Patents

Literature

301 results about "Test algorithm" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Testing Algorithms. This section provides an introduction to software testing and the testing of Artificial Intelligence algorithms. introduces software testing and focuses on a type of testing relevant to algorithms called unit testing. provides a specific example of an algorithm and a prepared suite of unit tests,...

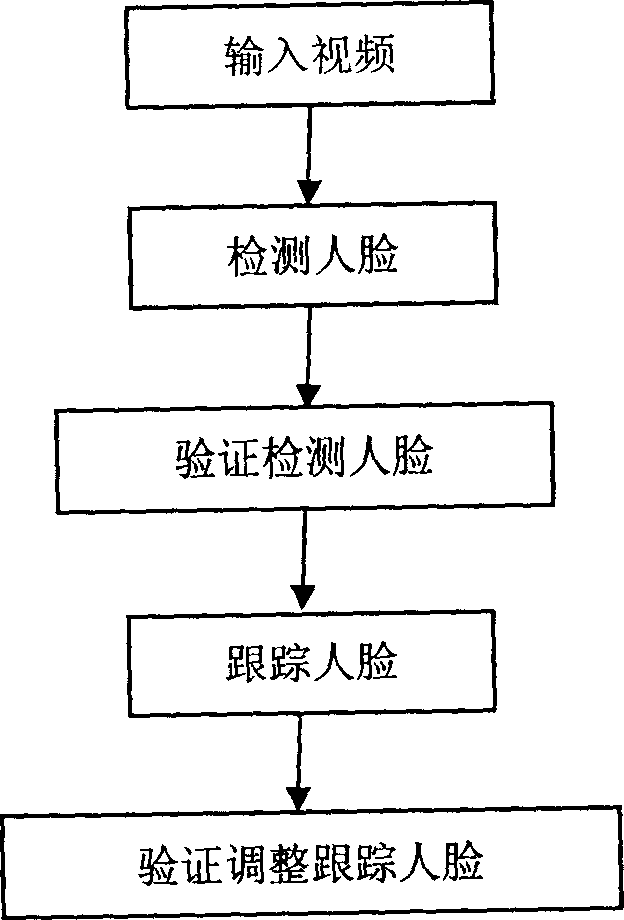

Method and system of real time detecting and continuous tracing human face in video frequency sequence

ActiveCN1794264AGood technical effectEliminate the effects of uneven lightingCharacter and pattern recognitionFace detectionMean-shift

This invention puts forward a method and a system for real time testing and continuous tracking of man-face in a video sequence including the following steps: carrying out a test algorithm to a man-face input video image, then applying a rough and fine two stages of test algorithm to verify the tested face, applying an object following algorithm to follow the verified one and verifying it by verifying the followed regions, which realizes a real time test to a positive and vertical man-face by a test method based on AdaBoost statistic hierarchical sorter and Mean shift and a square pattern property.

Owner:BEIJING VIMICRO ARTIFICIAL INTELLIGENCE CHIP TECH CO LTD

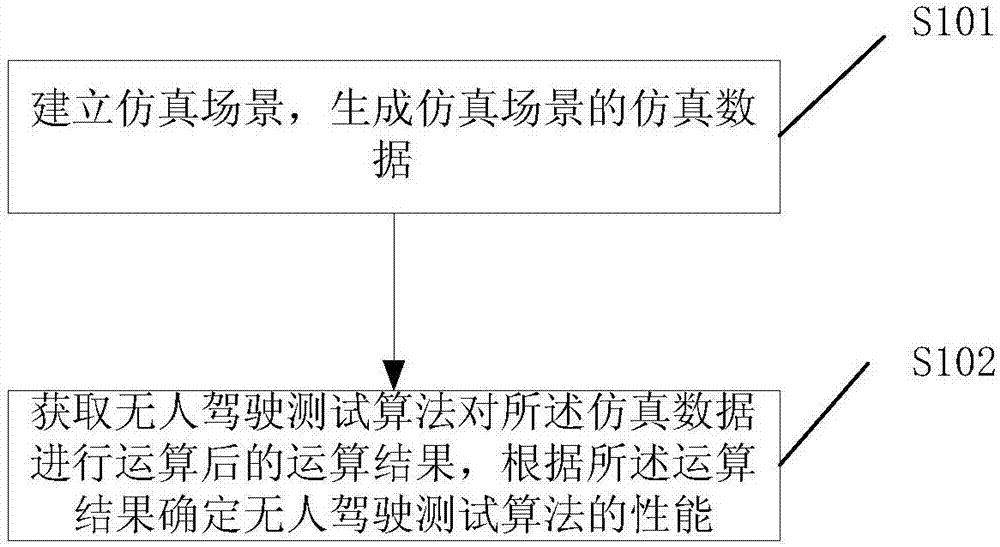

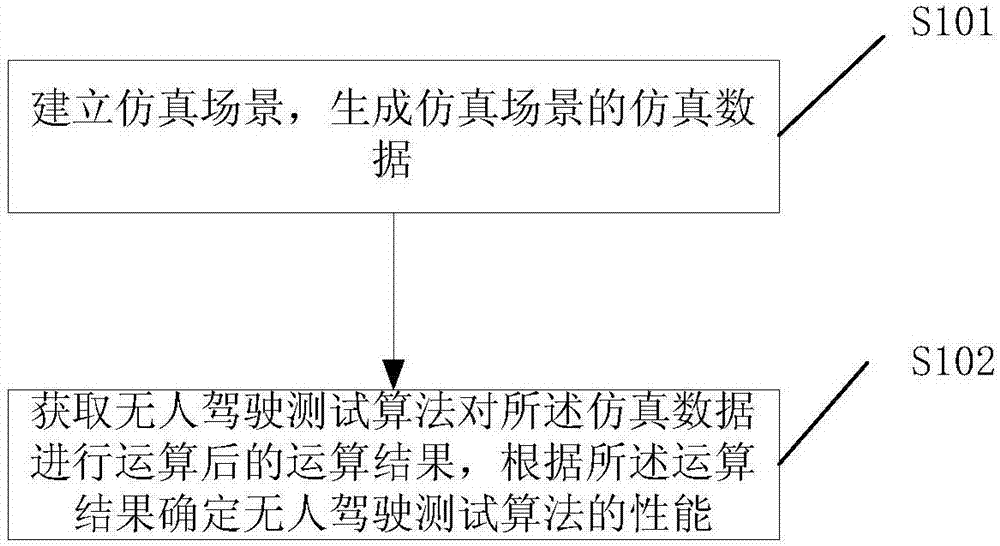

Driverless vehicle simulation test apparatus and electronic device

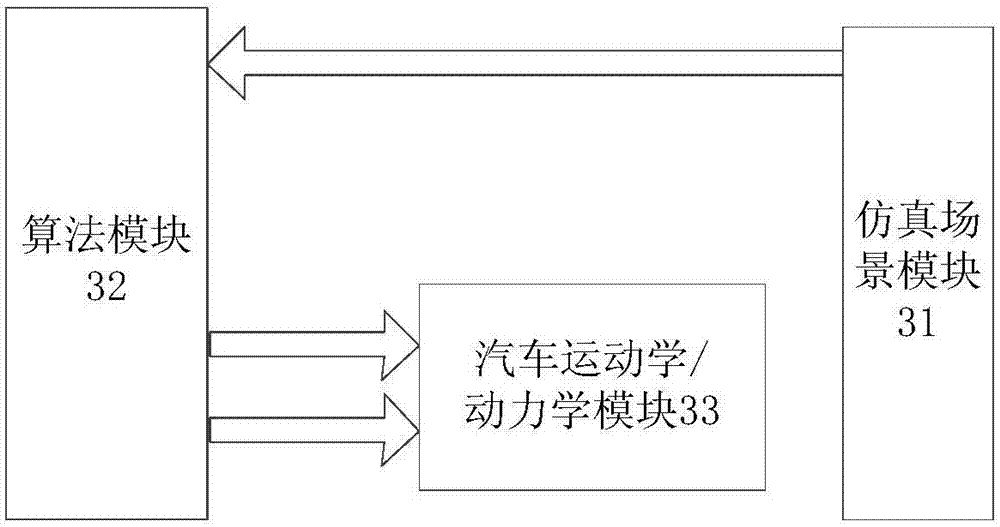

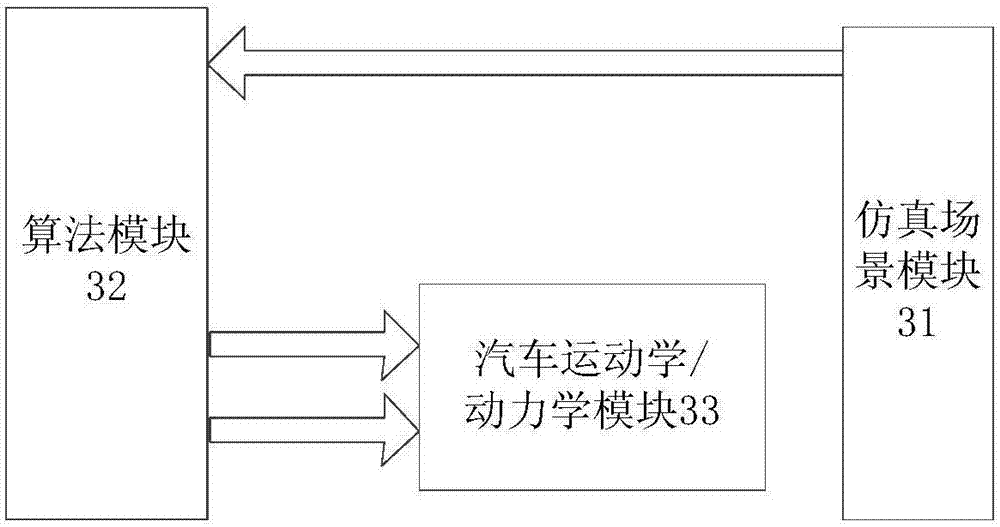

The embodiment of the invention discloses a driverless vehicle simulation test apparatus and an electronic device. The driverless vehicle simulation test apparatus comprises: a simulation scene establishing module, which is used for establishing a simulation scene and generating simulation data of the simulation scene; and a test operation module, which is used for obtaining an operation result after a driverless test algorithm conducts an operation on the simulation data and determining the performance of the driverless test algorithm on the basis of the operation result. The simulation sceneis established and the operation result of the driverless test algorithm is obtained, so that the performance of the driverless test algorithm is determined. In this way, an automobile simulation test scheme for testing complete automatic driving schemes is achieved.

Owner:FAFA AUTOMOBILE (CHINA) CO LTD

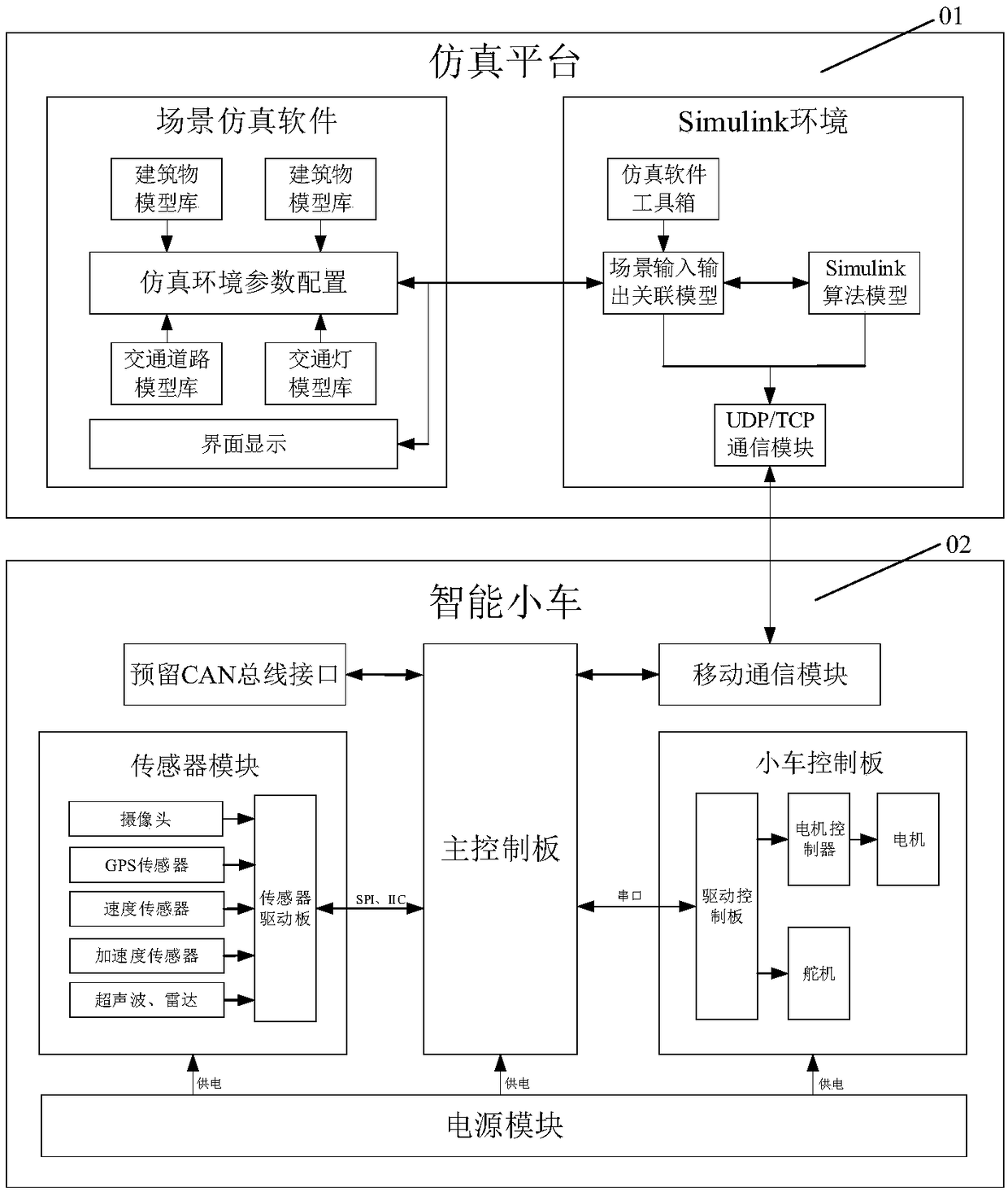

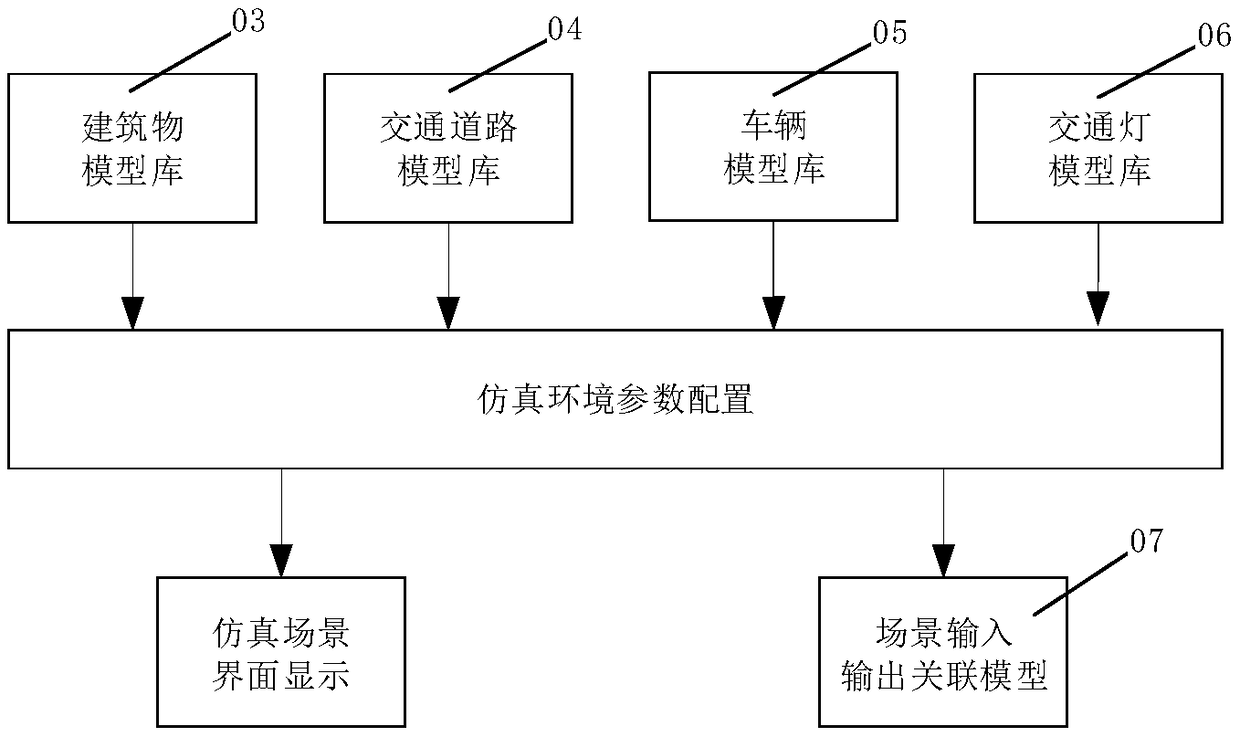

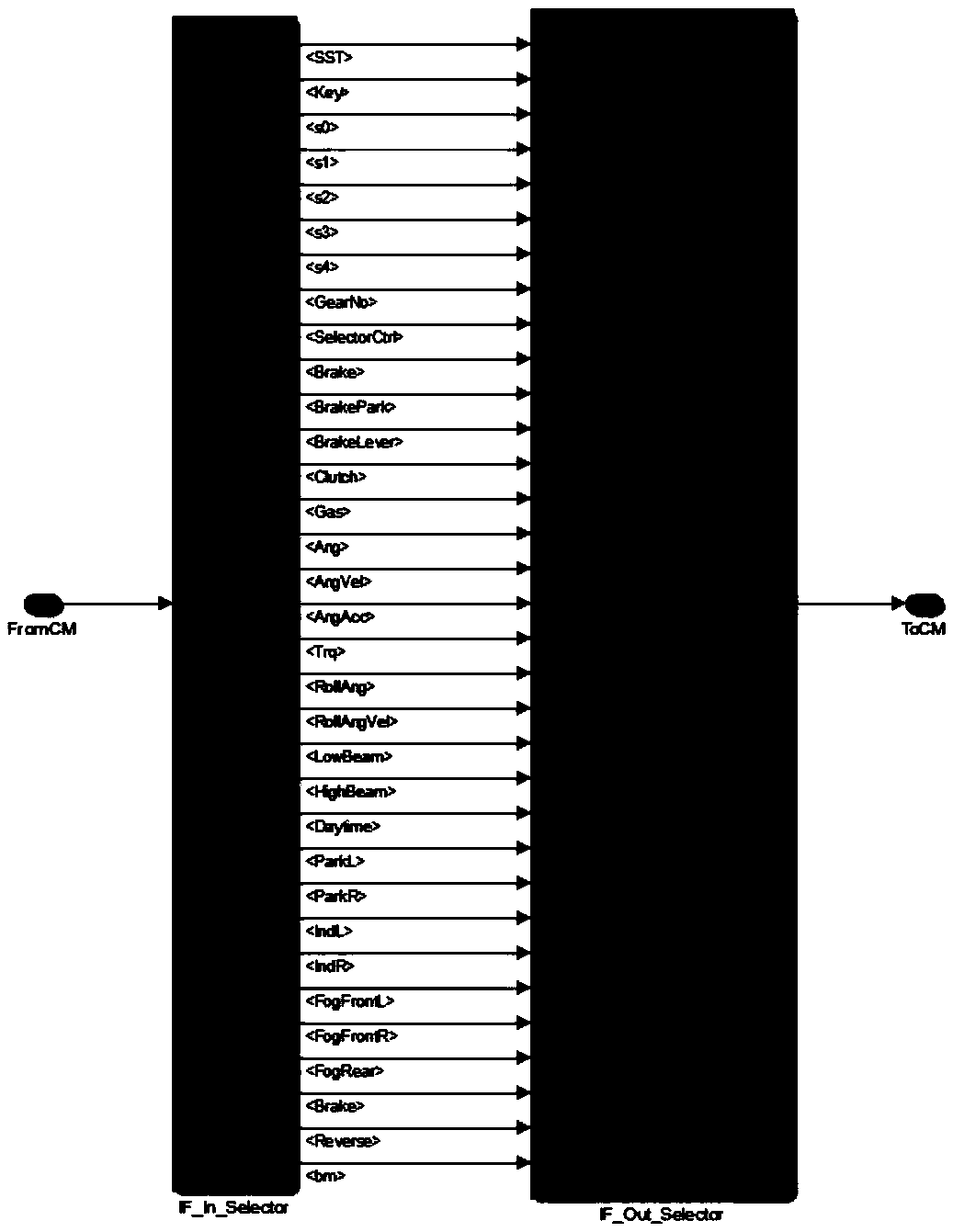

Intelligent connected vehicle in-the-loop simulation and test and verification system and method

The invention provides an intelligent connected vehicle in-the-loop simulation and test and verification system and method. Simulation of the intelligent trolley operation scene is performed mainly byIPG CarMaker, CarSIM and other tools. The system is composed of the functions of Simulink data simulation calculation, transmission of the simulation scene parameters to the intelligent trolley for simulation of the real scene, intelligent trolley image acquisition and display and test analysis. The intelligent trolley side is mainly responsible for environmental perception and control algorithmverification of the intelligent connected vehicle and is composed of a trolley and a control module, a driving module, a communication module and a sensor module to act as the carrier of loading the test algorithm software and the sensor and the communication module required to be tested. According to the system, the cost and the dangerousness of the intelligent connected vehicle test can be reduced, onsite verification of the intelligent vehicle system can be performed in the real site, the research work of modeling, simulation and control and other aspects for vehicle-road coordination and other application in different simulation traffic scenes and thus a lot of data support can be provided for the research of the intelligent connected vehicle.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

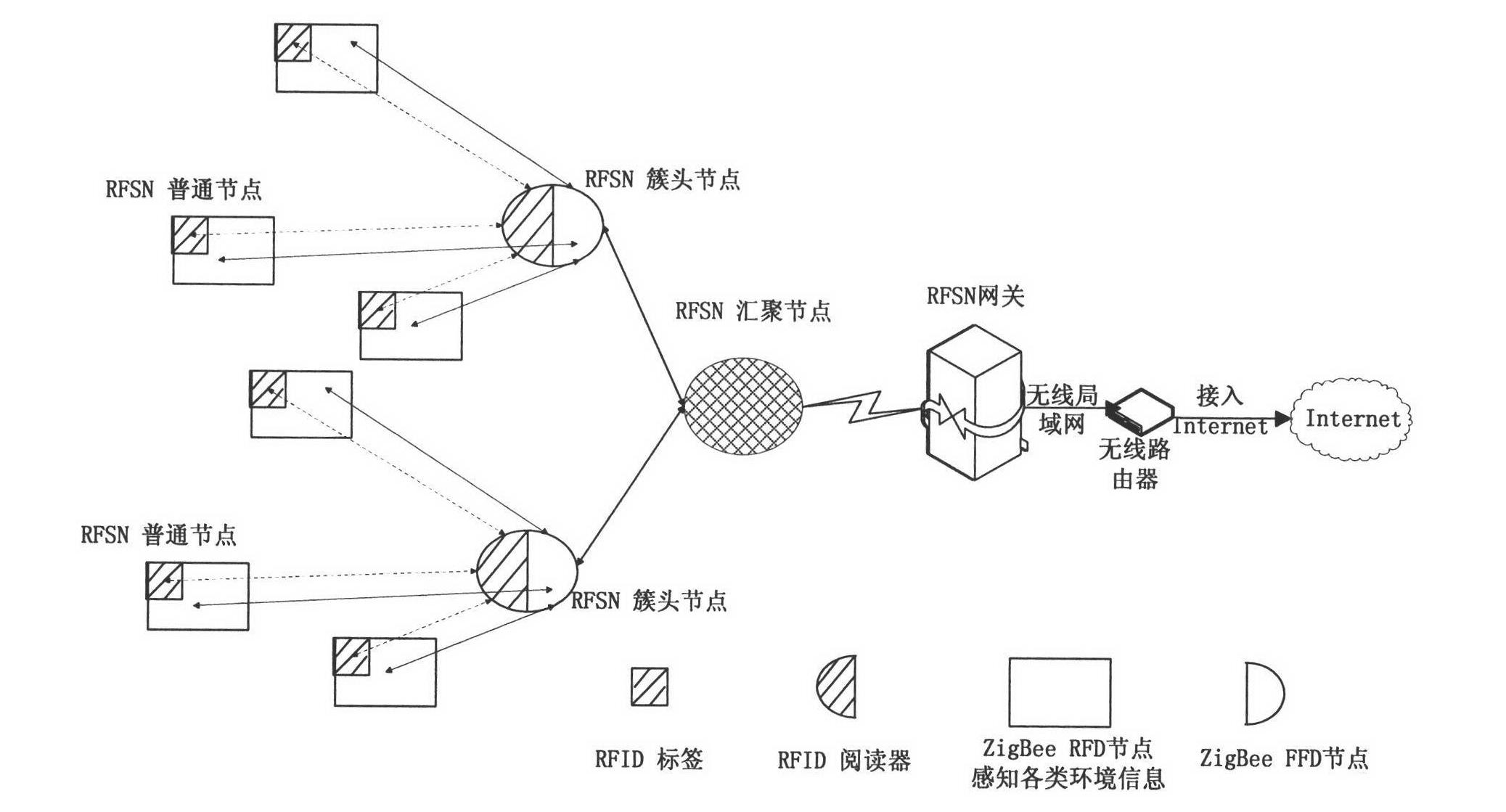

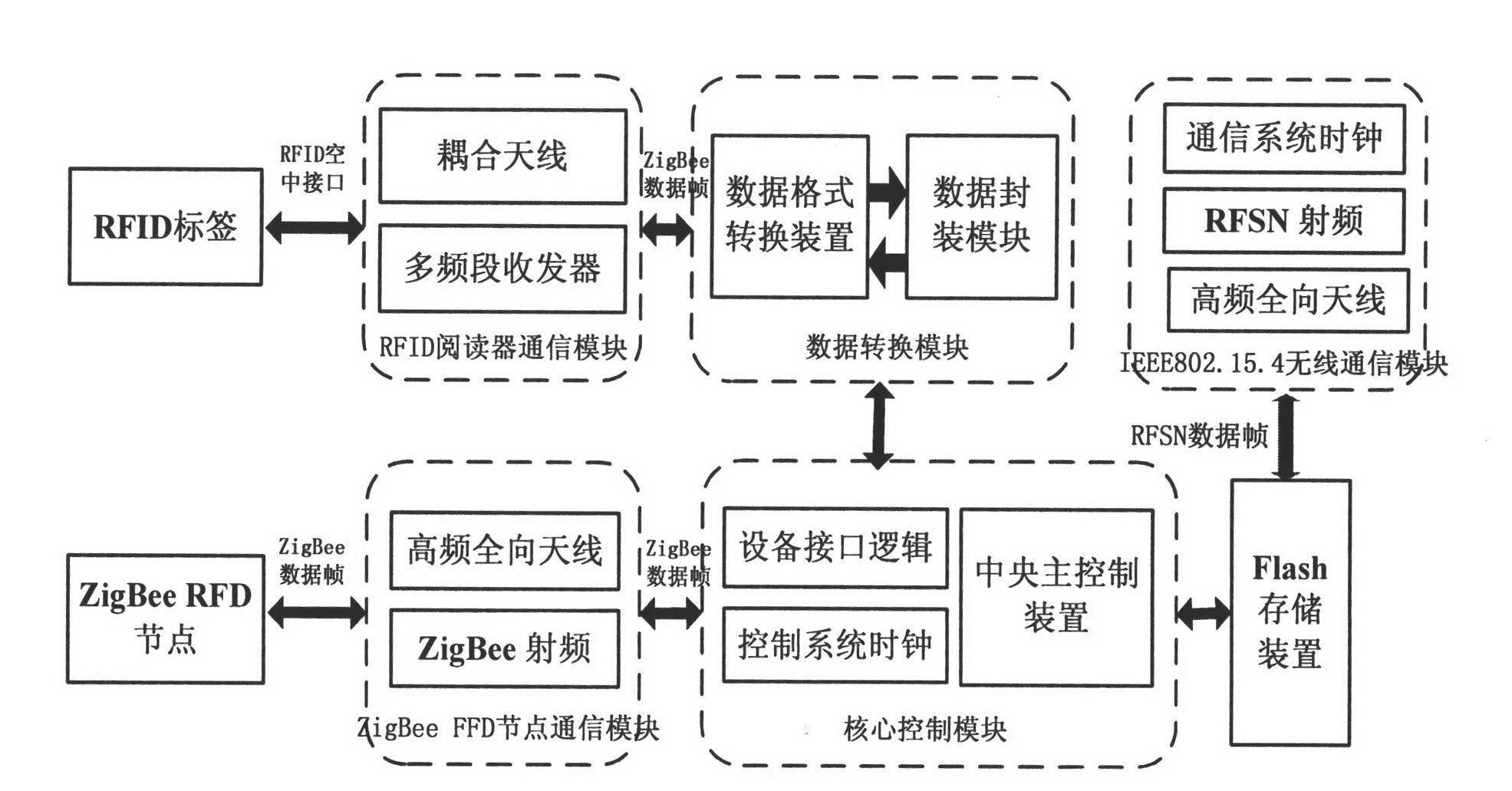

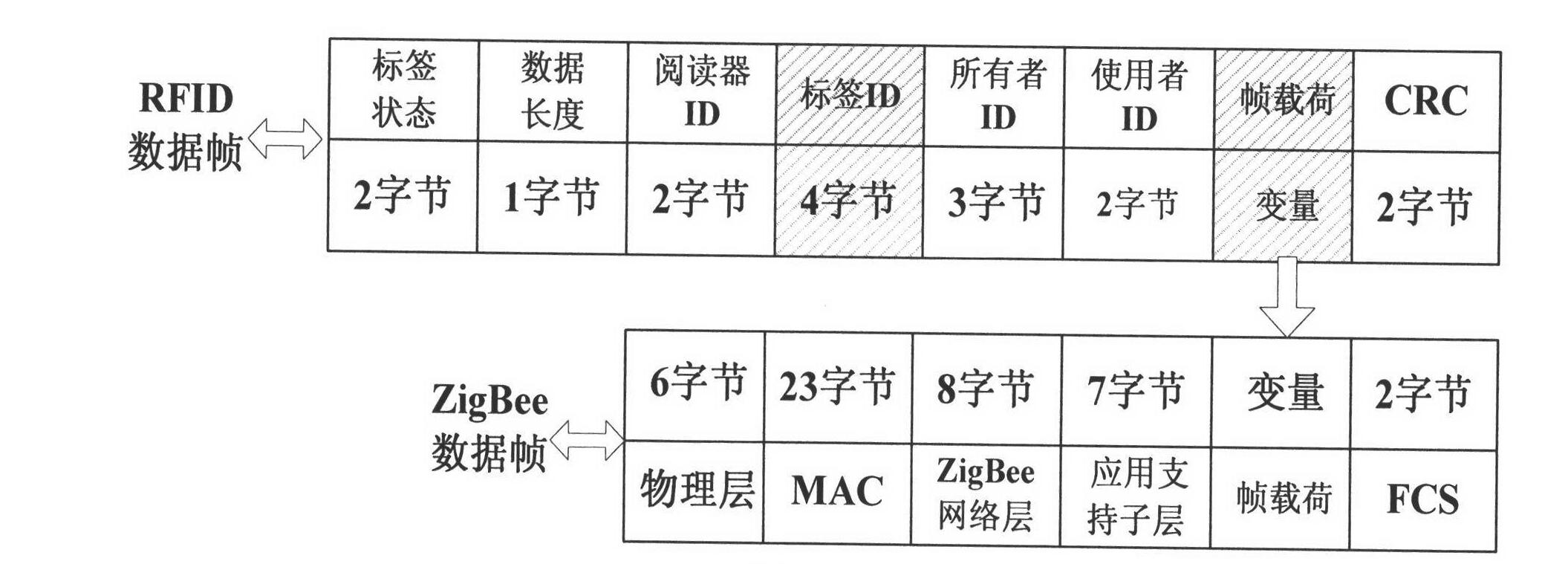

Method for tracking and locating container by adopting label sensor network

ActiveCN102325344AComprehensive monitoringImprove access to informationNetwork traffic/resource managementNetwork topologiesRelevant informationTest algorithm

At present, an RFID (Radio Frequency Identification Device) technology is used in the container physical distribution process, however, the application of the RFID technology in the field of container physical distribution tracking and locating is limited due to defects and limitations of an RFID per se. The invention provides a method for tracking and locating a container by adopting a label sensor network, and in the method, the sensor network is fused with an RFID network, so that transmitting various types of radio frequency label data is realized by a ZigBee network through gateway level design, hardware module design, protocol fusion and the like. By using the label sensor network, the transmission radius of the traditional RFID network is increased, and a series of problems such as incapability of sensing object states, poor an-interference performance and the like of the RFID are solved. Positional information of the container is calculated through a subtriangular inner pointer testing algorithm. Relevant information such as a position, a safety condition, humidity and temperature change and the like of the container can be gotten by a shipper or manager through a computer and a mobile phone, and once unforeseen circumstances such as container damage, transportation line change or delay and the like happen, alarm information can be received in time.

Owner:NANJING UNIV OF POSTS & TELECOMM

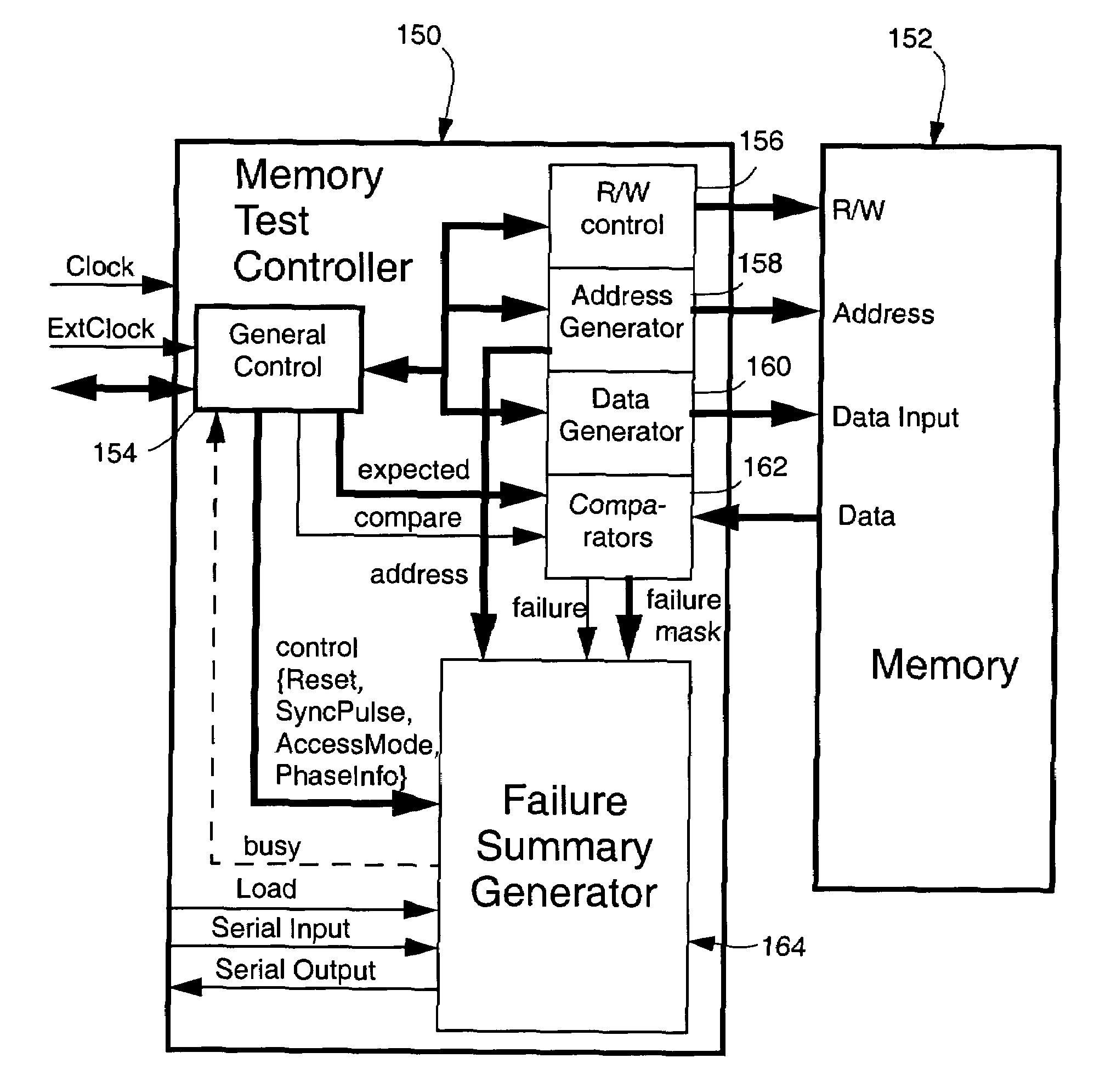

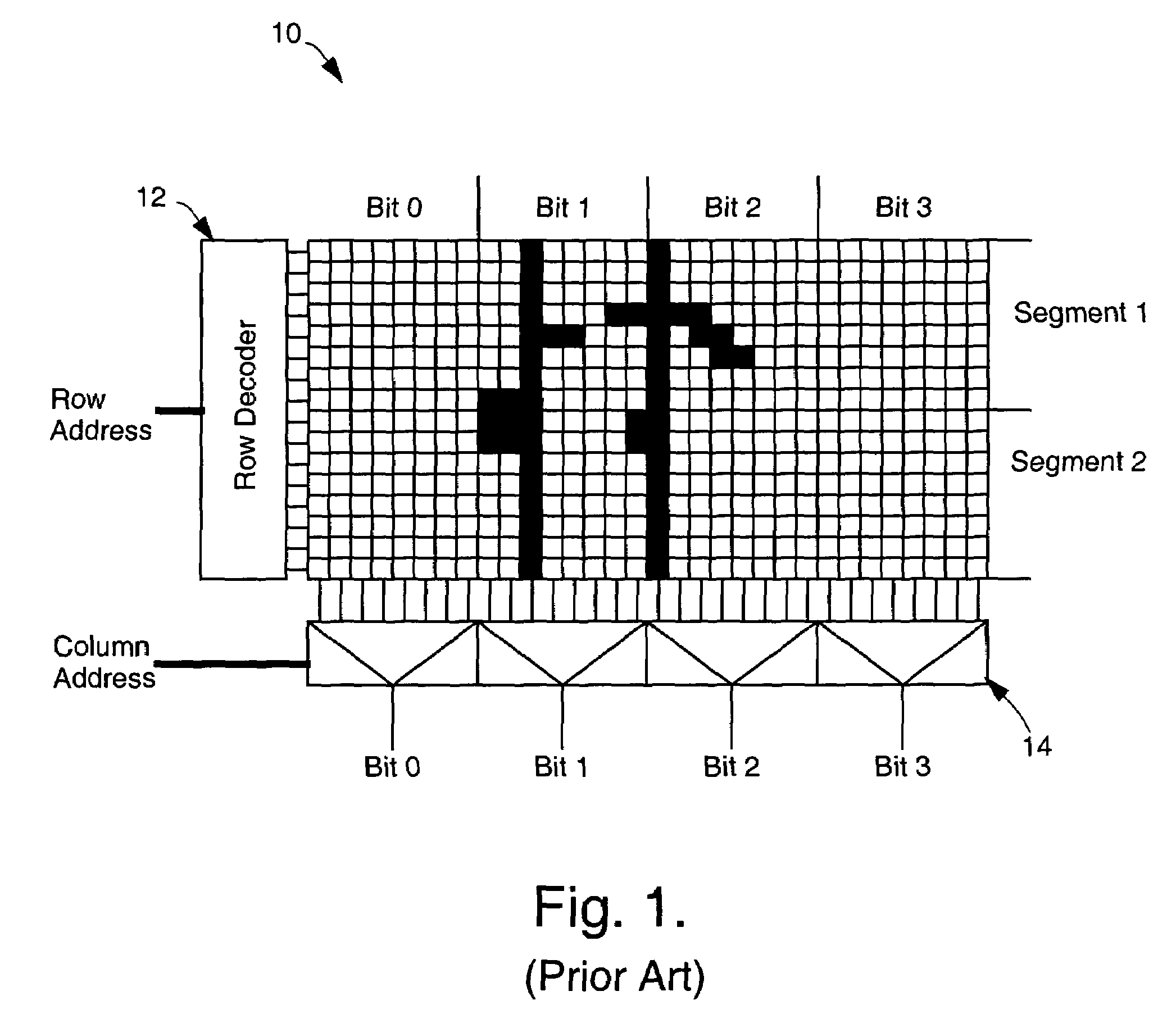

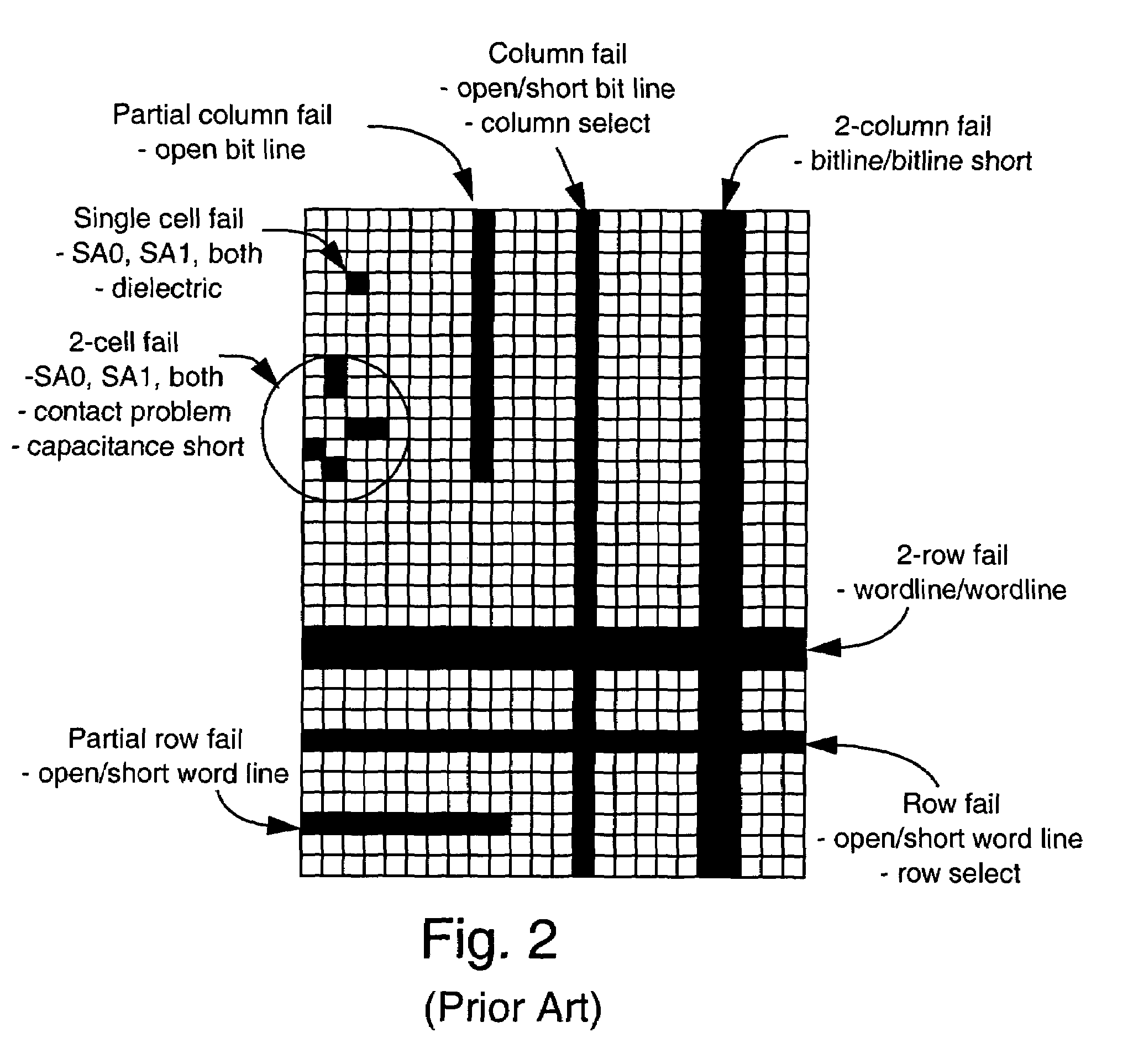

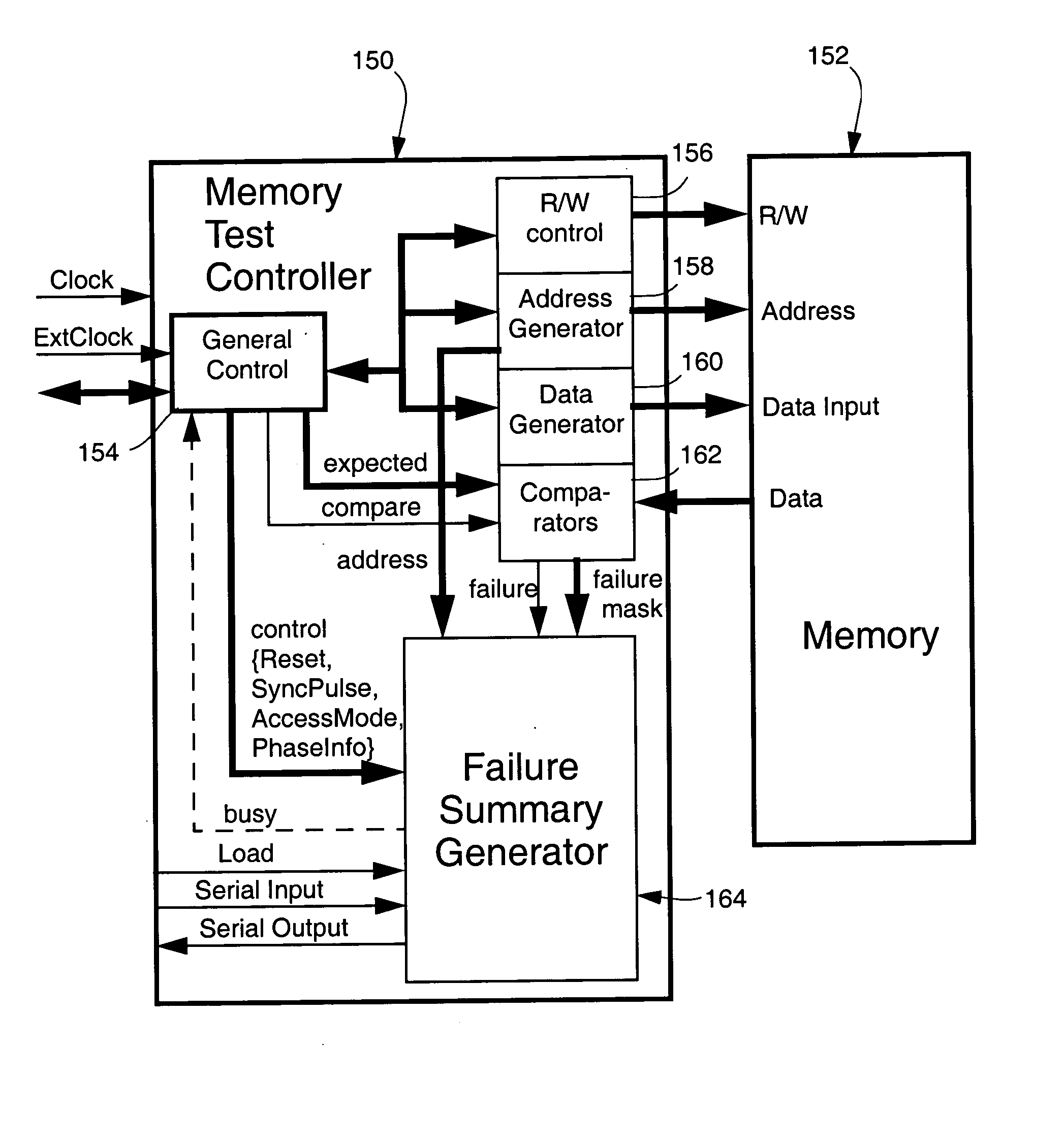

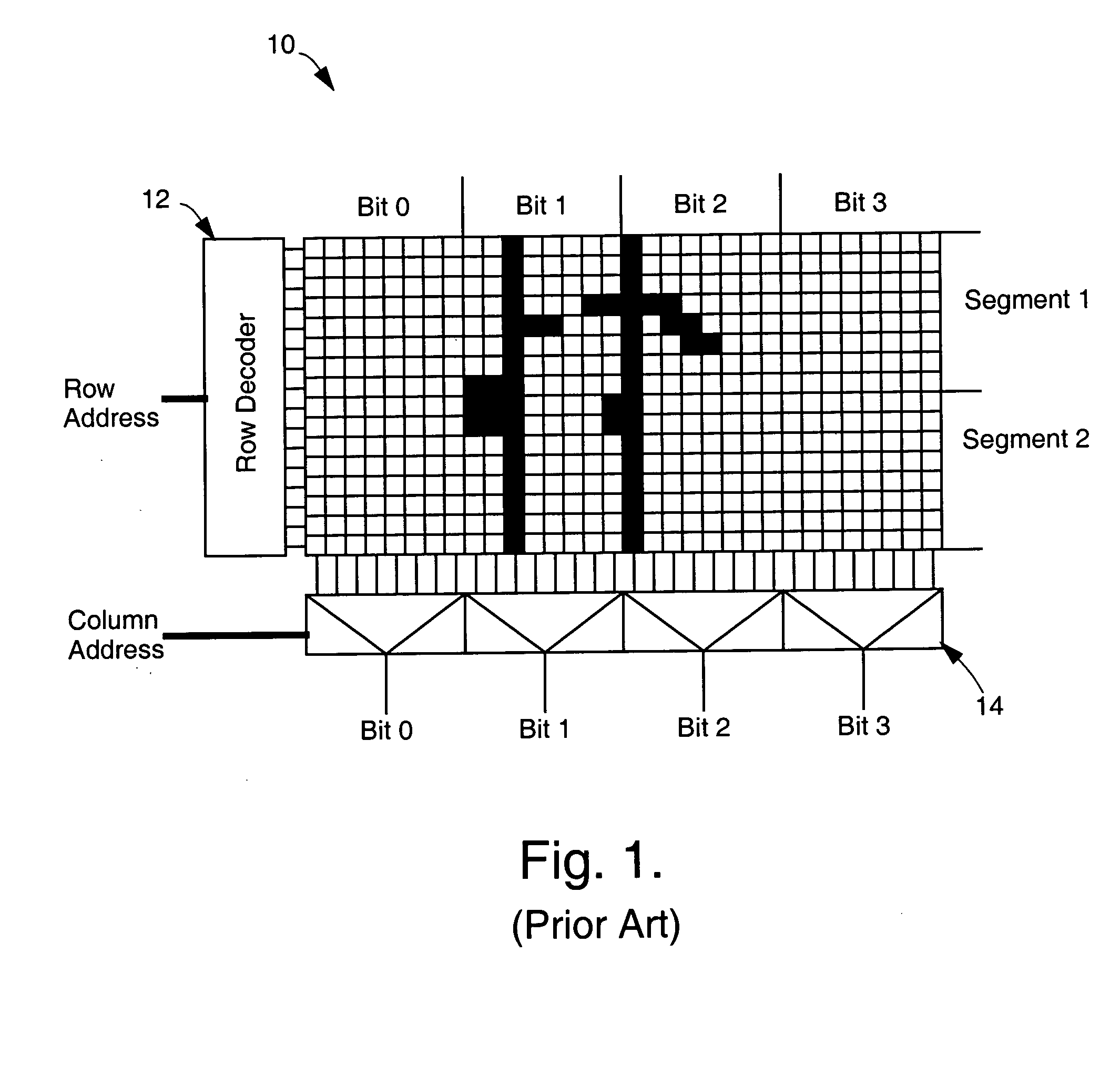

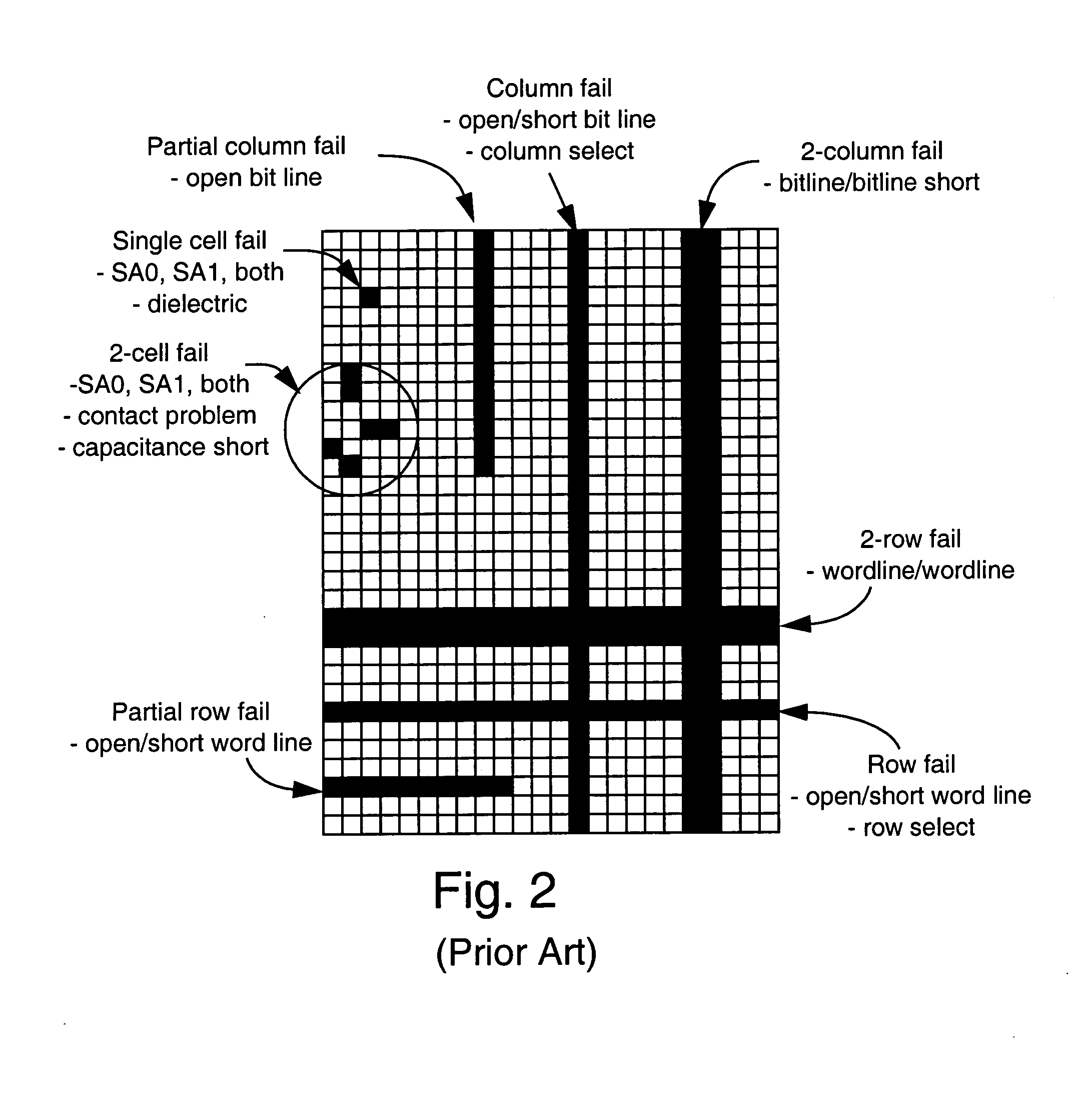

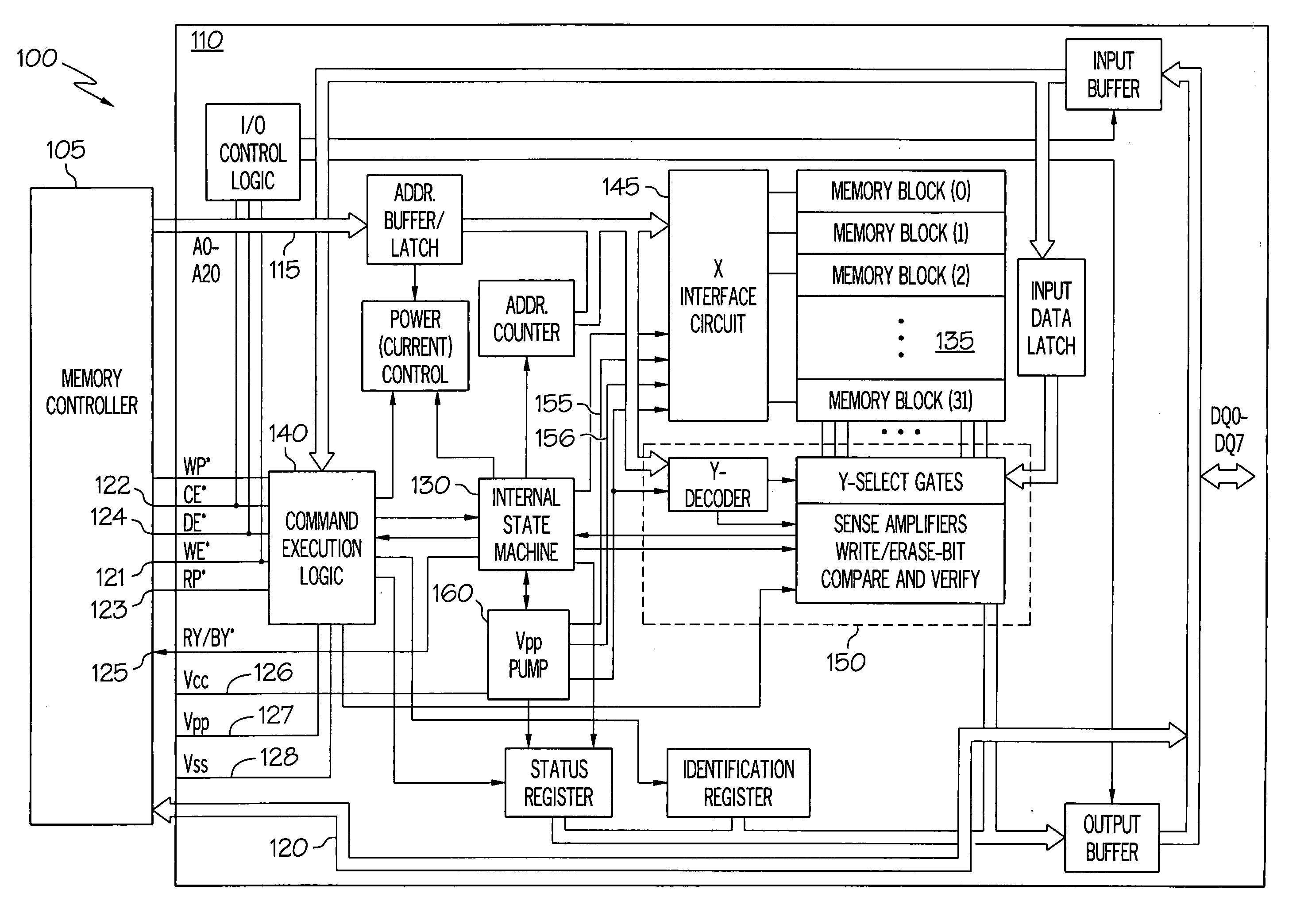

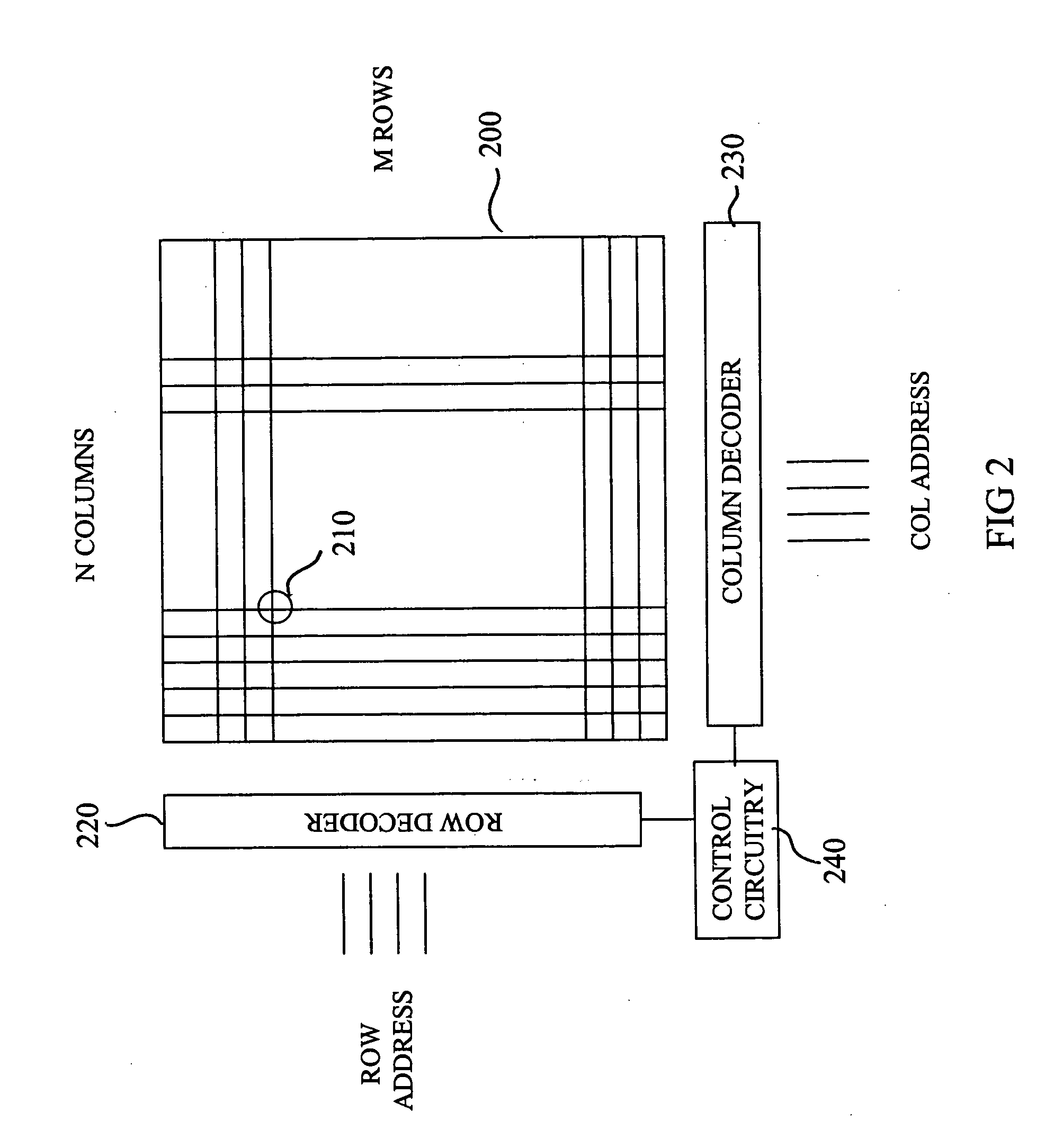

Method and circuit for collecting memory failure information

A method and circuit for collecting memory failure information on-chip and unloading the information in real time while performing a test of memory embedded in a circuit comprises, for each column or row of a memory under test, testing each memory location of the column or row according to a memory test algorithm under control of a first clock, selectively generating a failure summary on-circuit while testing each column or row of the memory; and transferring the failure summary from the circuit under control of a second clock within the time required to test the next column or row, if any, of the memory under test.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

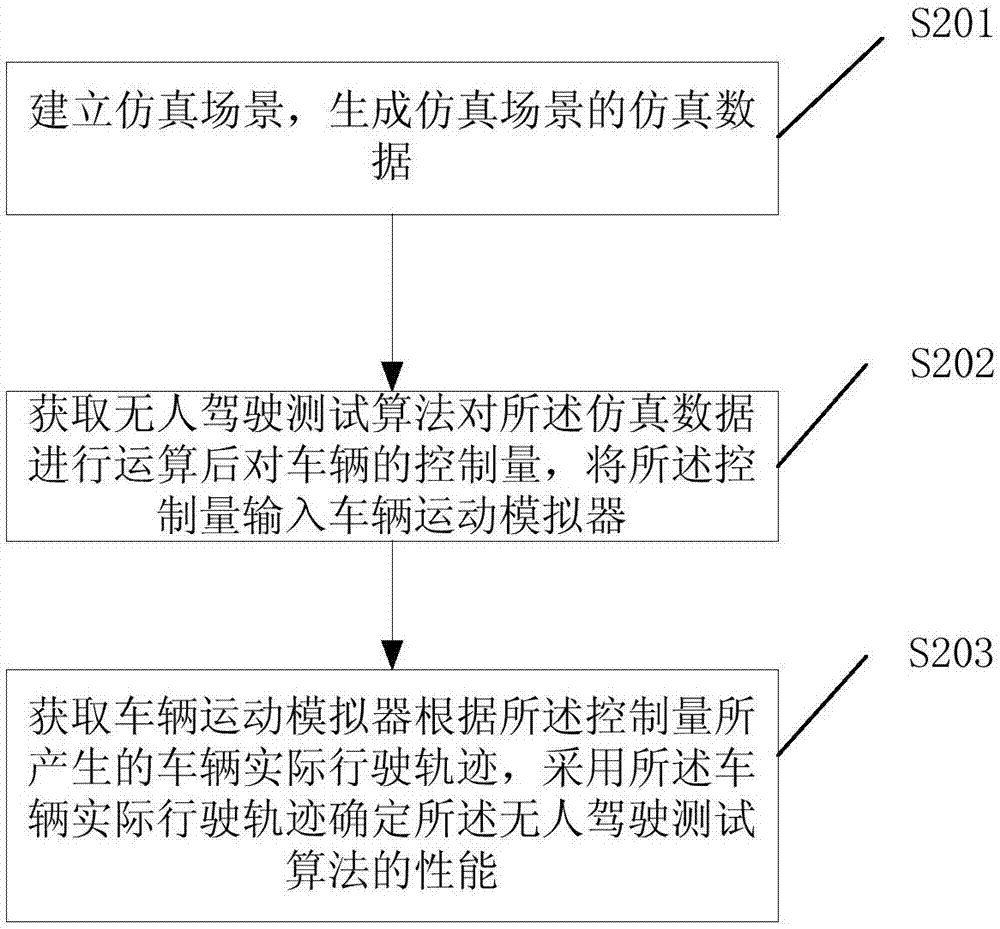

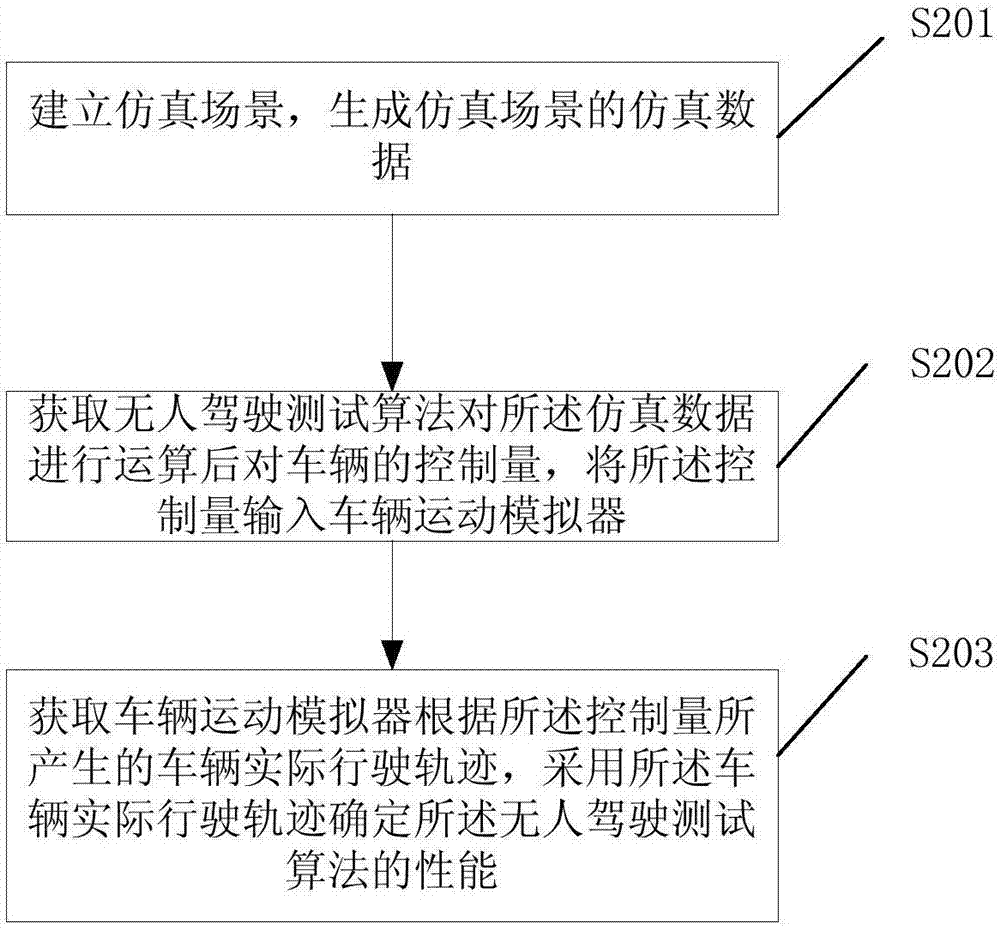

Driverless vehicle simulation test method

The embodiment of the invention discloses a driverless vehicle simulation test method. The driverless vehicle simulation test method includes the following steps: establishing a simulation scene, andgenerating simulation data of the simulation scene; and obtaining an operation result after a driverless test algorithm conducts an operation on the simulation data, and determining the performance ofthe driverless test algorithm on the basis of the operation result. The simulation scene is established and the operation result of the driverless test algorithm is obtained, so that the performanceof the driverless test algorithm is determined. In this way, an automobile simulation test scheme for testing complete automatic driving schemes is achieved.

Owner:FAFA AUTOMOBILE (CHINA) CO LTD

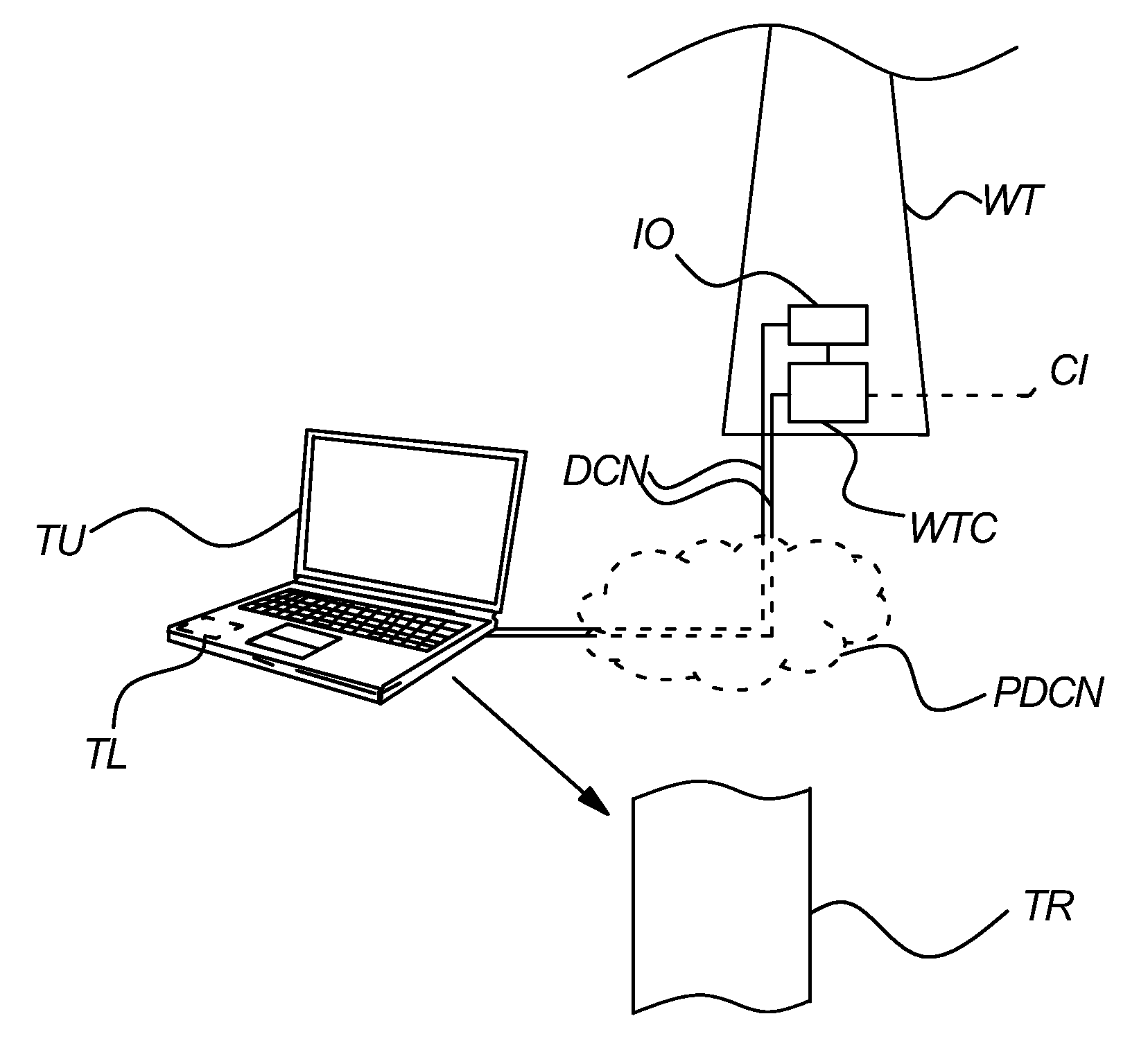

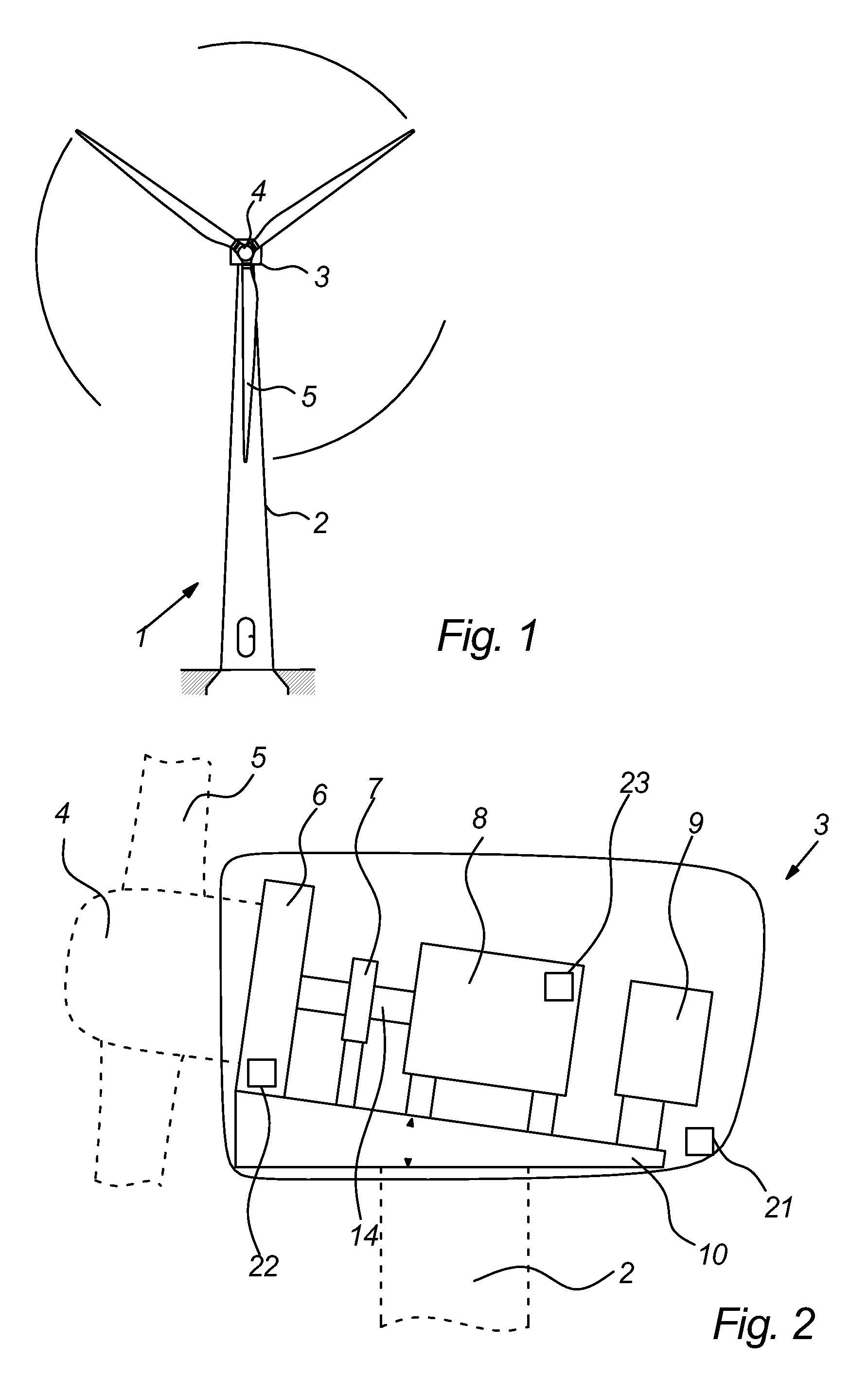

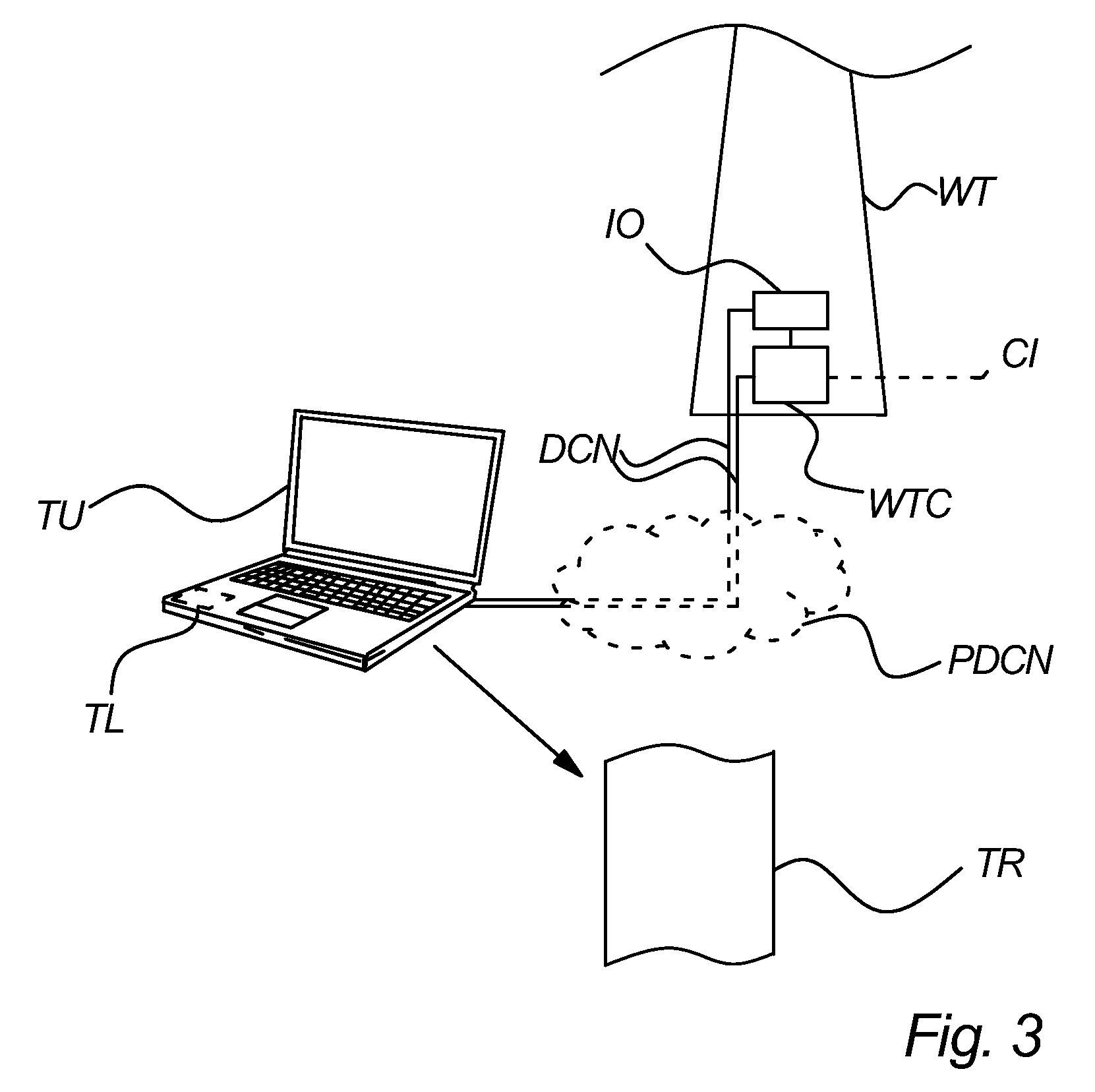

Method And System Of Performing A Functional Test Of At Least One Embedded Sub-Element Of A Wind Turbine

A method of performing a functional test of at least one embedded sub-element of a wind turbine, the wind turbine being controlled by a control algorithm of a wind turbine controller, includes the steps of: executing a predefined event pattern activating at least one sub-element of the wind turbine, obtaining measure data on the basis of measurements of at least one sub-element according to the predefined event pattern, and relating the measure data to predefined reference data and establishing a test result indicating the condition of the embedded sub-element on the basis thereof. The predefined event pattern is executed by a test algorithm overriding the control algorithm of the wind turbine controller at least partly. It is a very advantageous feature according to the present invention that the sub-elements may be tested while being embedded in the wind turbine.

Owner:VESTAS WIND SYST AS

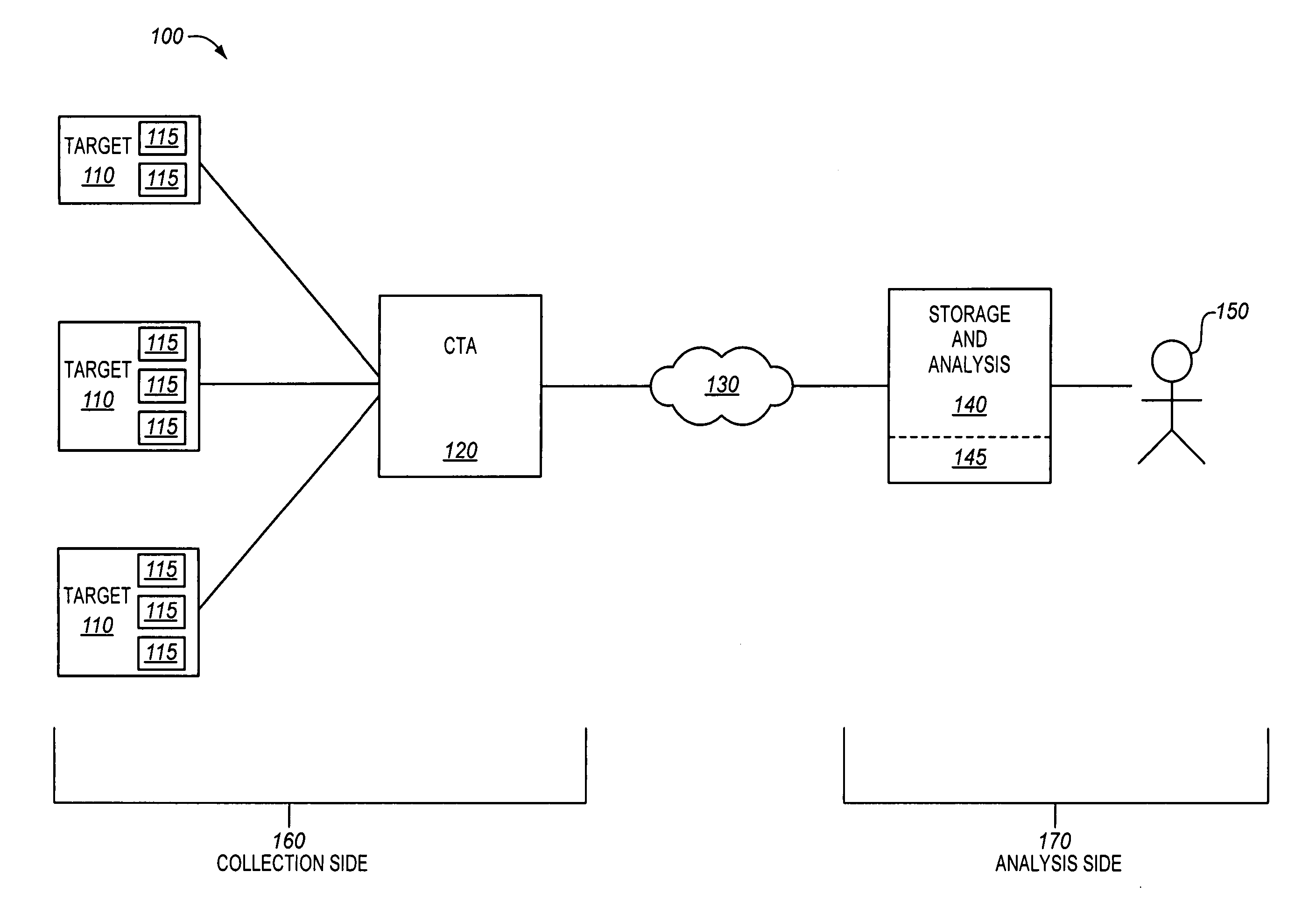

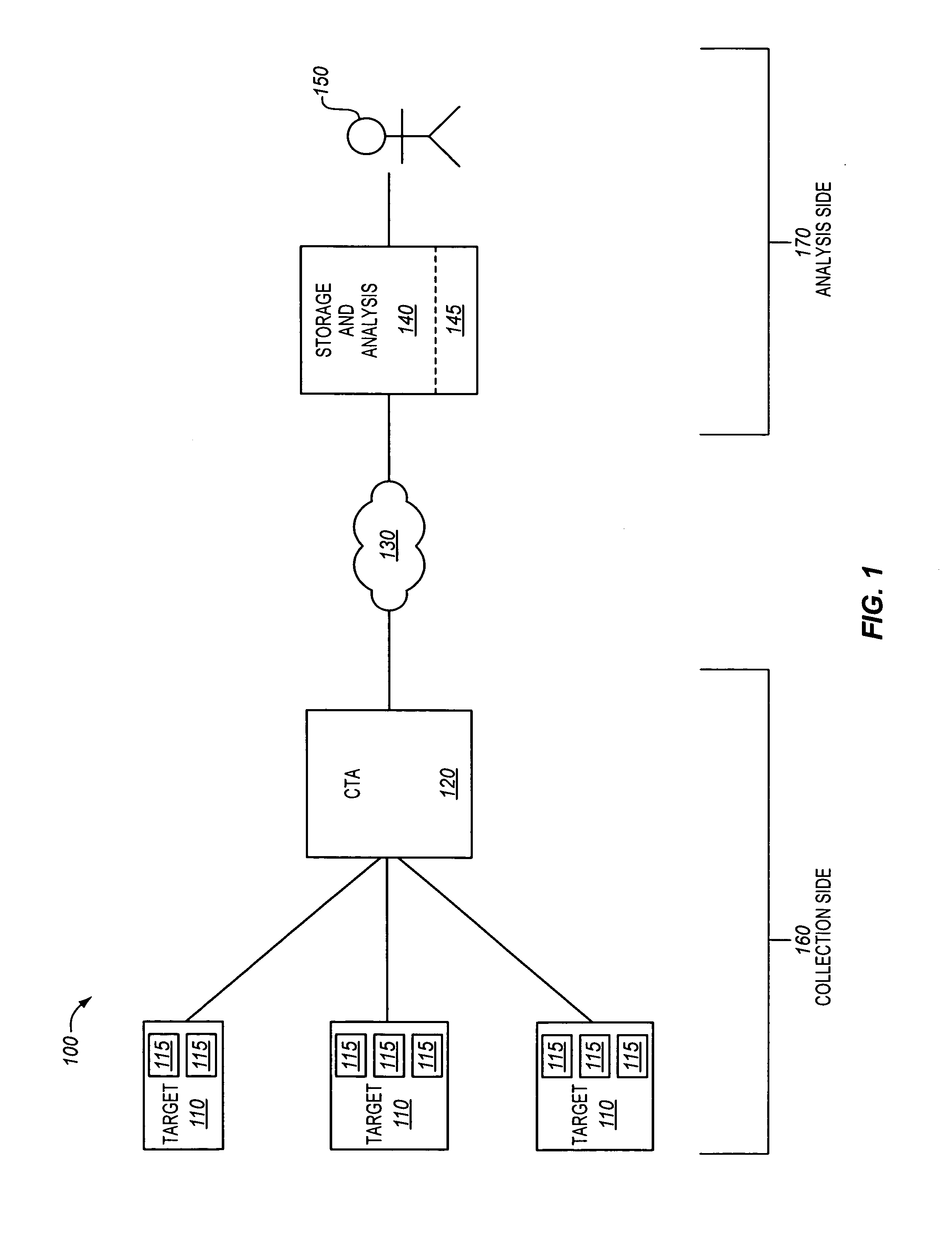

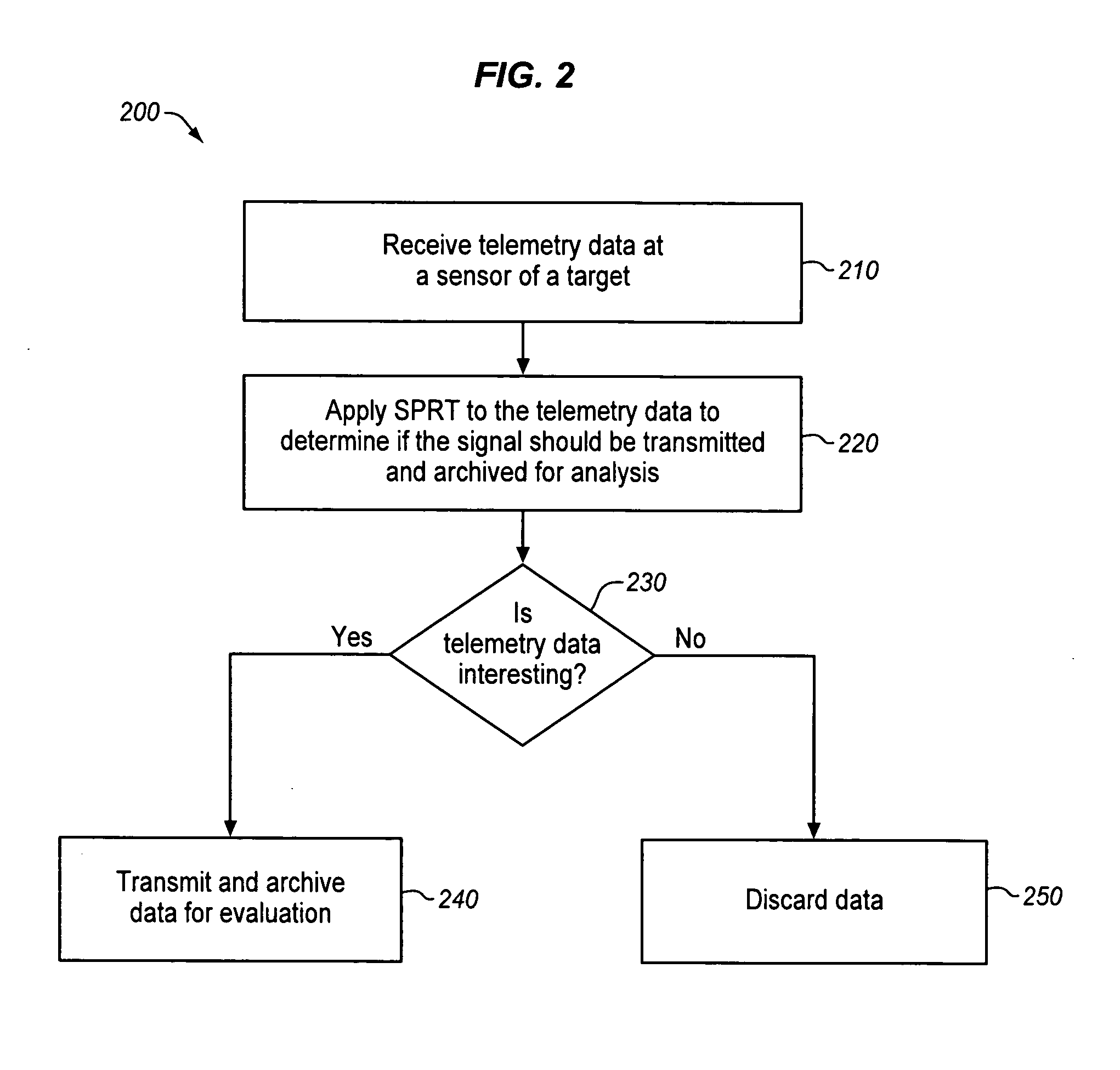

High-efficiency time-series archival system for telemetry signals

ActiveUS20070226554A1High-efficiency time-series archivingElectronic circuit testingError detection/correctionSequential probability ratio testTest algorithm

In one embodiment, a method and apparatus for high-efficiency time-series archiving for computer server telemetry signals is disclosed. The method includes selecting one or more telemetry signals of a plurality of telemetry signals by a sequential probability ratio test (SPRT) algorithm, the SPRT algorithm identifying the one or more telemetry signals as not consistent with normal behavior of the plurality of telemetry signals, injecting synthetic samples around the selected one or more telemetry signals to create a continuous time series telemetry sample, and analyzing the continuous time series telemetry sample to identify leading indicators of faults in the target. Other embodiments are also disclosed.

Owner:ORACLE INT CORP

Method and circuit for collecting memory failure information

ActiveUS20050047229A1Quantity minimizationError detection/correctionDigital storageTest algorithmComputer science

A method and circuit for collecting memory failure information on-chip and unloading the information in real time while performing a test of memory embedded in a circuit comprises, for each column or row of a memory under test, testing each memory location of the column or row according to a memory test algorithm under control of a first clock, selectively generating a failure summary on-circuit while testing each column or row of the memory; and transferring the failure summary from the circuit under control of a second clock within the time required to test the next column or row, if any, of the memory under test.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

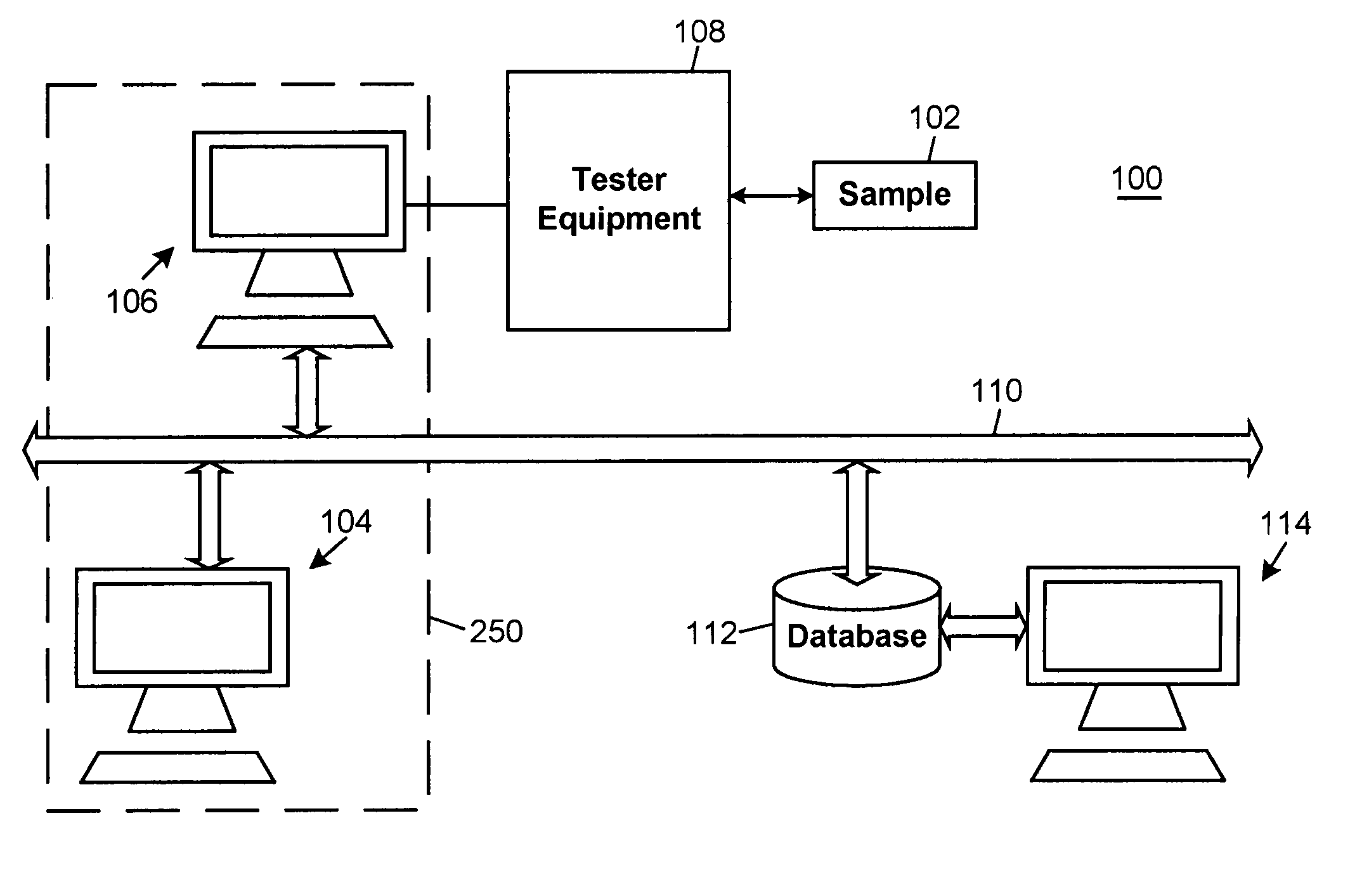

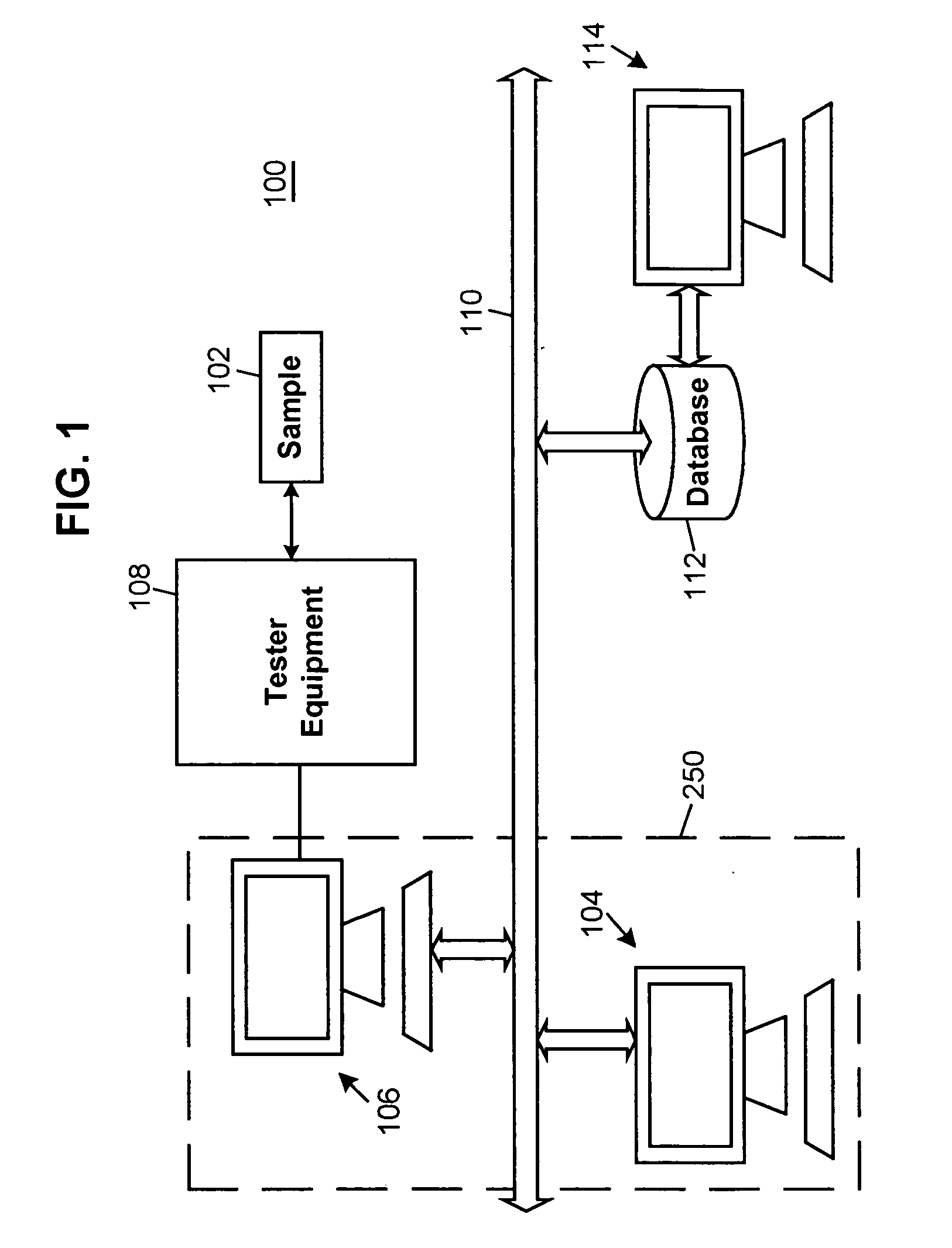

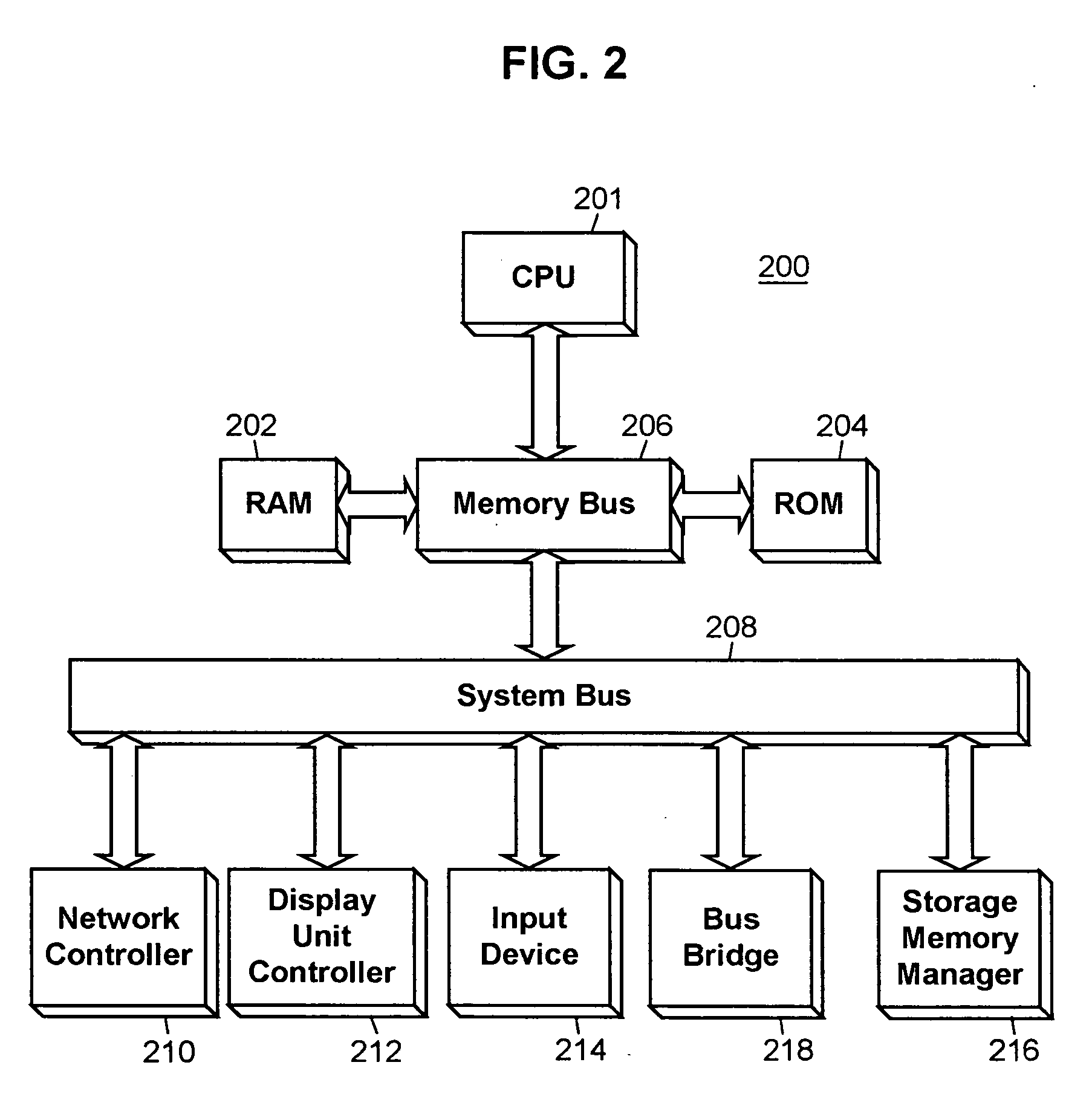

Automated and customizable generation of efficient test programs for multiple electrical test equipment platforms

InactiveUS20050273685A1Electronic circuit testingError detection/correctionDevice materialTest algorithm

Automating techniques provide a way to create efficient test programs for characterizing semiconductor devices, such as those on a silicon die sample. Typically, test program creation is a drawn out process involving data entry for every test to be run as part of the test program. The described techniques improve test algorithm selection and automatically populate the test algorithm data in creating the test program. The automatic population may occur by accessing test structure, header, and test algorithm catalogs. The test structure catalog contains physical data for the test program, while the header catalog contains global parameter values. The test algorithm catalog has all of the various test algorithms that may be run in a given test, where these test algorithms may be in a template form and specific to any number of different test language abstractions. After test program creation, a validation process is executed to determine if the test program data is valid. Invalid data may be flagged, in an example. Once validated, techniques are described for converting the validated test program into an executable form, by formatting the various test algorithm data in the test program into a form compatible with the applicable test language abstraction selected by the user or the tester.

Owner:INTEL CORP

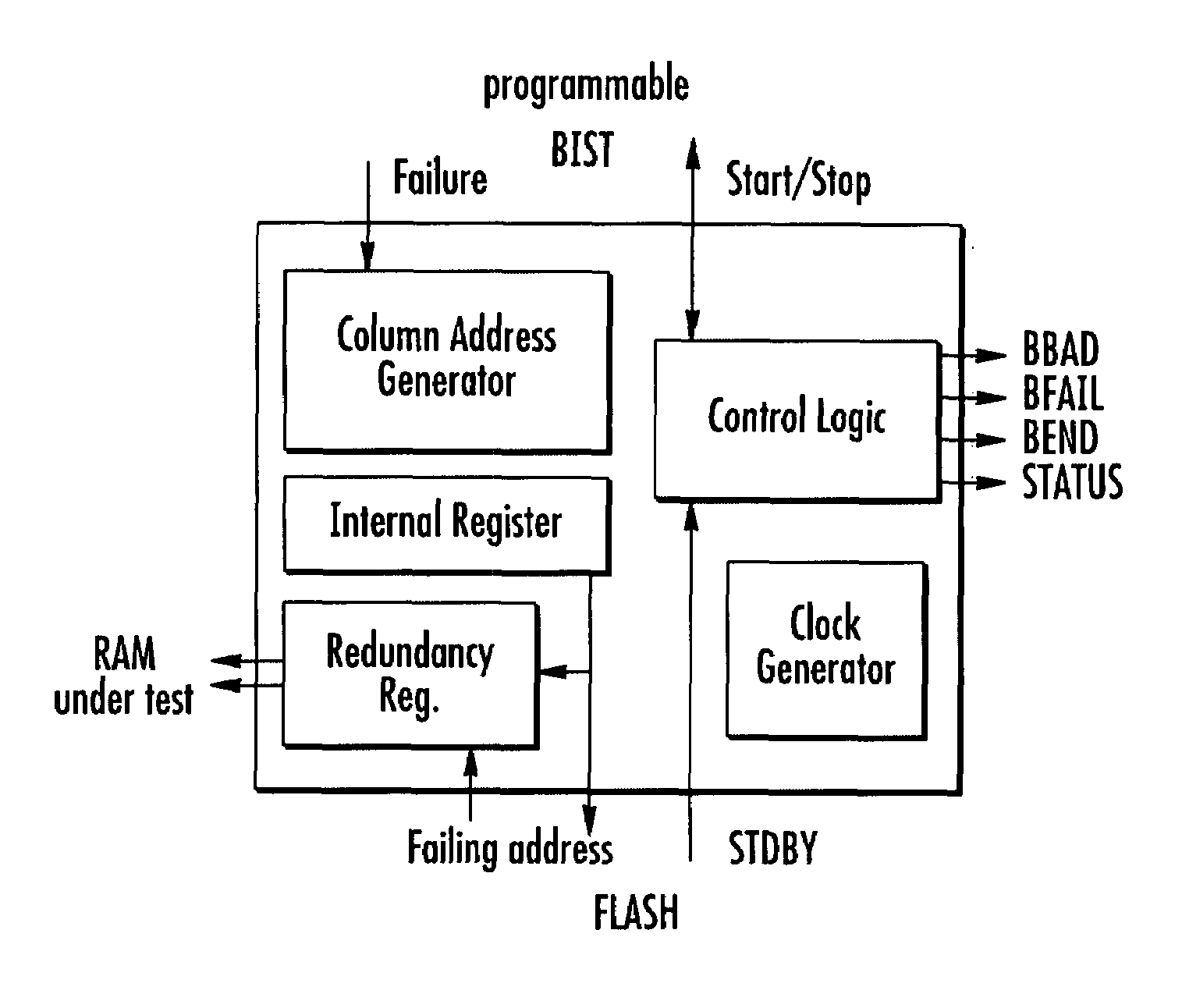

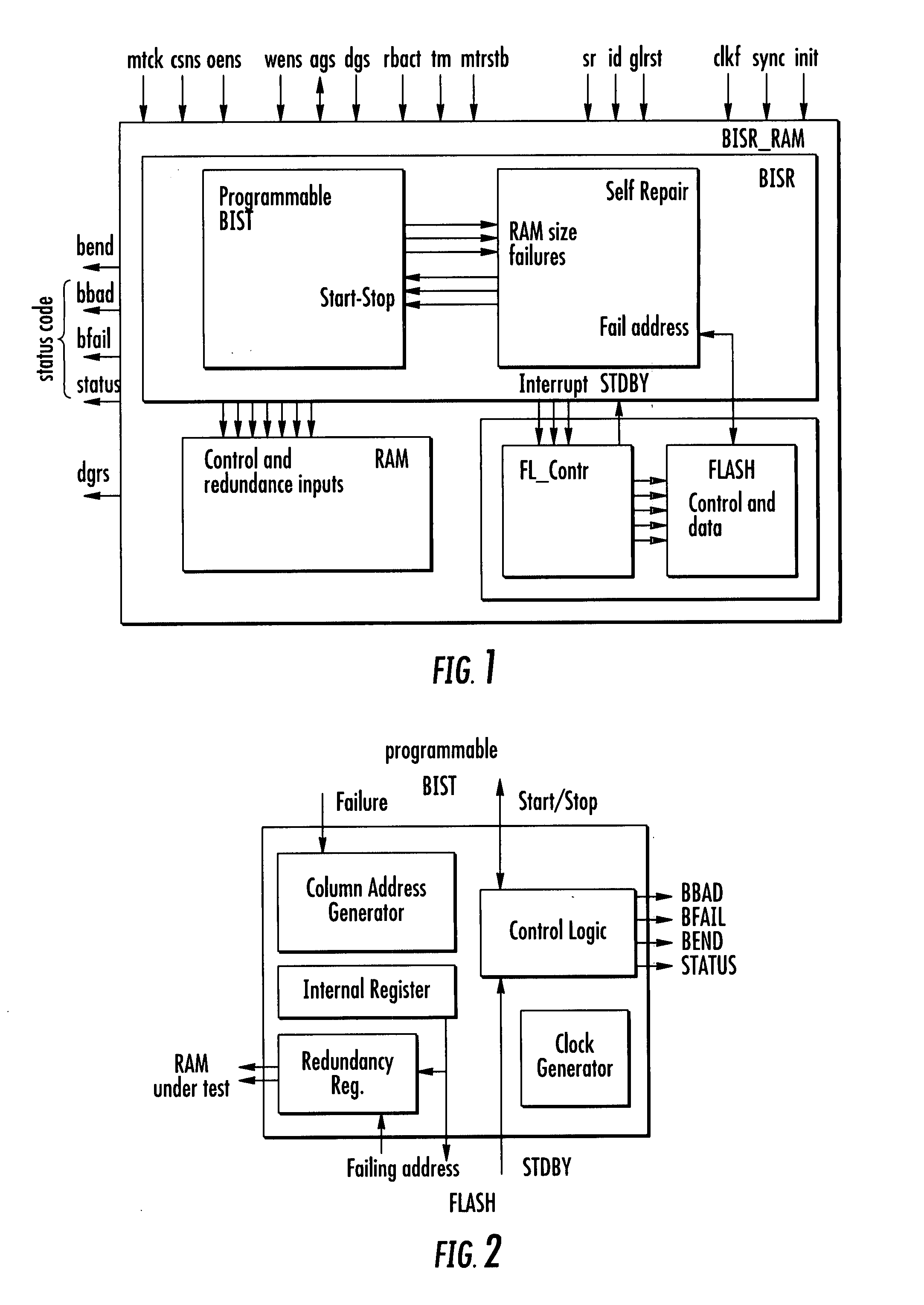

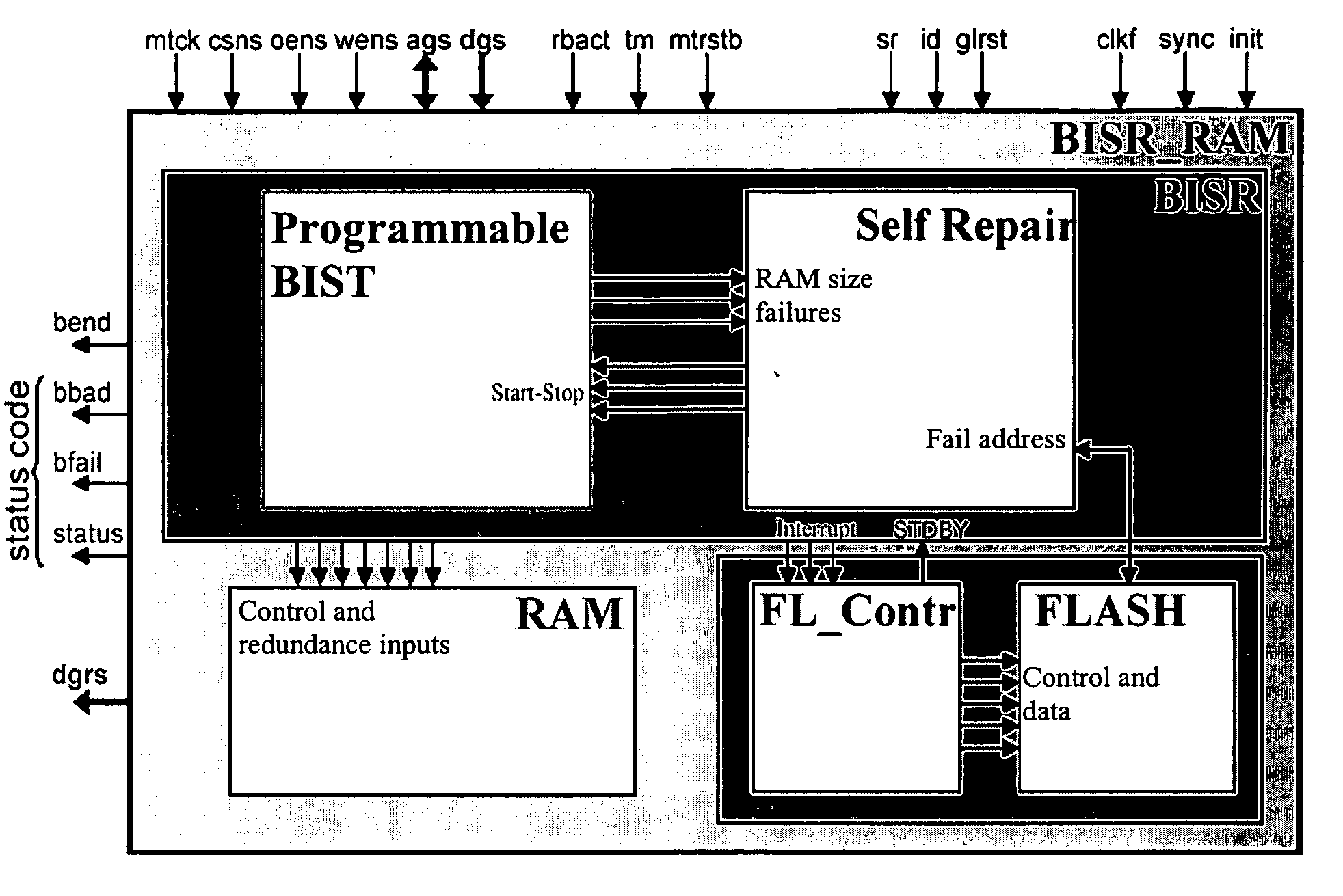

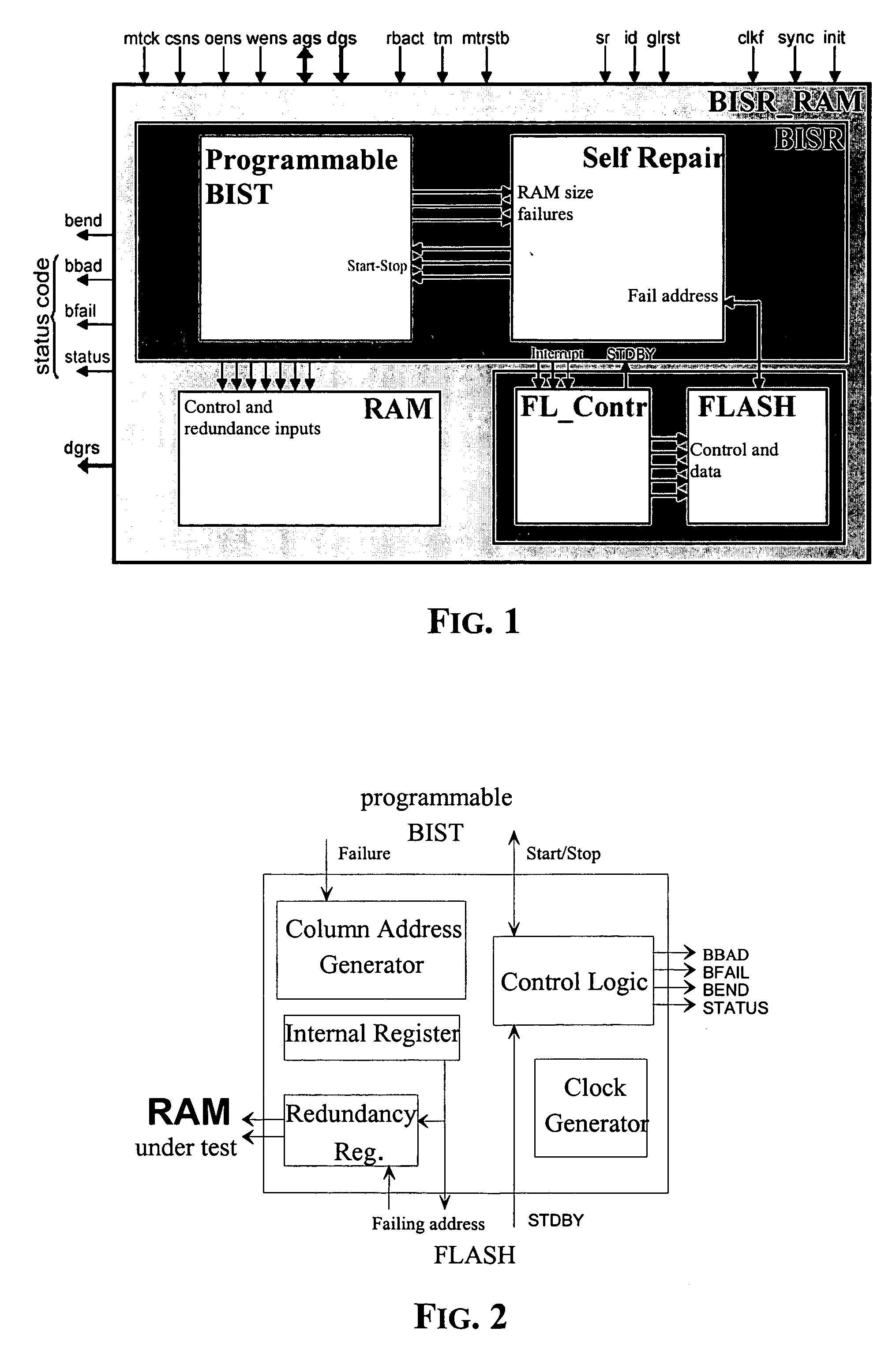

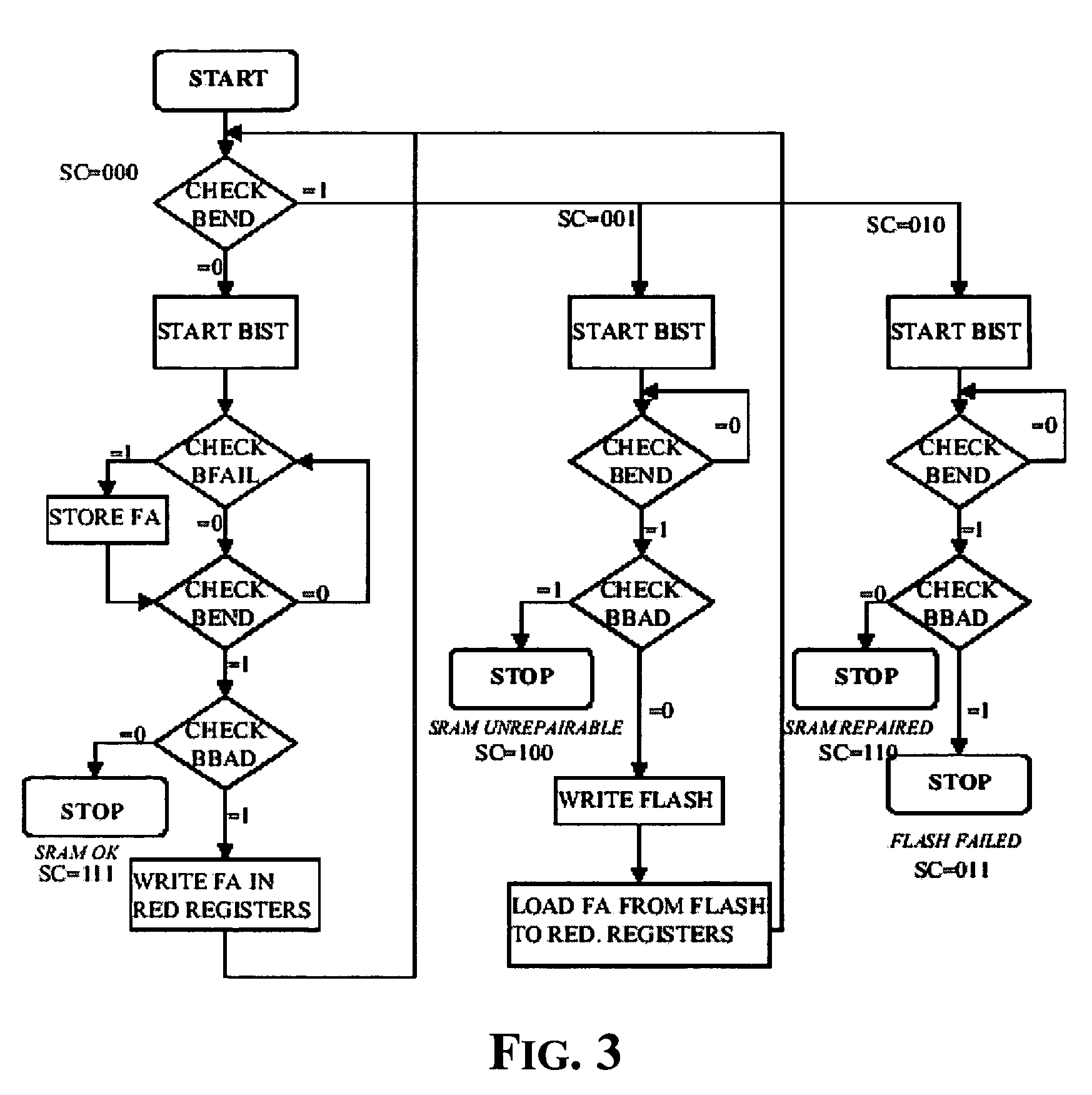

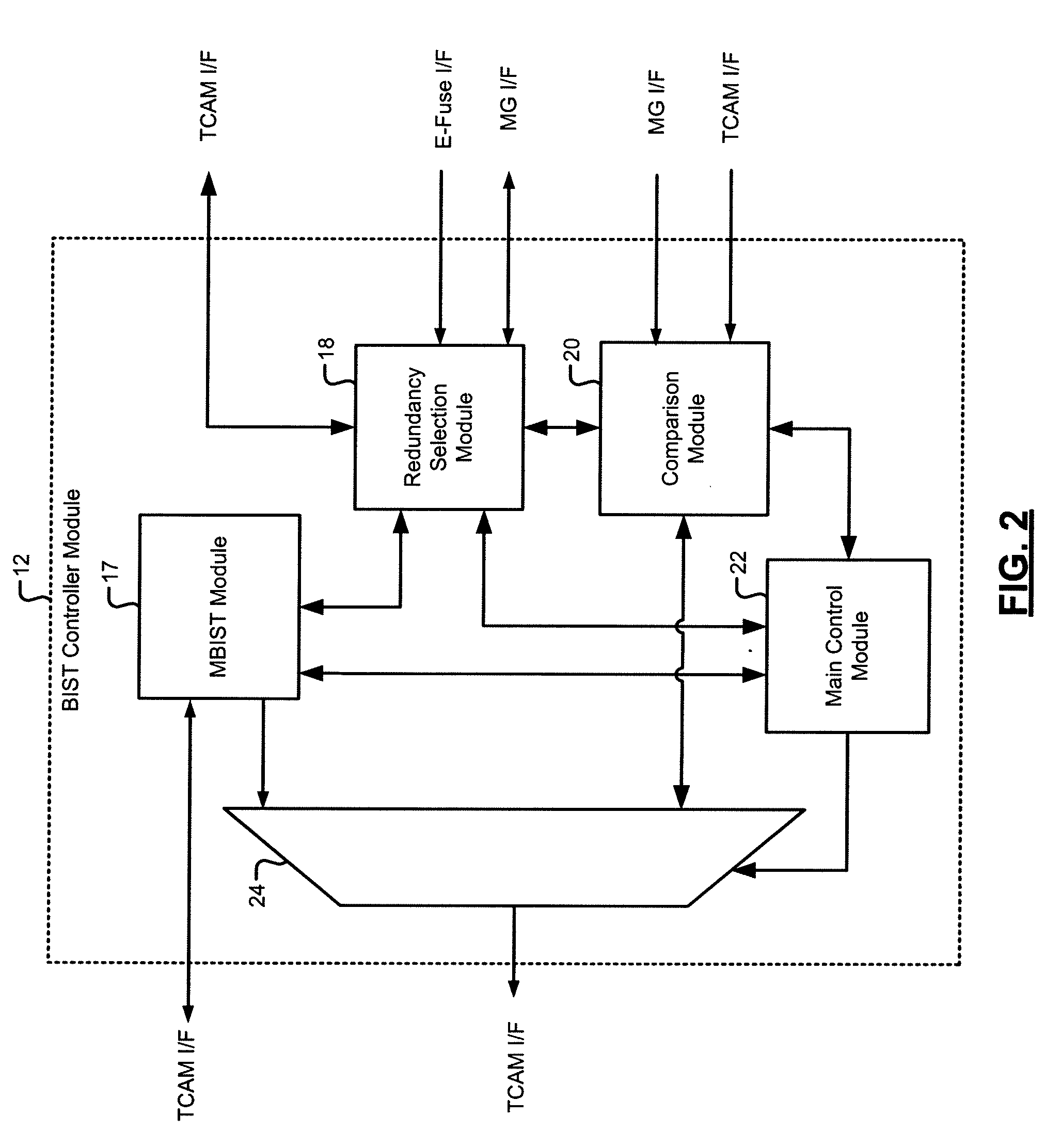

Programmable multi-mode built-in self-test and self-repair structure for embedded memory arrays

ActiveUS7284166B2Efficient and less cumbersomeIncrease flexibilityElectronic circuit testingStatic storageProcessor registerAddress generator

A built-in self-test and self-repair structure (BISR) of memory arrays embedded in an integrated device includes at least a test block (BIST) programmable to execute on a respective memory array of the device any of a certain number of test algorithms, and a self-repair block that includes a column address generator processing the faulty address information for allocating redundant resources of the tested memory array. The BISR may further include a redundancy register on which final redundancy information is loaded at each power-on of the device and control logic for managing data transfer from external circuitry to the built-in self-test and self-repair structure (BISR) and vice versa. The BIST structure serves any number of embedded memory arrays even of different types and sizes.

Owner:STMICROELECTRONICS SRL

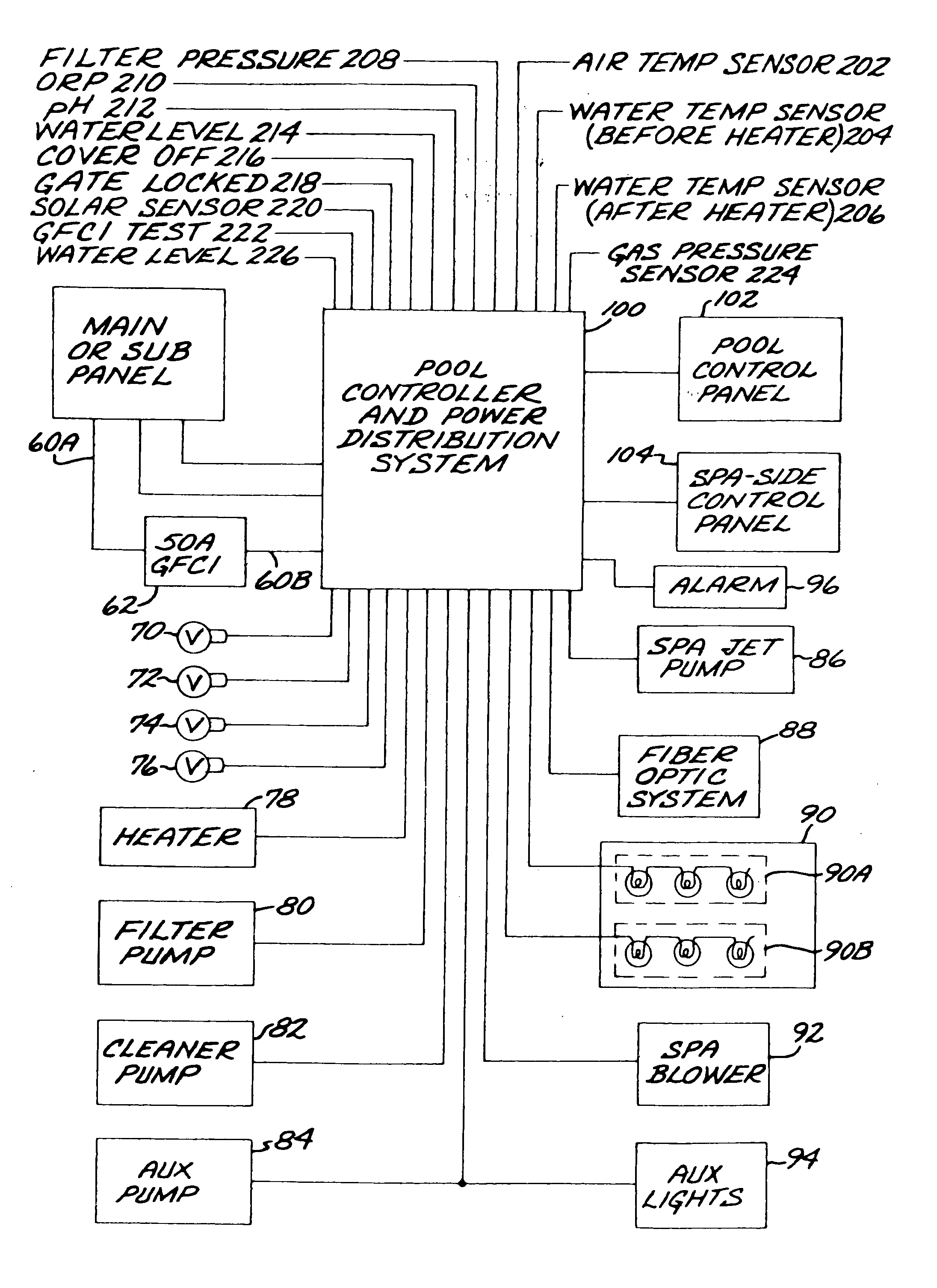

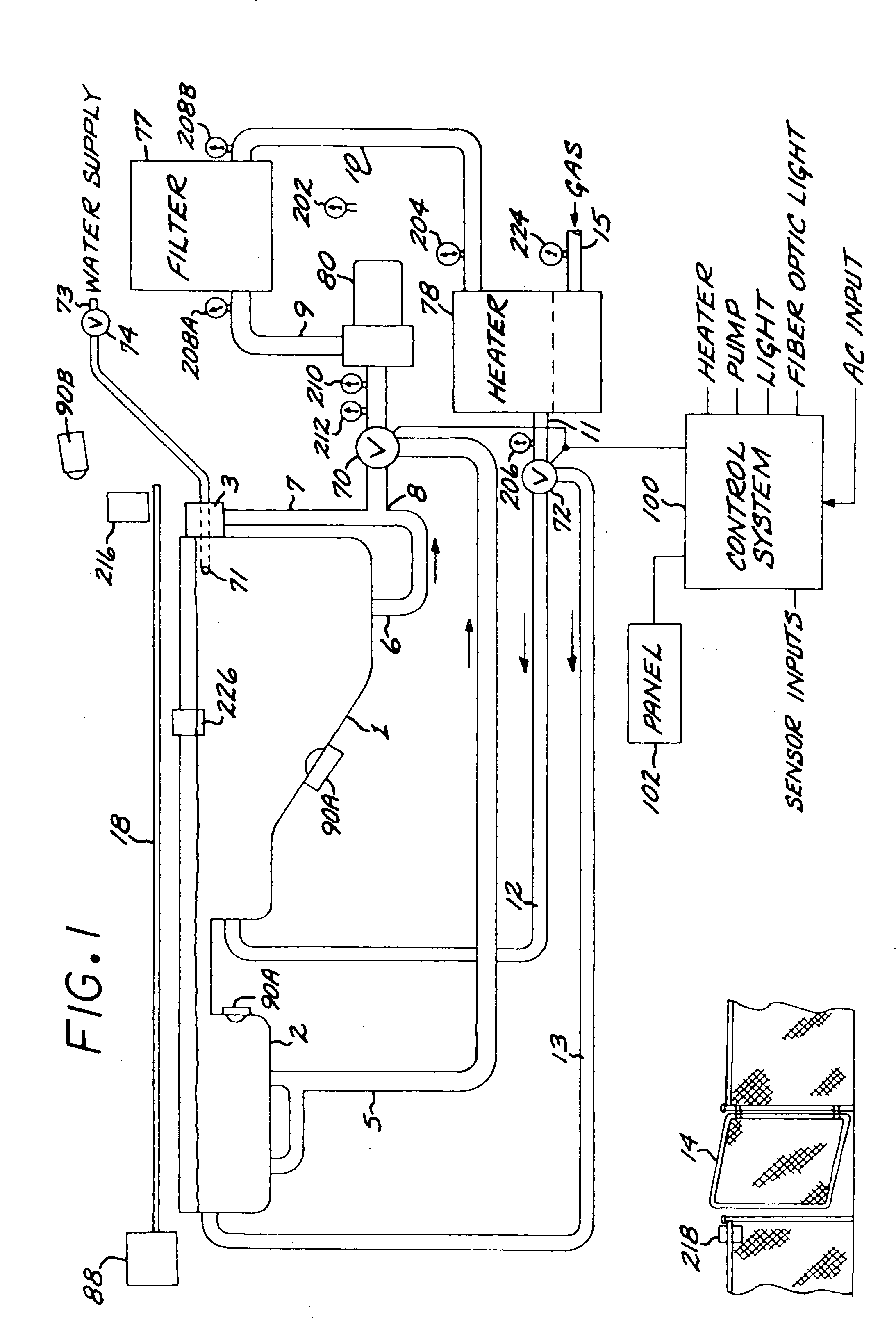

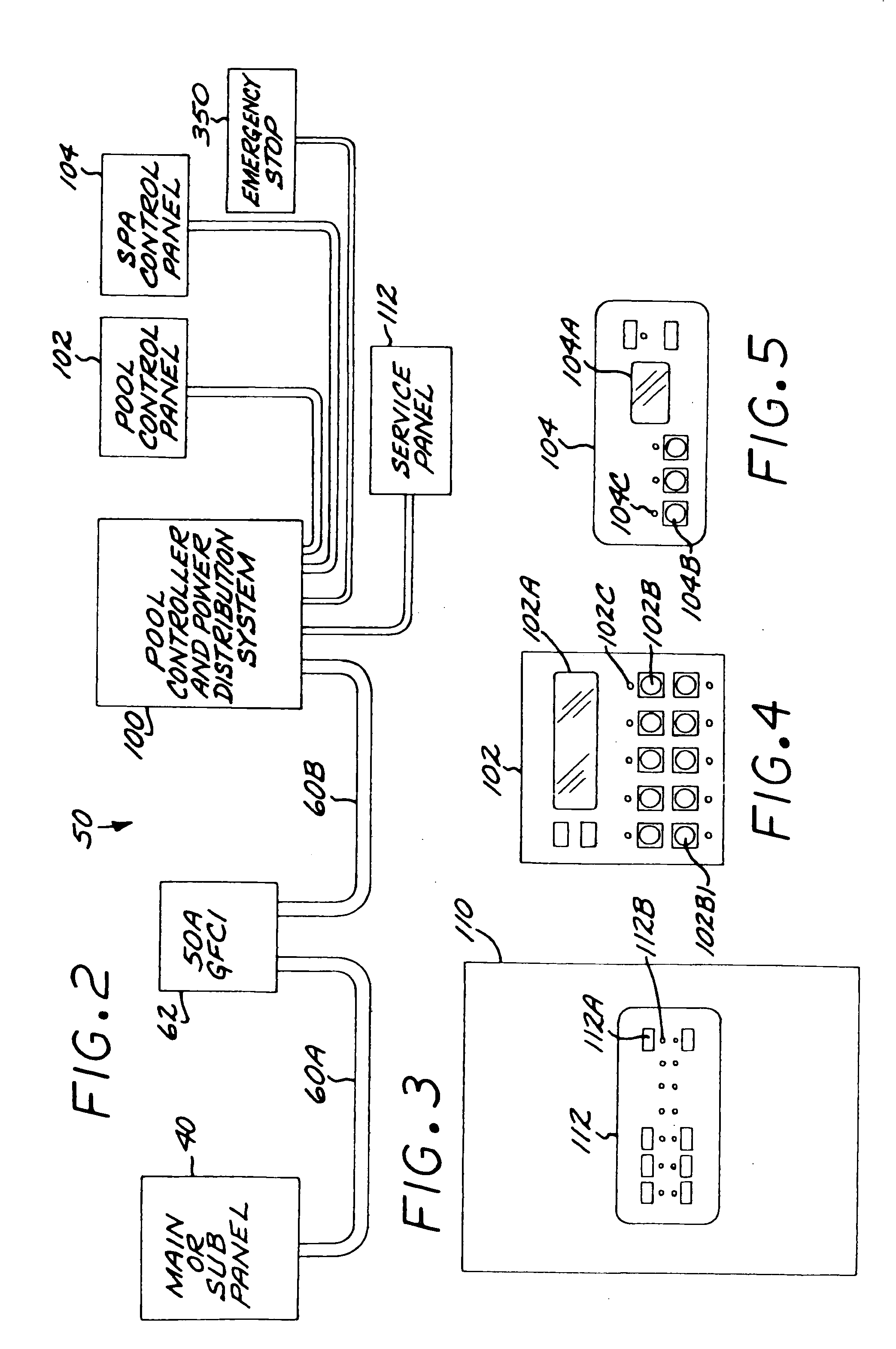

Controller system for pool and/or spa

InactiveUS20050063123A1Effective ground fault protectionEasy to testDc network circuit arrangementsLevel controlLow voltageControl system

A control system for a pool and spa. Main line voltage is provided through a single line voltage service and a single ground fault circuit interrupter circuit, facilitating a ground fault test and simplifying installation. The control system acts as a power distribution system for controlling the pool and spa equipment, with a circuit board assembly including individual fuse protection devices and switching circuits. A test algorithm is included, wherein the control system is disabled from normal operation if the GFCI test fails. The pool operator manually enters a water fill command, and the controller system automatically opens the fill valve for a predetermined time interval, and then automatically closes the valve. An emergency disconnect switch is mounted near the bathing area, connected by low voltage wiring to the controller system cabinet. The controller system senses the emergency switch closure and disconnects line voltage to the line voltage loads. The emergency switch closure also remotely induces a ground fault, tripping the GFCI. A sensing circuit allows the controller system to sense the presence of the emergency switch system, and issues a warning and prevents normal operation of the pool and spa system if not connected. A gas pressure sensor monitors the natural gas line, and the heater is disabled and a warning given under low pressure conditions. Abnormal filter backpressure triggers a warning when the filter needs service. A temperature sensor has parallel sensing elements in a common housing to provide separate sensing circuits.

Owner:DYMAS FUNDING COMPANY

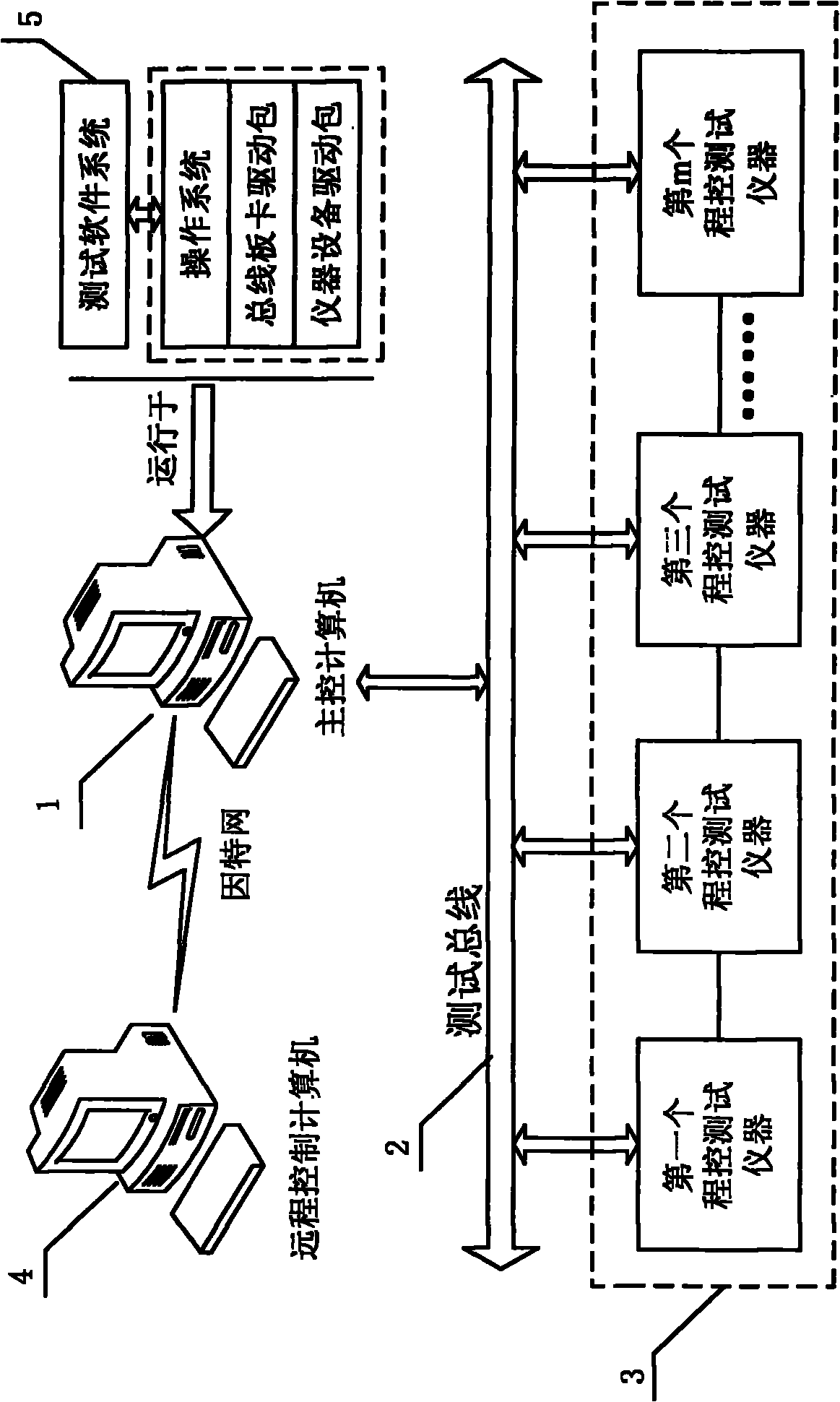

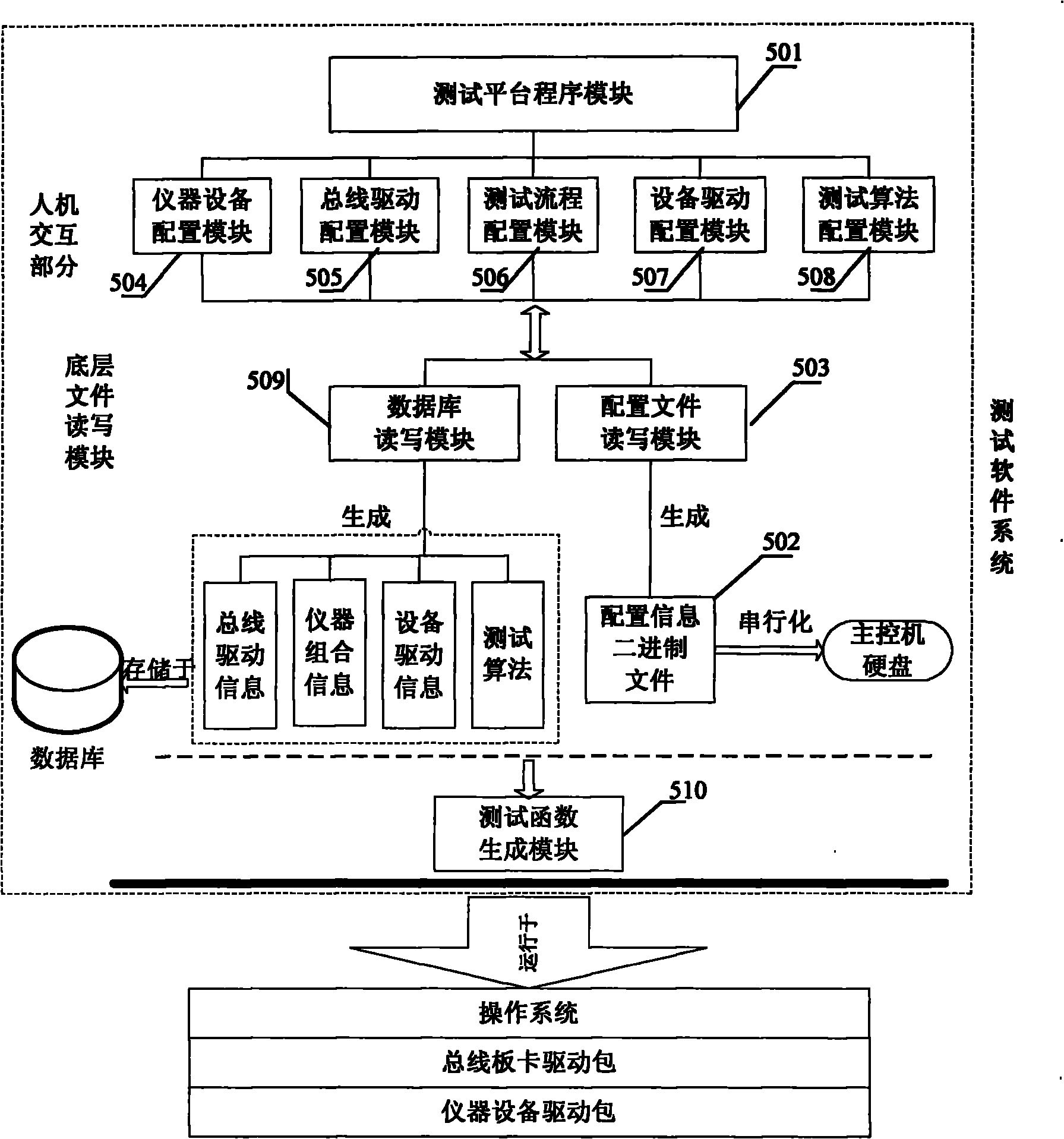

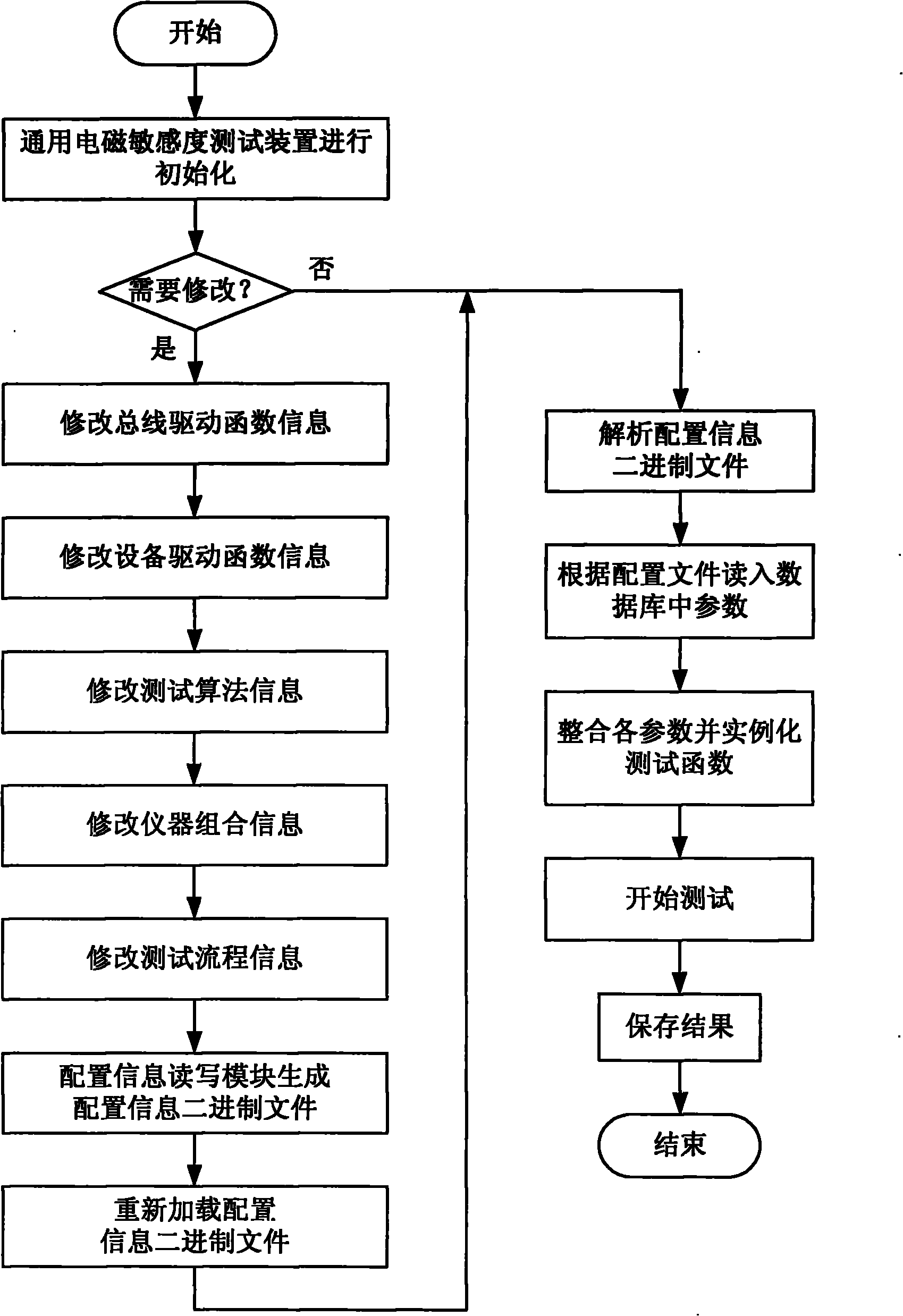

Bus technology-based universal electromagnetic susceptibility testing device and method

InactiveCN101915877AImprove scalabilityEnsure safetyElectrical testingElectromagentic field characteristicsComputer hardwareRemote control

The invention discloses a bus technology-based universal electromagnetic susceptibility testing device and a bus technology-based universal electromagnetic susceptibility testing method. The testing device comprises a main control computer, a program control testing instrument, a remote control computer and a testing software system. The testing method comprises the following steps of: 1, initializing the universal electromagnetic susceptibility testing device; 2, setting parameters aiming at the electromagnetic susceptibility test by a user; 3, starting an upper level test platform program to start the test; and 4, testing a function generation module-instantiated test function, and testing the electromagnetic susceptibility. The invention overcomes the defect of redesign of the conventional electromagnetic susceptibility testing system when new equipment, the type of a testing bus or the connection mode of the testing instrument needs to be replaced or a testing algorithm needs to be updated, realizes the universal electromagnetic susceptibility testing system with convenient function expansion, addition of node equipment and update of the testing algorithm, and reduces the cost and the energy for system expansion and maintenance.

Owner:BEIHANG UNIV

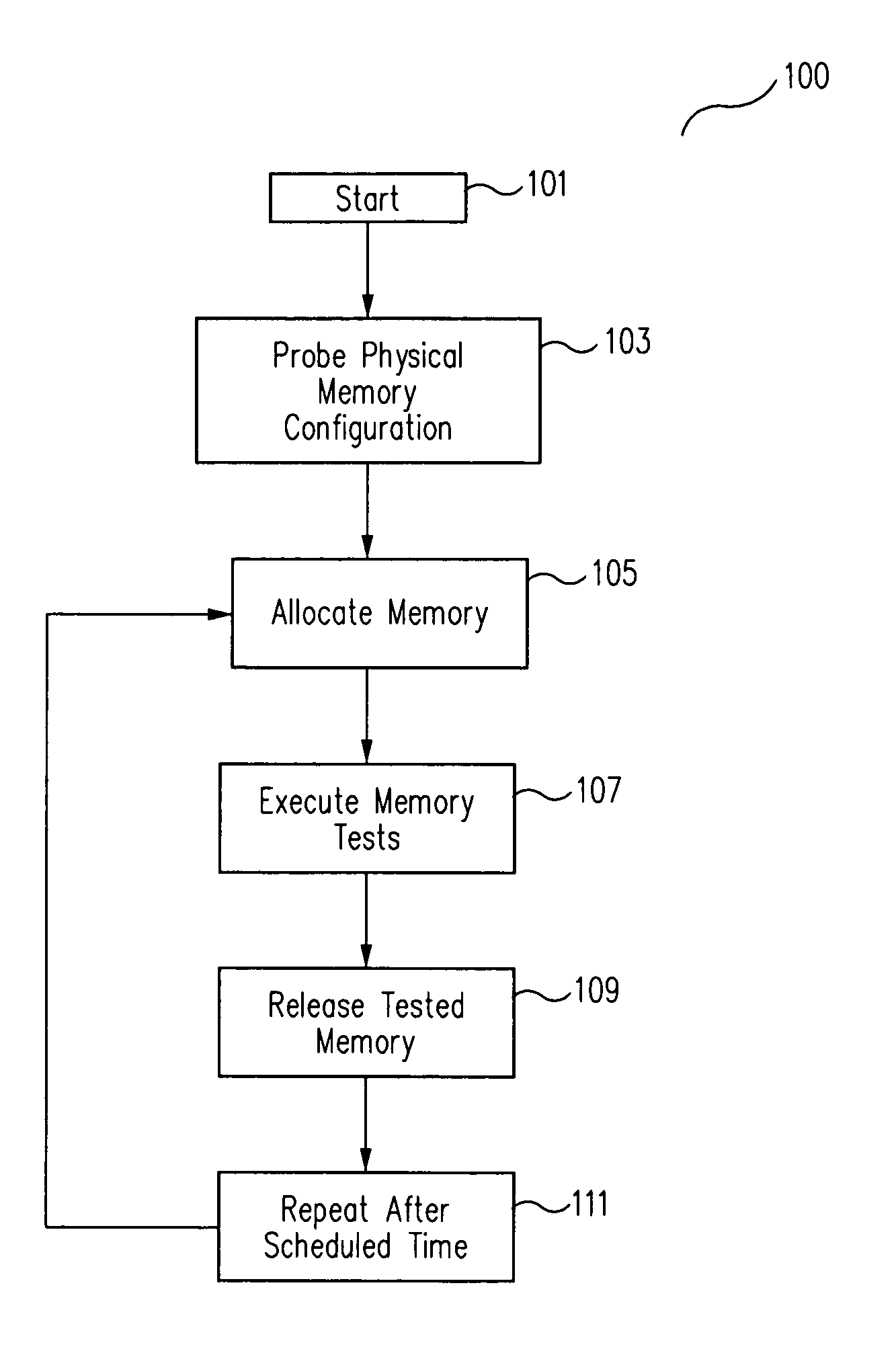

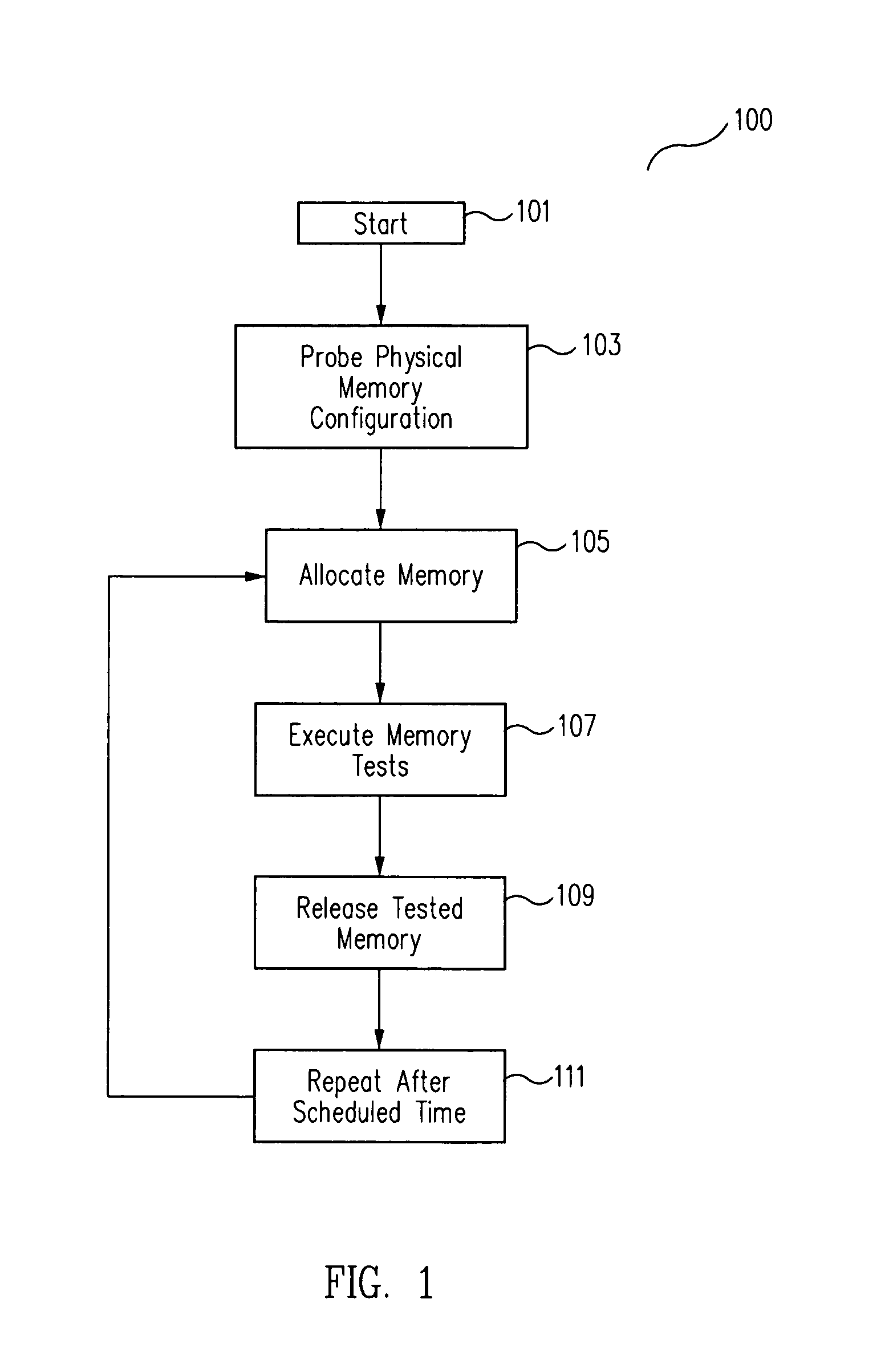

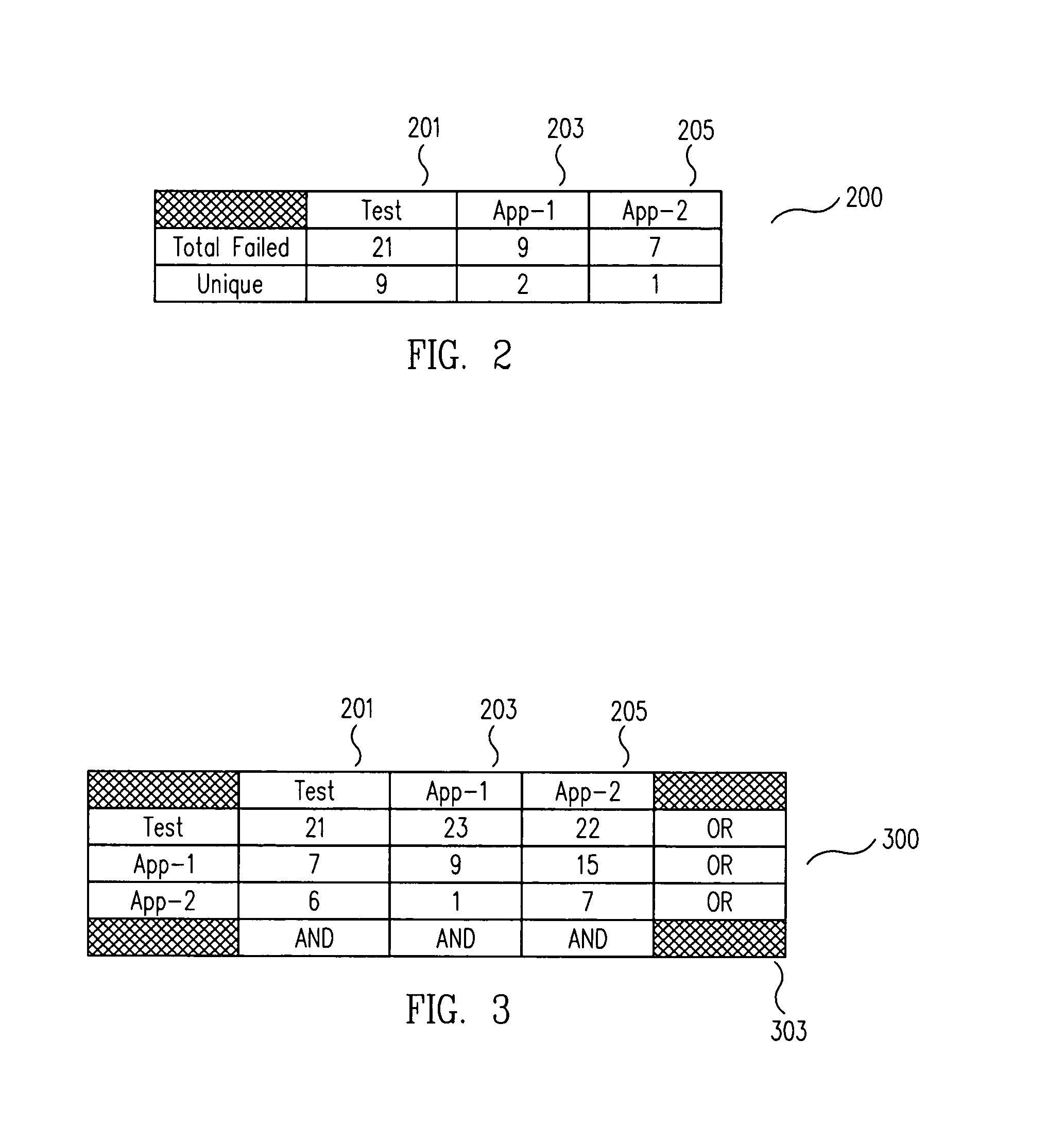

Method and template for physical-memory allocation for implementing an in-system memory test

An in-system memory testing method includes transparently selecting and “stealing” a portion of memory from the memory system for running memory tests, then running one or more of the numerous known memory system tests on the selected portion of memory, and then inserting the selected, and now tested, portion of memory back into the system for normal application use. The disclosed in-system memory testing method is capable of testing system memory in both offline and online environments, without imposing any additional hardware requirements or significantly affecting system performance. The disclosed in-system memory testing method is compatible with any conventional prior art functional test algorithm for in-system memory testing and can be performed under real life system environmental conditions. Therefore, the disclosed in-system memory testing method complements other test techniques like BIST / POST that are conventionally used only at the time of system boot up.

Owner:ORACLE INT CORP

Programmable multi-mode built-in self-test and self-repair structure for embedded memory arrays

ActiveUS20060031726A1SpeedIncrease flexibilityElectronic circuit testingStatic storageProcessor registerAddress generator

A built-in self-test and self-repair structure (BISR) of memory arrays embedded in an integrated device includes at least a test block (BIST) programmable to execute on a respective memory array of the device any of a certain number of test algorithms, and a self-repair block that includes a column address generator processing the faulty address information for allocating redundant resources of the tested memory array. The BISR may further include a redundancy register on which final redundancy information is loaded at each power-on of the device and control logic for managing data transfer from external circuitry to the built-in self-test and self-repair structure (BISR) and vice versa. The BIST structure serves any number of embedded memory arrays even of different types and sizes.

Owner:STMICROELECTRONICS SRL

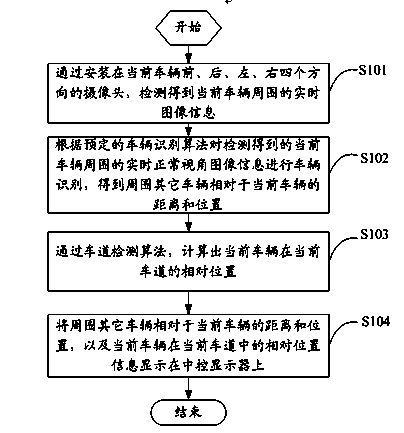

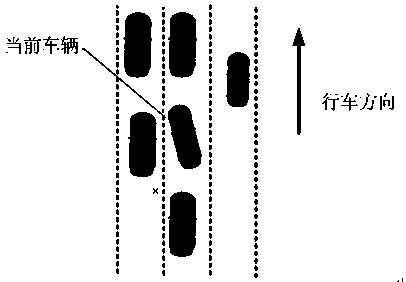

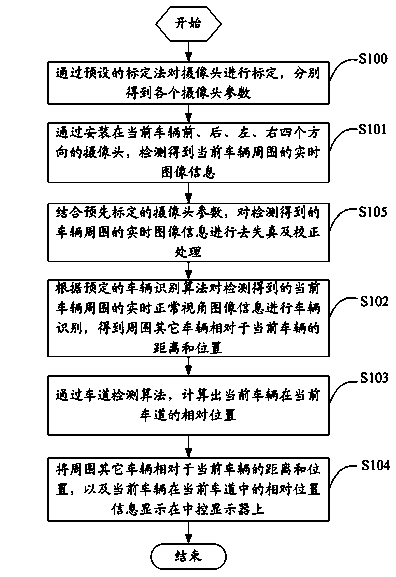

Panoramic auxiliary driving method and system

InactiveCN103950410AAssisted driving operationImprove driving safetyClosed circuit television systemsOptical viewingLeft directionDisplay device

The invention discloses a panoramic auxiliary driving method and system. The system comprises a detecting module, an identifying module, a calculating module and a display module. According to the system, all-round real-time images around a vehicle without a dead angle through fisheye cameras mounted in the front direction, the rear direction, the left direction and the right direction of the vehicle can be obtained; four images can be calibrated to normal angle images combing with parameters of the fisheye cameras calibrated in advance; surrounding vehicles can be identified real-timely through a vehicle identification algorithm; then the position of a current vehicle on a current lane can be calculated through a lane test algorithm; finally, according to a certain scaling factor, relative position information between the current vehicle and the surrounding vehicles and the current lane is simulatively displayed on the central control display with an overlook angle; therefore, a driver can clearly see the relative position of the current vehicle among the surrounding vehicles through a 360 degree of panoramic display, so that the driving safety of the driver is improved.

Owner:深圳前向启创数码技术有限公司

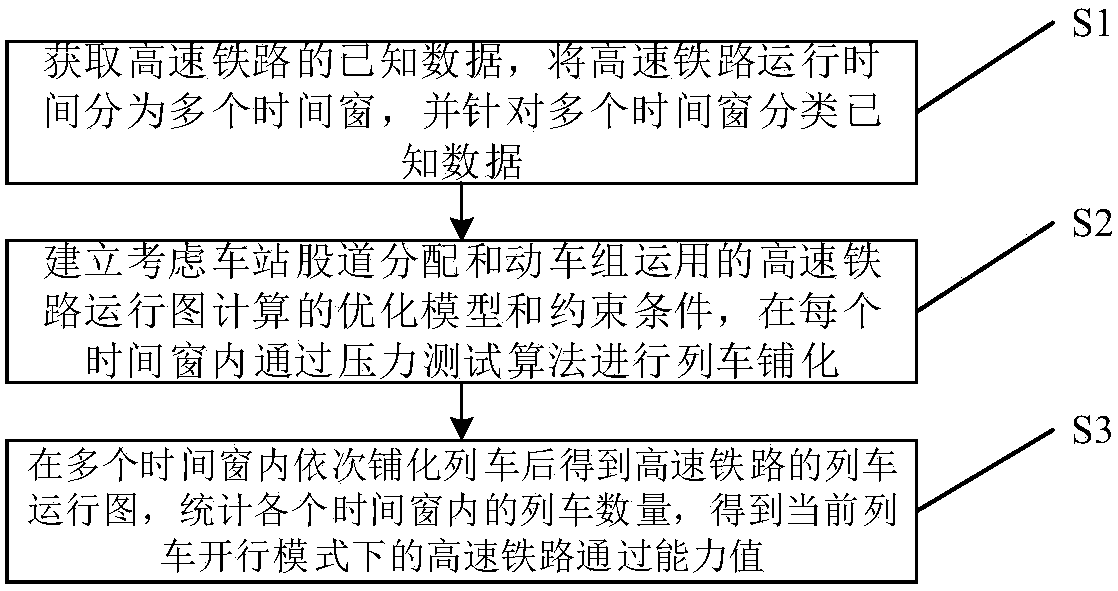

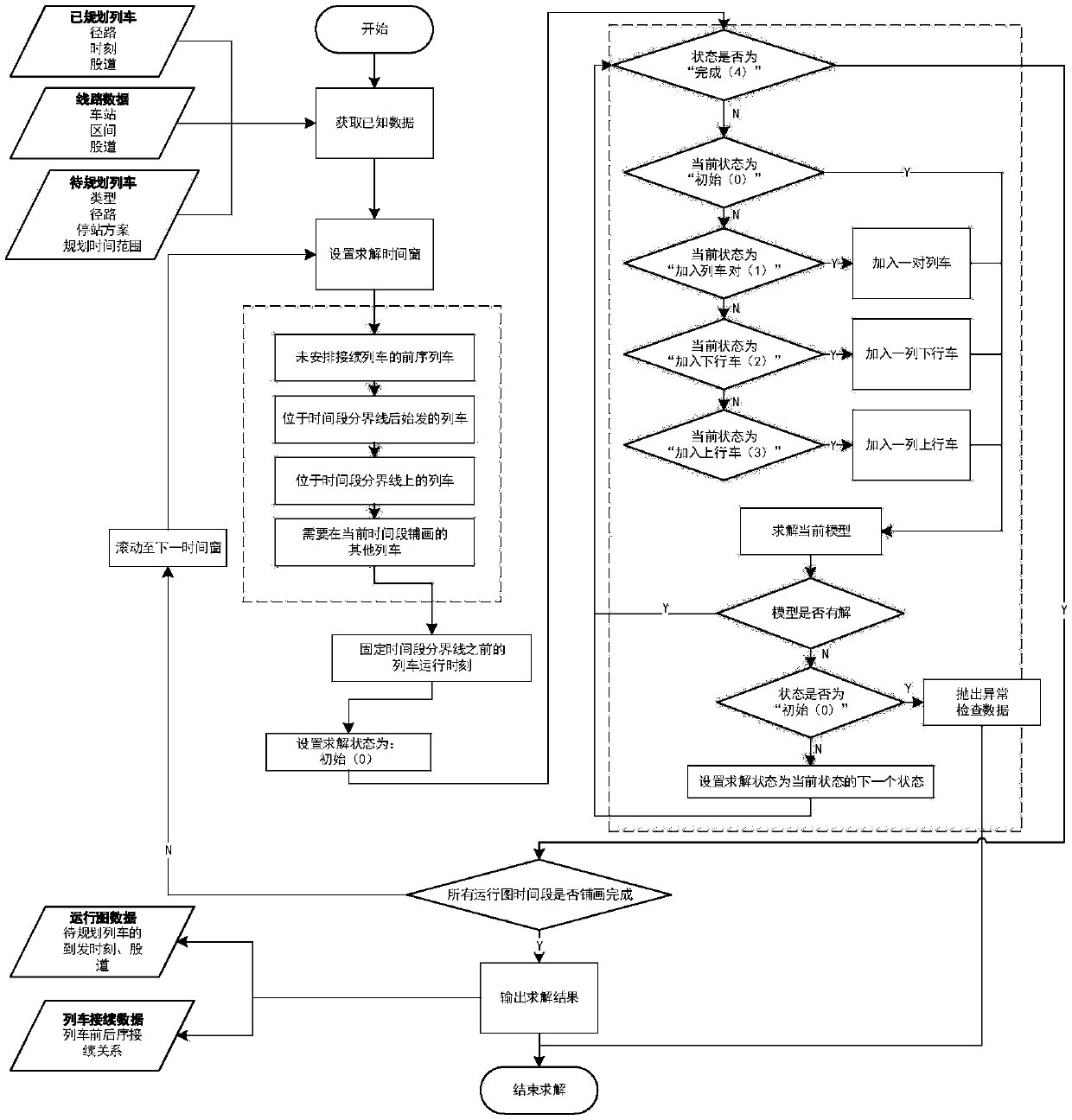

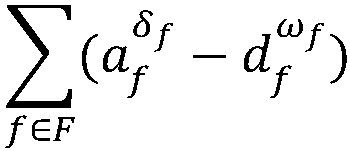

Multiple resource constraints-considered high-speed railway trafficability calculation method

InactiveCN108491950AEnsure cashabilityThe calculation result is accurateForecastingResourcesStatistical analysisTest algorithm

The invention discloses a multiple resource constraints-considered high-speed railway trafficability calculation method. The method comprises the following steps of: S1, obtaining known data of a high-speed railway, dividing an operation time of the high-speed railway into a plurality of time windows, and classifying the known data for the plurality of time windows; S2, establishing a station track distribution and CRH train application-considered high-speed railway running chart calculation optimization model and a constraint condition, and carrying out train painting in each time window through a pressure test algorithm; and S3, obtaining a train running chart full chart of the high-speed railway after painting the trains in the plurality of time windows in sequence, and carrying out statistical analysis on a train quantity in each time window so as to obtain a high-speed railway trafficability value under the current train running mode. According to the method, influences, on trafficability, of stopping schemes and running chart structures of trains are considered, and high-speed railway trafficability can be calculated by considering trafficability under a certain scale of redundancy and buffering time layout conditions, so that the correctness is high.

Owner:BEIJING JIAOTONG UNIV

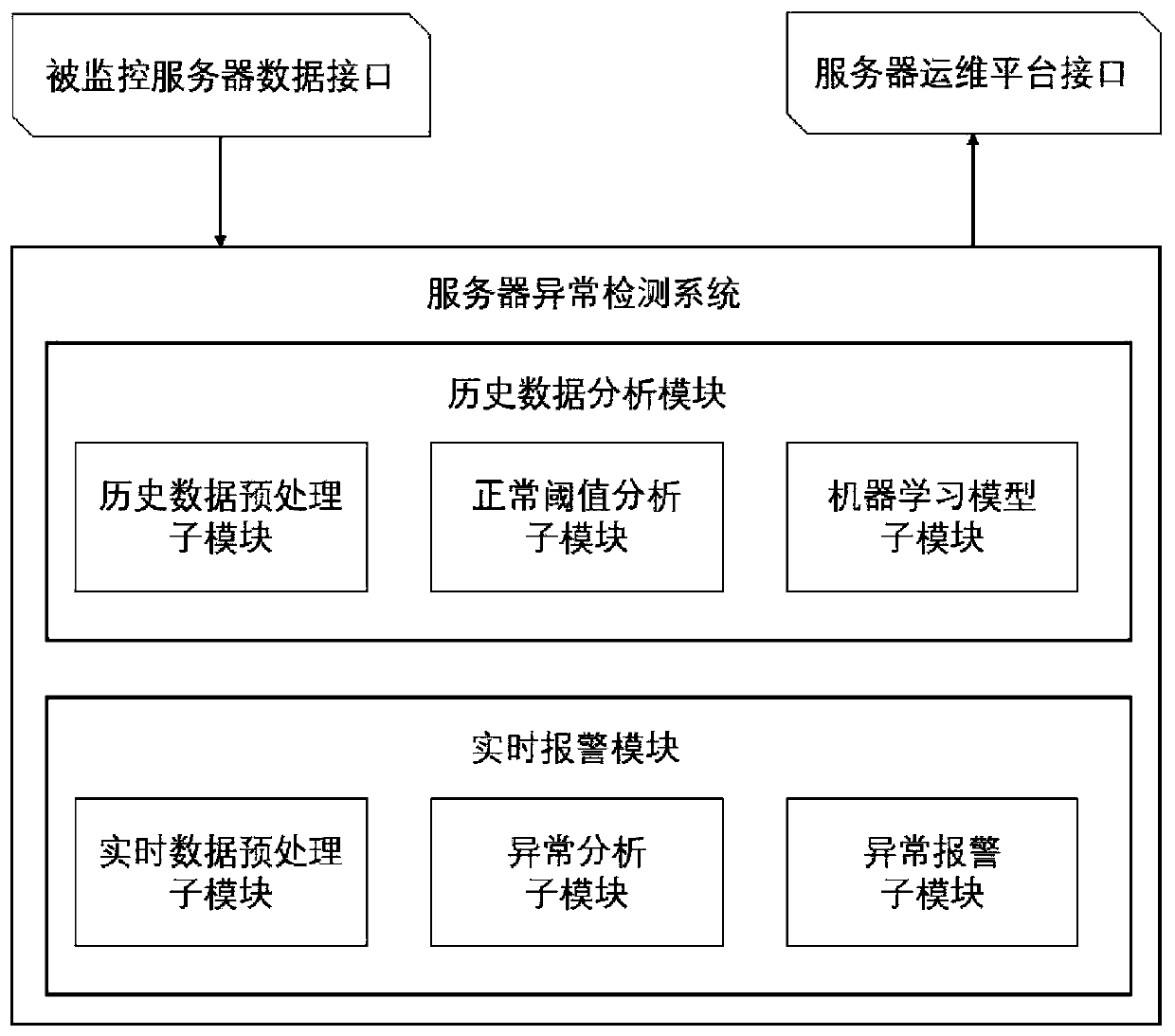

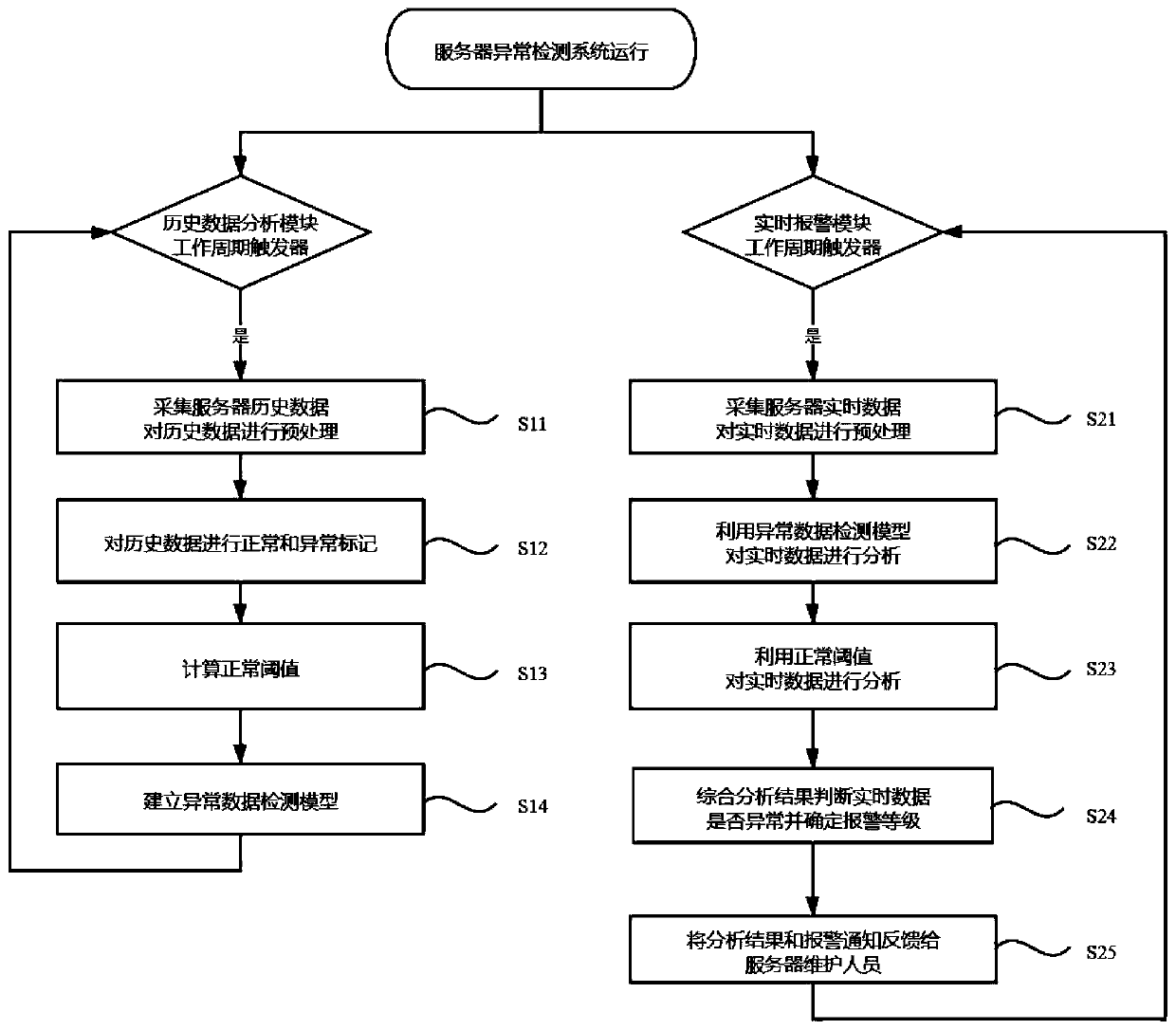

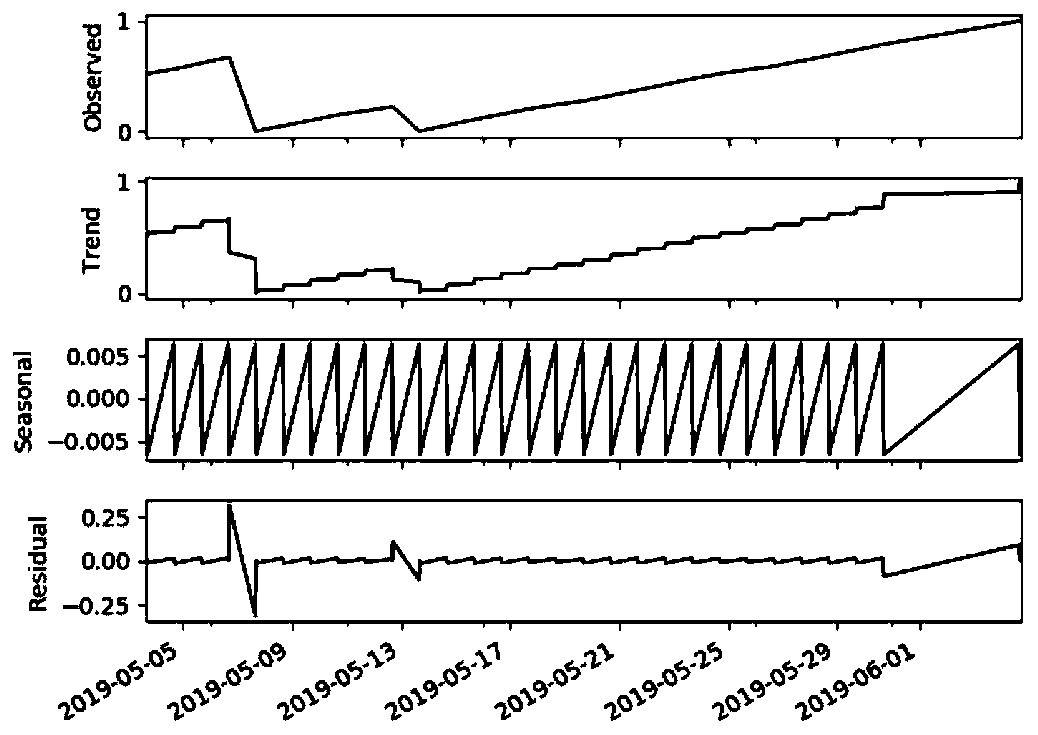

Intelligent detection method and detection system for server exception of hybrid strategy

ActiveCN111061620ADetect abnormalities in timeReduce maintenance costsHardware monitoringReal-time dataData acquisition

The invention discloses an intelligent detection method for server exception of a hybrid strategy. The method comprises a historical data acquisition and analysis step and a real-time anomaly alarm step, wherein the historical data acquisition and analysis step comprises the steps of acquiring server historical data in a preset time period, preprocessing the historical data, screening out featuresneeding to be analyzed, and taking data corresponding to each feature as a time sequence, determining a normal value and an abnormal value corresponding to each time sequence in the historical data in combination with a time sequence decomposition algorithm and a Grubbs test algorithm; calculating a normal threshold value corresponding to each feature in the historical data, i.e., a maximum valuerange and a minimum value range of a normal value in each time sequence; and taking all time sequences in the historical data as training samples, establishing a plurality of abnormal data detectionmodels to predict and judge the to-be-detected sample, and outputting the probability that the to-be-detected sample is abnormal, so as to analyze the real-time data in the real-time alarm step.

Owner:南京林科斯拉信息技术有限公司

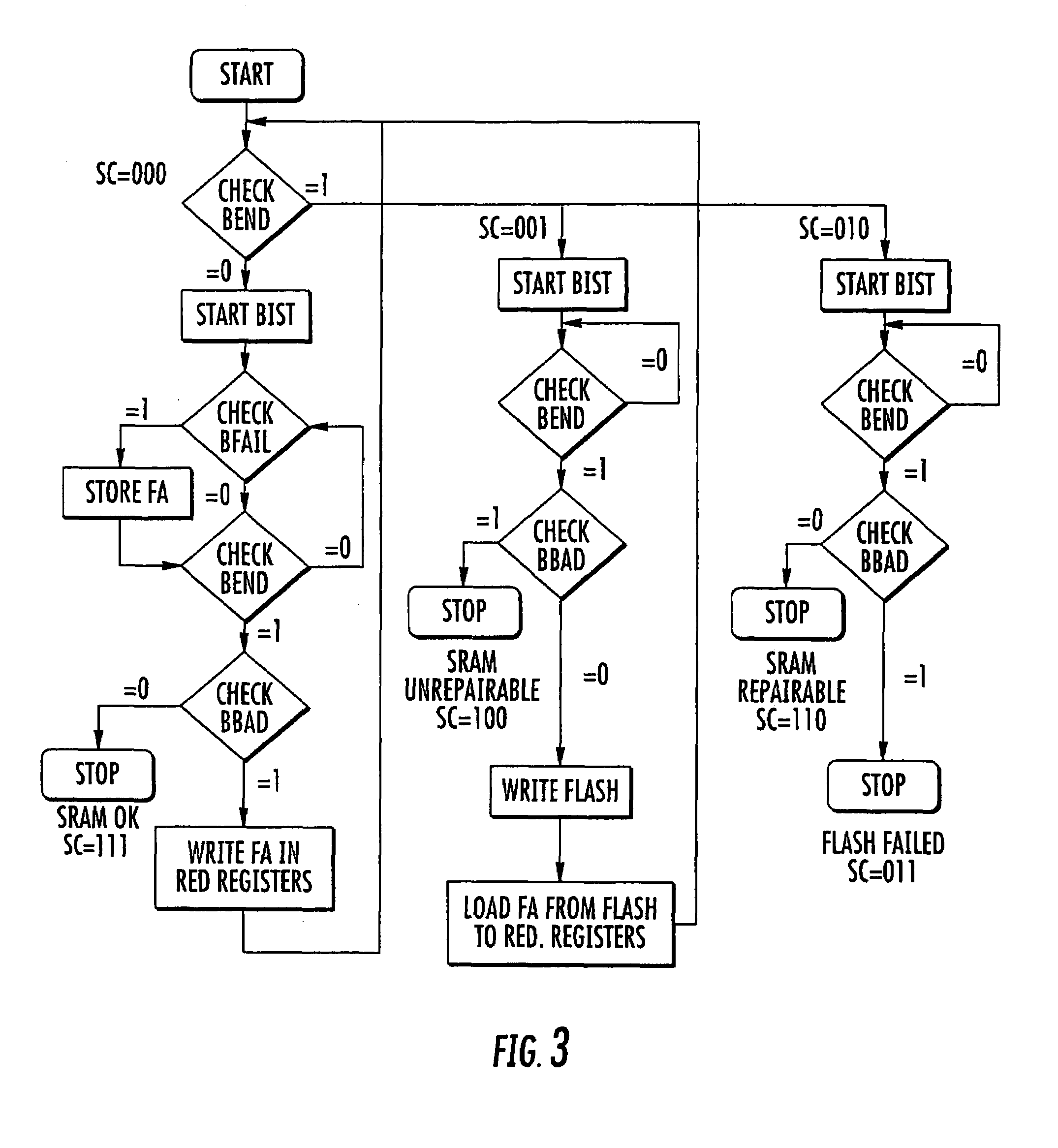

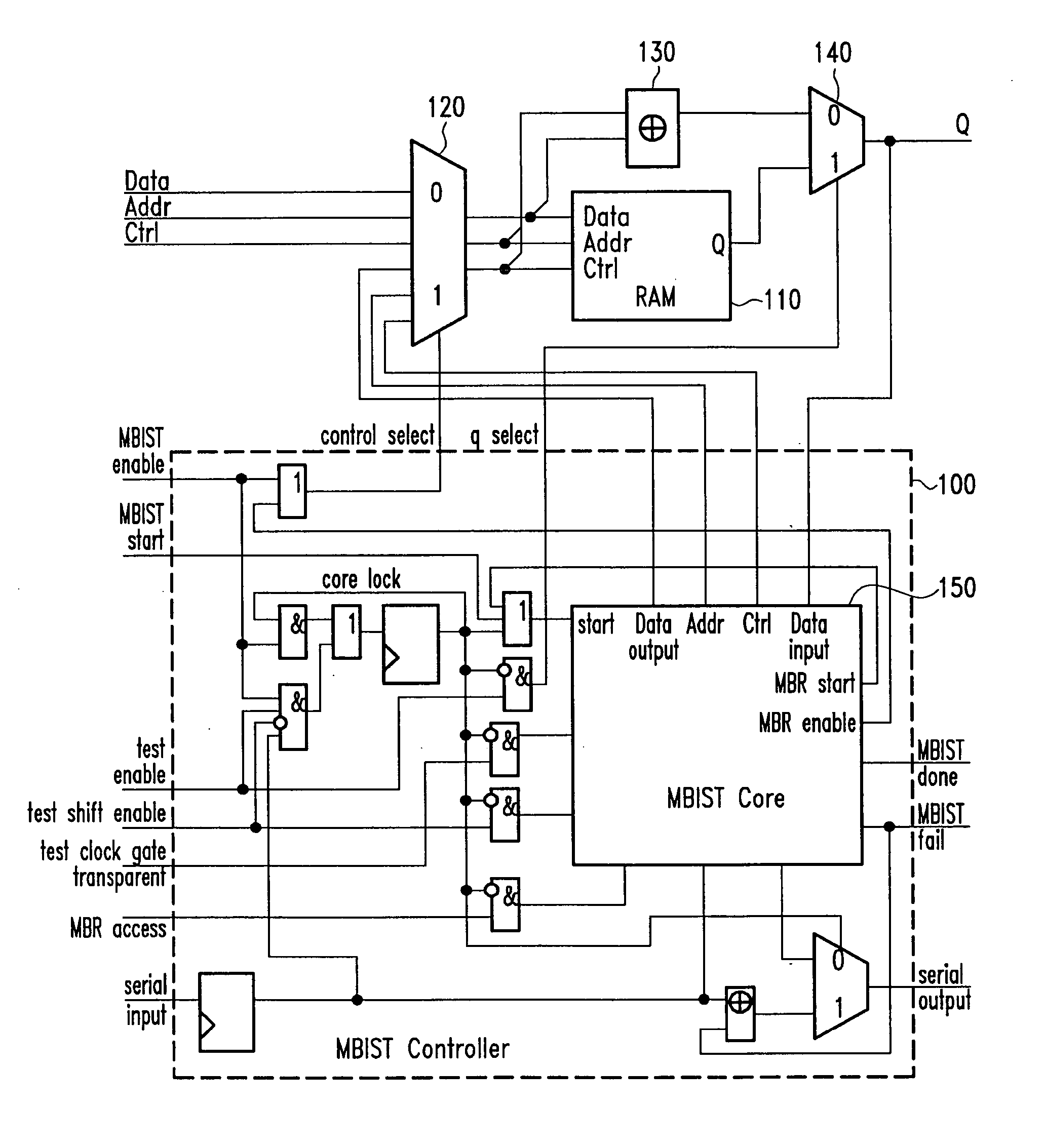

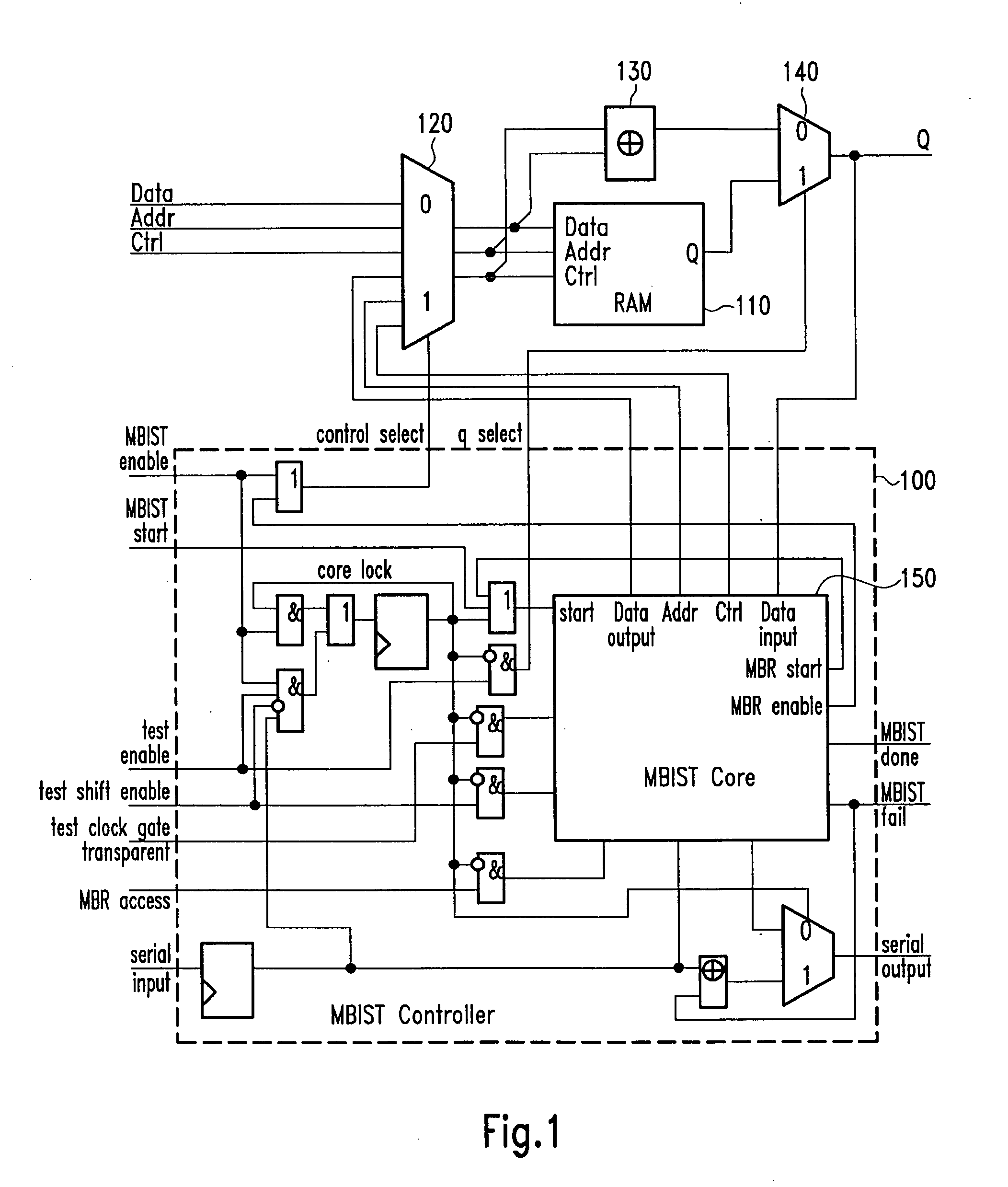

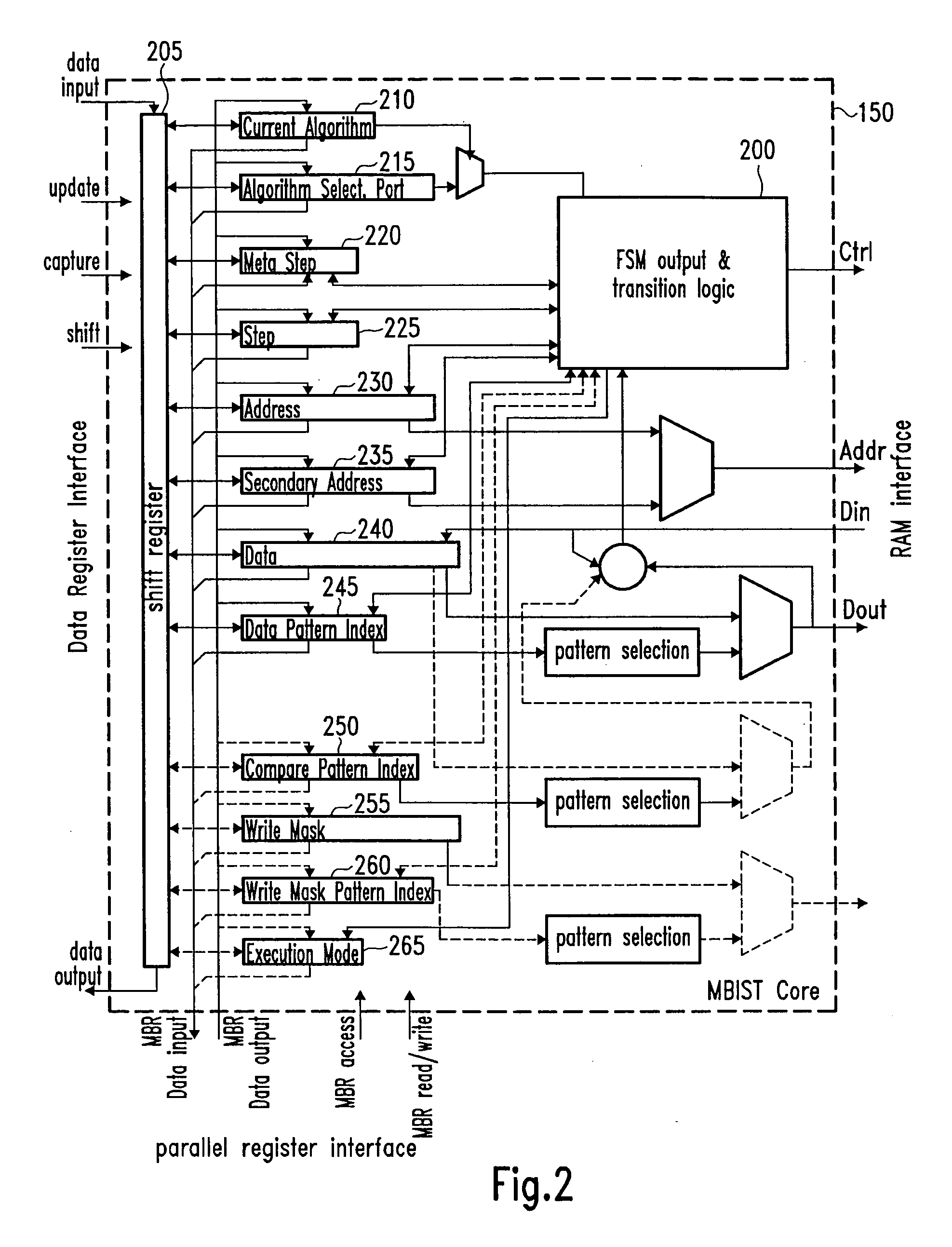

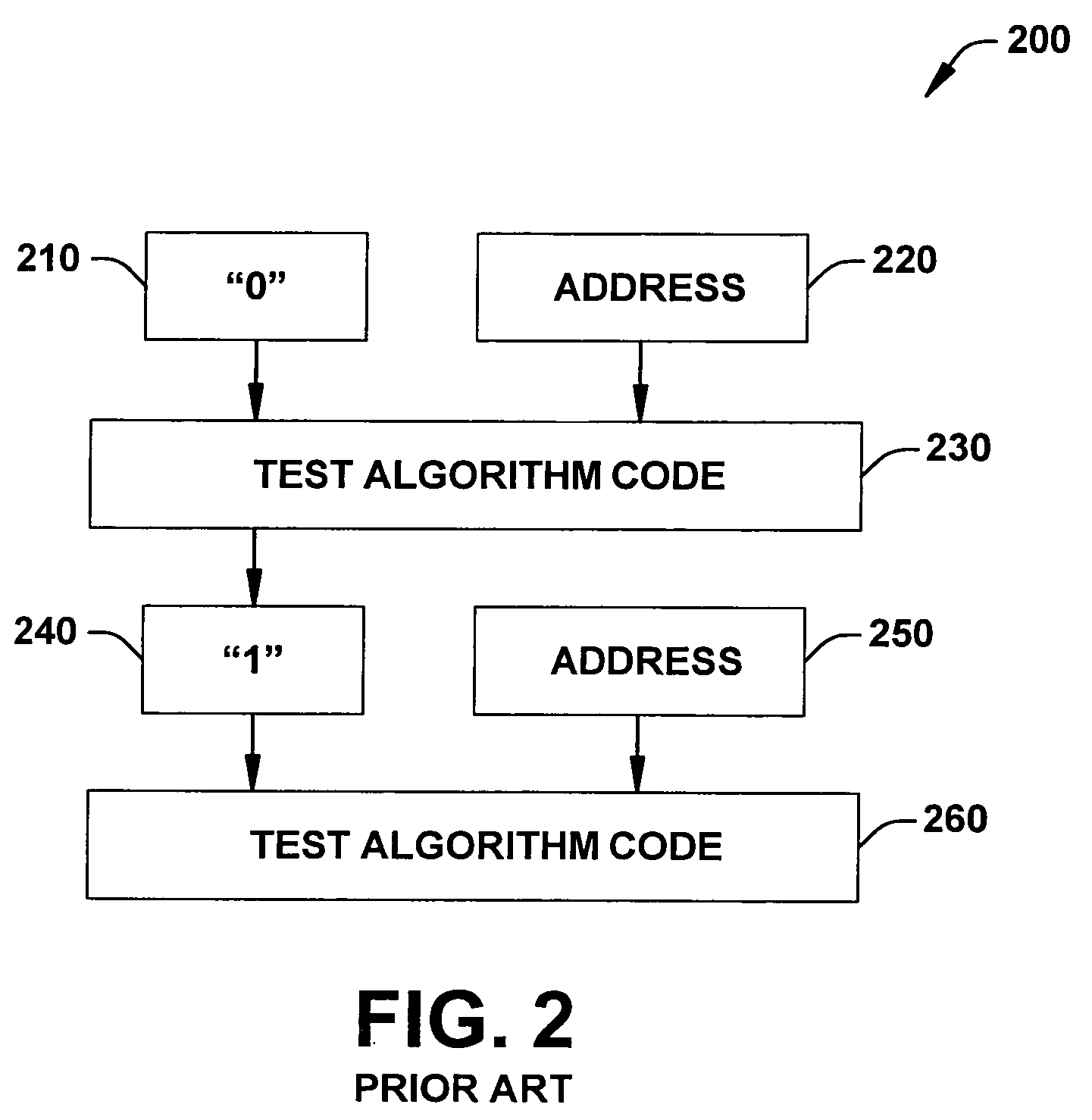

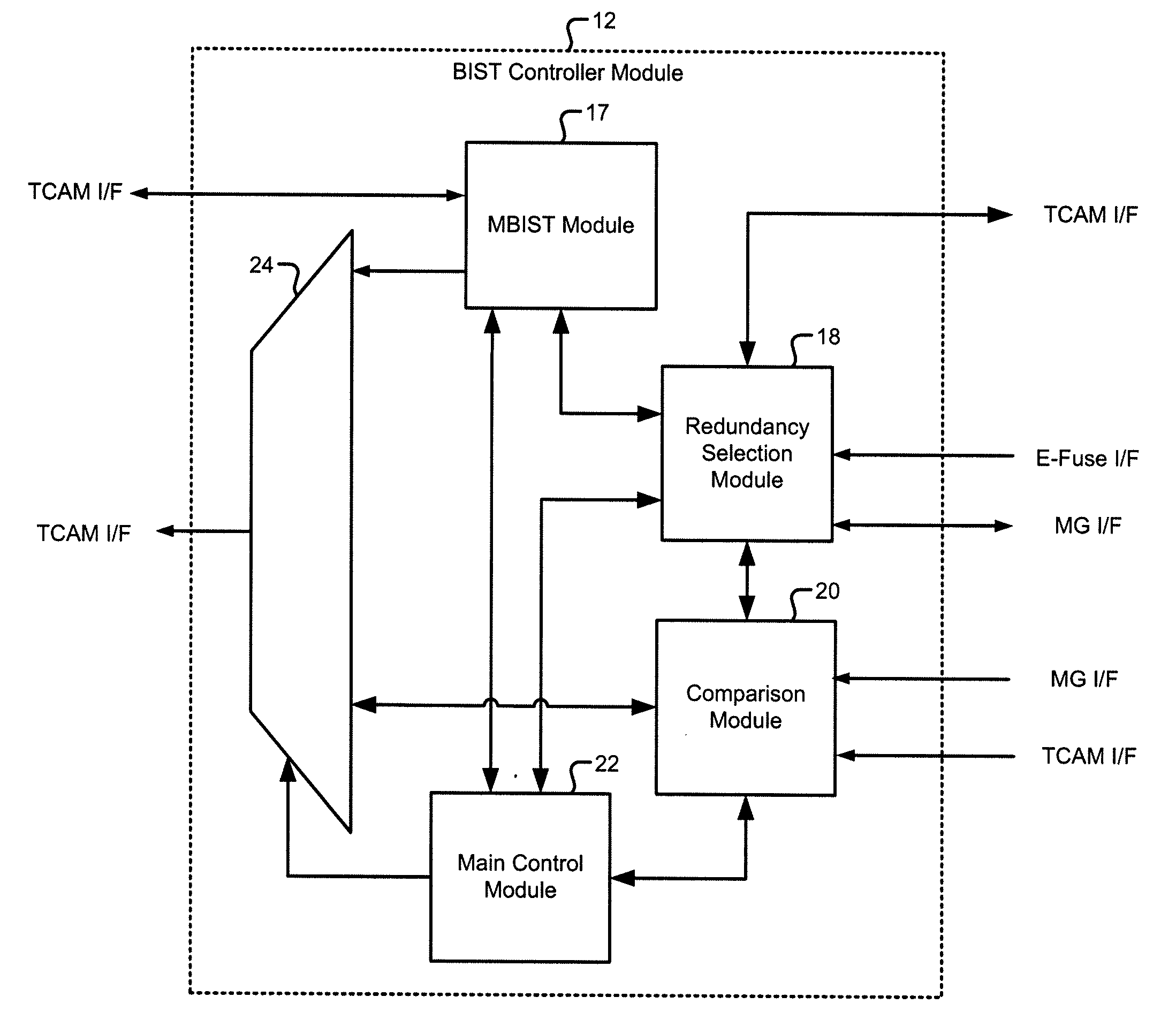

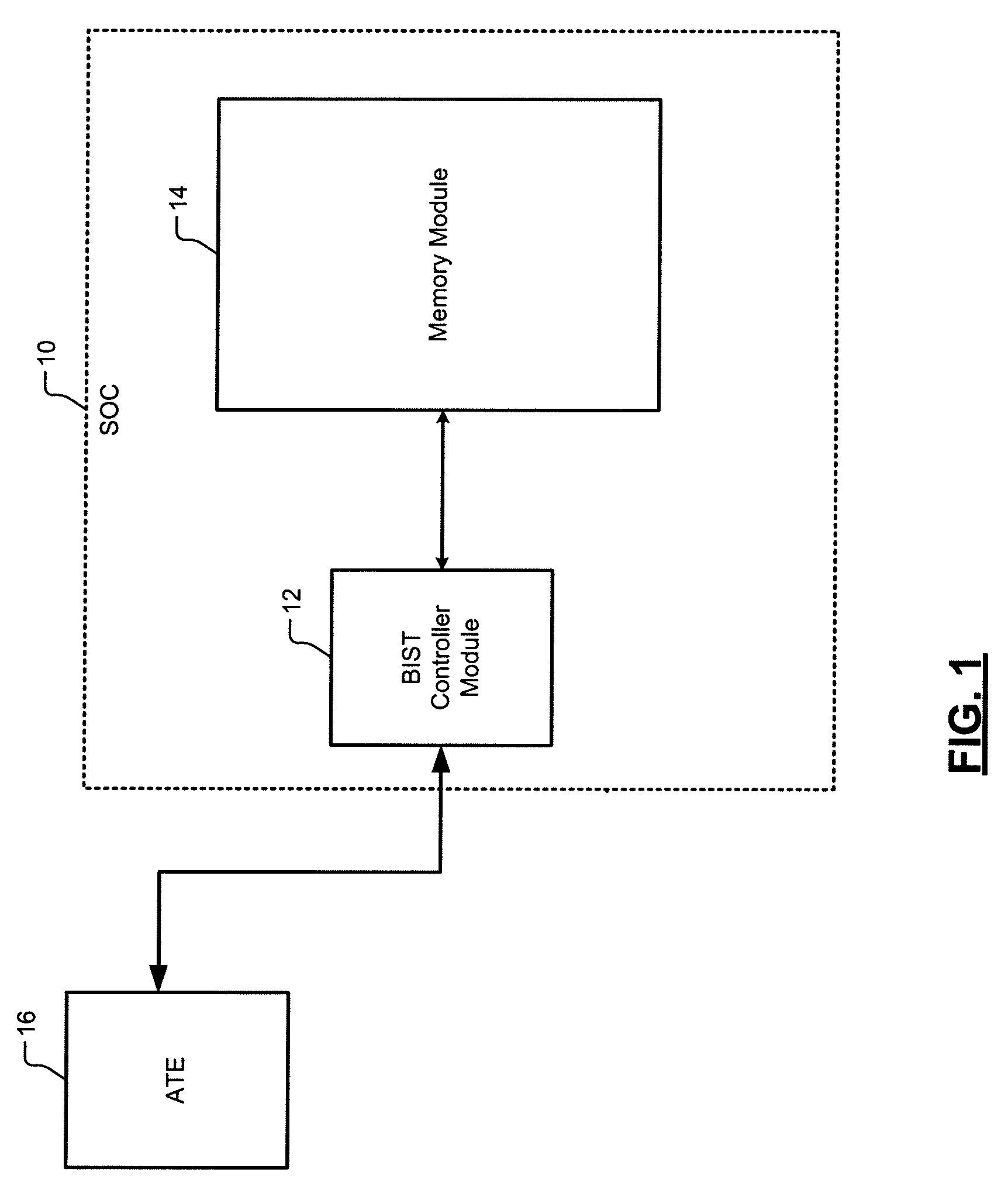

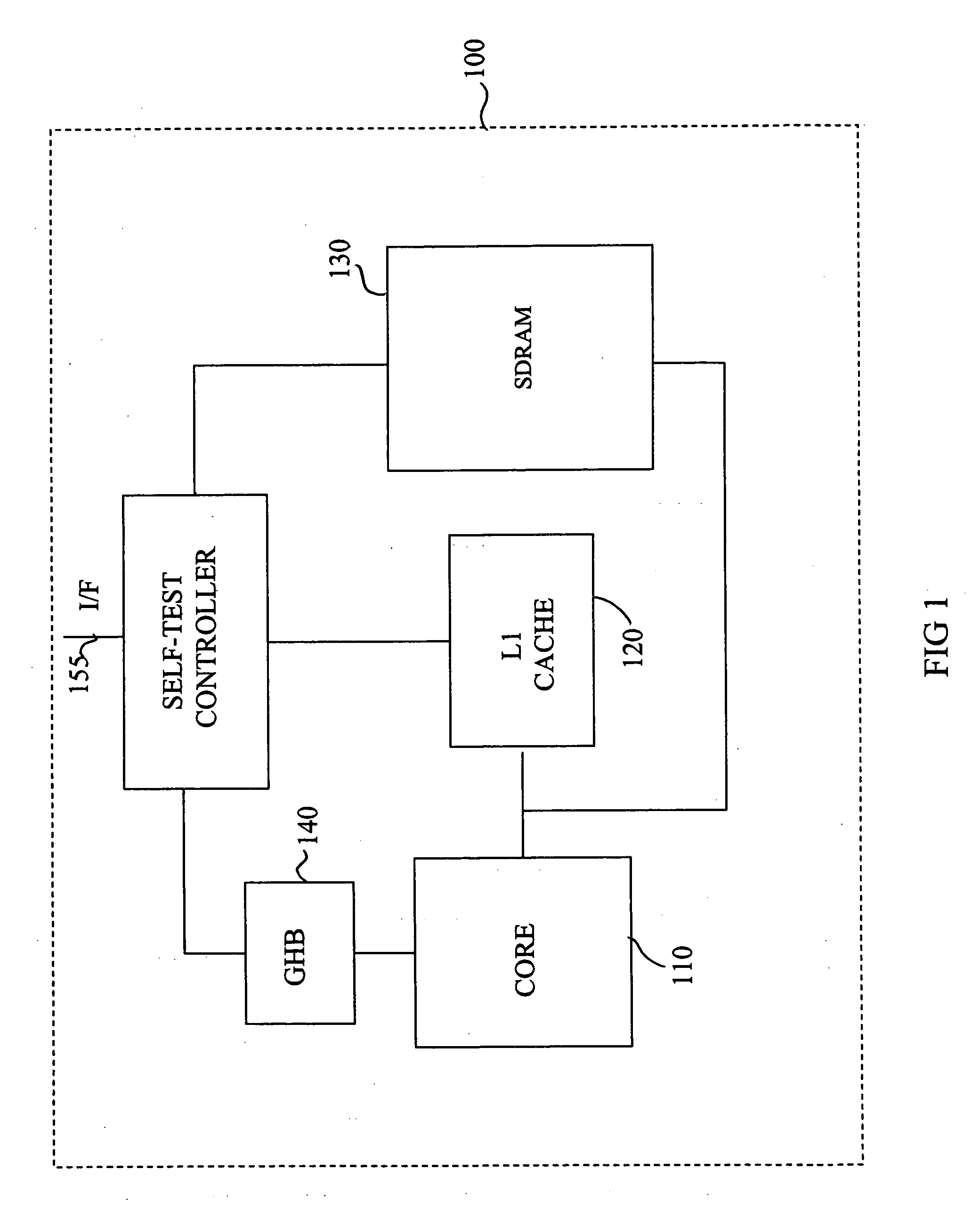

Test algorithm selection in memory built-in self test controller

InactiveUS20070204190A1Effective and flexibleImprove efficiencyElectronic circuit testingStatic storageComputer hardwareMemory faults

An integrated circuit chip is provided that comprises on-chip memory and test circuitry. The test circuitry is configured to perform operational testing of the on-chip memory. The test circuitry comprises a controller which is configured to perform a selection out of a plurality of test algorithms to perform the operational testing. The plurality of test algorithms includes a fault detection test algorithm to perform operational testing of the on-chip memory in order to detect whether or not there is a memory fault, without locating the memory fault. The plurality of test algorithms further includes a fault location test algorithm to perform operational testing of the on-chip memory in order to detect and locate a memory fault. Further, a method to perform a memory built-in self test and an MBIST (Memory Built-In Self Test) control circuit template are provided.

Owner:CHRONOCLOUD MEDTECH (SHANGHAI) CO LTD

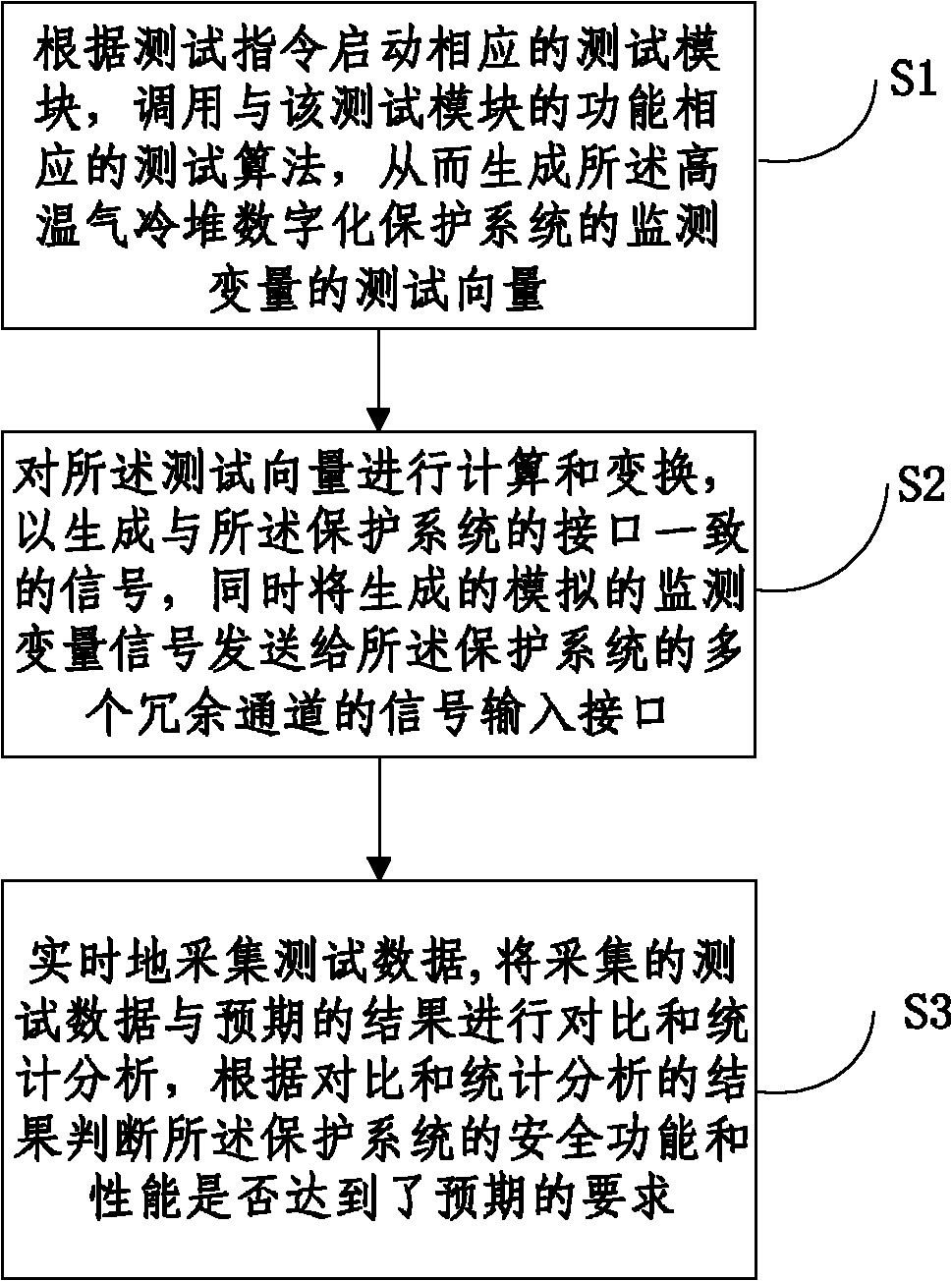

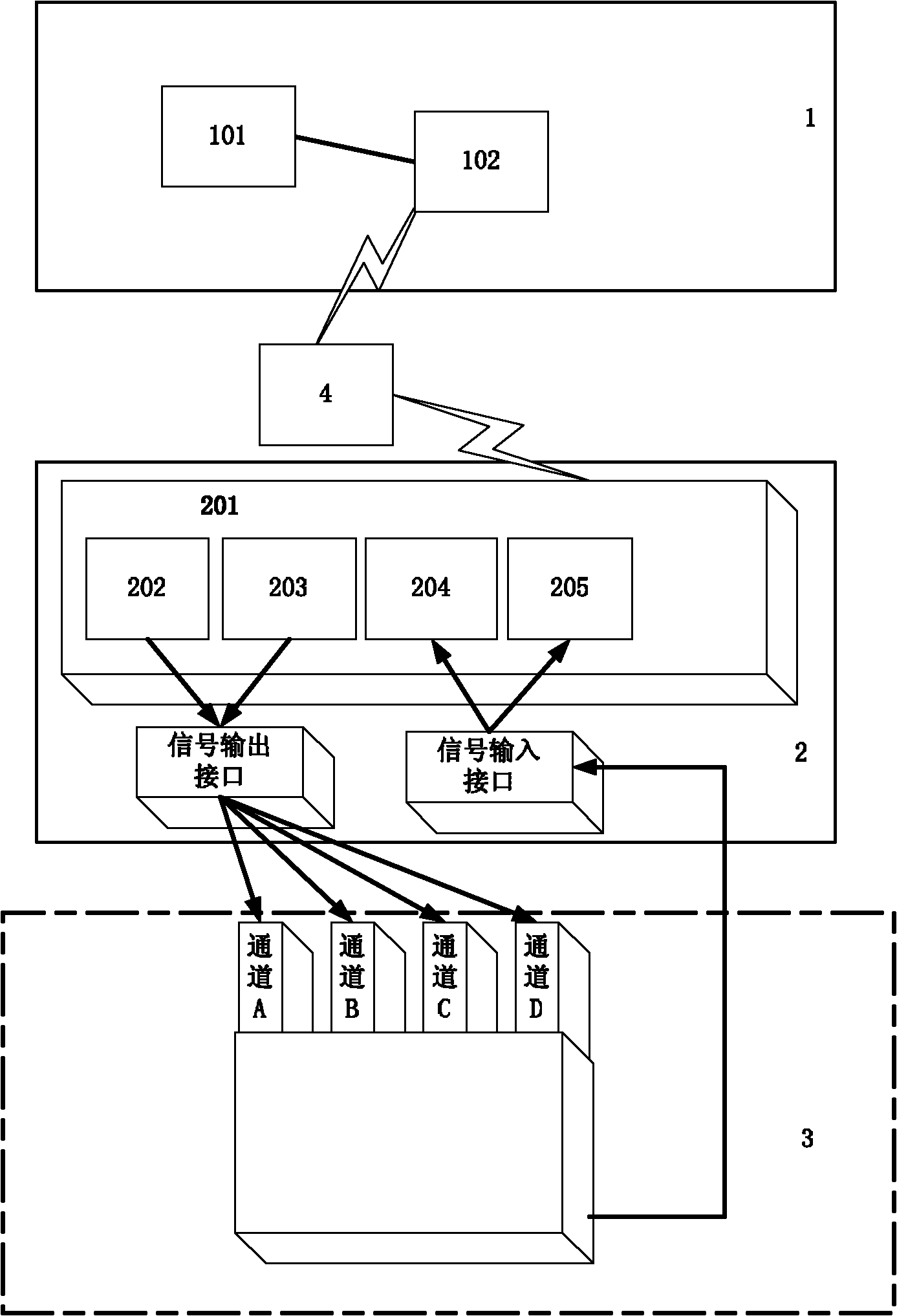

Integrated testing method and system for digital protection system of high temperature gas-cooled reactor

ActiveCN102280148AReal-time acquisitionImprove real-time performanceNuclear energy generationNuclear monitoringSystem integrationNuclear reactor

The invention discloses an integration testing method and system for a digital protection system of a high temperature gas cooled reactor and belongs to the technical field of the nuclear reactor. The method comprises the following steps of: S1, starting a corresponding testing module according to a testing instrument, and calling a testing algorithm corresponding to the function of the testing module so as to generating a testing vector of a monitoring variable of the digital protection system of the high temperature gas cooled reactor; S2, calculating and converting the testing vector to generating a signal in accordance with an interface of the protection system, and simultaneously, sending the generated simulated monitoring variable signal to signal input interfaces of a plurality of redundant channels of the protection system; and S3, acquiring testing data in real-time, carrying out comparison and statistic analysis on the acquired testing data and the predicted result, and judging whether the safety function and performance of the protection system has met the predicted requirements according to the results of comparison and statistic analysis. The invention can be used for determining whether the safety function and performance has met the predicted requirements at the system integration stage of the protection system.

Owner:CHINERGY CO LTD

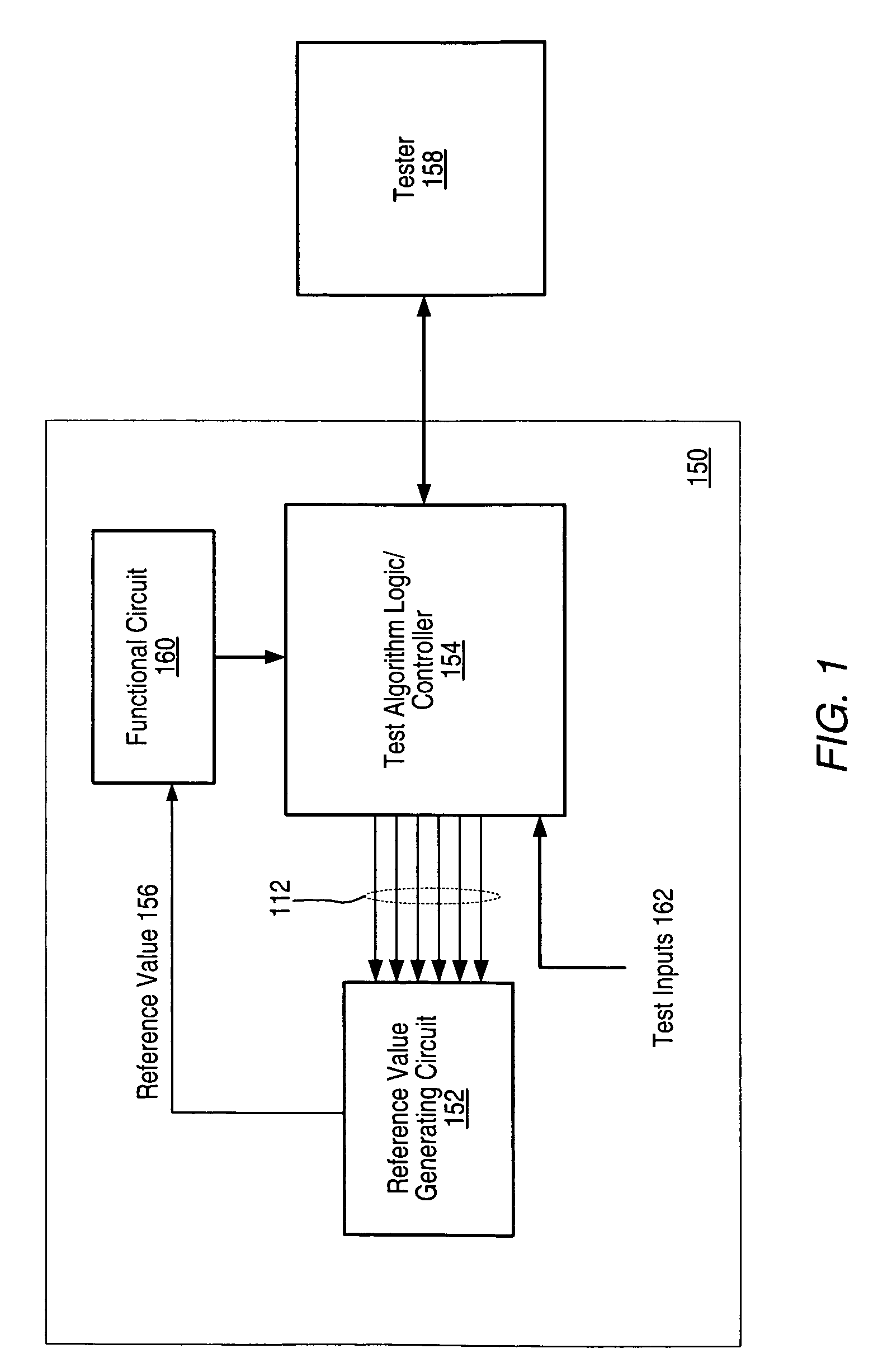

Intelligent video monitoring system and performance test method of algorithm thereof

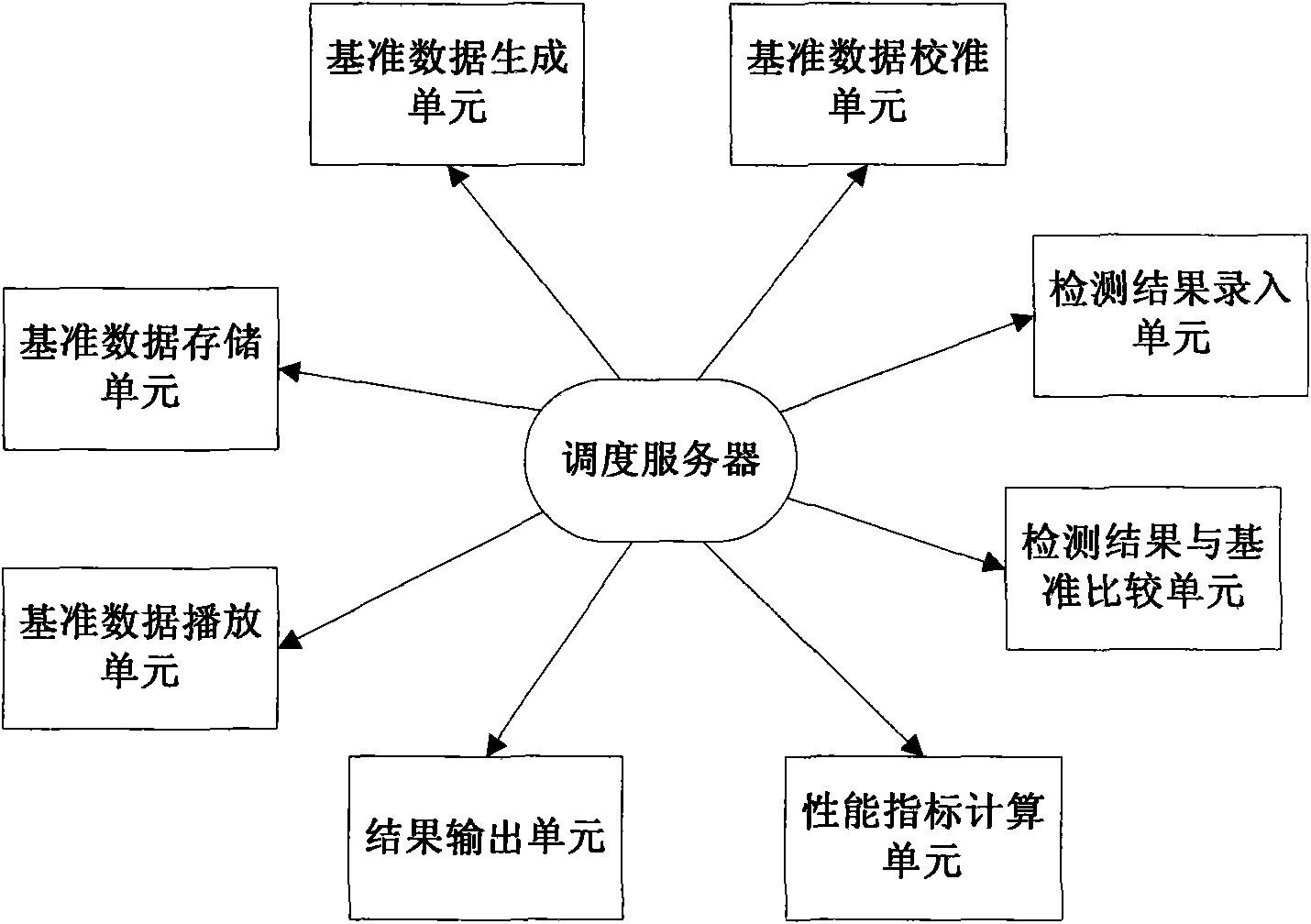

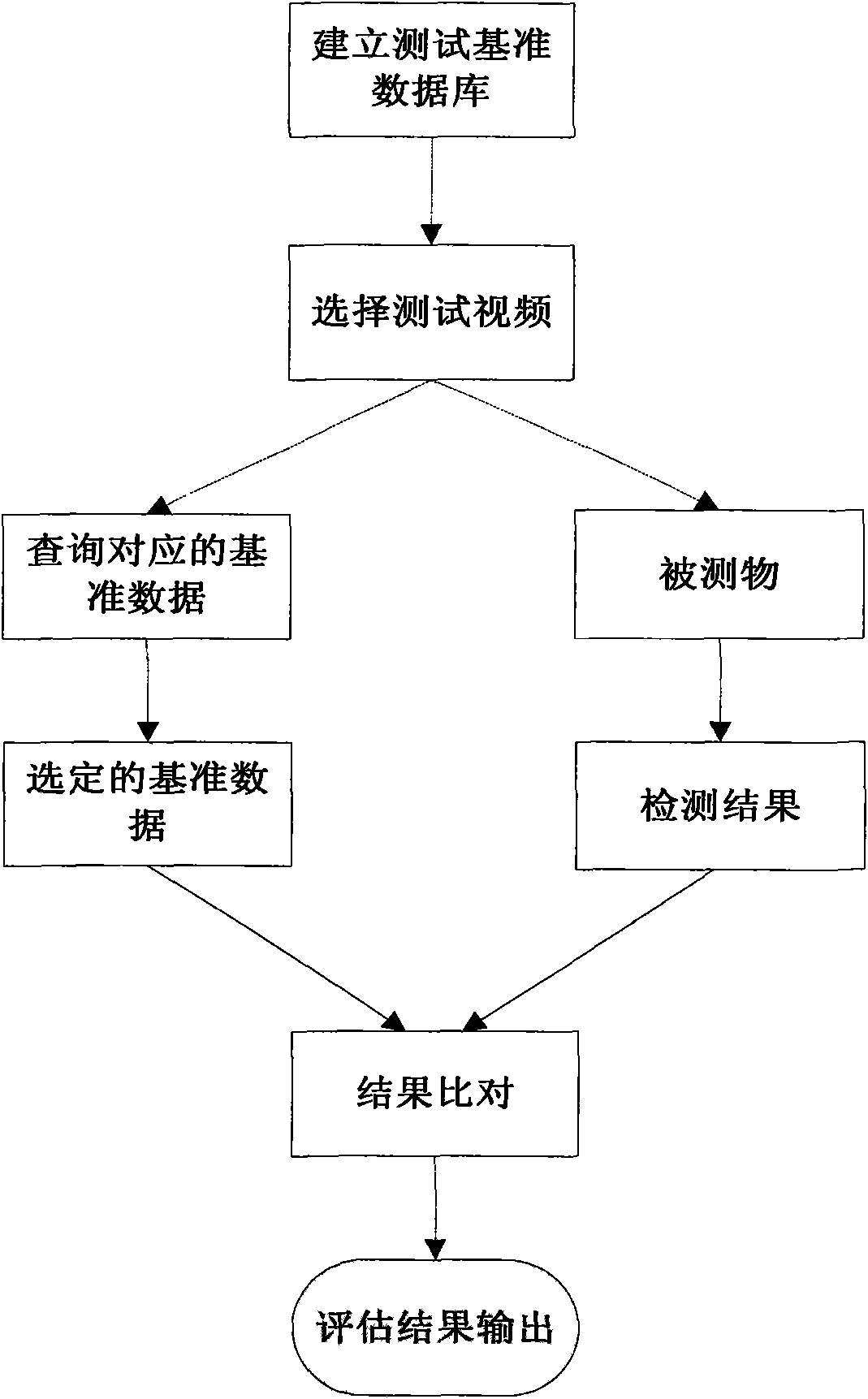

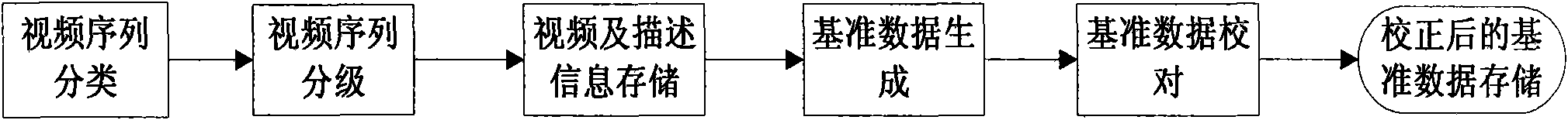

ActiveCN101656891APromote improvementRun fastClosed circuit television systemsSpecial data processing applicationsComputer hardwareVideo monitoring

The invention provides an intelligent video monitoring system and a performance test method of an algorithm thereof. The test method is completed by a test system composed of a reference data generation unit, a reference data calibration unit, a reference data storage unit, a reference data playing unit, a detection result input unit, a detection result and reference comparing unit, a performanceindex calculation unit, a result output unit and a scheduling server. The method for testing the intelligent video system or the algorithm comprises the following steps: firstly establishing a reference database for testing, and sequentially performing reference data generation, calibration and storage on a video for testing; then selecting the test video, performing function detection on the tested system or the tested algorithm on the selected test video, and storing a detection result as an XML file with a specified format; and finally comparing the file with the reference data corresponding to the video, and outputting a comparison and evaluation result in a text and graphics mode.

Owner:BEIJING ZHONGDUN SECURITY TECH DEV +1

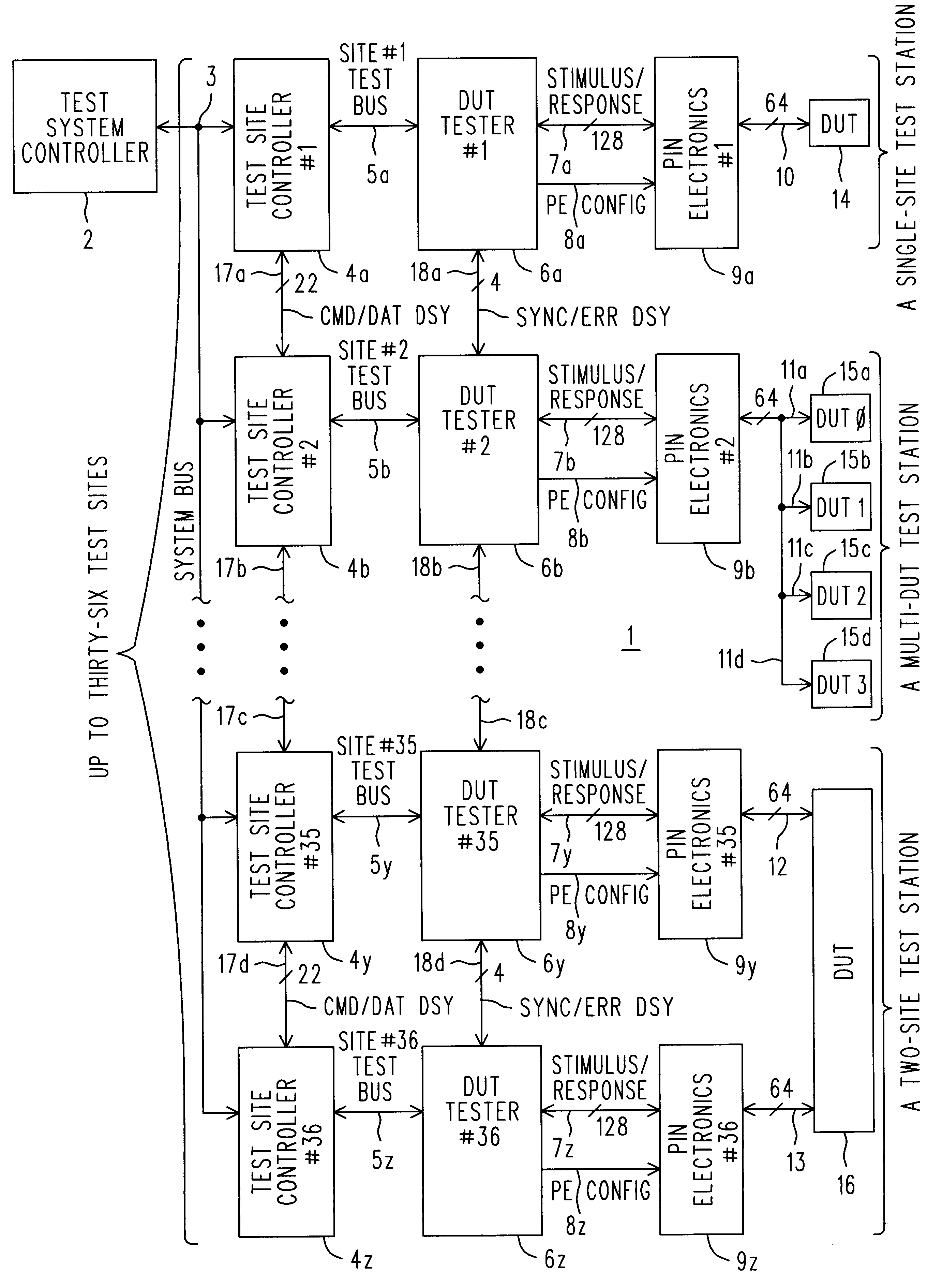

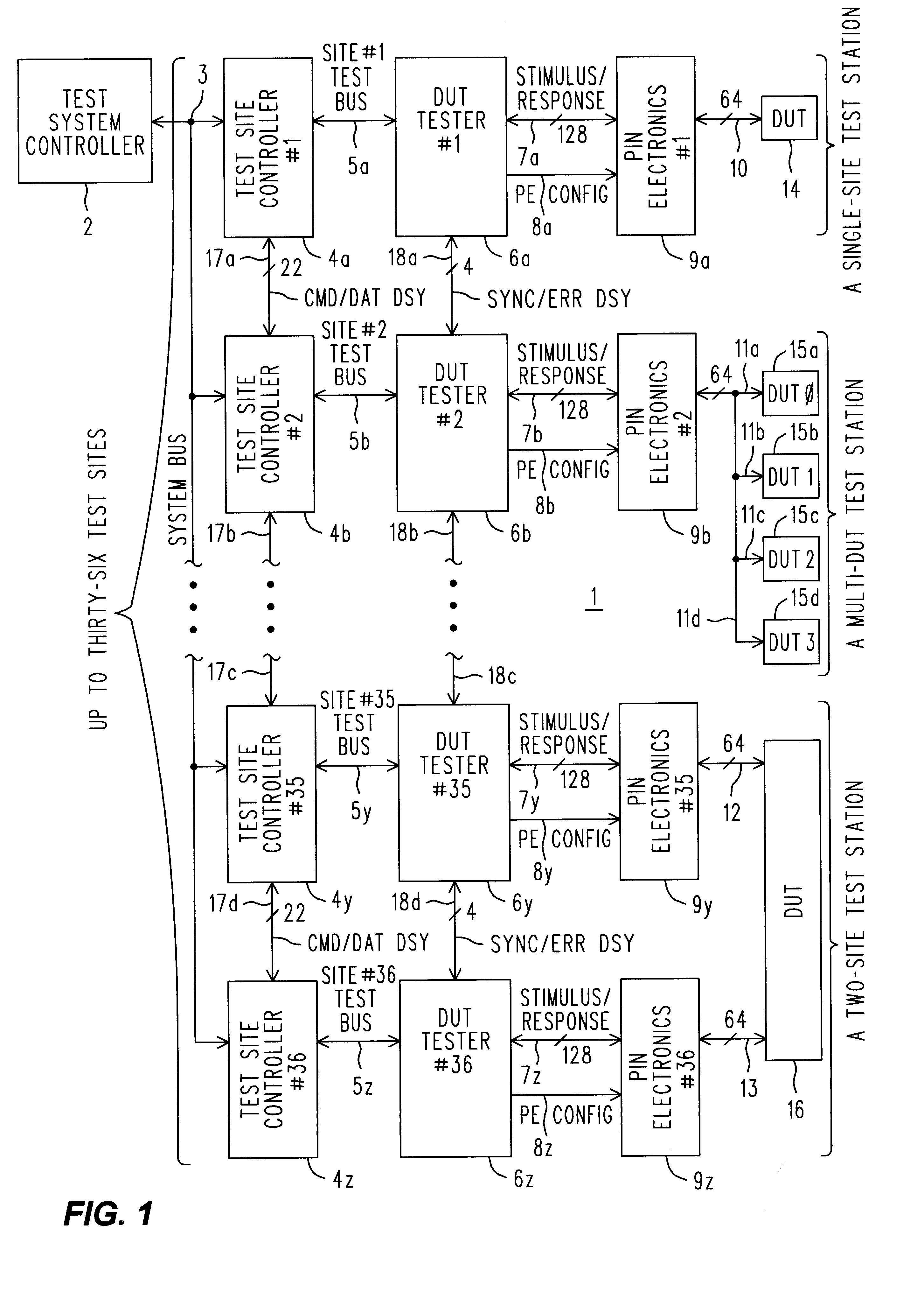

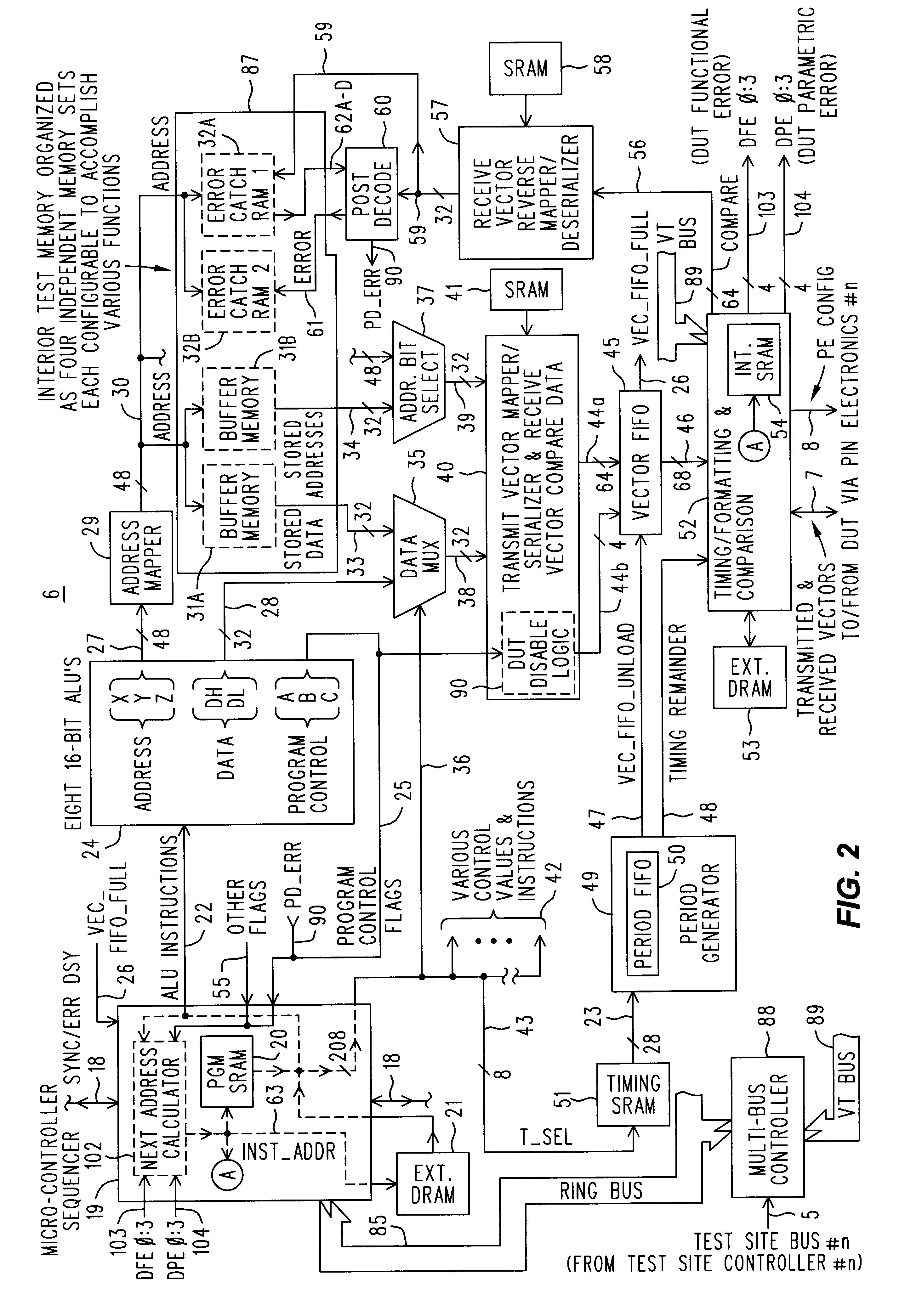

Algorithmically programmable memory tester with history FIFO's that aid in error analysis and recovery

InactiveUS6574764B2Increase overheadDigital circuit testingMarginal checkingMemory testerTester device

The problem is to branch back to an appropriate location within a memory tester test program, and also restore its state of algorithmic control, when an error associated therewith occurs later in time at the DUT. Owing to delays in pipelines connecting the program execution environment to the DUT and back again. These delays allow the program to arbitrarily advance beyond where the stimulus was given. The arbitrary advance makes it difficult to determine the exact circumstances that were associated with the error. A branch based on the error signal can restart a section of the test program, but it is likely only a template needing further test algorithm control information that varies dynamically as the test program executes. The solution is to equip the memory tester with History FIFO's whose depths are adjusted to account for the sum of the delays of the pipelines, relative to the location of that History FIFO. When the error flag is generated the desired program location and state information is present at the bottom of an appropriate History FIFO.

Owner:ADVANTEST CORP

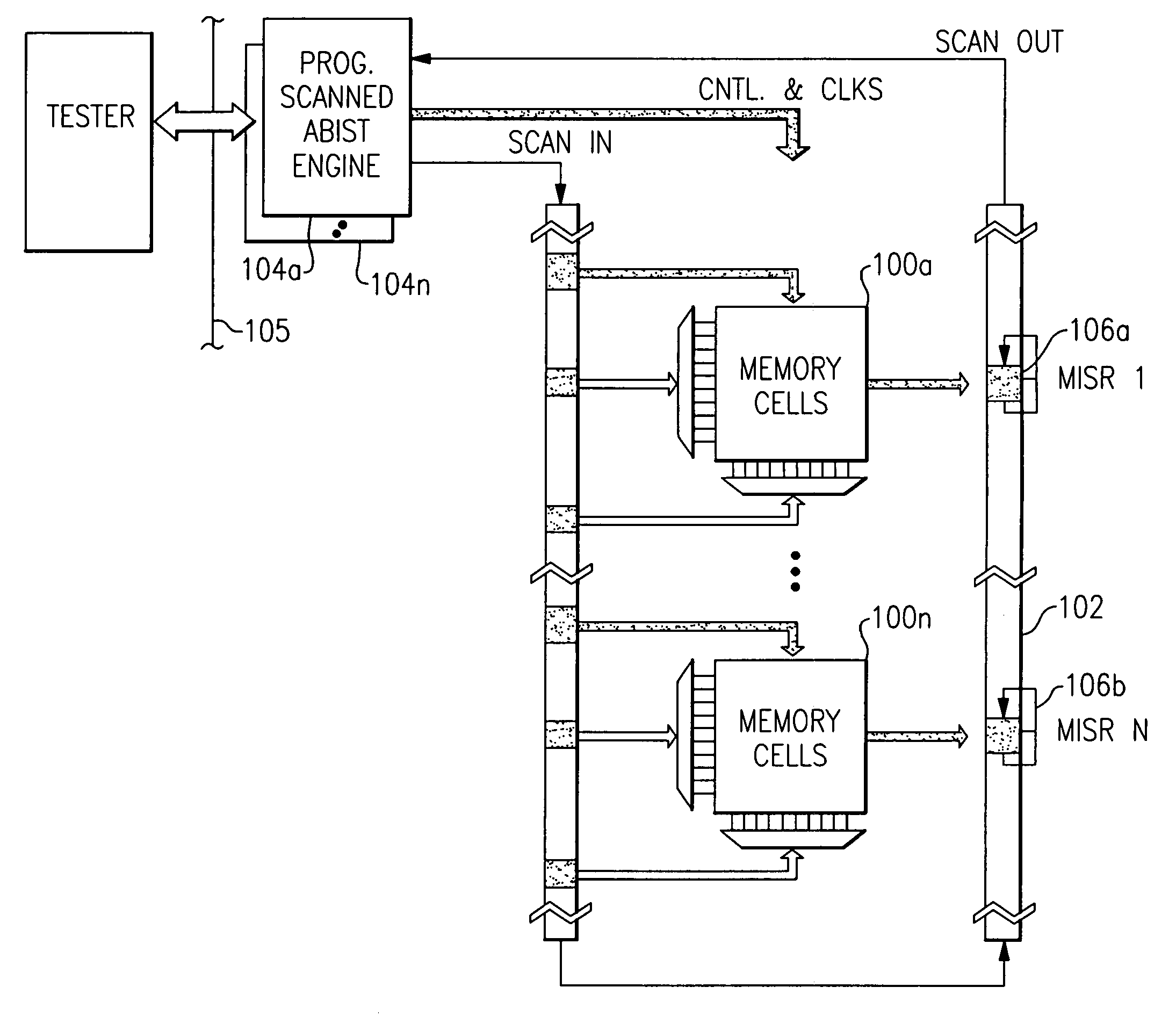

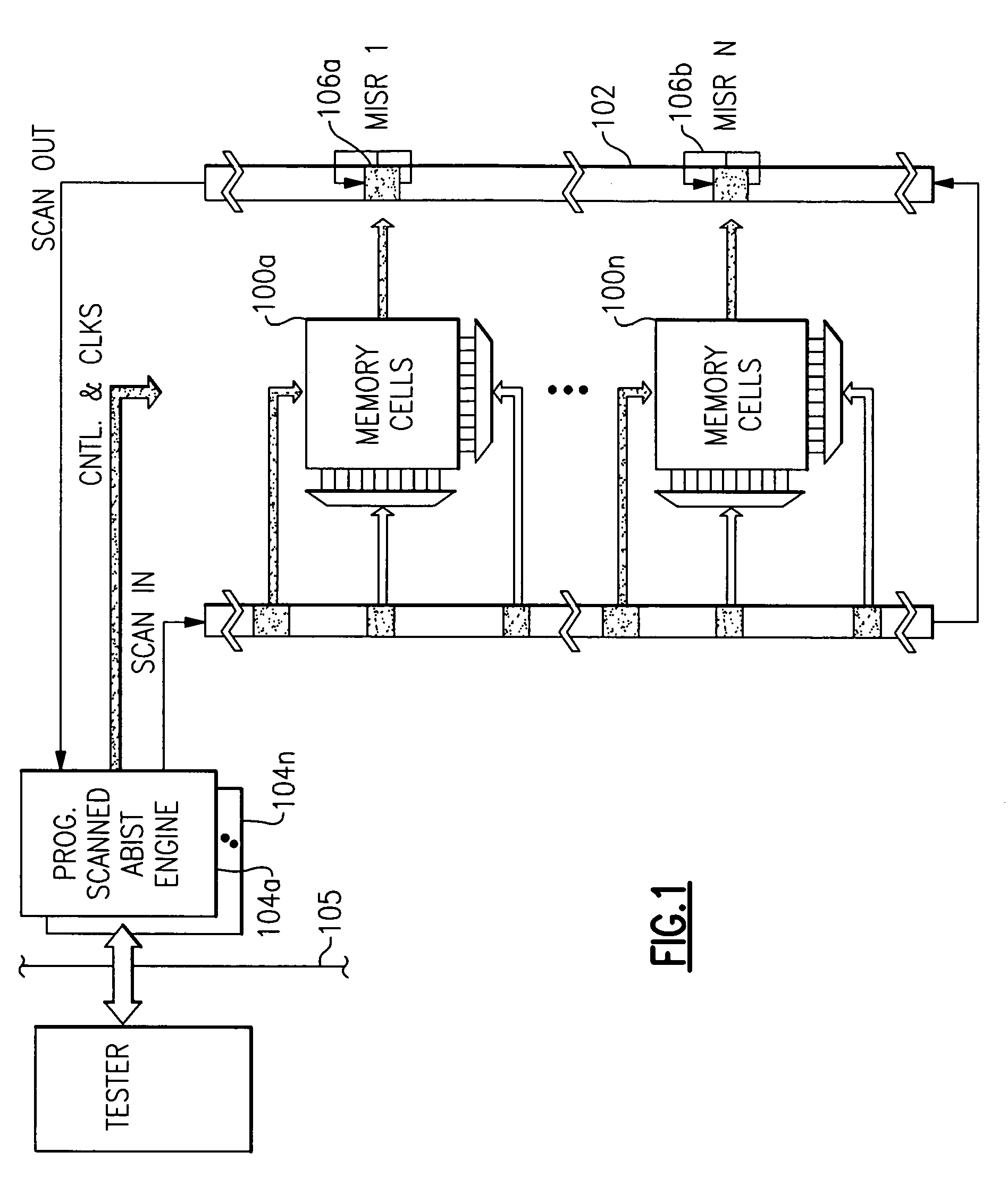

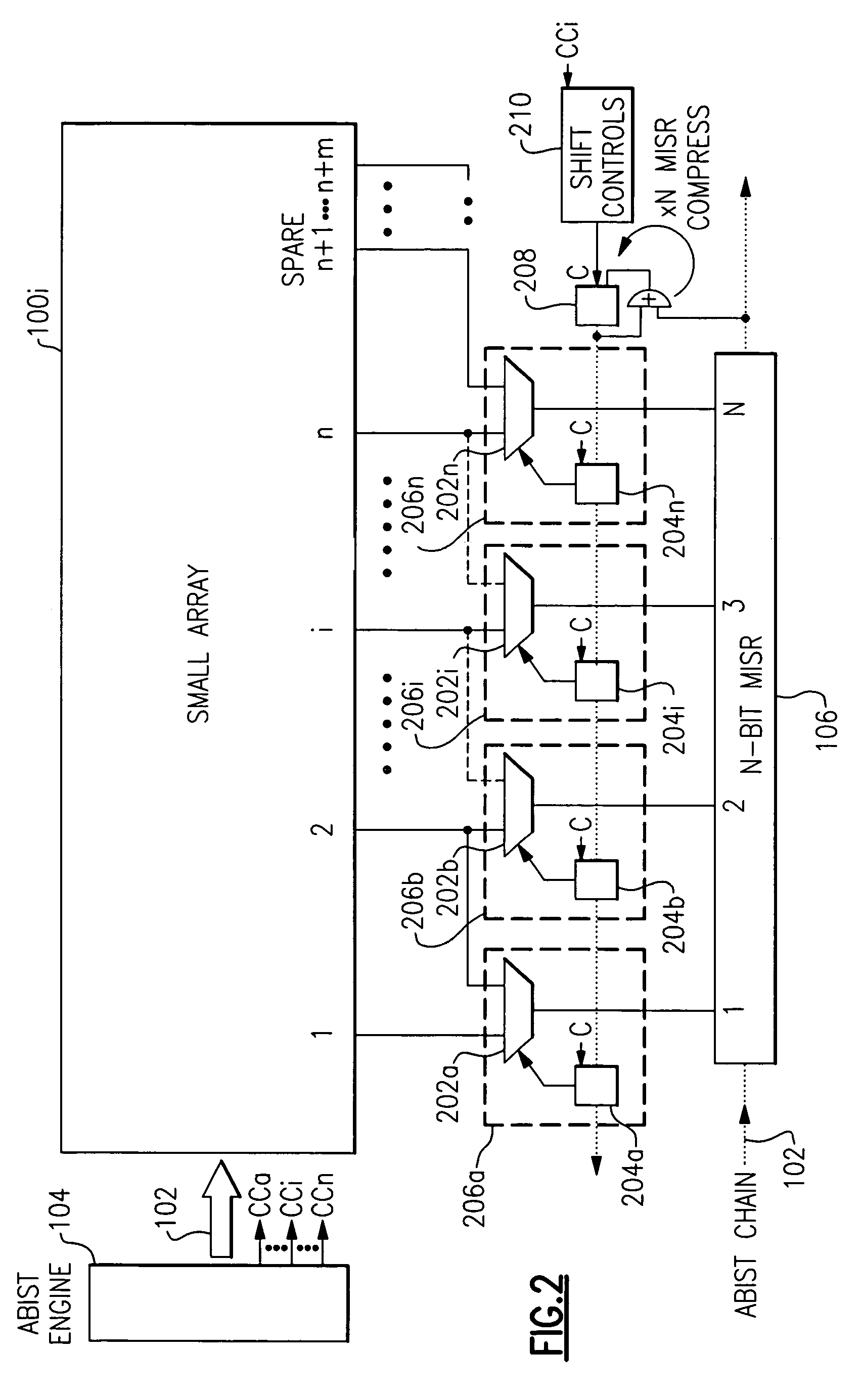

Array self repair using built-in self test techniques

InactiveUS7257745B2Not be accurately evaluatedRapid memory array diagnosis and repairElectronic circuit testingRead-only memoriesShift registerTest algorithm

A soft-fust test algorithm is distributed on-chip from an ABSIT engine through an LSSD shift register chain to dynamically evaluate a plurality of arrays with redundancy compensation for bad elements and repair those that are fixable. Using single-bit MISR error evaluation an ABSIT test sequence is executed concurrently on all arrays through the shift register chain. If any arrays are in error, redundancy compensation is employed and the ABIST test is repeated for all possible array redundant combinations until a functional configuration for each array is identified or all possible redundant combinations have been tried. Once functioning array configurations are verified, the associated soft-fuse states can be used to blow fuses and / or extracted for further system setup, permanent fuse-blowing and yield analysis. Multiple shift register chains driven by separate ABIST engines may be required to test all arrays on a chip.

Owner:INT BUSINESS MASCH CORP

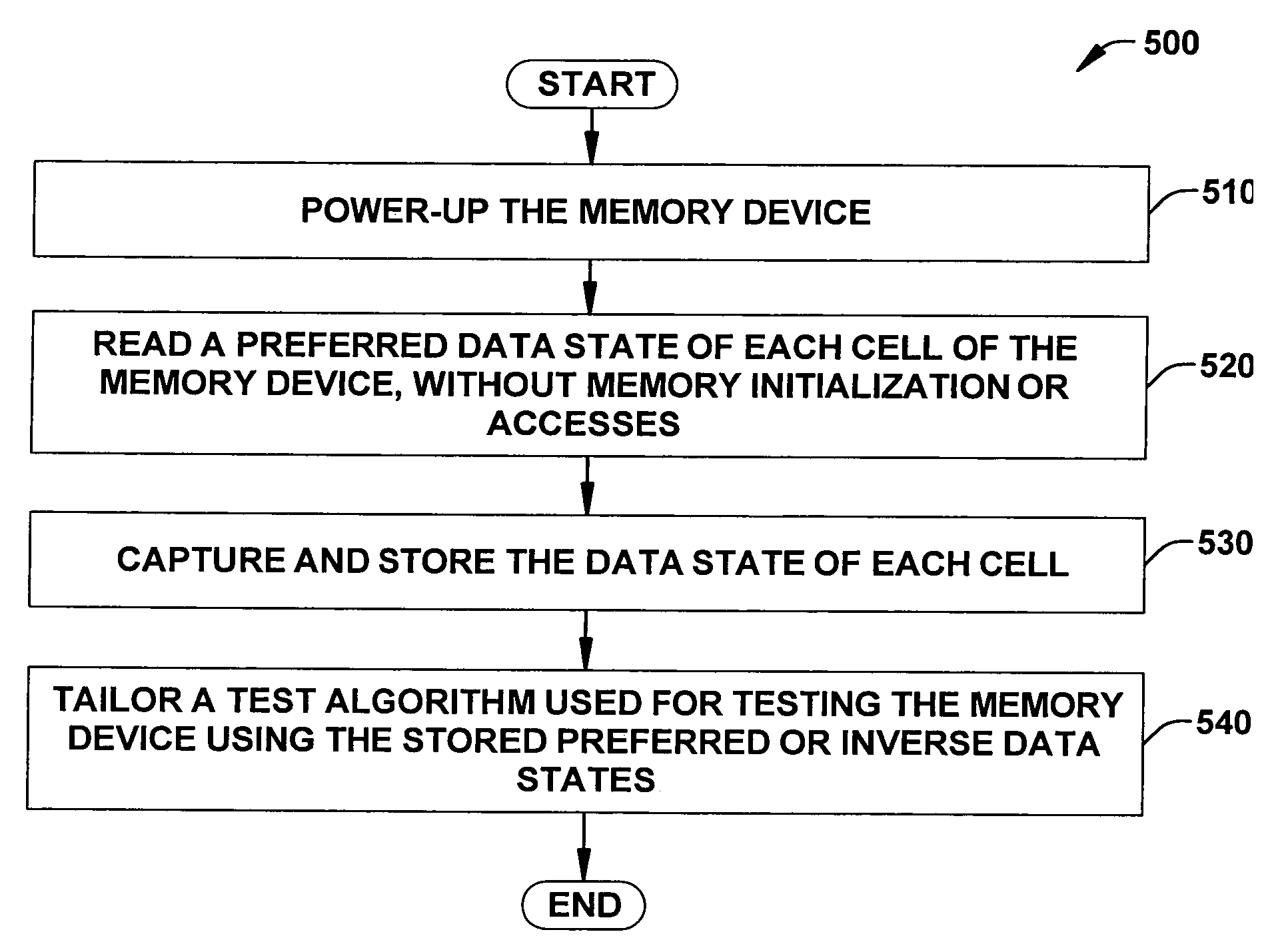

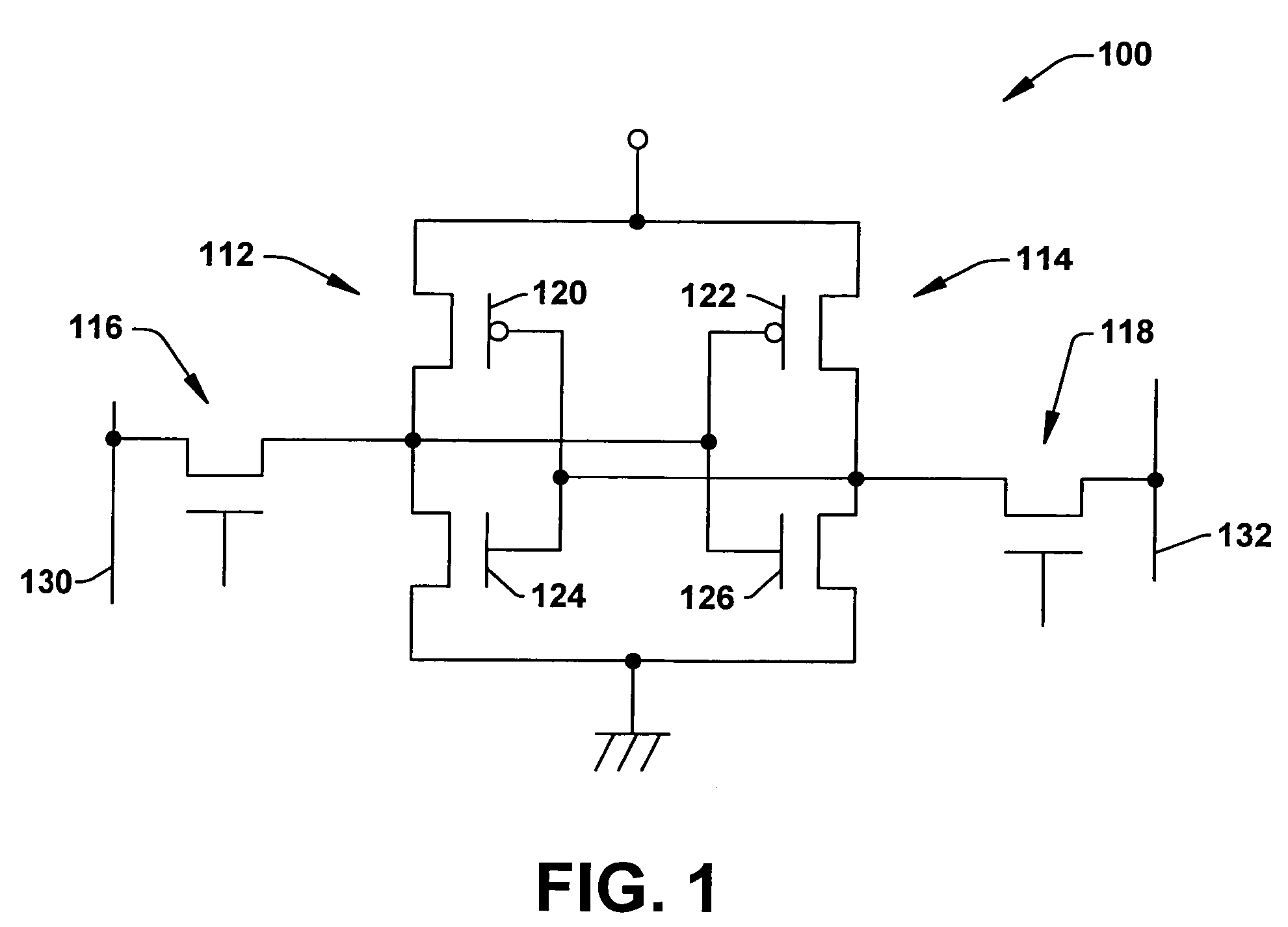

Method for reducing SRAM test time by applying power-up state knowledge

Owner:TEXAS INSTR INC

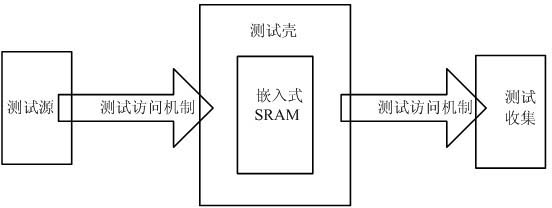

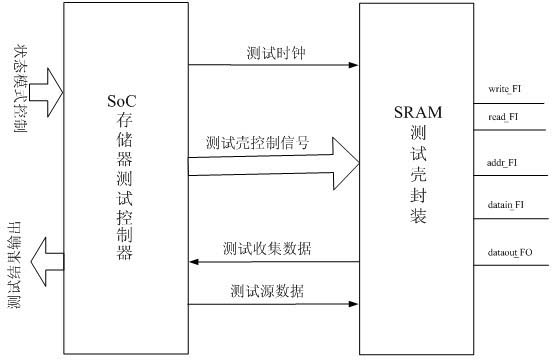

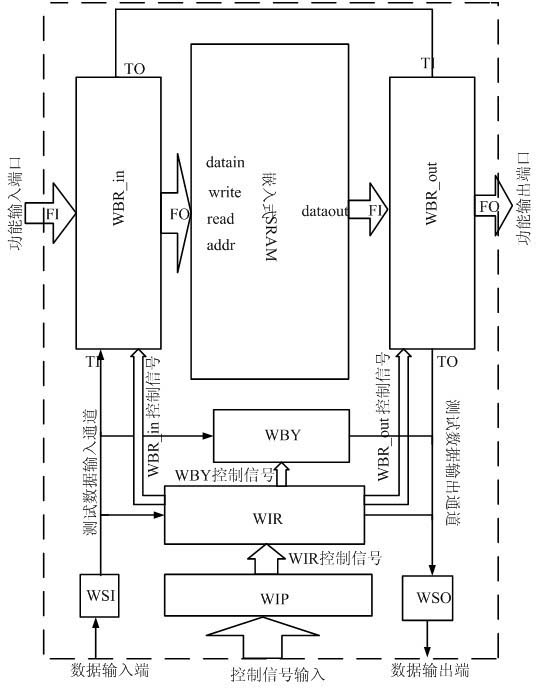

Embedded static random access memory (SRAM) test structure and test method based on institute of electrical and electronics engineers (IEEE) 1500

InactiveCN102332306AResolve Test AccessSolving Test IsolationStatic storageStatic random-access memoryTest algorithm

The invention discloses an embedded static random access memory (SRAM) test structure and an embedded SRAM test method based on institute of electrical and electronics engineers (IEEE) 1500. Methods for IEEE1500 standard for embedded core test and built-in self test (BIST) are combined in the test structure; the embedded SRAM test structure consists of a test shell package of an embedded SRAM and a SRAM test controller, wherein the test shell package is used for solving the problems of test access, test isolation and test control of the embedded SRAM; and the SRAM test controller is used for generating test incentive data, controlling a package shell Wrapper, performing response analysis and outputting a test result according to a test algorithm. By adoption of the test structure and the test method, a fault existing in the embedded SRAM can be detected, the test reuse of the embedded SRAM is facilitated, and the integration efficiency of system on a chip (SoC) can be effectively improved.

Owner:GUILIN UNIV OF ELECTRONIC TECH

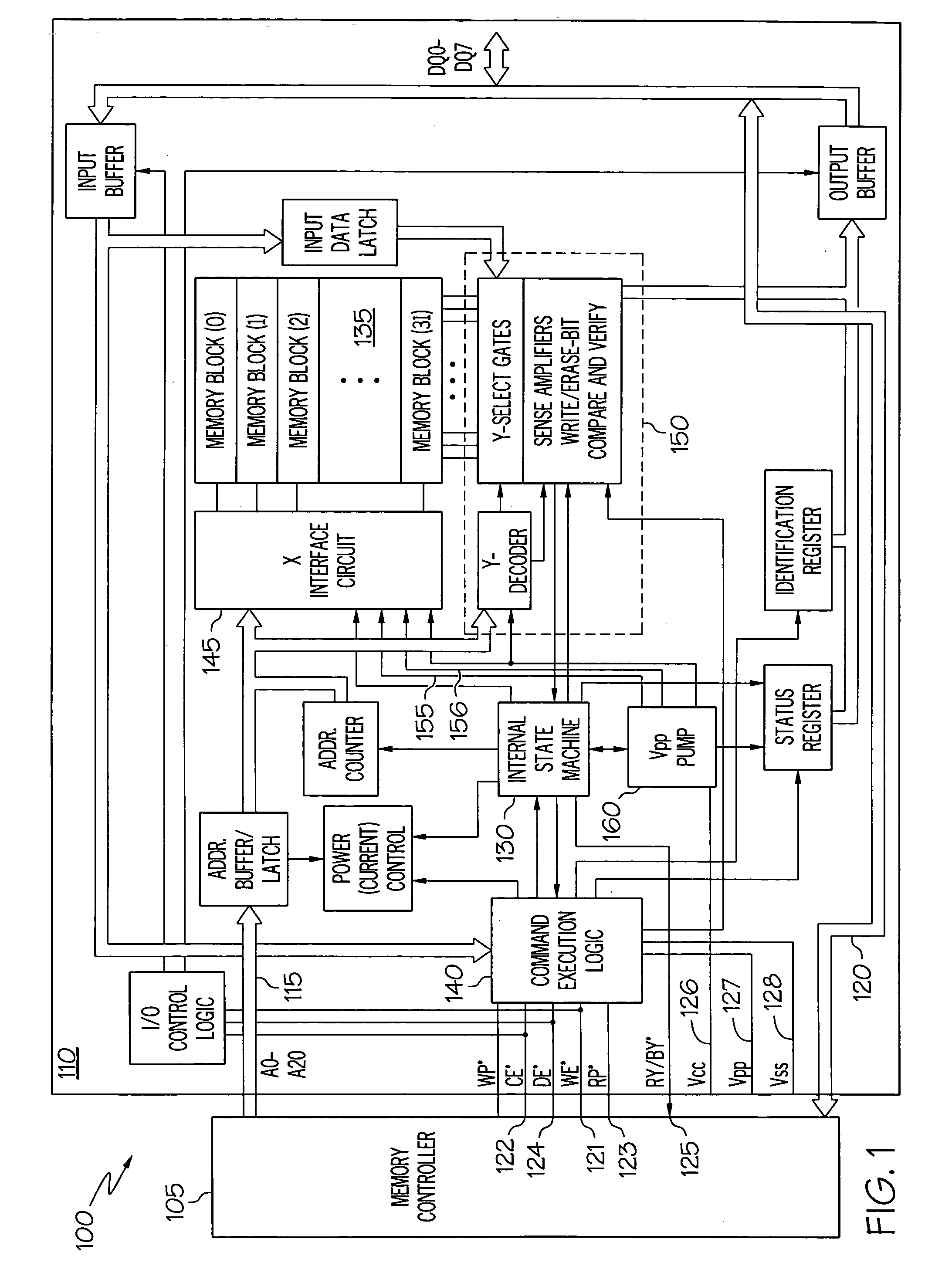

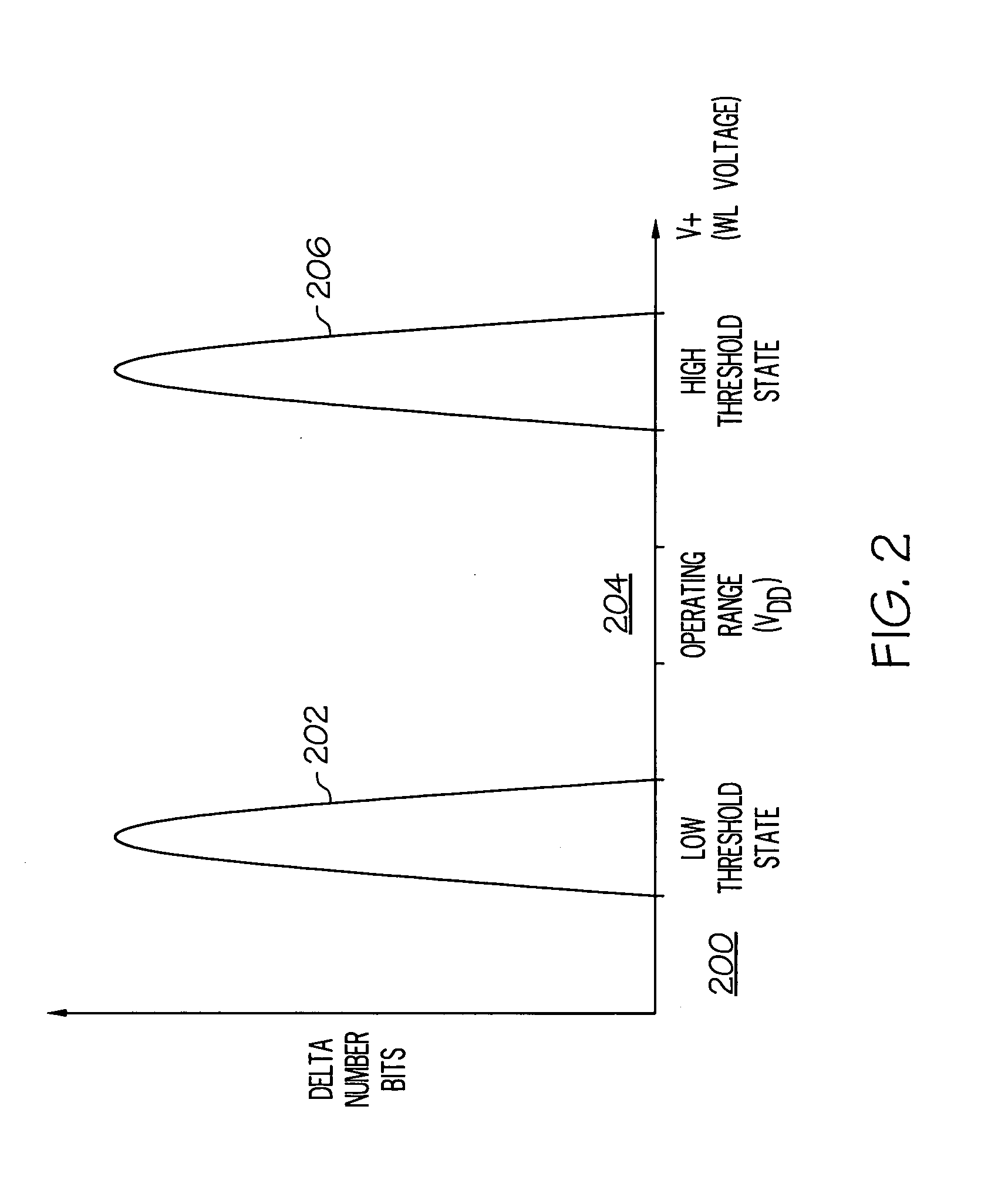

In-circuit Vt distribution bit counter for non-volatile memory devices

Integrated testing components and testing algorithm on a non-volatile memory module provide faster Vt (threshold voltage) distributions during the module verification process. The memory module includes address and voltage scanning components and a bit counter for storing the number of 0's or 1's for a specified voltage. As the range of addresses are scanned across a range of voltages, the instances of the count value being counted is accumulated by the bit counter. Automated Tester Equipment (ATE) reads the accumulated count value for each tested voltage.

Owner:NXP USA INC

Op-code based built-in-self-test

InactiveUS20080195901A1Electronic circuit testingFunctional testingComputer hardwareOperational system

A built-in-self-test (BIST) system for testing a memory that includes a scheduler module that generates a first test algorithm based on a set of operational codes. Each operational code defines a test operation to be performed by the first test algorithm on the memory. The BIST system also includes an execution module that applies the first test algorithm to the memory.

Owner:MARVELL ISRAEL MISL

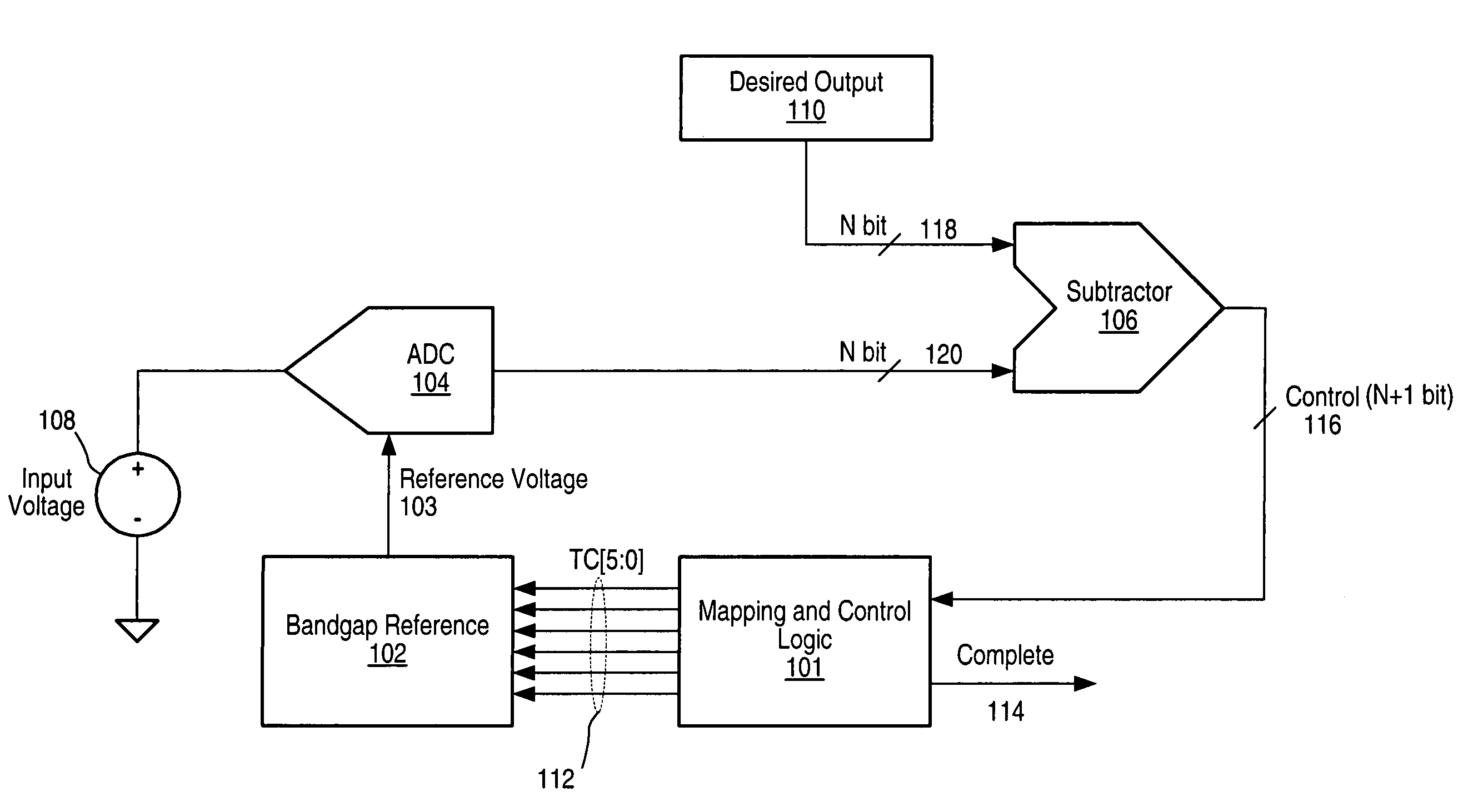

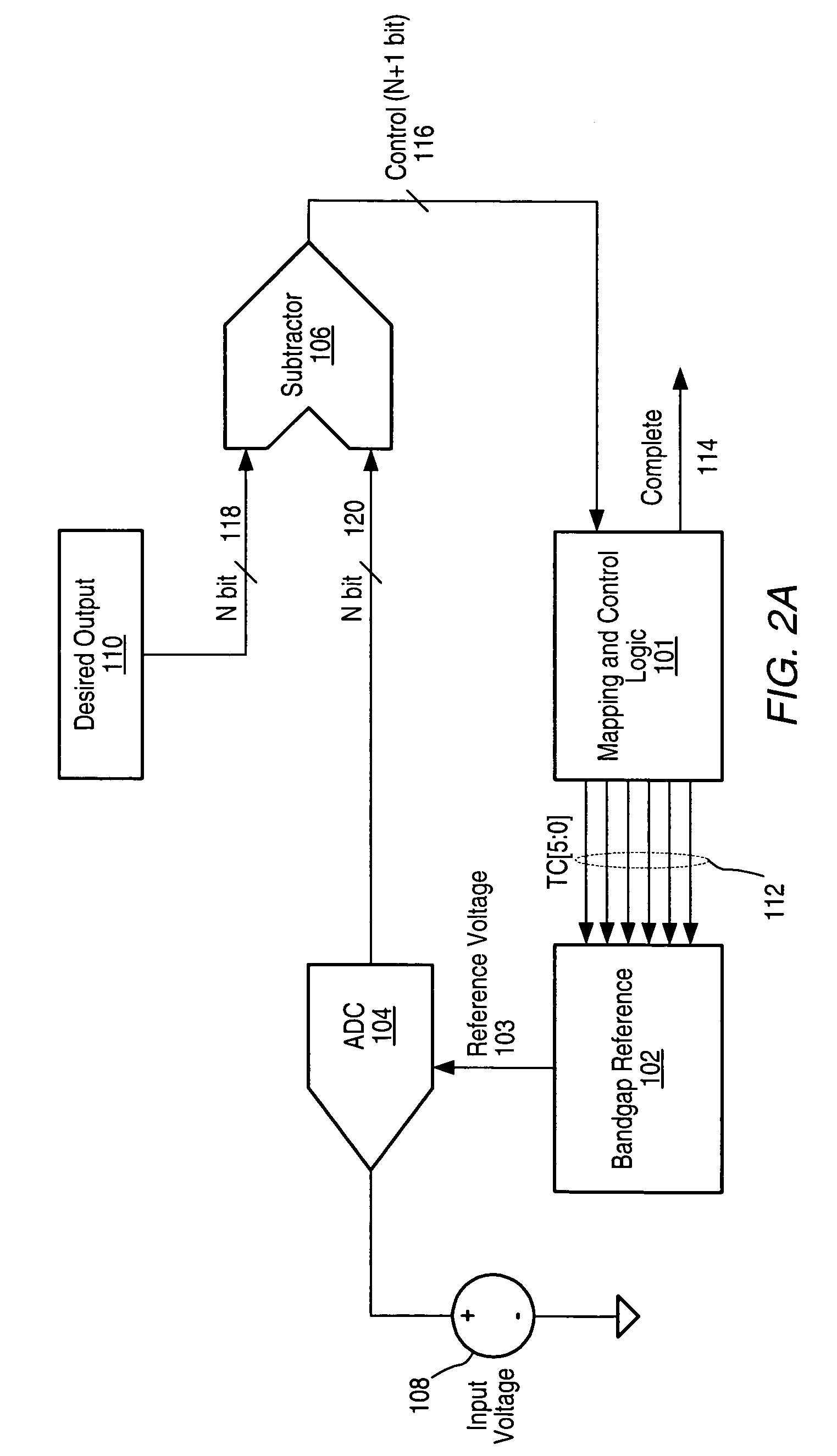

Automatic reference voltage trimming technique

ActiveUS7433790B2Precise designReduce controlThermometers using electric/magnetic elementsElectrical testingTest algorithmVoltage reference

Owner:MICROCHIP TECH INC

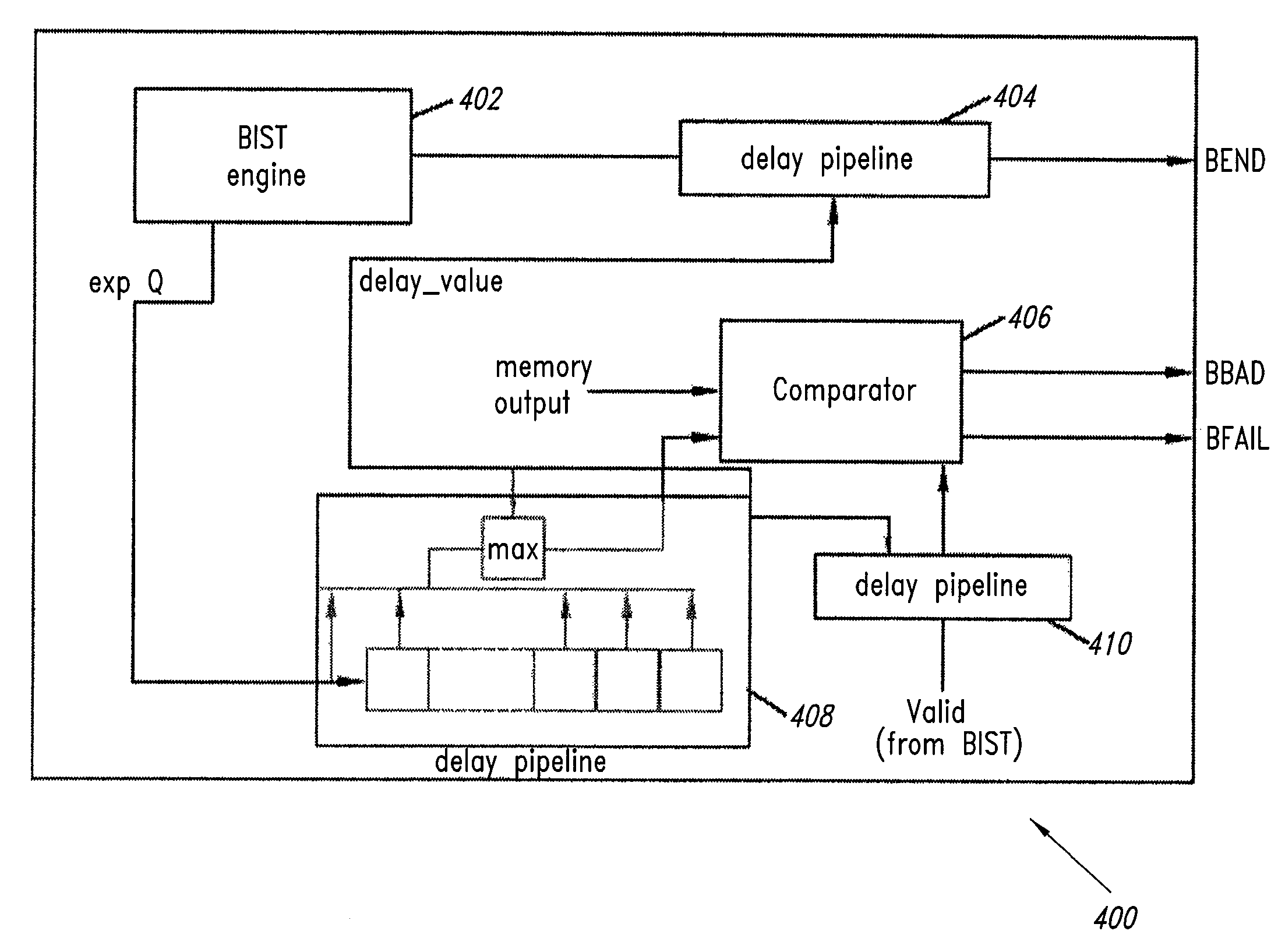

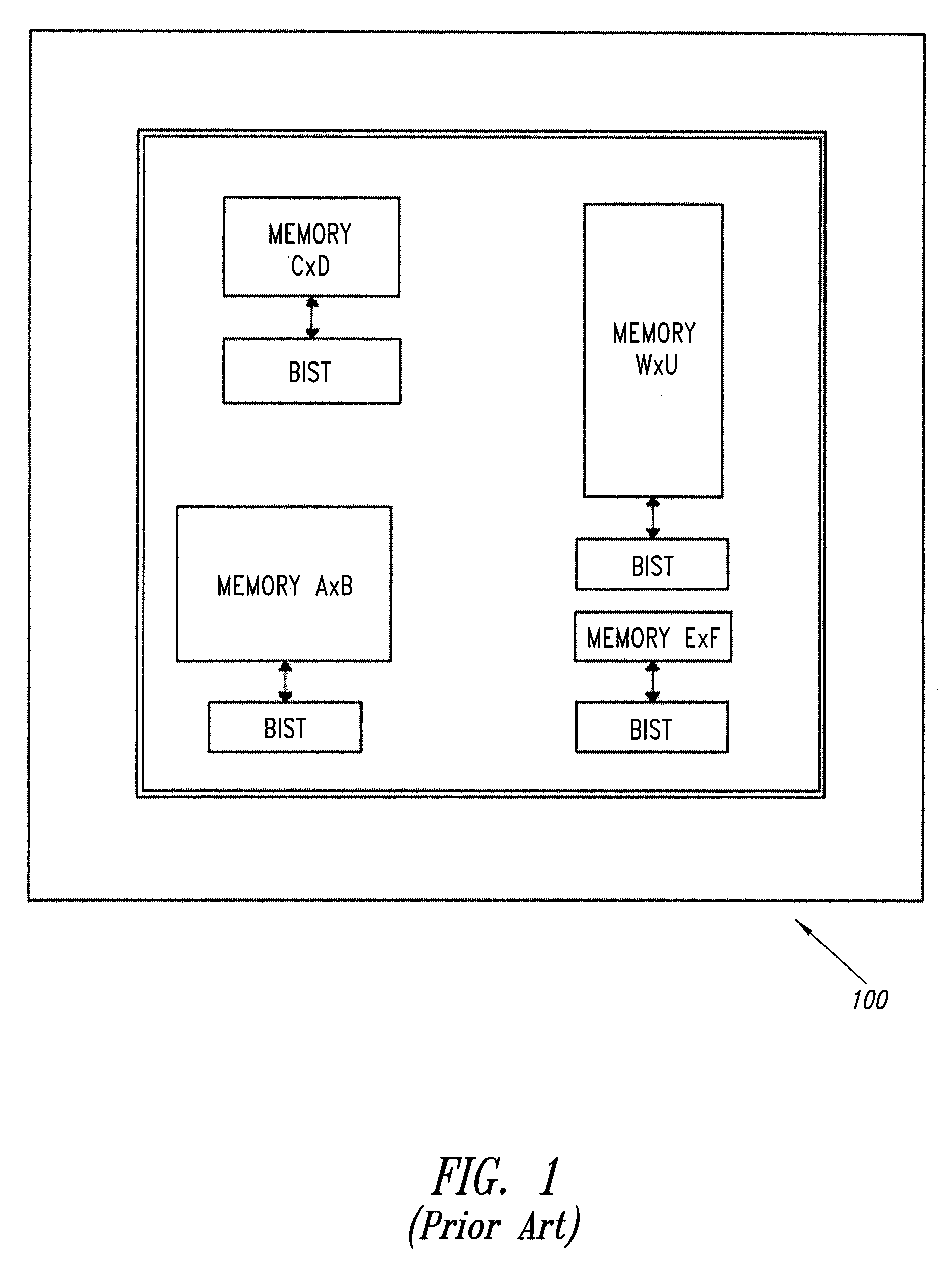

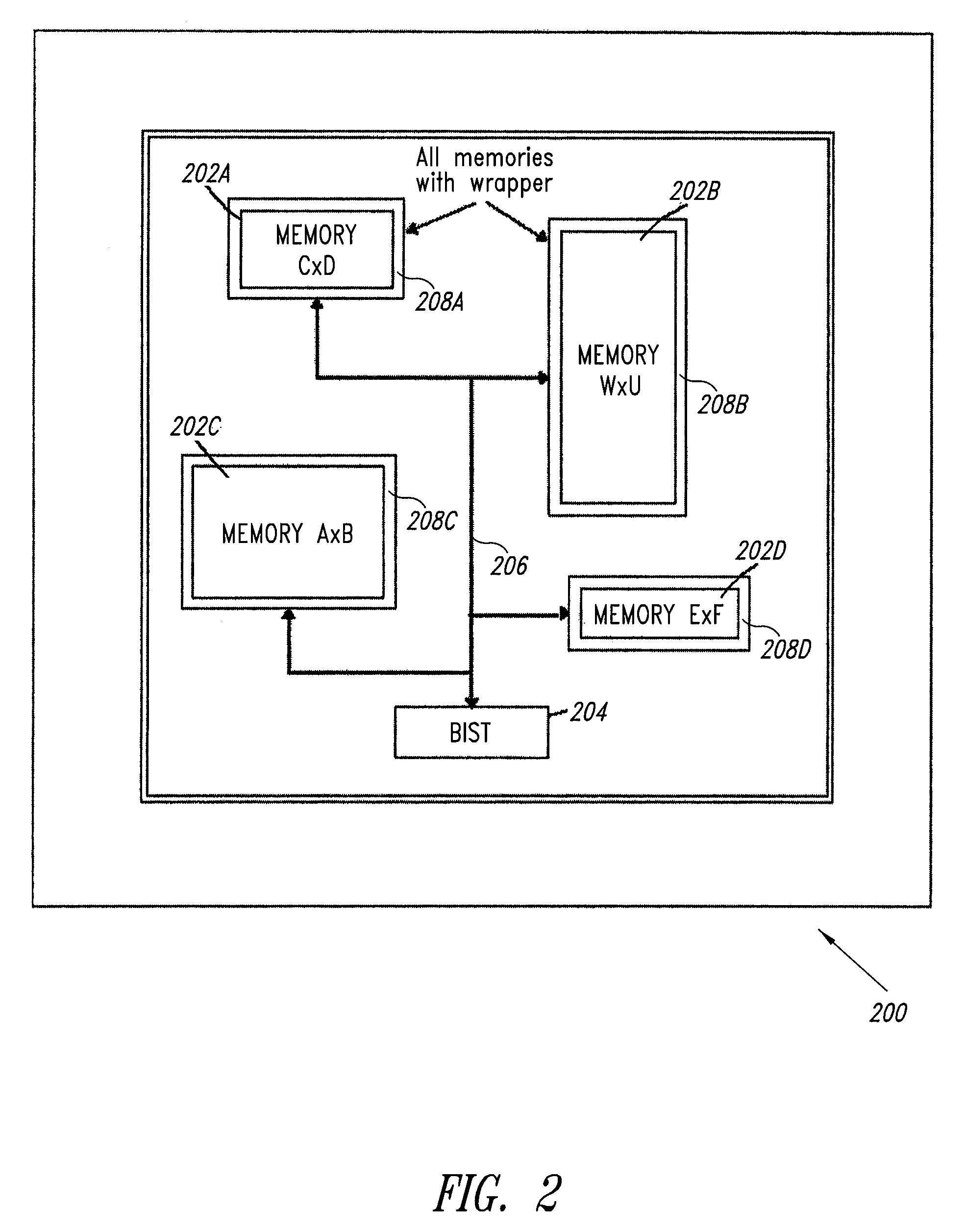

Self programmable shared BIST for testing multiple memories

A built-in self-test (BIST) device tests multiple embedded memories of different characteristics. The BIST includes a BIST controller, a delay generator, multiple interface modules, and a memory wrapper. The BIST controller generates an initialization sequence and a memory test algorithm. The delay generator provides a delay of an expected data, a valid signal, a BBAD signal, a BEND signal, and a BFAIL signal. The multiple interface modules provide signal pipelining for multiple memories through a bus. The bus carries signals form the BIST device to multiple memories and vice-versa. The memory wrapper decodes a selected memory for decompressing a memory data signal generated by said BIST device and further compresses a memory output signal.

Owner:STMICROELECTRONICS PVT LTD

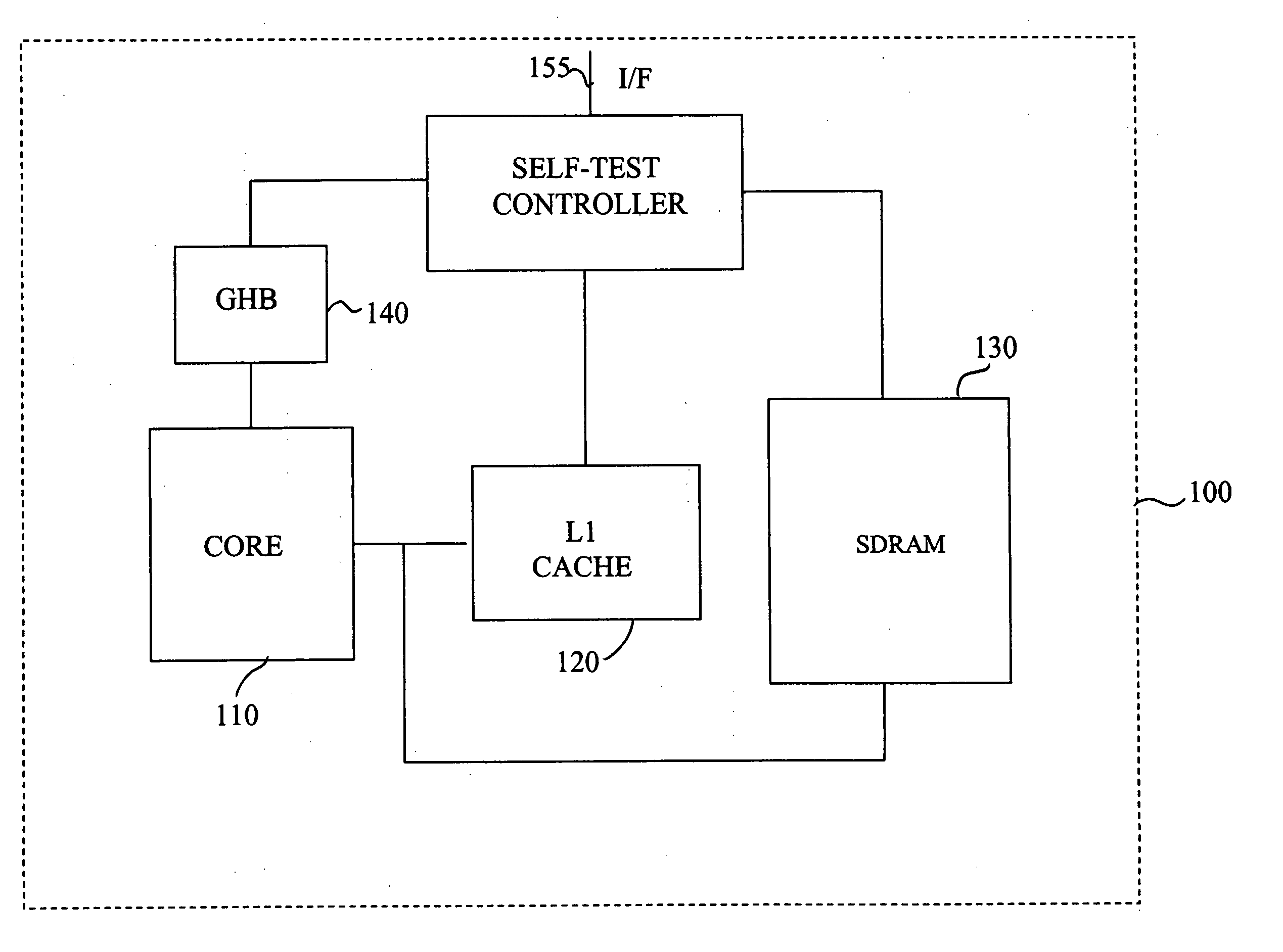

Method and apparatus for memory self testing

ActiveUS20060200713A1Efficiently re-assignedCompromise accuracy of testingStatic storageMemory addressParallel computing

A memory self-test system is provided comprising a self-test controller operable in self-test mode to generate a sequence of generated memory addresses for performing memory access operations associated with the memory test algorithm having an associated memory cell physical access pattern. A programmable re-mapper is operable to re-map the sequence of generated memory addresses derived from the self-test instruction to a sequence of re-mapped memory addresses. The programmable re-mapper performs this re-mapping in response to programmable mapping selection data. The re-mapping of the generated memory addresses to re-mapped memory addresses ensures that the memory cell accesses performed during execution of the memory self-test are consistent with the associated memory cell physical access pattern regardless of the particular implementation of the memory array.

Owner:ARM LTD