Patents

Literature

121 results about "Memory faults" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Memory faults. A memory fault occurs when a process either uses memory in an incorrect way or uses memory that does not belong to it, according to the OS . On a Linux system, a memory fault is called a segmentation fault. When a memory fault occurs, the OS terminates the process immediately .

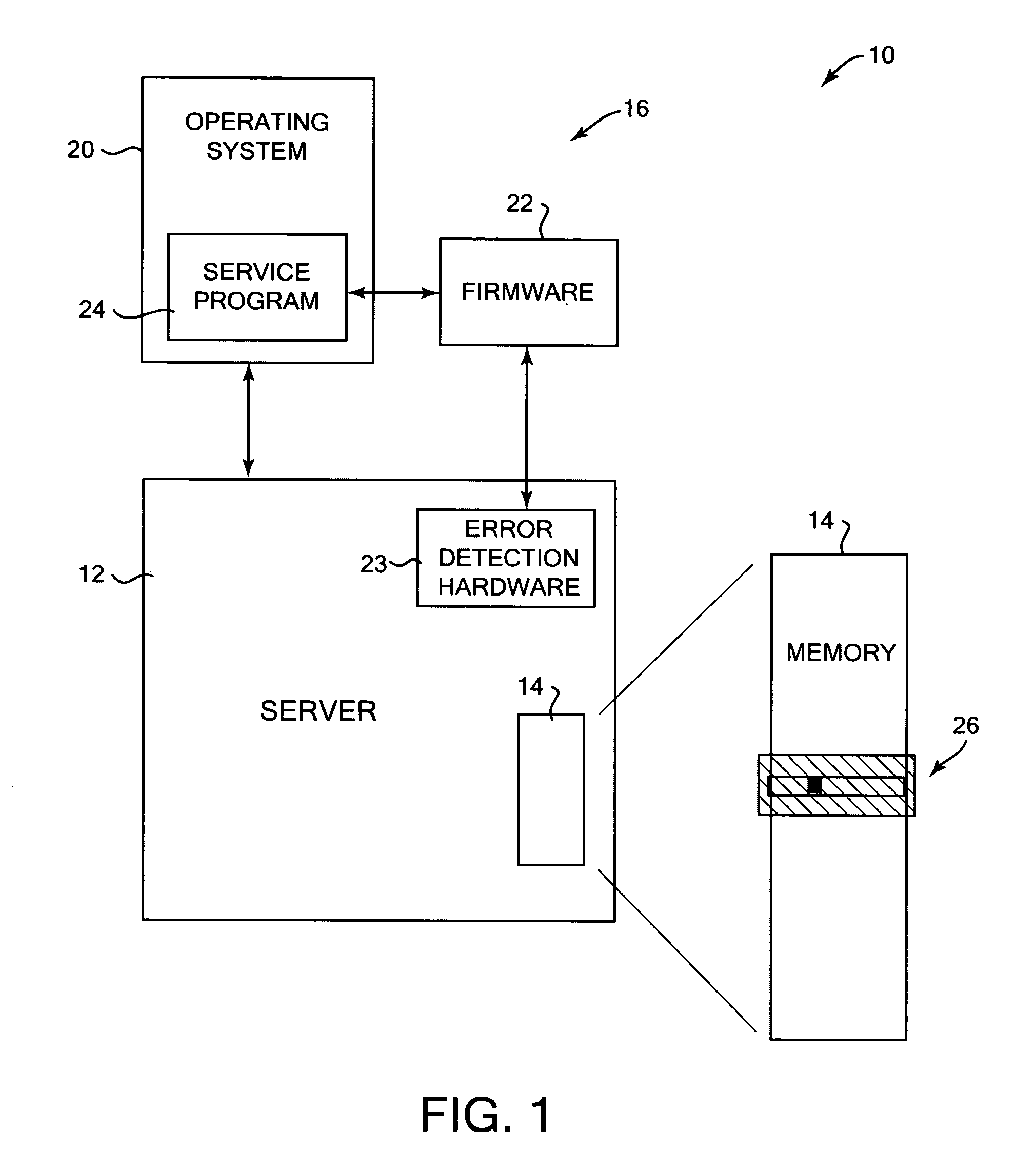

Memory protection system and method

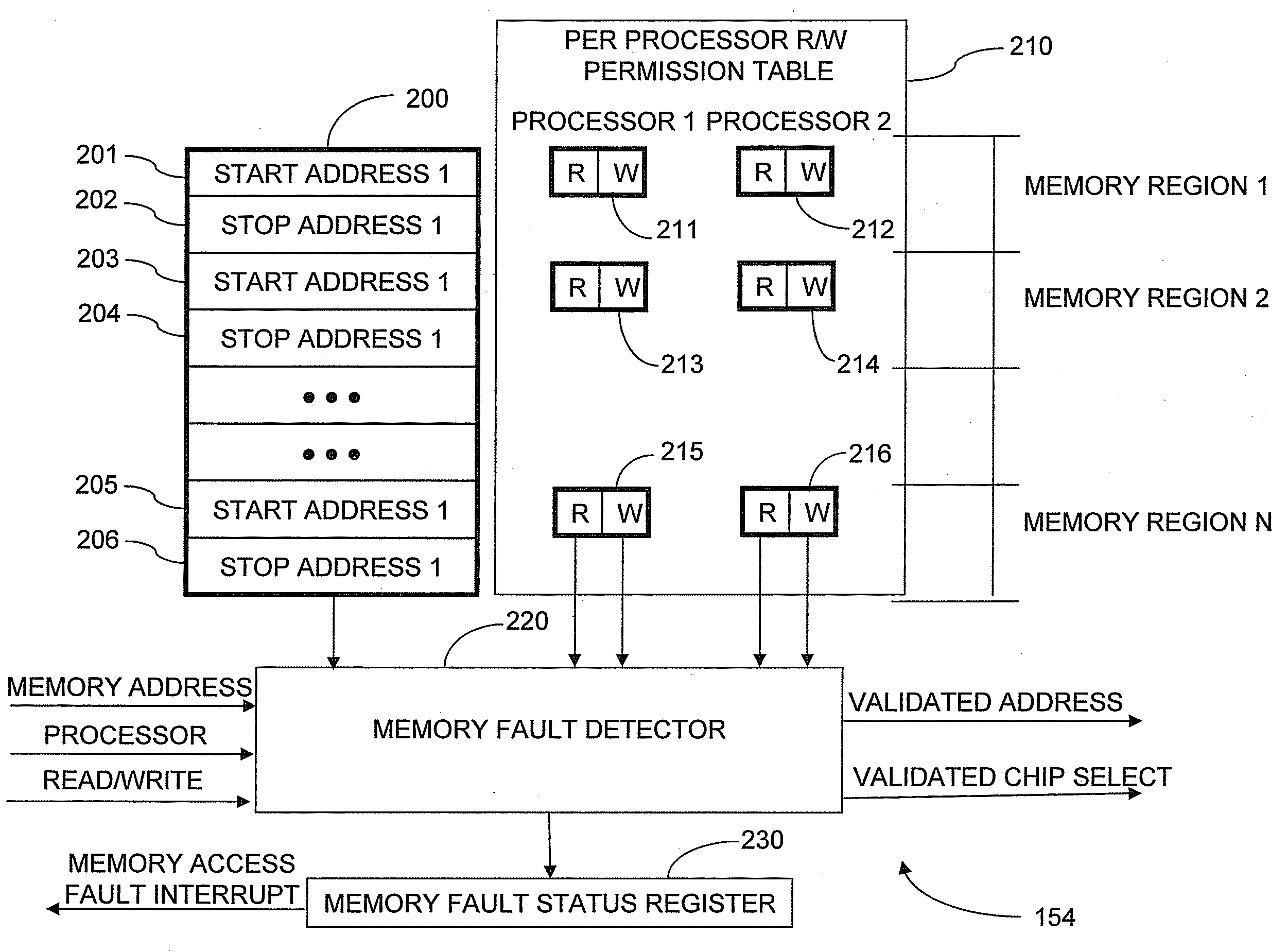

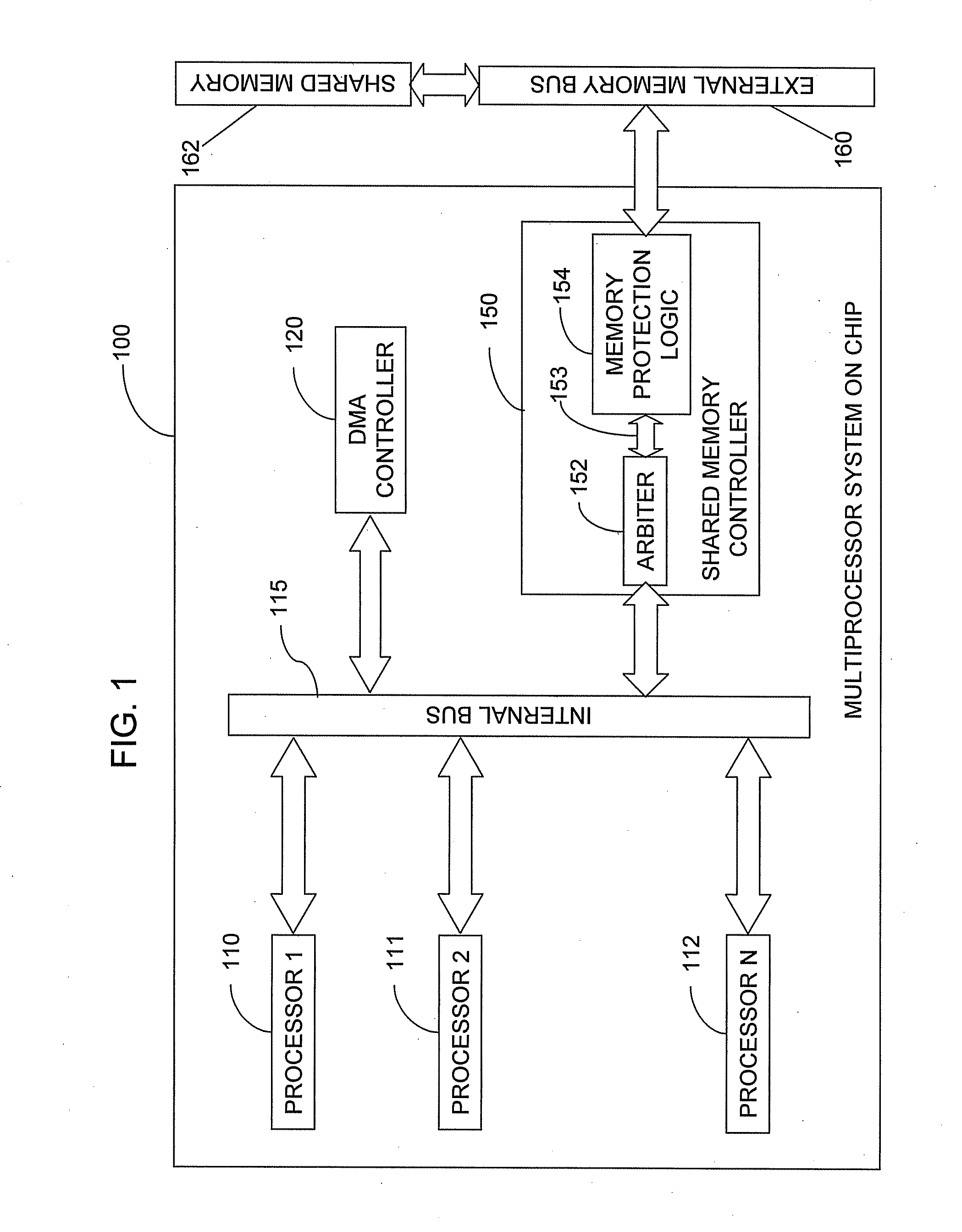

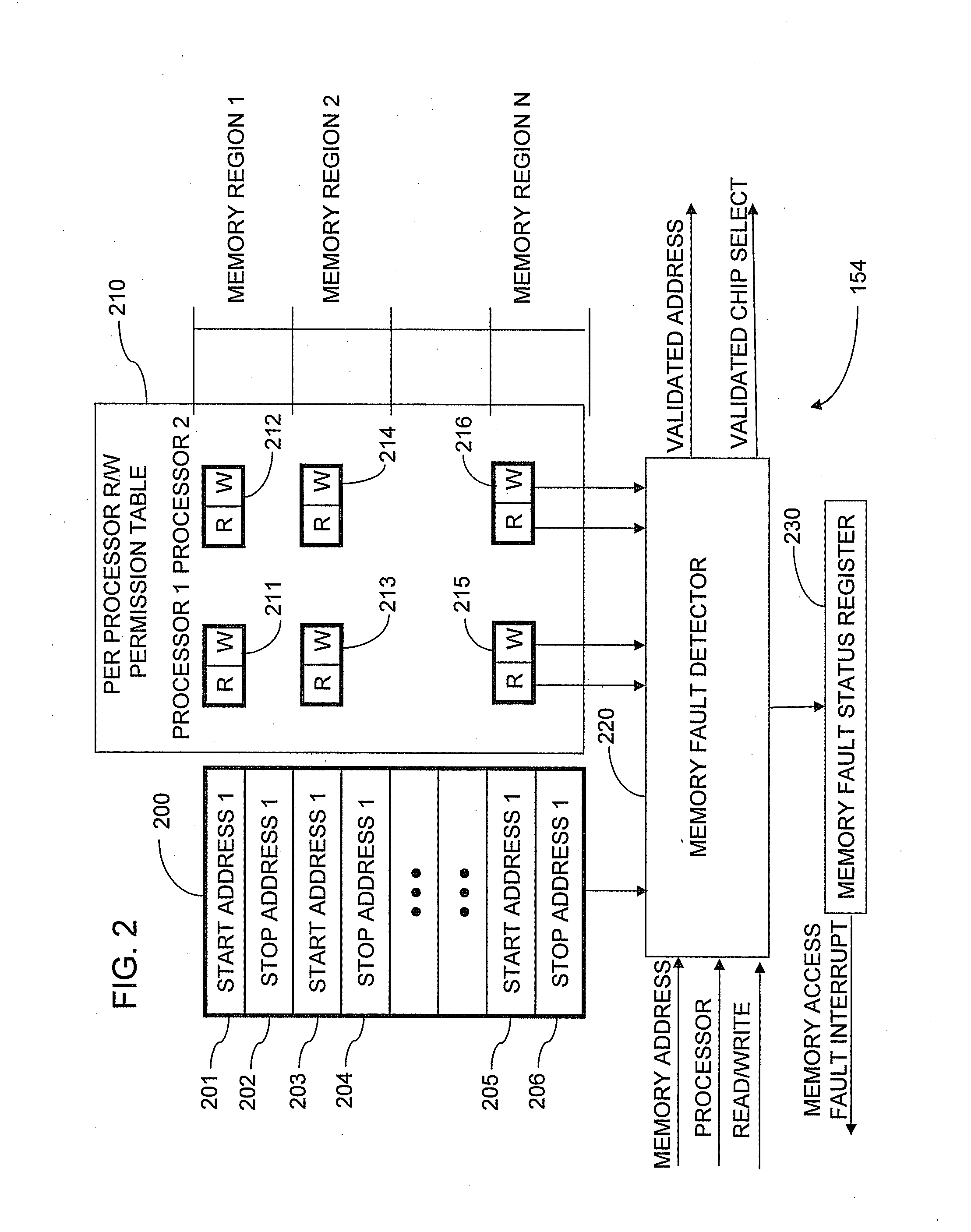

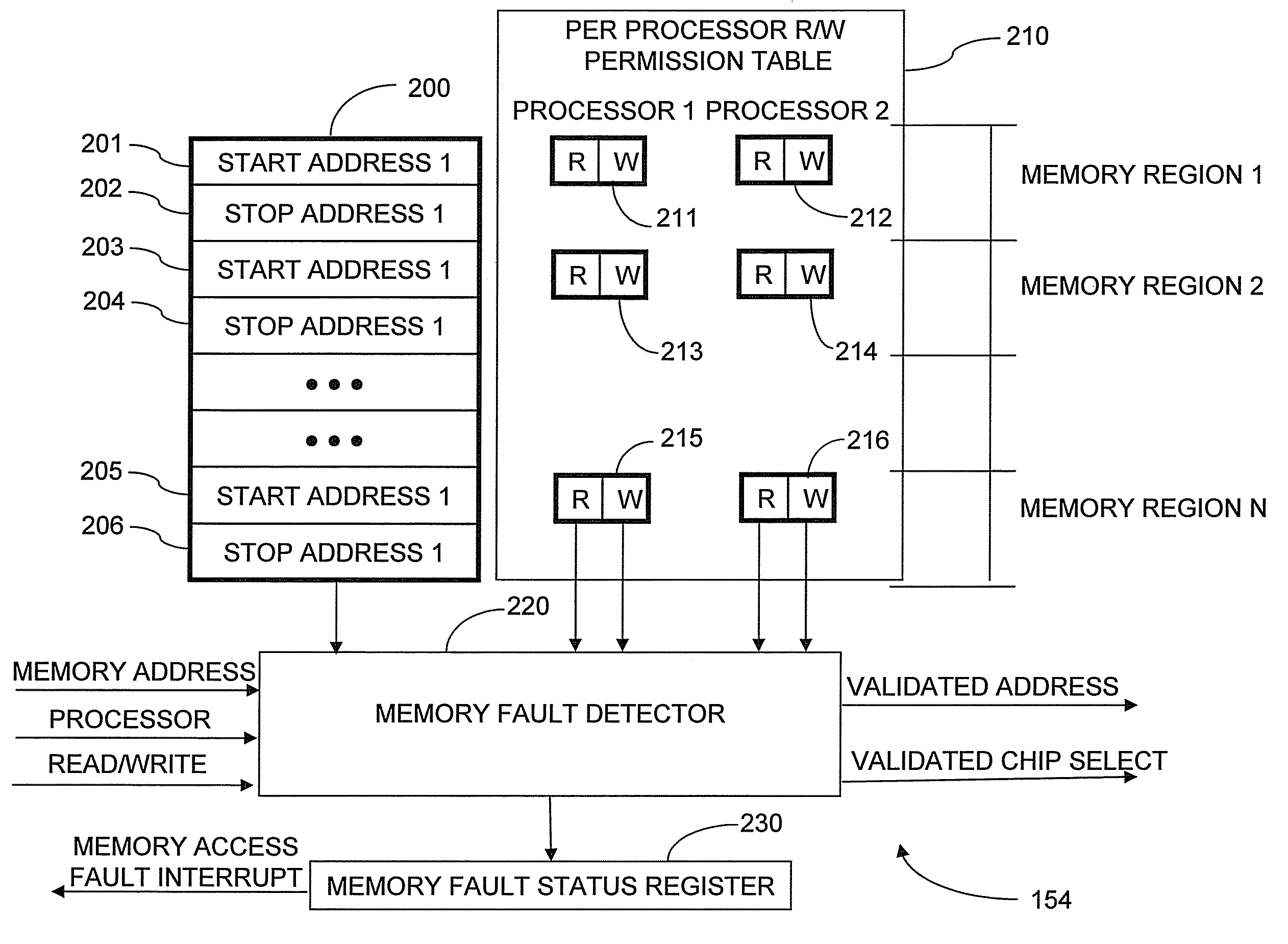

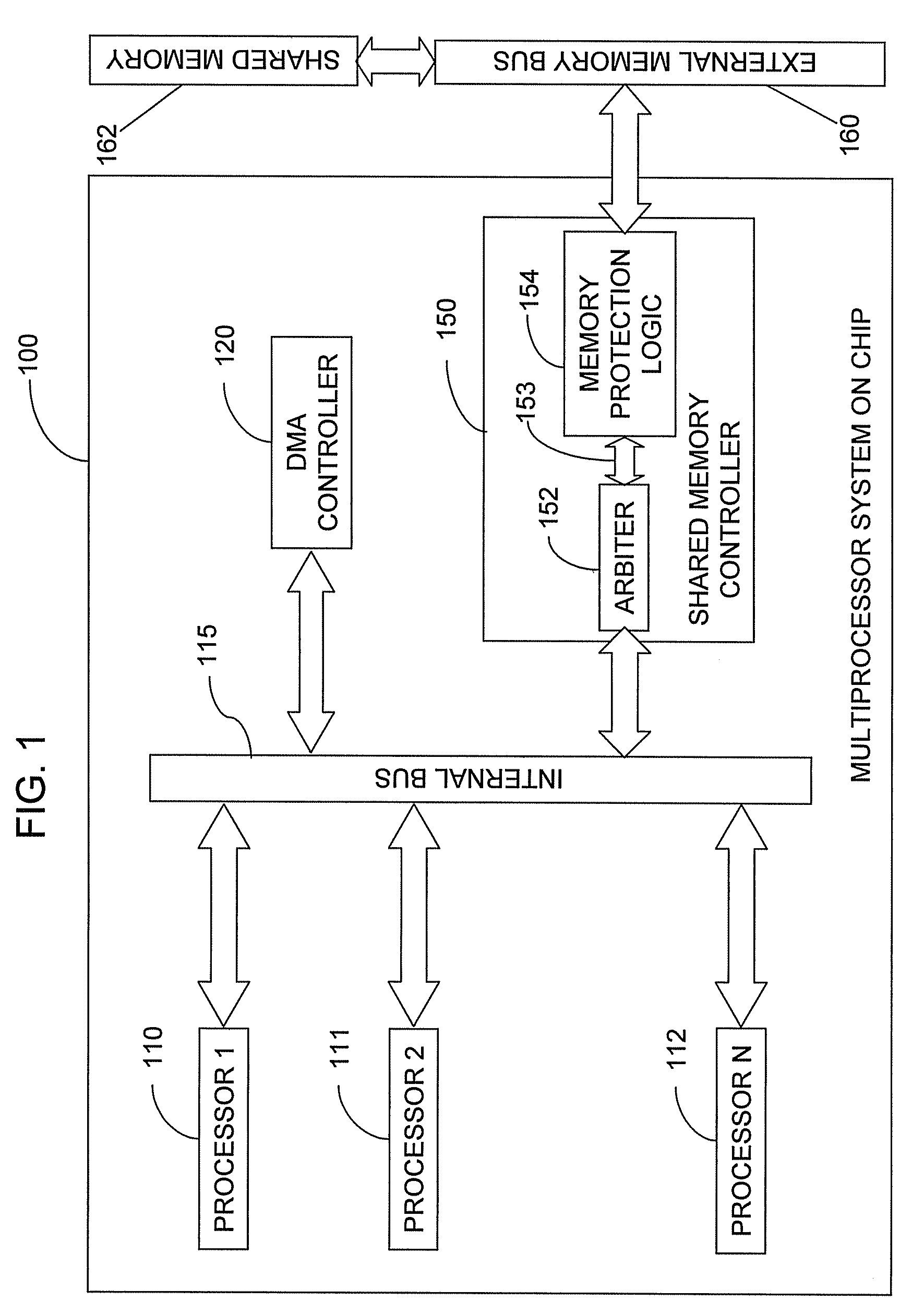

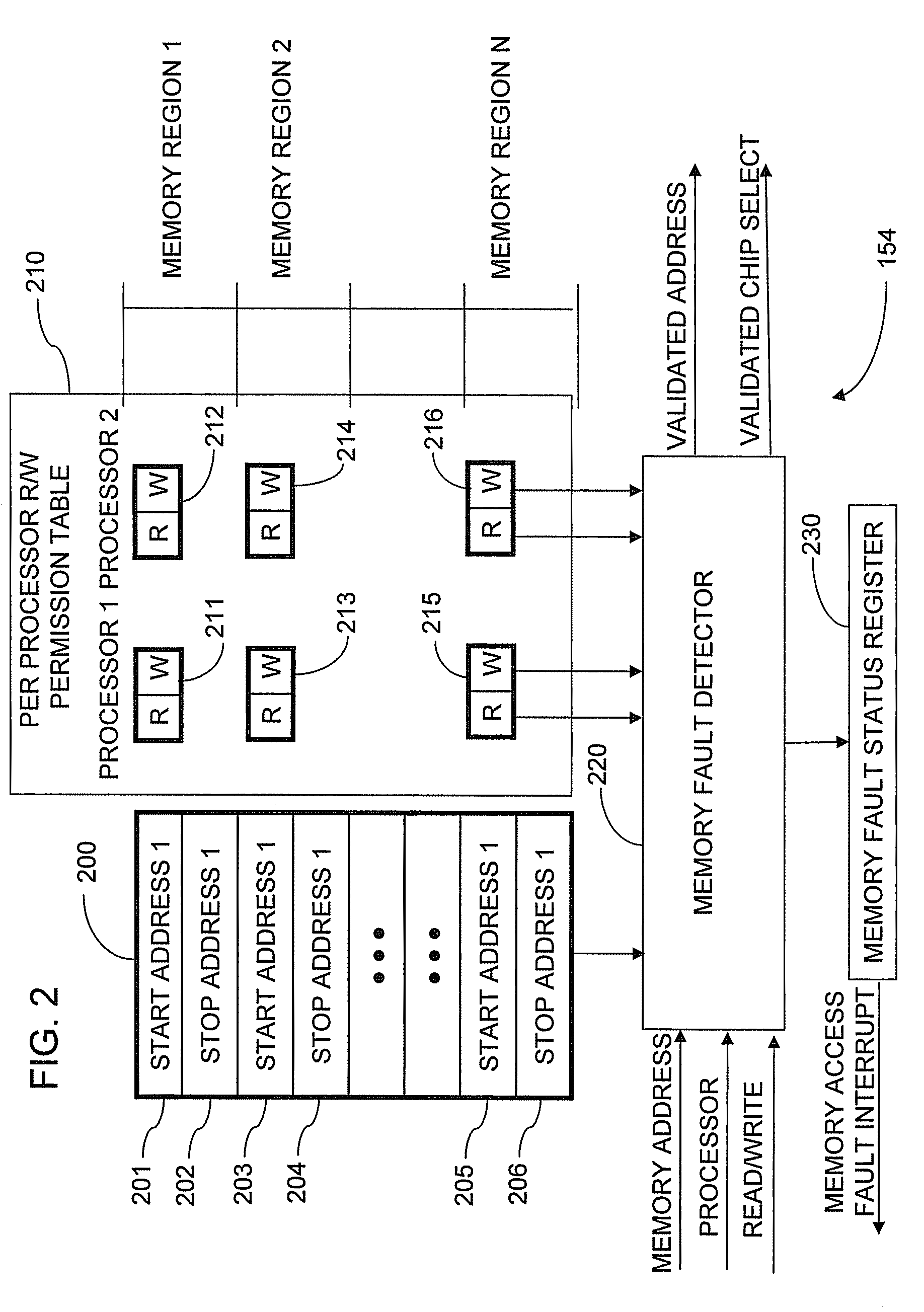

A shared memory controller is provided for controlling access to a shared memory by a plurality of processors. At least one device includes a storage area for storing a respective address range for each of a plurality of memory regions. The at least one device further includes a permission table containing, for each of the plurality of memory regions, read and write permission data for each of the plurality of processors. A memory fault detector is coupled to the at least one device and has an input for receiving a memory access request including a memory address, a processor identification and a read / write indicator. The memory fault detector includes logic for determining whether a memory access according to the memory access request would conflict with the read and write permission data in the permission table.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

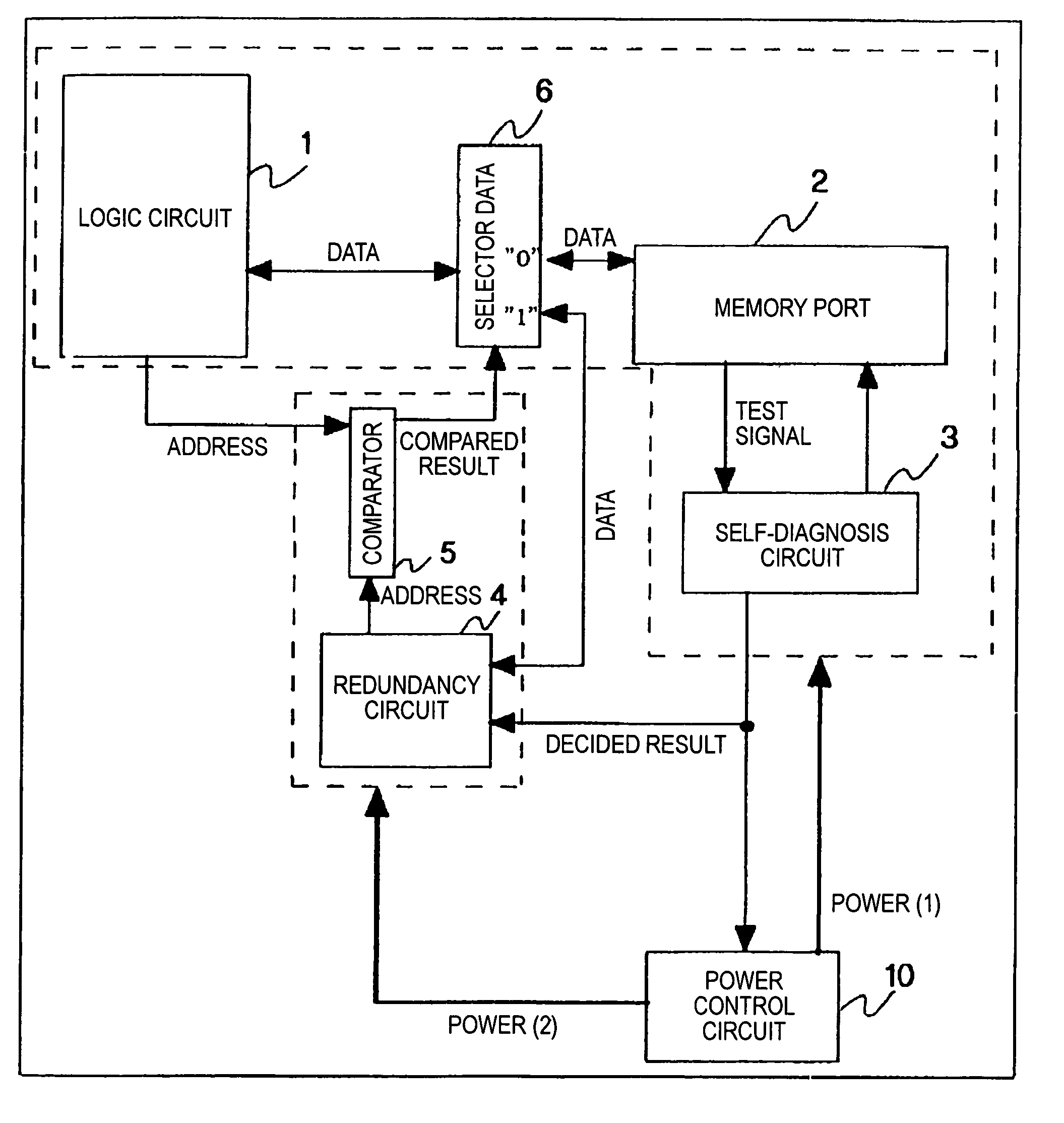

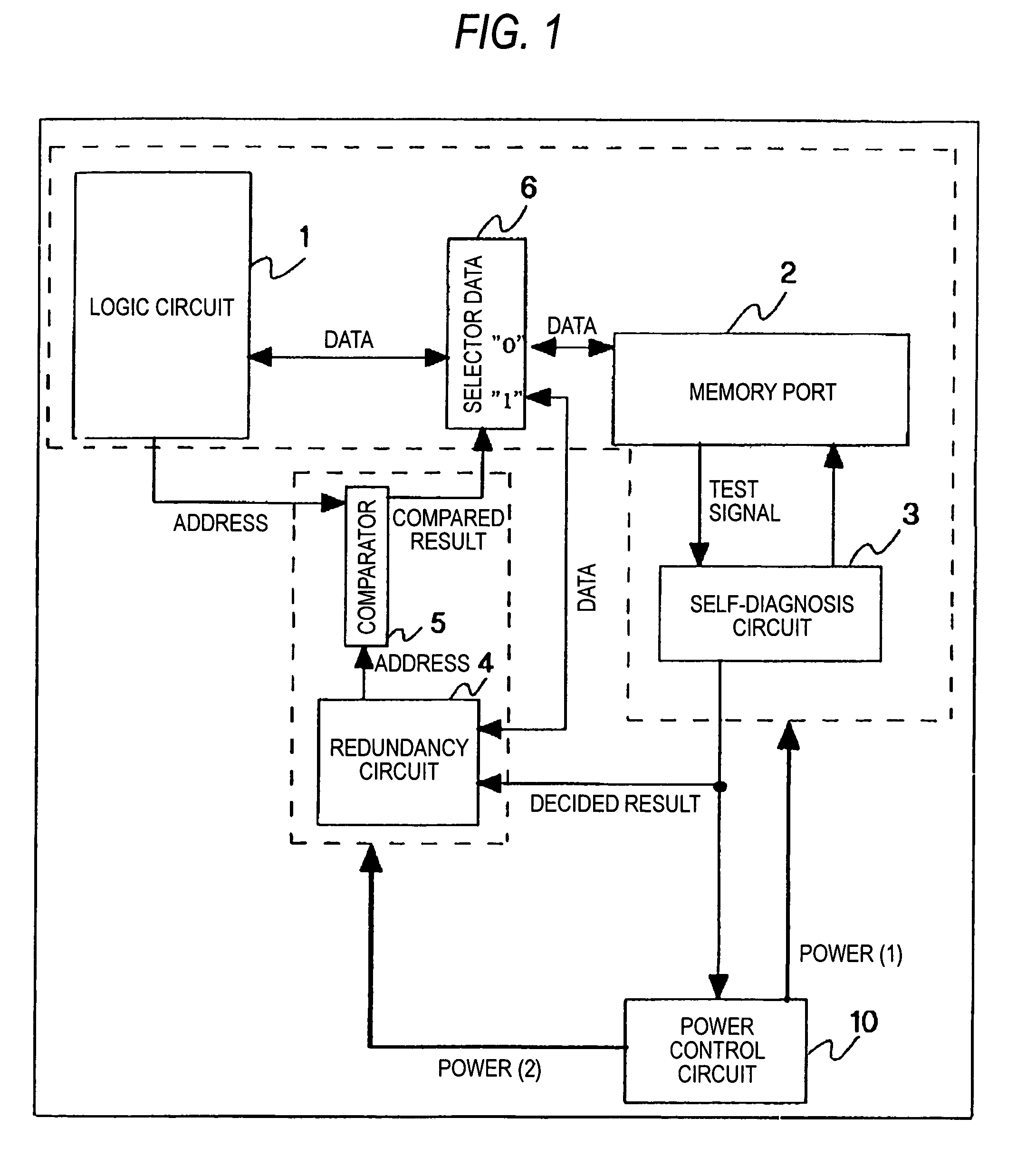

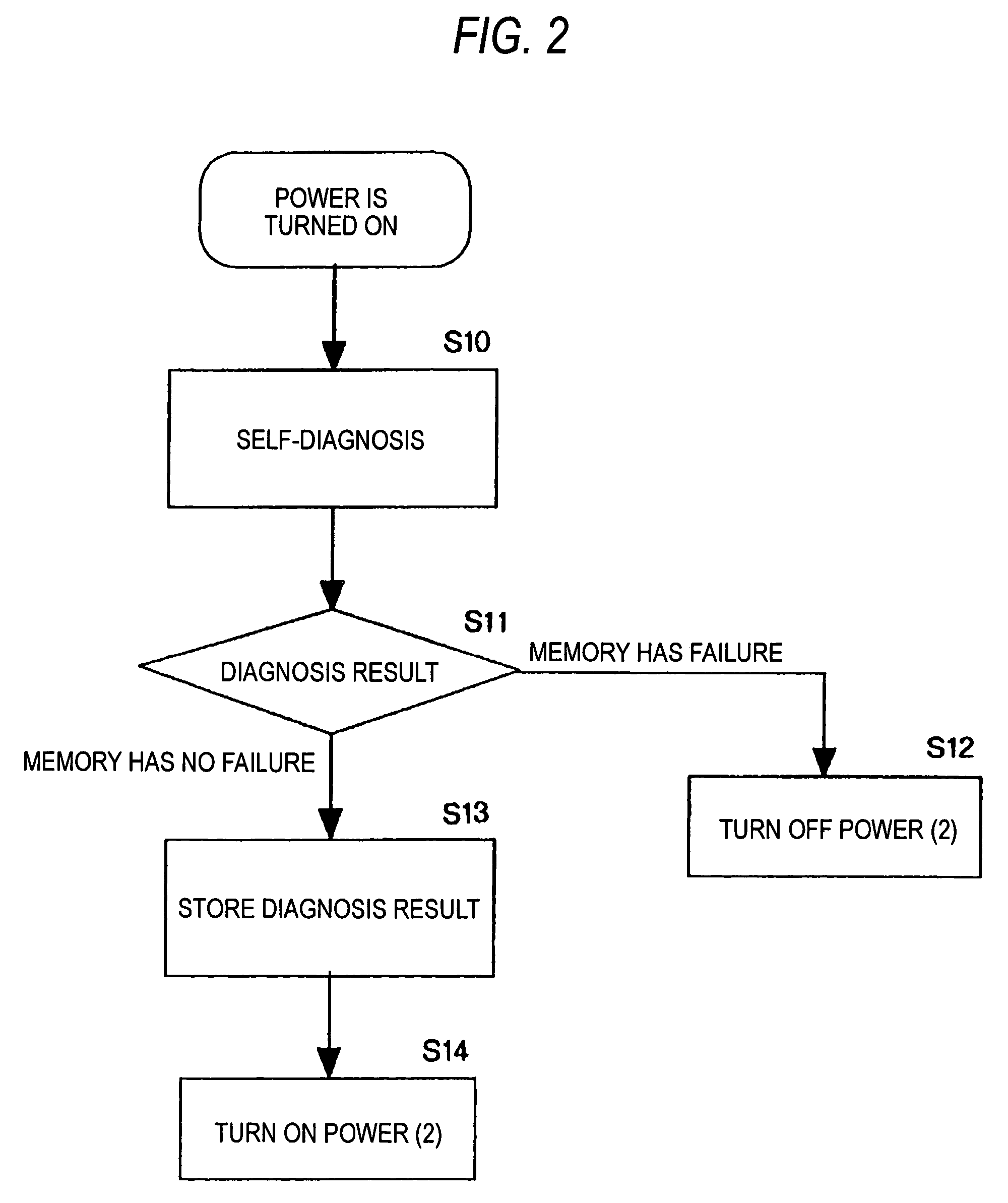

Memory trouble relief circuit

InactiveUS6967879B2Reduce leakage currentTotal current dropError detection/correctionSolid-state devicesMemory faultsSemiconductor storage devices

Owner:PANASONIC CORP

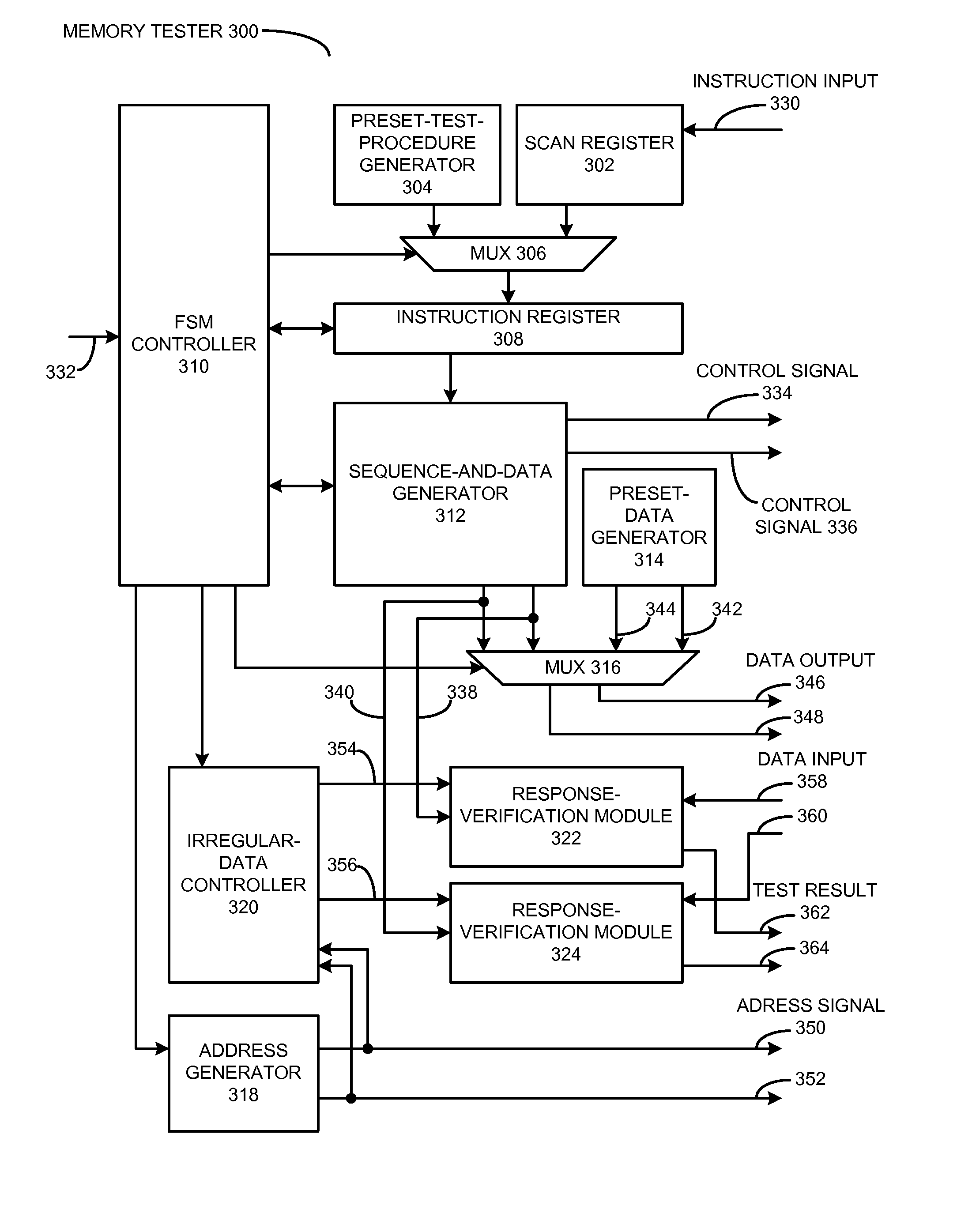

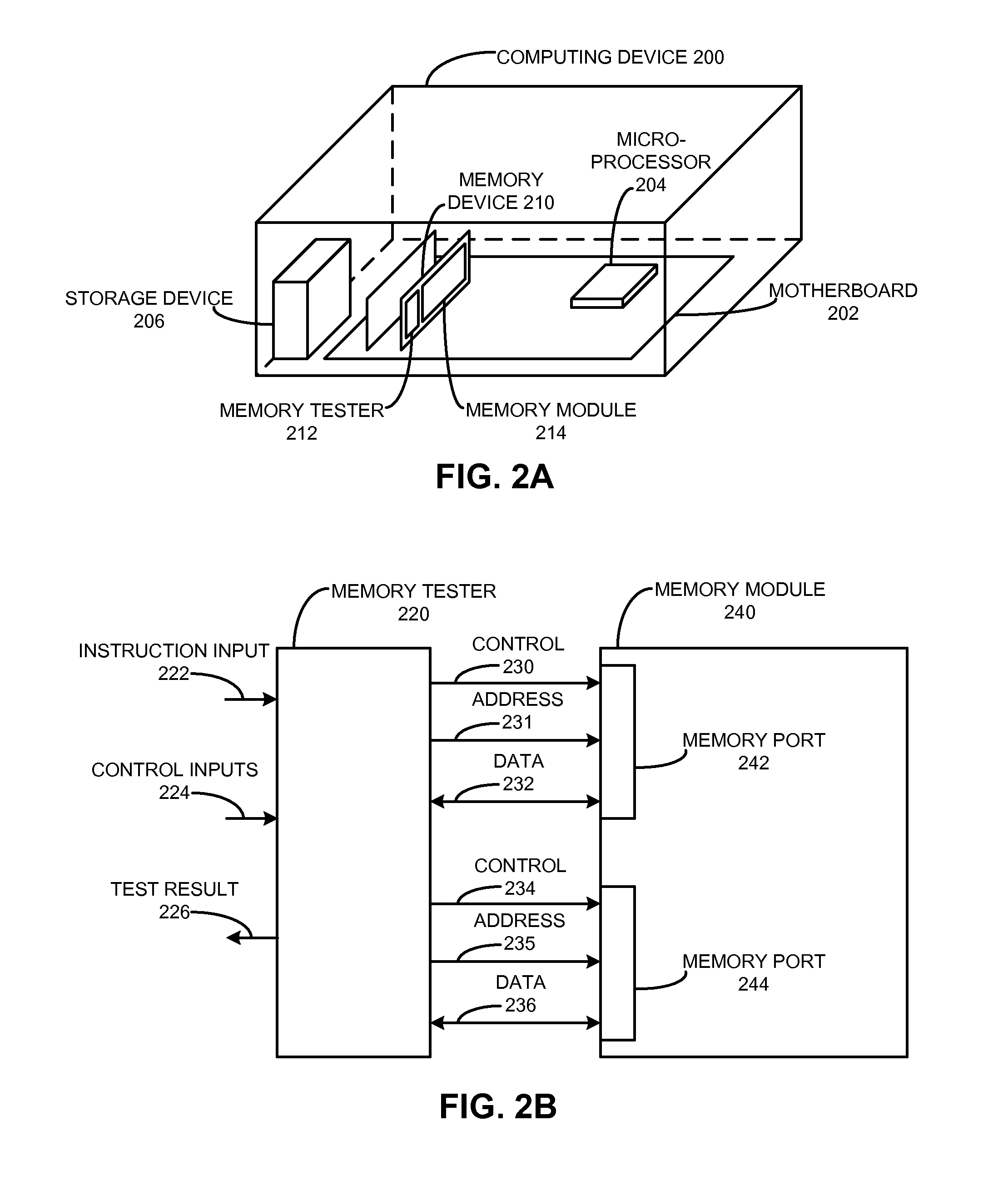

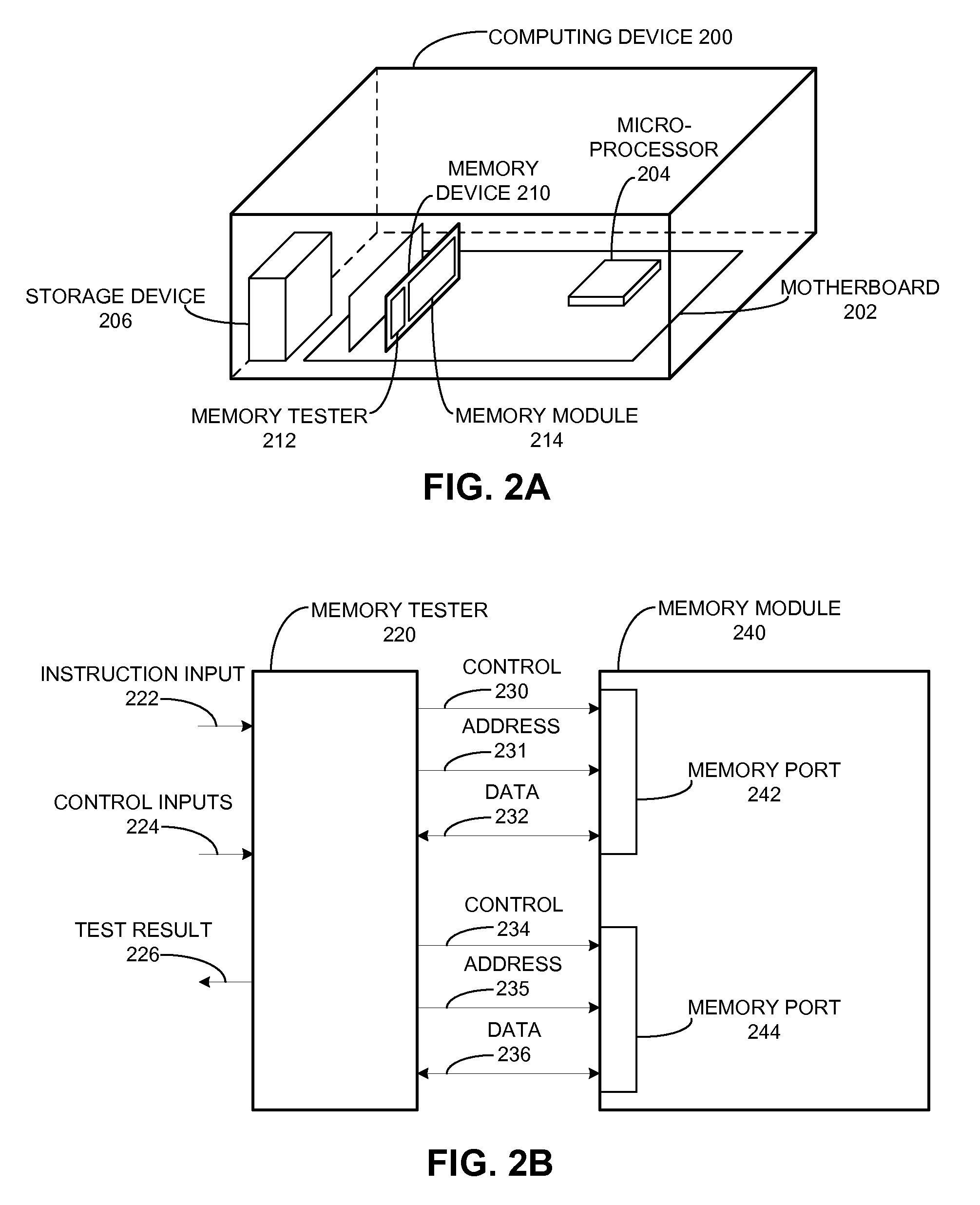

Runtime programmable BIST for testing a multi-port memory device

One embodiment provides a runtime programmable system which comprises methods and apparatuses for testing a multi-port memory device to detect a multi-port memory fault, in addition to typical single-port memory faults that can be activated when accessing a single port of a memory device. More specifically, the system comprises a number of mechanisms which can be configured to activate and detect any realistic fault which affects the memory device when two simultaneous memory access operations are performed. During operation, the system can receive an instruction sequence, which implements a new test procedure for testing the memory device, while the memory device is being tested. Furthermore, the system can implement a built-in self-test (BIST) solution for testing any multi-port memory device, and can generate tests targeted to a specific memory design based in part on information from the instruction sequence.

Owner:SYNOPSYS INC

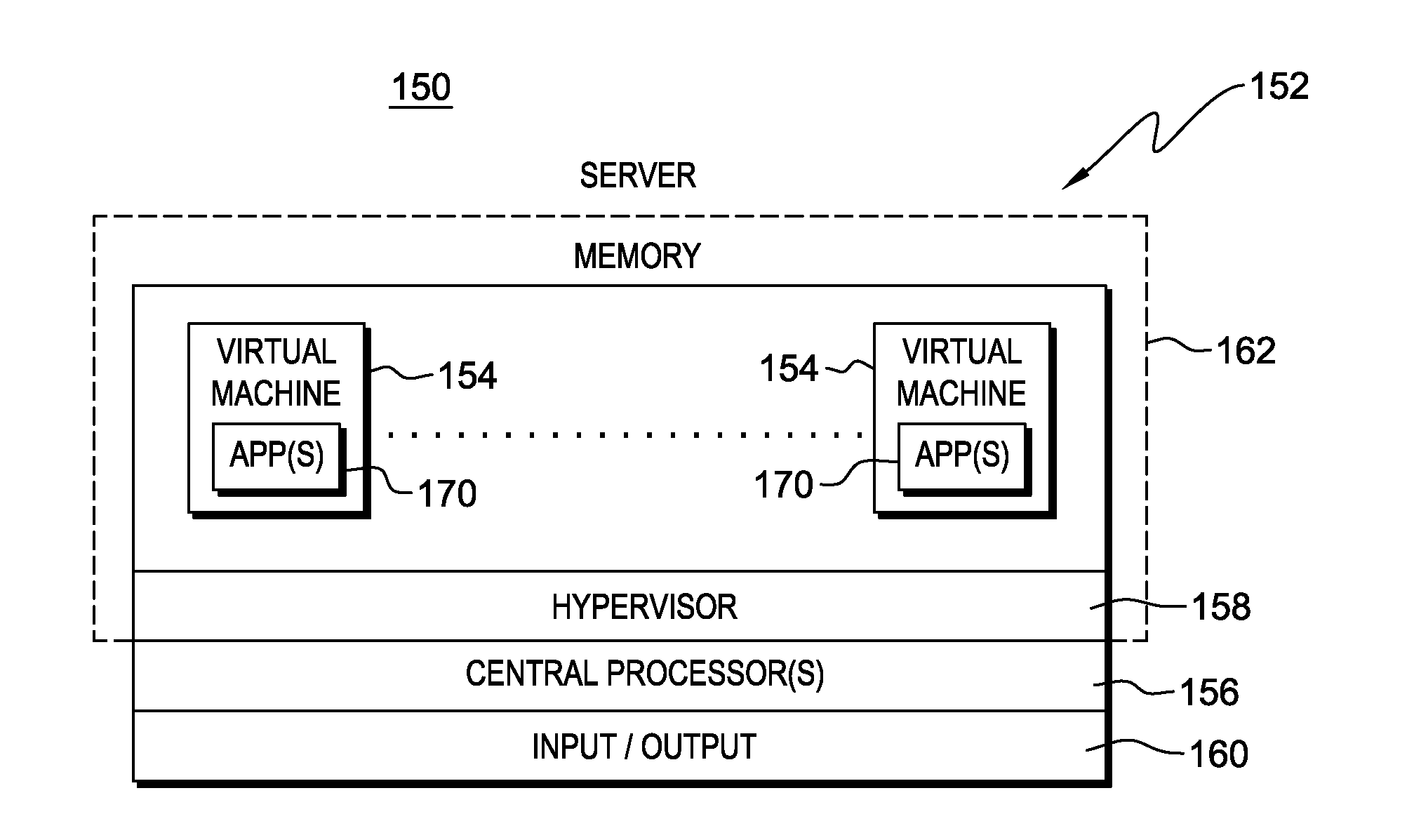

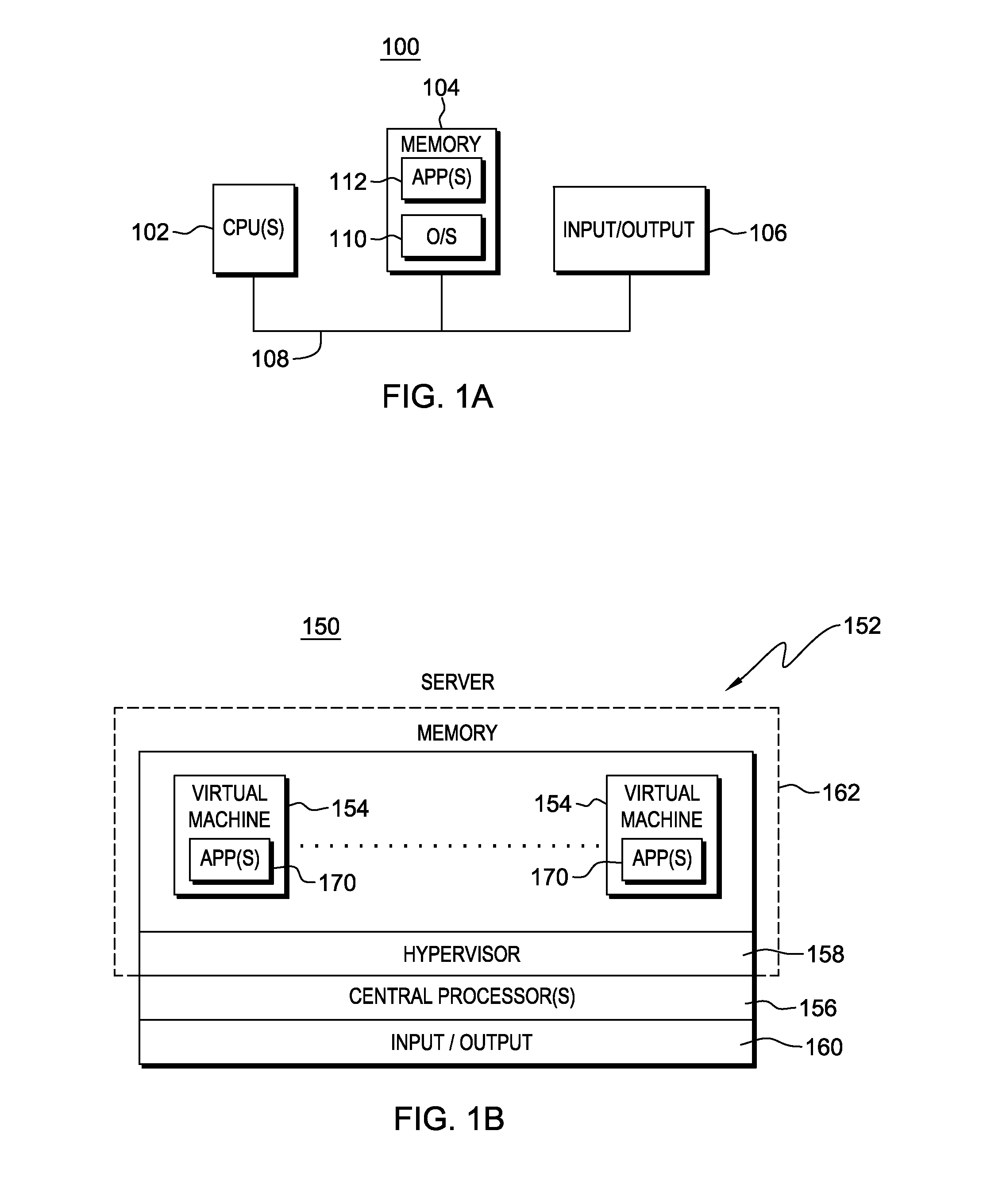

Physical memory fault mitigation in a computing environment

ActiveUS20140089725A1Reduce memory effectNone provides advantagesMemory adressing/allocation/relocationRecord information storageMemory faultsEnvironment effect

Effects of a physical memory fault are mitigated. In one example, to facilitate mitigation, memory is allocated to processing entities of a computing environment, such as applications, operating systems, or virtual machines, in a manner that minimizes impact to the computing environment in the event of a memory failure. Allocation includes using memory structure information, including, information regarding fault containment zones, to allocate memory to the processing entities. By allocating memory based on fault containment zones, a fault only affects a minimum number of processing entities.

Owner:IBM CORP

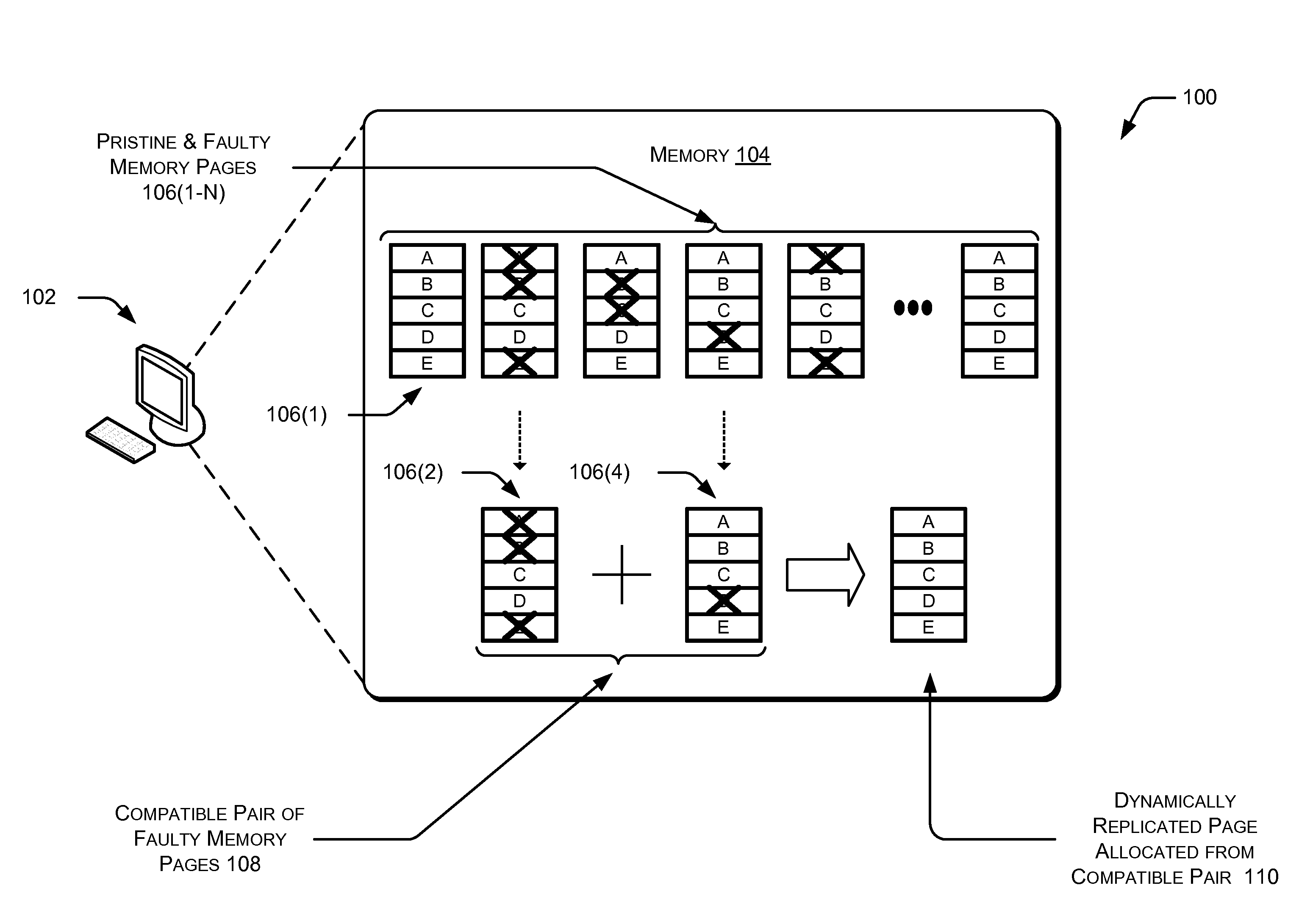

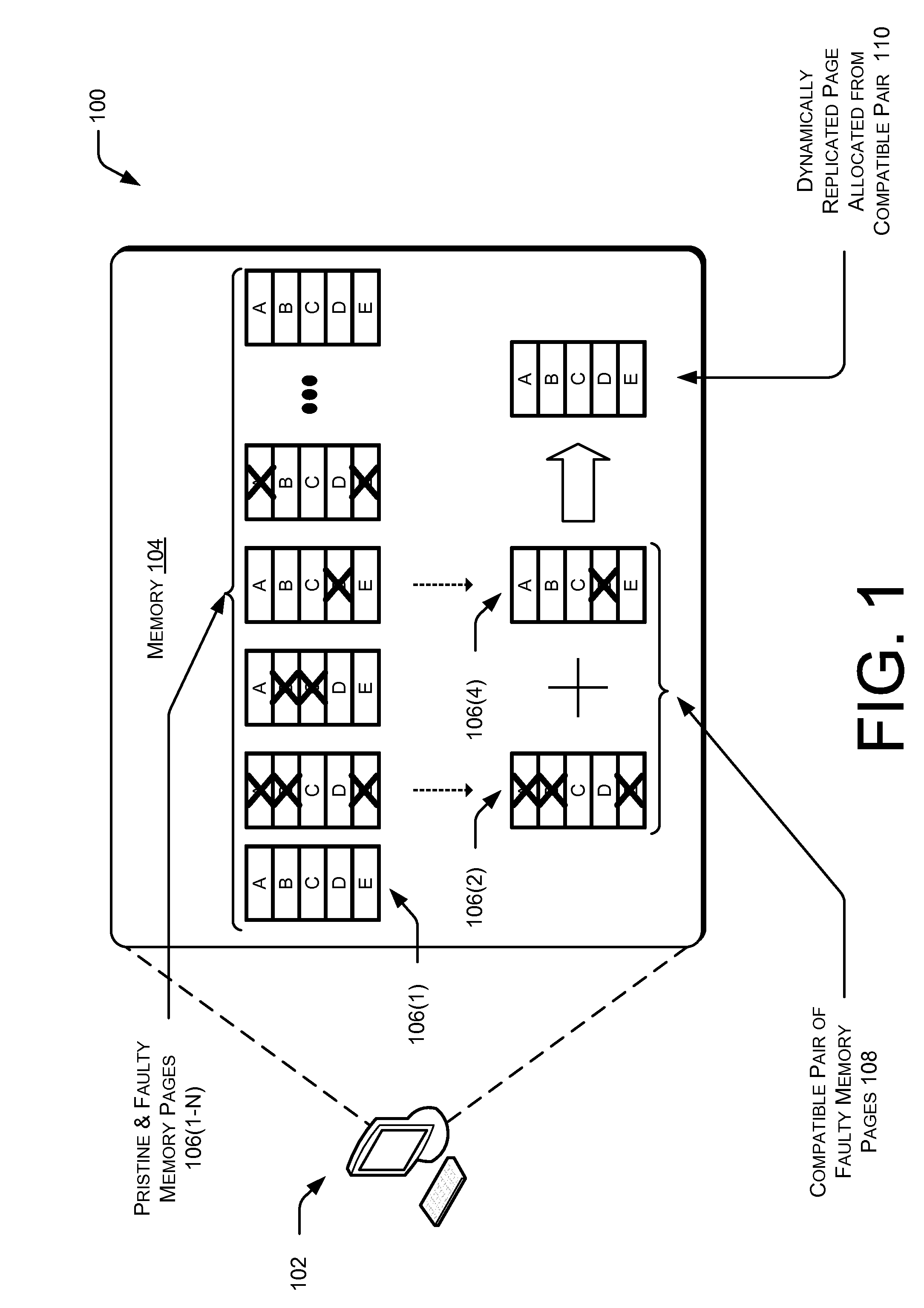

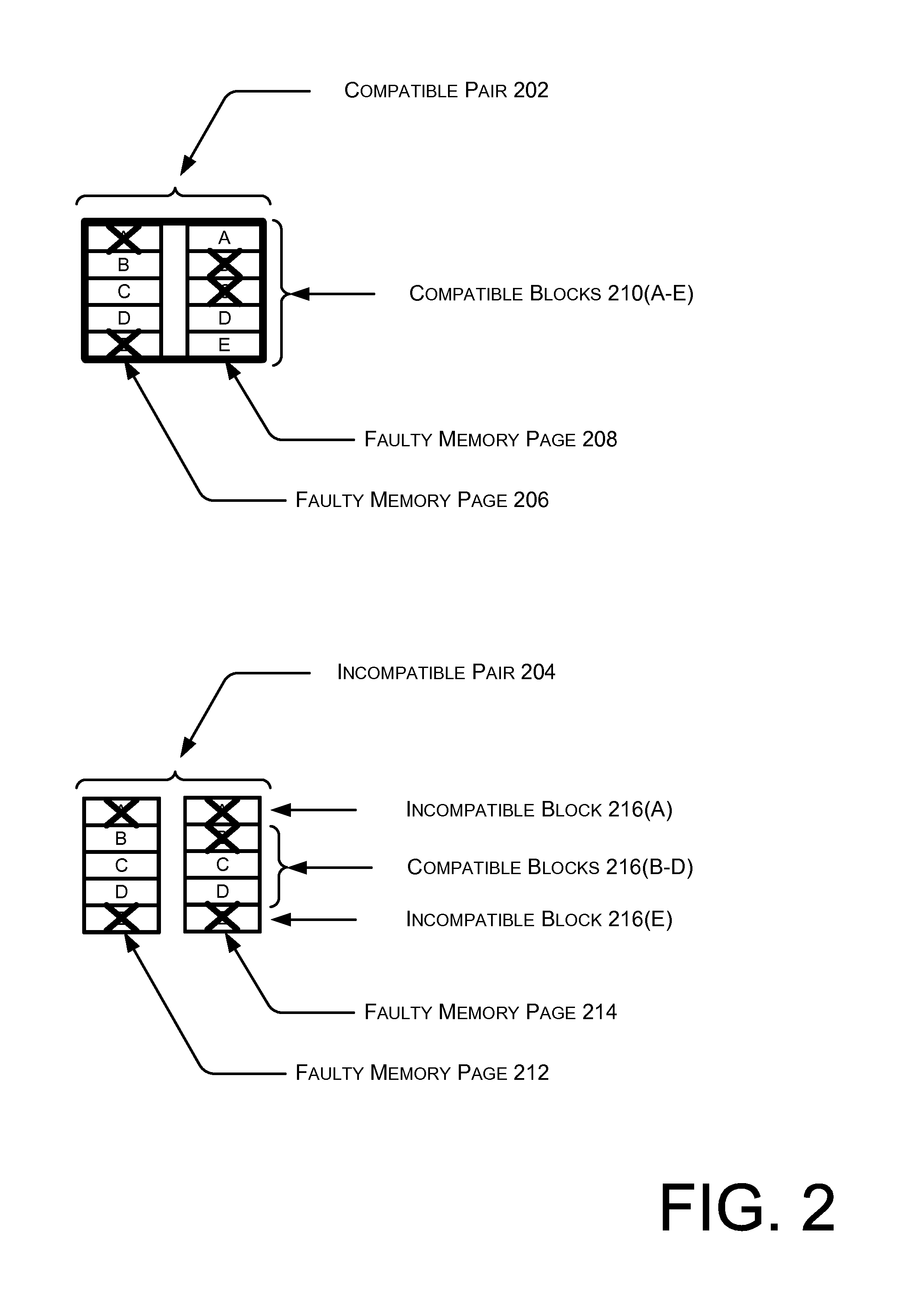

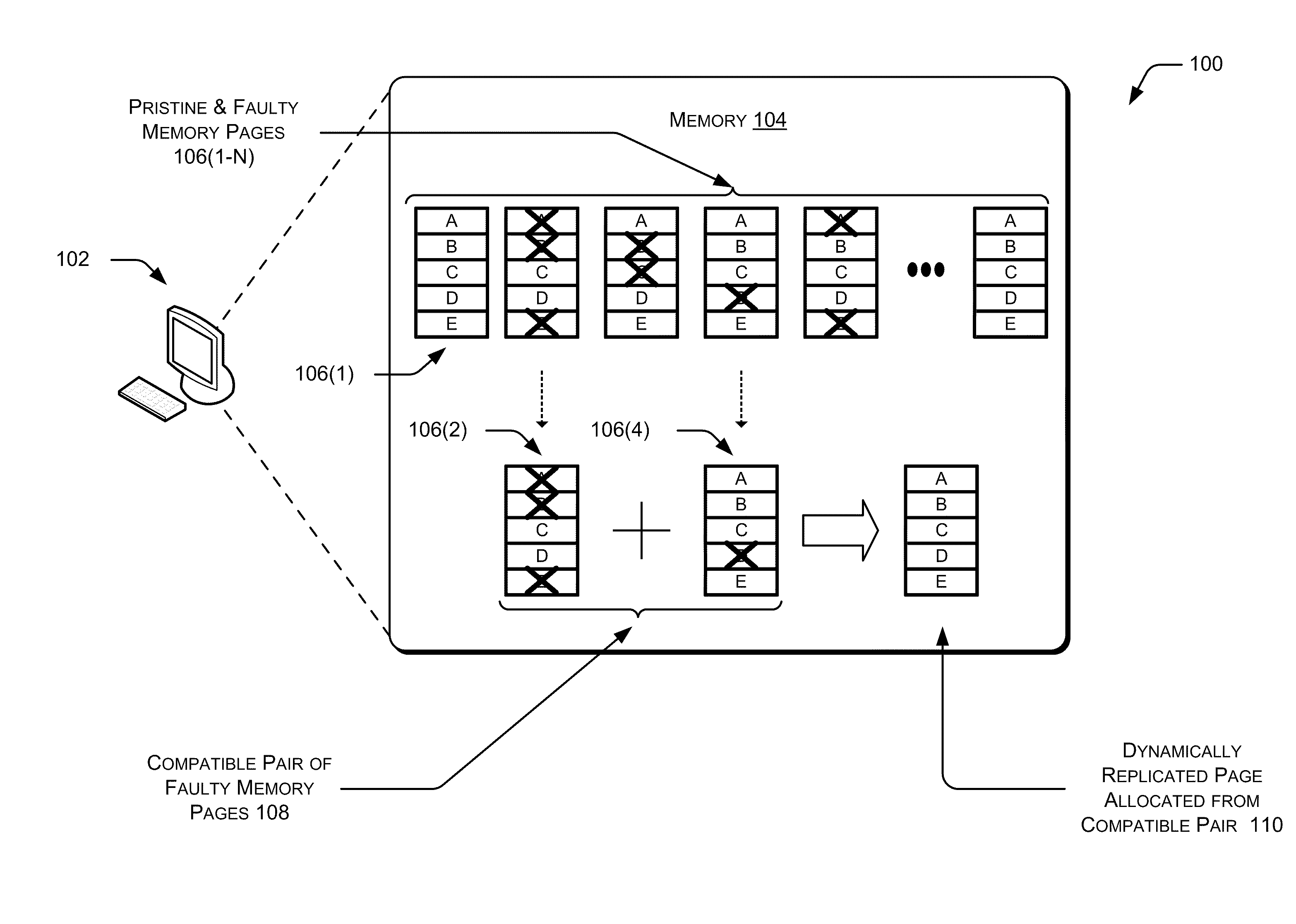

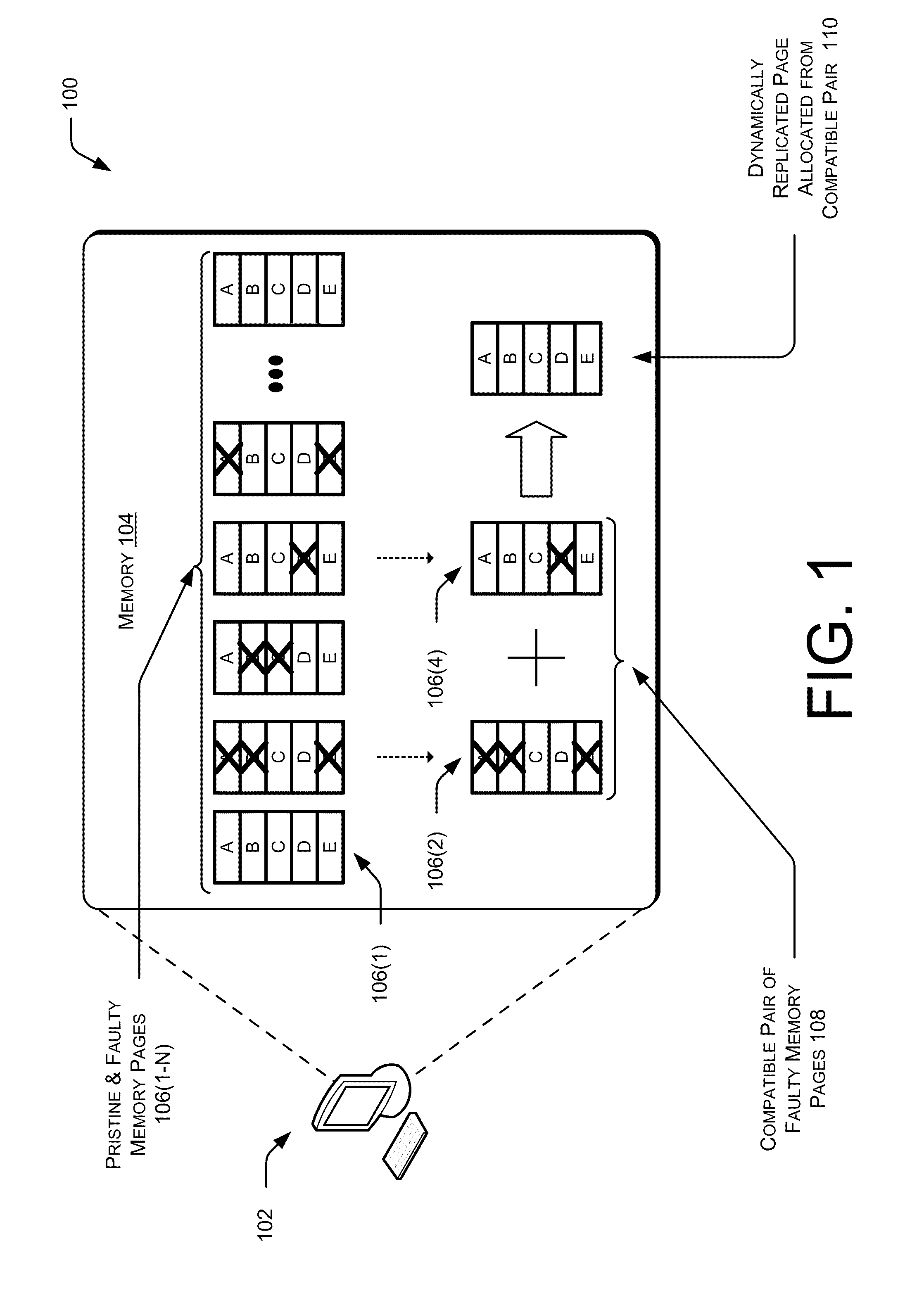

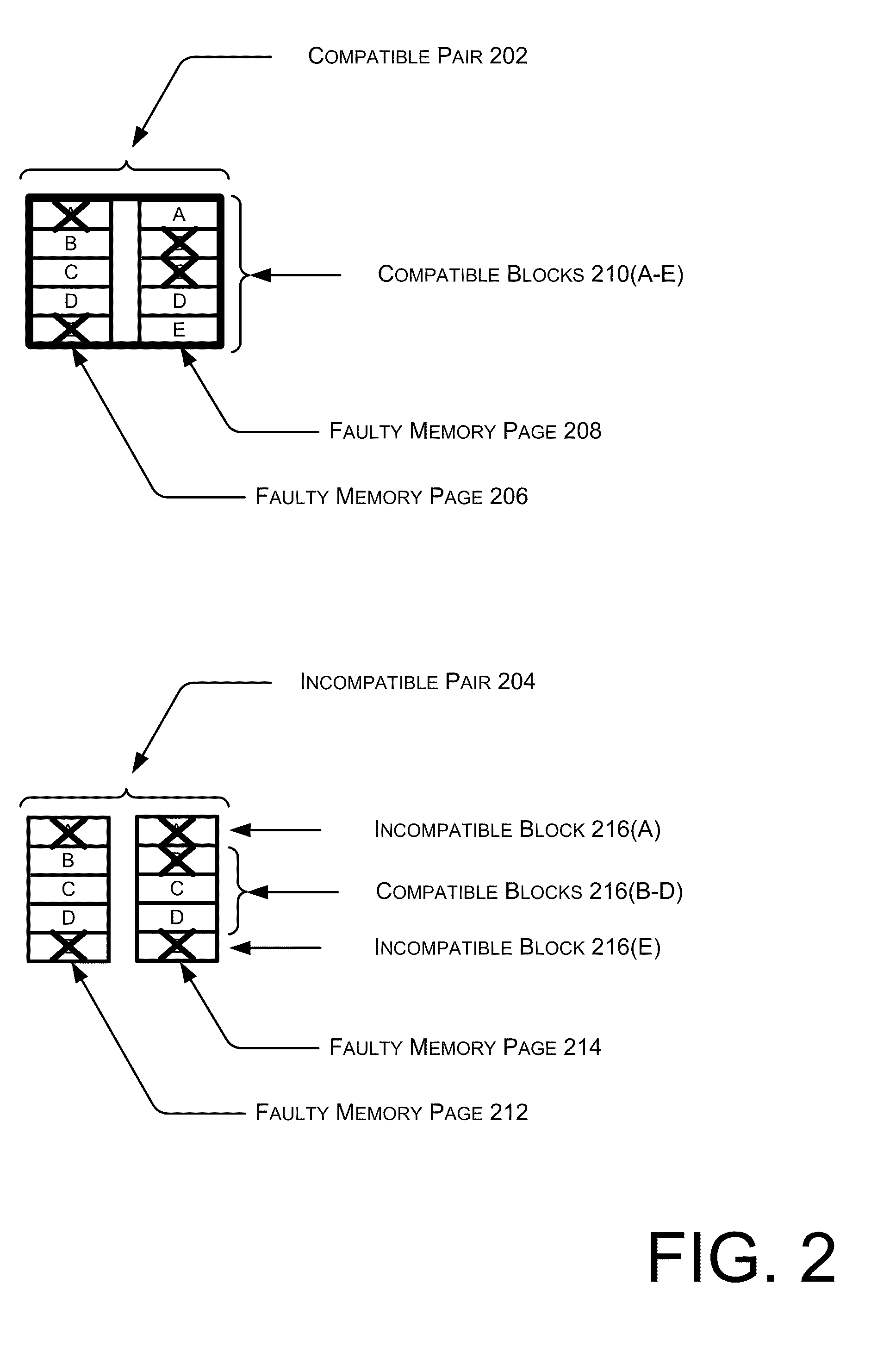

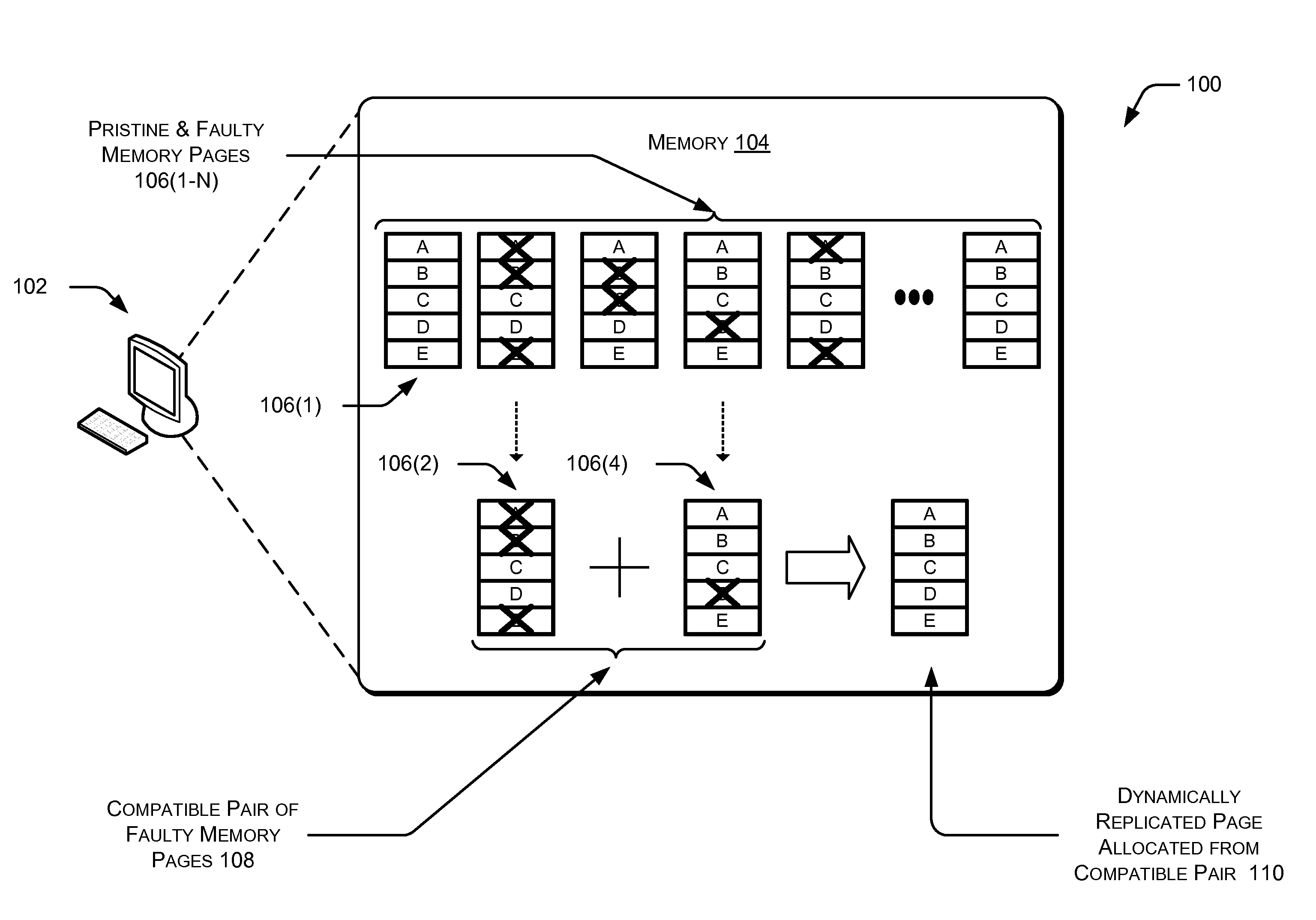

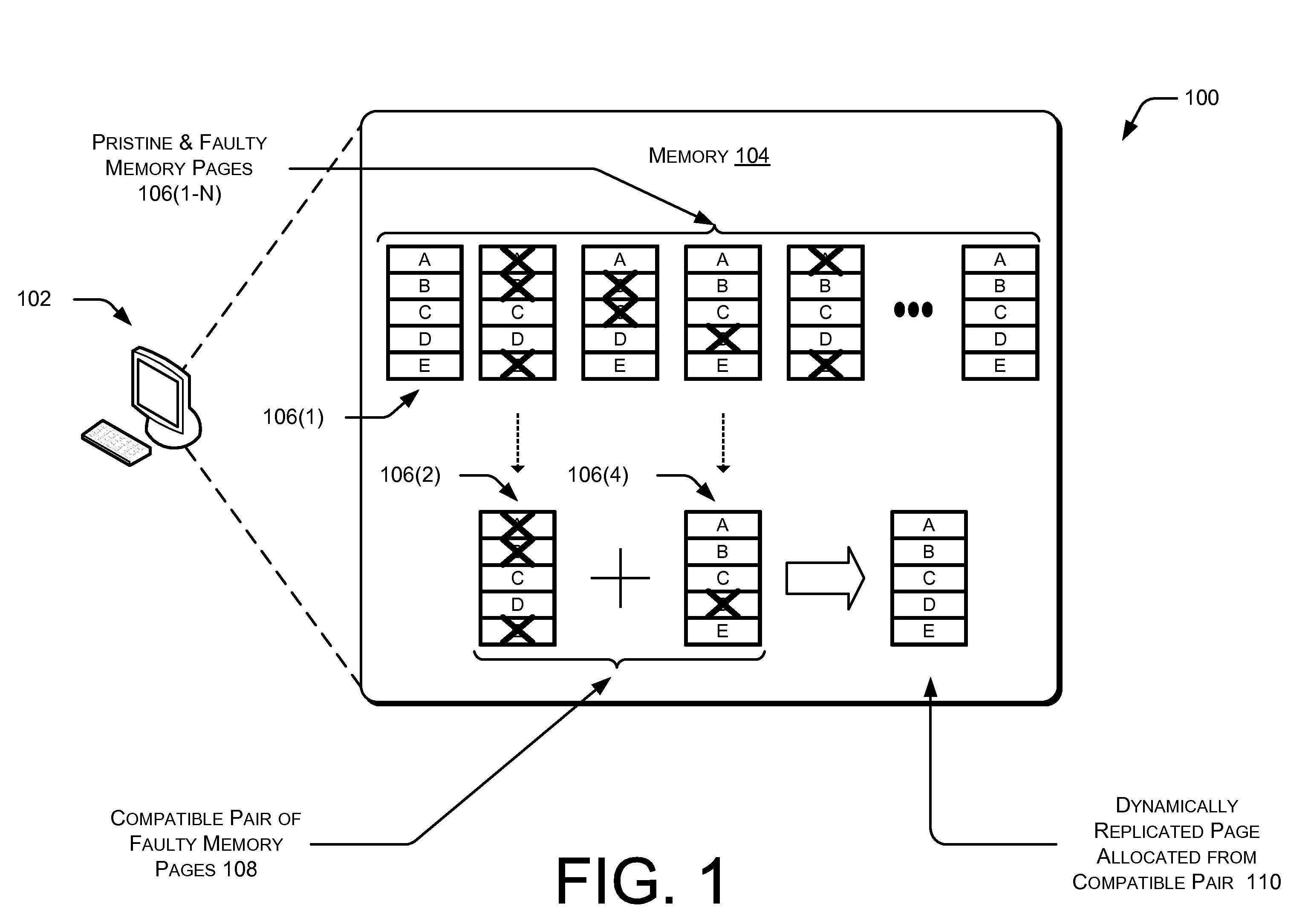

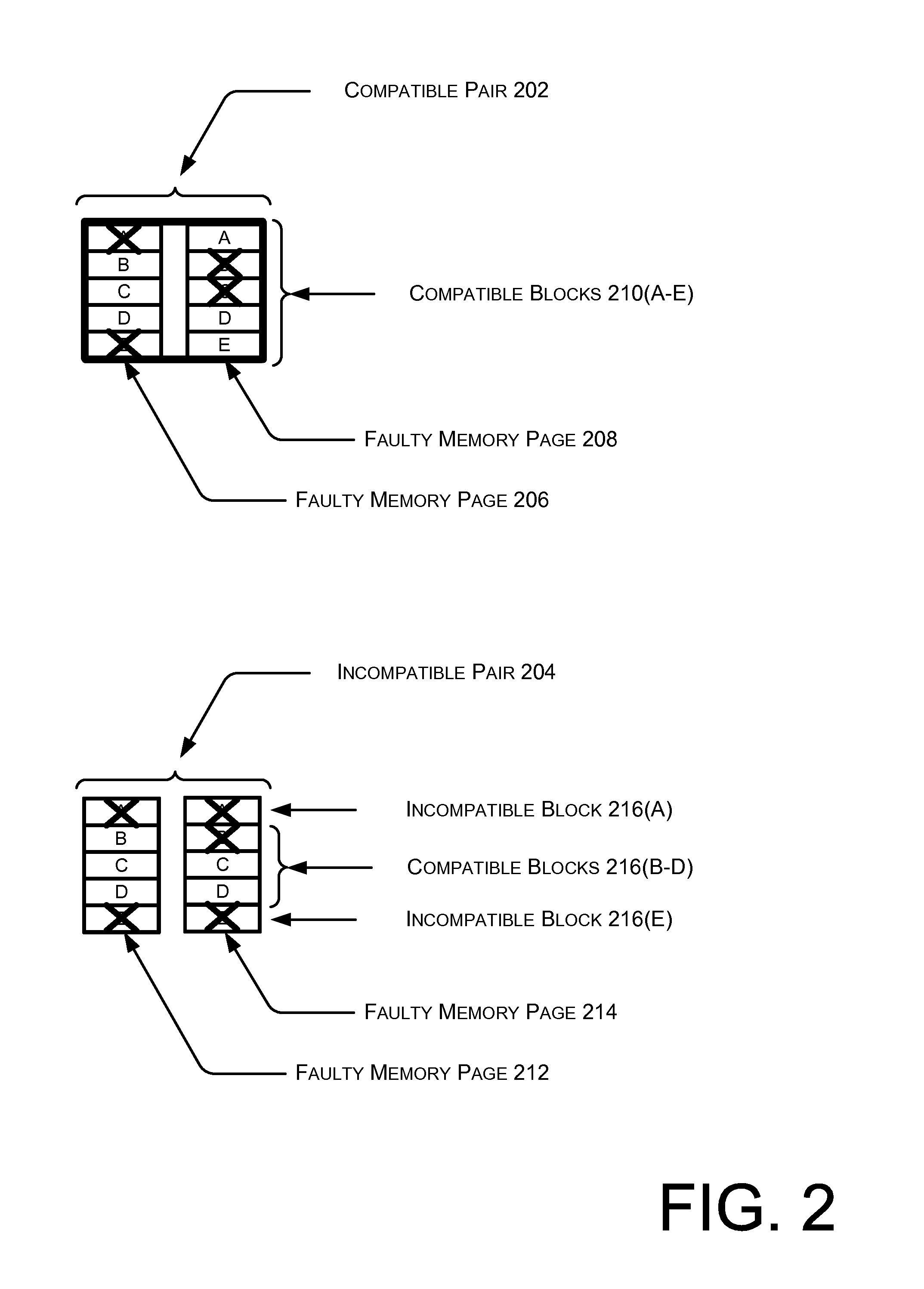

Dynamically replicated memory

Dynamically replicated memory is usable to allocate new memory space from failed memory pages by pairing compatible failed memory pages to reuse otherwise unusable failed memory pages. Dynamically replicating memory involves detecting and recording memory faults, reclaiming failed memory pages for later use, recovering from detected memory faults, and scheduling access to replicated memory pages.

Owner:MICROSOFT TECH LICENSING LLC

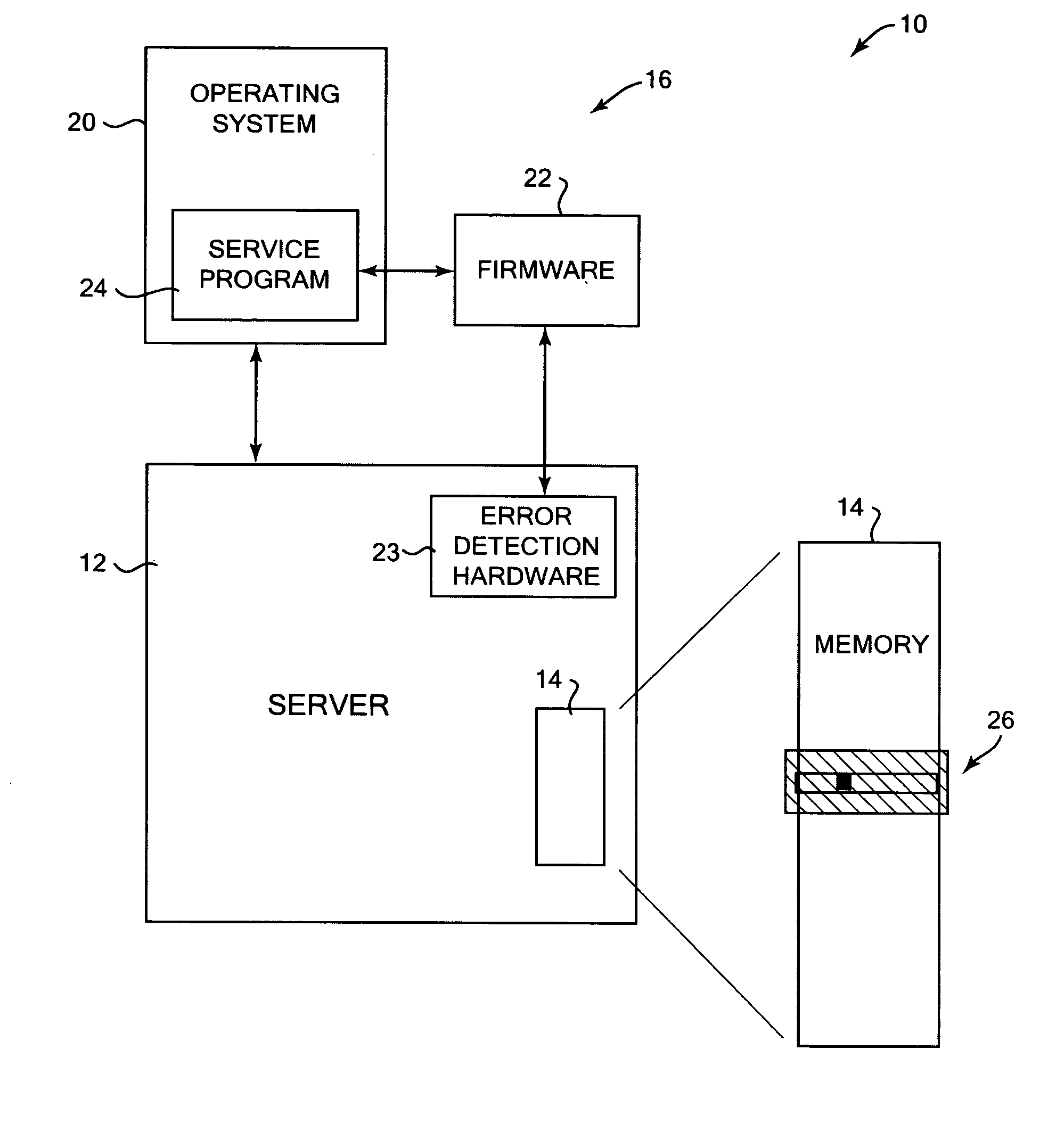

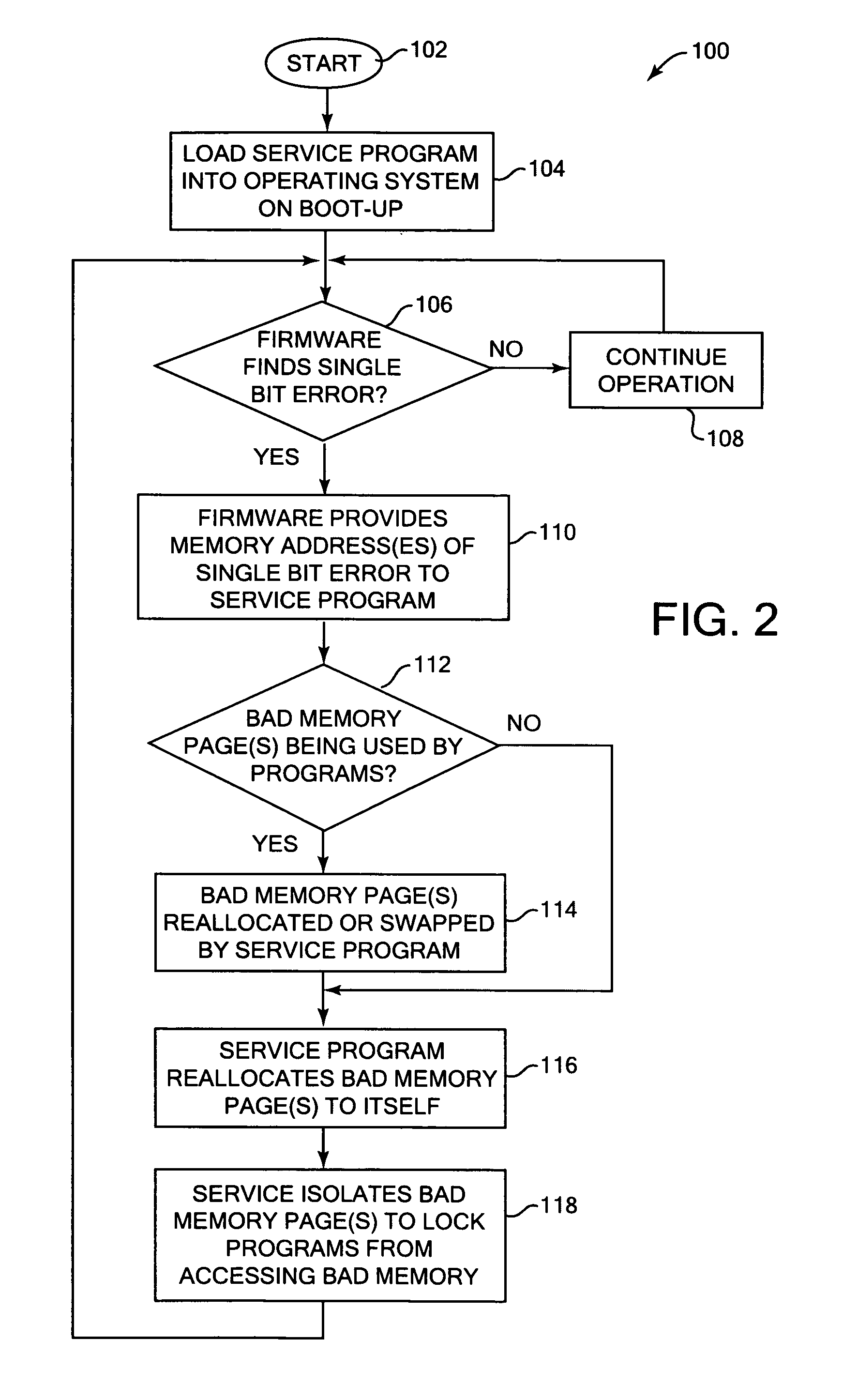

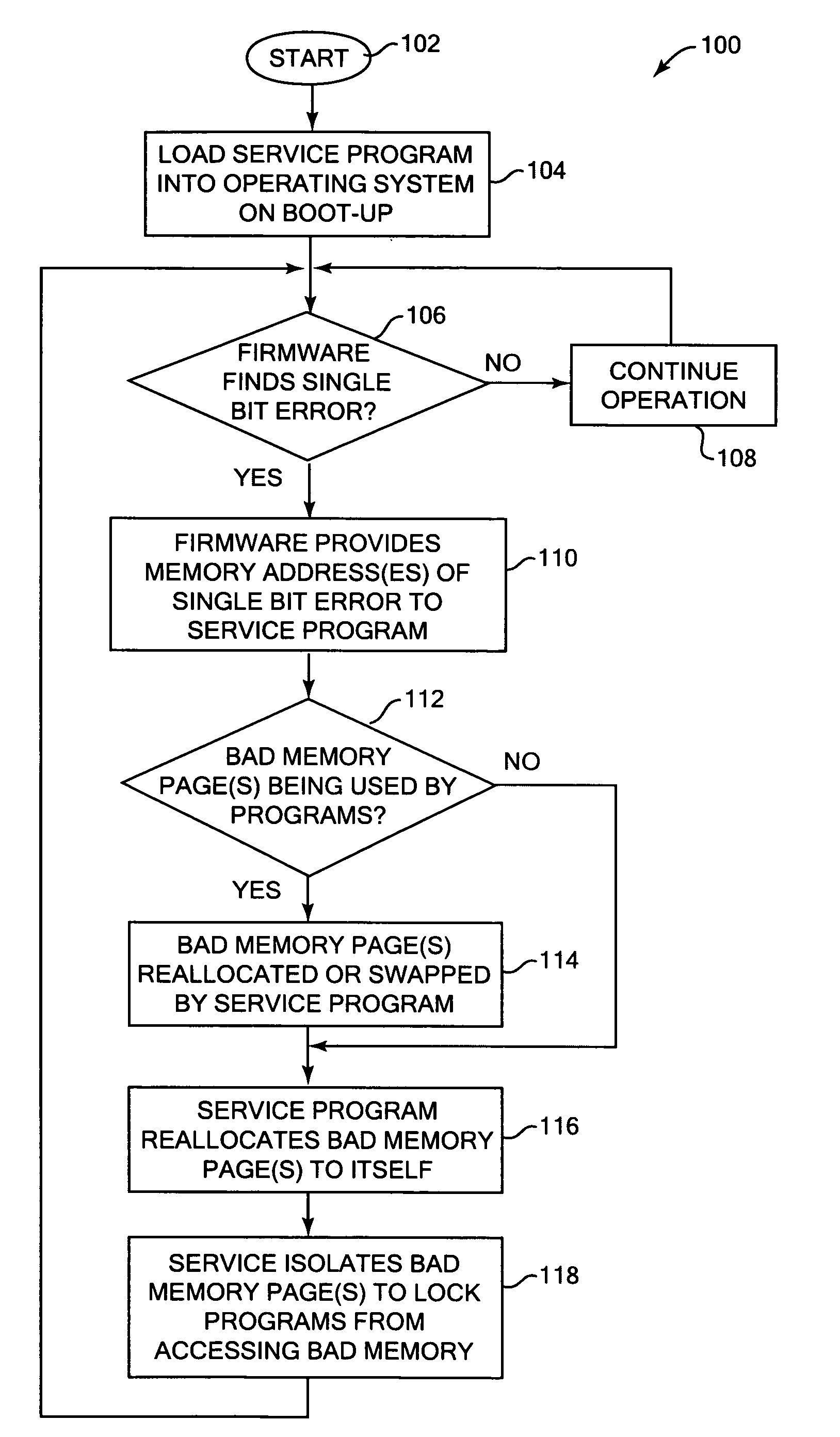

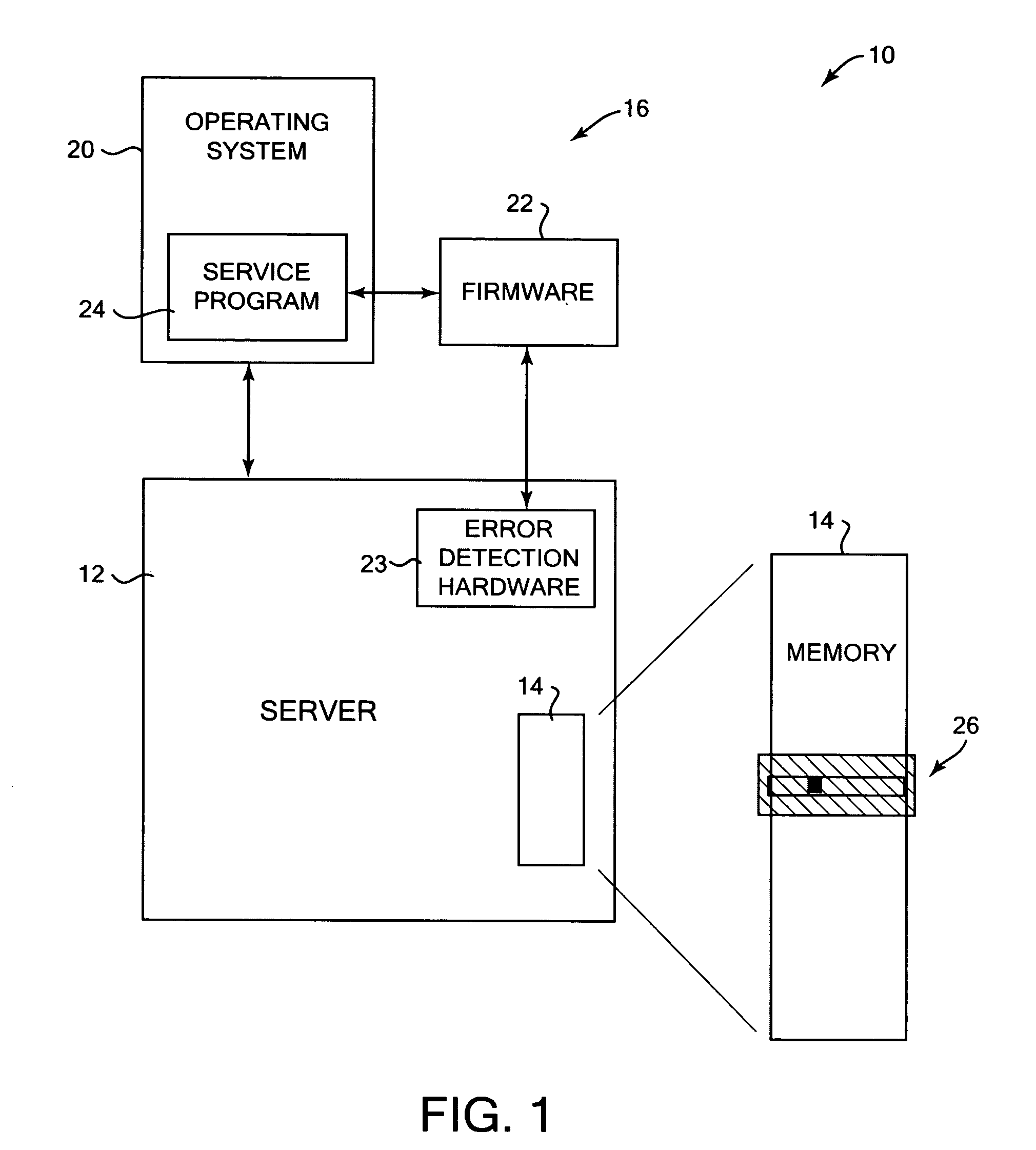

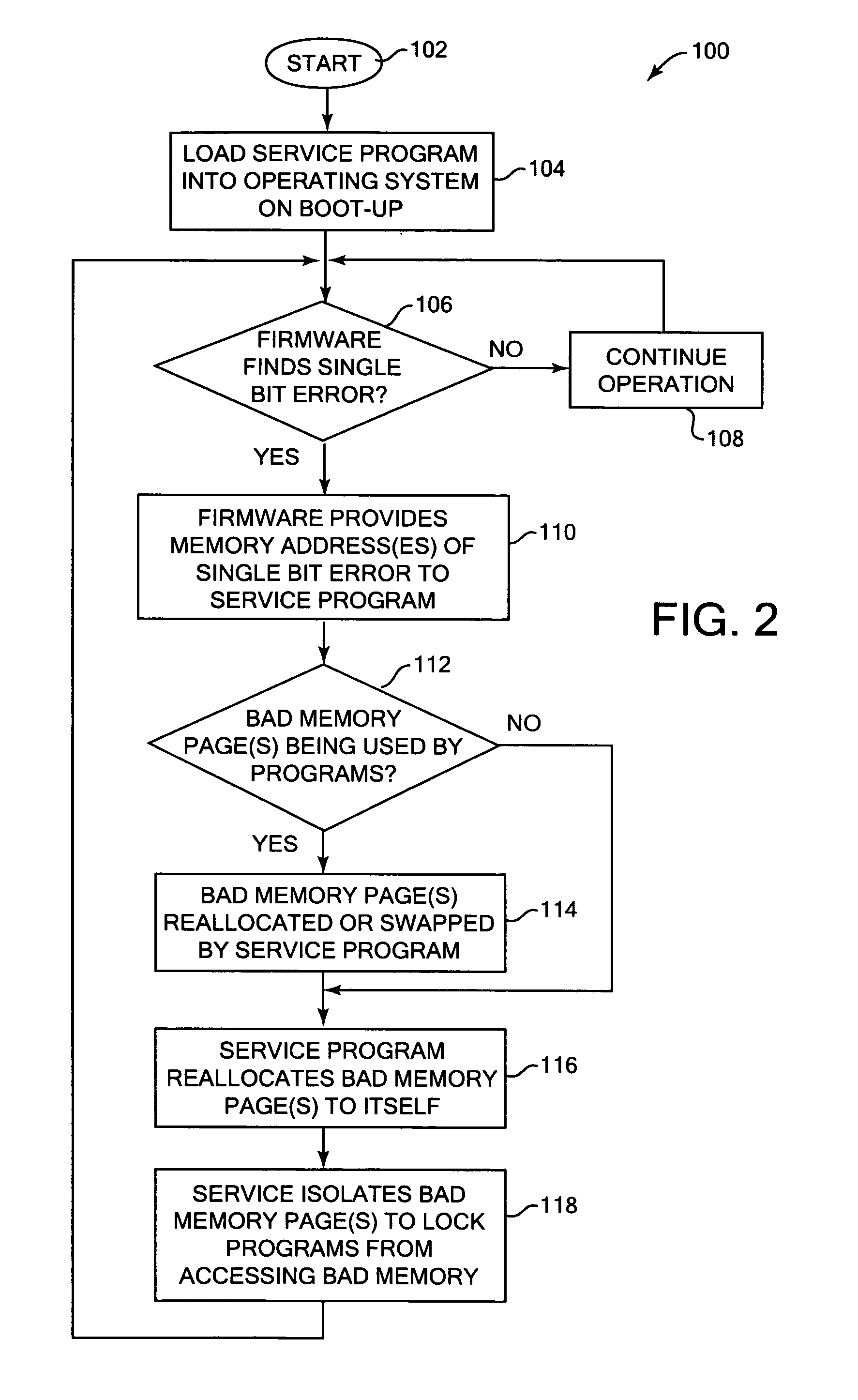

Method and system for reducing memory faults while running an operating system

ActiveUS20060085670A1Reduce failureError detection/correctionStatic storageOperational systemMemory faults

Method and system for reducing memory faults for computer systems. In one aspect, a notification is received that indicates that a single bit error has been detected in a portion of memory of the computer system. A service program is used to isolate the portion of the memory that includes the detected single bit error by allocating the portion of memory to itself, such that the portion of memory may no longer be accessed for data reading or writing by programs running on the computer system.

Owner:GOOGLE LLC

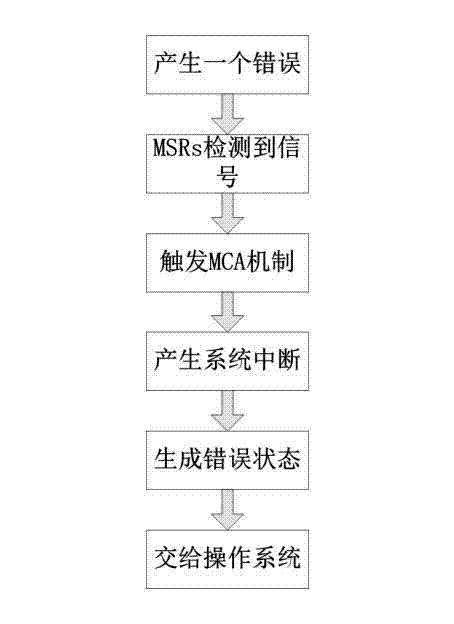

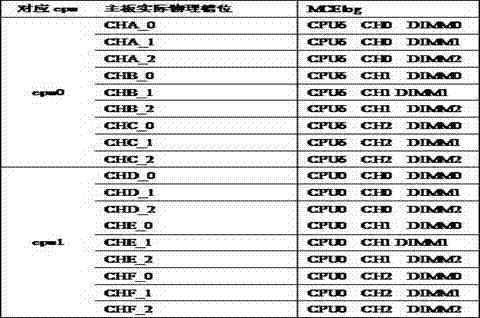

Method for positioning faulted memory in linux system

InactiveCN103198000ASolve the crash problemSolve problems such as blue screenDetecting faulty computer hardwareHardware monitoringMemory faultsGNU/Linux

The invention provides a method for positioning a faulted memory in a linux system. The method comprises that error types and fault positions of the faulted memory are judged quickly and problems such as server halting and blue screens caused by memory faults are solved quickly by usage of mcelog records produced by the system according to the actual physical slot comparison relationship without regard to judgments and records of memory faults provided by a mainboard baseboard management controller (bmc). Compared with existing memory fault judgment methods, the method has the advantages that the method is independent of a memory fault tracking and positioning function of the mainboard bmc; on-site repetition of pressure tests to wait for faults and exchange of memory tests to position the faulted memory are not required, and the fault appearance frequency, fault reasons and fault positions can be determined quickly according to generated mcelog logs; and the implementation method is simple, and the efficiency for judgment and solving of problems can be improved.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

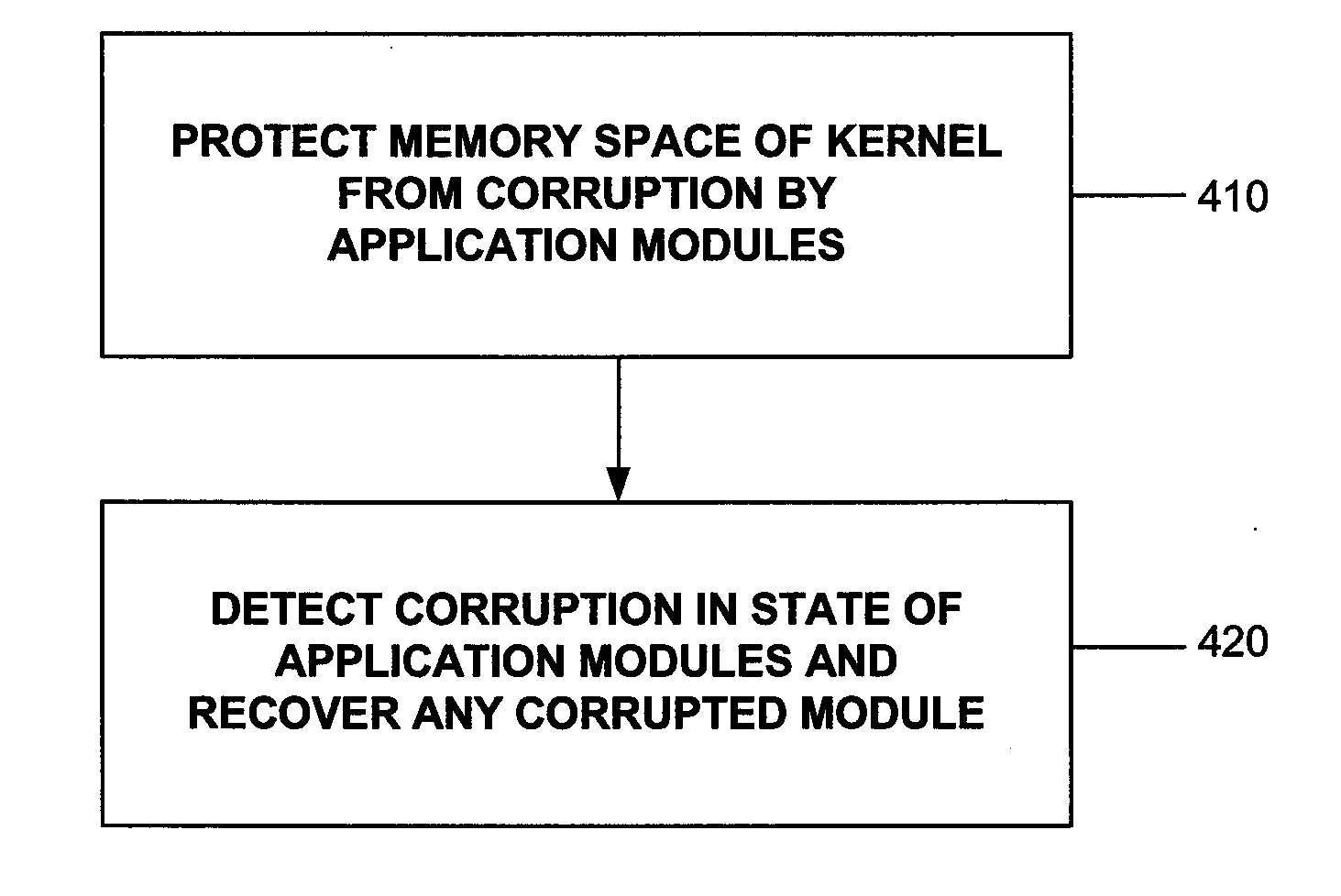

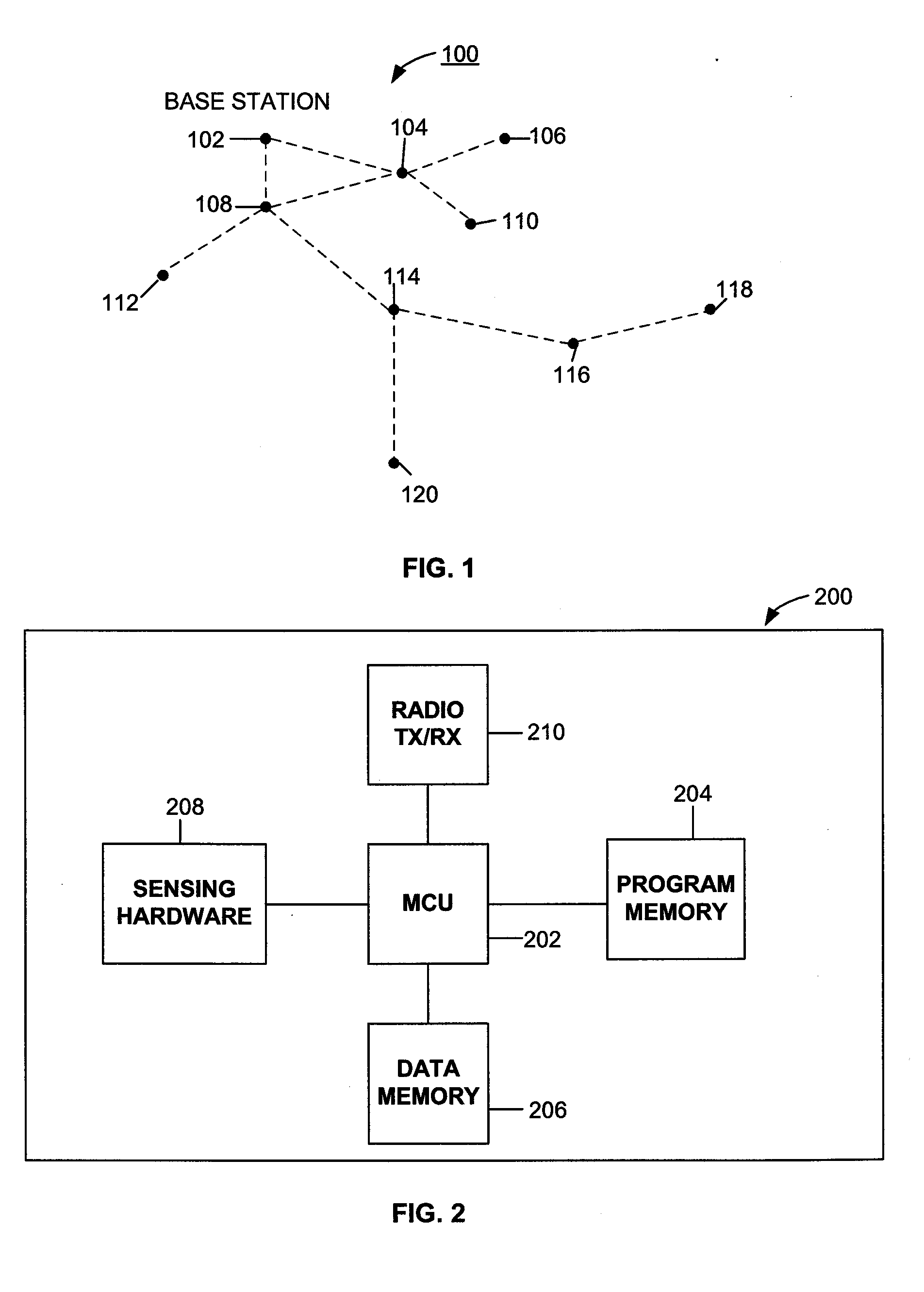

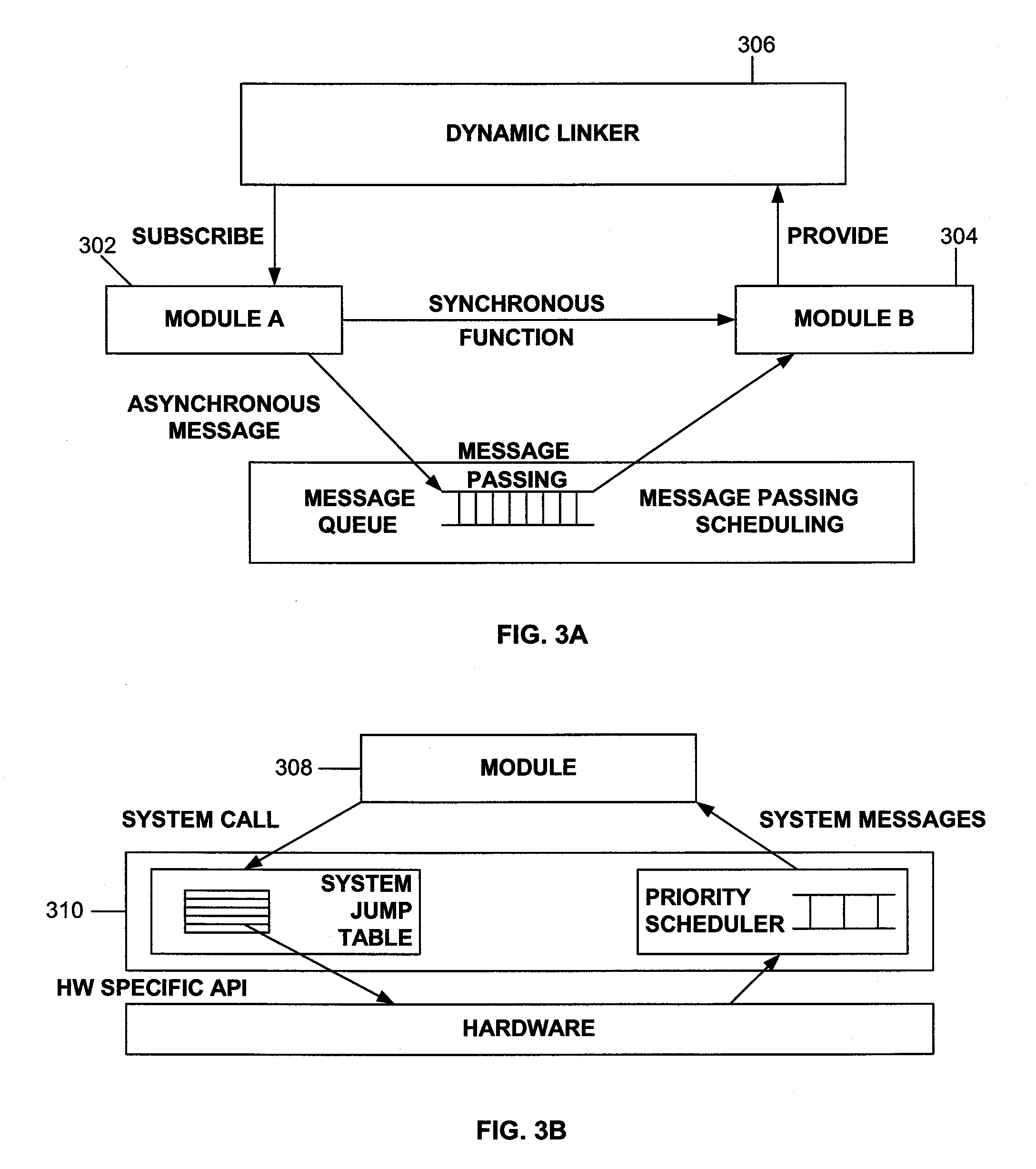

Method and system usable in sensor networks for handling memory faults

InactiveUS20070156951A1Corrupt stateProtection operationError detection/correctionMemory systemsMemory faultsOperational system

A method and system usable in sensor networks for handling memory faults is disclosed. In order to protect the operating system of a sensor node, coarse-grained memory protection is provided by creating and enforcing an application fault domain in the data memory address space of the sensor node. The data memory accessed by the application modules is restricted to the region (which defines the application fault domain) within the data memory address space. The application modules are prevented from accessing memory outside the application fault domain through software-based run-time checks. The state belonging to the operations system is maintained outside of the application fault domain, and is thus protected from memory corruption from any application module. In order to ensure that an application module does not operate on a corrupted state, fine-grained error detection and recovery is provided within the application fault domain. Any corruption of memory within the application fault domain is detected by a run-time memory integrity verifier implemented in the operating system kernel. Recovery involves purging the corrupted state and restarting only the affected application module to operate on an uncorrupted state.

Owner:NEC CORP

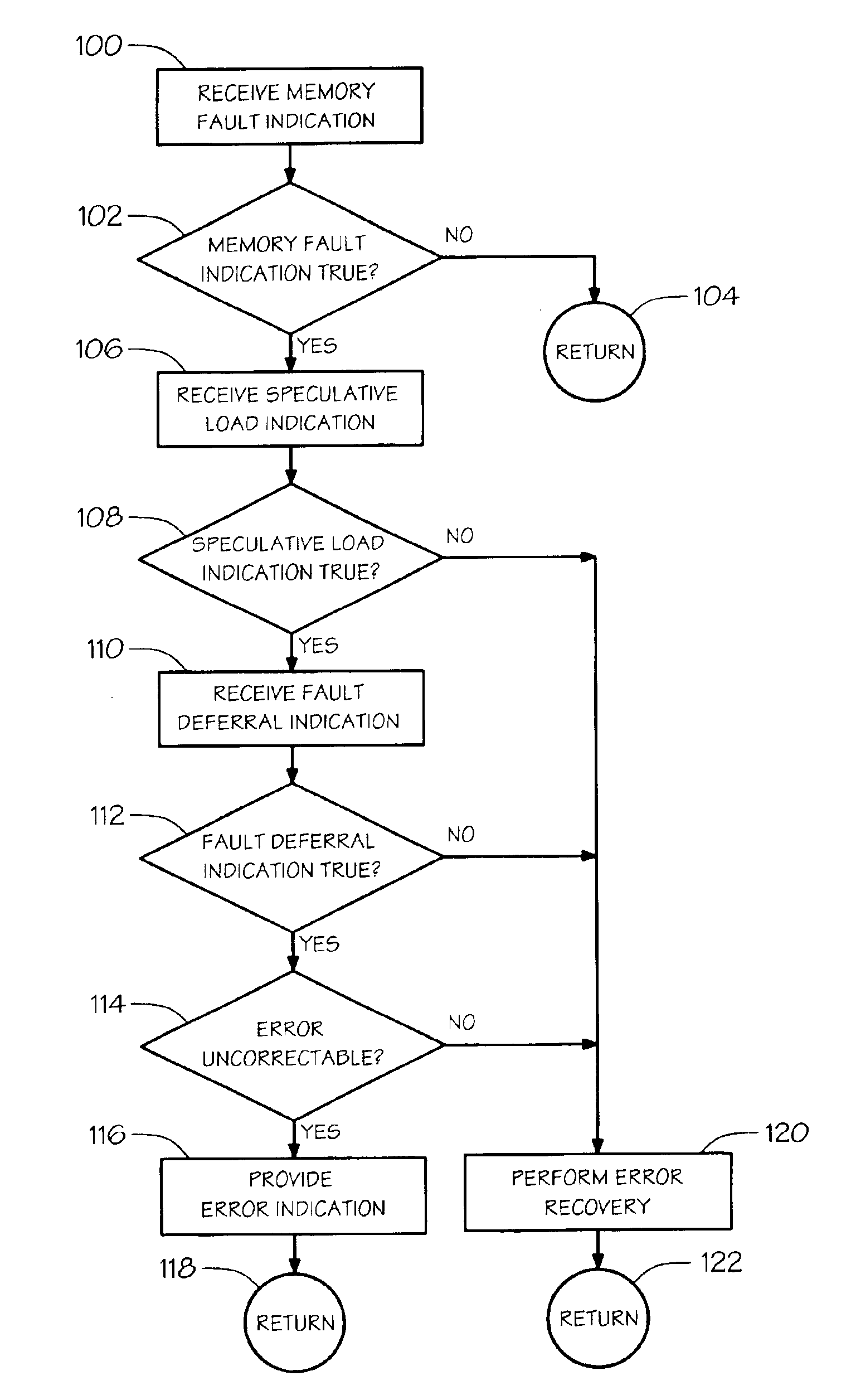

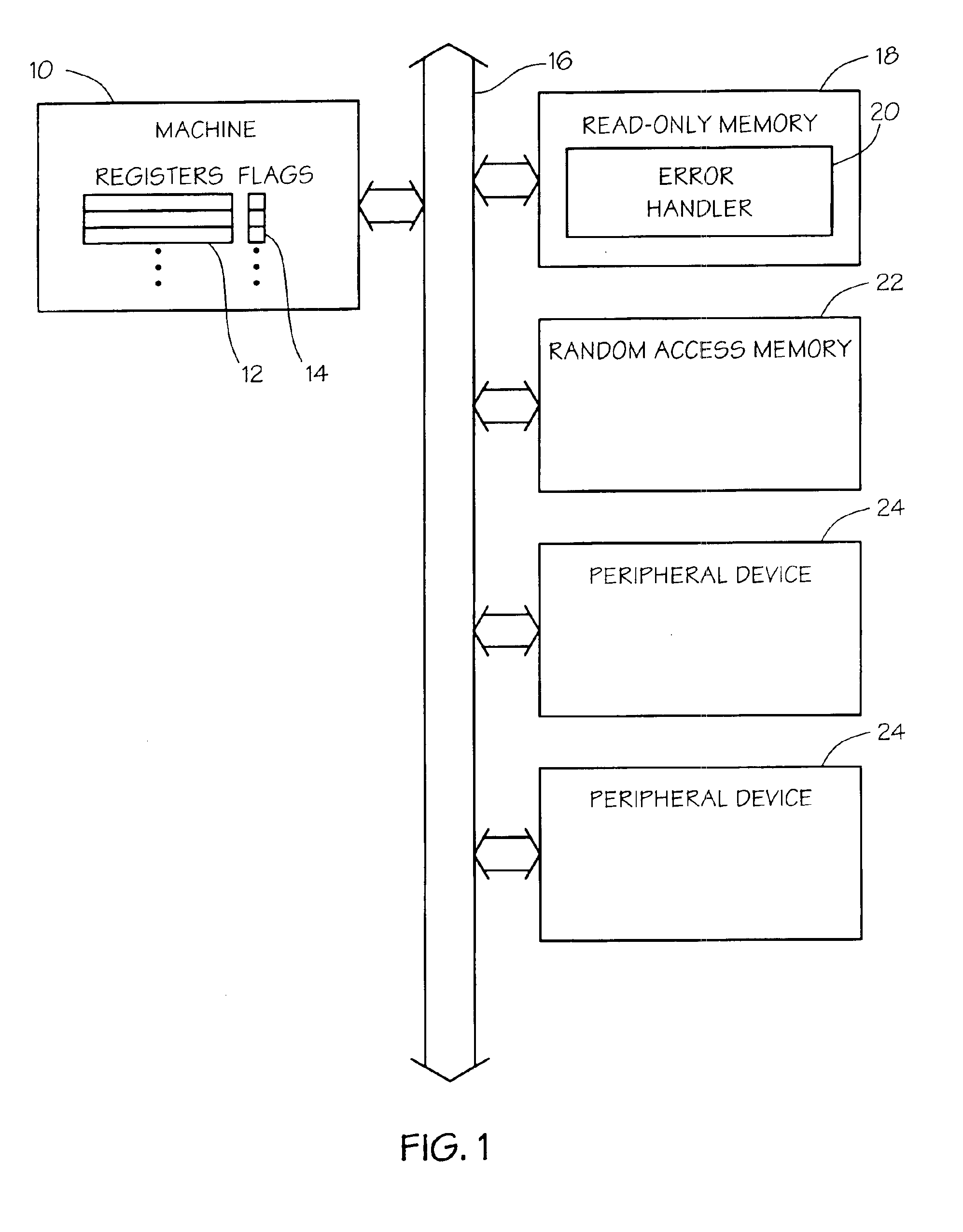

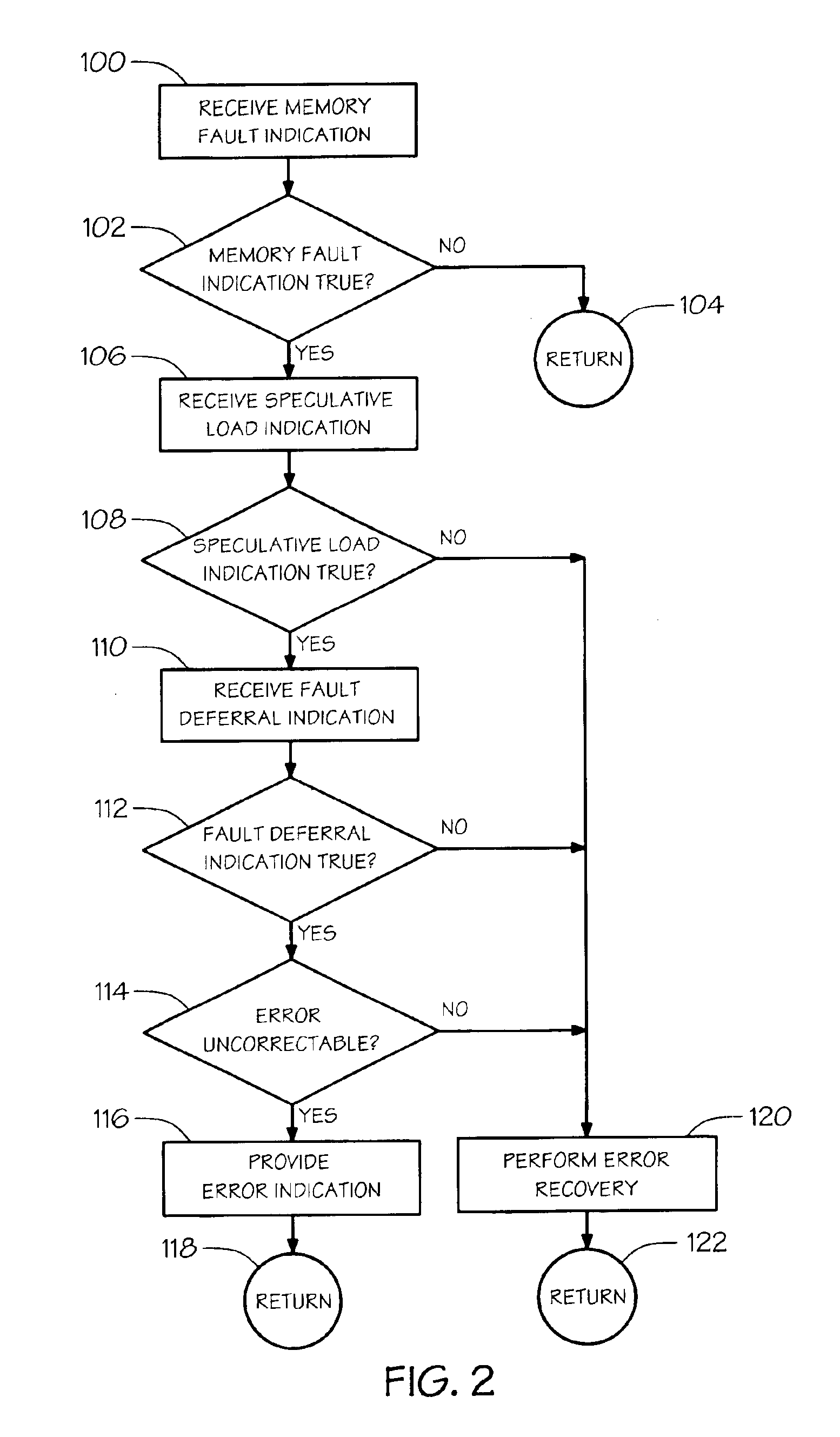

Error recovery for speculative memory accesses

A method of handling memory errors. A memory fault indication is received that is true if an error in the memory is detected while executing a memory load request to retrieve a value from the memory. A speculative load indication is received that is true if the memory load request was issued speculatively. If the memory fault indication is true and the speculative load indication is true, then an error indication that the returned value is invalid is provided, otherwise, error recovery is performed.

Owner:INTEL CORP

Efficiency of hardware memory access using dynamically replicated memory

InactiveUS20110119456A1Simple conceptDigital data processing detailsMemory adressing/allocation/relocationMemory faultsParallel computing

Dynamically replicated memory is usable to allocate new memory space from failed memory pages by pairing compatible failed memory pages to reuse otherwise unusable failed memory pages. Dynamically replicating memory involves detecting and recording memory faults, reclaiming failed memory pages for later use, recovering from detected memory faults, and scheduling access to replicated memory pages.

Owner:MICROSOFT TECH LICENSING LLC

Dynamically Replicated Memory

Dynamically replicated memory is usable to allocate new memory space from failed memory pages by pairing compatible failed memory pages to reuse otherwise unusable failed memory pages. Dynamically replicating memory involves detecting and recording memory faults, reclaiming failed memory pages for later use, recovering from detected memory faults, and scheduling access to replicated memory pages.

Owner:MICROSOFT TECH LICENSING LLC

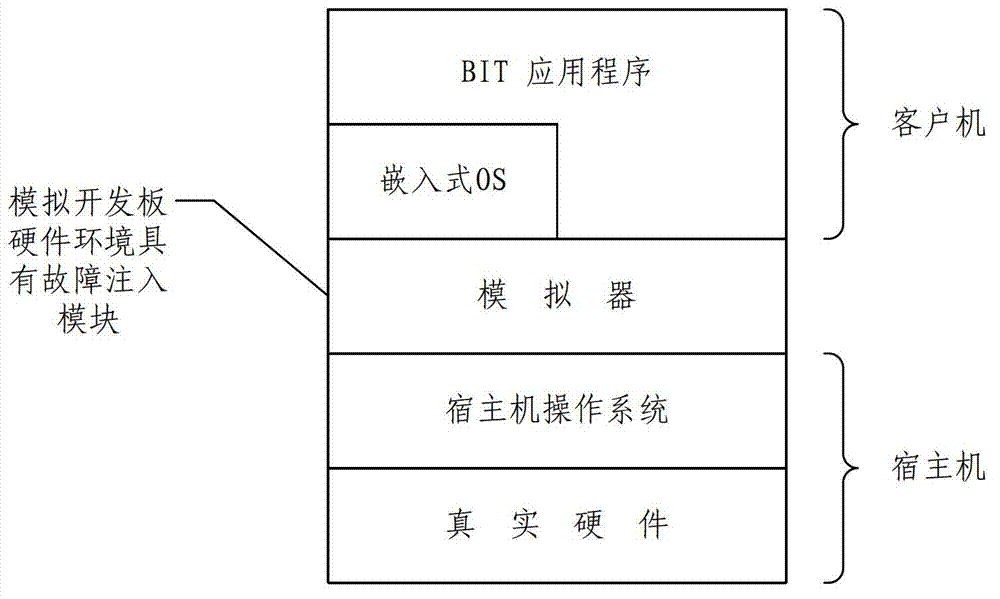

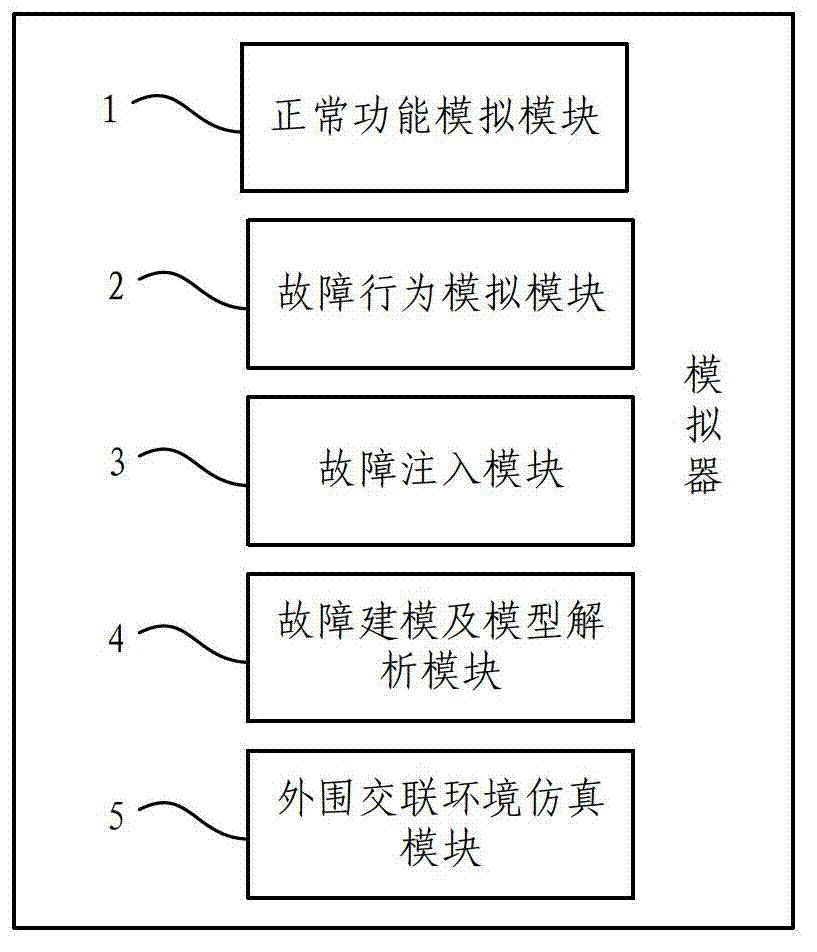

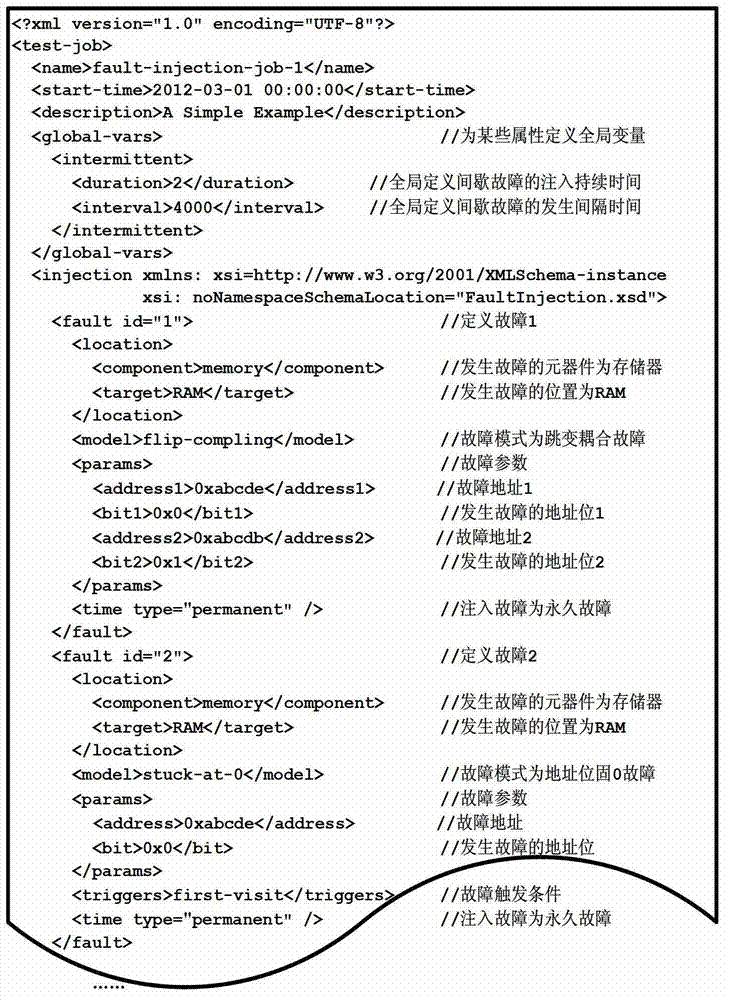

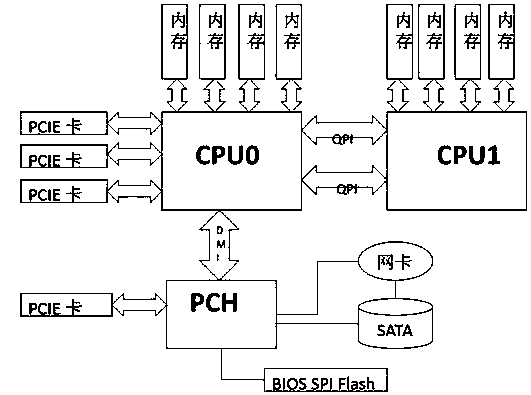

Memory fault injection method and simulator thereof for software built-in test (BIT)

InactiveCN102789416ASolve test problemsGuaranteed accuracySoftware testing/debuggingCross-linkMemory faults

The invention provides a memory fault injection method and a simulator thereof for a software BIT. A hardware circuit board carrying out BIT software serves as a mock object of the simulator. An analog module for simulating normal functions of a memory, a fault modeling and model analysis module for establishing and analyzing fault sequence files, a fault injection module for matching the faults to be injected, and a fault behavior analog module and a peripheral cross-linking environment simulation module are added to the simulator. The method includes establishing a fault mode base, writing and analyzing extensive makeup language (XML) fault sequence files into identifiable fault sequences, searching and injecting corresponding faults when a processor accesses the memory, and performing fault simulation when the faults are triggered. According to the method and the simulator, the injected fault modes are complete and fully cover test cases under each fault occurrence for the memory, sufficient tests can be performed on the BIT software on a circuit board level, and only the BIT software after the sufficient tests can guarantee accuracy and timeliness of BIT fault prediction of aeronautical airborne equipment and further guarantee system reliability and safety.

Owner:BEIHANG UNIV

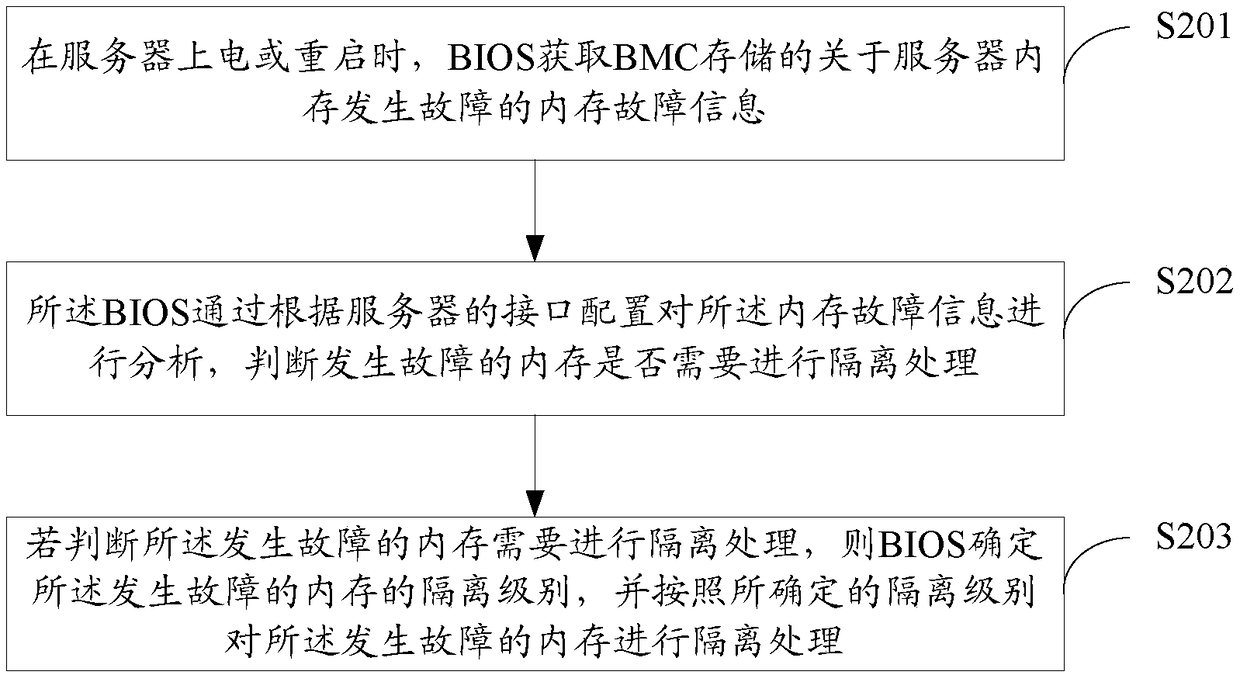

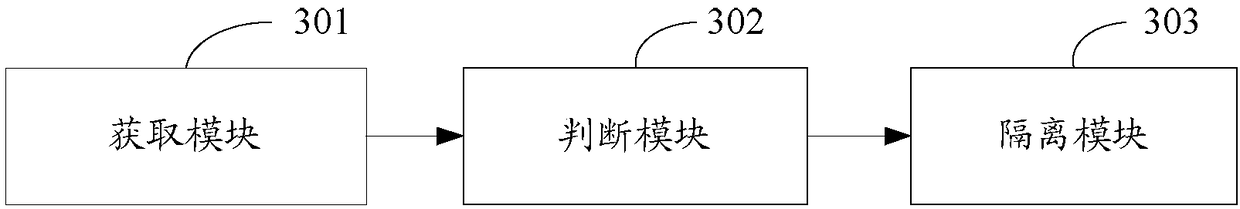

A method and apparatus for isolating memory failure on a server

InactiveCN109086151AStable and controllable businessNon-redundant fault processingElectricityMemory faults

The invention discloses a method and a device for isolating memory failure on a server, relating to the technical field of a server product. The method comprises: when a server is powered on or restarted, a BIOS obtains memory failure information about the memory failure of the server stored in a BMC; ; the BIOS analyzes the memory fault information according to the interface configuration of theserver, and judges whether the failed memory needs to be isolated or not; if it is judged that the faulty memory needs to be isolated, the BIOS determines the isolation level of the faulty memory, andisolates the faulty memory according to the determined isolation level.

Owner:ZTE CORP

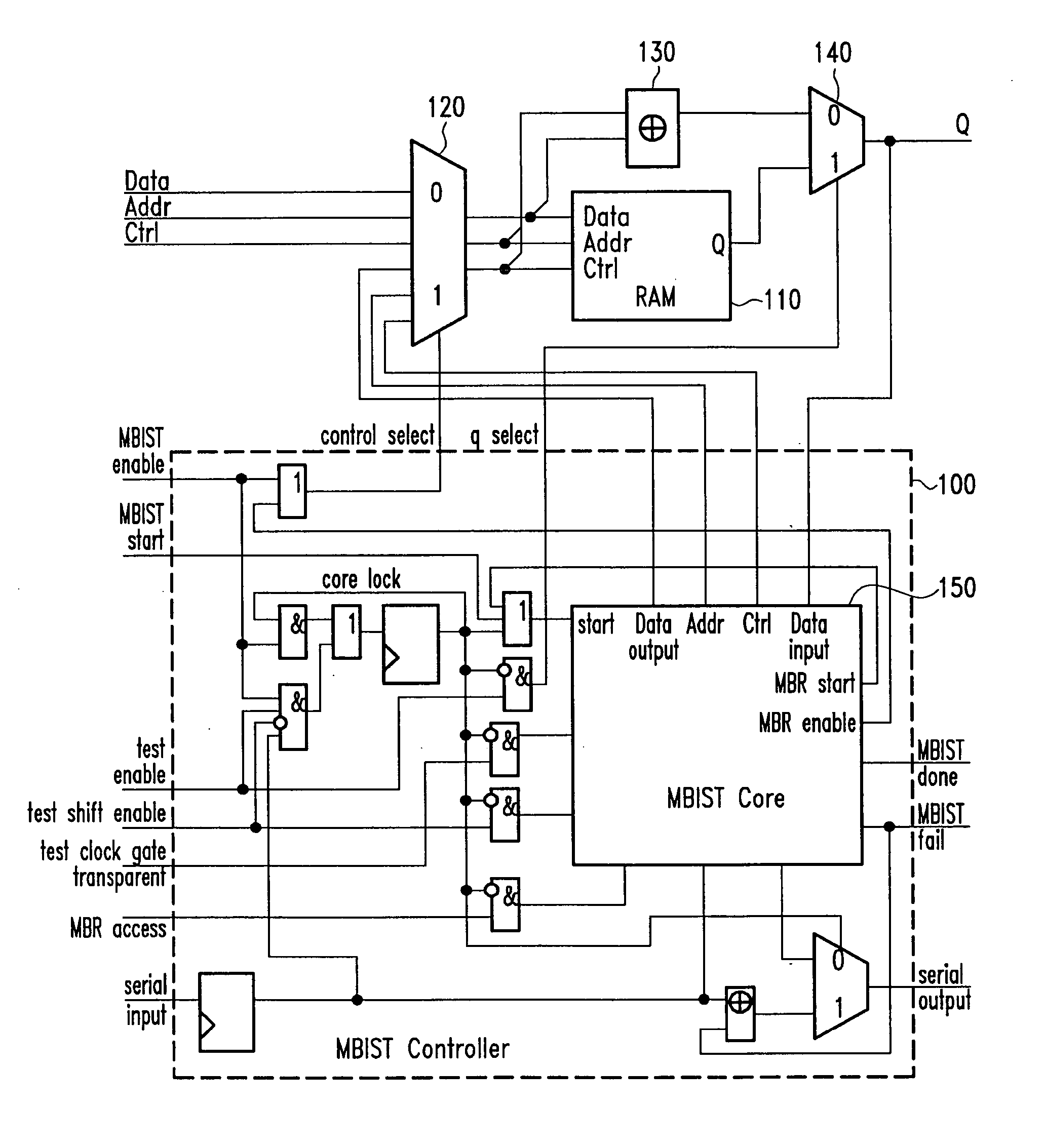

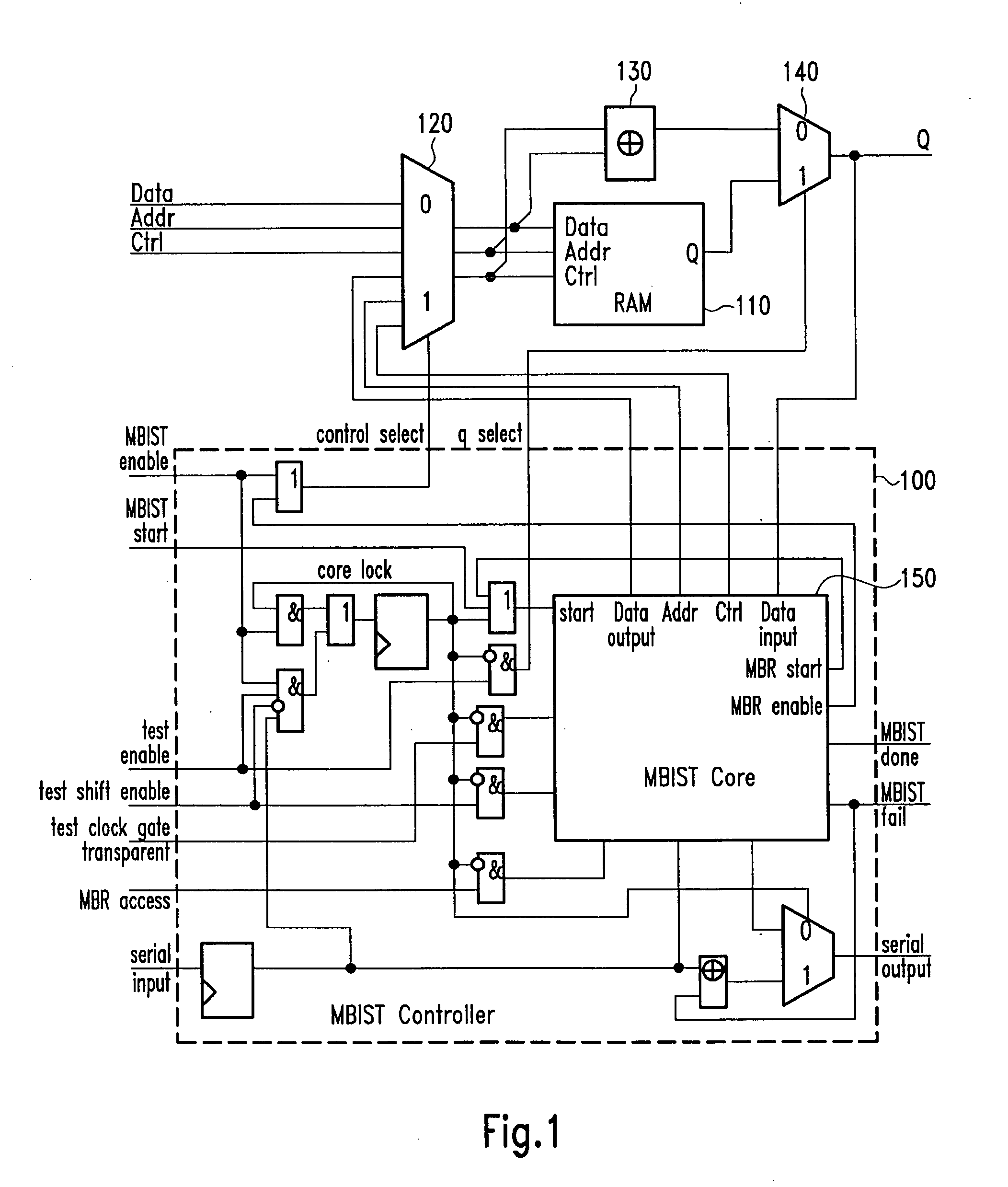

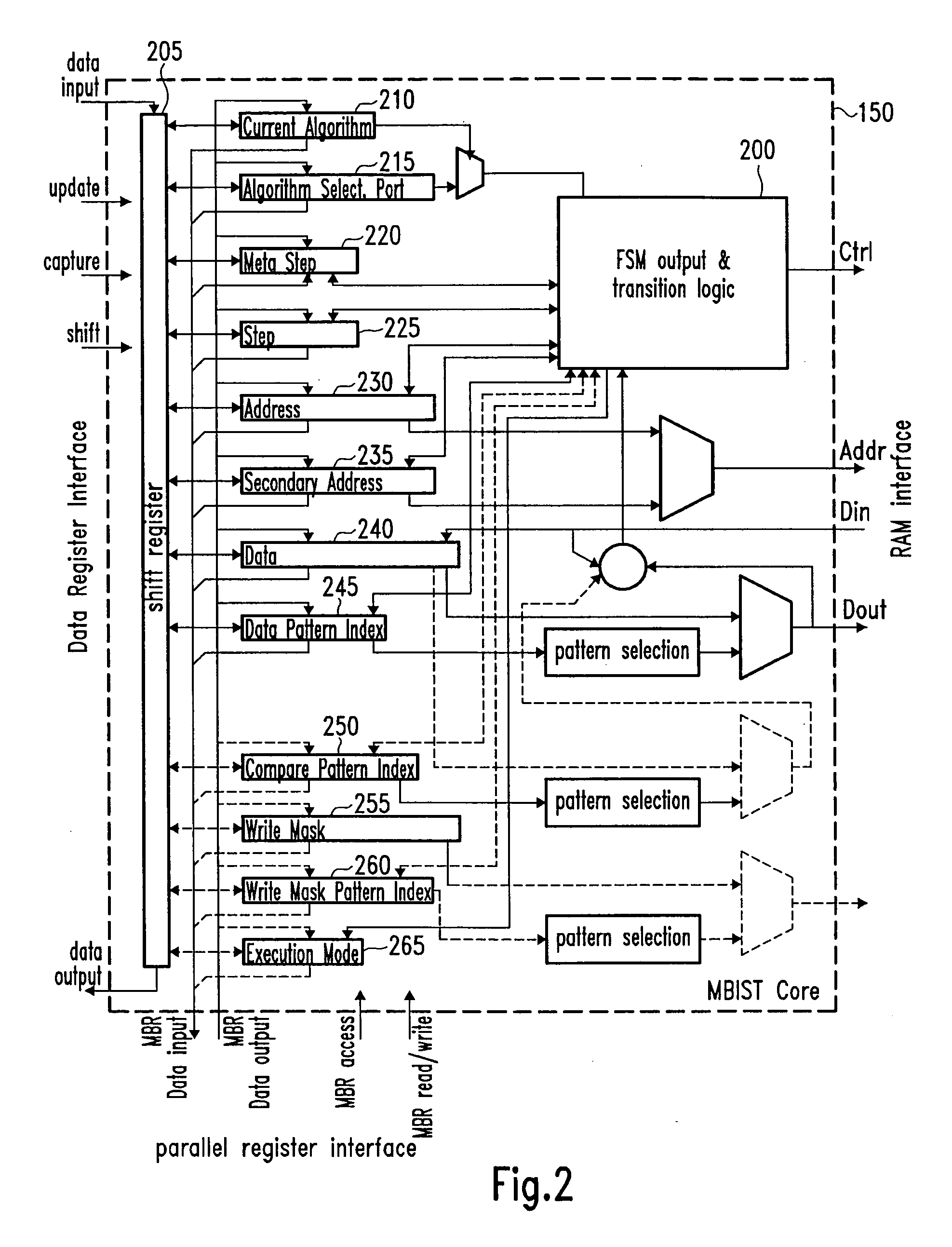

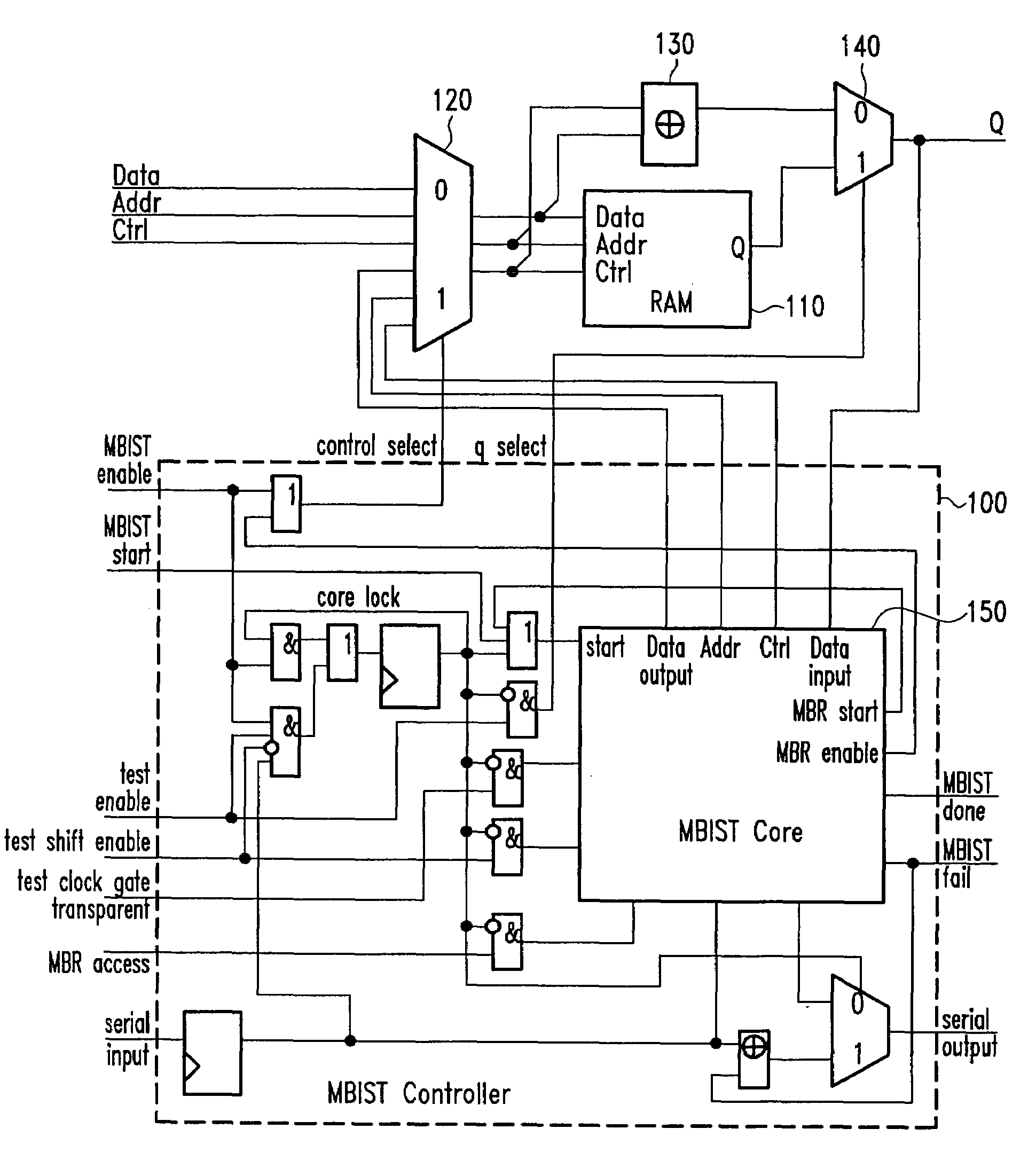

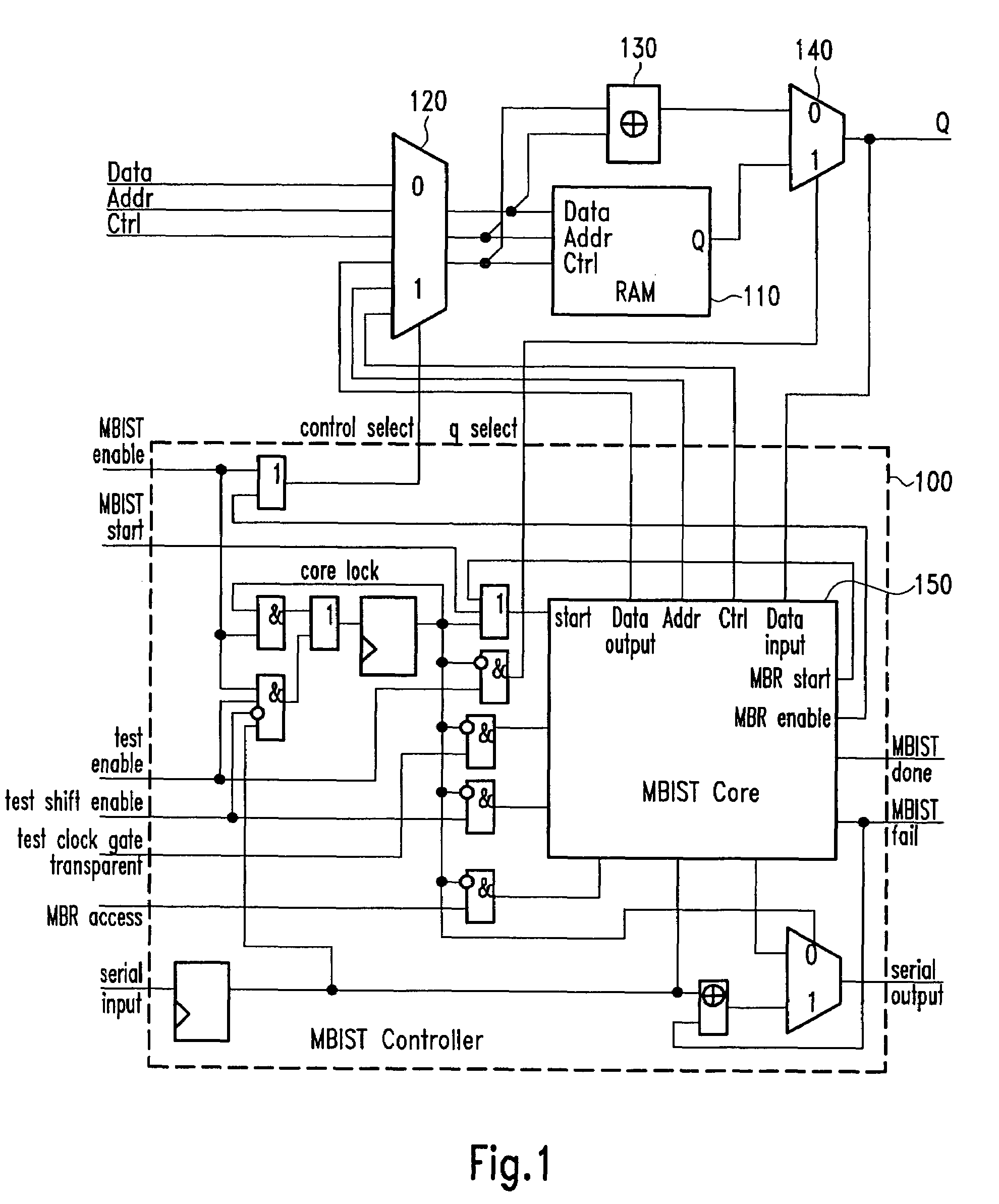

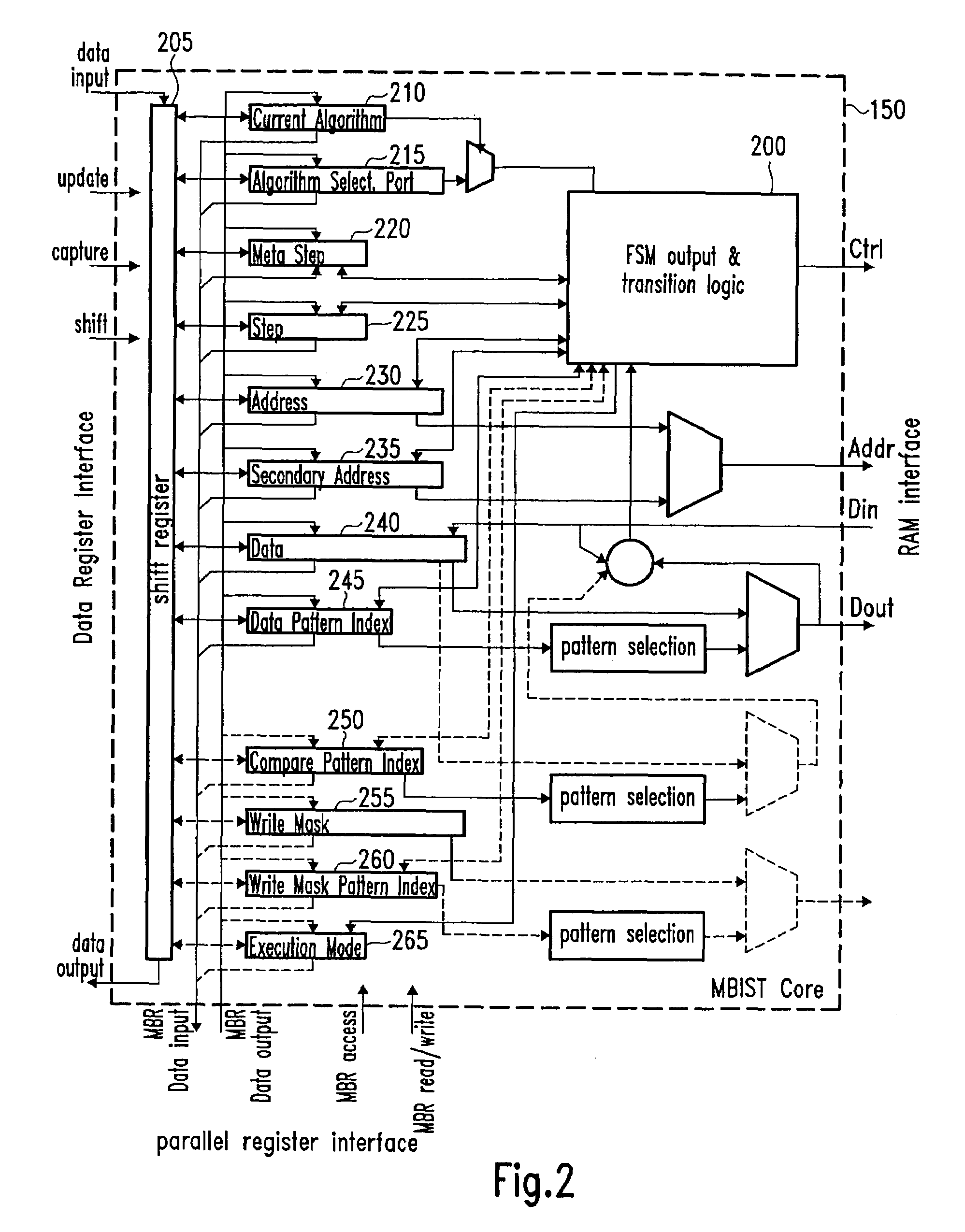

Test algorithm selection in memory built-in self test controller

InactiveUS20070204190A1Effective and flexibleImprove efficiencyElectronic circuit testingStatic storageComputer hardwareMemory faults

An integrated circuit chip is provided that comprises on-chip memory and test circuitry. The test circuitry is configured to perform operational testing of the on-chip memory. The test circuitry comprises a controller which is configured to perform a selection out of a plurality of test algorithms to perform the operational testing. The plurality of test algorithms includes a fault detection test algorithm to perform operational testing of the on-chip memory in order to detect whether or not there is a memory fault, without locating the memory fault. The plurality of test algorithms further includes a fault location test algorithm to perform operational testing of the on-chip memory in order to detect and locate a memory fault. Further, a method to perform a memory built-in self test and an MBIST (Memory Built-In Self Test) control circuit template are provided.

Owner:CHRONOCLOUD MEDTECH (SHANGHAI) CO LTD

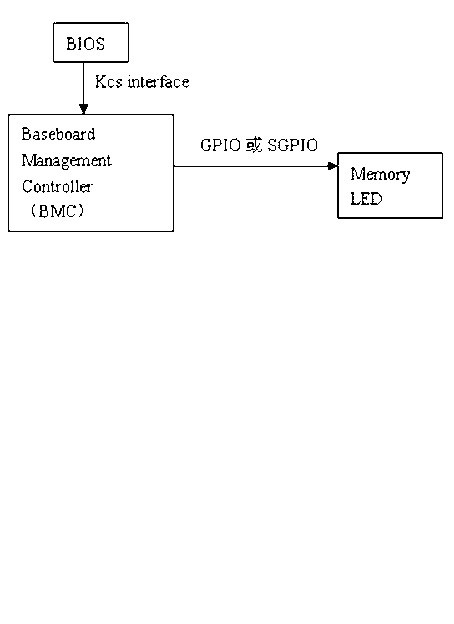

Method for positioning fault memory

InactiveCN102799506APrecise positioningEasy to replaceDetecting faulty computer hardwareHardware monitoringIntelligent Platform Management InterfaceMemory faults

The invention provides a method for positioning a fault memory. Each memory corresponds to a light emitting diode (LED) lamp; in system startup process, a basic input / output system (BIOS) detects memories; and if a memory fault is discovered, an intelligent platform management interface (IPMI) command is sent to a baseboard management controller (BMC), the BMC acquires the position of the fault memory according to the IPMI command, and the LED lamp corresponding to the fault memory is turned on, wherein the memory corresponding to the lighting position of the LED lamp is the fault memory. The method comprises the following steps of: (1) starting a system, and detecting the memories by the BIOS; (2) when the BIOS detects the memory fault, organizing the IPMI command according to the position information of the fault memory, and sending the IPMI command to the BMC; and (3) receiving the IPMI command sent by the BIOS by the BMC, resolving the position information of the acquired fault memory, and turning on the LED lamp corresponding to the fault memory.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

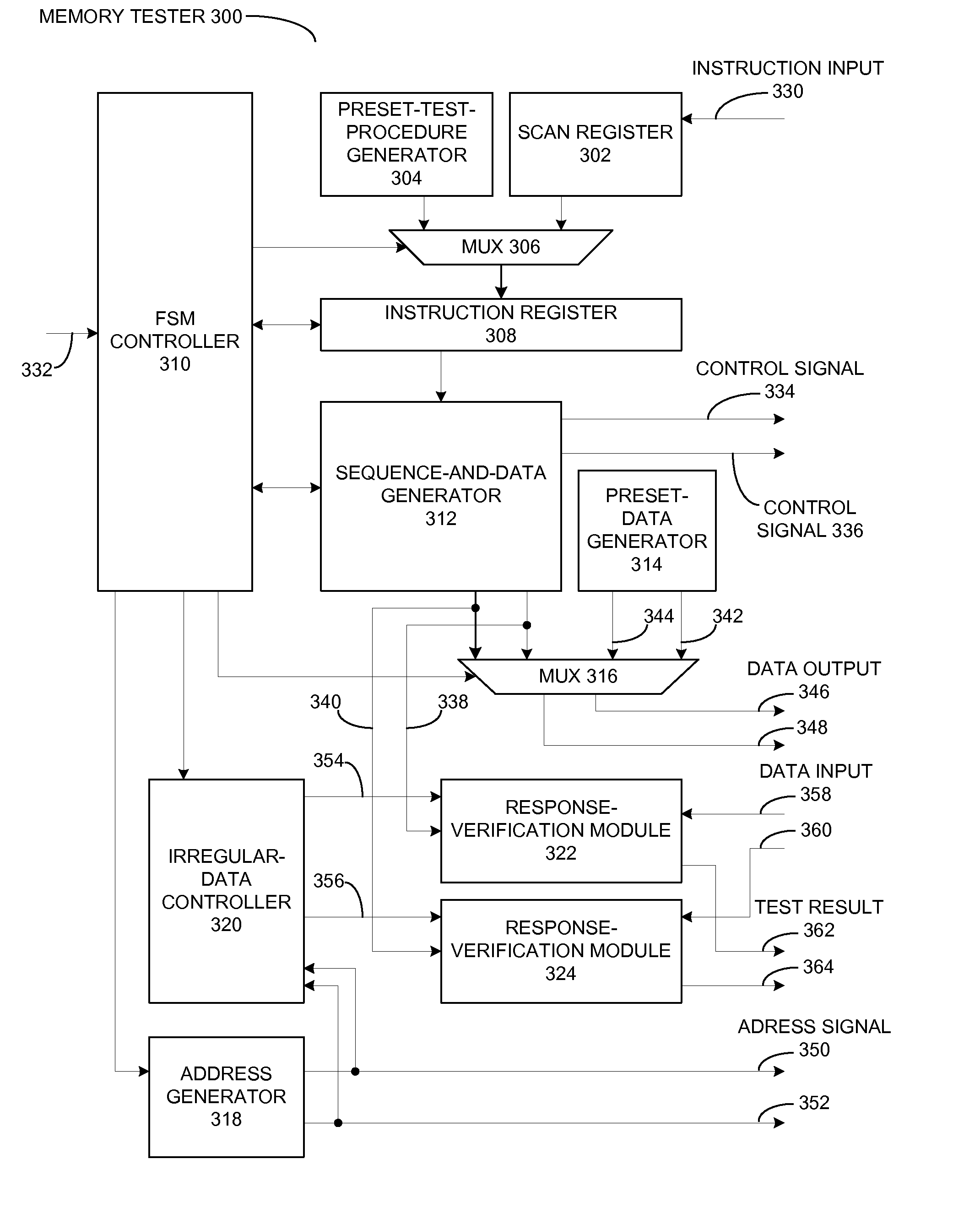

Runtime programmable bist for testing a multi-port memory device

ActiveUS20100275074A1Improve test qualityElectronic circuit testingFunctional testingMemory faultsTest procedures

One embodiment provides a runtime programmable system which comprises methods and apparatuses for testing a multi-port memory device to detect a multi-port memory fault, in addition to typical single-port memory faults that can be activated when accessing a single port of a memory device. More specifically, the system comprises a number of mechanisms which can be configured to activate and detect any realistic fault which affects the memory device when two simultaneous memory access operations are performed. During operation, the system can receive an instruction sequence, which implements a new test procedure for testing the memory device, while the memory device is being tested. Furthermore, the system can implement a built-in self-test (BIST) solution for testing any multi-port memory device, and can generate tests targeted to a specific memory design based in part on information from the instruction sequence.

Owner:SYNOPSYS INC

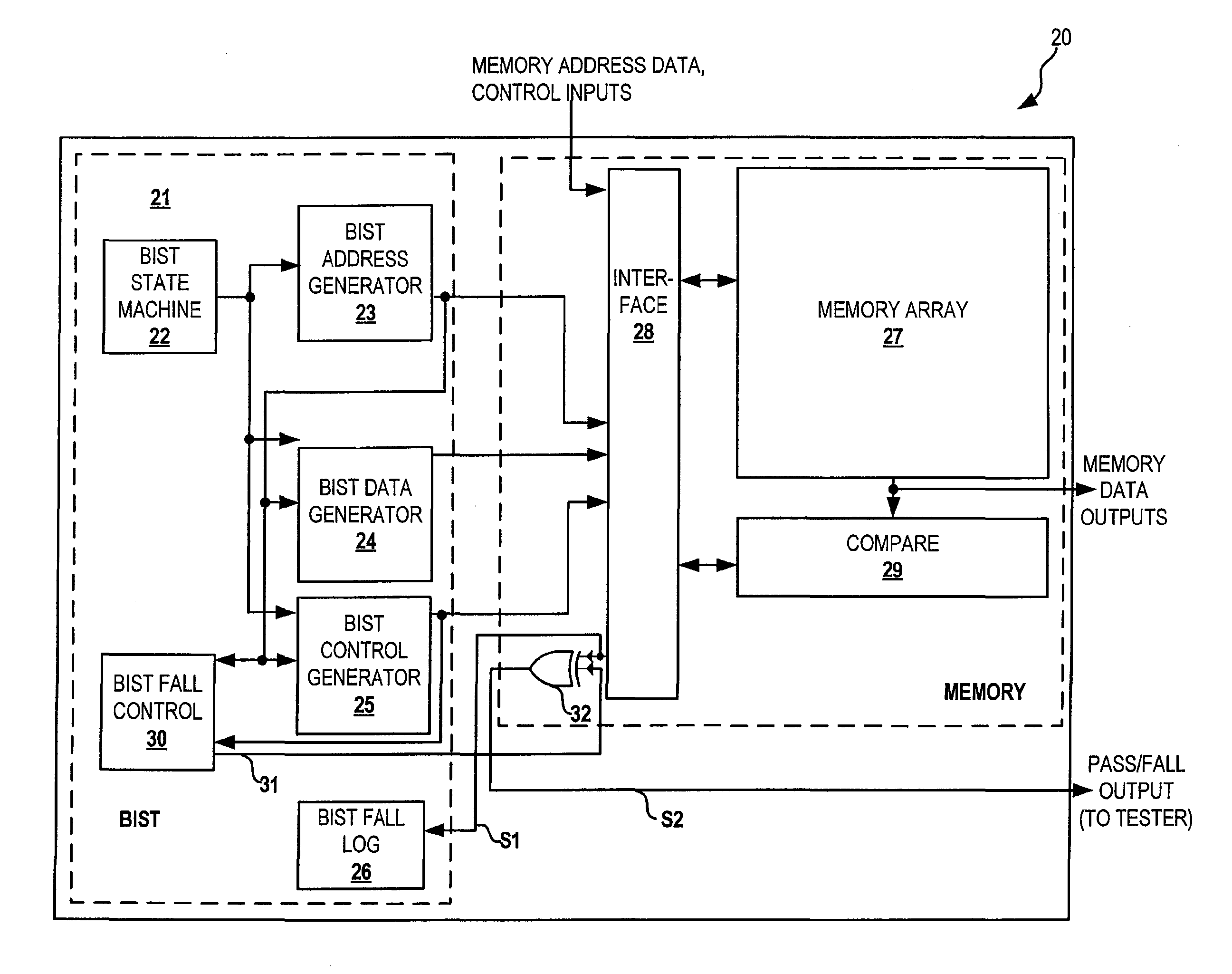

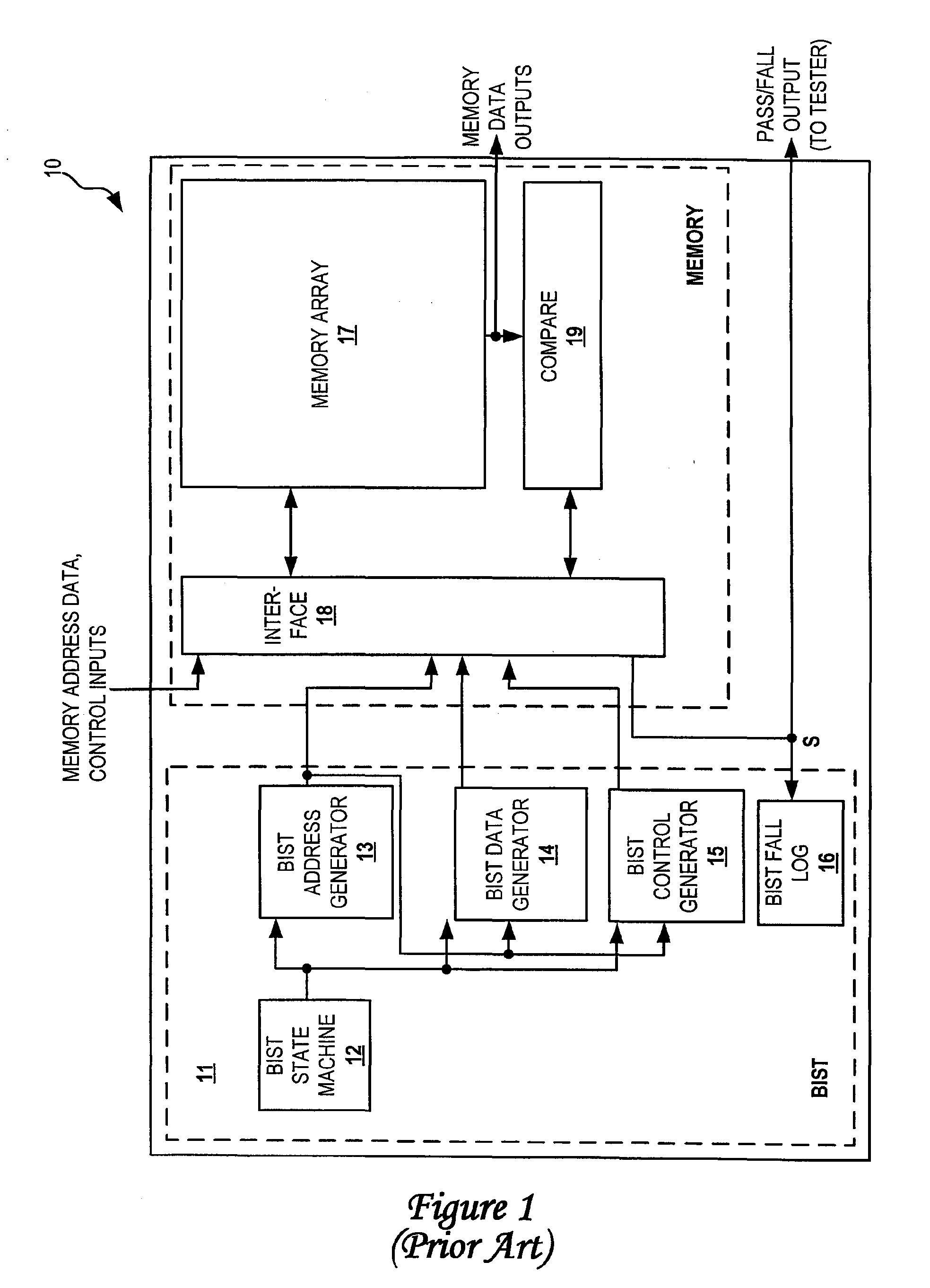

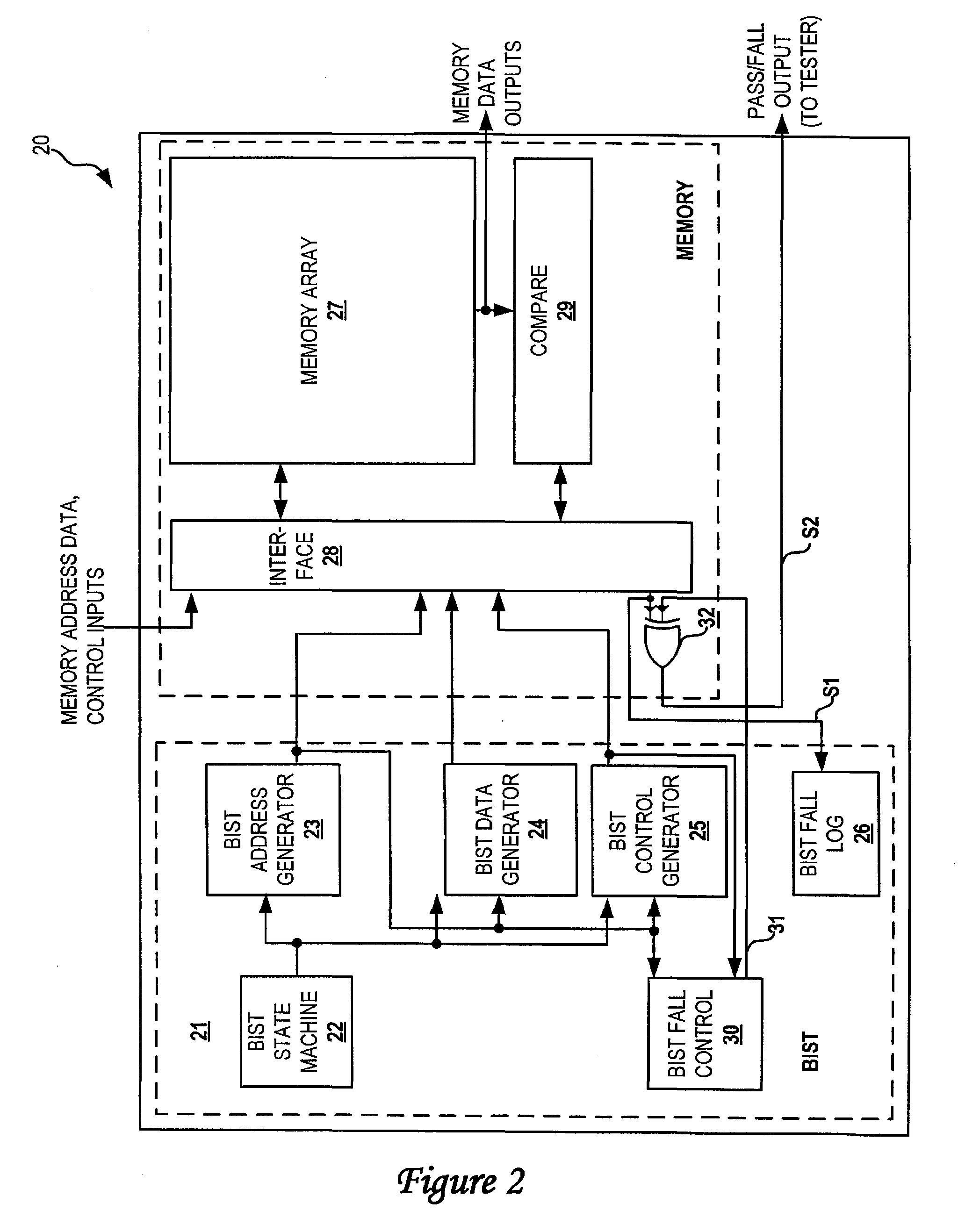

Method and apparatus for verifying memory testing software

ActiveUS20060190788A1Verify accuracyElectronic circuit testingError detection/correctionMemory faultsParallel computing

A method for verifying the accuracy of memory testing software is disclosed. A built-in self test (BIST) fail control function is utilized to generate multiple simulated memory fails at various predetermined locations within a memory array of a memory device. The memory array is then tested by a memory tester. Afterwards, a bit fail map is generated by the logical-to-physical mapping software based on all the memory fails indicated by the memory tester. The bit fail map provides all the fail memory locations derived by the logical-to-physical mapping software. The fail memory locations derived by the logical-to-physical mapping software are then compared to the predetermined memory locations to verify the accuracy of the logical-to-physical mapping software.

Owner:MARVELL ASIA PTE LTD

Method for batched server memory fault detection through IPMI tool

InactiveCN103970661ASuitable for configuration environmentEasy to implementSoftware testing/debuggingRedundant data error correctionMemory faultsBatch machine

The invention provides a method for batched server memory fault detection through an IPMI tool, and belongs to the field of fault detection. The method comprises the steps that recording and scanning bmc logs of all servers inside a network through the IPMI tool, analyzing machines with the memory problem from the result, conducting batched checking on the batched servers inside the network through a script, rapidly determining the machines with the memory ecc errors, and achieving memory batched checking of the batched machines. According to the method, the testing time is shortened, and working efficiency is improved.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

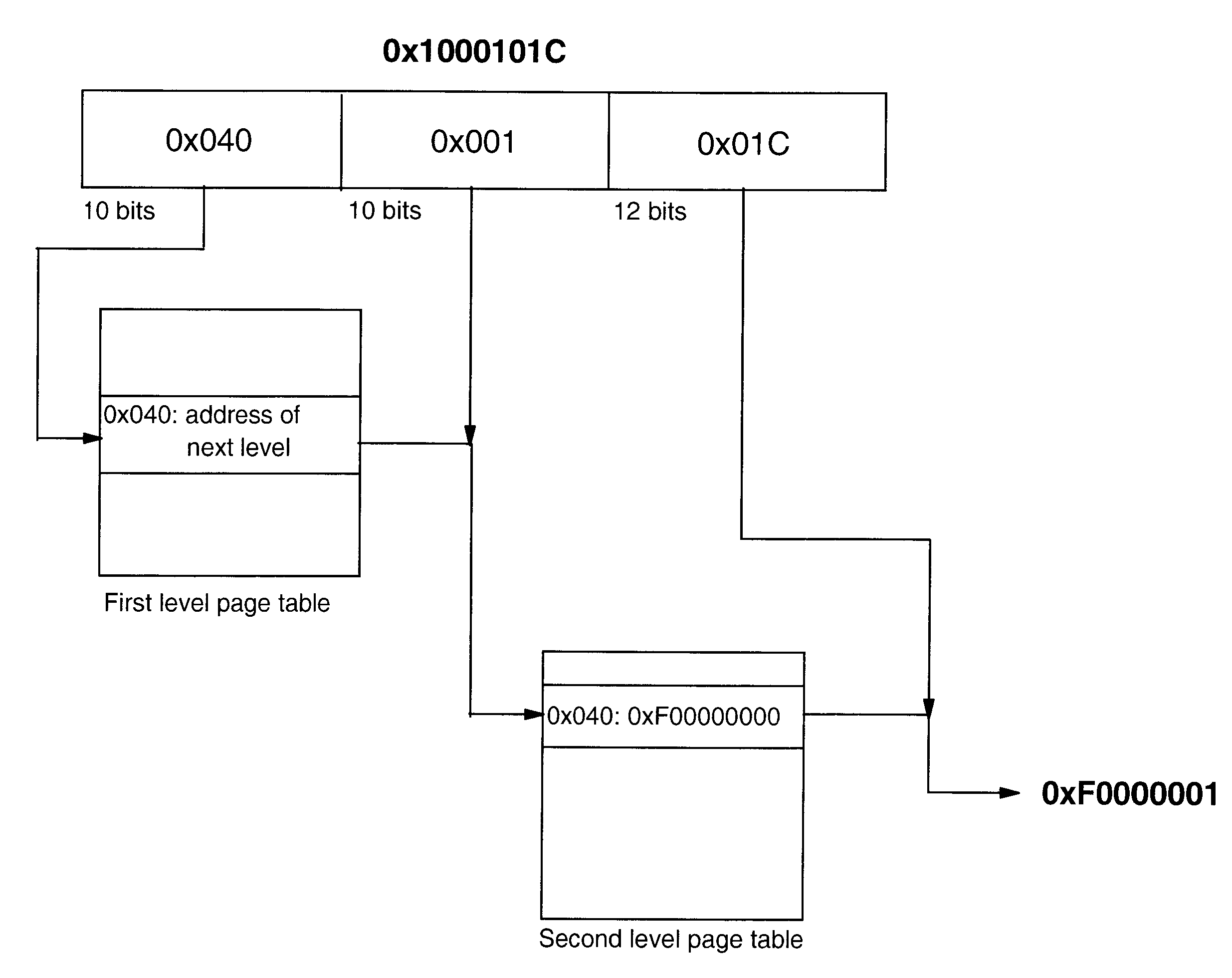

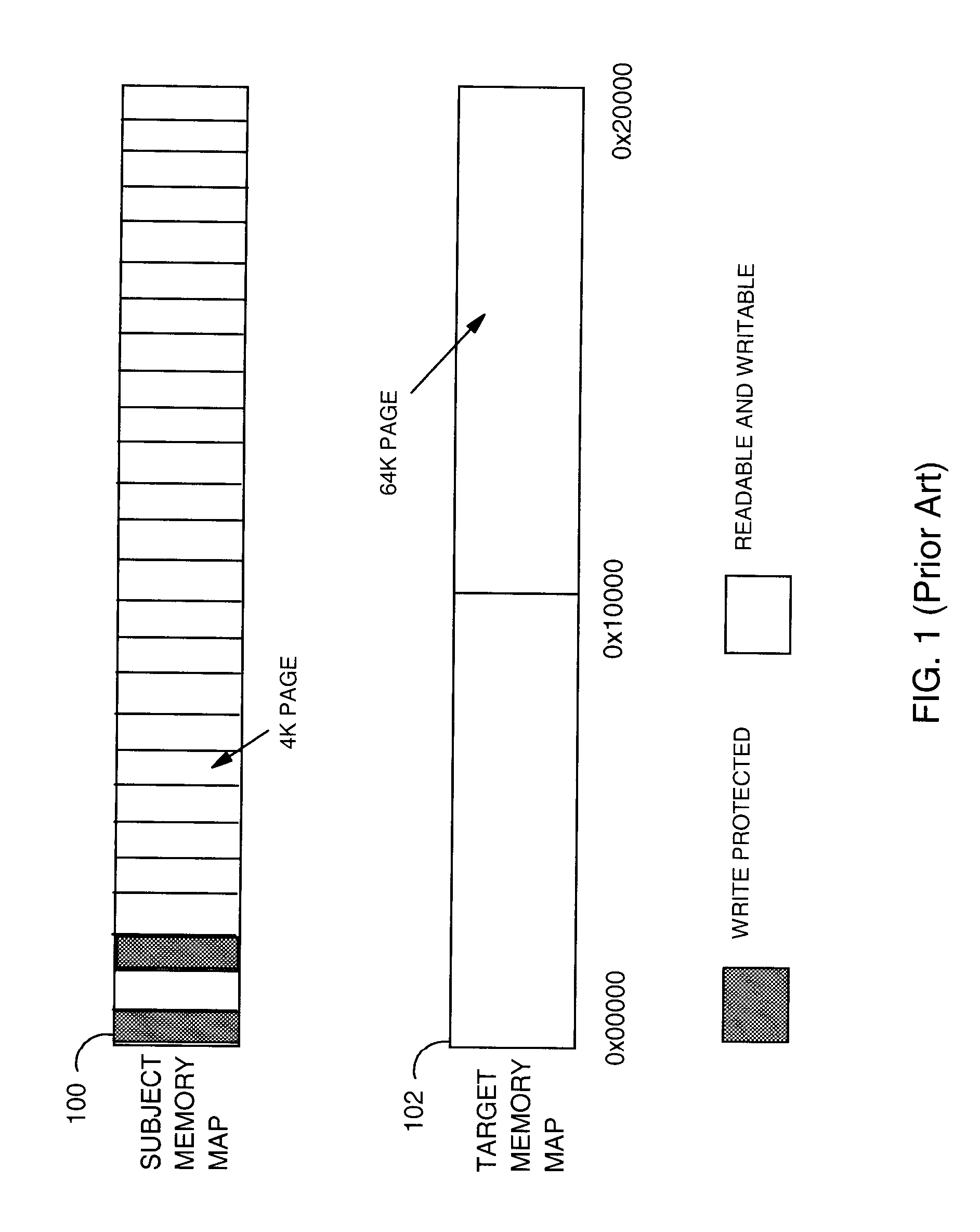

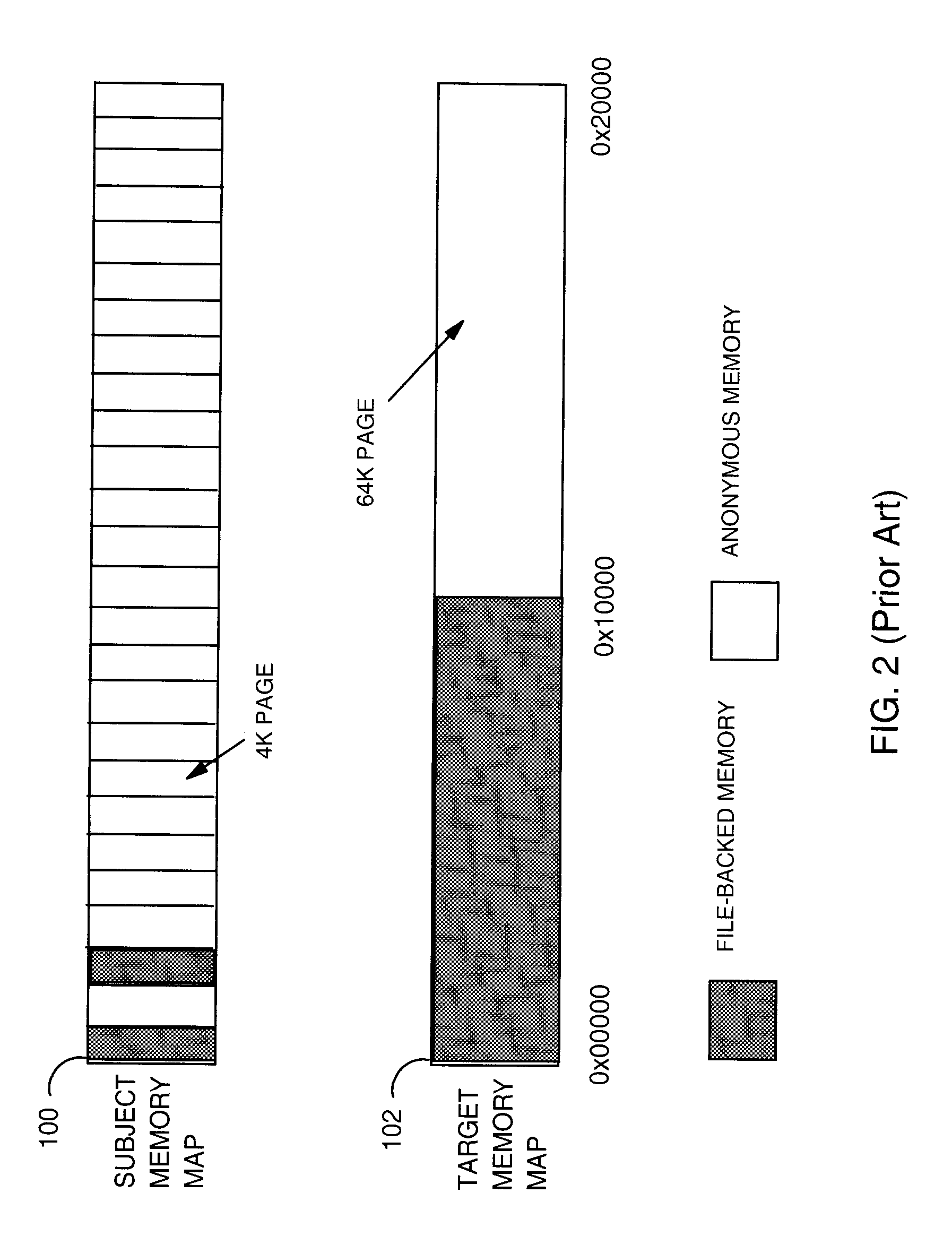

Memory Management for a Dynamic Binary Translator

InactiveUS20120117355A1Increase constraintsBinary to binaryMemory adressing/allocation/relocationMemory faultsParallel computing

A dynamic binary translator apparatus, method and program for translating a first block of binary computer code intended for execution in a subject execution environment having a first memory of one page size into a second block for execution in a second execution environment having a second memory of another page size, comprising a redirection page mapper responsive to a page characteristic of the first memory for mapping an address of the first memory to an address of the second memory; a memory fault behaviour detector operable to detect memory faulting during execution of the second block and to accumulate a fault count to a trigger threshold; and a regeneration component responsive to the fault count reaching the trigger threshold to discard the second block and cause the first block to be retranslated with its memory references remapped by a page table walk.

Owner:IBM CORP

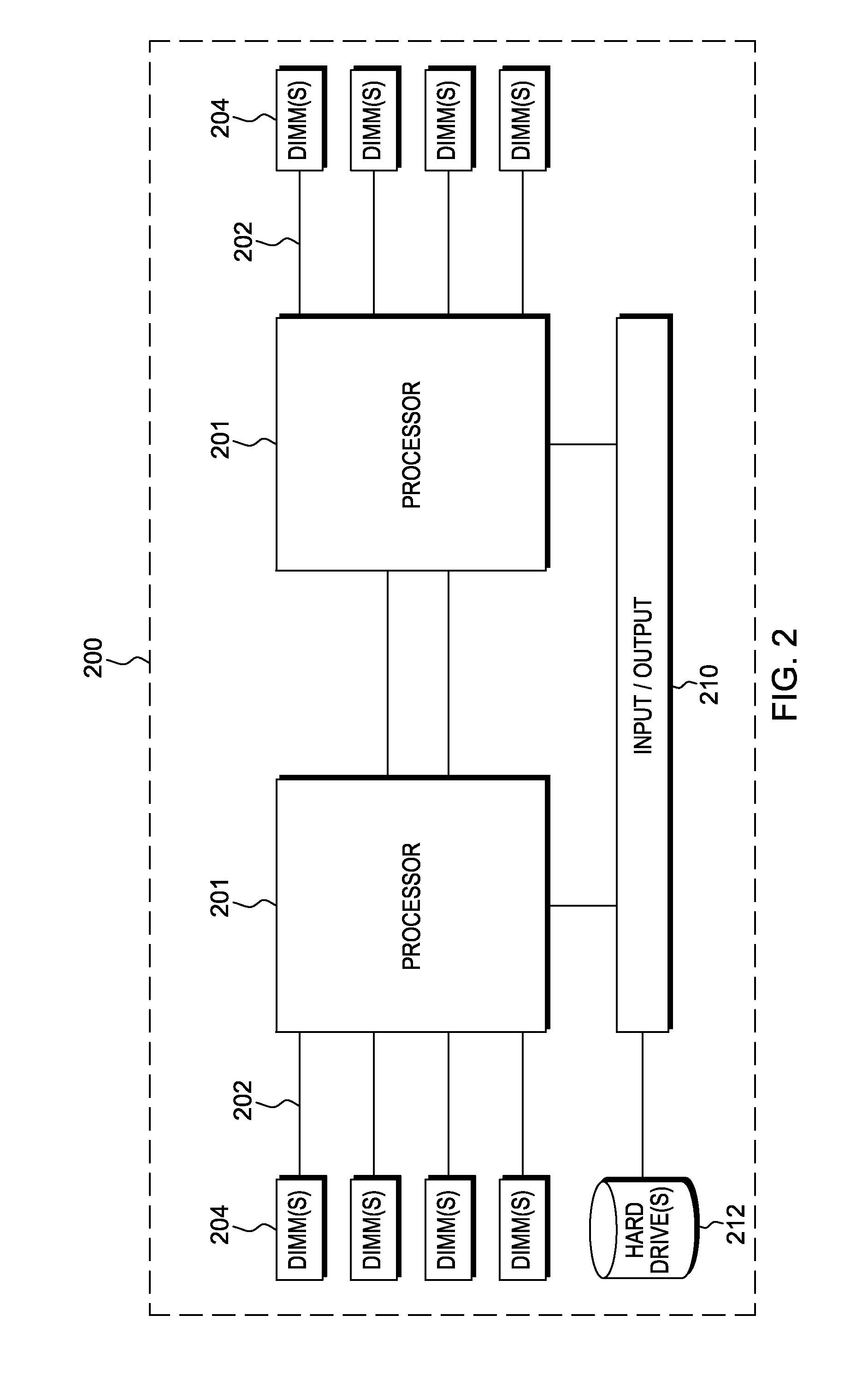

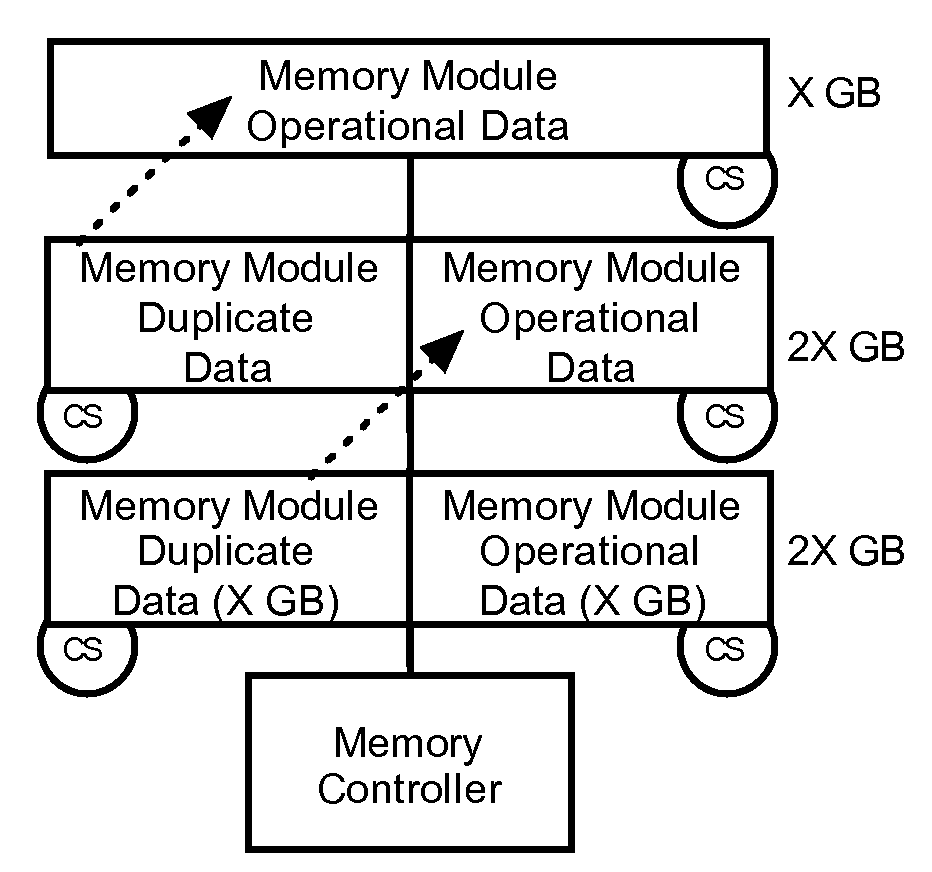

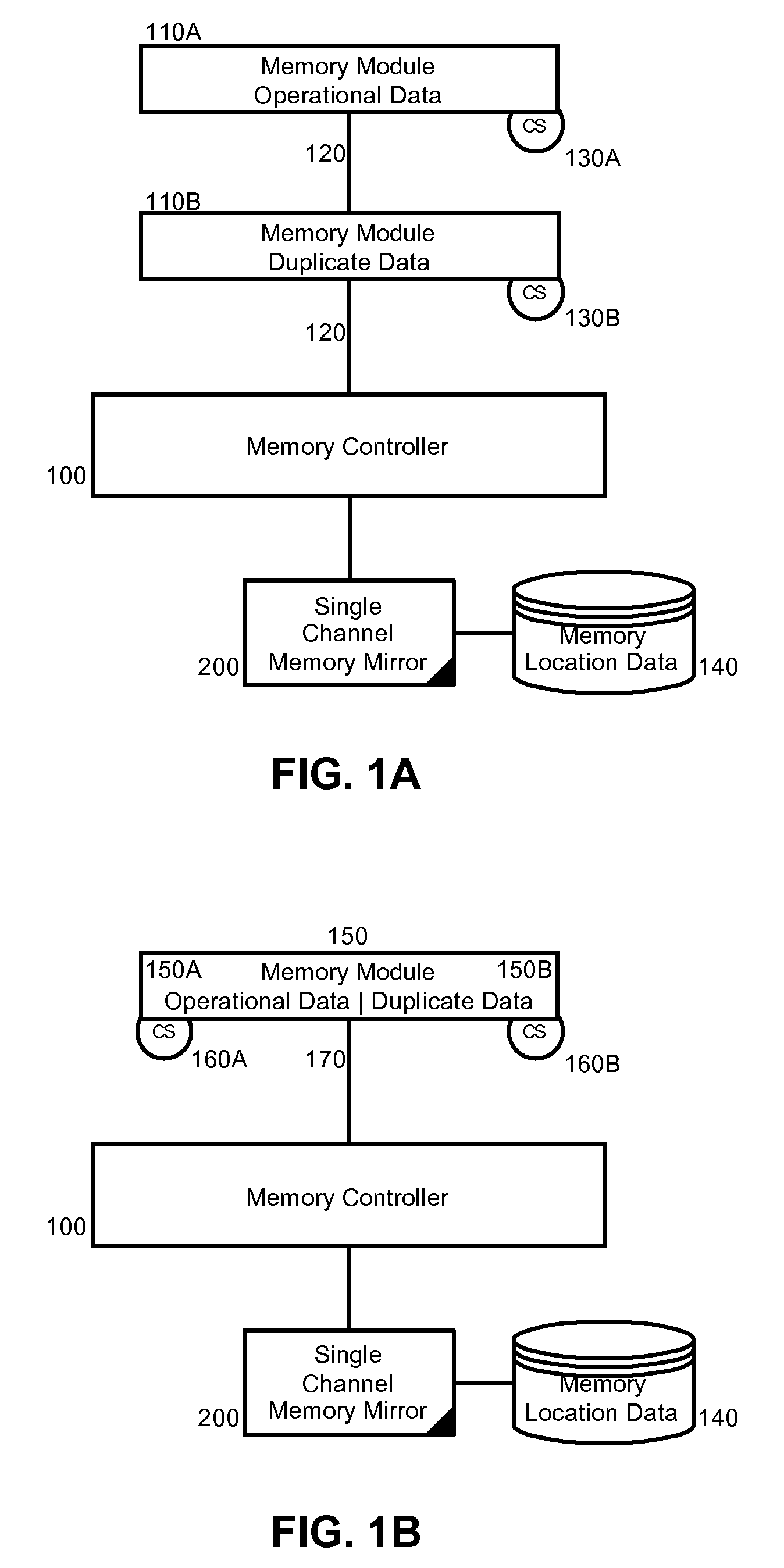

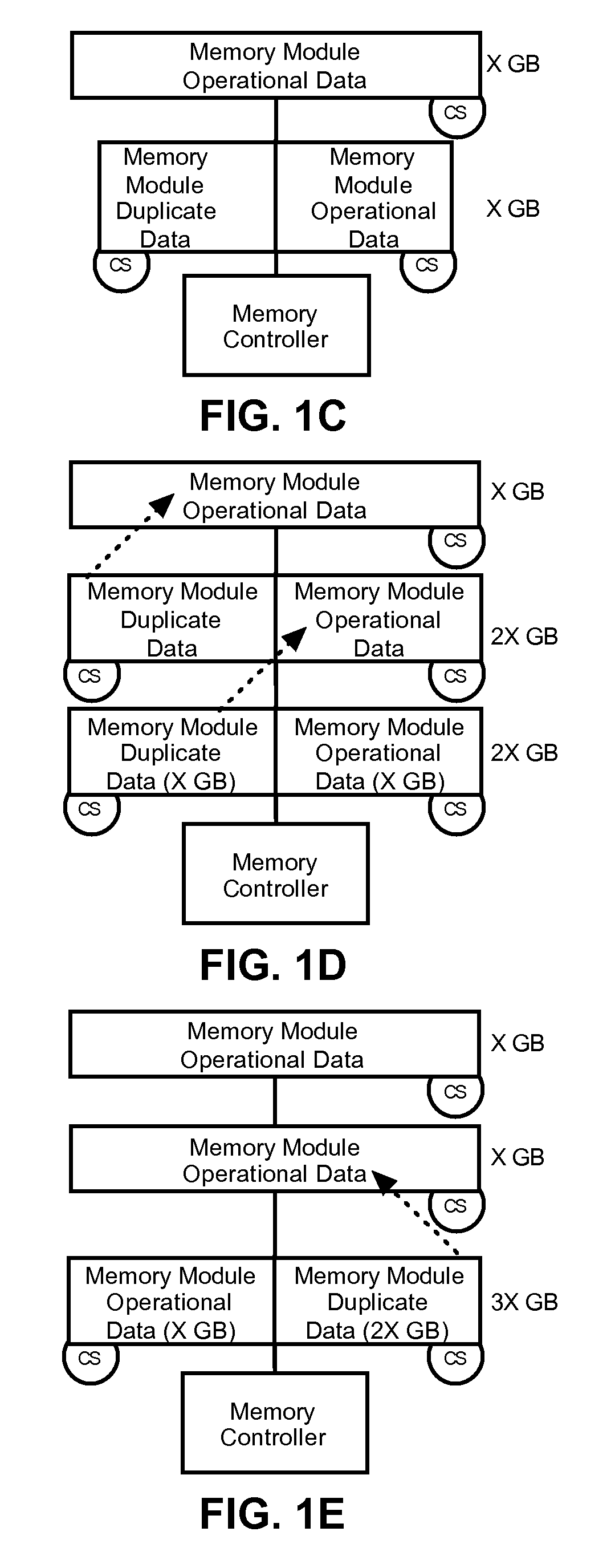

Single channel memory mirror

ActiveUS20080140961A1Memory loss protectionRedundant hardware error correctionFault toleranceMemory faults

Embodiments of the invention address deficiencies of the art in respect to memory fault tolerance, and provide a novel and non-obvious method, system and apparatus for single channel memory mirroring. In one embodiment of the invention, a single channel memory mirroring system can be provided. The single channel memory mirroring system can include a memory controller, a single communications channel, and an operational data portion of memory, and a duplicate data portion of memory, both portions being communicatively coupled to the memory controller over the single communications channel. Finally, the system can include single channel memory mirror logic. The logic can include program code enabled to mirror data in the operational data portion of memory in the duplicate data portion of memory.

Owner:LENOVO GLOBAL TECH INT LTD

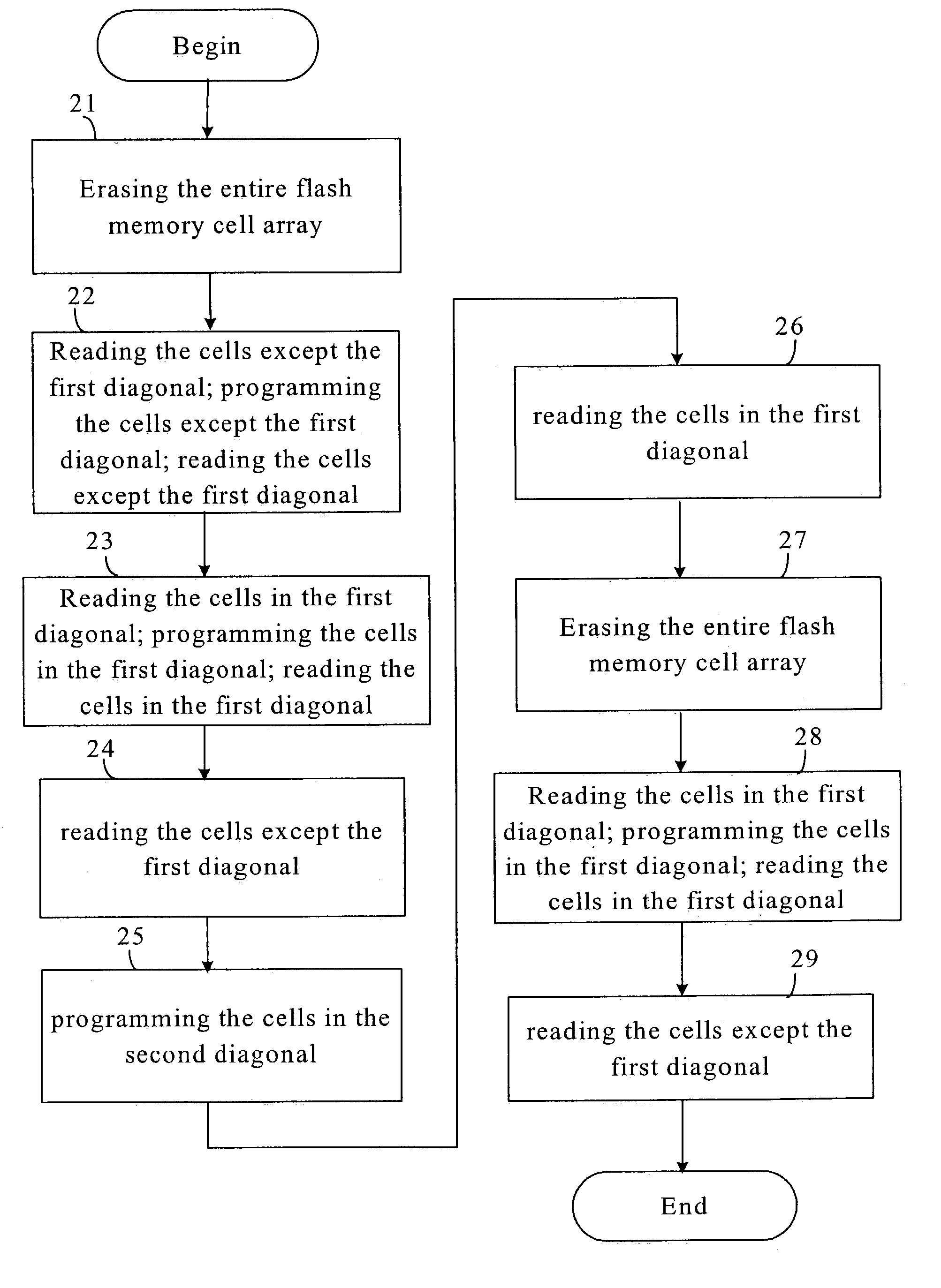

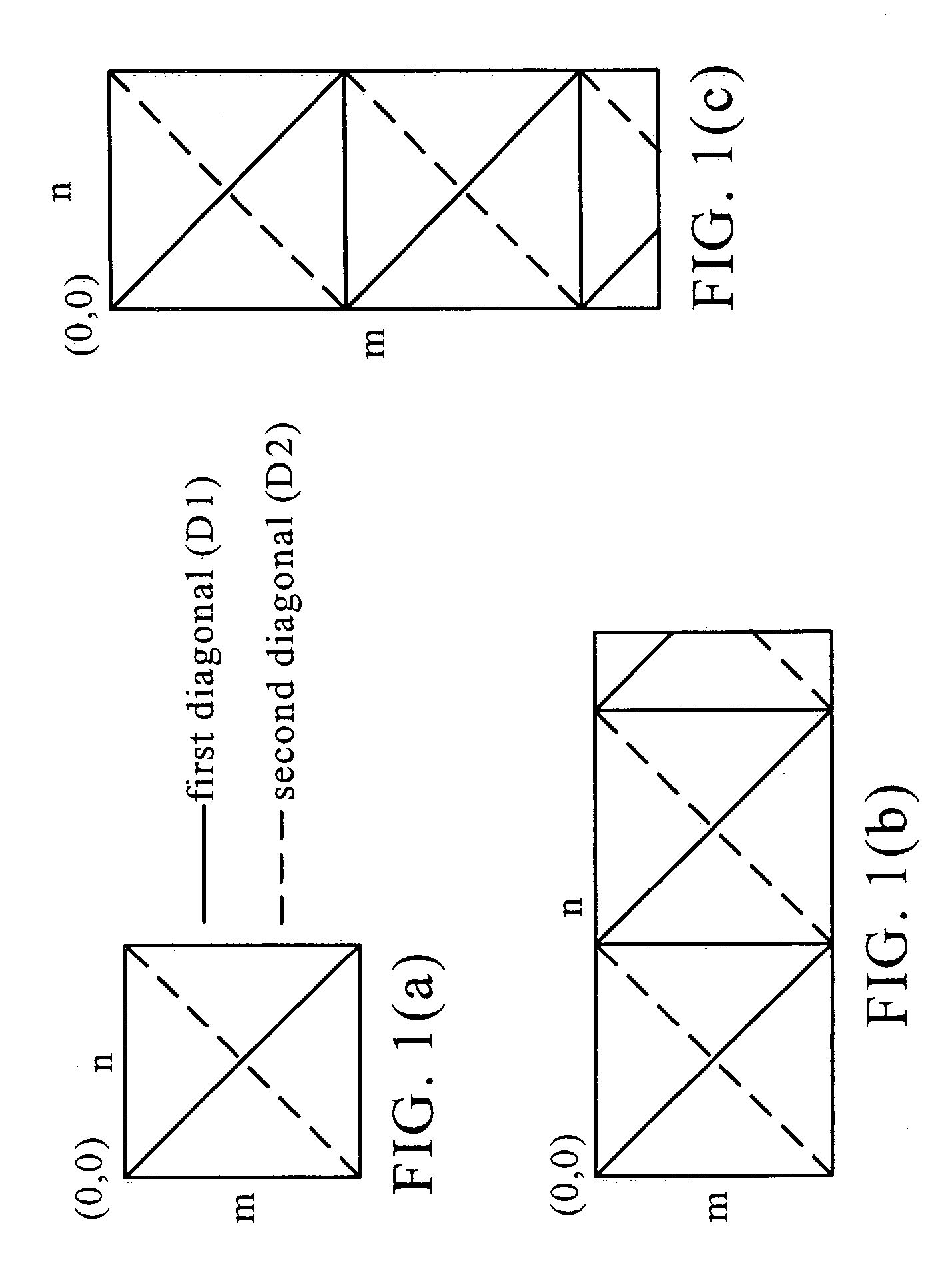

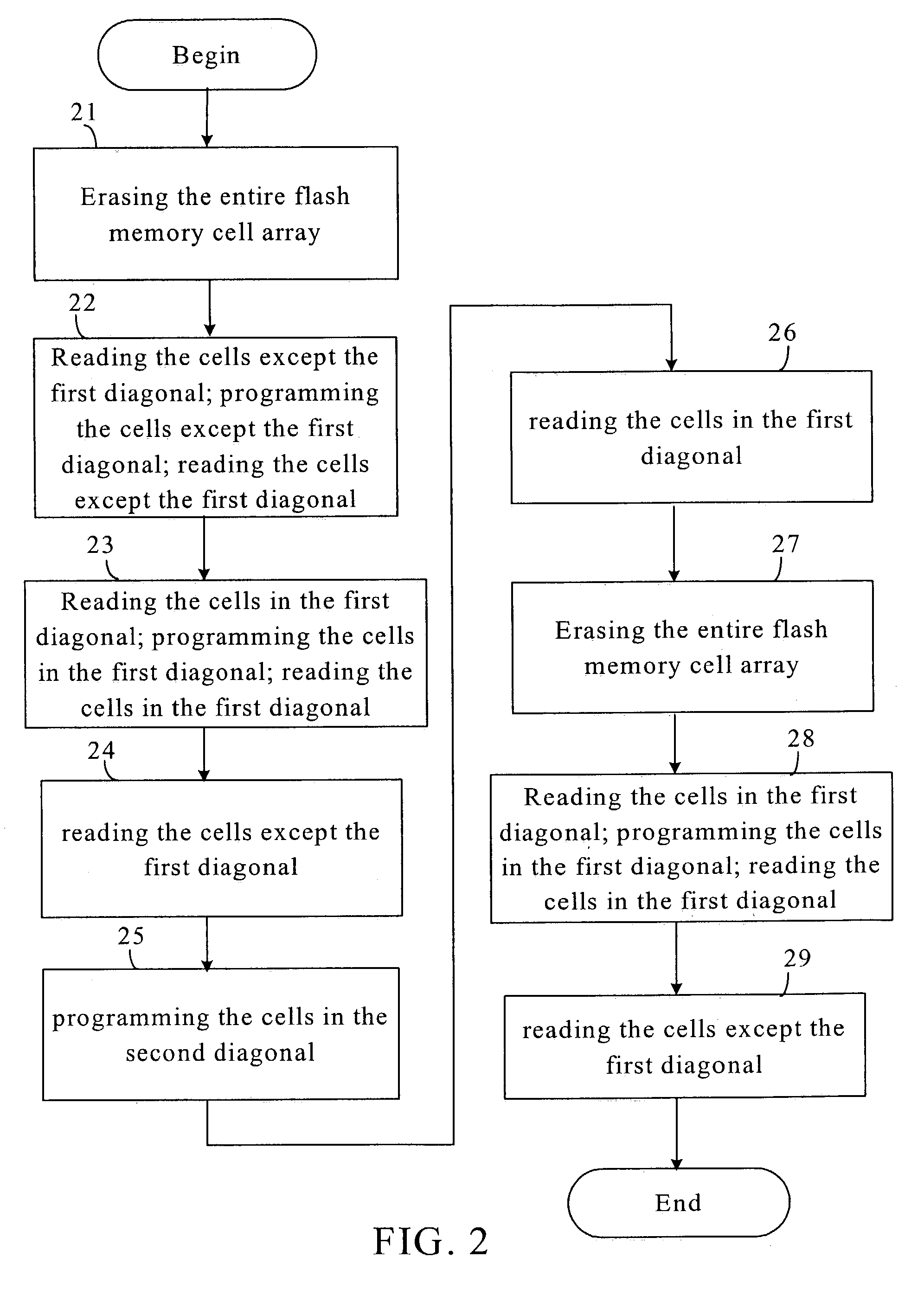

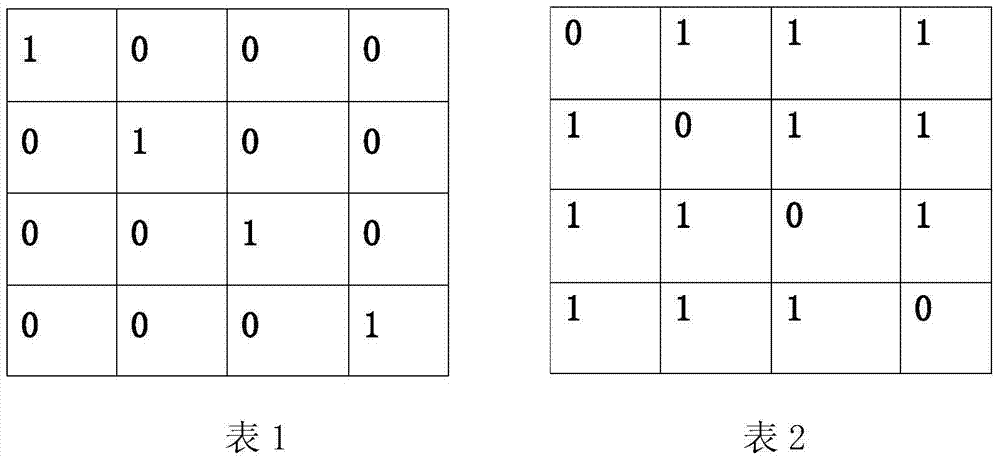

Diagonal testing method for flash memories

InactiveUS7065689B2Shorten test timeReducing fault coverageMemory loss protectionRead-only memoriesMemory faultsDiagonal

The present invention discloses a diagonal testing method for flash memories. The testing method regards the flash memory as several squares, and executes in the direction from top to bottom and from left to right. Each square is provided with a first diagonal in −45 degrees from the upper left to the lower right, and a second diagonal in +45 degrees from the lower left to the upper right. The present invention is to program the cells in the first diagonal or the second diagonal, and then read the cells except the first diagonal or the second diagonal; or, program the cells except the first diagonal or the second diagonal, and then read the cells in the first diagonal or the second diagonal so as to detect the disturb fault in the flash memories and normal memory fault models.

Owner:SPIROX NAT TSING HUA UNIV

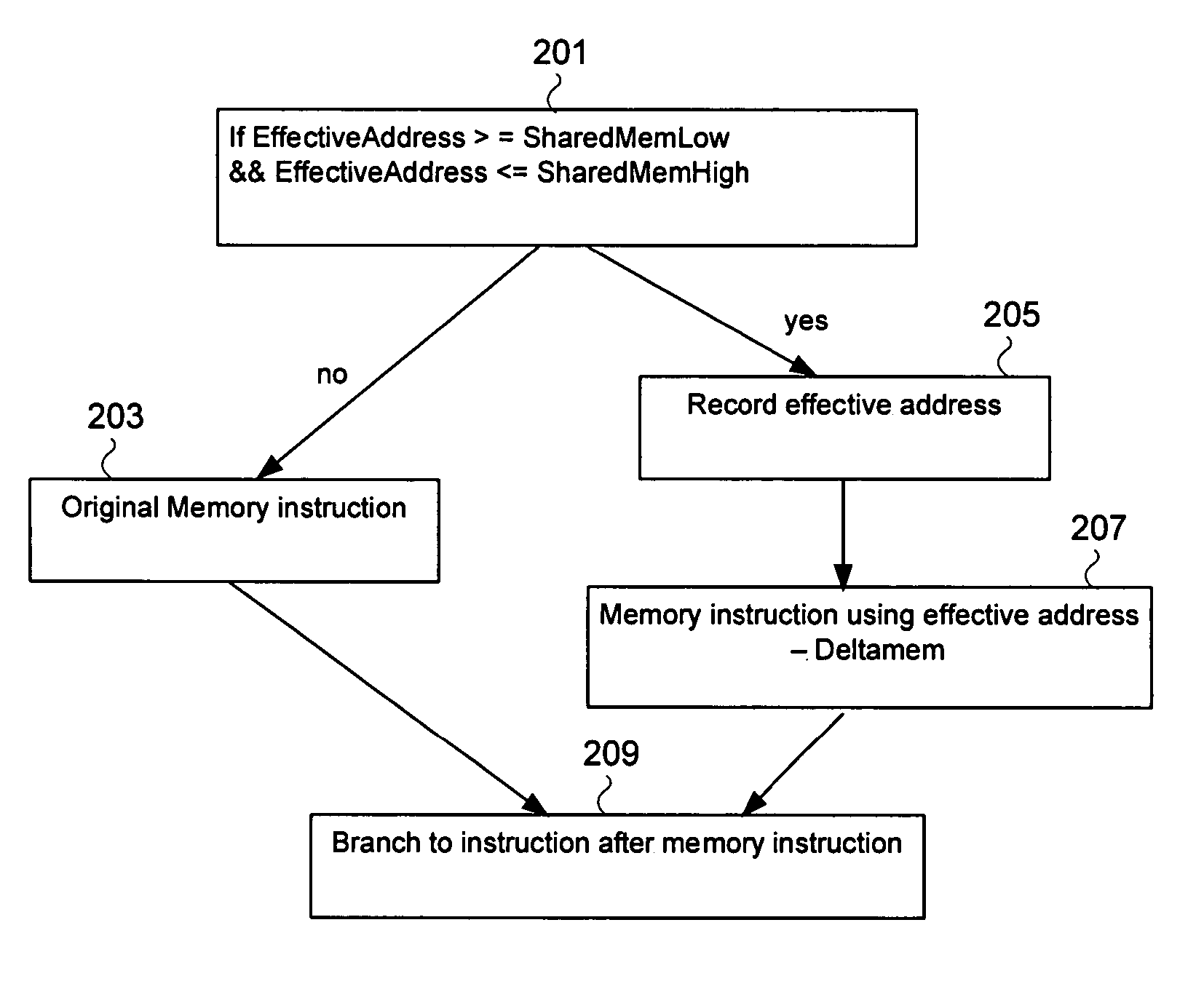

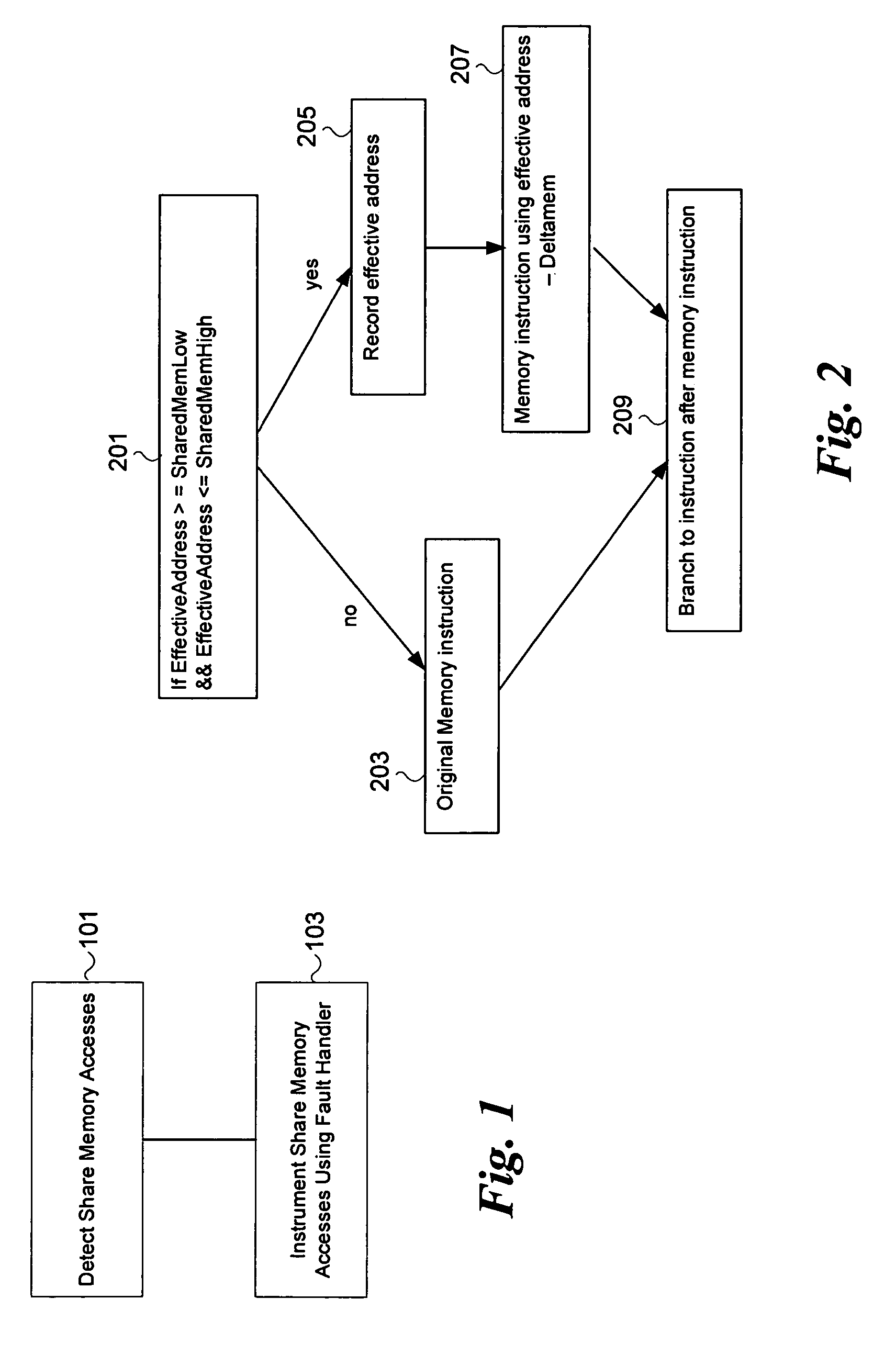

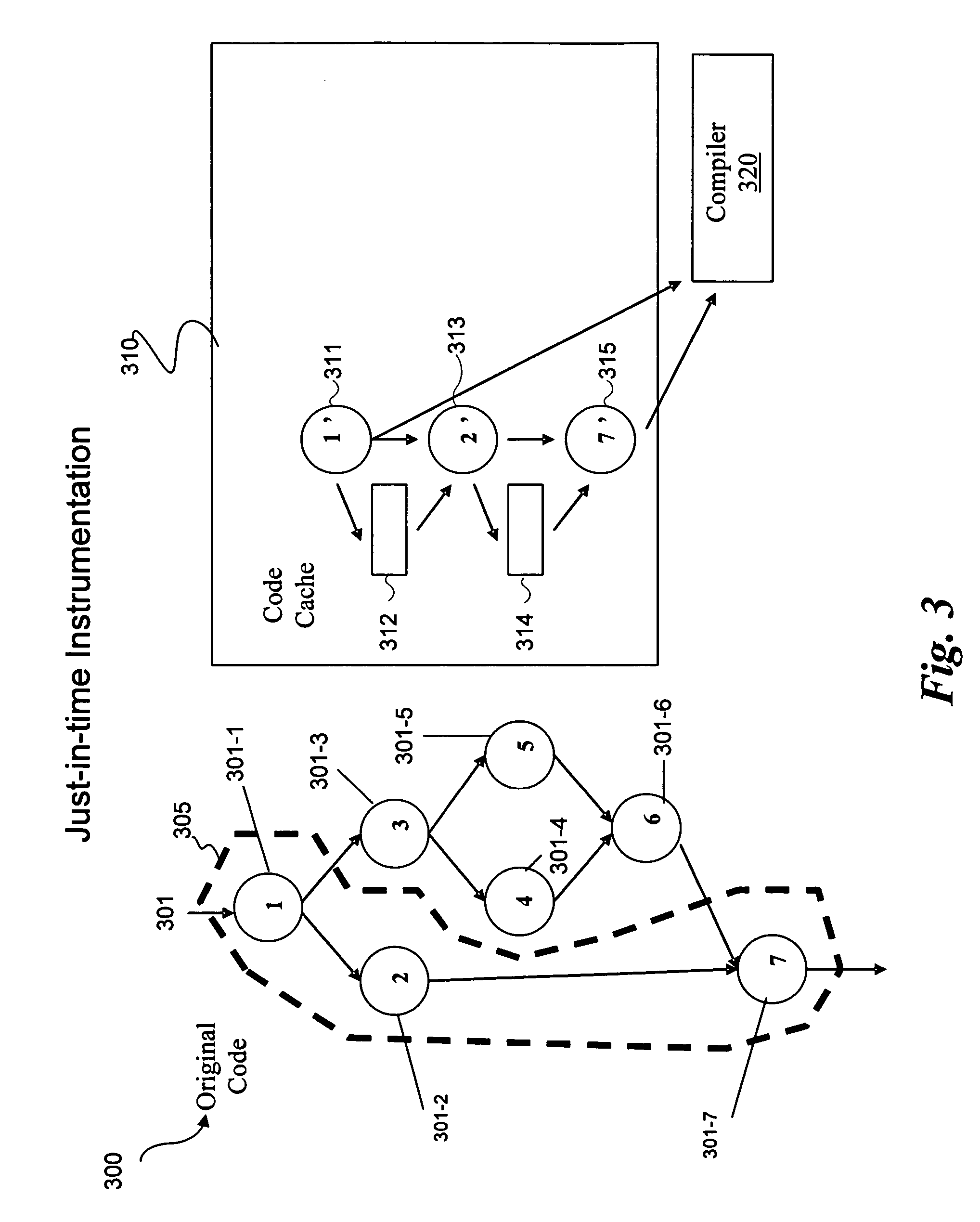

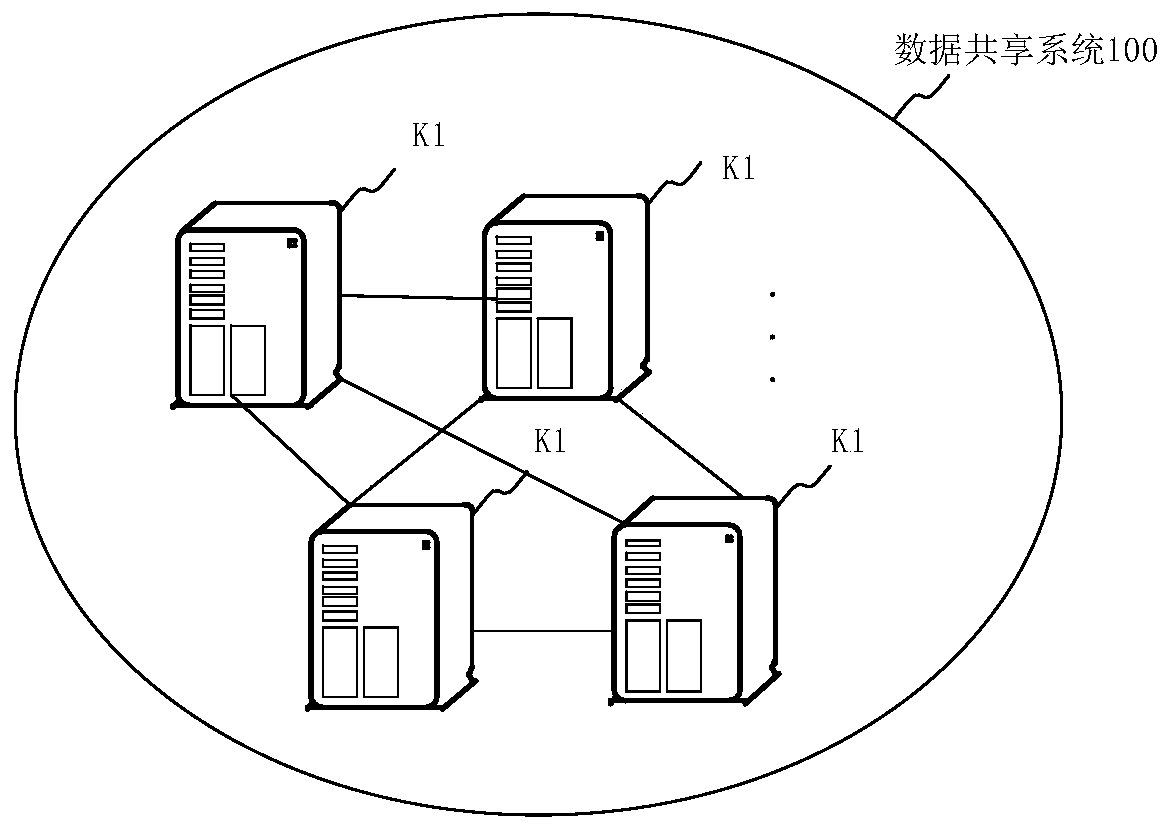

System and method to instrument references to shared memory

InactiveUS20060277371A1Execution timeReduce overheadError detection/correctionProgram controlMemory addressMemory faults

In some embodiments, the invention involves instrumentation of computer binary code and, more specifically, dynamically identifying shared memory accesses at runtime and instrumenting the shared memory access instruction code. Some embodiments use code caching to only hold the patched instrumentation. Other embodiments use code caching to hold the entire program and instrumentation. Shared memory accesses are identified using inaccessible memory address references to cause memory faults. The fault handler may emulate instrumentation in one instance and cause a just-in-time compilation of instruction traces with instrumentation into the code cache. Other embodiments are described and claimed.

Owner:INTEL CORP

Memory protection system and method

A shared memory controller is provided for controlling access to a shared memory by a plurality of processors. At least one device includes a storage area for storing a respective address range for each of a plurality of memory regions. The at least one device further includes a permission table containing, for each of the plurality of memory regions, read and write permission data for each of the plurality of processors. A memory fault detector is coupled to the at least one device and has an input for receiving a memory access request including a memory address, a processor identification and a read / write indicator. The memory fault detector includes logic for determining whether a memory access according to the memory access request would conflict with the read and write permission data in the permission table.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Memory detection model training method and memory detection method and device

ActiveCN110598802AImprove the accuracy of fault locationCharacter and pattern recognitionFaulty hardware testing methodsRisk levelData set

The invention discloses a memory detection model training method. The method comprises the steps of obtaining a memory state historical data set, generating a real fault label set according to the memory state historical data set, and generating a to-be-trained feature set according to the memory state historical data set, training the to-be-trained memory detection model according to the to-be-trained feature set to obtain a prediction fault label set, and if the prediction fault label set and the real fault label set meet a model verification condition, training according to the to-be-trained memory detection model to obtain a memory detection model. The invention further discloses a memory detection method and device. According to the memory detection model provided by the invention, the memory fault condition can be predicted according to the granularity of the memory module level, and the health condition and the risk level of the memory are fully considered, so that the fault positioning accuracy of memory detection is improved.

Owner:TENCENT TECH (SHENZHEN) CO LTD

Test algorithm selection in memory built-in self test controller

InactiveUS7653845B2Effective and flexibleImprove efficiencyElectronic circuit testingStatic storageComputer hardwareMemory faults

An integrated circuit chip is provided that comprises on-chip memory and test circuitry. The test circuitry is configured to perform operational testing of the on-chip memory. The test circuitry comprises a controller which is configured to perform a selection out of a plurality of test algorithms to perform the operational testing. The plurality of test algorithms includes a fault detection test algorithm to perform operational testing of the on-chip memory in order to detect whether or not there is a memory fault, without locating the memory fault. The plurality of test algorithms further includes a fault location test algorithm to perform operational testing of the on-chip memory in order to detect and locate a memory fault. Further, a method to perform a memory built-in self test and an MBIST (Memory Built-In Self Test) control circuit template are provided.

Owner:CHRONOCLOUD MEDTECH (SHANGHAI) CO LTD

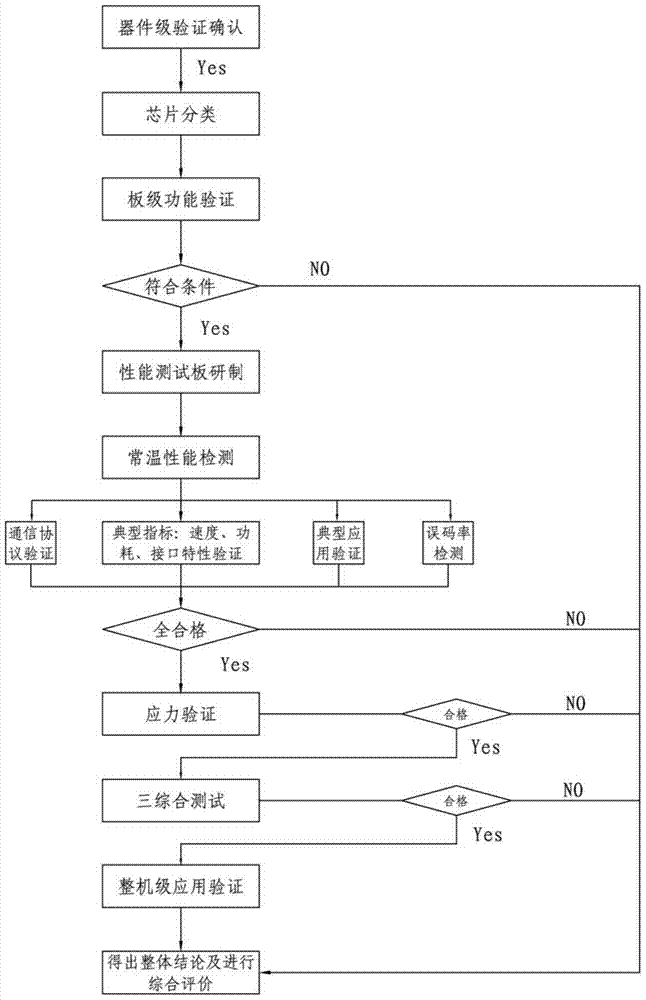

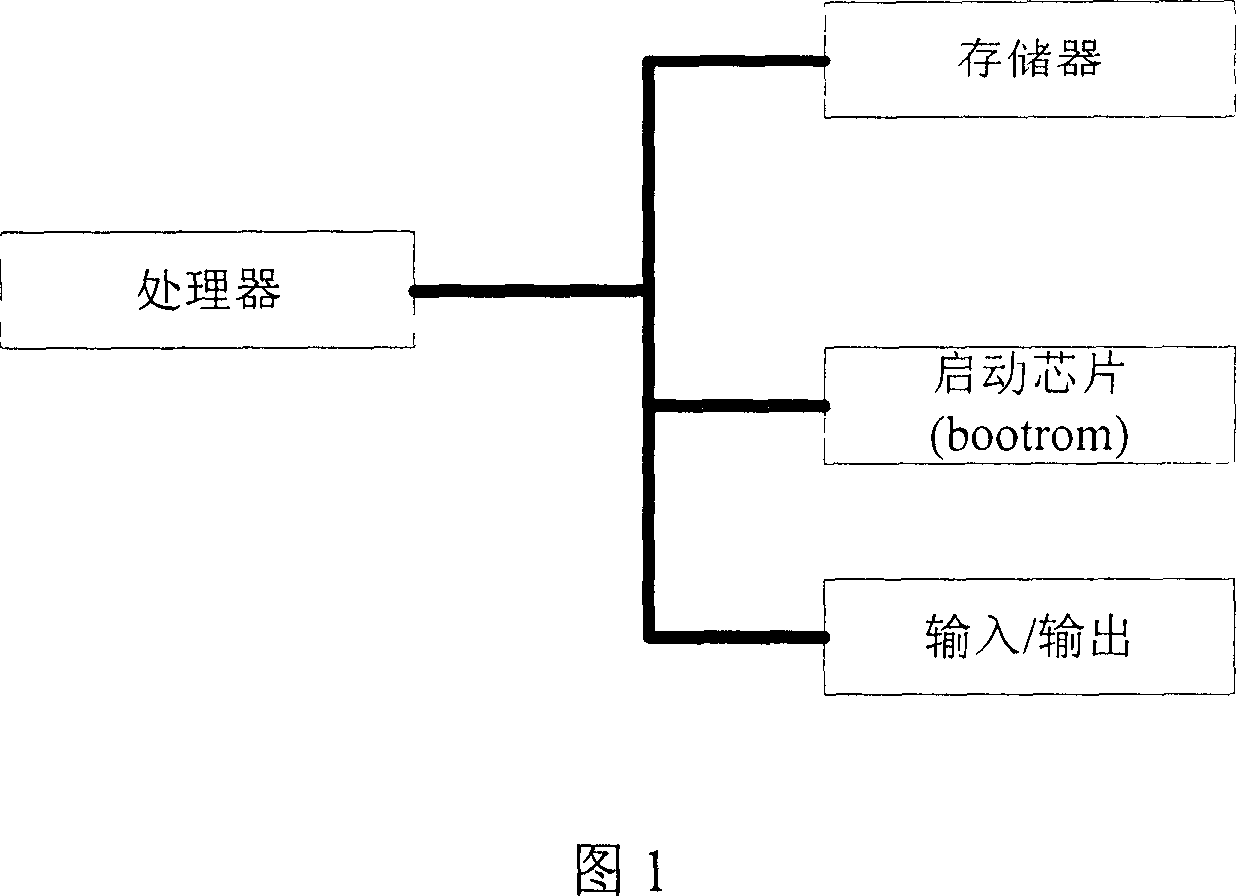

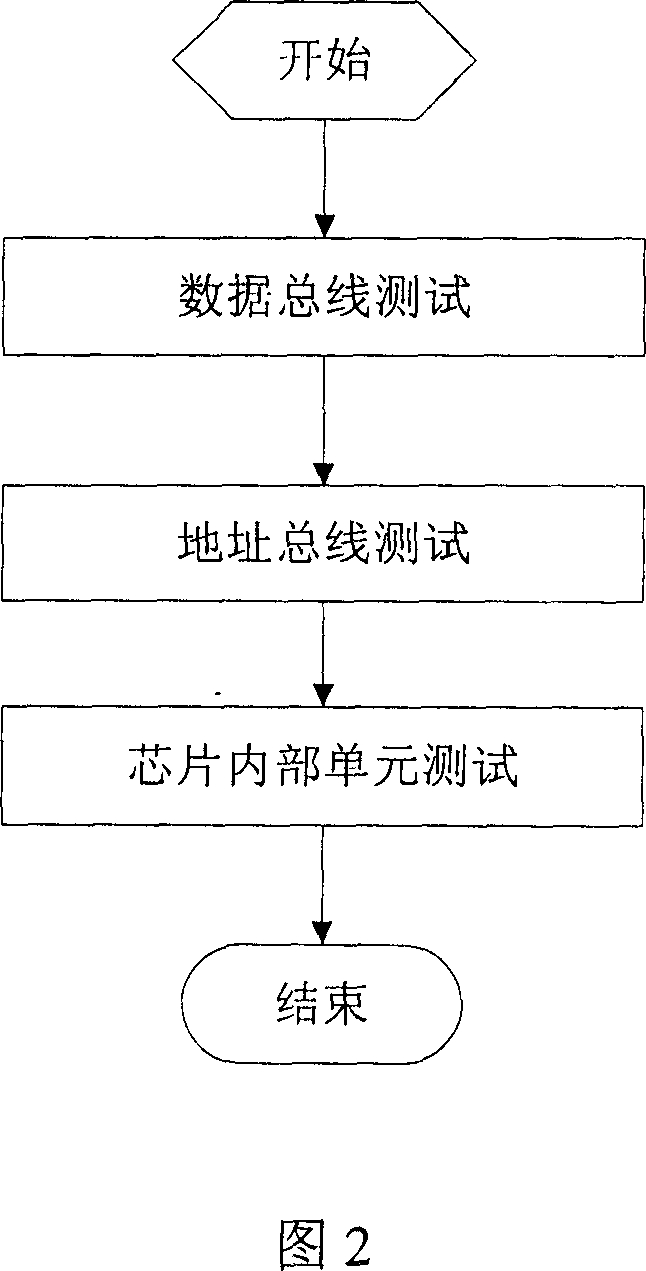

Aviation application-based verification method for domestic storages

ActiveCN103700407AVerify reverse failureValidation failureFunctional testingStatic storageAviationMemory faults

The invention provides an aviation application-based verification method for domestic storages. The aviation application-based verification method sequentially comprises the following steps: 1) storage chip detection; 2) board level functionality test; 3) board level performance test; 4) complete machine level verification; 5) comprehensive analysis and evaluation. According to the aviation application-based verification method disclosed by the invention, basic environment adaptation verification is performed on the applications of the domestic storages on aviation weapon systems, and the single memory unit faults, single memory unit reversal faults, inter-unit coupling faults and memory faults and unit sensitization faults of the various storages, as well as the data retention faults of the changes of unit logical values due to electric leakage after some periods, can be verified, thus providing a beneficial guarantee for domestic development of the aviation weapon systems.

Owner:AVIC NO 631 RES INST

Memory detection model training method and memory detection method and device

ActiveCN111078479AImprove the accuracy of fault locationCharacter and pattern recognitionFaulty hardware testing methodsData setMemory faults

The invention discloses a memory detection model training method. The method is applied to fault detection, and comprises the steps of obtaining a memory state historical data set, generating a real fault label set according to the memory state historical data set, generating a plurality of to-be-trained feature subsets according to the memory state historical data set, and obtaining a predictionfault label subset corresponding to the to-be-trained feature subset through the to-be-trained memory detection sub-model, and generating a memory detection sub-model according to the to-be-trained memory detection sub-model if the prediction fault label subset and the real fault label subset meet a model verification condition. The invention further discloses a memory detection device. Accordingto the memory detection model provided by the invention, the memory fault condition can be predicted according to the granularity of the memory module level, and the health condition and the risk level of the memory are fully considered, so that the fault positioning accuracy of memory detection is improved.

Owner:TENCENT TECH (SHENZHEN) CO LTD

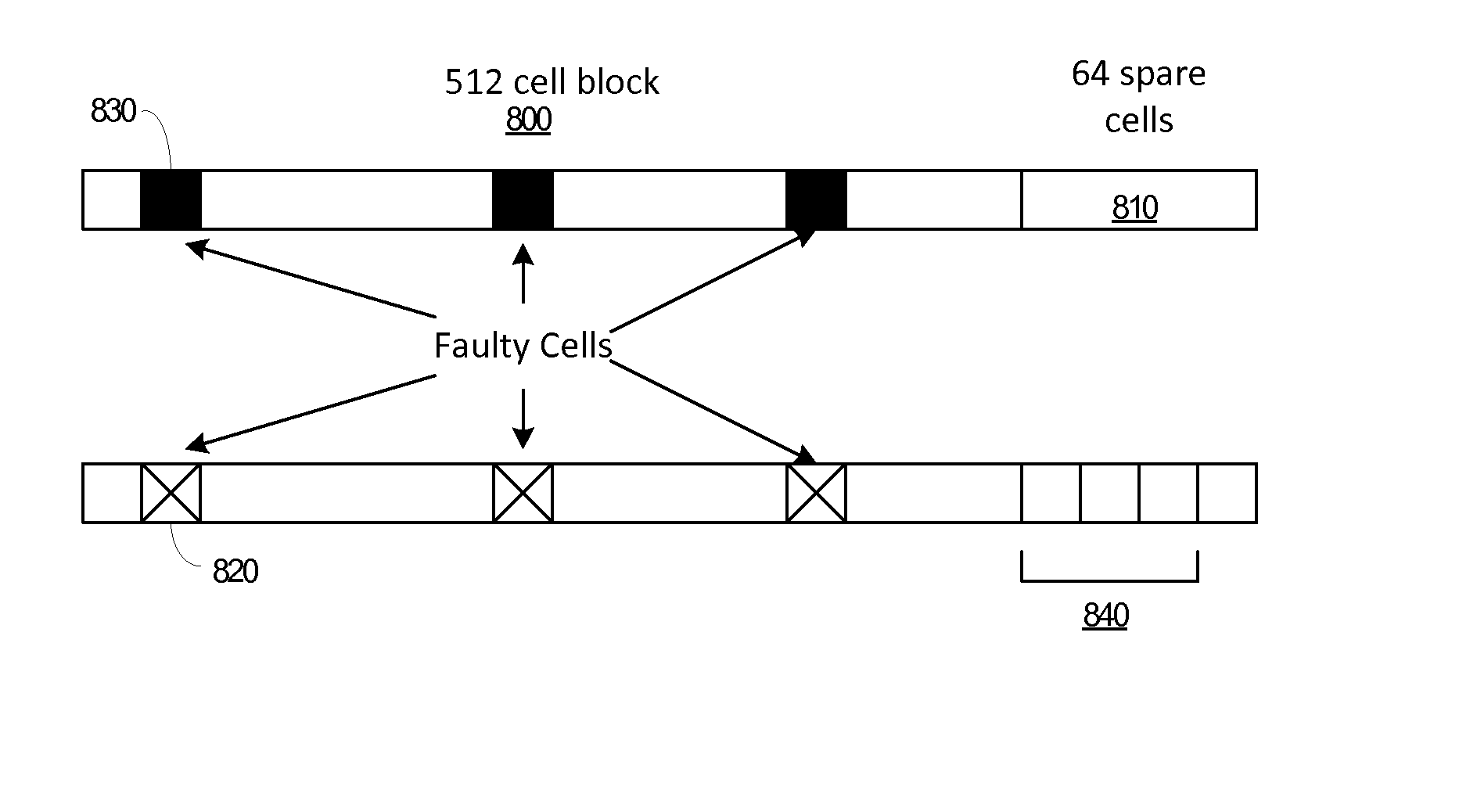

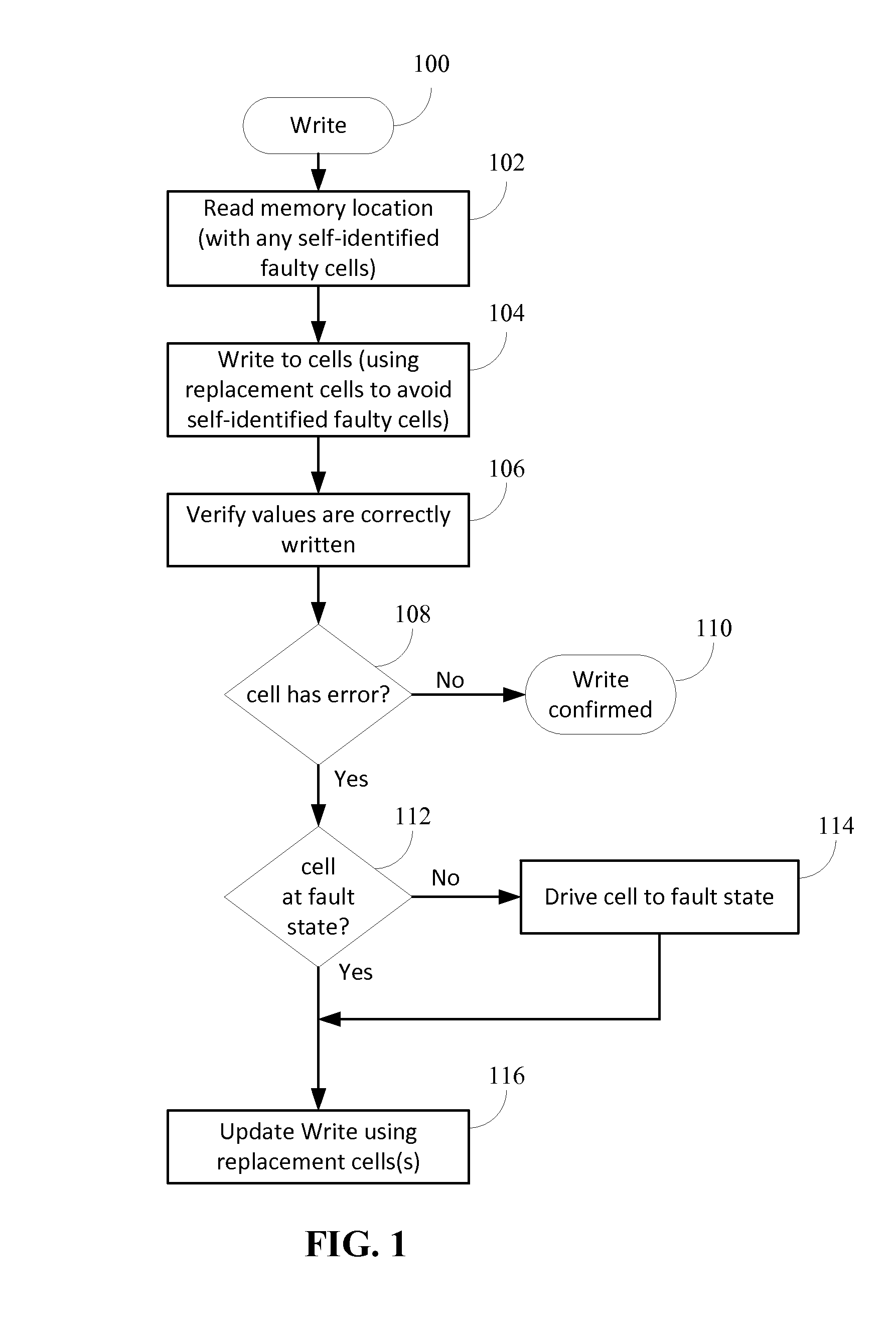

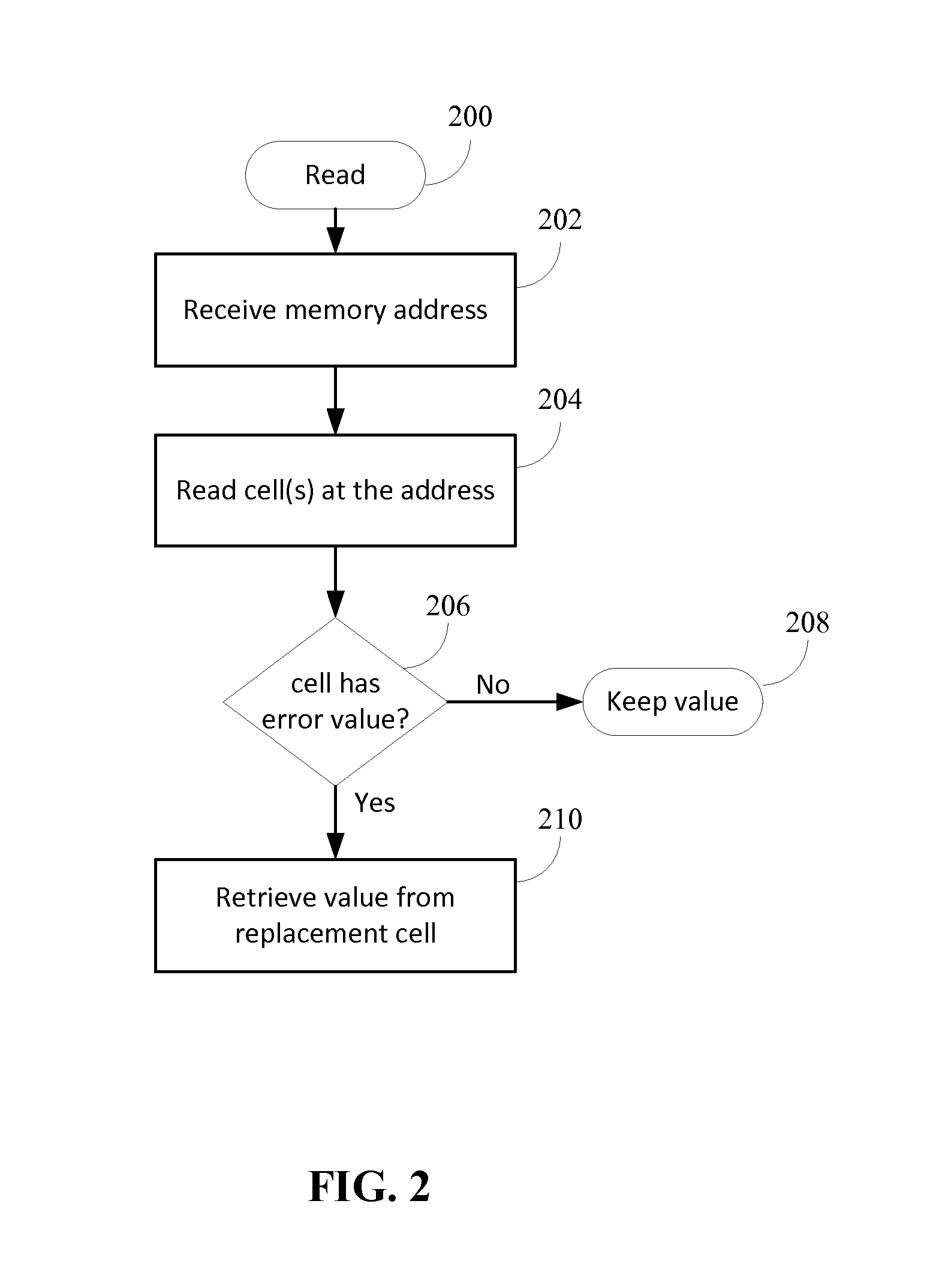

Self-identifying memory errors

ActiveUS20150033064A1Well formedError detection/correctionRead-only memoriesHigh resistanceMemory faults

A memory region can durably self-identify as being faulty when read. Information that would have been assigned to the faulty memory region can be assigned to another of that sized region in memory using a replacement encoding technique. For phase change memory, at least two fault states can be provided for durably self-identifying a faulty memory region; one state at a highest resistance range and the other state at a lowest resistance range. Replacement cells can be used to shift or assign data when a self-identifying memory fault is present. A memory controller and memory module, alone or in combination may manage replacement cell use and facilitate driving a newly discovered faulty cell to a fault state if the faulty cell is not already at the fault state.

Owner:MICROSOFT TECH LICENSING LLC

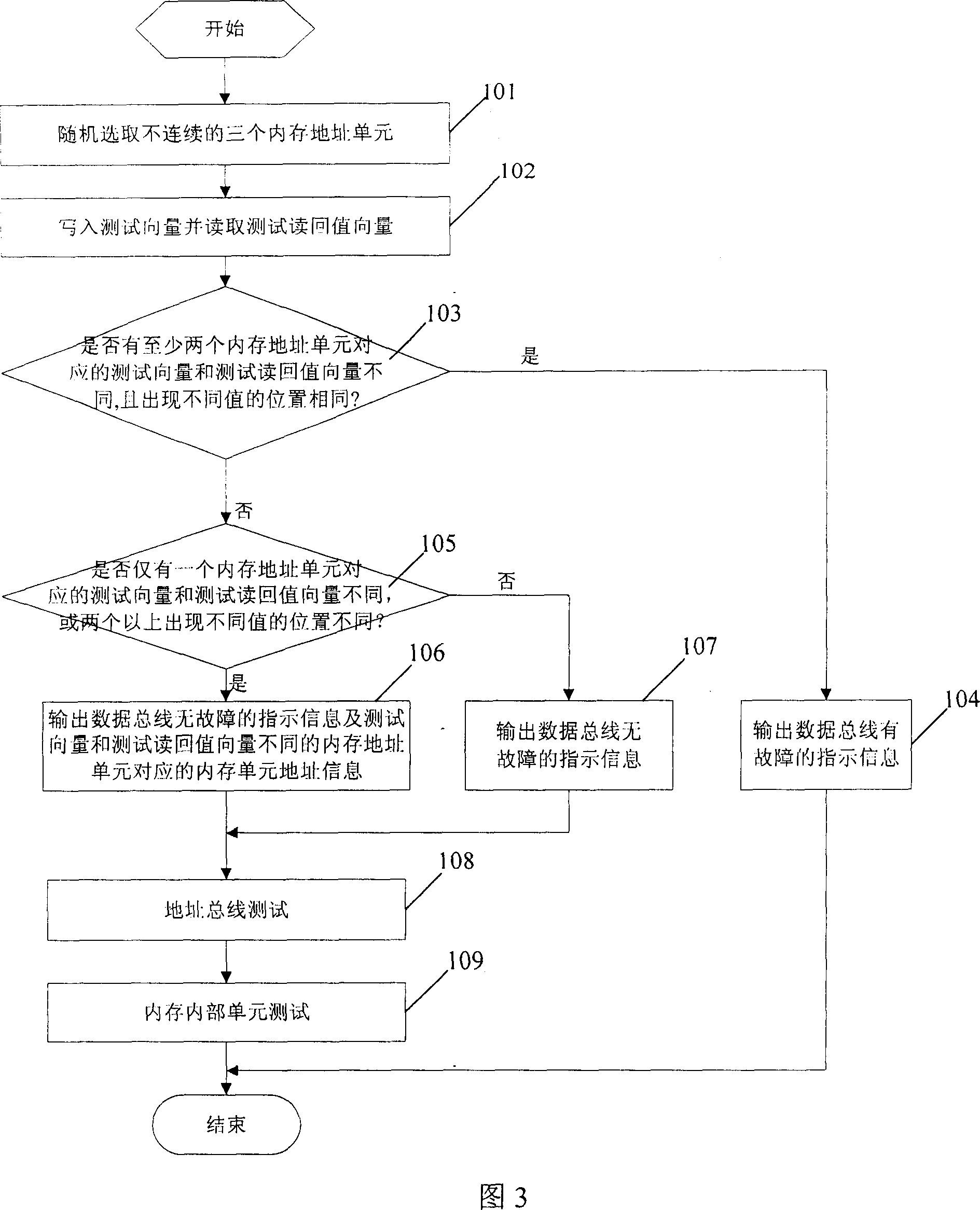

Method and system for RAM fault testing

InactiveCN1929034AGuaranteed reliabilityImprove reliabilityError detection/correctionStatic storageMemory addressMemory faults

The disclosed memory fault testing method comprises: from the target, selecting at least three address units with same bit width as the memory data bus; writing testing vectors into every selected unit to read the back vector for comparison with the original and final fault decision. This invention can ensure the testing accuracy and precision for embedded communication devices.

Owner:HUAWEI TECH CO LTD

Method and system for reducing memory faults while running an operating system

ActiveUS7308603B2Reduce failureError detection/correctionStatic storageMemory faultsOperational system

Method and system for reducing memory faults for computer systems. In one aspect, a notification is received that indicates that a single bit error has been detected in a portion of memory of the computer system. A service program is used to isolate the portion of the memory that includes the detected single bit error by allocating the portion of memory to itself, such that the portion of memory may no longer be accessed for data reading or writing by programs running on the computer system.

Owner:GOOGLE LLC