Patents

Literature

178results about How to "Simple concept" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Multi-screen synchronous slide gesture

ActiveUS20110209104A1Simple conceptInput/output for user-computer interactionDigital data processing detailsComputer scienceSecond screen

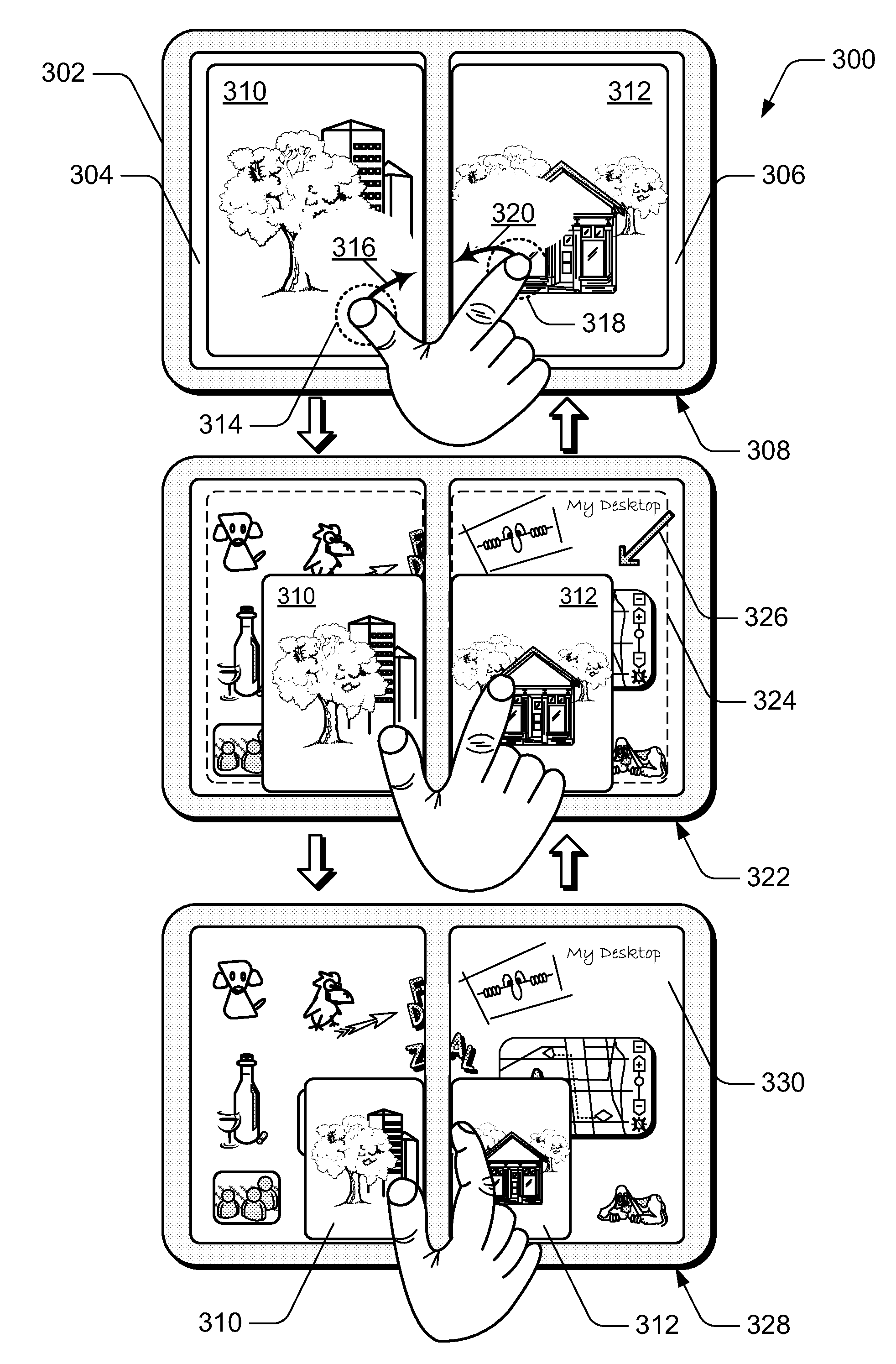

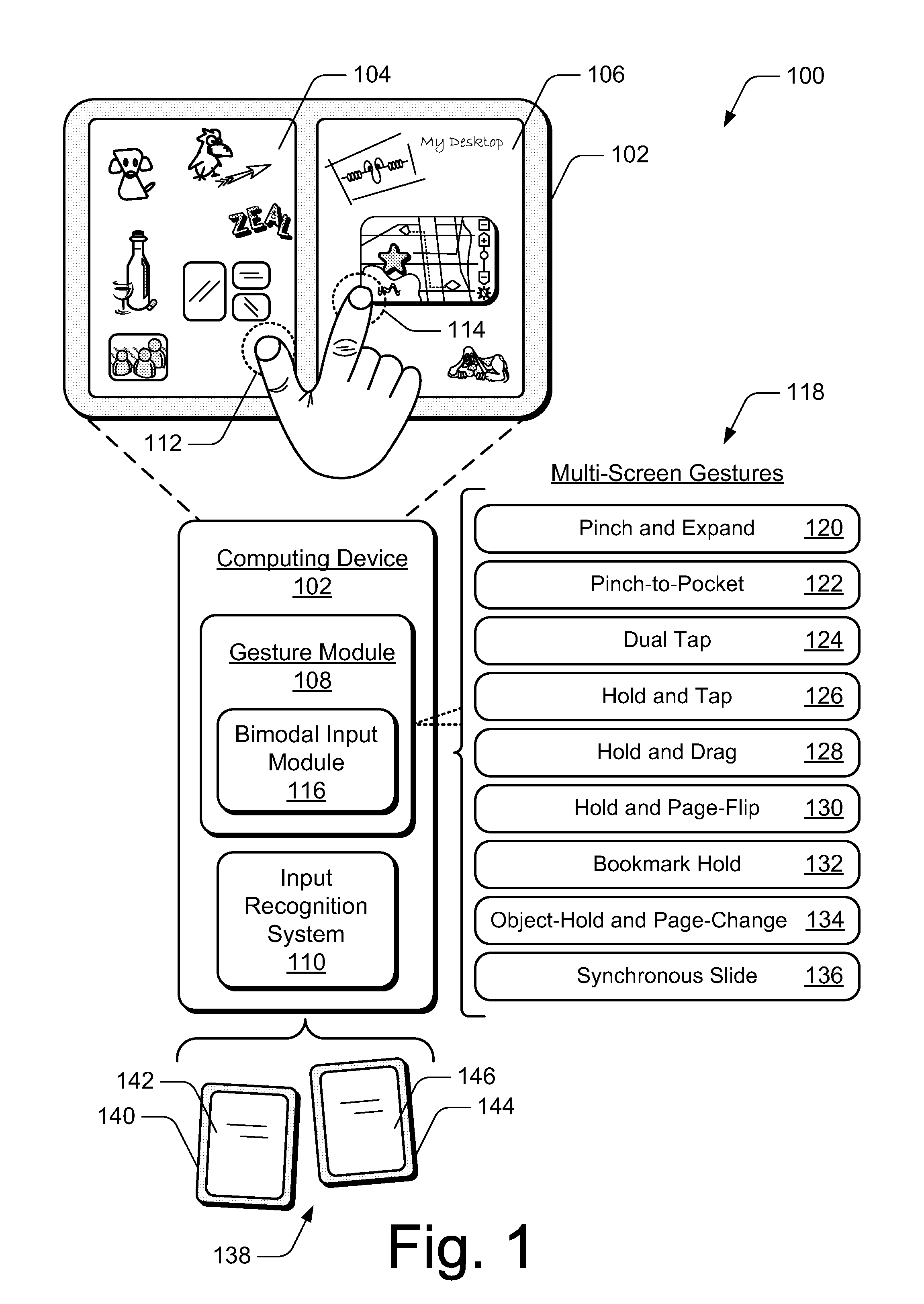

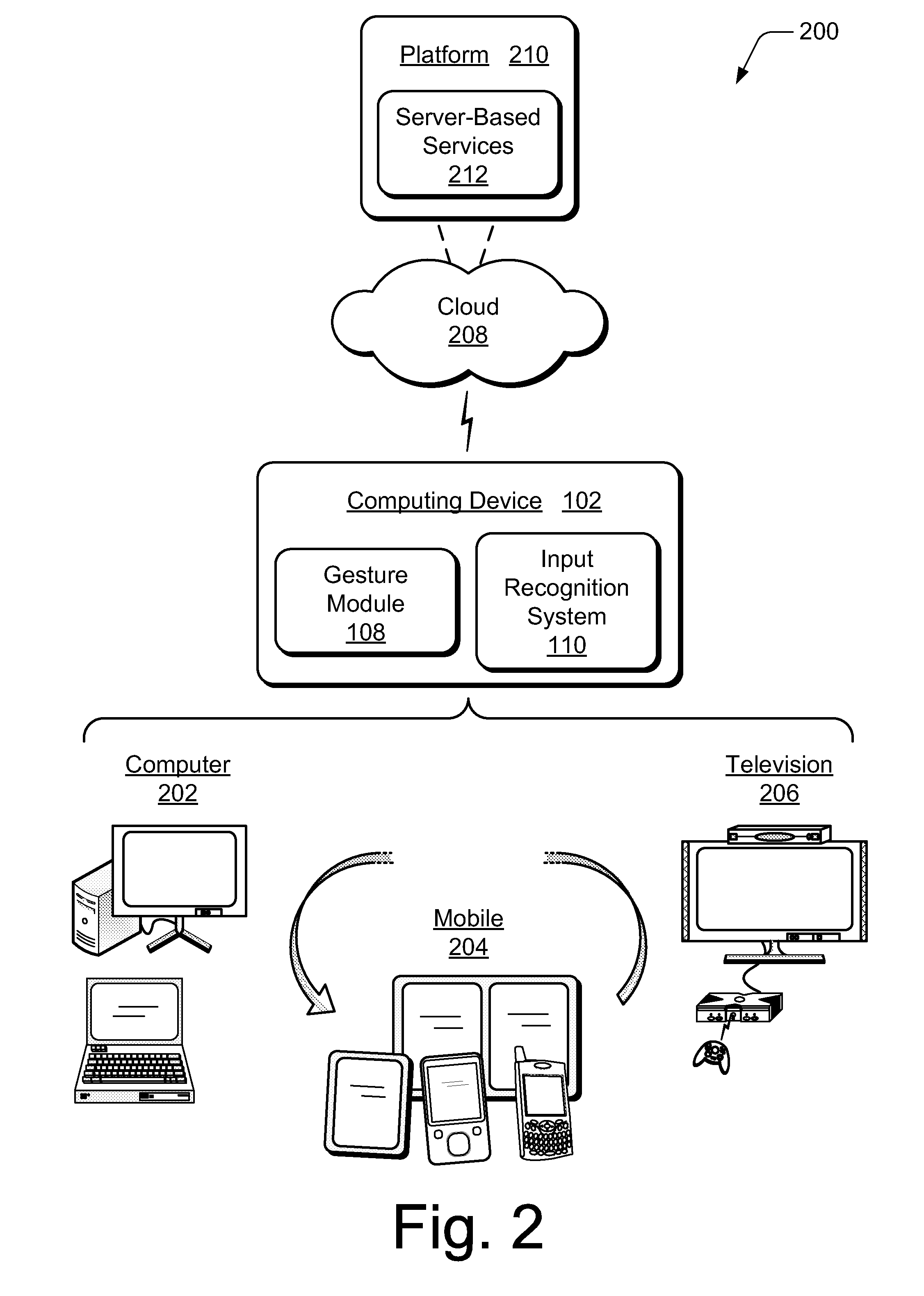

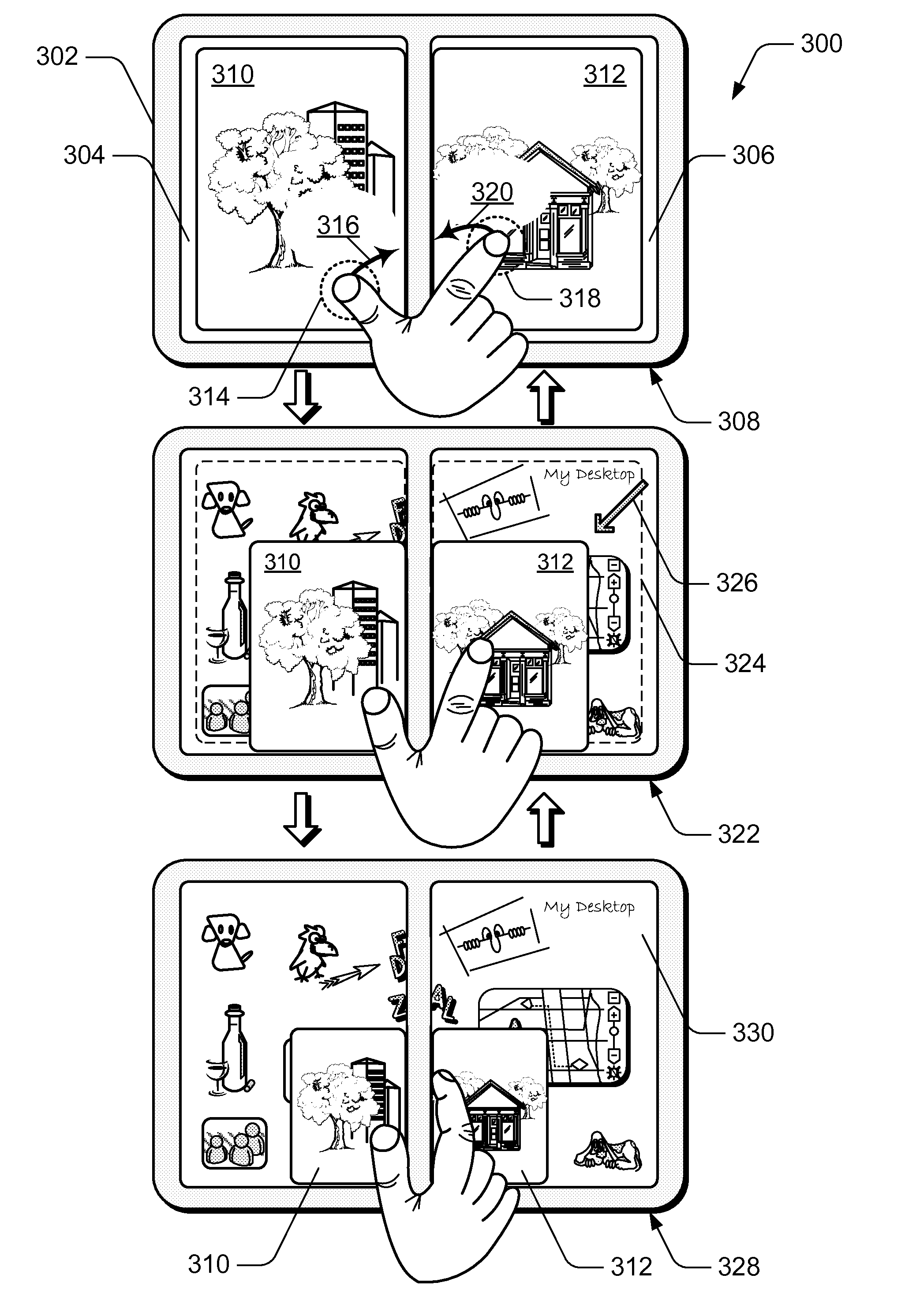

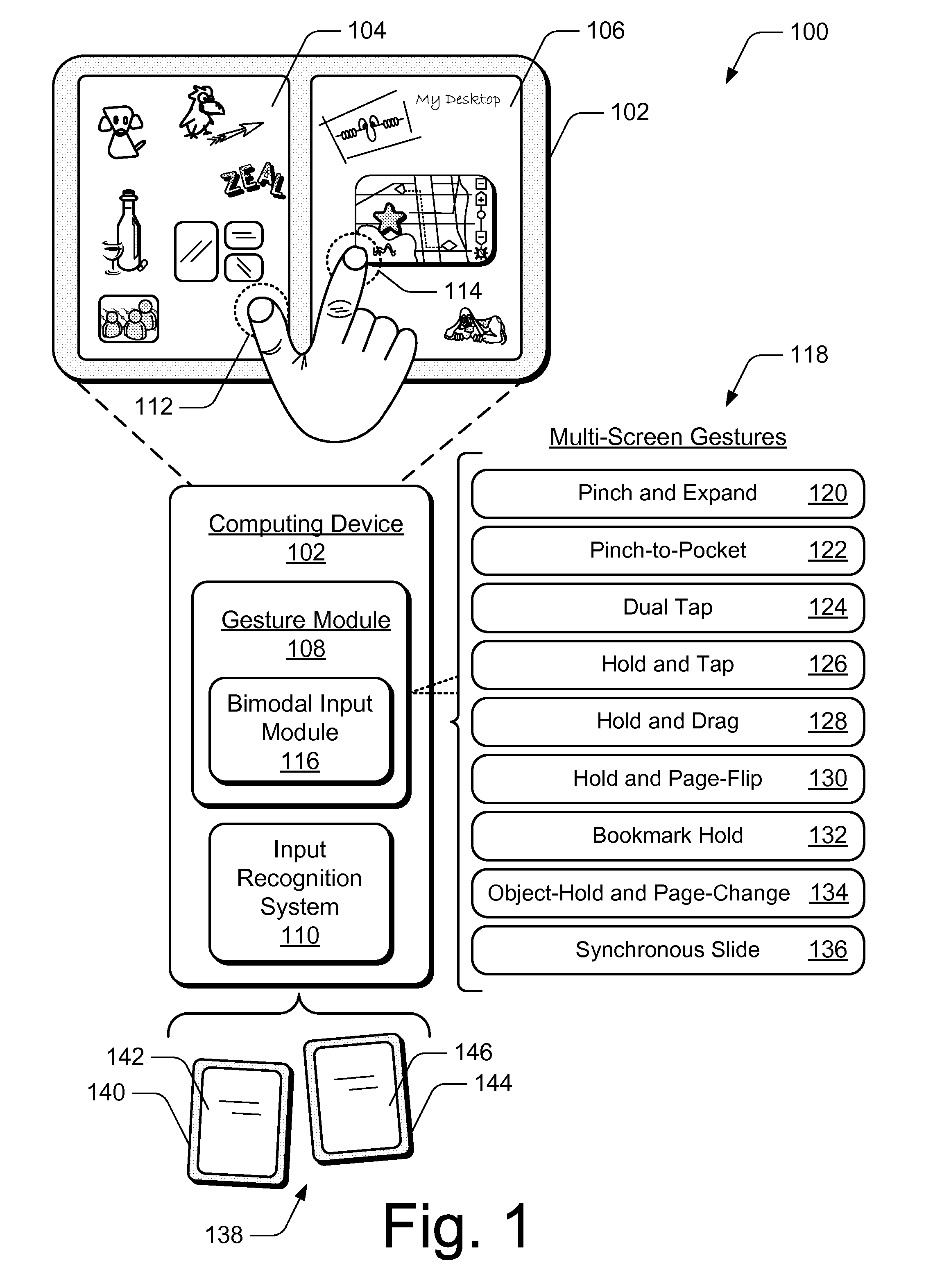

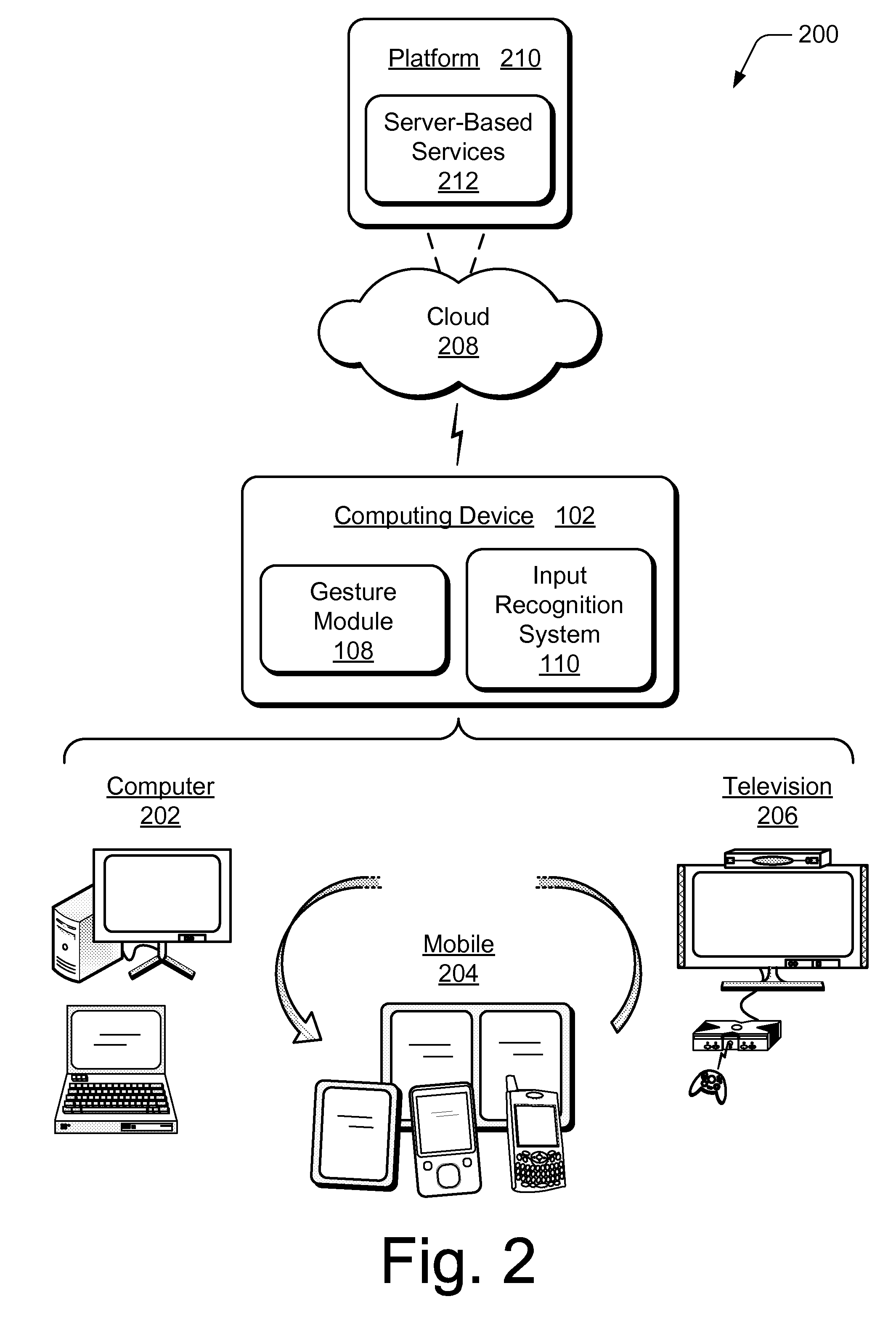

Embodiments of a multi-screen synchronous slide gesture are described. In various embodiments, a first motion input is recognized at a first screen of a multi-screen system, and the first motion input is recognized when moving in a particular direction across the first screen. A second motion input is recognized at a second screen of the multi-screen system, where the second motion input is recognized when moving in the particular direction across the second screen and approximately when the first motion input is recognized. A synchronous slide gesture can then be determined from the recognized first and second motion inputs.

Owner:MICROSOFT TECH LICENSING LLC

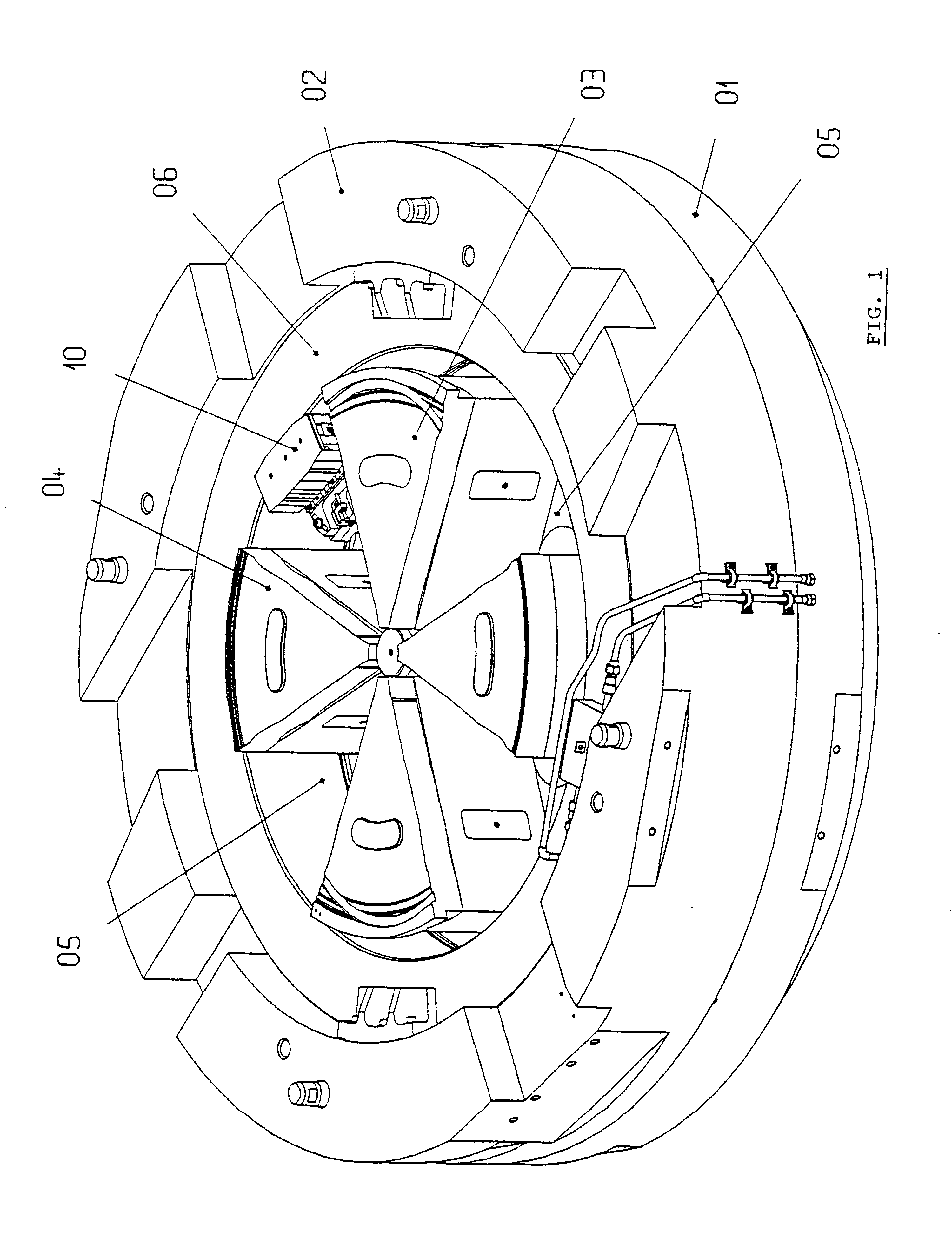

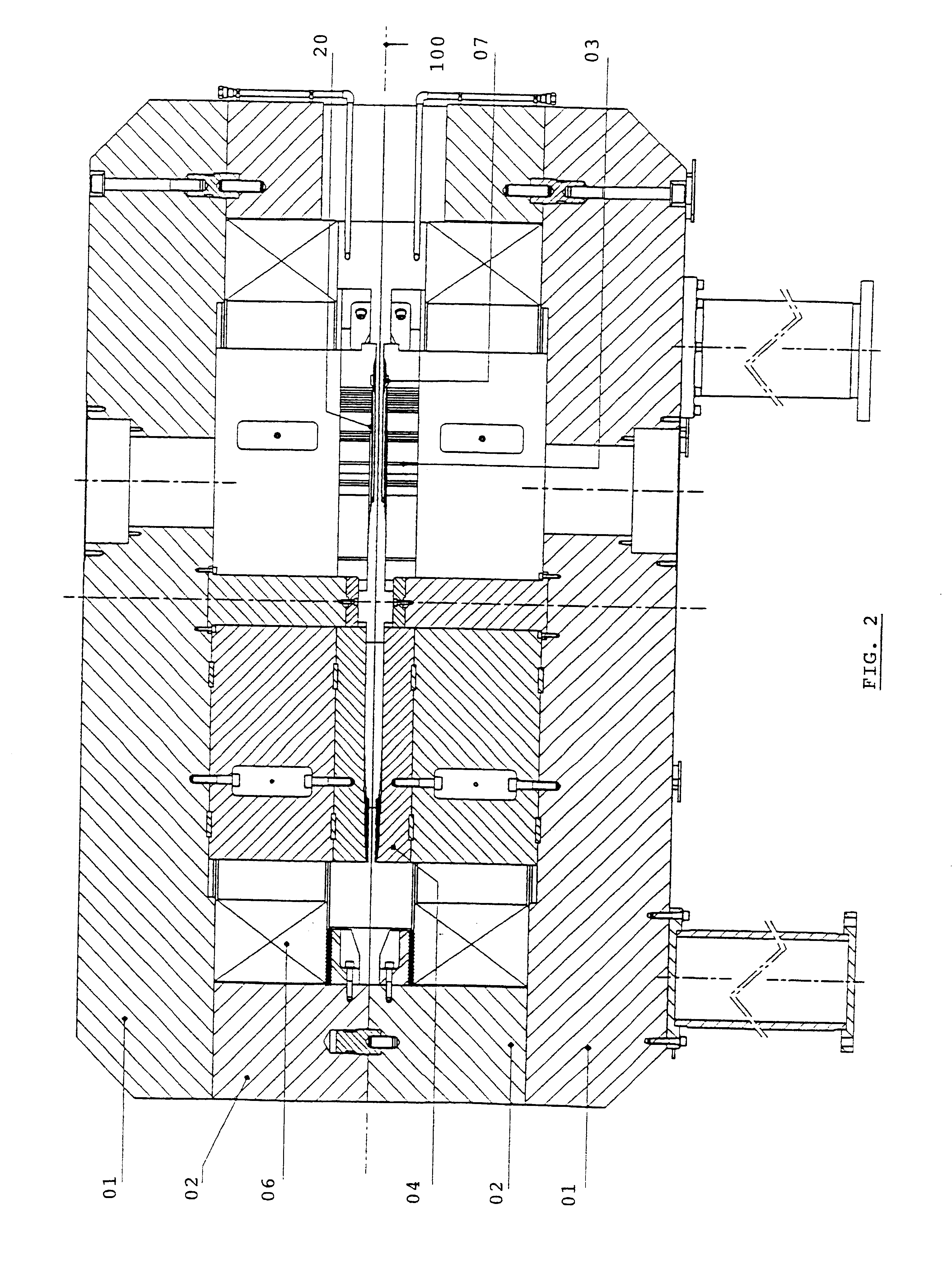

Isochronous cyclotron and method of extraction of charged particles from such cyclotron

InactiveUS6683426B1Simple conceptImprove extraction efficiencyTransit-time tubesMagnetic resonance acceleratorsLower polePlateau

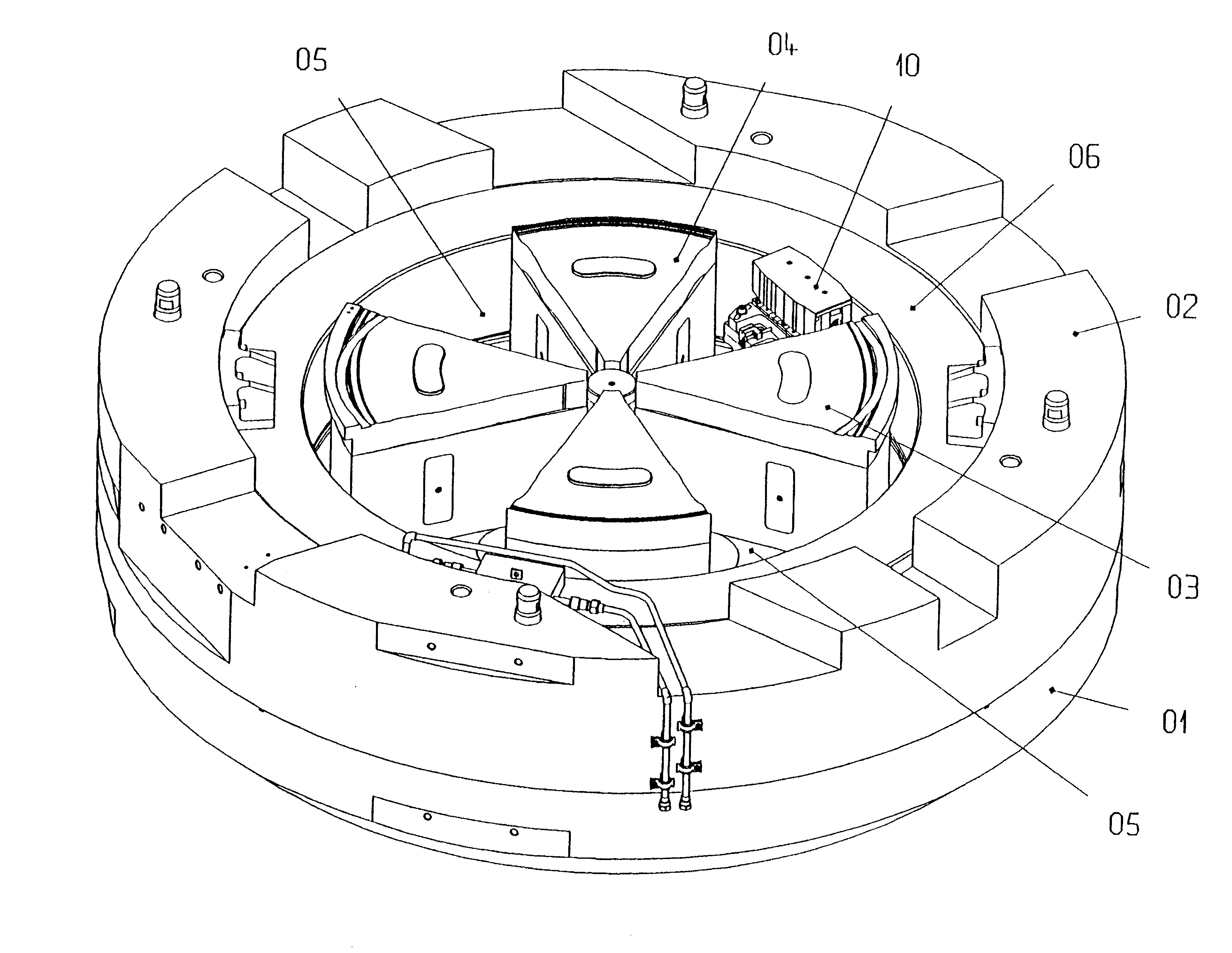

The present inventions is related to a superconducting or non-superconducting isochronous sector-focused cyclotron, comprising an electromagnet with an upper pole and a lower pole that constitute the magnetic circuit, the poles being made of at least three pair of sectors (3,4) called "hills" where the vertical gap between said sectors is small, these hill-sectors being separated by sector-formed spaces called "valleys" (5) where the vertical gap is large, said cyclotron being energized by at least one pair of main coils (6), characterised in that at least one pair of upper and lower hills is significantly longer than the remaining pair of hill sectors in order to have at least one pair of extended hill sectors (3) and at least one pair of non-extended hill sectors (4) in that a groove (7) or a "plateau" (7') which follows the shape of the extracted orbit is present in said pair of extended hill sectors (3) in order to produce a dip (200) in the magnetic field.

Owner:ION BEAM APPL

Multi-screen hold and drag gesture

ActiveUS20110209103A1Simple conceptInput/output for user-computer interactionDigital data processing detailsSecond screenHuman–computer interaction

Embodiments of a multi-screen hold and drag gesture are described. In various embodiments, a hold input is recognized at a first screen of a multi-screen system when the hold input is held in place. A motion input is recognized at a second screen of the multi-screen system, and the motion input is recognized to select a displayed object while the hold input remains held in place. A hold and drag gesture can then be determined from the recognized hold and motion inputs.

Owner:MICROSOFT TECH LICENSING LLC

Scalable Tenant Networks

InactiveUS20170170990A1Simple conceptProgram controlNetworks interconnectionVirtualizationData center

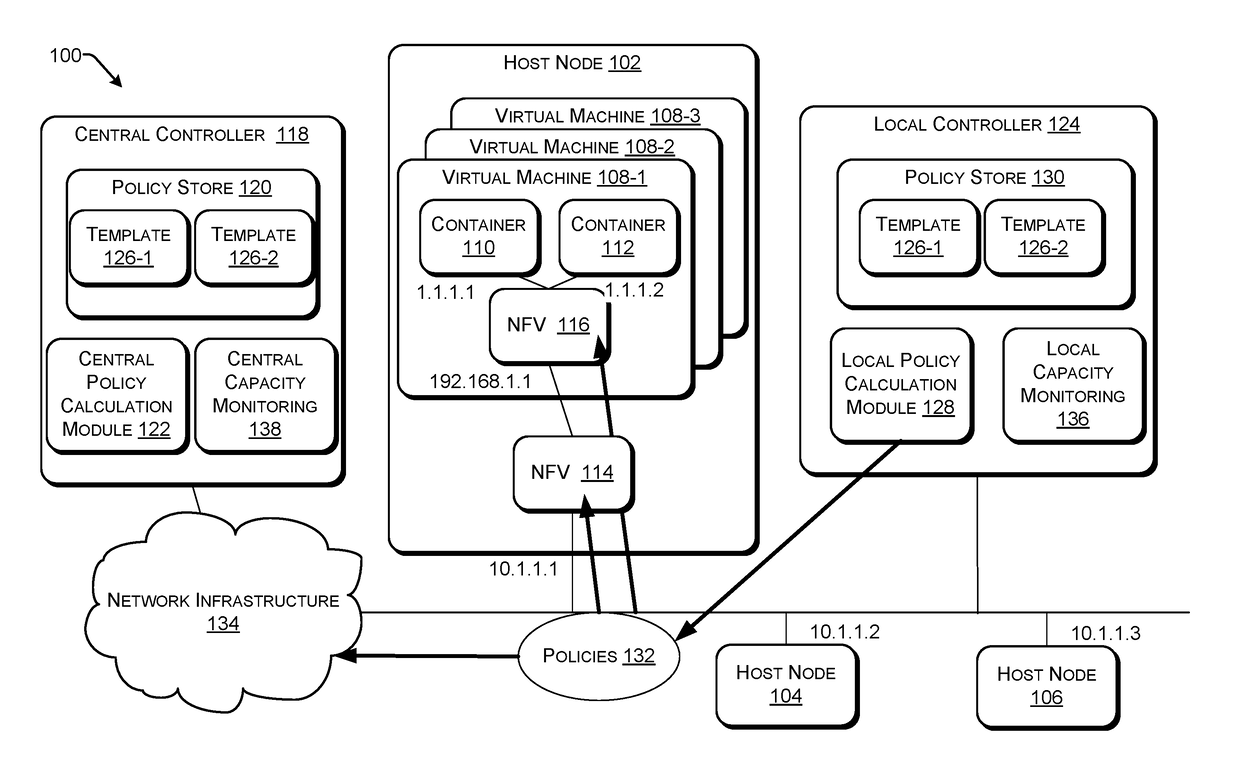

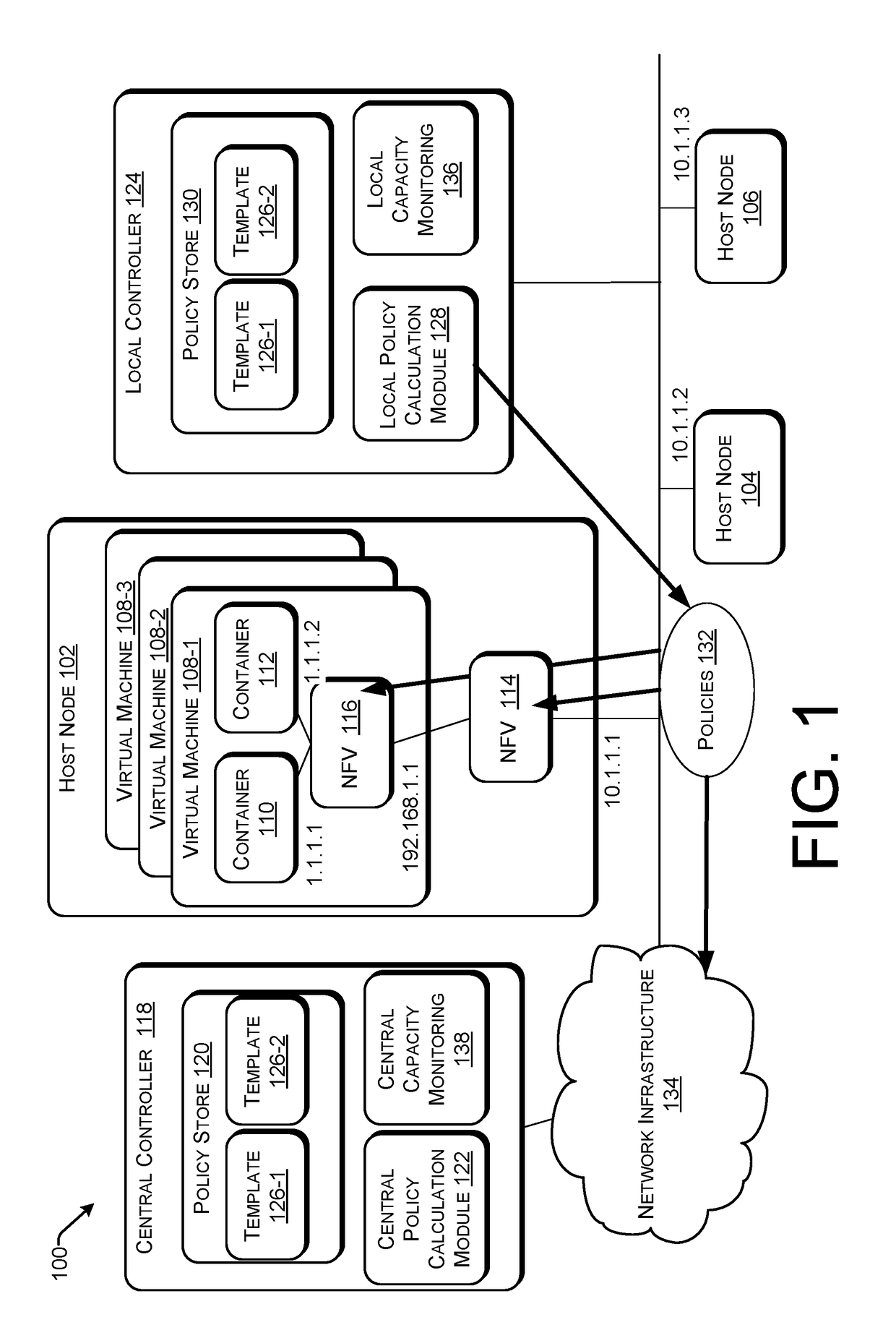

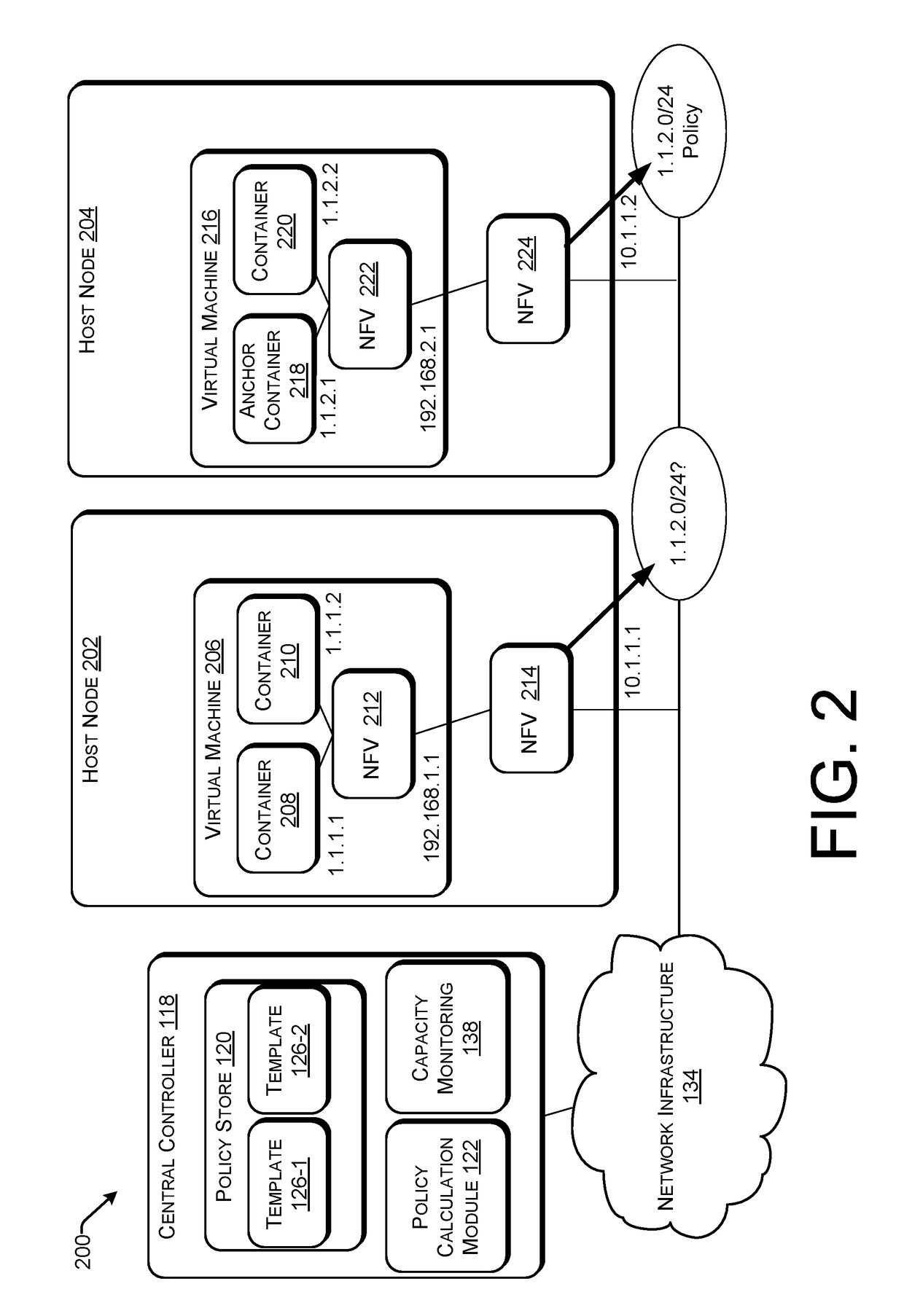

Template-driven locally calculated policy updates for virtualized machines in a datacenter environment are described. A central control and monitoring node calculates and pushes down policy templates to local control and monitoring nodes. The templates provide boundaries and / or a pool of networking resources, from which the local control and monitoring node is enabled to calculate policy updates for locally instantiated virtual machines and containers.

Owner:MICROSOFT TECH LICENSING LLC

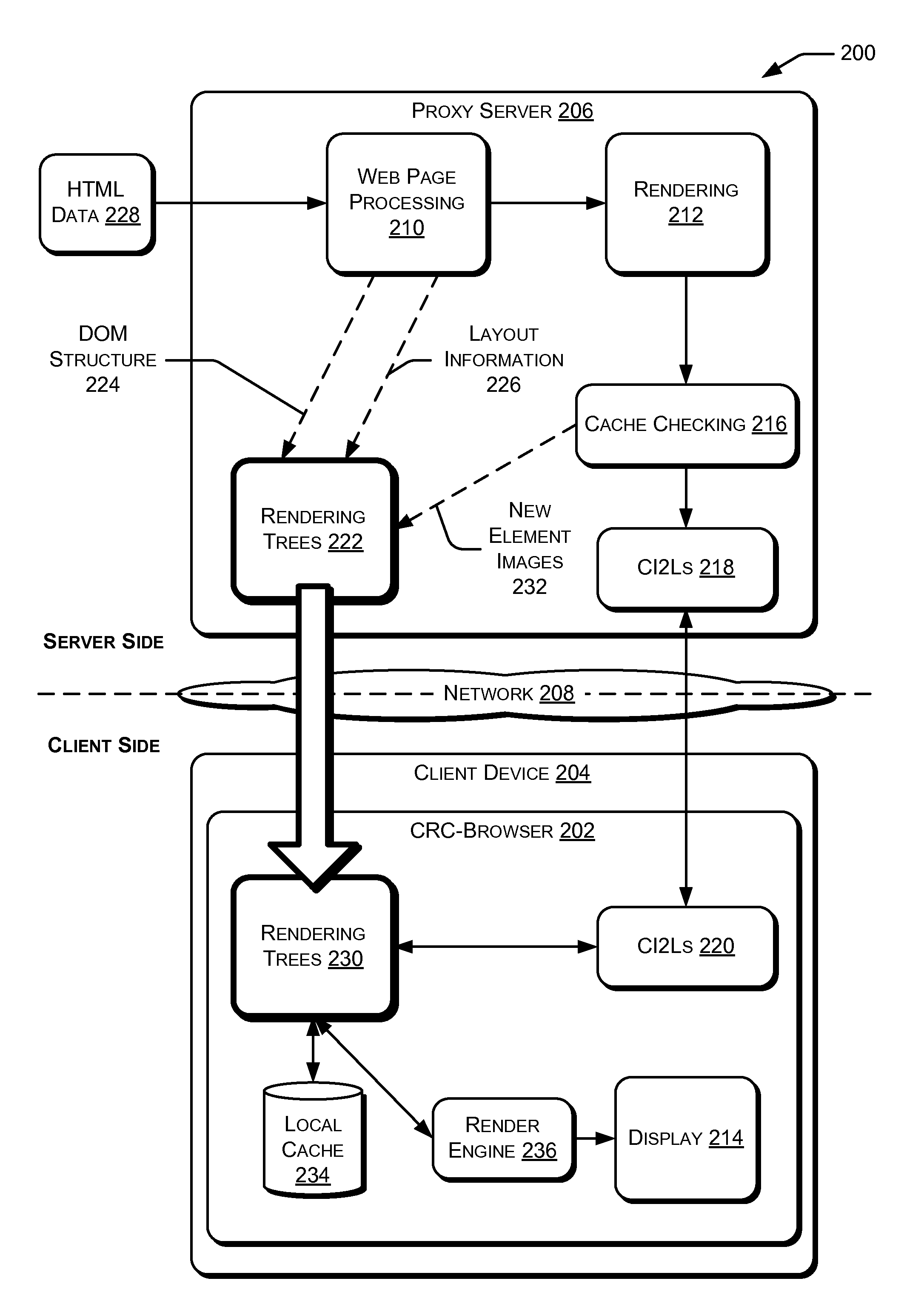

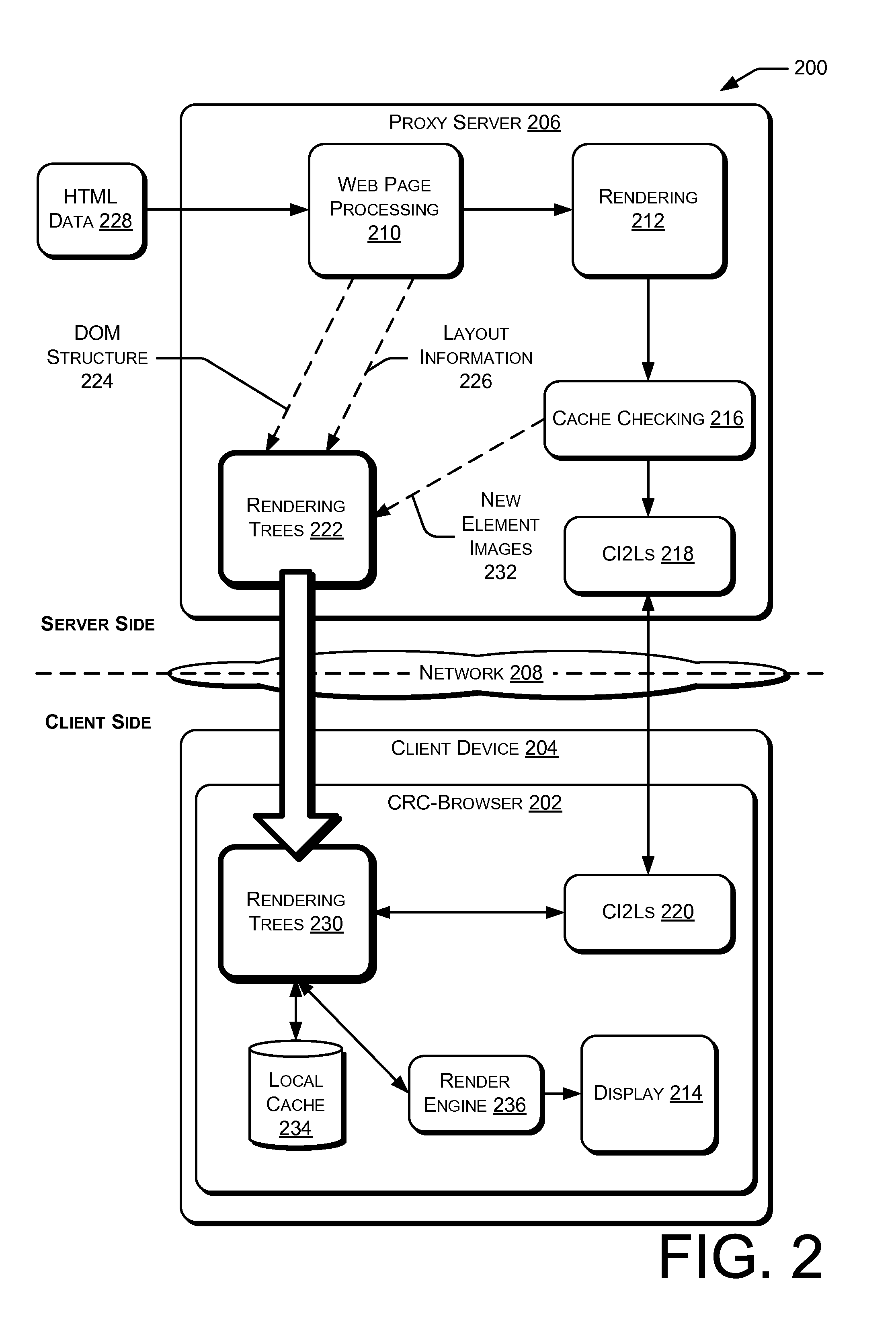

Cooperative Rendering Cache for Mobile Browser

ActiveUS20120260157A1Reduce redundant data transmissionImprove responsivenessDigital data information retrievalDigital computer detailsClient-sideMobile device

A cooperative rendering cache browser (CRC-Browser) for a mobile device may cooperatively manage cached content with a proxy server to reduce redundant transmissions of processed Web data. Additionally, the CRC-Browser may provide stateful, thin-client Web browsing to maintain synchronized information about rendering objects of a Web page. Further, the CRC-Browser may cache only stable and / or visible document object model (DOM) elements and communicate a list of IDs of the cached elements to the proxy. Such stateful thin-client browsers may be useful for reducing battery drain, poor responsiveness, and high wireless network costs of mobile Web browsing.

Owner:MICROSOFT TECH LICENSING LLC

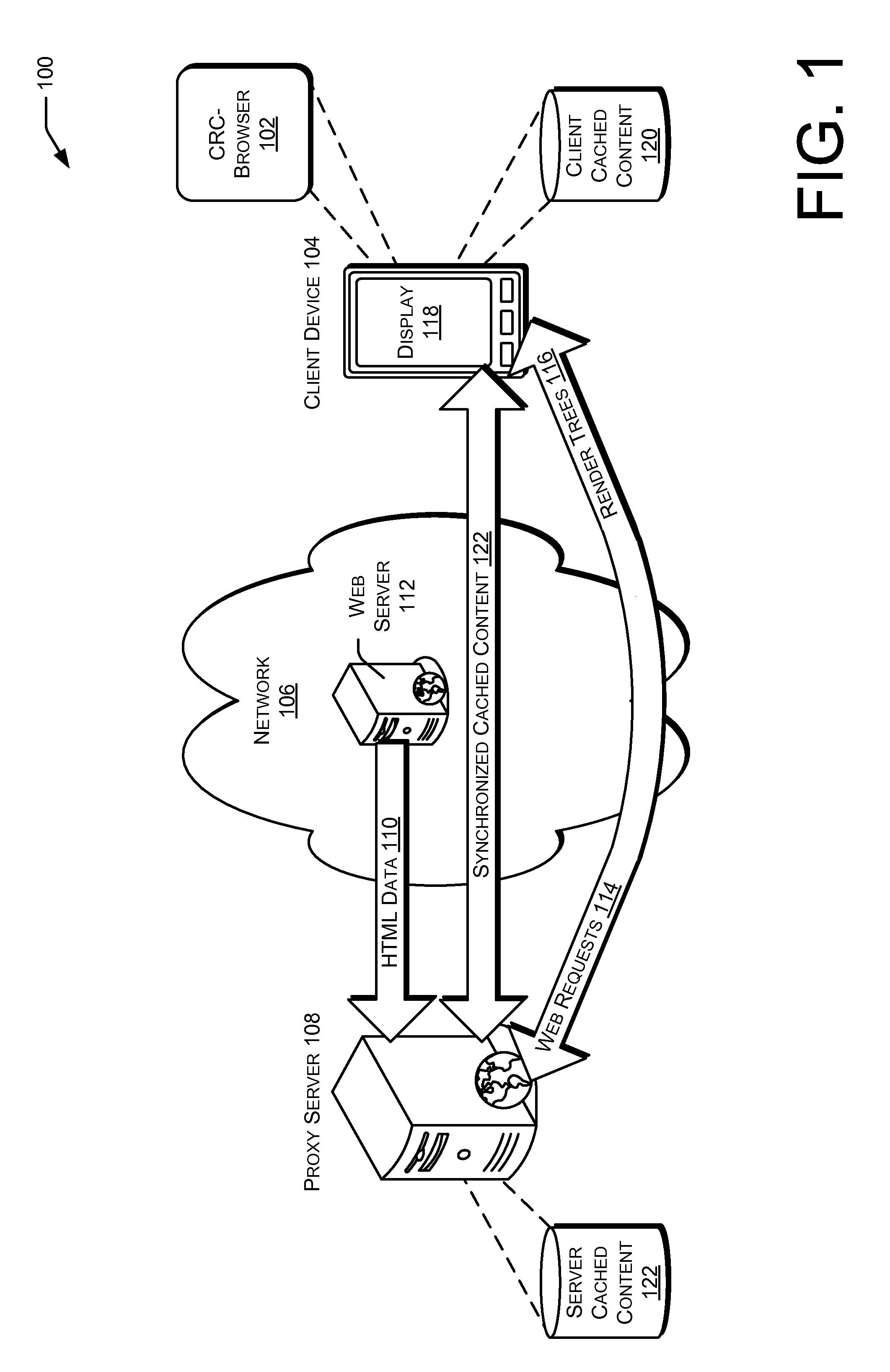

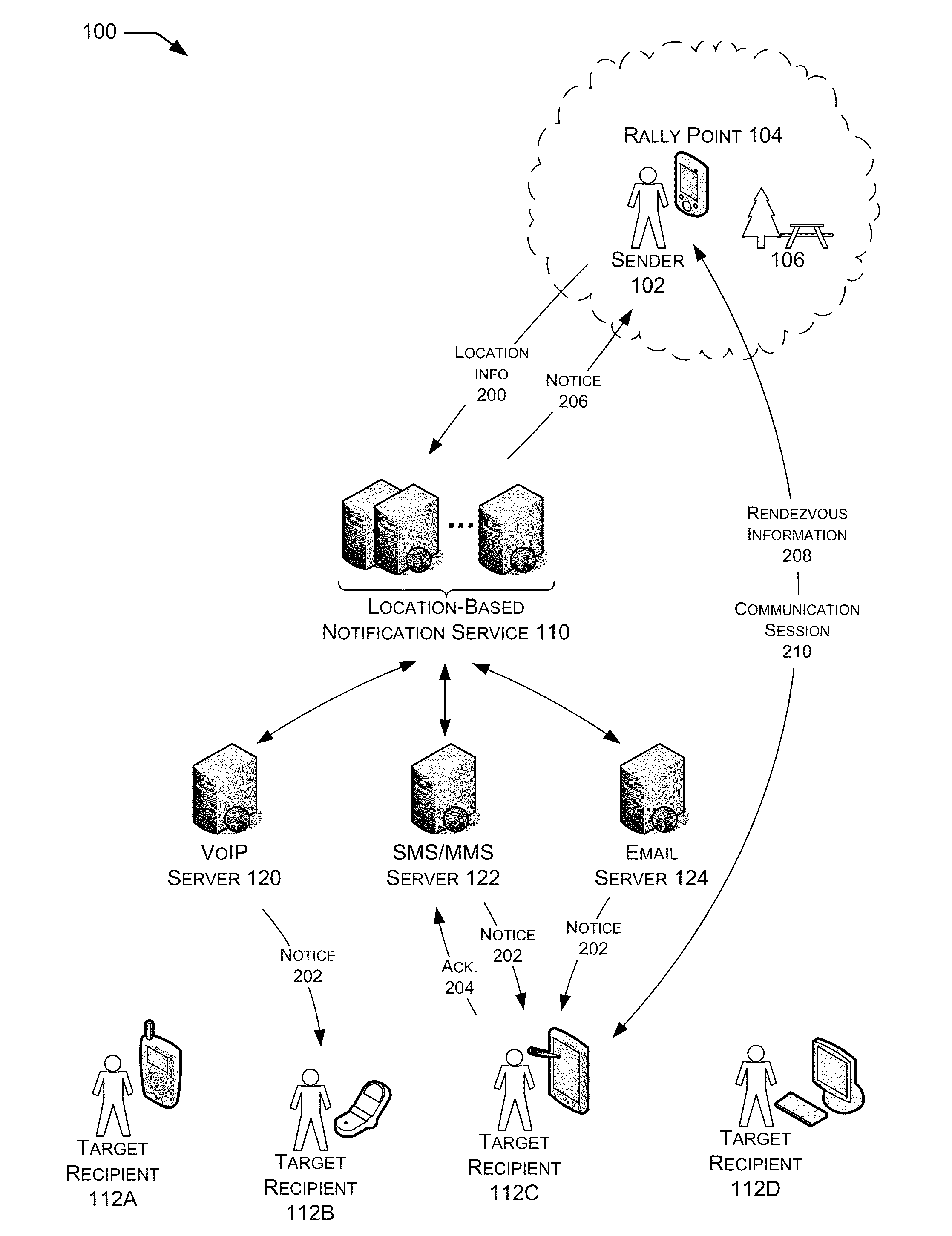

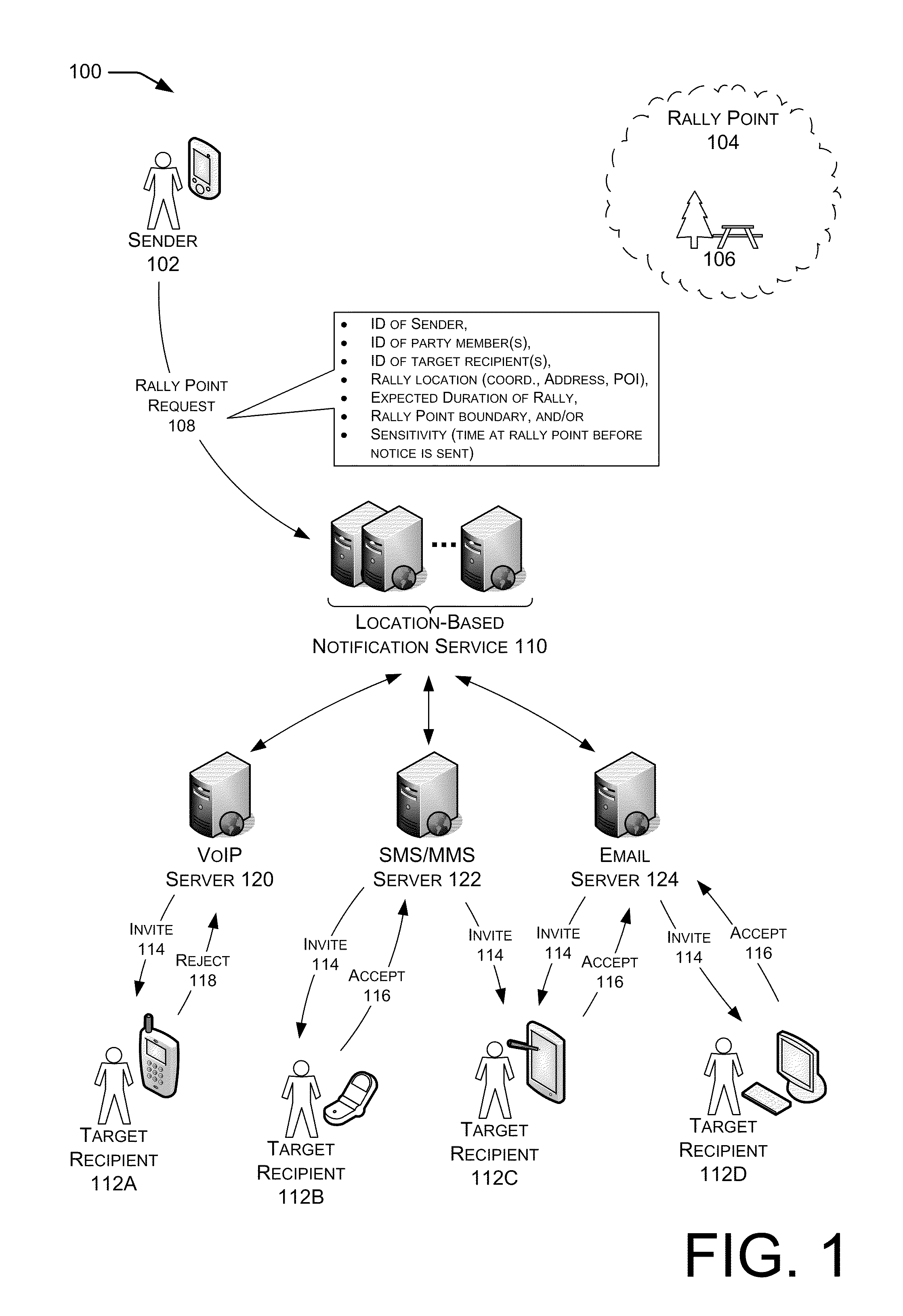

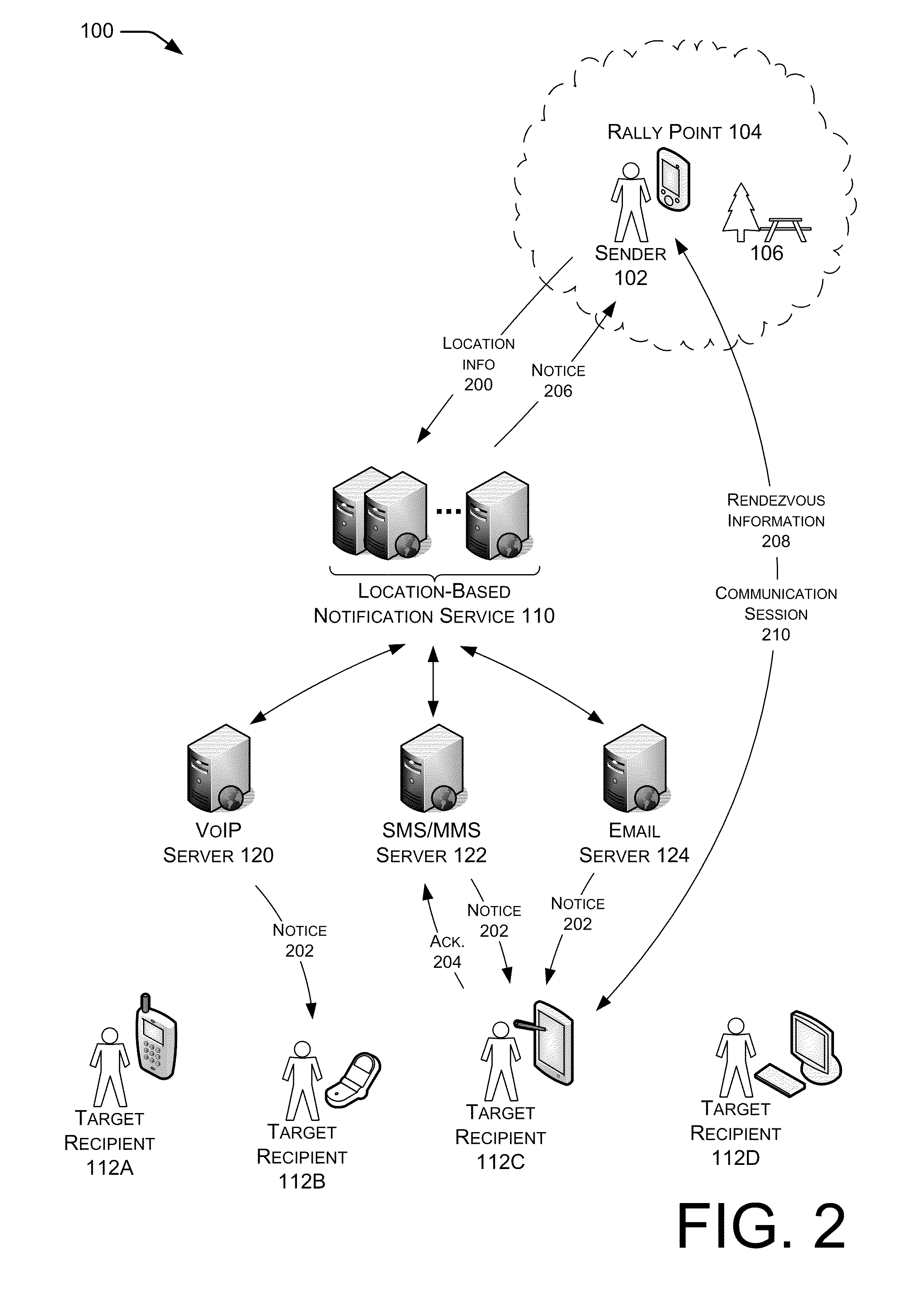

Location-based notification

InactiveUS20110231493A1Simple conceptMultiple digital computer combinationsTransmissionComputer scienceReal-time computing

Location-based notification includes establishment of a rally point and subsequent notification of a user when another user enters the rally point. Senders may set up rally points at various physical locations and specify one or more target recipients that are to be notified when the sender enters the rally point. Target recipients may specify communication settings that dictate whether and / or how they wish to receive notifications under a variety of circumstances. When a sender having a computing device enters a rally point location, a notification is sent from the computing device to a location-based notification service, which notifies each of the target recipients in a manner that complies with the target recipient's individual communication settings.

Owner:MICROSOFT TECH LICENSING LLC

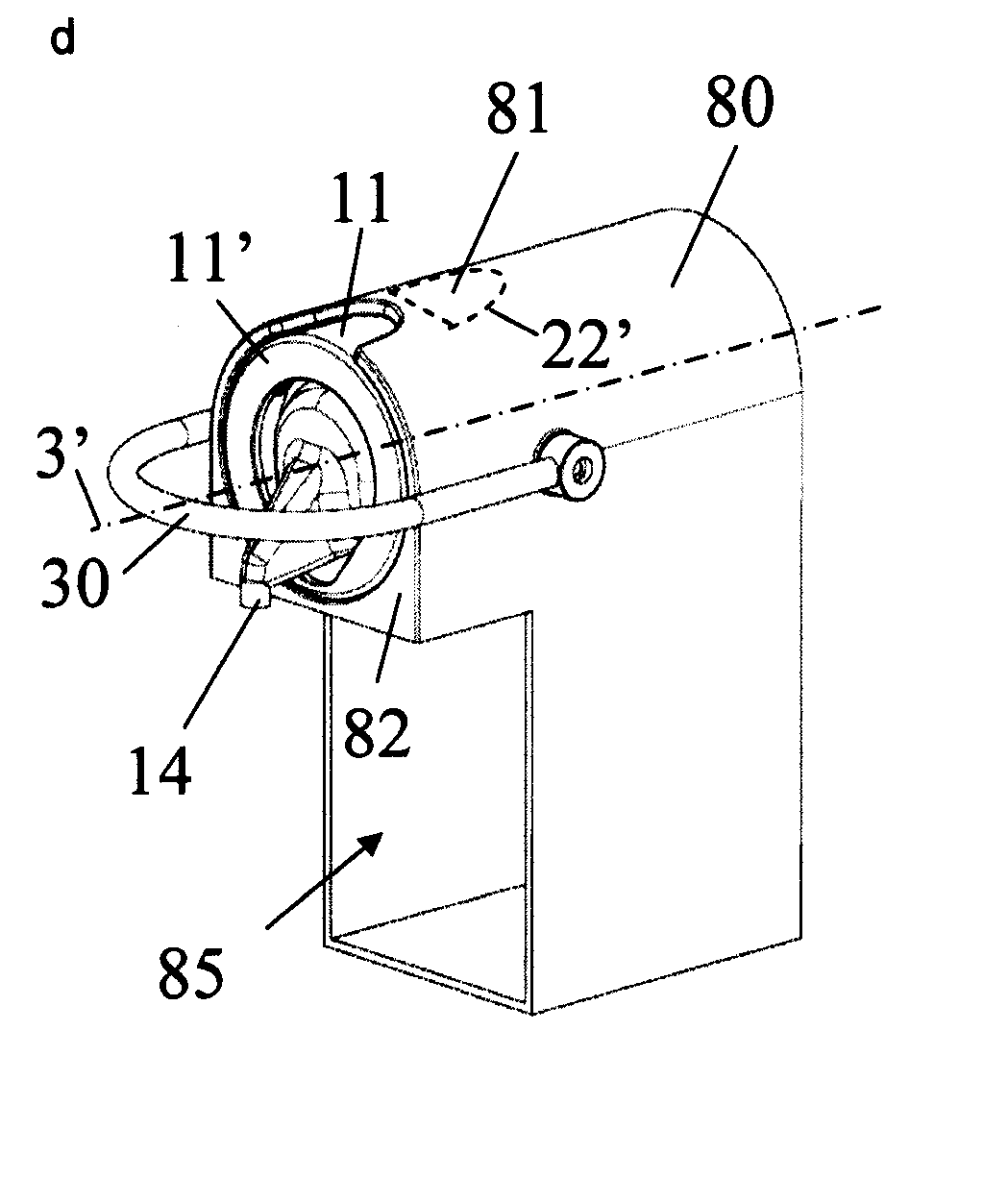

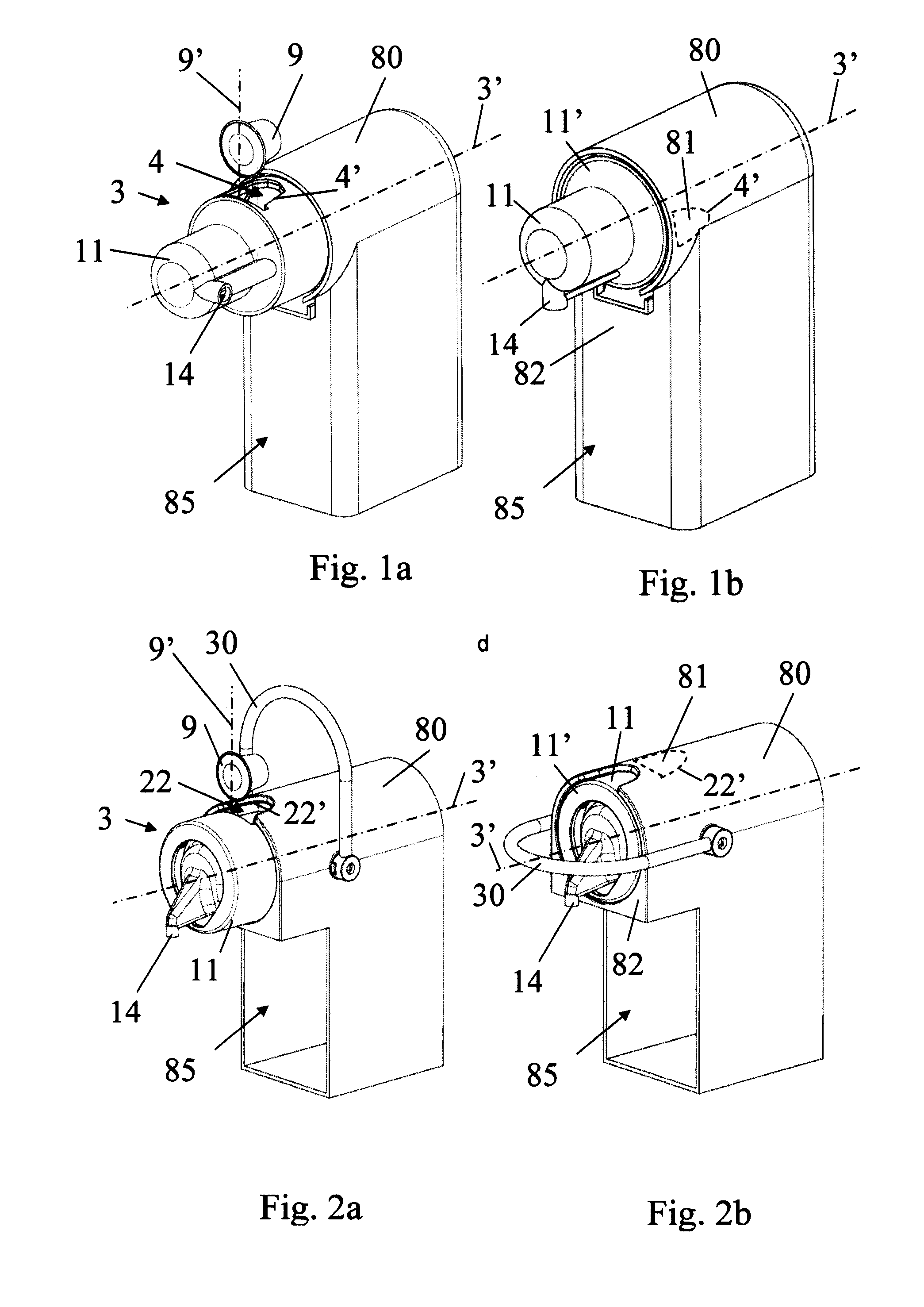

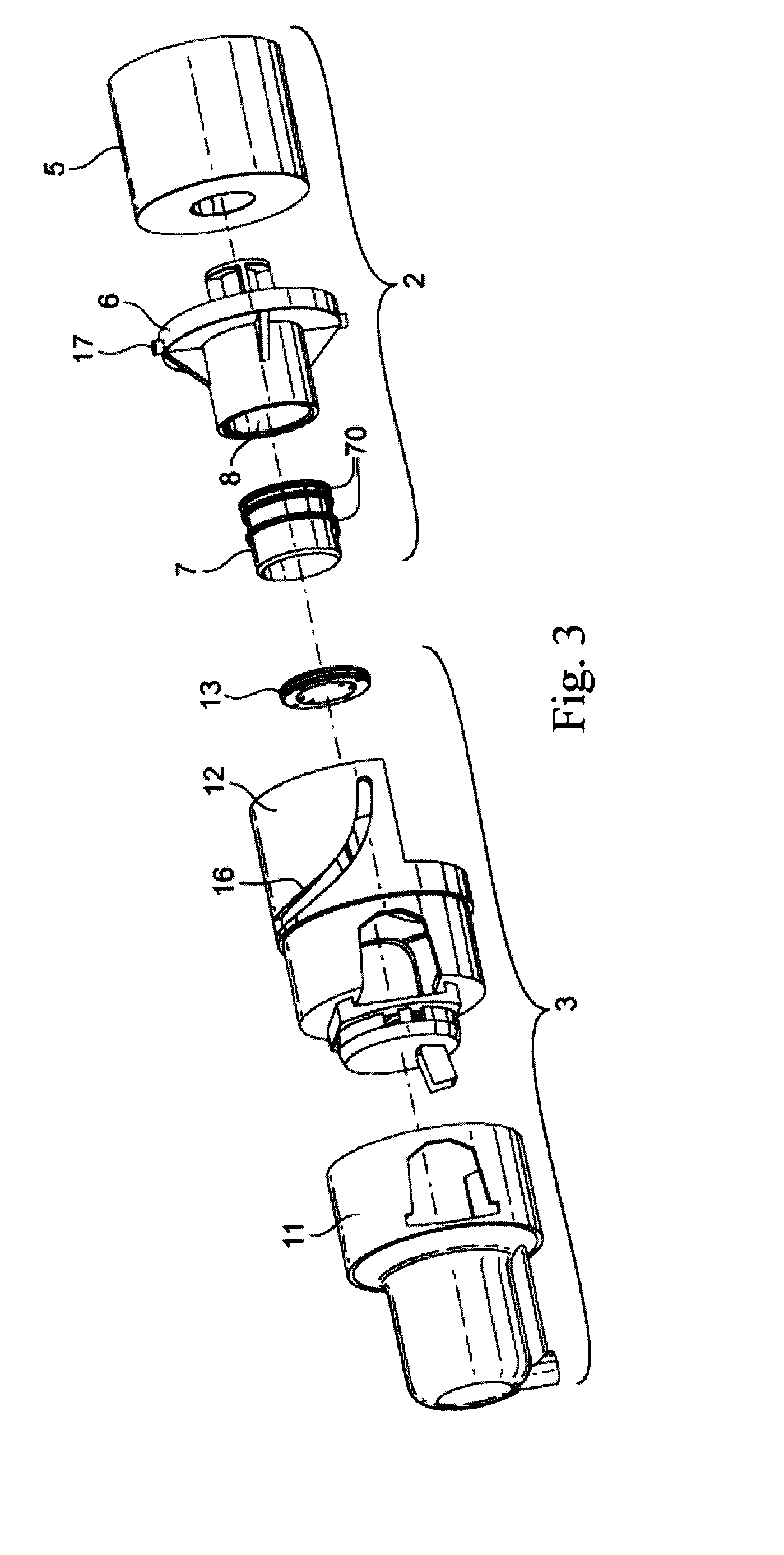

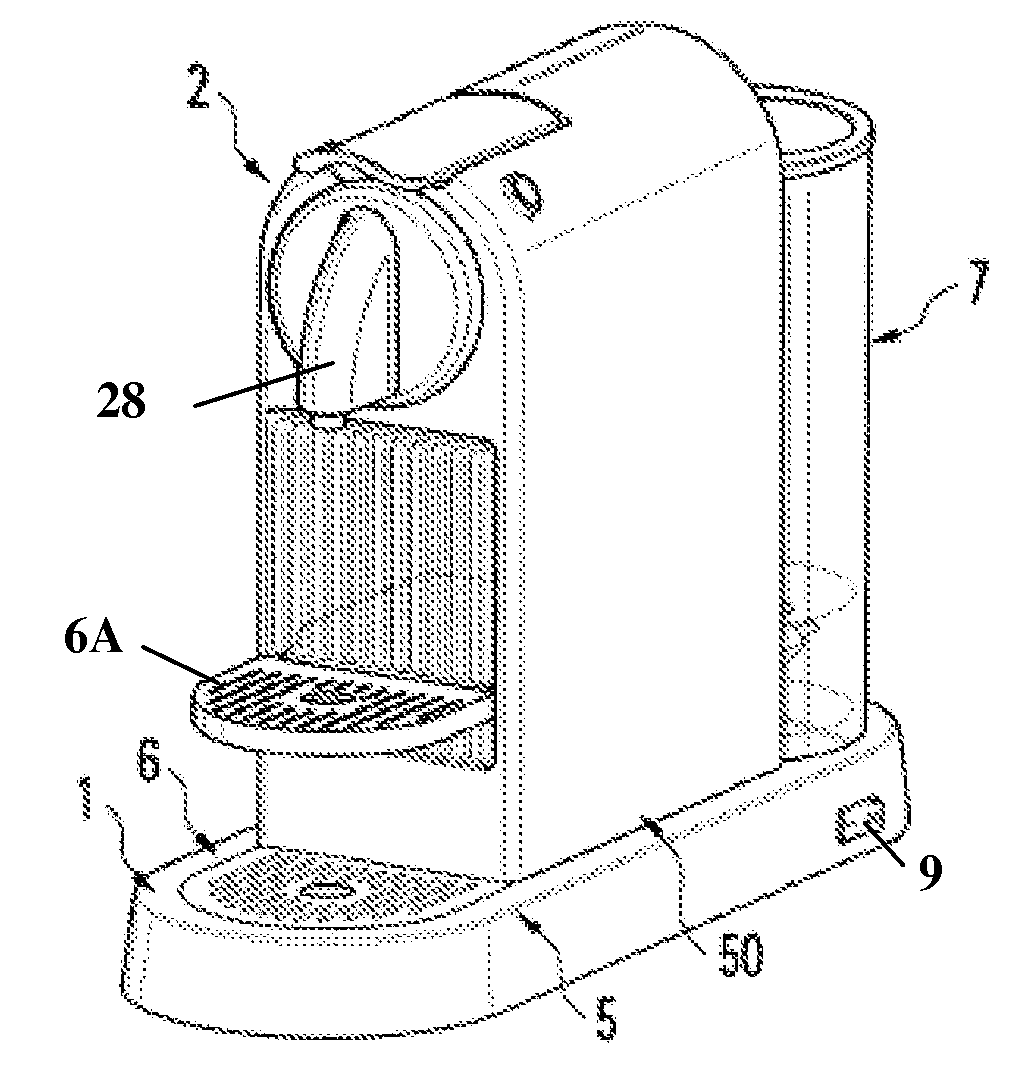

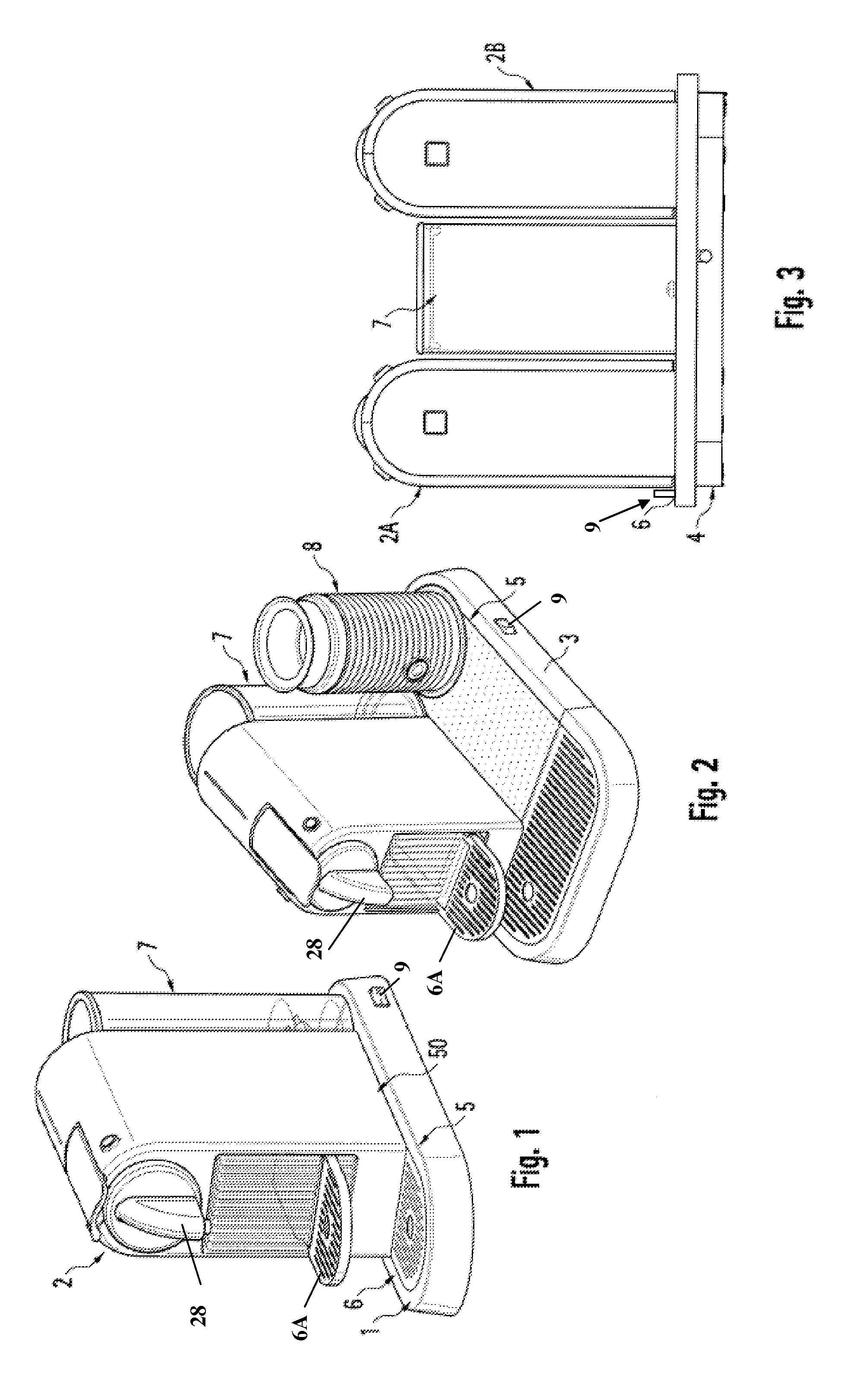

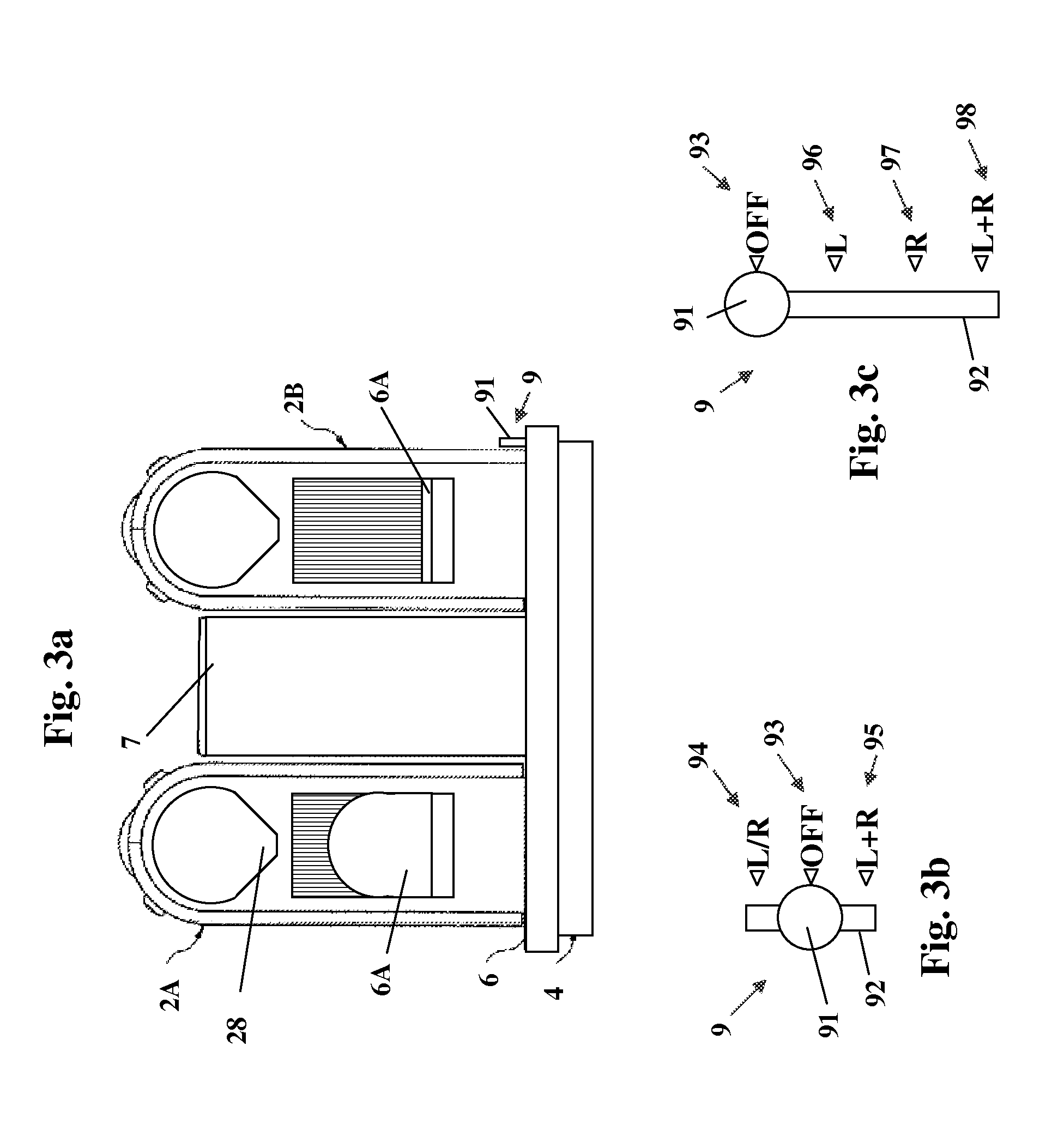

Beverage brewing unit

ActiveUS20100288132A1Direct fluid connectionFew moving partsBeverage vesselsAdditive ingredientBiomedical engineering

A beverage machine having a beverage brewing unit for receiving a single-serve capsule and including a capsule holding assembly for holding a capsule in a position during insertion by gravity of the capsule in the brewing unit; and a water injection assembly for at least partially enclosing the capsule and providing water in the capsule. The capsule holding part forms a front part of the unit and is mounted to the capsule injection assembly in a manner to be displaceable along a substantially horizontal path whereas the water injection assembly is located in a rear fixed part of the unit. The beverage machine has an outermost casing. One of these brewing unit assemblies can be moved or telescoped out or through this casing for inserting / removing the ingredient capsule and retracted into the outermost casing for bringing the brewing unit into its capsule extraction configuration.

Owner:SOC DES PROD NESTLE SA

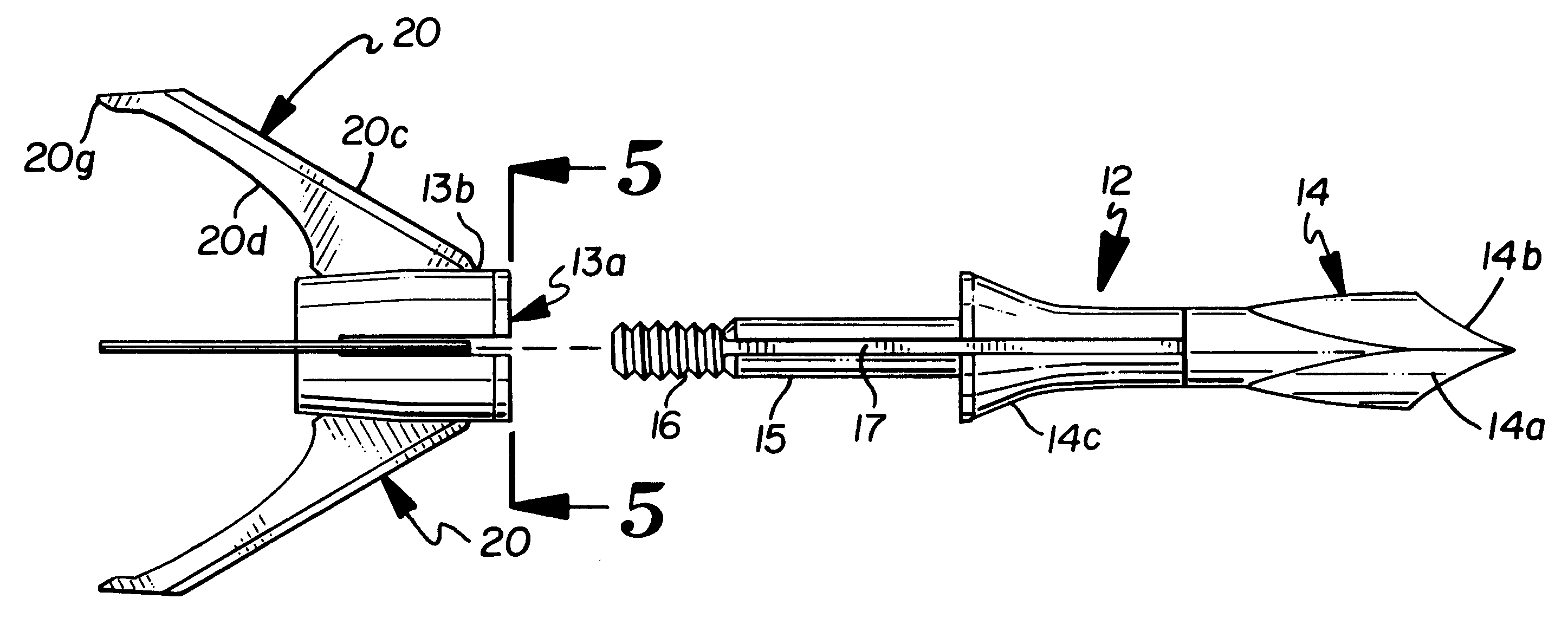

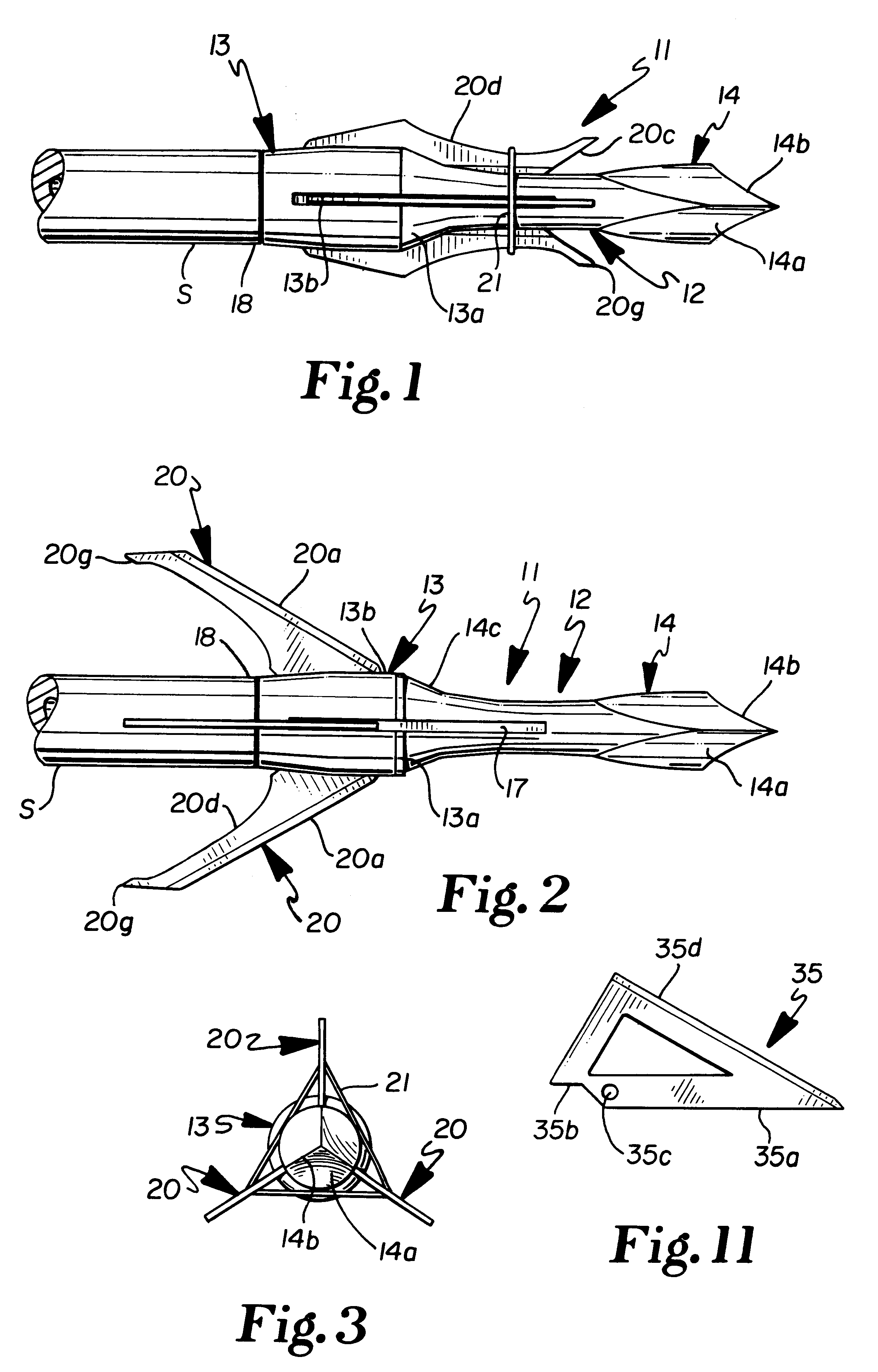

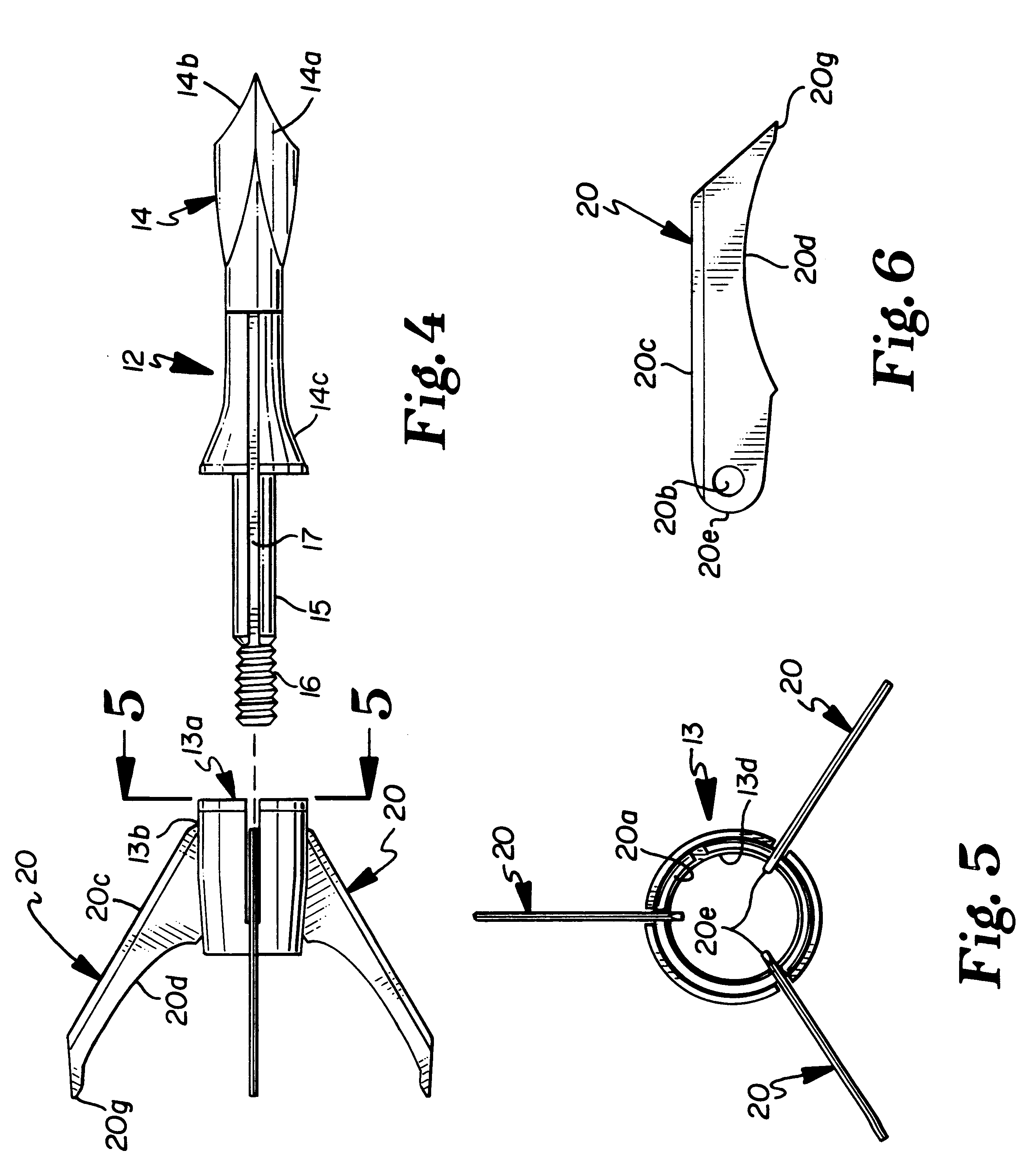

Broadhead with replaceable blade carrying section

InactiveUS6283880B1Small diameterConstant cutting diameterAmmunition projectilesThrow gamesEngineeringKnife blades

A broadhead including a main body portion and a replaceable blade carrying portion having at least a pair of blades on the blade portion. This structure permits removal and replacement of the blade portion to provide new blades of the same style or provide blades of another selected style. Such a selected style may include pivotally mounted blades which are folded for in-flight and travel and which expand rearwardly upon striking a target to present a large cutting dimension or may include stationary blades of predetermined cutting dimension. This concept allows the user to simply switch from dull to sharp blades or change styles from an expandable to a stationary type broadhead or vice-versa, by simply changing the blade carrying portion while utilizing the same man body portion. The pivotally mounted blades provide a folded, in-flight, position. When this style impacts the target, the blades pivot to their expanded cutting position exposing the cutting edge of each blade. When selecting the stationary style which provides a fixed position blade wherein the cutting edges will always be exposed. In either instance, the blade carrying body is prevented from rotating about the main body portion in the in-flight or target striking position.

Owner:OUT RAGE

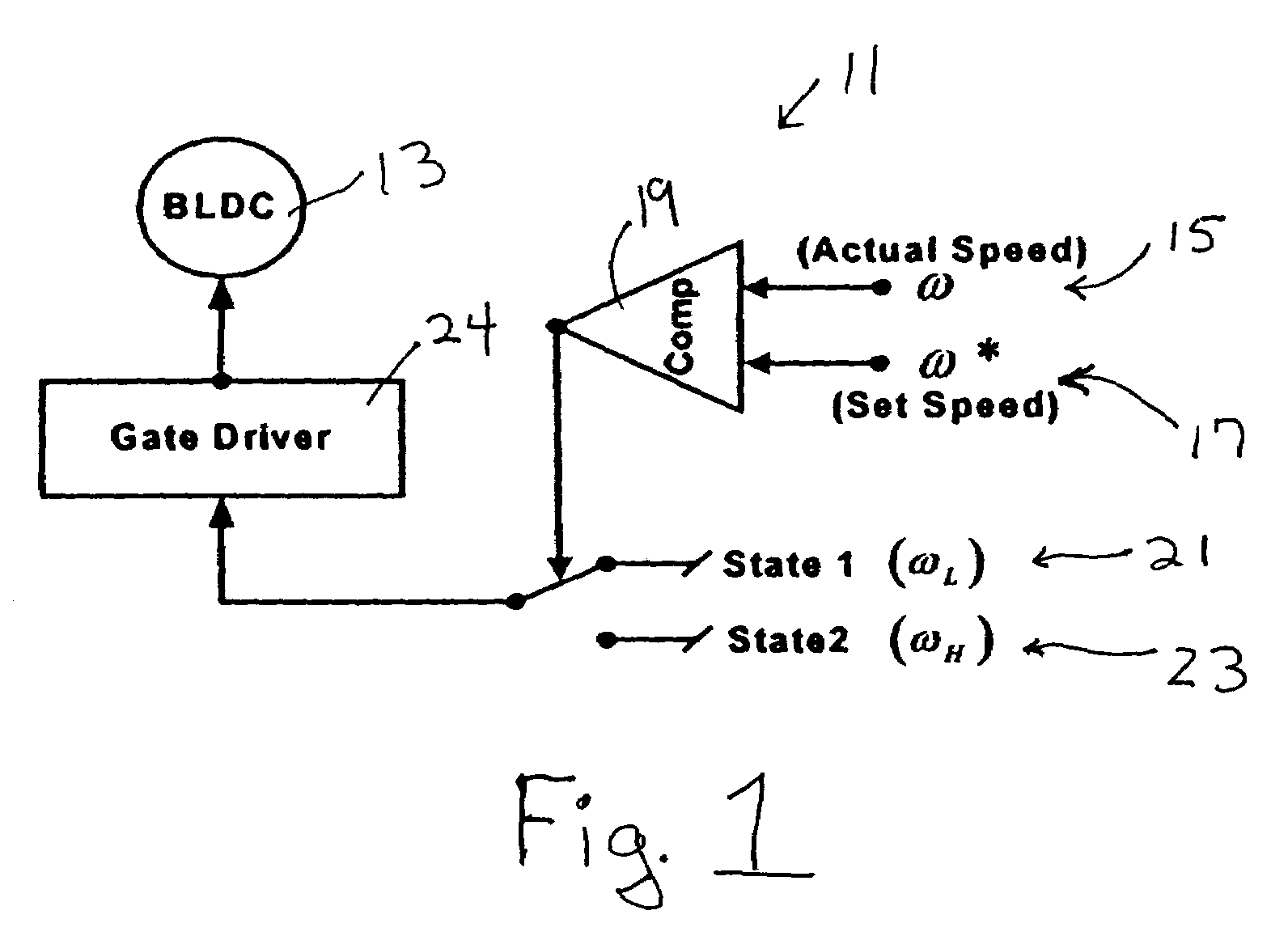

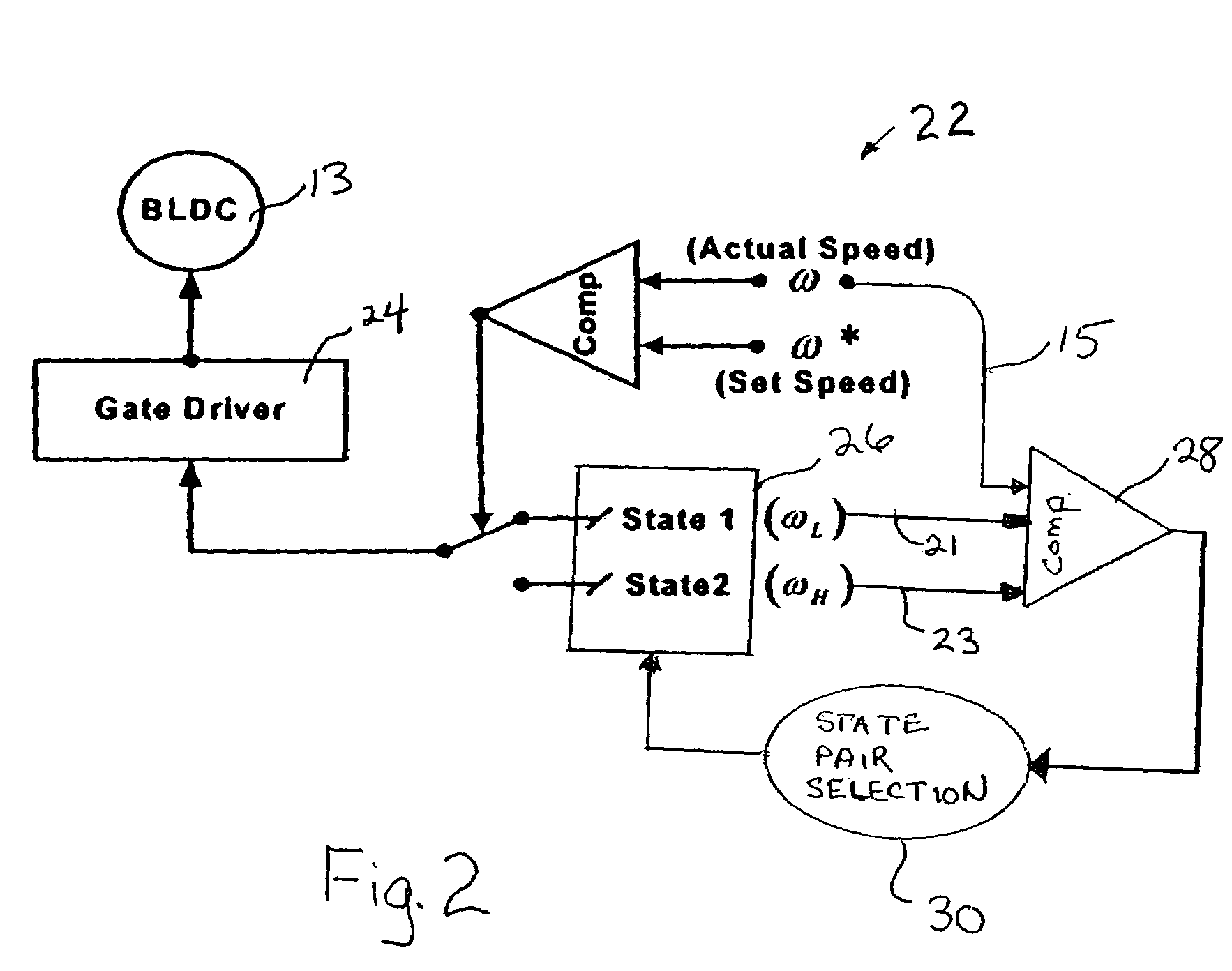

Digital control of motor drives

ActiveUS7193385B2Low costEasy to implementAC motor controlDC motor speed/torque controlMotor driveElectric machine

A digital controller is easily implemented for variable speed or torque control of an electric motor or generator by using a comparator to determine a choice of control state outputs.

Owner:ILLINOIS INSTITUTE OF TECHNOLOGY

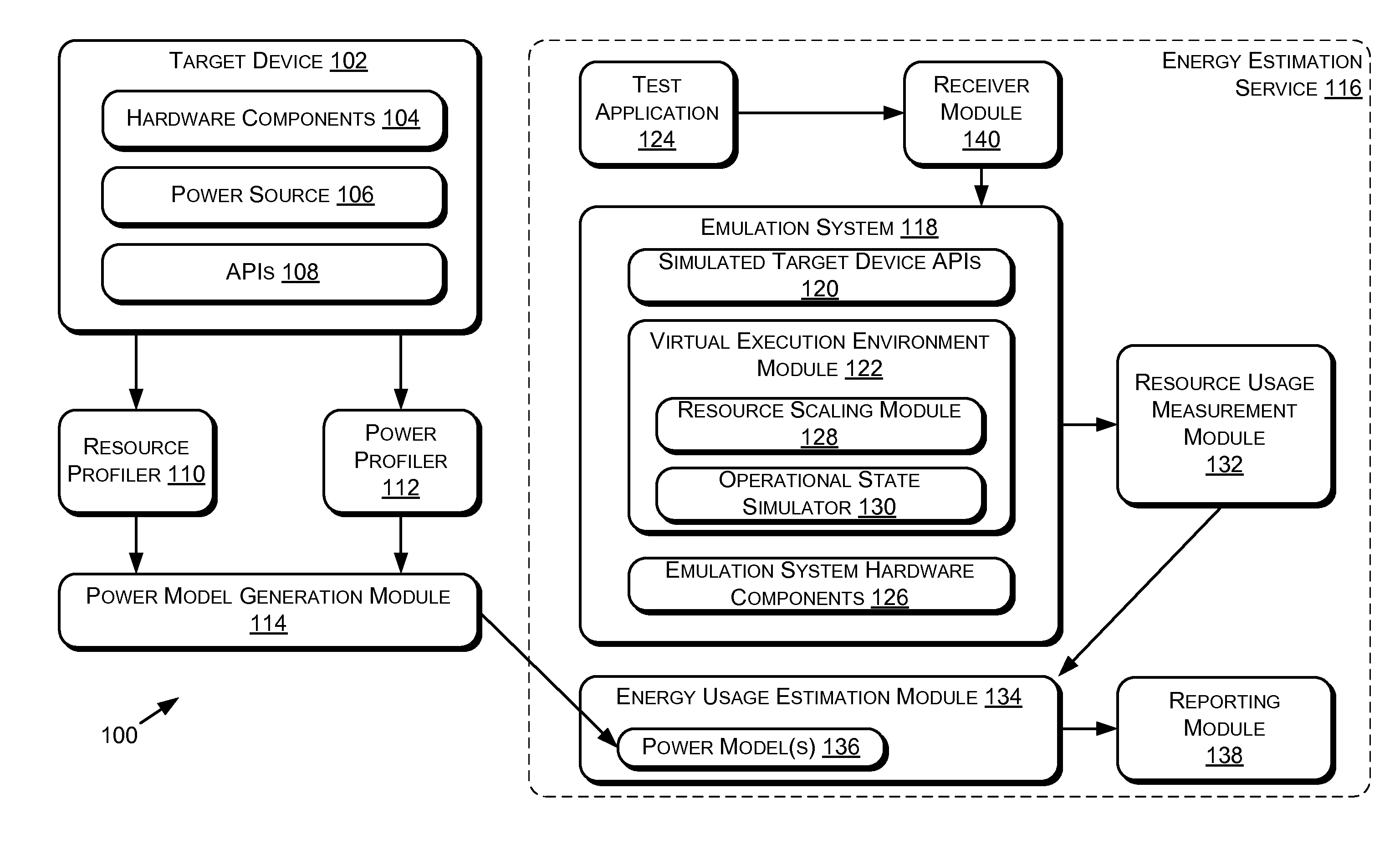

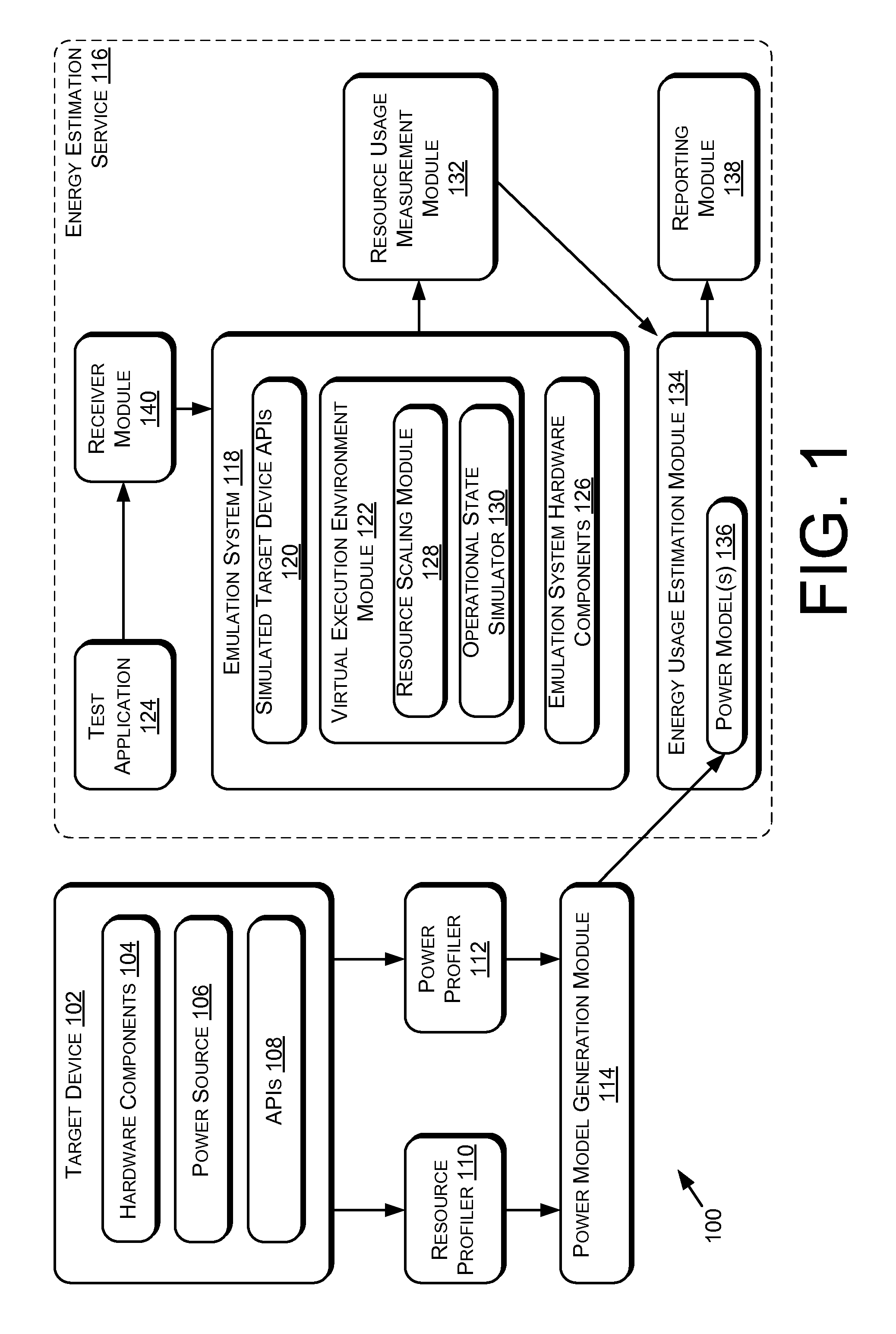

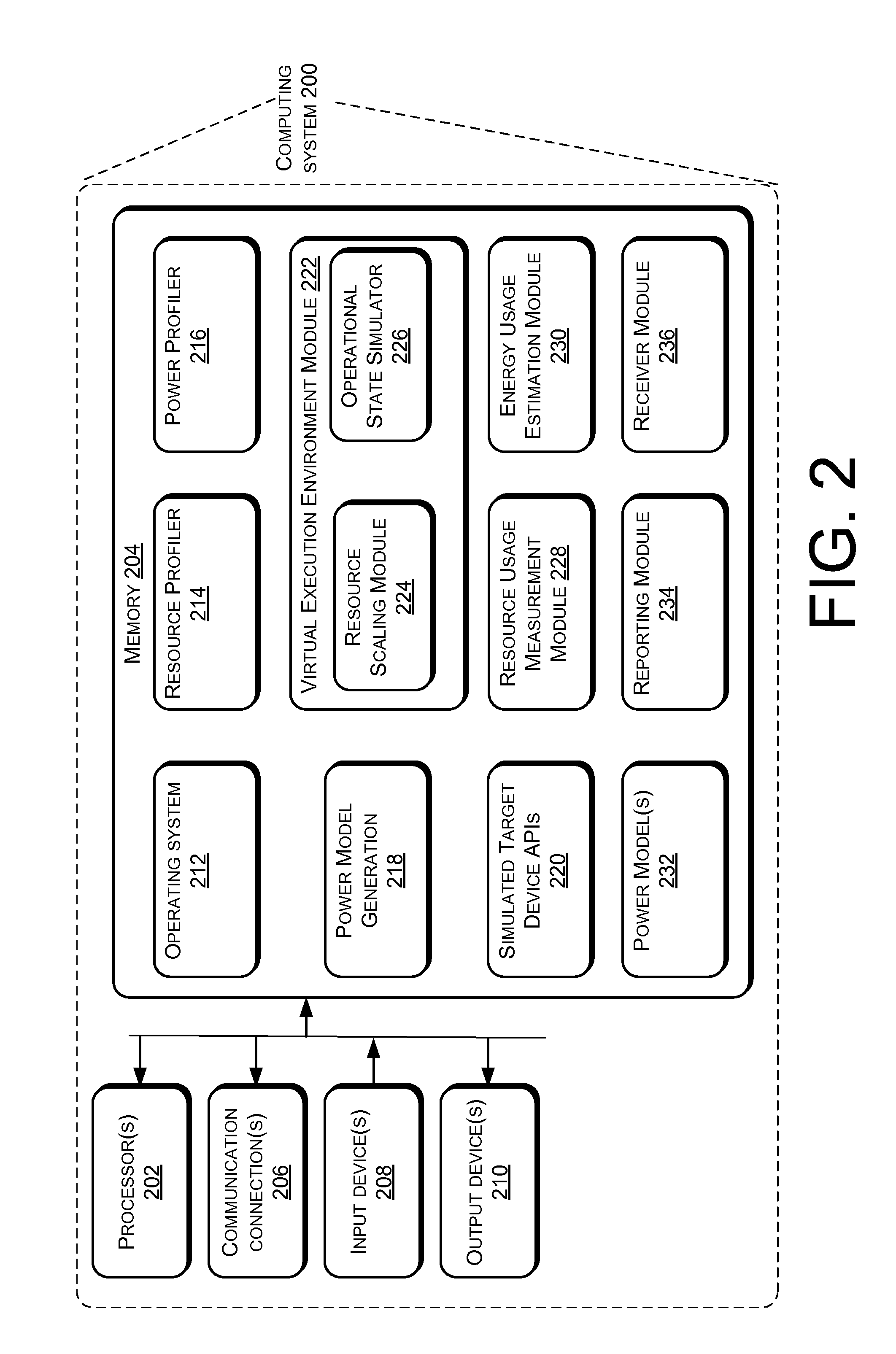

Estimating Application Energy Usage in a Target Device

ActiveUS20130174128A1Simple conceptEnergy efficient ICTError detection/correctionApplication programming interfaceParallel computing

Embodiments provide implementations for estimating a test application's energy usage on a target device based on execution of the test application. Resource usage associated with the execution of the test application is measured. The measured resource usage is input into a power model of the target device to estimate the energy that the test application uses when executed on the target device. An emulation system is configured to execute the test application in a virtual execution environment using resource scaling and simulated target device application programming interfaces to substantially simulate the corresponding capabilities of the target device.

Owner:MICROSOFT TECH LICENSING LLC

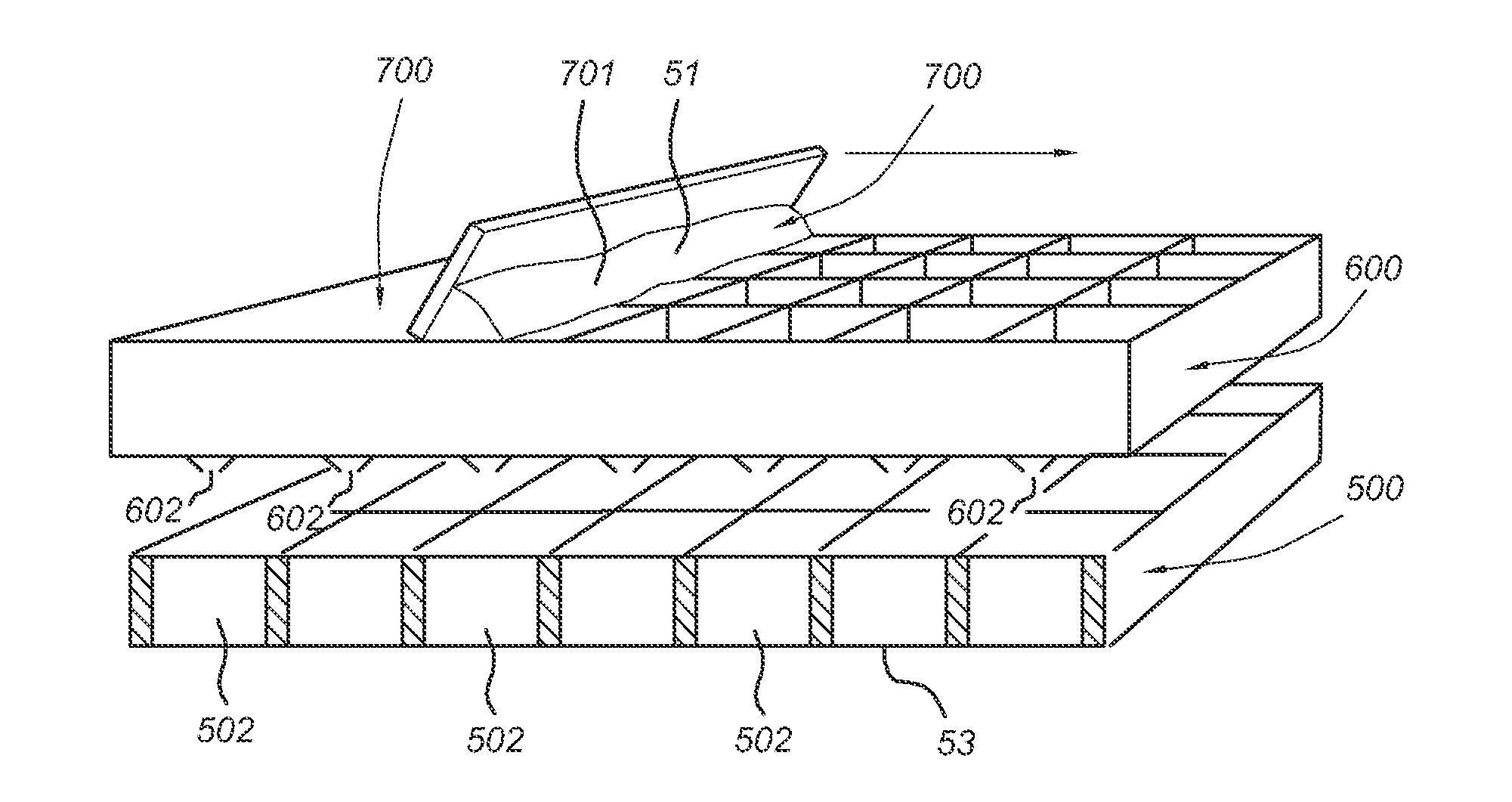

Modular manufacturing of beverage production machines

ActiveUS20100263543A1Reduce in quantitySimple conceptLiquid transferring devicesBeverage vesselsControl circuitWater reservoir

A modular method of manufacturing a set of beverage production machines with different beverage-related functions. The machines are designed for producing a beverage on the basis of pre-portioned ingredient packages. The method includes providing a plurality of identical core units having control circuitry and a beverage production module for housing an ingredient package and feeding a liquid to the interior of the ingredient package, providing a plurality of different base platforms that differ as to beverage production functions, and manufacturing a set of different beverage production machines by mounting respectively at least one of the core units on a top surface of one of the differing base platforms while also mounting water reservoirs on the base platforms.

Owner:SOC DES PROD NESTLE SA

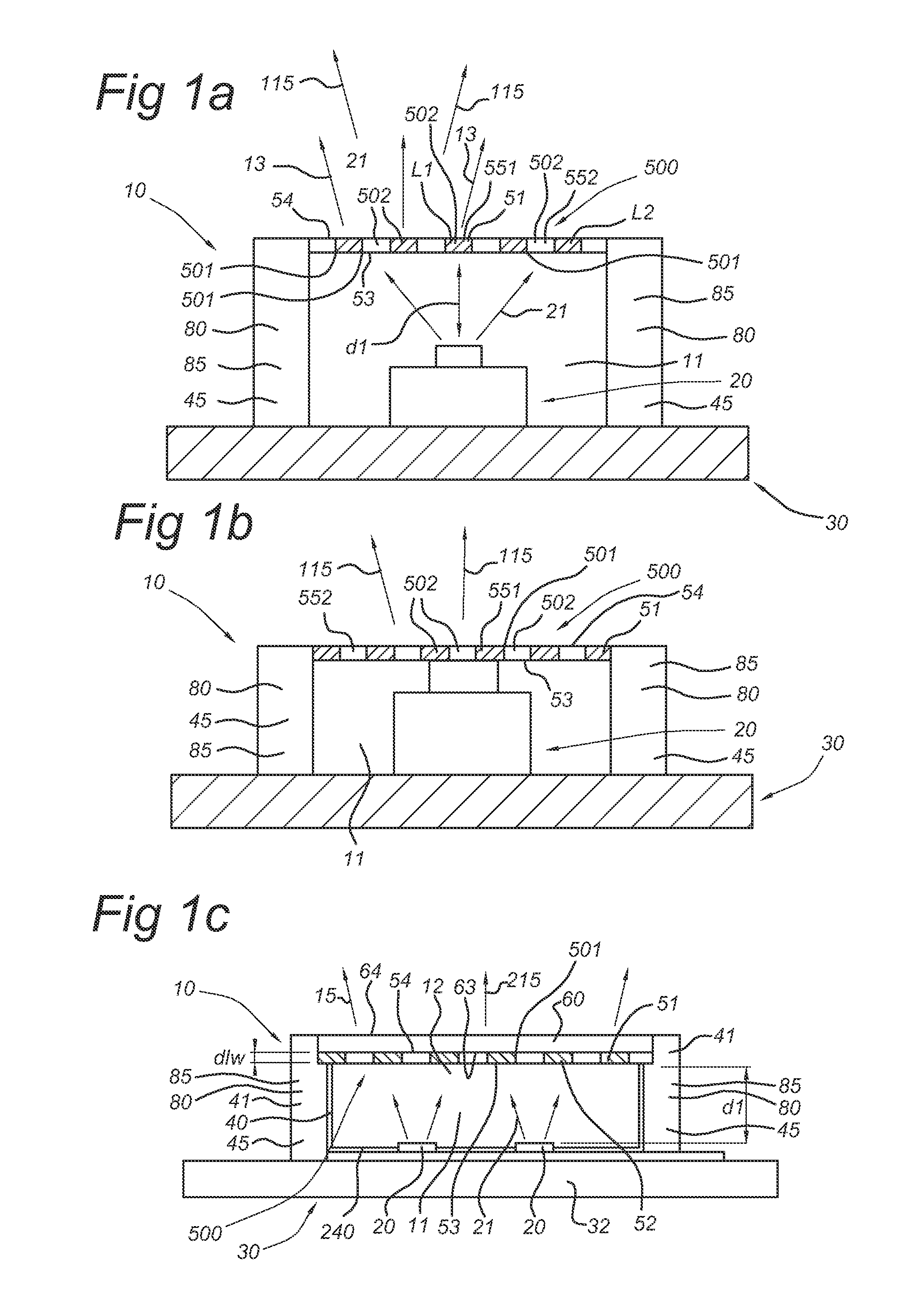

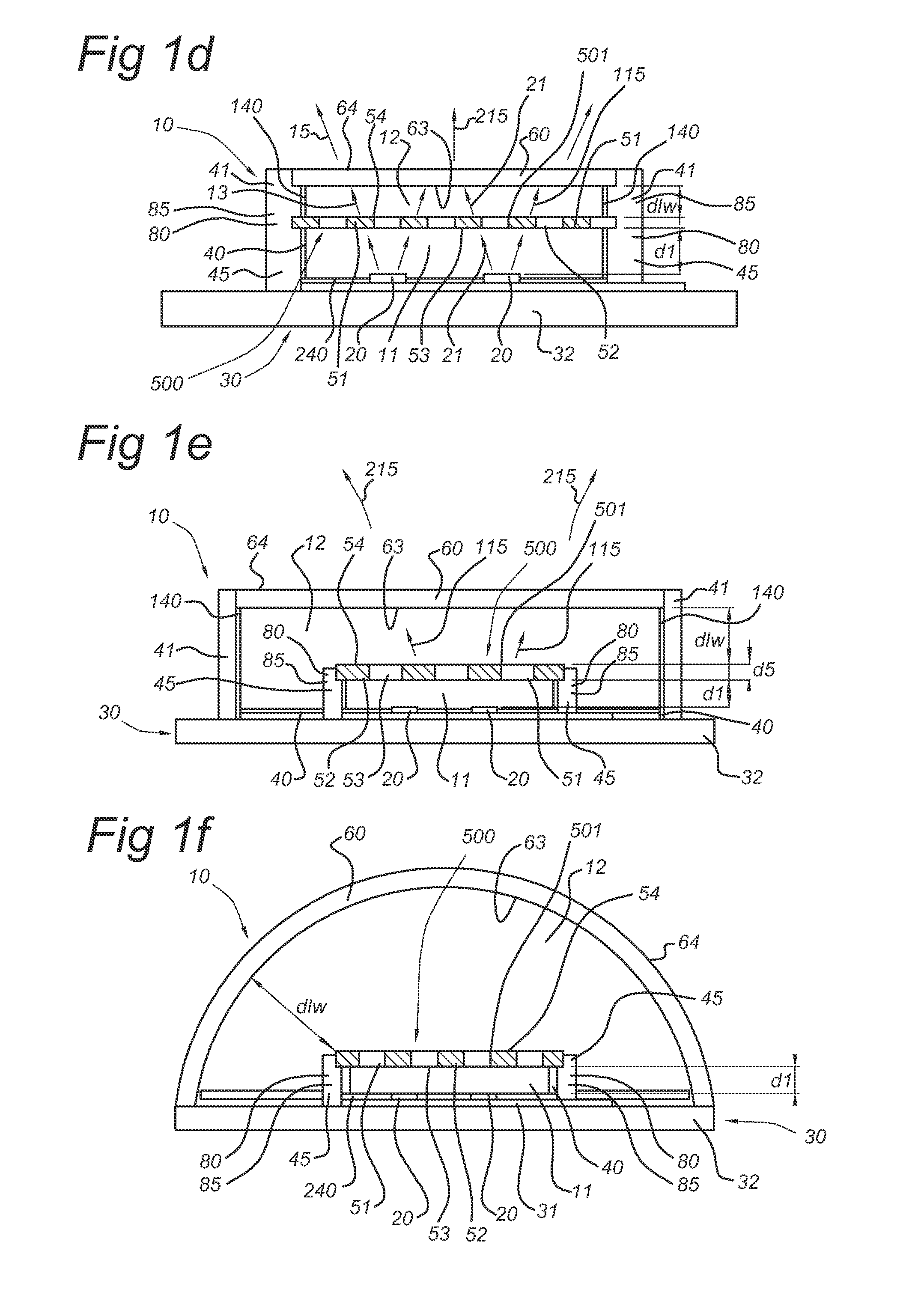

Illumination device with LED with a self-supporting grid containing luminescent material and method of making the self-supporting grid

InactiveUS20110044026A1Less back reflection/reabsorptionSimple conceptPoint-like light sourceLighting heating/cooling arrangementsEngineeringLight-emitting diode

The invention provides an illumination device (10) comprising (a) a light emitting diode (LED), (b) a heat sink (85) and (c) a self-supporting grid (500). This grid (500) is arranged downstream of the LED (20) and arranged so as to be in contact with the heat sink 85. The self-supporting grid (500) comprises a plurality of grid structures (501) and a plurality of grid openings 502) between the grid structures (501). At least part of the total number of grid openings (502) encloses luminescent material (51), thereby providing luminescent material-filled grid openings (551). The luminescent material (51) is arranged to absorb at least part of the LED emission (21) and emit luminescent material emission (13). The LED (20) and the luminescent material (51) are arranged to provide light (115) of a predetermined color downstream of the self-supporting grid (500).

Owner:SIGNIFY HLDG BV

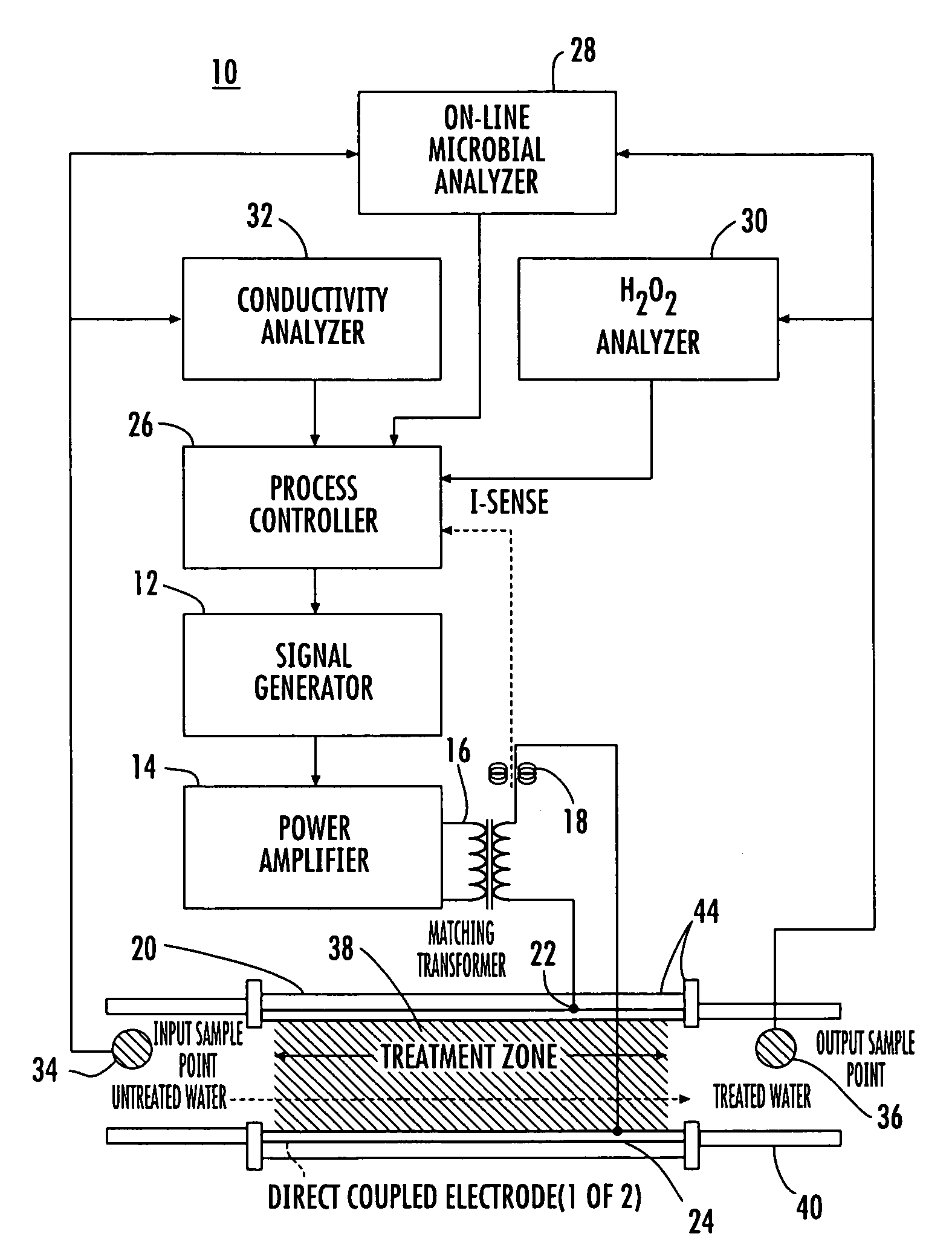

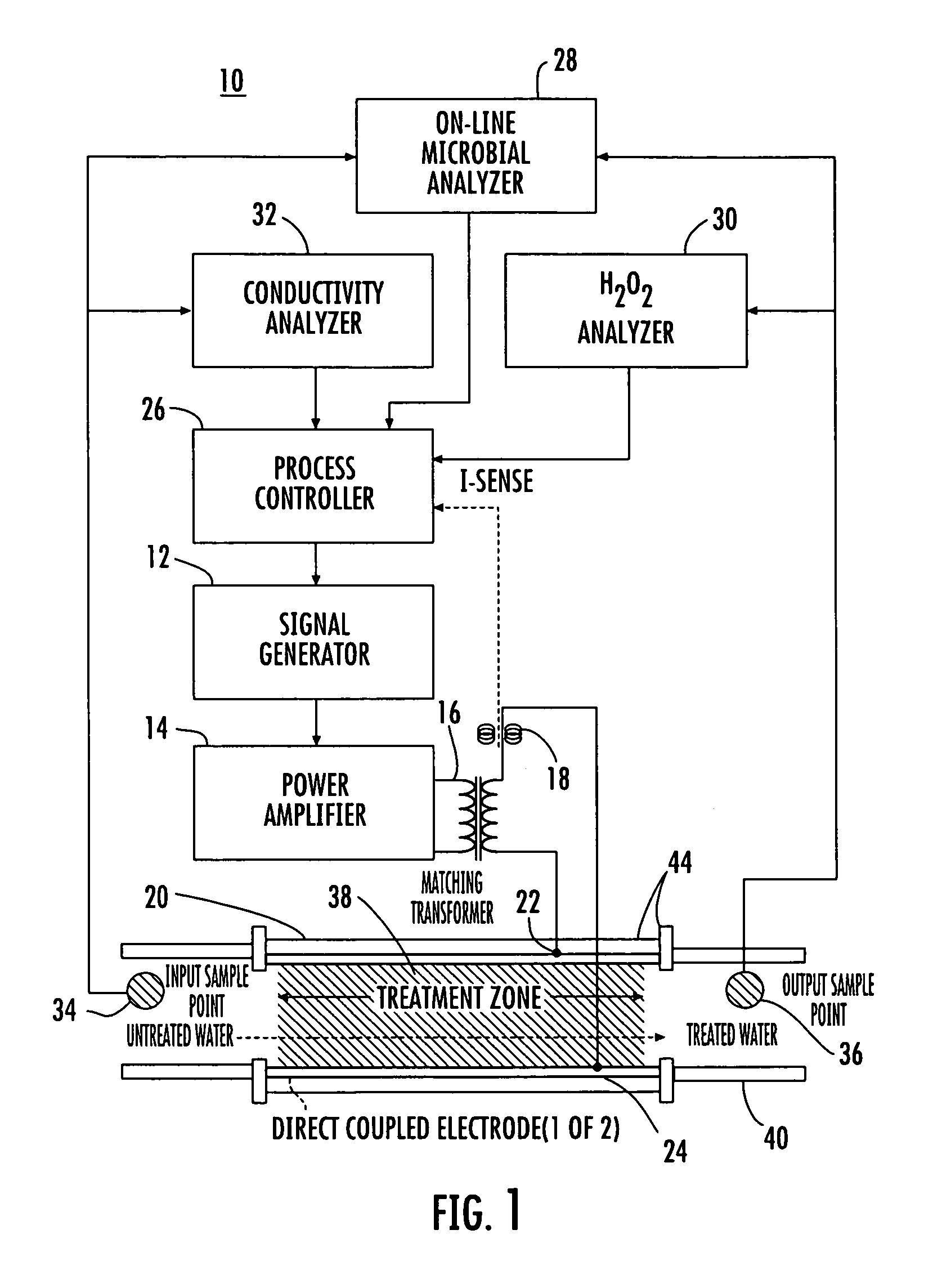

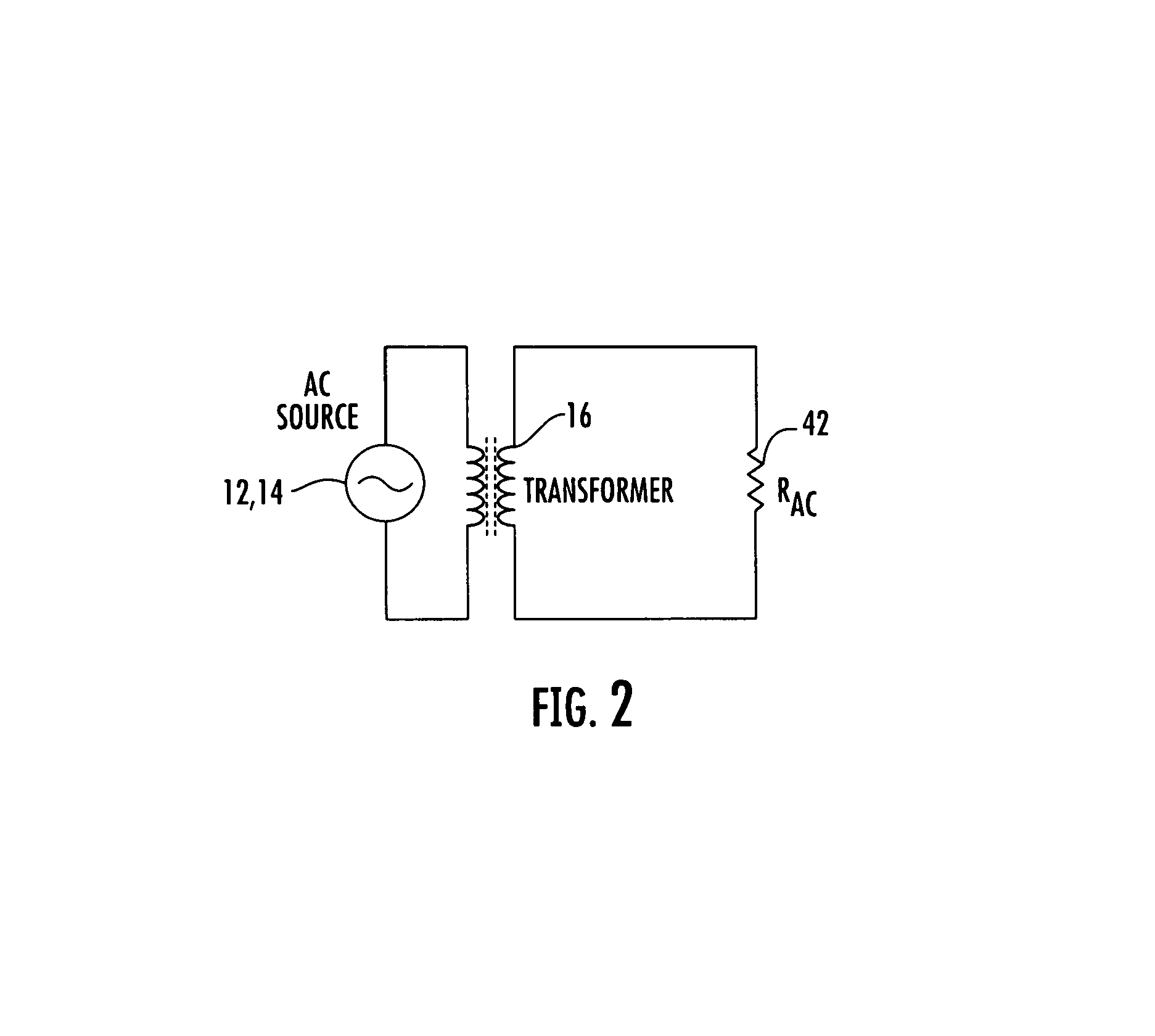

Electroionic processing system

ActiveUS7033481B1Improve conductivityReduce conductivityLiquid separation by electricityCell componentsCapacitanceAlternating current

The present invention provides an electroionic processing system having a high frequency alternating current (AC) power source for treating potable water, process water, wastewater, biosolids, sludge, primary effluent, secondary effluent, and other biochemical processing functions, including producing hydrogen peroxide and other useful chemicals. An electromagnetic field is generated and coupled to an electrolytic treatment apparatus by a direct coupling apparatus and method, a capacitive coupling apparatus and method, and an inductive coupling apparatus and method. The present invention further comprises a process controller and a plurality of analyzers for monitoring various treatment process variables to adjust and optimize the process as necessary.

Owner:BIOIONIX

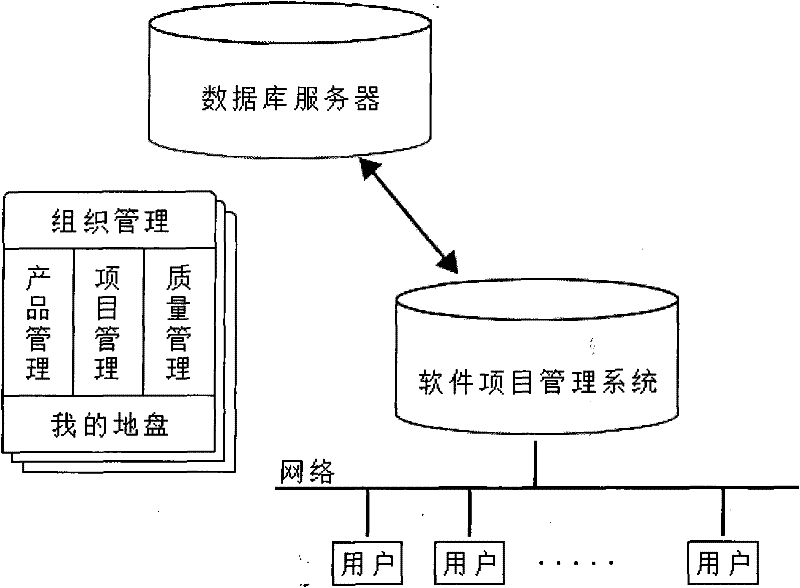

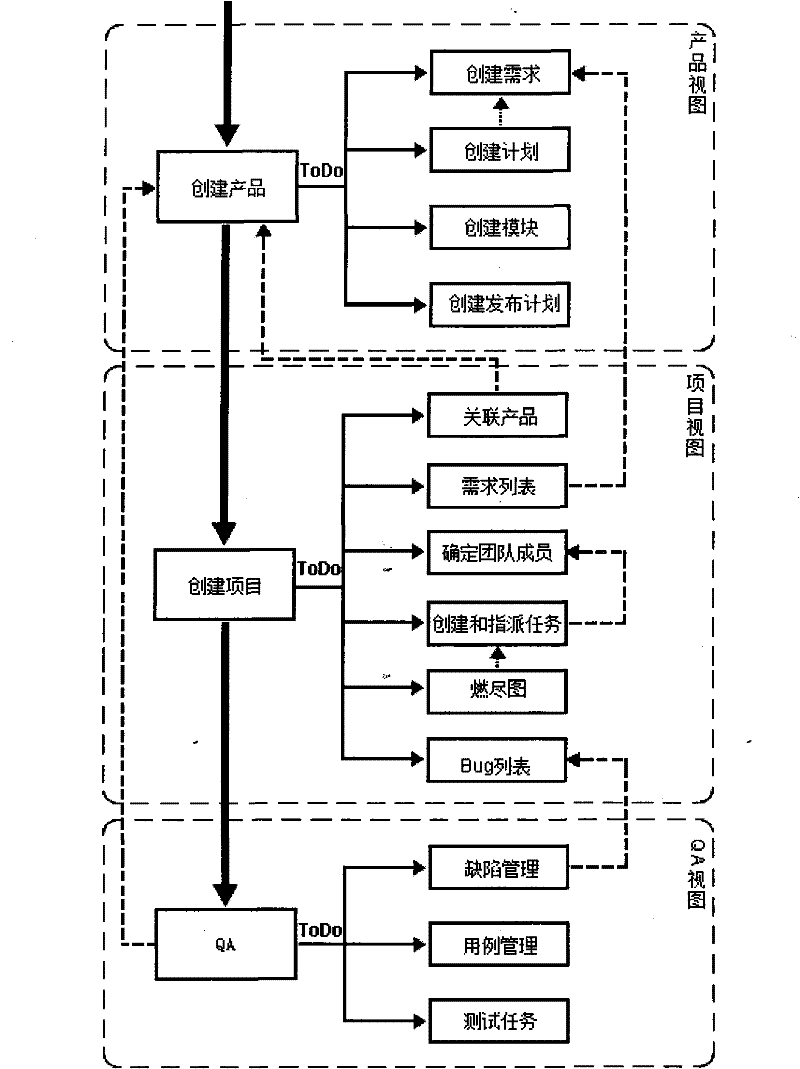

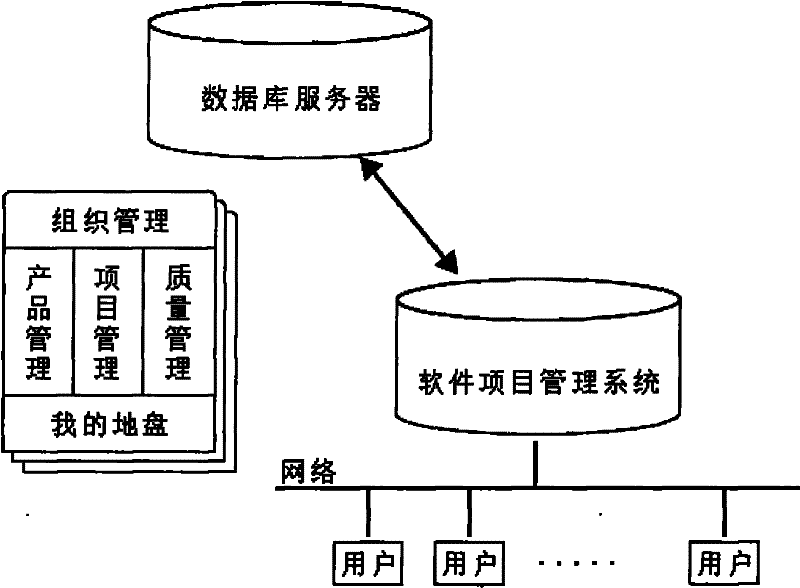

Software project management system

The invention relates to a software project management system used for the control management of the software product developing process. The software project management system comprises a database server, an organization and management module, a product management module, a project management module, a quality management module and a private zone module as well as a terminal equipment. Each module is connected with the database. The user terminal equipment is connected to the software project management system via network. The software project management system provided by the invention is integrated with product management, project management and testing management and also includes a plurality functions like event management, organization, management and the like; and the project developing speed is monitored in time to realize informatization and electronization of the software research and development process management and improve the efficiency and achievement of the project management so that the operation of the project is effectively managed.

Owner:ZHENJIANG HUAYANG INFORMATION TECH

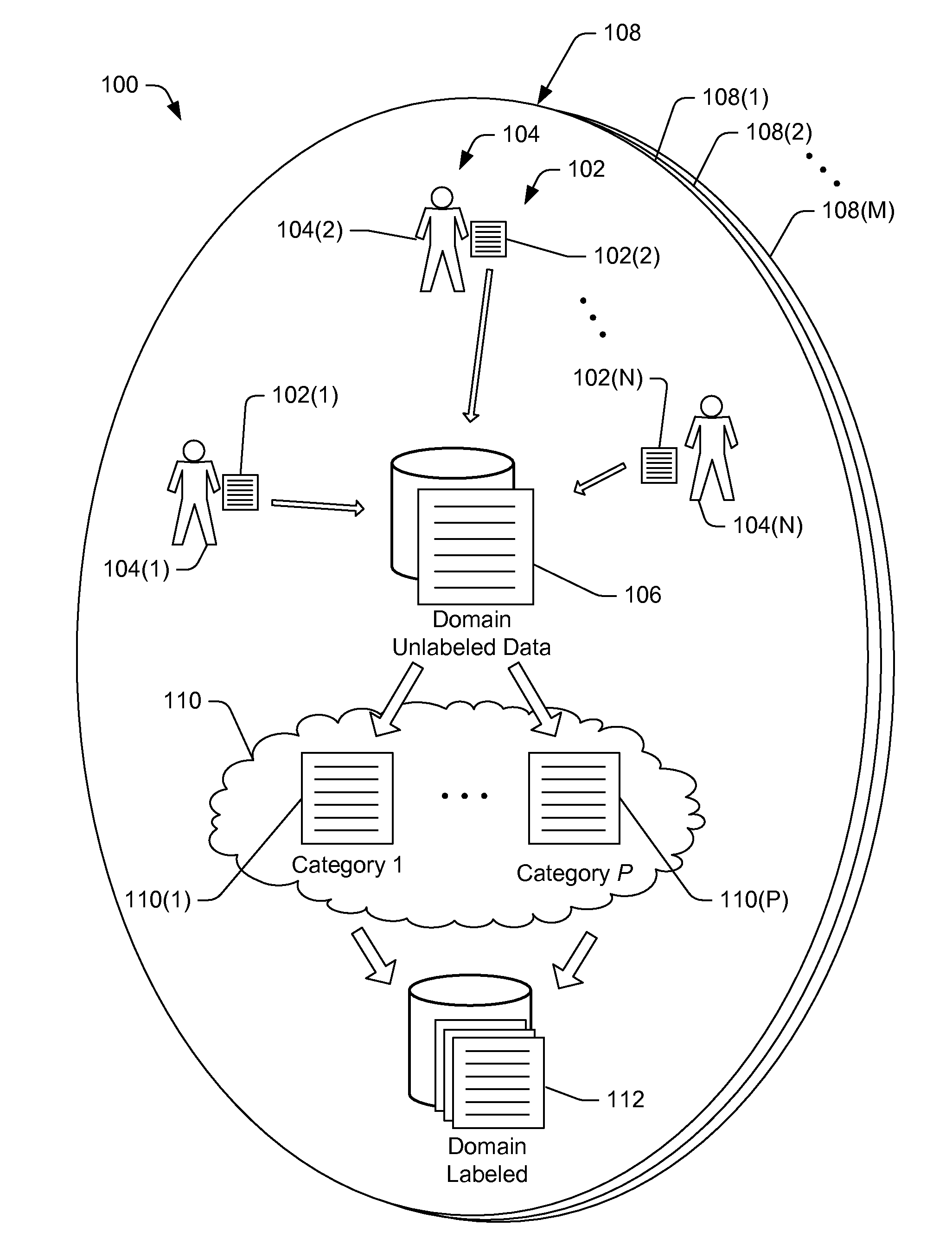

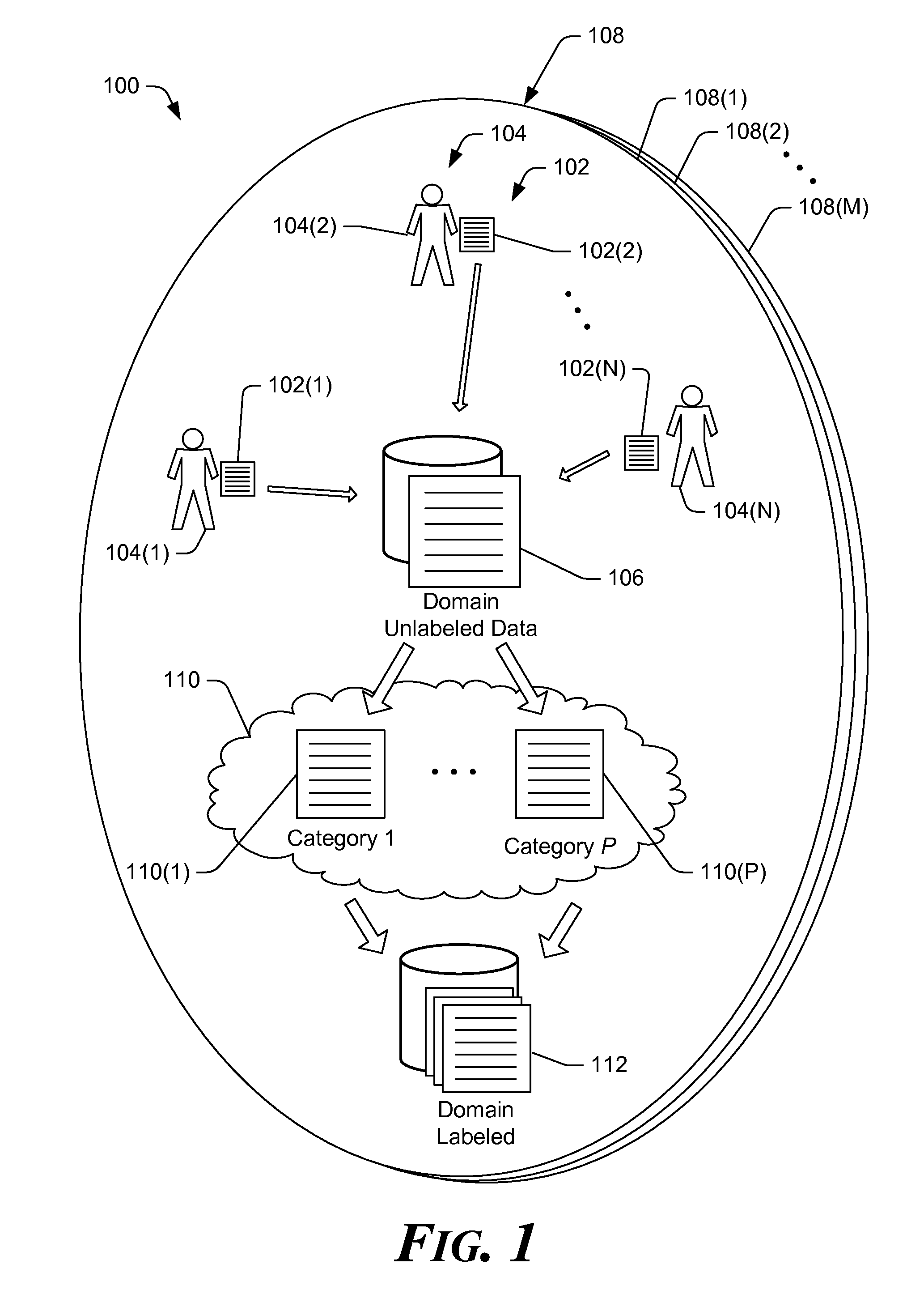

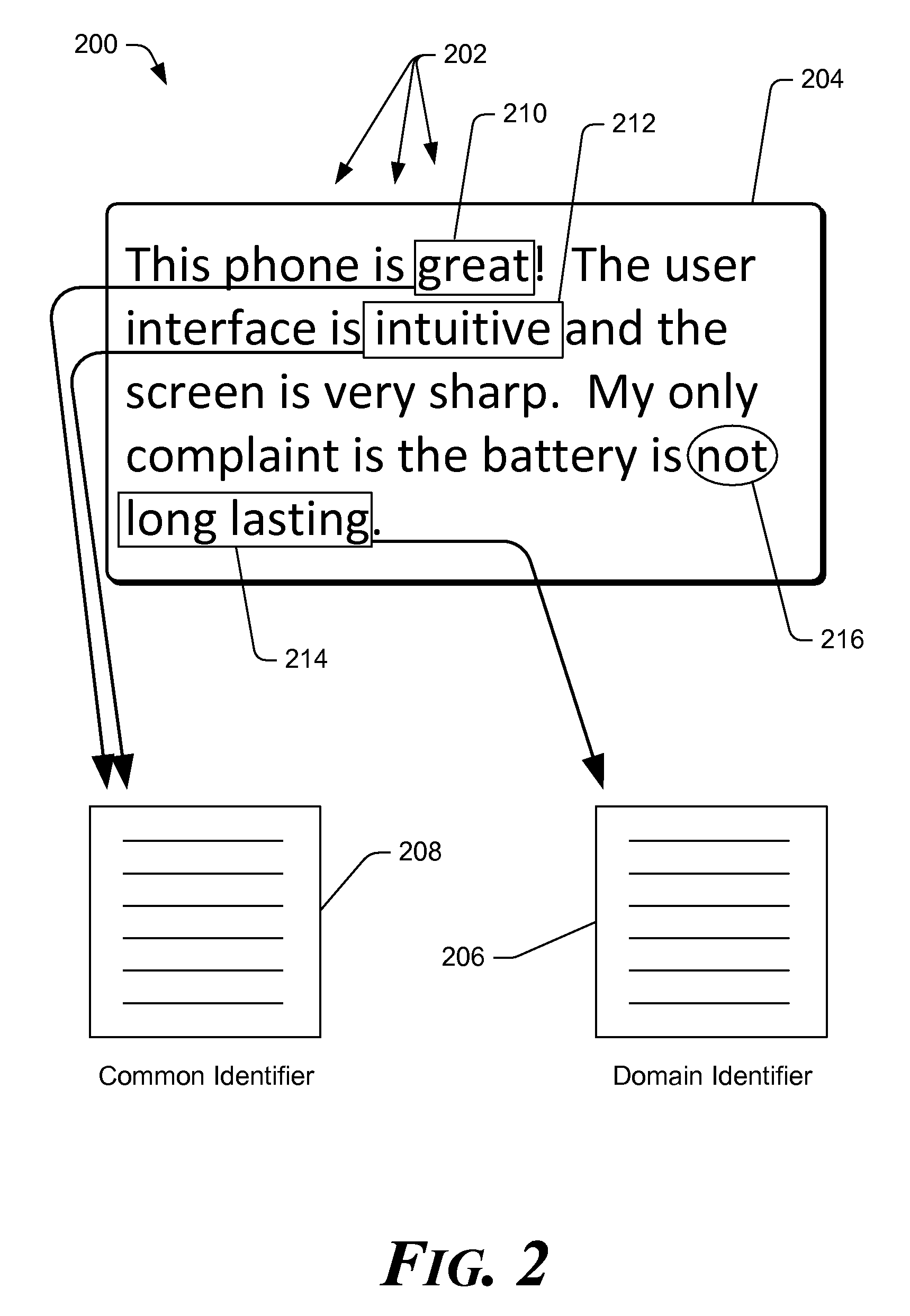

Sentiment classification using out of domain data

ActiveUS20100150393A1Simple conceptDigital data information retrievalSemantic analysisMachine learning

Owner:MICROSOFT TECH LICENSING LLC

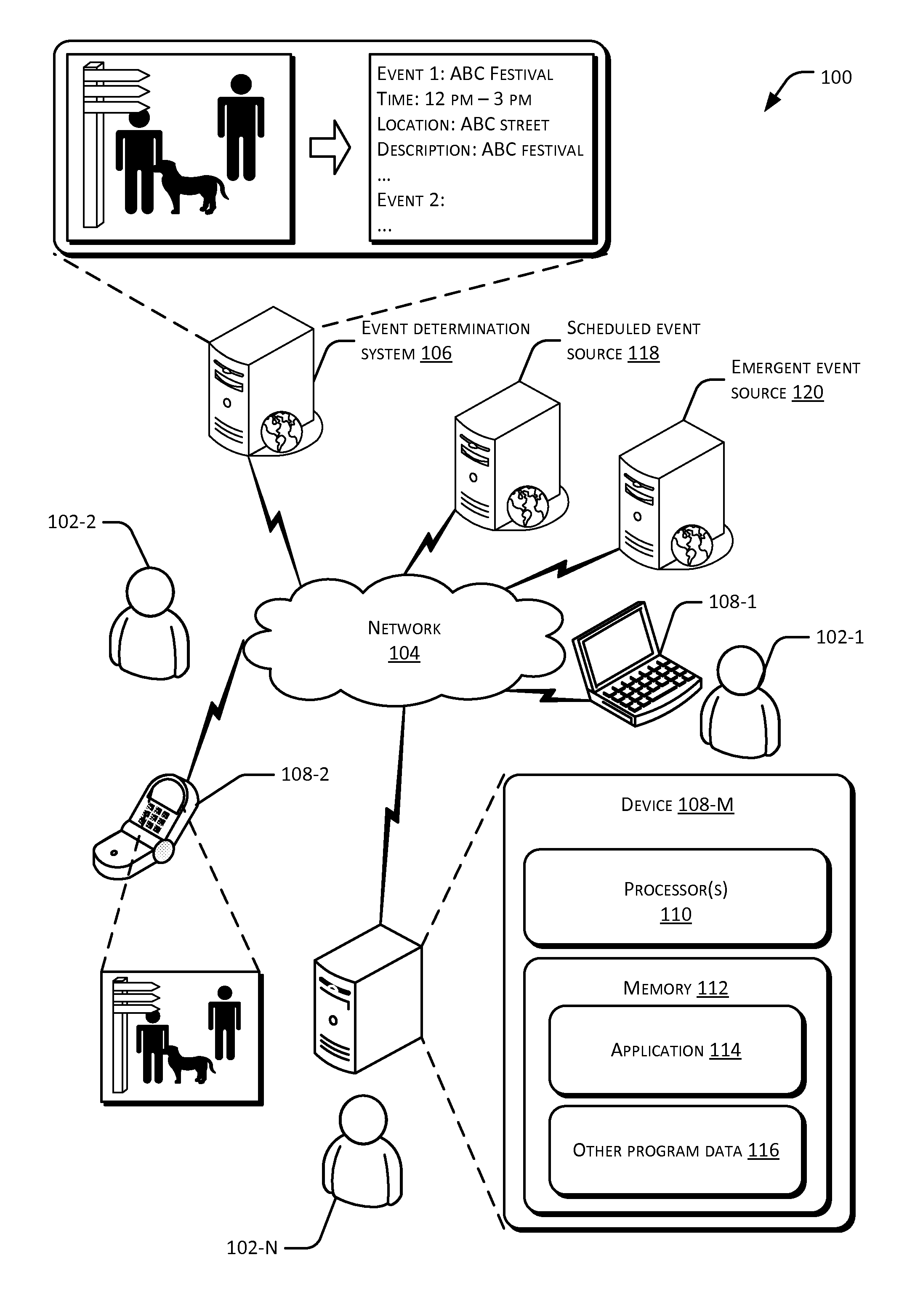

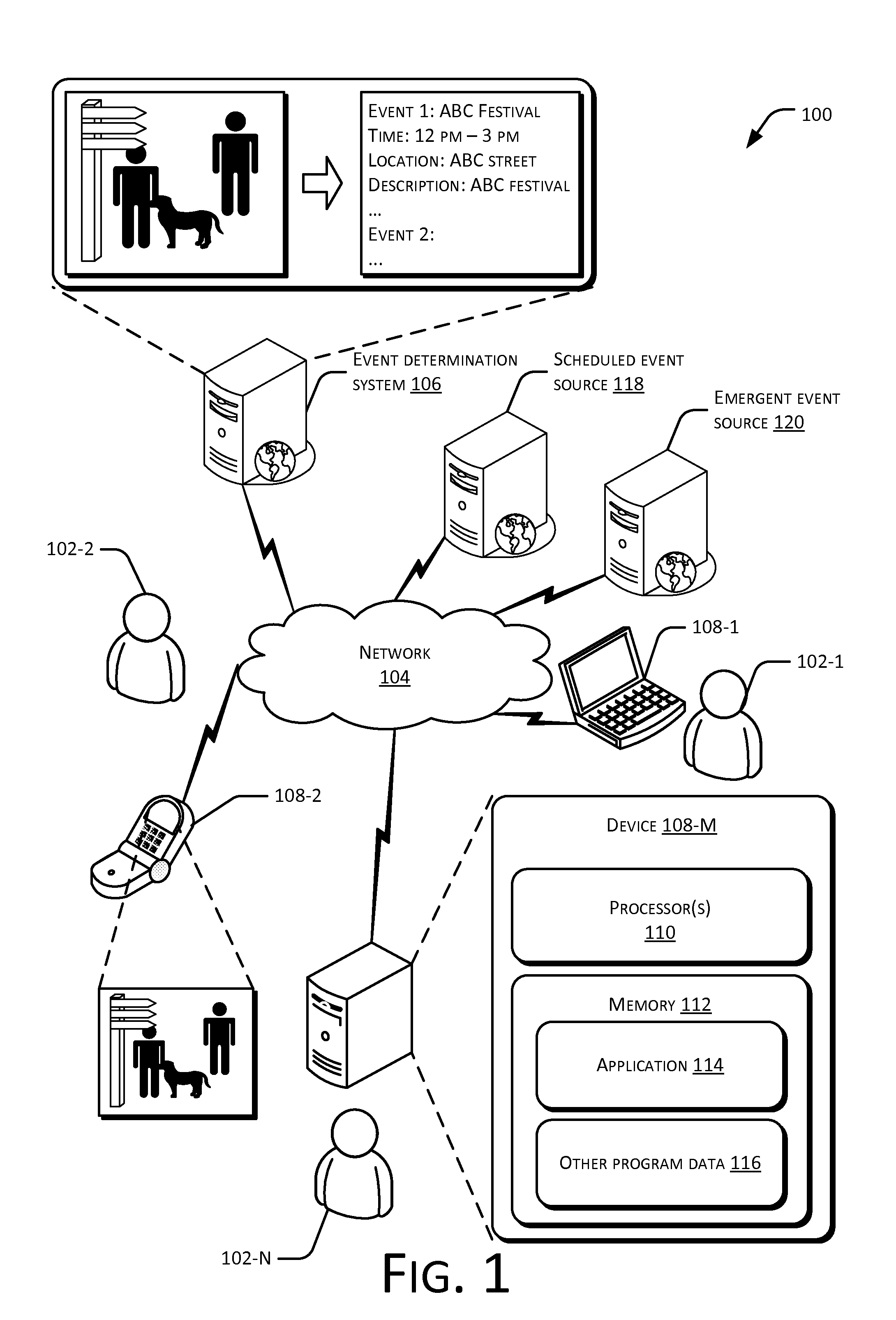

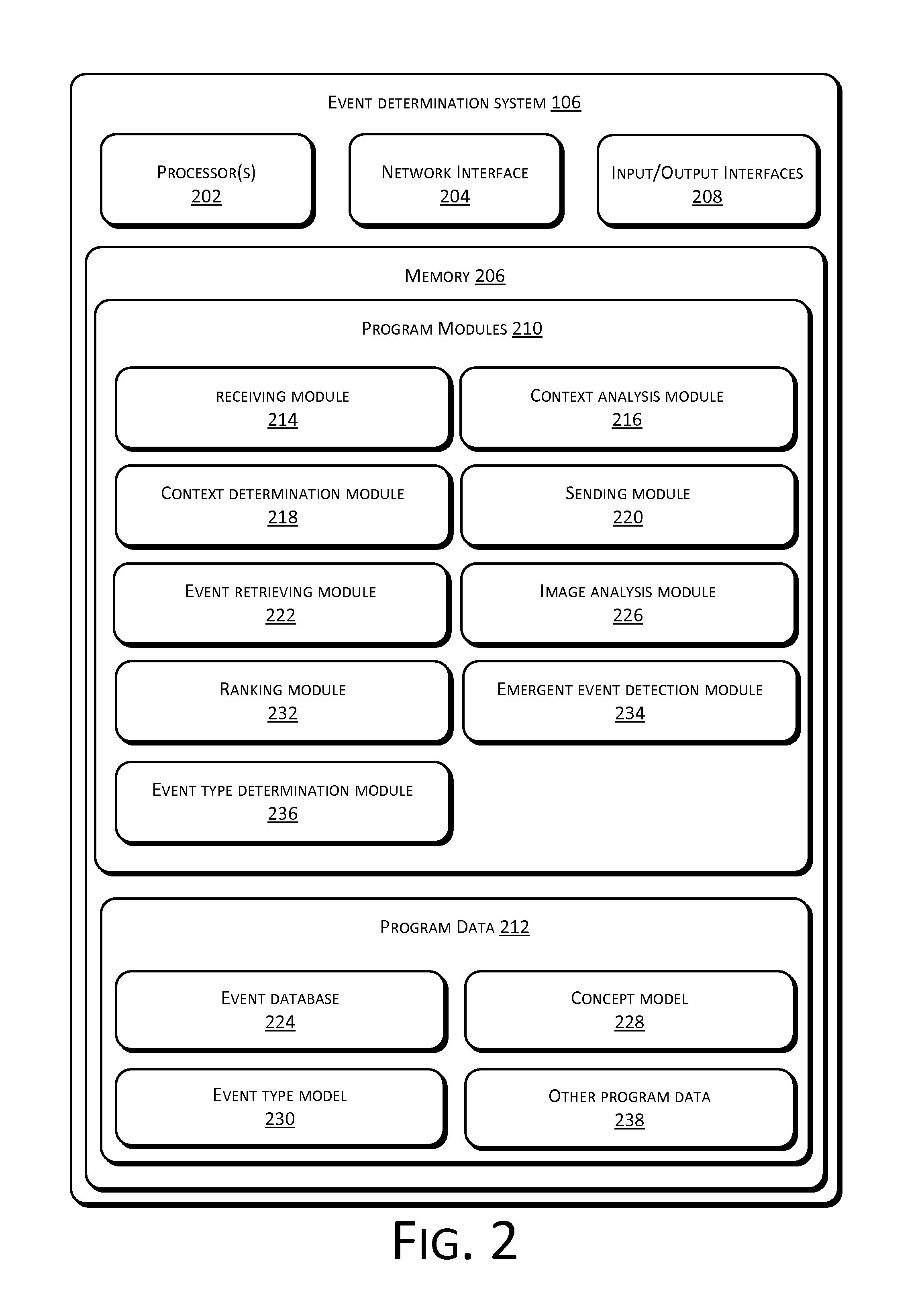

Event determination from photos

ActiveUS8831352B2Simple conceptDigital data processing detailsDigital computer detailsContext basedImage based

Events may be determined based on an image and context data associated with the image. An event type associated with the image may be determined based on a concept of the image. A list of events may be retrieved from an event database based on the context data. The retrieved list of events may then be ranked based on the determined event type and the context data. Through this event determination, a user may obtain information of one or more events happening at a specific location simply by capturing an image of that specific location, thereby saving the user from searching and browsing the Internet or brochure to locate the information of the one or more events at the specific location.

Owner:MICROSOFT TECH LICENSING LLC

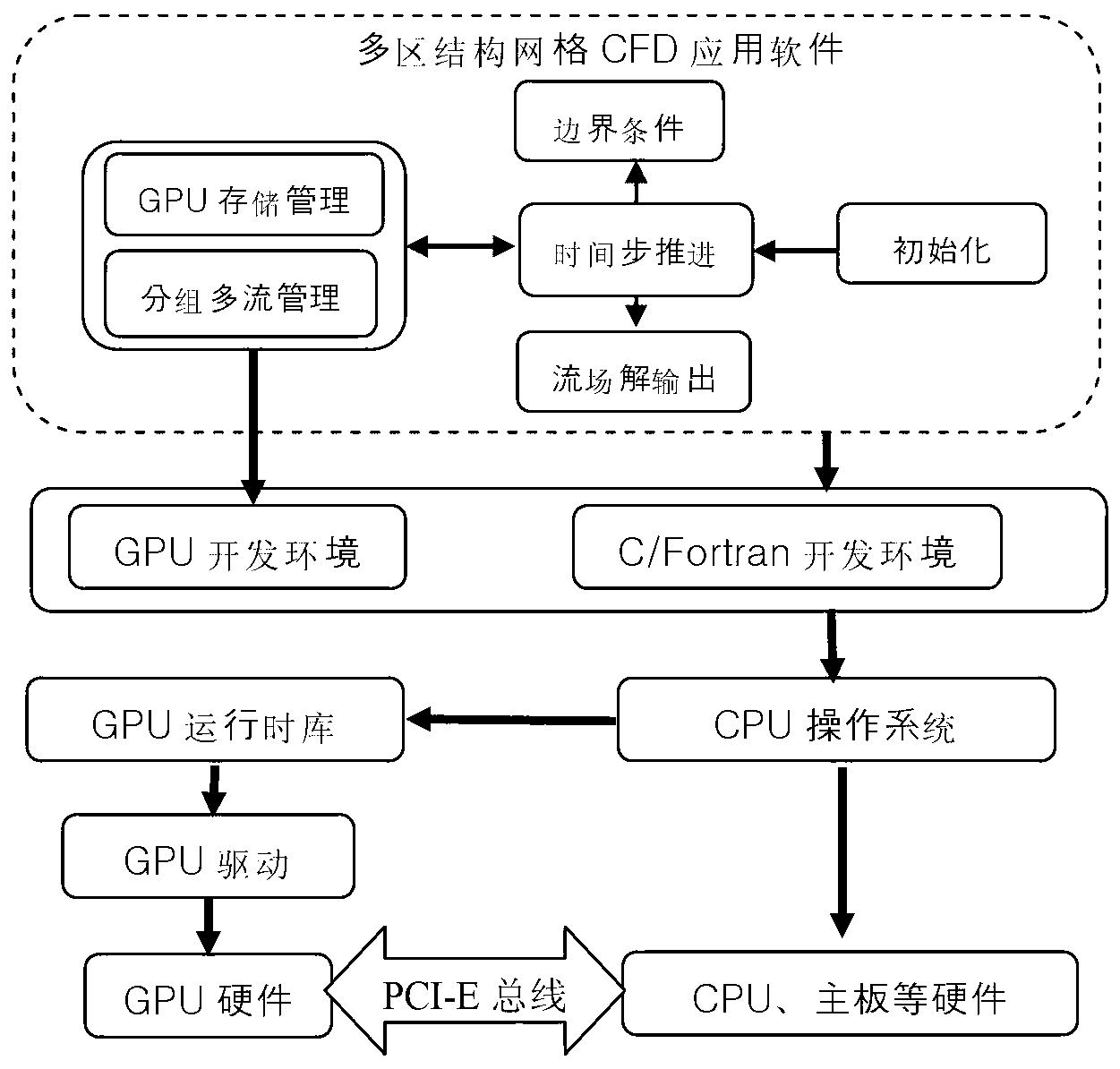

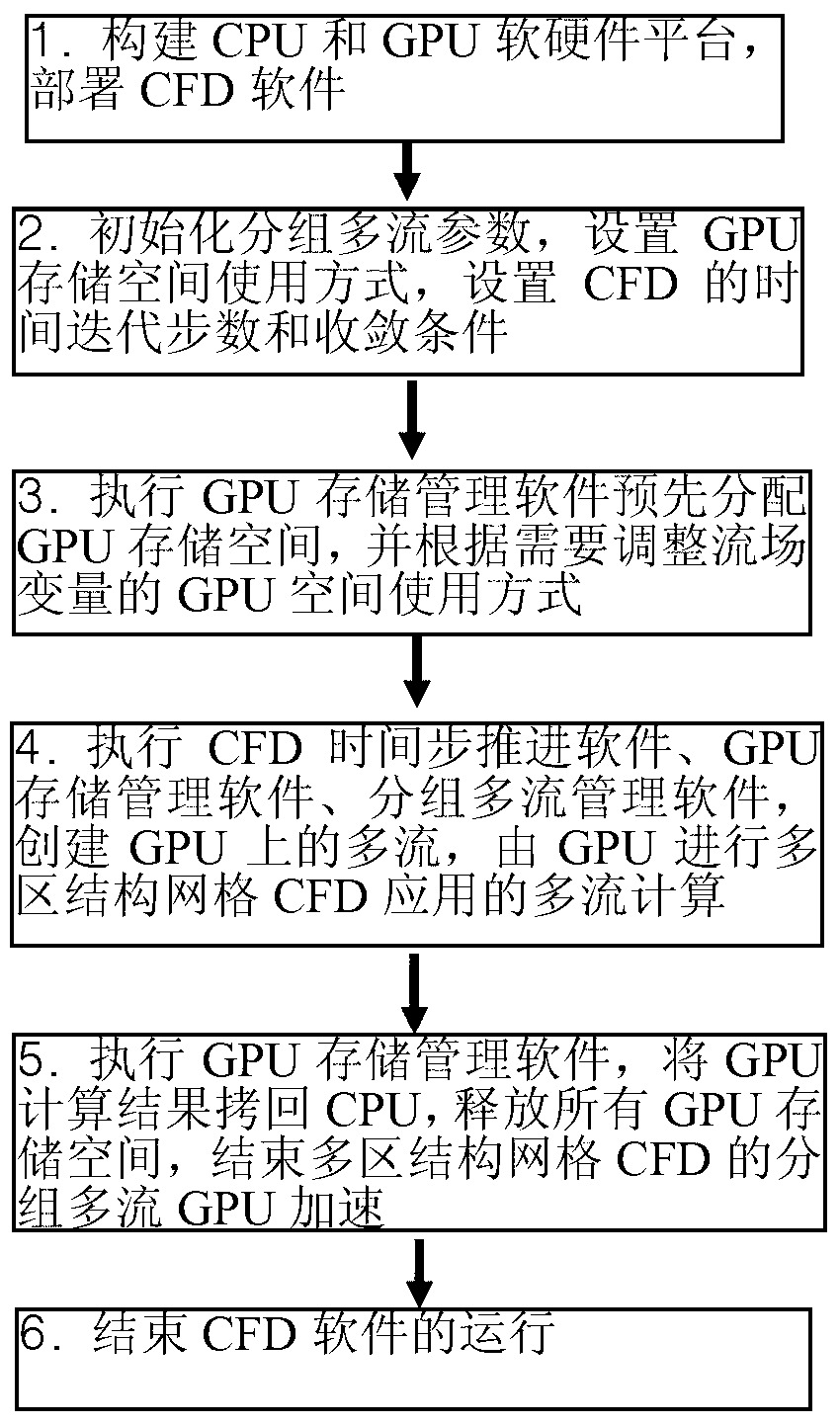

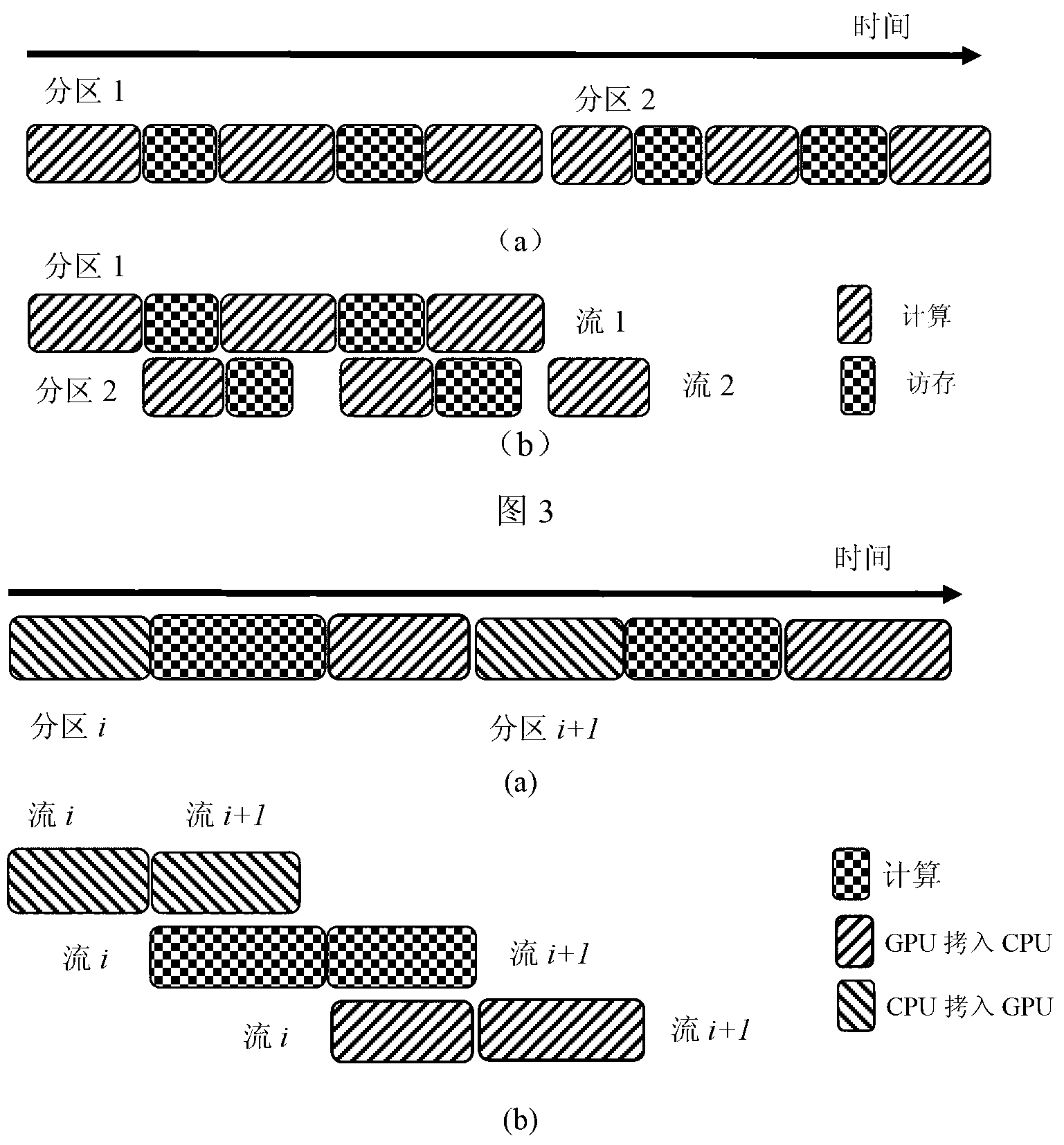

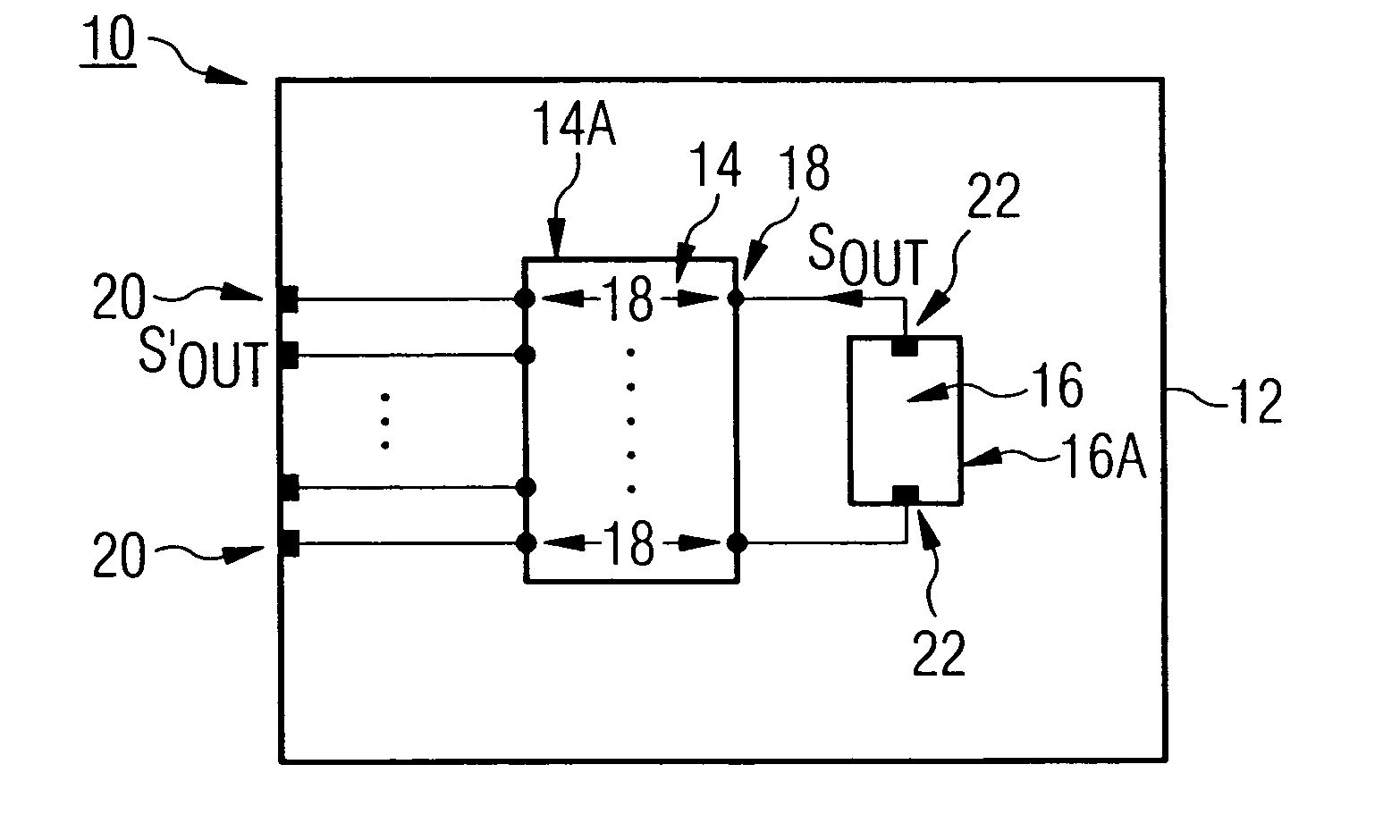

CFD (Computational Fluid Dynamics) accelerating method for multi-region structured grids on GPU (Ground Power Unit) based on grouped multi-streams

ActiveCN103226540AQuick calculationImprove efficiencyDigital computer detailsElectric digital data processingData transmissionPower unit

The invention discloses a CFD (Computational Fluid Dynamics) accelerating method for multi-region structured grids on a GPU (Ground Power Unit) based on grouped multi-streams, and aims to accelerate the CFD application of the multi-region structured grids running on the GPU. The technical scheme is as follows: the method comprises the following steps of: constructing a CPU (Central Processing Unit) and GPU software and hardware platform, and deploying CFD application software of the multi-region structured grids; implementing grouped multi-stream management software and time step advancing software, setting a grouped multi-stream parameter, a CFD time iteration step number and a convergence condition, implementing GPU storage management software to initialize the usage mode of a storage space of the GPU, pre-assigning the storage space of the GPU, and adjusting the storage of the GPU as required; and implementing the grouped multi-stream management software in time step iteration, and finishing the multi-stream calculation for the CFD application of the multi-region structured grids by using the GPU. The CFD accelerating method can be used for effectively accelerating the CFD application of the multi-region structured grids running on the GPU, calculating multiple grid sub-regions on the overlapped GPUs and realizing the communication between the CPU and the GPU, so that the expense for data transmission between the CPU and the GPU is hidden, and the limitation of smaller whole video memory volume of the GPU is relieved. In addition, the CFD accelerating method is simple and easy to realize and strong in universality.

Owner:NAT UNIV OF DEFENSE TECH

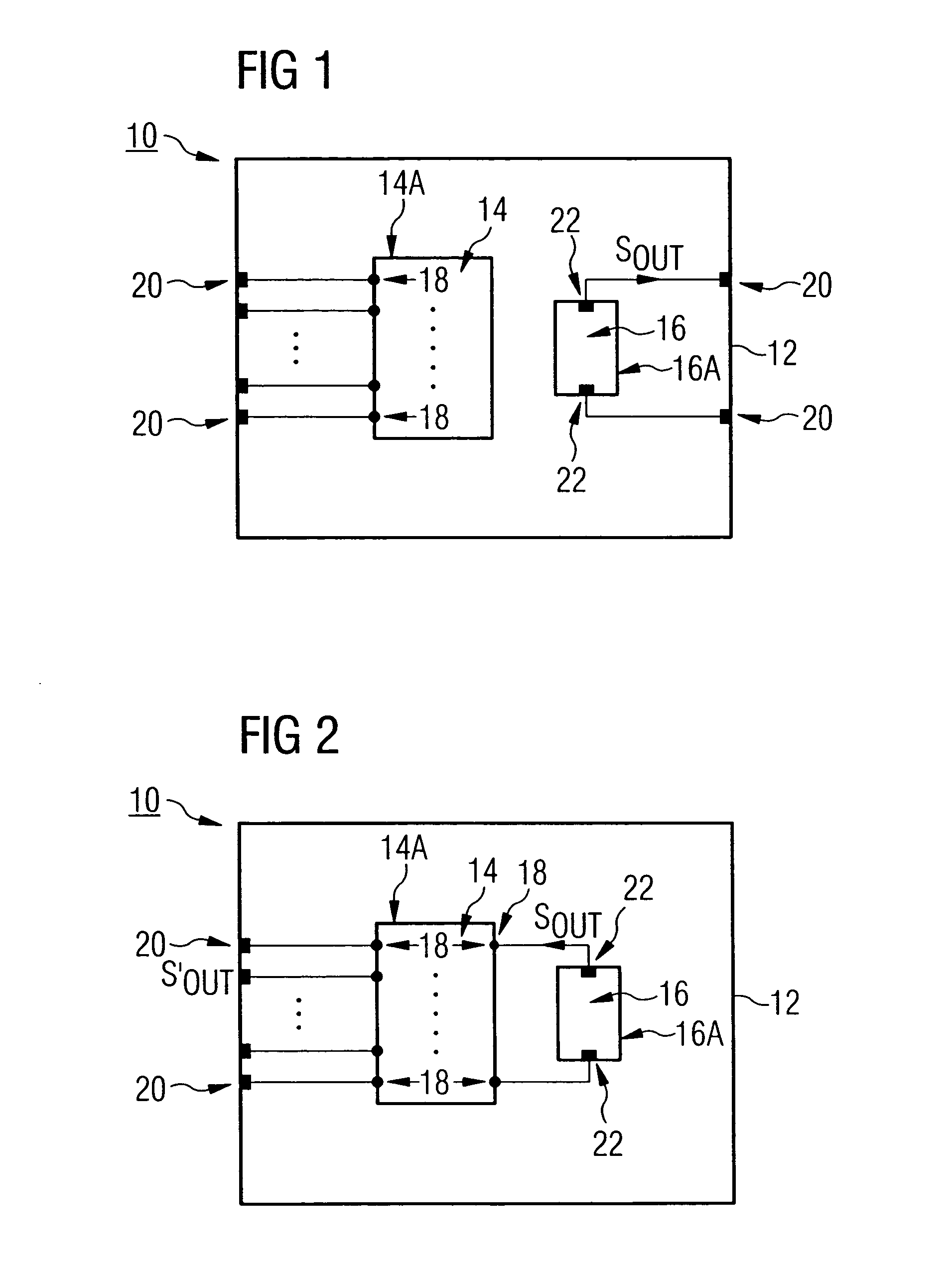

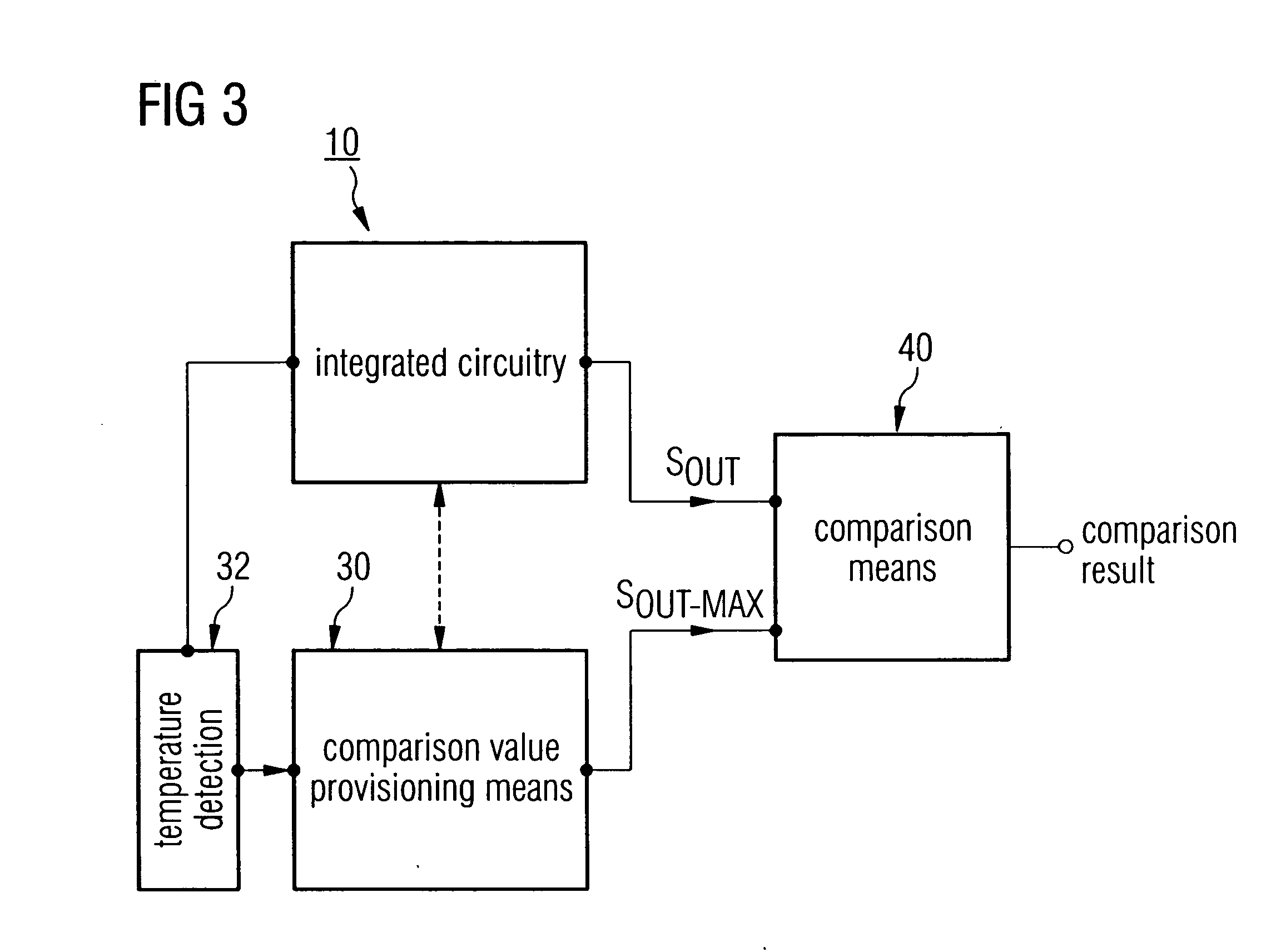

Integrated circuitry and method for manufacturing the same

ActiveUS20050045879A1Reliable functionSimple conceptAcceleration measurement using interia forcesSemiconductor/solid-state device testing/measurementEngineeringSemiconductor

The integrated circuitry on a semiconductor substrate includes an integrated circuit arranged in a circuit area of the semiconductor substrate and a stress-sensitive structure on the semiconductor substrate for detecting a mechanical stress component in the semiconductor substrate, wherein the stress-sensitive structure is implemented to provide an output signal depending on the mechanical stress component in response to an excitation and to a mechanical stress component, wherein the stress-sensitive structure is arranged in a sensor area of the semiconductor substrate and wherein the circuit area and the sensor area are spatially separated.

Owner:INFINEON TECH AG

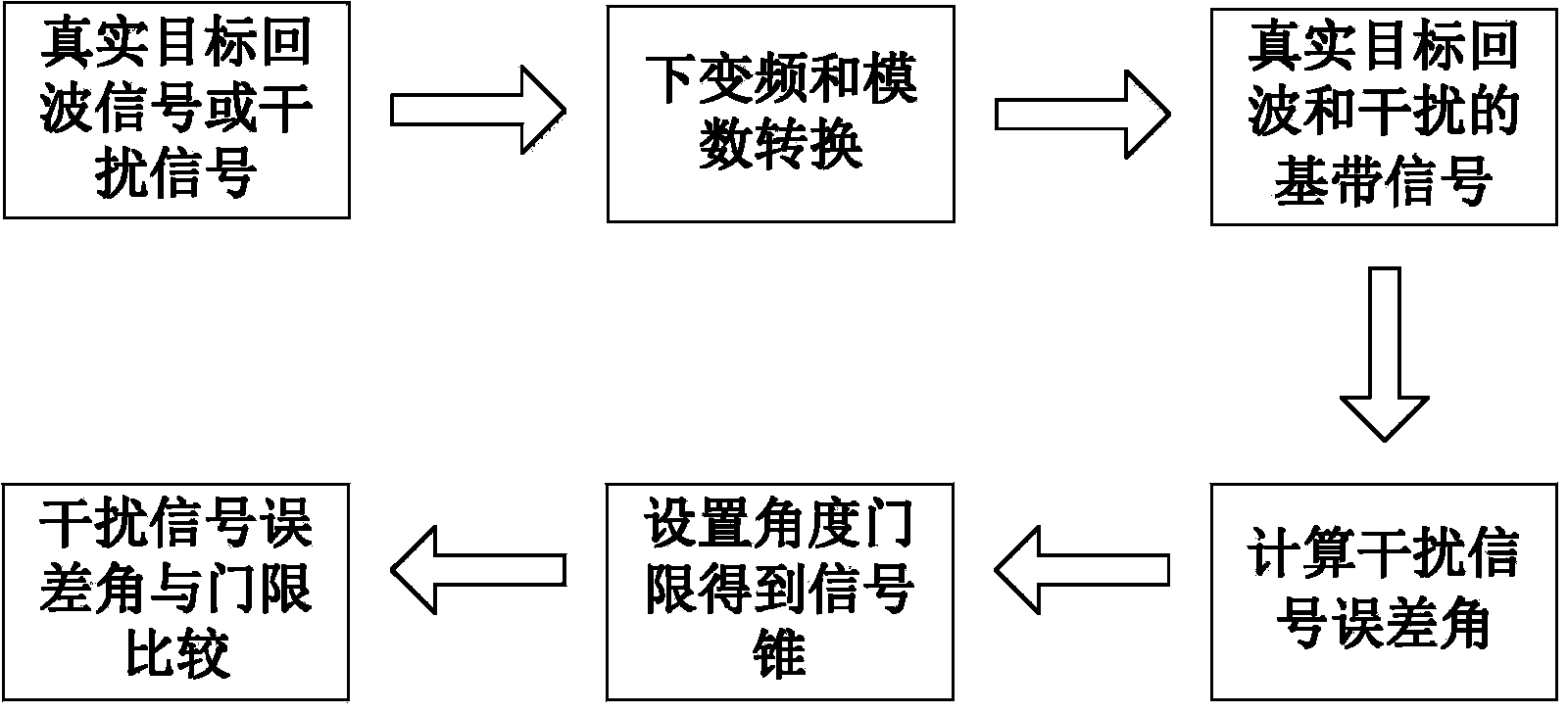

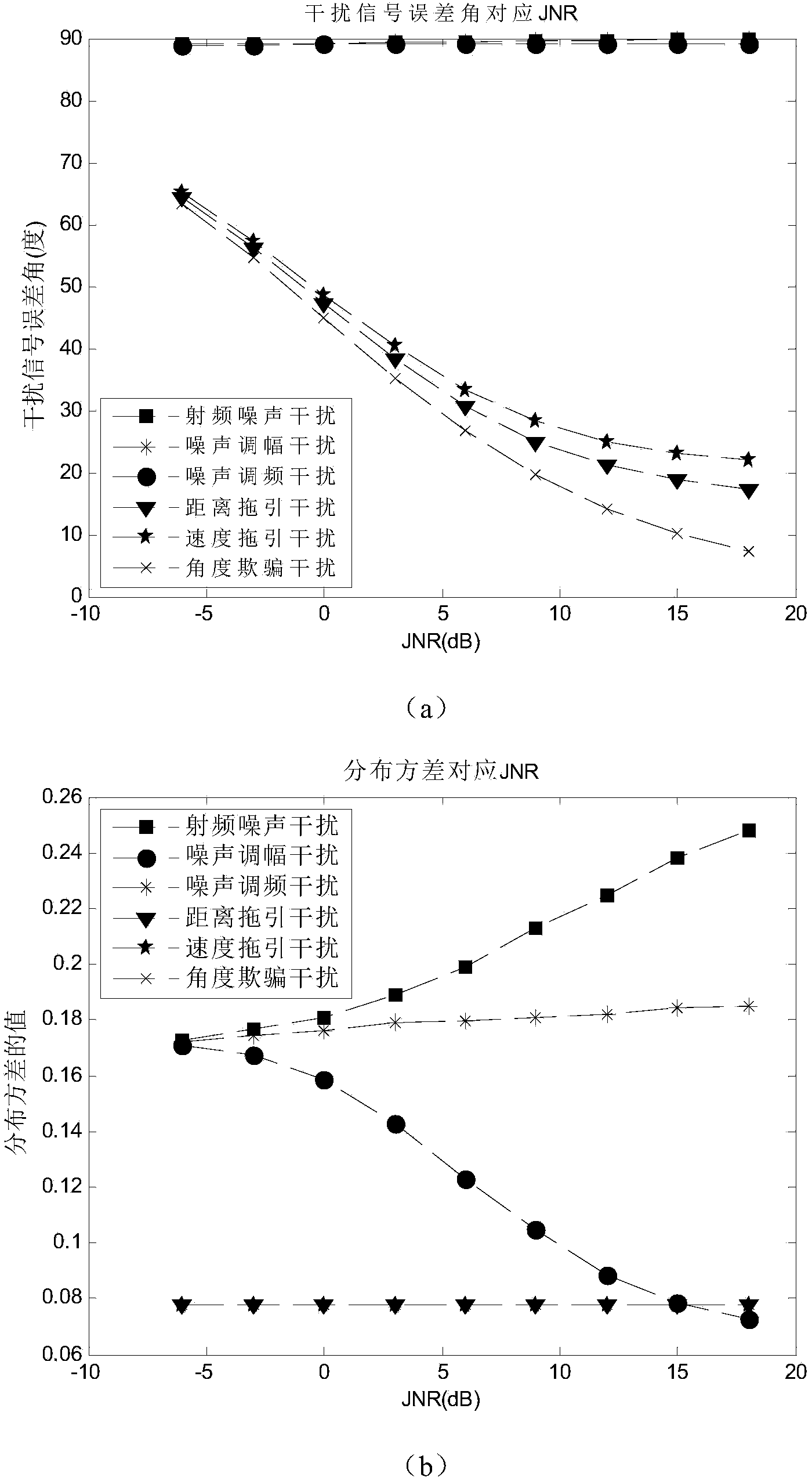

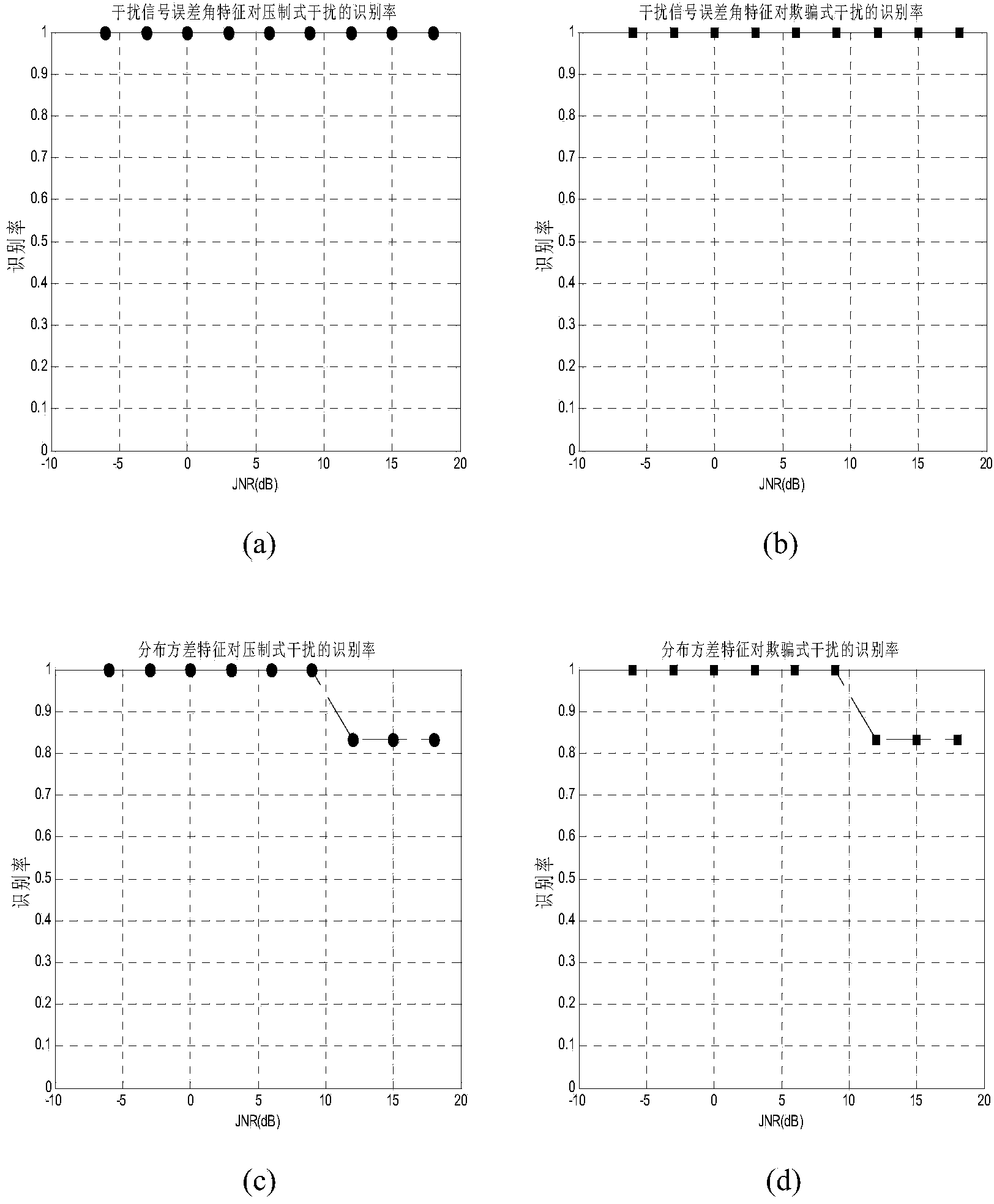

Radar suppressing jamming and deception jamming identification method based on signal cone

ActiveCN103760530ASmall amount of calculationEasy to implementWave based measurement systemsAnti jammingRadar

The invention discloses a radar suppressing jamming and deception jamming identification method based on a signal cone. The radar suppressing jamming and deception jamming identification method mainly aims to solve the problems that jamming characteristics extracted in the prior art are not steady, and the identification rate of jamming types is low under the condition of a low or high jamming to noise ratio. The radar suppressing jamming and deception jamming identification method comprises the steps that 1, target or jammed baseband signals are obtained; 2, jamming signal error angles mu between jamming signals and a real target echo signal are calculated; 3, a threshold angle theta is set as 80 degrees, the signal cone is obtained by using theta as a cone angle and using the real target echo signal as a center axis, the jamming signals located outside the cone are defined as suppressing jamming, and the jamming signals located inside the cone are defined as deception jamming; 4 the jamming signal error angles mu are compared with the threshold angle theta, and the types of jamming are determined. Jamming characteristics extracted in the radar suppressing jamming and deception jamming identification method are steady, the types of the suppressing jamming and the deception jamming are effectively identified by using the conception of the signal cone under the condition of the high or low jamming to noise ratio, and the radar suppressing jamming and deception jamming identification method can be used for anti-jamming, target detection and target tracking of radar.

Owner:XIDIAN UNIV

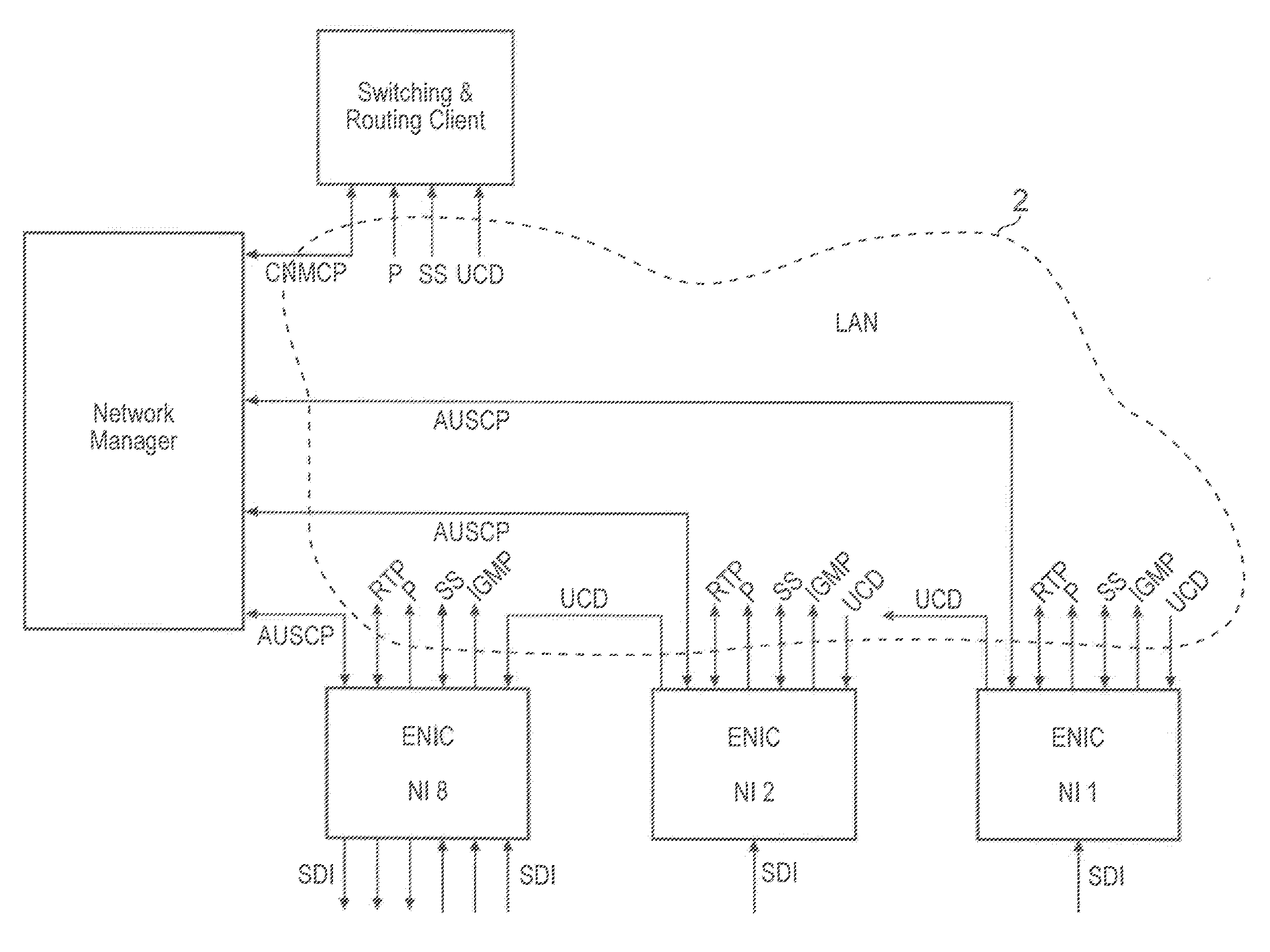

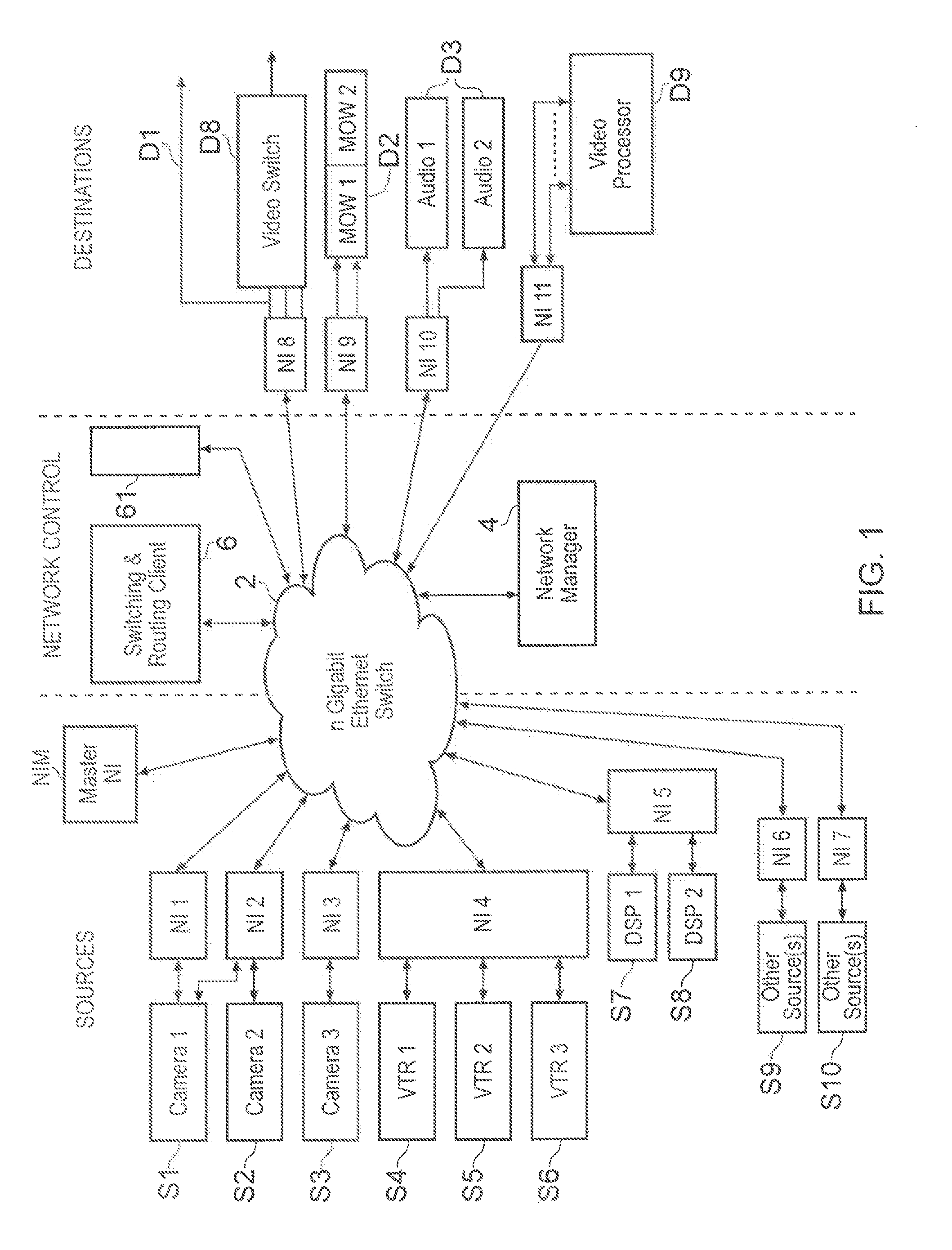

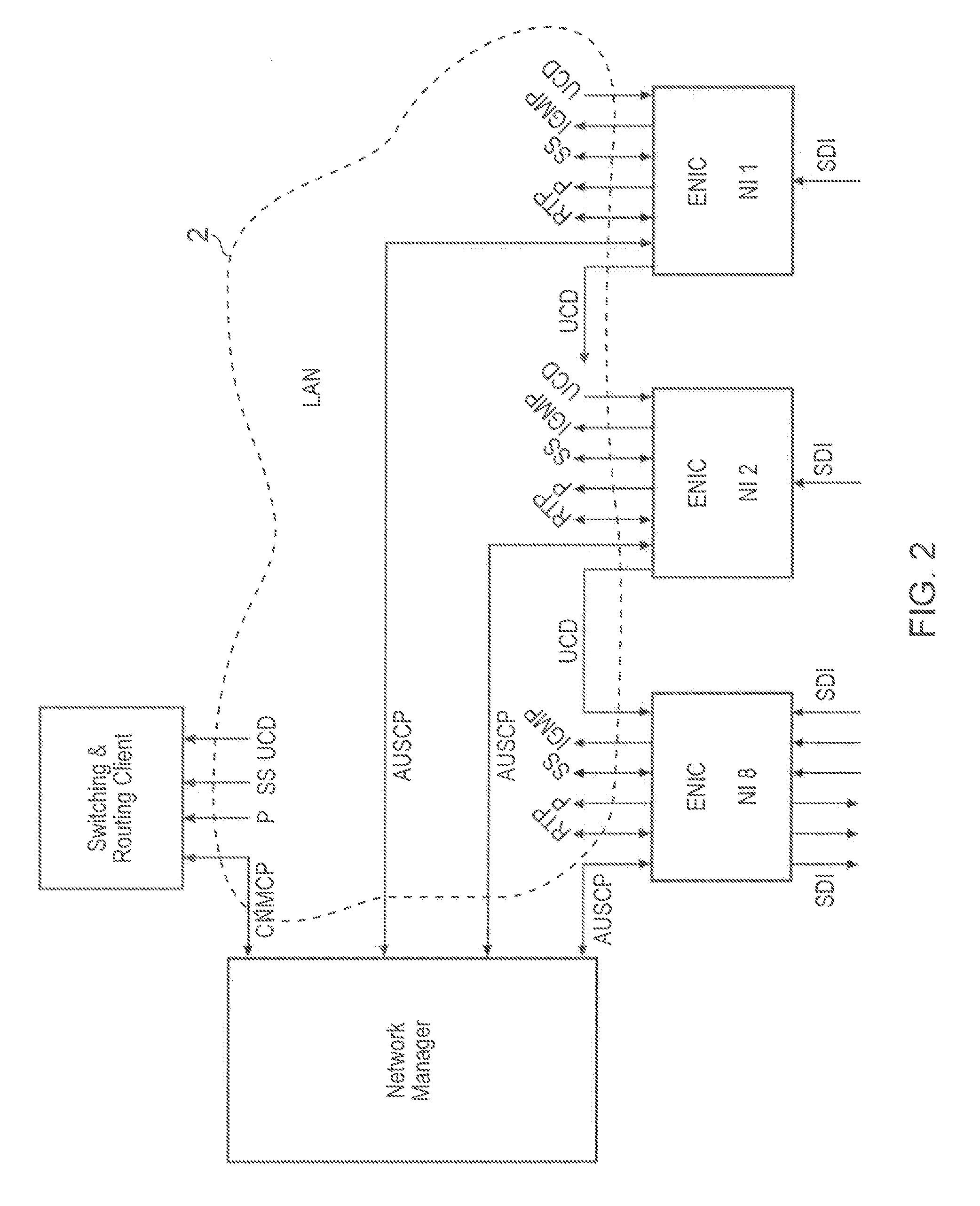

Video/audio network

ActiveUS20110055416A1Avoid restrictionsSimple conceptSpecial service provision for substationMultiple digital computer combinationsGraphicsComputer network

A packet-based data network including: an audio / video network comprising:a packet-switched network over which data including audio and / or video data packets can be carried; at least one data source connected to the network and operable to assemble packetised data comprising audio / video data at a first resolution and at a second resolution greater than the first resolution, and to transmit data packets carrying multiple audio / video streams at the first resolution by multicast network transmission; at least one client connected to the network, being a data handling device for handling packetised audio / video data and being arranged to join the multicast group to receive the multiple audio / video streams at the first resolution, wherein the client is associated with a graphical user interface configured in conjunction with a processor to select an audio / video stream, and the processor is arranged to issue a unicast command to cause transmission of a selected audio / video stream at the second resolution from the source to the client.

Owner:SONY EUROPE BV

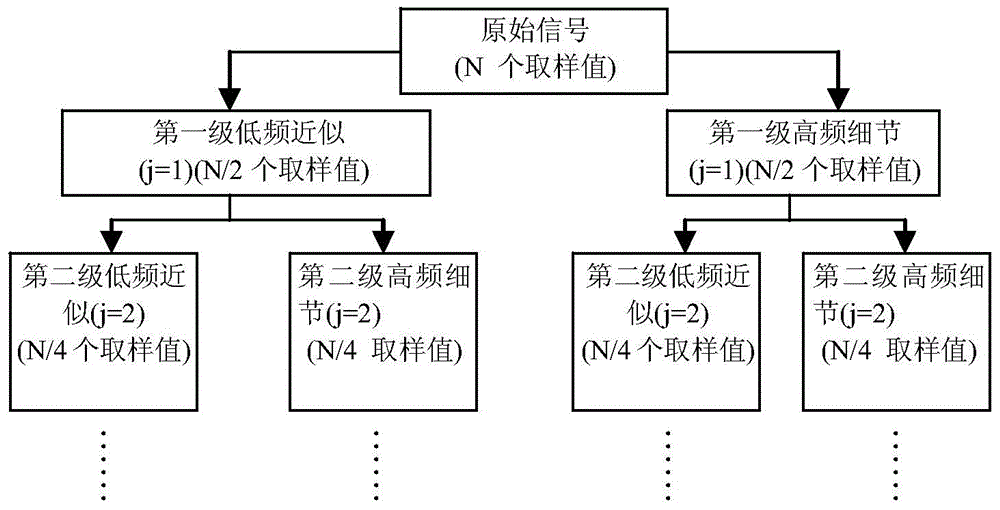

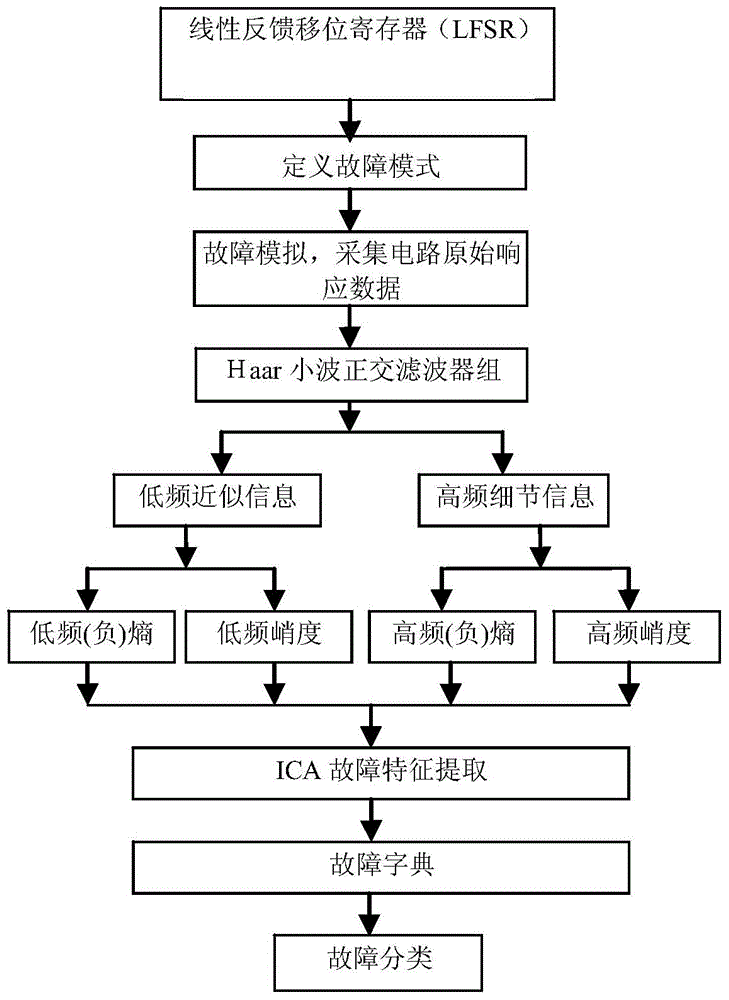

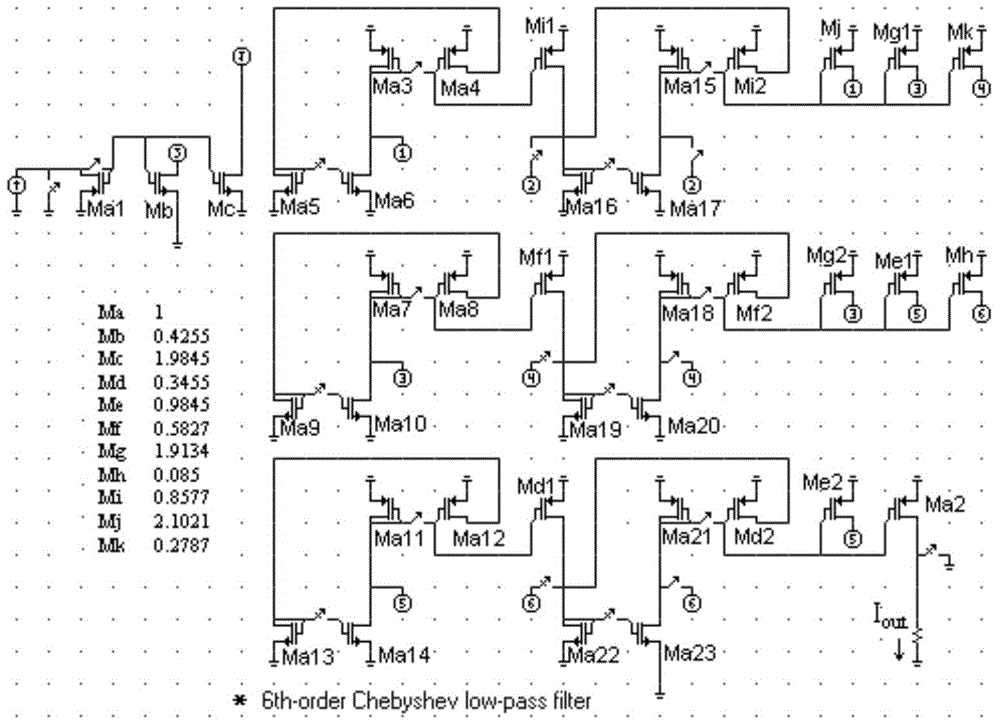

Switched circuit fault diagnosis method based on wavelet transformation and ICA (independent component analysis) feature extraction

InactiveCN104793124AThe classification result is accurateAccurate diagnosisElectronic circuit testingFeature extractionSwitched current

The invention discloses a switched circuit fault diagnosis method based on wavelet transformation and ICA (independent component analysis) feature extraction. The switched circuit fault diagnosis method includes the steps of firstly, performing classifier training and fault dictionary construction, namely, based on circuit simulation, acquiring feature parameters by a method based on wavelet transformation and ICA feature extraction, and constructing a fault dictionary and a training classifier based on the feature parameters; secondly, performing fault diagnosis, namely, acquiring the feature parameters aiming at a switched current circuit to be diagnosed by referring to the fault dictionary and by the method based on wavelet transformation and ICA feature extraction, inputting the feature parameters into a trained classifier, and subjecting the switched current circuit to be diagnosed to fault diagnosis to obtain output signals of the classifier, namely, fault diagnosis results. The switched circuit fault diagnosis method based on wavelet transformation and ICA feature extraction has the advantages of ingenious concept, easiness in implementation, simulation proving and capability of distinguishing various fault types more accurately as compared with an existing method.

Owner:CHANGSHA UNIVERSITY

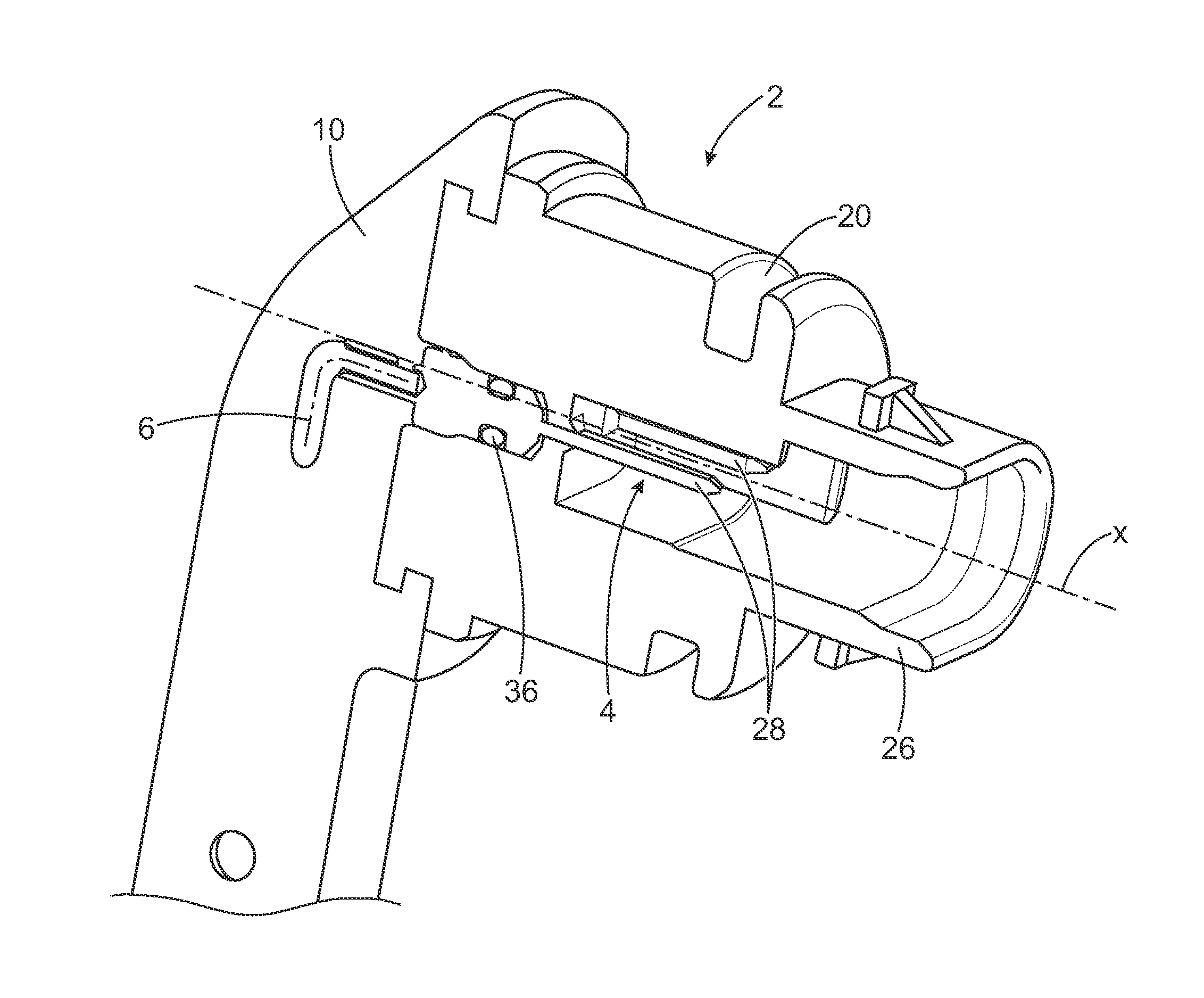

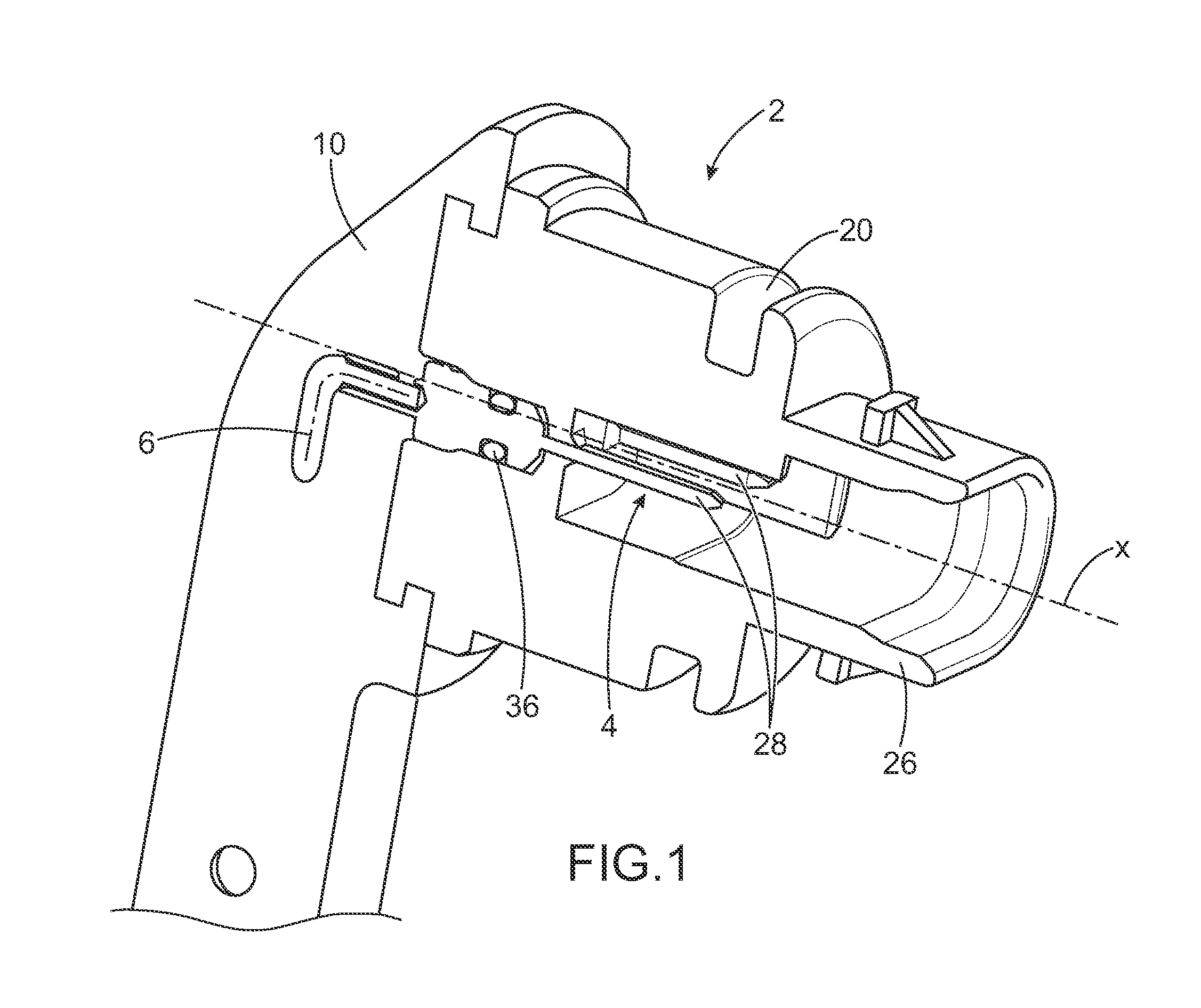

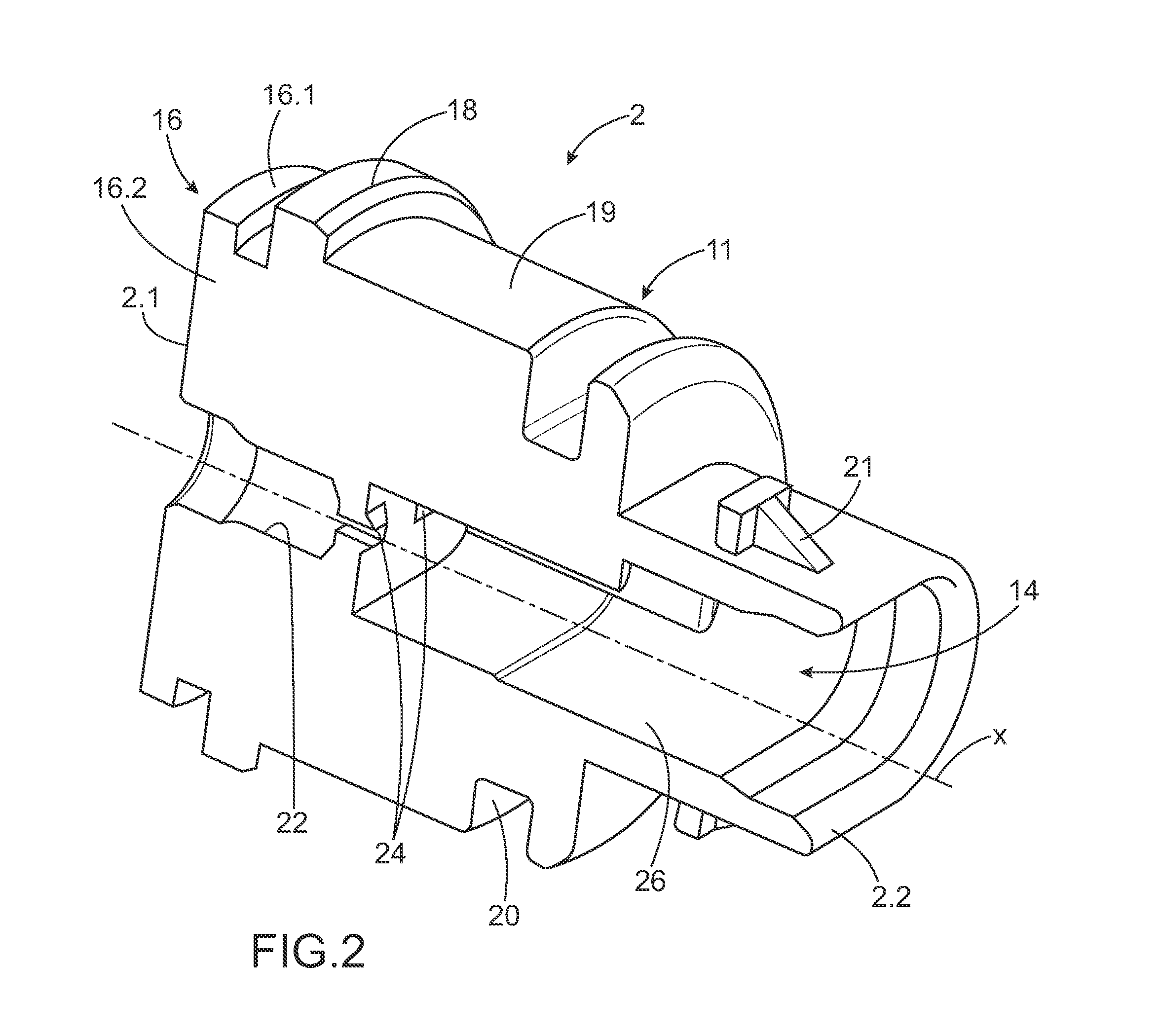

Device for producing a sealed electrical connection through a wall

ActiveUS20130203284A1Reduce in quantitySimple conceptVehicle connectorsContact member assembly/disassemblyElectricityElectrical connection

The invention relates to a device for producing a sealed electrical connection through an engine block crankcase wall in order to connect a sensor or actuating unit contained in the engine block to a central unit comprising a connector provided with at least one bore, which is intended to be arranged in an opening of said wall, at least one electrical contact connected to a wiring harness, said electric contact being surrounded by at least one O-ring seal and arranged in the bore of the connector, said device also comprising an over-moulded part on the wiring harness, an end of the electrical contact connected to the wiring harness and an end of the connector, such that, after the device has been mounted in the opening, the junction between said over-moulded part and the connector is situated on one side of the wall.

Owner:BONTAZ CENT

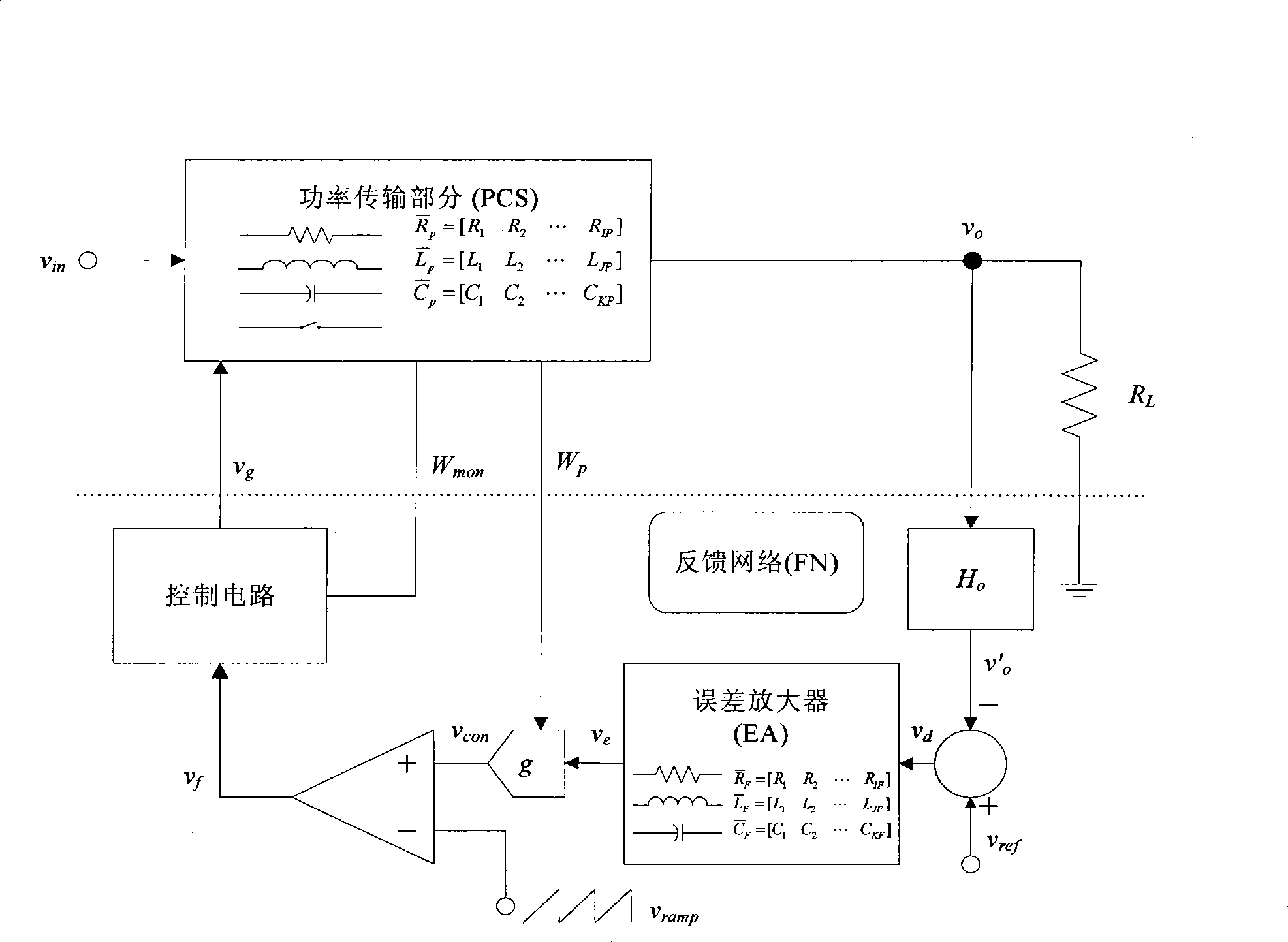

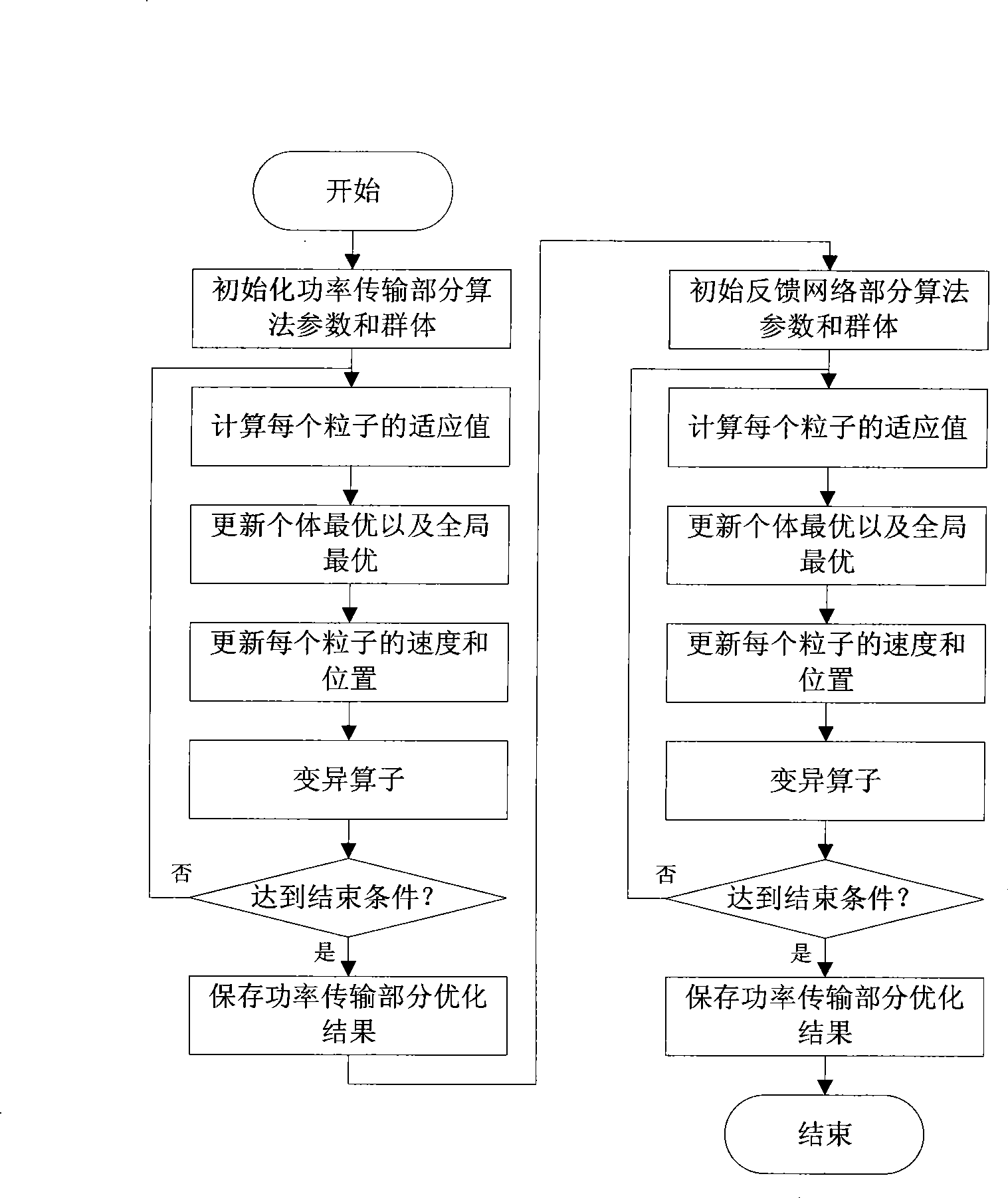

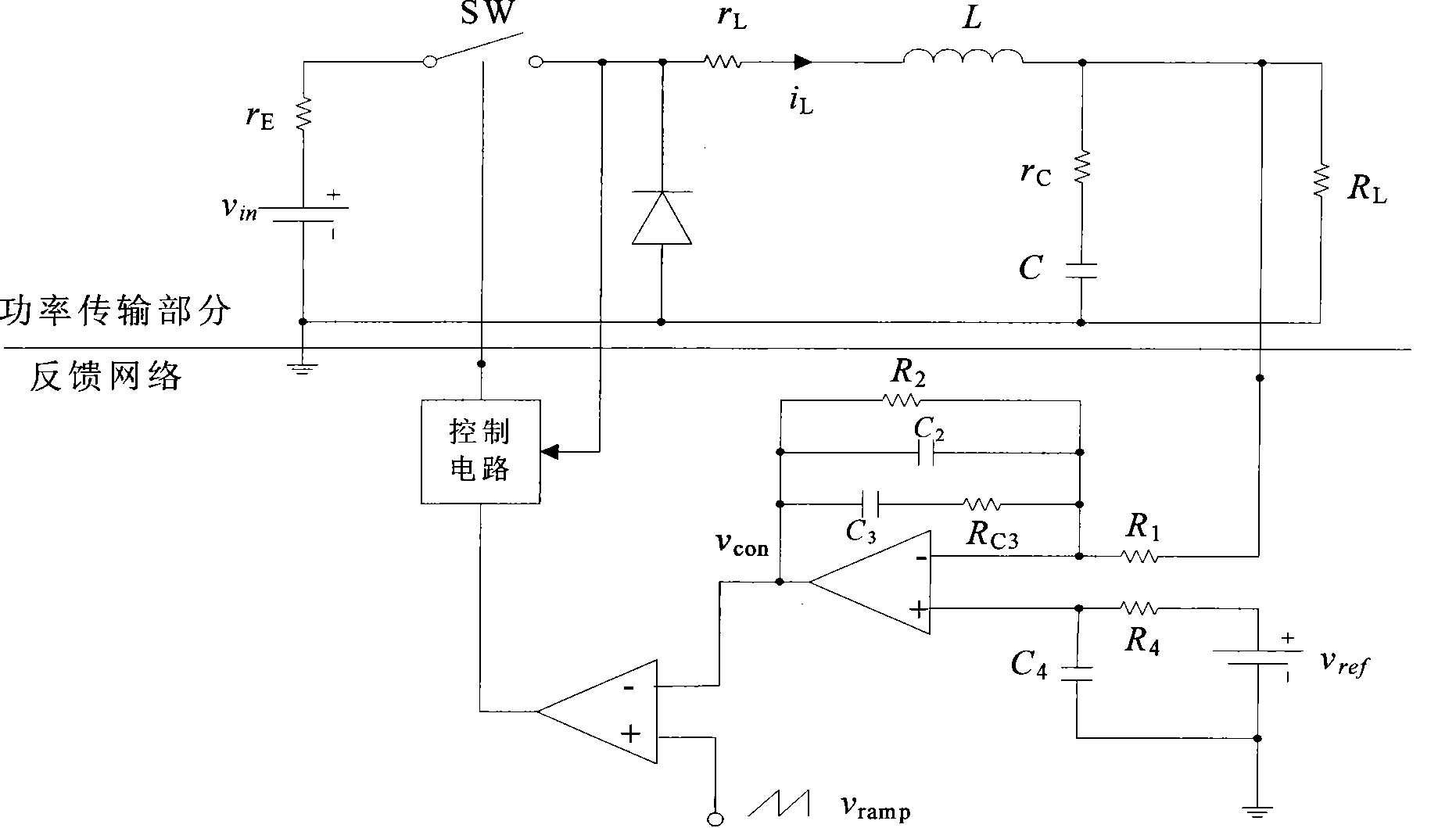

Power electronic circuit optimization method based on particle swarm algorithm

InactiveCN101446997ASimple conceptEasy to implementBiological modelsSpecial data processing applicationsElectric power transmissionMutation operator

The demand for automation design of power electronic circuits becomes higher and higher with the development of the power electronic technology. In the invention, a particle swarm algorithm is applied to the design and optimization of the power electronic circuits, and the invention mainly relates to the power electronics field and the intelligent computation field. In the optimization method, an optimization process is divided into two parts by a decoupling technology to respectively optimize the power transmission of the power electronic circuit and a feedback network. Meanwhile, a mutation operator is introduced into the particle swarm algorithm to increase diversity of the swarm and improve the optimization efficiency of the algorithm. The optimization design of a buck converter is taken as an example for testing, which proves that the optimization method is very effective.

Owner:SUN YAT SEN UNIV

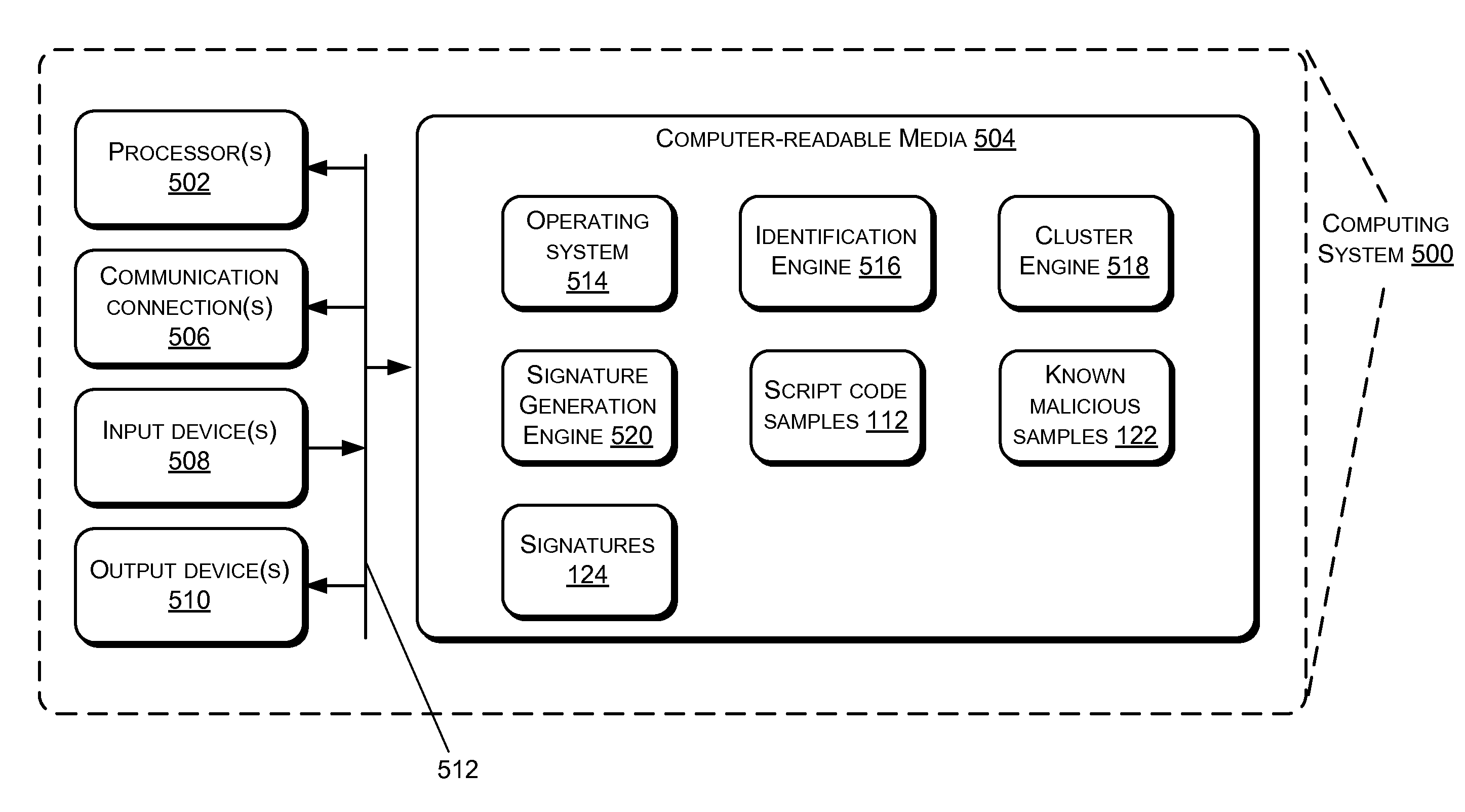

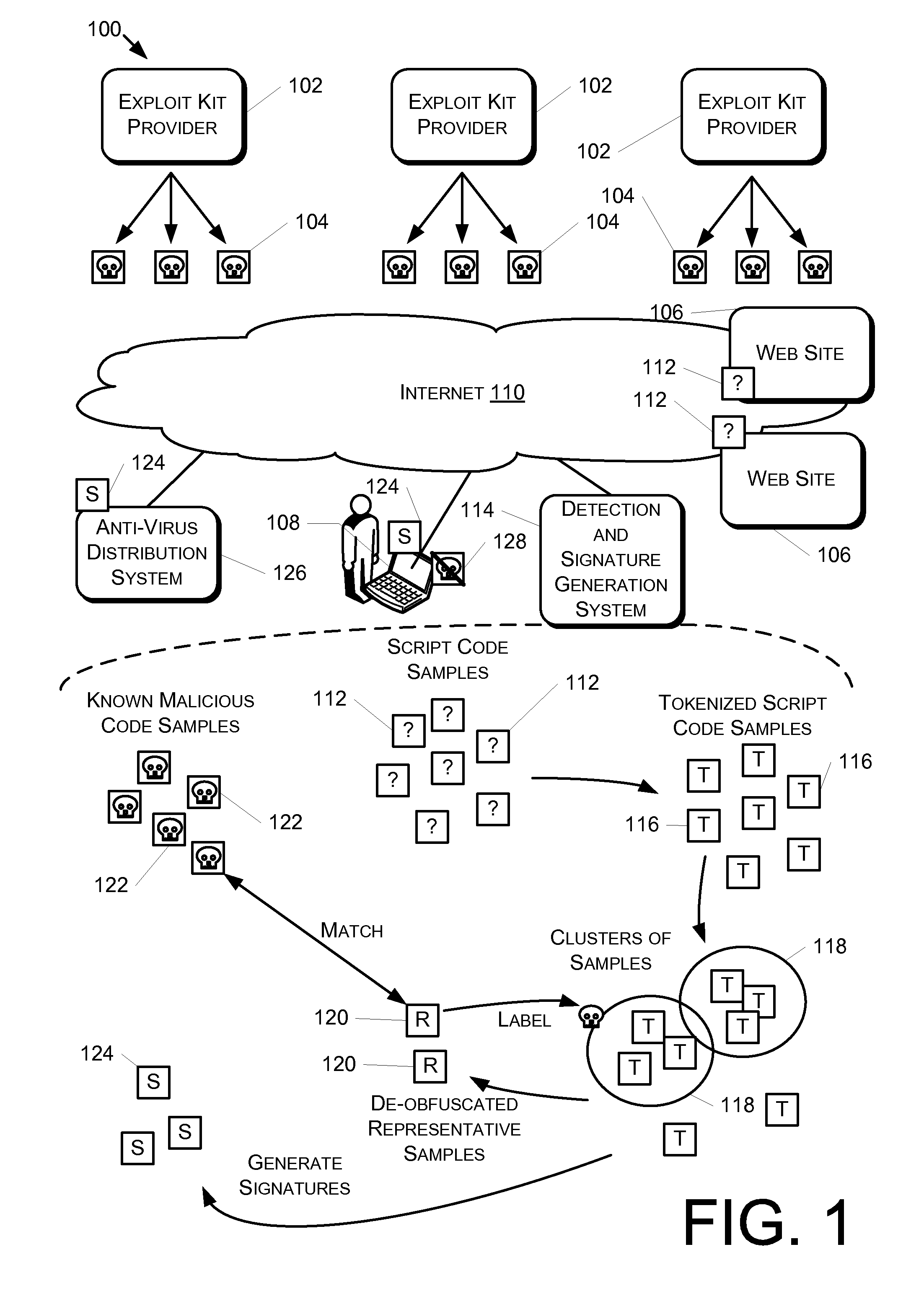

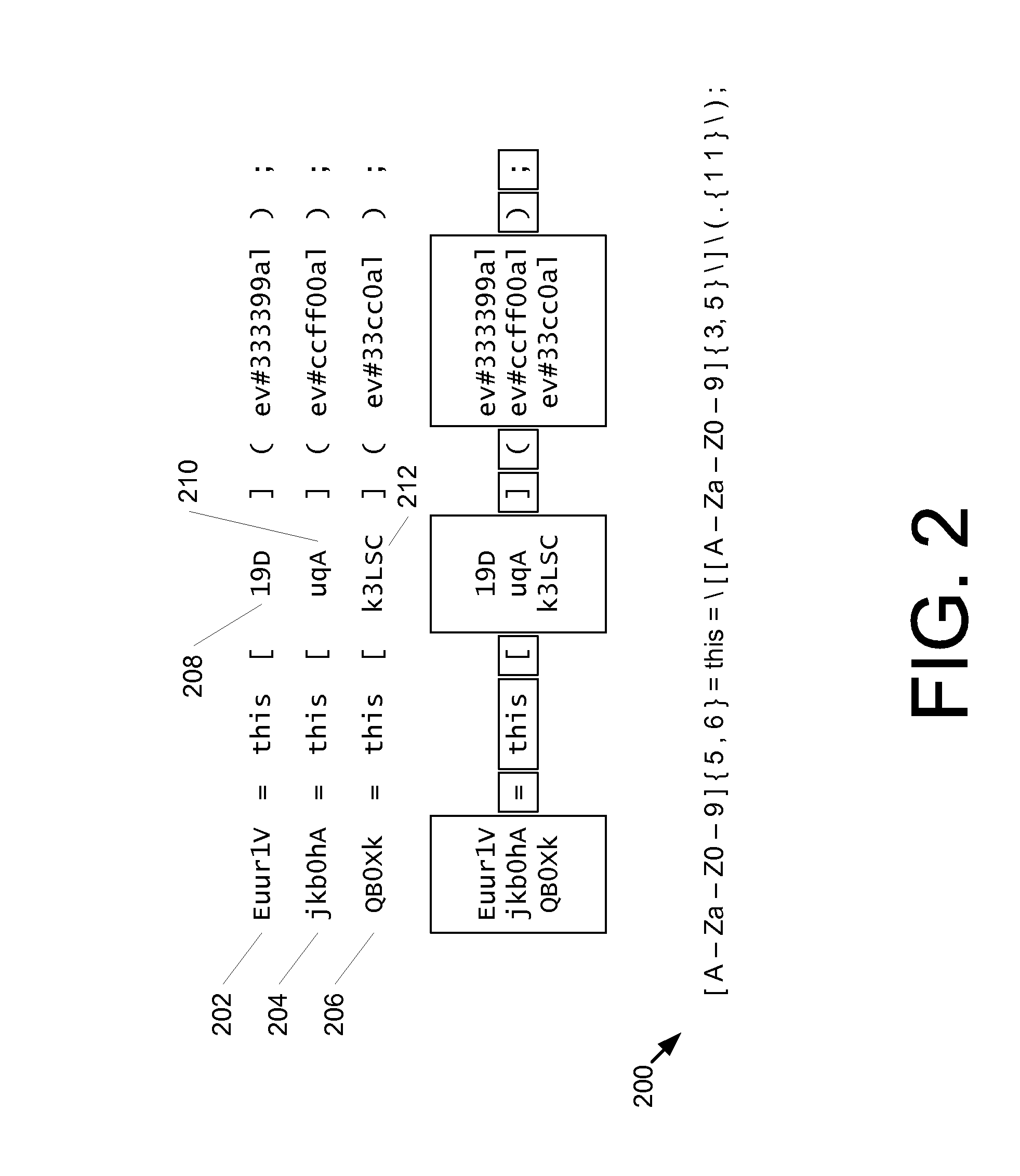

Code Labeling Based on Tokenized Code Samples

ActiveUS20160212153A1Simple conceptMemory loss protectionError detection/correctionPattern recognitionMalware

Disclosed herein are systems and methods for detecting script code malware and generating signatures. A plurality of script code samples are received and transformed into a plurality of tokenized samples. The tokenized samples are based on syntactical elements of the plurality of script code samples. One or more clusters of samples are determined based on similarities in different ones of the plurality of tokenized samples, and known malicious code having a threshold similarity to a representative sample of the cluster of samples is identified. Based on the identifying, the cluster of samples is identified as malicious. Based at least on respective ones of the plurality of tokenized samples associated with the cluster of samples, a generalized code signature usable to identify the script code samples in the cluster of samples is generated.

Owner:MICROSOFT TECH LICENSING LLC

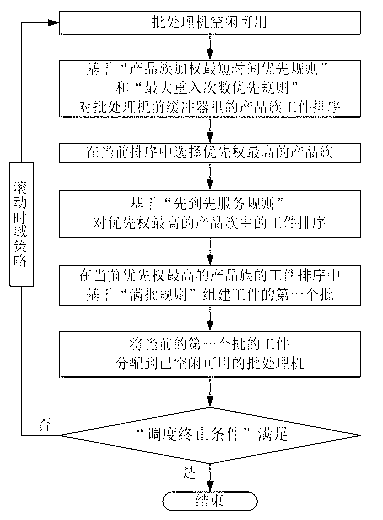

Batch scheduling method achieving minimum total completion time based on product family sorting

Owner:ANHUI UNIVERSITY OF TECHNOLOGY AND SCIENCE

Overlapping peak treatment method and device applied to chromatographic analysis

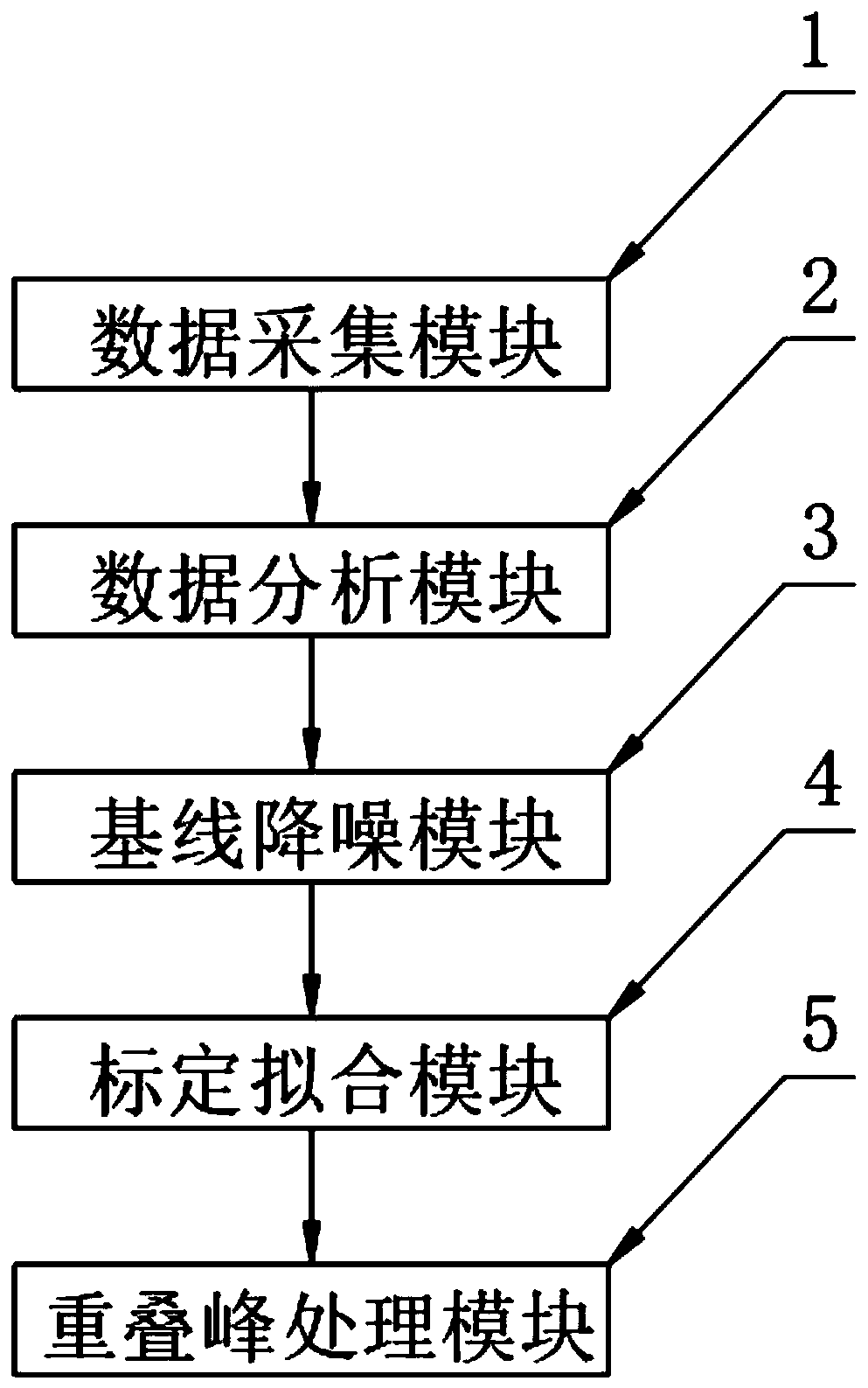

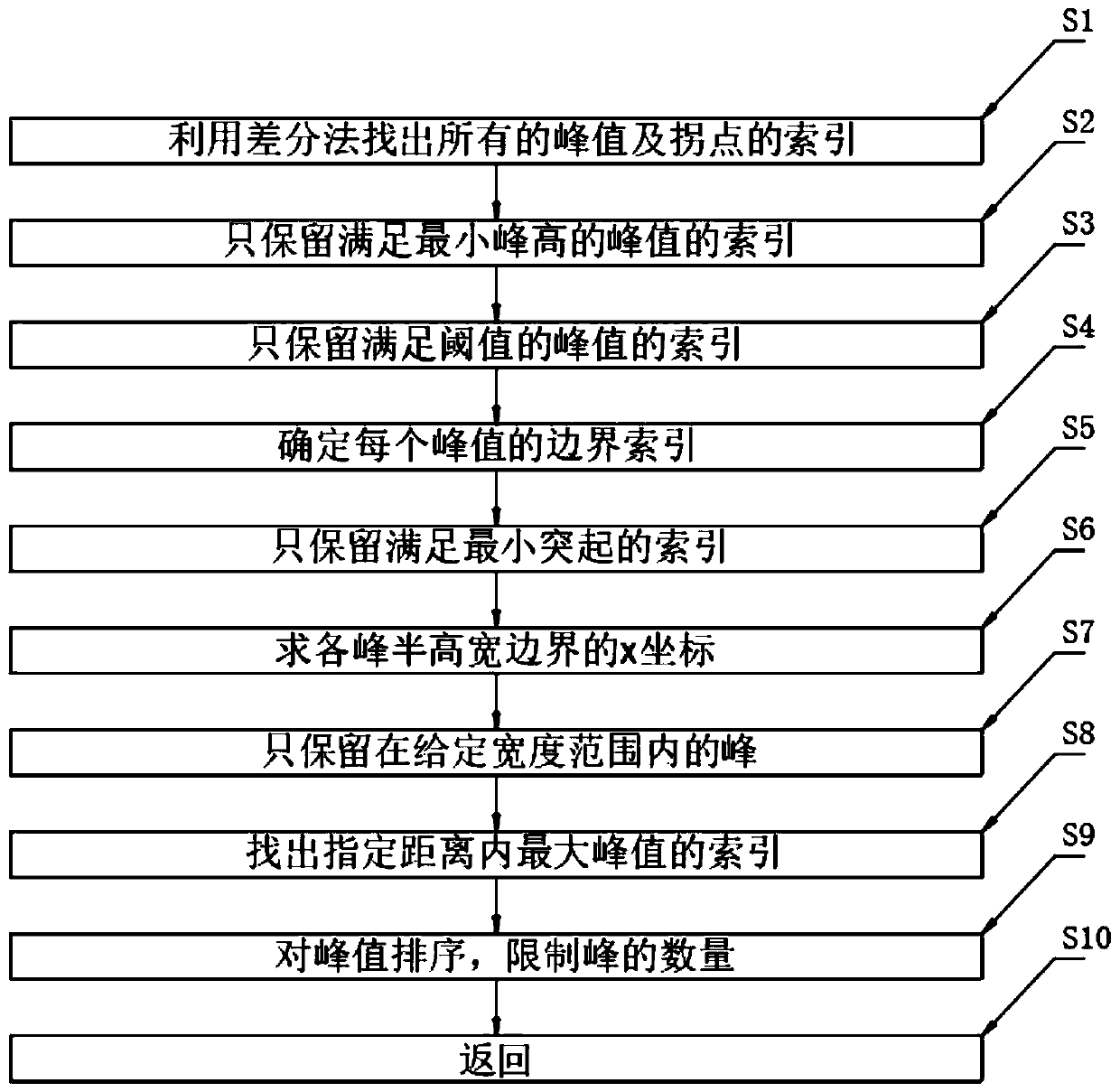

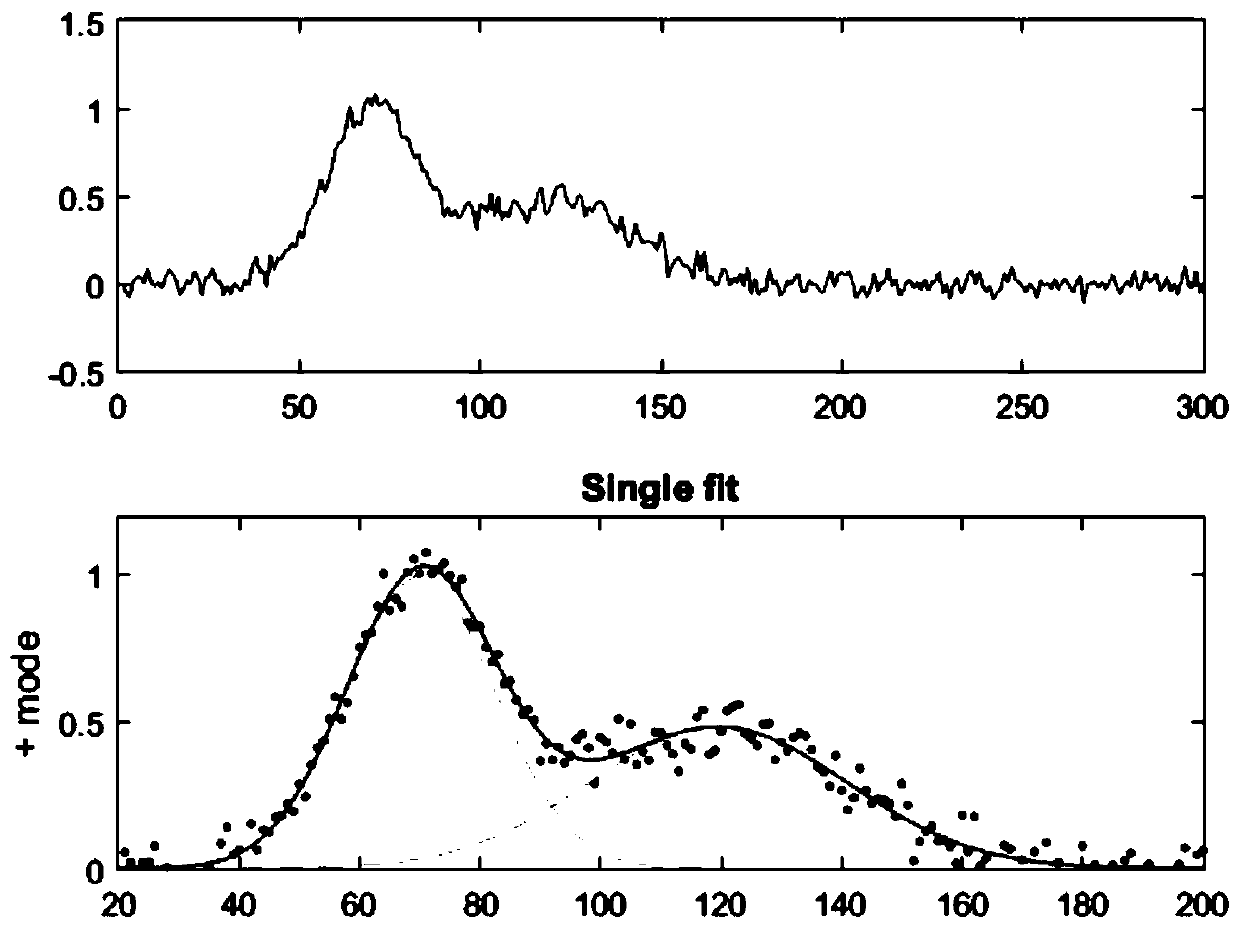

ActiveCN111337606AAccurately determineNot easy to fall intoComponent separationPhysical chemistryData profiling

The invention discloses a chromatographic overlapping peak treatment device. The device comprises a data collection module, a data analysis module, a baseline noise reduction module, a calibration fitting module and an overlapping peak treatment module. Wherein the data collection module is connected with the data analysis module, the data analysis module is connected with the baseline noise reduction module, the baseline noise reduction module is connected with the calibration fitting module, and the marking fitting module is connected with the overlapping peak treatment module. According tothe invention, the overlapped peak treatment module firstly determines a peak position by adopting a derivative method; overlapped peaks are determined through base point grouping, a simplex method isused for fitting a peak shape curve, so that information such as peak heights, peak widths and protrusions of all components of the overlapped peaks is determined, the peak position determining precision is high, the information precision of all the components of the overlapped peaks is high, peak division intervals can be automatically defined, and the number of sub-peaks in the overlapped peakscan be automatically determined.

Owner:江苏乐尔环境科技股份有限公司

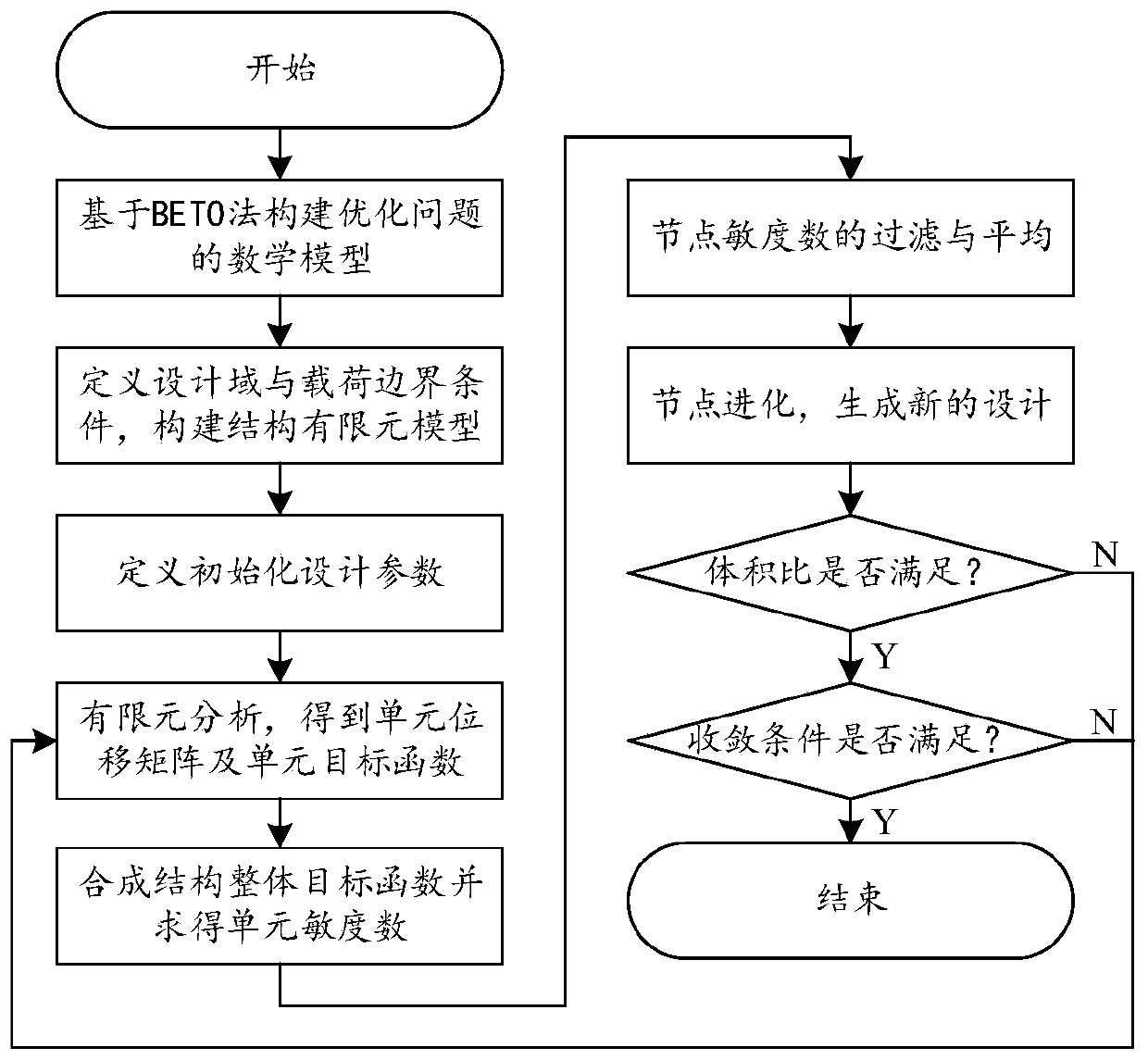

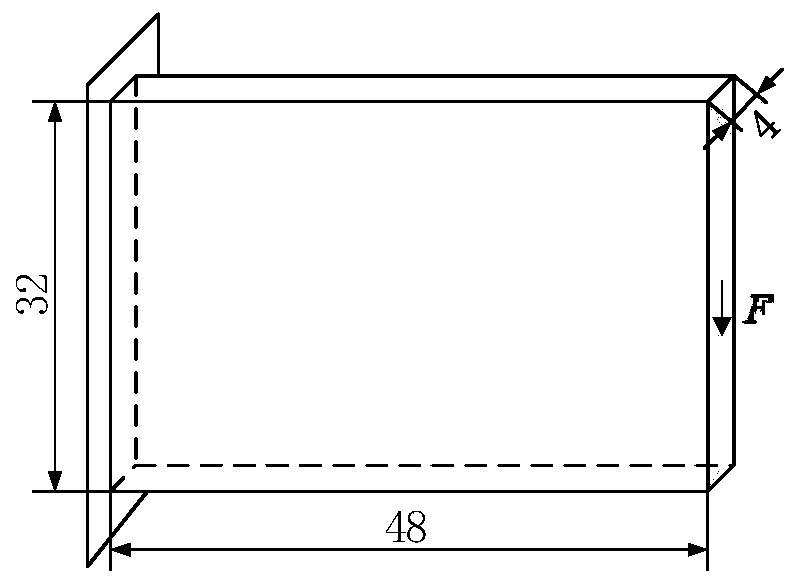

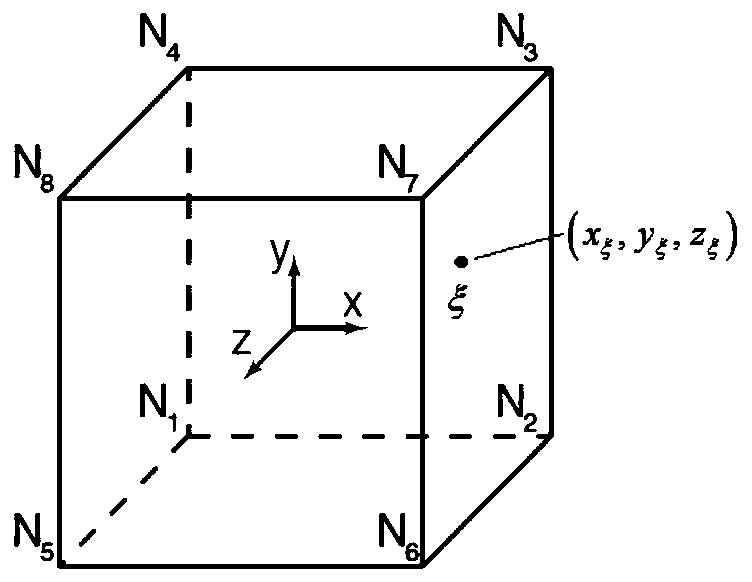

Three-dimensional structure topology optimization design method and device with smooth boundary expression

ActiveCN110069800ASimple conceptSimple procedureGeometric CADDesign optimisation/simulationElement modelMathematical model

The invention discloses a three-dimensional structure topology optimization design method and device with smooth boundary expression, and belongs to the field of structure topology optimization. The method comprises steps of establishing a mathematical model of an optimization problem based on bidirectional progressive topological optimization, and carrying out parameter initialization and finiteelement analysis by combining a finite element model of a target structure, so that a unit displacement matrix and a unit target function are obtained, and a unit sensitivity degree is obtained; filtering and averaging the node sensitivity degrees of the units, and then performing node evolution to generate a new design; judging whether the volume ratio and the convergence condition are simultaneously met or not for the new design; and if yes, obtaining an optimal design scheme, otherwise, returning to the finite element analysis step, and starting loop iteration optimization. According to themethod, the designed three-dimensional structure can always have a smooth structure boundary under the condition of dividing the small grid size, post-processing operations such as curve / surface fitting are not needed, and the defect that an existing method seriously depends on the grid size is effectively avoided.

Owner:HUAZHONG UNIV OF SCI & TECH

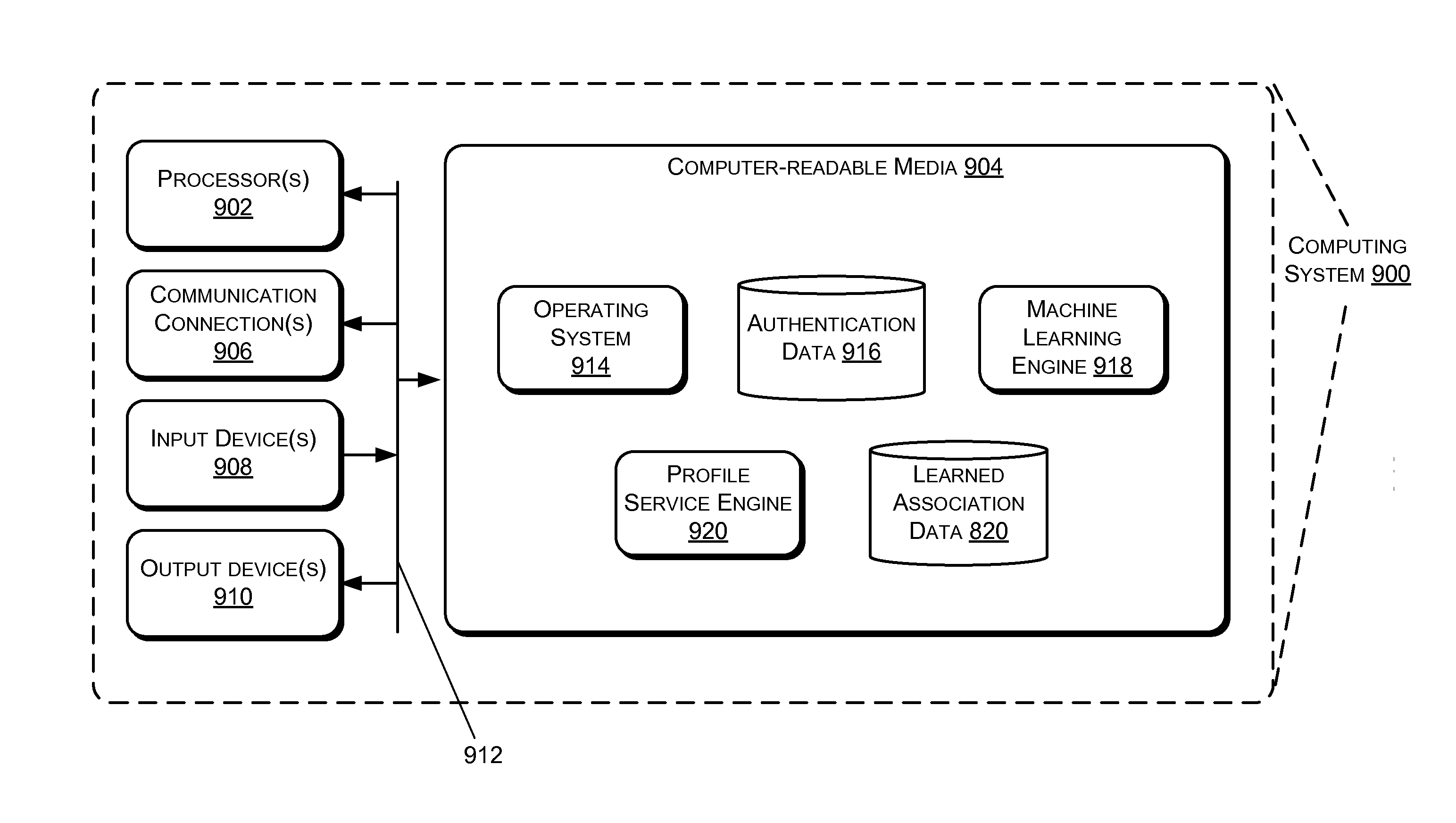

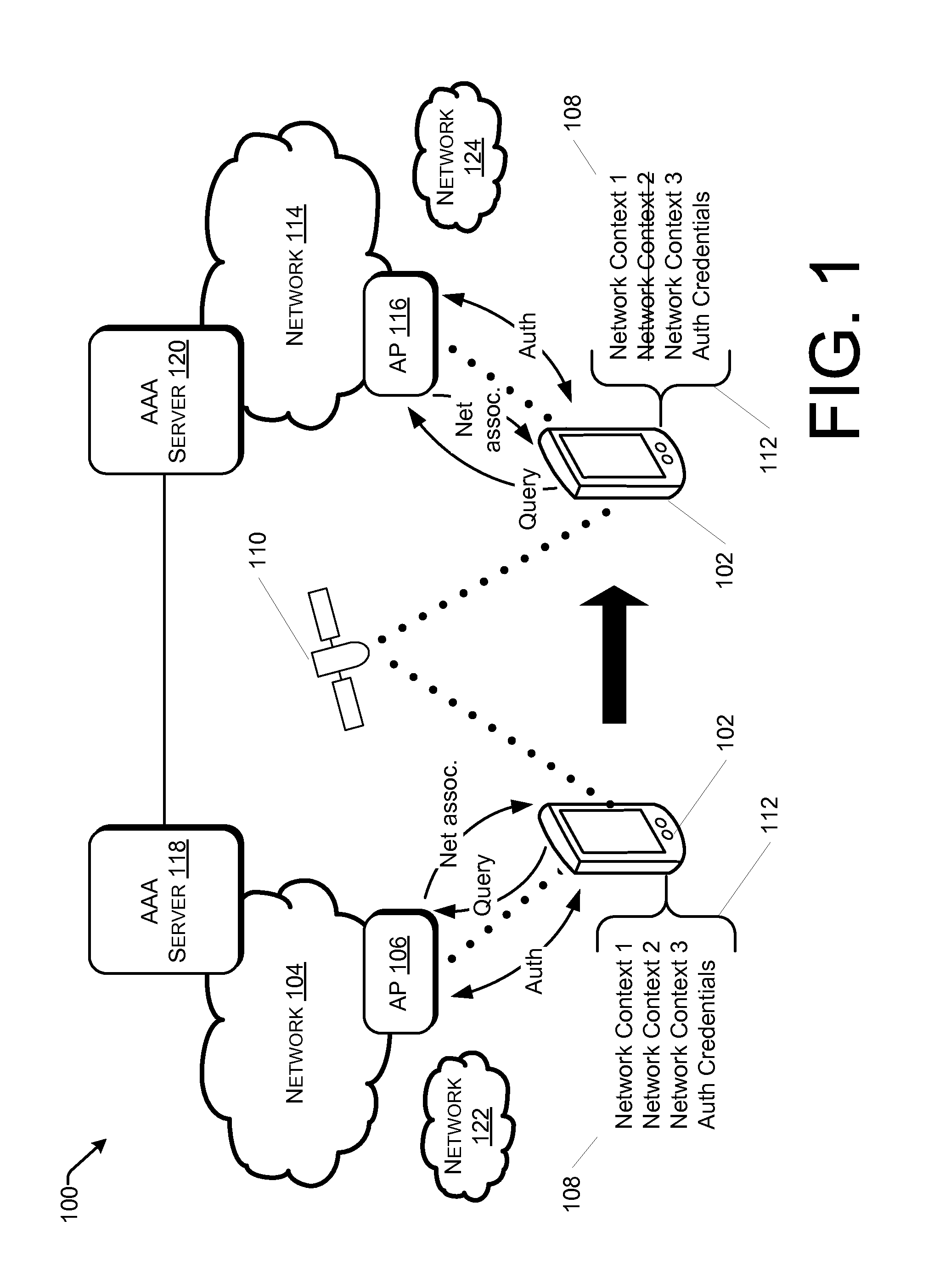

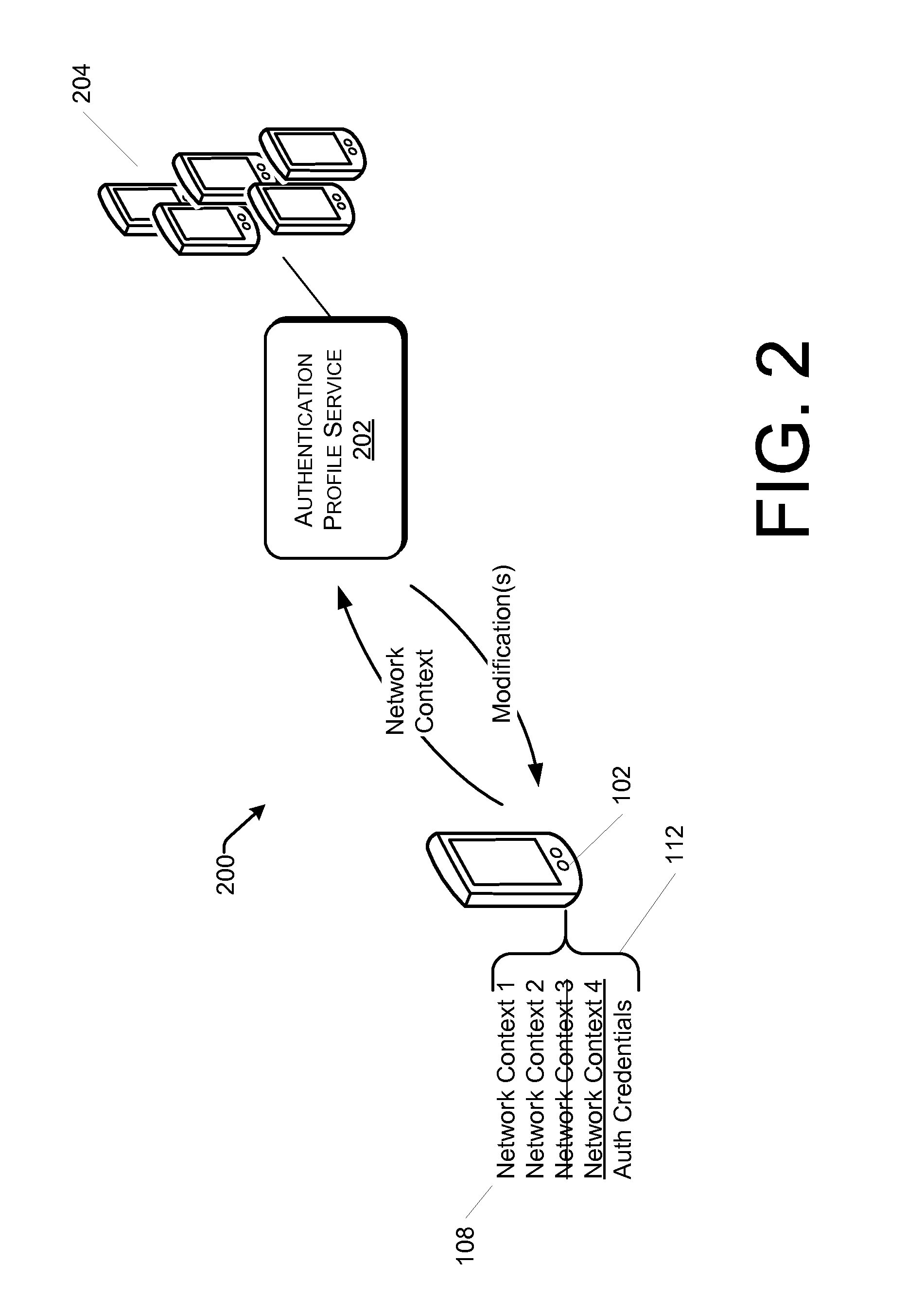

Learned roving authentication profiles

ActiveUS20160380989A1Simple conceptDigital data processing detailsMultiple digital computer combinationsMobile deviceDistributed computing

Disclosed herein are systems and methods for determining learned associations between authentication credentials and network contextual data, such as may be utilized in a network that supports network roving. A mobile device attempts to rove to a visited network using authentication credentials associated with another network, based at least in part on first contextual information associated with the other network and second contextual information associated with the visited network indicating that the visited network is part of a common association of networks that supports roving internetworking between the networks of the common association.

Owner:MICROSOFT TECH LICENSING LLC

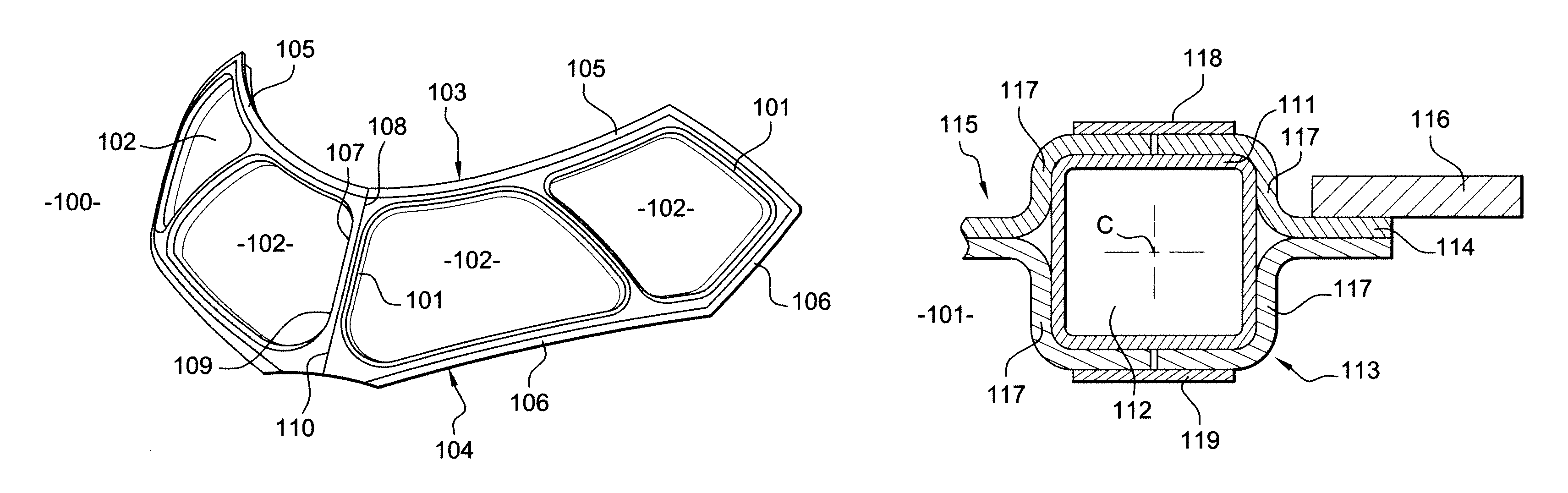

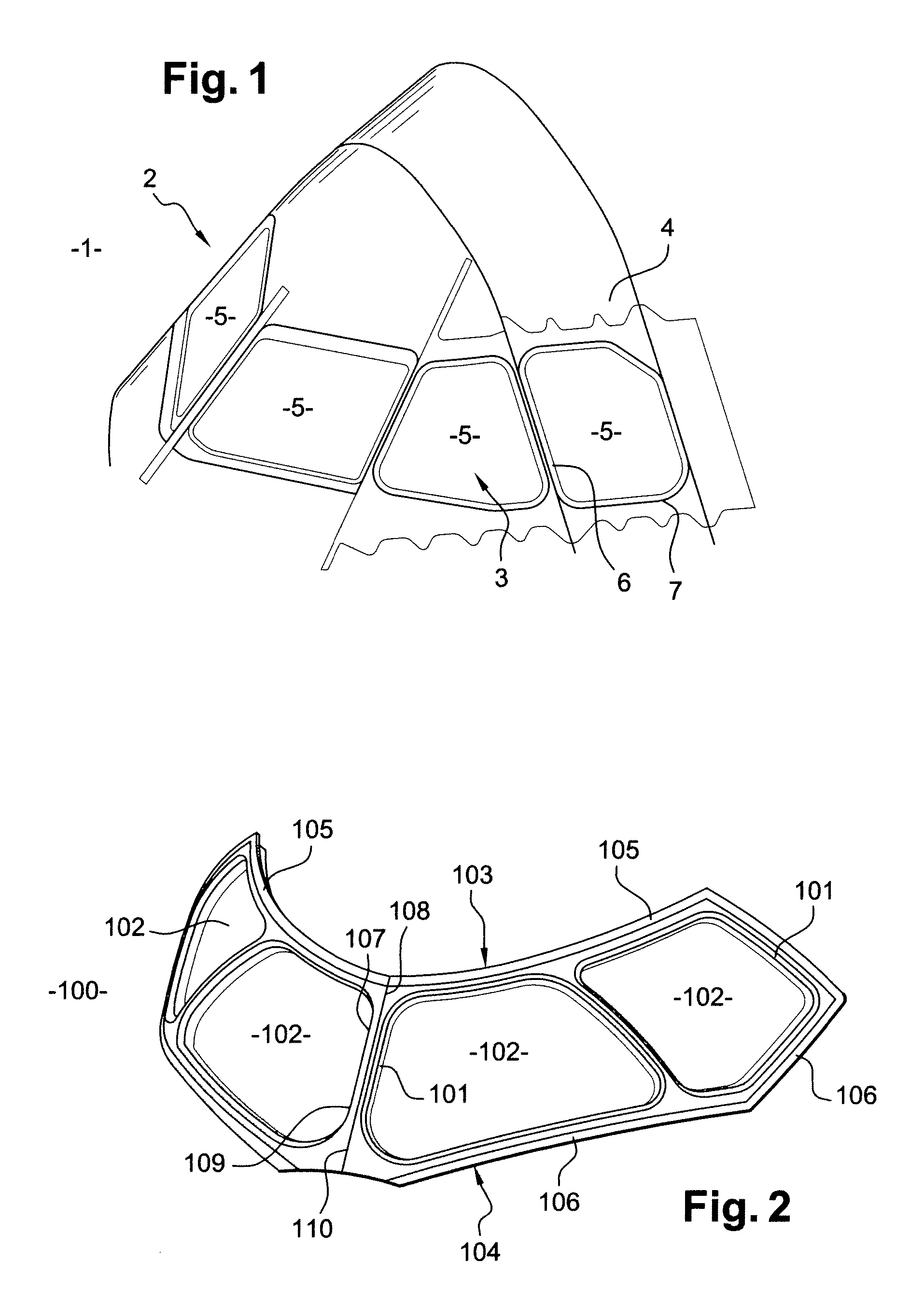

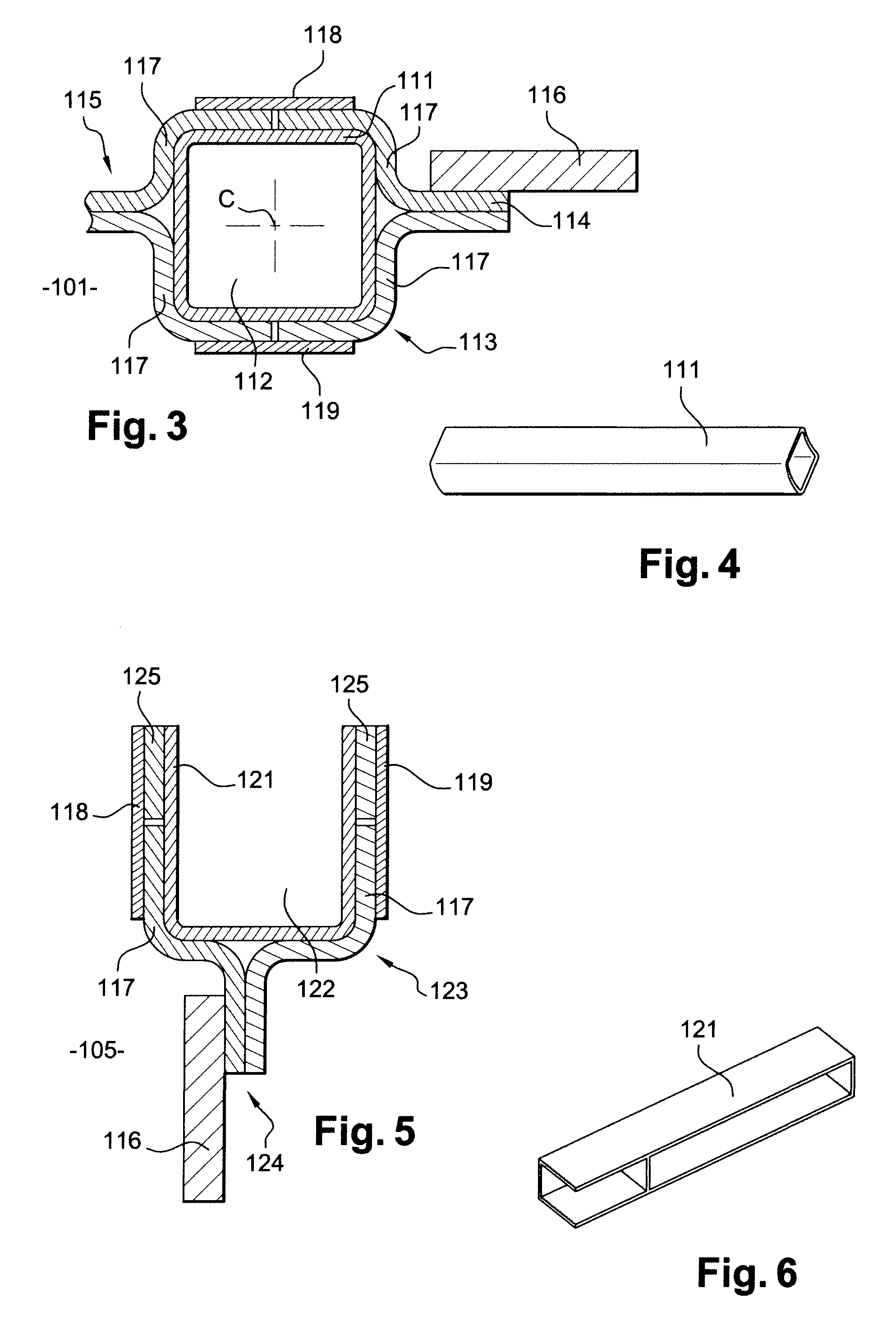

Windscreen frame and a method of production for a windscreen frame

InactiveUS7942369B2Simple conceptEasy to fit into wallWindowsWindscreensEngineeringMethods of production

A windscreen frame, and a method of production for a windscreen frame, designed to hold a windscreen in an opening in a wall, the frame including at least one upper horizontal frame section element, at least one lower horizontal frame section element and at least one vertical mounting, characterized in that it is a single unit in composite material.

Owner:AIRBUS OPERATIONS (SAS)

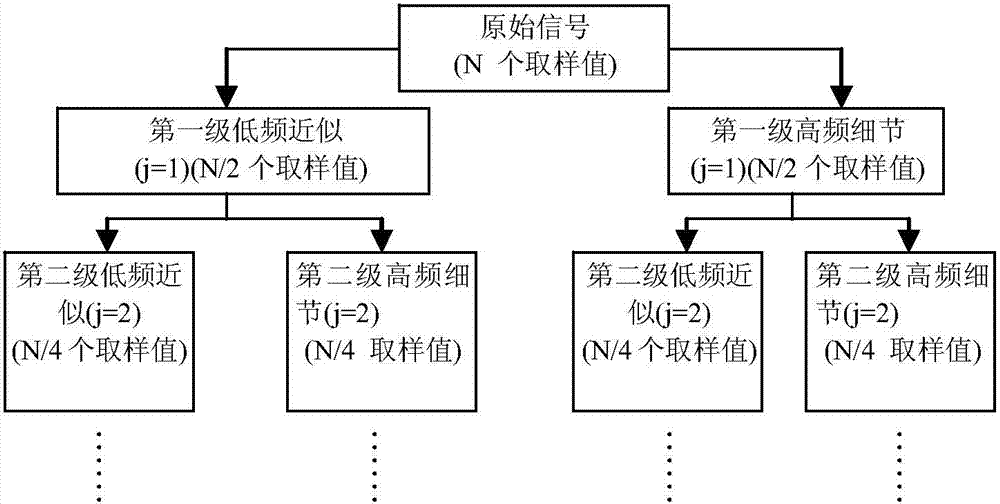

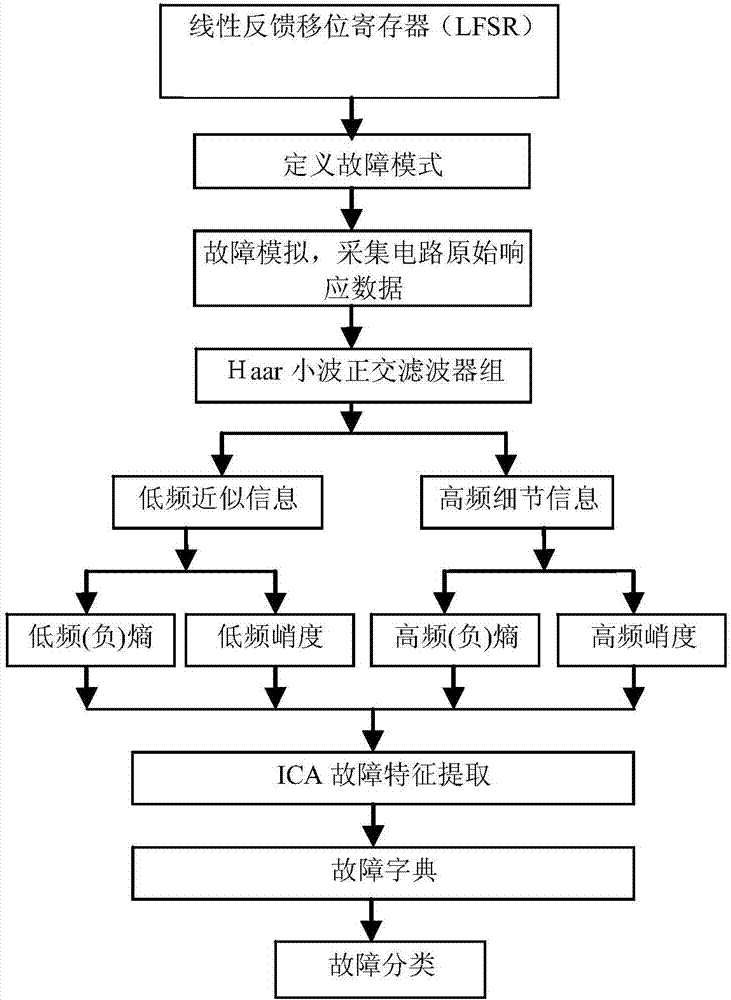

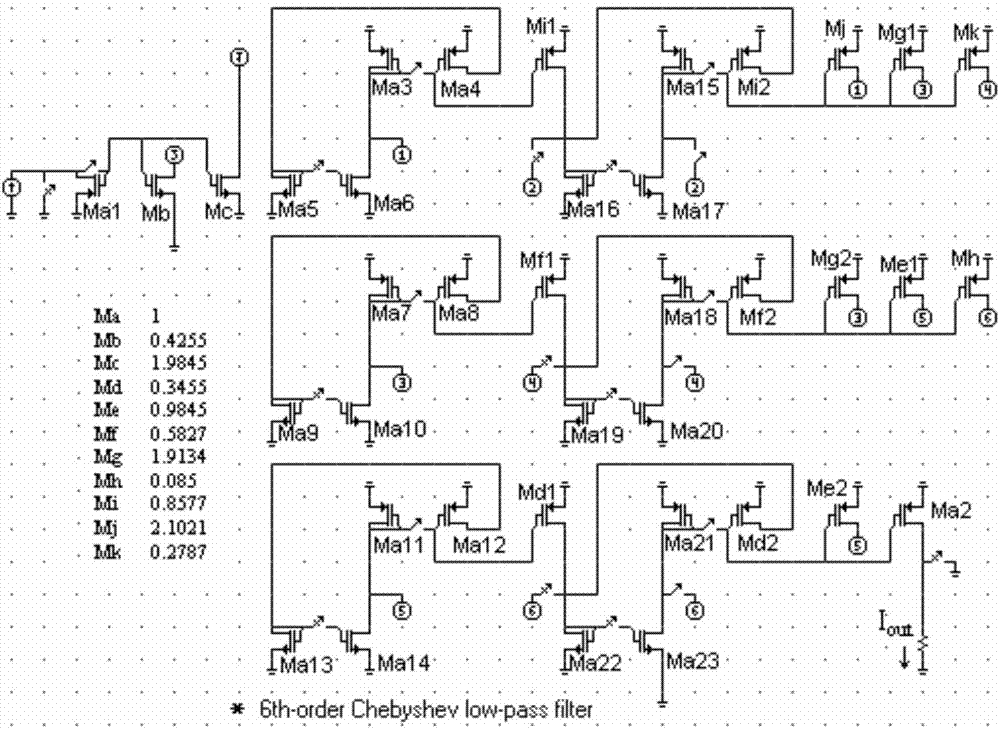

Switching circuit fault classifying method based on wavelet transform and ICA feature extraction

InactiveCN104714171AThe result is accurateHigh fault classification accuracyElectronic circuit testingCircuit interrupters testingFeature extractionAlgorithm

The invention discloses a switching circuit fault classifying method based on wavelet transform and ICA feature extraction. The method comprises the following steps: (1) generating a pseudo random signal as a test stimulation signal; (2) defining a fault mode; (3) acquiring the original response data of the circuit; (4) pre-treating the original response data by a Haar wavelet orthogonal filter; (5) extracting the fault feature parameters, and calculating the entropy and kurtosis as well as fuzzy sets thereof of low-frequency approximate information and high-frequency detail information for the pre-treated signal respectively; and (6) constructing a fault dictionary based on the extracted fault feature parameters so as to realize fault classification of the switching circuit. The method disclosed by the invention has the advantages of skillful concept, easiness in implementation and simulation proof and can distinguish the fault types more accurately than the existing method.

Owner:CHANGSHA UNIVERSITY