Patents

Literature

347results about How to "Design more" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

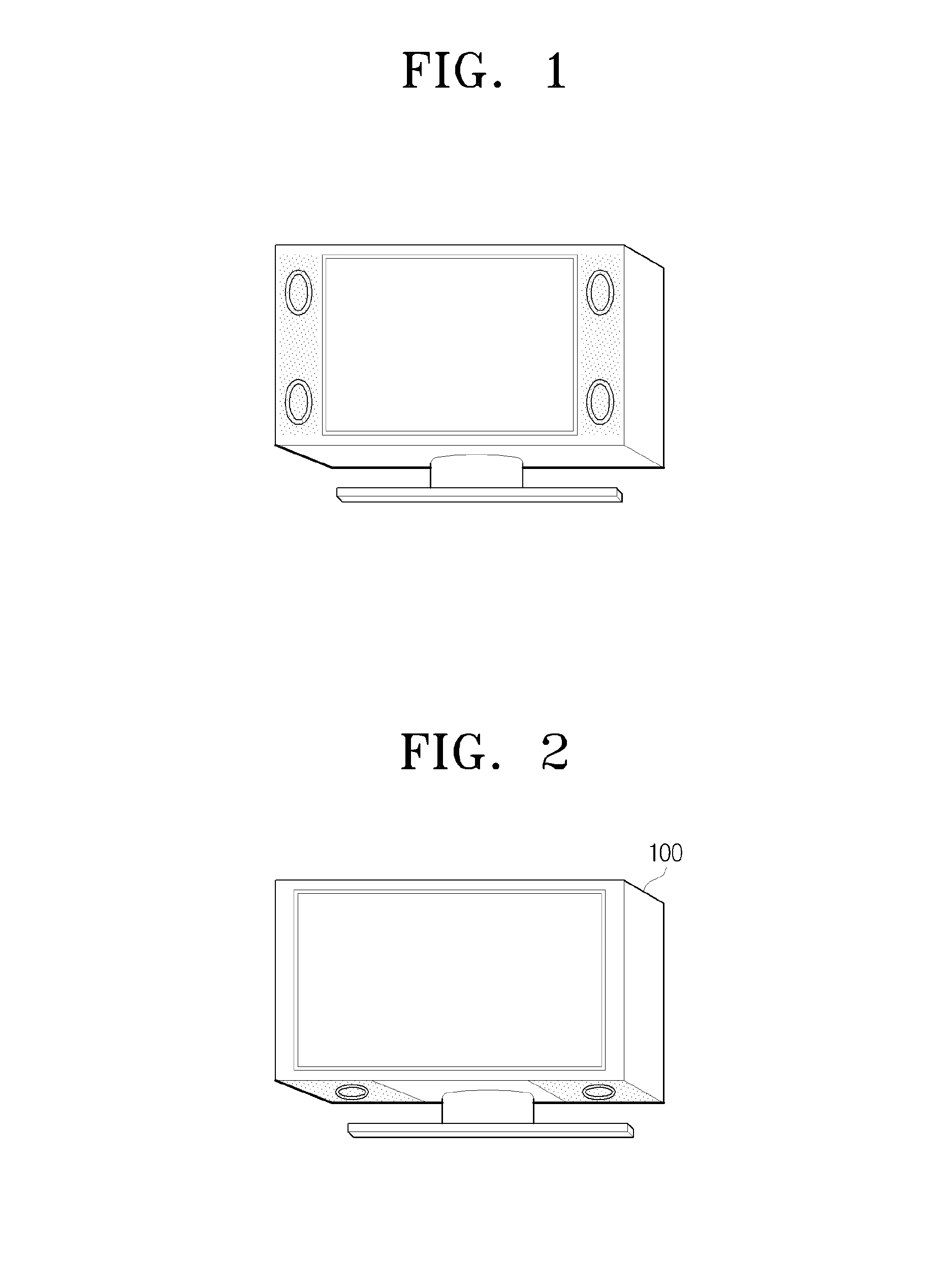

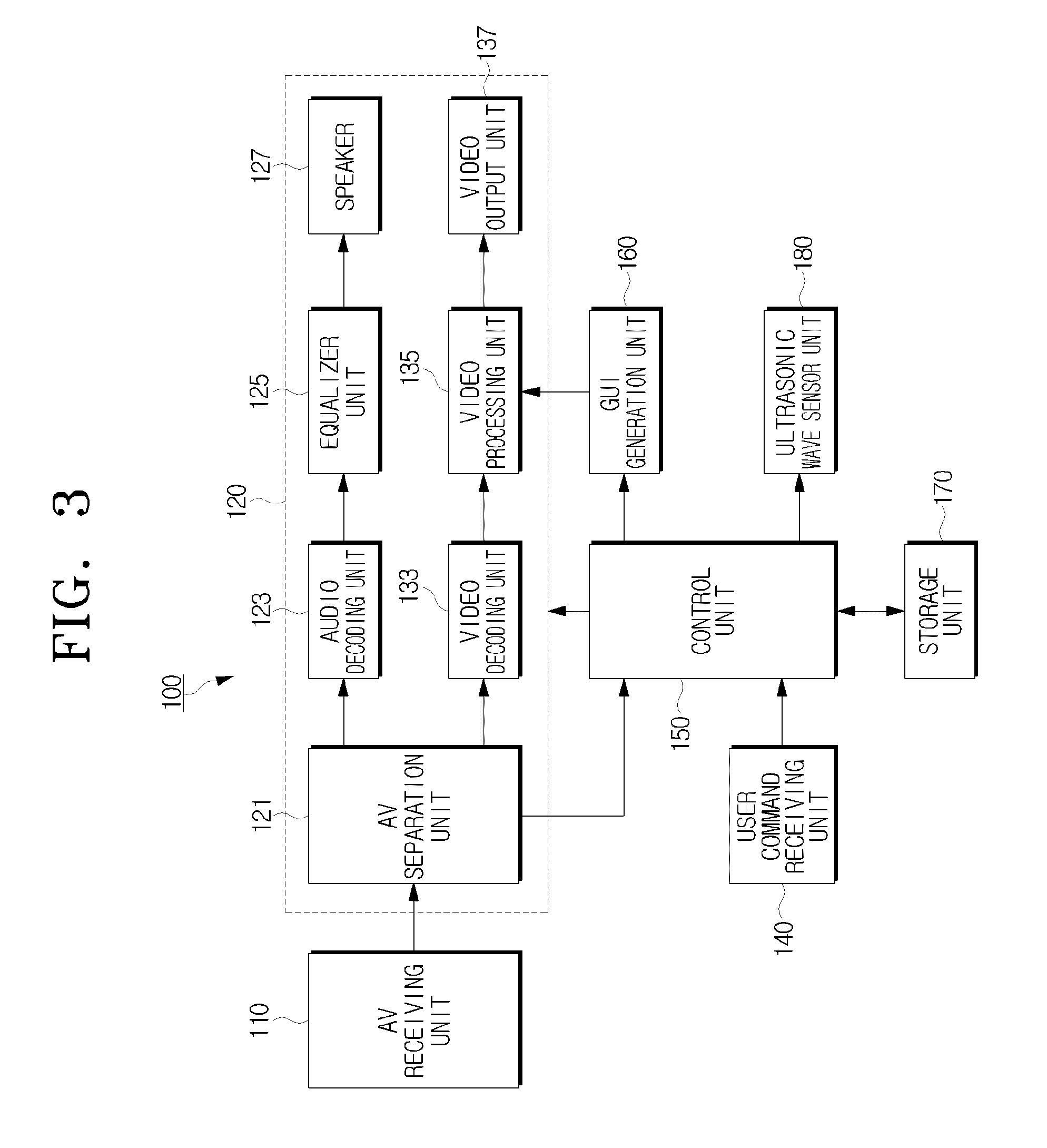

Method for equalizing audio, and video apparatus using the same

InactiveUS8600075B2Prevent audio attenuationDesign moreTelevision system detailsStereophonic systemsUltrasound attenuationLoudspeaker

A method for equalizing audio and a video apparatus using the audio equalizing method are provided. The method for equalizing audio includes detecting the distance between a speaker mounted in a video apparatus and a reflective surface, and equalizing an audio signal to be output from the speaker based on the detected distance. Accordingly, attenuation of audio output is reduced, so audio output is optimized.

Owner:SAMSUNG ELECTRONICS CO LTD

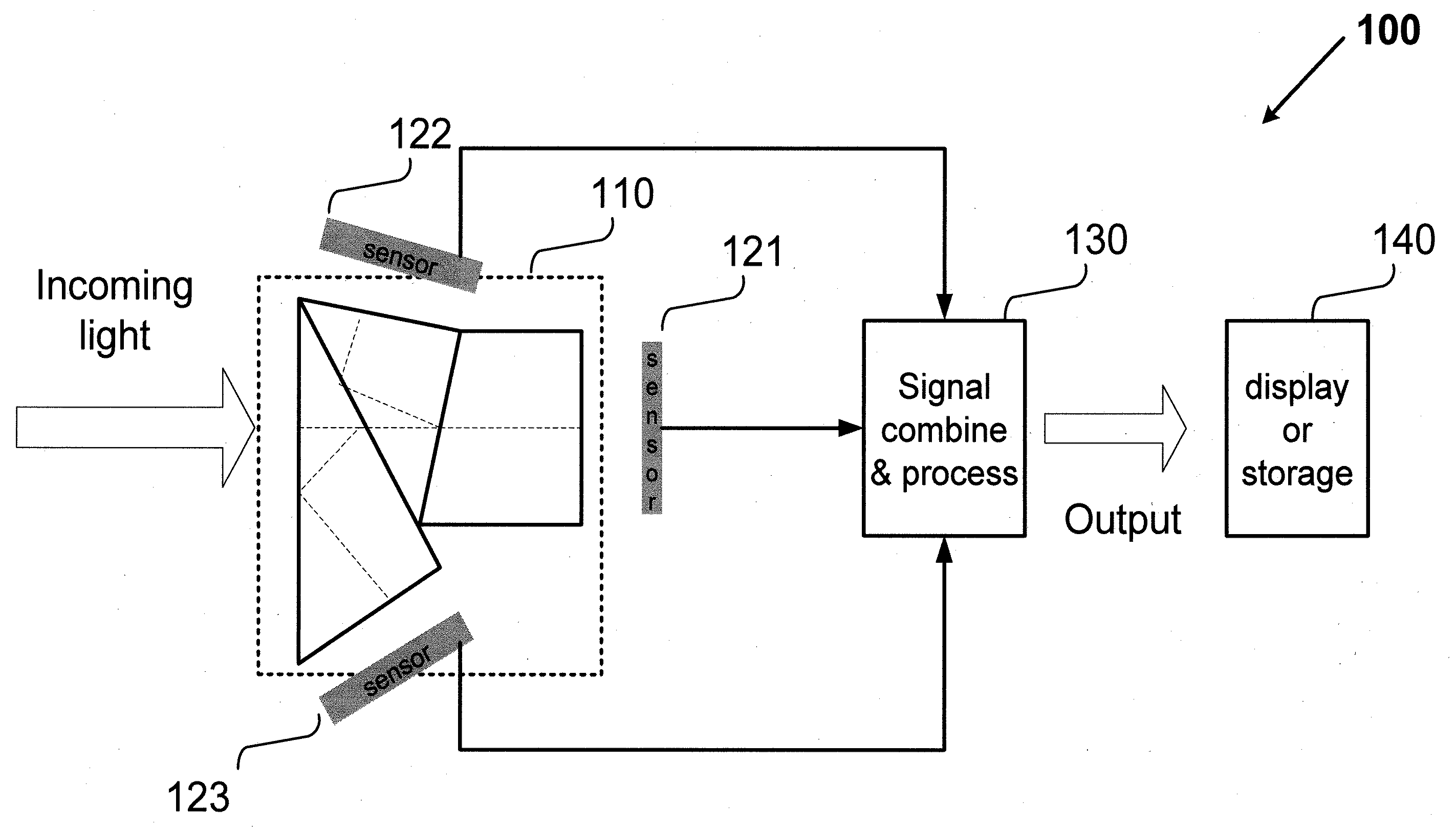

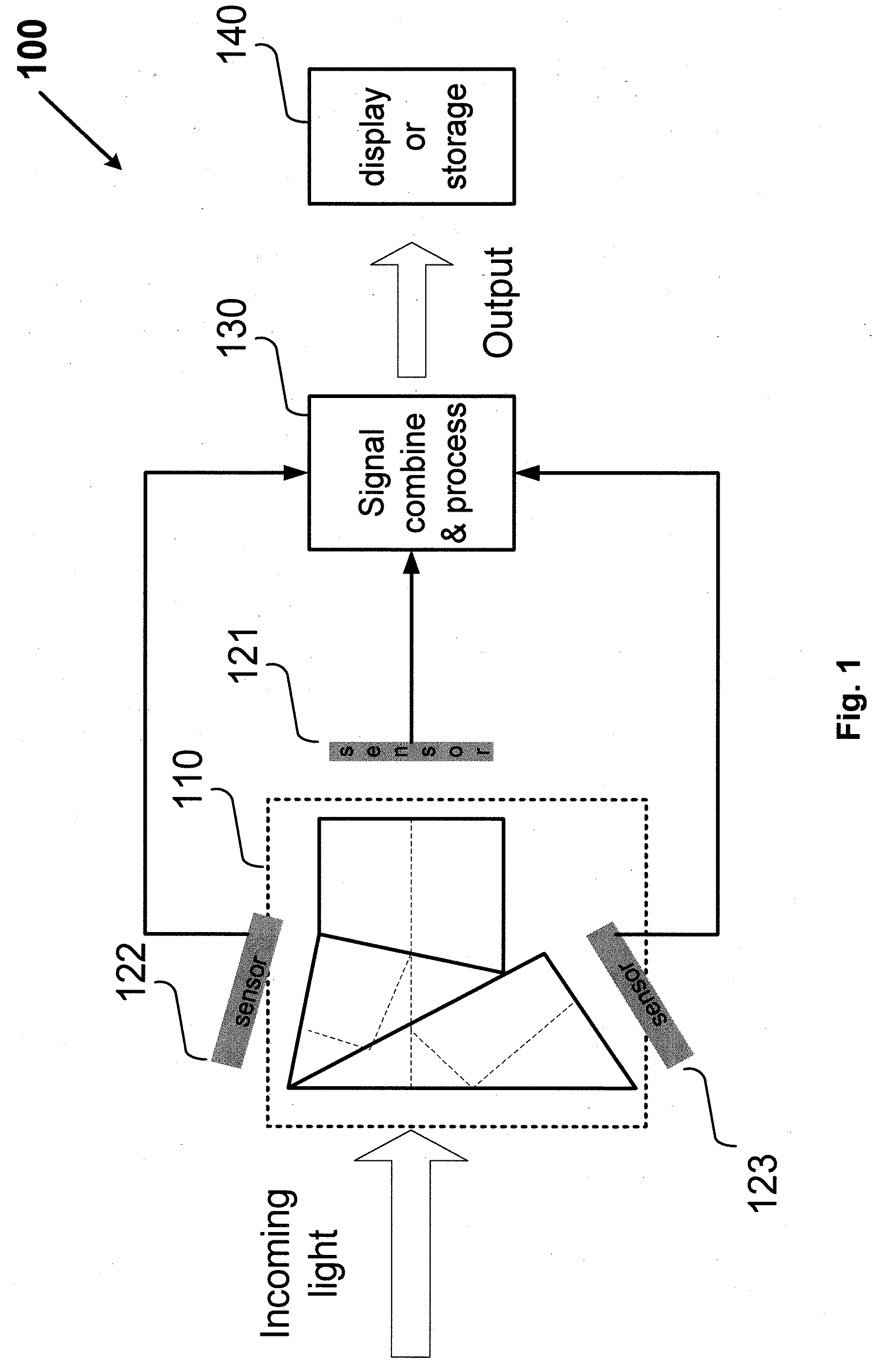

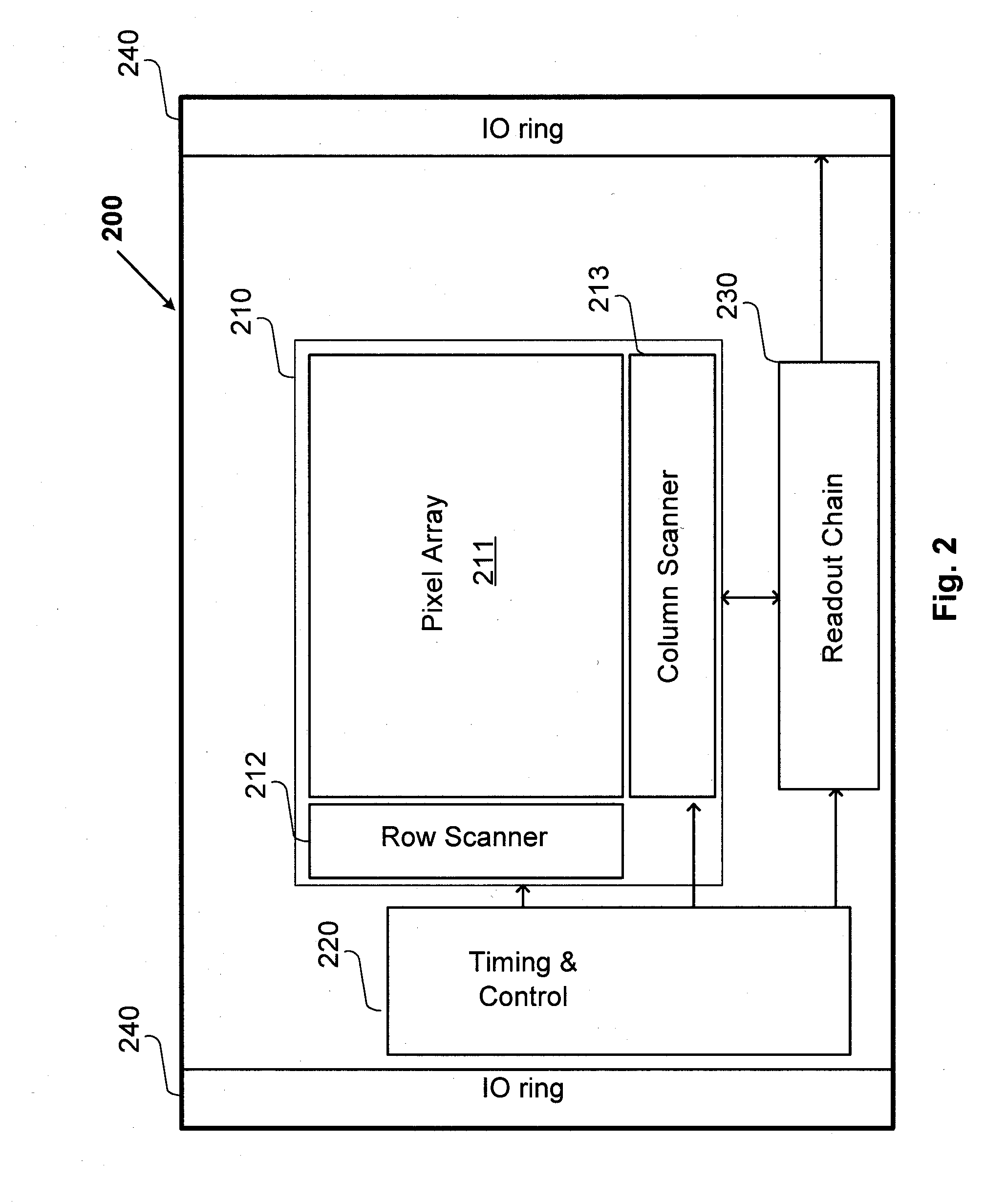

Camera system with multiple pixel arrays on a chip

ActiveUS20090135245A1Compact designEasy to makeTelevision system detailsPulse modulation television signal transmissionTelecommunications linkDigital storage

A camera system uses one or more image sensor IC chips each having multiple pixel arrays on the same semiconductor substrate (i.e., “multiple pixel arrays on a chip”). In one embodiment, such a camera system includes: (a) optical components that create multiple images in close physical proximity of each other (e.g., within a few millimeters or centimeters); and (b) a single sensor substrate (“chip”) containing multiple 2-dimensional pixel arrays that are aligned to capture these multiple images, so as to convert the multiple images into electrical signal. The pixel arrays can be manufactured using a CCD or a CMOS compatible process. For manufacturing reasons, such a chip is typically two centimeters or less on a side. However, large chips can also be made. Optional electronic components for further signal processing of the captured images may be formed either on the sensor chip (i.e., in a “system-on-a-chip” implementation), or in a separate back-end application specific integrated circuit (ASIC). In addition, digital storage components, display elements, and wired or wireless communication links may also be included in any suitable combination to allow review and further processing of the captured images.

Owner:CAPSO VISION INC

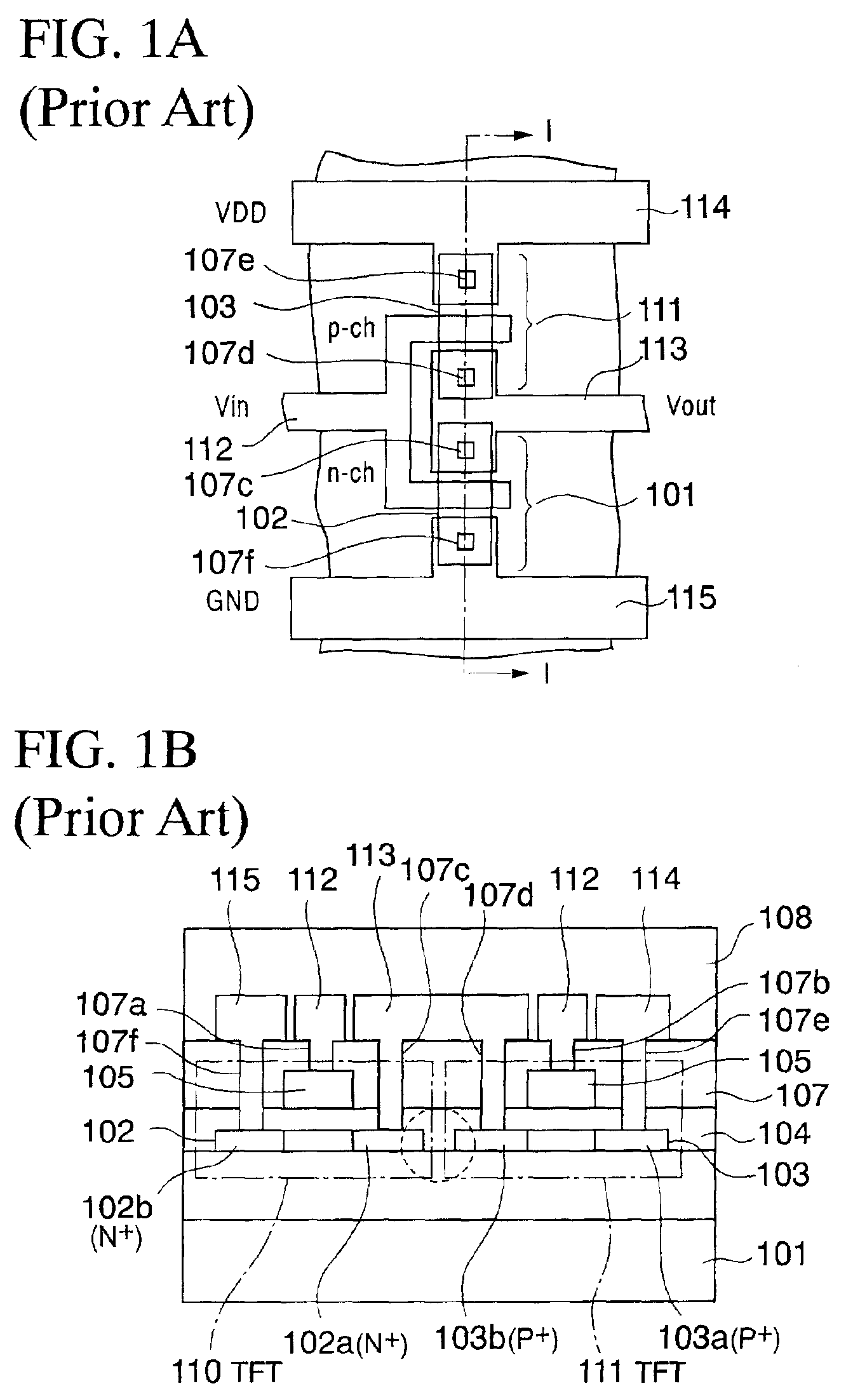

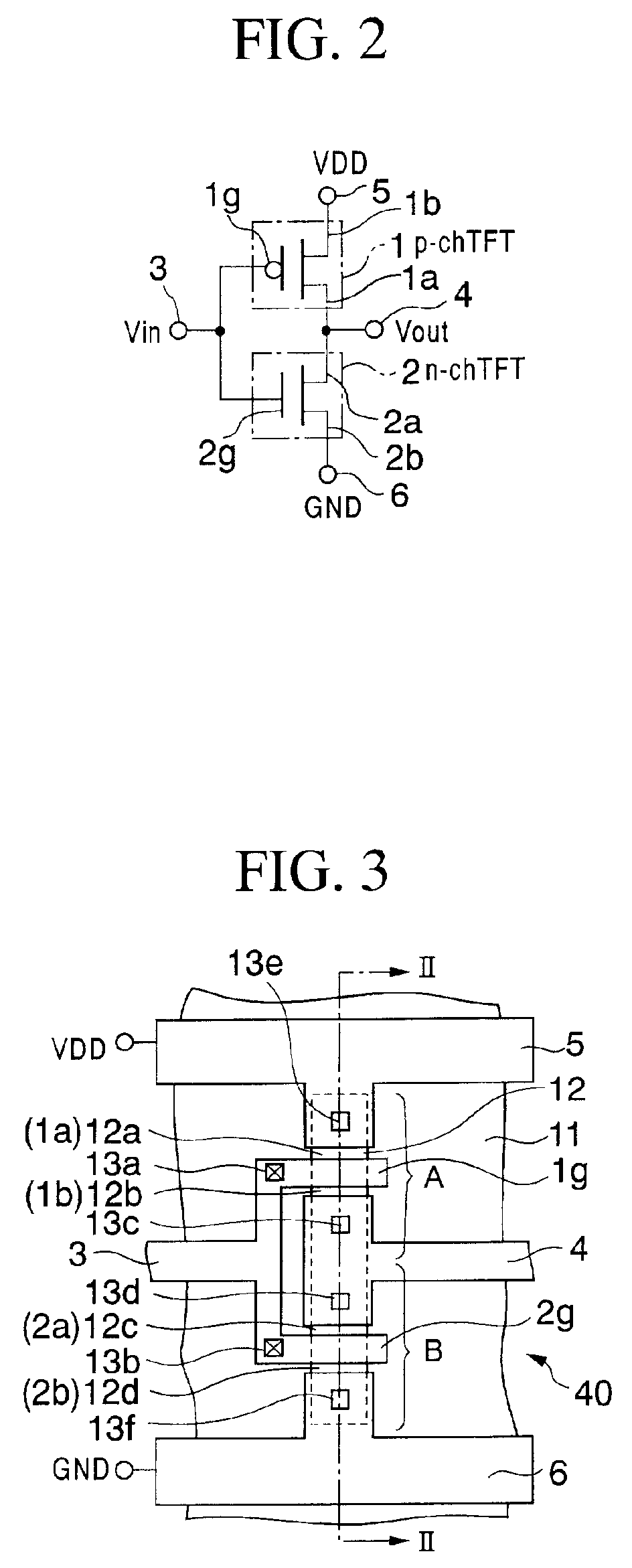

Display device and method of manufacturing the same

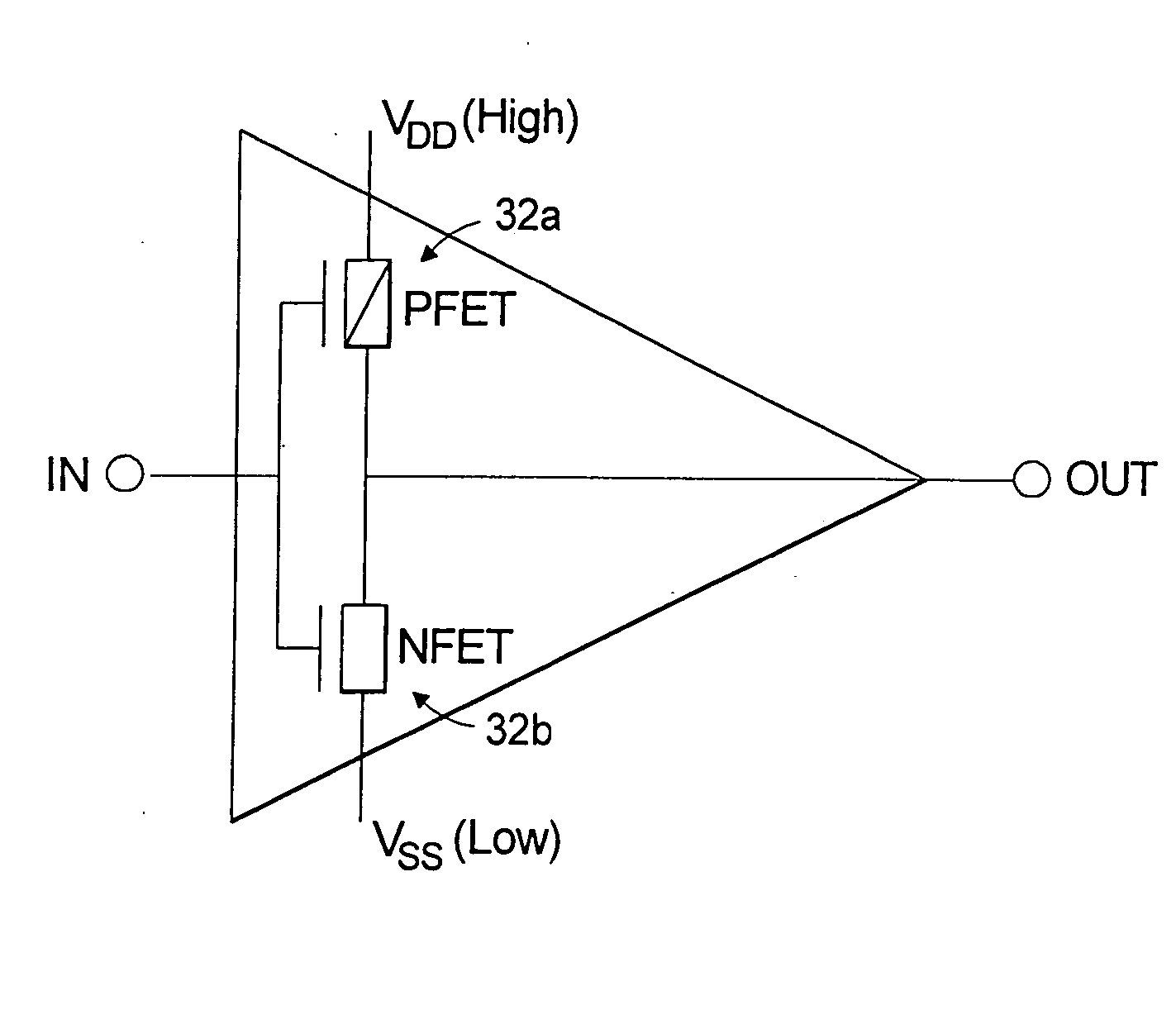

InactiveUS6919933B2Margin region required to add the impurity can be eliminatedReduce areaTransistorSolid-state devicesDisplay deviceSemiconductor

In a semiconductor circuit in a display device, there are provided a first gate electrode of a first MOS transistor formed on a semiconductor layer via a gate insulating film, a second gate electrode of a second MOS transistor formed on the semiconductor layer via the gate insulating film at a distance from the first gate electrode, first and second one conductivity type impurity introduced regions formed in the semiconductor layer on both sides of the first gate electrode to serve as source / drain of the first MOS transistor, and first and second opposite conductivity type impurity introduced regions formed in the semiconductor layer on both sides of the second gate electrode to serve as source / drain of the second MOS transistor. One of the first and second opposite conductivity type impurity introduced regions is formed to contact mutually to the second one conductivity type impurity introduced region.

Owner:SHARP KK

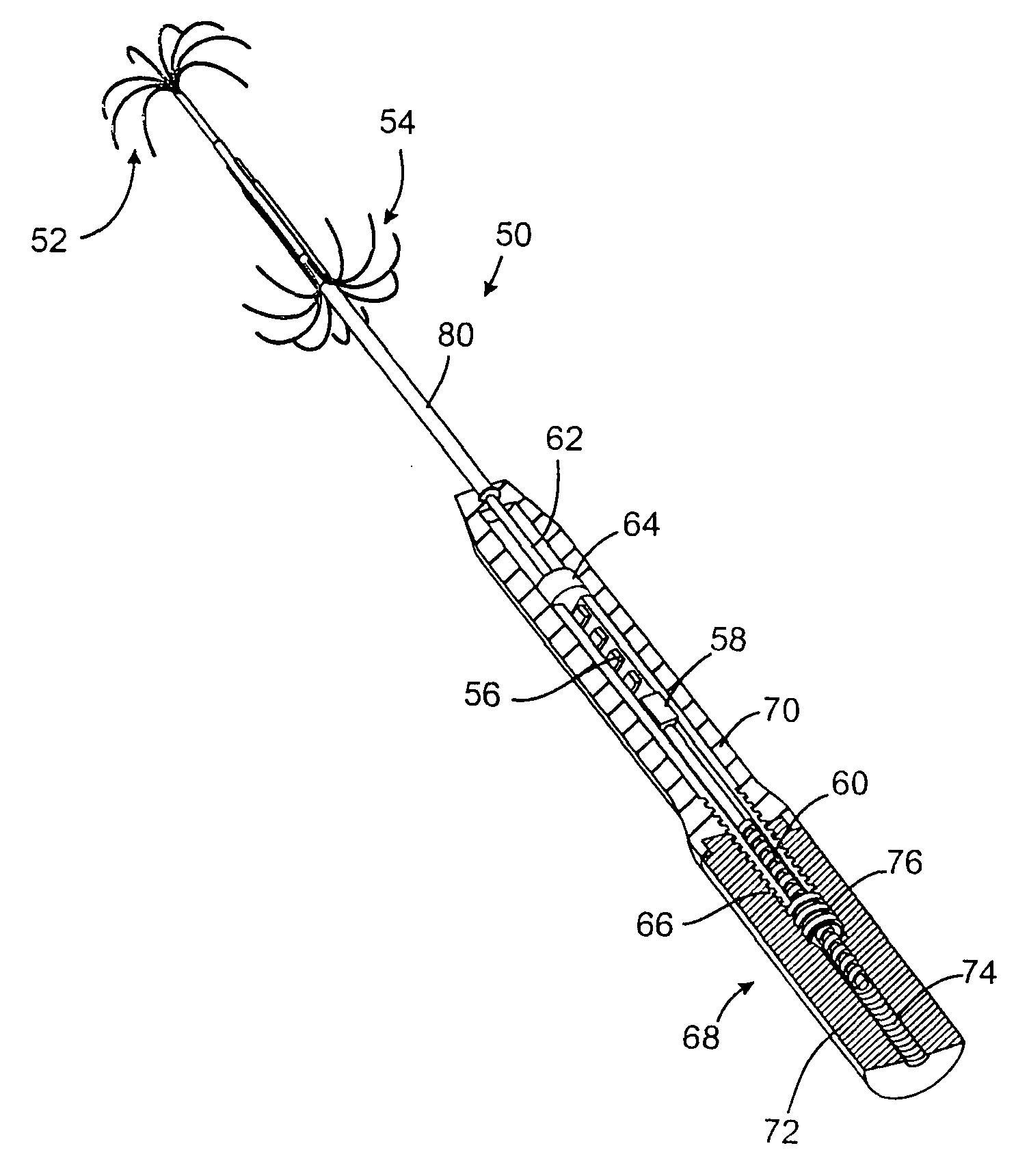

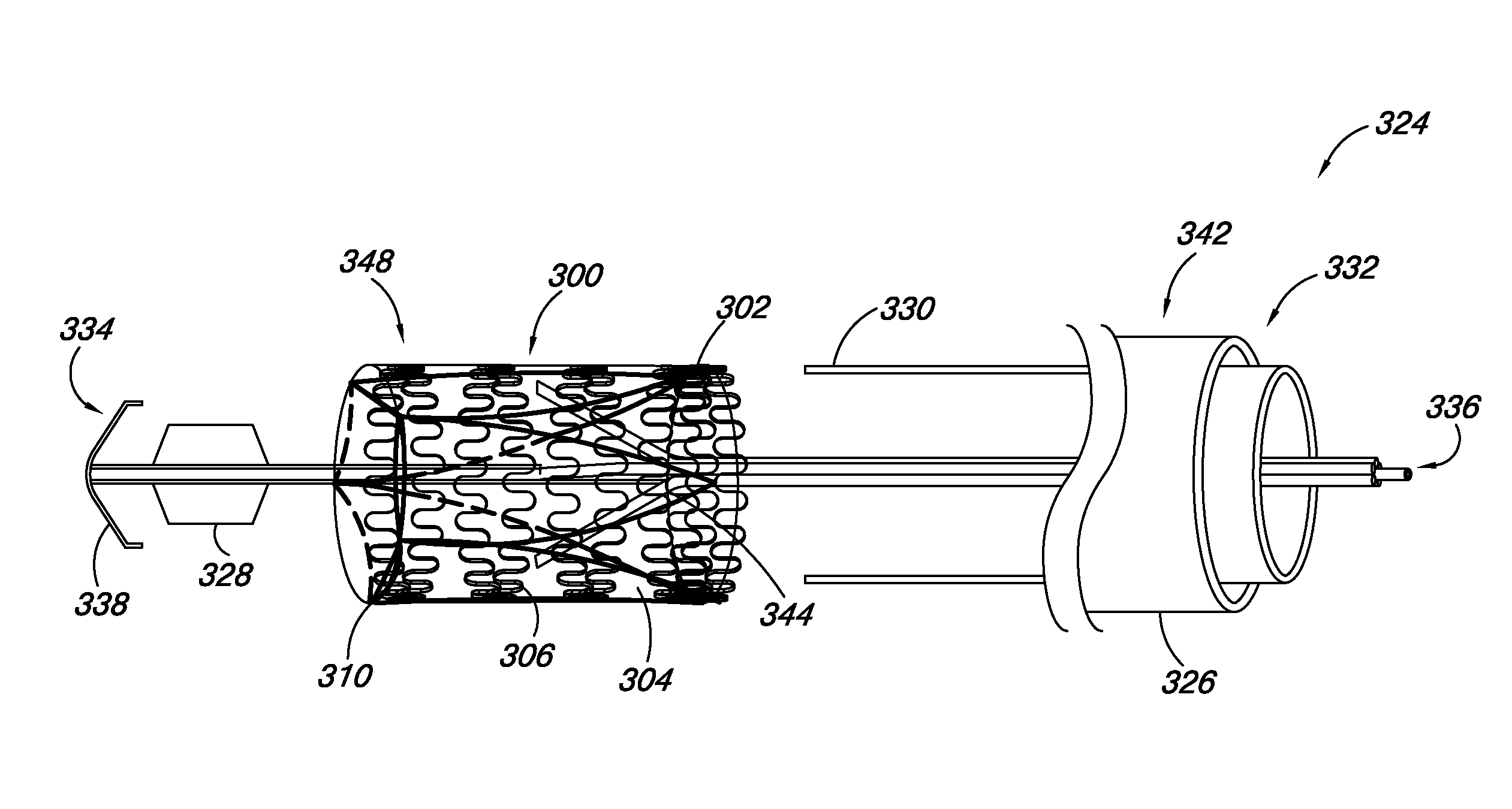

Methods and systems for focused bipolar tissue ablation

InactiveUS20040158239A1Design moreSurgical needlesSurgical instruments for heatingElectrical conductorElectrode array

Large tissue regions are treated using pairs of electrode arrays. The electrode arrays may be concave and disposed in tissue so that their concave portions are opposed to each other. Axial conductors may be provided extending from the arrays and toward each other in order to increase the heating of tissues lying along the axis between the deployed electrode arrays. By properly spacing the electrode arrays apart and selecting the diameters of the arrays, desired volumes of tissue may be treated, typically with a bipolar, radiofrequency current.

Owner:BOSTON SCI SCIMED INC

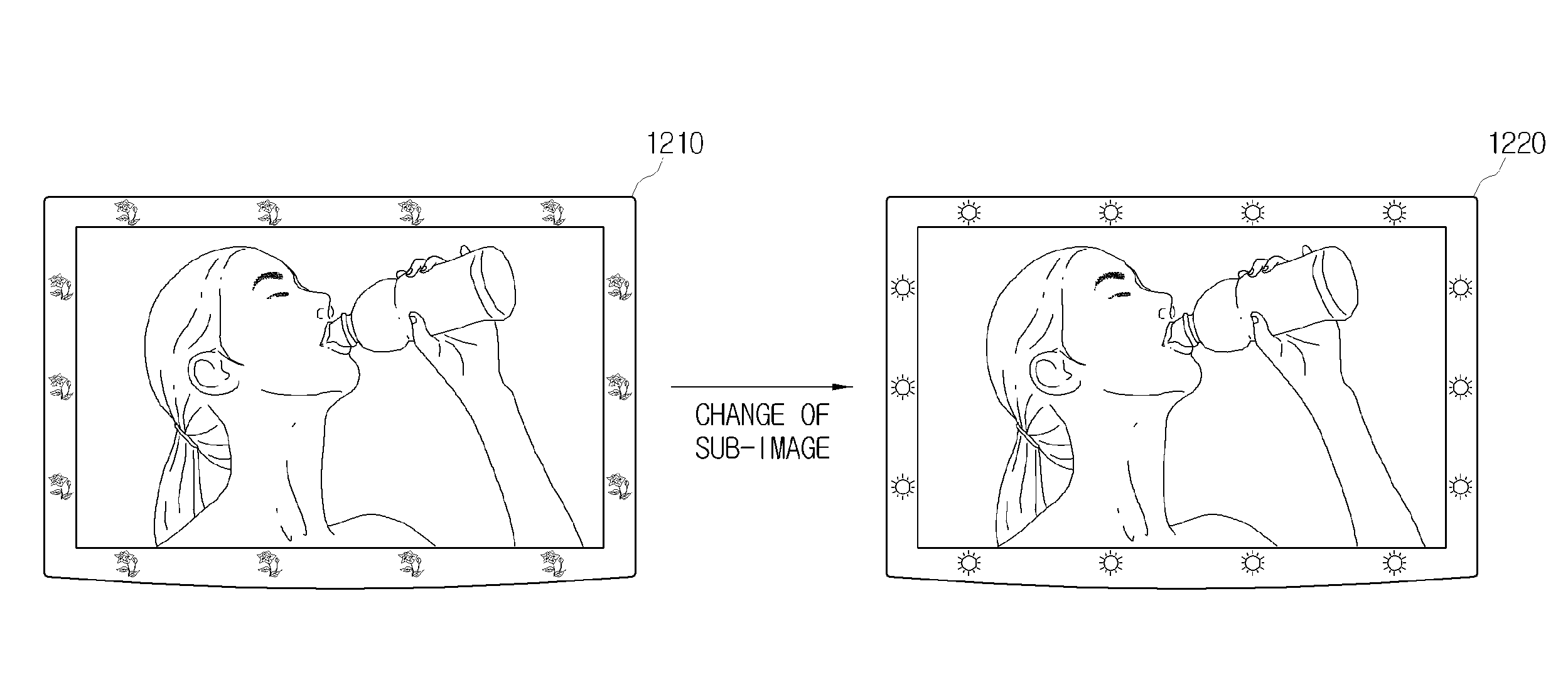

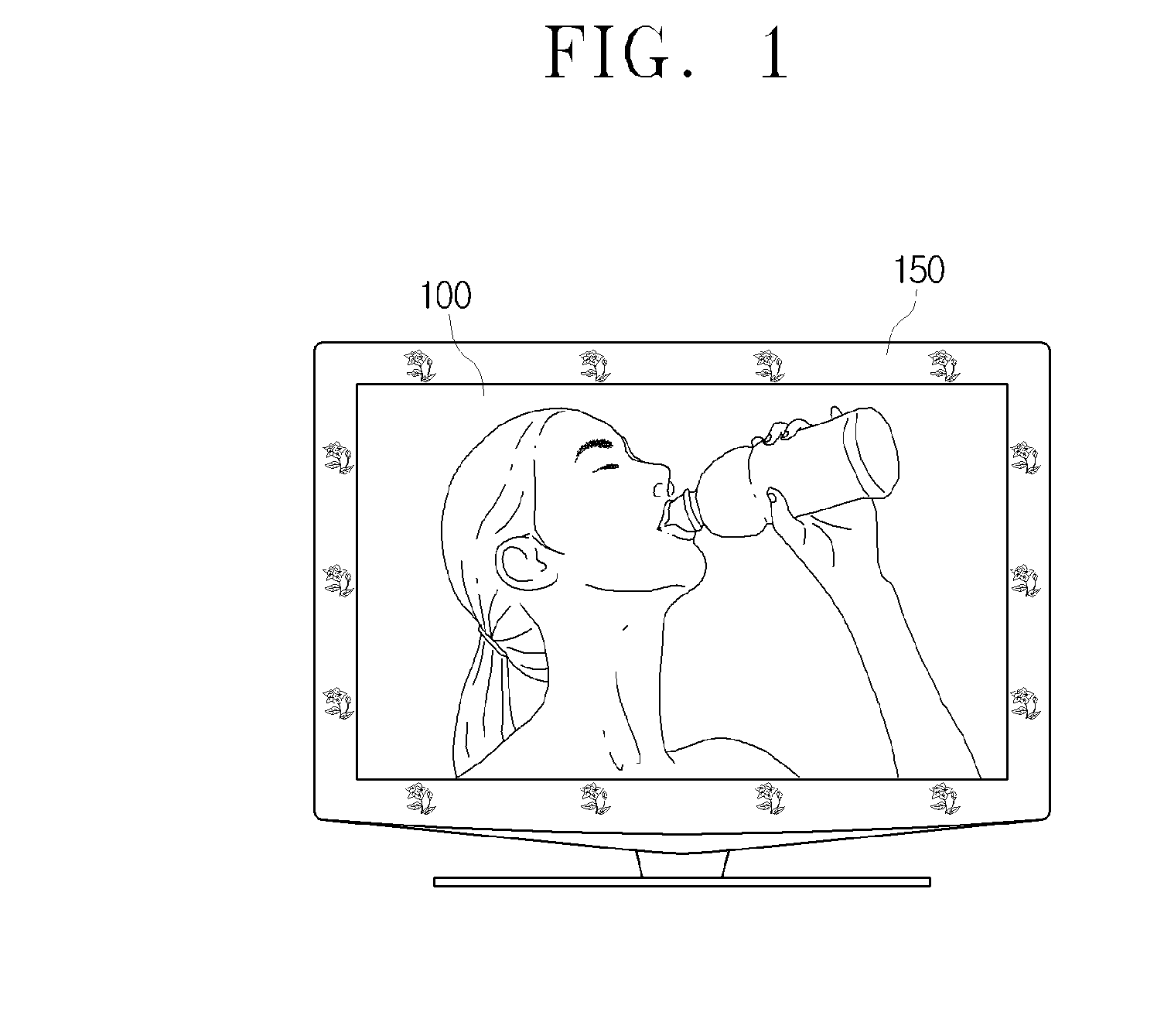

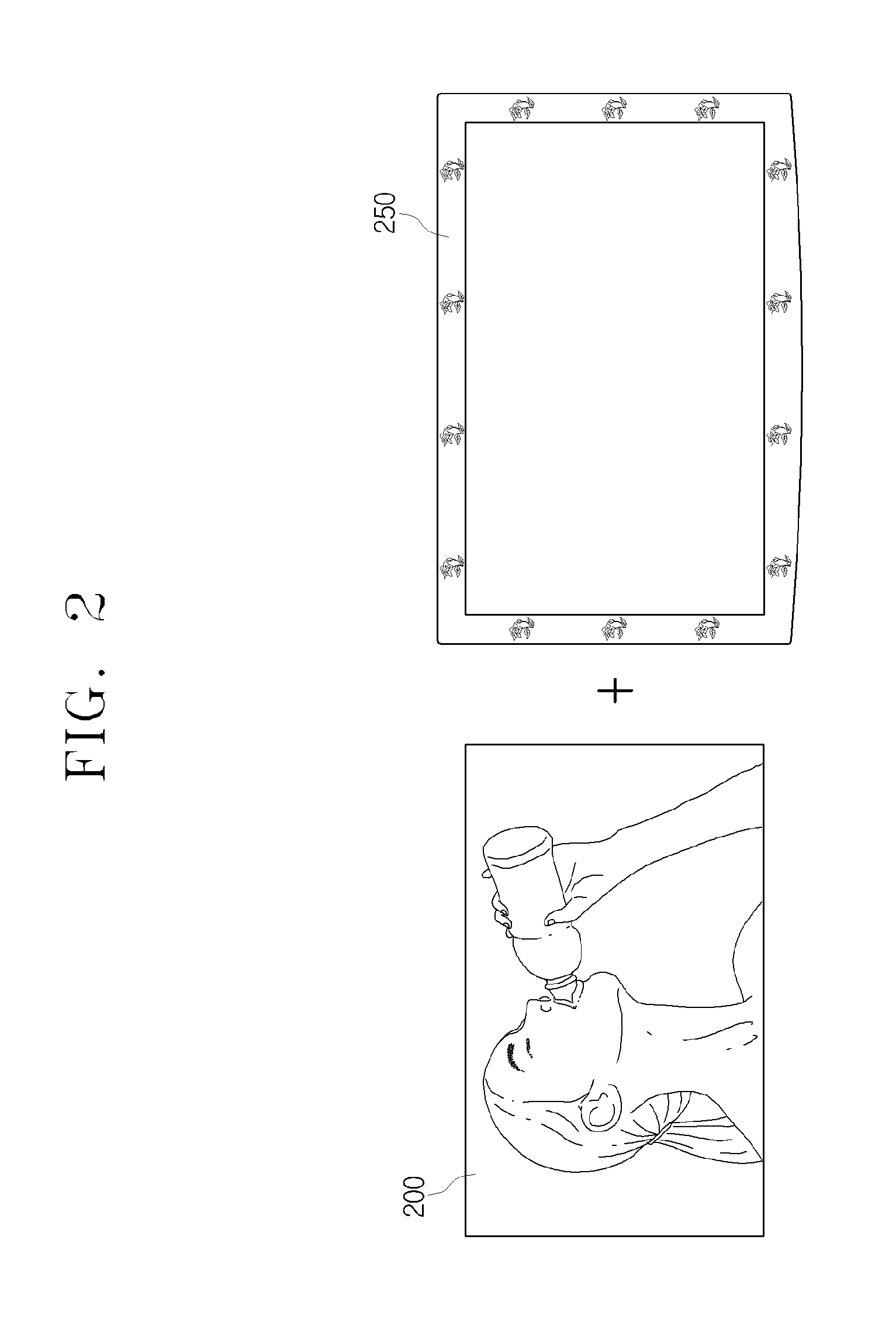

Image display apparatus of which display is disposed on border area and image display method thereof

InactiveUS20090289874A1Design moreTelevision system detailsColor television detailsComputer graphics (images)Display device

An image display apparatus and an image display method are disclosed. The image display apparatus includes a first display unit which displays a main image, and a second display unit which is disposed on a border of the first display unit and forms at least one side of a bezel. A user can thereby modify the design of the image display apparatus more diversely and easily.

Owner:SAMSUNG ELECTRONICS CO LTD

Method for producing high strength aluminum alloy welded structures

The present invention relates to a method for fabricating lightweight alloy feedstock for welded structures. Specifically, the method for producing the tubular stock proposed in the present invention enables a bicycle manufacturer to readily weld a lightweight yet high strength bicycle frame. The properties attained in the final product allow the bicycle manufacturer to reduce the overall weight of the bicycle without sacrificing durability.

Owner:TRI KOR ALLOYS

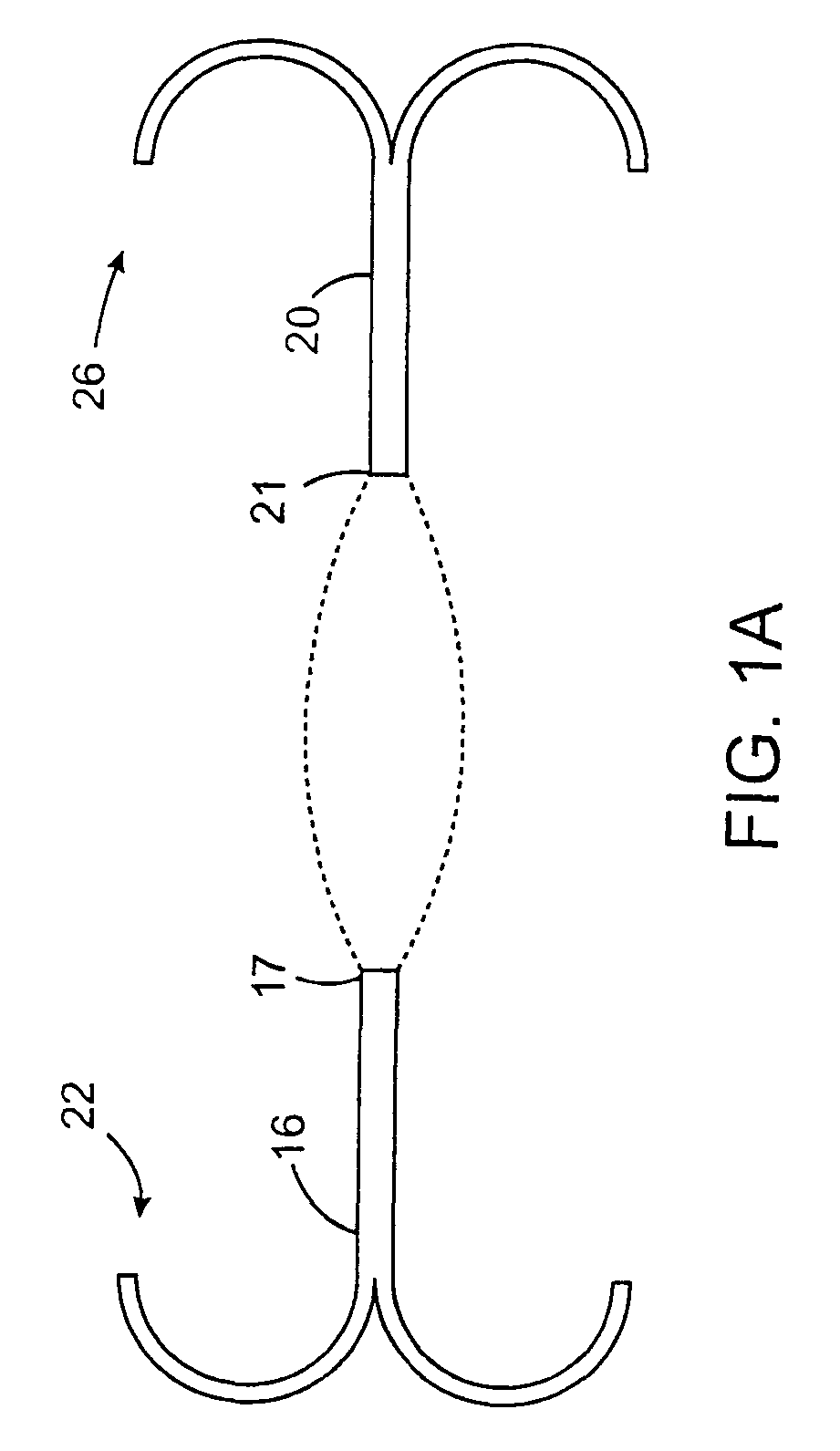

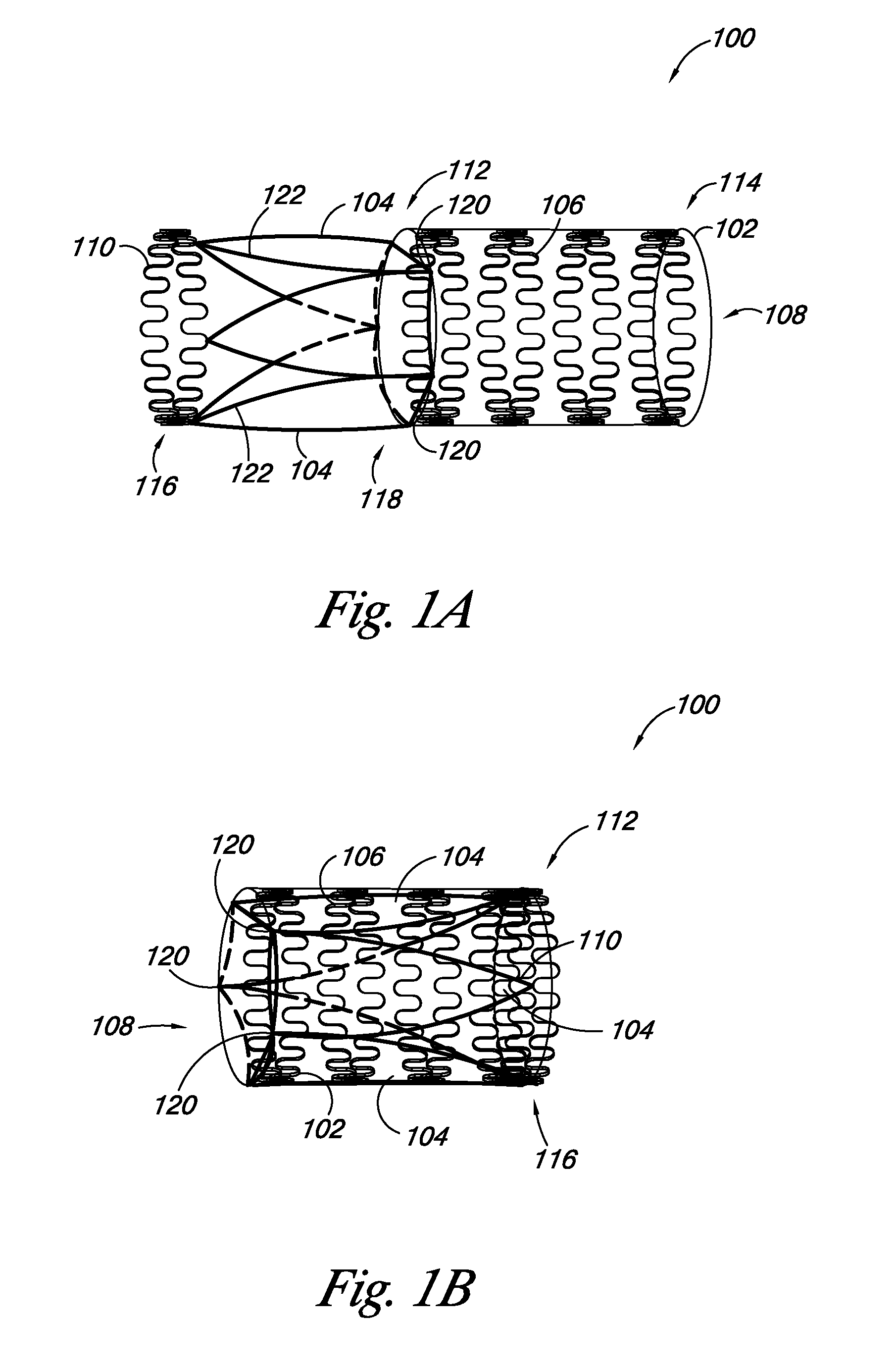

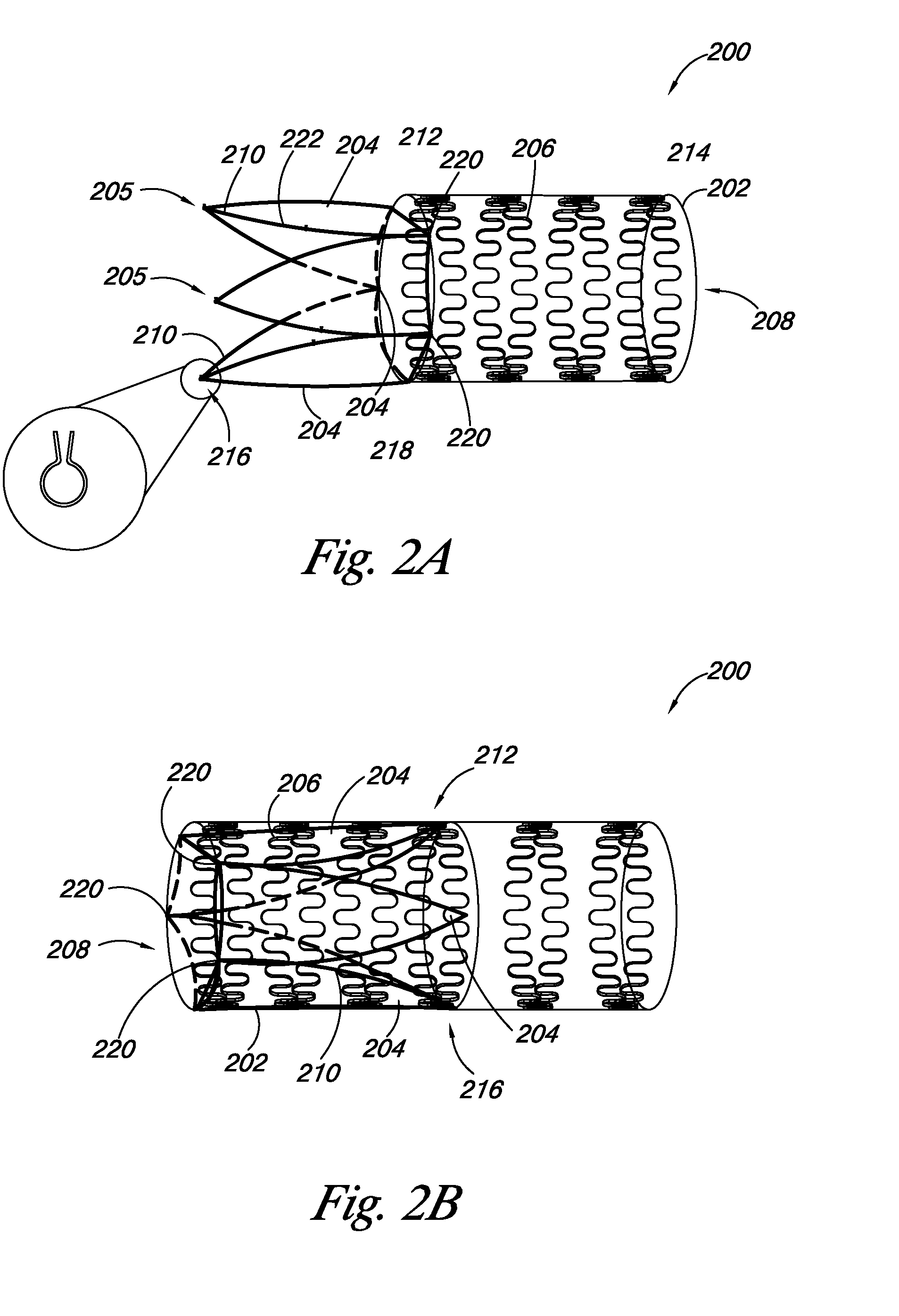

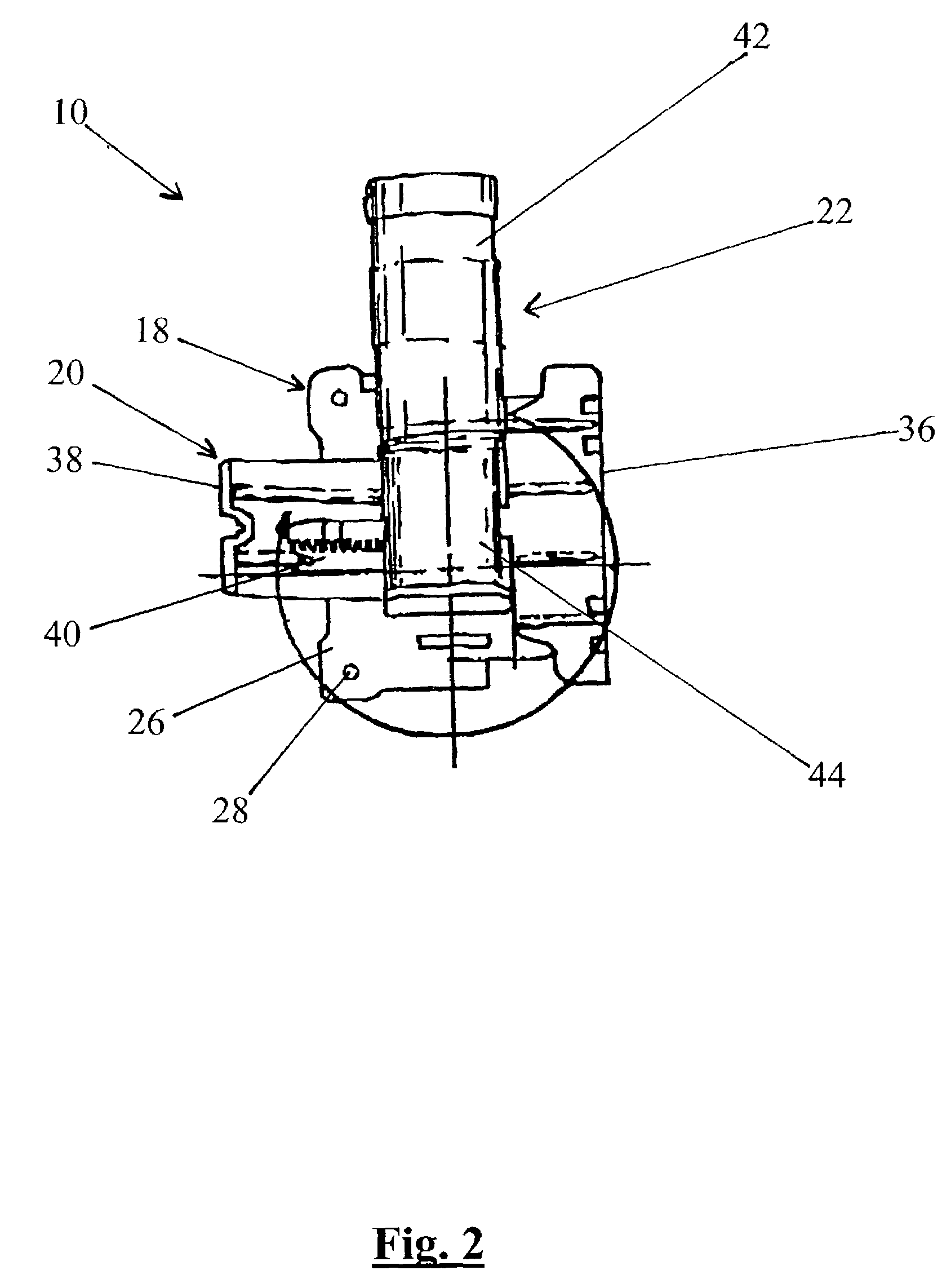

Percutaneous Valve, System and Method

Apparatus, systems, and methods for percutaneous valve replacement and / or augmentation are provided. The apparatus includes a valve having a valve frame, a valve leaflet coupled to the valve frame, and a leaflet transition member coupled to the valve leaflet. The valve leaflet and leaflet transition member can transition from a first position where the valve leaflet and leaflet frame are at least partially outside a lumen of the valve frame to a second position where the valve leaflet and the leaflet transition member are within the lumen of the valve frame.

Owner:BOSTON SCI SCIMED INC

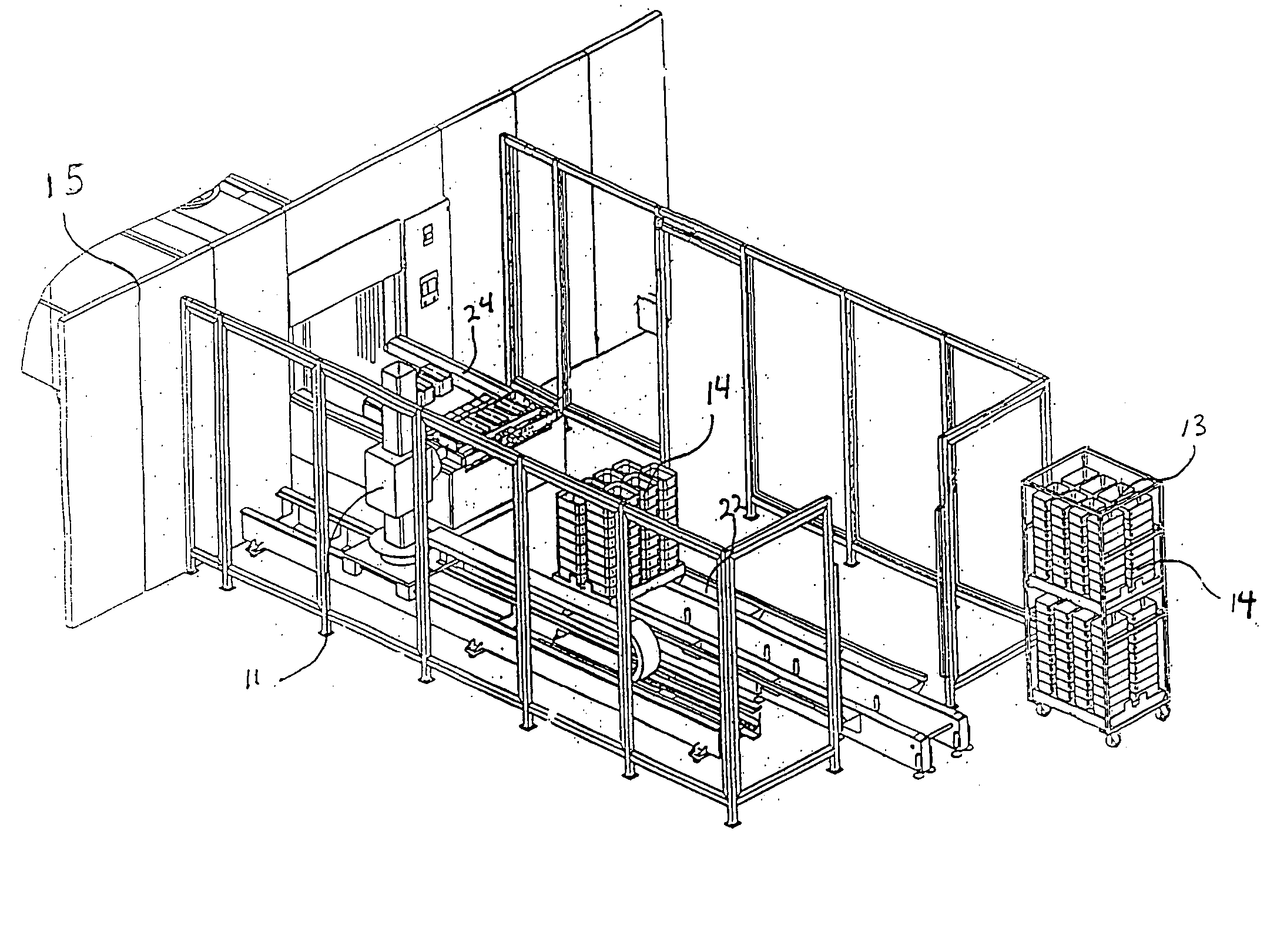

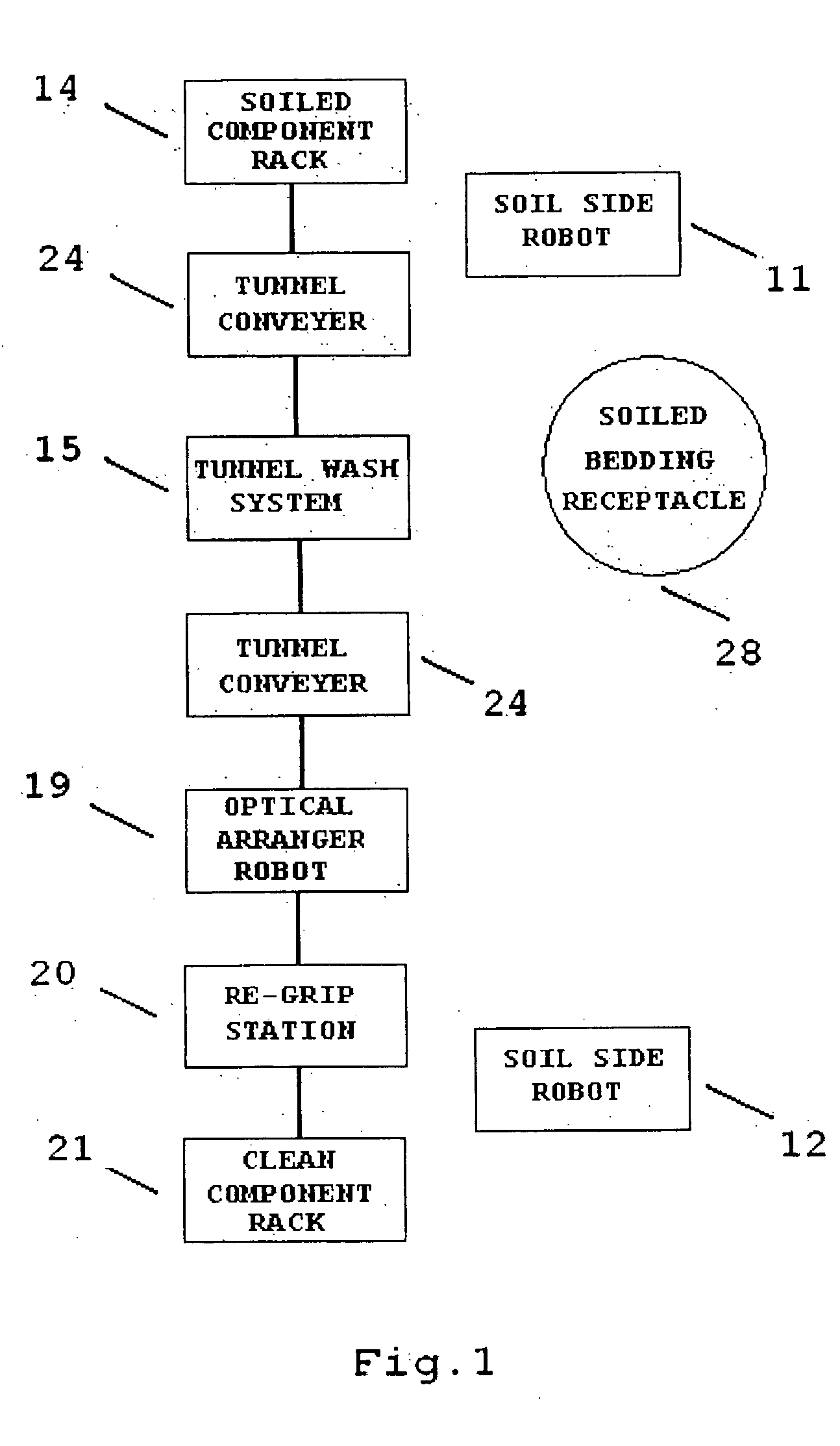

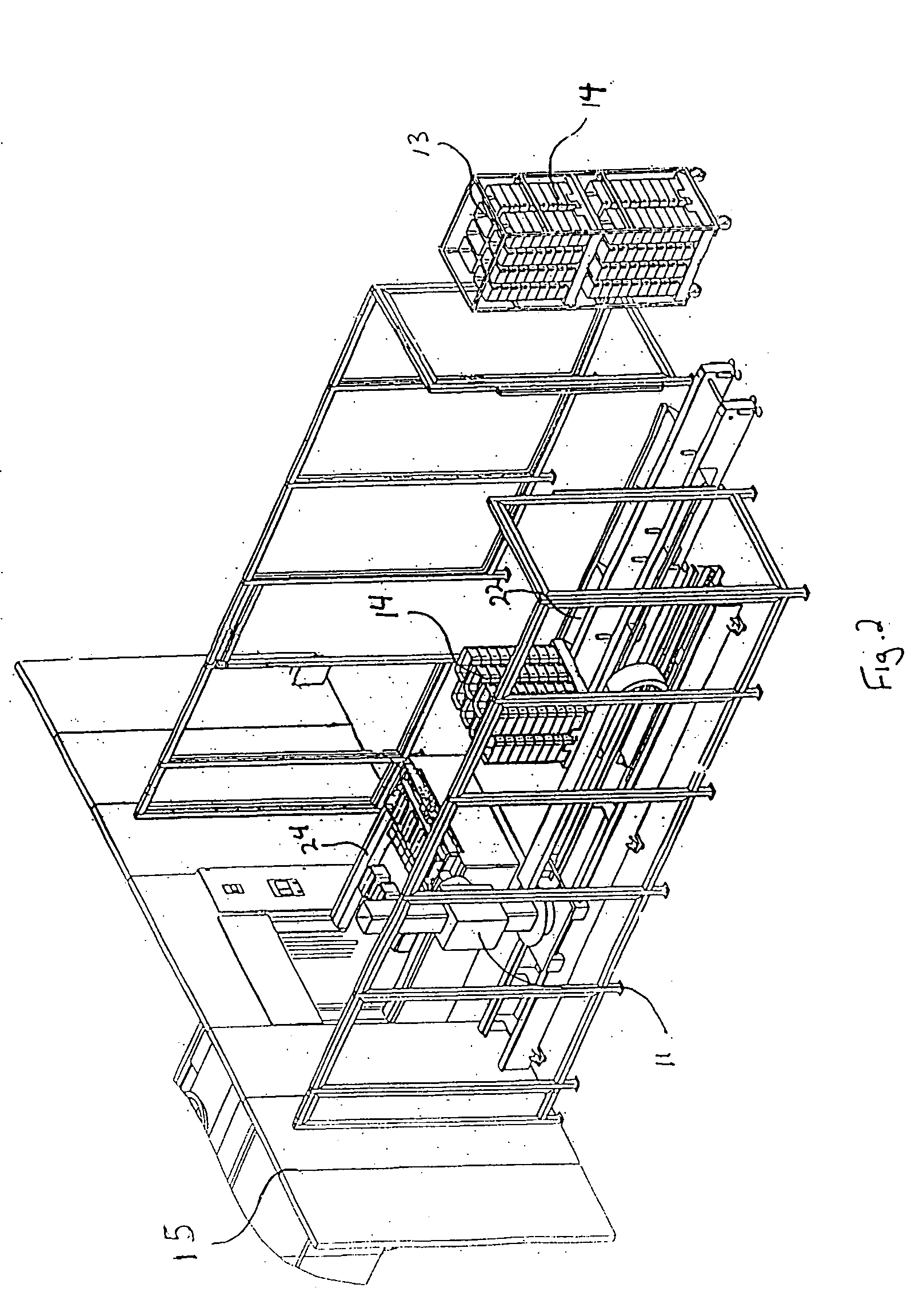

Automated cage cleaning apparatus and method

InactiveUS20050166860A1Design moreLimit human exposureAnimal housingCleaning using liquidsVision processingRobotic arm

The automated cage cleaning system is comprised of a pair of robotic arms, a soil side robot and a clean side robot. The soil side robot is utilized for removing the dirty cage bottoms from a cart, rack, pallet, or fixture, emptying soiled bedding from the cage bottoms, and placing the cage bottoms on a conveyer leading to the tunnel washing equipment. The clean side robot is used to grip the clean cage bottoms, and place the cage bottoms on a cart, rack, pallet, or fixture. Additionally, the present invention comprises an optical arranger robot with vision processing for detecting, and moving skewed cage bottoms to a re-grip station. From the re-grip station, the clean side robot places the cage bottoms on a rack, pallet, fixture, or any other device suitable for holding a plurality of cage bottoms.

Owner:MATRIX SCI

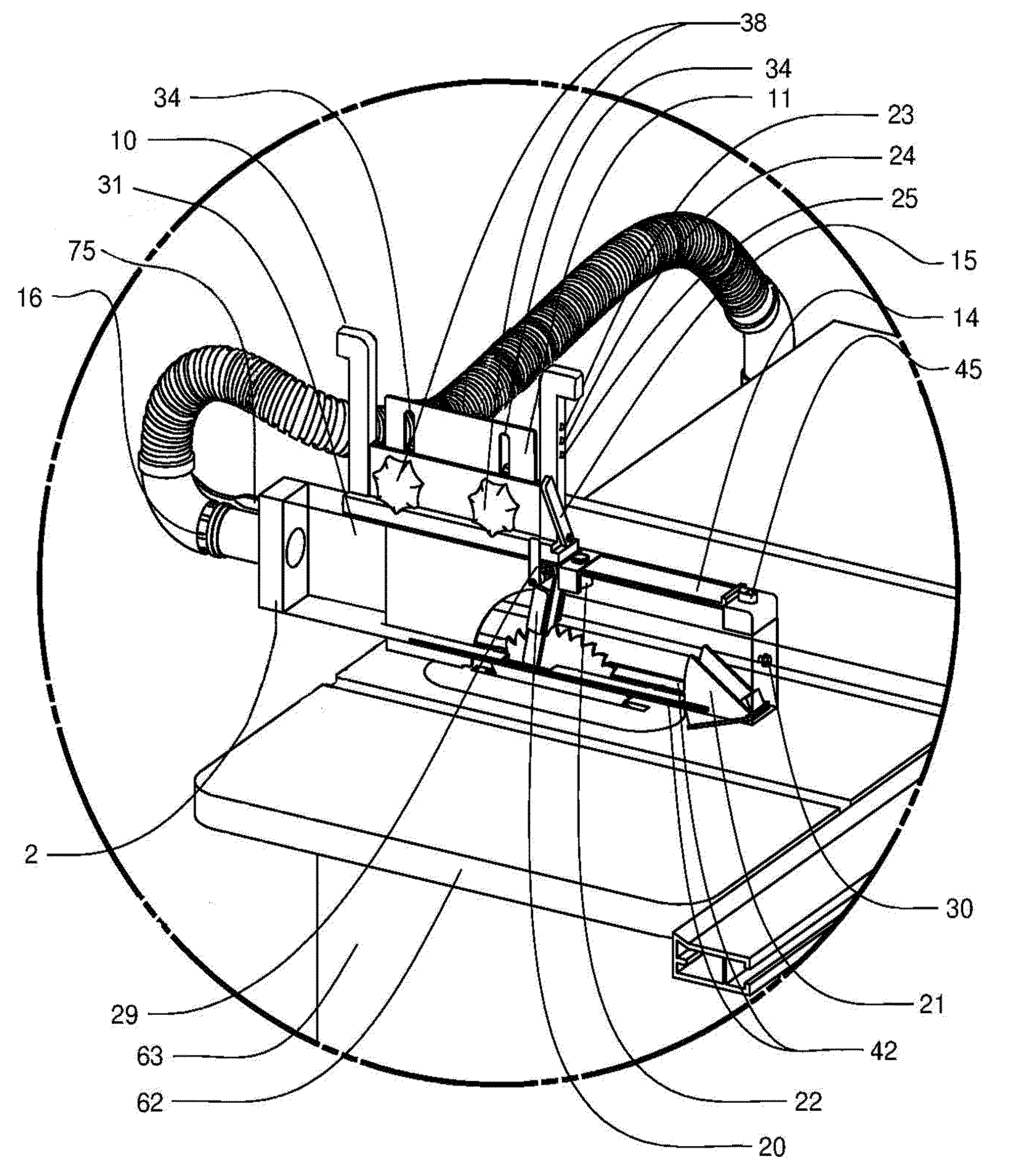

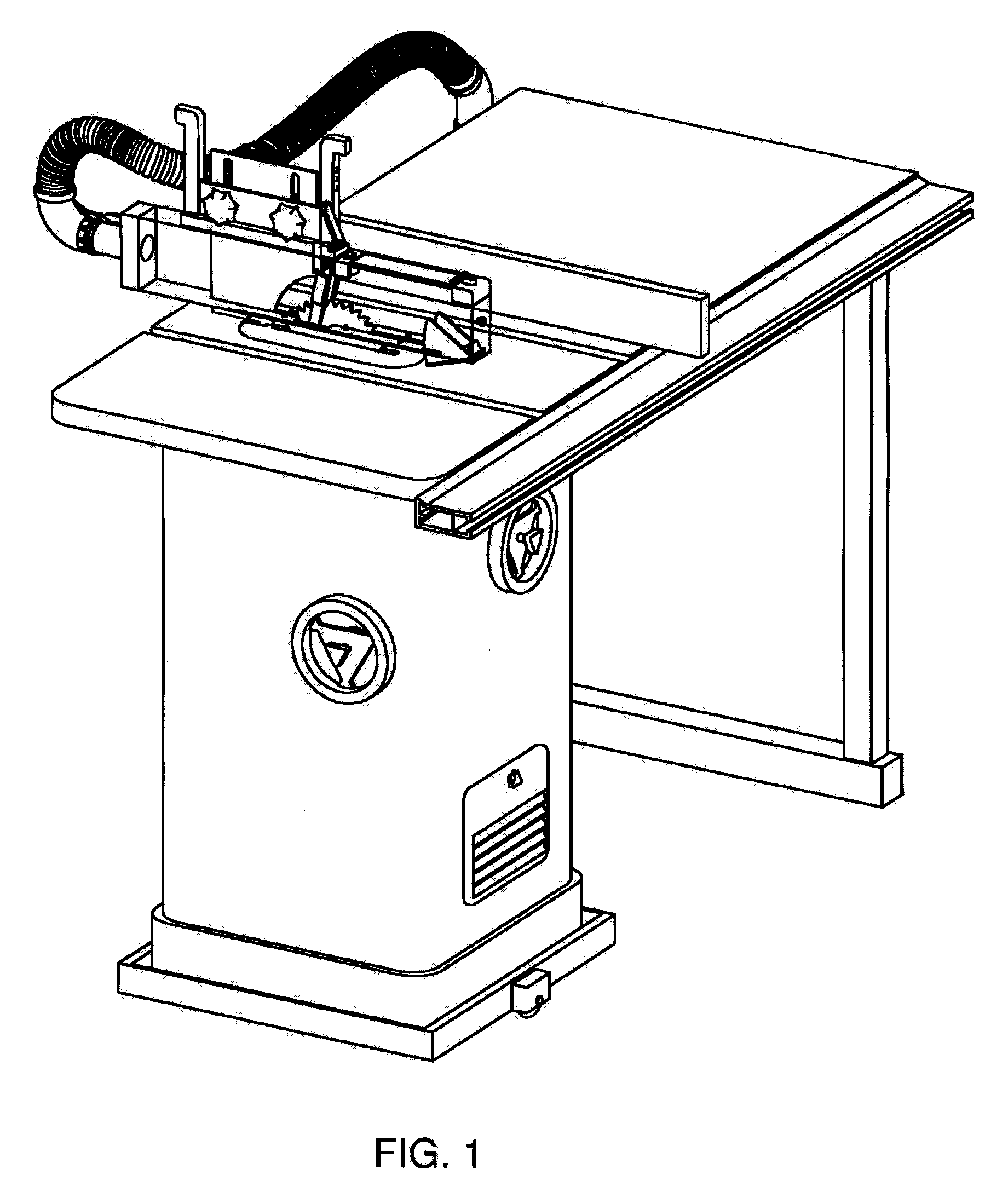

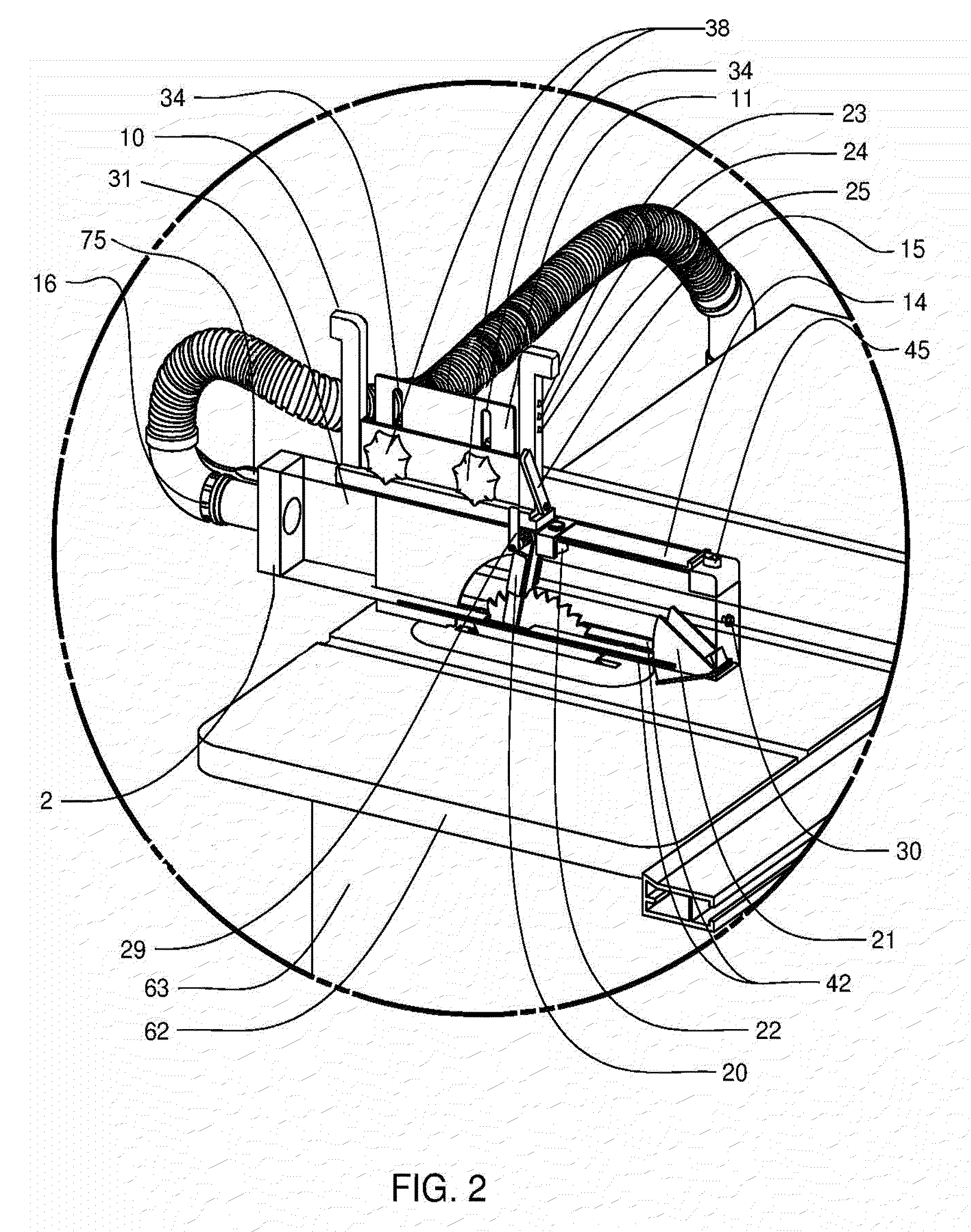

Health and safety system for a table saw

InactiveUS20100307307A1Reduces long-term riskEasy accessMetal sawing accessoriesGuide fencesInjury causeCollection system

An improved health and safety system for a table saw includes one or more of: a blade guard that protects the operator from the saw blade, and contains and collects sawdust; a proximity detector and emergency saw motor braking means for use in connection with such blade guard; an anti-kickback device for use in connection with such blade guard, a rip fence adapter for use in connection with such a blade guard, and hoses and fittings to connect the dust containment and collection system of said blade guard to a shop dust collection blower or vacuum system. The system protects the saw operator from potential traumatic injury to a hand, and from ingesting potentially carcinogenic sawdust.

Owner:BUTLER DAVID J

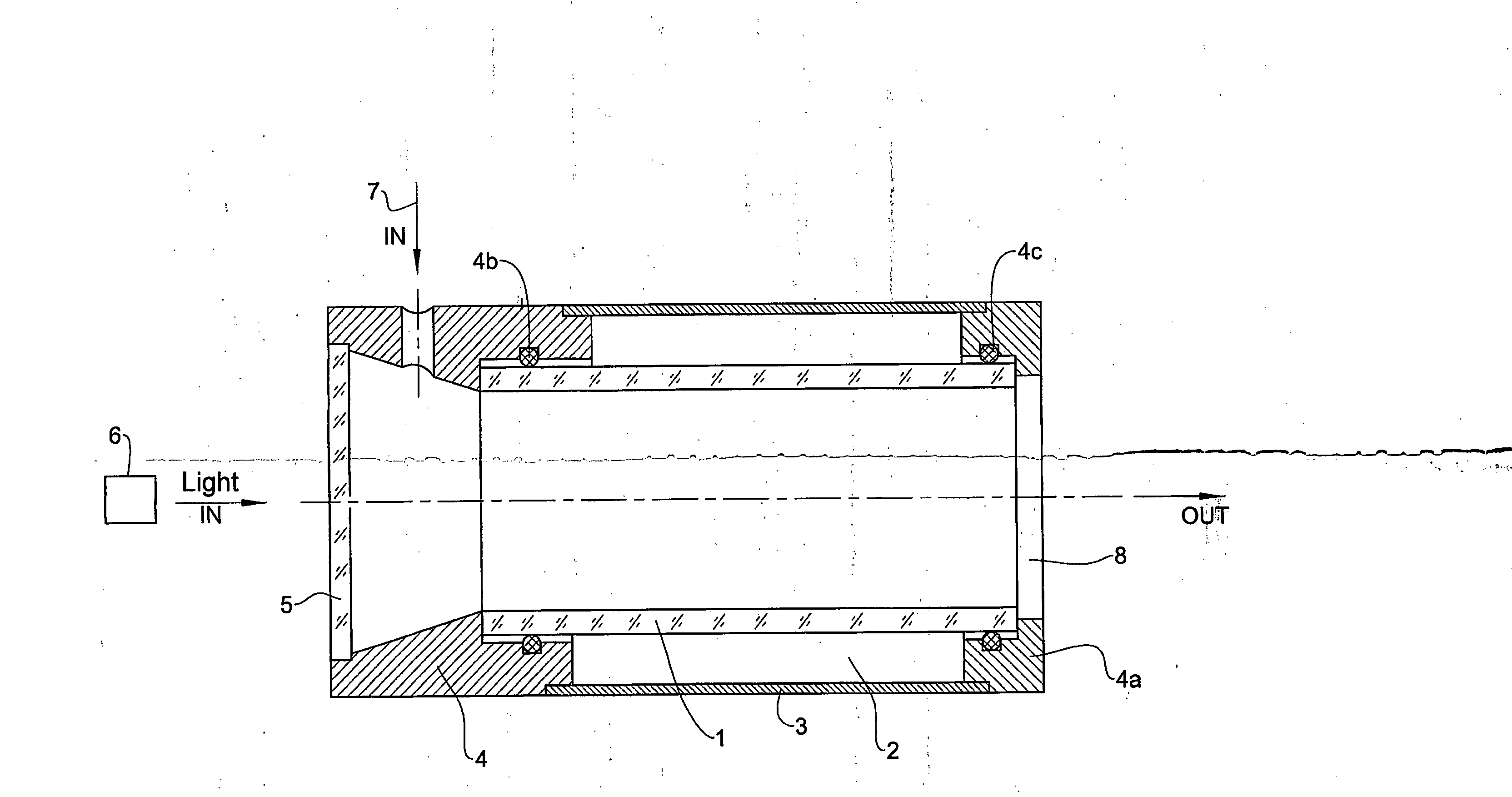

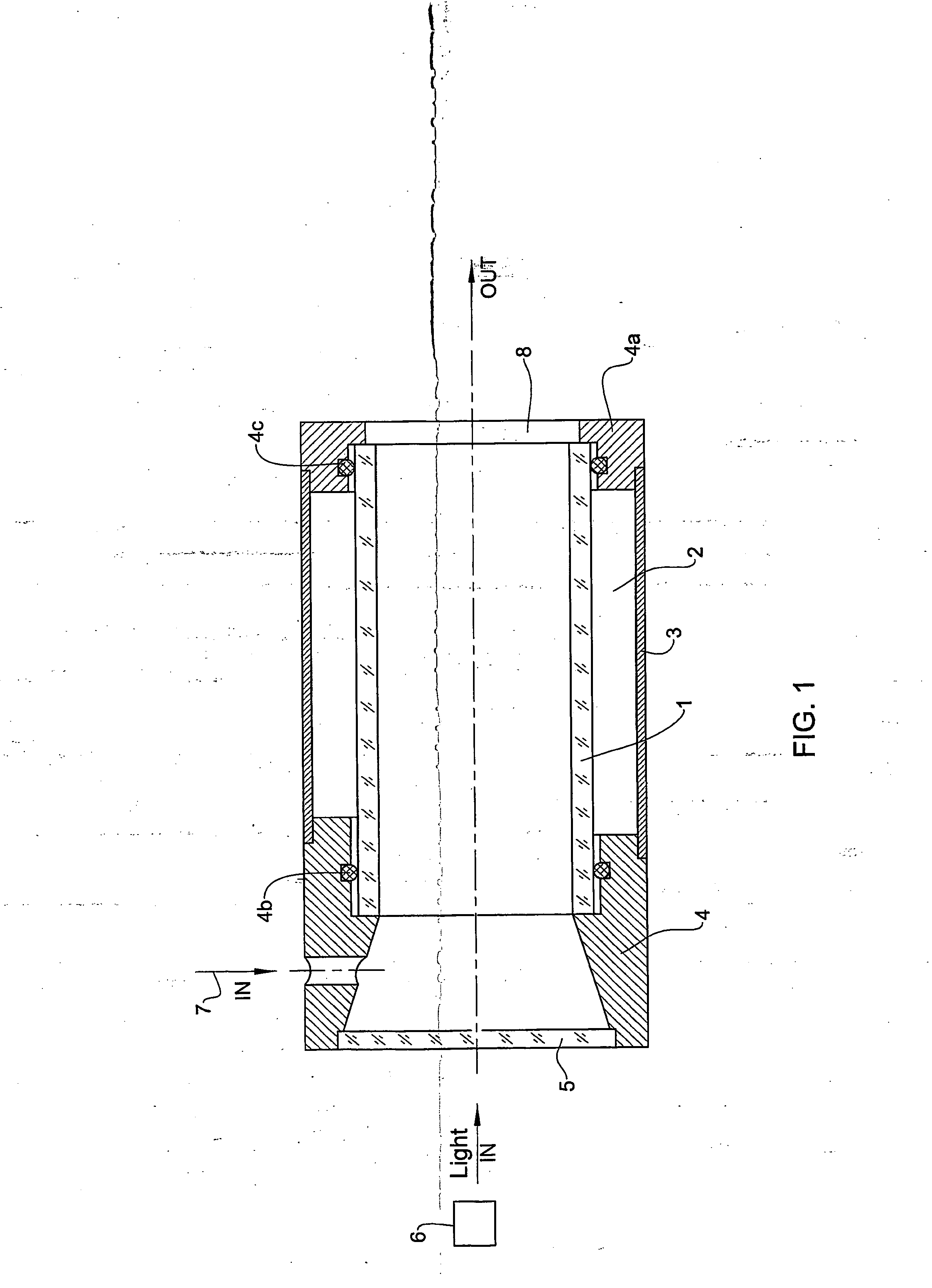

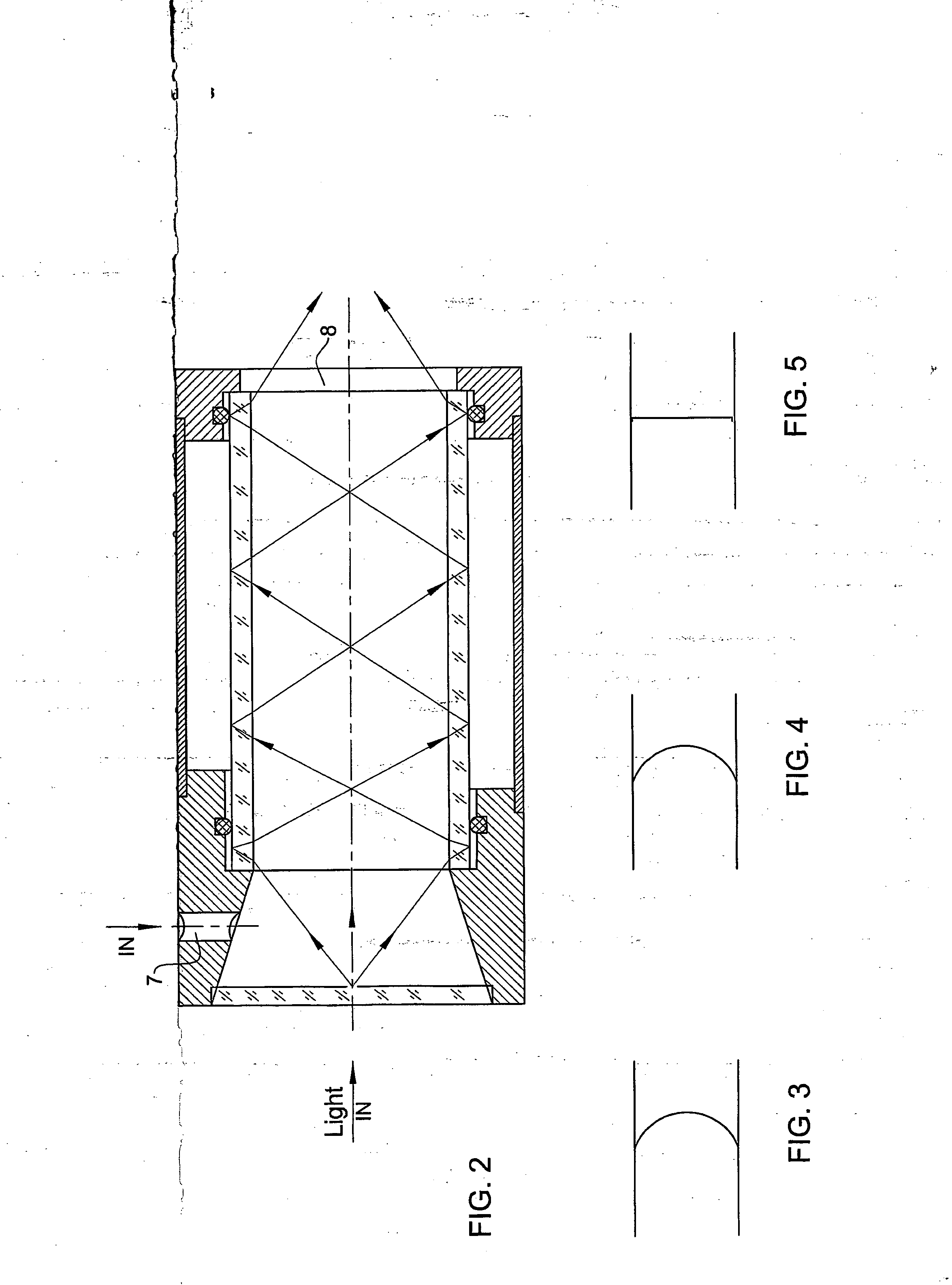

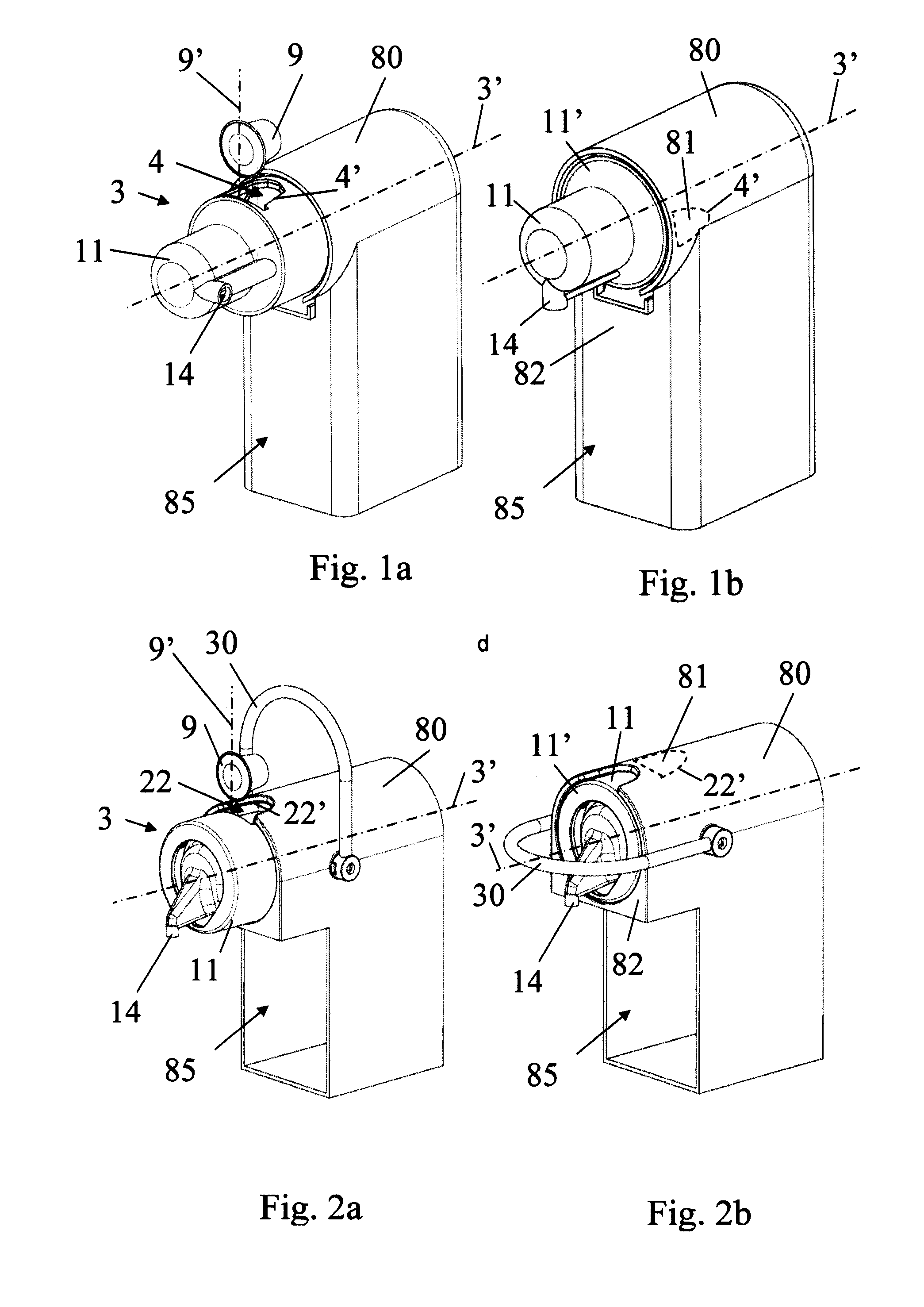

In-Line Treatment of Liquids and Gases by Light Irradiation

ActiveUS20070272877A1Design moreEasy to adaptWater/sewage treatment by irradiationWater/sewage treatment with mechanical oscillationsSpray nozzleWater jet

Owner:ATLANTIUM TECHNOLOGIES LTD

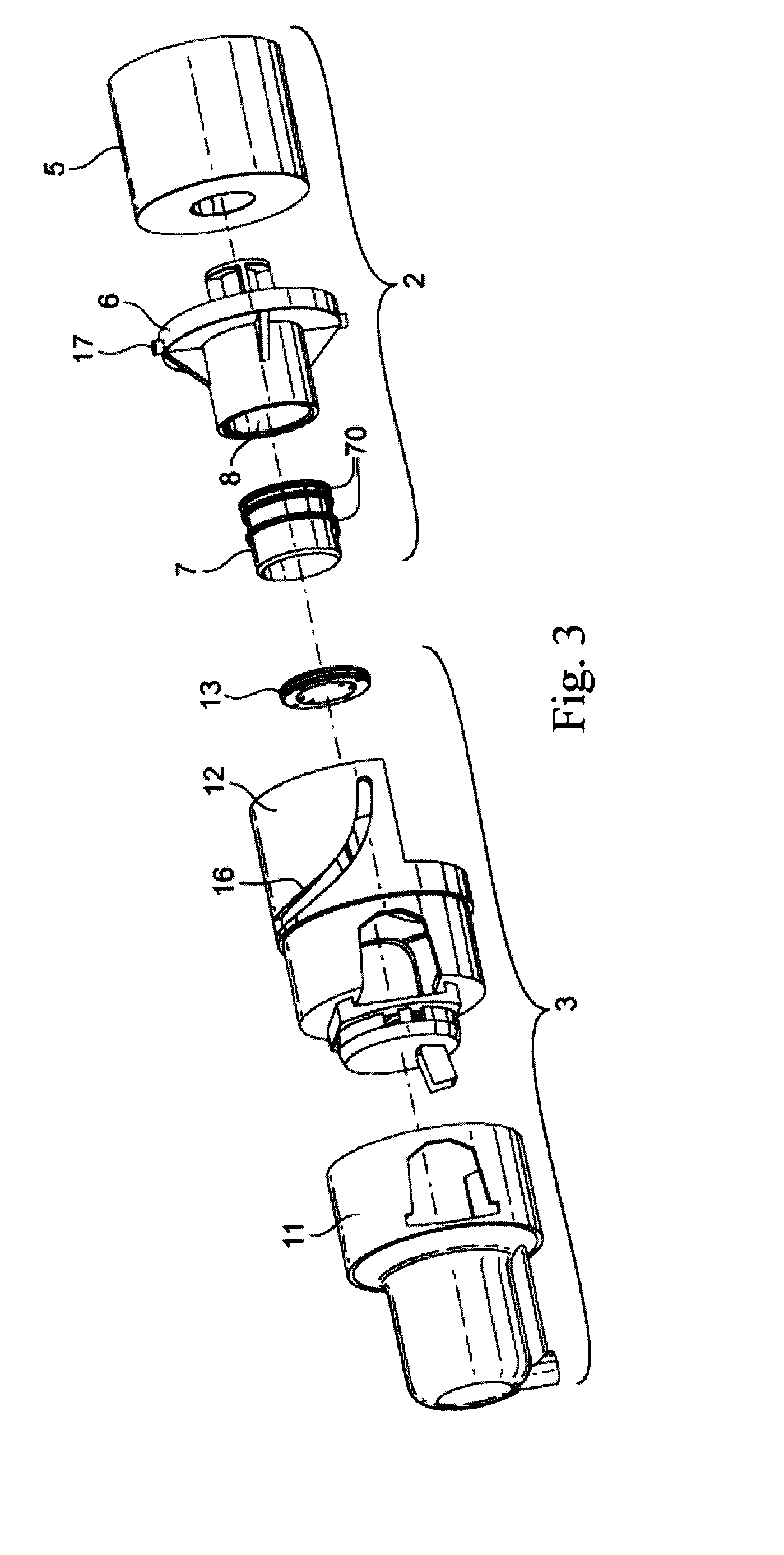

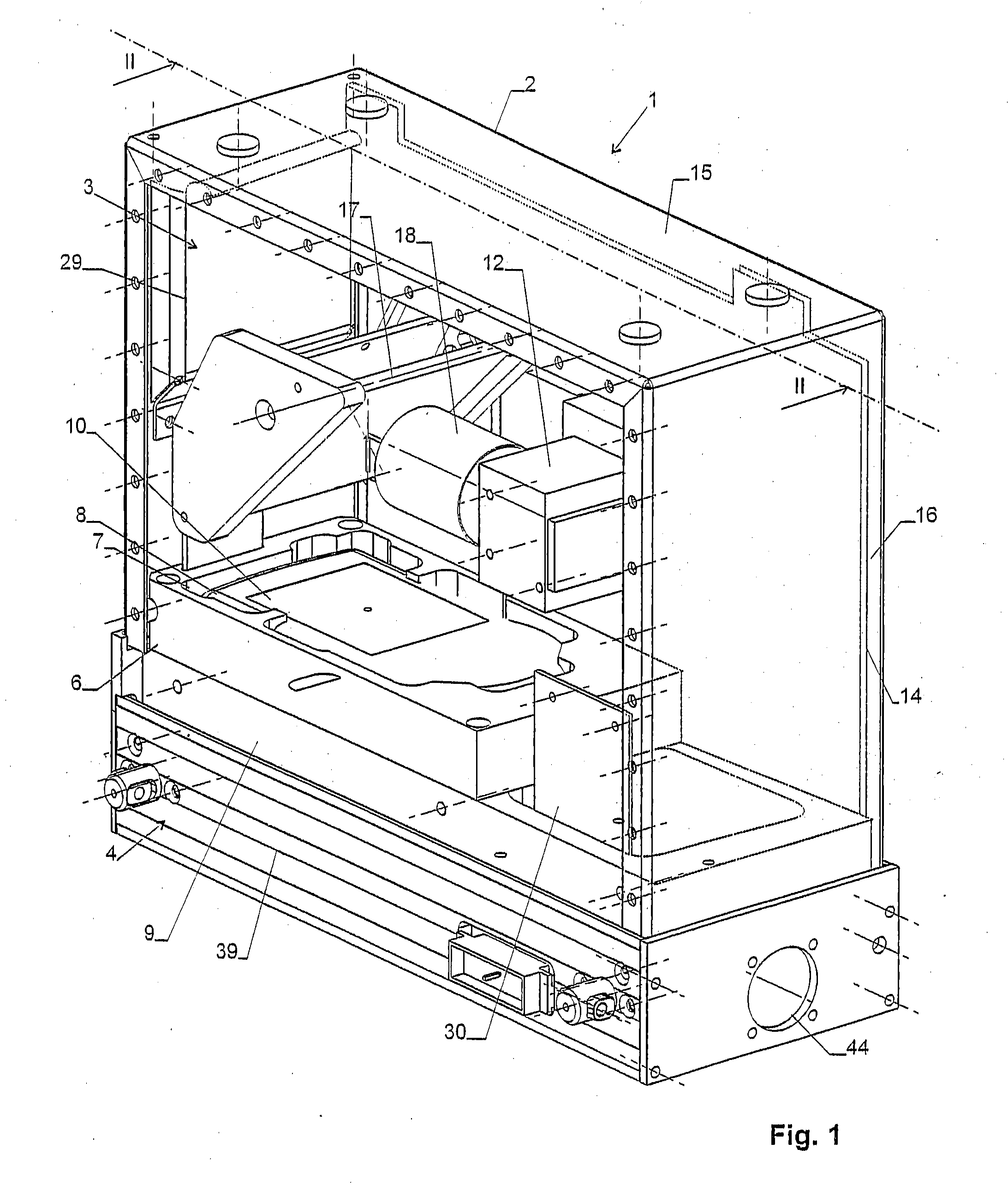

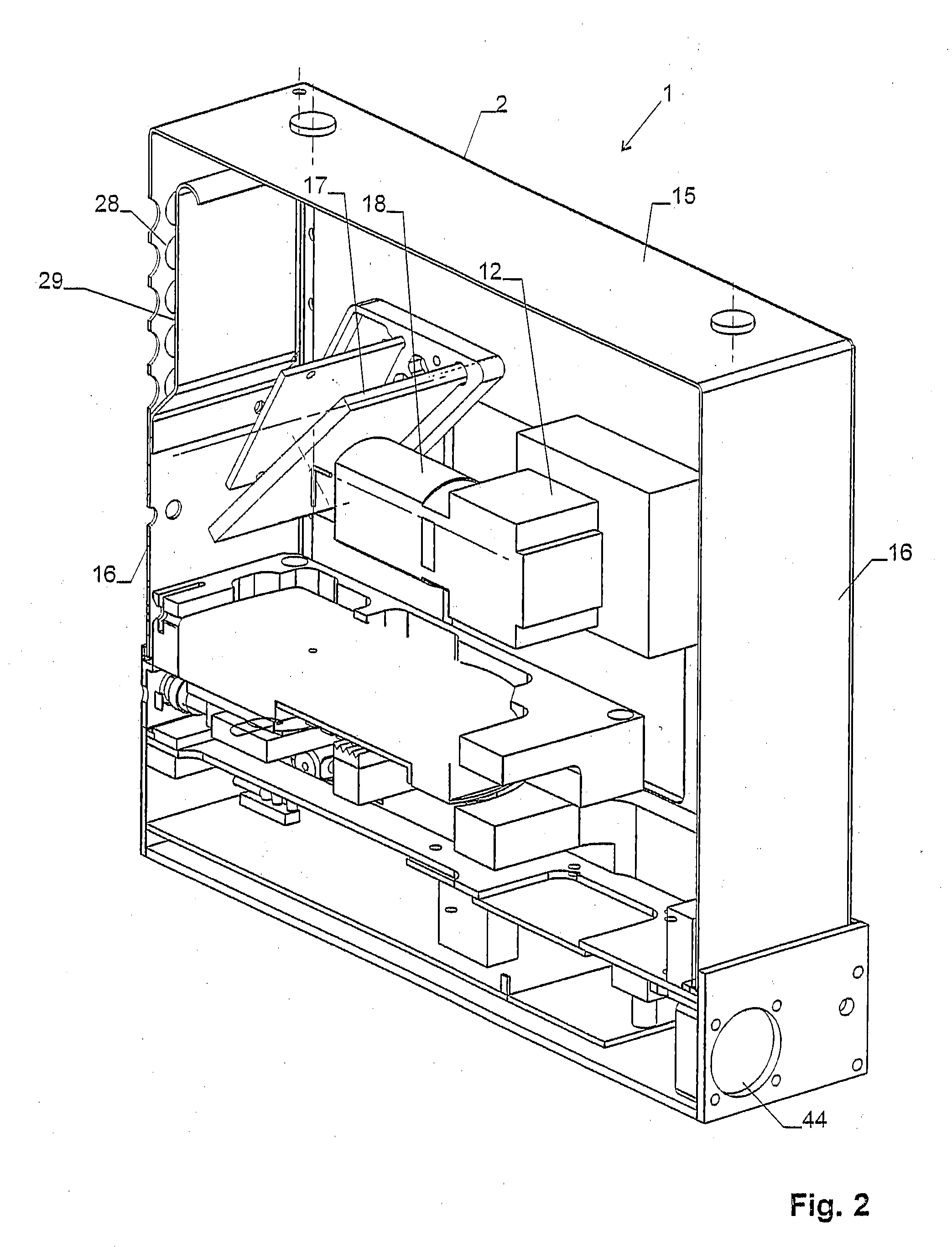

Beverage brewing unit

ActiveUS20100288132A1Direct fluid connectionFew moving partsBeverage vesselsAdditive ingredientBiomedical engineering

A beverage machine having a beverage brewing unit for receiving a single-serve capsule and including a capsule holding assembly for holding a capsule in a position during insertion by gravity of the capsule in the brewing unit; and a water injection assembly for at least partially enclosing the capsule and providing water in the capsule. The capsule holding part forms a front part of the unit and is mounted to the capsule injection assembly in a manner to be displaceable along a substantially horizontal path whereas the water injection assembly is located in a rear fixed part of the unit. The beverage machine has an outermost casing. One of these brewing unit assemblies can be moved or telescoped out or through this casing for inserting / removing the ingredient capsule and retracted into the outermost casing for bringing the brewing unit into its capsule extraction configuration.

Owner:SOC DES PROD NESTLE SA

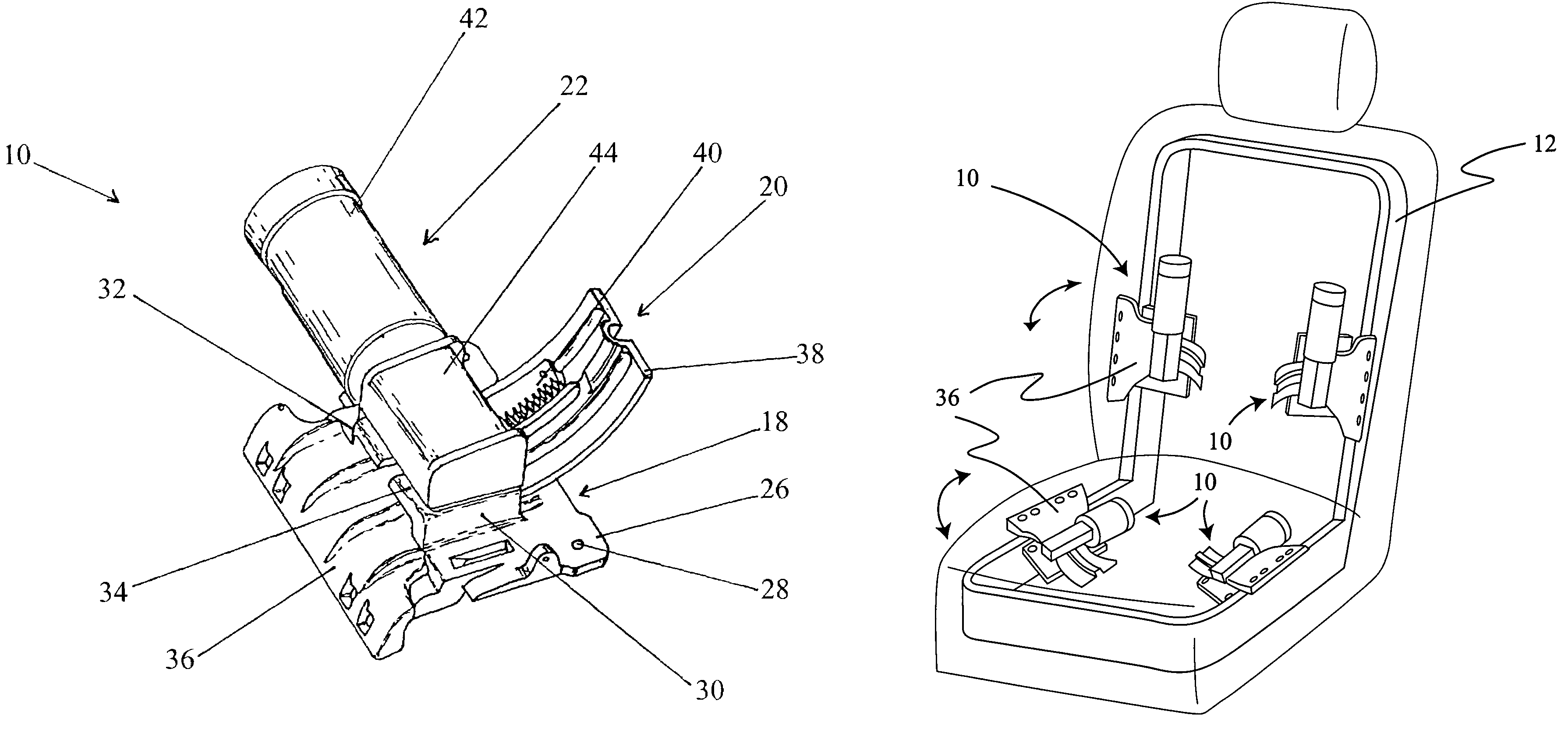

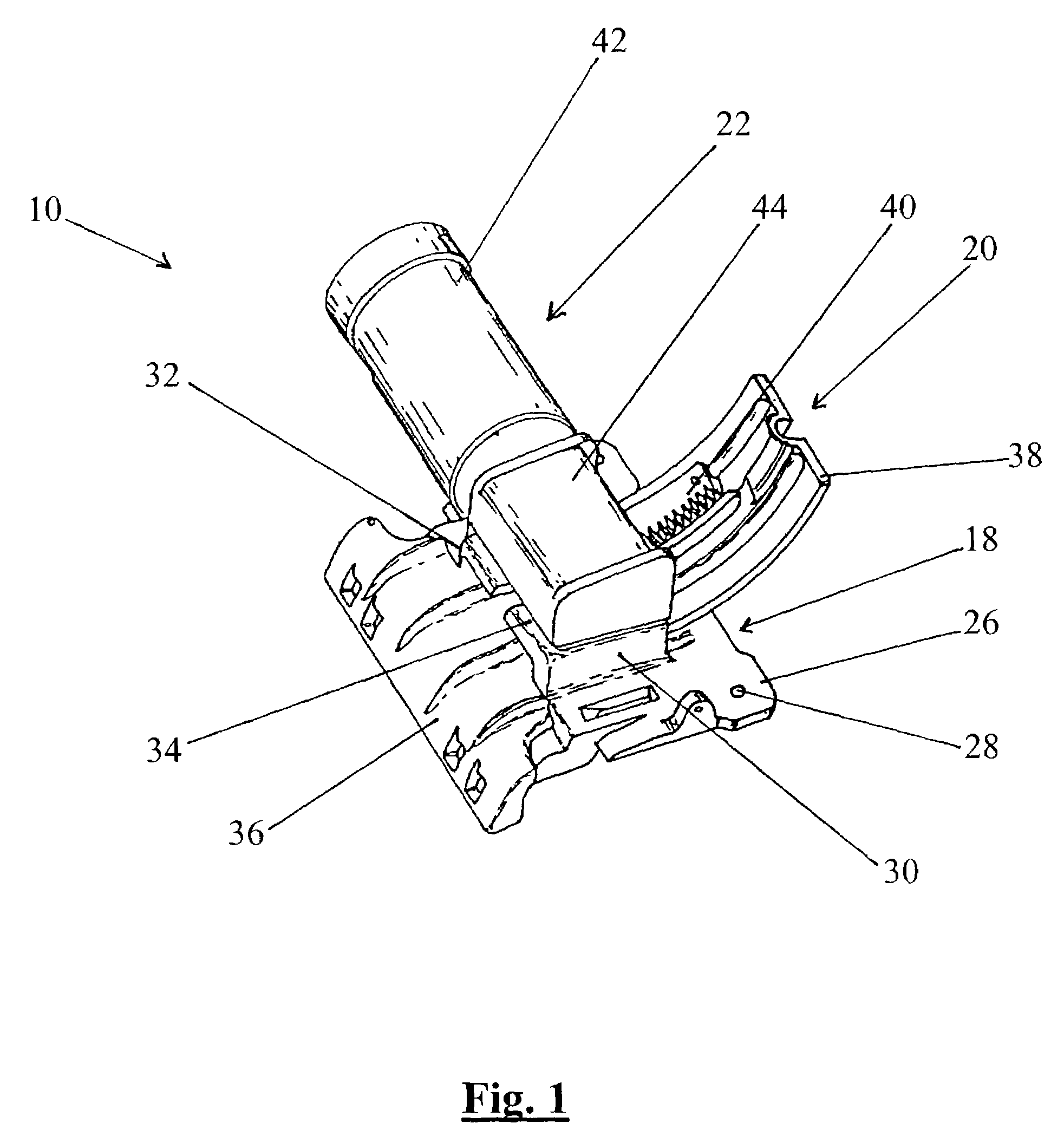

Seat bolster adjustment apparatus and method

An active bolster adjustment apparatus for use in vehicle seats includes a mounting plate connected with the vehicle seat. An adjustable bolster slider is in sliding communication with the mounting plate, and has an adjustment arm and a pressure surface. A drive unit having an actuator and a gear set and the gear set is in direct communication with the adjustable bolster slider.

Owner:L & P PROPERTY MANAGEMENT CO

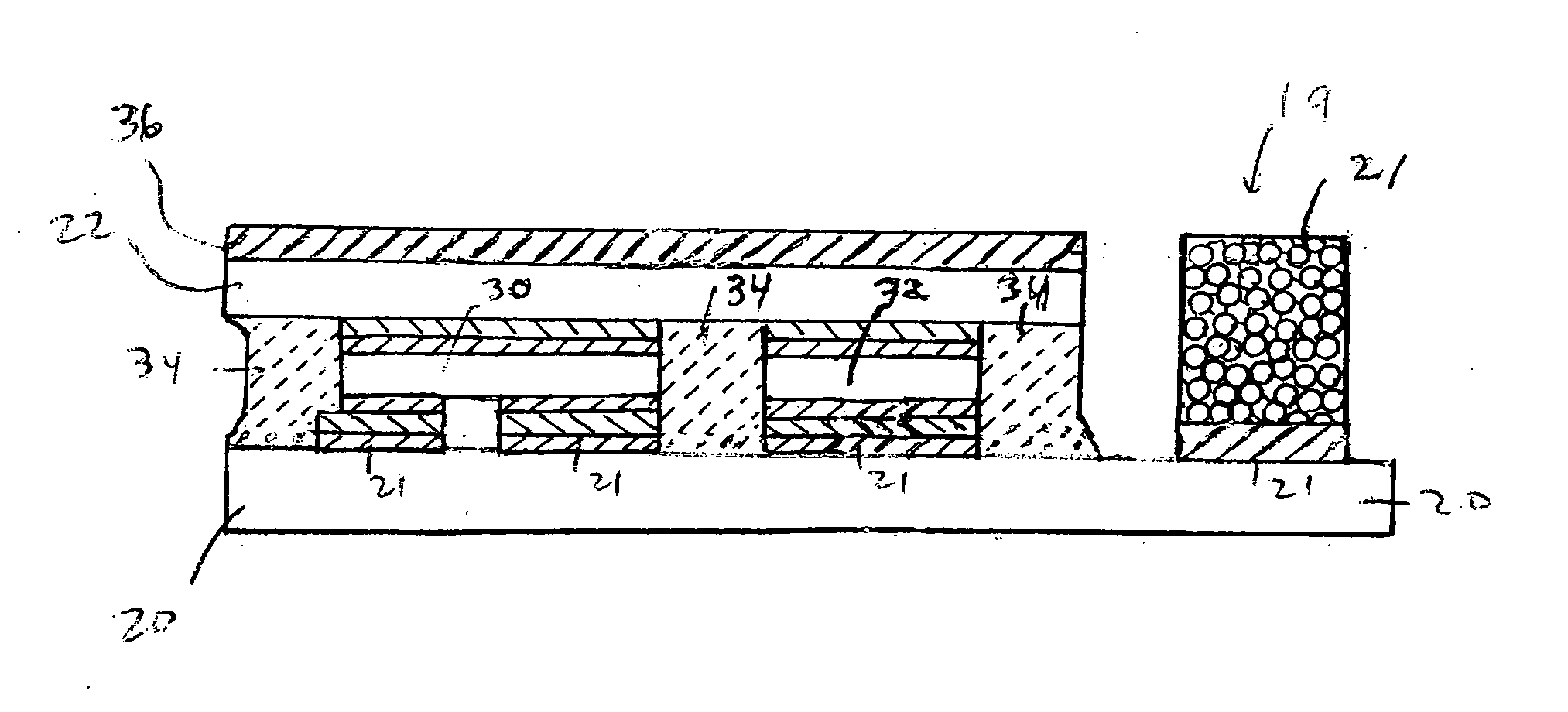

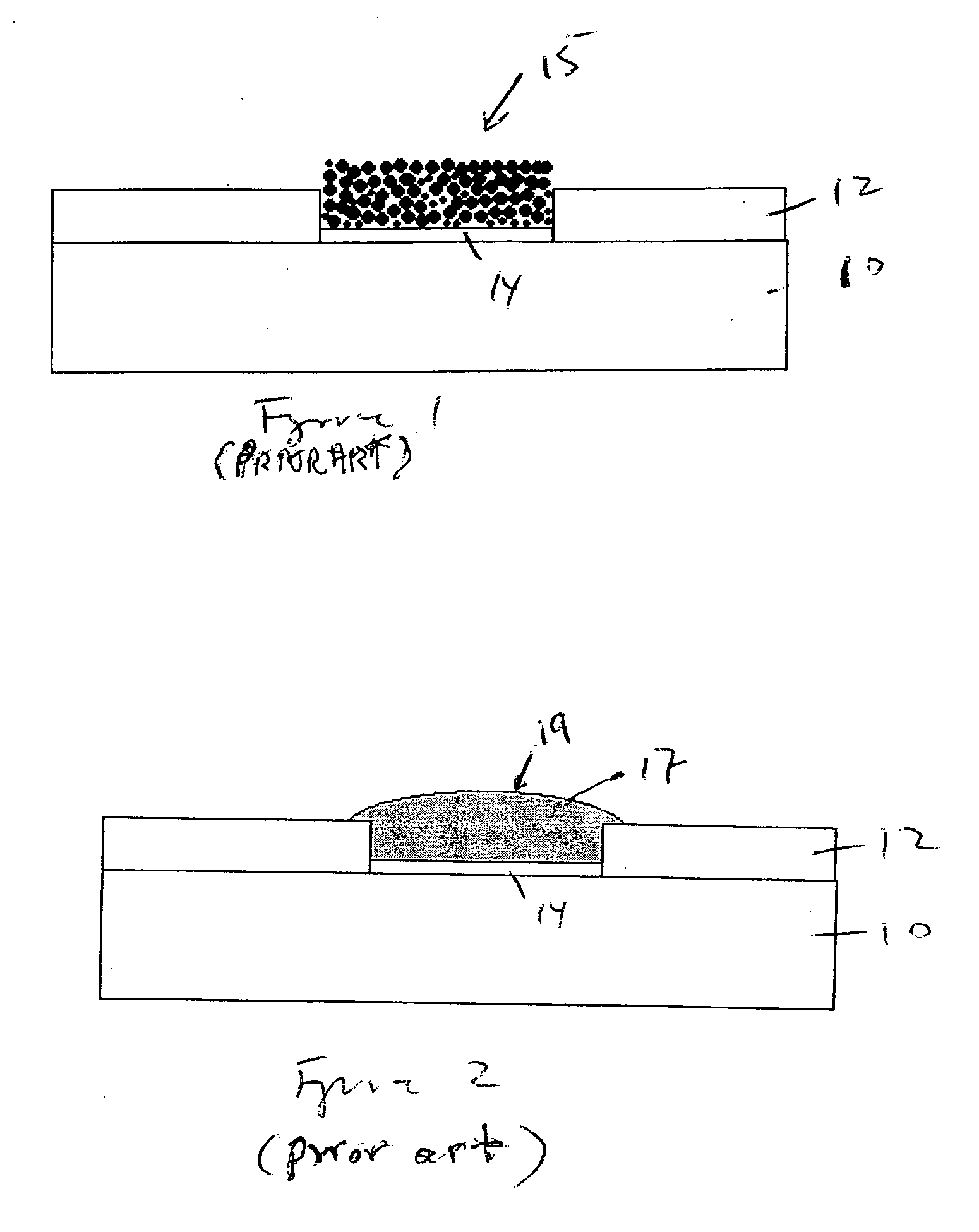

Semiconductor device package utilizing proud interconnect material

InactiveUS20050121784A1Reduce critical manufacturing toleranceEasy to produceSemiconductor/solid-state device detailsSolid-state devicesDevice materialSemiconductor package

A semiconductor package which includes a conductive can, a semiconductor die received in the interior of the can and connected to an interior portion thereof at one of its sides, at least one interconnect structure formed on the other side of the semiconductor die, and a passivation layer disposed on the other side of the semiconductor die around the interconnect structure and extending at least to the can.

Owner:INFINEON TECH AMERICAS CORP

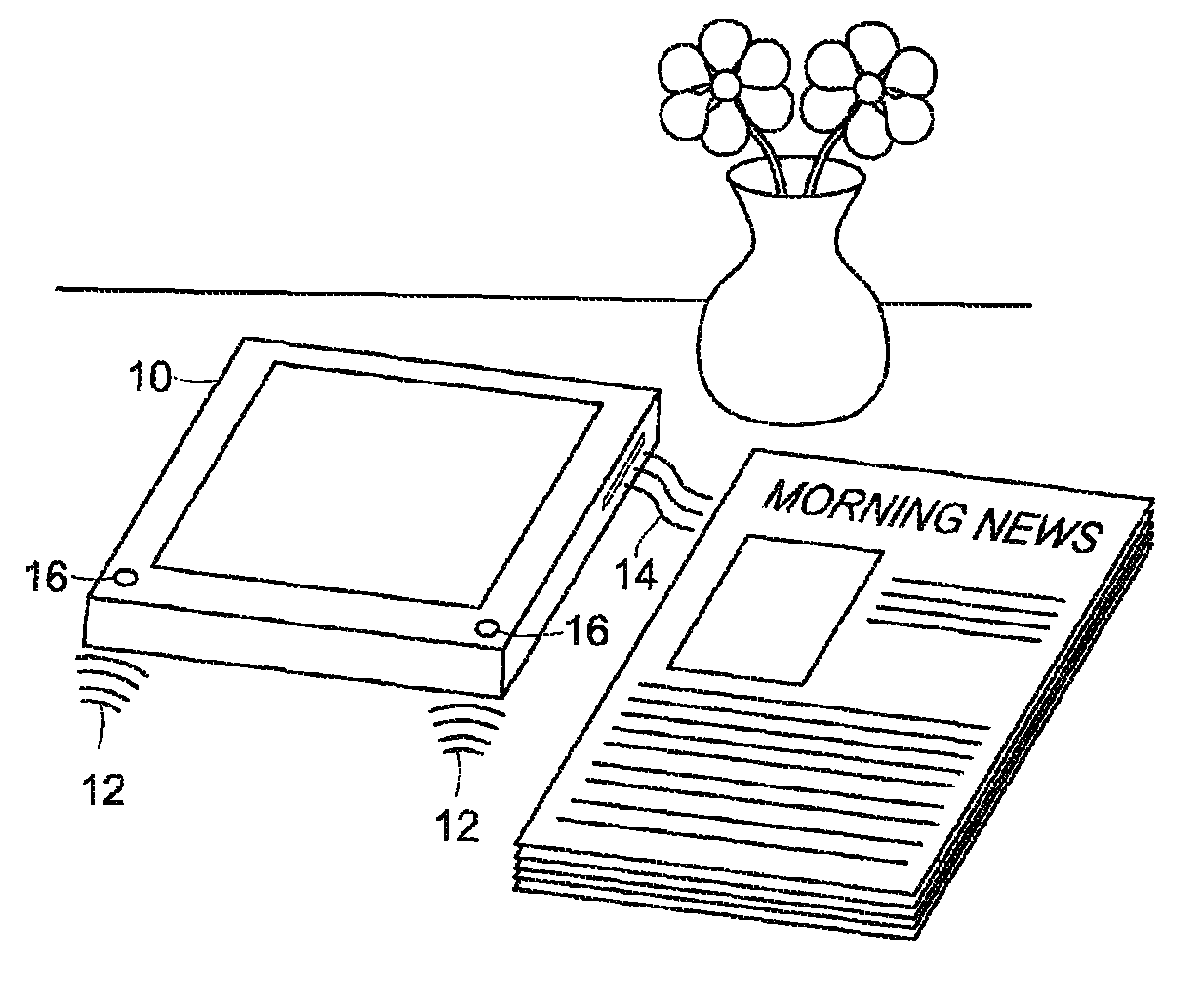

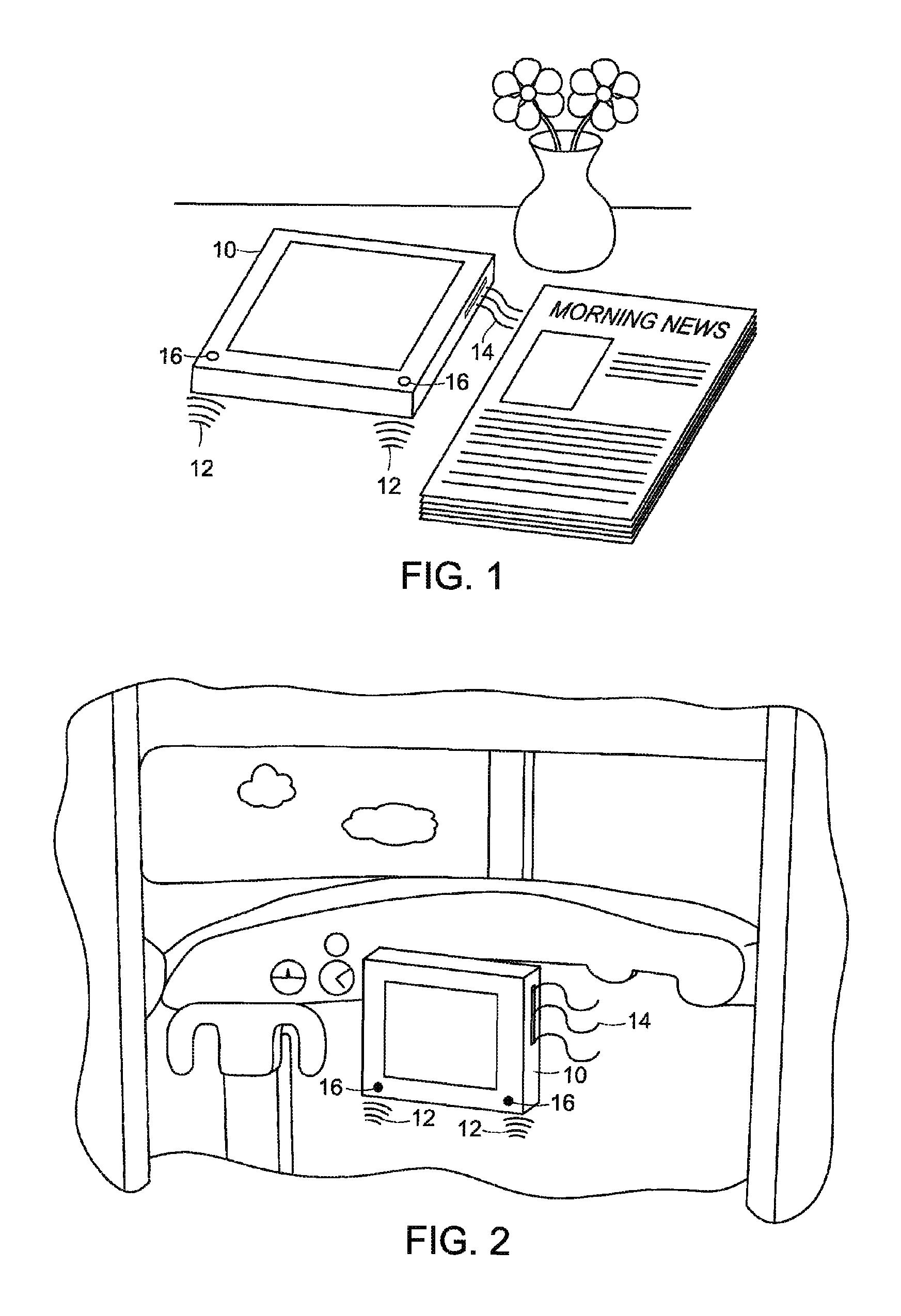

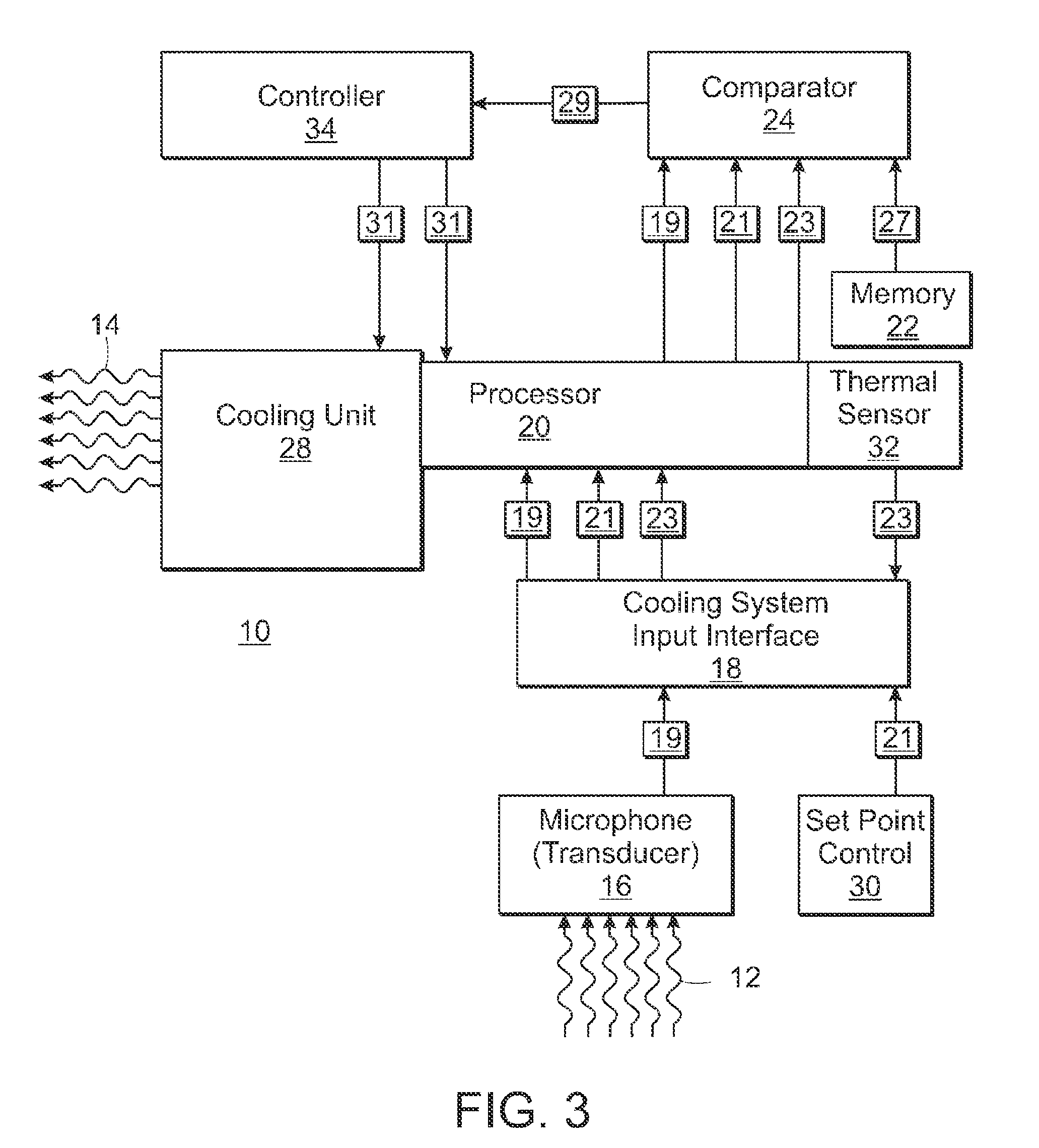

Ambient noise level sampling system for cooling an electronic device

ActiveUS7941231B1More compact designPerformance maximizationVibration measurement in solidsMachine part testingEnvironmental noiseEngineering

An electronic device is provided that is able to detect noise to which the electronic device is exposed and an internal temperature of the device. The device contains a cooling unit to cool at least a portion of the electronic device and a subsystem coupled to the microphone and / or a thermal sensor and further coupled to the cooling unit. The cooling unit adjusts according to the detected noise and internal temperature. A method for cooling an electronic device is also provided. The method comprises monitoring the noise of the device's ambient environment, monitoring an internal temperature of the device, and actuating a user interface. The method provides for cooling the device by adjusting fan speed, clock speed, or power supply voltage applied to the device based on the noise of the ambient environment, an internal temperature of the device, and actuation of the user interface.

Owner:ZEBRA TECH CORP

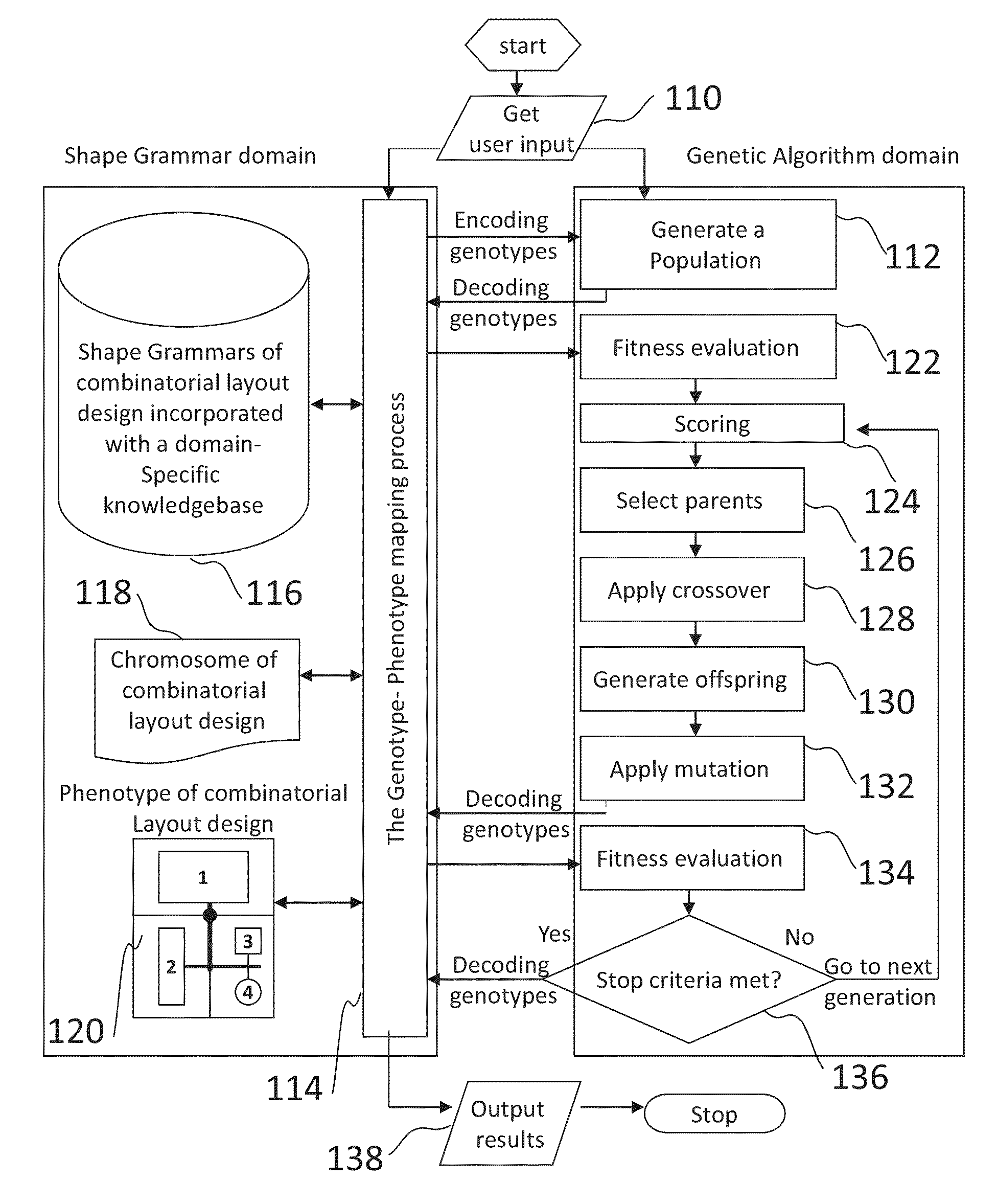

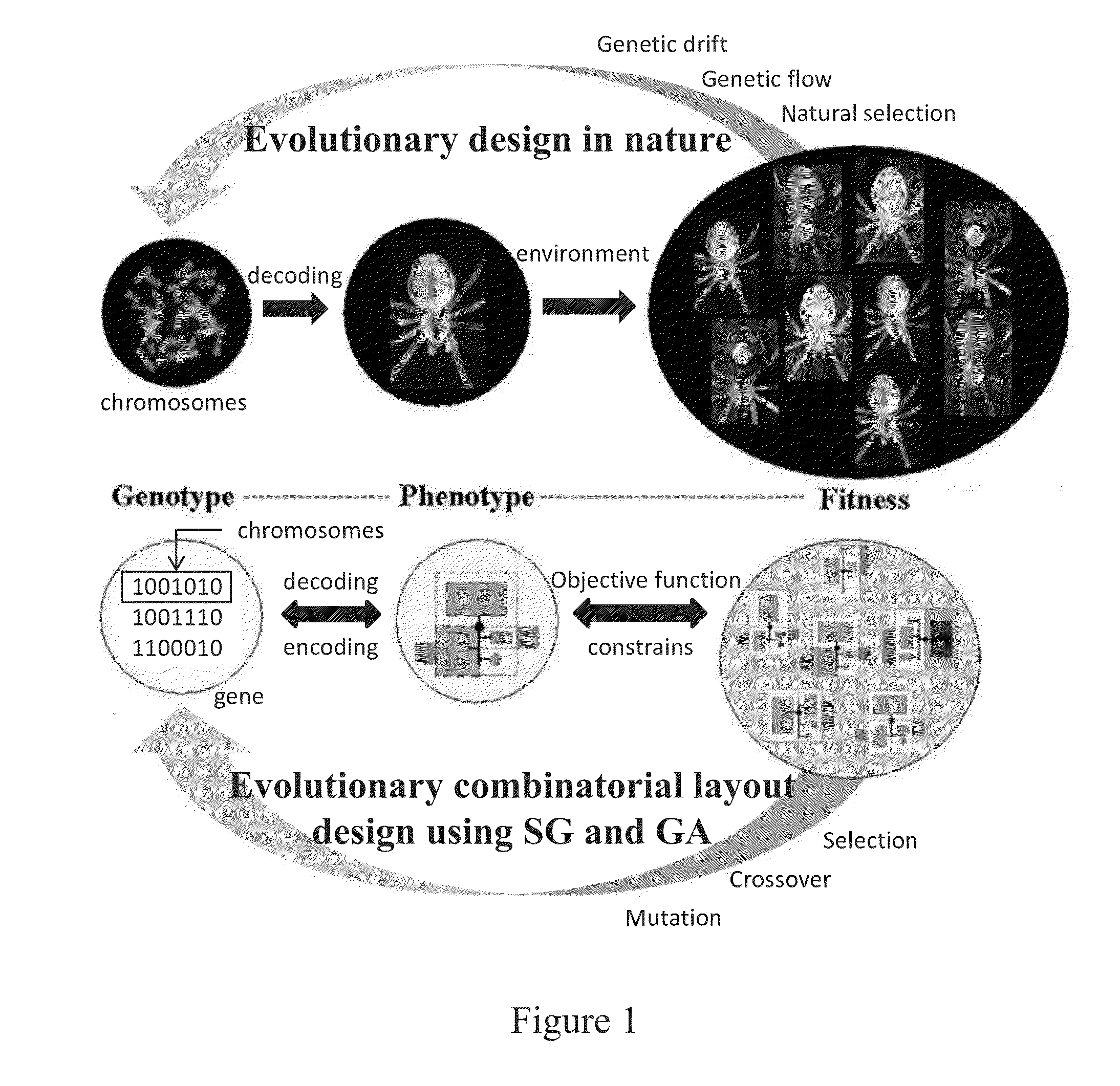

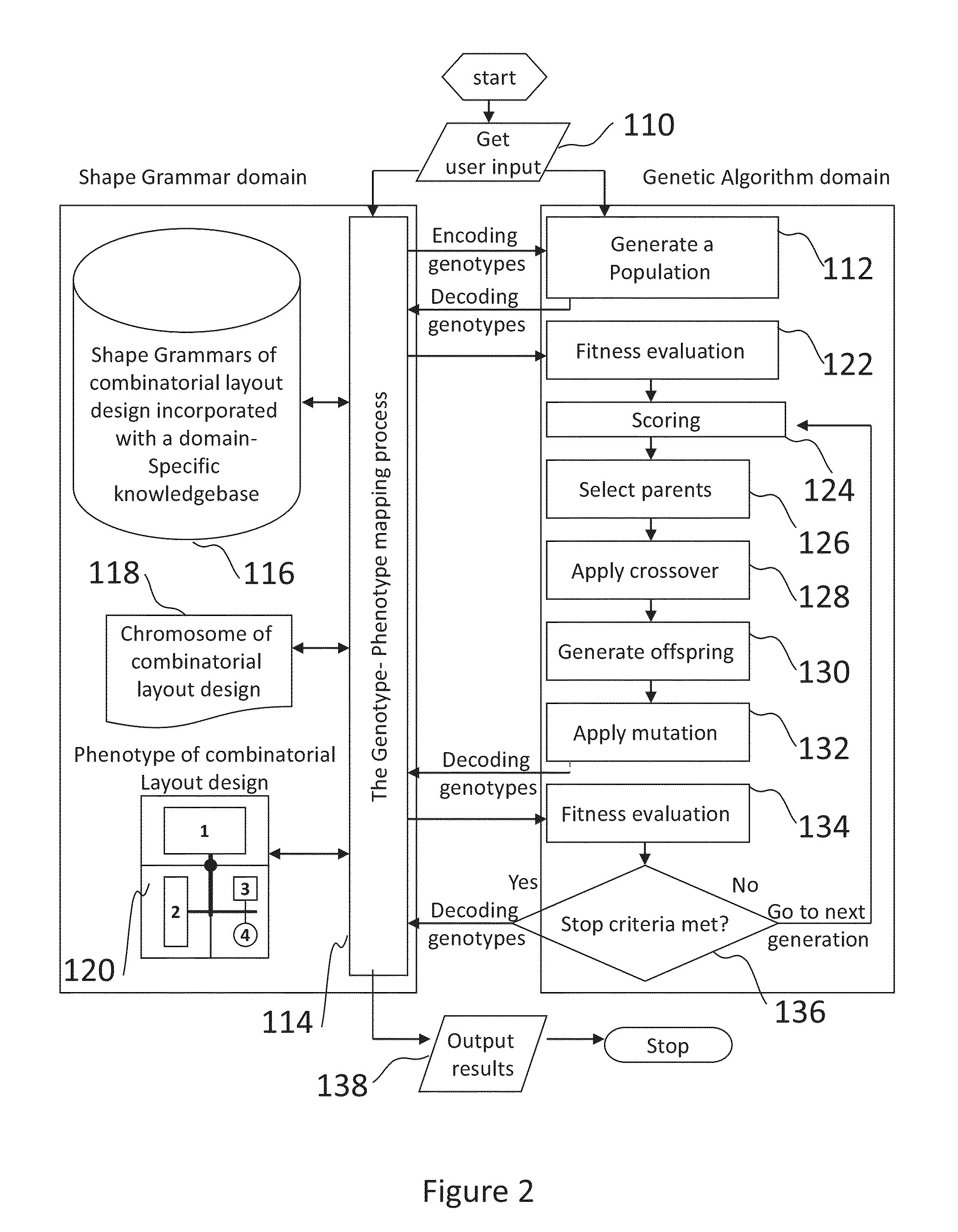

Method and System for Combinatorial Layout Design

InactiveUS20130132042A1Reduce timeImprove design qualityMulti-objective optimisationSpecial data processing applicationsGenotypes phenotypesPopulation

The present invention discloses a method for combinatorial layout design, in particular family mould layout design, using a computer. The method starts with receiving design specific parameters and information about moulding parts from user. A Genetic Algorithm module is then invoked to generate a population of layout designs which satisfies the design specific parameters. The Genetic Algorithm module first automatically generates a population of specially designed chromosome with three interdependent sessions. Crossover, mutation and replacement operation are applied on the population subsequently to evolve such towards a more optimal population over successive generations. In each generation step, a Genotype-Phenotype mapping module is utilised to decode the chromosome to corresponding layout design for fitness evaluation. A system for combinatorial layout design automation and optimisation using this evolutionary design approach is also disclosed in the present invention.

Owner:CHAN WAI MAN

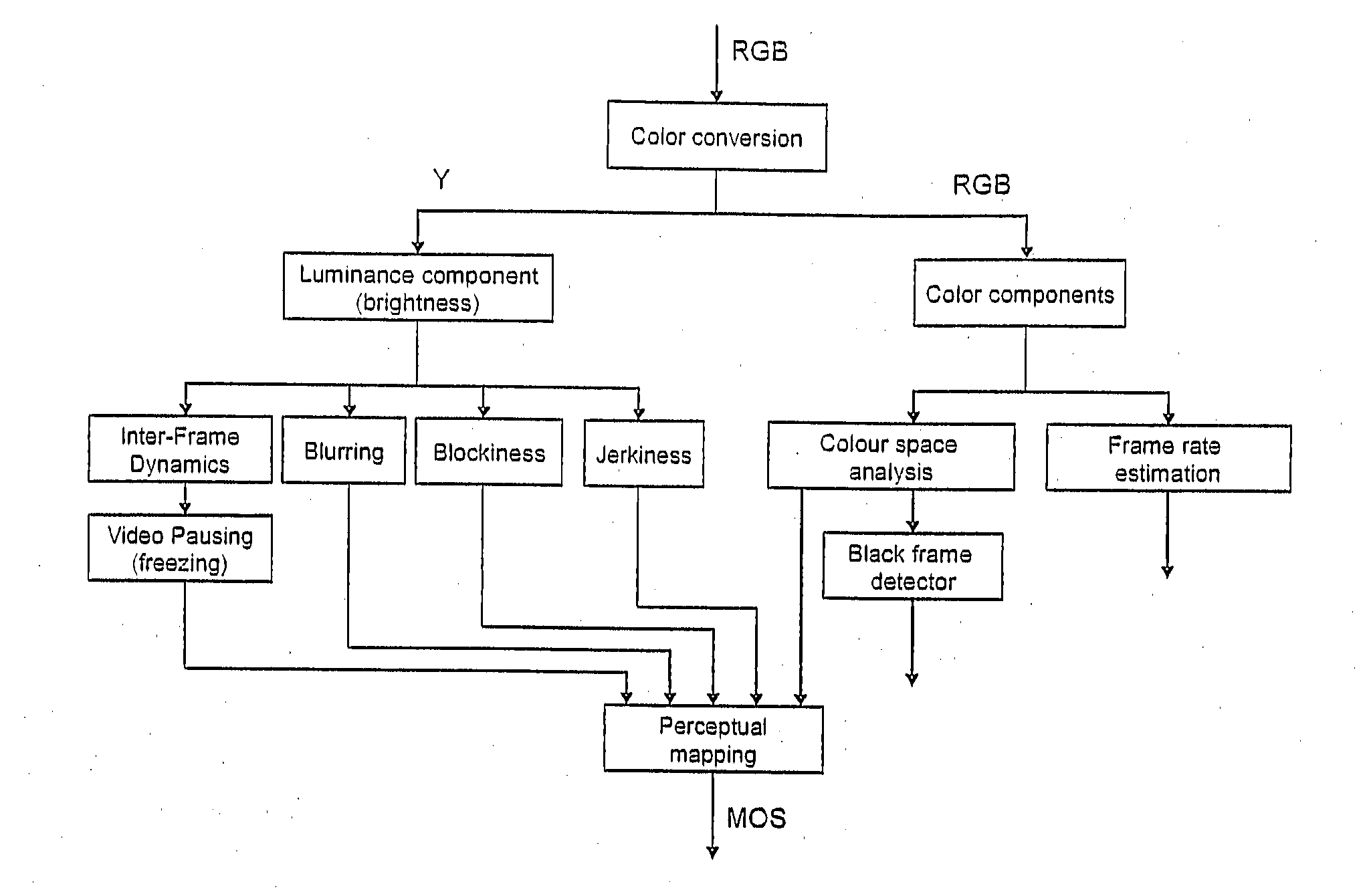

Device and Method for Assessing the Quality of a Mobile Phone or Mobile Phone Network

InactiveUS20080207198A1Easy to adaptReduce adjustmentReceivers monitoringCharacter and pattern recognitionQuality assessmentDisplay device

The problem to be solved by the present invention is to provide a system that allows a realistic quality assessment of a mobile phone and / or mobile phone network. For this purpose, imaging optics are used to project the image from at least part of the phone display onto a camera. The image or video data from the camera is then processed in image processing circuitry for deriving at least one quality parameter for the received image or video.

Owner:SWISSQUAL LICENSE

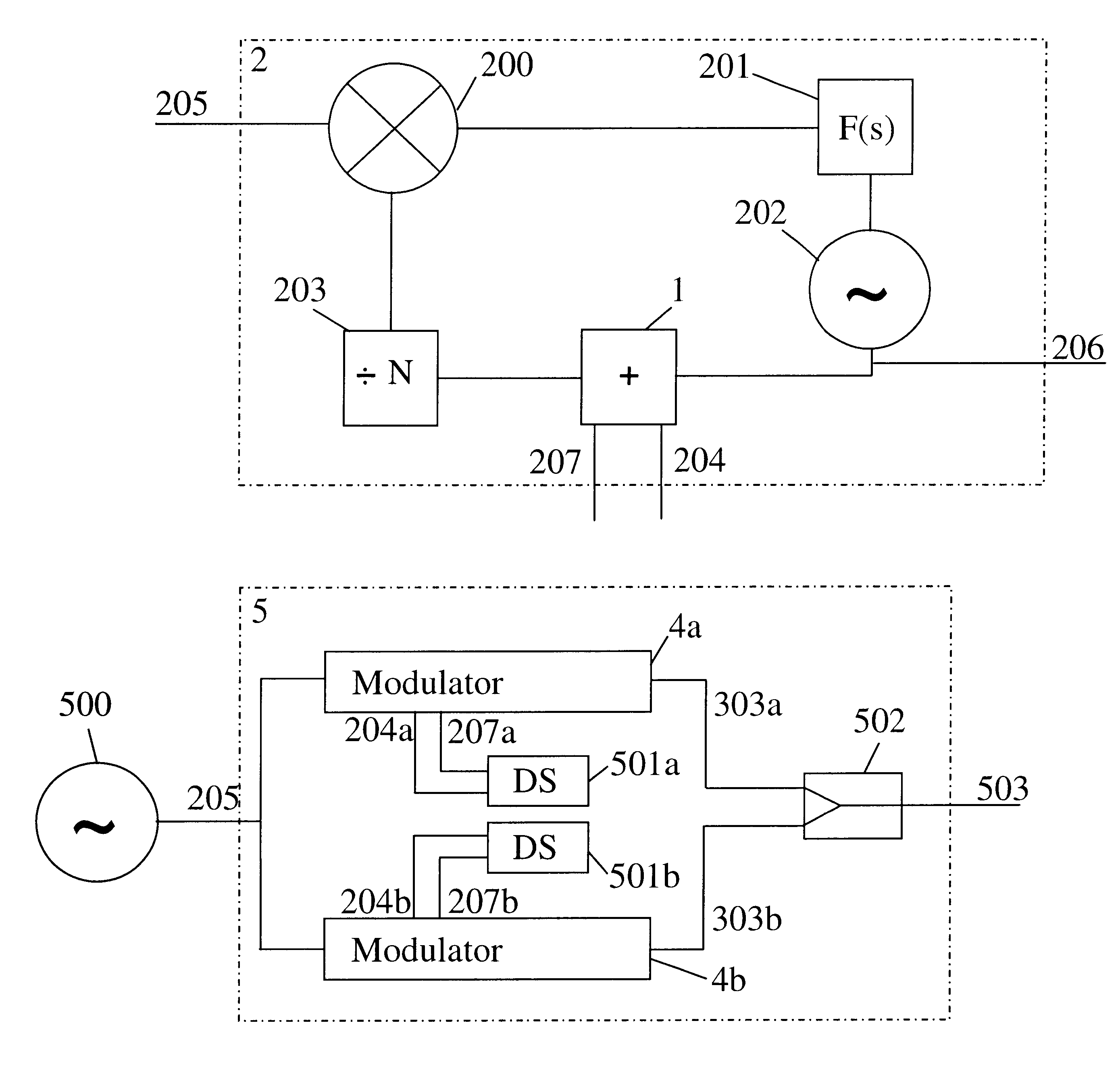

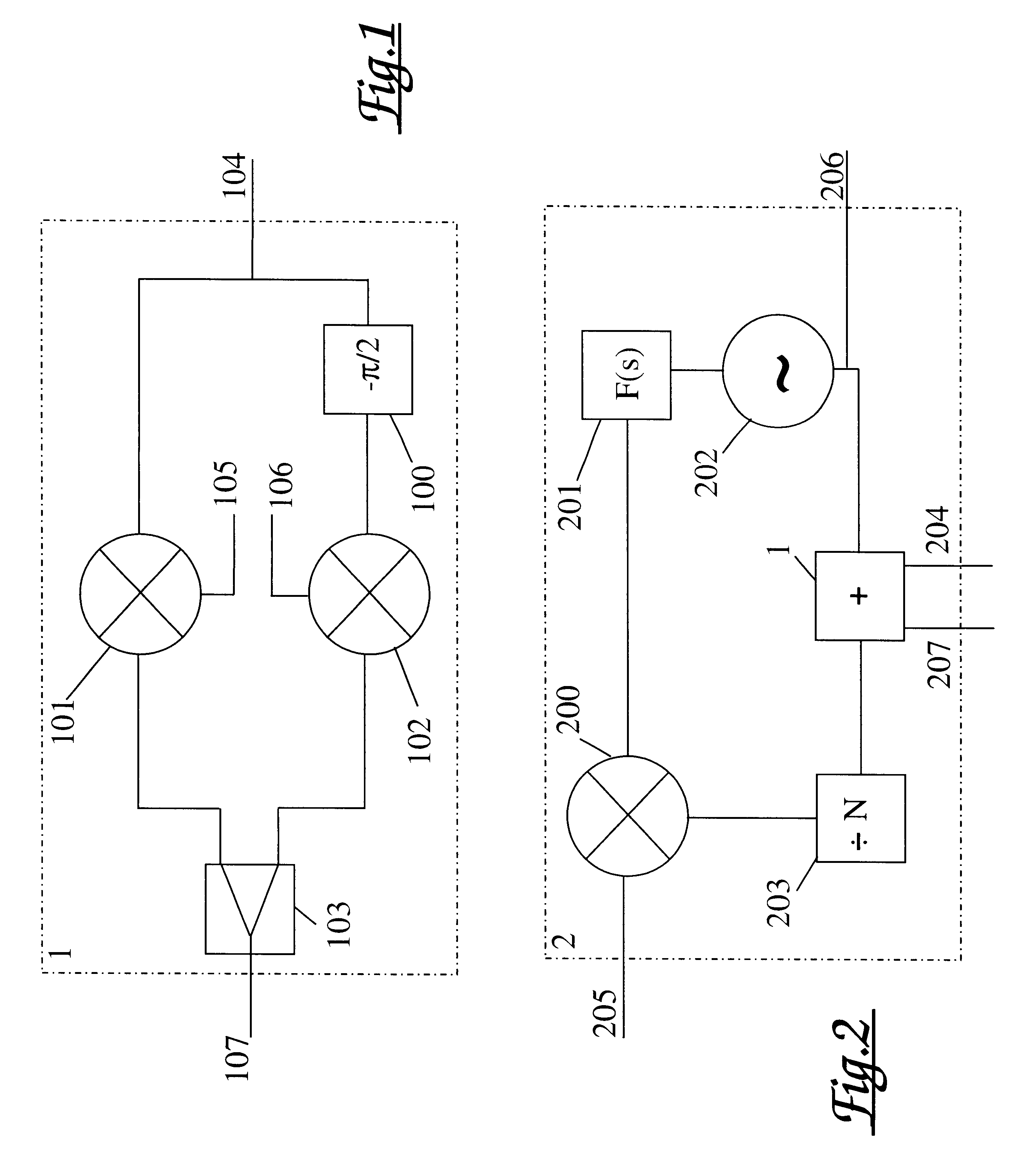

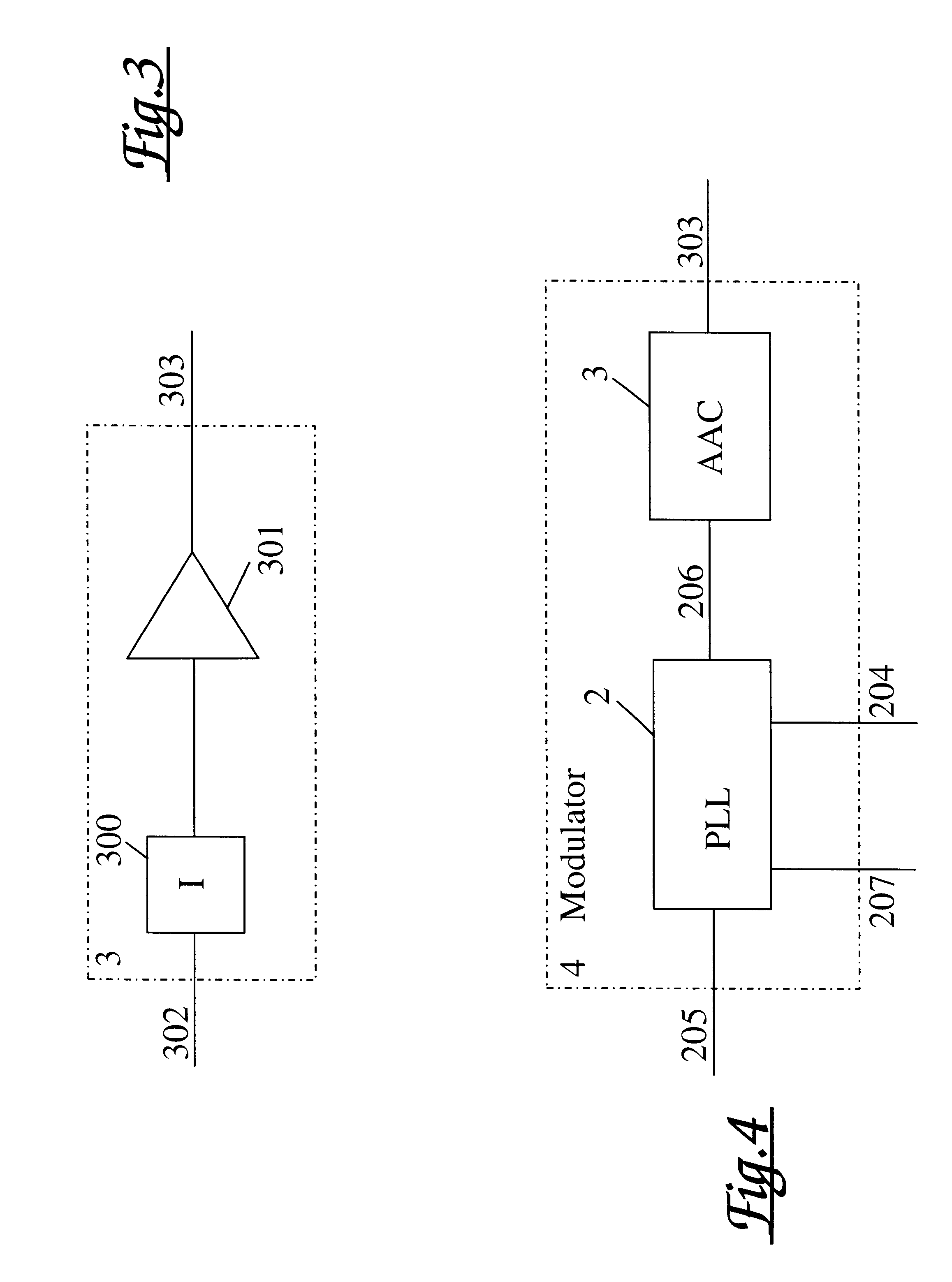

Phase and amplitude modulation of baseband signals

InactiveUS6415002B1Easy to changeReduce manufacturing costSimultaneous amplitude and angle modulationAngle modulation detailsCarrier signalPhysics

A baseband signal modulator provides a phase and amplitude modulated carrier signal. First and second phase modulators each receive a common reference signal and derive therefrom a carrier signal frequency. The phase modulators each receive a respective pair of phase-encoded data signals so as to provide respective first and second phase-encoded carrier. The modulator outputs are summed to provide the phase and amplitude modulated carrier signal. Each phase modulator includes a respective phase locked loop incorporating an oscillator locked via the common reference signal to the carrier signal frequency, and a phase adder having a first input for receiving the carrier frequency signal and having second and third inputs for receiving the respective pair of data encoded signals.

Owner:APPLE INC

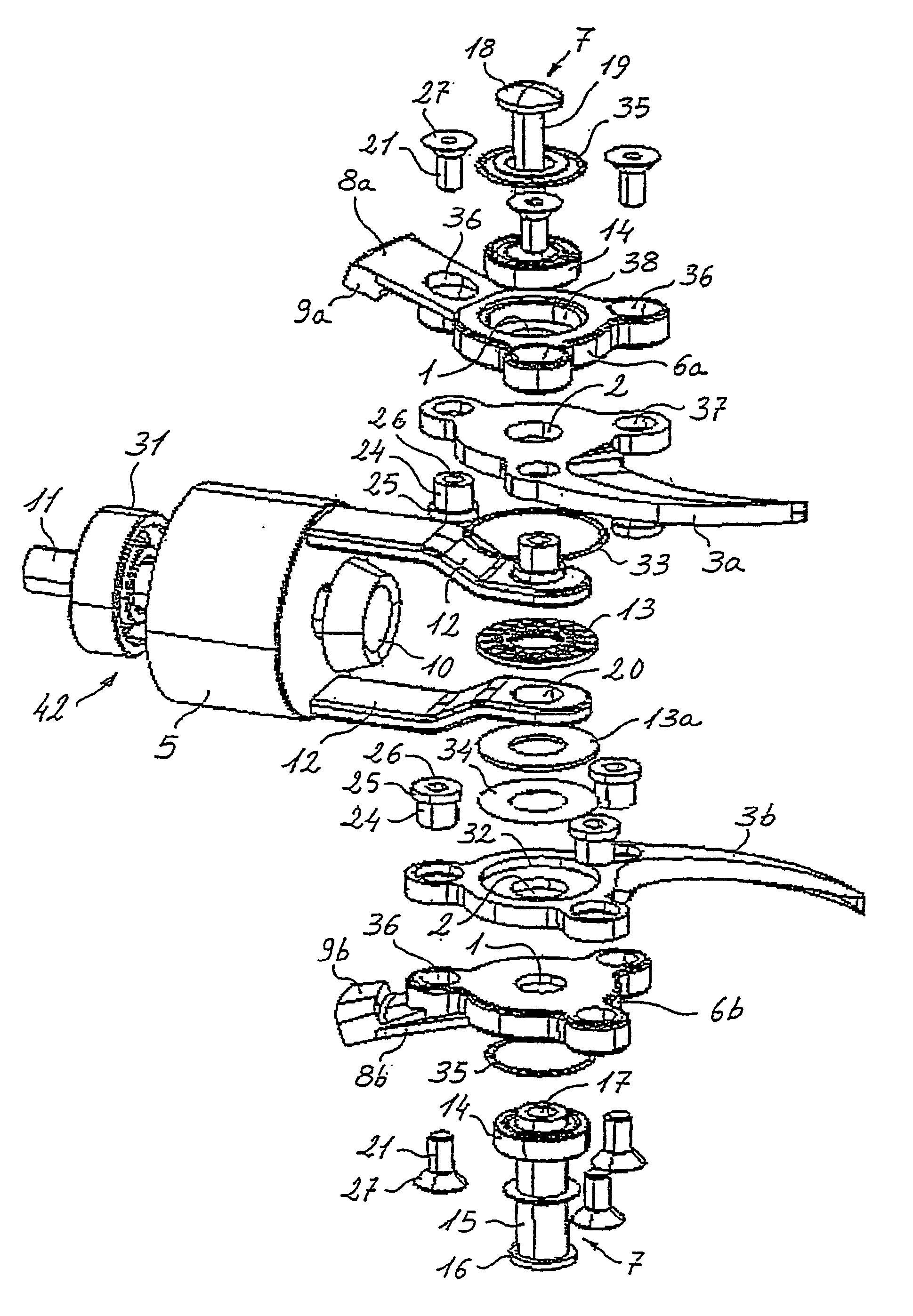

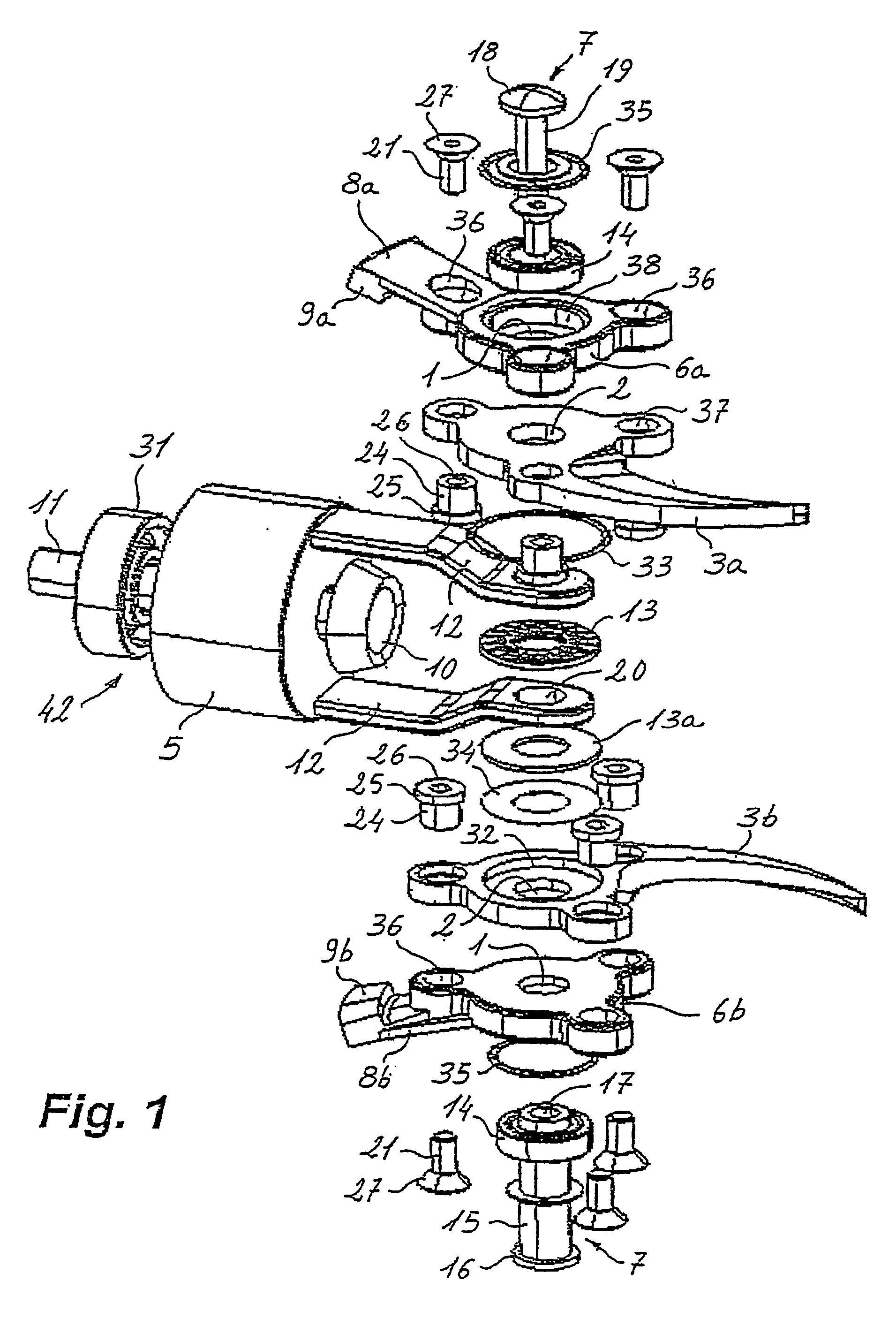

Portable motor-powered shears

InactiveUS20040055164A1High mechanic efficiencyImprove energy consumptionCuttersCutting implementsGear wheelEngineering

It comprises a support (5) associated to a current takeoff (42) from a motor (43) and a cutting mouth (44) comprising two jaws (3a, 3b), at least one of which is a working cutting jaw (3a) rotatably mounted on the said support (5) and connected to the said power takeoff (42) by means of a drive (47) for carrying out the closing-opening operation with respect to the other jaw (3b). The working cutting jaw (3a), which is at least one, is fixed on a power drive part (6a) which can rotate about an axis (7) mounted on the support (5), the said power drive part (6a) includes a lever arm (8a) at the end of which is arranged a sector of conical gear wheel (9a) which interlocks with a conical gear (10) joined to an axis (11) of the said power takeoff (42).

Owner:HISPAES

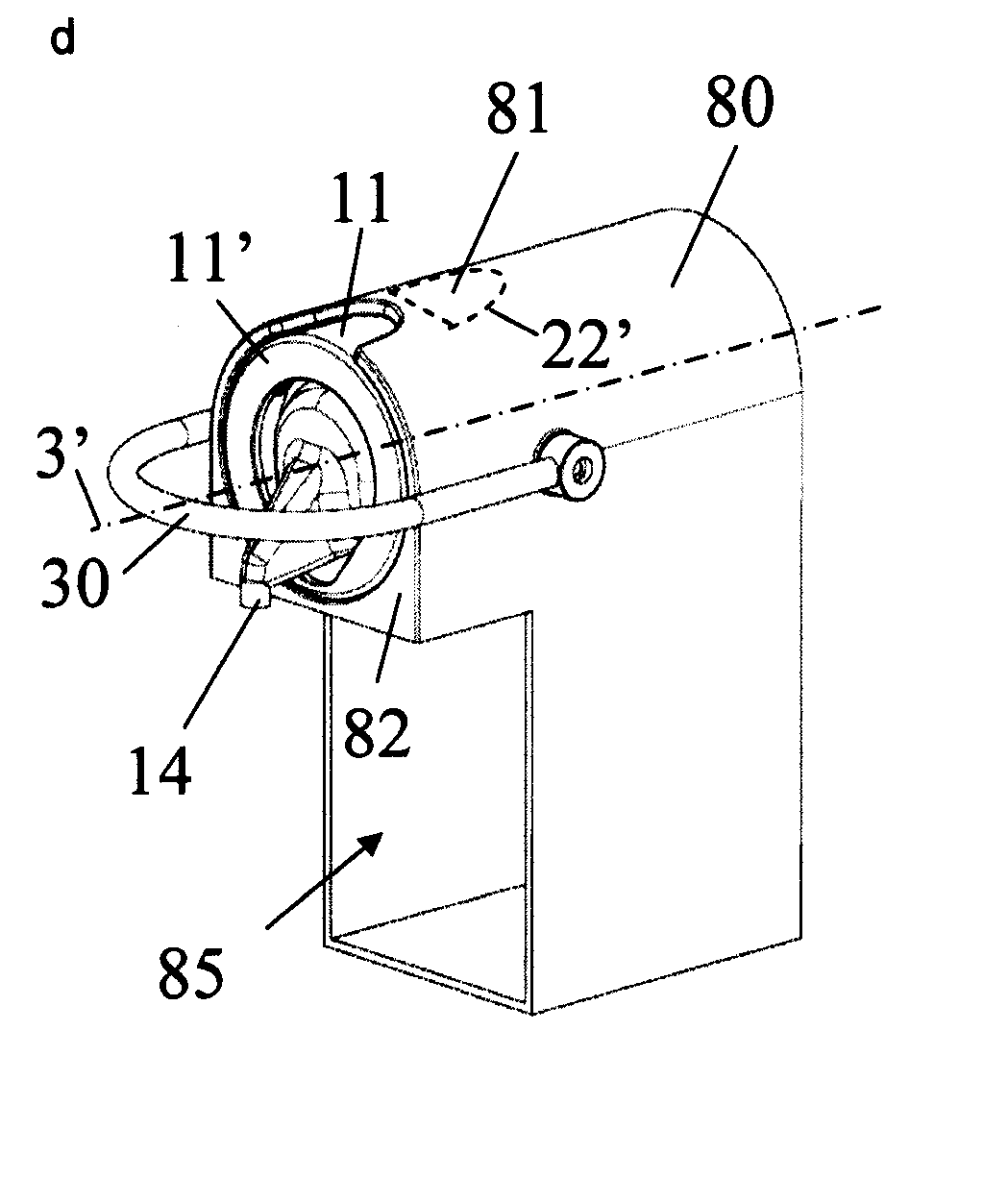

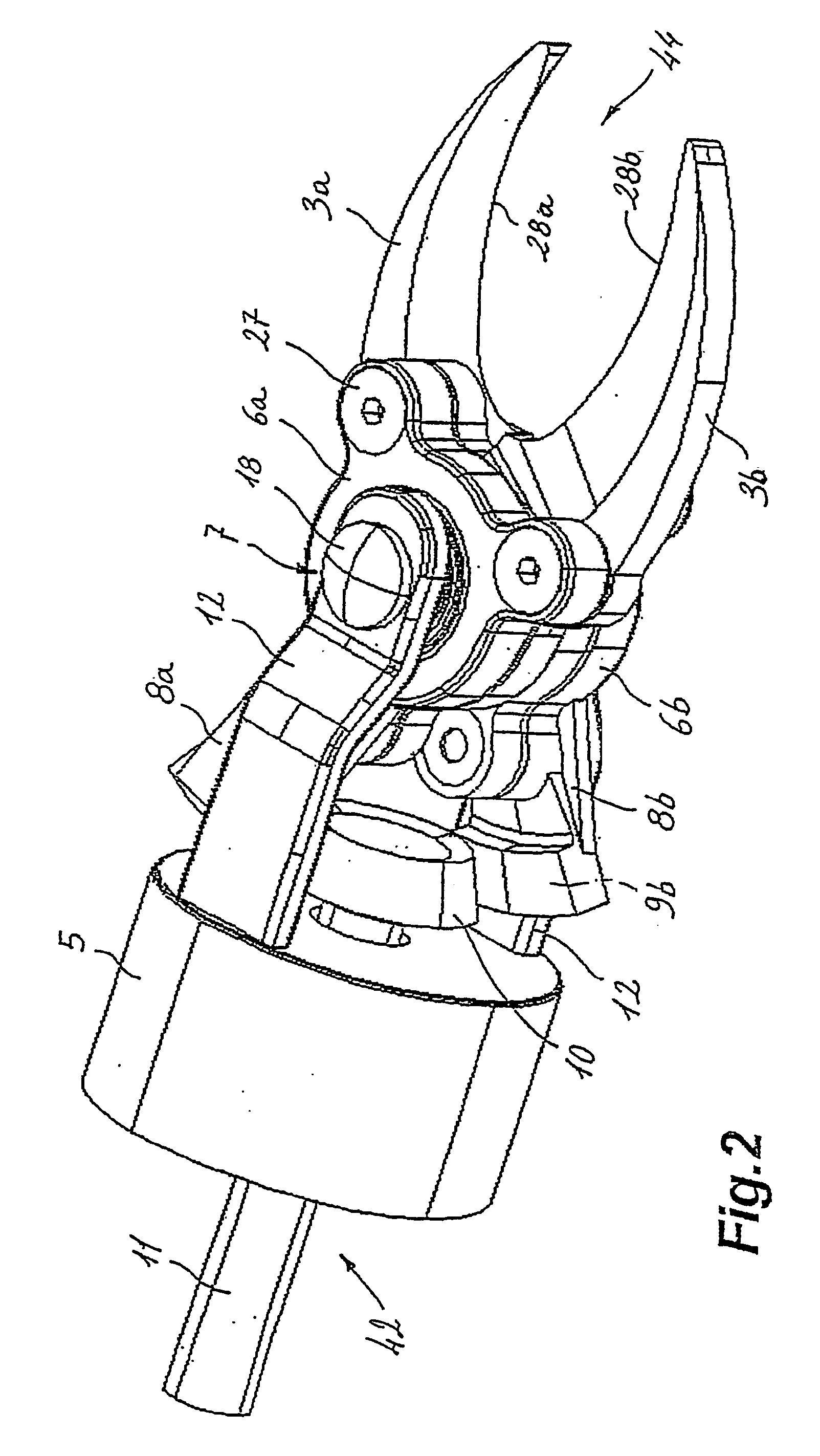

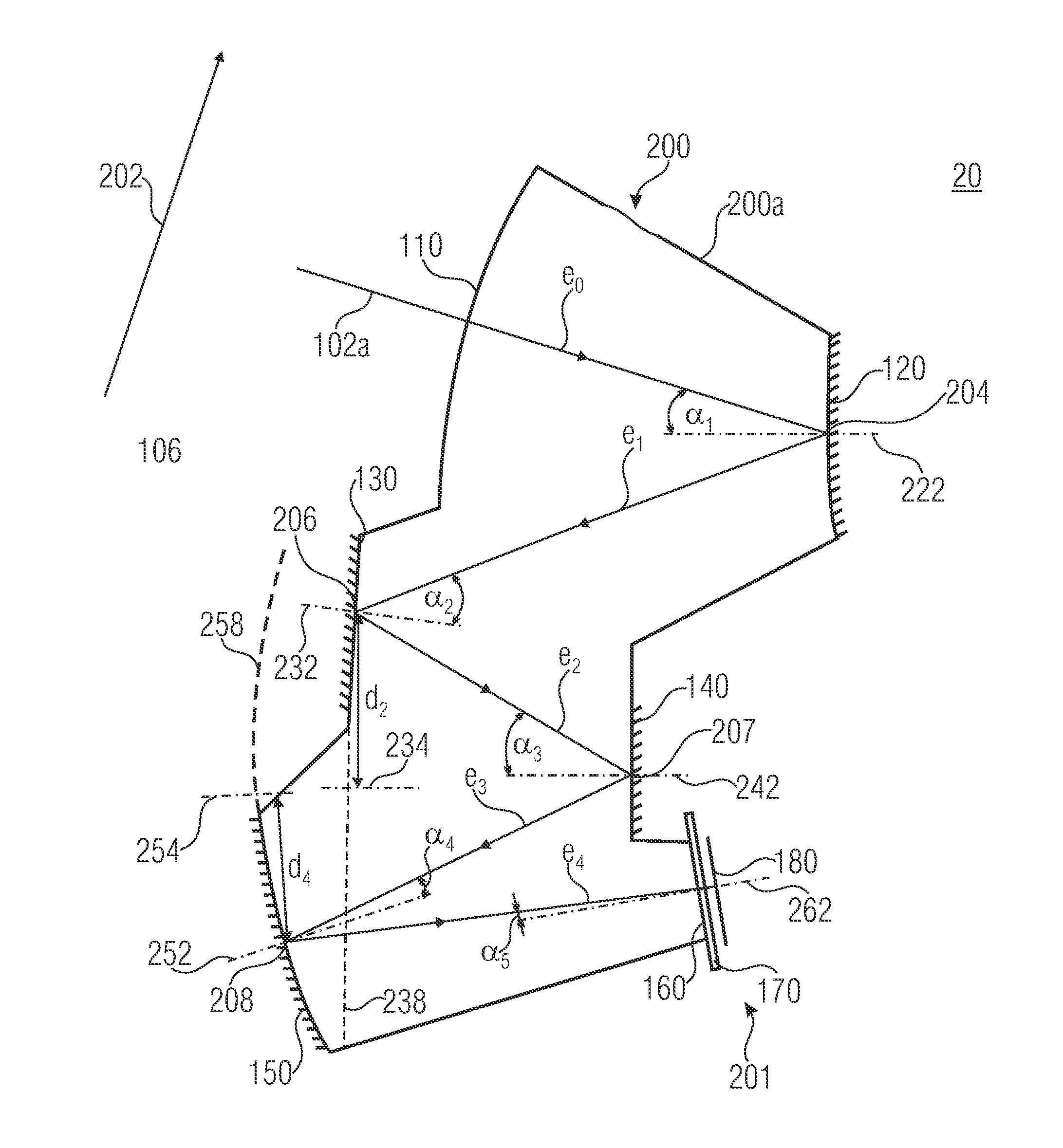

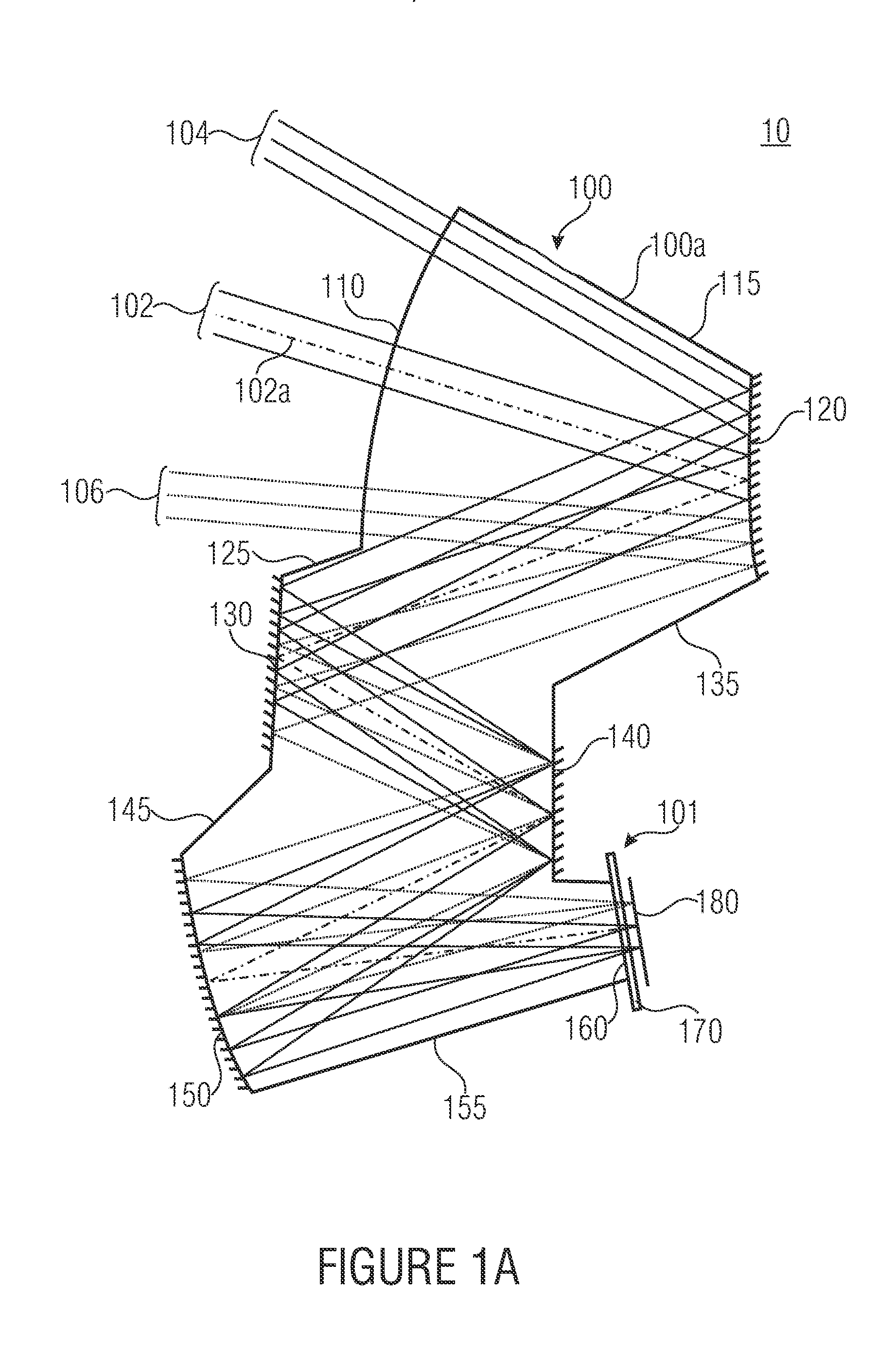

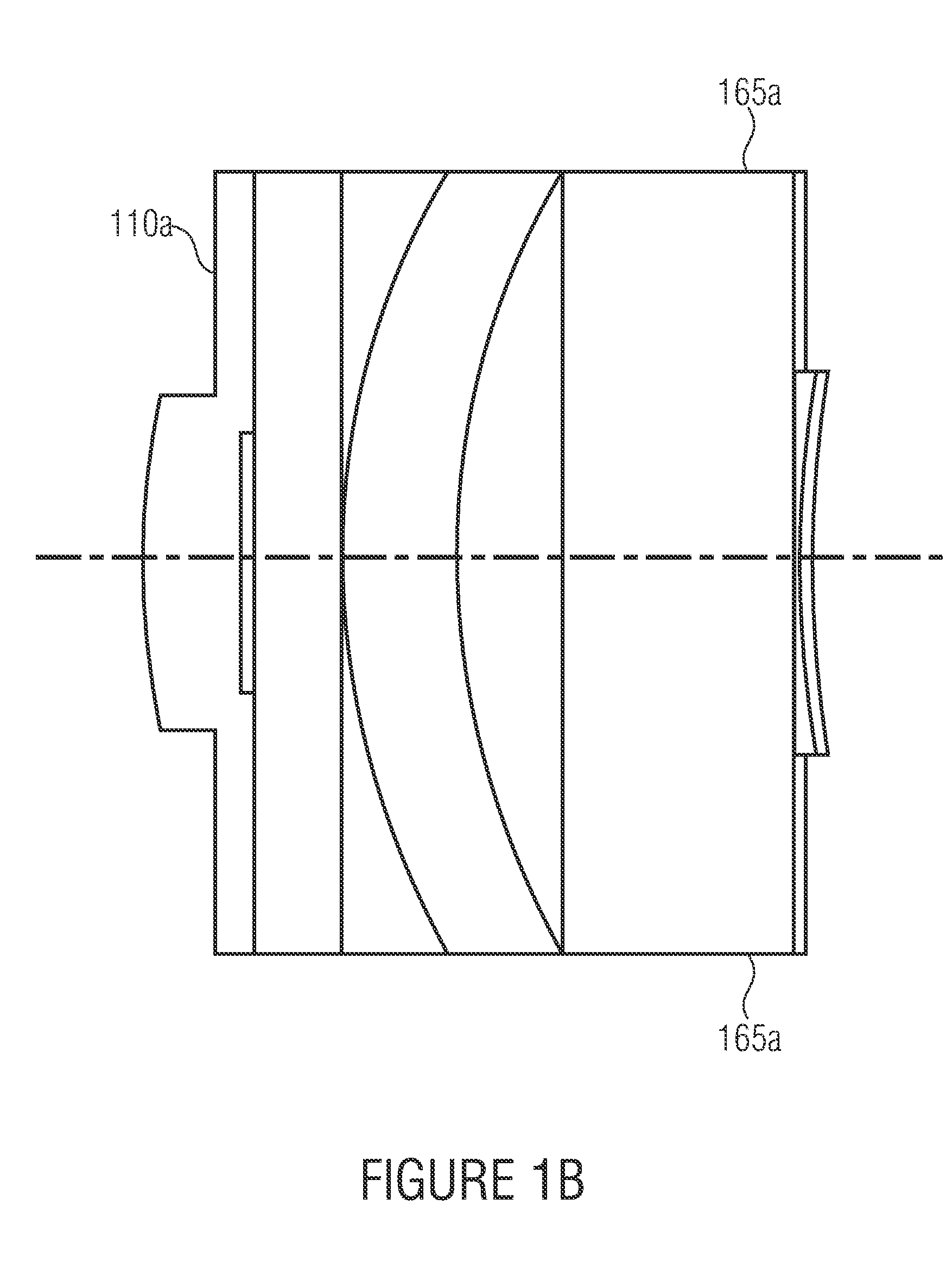

Objective

InactiveUS20120050891A1Low production costRobust and inexpensive productionLensOptical reflectionIntermediate image

An objective is described consisting of a monolithic body of a material at least partly transparent for a part of an electromagnetic spectrum, and whose surfaces include a first optical refractive functional area serving as entrance area through which electromagnetic radiation can enter the objective, a second optical reflective functional area serving as a first mirror, a third optical reflective functional area serving as a second mirror, a fourth optical reflective functional area serving as a third mirror, a fifth optical reflective functional area serving as a fourth mirror, and a sixth optical refractive functional area serving as an exit area through which electromagnetic radiation can exit the objective, wherein the first to sixth optical functional areas are implemented such that a center shading-free, folded optical path extends from the entrance area through the monolithic body via first to fourth mirrors to the exit area, wherein no intermediate image level is located in the same between the entrance area and the exit area.

Owner:FRAUNHOFER GESELLSCHAFT ZUR FOERDERUNG DER ANGEWANDTEN FORSCHUNG EV

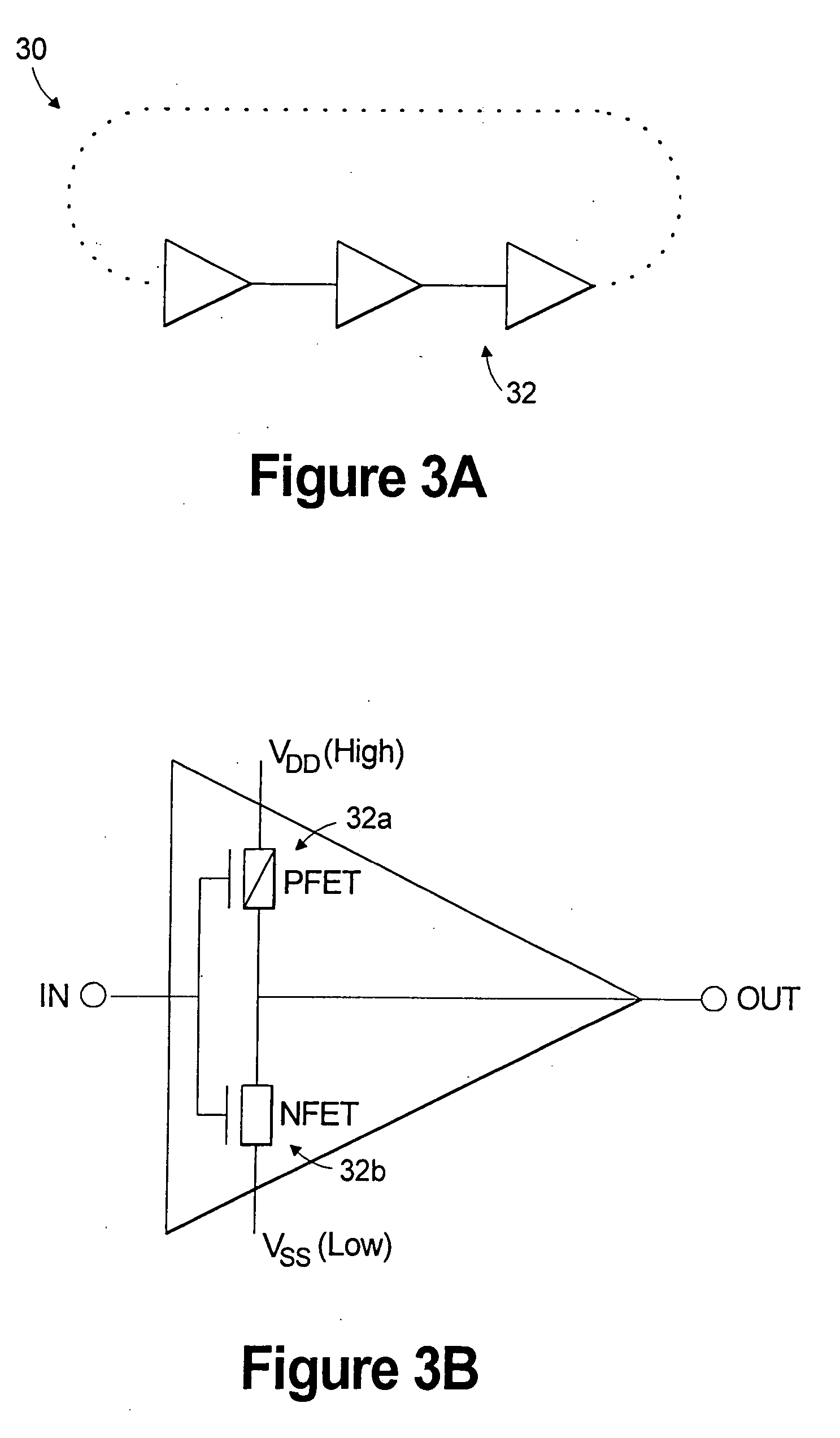

Circuitry and methodology to establish correlation between gate dielectric test site reliability and product gate reliability

InactiveUS20050184720A1Thinner oxideDesign moreElectronic circuit testingResistance/reactance/impedenceElectricityGate dielectric

A method and system for predicting gate reliability. The method comprises the steps of stressing a gate dielectric test site to obtain gate dielectric test site data and using the test site data to predict gate reliability. Preferably, the test structure and the product structure are integrated in such a manner that a test site occupies some of the product area and the product itself occupies the remainder of the product area. A preferred methodology, more specifically, is as follows: (1) Test structures at start both in parallel stress mode and in ring oscillator or “product” mode; (2) Analyze the breakdown data as per the present state of the art for each of the areas based on the parallel stress mode; (3) Combine the above breakdown distributions using the area scaling to improve the confidence bounds of the Weibull slope of the cumulative distribution function; (4) Test the ring oscillators in the product mode to determine how many of the stress fails are also product fails as defined by an operational degradation; (5) Subdivide the failures to determine the relationship between the first fail, and the second fail, and the nth fail; (6) Investigate which stress fail, if not the first stress fail, is more likely to cause a product fail as defined by operational degradation; and (7) Based on the subdivision in step 5 and the results in step 6, make projection based on that fail which is most likely to cause fail. The methodology as outlined above bridges between dielectric stress fails and product degradation both in the case of each stress fail causing a product degradation, as well as in the case where more than one stress fail occurs before any product degradation occurs. And this relationship can be quantified.

Owner:INT BUSINESS MASCH CORP

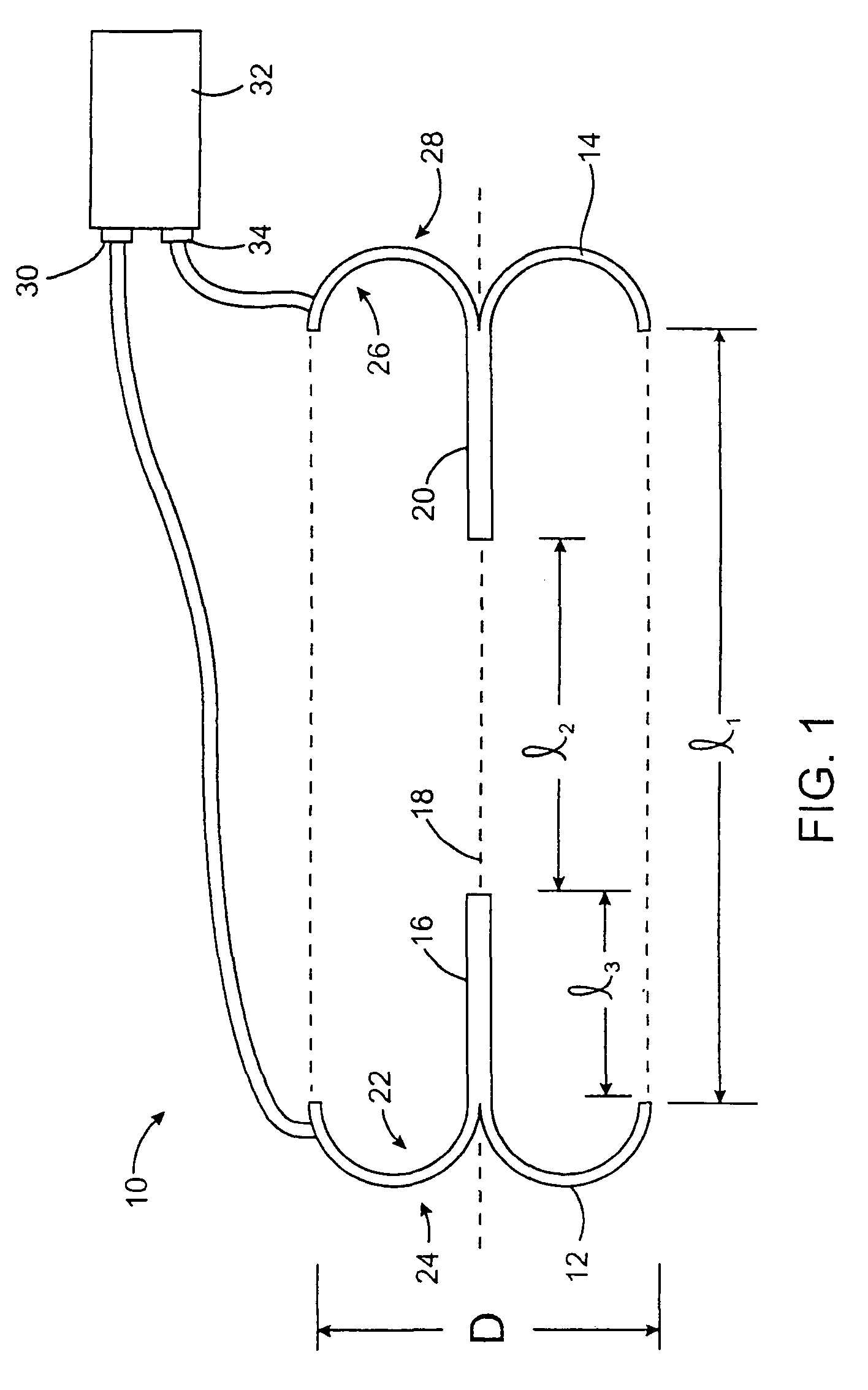

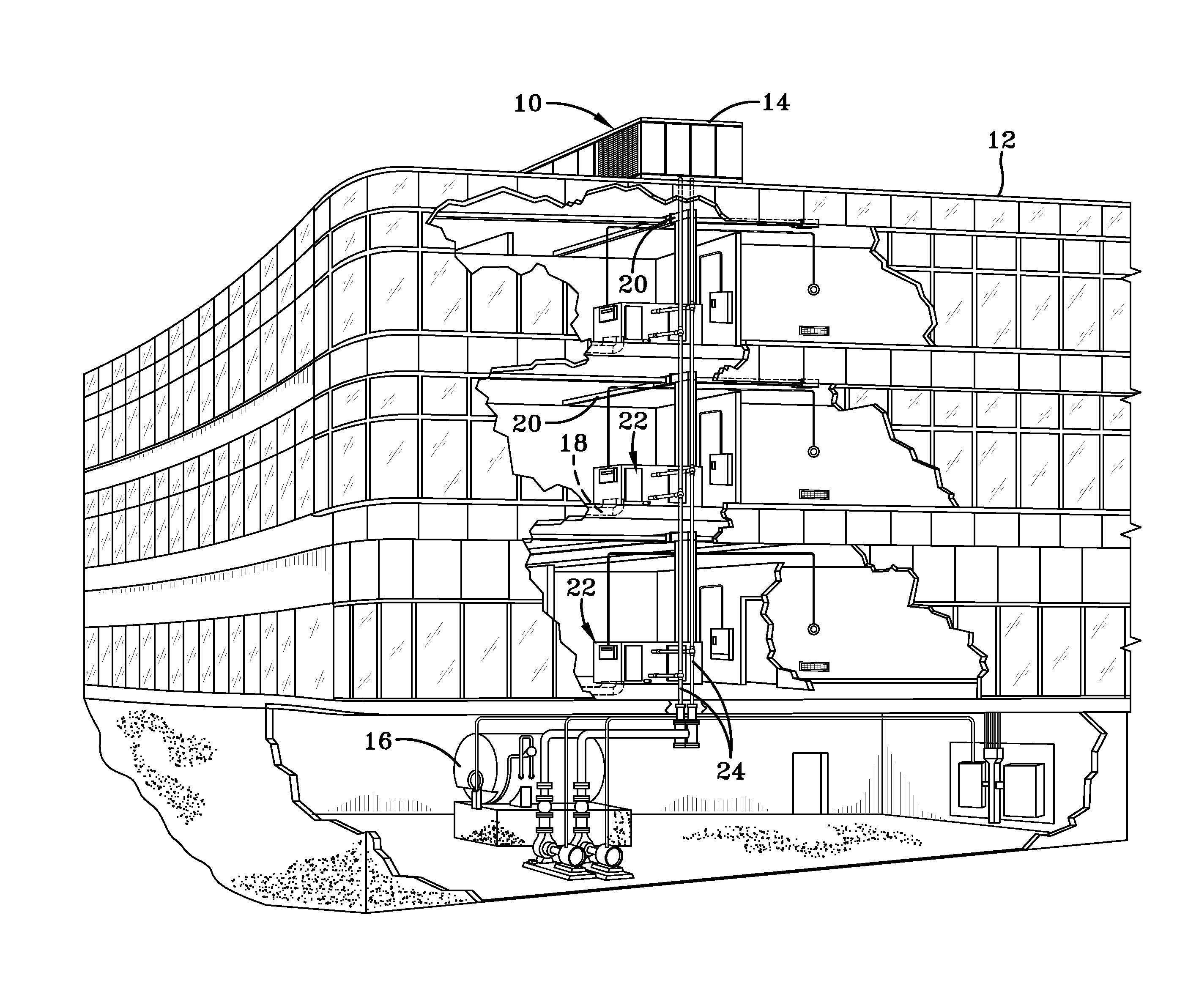

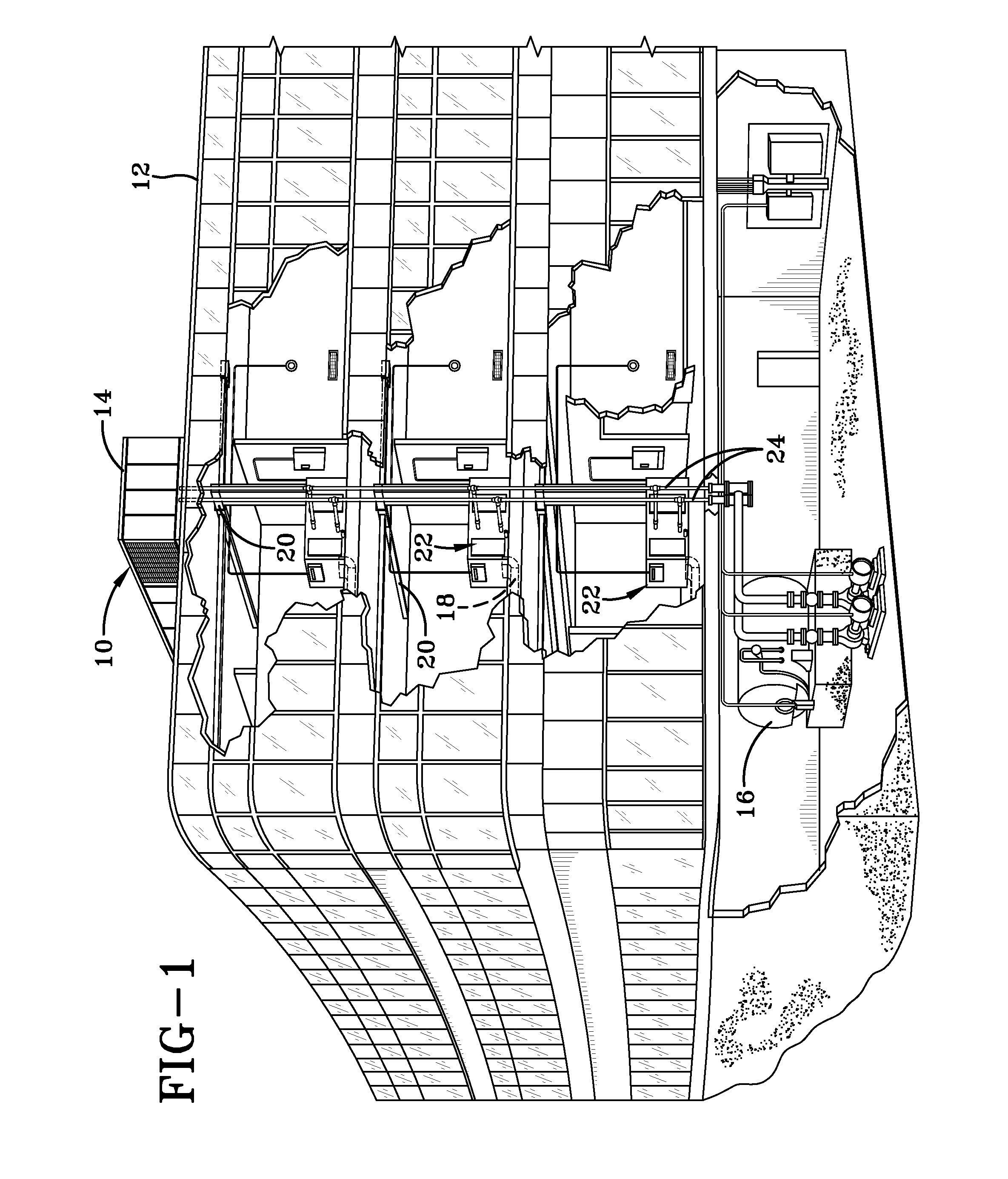

Heat exchanger having stacked coil sections

ActiveUS20110192188A1Increase system capacityUniform processEvaporators/condensersSteam/vapor condensersAir cyclePlate heat exchanger

A heat exchanger is provided with stacked coil sections. Each of the stacked coil sections is configured to circulate a fluid independent from the other coil section. An air moving device is used to circulate air through both of the stacked coil sections. The stacked coil sections are positioned to have the air exiting the one coil section entering the other coil section.

Owner:JOHNSON CONTROLS TYCO IP HLDG LLP

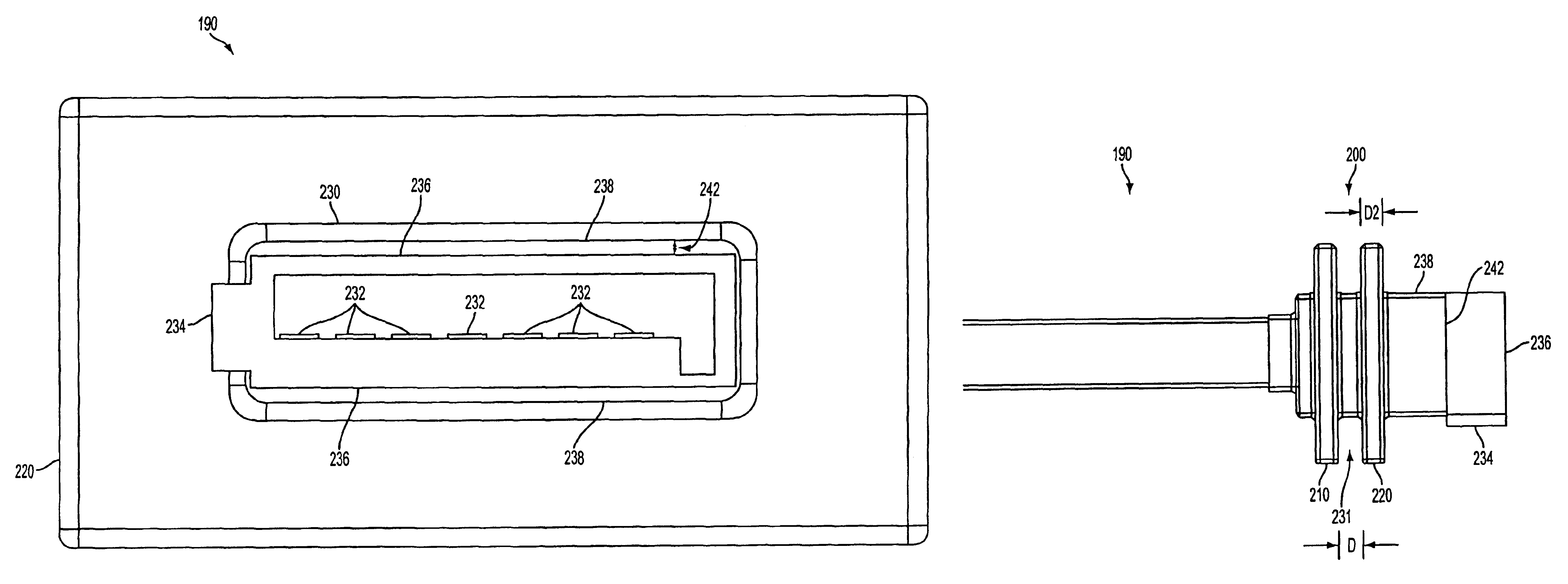

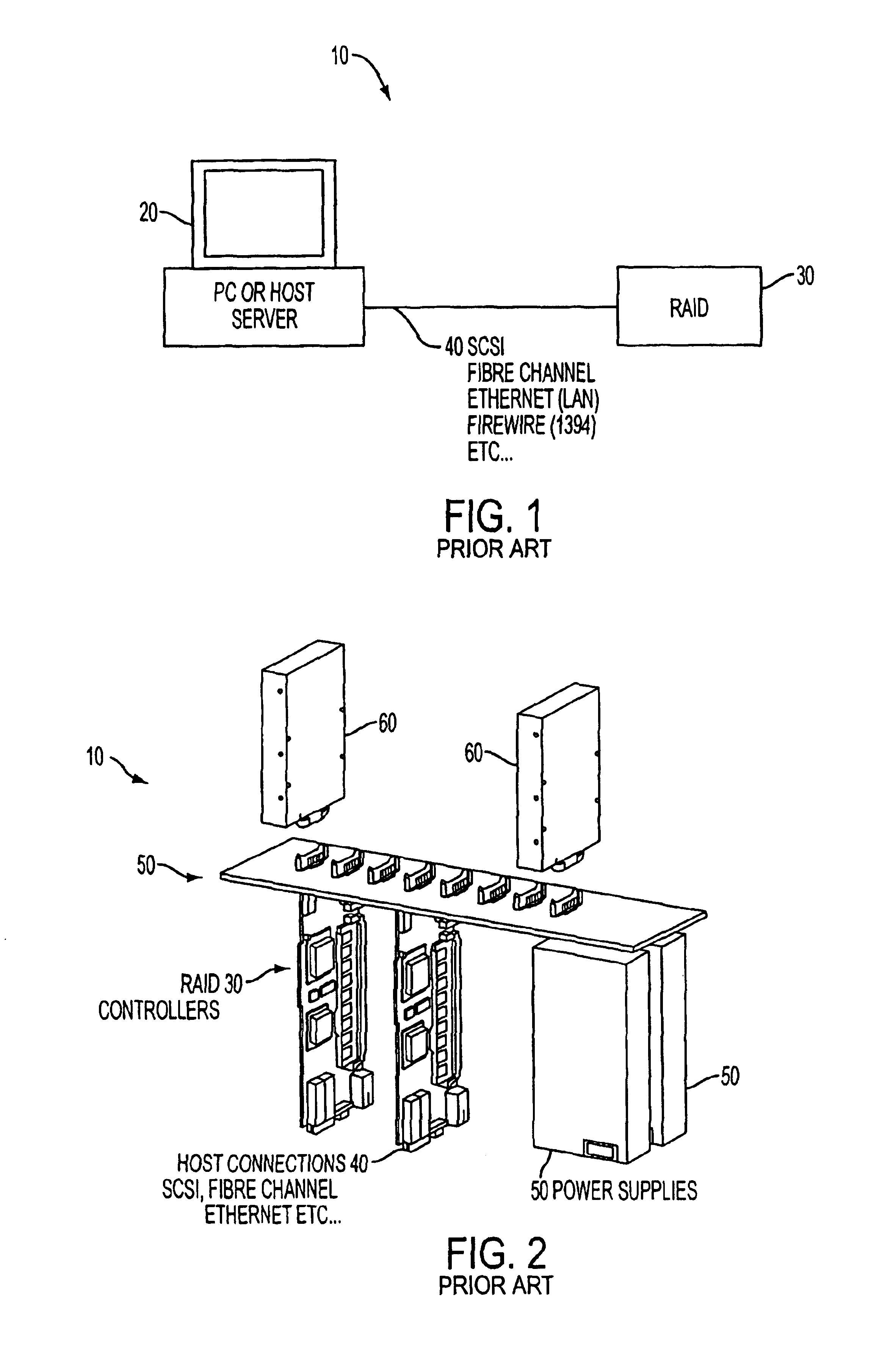

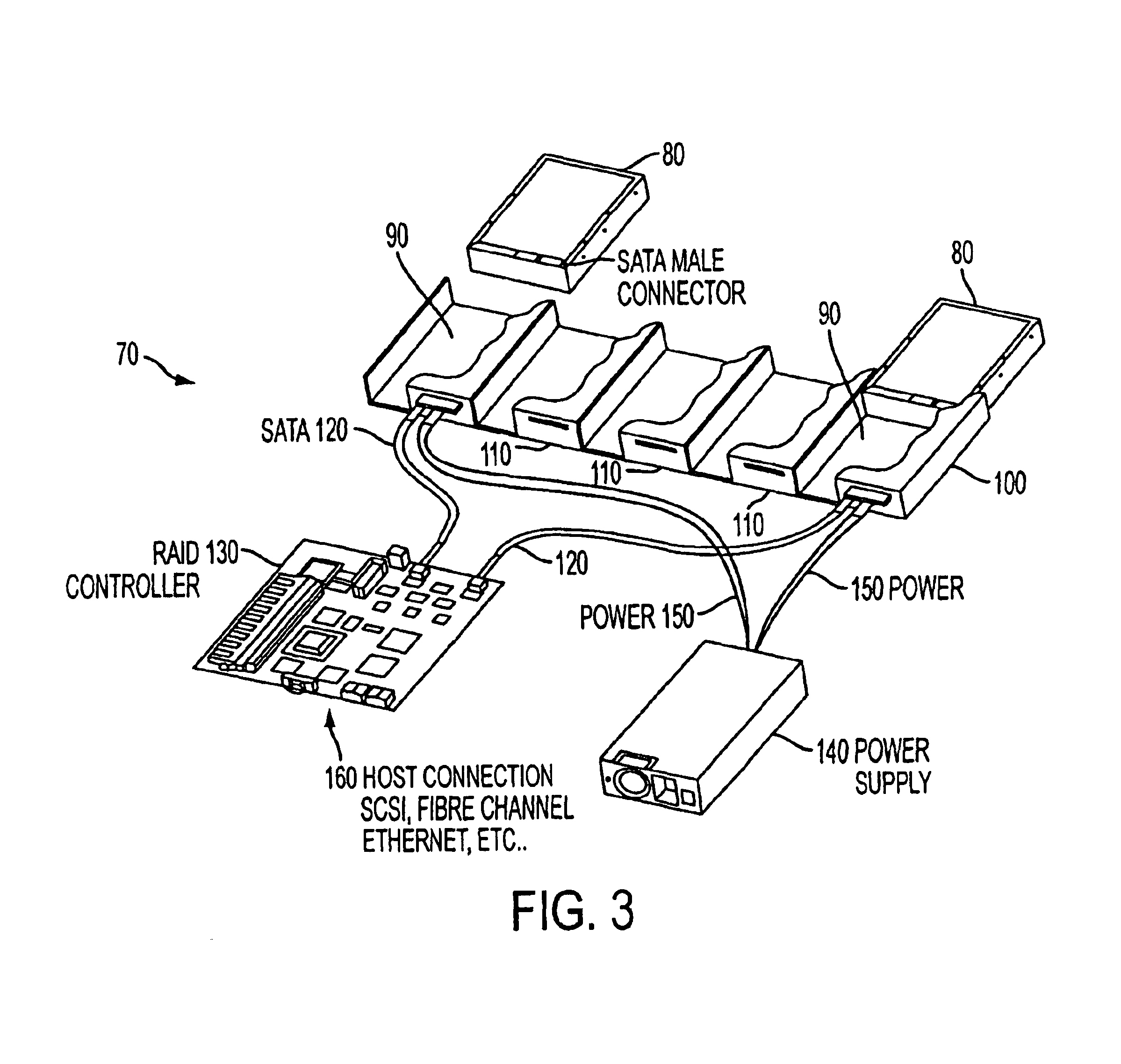

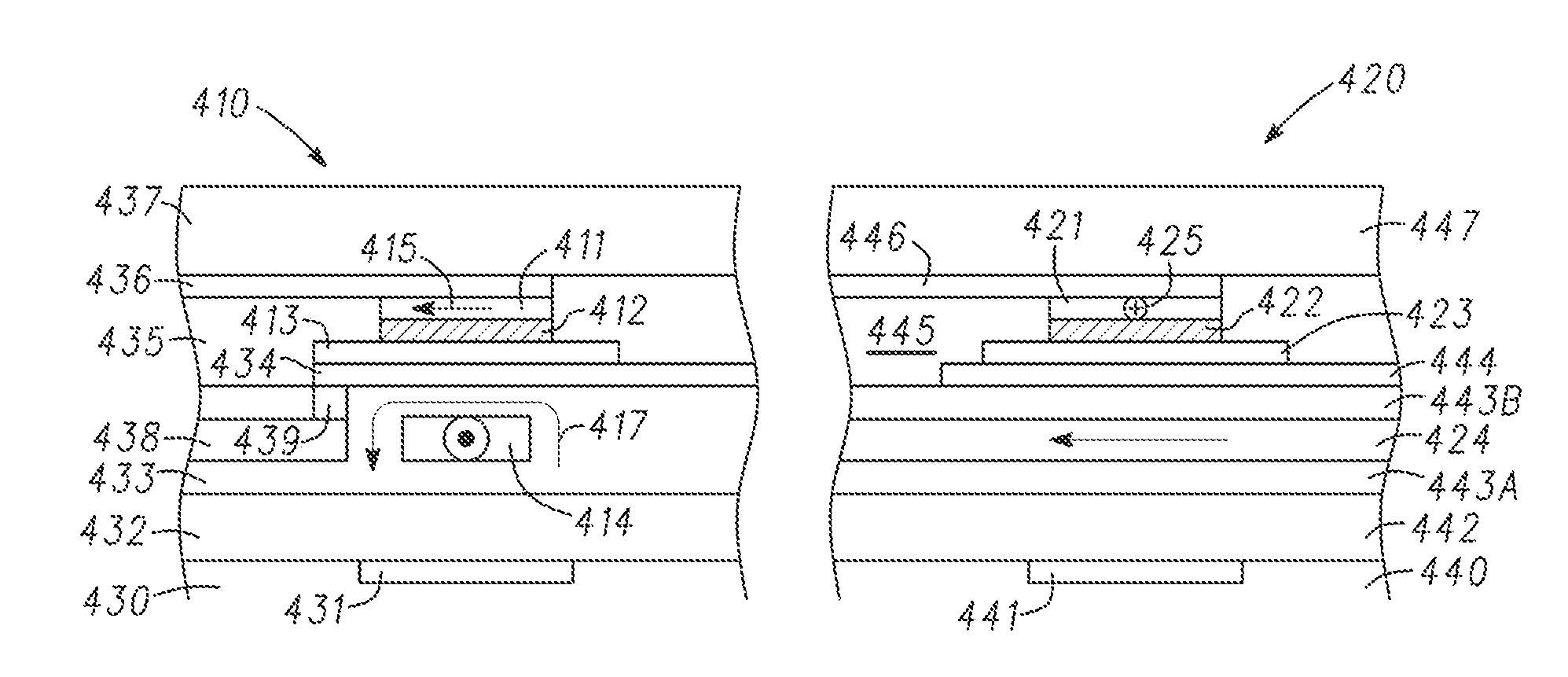

Method and apparatus for connecting serial ATA storage components

InactiveUS6843674B1Low costLimited maintenanceSubstation/switching arrangement detailsIncorrect coupling preventionEngineeringSerial ATA

A method for connecting to an SATA storage component includes a chassis having an interior and an exterior, and a wall portion provided with an opening. An SATA compatible connector, provided with a first restraining flange and a second restraining flange spaced from the first restraining flange, is inserted into the opening in the wall portion, wherein an interior surface of the first restraining flange faces a first surface of the wall portion and an interior surface of the second restraining flange faces a second surface of the wall portion. An SATA storage component is then inserted into the chassis such that it connects with the SATA compatible connector, whereby the first and second flange allows the SATA compatible connector to float in a limited fashion within the opening.

Owner:LATTICE SEMICON CORP

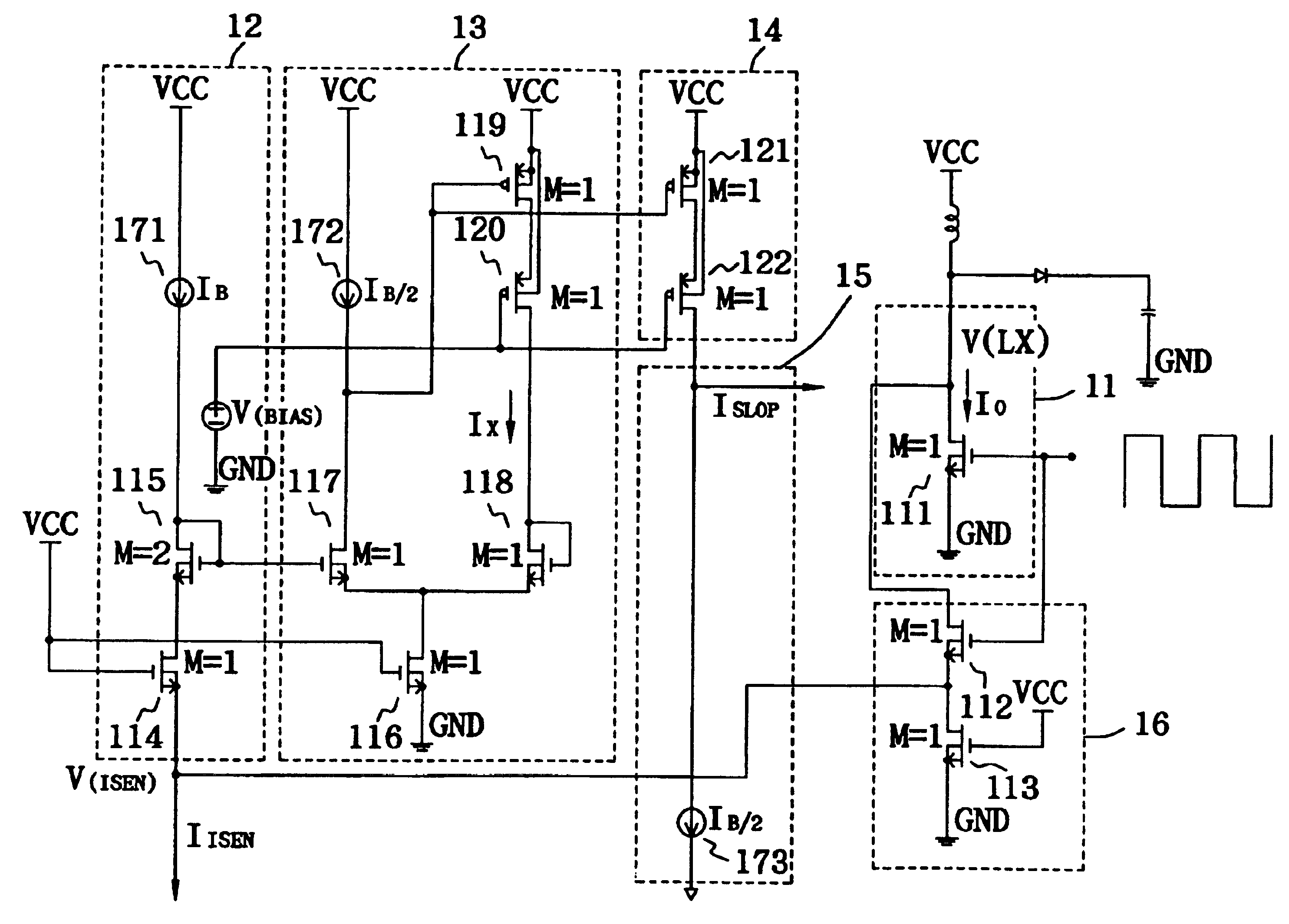

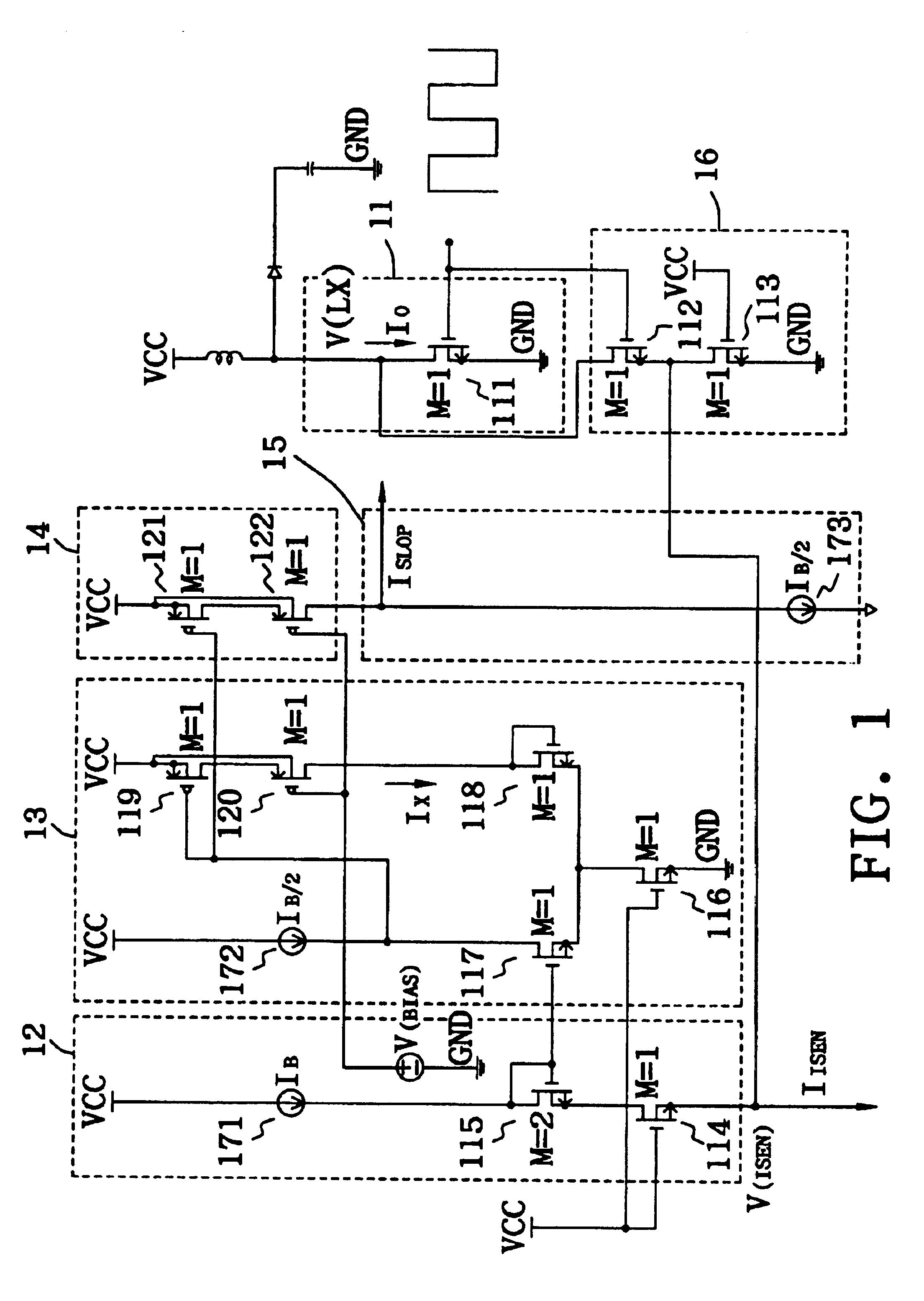

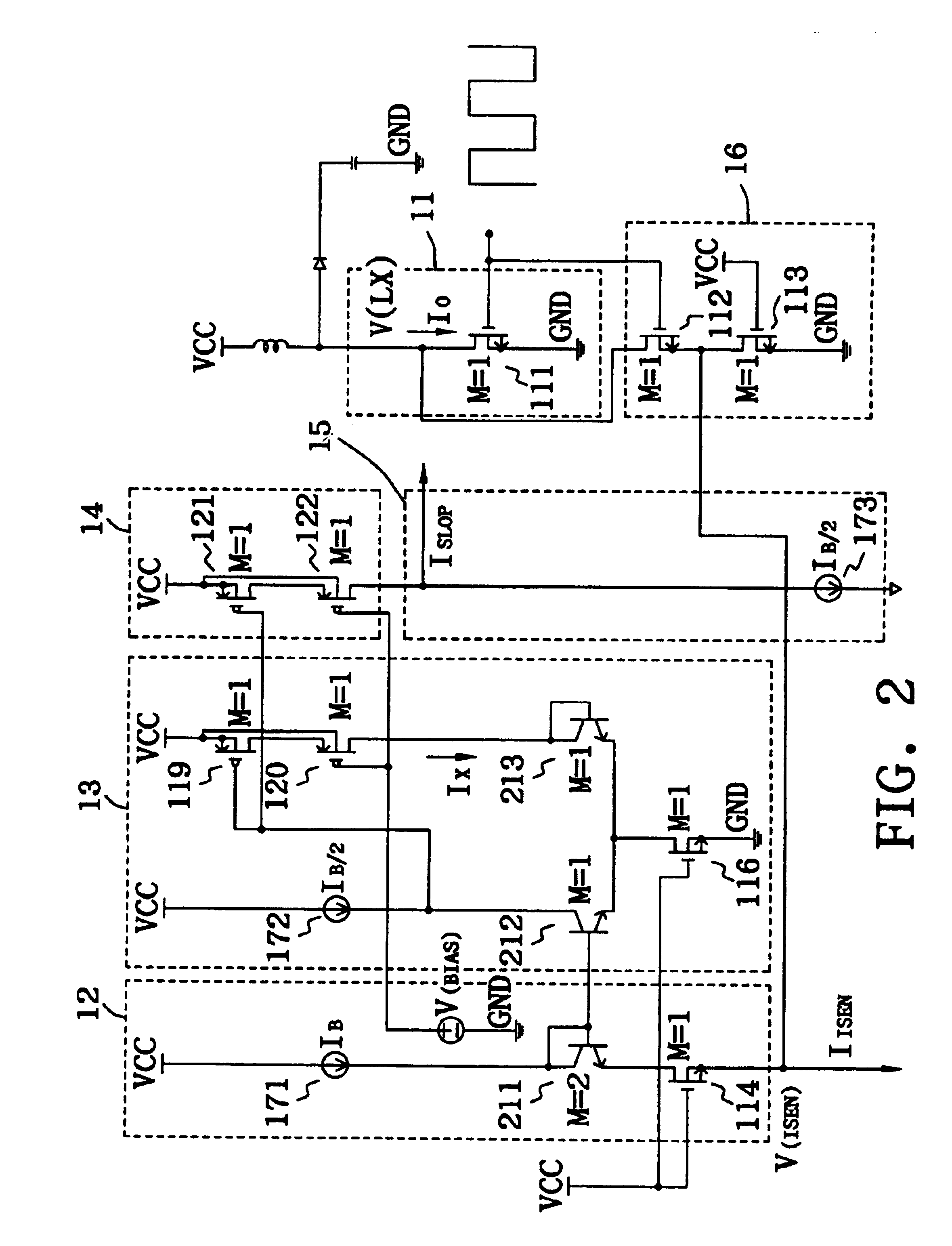

Current sensing circuit and method of a high-speed driving stage

InactiveUS6791368B2Design moreTakes up more chip spaceTransistorMultiple input and output pulse circuitsSignal processing circuitsEngineering

The present invention discloses a current sensing circuit and method of a high-speed driving stage, which comprises an input stage, a level converting unit, a feedback unit, a current mirror unit and a current shunting unit. The current sensing circuit is capable of linearly detecting the output current of the driving stage transistors, and directly condensing the detected current to an appropriate value using the geometric ratio of the transistors, so as to facilitate the subsequent signal processing circuit to use it for control purposes.

Owner:GLOBAL MIXED MODE TECH

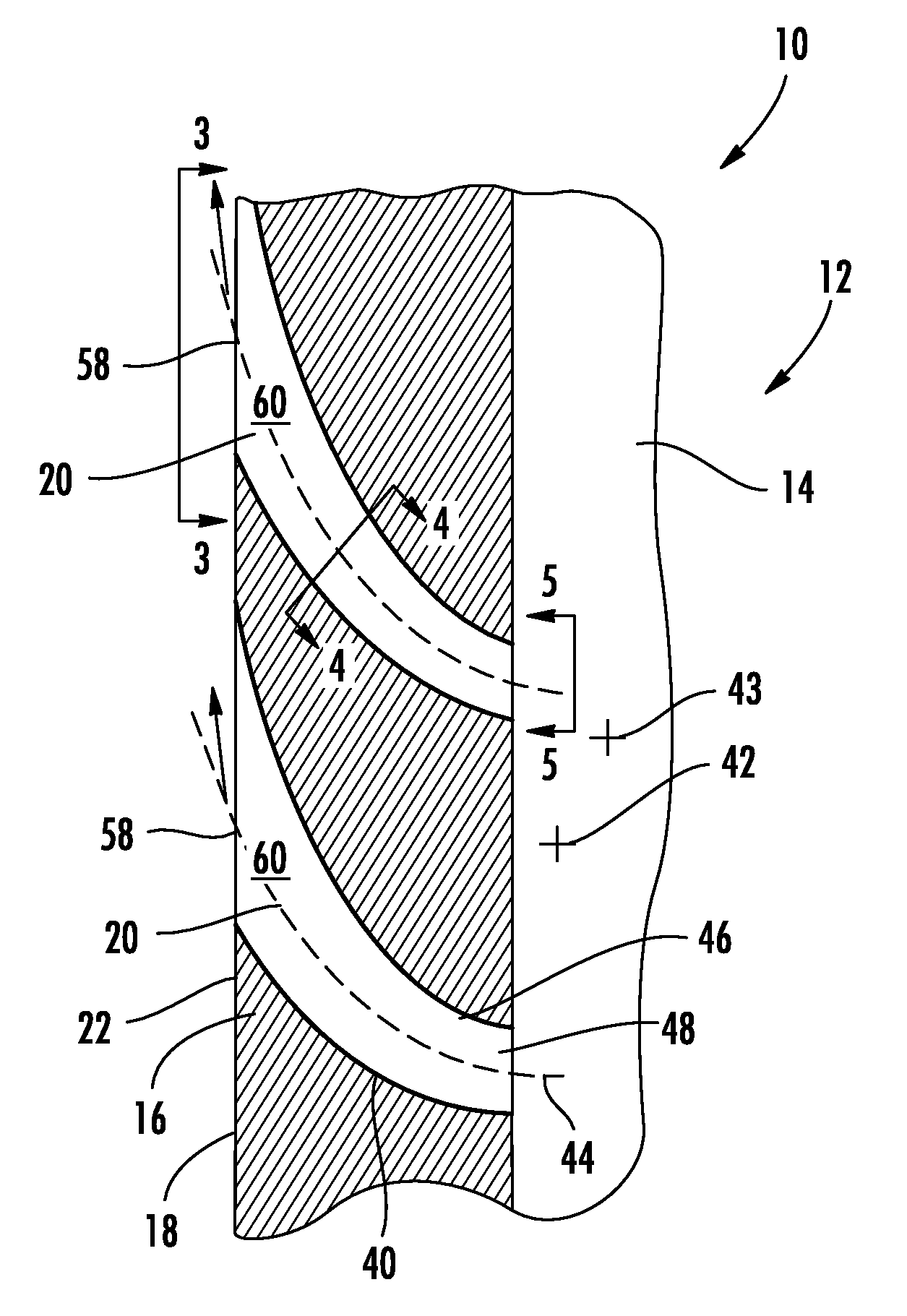

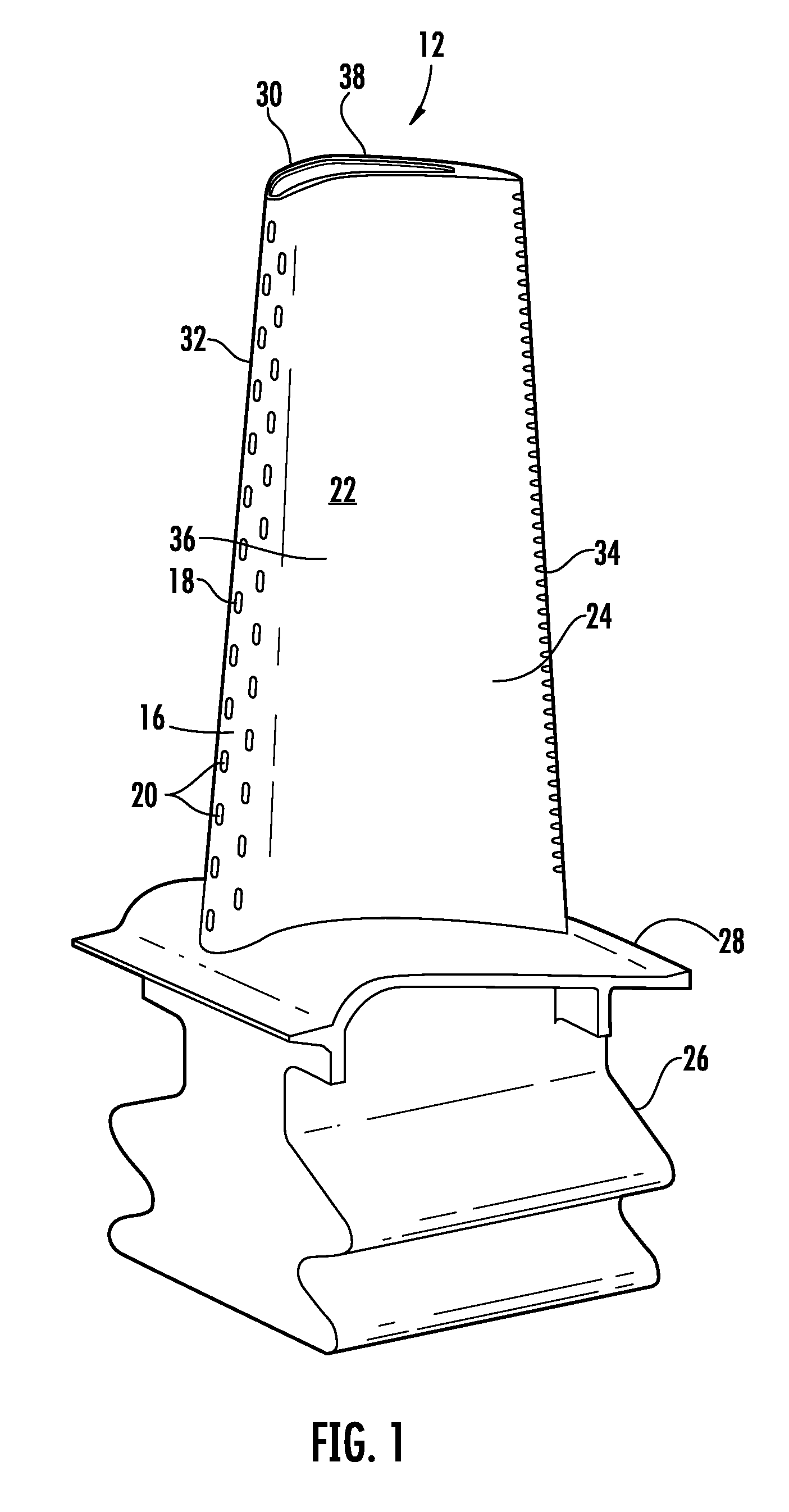

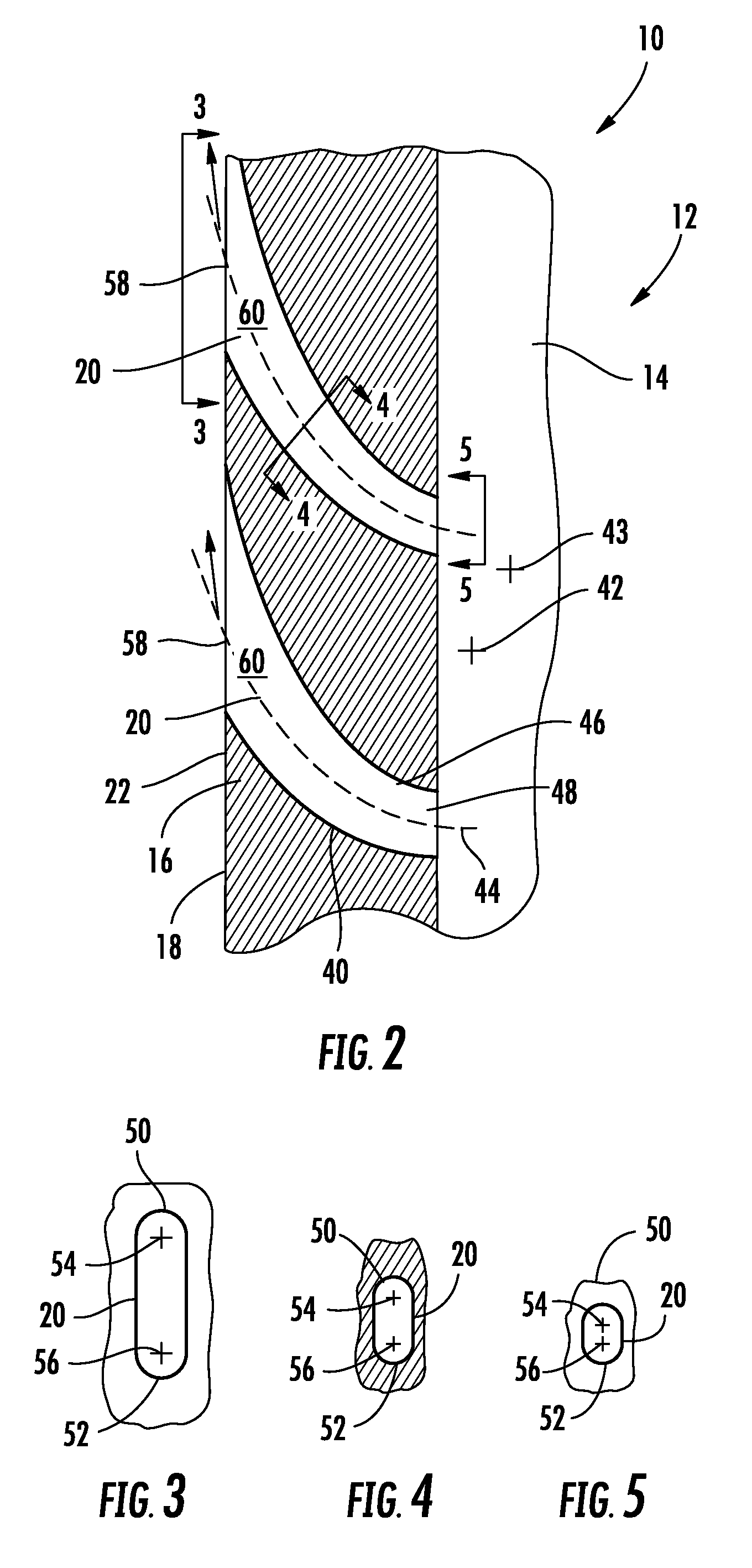

Turbine airfoil cooling system with curved diffusion film cooling hole

A cooling system for a turbine airfoil of a turbine engine having at least one diffusion film cooling hole positioned in an outer wall defining the turbine airfoil is disclosed. The diffusion film cooling hole includes a first sidewall having a first radius of curvature about an axis generally orthogonal to a centerline of cooling fluid flow through the diffusion film cooling hole and a second sidewall having a second radius of curvature about an axis generally orthogonal to the centerline of cooling fluid flow through the at least one diffusion film cooling hole. The radii of curvature of the first and second sidewalls are different such that the diffusion film cooling hole includes an ever increasing cross-sectional area moving from an inlet to an outlet, thereby diffusing and reducing the velocity of cooling fluids flowing there through.

Owner:SIEMENS ENERGY INC

LED retrofit for fluorescent backlit signs

InactiveUS20110019413A1Quick installationMany componentLighting support devicesPoint-like light sourceSmart lightingLed array

Owner:ZIMMERMAN JAMES WILLIAM +2

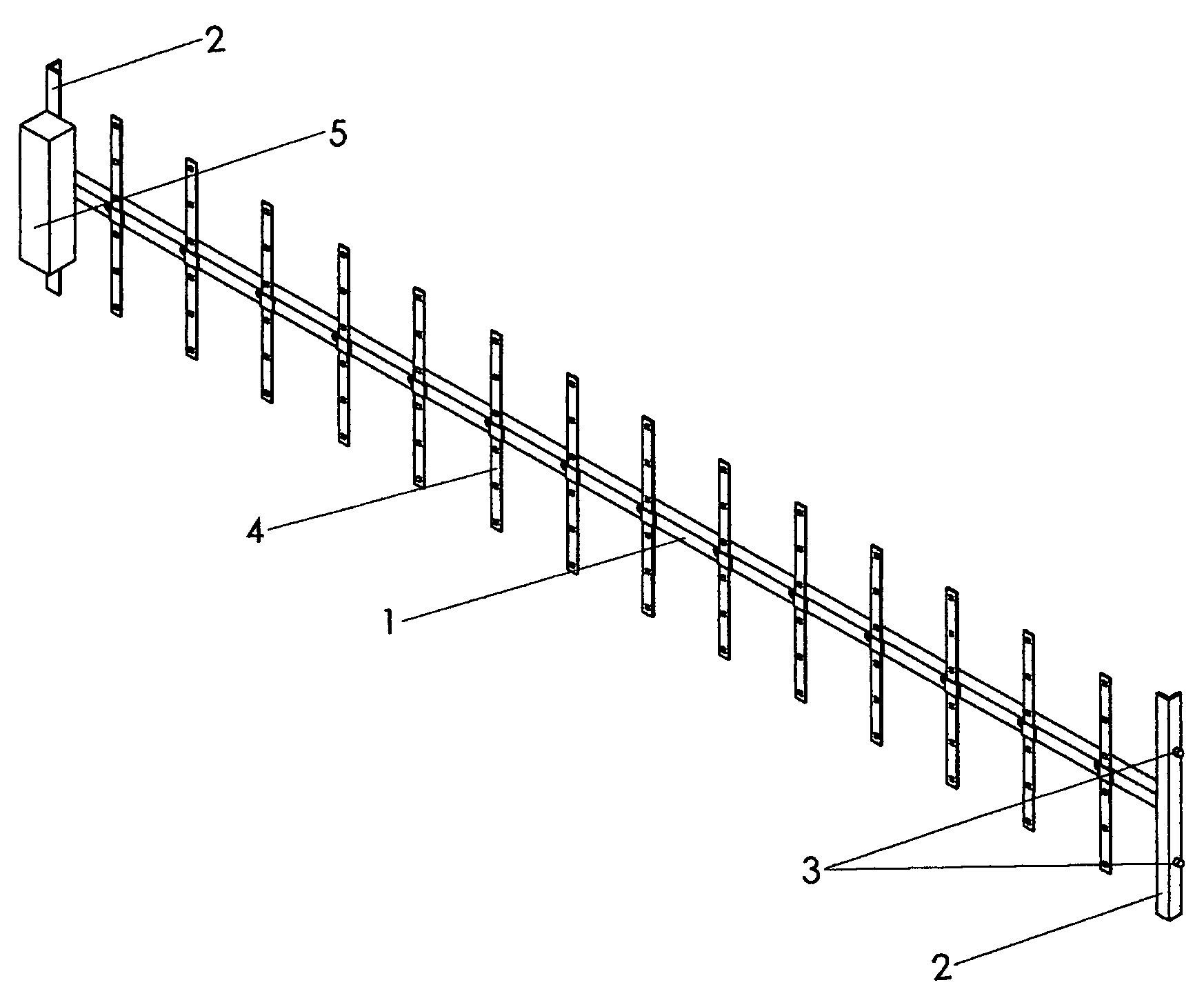

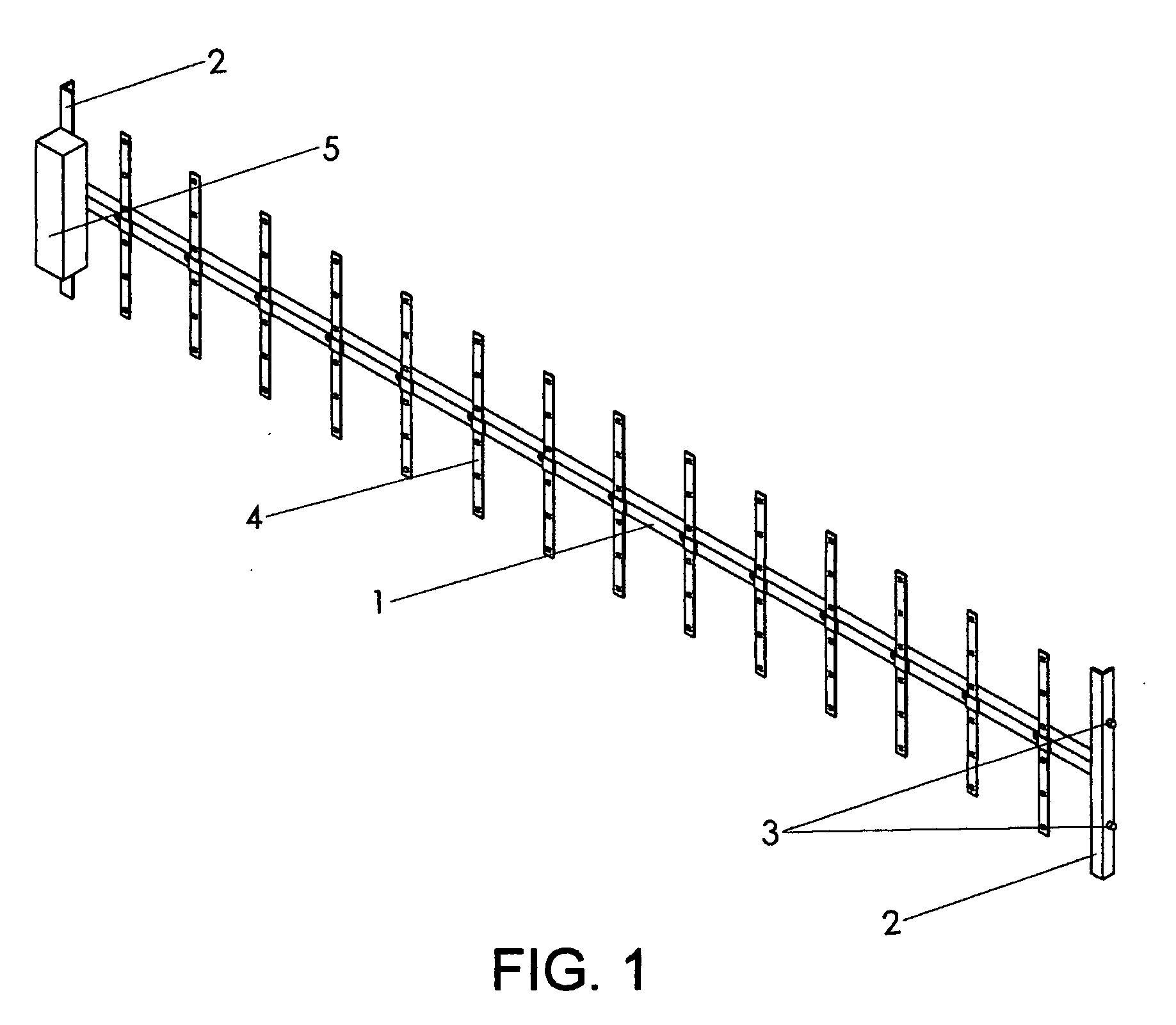

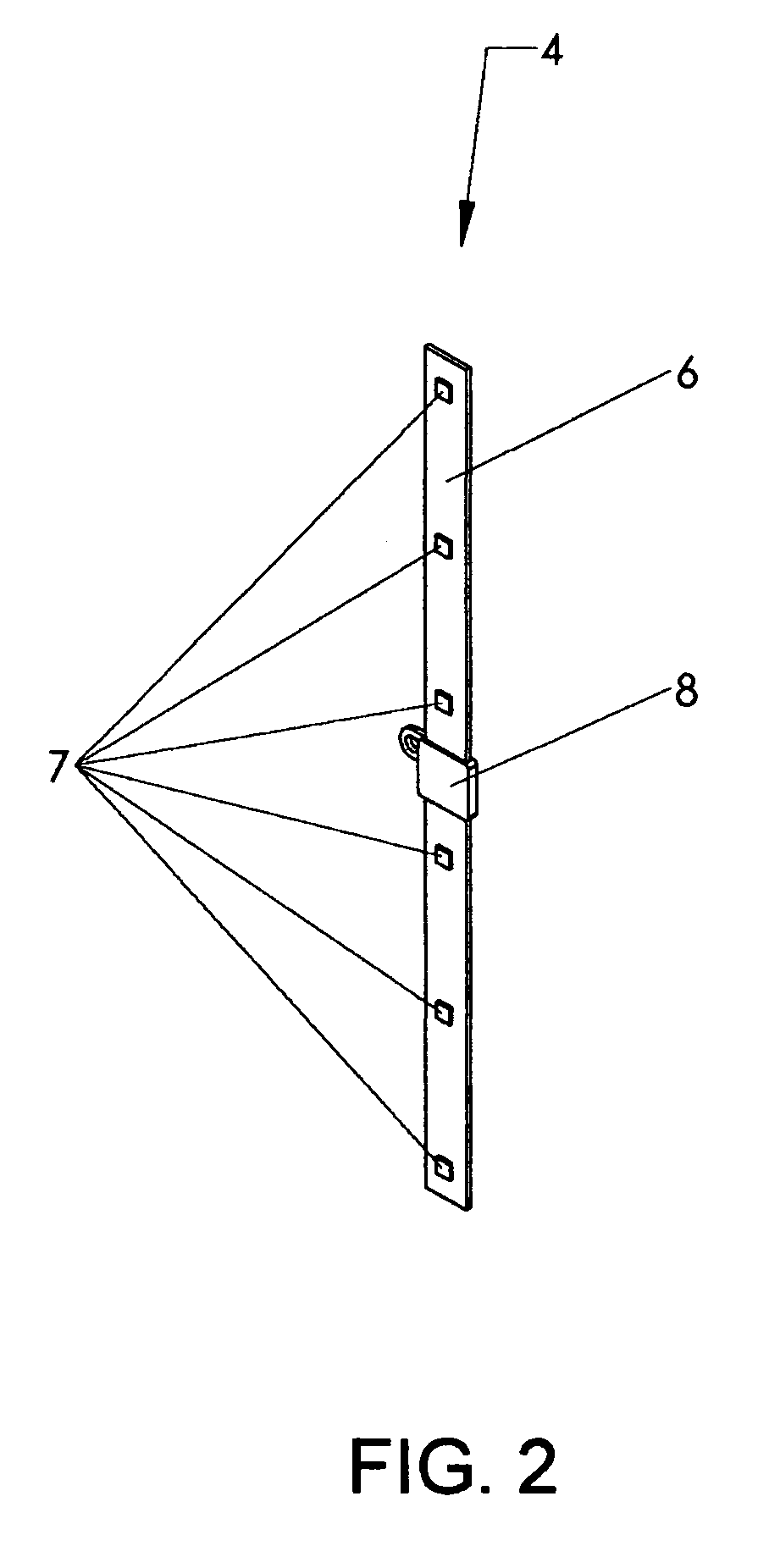

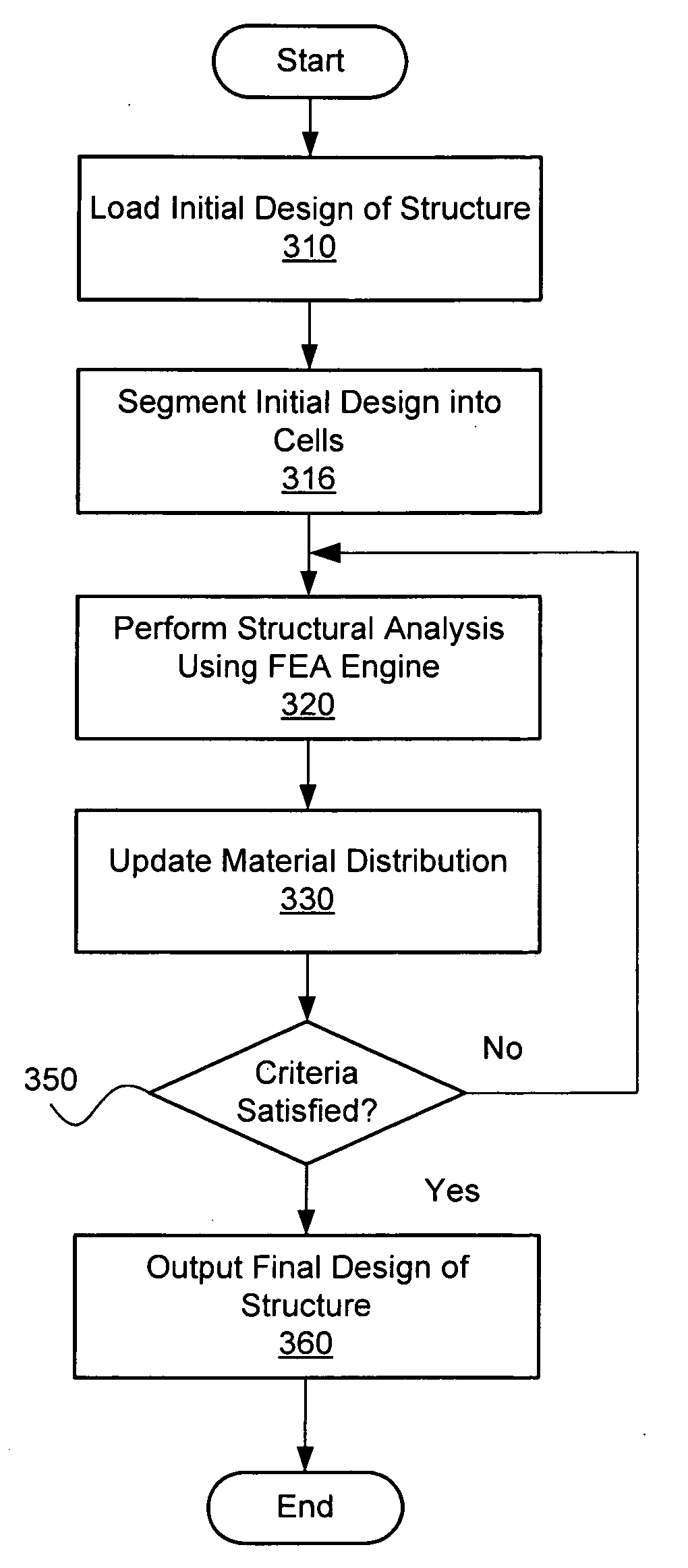

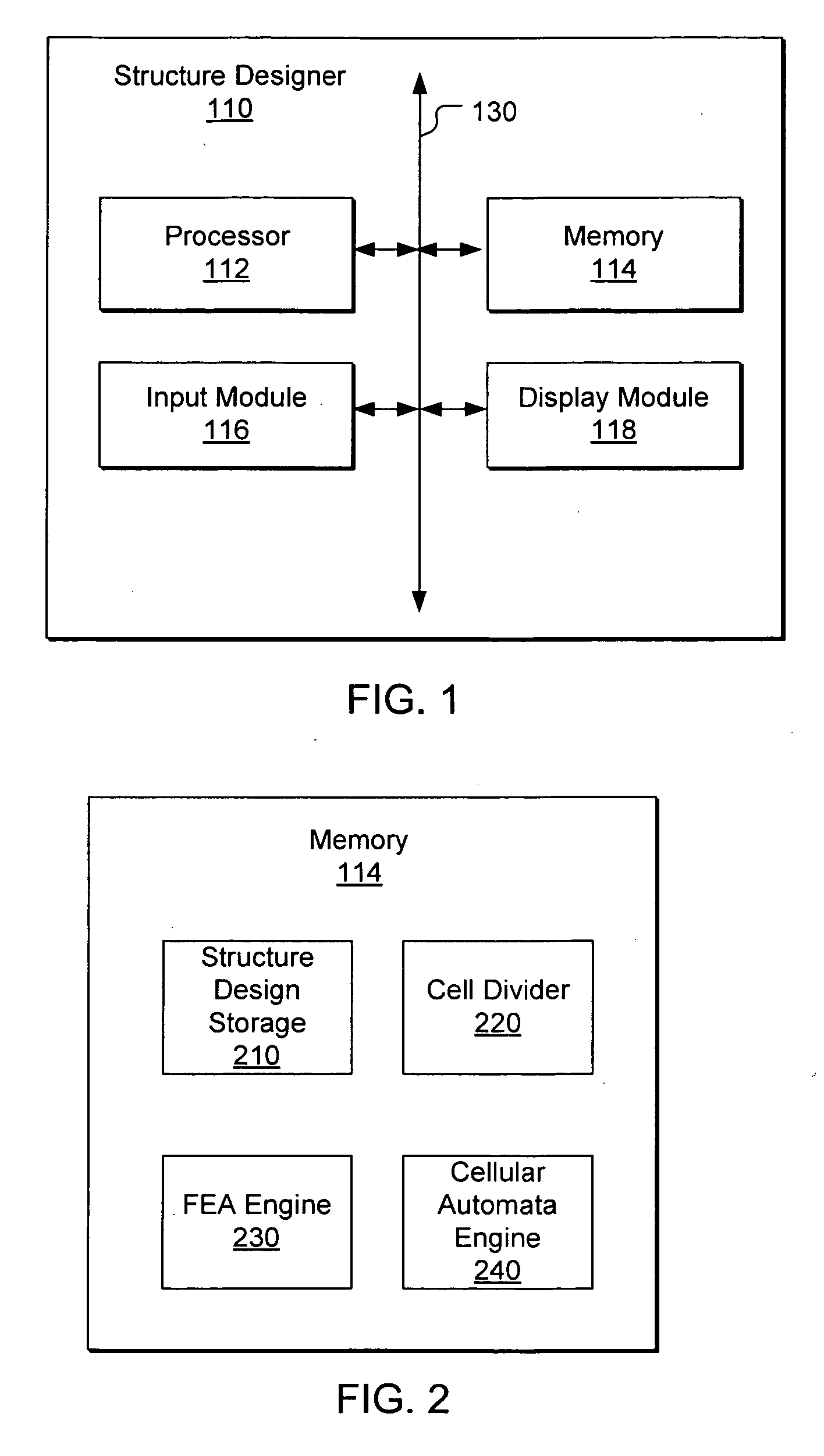

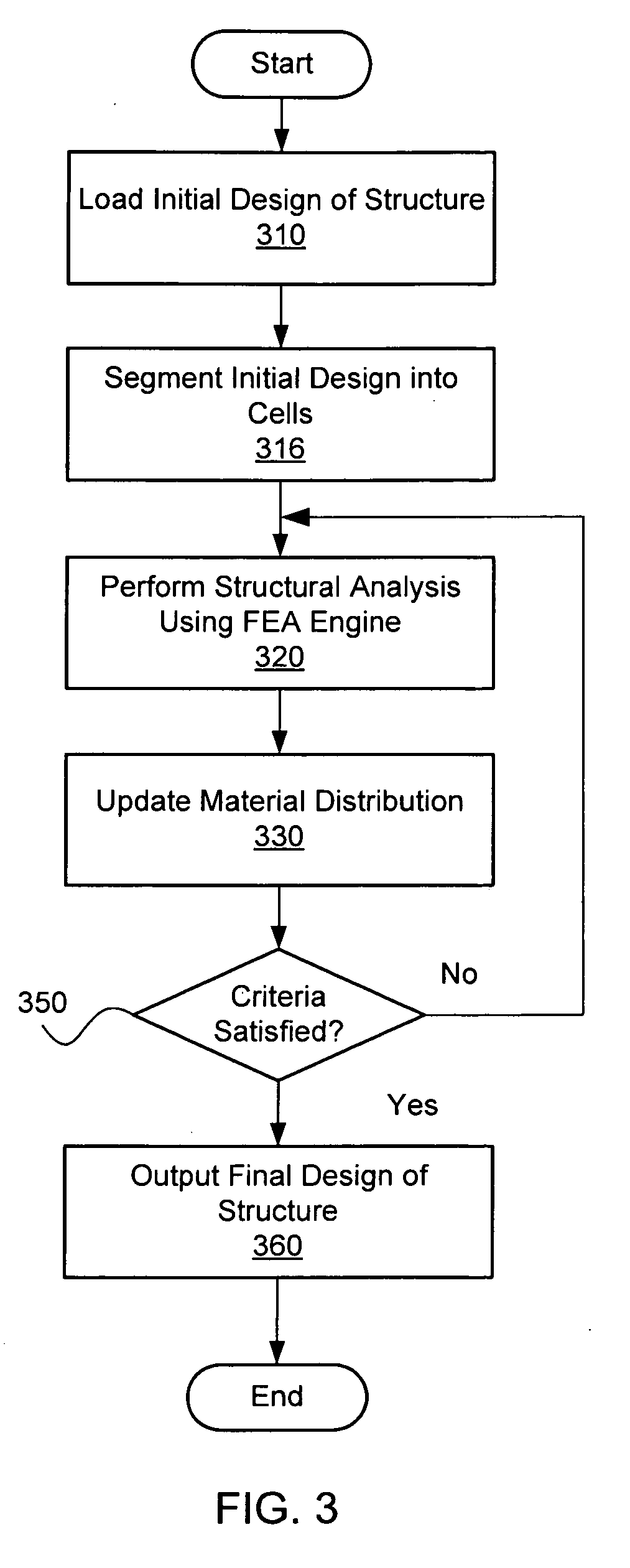

Crashworthiness design methodology using a hybrid cellular automata algorithm for the synthesis of topologies for structures subject to nonlinear transient loading

InactiveUS20090164178A1Design moreEqually distributedGeometric CADDesign optimisation/simulationElement analysisEngineering

Crashworthiness designing of a structure using a Hybrid Cellular Automata (HCA) algorithm where field states are computed using finite element analysis (FEA) and the material distribution of the structure is updated at each iteration using cellular automata method. The HCA algorithm optimizes the topology of the structures to achieve certain performance within the limits of various constraints applied to ensure crashworthiness of the structures. The HCA algorithm may also be applied to designing of structures to be fabricated by an extrusion method having the same cross section along the direction of extrusion or stamped structures having thickness varying across the structure.

Owner:UNIV OF NOTRE DAME DU LAC +1

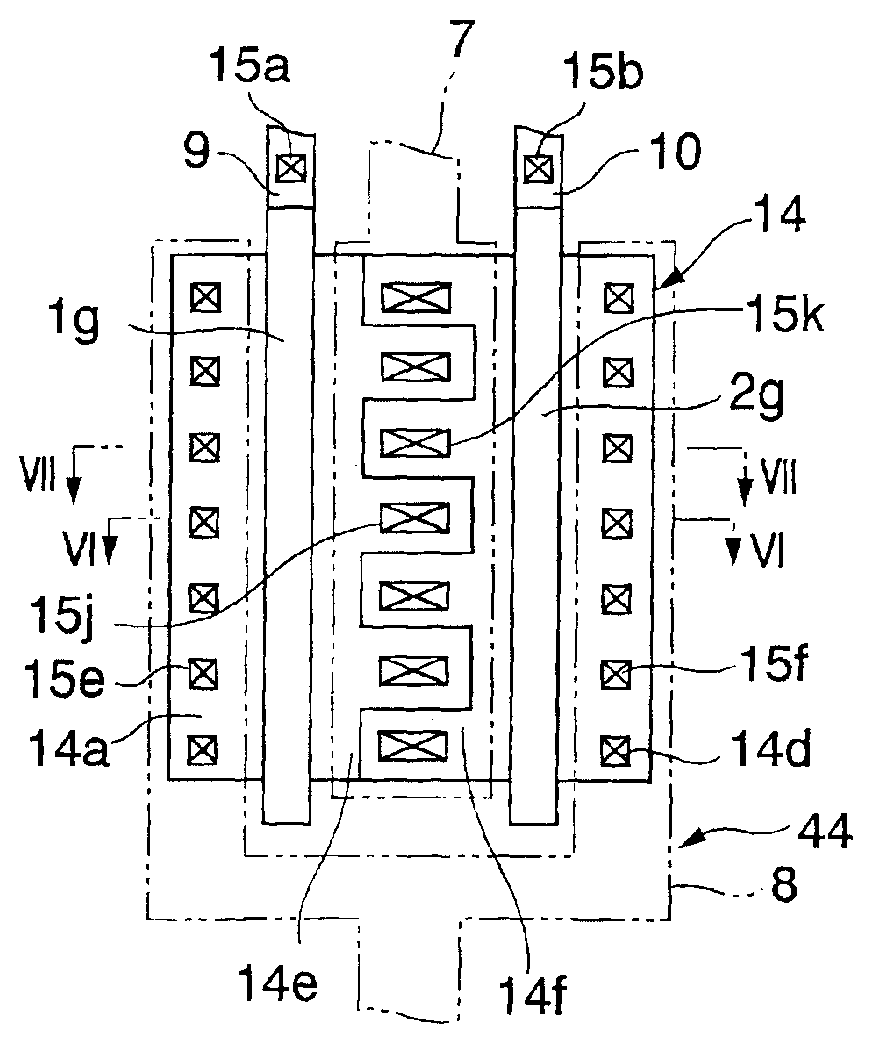

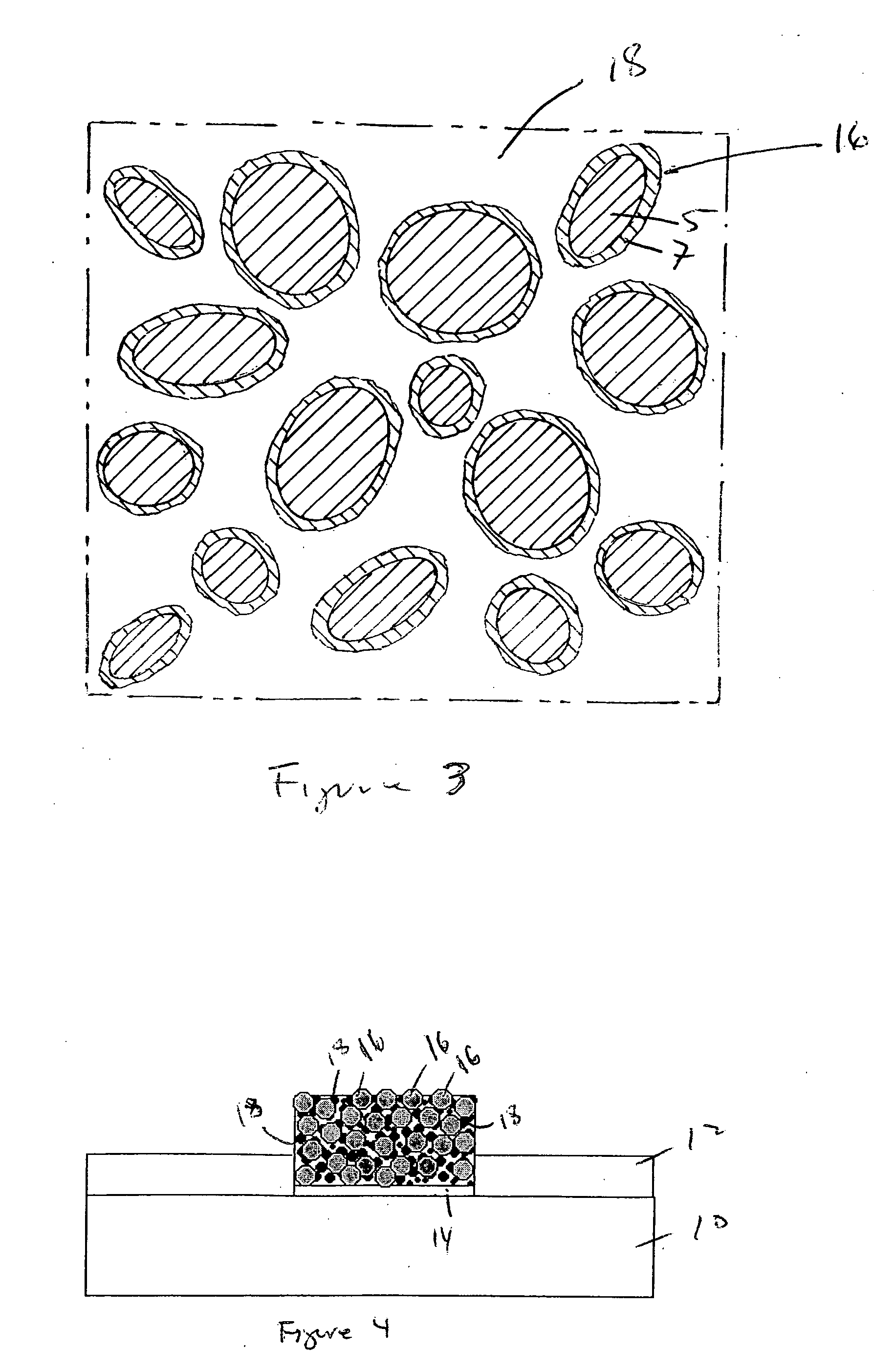

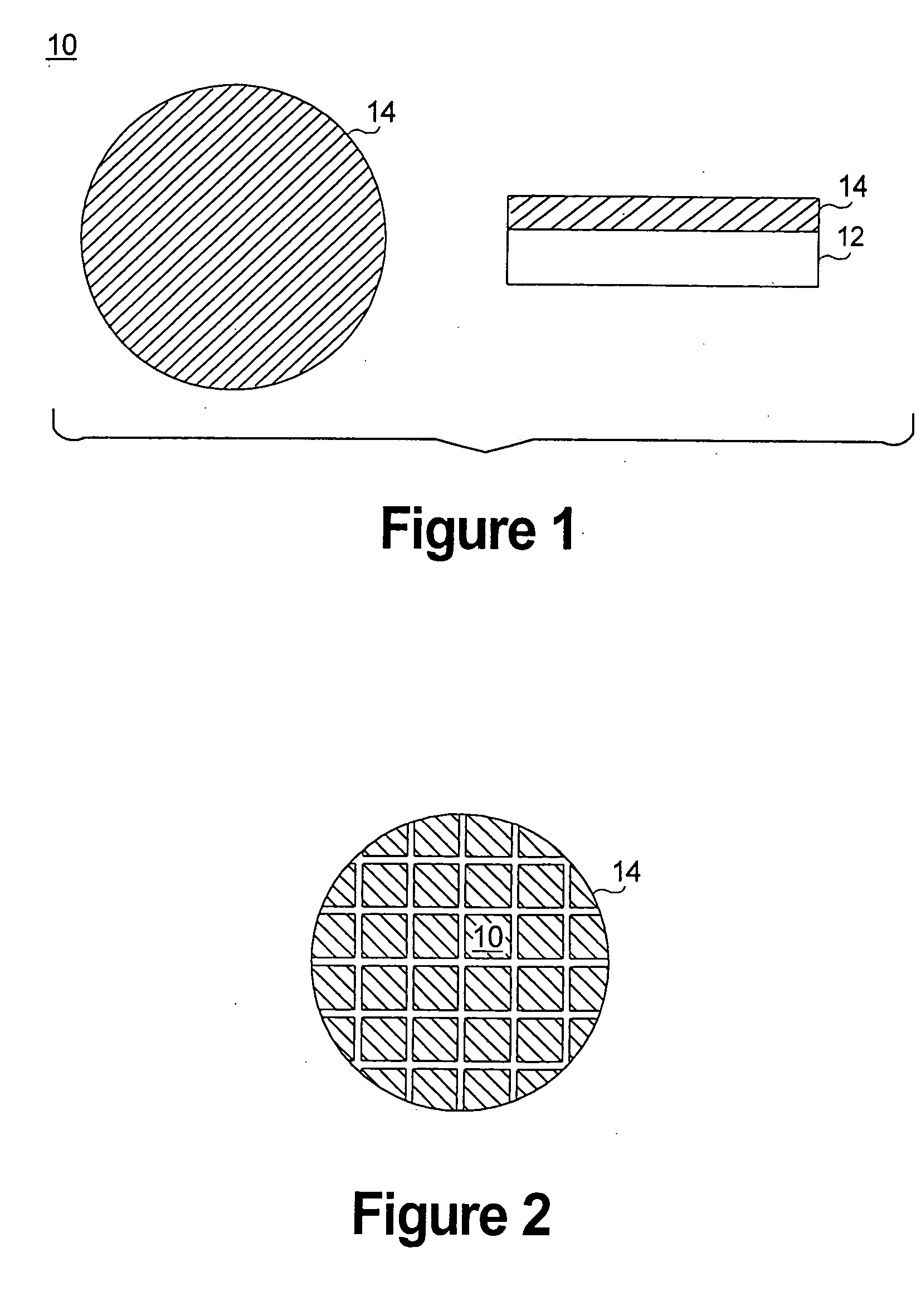

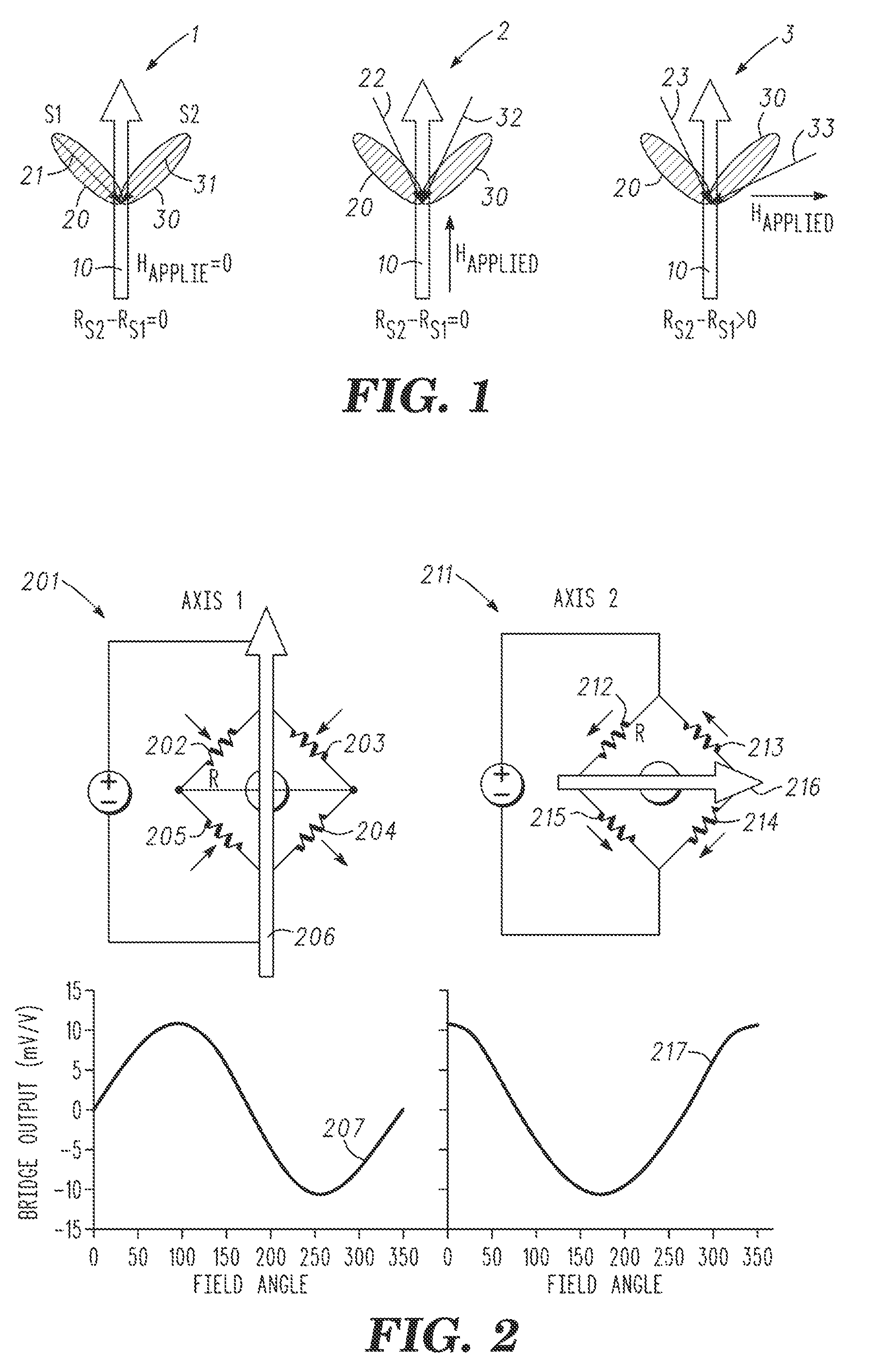

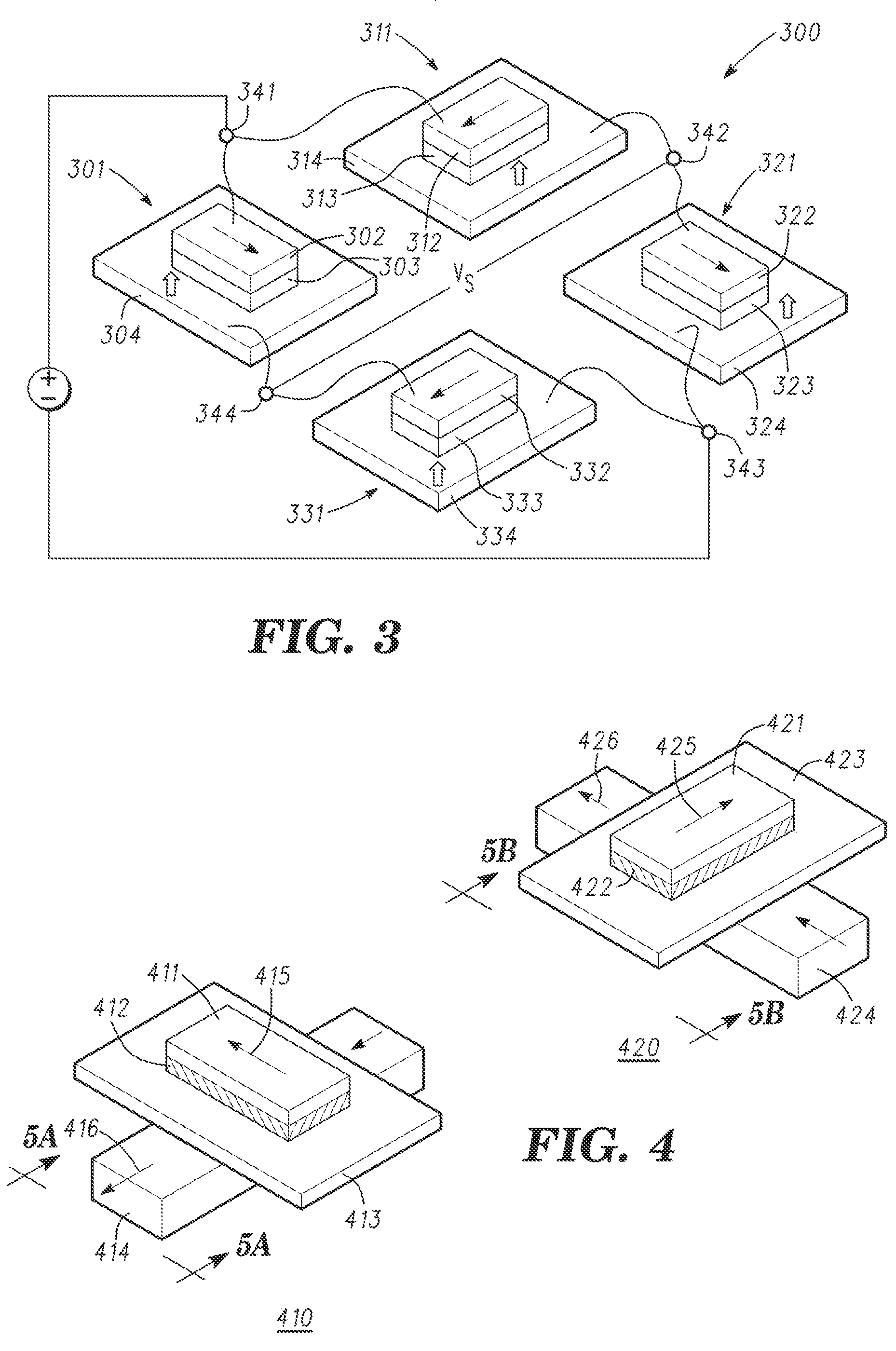

Fabrication process and layout for magnetic sensor arrays

ActiveUS20120193736A1Diminish read signalMore freedom in device designMagnetic measurementsMagnetic-field-controlled resistorsSensor arrayCMOS

A magnetic sensor includes a plurality of groups, each group comprising a plurality of magnetic tunnel junction (MTJ) devices having a plurality of conductors configured to couple the MTJ devices within one group in parallel and the groups in series enabling independent optimization of the material resistance area (RA) of the MTJ and setting total device resistance so that the total bridge resistance is not so high that Johnson noise becomes a signal limiting concern, and yet not so low that CMOS elements may diminish the read signal. Alternatively, the magnetic tunnel junction devices within each of at least two groups in series and the at least two groups in parallel resulting in the individual configuration of the electrical connection path and the magnetic reference direction of the reference layer, leading to independent optimization of both functions, and more freedom in device design and layout. The X and Y pitch of the sense elements are arranged such that the line segment that stabilizes, for example, the right side of one sense element; also stabilizes the left side of the adjacent sense element.

Owner:EVERSPIN TECHNOLOGIES

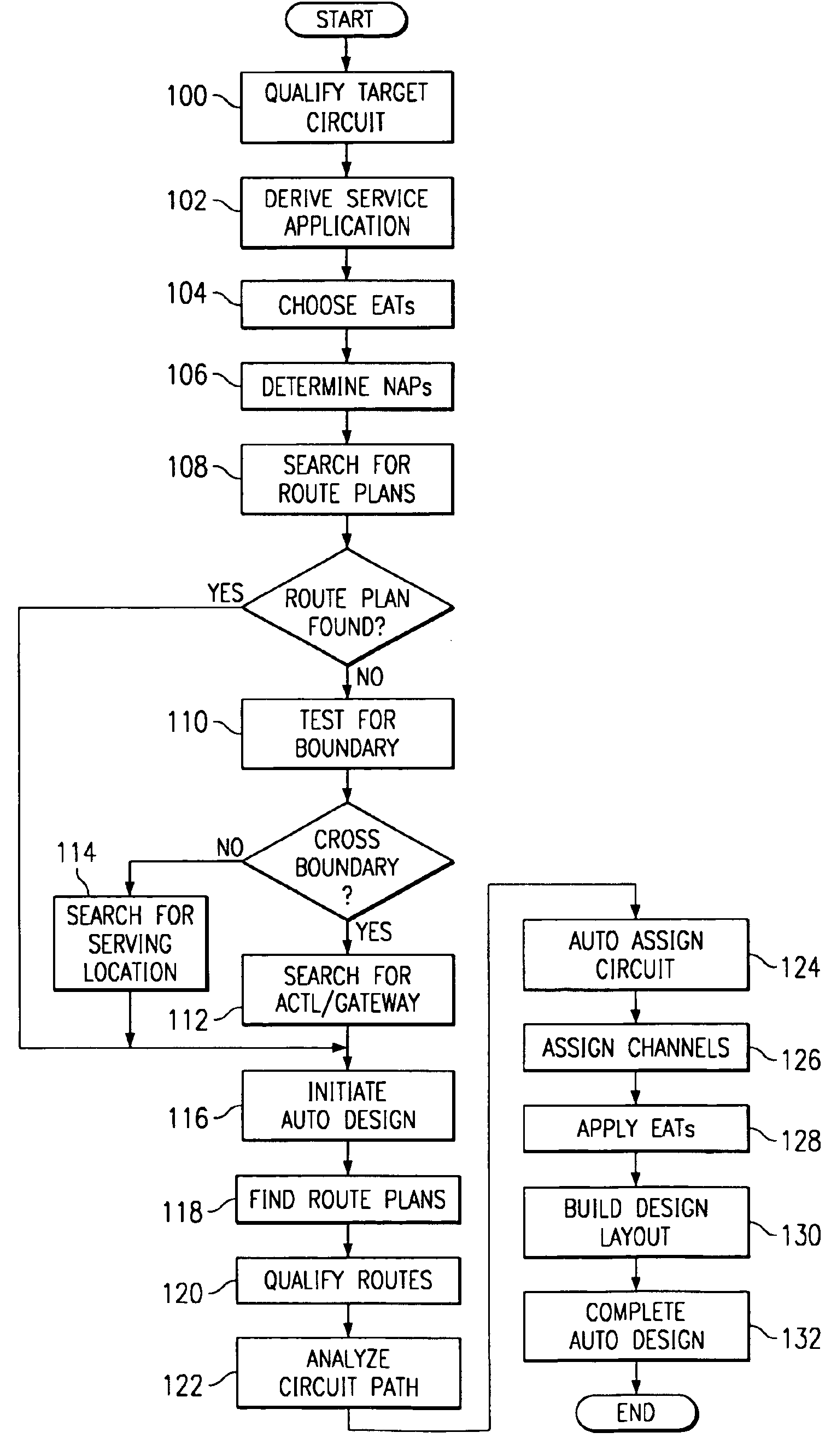

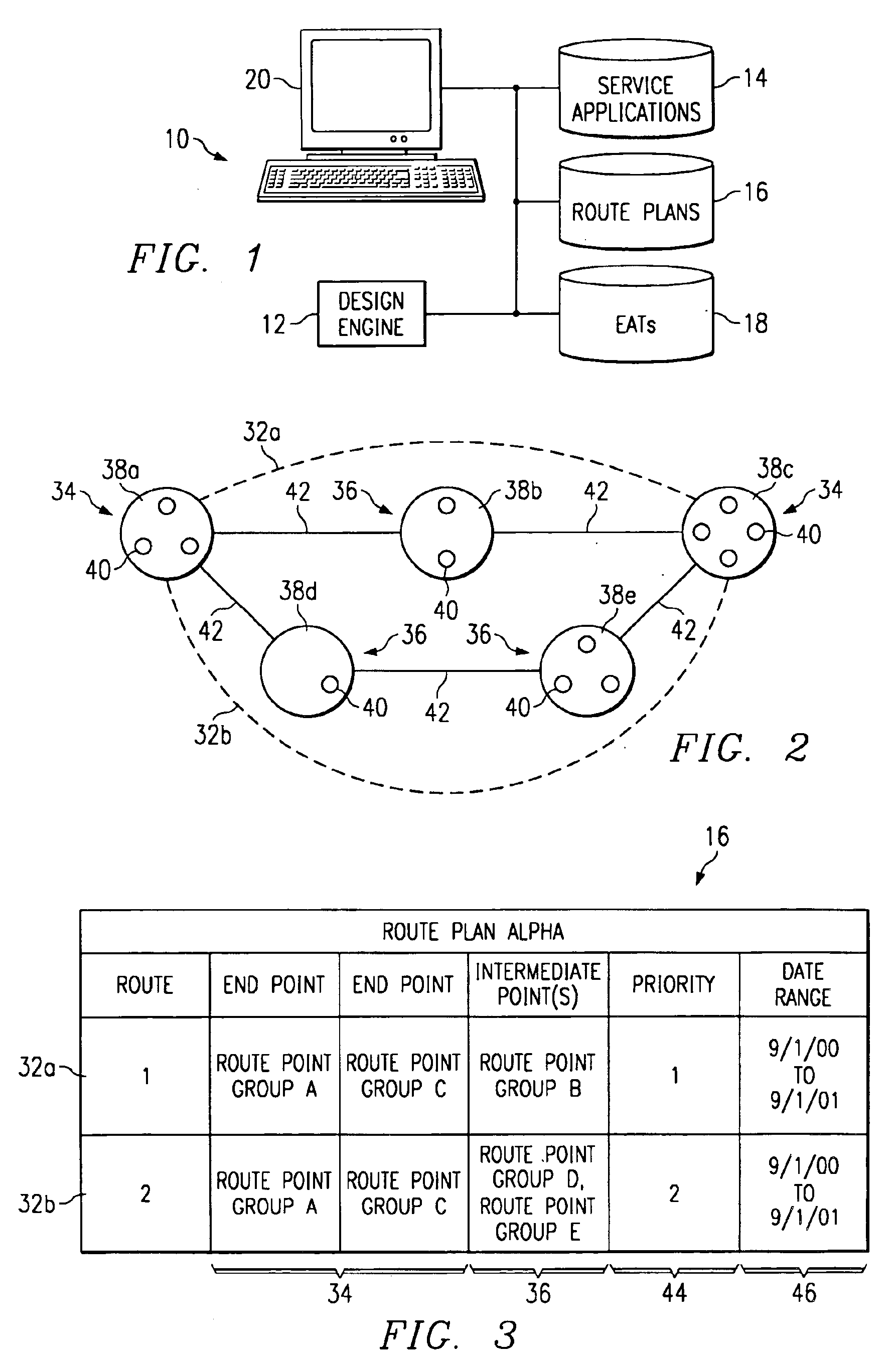

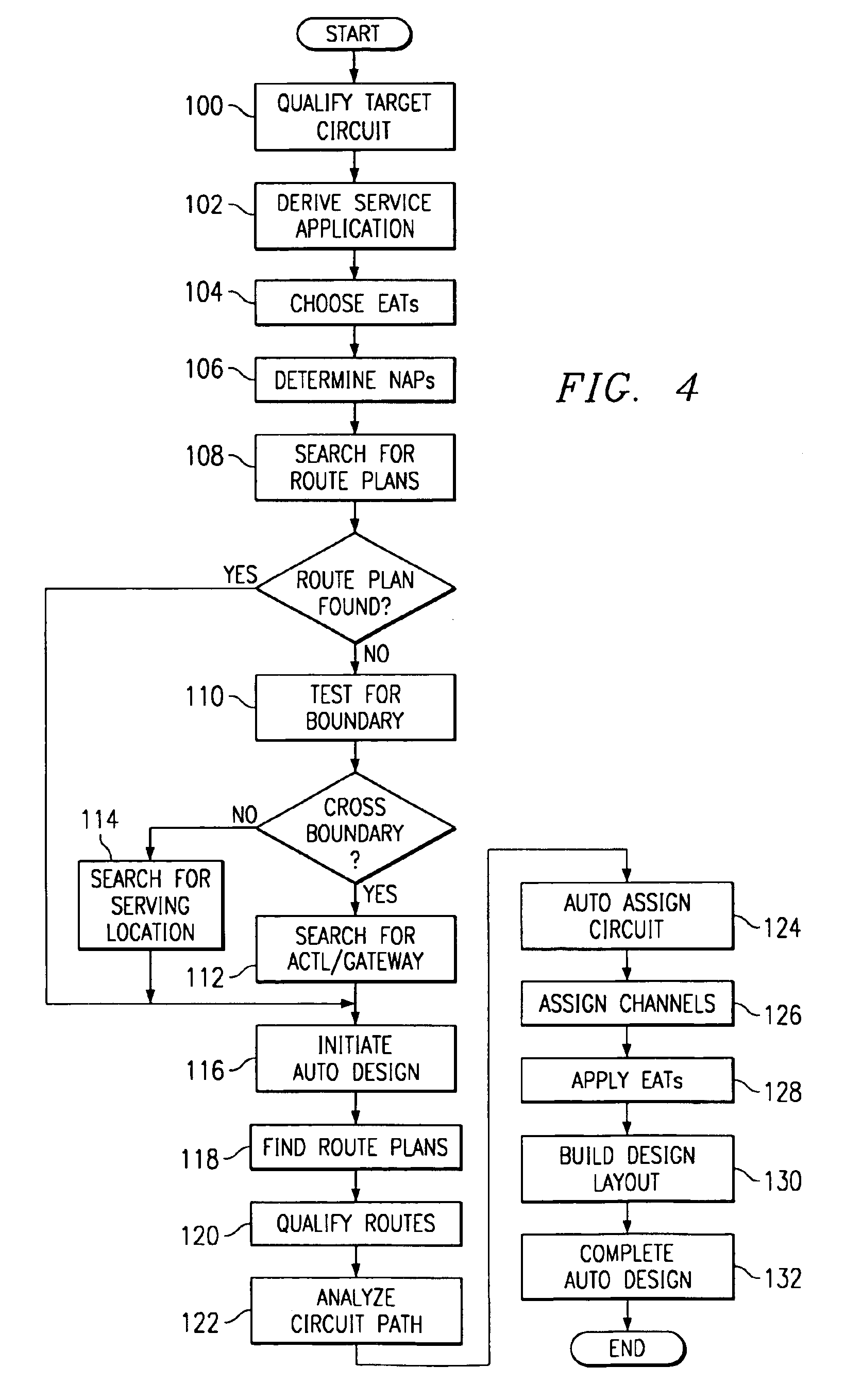

System and method for automatically designing communications circuits

InactiveUS6892169B1Communications reduced eliminatedDisadvantages and reduced eliminatedMultiplex system selection arrangementsCircuit switching systemsDesign communicationRoute planning

A software interface used in designing communications circuits receives input from a user (20). In response, the software interface initiates accessing of a route plan (16) comprising a first route point group (38) associated with a first circuit end point (34), a second route point group (38) associated with a second circuit end point (34), and one or more routes (32) connecting the first and second route point groups (38). Each route (32) is available for use in designing the circuit. The software interface also initiates selection of a route (32) according to the route plan (16) and initiates the automatic assignment of the selected route (32) to the circuit in designing the circuit. The software interface provides information to the user (20) reflecting assignment of the route (32) to the circuit. The route plan (16) may be selected from among multiple route plans (16) according to a service application (14) automatically derived from an associated circuit order. The software interface may initiate assignment of equipment to the circuit at one or more points along the selected route (32) according to an equipment assignment template (18) specifying characteristics of the equipment. The template (18) may be selected from among multiple templates (18) according to a service application (14).

Owner:AGILE SOFTWARE CORPORATION

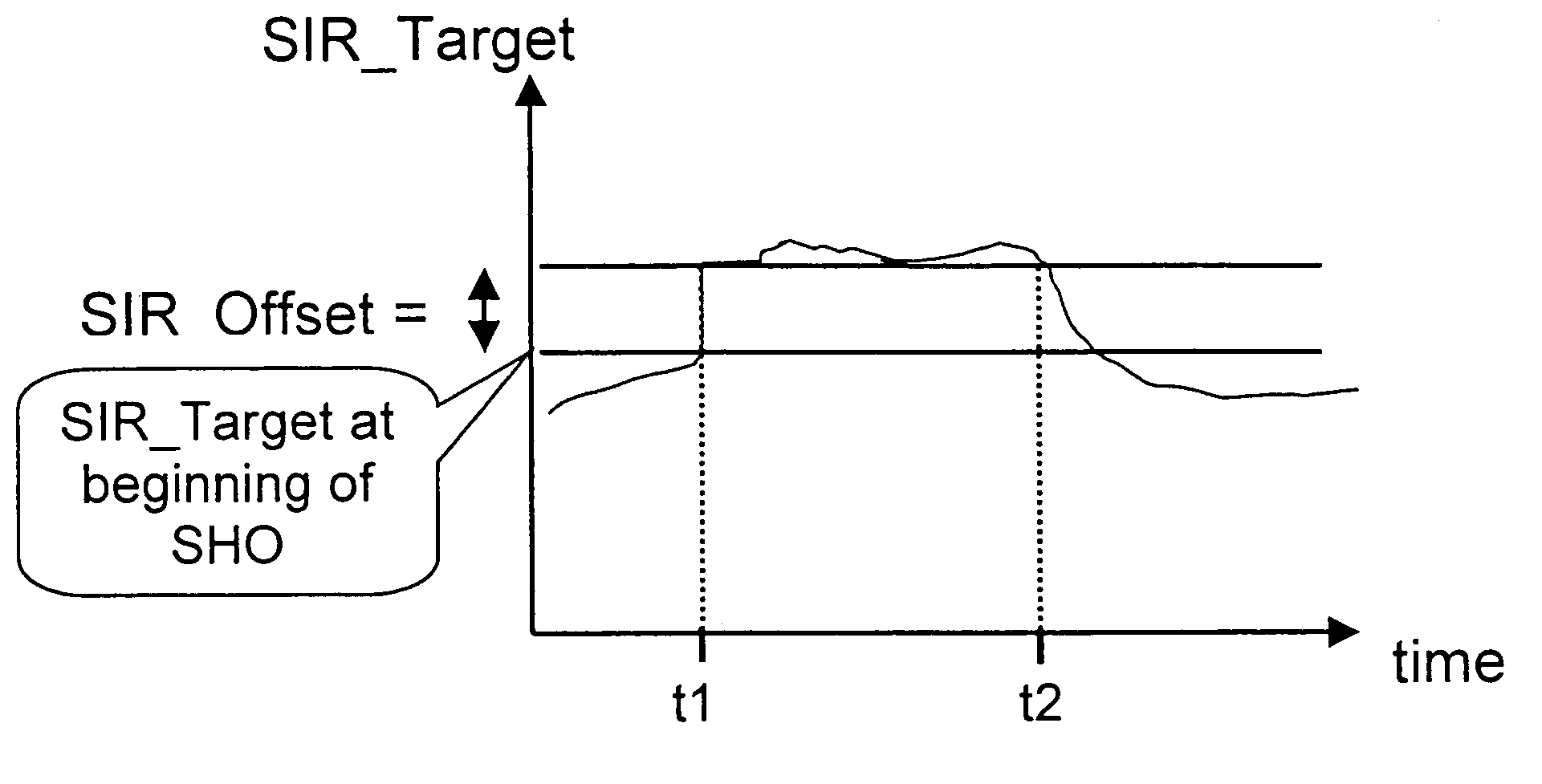

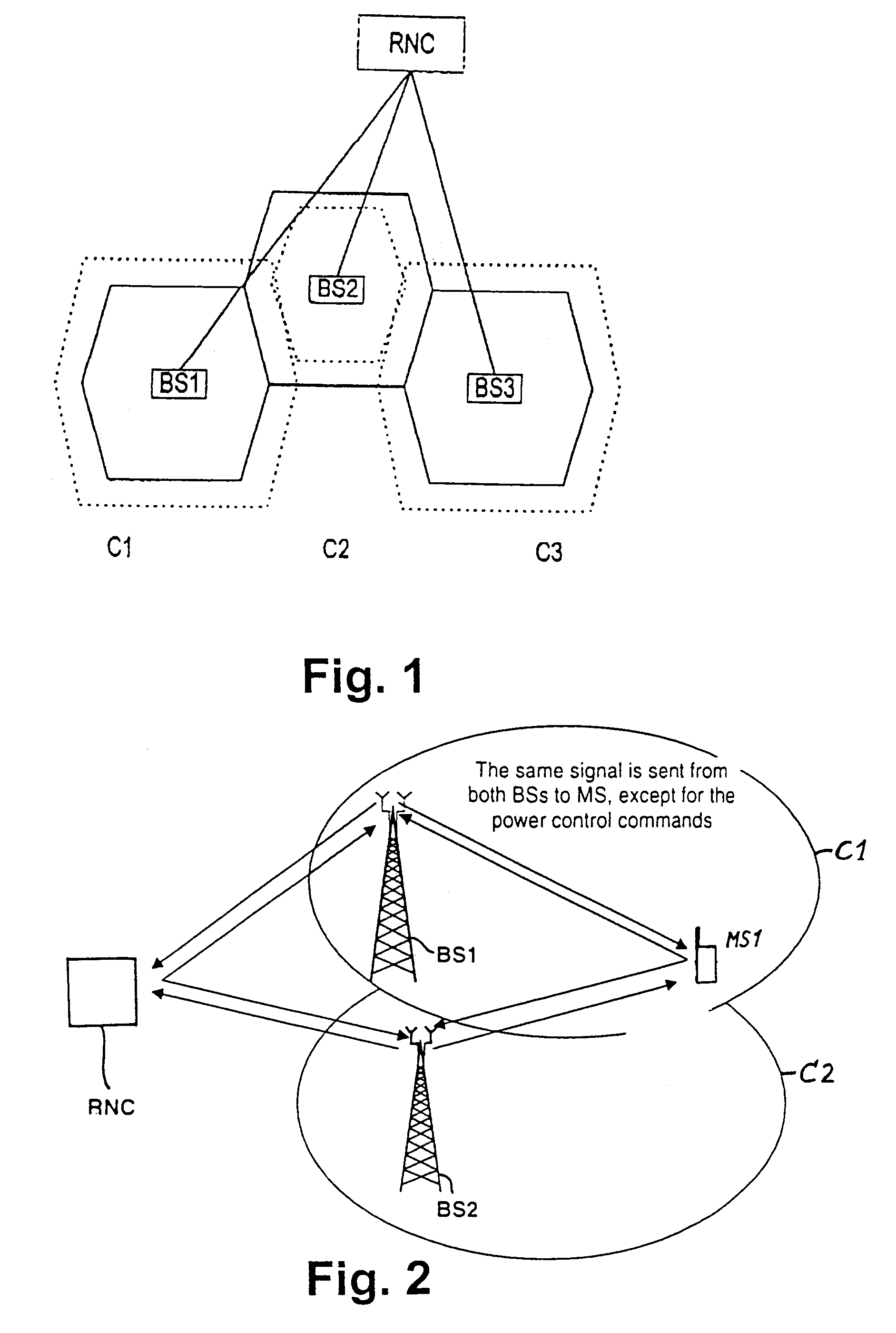

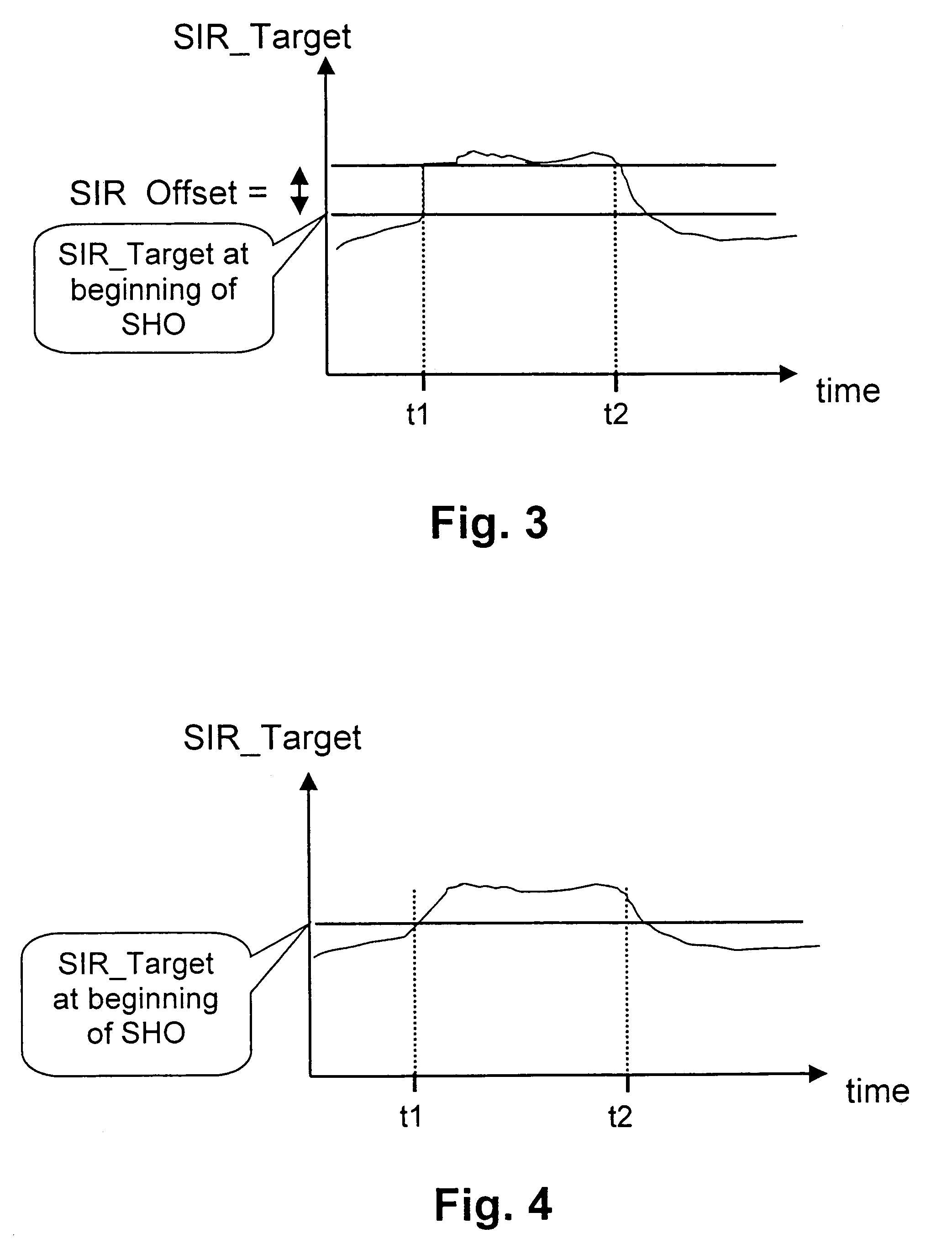

Method and device for controlling the power in an asymmetric soft handover condition

InactiveUS7248889B2Weak linkDesign morePower managementTransmission control/equalisingSoft handoverComputer science

A method and a device for controlling a method for controlling the power in an asymmetric soft handover condition in a communication network, including at least two cellseach cell being served by a first type network device adapted to serve second type network devices in the respective cell. The method comprises:temporarily adjusting (step S3) a communication parameter of at least one second type network deviceto set up and / or maintain the communication of the second type network device with the first type network device of at least one of said cells.

Owner:NOKIA CORP

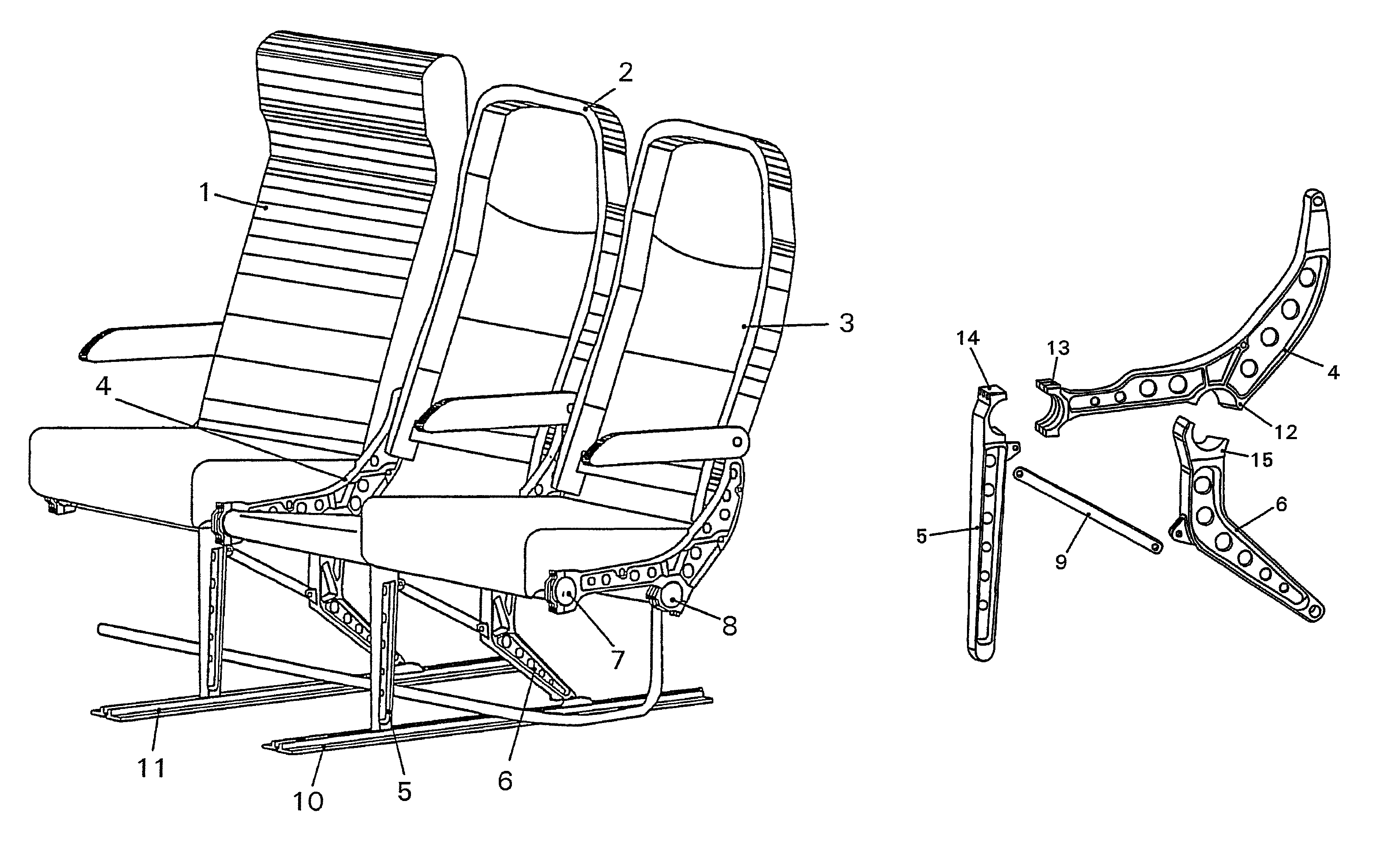

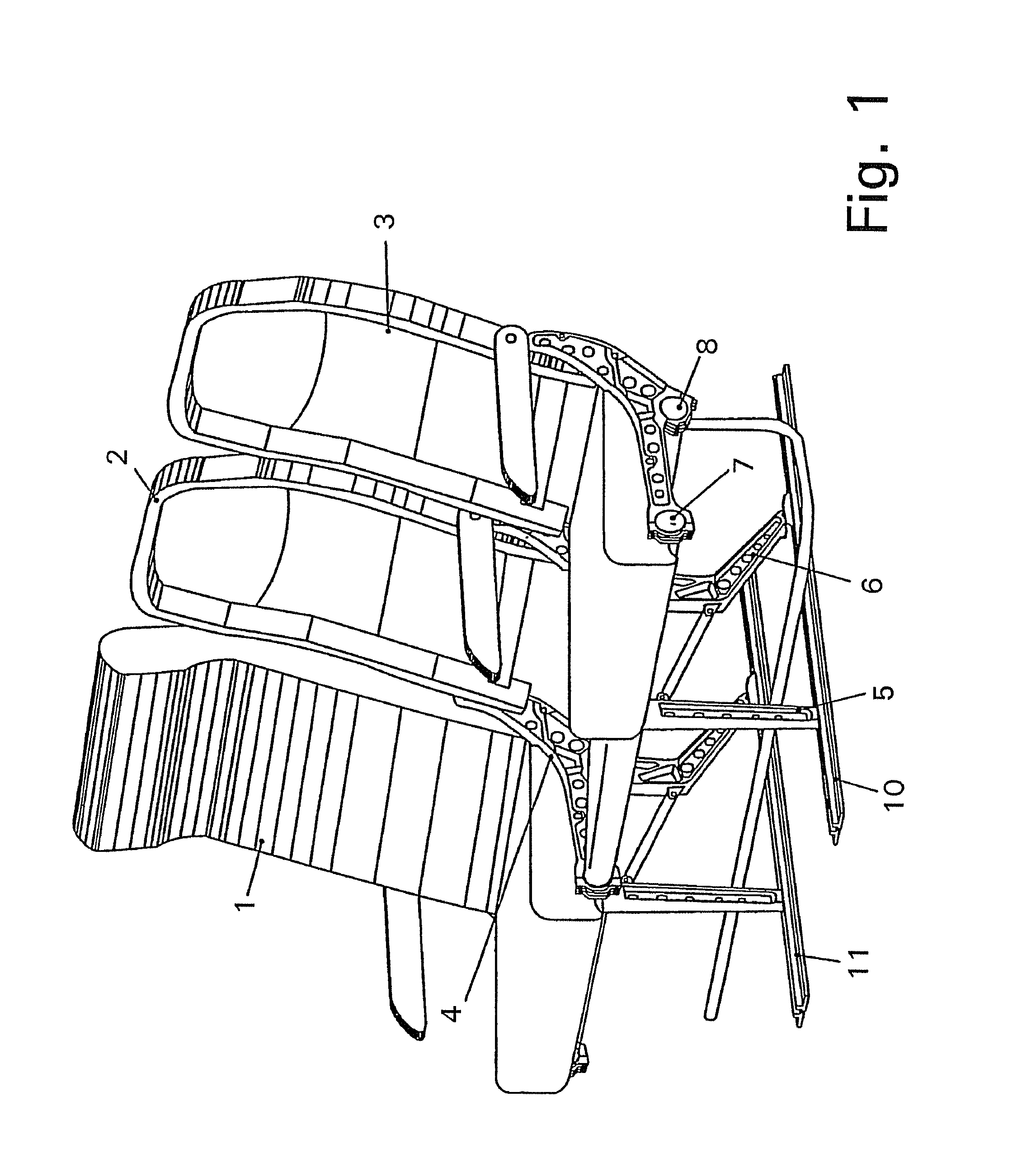

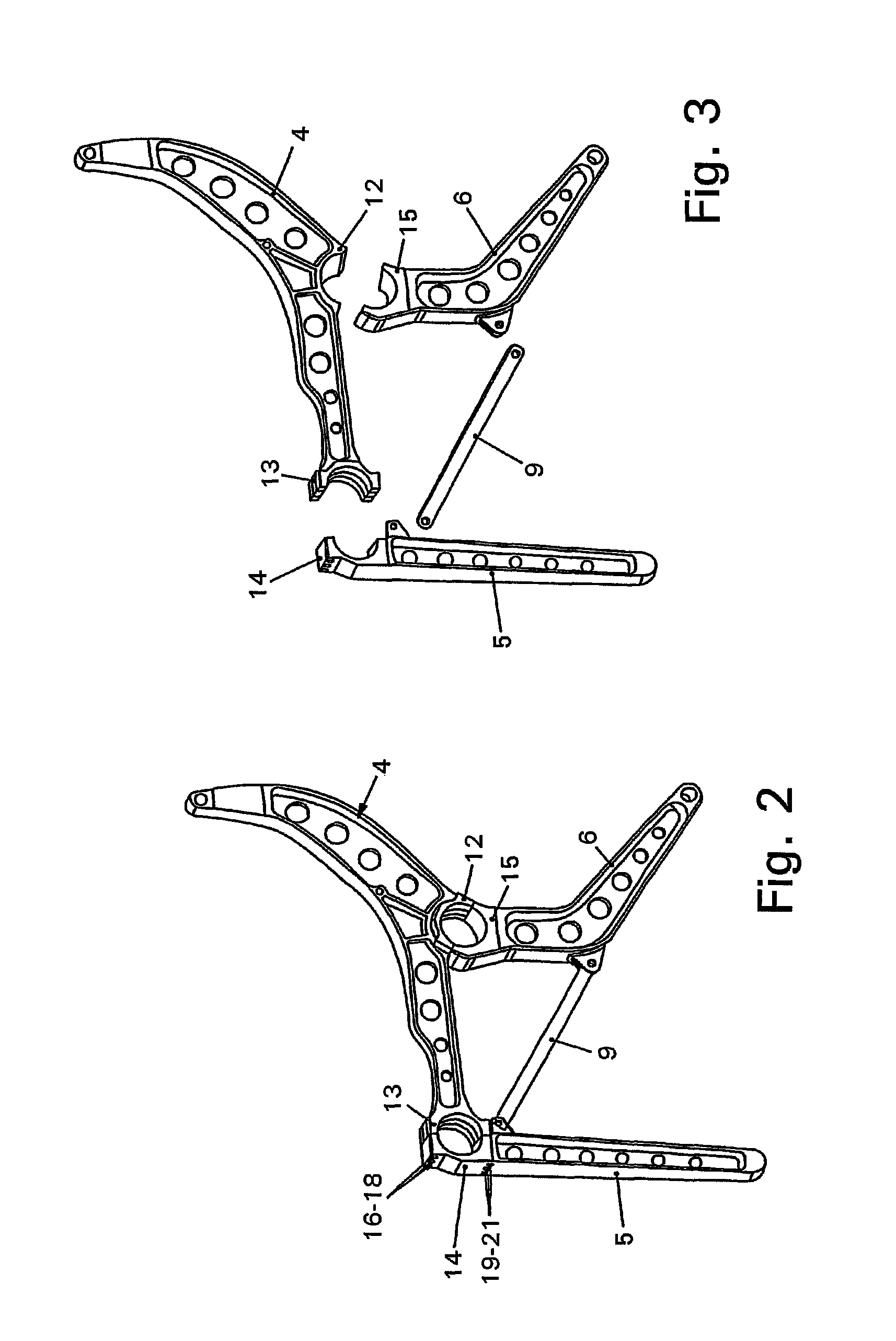

Kit for seat rows in aircraft

ActiveUS8393680B2Improve the level ofDesign moreSeating arrangementsAir-treatment apparatus arrangementsEngineeringAirplane

In seat rows, in particular in aircraft, the individual seats thereof being able to be adjusted in their usable seat width, and comprising seat dividers with support legs, which are held by spars running transversely to the seat direction, at least one seat divider may be adjusted in the direction of the spars.

Owner:ZIM AIRCRAFT SEATING GMBH