Patents

Literature

28149results about How to "Reduce area" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

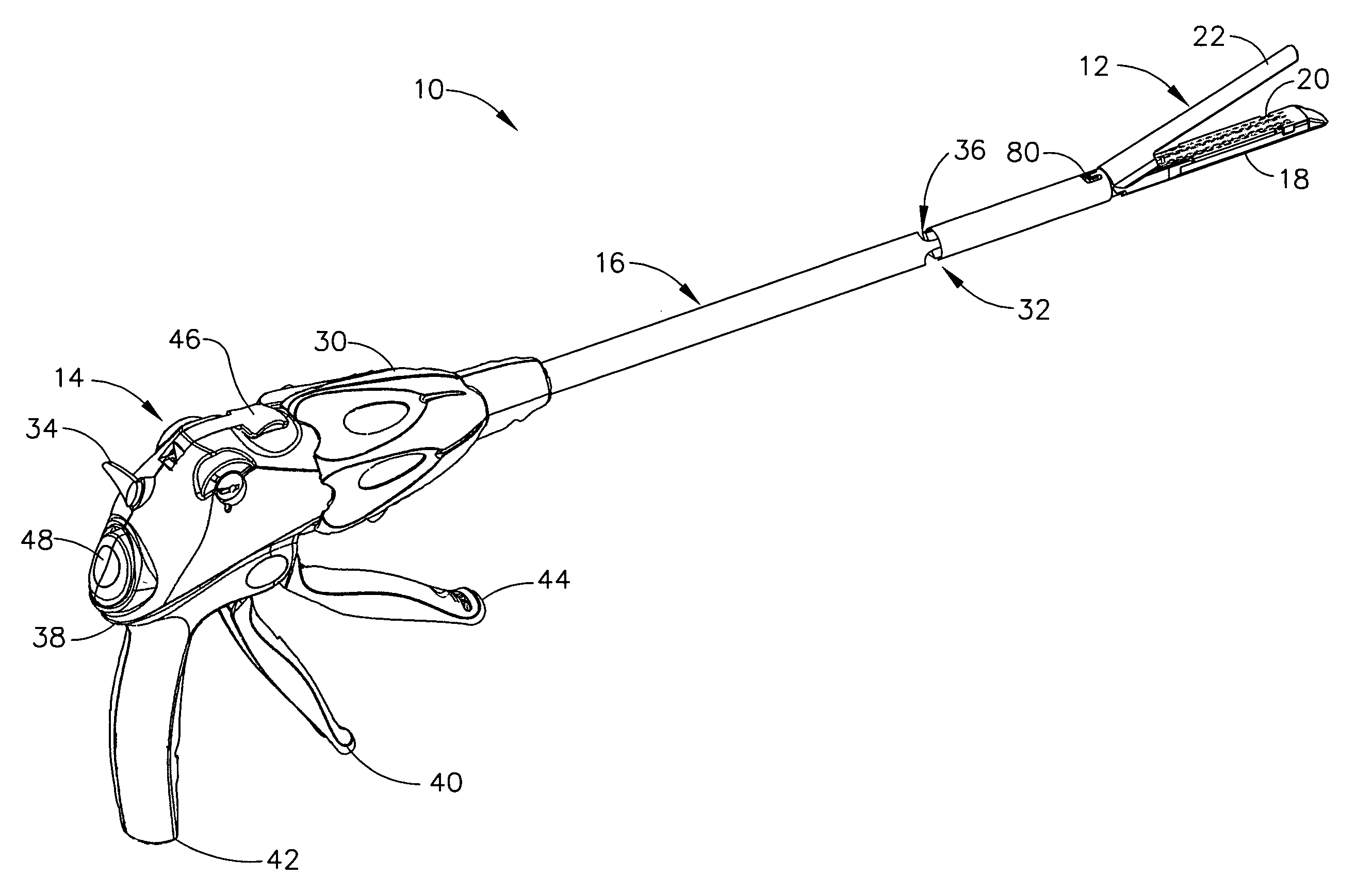

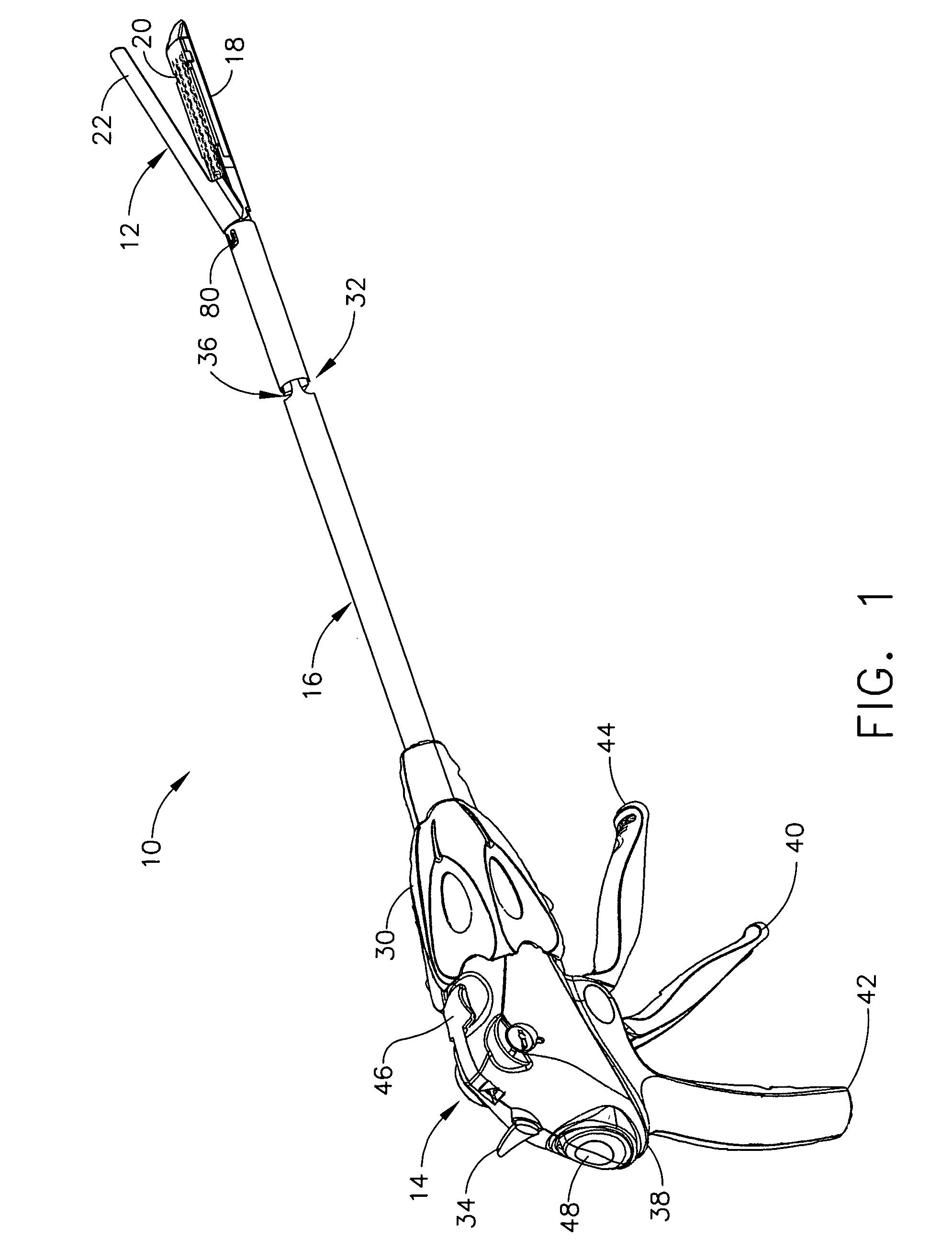

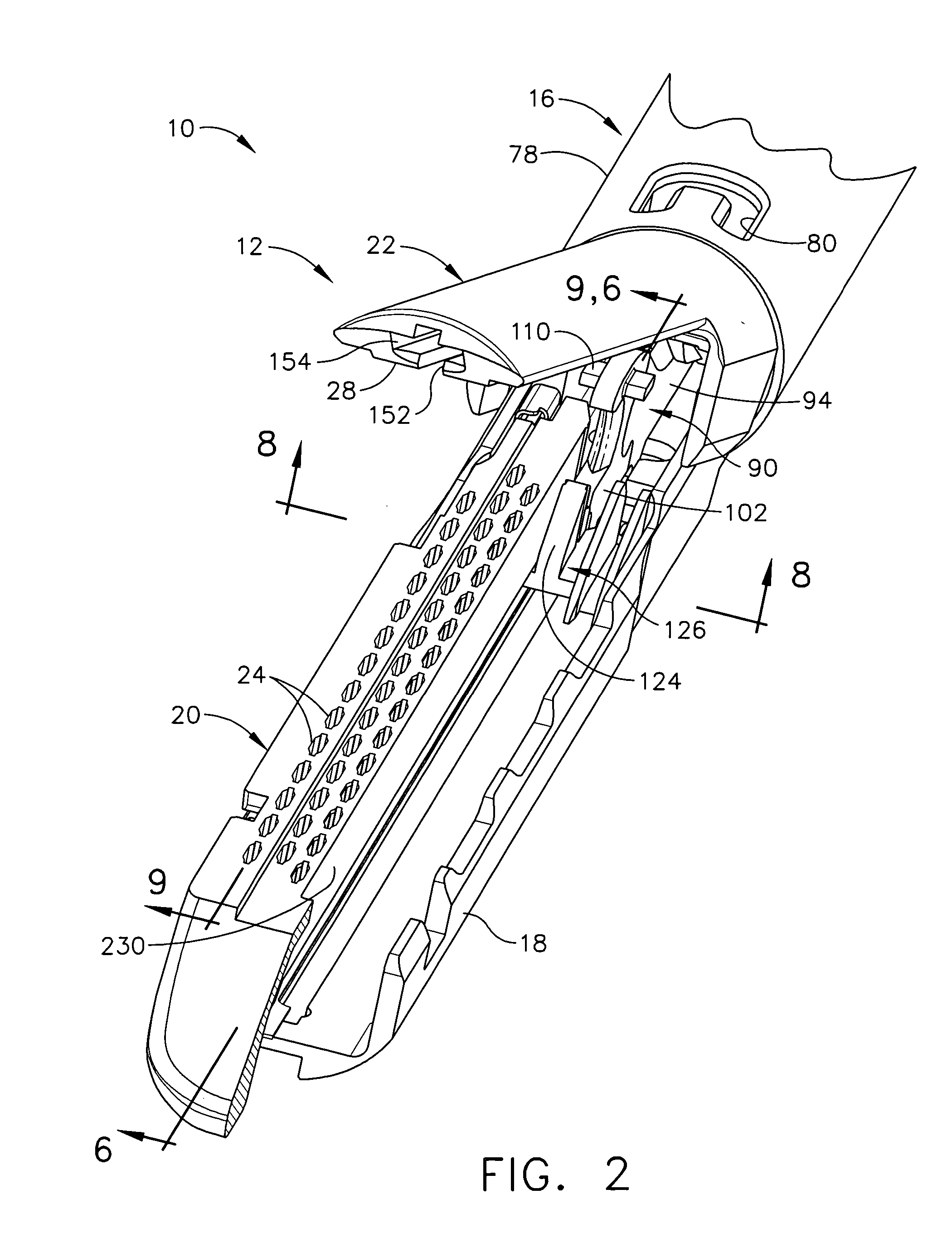

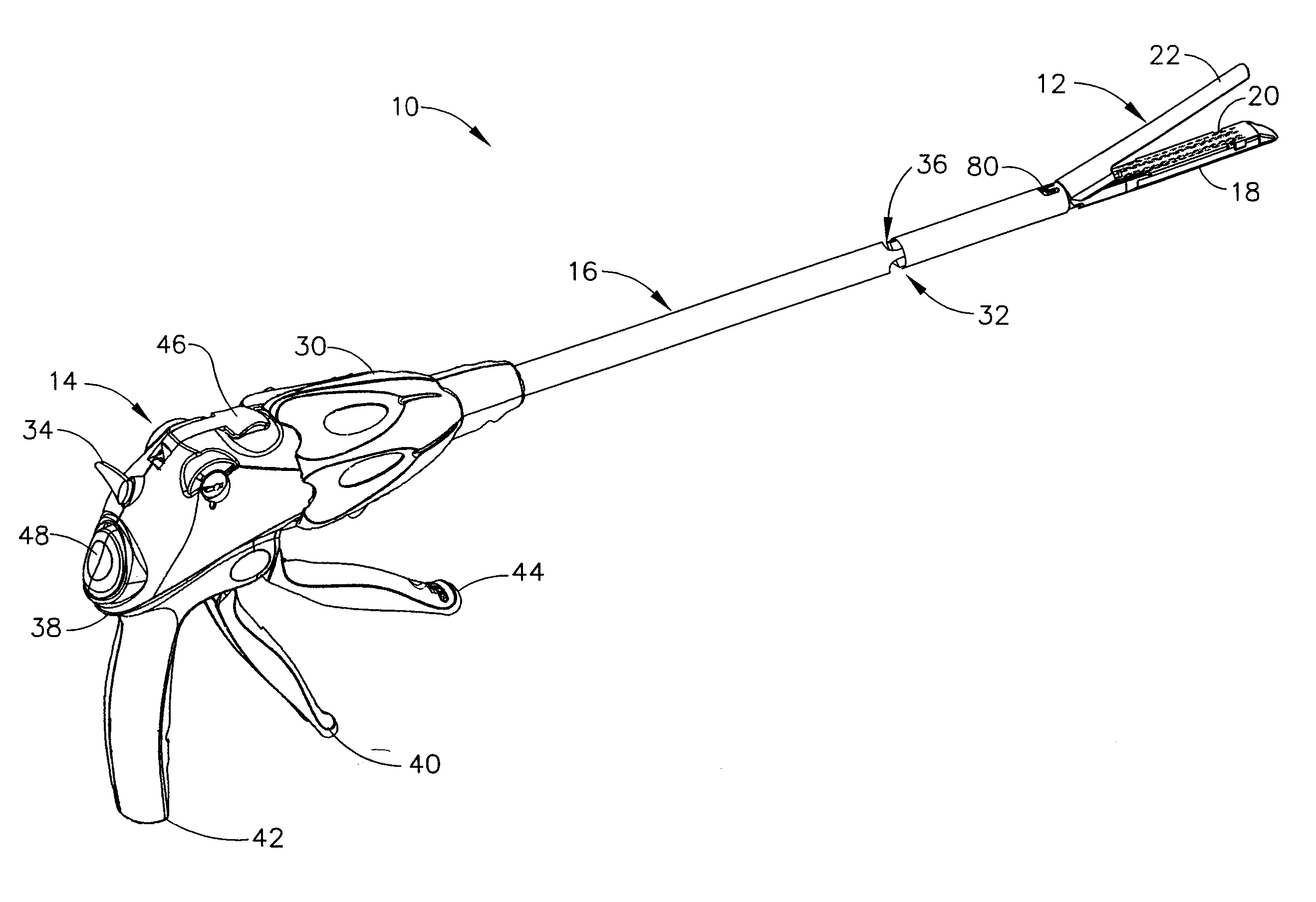

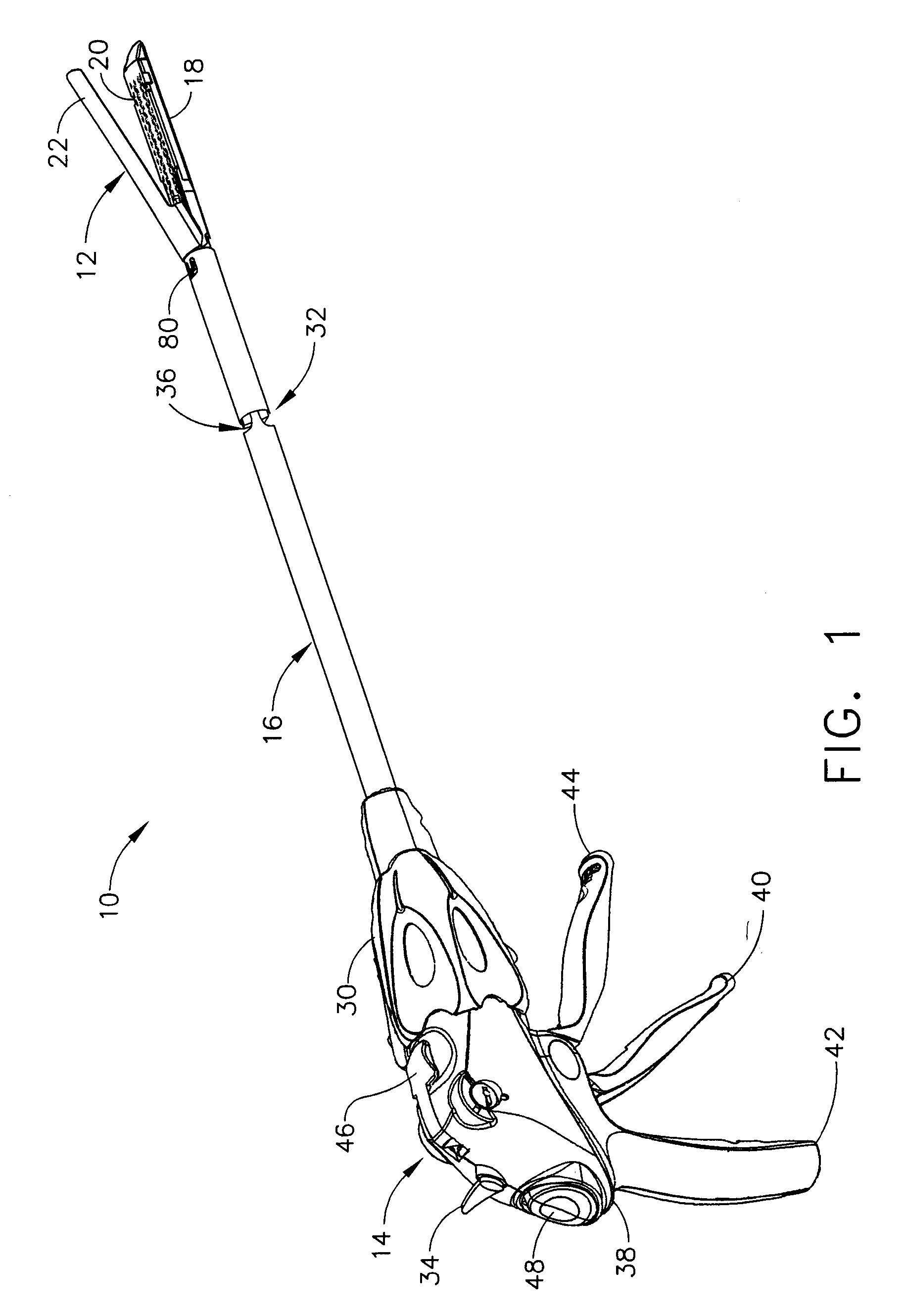

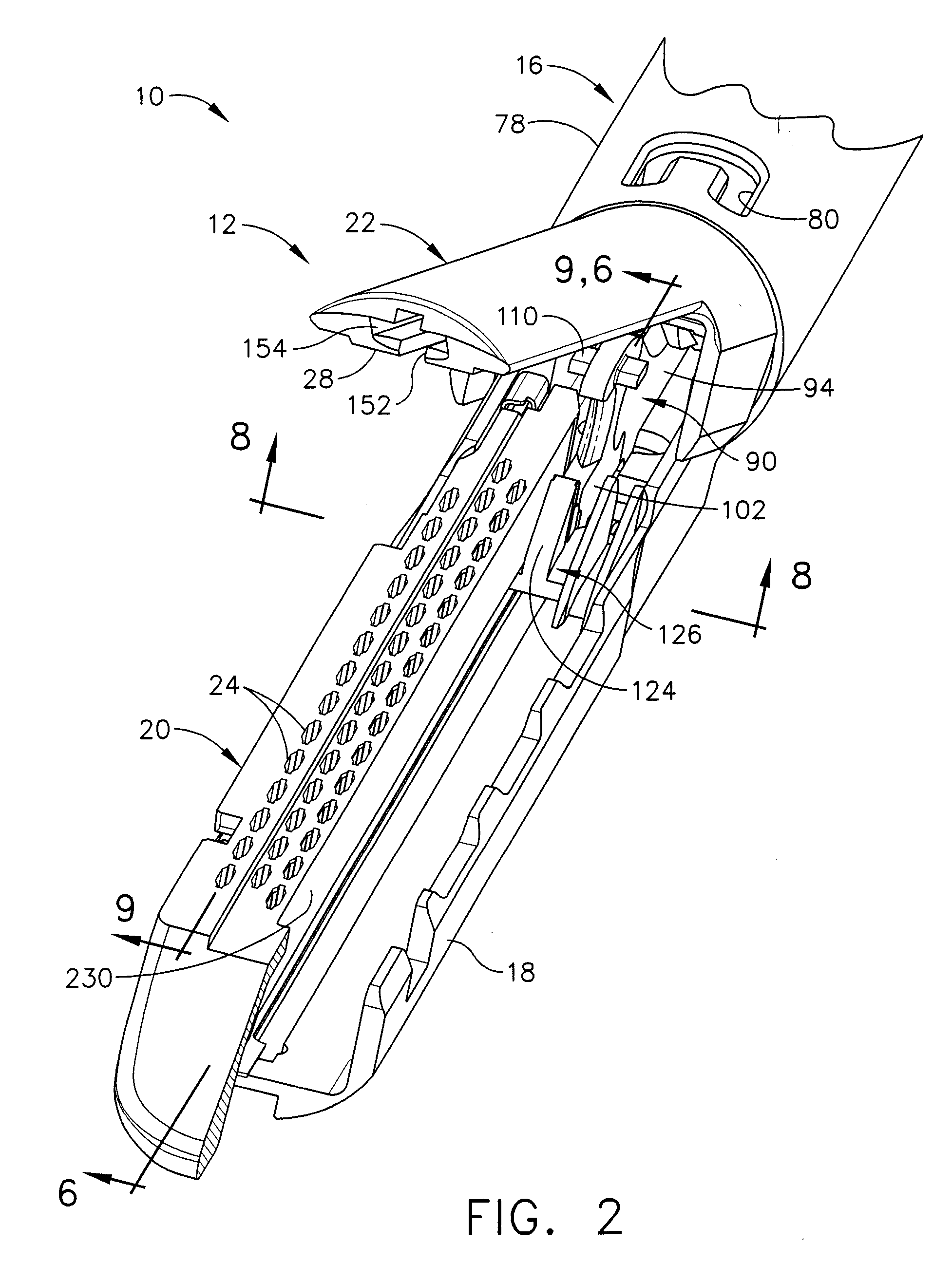

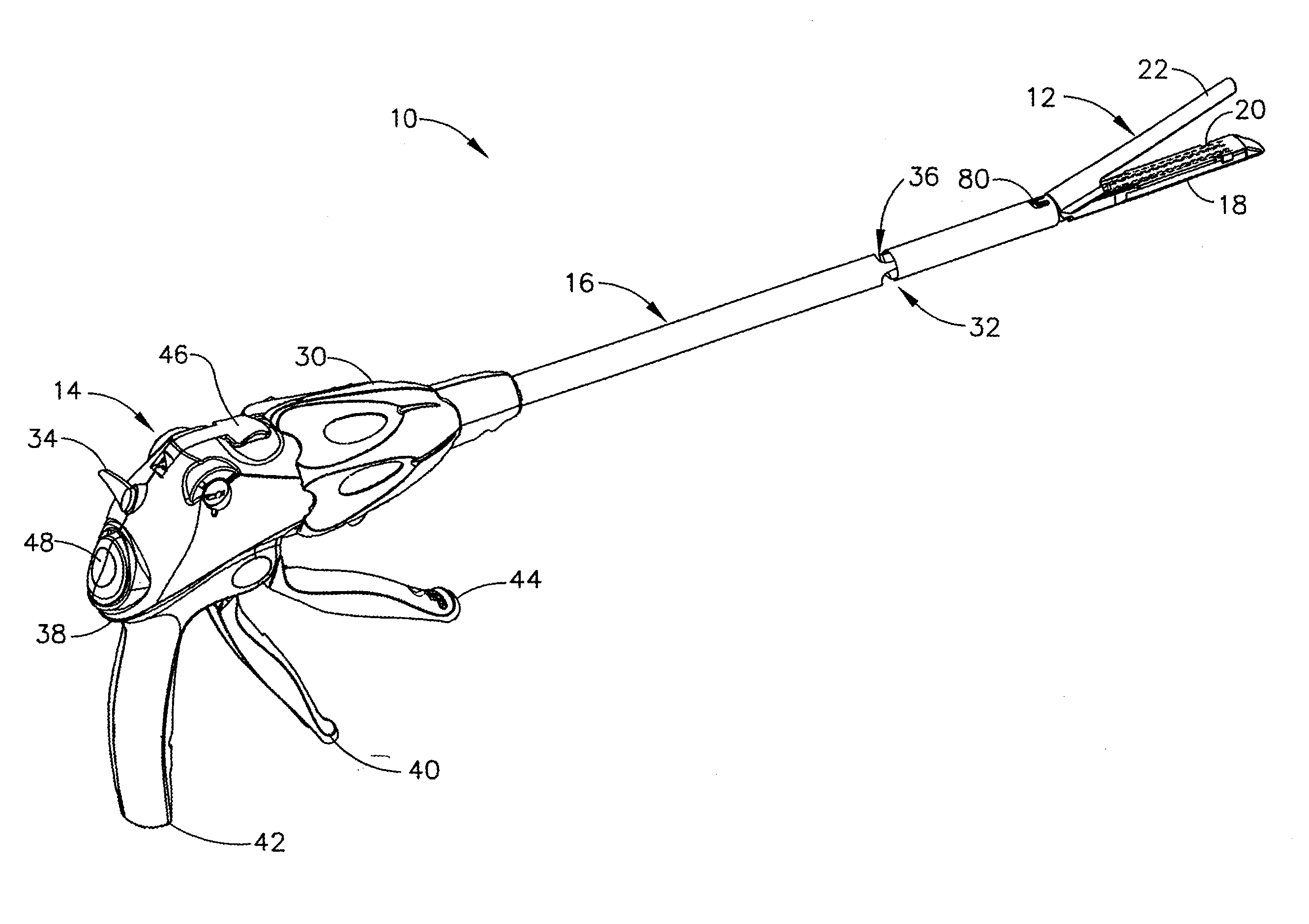

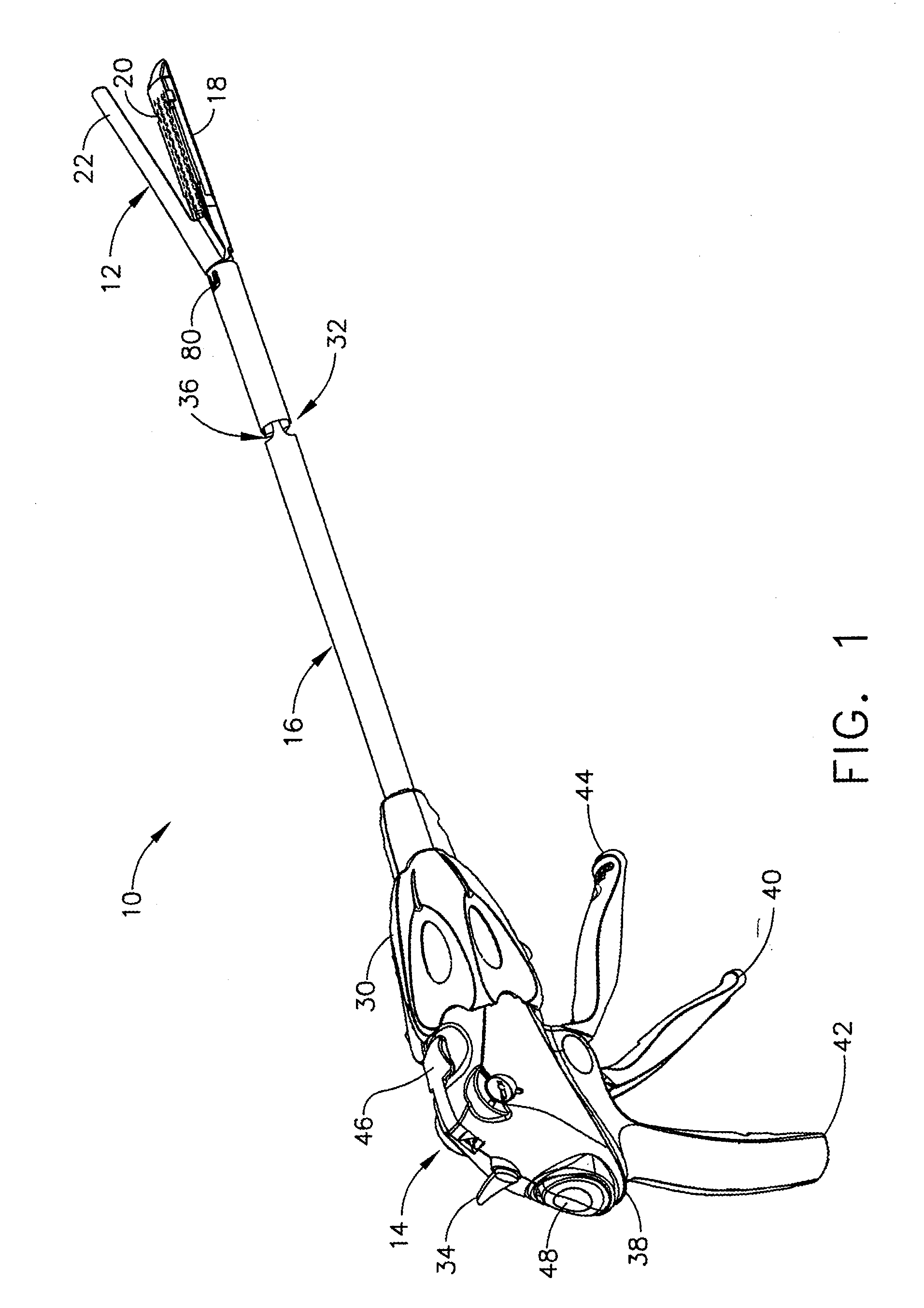

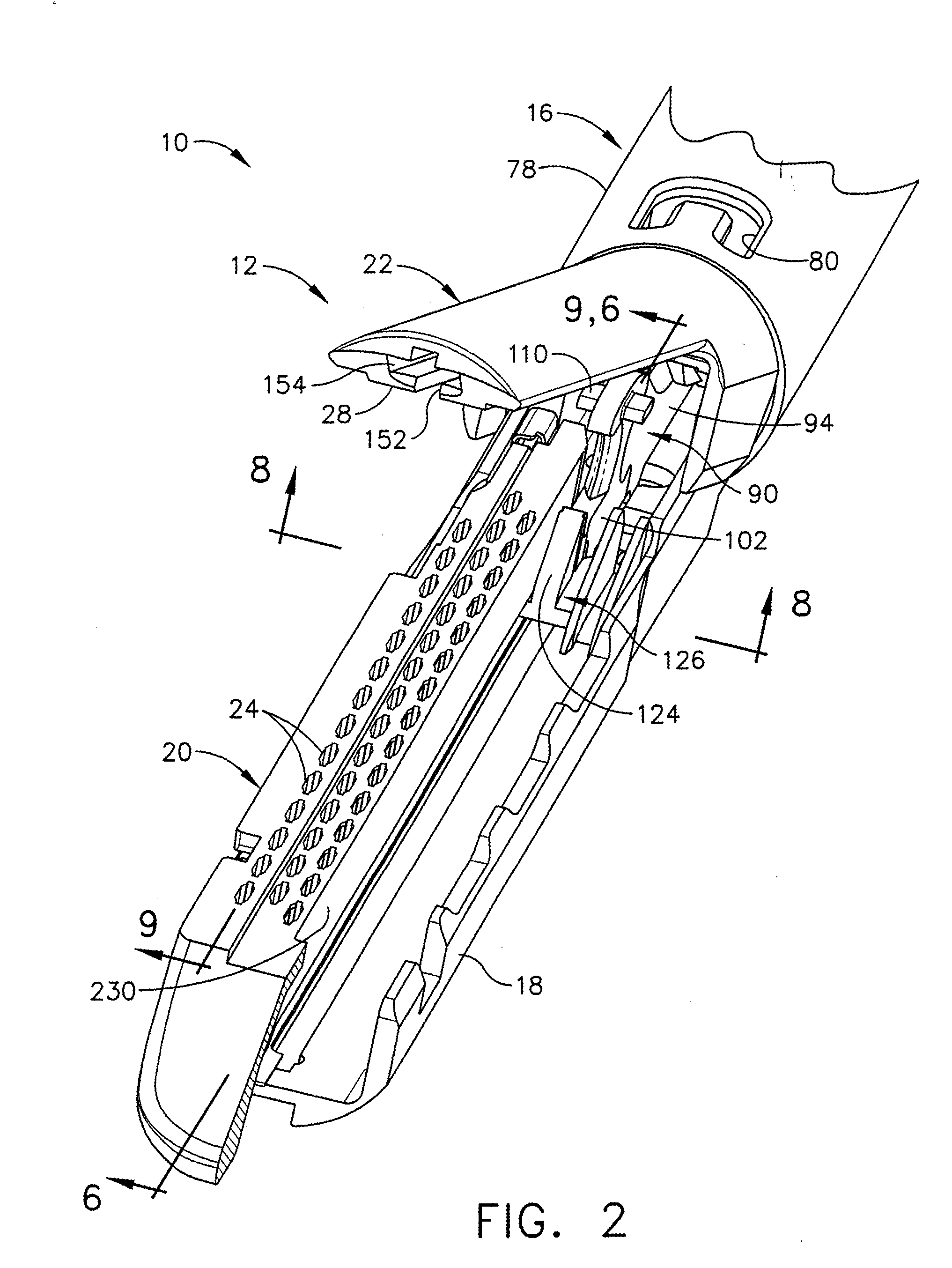

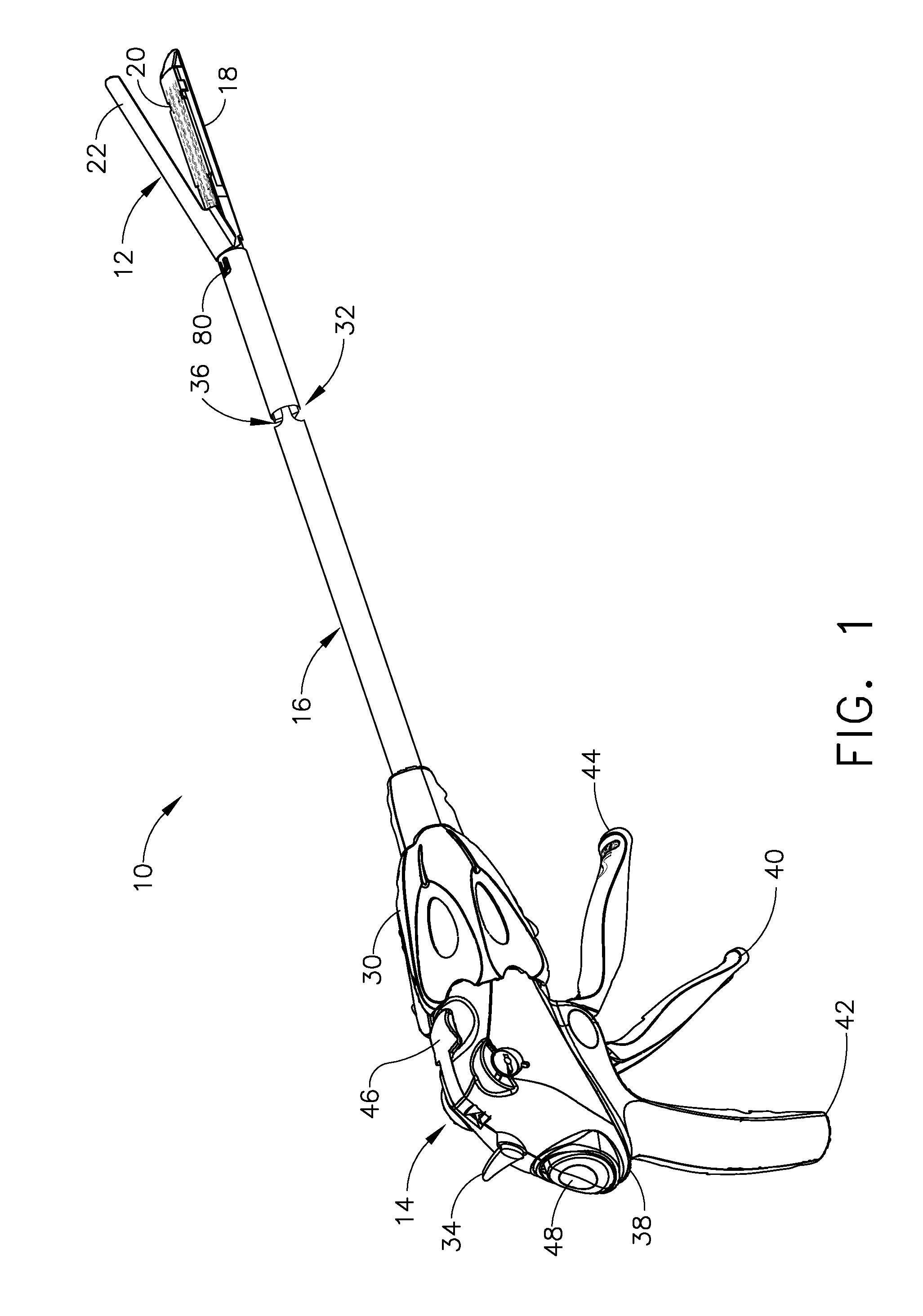

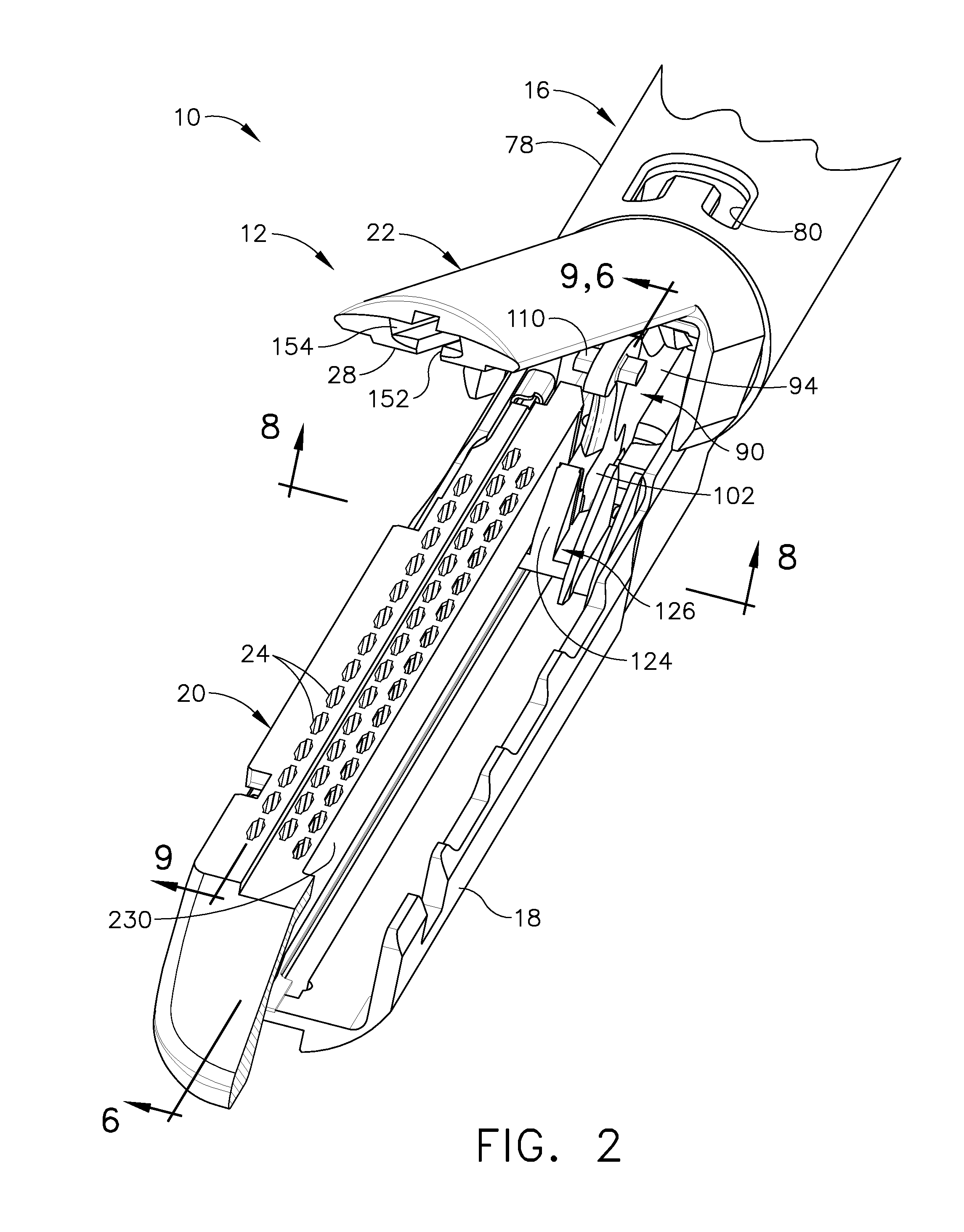

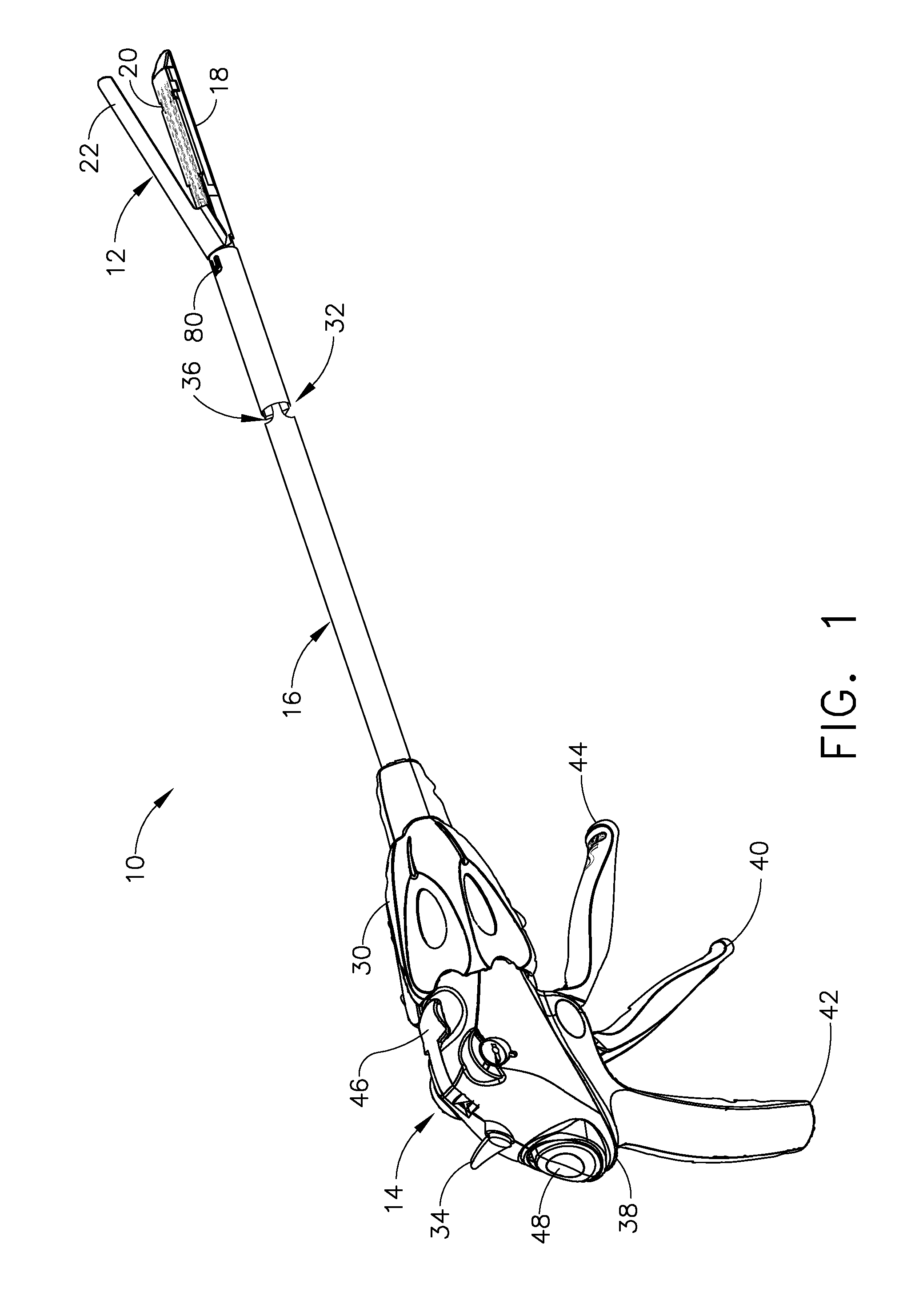

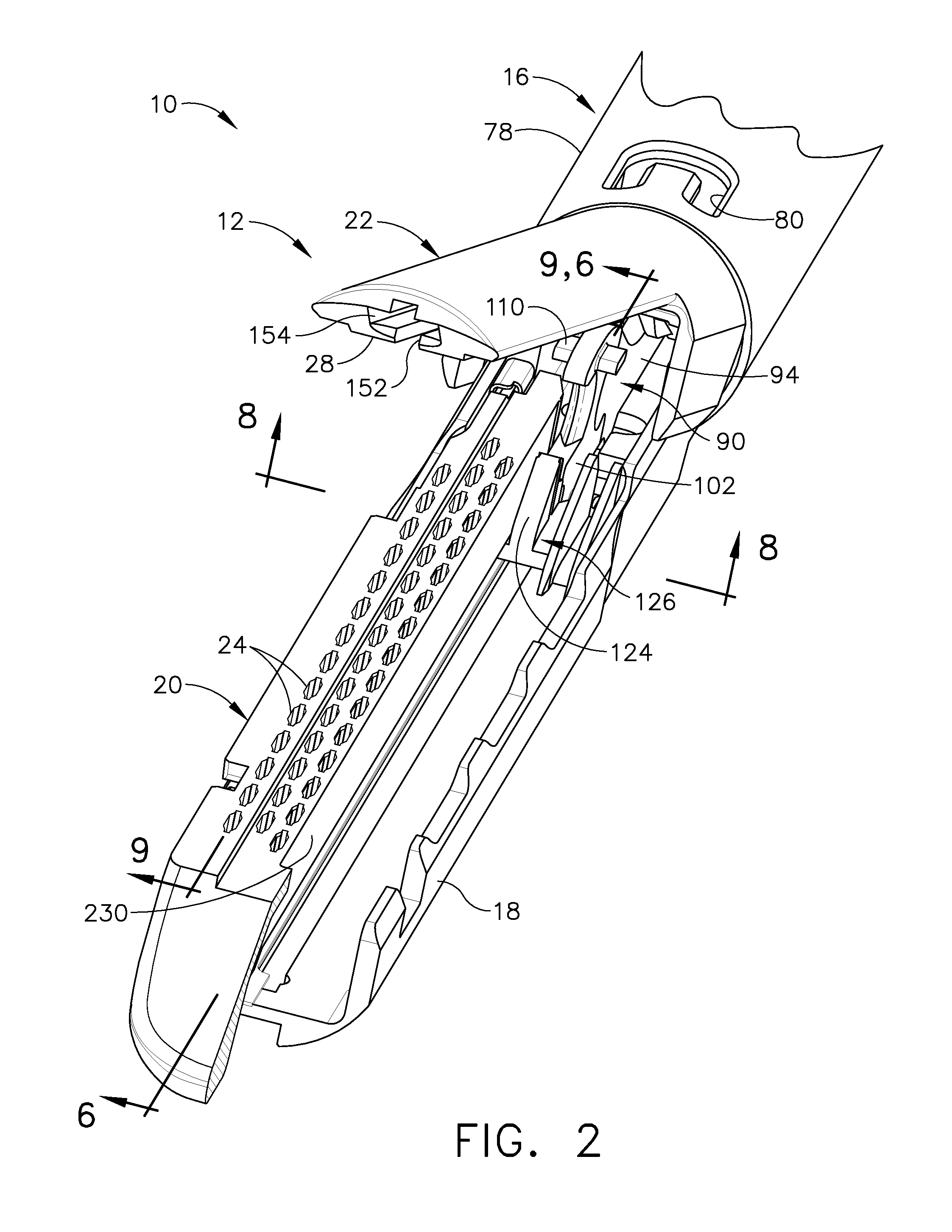

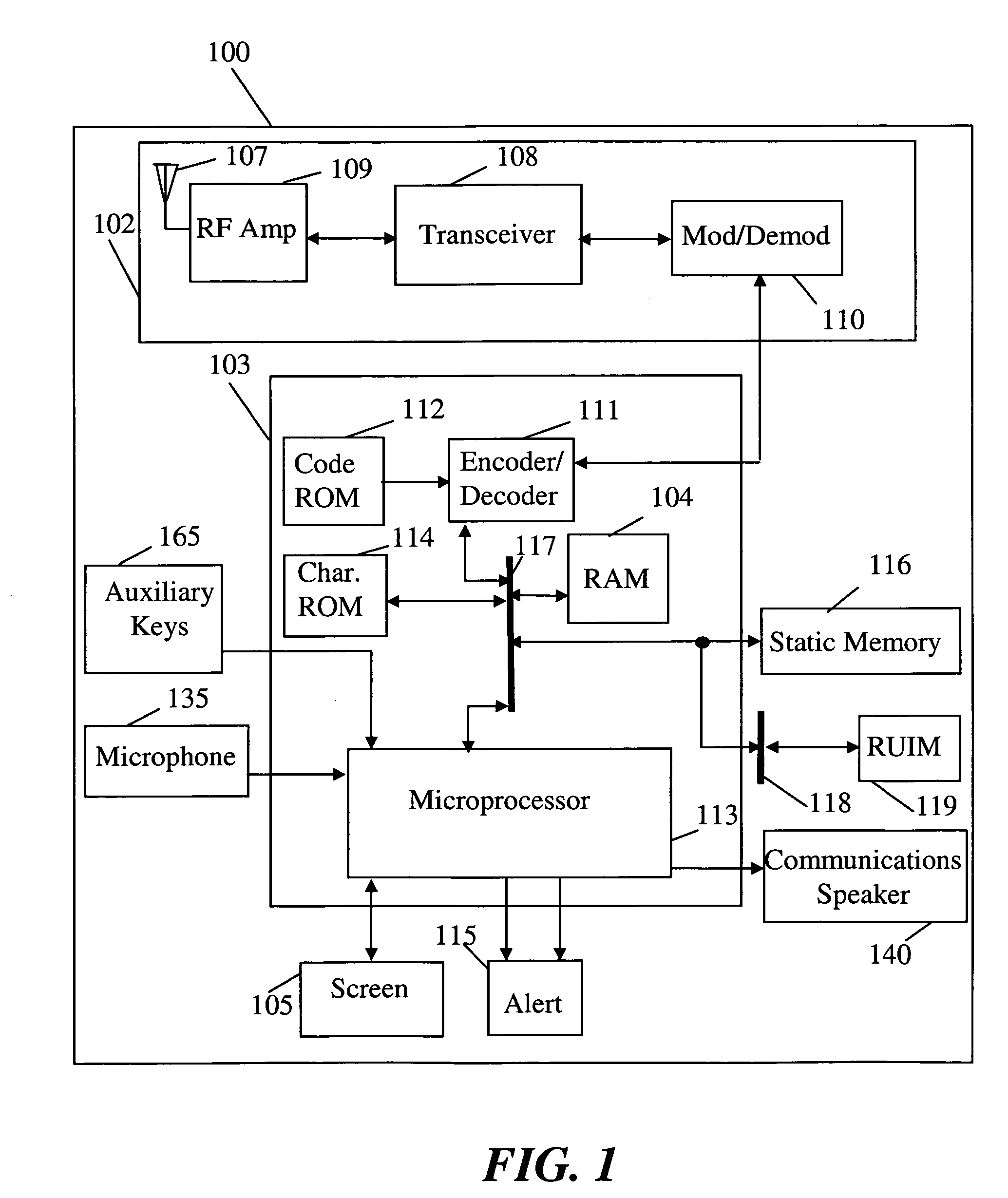

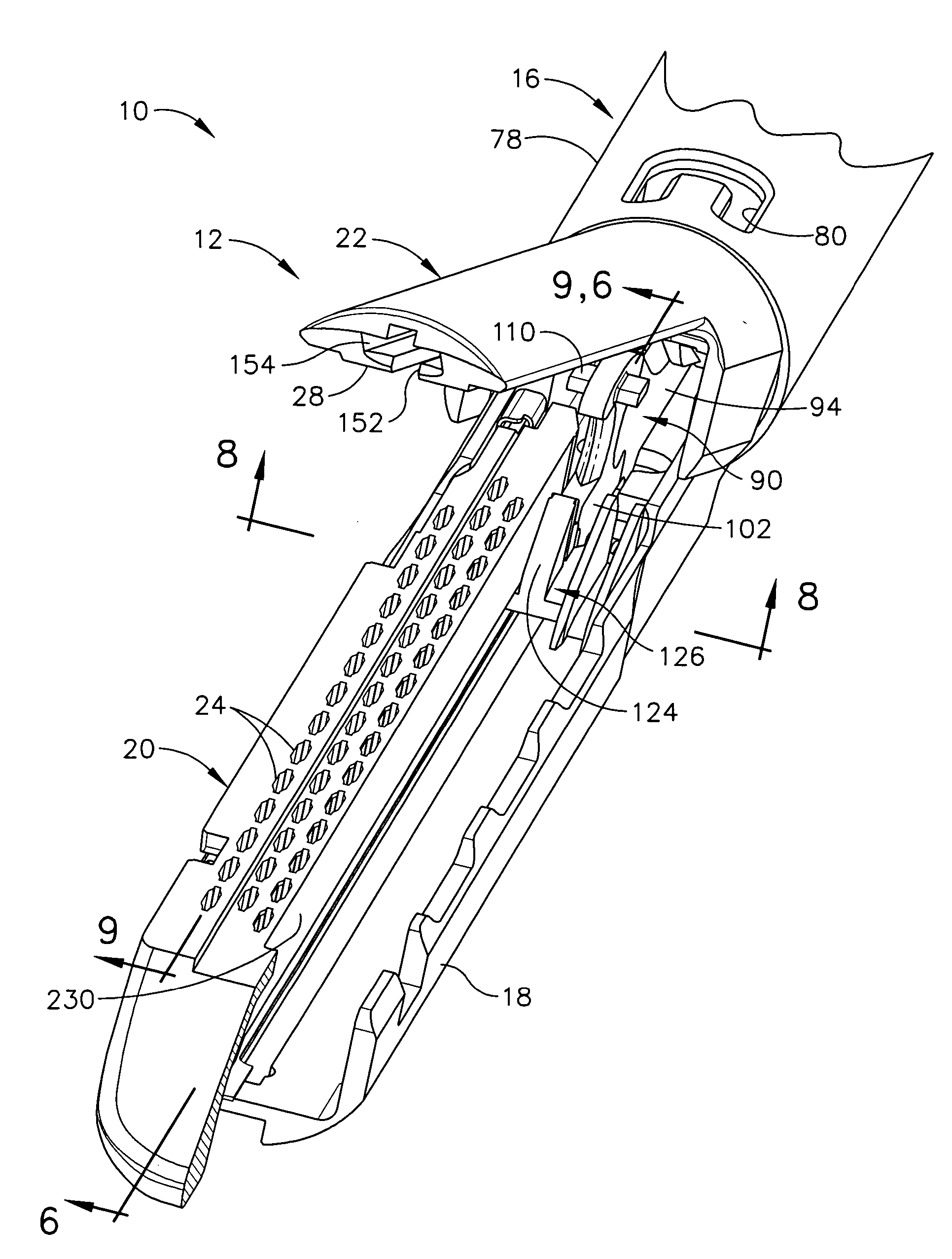

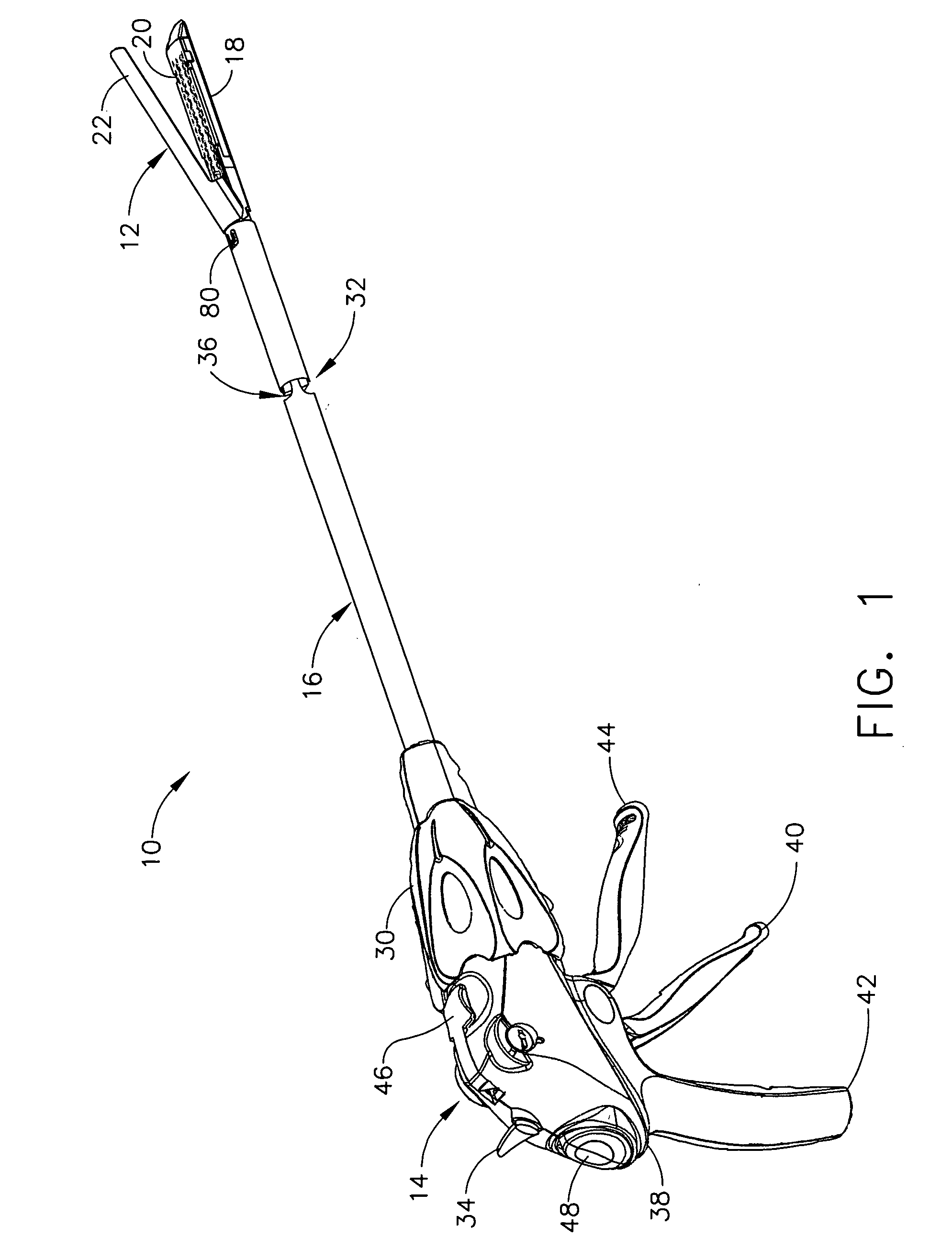

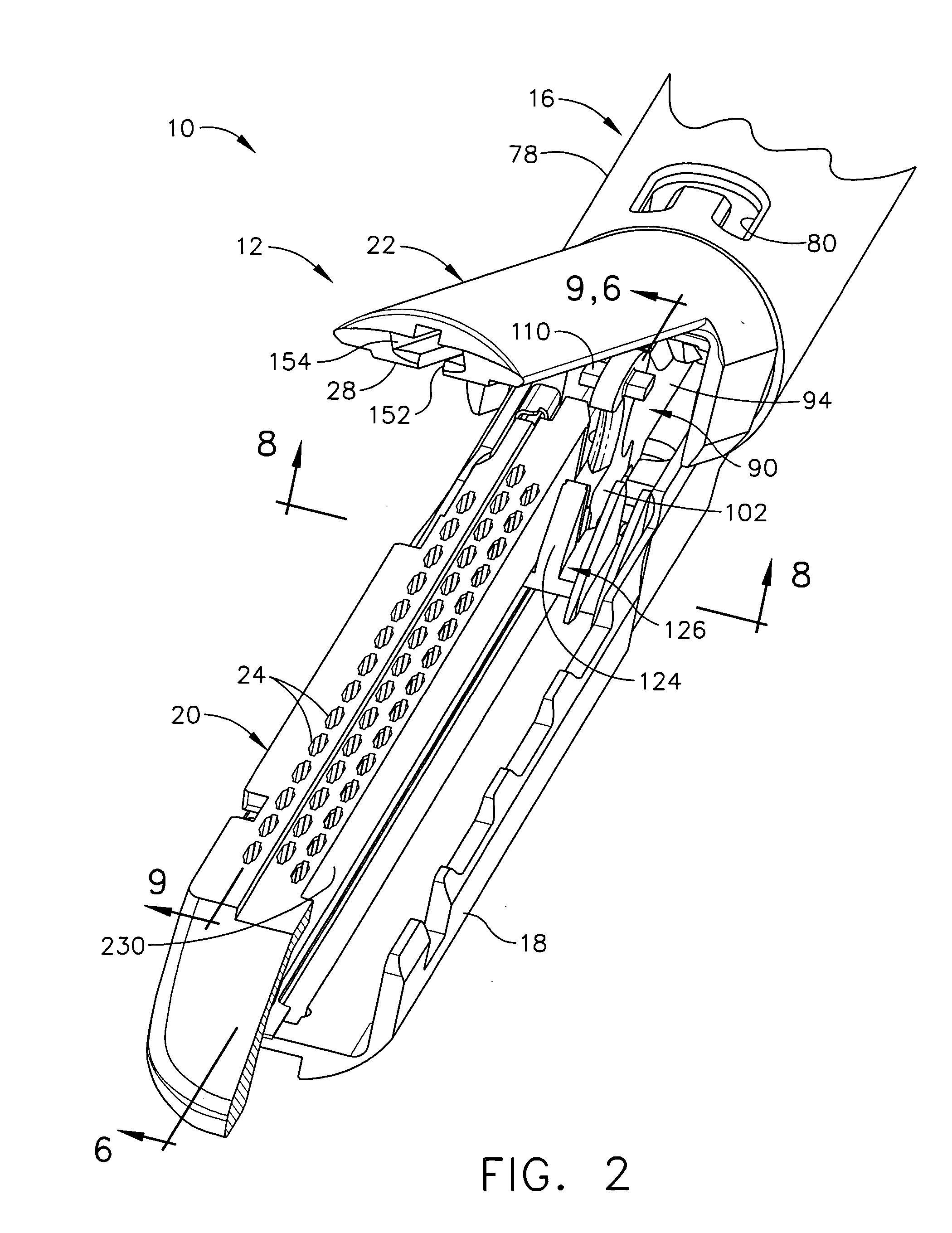

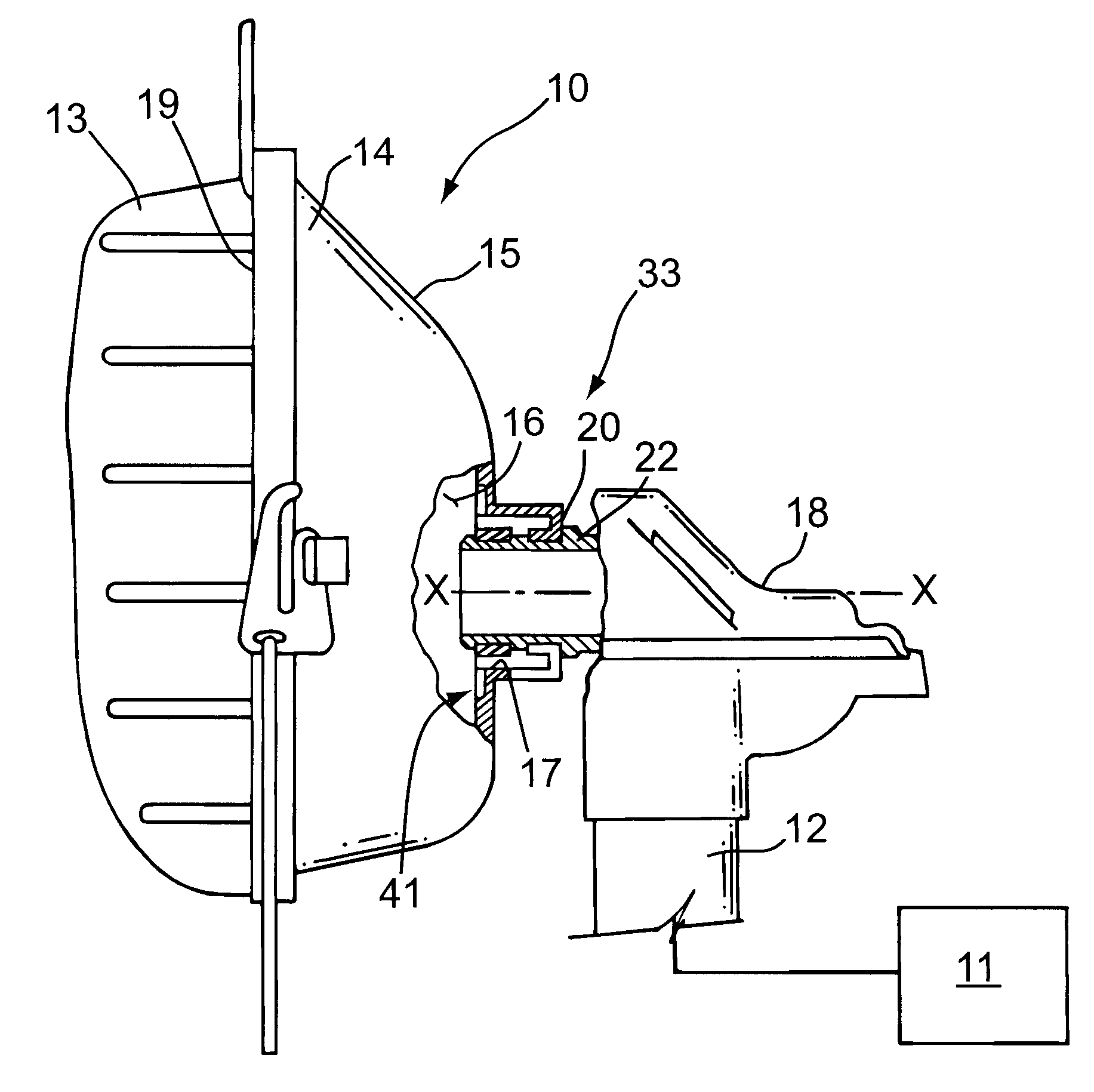

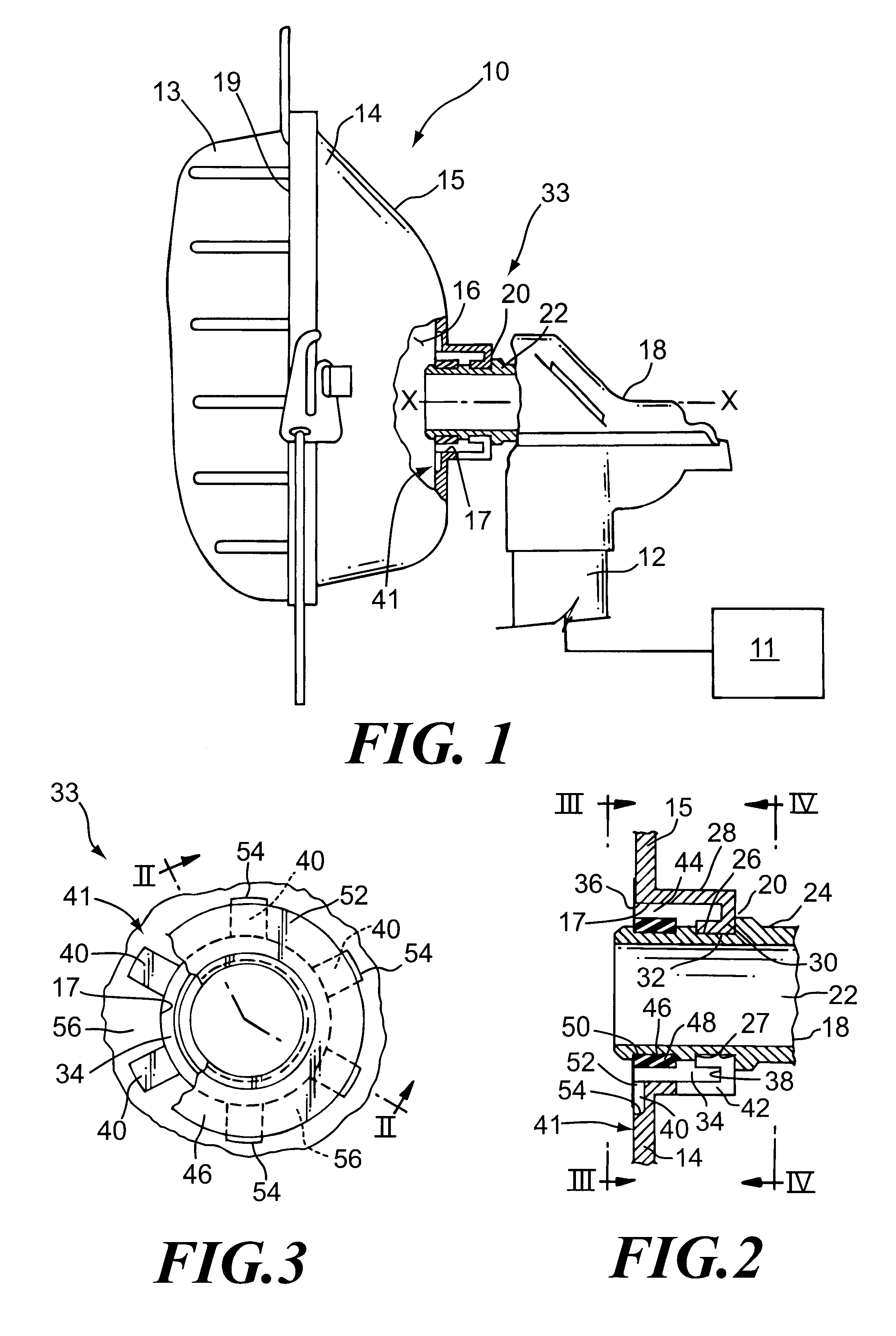

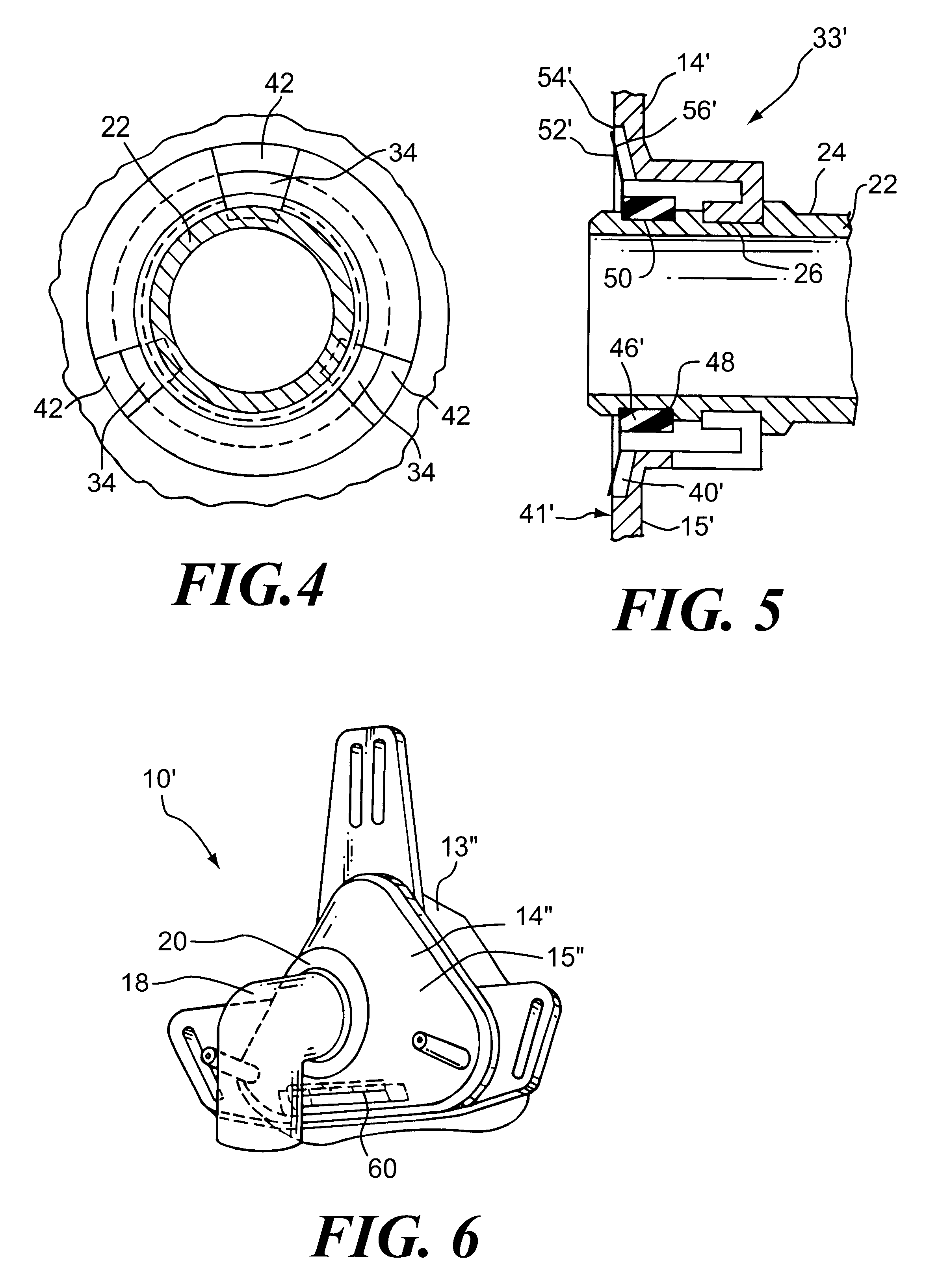

Articulating surgical stapling instrument incorporating a two-piece E-beam firing mechanism

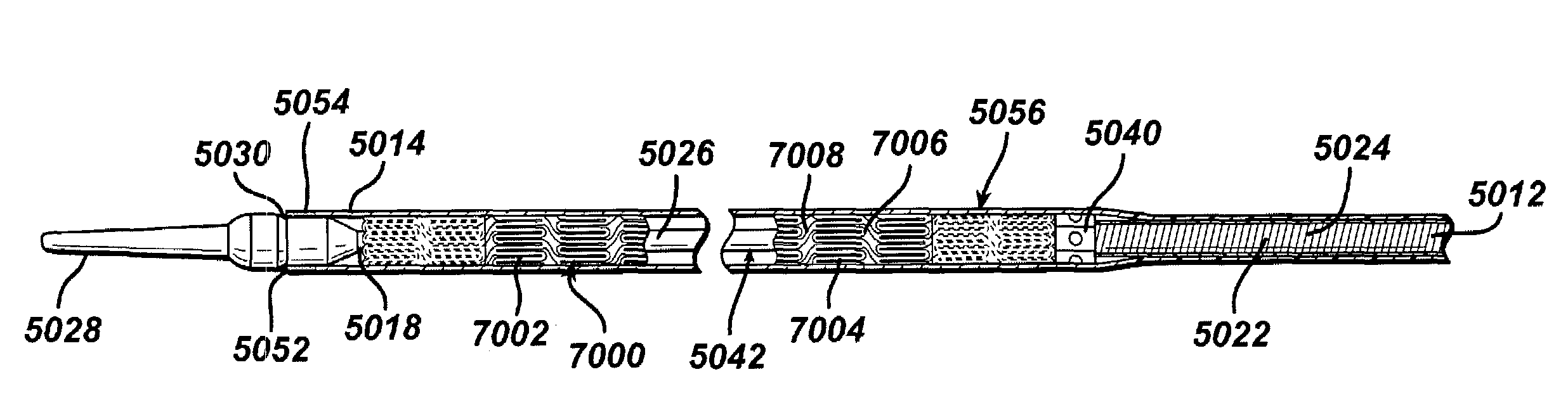

InactiveUS7380696B2Solve the lack of spaceEasy to useSuture equipmentsStapling toolsPERITONEOSCOPEDistal portion

A surgical severing and stapling instrument, suitable for laparoscopic and endoscopic clinical procedures, clamps tissue within an end effector of an elongate channel pivotally opposed by an anvil. An E-beam firing bar moves distally through the clamped end effector to sever tissue and to drive staples on each side of the cut. The E-beam firing bar affirmatively spaces the anvil from the elongate channel to assure properly formed closed staples, especially when an amount of tissue is clamped that is inadequate to space the end effector. In particular, an upper pin of the firing bar longitudinally moves through an anvil slot and a channel slot is captured between a lower cap and a middle pin of the firing bar to assure a minimum spacing. Forming the E-beam from a thickened distal portion and a thinned proximal strip enhances manufacturability and facilitates use in such articulating surgical instruments.

Owner:ETHICON ENDO SURGERY INC +1

Articulating surgical stapling instrument incorporating a two-piece e-beam firing mechanism

InactiveUS20070084897A1Solve the lack of spaceEasy to useSuture equipmentsStapling toolsSurgical stapleEngineering

A surgical severing and stapling instrument, suitable for laparoscopic and endoscopic clinical procedures, clamps tissue within an end effector of an elongate channel pivotally opposed by an anvil. An E-beam firing bar moves distally through the clamped end effector to sever tissue and to drive staples on each side of the cut. The E-beam firing bar affirmatively spaces the anvil from the elongate channel to assure properly formed closed staples, especially when an amount of tissue is clamped that is inadequate to space the end effector. In particular, an upper pin of the firing bar longitudinally moves through an anvil slot and a channel slot is captured between a lower cap and a middle pin of the firing bar to assure a minimum spacing. Forming the E-beam from a thickened distal portion and a thinned proximal strip enhances manufacturability and facilitates use in such articulating surgical instruments.

Owner:CILAG GMBH INT +1

Articulating surgical stapling instrument incorporating a two-piece e-beam firing mechanism

InactiveUS20110147433A1Solve the lack of spaceEasy to useSuture equipmentsStapling toolsSurgical stapleEngineering

A surgical severing and stapling instrument, suitable for laparoscopic and endoscopic clinical procedures, clamps tissue within an end effector of an elongate channel pivotally opposed by an anvil. An E-beam firing bar moves distally through the clamped end effector to sever tissue and to drive staples on each side of the cut. The E-beam firing bar affirmatively spaces the anvil from the elongate channel to assure properly formed closed staples, especially when an amount of tissue is clamped that is inadequate to space the end effector. In particular, an upper pin of the firing bar longitudinally moves through an anvil slot and a channel slot is captured between a lower cap and a middle pin of the firing bar to assure a minimum spacing. Forming the E-beam from a thickened distal portion and a thinned proximal strip enhances manufacturability and facilitates use in such articulating surgical instruments.

Owner:CILAG GMBH INT

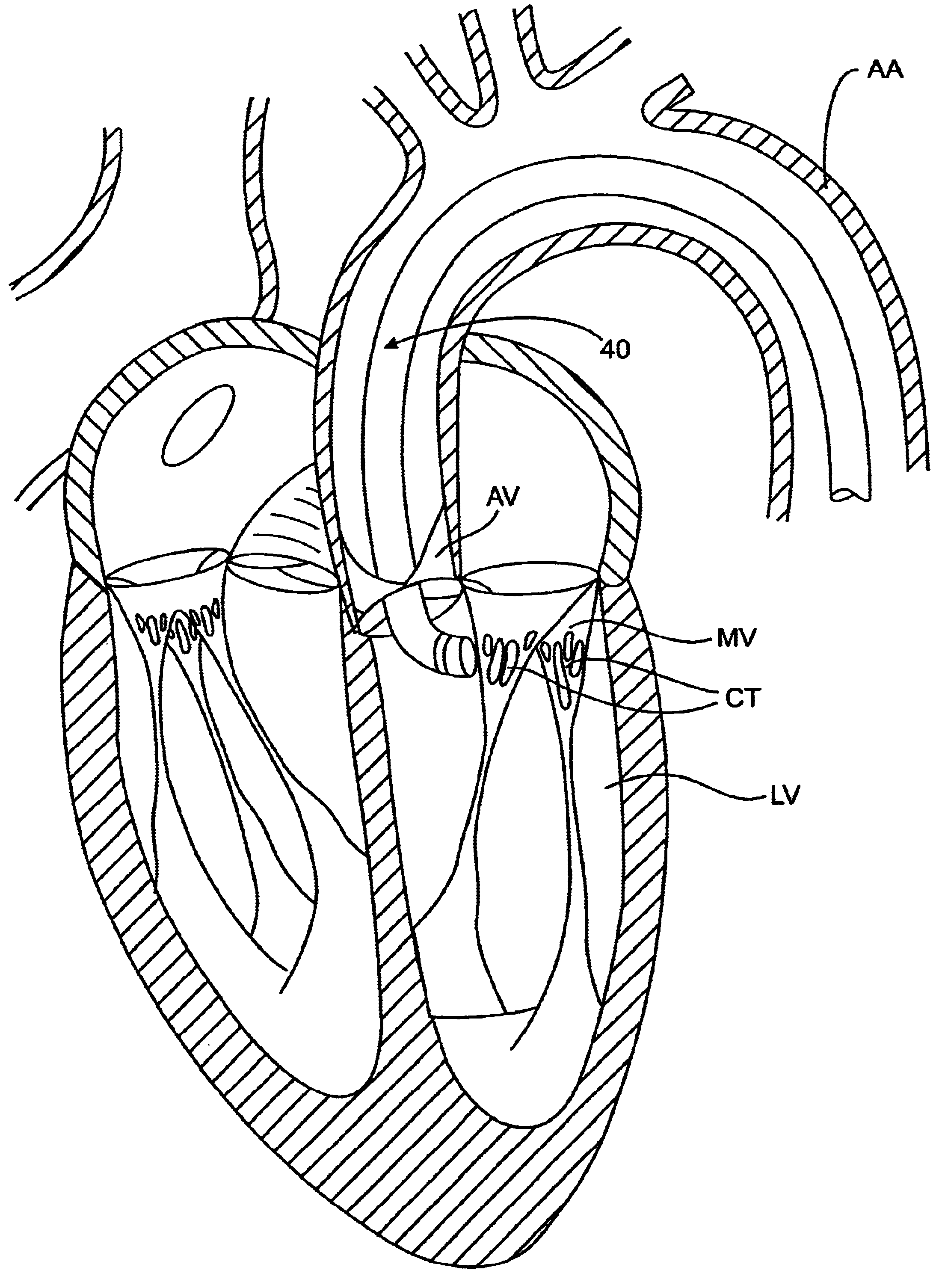

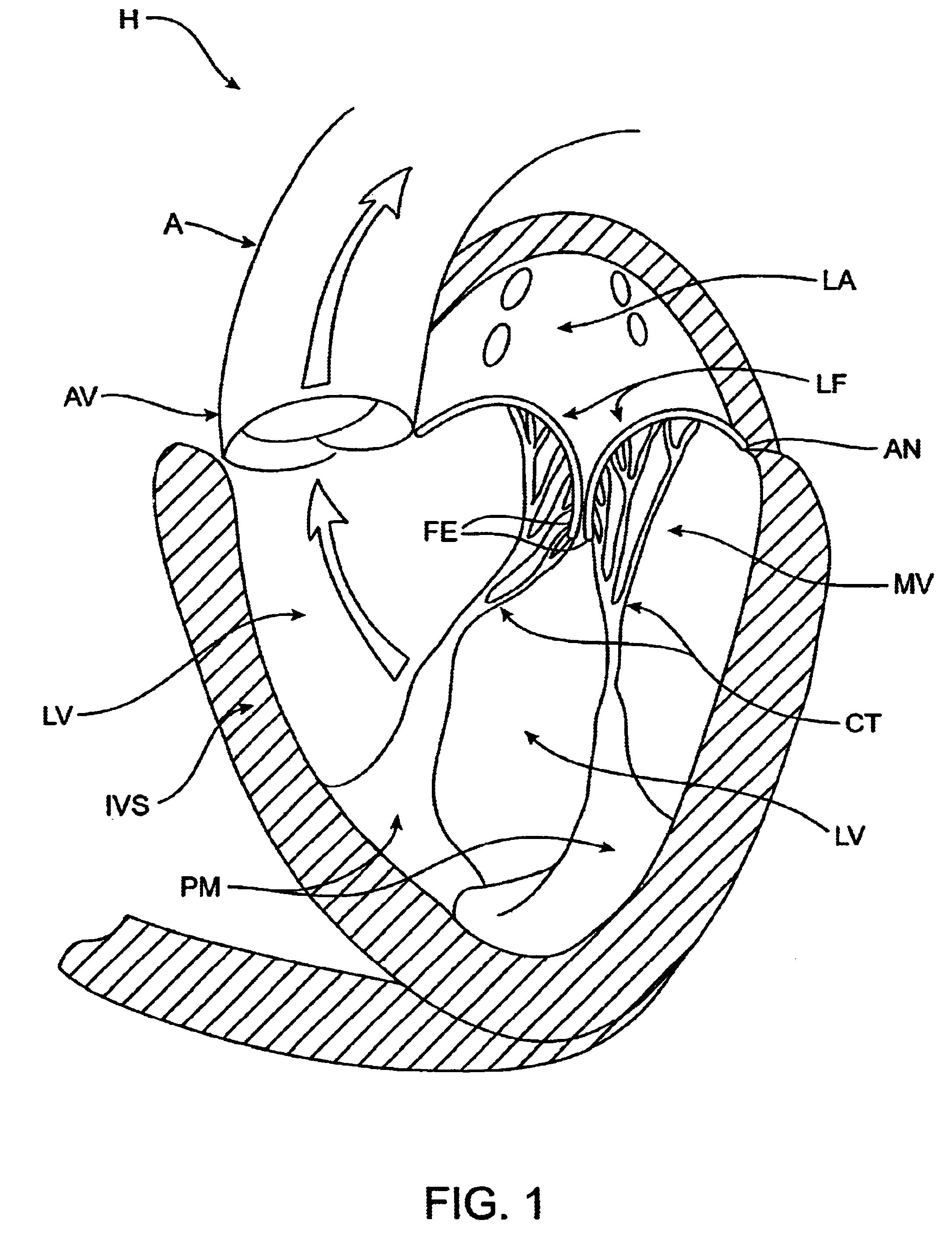

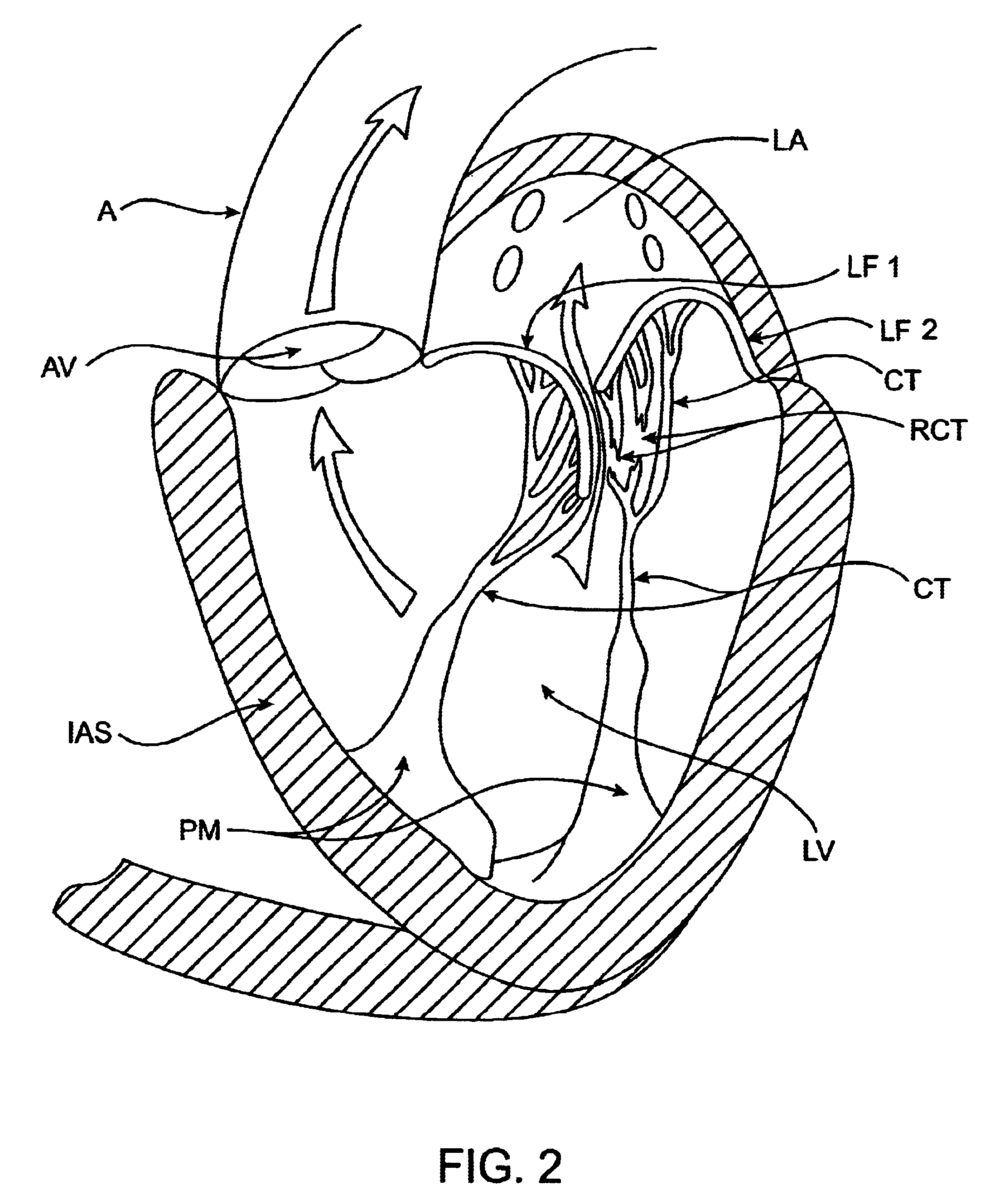

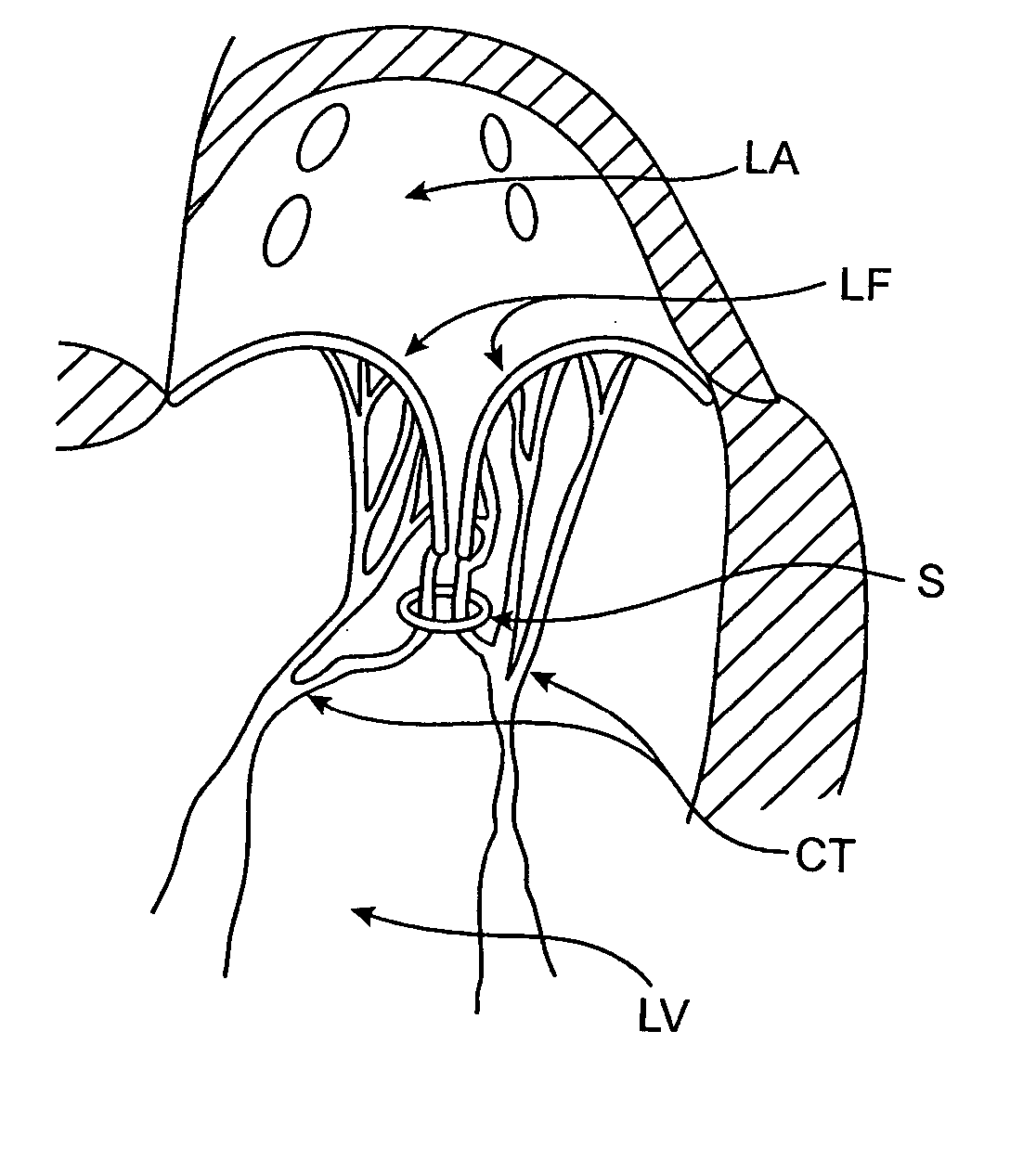

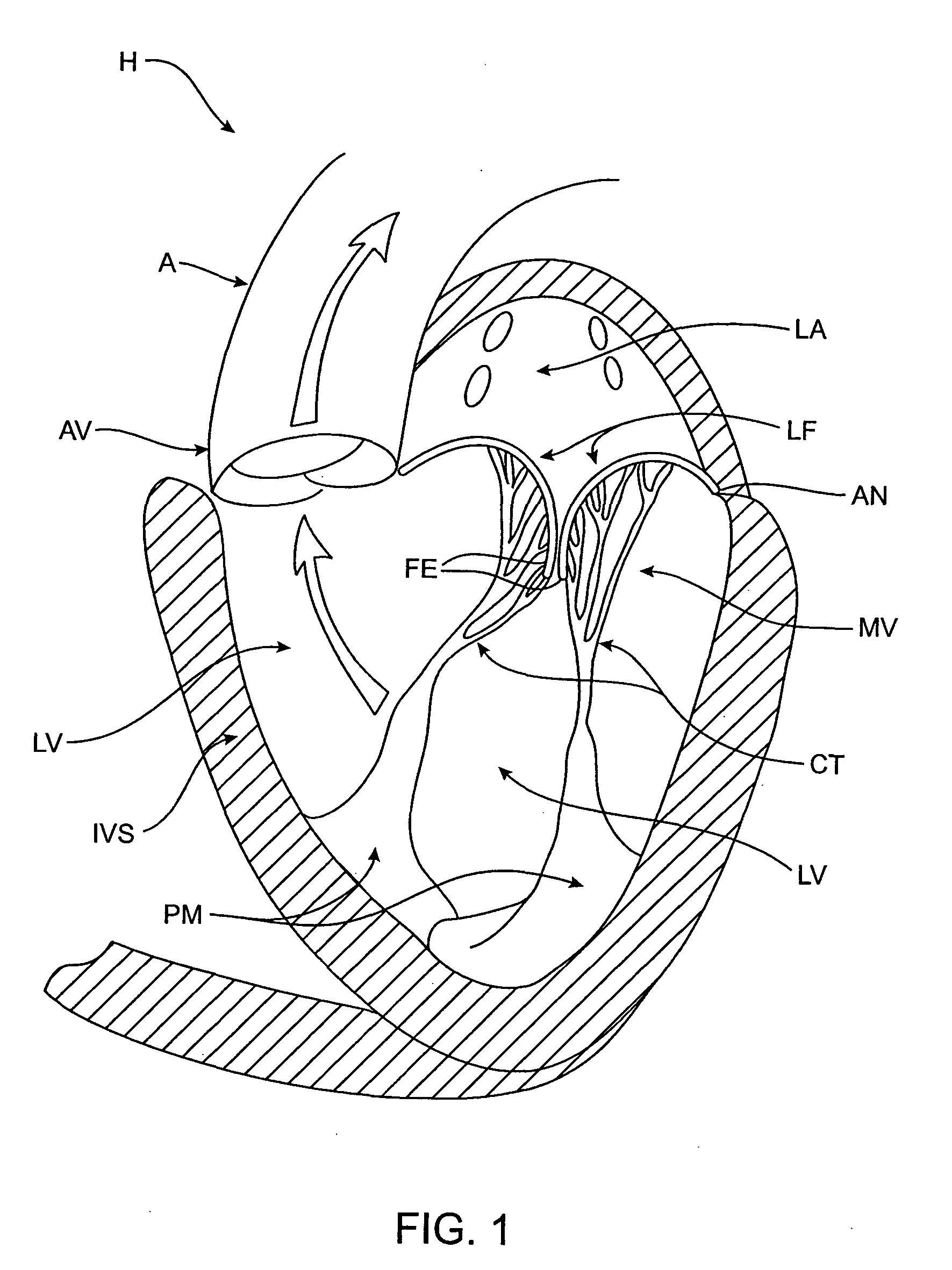

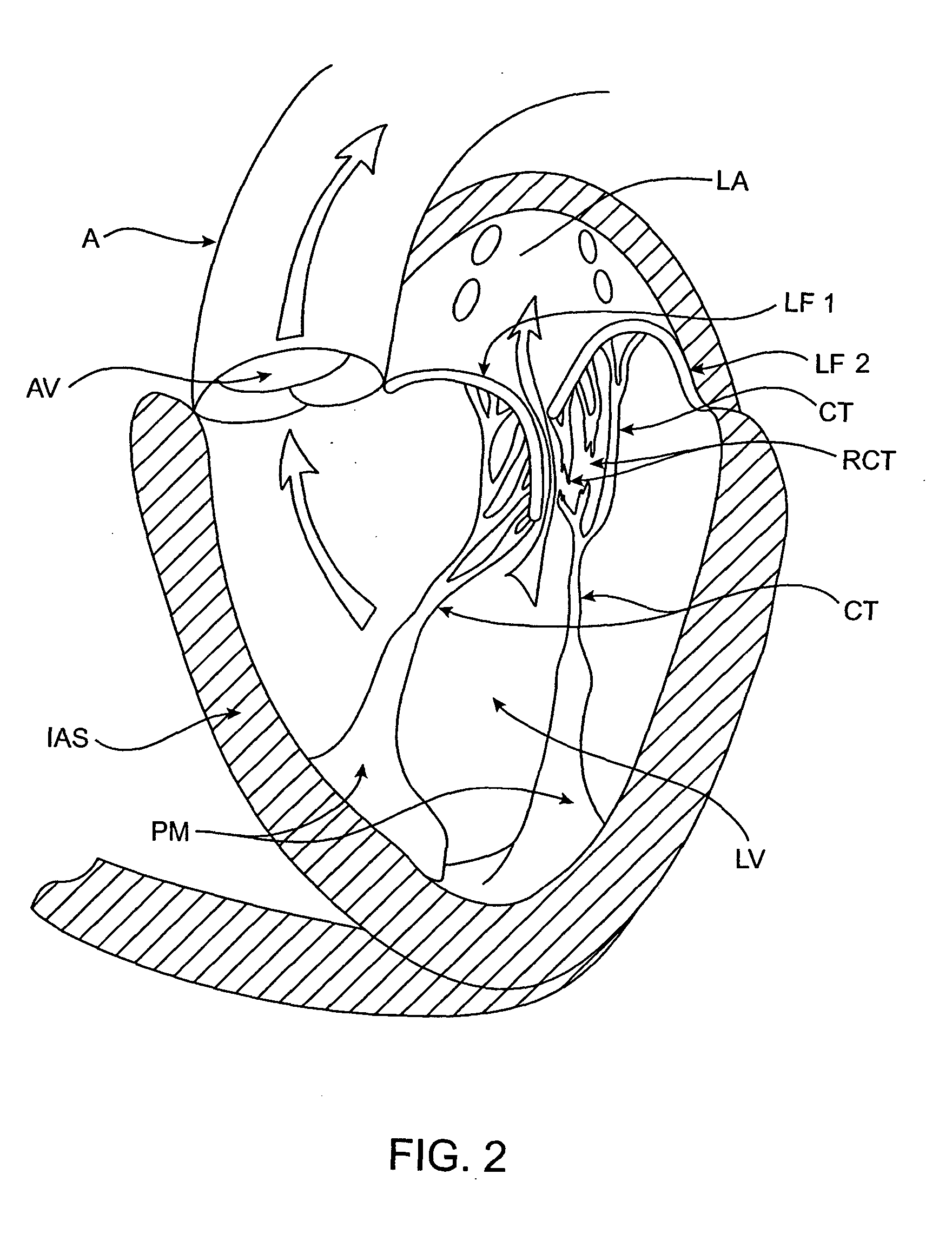

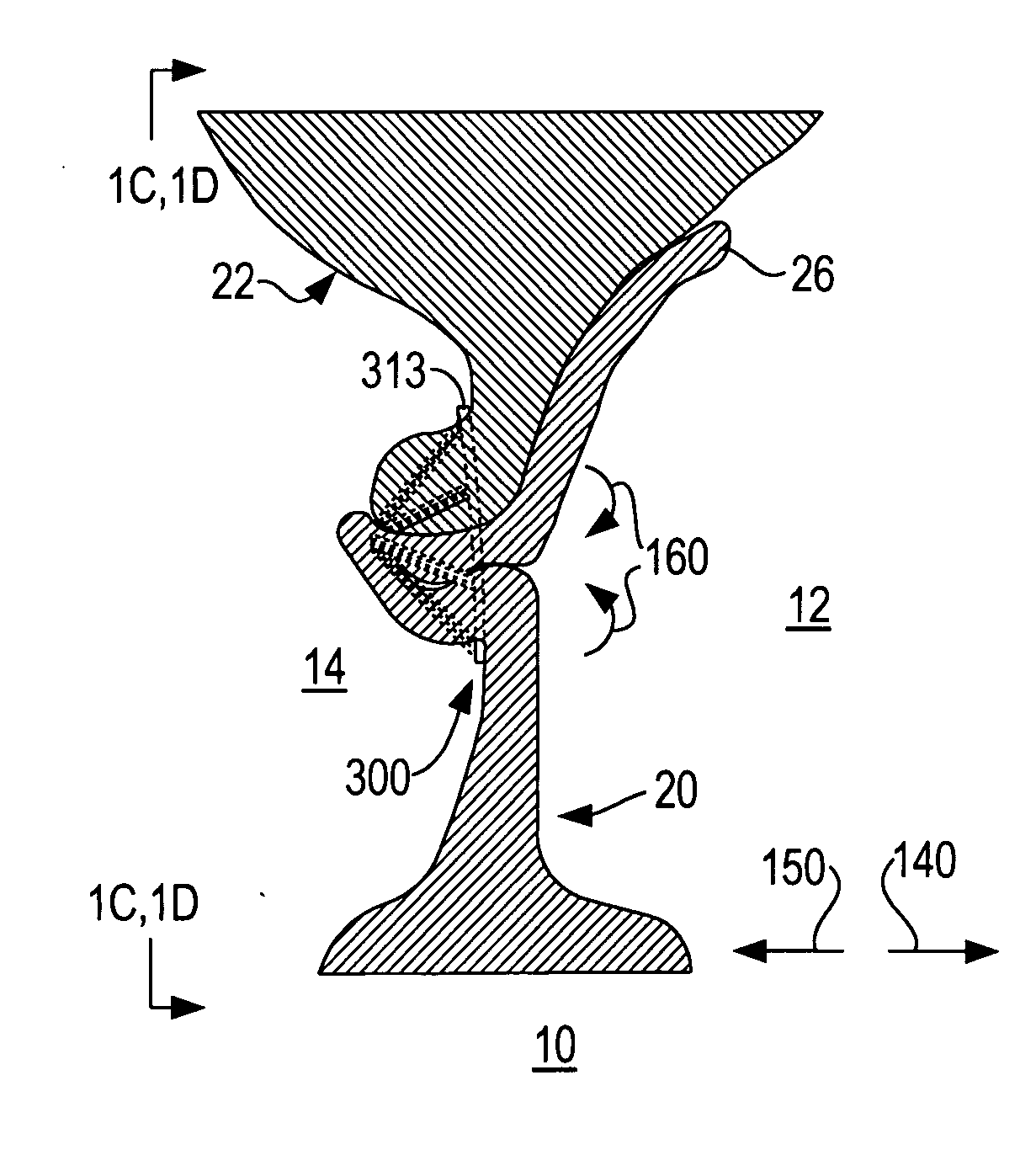

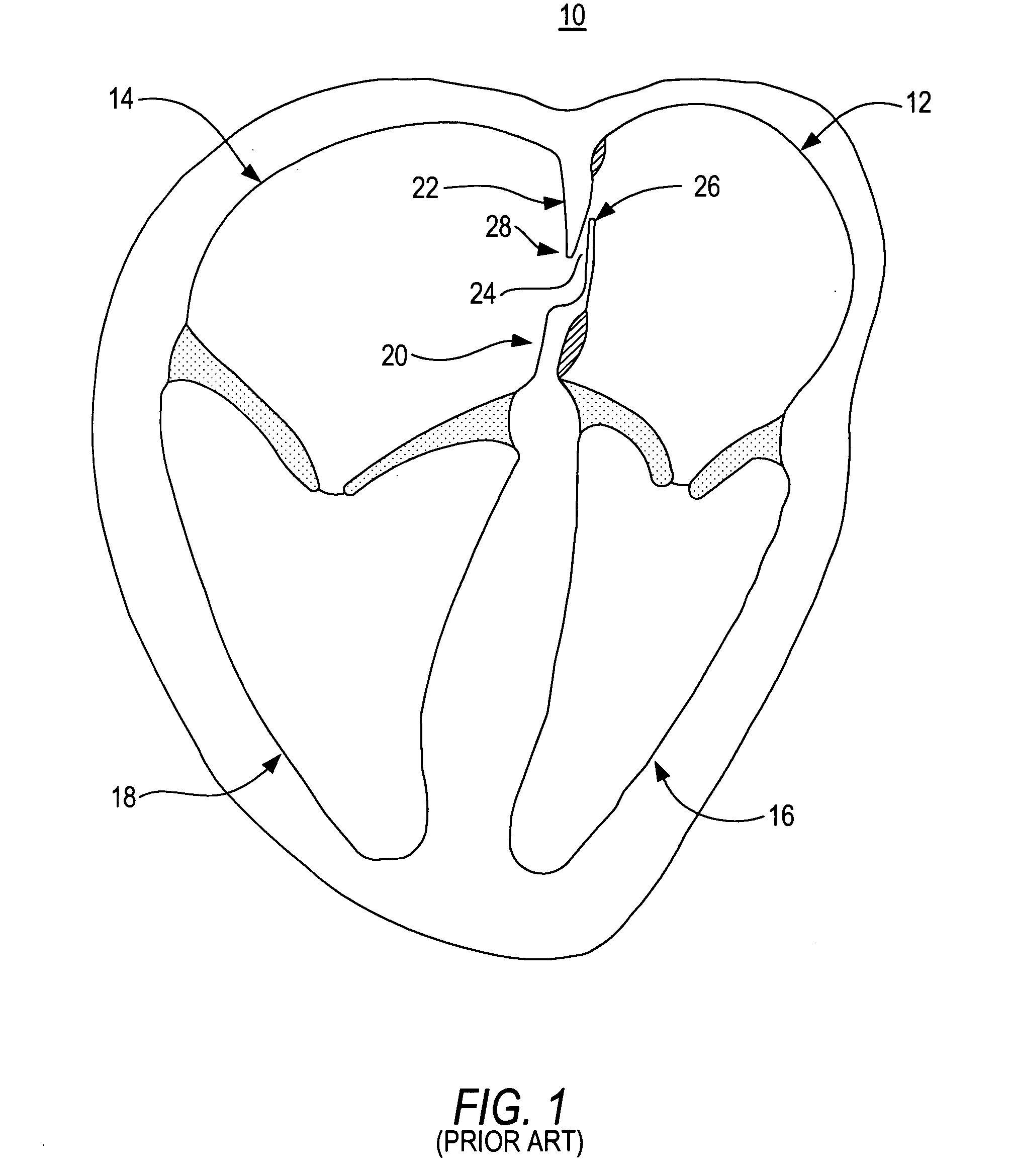

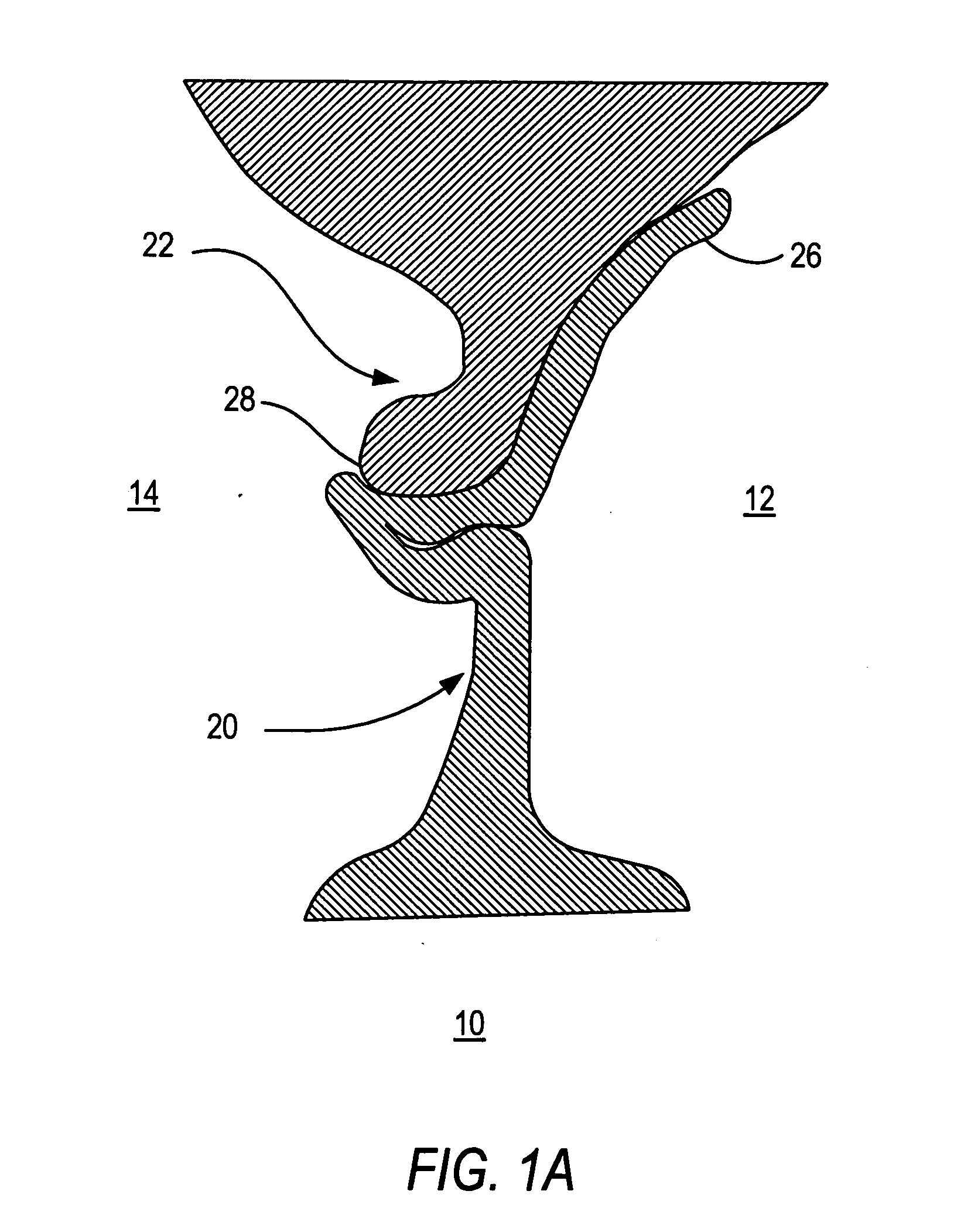

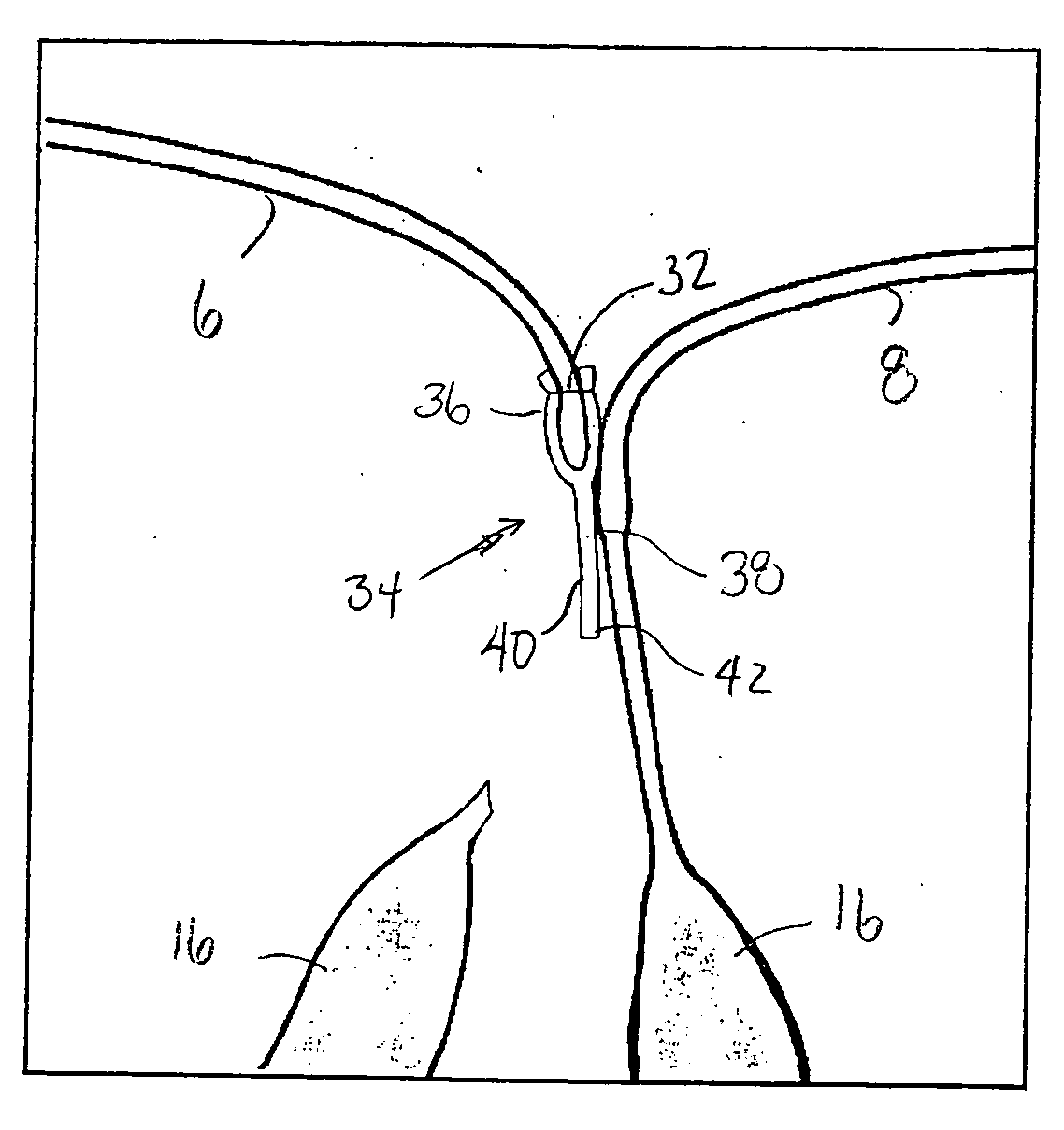

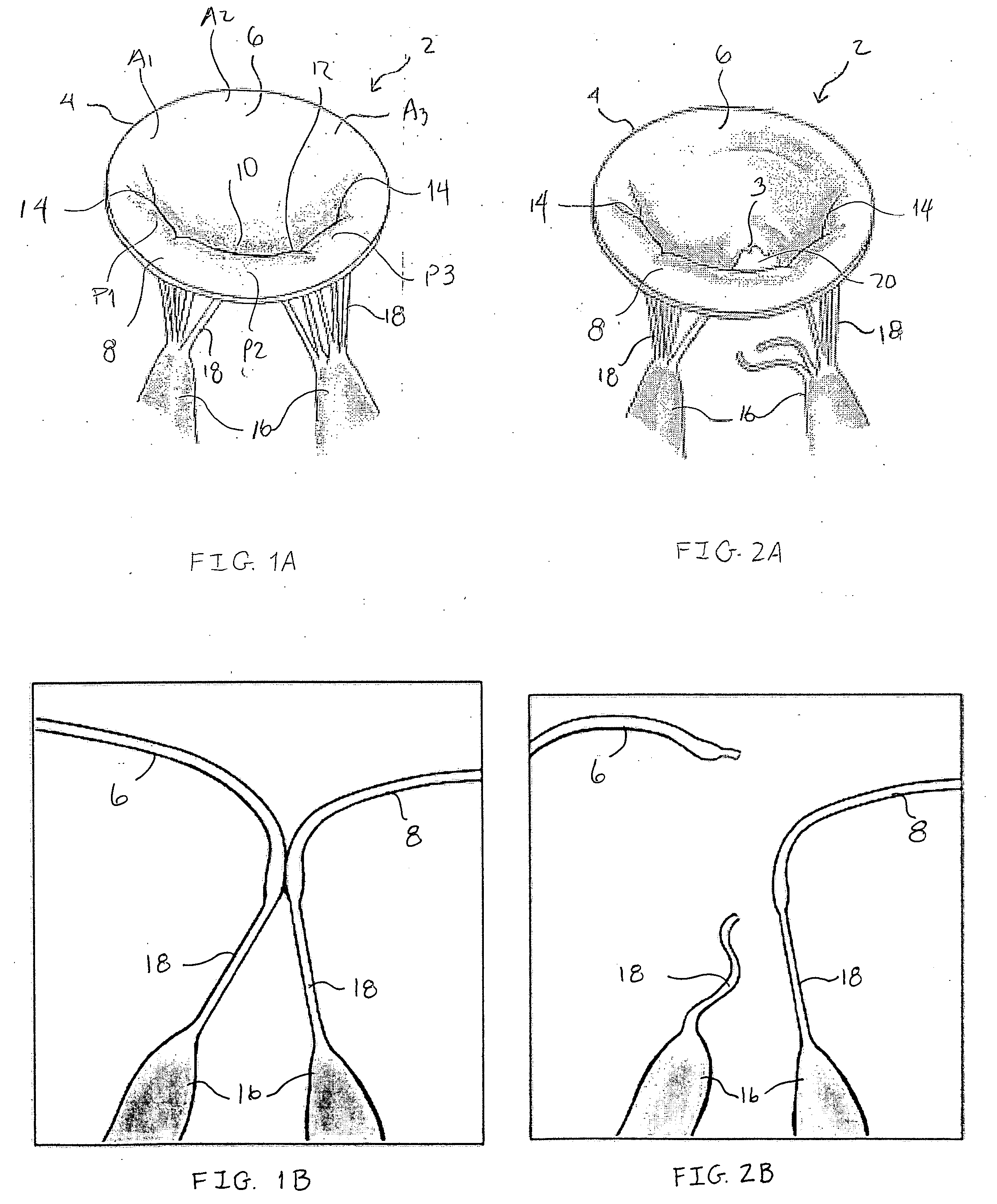

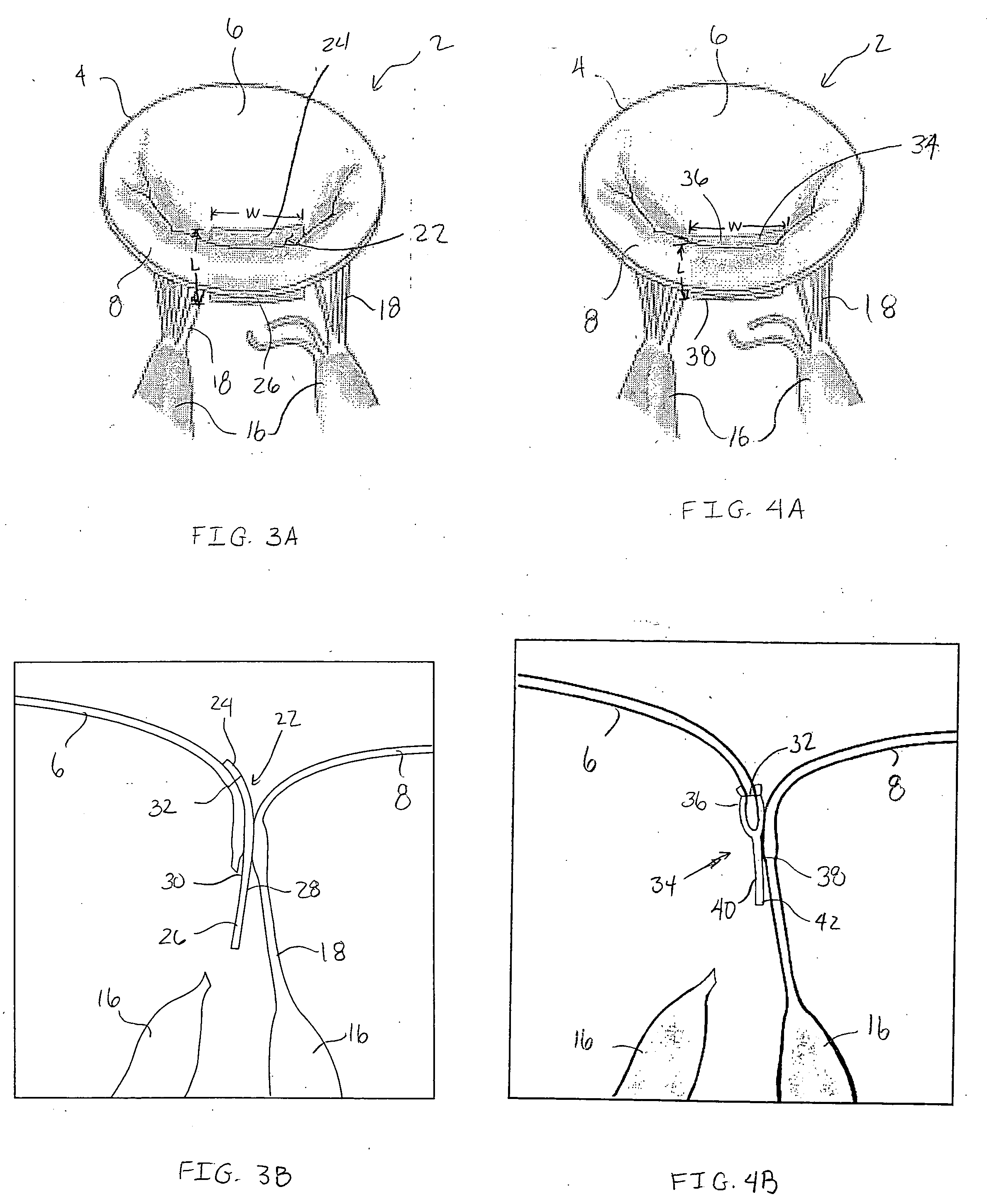

Methods and apparatus for cardiac valve repair

InactiveUS6629534B1Reduce leakageReduce regurgitationSuture equipmentsSurgical needlesHeart chamberPapillary muscle

The methods, devices, and systems are provided for performing endovascular repair of atrioventricular and other cardiac valves in the heart. Regurgitation of an atrioventricular valve, particularly a mitral valve, can be repaired by modifying a tissue structure selected from the valve leaflets, the valve annulus, the valve chordae, and the papillary muscles. These structures may be modified by suturing, stapling, snaring, or shortening, using interventional tools which are introduced to a heart chamber. Preferably, the tissue structures will be temporarily modified prior to permanent modification. For example, opposed valve leaflets may be temporarily grasped and held into position prior to permanent attachment.

Owner:EVALVE

Modified delivery device for coated medical devices

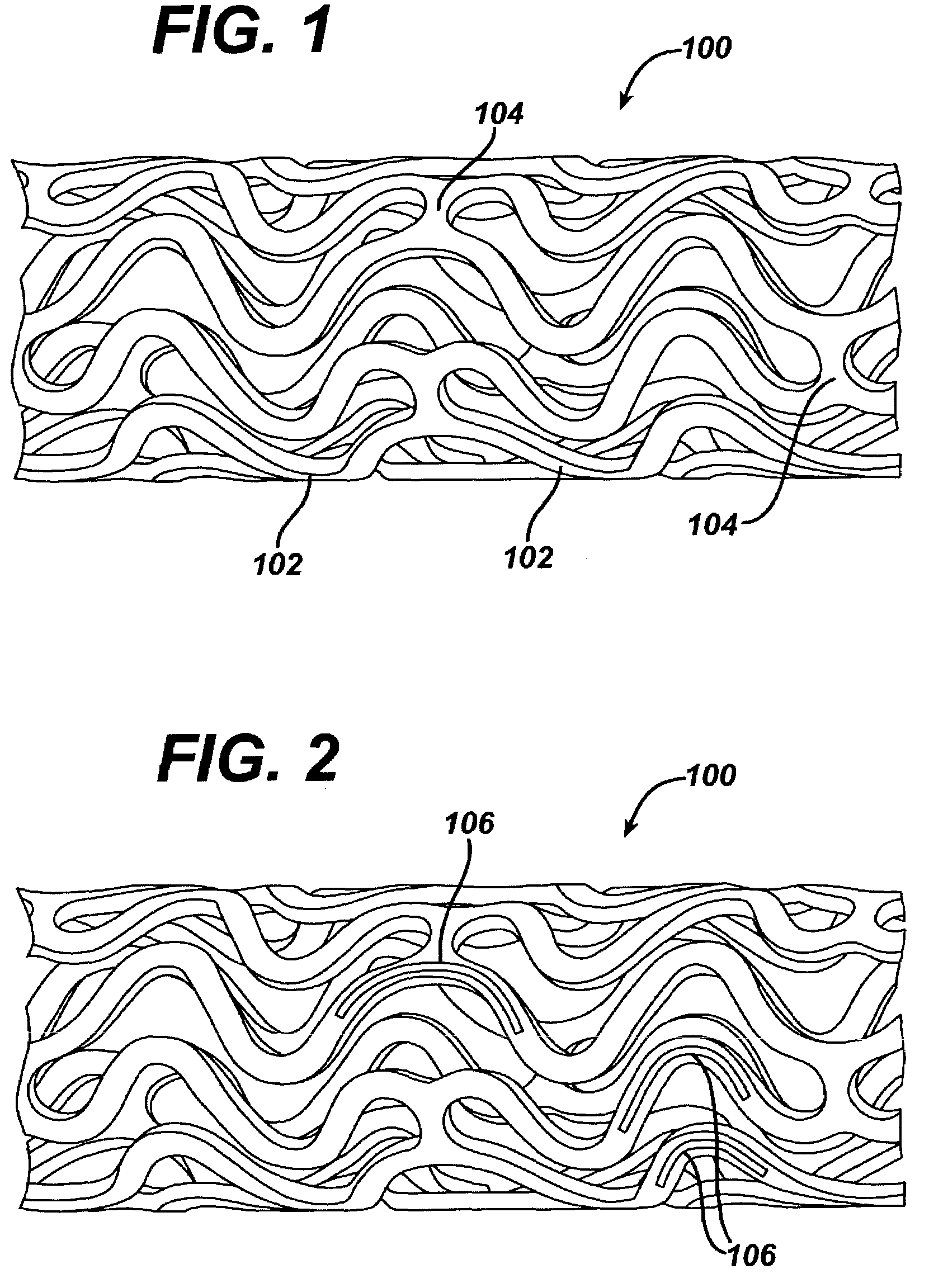

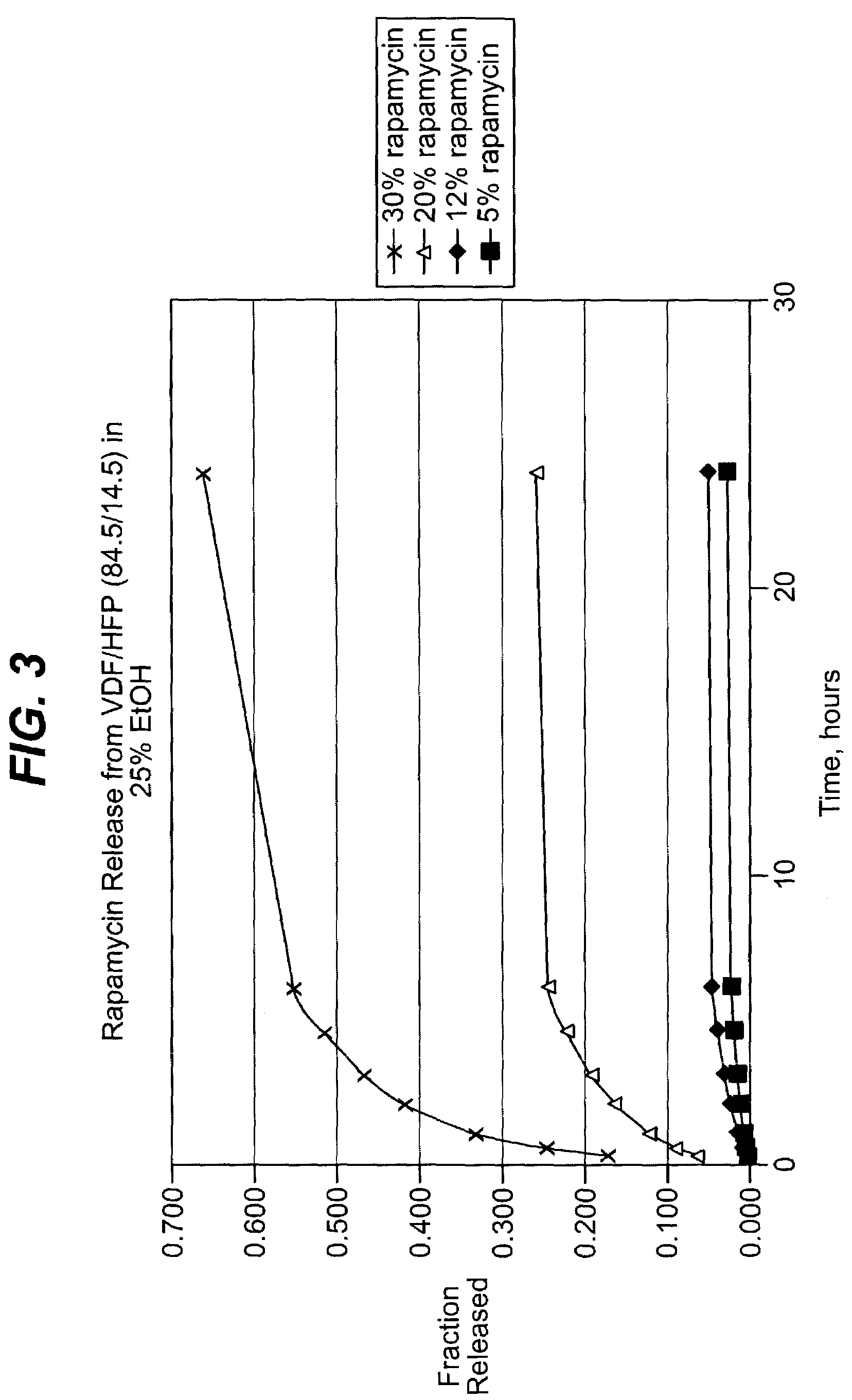

InactiveUS7527632B2Minimize potential risk of damageReduce frictionStentsEar treatmentBiological bodyMedical device

Medical devices, and in particular implantable medical devices, including self-expanding stents, may be coated to minimize or substantially eliminate a biological organism's reaction to the introduction of the medical device to the organism. The devices utilized to deliver the implantable medical devices may be modified to reduce the potential for damaging the implantable medical device during deployment.

Owner:CARDINAL HEALTH SWITZERLAND 515 GMBH

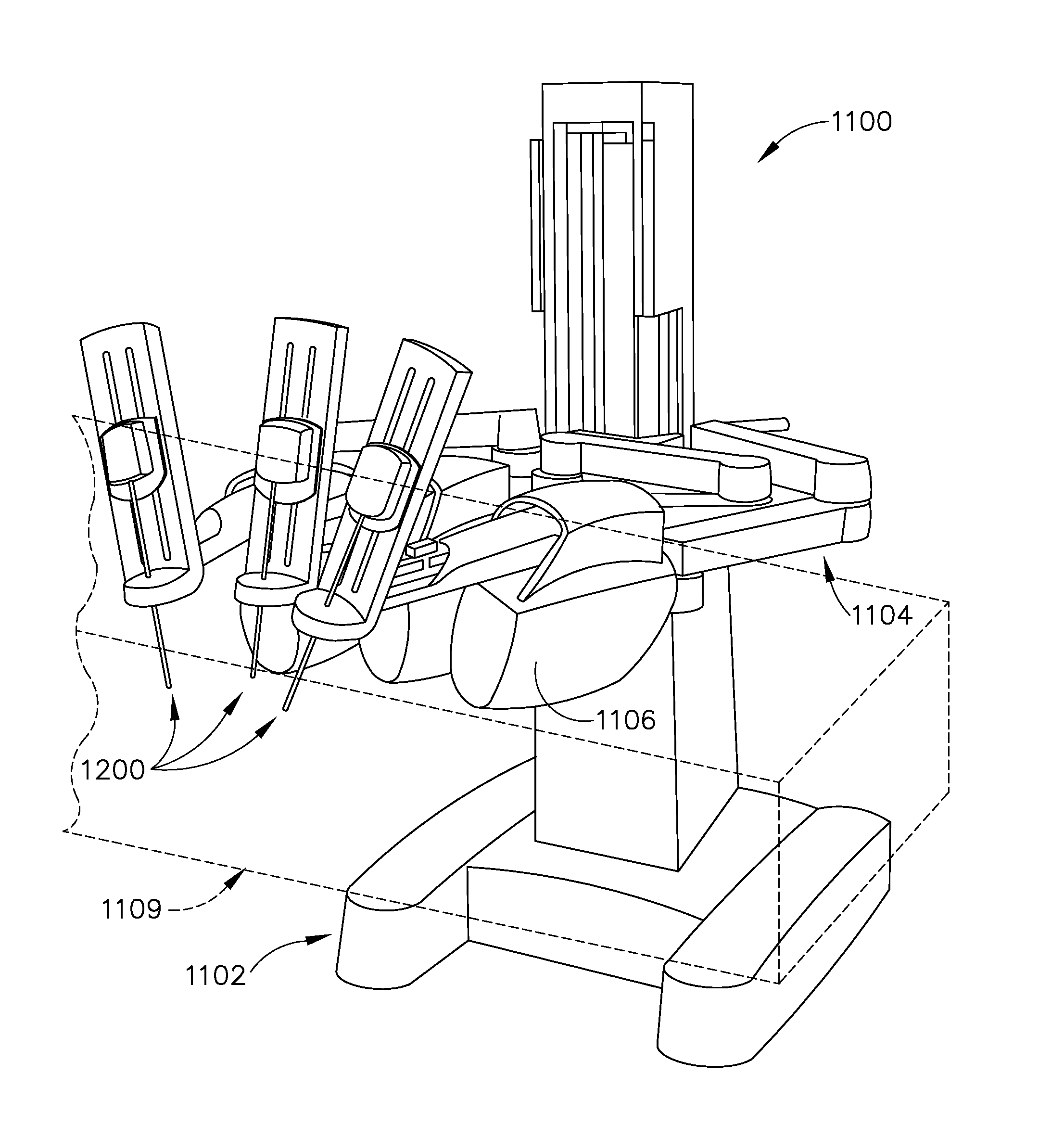

Robotically-driven surgical instrument with e-beam driver

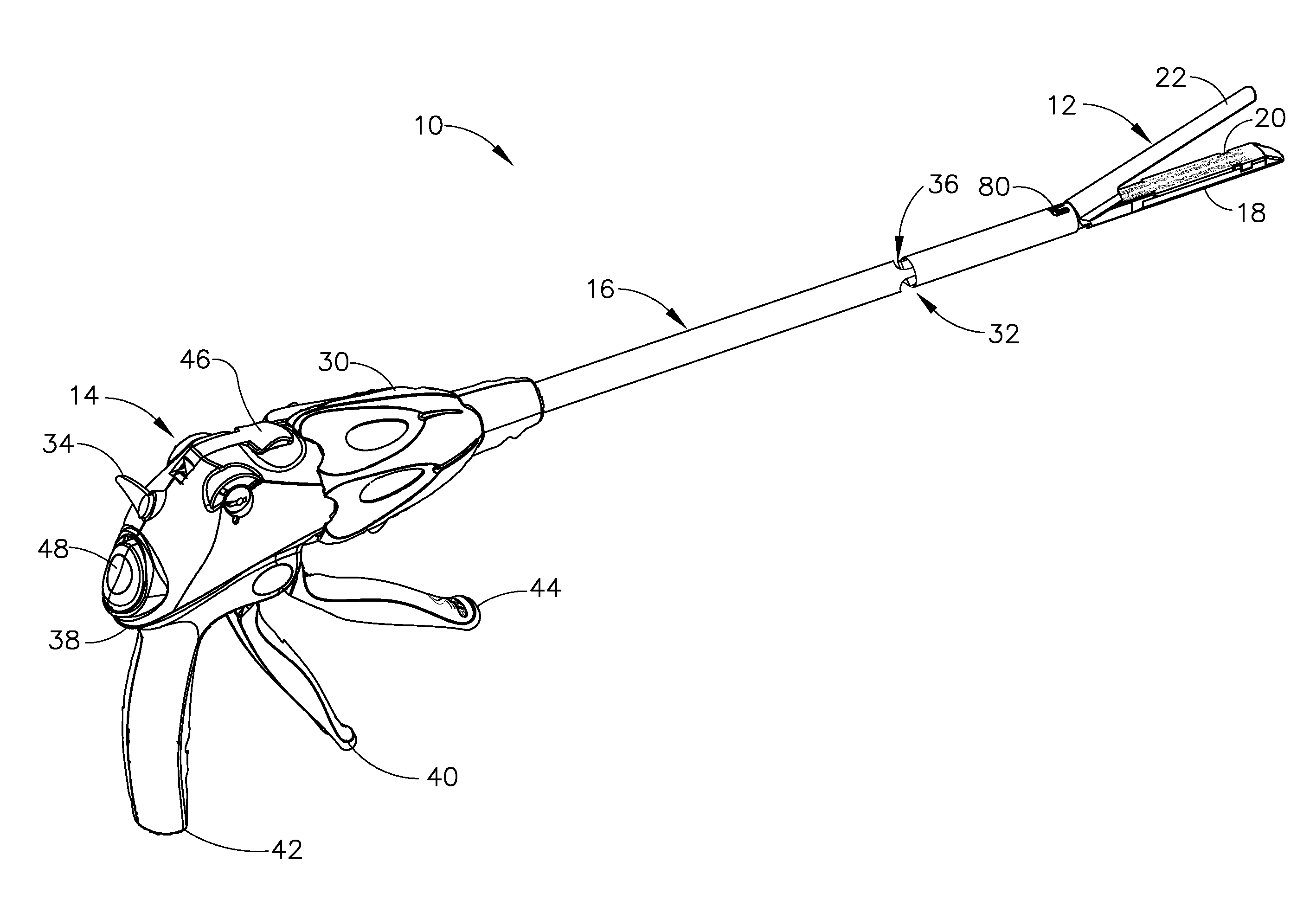

ActiveUS20110290853A1Solve the lack of spaceEasy to useSuture equipmentsStapling toolsRobotic systemsSurgical instrumentation

A surgical severing and stapling instrument, suitable for laparoscopic and endoscopic clinical procedures, clamps tissue within an end effector of an elongate channel pivotally opposed by an anvil. Various embodiments are configured to be operably attached to a robotic system to receive actuation / control motions therefrom.

Owner:CILAG GMBH INT

Robotically-controlled surgical end effector system

ActiveUS20120203247A1Solve the lack of spaceEasy to useSuture equipmentsStapling toolsRobotic systemsPERITONEOSCOPE

A surgical severing and stapling instrument, suitable for laparoscopic and endoscopic clinical procedures, clamps tissue within an end effector of an elongate channel pivotally opposed by an anvil. Various embodiments are configured to be operably attached to a robotic system to receive actuation / control motions therefrom.

Owner:CILAG GMBH INT

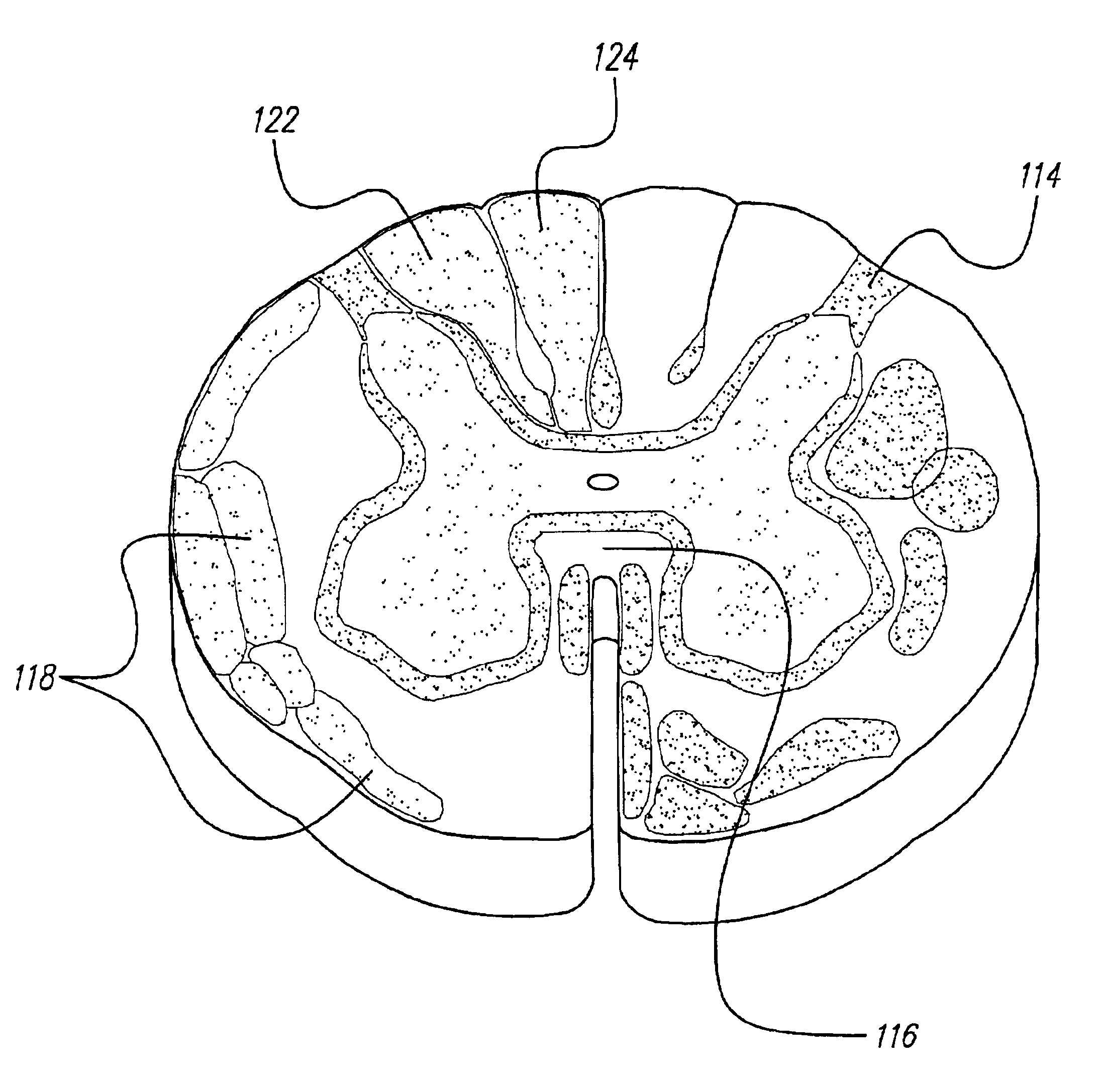

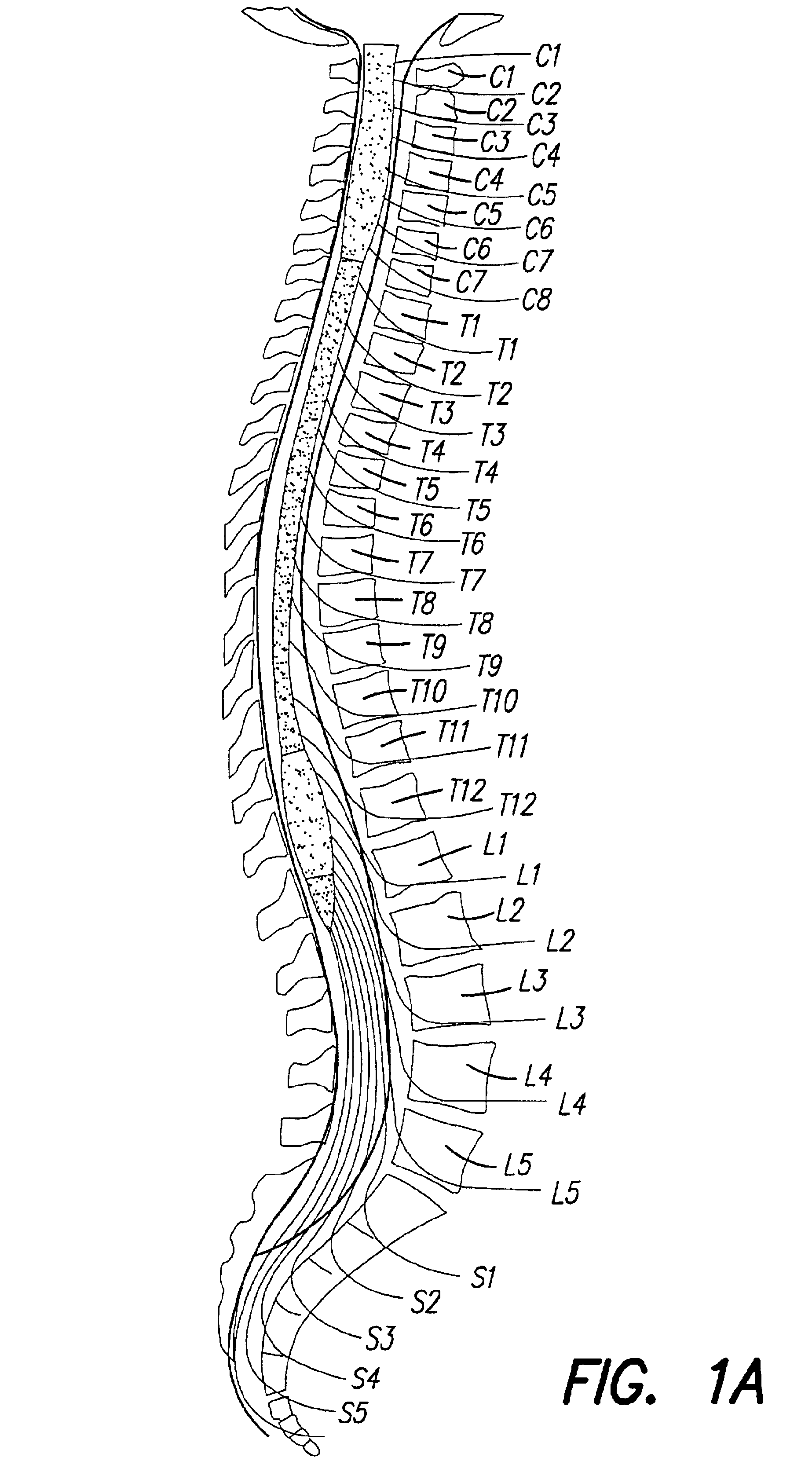

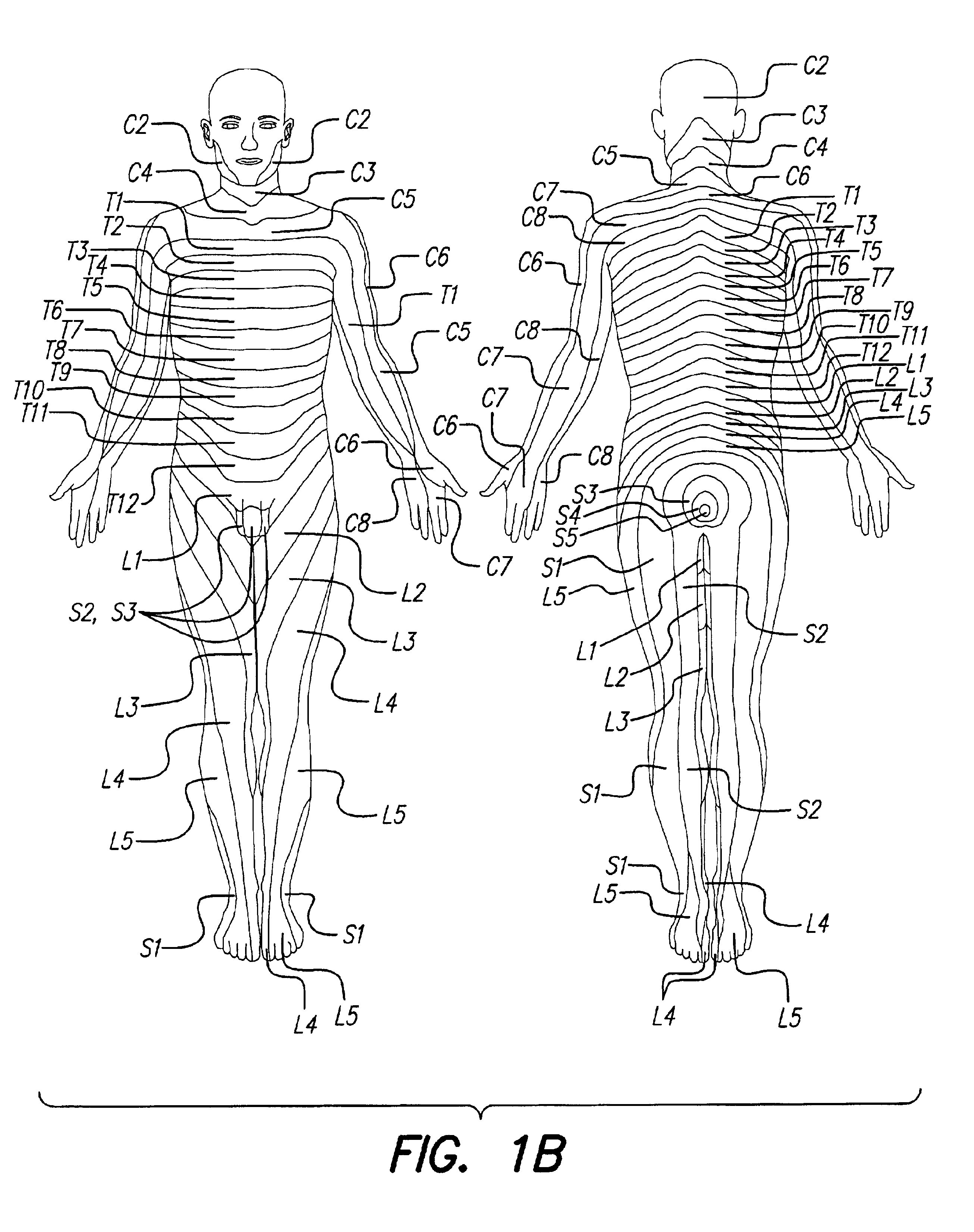

Fully implantable microstimulator for spinal cord stimulation as a therapy for chronic pain

An implantable stimulator(s), small enough to be located near or within an area of the spine responsible for sensations in a region experiencing chronic pain uses a power source / storage device, such as a rechargeable battery. Periodic recharging of such a power source / storage device is accomplished, for example, by inductive coupling with an external appliance. The small stimulator provides a means of stimulating a nerve(s) or other tissue when desired, without the need for external appliances during the stimulation session. When necessary, external appliances are used for the transmission of data to and / or from the stimulator(s) and for the transmission of power, it necessary. In a preferred embodiment, the system is capable of open- and closed-loop operation. In closed-loop operation, at least one implant includes at least one sensor, and the sensed condition is used to adjust stimulation parameters.

Owner:BOSTON SCI NEUROMODULATION CORP

Methods and apparatus for cardiac valve repair

ActiveUS20040030382A1Reduce leakageReduce regurgitationSuture equipmentsBone implantHeart chamberPapillary muscle

The methods, devices, and systems are provided for performing endovascular repair of atrioventricular and other cardiac valves in the heart. Regurgitation of an atrioventricular valve, particularly a mitral valve, can be repaired by modifying a tissue structure selected from the valve leaflets, the valve annulus, the valve chordae, and the papillary muscles. These structures may be modified by suturing, stapling, snaring, or shortening, using interventional tools which are introduced to a heart chamber. Preferably, the tissue structures will be temporarily modified prior to permanent modification. For example, opposed valve leaflets may be temporarily grasped and held into position prior to permanent attachment.

Owner:EVALVE

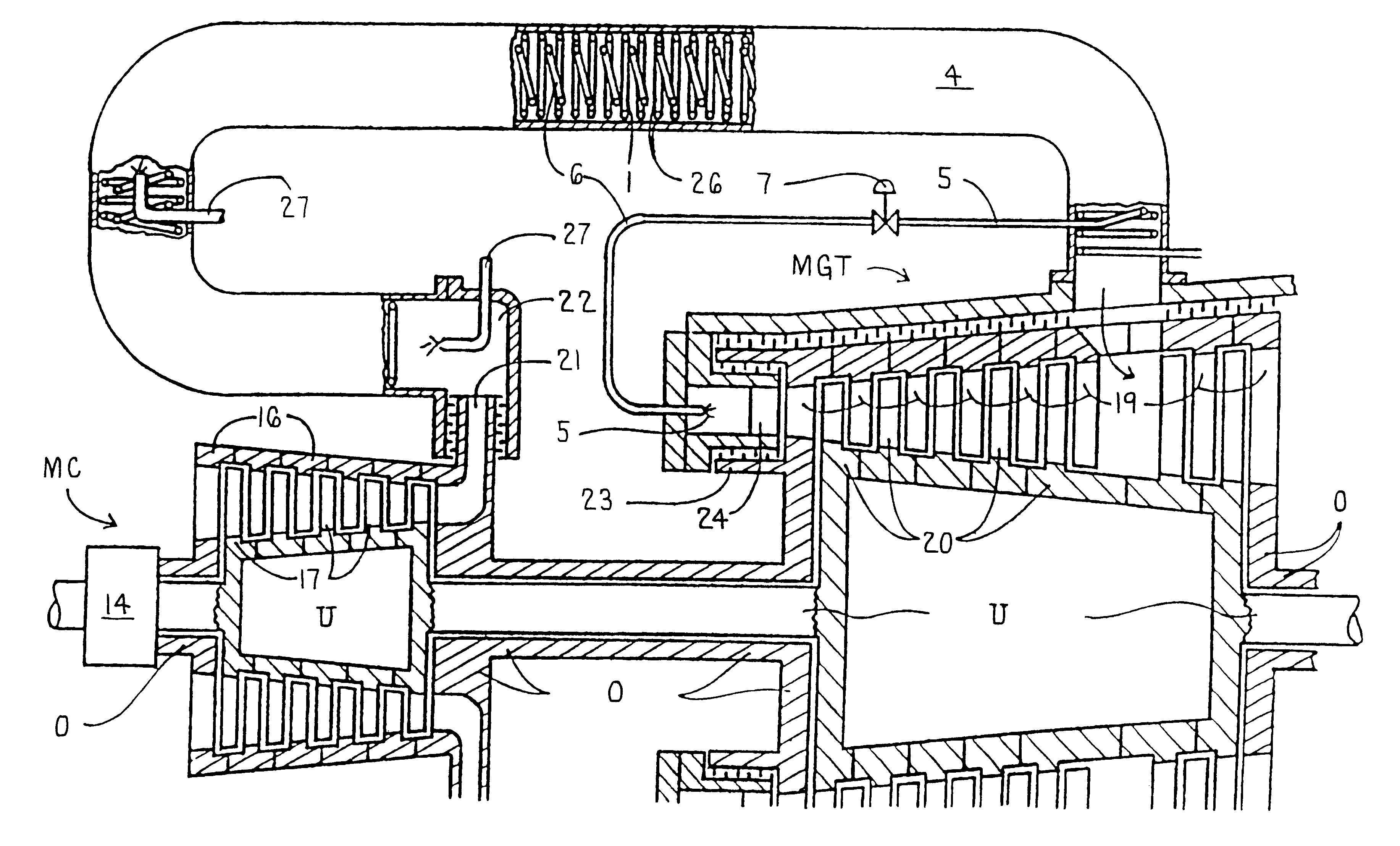

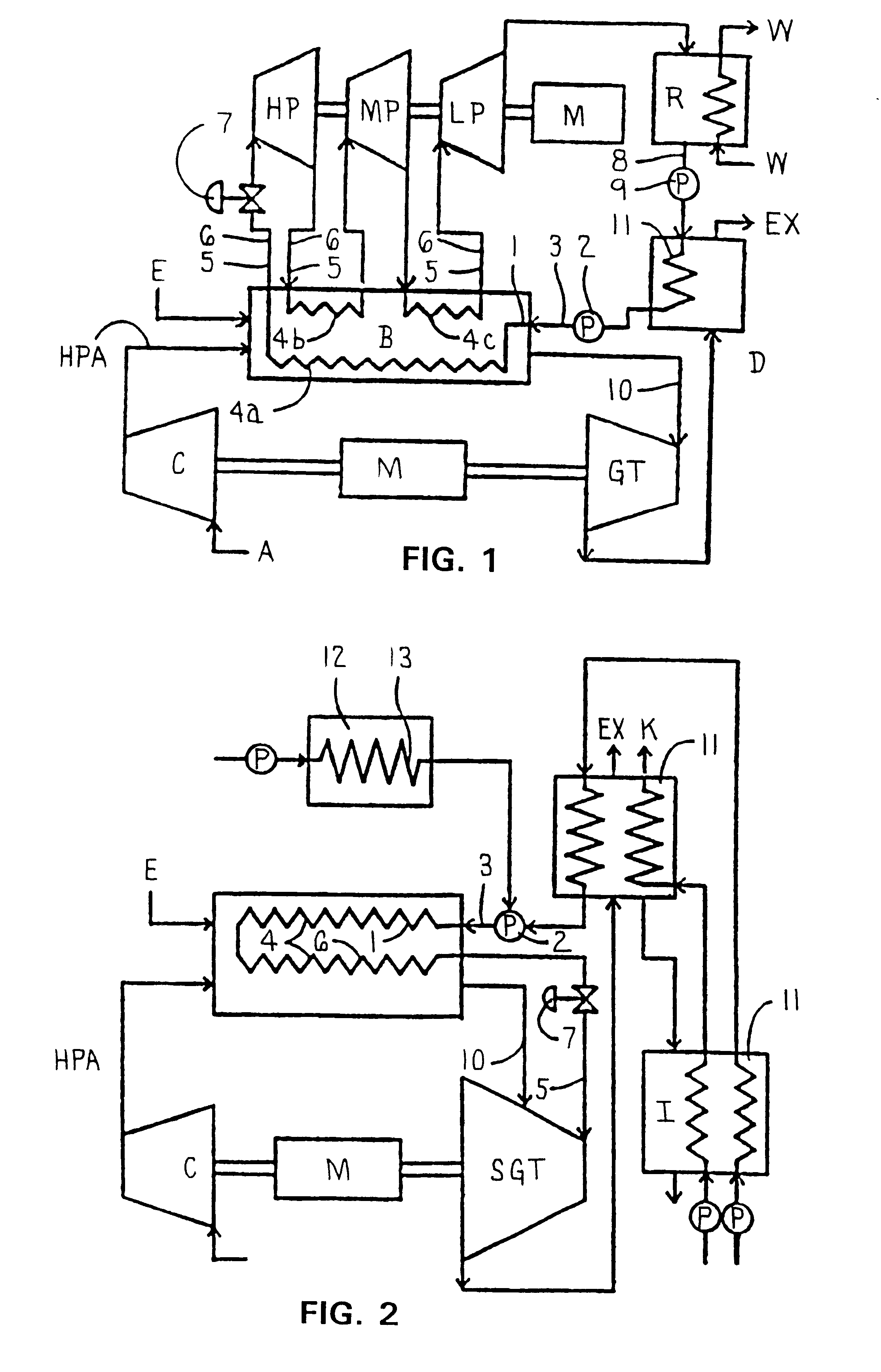

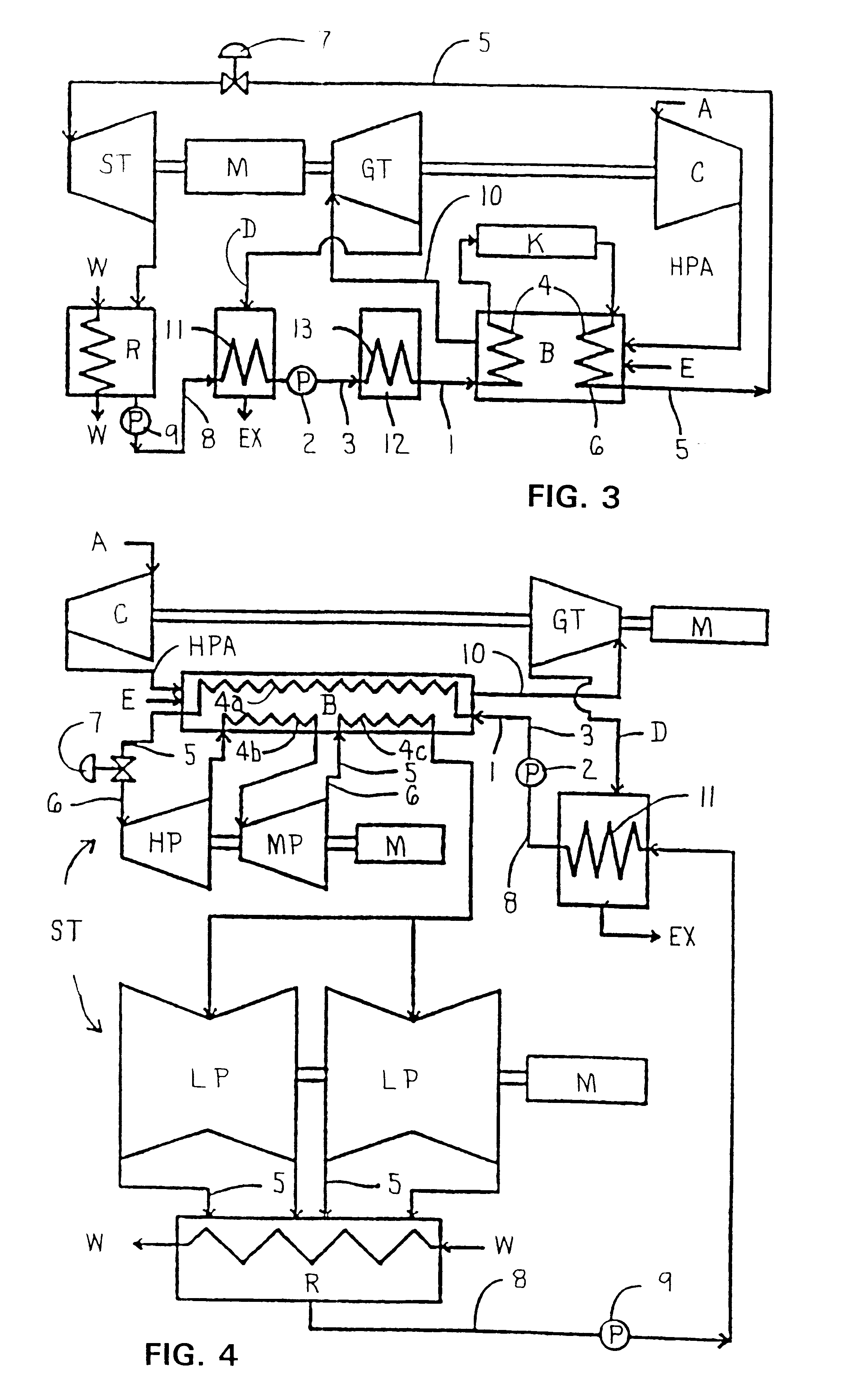

Combined steam and gas turbine engine with magnetic transmission

InactiveUS6263664B1Wide areaImprove system efficiencyContinuous combustion chamberGearingThermal energyCombustion chamber

In a combined steam and gas turbine engine cycle, a combustion chamber is made durable against high pressure and enlarged in length to increase the operation pressure ratio, without exceeding the heat durability temperature of the system while increasing the fuel combustion gas mass flow four times as much as the conventional turbine system and simultaneously for greatly raising the thermal efficiency of the system and specific power of the combined steam and gas turbine engine.Water pipes and steam pipes are arranged inside the combustion chamber so that the combustion chamber can function as a heat exchanger and thereby convert most of the combustion thermal energy into super-critical steam energy for driving a steam turbine and subsequently raising the operation pressure ratio and the thermal efficiencies of the steam turbine cycle and gas turbine cycle. The combustion gas mass flow can be also increased by four times as much as the conventional turbine system (up to the theoretical air to fuel ratio) and the thermal efficiency and the specific power of the gas turbine cycle are considerably increased.Further, the thermal efficiency of the combined system is improved by installing a magnetic friction power transmission system to transmit the power of the system to outer loads.

Owner:TANIGAWA HIROYASU +1

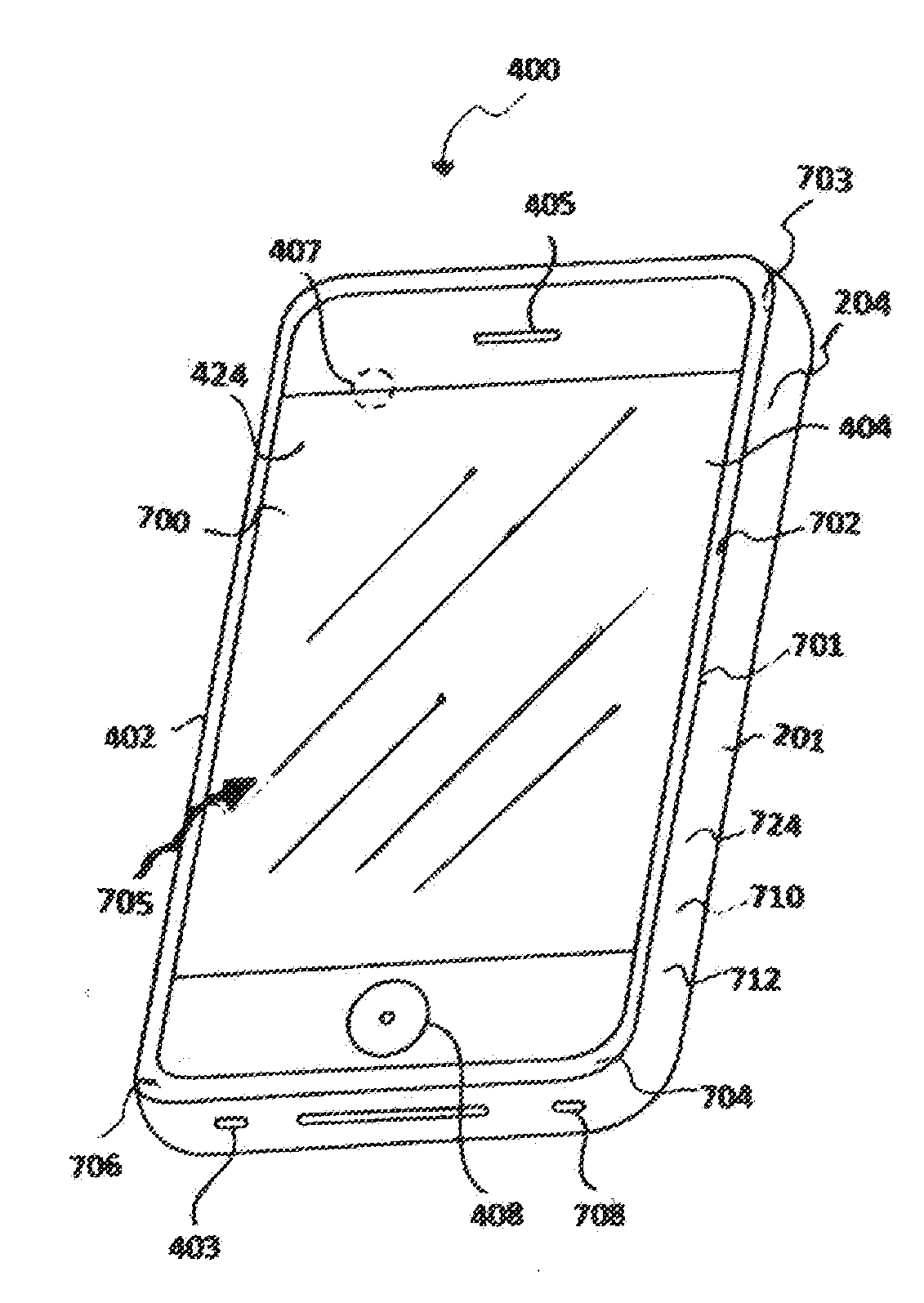

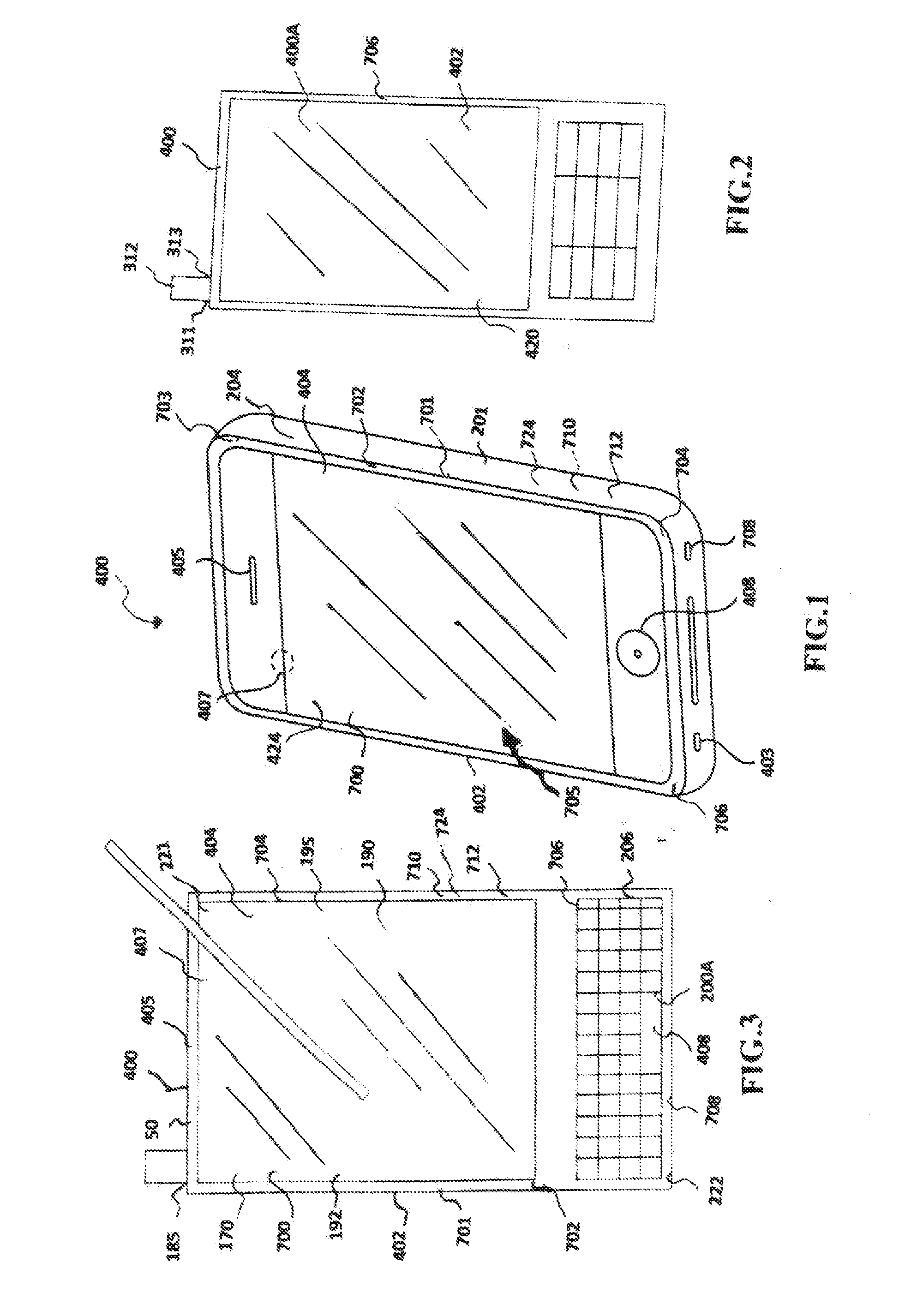

Energy harvesting computer device in association with a communication device configured with apparatus for boosting signal reception

ActiveUS20130157729A1Improve consumer electronics hybrid consumer electronics performanceLow densityMaterial nanotechnologyEnergy efficient ICTCellular telephoneCommunication device

Disclosed embodiments comprise an energy harvesting computer device in association with a communication device comprising interactive user interface operatively configured with CMOS multiple antennas on chip for boosting signal receptions and for providing faster data transmission speed. Disclosed embodiment encompasses three modes of communications—the Cell phone, wireless Internet applications, and Global communication and media information. Embodiments provide communication apparatus operable to enhance mobile communication efficiency with touch sensitive display comprising energy harvesting platform in communication with a charging circuit board configured with memories, processors, sensors, and modules. Embodiments further provide a gaming device, a wireless media device configured with touch pads comprising sensors being embedded in silicon substrate and fused in nano-fiber / microfiber material having excellent electrical characteristics. Certain embodiments provide communication apparatus configured for voice enabled applications comprising human voice auditory operable to convert text into voice auditory and / or voice auditory into text applications.

Owner:TABE JOSEPH AKWO

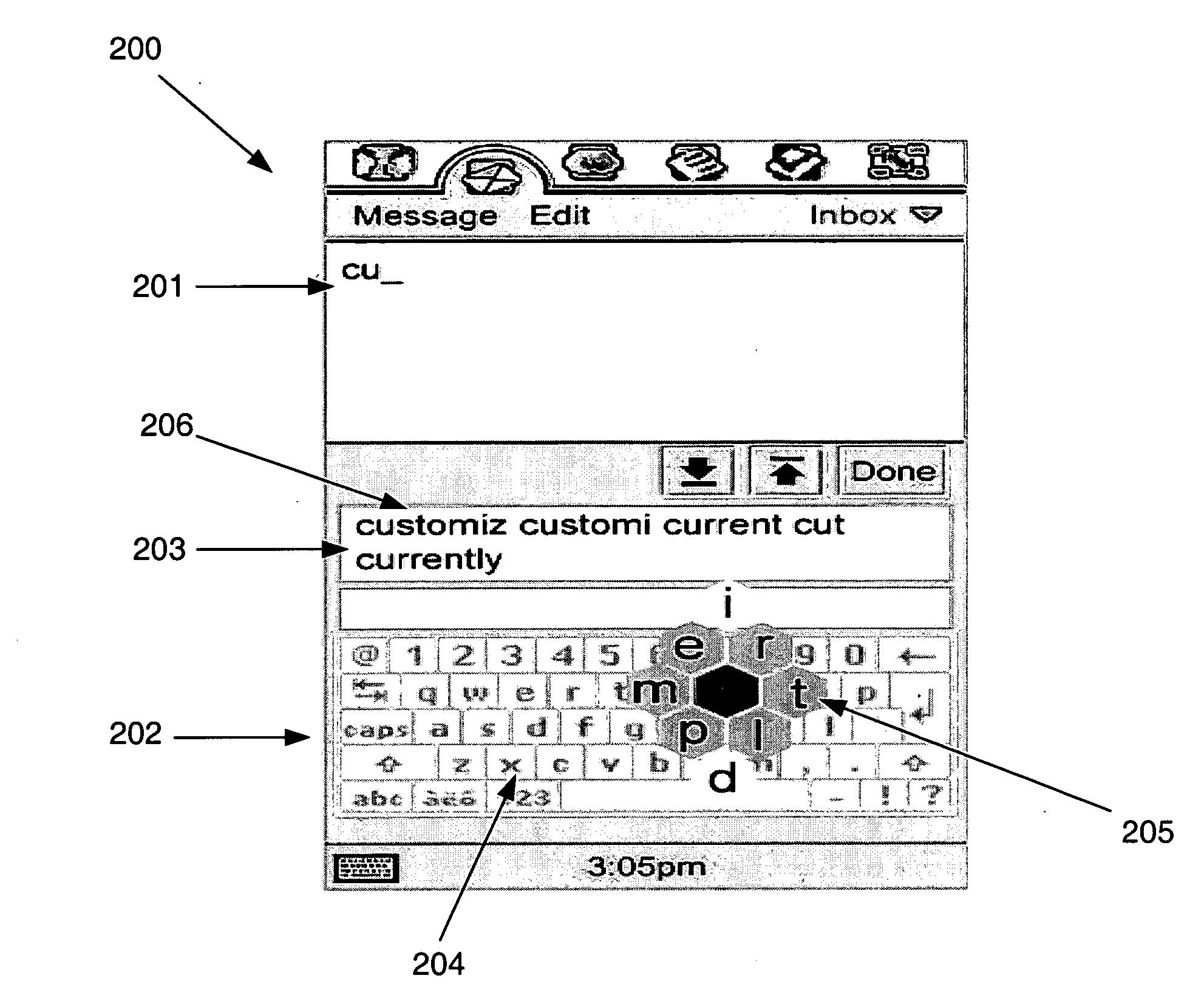

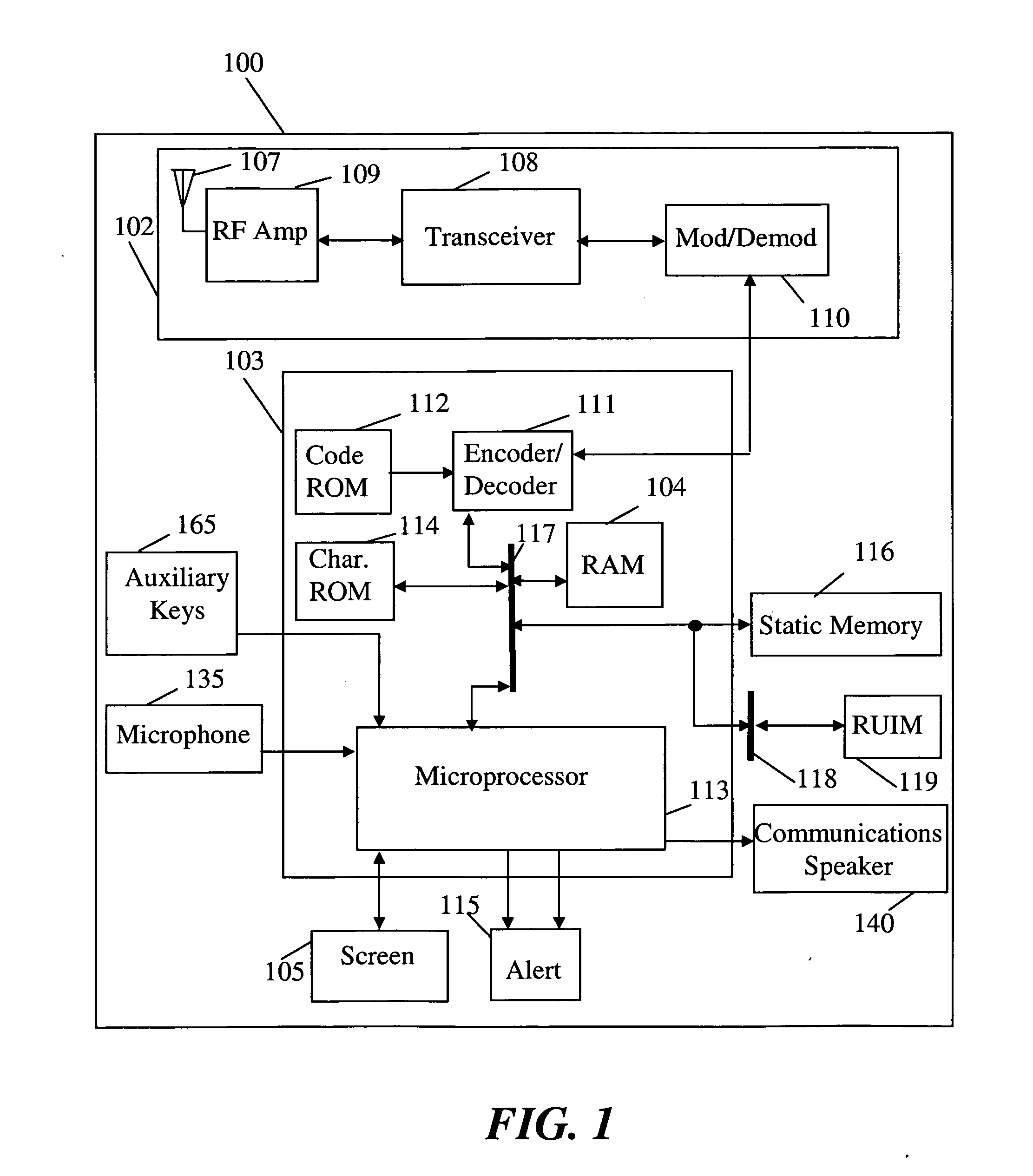

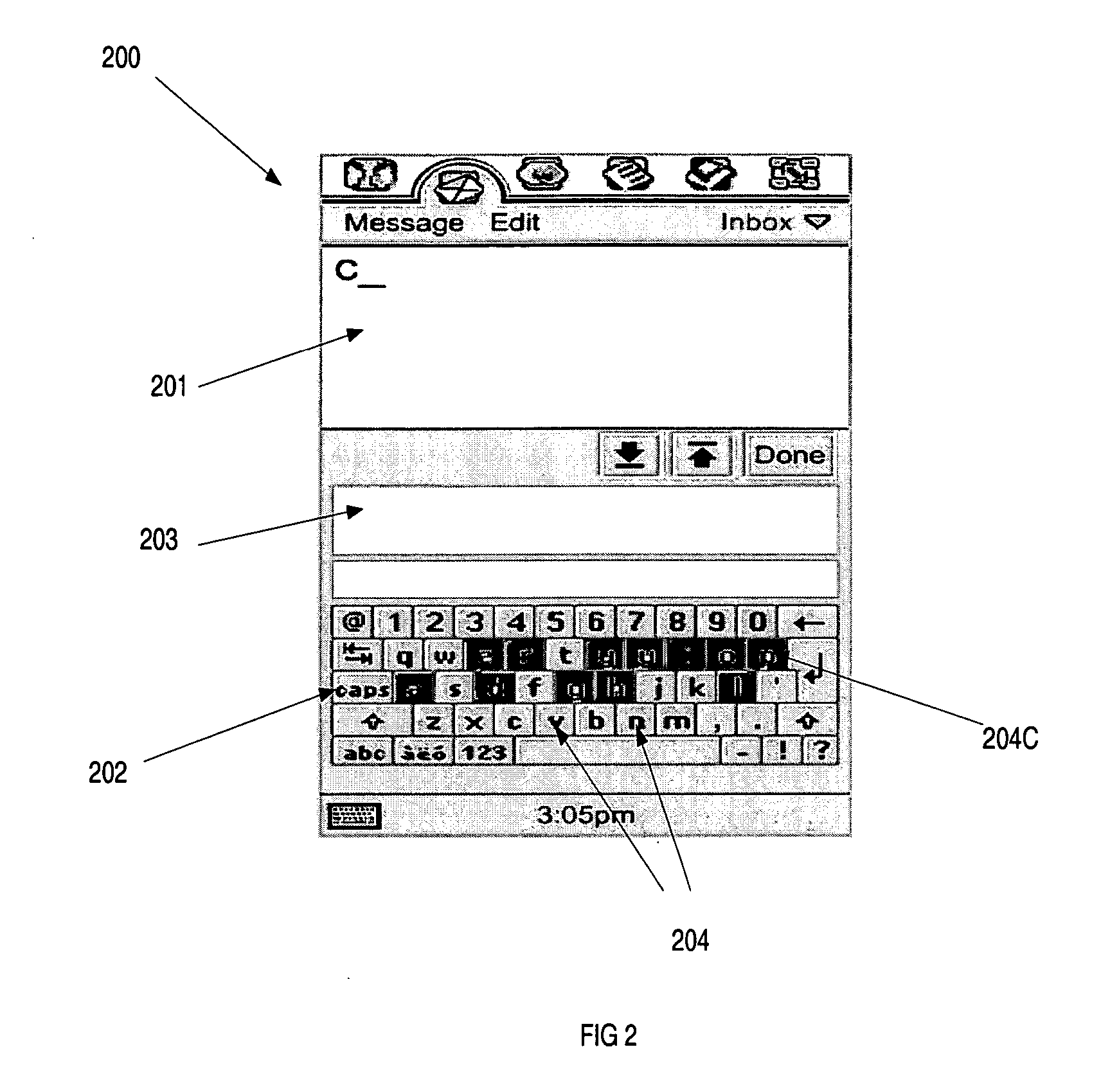

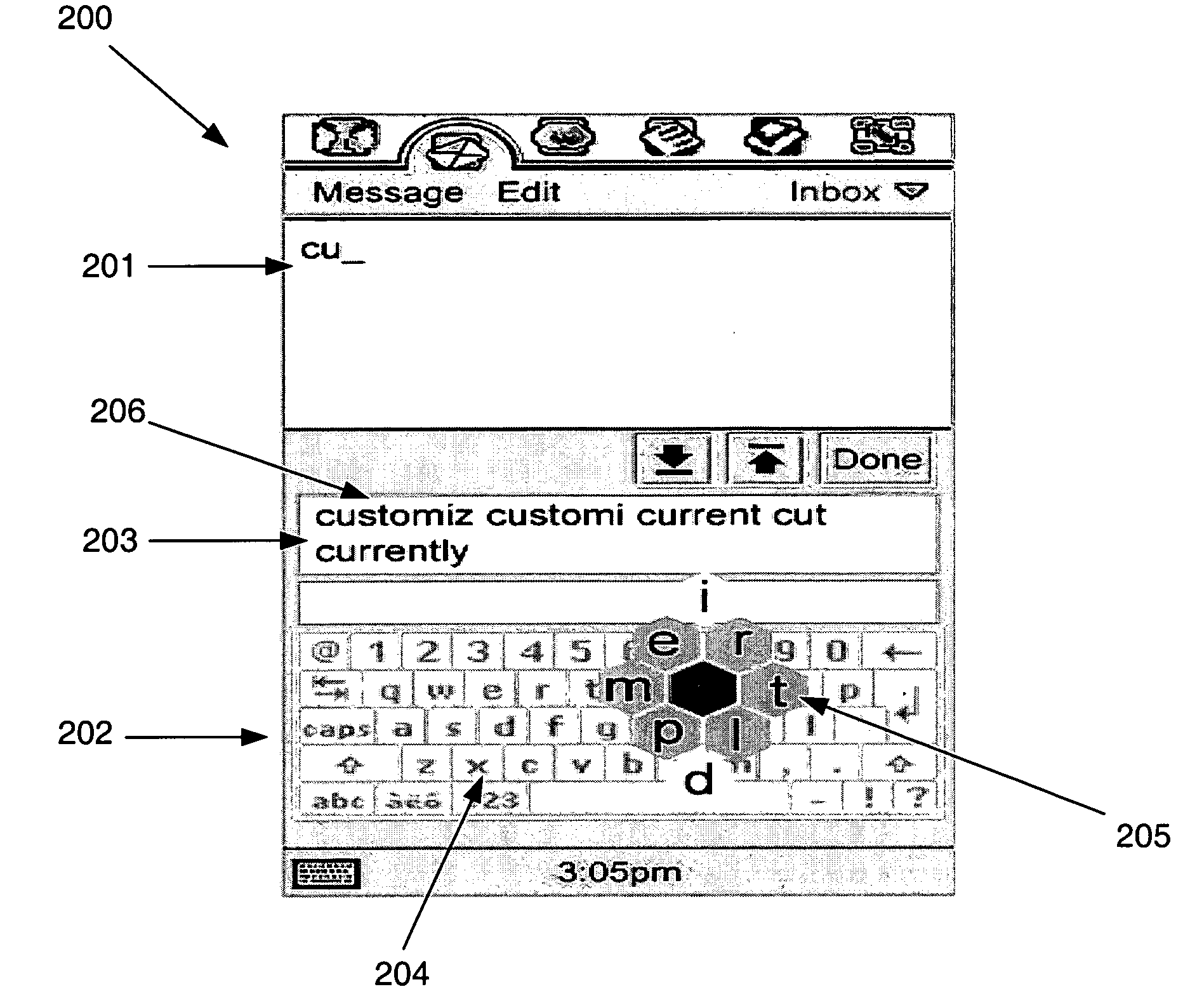

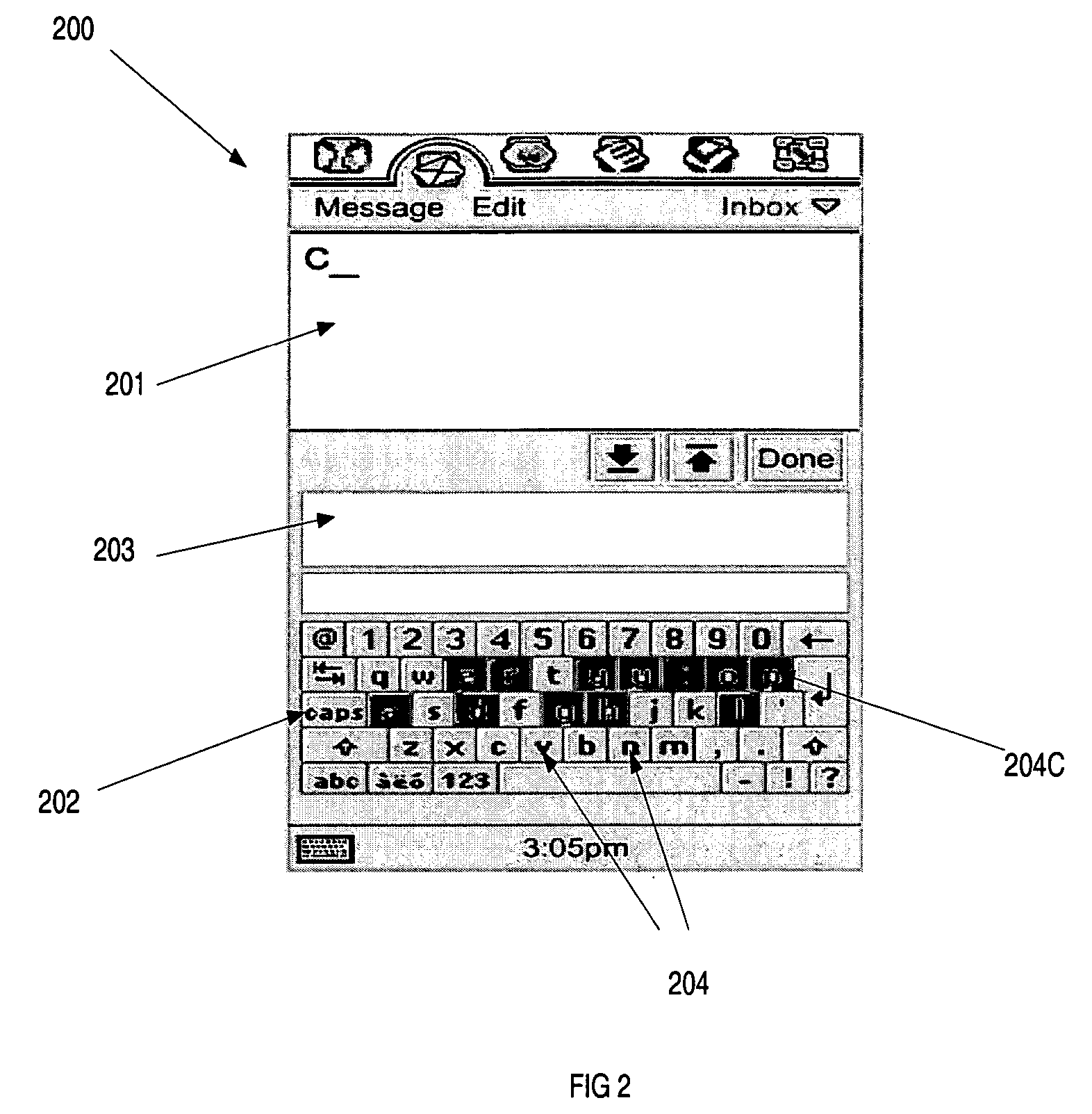

Entering a character into an electronic device

ActiveUS20070046641A1Reduced user hand movementReduce fatigueInput/output for user-computer interactionElectronic switchingArtificial intelligenceElectronic equipment

Owner:GOOGLE TECH HLDG LLC

Entering a character into an electronic device

ActiveUS7443316B2Easy for to identify wantedEasy for to see and also to selectInput/output for user-computer interactionCharacter and pattern recognitionAlgorithmEngineering

Owner:GOOGLE TECH HLDG LLC

Articulating surgical stapling instrument incorporating a two-piece E-beam firing mechanism

ActiveUS20050263562A1Solve the lack of spaceEasy to useSuture equipmentsStapling toolsDistal portionPERITONEOSCOPE

A surgical severing and stapling instrument, suitable for laparoscopic and endoscopic clinical procedures, clamps tissue within an end effector of an elongate channel pivotally opposed by an anvil. An E-beam firing bar moves distally through the clamped end effector to sever tissue and to drive staples on each side of the cut. The E-beam firing bar affirmatively spaces the anvil from the elongate channel to assure properly formed closed staples, especially when an amount of tissue is clamped that is inadequate to space the end effector. In particular, an upper pin of the firing bar longitudinally moves through an anvil slot and a channel slot is captured between a lower cap and a middle pin of the firing bar to assure a minimum spacing. Forming the E-beam from a thickened distal portion and a thinned proximal strip enhances manufacturability and facilitates use in such articulating surgical instruments.

Owner:ETHICON ENDO SURGERY INC +1

Apparatus and methods for tissue gathering and securing

InactiveUS20050075665A1Reduce areaMinimize and eliminate and of and activityStaplesNailsTissue CollectionTissue fixing

Methods and apparatus are provided that gather a patient's body tissue and then secure the gathered tissue in a reduced area utilizing a securing structure. The securing structure mainly resides on one side of the tissue to minimize or eliminate both foreign material and the amount of manipulation or activity on the other side of the tissue. The securing device is matched to the desired amount of tissue manipulation to minimize the structure. The gathered and secured tissue can surround a septal defect to obstruct or close the defect itself.

Owner:ST JUDE MEDICAL LLC

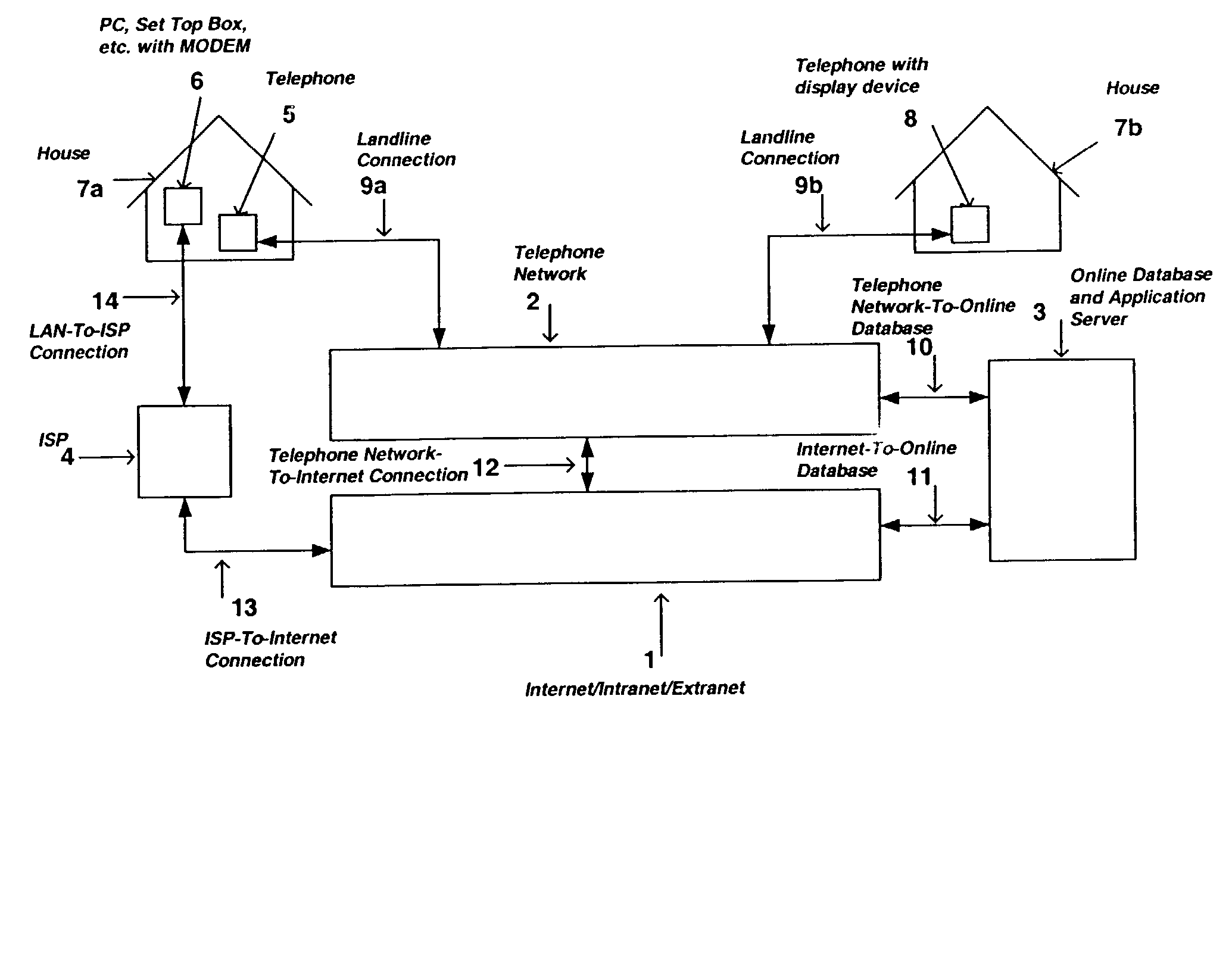

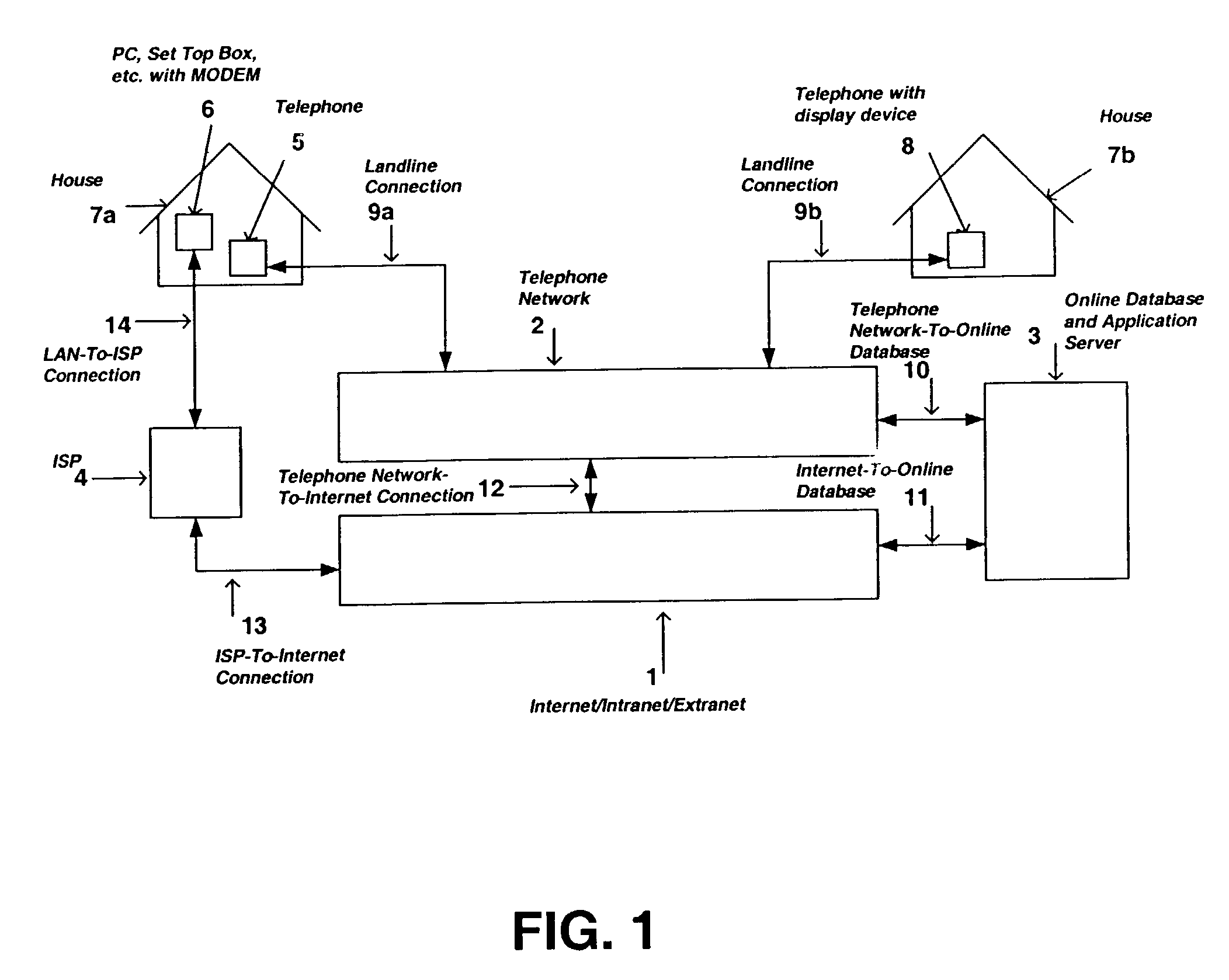

Position determination system

InactiveUS20030016804A1Limited resourceReduce areaInstruments for road network navigationDevices with GPS signal receiverTelecommunications networkThe Internet

The present invention is directed to a system and method for providing real-time position information of one party to another party by utilizing a conventional telecommunication network system such as the convention telephone network, a mobile telecommunications network, a computer network, or the Internet. More specifically, the preferred embodiments of the present invention allow a caller and a receiver of a telephone call to provide to and receive from each other position information related to the caller and / or receiver's physical location, including address information, GPS coordinates, nearby fixed locations such as a parking structure, etc. Additionally, the preferred embodiments of the present invention allow a caller and receiver to retrieve routing instructions or maps for traveling to or from each other. In another embodiment of the present invention, a party may locate the position of another party via the entry of the other party's unique identifier such as a phone number of the other party's mobile phone. In yet another embodiment of the present invention, the position information of a party may be concurrently delivered to another party's computer terminal whereby the other party can process the information in further detail.

Owner:ARTAX LLC

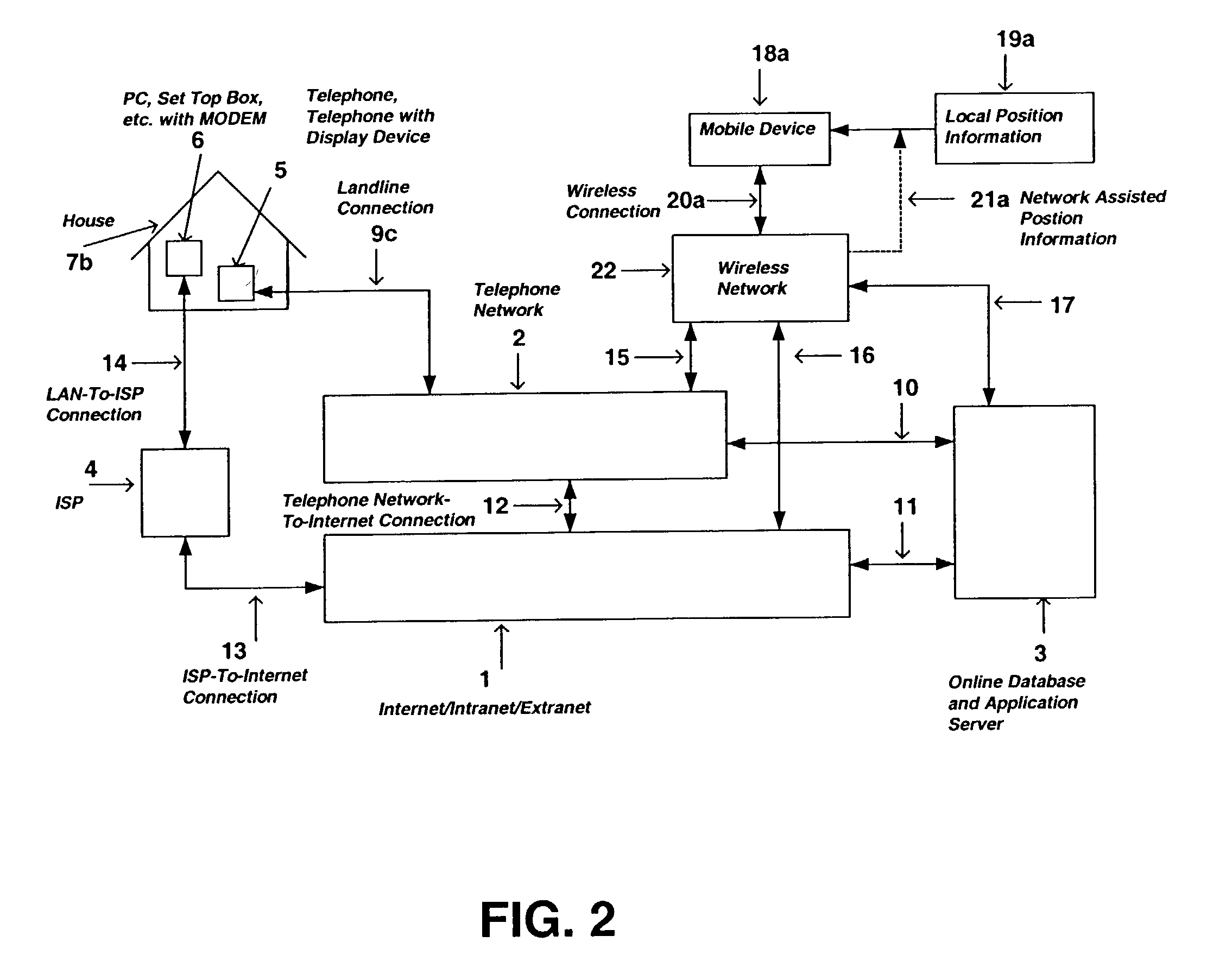

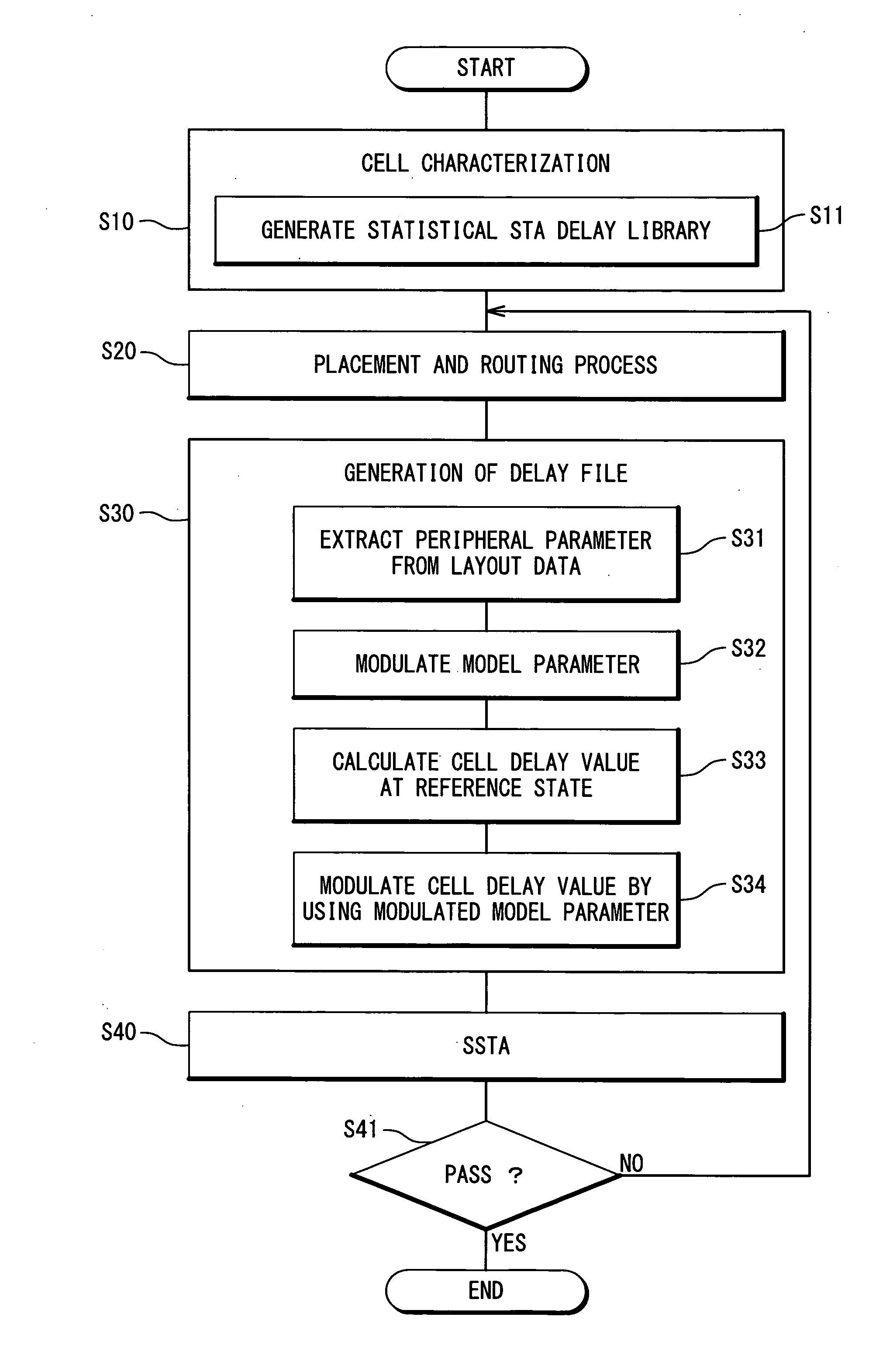

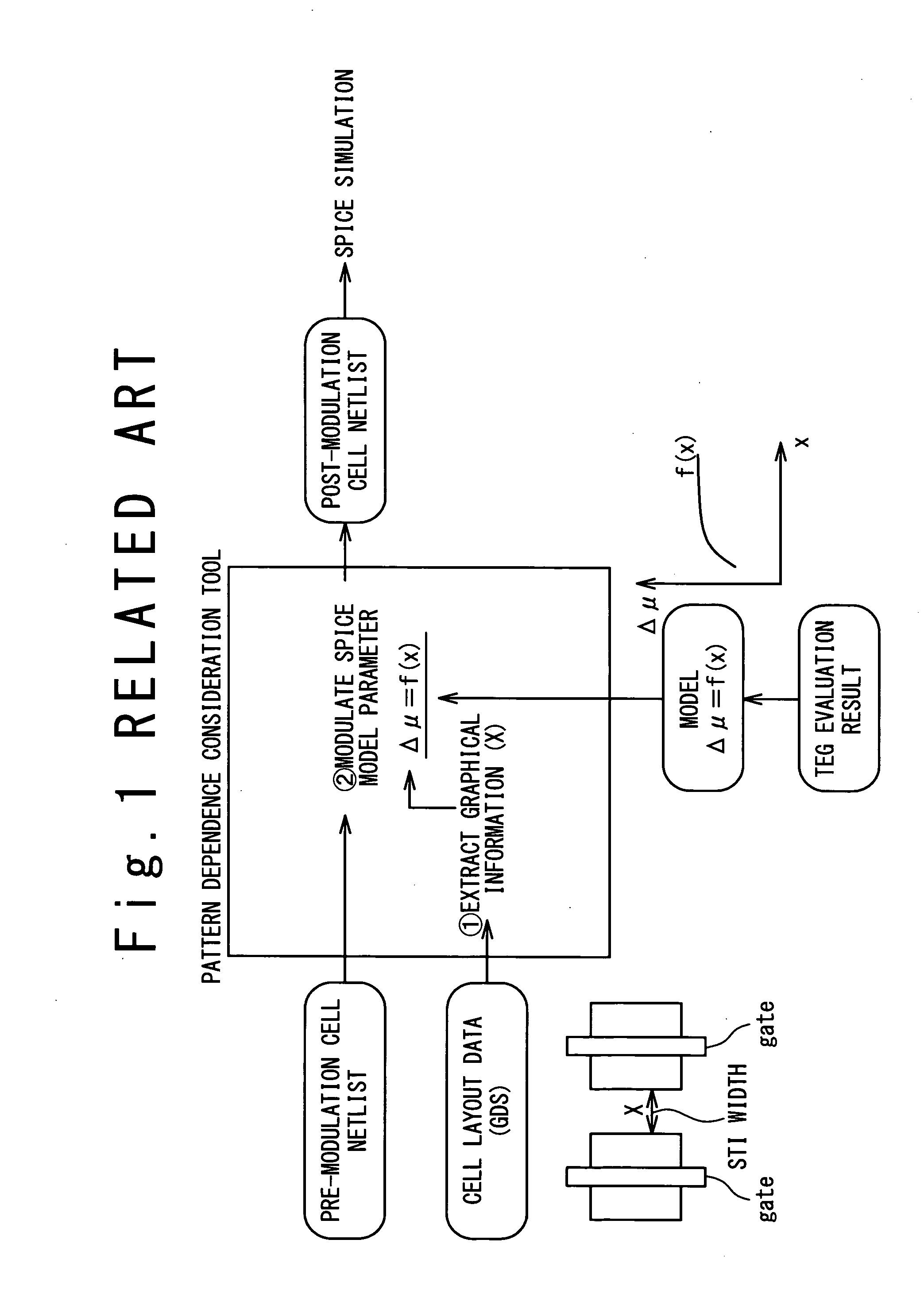

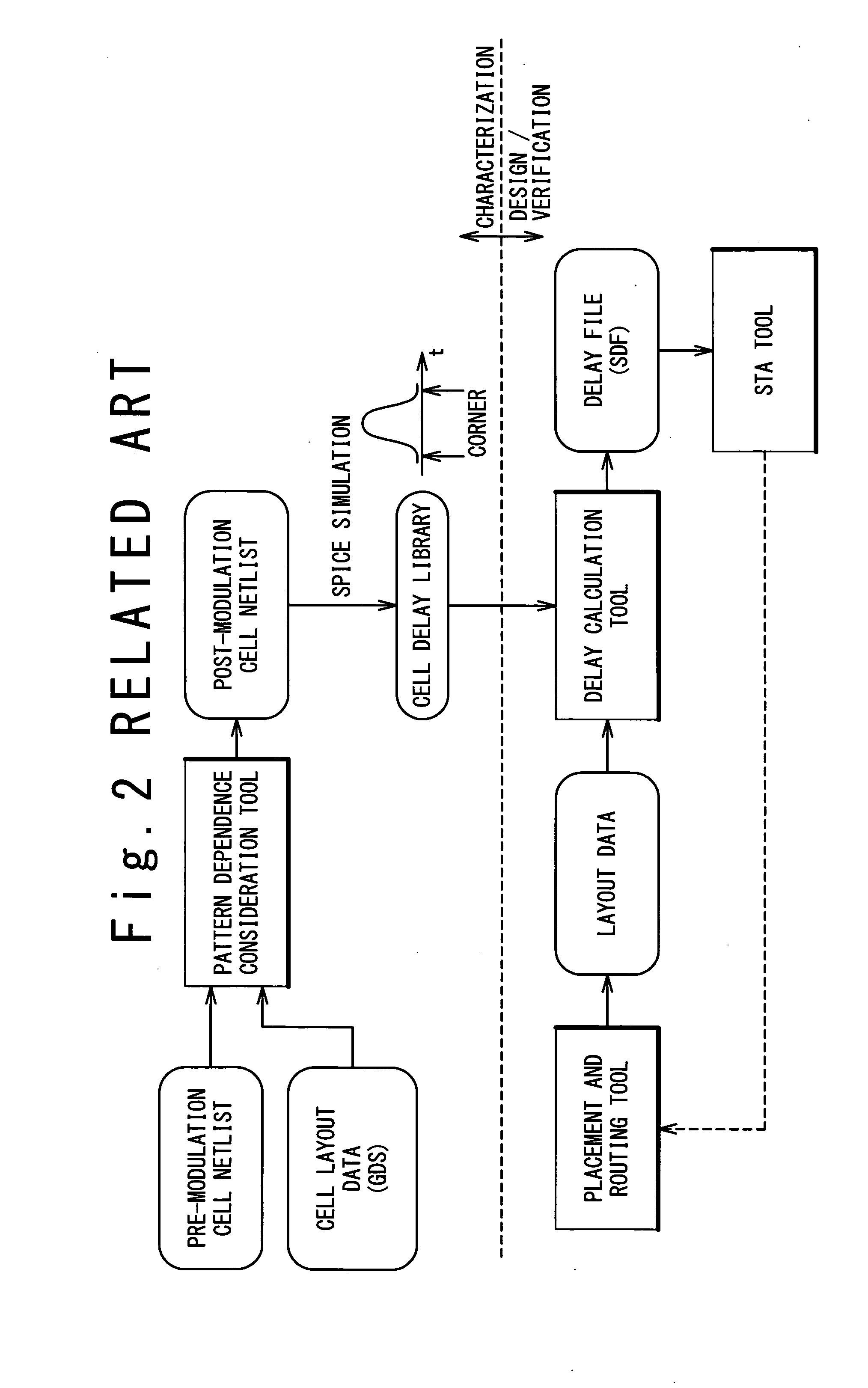

Method and program for designing semiconductor integrated circuit

InactiveUS20090024974A1Increase in design/verification TAT can be preventedHigh delay accuracyCAD circuit designSoftware simulation/interpretation/emulationModel parametersCell based

A design method for an LSI includes: generating a delay library for use in a statistical STA, wherein the delay library provides a delay function that expresses a cell delay value as a function of model parameters of a transistor; generating a layout data; and calculating a delay value of a target cell based on the delay library and the layout data. The calculating includes: referring to the layout data to extract a parameter specifying a layout pattern around a target transistor; modulating model parameters of the target transistor such that the characteristics corresponding to the extracted parameter is obtained in a circuit simulation; calculating, by using the delay function, a reference delay value of the target cell; and calculating, by using the delay function and the modulation amount of the model parameter, a delay variation from the reference delay value depending on the modulation amount.

Owner:RENESAS ELECTRONICS CORP

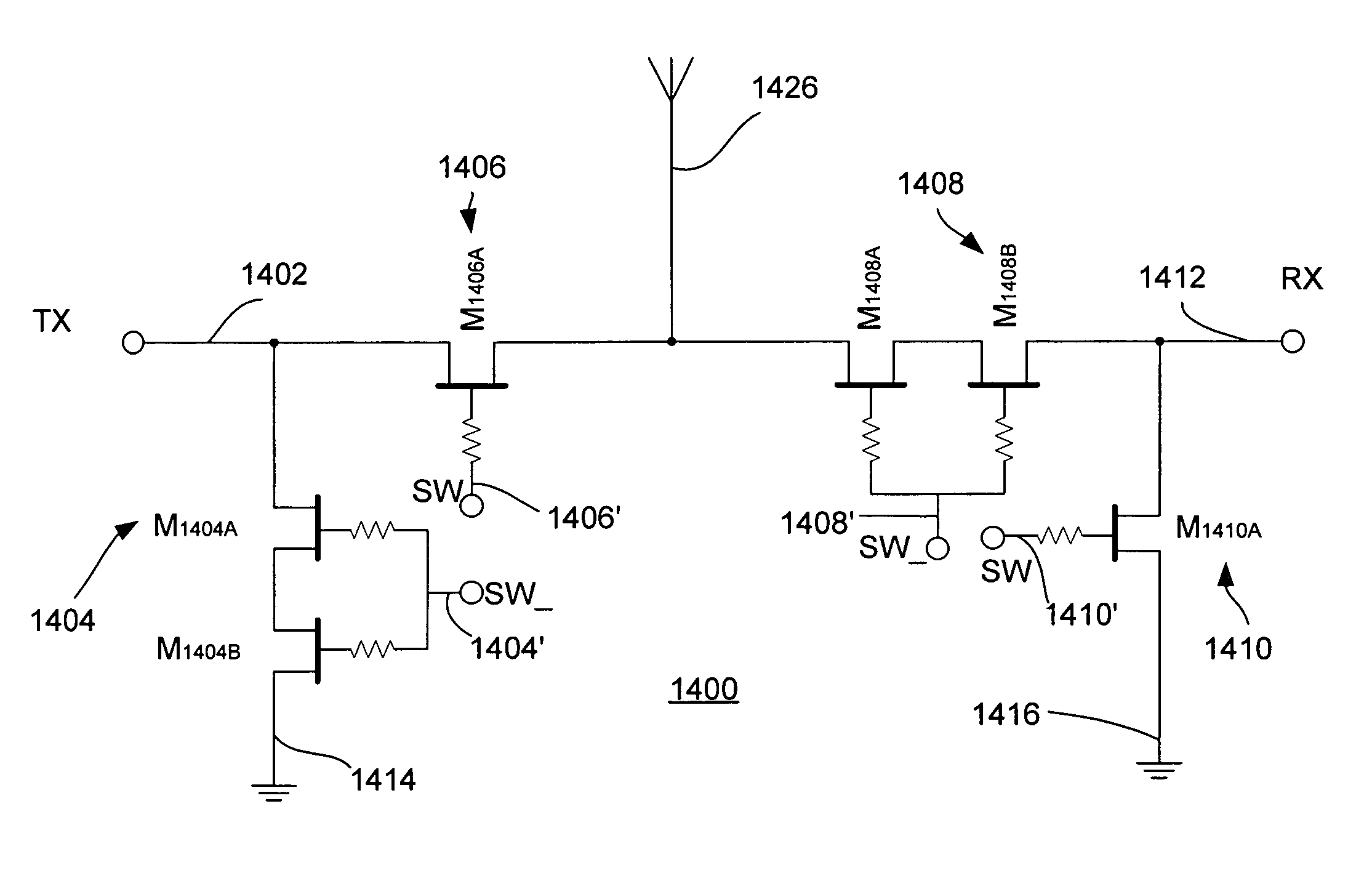

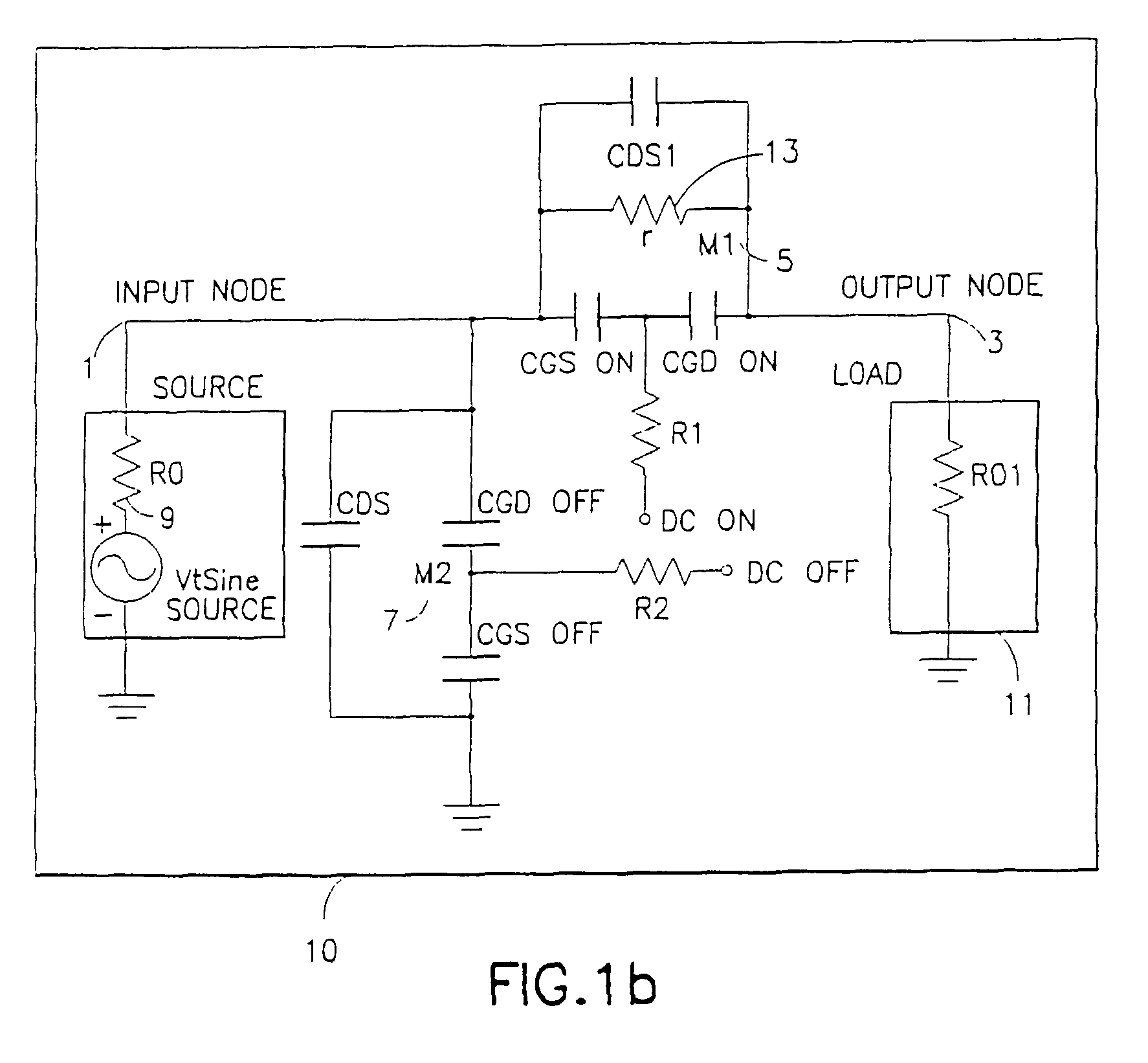

Symmetrically and asymmetrically stacked transistor group RF switch

A silicon-on-insulator (SOI) RF switch adapted for improved power handling capability using a reduced number of transistors is described. In one embodiment, an RF switch includes pairs of switching and shunting stacked transistor groupings to selectively couple RF signals between a plurality of input / output nodes and a common RF node. The switching and shunting stacked transistor groupings comprise one or more MOSFET transistors connected together in a “stacked” or serial configuration. In one embodiment, the transistor groupings are “symmetrically” stacked in the RF switch (i.e., the transistor groupings all comprise an identical number of transistors). In another embodiment, the transistor groupings are “asymmetrically” stacked in the RF switch (i.e., at least one transistor grouping comprises a number of transistors that is unequal to the number of transistors comprising at least one other transistor grouping). The stacked configuration of the transistor groupings enable the RF switch to withstand RF signals of varying and increased power levels. The asymmetrically stacked transistor grouping RF switch facilitates area-efficient implementation of the RF switch in an integrated circuit. Maximum input and output signal power levels can be withstood using a reduced number of stacked transistors.

Owner:PSEMI CORP

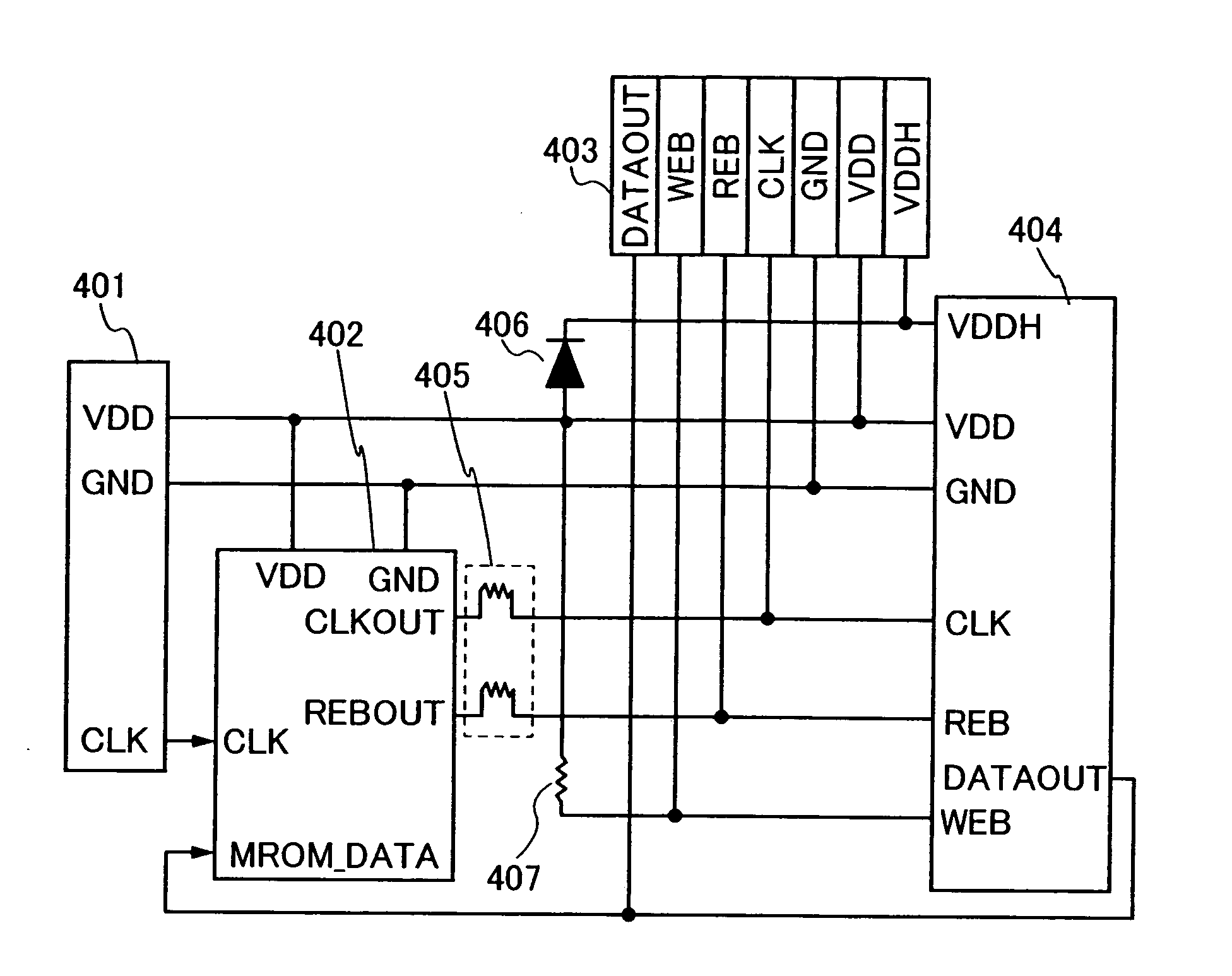

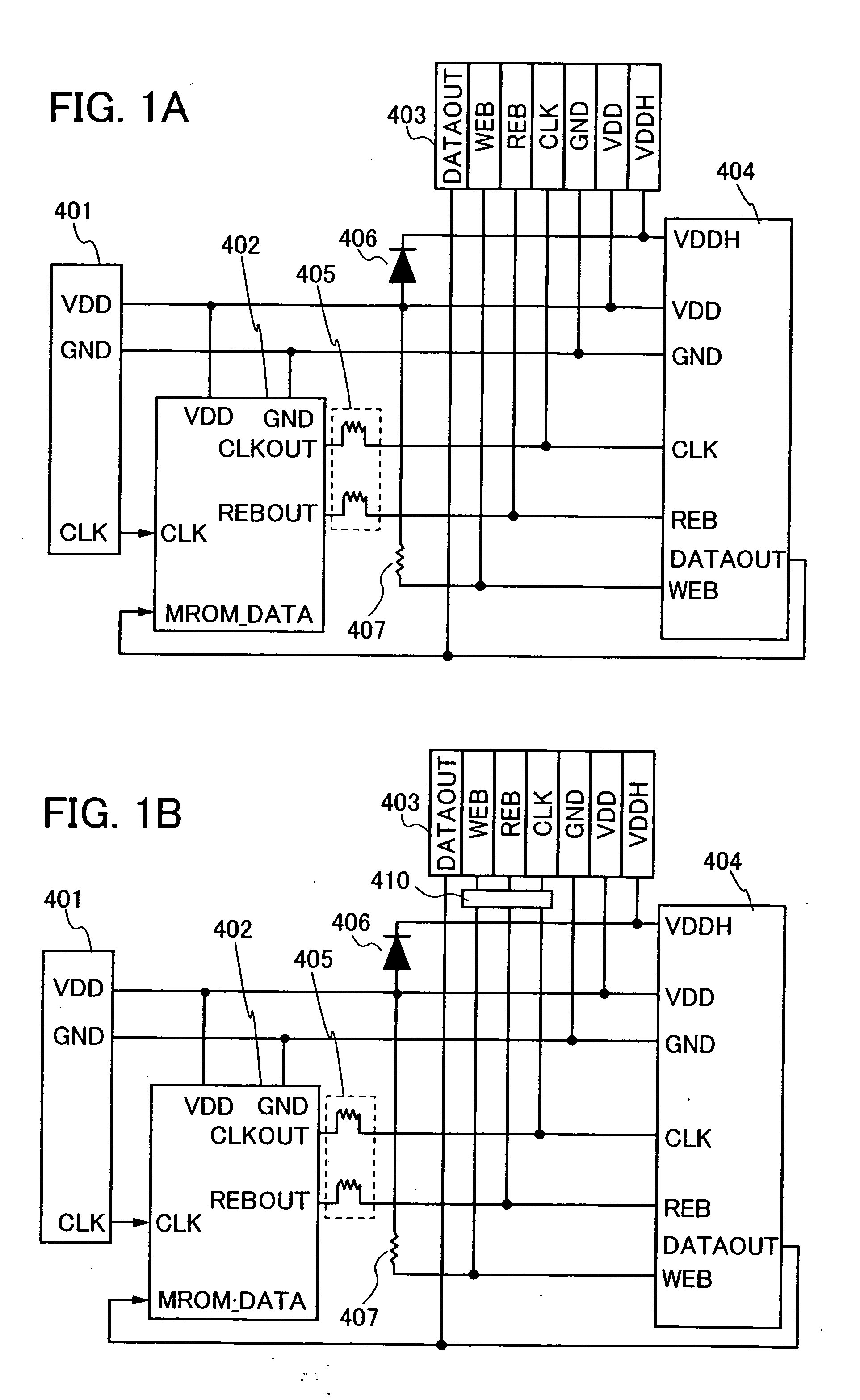

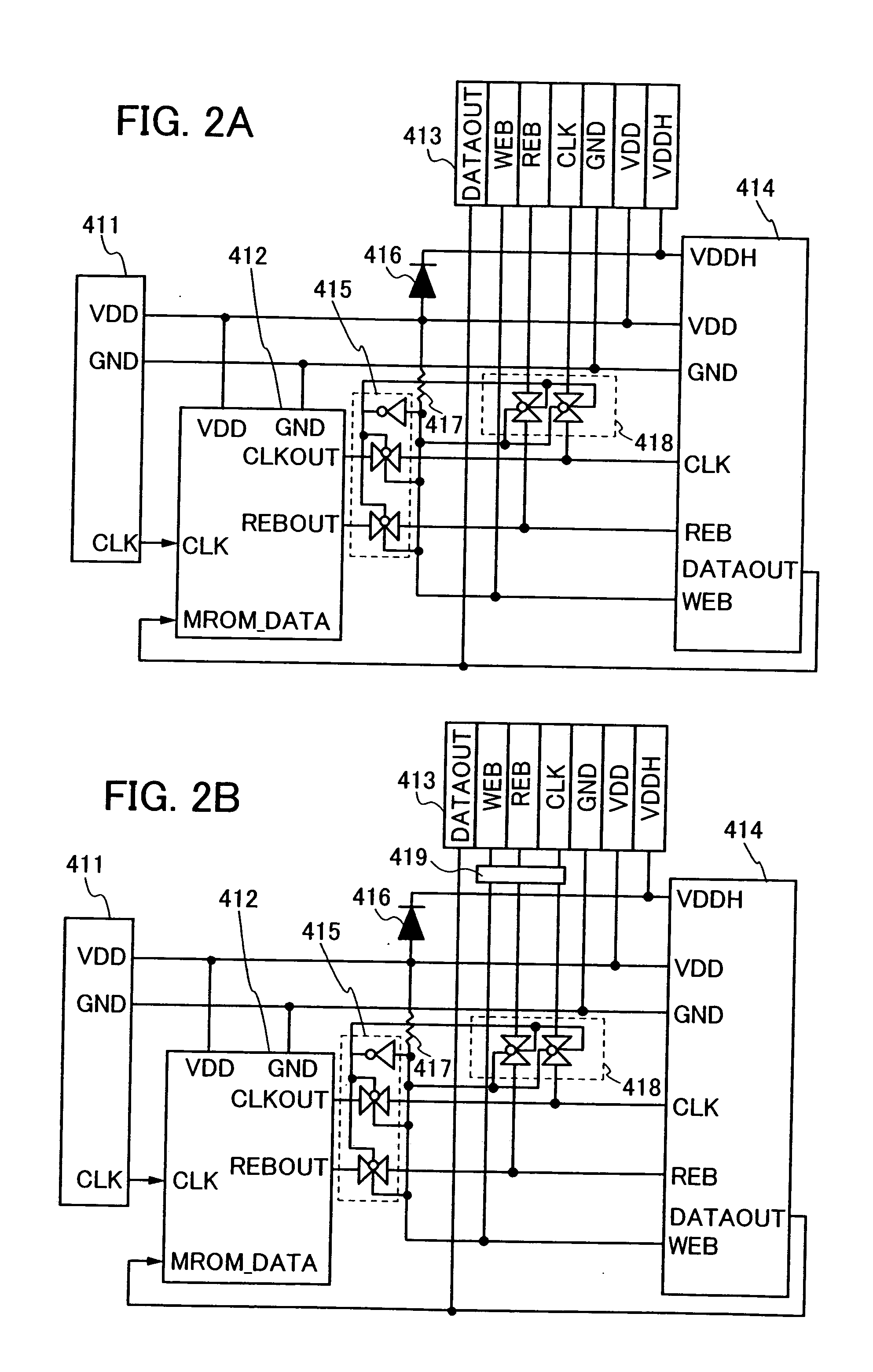

Semiconductor device and operating method thereof

InactiveUS20070123189A1Lower unit costReduce memory areaNanoinformaticsSolid-state devicesOrganic memoryBit line

In an organic memory which is included in a radio chip formed from a thin film, data are written to the organic memory by a signal inputted with a wired connection, and the data is read with a signal by radio transmission. A bit line and a word line which form the organic memory are each selected by a signal which specifies an address generated based on the signal inputted with a wired connection. A voltage is applied to a selected memory element. Thus writing is performed. Reading is performed by a clock signal or the like which are generated from a radio signal.

Owner:SEMICON ENERGY LAB CO LTD

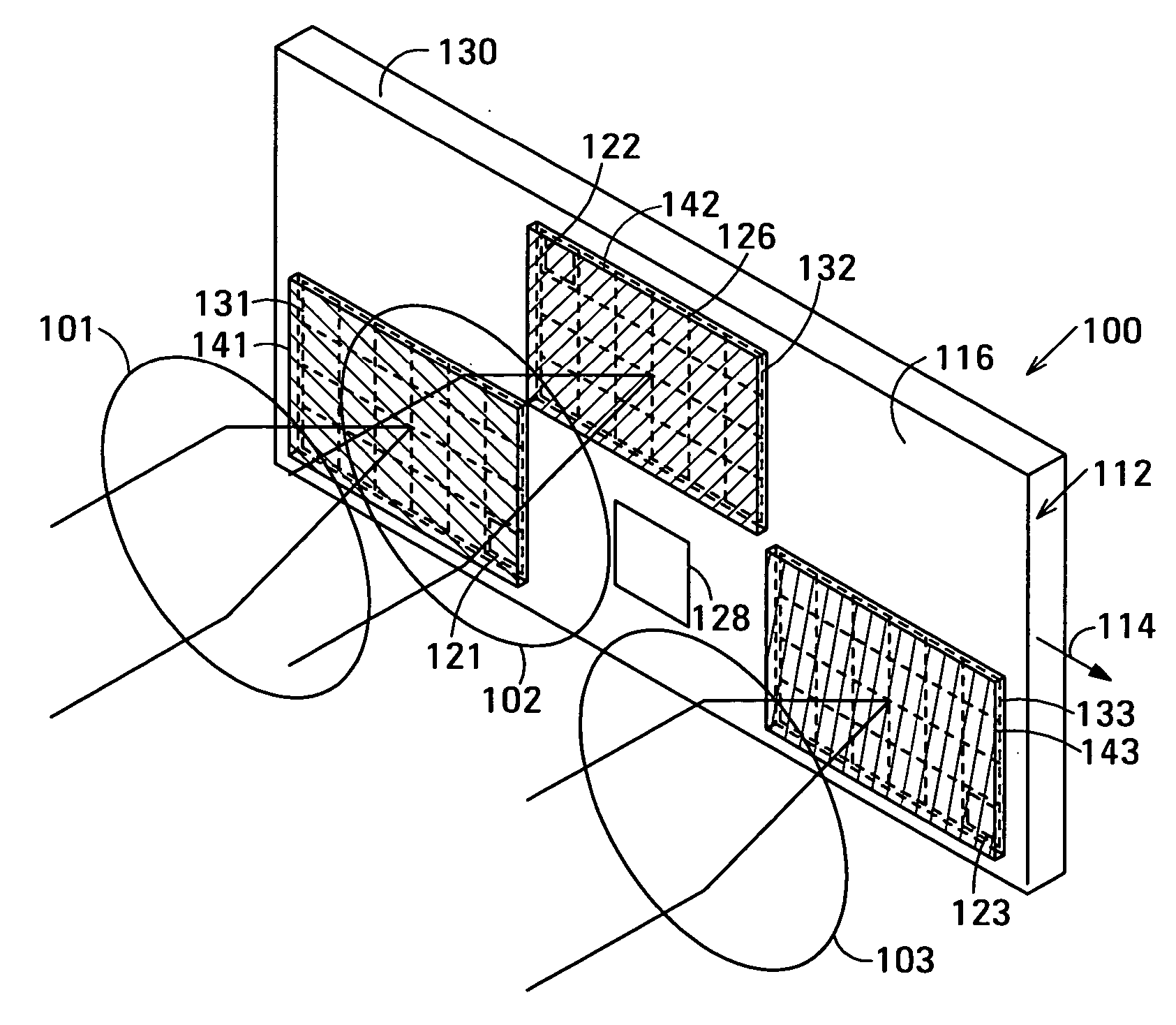

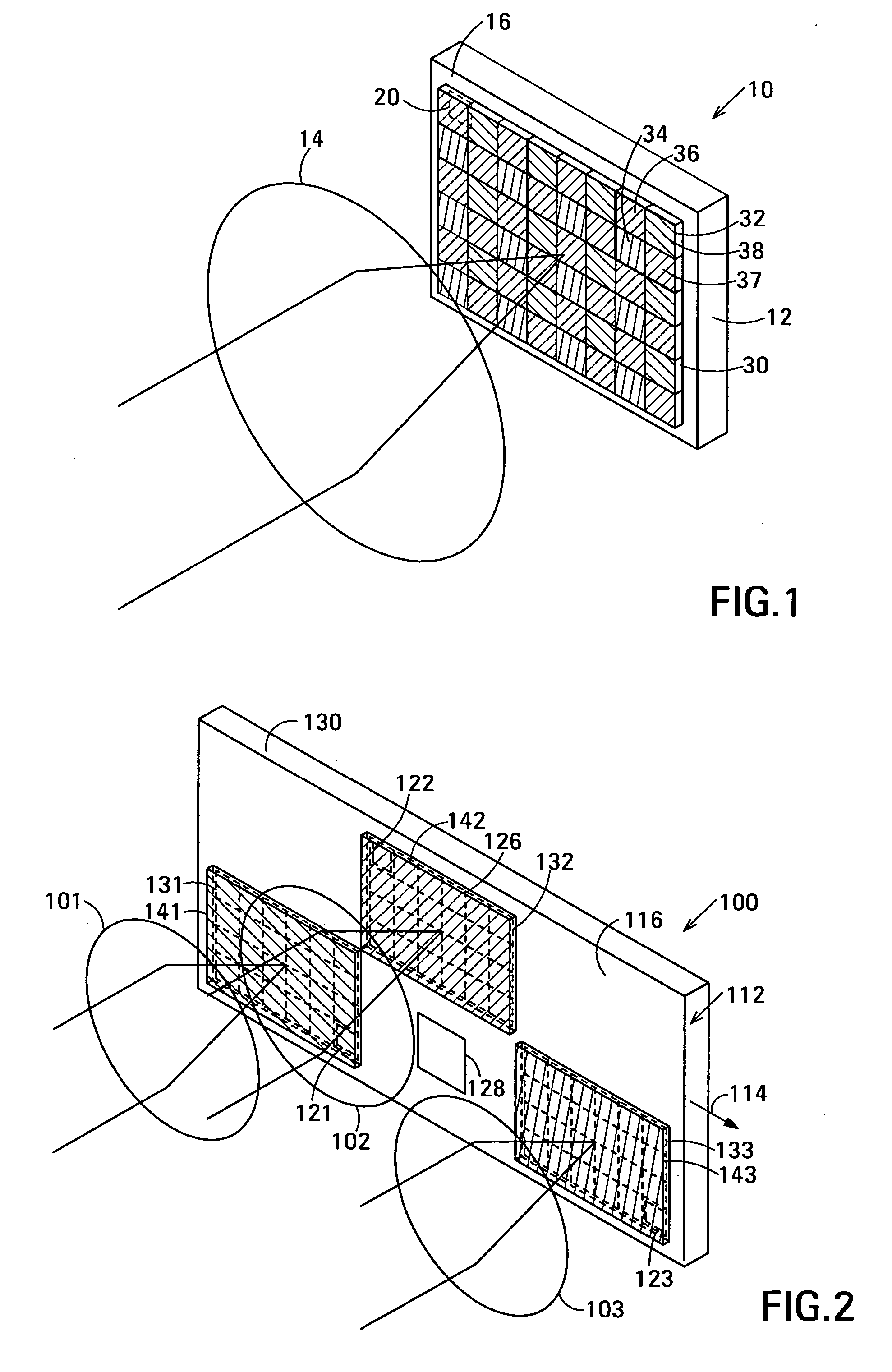

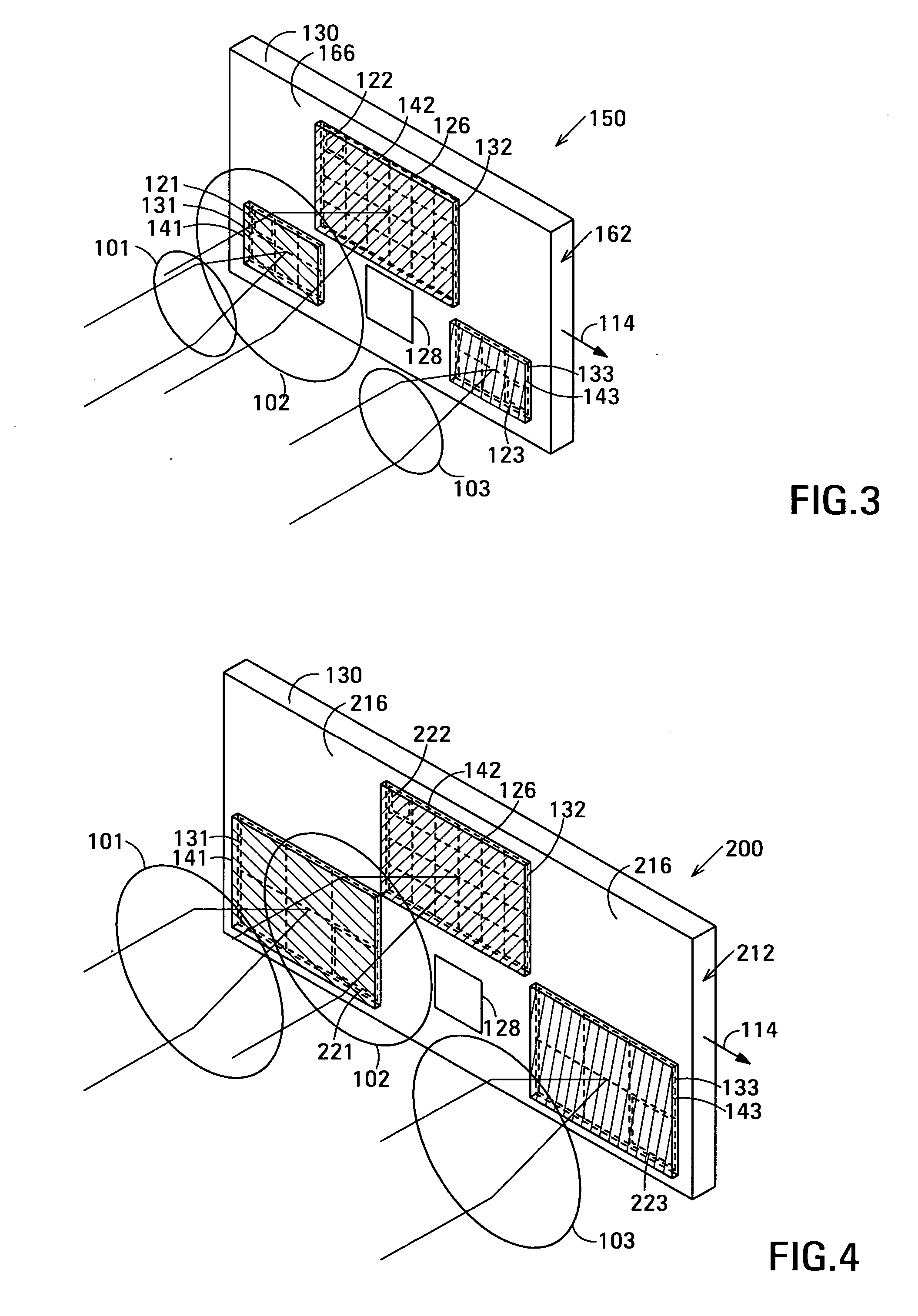

Color image sensor having imaging element array forming images on respective regions of sensor elements

The color image sensor generates a color image signal representing a subject and includes an optical substrate and a light sensor. The optical substrate includes spatially-separated imaging elements. Each of the imaging elements is configured to image light of a respective color. The light sensor includes regions of sensor elements disposed opposite respective ones of the imaging elements. The sensor elements in each of the regions are operable to generate a component of the color image signal in response to the light of the respective color incident on them.

Owner:APTINA IMAGING CORP

Devices and methods for repairing cardiac valves

InactiveUS20050159810A1Without reducing effective valve areaPermit leaflet coaptationHeart valvesWound clampsHeart valveVALVE PORT

Devices and methods for the repair of a defective cardiac valve are provided. The implantable devices provide a leaflet coaptation surface and correct for one or more prolapsing segments of a valve leaflet. The methods involve implanting one or more devices within the defective cardiac valve. In certain embodiments, the devices and methods correct for billowing leaflets and / or a dilated valve annulus.

Owner:MT SINAI SCHOOL OF MEDICINE

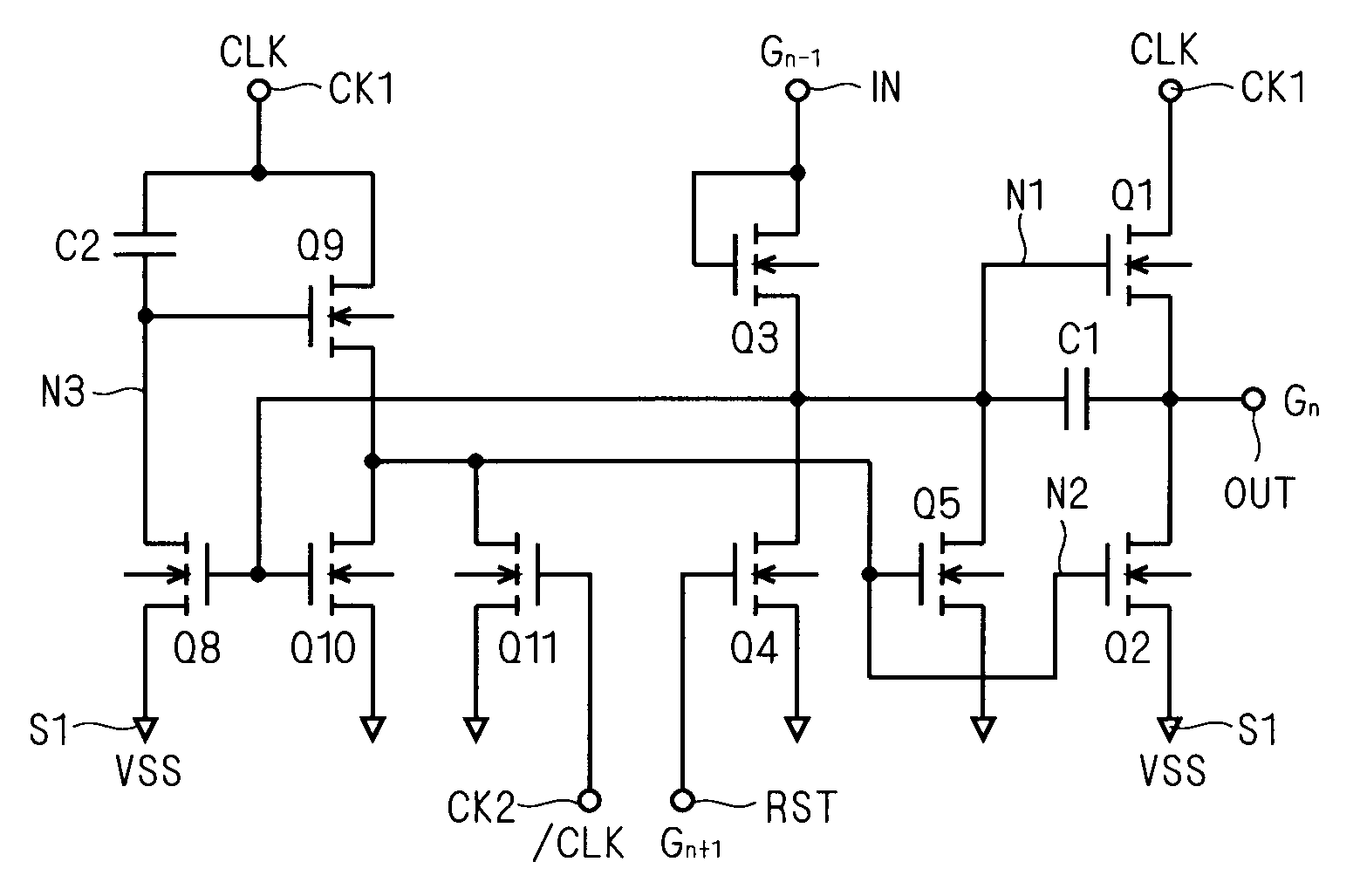

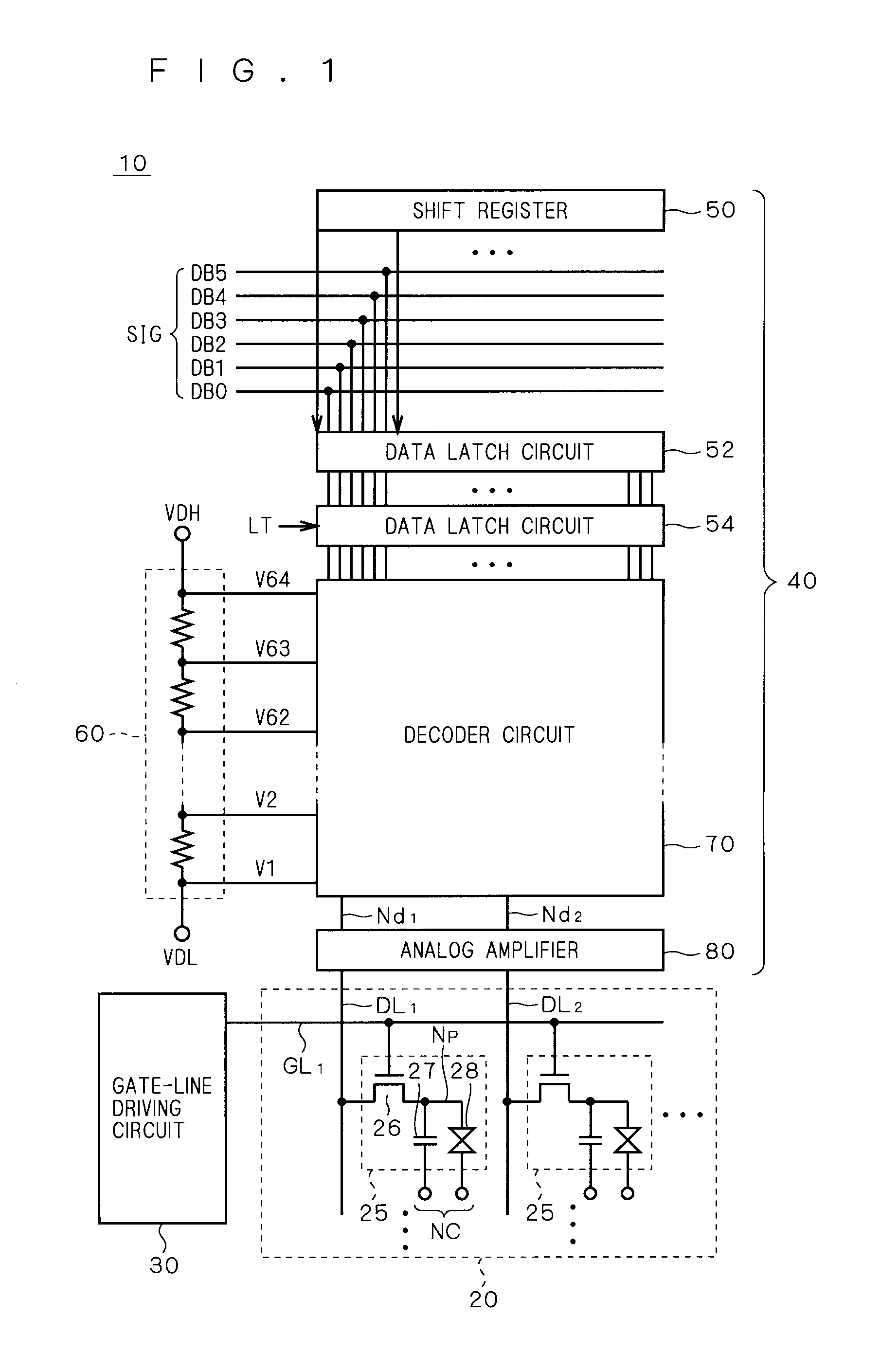

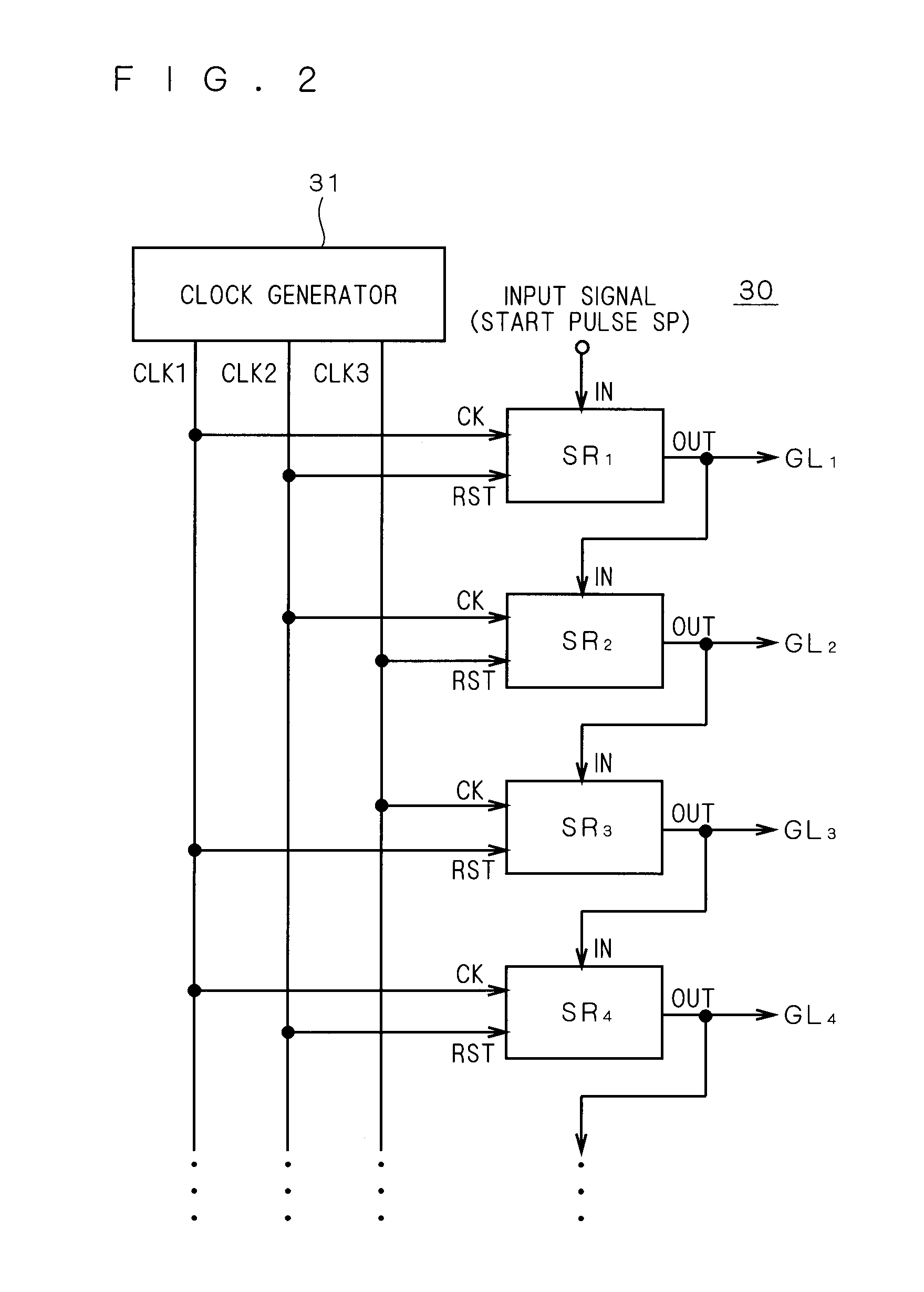

Shift register and image display apparatus containing the same

ActiveUS20080101529A1Increased circuit areaImprove driving reliabilityStatic indicating devicesDigital storagePower inverterShift register

A shift register includes a first transistor supplying an output terminal with a clock signal input to a first clock terminal and a second transistor discharging the output terminal. Defining the gate node of the first transistor as a first node, and the gate node of the second transistor as a second node, the shift register includes an inverter circuit in which the first node serves as its input node and a capacitive element serves as a load, and a buffer circuit receiving the output from the inverter circuit and outputting a signal to the second node.

Owner:TRIVALE TECH

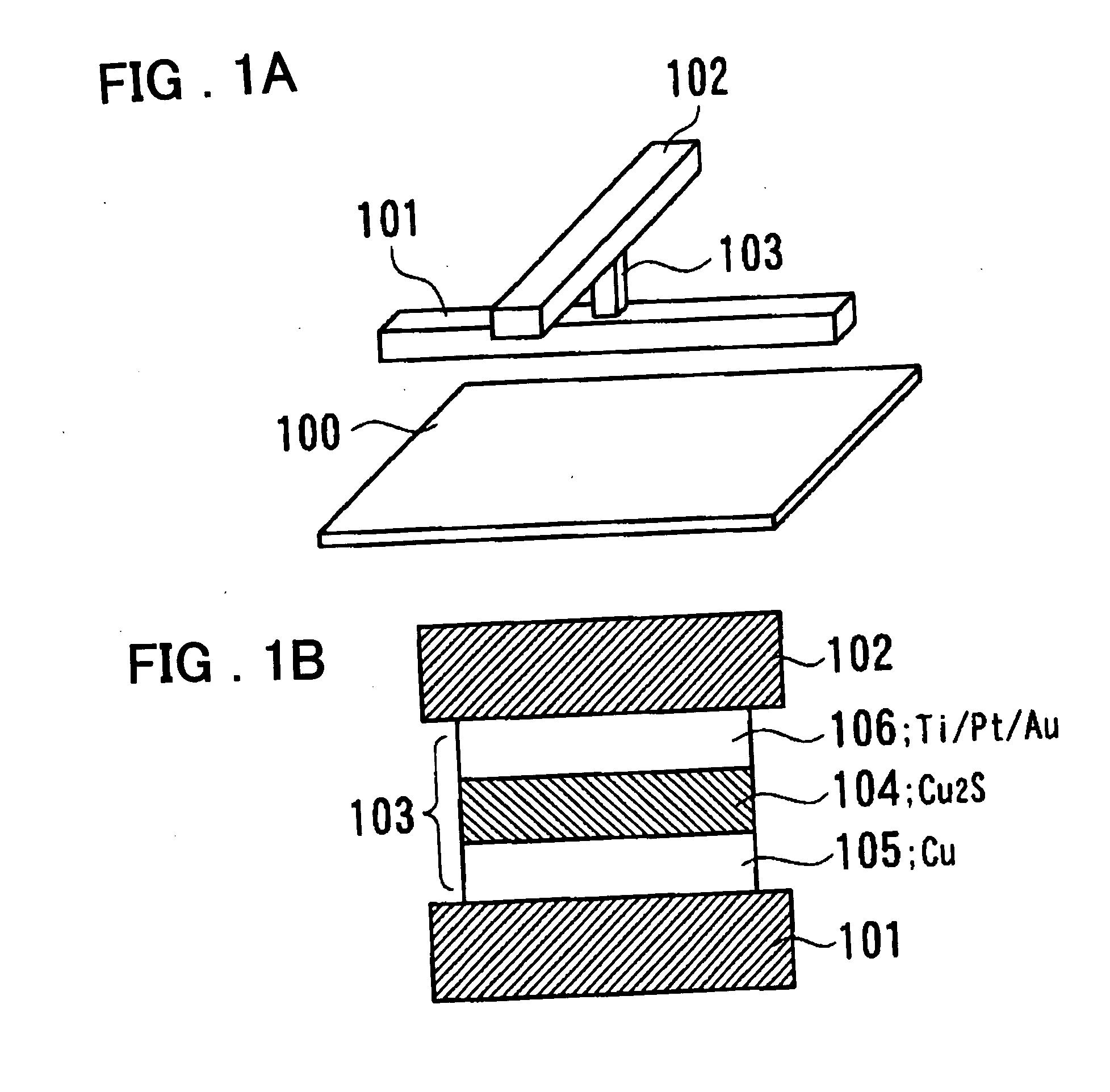

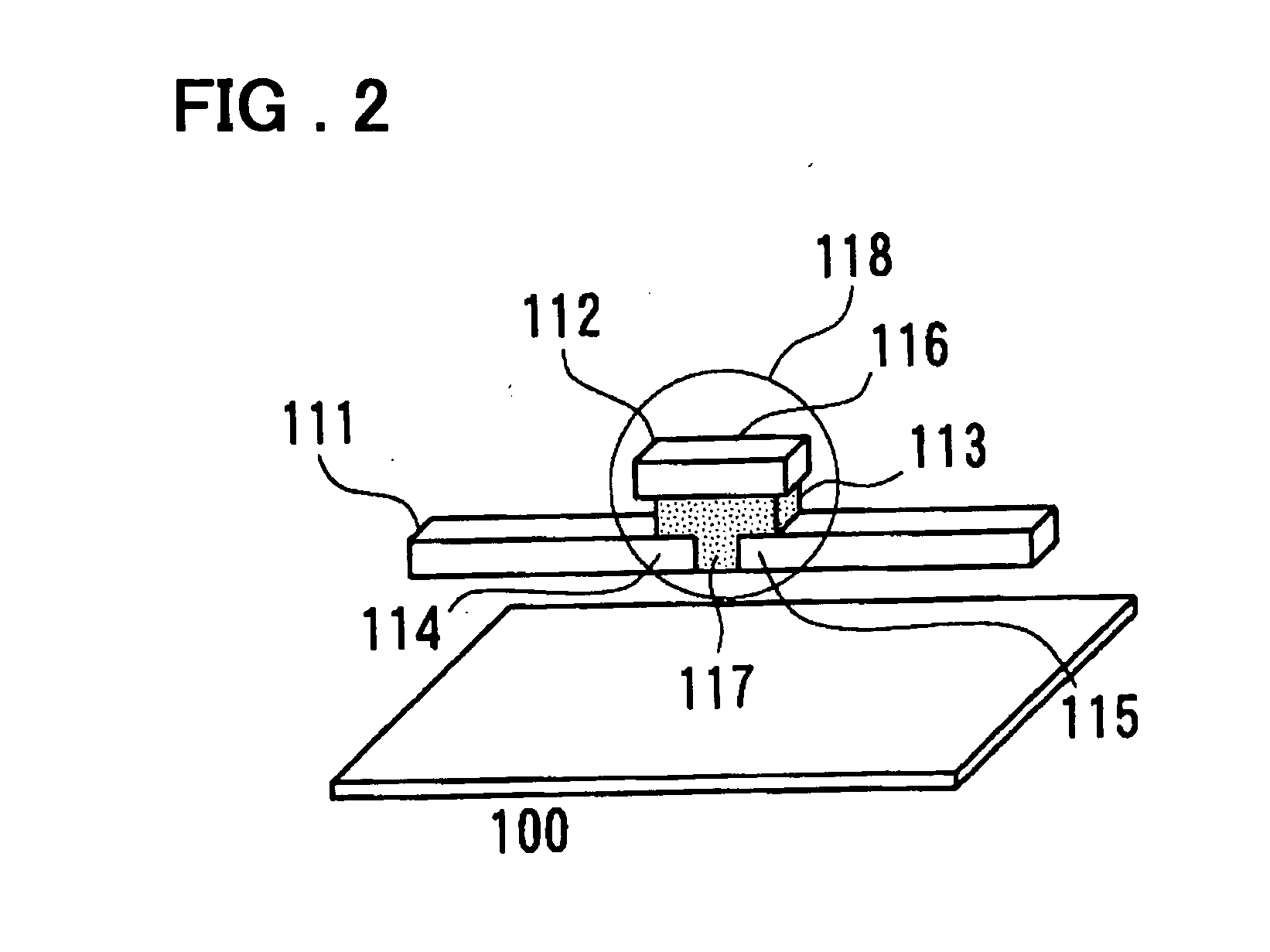

Semiconductor device

InactiveUS20050045919A1Increase the areaFine granularitySemiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

A programmable semiconductor device has a switch element in an interconnection layer, wherein in at least one of the inside of a via, interconnecting a wire of a first interconnection layer and a wire of a second interconnection layer, a contact part of the via with the wire of the first interconnection layer and a contact part of the via with the wire of the second interconnection layer, there is provided a variable electrical conductivity member, such as a member of an electrolyte material. The via is used as a variable electrical conductivity type switch element or as a variable resistance device having a contact part with the wire of the first interconnection layer as a first terminal and having a contact part with the wire of the second interconnection layer as a second terminal. By varying the electrical conductivity of the switch element, the state of connection of the via with the wire of the first interconnection layer and the state of connection of the via with the wire of the second interconnection layer may be variably set to a shorted state, an open-circuited state or to an intermediate state A two-state switch element includes an ion conductor for conducting metal ions interposed between the first and second electrodes. The second electrode is formed of a material lower in reactivity than the first electrode. The electrical conductivity across the first and second electrodes is changed by the oxidation-reduction reaction of the metal ions. There are provided first and second transistors of opposite polarities, connected to the first electrode, and third and fourth transistors of opposite polarities, connected to the second electrode.

Owner:NEC CORP

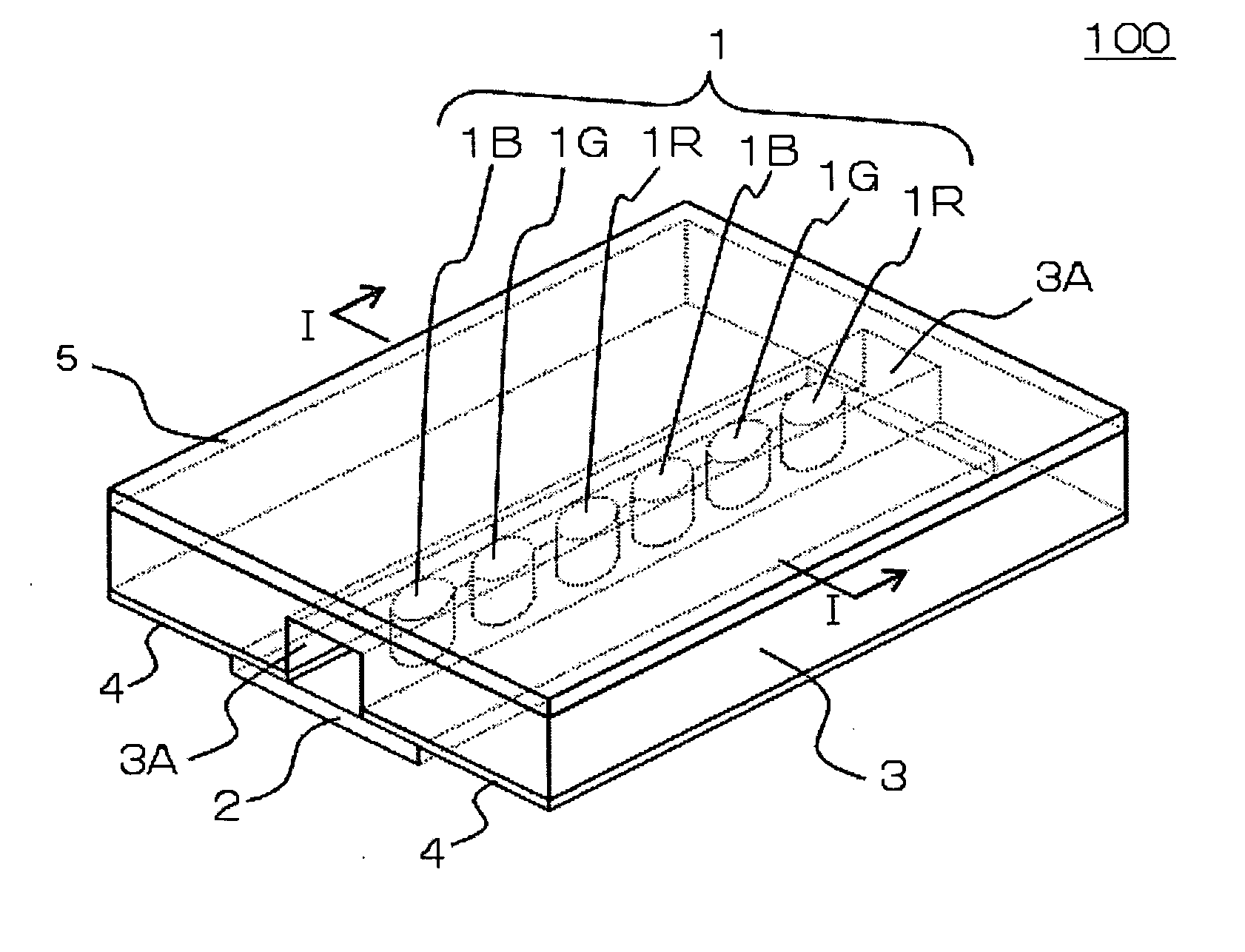

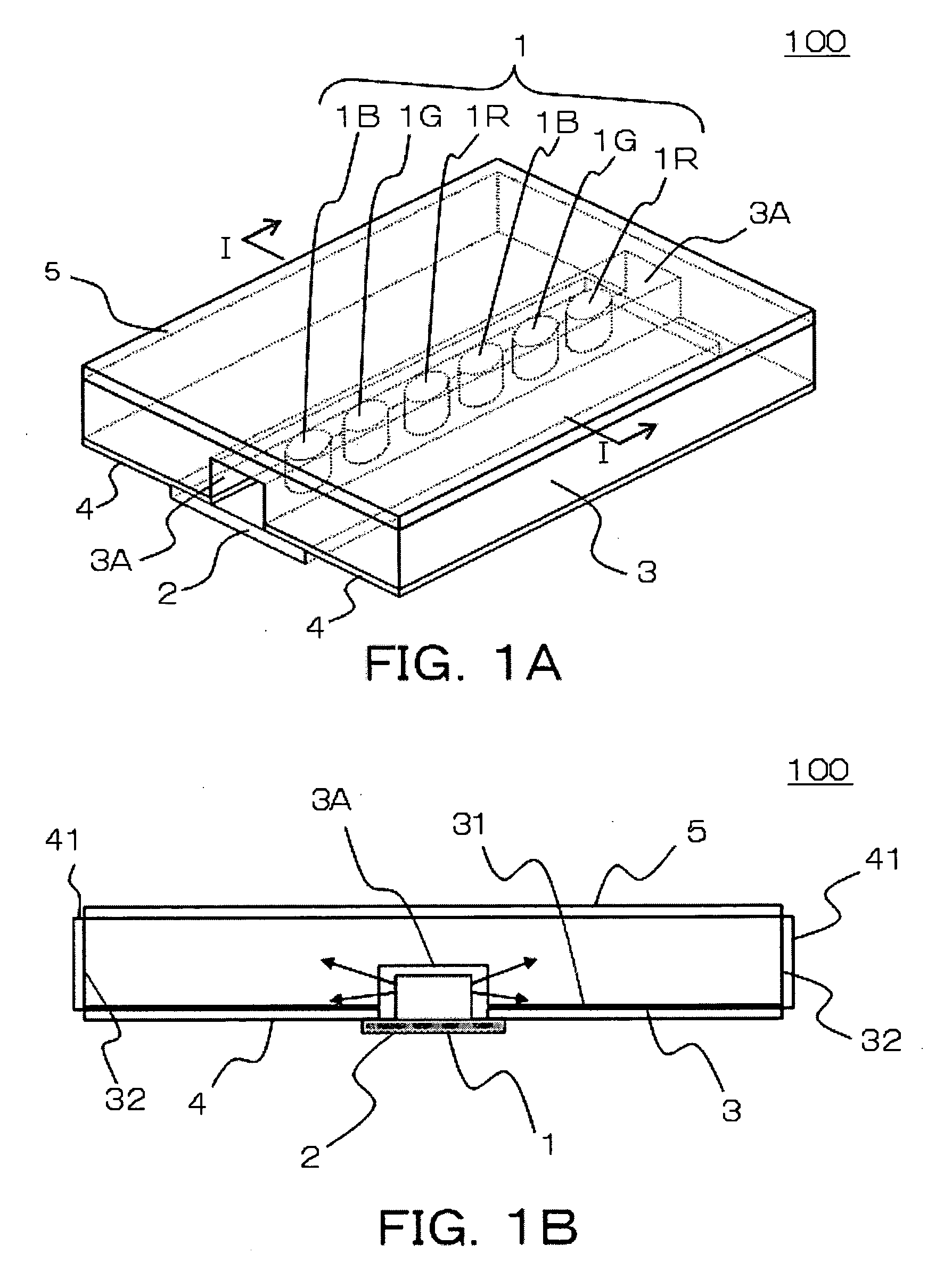

Backlight unit and liquid crystal display device using the same

InactiveUS20060002146A1Efficient mixingLittle color changeOptical light guidesNon-linear opticsLiquid-crystal displayLight guide

Light emitted in side surface directions from side-emitting red, green, and blue LEDs which are arranged on an LED array substrate is introduced into a light guide from side surfaces of a groove-shaped recessed portion, and propagates in the light guide. Thus, the three colors are mixed. The light further propagates in the light guide while being reflected at both side end surfaces of the light guide by the function of a reflective sheet and the like. Thus, color mixing progresses. Further, the light is reflected upward by diffuse reflective means provided on the lower surface of the light guide, and emitted as backlight light to the outside through a diffuse sheet.

Owner:NEC LCD TECH CORP

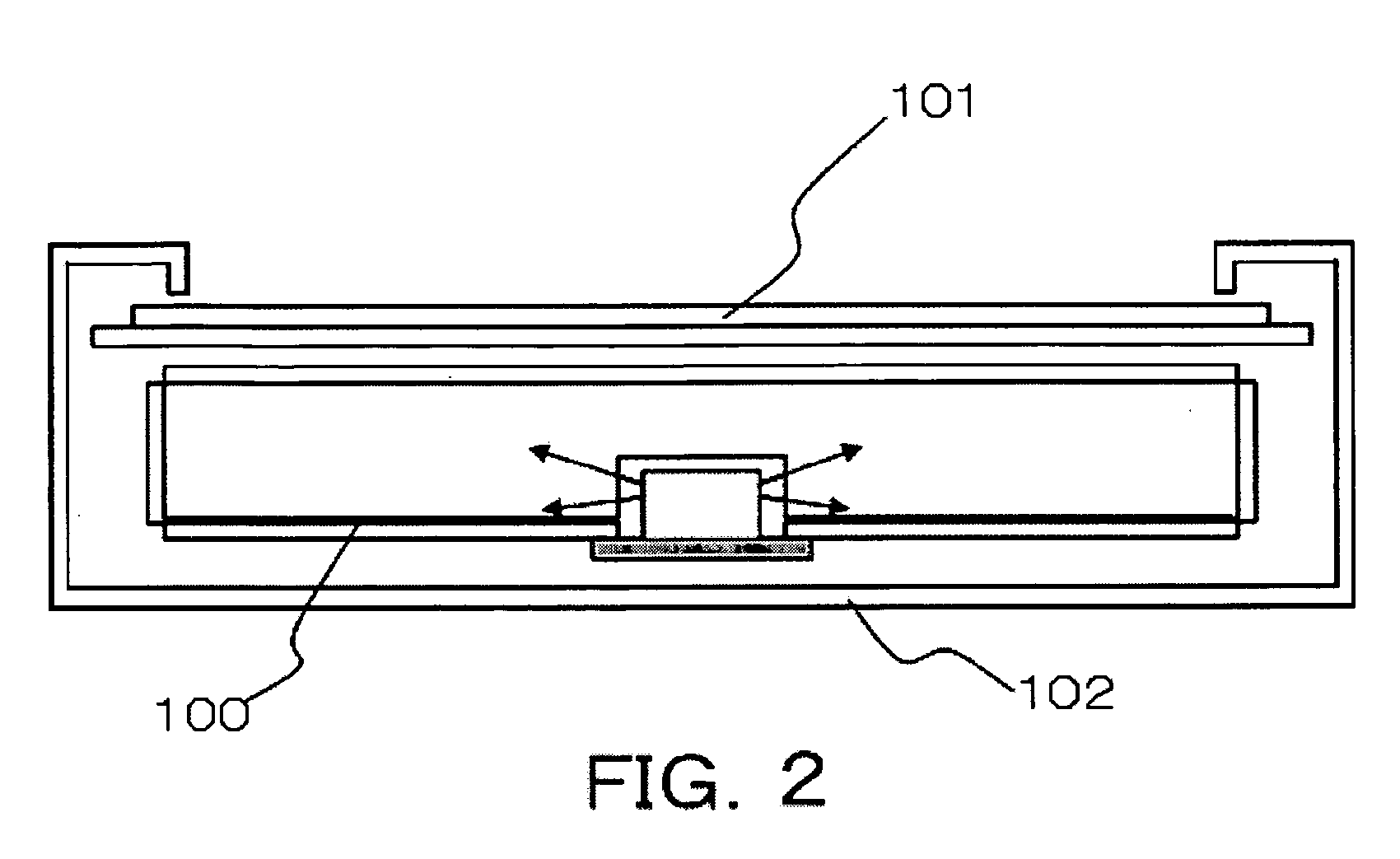

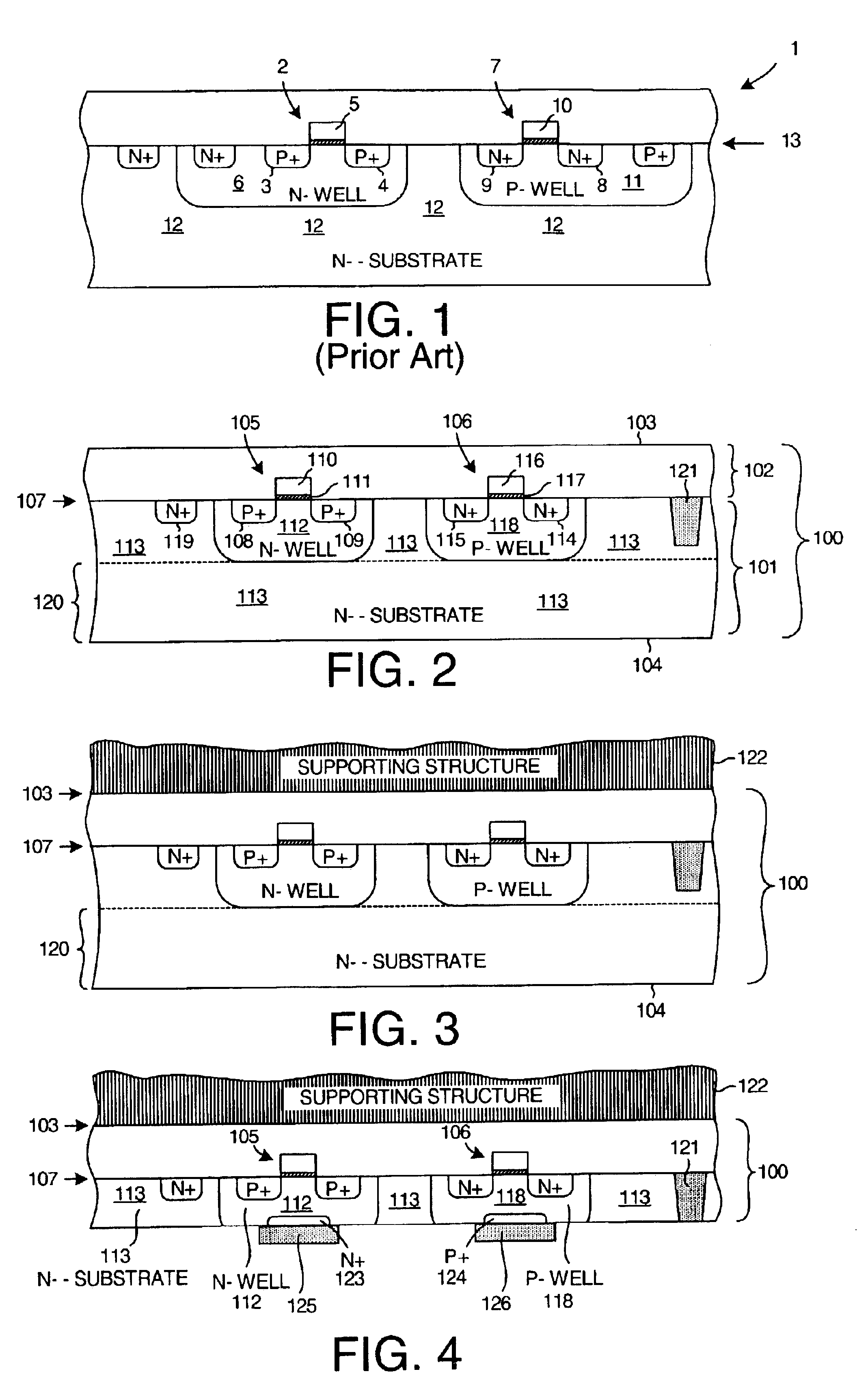

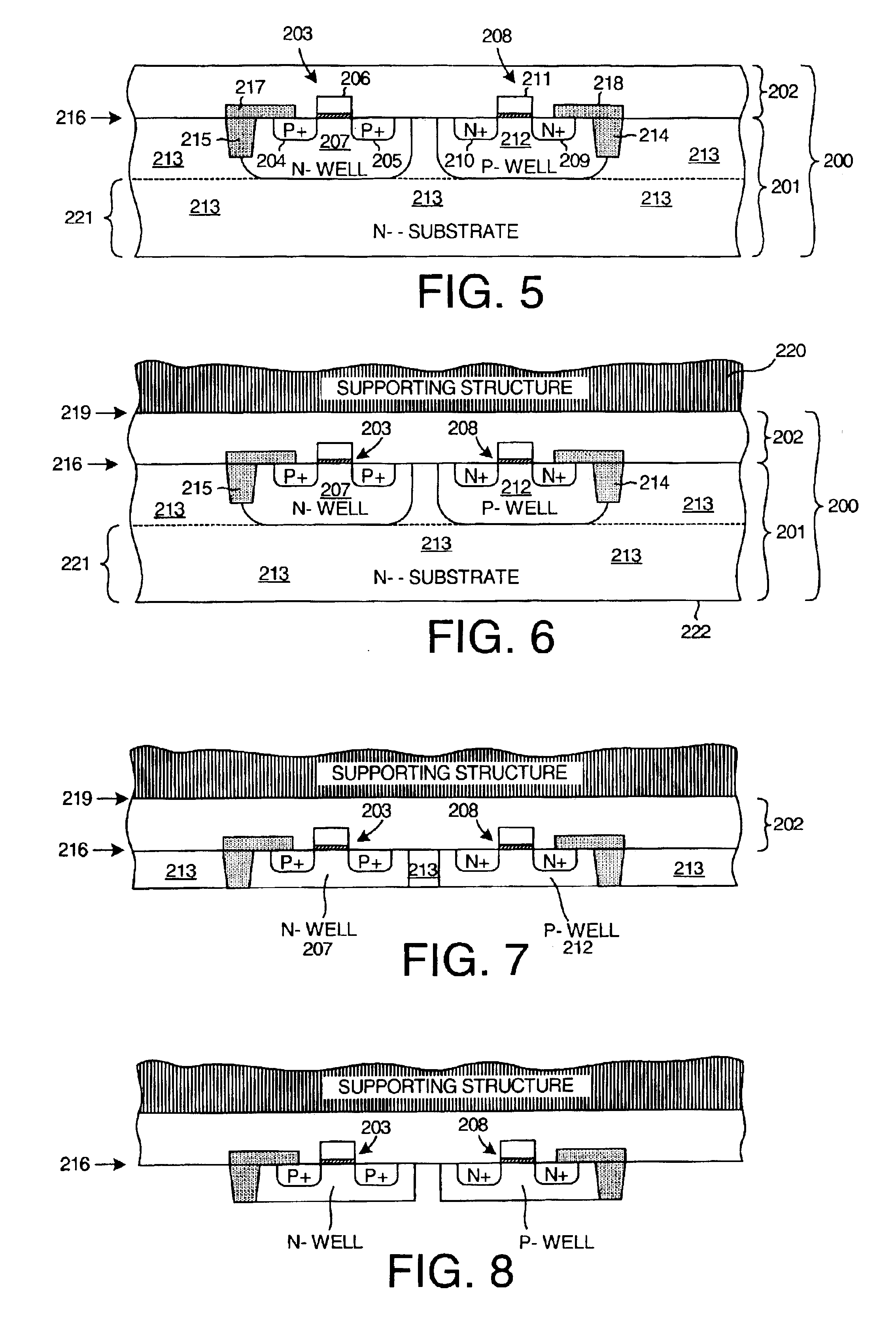

Semiconductor wafer with well contacts on back side

InactiveUS6864156B1Little source-to-wellImprove leakageTransistorSolid-state devicesCapacitanceEngineering

A supporting structure is wafer-bonded to the upper face side of a partially or fully processed device wafer. The device wafer includes a transistor having a well region that extends into the substrate material of the device wafer. The source and drain regions of the transistor extend into the well region. After attachment of the supporting structure, the device wafer is thinned from the back side until the bottom of the well region is reached. To reduce source and drain junction capacitances, etching can continue until the source and drain regions are reached. In one embodiment, all of the well-to-substrate junction is removed in a subsequent etching step, thereby reducing or eliminating the well-to-substrate junction capacitance of the resulting transistor. Resistance between the well electrode and the transistor channel is reduced because the well contact is disposed on the back side of the device wafer directly under the gate of the transistor.

Owner:XILINX INC

Combined patient interface and exhaust assembly

InactiveUS6584977B1Narrowing the exhaust pathReduce the effective cross-sectional areaBreathing masksRespiratory masksMedicineMechanical engineering

A combined patient interface and integrated exhaust assembly that passes a controlled flow of gas from an interior of a patient interface to ambient atmosphere at a predetermined flow rate irrespective of variations of pressure in the interior of the patient interface device relative to ambient atmosphere. Control of the flow of exhaust gas is achieved by varying the effective cross sectional area of the exhaust path communicating the interior of the patient interface with ambient atmosphere based on the pressure in the interior of the patient interface relative to ambient atmospheric pressure.

Owner:RIC INVESTMENTS LLC

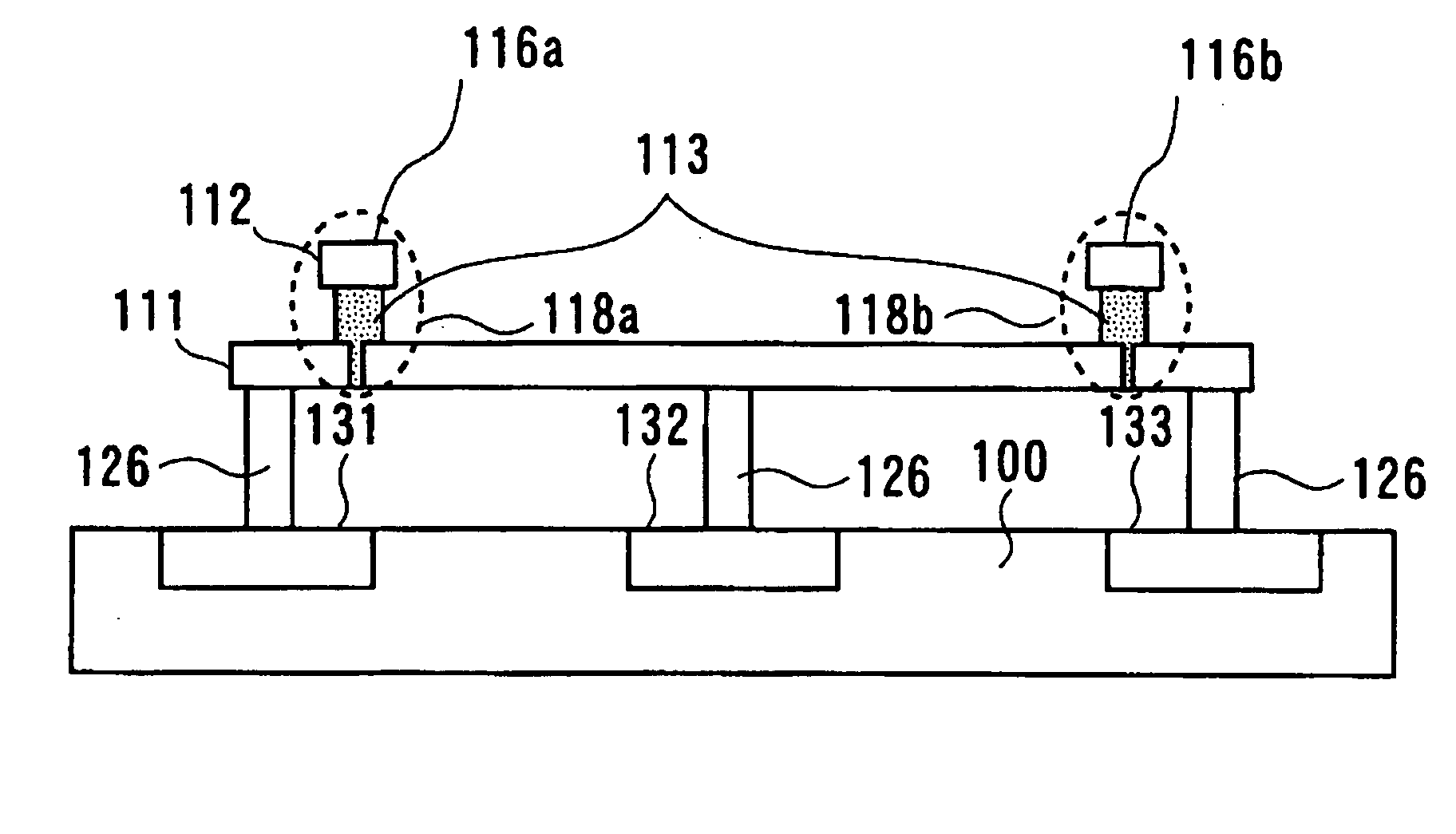

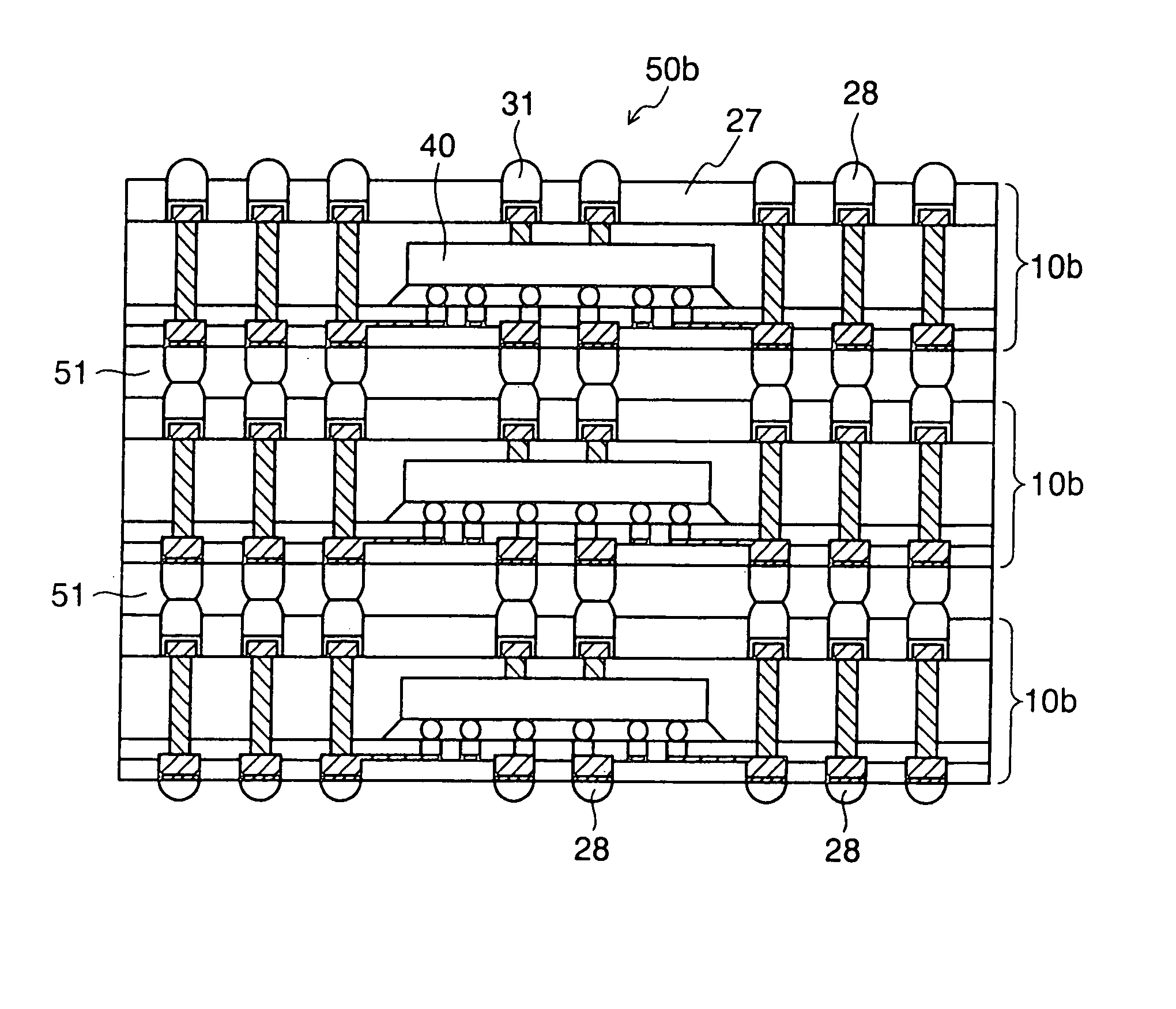

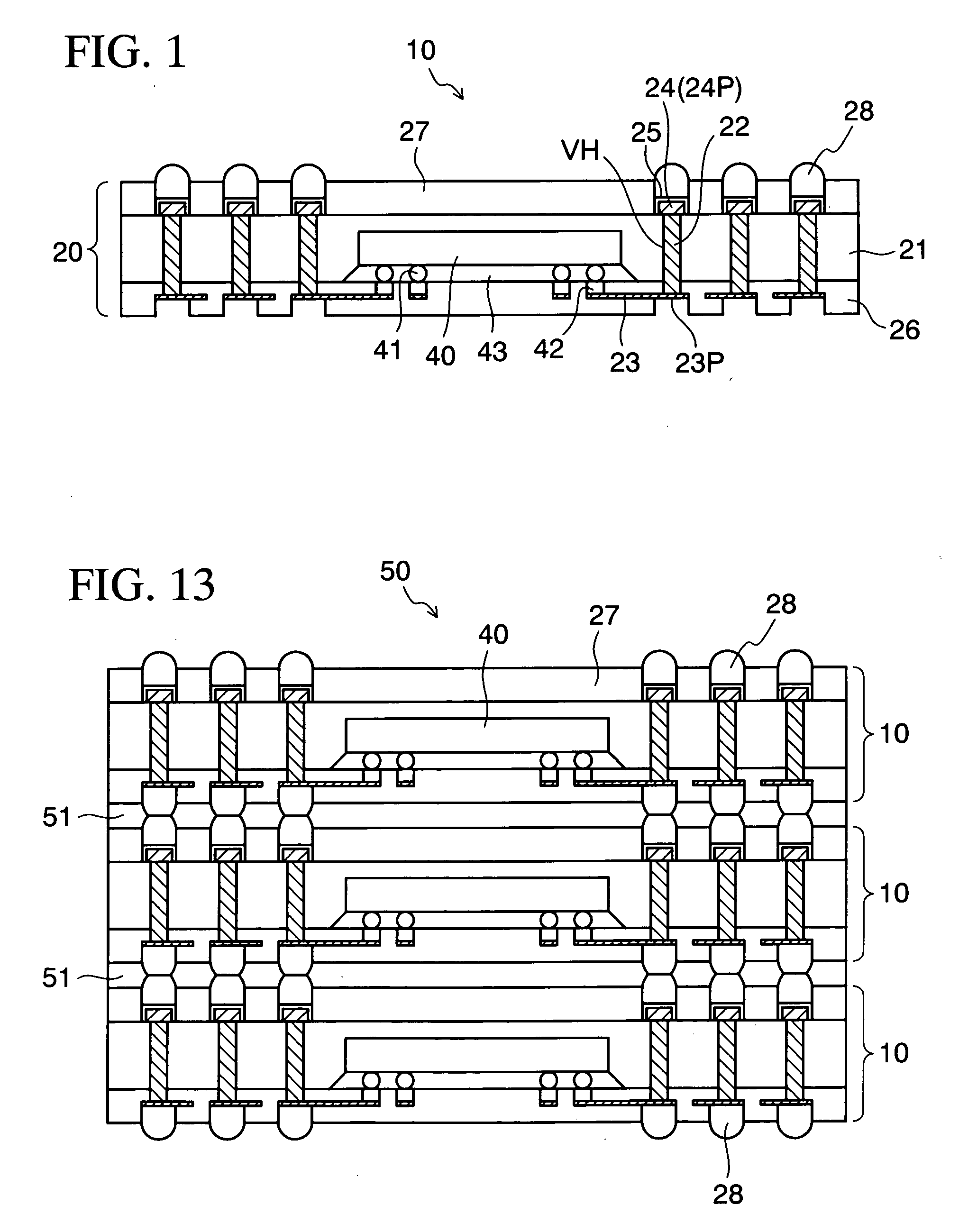

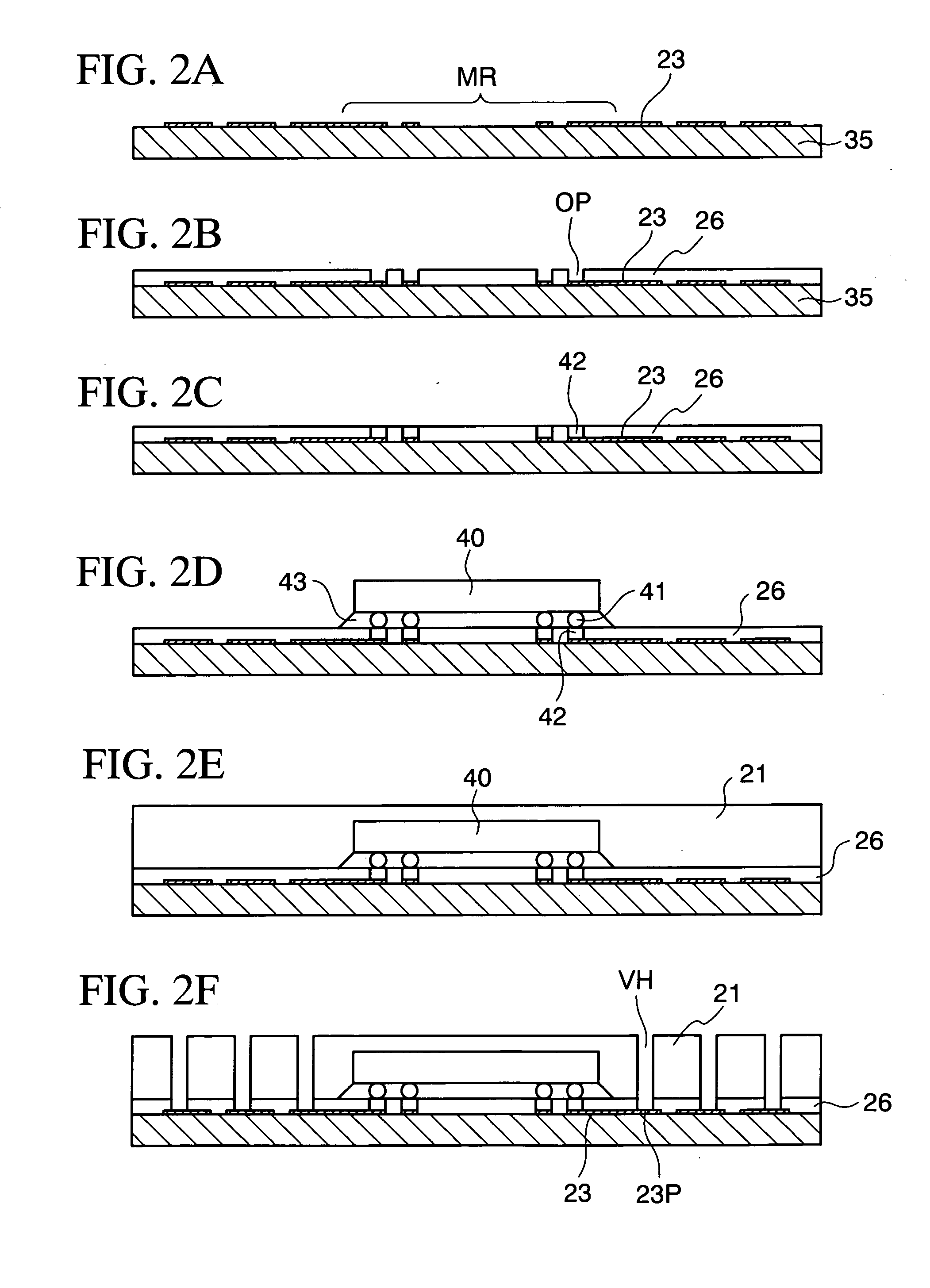

Semiconductor device and method of manufacturing the same

InactiveUS20050184377A1Increase freedomFunction increaseSemiconductor/solid-state device detailsSolid-state devicesTectorial membraneElectrical conductor

In a semiconductor device, via holes are formed around a chip buried in a package, and conductor layers are respectively formed to be connected to one end and another end of the conductor filled in the individual via hole. Portions (pad portions) of the conductor layers which correspond to the conductors are exposed from protective films, or external connection terminals are bonded to the pad portions. The chip is mounted with flip-chip technology so that at least some of electrode terminals thereof are electrically connected to the conductor layers.

Owner:SHINKO ELECTRIC IND CO LTD

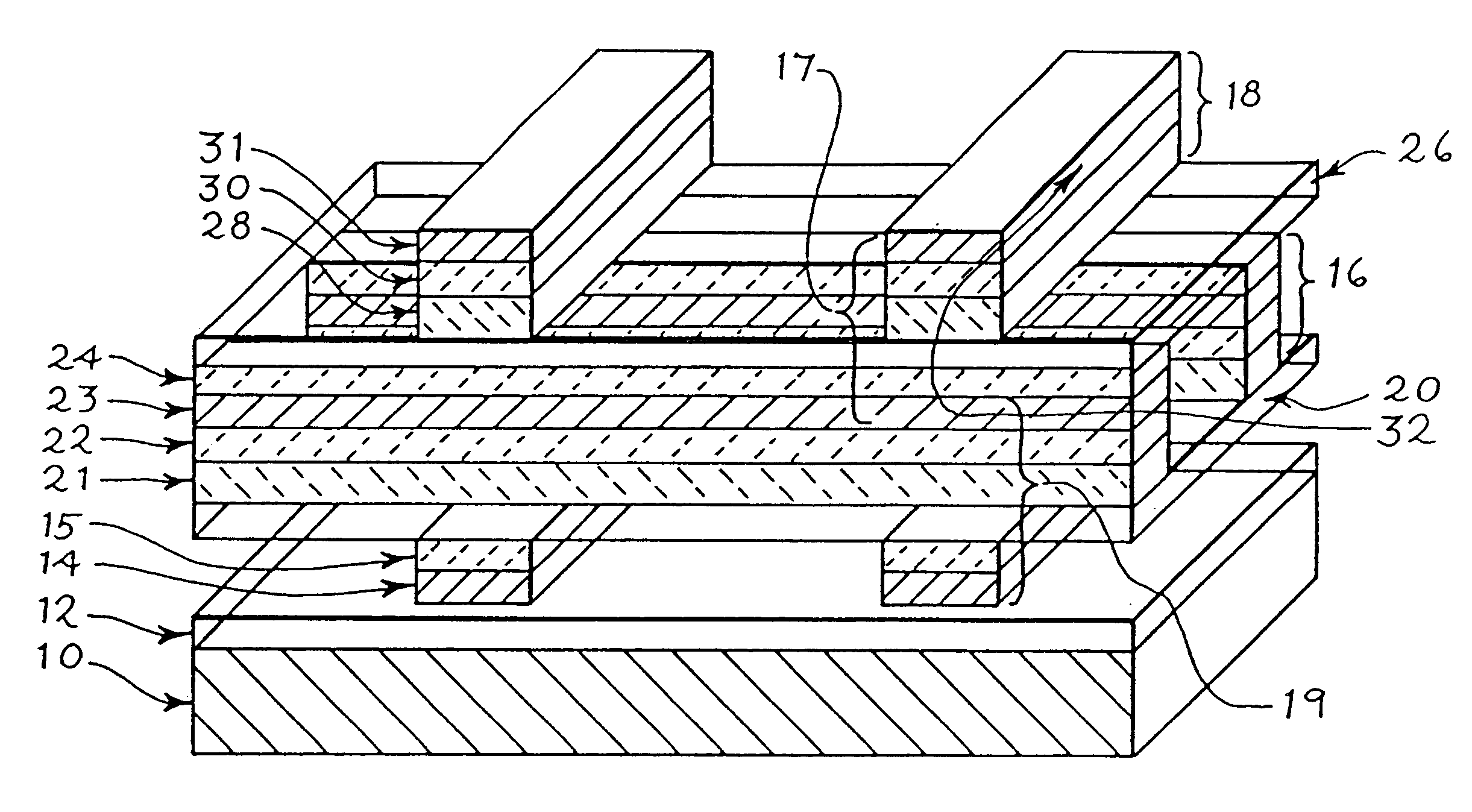

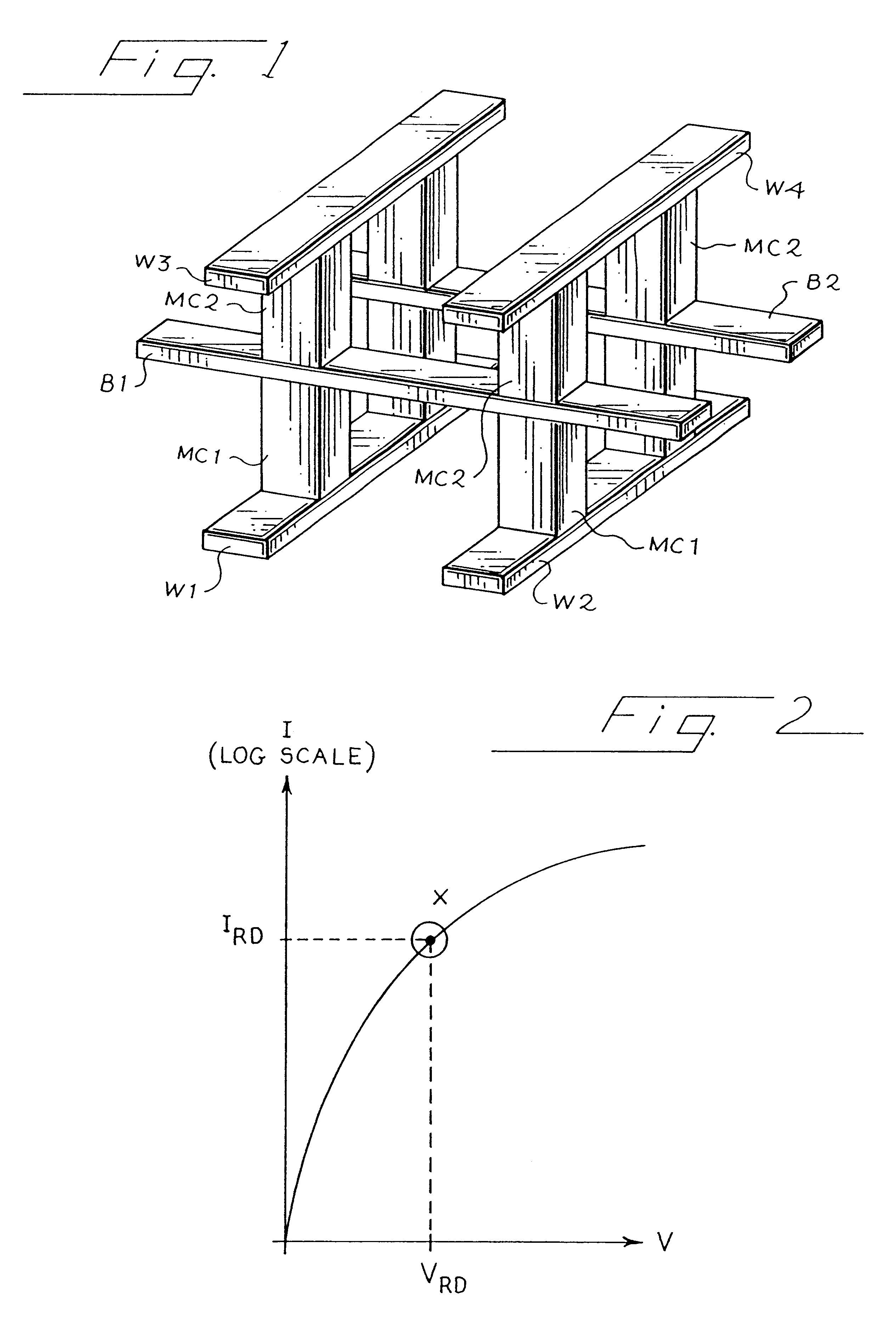

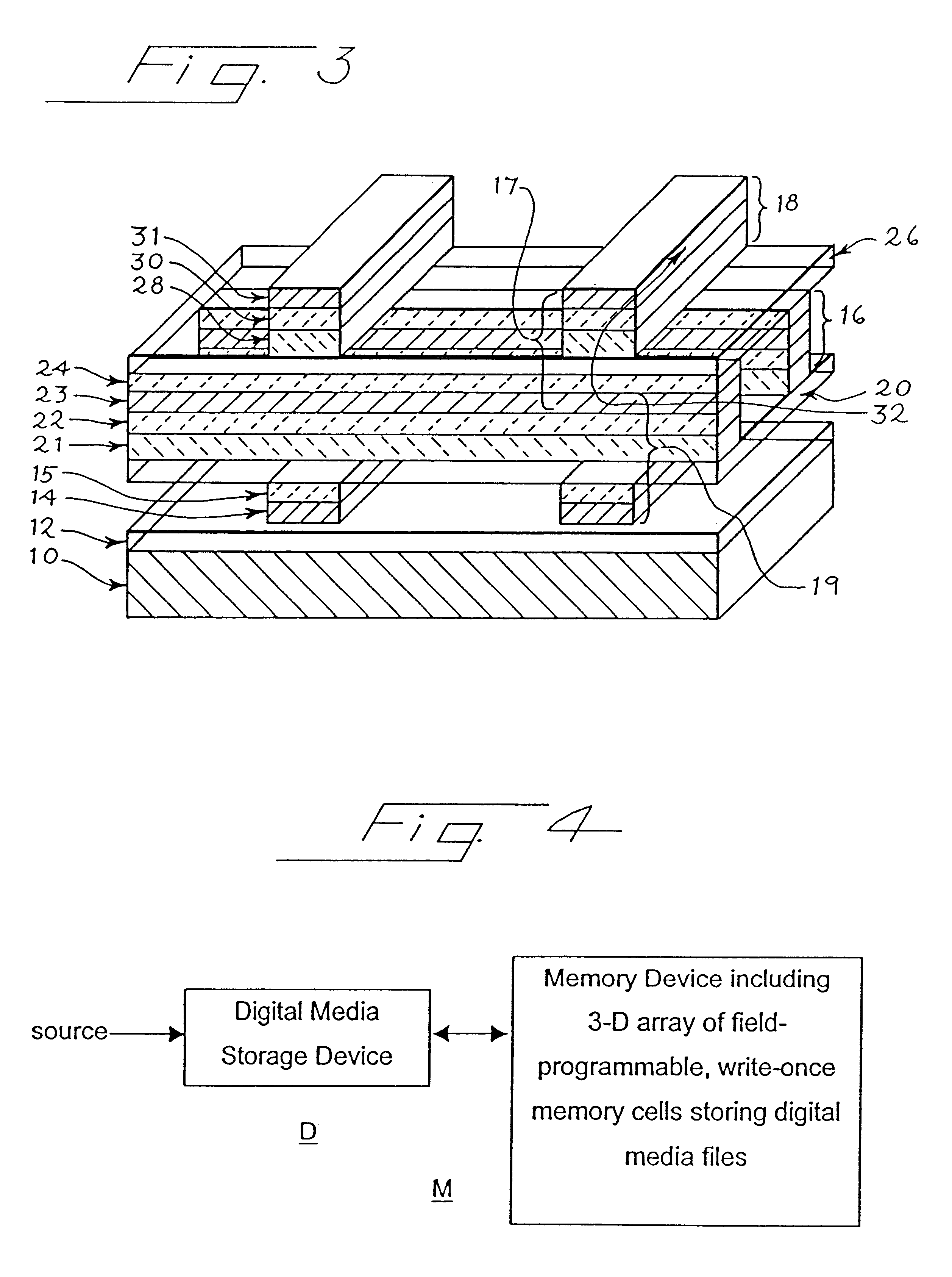

Low cost three-dimensional memory array

InactiveUS6515888B2Reduce areaReduce manufacturing costSolid-state devicesRead-only memoriesDopantAccess time

A low-cost memory cell array includes multiple, vertically-stacked layers of memory cells. In one form, each memory cell is characterized by a small cross-sectional area and a read current less than 6.3 microamperes. The resulting memory array has a slow access time and is well-suited for digital media storage, where access time requirements are low and the dramatic cost reductions associated with the disclosed memory arrays are particularly attractive. In another form, each memory cell includes an antifuse layer and diode components, wherein at least one diode component is heavily doped (to a dopant concentration greater than 1019 / cm3), and wherein the read current is large (up to 500 mA).

Owner:SANDISK TECH LLC

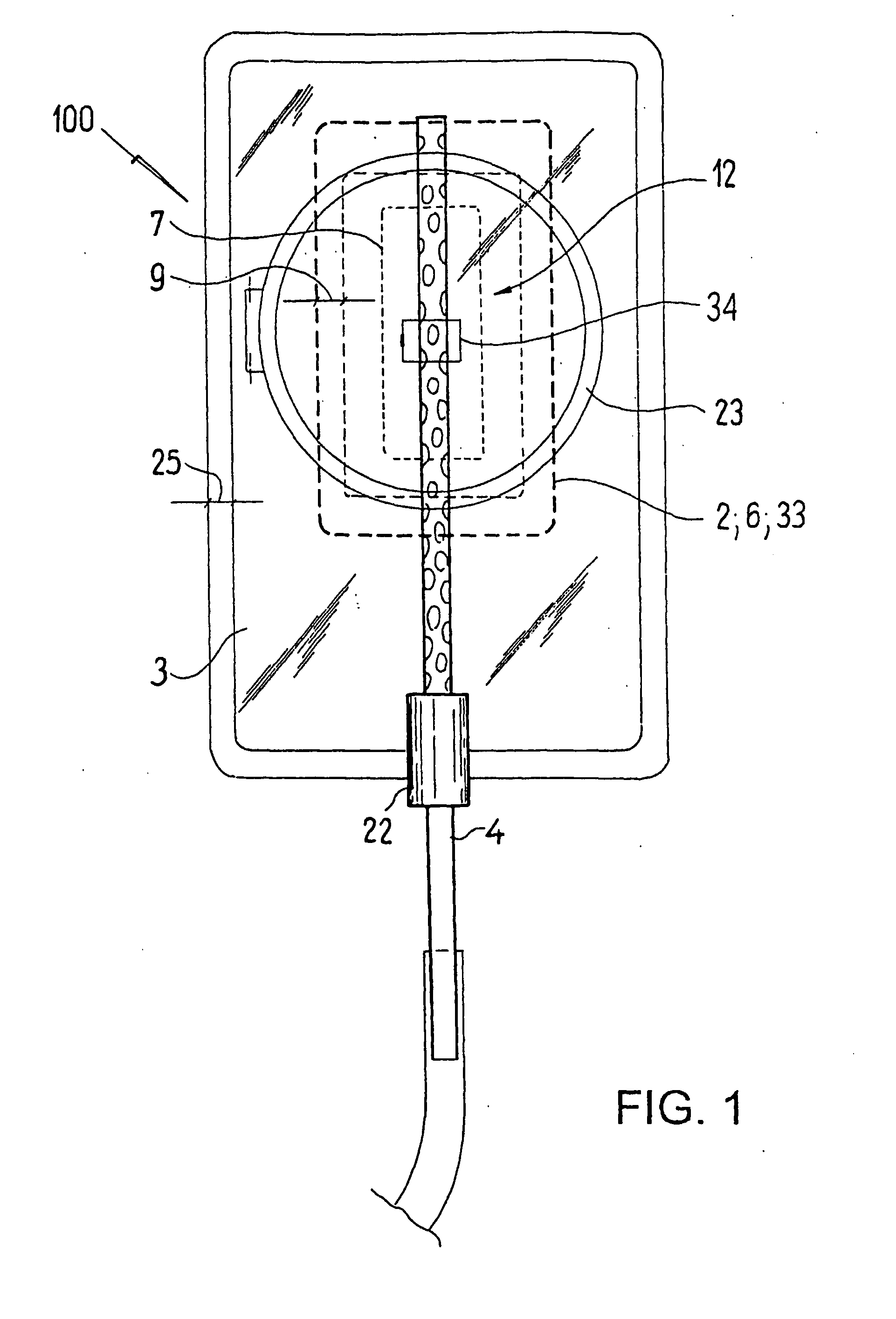

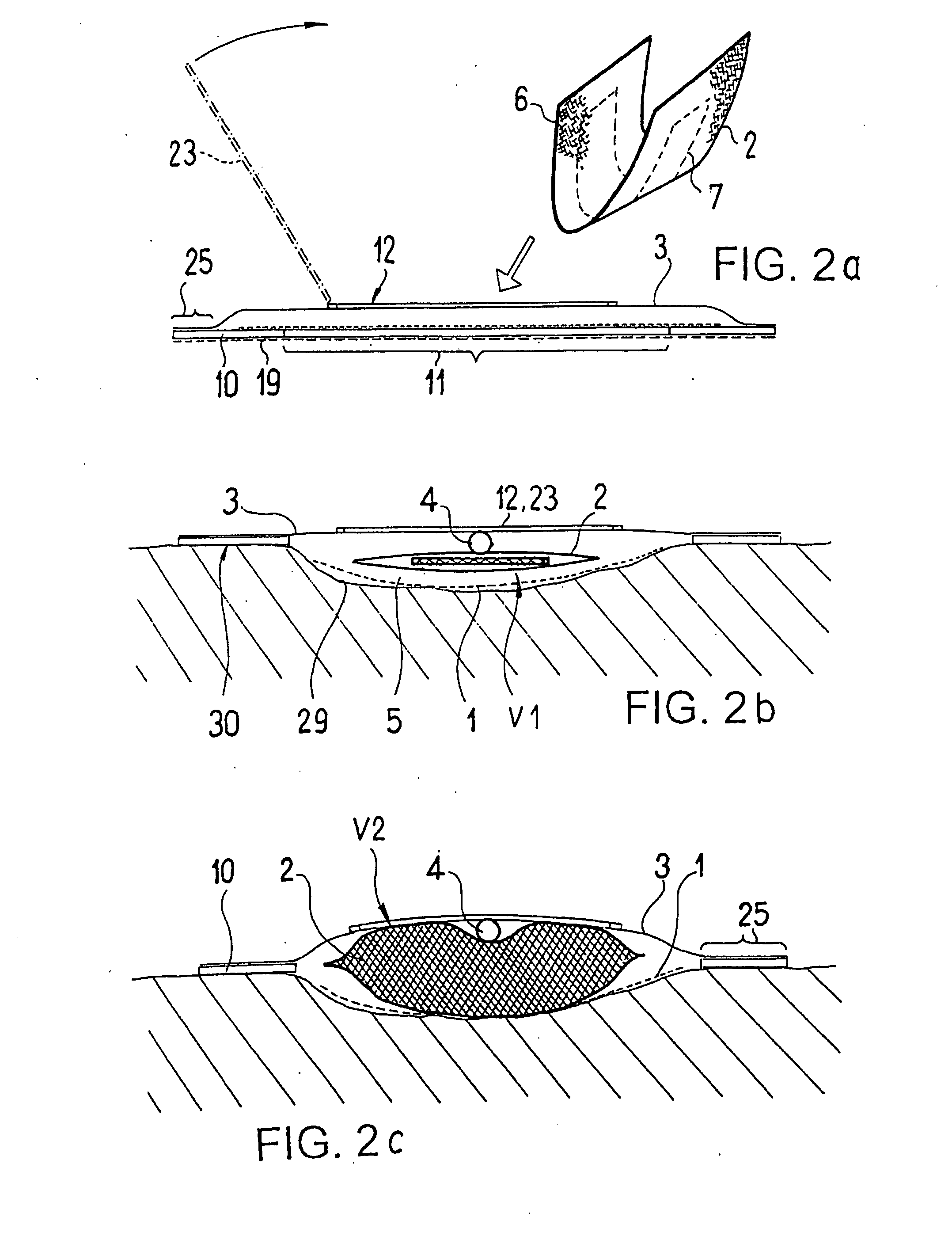

Drainage Device for the Treating Wounds Using a Reduced Pressure

ActiveUS20080119802A1Cost-effectiveSimple designSurgical needlesWound drainsSkin surfaceDrainage tubes

The invention relates to a drainage device (100) for the treatment of wounds using reduced pressure, comprising (a) a gas-type wound-covering element (3), which, in the state in contact with the body of the patient, is fastened cohesively at the skin surface around the region of the wound and forms a sealed wound space, remaining between the respective wound and the wound-covering element (3); (b) at least one drainage tube (4), which can be connected to means generating the reduced pressure and can be inserted into the wound space approximately parallel to the wound-covering element (3); and (c) at least one absorption body (2) in the form of at least one layer (7) of a textile section (33), which is interspersed with super-absorbing particles and enclosed in an envelope. Due to the size of the pores of the envelope, the absorbed wound secretions remain within the absorption body (2) and, with that, underneath the wound-covering element (3) until the absorption body is removed from the wound space. An air opening (34) is provided for the wound-covering element (3).

Owner:BR ENTWICKLUNGS

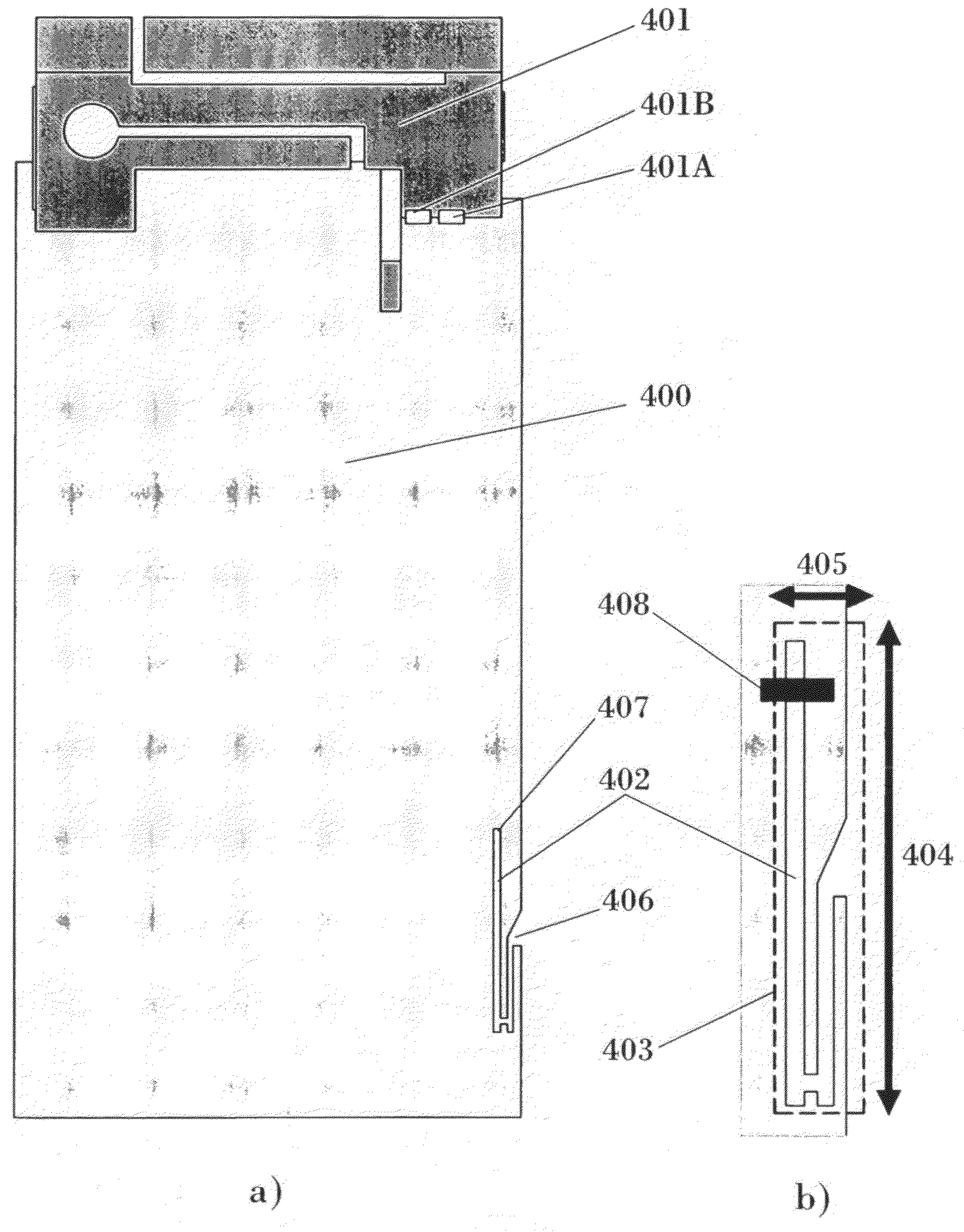

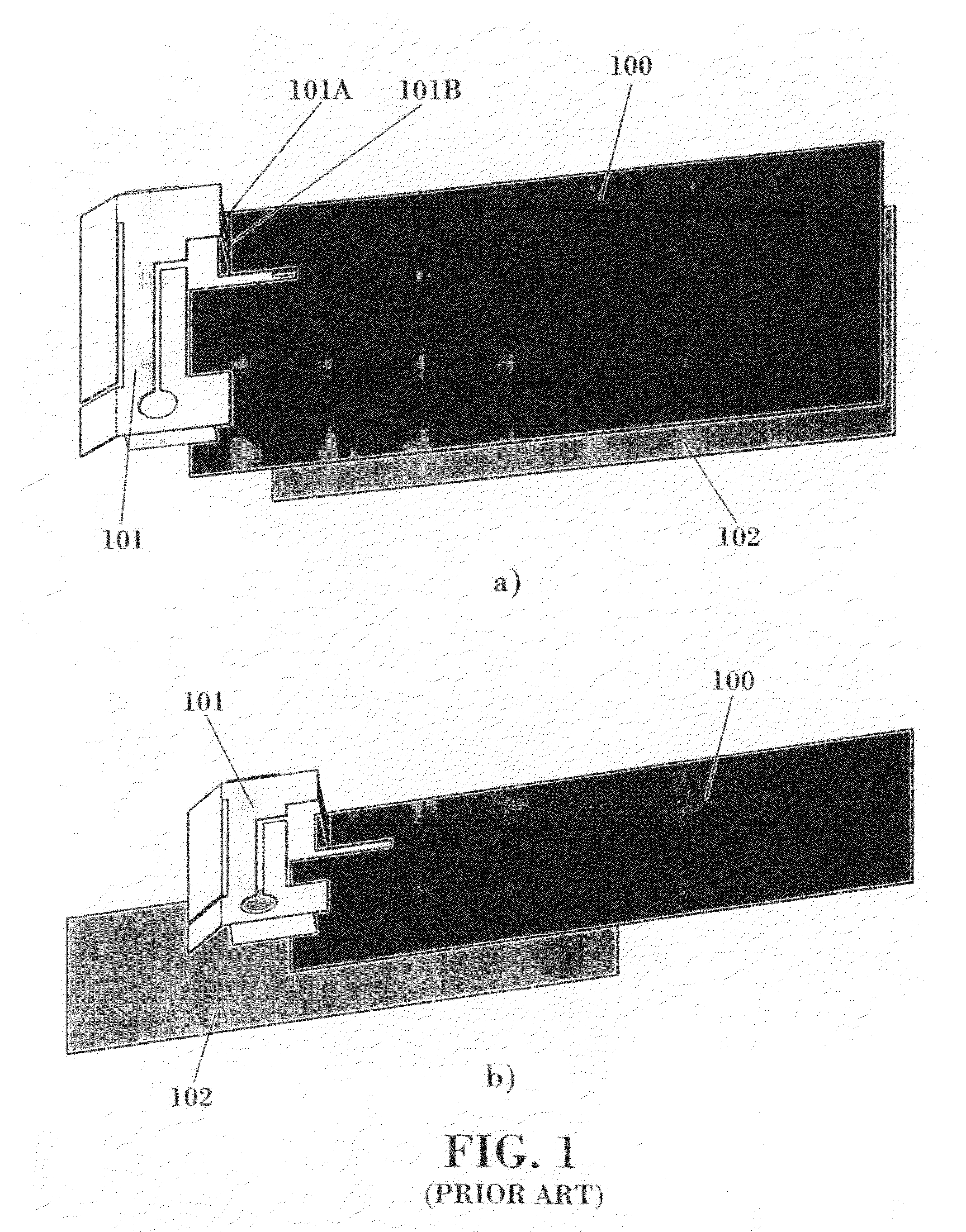

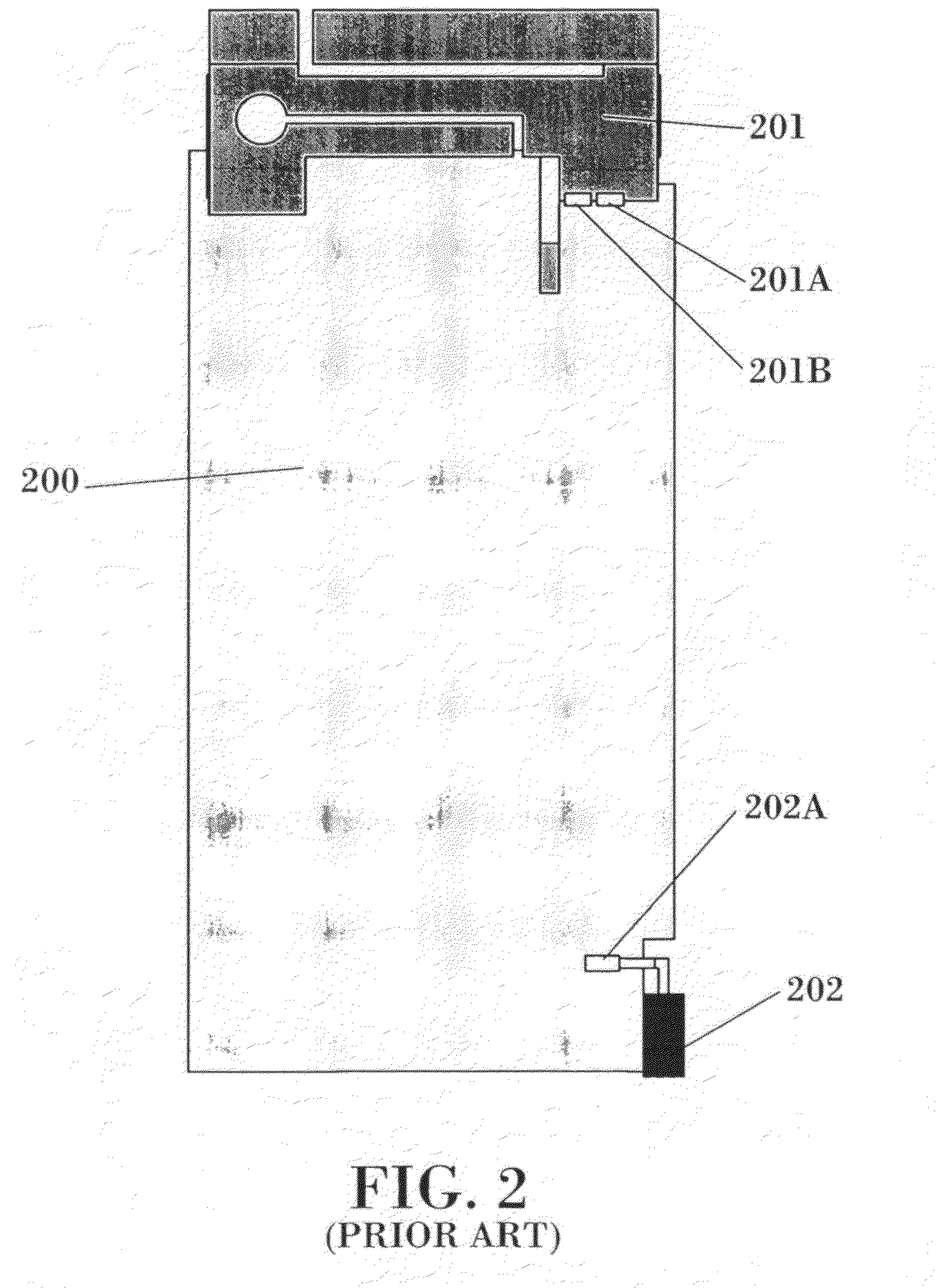

Handheld device with two antennas, and method of enhancing the isolation between the antennas

ActiveUS20090262028A1Avoid less flexibilityDistance minimizationSimultaneous aerial operationsAntenna supports/mountingsHand held devicesSlot antenna

The invention relates to a handheld device comprising a first antenna (401, 701, 901, 931, 961, 1101, 1151, 1301, 1501) arranged to operate in at least a first frequency band, and a second antenna (402, 702, 902, 1102, 1302, 1502, 2210) arranged to operate in at least a second frequency band, wherein said second frequency band is different from said first frequency band. According to the invention, the second antenna comprises a slot antenna comprising at least one slot in at least one conductive layer. The invention also relates to enhancement of the isolation between first and second antennas in a handheld device.

Owner:FRACTUS