Patents

Literature

36results about How to "Increased circuit area" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

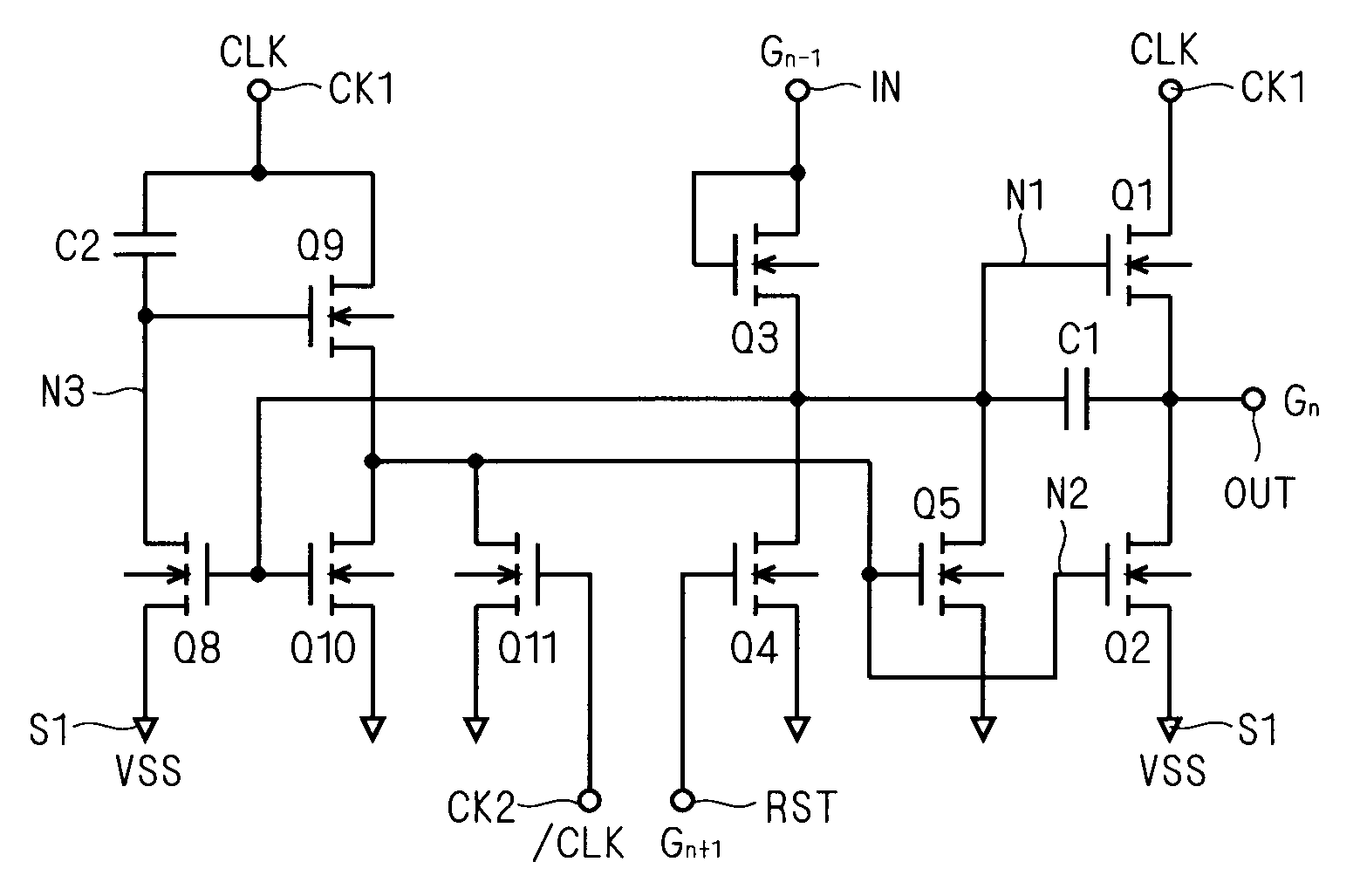

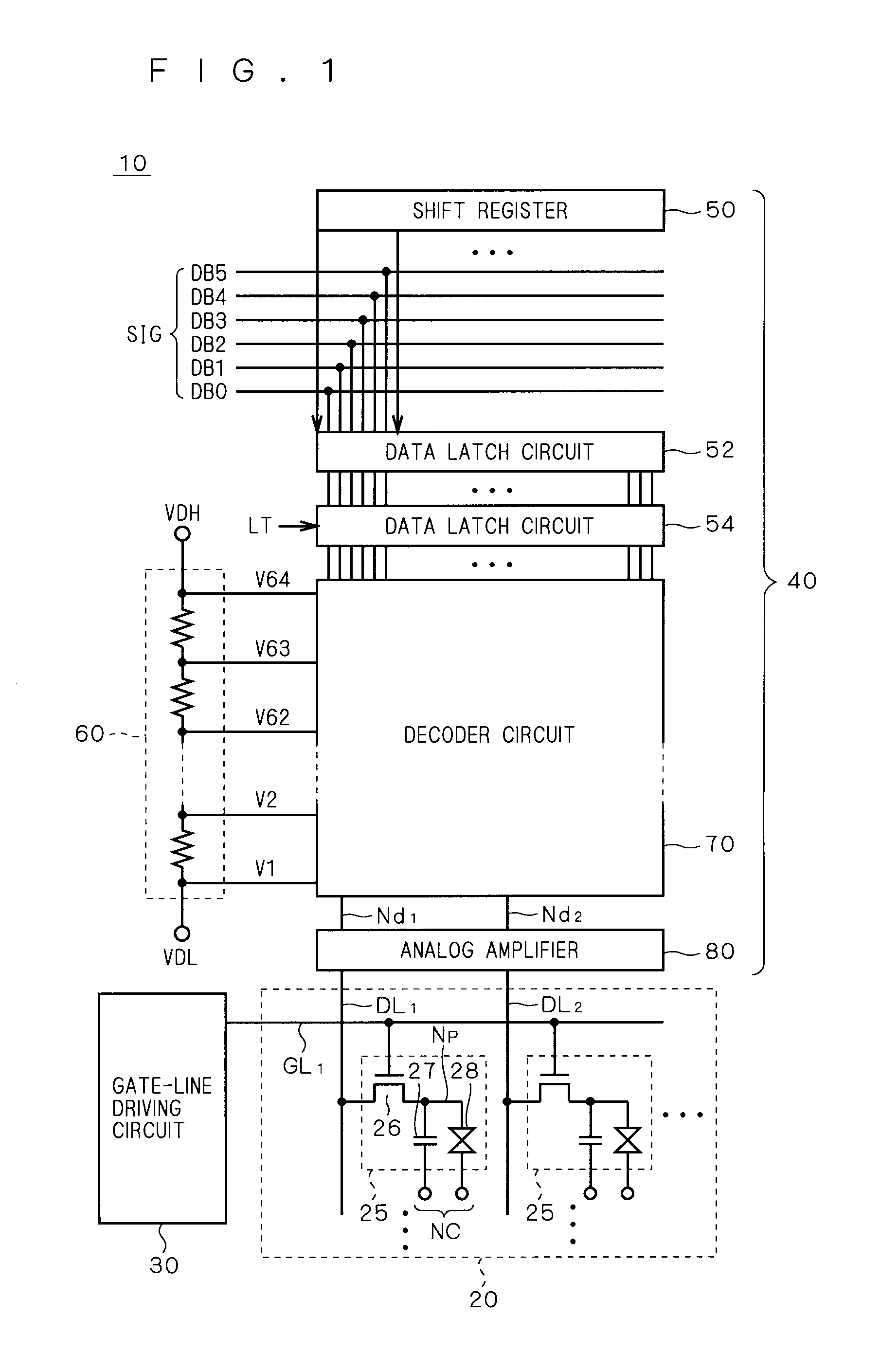

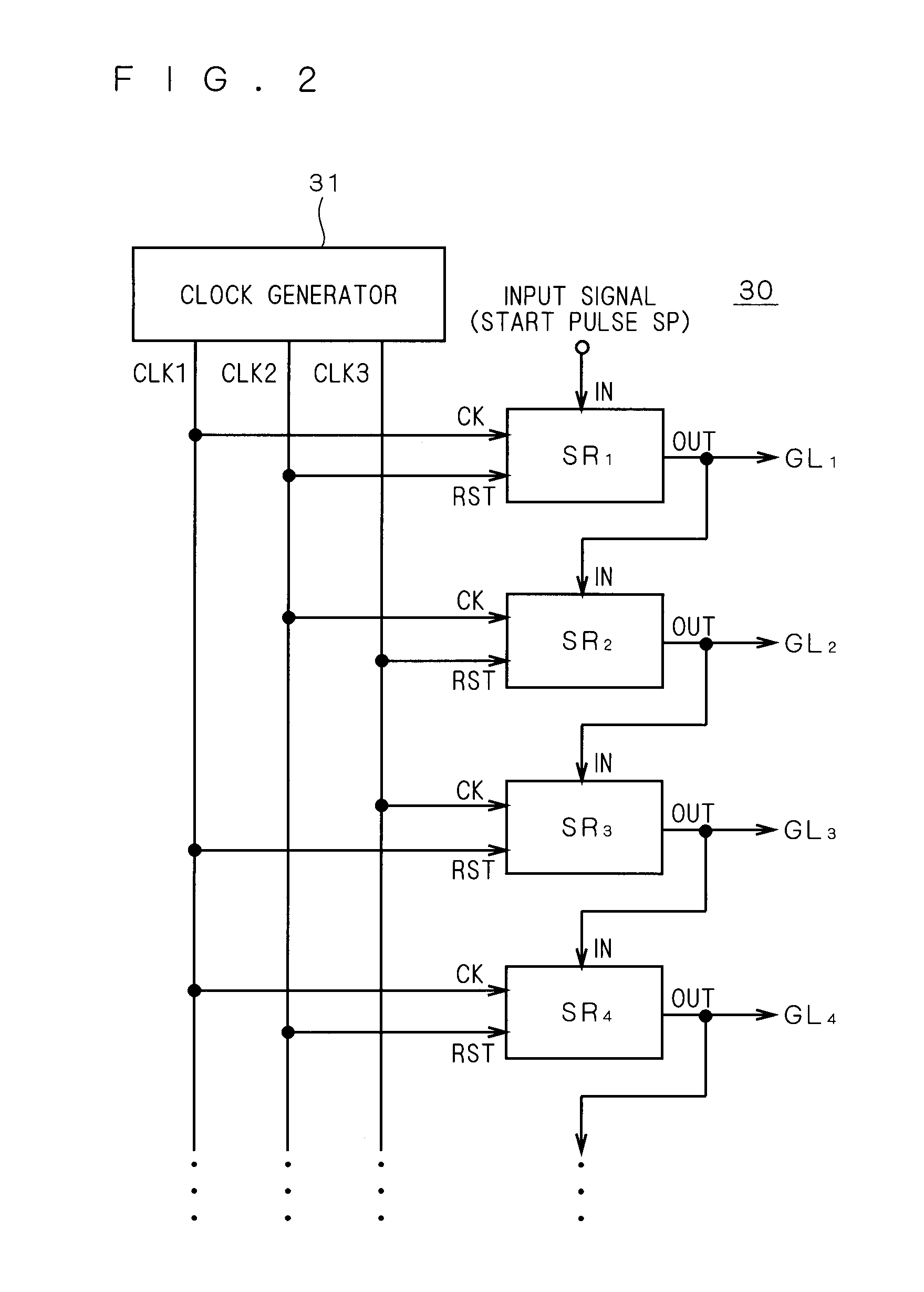

Shift register and image display apparatus containing the same

ActiveUS20080101529A1Increased circuit areaImprove driving reliabilityStatic indicating devicesDigital storagePower inverterShift register

A shift register includes a first transistor supplying an output terminal with a clock signal input to a first clock terminal and a second transistor discharging the output terminal. Defining the gate node of the first transistor as a first node, and the gate node of the second transistor as a second node, the shift register includes an inverter circuit in which the first node serves as its input node and a capacitive element serves as a load, and a buffer circuit receiving the output from the inverter circuit and outputting a signal to the second node.

Owner:TRIVALE TECH

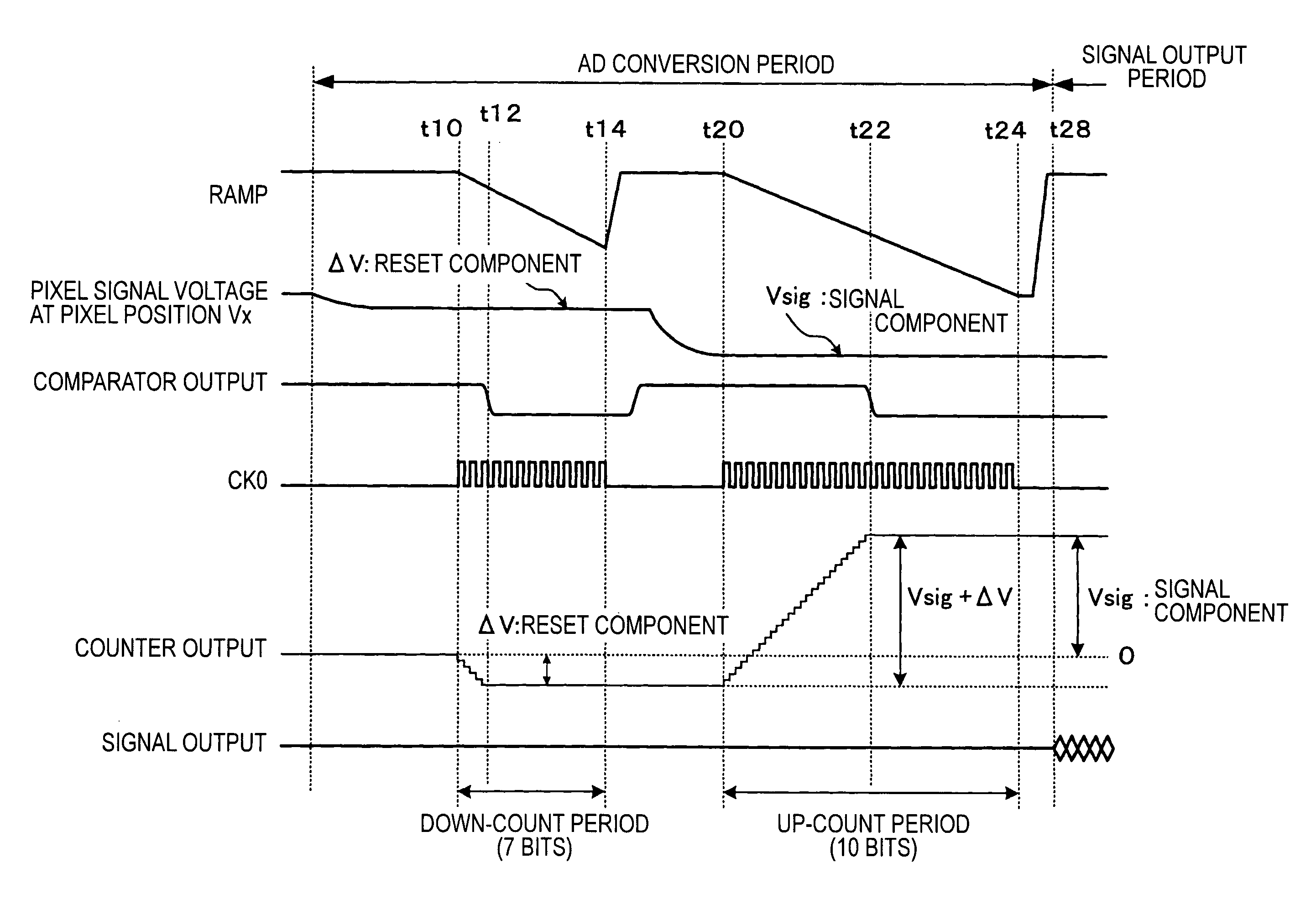

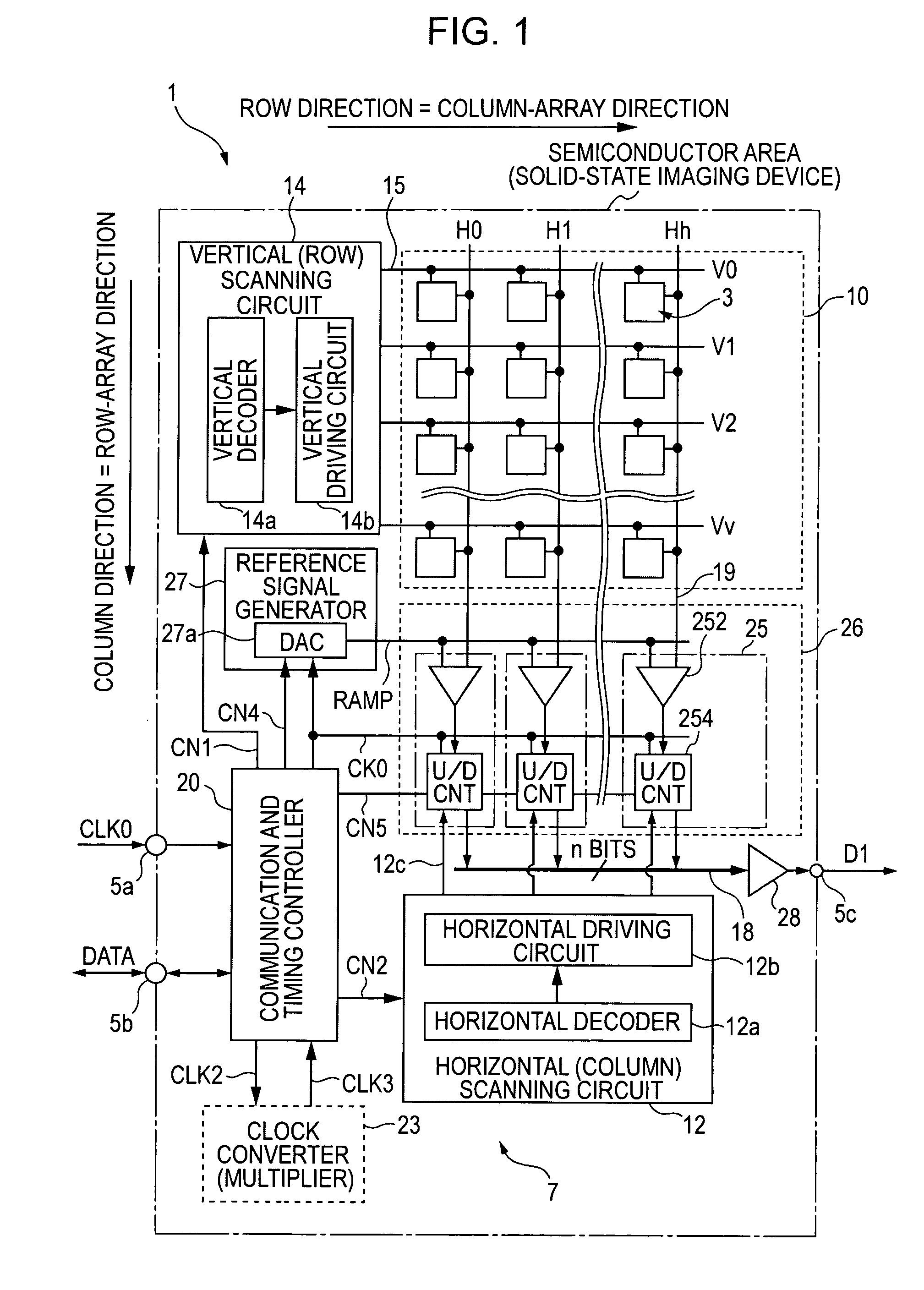

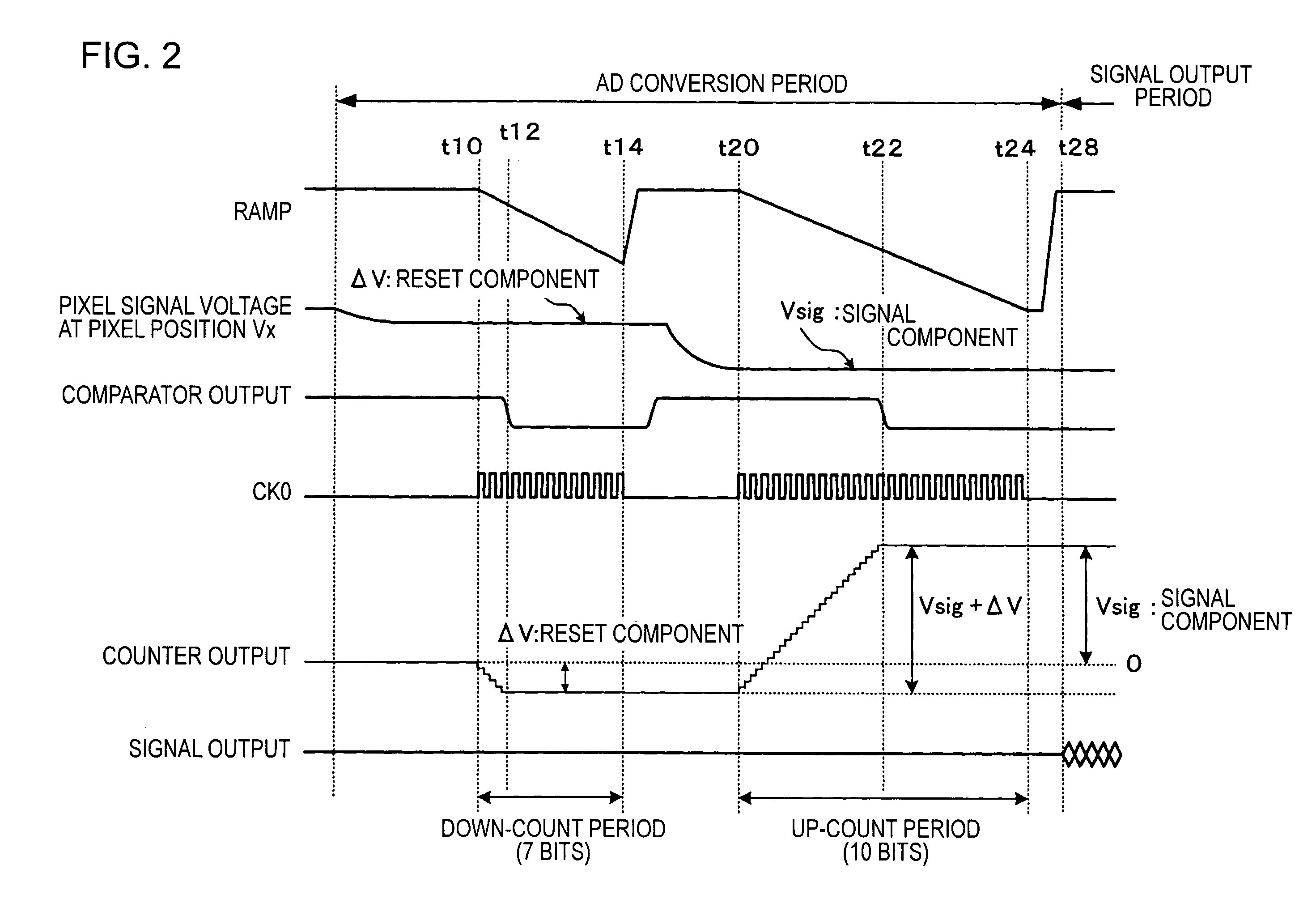

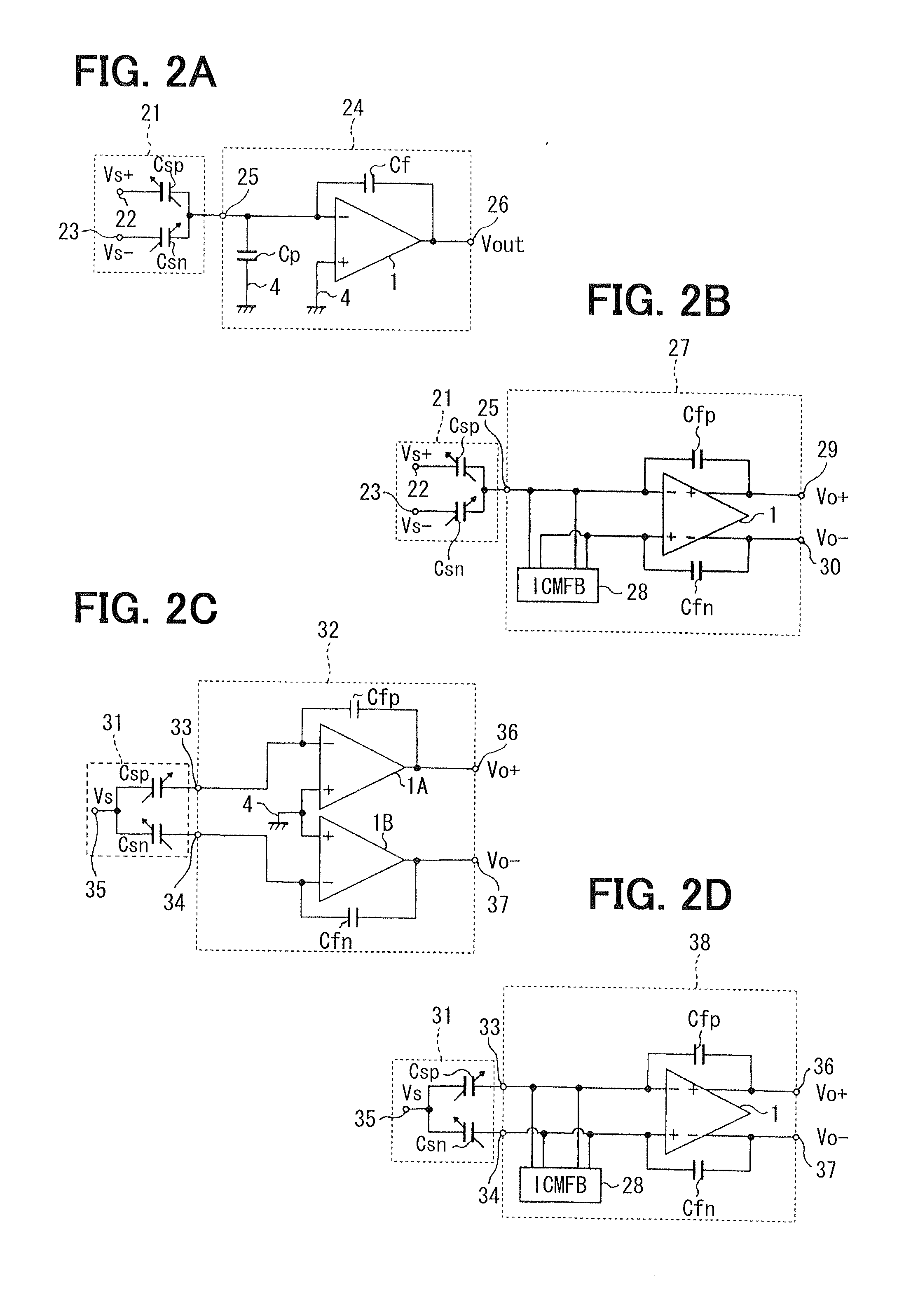

Analog-to-digital conversion method, analog-to-digital converter, semiconductor device for detecting distribution of physical quantity, and electronic apparatus

ActiveUS20060097902A1Increase currentImprove noiseTelevision system detailsElectric signal transmission systemsDigital dataA d converter

In an analog-to-digital conversion method for converting a difference signal component representing a difference between a reference component and a signal component in an analog signal to be processed into digital data, in a first process, a signal corresponding to one of the reference component and the signal component is compared with a reference signal for conversion into the digital data. Concurrently with the comparison, counting is performed in one of a down-count mode and an up-count mode, and a count value at a time of completion of the comparison is held. In a second process, a signal corresponding to the other one of the reference component and the signal component is compared with the reference signal. Concurrently with the comparison, counting is performed in the other one of the down-count mode and the up-count mode, and a count value at a time of completion of the comparison is held.

Owner:SONY CORP

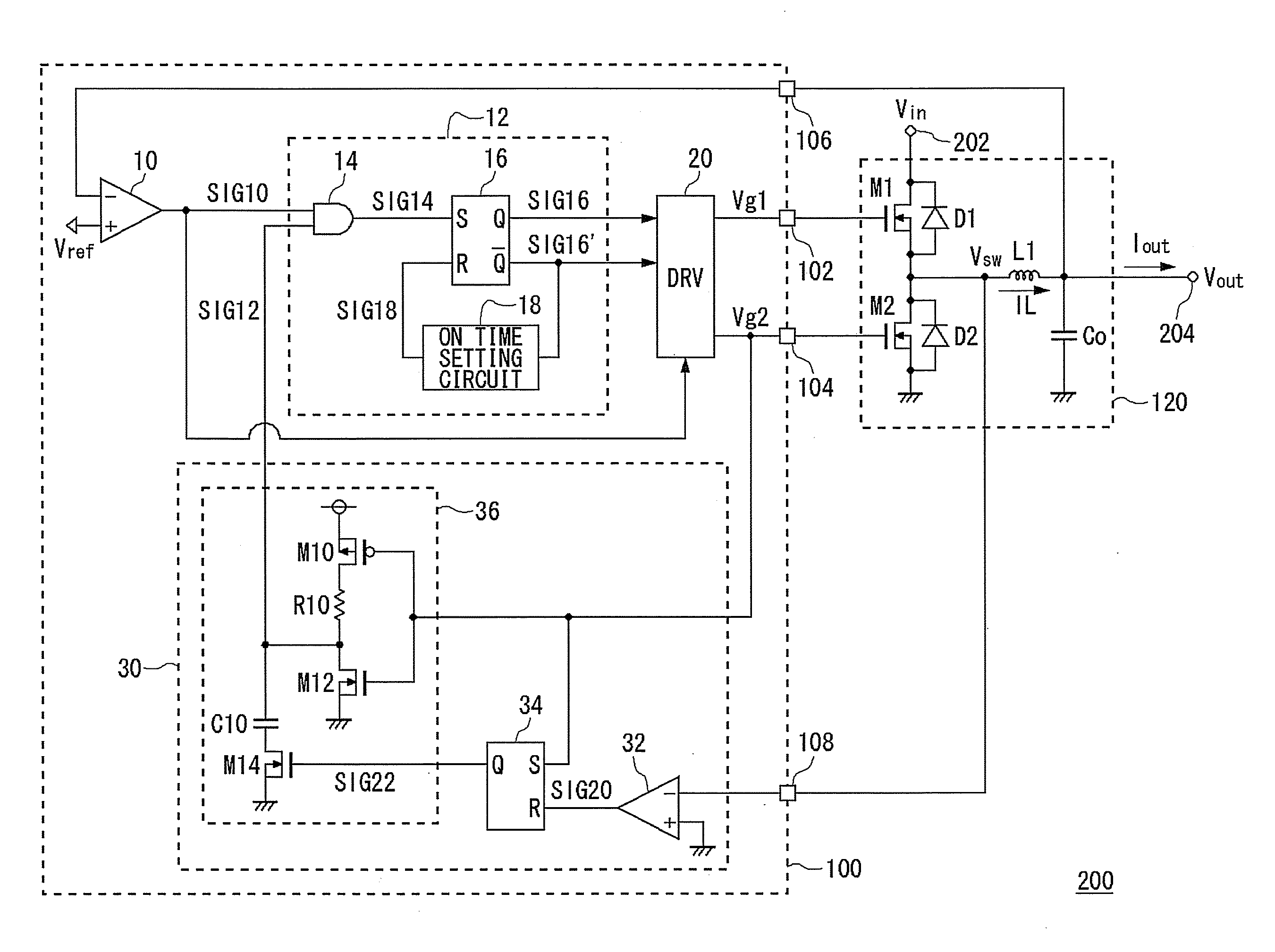

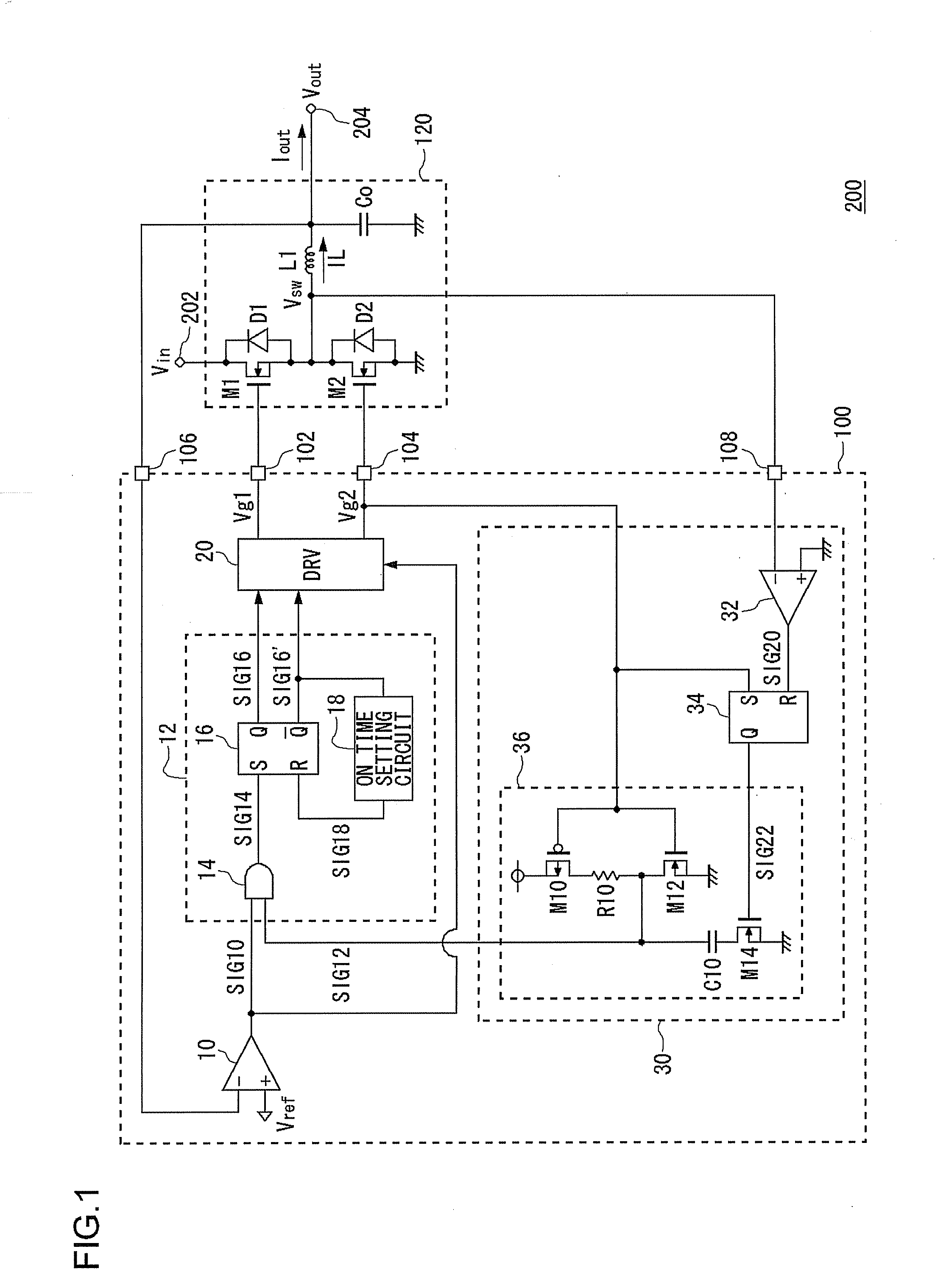

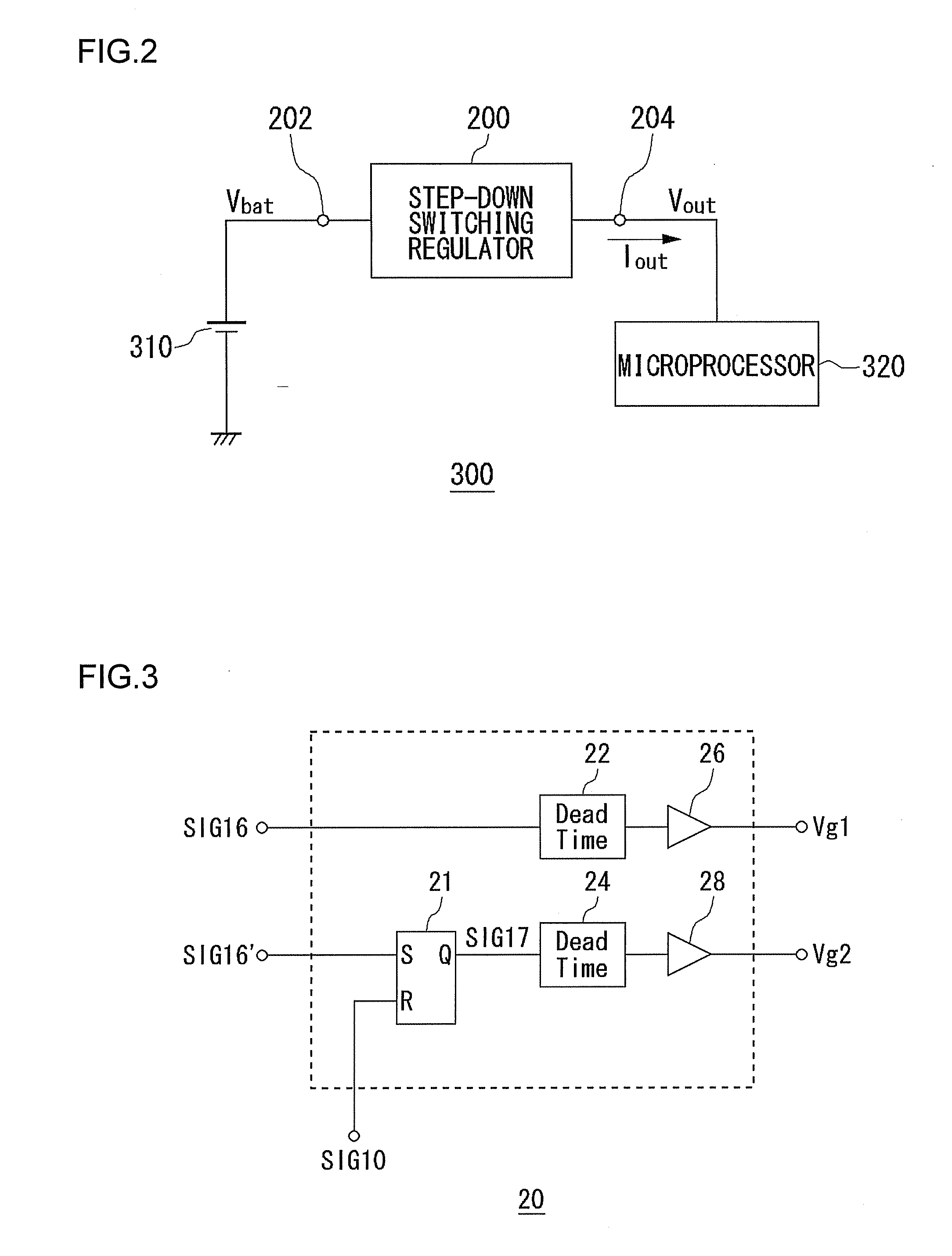

Step-down switching regulator, control circuit thereof, and electronic device using the same

ActiveUS20100156366A1Improve efficiencyIncreased circuit areaAc-dc conversion without reversalEfficient power electronics conversionDriver circuitEngineering

An output monitoring comparator outputs an ON signal when an output voltage becomes lower than a reference voltage. A pulse modulator generates a pulse signal at a predetermined level, an ON time-period from when the ON signal is outputted. A driver circuit alternately turns ON, after a dead time, a switching transistor and a synchronous rectification transistor, based on the pulse signal. A light load mode detector compares a switching voltage at a connection point of the switching transistor and the synchronous rectification transistor, and ground potential, and at timing at which the ON signal is outputted from the output monitoring comparator, when the switching voltage is higher than the ground potential, nullifies the ON signal.

Owner:ROHM CO LTD

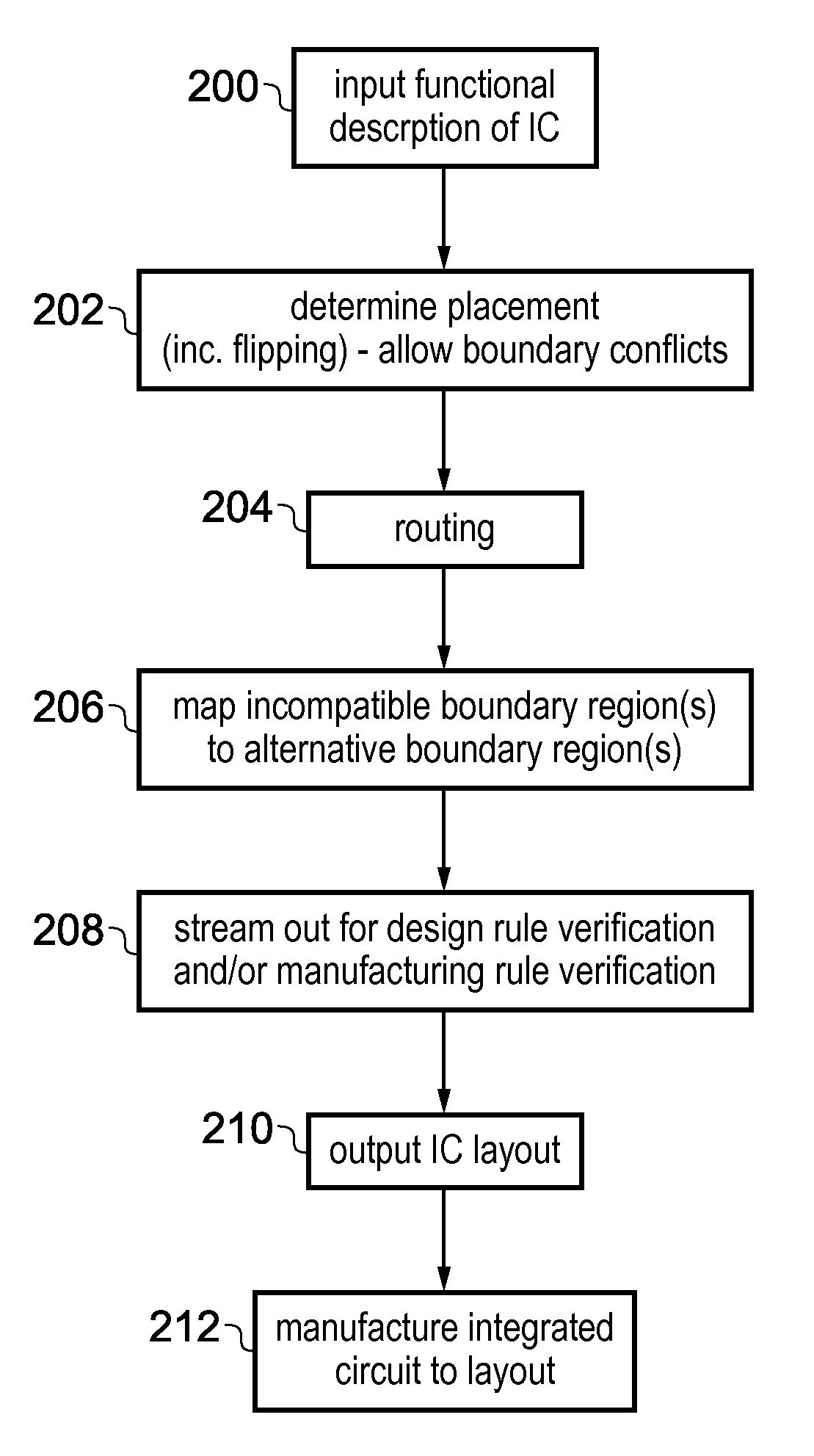

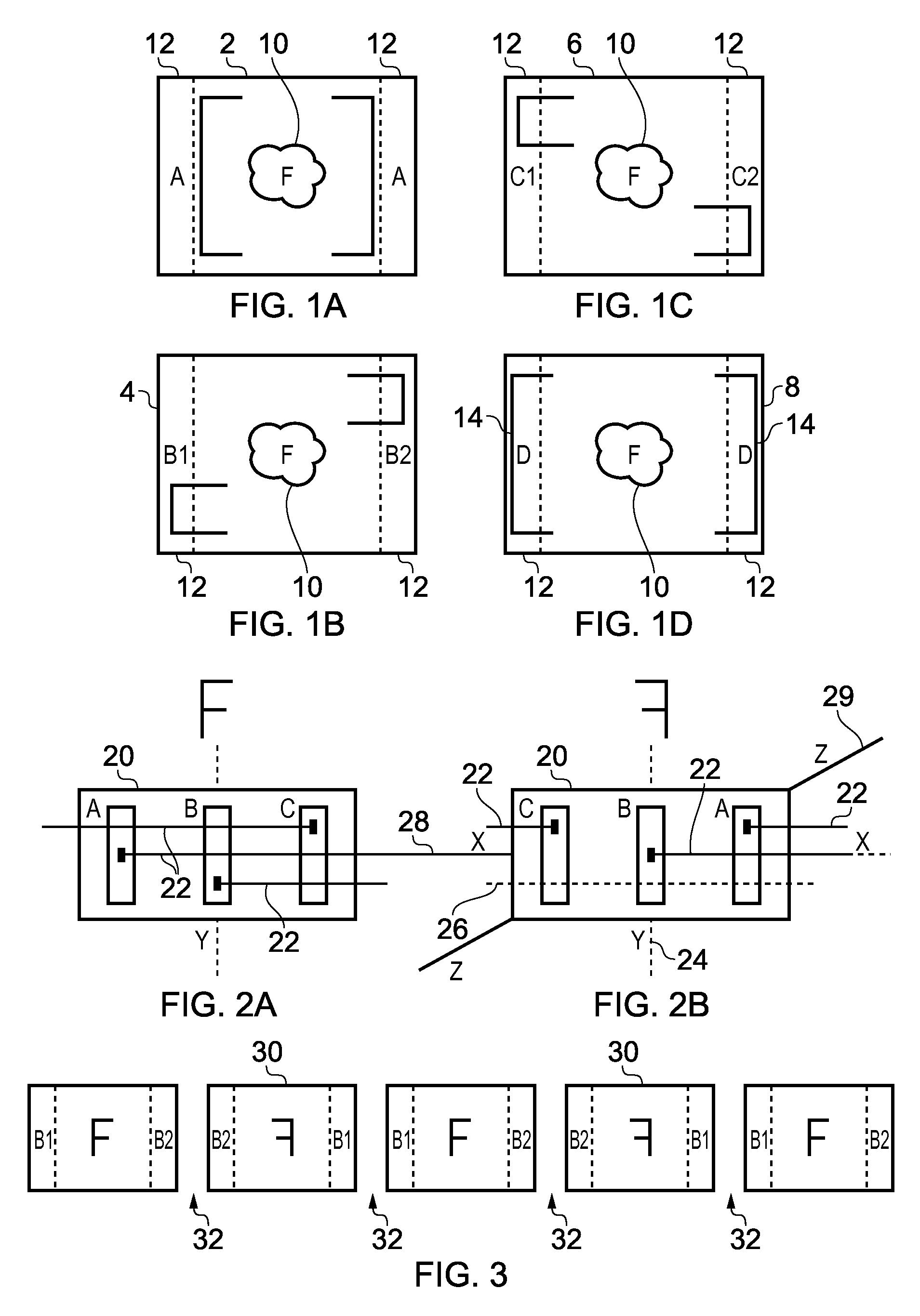

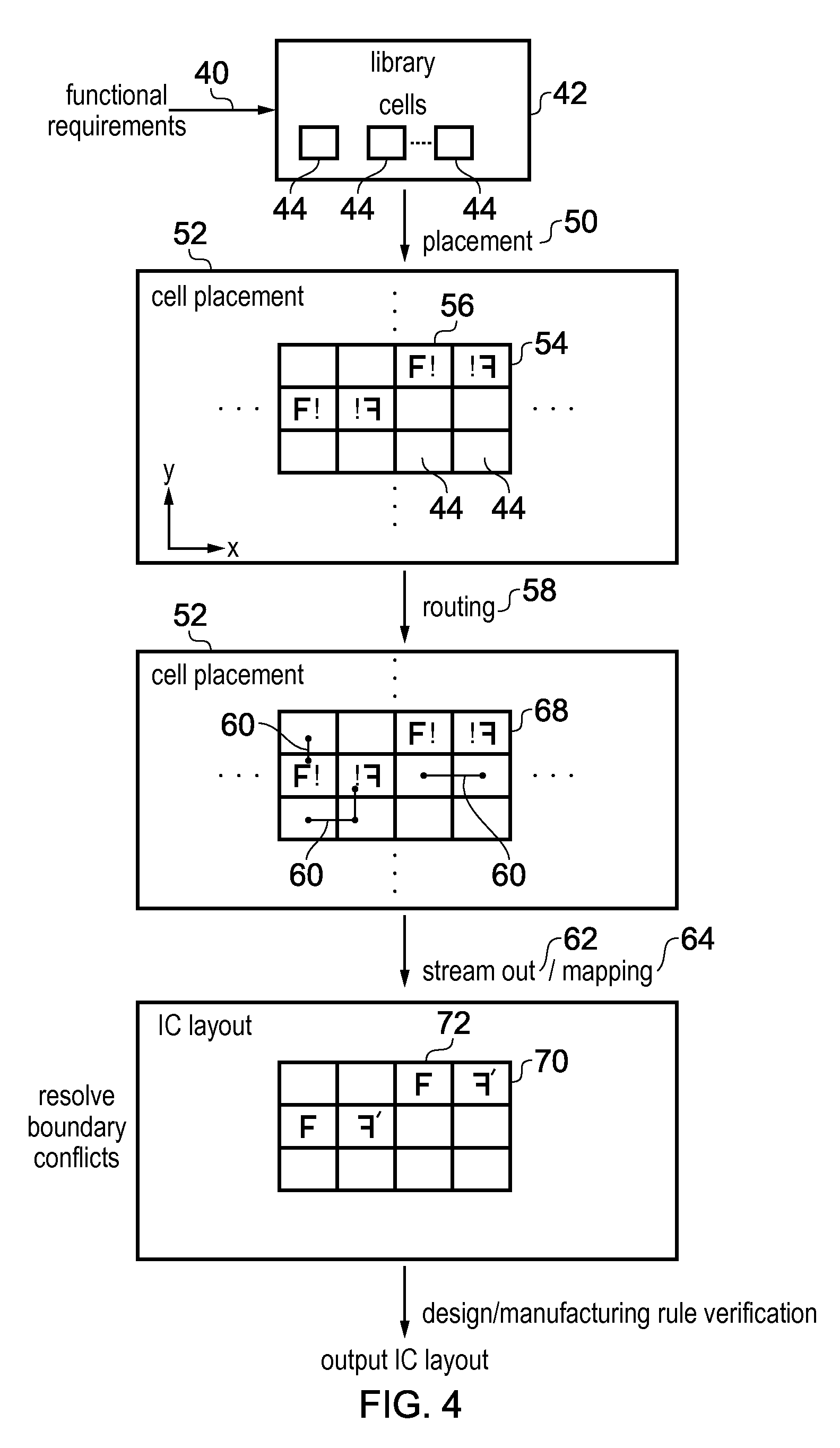

Considering compatibility of adjacent boundary regions for standard cells placement and routing

ActiveUS8959472B1Good flexibilityEasy to routeComputer aided designSoftware simulation/interpretation/emulationComputer architectureComputer compatibility

A method of generating an integrated circuit layout comprises a step of determining a placement of standard cells selected from a standard cell library while permitting boundary conflicts in which incompatible boundary regions of standard cells are placed next to each other. After determining routing connections between the standard cells, the integrated circuit layout is generated. The generation of the integrated circuit layout includes a mapping step of mapping at least one incompatible boundary region to an alternative boundary region to resolve at least one boundary conflict.

Owner:ARM LTD

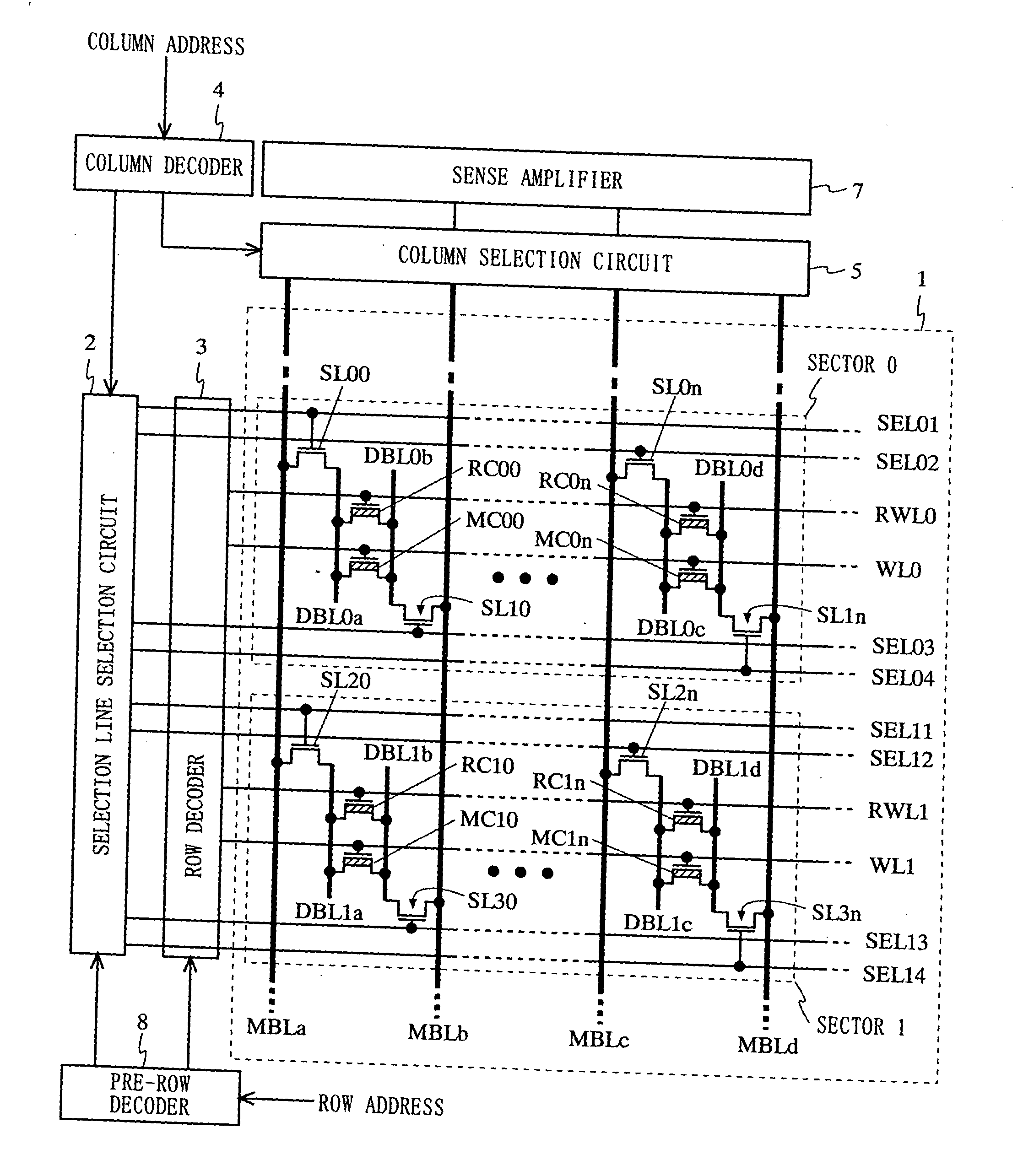

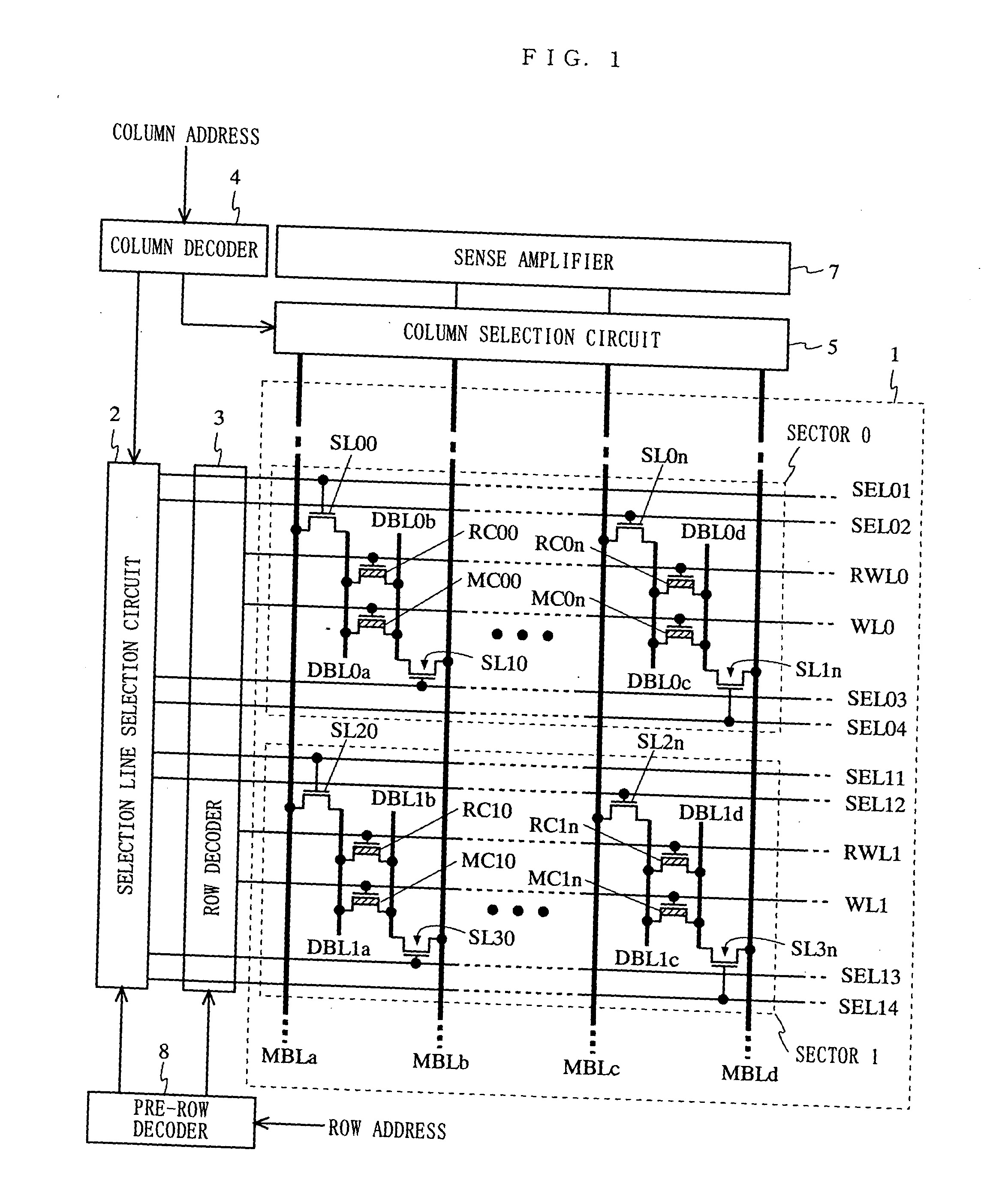

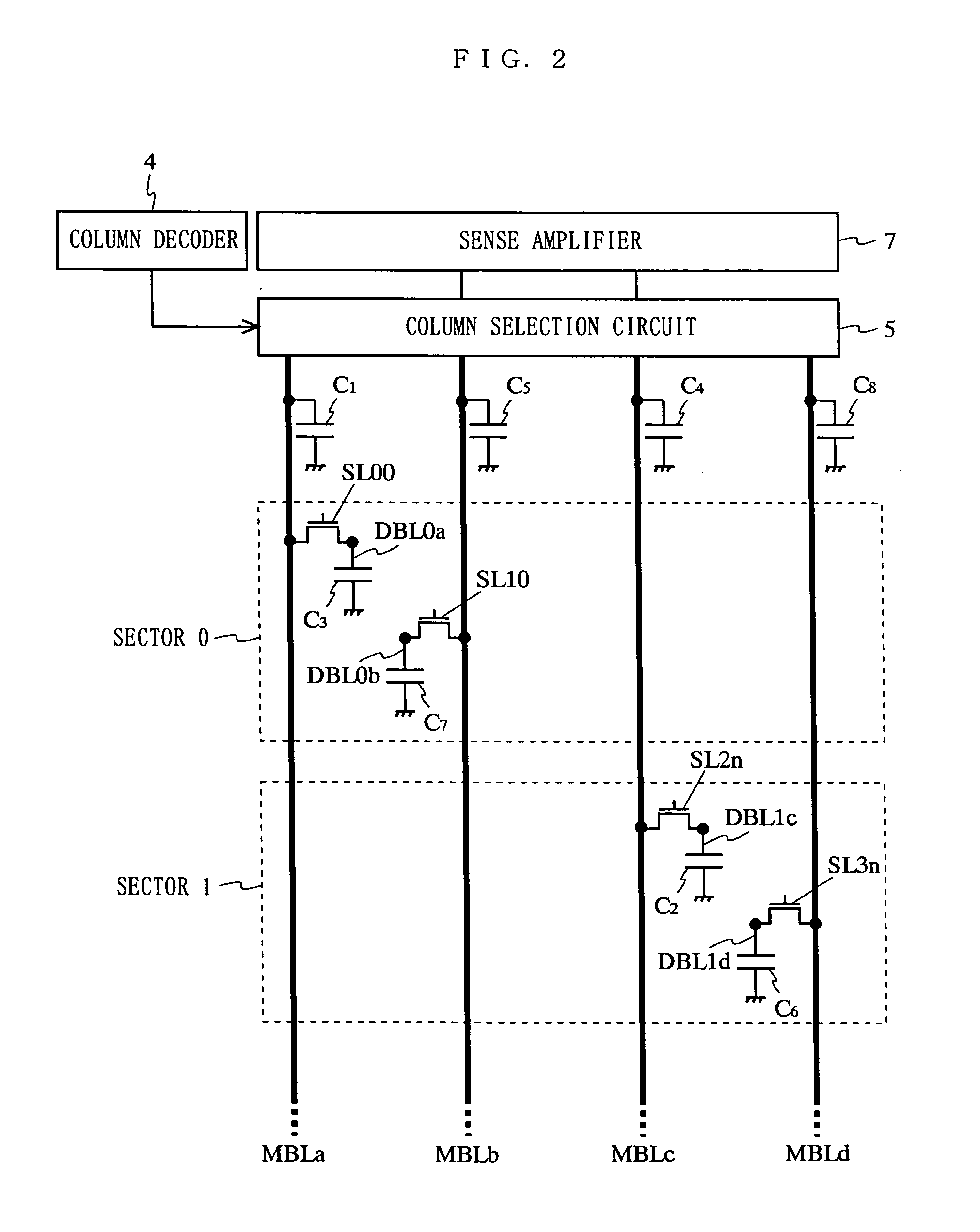

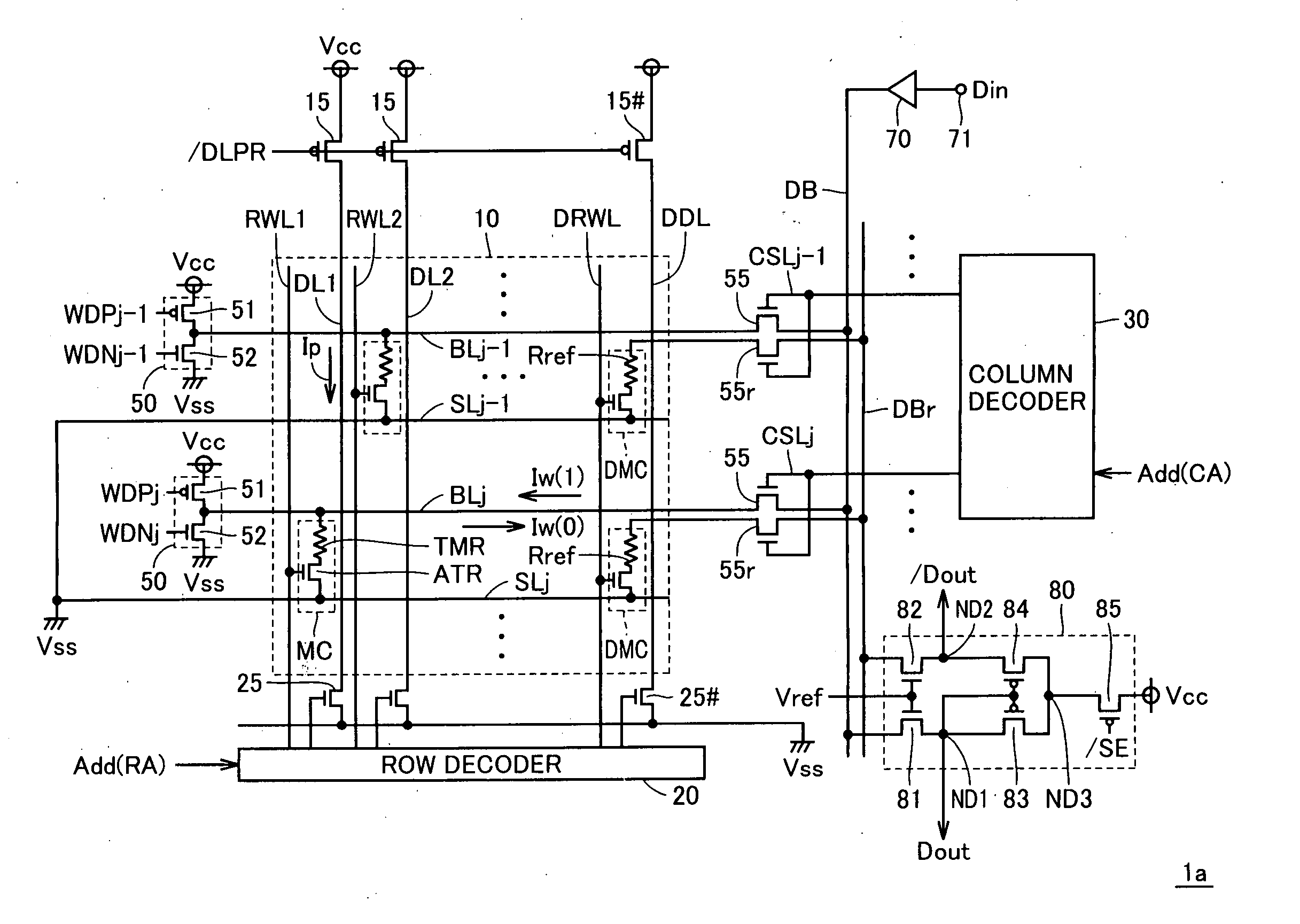

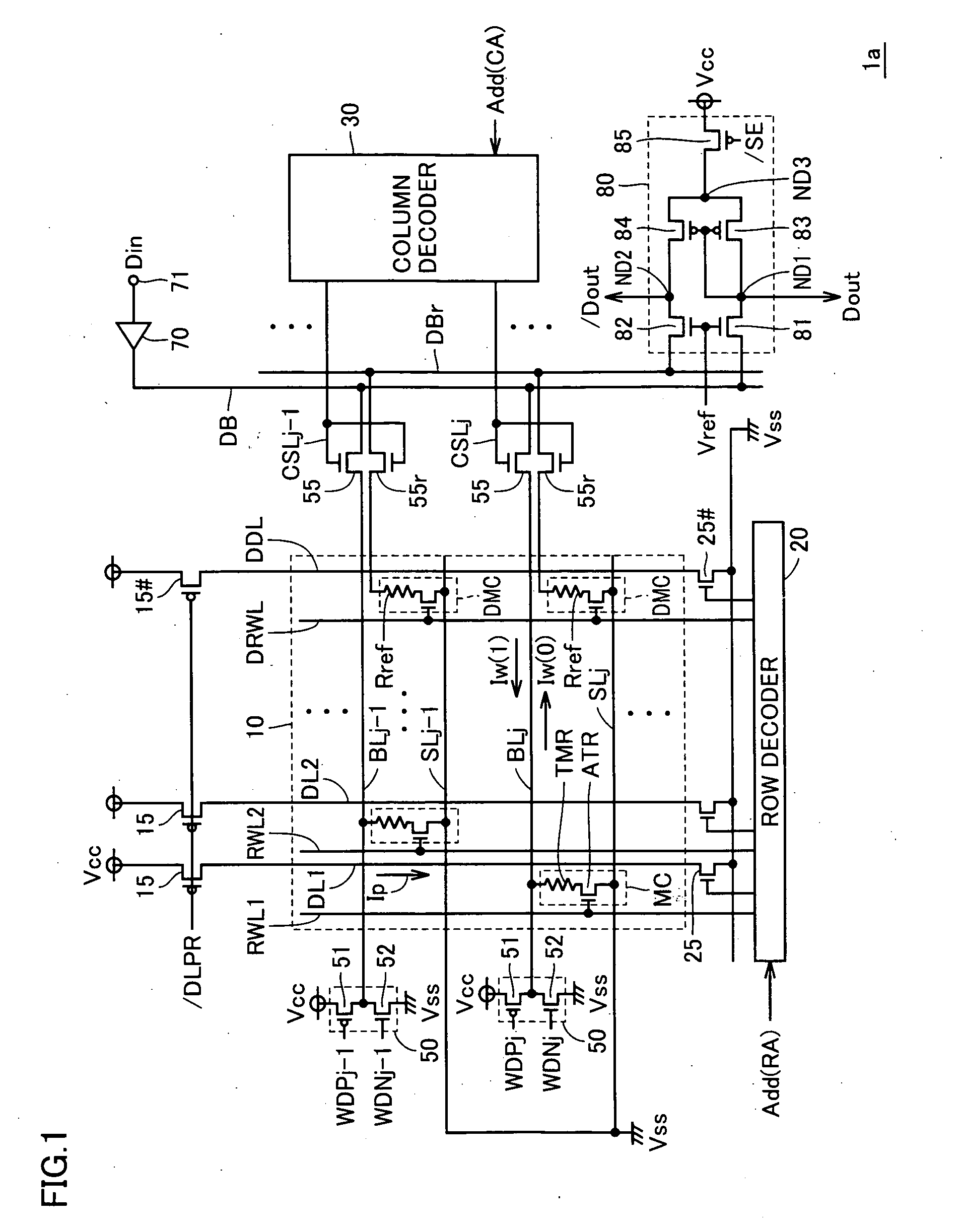

Non-volatile semiconductor memory device

InactiveUS20050180212A1Accurate dataIncreased circuit areaRead-only memoriesDigital storageStorage cellVoltage

A plurality of memory cells are connected between two adjacent sub-bit lines. A row decoder 3 selects a word line connected to a memory cell to be read. A selection line selection circuit 2 and a column selection circuit 5 include first and second selection portions that perform selection operations simultaneously and independently. The first selection portion selects a first pair of main bit lines and selection lines in order to select the memory cell to be read. The second selection portion selects a second pair of main bit lines that is different from the first pair of main bit lines and selection lines for selecting a sector different from that for the memory cell to be read in order to select a line to be used for reading a reference voltage.

Owner:PANASONIC CORP

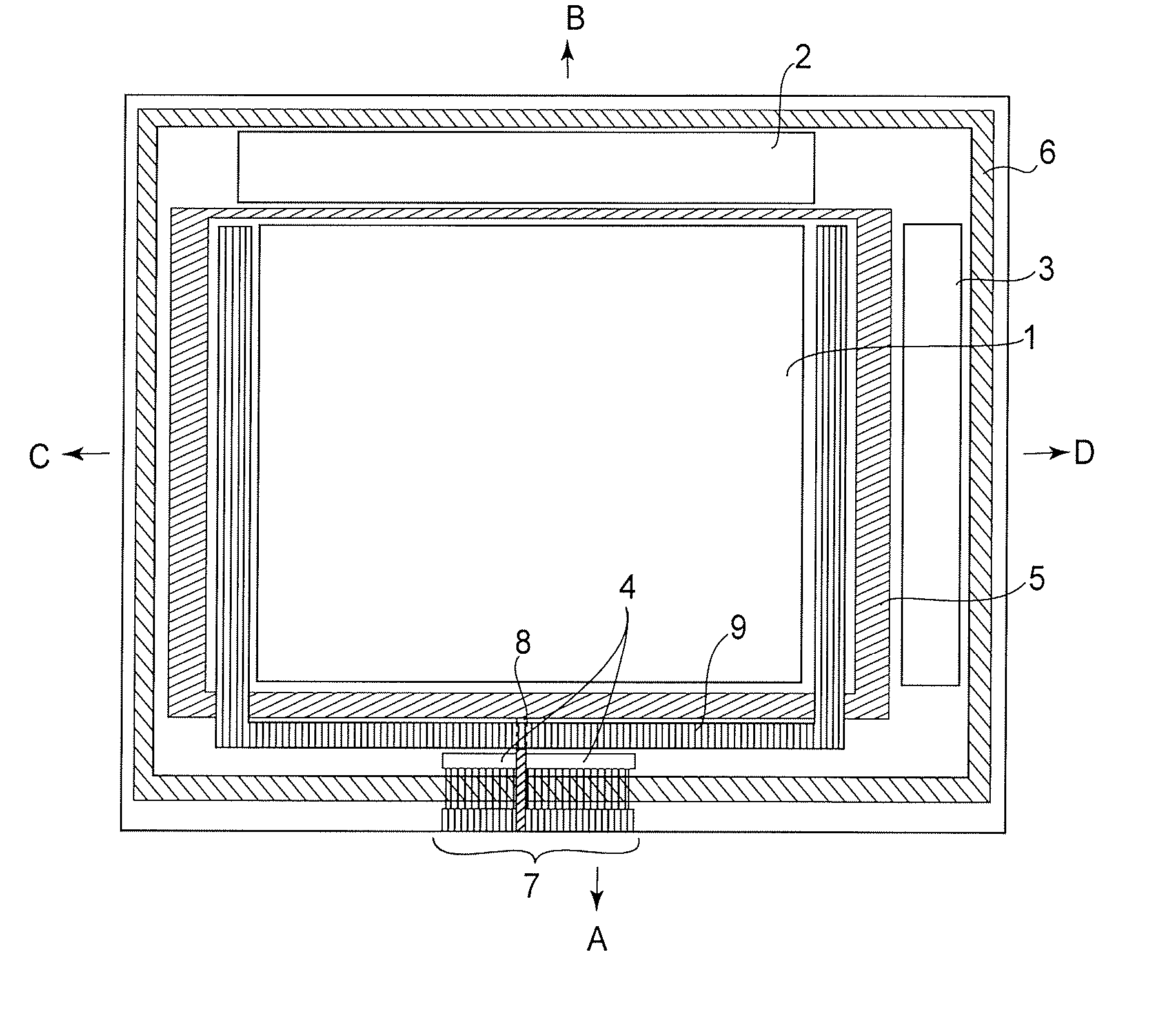

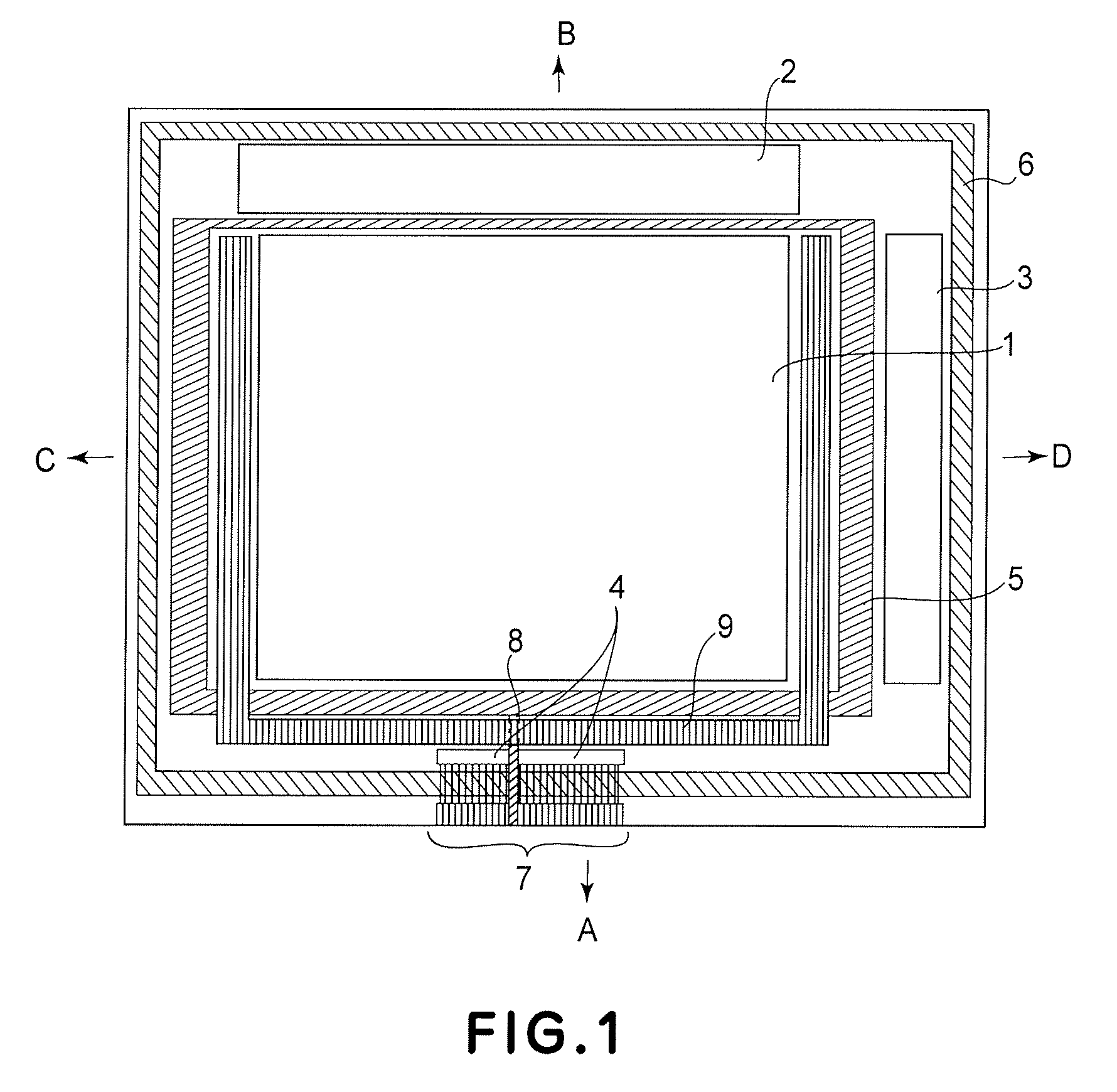

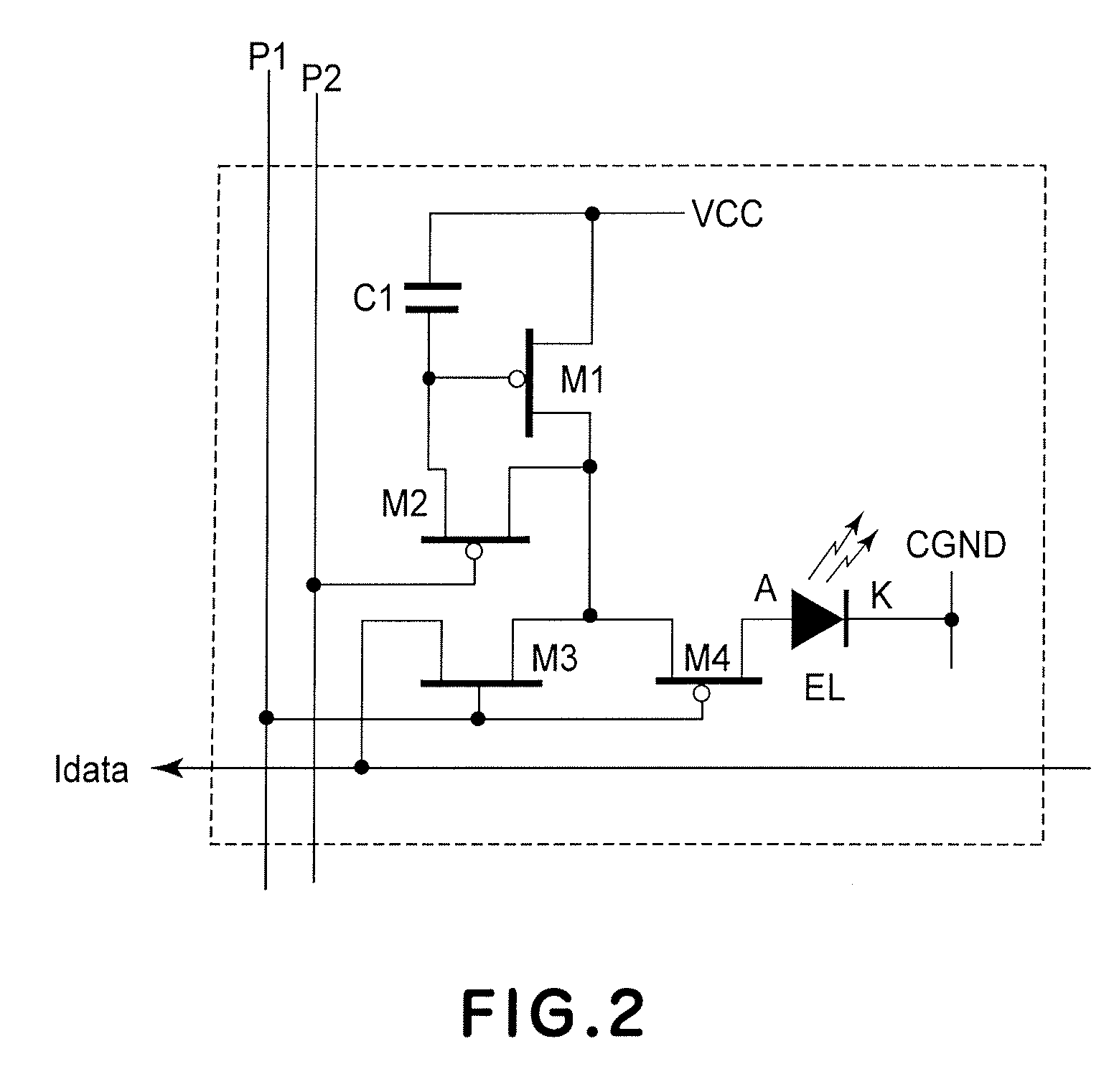

Display apparatus

InactiveUS20070146245A1Reduce layout areaReduce circuit areaStatic indicating devicesElectrical connectionHemt circuits

A display apparatus includes, on a substrate, an area in which a plurality of constituents each including a light-emitting device and a device control circuit for controlling current passing through the light-emitting device is disposed, a common interconnecting line disposed to surround a periphery of the area, a terminal portion for permitting electrical connection to an external circuit, and a wiring lead-out portion for electrically connecting the common interconnecting line to the terminal portion. The light-emitting device is disposed, on the substrate, between a lower first electrode and an upper second electrode. The first electrode is electrically connected to the device control circuit, and the second electrode is electrically connected to the common interconnecting line through a contact hole. The common interconnecting line disposed along a side of the area most distant from the wiring lead-out portion has a narrower width than a width of the common interconnecting line disposed along a side of the area closer to the wiring lead-out portion.

Owner:CANON KK

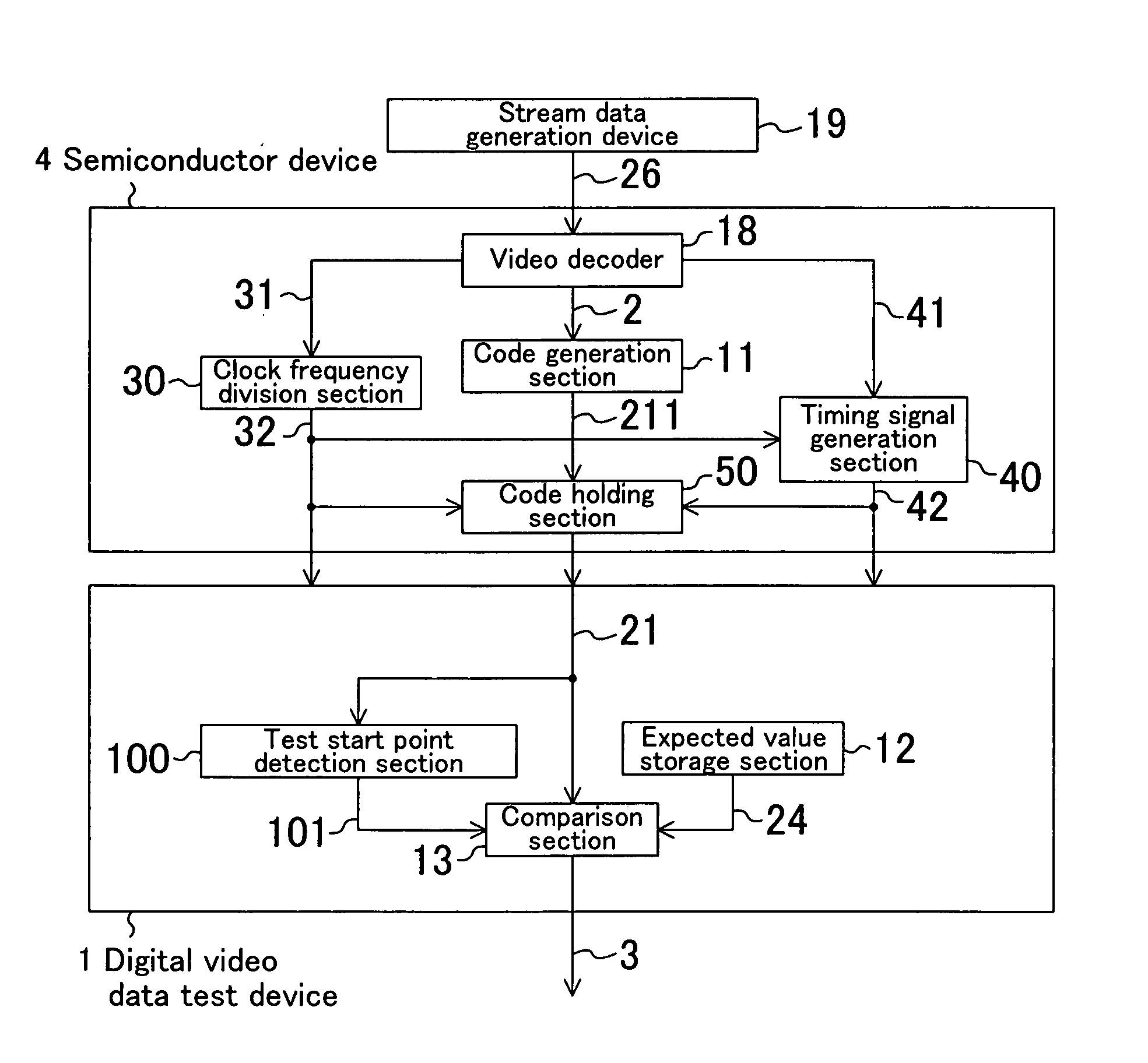

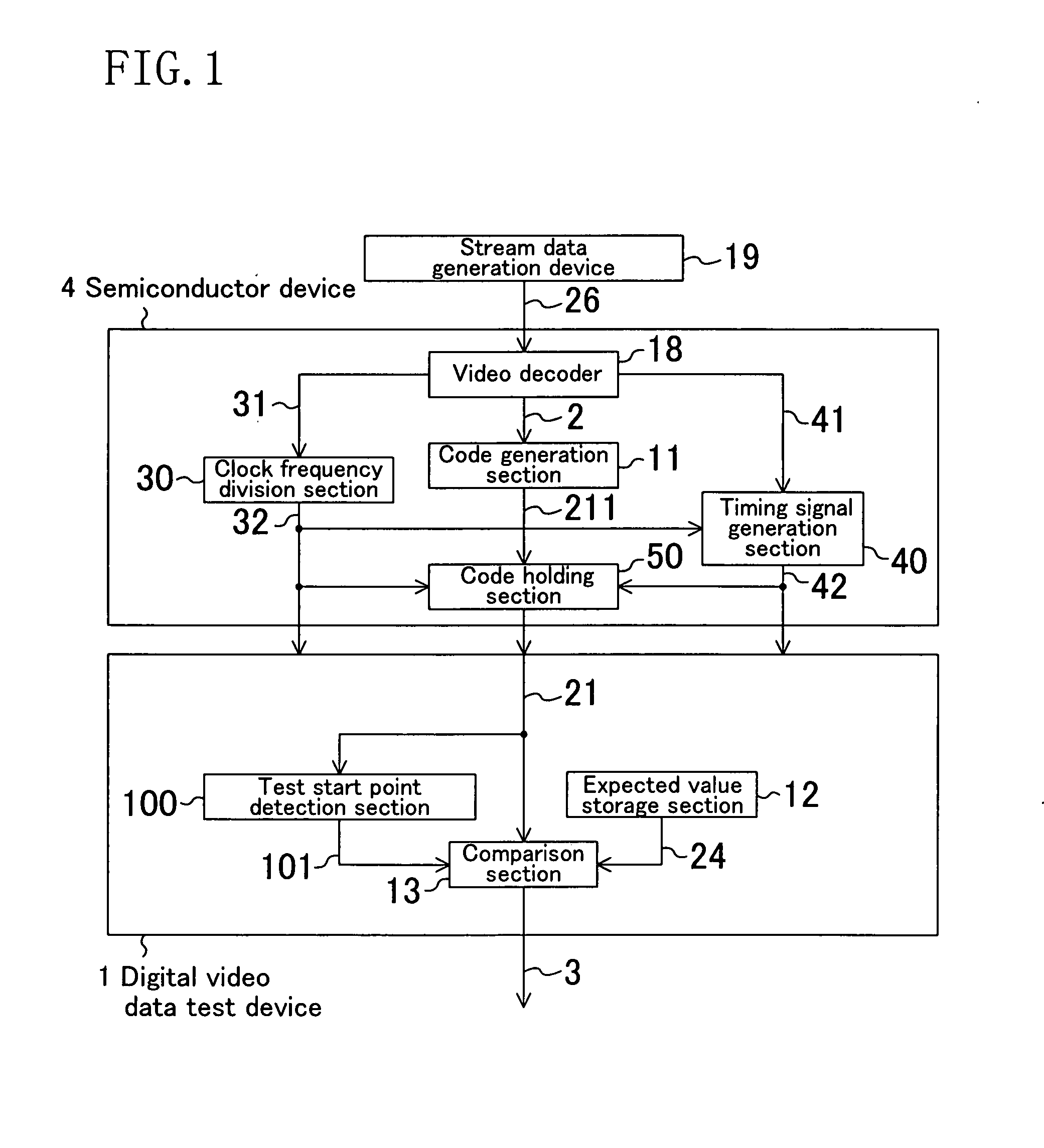

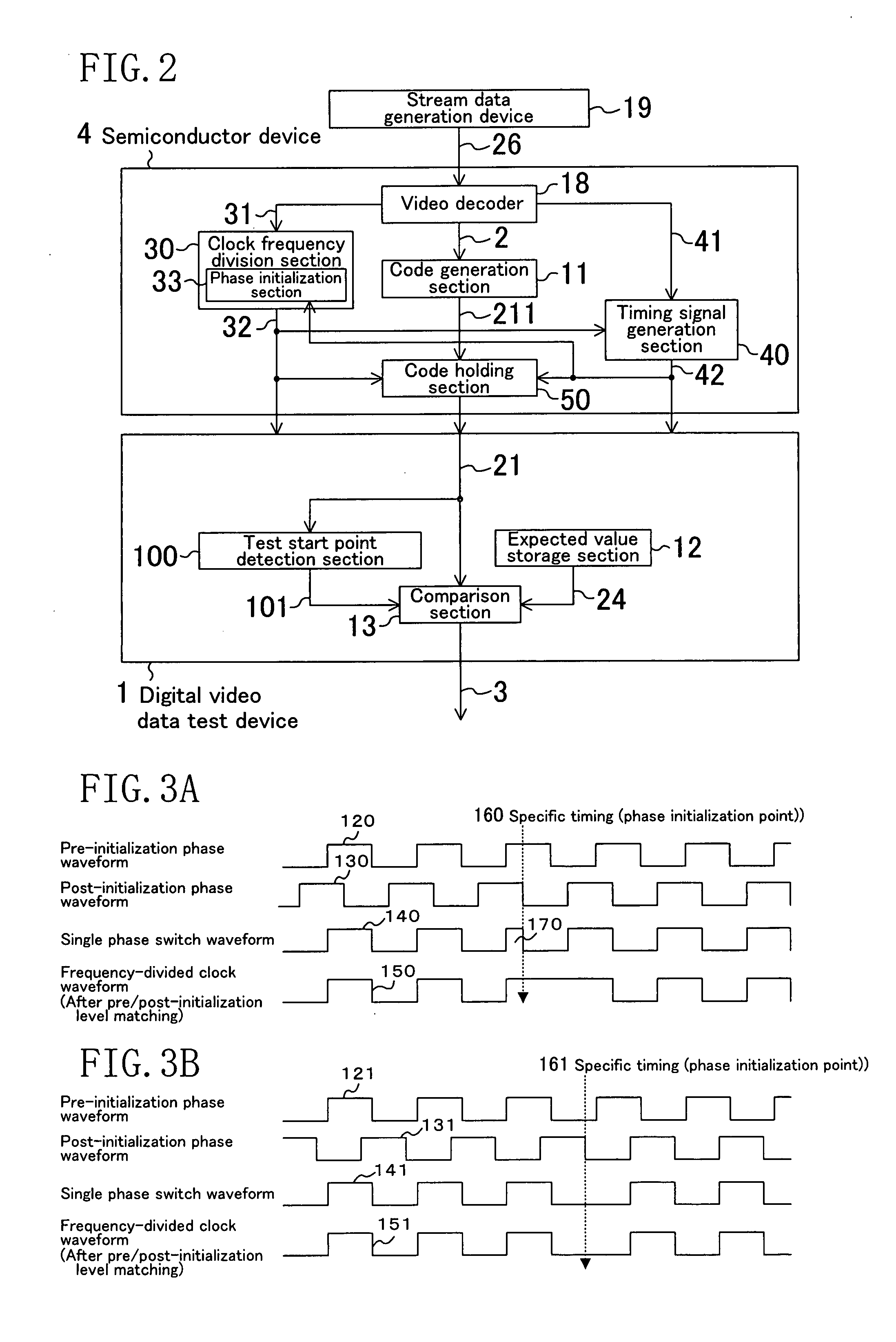

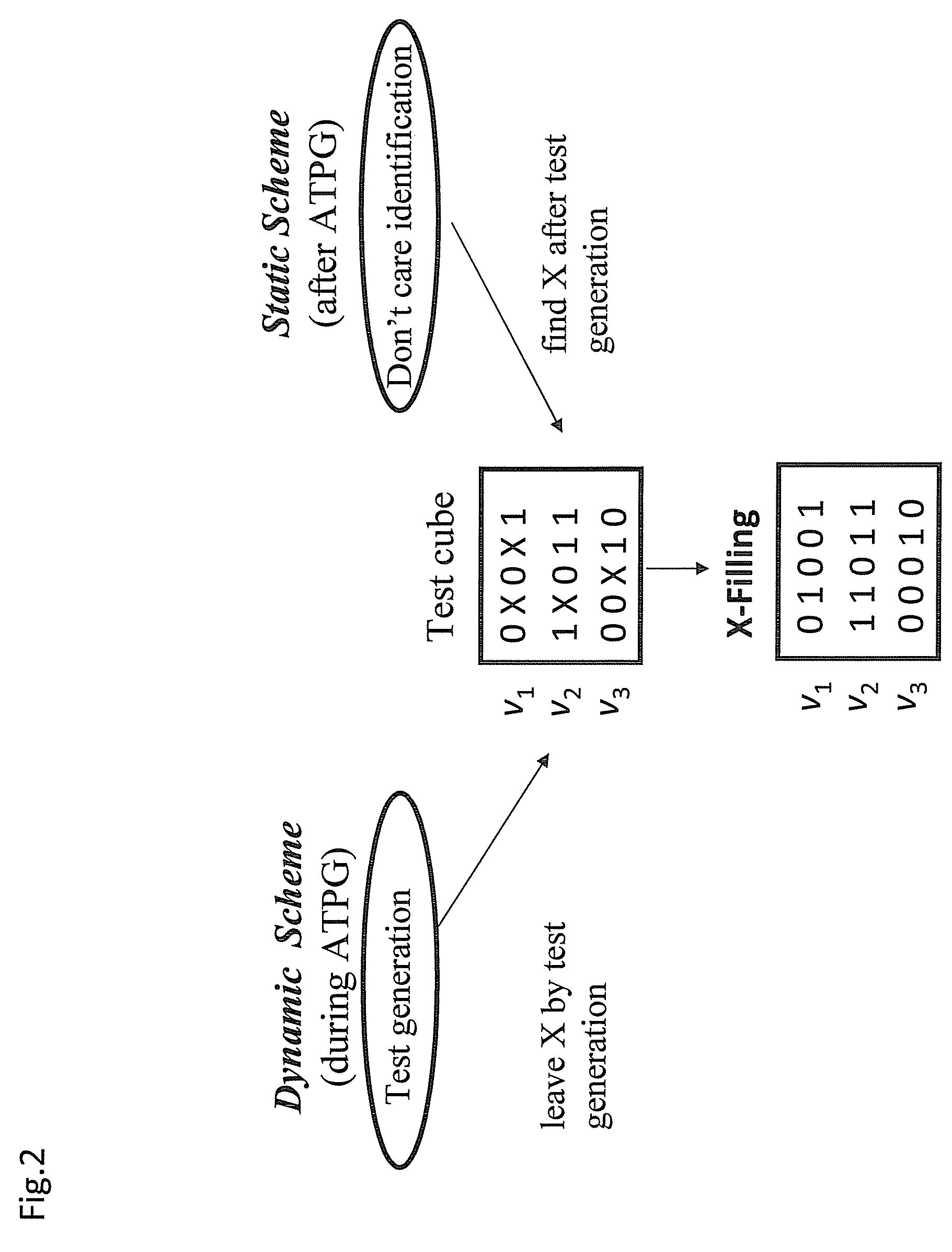

Test system of digital video data and semiconductor device

InactiveUS20080101468A1Increased circuit areaIncrease the areaColor television with pulse code modulationColor television with bandwidth reductionDigital videoSemiconductor

The digital video data test system includes a semiconductor device to be tested and a digital video data test device. In the semiconductor device, a clock frequency division section divides the frequency of a digital video clock to generate a frequency-divided clock. A timing signal generation section generates a timing signal synchronizing with the frequency-divided clock using a sync signal in digital video data. A code holding section outputs a generated code generated by a code generation section to the digital video data test device in synchronization with the timing signal and the frequency-divided clock.

Owner:PANASONIC CORP

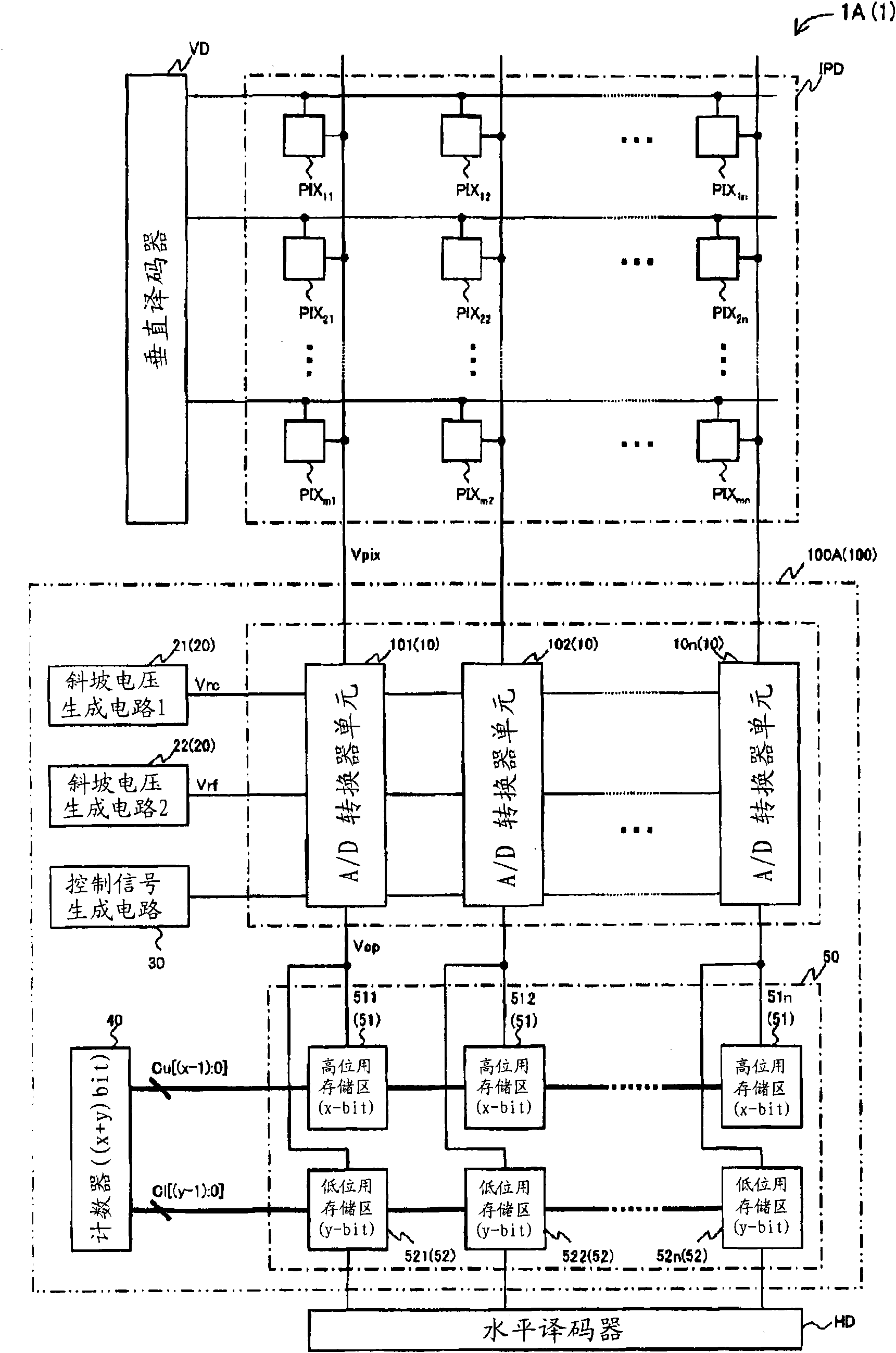

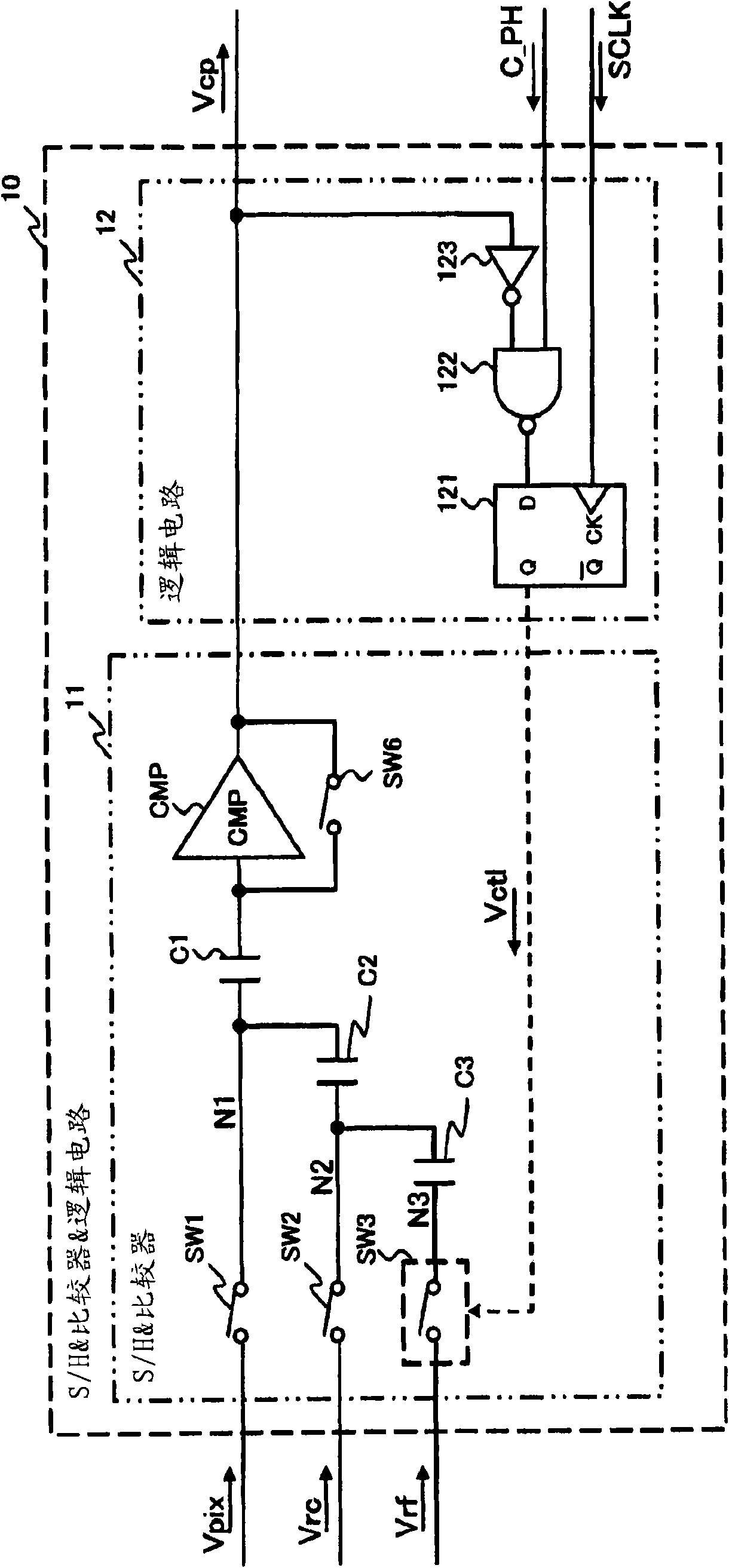

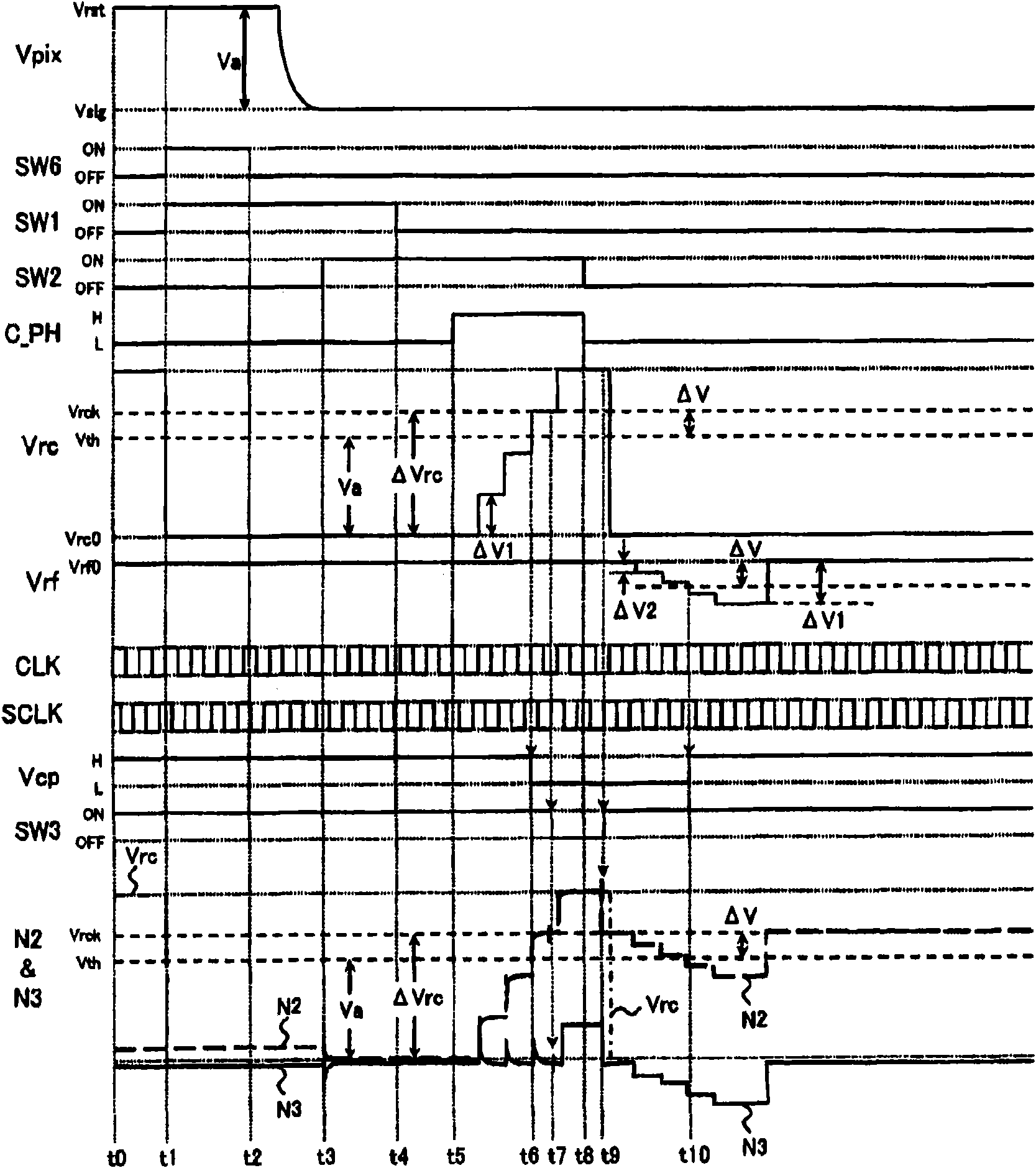

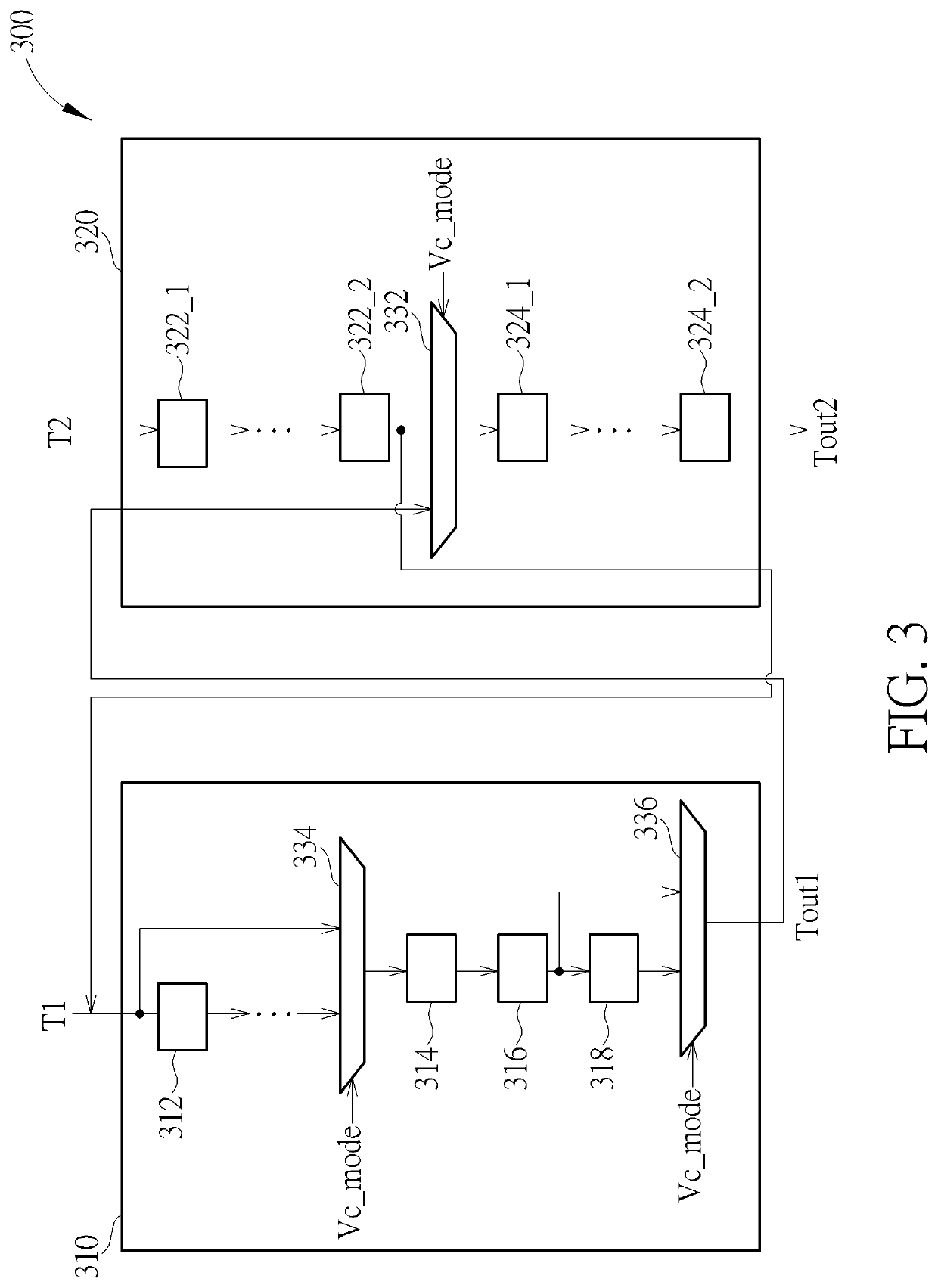

A/D converter circuit and solid-state imaging device

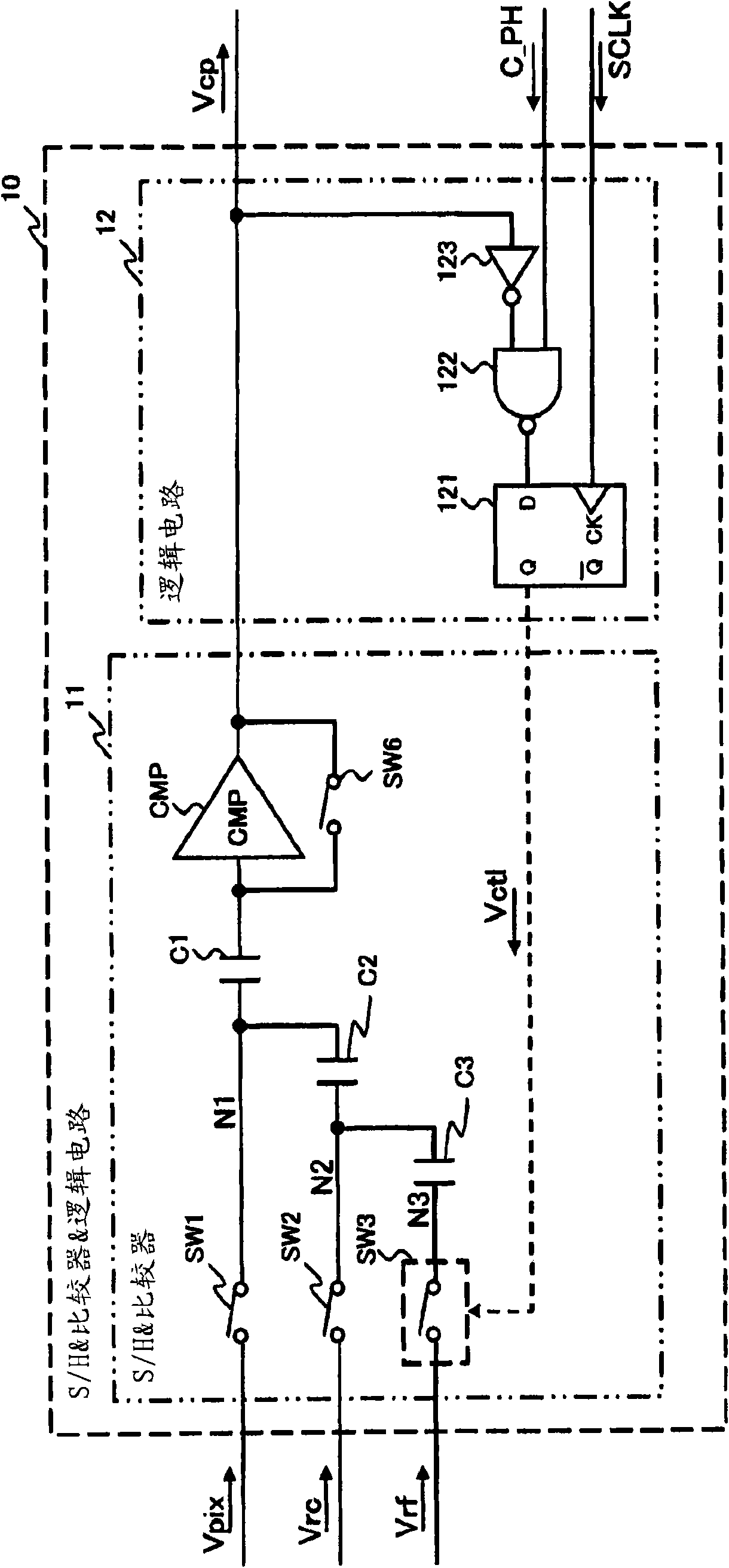

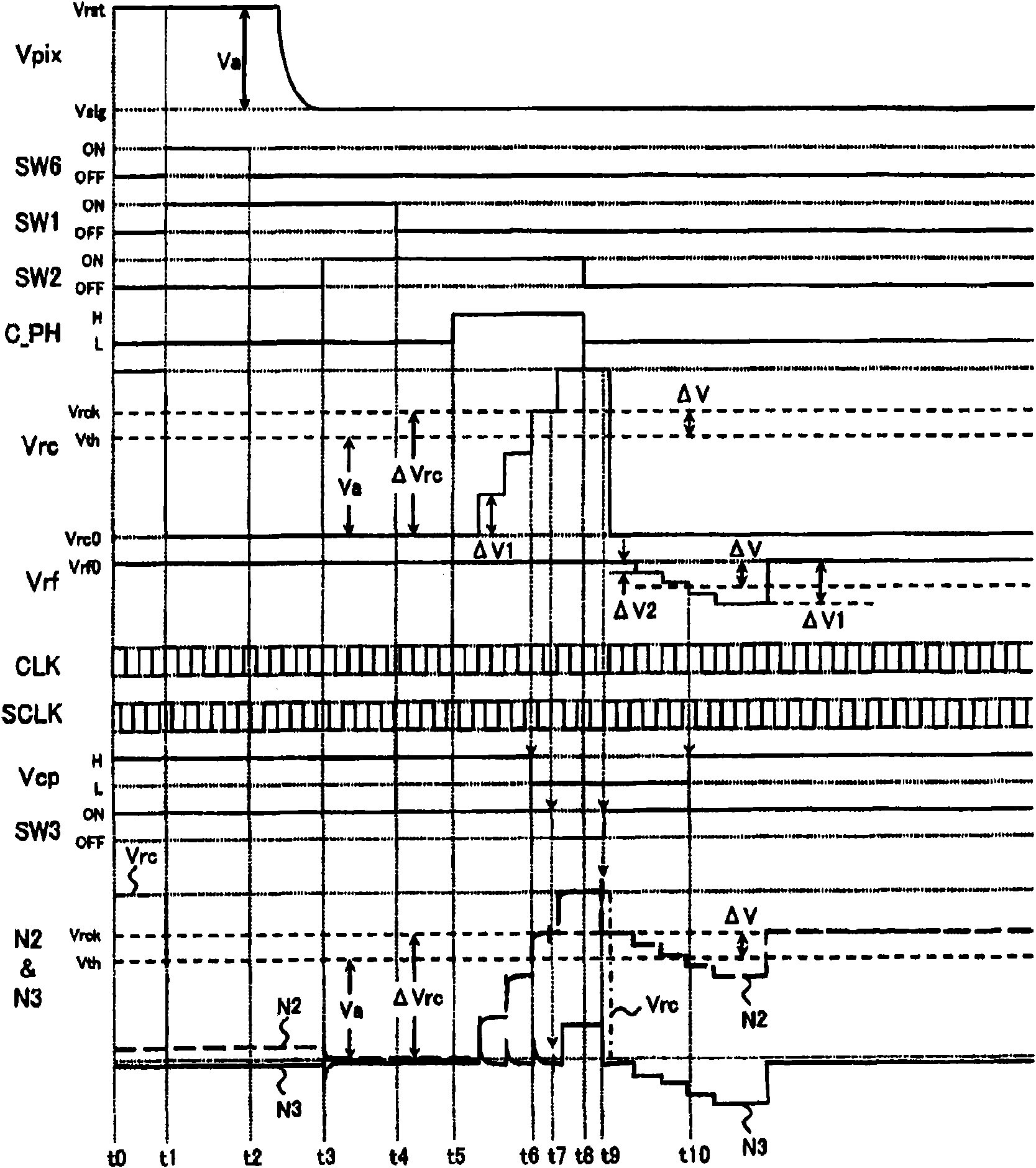

ActiveCN101939917AScale upAvoid noiseTelevision system detailsElectric signal transmission systemsCapacitanceControl signal

Provided are a solid-state image pickup device and subranging A / D converter circuit that can effectively realize both preventing the conversion accuracy from degrading due to characteristic variations and preventing the circuit scale from increasing. There are included series-connected capacitive elements (C1-C3); a voltage comparator circuit (CMP) that compares an output value of the capacitive element (C1) with a threshold voltage value (Vth); a first input circuit that supplies an analog voltage signal (Vpix), which is to be converted, to a node between the capacitive elements (C1 and C2);a second input circuit that supplies a first reference voltage, the voltage value of which monotonously varies, to a node between the capacitive elements (C2 and C3) during execution of a first conversion process obtaining the values of higher-order bits; a third input circuit that supplies a second reference voltage, the voltage value of which monotonously varies, to an input terminal of the capacitive element (C3) during execution of a second conversion process obtaining the values of unconverted bits after completion of the first conversion process; and a control circuit (12) that generates a control signal (Vctl) for holding the first reference voltage in the capacitive element (C3) at occurrence of a change in the output of the voltage comparator circuit (CMP) in the first conversionprocess.

Owner:思特威(上海)电子科技股份有限公司

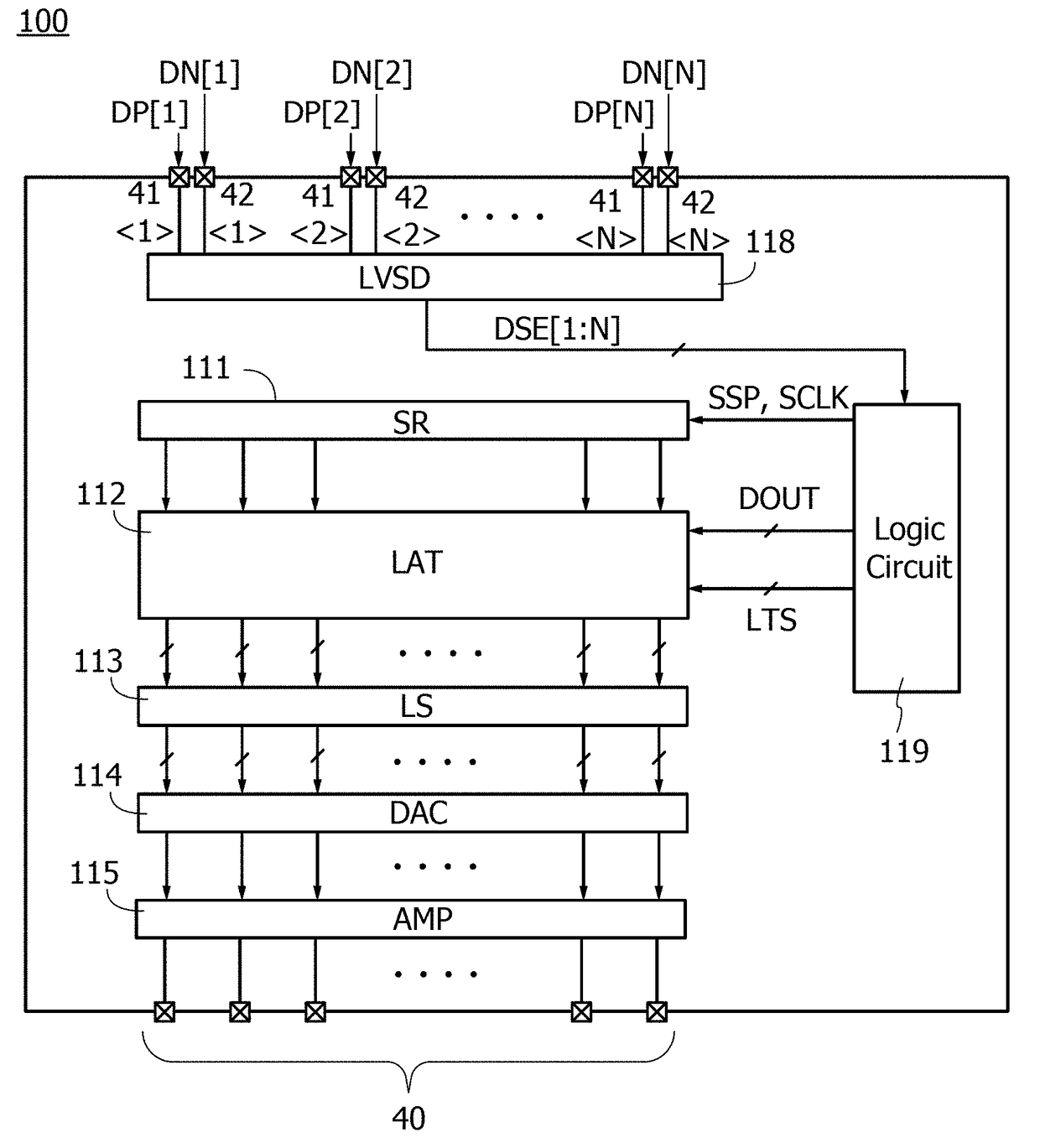

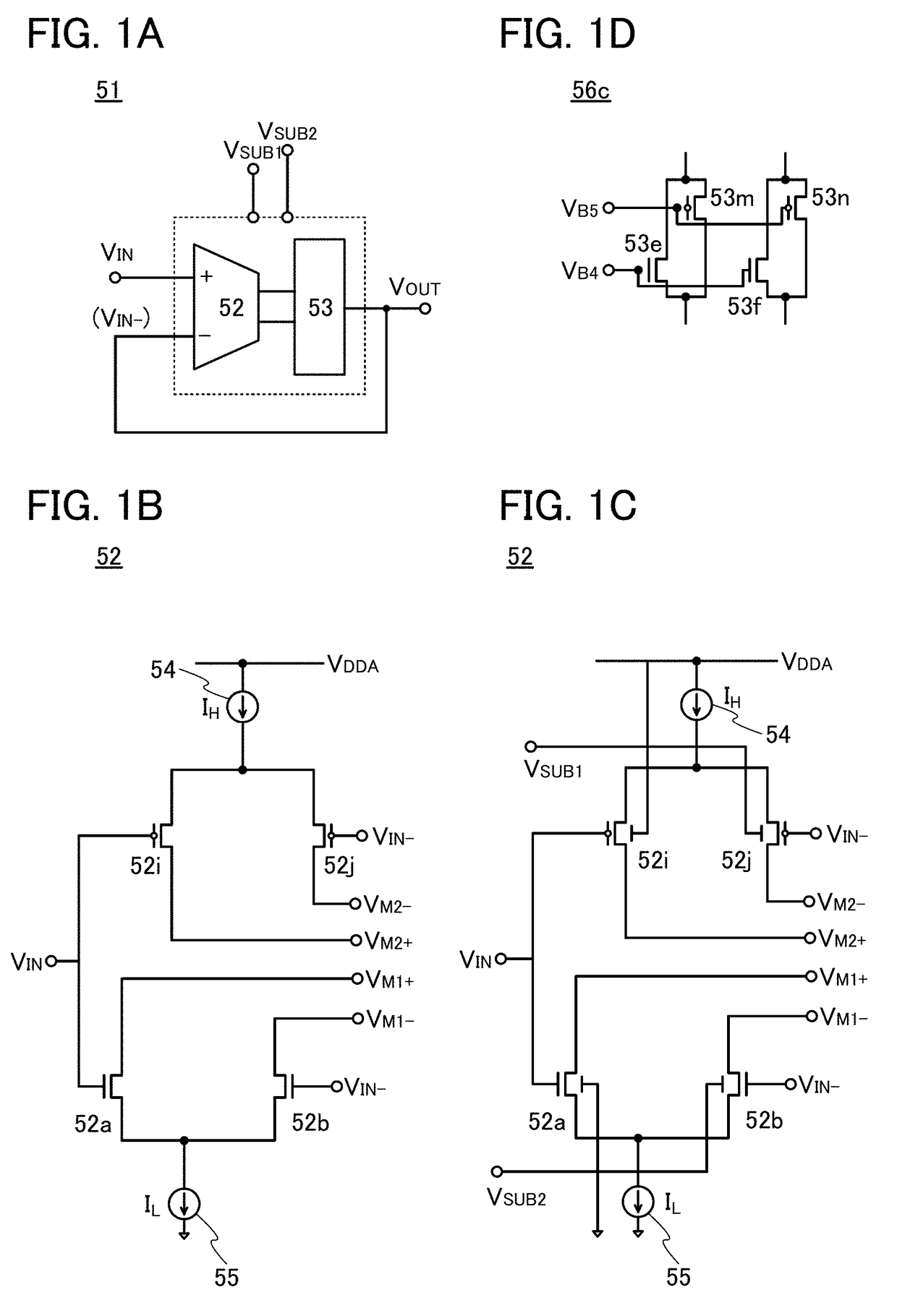

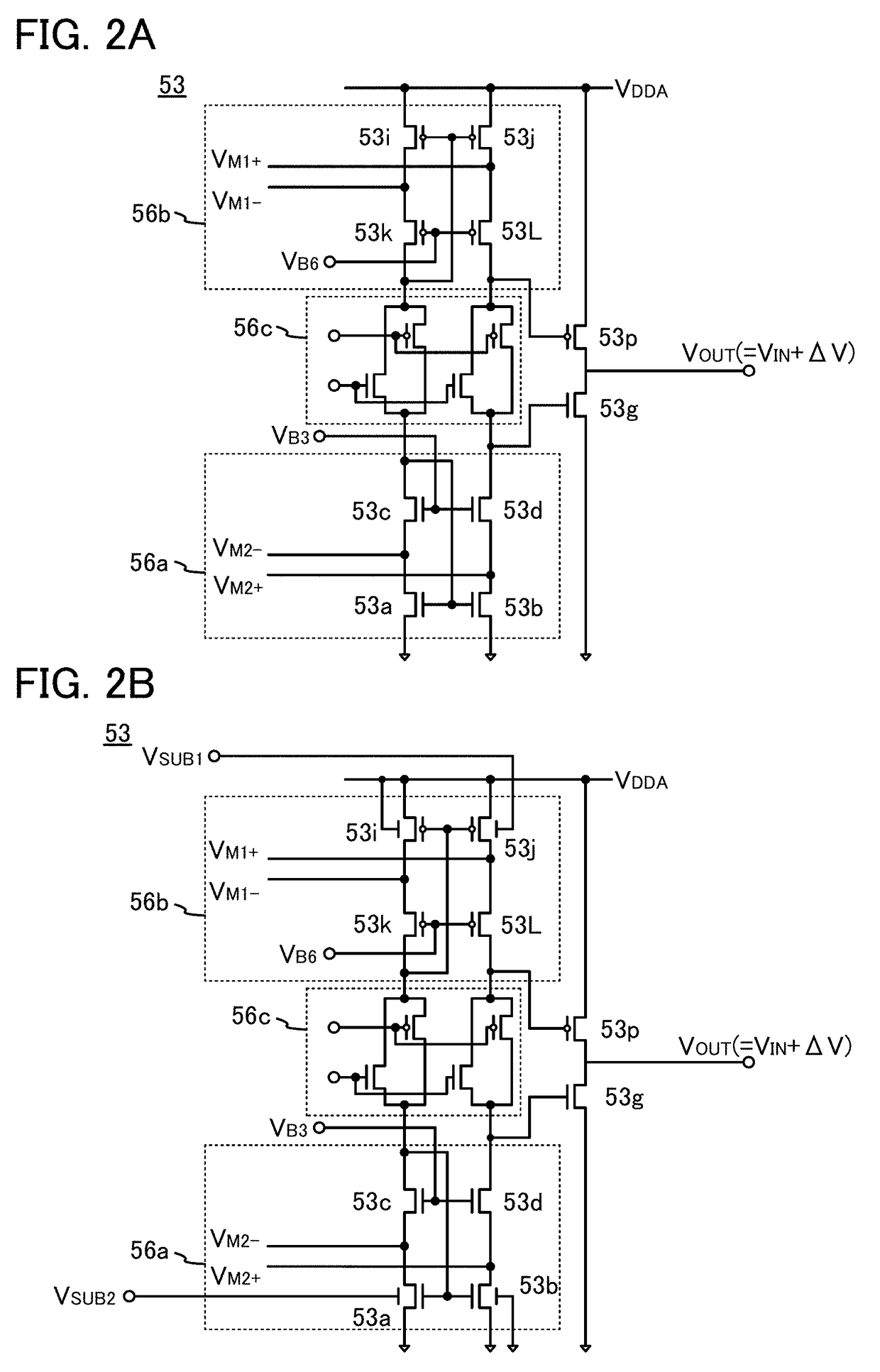

Circuit, semiconductor device, display device, electronic device, and driving method of circuit

ActiveUS20170186355A1Increased circuit areaResponse speed is loweredTransistorStatic indicating devicesDigital analog converterSemiconductor

A semiconductor device with lower power consumption or a display device including the semiconductor device is provided. A circuit to which an N-bit signal is input includes a first digital-to-analog converter circuit to which an upper M-bit signal is input, a second digital-to-analog converter circuit to which a lower (N−M)-bit signal is input, and an amplifier circuit. The amplifier circuit includes a first transistor and a second transistor. An output terminal of the first digital-to-analog converter circuit is electrically connected to a gate of the first transistor. An output terminal of the second digital-to-analog converter circuit is electrically connected to a substrate potential of the second transistor. One of a source and a drain of the first transistor is electrically connected to one of a source and a drain of the second transistor. An output terminal of the amplifier circuit is electrically connected to a gate of the second transistor.

Owner:SEMICON ENERGY LAB CO LTD

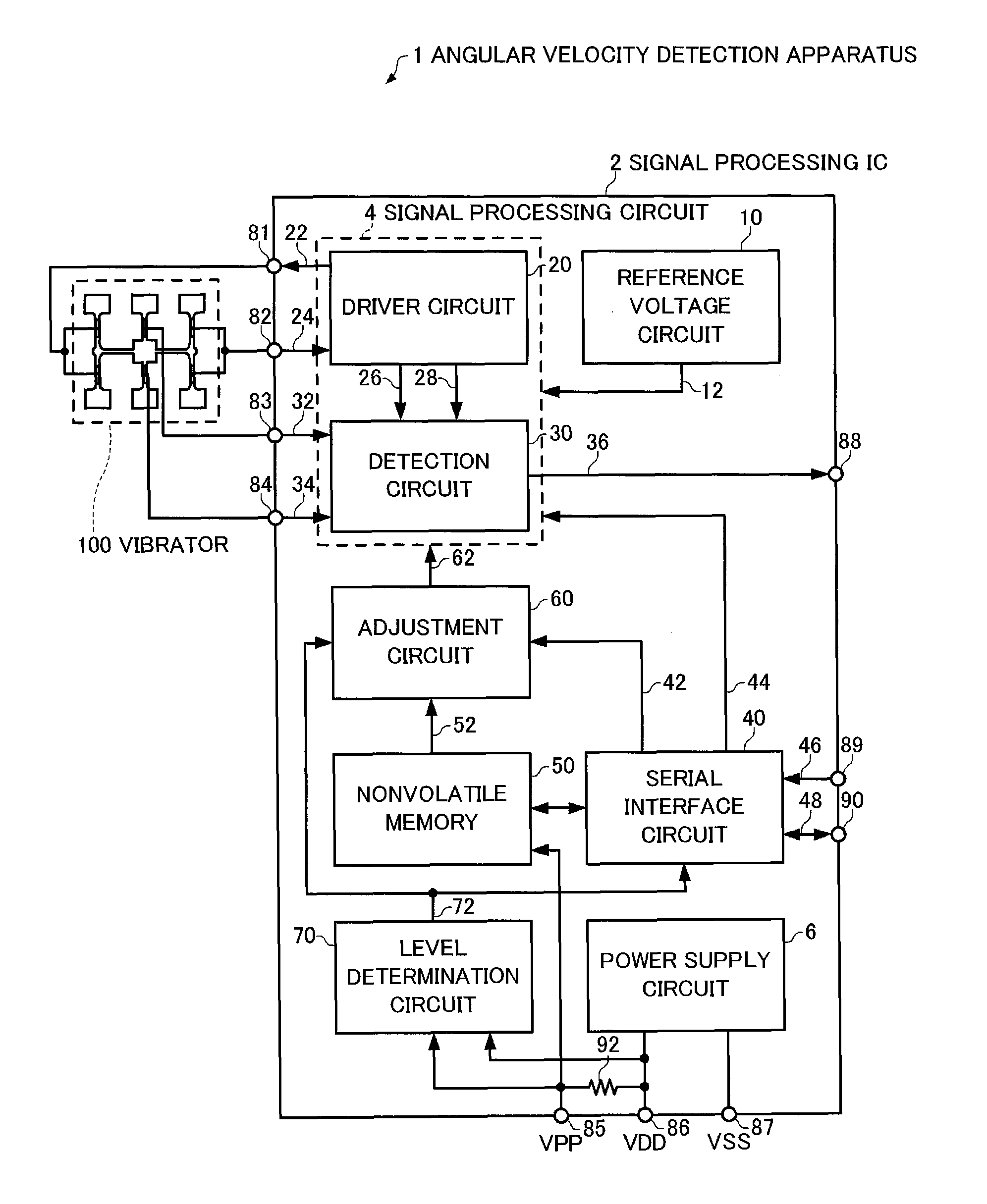

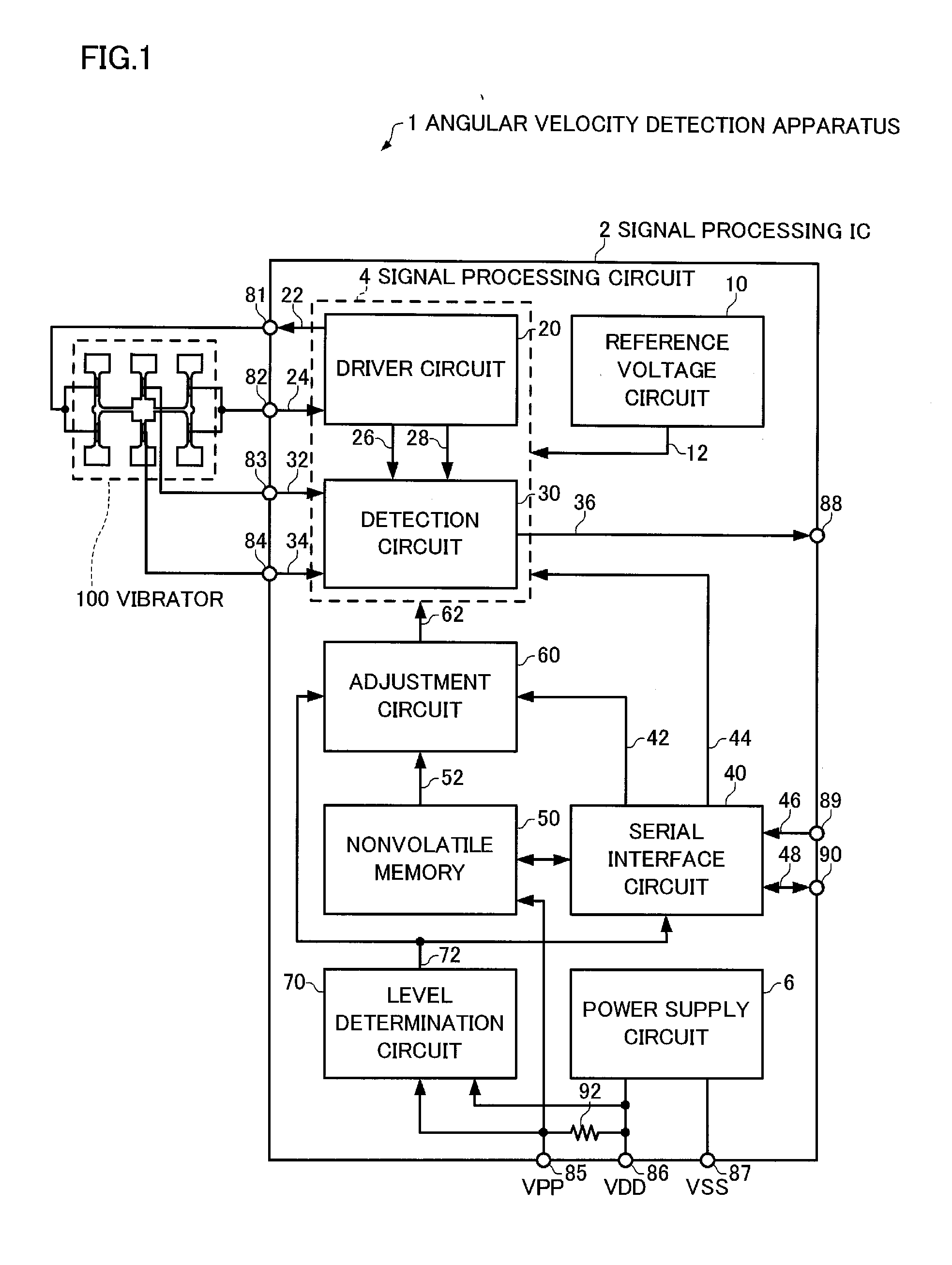

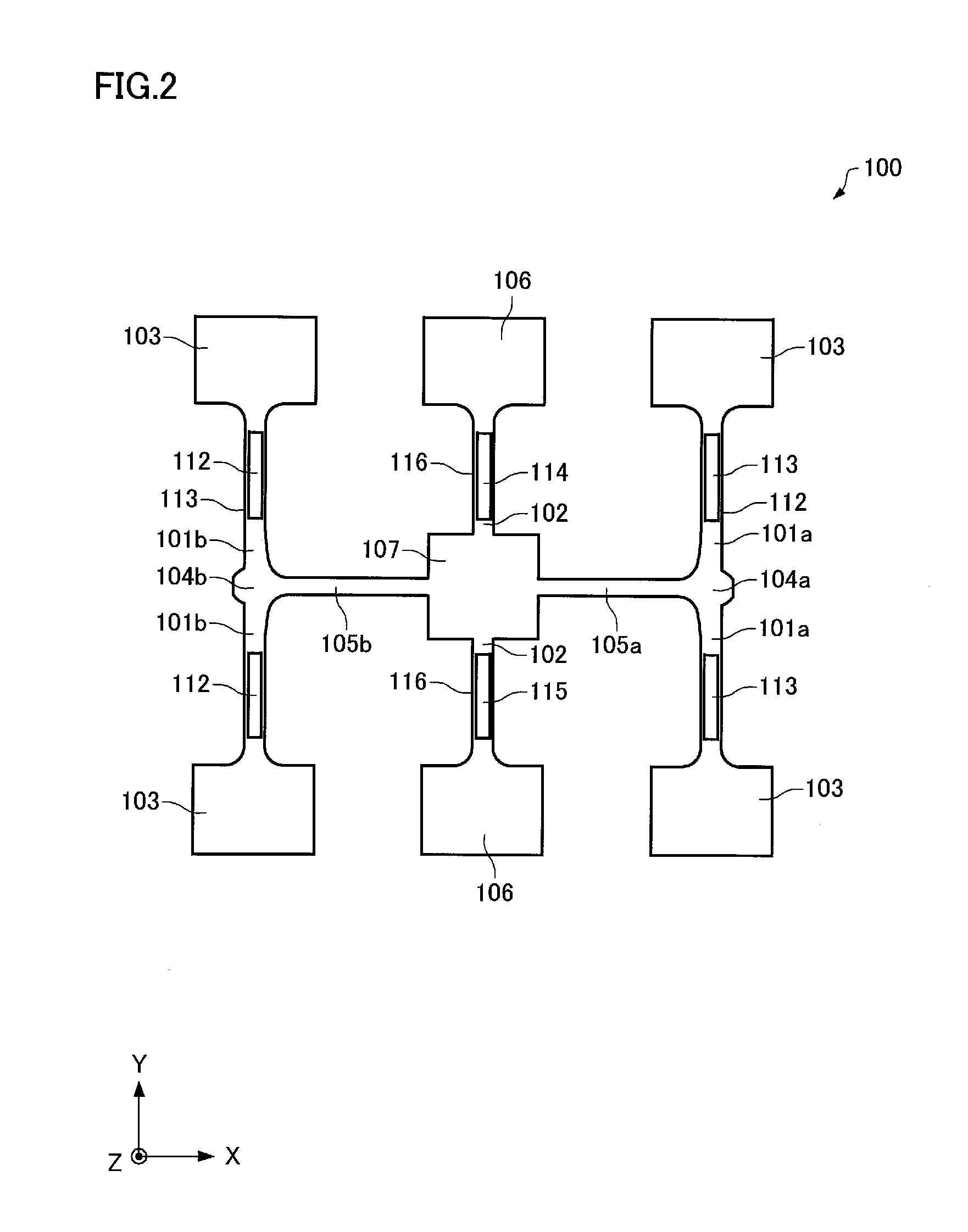

Signal processing circuit, physical quantity detection apparatus, angular velocity detection apparatus, integrated circuit device, and electronic instrument

ActiveUS20130055815A1Reduce noiseIncreased circuit areaVibration measurement in solidsAnalysing solids using sonic/ultrasonic/infrasonic wavesSignal processing circuitsPhase difference

A signal processing circuit includes an I / V conversion circuit (current / voltage conversion section) that converts an oscillation current of a vibrator into a voltage, an RC filter (phase shift section) that shifts a phase of the output signal of the I / V conversion circuit, a full-wave rectifier (part of a drive amplitude control section) that binarizes a signal that has been shifted in phase to generate a switch control signal, a comparator (reference signal generation section) that generates a reference signal for synchronous detection based on the output signal of the I / V conversion circuit, and an EXOR circuit (clock signal generation section) that generates a clock signal for a switched capacitor filter (SCF) that has a frequency twice a frequency of a drive signal based on a phase difference between the reference signal and the switch control signal.

Owner:SEIKO EPSON CORP +1

Electronic Apparatus

ActiveUS20130145084A1Increased circuit areaImprove accuracyMemory adressing/allocation/relocationData rate detection arrangementsComputer scienceBaud

An electronic apparatus provided with a serial communication circuit achieving a baud rate adjustment with high precision is provided. For example, a bit width of each of a plurality of bits in received serial data is measured by a clock counter, and an average value of the bit width is calculated detecting its maximum value and minimum value. Moreover, for example, a maximum tolerance and a minimum tolerance are calculated as a value substantially 1.5 times the average value and a value substantially 0.5 times the average value, and determination is made as to whether or not the maximum value and the minimum value are within a range between the maximum tolerance and the minimum tolerance. If they are within the range, the corresponding average value is set in a baud rate setting register.

Owner:SANKEN ELECTRIC CO LTD

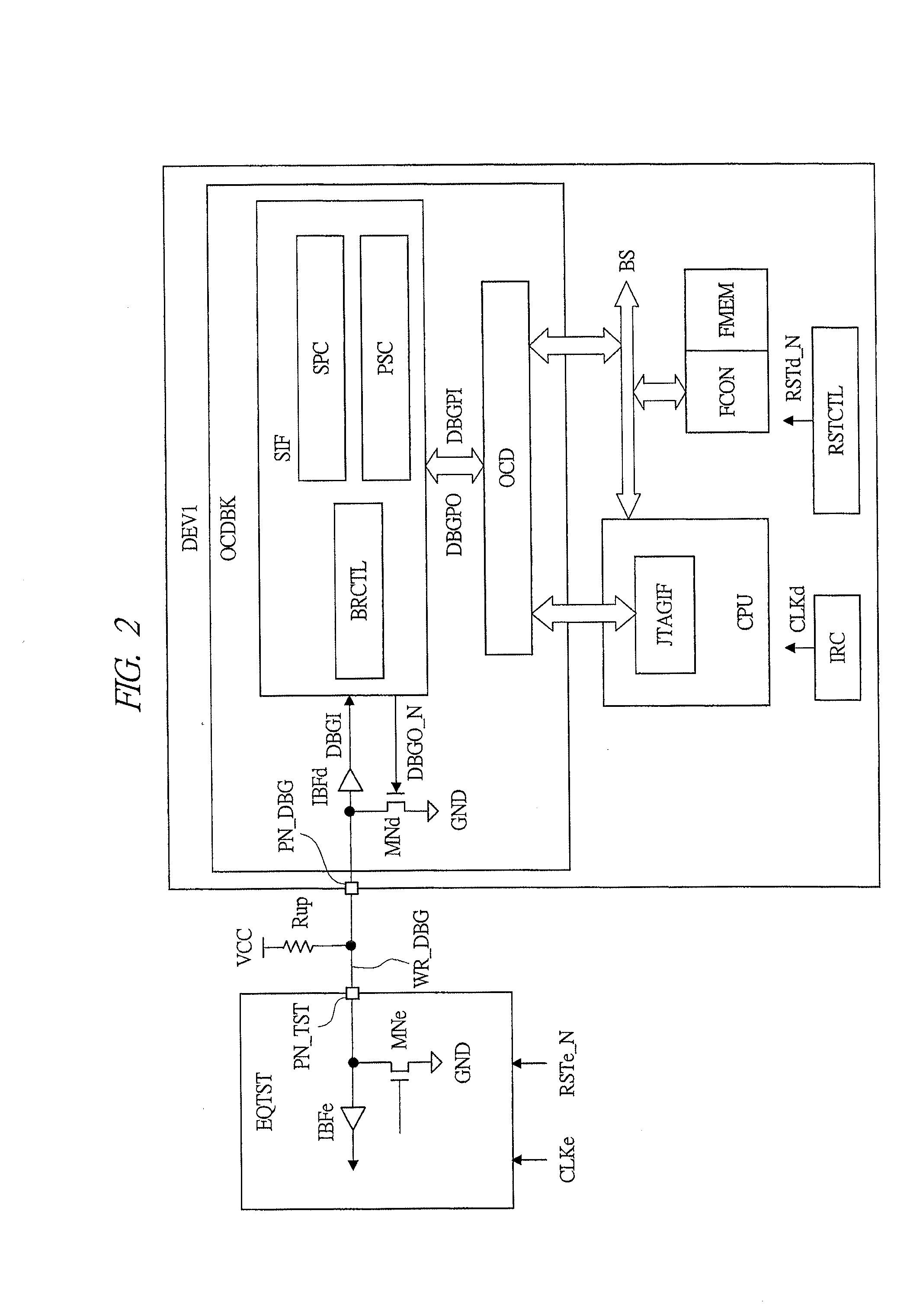

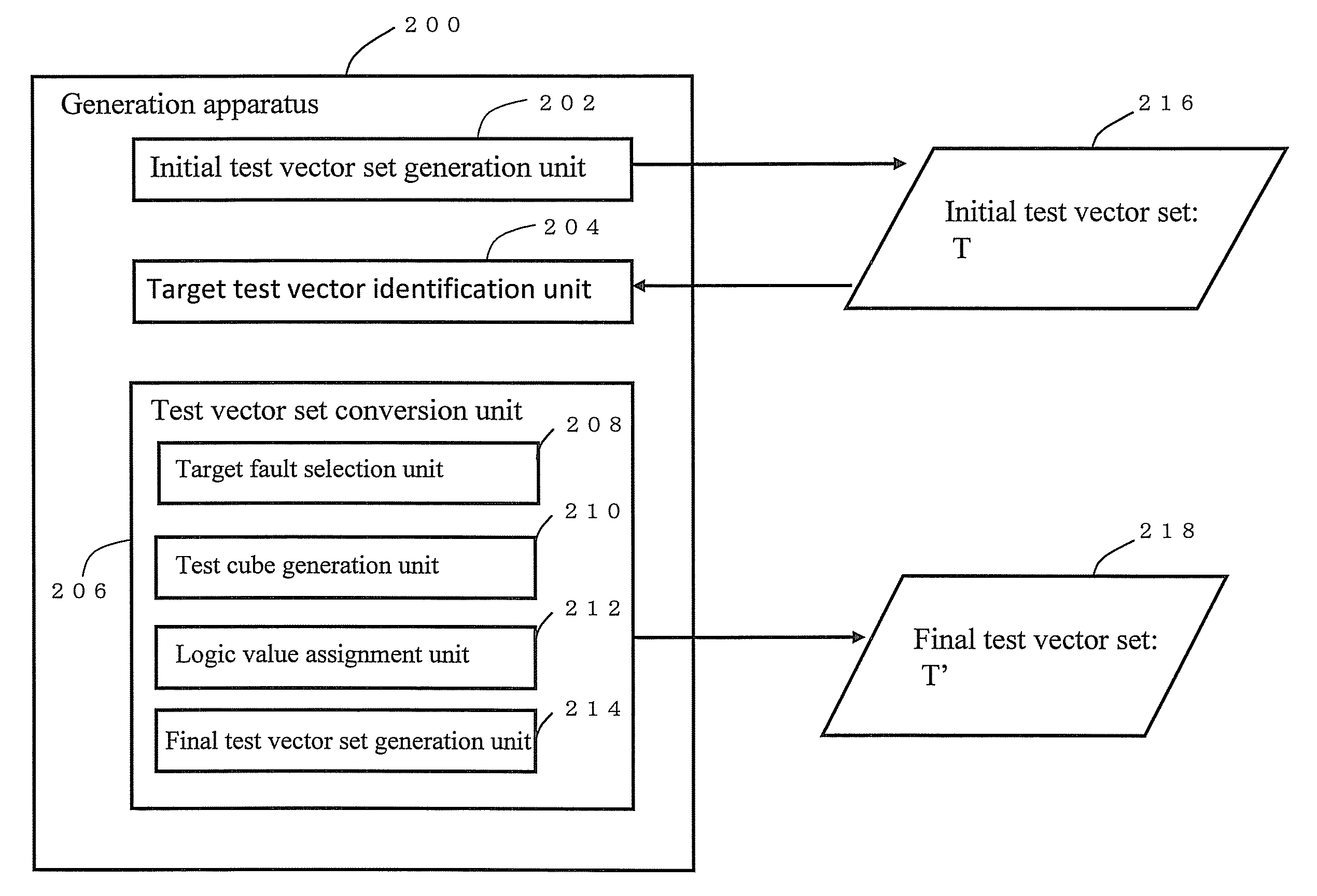

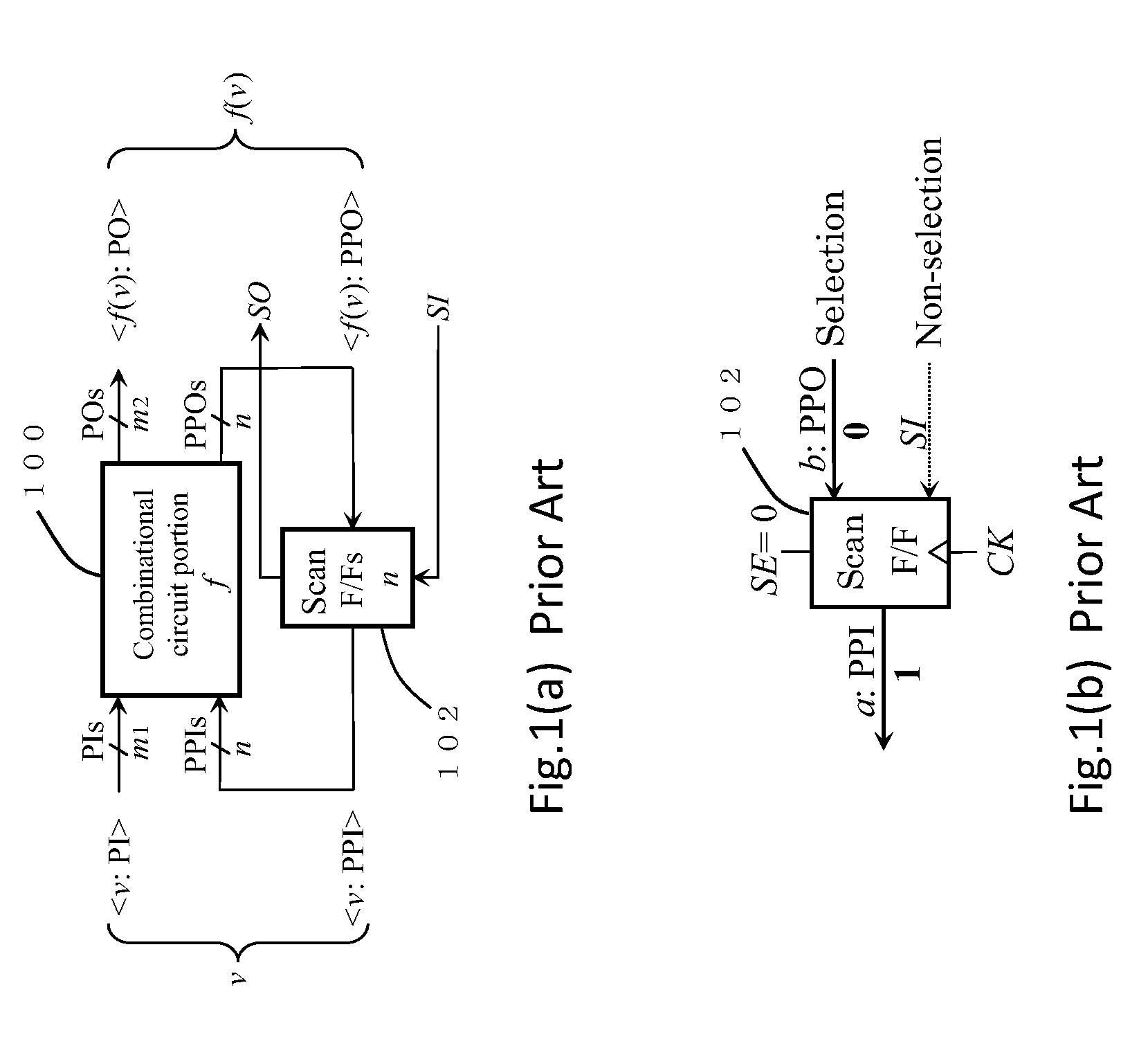

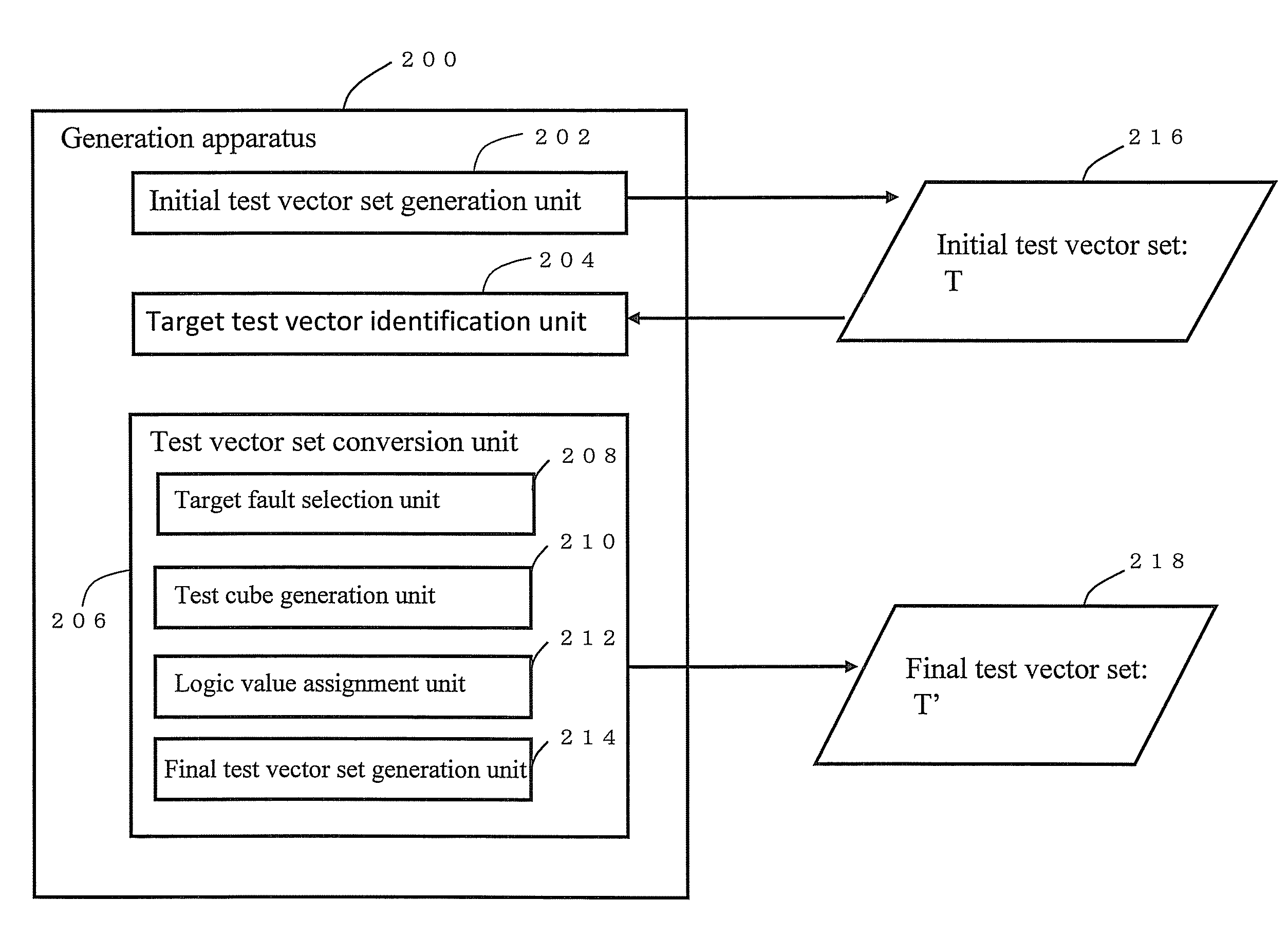

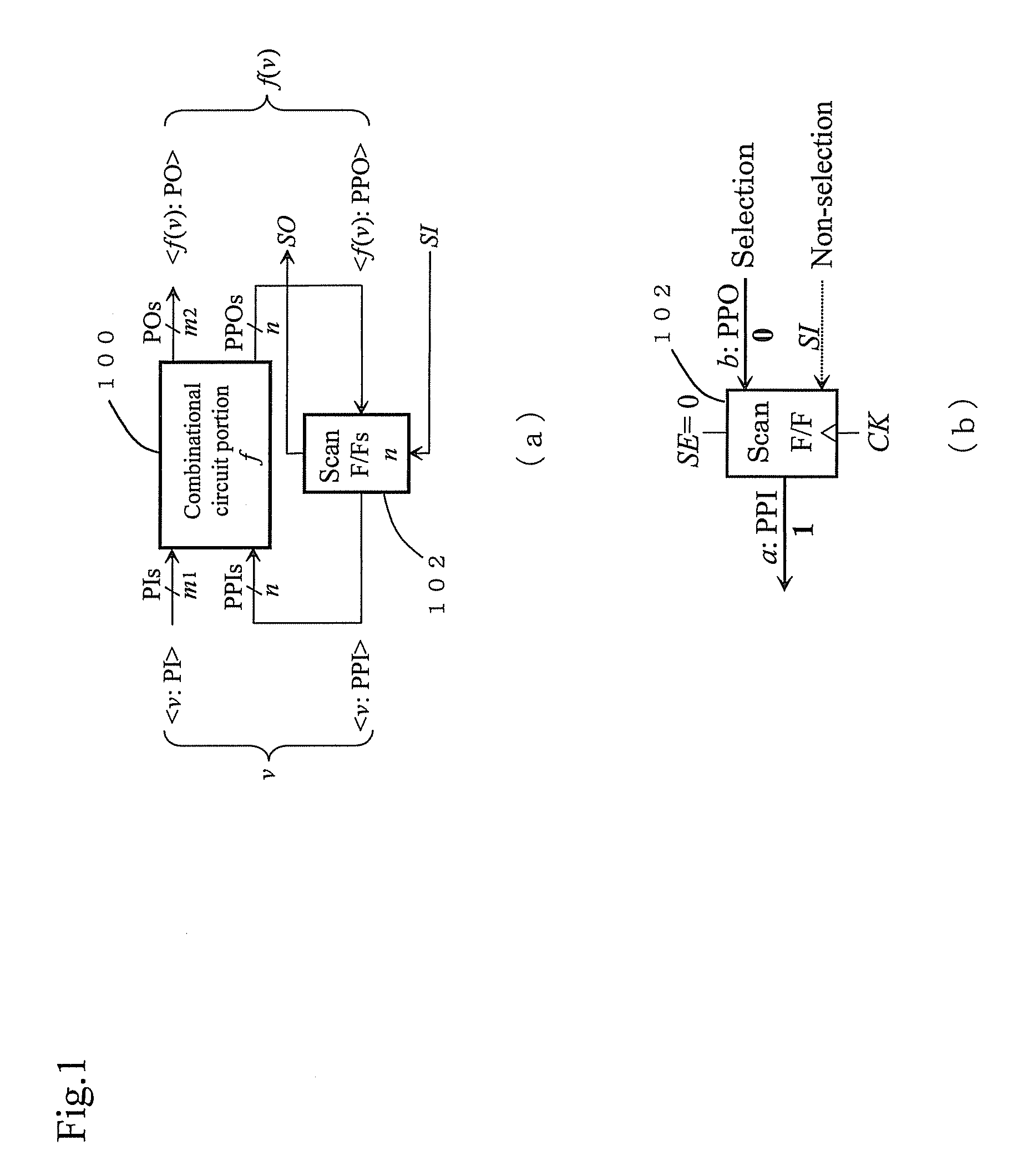

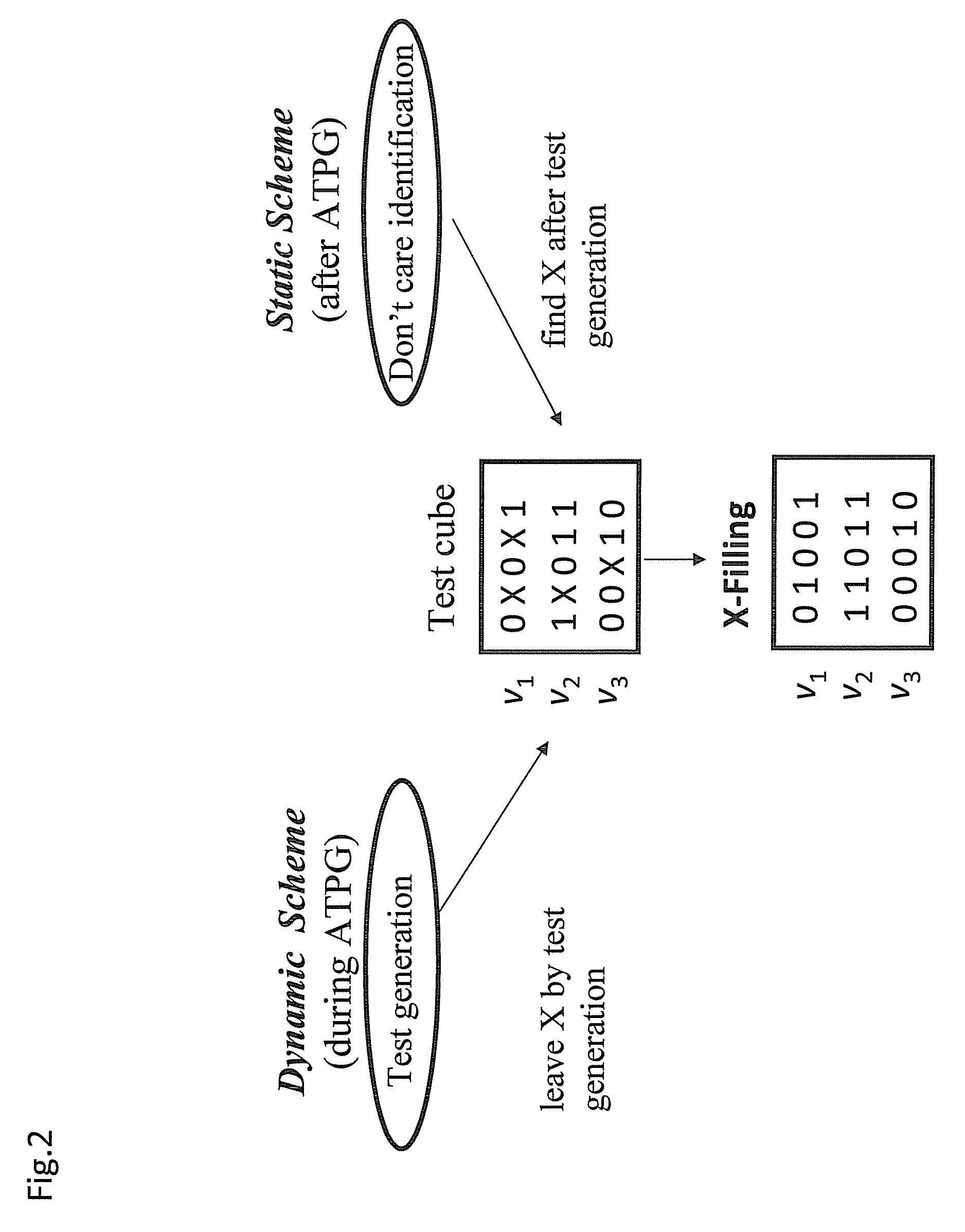

Generating device, generating method, program and recording medium

InactiveUS7962822B2Reduce the differenceScan capture power dissipation can be thereby suppressedElectronic circuit testingError detection/correctionParallel computingTest vector

A generation apparatus and the like for generating a test vector set capable of reducing differences in a logic value generated before and after a scan capture for outputs from scan cells included in a full-scan sequential circuit are provided. A generation apparatus 200 generating an initial test vector set 216 for a logic circuit includes a target vector identification unit 204 identifying a test vector satisfying a predetermined criterion and to be selected for the number of bits (the number of bit transitions) whose logic values differ before and after scan capture with respect to outputs from scan cells included in the sequential circuit, from among test vectors in the initial test vector set 216, and a test vector set conversion unit 206 converting the test vector identified by the test vector identification unit 204 and to be selected so as to reduce the number of bit transitions with respect to outputs from the scan cells included in the sequential circuit.

Owner:JAPAN SCI & TECH CORP +2

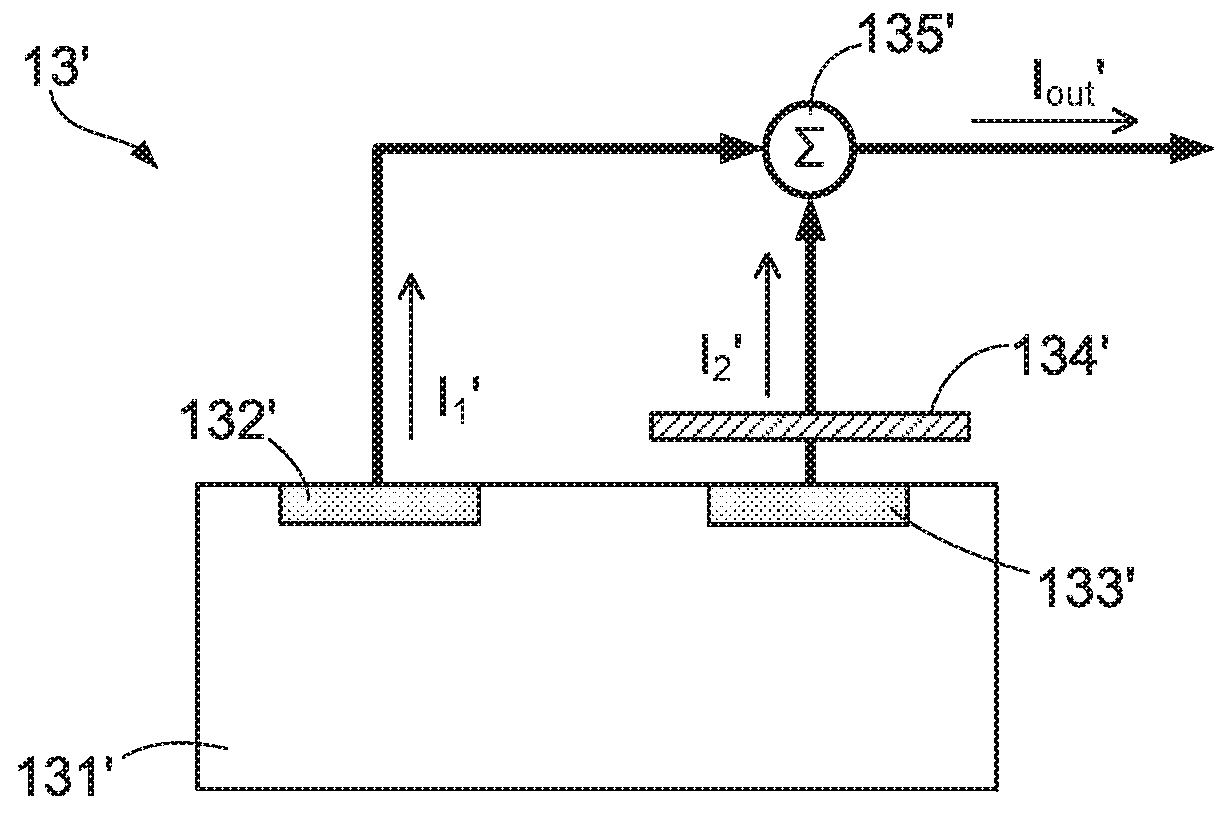

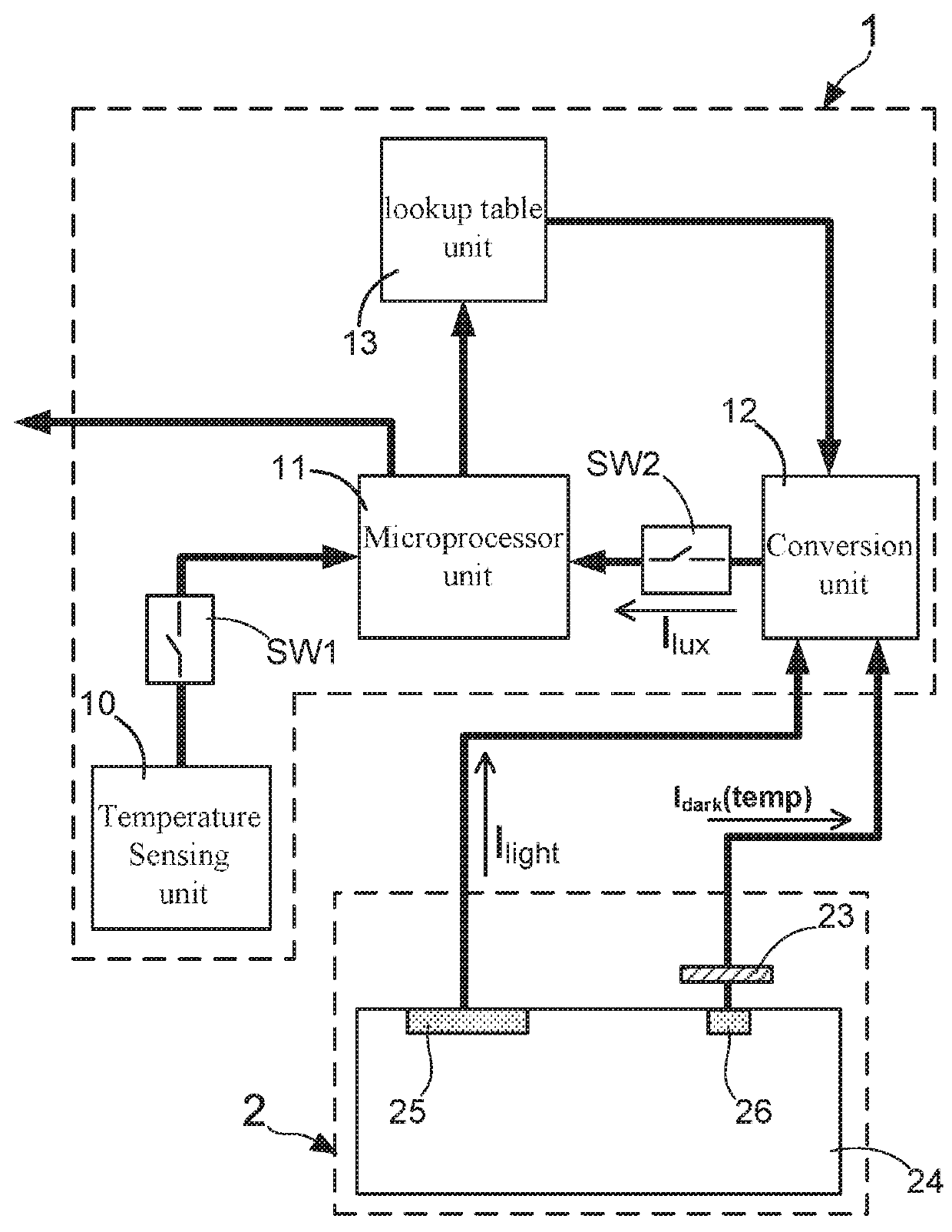

Ambient light sensor with photodiode leakage current compensation

InactiveUS20180266879A1Reduce circuit areaReduce manufacturing costPhotometry electrical circuitsPhotometry using multiple detectorsEngineeringTransducing Unit

Differing from conventional ambient light sensors at least having drawbacks of huge circuit area and high manufacturing cost, the present invention discloses an ambient light sensor showing advantages of small circuit area and low manufacturing cost. This ambient light sensor has functionality of photodiode leakage current compensation, and comprises: a temperature sensing unit, a microprocessor unit, a conversion unit, and a lookup table unit. The microprocessor unit is configured to find out a reference parameter for a first dark current from the lookup table unit according to a measured data of ambient temperature. Subsequently, the conversion unit is controlled to apply a current amplifying process to a second dark current. Therefore, after subtracting an output current of the first photodiode from the second dark current been treated with the current amplifying process, the output current been treated with a leakage current compensating process is produced and outputted.

Owner:DYNA IMAGE CORPORATION

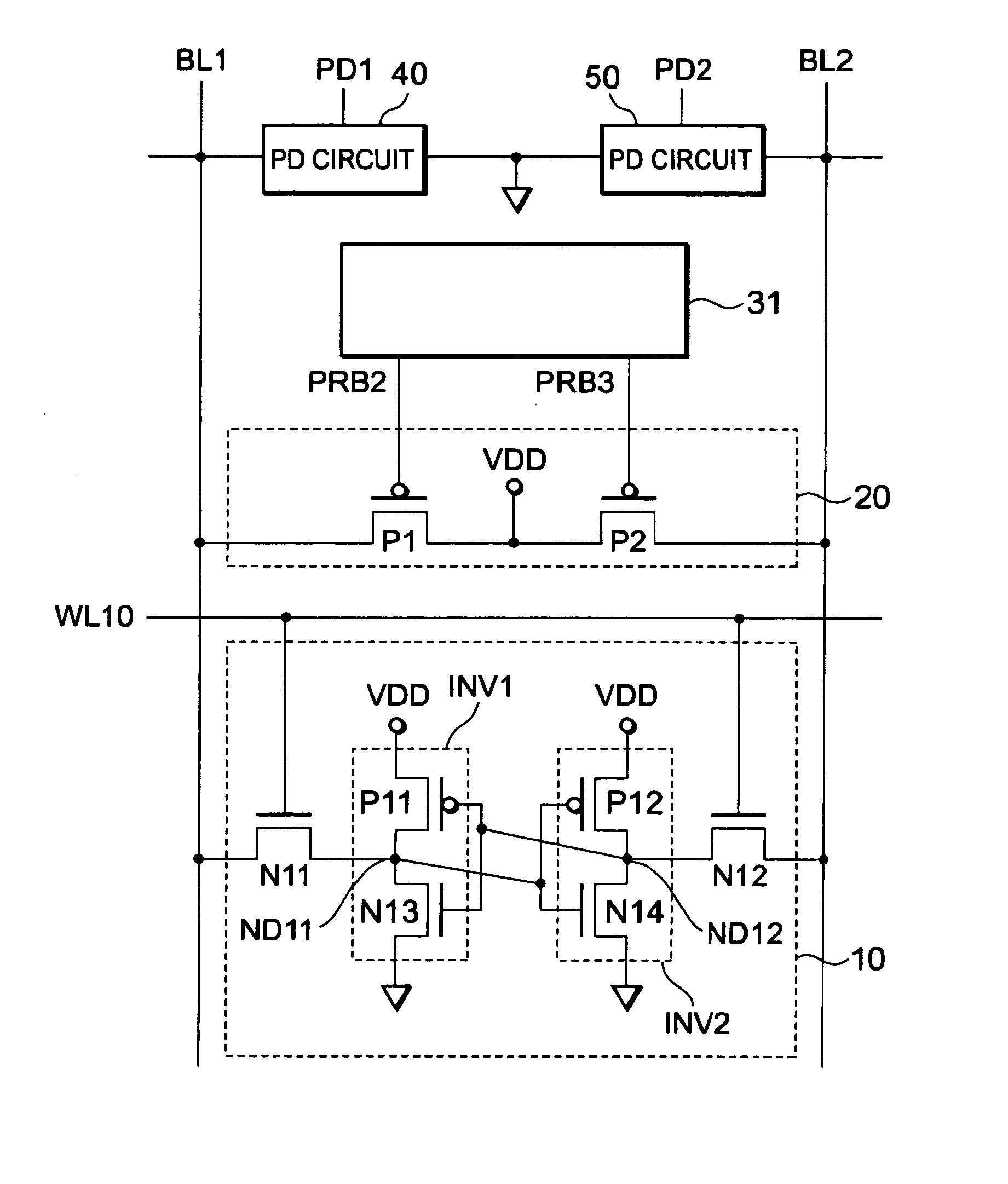

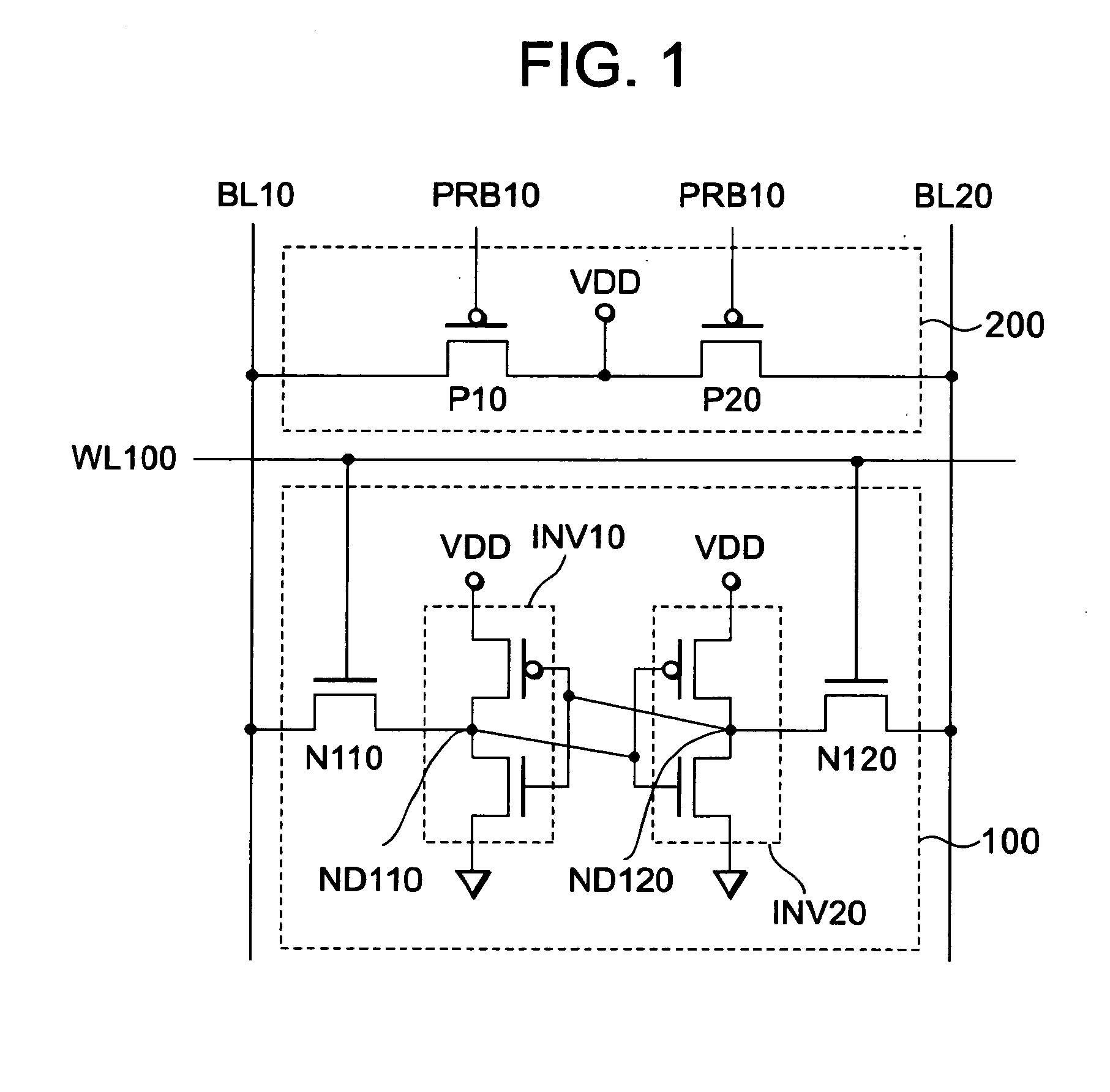

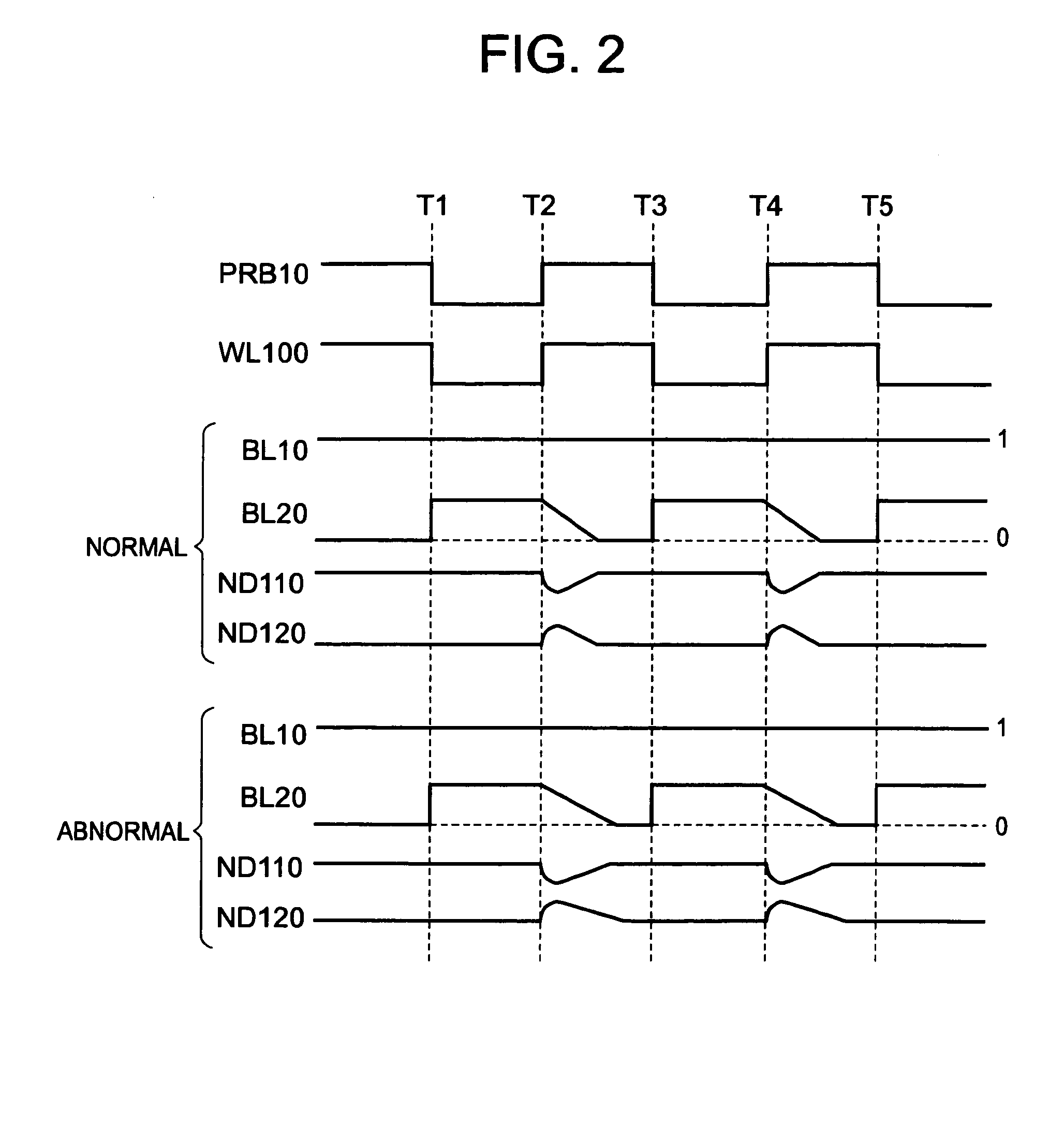

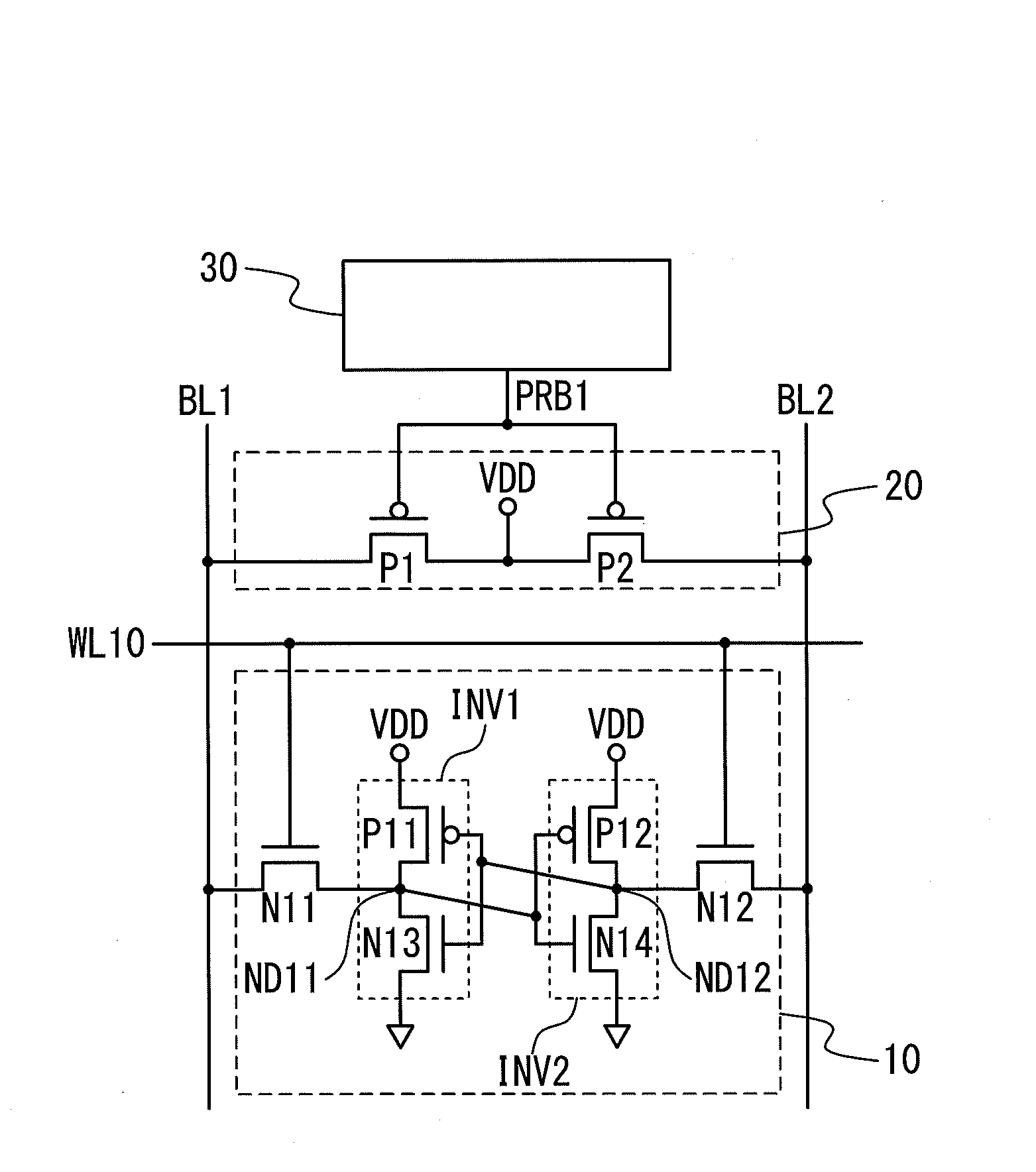

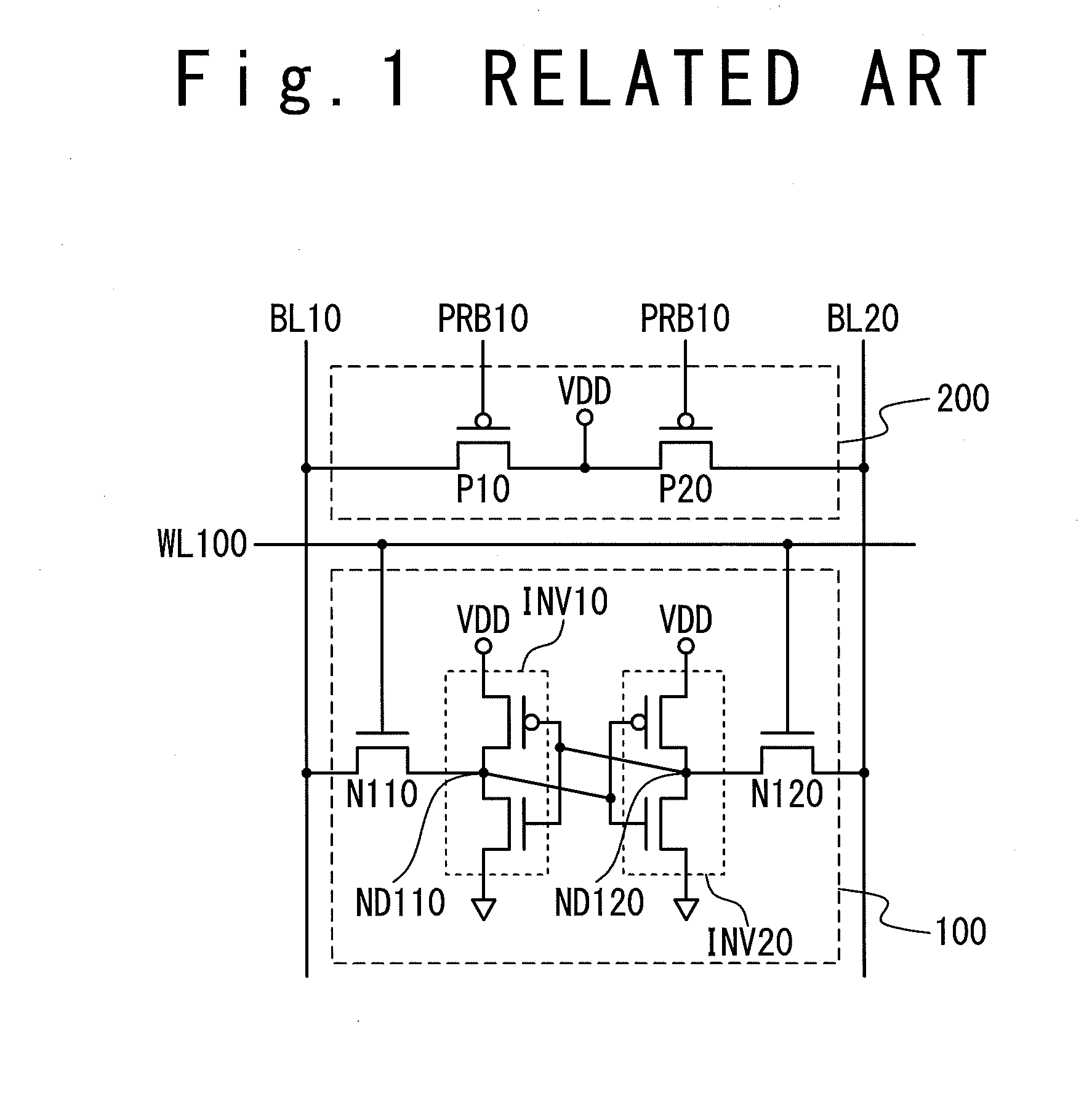

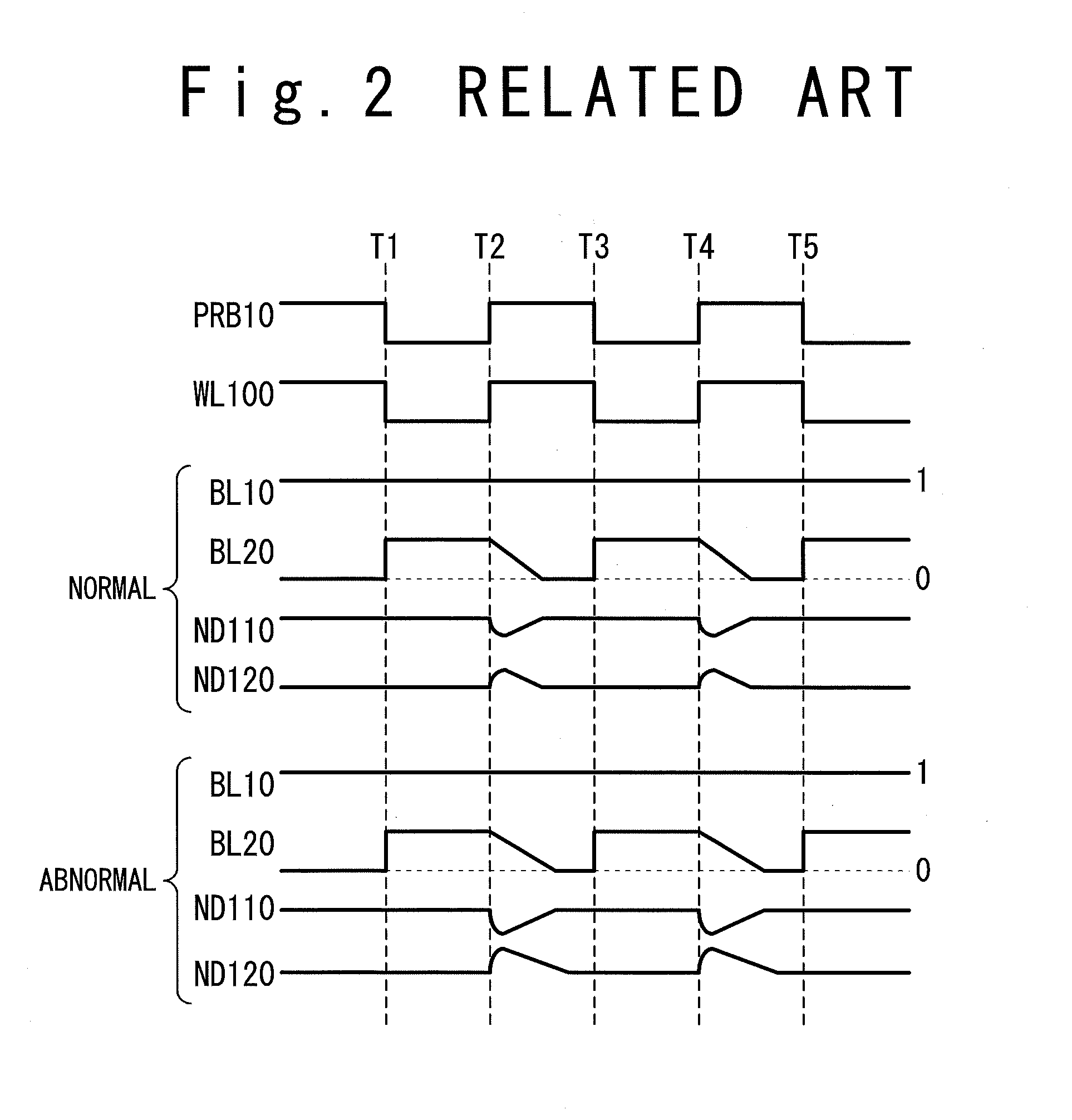

Static random access memory (SRAM) and test method of the SRAM having precharge circuit to precharge bit line

ActiveUS20100054062A1High detection sensitivityIncreased circuit areaDigital storageBit lineStatic random-access memory

An SRAM includes a memory cell and a precharge circuit. The precharge circuit precharges a bit line pair with a power supply voltage before writing a data in the memory cell or before reading a data therefrom at a time of a normal mode, and which feeds a power supply voltage to at least a low level data-holding node of a node pair of the memory cell at a time of a read test mode, between time for writing a data in the memory cell and time for reading a data therefrom.

Owner:RENESAS ELECTRONICS CORP

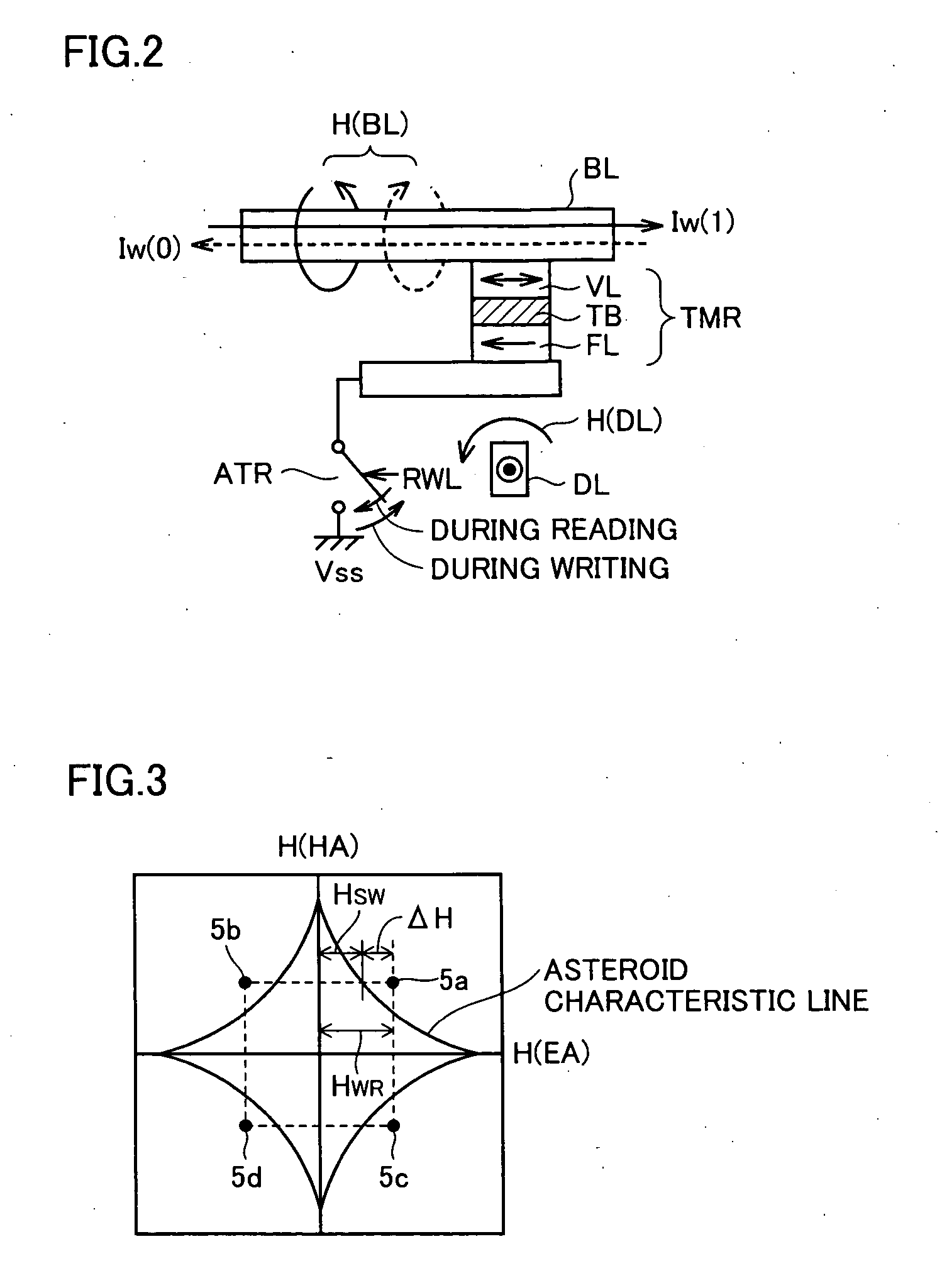

Thin film magnetic memory device suitable for drive by battery

InactiveUS20050219894A1Improved and gentle waveformExtension of timeDigital storageCapacitanceBit line

After a digit line is charged to a power supply voltage by turn-on of a first switching element, the first switching element is turned off and a second switching element is turned on, whereby the digit line is connected to a ground voltage. Similarly, in order to feed data write current, a bit line is charged to a data voltage in accordance with write data through a third switching element. Then, the bit line is connected to a voltage different from the data voltage by a fourth switching element while the third switching element is turned off. Therefore, a load current from a power supply to an MRAM device is supplied during charging of a digit line capacitance and a bit line capacitance, without being consumed when the data write current flows. Consequently, a peak of the load current supplied from the power supply is suppressed.

Owner:RENESAS ELECTRONICS CORP

Generating device, generating method, program and recording medium

InactiveUS20090019327A1Reduce differenceReduce rateElectronic circuit testingLogical operation testingLogical circuitTest vector

A generation apparatus and the like for generating a test vector set capable of reducing differences in a logic value generated before and after a scan capture for outputs from scan cells included in a full-scan sequential circuit are provided. A generation apparatus 200 generating an initial test vector set 216 for a logic circuit includes a target vector identification unit 204 identifying a test vector satisfying a predetermined criterion and to be selected for the number of bits (the number of bit transitions) whose logic values differ before and after scan capture with respect to outputs from scan cells included in the sequential circuit, from among test vectors in the initial test vector set 216, and a test vector set conversion unit 206 converting the test vector identified by the test vector identification unit 204 and to be selected so as to reduce the number of bit transitions with respect to outputs from the scan cells included in the sequential circuit.

Owner:JAPAN SCI & TECH CORP +2

Semiconductor element, memory circuit, integrated circuit, and driving method of the integrated circuit

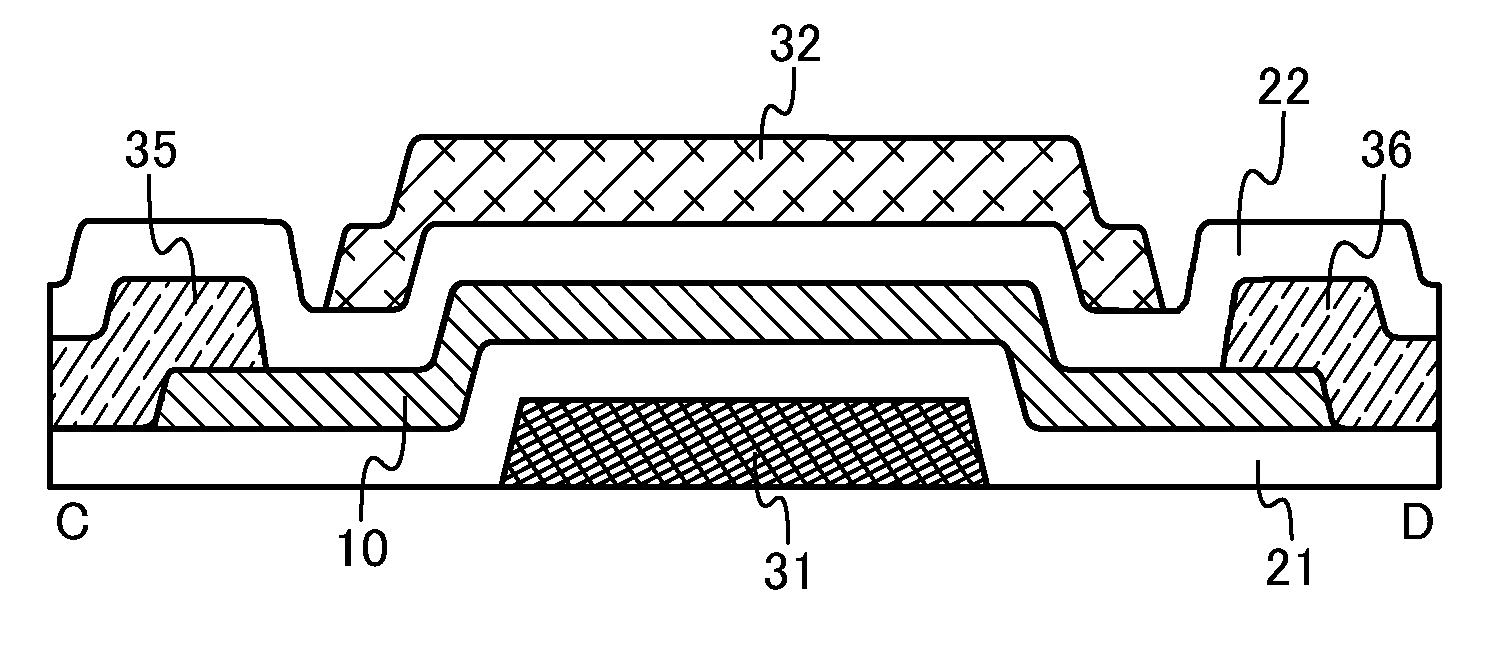

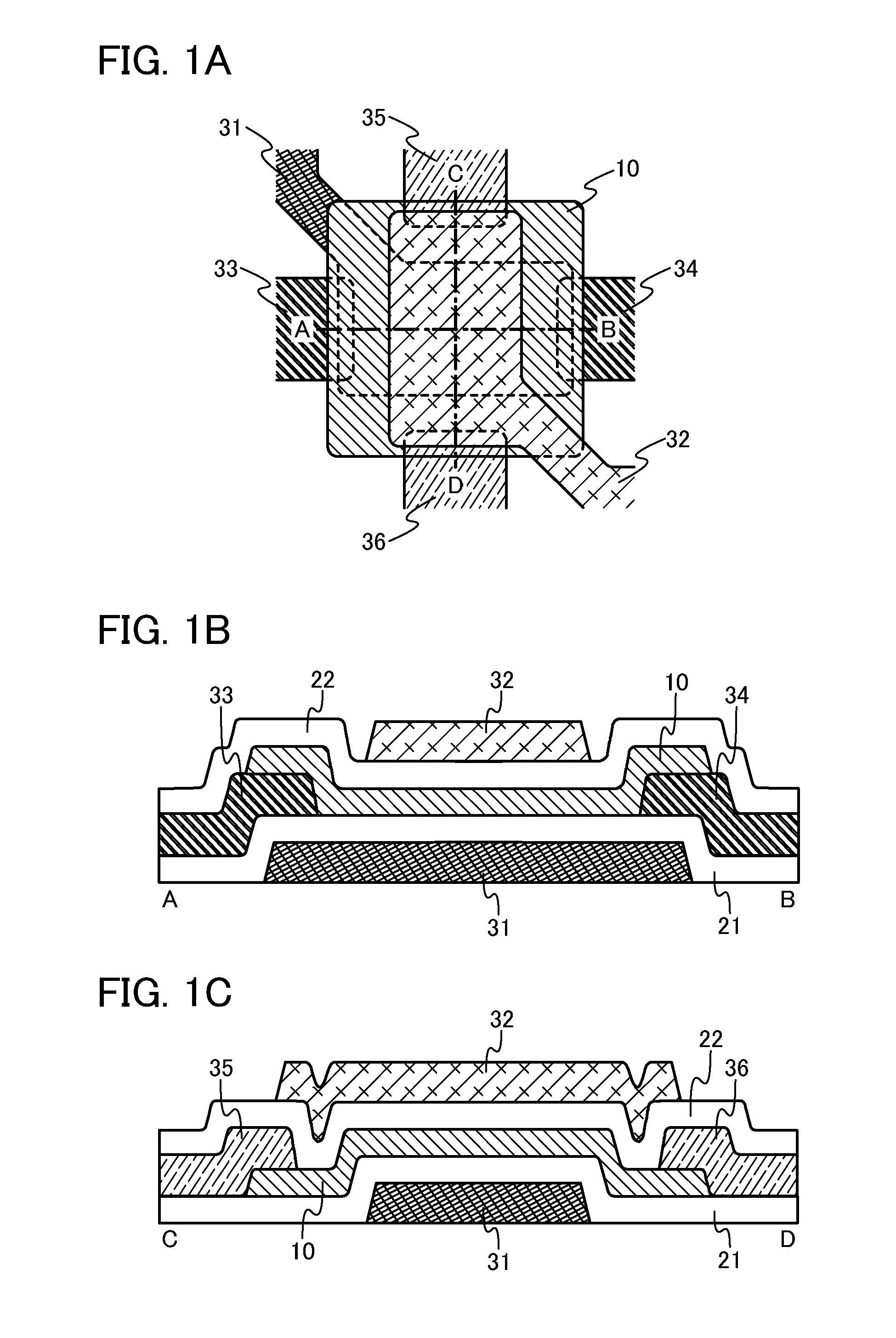

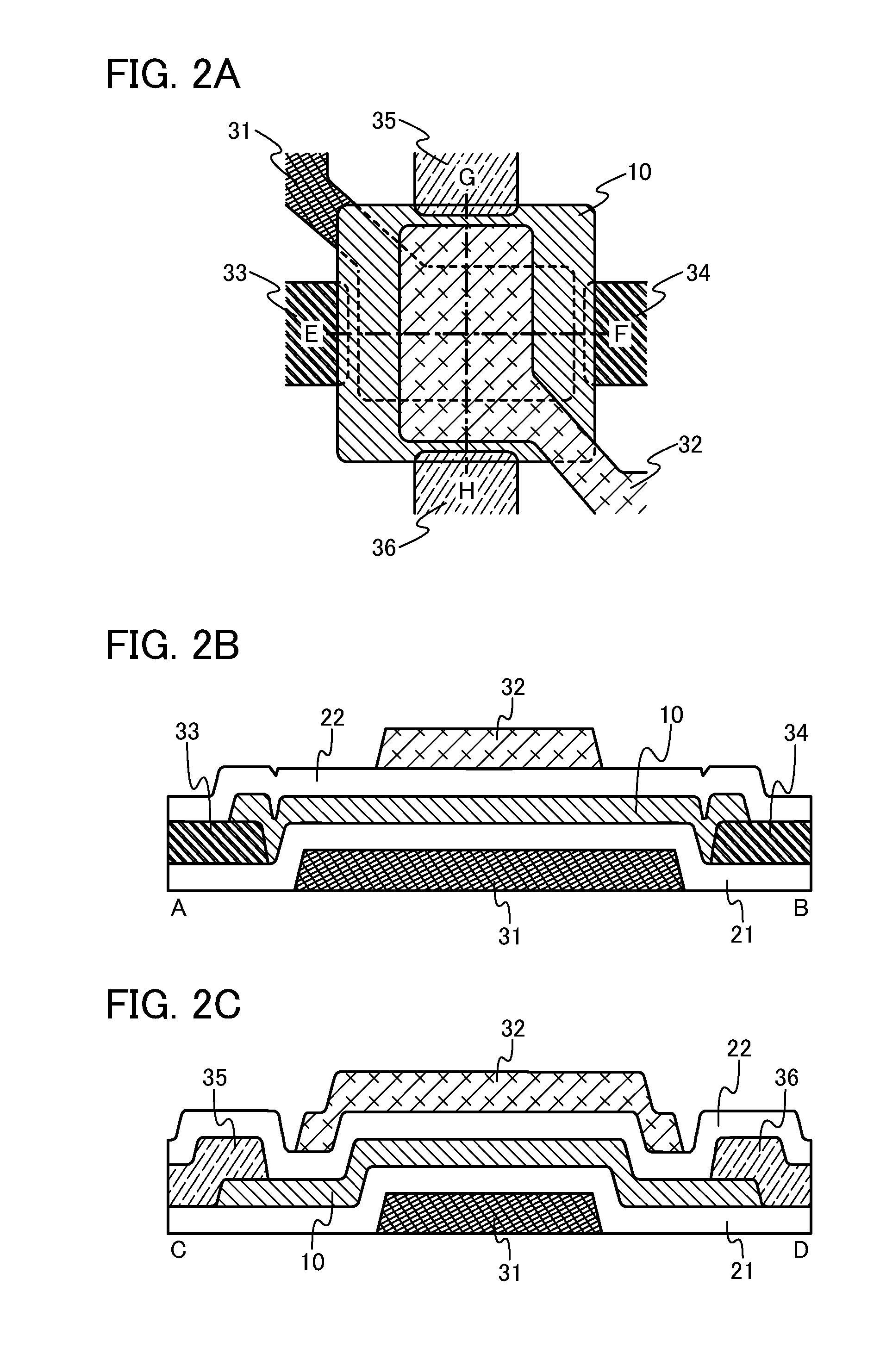

InactiveUS20120262995A1Reduce circuit areaIncreased circuit areaTransistorSolid-state devicesElectricityMemory circuits

A novel semiconductor element contributing to an increase in circuit scale is provided. In the semiconductor element, two different electrical switches are formed using a single oxide semiconductor layer. For example, in the semiconductor element, formation of a channel (a current path) in the vicinity of a bottom surface (a first surface) of the oxide semiconductor layer and formation of a channel in the vicinity of a top surface (a second surface) of the oxide semiconductor layer are independently controlled. Therefore, the circuit area can be reduced as compared to the case two electrical switches are separately provided (for example, the case where two transistors are separately provided). That is, a circuit is formed using the semiconductor element, whereby an increase in the circuit area due to an increase in circuit scale can be suppressed.

Owner:SEMICON ENERGY LAB CO LTD

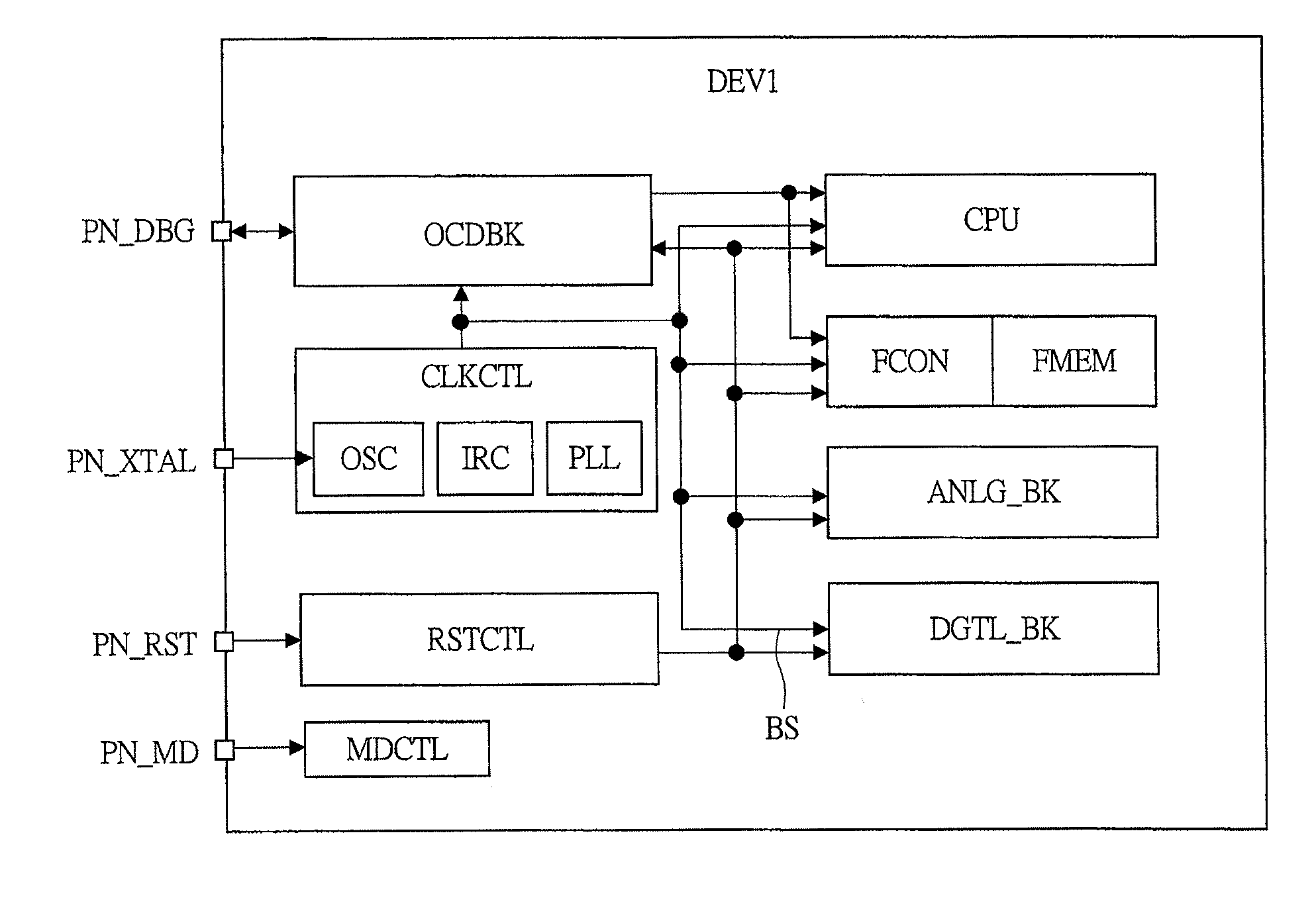

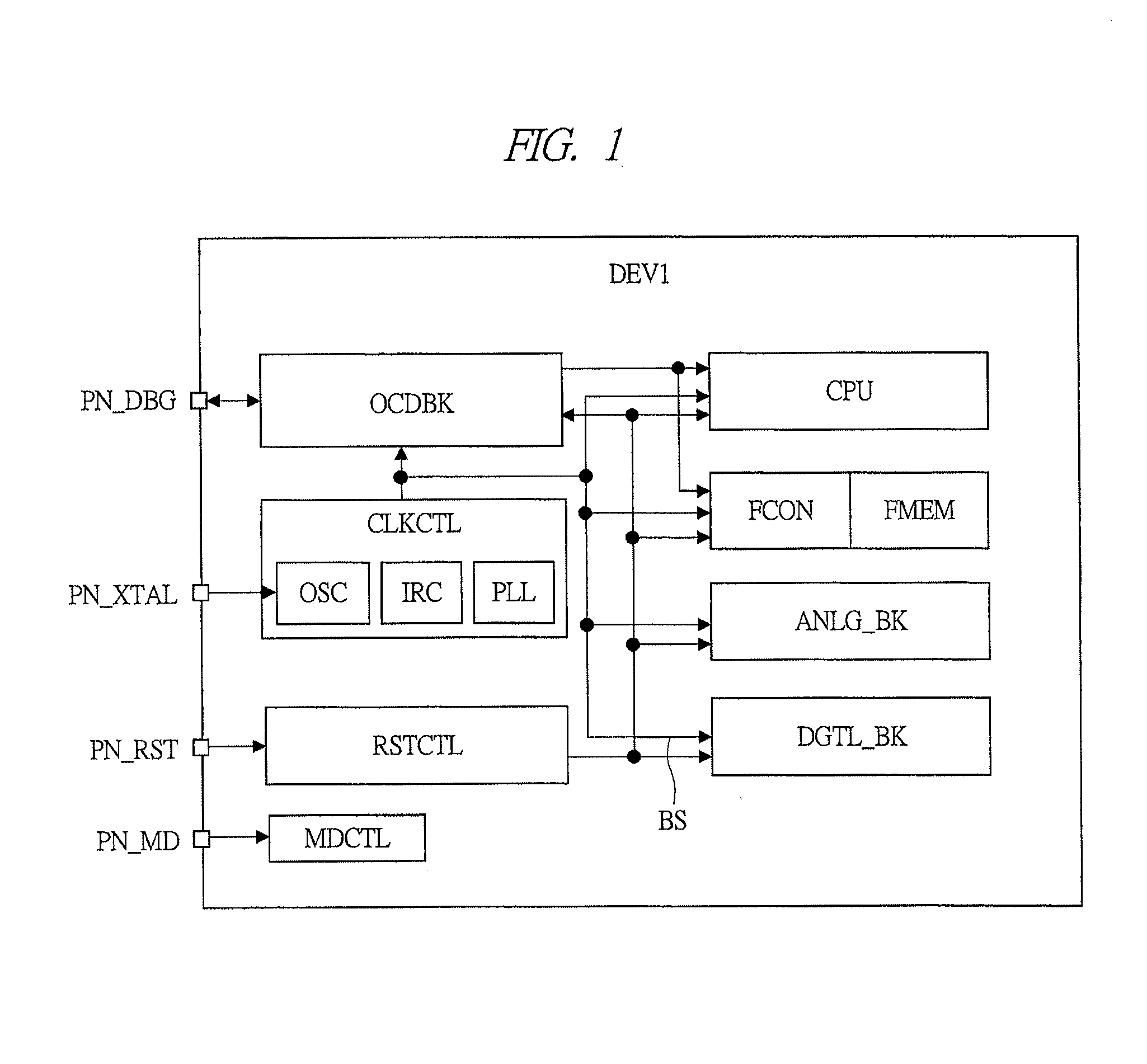

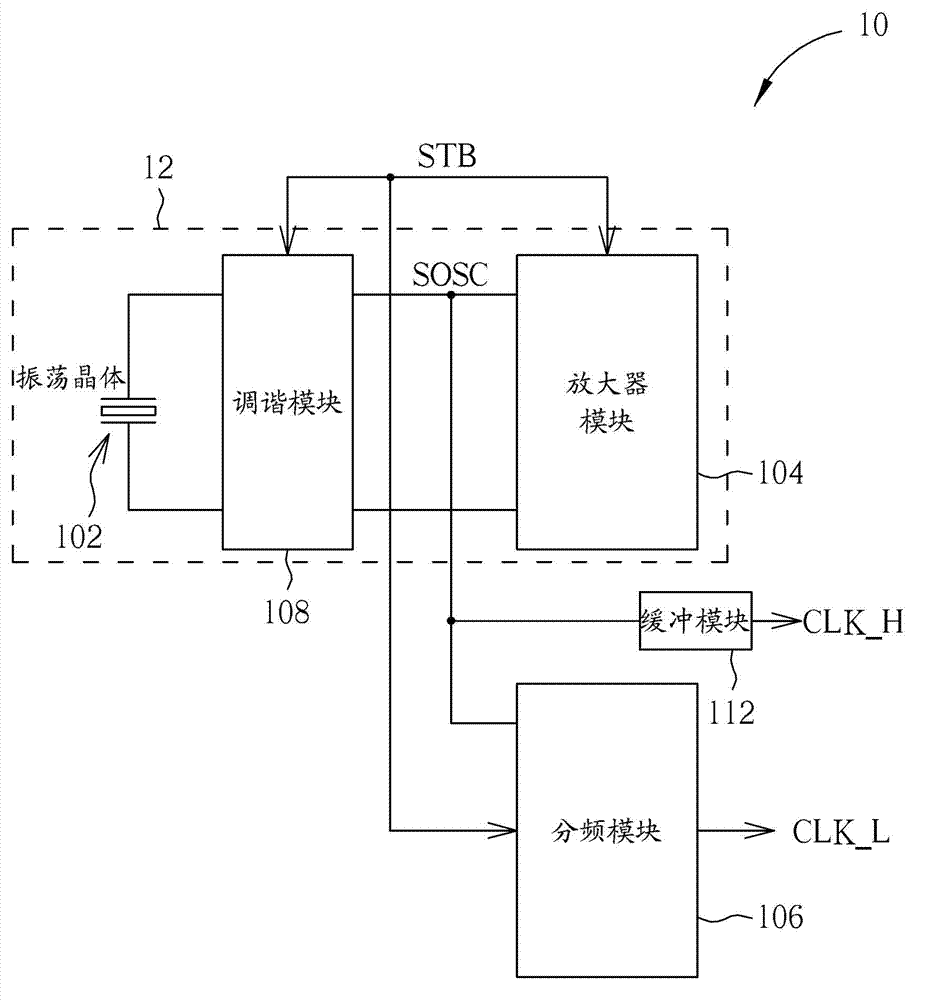

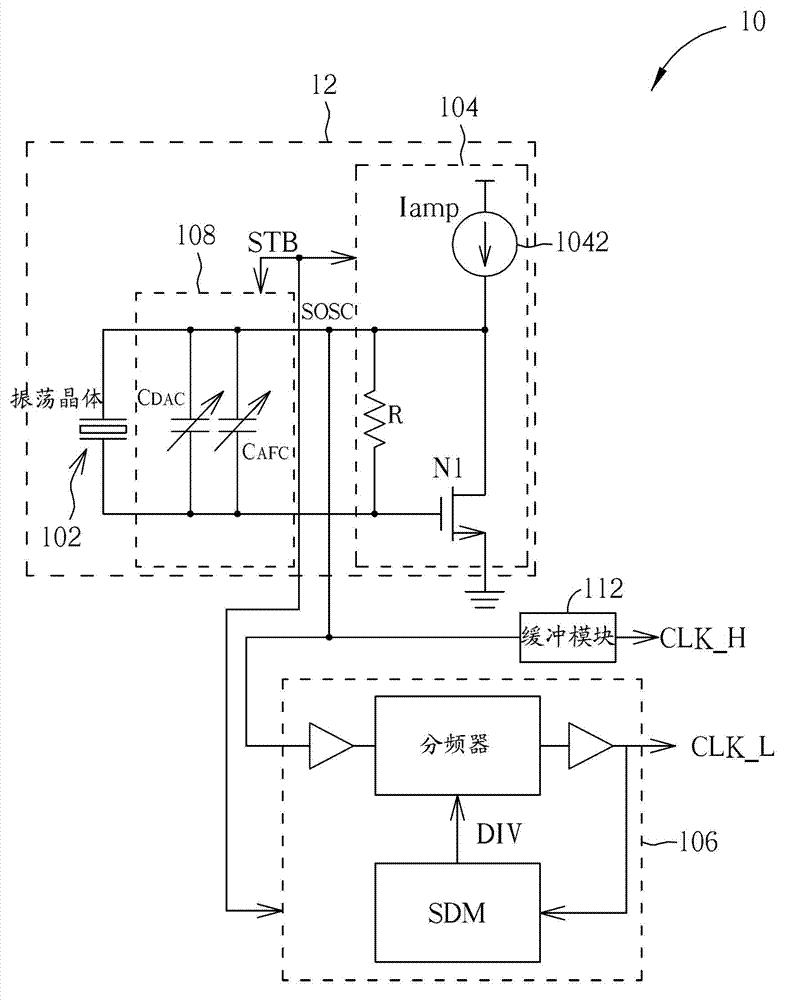

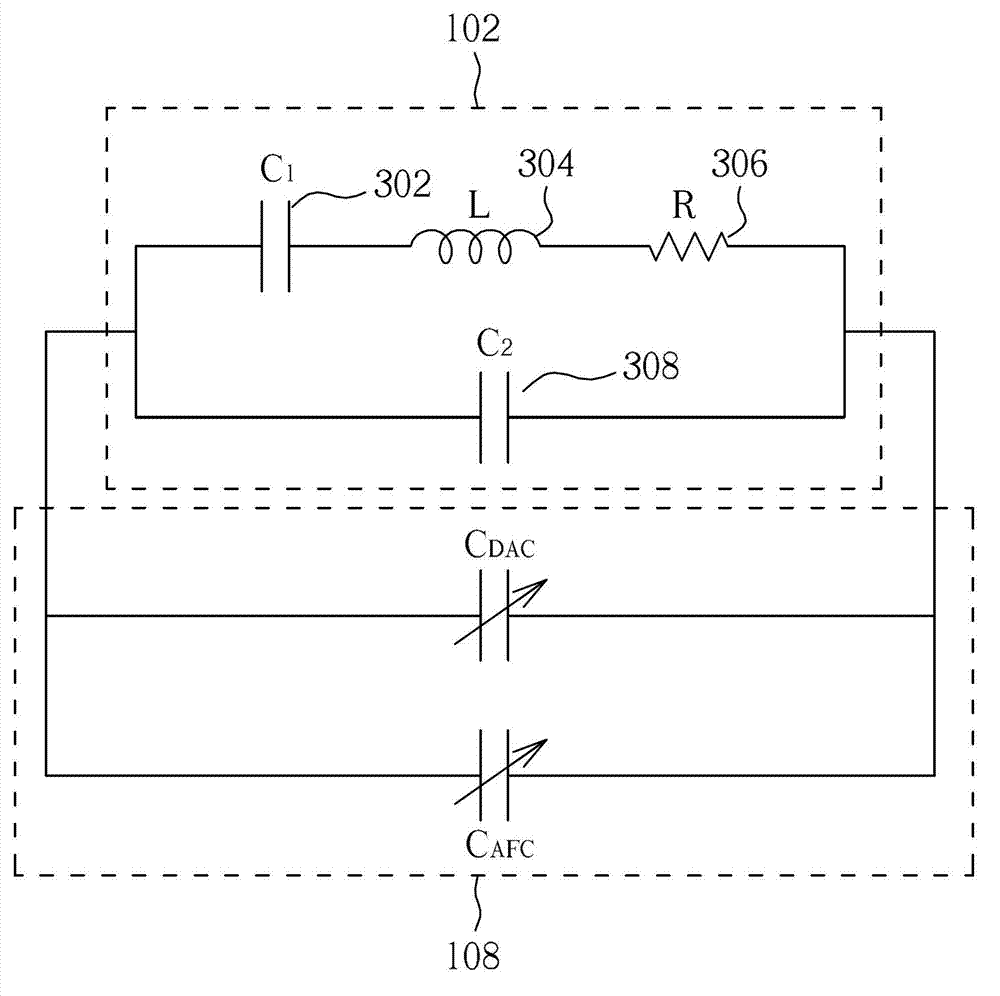

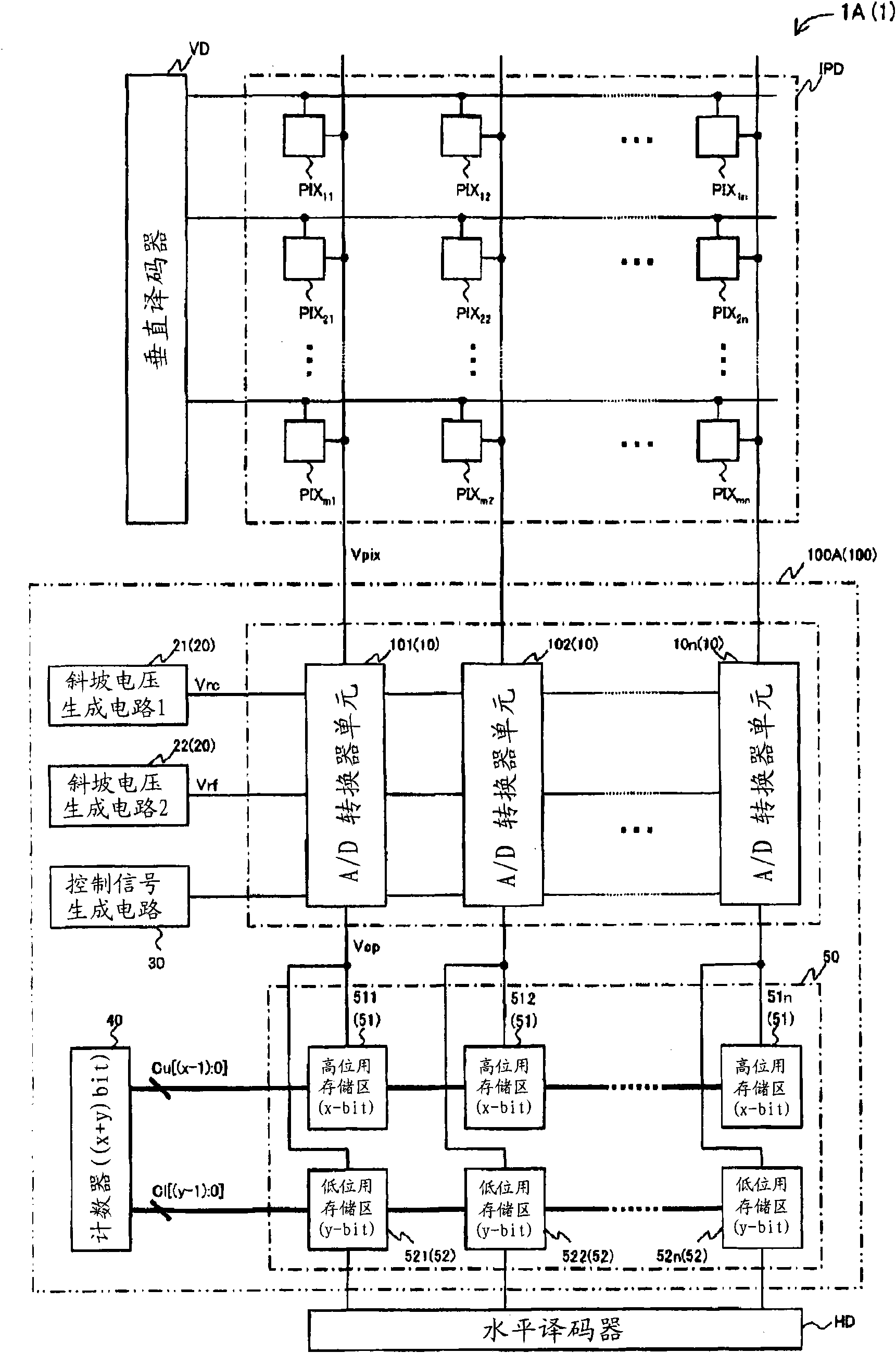

Clock generator and mobile device using the same

InactiveCN103199859AIncrease production costIncreased circuit areaPulse automatic controlPower supply for data processingPower modeComputer module

The invention provides a clock generator for a mobile device, capable of operating in one of a full-power mode and a low-power mode according to a standby signal to generate a high-frequency clock signal and a low-frequency clock signal is disclosed. The clock generator includes a crystal oscillator, for generating an oscillation signal of a specific frequency according to the power mode of the clock generator; a frequency division block, for dividing the oscillation signal by a specific divisor according to the power mode of the clock generator to generate the low-frequency clock signal; and a buffer block, for amplifying the oscillation signal to generate the high-frequency clock signal; wherein during each power mode, a frequency of the low-frequency clock signal is substantially the same. The invention also provides a mobile device using the clock generator.

Owner:MEDIATEK INC

SRAM and testing method of SRAM

InactiveUS20100226190A1High detection sensitivityIncreased circuit areaDigital storageComputer hardwareControl circuit

An SRAM includes a memory cell; and a control circuit configured to change a signal level of a signal which is used in an ordinary mode for access to the memory cell in a test mode to apply a disturbance to the memory cell. The control circuit can change the signal level to set a level of the disturbance optionally.

Owner:RENESAS ELECTRONICS CORP

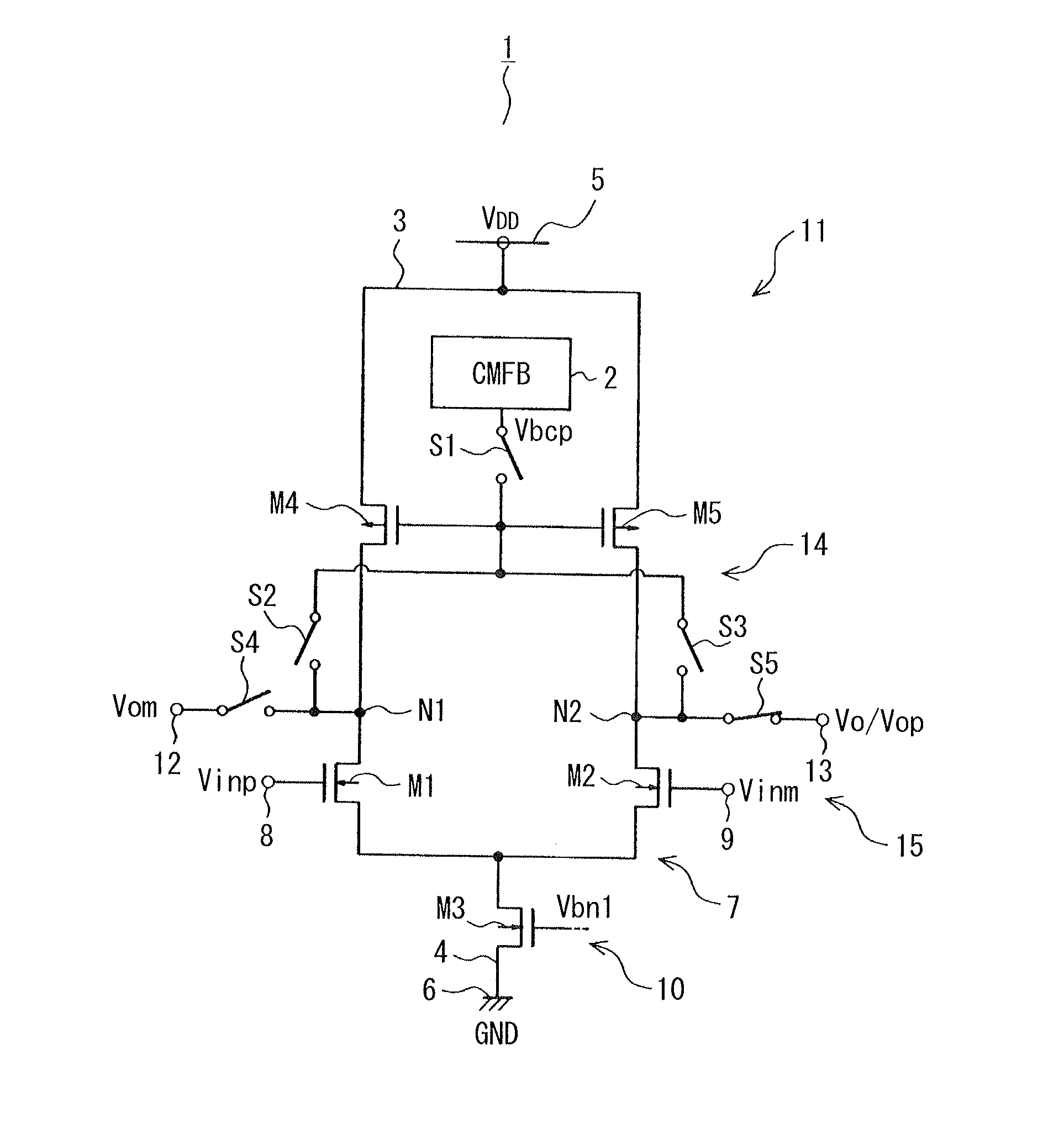

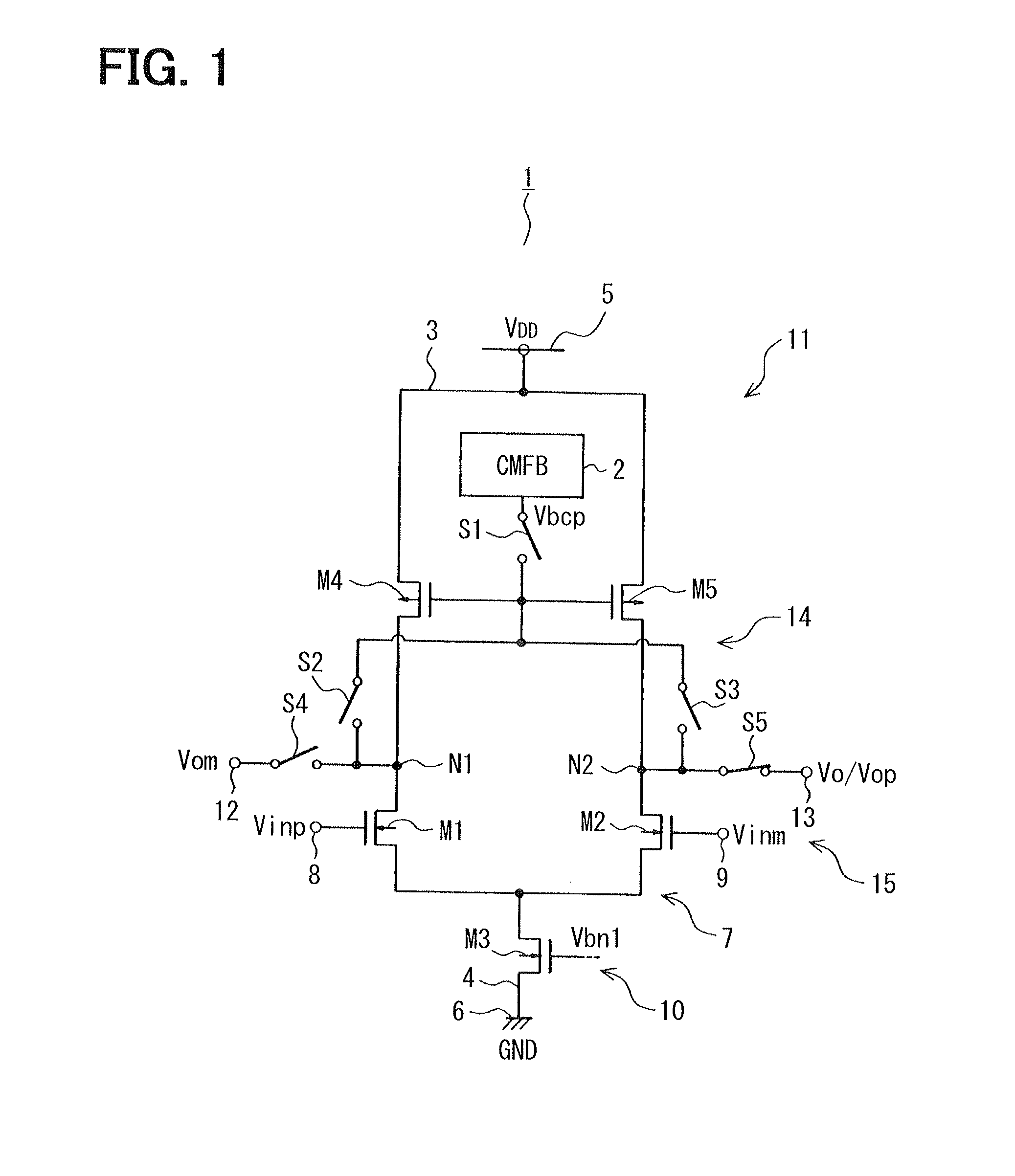

Amplifier circuit, signal processor circuit, and semiconductor integrated circuit device

InactiveUS20110241780A1Increased circuit areaDifferential amplifiersAmplifier detailsLoad circuitAudio power amplifier

An amplifier circuit is provided to be switchable between a single end output configuration and a differential output configuration without increasing a circuit area. When first and fourth switches are turned off and a second switch is turned on, a load circuit functions as an active load on a differential pair and a first output terminal is internally disconnected. The amplifier circuit is provided with a single end output configuration and differentially amplifies input voltages inputted to input terminals and outputs an imbalanced signal from a second output terminal. When the first and fourth switches are turned on and the second switch is turned off, the load circuit functions as a load on the differential pair and the first output terminal is internally connected. The amplifier circuit is provided with a differential output configuration and differentially amplifies the input voltages inputted to the input terminals and outputs balanced signals from the output terminals.

Owner:DENSO CORP

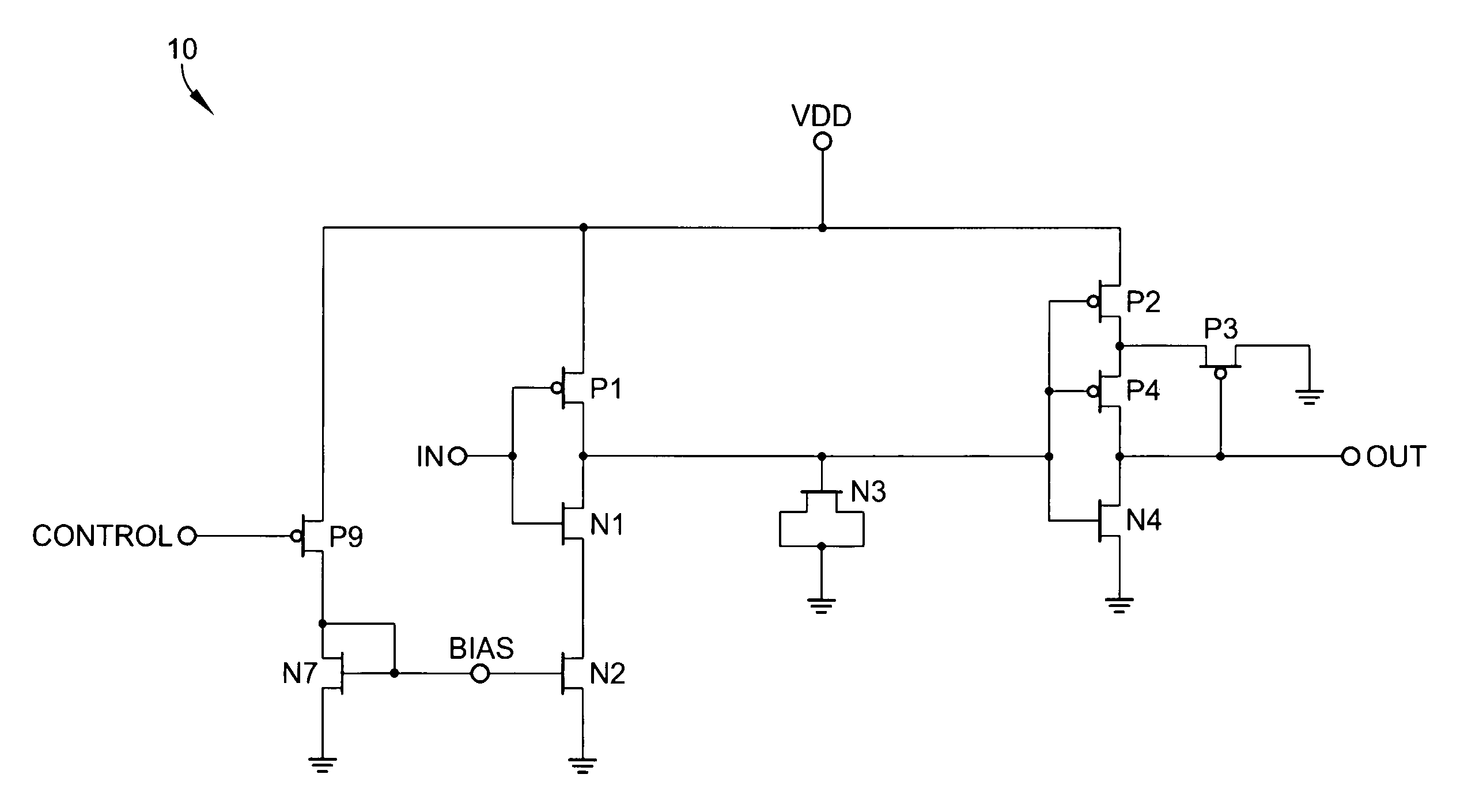

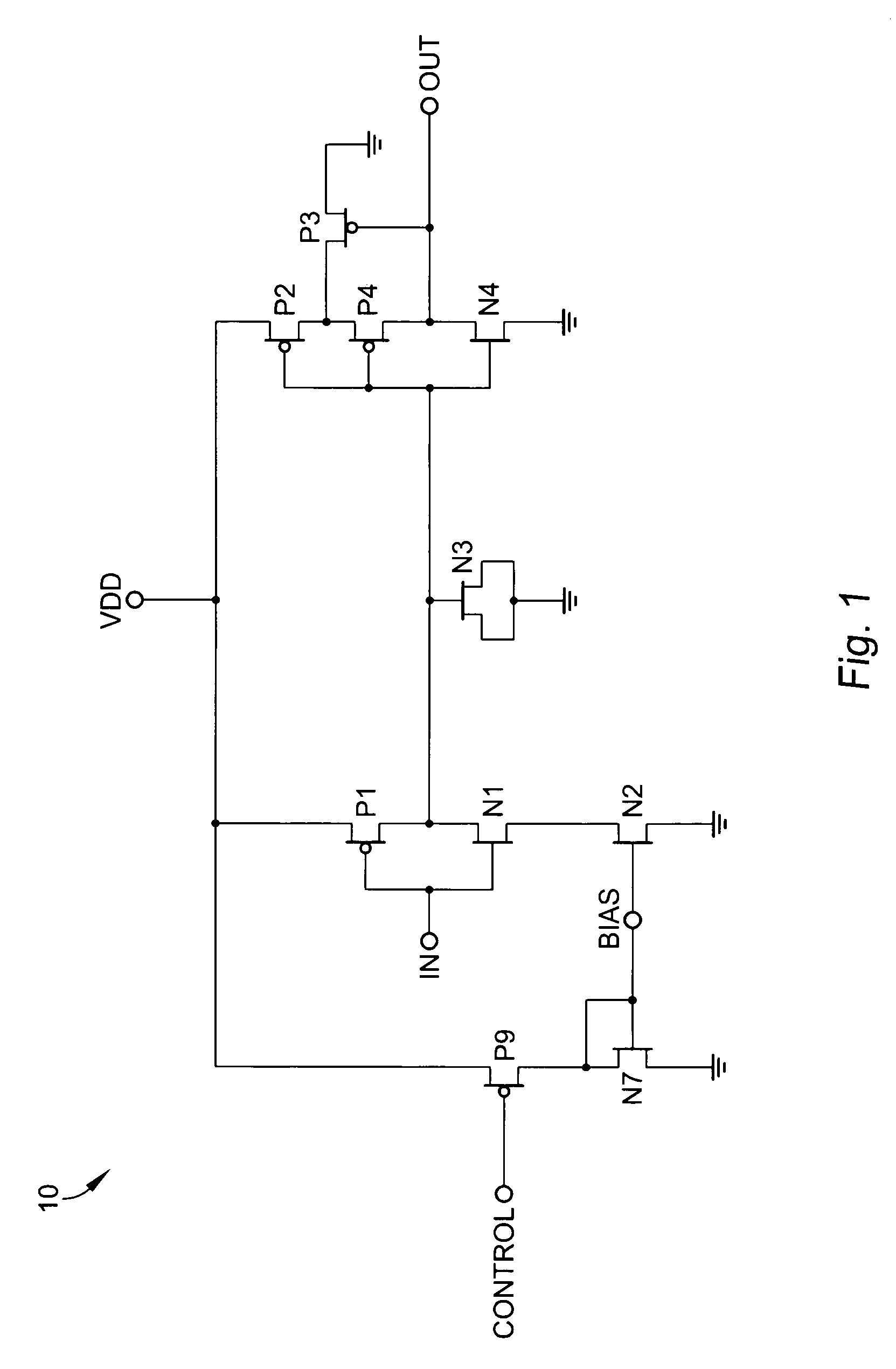

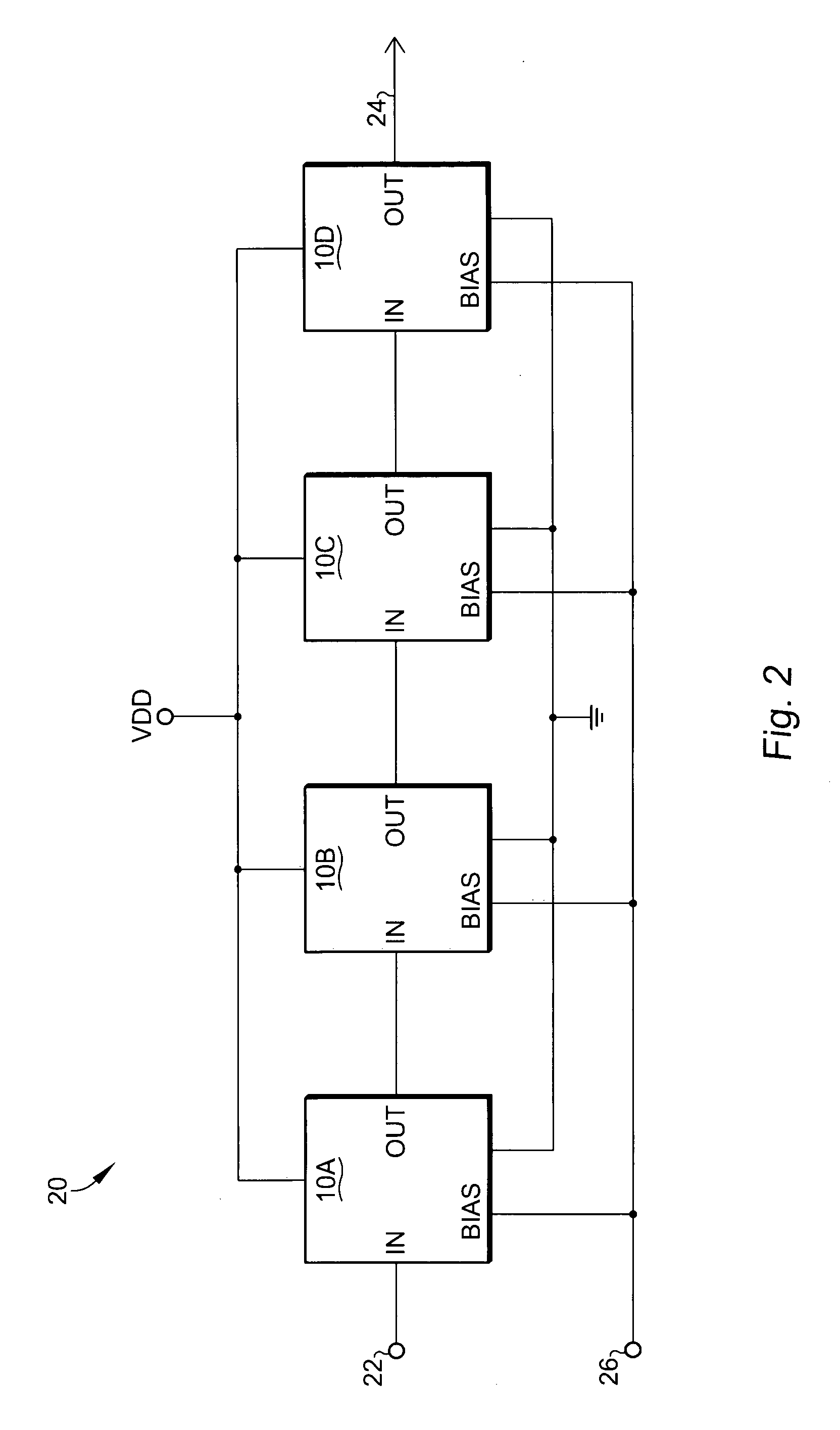

SET and SEGR resistant delay cell and delay line for Power-On Reset circuit applications

ActiveUS7733146B2Increased circuit areaImprove performancePulse shapingTime-delay networksElectrical resistance and conductancePower-on reset

Owner:CAES COLORADO SPRINGS LLC

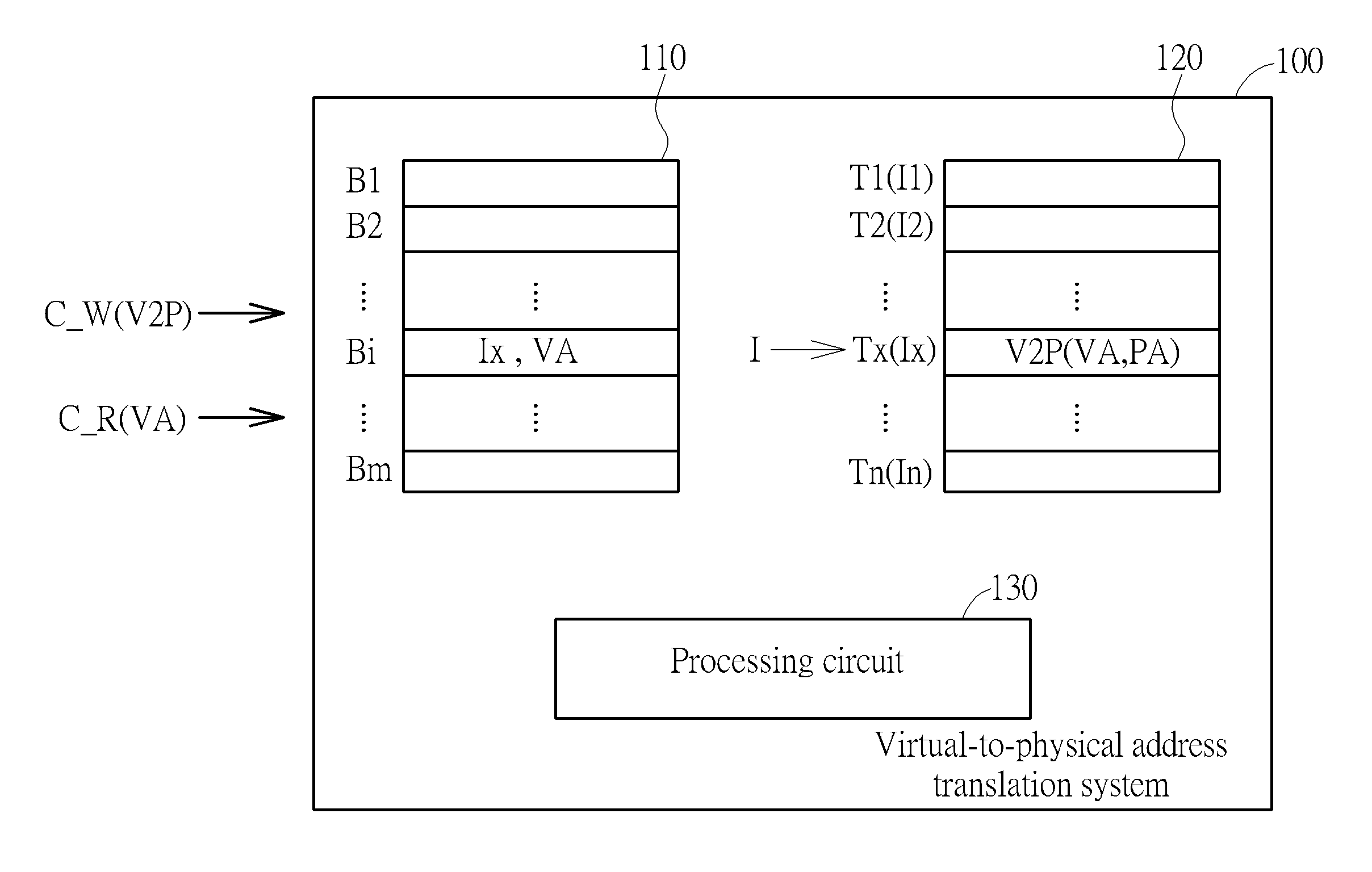

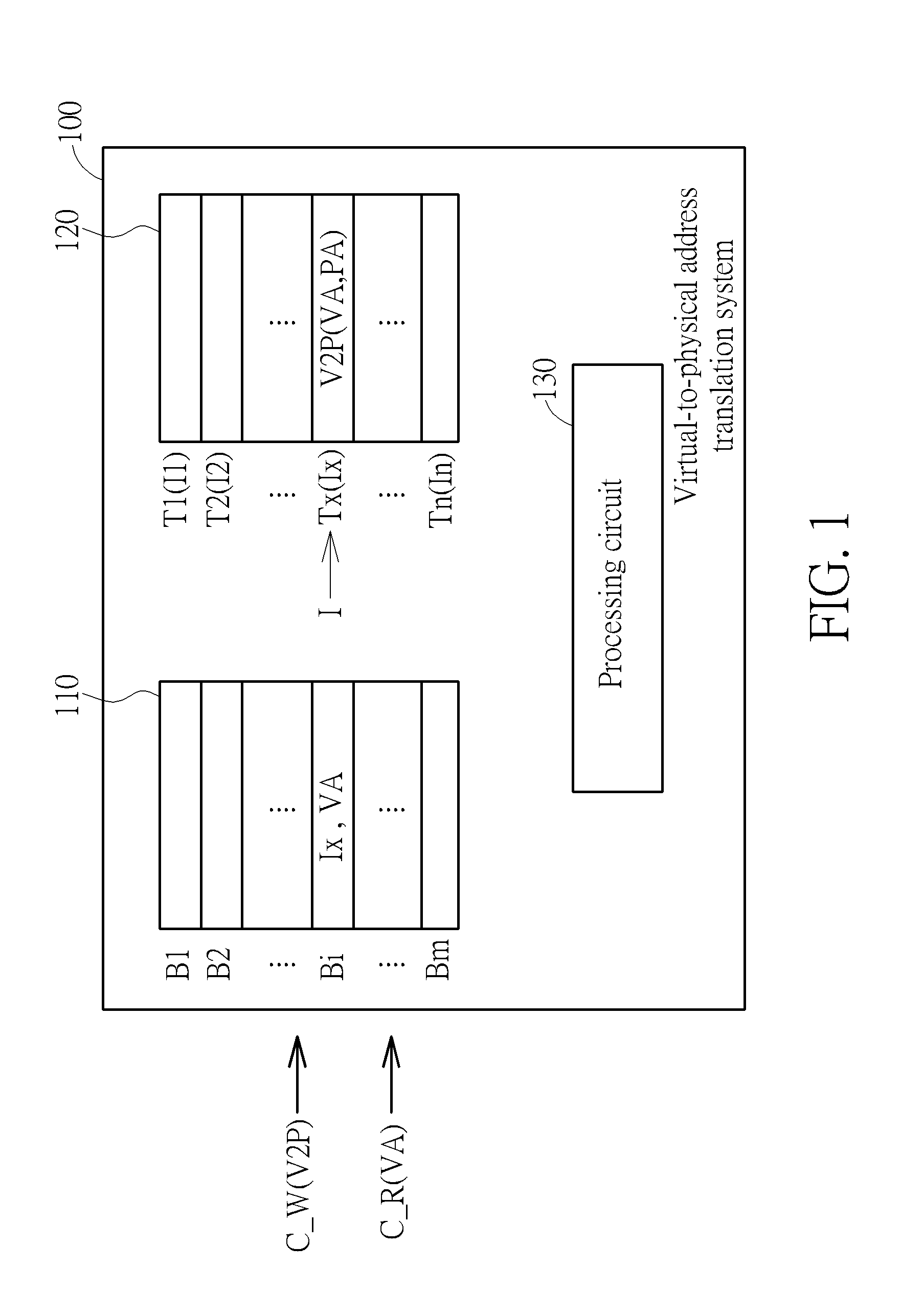

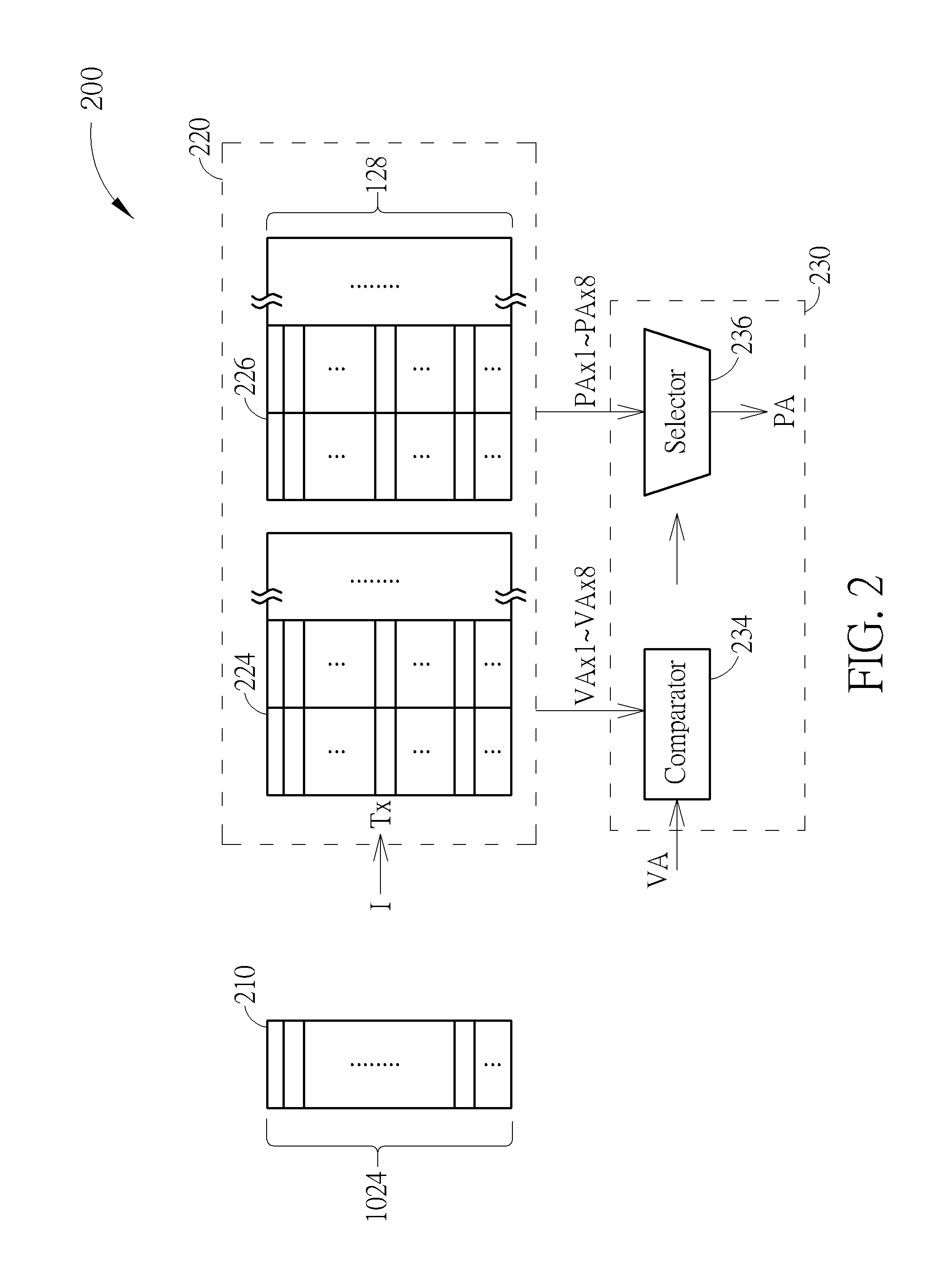

Management method of virtual-to-physical address translation system using part of bits of virtual address as index

ActiveUS20150149743A1Improve system performanceReduce processing speedMemory architecture accessing/allocationMemory adressing/allocation/relocationOperating systemVirtual address space

A management method of a virtual-to-physical address translation system includes the following steps: providing a first storage space, wherein the first storage space includes a plurality of buffer entries; providing a second storage space, wherein the second storage space includes a plurality of translation entries, and the translation entries correspond to a plurality of translation indices; and when receiving a write instruction to write a first virtual-to-physical address translation into a specific buffer entry of the buffer entries, storing the first virtual-to-physical address translation in a write translation entry of the translation entries according to a first part of bits of a first virtual address corresponding to the first virtual-to-physical address translation, and storing the first virtual address and a write translation index corresponding to the write translation entry in the specific buffer entry.

Owner:REALTEK SEMICON CORP

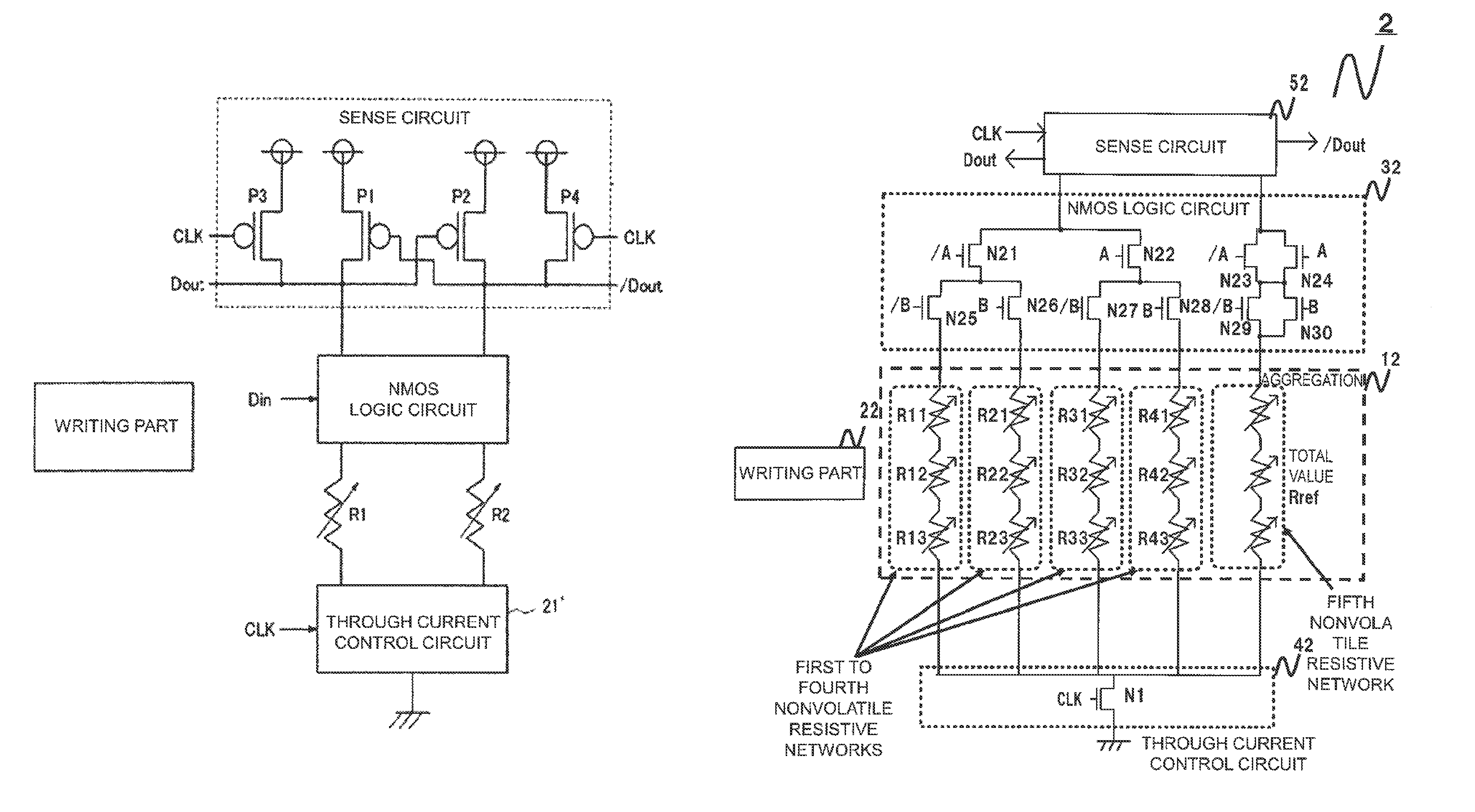

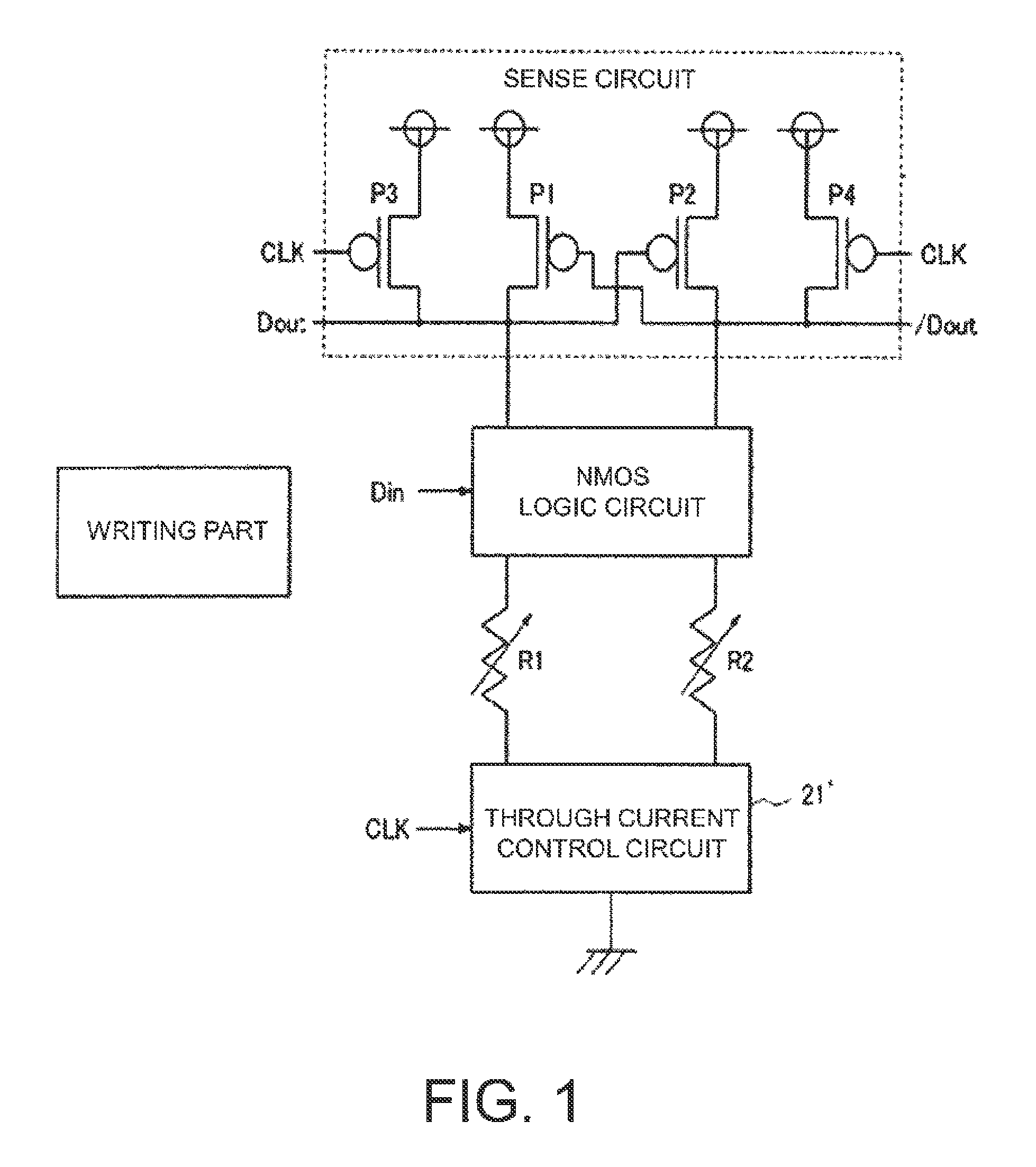

Nonvolatile logic gate device

ActiveUS9536584B2Improve fault toleranceIncreased circuit areaDigital storageElectric pulse generatorLogic gateComputer science

A nonvolatile logic gate device is configured to include a resistive network of a memory structure in which at least three nonvolatile resistive elements are connected, a reference resistive network as a reference resistance providing a tolerance of the memory structure to a resistance value of the resistive network of the memory structure, a writing part operable to selectively write or rewrite a value of each of the nonvolatile resistive elements in the resistive network into a maximum or a minimum corresponding to a logical value to be read when data are stored into the resistive network, and a logic circuit structure operable to use, as a logical value of the memory structure, a value obtained by comparison between the resistance value of the resistive network and the resistance value of the reference resistive network.

Owner:NEC CORP +1

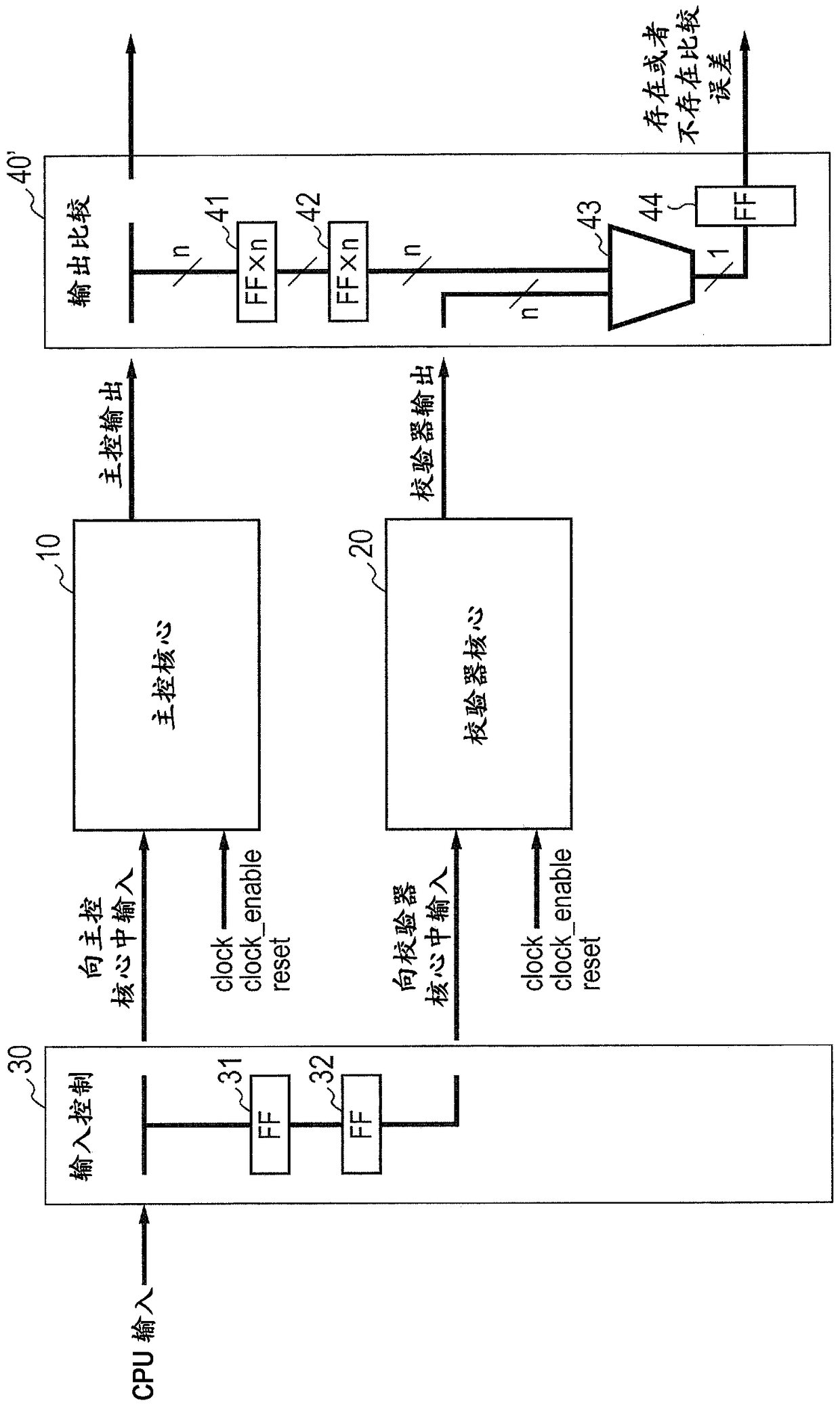

Semiconductor device

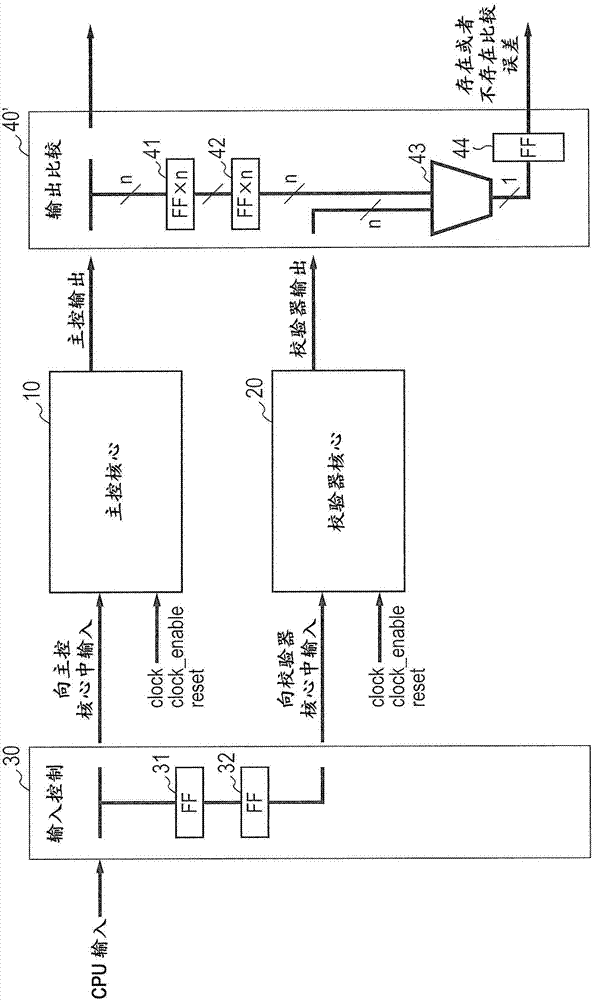

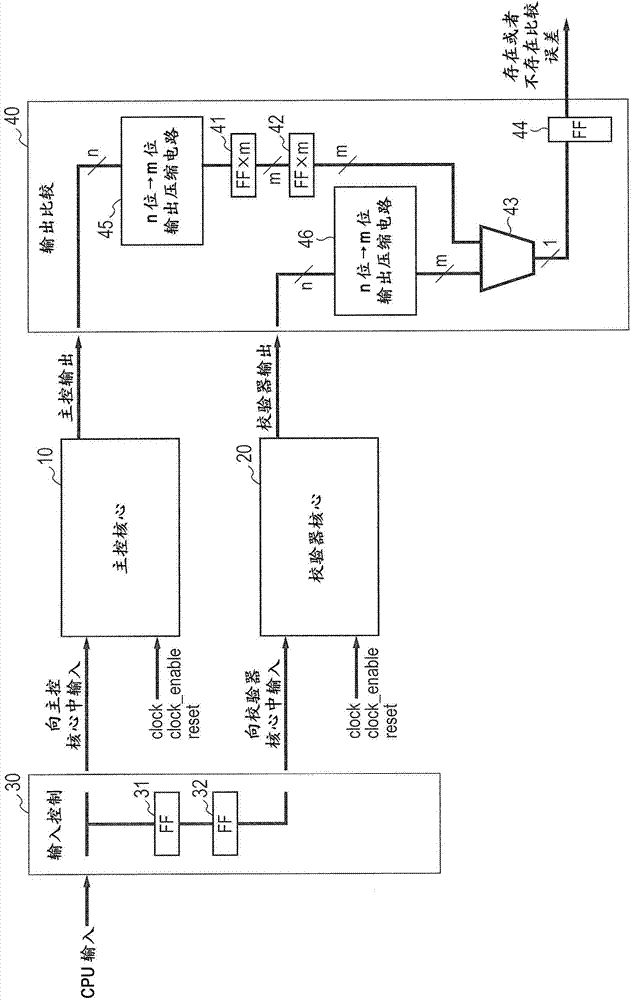

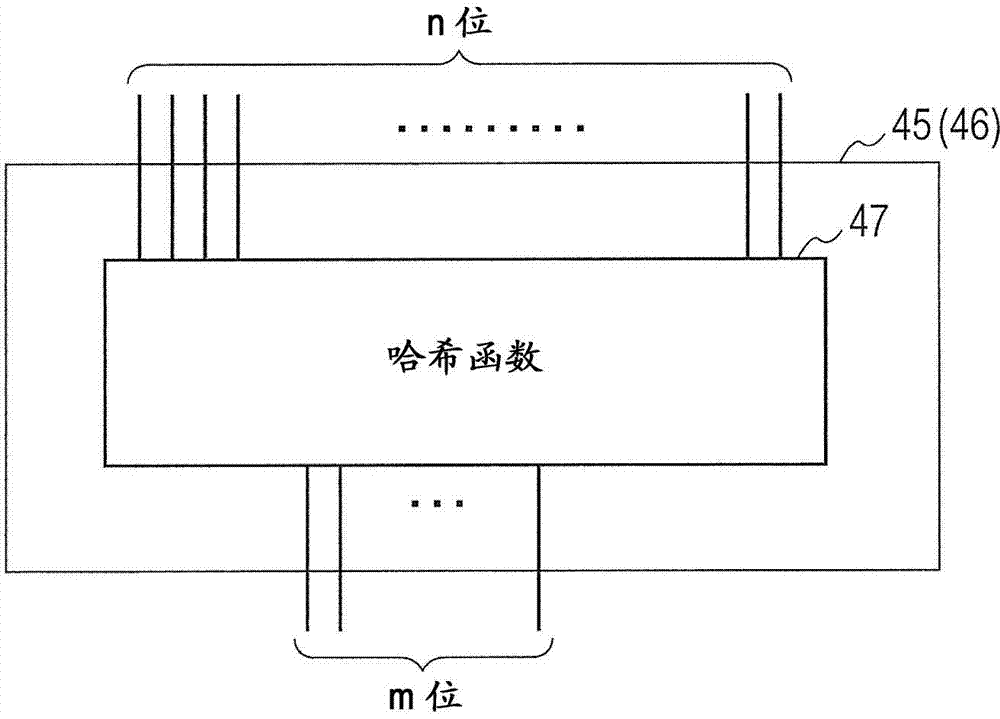

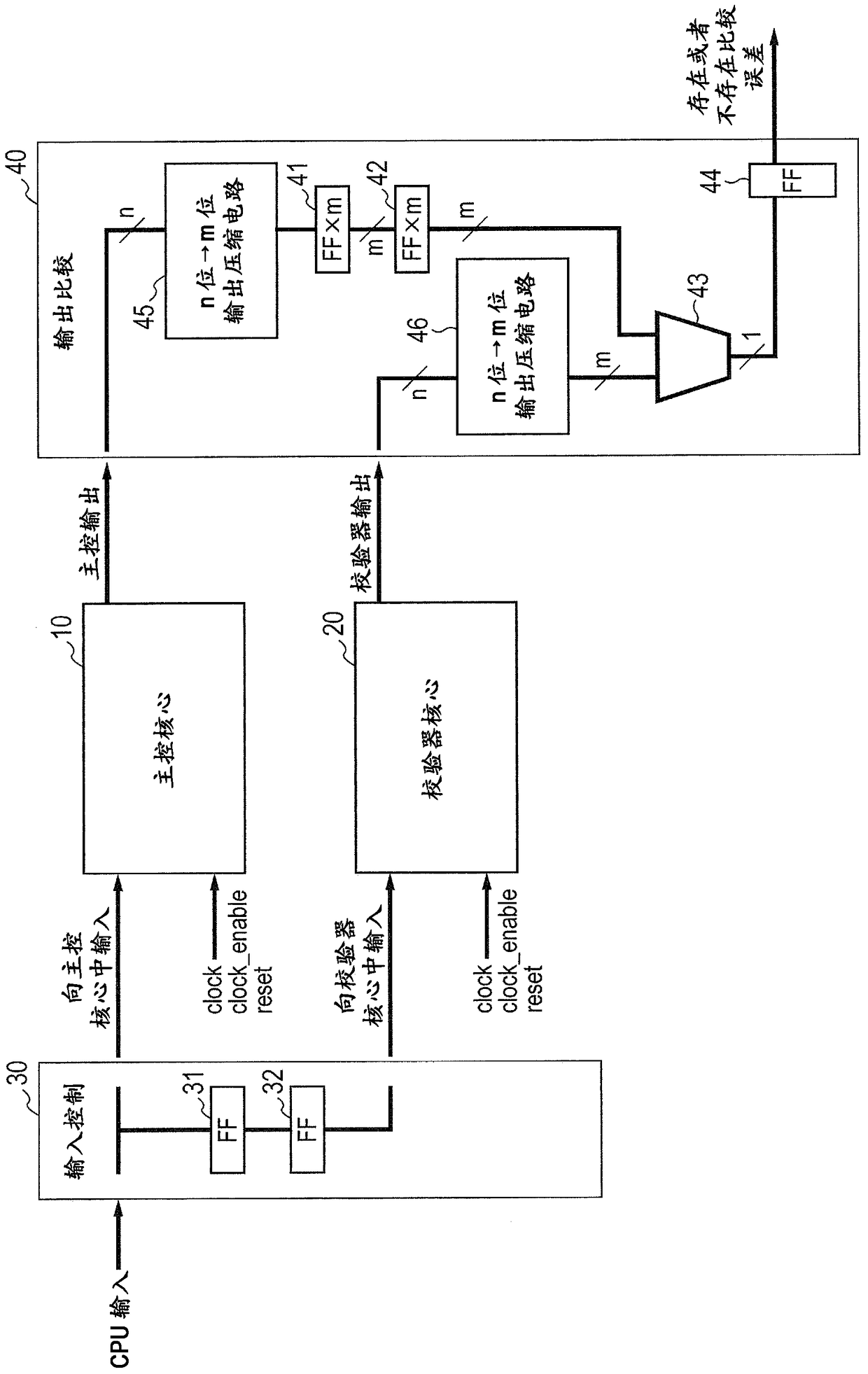

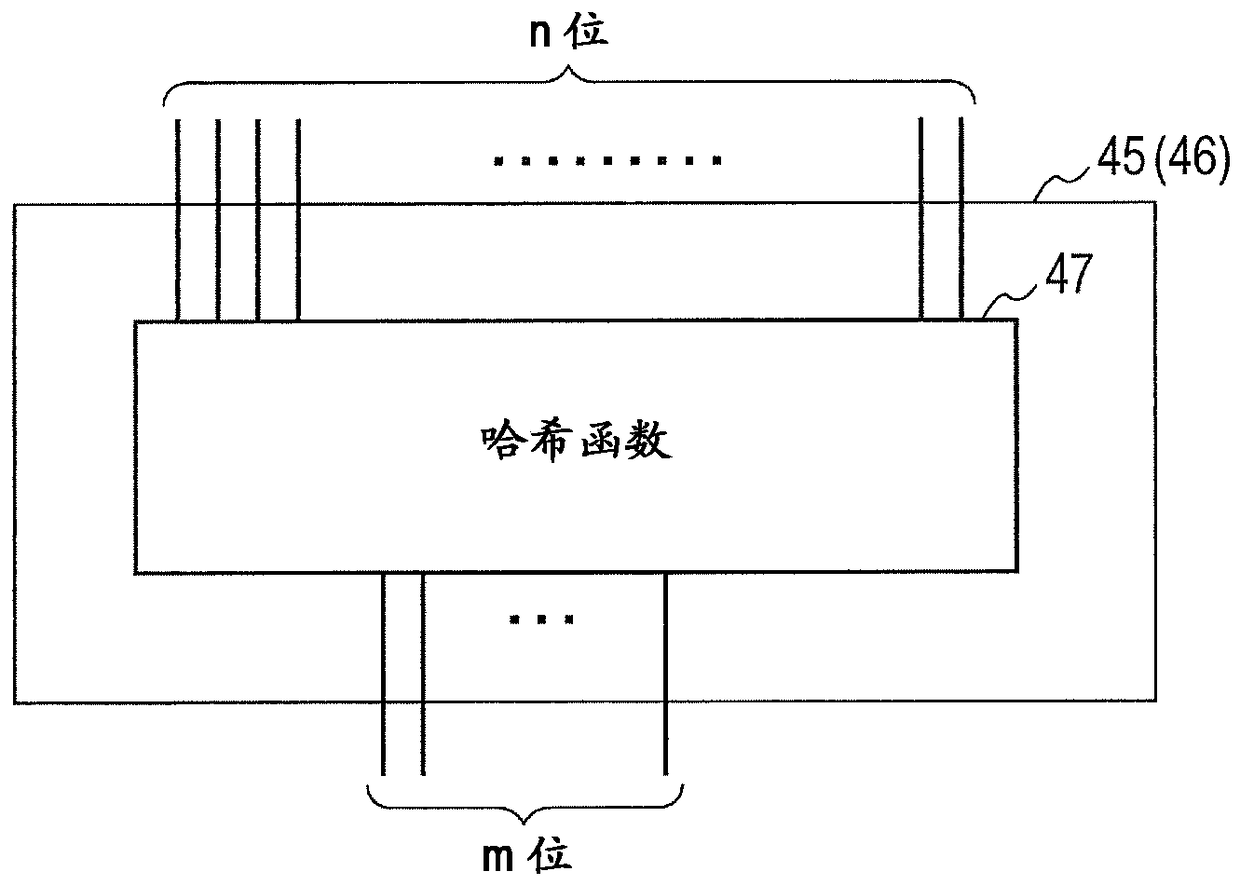

ActiveCN103778028AIncreased circuit areaIncreased power consumptionRedundant data error correctionCoincidencePower semiconductor device

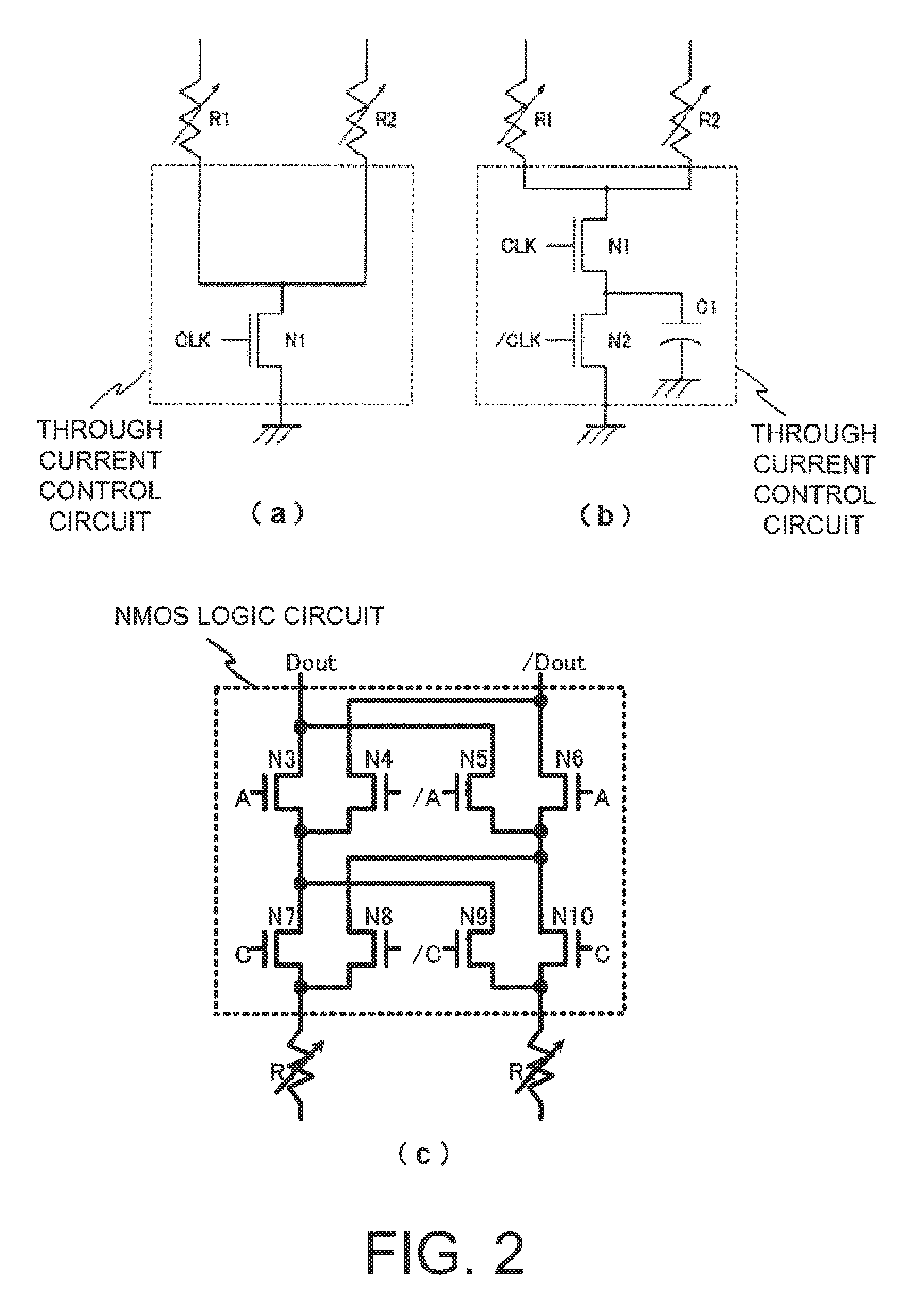

A semiconductor device comprising: a first processor; a second processor; a first delay circuit delaying a signal input into the first processor by a predefined number of cycles and inputting the signal into the second processor; a first compression circuit compressing a signal of n-bit width from the first processor into a signal of m-bit width (m<n) and outputting the signal of m-bit width; a second compression circuit compressing a signal of n-bit width from the second processor into a signal of m-bit width and outputting the signal of m-bit width; a second delay circuit delaying the signal from the first compressor by the predefined number of cycles and outputting the delayed signal; and a coincidence comparison circuit comparing bit-wise the corresponding bits of the signals from the second delay circuit and from the second compression circuit to check whether the corresponding bits coincide with each other or not.

Owner:RENESAS ELECTRONICS CORP

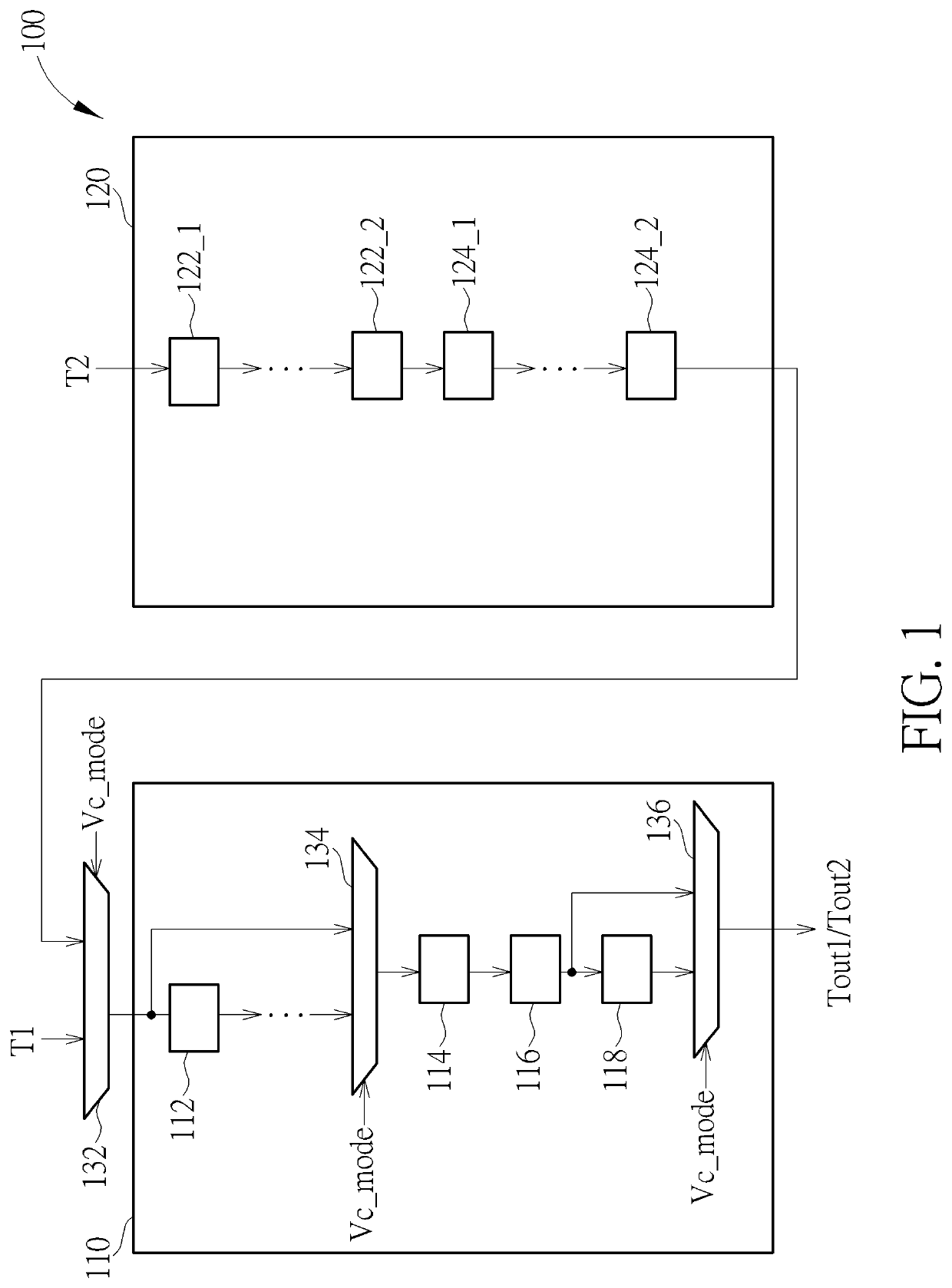

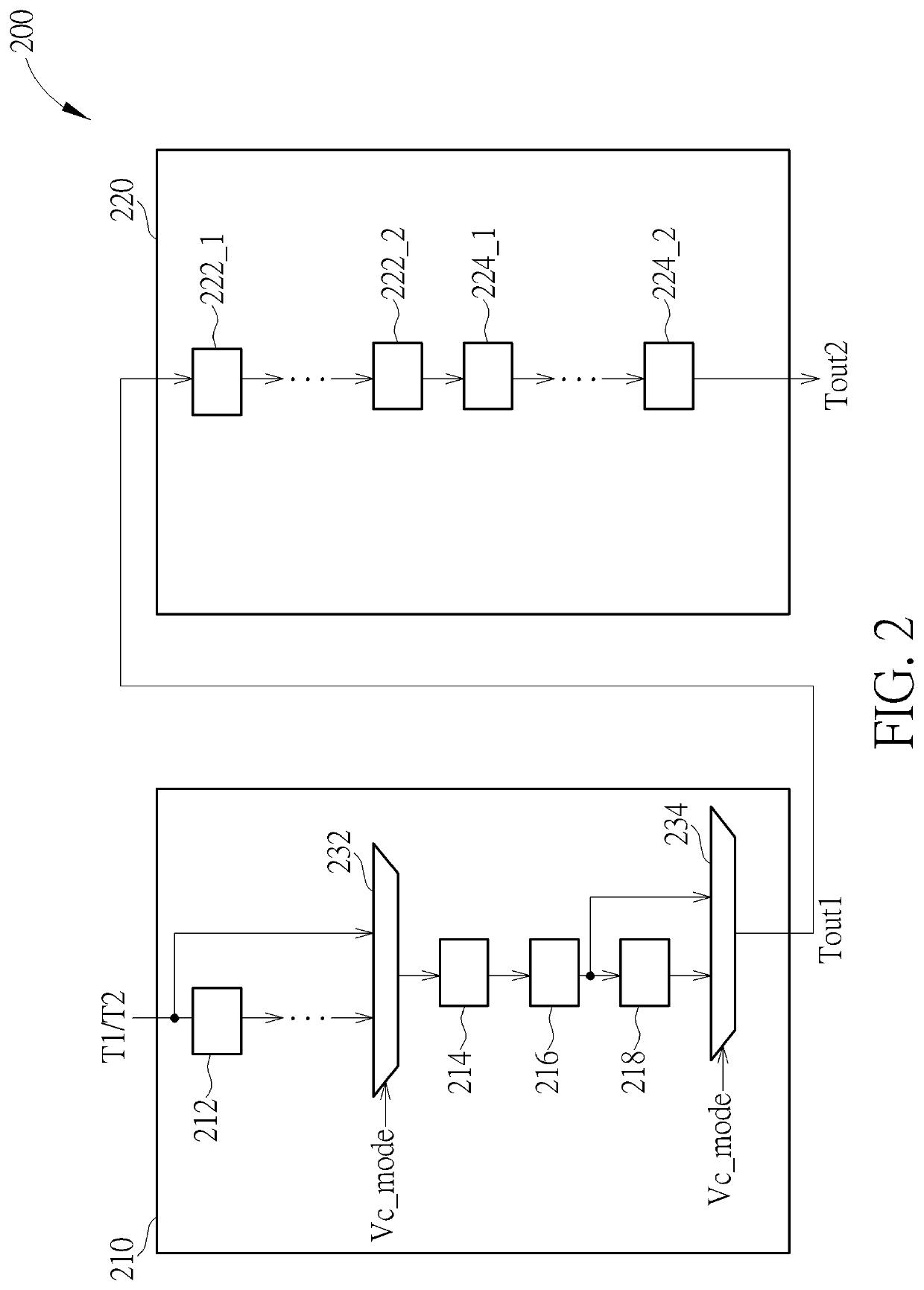

Circuit applied to multiple scan modes for testing

A circuit applied to multiple scan modes is disclosed, wherein the circuit can increase fault coverage during chip testing without using scan chain wrappers. The circuit includes a first circuit block and a second circuit block. The first circuit block corresponds to a first scan mode of the multiple scan modes, and the first circuit block includes at least one first scan chain for receiving a test signal from an external automatic test equipment. The second circuit block corresponds to a second scan mode of the multiple scan modes, and the second circuit block includes at least one second scan chain for receiving another test signal from the external automatic test equipment. The second scan chain includes at least one specific flip-flop positioned in the first circuit block, and the specific flip-flop is configured to drive the second circuit block.

Owner:REALTEK SEMICON CORP

A/D converter circuit and solid-state imaging device

ActiveCN101939917BScale upAvoid noiseTelevision system detailsColor television detailsCapacitanceControl signal

Provided are a solid-state imaging device and A / D converter circuit comprising: series-connected capacitative elements; a voltage comparator circuit comparing the output of the capacitative element C1 with a threshold voltage; a first input circuit inputting an analog voltage signal to the node between the capacitative elements C1 and C2; a second input circuit inputting a first reference voltage, monotonously changing in a first conversion process for finding the upper-order bit value, to the node between the capacitative elements C2 and C3; a third input circuit inputting a second reference voltage, monotonously changing in a second conversion process for finding an unconverted bit value after the first conversion process, to the input terminal of the capacitative element C3; and a control circuit generating a control signal to hold the first reference voltage in the capacitative element C3 when the output of the voltage comparator circuit changes in the first conversion process.

Owner:思特威(上海)电子科技股份有限公司

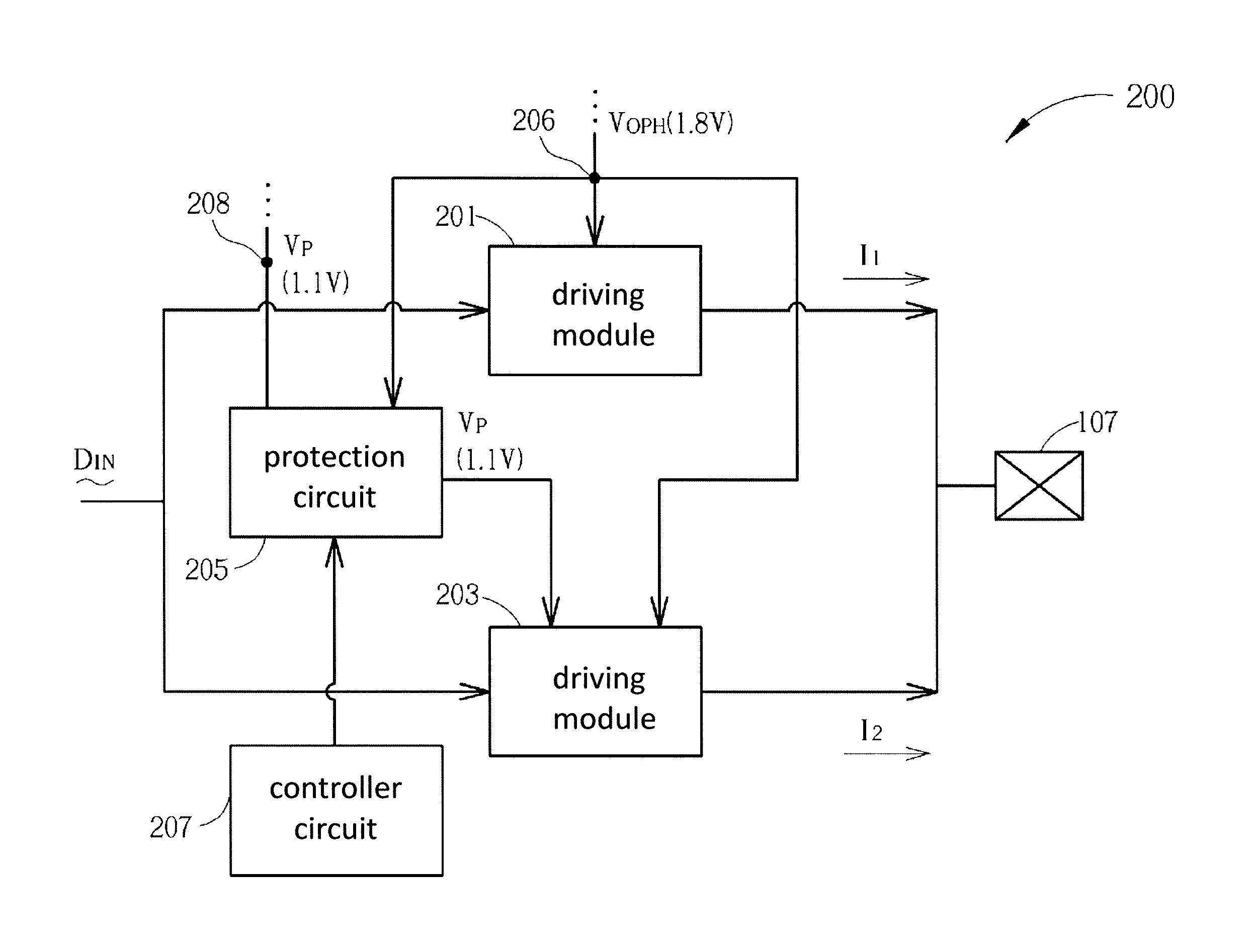

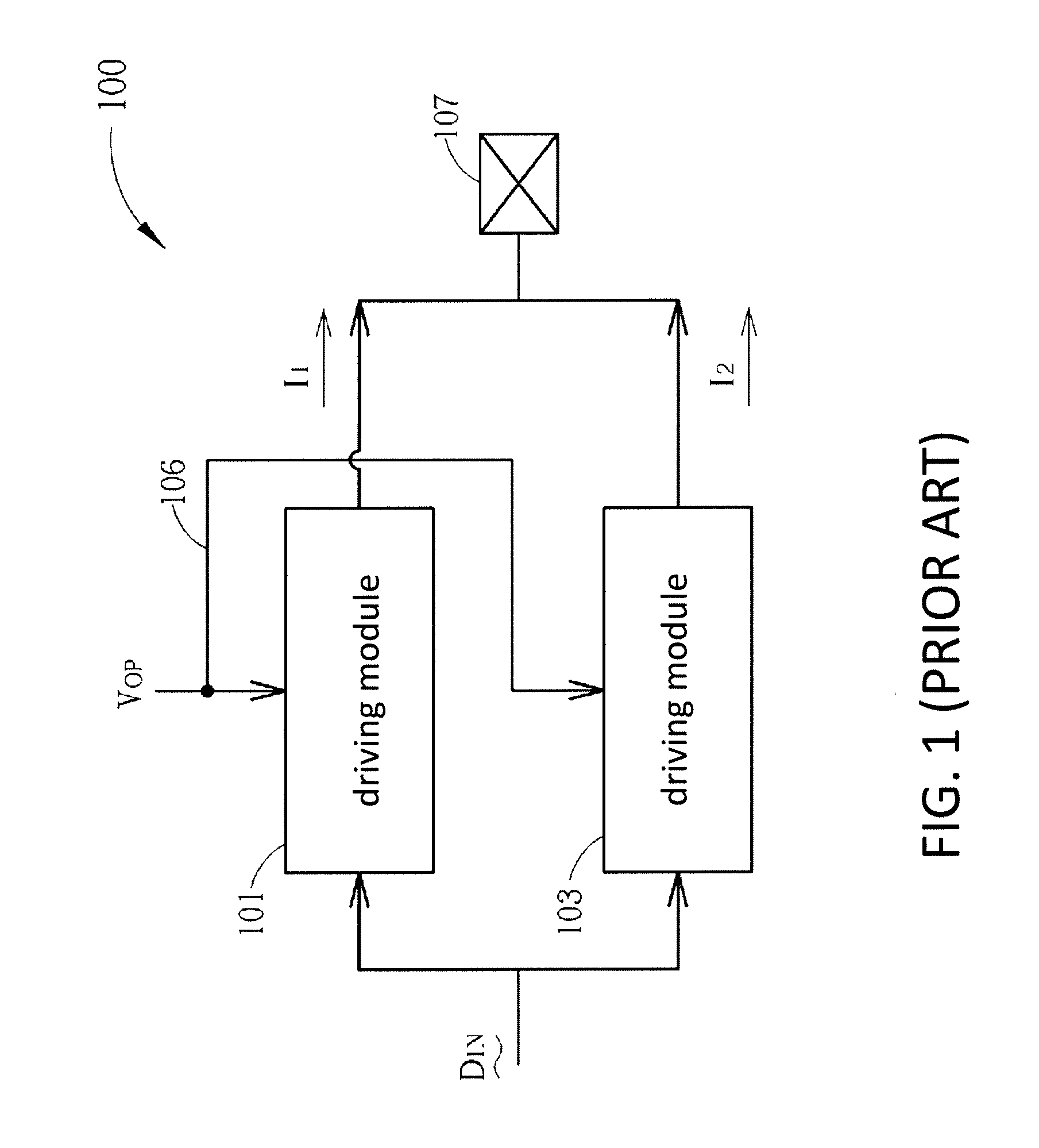

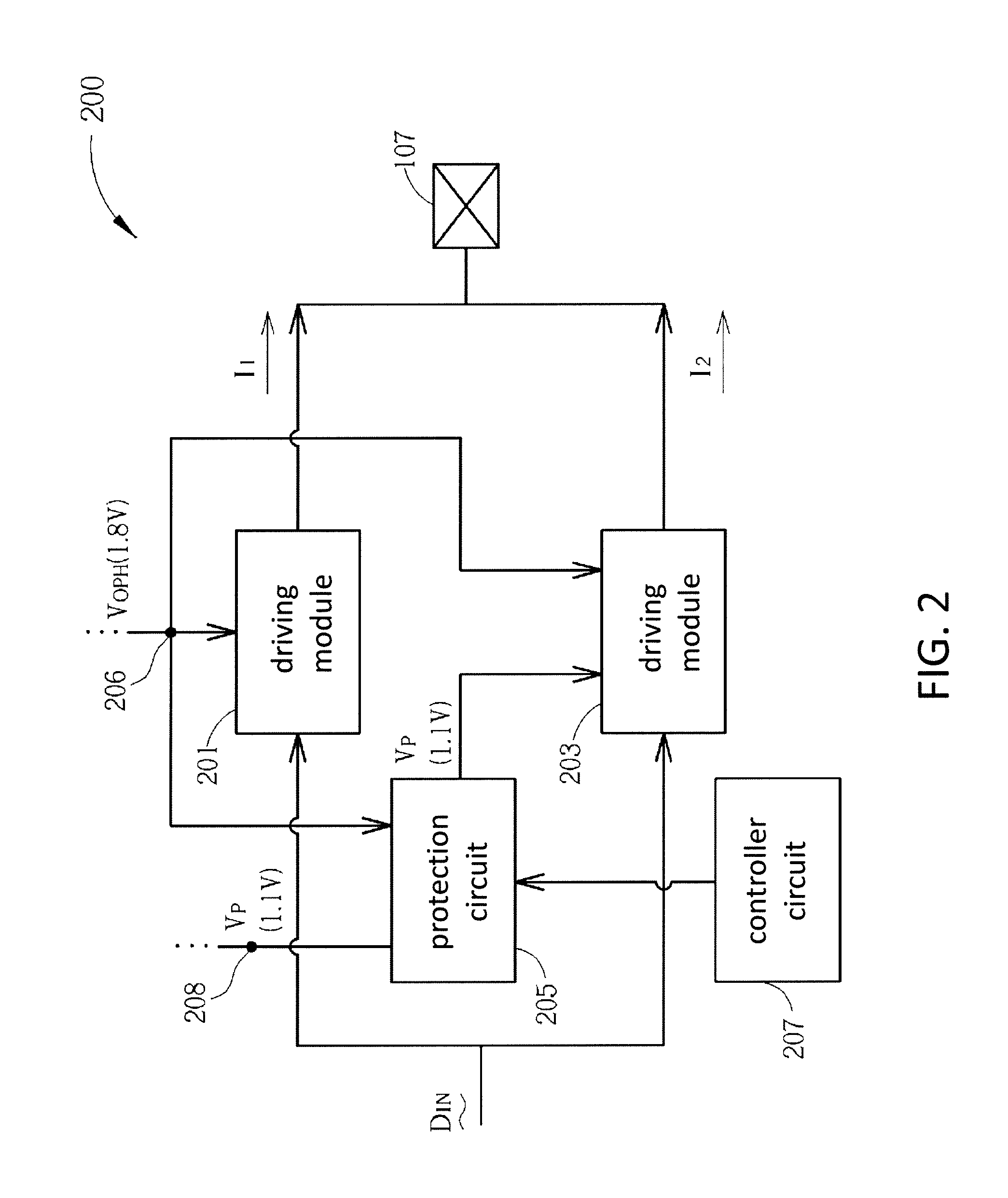

Driving circuit and driving method

ActiveUS20150194958A1Increased circuit areaPrecise functionElectric pulse generatorOscillations generatorsDriver circuitEngineering

A driving circuit includes a first driving module, configured to operate at a first operating voltage in a first mode and configured to be deactivated in a second mode; and a second driving module, wherein at least part of the second driving module operates at a protection voltage in the first mode and operates at a second operating voltage in the second mode, wherein the second operating voltage and the protection voltage are lower than the first operating voltage.

Owner:MEDIATEK INC

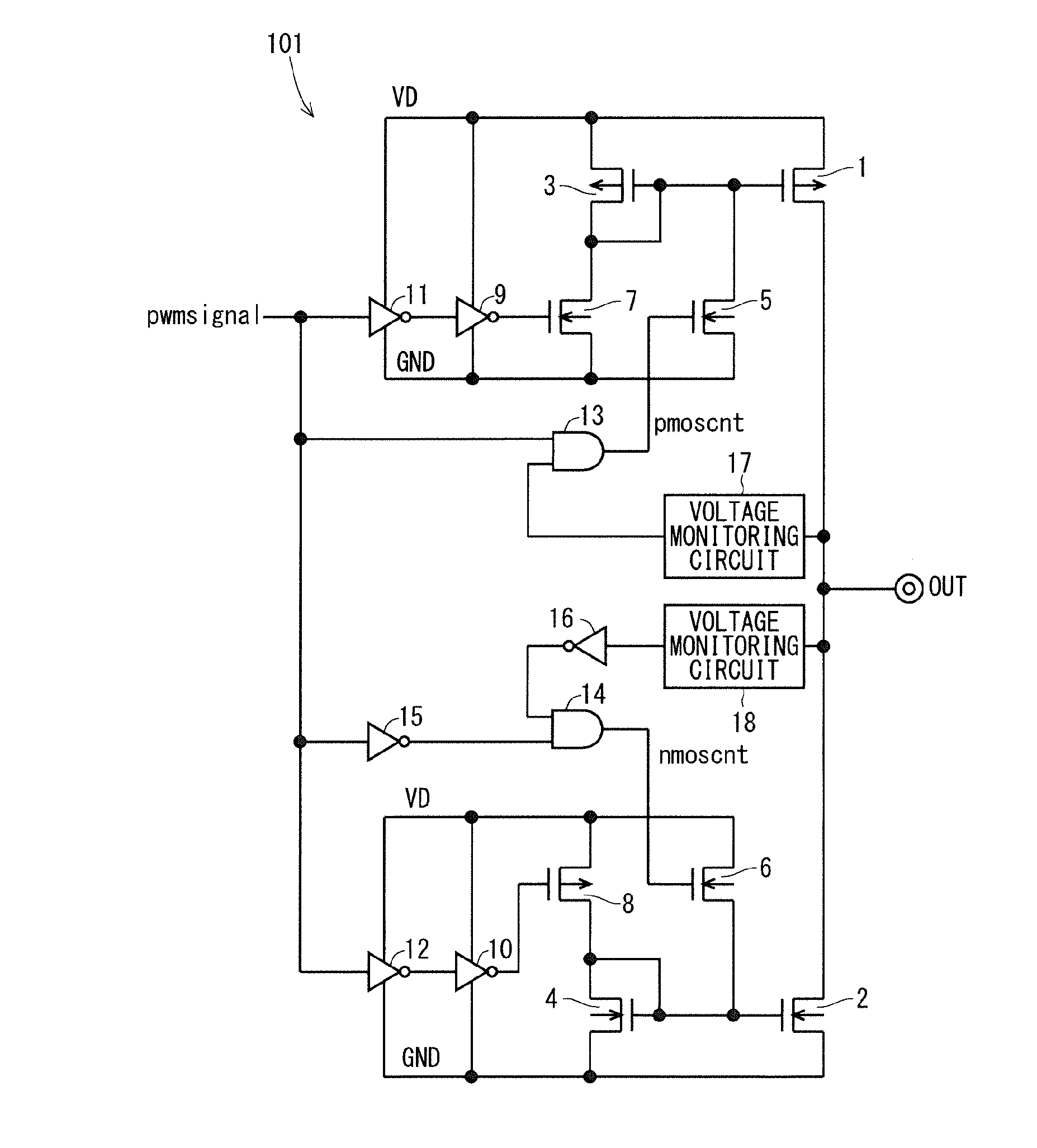

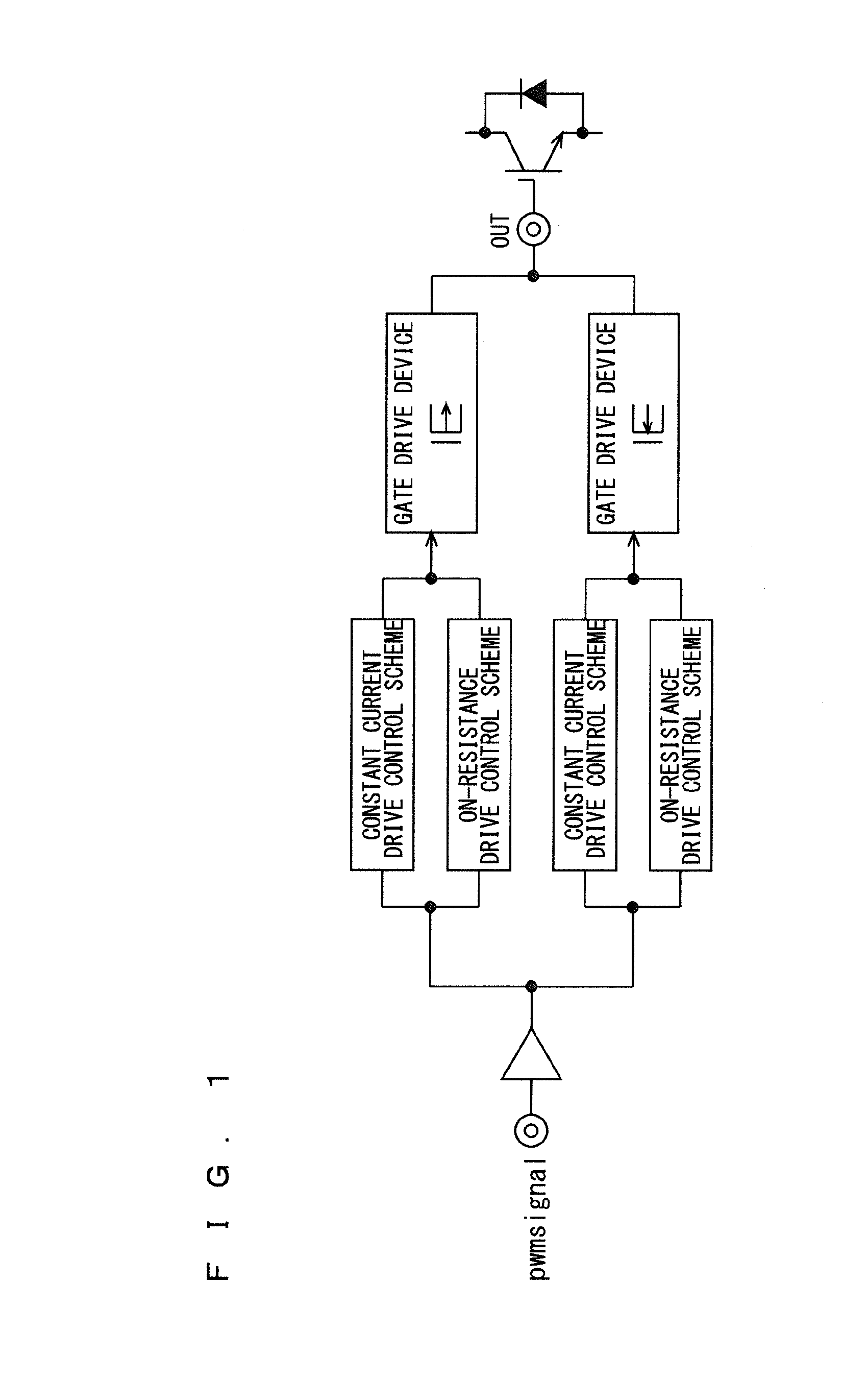

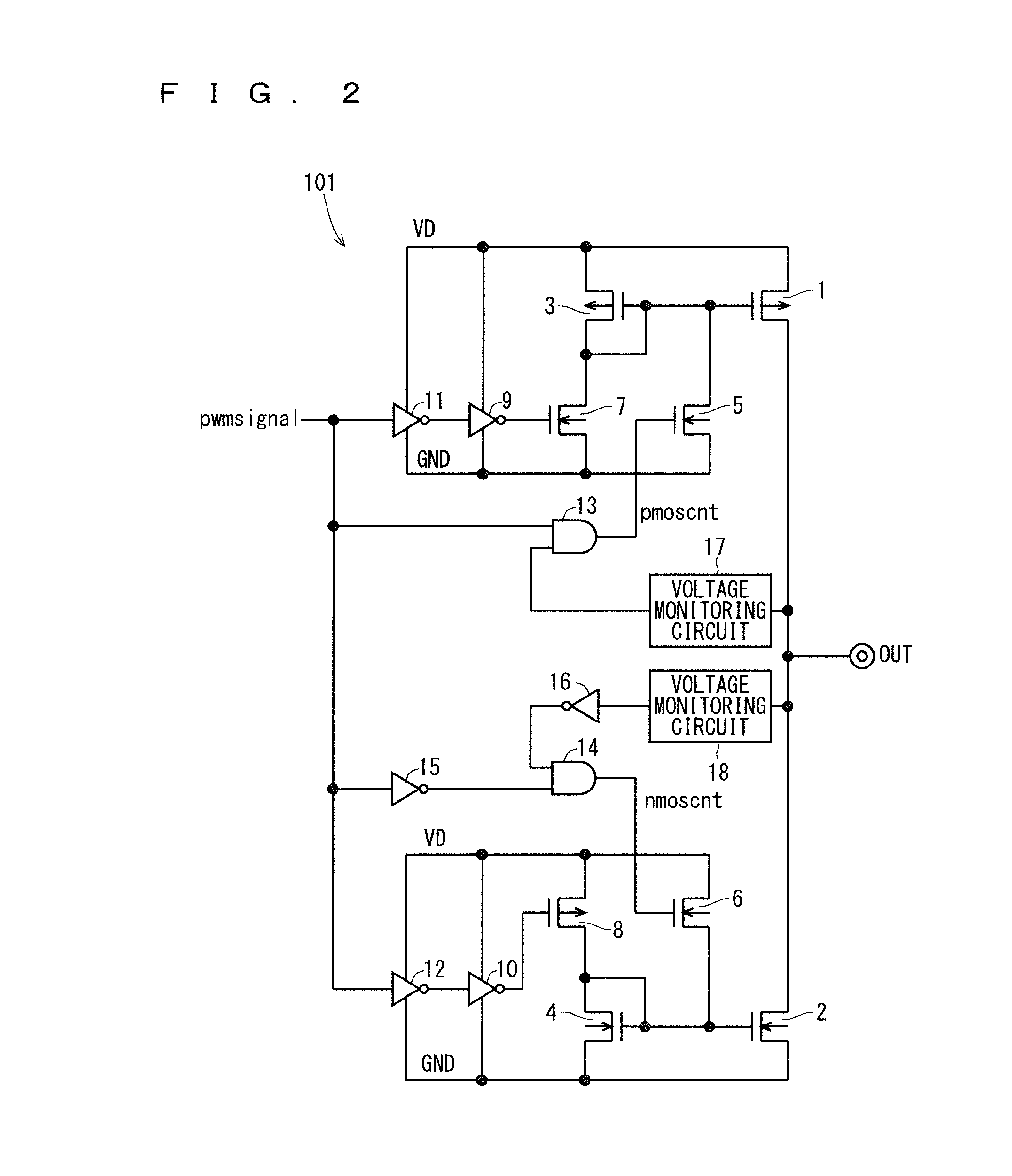

Drive circuit

ActiveUS20160116929A1Increased circuit areaElectric variable regulationPotential changeControl signal

A drive circuit of the present invention, which drives a switching device in response to a control signal, includes: a current mirror circuit including an output transistor connected to a control electrode of the switching device and a reference transistor that is connected to the output transistor in a current mirror manner and supplies a mirror current to the output transistor; and a potential change circuit that is connected to the reference transistor and changes a control potential of the output transistor from a potential during mirror operation of the current mirror circuit.

Owner:MITSUBISHI ELECTRIC CORP

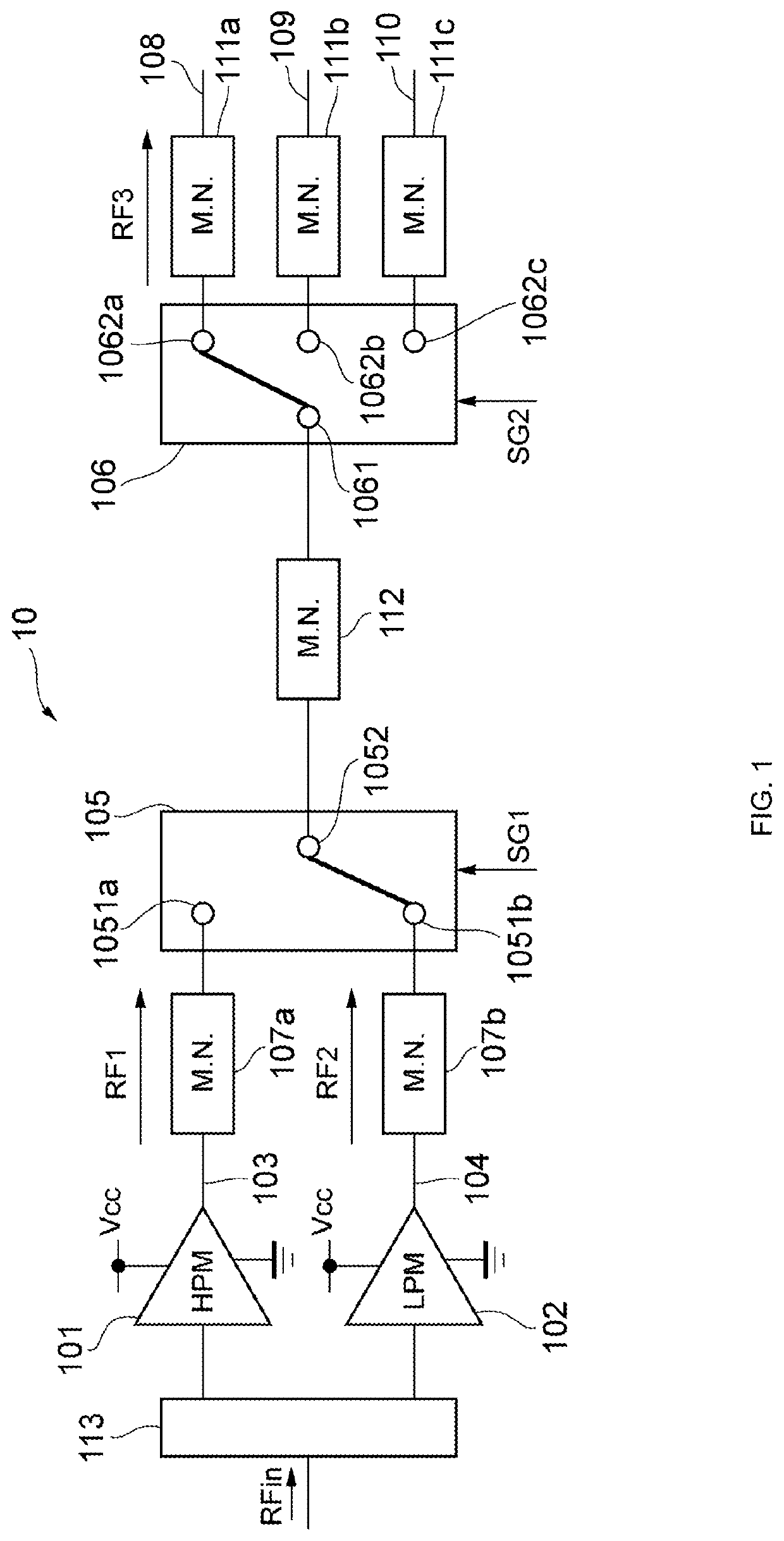

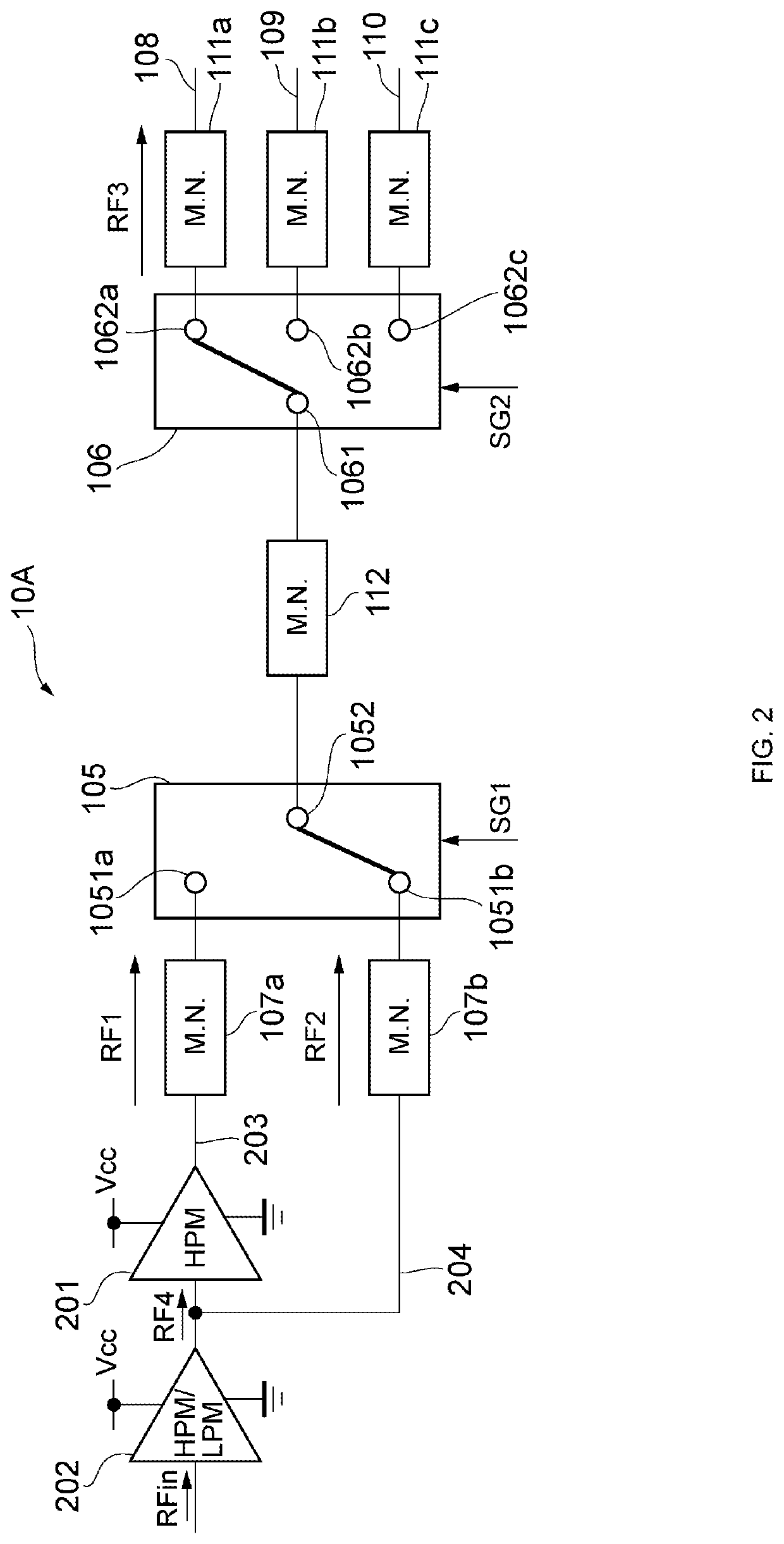

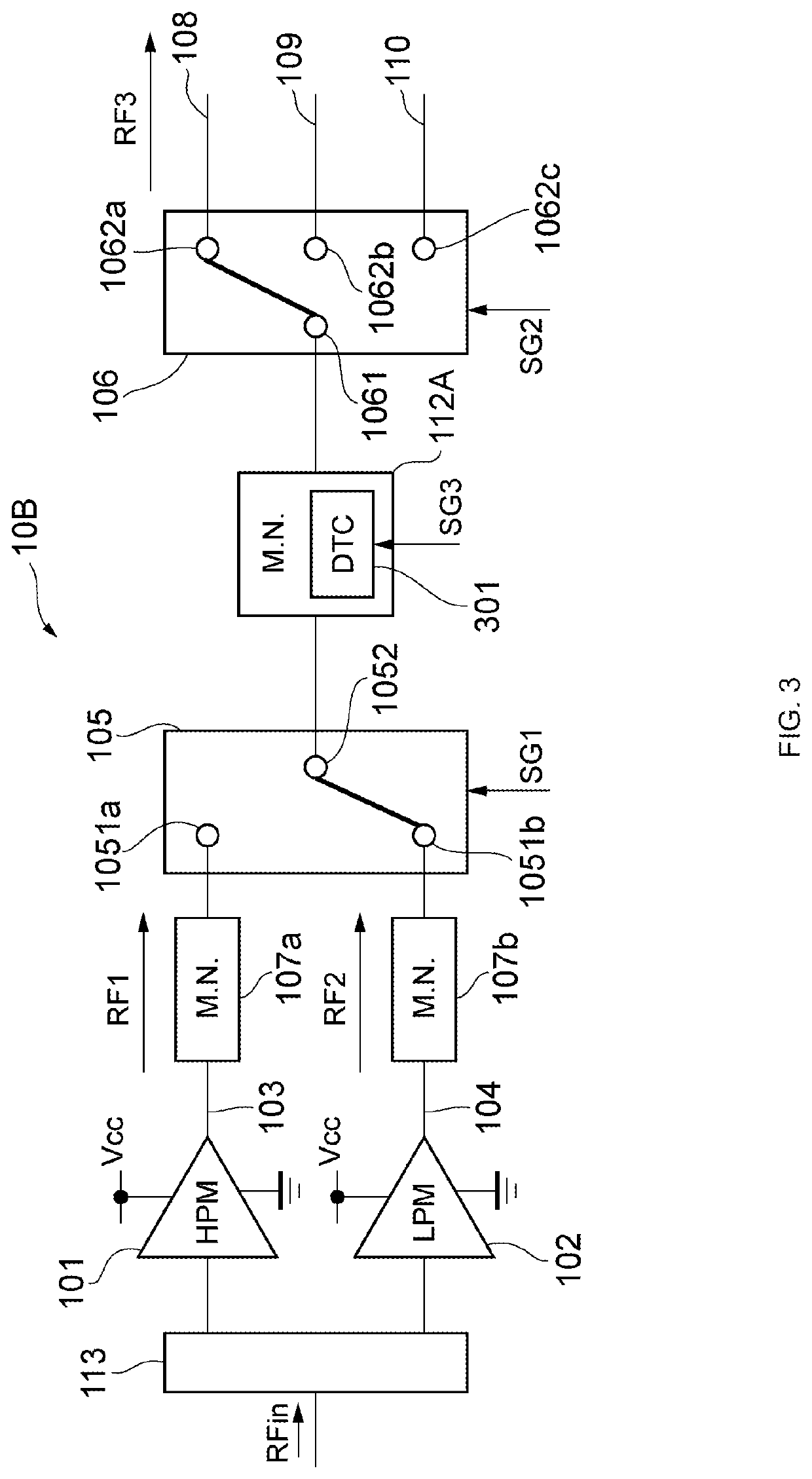

Power amplifier circuit

PendingUS20210328558A1Increased circuit areaIncrease the areaGated amplifiersPower amplifiersHemt circuitsEngineering

A power amplifier circuit includes a first amplification path including a first power amplifier, a second amplification path including a second power amplifier, a first switching circuit configured to electrically connect either the first amplification path or the second amplification path and a first output terminal to each other, a second switching circuit configured to electrically connect an input terminal and any one of a plurality of second output terminals to each other, and a matching circuit configured to electrically connect the first output terminal and the input terminal to each other and achieve impedance matching between the first output terminal and the input terminal.

Owner:MURATA MFG CO LTD

Semiconductor device

ActiveCN103778028BIncreased circuit areaIncreased power consumptionRedundant data error correctionPower semiconductor deviceCircuit delay

A semiconductor device comprising: a first processor; a second processor; a first delay circuit delaying a signal input into the first processor by a predefined number of cycles and inputting the signal into the second processor; a first compression circuit compressing a signal of n-bit width from the first processor into a signal of m-bit width (m<n) and outputting the signal of m-bit width; a second compression circuit compressing a signal of n-bit width from the second processor into a signal of m-bit width and outputting the signal of m-bit width; a second delay circuit delaying the signal from the first compressor by the predefined number of cycles and outputting the delayed signal; and a coincidence comparison circuit comparing bit-wise the corresponding bits of the signals from the second delay circuit and from the second compression circuit to check whether the corresponding bits coincide with each other or not.

Owner:RENESAS ELECTRONICS CORP