Patents

Literature

1358results about How to "Reduce layout area" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

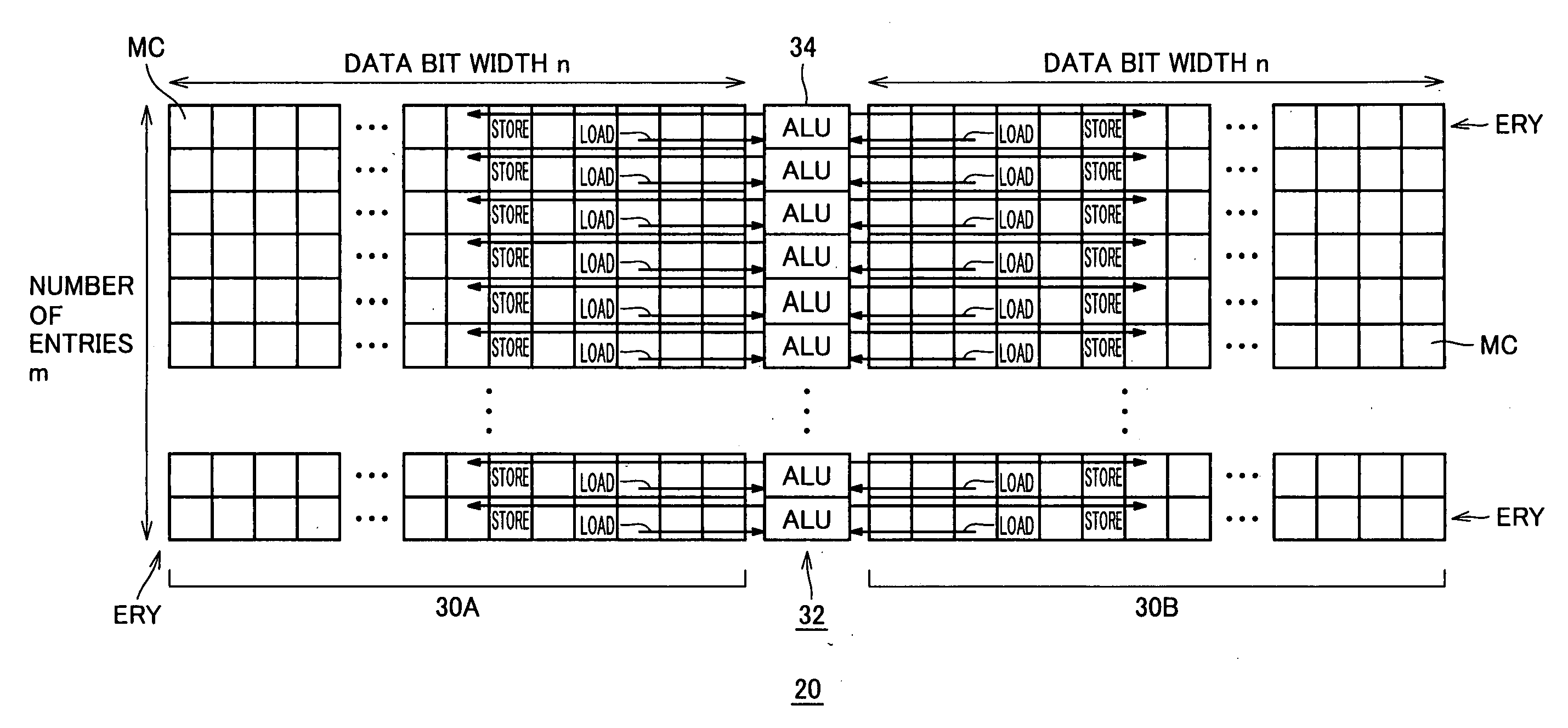

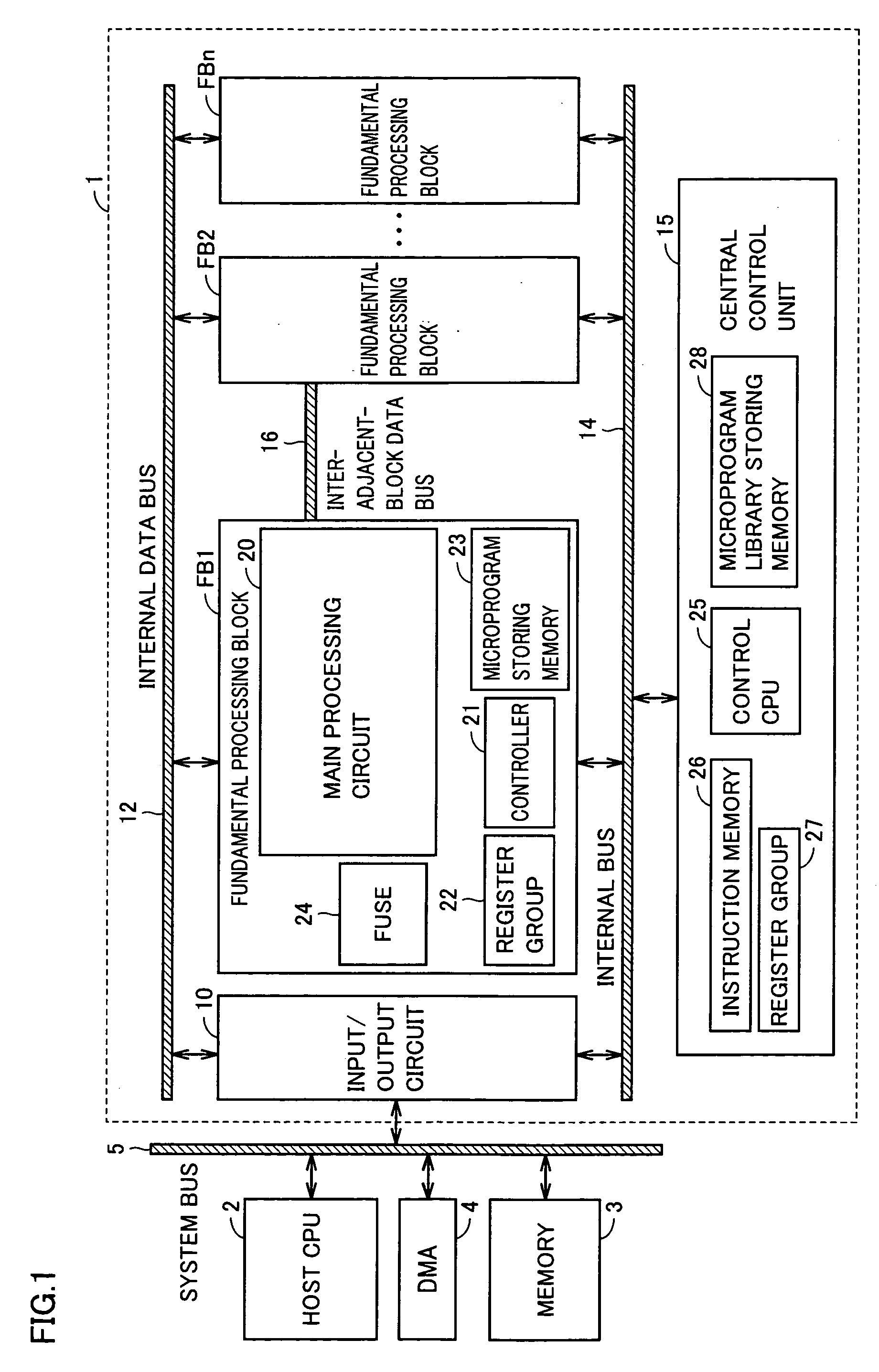

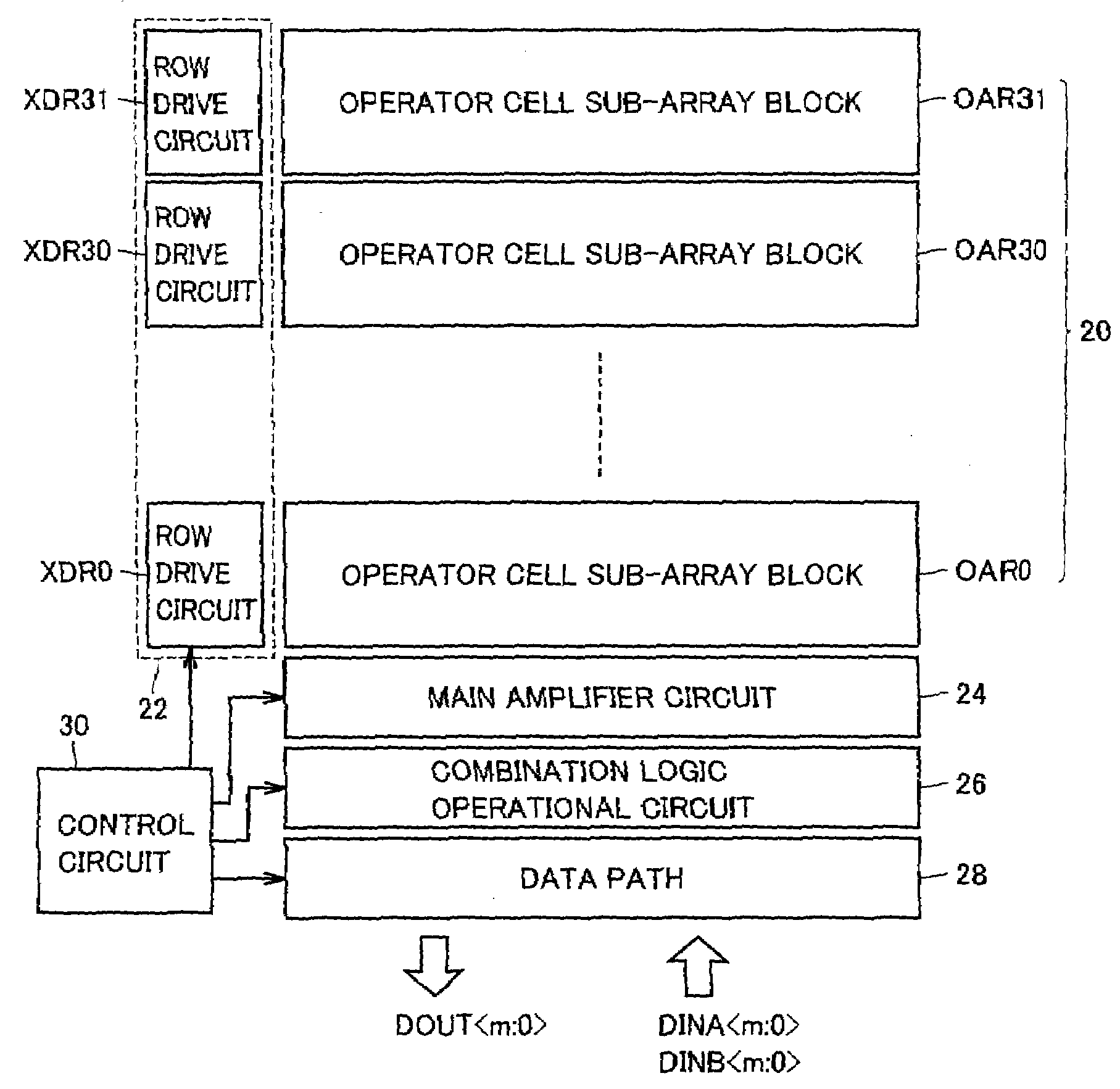

Parallel operational processing device

InactiveUS20070180006A1Easy to operateReduce power consumptionEnergy efficient ICTDigital data processing detailsAudio power amplifierParallel computing

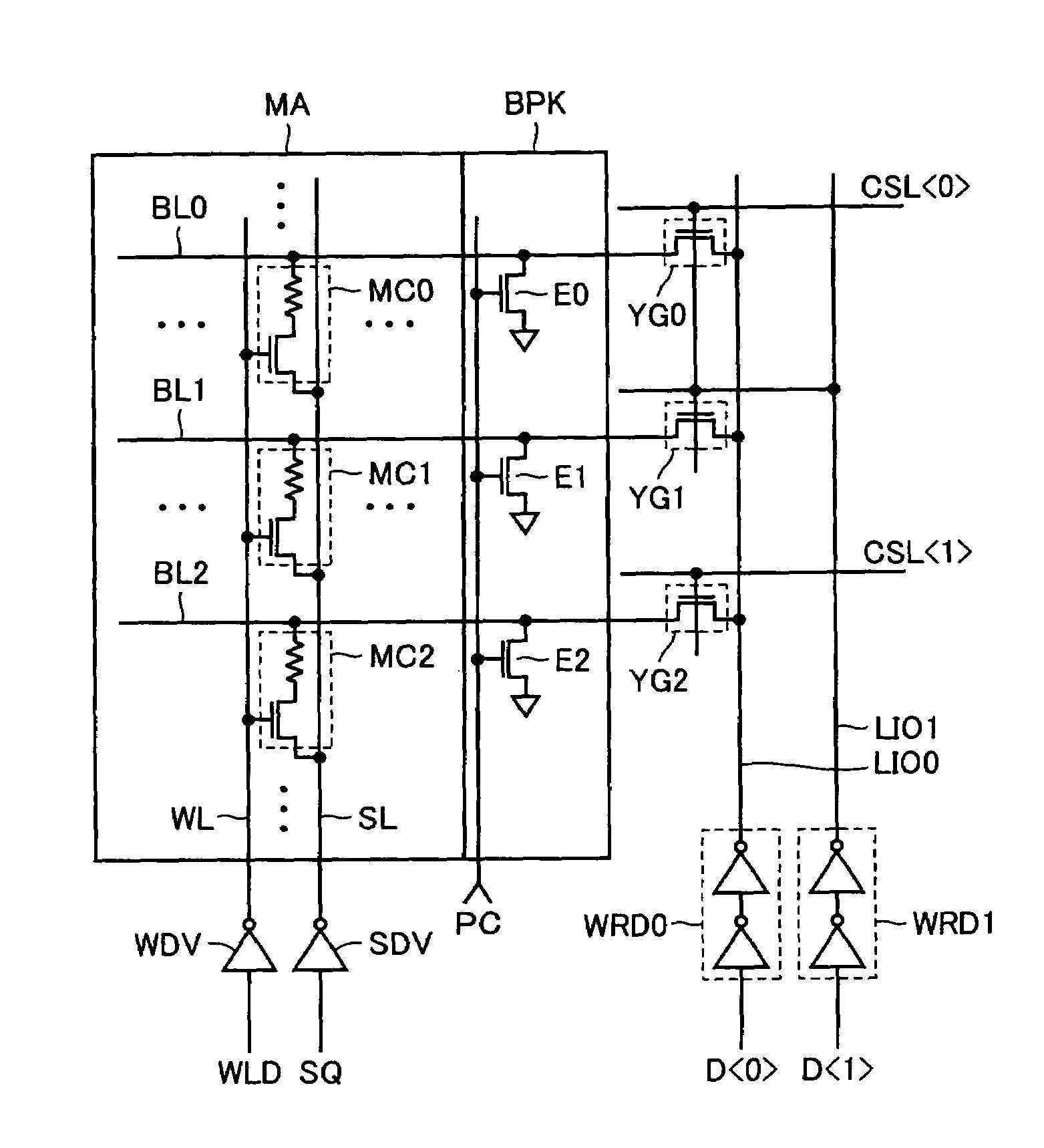

In a parallel operational processing device having an operational processing unit arranged between memory blocks each having a plurality of memory cells arranged in rows and columns, the respective columns of each memory block are alternately connected to the operational processing units on the opposite sides of the memory block. By selecting one word line in one memory block, data can be transferred to two operational processing units. The number of the word lines selected per one operational processing unit is reduced, and power consumption is reduced. The bit operation units and sense amplifiers / write drivers of the operational processing units have arrangement pitch conditions mitigated and are reduced in number, and an isolation region between the memory blocks is not required and the layout area is reduced. Thus, the parallel operational processing device with a layout area and the power consumption reduced, can achieve a fast operation.

Owner:RENESAS ELECTRONICS CORP

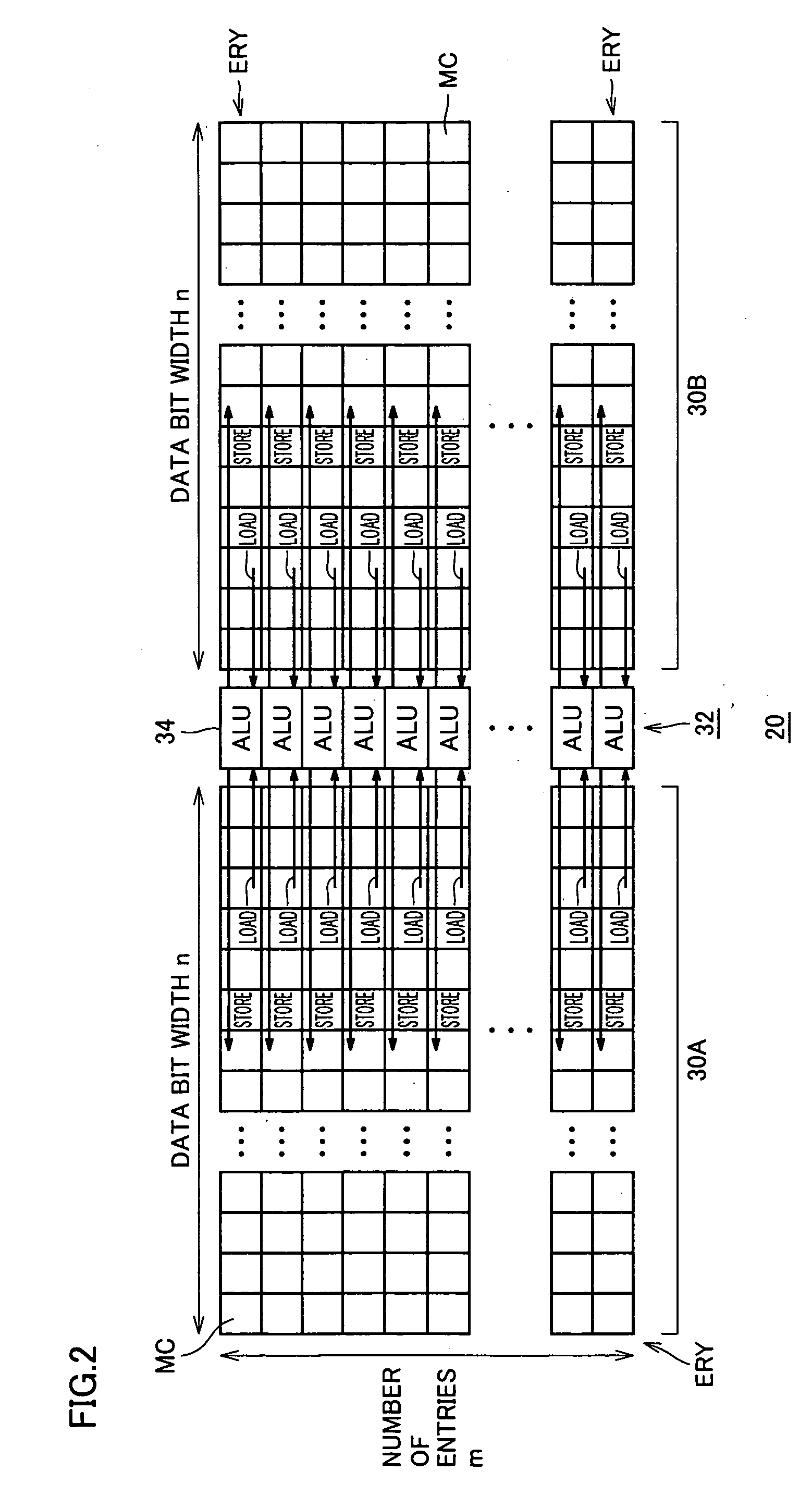

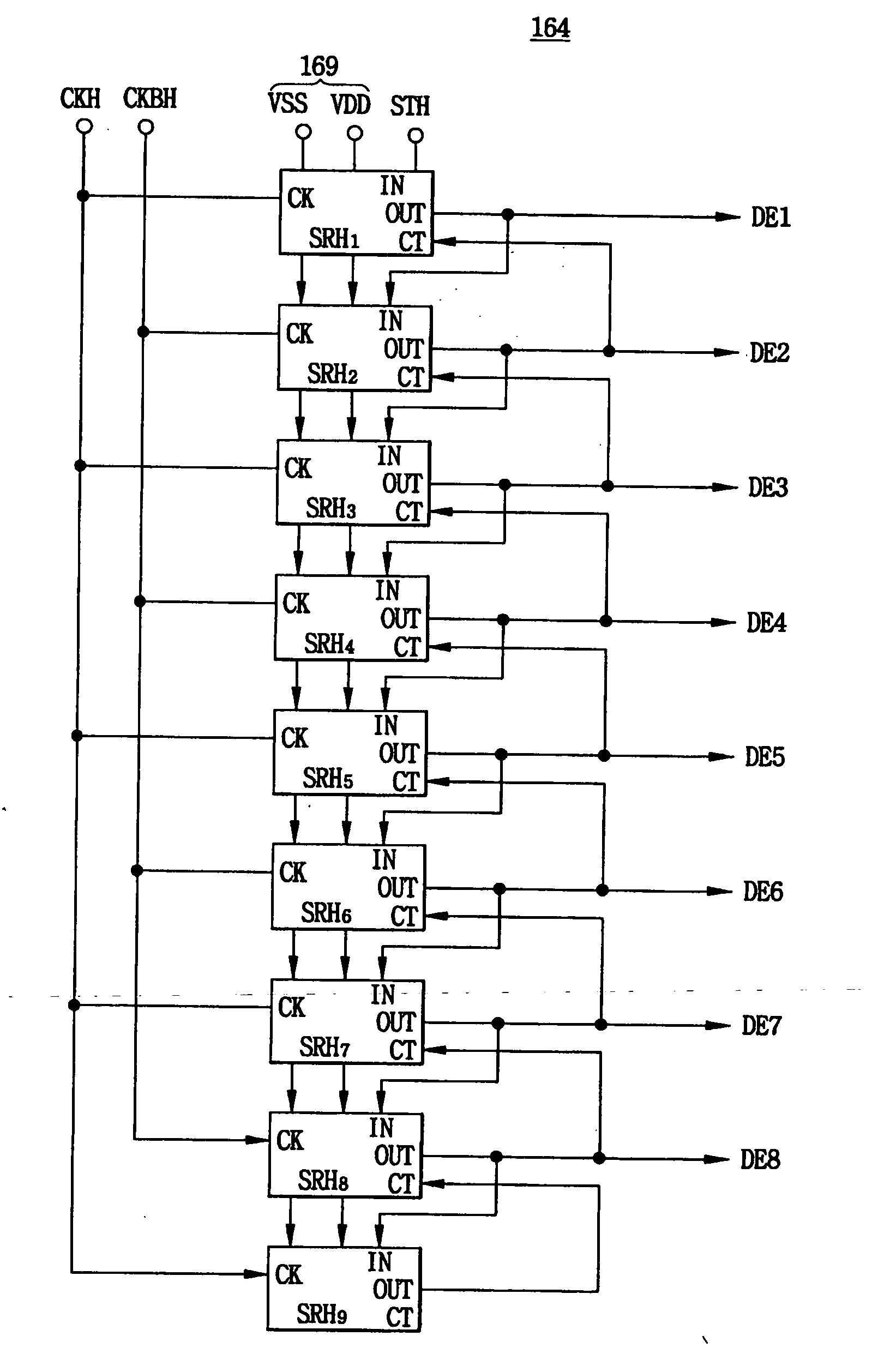

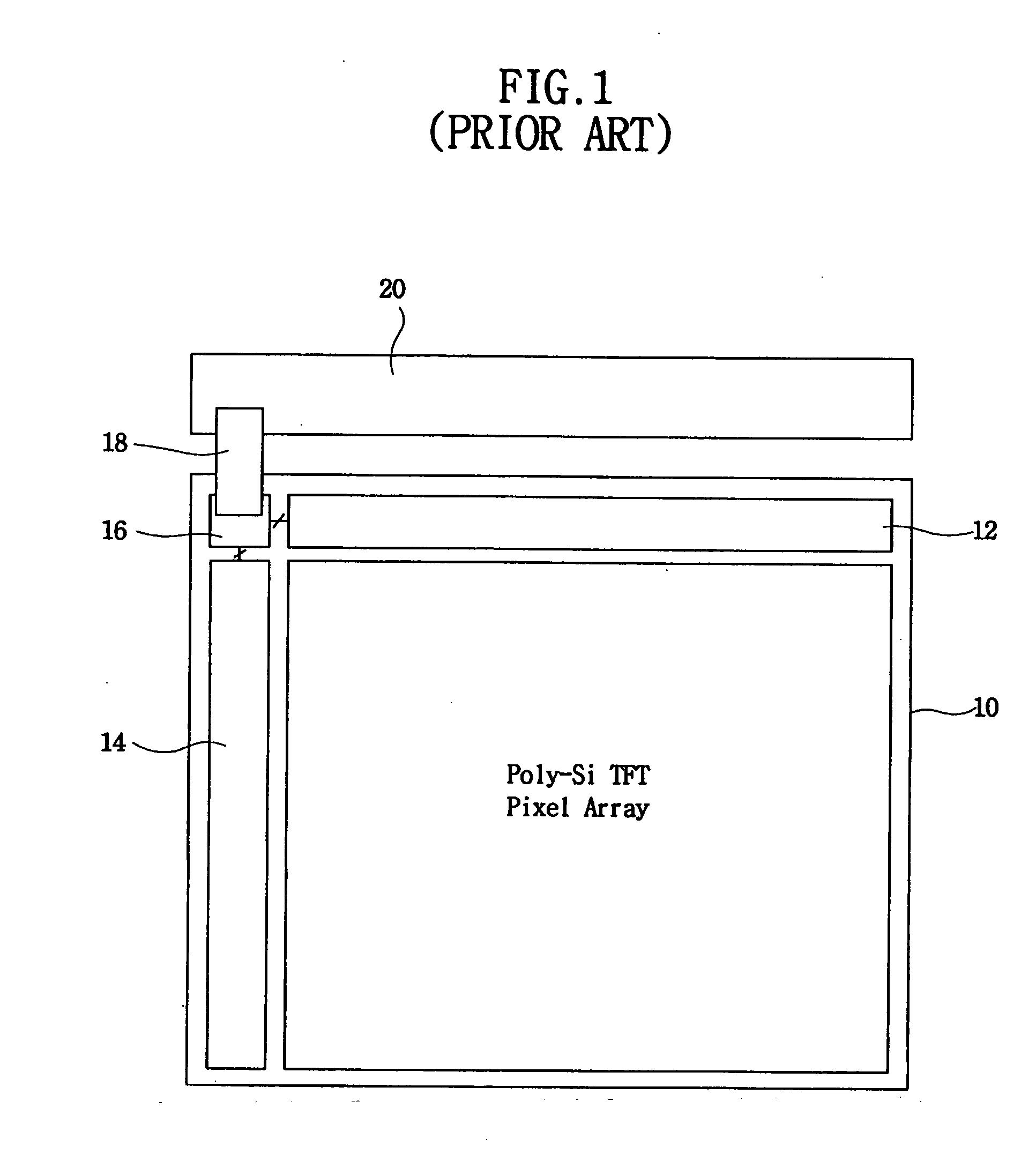

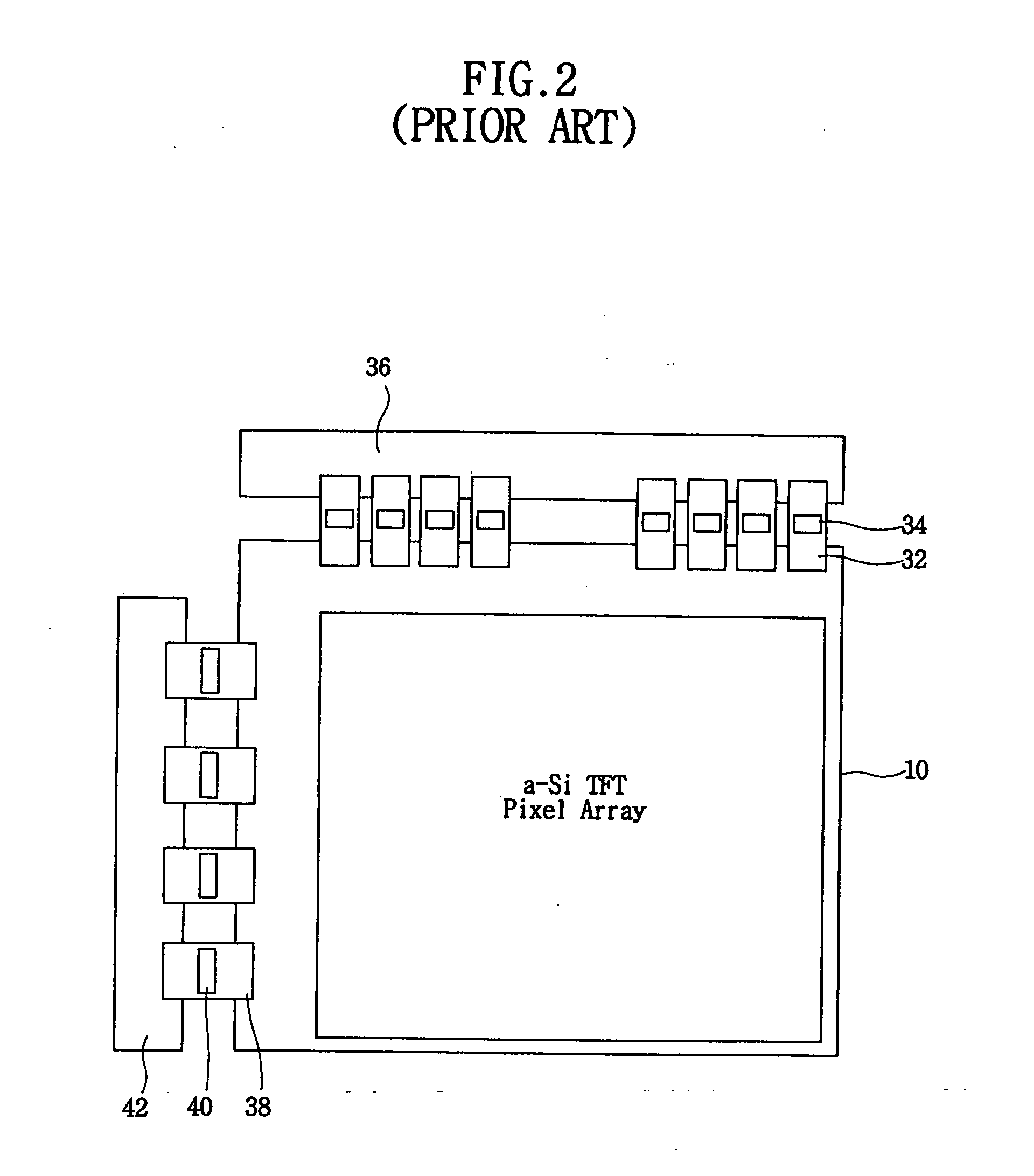

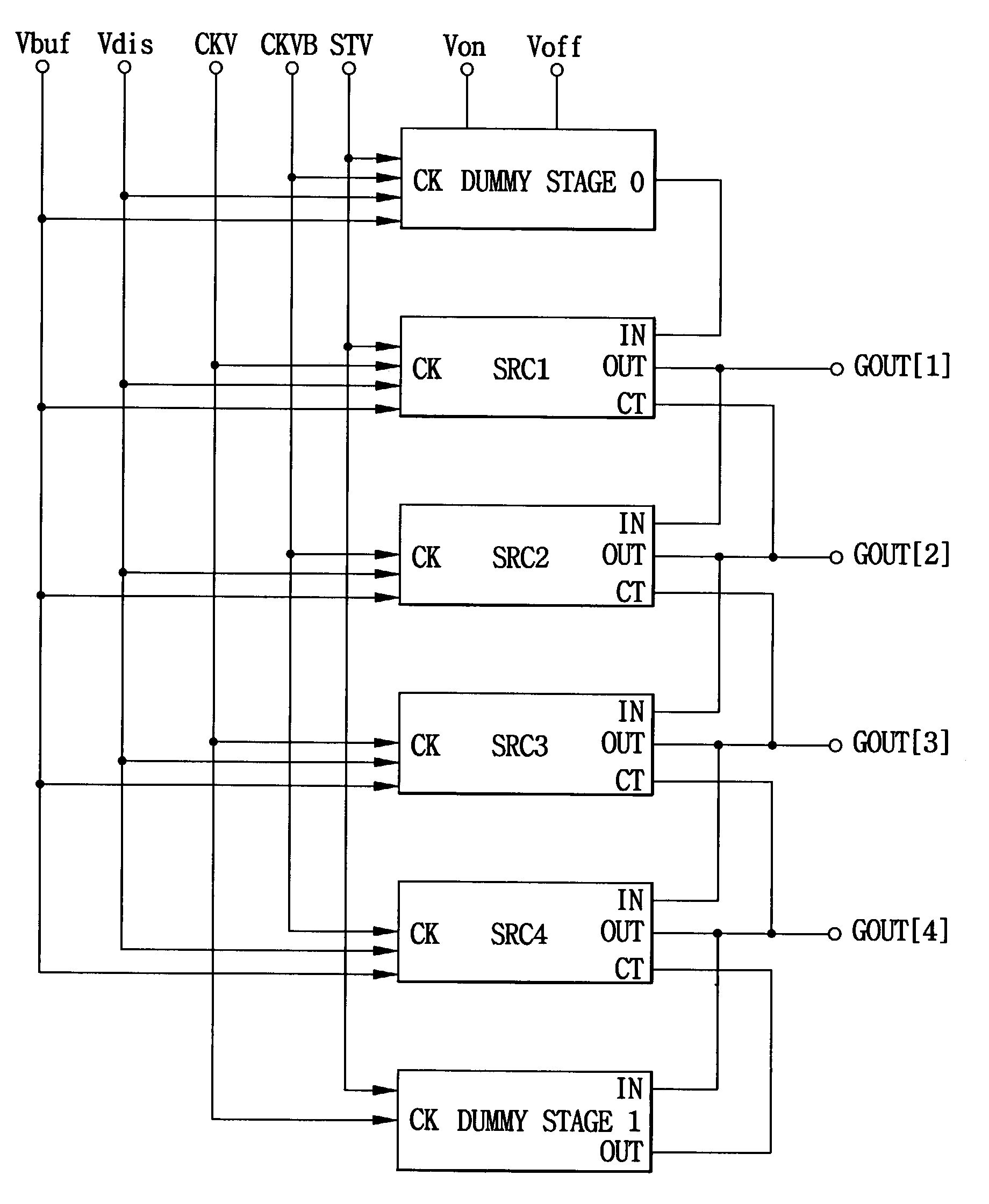

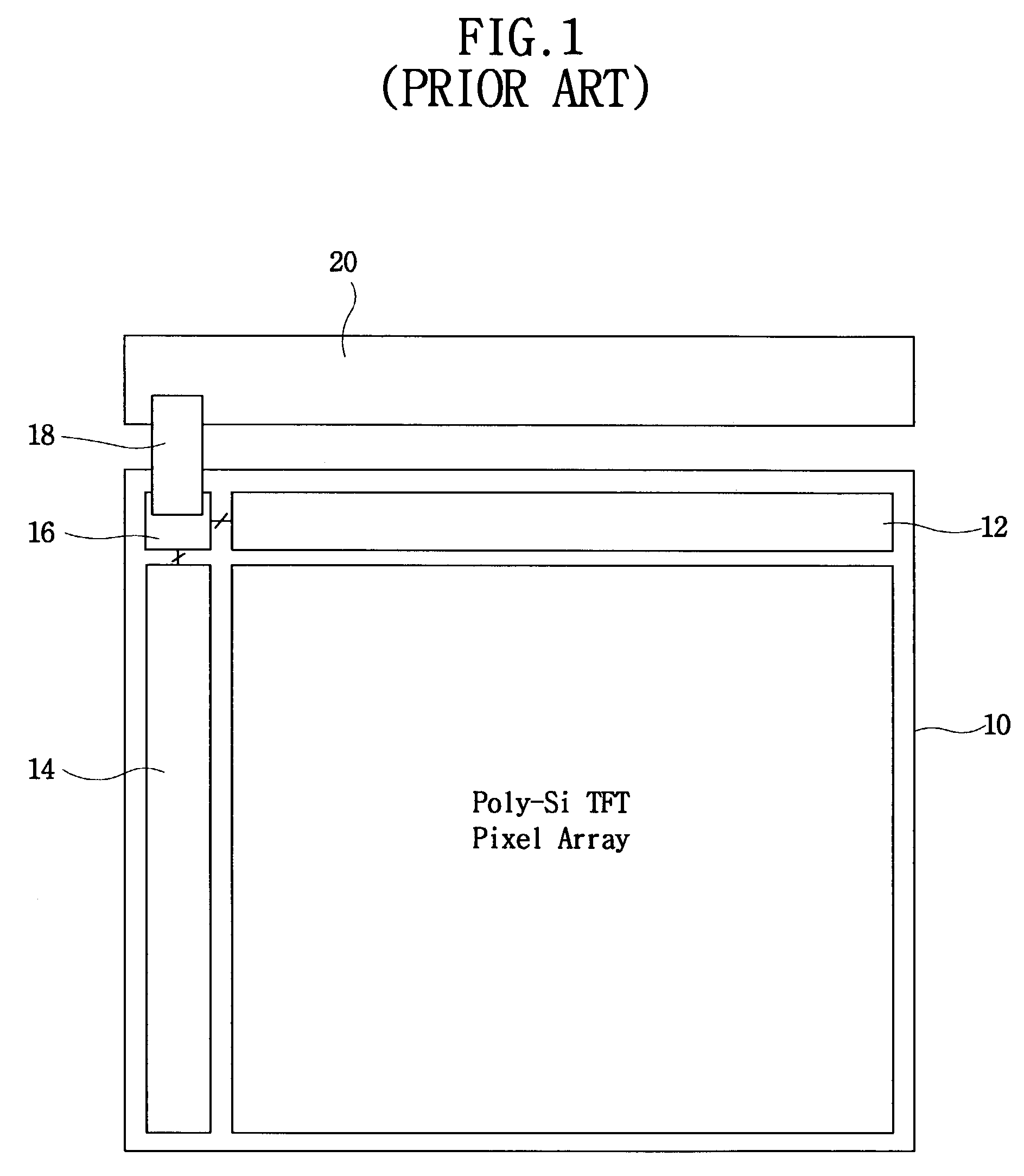

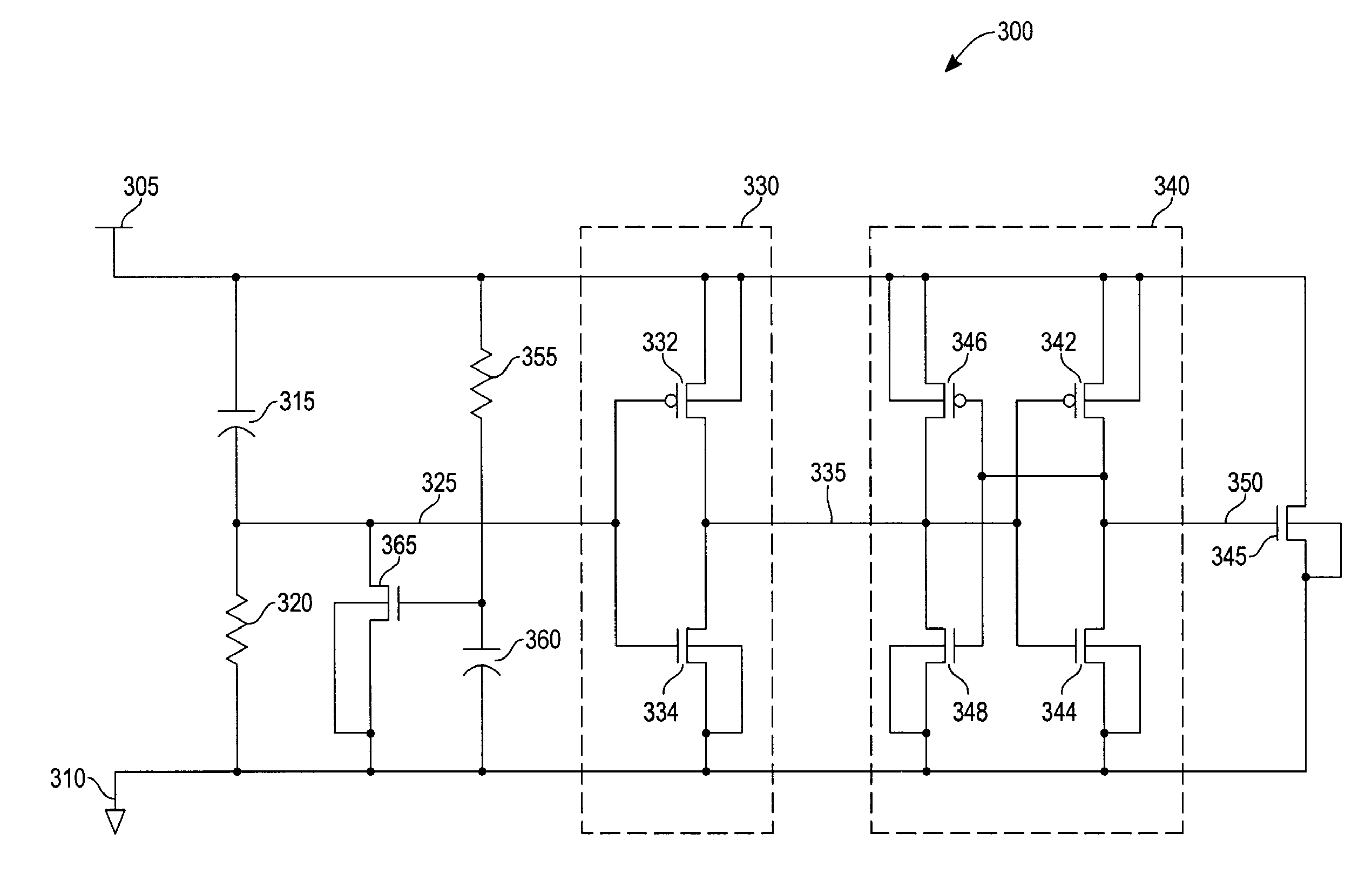

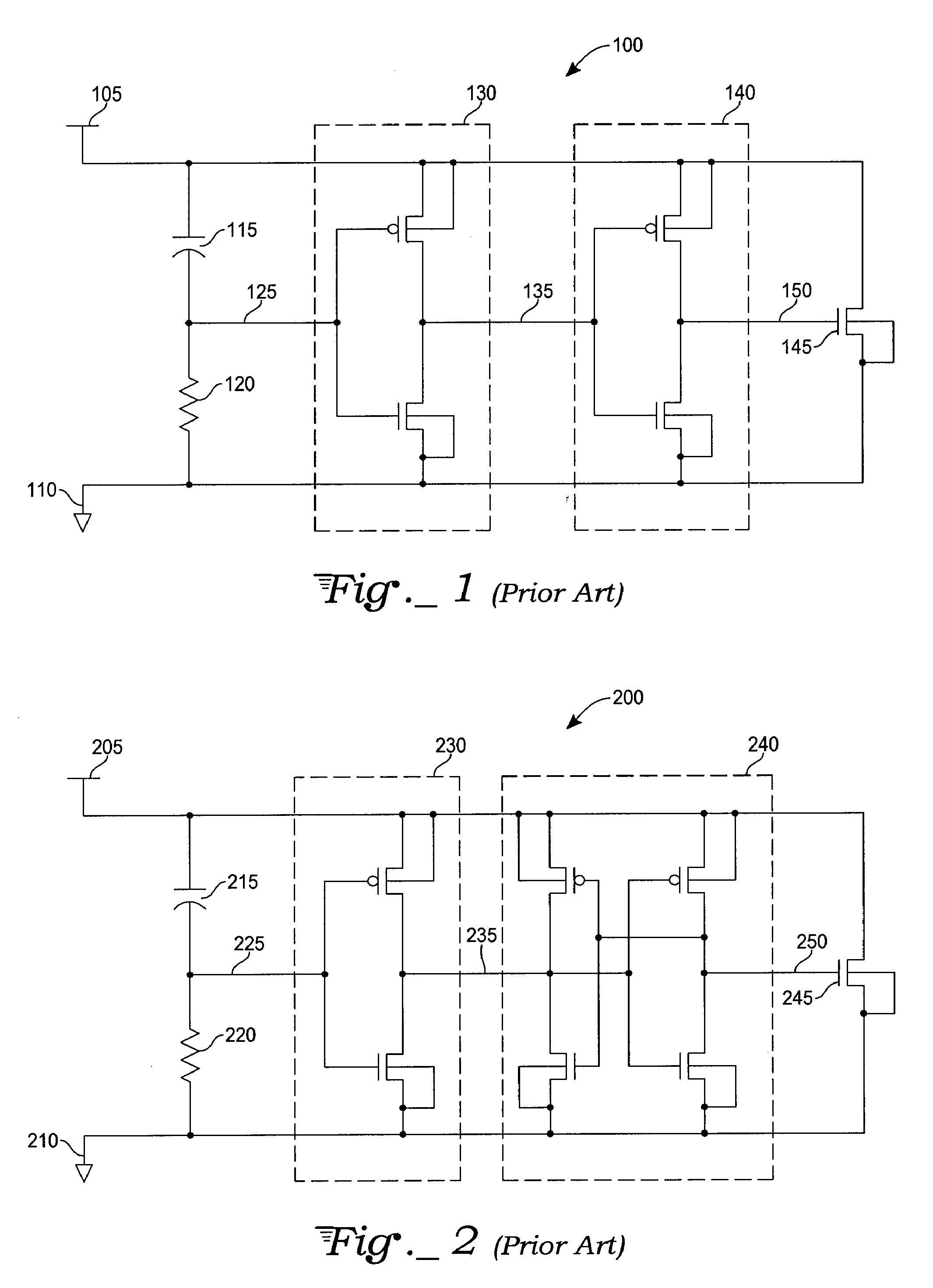

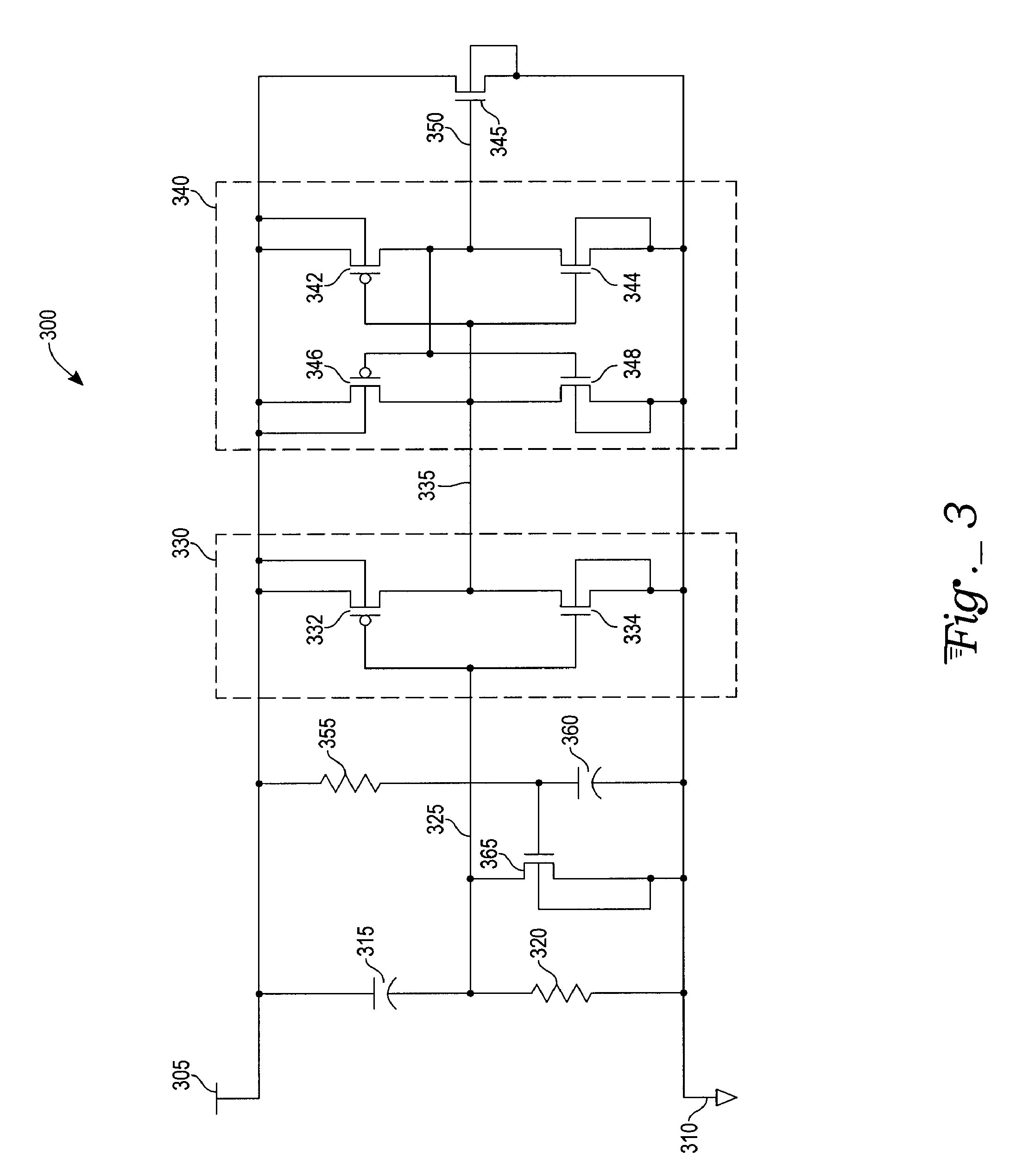

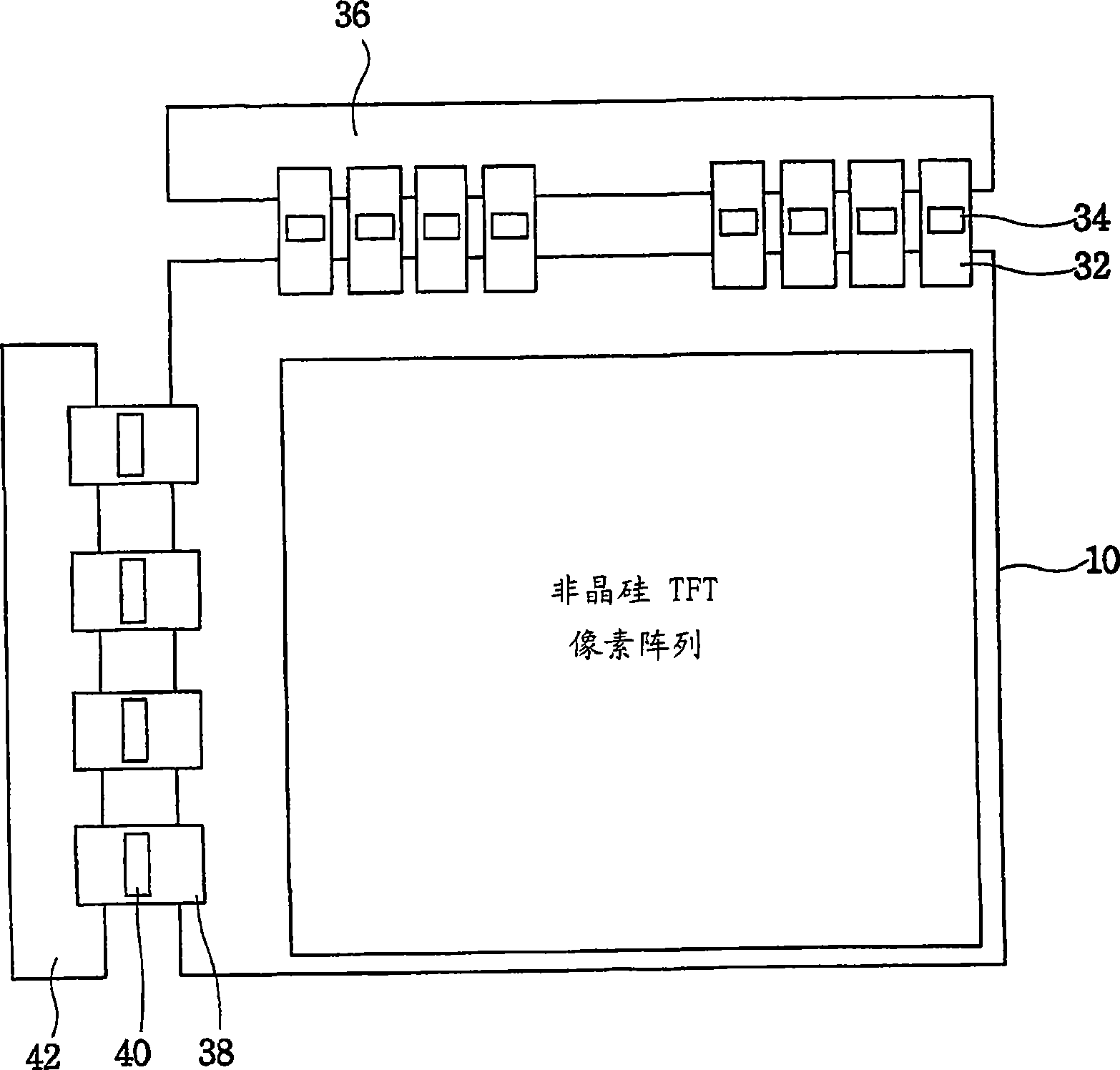

Shift register, liquid crystal display device having the shift register and method of driving scan lines using the same

ActiveUS20060256066A1Reduce power consumptionReduce layout areaStatic indicating devicesDigital storageShift registerLiquid-crystal display

In a bi-directional shift register and a liquid crystal display device having the bi-directional shift register, the shift register further includes a dummy stage for resetting a last stage. The dummy stage is reset by a control signal of the last stage or by the output signal of the dummy stage. Therefore, power consumption and layout area may be reduced. The shift register includes a plurality of stages and two dummy stages, and two selection signals for selecting shift direction is applied to each of the stages.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

Shift register, liquid crystal display device having the shift register and method of driving scan lines using the same

ActiveUS7106292B2Reduce power consumptionReduce layout areaCathode-ray tube indicatorsDigital storageShift registerLiquid-crystal display

In a bi-directional shift register and a liquid crystal display device having the bi-directional shift register, the shift register further includes a dummy stage for resetting a last stage. The dummy stage is reset by a control signal of the last stage or by the output signal of the dummy stage. Therefore, power consumption and layout area may be reduced. The shift register includes a plurality of stages and two dummy stages, and two selection signals for selecting shift direction is applied to each of the stages.

Owner:HEWLETT PACKARD DEV CO LP +1

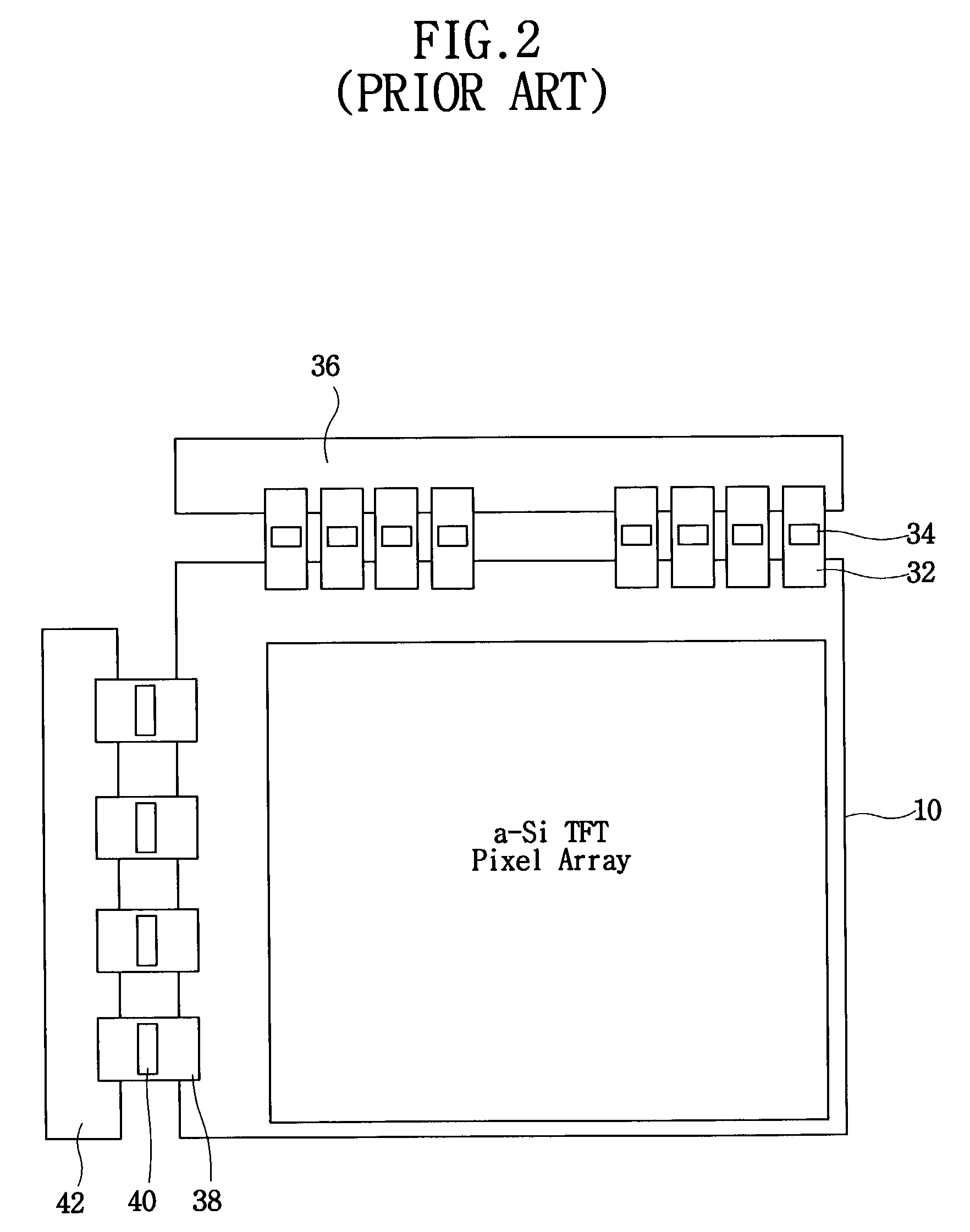

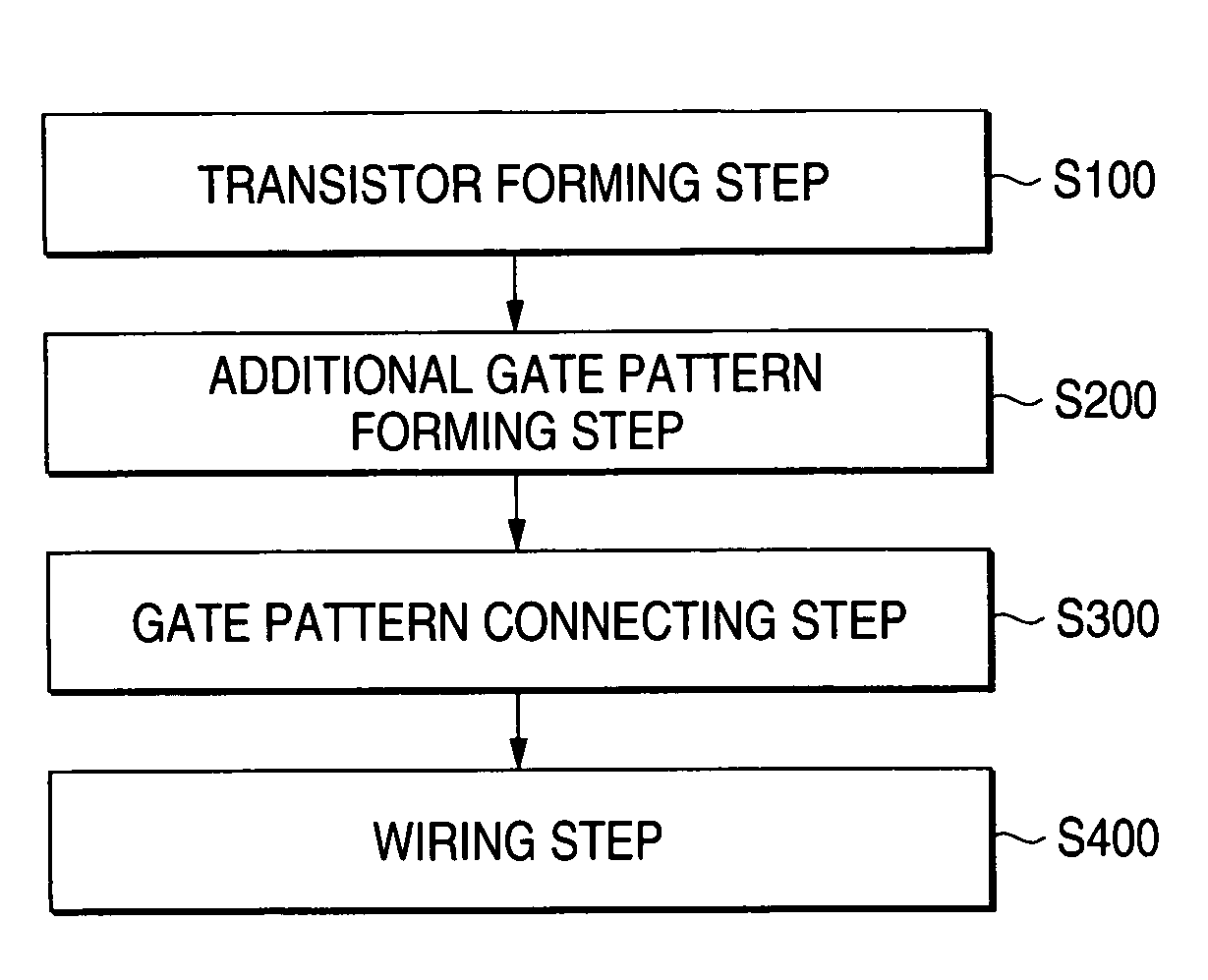

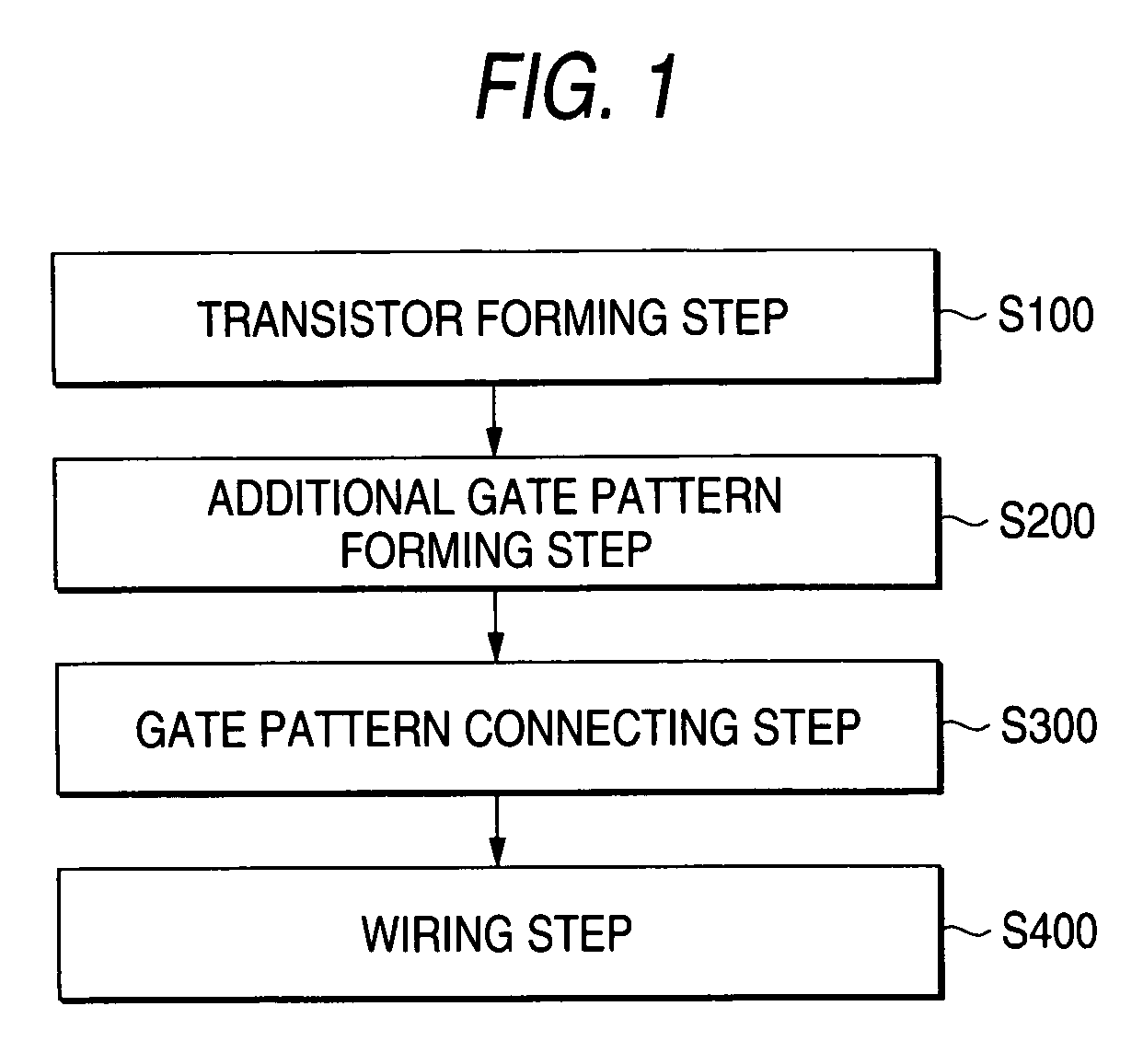

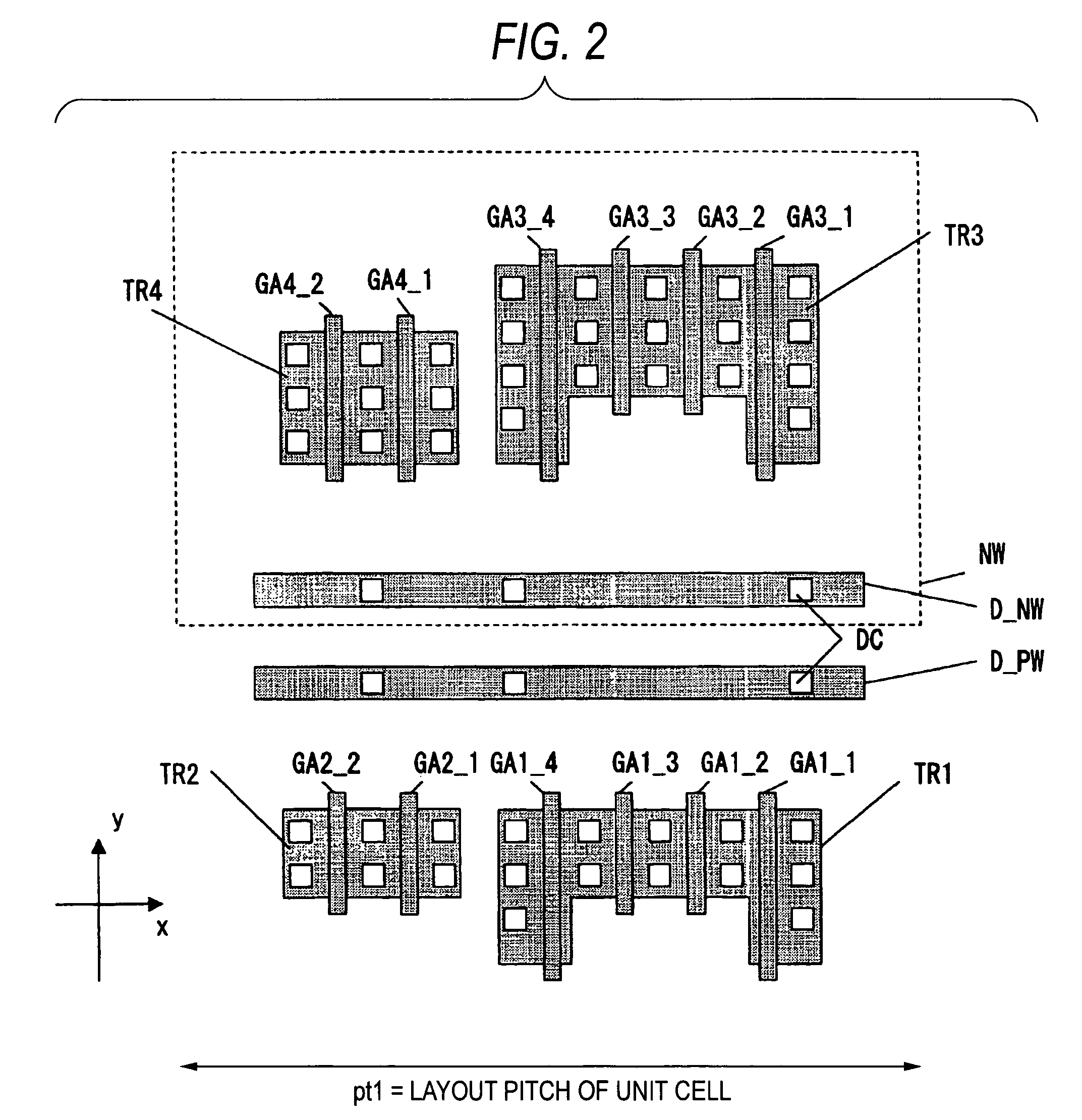

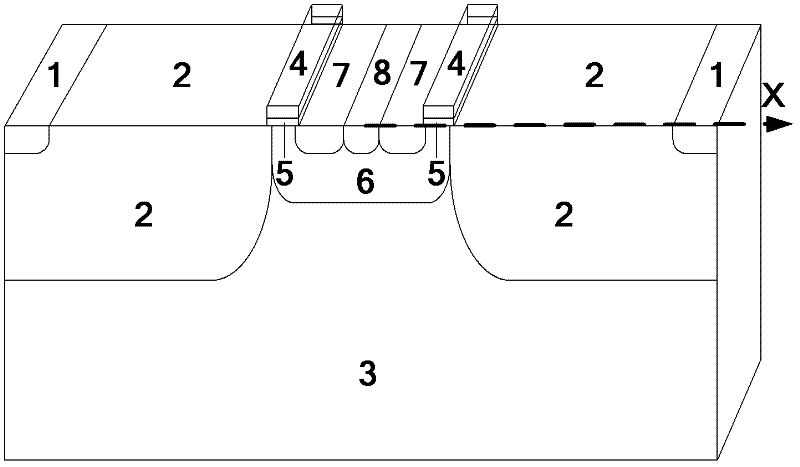

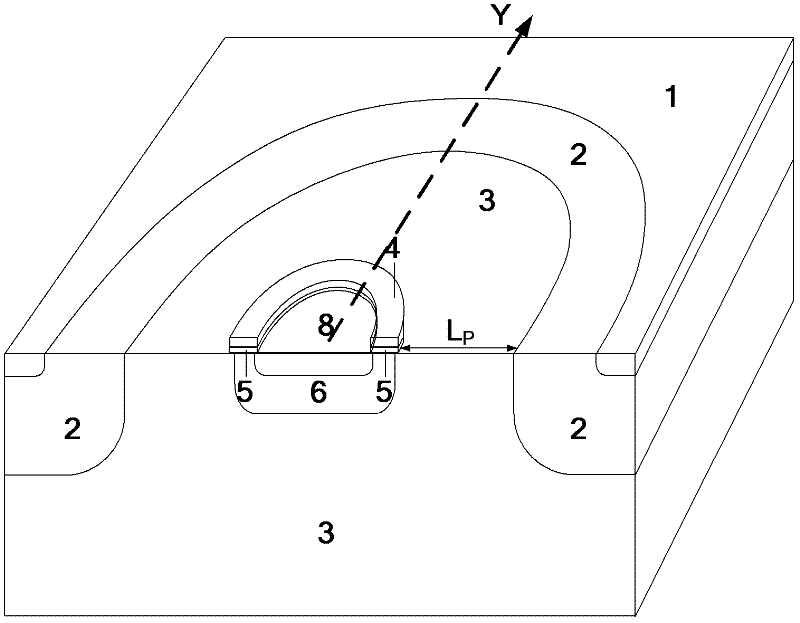

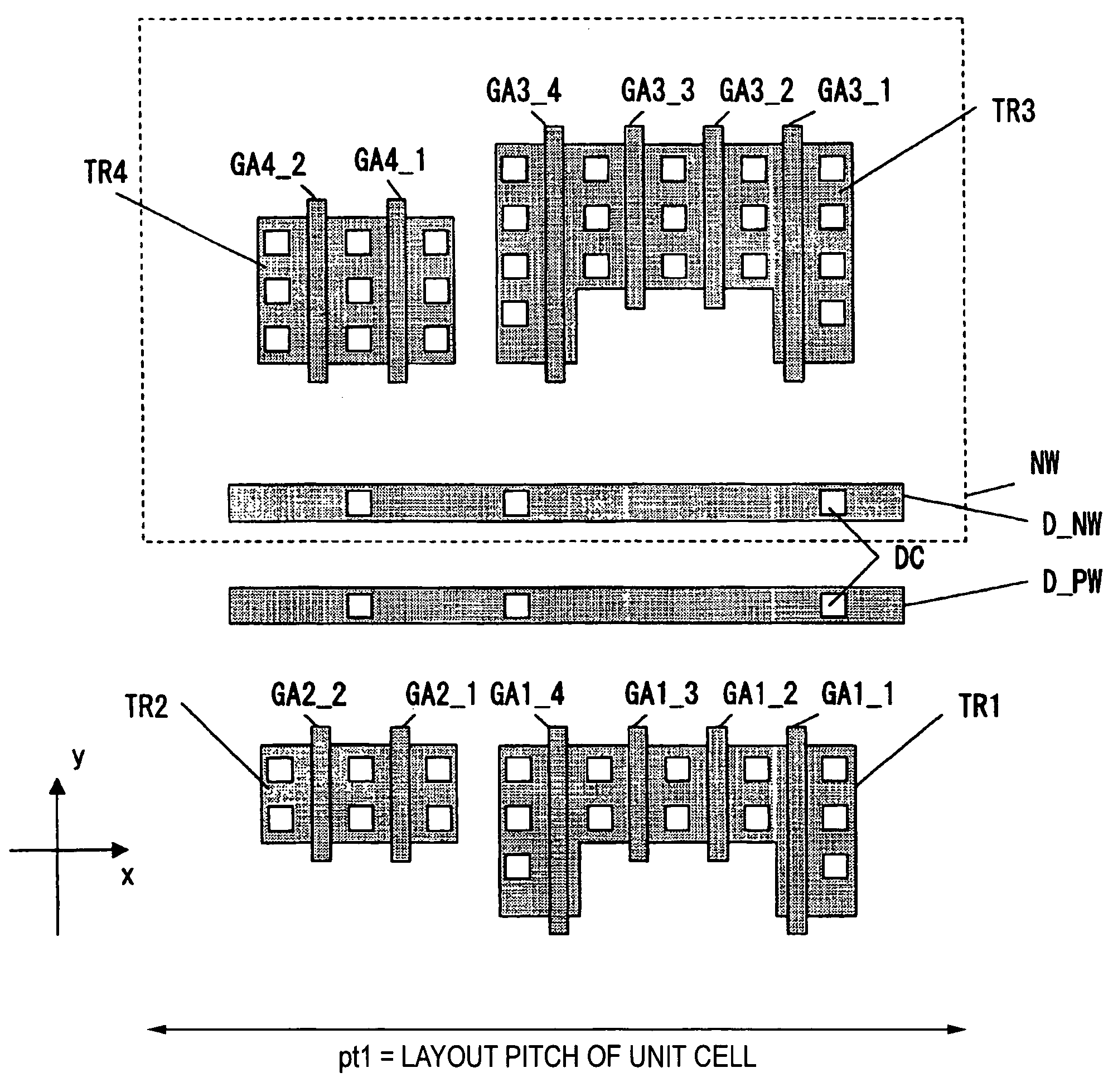

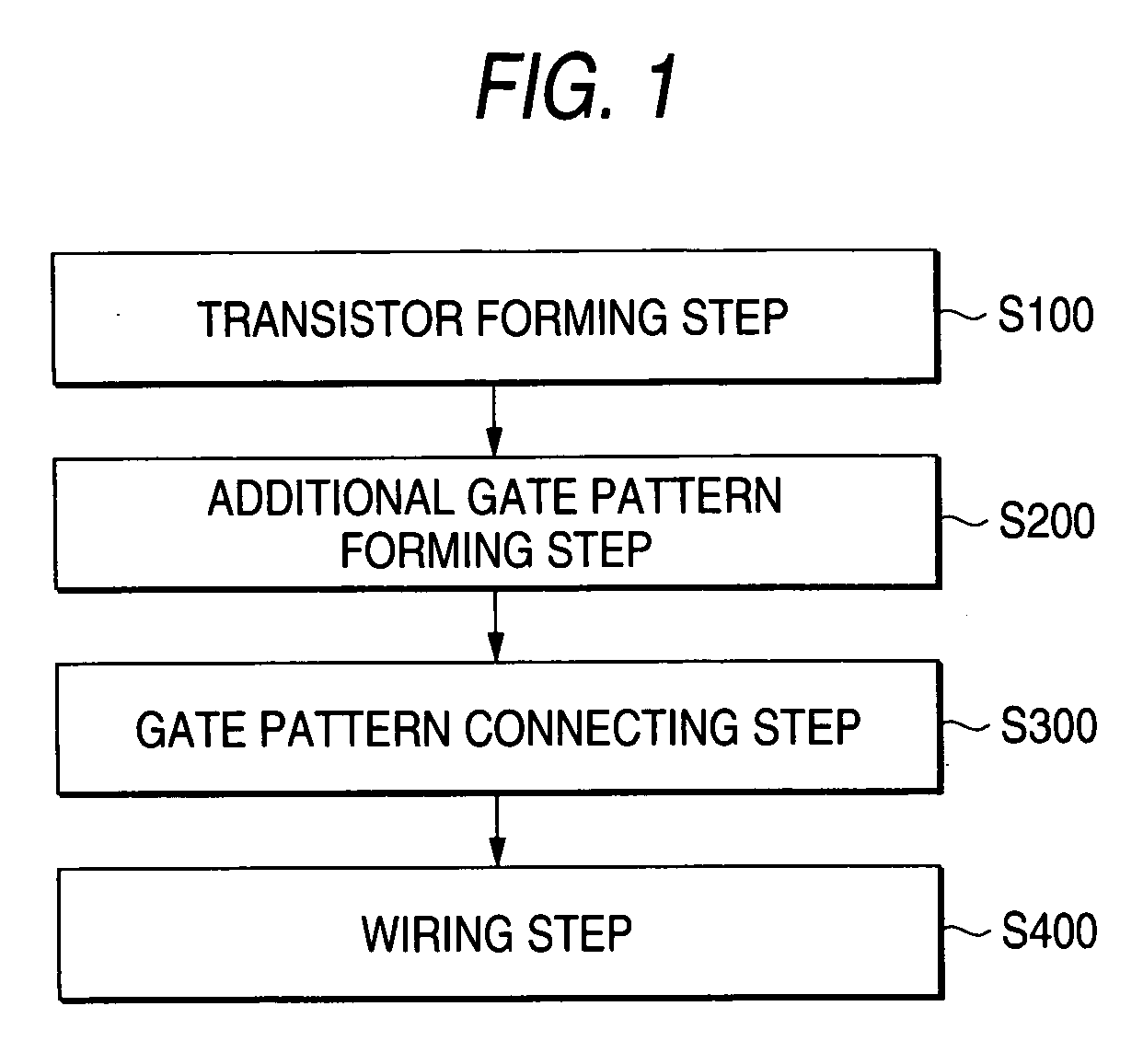

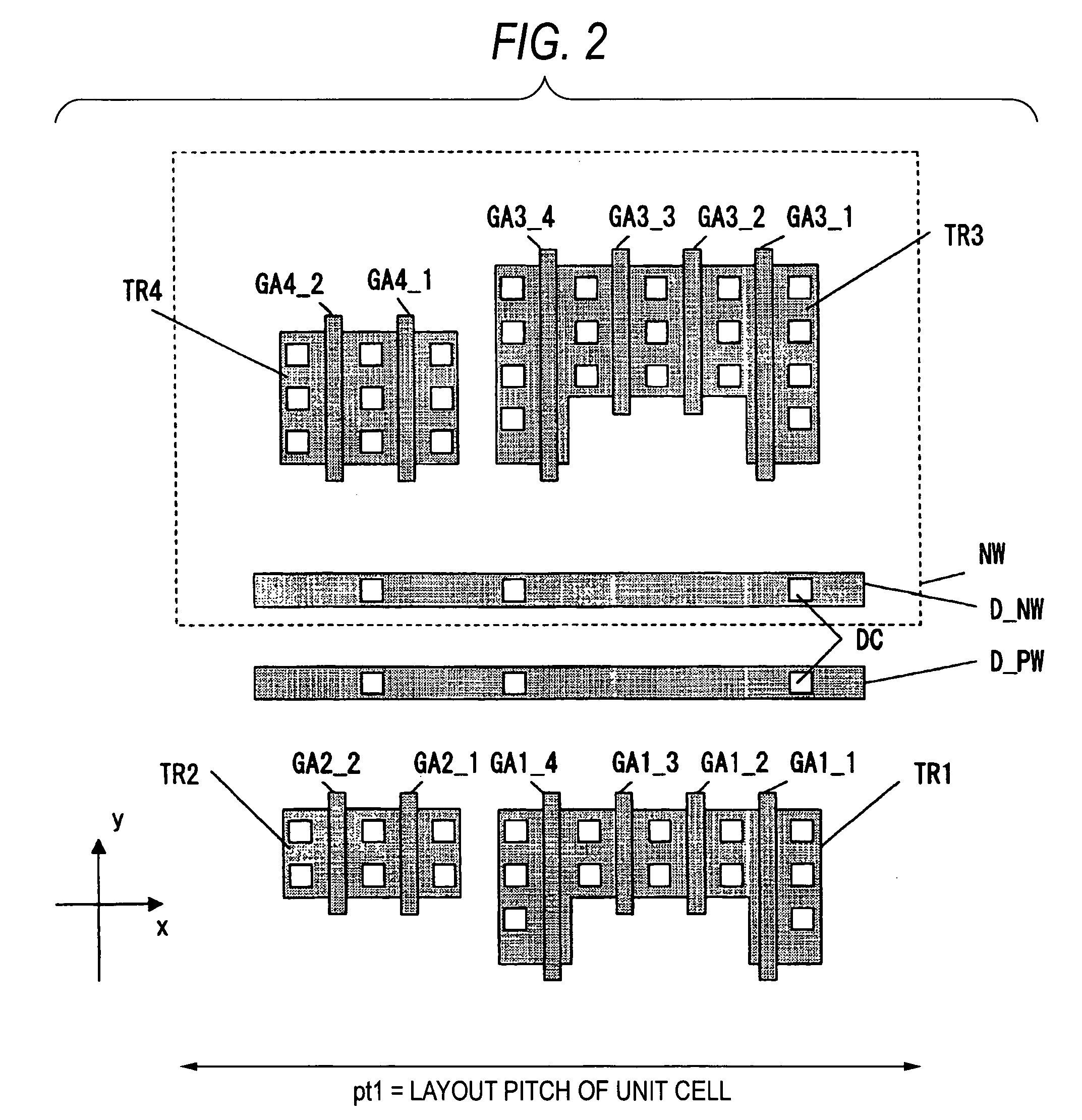

Semiconductor device and layout design method therefor

A layout design method for a semiconductor device includes a step of arranging transistors, a dummy gate forming step of forming dummy gates, which has a shape identical with a shape including gate electrodes or the gate electrodes and projected parts from active regions of the gate electrodes, in positions in parallel with and a fixed distance apart from the gate electrodes arranged at both ends in a gate length direction on active regions of the transistors and, when the transistors have plural gate electrodes with different gate widths, extending the projected parts to the outside of the active regions by a necessary length, a gate connecting step of, when gate patterns and contact regions are connected to the gate electrodes of the transistors, connecting the gate electrodes and the dummy gates according to a positional relation between the gate electrodes and the dummy gates, and a wiring step of wiring a metal layer. It is possible to design a semiconductor device having a smaller area than that in the past and with a less design man-hour.

Owner:SOCIONEXT INC

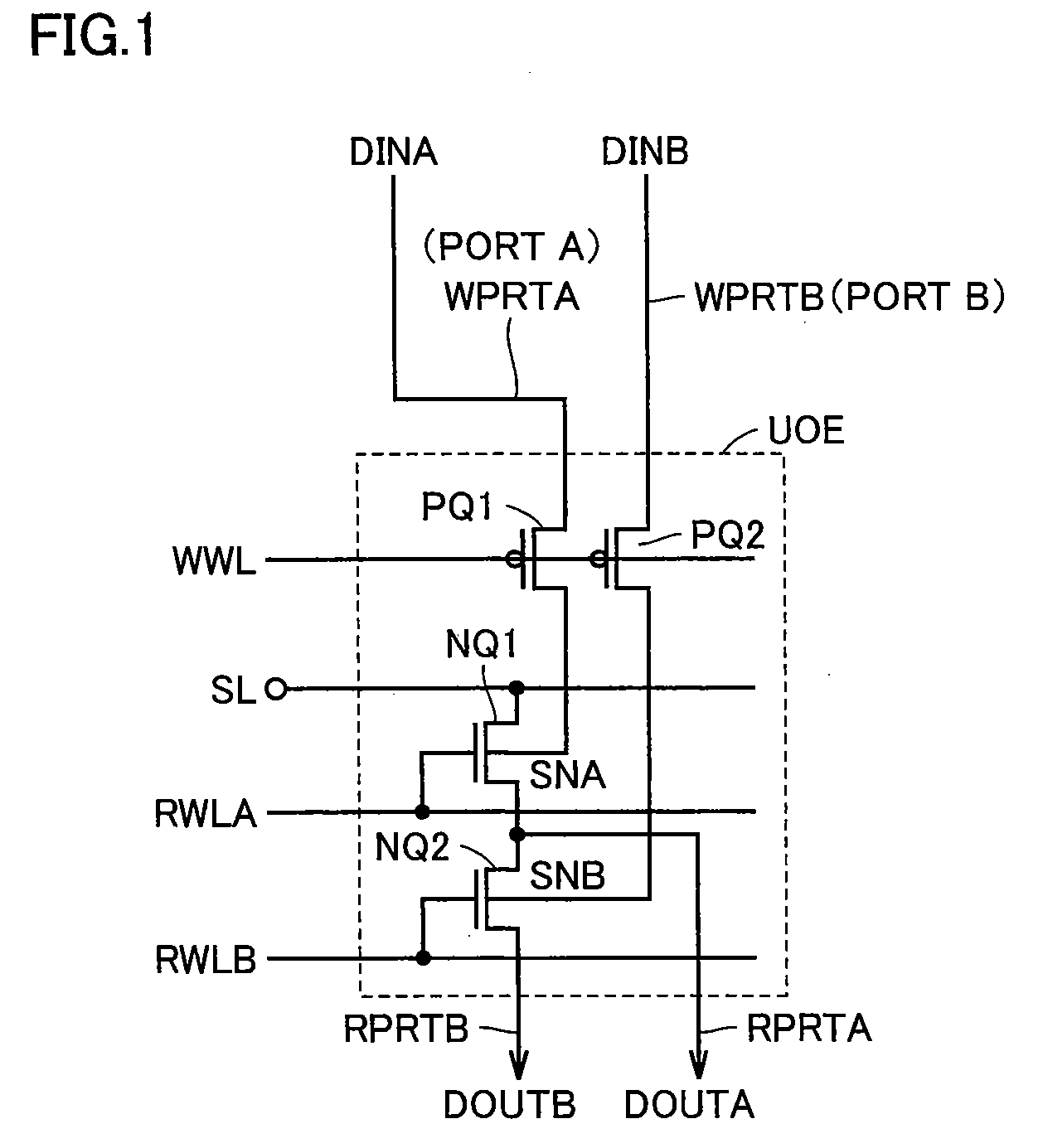

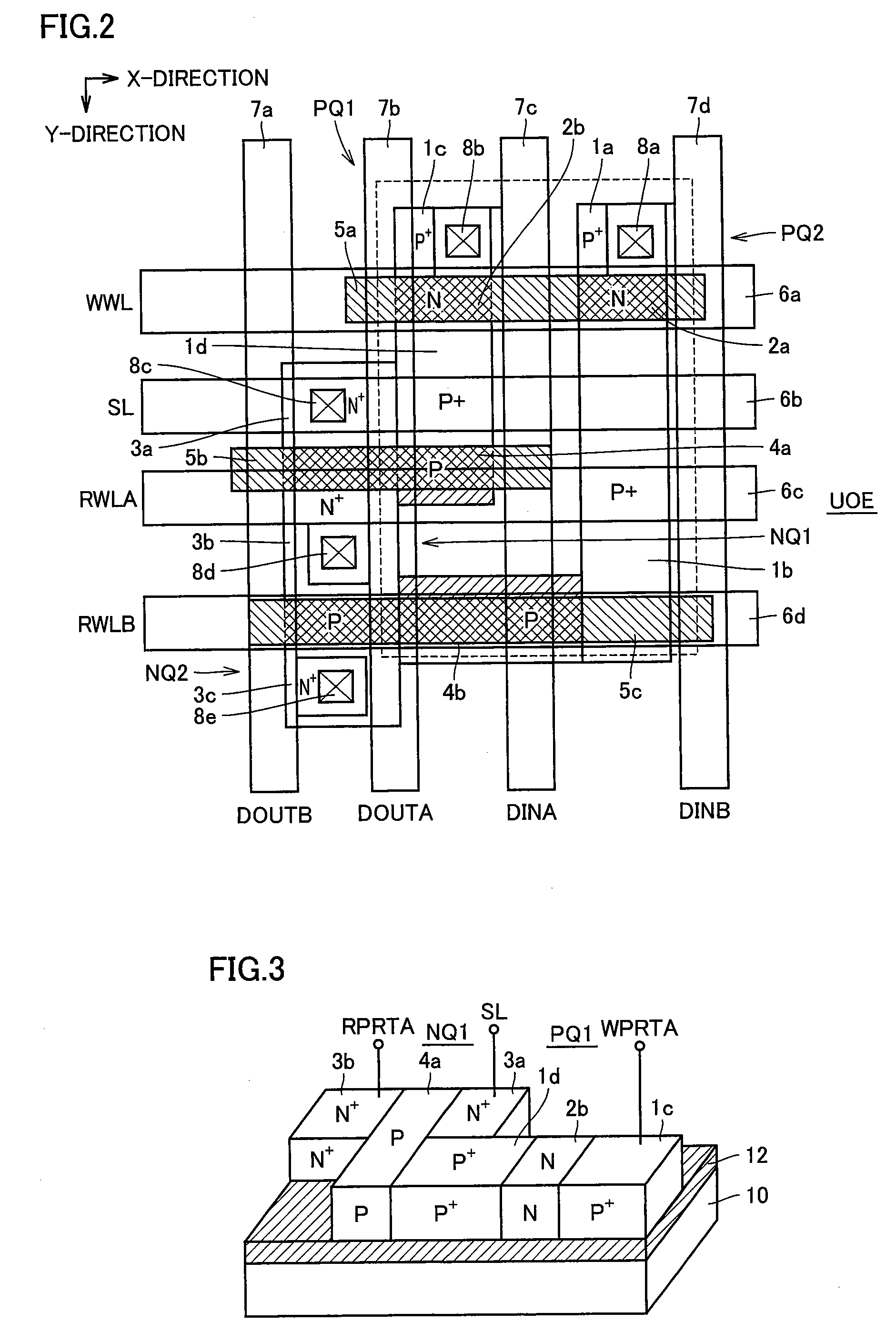

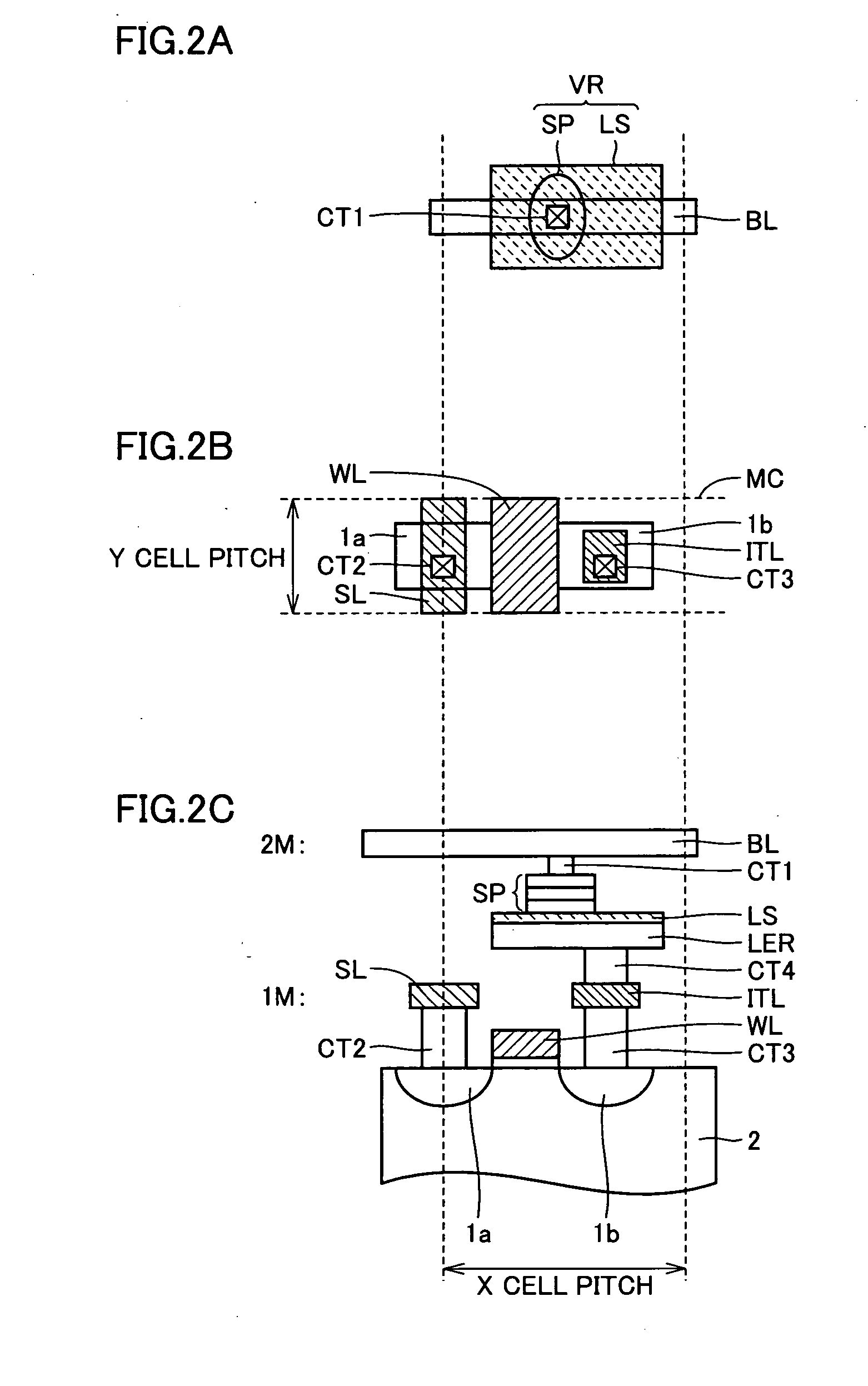

Semiconductor signal processing device

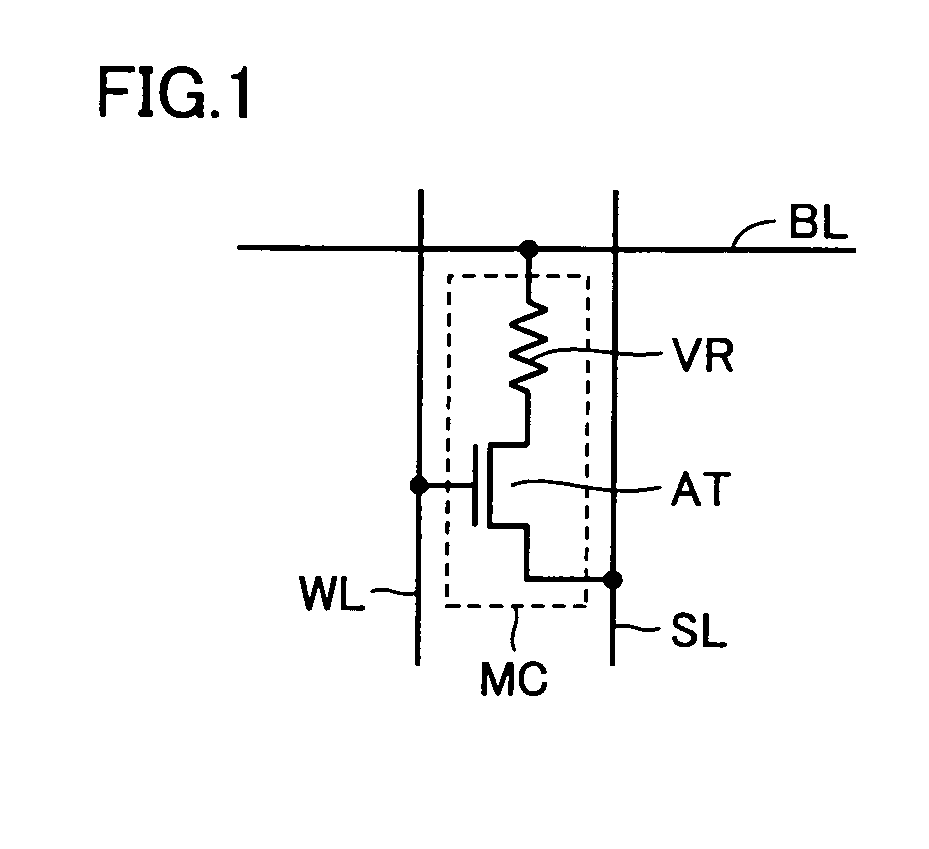

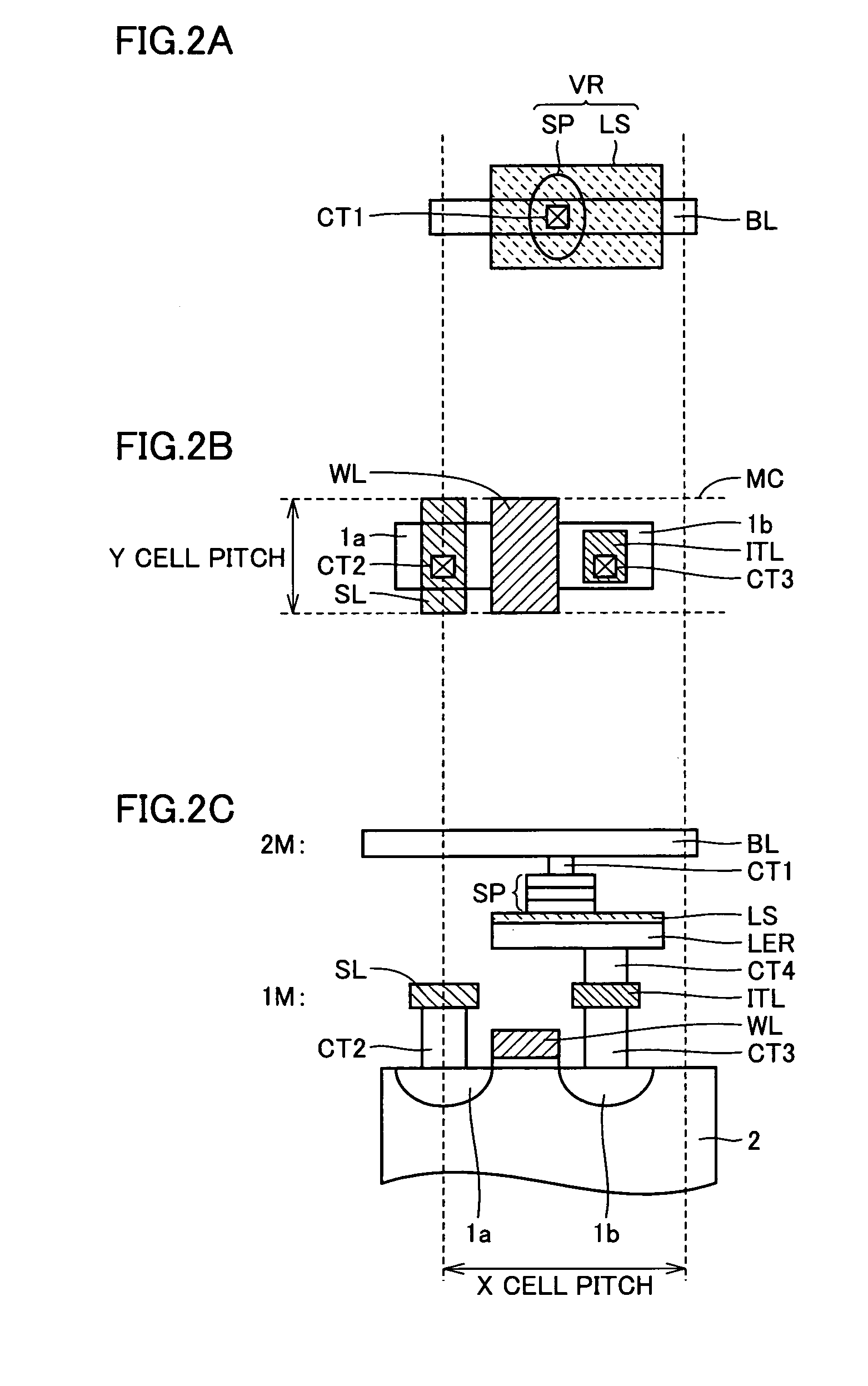

InactiveUS20090207642A1Small footprintIncrease speedSolid-state devicesDigital storageSoftware engineeringData storing

A unit operator cell includes a plurality of SOI (Silicon on Insulator) transistors, write data is stored in a body region of at least two SOI transistors, and the storage SOI transistors are connected in series with each other to a read port or each of the storage SOI transistors is singly connected to the read port. Therefore, an AND operation result or a NOT operation result of data stored in the unit operator cells can be obtained, and operation processing can be performed only by writing and reading data. A semiconductor signal processing device that can perform logic operation processing and arithmetic operation processing at high speed is implemented with low power consumption and a small occupation area.

Owner:RENESAS ELECTRONICS CORP

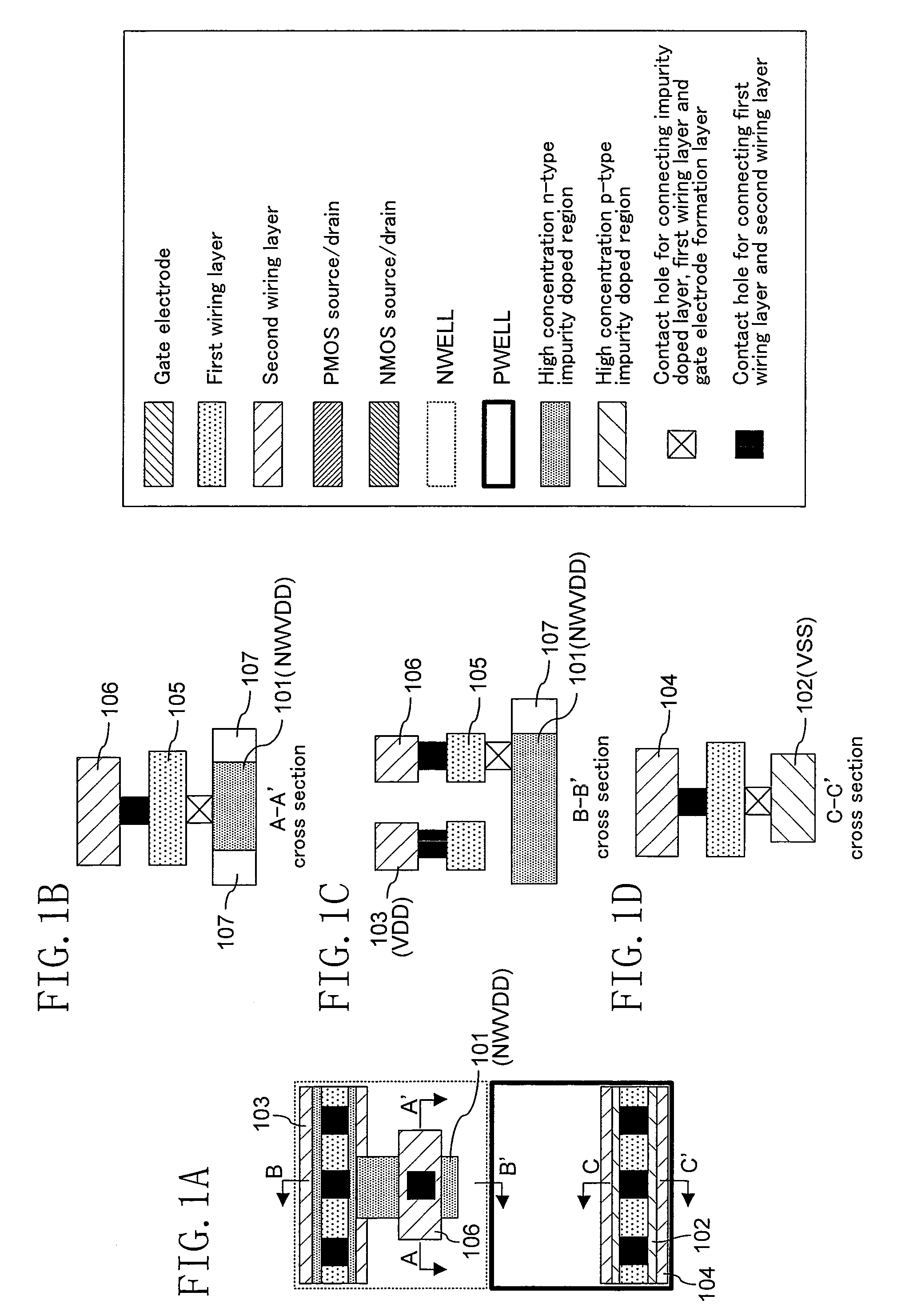

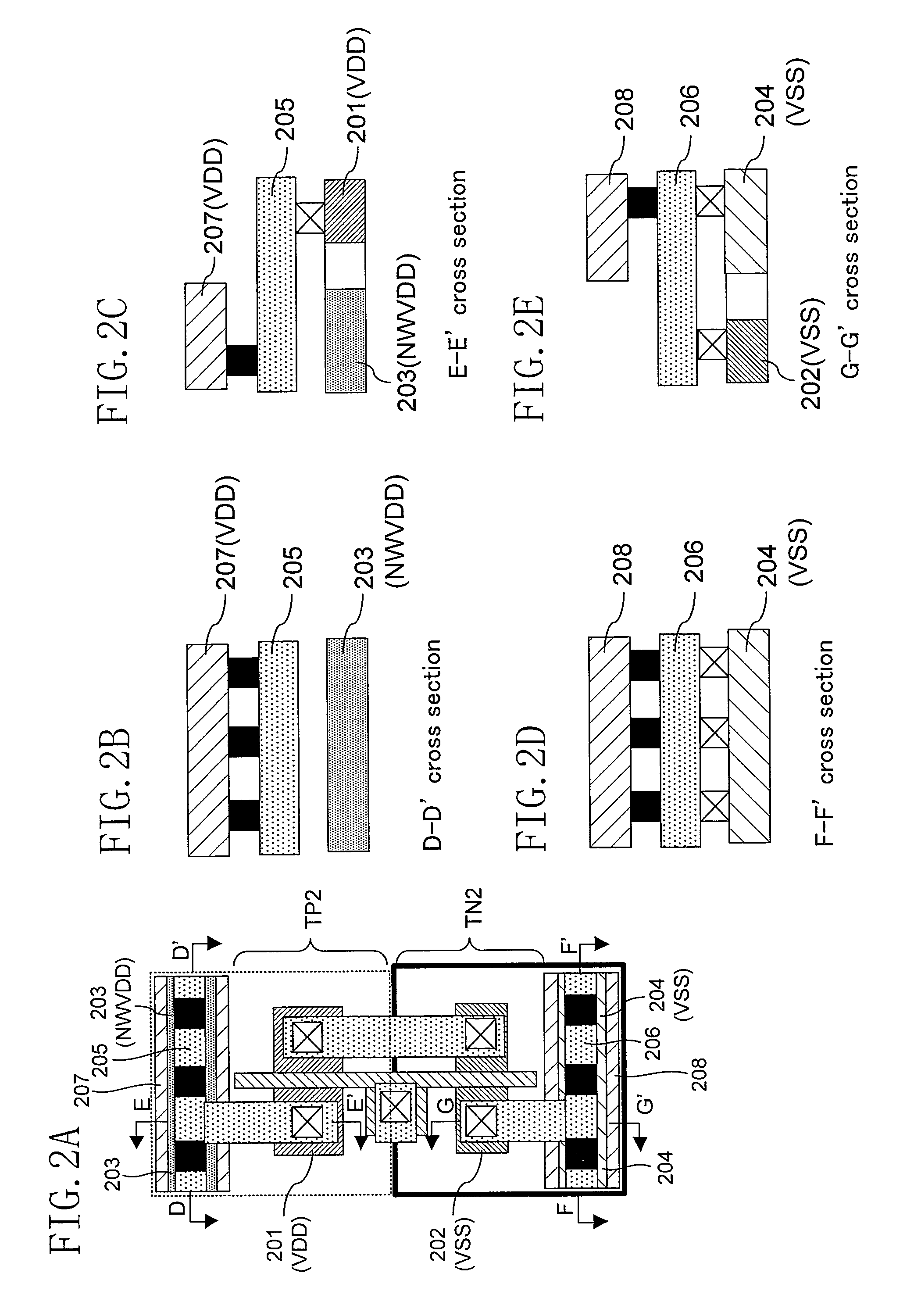

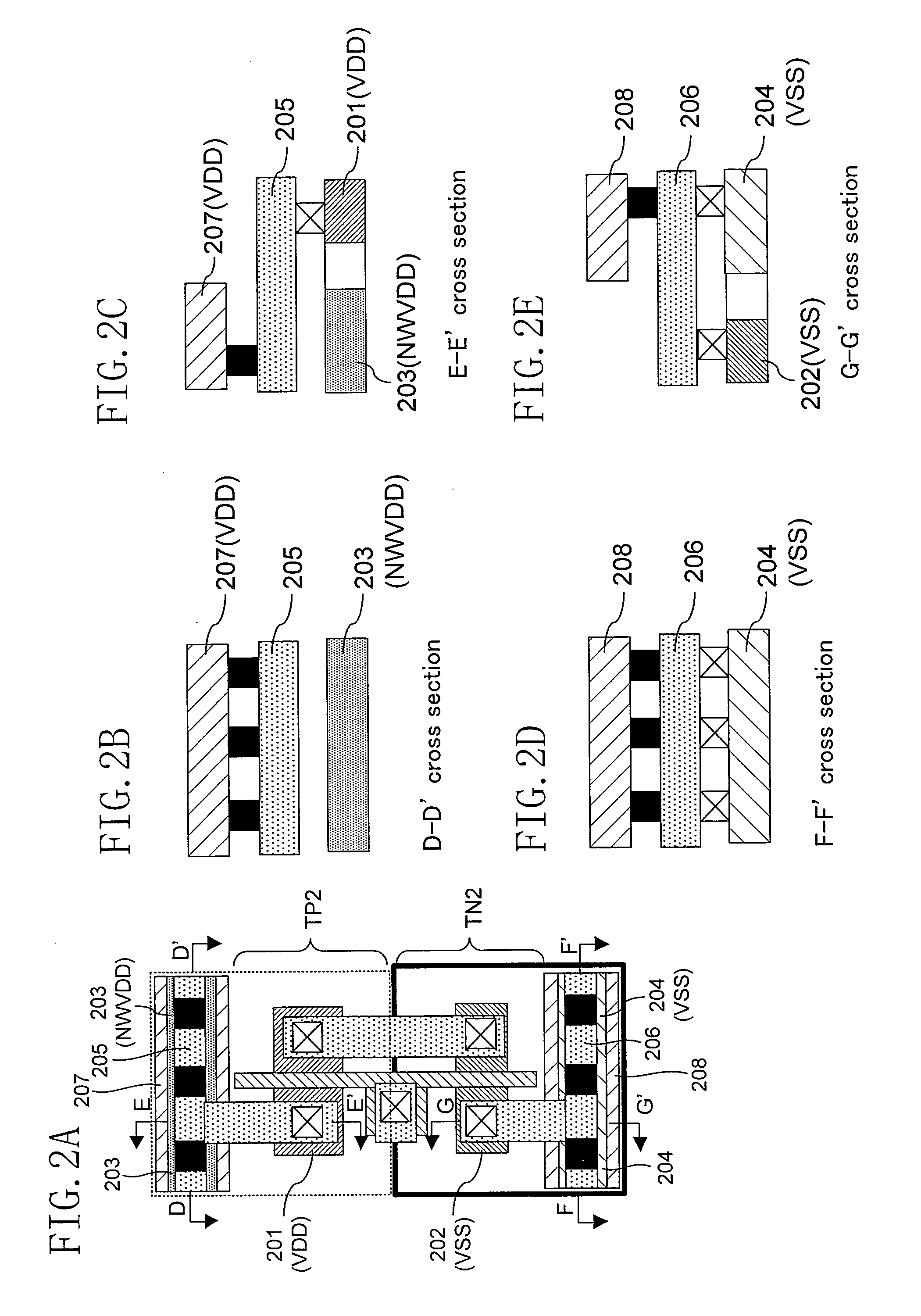

Layout structure of semiconductor device

InactiveUS8178905B2Reduce layout areaTransistorSemiconductor/solid-state device detailsElectricityPositive power

In a layout structure capable of independent supply of a substrate or well potential from a power supply potential, further reduction in layout area is achieved. A reinforcing power supply cell is inserted in a cell line in which a plurality of cells are arranged in series. Each of the cells includes an impurity doped region for supplying a substrate or well potential NWVDD which is different from a positive power supply potential VDD to a p-type transistor arranging region. The reinforcing power supply cell includes a power supply impurity doped region to which an impurity doped region of an adjacent cell is electrically connected and a power supply wire provided in a wiring layer formed above the power supply impurity doped region and electrically connected to the power supply impurity doped region.

Owner:SOCIONEXT INC

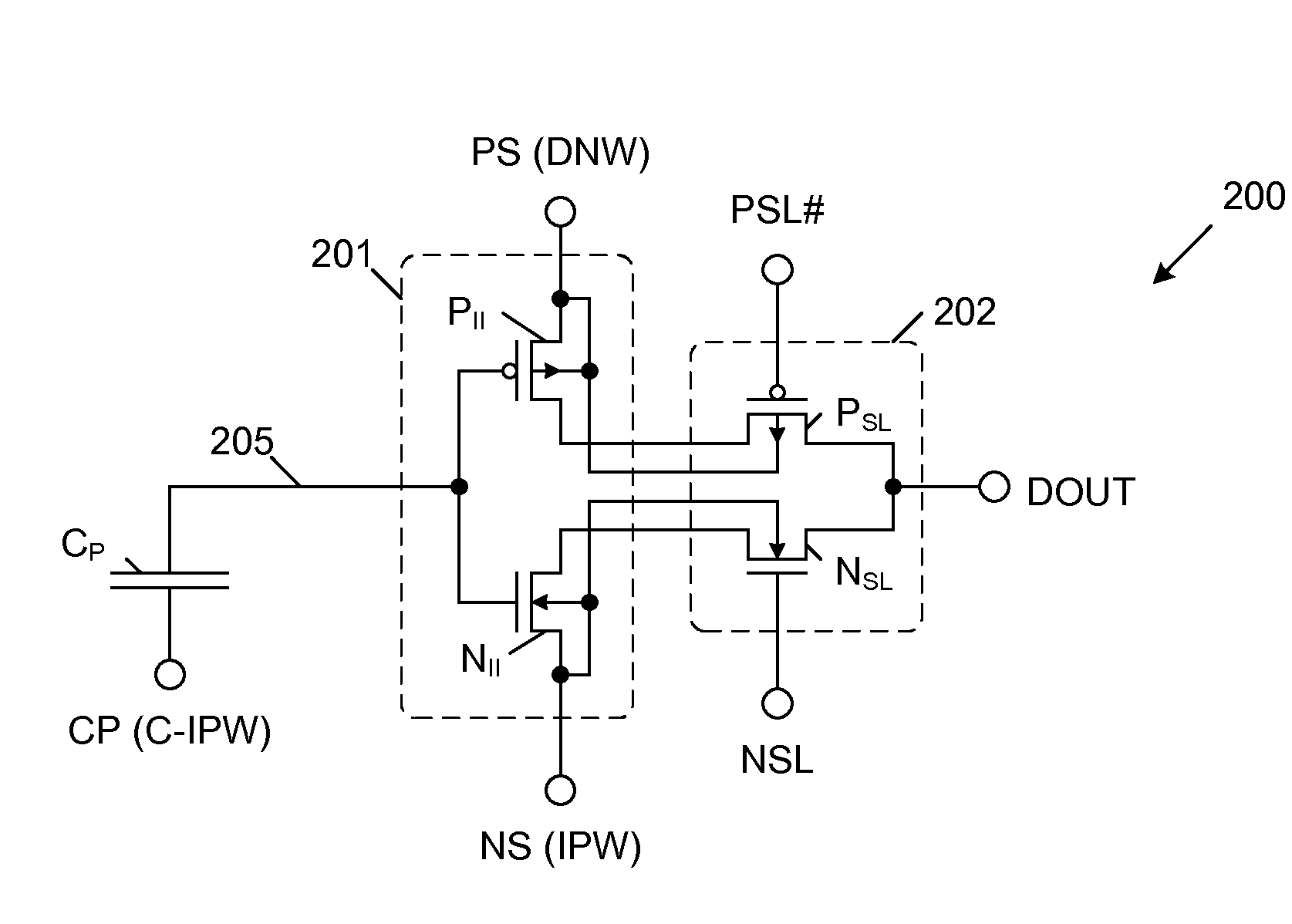

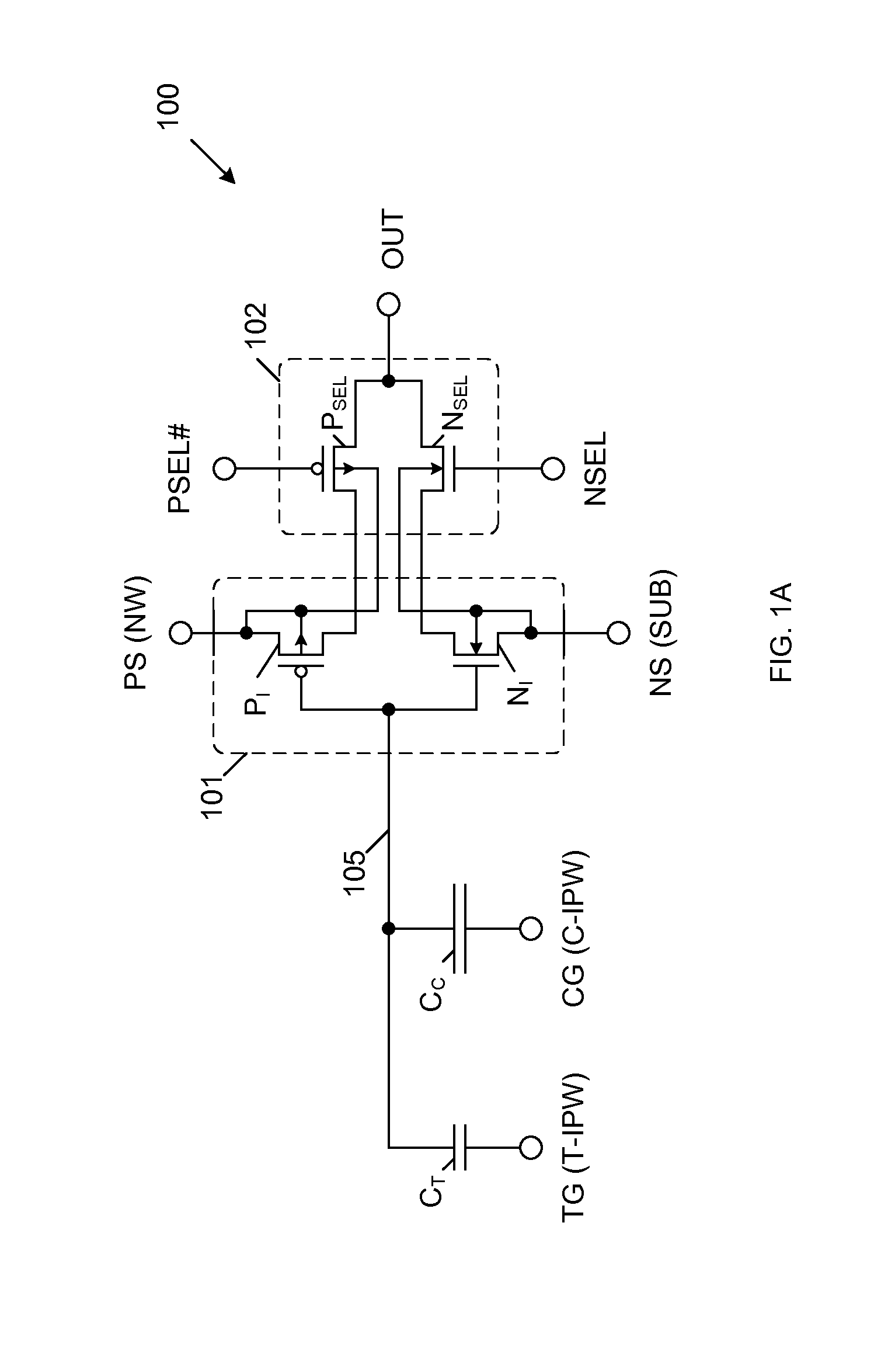

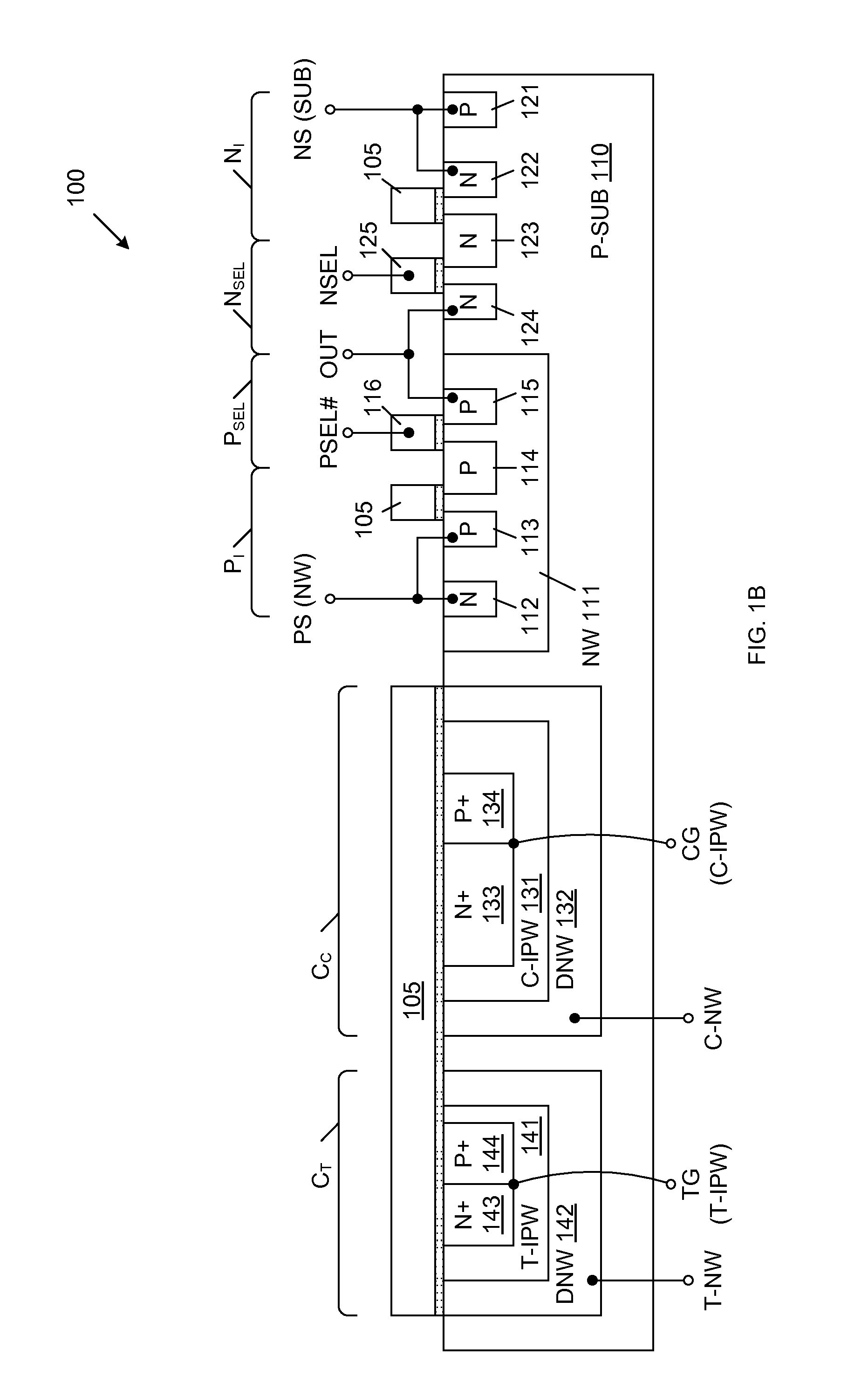

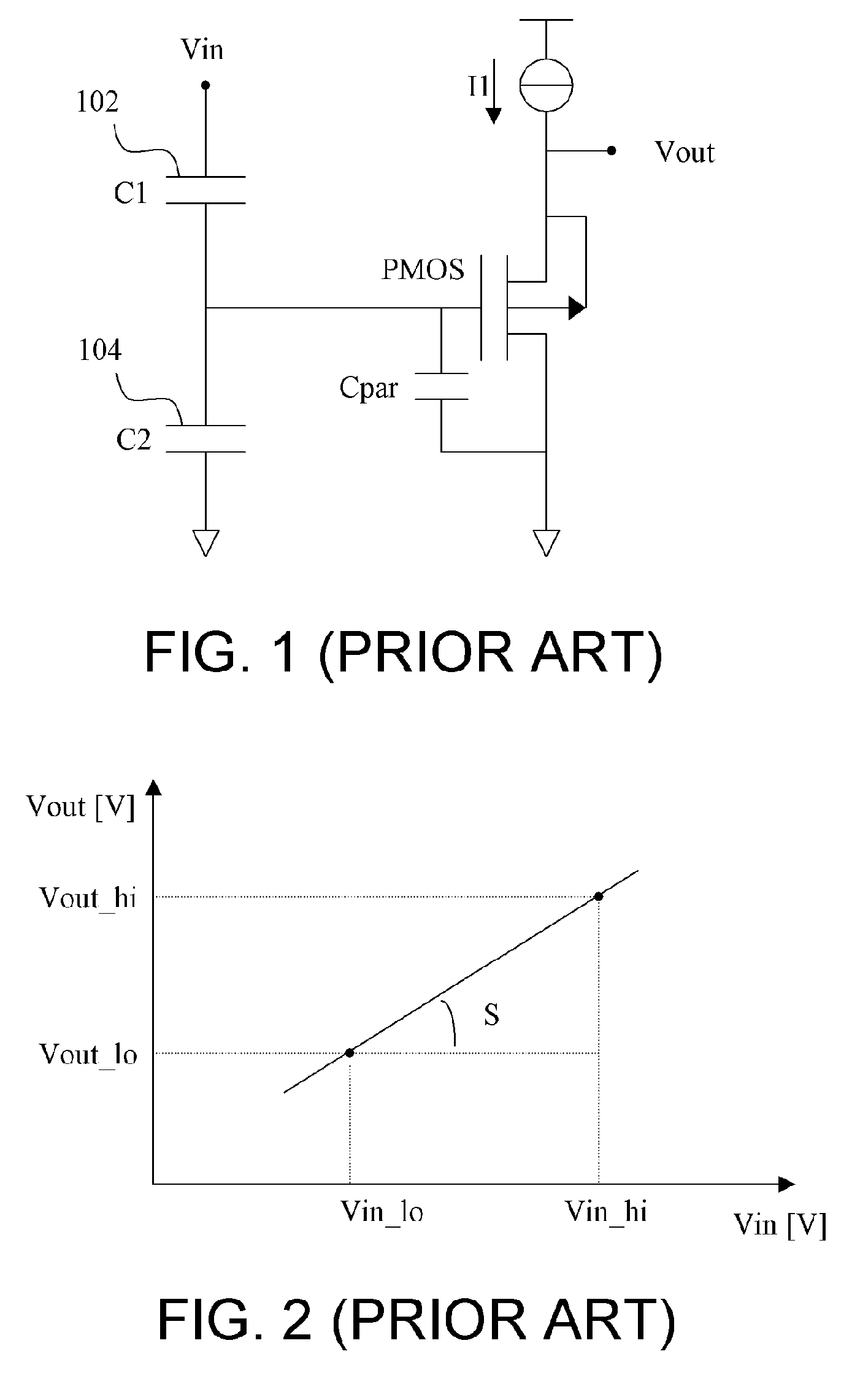

Floating Gate Inverter Type Memory Cell And Array

ActiveUS20100157669A1Optimize layoutReduce layout areaTransistorSolid-state devicesCMOSFowler nordheim

A non-volatile memory (NVM) cell and array includes a control capacitor, tunneling capacitor, CMOS inverter and output circuit. The CMOS inverter includes PMOS and NMOS inverter transistors. The control capacitor, tunneling capacitor and PMOS and NMOS inverter transistors share a common floating gate, which is programmed / erased by Fowler-Nordheim tunneling. The output circuit includes PMOS and NMOS select transistors. The PMOS inverter and select transistors share a common source / drain region. Similarly, the NMOS inverter and select transistors share a common source / drain region. This configuration minimizes the required layout area of the non-volatile memory cell and allows design of arrays with smaller footprints. Alternately, the tunneling capacitor may be excluded, further reducing the required layout area of the NVM cell. In this case, the NMOS inverter transistor functions as a tunneling capacitor for programming and erasing the cell, and the PMOS inverter transistor functions as a tunneling capacitor for erasing the cell.

Owner:TOWER SEMICONDUCTOR

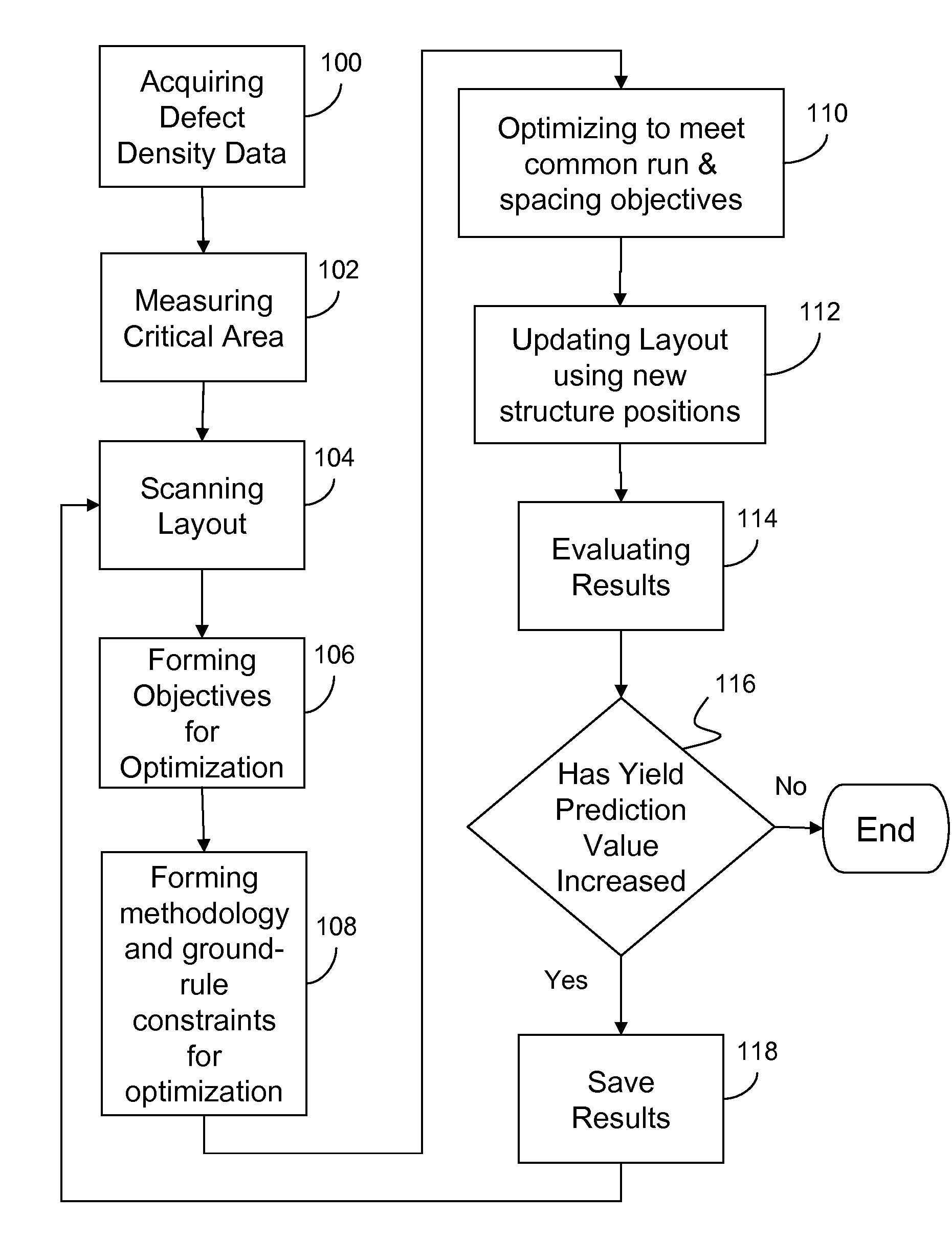

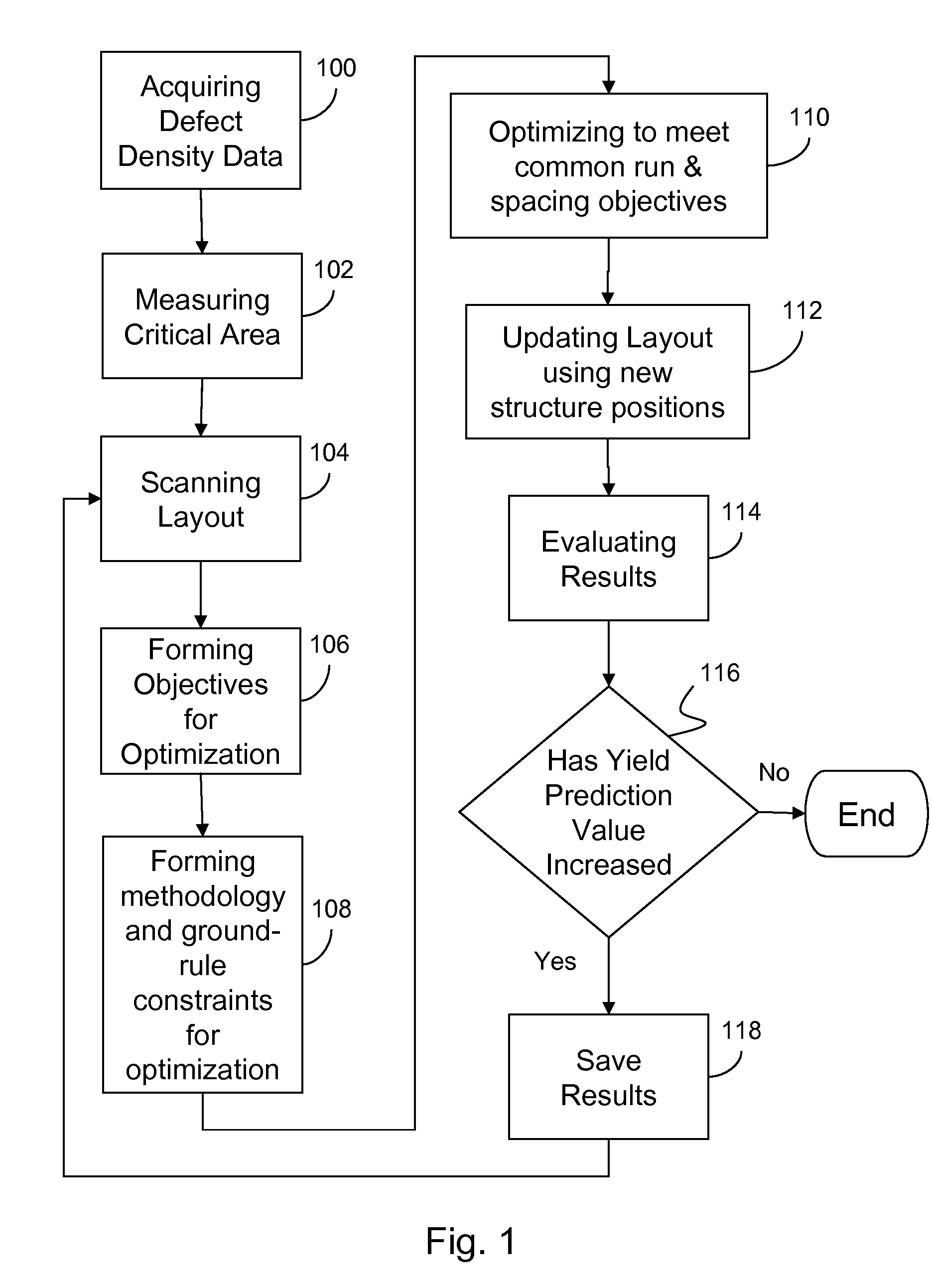

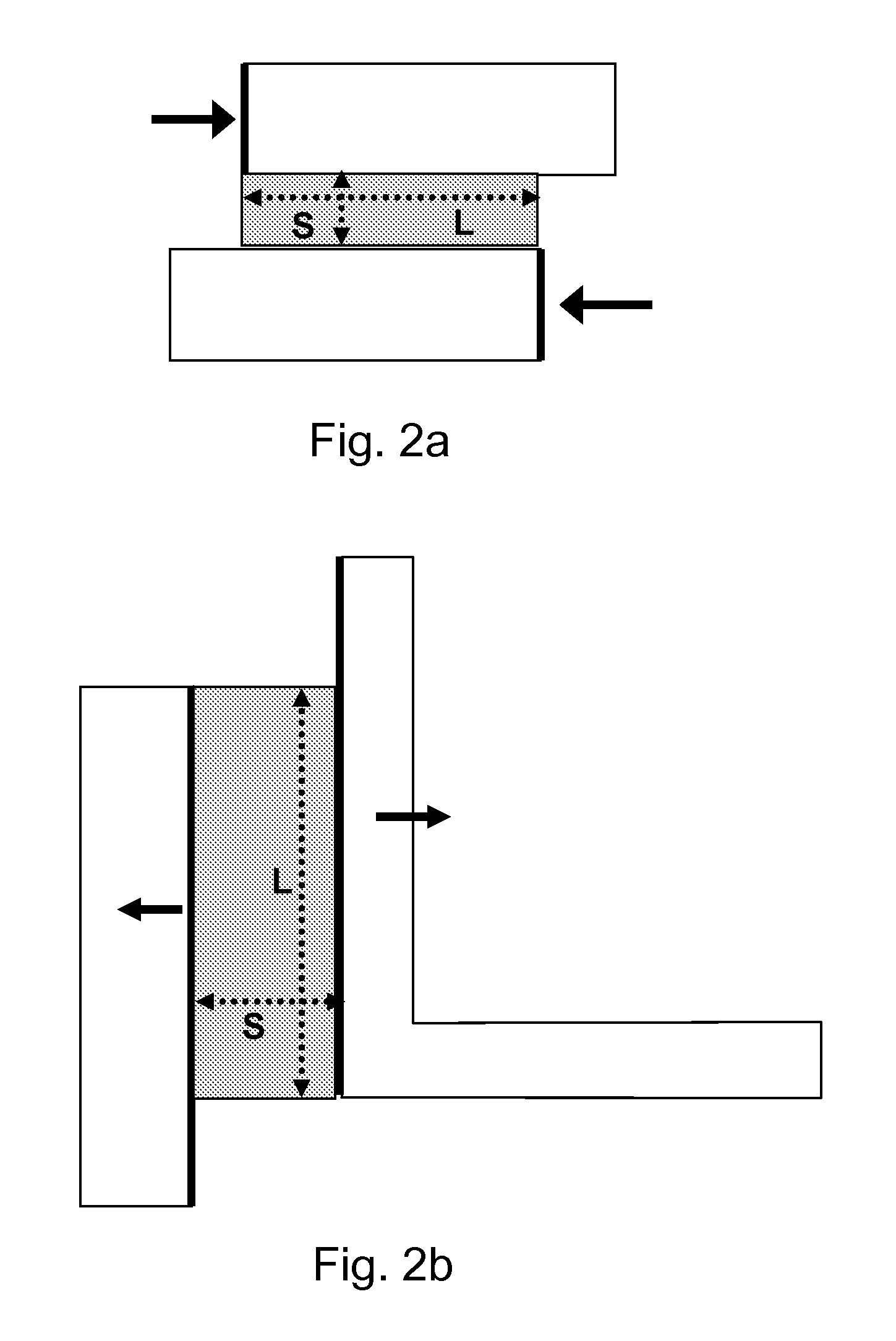

IC layout optimization to improve yield

InactiveUS7503020B2Low costReduce layout areaCAD circuit designSoftware simulation/interpretation/emulationHigh probabilityManufacturing data

A method of and service for optimizing an integrated circuit design to improve manufacturing yield. The invention uses manufacturing data and algorithms to identify areas with high probability of failures, i.e. critical areas. The invention further changes the layout of the circuit design to reduce critical area thereby reducing the probability of a fault occurring during manufacturing. Methods of identifying critical area include common run, geometry mapping, and Voronoi diagrams. Optimization includes but is not limited to incremental movement and adjustment of shape dimensions until optimization objectives are achieved and critical area is reduced.

Owner:GLOBALFOUNDRIES INC

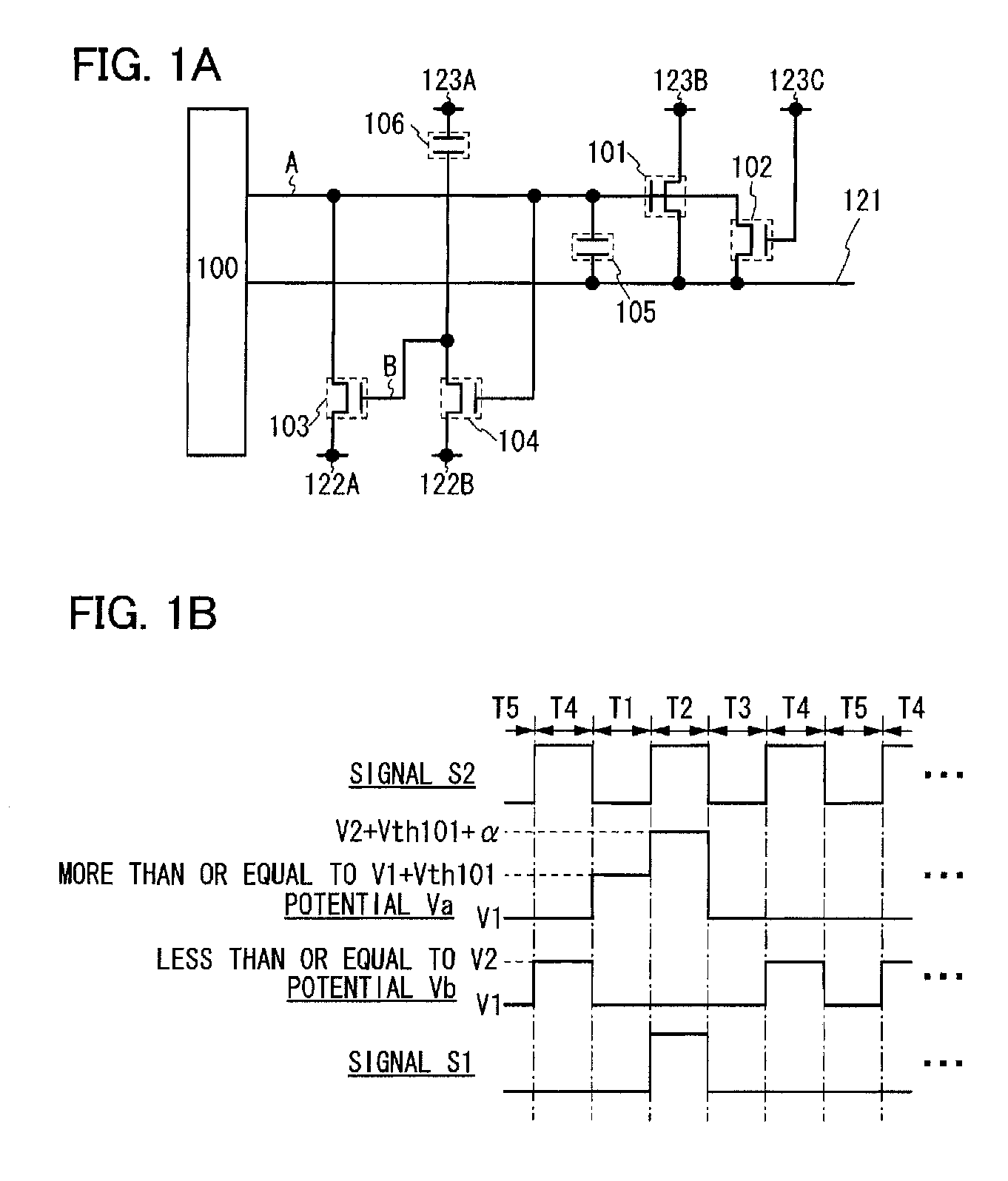

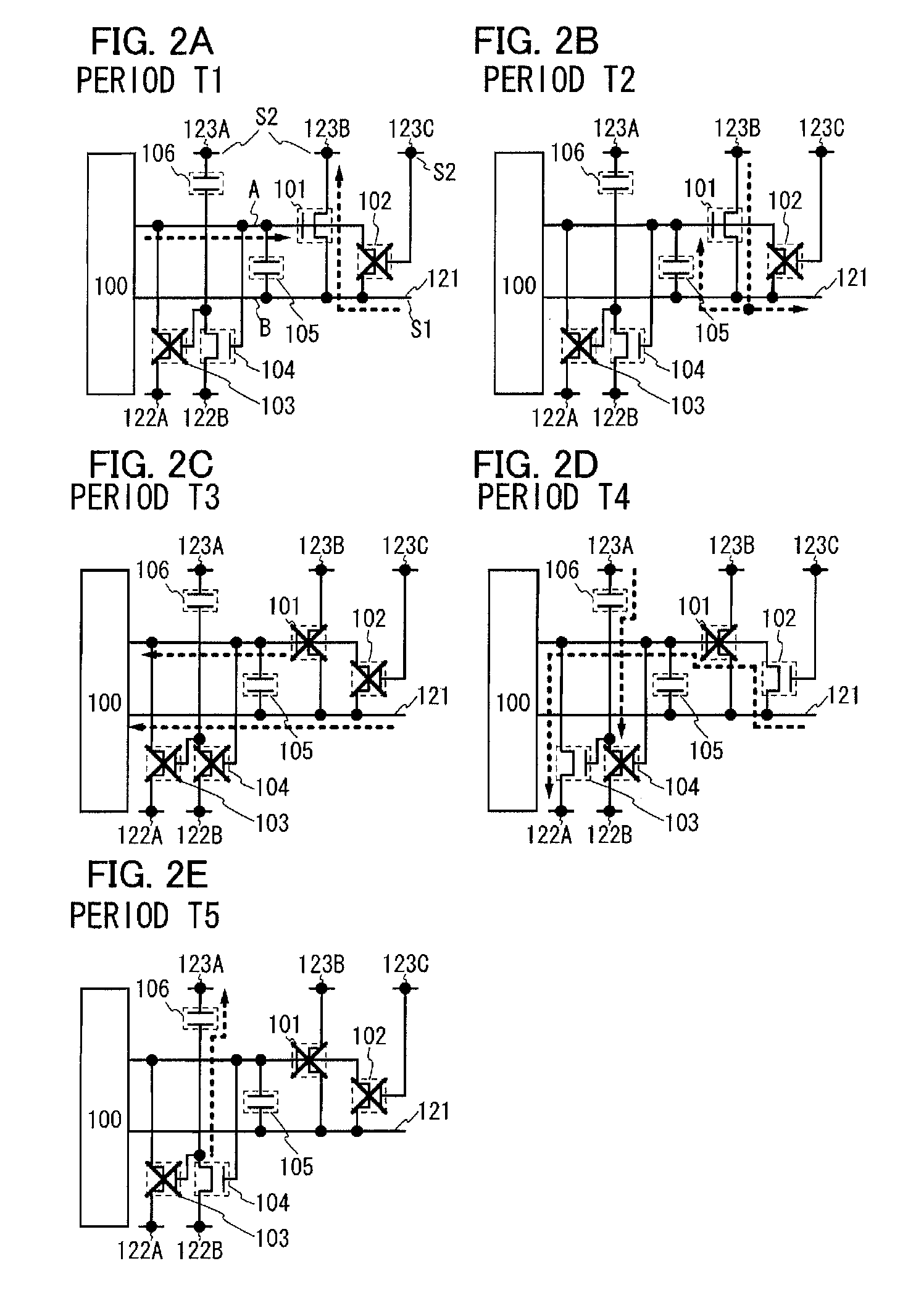

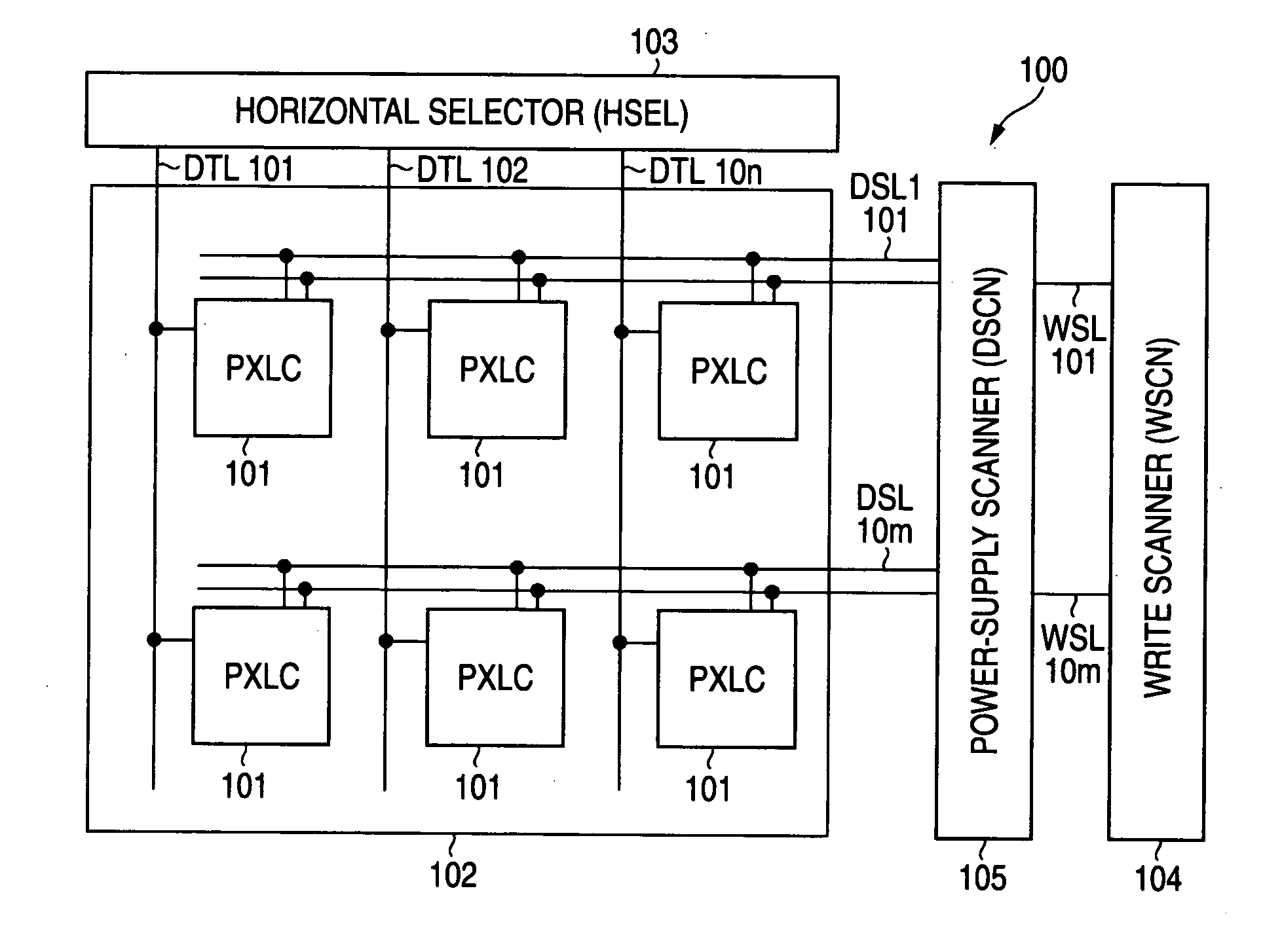

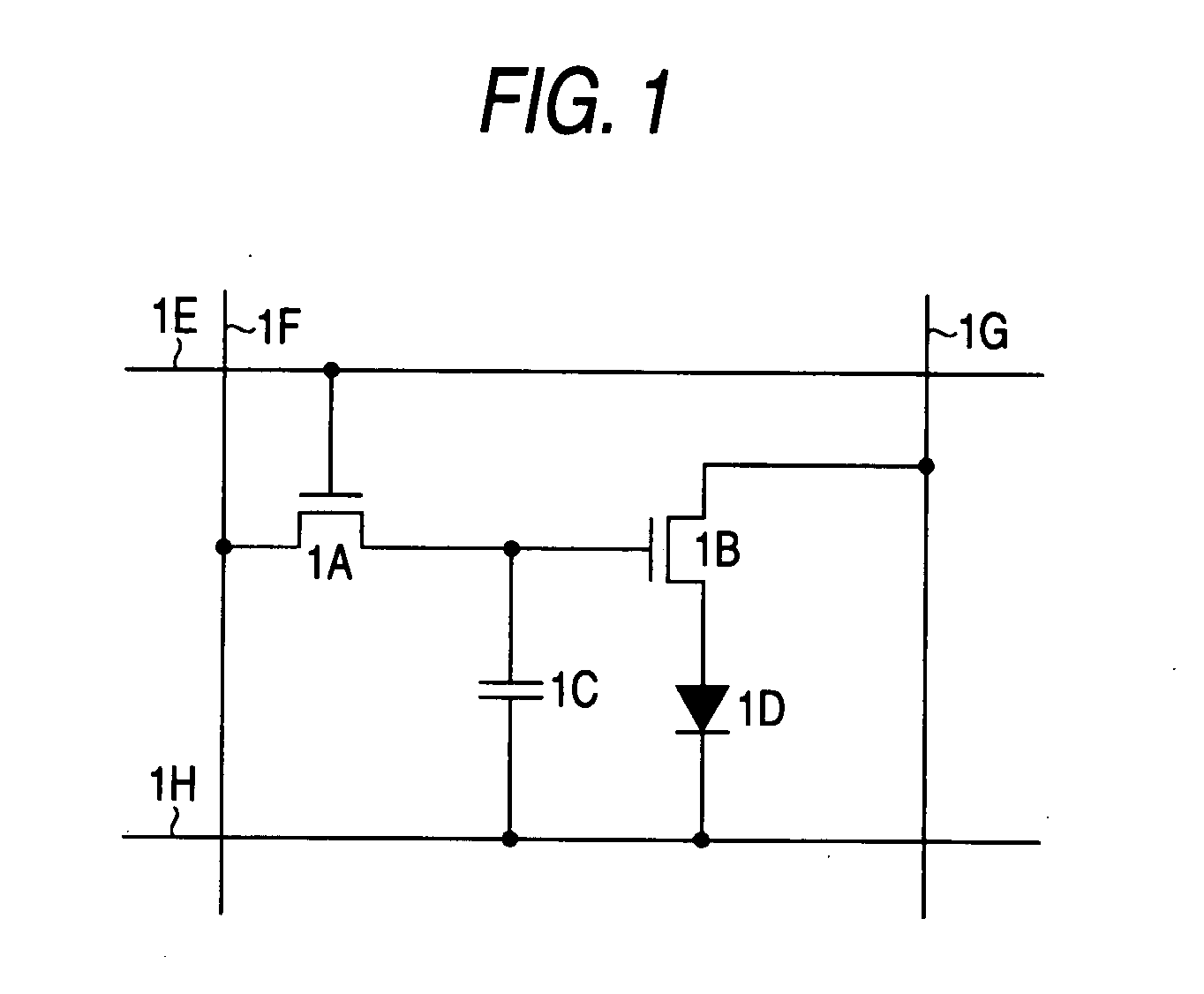

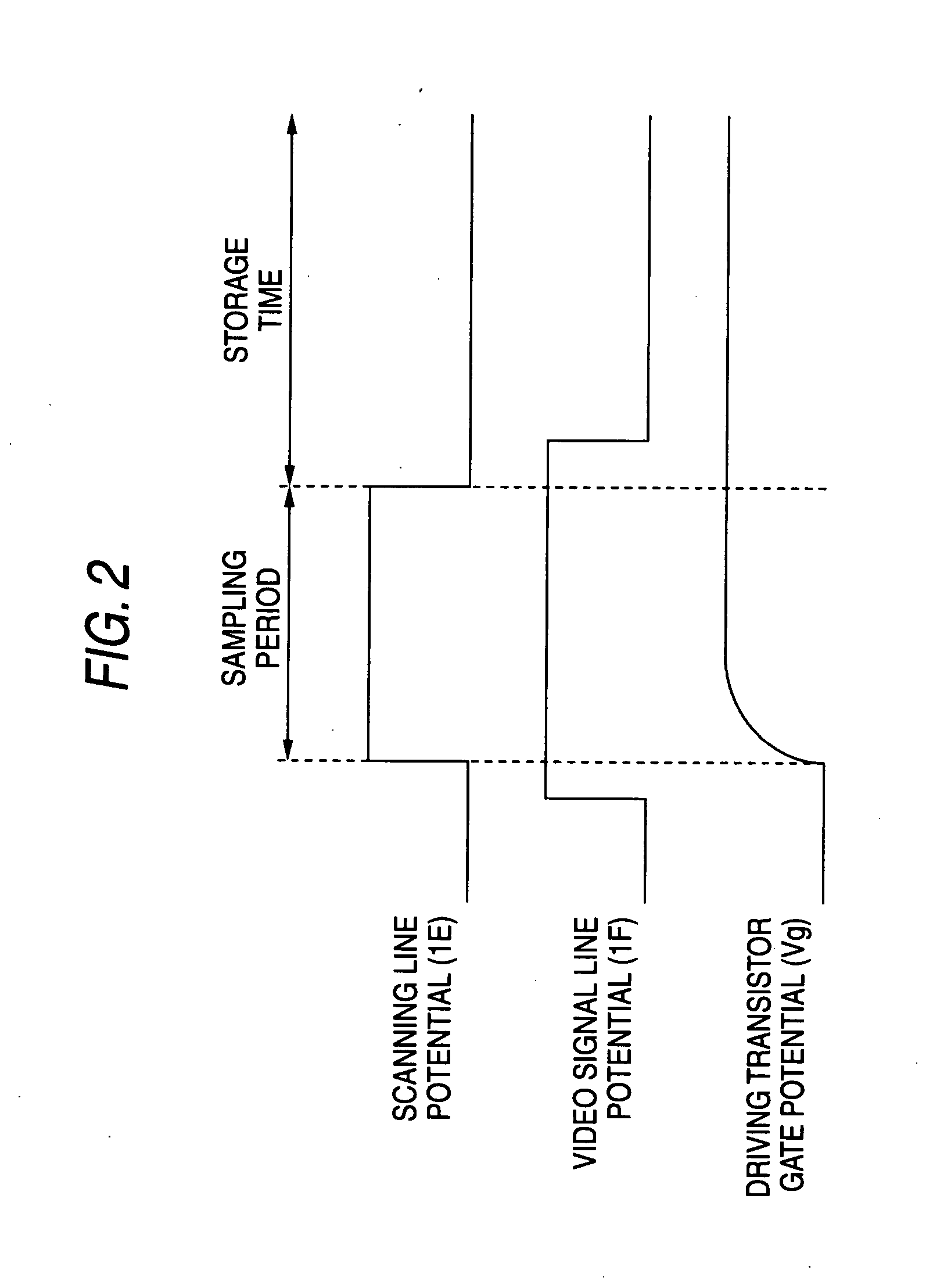

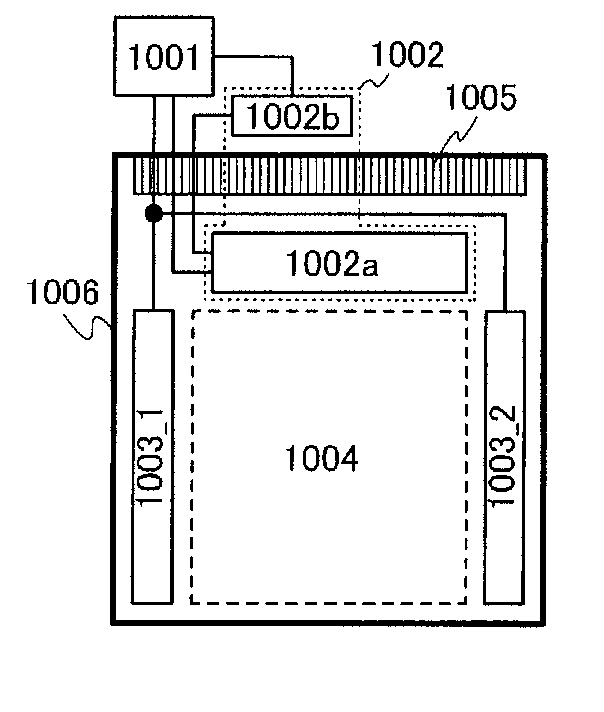

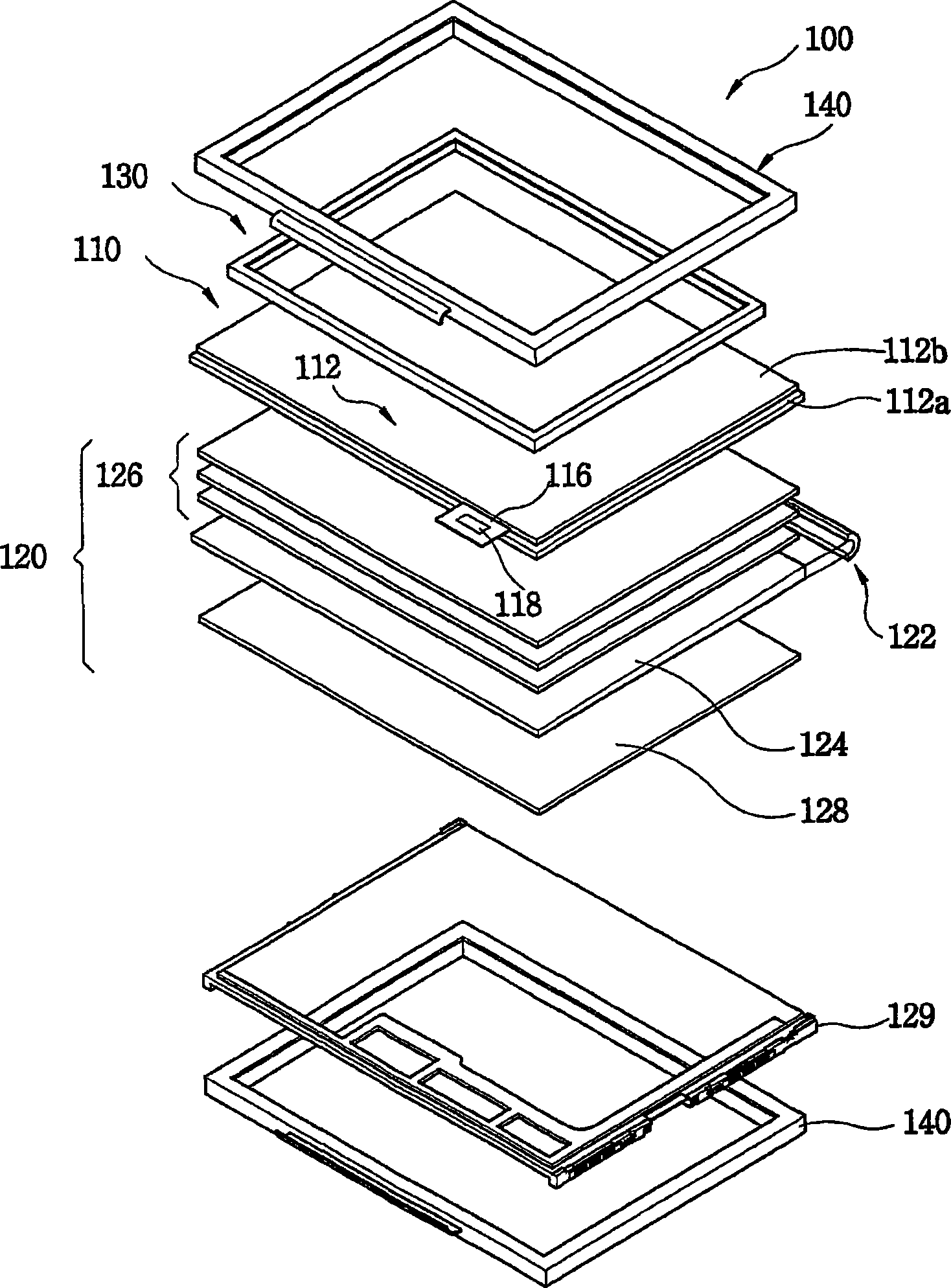

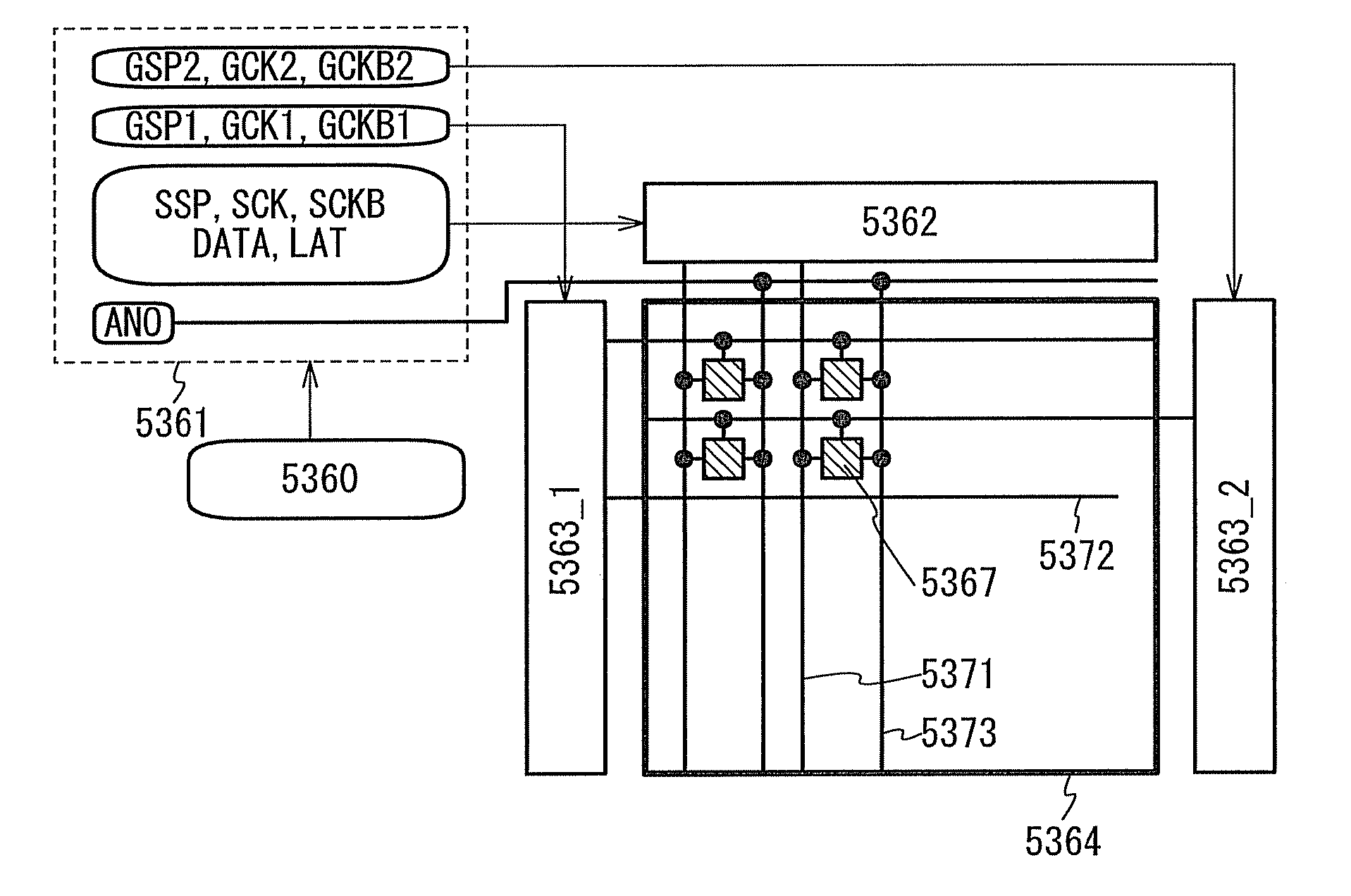

Display device, method of driving same, and electonic device

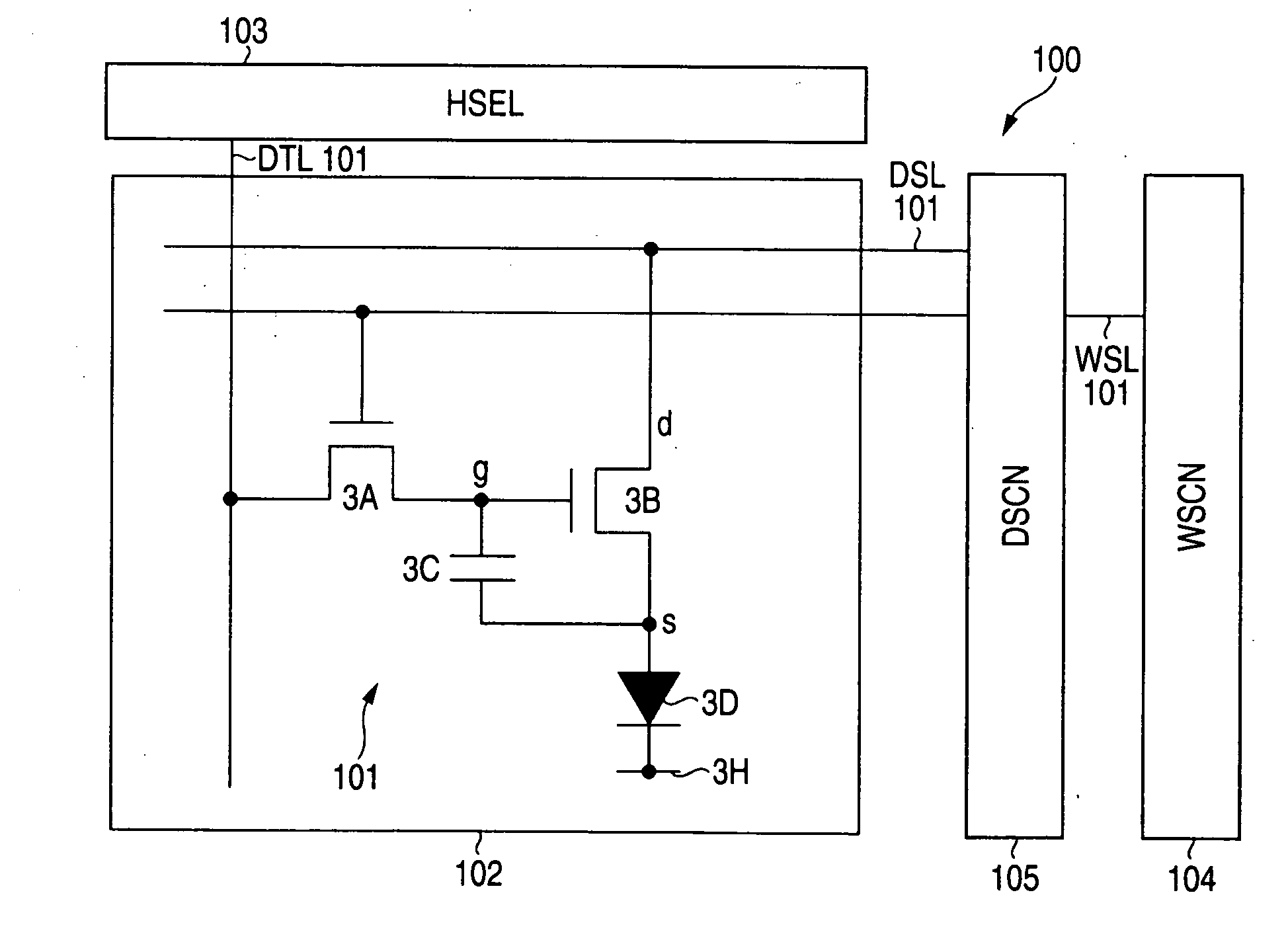

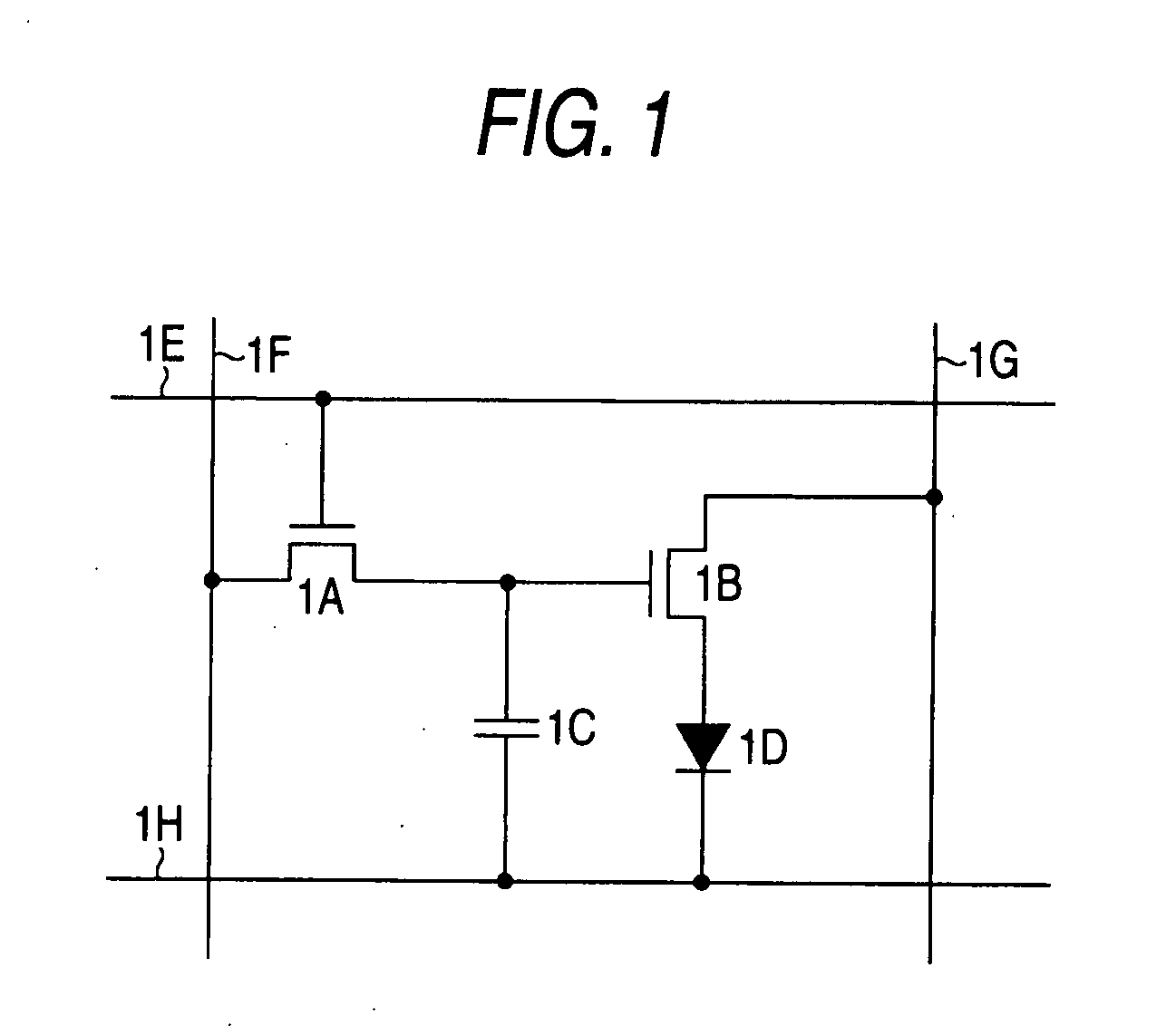

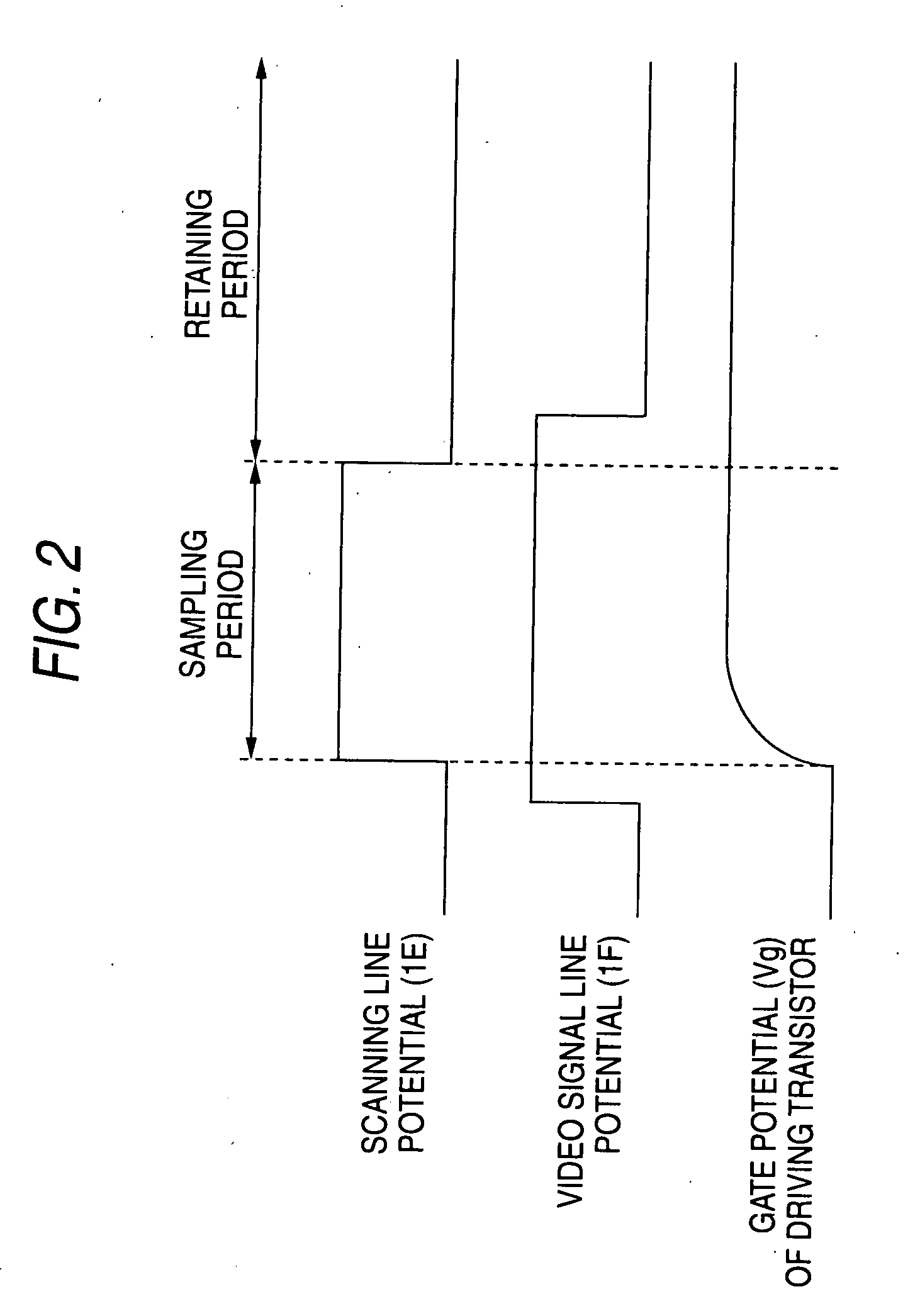

ActiveUS20080030436A1Increase the number ofIncrease display resolutionElectrical apparatusElectroluminescent light sourcesComputer hardwareScan line

A display device is disclosed. The display device includes: a pixel array portion and a driver portion for driving the pixel array portion. The pixel array portion has rows of scanning lines, columns of signal lines, pixels arranged in rows and columns at intersections of the scanning lines and the signal lines, and power lines disposed in a corresponding manner to the rows of the pixels. The driver portion includes a main scanner, a power-supply scanner, and a signal selector. Each of the pixels includes light-emitting devices, a sampling transistor, a driving transistor, a retaining capacitor.

Owner:JOLED INC

Display device and electronic device including the same

ActiveUS20100134396A1Reduce in quantityReduce parasitic capacitanceTransistorStatic indicating devicesDisplay deviceCapacitor

It is an object to decrease the number of transistors connected to a capacitor. In a structure, a capacitor and one transistor are included, one electrode of the capacitor is connected to a wiring, and the other electrode of the capacitor is connected to a gate of the transistor. Since a clock signal is input to the wiring, the clock signal is input to the gate of the transistor through the capacitor. Then, on / off of the transistor is controlled by a signal which synchronizes with the clock signal, so that a period when the transistor is on and a period when the transistor is off are repeated. In this manner, deterioration of the transistor can be suppressed.

Owner:SEMICON ENERGY LAB CO LTD

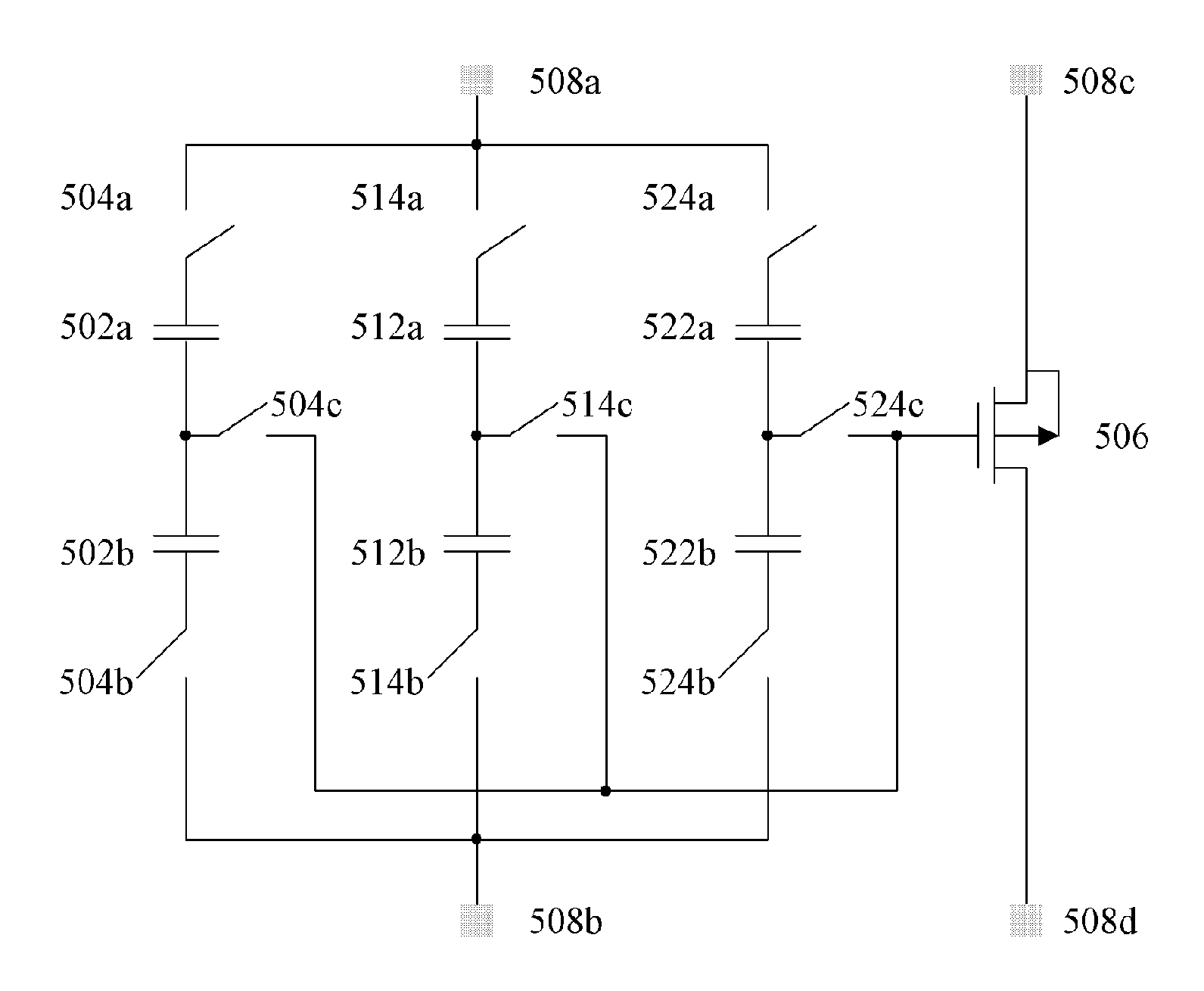

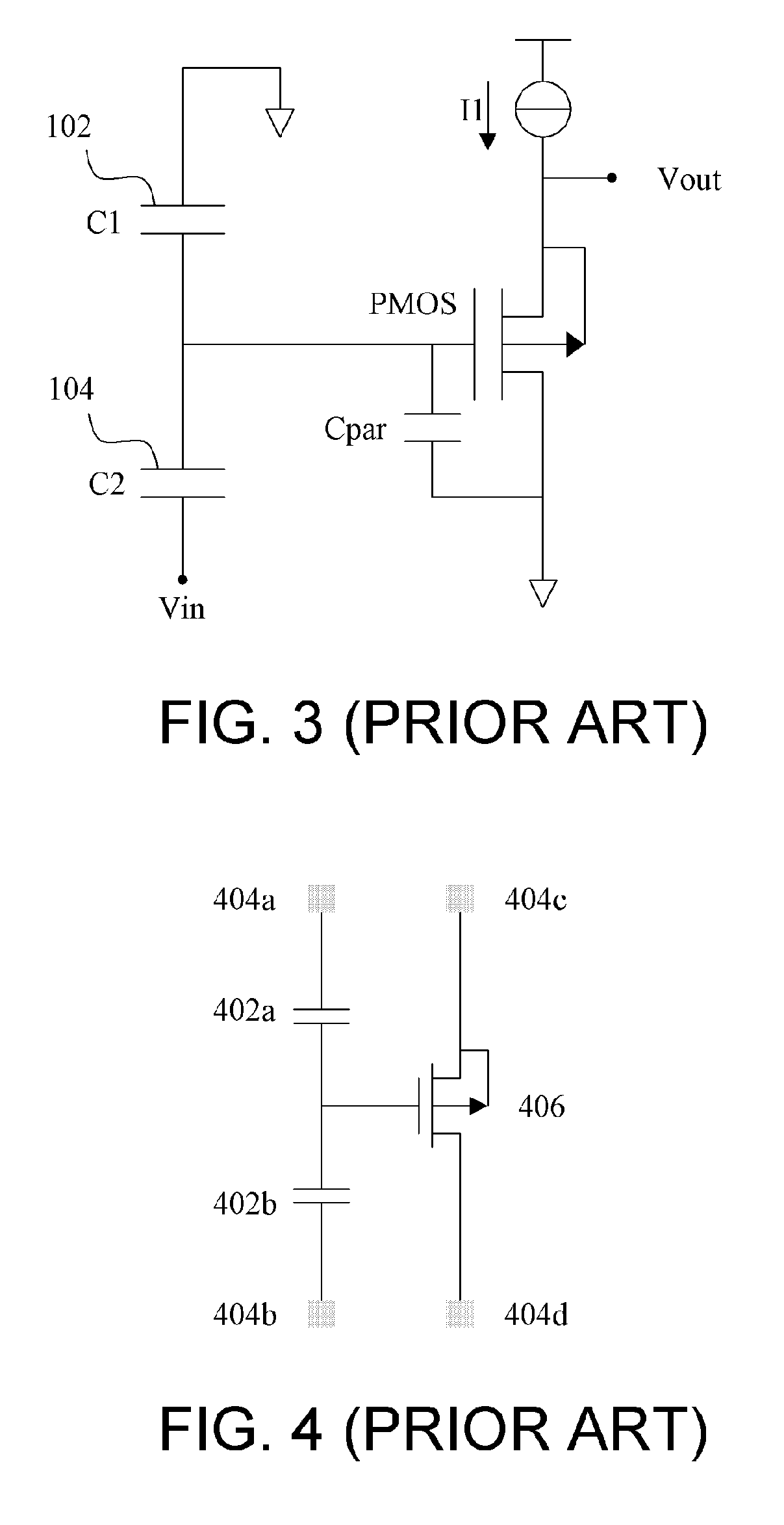

Method and circuit for measuring capacitance and capacitance mismatch

ActiveUS7323879B2Reduce layout areaImprove measurement efficiencyCapacitance measurementsFault locationCapacitanceHemt circuits

A circuit and method for measuring capacitance and capacitance mismatch of at least one capacitor pair are provided. The circuit includes a first switch, a second switch, a third switch and a P-type transistor. A terminal of the first switch is connected to a terminal of a first capacitor, and a terminal of the second switch is connected to a terminal of a second capacitor. A terminal of the third switch is connected to another terminal of the first capacitor and another terminal of the second capacitor, and a gate of the P-type transistor is connected to another terminal of the third switch. When the first, second and third switches are turned on, a capacitance of the first capacitor, a capacitance of the second capacitor, or a capacitance mismatch between the first and second capacitances is measured.

Owner:UNITED MICROELECTRONICS CORP

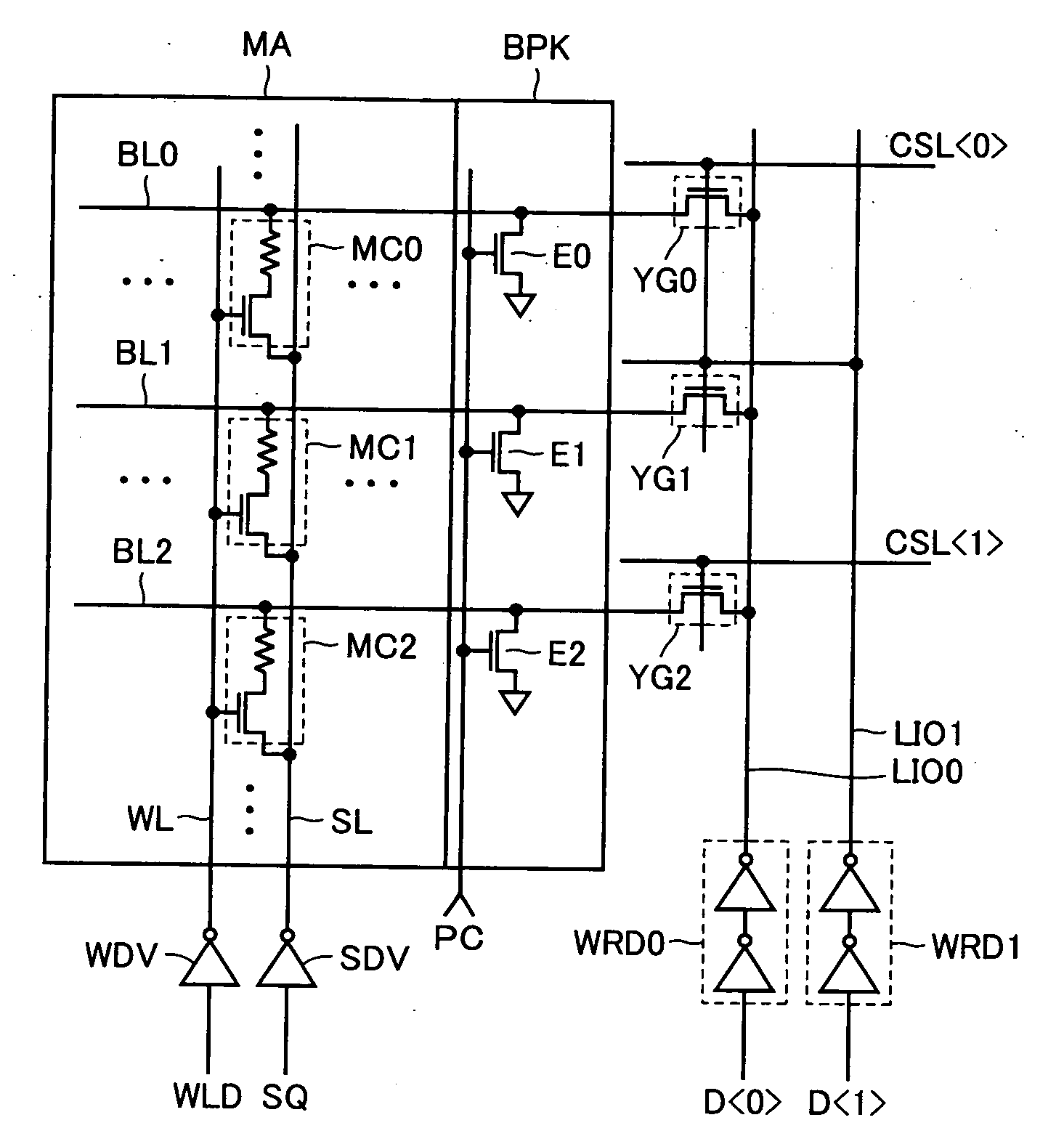

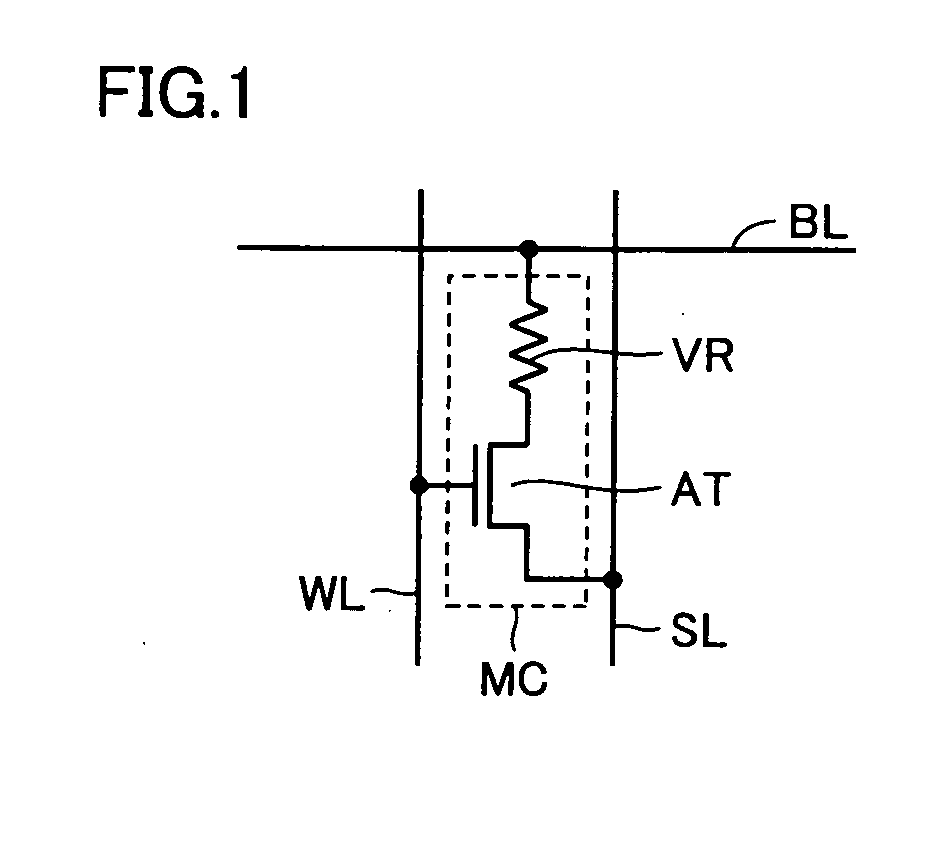

Nonvolatile semiconductor memory device

InactiveUS20070159870A1Reduce in quantityReduce layout areaDigital storageSpin injectionSemiconductor memory

Source lines for a spin injection magnetic memory cell are arranged parallel to word lines for executing writing / reading of data multiple bits at a time. In a write operation, a source line potential changes in a predetermined sequence such that the source line commonly connected to a plurality of selected memory cells is set to pass a current only in one direction in each stage of the operation sequence. For the data write sequence, a current is caused to flow through memory cells according to write data sequentially, or the memory cell has a resistance state set to an initial resistance state before writing, and then changed to a state according to the write data Fast writing can be achieved in the magnetic memory without increasing a memory cell layout area.

Owner:RENESAS ELECTRONICS CORP

Nonvolatile semiconductor memory device

InactiveUS7436699B2Reduce in quantityReduce layout areaDigital storagePotential changeParallel computing

Source lines for a spin injection magnetic memory cell are arranged parallel to word lines for executing writing / reading of data multiple bits at a time. In a write operation, a source line potential changes in a predetermined sequence such that the source line commonly connected to a plurality of selected memory cells is set to pass a current only in one direction in each stage of the operation sequence. For the data write sequence, a current is caused to flow through memory cells according to write data sequentially, or the memory cell has a resistance state set to an initial resistance state before writing, and then changed to a state according to the write data Fast writing can be achieved in the magnetic memory without increasing a memory cell layout area.

Owner:RENESAS ELECTRONICS CORP

Low-voltage difference linear constant voltage regulator with novel structure

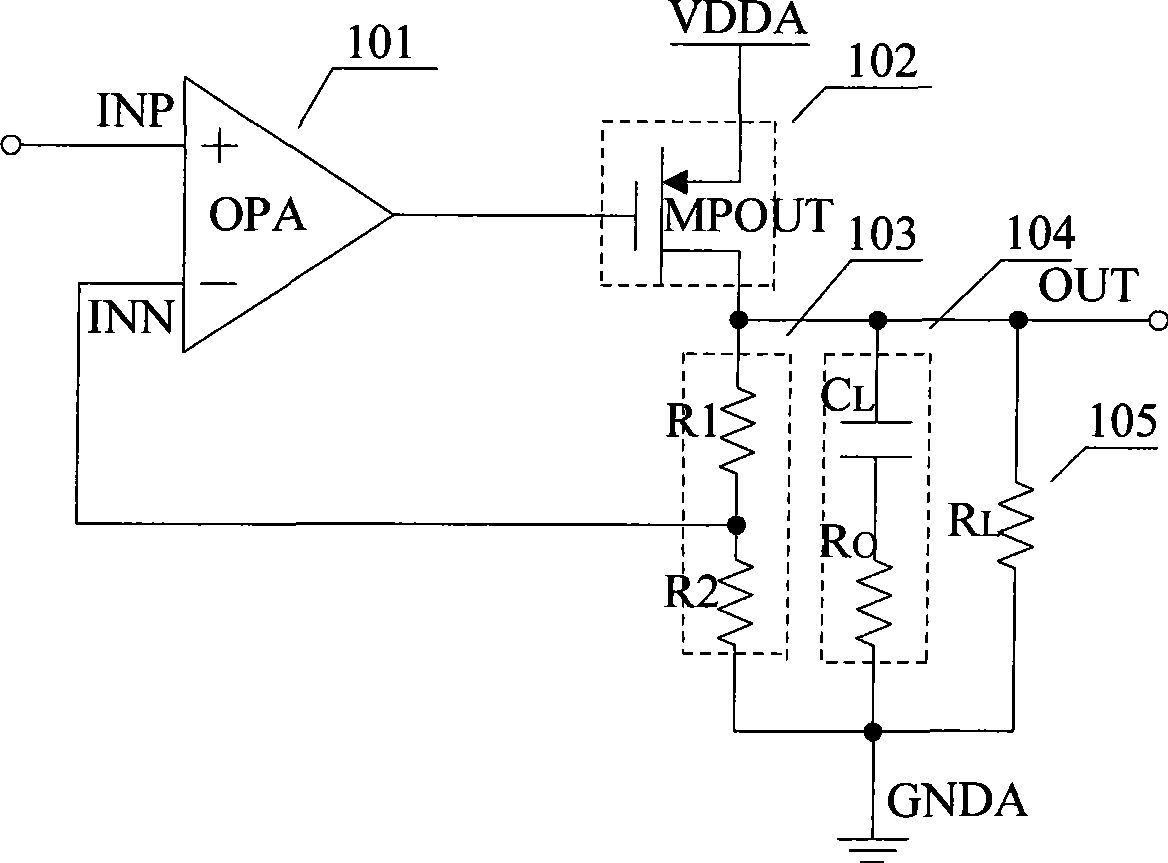

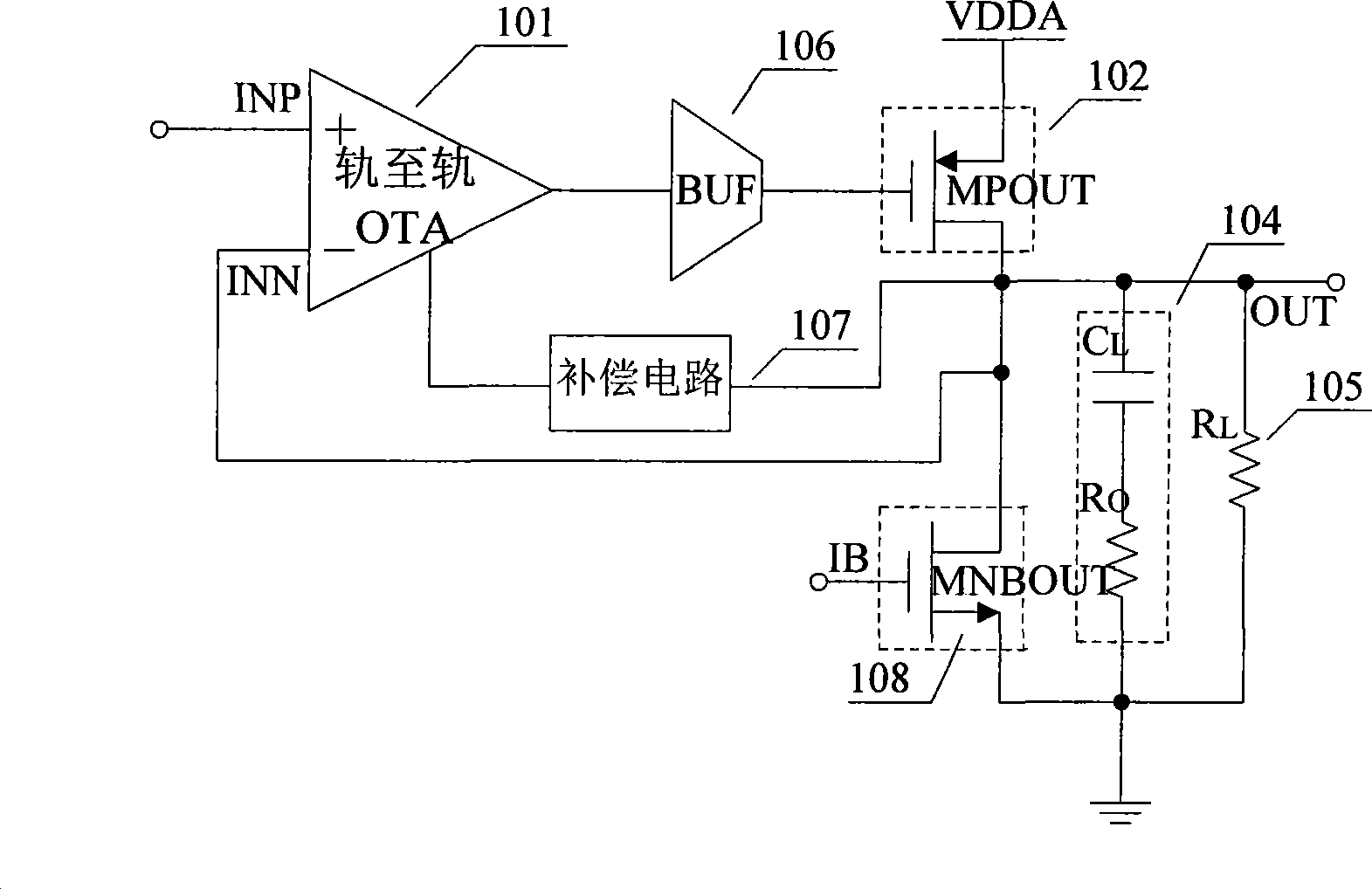

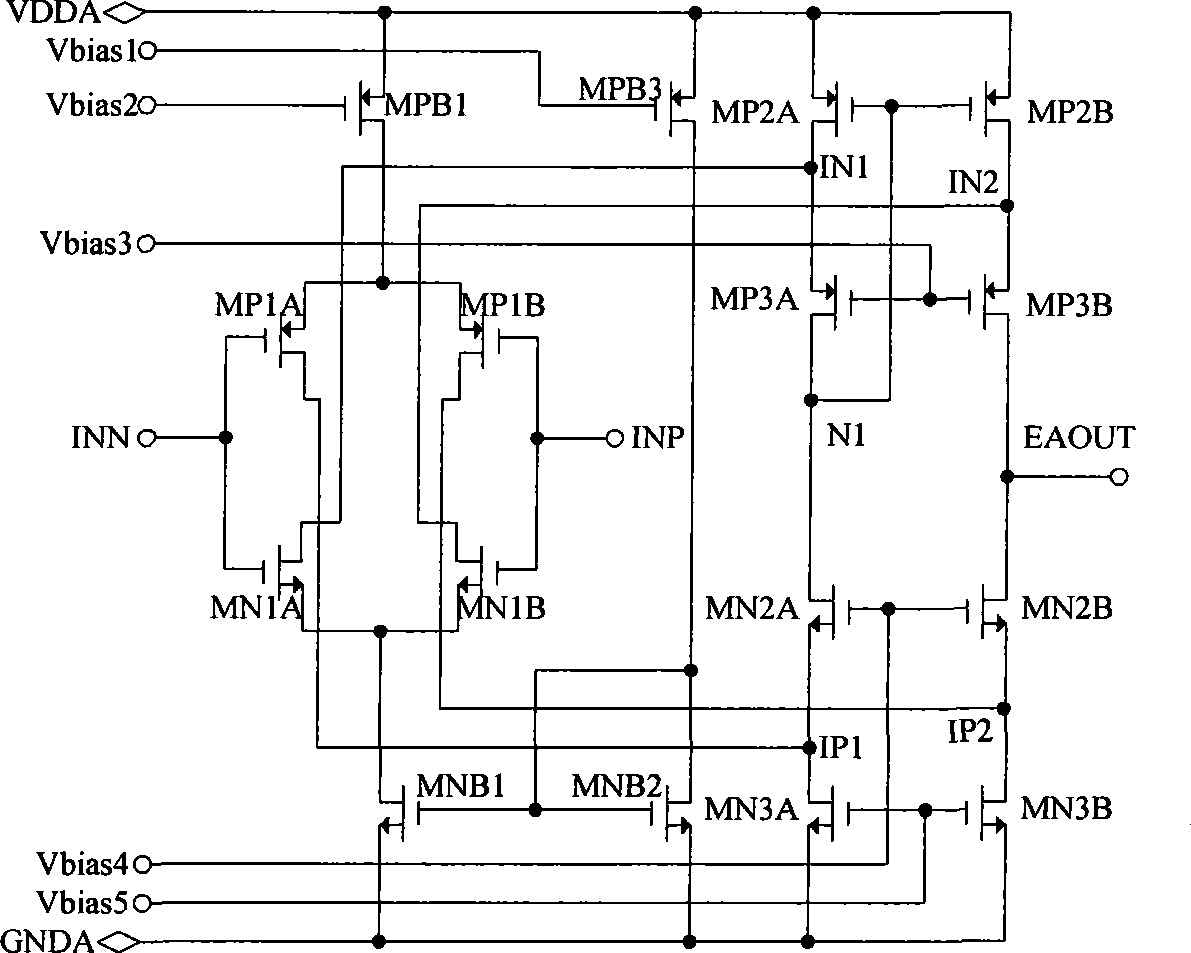

InactiveCN101419479AFeedback structure is omittedThe output voltage is accurate and stableElectric variable regulationCushionOperational transconductance amplifier

The invention relates to a low dropout linear regulator with a novel structure, which comprises an error amplifier, a driving component, a cushion circuit, a driving component biasing circuit for providing static current for the driving component, and a compensating circuit, wherein the error amplifier adopts a rail-to-rail folding common-source common-mesh operation transconductance amplifier structure, and the cushion circuit comprises a source follower circuit device and a conversion rate intensifier circuit. The regulator adopts the full feedback structure and the driving component biasing circuit to replace a resistor potential-divider network, saves the area of a domain, reduces the power consumption of the system, improves the precision and the stability of output voltage, and reduces the nonlinear distortion, and the like of the system; the error amplifier adopts a rail-to-rail folding common-source common-mesh operation transconductance amplifier structure, and realizes the rail to rail of input and output voltage; the conversion rate intensifier circuit increases the conversion rate of the system; the source follower circuit device and the compensating circuit change the position displacement of zero poles of the system, improves phase margin, and improves the stability of the system.

Owner:WUHAN UNIV

Presentation of large objects on small displays

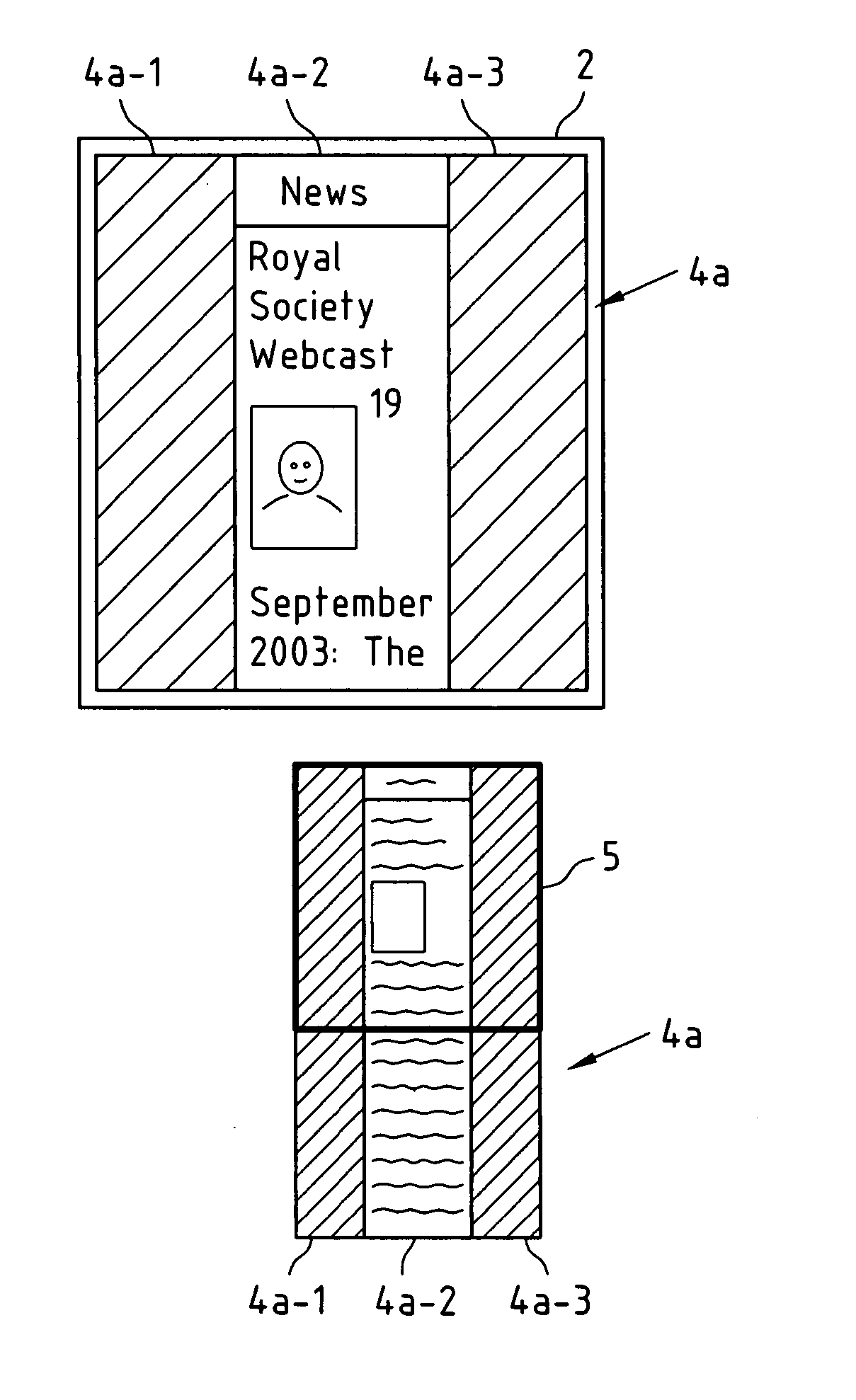

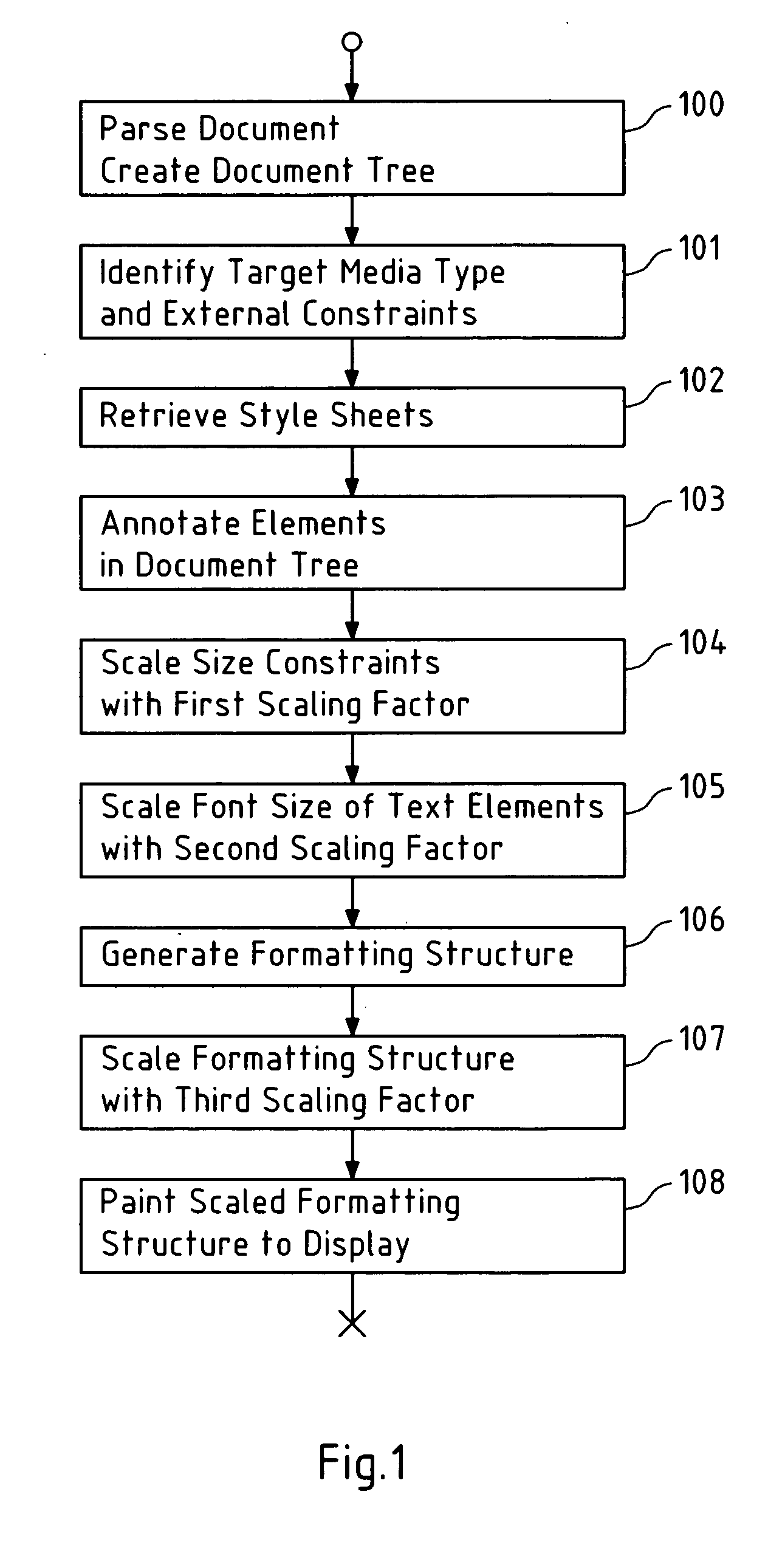

ActiveUS20060195784A1Reduce layout areaIncrease display areaDigital data information retrievalDigital computer detailsDisplay deviceComputer vision

This invention relates to a method, a computer program product, a device and a system for formatting an object to obtain a formatted object, wherein the object comprises a plurality of elements, and wherein the formatted object is affected by at least one constraint, wherein the constraint is scaled by a first scaling factor to obtain a scaled constraint; wherein at least one of the elements is scaled by a second scaling factor to obtain a scaled element; wherein a layout structure is generated for the plurality of elements including the scaled element under consideration of the scaled constraint; and wherein the layout structure is scaled by a third scaling factor to obtain the formatted object.

Owner:TEENSHARE LTD

Display device and electronic equiipment

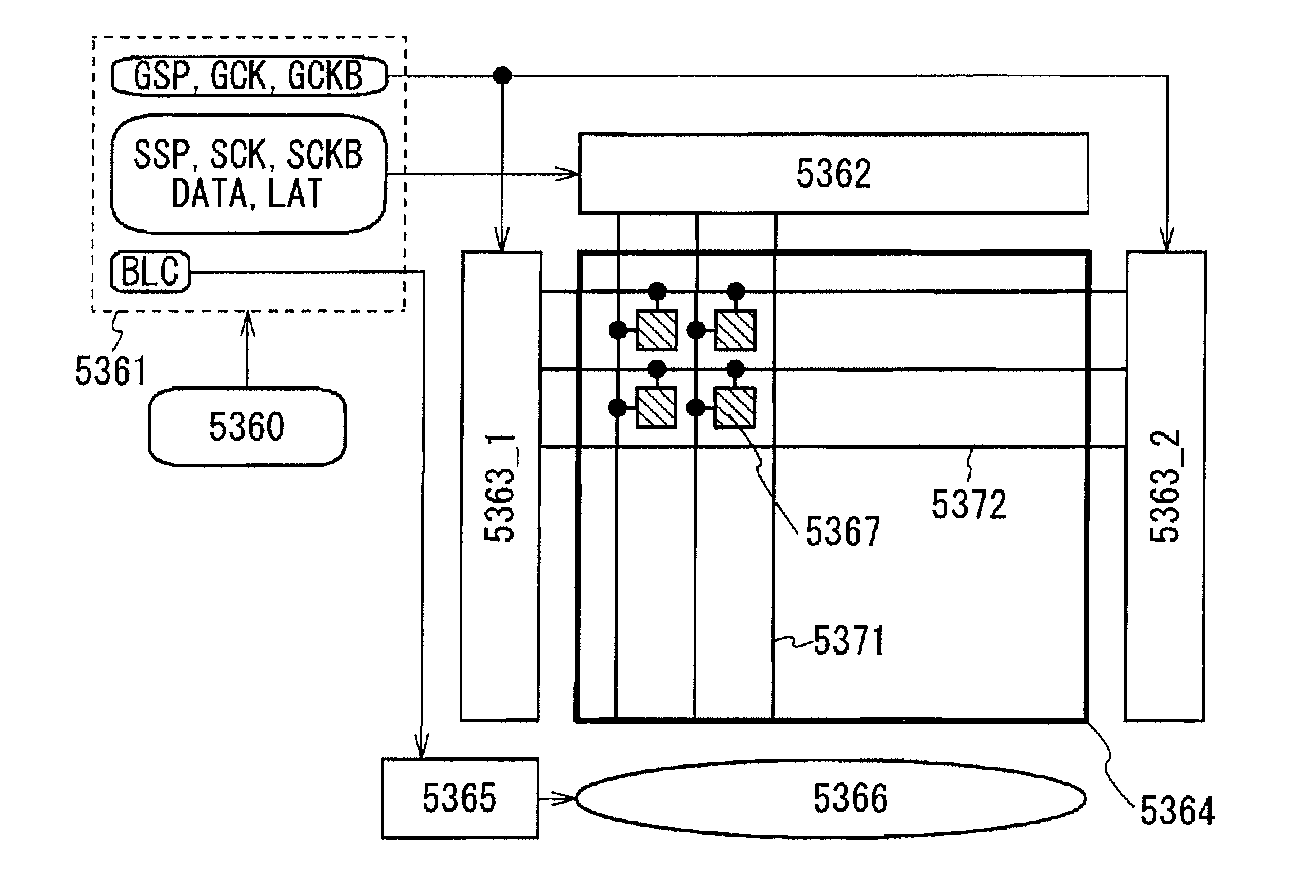

InactiveUS20080030437A1Correction of mobilityMaintaining light emissionElectrical apparatusStatic indicating devicesControl signalDisplay device

A display device is disclosed. The display device includes: a pixel array unit and a driving unit which drives the pixel array unit. The pixel array unit includes rows of scanning line, columns of signal lines, pixels in a matrix state arranged at portions where scanning lines and signal lines cross each other and power supply lines arranged corresponding to respective rows of pixels. The driving unit includes a main scanner performing line-sequential scanning to pixels by each row by supplying a control signal to each scanning line sequentially, a power supply scanner supplying a power supply voltage which is switched to a first potential and a second potential to each power supply line so as to correspond to the line-sequential scanning, and a signal selector supplying a signal potential and a reference potential to be video signal to columns of signal lines so as to correspond to the line-sequential scanning.

Owner:SONY CORP

Noise immune rc trigger for ESD protection

ActiveUS20080007882A1Risk minimizationGain is not constantEmergency protective arrangements for limiting excess voltage/currentArrangements responsive to excess voltageShunt DeviceTime range

An ESD protection circuit incorporates an ESD shunt device triggered by an ESD trigger network. In non-powered situations, a first RC time constant in the ESD trigger network, corresponds with the time range of the onset an ESD event and controls application of the ESD shunt device in response to the ESD event. A second RC time constant in a shunt trigger network is selected to be longer than the first RC time constant and holds-off triggering of a shunt device during ESD shunt protection. When activated during powered-on operation, the shunt device shunts a resistive element in the ESD trigger network forming a third time constant. The shunt device guards against false triggering during noise on a power rail by maintaining the third time constant in the ESD trigger network. The third time constant ensures that power rail voltage buildup due to noise dissipates before a false trigger develops.

Owner:ATMEL ROUSSET SAS

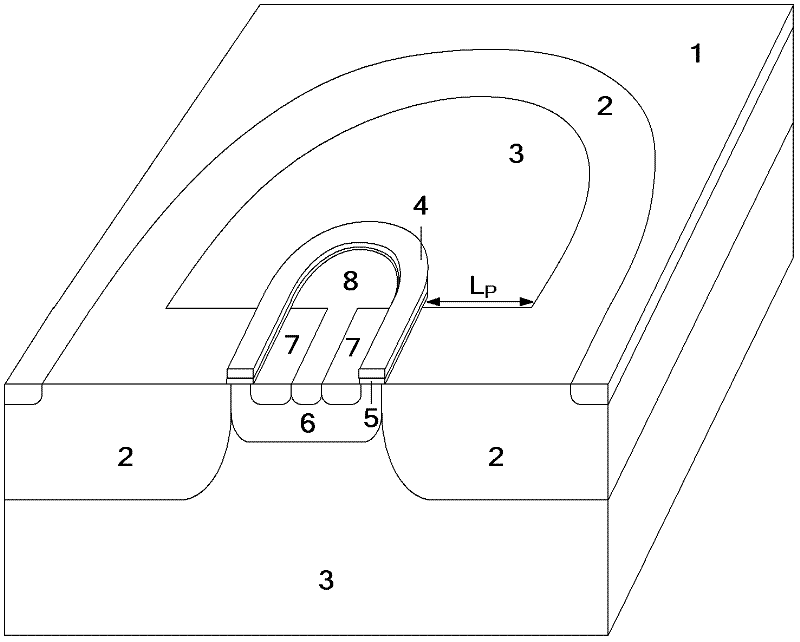

Junction termination structure of transverse high-pressure power semiconductor device

InactiveCN102244092AImprove breakdown voltageReduce widthSemiconductor devicesPower semiconductor deviceCMOS

The invention relates to a junction termination structure of a transverse high-pressure power semiconductor device, belonging to the technical field of semiconductor power devices. An N-type drift region at a curvature termination of the transverse high-pressure power semiconductor device is shortened in length to ensure that the N-type drift region is spaced with a P-well region by a certain displace, wherein the spaced part is replaced by a P-type substrate, which is equivalent that additional electric charges of the P-type substrate are introduced so that the peak value of an electric field at a pn junction formed the original P-well region and the N-type drift region is reduced, meanwhile, a new peak value of the electric field is introduced at a pn junction formed by the P-type substrate and the N-type drift region, the radius of curvature of the curvature terminal is increased, the excessive concentration of a power line is avoided, and the puncture voltage of the device is increased, wherein the surface of the N-type drift region also can be combined with a surface RESURF structure or an ultra-junction structure. The junction termination structure has the advantages of being capable of decreasing the width of the curvature terminal of the device, saving the layout area of the device and being compatible with a CMOS (Complementary Metal-Oxide-semiconductor Transistor) process, and can be used for manufacturing the transverse high-pressure power device with the advantages of excellent performance, high voltage, high speed and low conduction loss.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Semiconductor device and layout design method therefor

A layout design method for a semiconductor device includes a step of arranging transistors, a dummy gate forming step of forming dummy gates, which has a shape identical with a shape including gate electrodes or the gate electrodes and projected parts from active regions of the gate electrodes, in positions in parallel with and a fixed distance apart from the gate electrodes arranged at both ends in a gate length direction on active regions of the transistors and, when the transistors have plural gate electrodes with different gate widths, extending the projected parts to the outside of the active regions by a necessary length, a gate connecting step of, when gate patterns and contact regions are connected to the gate electrodes of the transistors, connecting the gate electrodes and the dummy gates according to a positional relation between the gate electrodes and the dummy gates, and a wiring step of wiring a metal layer. It is possible to design a semiconductor device having a smaller area than that in the past and with a less design man-hour.

Owner:SOCIONEXT INC

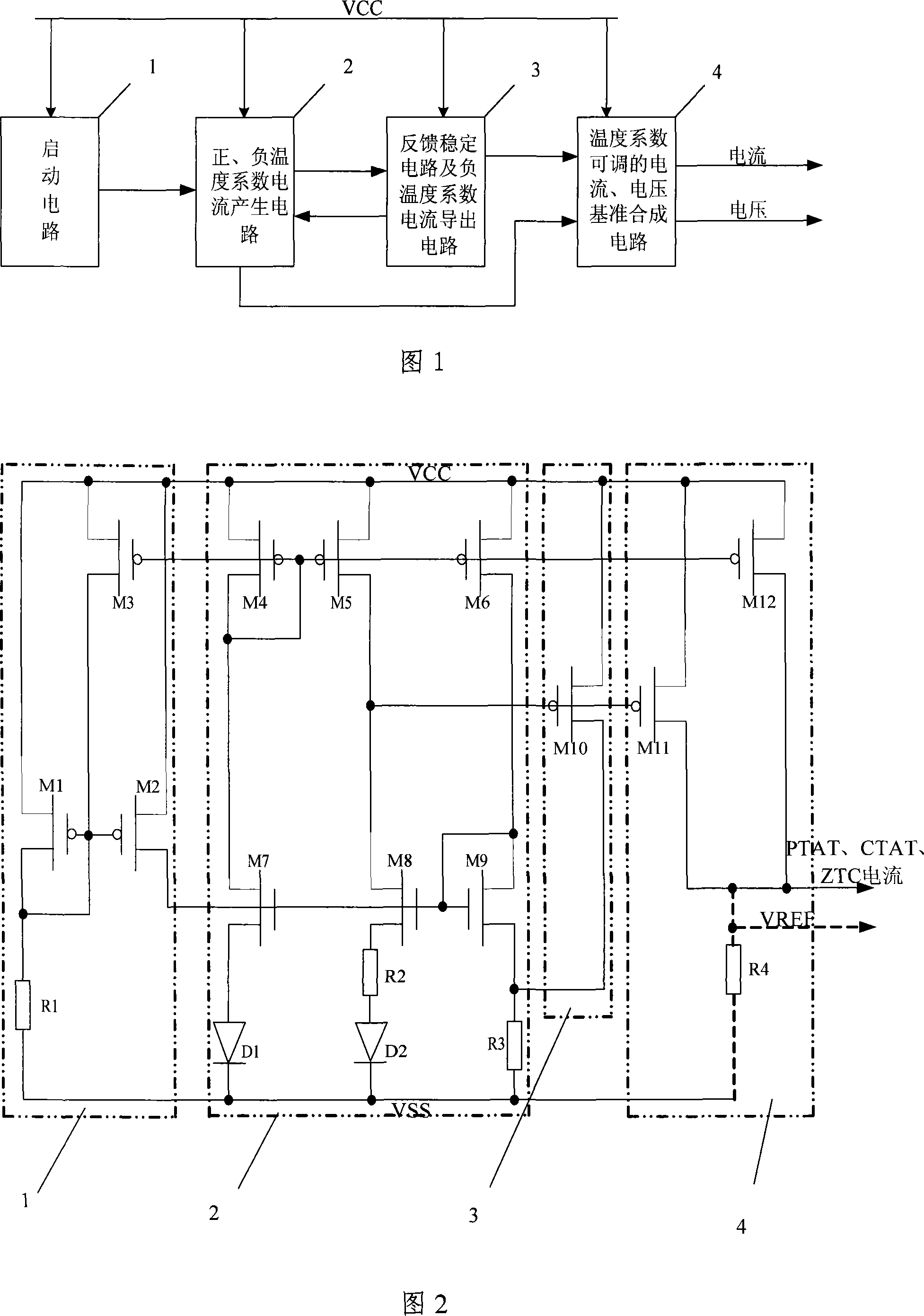

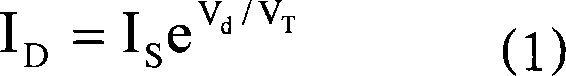

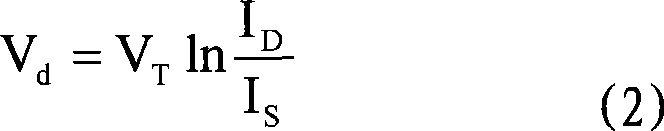

Circuit outputting adjustable positive and negative or zero-temperature coefficient electrical current and voltage reference

InactiveCN101178610ASimple structureReduce layout areaElectric variable regulationNegative temperatureReference current

The invention provides a circuit for outputting adjustable positive, negative or zero temperature coefficient current and voltage reference, including: a start-up circuit, a positive and negative temperature coefficient current generation circuit, a feedback stable and negative temperature coefficient current derivation circuit, and the temperature coefficient can be Adjusted current reference, voltage reference synthesis circuit. The invention is realized under the standard CMOS technology, has simple structure, low input voltage, and can generate current reference and voltage (VREF) reference with adjustable temperature coefficient, which can be positive, negative or zero temperature coefficient.

Owner:XIAN BIAOXIN ELECTRONICS SCI & TECH

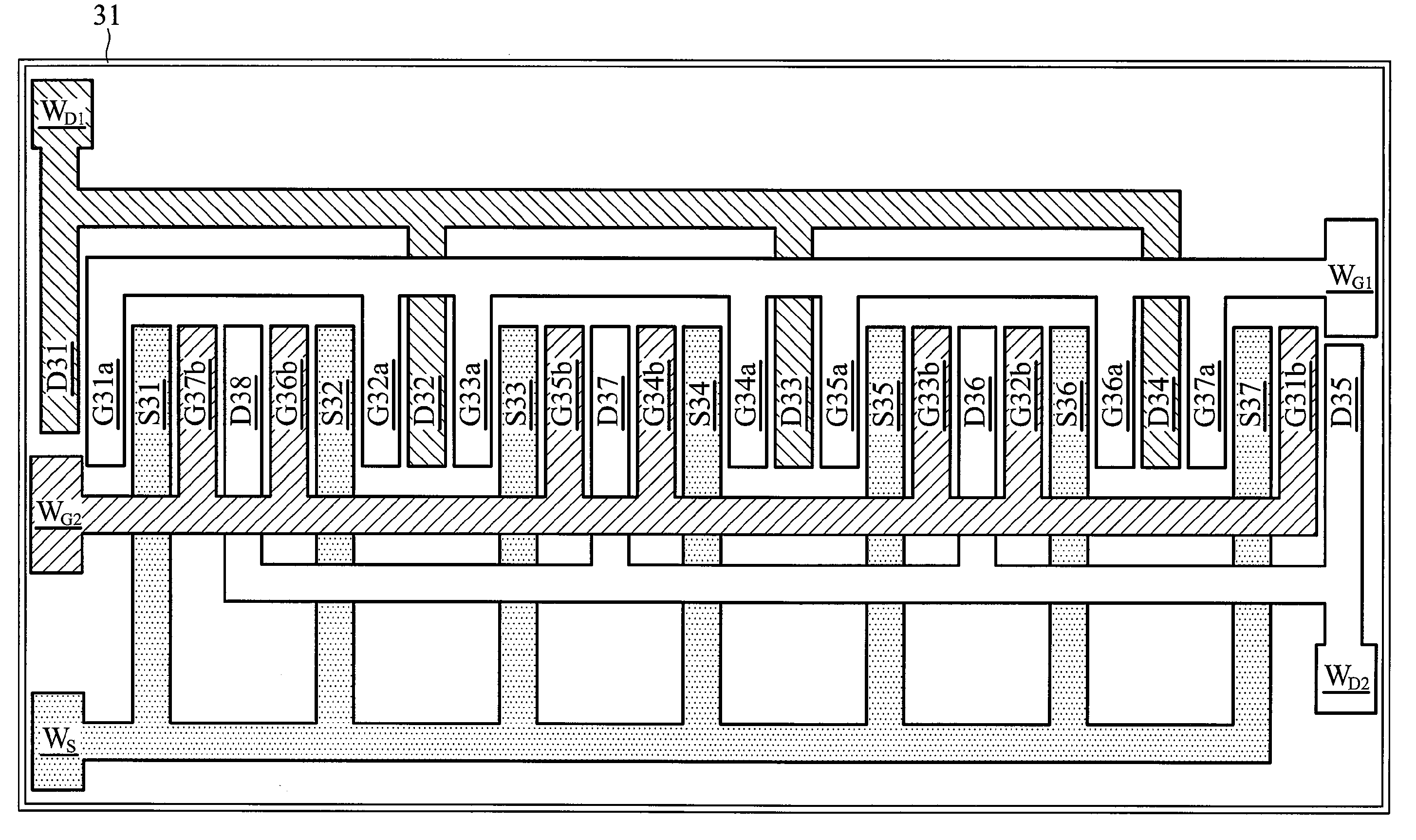

RF integrated circuit device

InactiveUS20080157222A1Reduce layout areaReduce parasitic capacitanceTransistorSolid-state devicesIntegrated circuitEngineering

A differential pair of an RF integrated circuit device is disclosed. The differential pair of the integrated circuit device includes a first MOS formed by a multiple finger configuration, having a plurality of first gate fingers; a second MOS formed by the multiple fingers configuration, having a plurality of second gate fingers, wherein each two first gate fingers interdigitate with each two second gate fingers.

Owner:MEDIATEK INC

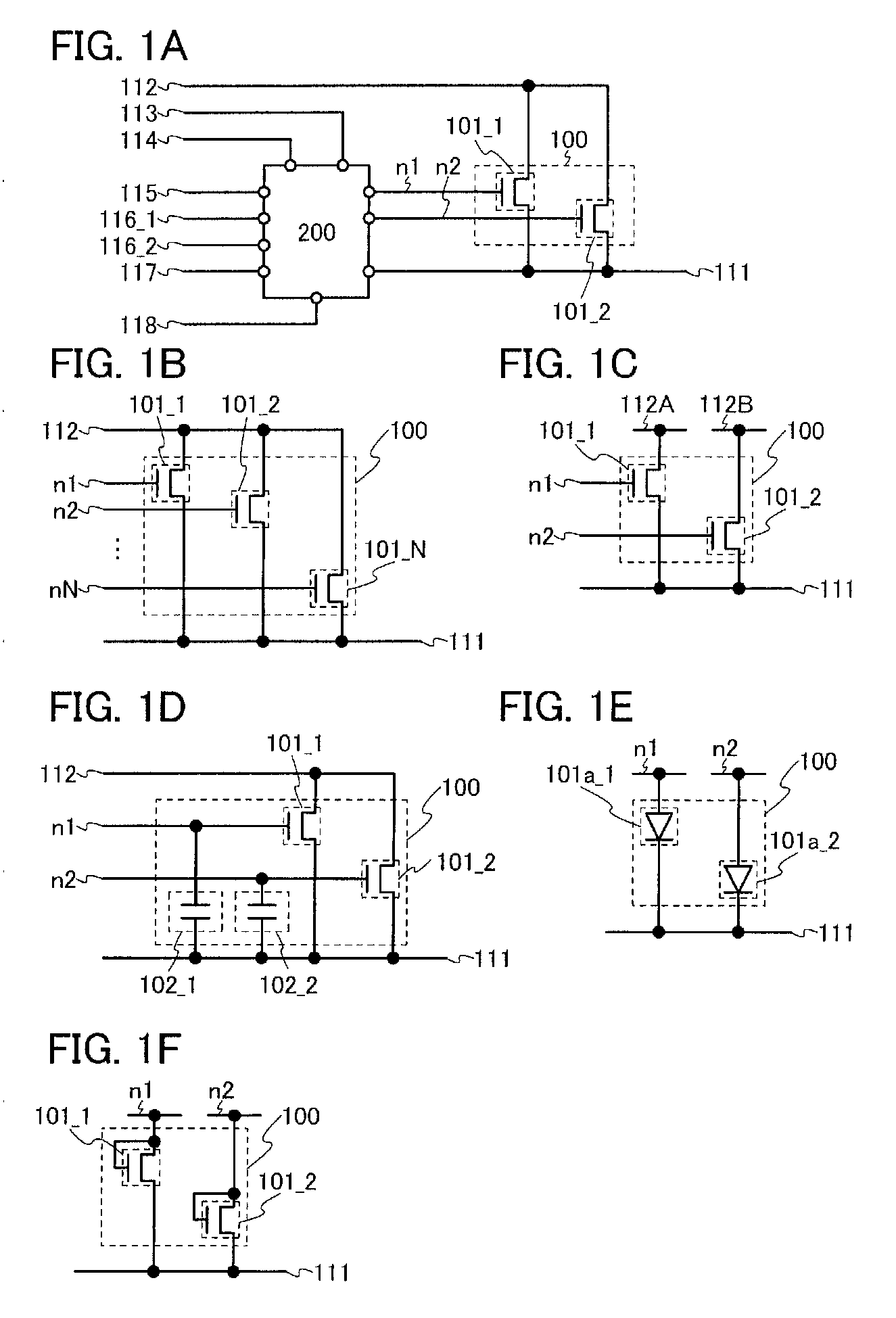

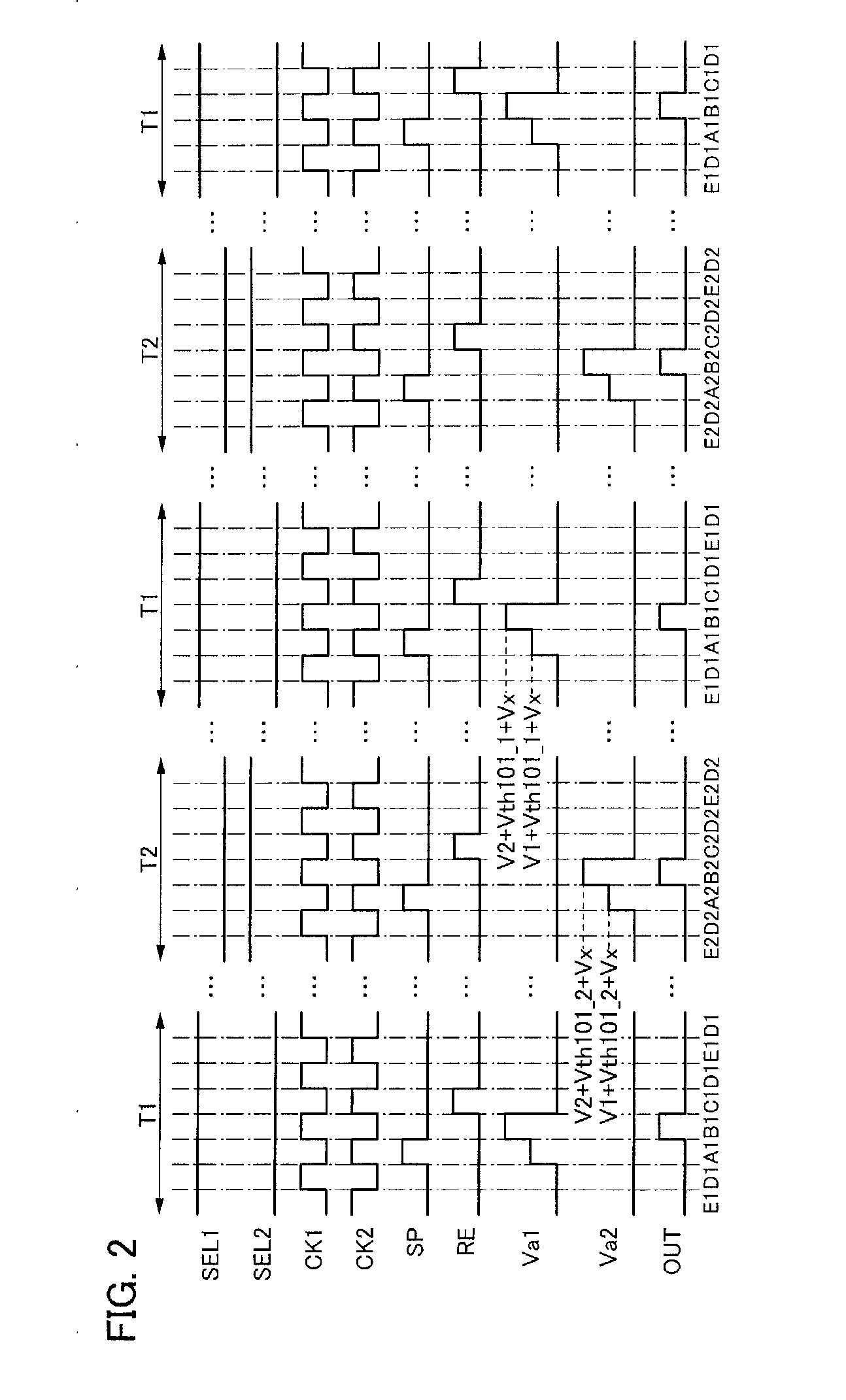

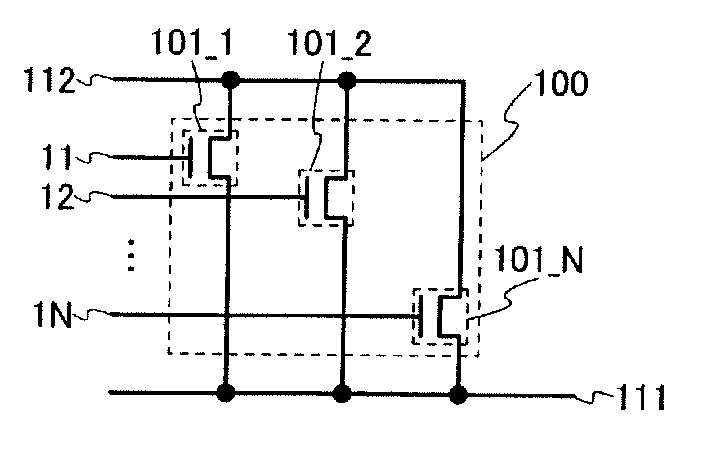

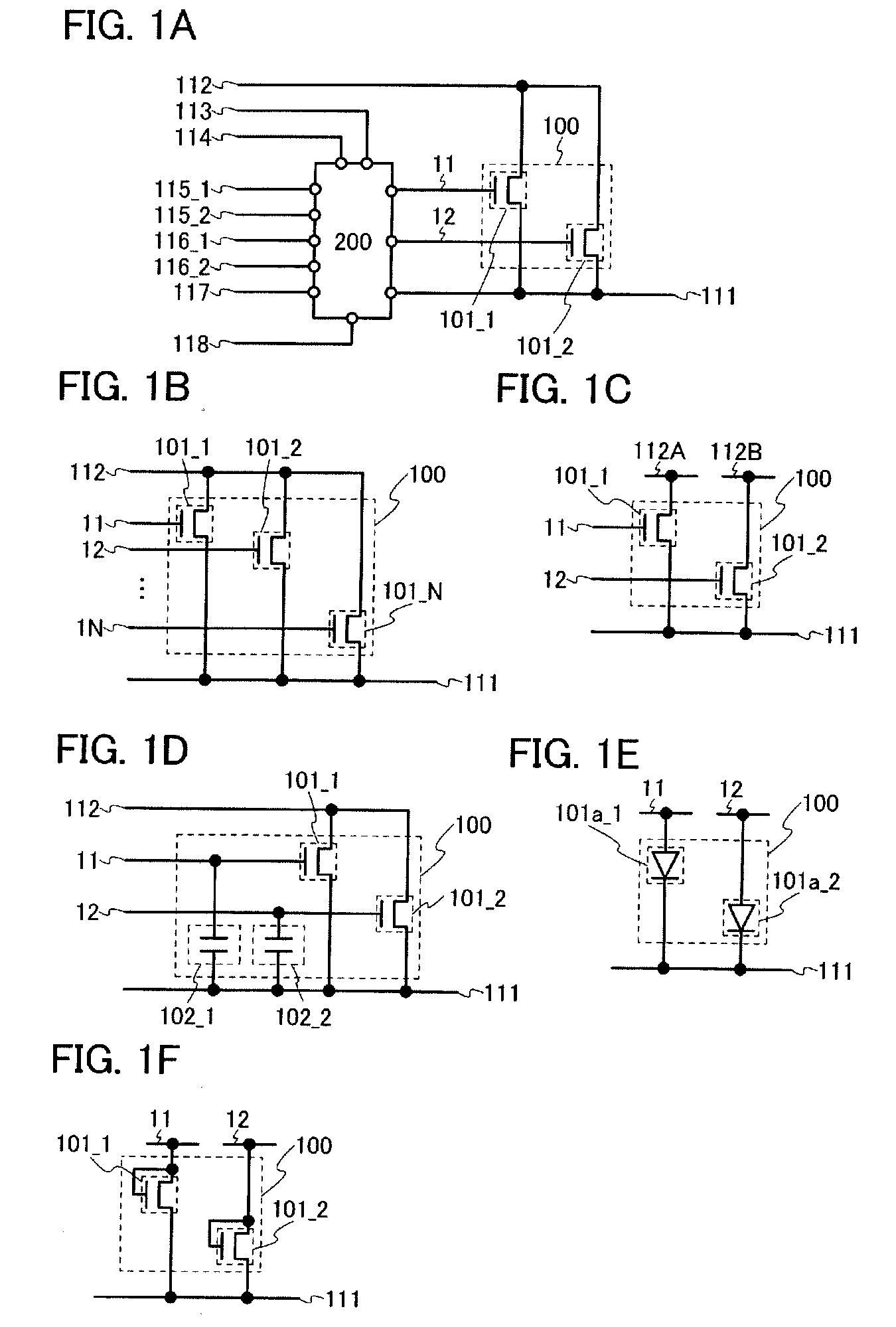

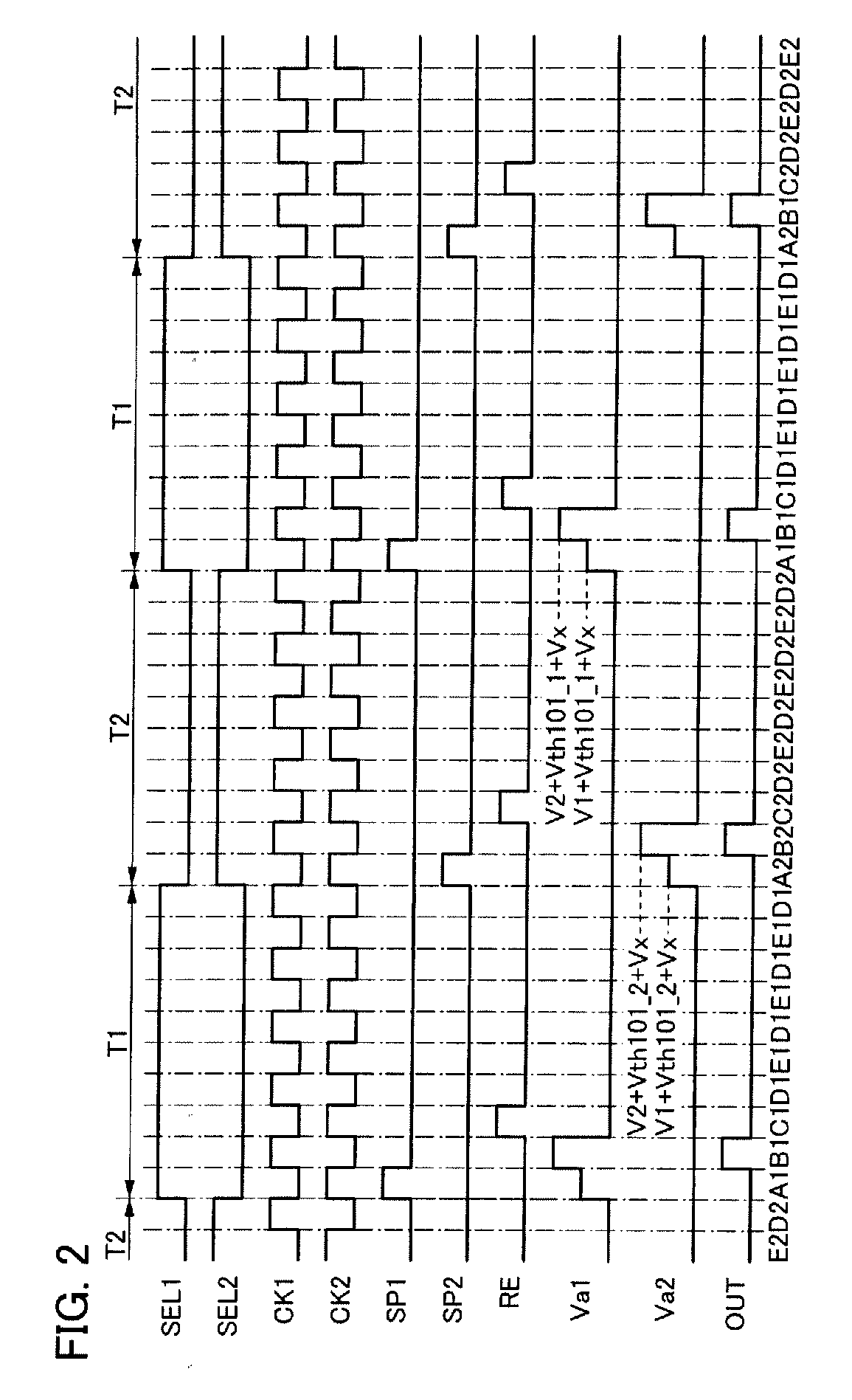

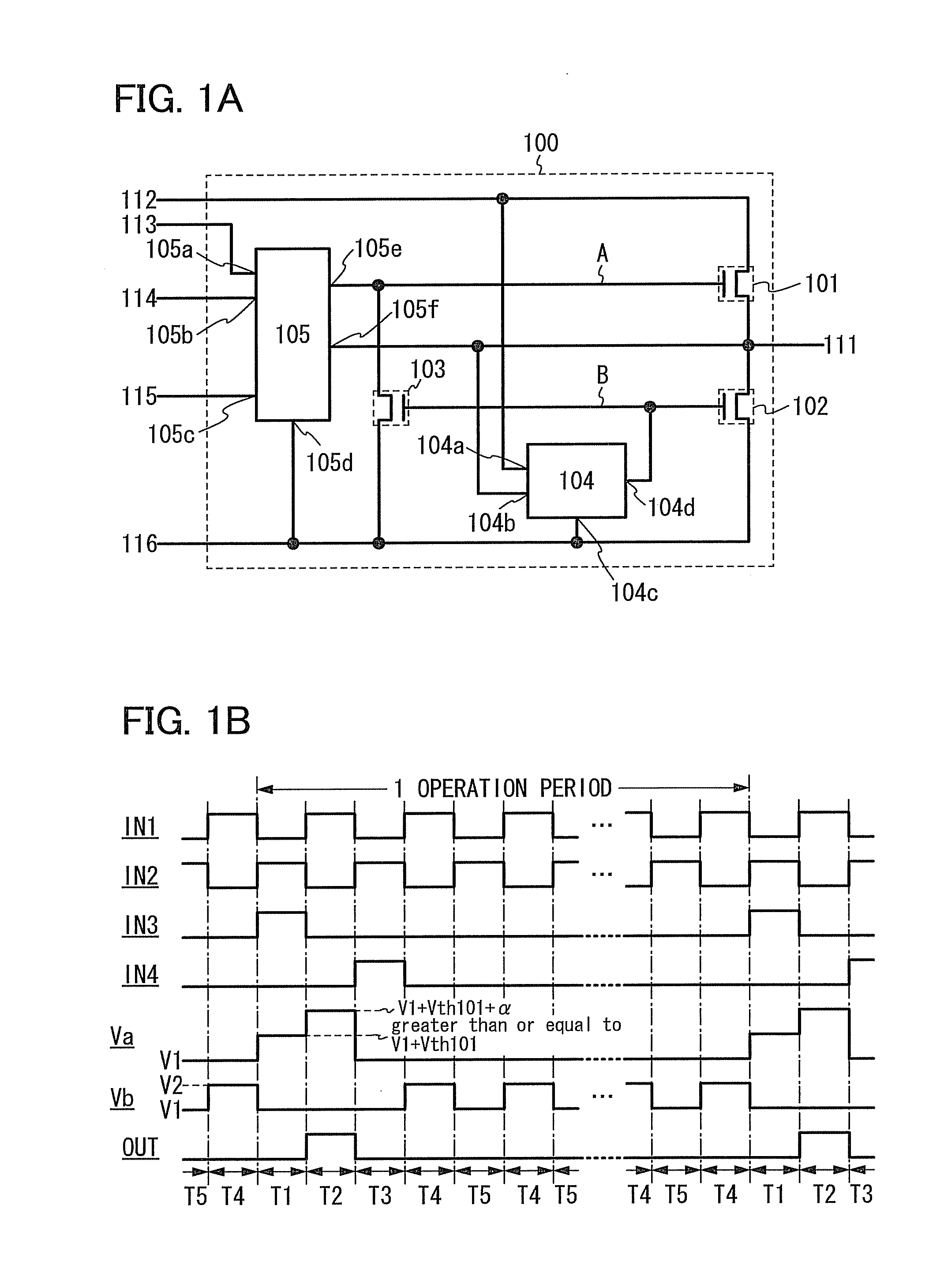

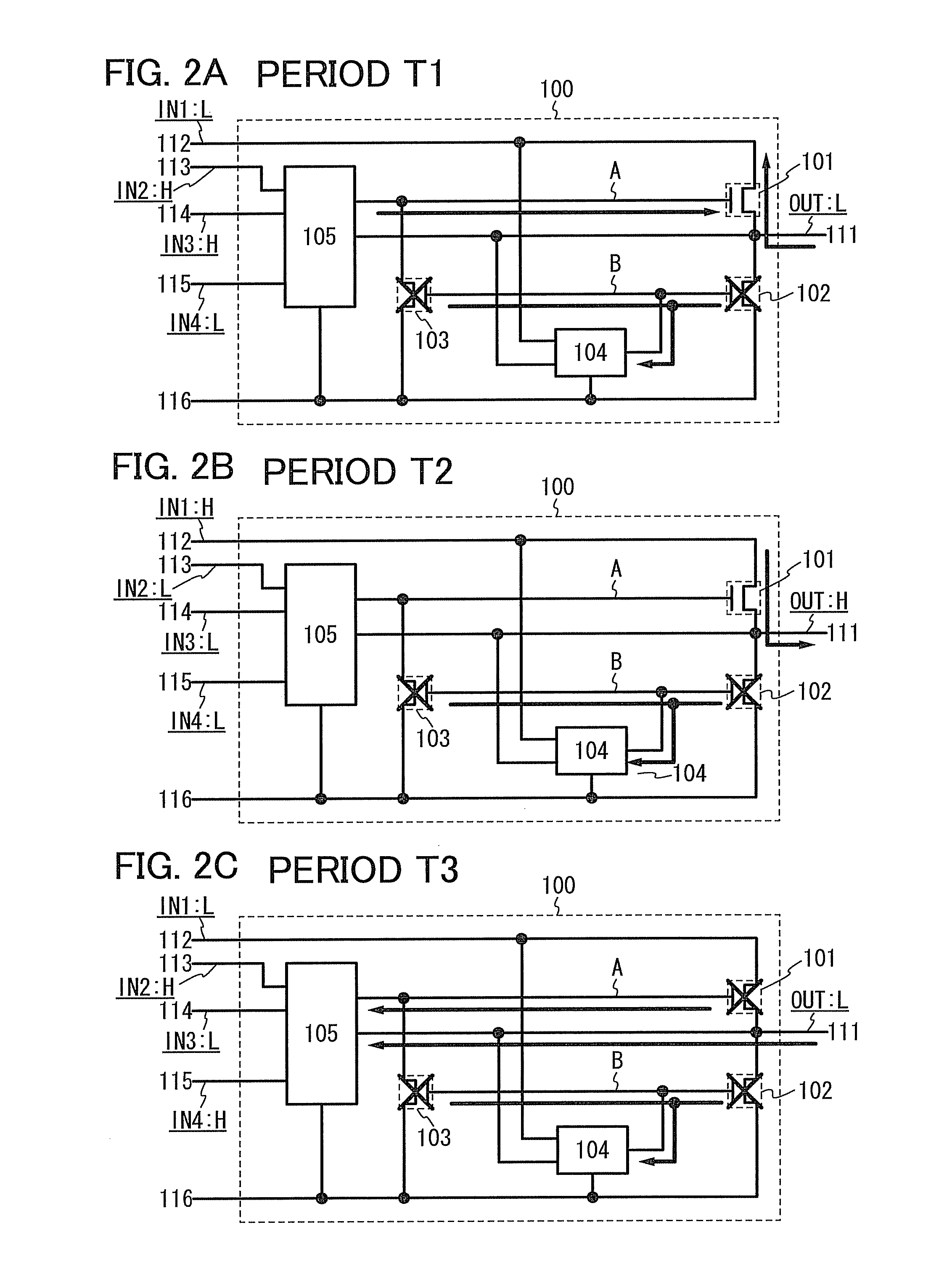

Liquid Crystal Display Device and Electronic Device Including the Same

ActiveUS20100245307A1Prevent degradationChannel width reductionSolid-state devicesCathode-ray tube indicatorsDriver circuitLiquid-crystal display

A driver circuit includes a circuit 200, a transistor 101—1, and a transistor 101—2. A signal is selectively input from the circuit 200 to a gate of the transistor 101—1 and the transistor 101—2, so that the transistor 1011 and the transistor 101—2 are controlled to be on or off. The transistor 101—1 and the transistor 101—2 are turned on or off; thus, the wiring 112 and the wiring 111 become conducting or non-conducting.

Owner:SEMICON ENERGY LAB CO LTD

Shift register, liquid crystal display device having the shift register and method of driving scan lines using the same

ActiveCN1868003AReduce power consumptionReduce layout areaStatic indicating devicesDigital storageLiquid-crystal displayEngineering

In a bi-directional shift register and a liquid crystal display device having the bi-directional shift register, the shift register further includes a dummy stage for resetting a last stage. The dummy stage is reset by a control signal of the last stage or by the output signal of the dummy stage. Therefore, power consumption and layout area may be reduced. The shift register includes a plurality of stages and two dummy stages, and two selection signals for selecting shift direction is applied to each of the stages.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

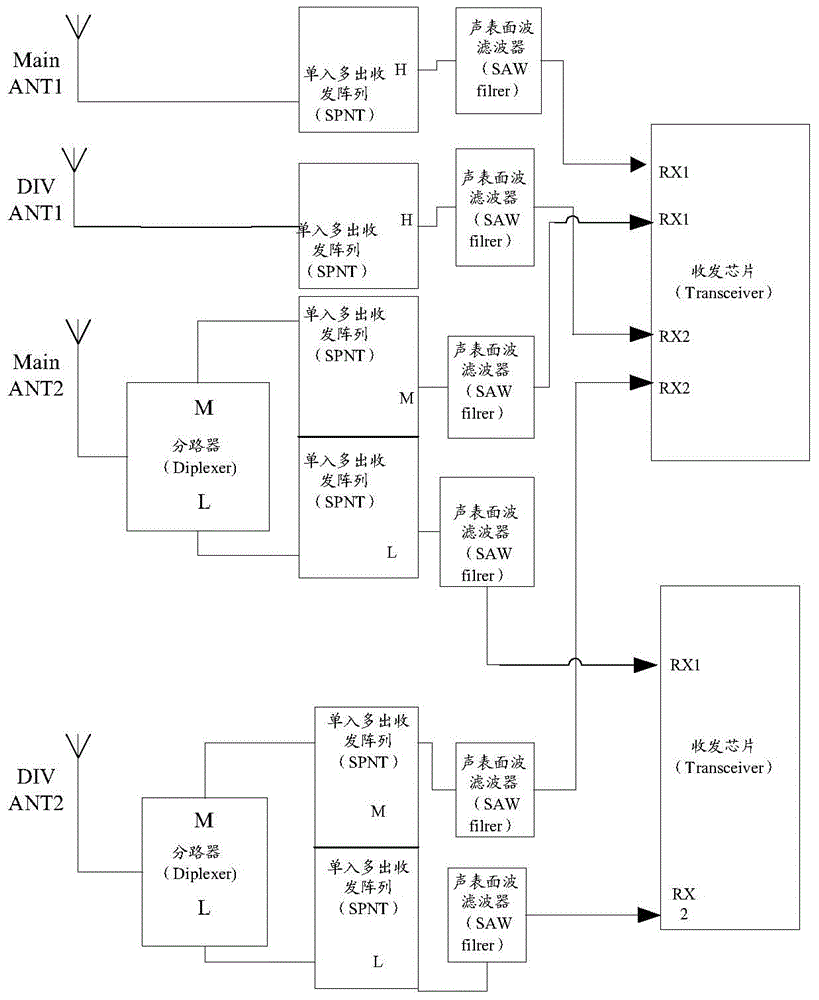

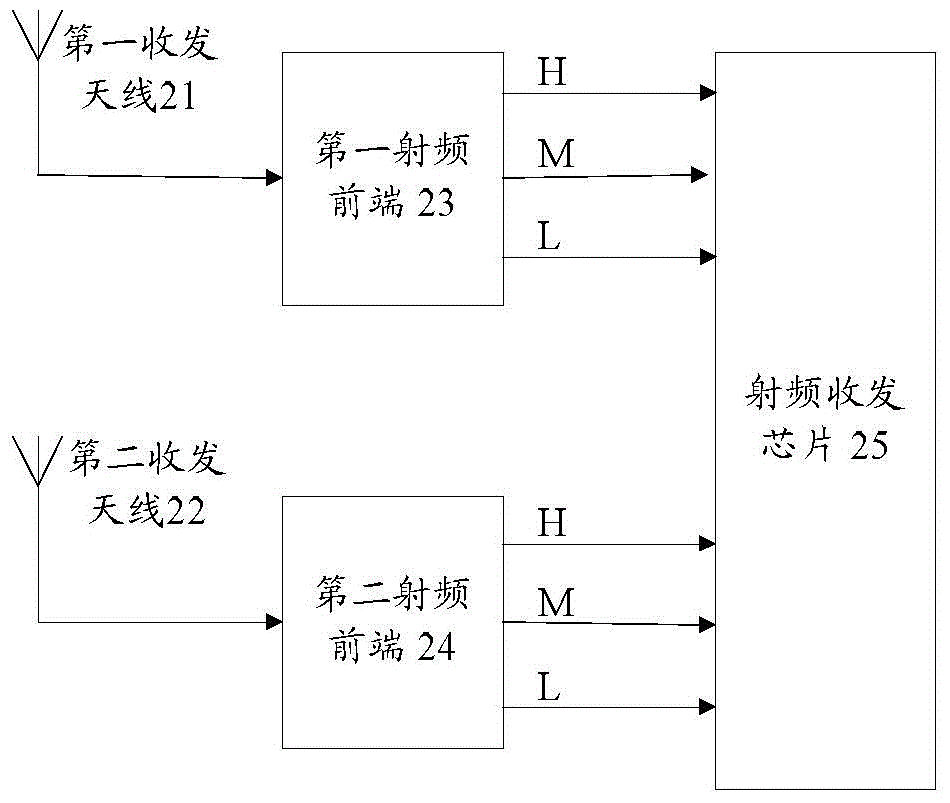

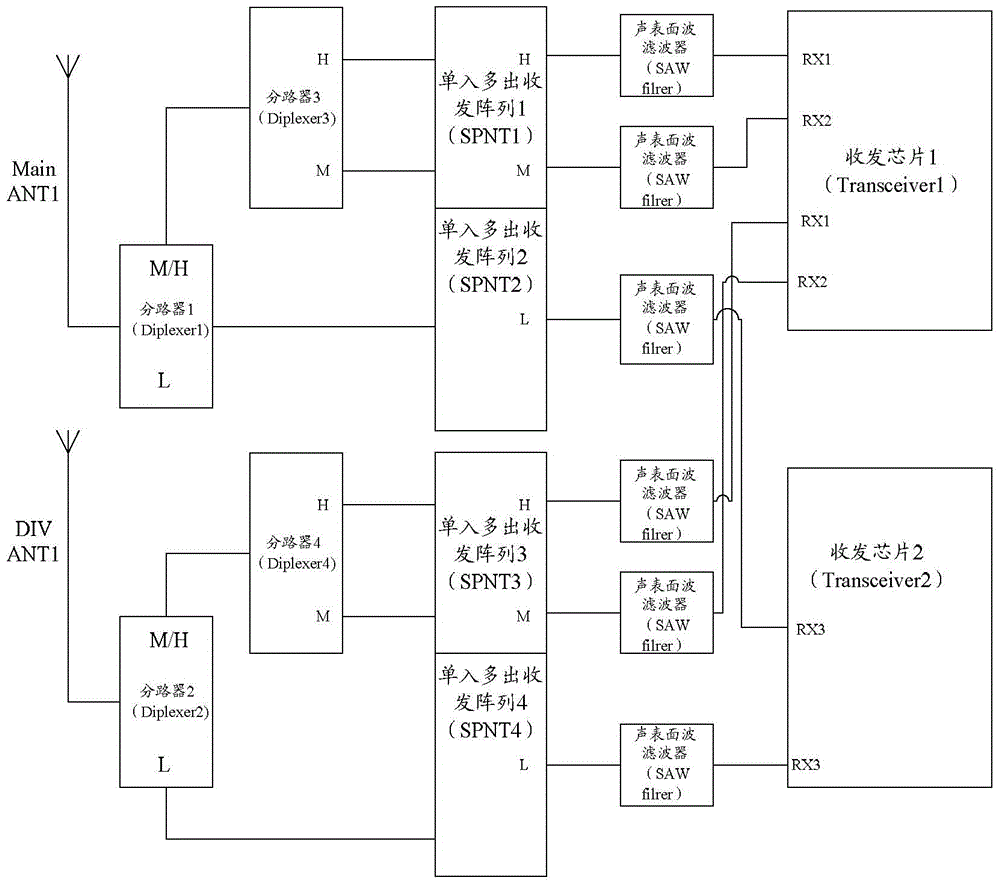

Carrier aggregation device

ActiveCN105471557AReduce layout areaReduce distractionsTransmission path divisionDuplex signal operationIntermediate frequencyEngineering

The invention discloses a carrier aggregation device, which comprises a first transmitting and receiving antenna, a second transmitting and receiving antenna, a first radio frequency front end, a second radio frequency front end and a radio frequency transmitting and receiving chip, wherein signals received by the first transmitting and receiving antenna are divided into a way of high-frequency signals, a way of intermediate-frequency signals and a way of low-frequency signals through the first radio frequency front end, and the three ways of signals enter the radio frequency transmitting and receiving chip respectively; and signals received by the second transmitting and receiving antenna are divided into a way of high-frequency signals, a way of intermediate-frequency signals and a way of low-frequency signals through the second radio frequency front end, and the three ways of signals enter the radio frequency transmitting and receiving chip respectively.

Owner:SANECHIPS TECH CO LTD

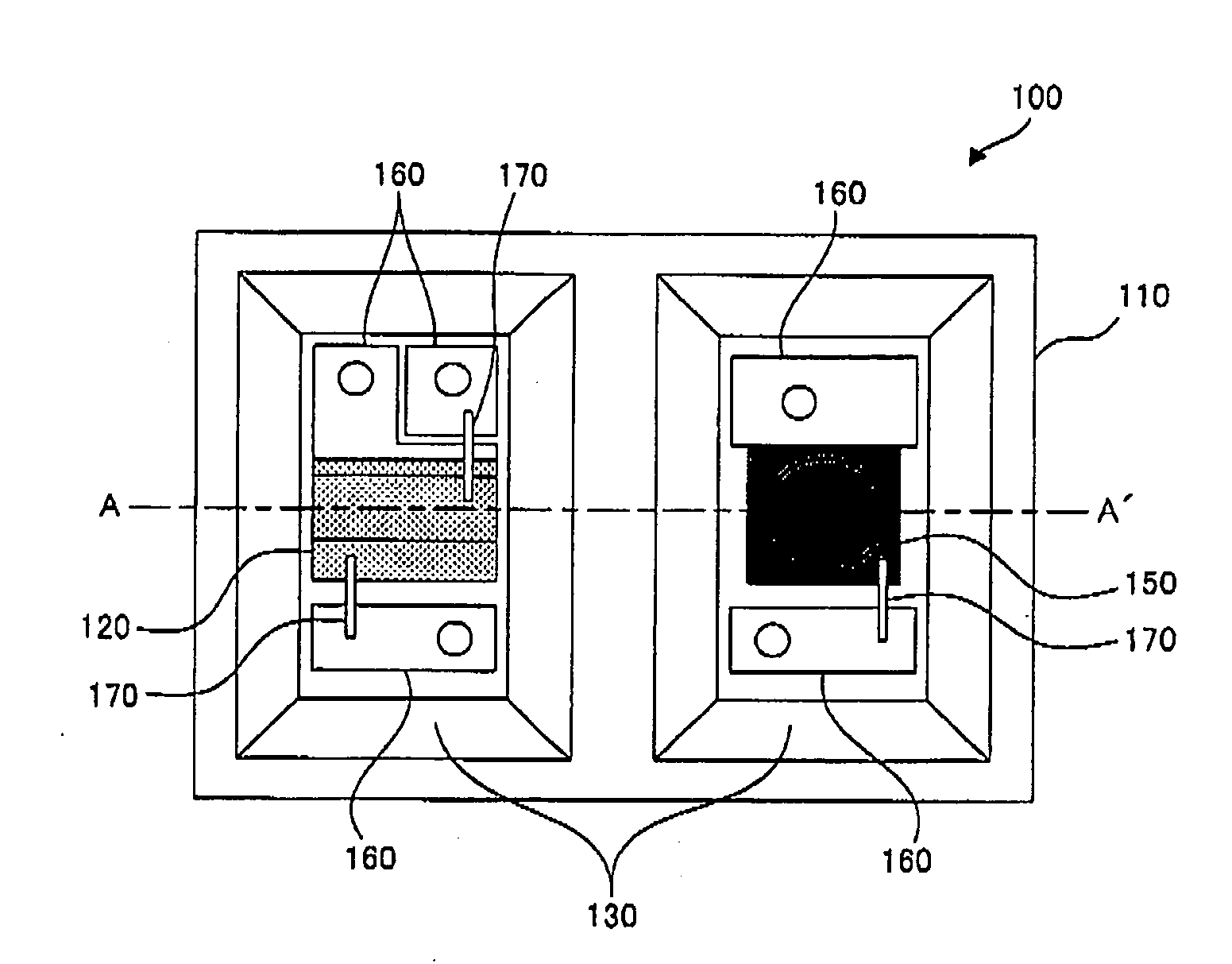

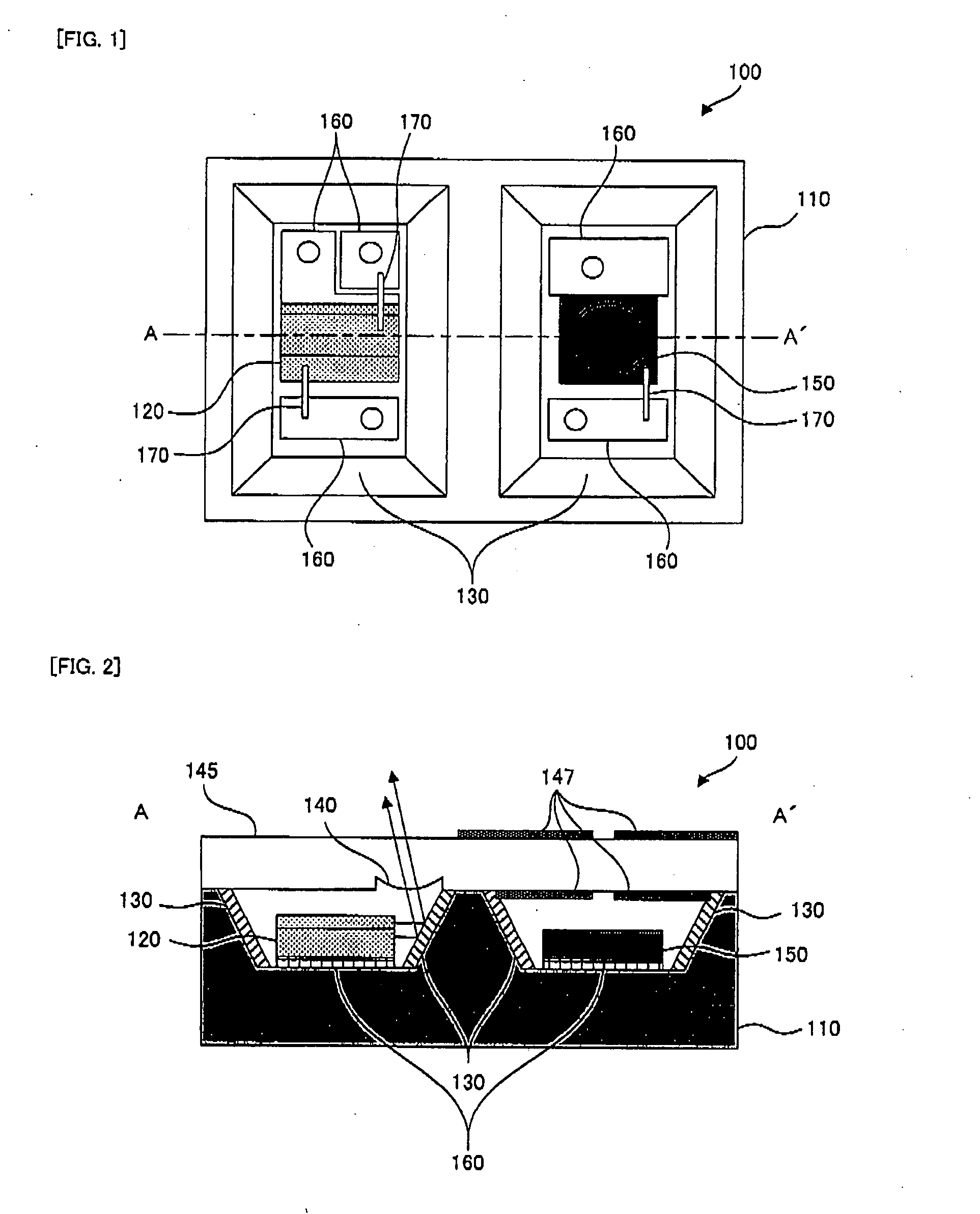

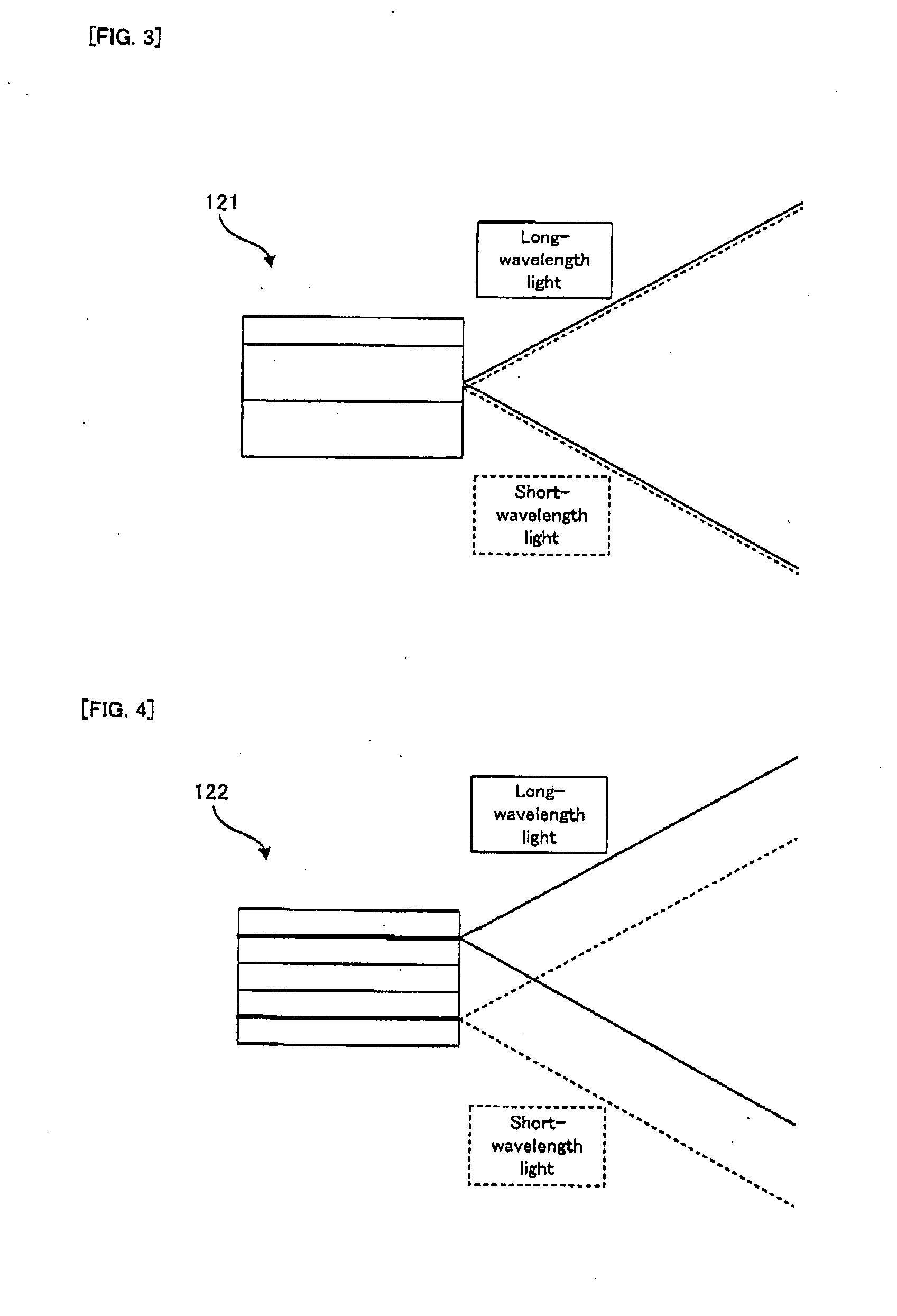

Emission sensor device and bioinformation detecting method

InactiveUS20100056887A1MiniaturizationLess difficultyCatheterColor/spectral properties measurementsLight beamLength wave

An emission sensor device includes a base (110), a light applying section (120) disposed on the base and adapted for applying light beams having different wavelengths to a subject in such a way that the light beams at least overlap with one another, and a light receiving section (150) disposed on the base and adapted for detecting light from the subject attributed to the applied light beams for each wavelength. The device has a small size and can collect predetermined types of information on the subject such as bioinformation with high accuracy.

Owner:PIONEER CORP +1

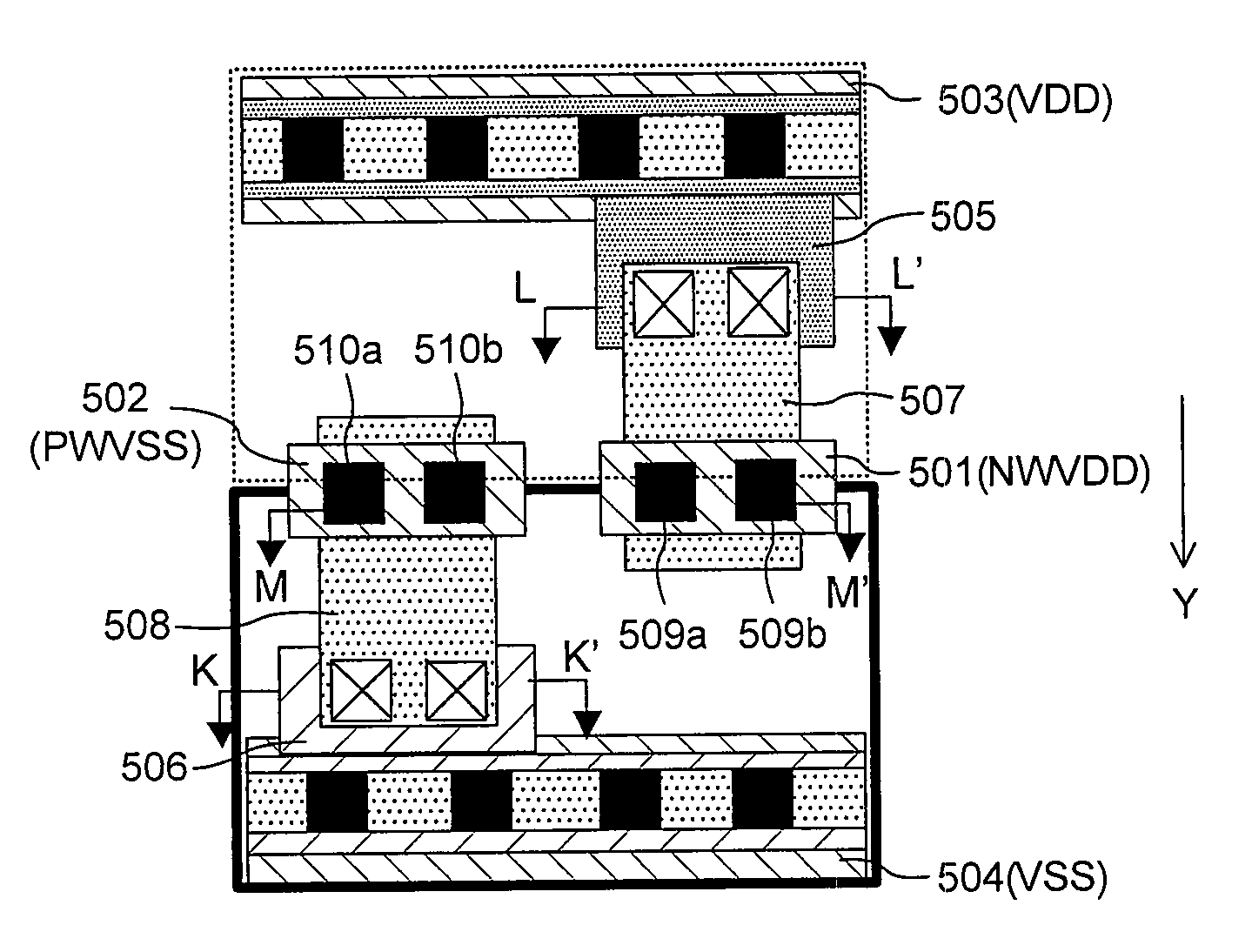

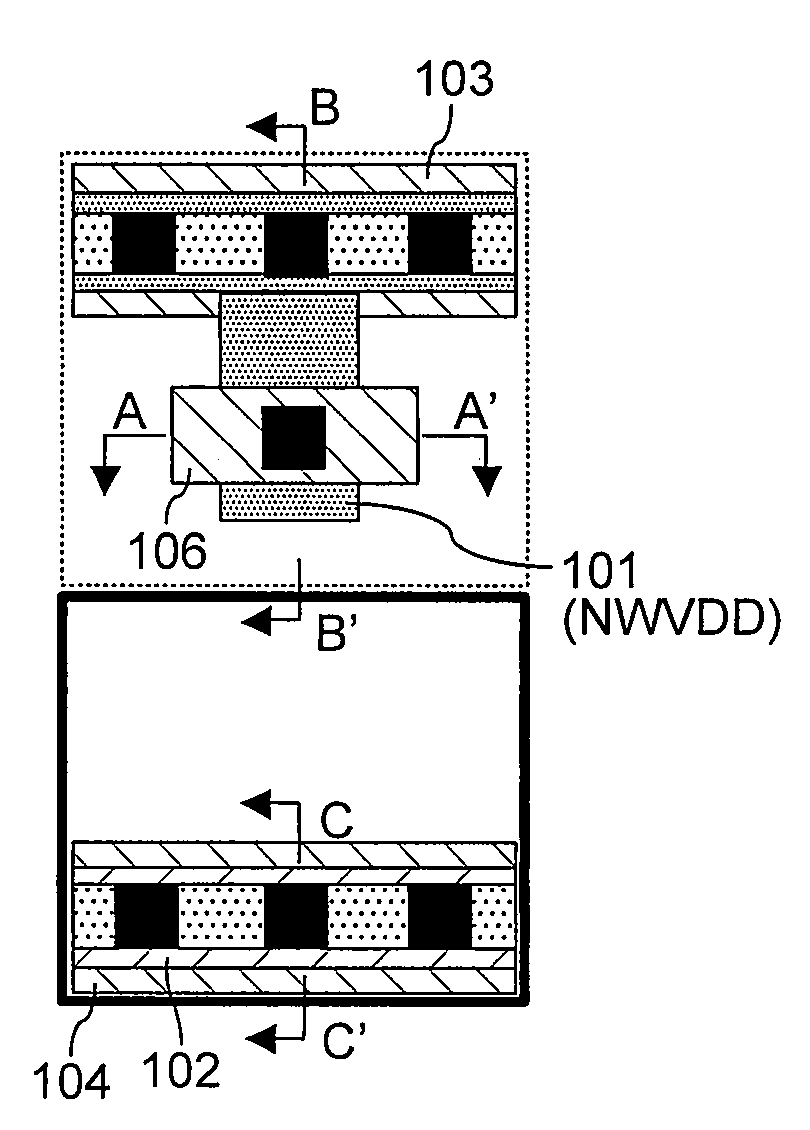

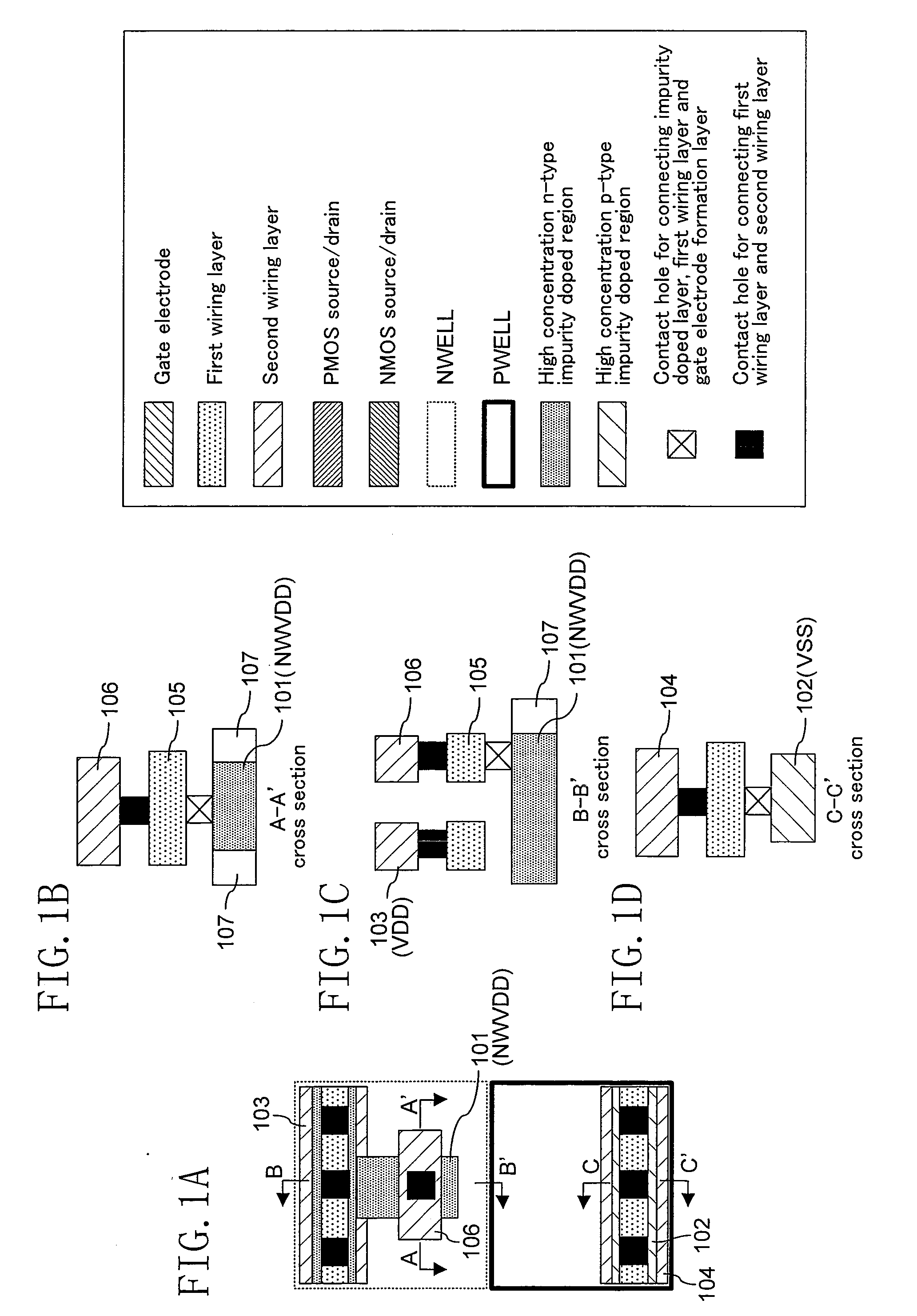

Layout structure of semiconductor device

InactiveUS20080169868A1Reduce chip areaReduce in quantityTransistorSemiconductor/solid-state device detailsElectricityEngineering

In a layout structure capable of independent supply of a substrate or well potential from a power supply potential, further reduction in layout area is achieved. A reinforcing power supply cell is inserted in a cell line in which a plurality of cells are arranged in series. Each of the cells includes an impurity doped region for supplying a substrate or well potential NWVDD which is different from a positive power supply potential VDD to a p-type transistor arranging region. The reinforcing power supply cell includes a power supply impurity doped region to which an impurity doped region of an adjacent cell is electrically connected and a power supply wire provided in a wiring layer formed above the power supply impurity doped region and electrically connected to the power supply impurity doped region.

Owner:SOCIONEXT INC

Semiconductor Device and Electronic Device Including Semiconductor Device

ActiveUS20100246750A1Suppress characteristicImprove the shortageTransistorStatic indicating devicesDriver circuitEngineering

It is an object to suppress deterioration in characteristics of a transistor in a driver cricuit. A driver circuit includes a first transistor, a second transistor including a gate and one of a source and a drain to which a second signal is inputted, a third transistor whose gate is electrically connected to one of a source and a drain of the first transistor and which controls whether a voltage state of an output signal is set or not by being turned on / off, and a fourth transistor whose gate is electrically connected to the other of the source and the drain of the second transistor and which controls whether a voltage state of an output signal is set or not by being turned on / off.

Owner:SEMICON ENERGY LAB CO LTD

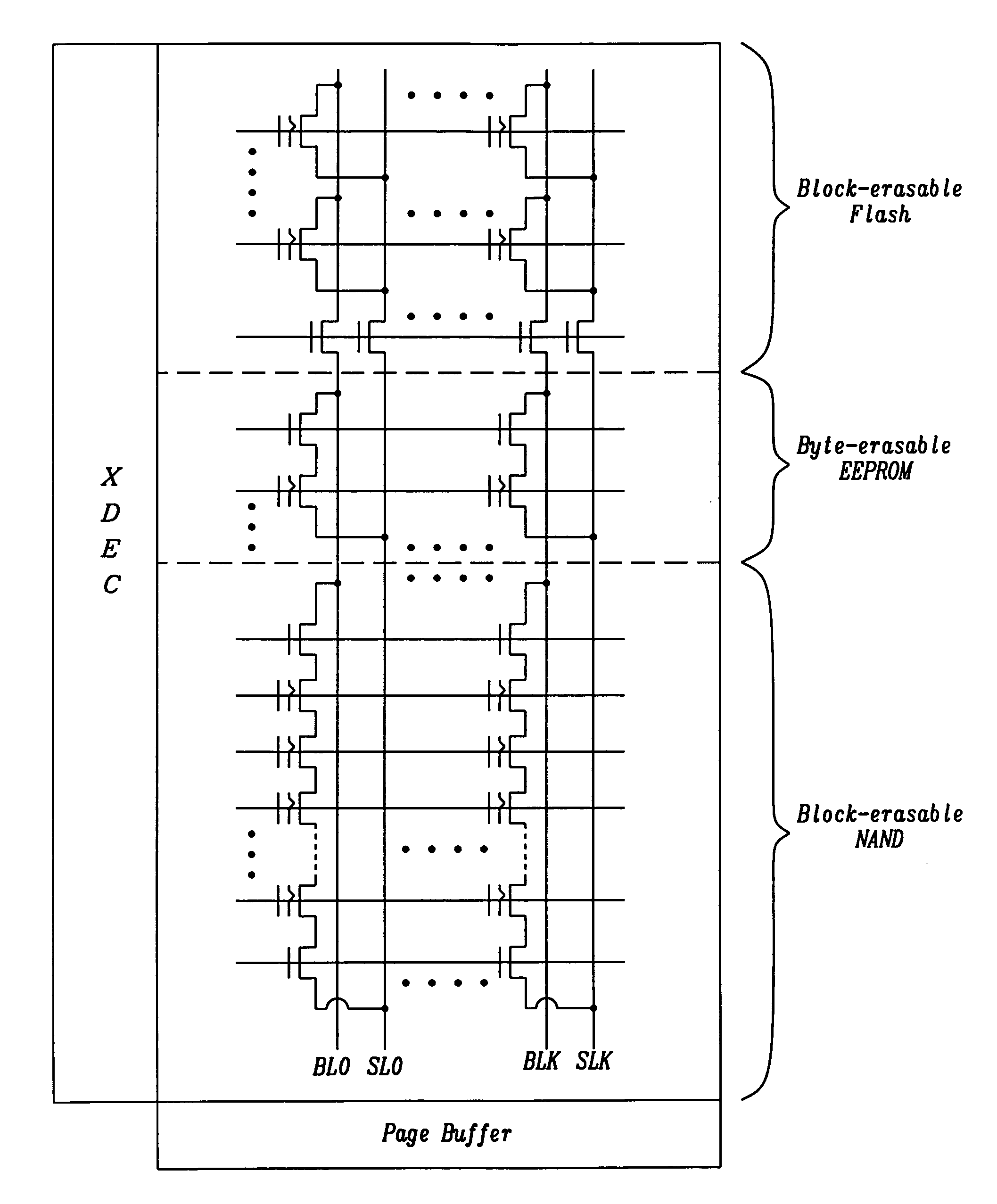

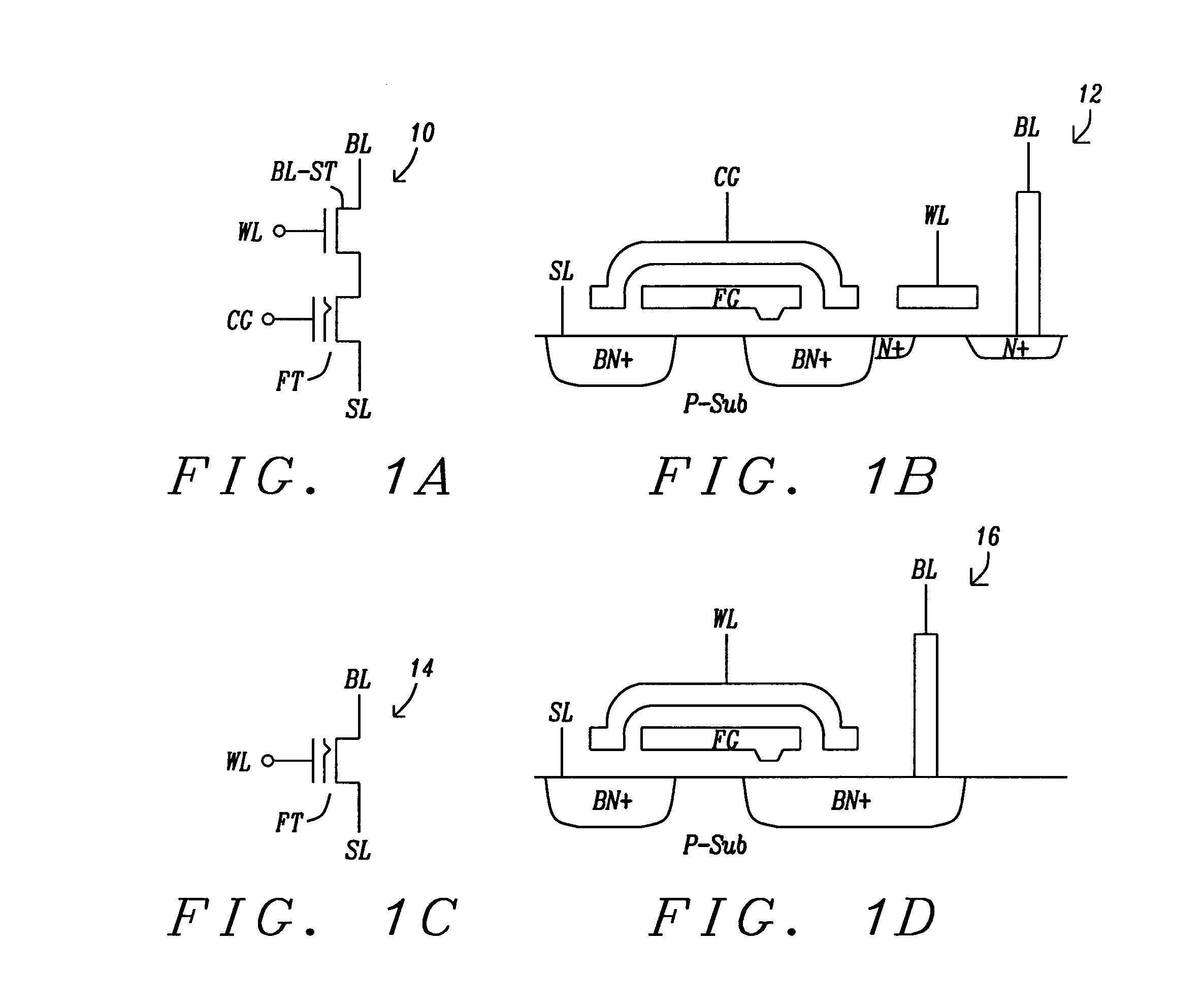

Most compact flotox-based combo NVM design without sacrificing EEPROM endurance cycles for 1-die data and code storage

InactiveUS20120063223A1Increase data rateReduce layout areaRead-only memoriesDigital storageByteComputer science

Disclosed is a low-cost hybrid storage solution that allows Code like sector-alterable NOR and Data like block-alterable NAND and byte-alterable EEPROM being integrated on a same die. The disclosed combo NVM design of the present invention is a truly Data-oriented NVM design that allows 2T-EEPROM to integrate both 0.5T-NAND and 1T-NOR without sacrificing any EEPROM's byte-write performance in the same die. The invention provides several new embodiment sets of preferable bias conditions of Program, Program-Inhibit, Erase and Erase-Inhibit for operating bit-write, byte-write, sector-write and page-write for several preferable Flotox-based EEPROM, NOR and NAND or combo NVM arrays that include types of shared SL, 8-pair BLs and SLS, with or without GBL, normally Erased Vt and Programmed Vt, or the reversed Erased-Vt or Programmed-Vt, etc. Further disclosed is a flexible X-decoder design to allow the flexible selection of pages to be erased to save erase time. Also disclosed is using on-chip negative voltage for FT's gate along with the less positive HV applied to FTs' channel region for same write performance but with the benefits of channel length reduction in cell and less BVDS electric requirement in peripheral devices for more scalable manufacturing process.

Owner:APLUS FLASH TECH

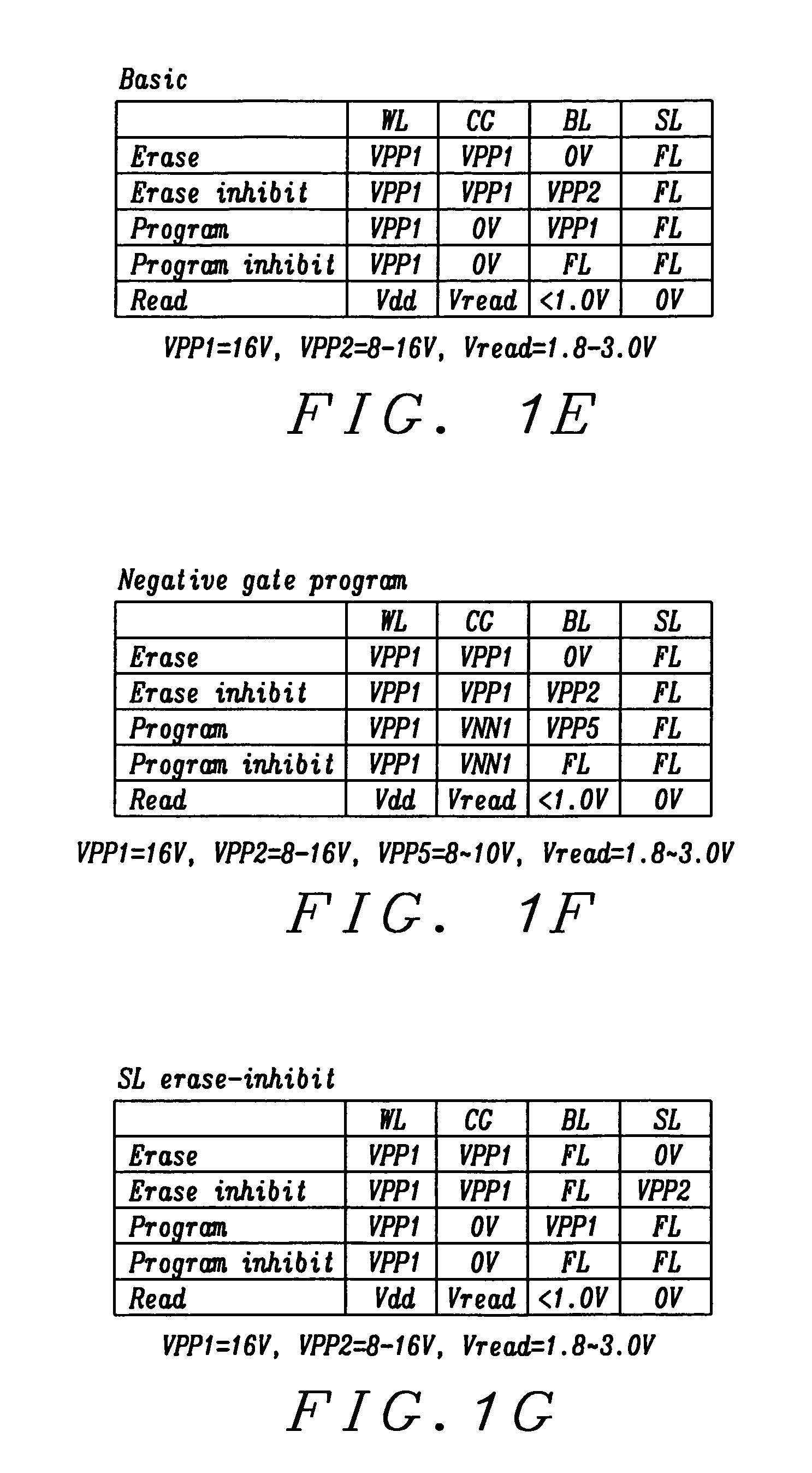

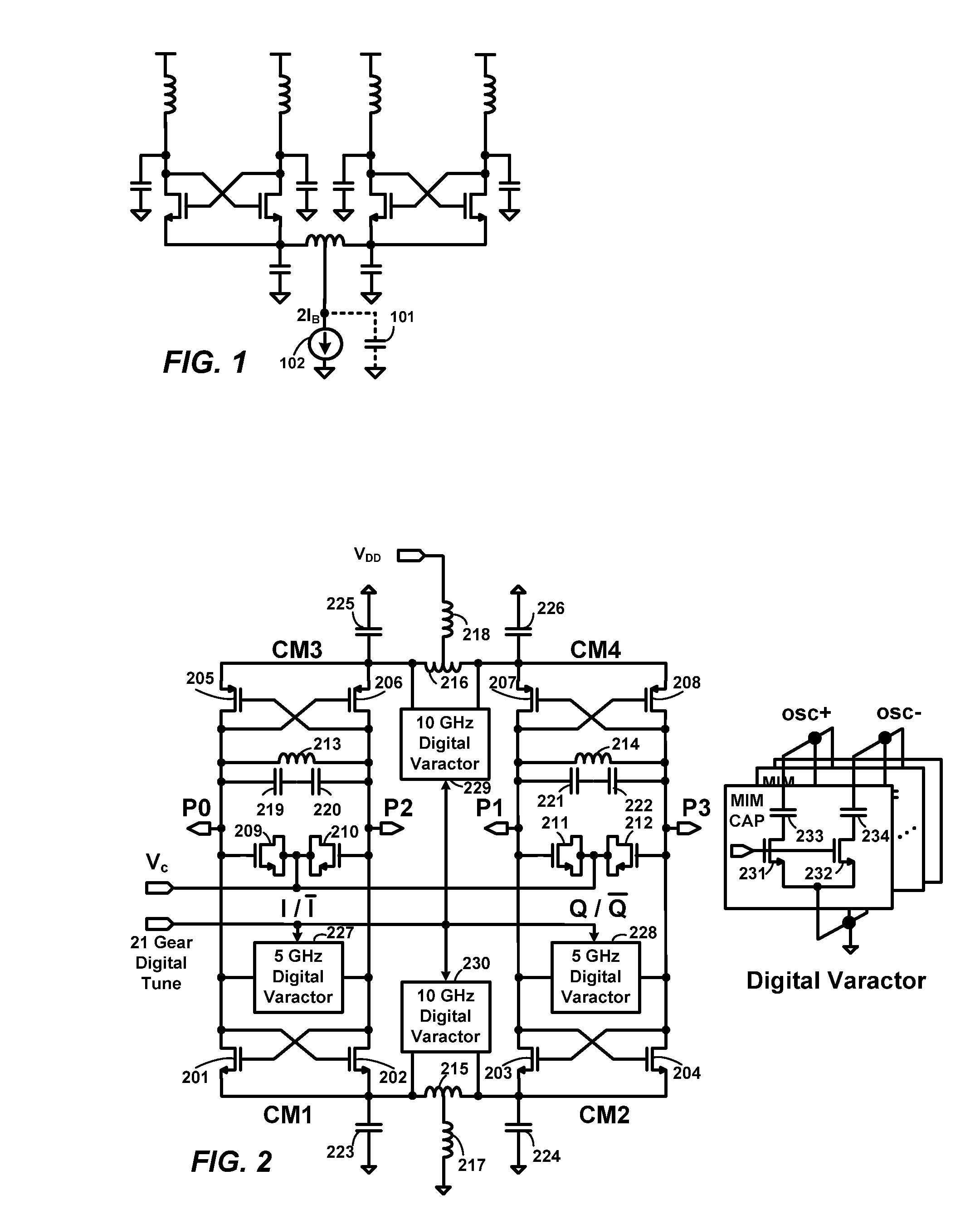

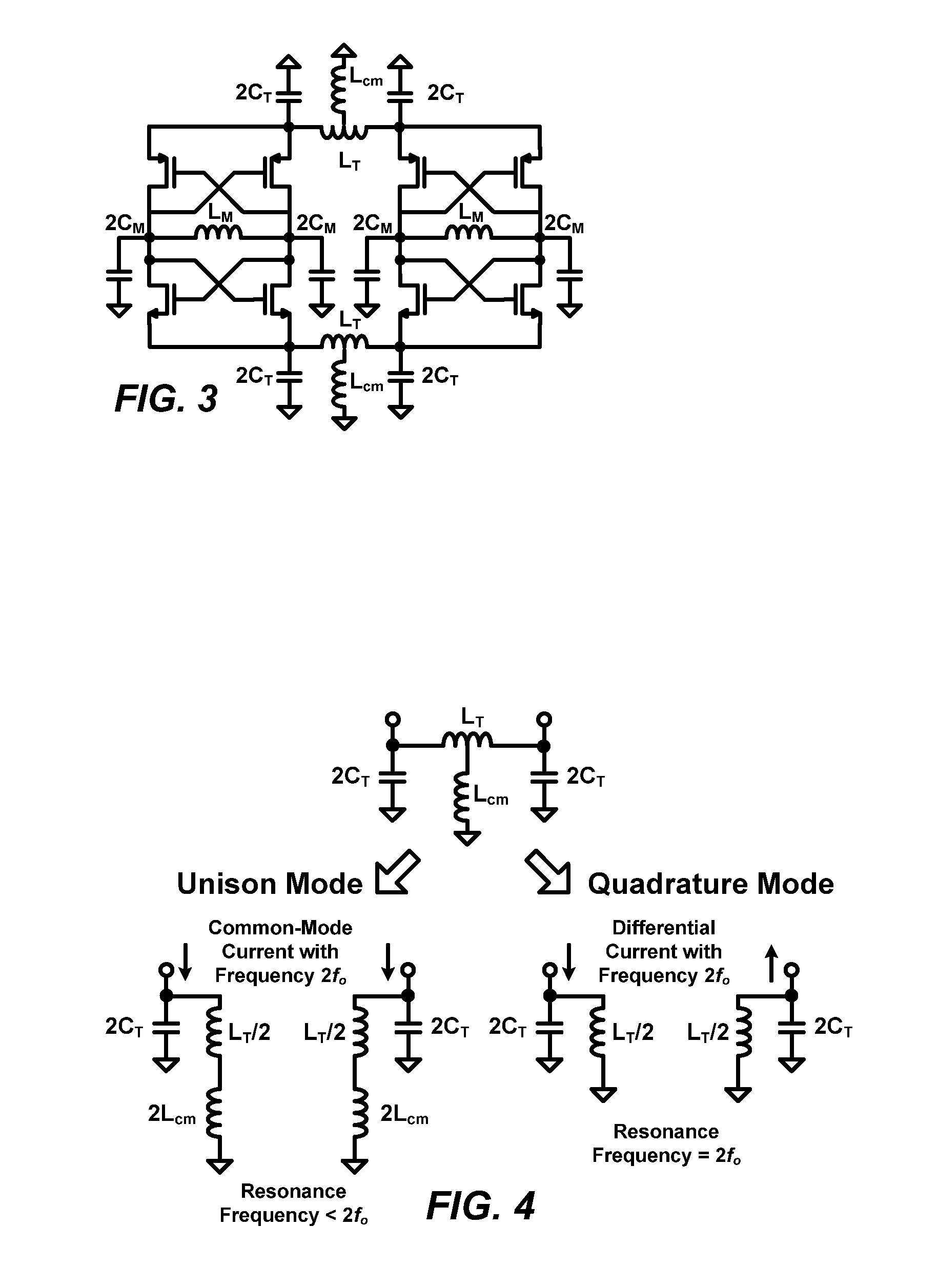

Low Phase-Noise Oscillator

InactiveUS20080143446A1Reduce impactTotal current dropPulse automatic controlElectric pulse generatorPhase noiseCoupling

A tail-tank coupling technique combines two complementary differential LC-VCOs to form a quadrature LC-VCO. The technique reduces phase noise by providing additional energy storage for noise redistribution and by cancelling noise injected by transistors when they operate in the triode region. The resulting noise factor is close to the theoretical minimum 1+γ, similar to a differential LC-VCO driven by an ideal noiseless current source. However, its figure-of-merit is higher, due to the absence of voltage head-room being consumed by a current source. The optimal ratio of tail-tank capacitor to main-tank capacitor for minimizing phase noise is approximately 0.5. The method can be extended to combine any even number of LC tanks resonating at fo and 2fo to form an integrated oscillator producing quadrature phase at frequency fosc and differential output at 2fosc.

Owner:WILLSON ALAN N JR

Liquid Crystal Display Device and Electronic Device Including the Same

ActiveUS20100182226A1Avoid failureReduce decreaseTransistorStatic indicating devicesDriver circuitLiquid-crystal display

A driver circuit includes first to third transistors, a first circuit, and a second circuit. In the first transistor, a first terminal is electrically connected to a second wiring, a second terminal is electrically connected to a first wiring, and a gate is electrically connected to the second circuit and a first terminal of the third transistor. In the second transistor, a first terminal is electrically connected to the first wiring, a second terminal is electrically connected to a sixth wiring, a gate is electrically connected to the first circuit and a gate of the third transistor. A second terminal of the third transistor is electrically connected to the sixth wiring. The first circuit is electrically connected to a third wiring, a fourth wiring, a fifth wiring, and the sixth wiring. The second circuit is electrically connected to the first wiring, the second wiring, and the sixth wiring.

Owner:SEMICON ENERGY LAB CO LTD