Patents

Literature

908results about How to "Reduce chip area" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

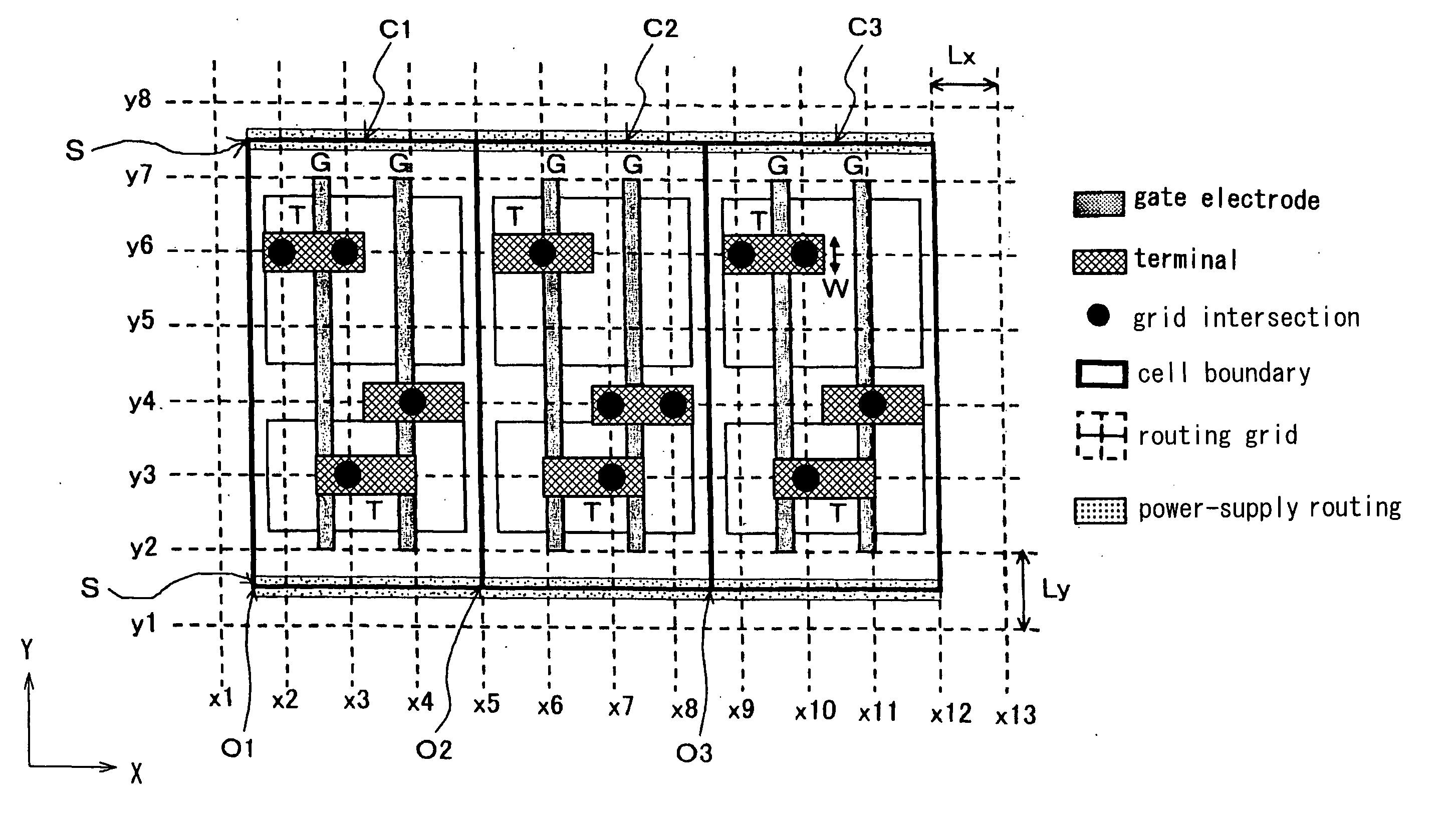

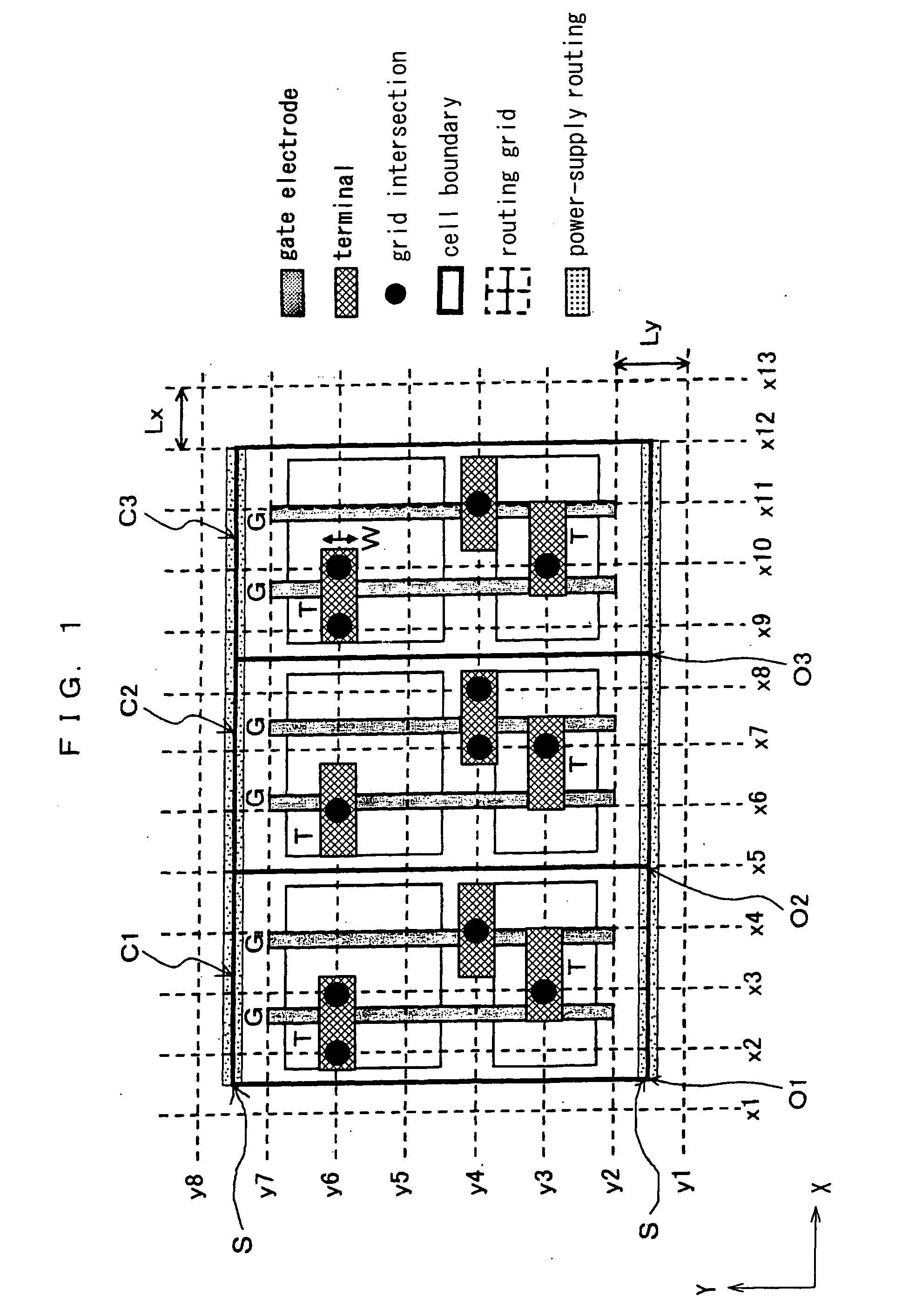

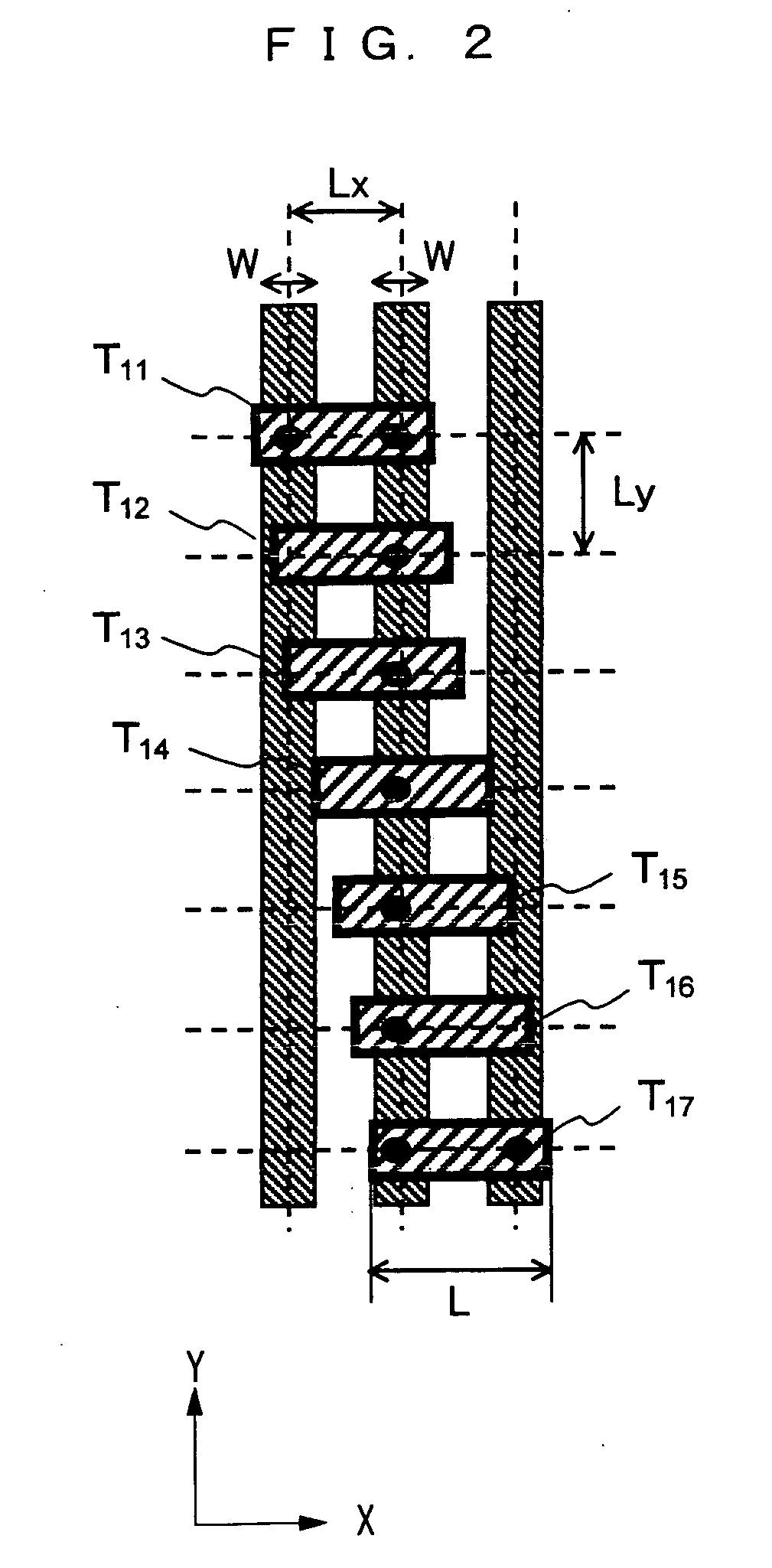

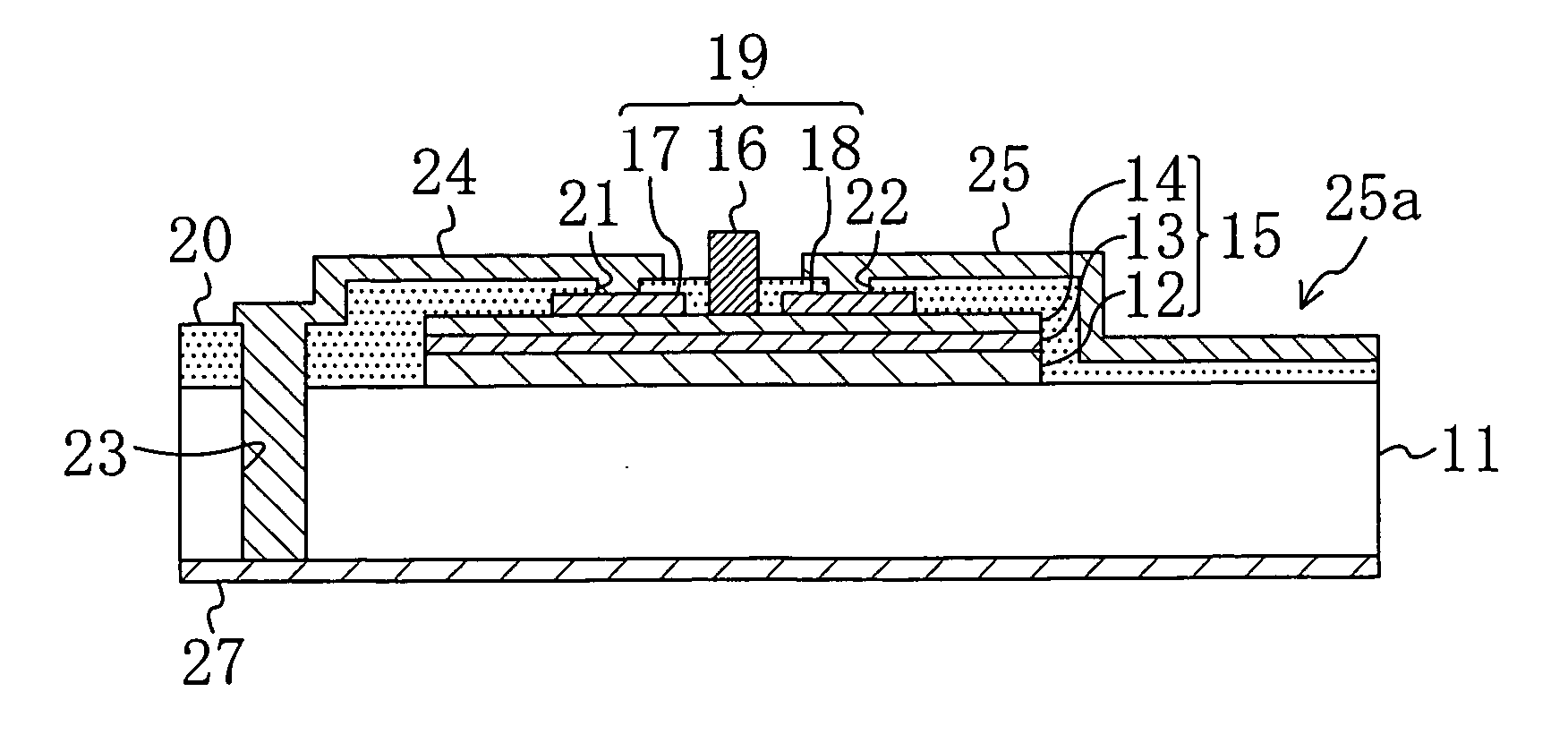

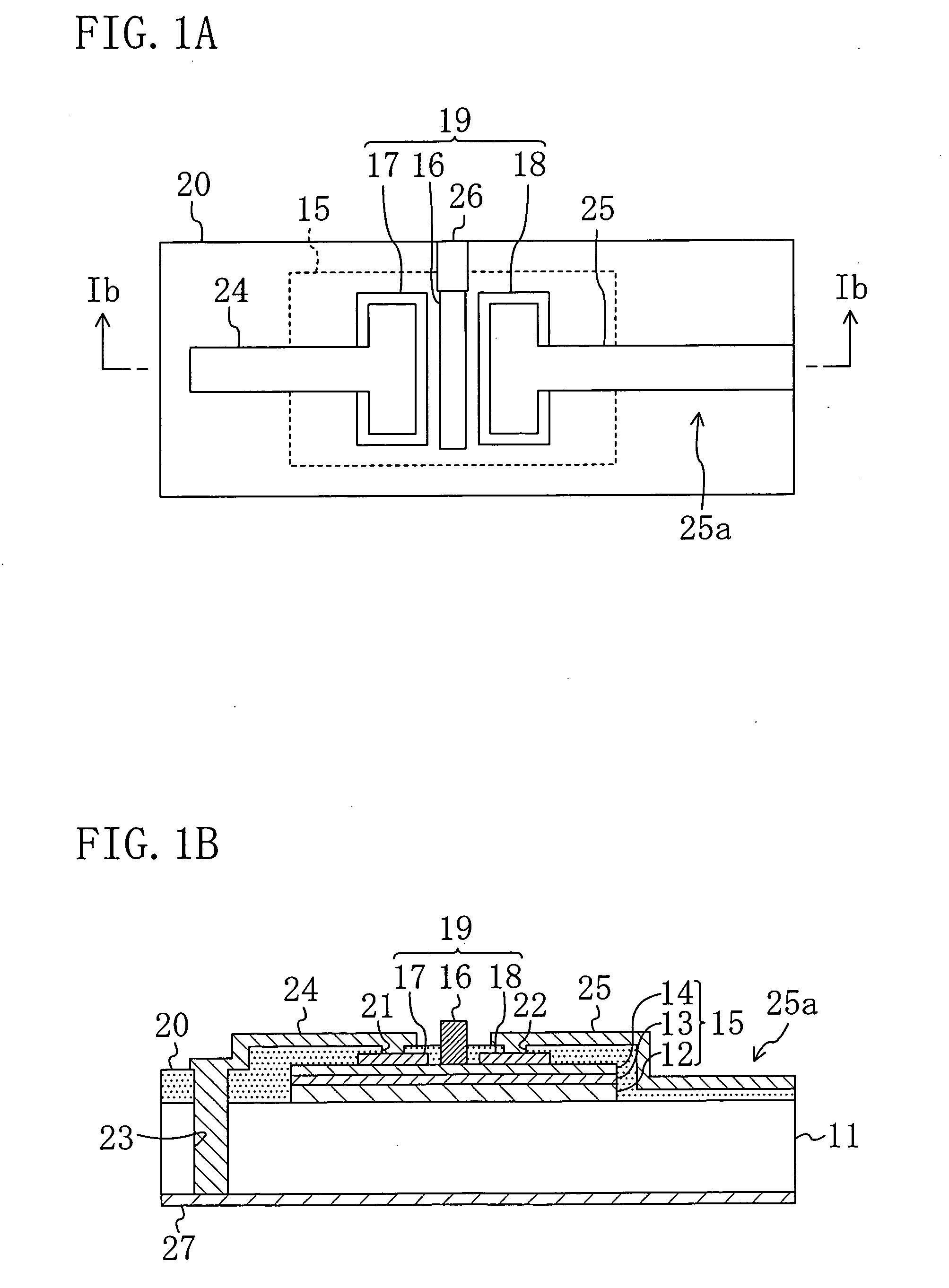

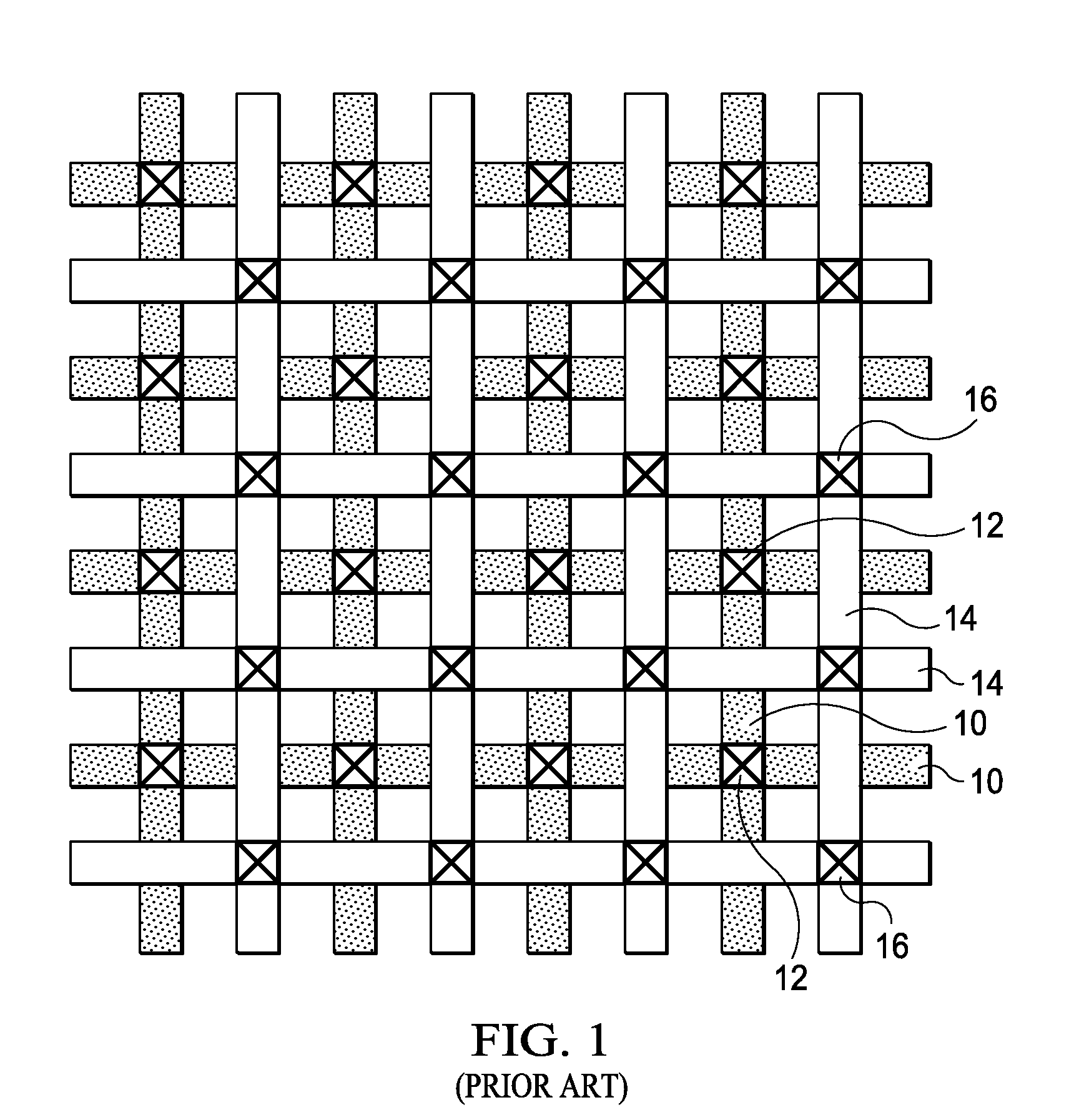

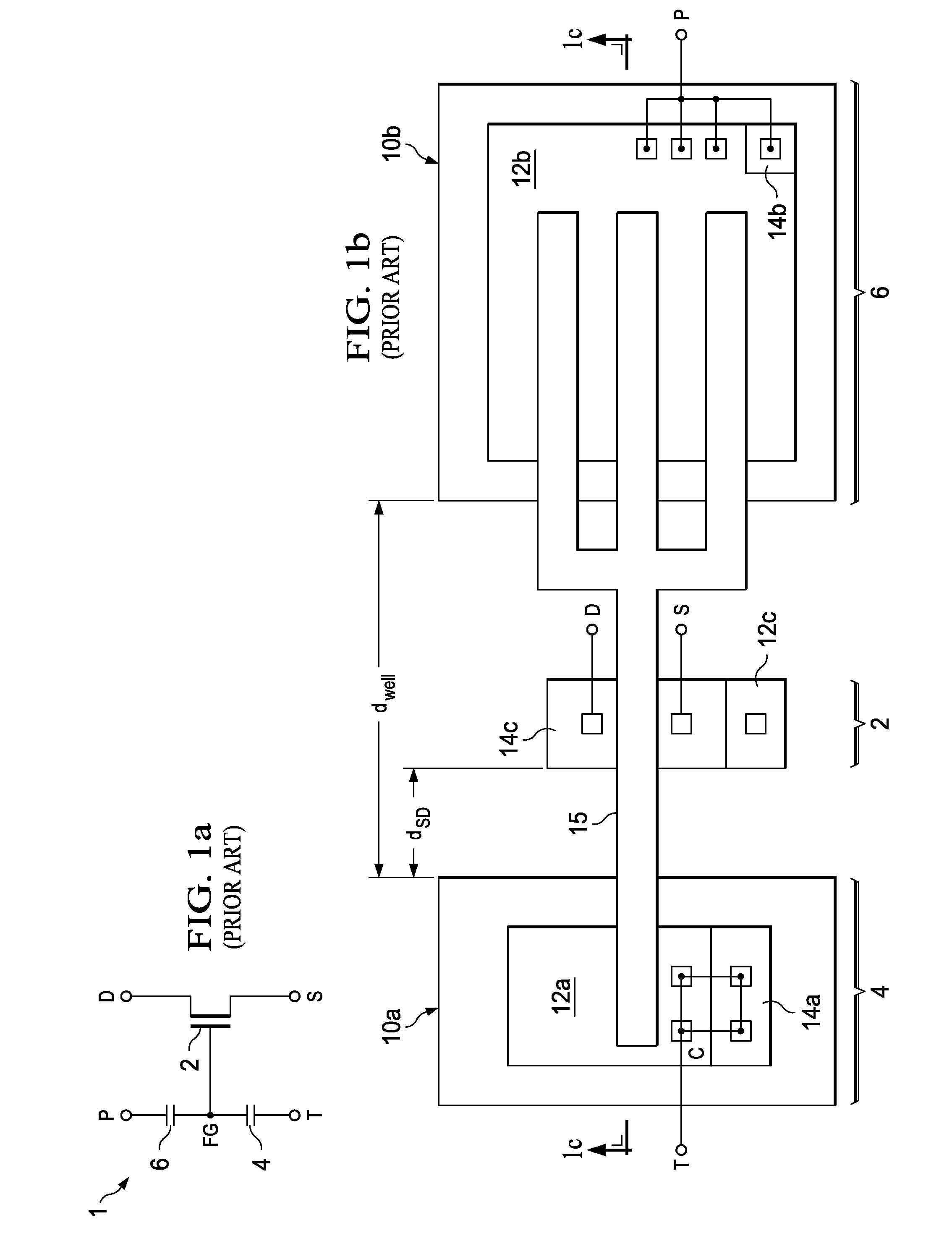

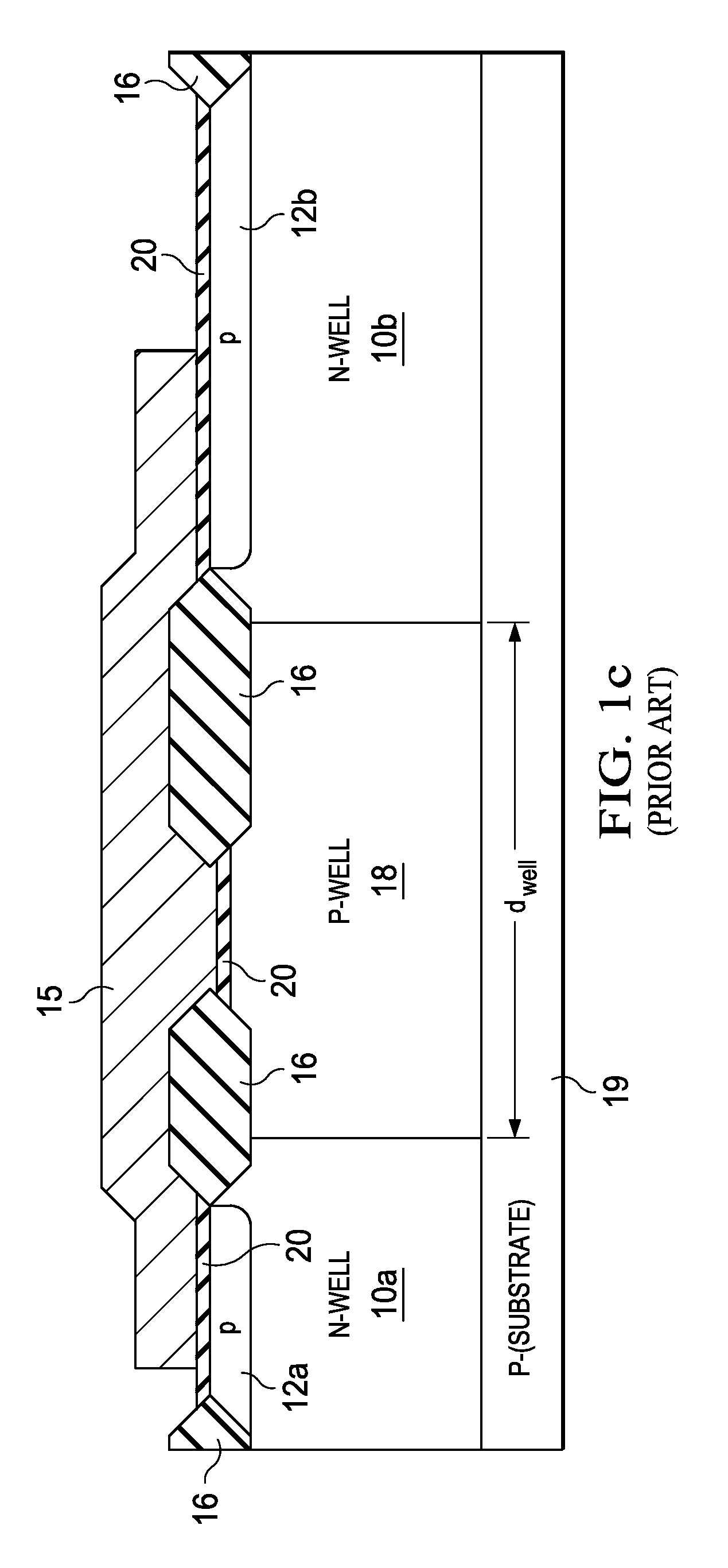

Cell, standard cell, standard cell library, a placement method using standard cell, and a semiconductor integrated circuit

ActiveUS20060136848A1Reducing cell area areaReduce chip areaSolid-state devicesProgram controlEngineeringSemiconductor

A cell according to the present invention comprises a plurality of terminals capable of transmitting an input signal or an output signal and serving as a minimum unit in designing a semiconductor integrated circuit, wherein the plurality of terminals is located on routing grids lined in a Y direction which is a direction vertical to a power-supply wiring of the cell used in automatic placement & routing and has a shape extended in an X direction which is a direction in parallel with the power-supply wiring, more specifically such a shape that, for example, a longer-side dimension of the terminal is equal to “a routing grid interval in the X direction+a wiring width. According to the constitution, a cell area is reduced, which advantageously leads to the reduction of a chip area.

Owner:SOCIONEXT INC

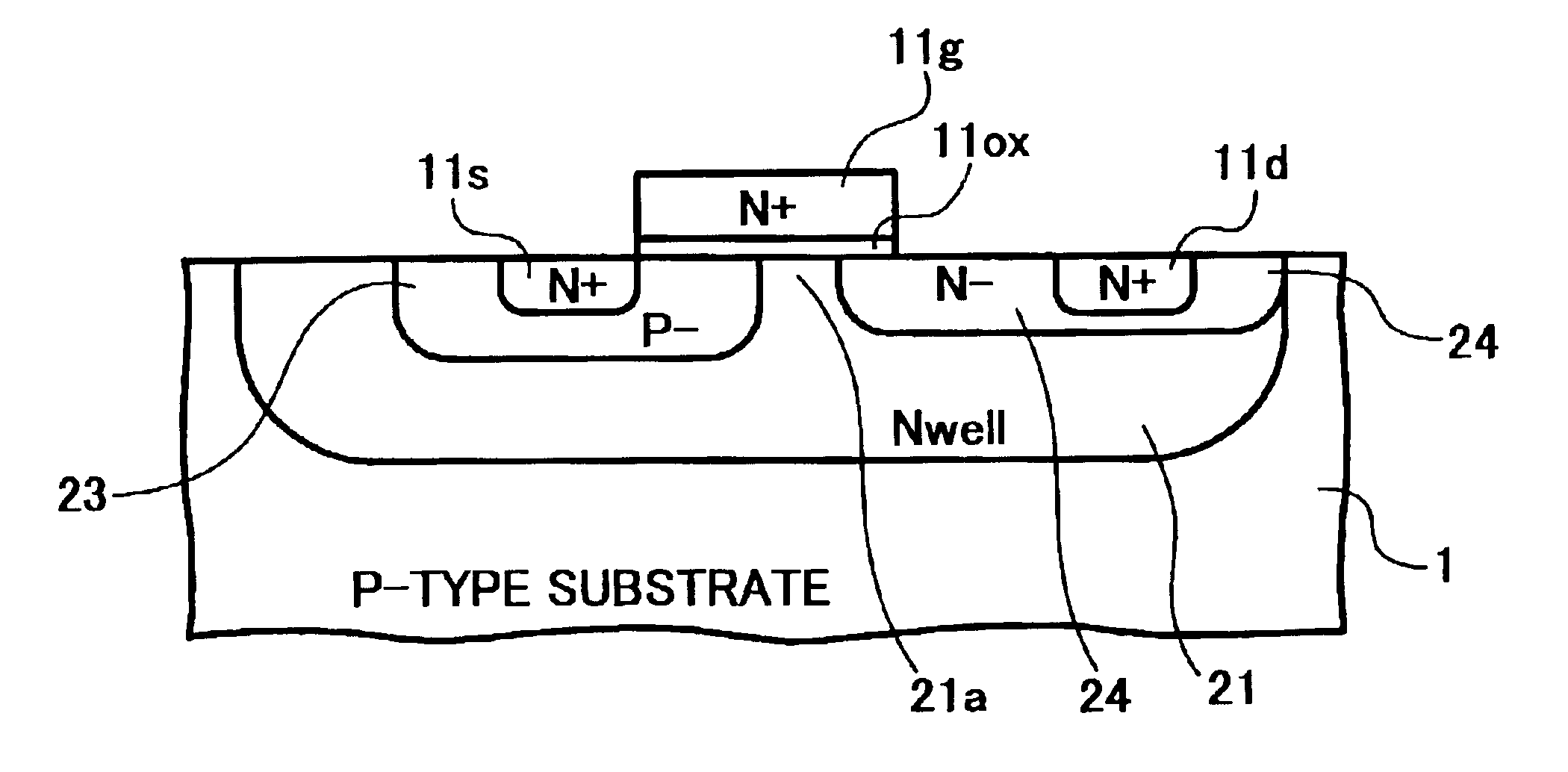

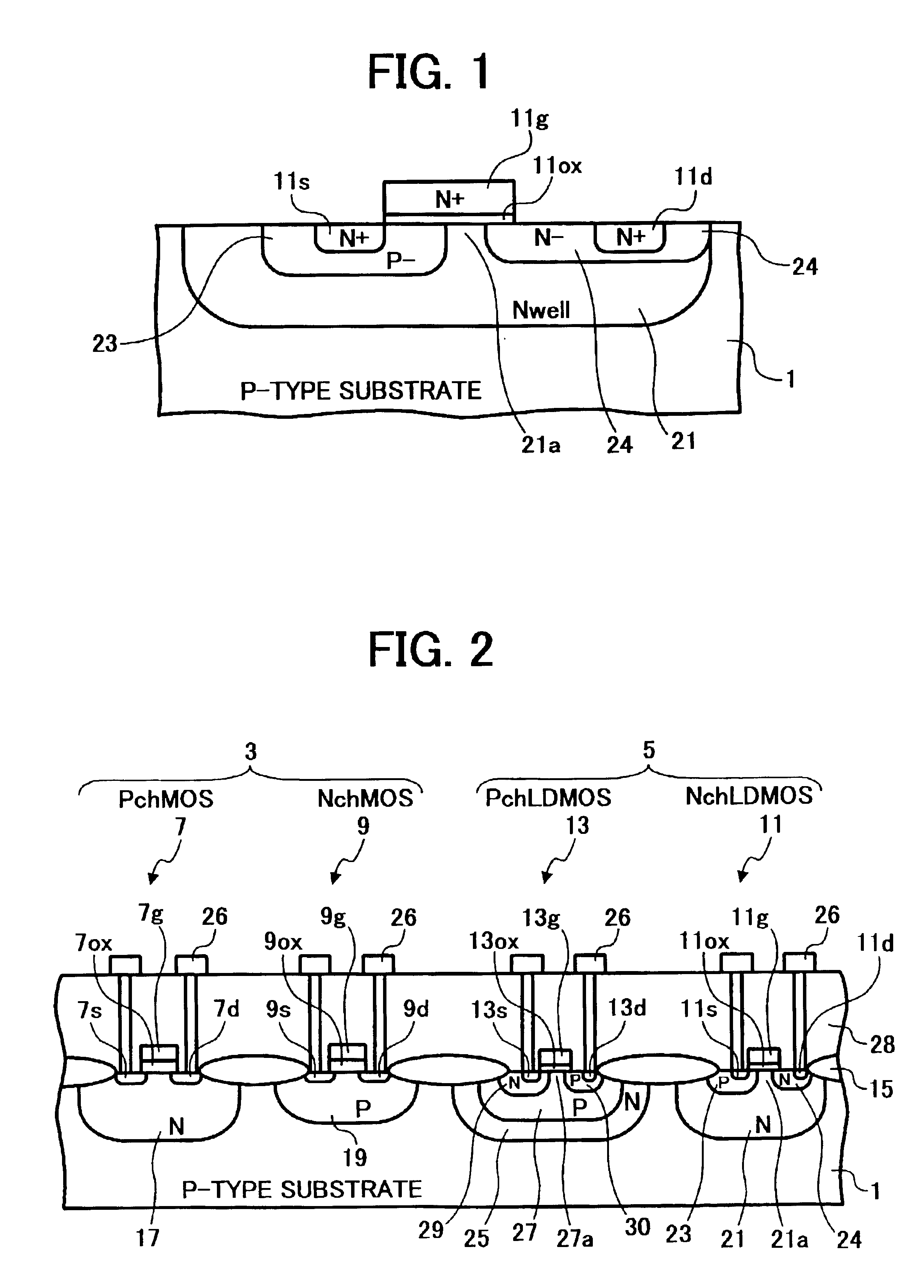

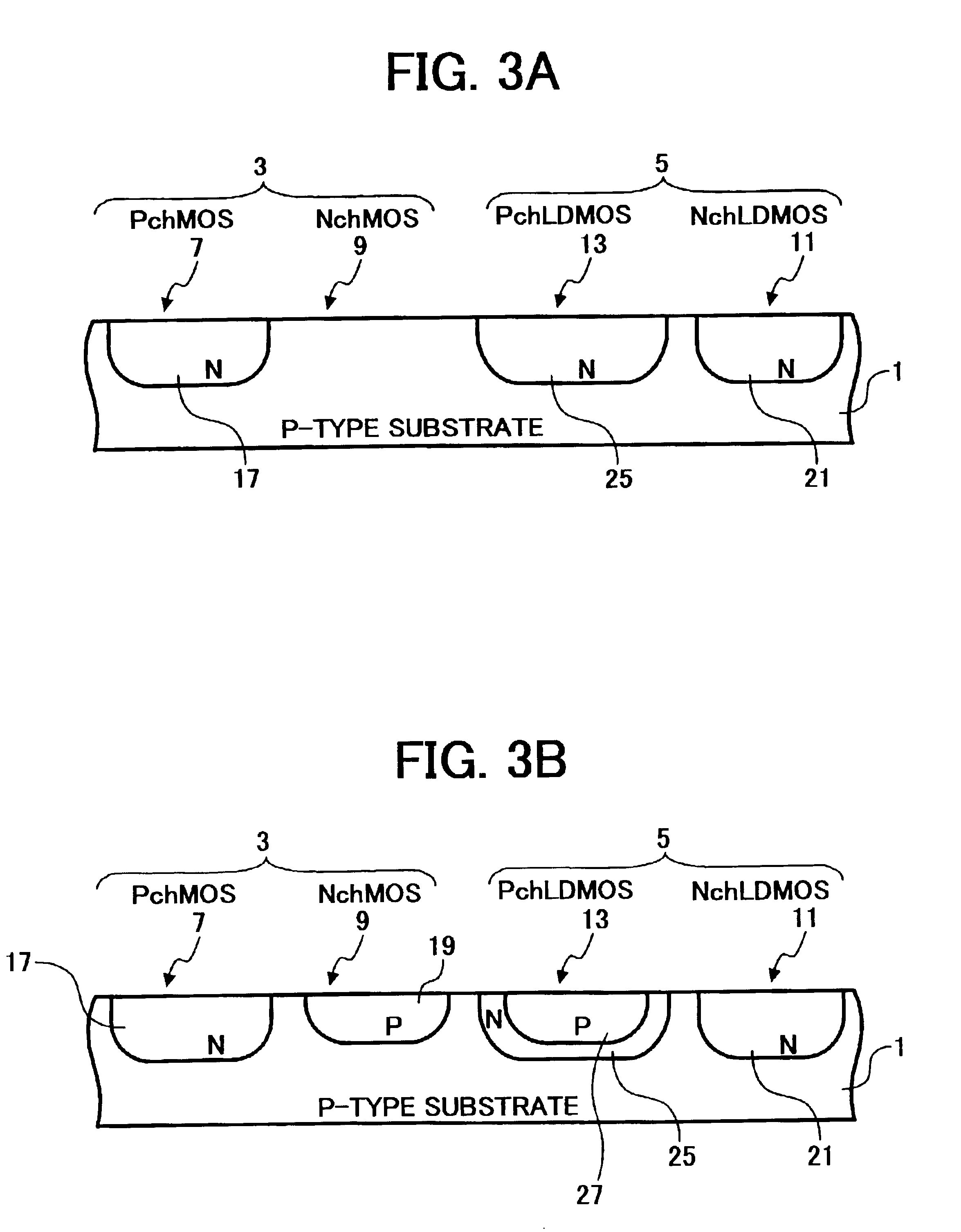

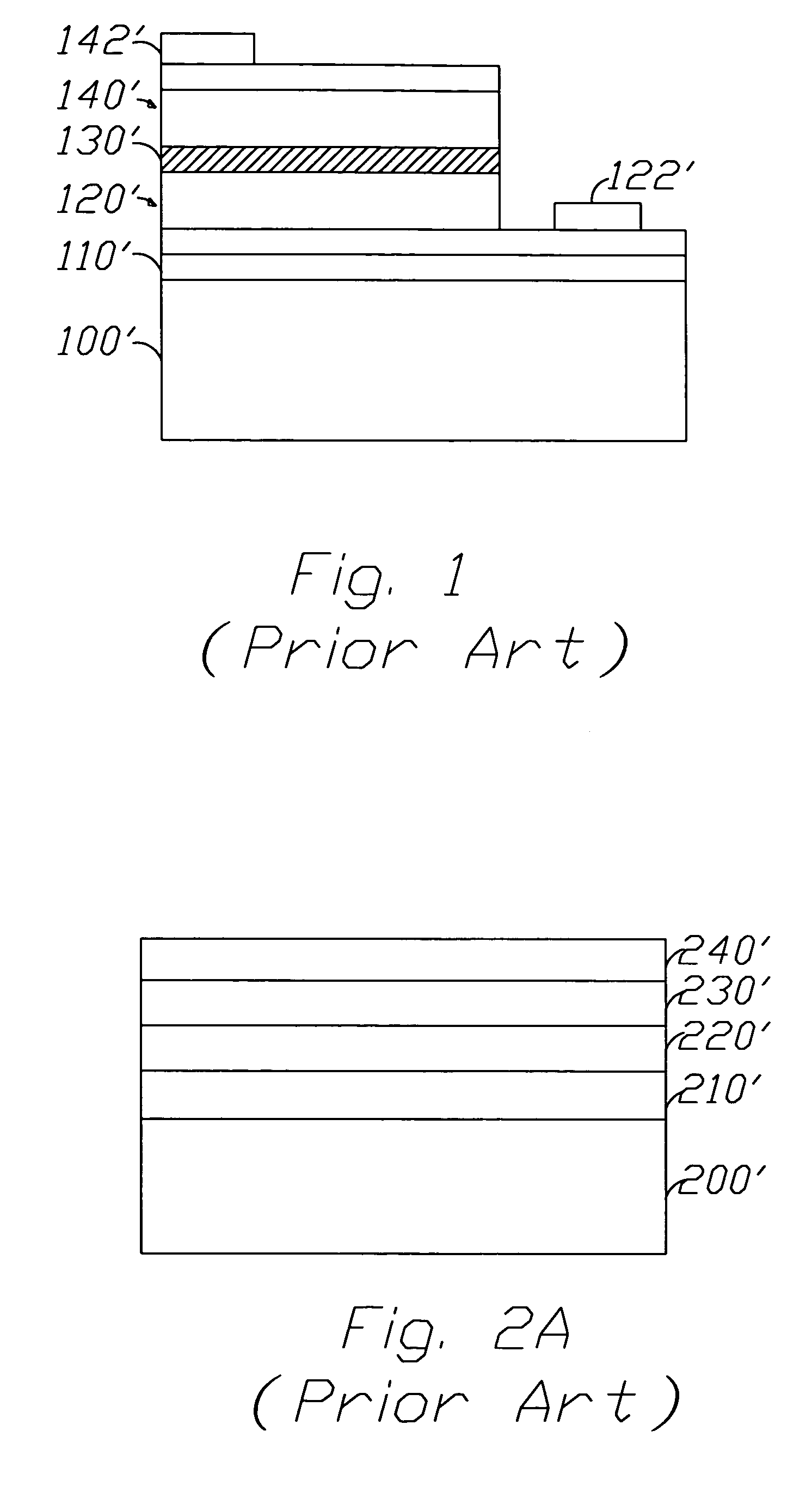

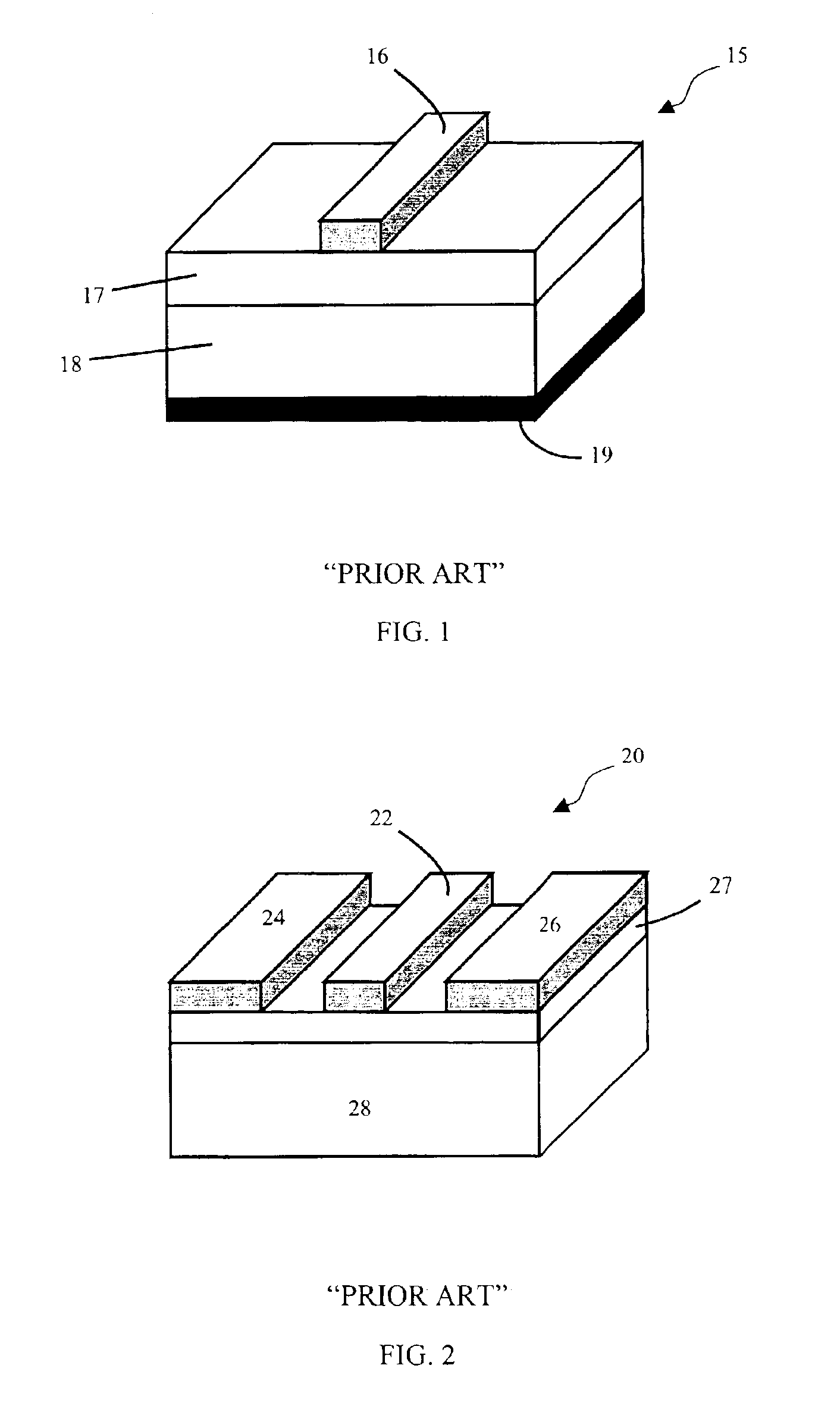

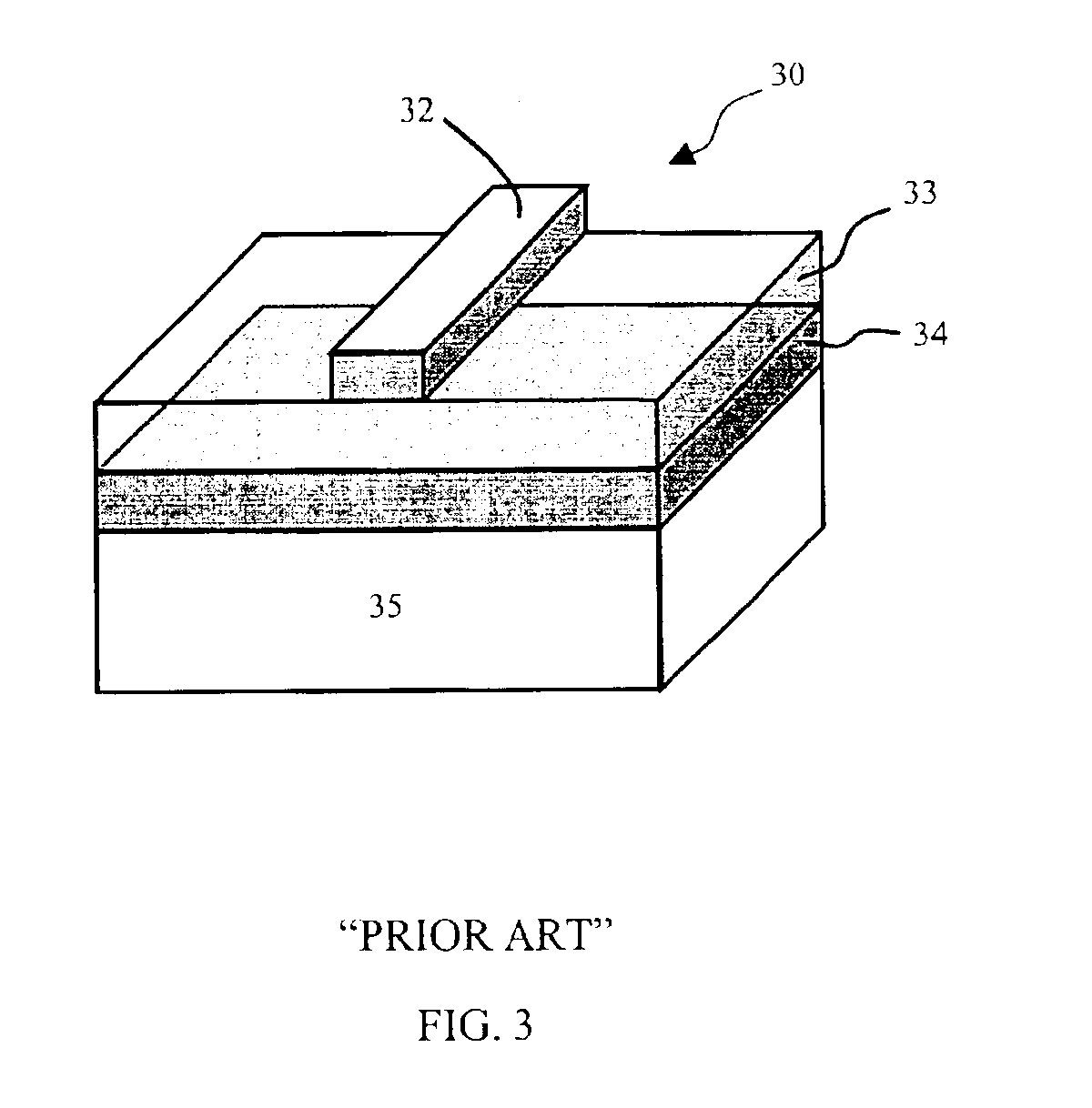

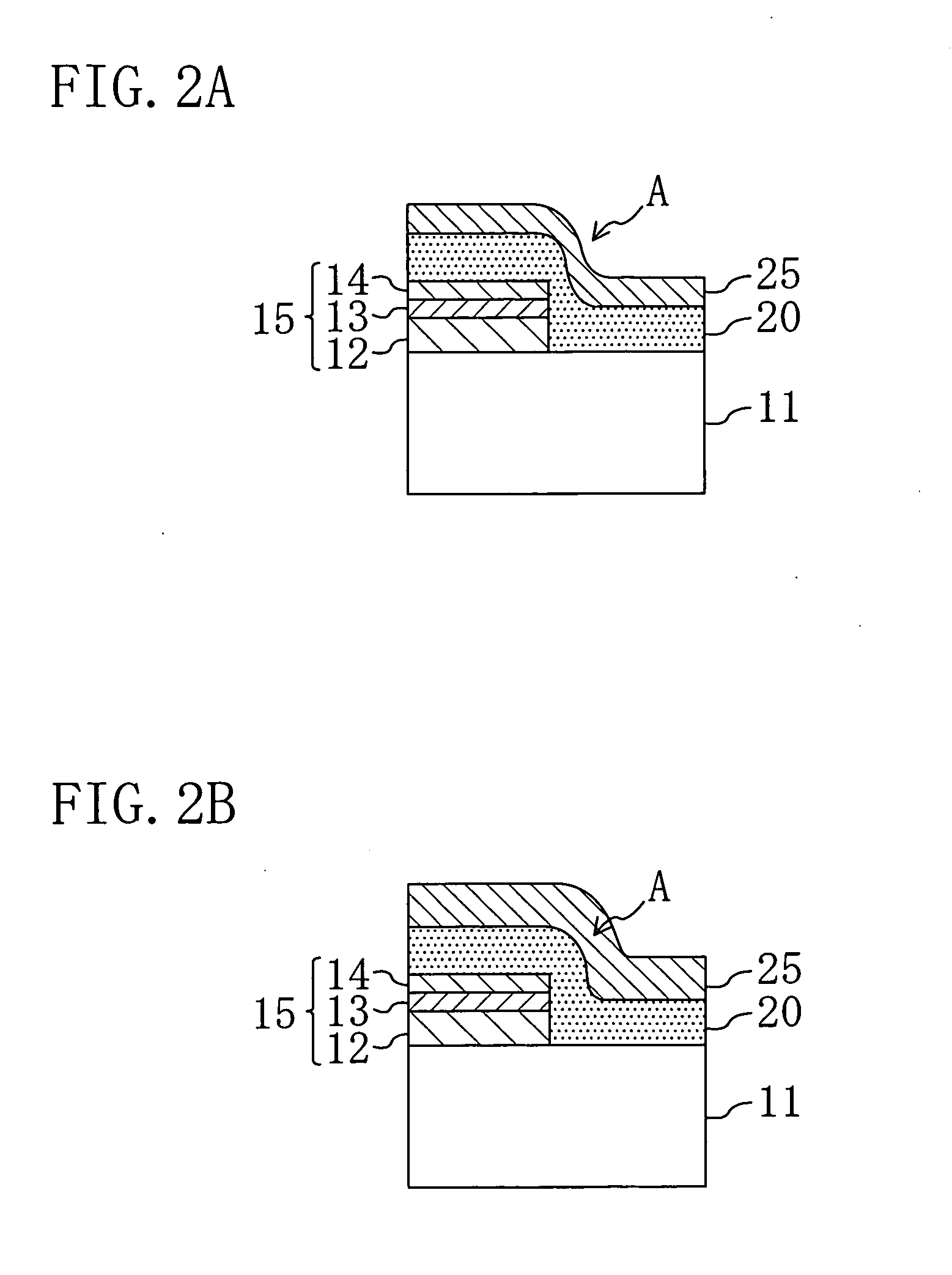

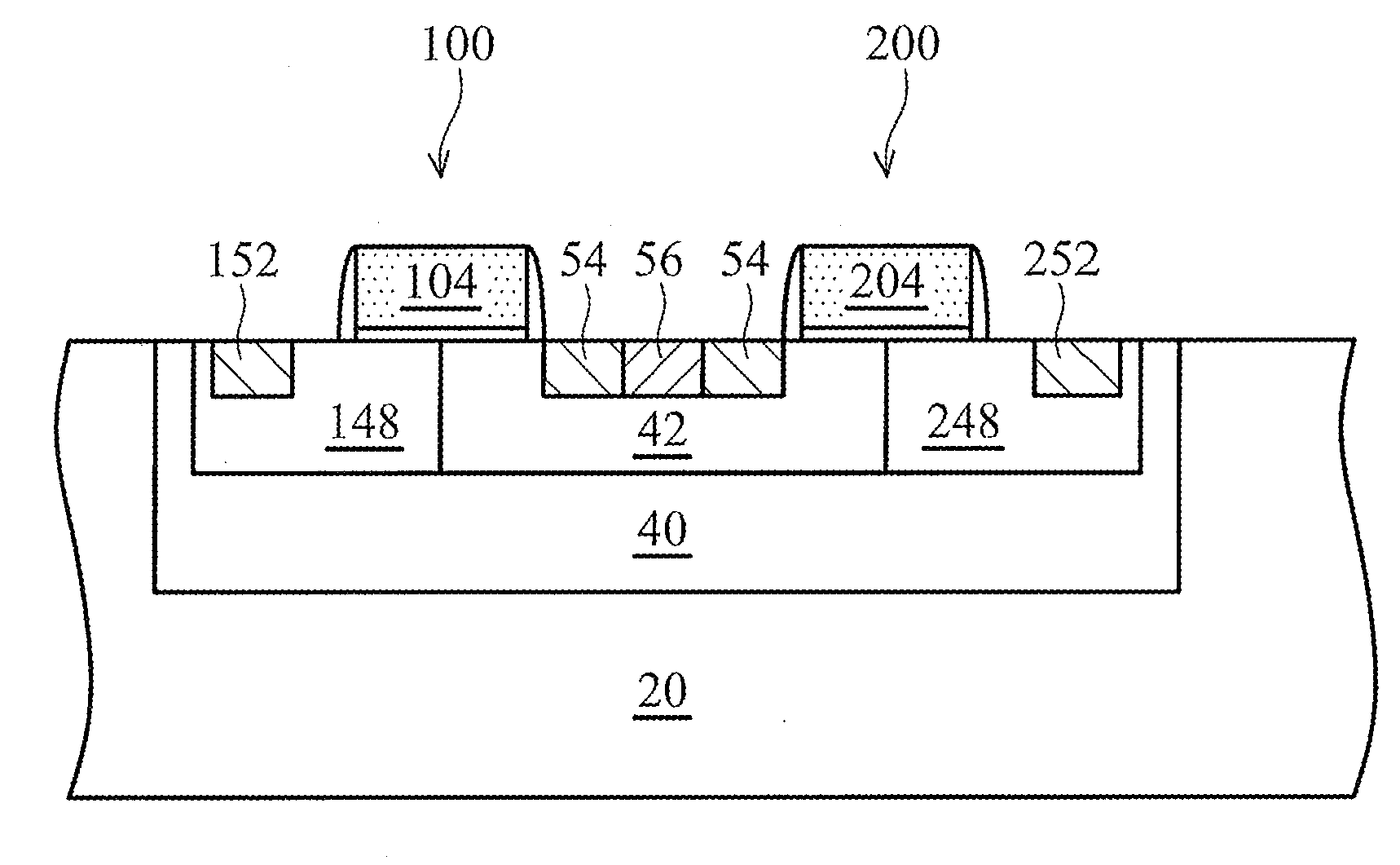

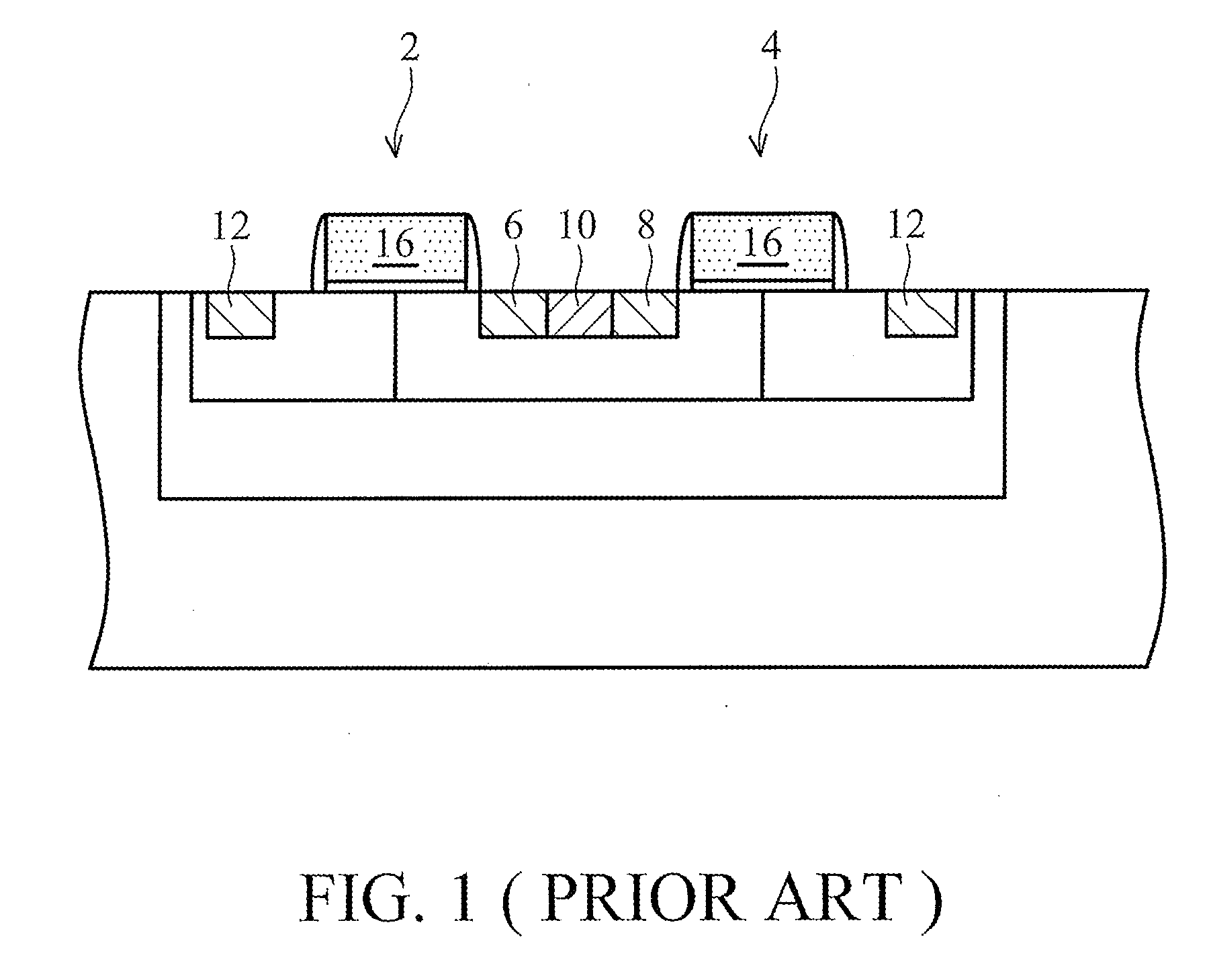

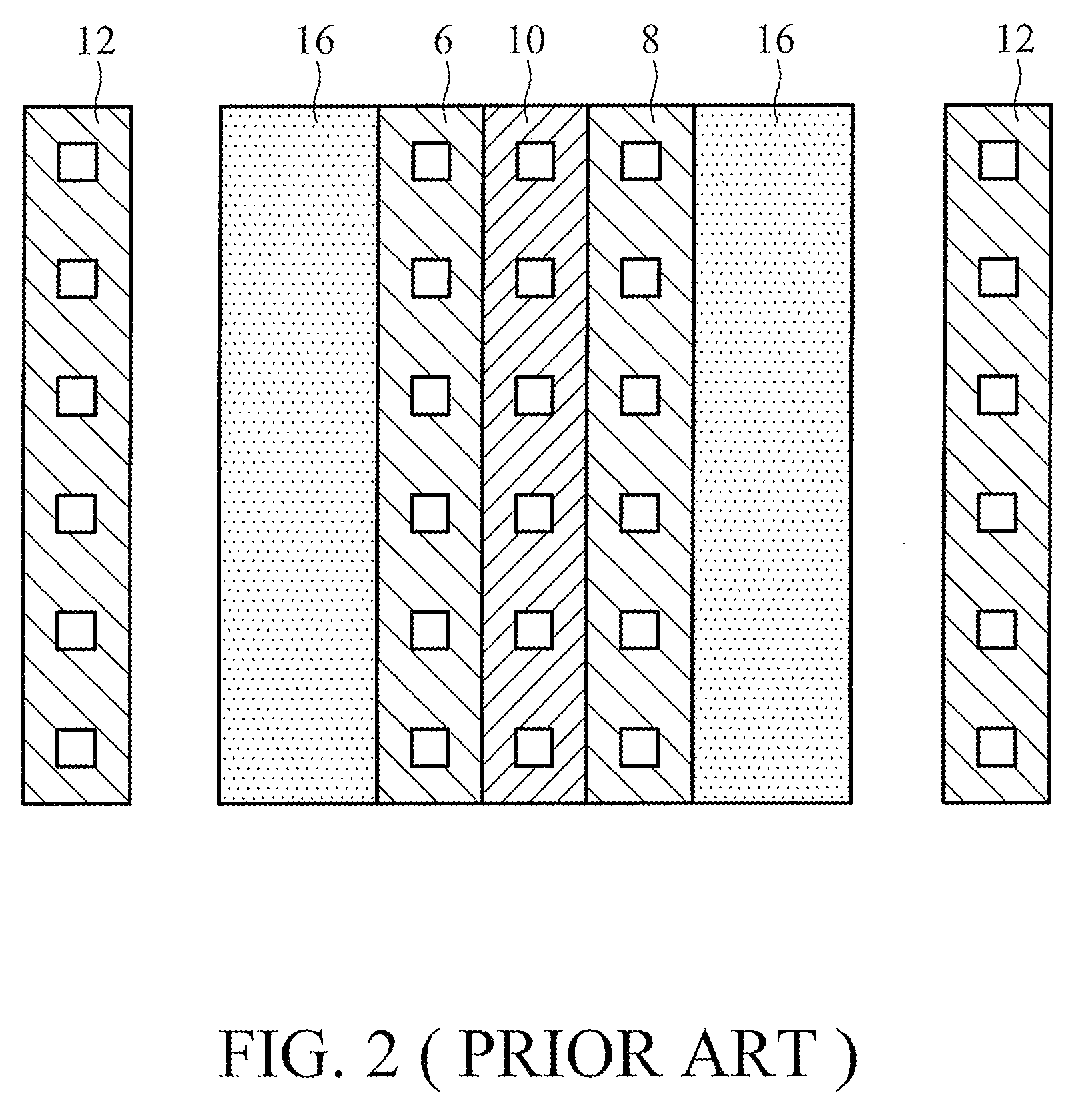

Semiconductor device and method for fabricating such device

InactiveUS6911694B2Stable operational characteristicAvoid layeringTransistorSolid-state devicesLDMOSGate dielectric

An LDMOS transistor and a bipolar transistor with LDMOS structures are disclosed for suitable use in high withstand voltage device applications, among others. The LDMOS transistor includes a drain well region 21 formed in P-type substrate 1, and also formed therein spatially separated one another are a channel well region 23 and a medium concentration drain region 24 having an impurity concentration larger than that of drain well region 21, which are simultaneously formed having a large diffusion depth through thermal processing. A source 11s is formed in channel well region 23, while a drain 11d is formed in drain region 24 having an impurity concentration larger than that of drain region 24. In addition, a gate electrode 11g is formed over the well region, overlying the partially overlapped portions with well region 23 and drain region 24 and being separated from drain 11d. Since the source 11s, well region 23, and drain region 24 are respectively self-aligned to the gate electrode 11g, resultant transistor characteristics are stabilized, and the decrease in the on resistance and improved drain threshold voltages can be achieved. Also disclosed herein are bipolar transistors with LDMOS structures, which are capable of obviating the breakdown of gate dielectric layers even at high applied voltage and achieving improved stability in transistor characteristics.

Owner:RICOH KK

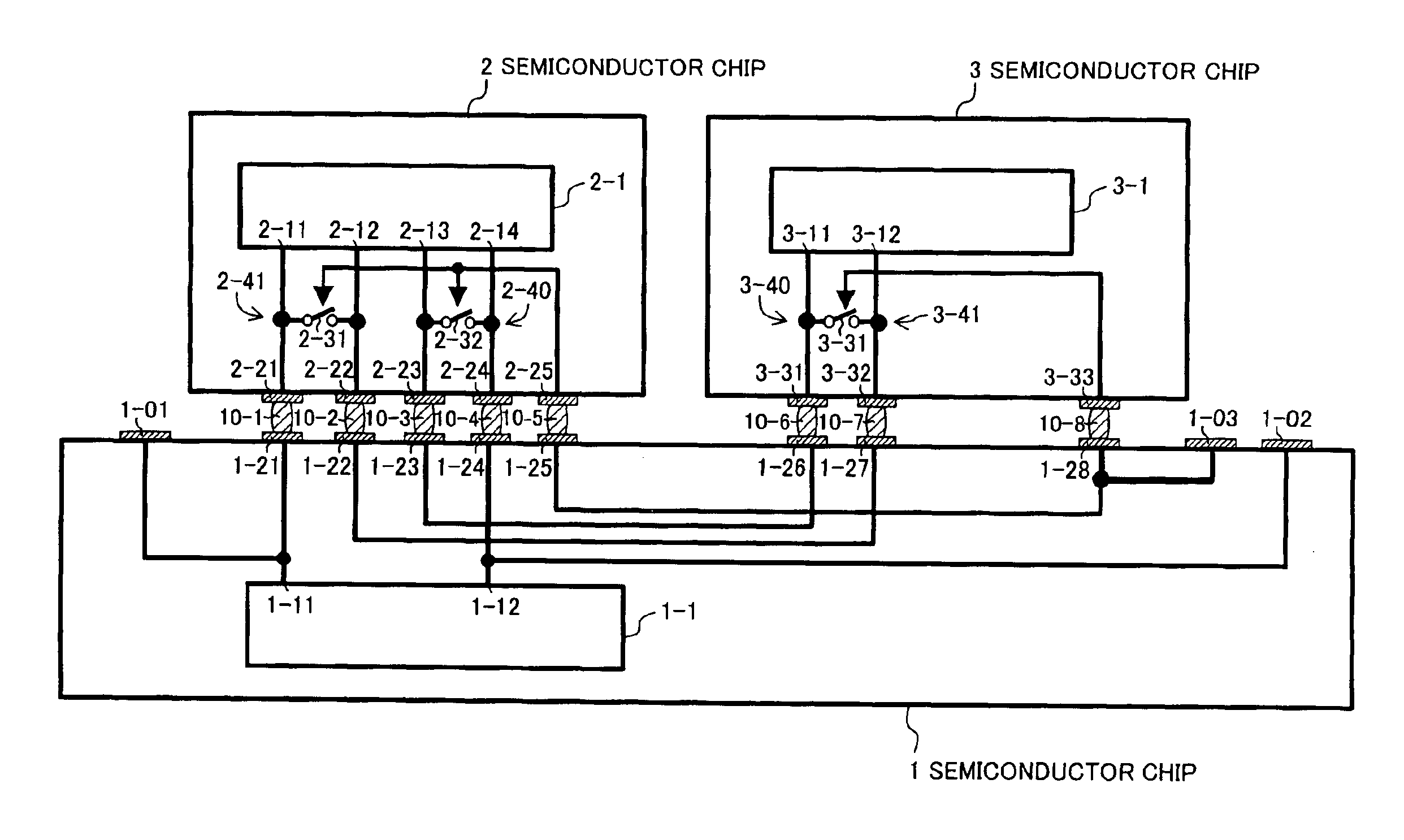

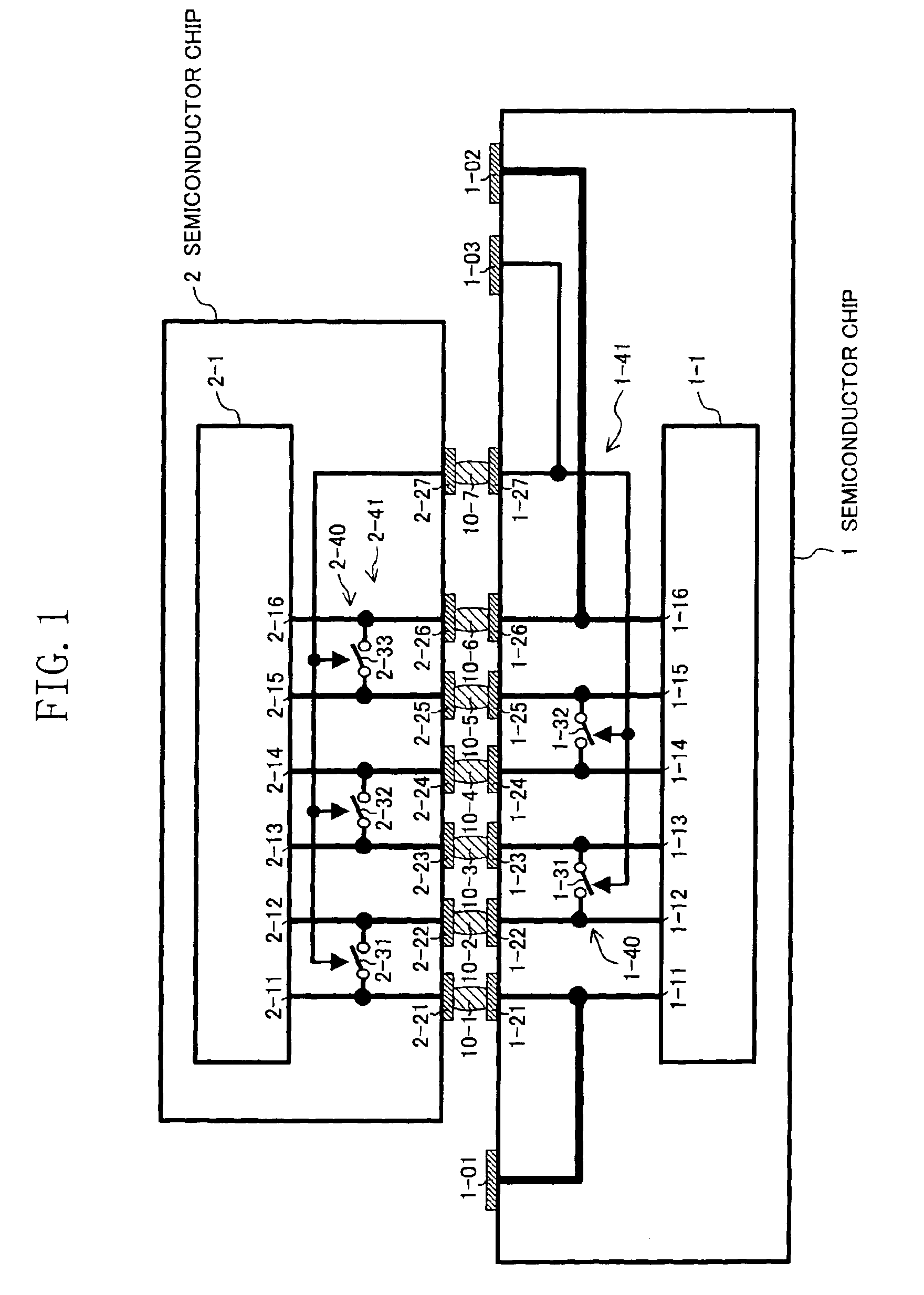

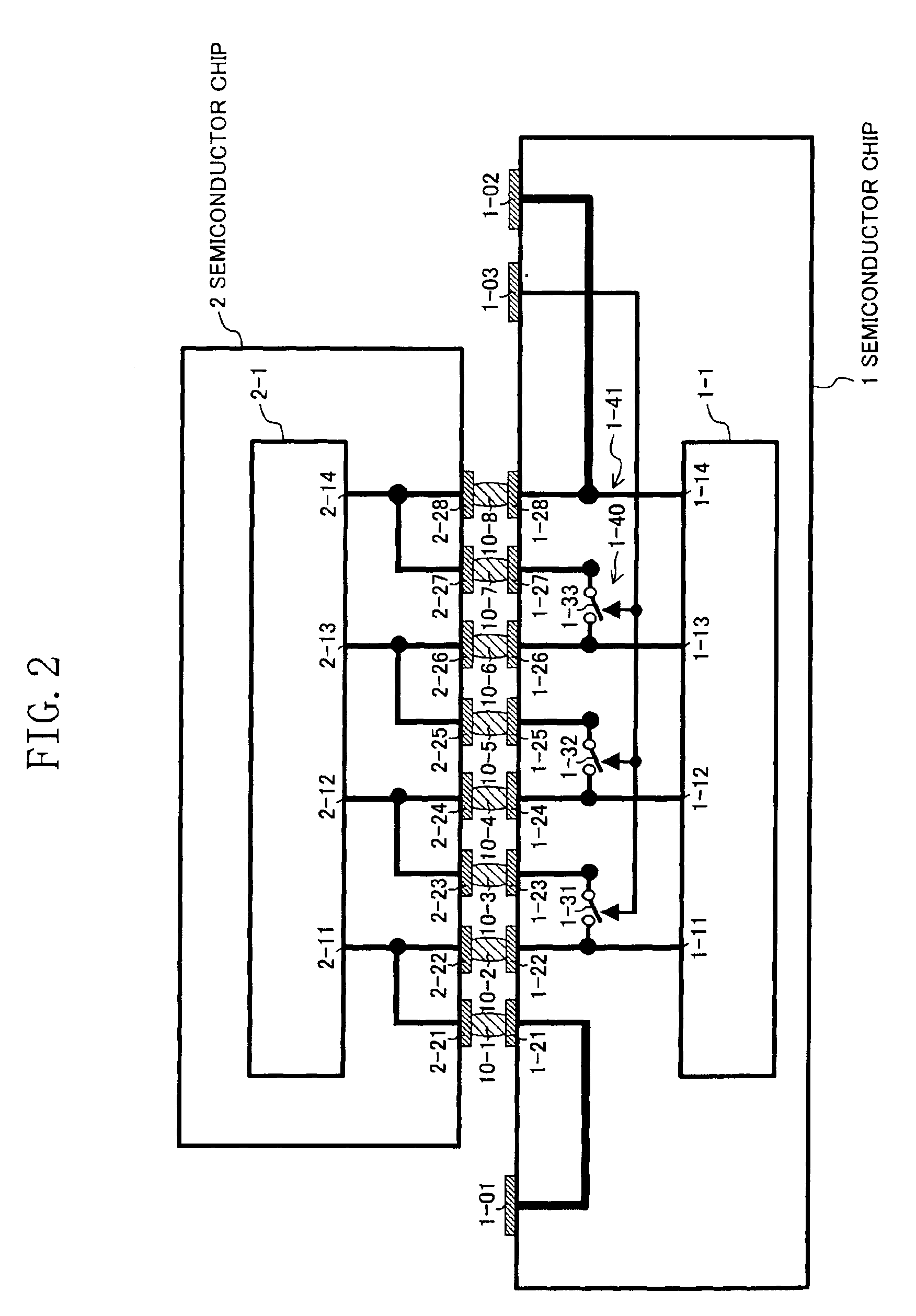

Multi-chip module, semiconductor chip, and interchip connection test method for multi-chip module

InactiveUS6914259B2Reduce chip areaAvoid crosstalkElectronic circuit testingSemiconductor/solid-state device detailsSemiconductor chipMulti-chip module

A multi-chip module is implemented by connecting a plurality of connection pads provided on, for example, two semiconductor chips via a plurality of conductive connecting members. To carry out a test for determining the quality of the connection between the two semiconductor chips, the multi-chip module is further provided with a plurality of switch elements so that the plurality of connecting members can be electrically conducted in a serial manner via the connection pads of the semiconductor chips. During the connection test, all the switch elements are turned on, and the impedance between both ends of the line including the plurality of connecting members conducted in a serial manner is measured using two probing pads.

Owner:PANASONIC CORP

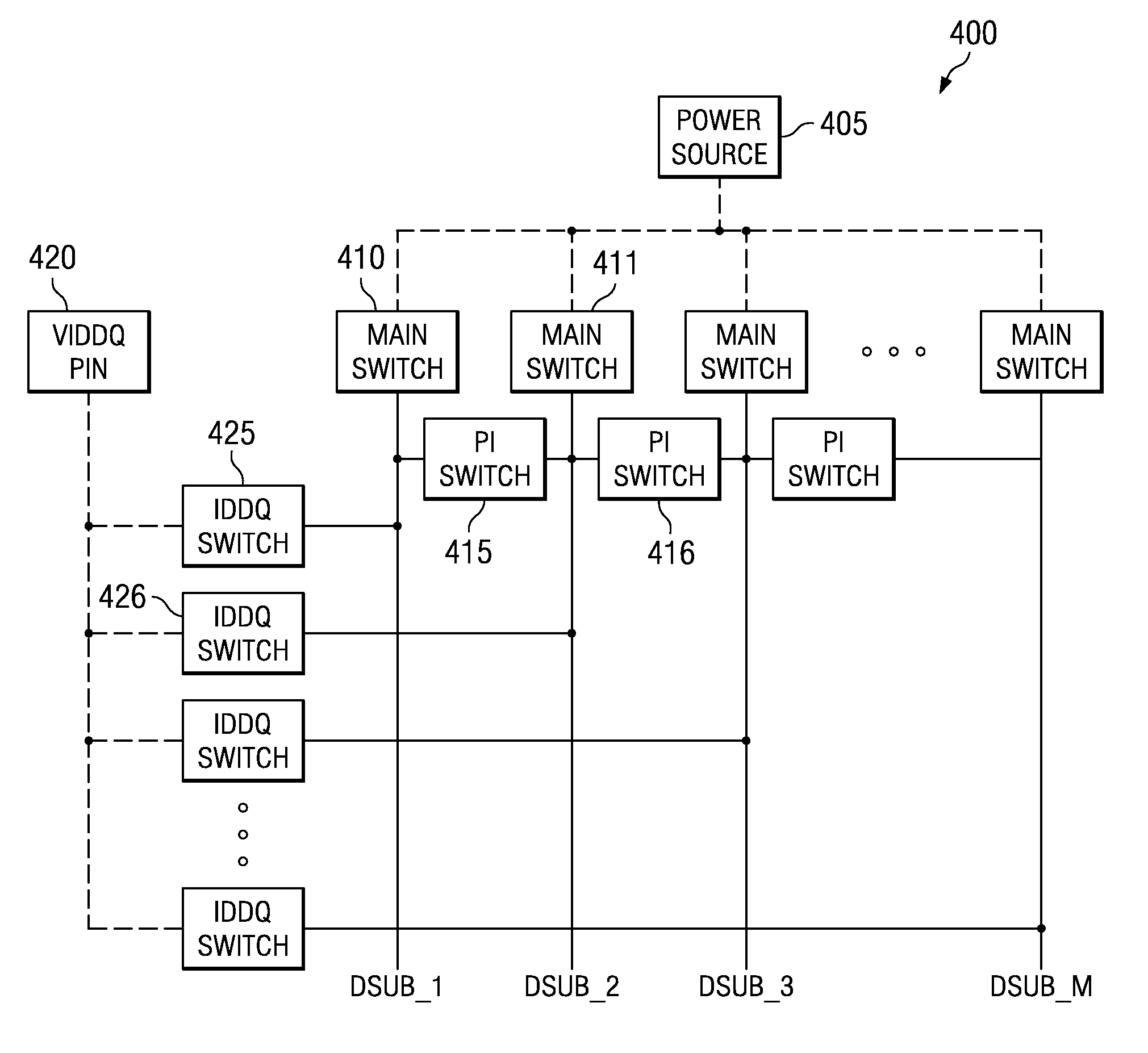

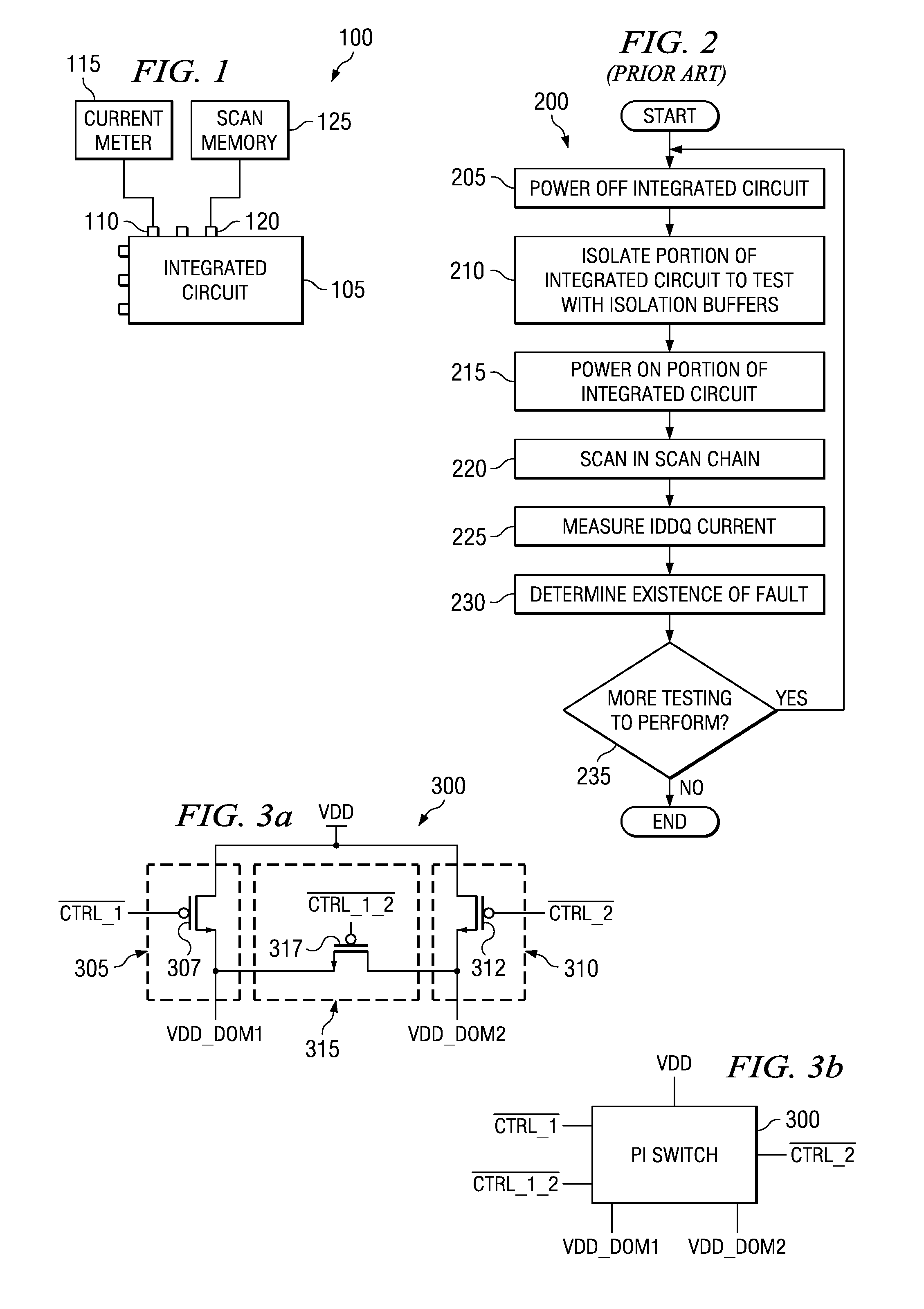

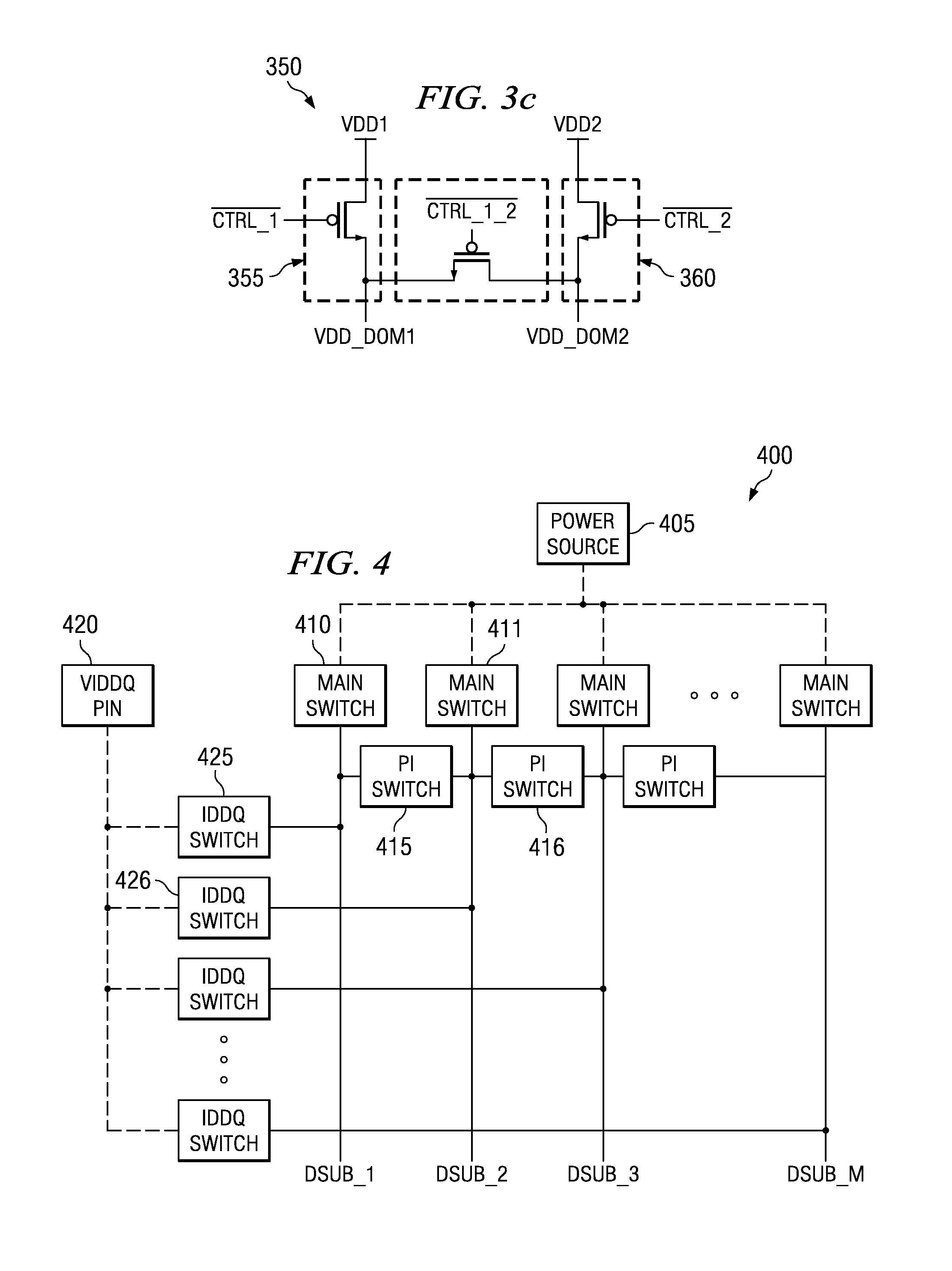

System and method for IDDQ measurement in system on a chip (SOC) design

ActiveUS7282905B2Short test timeReduce chip areaMarginal circuit testingIndividual semiconductor device testingElectricityEngineering

System and method for detecting transistor failure in large-scale integrated circuits by measuring IDDQ. A preferred embodiment comprises a switch structure for an integrated circuit made up of a plurality of main switches (such as main switch 410) selectively coupling a power sub-domain to a power source pin, a plurality of pi-switches (such as pi-switch 415) selectively coupling pairs of power sub-domains, and a plurality of IDDQ switches (such as IDDQ switch 425) selectively coupling the power sub-domains to a VIDDQ pin. The pi-switches can decouple the power sub-domains while the IDDQ switches can enable the measurement of the quiescent current in the power sub-domains. The use of pi-switches and IDDQ switches can permit the measurement of the quiescent current in the power sub-domains without requiring the use of isolation buffers and needed to powering on and off the integrated circuit between current measurements in the different power sub-domains.

Owner:TEXAS INSTR INC

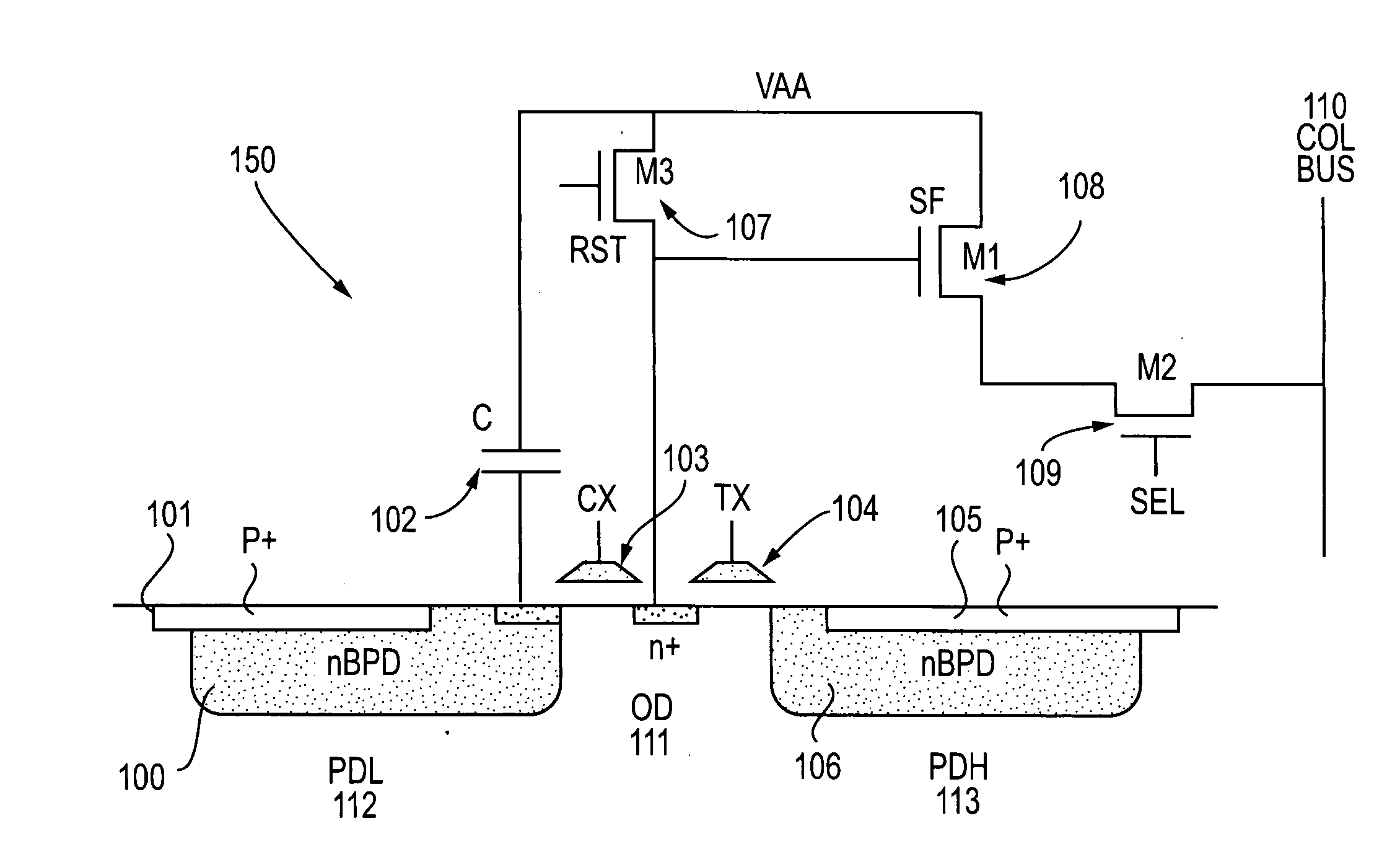

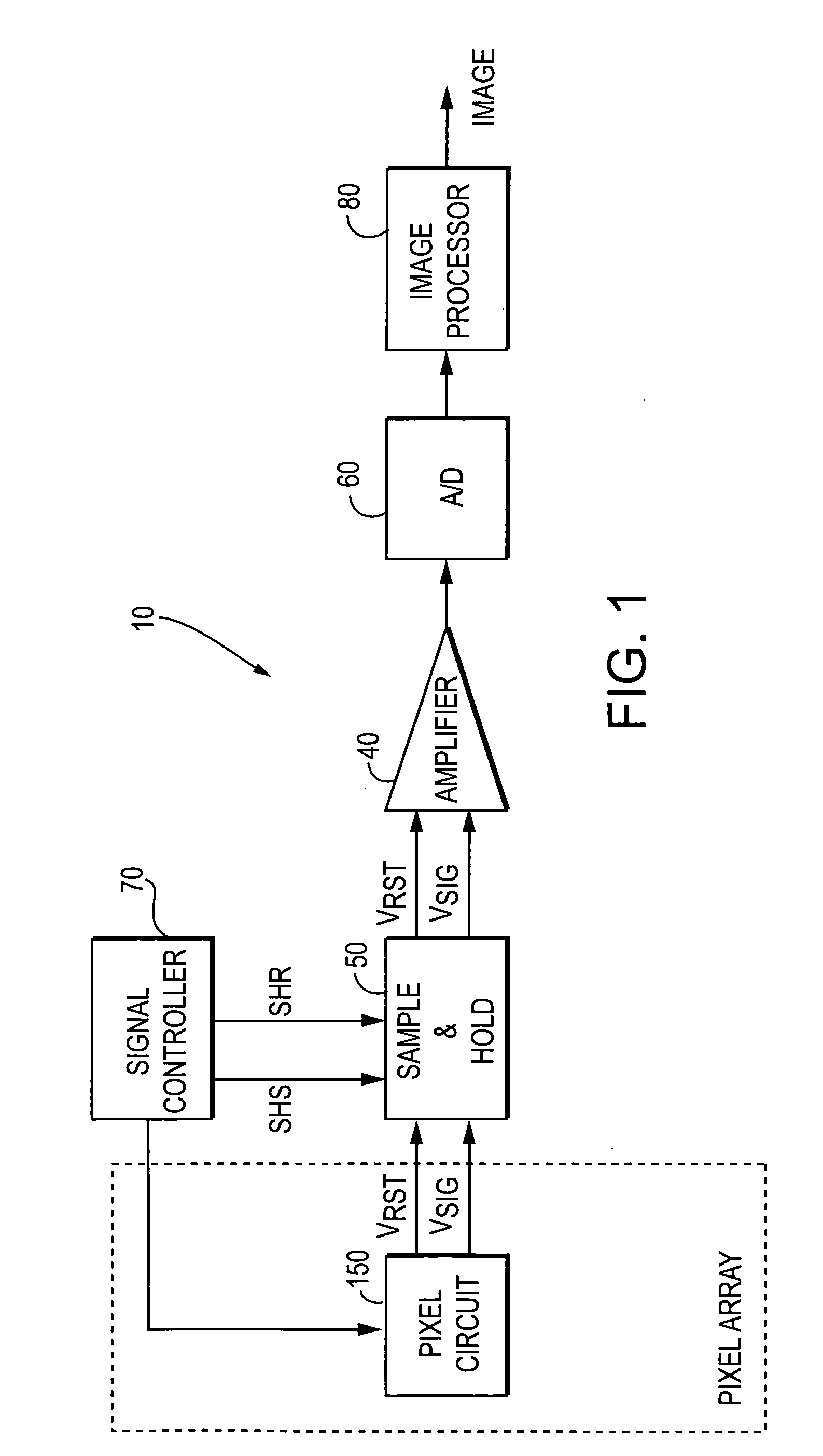

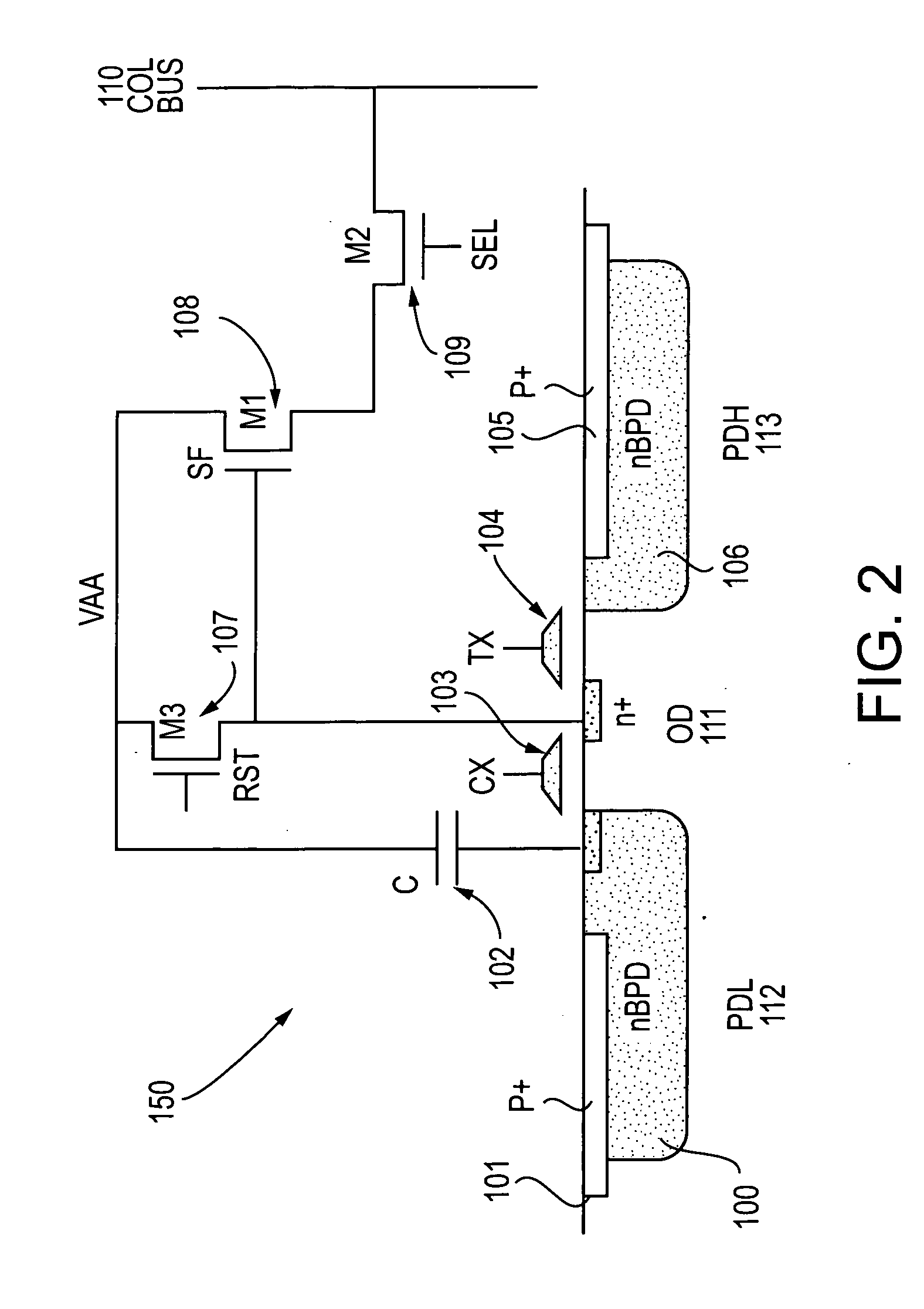

High-low sensitivity pixel

ActiveUS20050092894A1Increase pixel densityReduce chip areaTelevision system detailsTelevision system scanning detailsFloating diffusionPhotodiode

A pixel circuit, and a method for operating a high-low sensitivity (HLS) pixel circuit, to provide increased dynamic range in an imager. The pixel circuit combines a four transistor (“4T”) and a three-transistor plus capacitor (“3TC”) configuration in one pixel, where the 4T portion of the pixel is coupled to a high sensitivity buried photodiode region, and the 3TC portion of the pixel is coupled to a low sensitivity buried photodiode region. The pixel circuit first reads out charge from the high sensitivity photodiode region and compares it to a reset voltage, then reads out charge from the low sensitivity photodiode region. Under an alternate embodiment, multiple HLS pixels are coupled through a common floating diffusion node.

Owner:APTINA IMAGING CORP

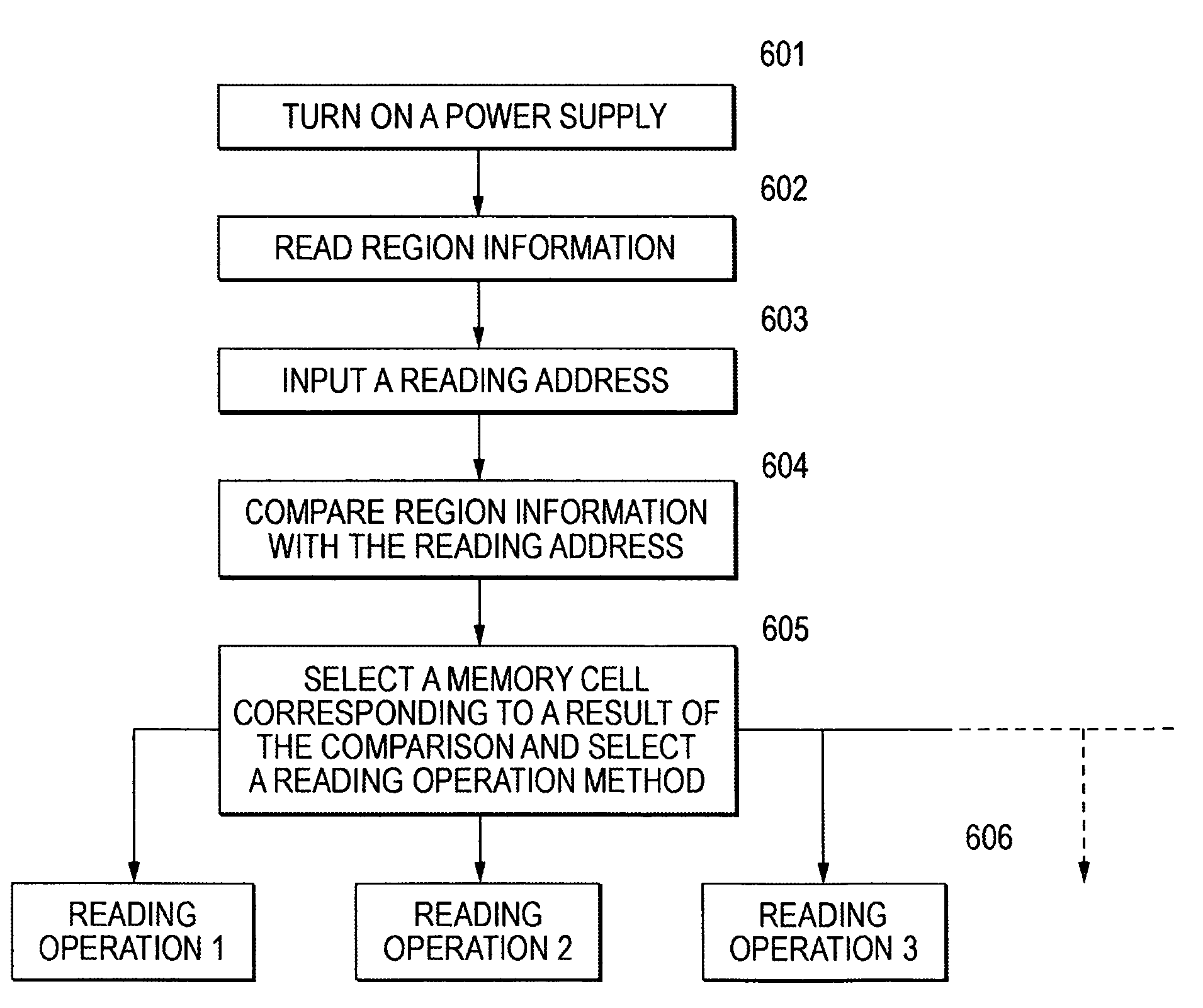

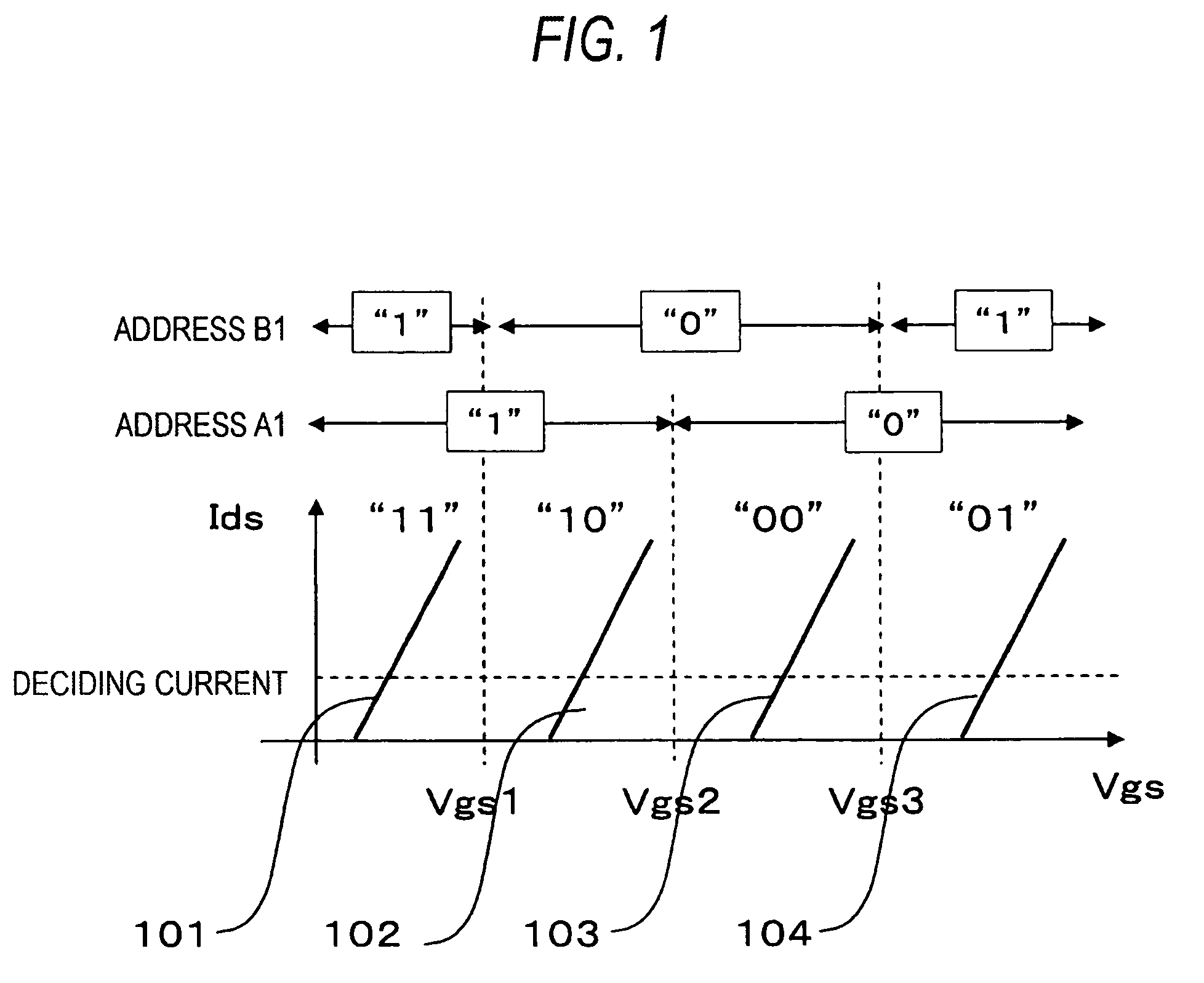

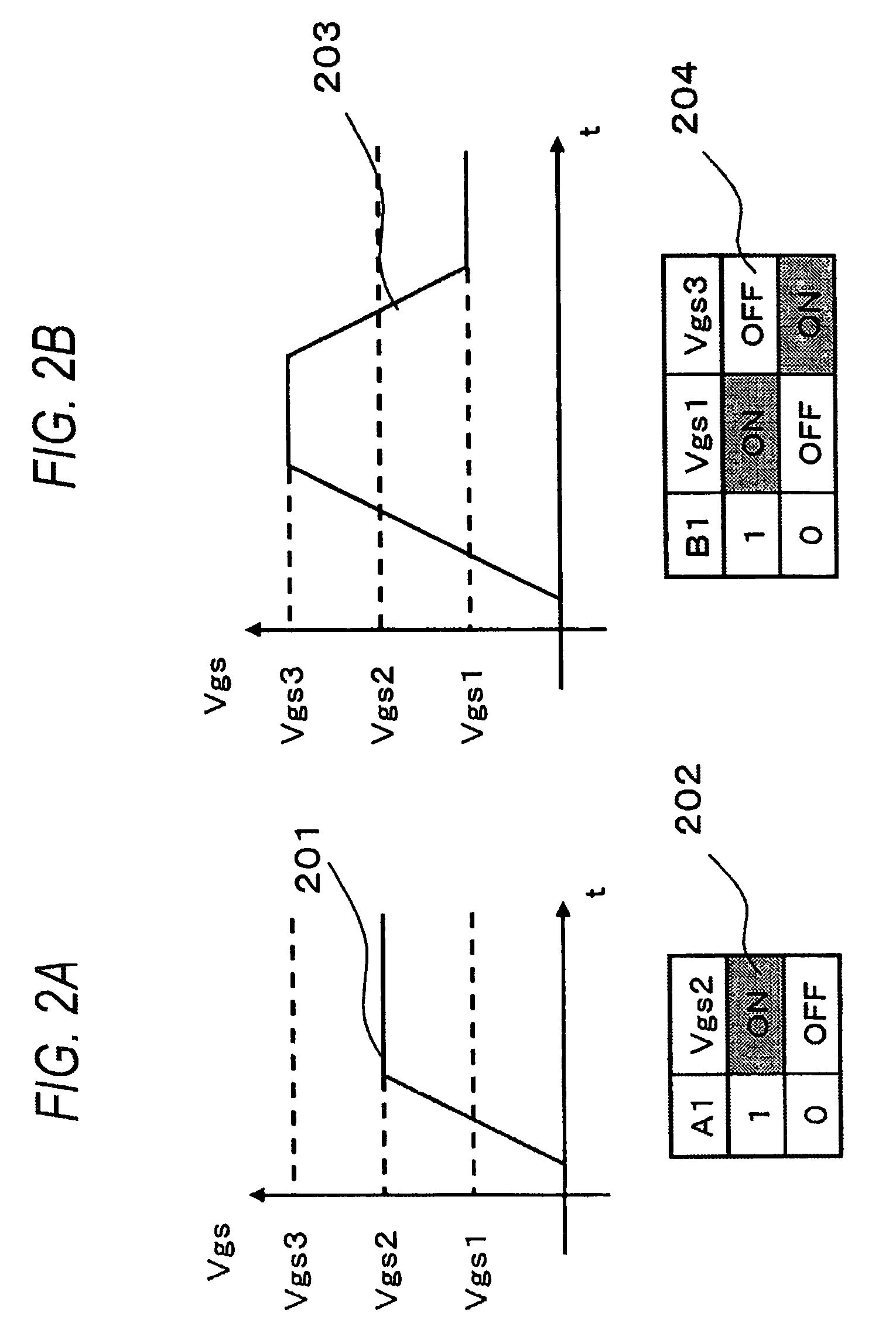

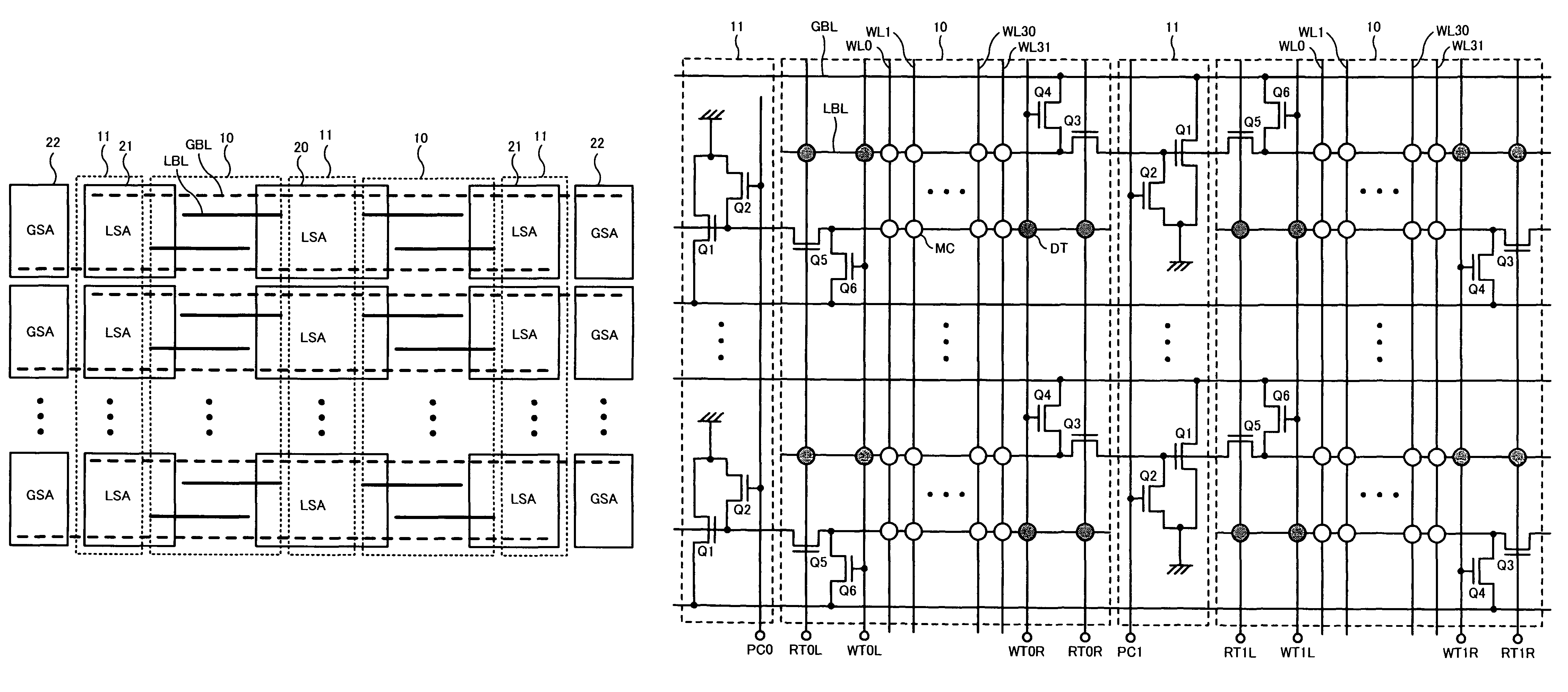

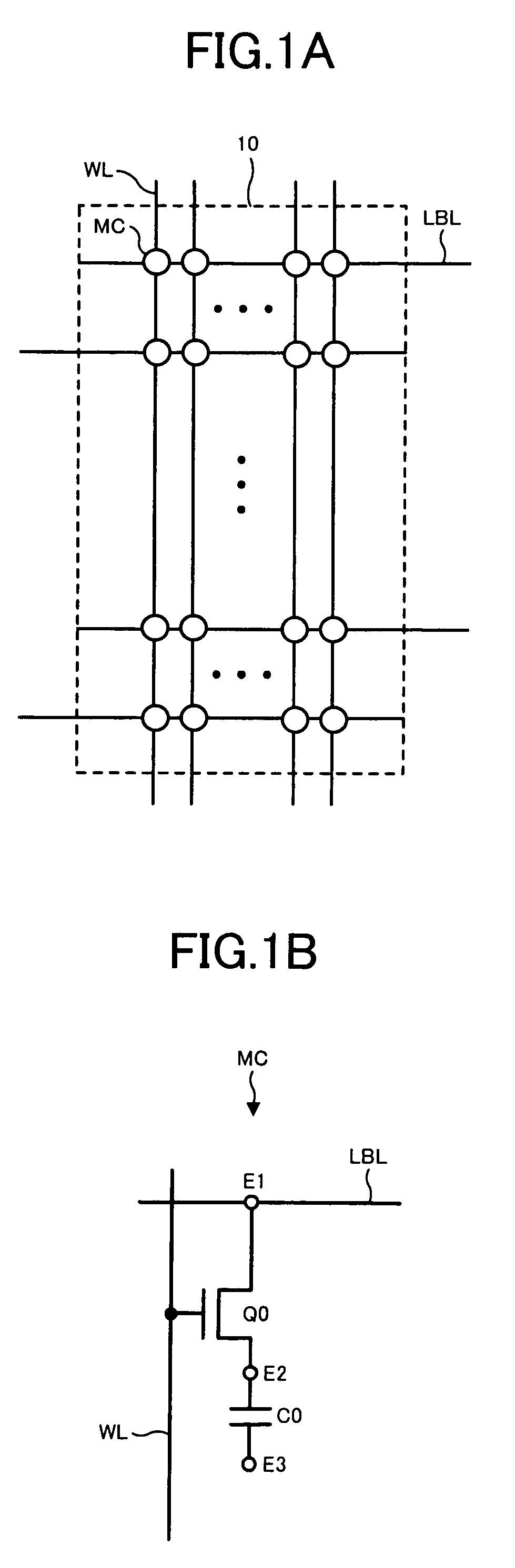

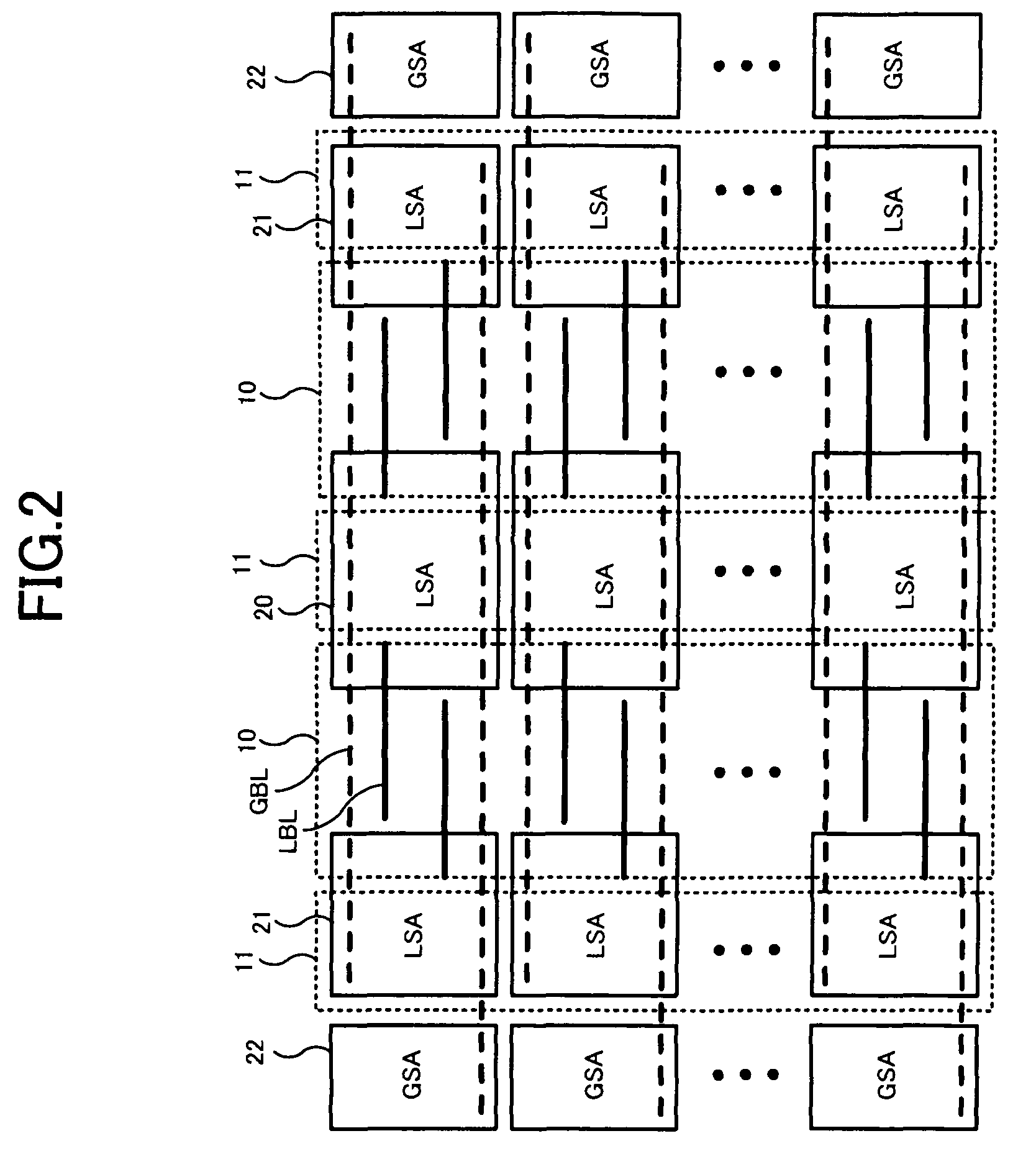

Nonvolatile semiconductor storage apparatus and method of driving the same

InactiveUS7339823B2Increase speedEfficiently and read informationRead-only memoriesDigital storageComputer architectureControl circuit

A memory cell array is logically divided into a plurality of regions having different reading speeds, the respective regions having the different reading speeds include region information storage regions for storing region information in which at least two addresses present in the memory cell at the same time are set to be different regions, a reading control circuit is constituted to carry out a reading operation by determining any of the divided regions which is to be read, selecting an optimum reading method and controlling the reading circuit based on the region information stored in the region information storage region, and an address which can be read in a short time in multivalued information stored in one memory cell is set to be a high speed reading region and is distinguished from regions having the other reading speeds. Consequently, it is possible to efficiently write and read information of 2 bits or more in one memory cell array without reducing a using efficiency of the memory cell array.

Owner:PANASONIC CORP

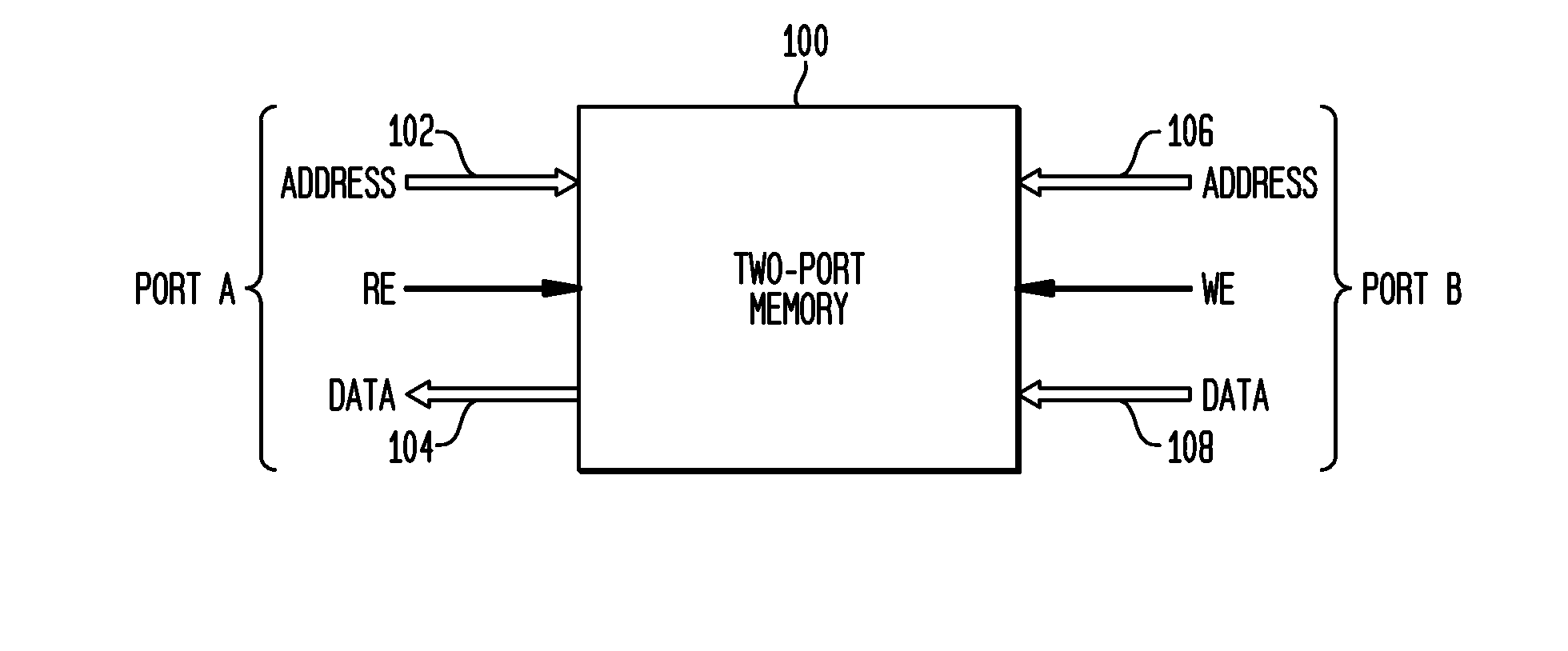

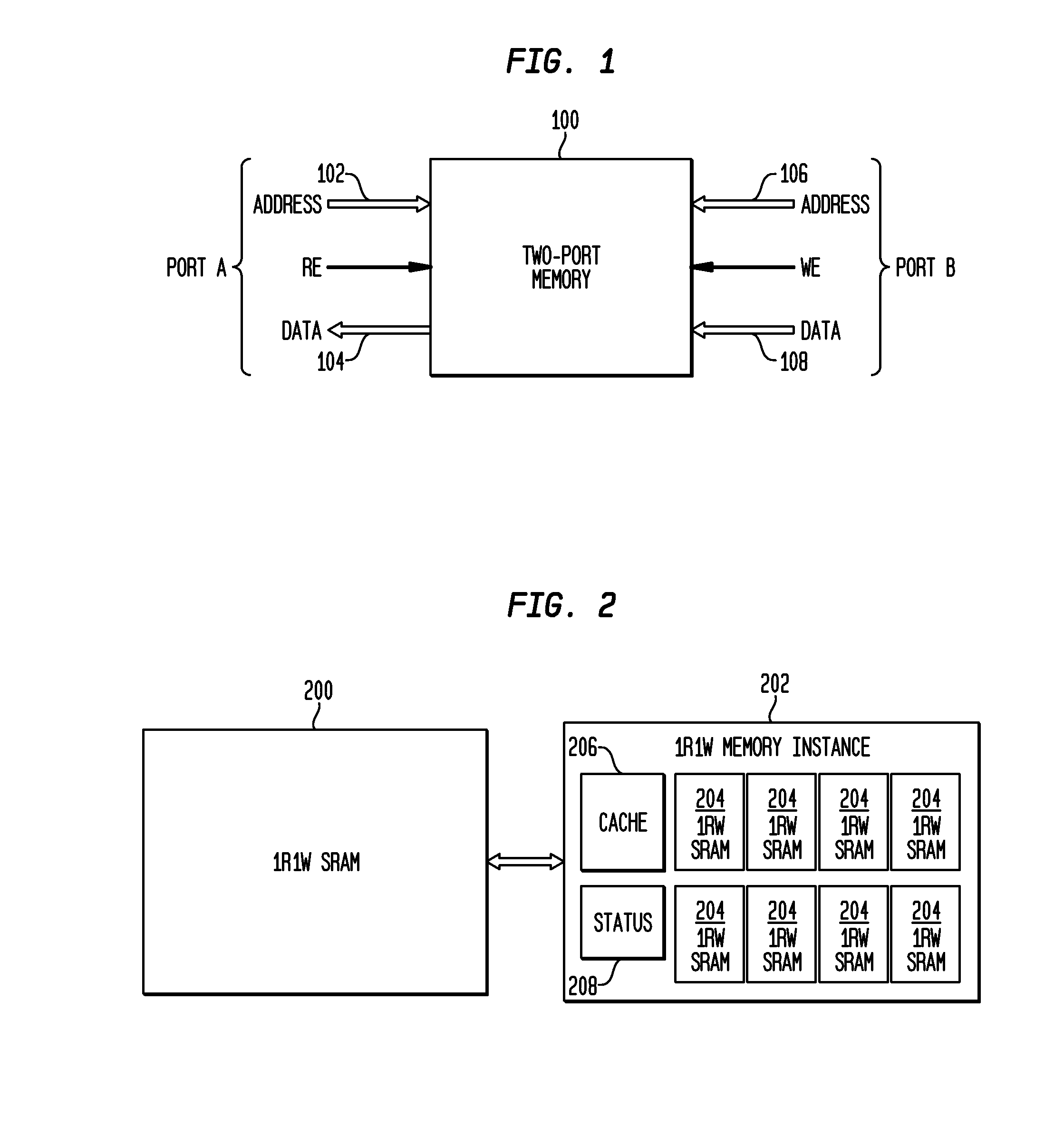

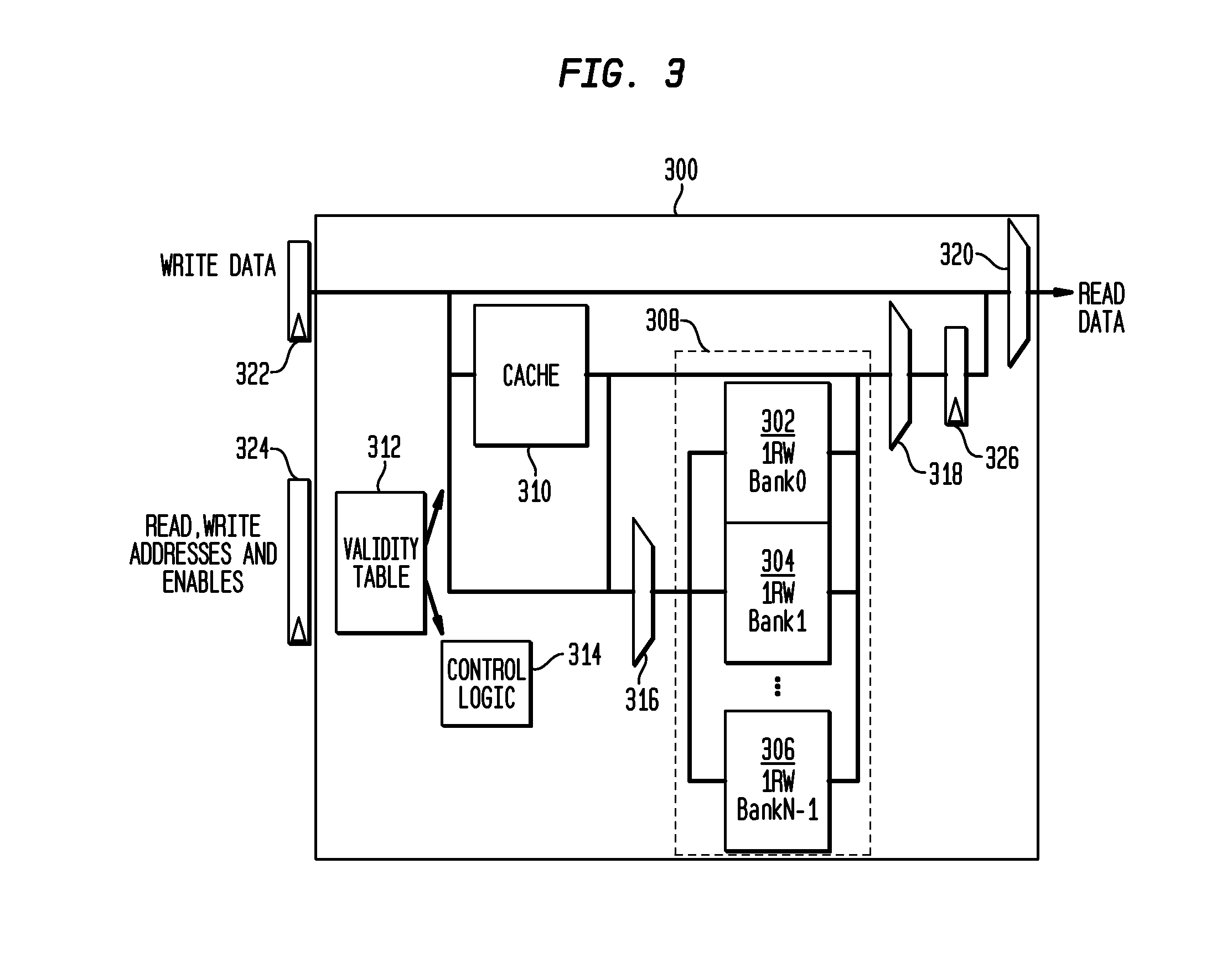

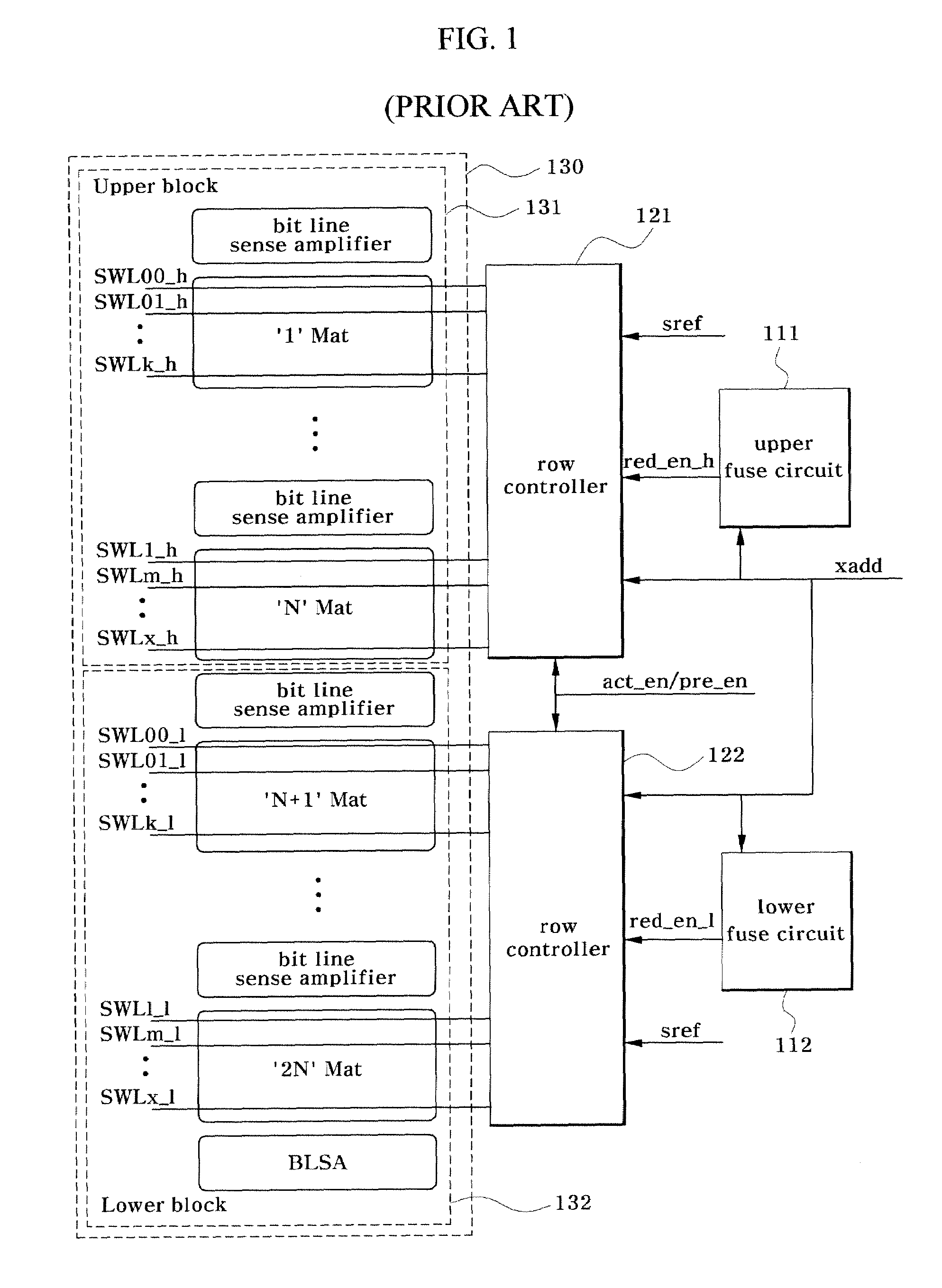

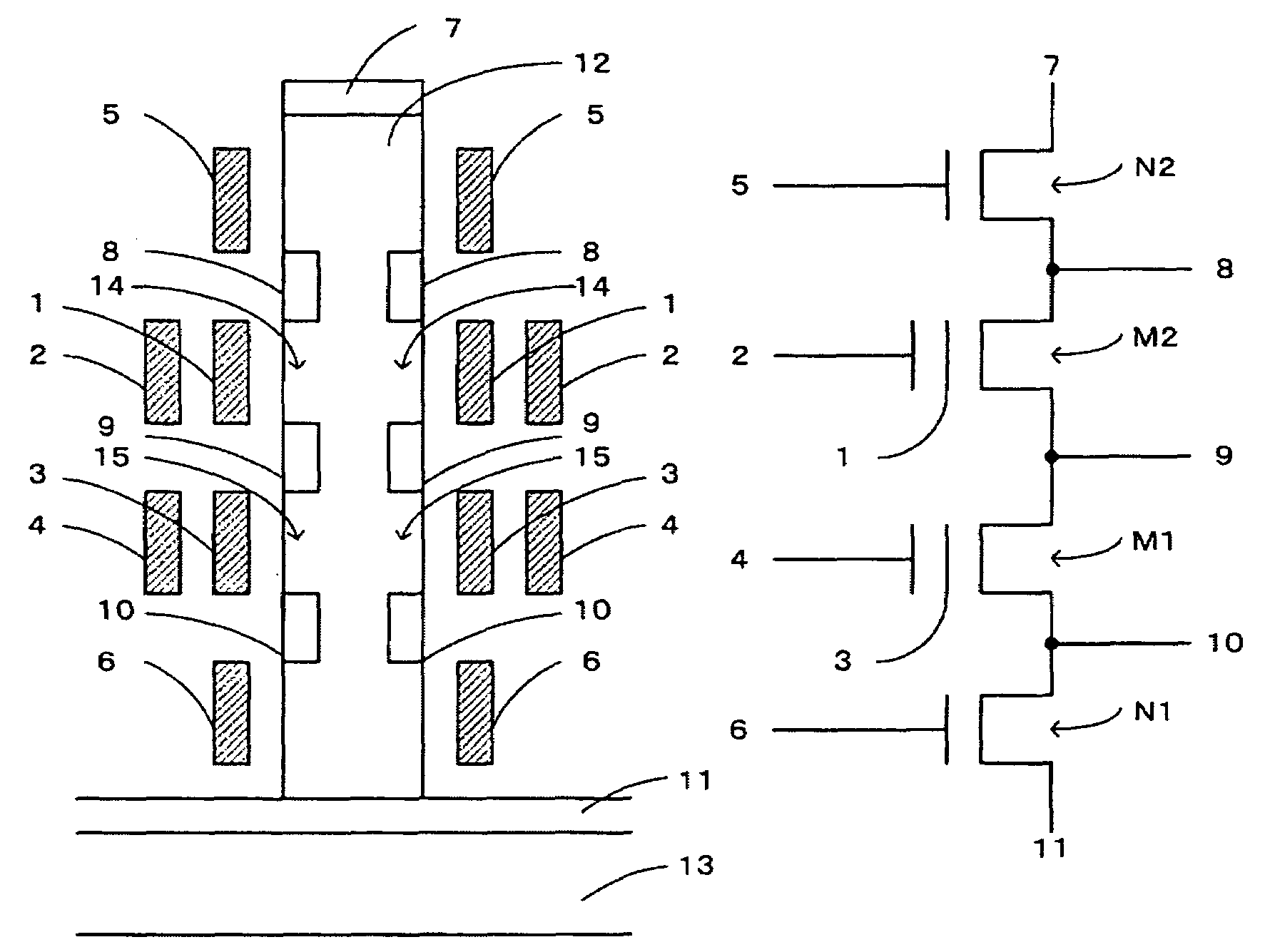

Multi-Port Memory Using Single-Port Memory Cells

InactiveUS20110310691A1Consume areaConsume powerEnergy efficient ICTMemory adressing/allocation/relocationMemory bankParallel computing

A memory operative to provide multi-port functionality includes multiple single-port memory cells forming a first memory array. The first memory array is organized into multiple memory banks, each of the memory banks comprising a corresponding subset of the single-port memory cells. The memory further includes a second memory array including multiple multi-port memory cells and is operative to track status information of data stored in corresponding locations in the first memory array. At least one cache memory is connected with the first memory array and is operative to store data for resolving concurrent read and write access conflicts in the first memory array. The memory includes a controller operative: to receive the status information and to determine a validity of data stored in the first memory array as a function of the status information; to control a manner in which data is stored in the memory for avoiding data overflow in the cache memory; and to resolve concurrent read and write access conflicts in the first memory array during the same memory cycle.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

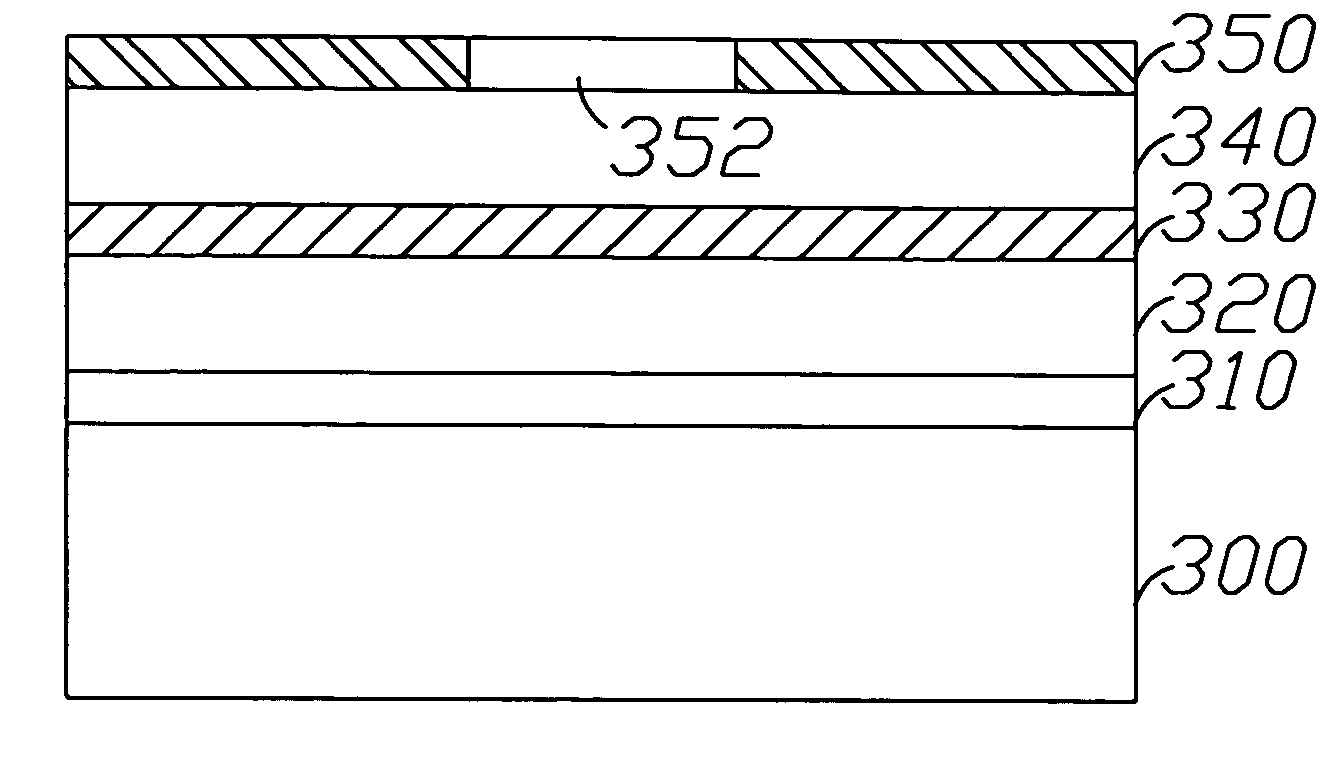

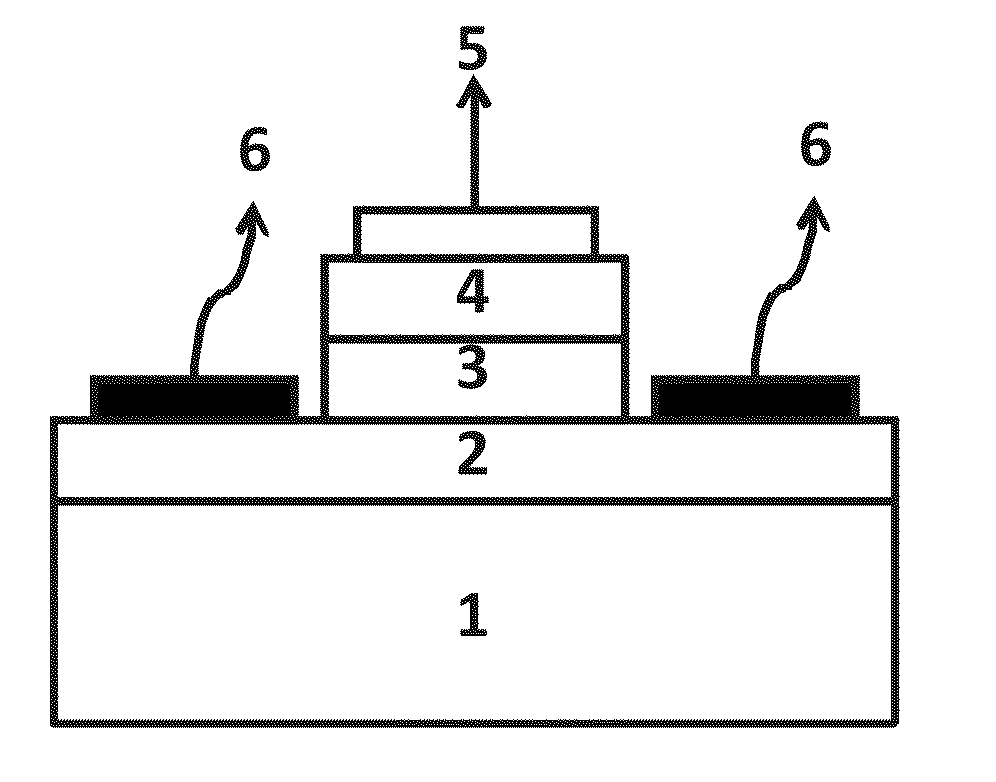

Vertical electrode structure of gallium nitride based light emitting diode

InactiveUS20050236632A1Reduce reflectionImprove external luminous efficiencySemiconductor devicesAngle of incidenceReflection loss

A vertical electrode structure of GaN-based light emitting diode discloses an oxide window layer constructing the GaN-based light emitting diode of vertical electrode structure, which effectively decreases the Fresnel reflection loss and total reflection, and further advances the luminous efficiency. Moreover, the further included metal reflecting layer causes the reflection without the selective angle of incidence, thus increasing the coverage of the reflecting angles and further reflecting the light emitted from a light emitting layer effectively. In addition, the invented structure can also advance the function of heat elimination and the electrostatic discharge (ESD) so as to the increase the operating life of the component and to be applicable to the using under the high current driving. Moreover, the vertical electrode structure of the present invention is able to lower down the manufacturing square of the chip and facilitate the post stage of the conventional wire bonding process.

Owner:SUPERNOVA OPTOELECTRONICS

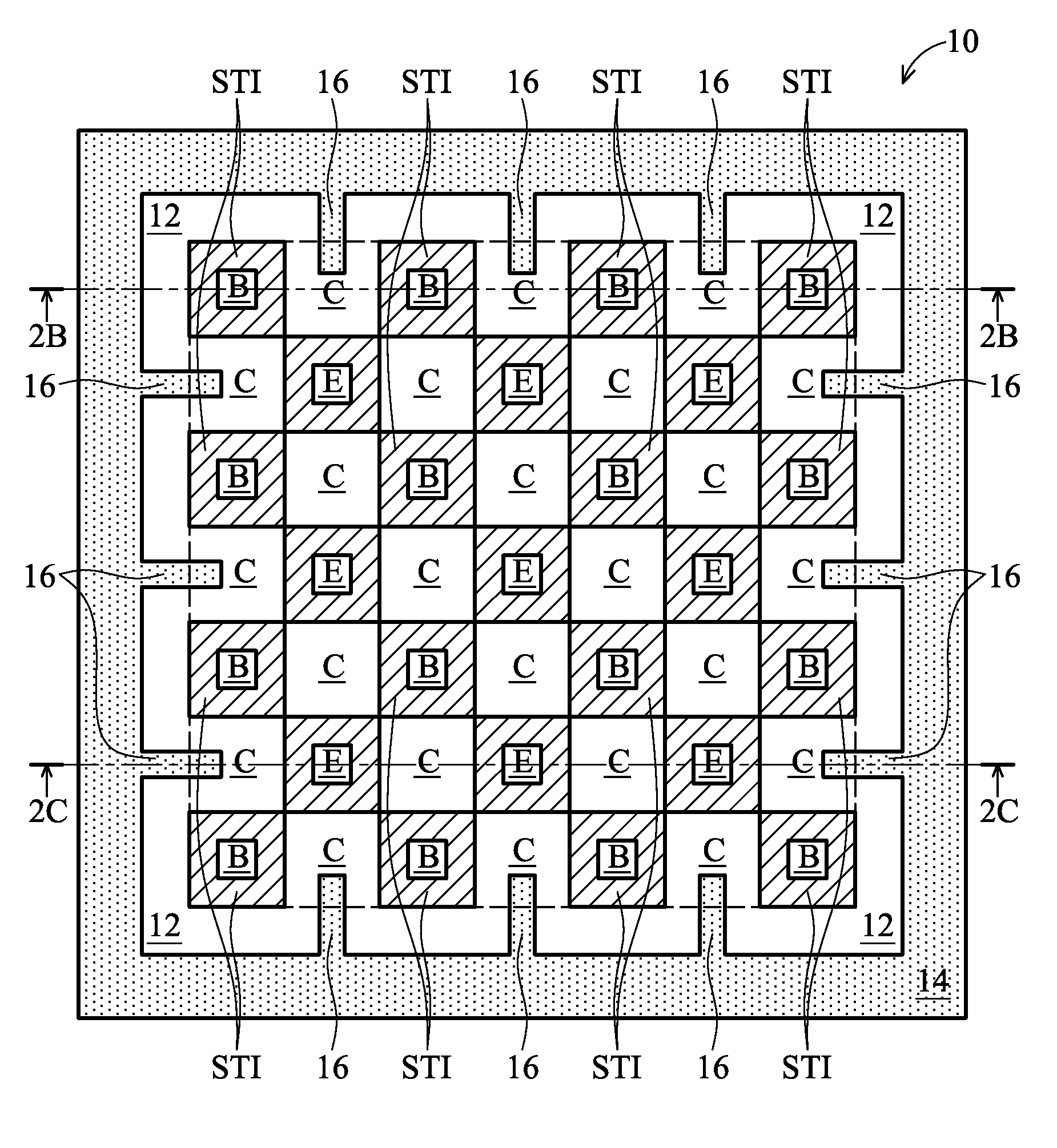

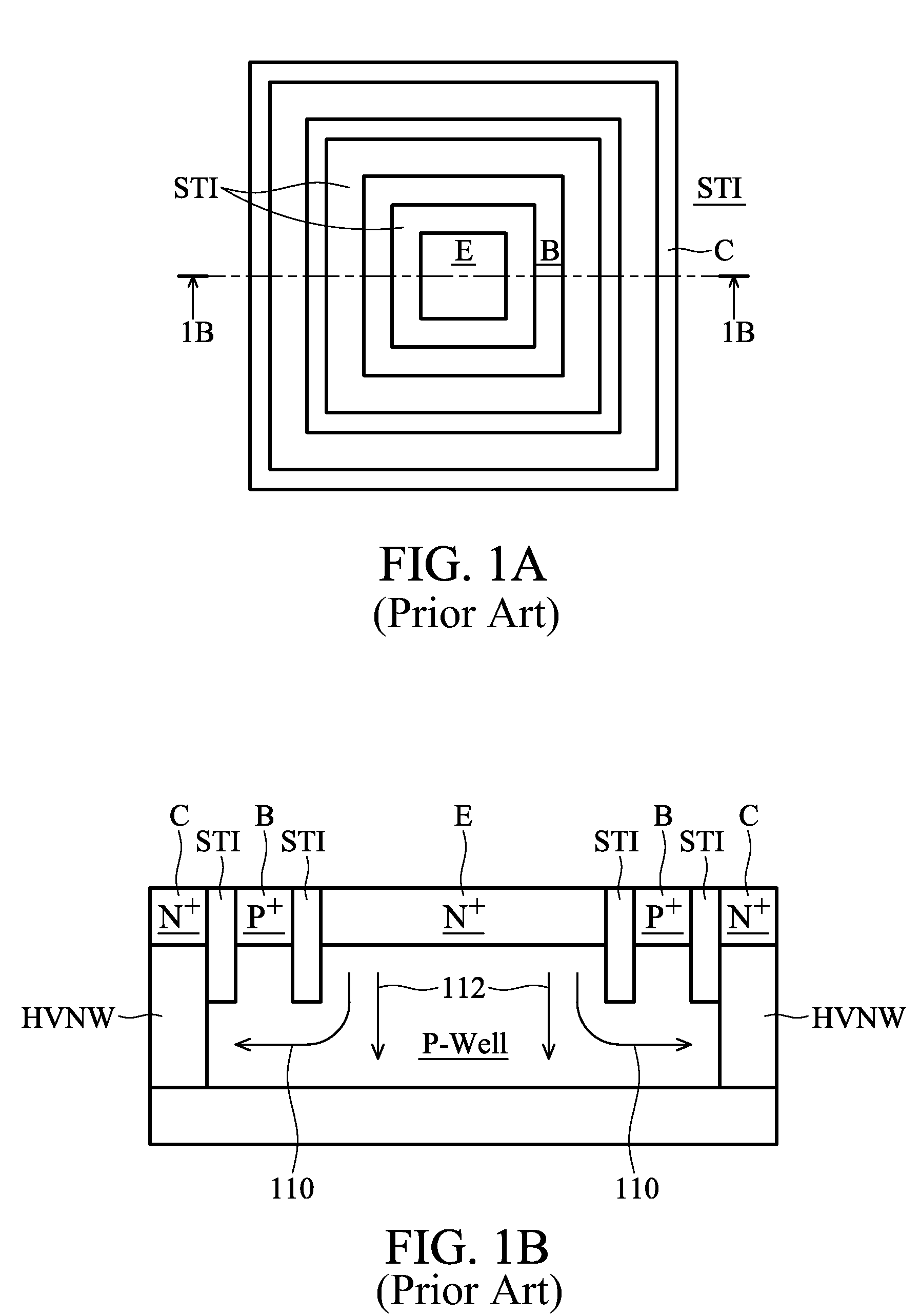

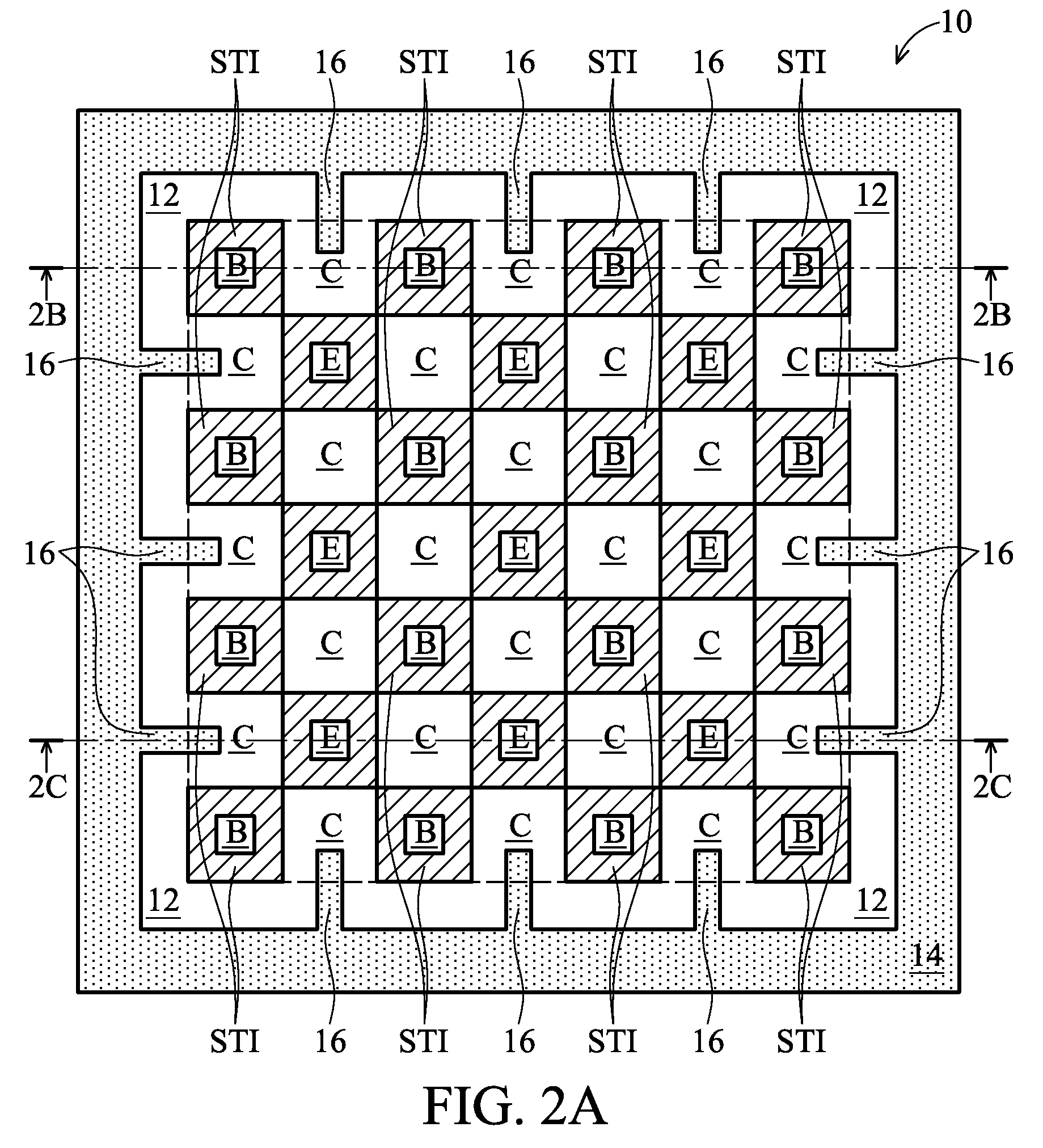

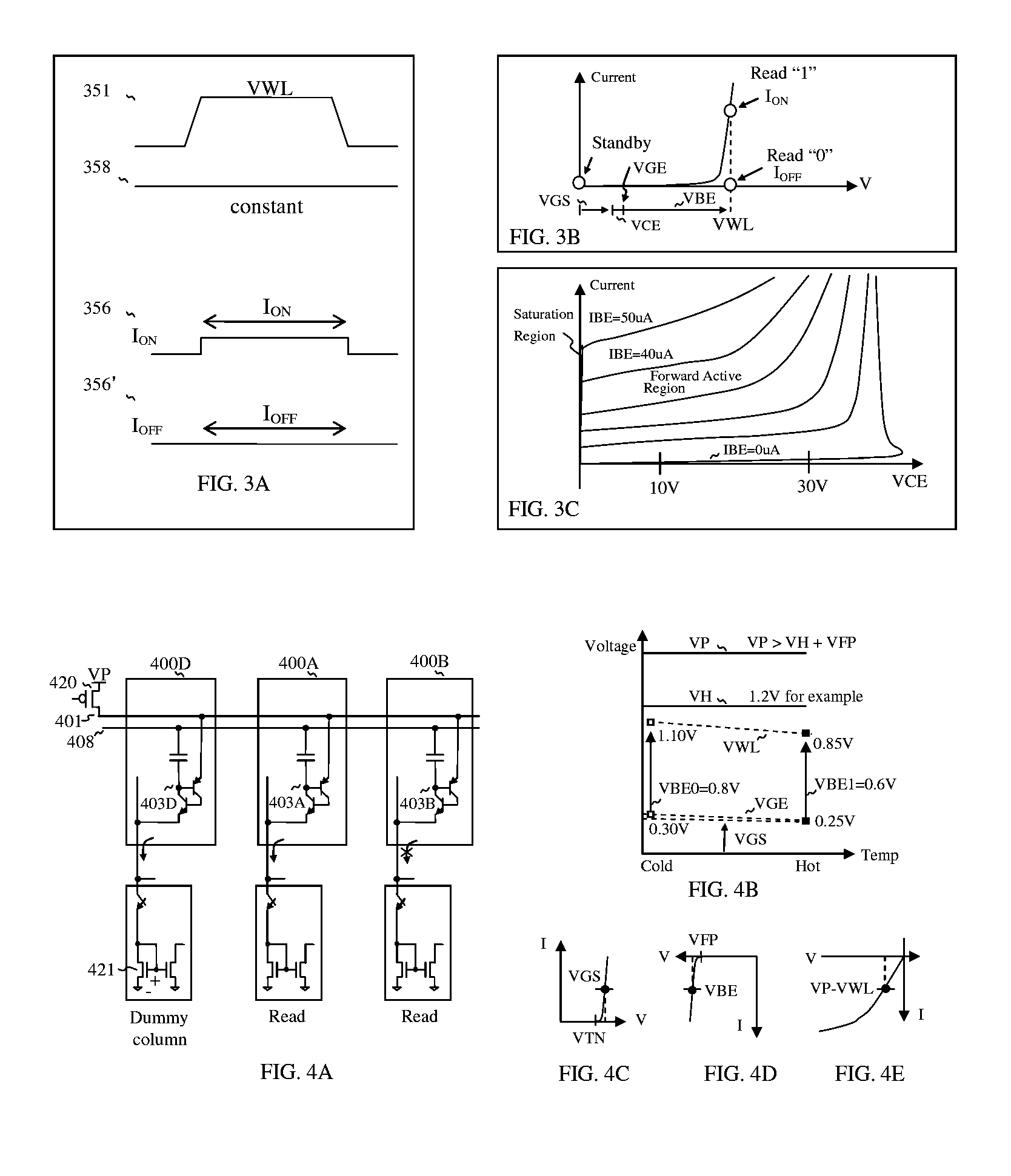

High-voltage BJT formed using CMOS HV processes

An integrated circuit device includes a semiconductor substrate having a top surface; at least one insulation region extending from the top surface into the semiconductor substrate; a plurality of base contacts of a first conductivity type electrically interconnected to each other; and a plurality of emitters and a plurality of collectors of a second conductivity type opposite the first conductivity type. Each of the plurality of emitters, the plurality of collectors, and the plurality of base contacts is laterally spaced apart from each other by the at least one insulation region. The integrated circuit device further includes a buried layer of the second conductivity type in the semiconductor substrate, wherein the buried layer has an upper surface adjoining bottom surfaces of the plurality of collectors.

Owner:TAIWAN SEMICON MFG CO LTD

Transmission lines and components with wavelength reduction and shielding

InactiveUS6950590B2Reduce couplingReduce energy lossCoupling light guidesDelay linesWave structureMetal strips

A slow-wave transmission line component having a slow-wave structure. The slow-wave structure includes a floating shield employing one of electric and magnetic induction to set a potential on floating strips of said floating shield to about 0, thereby reducing losses caused by electric coupling to a substrate. A spacing between the strips is small to inhibit electric field from passing the metal strips to the substrate material.

Owner:CHEUNG TAK SHUN +1

Semiconductor integrated circuit device and vehicle-mounted radar system using the same

ActiveUS20060226415A1Reduce chip areaReduce the high-frequency lossWave based measurement systemsSemiconductor/solid-state device detailsRadar systemsSapphire

A semiconductor integrated circuit device includes a HFET formed on part of a substrate made of sapphire and including a Group III-V nitride semiconductor layer, a dielectric film formed on the substrate to cover the top and side surfaces and upper corners of the Group III-V nitride semiconductor layer, a microstrip line formed with the dielectric film interposed between the substrate and the microstrip line, and a drain lead which is formed on part of the dielectric film and through which the HFET is electrically connected to the microstrip line.

Owner:PANASONIC CORP

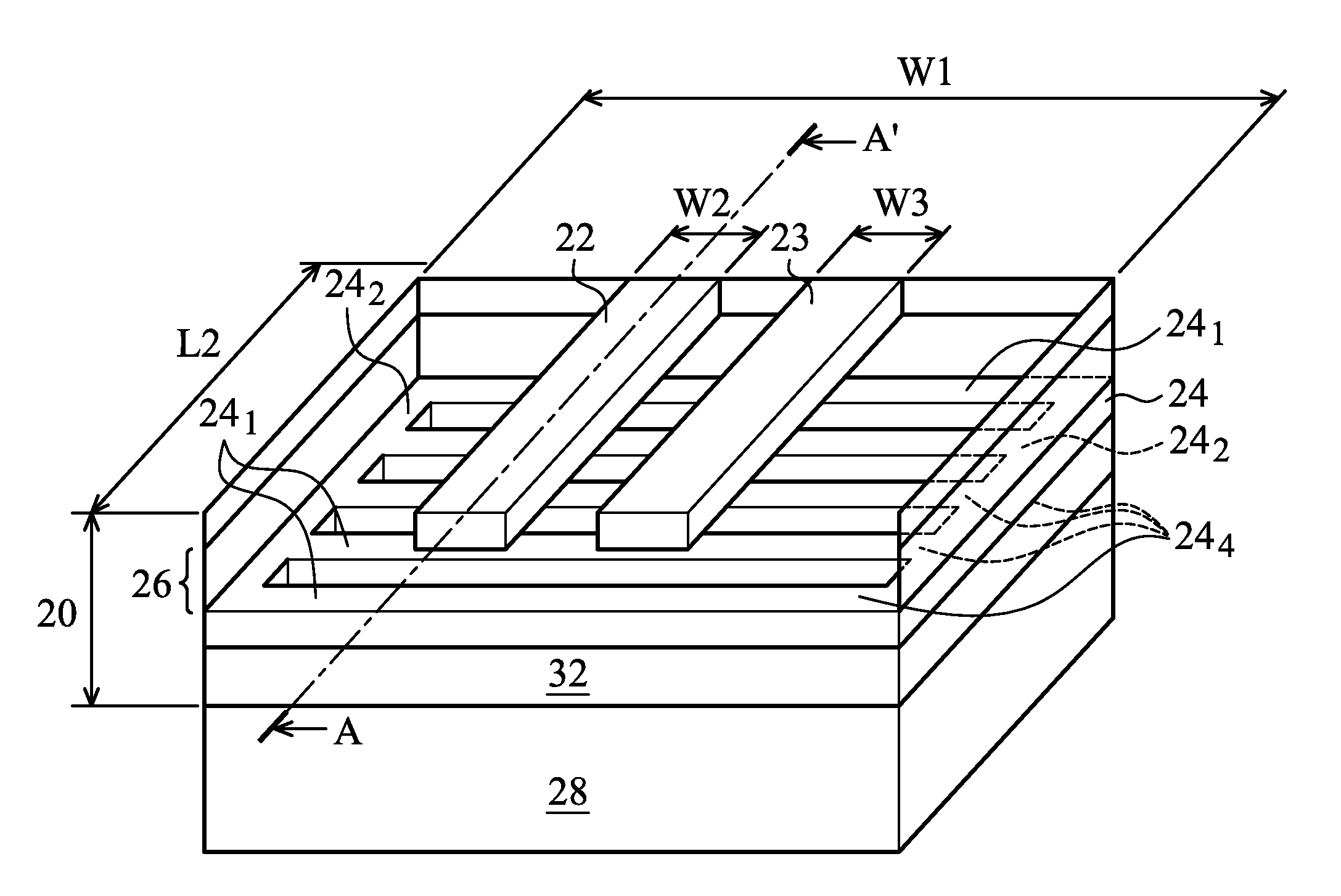

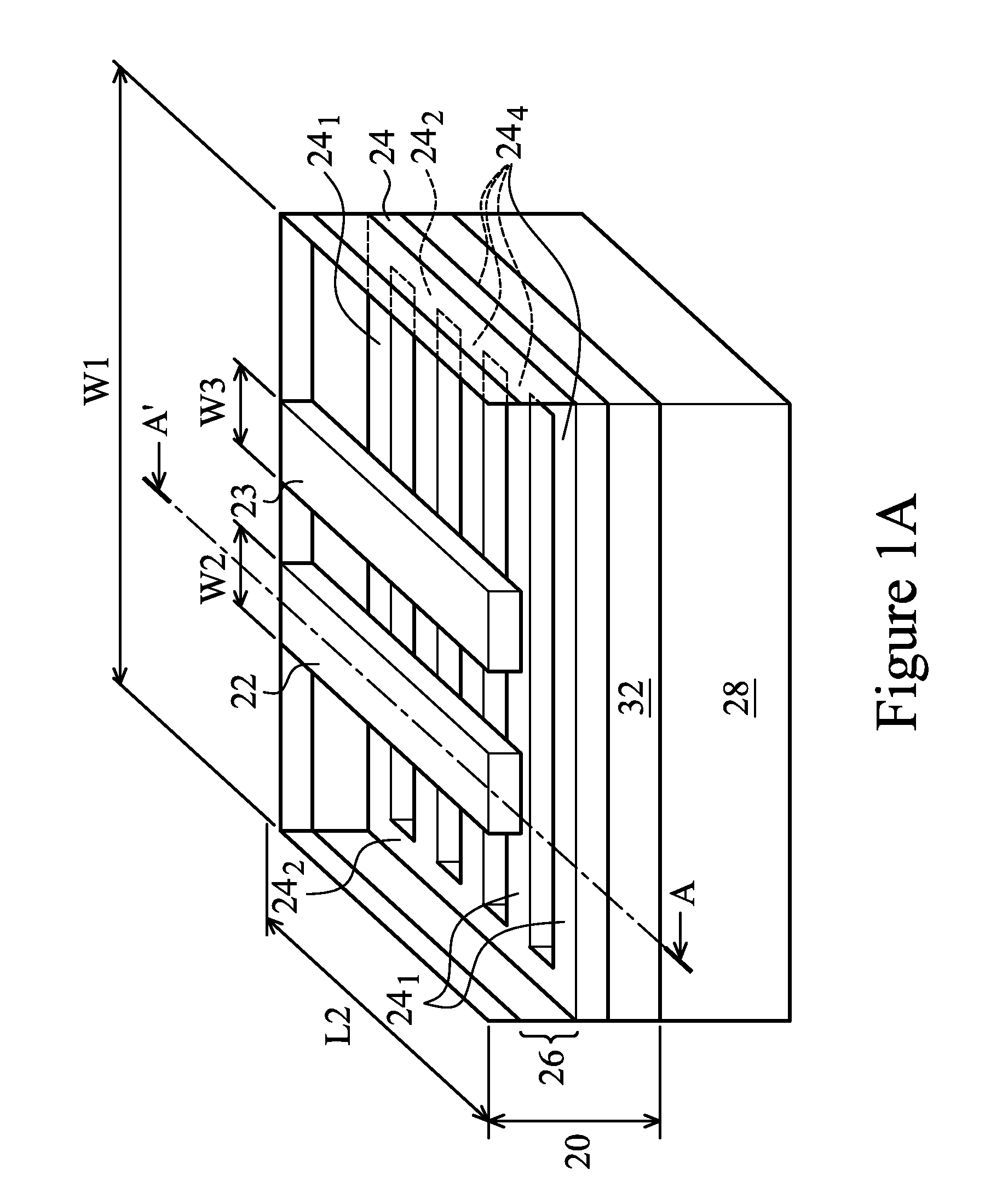

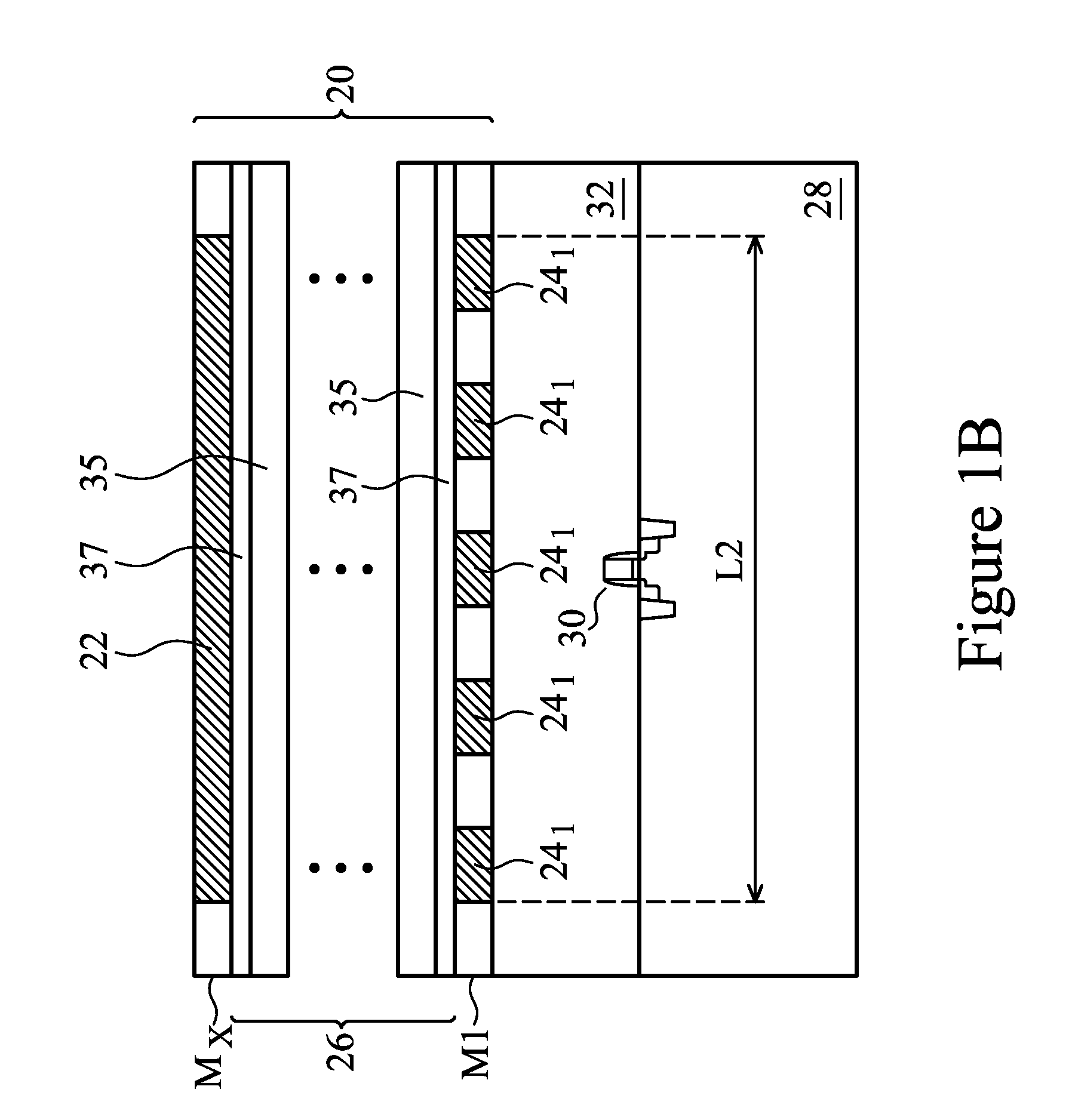

Semiconductor memory device having vertical transistors

A semiconductor memory device includes a memory cell array region in which vertical transistors each having a lower electrode connected to a bit line is regularly arranged with a predetermined pitch, including memory cells formed using at least the vertical transistors; a peripheral circuit region arranged adjacent to the memory cell array region in a bit line extending direction; and a predetermined circuit arranged overlapping the peripheral circuit region and the memory cell array region. In the semiconductor memory device, the vertical transistors each having an upper electrode connected to the predetermined circuit are included in an end region of the memory cell array region, in which no word line is provided.

Owner:LONGITUDE LICENSING LTD

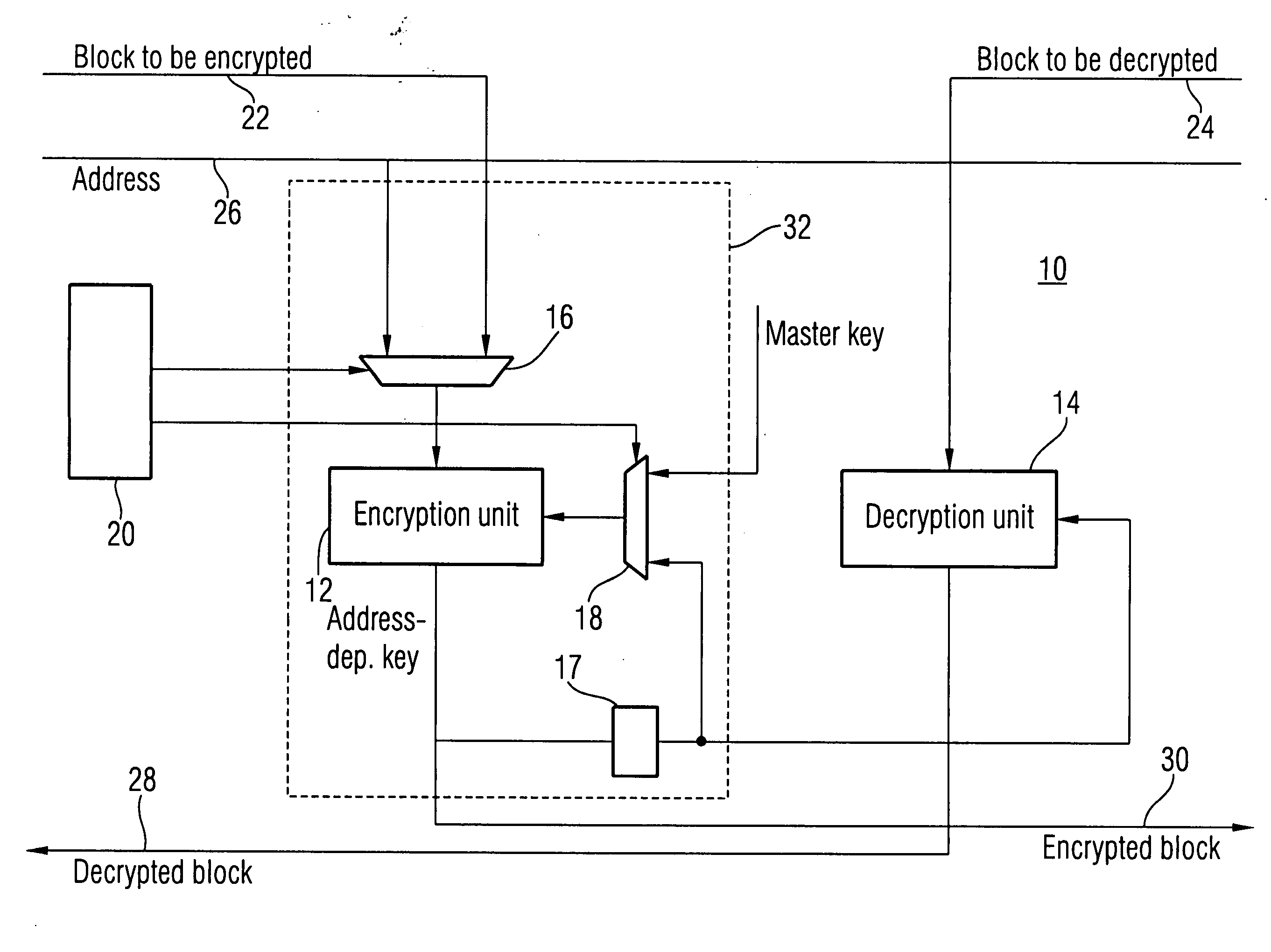

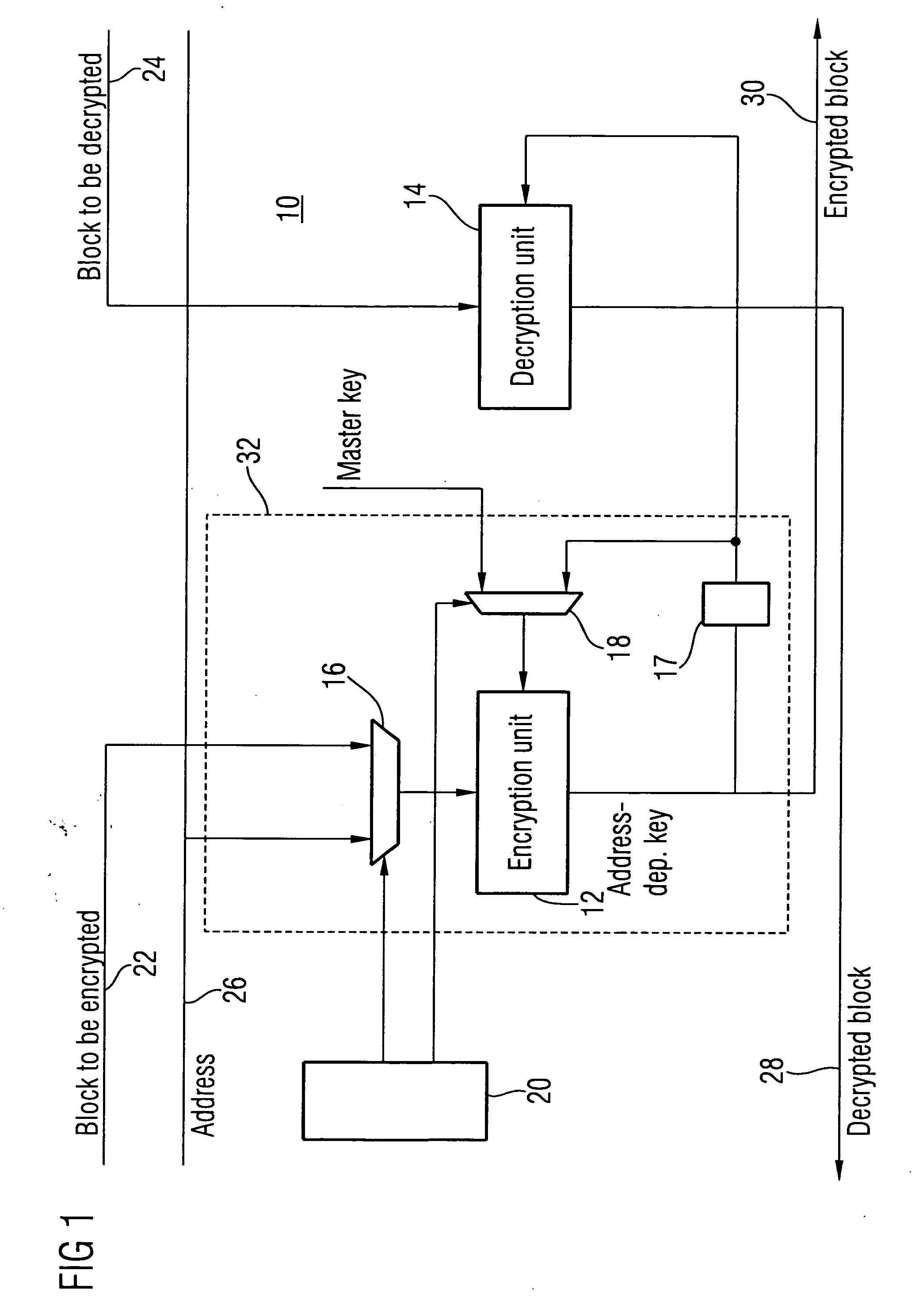

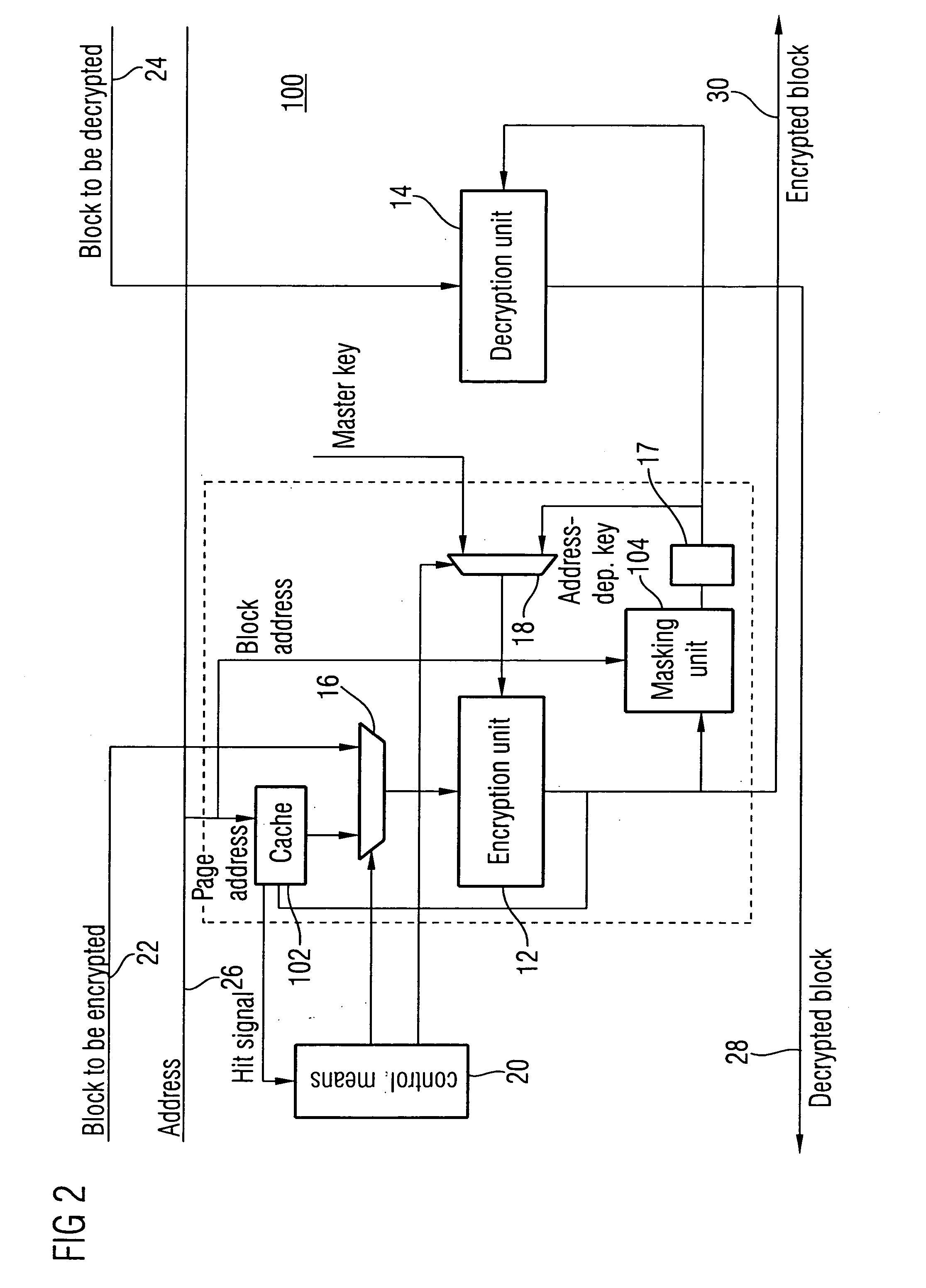

Decryption and encryption during write accesses to a memory

ActiveUS20070192592A1Efficient implementationExtended latencyUnauthorized memory use protectionHardware monitoringComputer hardwareEncryption decryption

An encryption part or a decryption part of an encryption / decryption apparatus or a part common to both parts is used both for encryption and decryption of a datum to be stored and the encrypted memory content and for the generation of the address-individual key and the address-dependent key, respectively.

Owner:INFINEON TECH AG

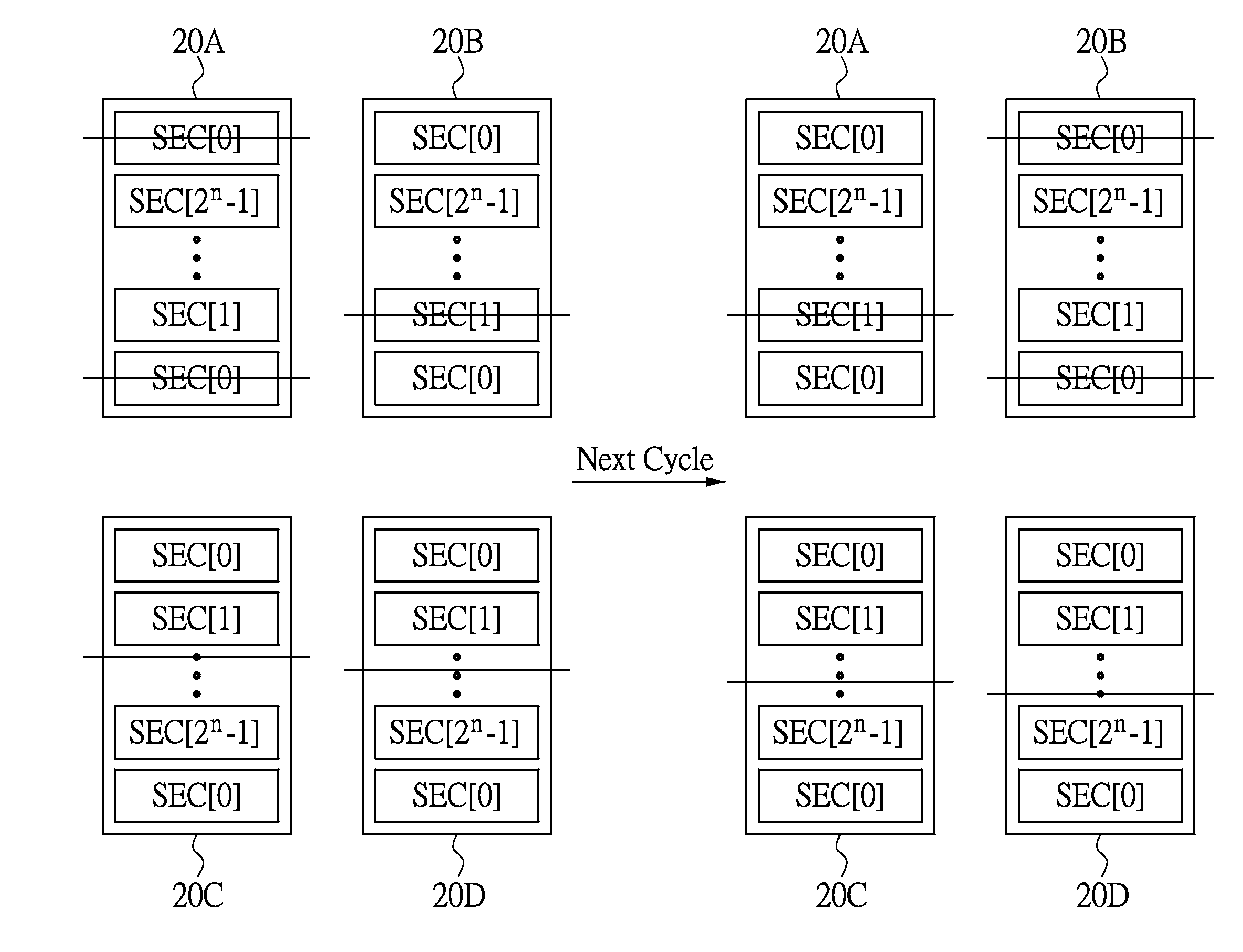

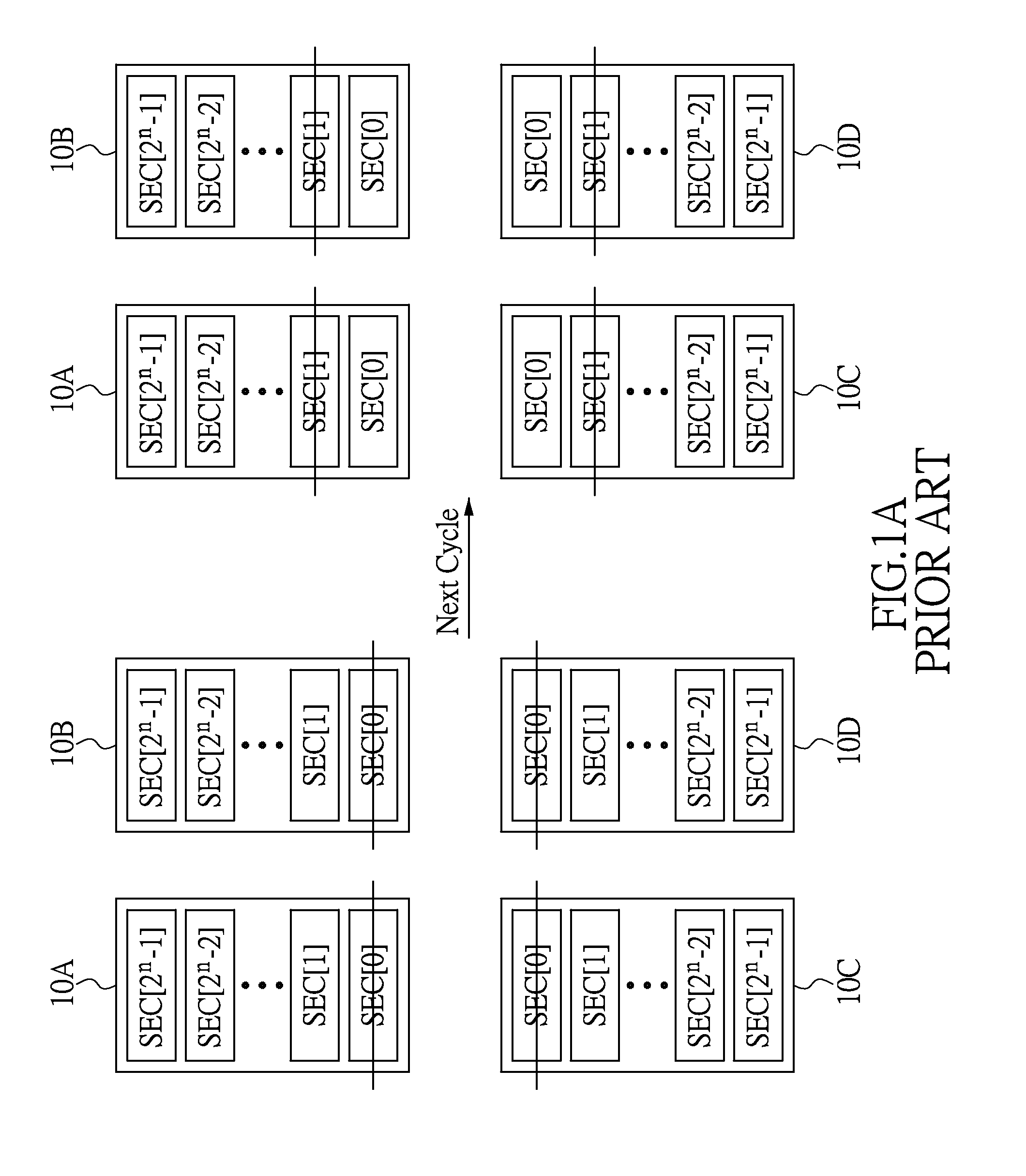

Method for auto-refreshing memory cells in semiconductor memory device and semiconductor memory device using the method

An exemplary embodiment of the present disclosure illustrates a method for auto-refreshing memory cells in a semiconductor memory device with an open bit line architecture, wherein the semiconductor memory device comprises M memory banks, and each of the M memory banks has two particular sectors with a same index and L remained sectors with different indices. Two word lines of the two particular sectors with the same index in the memory bank and (M−1) word lines of the L remained sectors respectively in the other (M−1) memory banks are selected in one cycle. Then, memory cells of the selected word lines are refreshed.

Owner:ELITE SEMICON MEMORY TECH INC

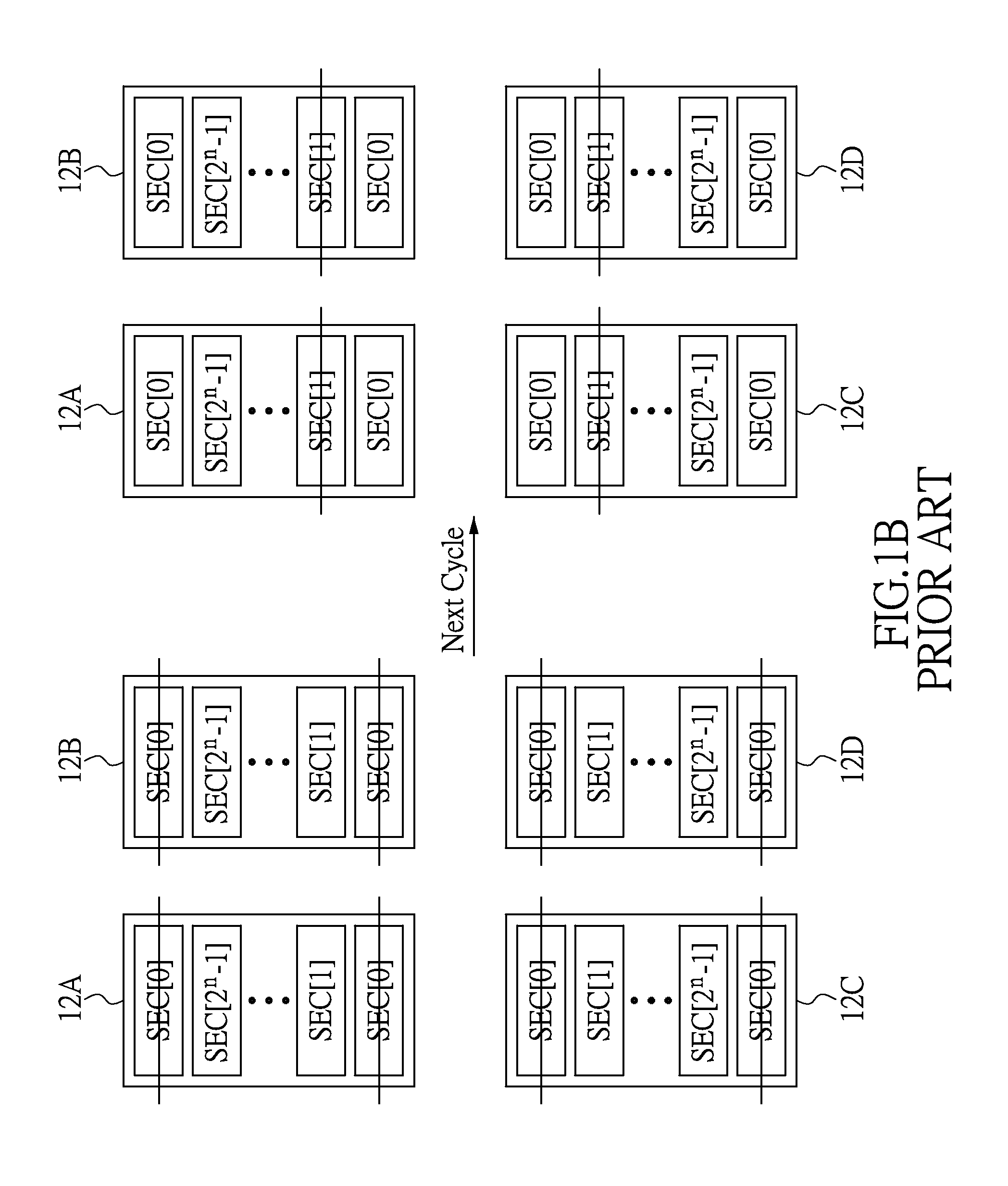

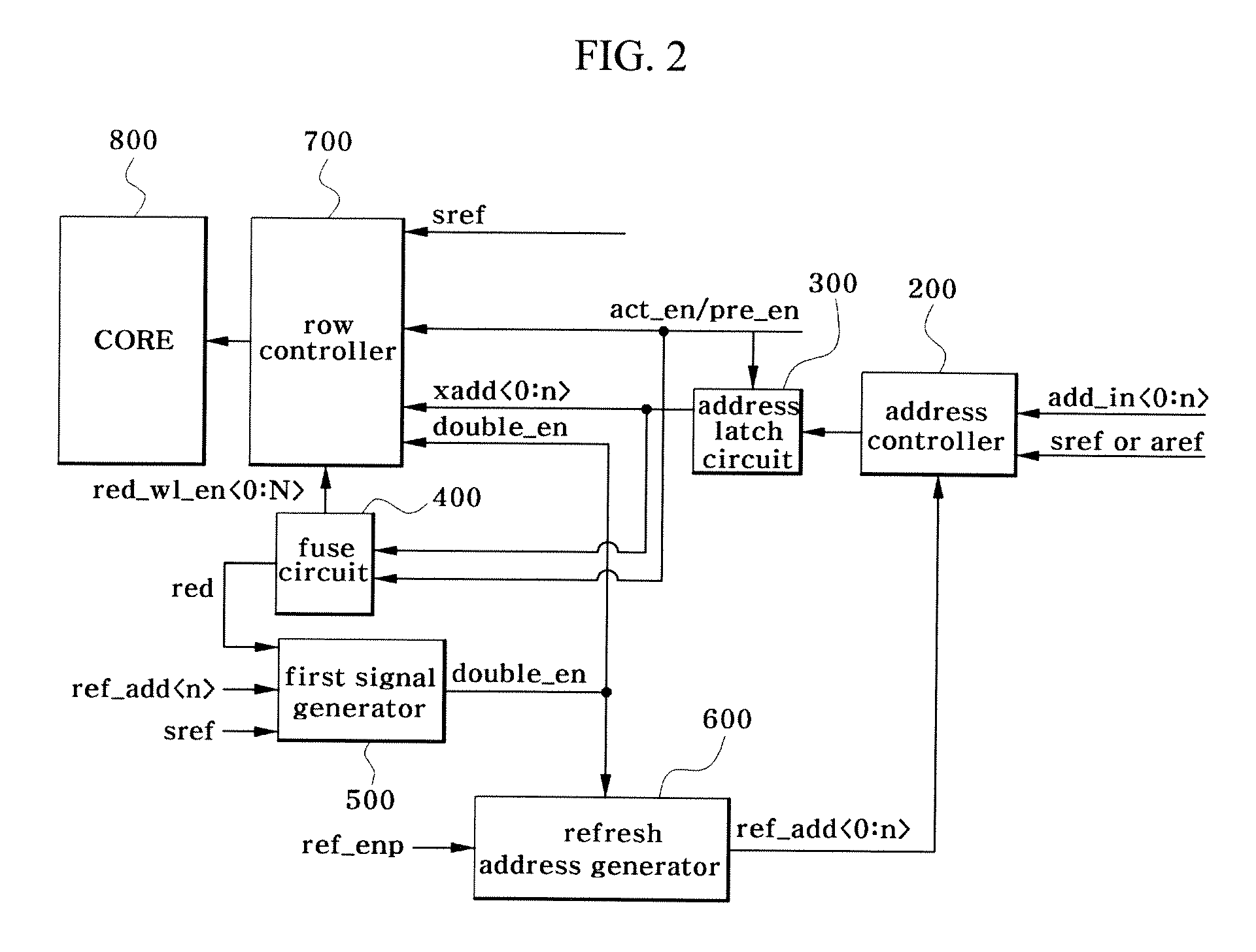

Semiconductor Device

InactiveUS20070147154A1Improve maintenance efficiencyReduce chip areaRead-only memoriesDigital storageAddress generatorSemiconductor

A multi-word line refresh-type semiconductor device may have a plurality of memory banks and performs a refresh operation simultaneously with respect to a plurality of word lines for each of the banks in a self-refresh mode. The semiconductor device includes an address controller for receiving a normal address and a refresh address and selectively outputting the received refresh address in a refresh mode, a fuse circuit for receiving the refresh address, determining whether the received refresh address corresponds to a word line to be repaired and outputting a redundancy word line enable signal and a first control signal according to a result of the determination, a first signal generator for, in response to a bit value for block selection of the refresh address and the first control signal, outputting a second control signal which defines a multi-word line refresh period, a refresh address generator for generating the refresh address in response to the second control signal, and a row controller for receiving the refresh address, second control signal and redundancy word line enable signal and controlling the refresh operation with respect to a memory core.

Owner:SK HYNIX INC

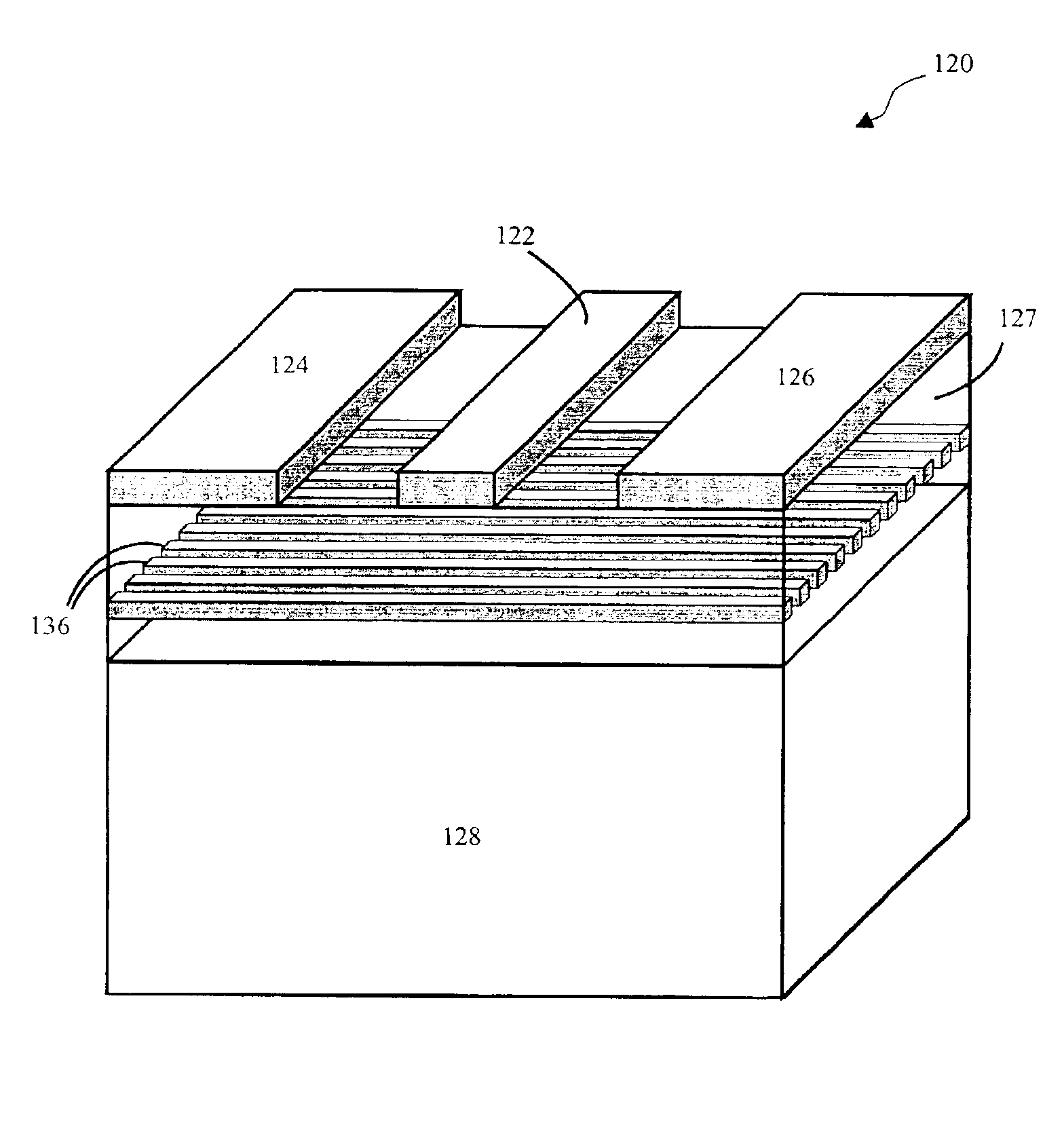

Coupled Microstrip Lines with Tunable Characteristic Impedance and Wavelength

ActiveUS20100214041A1Reduce chip areaMultiple-port networksSemiconductor/solid-state device detailsGround planeLength wave

A coupled microstrip line structure having tunable characteristic impedance and wavelength are provided. In accordance with one aspect of the invention, a coupled microstrip line structure comprises a first ground plane having a plurality of first conductive strips separated by a dielectric material, and a first dielectric layer over the first ground plane. The coupled microstrip line further comprises a first signal line over the first dielectric layer, wherein the first signal line is directly above the plurality of first conductive strips, and wherein the first signal line and the plurality of first conductive strips are non-parallel, and a second signal line over the first dielectric layer, wherein the second signal line is directly above the plurality of first conductive strips, and wherein the second signal line and the plurality of first conductive strips are non-parallel, and wherein the second signal line is substantially parallel to the first signal line.

Owner:TAIWAN SEMICON MFG CO LTD

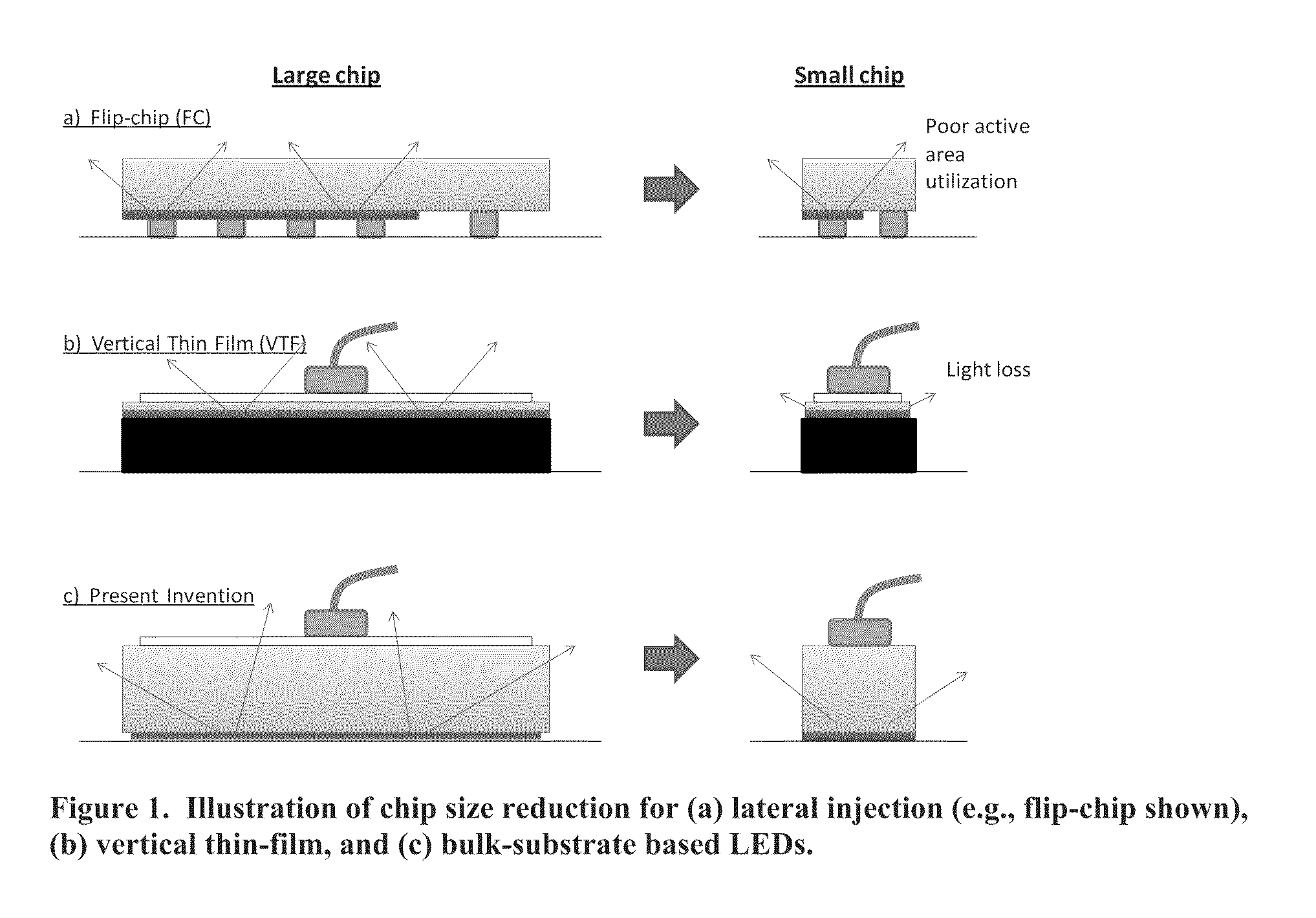

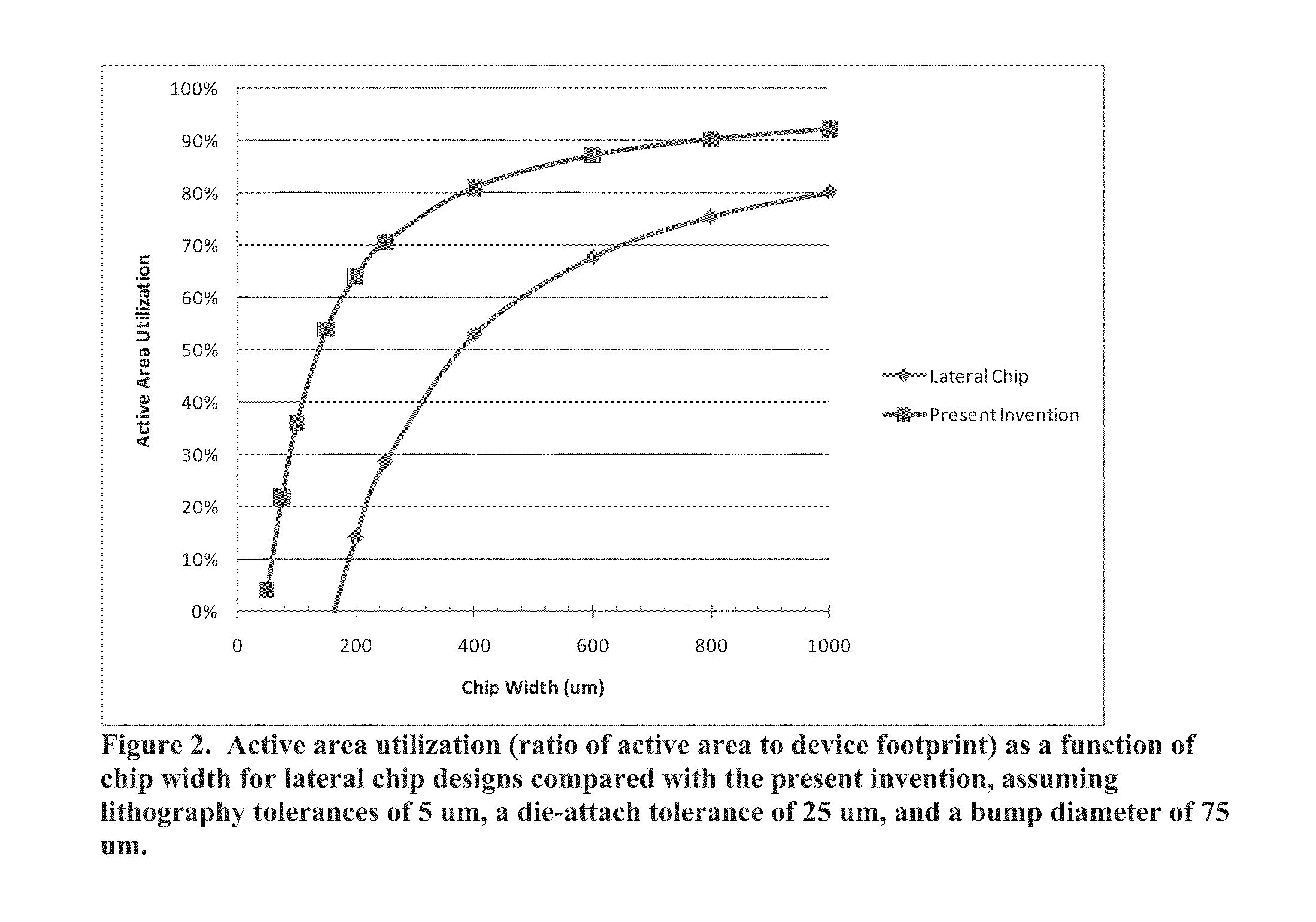

Power light emitting diode and method with current density operation

ActiveUS8502465B2Reduce chip areaLow costSolid-state devicesSemiconductor/solid-state device manufacturingQuantum efficiencyNitrogen

A light emitting diode device emitting at a wavelength of 390-415 nm has a bulk gallium and nitrogen containing substrate with an active region. The device has a current density of greater than about 175 Amps / cm2 and an external quantum efficiency with a roll off of less than about 5% absolute efficiency.

Owner:KORRUS INC

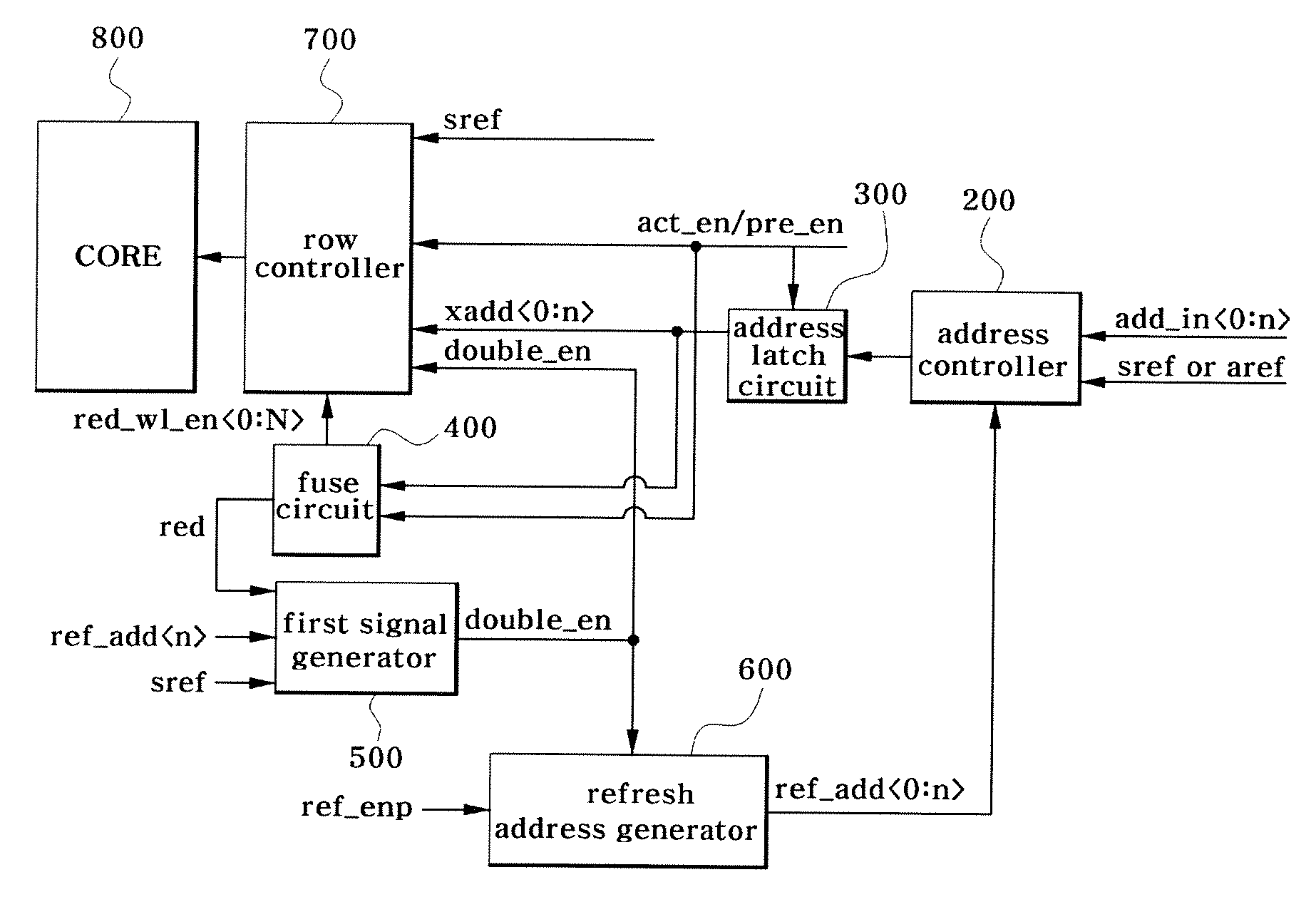

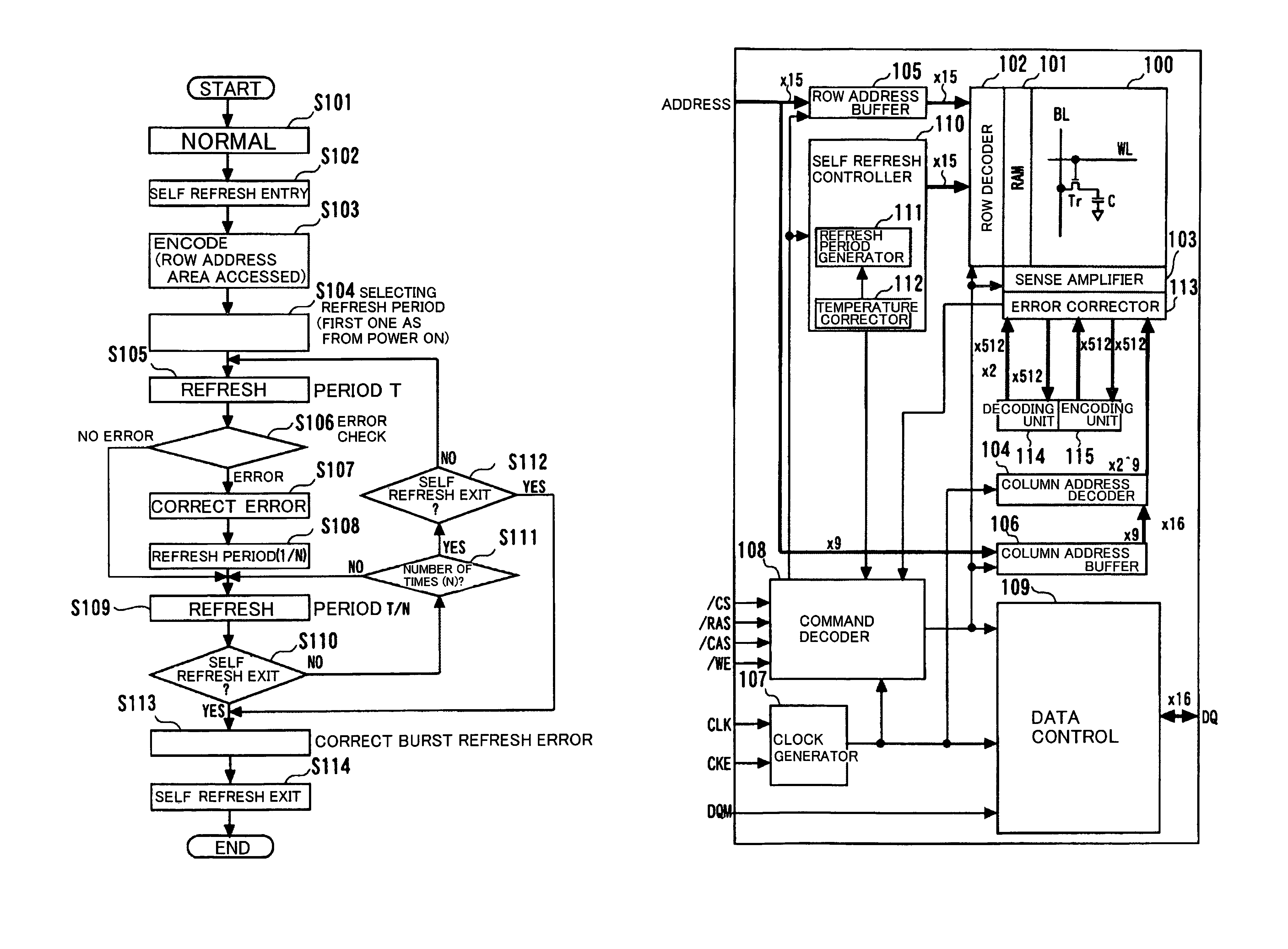

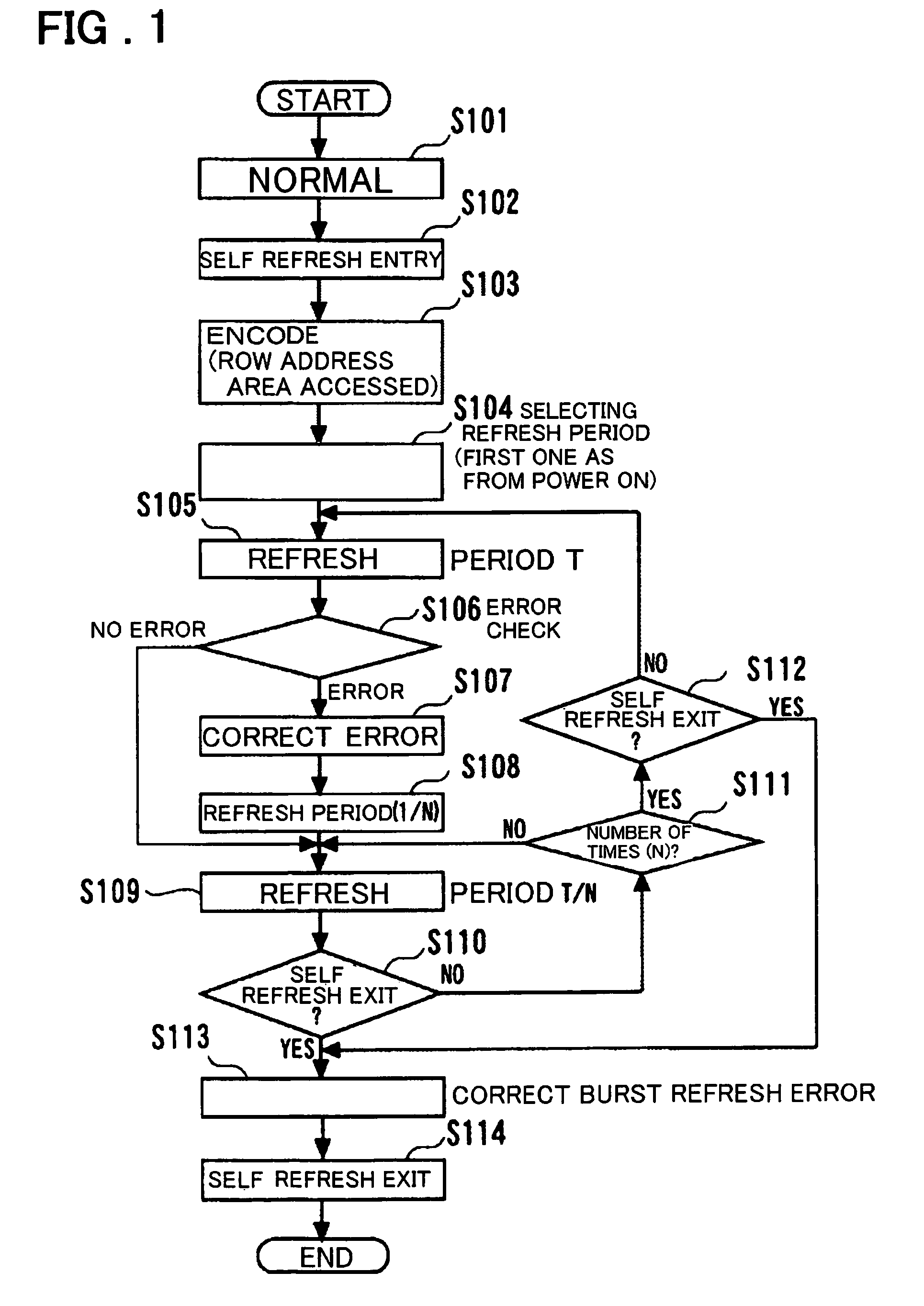

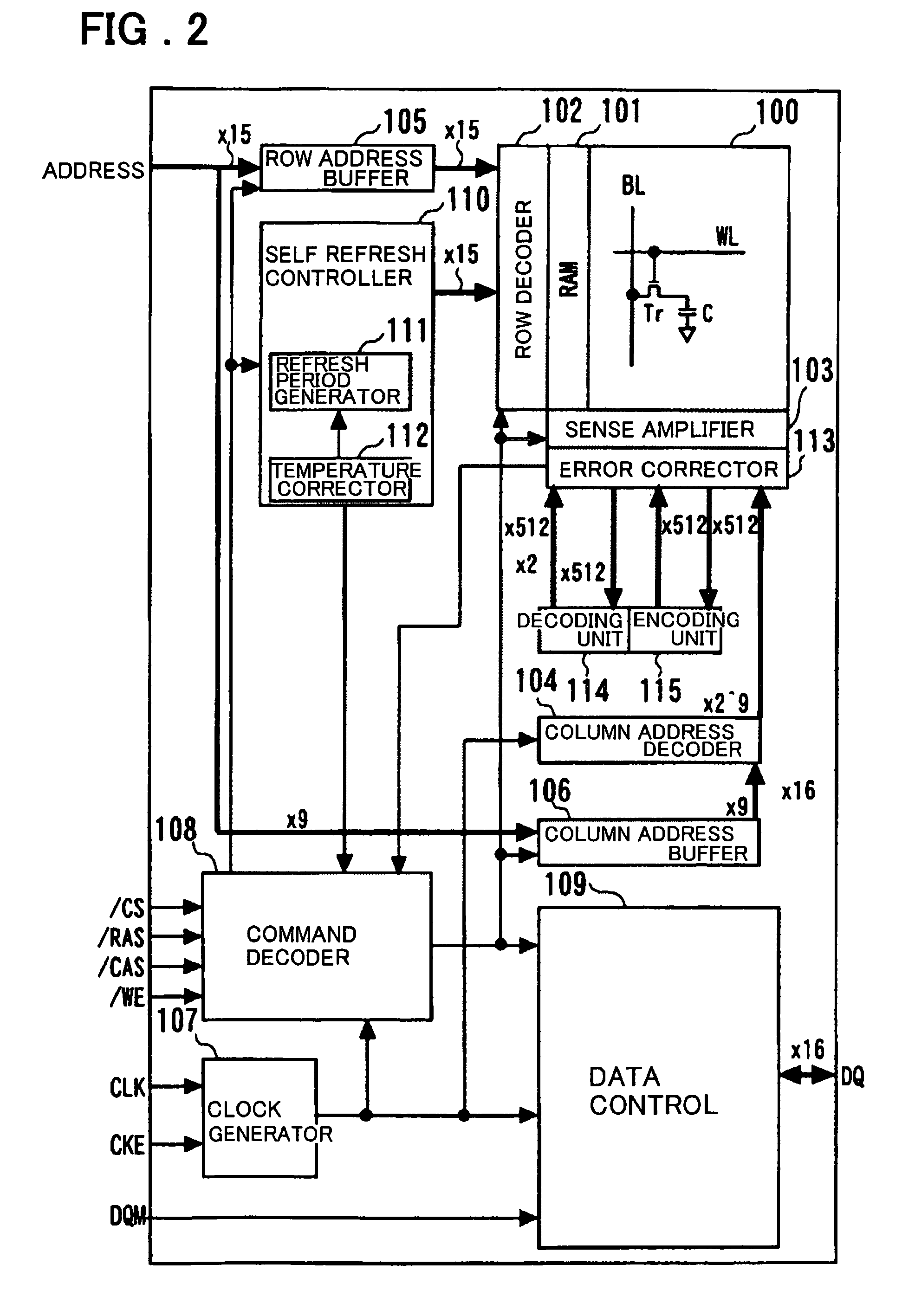

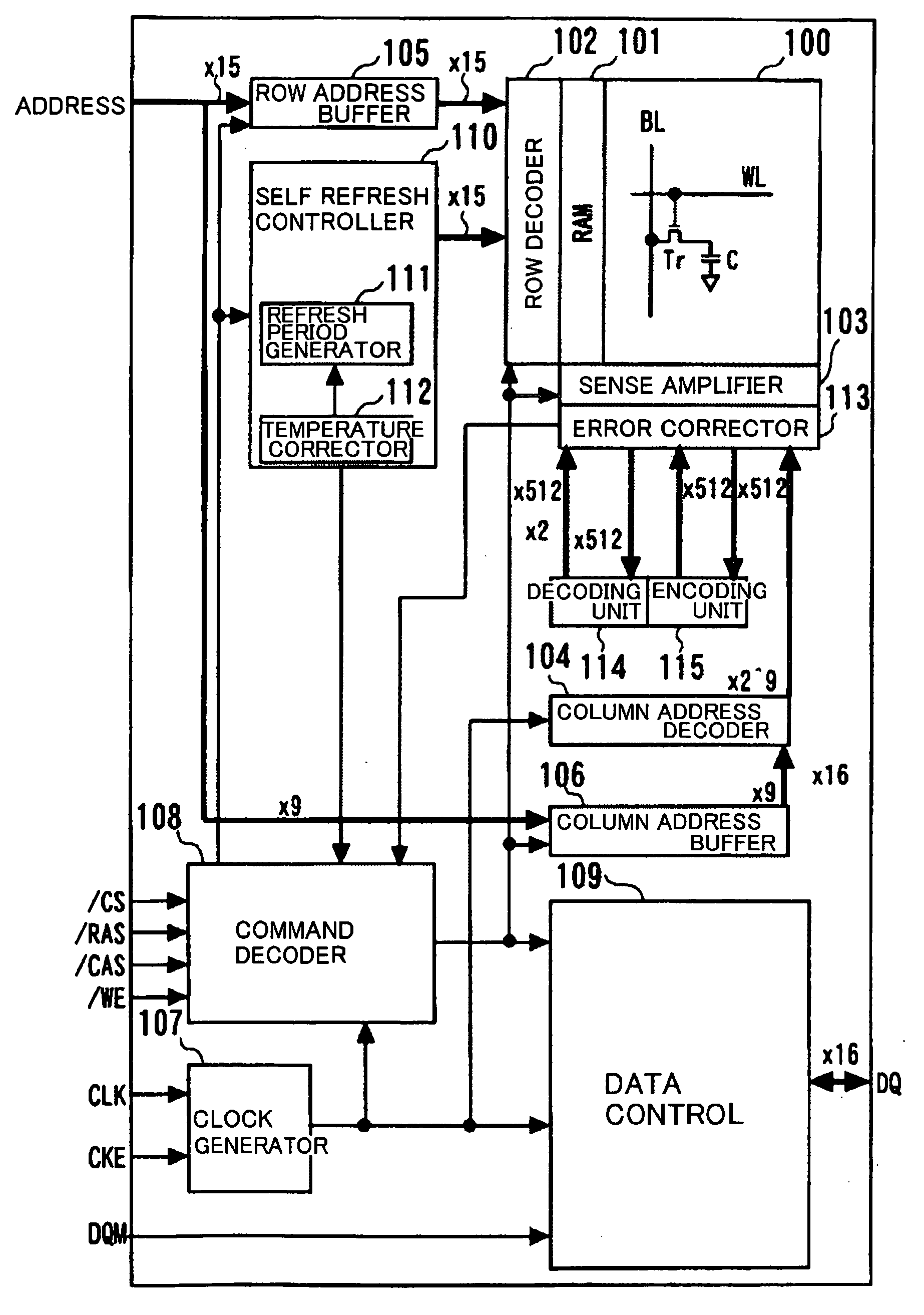

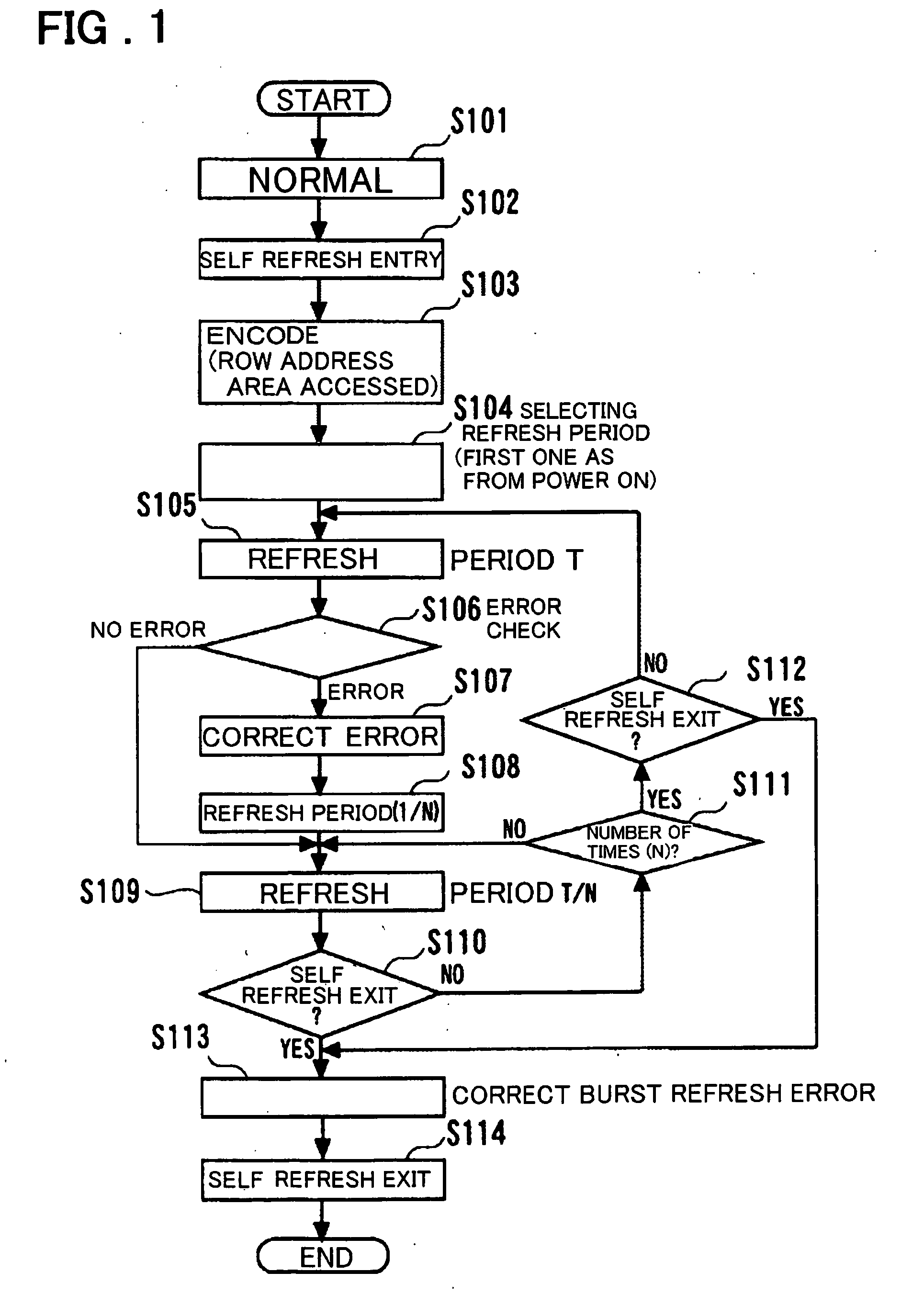

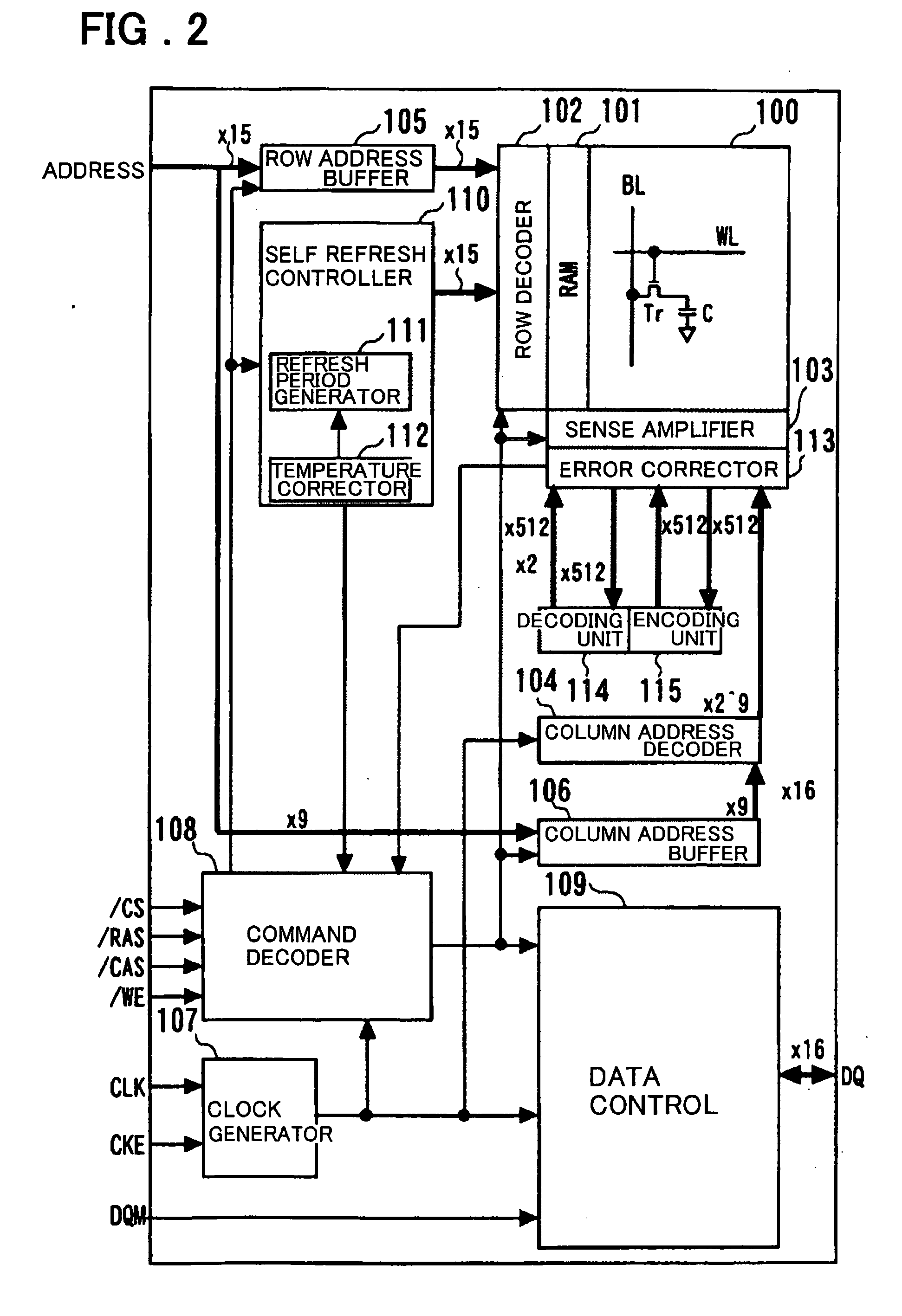

Semiconductor storage device and refresh control method therefor

InactiveUS7167403B2Reduce chip areaSimple structureDigital storageRedundant data error correctionError checkSemiconductor storage devices

A dynamic semiconductor storage device in which the power supply current during the standby time is diminished to decrease the power consumption and to suppress the chip area from increasing. During the normal operation, the information as to a word line associated with a row address accessed during the normal operation is stored in a RAM. In entering self refresh, data of memory cells connected to a word line associated with a row address accessed during the normal operation time is read out and check bits for the data are appended in an encoder and written in a check bit area. As an initializing operation for the first self refresh entry after power up sequence, the data retention time of the memory cells is inspected every word line. Based on the results of inspection, the setting value of the refresh period of the word line is determined and written in the RAM to set the word line based refresh period. During error check for the refresh operation, any error is corrected by an error correction circuit.

Owner:LONGITUDE SEMICON S A R L

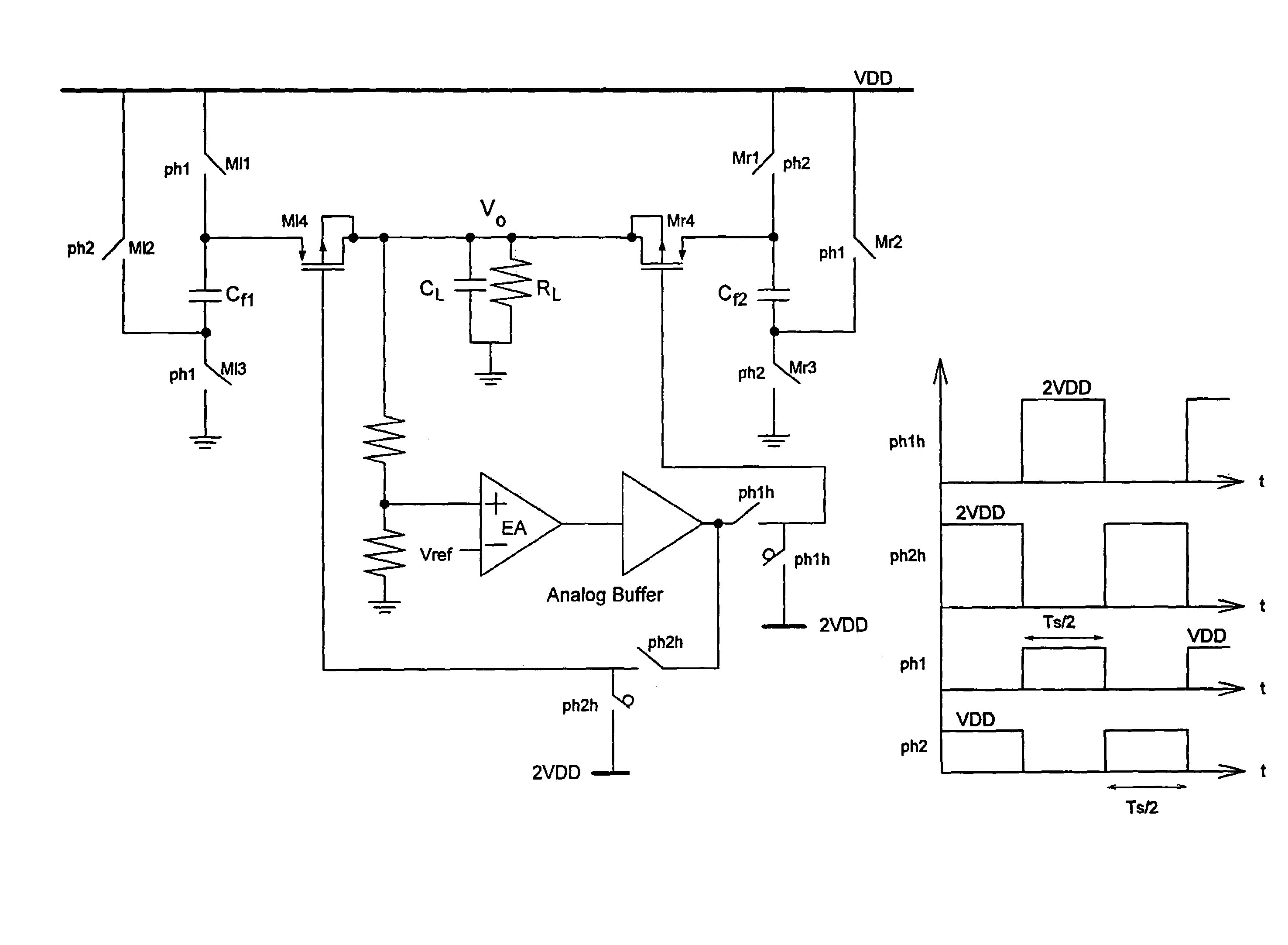

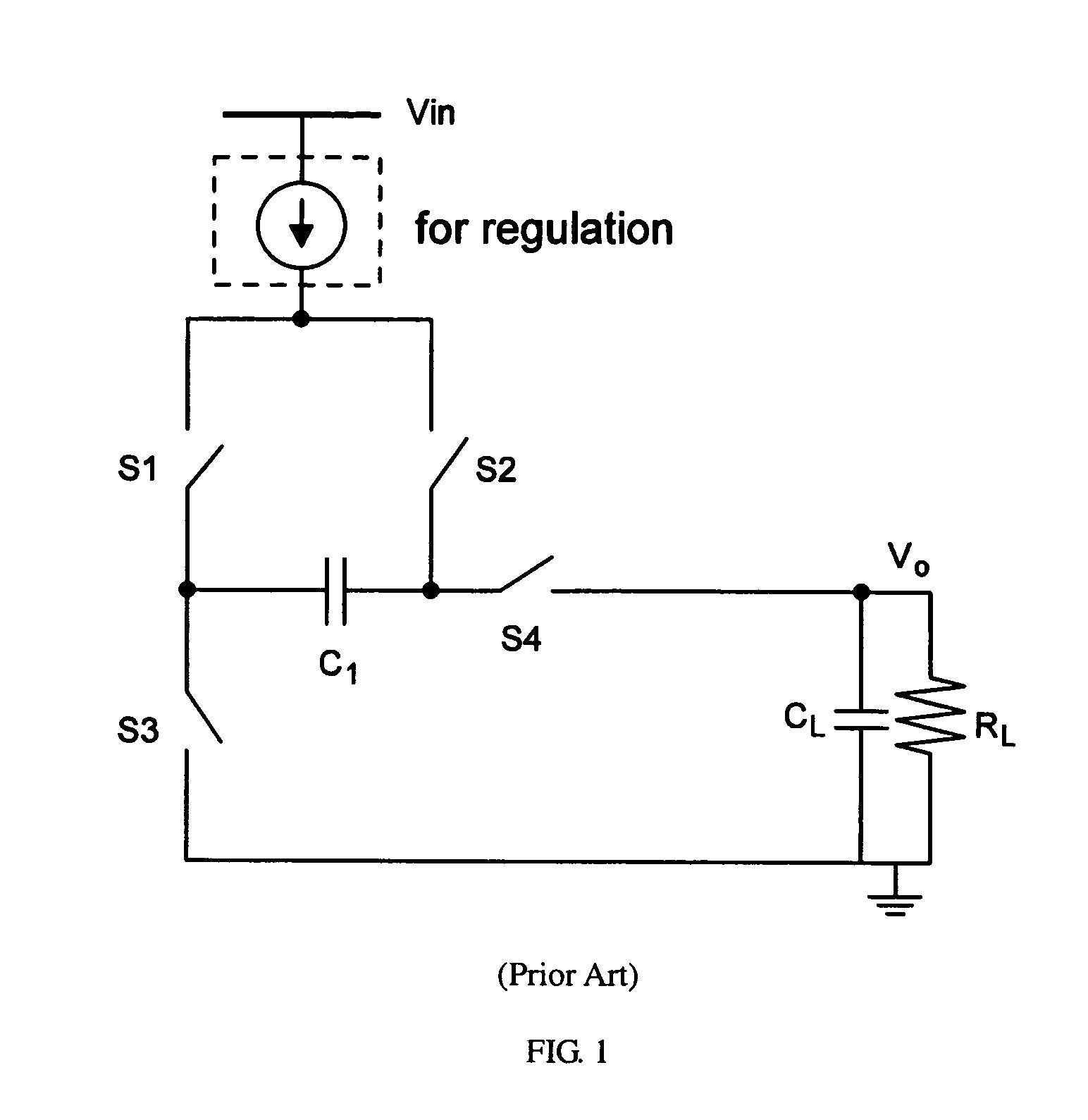

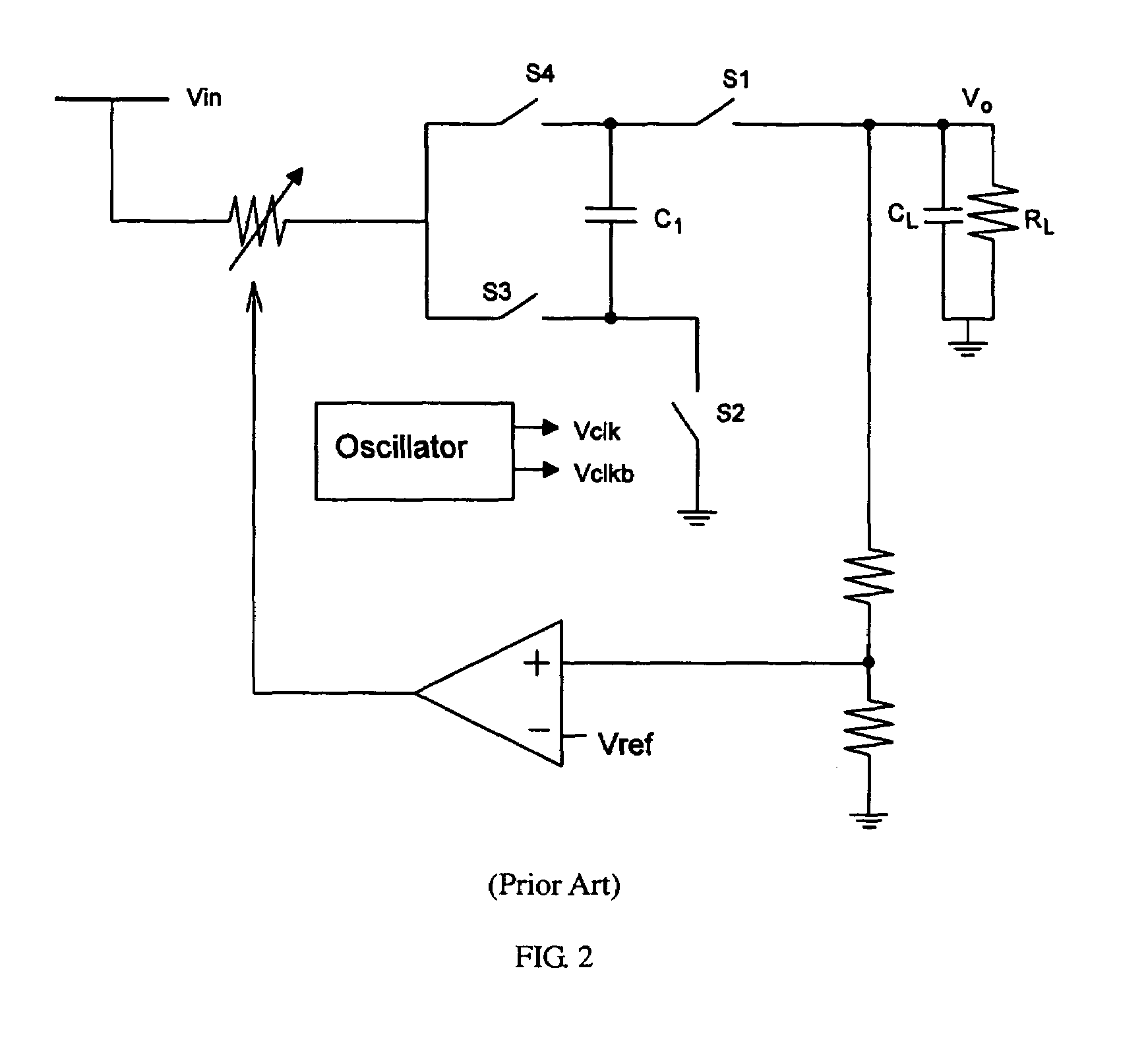

Switched-capacitor regulators

ActiveUS7375992B2Improve area efficiencyIncreases magnitudeAc-dc conversionApparatus without intermediate ac conversionCapacitancePole splitting

A switched-capacitor regulator is provided for regulating the output voltage of a voltage supply. The switched-capacitor regulator includes a supply input terminal capable of receiving a supply voltage, two or more flying capacitors, a regulation switch located between each flying capacitor and the supply input terminal, and a voltage control circuit. The activity of the regulation switches is controlled by the voltage control circuit. In one embodiment of the invention, the voltage control circuit includes a feedback resistance area having one or more feedback resistors located between the output of the flying capacitors and a ground terminal, a first gain stage connected to the feedback resistance area, and two or more second switchable gain stages, which are each connected to a regulation switch and the first gain stage. The switched-capacitor regulator operates in pseudo-continuous regulator mode using three-stage switchable operational amplifiers with time-multiplexed pole-splitting compensation.

Owner:THE HONG KONG UNIV OF SCI & TECH

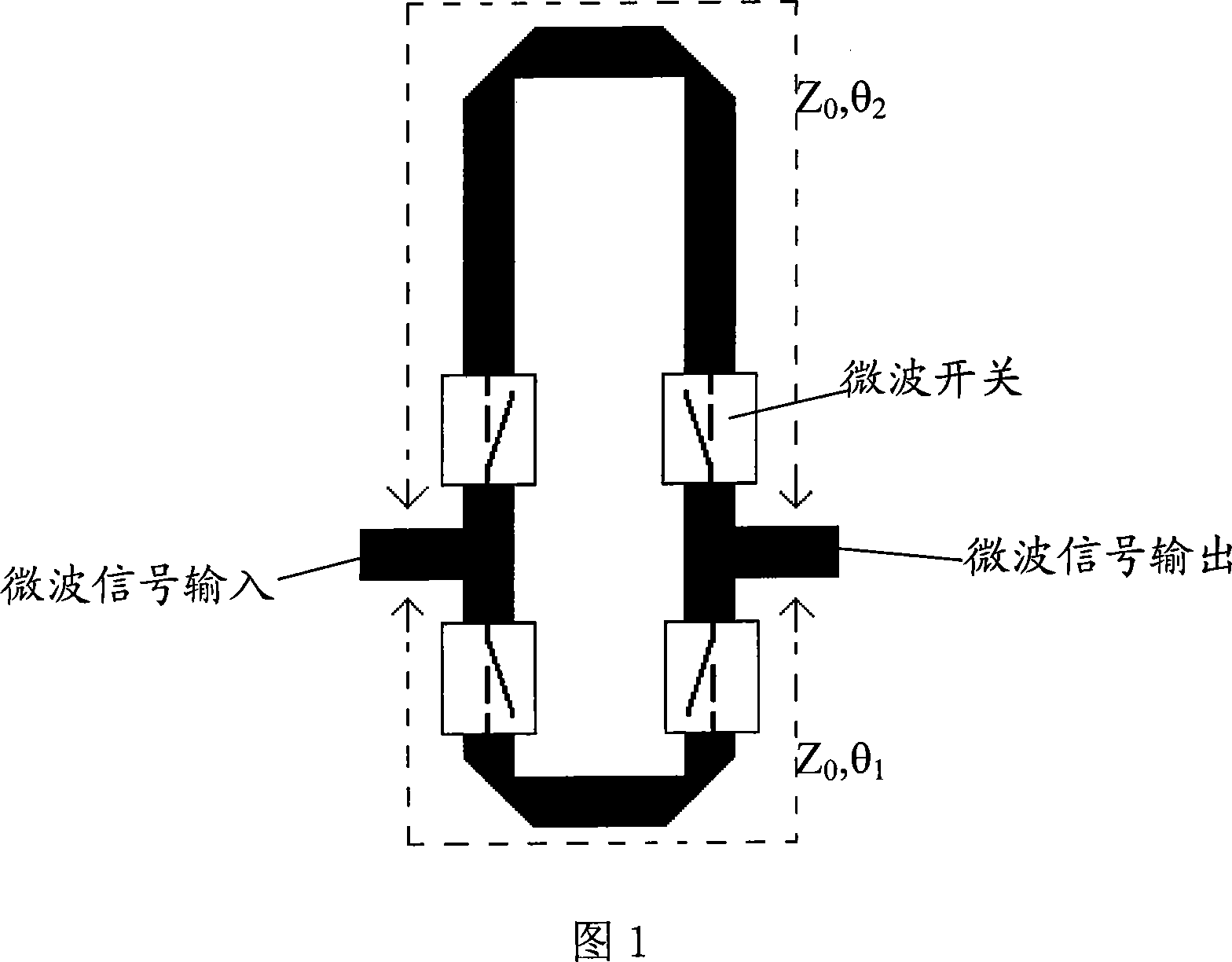

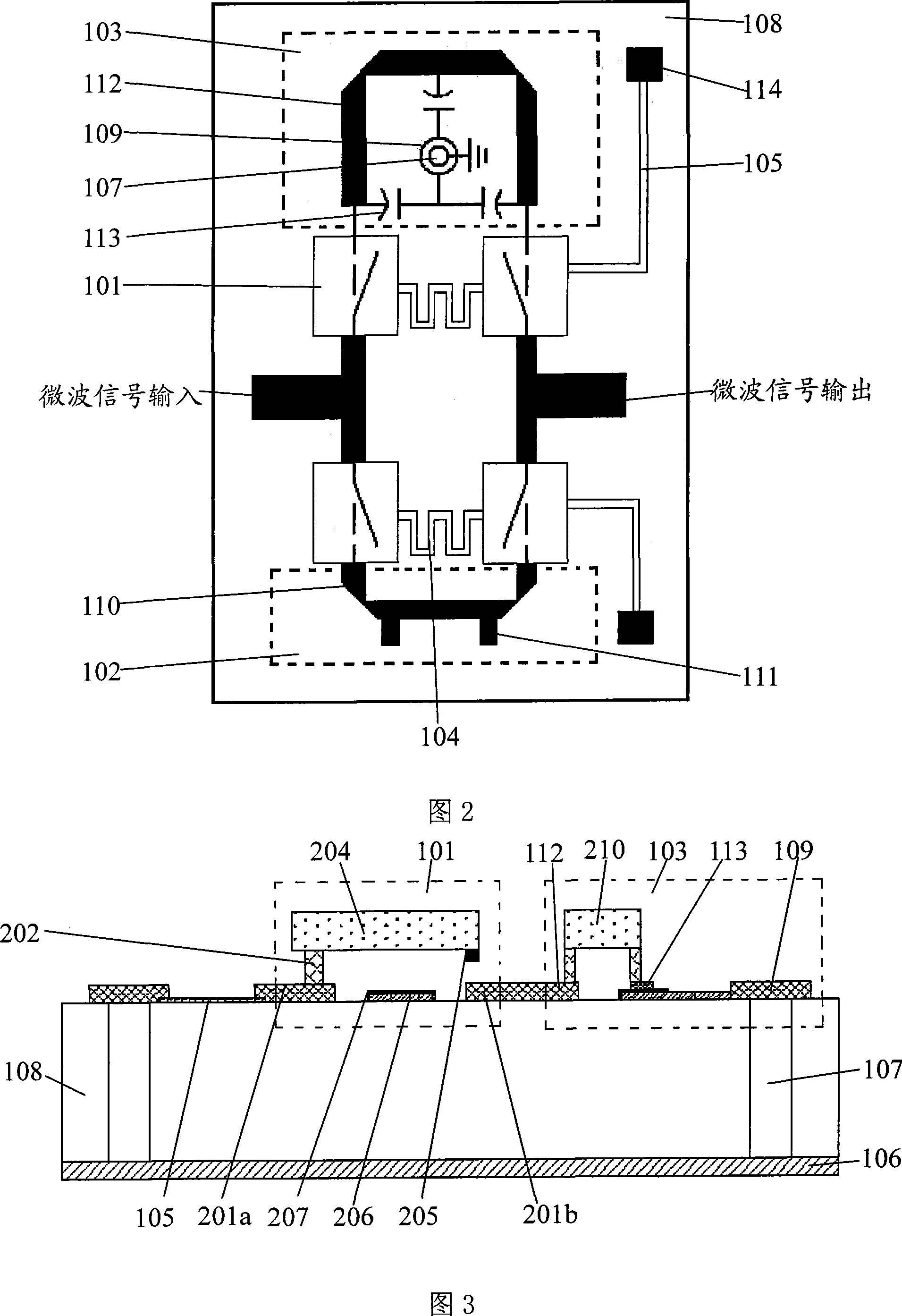

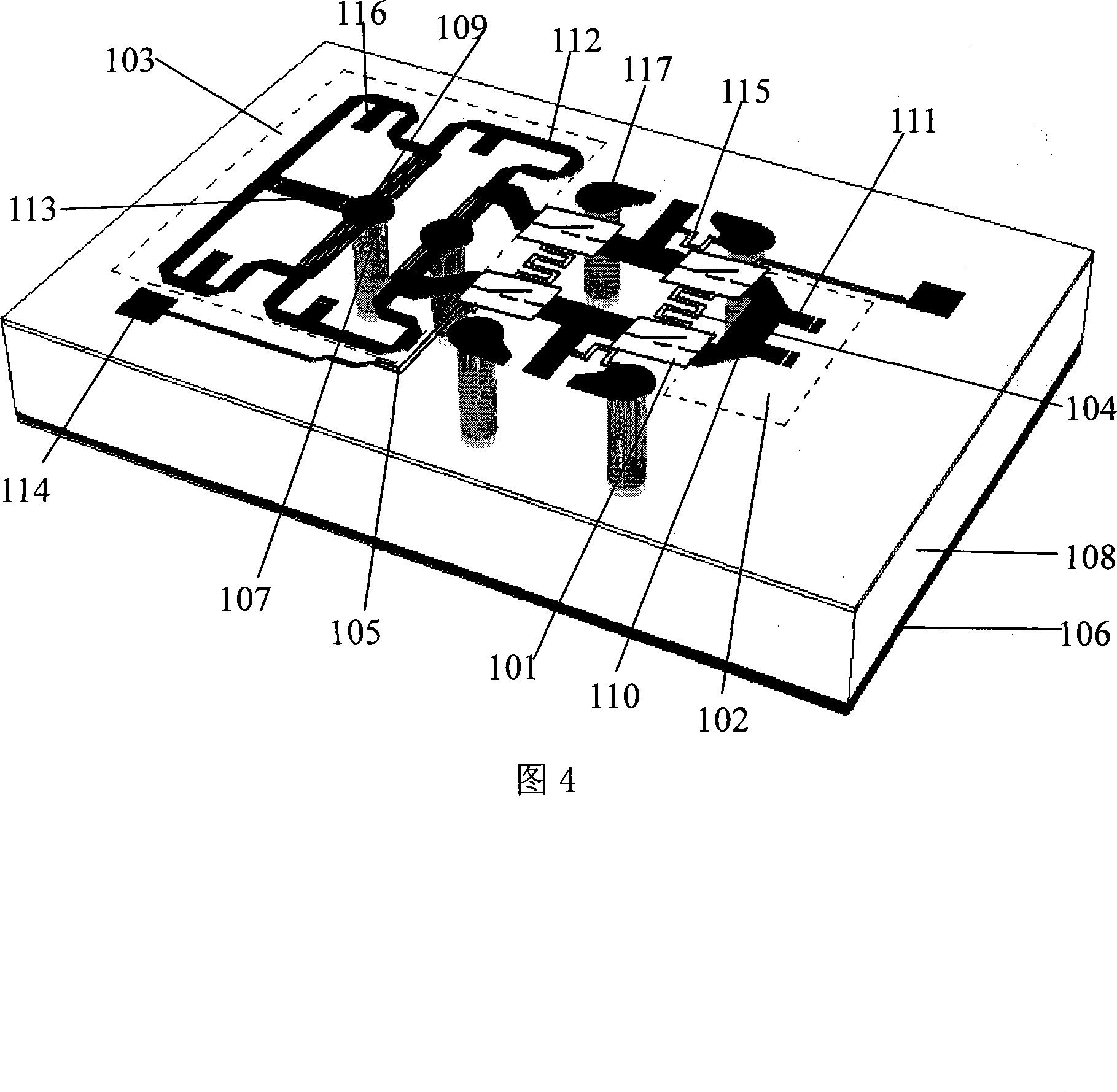

Miniature MEMS switching line phase shifter

ActiveCN101202369ALow insertion loss performanceReduce chip areaWaveguide type devicesAntennasHigh resistanceEngineering

The invention provides a miniaturized MEMS switch-line phase shifter, comprising an MEMS switch, a reference phase shifting transmission line, a phase delay transmission line, a switch offset line, a back surface grounding layer, a medium liner, a microwave grounding terminal, and a micro-mechanical through hole. The invention has the advantages of keeping low insertion loss of a transmission passage and reducing the chip area of a large phase shifting unit bit transmission line of the phase shifter by distribution-typed elements with high resistance and a phase delay transmission network formed by the microwave grounding of a collecting element and the micro-mechanical through hole, reducing the chip area of a small phase shifting unit bit delay line of the phase shifter, reducing the area of the chip, minimizing the chip area occupied by the MEME switch by selecting miniaturized MEMS switches such as a built-in cantilever MEMS switch, keeping the broad band performance of the MEMS switch and the phase shifter and minimizing the chip area occupied by the MEMS switch offset circuit by separating a microwave signal from a switch driving signal, and leading to simple and convenient design of microwave grounding of the chip and reducing the area of the chip to the most extent by the micro-mechanical through hole technology.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

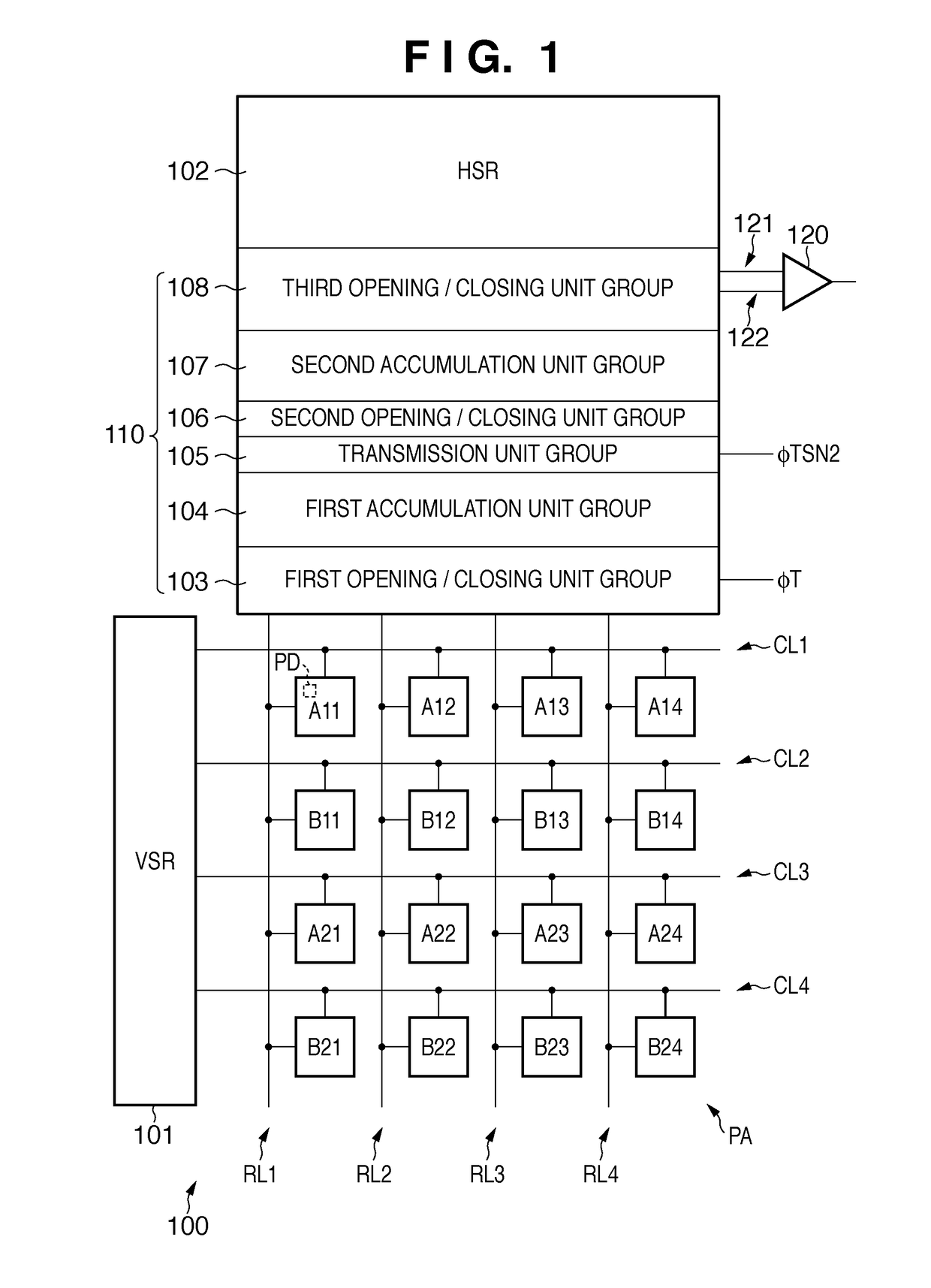

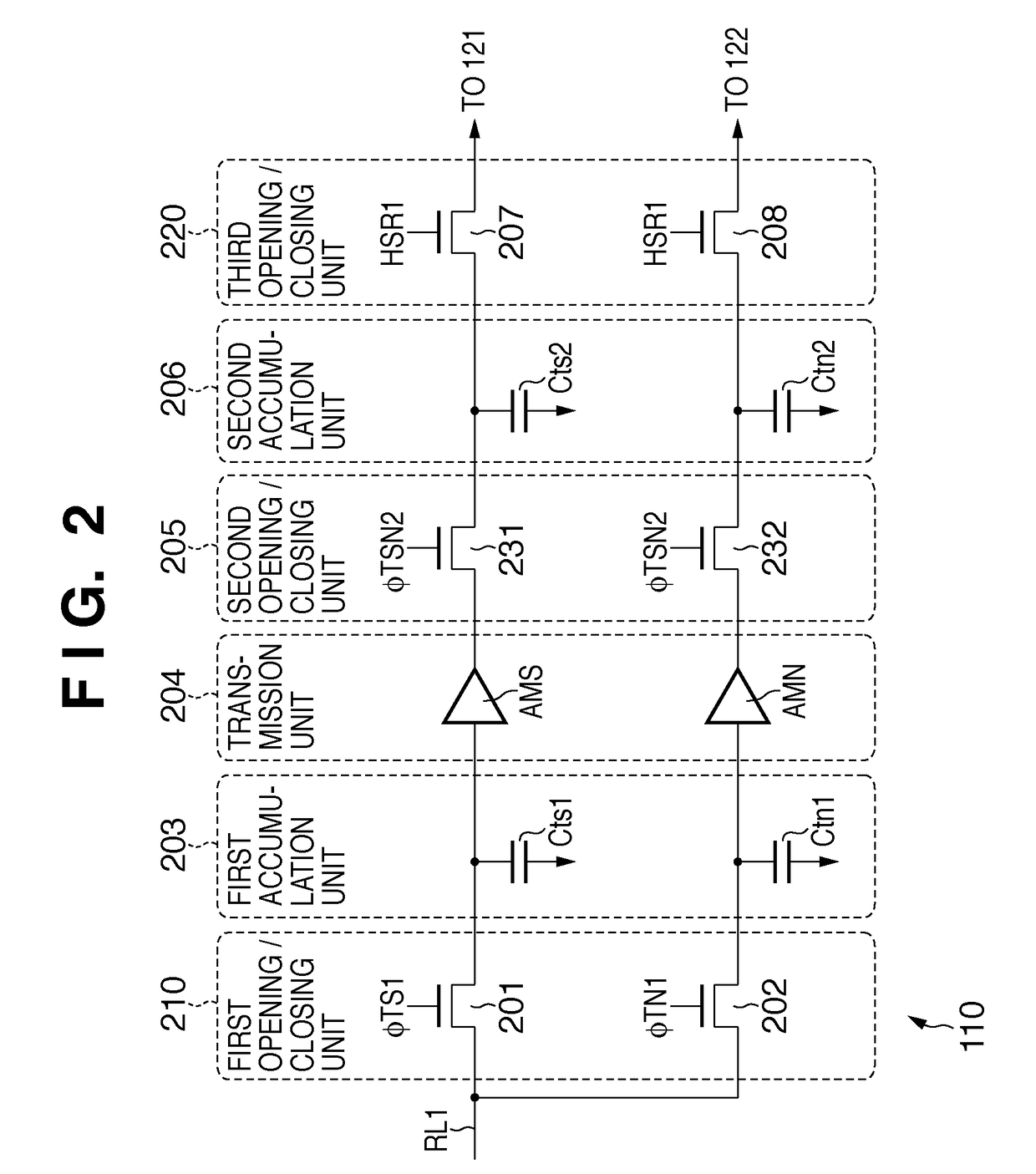

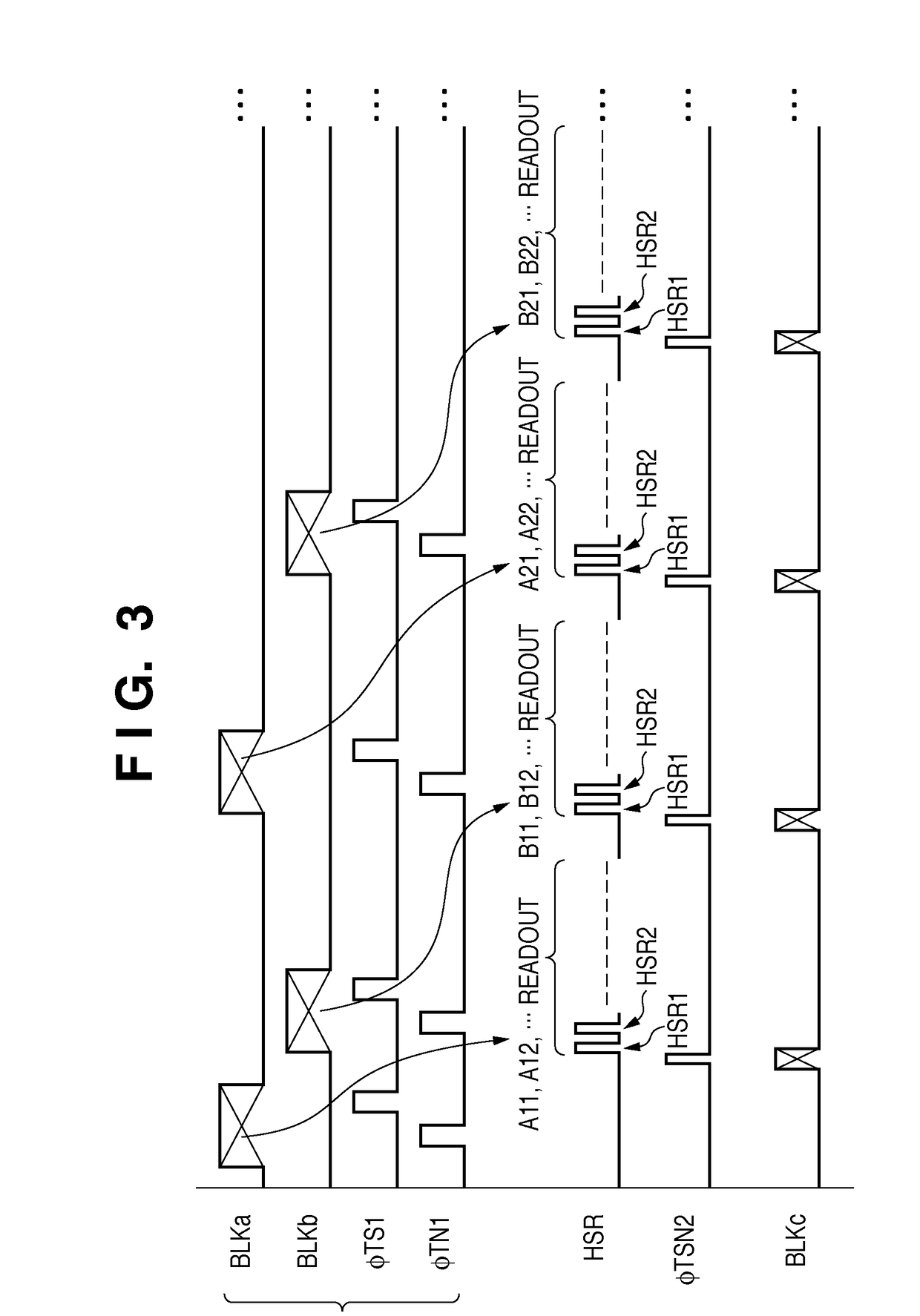

Image sensing apparatus and imaging system

InactiveUS7907196B2Reduce power consumptionReduce chip areaTelevision system detailsTelevision system scanning detailsCapacitanceEngineering

Owner:CANON KK

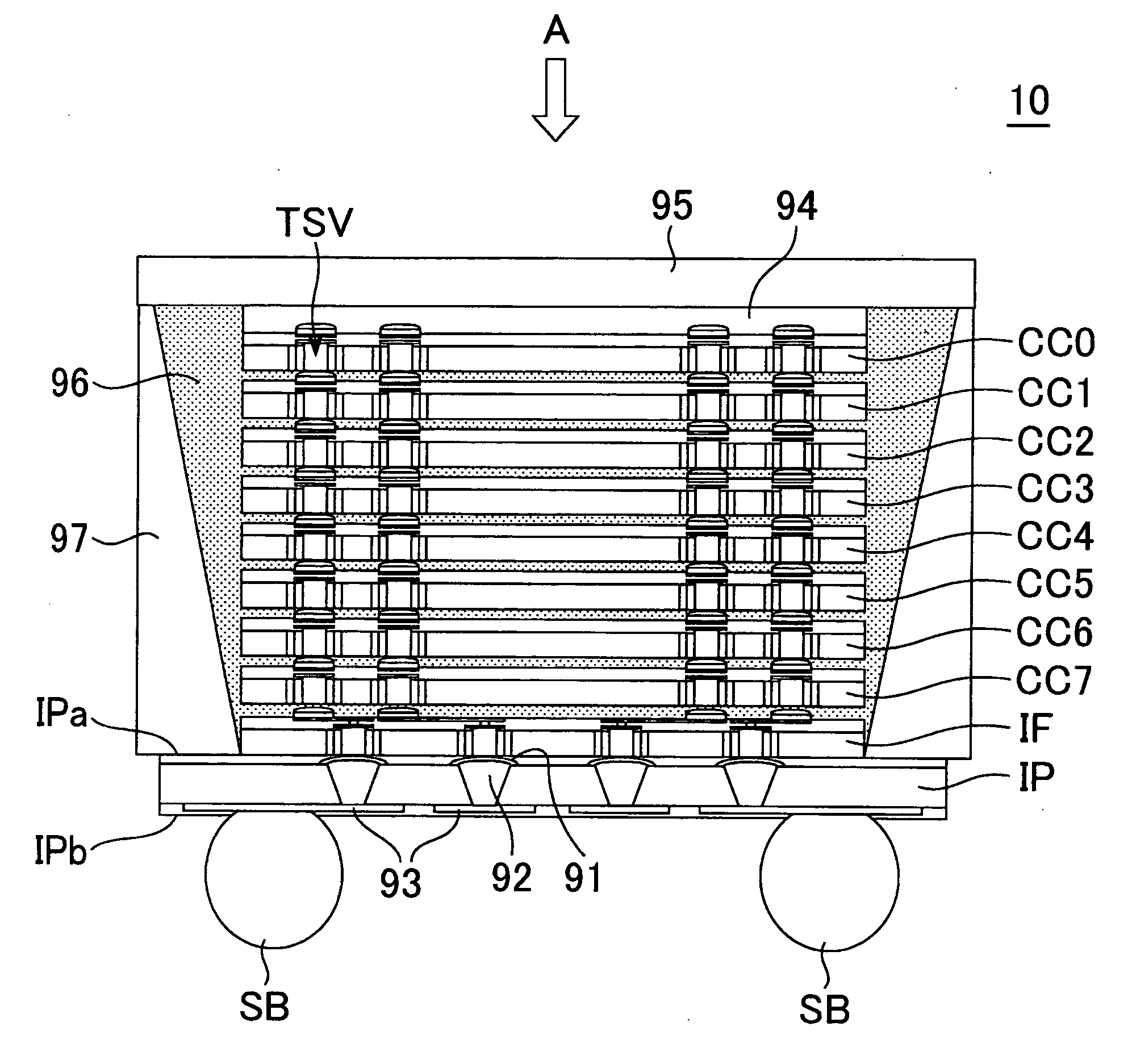

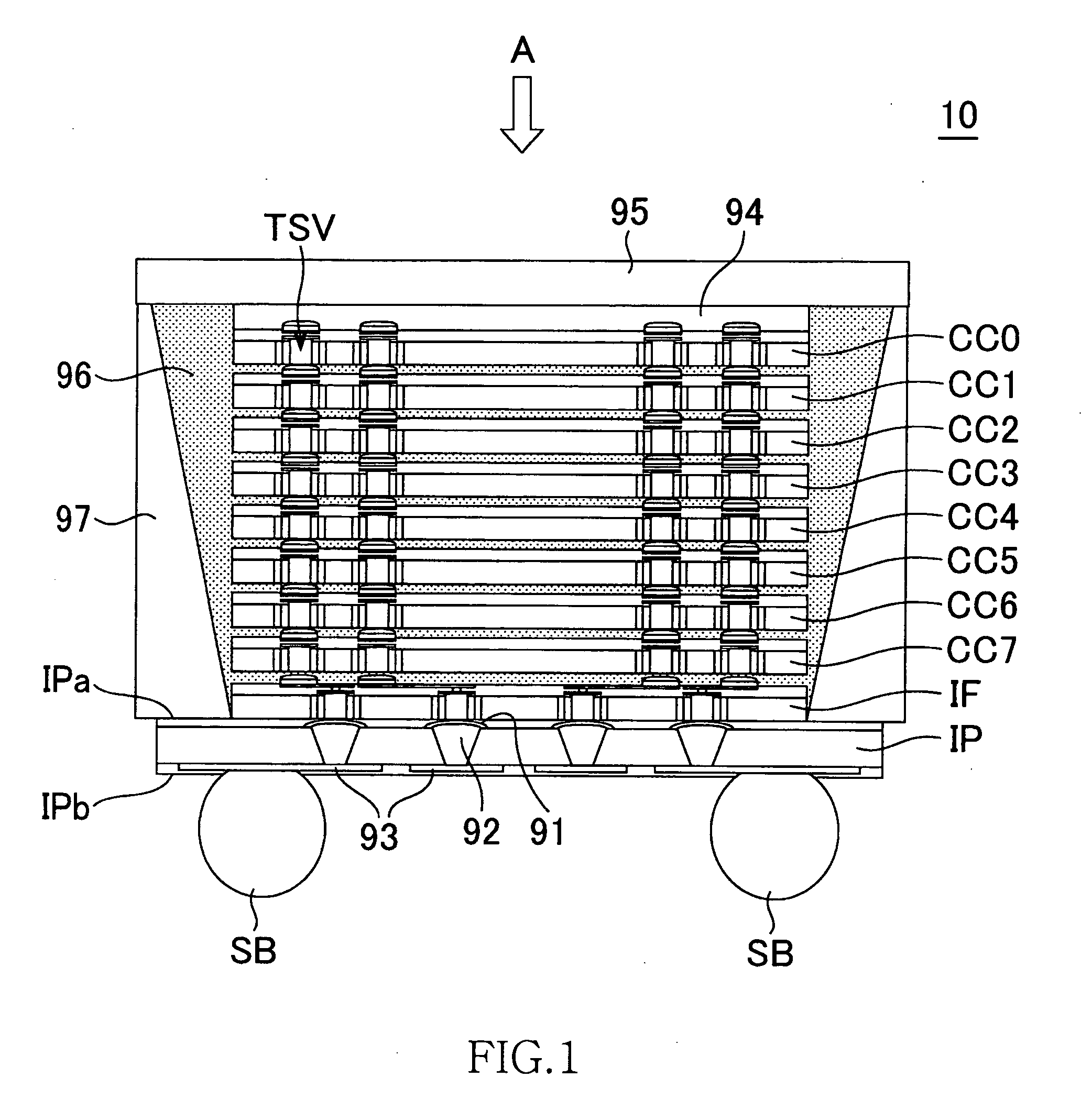

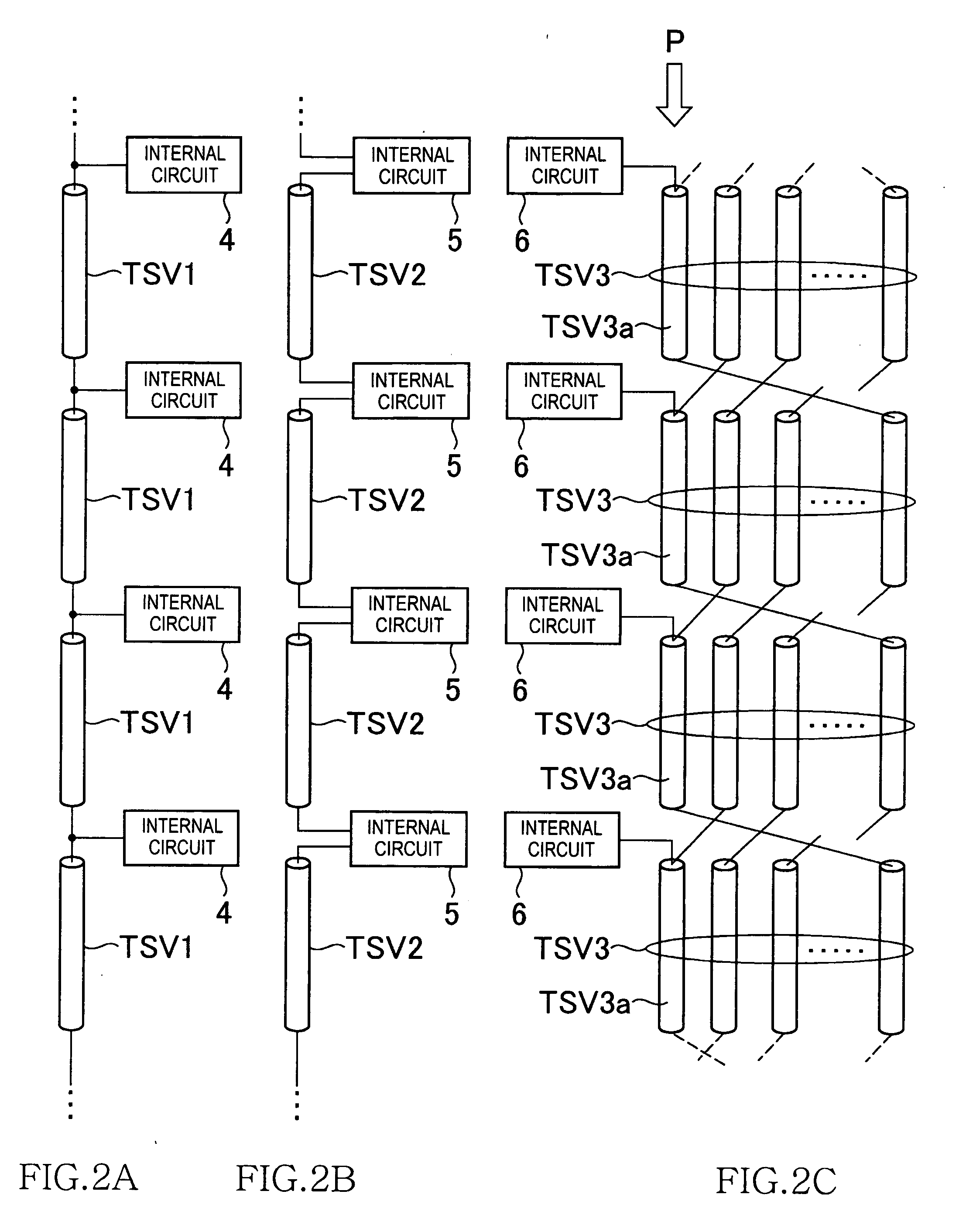

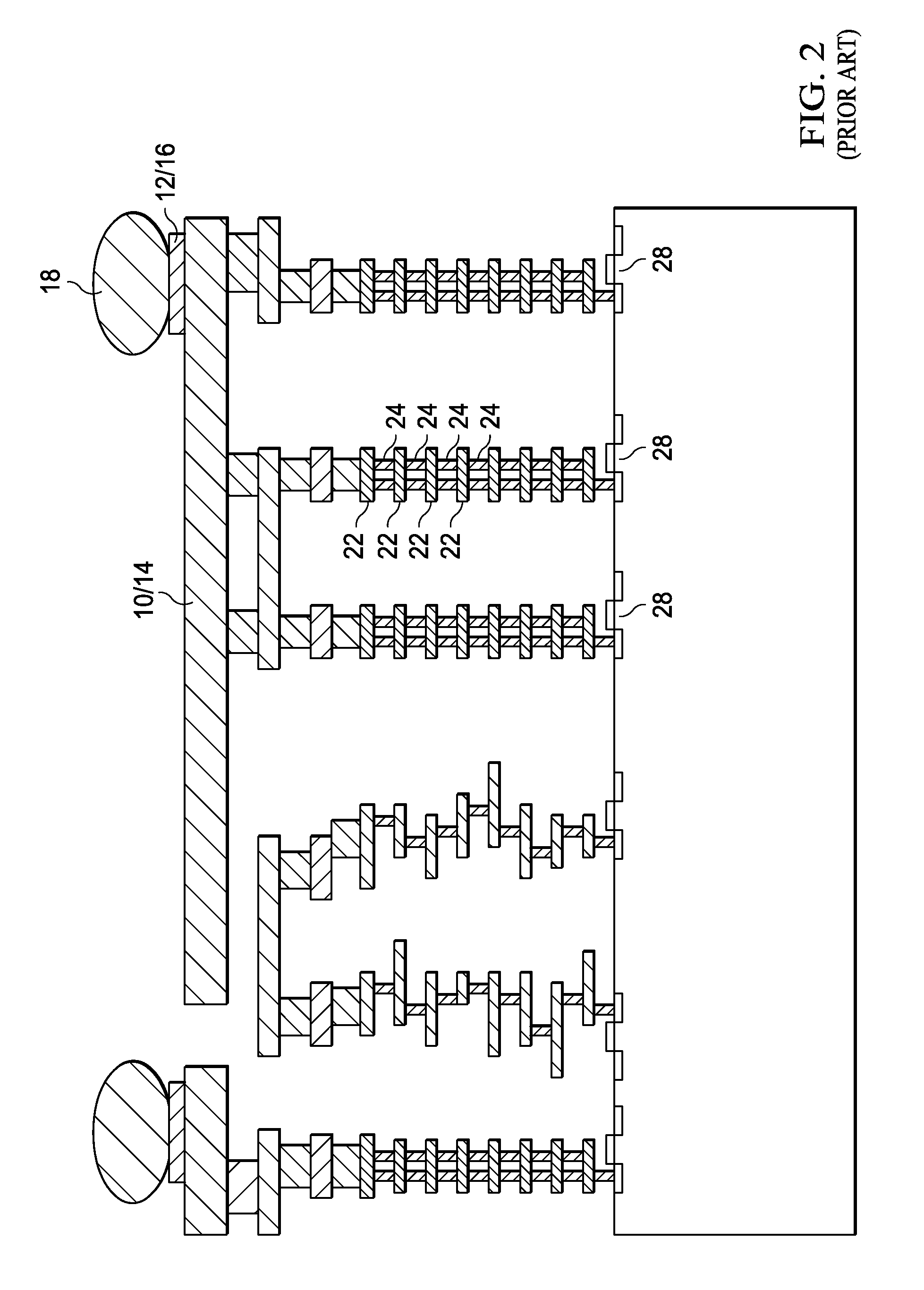

Semiconductor device having plural semiconductor chips laminated to each other

ActiveUS20110057819A1Reduce areaReduce chip areaParallel/series conversionSemiconductor/solid-state device detailsPower semiconductor deviceSemiconductor chip

In a stacked semiconductor device in which a plurality of through silicon vias used for data transfer are shared among a plurality of semiconductor chips, a first semiconductor chip included in the semiconductor chips holds through silicon via switching information for specifying a through silicon via among the through silicon vias to be used for data transfer, and transfers the through silicon via switching information to a second semiconductor chip included in the semiconductor chips. According to the present invention, because the through silicon via switching information is transferred from the first semiconductor chip to the second semiconductor chip, a circuit for storing the through silicon via switching information in a nonvolatile manner is not required in the second semiconductor chip. With this arrangement, a chip area of the second semiconductor chip can be reduced.

Owner:LONGITUDE LICENSING LTD

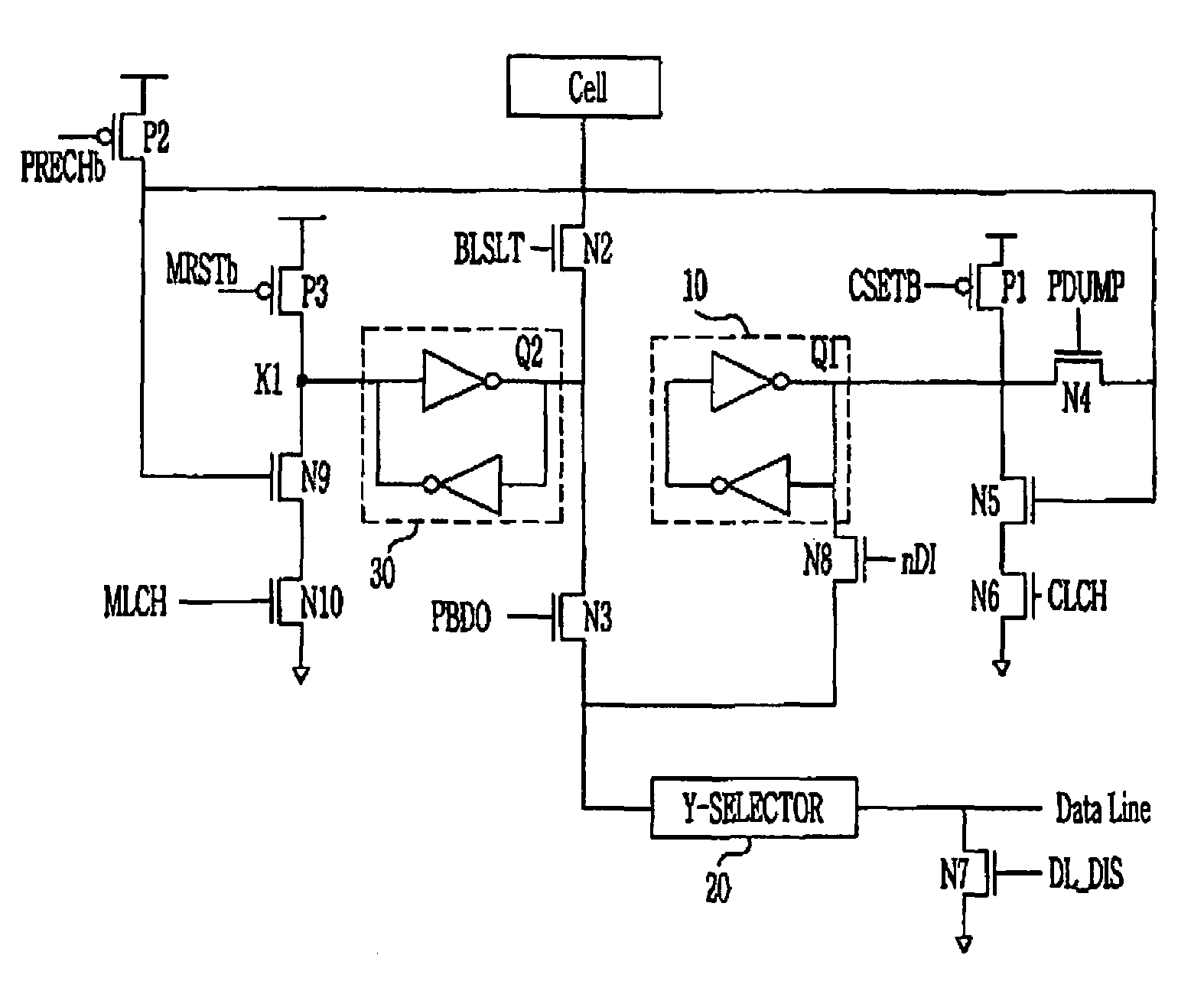

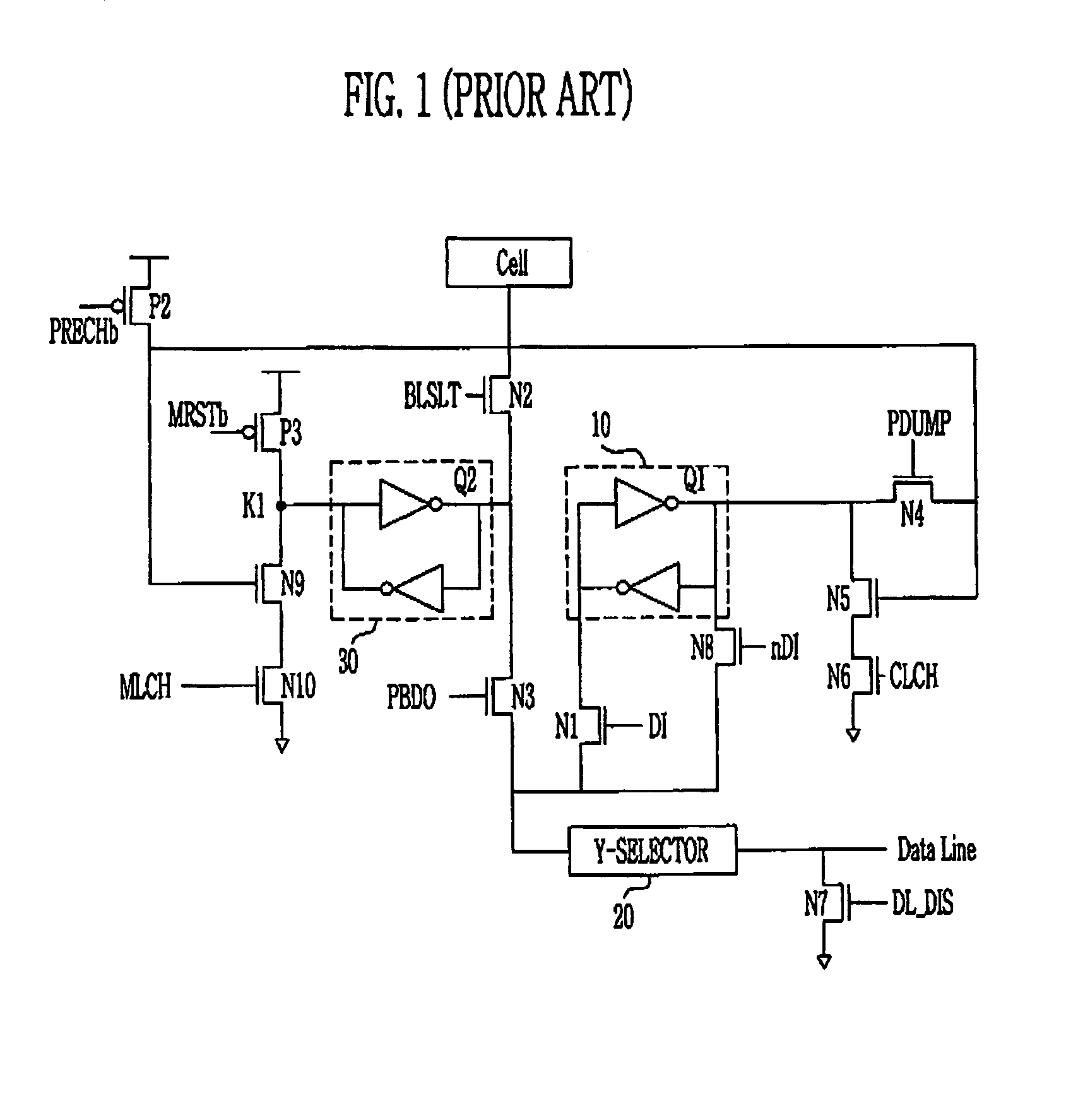

Page buffer for NAND flash memory

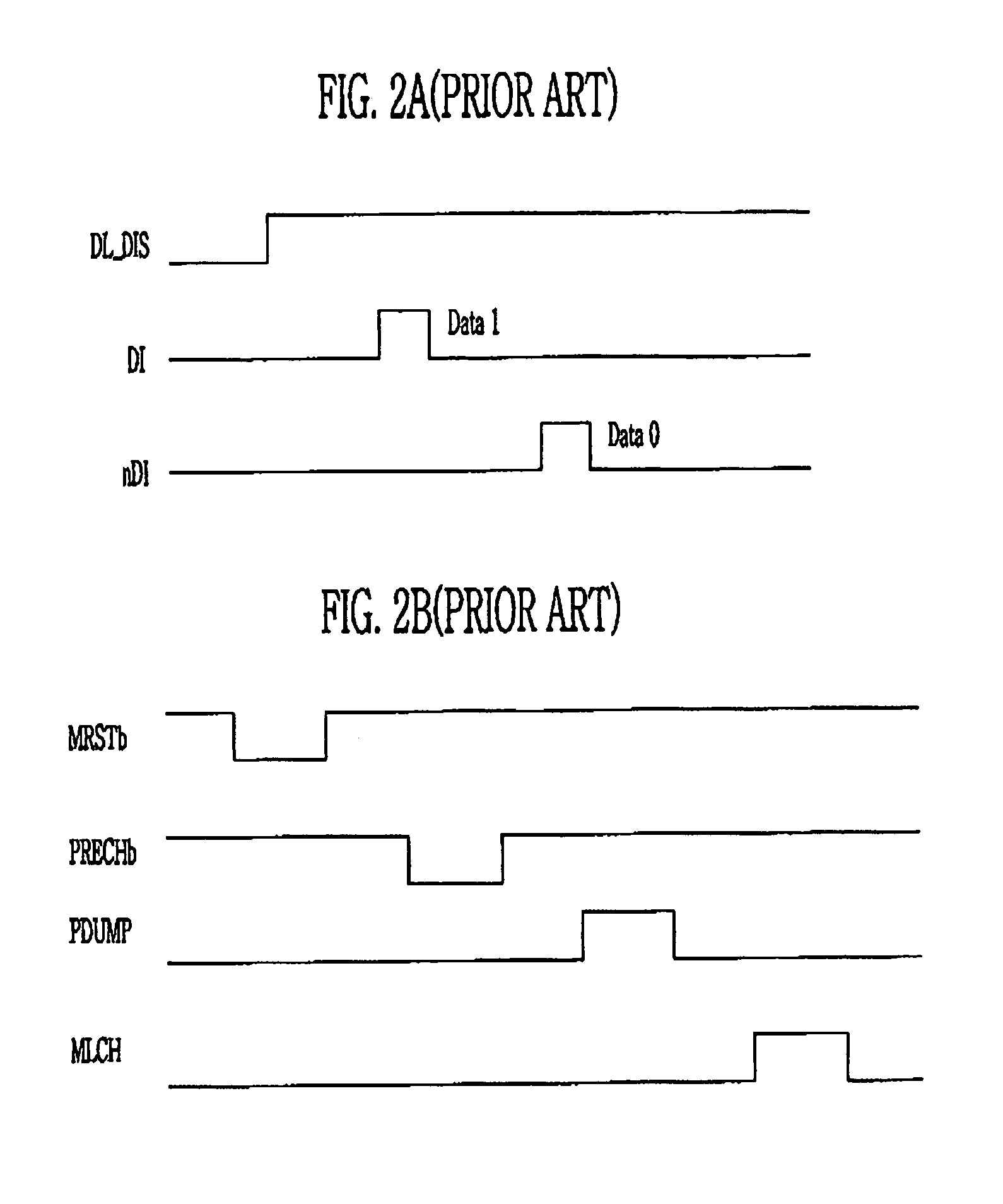

InactiveUS7016229B2Reduce decreaseImprove data loading speedRead-only memoriesDigital storageData controlControl signal

A page buffer for an NAND flash memory, including: a first latch for loading data; a second latch for storing data stored on a cell depending on a bit line selection signal; a setting circuit for setting the first latch to a high level to load data in a high level; a first switching circuit for transferring the data stored on the second latch depending on a data output signal of a page buffer; a discharging circuit for discharging charges on a data line; a second switching circuit for connecting the data line discharged by the discharging circuit to the first latch depending on a data control signal to load the data in a low level to the first latch; and a data transferring circuit for transferring the data of the first latch to the second latch.

Owner:SK HYNIX INC

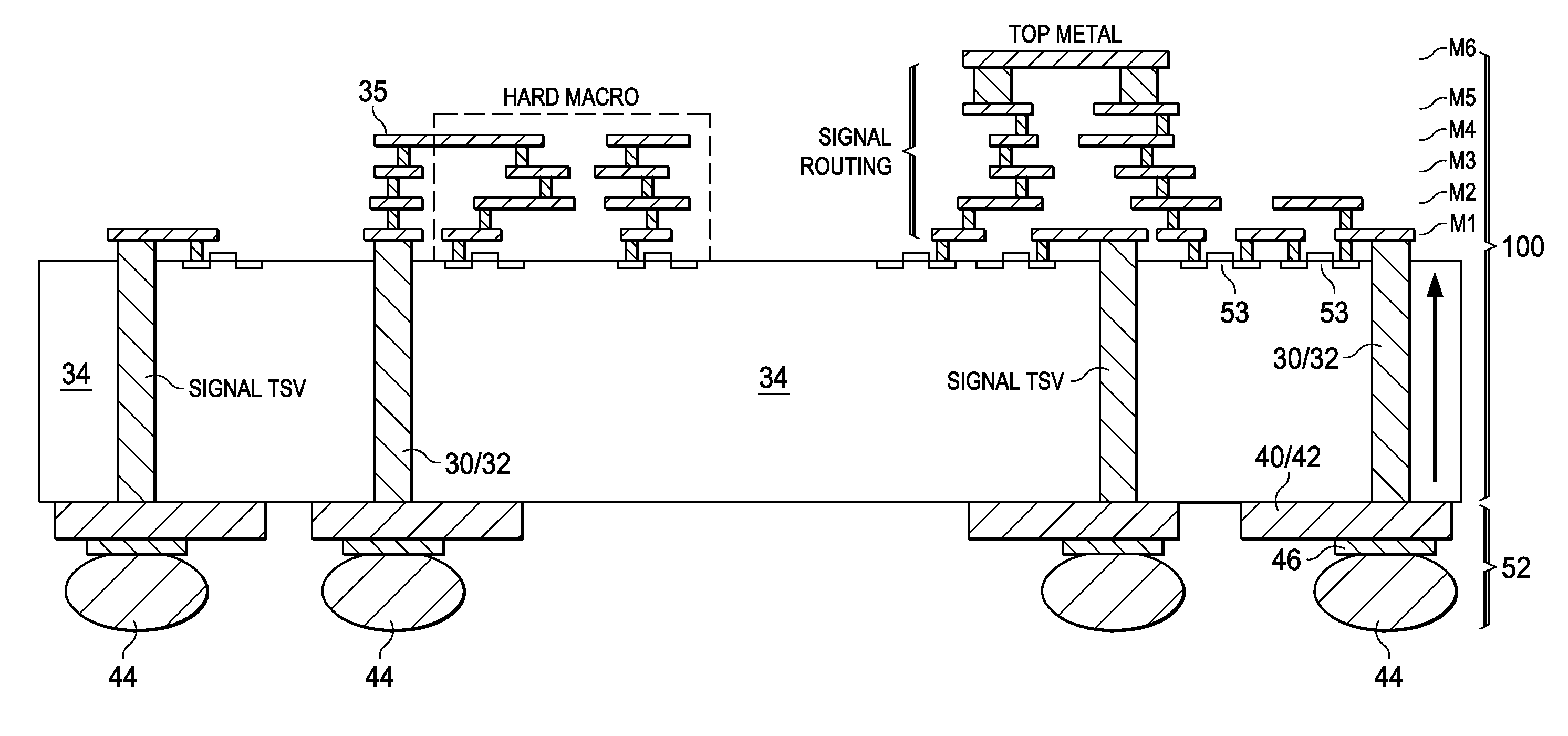

Supplying Power to Integrated Circuits Using a Grid Matrix Formed of Through-Silicon Vias

ActiveUS20110001249A1Reduce chip areaAvoid signalingSemiconductor/solid-state device detailsSolid-state devicesEngineeringSilicon

An integrated circuit structure includes a chip including a substrate and a power distribution network. The power distribution network includes a plurality of power through-silicon vias (TSVs) penetrating the substrate, wherein the plurality of power TSVs forms a grid; and a plurality of metal lines in a bottom metallization layer (M1), wherein the plurality of metal lines couples the plurality of power TSVs to integrated circuit devices on the substrate.

Owner:TAIWAN SEMICON MFG CO LTD

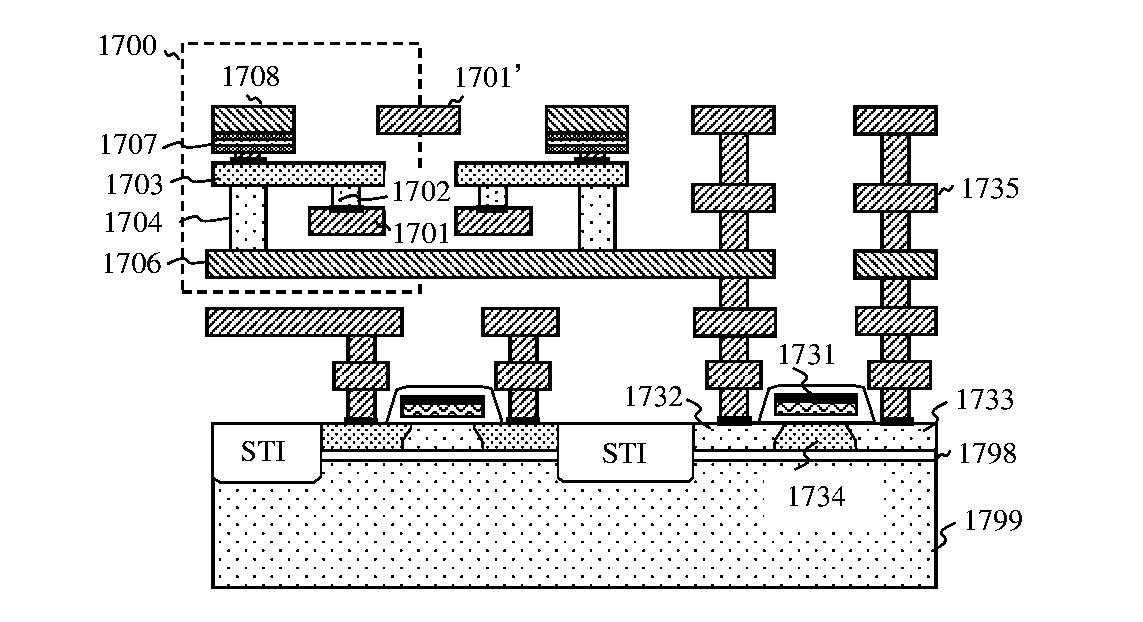

Area-Efficient Electrically Erasable Programmable Memory Cell

ActiveUS20100302854A1Reduce chip areaEliminate leaksTransistorSolid-state devicesBuried oxideIntegrated circuit

Electrically erasable programmable “read-only” memory (EEPROM) cells in an integrated circuit, and formed by a single polysilicon level. The EEPROM cell consists of a coupling capacitor and a combined read transistor and tunneling capacitor. The capacitance of the coupling capacitor is much larger than that of the tunneling capacitor. In one embodiment, field oxide isolation structures isolate the devices from one another; a lightly-doped region at the source of the read transistor improves breakdown voltage performance. In another embodiment, trench isolation structures and a buried oxide layer surround the well regions at which the coupling capacitor and combined read transistor and tunneling capacitor are formed.

Owner:TEXAS INSTR INC

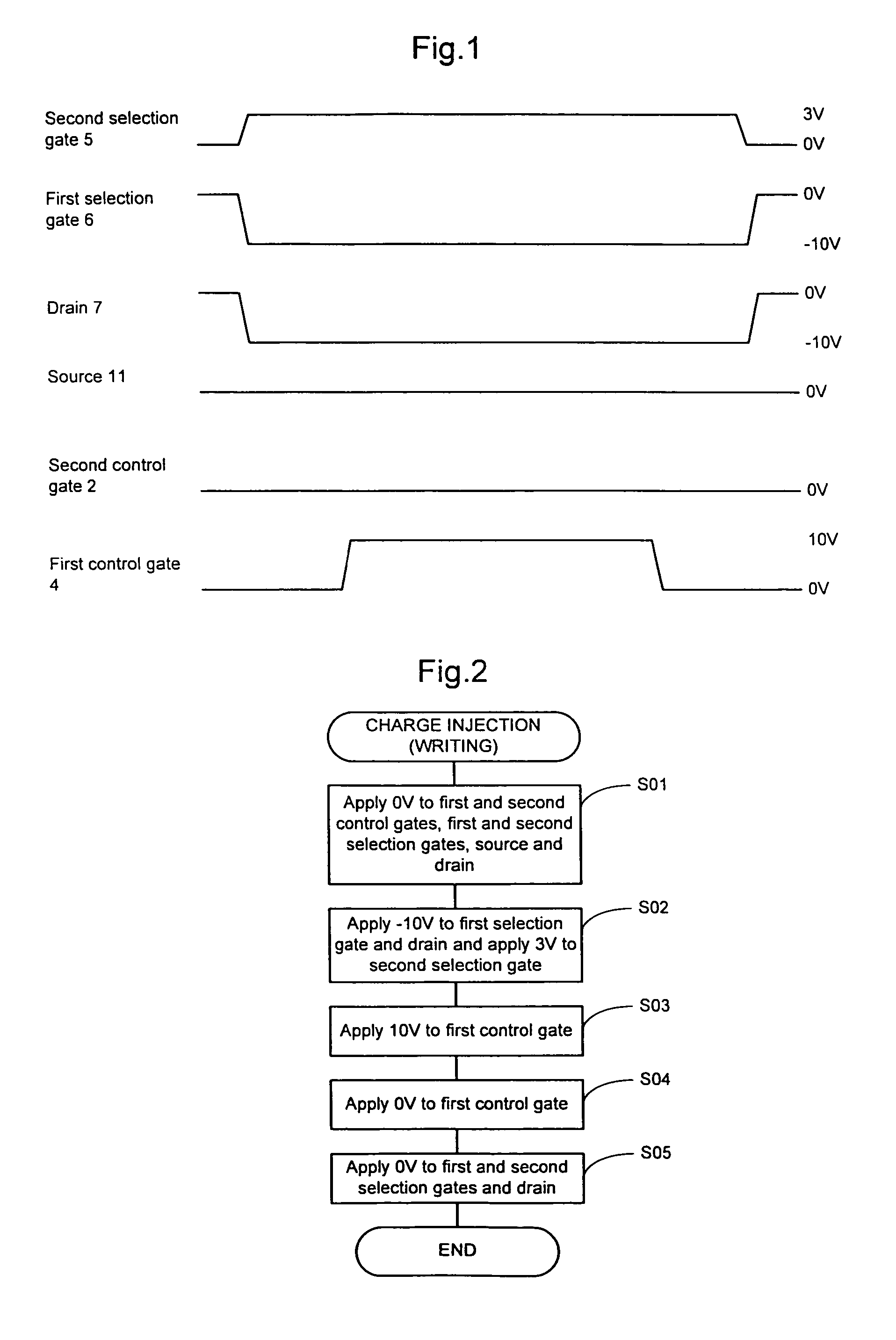

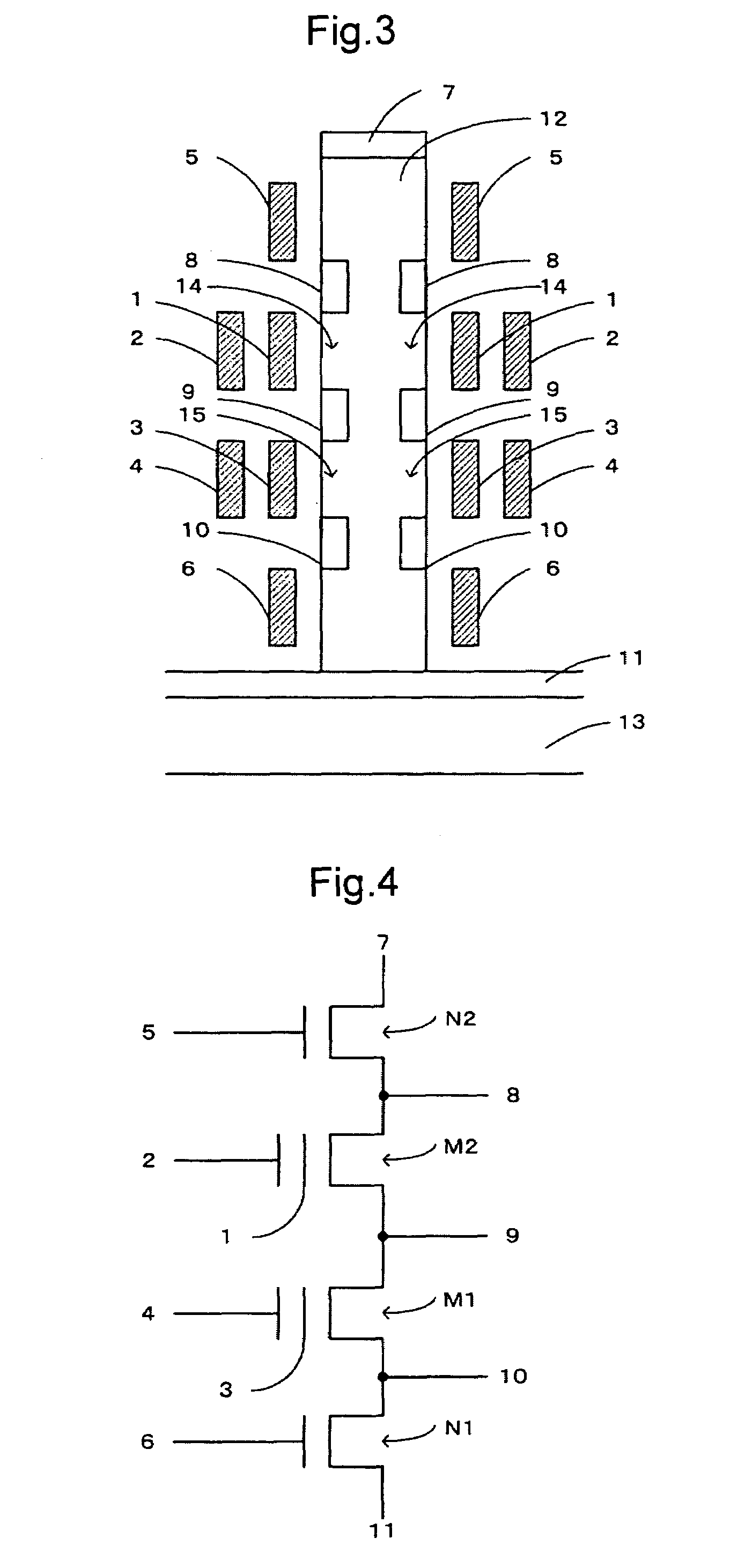

Low voltage, island-layer-based nonvolatile semiconductor storage device with floating biased memory cell channel

ActiveUS7009888B2Less susceptible to the back bias effectWeakening rangeTransistorStatic indicating devicesLow voltageSemiconductor storage devices

A method for driving a nonvolatile memory device including a semiconductor substrate, an island semiconductor layer on the substrate, a memory cell having a control gate and a charge storage layer surrounding a peripheral surface of the island semiconductor layer, a first selection transistor provided between the memory cell and the substrate and having a first selection gate, a source diffusion layer between the substrate and the island semiconductor layer, a drain diffusion layer provided in an opposing end of the island semiconductor layer from the source diffusion layer, and a second selection transistor provided between the memory cell and the drain diffusion layer and having a second selection gate, the method comprising the steps of: applying a negative first voltage to the drain and the first selection gate, applying a positive second voltage to the second selection gate, and applying 0V or a positive third voltage to the source; and applying a positive fourth voltage higher than the second voltage to the control gate of the memory cell for injecting electric charges into the charge storage layer.

Owner:MASUOKA FUJIO +1

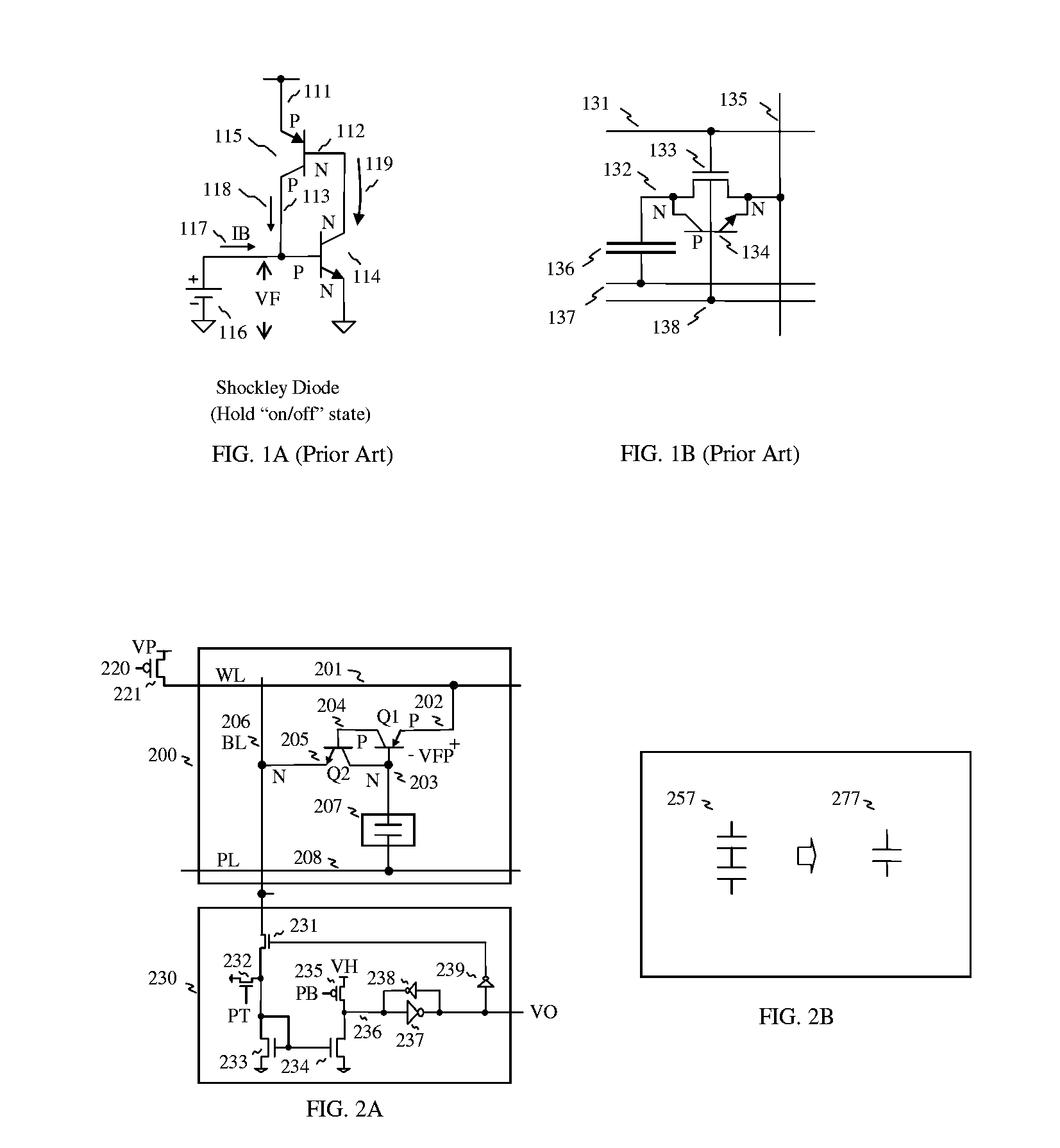

Stacked capacitor memory

InactiveUS20070183191A1Reduce chip areaLess complicated to fabricateSolid-state devicesDiodeEngineeringMulti port

Stacked capacitor memory is realized, wherein a capacitor stores data and a diode serves as an access device instead of MOS transistor, the first terminal is connected to a word line, the second terminal is connected to the first electrode of the capacitor which serves as a storage node while the second electrode is connected to a plate line, the third terminal is floating, and the fourth terminal is connected to a bit line. When write, the storage node is charged or not, depending on the conducting state of the diode which is controlled by the bit line. When read, the diode also serves as a sense amplifier to detect whether the storage node is forward bias or not, and it sends binary data to a latch device wherein includes a current mirror and a feedback loop which cuts off the current path after latching, thus it reduces active current, minimizes data pattern sensitivity, and also rejects coupling noise. And dummy rows and columns generate replica delay signals which guarantee timing margin and reduce cycle time. And its applications are extended to single port, multi port and content addressable memory. In addition, the memory cells are formed in between the routing layers, which memory cells can be stacked over the transistor or another capacitor memory cell.

Owner:KIM JUHAN

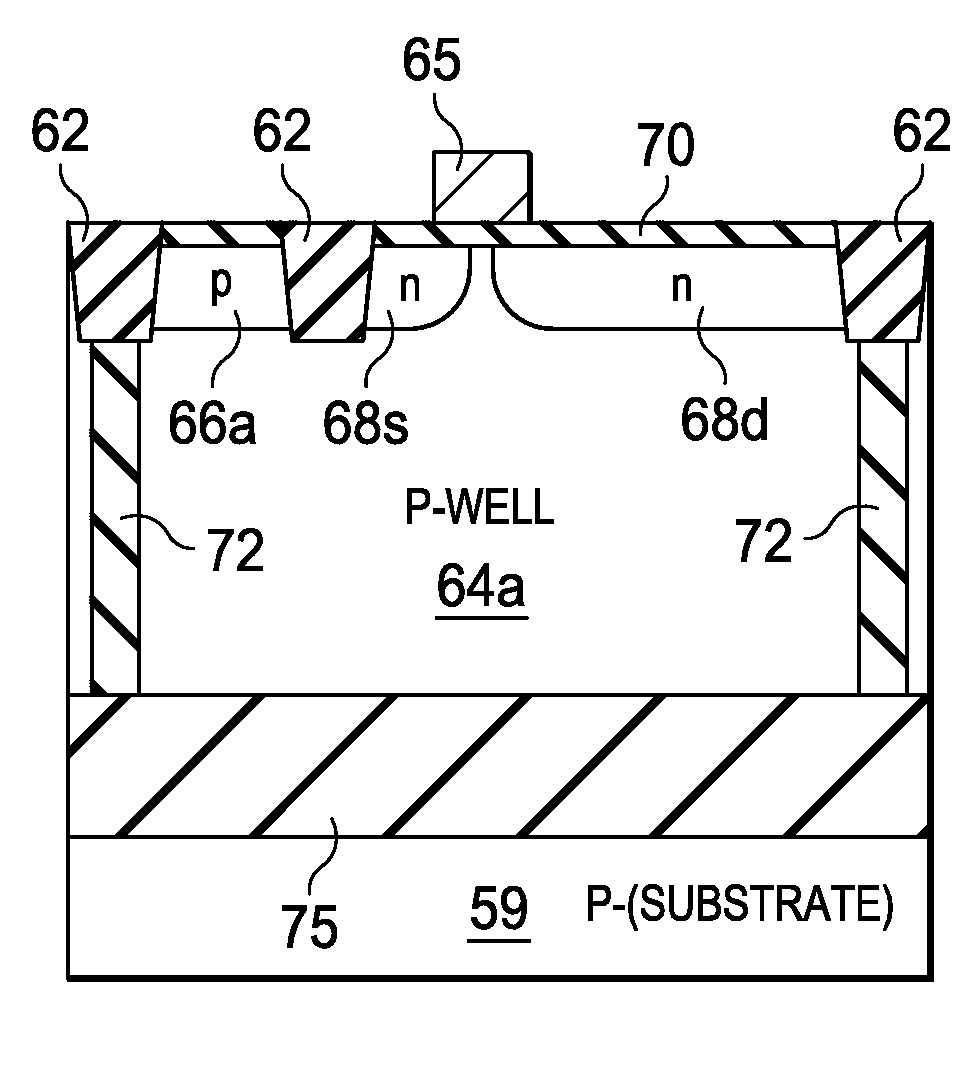

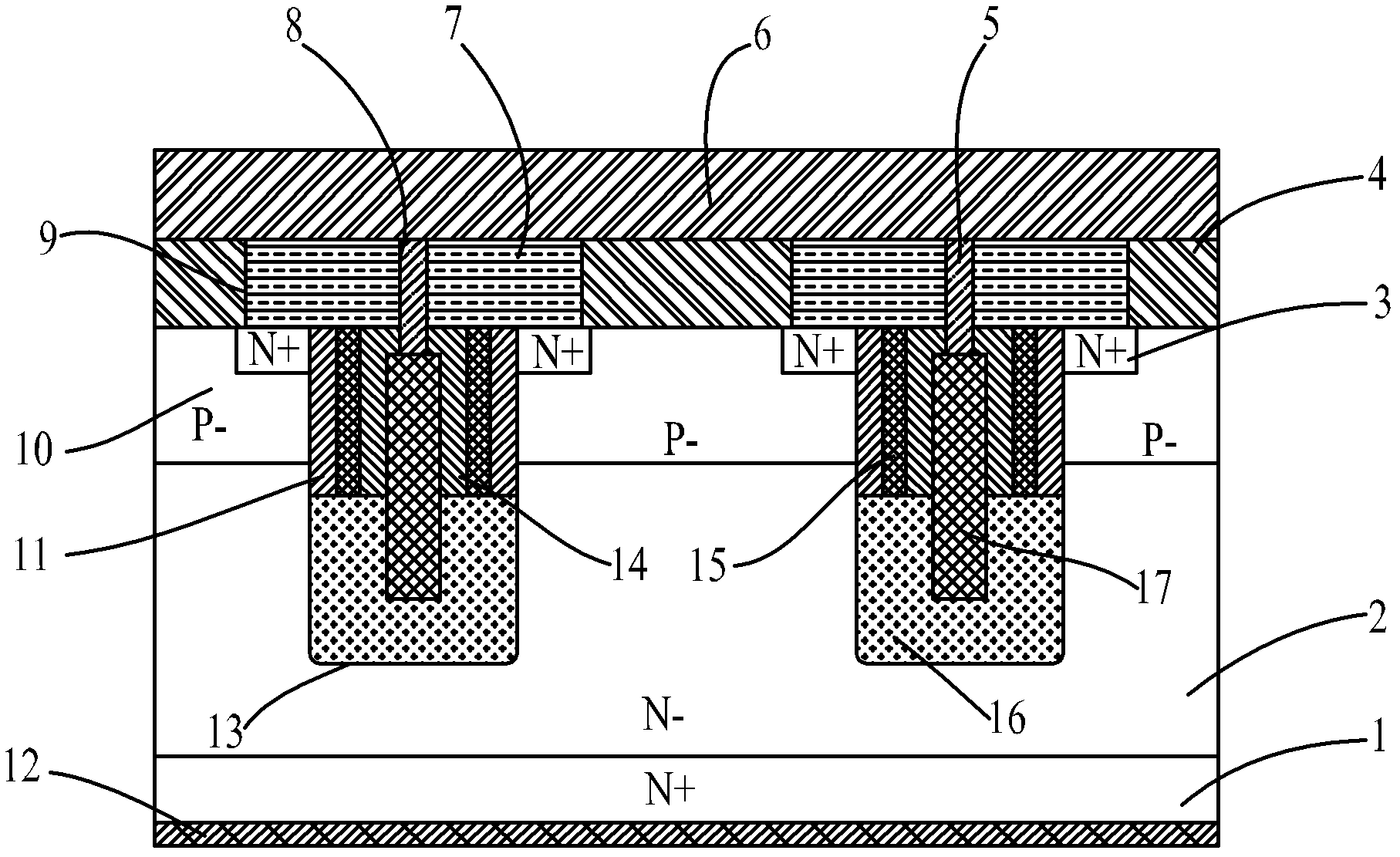

Robust ESD LDMOS Device

ActiveUS20090008710A1Improved electrostatic discharging abilityReduced chip area usageSemiconductor devicesLDMOSSemiconductor

A semiconductor device includes a gate electrode over a semiconductor substrate, wherein the gate electrode has a gate width direction; a source / drain region in the semiconductor substrate and adjacent the gate electrode, wherein the source / drain region has a first width in a direction parallel to the gate width direction; and a bulk pick-up region in the semiconductor substrate and abutting the source / drain region. The bulk pick-up region and the source / drain region have opposite conductivity types. The bulk pick-up region has a second width in the width direction, and wherein the second width is substantially less than the first width.

Owner:TAIWAN SEMICON MFG CO LTD

Semiconductor storage device and refresh control method therefor

InactiveUS20050169083A1Reduce chip areaSimple structureDigital storageRedundant data error correctionError checkSemiconductor storage devices

Disclosed is a dynamic semiconductor storage device in which the power supply current during the standby time is diminished to decrease the power consumption and to suppress the chip area from increasing. During the normal operation, the information as to a word line associated with a row address accessed during the normal operation is stored in a RAM. In entering self refresh, data of memory cells connected to a word line associated with a row address accessed during the normal operation time is read out and check bits for the data are appended in an encoder and written in a check bit area. As an initializing operation for the first self refresh entry after power up sequence, the data retention time of the memory cells is inspected every word line. Based on the results of inspection, the setting value of the refresh period of the word line is determined and written in the RAM to set the word line based refresh period. During error check for the refresh operation, any error is corrected by an error correction circuit.

Owner:LONGITUDE SEMICON S A R L

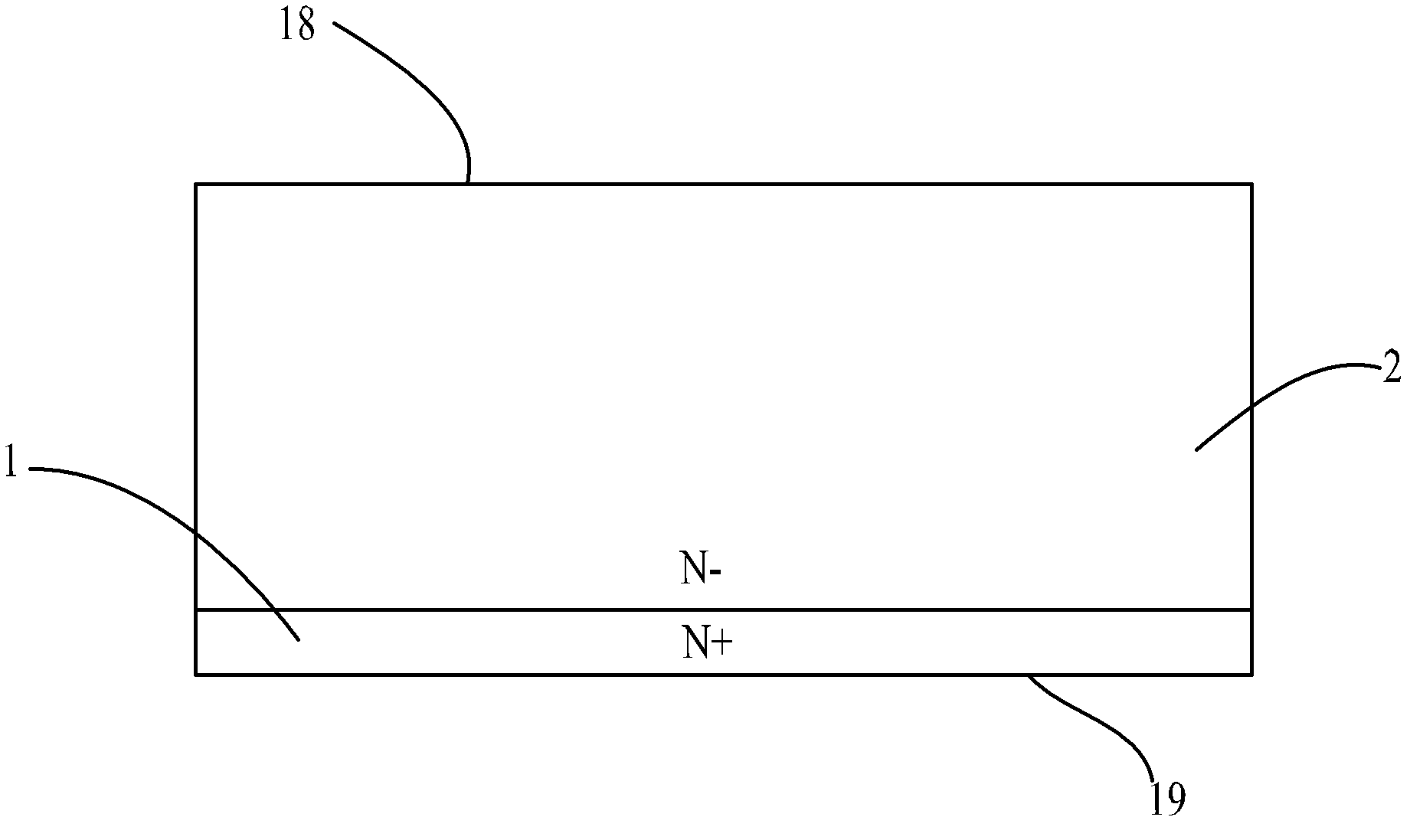

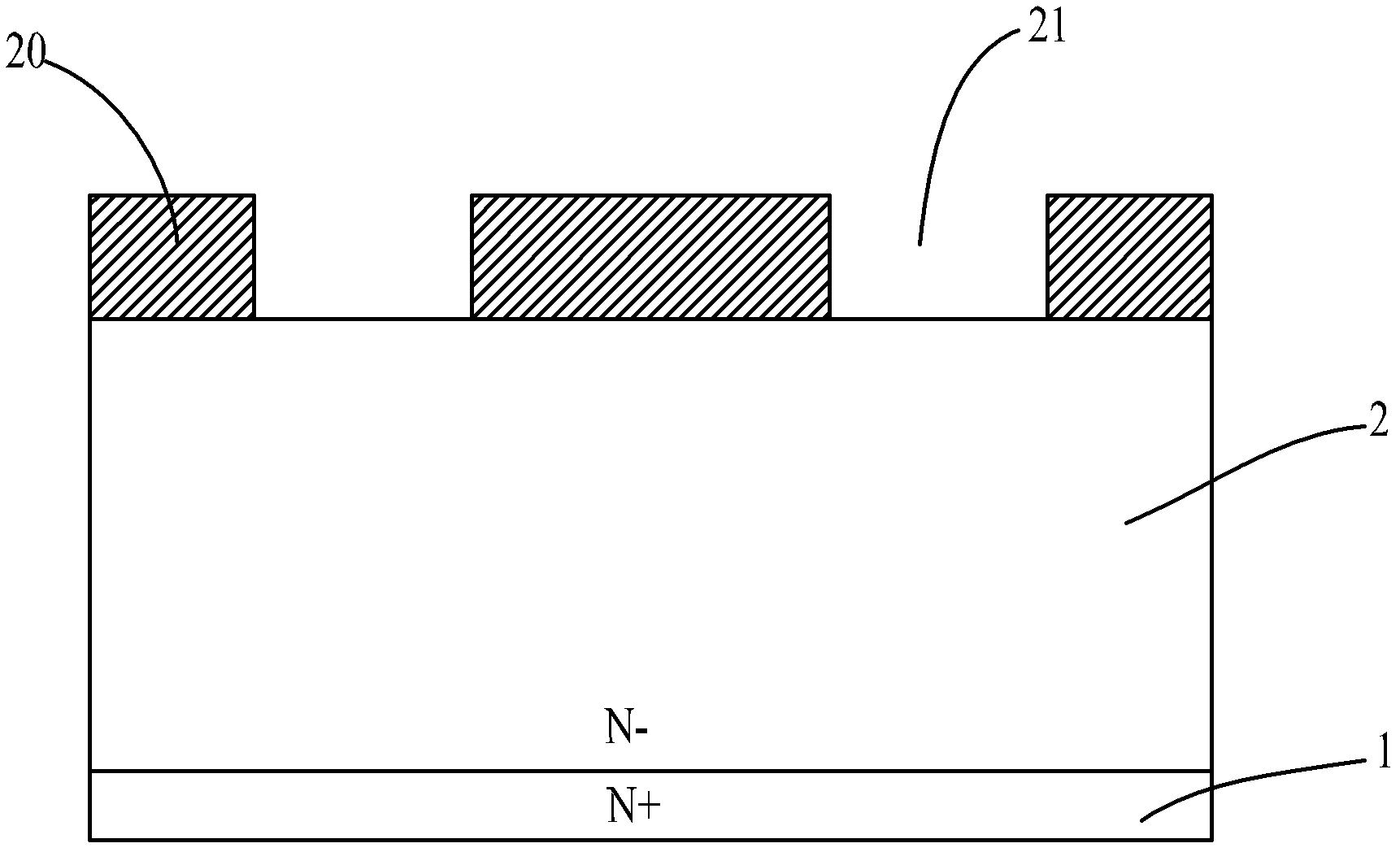

A novel trench structure power mosfet device and its manufacturing method

ActiveCN102280487ALower on-resistanceHigh resistivitySemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactElectrode Contact

The invention relates to a power MOSFET (Metal-Oxide -Semiconductor Field Effect Transistor) device of a novel groove structure and a manufacture method thereof. The unit cell of the element zone of the power MOSFET device adopts groove structure; an insulating oxide layer is arranged in the unit cell groove; the thickness of a second isolated gate oxide layer in the unit cell groove is more thanthe thickness of a first isolated gate oxide layer; conductive polysilicon is deposited in the cell unit groove; the extending distance of the first conductive polysilicon is more than the extending distance of the second conductive polysilicon in the unit cell groove; the groove mouth of the unit cell groove is covered by an insulating medium layer; a source electrode contact hole is filled withsecond contract hole filling metal; the second contract hole filling metal, a first conductive type filling zone and a second conductive type layer are in ohmic contact; source electrode metal is arranged above the unit cell groove; the source electrode metal and the second contact hole filling metal are electrically connected; and the first conductive polysilicon, the source electrode metal and the like are in potential connection. The power MOSFET device has the advantages of low conduction resistance, small grid leak electric charge Qgd, low switching speed, low switching loss, simple technology and low cost.

Owner:WUXI NCE POWER