Patents

Literature

84 results about "Memory cycle" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Methods and apparatuses for reducing power consumption in a pattern recognition processor

ActiveUS20110145271A1Energy efficient ICTDigital data information retrievalData streamParallel computing

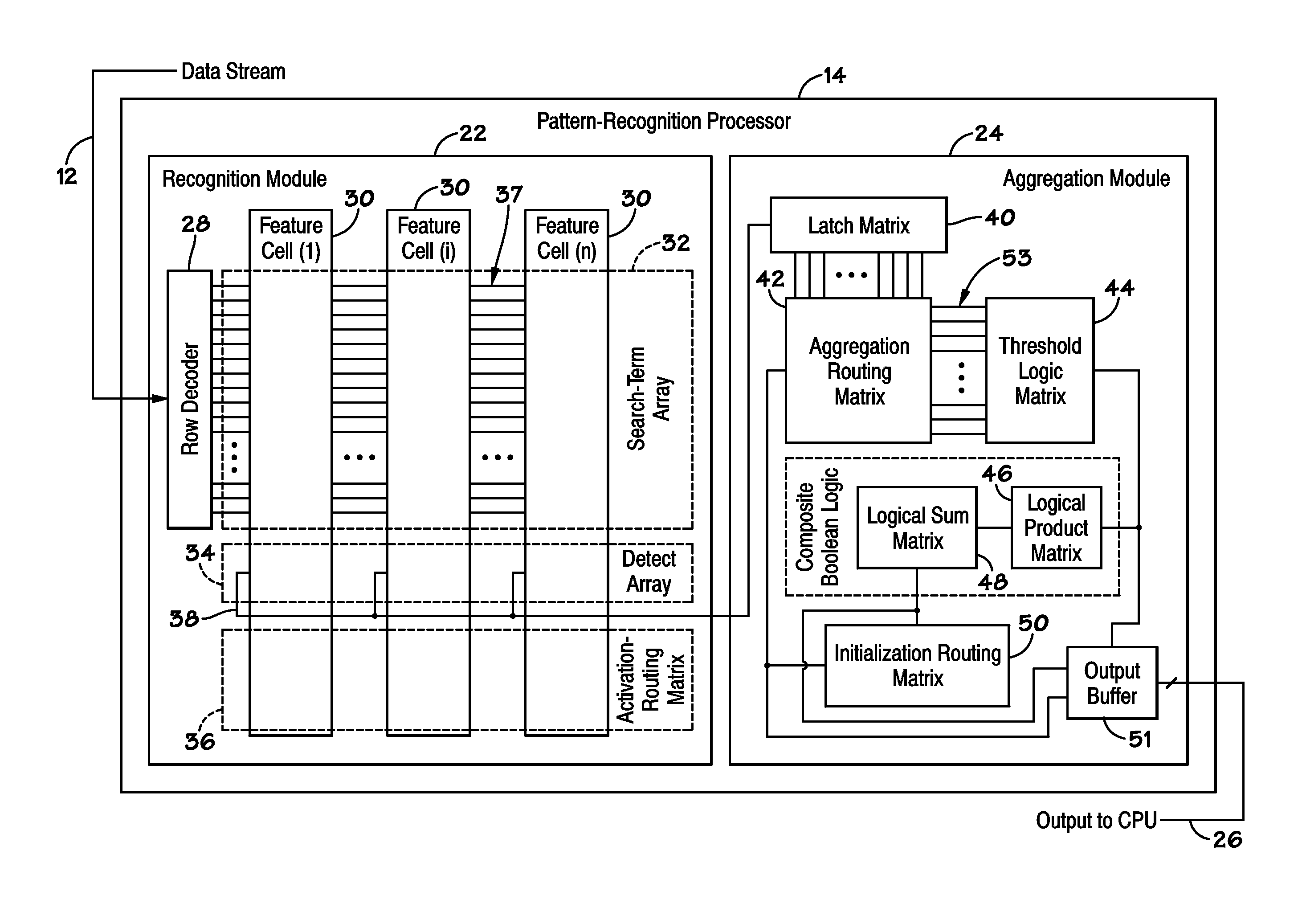

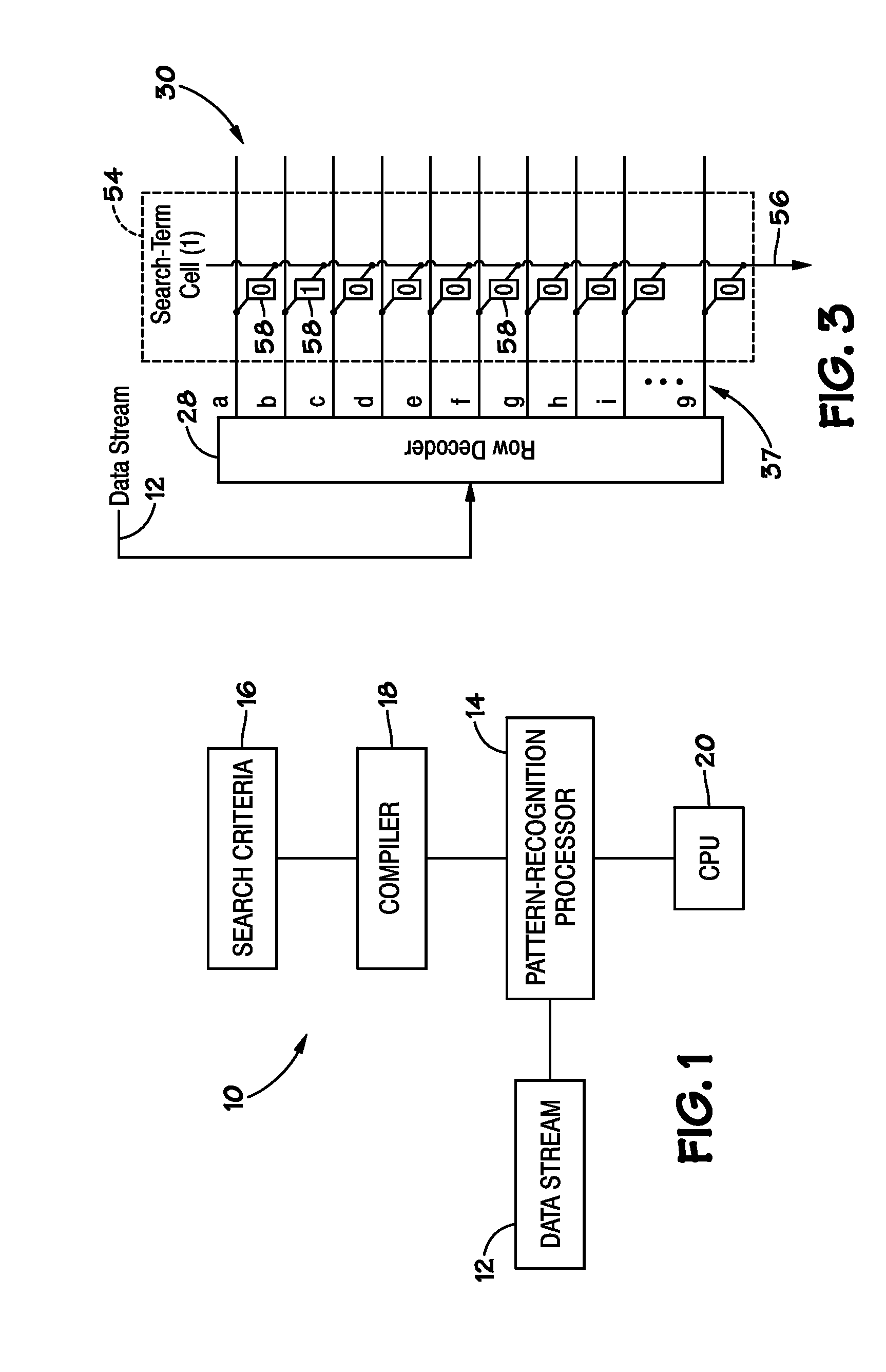

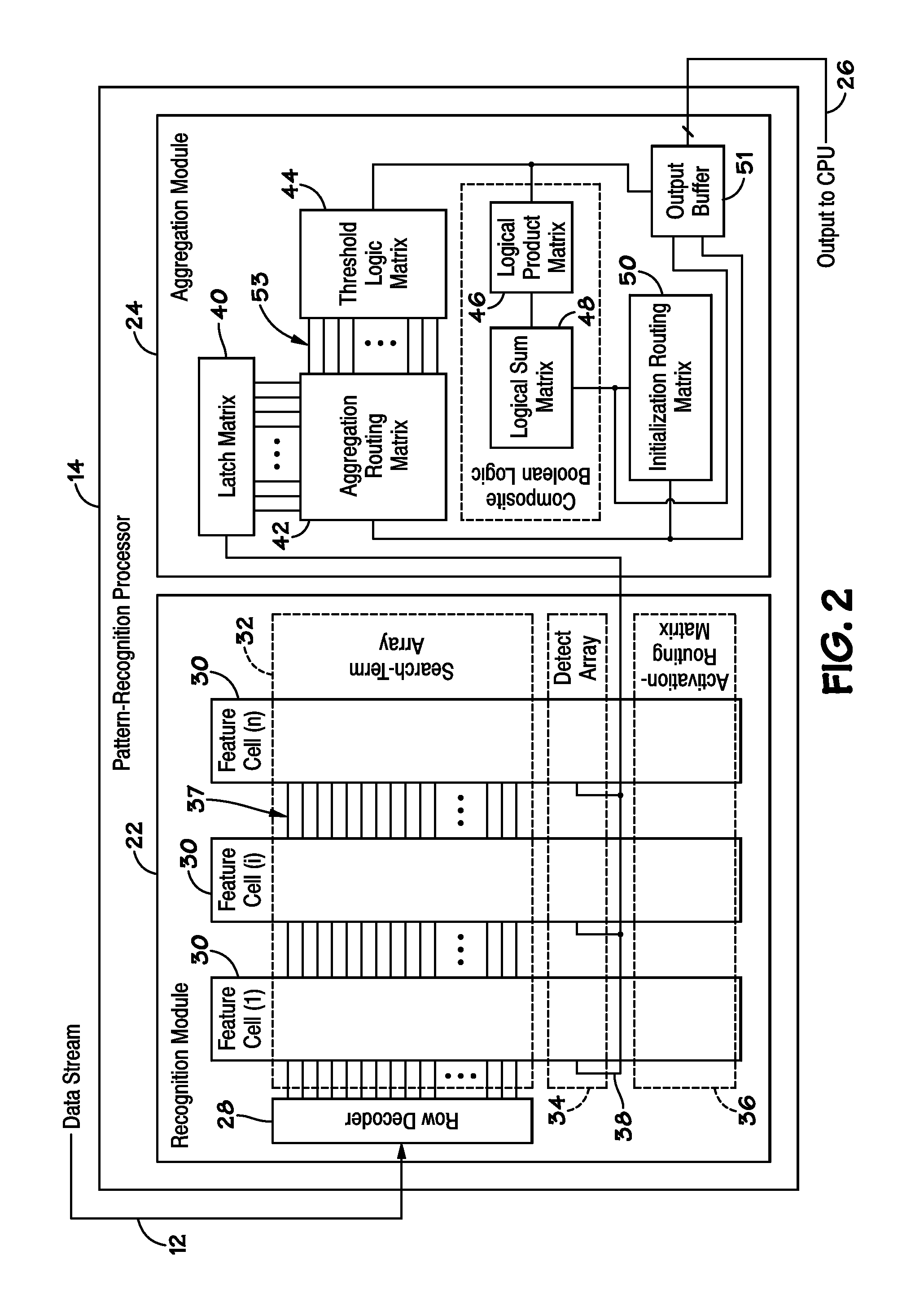

Apparatuses and methods are provided for reducing power consumption in a pattern-recognition processor. A power control circuit may be coupled to a block of programmed state machines to enable selective activation and deactivation of the block during a pattern search. The block may be deactivated if the pattern search is no longer active in that block and activated when needed by the pattern search. Additionally, the block may be deactivated based on an identifier of the data stream being searched. Excess blocks not used for any programmed state machines may be disabled such that they are not refreshed during a memory cycle.

Owner:MICRON TECH INC

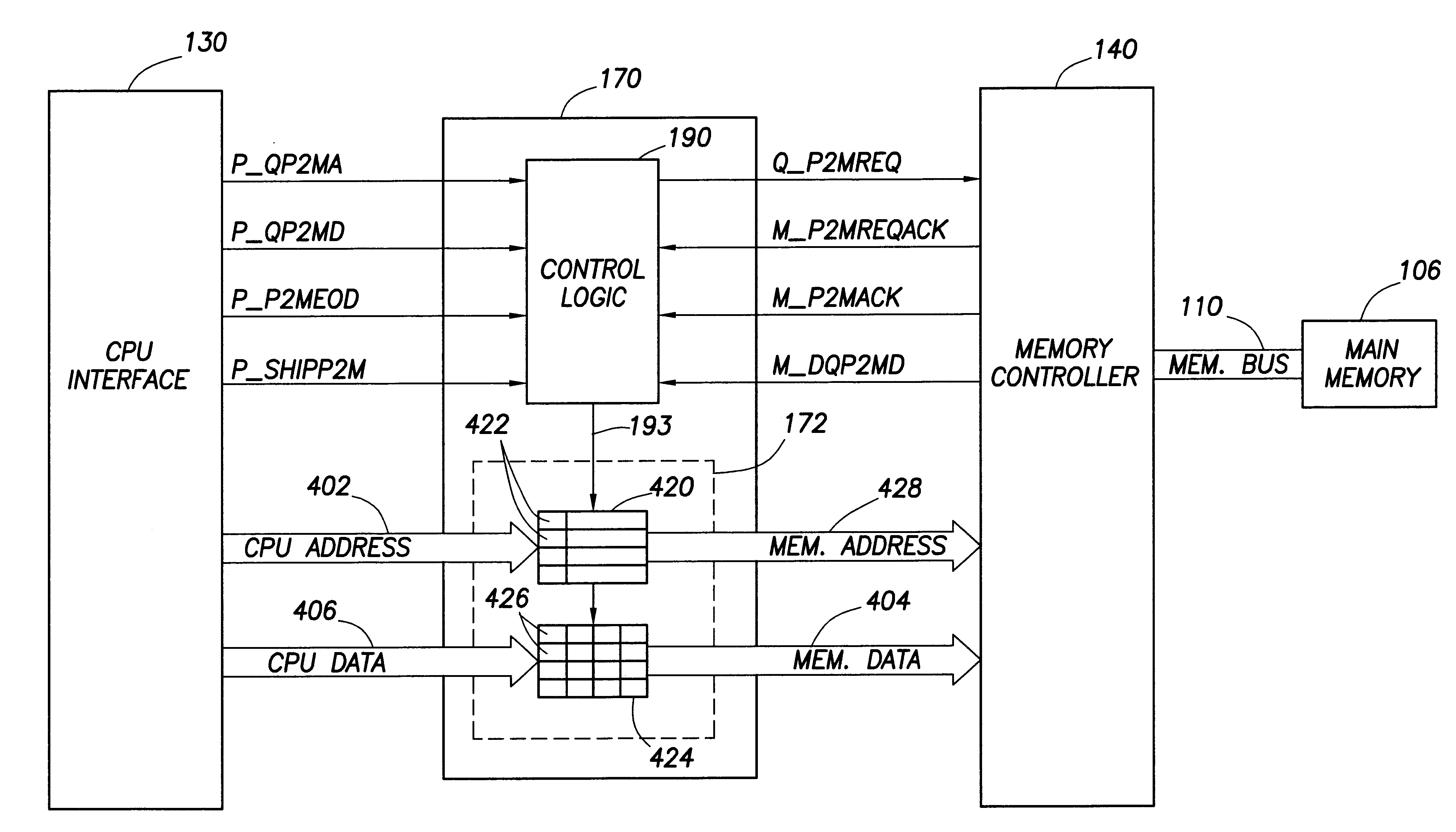

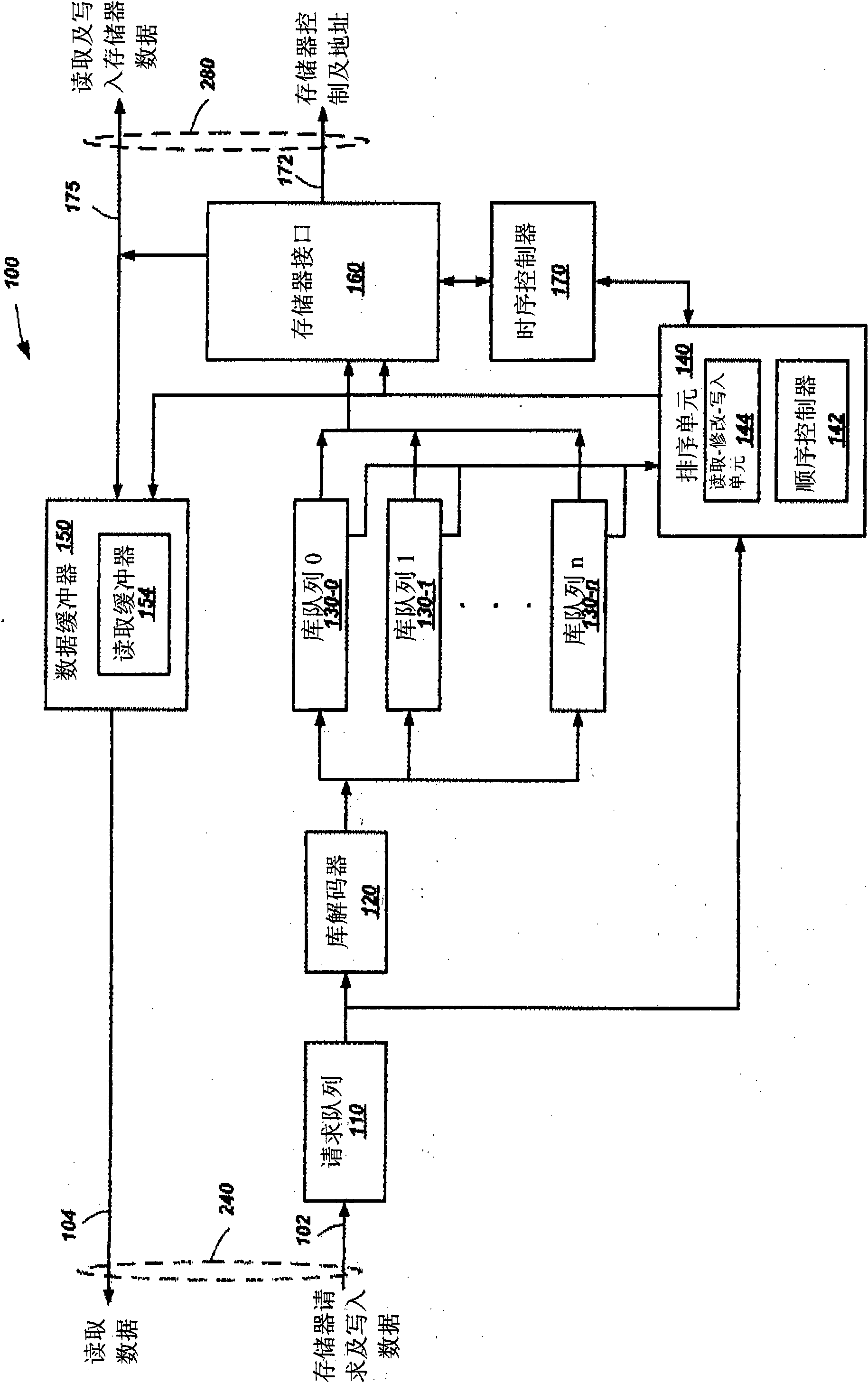

Reordering and flushing commands in a computer memory subsystem

InactiveUS6895482B1Avoid deadlockDetermining memory cycle performance penaltiesConcurrent instruction executionMemory systemsParallel computingMemory controller

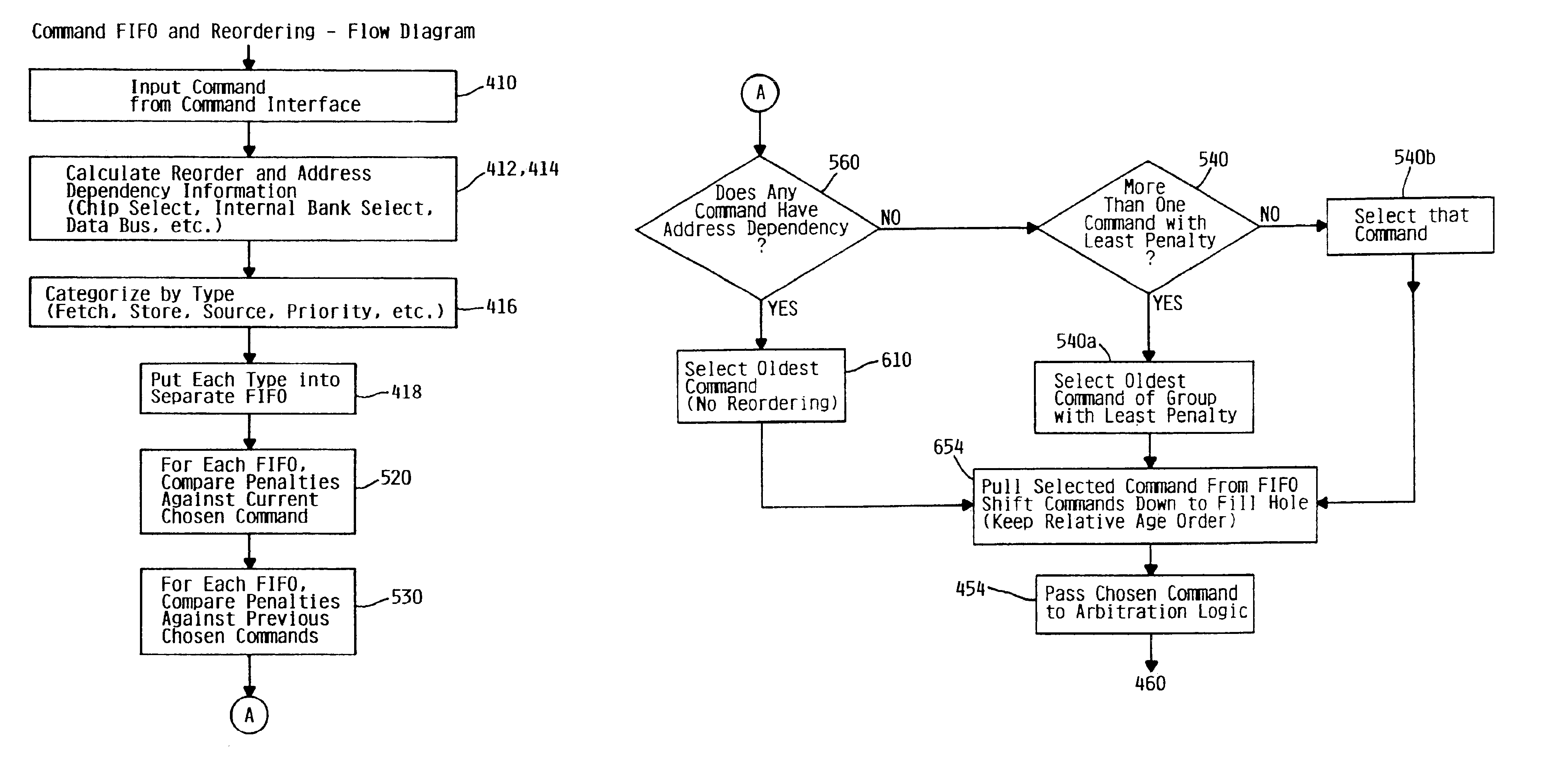

An improved computer memory subsystem determines the most efficient memory command to execute. The physical location and any address dependency of each incoming memory command to a memory controller is ascertained and that information accompanies the command for categorization into types of command. For each type of memory command, there exists a command FIFO and associated logic in which a programmable number of the memory commands are selected for comparison with each other, with the memory command currently executing, and with the memory command previously chosen for execution. The memory command having the least memory cycle performance penalty is selected for execution unless that memory command has an address dependency. If more than one memory command of that type has the least memory cycle performance penalty, then the oldest is selected for execution. Memory commands of that type are selected for execution each subsequent cycle until a valid memory command of that type is no longer available, or until a predetermined number has been executed, or until a memory command of another type has higher priority. If an address dependency exists between memory commands of different types, then memory commands of the same type of the oldest memory command is executed to avoid deadlock.

Owner:IBM CORP

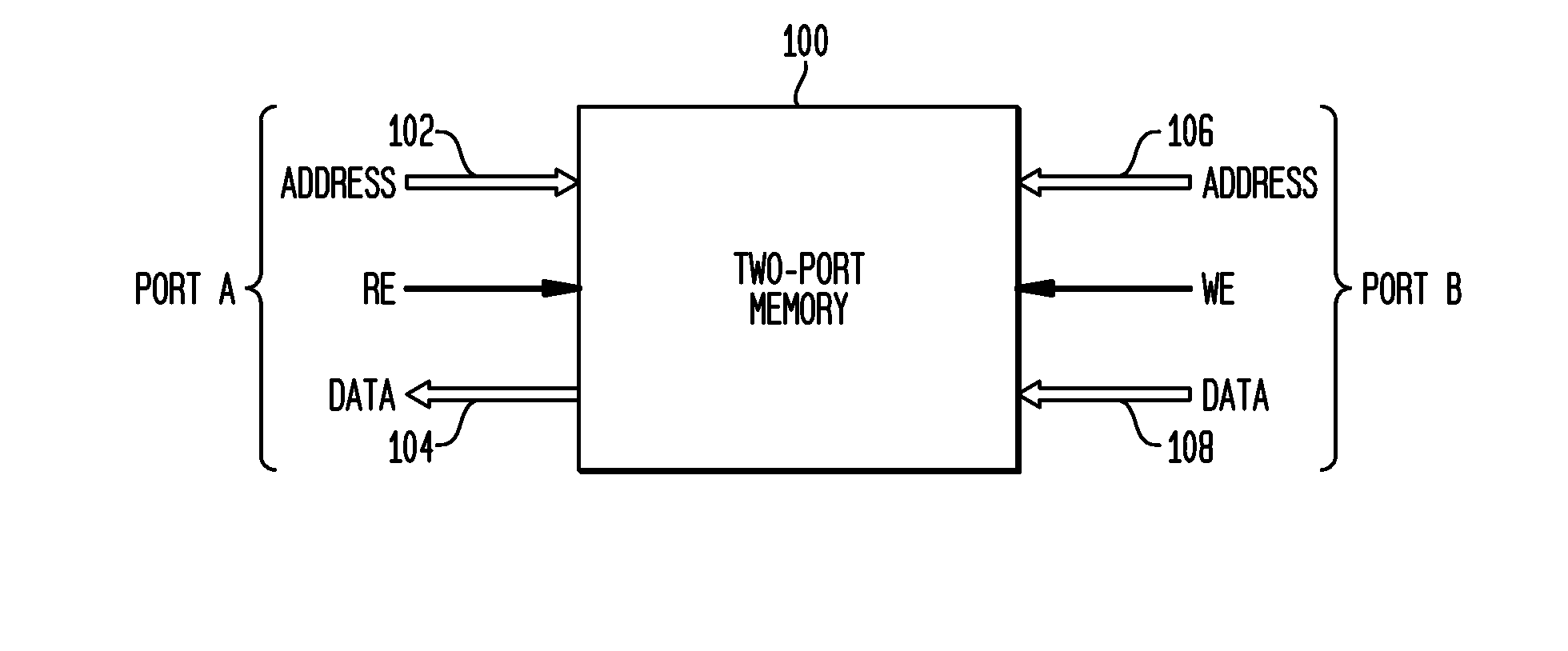

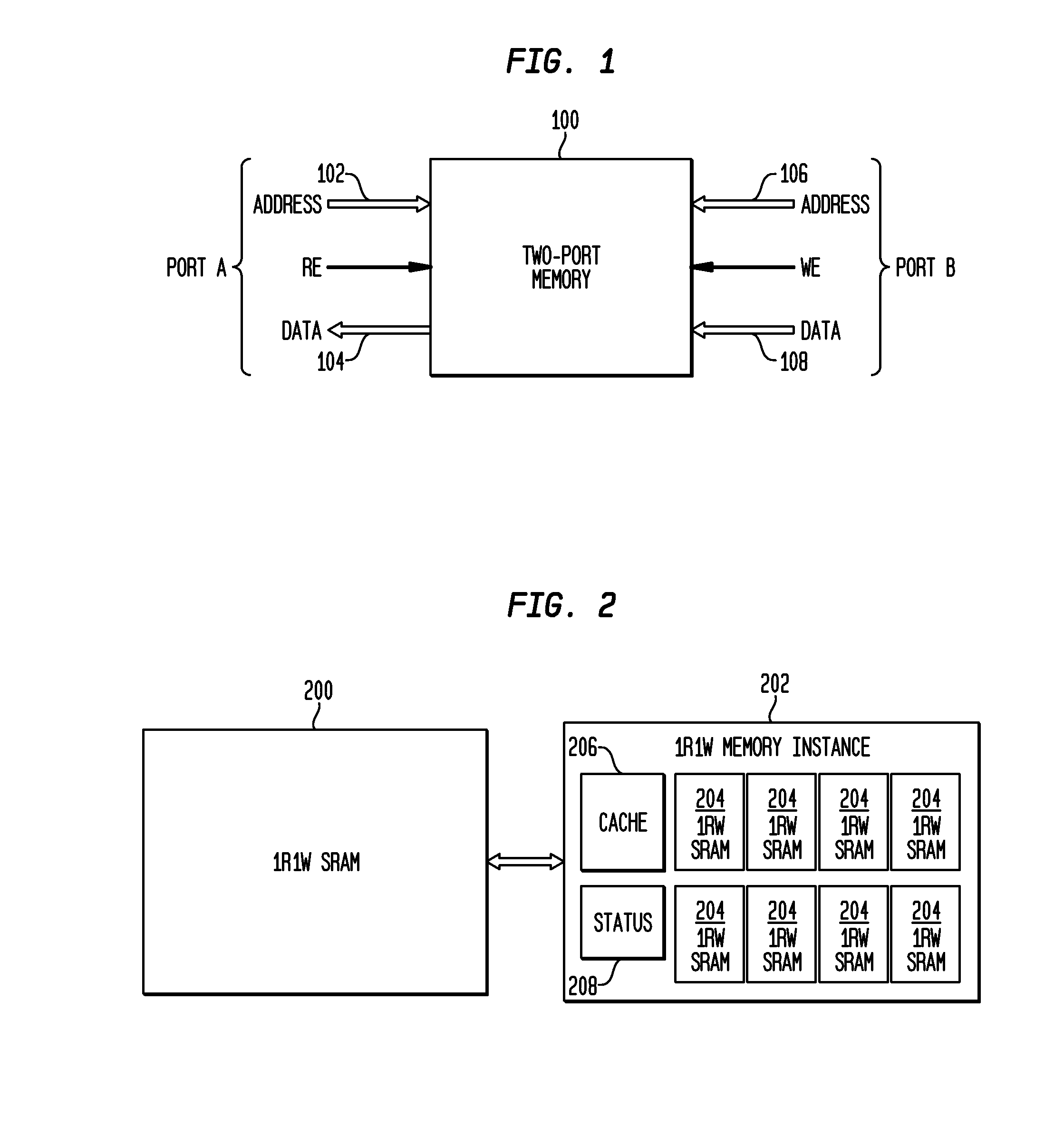

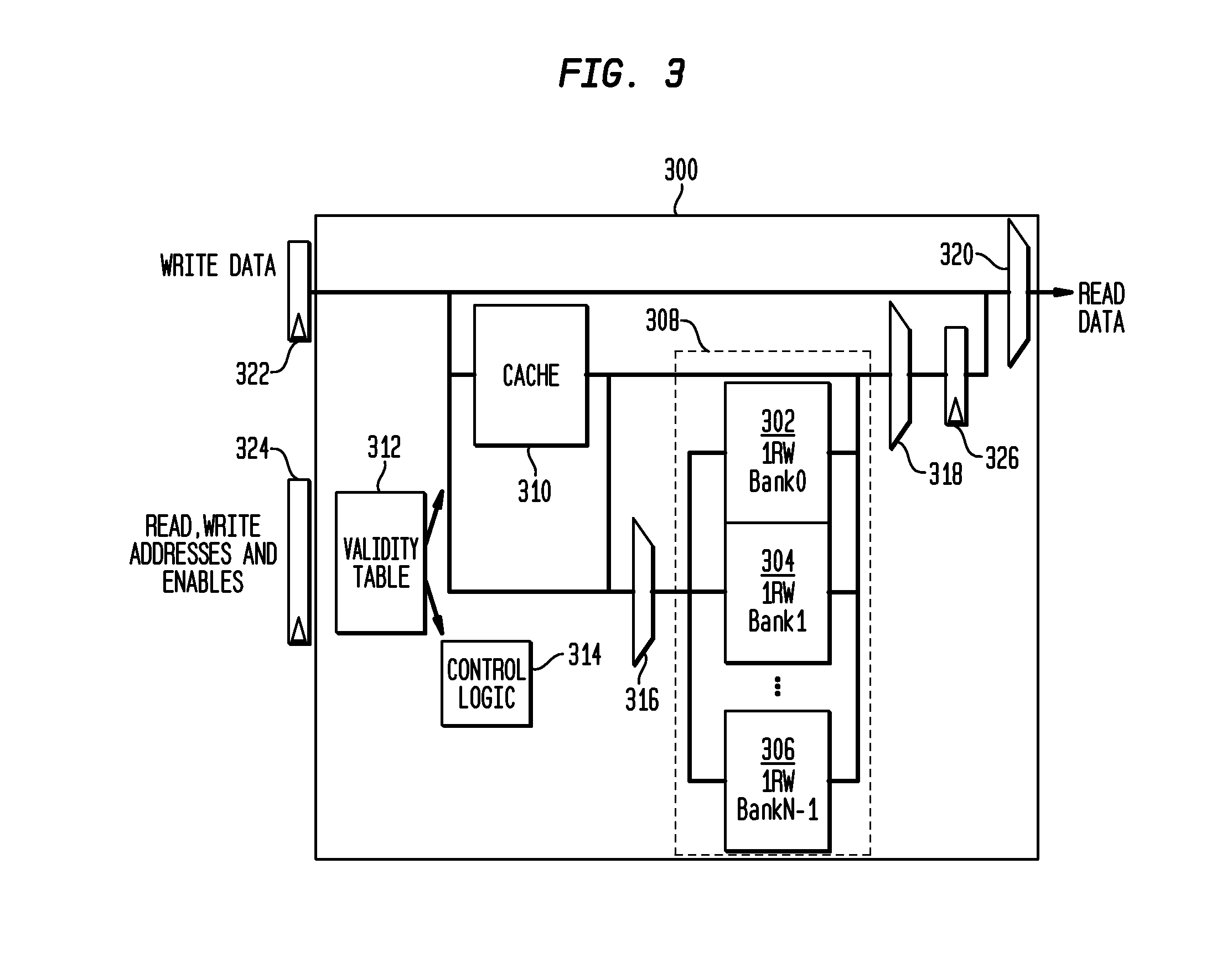

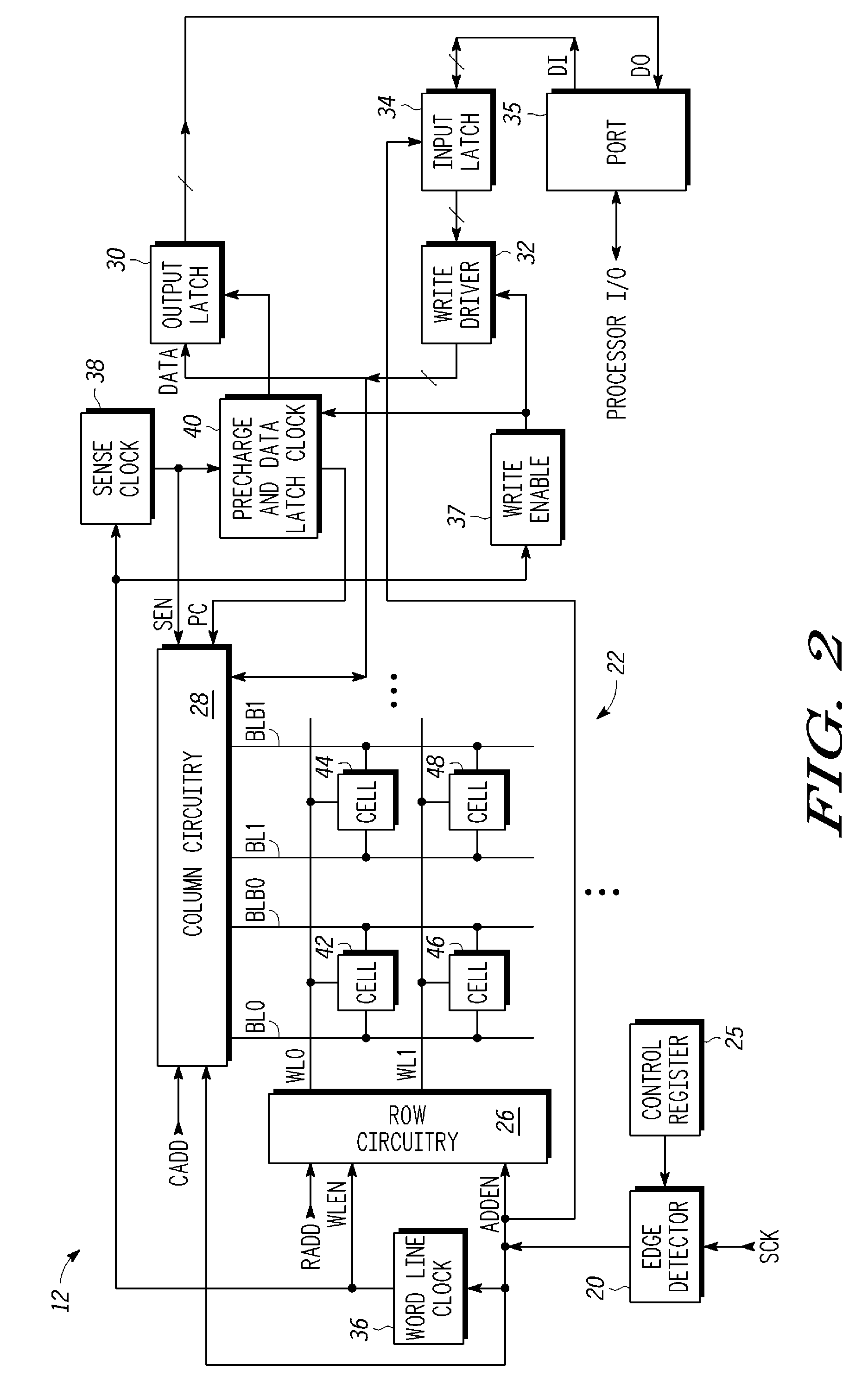

Multi-Port Memory Using Single-Port Memory Cells

InactiveUS20110310691A1Consume areaConsume powerEnergy efficient ICTMemory adressing/allocation/relocationMemory bankParallel computing

A memory operative to provide multi-port functionality includes multiple single-port memory cells forming a first memory array. The first memory array is organized into multiple memory banks, each of the memory banks comprising a corresponding subset of the single-port memory cells. The memory further includes a second memory array including multiple multi-port memory cells and is operative to track status information of data stored in corresponding locations in the first memory array. At least one cache memory is connected with the first memory array and is operative to store data for resolving concurrent read and write access conflicts in the first memory array. The memory includes a controller operative: to receive the status information and to determine a validity of data stored in the first memory array as a function of the status information; to control a manner in which data is stored in the memory for avoiding data overflow in the cache memory; and to resolve concurrent read and write access conflicts in the first memory array during the same memory cycle.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

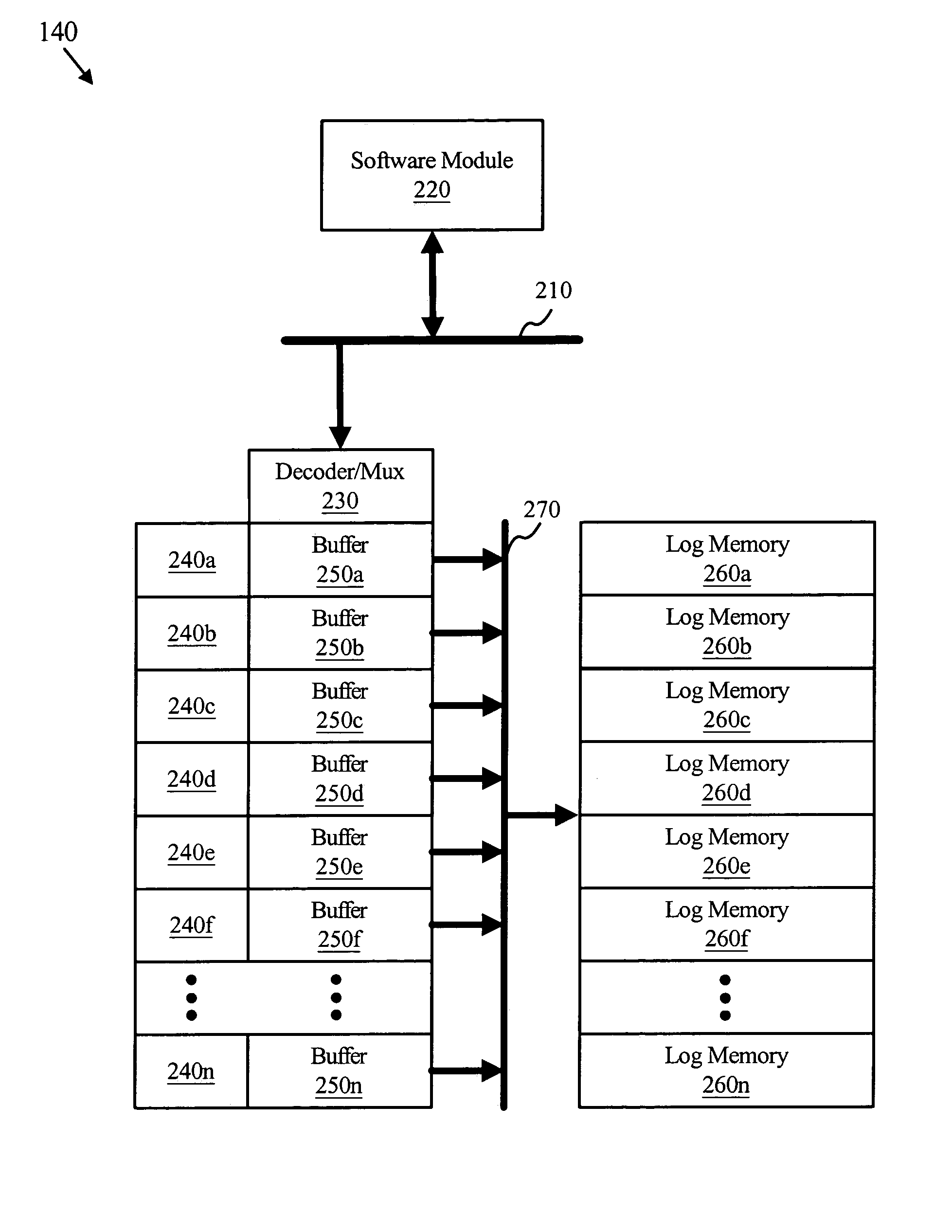

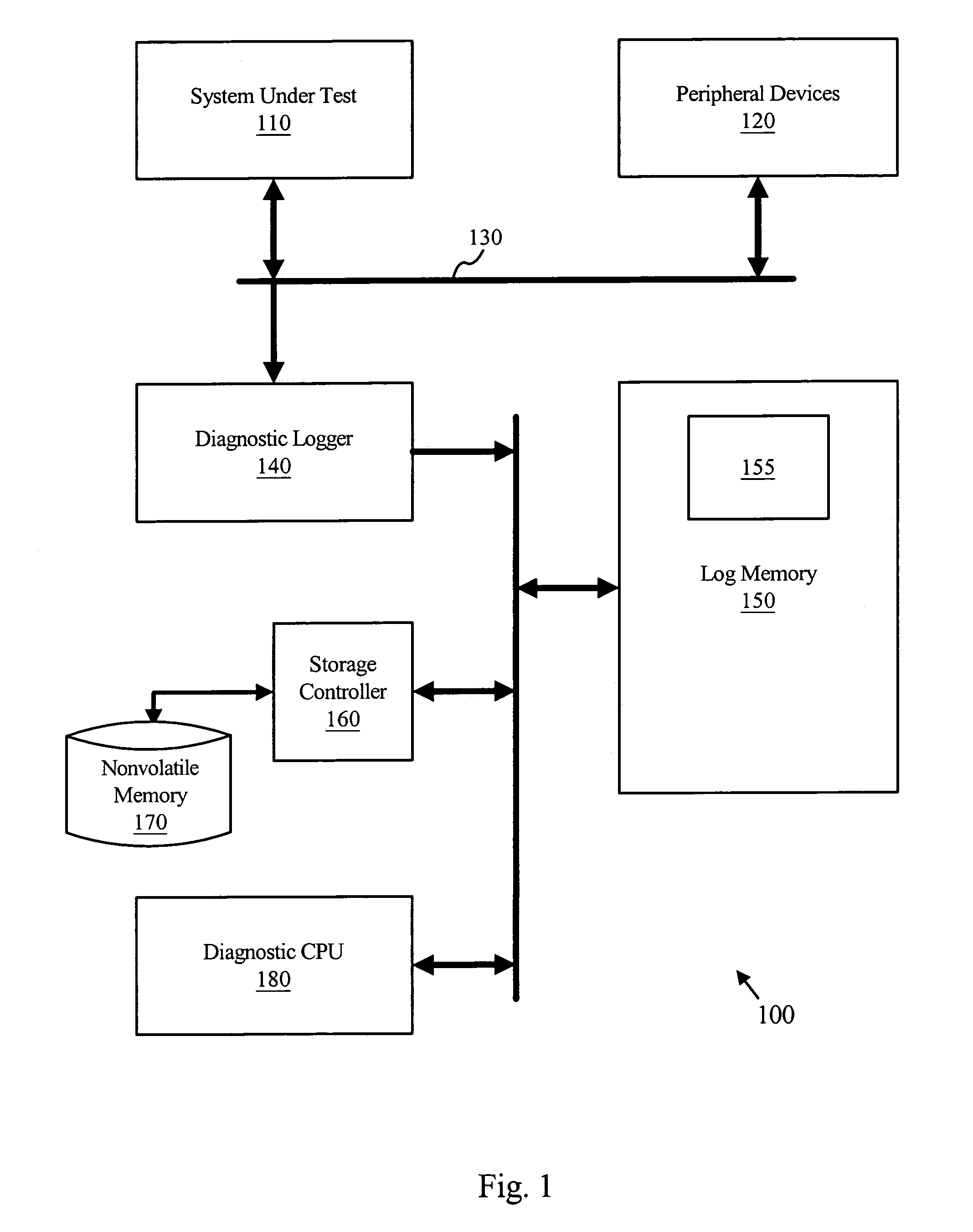

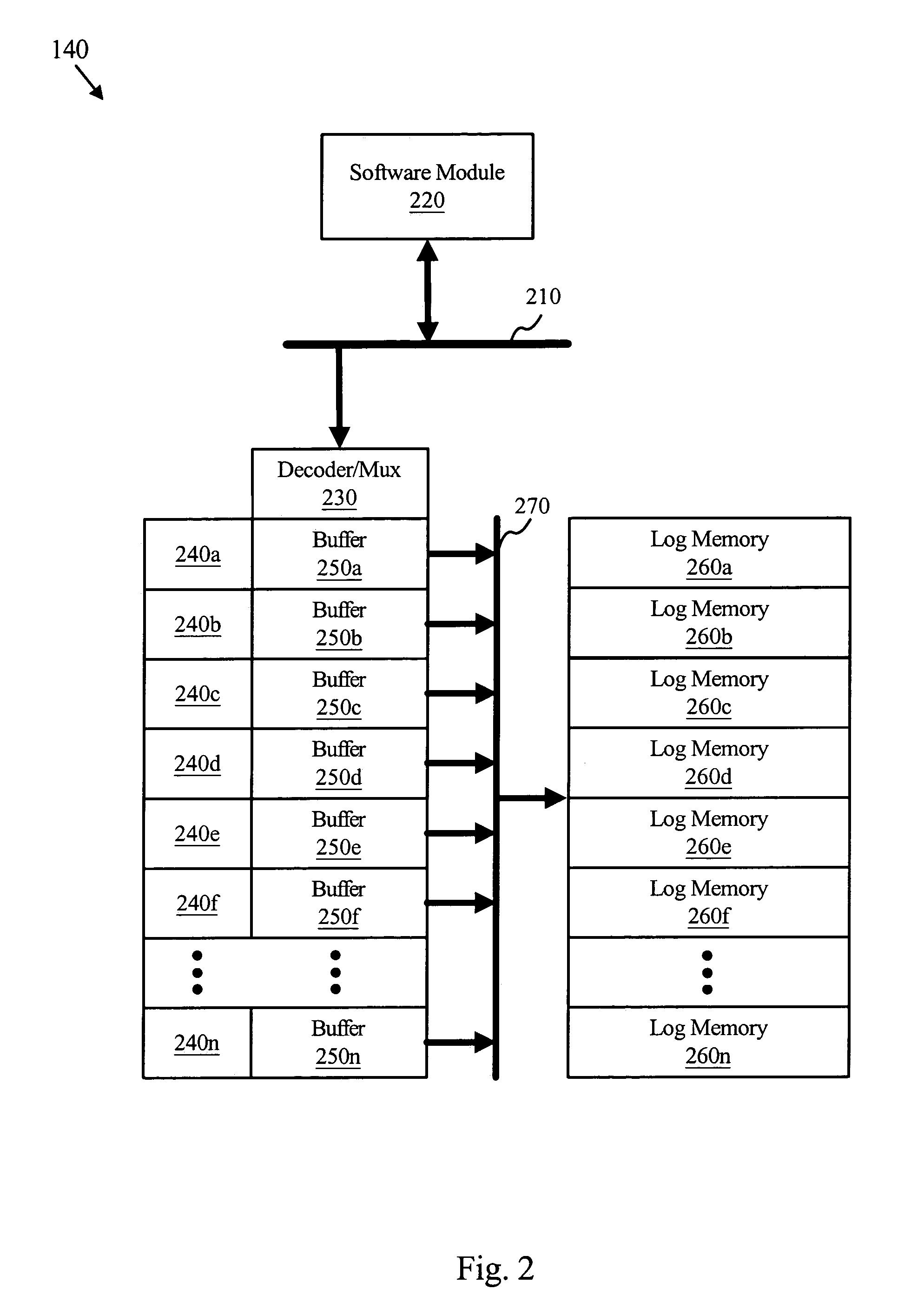

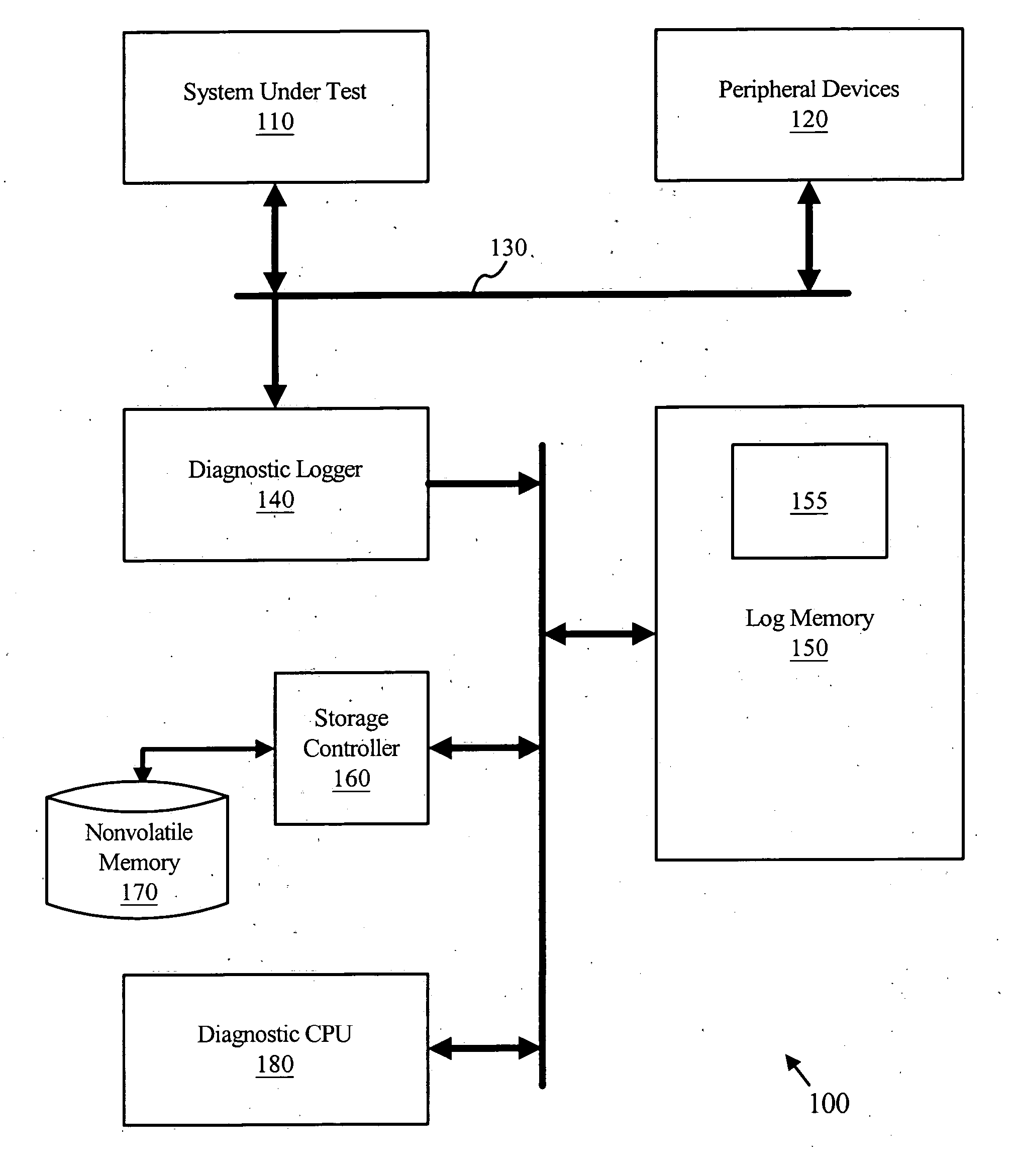

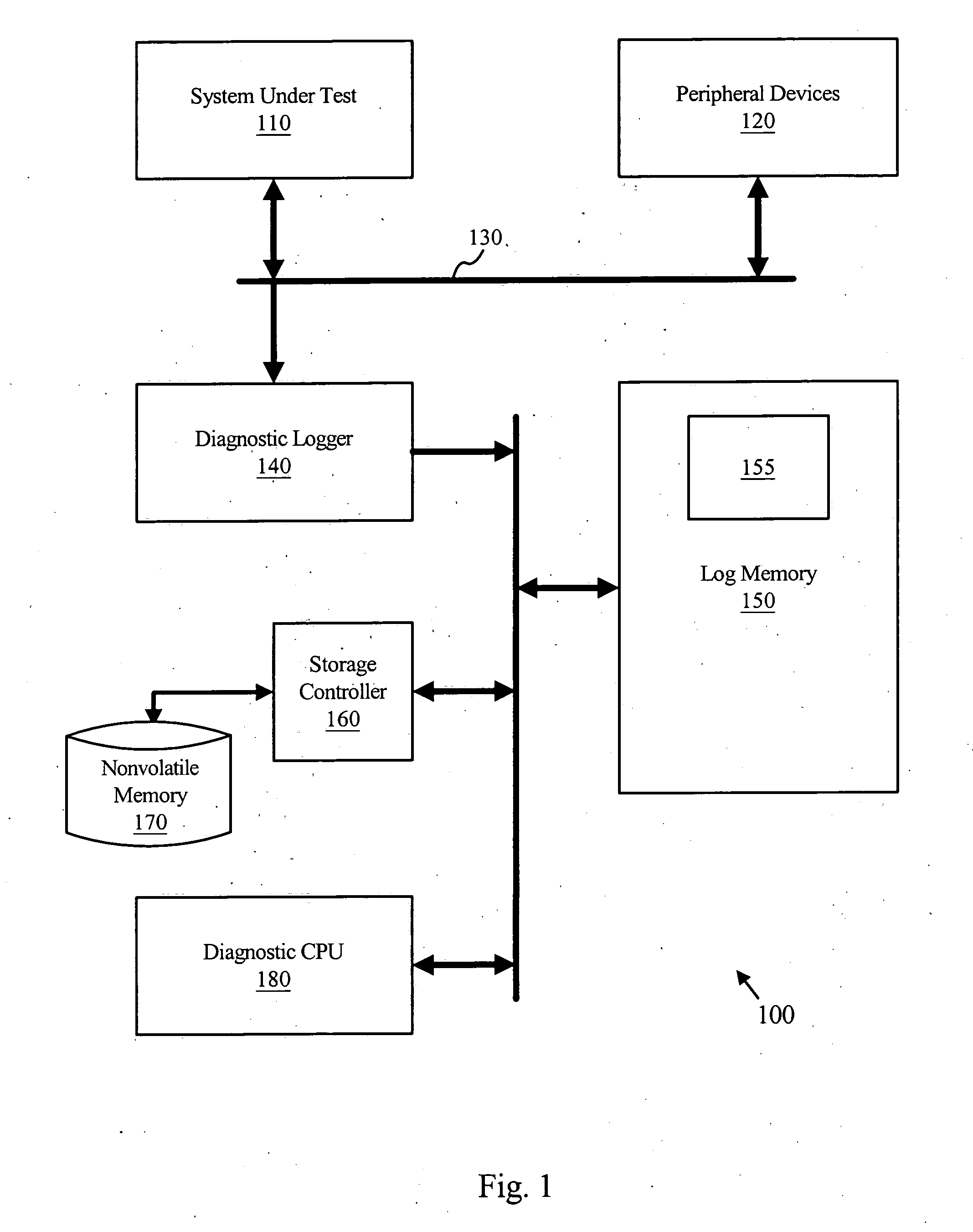

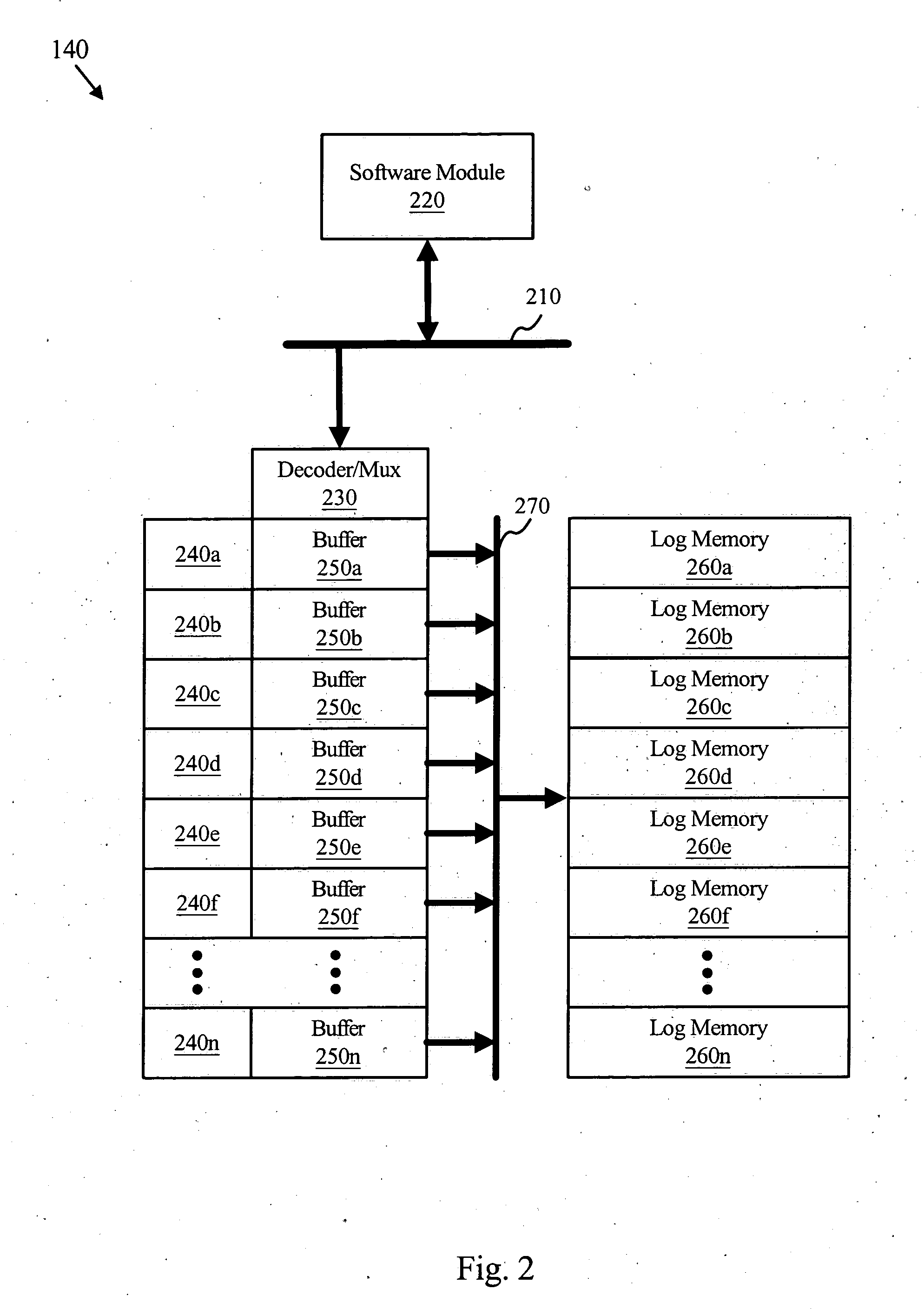

Apparatus, method, and system for logging diagnostic information

ActiveUS7284153B2Minimal impactEasy diagnosisError detection/correctionMemory addressProcessor register

Owner:GOOGLE LLC

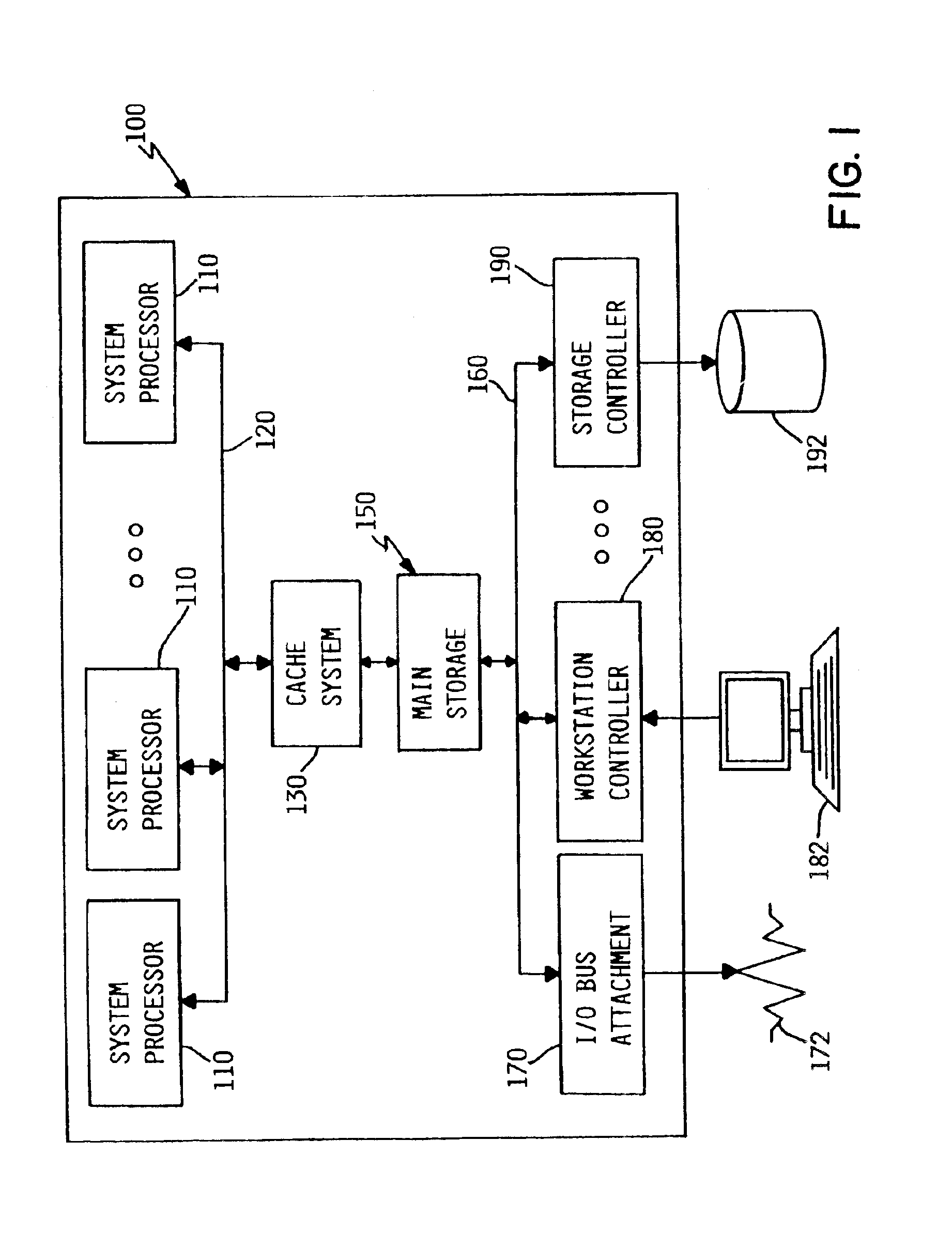

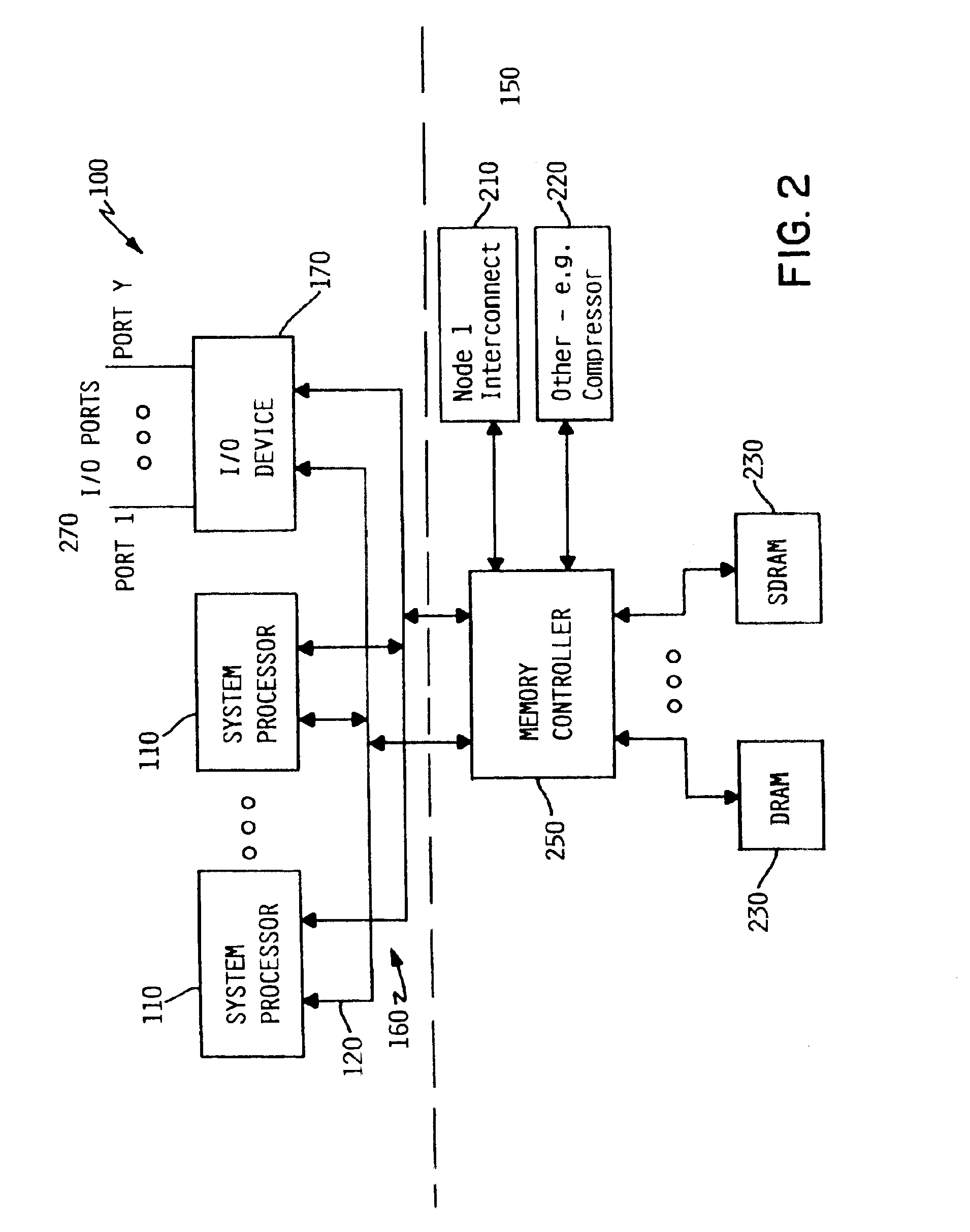

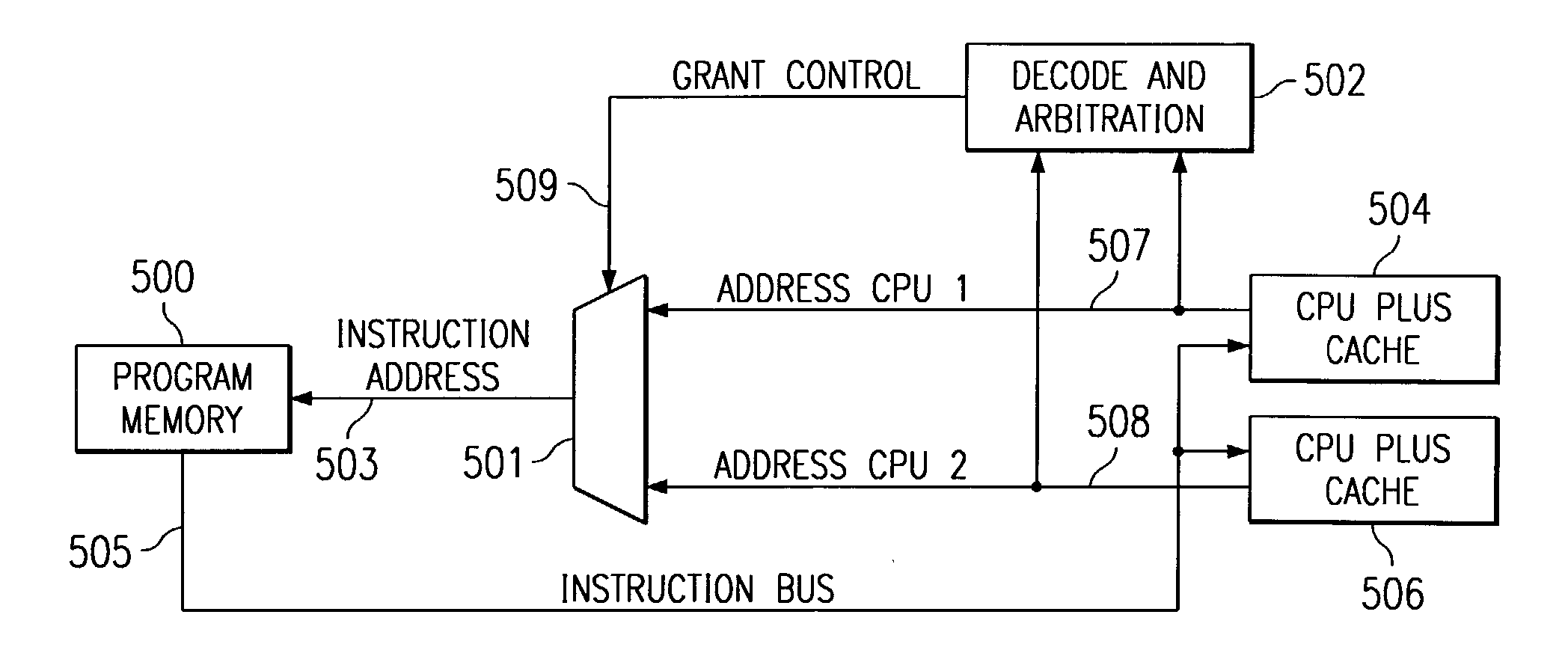

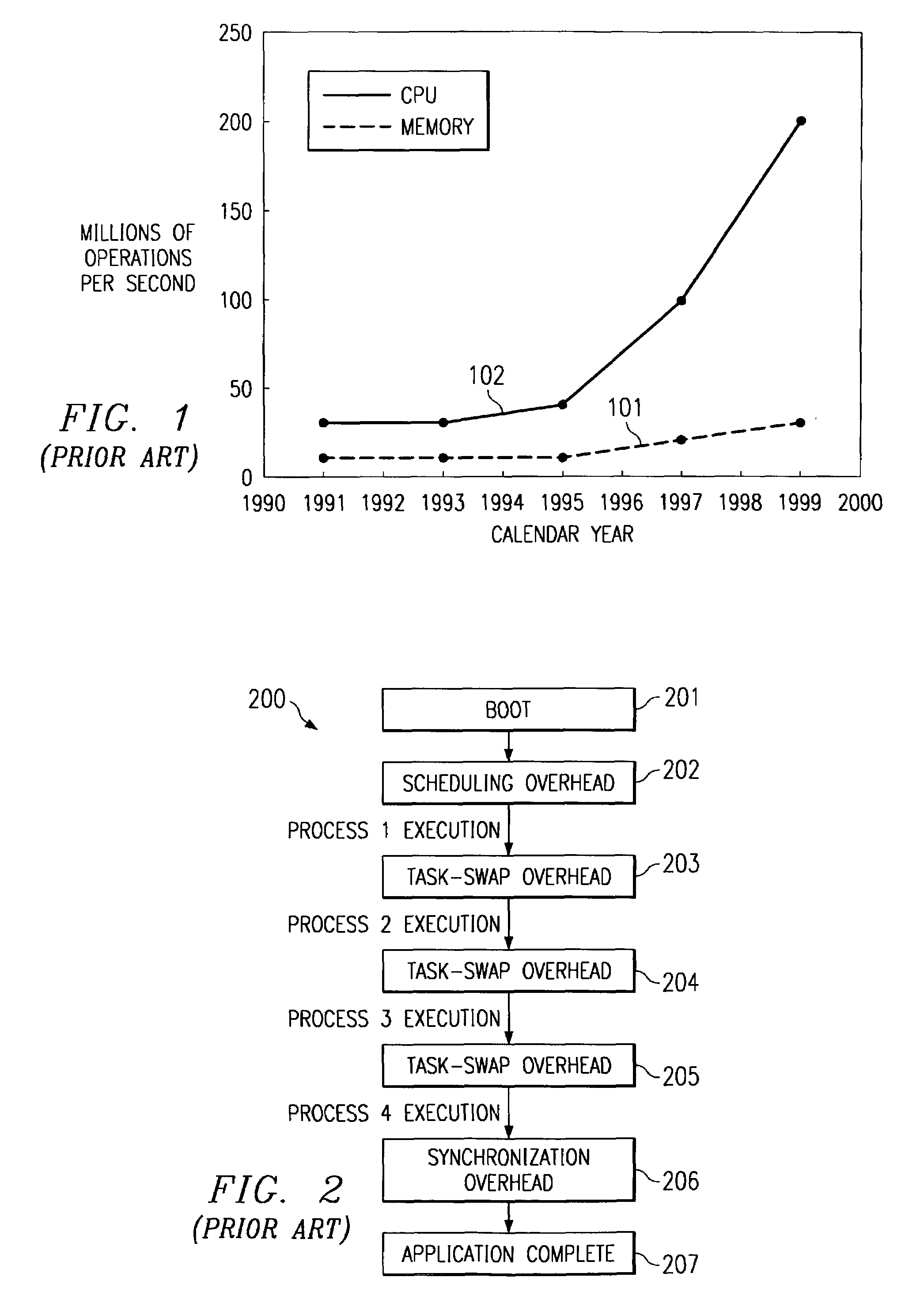

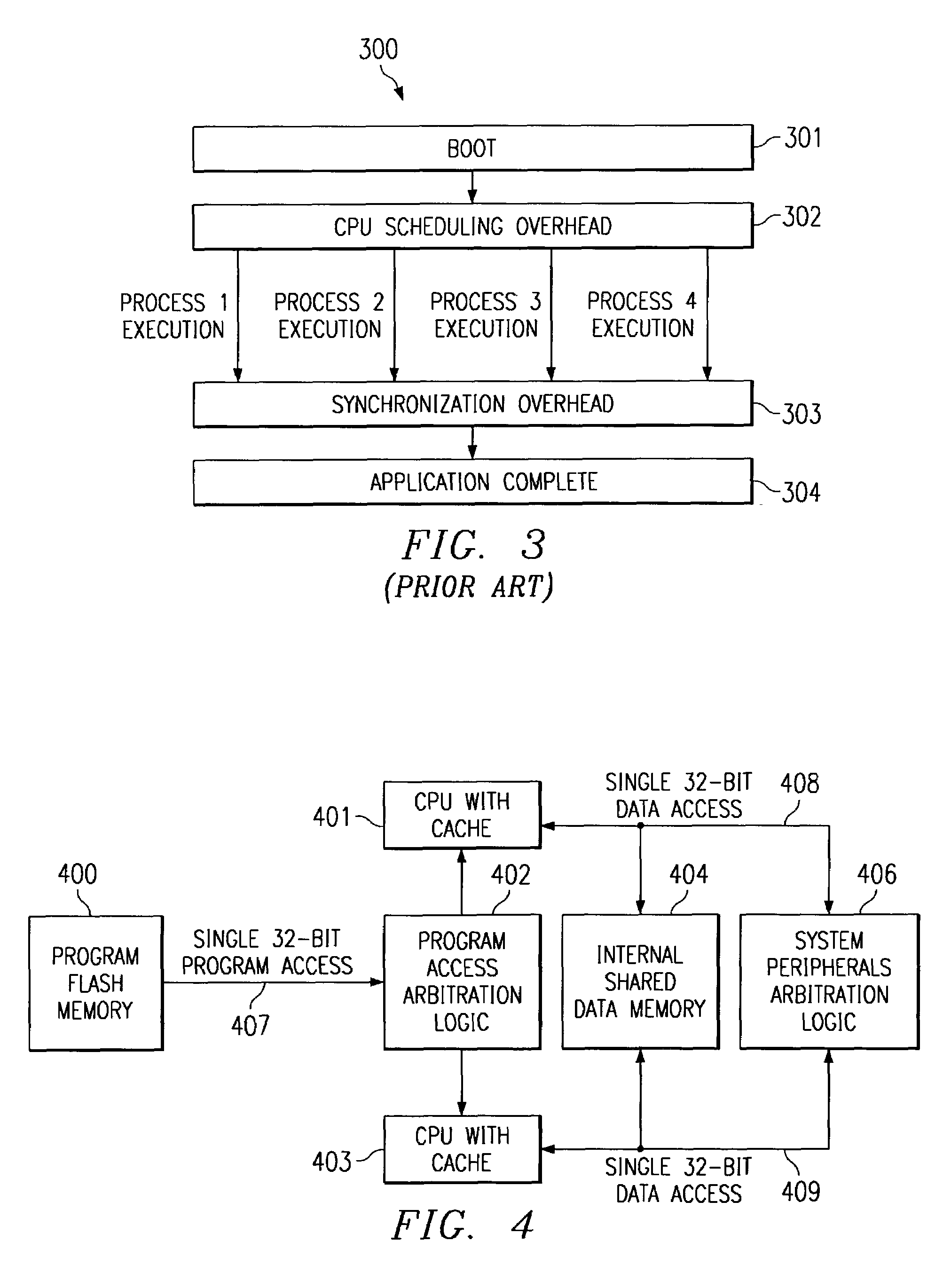

Embedded symmetric multiprocessor system with arbitration control of access to shared resources

InactiveUS7237071B2Low costImprove performanceEnergy efficient ICTMemory adressing/allocation/relocationMemory bankSingle chip

A single chip, embedded symmetric multiprocessor (ESMP) having parallel multiprocessing architecture composed of identical processors includes a single program memory. Program access arbitration logic supplies an instruction to a single requesting central processing unit at a time. Shared memory access arbitration logic can supply data from separate simultaneously accessible memory banks or arbitrate among central processing units for access. The system may simulate an atomic read / modify / write instruction by prohibiting access to the one address by another central processing unit for a predetermined number of memory cycles following a read access to one of a predetermined set of addresses in said shared memory.

Owner:TEXAS INSTR INC

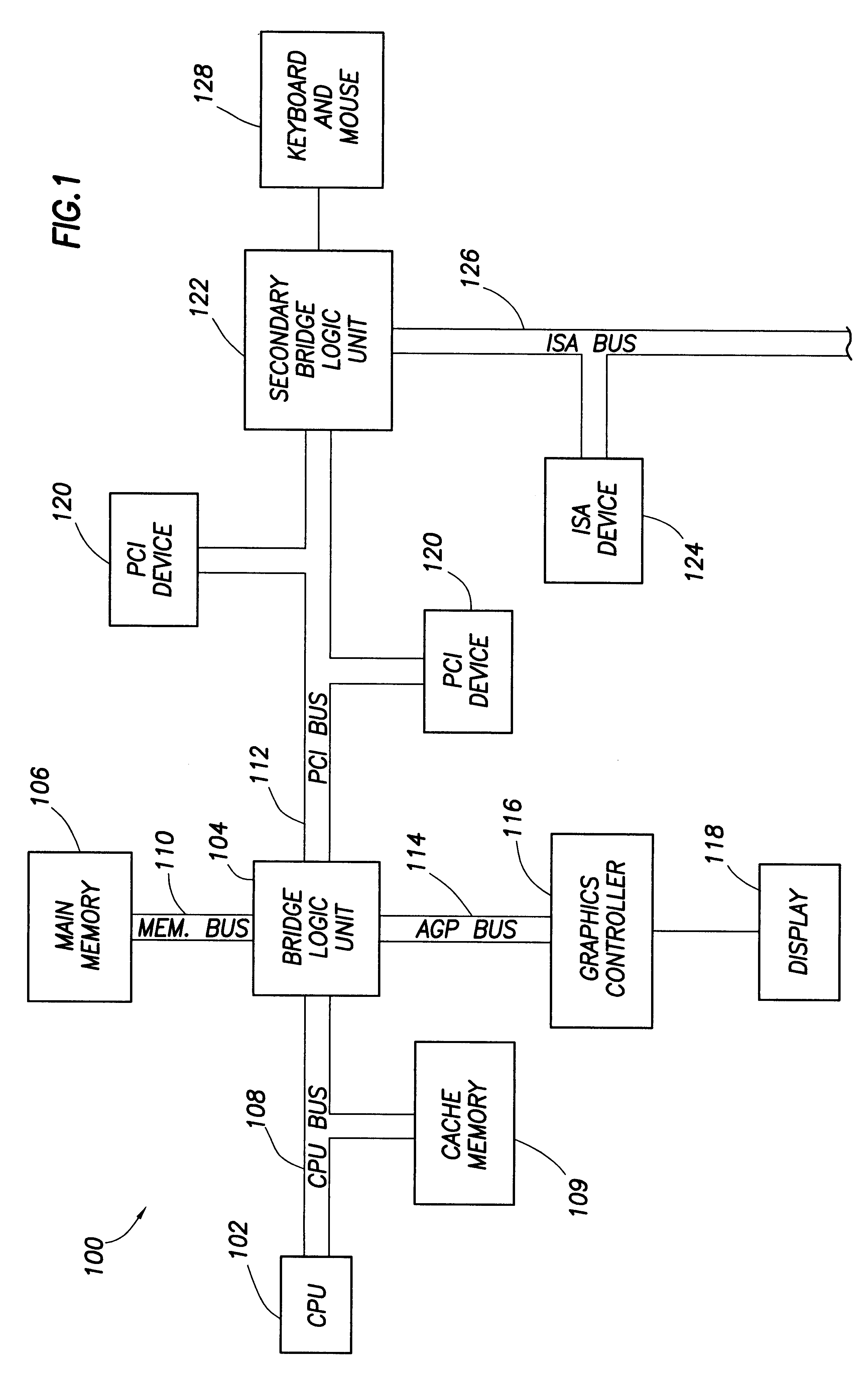

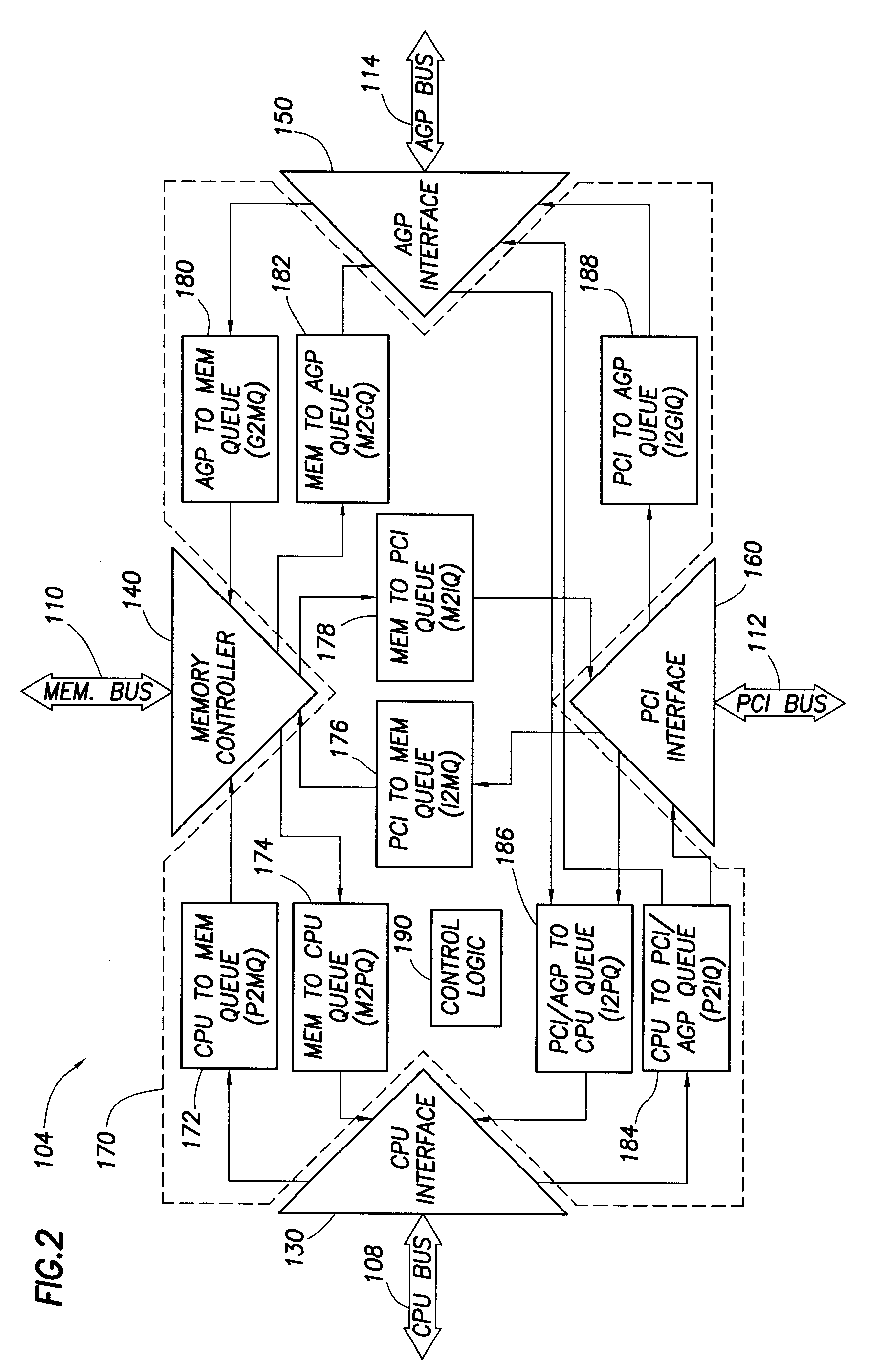

Computer system with improved memory access

InactiveUS6279065B1Multiple digital computer combinationsMemory systemsLogic cellComputerized system

A computer system includes a CPU and a memory device coupled by a bridge logic unit. CPU to memory write requests (including the data to be written) are temporarily stored in a queue in the bridge logic unit. The bridge logic unit preferably begins a write cycle to the memory device before all of the write data has been stored in the queue and available to the memory device. By beginning the memory cycle as early as possible, the total amount of time required to store all of the write data in the queue and then de-queue the data from the queue is reduced. Consequently, many CPU to memory write transactions are performed more efficiently and generally with less latency than previously possible.

Owner:HEWLETT PACKARD DEV CO LP

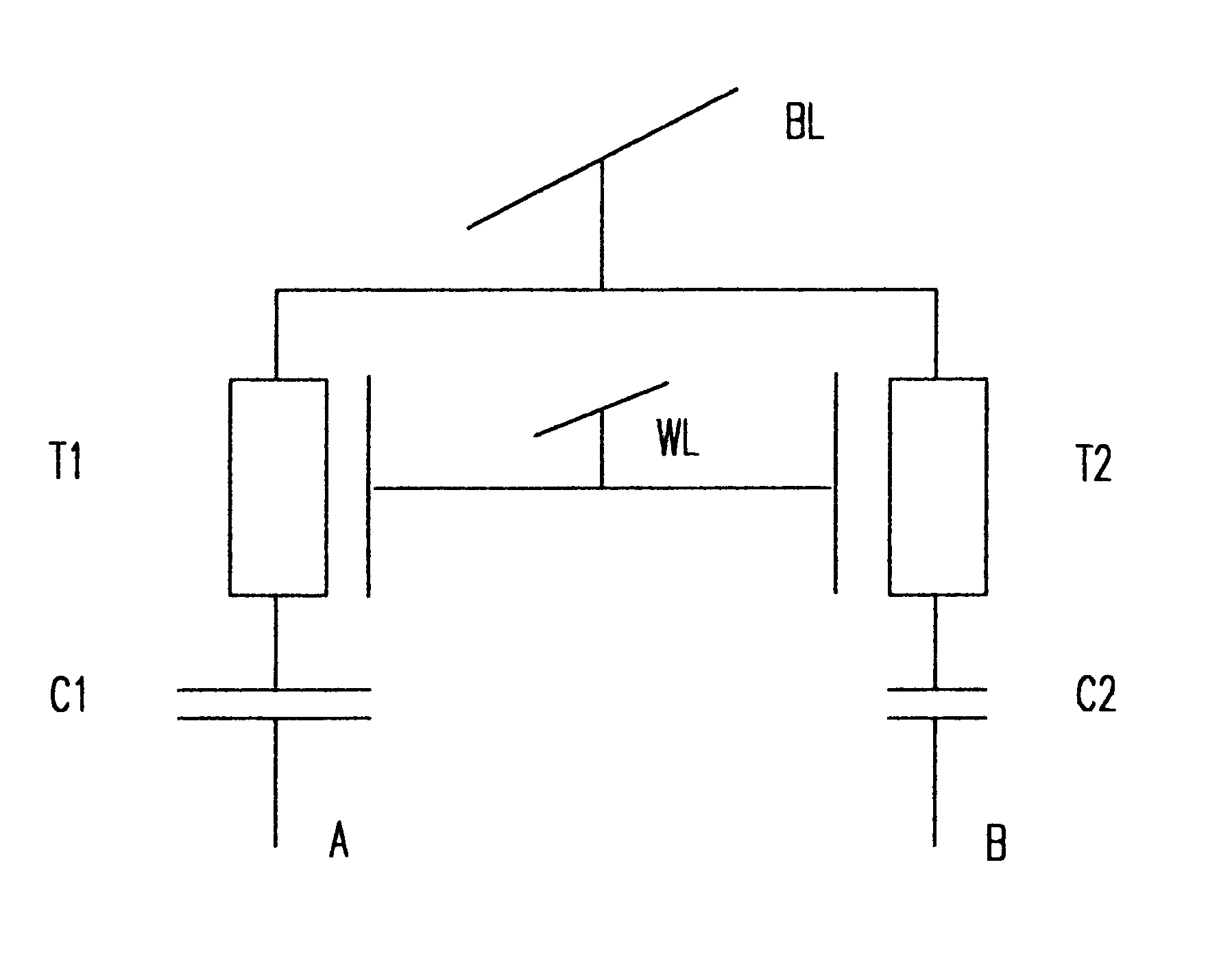

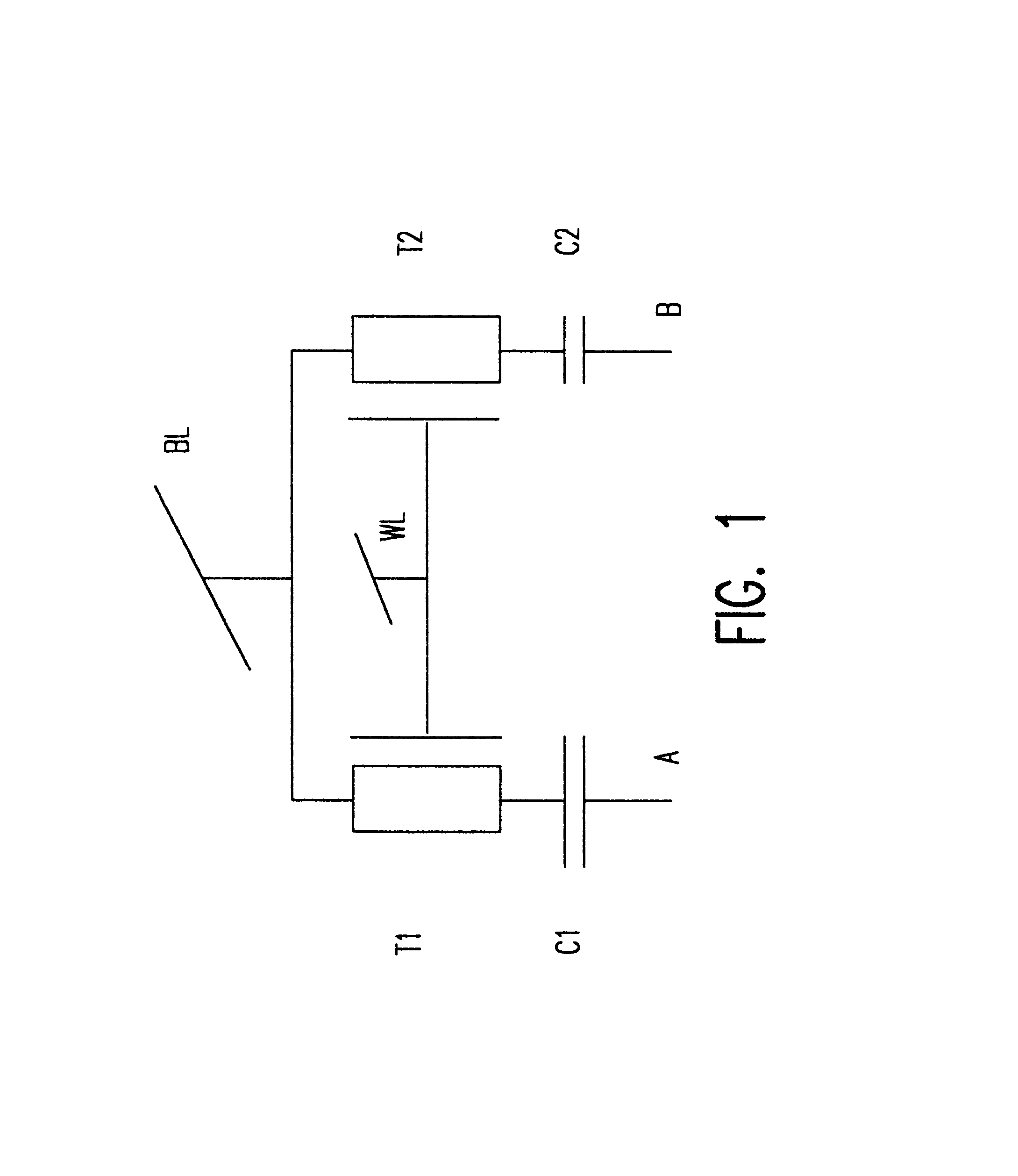

Multi-level DRAM trench store utilizing two capacitors and two plates

InactiveUS6282115B1Efficient storage densityImprove performanceTransistorSolid-state devicesDigital dataSemiconductor materials

A multi-level memory cell capable of storing two or three bits of digital data occupies only four lithographic squares and requires only one or two logic level voltage sources, respectively. High noise immunity derives from integration of the multi-level signal in the memory cell directly from logic level digital signals applied to two capacitors (as well as the bit line for the eight level mode of operation) by using capacitors having different values in order to avoid digital-to-analog conversion during writing. The capacitors can be simultaneously written and read to reduce memory cycle time. Transistor channels and capacitor connections are formed on adjacent semiconductor pillars using plugs of semiconductor material between pillars as common gate structures and connections. Opposite surfaces of the pillars also serve as storage nodes with common capacitor plates formed by conformal deposition between rows of plugs and pillars.

Owner:IBM CORP

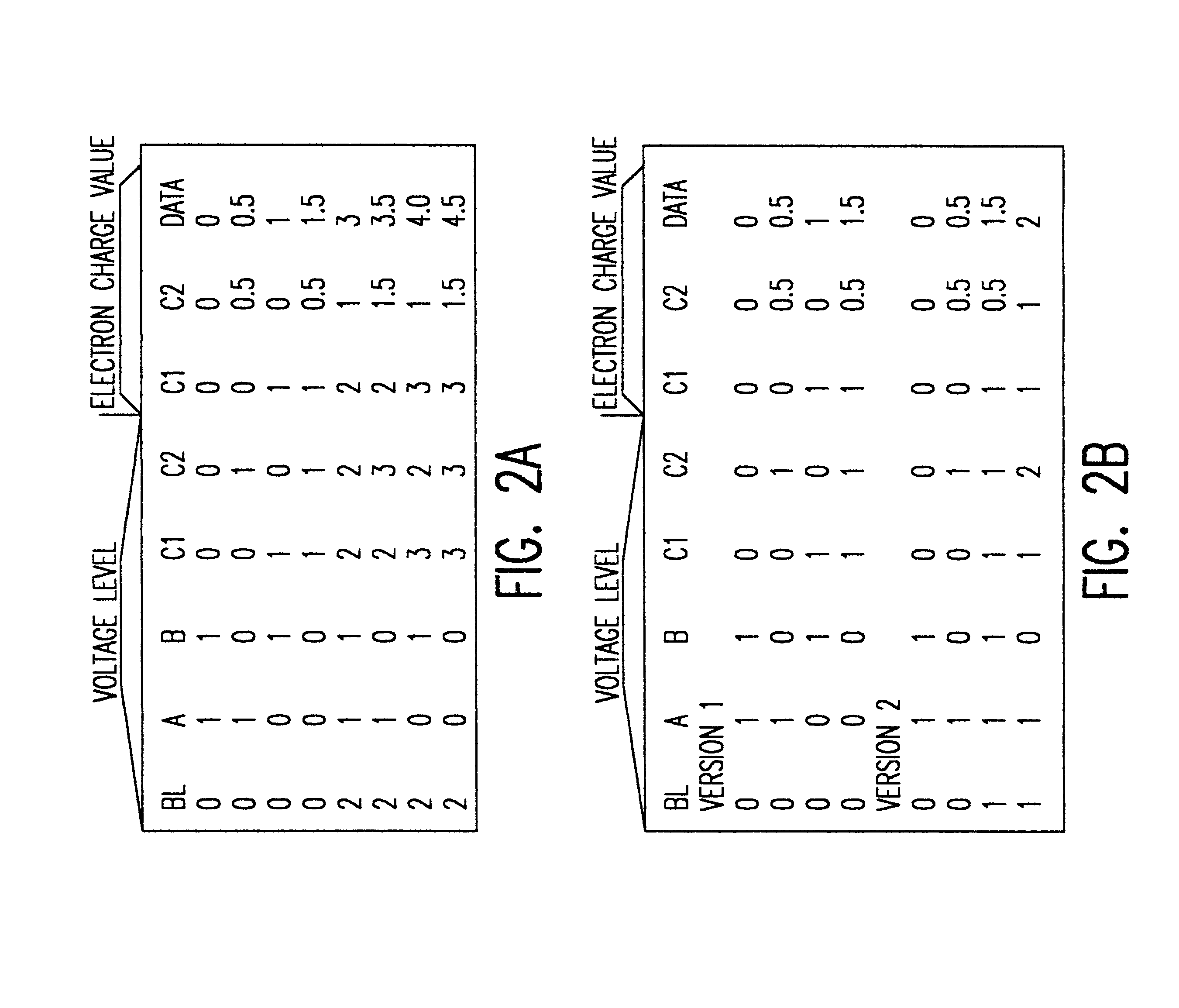

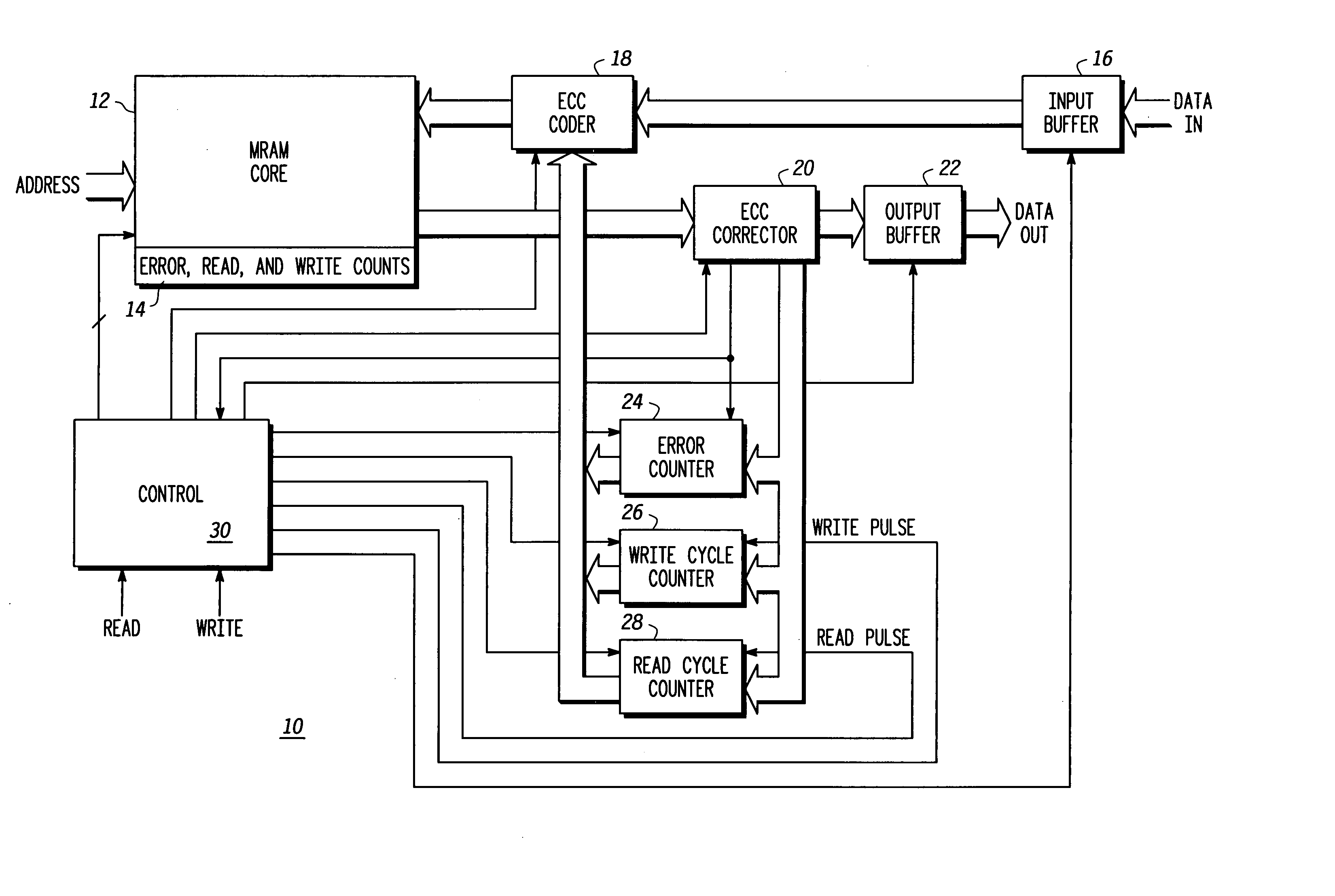

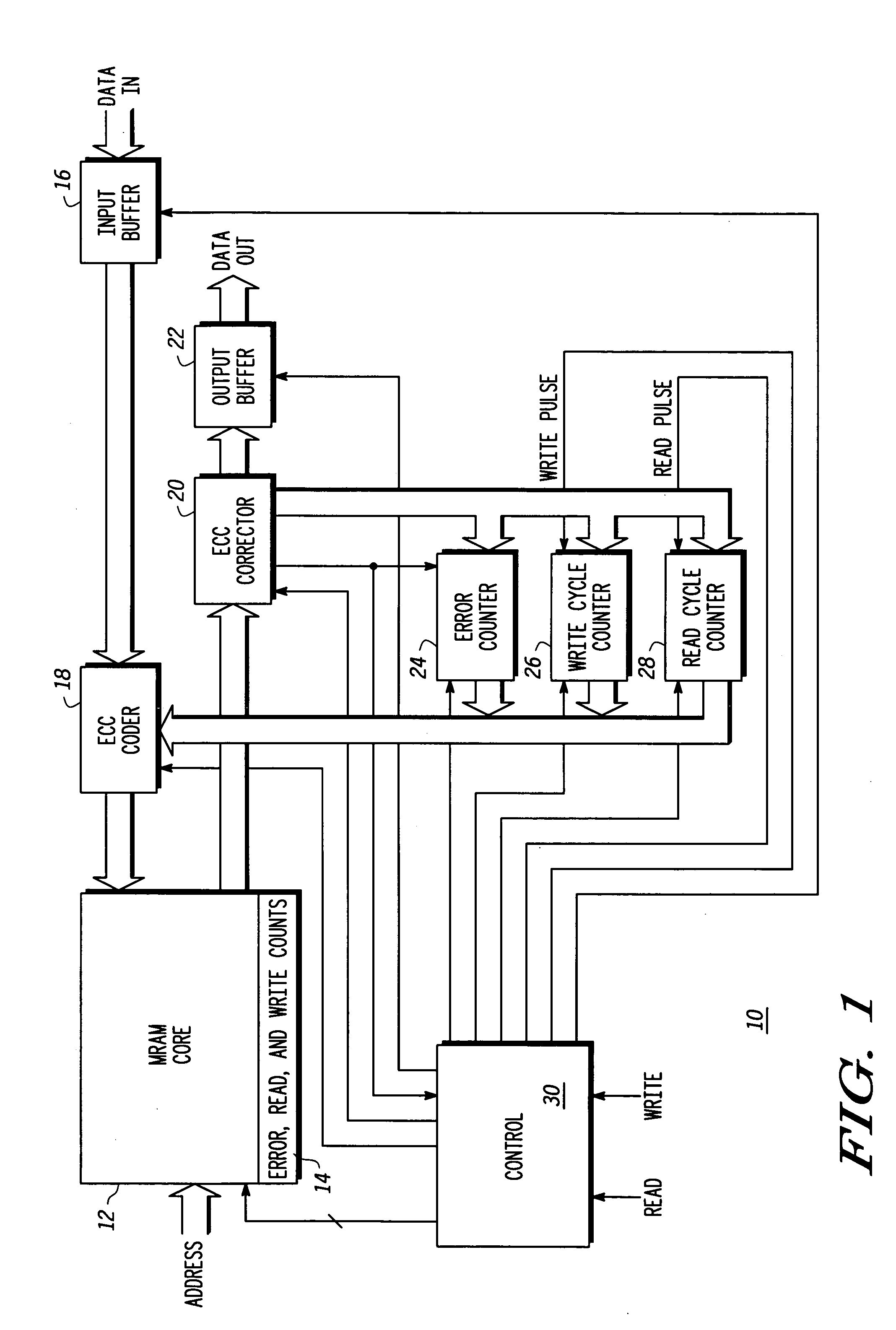

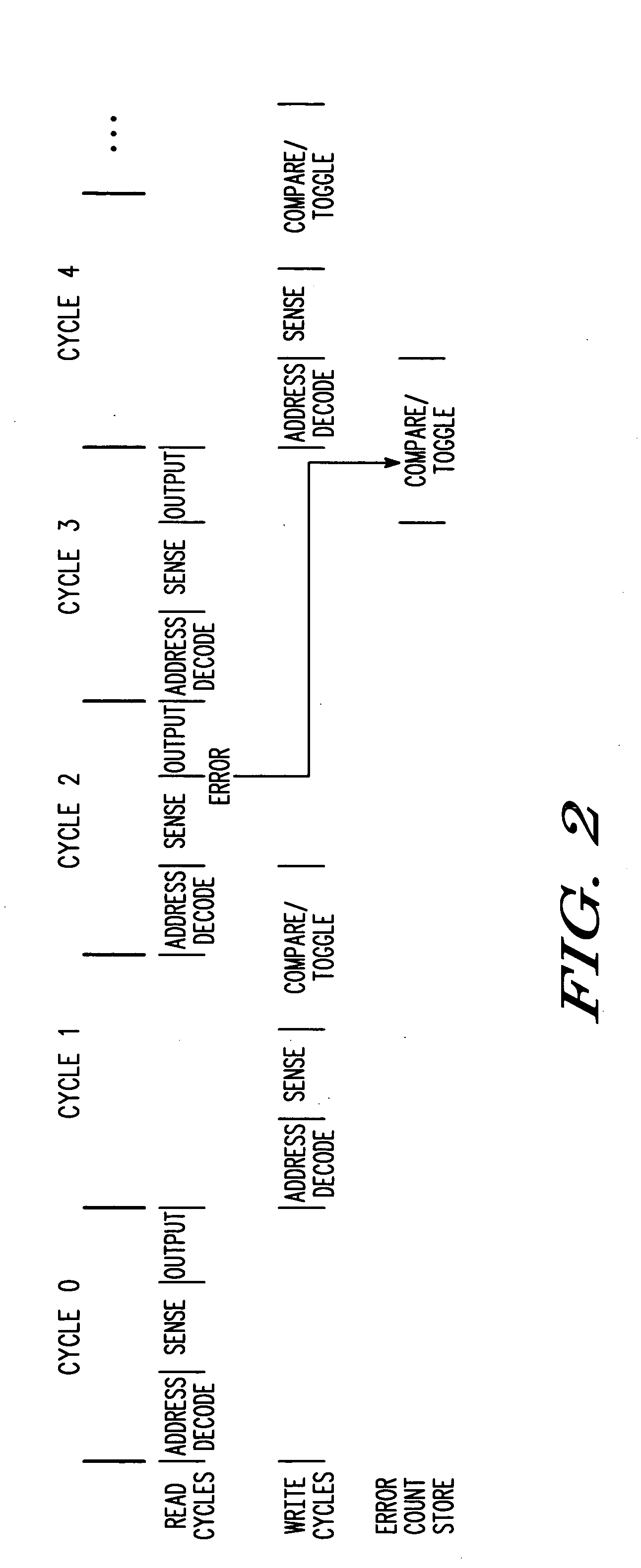

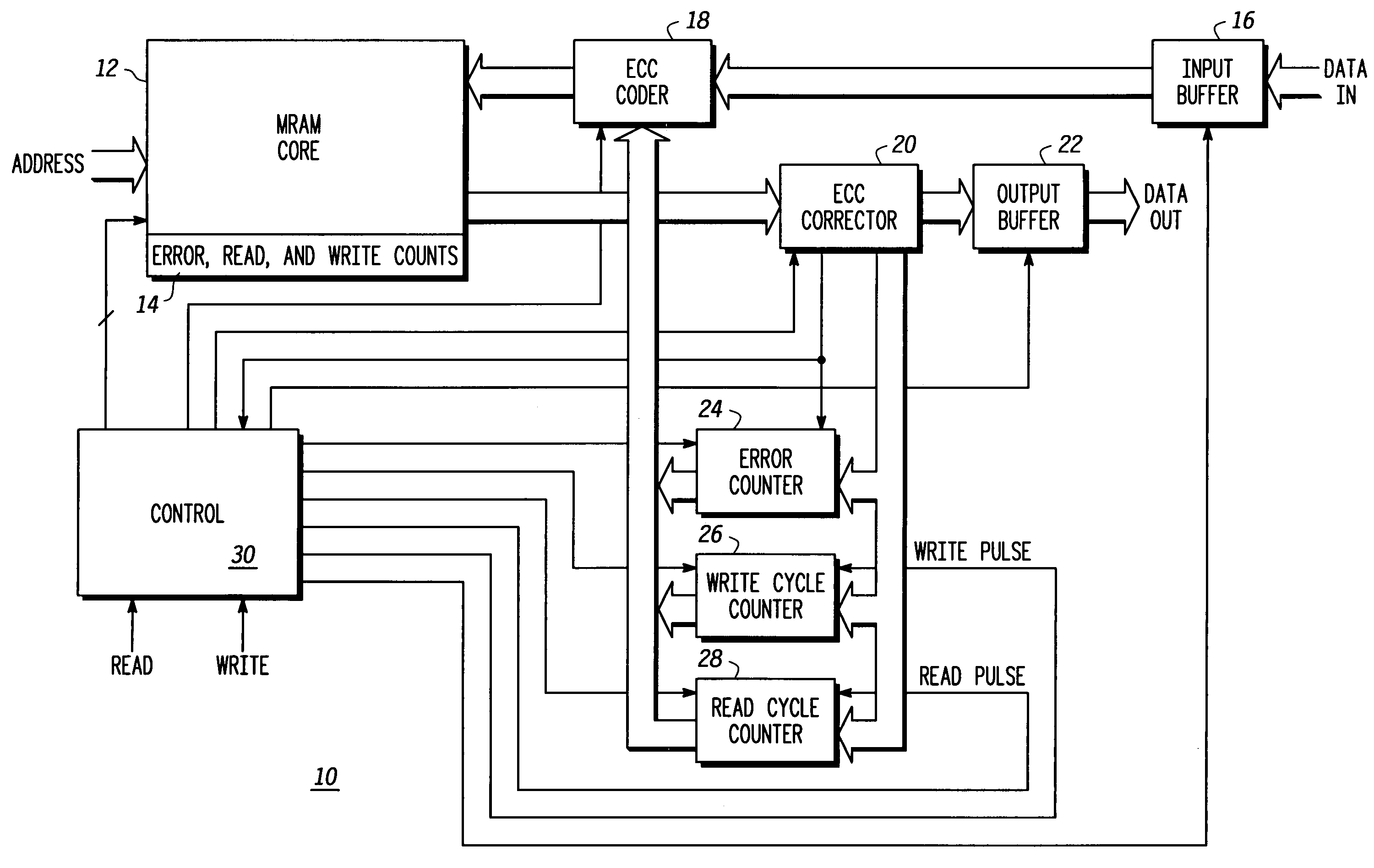

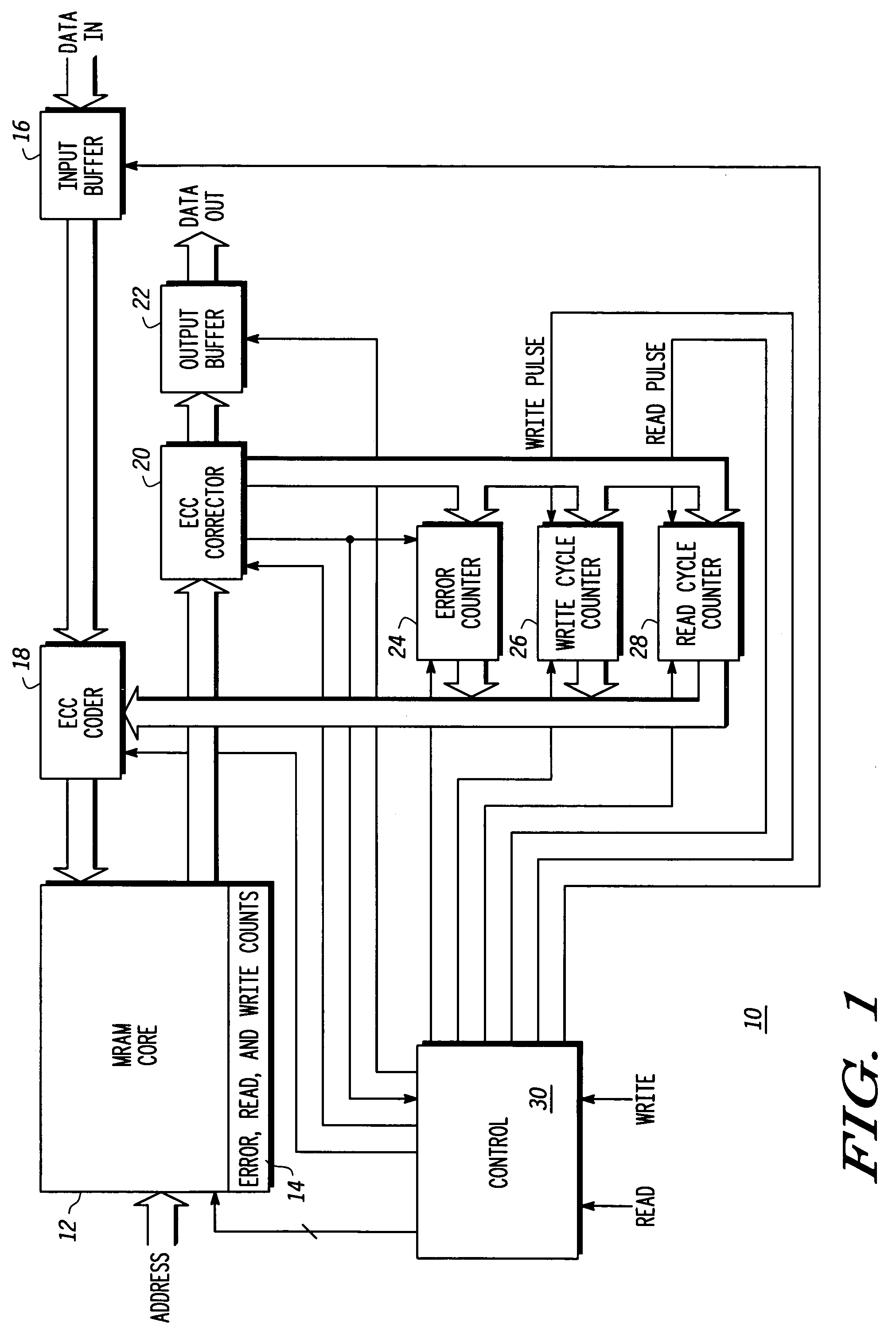

MRAM having error correction code circuitry and method therefor

An embedded memory system (10) uses an MRAM core (12) and error correction code (ECC) corrector circuitry (20). The ECC corrector circuitry identifies soft memory bit errors which are errors primarily resulting from an MRAM bit not being correctly programmed. The errors are identified and corrected during a read or a write cycle and not necessarily when the memory is in a special test mode. As errors are corrected, the error corrections are counted by an error counter (24) to create a count value. The count value is stored in the MRAM core itself and can later be retrieved and read during a test mode for an indication of how many bit corrections are required for the MRAM core over a period of time. The count value is stored by using an unused portion of a write memory cycle during a read operation.

Owner:EVERSPIN TECHNOLOGIES

Apparatus, method, and system for logging diagnostic information

ActiveUS20050138471A1Minimal impactEasy diagnosisError detection/correctionMemory addressProcessor register

A diagnostic tracing logger is presented for use in a multithread environment in which diagnostic trace log entries are captured and recorded. The trace logs are composed of sequences of memory addresses used to access instructions and operands, instruction op-codes and register specifiers, sequences of memory addresses, branch instructions or exceptions, the contents of registers or semiconductor memory locations, and the like. In one embodiment, a software module configures a plurality of buffers to capture bus traces, each trace triggered by a specific pattern. A buffer controller manages transfer of diagnostic trace information from the plurality of buffers to a diagnostic log without using processor memory cycles. The trace information is transferred to a selected buffer using a processor cache flush instruction. Diagnostic trace logging facilitates diagnosis of complex system and software interactions without the cost and overhead of prior art trace logging techniques.

Owner:GOOGLE LLC

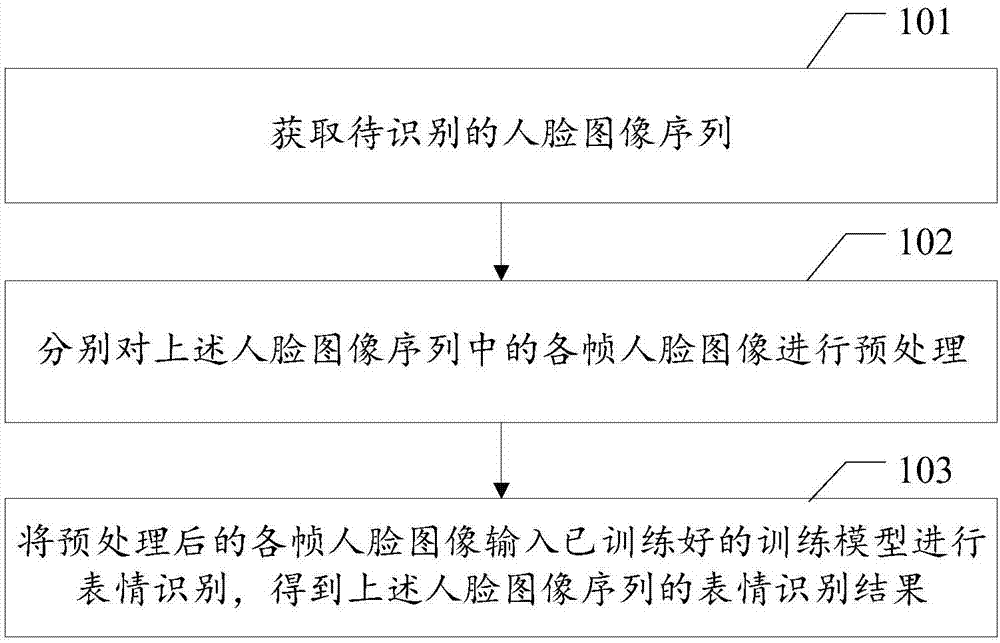

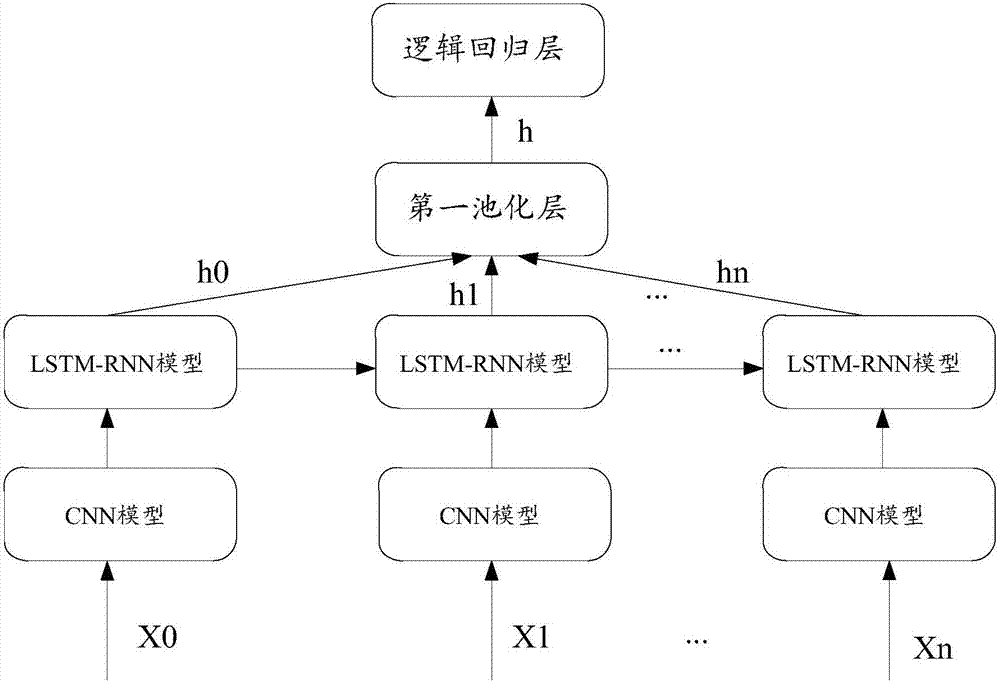

Face expression identification method and device

InactiveCN106980811AImprove forecast accuracyImprove robustnessAcquiring/recognising facial featuresNeural learning methodsNetwork modelConsecutive frame

The invention discloses a face expression identification method and device. The method comprises steps that a to-be-identified face image sequence is acquired, and the face image sequence comprises one or more than two face images; each face image of the face image sequence is pre-processed; the pre-processed face images are inputted to a trained training model to carry out expression identification to acquire expression identification results of the face image sequence; a convolutional neural network model, a long-time short-time memory cycle neural network model, a first pooling layer and a logic regression model are sequentially constructed from an input end to an output end of the training model, and the training model is acquired through training a continuous-image set marked with expression categories. The method is advantaged in that face expression identification performance can be effectively improved.

Owner:SENSETIME GRP LTD

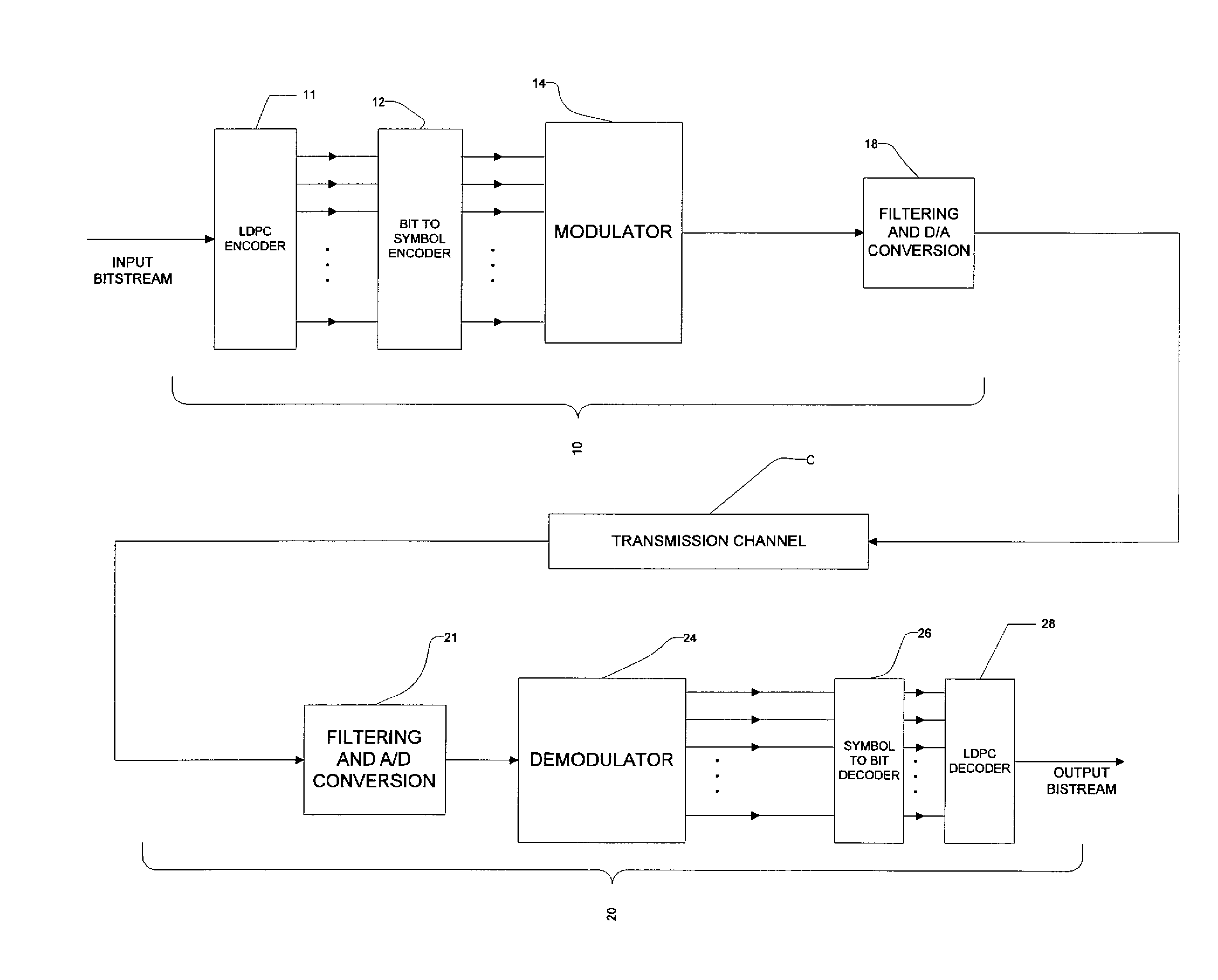

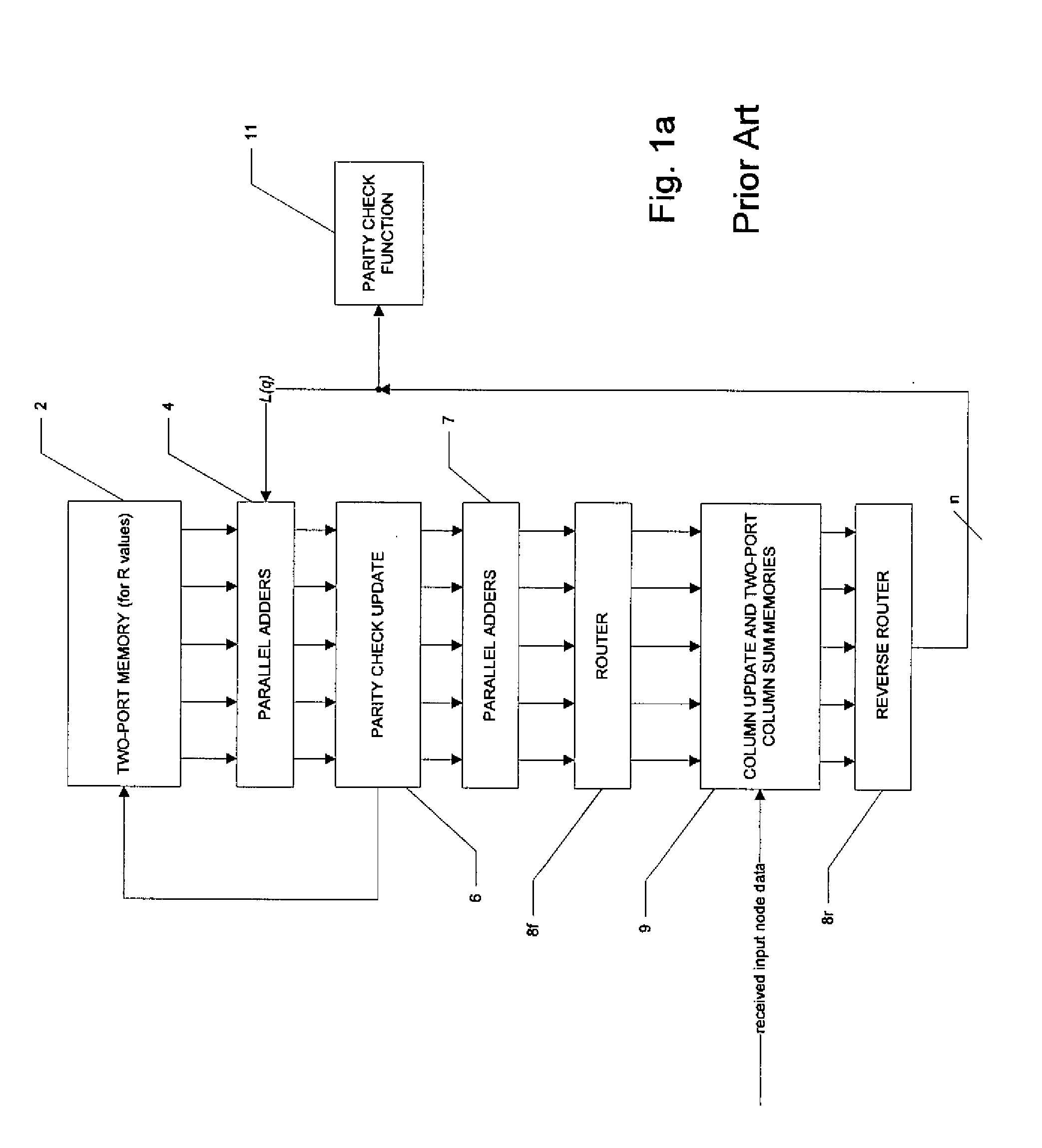

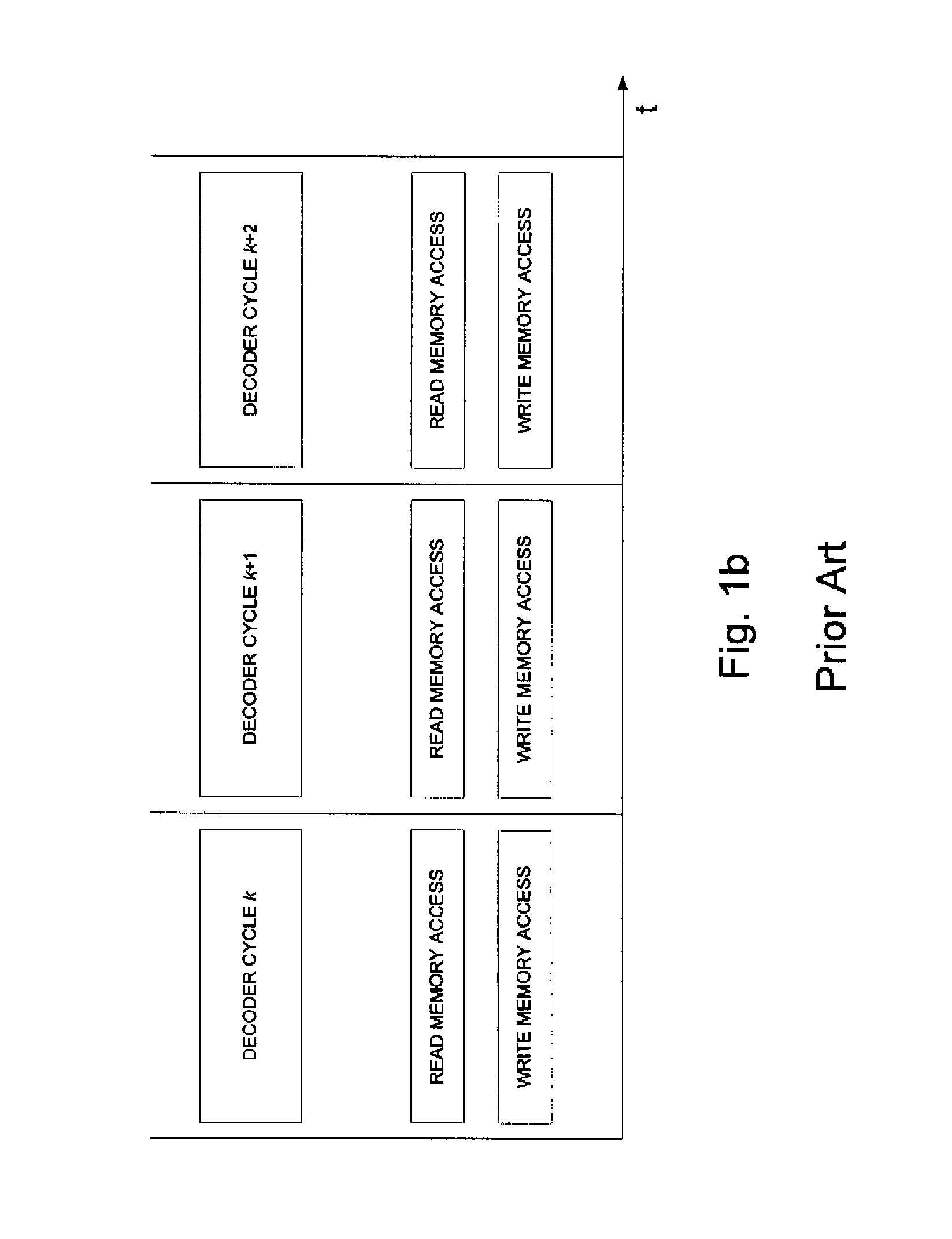

Memory Access in Low-Density Parity Check Decoders

InactiveUS20090282316A1Adversely impacting performanceImprove area efficiencyError correction/detection using multiple parity bitsCode conversionComputer architectureParity-check matrix

Low Density Parity Check (LDPC) decoder circuitry in which memory resources are realized as single-port memory. The decoder circuitry includes a single port memory for storing log-likelihood ratio (LLR) estimates of input node data states for individual rows of a parity check matrix. The decoder circuitry also includes multiple instances of single-port column sum memories, which store updated LLR estimates for each input node. In each case, the memory resources include logic circuitry that executes at least one write cycle and one read cycle to the memory within each decoder cycle. Because the decoder cycle time is much longer than the necessary memory cycle time, particularly in LDPC decoding, data can be written to and read from single-port memory resources in ample time for the decoding operation.

Owner:TEXAS INSTR INC

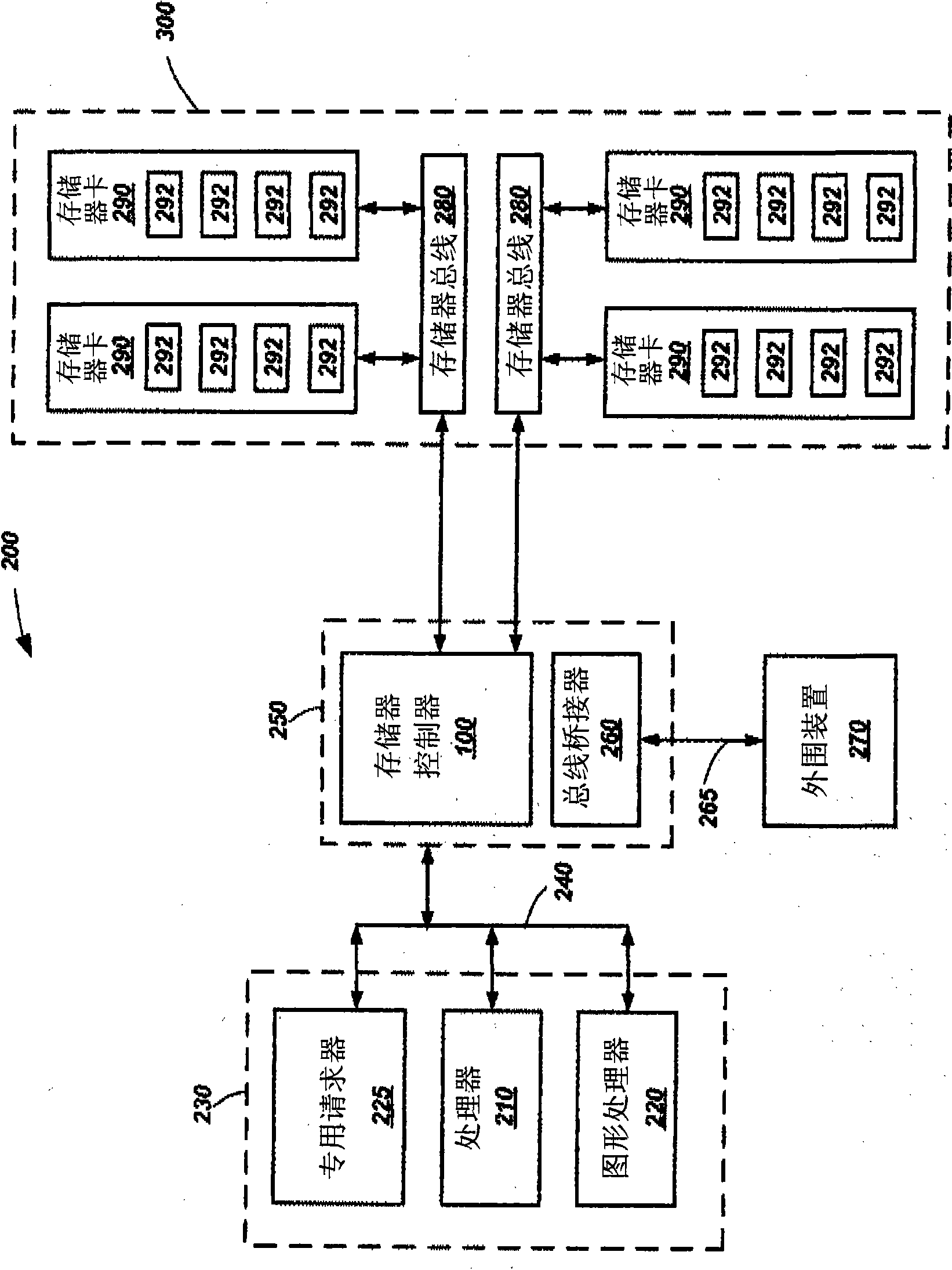

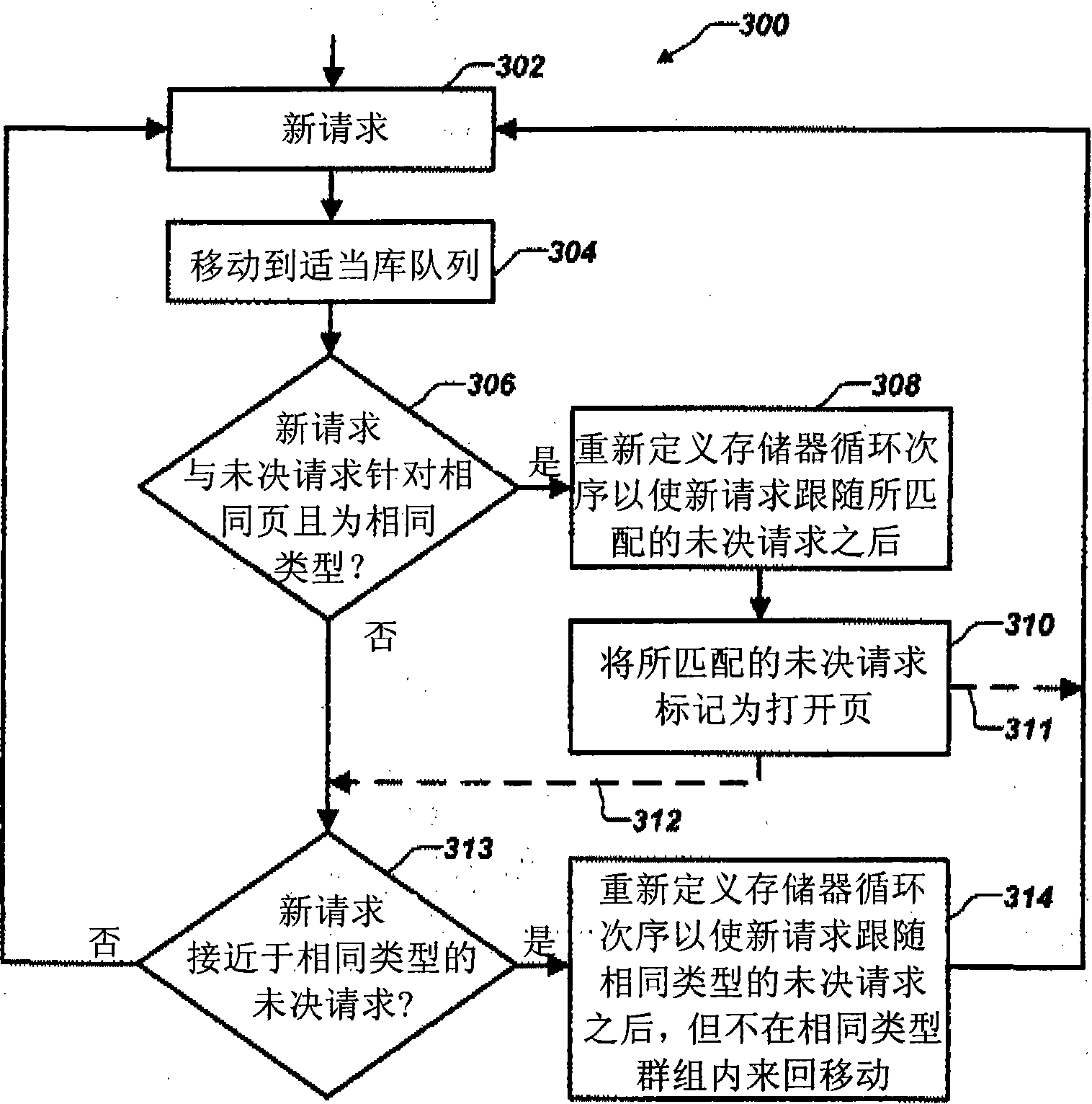

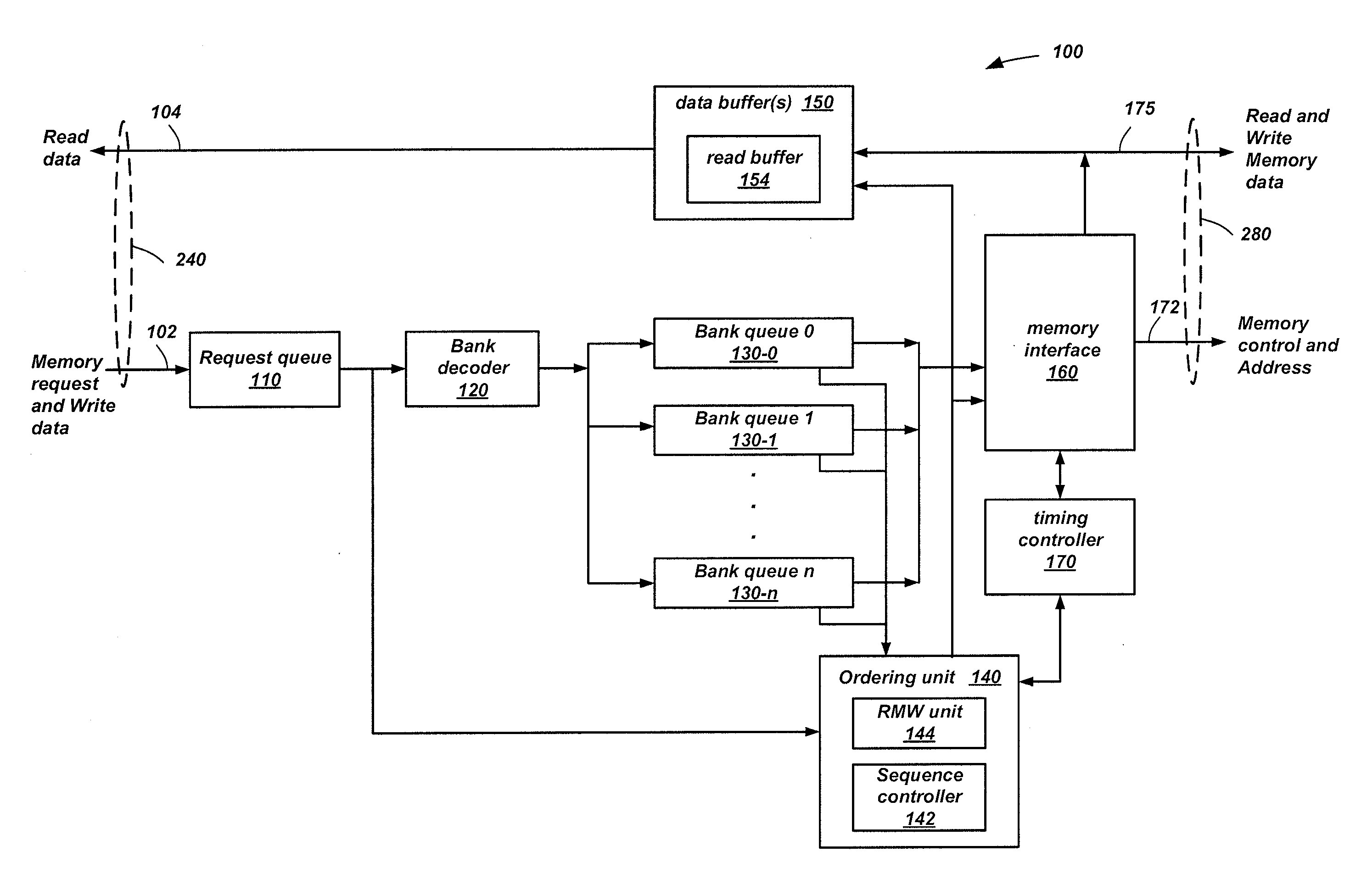

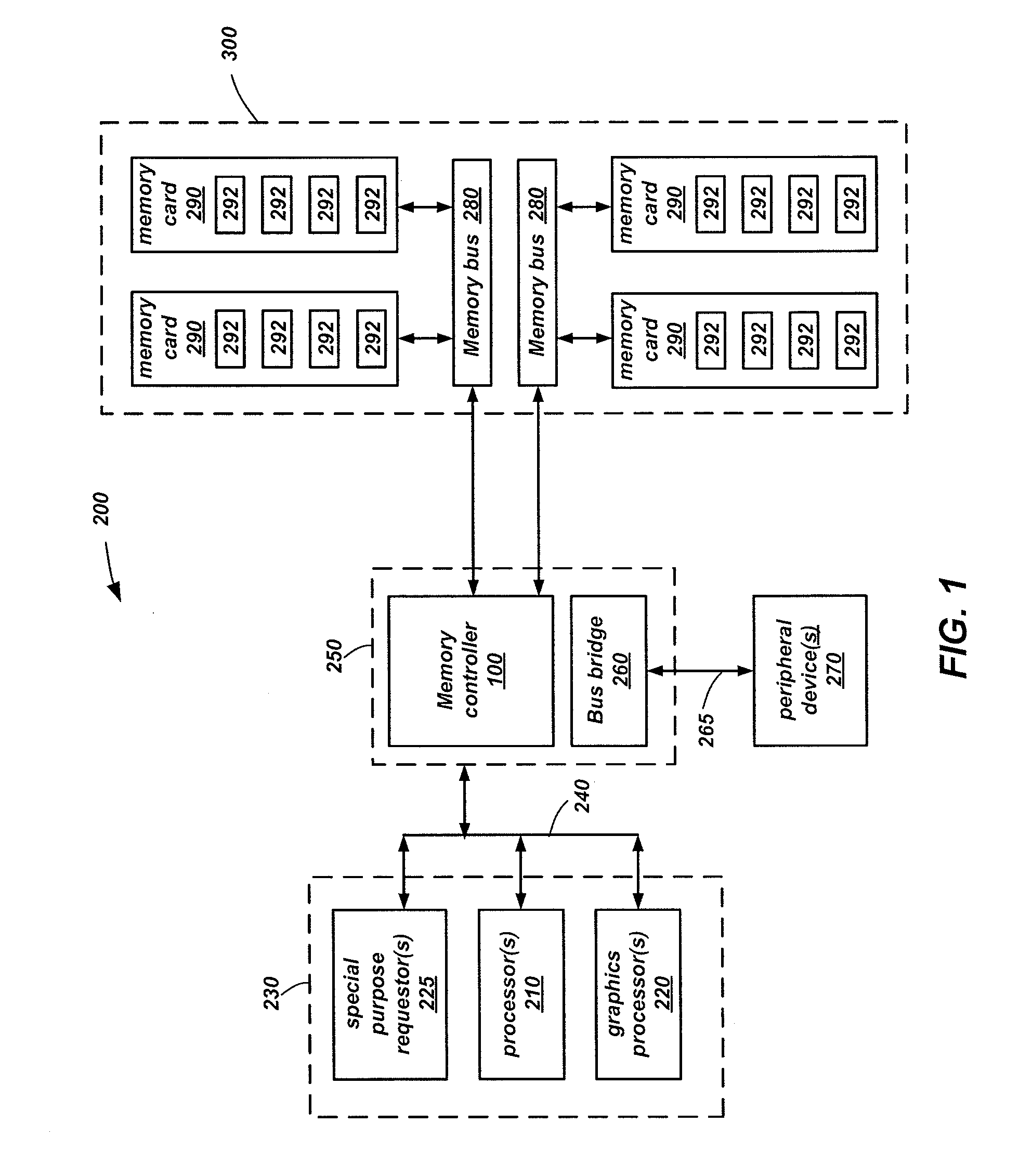

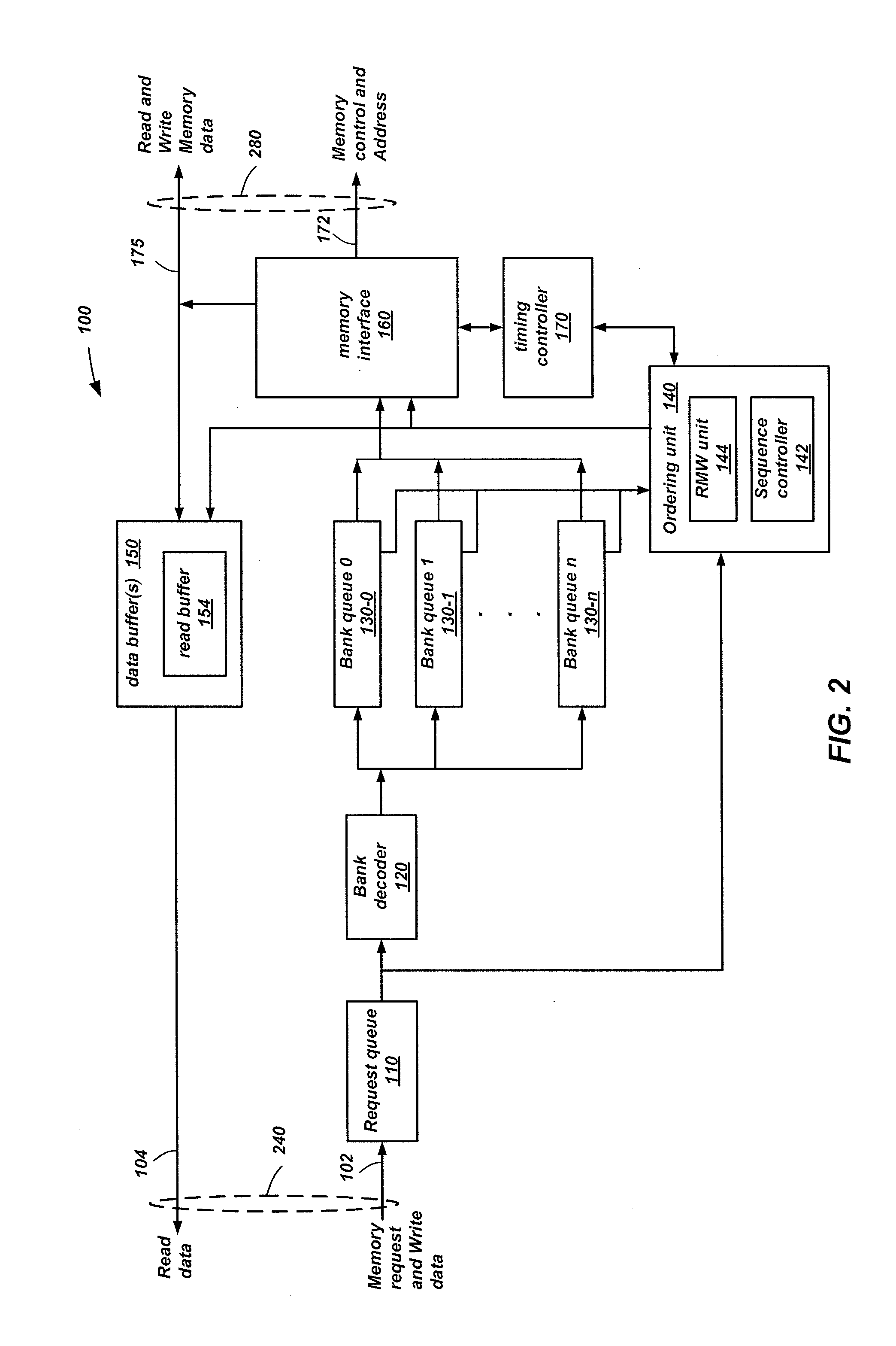

System, apparatus, and method for modifying the order of memory accesses

Systems and methods for controlling memory access operation are disclosed. The system may include one or more requestors performing requests to memory devices. Within a memory controller, a request queue receives requests from a requestor, a bank decoder determines a destination bank, and the request is placed in an appropriate bank queue. An ordering unit determines if the current request can be reordered relative to the received order and generates a new memory cycle order based on the reordering determination. The reordering may be based on whether there are multiple requests to the same memory page, multiple reads, or multiple writes. A memory interface executes each memory request in the memory cycle order. A data buffer holds write data until it is written to the memory and read data until it is returned to the requestor. The data buffer also may hold memory words used in read-modify- write operations.

Owner:MICRON TECH INC

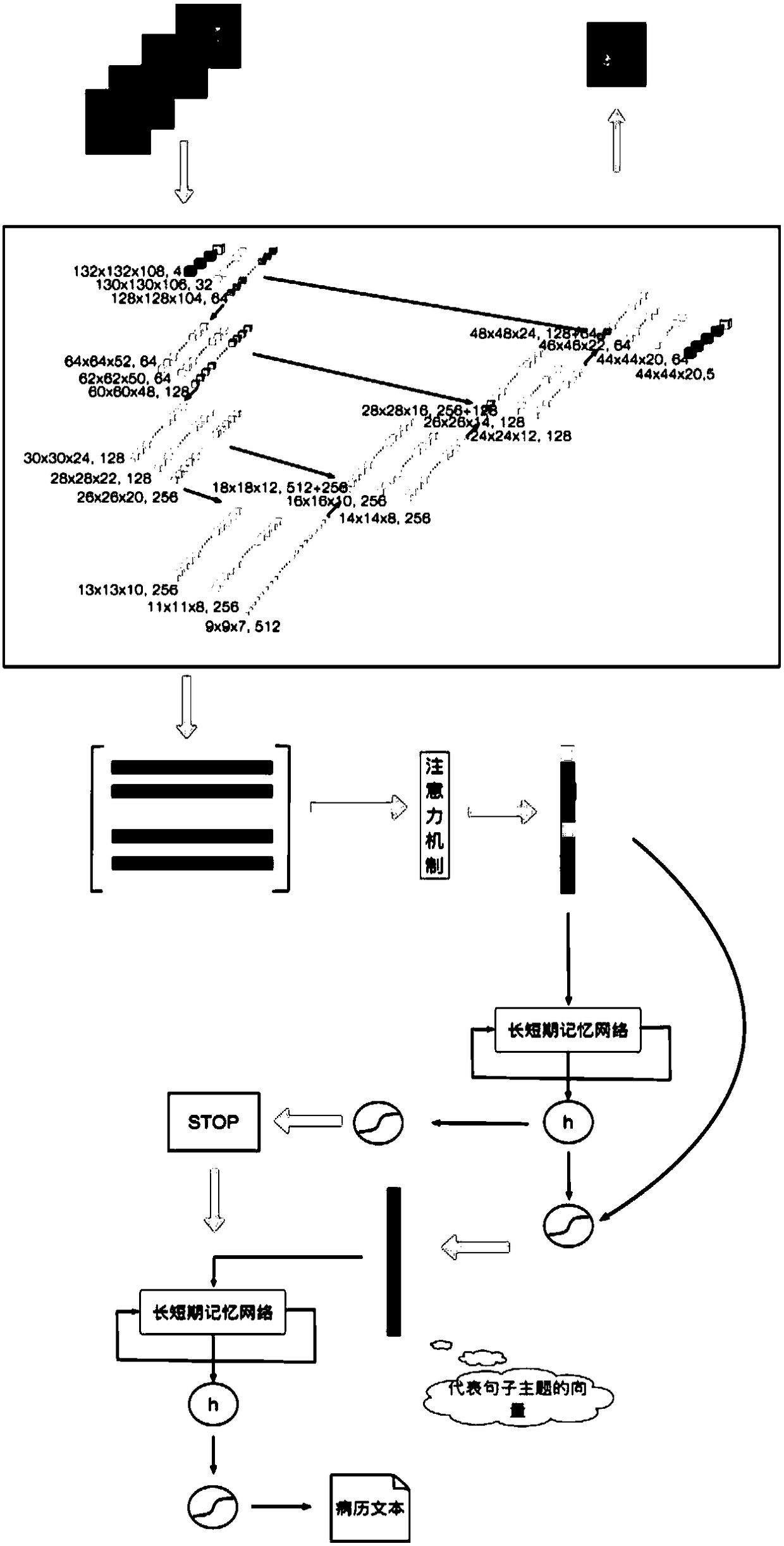

Multi-modal nuclear magnetic resonance image case report automatic generation method

ActiveCN108376558ANo human intervention requiredEase workMedical automated diagnosisMedical imagesMedical recordNerve network

The invention belongs to the medical data analysis and intelligent processing technical field, and specifically relates to a multi-modal nuclear magnetic resonance image case report automatic generation method employing a deep learning model; the method comprises the following steps: importing an attention matrix on the basis of using a convolution nerve network to extract image characteristics; giving different weights on characteristics of different positions via point multiplication operation, thus obtaining image characteristics under different attentions; using a long-short period memorycycle nerve network to form a subject vector of each sentence in a case report according to the image characteristics under different attentions; using another long-short period memory cycle nerve network to form each word according to the subject vector of the sentence; connecting the words so as to obtain the final case report. The method can automatically form a description text of a magnetic resonance image case without using a case template, thus providing deep meanings for mitigating works of radiology department doctors and building an intelligent computer auxiliary diagnosis system.

Owner:FUDAN UNIV

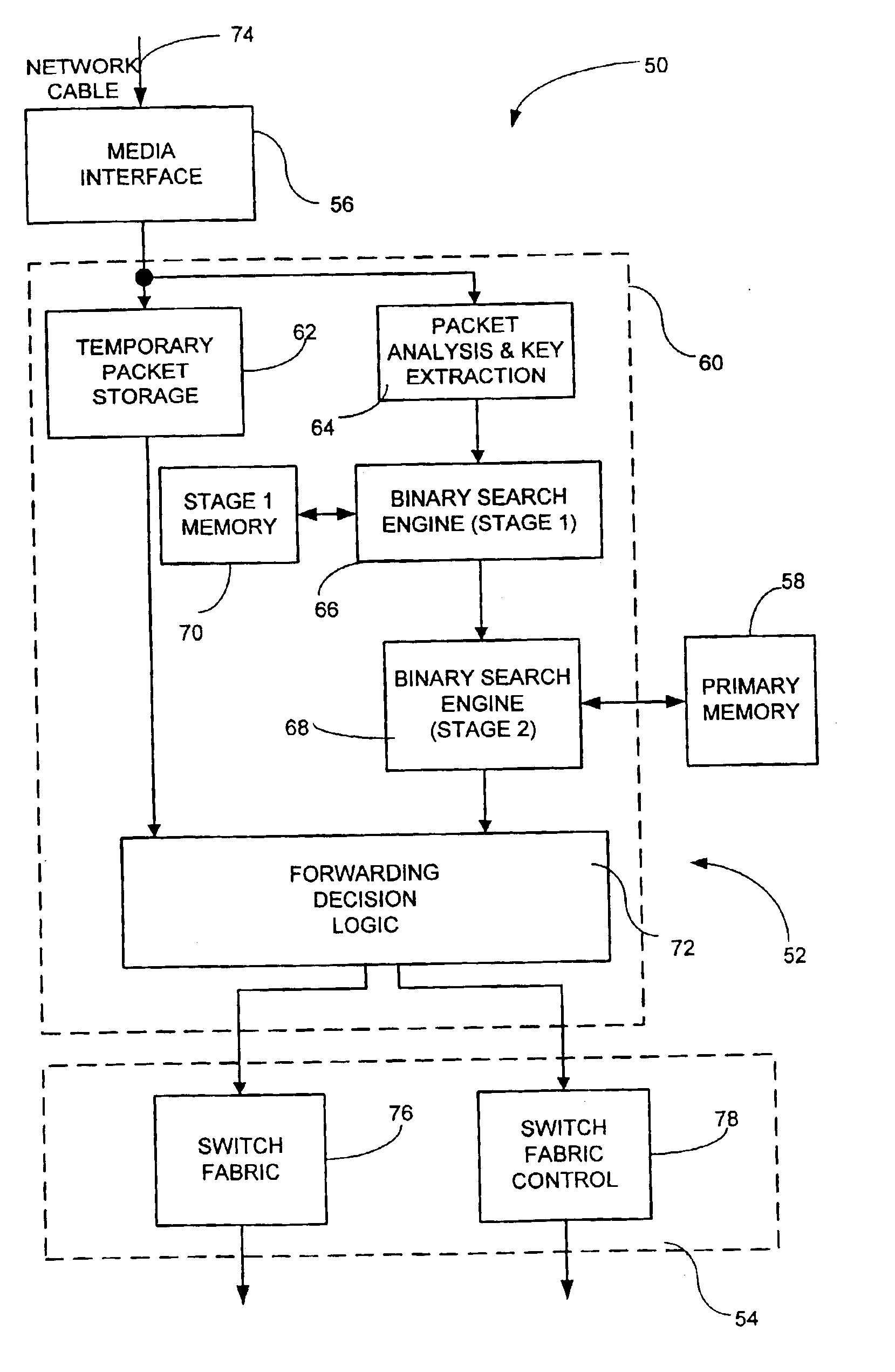

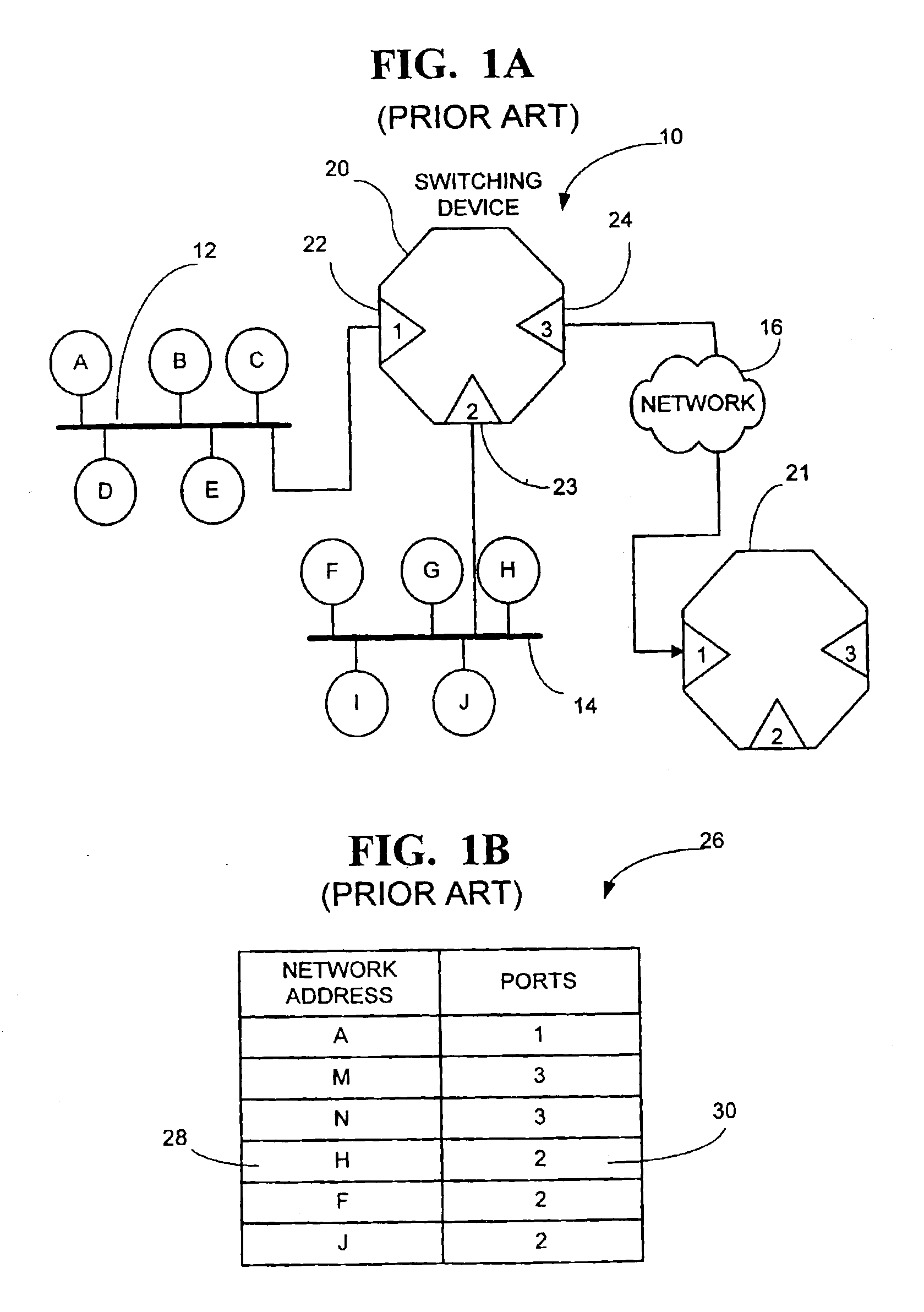

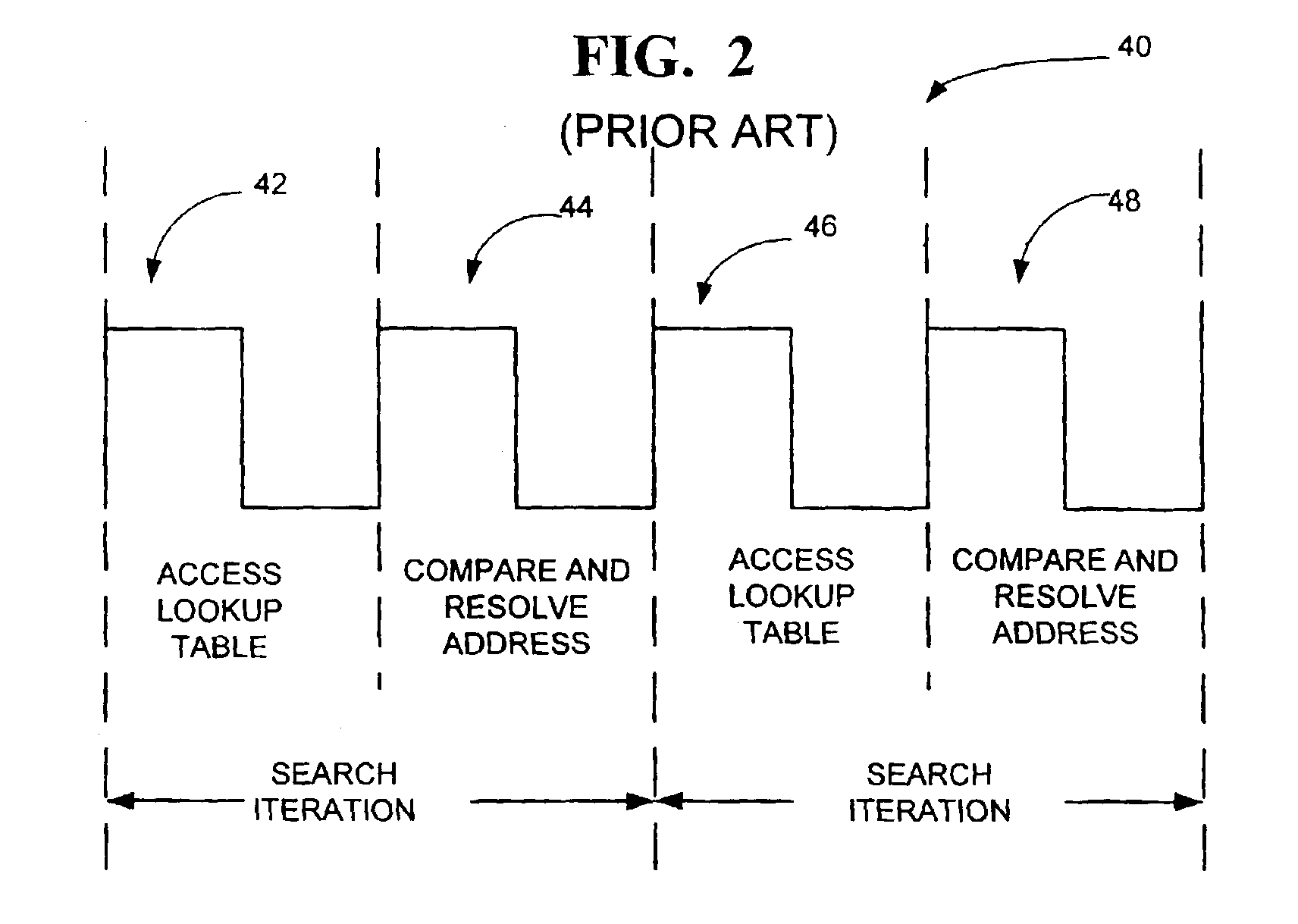

Network switching device with pipelined search engines

A switching device for forwarding network traffic to a desired destination on a network, such as a telephone or computer network. The switching device includes multiple ports and uses a lookup table to determine which port to forward network traffic over. The lookup table includes network addresses that are maintained in ascending or descending order. The switching device includes multiple binary search engines coupled in series including one or more precursor binary search engines and a final stage binary search engine. Together, the binary search engines perform an N iteration binary search. Additionally, a single search engine can perform multiple concurrent searches so that source and destination addresses can be obtained simultaneously and without wasted memory cycles.

Owner:MICHELS TIMOTHY SCOTT +3

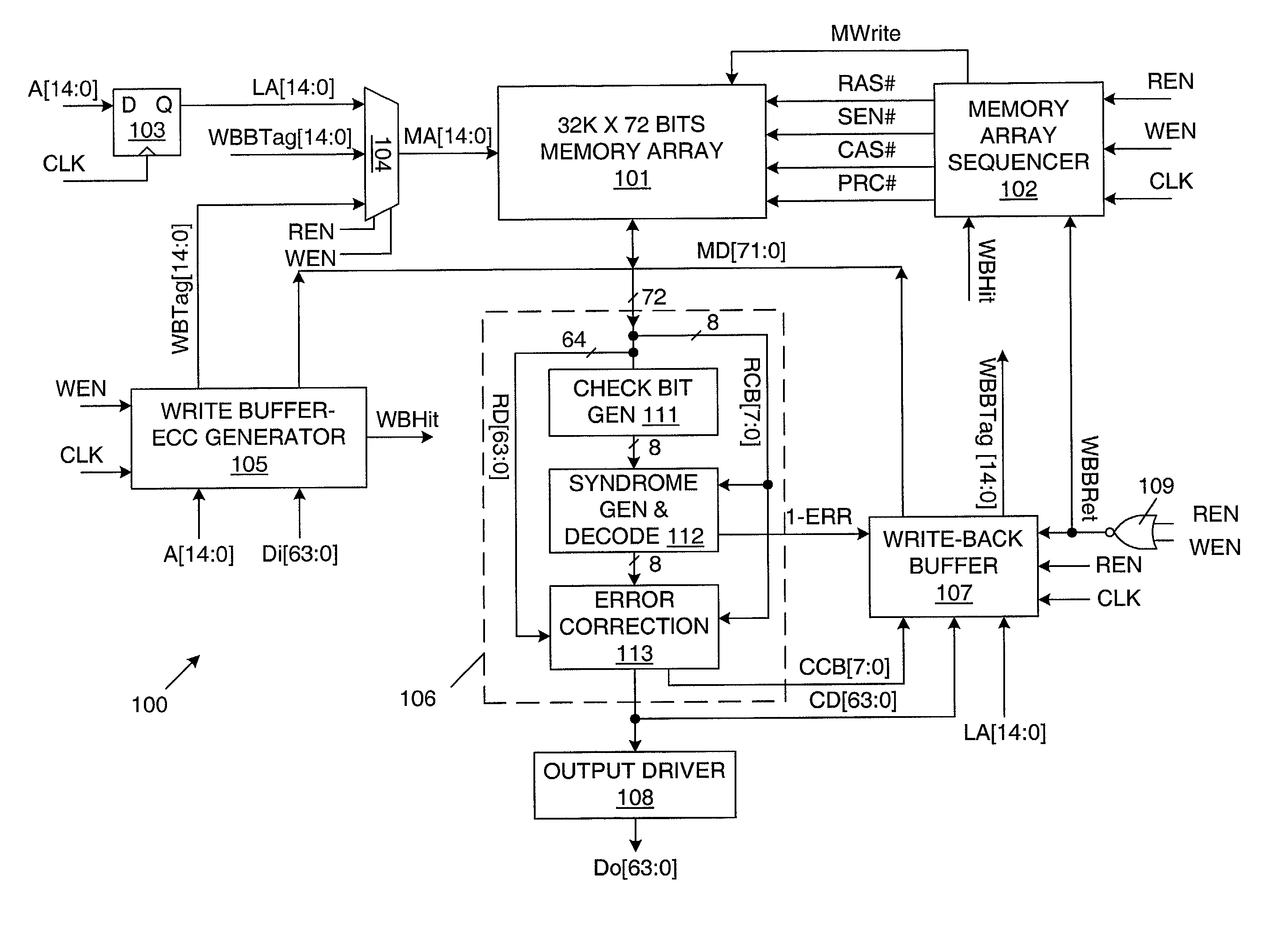

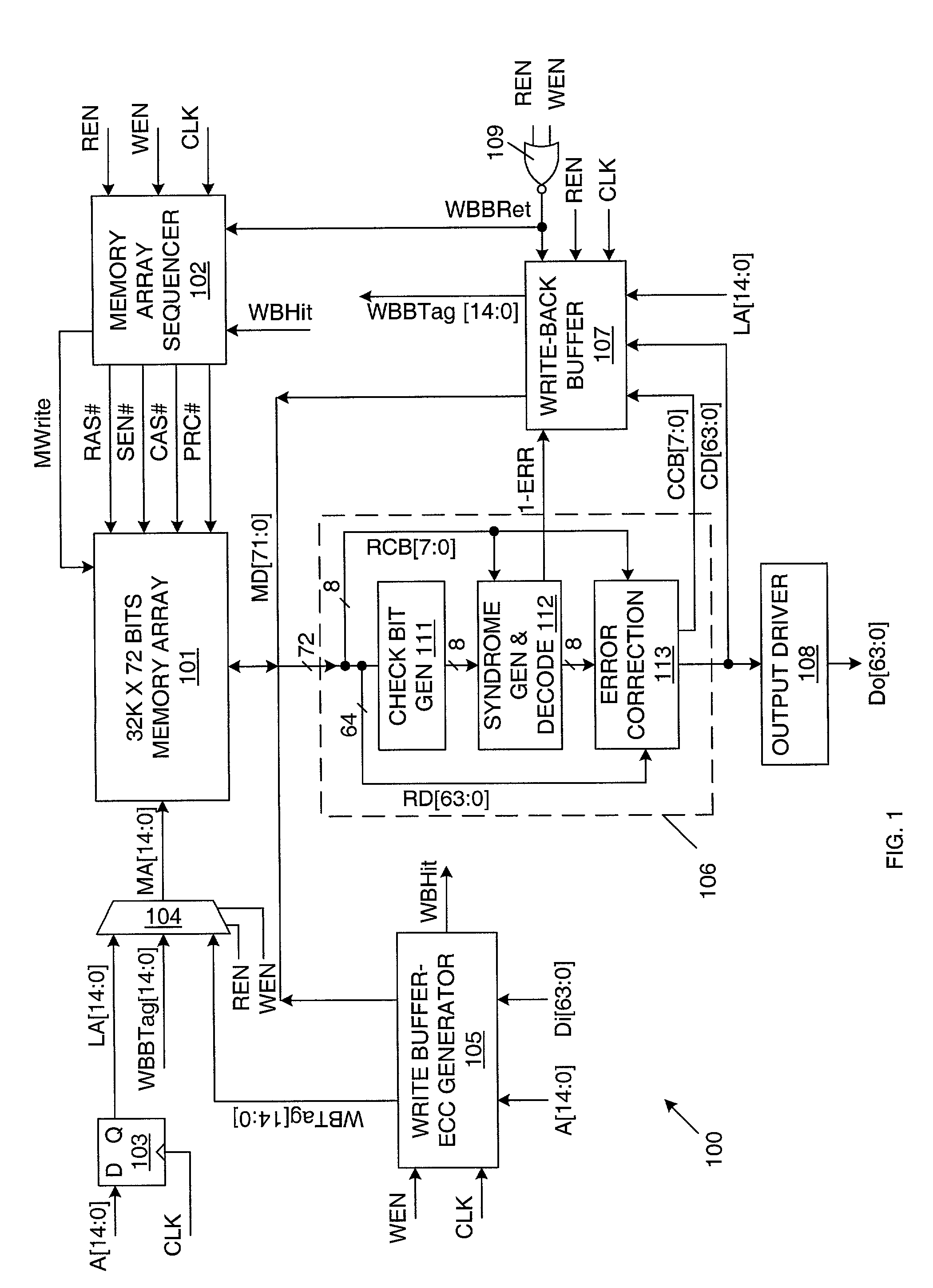

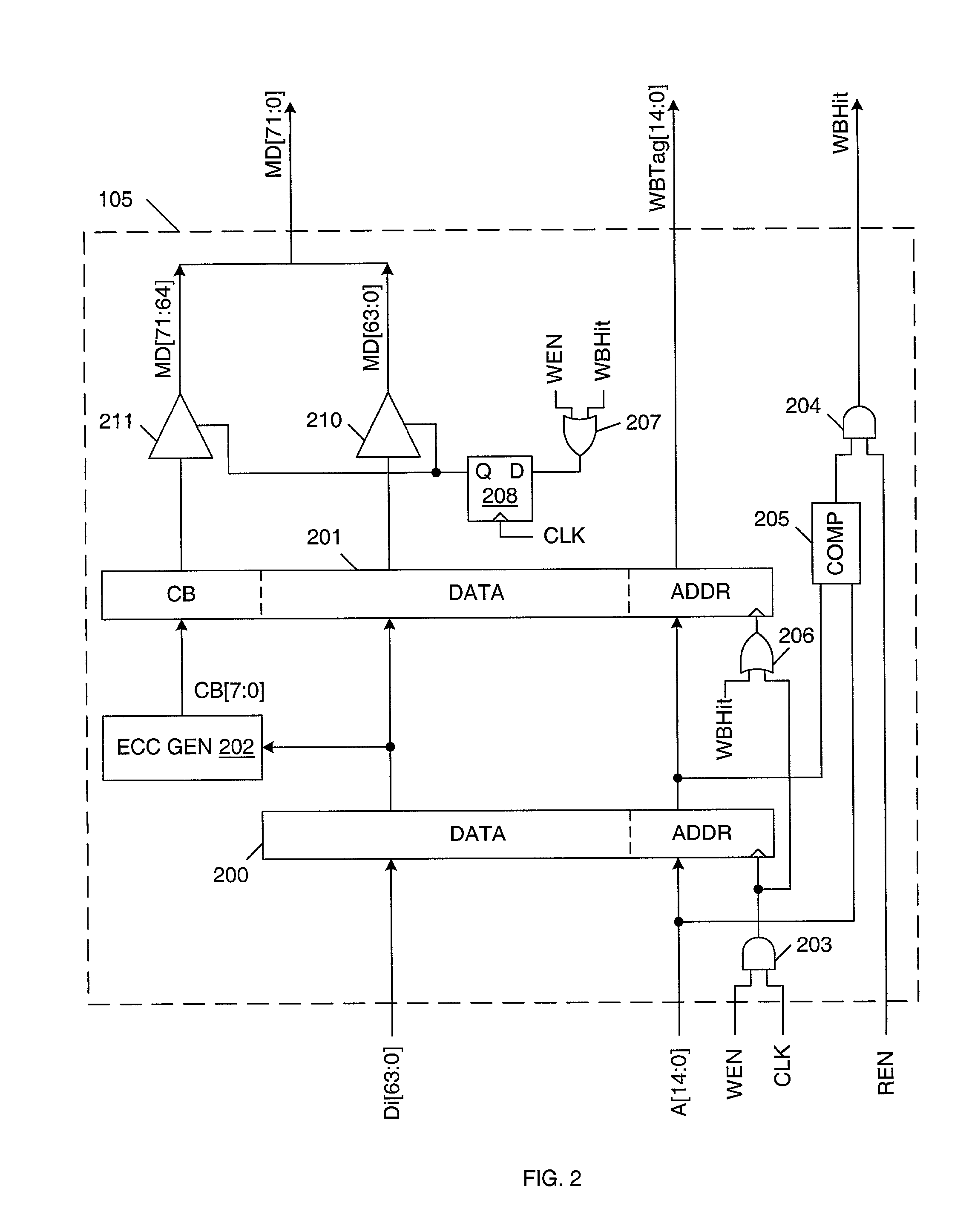

Error correcting memory and method of operating same

InactiveUS7051264B2Shorten the timeEliminate the effects ofCode conversionCoding detailsWrite bufferExternal storage

A memory device that uses error correction code (ECC) circuitry to improve the reliability of the memory device in view of single-bit errors caused by hard failure or soft error. A write buffer is used to post write data, so that ECC generation and memory write array operation can be carried out in parallel. As a result there is no penalty in write latency or memory cycle time due to ECC generation. A write-back buffer is used to post corrected ECC words during read operations, so that write-back of corrected ECC words does not need to take place during the same cycle that data is read. Instead, write-back operations are performed during idle cycles when no external memory access is requested, such that the write back operation does not impose a penalty on memory cycle time or affect memory access latency.

Owner:MOSYS INC

MRAM having error correction code circuitry and method therefor

An embedded memory system (10) uses an MRAM core (12) and error correction code (ECC) corrector circuitry (20). The ECC corrector circuitry identifies soft memory bit errors which are errors primarily resulting from an MRAM bit not being correctly programmed. The errors are identified and corrected during a read or a write cycle and not necessarily when the memory is in a special test mode. As errors are corrected, the error corrections are counted by an error counter (24) to create a count value. The count value is stored in the MRAM core itself and can later be retrieved and read during a test mode for an indication of how many bit corrections are required for the MRAM core over a period of time. The count value is stored by using an unused portion of a write memory cycle during a read operation.

Owner:EVERSPIN TECHNOLOGIES

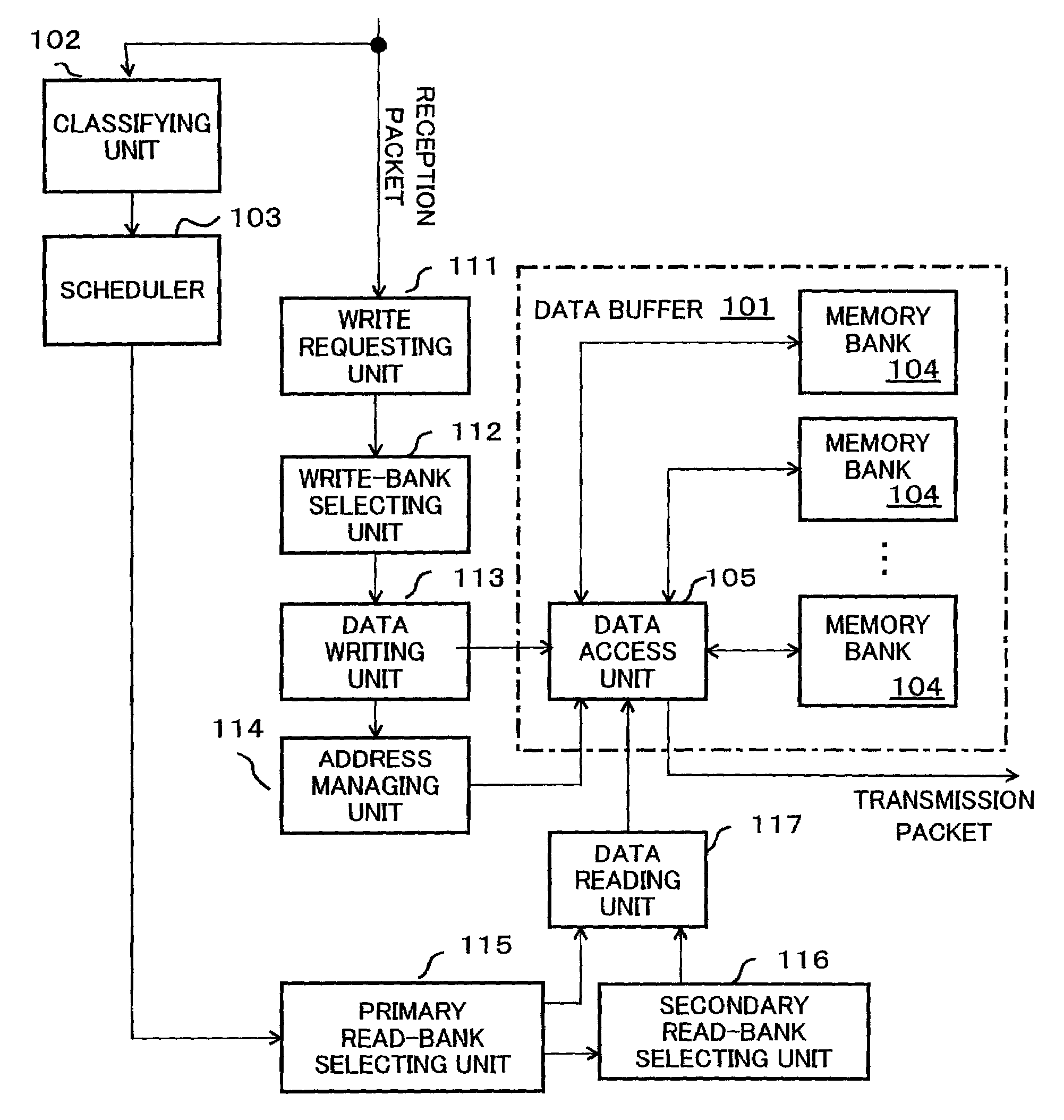

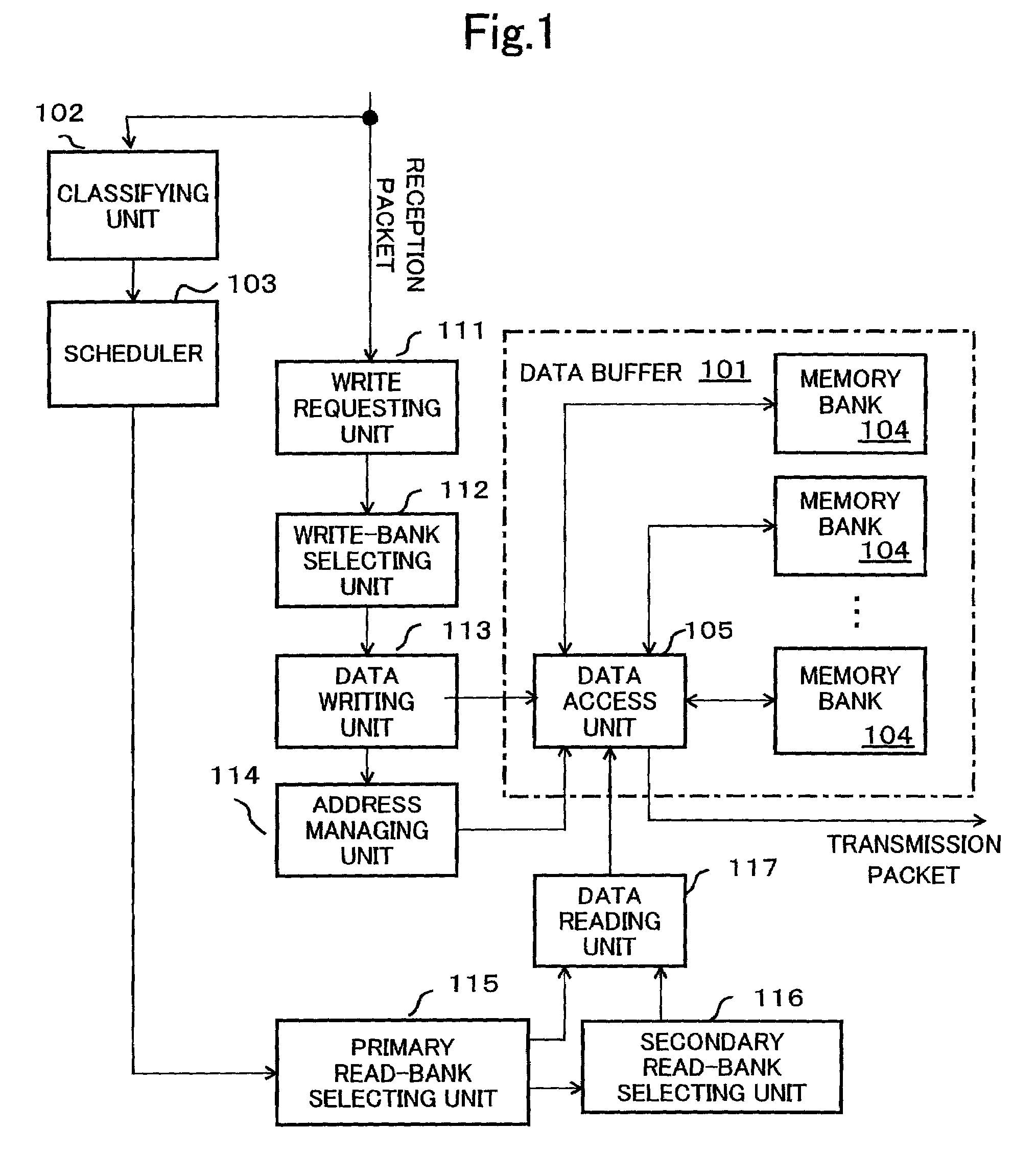

Packet buffer

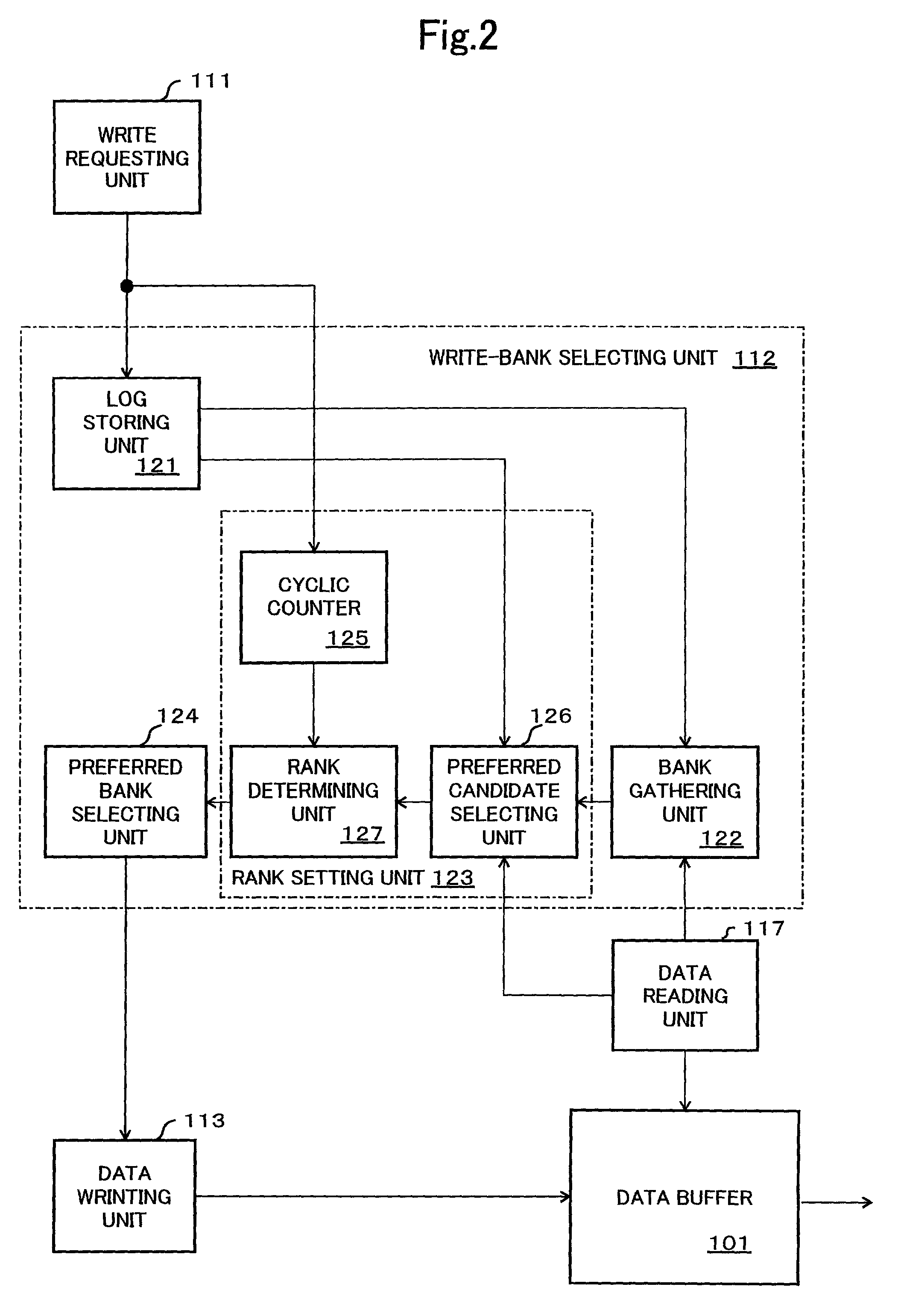

InactiveUS7295553B2Low priceShort processing cycleMemory adressing/allocation/relocationData switching by path configurationMemory bankData access

A write-bank selecting unit selects different memory banks in response to N+1 consecutive write requests, respectively. In each memory cycle, a data writing unit inputs N or less write commands to a data access unit. On the other hand, a primary read-bank selecting unit selects readable memory banks in each memory cycle. A secondary read-bank selecting unit selects memory banks corresponding to read requests for which data blocks could not be read out in the preceding memory cycle. A data reading unit generates read commands for those read banks and inputs the generated read commands to a data access unit. With this configuration, a packet buffer capable of satisfying both of short processing cycles and high memory use efficiency can be provided by using memory devices at a relatively low price.

Owner:FUJITSU LTD

Reduced Leakage Driver Circuit and Memory Device Employing Same

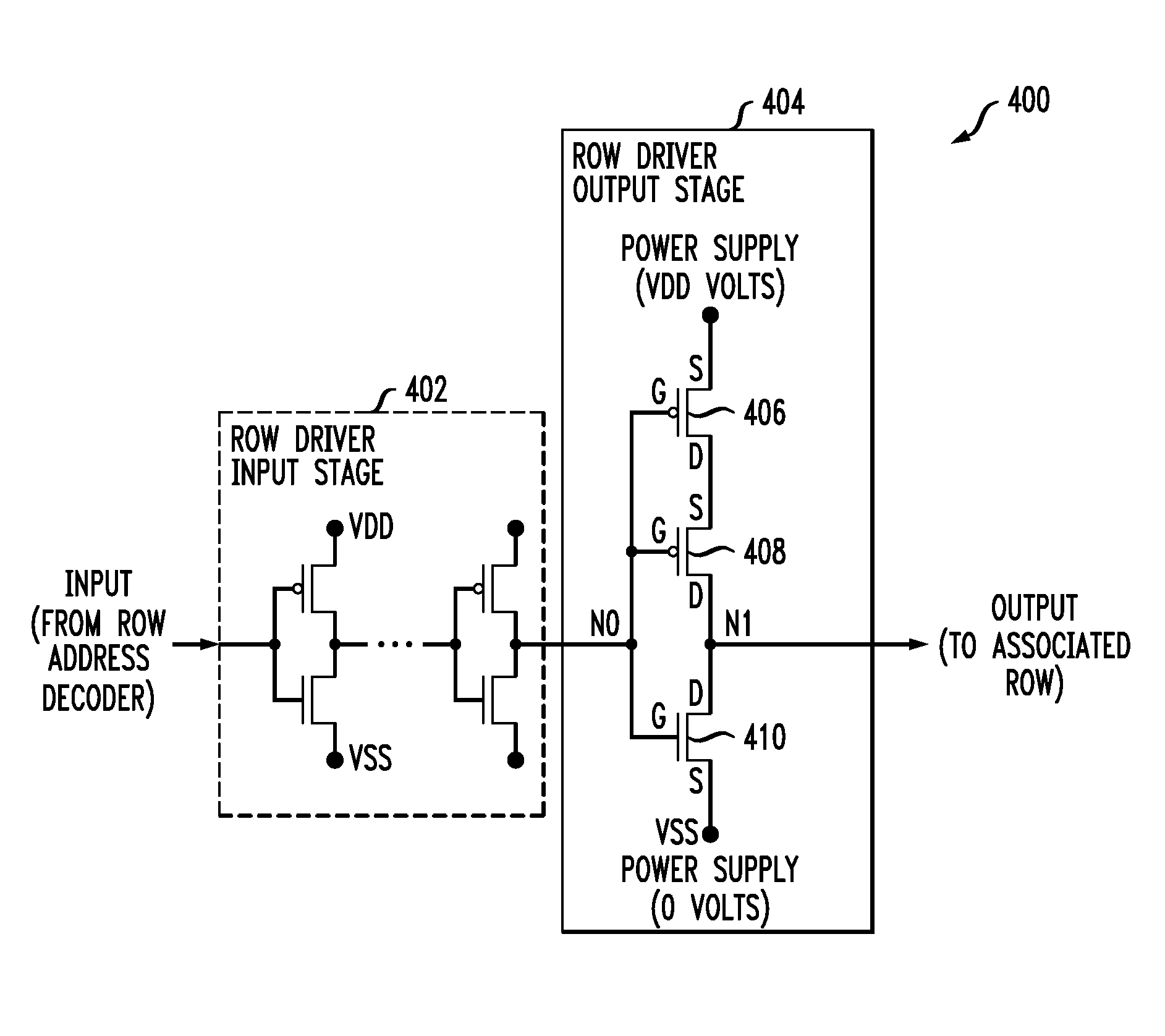

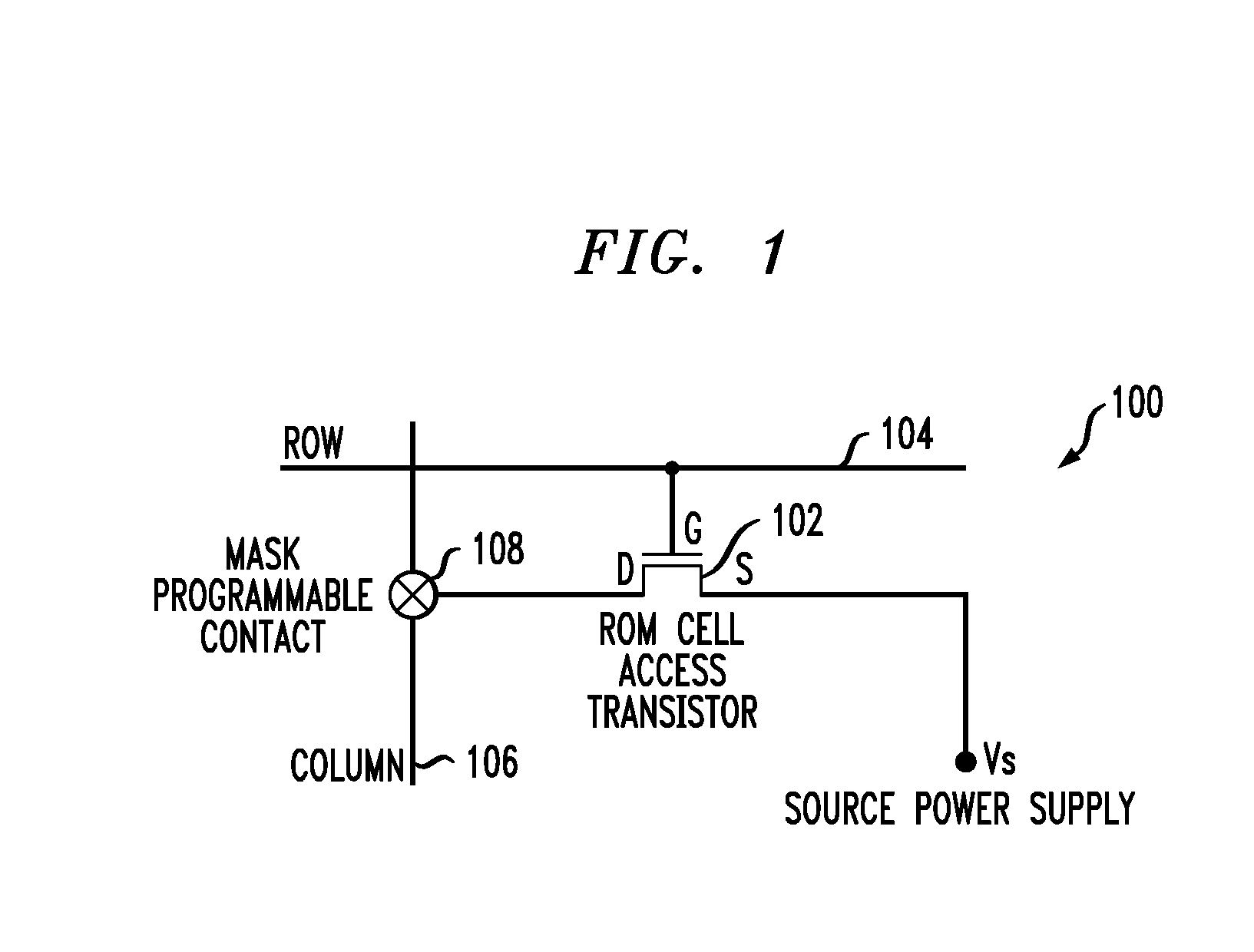

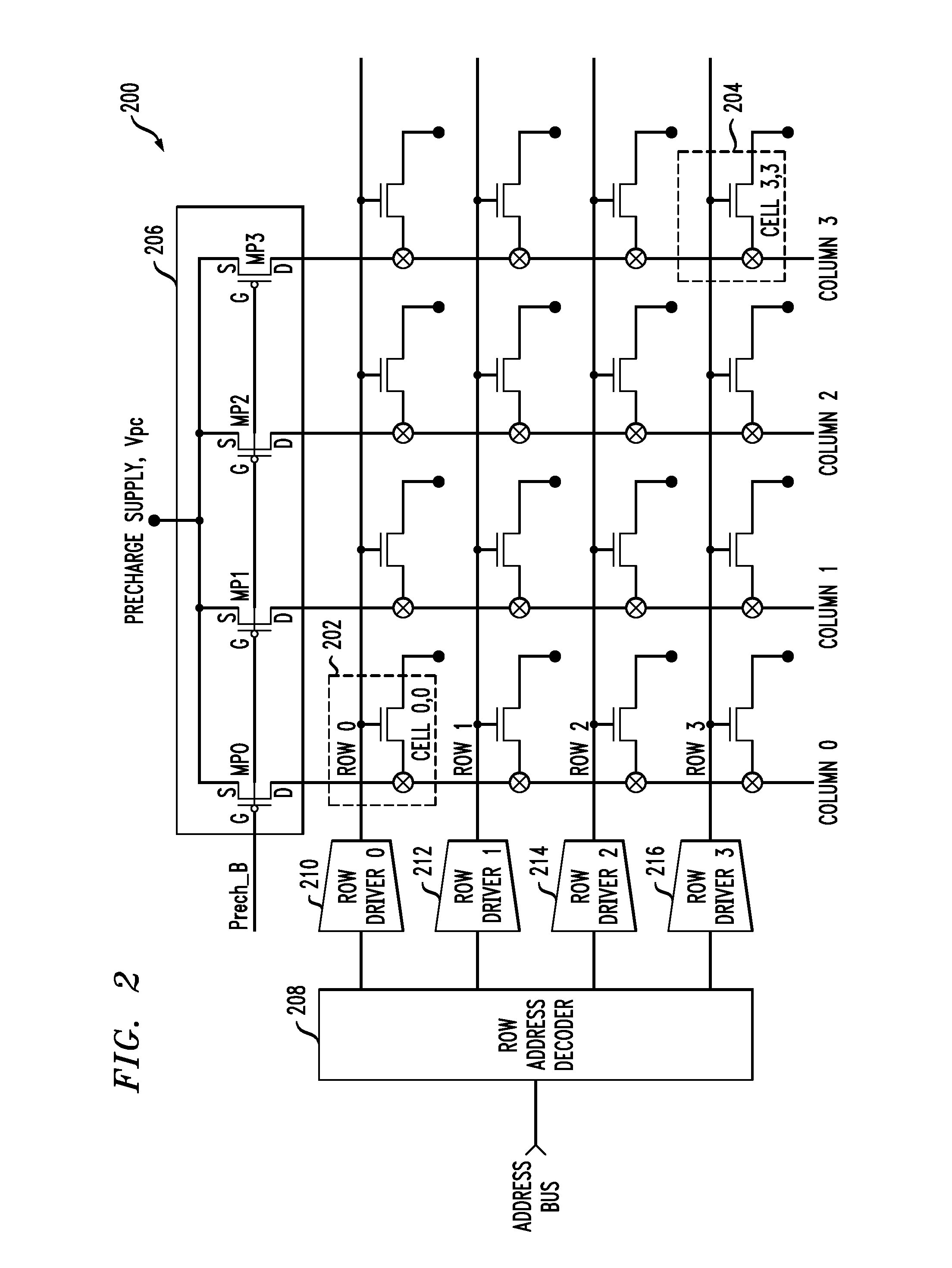

ActiveUS20090141580A1Reduce leakage currentIncreasing performance of circuitDigital storageDriver circuitControl signal

A row line driver circuit for use in a memory array including multiple memory cells and multiple row lines coupled to the memory cells for selectively accessing the memory cells includes an output stage adapted for connection to a corresponding one of the row lines and a control circuit connected to the output stage. The output stage is operative during an active phase of a given memory cycle to drive the corresponding row line to a potential as a function of at least one address signal received by the driver circuit. The control circuit is operative to generate at least one control signal for disabling the output stage at least during an inactive phase of the memory cycle to thereby substantially eliminate a leakage current path in the driver circuit.

Owner:AVAGO TECH INT SALES PTE LTD

System, apparatus, and method for modifying the order of memory accesses

ActiveUS20110099341A1Memory adressing/allocation/relocationProgram controlMemory interfaceParallel computing

Systems and methods for controlling memory access operations are disclosed. The system may include one or more requestors performing requests to memory devices. Within a memory controller, a request queue receives requests from a requestor, a bank decoder determines a destination bank, and the request is placed in an appropriate bank queue. An ordering unit determines if the current request can be reordered relative to the received order and generates a new memory cycle order based on the reordering determination. The reordering may be based on whether there are multiple requests to the same memory page, multiple reads, or multiple writes. A memory interface executes each memory request in the memory cycle order. A data buffer holds write data until it is written to the memory and read data until it is returned to the requestor. The data buffer also may hold memory words used in read-modify-write operations.

Owner:MICRON TECH INC

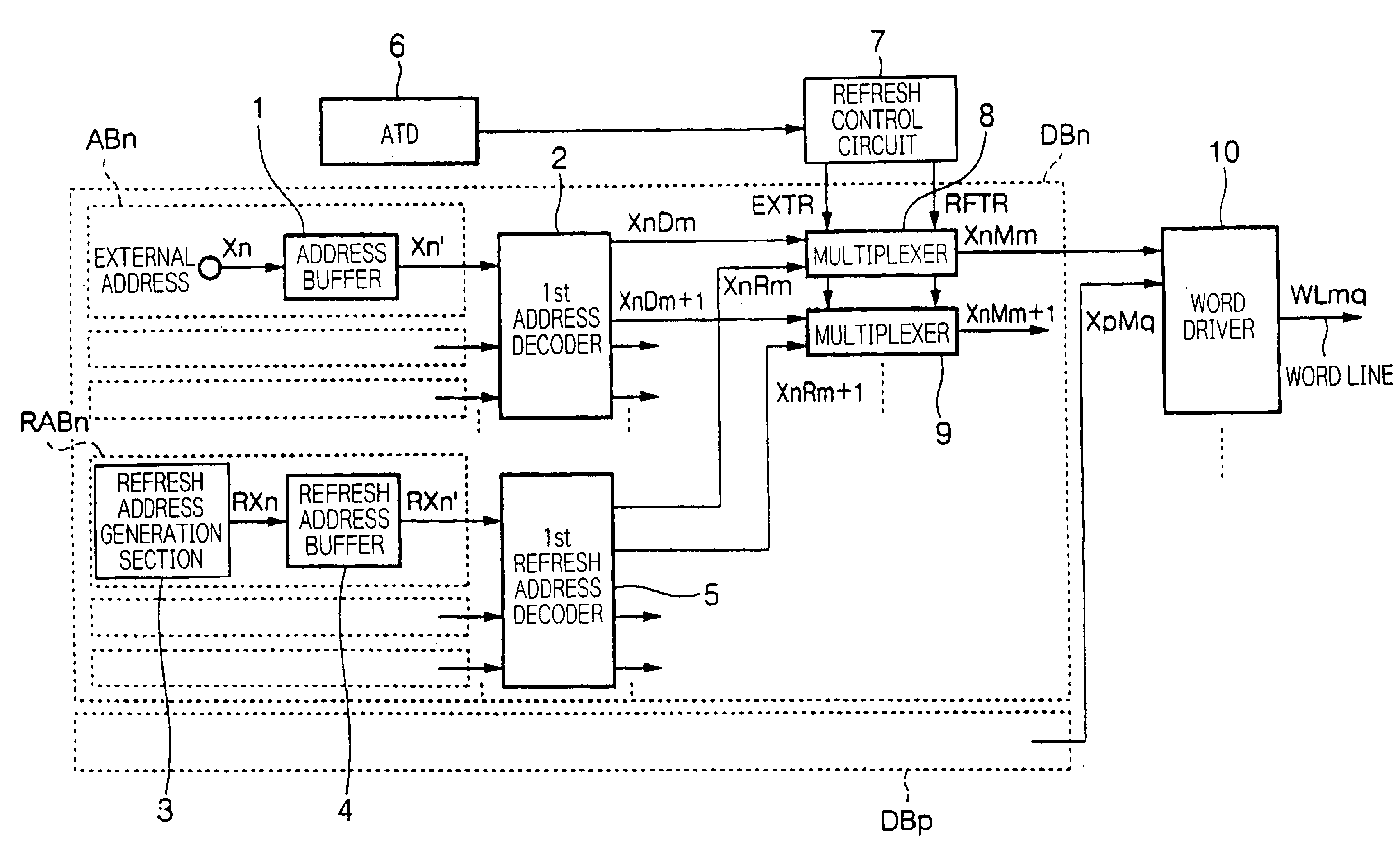

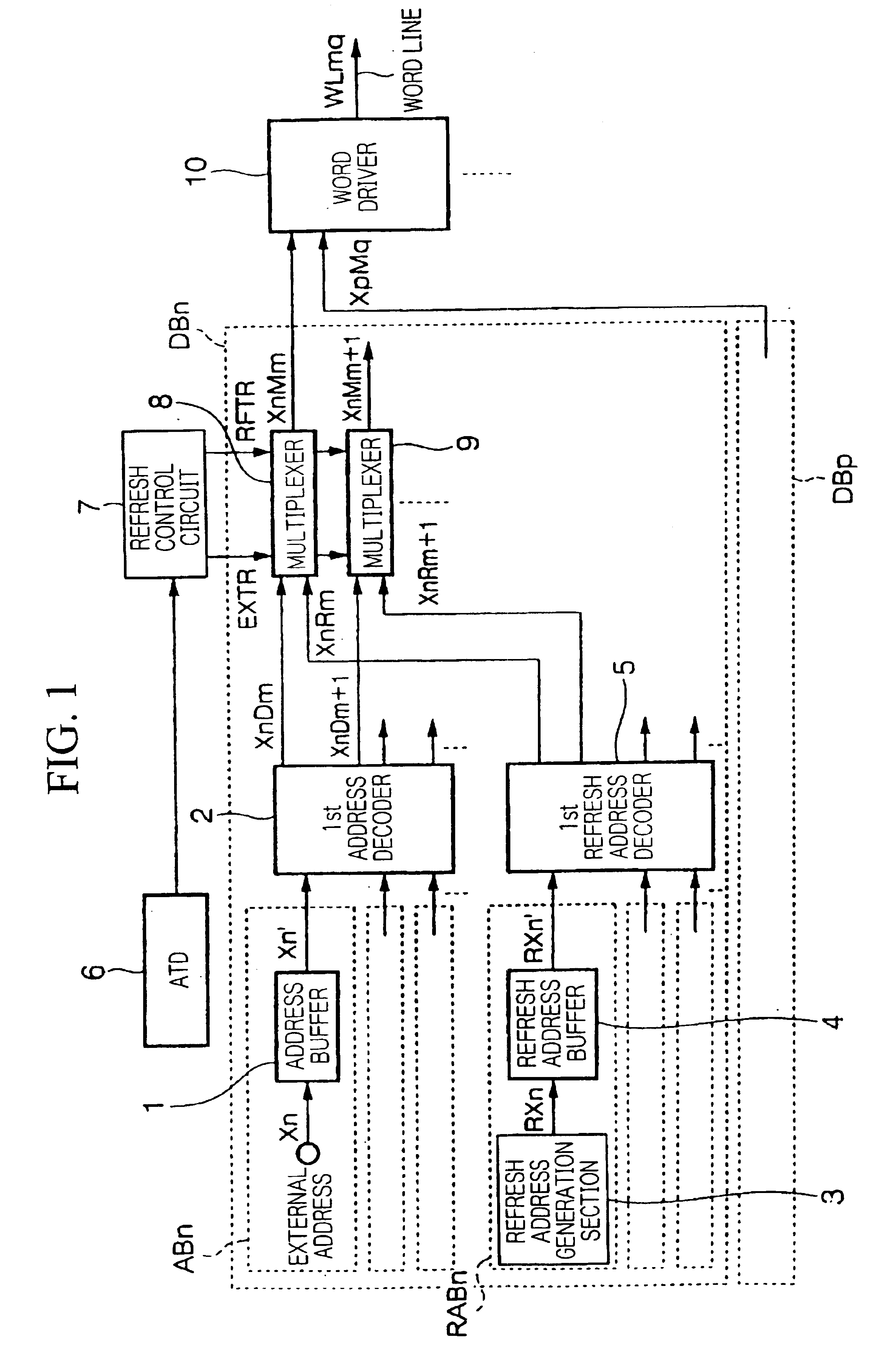

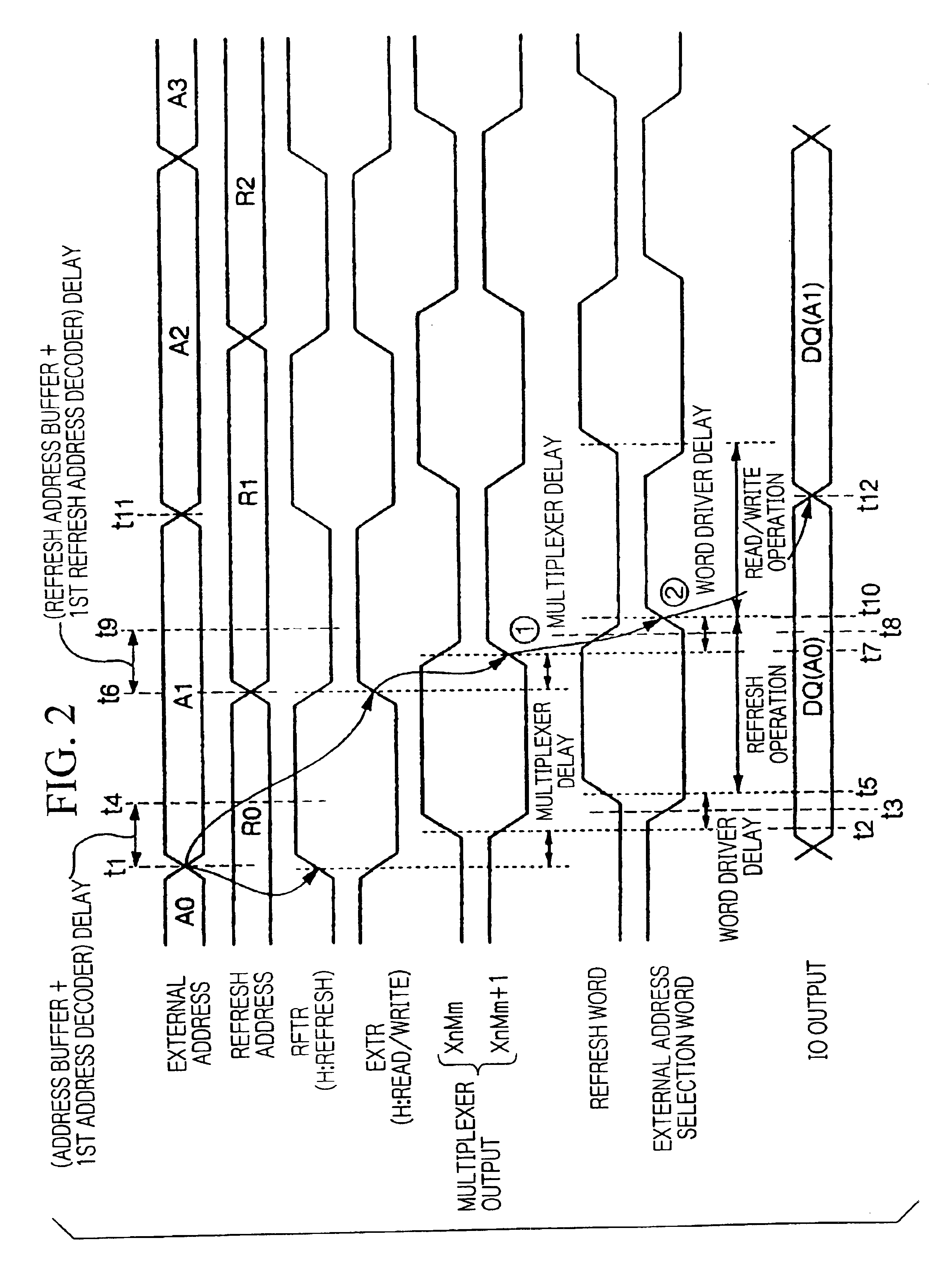

Semiconductor memory device

InactiveUS6876592B2Accelerate address accessShorten cycle timeDigital storageAddress decoderMultiplexer

A semiconductor memory device capable of accelerating address access and shortening cycle time is provided. A first address decoder (2) and first refresh address decoder (5) respectively decode an external address (Xn) supplied from outside the semiconductor memory device and a refresh address (RXn) used for refreshing within the semiconductor memory device. A multiplexer (8) selects the external address side decode signal (XnDm) or the refresh address side decode signal (XnRm) and outputs the signal as a decode signal (XnMm) based on an external address transmission signal (EXTR) and refresh address transmission signal (RFTR) so that a refresh operation and a read / write operation is performed continuously within one memory cycle. A word driver (10) then decodes decode signals (XnMm, XpMq) selected with multiplexer (8) and so forth, and activates a word line (WLmq).

Owner:RENESAS ELECTRONICS CORP

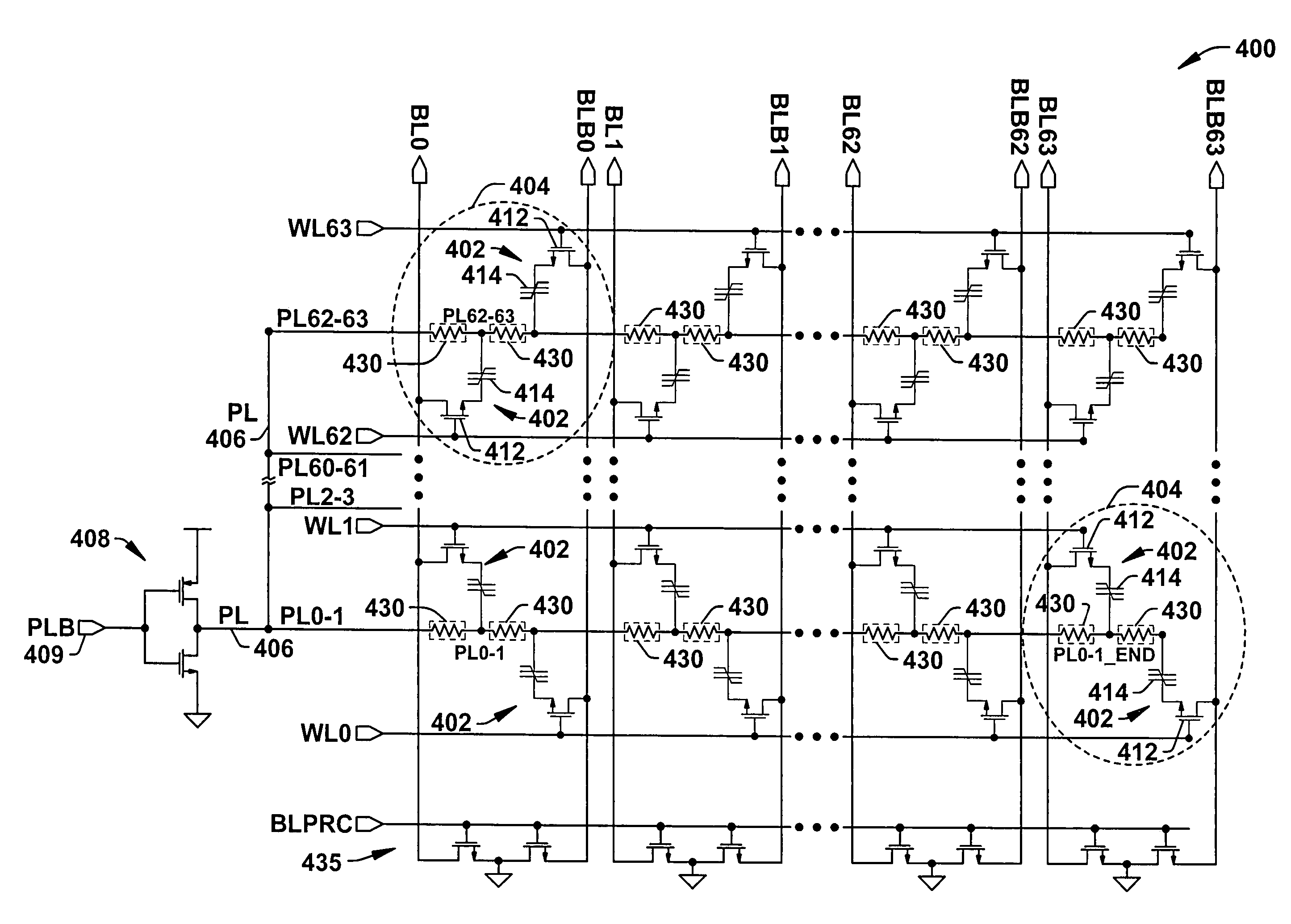

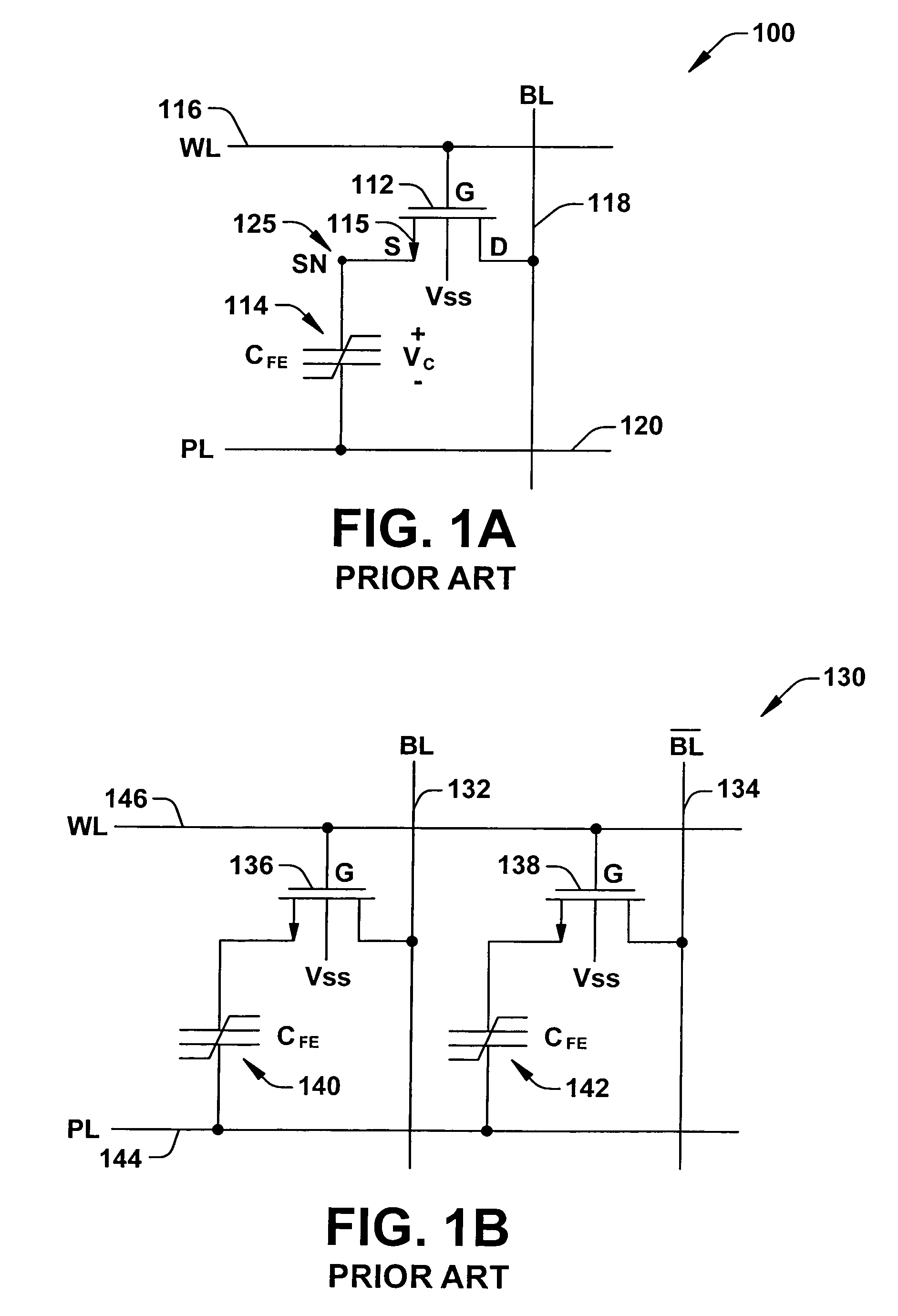

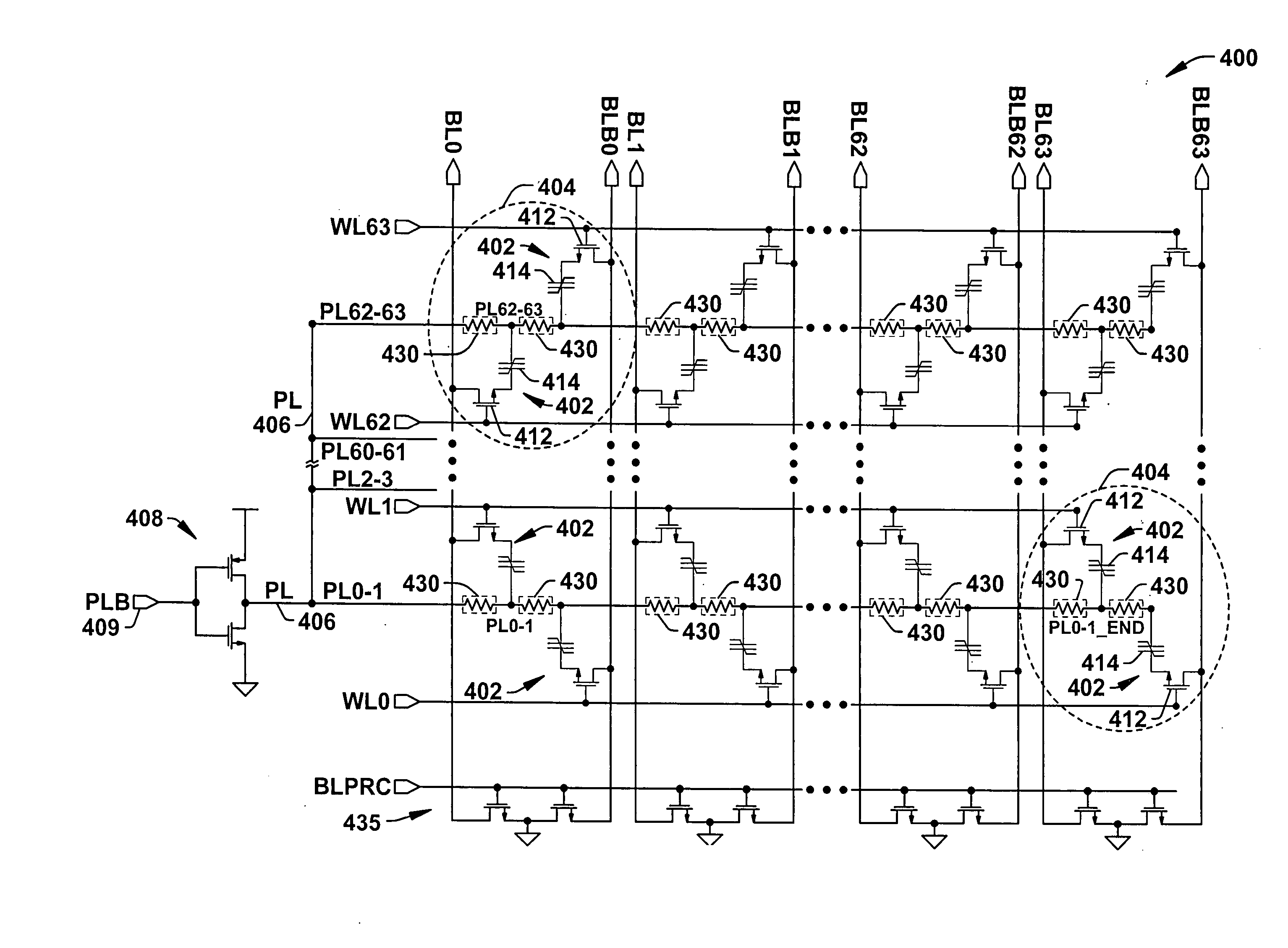

Low resistance plate line bus architecture

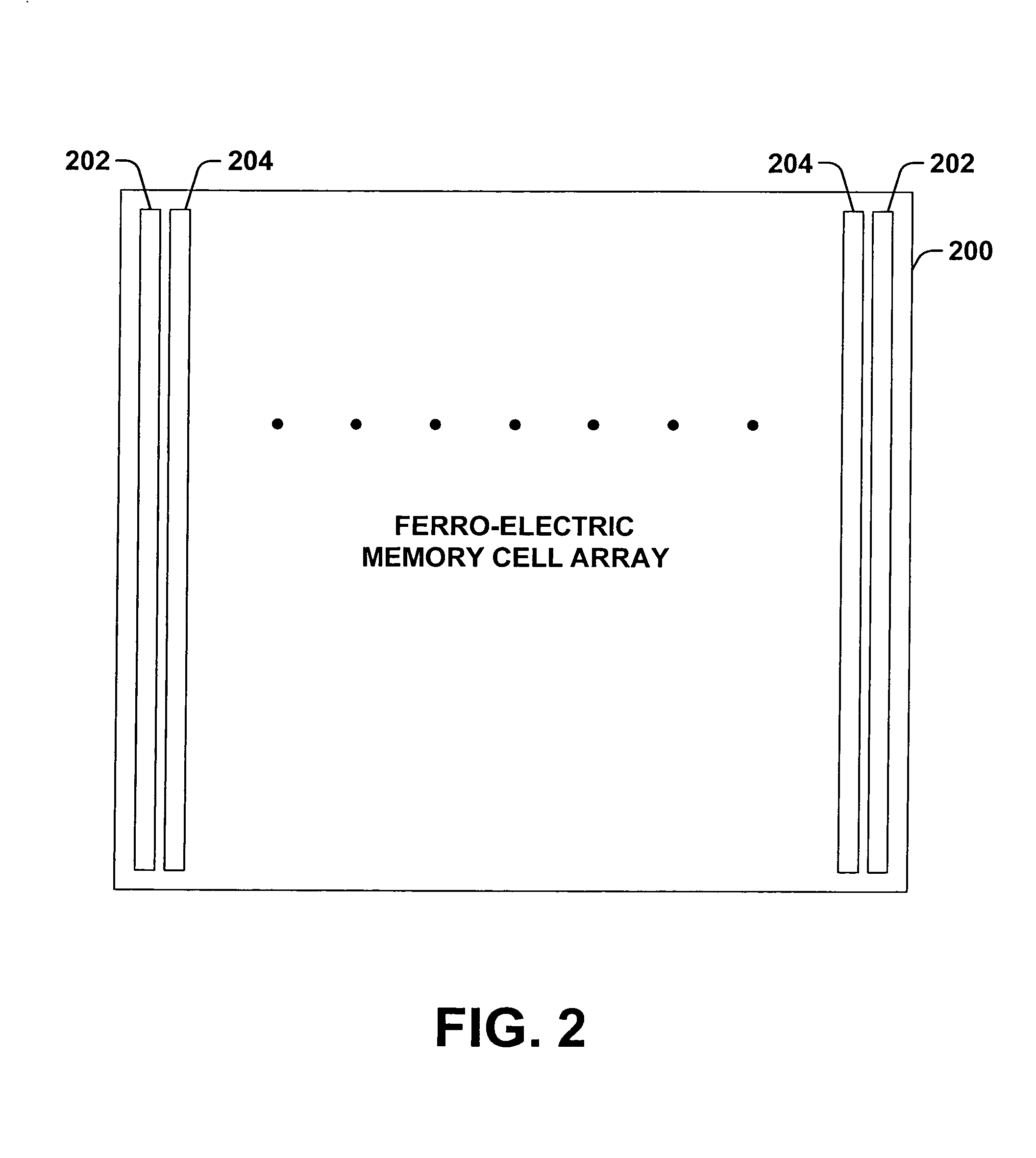

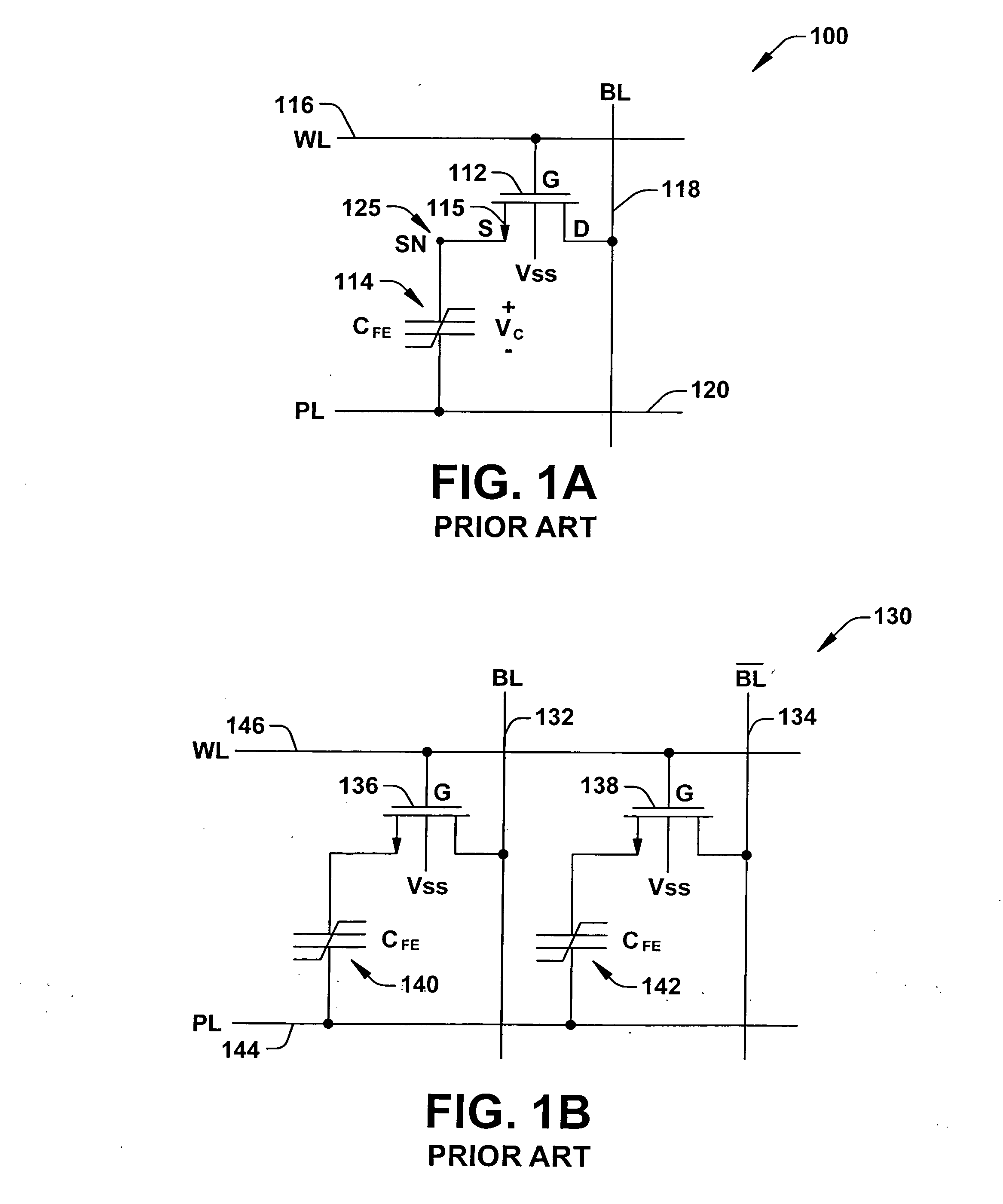

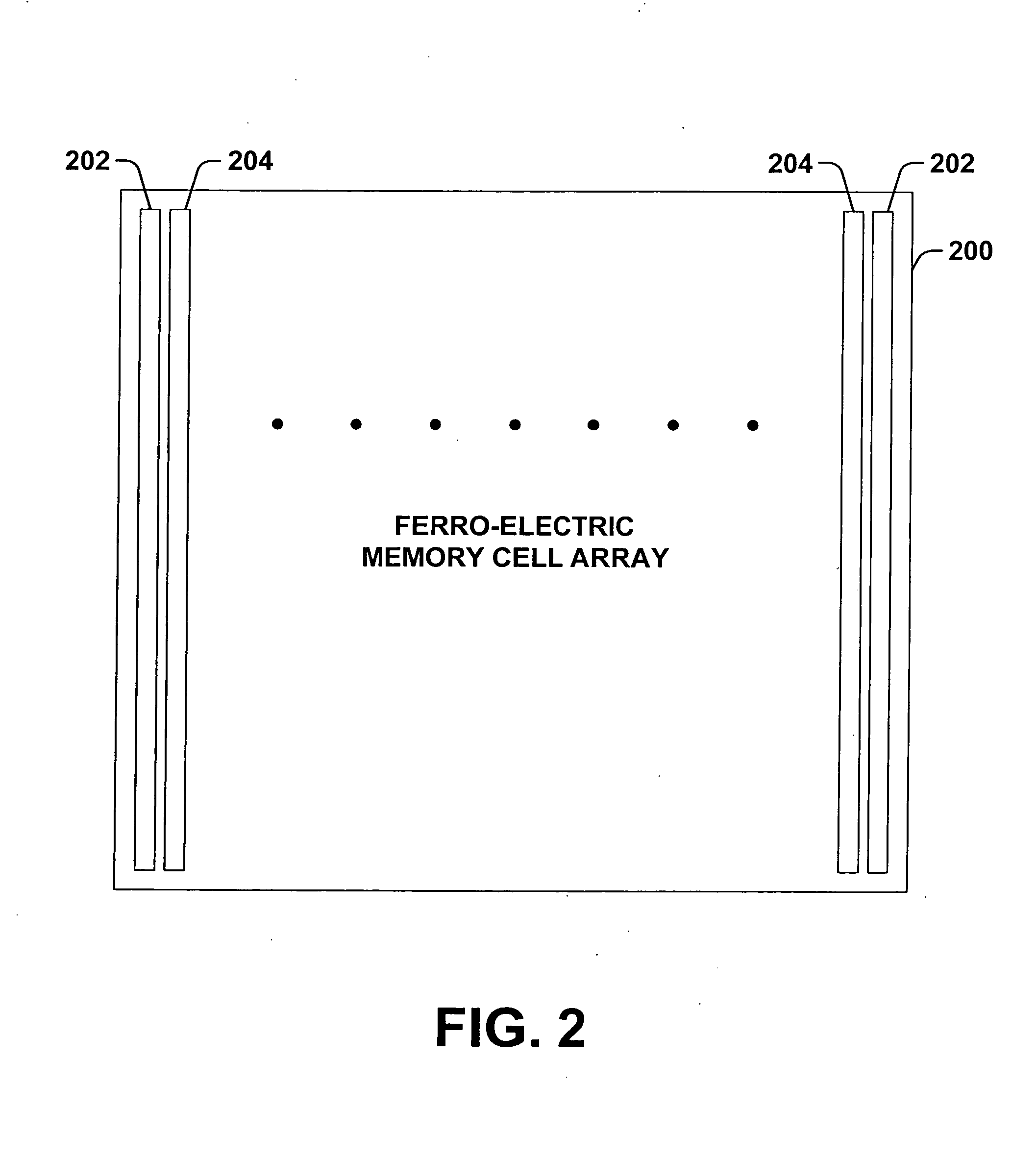

ActiveUS7443708B2Weakening rangeReduce resistanceSolid-state devicesDigital storageCapacitanceLine resistance

An FeRAM memory array wherein the plate lines run in the direction of word lines is described that provides a reduced plate line resistance in arrays having a common plate line connection. The lower plate line resistance reduces the magnitude of negative spikes on the plate line to reduce the potential for FeCap depolarization. Two or more plate lines of a plurality of columns of memory cells are interconnected along a bit line direction. Some or all of the plate lines of one or more columns of dummy memory cells may also be interconnected to reduce the plate line resistance and minimize any increase in the bit line capacitance for the active cells of the array. The improved FeRAM array provides a reduced data error rate, particularly at fast memory cycle times.

Owner:TEXAS INSTR INC

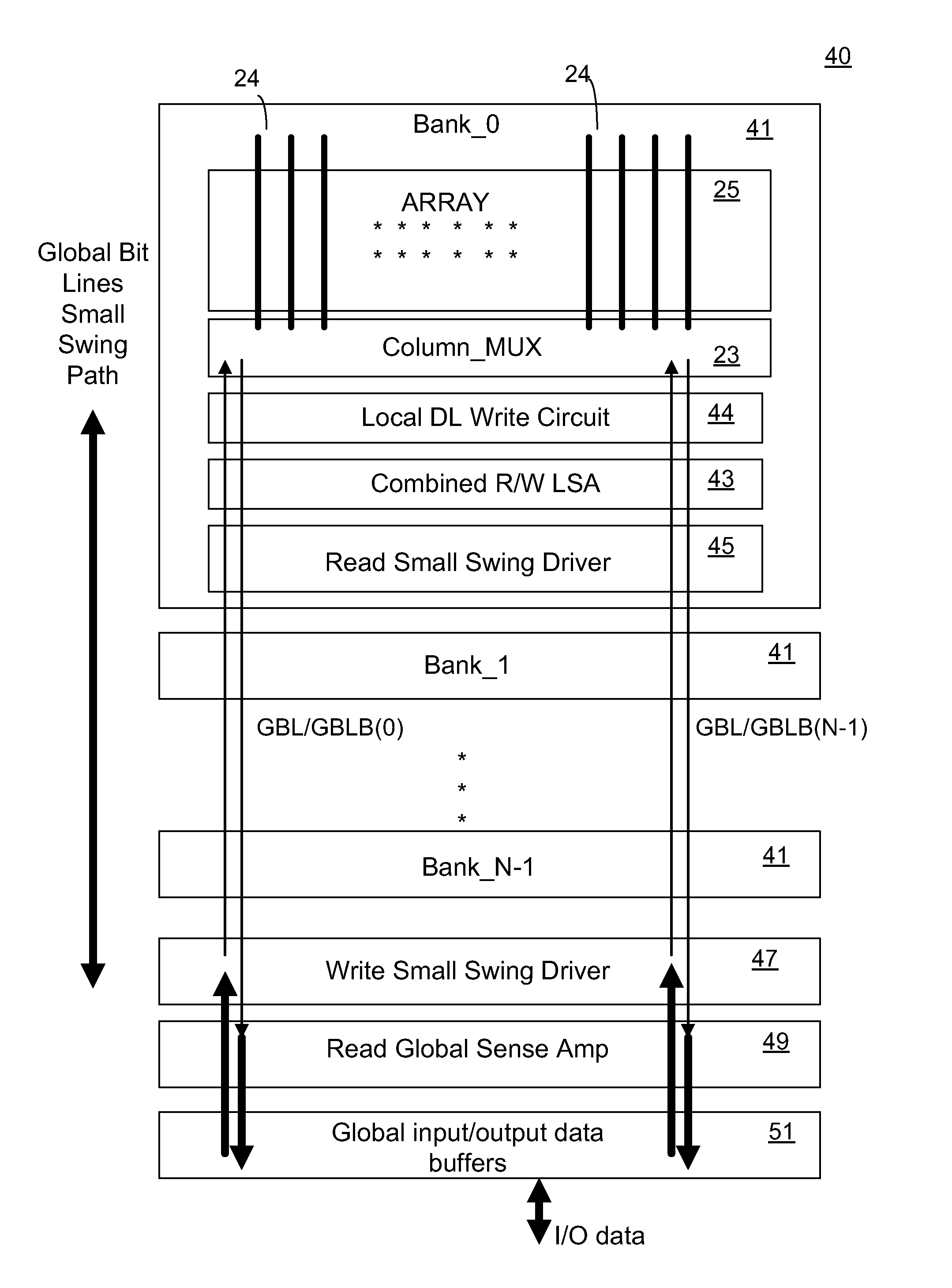

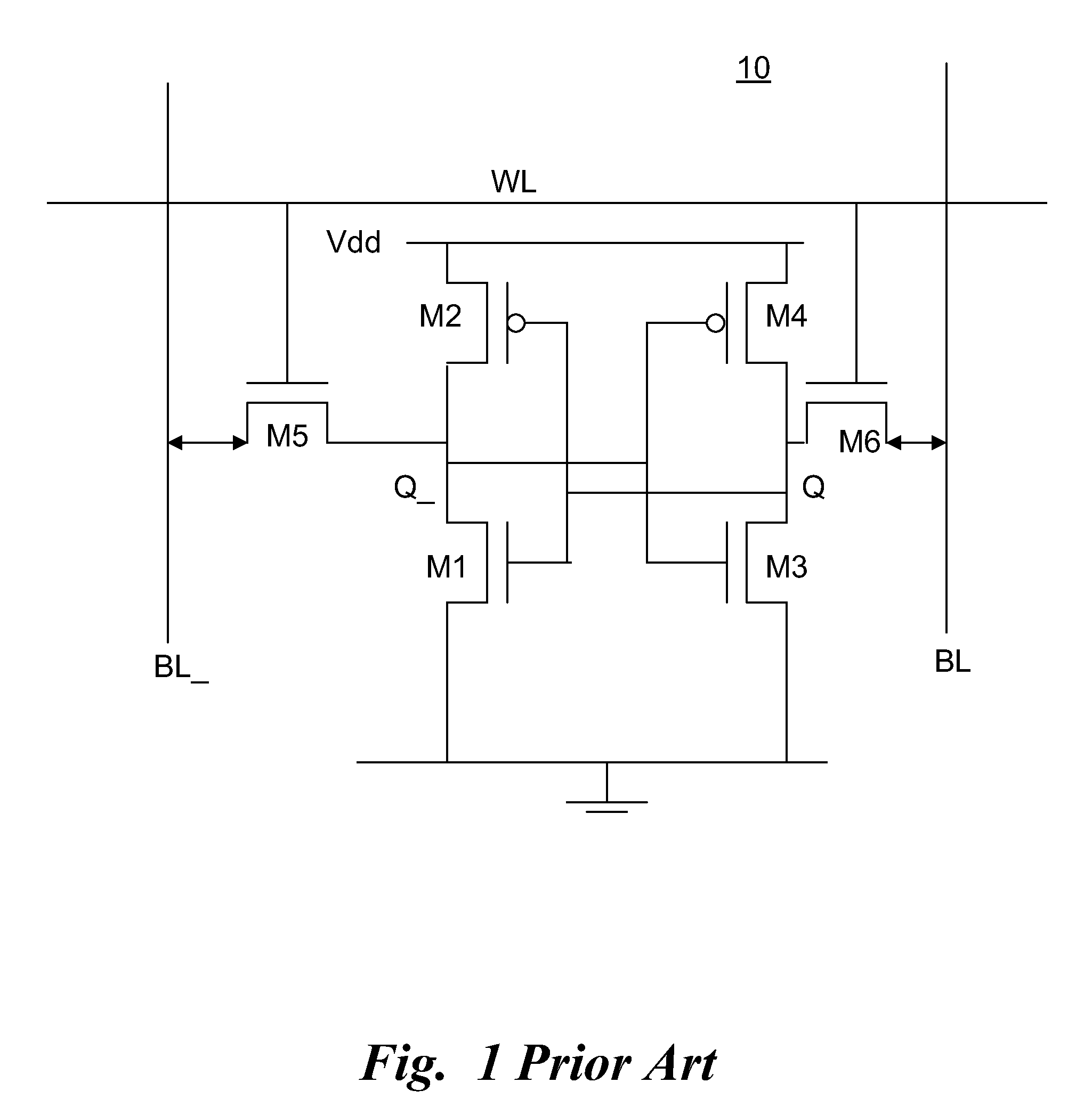

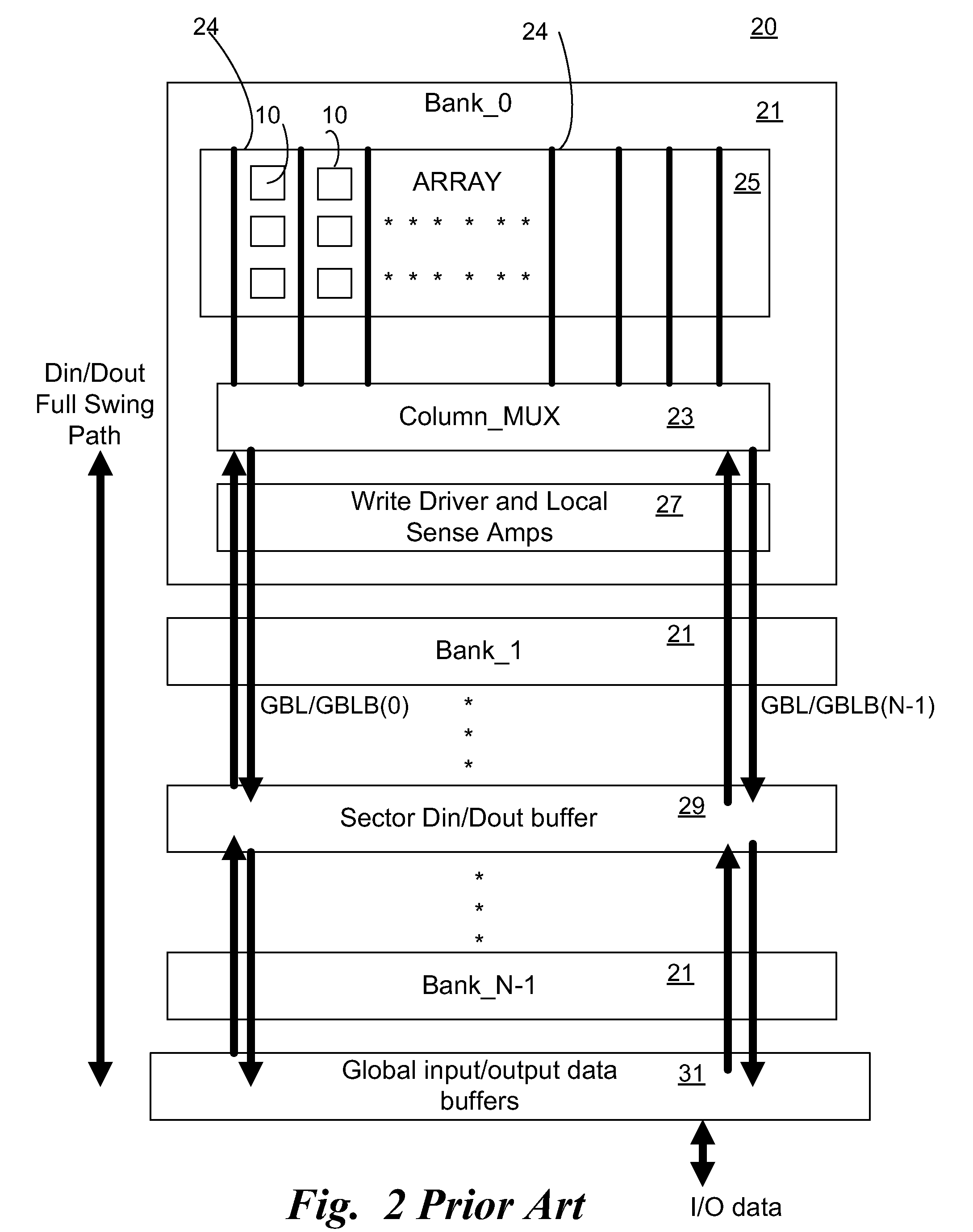

Circuit and method for small swing memory signals

InactiveUS8116149B2Time neededRead cycle in the memory is reducedDigital storageBit lineDriver circuit

Circuits and methods for transmitting and receiving small swing differential voltage data to and from a memory are described. A plurality of memory cells is formed in arrays within a plurality of memory banks. Each memory bank is coupled to a pair of small swing differential voltage global bit lines that extend across the memory. A small signal write driver circuit is coupled to the global bit lines and configured to output a small signal differential voltage on the global bit lines during write cycles. A global sense amplifier is coupled to the global bit line pairs and configured to output a full swing voltage on a data line during a read cycle. Methods for providing small swing global bit line signals to memory cells are disclosed. The use of small swing differential voltage signals across the memory reduces power consumption and shortens memory cycle time.

Owner:TAIWAN SEMICON MFG CO LTD

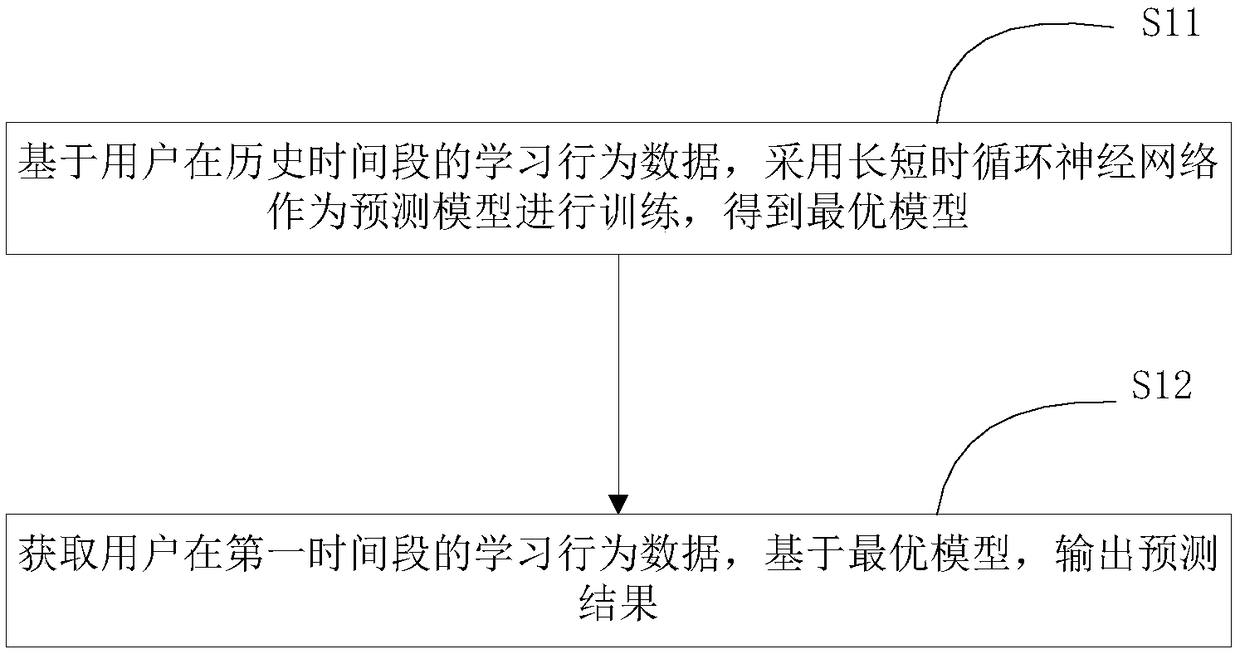

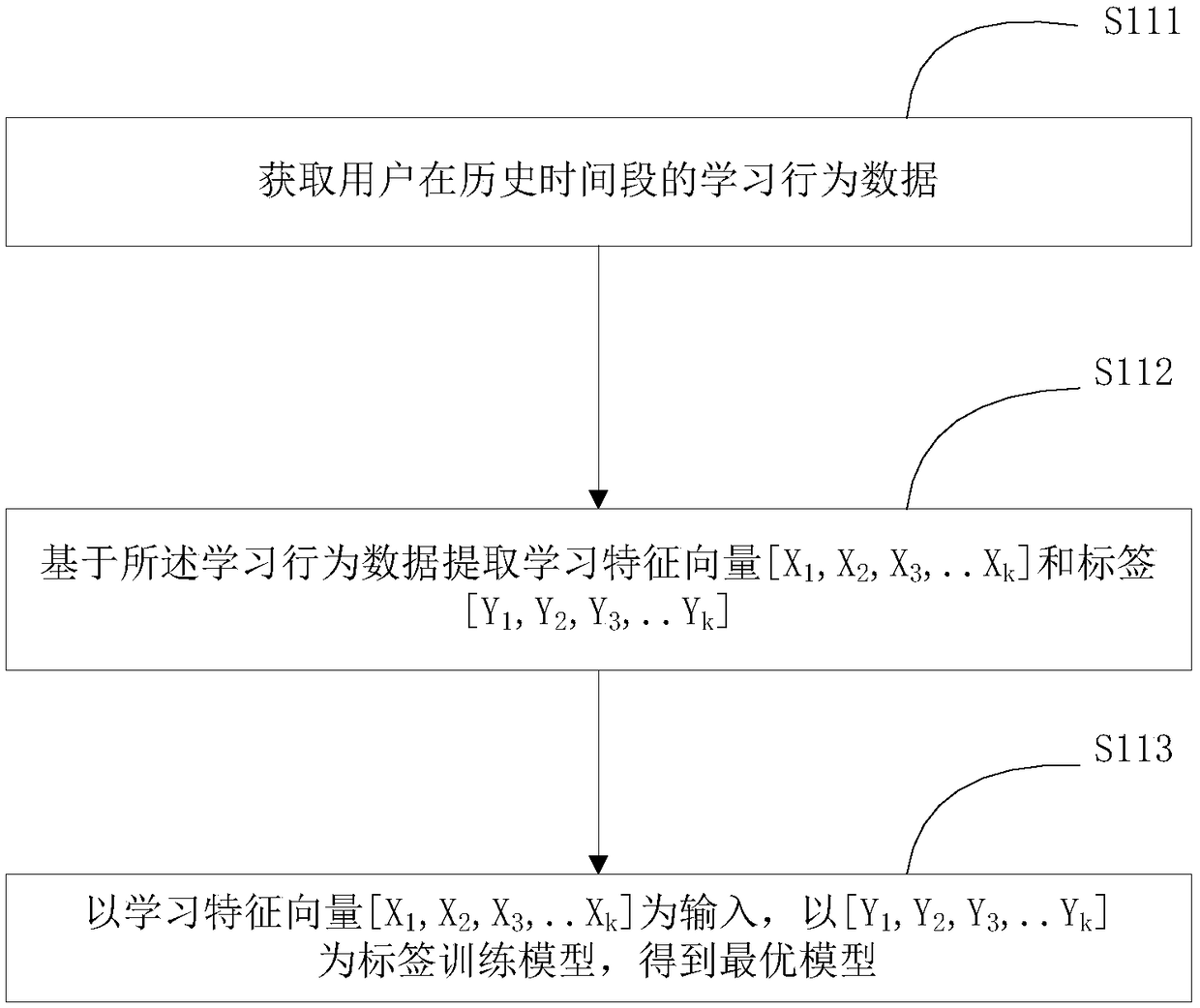

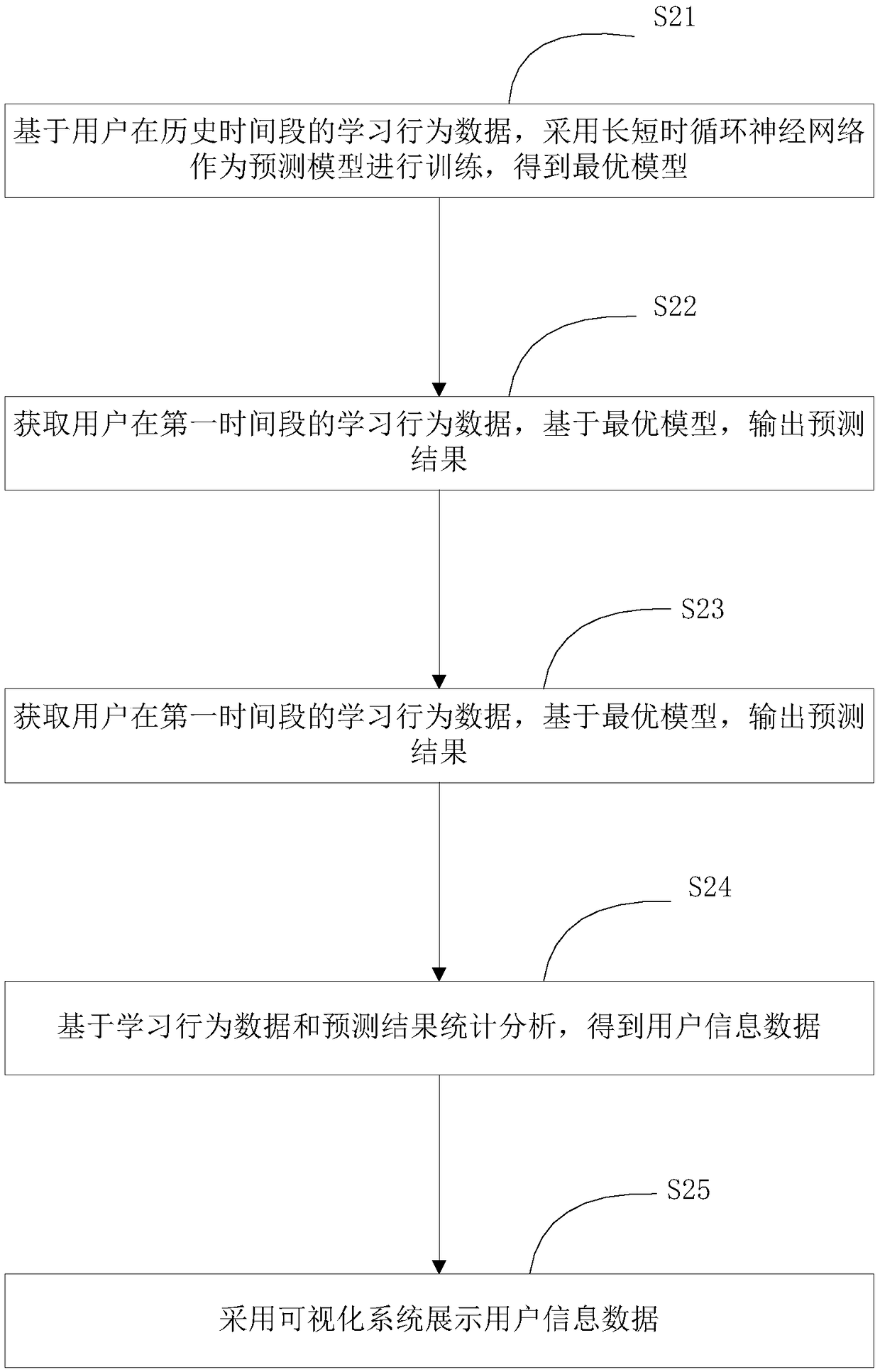

Learning behavior dynamic prediction method and apparatus, equipment and storage medium

ActiveCN109272164AImprove forecast accuracyEasy to analyzeForecastingNeural architecturesData informationClosed loop

The invention discloses a learning behavior dynamic prediction method and device, equipment and a storage medium. The prediction method comprises the following steps: based on the learning behavior data of a user in a historical period, adopting a long-short-time memory cycle neural network as a prediction model for training to obtain an optimal model; and acquiring learning behavior data of the user in the first time period, and outputting a prediction result based on the optimal model. The invention adopts LSTM-RNN as a prediction model to predict the output results, can improve the accuracyof the prediction, and uses an interactive visual analysis mode to display user information data, facilitates viewing and analysis of user data information at the background of the system, so as to help teachers to timely and intuitively know the results of data analysis, and then achieve the ''closed loop'' of the teaching process. The invention can be widely applied to various learning behaviorprediction systems.

Owner:SHENZHEN GRADUATE SCHOOL TSINGHUA UNIV

Low resistance plate line bus architecture

ActiveUS20070211510A1Reduce plate line resistanceSave chip areaSolid-state devicesDigital storageCapacitanceBit line

An FeRAM memory array wherein the plate lines run in the direction of word lines is described that provides a reduced plate line resistance in arrays having a common plate line connection. The lower plate line resistance reduces the magnitude of negative spikes on the plate line to reduce the potential for FeCap depolarization. Two or more plate lines of a plurality of columns of memory cells are interconnected along a bit line direction. Some or all of the plate lines of one or more columns of dummy memory cells may also be interconnected to reduce the plate line resistance and minimize any increase in the bit line capacitance for the active cells of the array. The improved FeRAM array provides a reduced data error rate, particularly at fast memory cycle times.

Owner:TEXAS INSTR INC

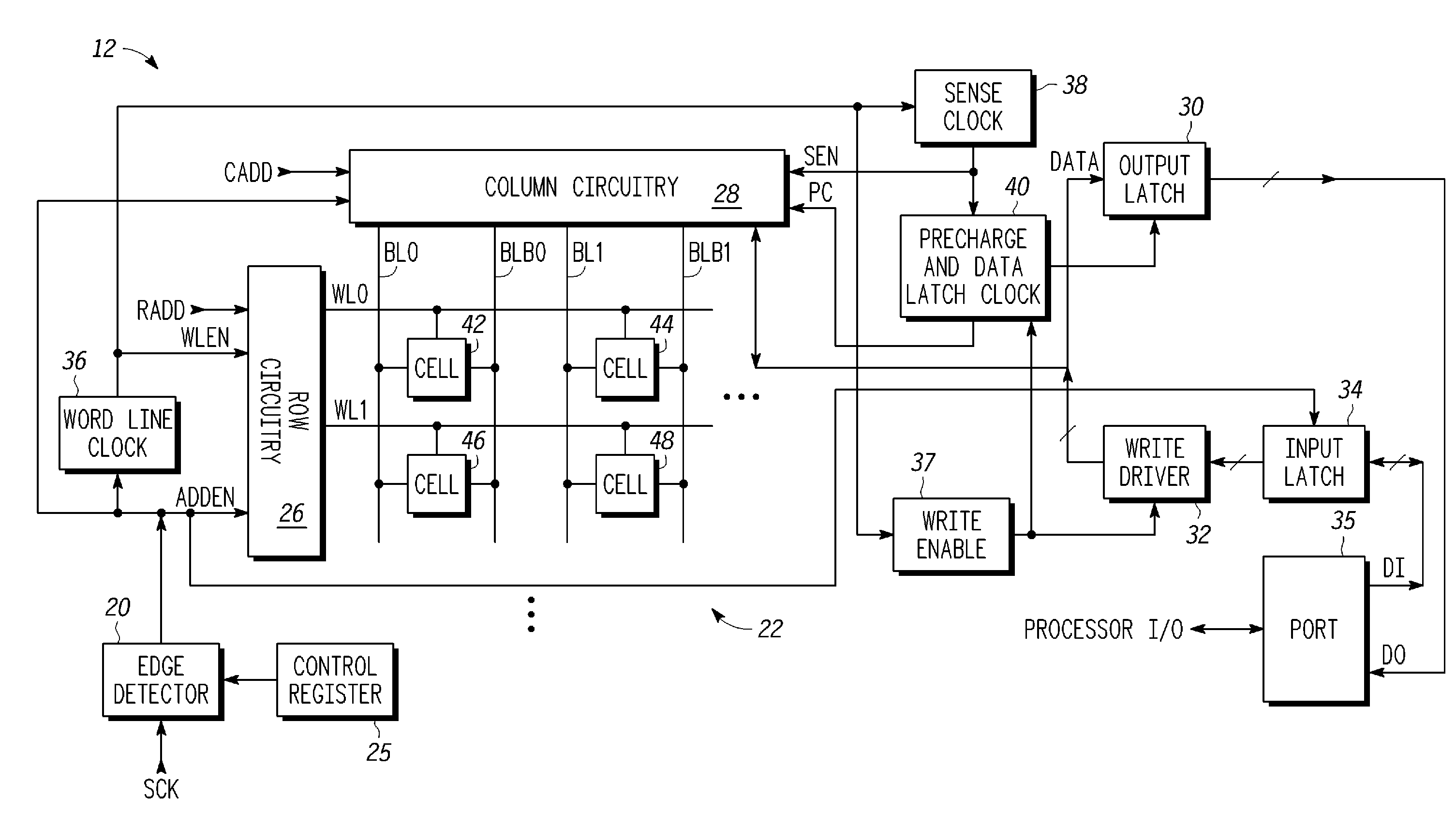

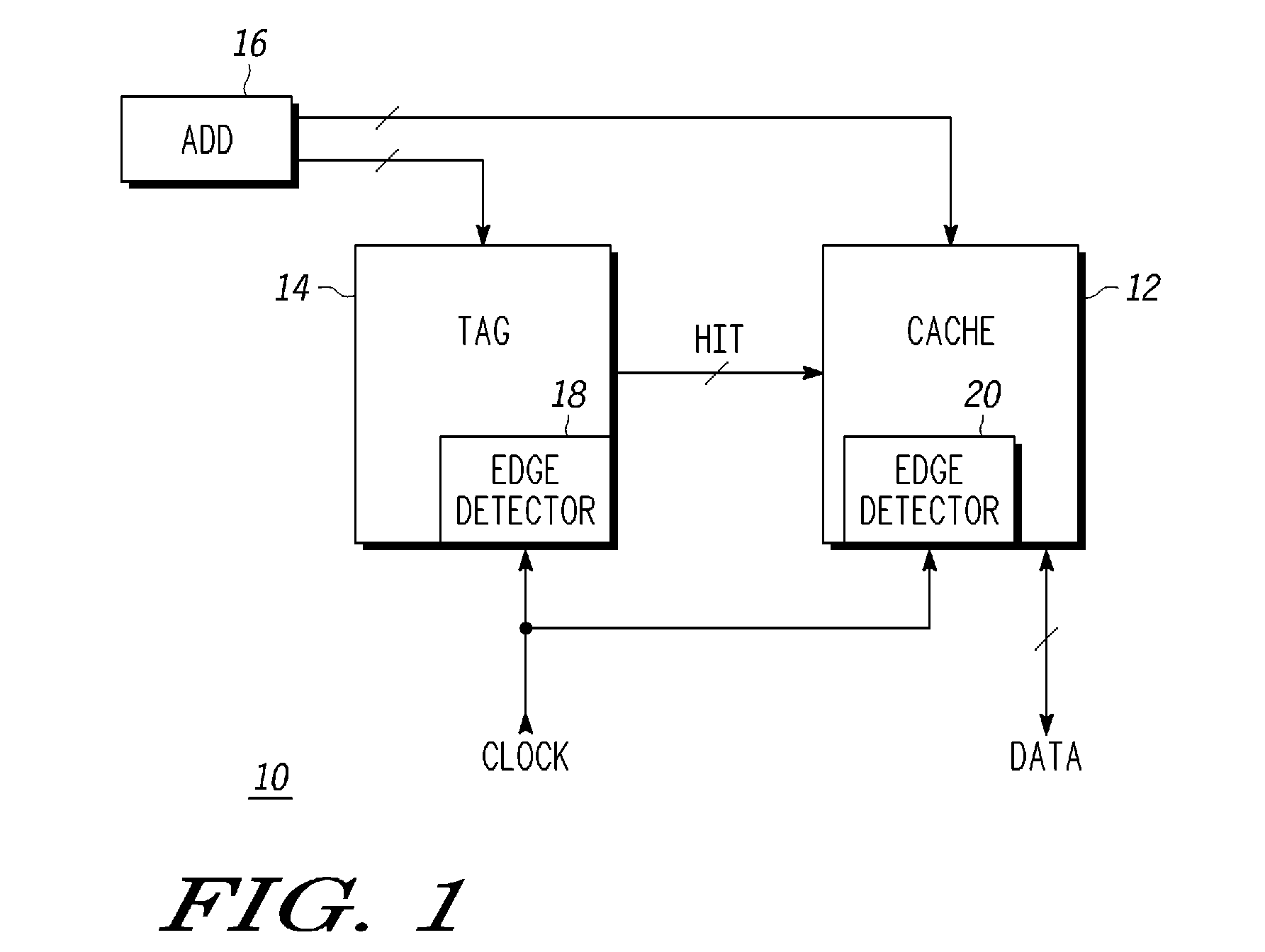

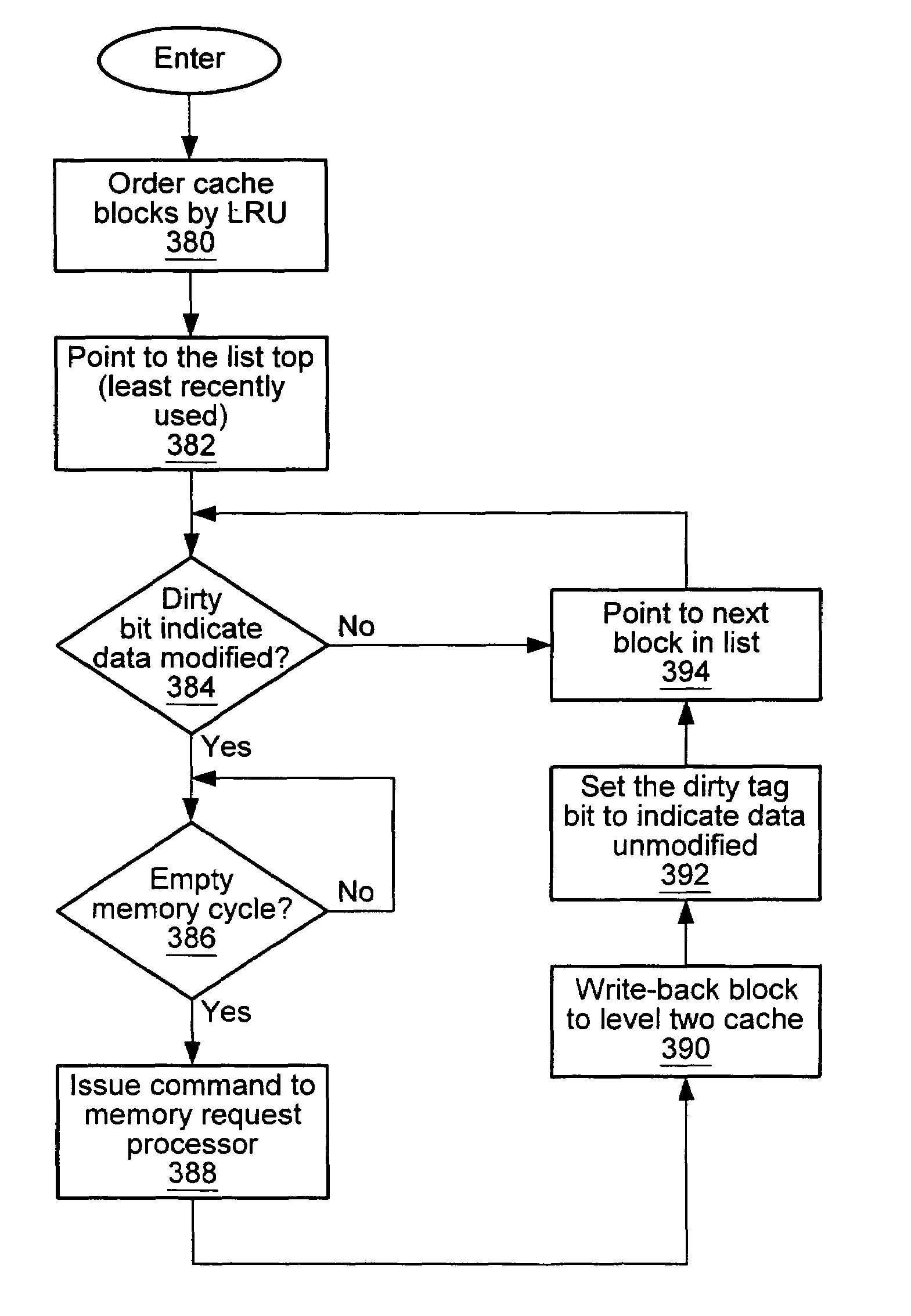

Double-rate memory

A double-rate memory has an array of single word line memory cells arranged in rows and columns. The single word line memory cells provide and store data via a first port. Addressing and control circuitry is coupled to the array of single word line memory cells. The addressing and control circuitry receives an address enable signal to initiate an access of the array whereby an address is received, decoded, and corresponding data retrieved or stored. Edge detection circuitry receives a memory clock and provides the address enable signal upon each rising edge and each falling edge of the memory clock to perform two memory operations in a single cycle of the memory clock. A memory operation includes addressing the memory and storing data in the memory or retrieving and latching data from the memory. In another form a double-rate dual port memory permits two independent read / write memory accesses in a single memory cycle.

Owner:NXP USA INC

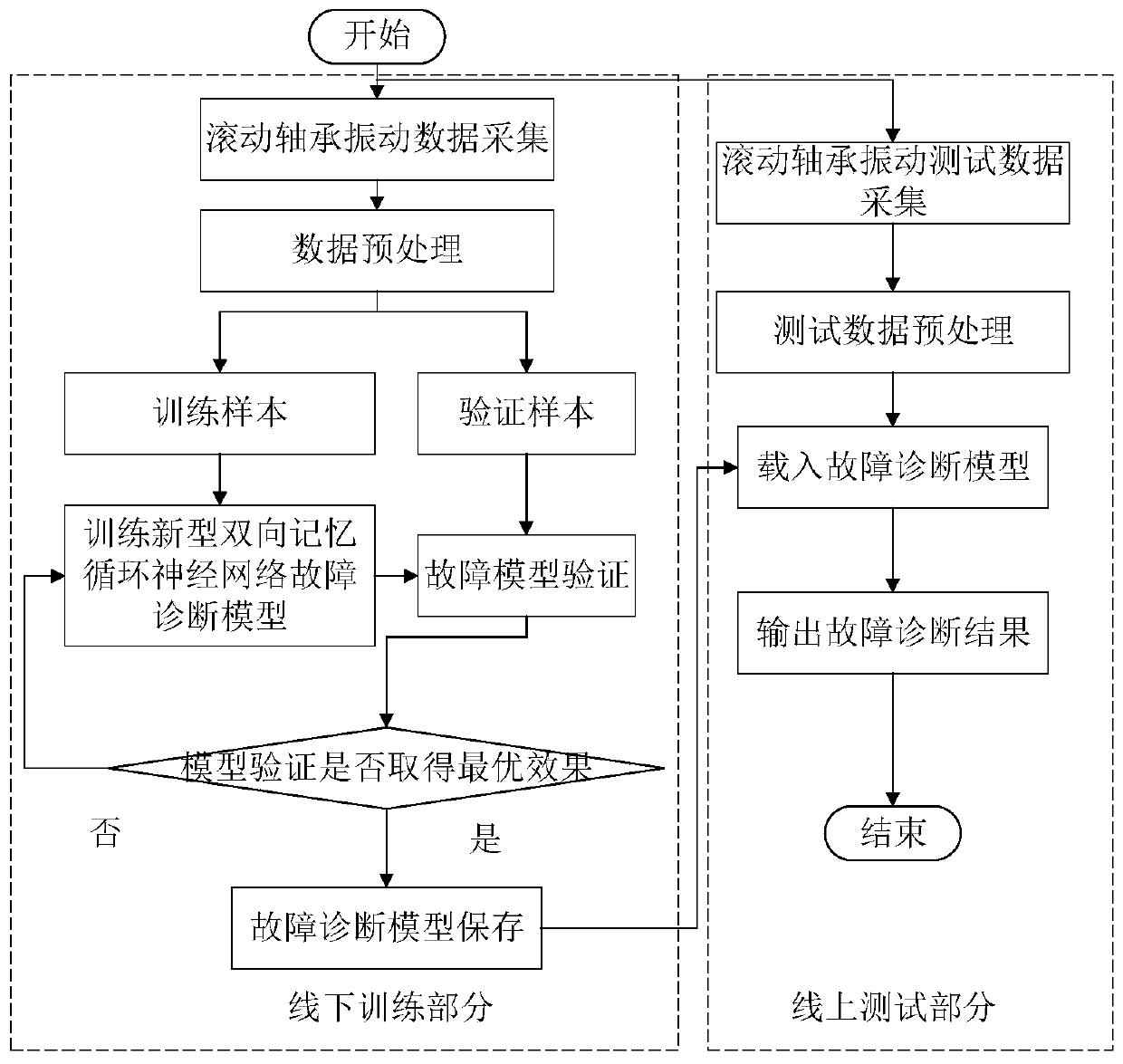

Rolling bearing fault diagnosis method based on two-way memory cycle neural network

ActiveCN110261109AStructuredImprove estimation performanceMachine bearings testingCharacter and pattern recognitionMemory typeVibration acceleration

The invention discloses a rolling bearing fault diagnosis method based on a two-way memory cycle neural network. An existing rolling bearing fault diagnosis method does not consider a single logical structure characteristic of data after characteristic extraction and a fault type can not be integrally determined from the data when fault data is processed. Aiming at the above defects, the method of the invention comprises the following steps of firstly, acquiring a program data sample, carrying out standardized preprocessing on vibration acceleration data, making the collected data accord with standard normal distribution, and then using a time-frequency domain characteristic extraction algorithm to obtain 512 time-frequency domain characteristic vectors; then, constructing an improved two-way memory type cycle neural network fault diagnosis model, using an idea of a simple design, and then using sample data to train a neural network weight parameter, after iteration training, generating a model which can map a relationship between bearing data and a fault type, wherein the designed memory-type cycle neural network includes a forgetting gate, an input gate and a cellular state; and finally, using the model to carry out fault analysis so as to achieve accurate diagnosis of a rolling bearing fault.

Owner:洛阳中科晶上智能装备科技有限公司

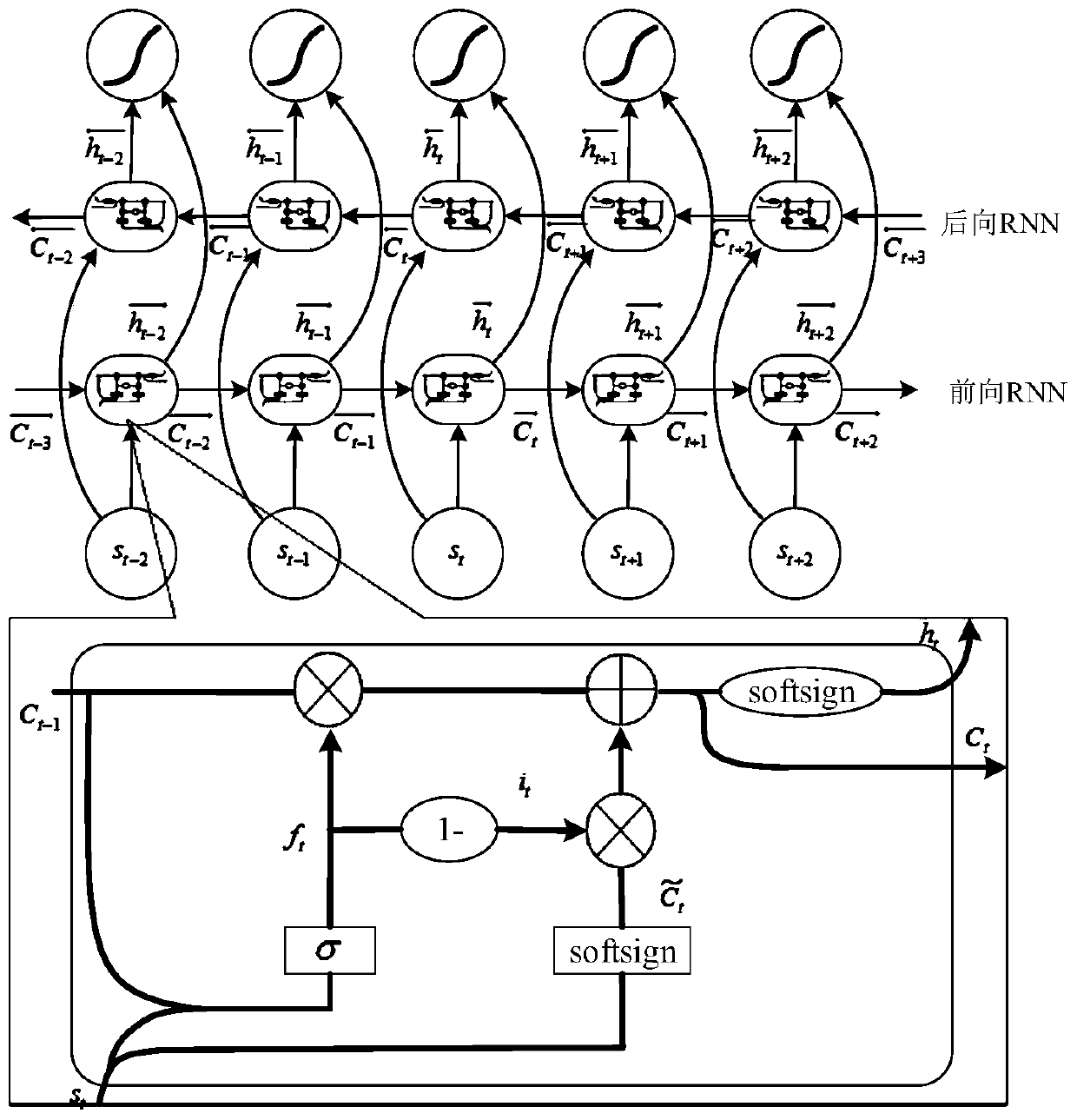

Active block write-back from SRAM cache to DRAM

InactiveUS7027064B2Memory architecture accessing/allocationImage memory managementGraphicsParallel computing

An external cache management unit for use with 3D-RAM and suitable for use in a computer graphics system is described. The unit maintains and tracks the status of level one cache memory in the 3D-RAM. The unit identifies dirty blocks of cache memory and prioritizes block cleansing based on a least used algorithm. Periodic block cleansing during empty memory cycles is provided for, and may also be prompted on demand.

Owner:ORACLE INT CORP

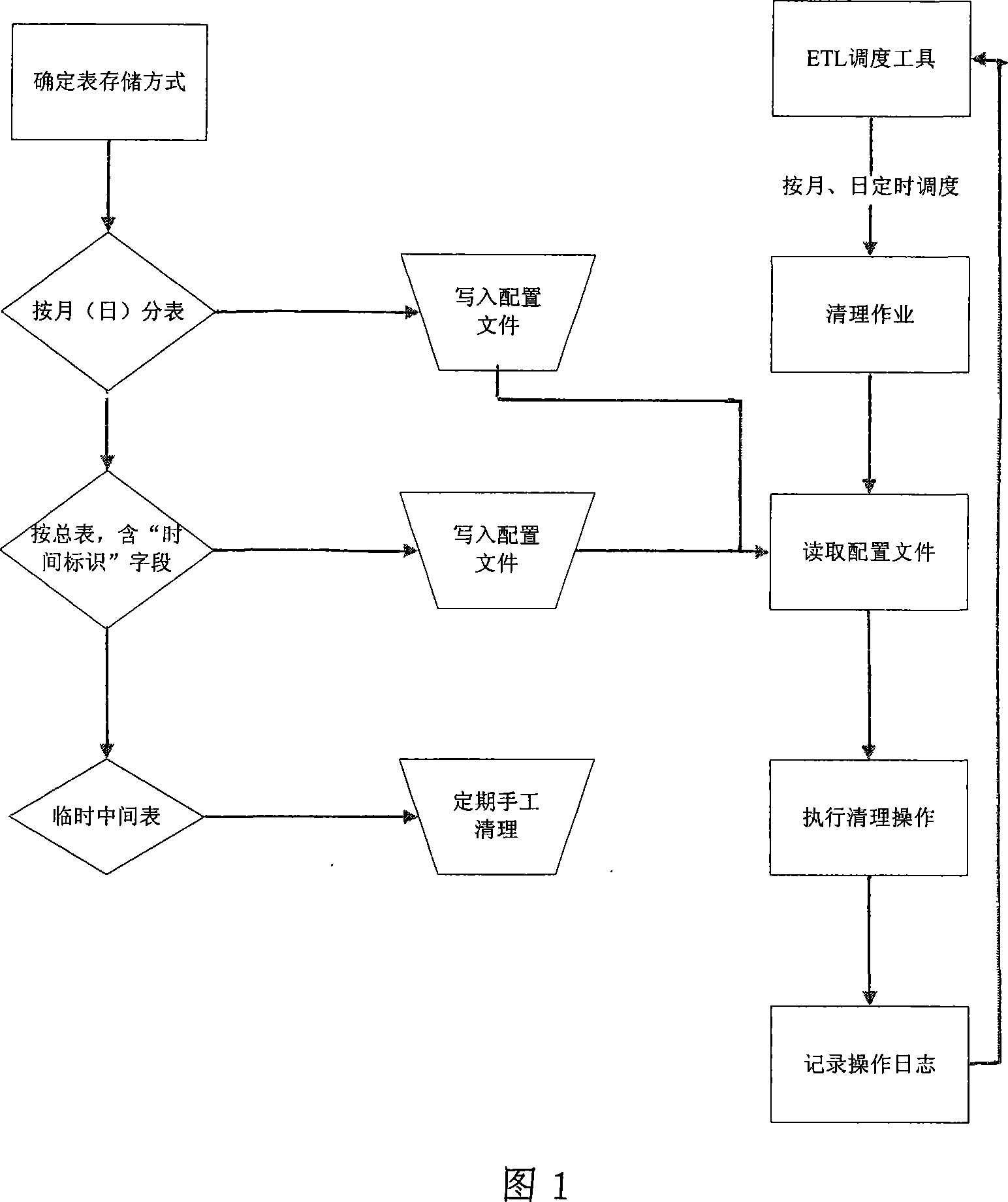

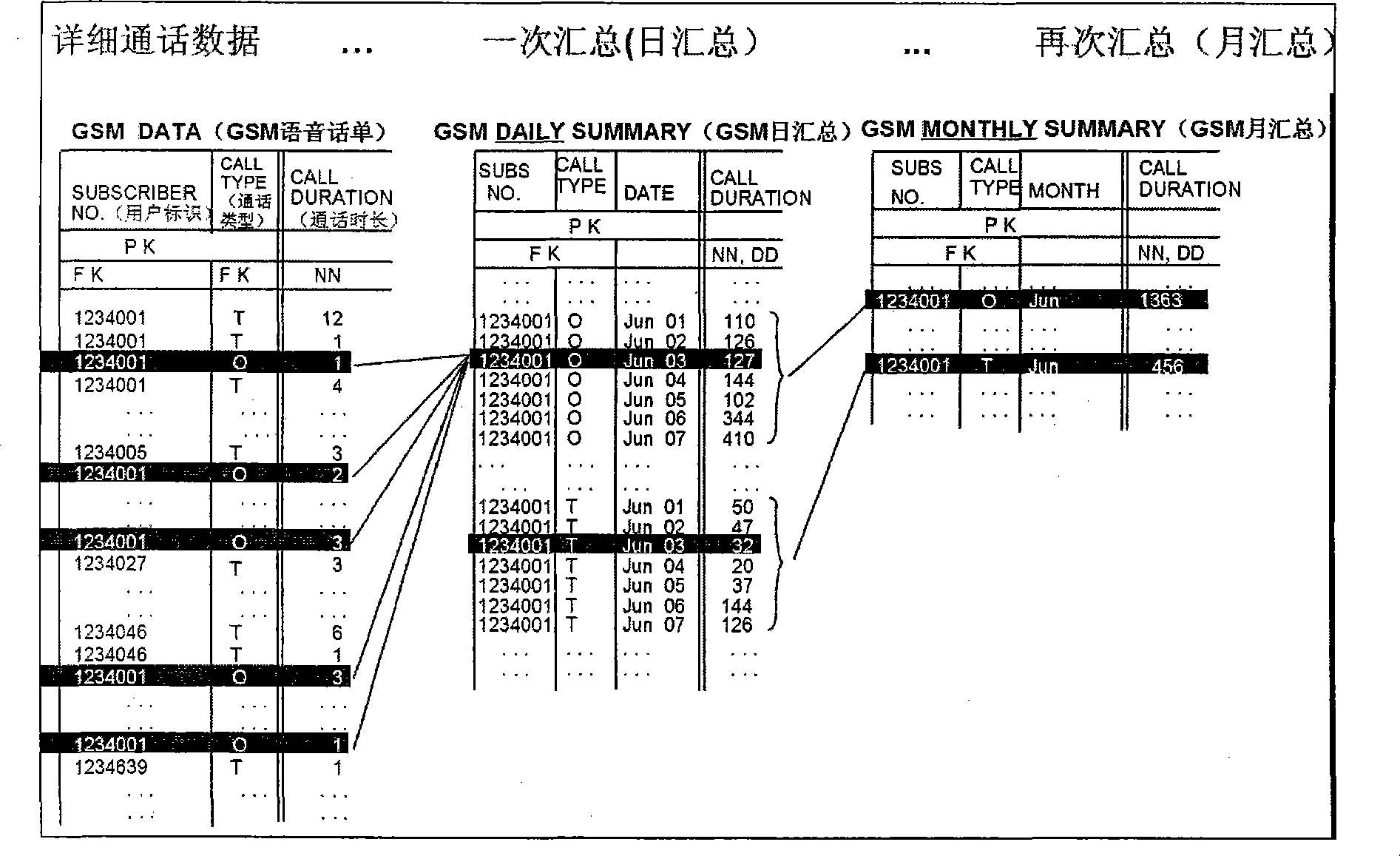

Method for economized storage, construction í‹greeníŒ database

InactiveCN101183986AAutomatic cleaningReduce storageSupervisory/monitoring/testing arrangementsData switching networksData compressionData warehouse

The invention relates to a method of saving memory and constructing a green data warehouse, comprising procedures as follows: (1) Saving memory of a base layer using method of data compression; (2) Saving memory of a collection layer using method of granularity memory such as user class-fine-grained class-coarse-grained class; establishing automatic, configurable and regular data cleaning mechanism for business data which exceeds memory cycle; (3) Adjusting memory cycle according to life cycle of application analysis for application layer; establishing automatic, configurable and regular data cleaning mechanism for business data which exceeds memory cycle. The invention has the advantage of effectively saving memory, automatically cleaning data garbage in time, and enabling clean and neat green data warehouse.

Owner:CHINA MOBILE QUANTONG SYST INTEGRATION CO LTD

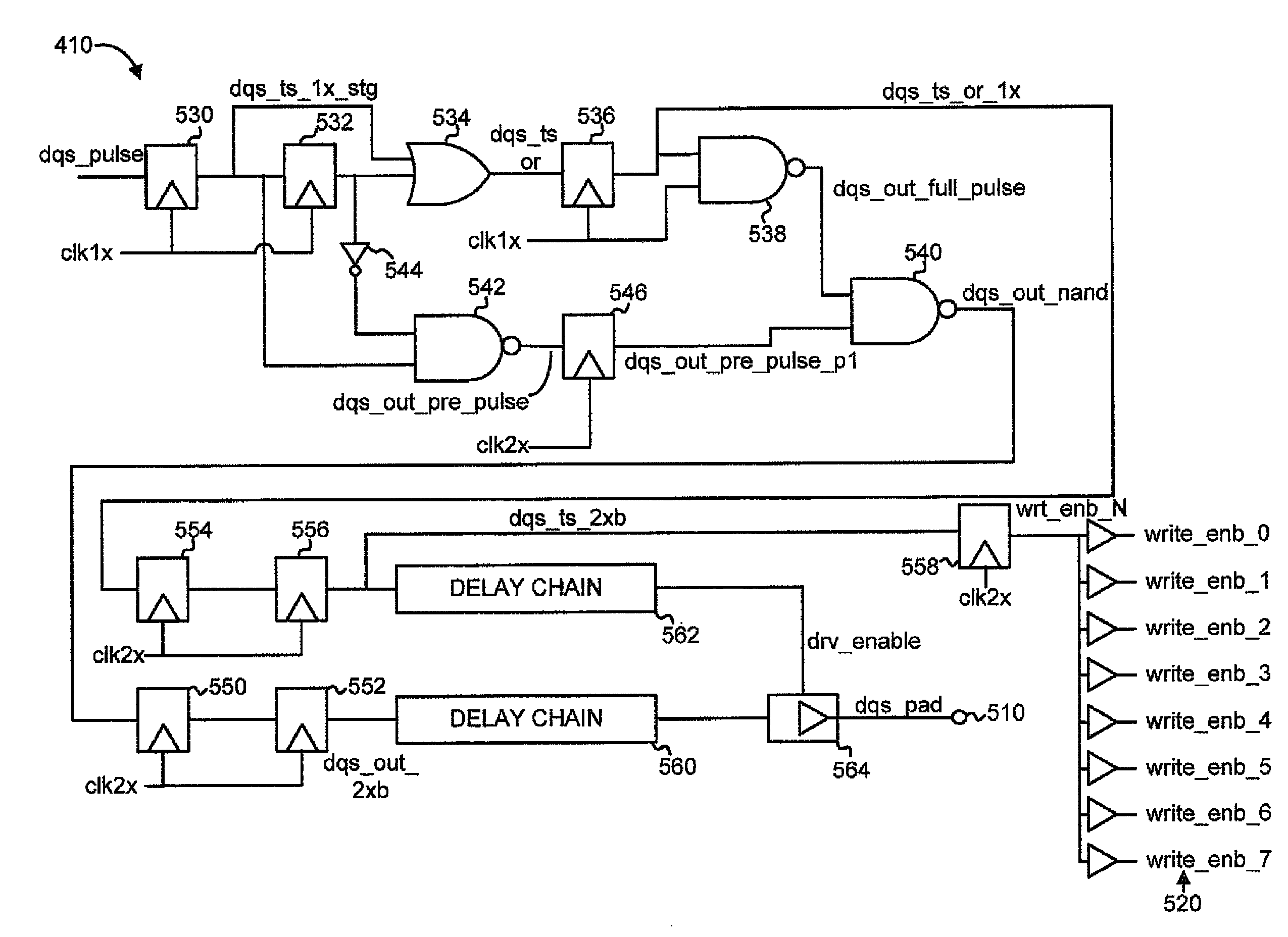

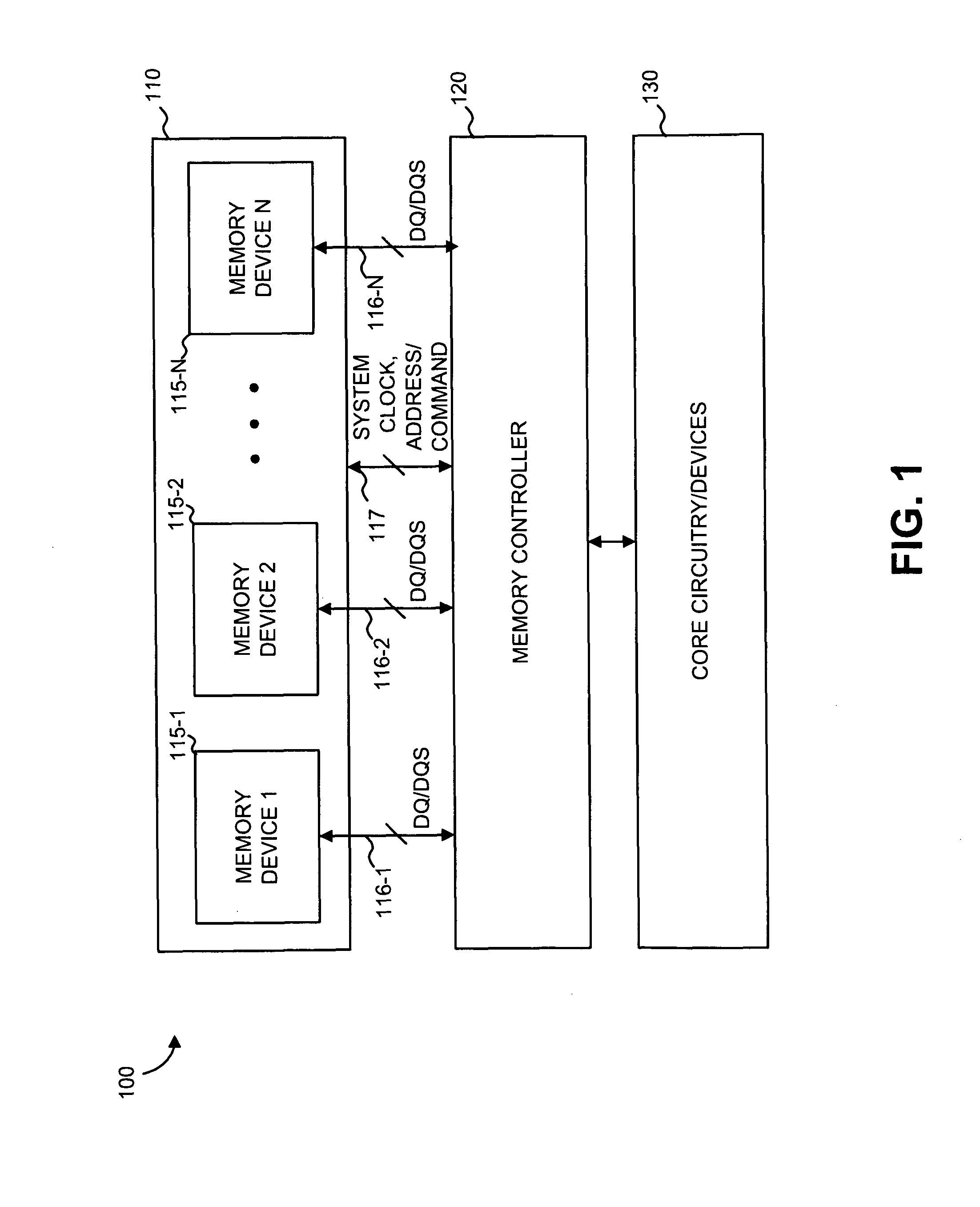

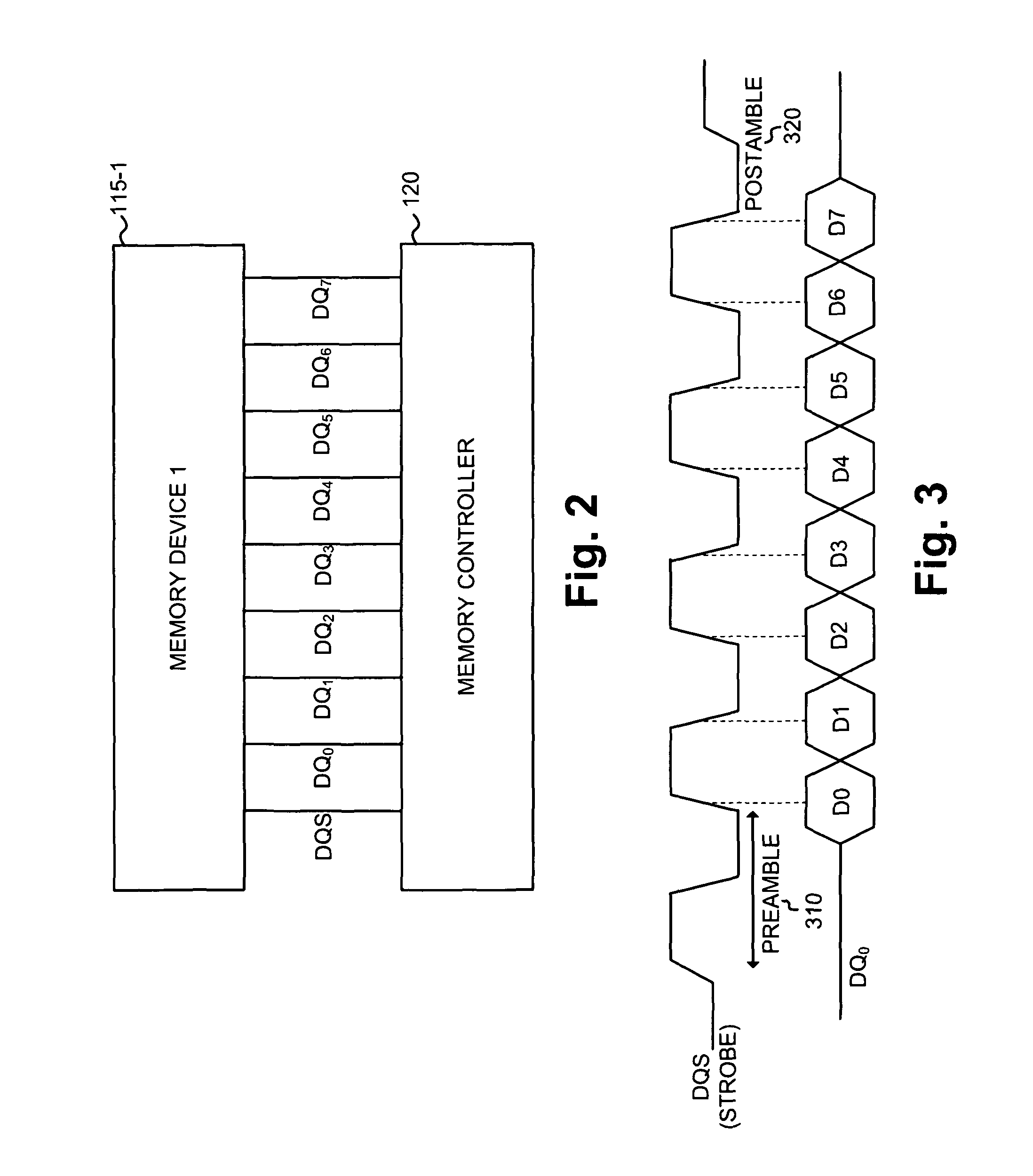

Write strobe generation for a memory interface controller

A memory controller includes a circuit to generate a strobe signal for write operations to a DDR SDRAM. The circuit efficiently generates a glitch free strobe signal for a group of data lines. In one implementation, the memory controller includes a write data generation circuits to each transmit a data signal to the memory on a data line, the write data generation circuits being controlled by write enable signals. A write strobe generation circuit generates the strobe signal and the write enable signals, the strobe signal including a preamble window to signal the beginning of the data burst, a data transfer window, and a postamble window to signal the end of the data burst, the write strobe generation circuit generating the write enable signals a half memory cycle early and terminating the write enable signals a half memory cycle late with respect to the data signals generated by the write data generation circuits.

Owner:JUMIPER NETWORKS INC

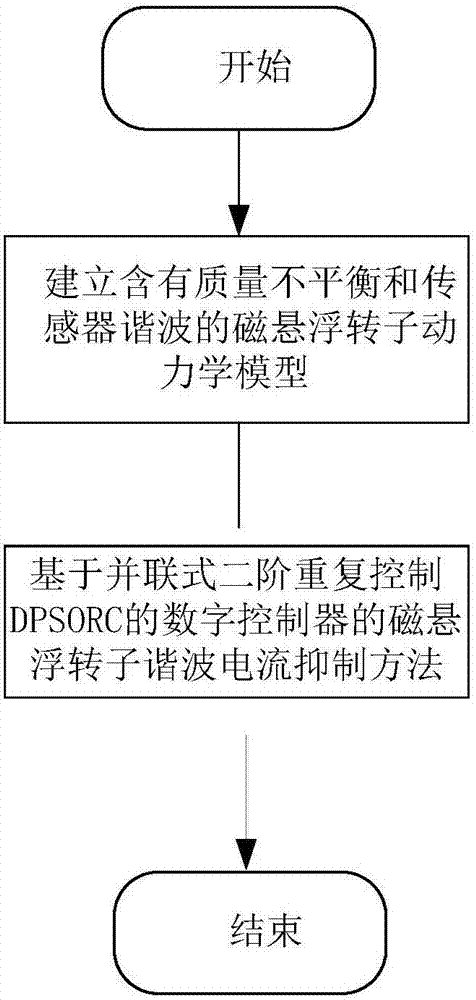

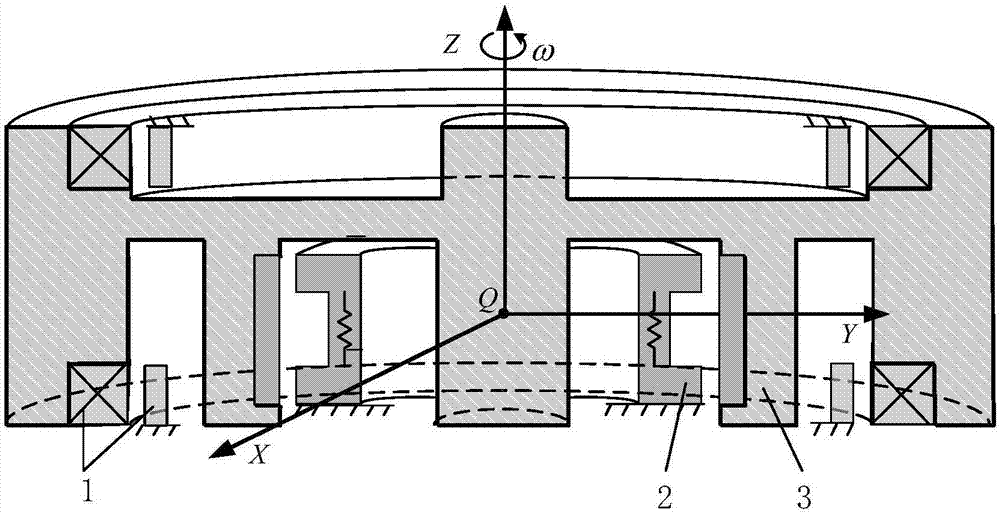

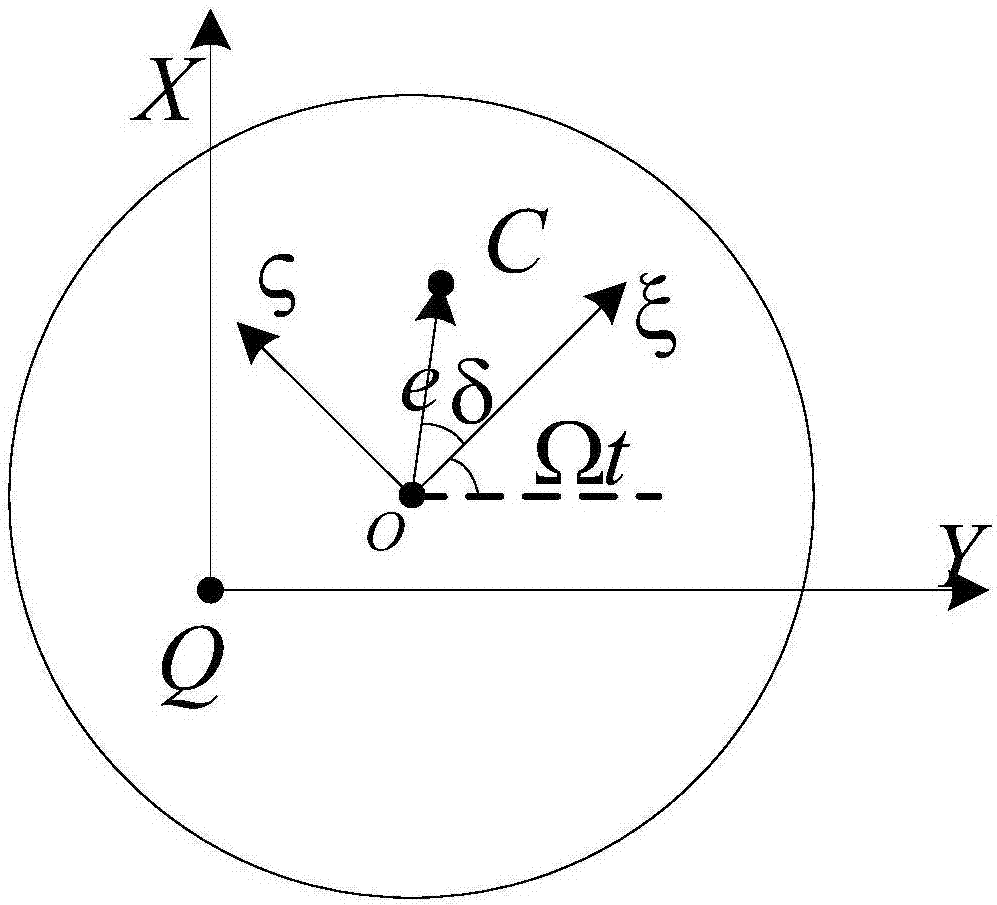

Magnetic suspension rotor harmonic current inhibition method of digital controller based on DPSORC

ActiveCN106896726AReduce sensitivityWiden the notch rangeMagnetic holding devicesAdaptive controlMagnetic bearingHarmonic

The present invention discloses a magnetic suspension rotor harmonic current inhibition method of a digital controller based on dual parallel structure digital second-order repetitive control (DPSORC). The method comprises: establishing a magnetic suspension rotor kinetic model including quality unbalance and sensor harmonic wave, and employing the magnetic suspension rotor harmonic current inhibition method of the digital controller based on DPSORC. The digital controller employs parallel dual memory cycle and one weighting factor to connect into a magnetic suspension rotor closed loop system so as to improve the robustness of rotating speed nondeterminacy. A traditional first-order repetitive controller phase compensation link can be completely planted into the DPSORC to provide convenience for the actual usage of the DPSORC and allow the controller to have good versatility. The method provided by the invention can perform inhibition of the harmonic wave components of the magnetic bearing coil current in the magnetic suspension rotor, and is suitable for the magnetic suspension rotor system harmonic wave current inhibition including quality unbalance and sensor harmonic wave.

Owner:BEIHANG UNIV