Patents

Literature

4109results about "Error correction/detection using multiple parity bits" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Fixed content distributed data storage using permutation ring encoding

InactiveUS7240236B2Highly available and reliable and persistent storageError correction/detection using multiple parity bitsCode conversionCoding blockDatabase

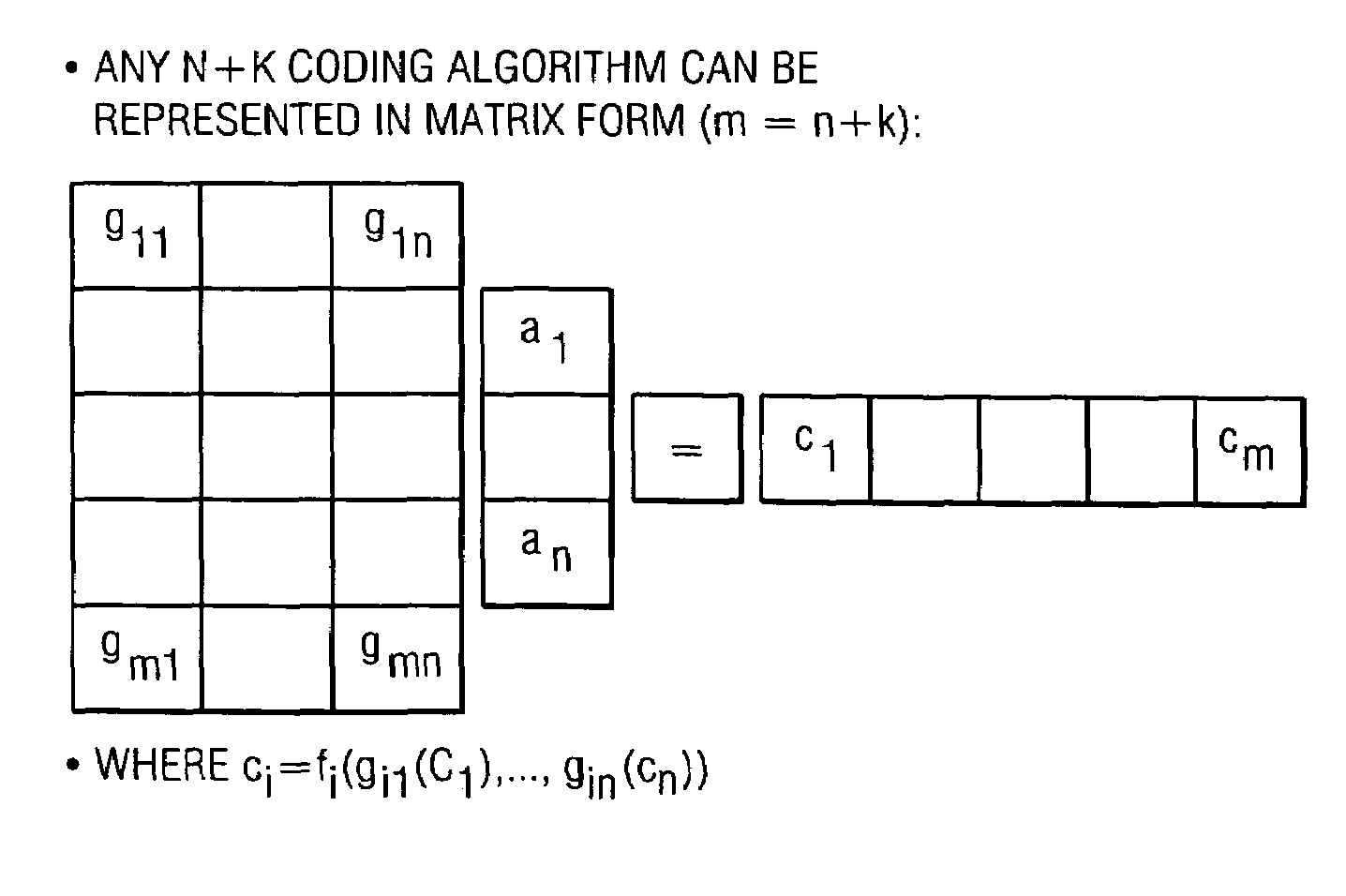

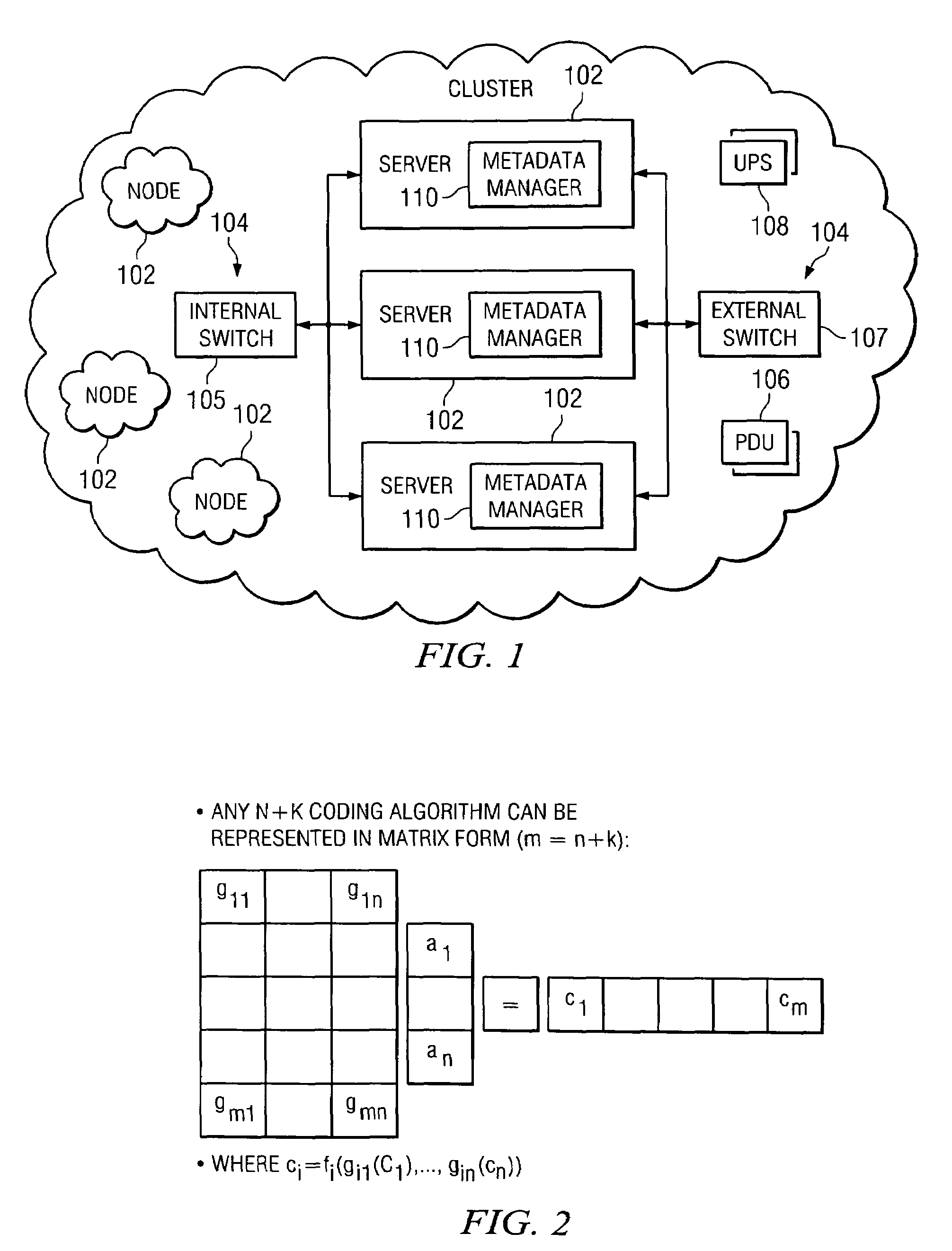

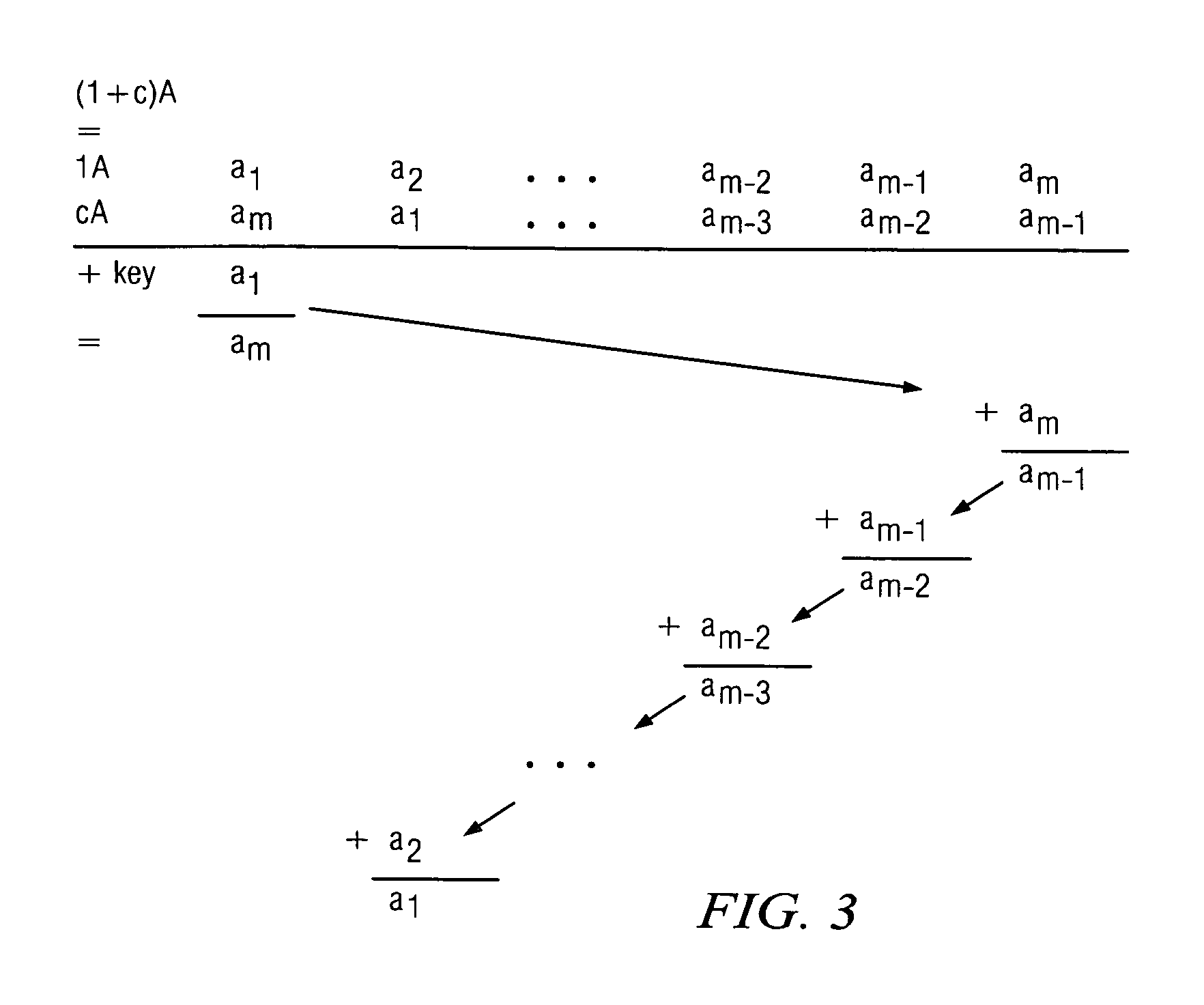

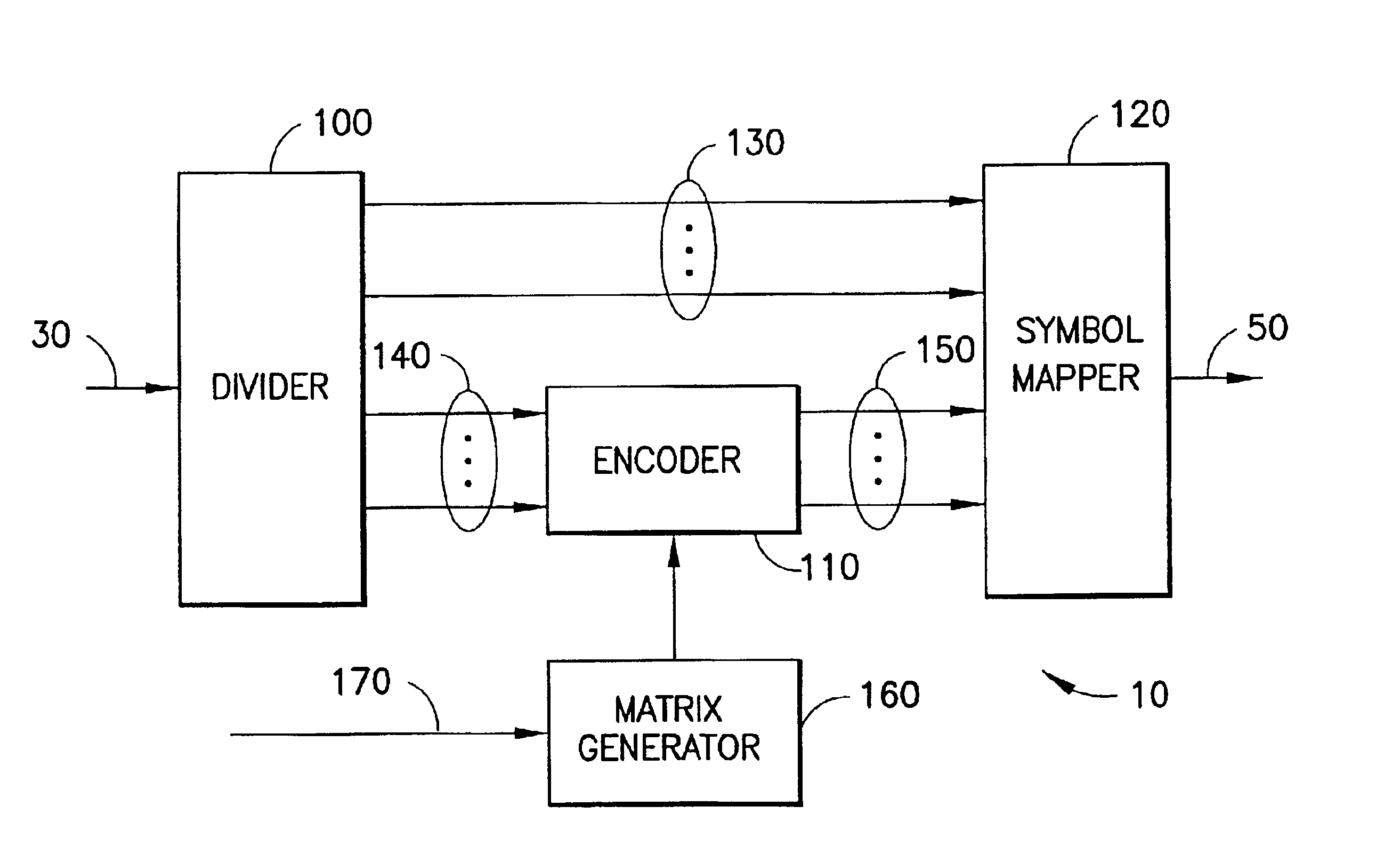

A file protection scheme for fixed content in a distributed data archive uses computations that leverage permutation operators of a cyclic code. In an illustrative embodiment, an N+K coding technique is described for use to protect data that is being distributed in a redundant array of independent nodes (RAIN). The data itself may be of any type, and it may also include system metadata. According to the invention, the data to be distributed is encoded by a dispersal operation that uses a group of permutation ring operators. In a preferred embodiment, the dispersal operation is carried out using a matrix of the form [IN<sub2>—< / sub2>C] where IN is an n×n identity sub-matrix and C is a k×n sub-matrix of code blocks. The identity sub-matrix is used to preserve the data blocks intact. The sub-matrix C preferably comprises a set of permutation ring operators that are used to generate the code blocks. The operators are preferably superpositions that are selected from a group ring of a permutation group with base ring Z2.

Owner:HITACHI VANTARA CORP

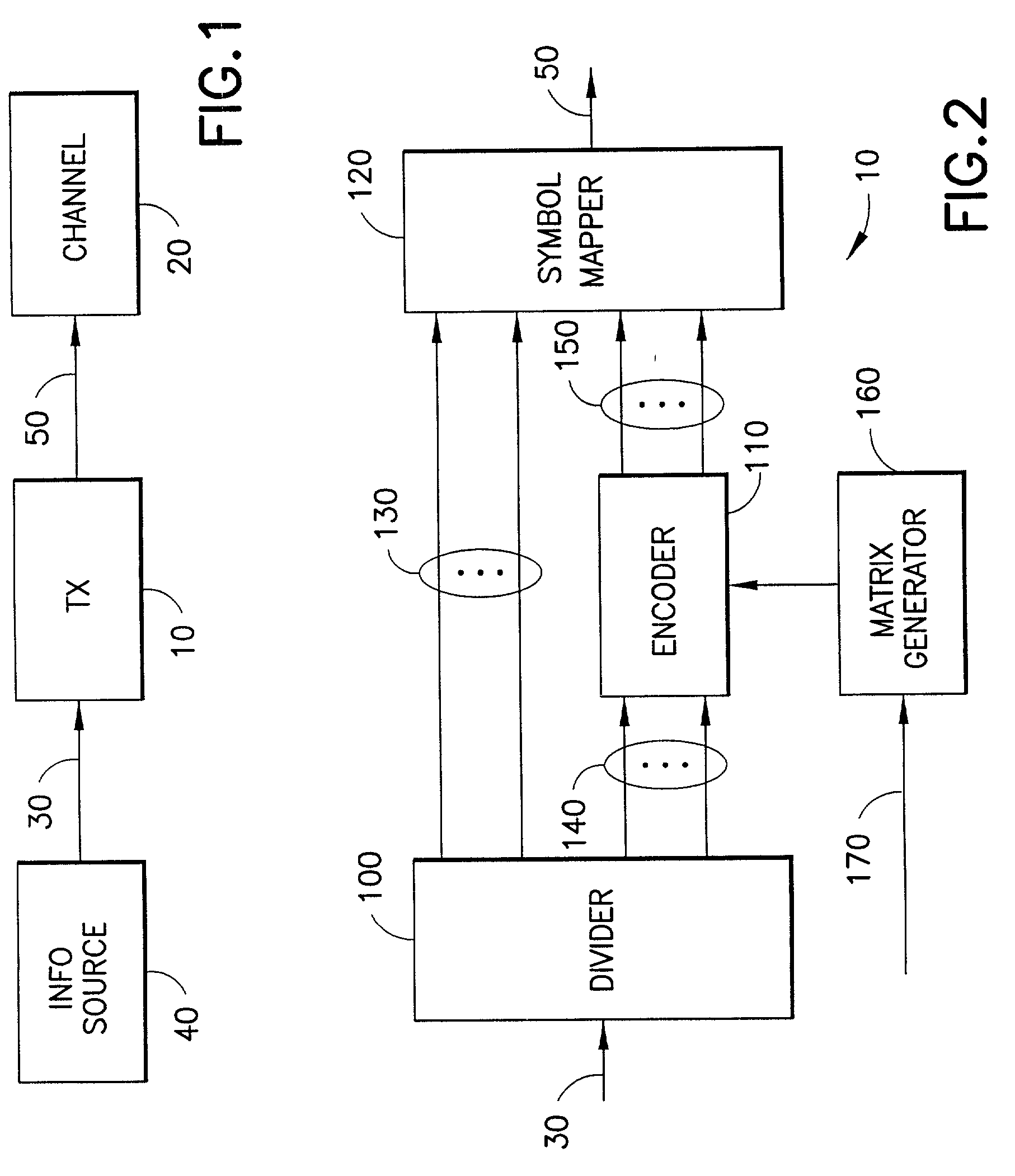

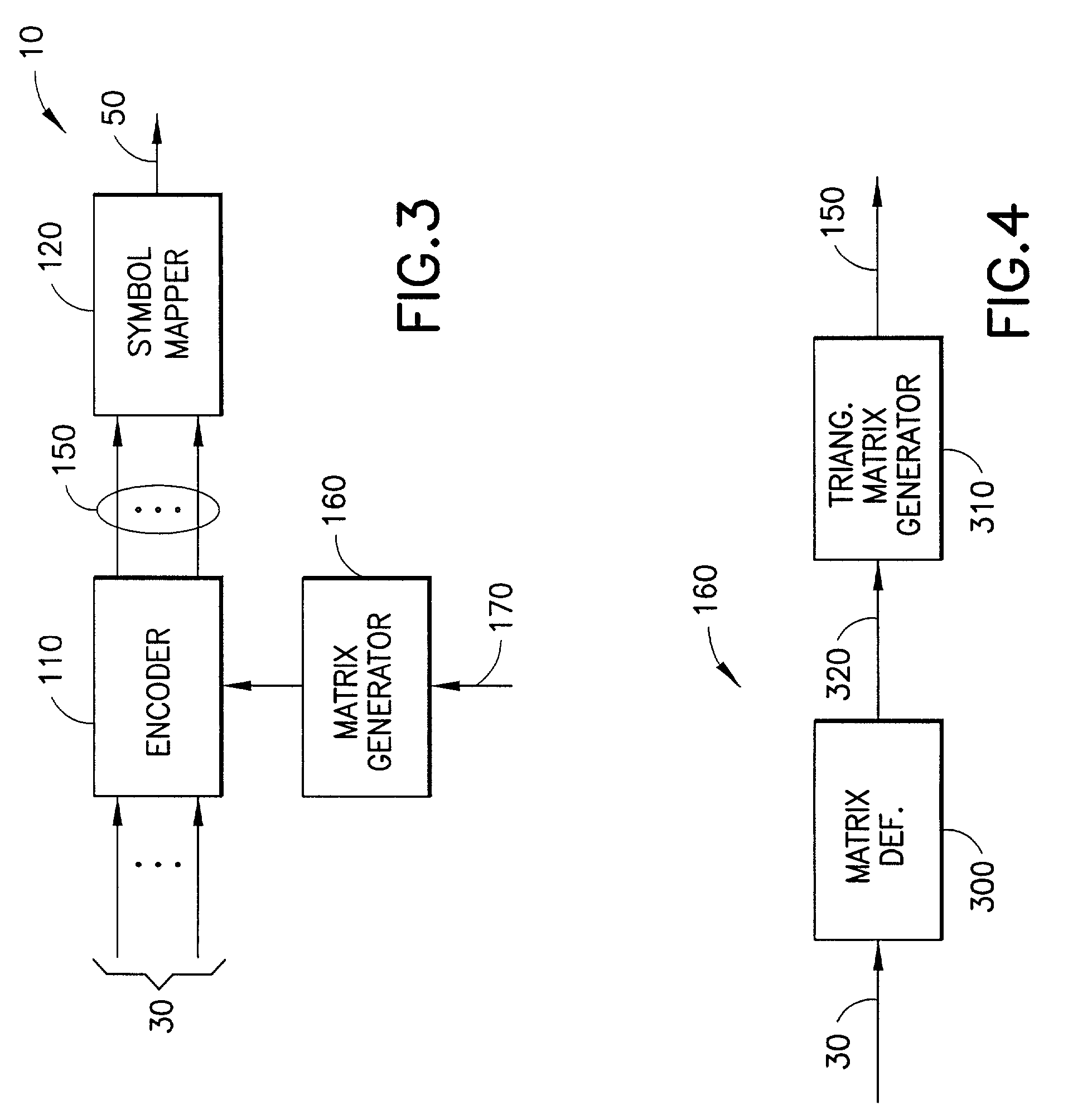

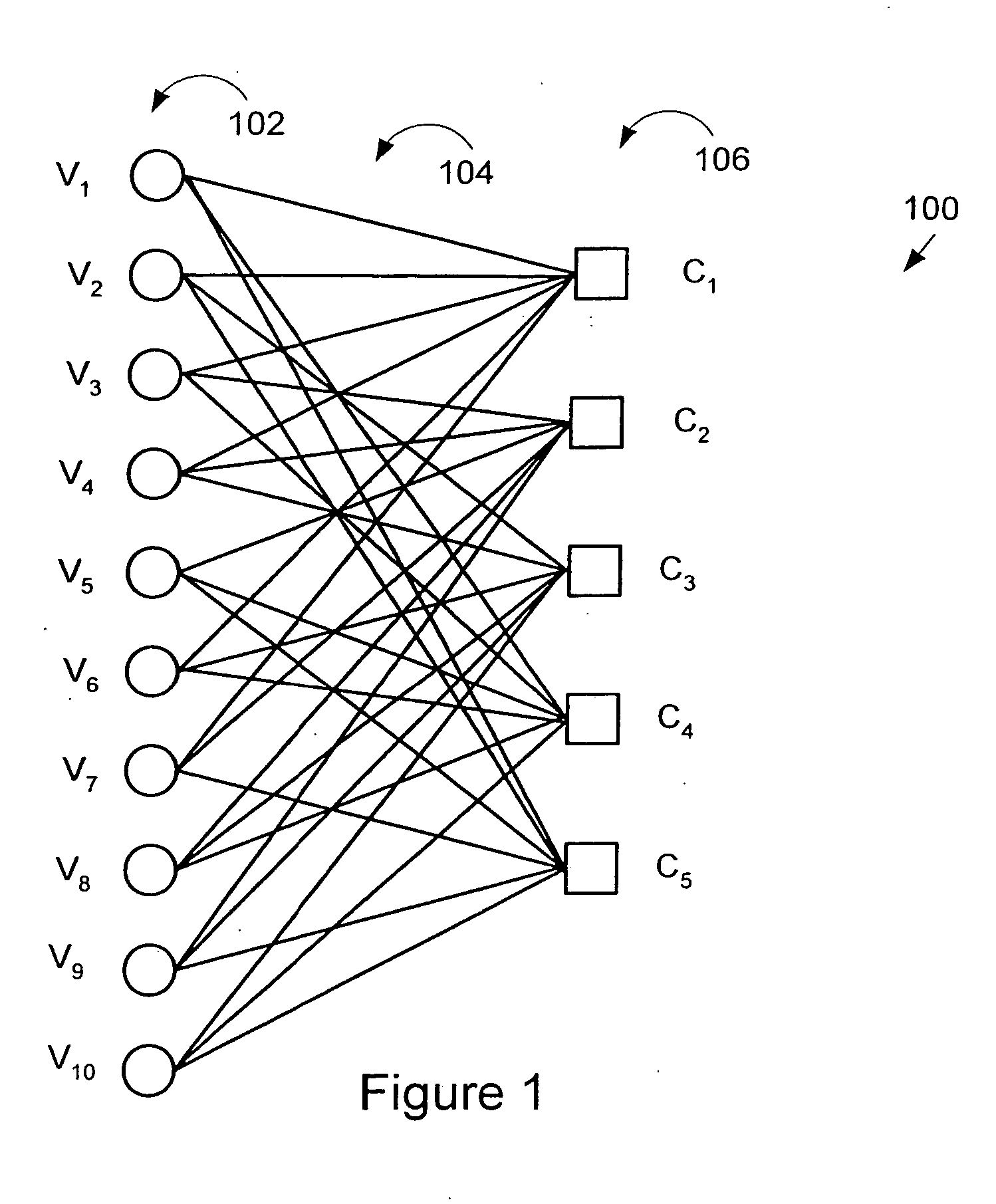

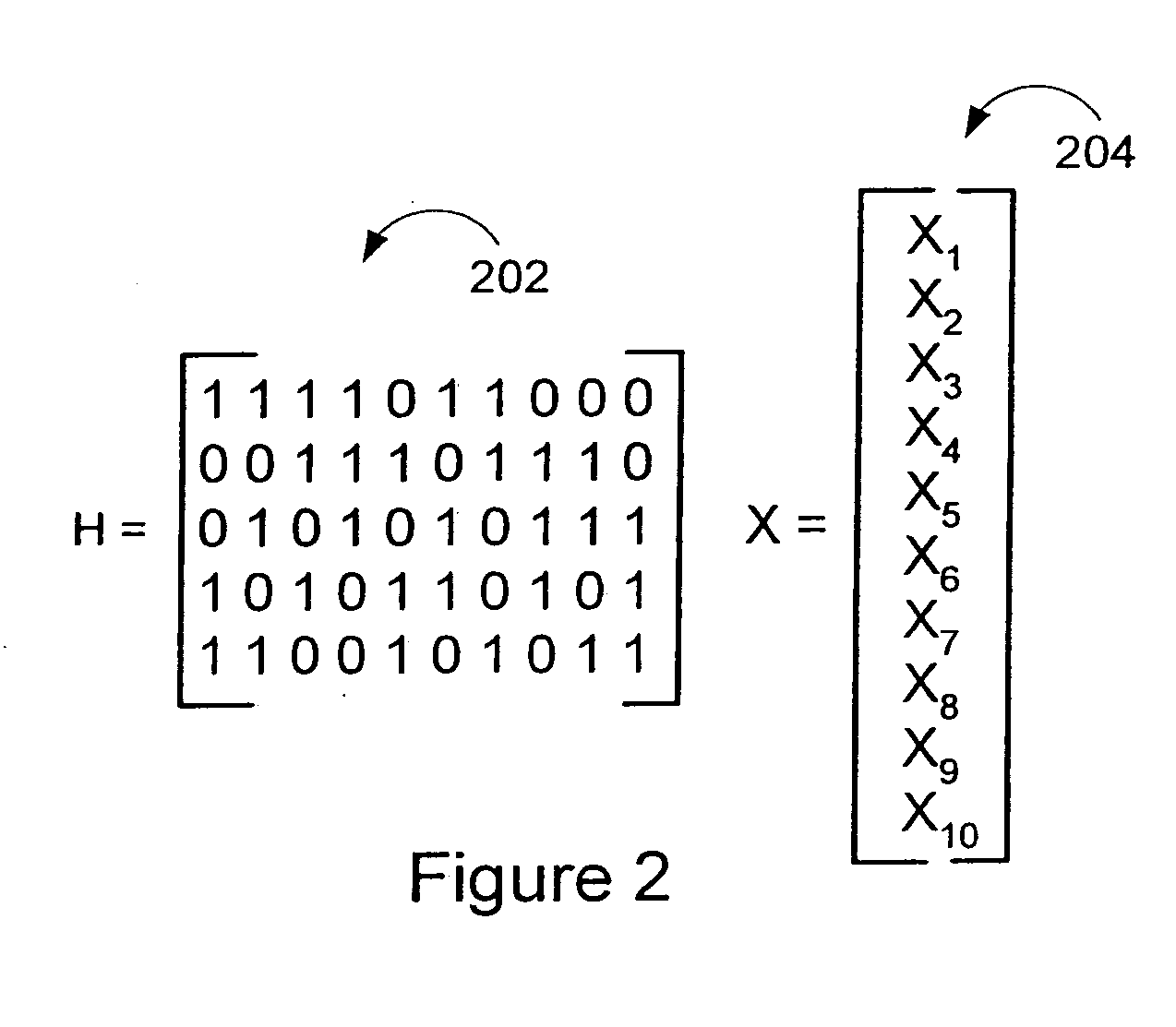

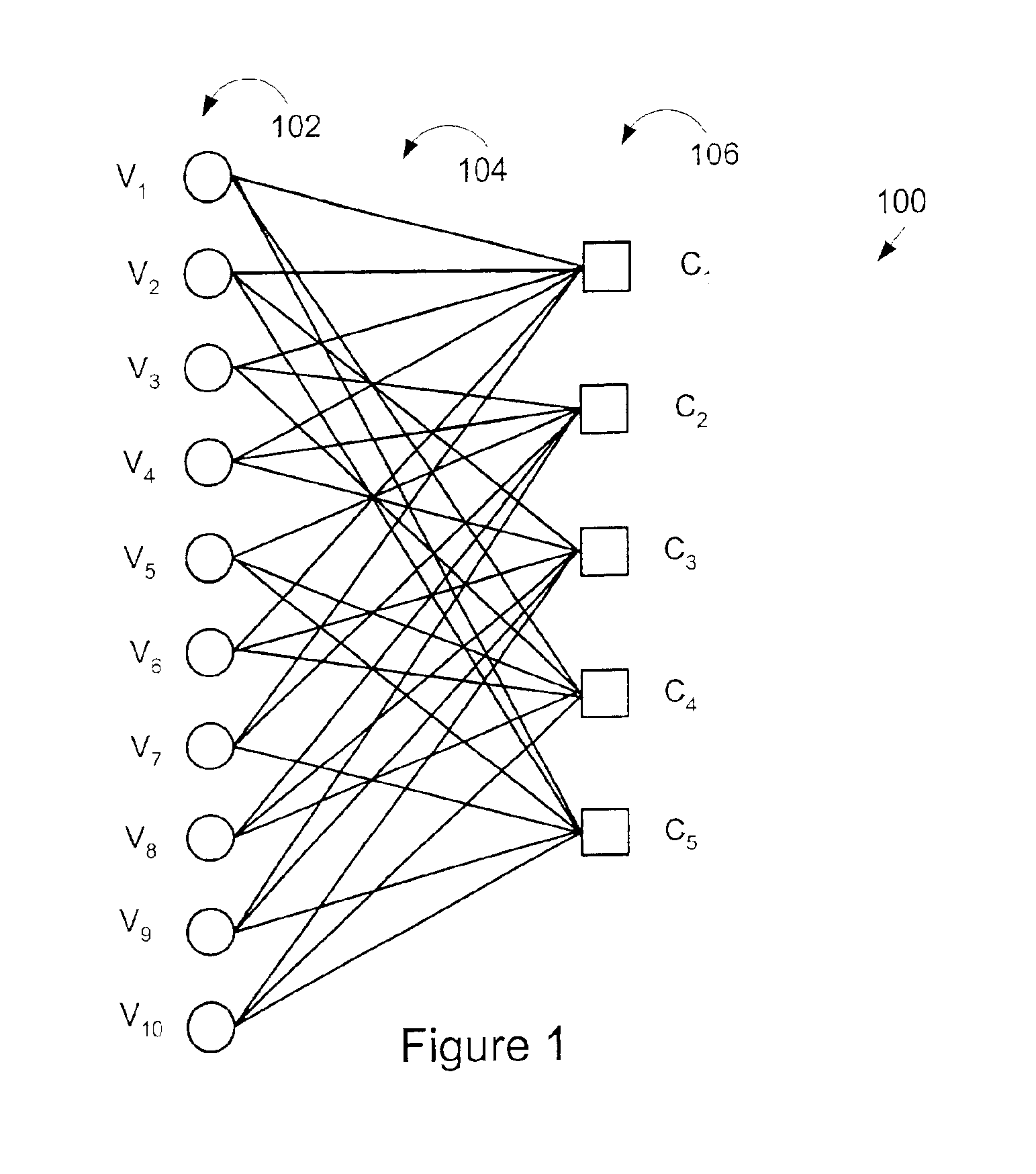

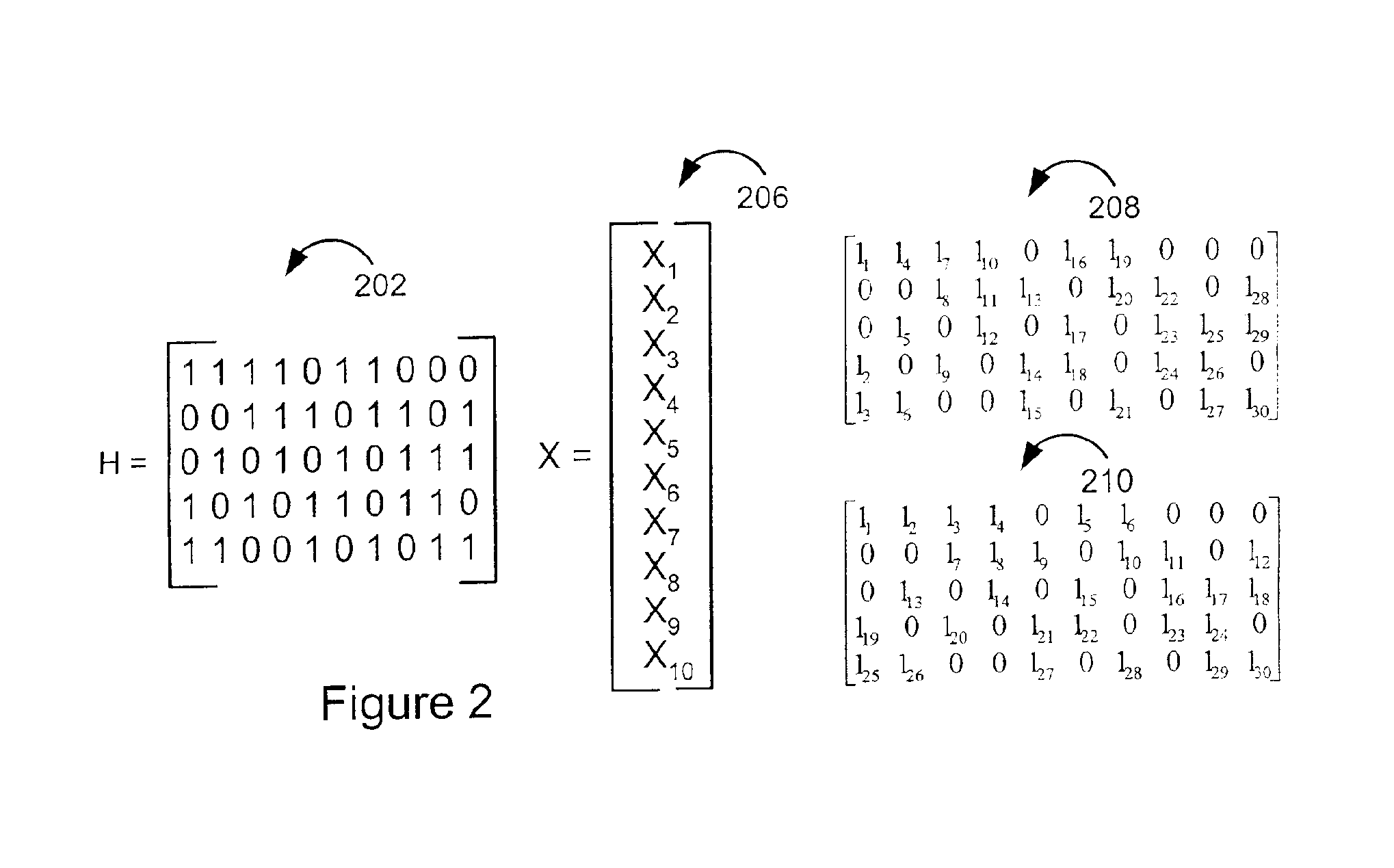

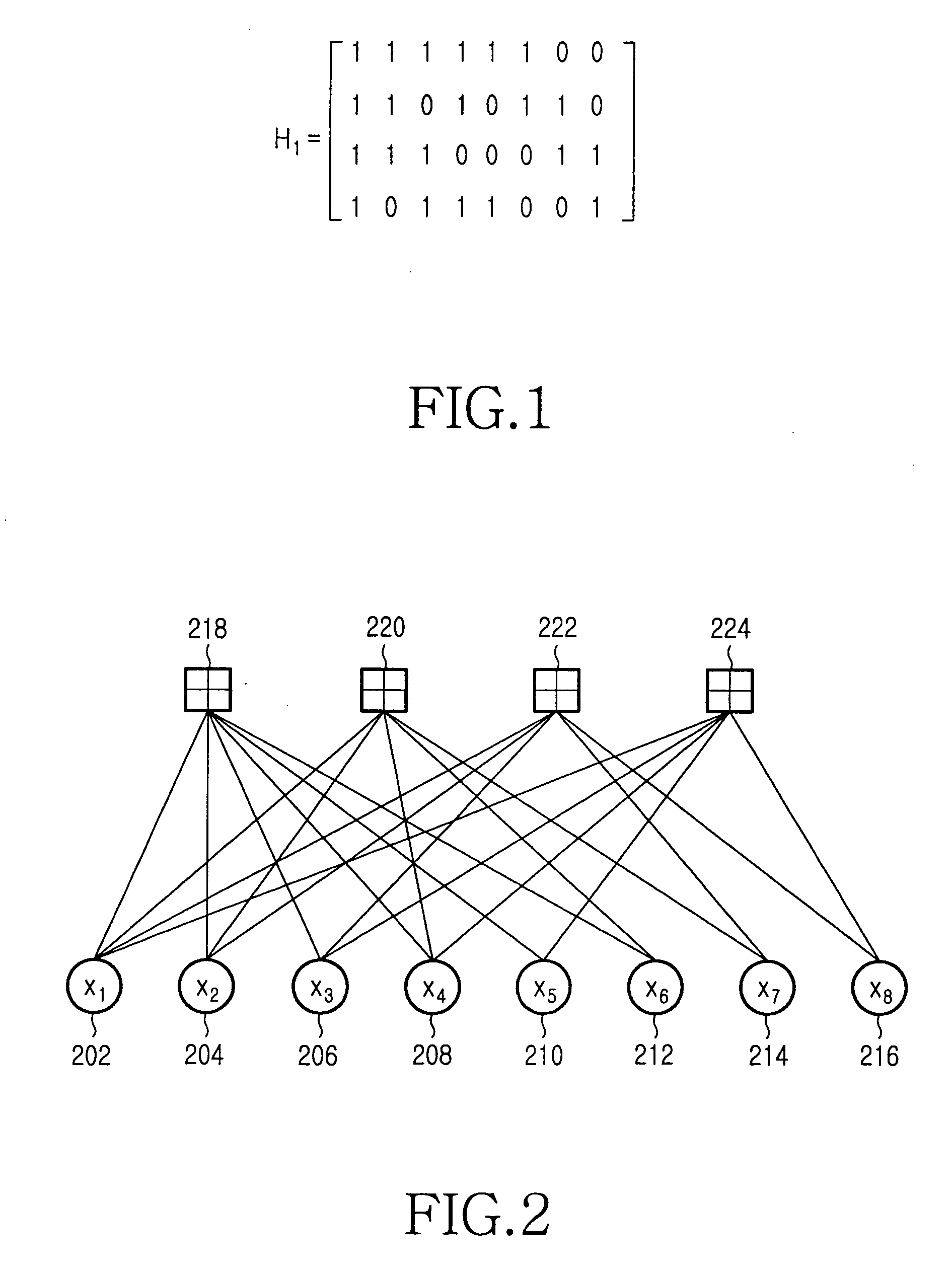

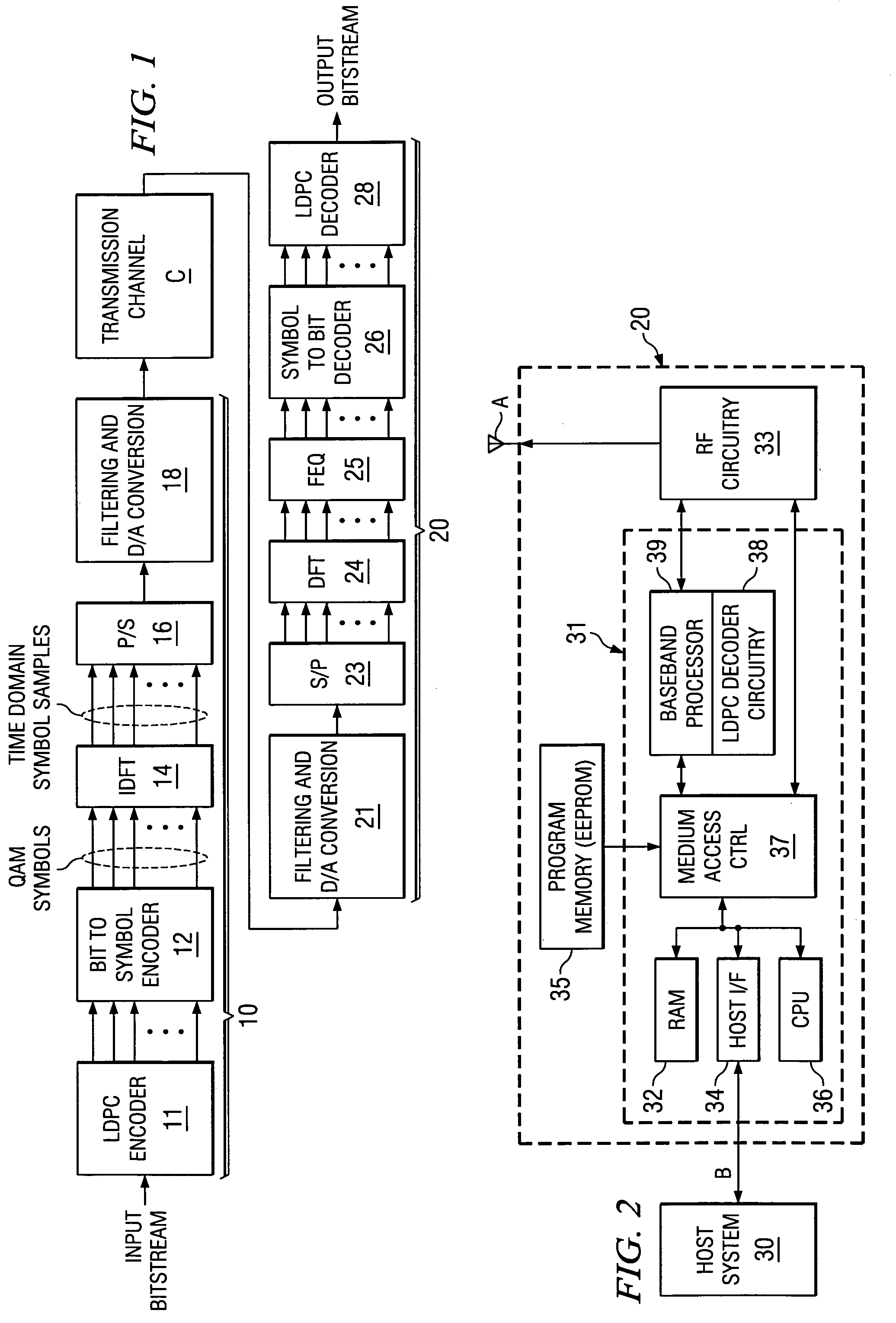

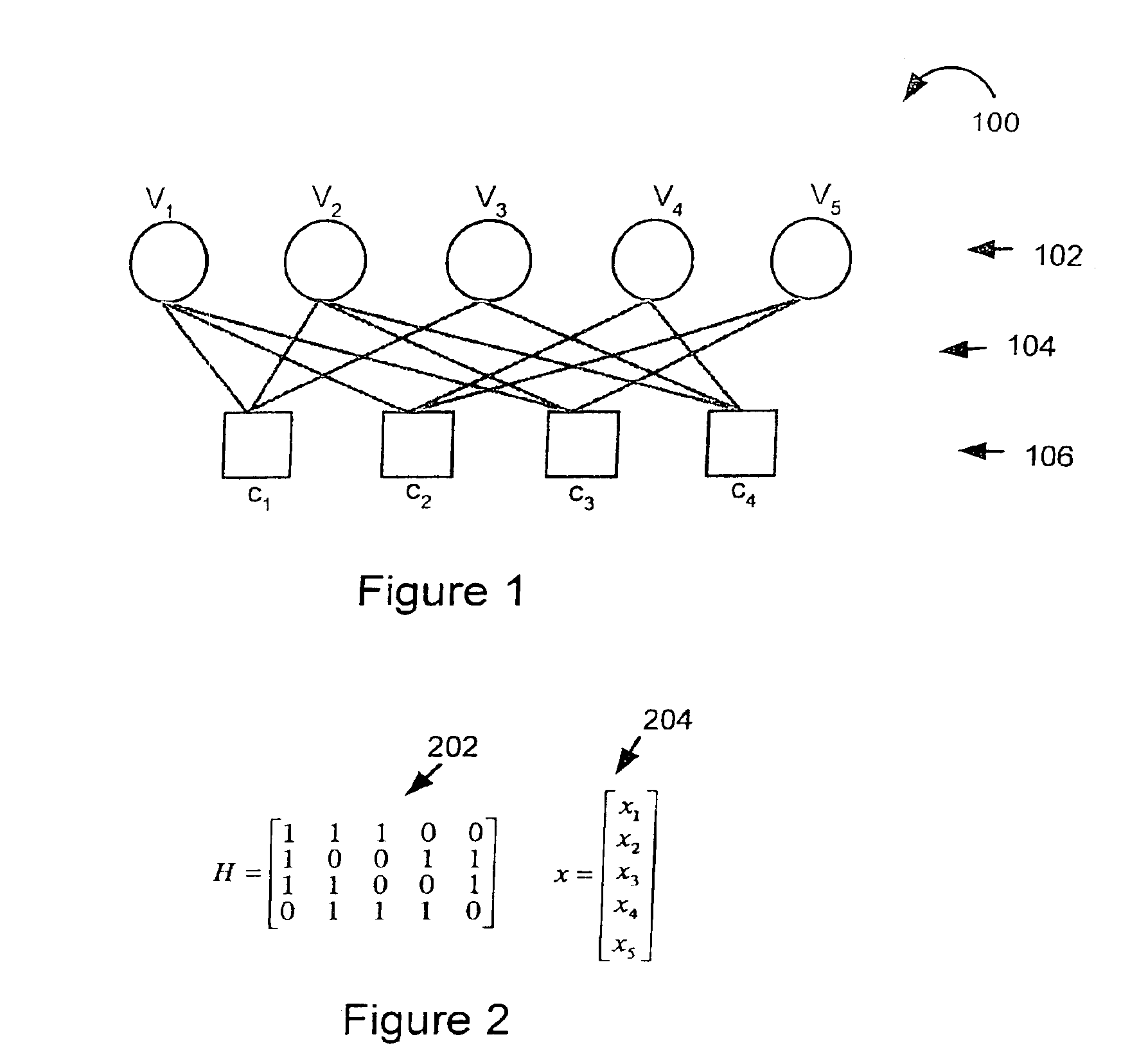

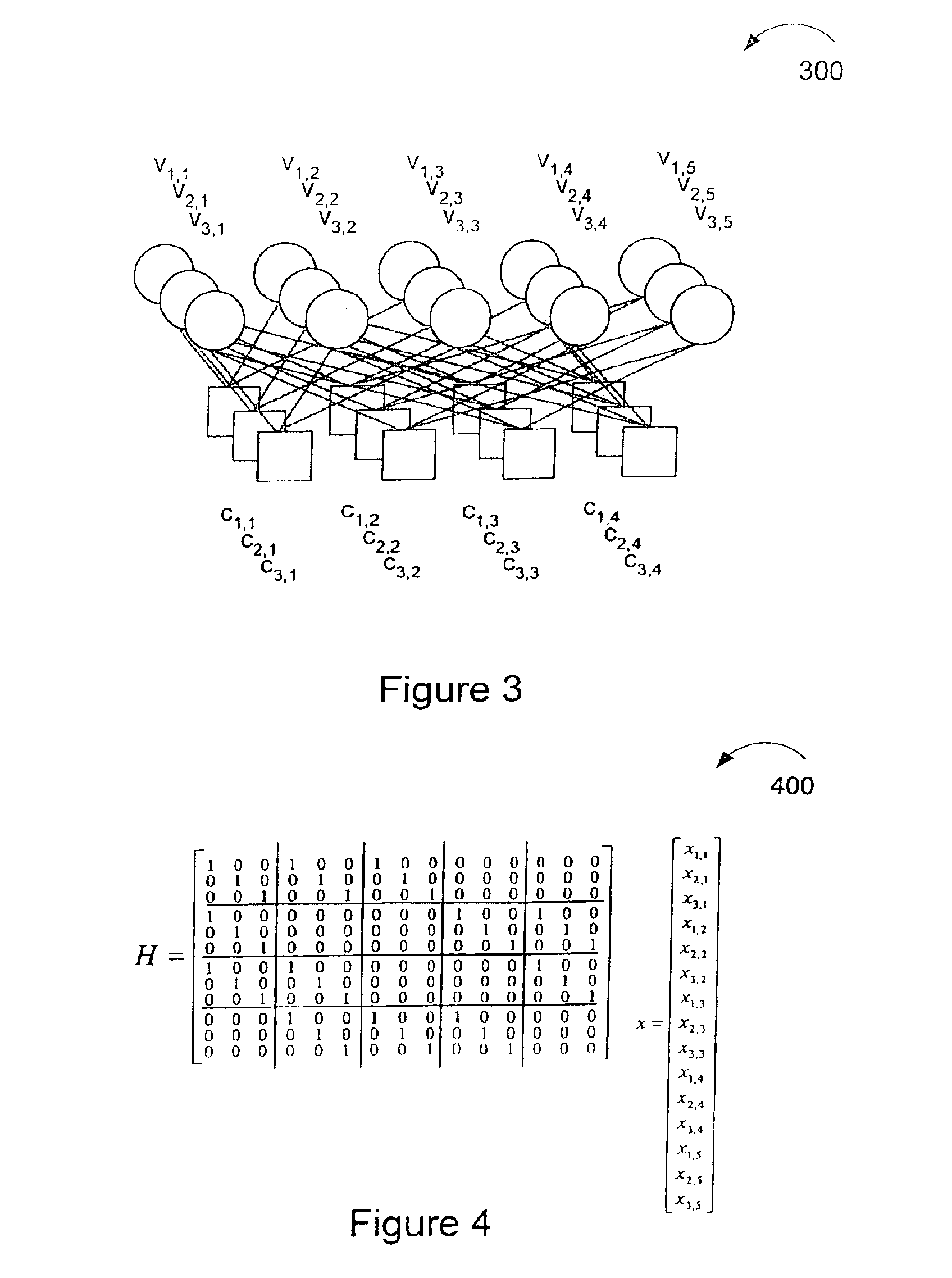

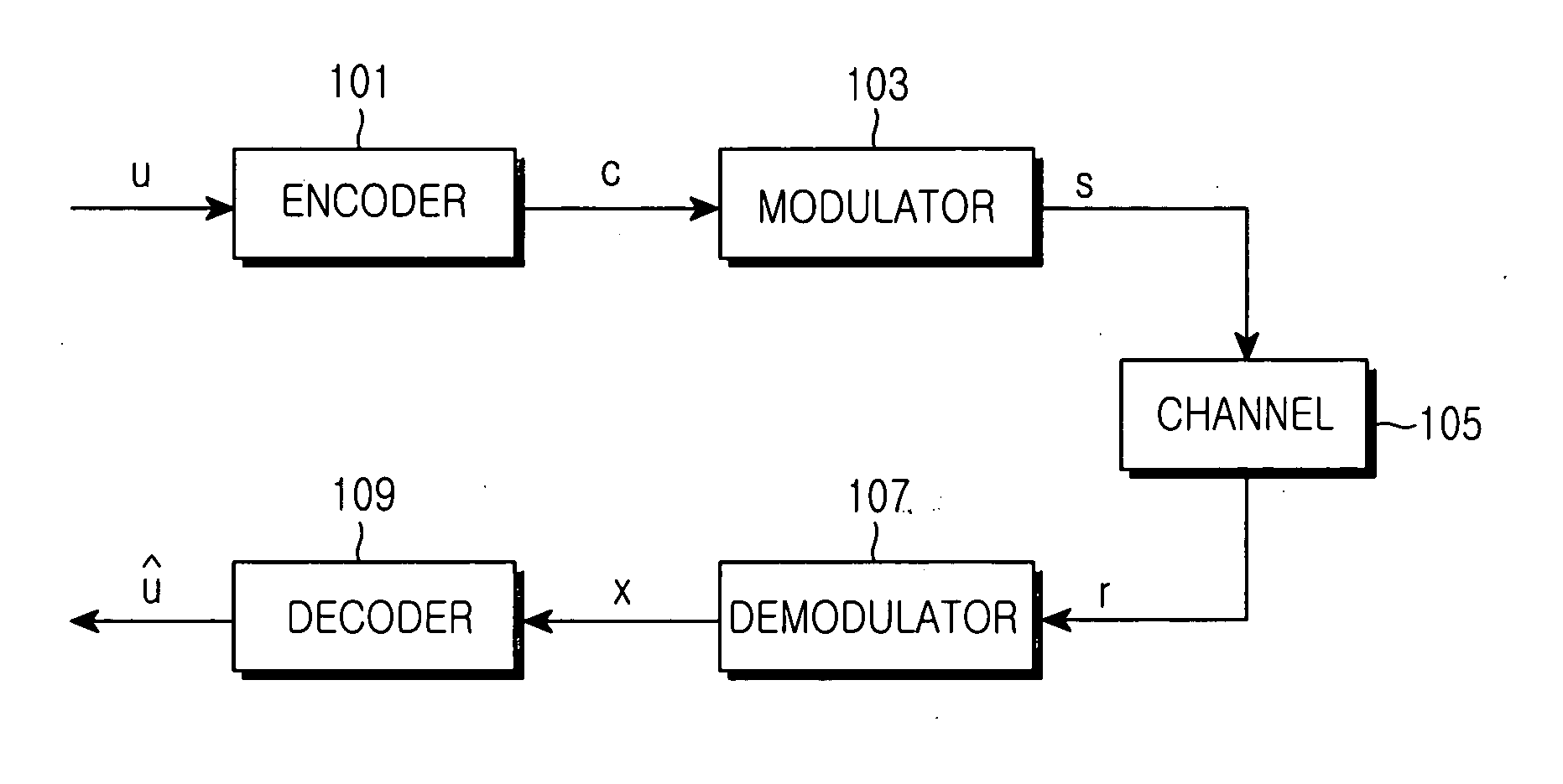

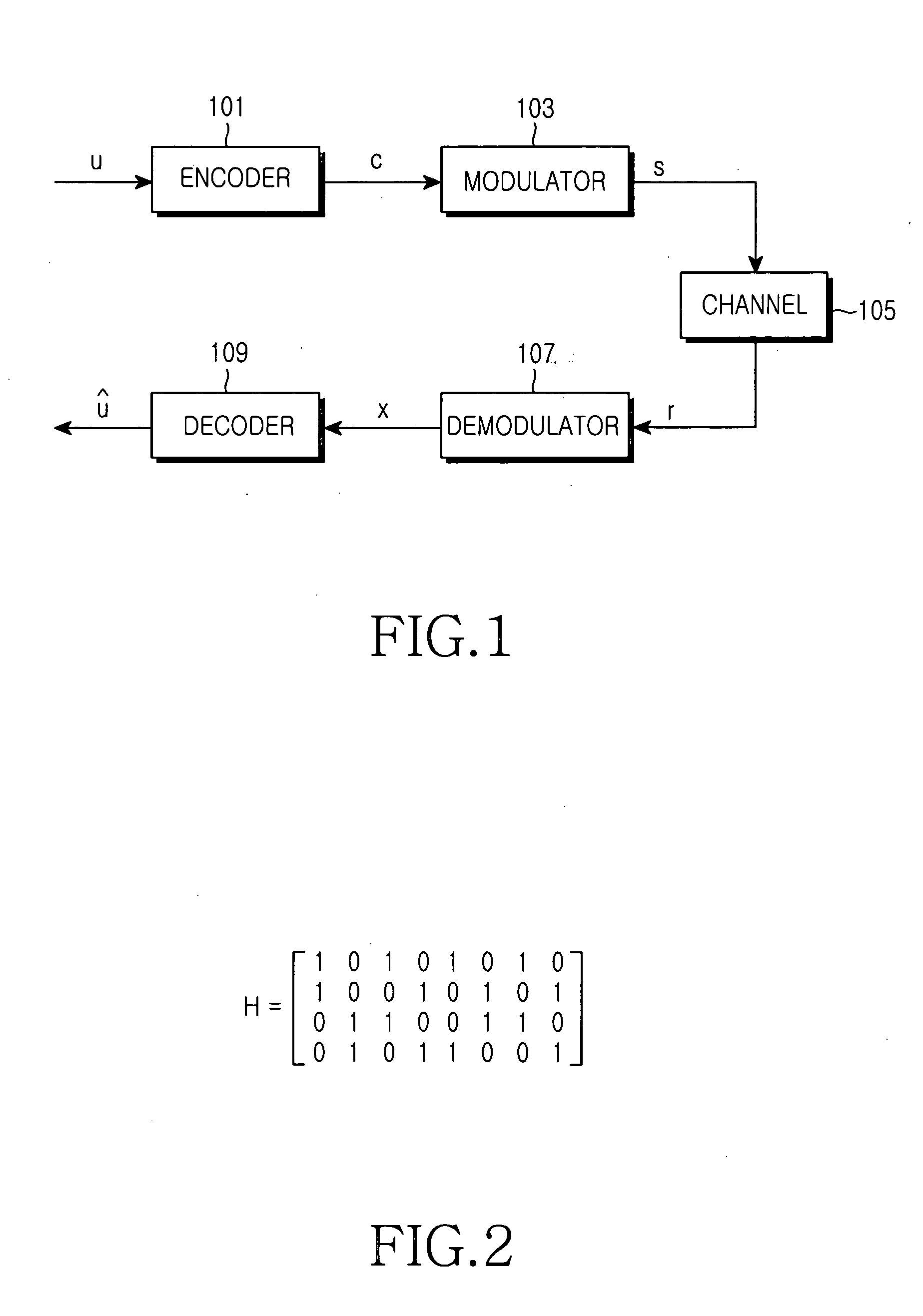

Method and apparatus for low density parity check encoding of data

InactiveUS6895547B2Improve performanceError preventionError detection/correctionTheoretical computer scienceParity-check matrix

A method for low-density parity-check (LDPC) encoding of data comprises defining a first M×N parity check matrix; generating, based on the first parity check matrix, a second parity check matrix having an M×M triangular sub-matrix; and, mapping the data into an LDPC code word based on the second parity check matrix. The method is particularly useful for data communications applications, but may also be employed in other applications such as, for example, data storage.

Owner:GLOBALFOUNDRIES US INC

Method and system for providing low density parity check (LDPC) encoding

ActiveUS7191378B2Readily apparentInterconnection arrangementsError correction/detection using LDPC codesAlgorithmParity-check matrix

An approach is provided for a method of encoding structure Low Density Parity Check (LDPC) codes. Memory storing information representing a structured parity check matrix of Low Density Parity Check (LDPC) codes is accessed during the encoding process. The information is organized in tabular form, wherein each row represents occurrences of one values within a first column of a group of columns of the parity check matrix. The rows correspond to groups of columns of the parity check matrix, wherein subsequent columns within each of the groups are derived according to a predetermined operation. An LDPC coded signal is output based on the stored information representing the parity check matrix.

Owner:DTVG LICENSING INC

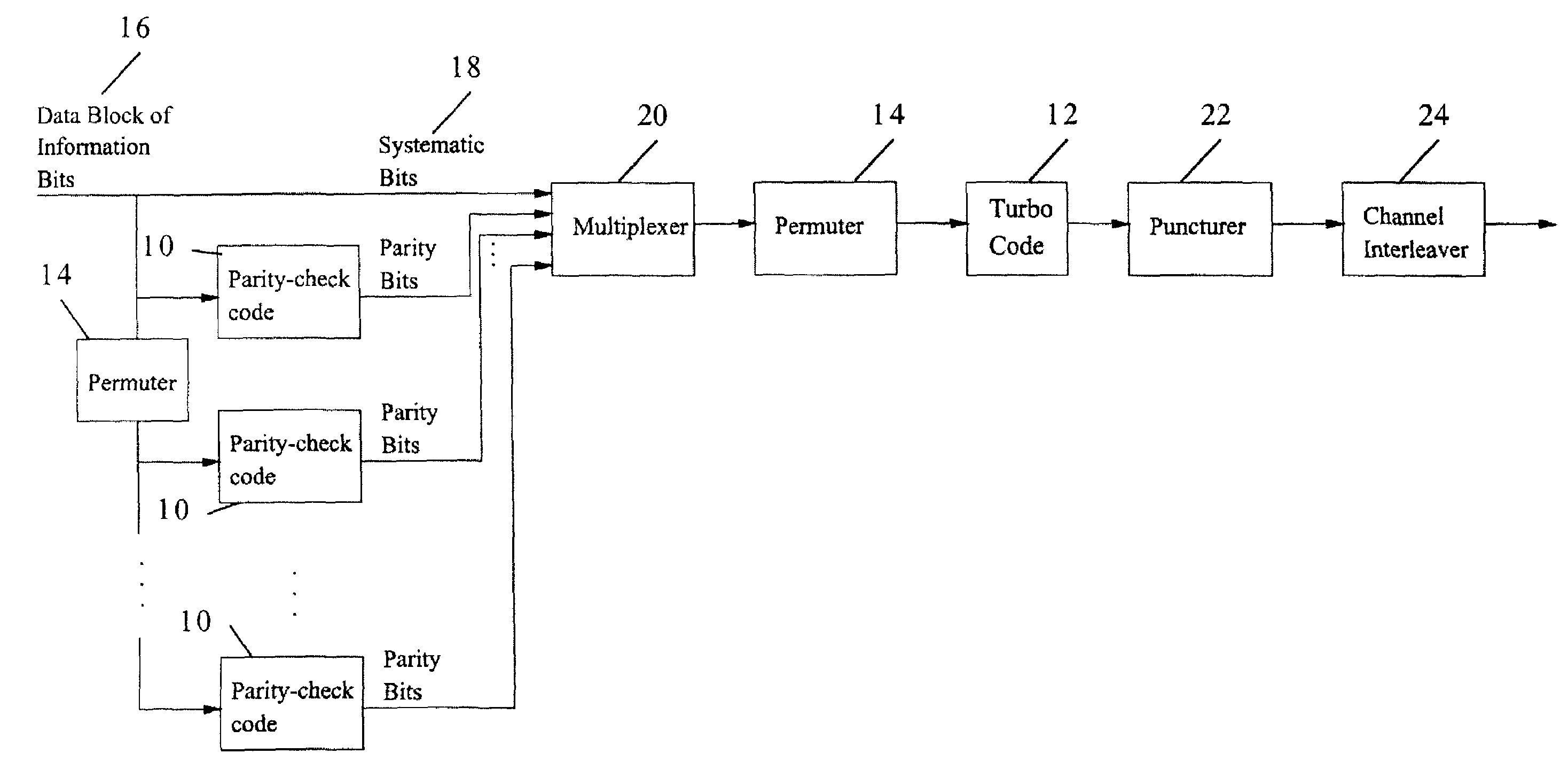

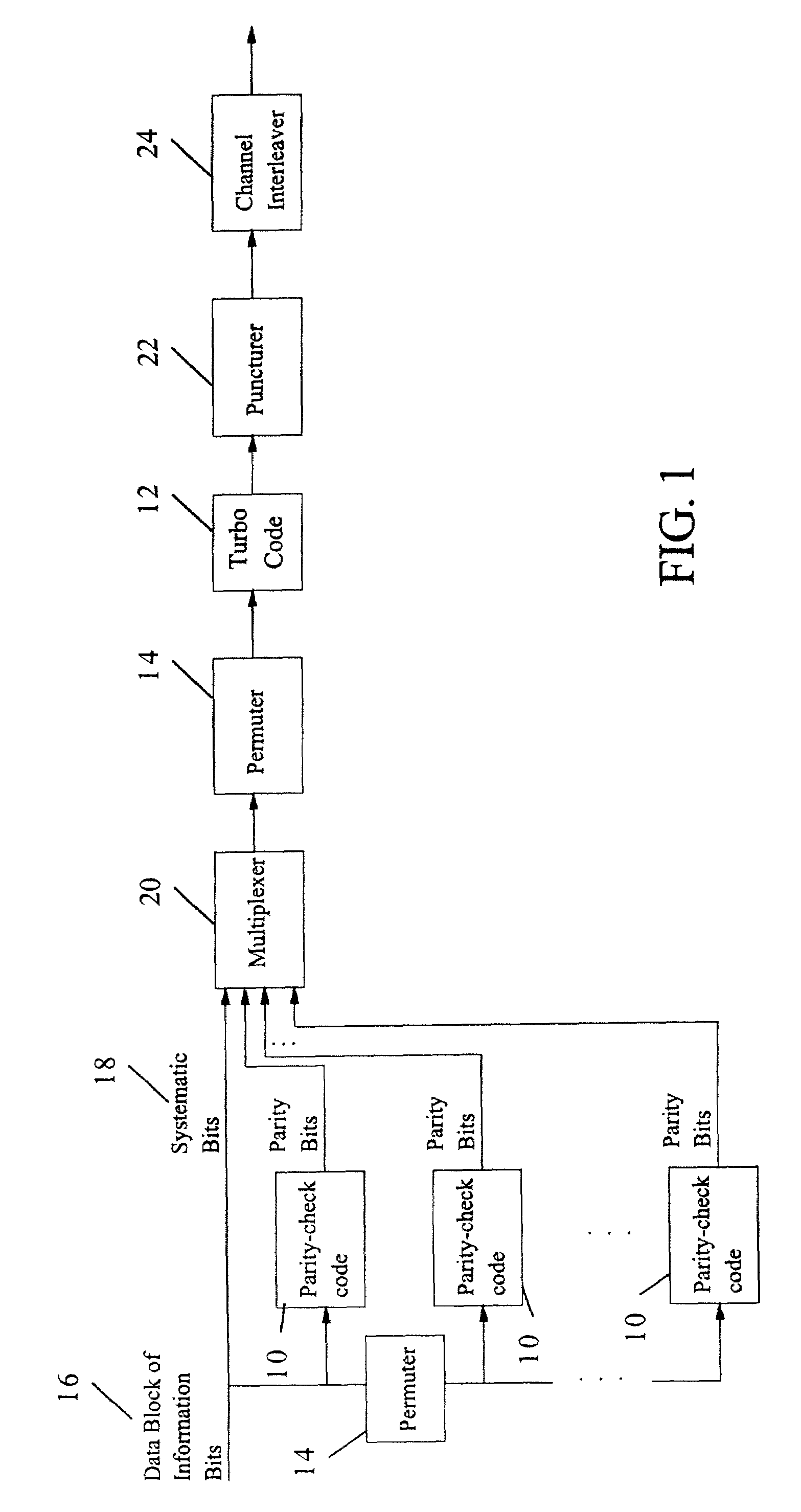

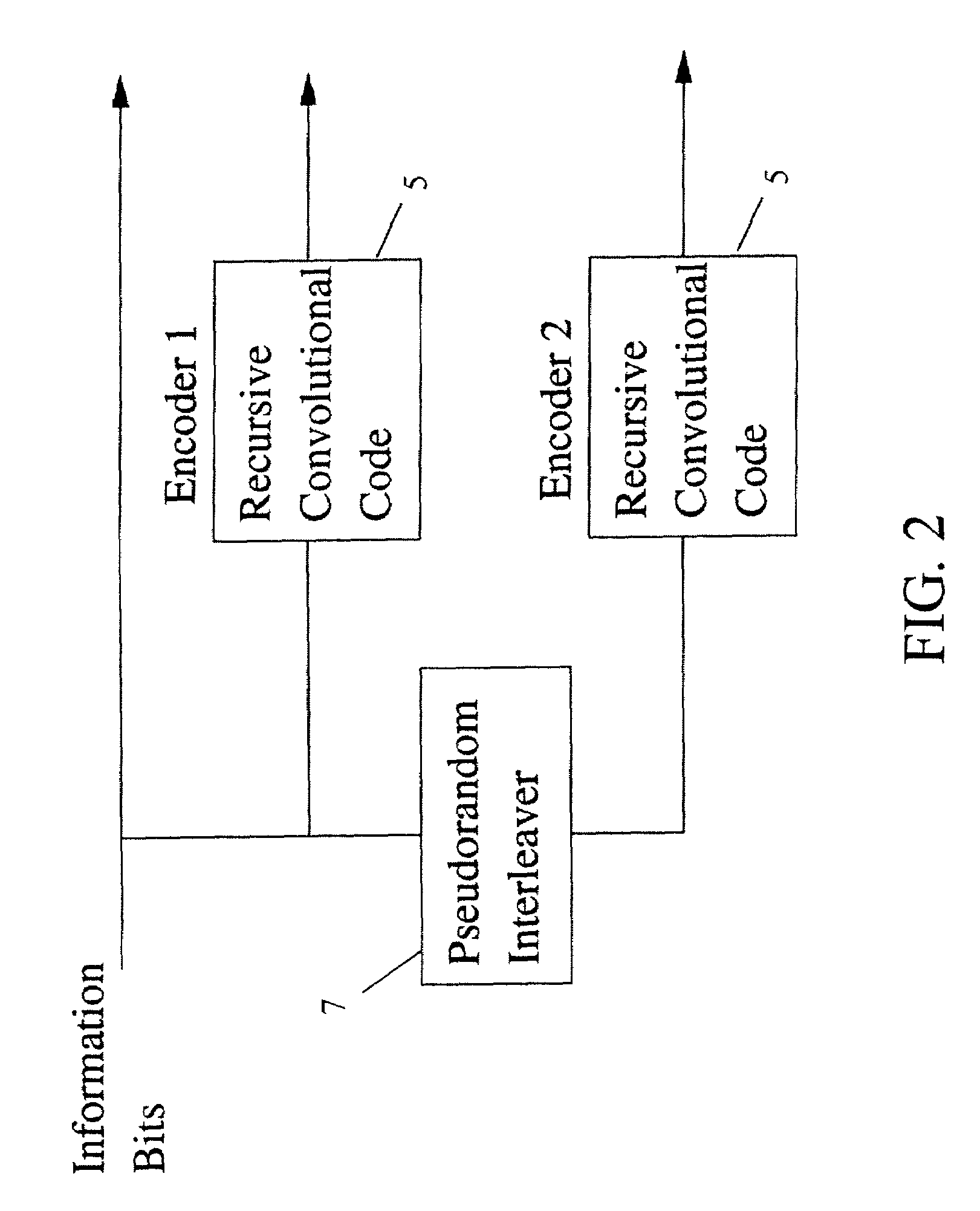

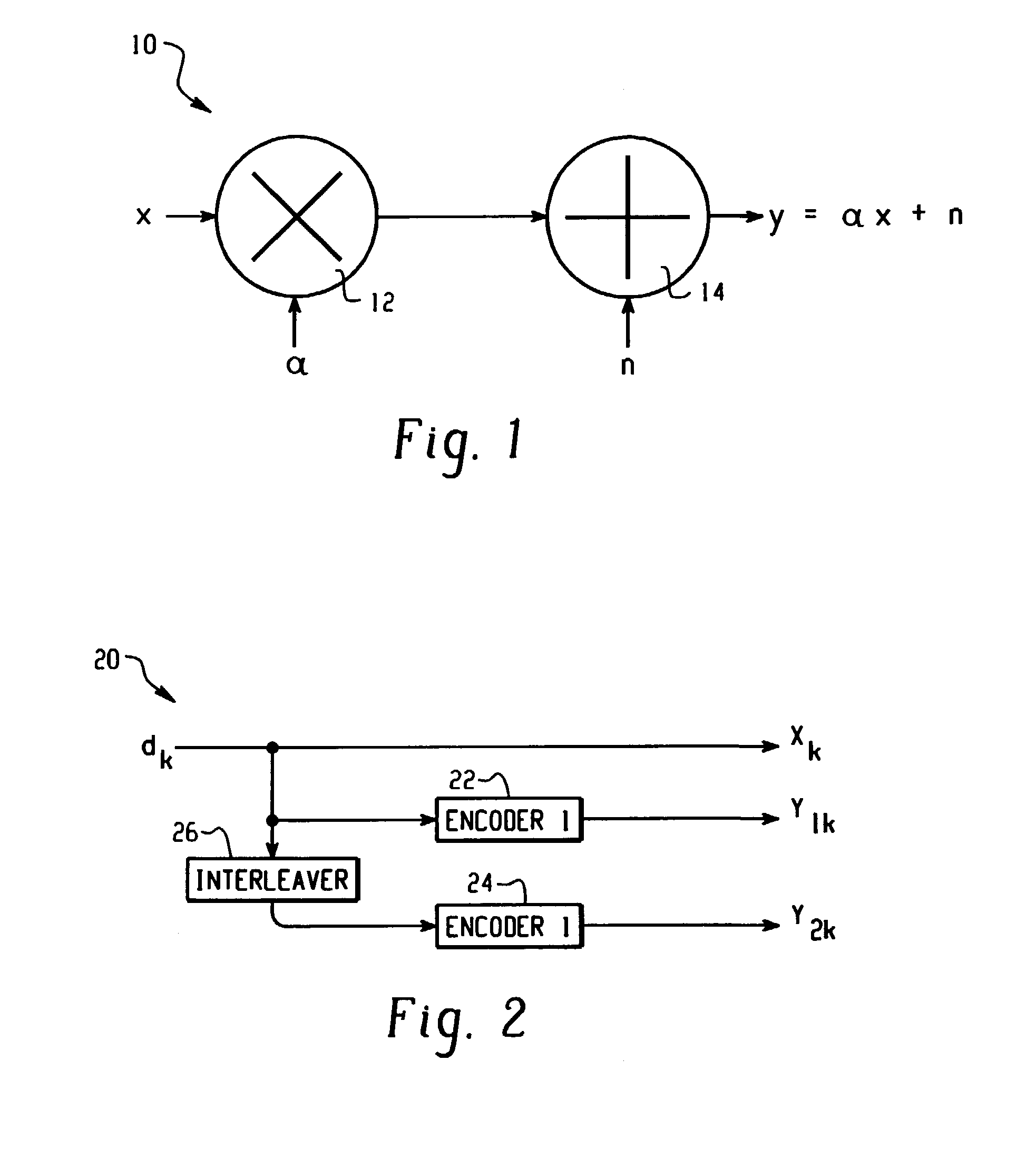

Method and coding means for error-correction utilizing concatenated parity and turbo codes

InactiveUS7093179B2Reduction in rateImprove overall utilizationError preventionError detection/correctionParallel computingTurbo coded

A method and apparatus for encoding and decoding data using an overall code comprising an outer parity-check and an inner parallel concatenated convolutional, or turbo code. The overall code provides error probabilities that are significantly lower than can be achieved by using turbo codes alone. The output of the inner code can be punctured to maintain the same turbo code rate as the turbo code encoding without the outer code. Multiple parity-check codes can be concatanated either serially or in parallel as outer codes. Decoding can be performed with iterative a posteriori probability (APP) decoders or with other decoders, depending on the requirements of the system. The parity-check code can be applied to a subset of the bits to achieve unequal error protection. Moreover, the techniques presented can be mapped to higher order modulation schemes to achieve improved power and bandwidth efficiency.

Owner:FLORIDA UNIV OF A FLORIDA +1

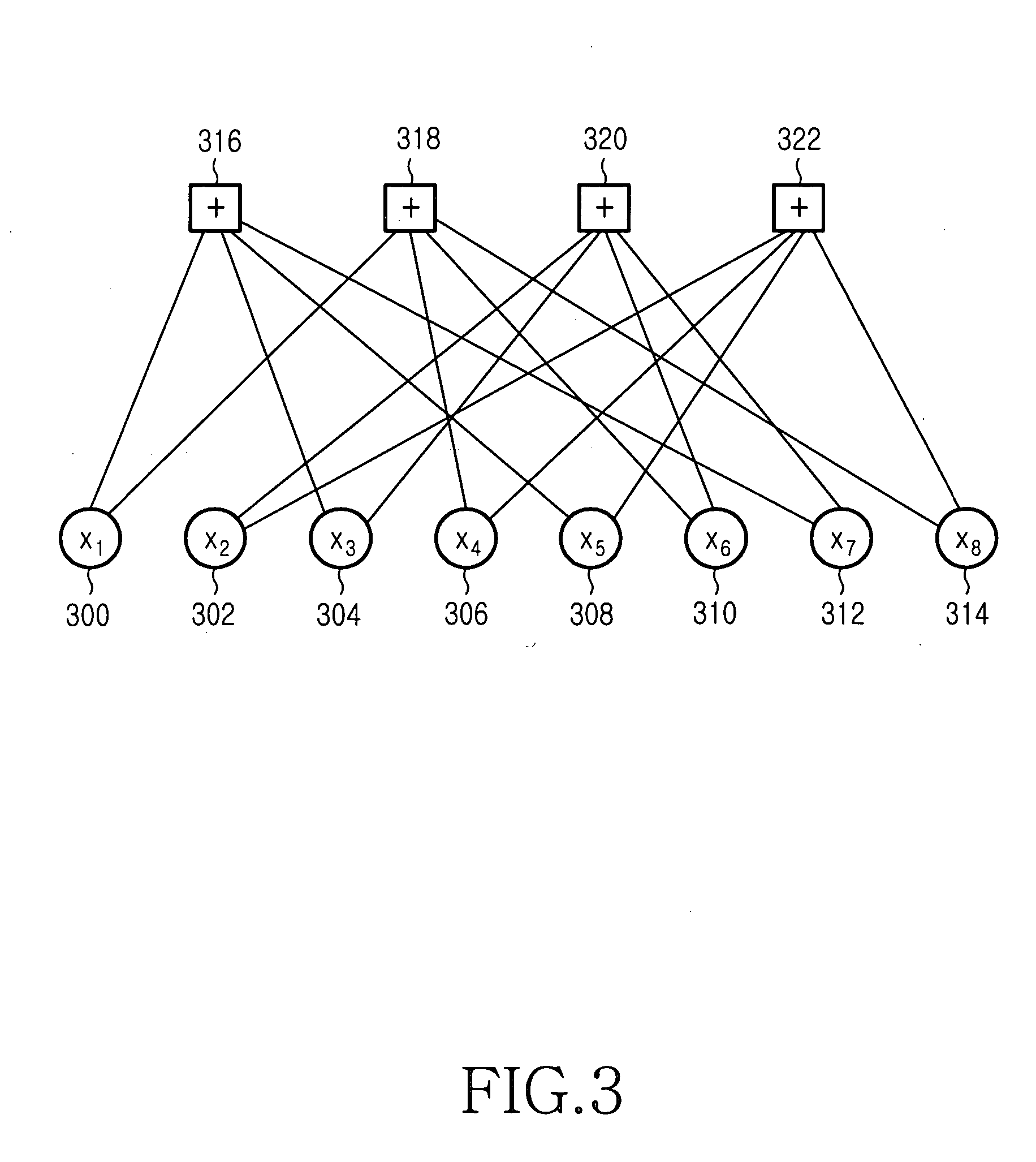

Encoding method using a low density parity check code with a column weight of two

ActiveUS7058873B2Facilitate the processOther decoding techniquesError correction/detection using multiple parity bitsTanner graphCommunications system

A method for communicating binary data and a digital communication system are presented. According to one embodiment, the method includes encoding a message word by multiplying the message word with a generator matrix, wherein the generator matrix multiplied by the transpose of a parity check matrix for a low density parity check code yields a null set, and wherein the parity check matrix has a column weight of two. Additionally disclosed is an encoding scheme based on a three-tier Tanner graph having a girth of twelve.

Owner:CARNEGIE MELLON UNIV

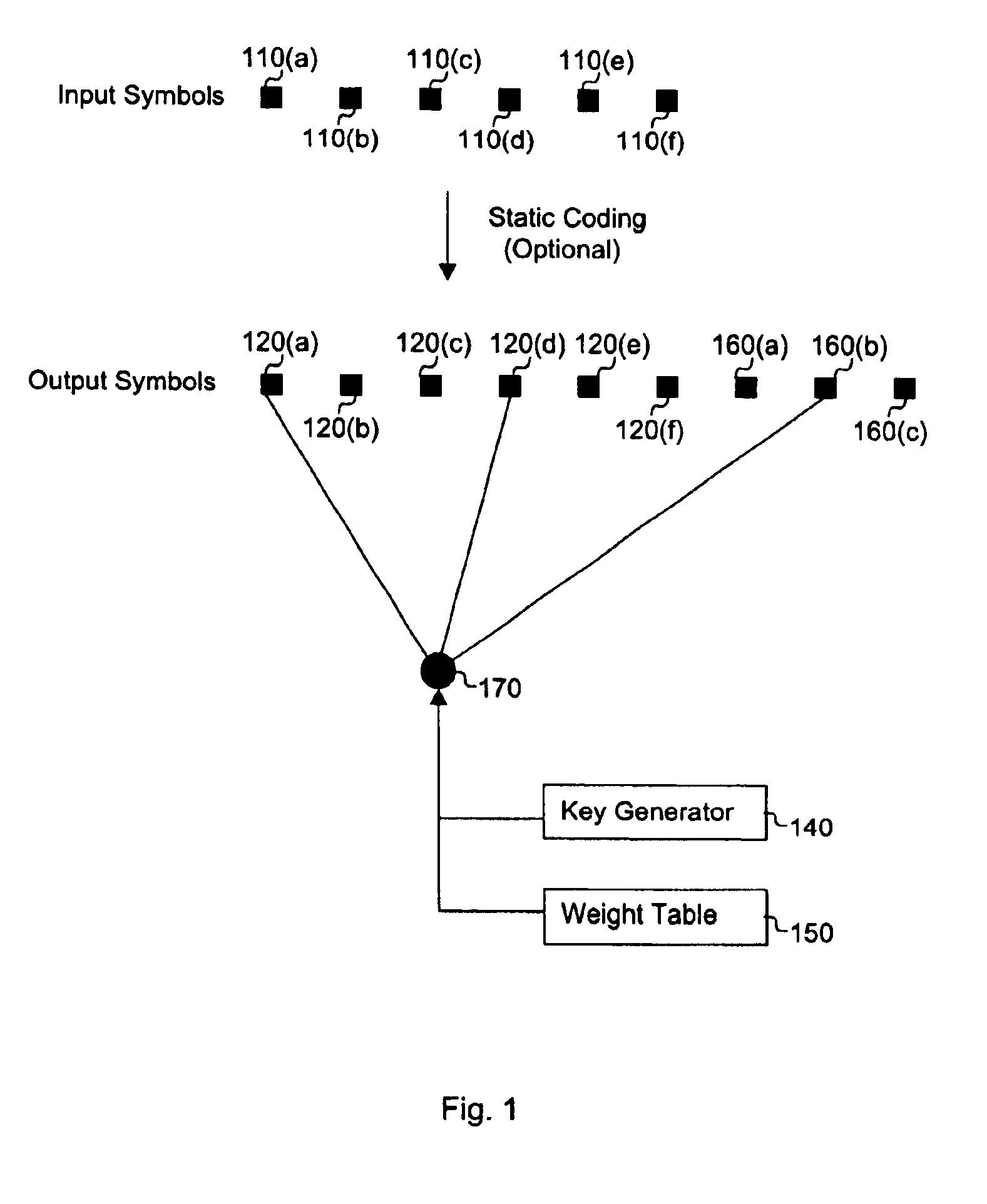

Multi-stage code generator and decoder for communication systems

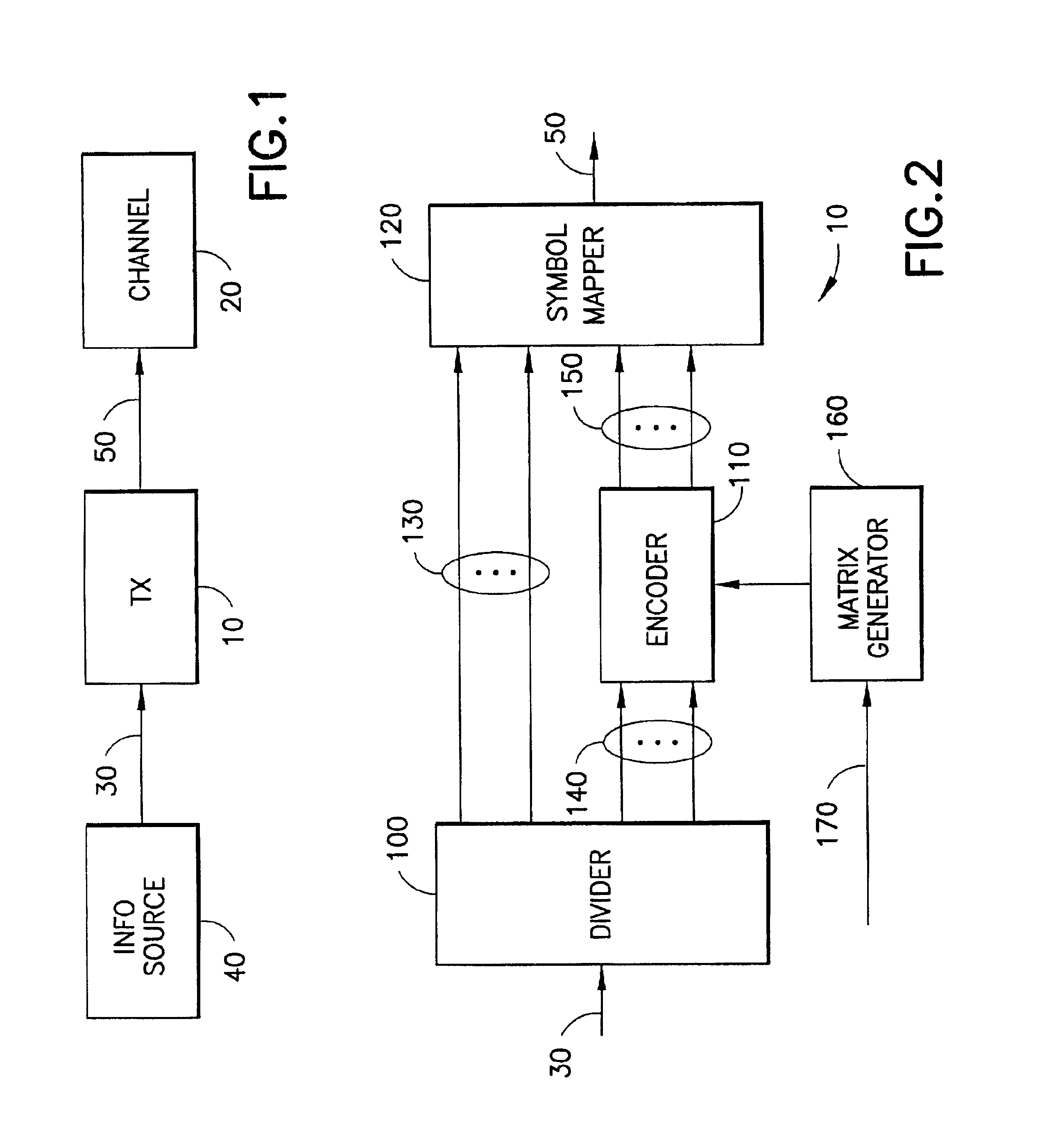

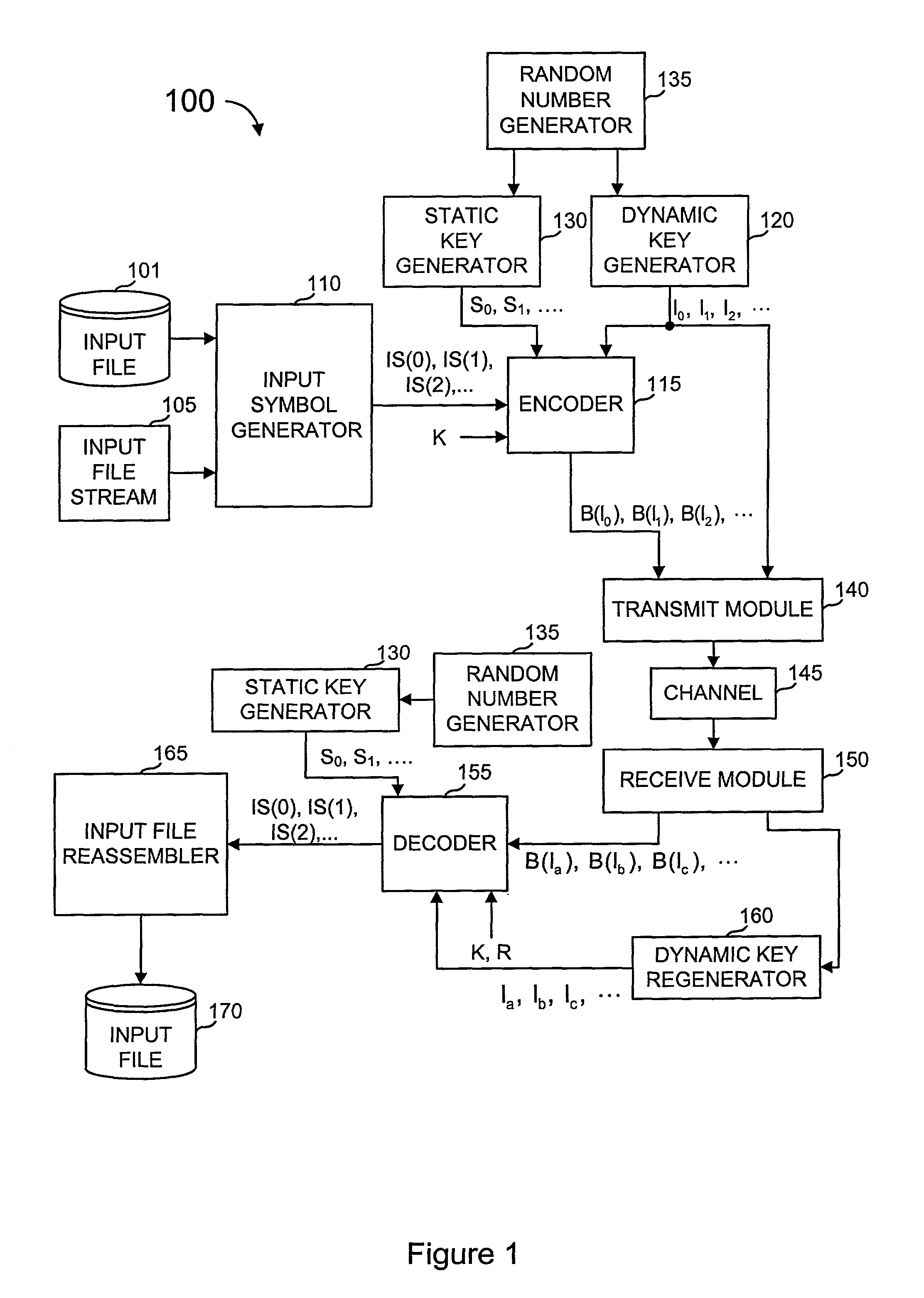

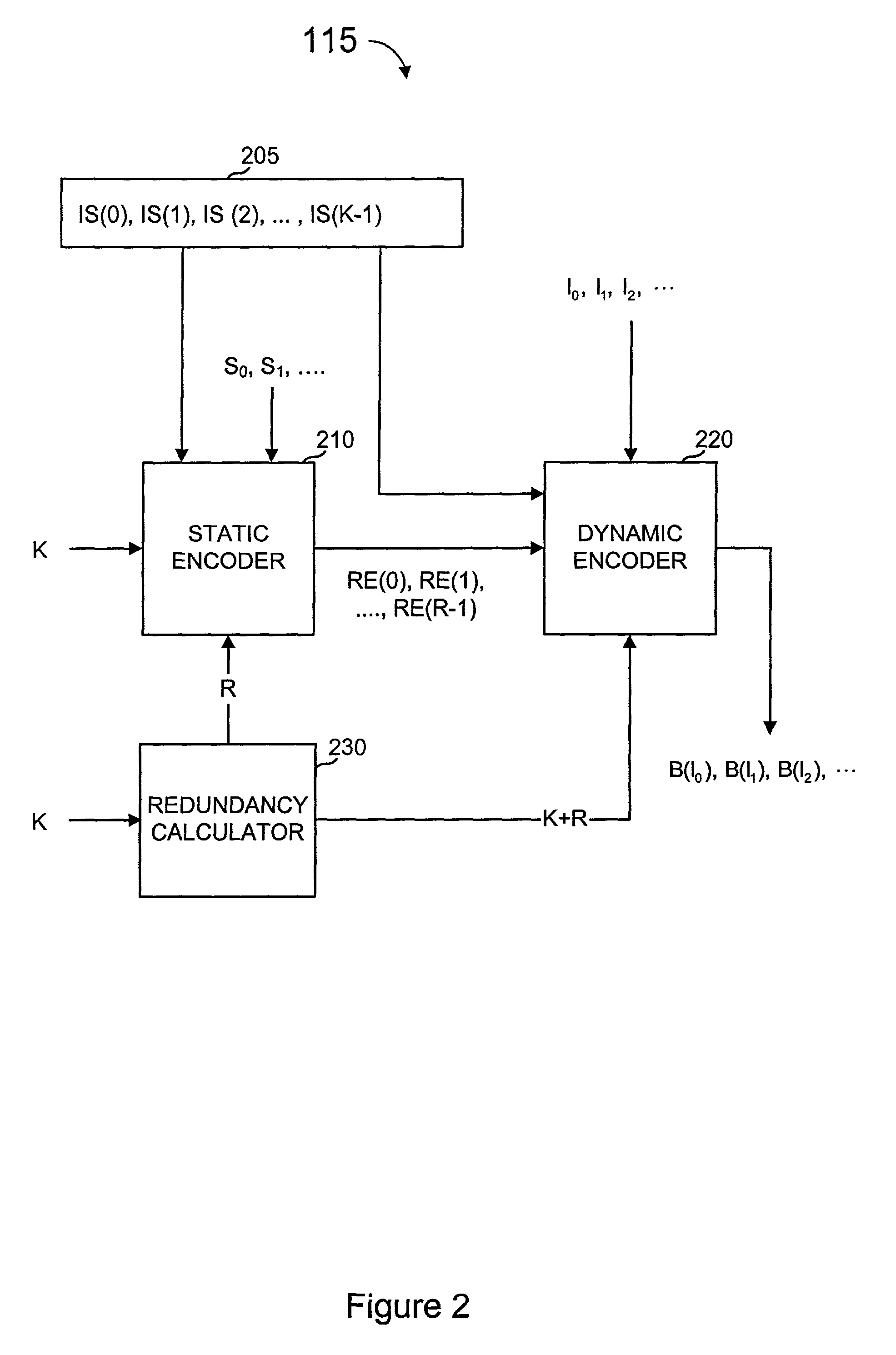

InactiveUS7068729B2Reduce expensesOther decoding techniquesOther error detection/correction/protectionCommunications systemOrder set

Owner:QUALCOMM INC

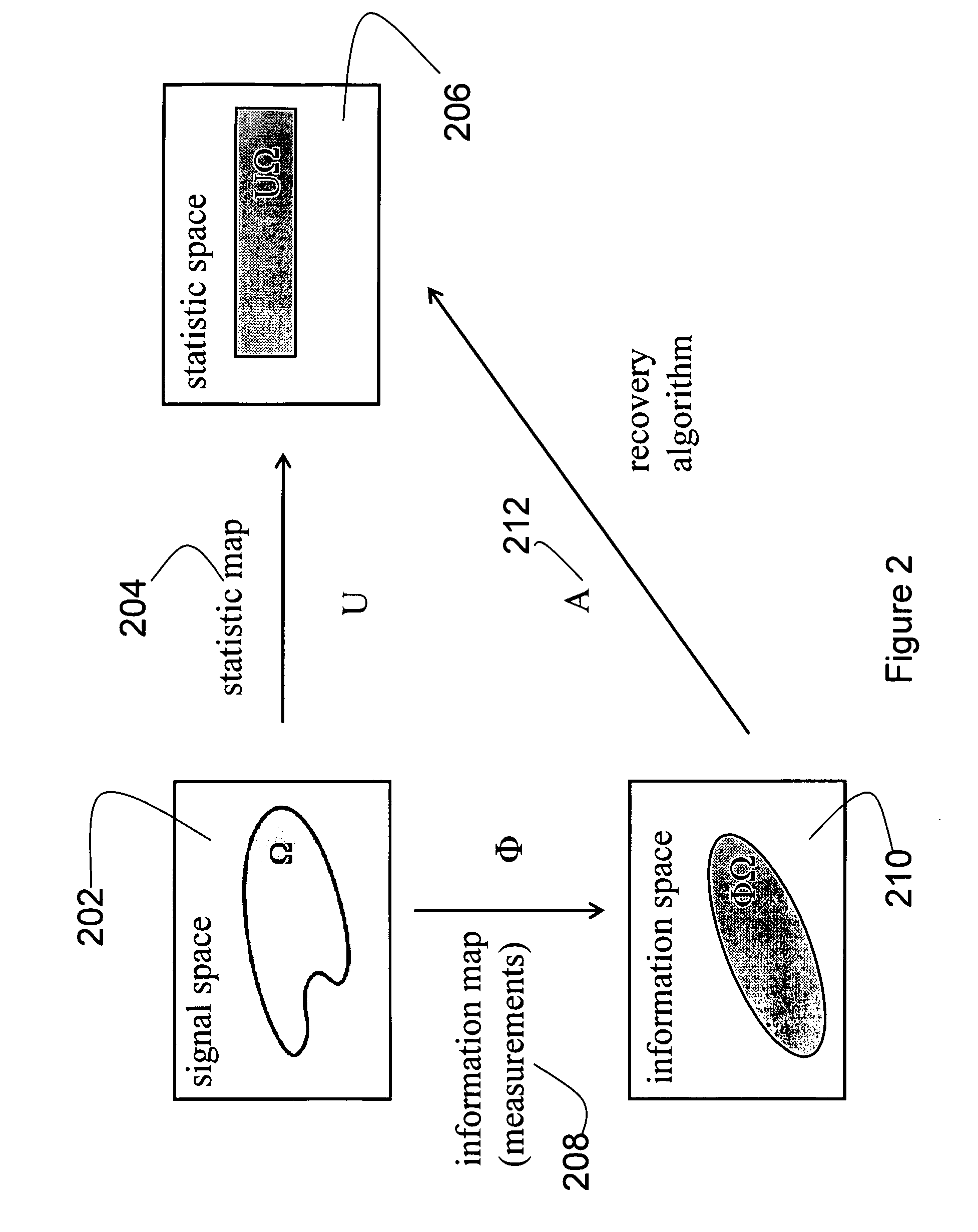

Method and Apparatus for On-Line Compressed Sensing

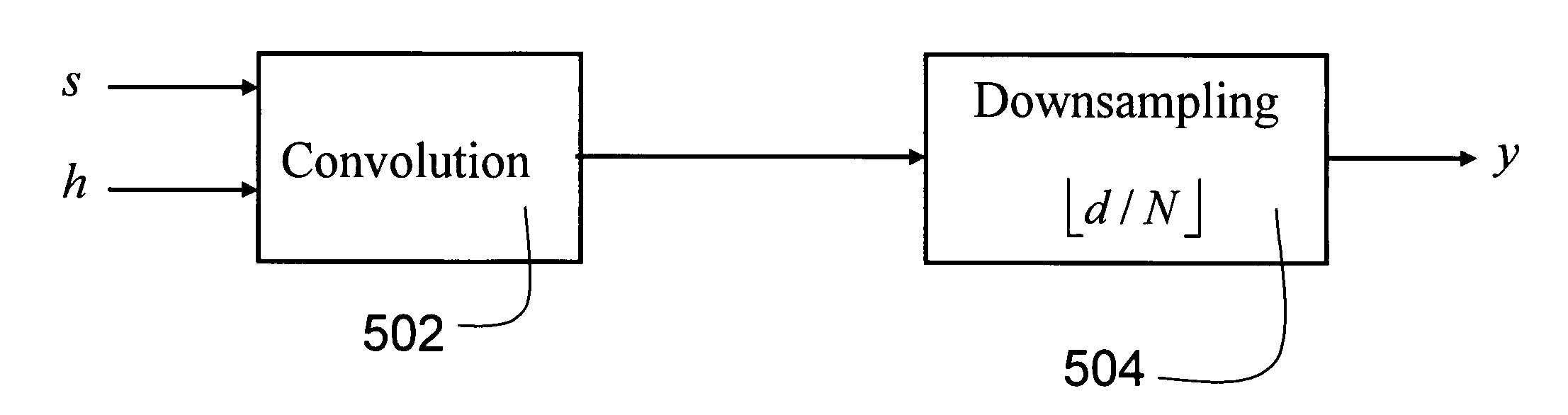

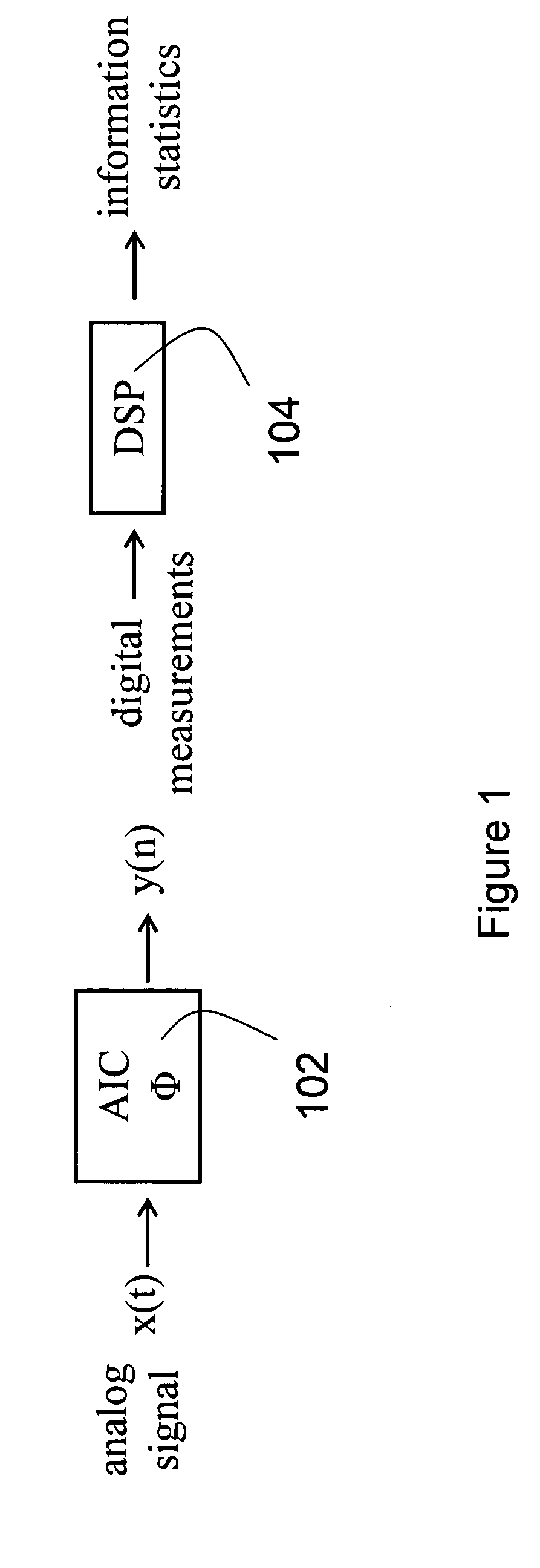

ActiveUS20090222226A1Improve system performanceAnalogue/digital conversionError correction/detection using multiple parity bitsHigh rateDiscrete-time signal

A typical data acquisition system takes periodic samples of a signal, image, or other data, often at the so-called Nyquist / Shannon sampling rate of two times the data bandwidth in order to ensure that no information is lost. In applications involving wideband signals, the Nyquist / Shannon sampling rate is very high, even though the signals may have a simple underlying structure. Recent developments in mathematics and signal processing have uncovered a solution to this Nyquist / Shannon sampling rate bottlenck for signals that are sparse or compressible in some representation. We demonstrate and reduce to practice methods to extract information directly from an analog or digital signal based on altering our notion of sampling to replace uniform time samples with more general linear functionals. One embodiment of our invention is a low-rate analog-to-information converter that can replace the high-rate analog-to-digital converter in certain applications involving wideband signals. Another embodiment is an encoding scheme for wideband discrete-time signals that condenses their information content.

Owner:RGT UNIV OF MICHIGAN +1

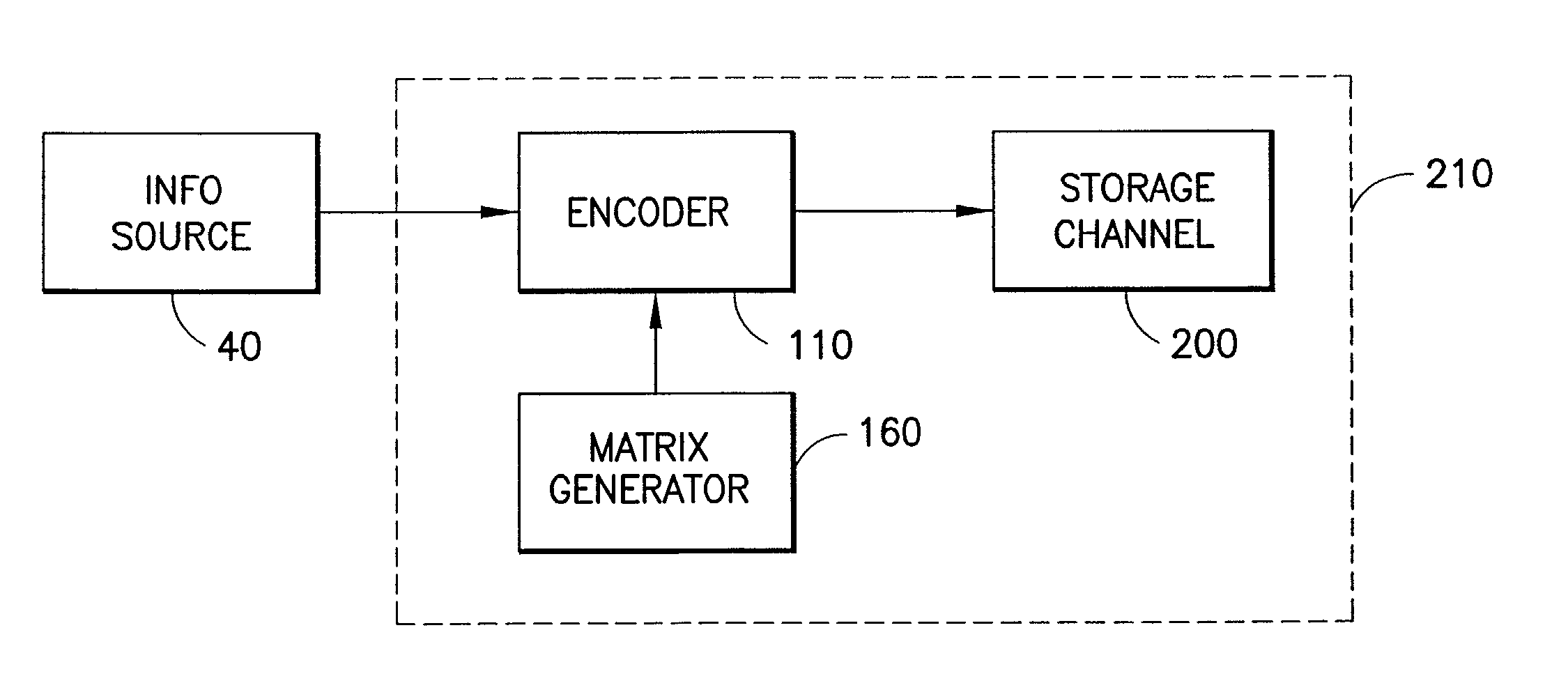

Method and apparatus for low density parity check encoding of data

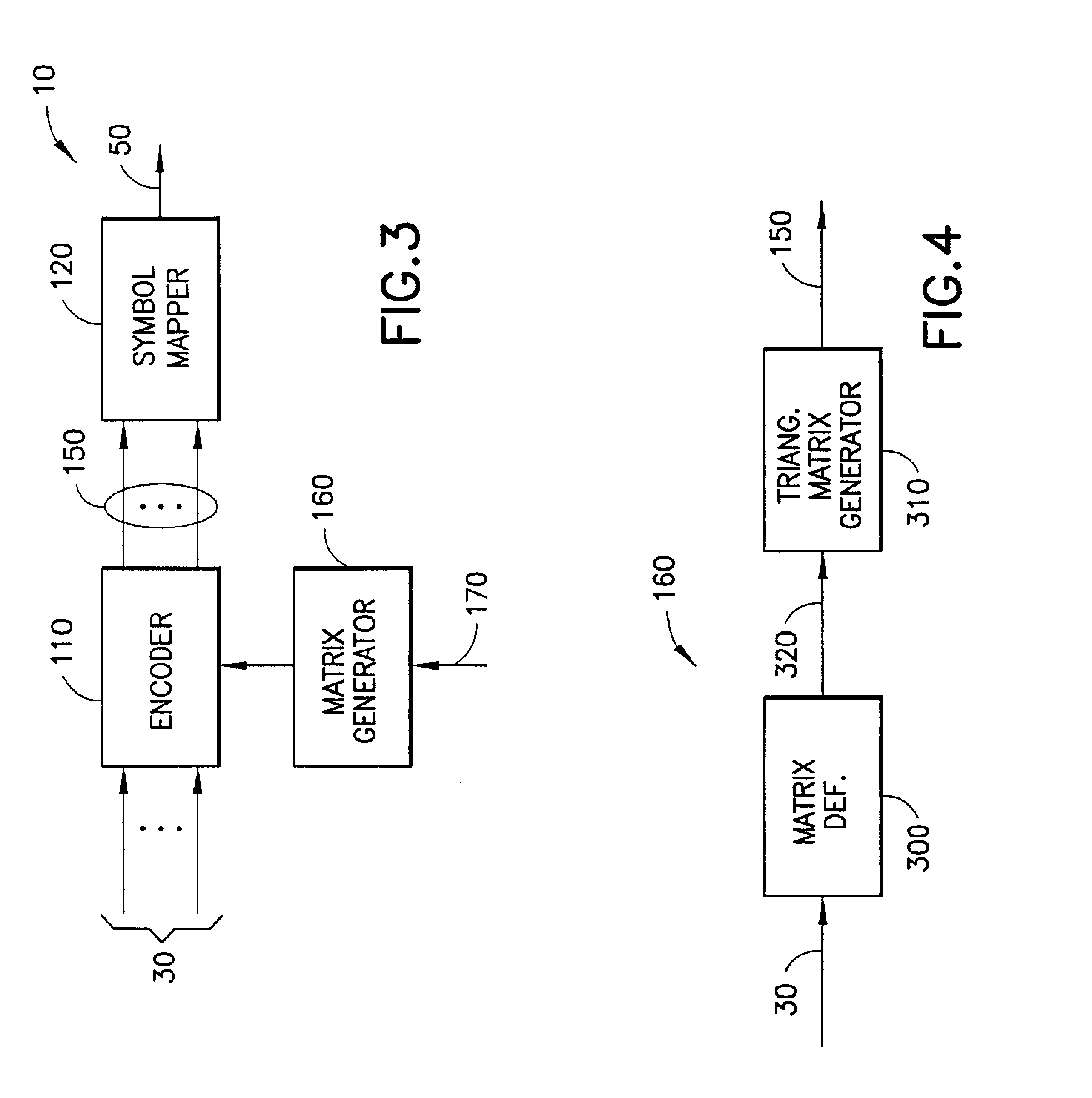

InactiveUS20030037298A1Improve performanceError preventionError detection/correctionParity-check matrixTheoretical computer science

A method for low-density parity-check (LDPC) encoding of data comprises defining a first MxN parity check matrix; generating, based on the first parity check matrix, a second parity check matrix having an MxM triangular sub-matrix; and, mapping the data into an LDPC code word based on the second parity check matrix. The method is particularly useful for data communications applications, but may also be employed in other applications such as, for example, data storage.

Owner:GLOBALFOUNDRIES US INC

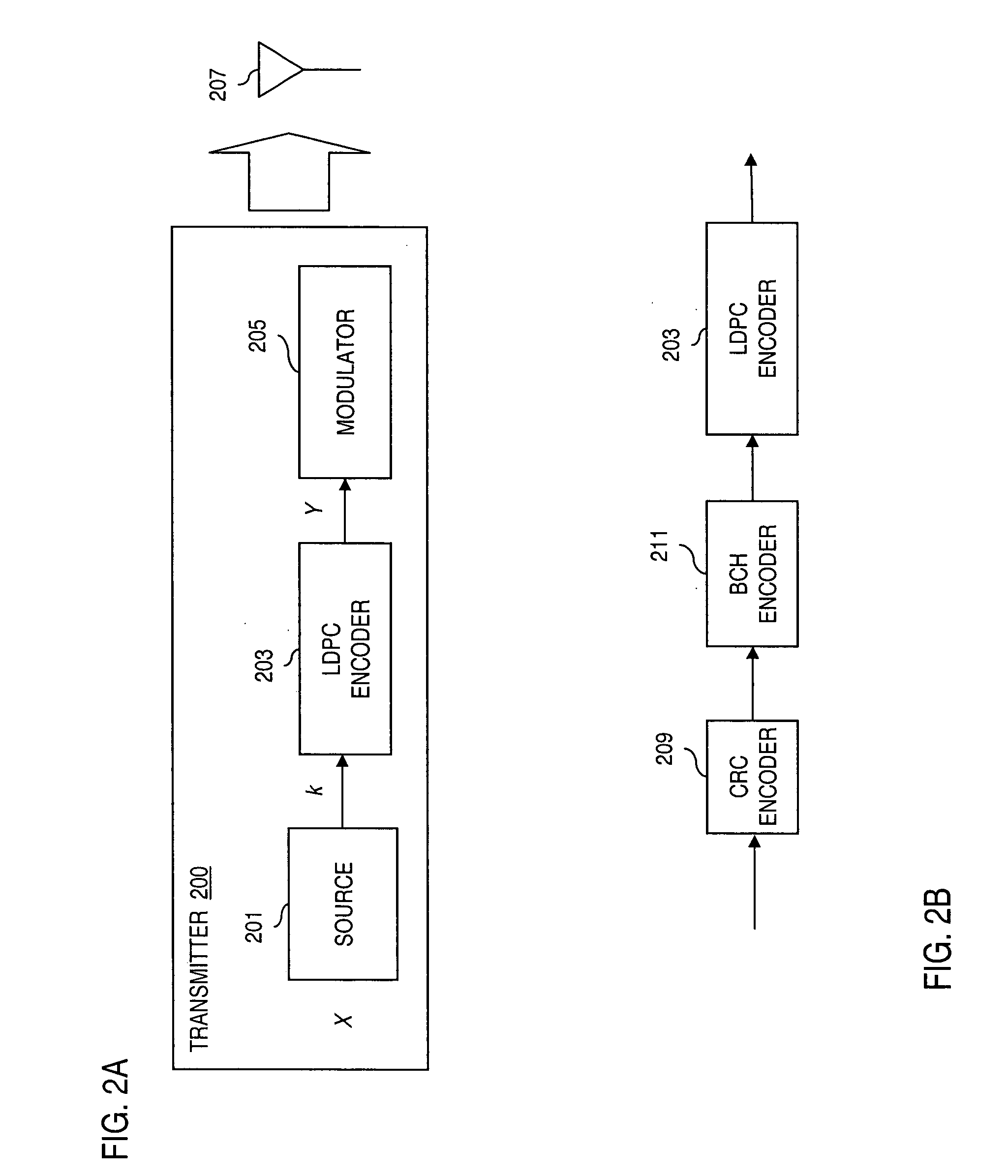

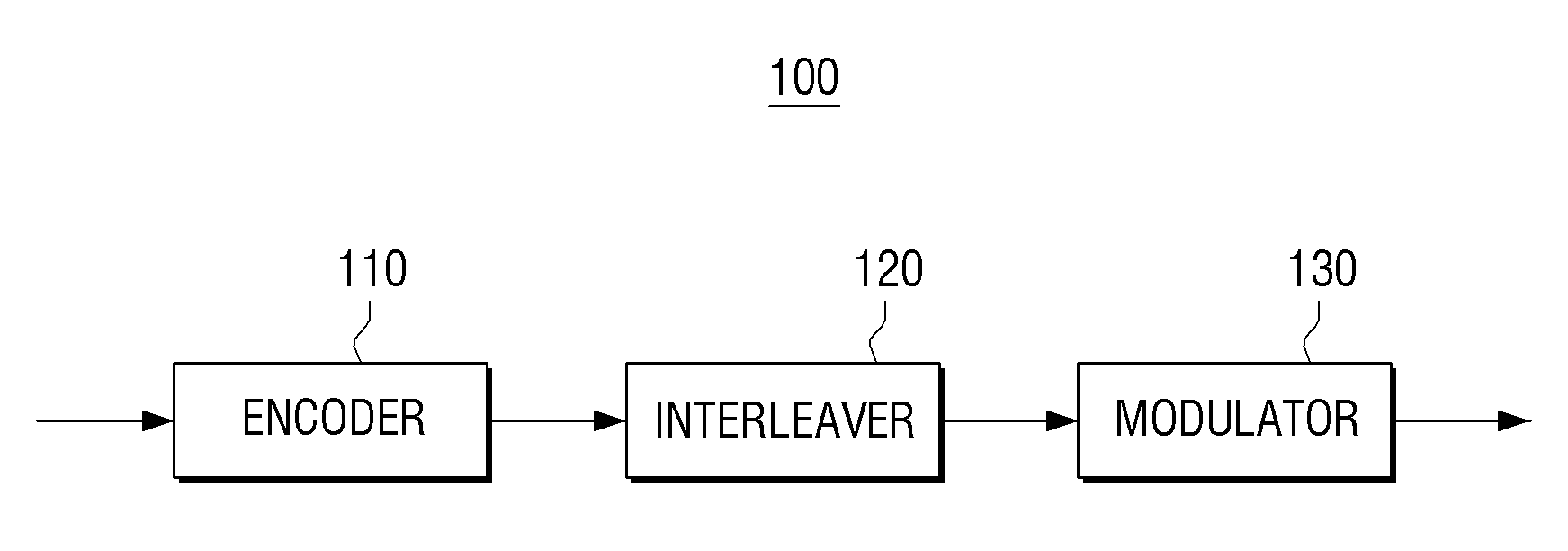

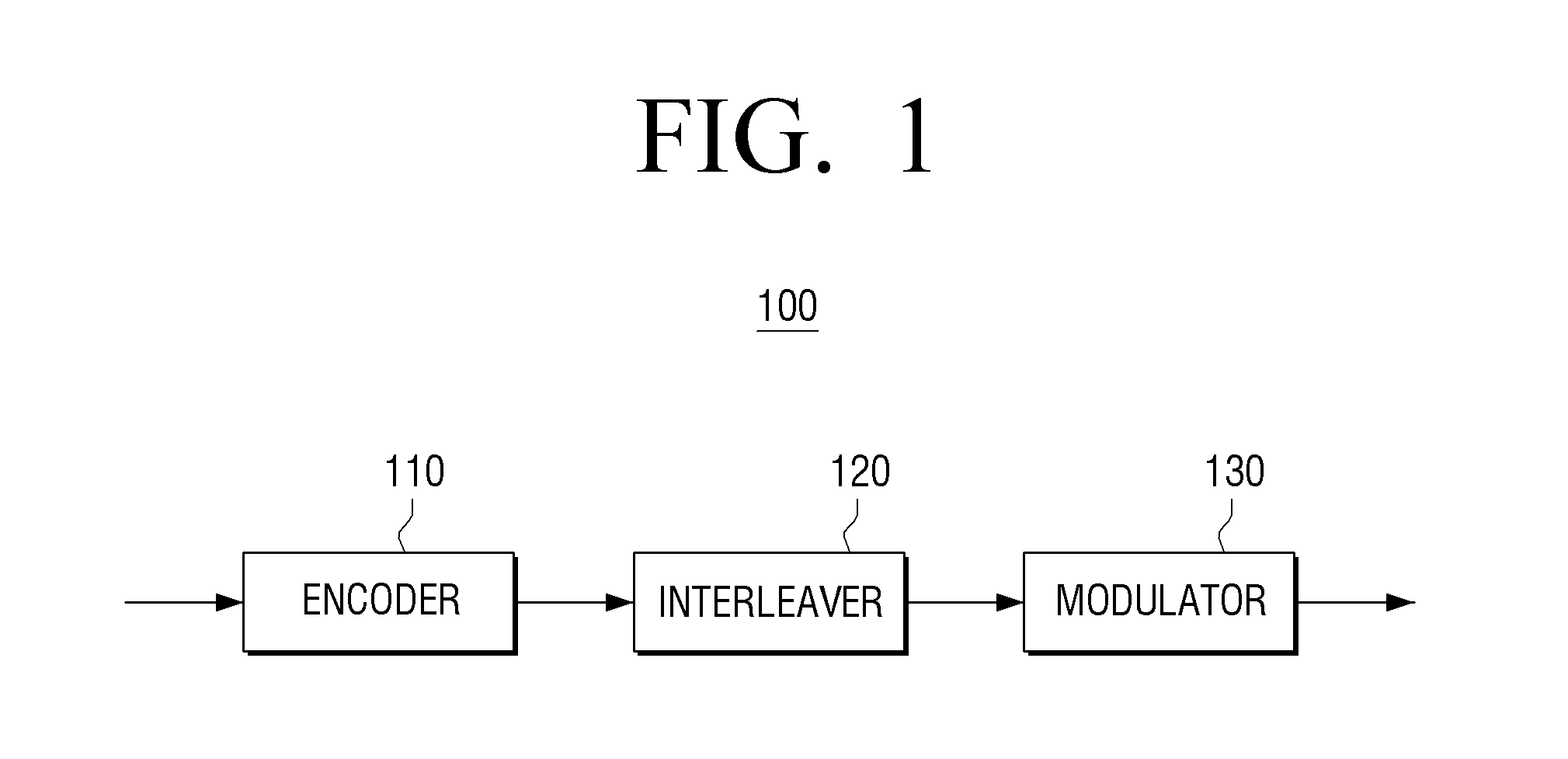

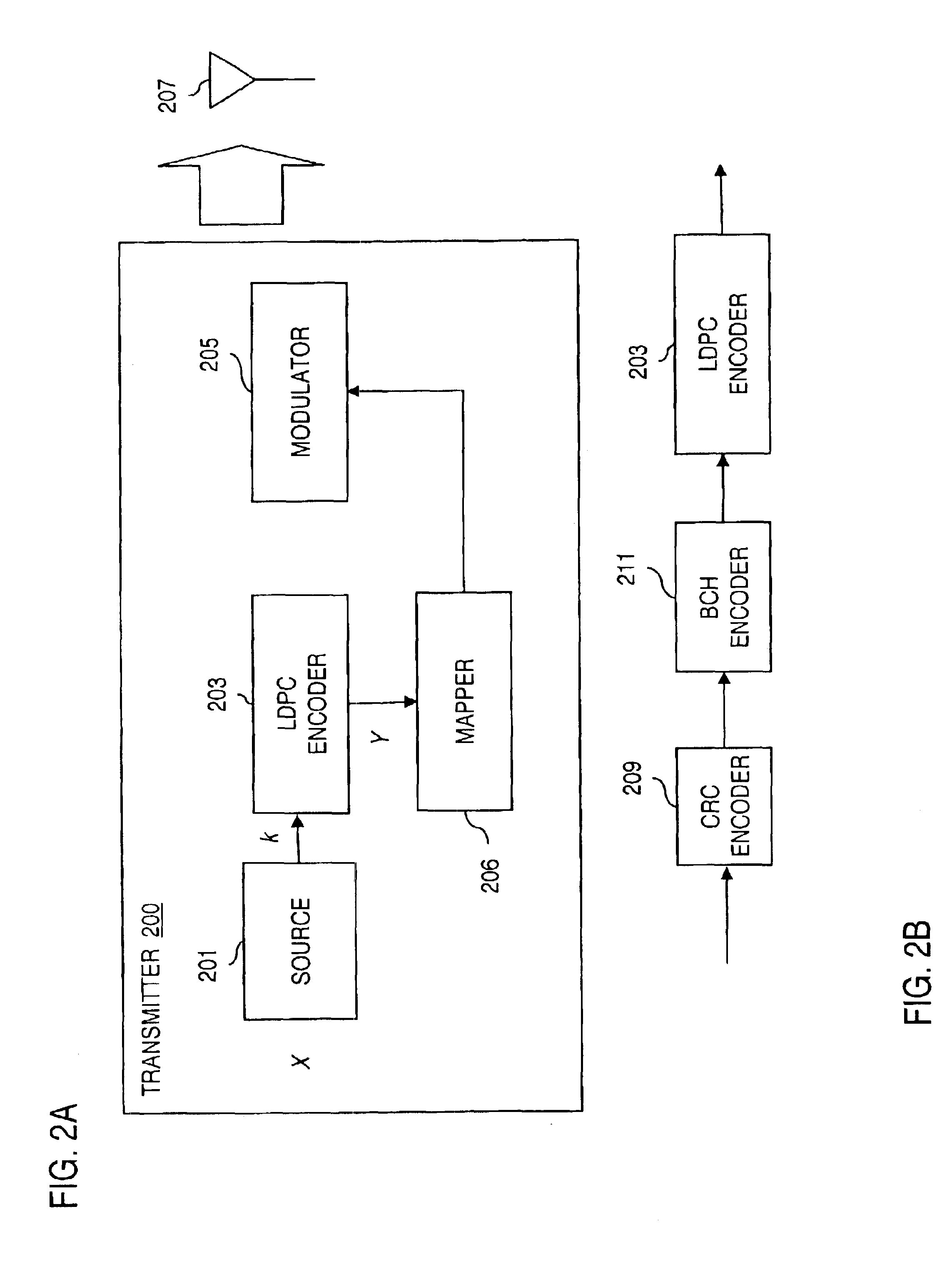

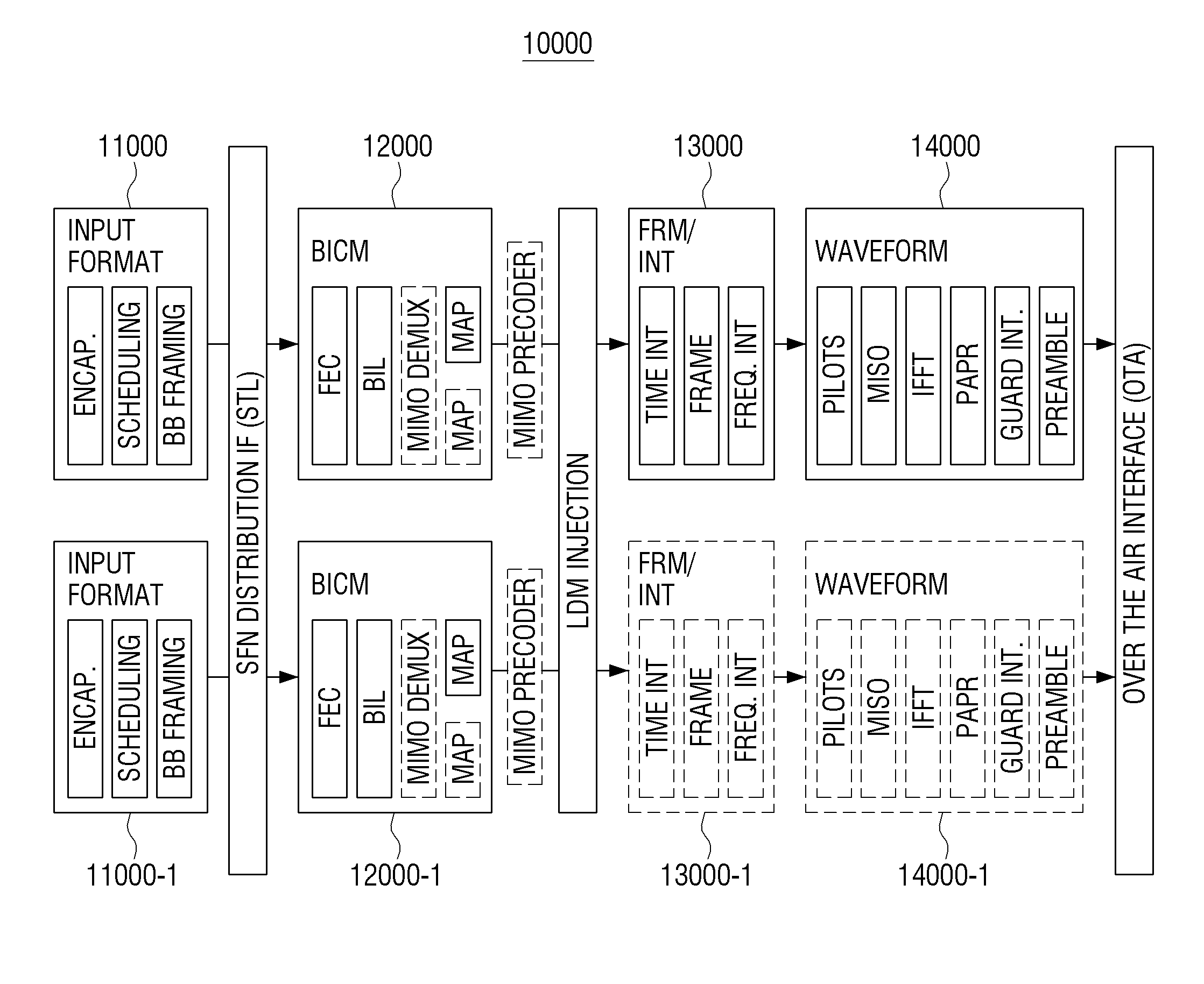

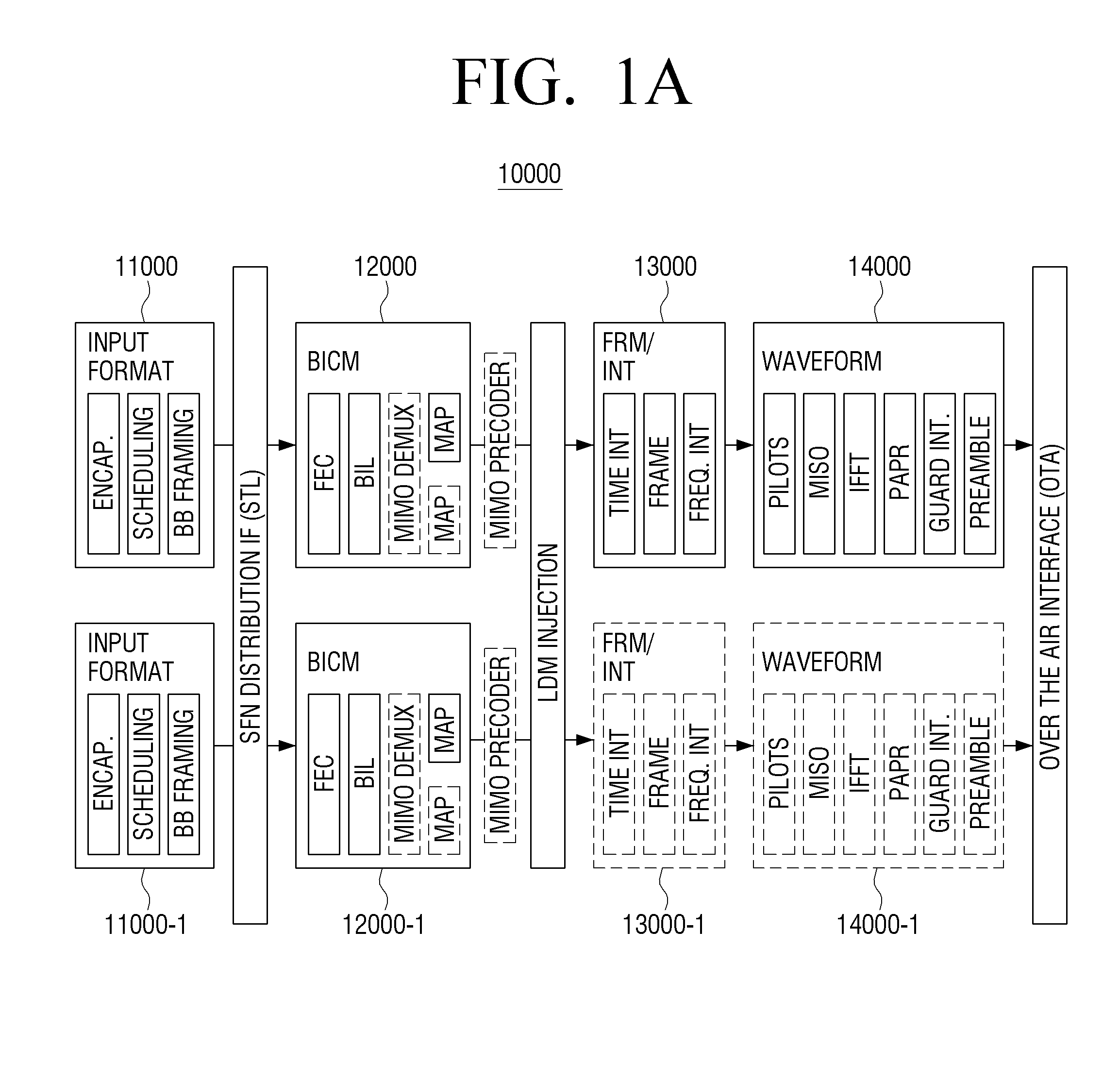

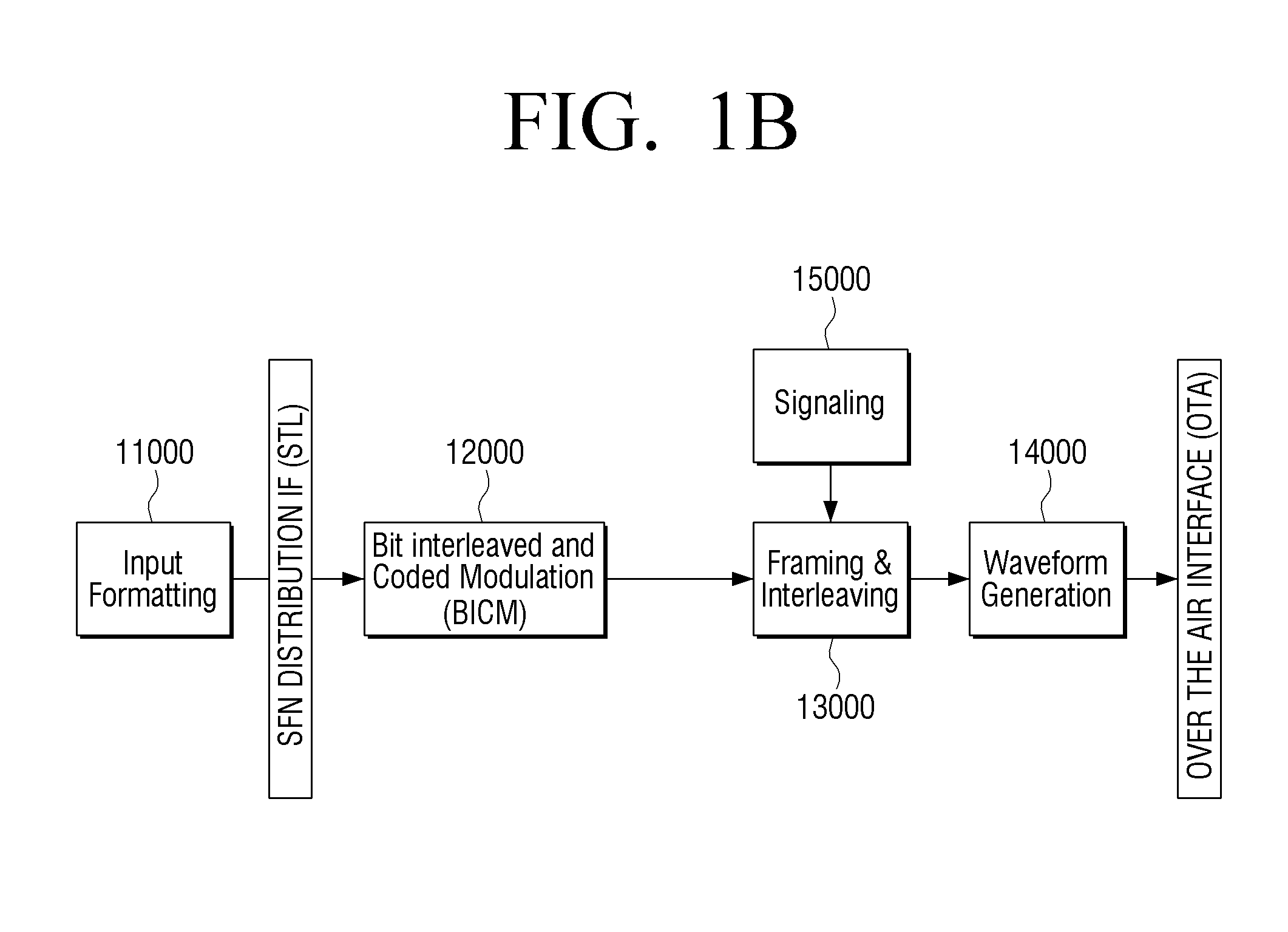

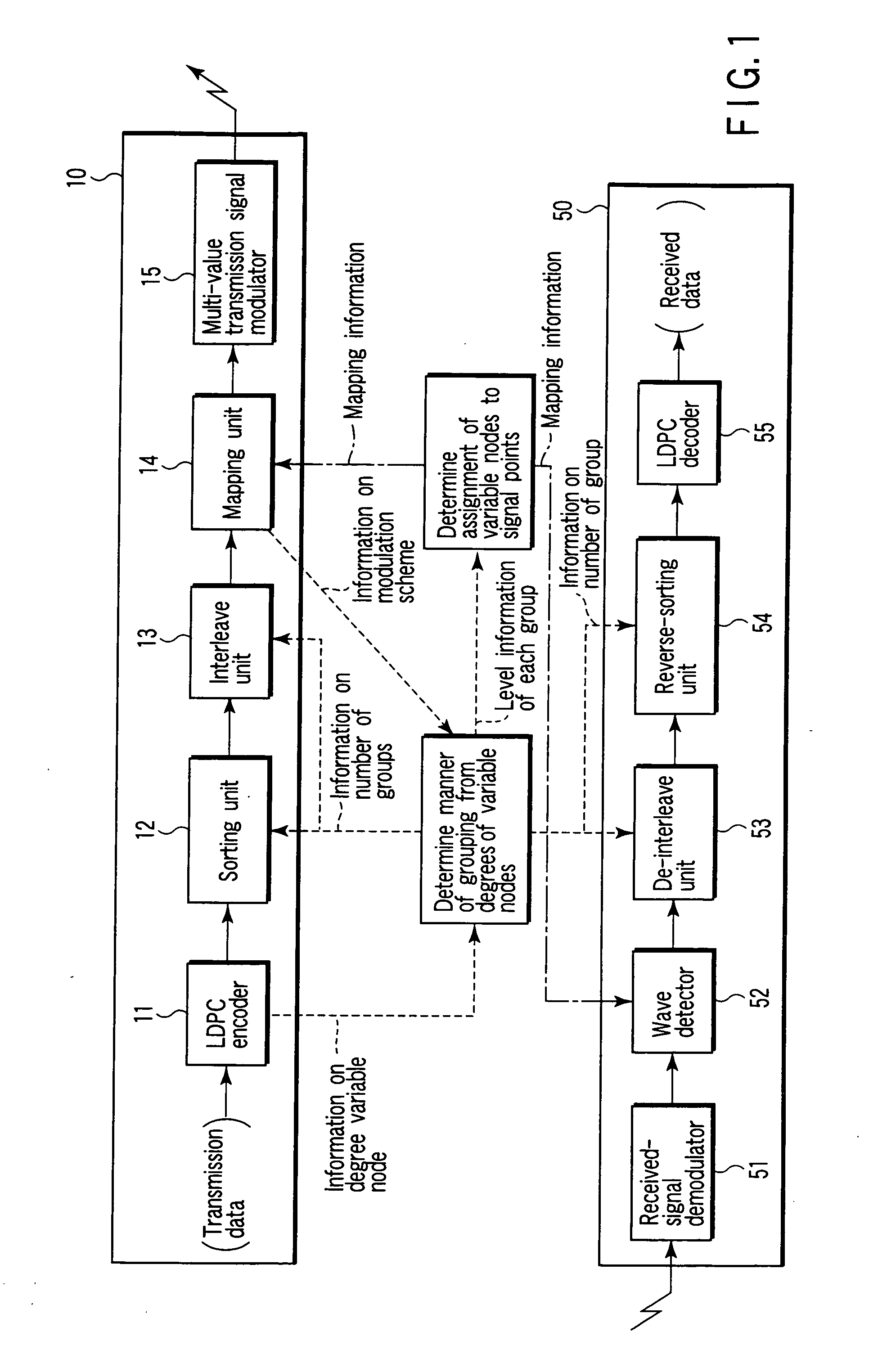

Transmitter apparatus and signal processing method thereof

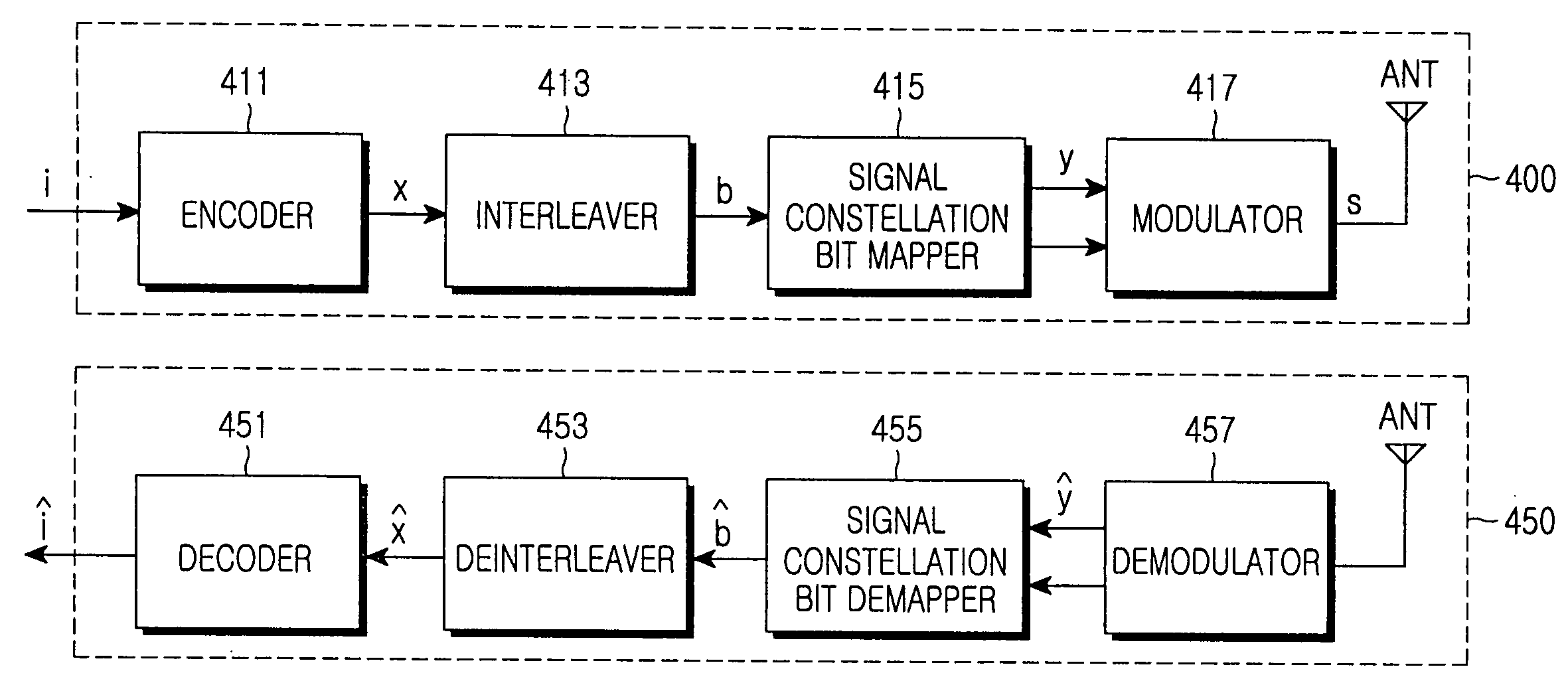

ActiveUS20150039973A1Improve decoding performanceImprove reception performanceError correction/detection using LDPC codesError correction/detection using multiple parity bitsLow densityComputer science

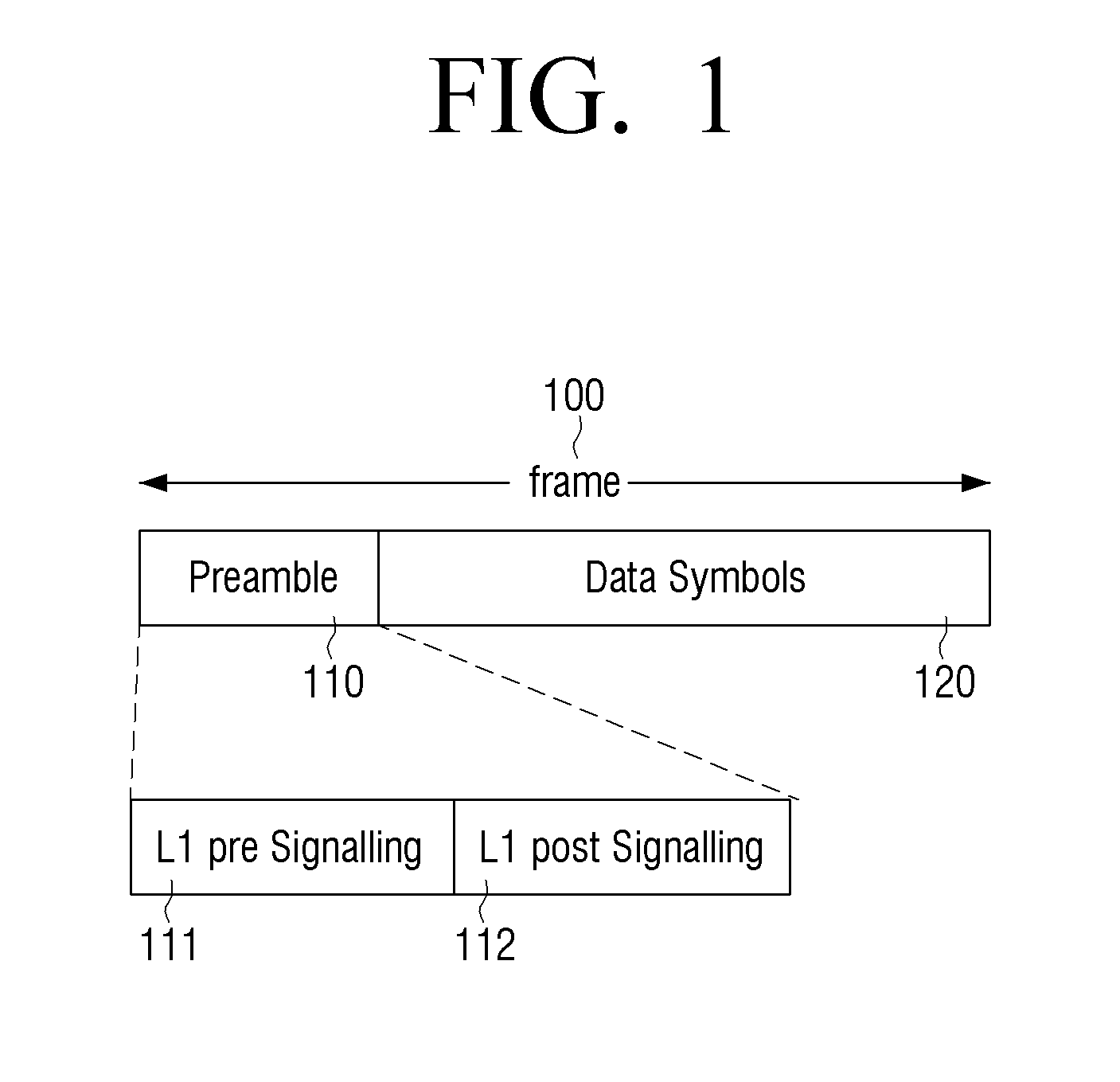

A transmitter apparatus and a receiver apparatus are provided. The transmitter apparatus includes: an encoder configured to generate a low density parity check (LDPC) by performing LDPC encoding; an interleaver configured to interleave the LDPC codeword; and a modulator configured to map the interleaved LDPC codeword onto a modulation symbol. The modulator maps a bit included in a predetermined group from among a plurality of groups constituting the LDPC codeword onto a predetermined bit in the modulation symbol.

Owner:SAMSUNG ELECTRONICS CO LTD

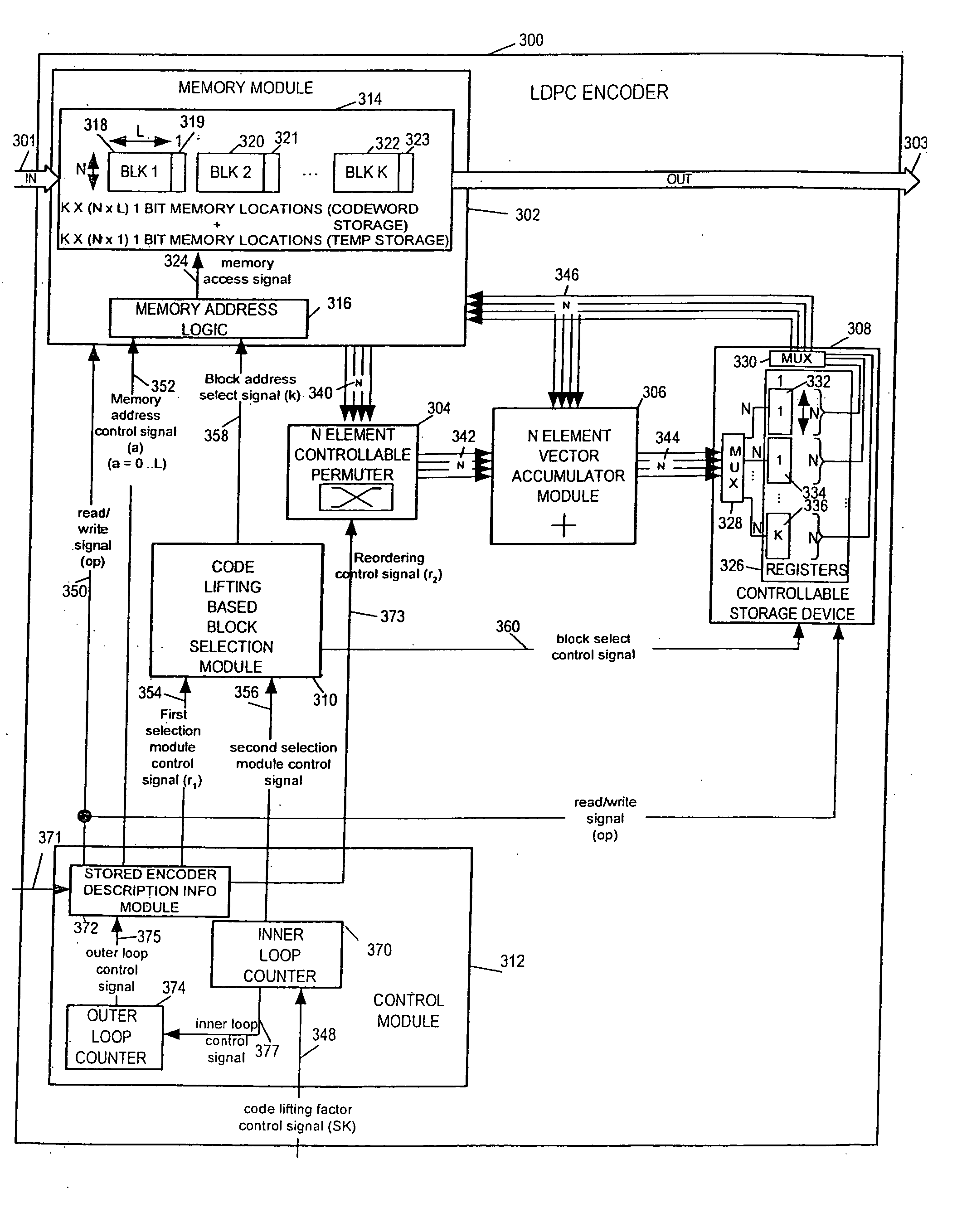

LDPC encoding methods and apparatus

ActiveUS20060020872A1Simple microcodeEasy to modifyError correction/detection using multiple parity bitsCode conversionDegree of parallelismInstruction set

A flexible and relatively hardware efficient LDPC encoder is described. The encoder can be implemented with a level of parallelism which is less than the full parallelism of the code structure used to control the encoding process. Each command of a relatively simple microcode used to describe the code structure can be stored and executed multiple times to complete the encoding of a codeword. Different codeword lengths can be supported using the same set of microcode instructions but with the code being implemented a different number of times depending on the lifting factor selected to be used. The LDPC encoder can switch between encoding codewords of different lengths, without the need to change the stored code description information, by simply changing a code lifting factor used to control the encoding processes. When coding codewords shorter than the maximum supported codeword length some block storage locations and / or registers may go unused.

Owner:QUALCOMM INC

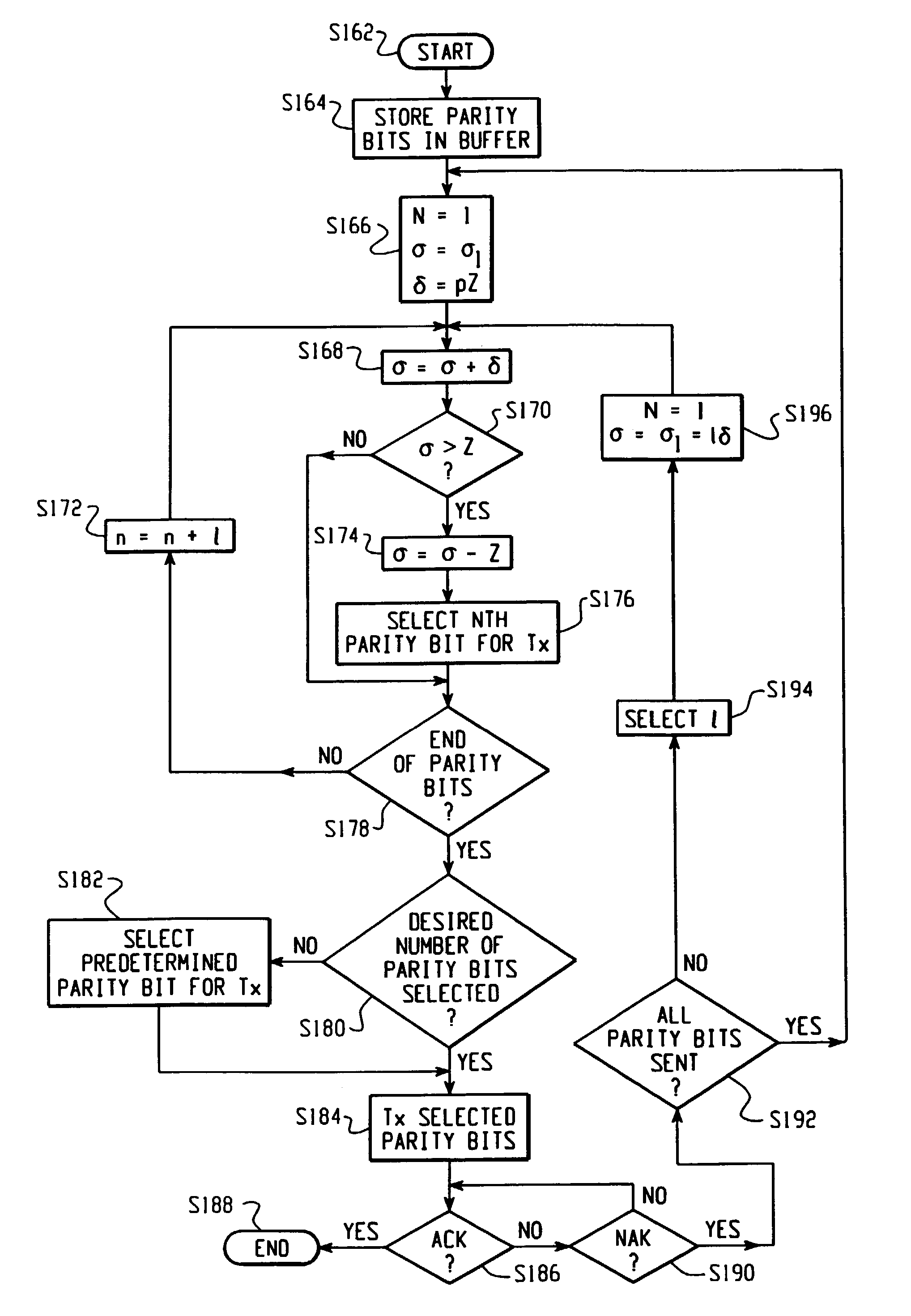

Hybrid automatic repeat request system and method

InactiveUS7000174B2Uniform puncturingError prevention/detection by using return channelTransmission systemsTheoretical computer scienceLow density

A data communication method and system for uniform arbitrary puncturing of parity bits generated by an encoder. The parity bits are stored in a buffer, and an a-bit accumulator is incremented to a predetermined initial value. For each parity bit in the buffer, the following steps are performed: the accumulator is incremented by a predetermined increment value, and if the accumulator overflows, the parity bit is selected for transmission. The predetermined initial value and the predetermined increment value are selected to achieve a desired amount of puncturing. In a further hybrid automatic repeat request (HARQ) communication method and system, the parity bits are generated by a low density parity check (LDPC) coder.

Owner:MALIKIE INNOVATIONS LTD

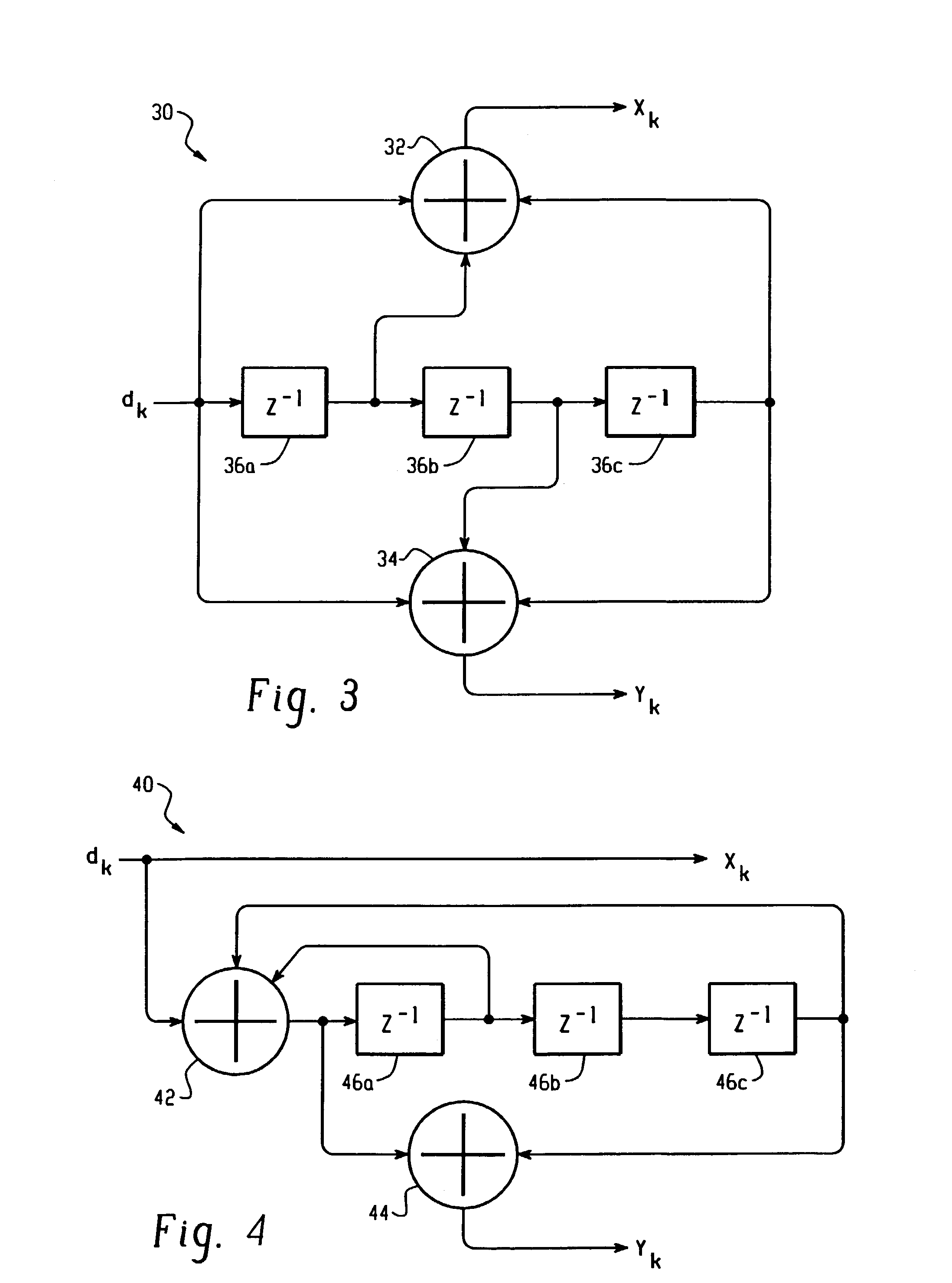

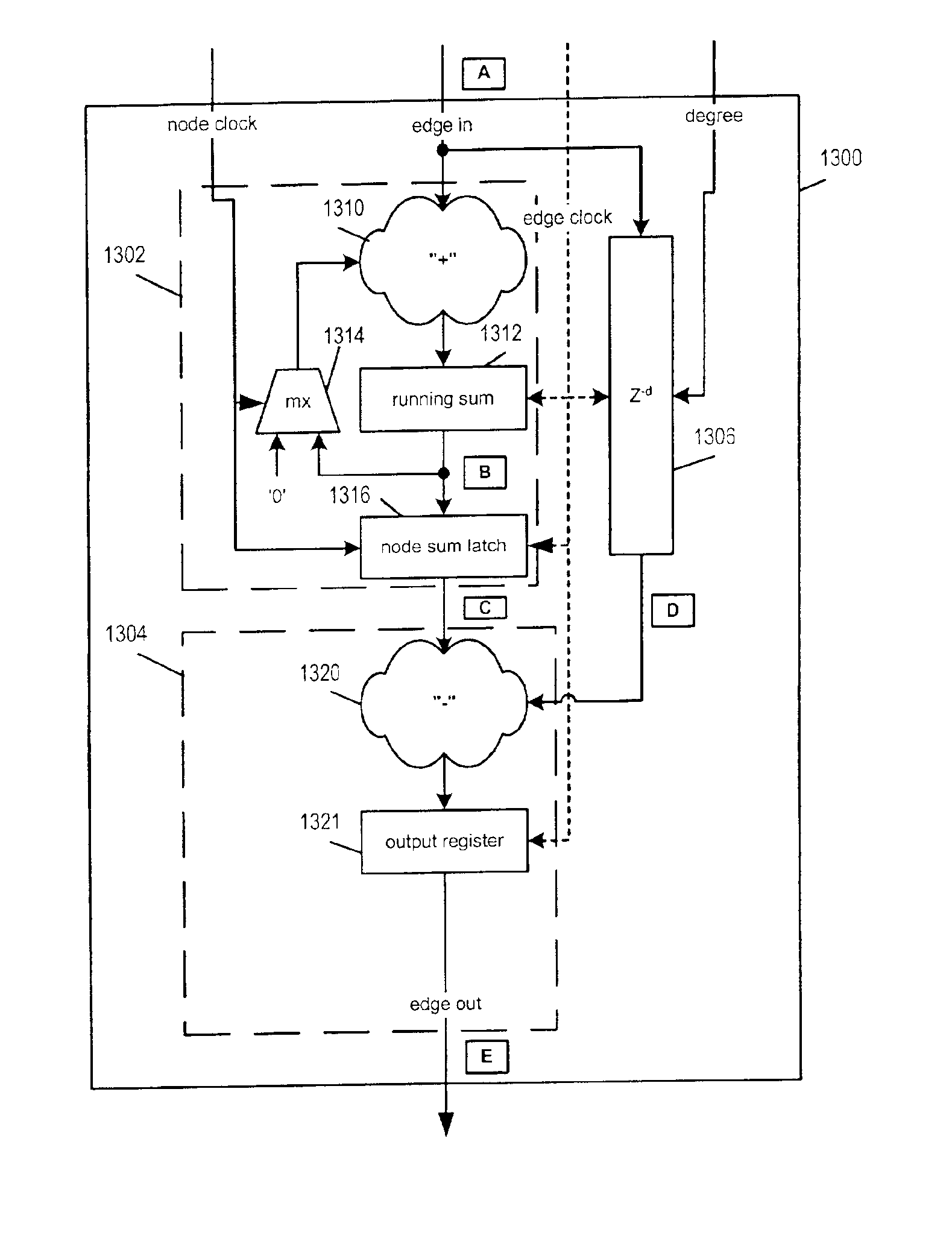

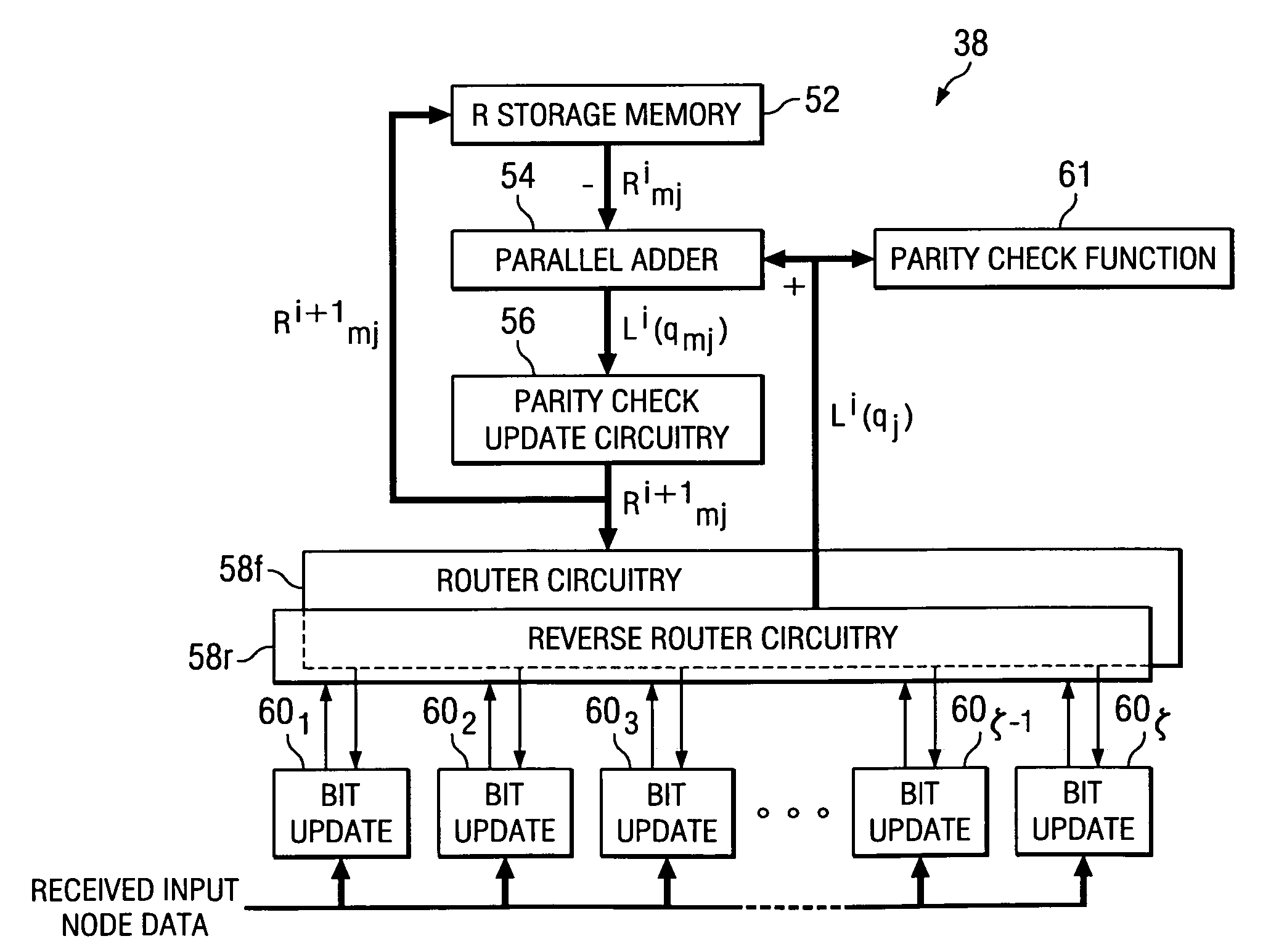

Node processors for use in parity check decoders

InactiveUS6938196B2Big errorCompensating for such errorError prevention/detection by using return channelOther decoding techniquesComputer moduleMessage processing

Techniques for implementing message passing decoders, e.g., LDPC decoders, are described. To facilitate hardware implementation messages are quantized to integer multiples of ½ ln2. Messages are transformed between more compact variable and less compact constraint node message representation formats. The variable node message format allows variable node message operations to be performed through simple additions and subtractions while the constraint node representation allows constraint node message processing to be performed through simple additions and subtractions. Variable and constraint nodes are implemented using an accumulator module, subtractor module and delay pipeline. The accumulator module generates an accumulated message sum. The accumulated message sum for a node is stored and then delayed input messages from the delay pipeline are subtracted there from to generate output messages. The delay pipeline includes a variable delay element making it possible to sequentially perform processing operations corresponding to nodes of different degrees.

Owner:QUALCOMM INC

Apparatus and method for transmitting and receiving data in a communication system using low density parity check codes

ActiveUS20090063929A1Reduce signal distortionImprove performanceError prevention/detection by using return channelTransmission systemsCommunications systemLow-density parity-check code

An apparatus for transmitting data in a communication system using a Low Density Parity Check (LDPC) matrix is provided. The apparatus includes an interleaver for interleaving a descending bit-ordered codeword having a predetermined size and in accordance with a predetermined modulation scheme; and a bit mapper for mapping codeword bits constituting the interleaved codeword in accordance with a predetermined mapping scheme that takes into account degrees of the codeword bits and reliability characteristics of modulation symbol-constituting bits based on the predetermined modulation scheme.

Owner:SAMSUNG ELECTRONICS CO LTD

Transmitter apparatus and interleaving method thereof

ActiveUS20150236816A1Improve decoding performanceImprove reception performanceModulated-carrier systemsError correction/detection using LDPC codesComputer hardwareParity-check matrix

A transmitting apparatus is provided. The transmitting apparatus includes: an encoder configured to generate a low-density parity check (LDPC) codeword by LDPC encoding based on a parity check matrix; an interleaver configured to interleave the LDPC codeword; and a modulator configured to map the interleaved LDPC codeword onto a modulation symbol, wherein the modulator is further configured to map a bit included in a predetermined bit group from among a plurality of bit groups constituting the LDPC codeword onto a predetermined bit of the modulation symbol.

Owner:SAMSUNG ELECTRONICS CO LTD

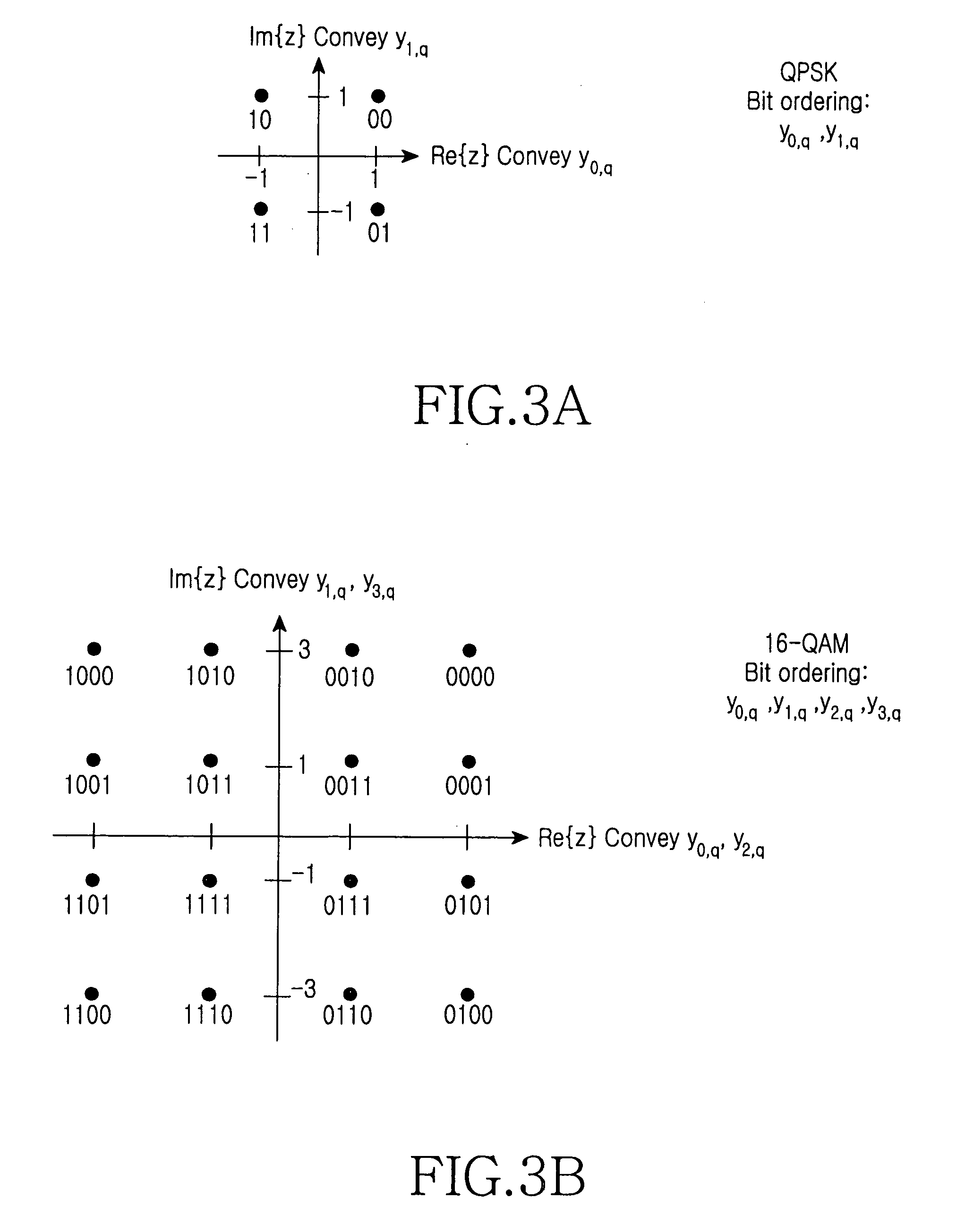

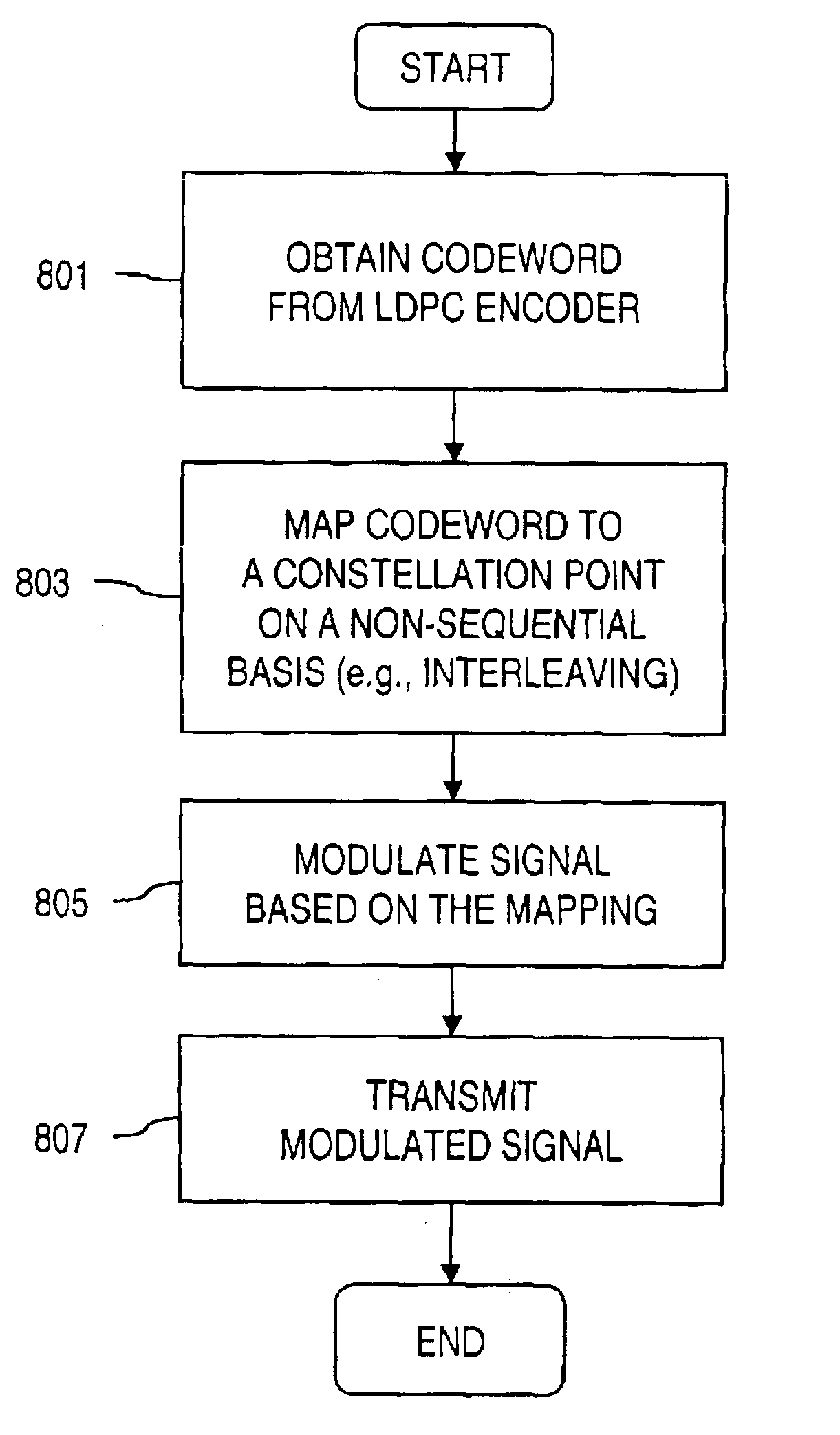

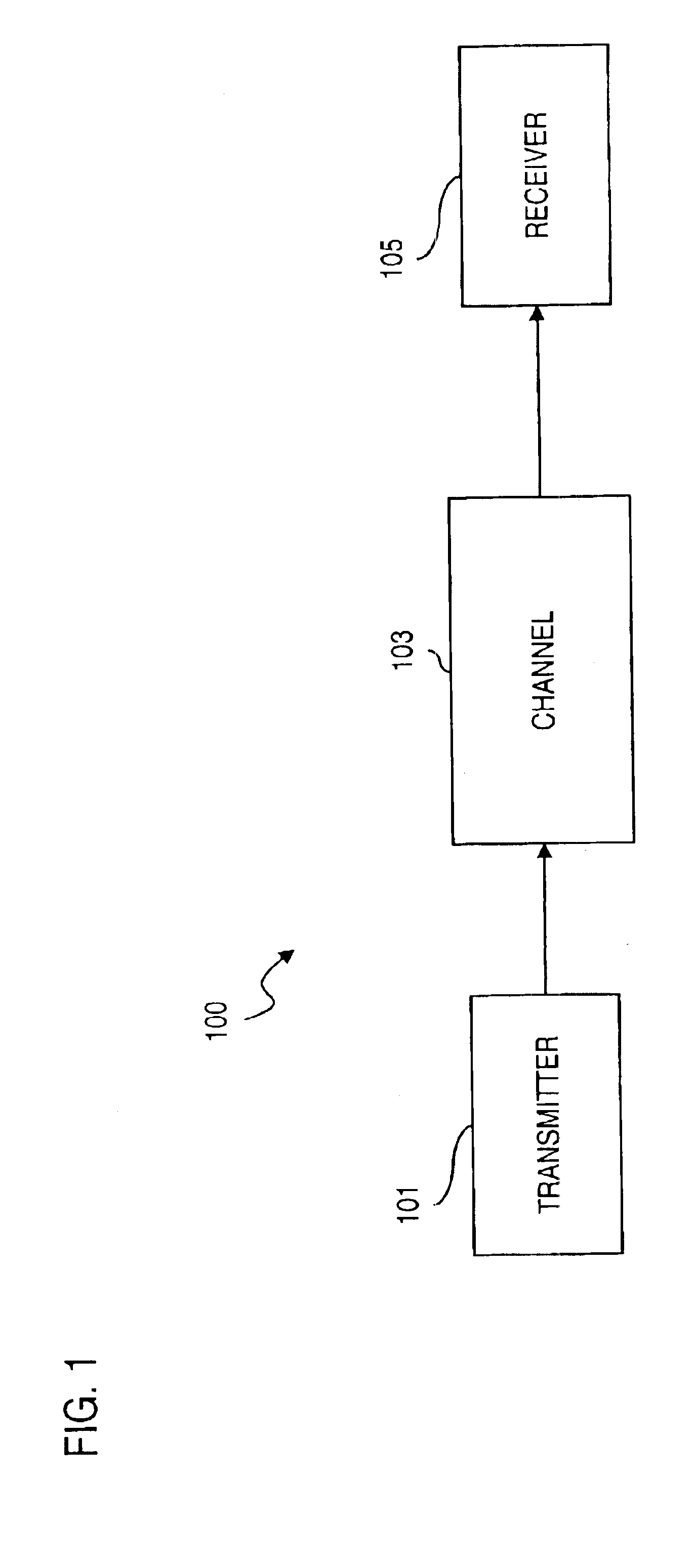

Bit labeling for amplitude phase shift constellation used with low density parity check (LDPC) codes

InactiveUS6963622B2Improve performanceError correction/detection using LDPC codesCode conversionParity-check matrixEngineering

An approach is provided for bit labeling of a signal constellation. A transmitter generates encoded signals using, according to one embodiment, a structured parity check matrix of a Low Density Parity Check (LDPC) code. The transmitter includes an encoder for transforming an input message into a codeword represented by a plurality of set of bits. The transmitter includes logic for mapping non-sequentially (e.g., interleaving) one set of bits into a higher order constellation (Quadrature Phase Shift Keying (QPSK), 8-PSK, 16-APSK (Amplitude Phase Shift Keying), 32-APSK, etc.), wherein a symbol of the higher order constellation corresponding to the one set of bits is output based on the mapping.

Owner:DTVG LICENSING INC

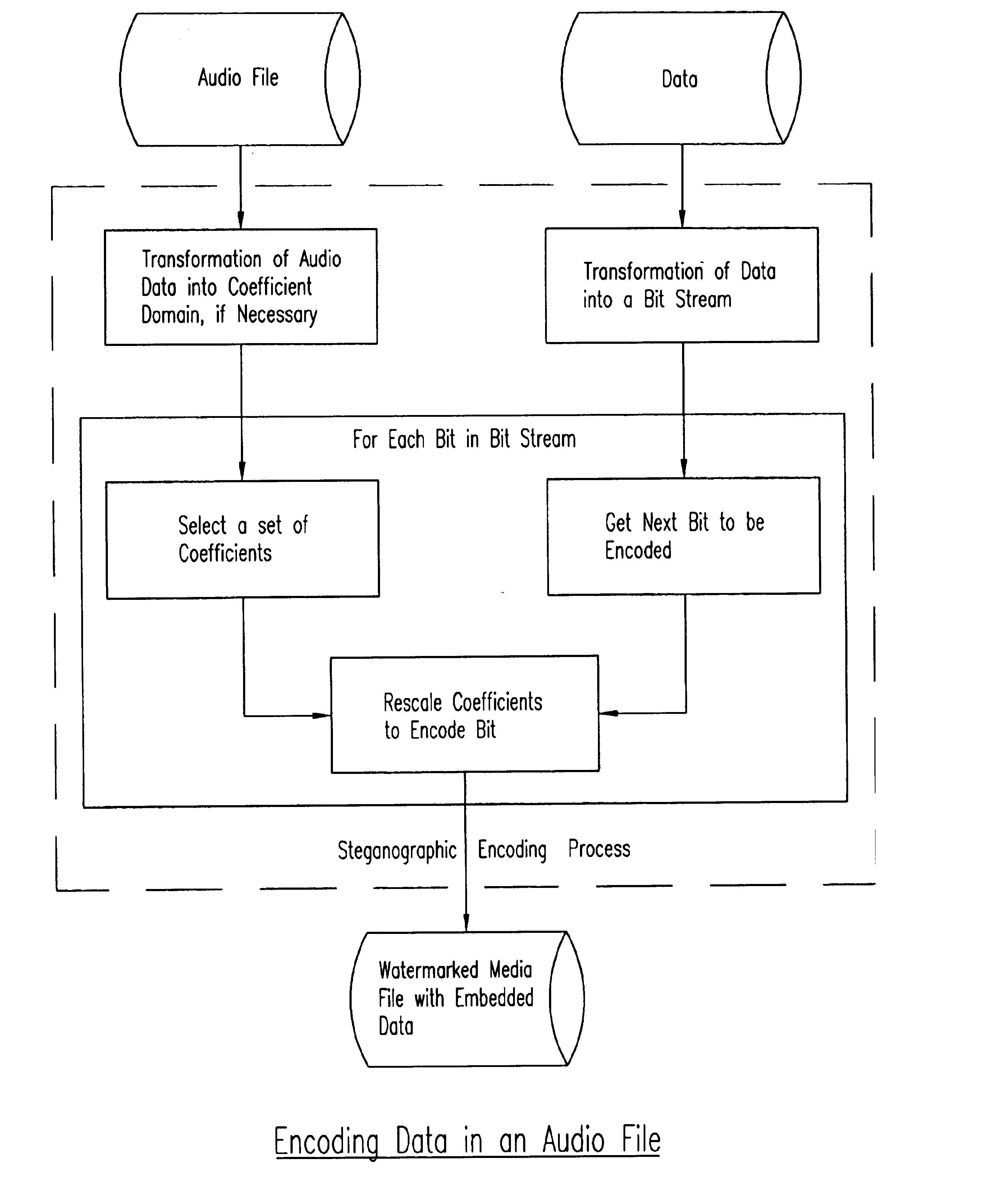

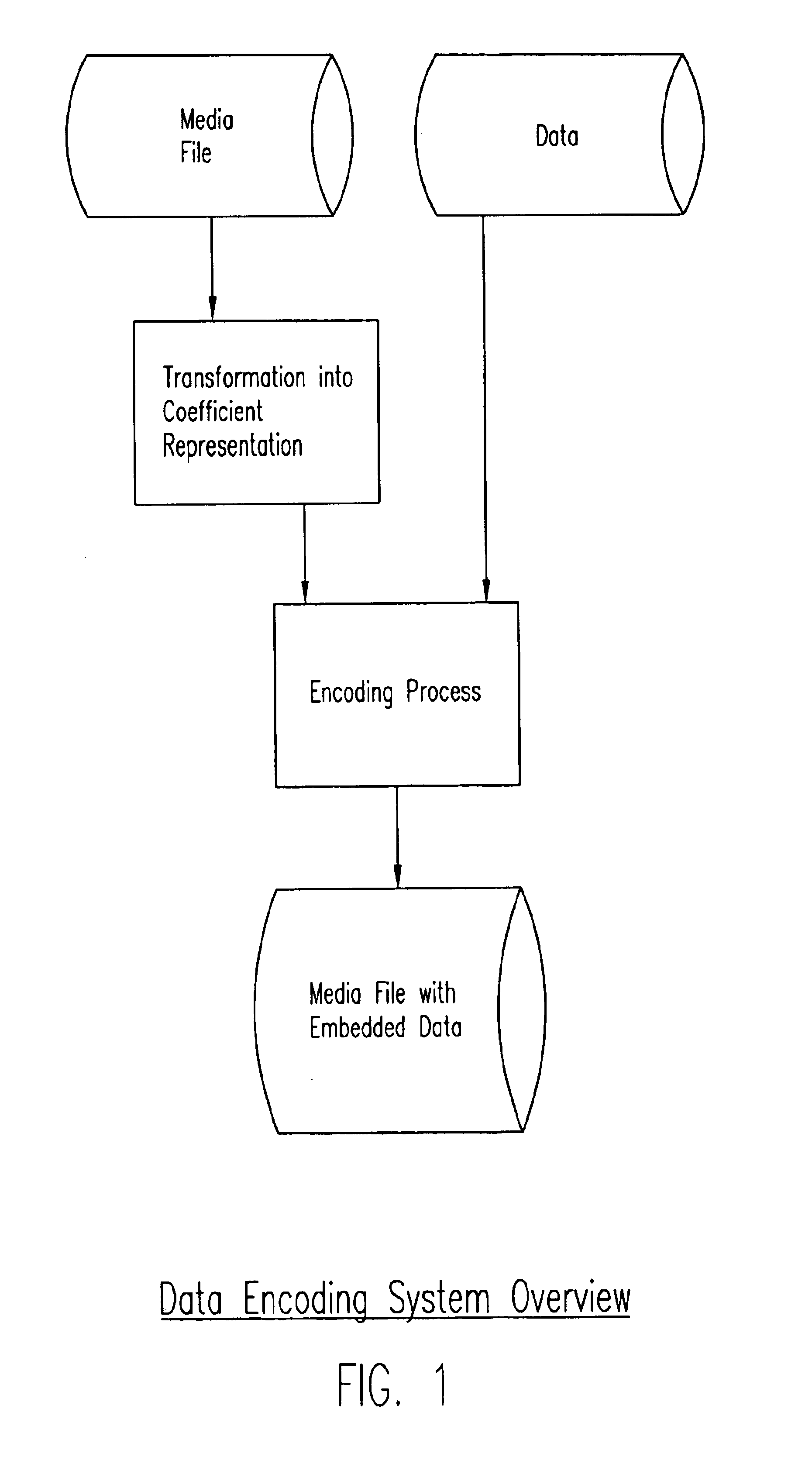

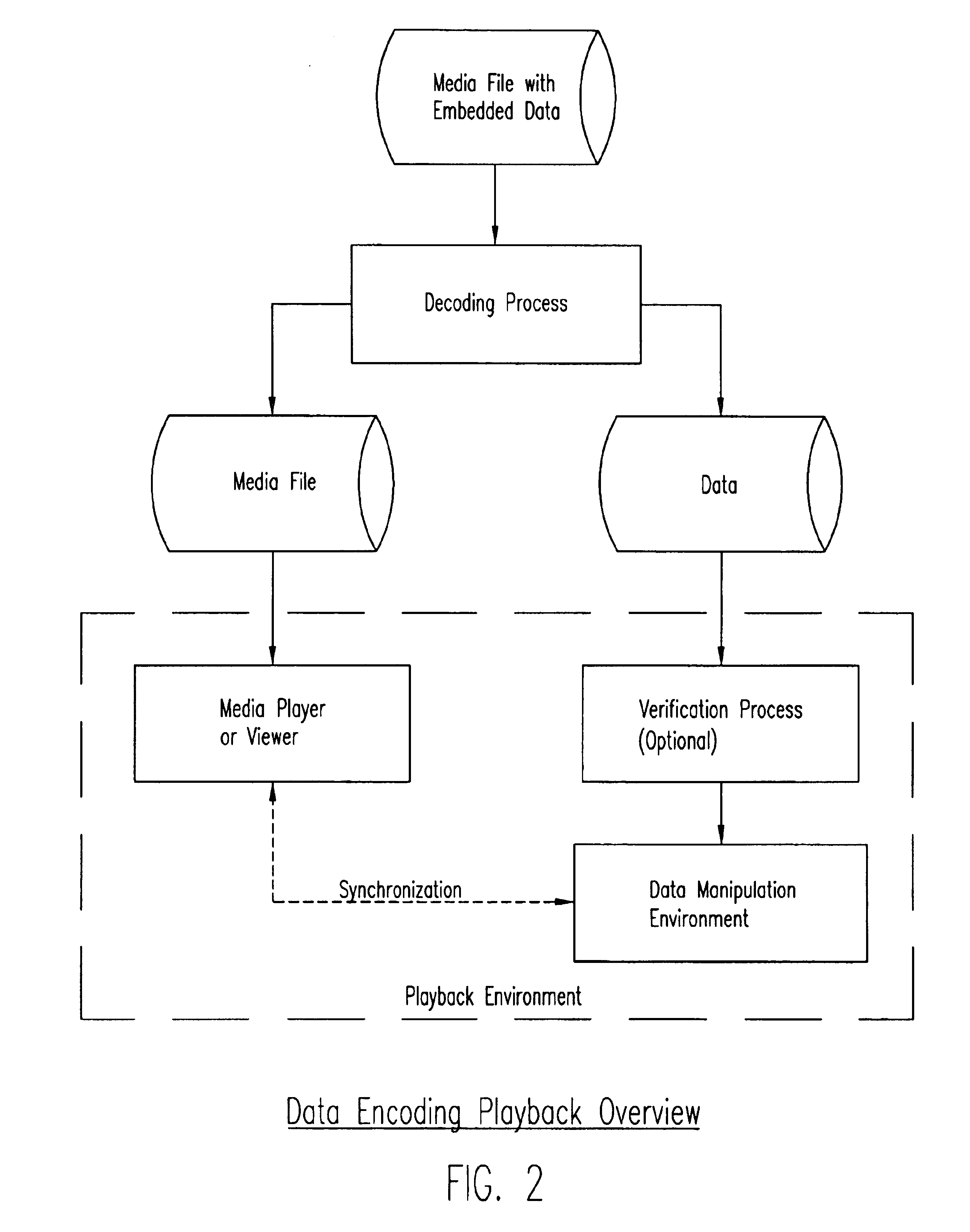

Process, system, and apparatus for embedding data in compressed audio, image video and other media files and the like

InactiveUS6748362B1User identity/authority verificationError correction/detection using multiple parity bitsDigital dataComputer graphics (images)

A novel process and system for enabling the seamless and facile embedding of relatively large quantities of supplemental digital data into pre-prepared digital media files (audio, image, video, 3D, volumetric and multimedia and the like) by compressing such files and encoding them into sets of coefficient representations (preferably frequency-domain coefficient representations) of the pre-prepared media file information, and embedding bits of the supplemental digital data at selected coefficients, preferably, though not exclusively, using the least significant bit of the selected coefficients, and with stenographic encoding processes.

Owner:TIME WARNER CABLE ENTERPRISES LLC

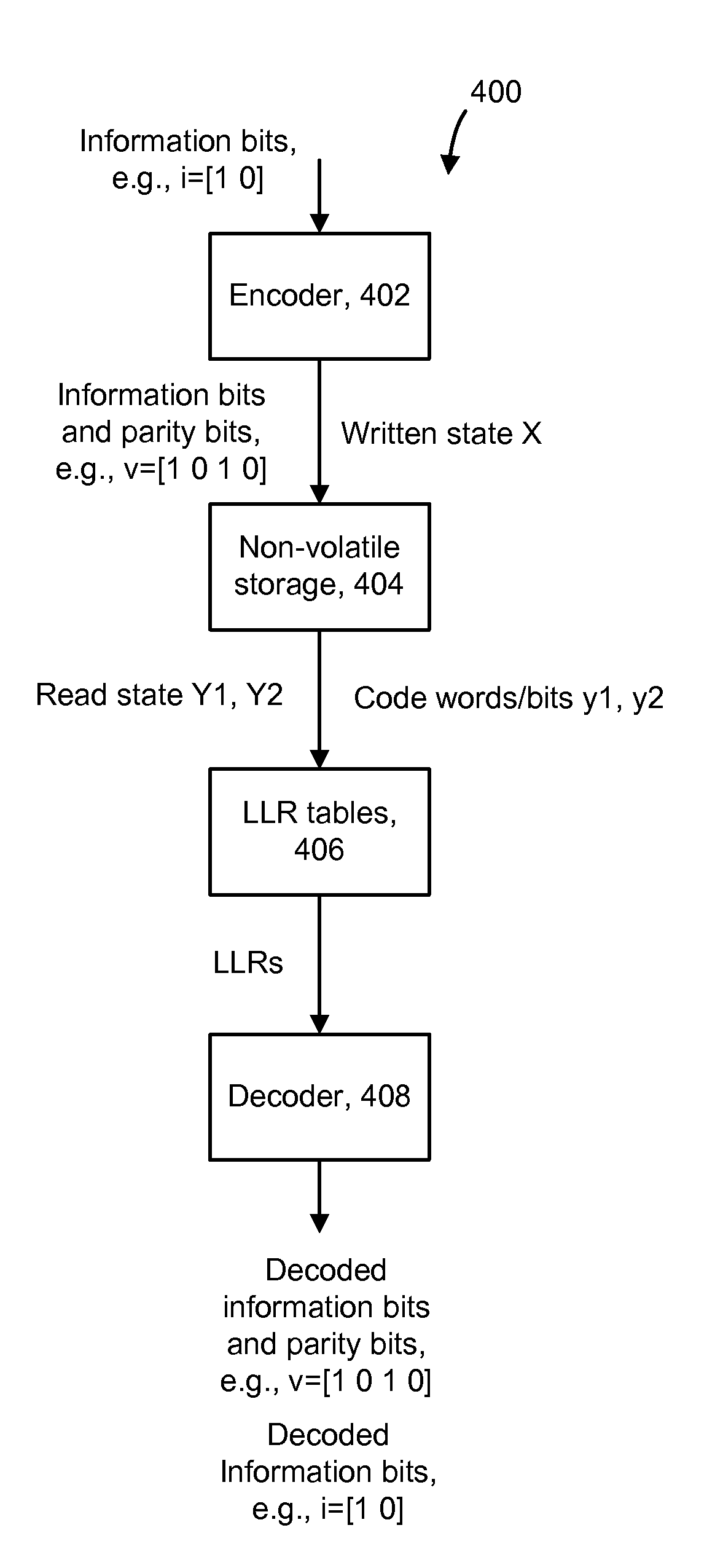

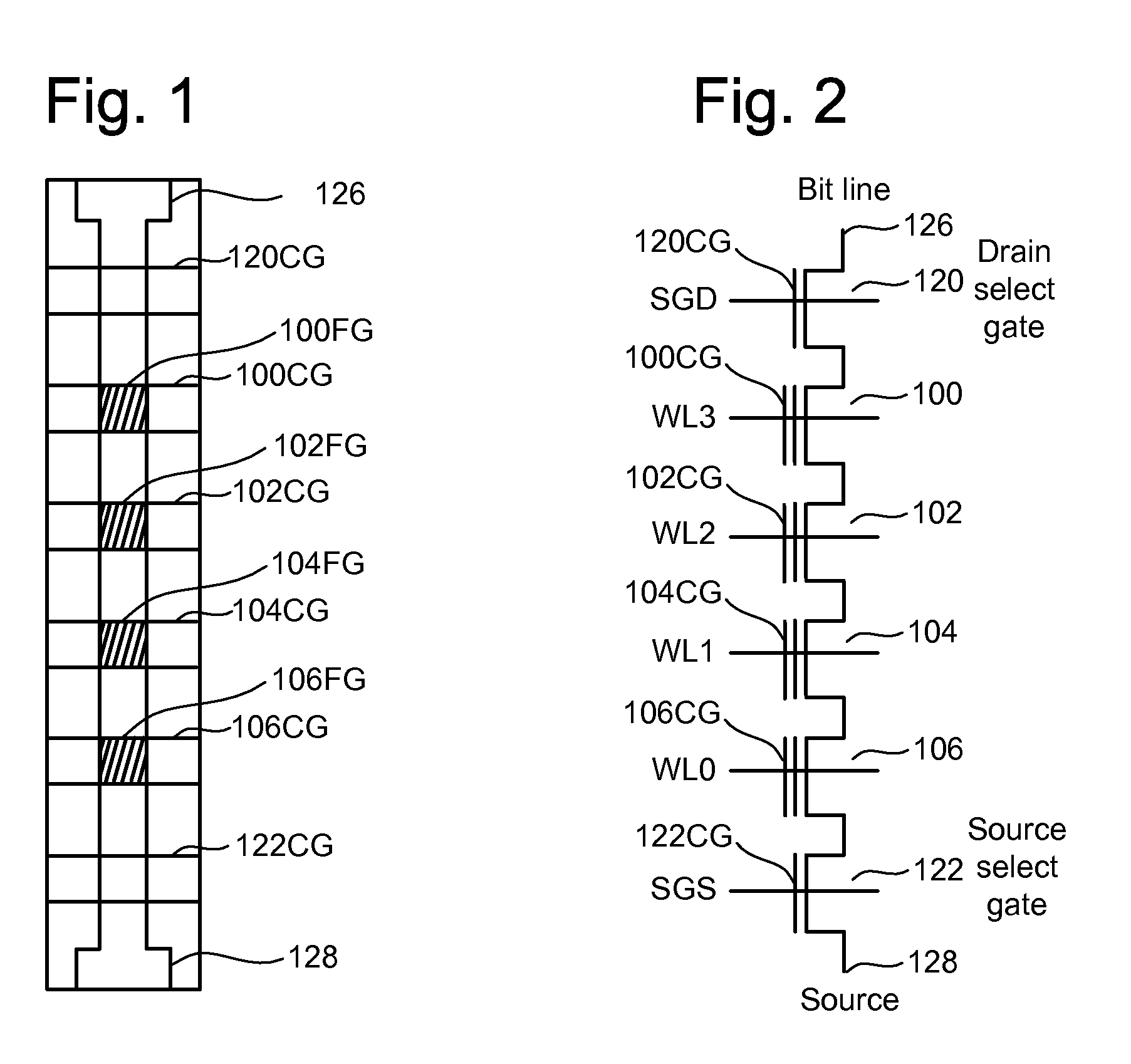

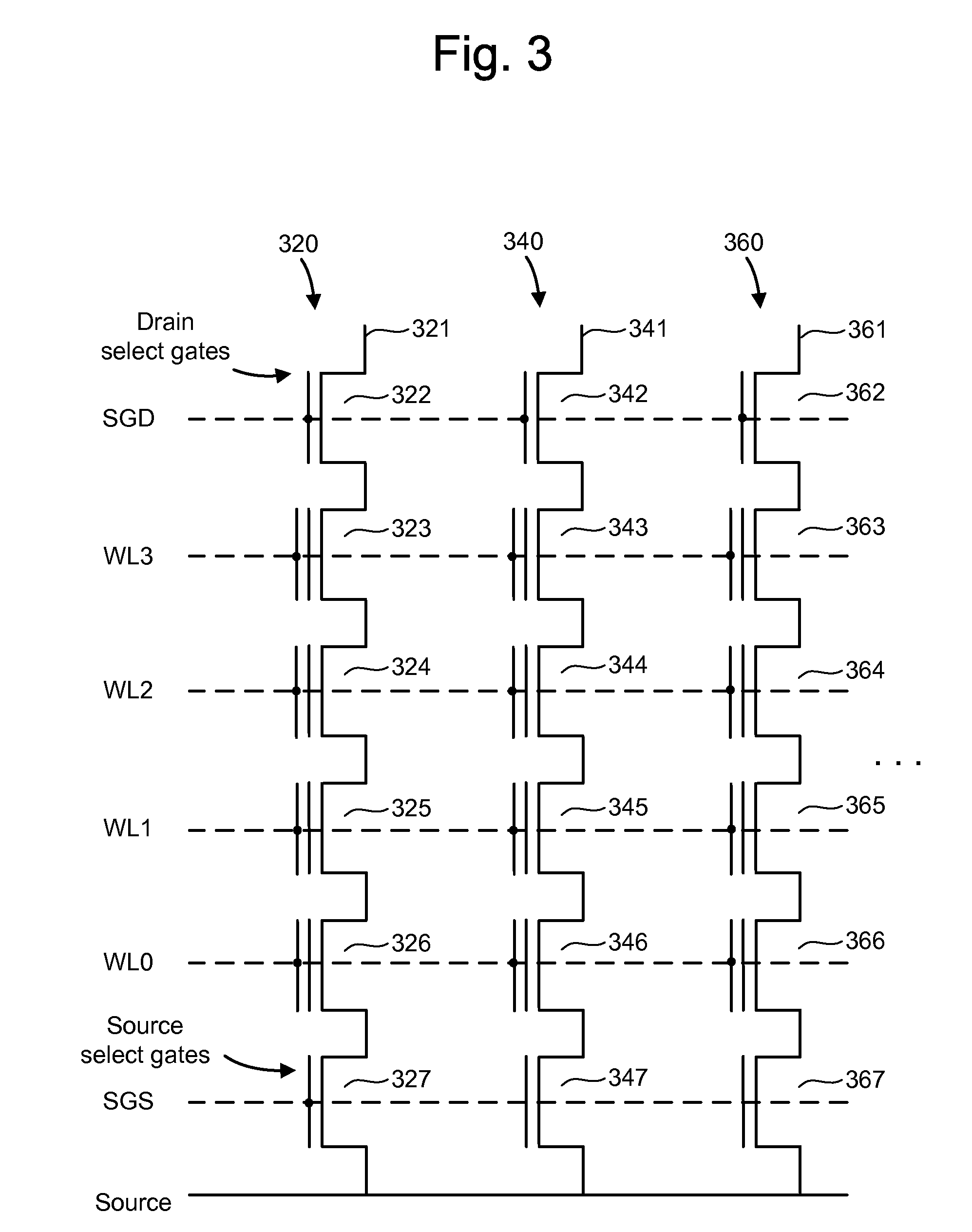

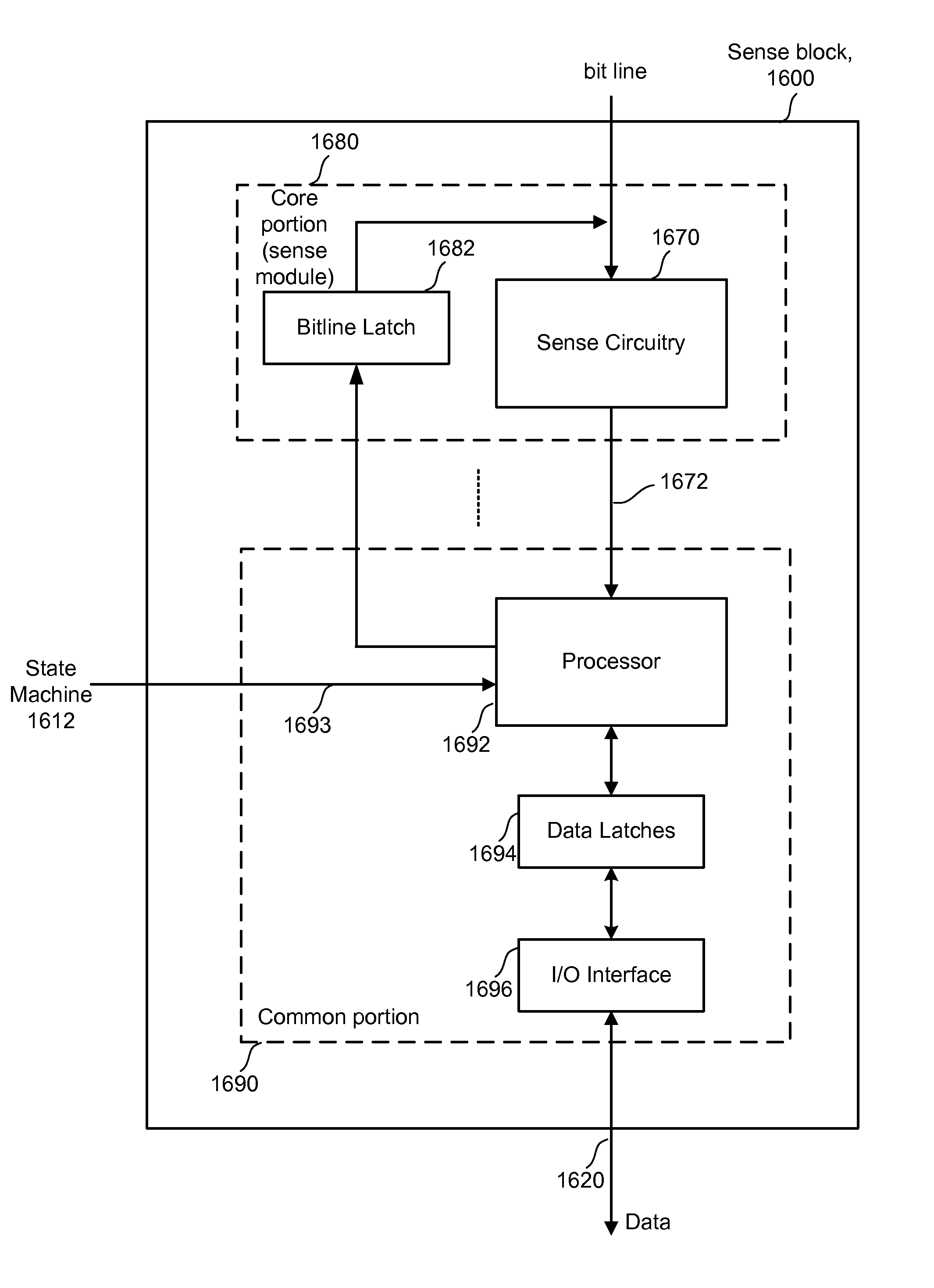

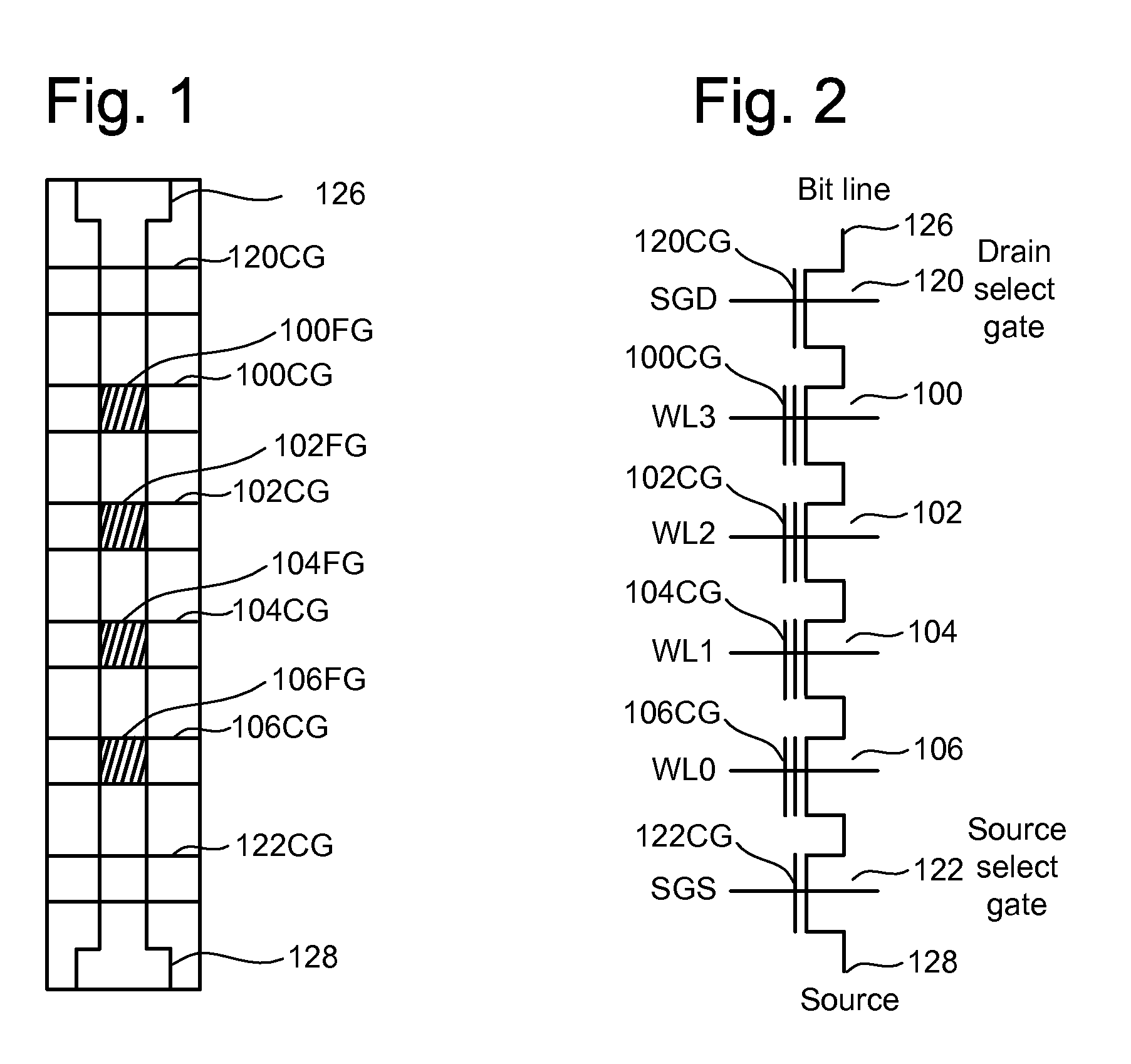

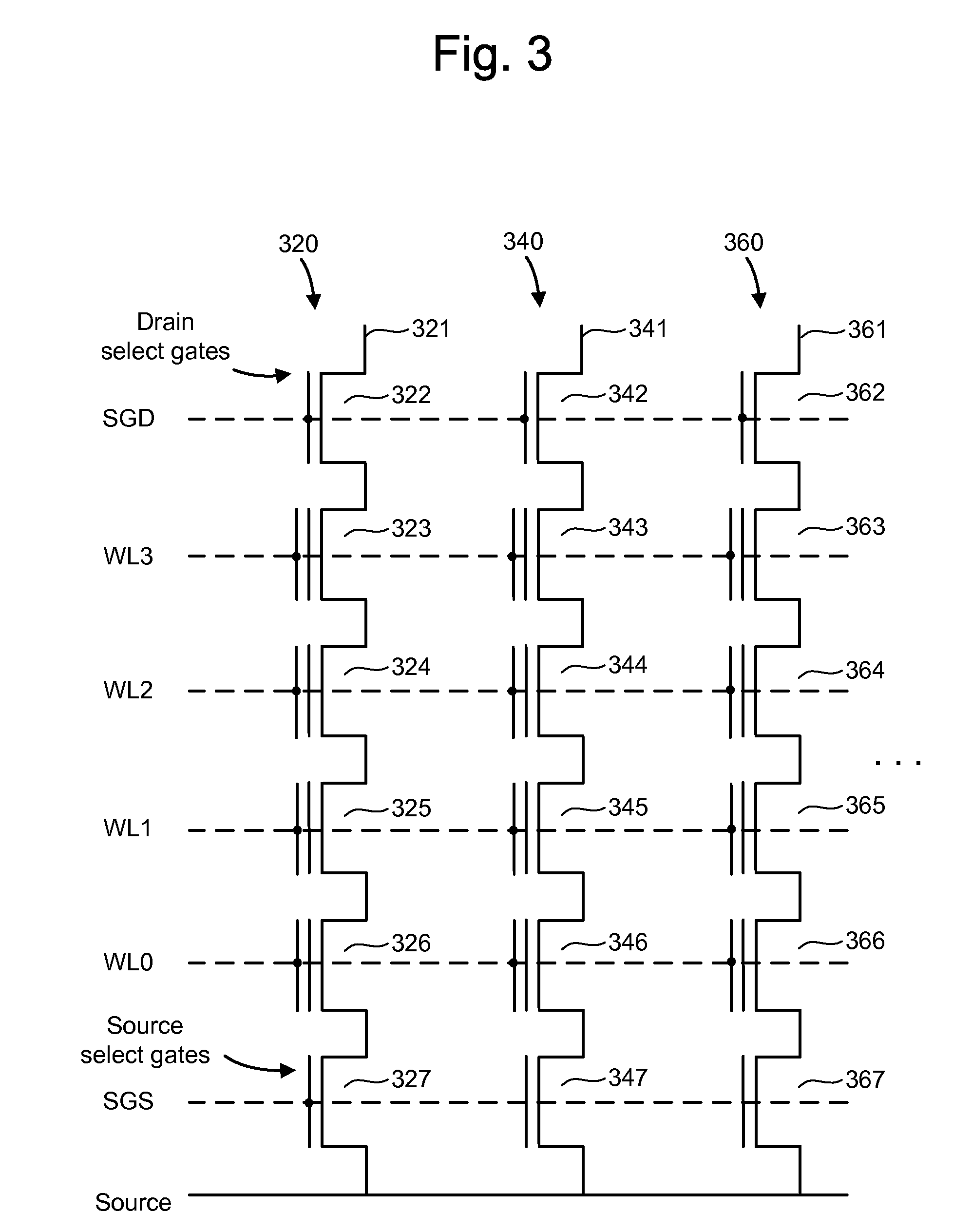

Method for decoding data in non-volatile storage using reliability metrics based on multiple reads

ActiveUS20080250300A1Other decoding techniquesError correction/detection using multiple parity bitsLow-density parity-check codeDependability

Data stored in non-volatile storage is decoded using iterative probabilistic decoding and multiple read operations to achieve greater reliability. An error correcting code such as a low density parity check code may be used. In one approach, initial reliability metrics, such as logarithmic likelihood ratios, are used in decoding read data of a set of non-volatile storage element. The decoding attempts to converge by adjusting the reliability metrics for bits in code words which represent the sensed state. If convergence does not occur, e.g., within a set time period, the state of the non-volatile storage element is sensed again, current values of the reliability metrics in the decoder are adjusted, and the decoding again attempts to converge. In another approach, the initial reliability metrics are based on multiple reads. Tables which store the reliability metrics and adjustments based on the sensed states can be prepared before decoding occurs.

Owner:SANDISK TECH LLC

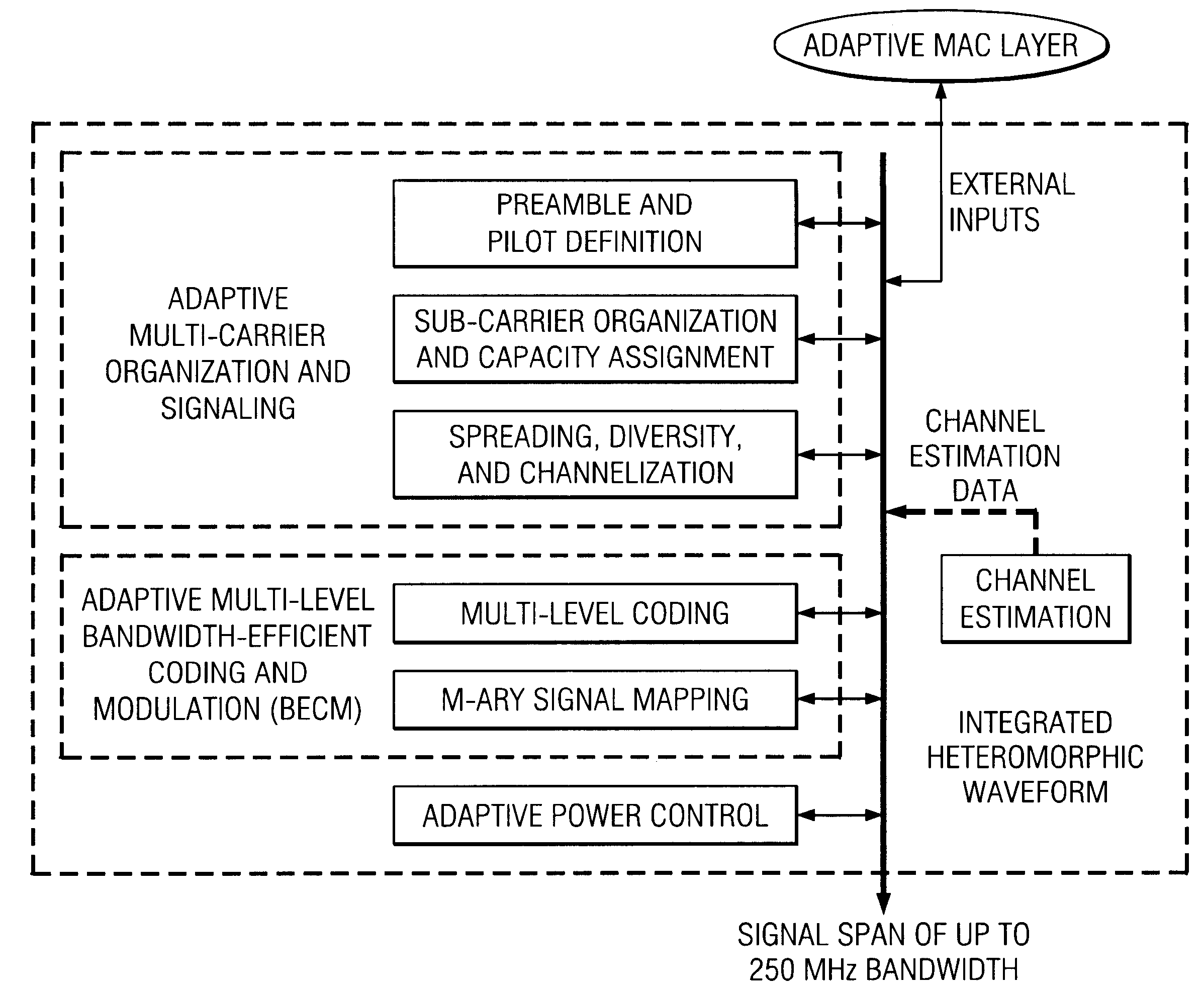

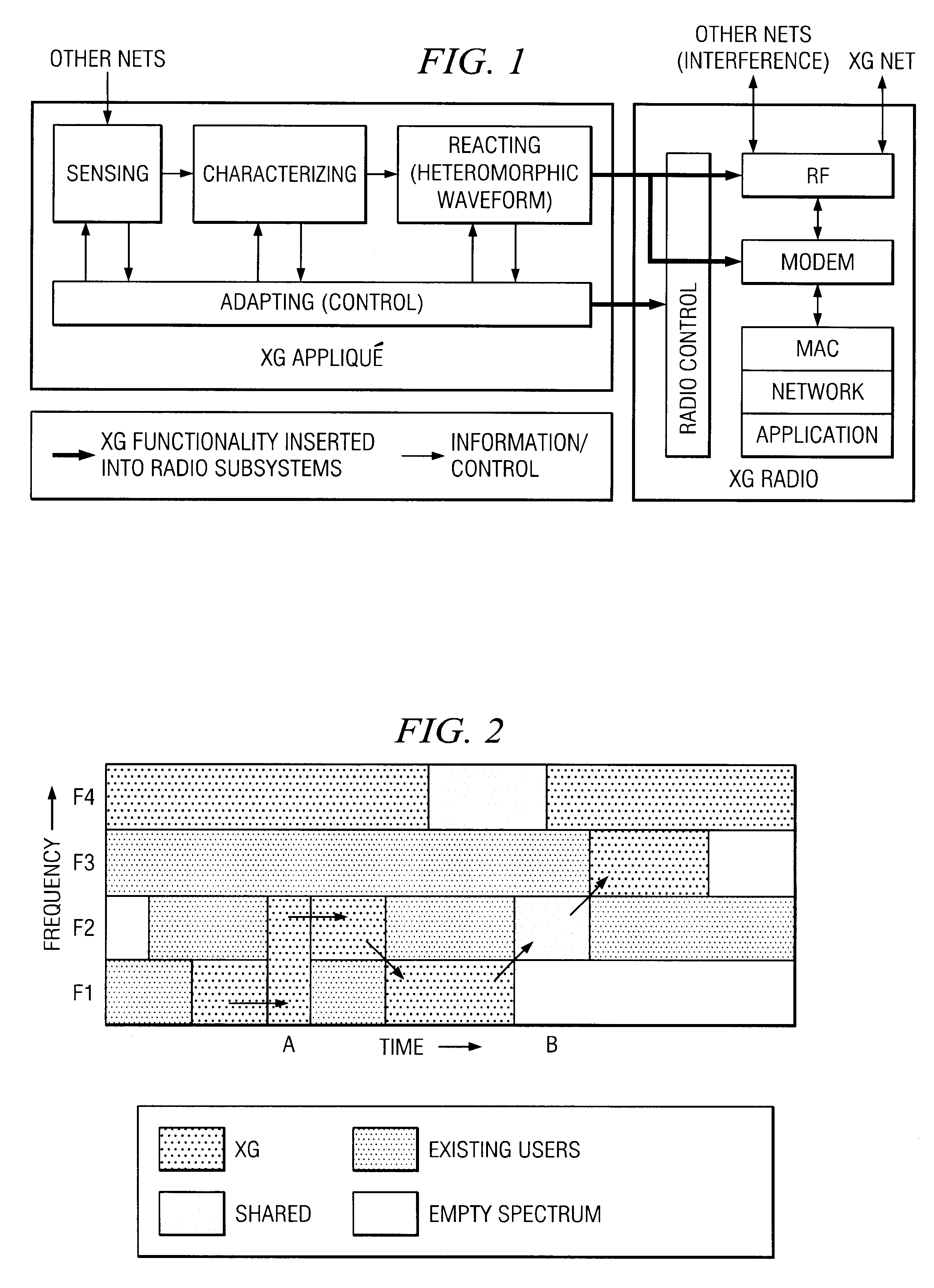

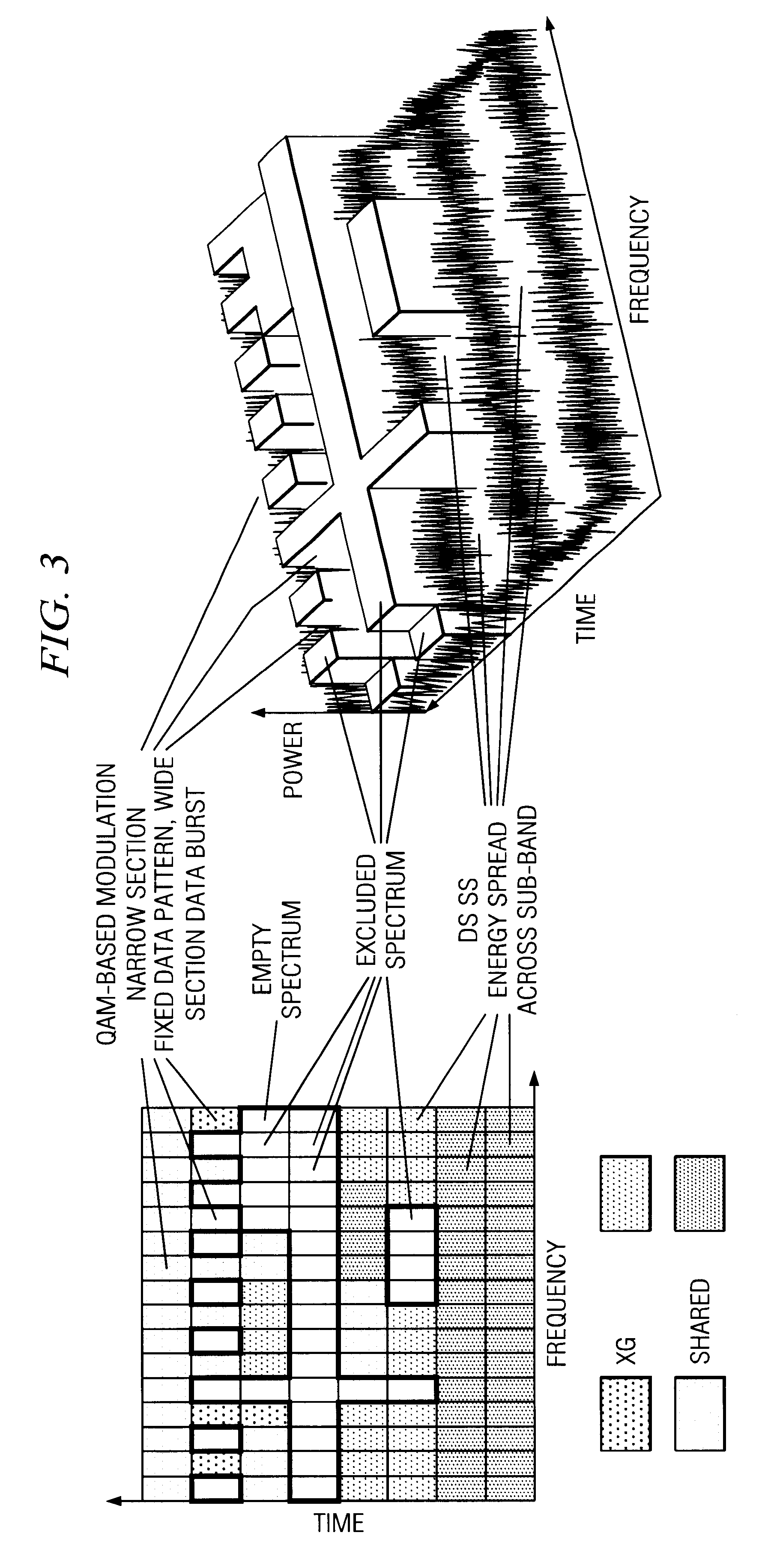

Adaptive air interface waveform

InactiveUS6847678B2Reduce and eliminate disadvantageReduce and eliminate and problemError correction/detection using LDPC codesCriteria allocationFrequency spectrumSpectral efficiency

In one embodiment, a method for generating an adaptive air interface waveform includes generating a waveform that includes a variable carrier frequency and variable bandwidth signal. The variable bandwidth signal includes one or more subcarriers that are dynamically placeable over a range of frequencies, and each subcarrier is separately modulated according to a direct sequence (DS) spread spectrum (SS) technique. The waveform has an embedded pilot usable to optimize one or more spectrum efficiencies of the waveform. A modulation constellation, a code rate, and a code length of the generated waveform are adapted according to an available spectrum and one or more sub-carrier conditions.

Owner:POWERWAVE COGNITION INC

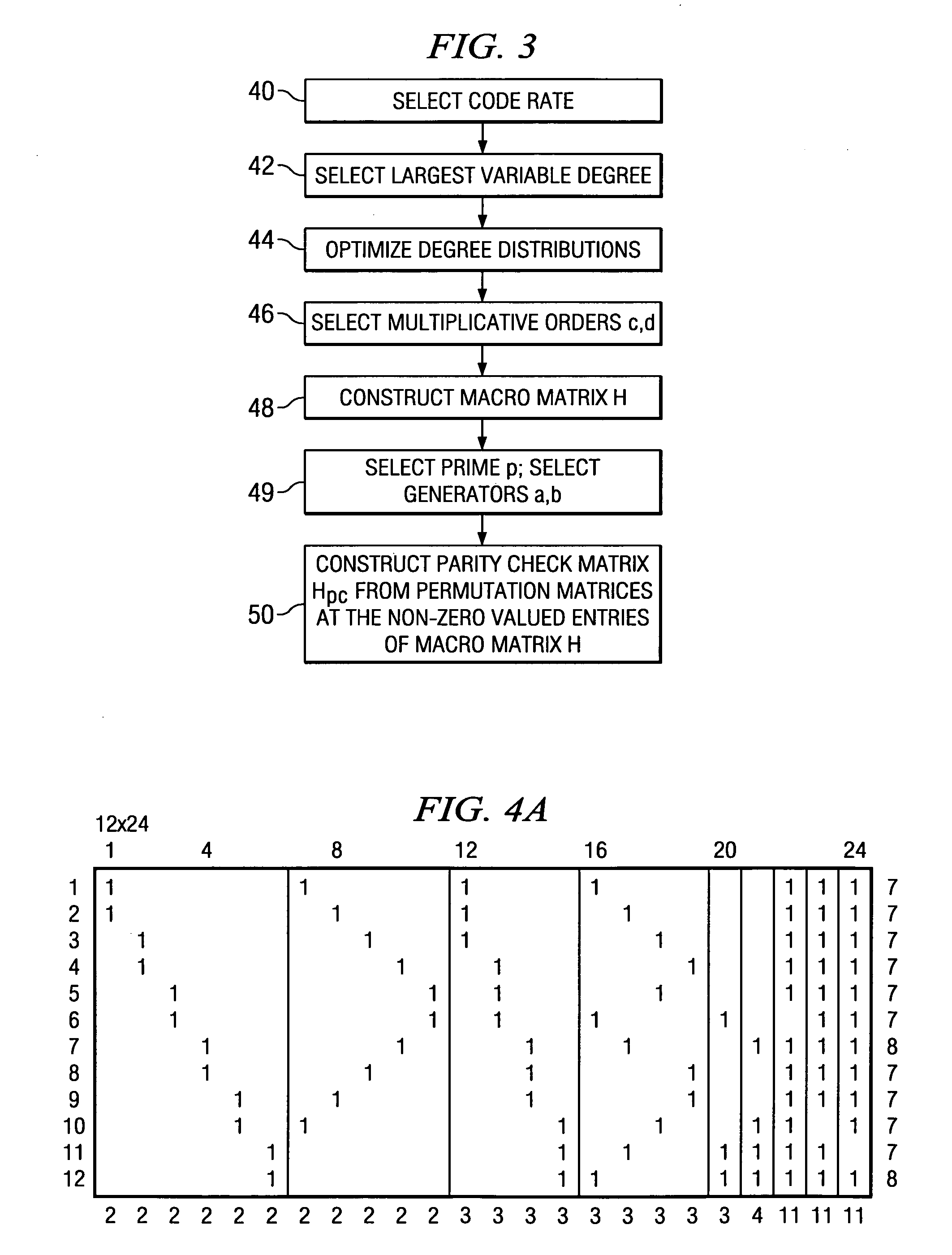

Hardware-efficient low density parity check code for digital communications

ActiveUS7178080B2Efficient implementationEfficient constructionError correction/detection using multiple parity bitsCode conversionMatrix groupParity-check matrix

Owner:TEXAS INSTR INC

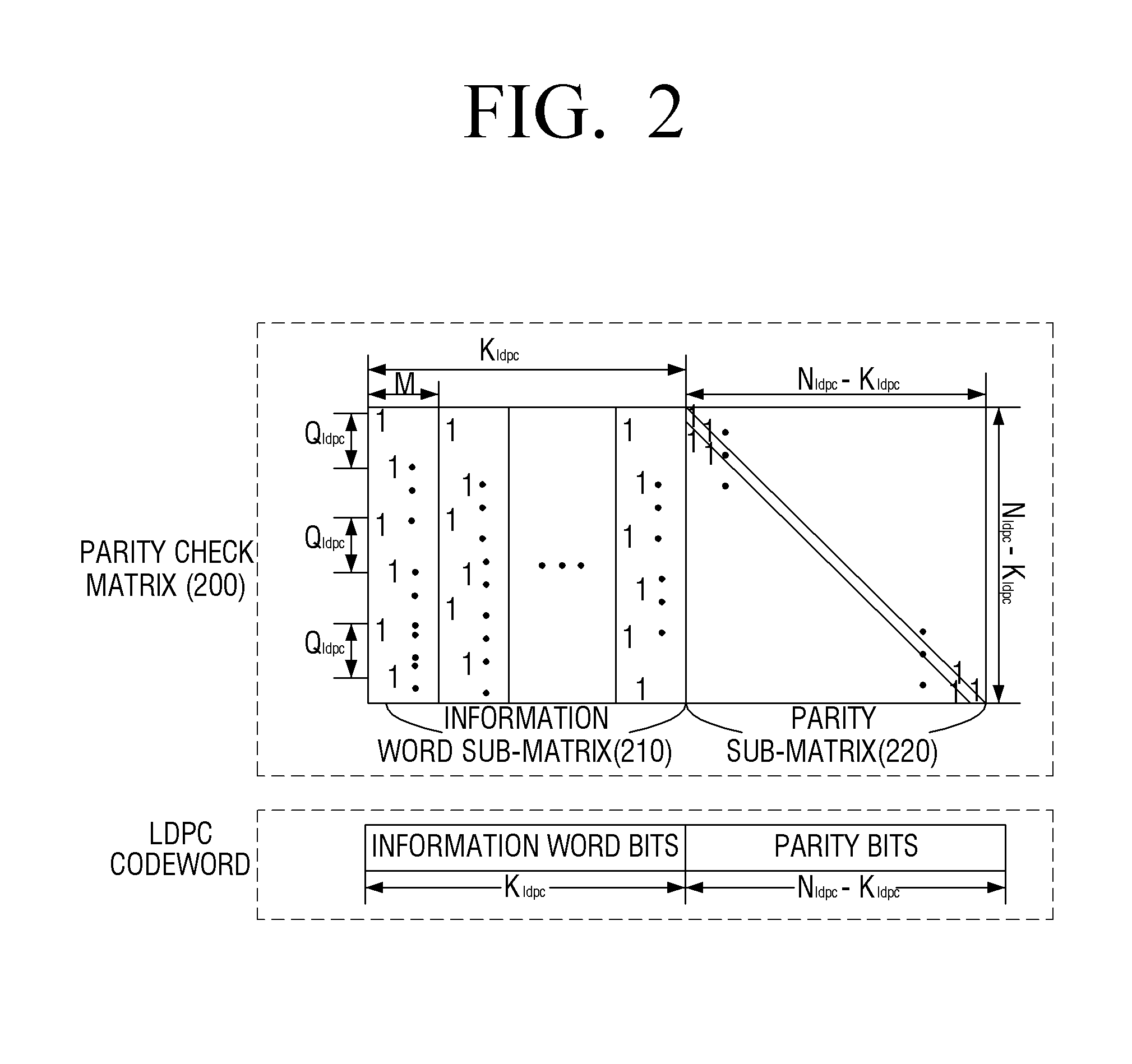

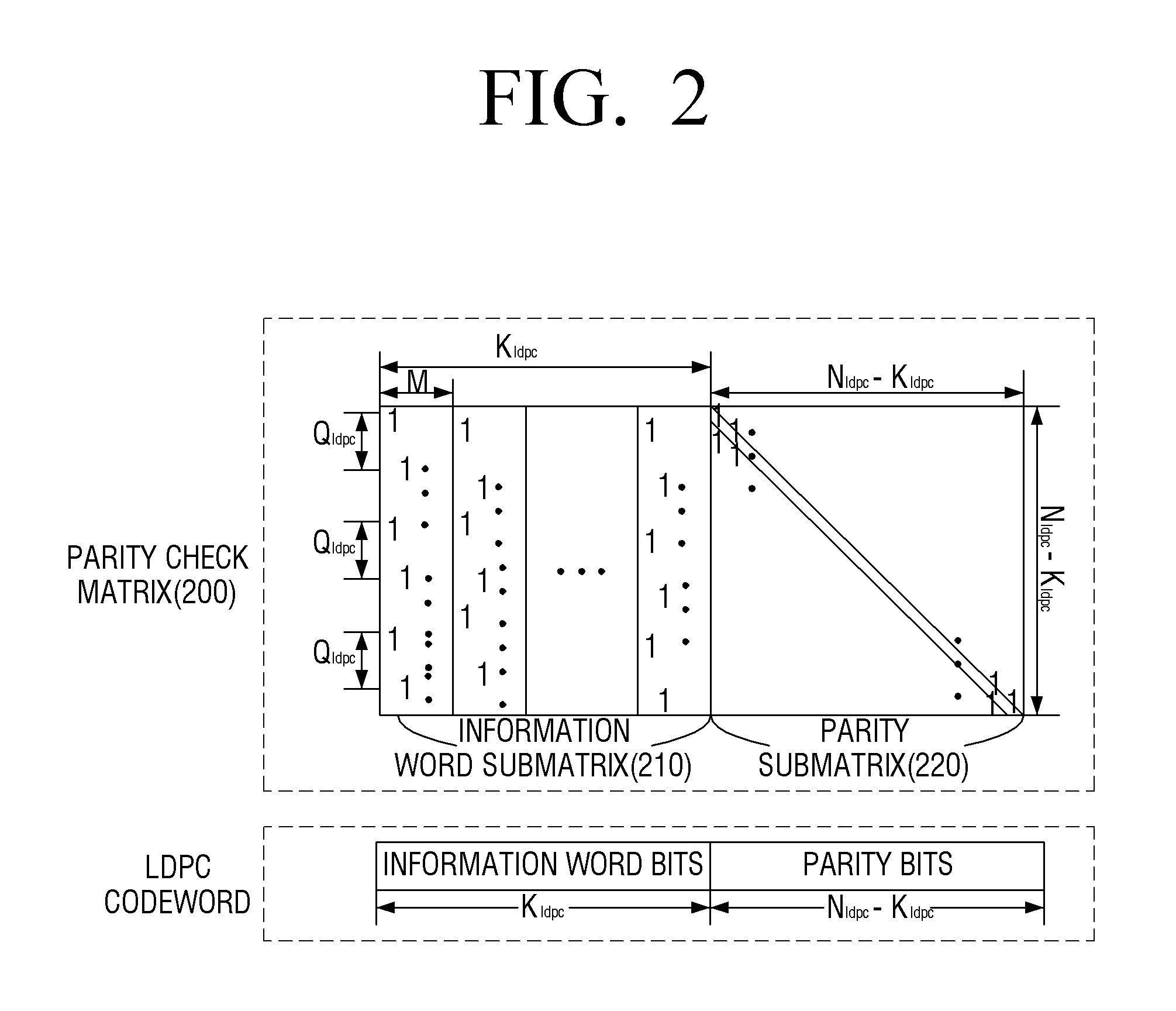

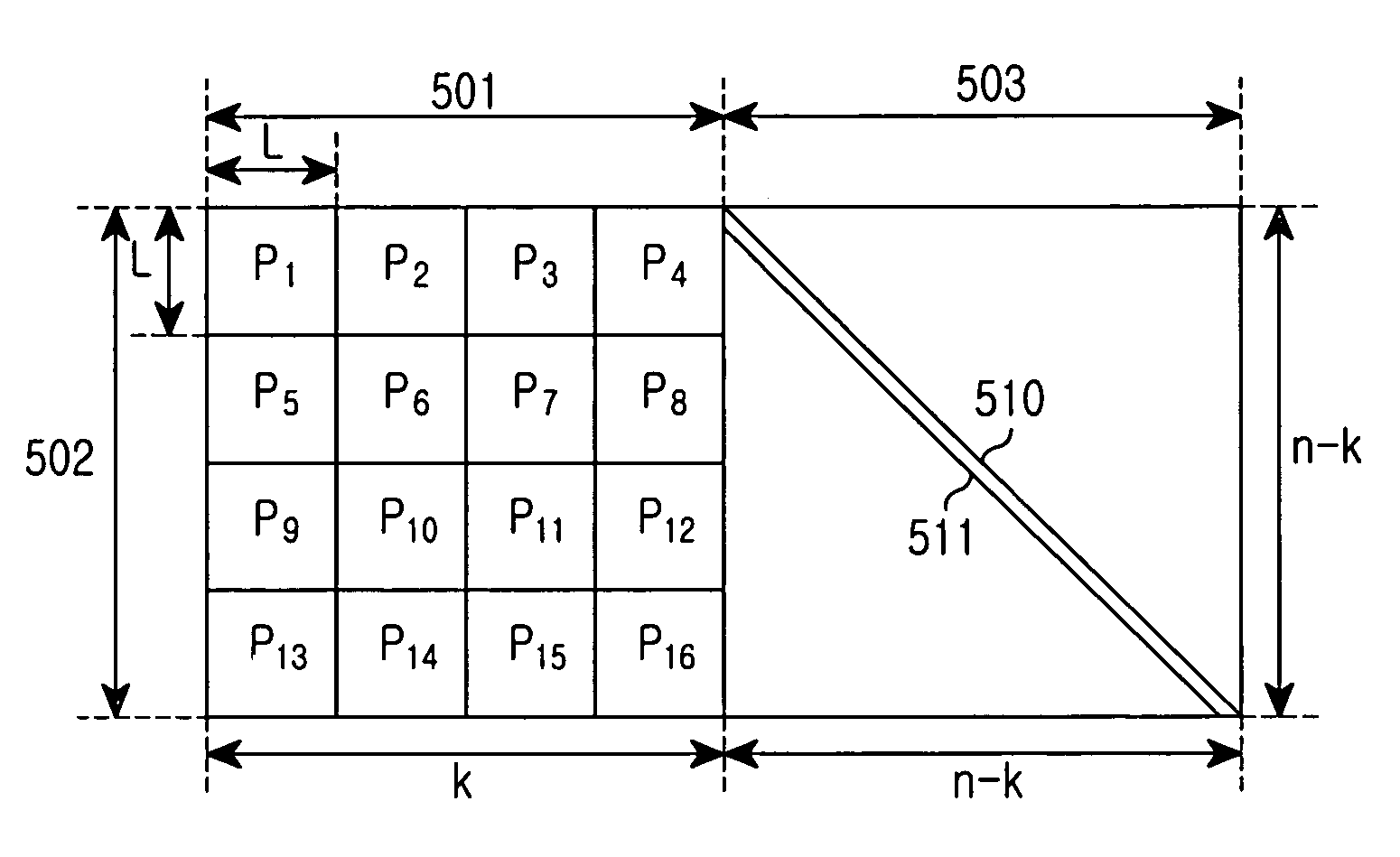

Apparatus and method for encoding a low density parity check code

ActiveUS7178082B2Low Density Parity CheckEasy to calculateError detection/correctionError correction/detection using multiple parity bitsTheoretical computer scienceDiagonal matrix

An apparatus and method for generating an encoding matrix for a low density parity check (LDPC) code having a dual-diagonal matrix as a parity check matrix are disclosed. The apparatus and method construct an information sub-matrix of the encoding matrix with a predetermined number of square matrixes according to a predetermined code rate such that each of the square matrixes has columns and rows with a weight of 1 and has a different offset value, combine the square matrixes with the dual-diagonal matrix, and perform inter-row permutation on the information sub-matrix.

Owner:SAMSUNG ELECTRONICS CO LTD

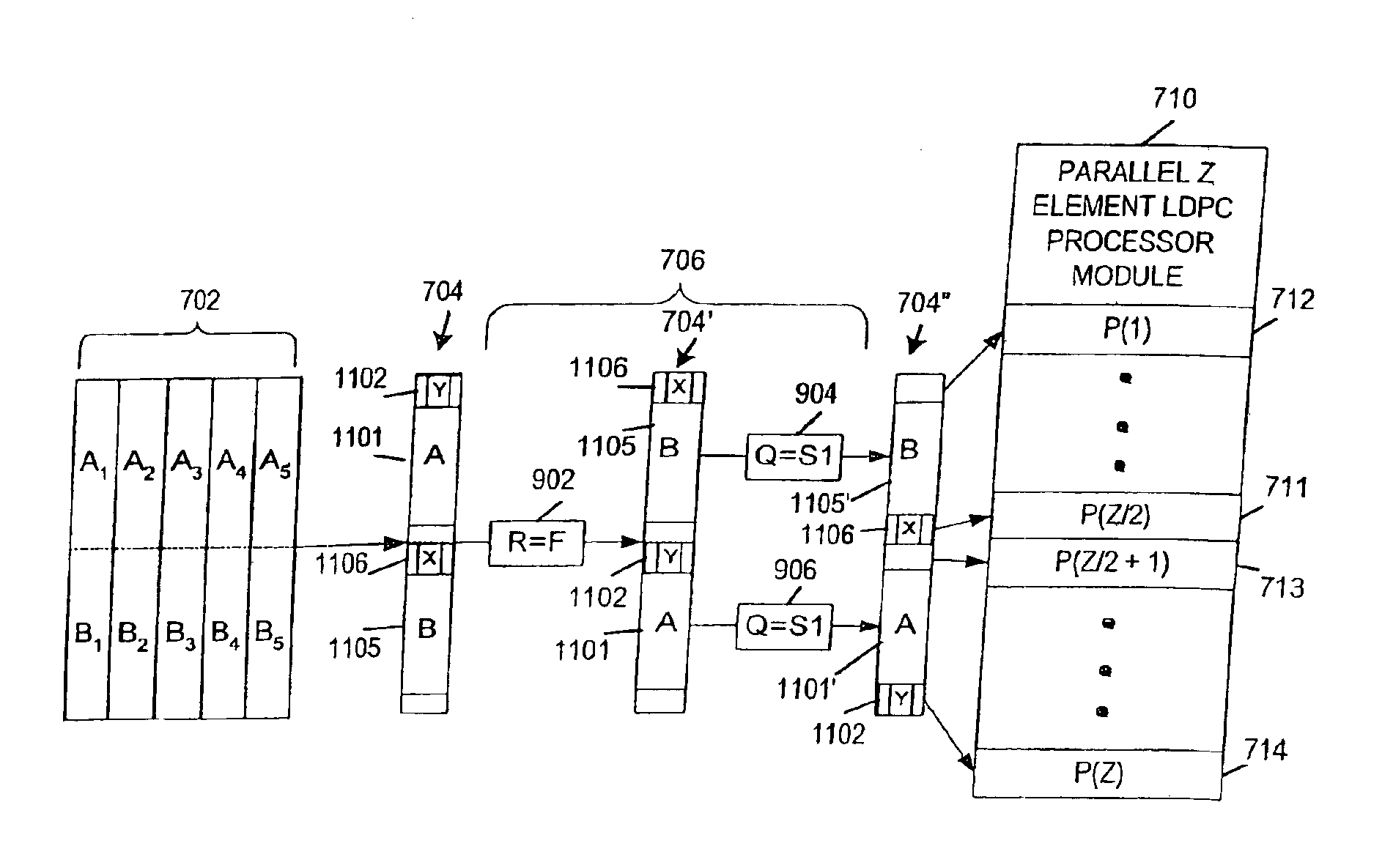

Method and apparatus for performing low-density parity-check (LDPC) code operations using a multi-level permutation

ActiveUS6957375B2Easy to implementError correction/detection using multiple parity bitsCode conversionGraphicsCommunications system

Methods and apparatus of the present invention can be used to implement a communications system wherein different devices using the same LDPC code can be implemented using different levels of parallelism. The use of a novel class of LDPC codes makes such differences in parallelism possible. Use of a factorable permuter in various embodiments of the invention make LDPC devices with different levels of parallelism in the encoder and decoder relatively easy to implement when using the codes in the class of LDPC codes discussed herein. The factorable permuter may be implemented as a controllable multi-stage switching devices which performs none, one, or multiple sequential reordering operations on a Z element vector passed between memory and a Z element vector processor, with the switching one individual vectors being controlled in accordance with the graph structure of the code being implemented.

Owner:QUALCOMM INC

Transmitter apparatus and bit interleaving method thereof

ActiveUS20150341054A1Improve decoding performanceImprove reception performanceError correction/detection using concatenated codesError correction/detection using LDPC codesParity-check matrixCheck digit

A transmitting apparatus is provided. The transmitting apparatus includes: an encoder configured to generate a low-density parity check (LDPC) codeword by LDPC encoding of input bits based on a parity check matrix including information word bits and parity bits, the LDPC codeword including a plurality of bit groups each including a plurality of bits; an interleaver configured to interleave the LDPC codeword; and a modulator configured to map the interleaved LDPC codeword onto a modulation symbol, wherein the interleaver is further configured to interleave the LDPC codeword such that a bit included in a predetermined bit group from among the plurality of bit groups constituting the LDPC codeword onto a predetermined bit of the modulation symbol.

Owner:SAMSUNG ELECTRONICS CO LTD

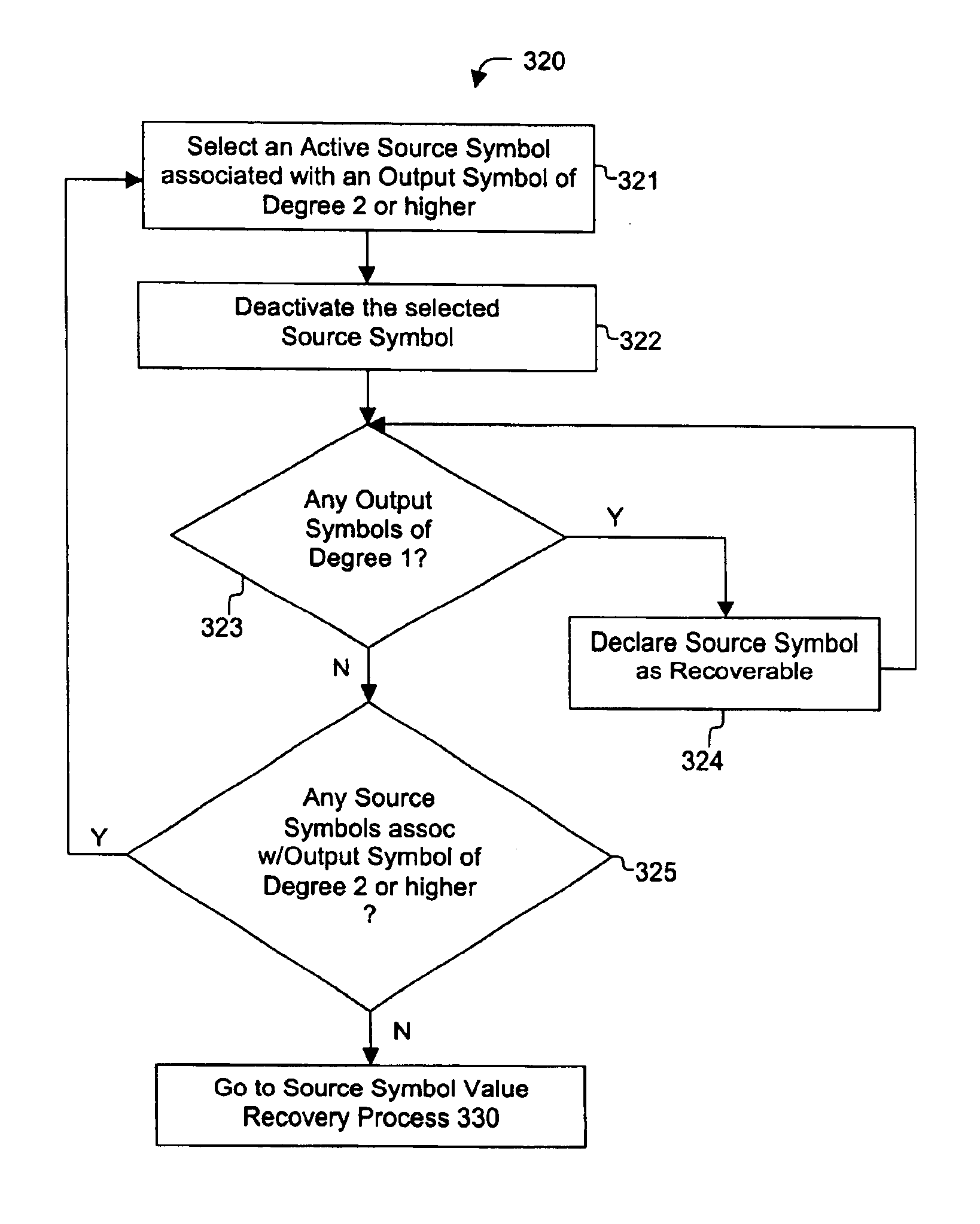

Systems and processes for decoding chain reaction codes through inactivation

InactiveUS6856263B2Error prevention/detection by using return channelOther decoding techniquesAlgorithmChain reaction

A method for processing a chain reaction codes includes first selecting a source symbol which is associated an output symbol of degree two or higher (i.e., an output symbol which is itself associated with two or more input symbols), and subsequently deactivating the selected source symbol in an attempt to produce an output symbol of degree one. The inactivation process can be repeated either successively until an output symbol of degree one is identified, and / or whenever the decoding process is unable to locate an output symbol of degree one.

Owner:QUALCOMM INC

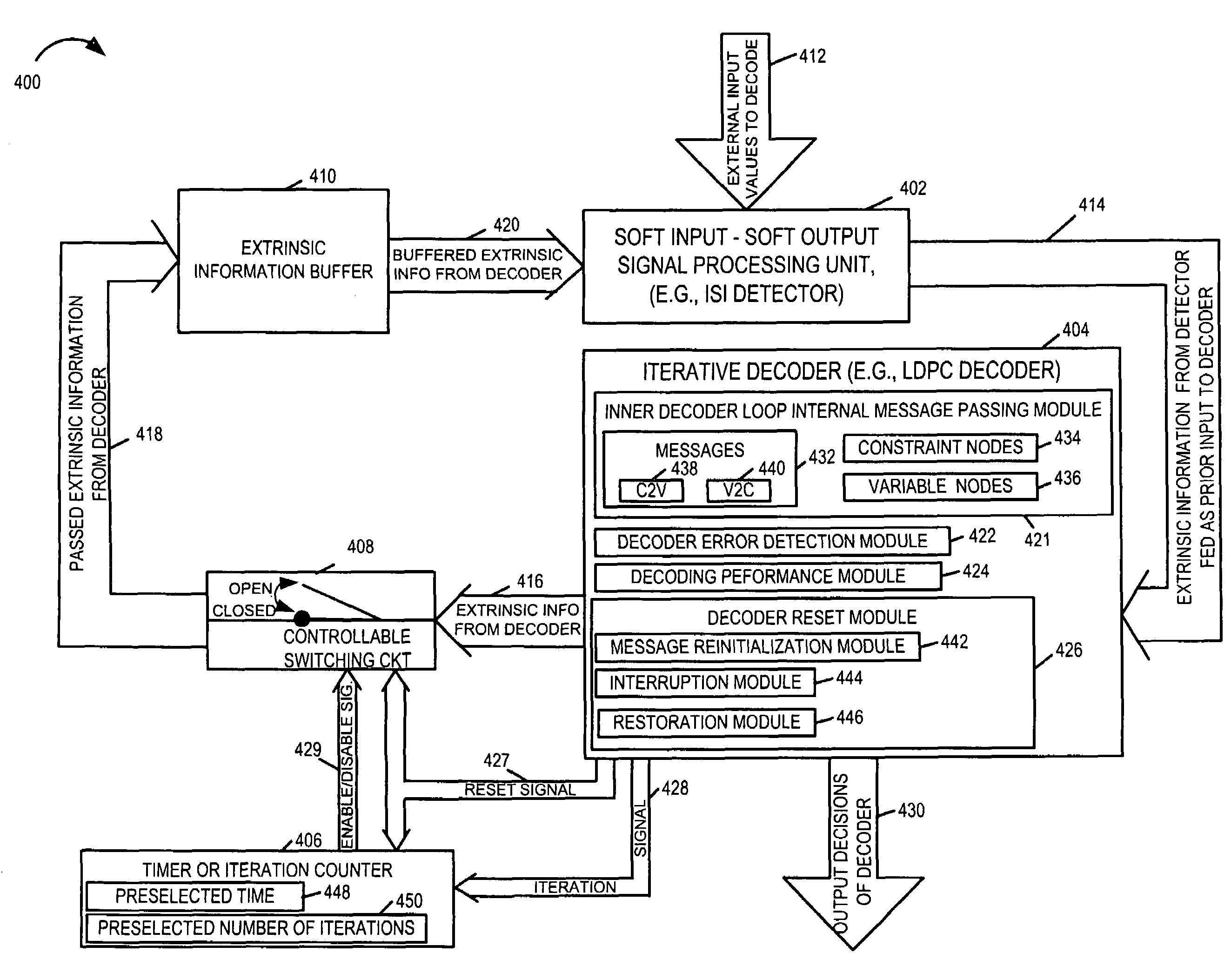

Methods and apparatus for reducing error floors in message passing decoders

ActiveUS7237181B2Reduce the numberReduce quality problemsError preventionError correction/detection using multiple parity bitsComputer hardwareEdge states

An iterative message passing decoder, e.g., an LDPC decoder, operating in conjunction with a soft input-soft output signal processing unit, e.g., an ISI detector, has an error floor performance region influenced by the decoder's sub-optimal message passing nature. Error floor reduction is achieved by a simple message re-initialization mechanism. Decoder edge states, e.g., constraint to variable node messages in decoder memory, are reinitialized, e.g., for an iteration, during the decoding after soft values provided by signal processing unit have improved. During the message re-initialization and for some subsequent amount of iterative decoder processing, extrinsic information fed back from the decoder to the signal processing unit and / or soft values delivered to the decoder from the signal processing unit, in an outer communications loop, is temporarily frozen, e.g., using a switch and a buffer. Then, the outer communications loop is restored as the decoding continues, achieving improved decoding performance.

Owner:QUALCOMM INC

Method for decoding data in non-volatile storage using reliability metrics based on multiple reads

ActiveUS7904793B2Other decoding techniquesRead-only memoriesLow-density parity-check codeDependability

Data stored in non-volatile storage is decoded using iterative probabilistic decoding and multiple read operations to achieve greater reliability. An error correcting code such as a low density parity check code may be used. In one approach, initial reliability metrics, such as logarithmic likelihood ratios, are used in decoding read data of a set of non-volatile storage element. The decoding attempts to converge by adjusting the reliability metrics for bits in code words which represent the sensed state. If convergence does not occur, e.g., within a set time period, the state of the non-volatile storage element is sensed again, current values of the reliability metrics in the decoder are adjusted, and the decoding again attempts to converge. In another approach, the initial reliability metrics are based on multiple reads. Tables which store the reliability metrics and adjustments based on the sensed states can be prepared before decoding occurs.

Owner:SANDISK TECH LLC

Channel coding/decoding apparatus and method using a parallel concatenated low density parity check code

InactiveUS20050149841A1Reduce complexityError prevention/detection by using return channelError detection/correctionComputer hardwareLow-density parity-check code

A parallel concatenated low density parity check (LDPC) code having a variable code rate is provided by generating, upon receiving information bits, a first component LDPC code according to the information bits, interleaving the information bits according to a predetermined interleaving rule, and generating a second component LDPC code according to the interleaved information bits. With use of the parallel concatenated LDPC code, a mobile communication system can use a Hybrid Automatic Retransmission Request (HARQ) scheme and an Adaptive Modulation and Coding (AMC) scheme without restriction.

Owner:SAMSUNG ELECTRONICS CO LTD

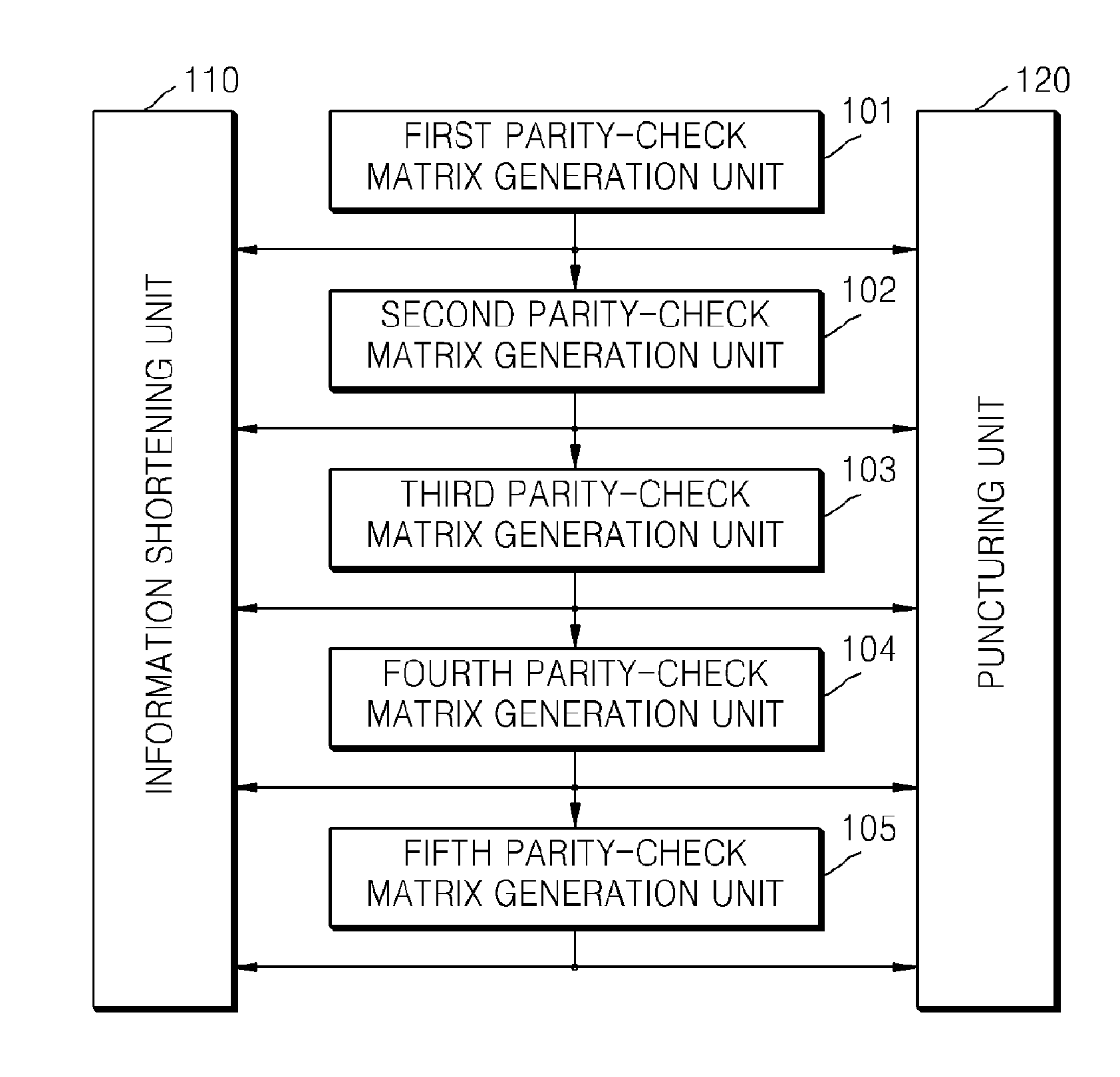

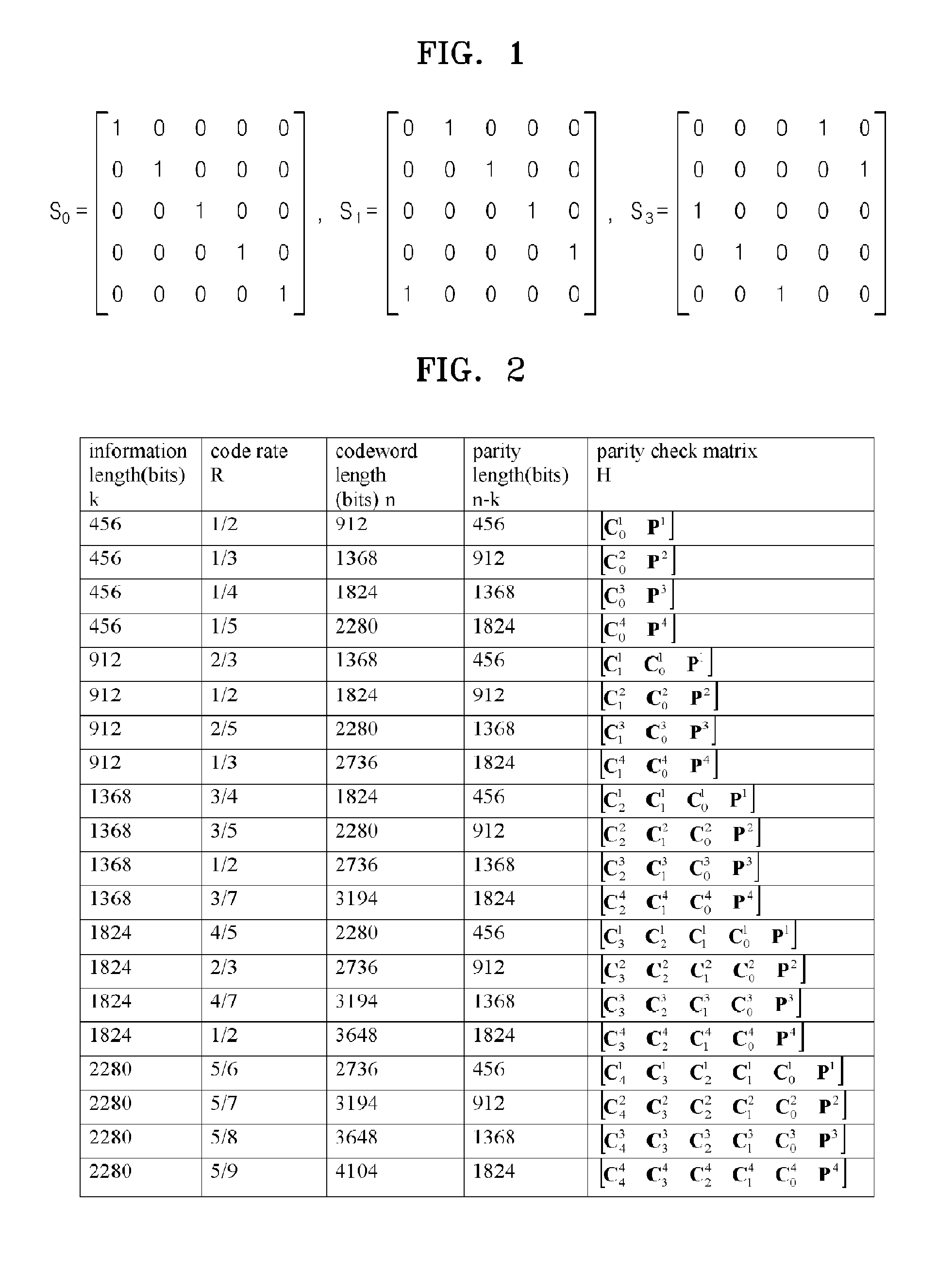

Method of generating parity-check matrix, encoding/decoding method for low density parity-check code with variable information length and variable code rate and apparatus using the same

InactiveUS20100325511A1Easily embodiedIncrease speedError correction/detection using multiple parity bitsCode conversionGeneration processParity-check matrix

A method of generating a parity-check matrix of a low density parity-check (LDPC) code with a variable information length and a variable code rate, an encoding / decoding method, and an apparatus using the same are provided. The method of generating a parity-check matrix of an LDPC code includes: a first parity-check matrix generation process of generating a first parity-check matrix constructed with a first information block and a parity block; and an m-th parity-check matrix generation process of generating an m-th parity-check matrix by an m-th information block to a generated (m−1)-th parity-check matrix (1<m≦M, where M is a natural number equal to or greater than two). Accordingly, it is possible to provide an LDPC code with a variable information length and a variable code rate which has a low complexity for encoding / decoding and a high quality of correction and detection of errors.

Owner:ELECTRONICS & TELECOMM RES INST

Transmitting apparatus and interleaving method thereof

ActiveUS20150341052A1Improve decoding performanceImprove reception performanceError correction/detection using concatenated codesError detection/correctionParity-check matrixComputer engineering

A transmitting apparatus is provided. The transmitting apparatus includes: an encoder configured to perform a low-density parity check (LDPC) encoding on input bits using a parity check matrix to generate an LDPC codeword comprising information word bits and parity bits; an interleaver configured to interleave the LDPC codeword; and a modulator configured to map the interleaved LDPC codeword onto a modulation symbol, wherein the modulator is further configured to map a bit included in a predetermined bit group from among a plurality of bit groups constituting the LDPC codeword onto a predetermined bit of the modulation symbol.

Owner:SAMSUNG ELECTRONICS CO LTD

Transmitting apparatus and puncturing method thereof

InactiveUS20150082118A1Improve decoding performanceError correction/detection using multiple parity bitsCode conversionLow-density parity-check codeLow density

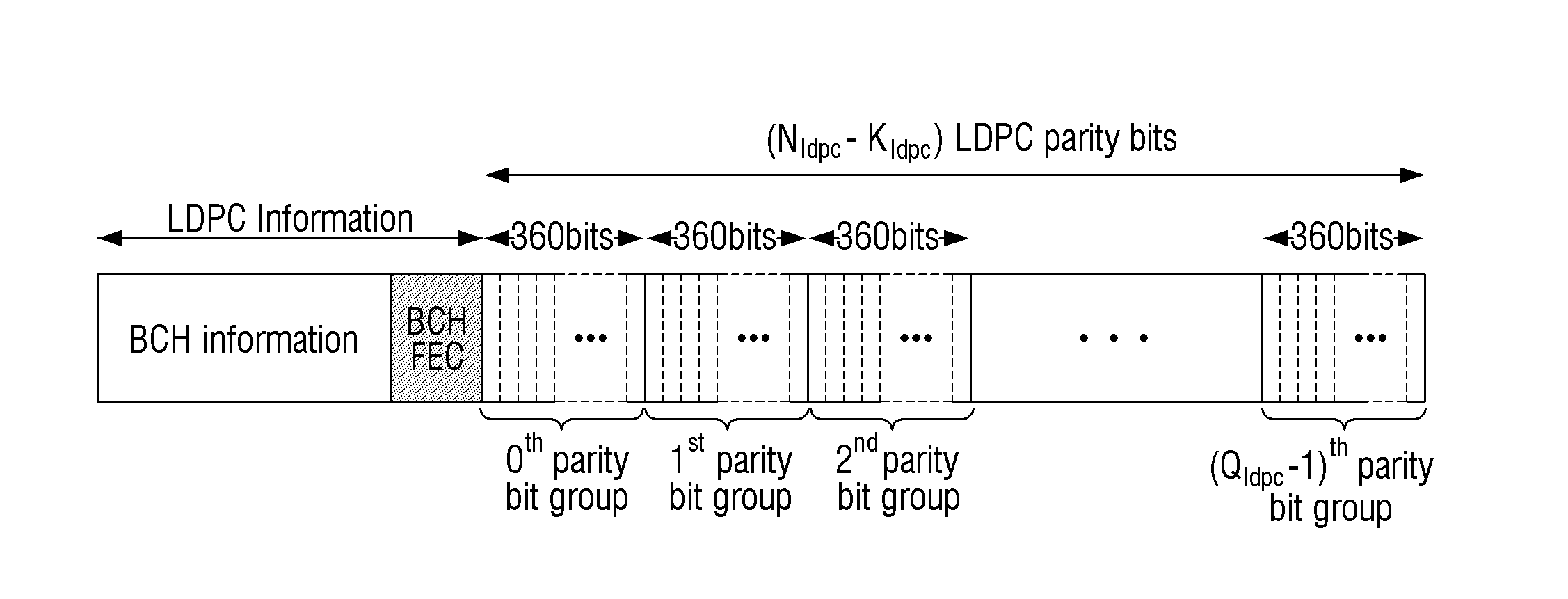

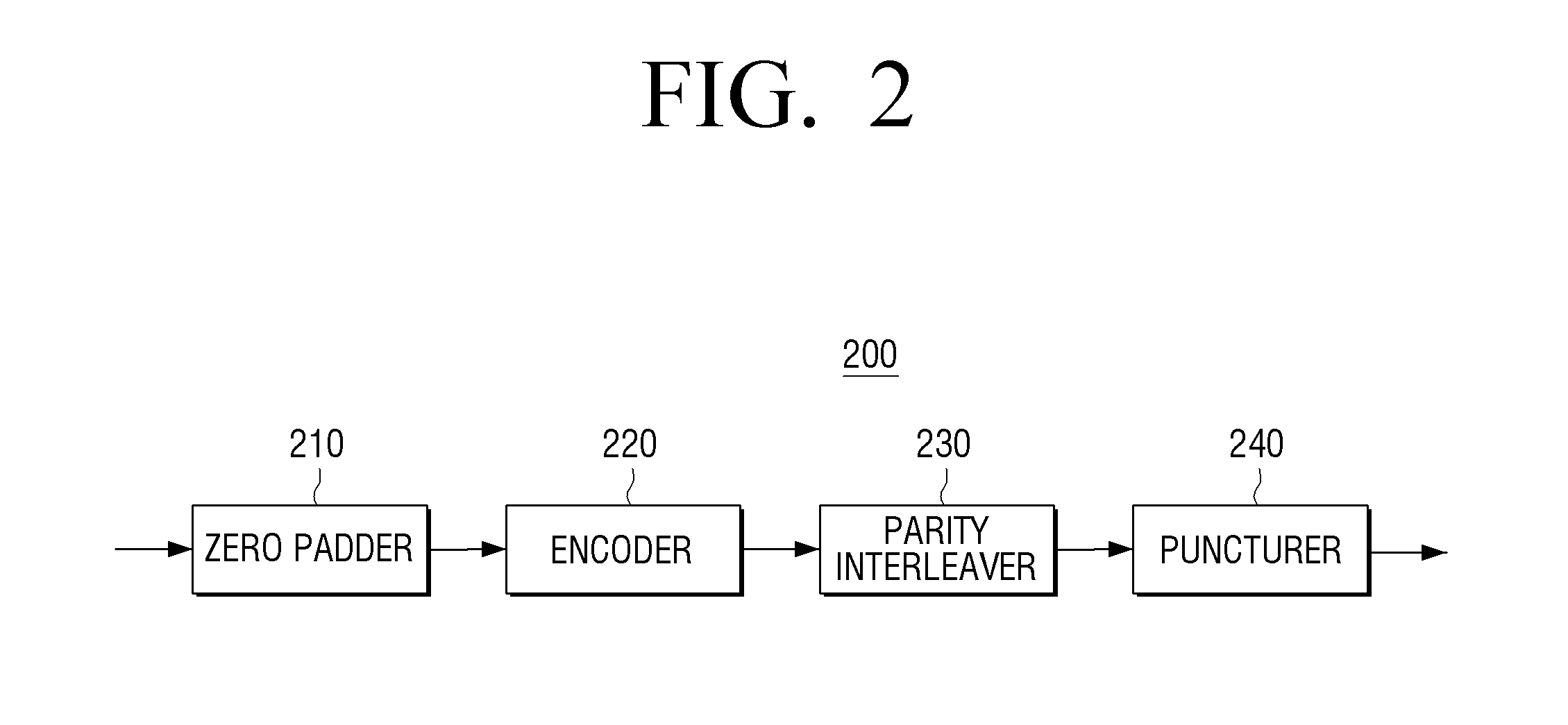

Provided are a transmitting apparatus, a receiving apparatus and methods of puncturing and depuncturing of parity bits. The transmitting apparatus includes: a zero padder configured to pad at least one zero bit to input bits; an encoder configured to generate a Low Density Parity Check (LDPC) codeword by performing LDPC encoding with respect to the bits to which the at least one zero bit is padded; a parity interleaver configured to interleave LDPC parity bits constituting the LDPC codeword; and a puncturer configured to puncture at least a part of the interleaved LDPC parity bits based on a pre-set puncturing pattern.

Owner:SAMSUNG ELECTRONICS CO LTD

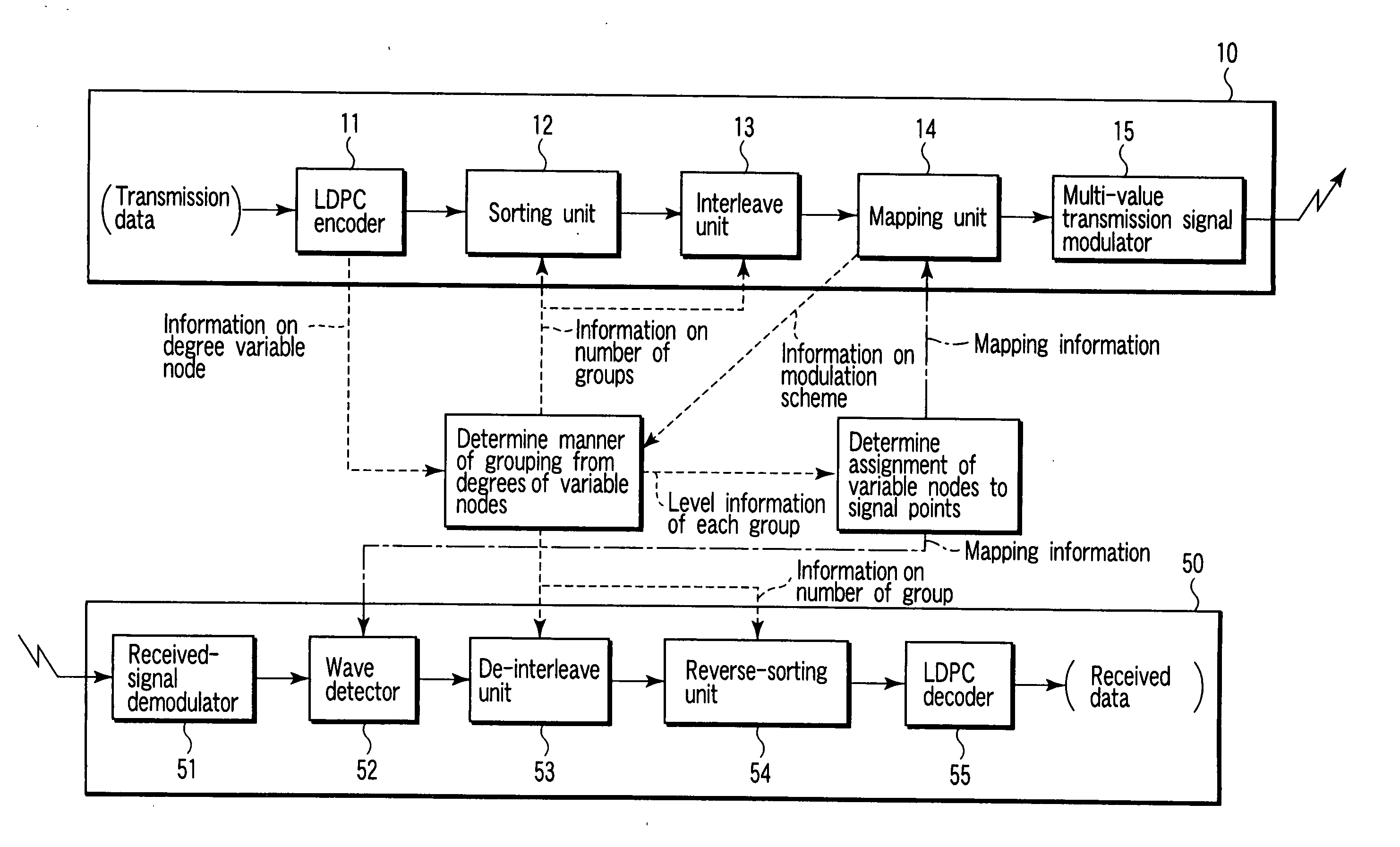

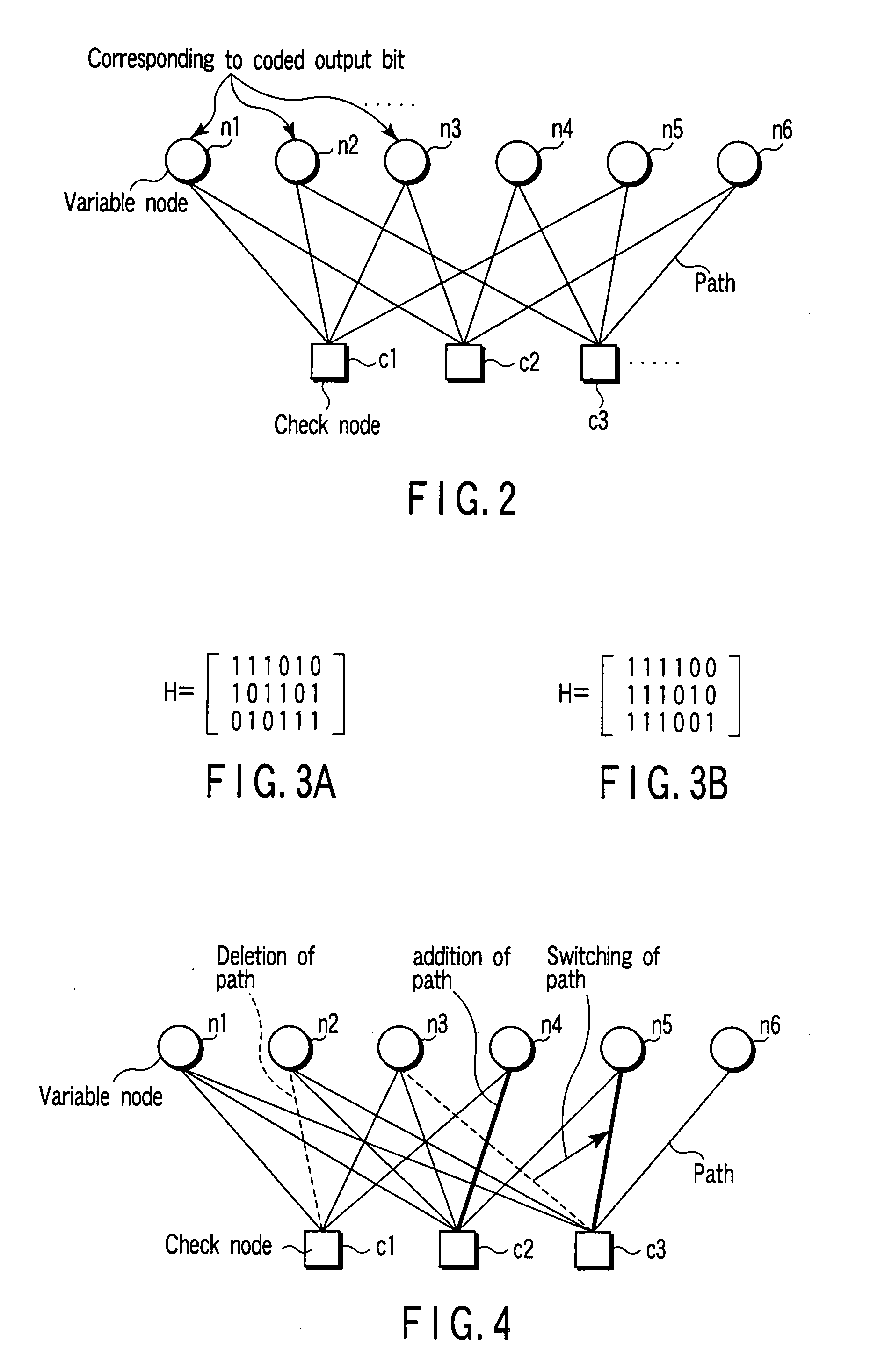

Mapping method for encoded bits using LDPC code, transmitting and receiving apparatuses employing this method, and program for executing this method

InactiveUS20050216821A1Transmission path divisionError correction/detection using LDPC codesTheoretical computer scienceParity-check matrix

A method for mapping of coded bits using a low density parity check (LDPC) code, comprises encoding information bits by using the LDPC code to generate coded bits, sorting the coded bits in accordance with degrees of variable nodes represented by a parity check matrix of the LDPC code, dividing the sorted coded bits into a plurality of groups in accordance with a using modulation scheme, and mapping the coded bits to respective modulation signal points by considering an error resistance of each of the groups and an error resistance of a corresponding one of the modulation signal points.

Owner:KK TOSHIBA

Popular searches

Cyclic codes Redundant data error correction Single error correction Record information storage Error correction/detection by combining multiple code structures Error detection only Digital signal error detection/correction Substation equipment Error correction/detection using interleaving techniques Baseband systems