Patents

Literature

2337results about "Error detection only" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

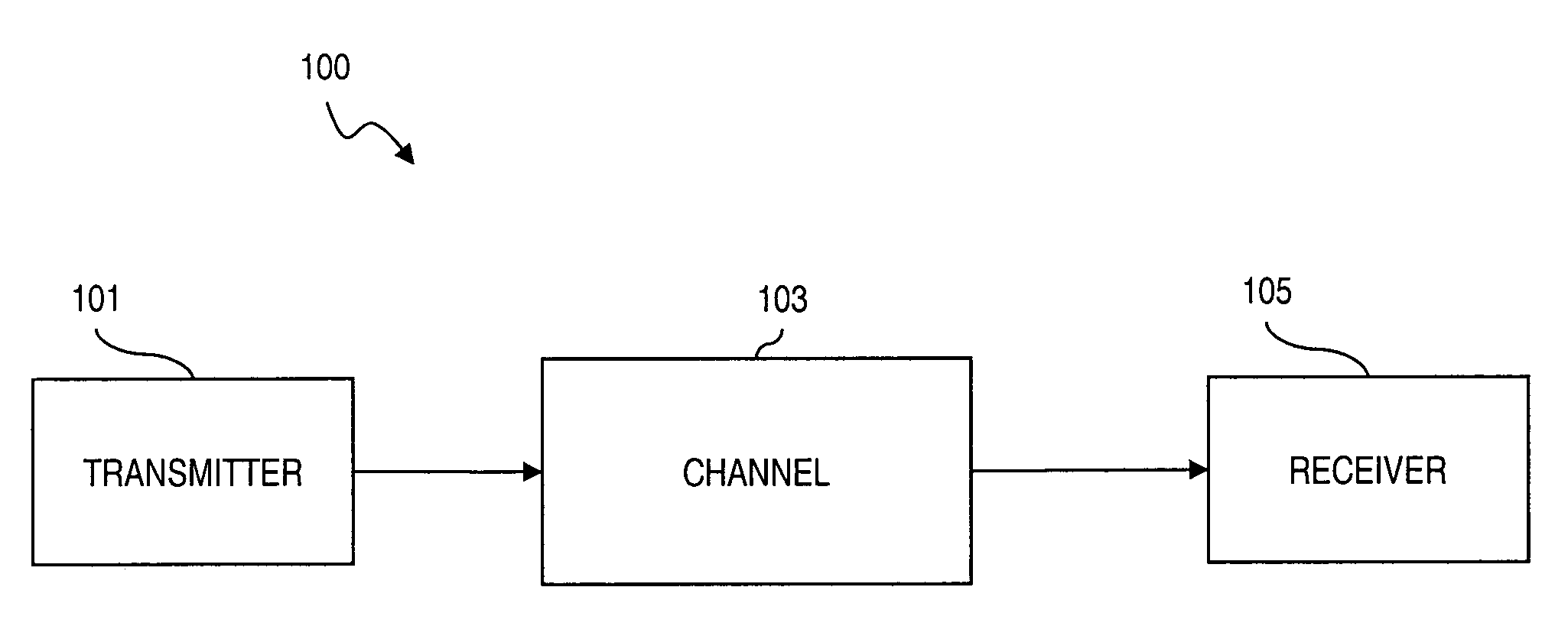

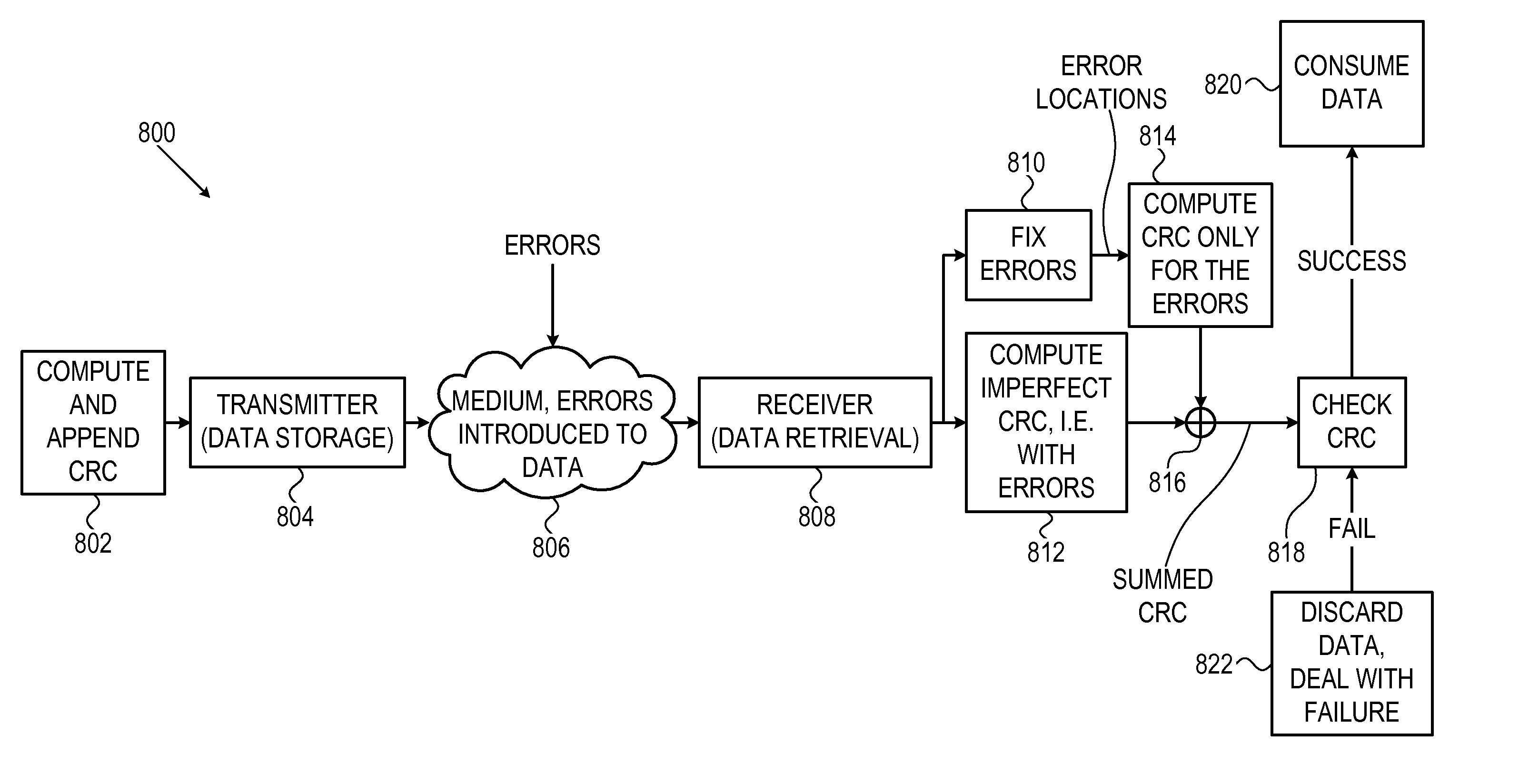

Method and system for calculating and verifying the integrity of data in a data transmission system

ActiveUS7987405B2Not having capability to accuratelyStay flexibleError preventionMemory record carrier reading problemsComputer hardwareData integrity

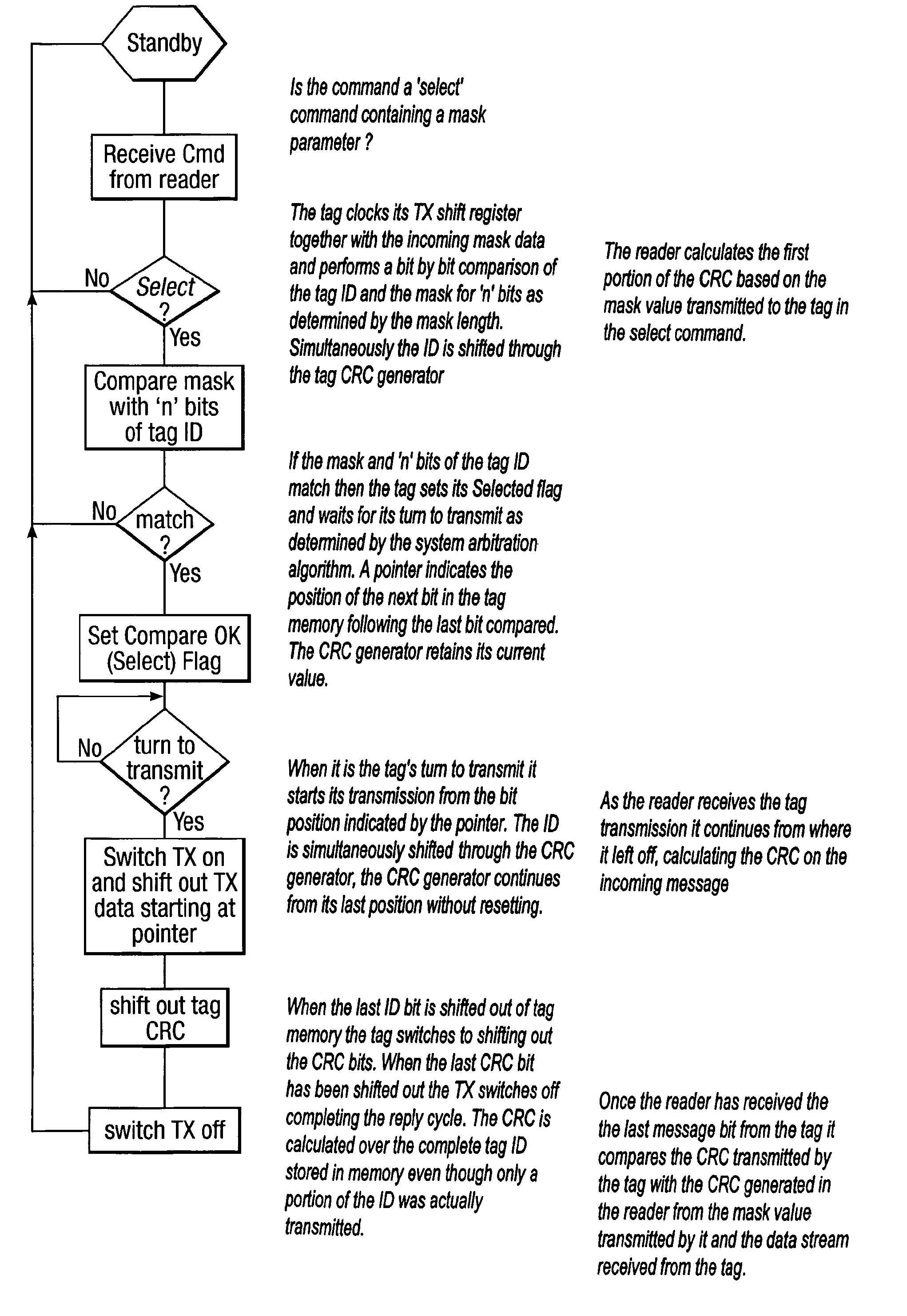

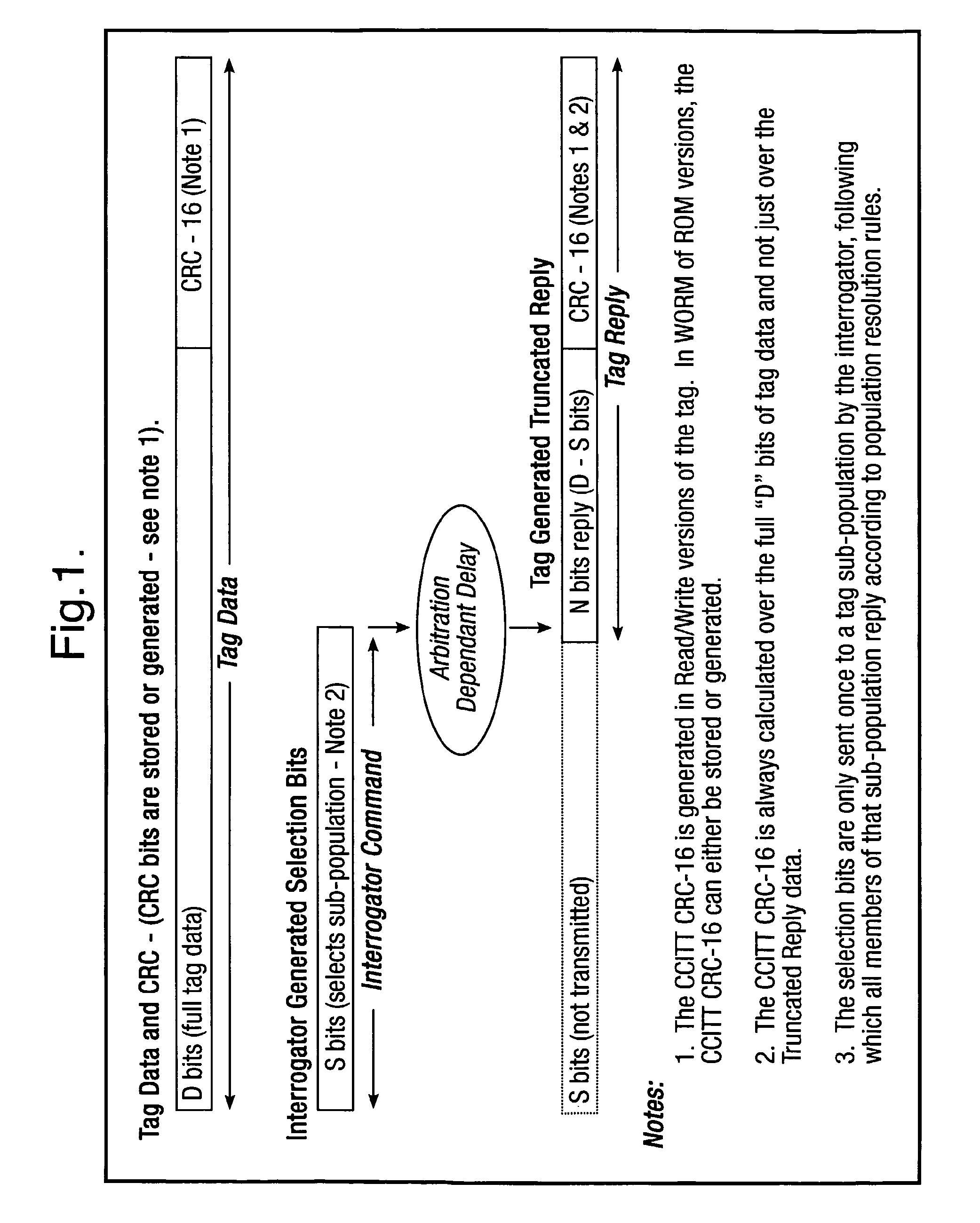

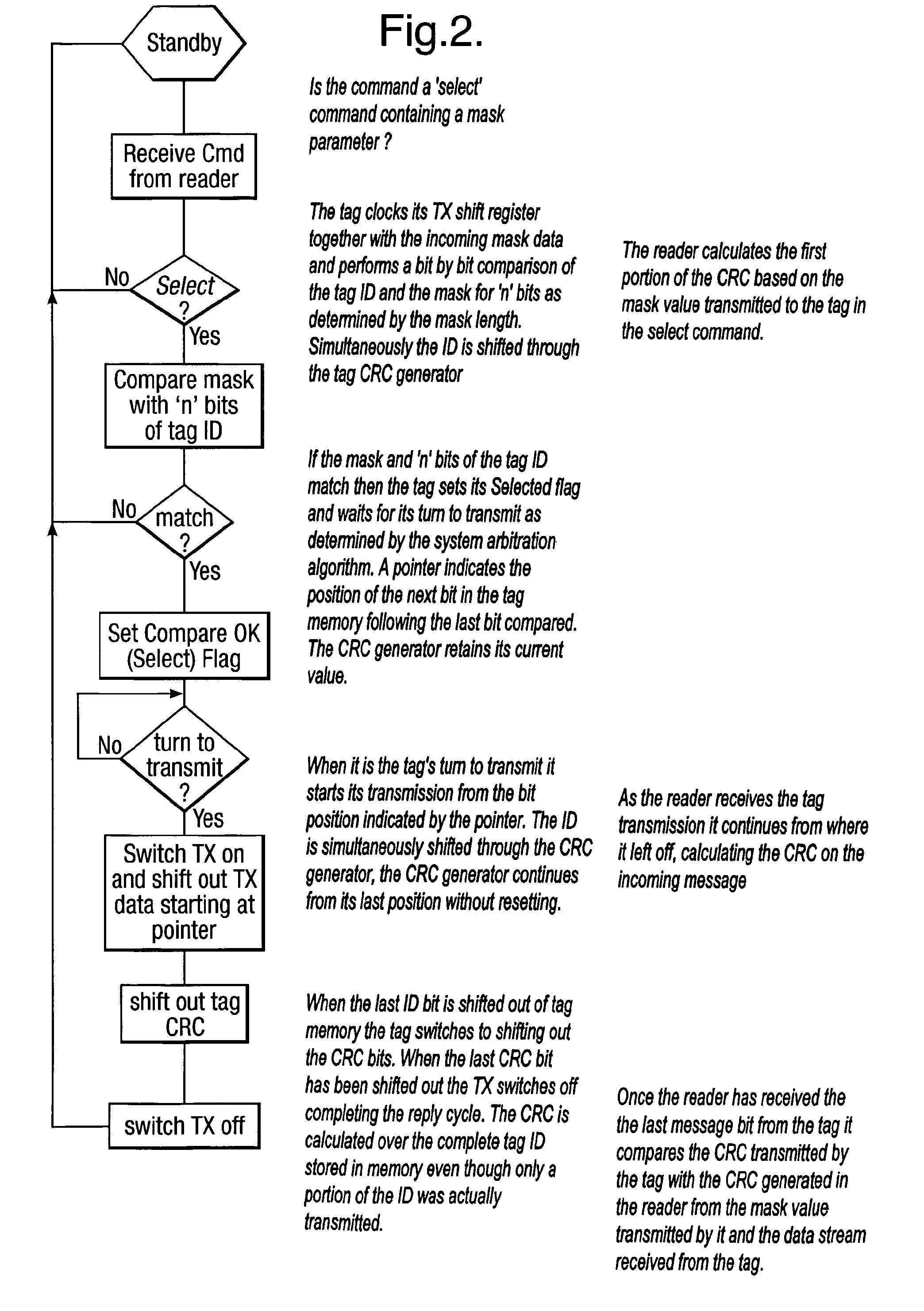

A method is described of calculating and verifying the integrity of data in a data communication system. The system comprises a base station and one or more remote stations, such as in an RFID system. The method includes transmitting a select instruction from the base station to the one or more remote stations, the select instruction containing a data field which matches a portion of an identity or other data field in one or more of the remote stations; transmitting from a selected remote station or stations a truncated reply containing identity data or other data of the remote station but omitting the portion transmitted by the base station; calculating in the base station a check sum or CRC from the data field originally sent and the truncated reply data received and comparing the calculated check sum or CRC with the check sum or CRC sent by the remote station.

Owner:ZEBRA TECH CORP

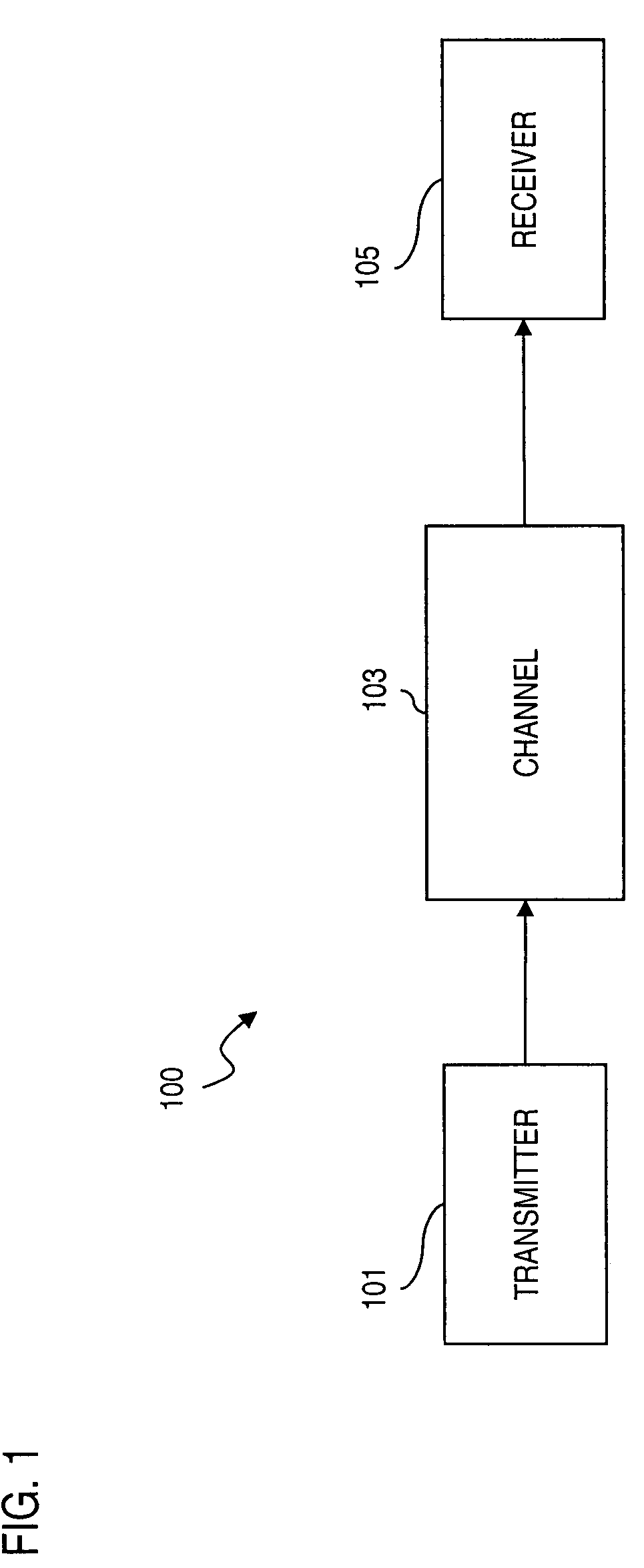

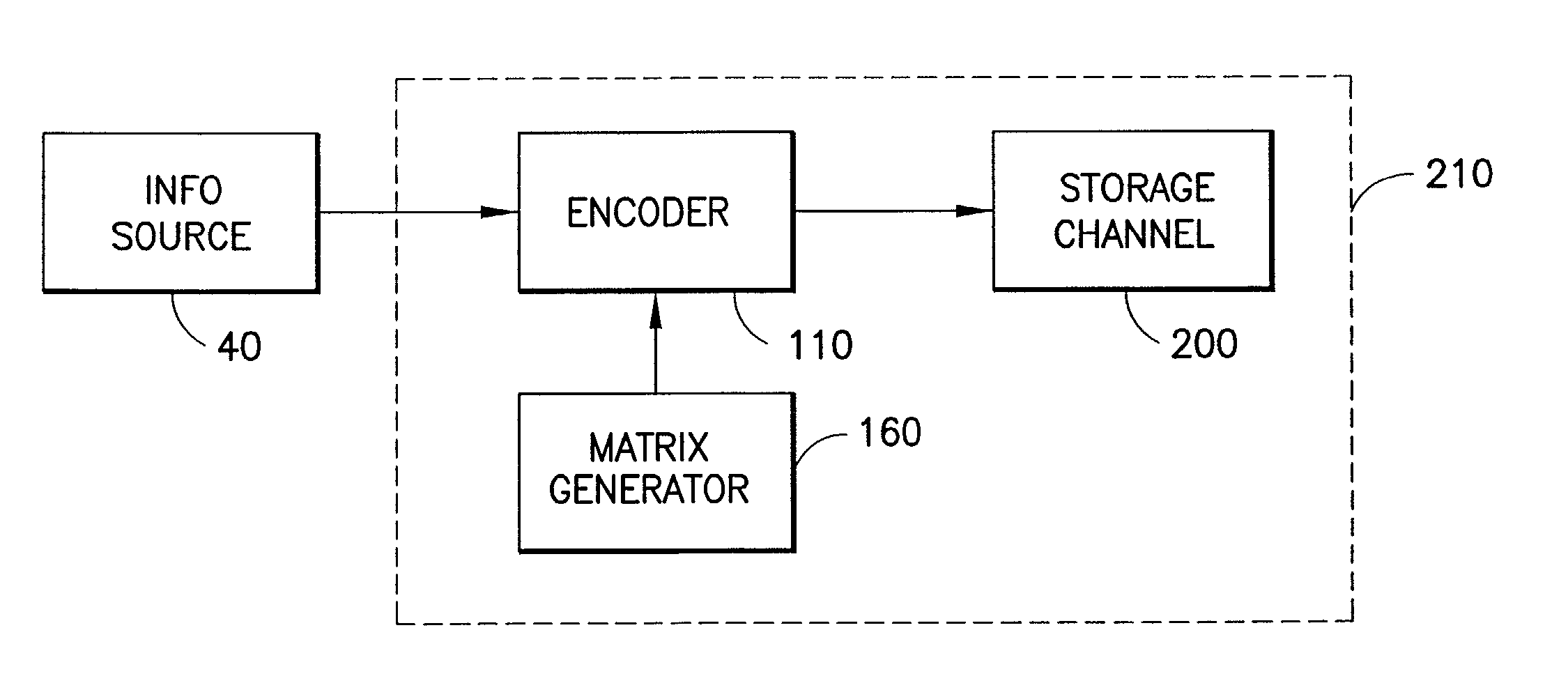

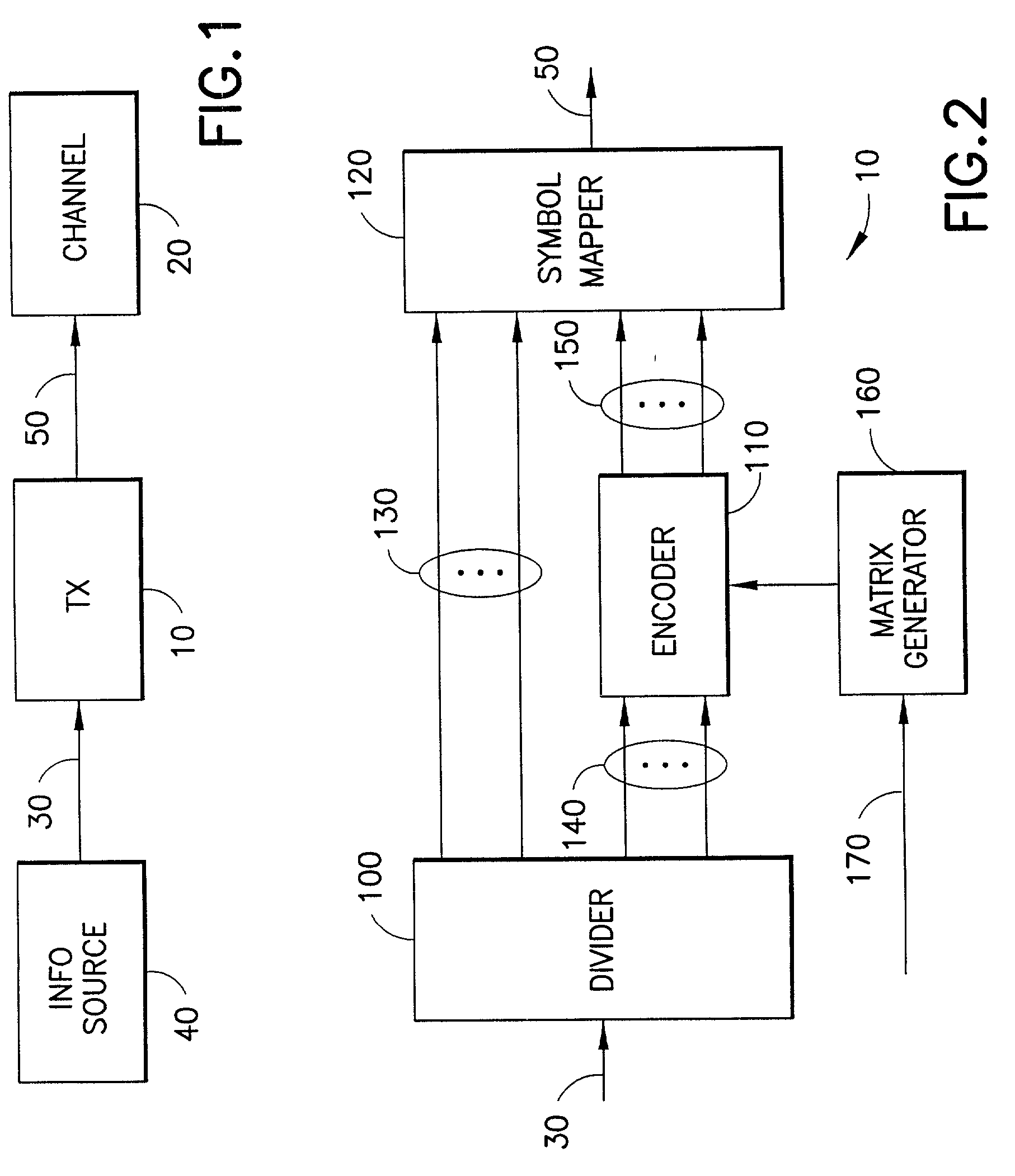

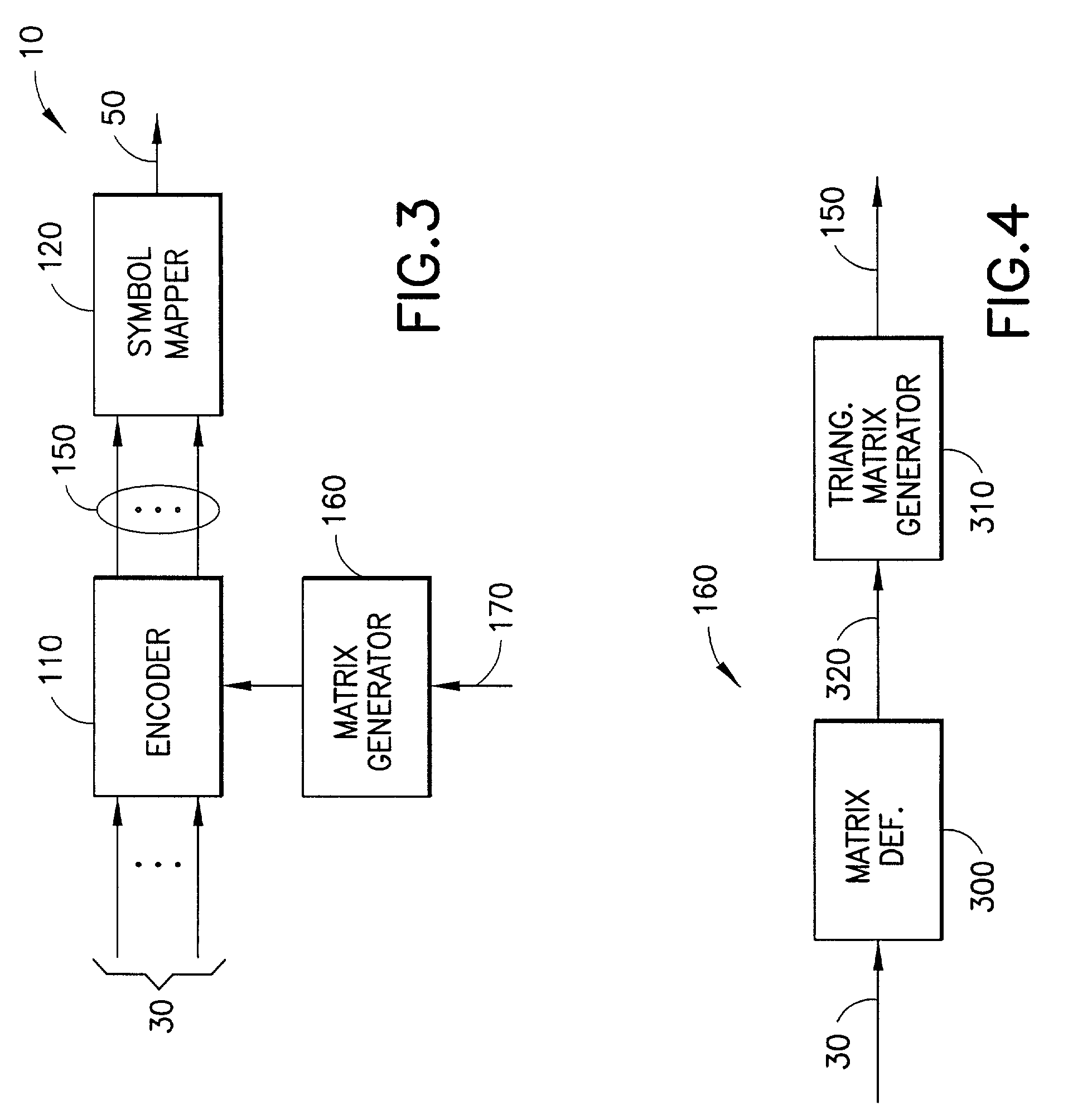

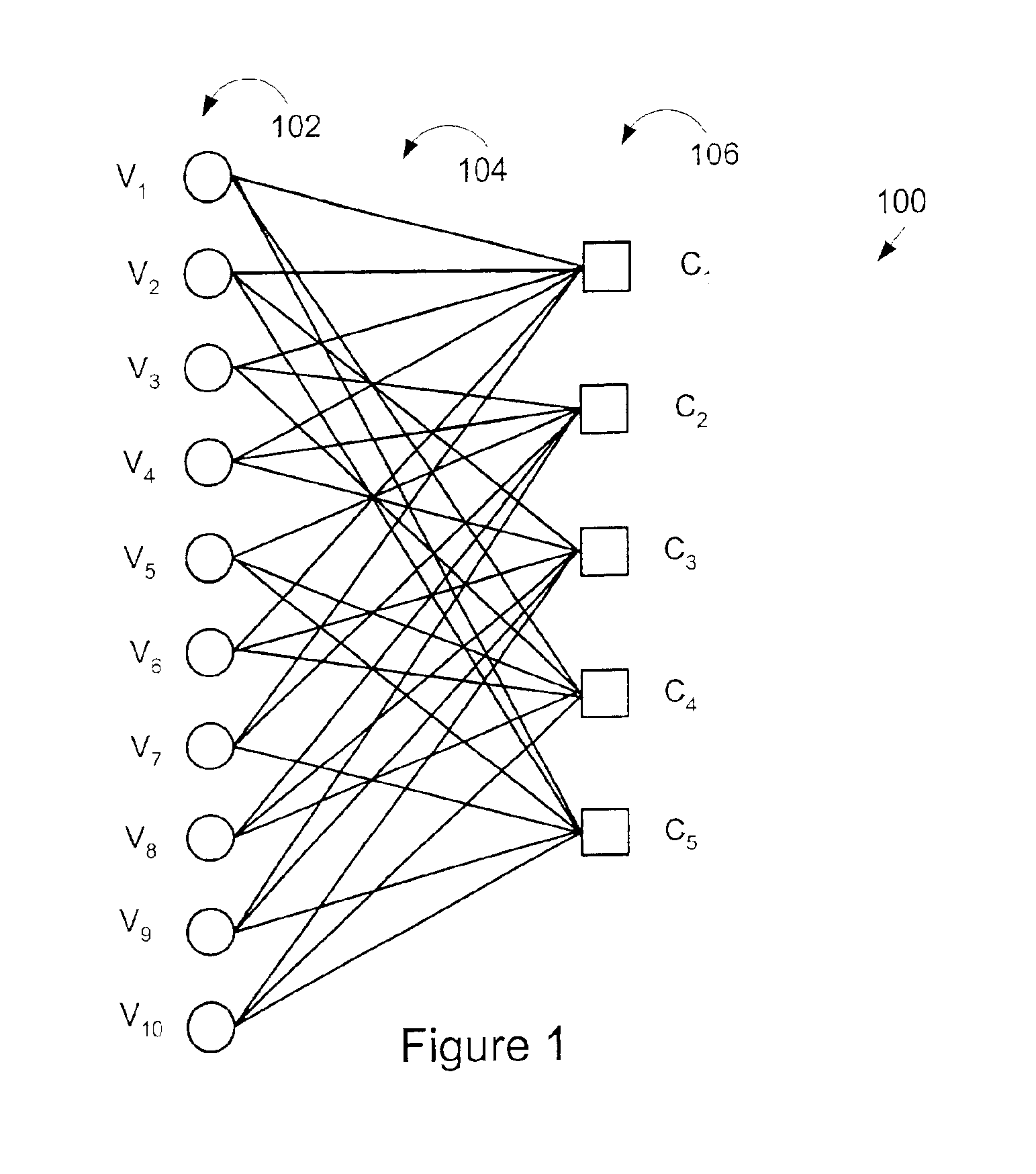

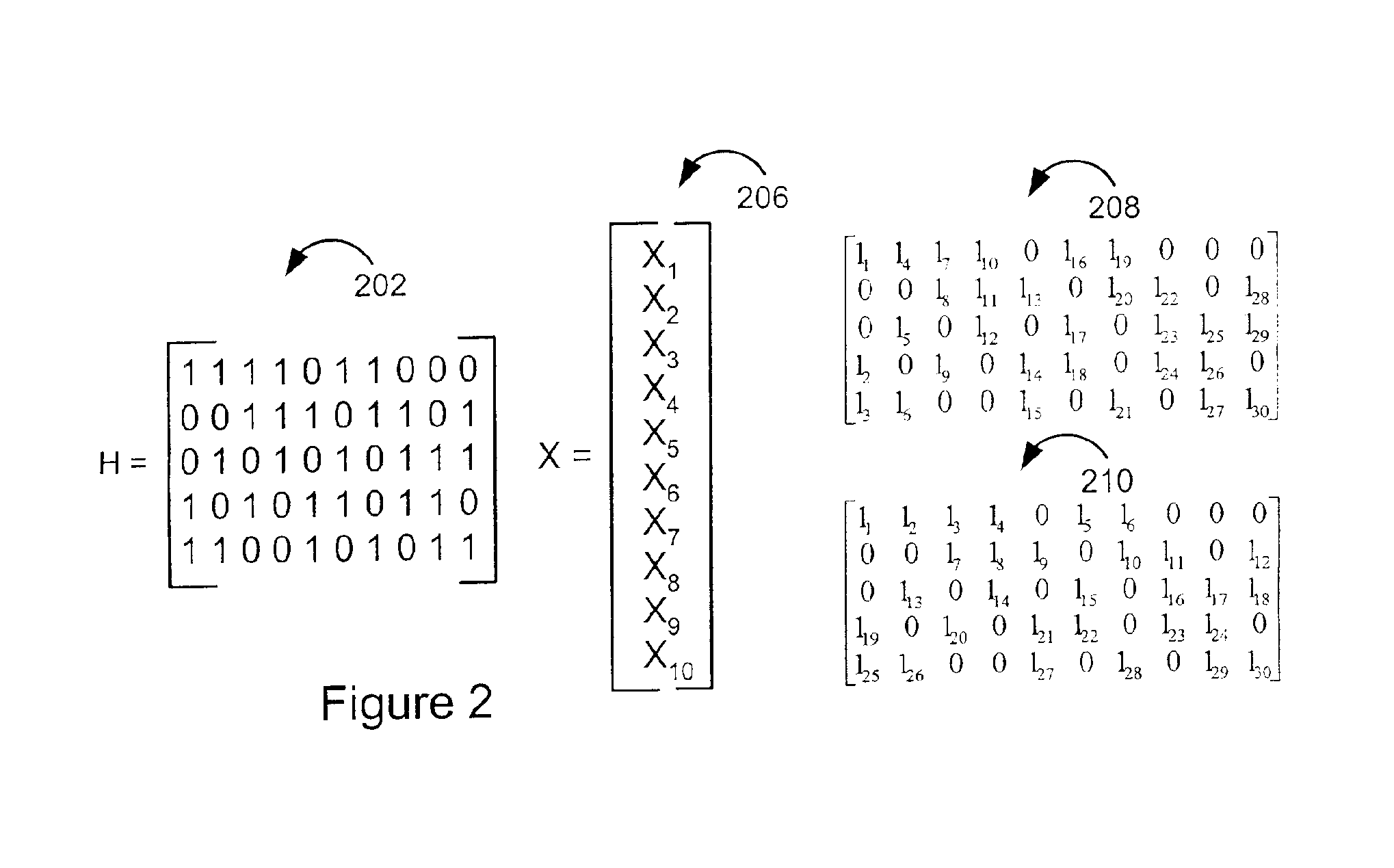

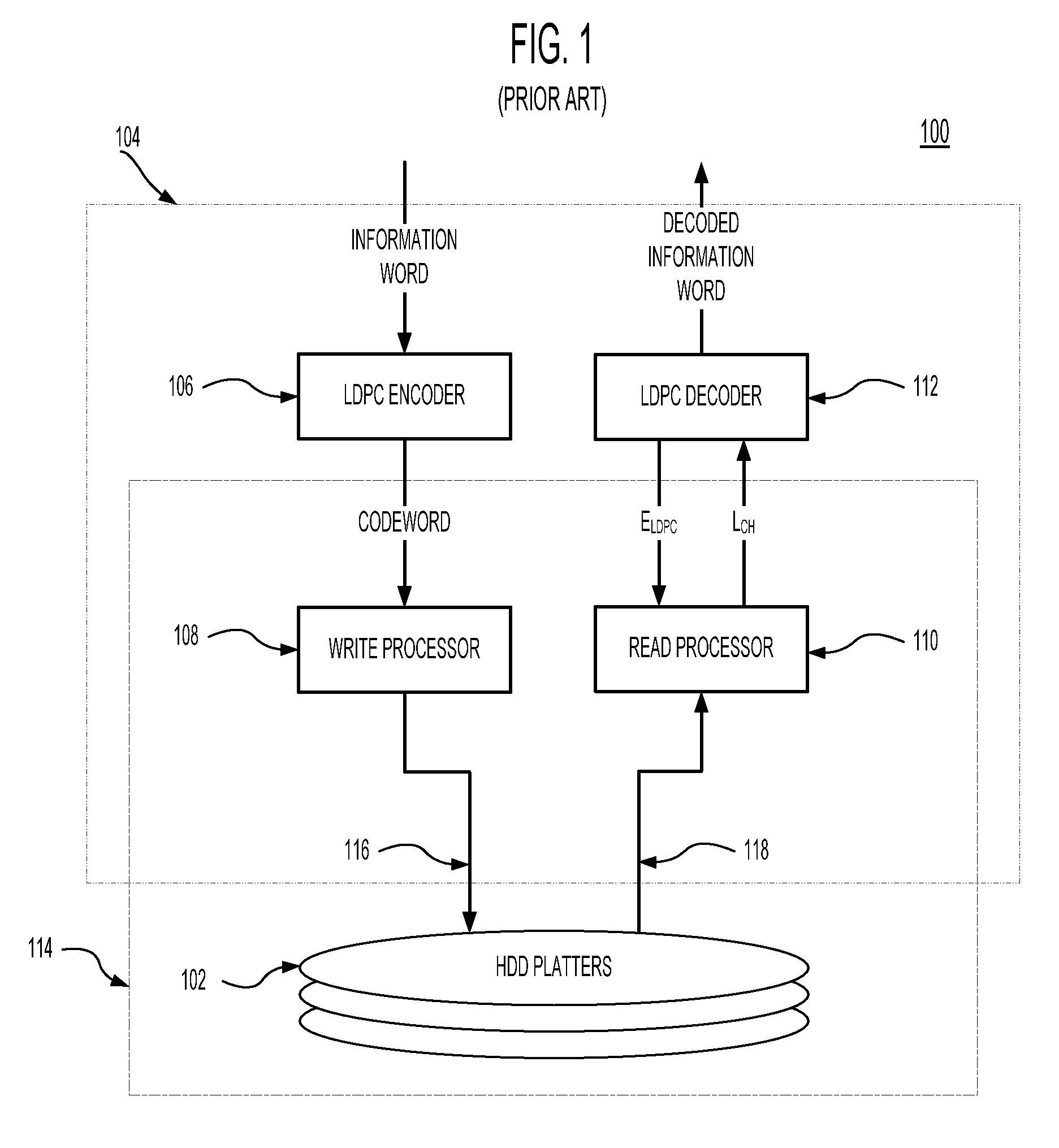

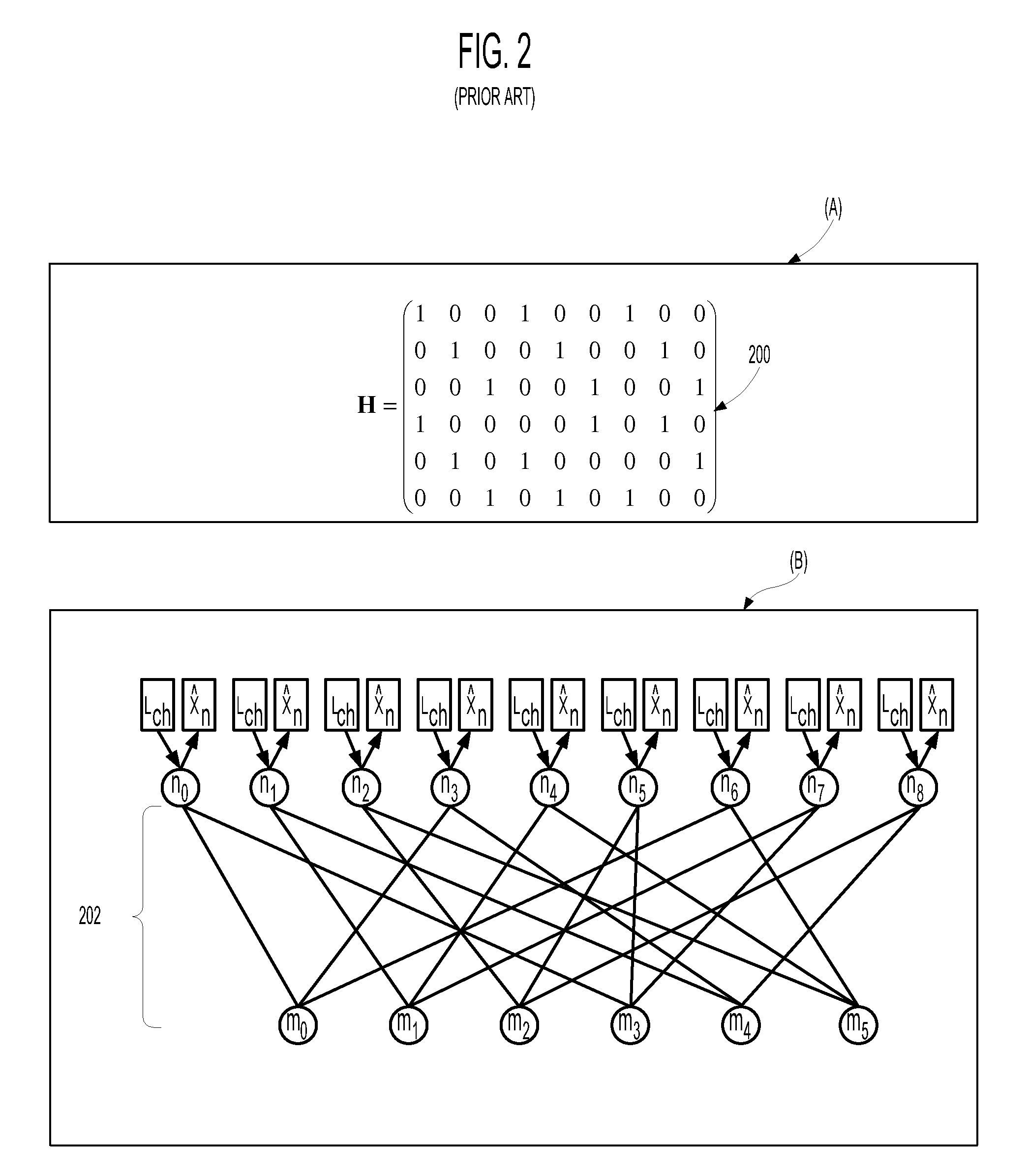

Method and apparatus for low density parity check encoding of data

InactiveUS6895547B2Improve performanceError preventionError detection/correctionTheoretical computer scienceParity-check matrix

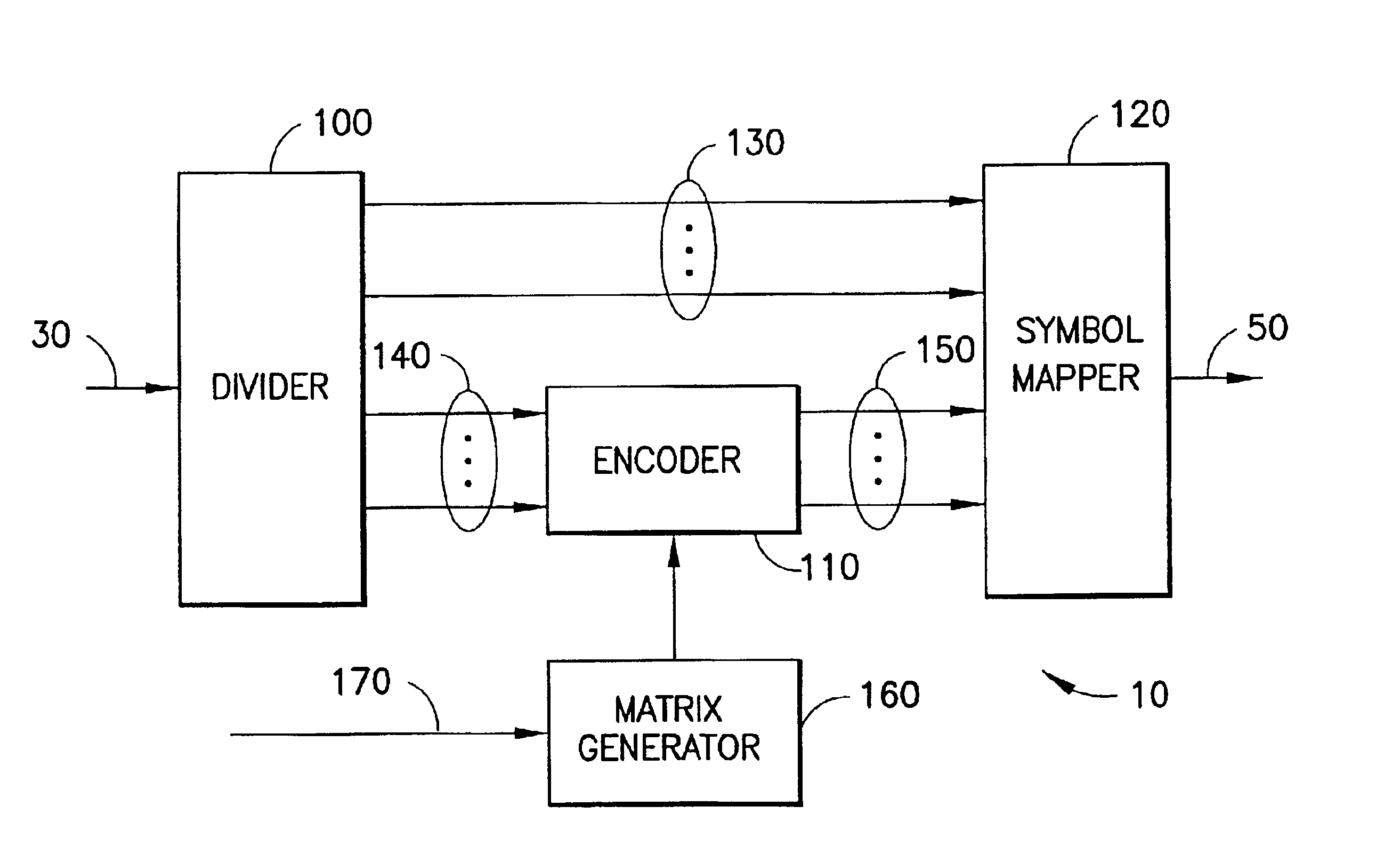

A method for low-density parity-check (LDPC) encoding of data comprises defining a first M×N parity check matrix; generating, based on the first parity check matrix, a second parity check matrix having an M×M triangular sub-matrix; and, mapping the data into an LDPC code word based on the second parity check matrix. The method is particularly useful for data communications applications, but may also be employed in other applications such as, for example, data storage.

Owner:GLOBALFOUNDRIES US INC

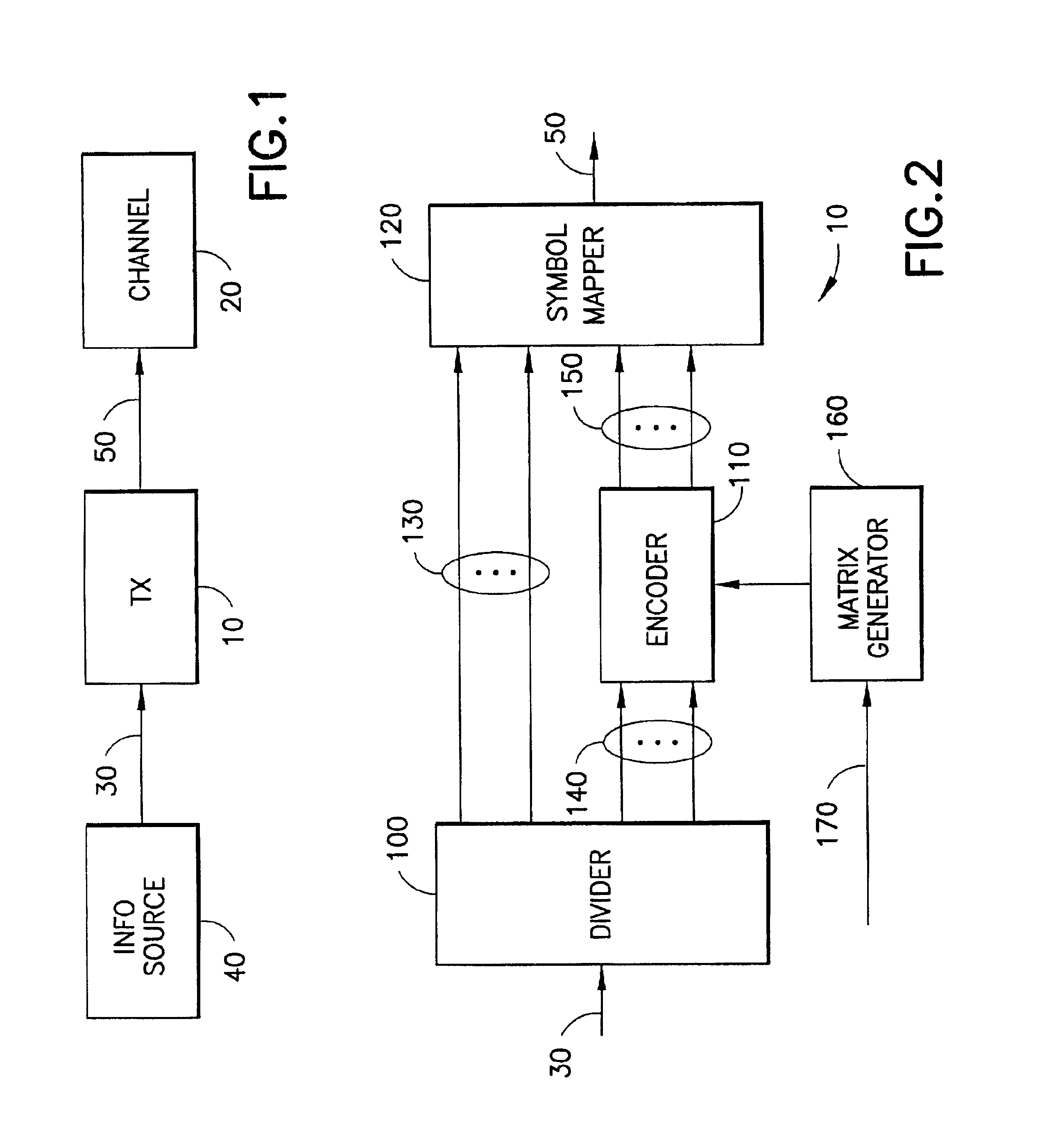

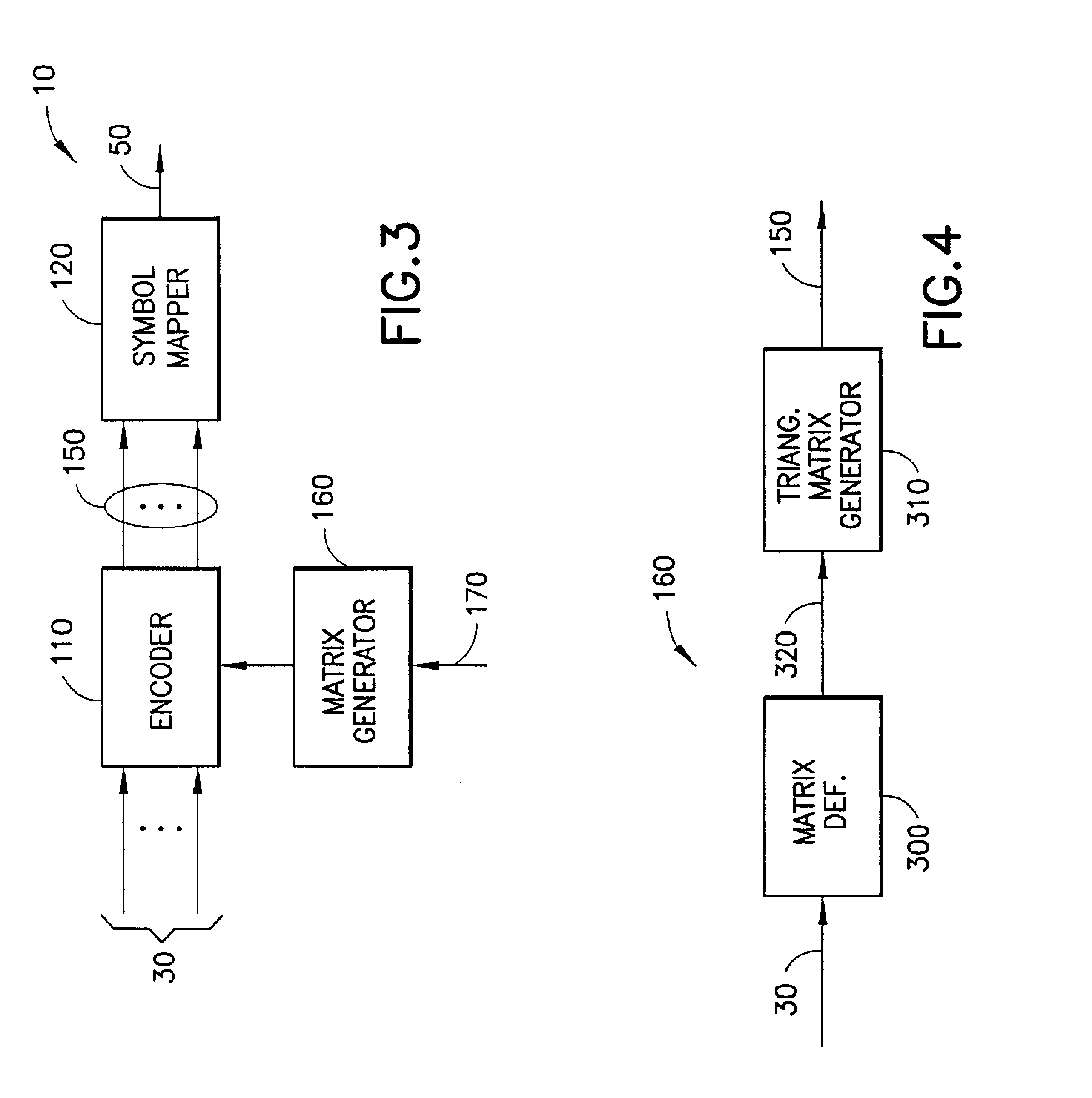

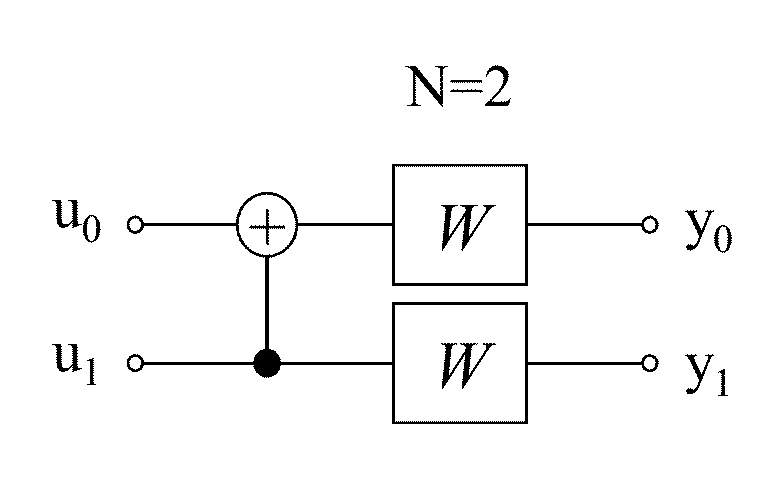

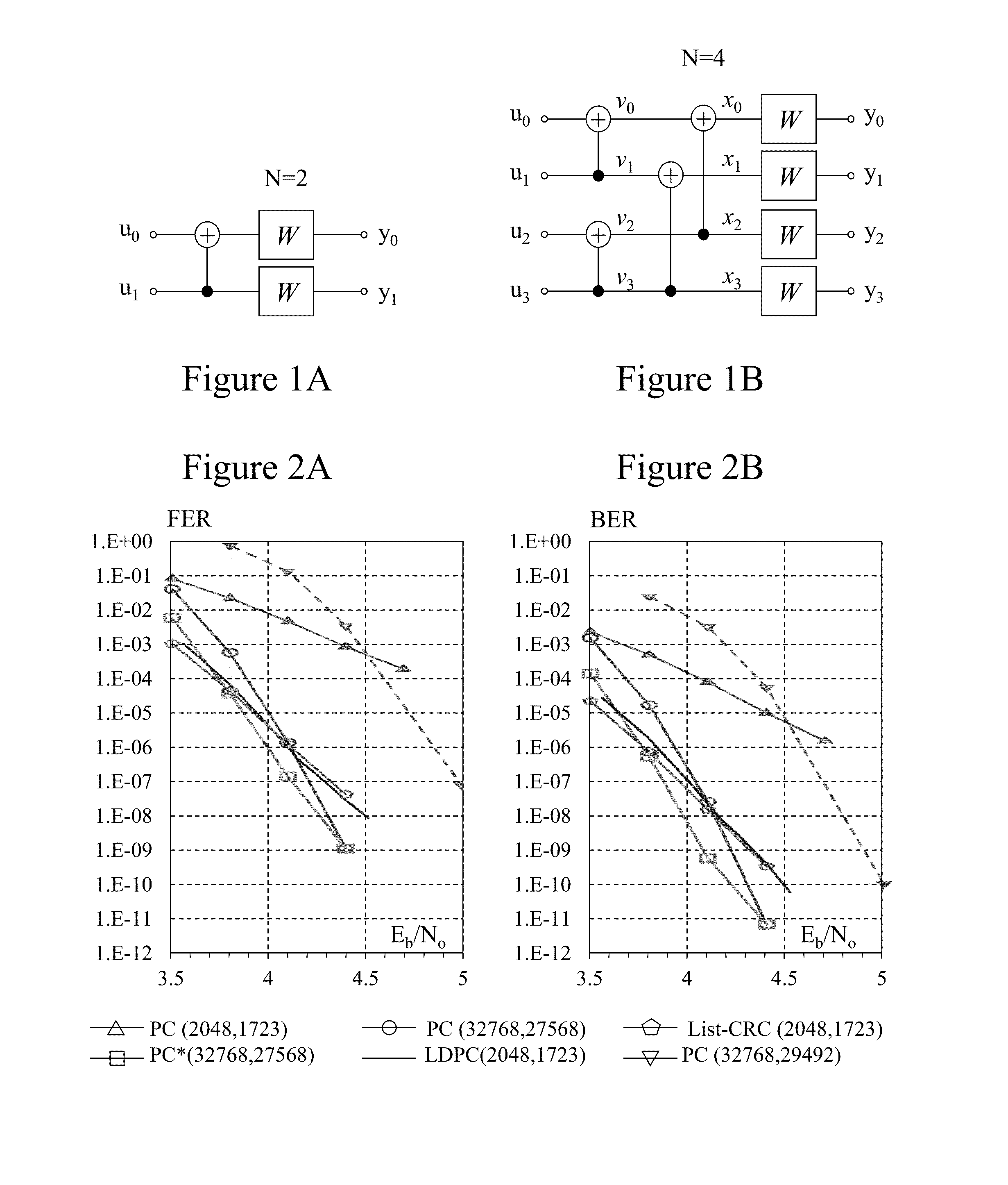

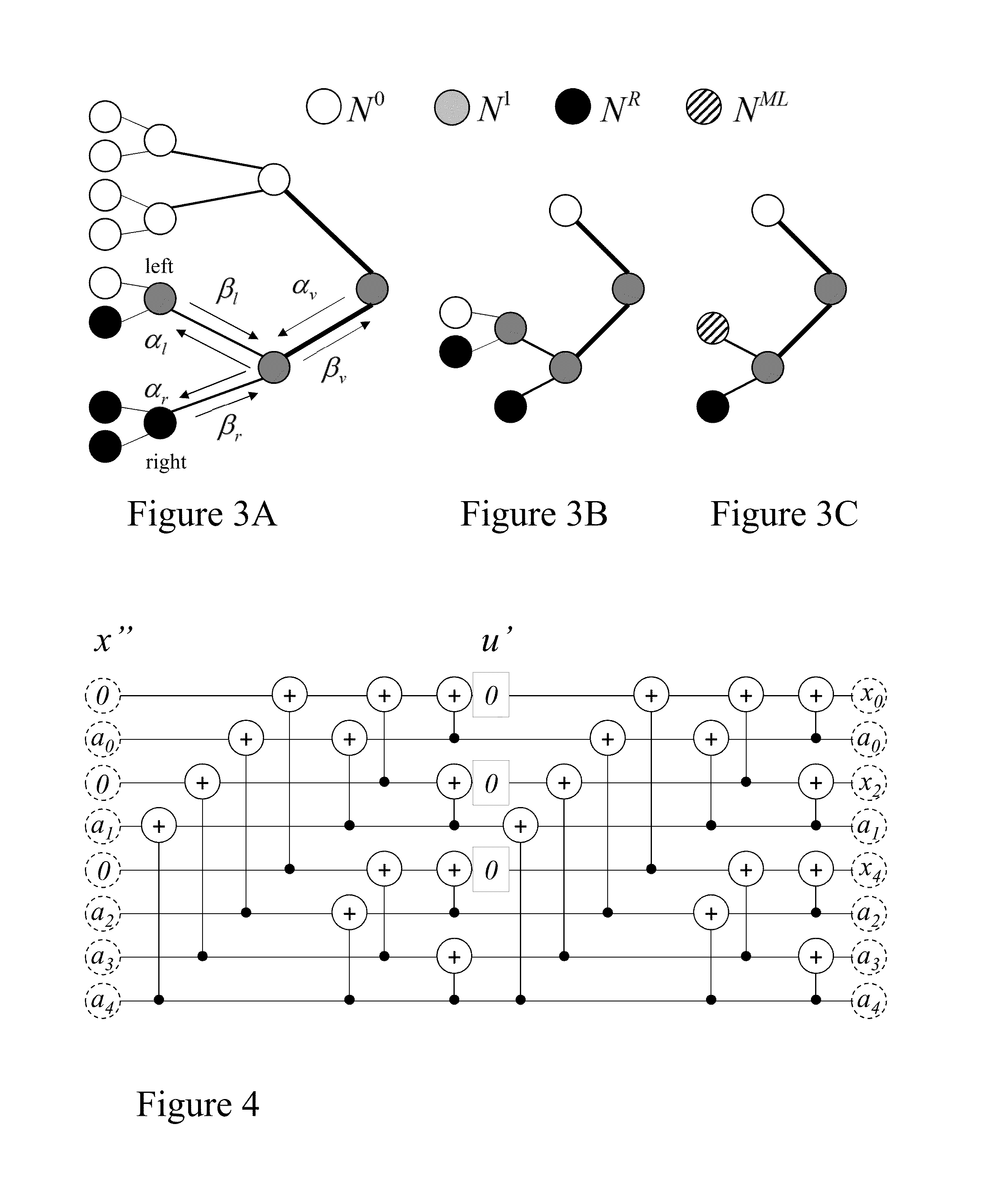

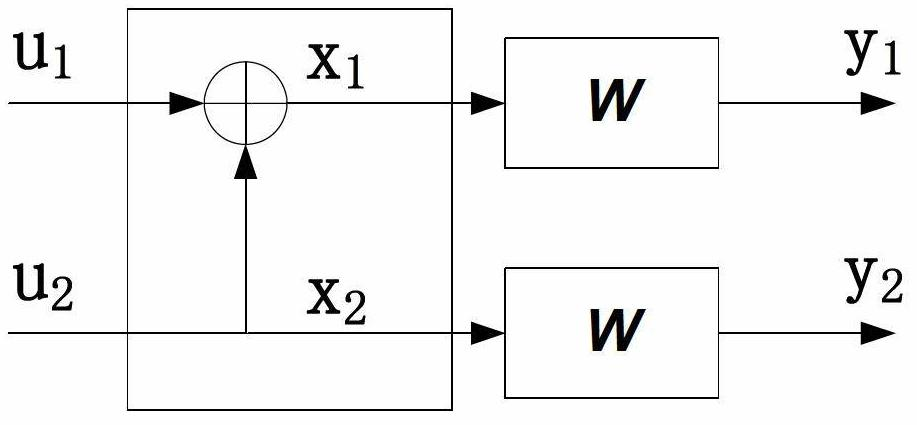

Flexible polar encoders and decoders

Modern communication systems must cope with varying channel conditions and differing throughput constraints. Polar codes despite being the first error-correcting codes with an explicit construction to achieve the symmetric capacity of memoryless channels are not currently employed against other older coding protocols such as low-density parity check (LDPC) codes as their performance at short / moderate lengths has been inferior and their decoding algorithm is serial leading to low decoding throughput. Accordingly techniques to address these issues are identified and disclosed including decoders that decode constituent codes without recursion and / or recognize classes of constituent directly decodable codes thereby increasing the decoder throughput. Flexible encoders and decoders supporting polar codes of any length up to a design maximum allow adaptive polar code systems responsive to communication link characteristics, performance, etc. whilst maximizing throughput. Further, designers are provided flexibility in implementing either hardware or software implementations.

Owner:POLAR TECH

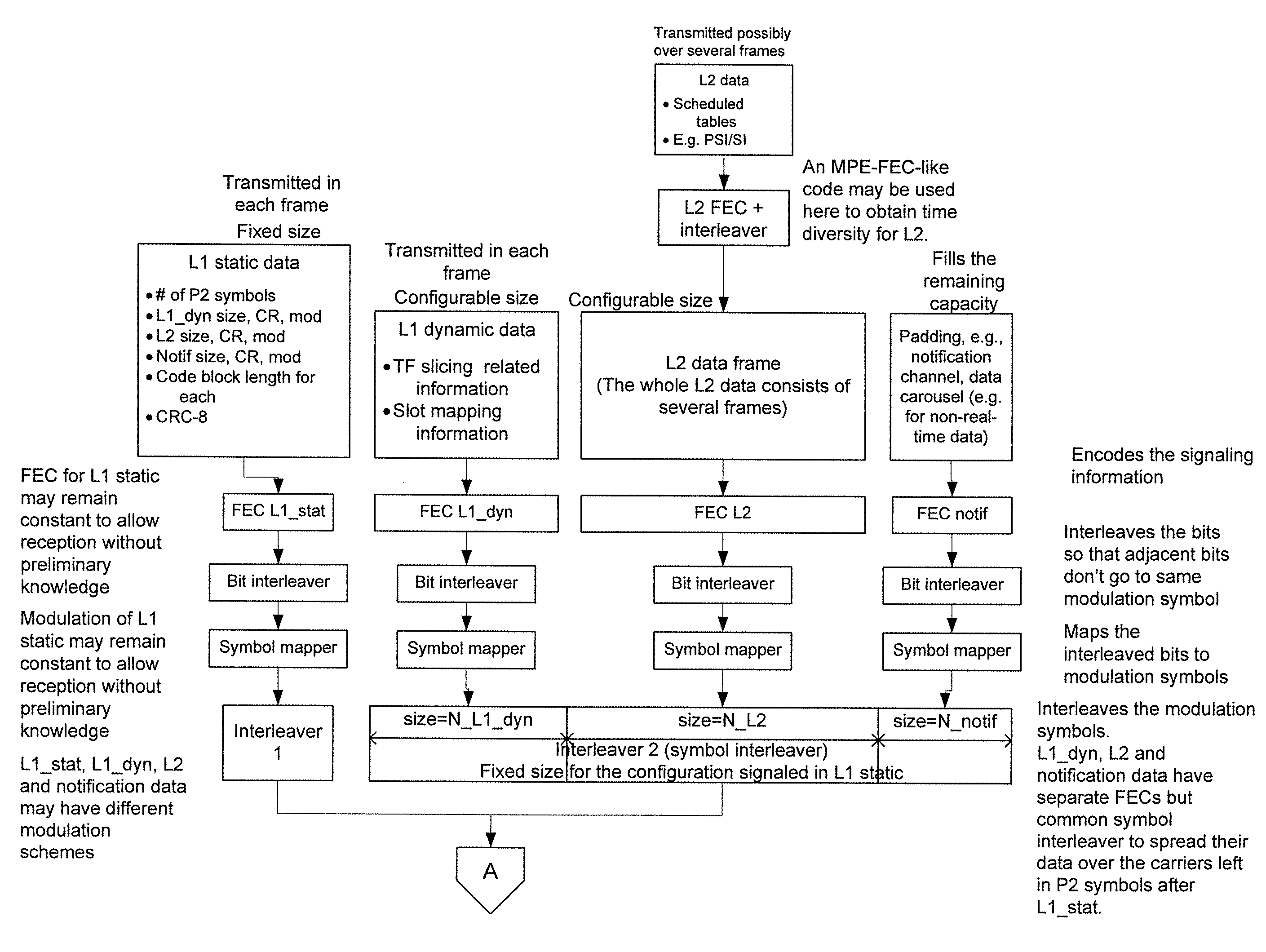

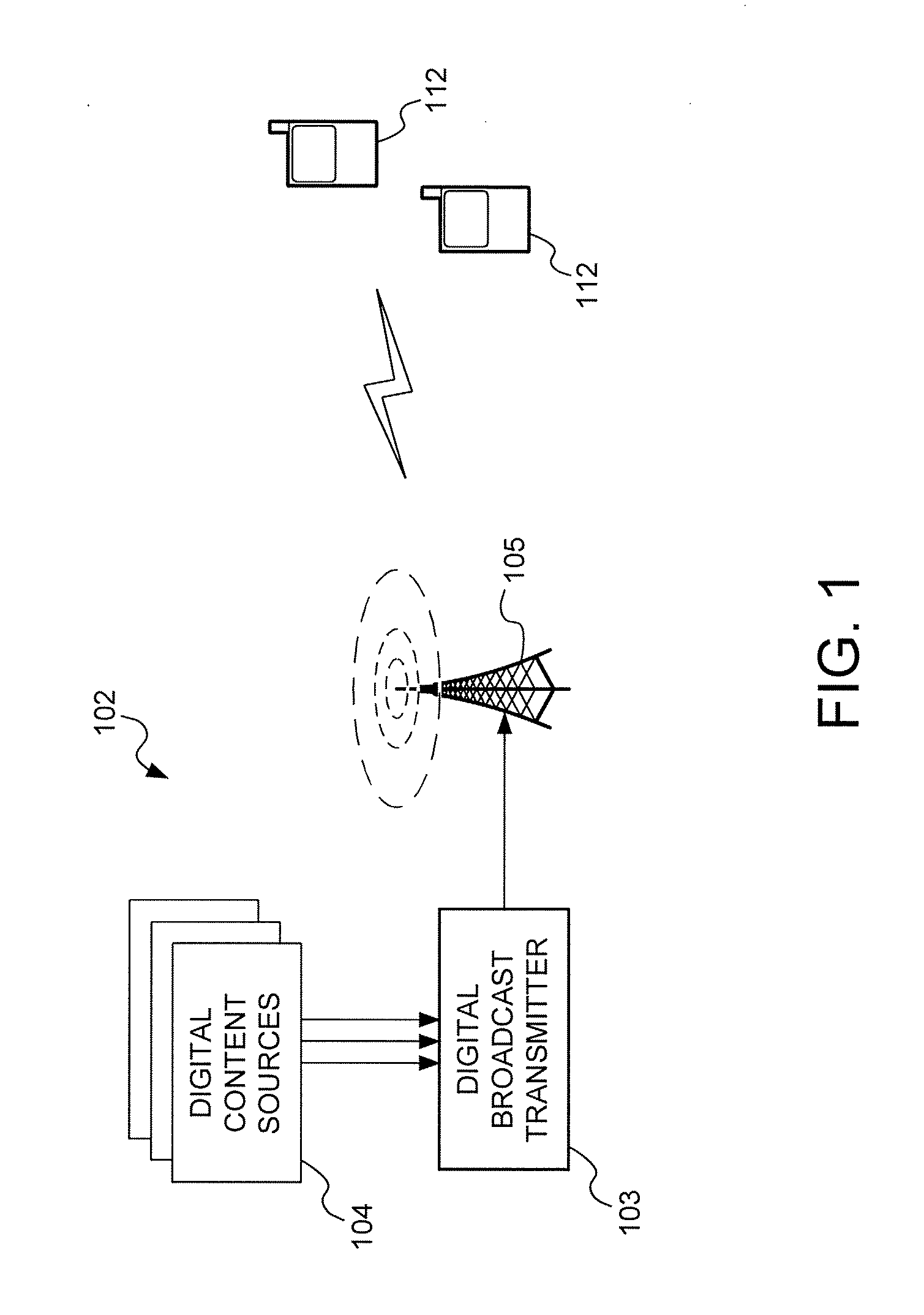

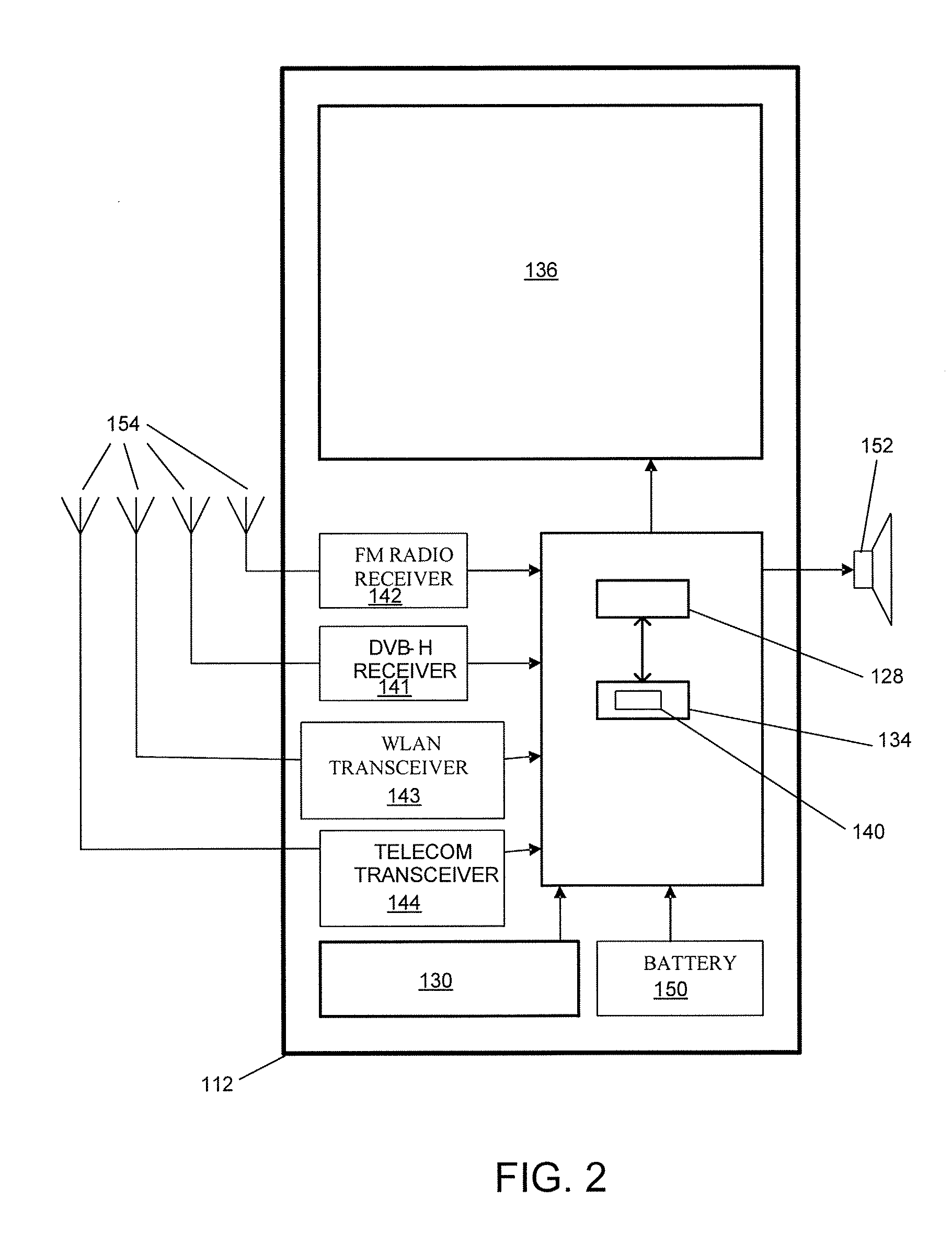

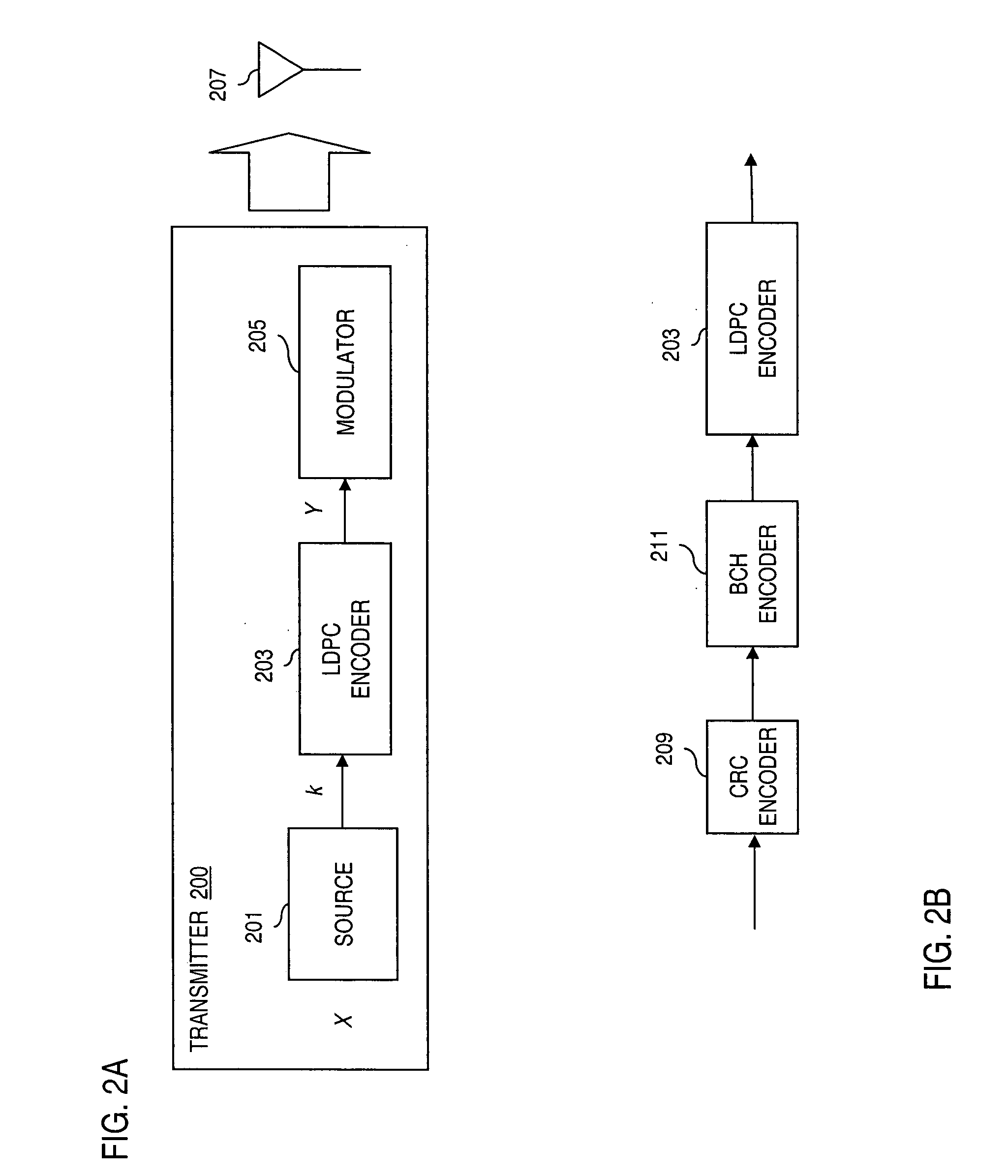

Digital Broadcast Signaling Metadata

ActiveUS20090103649A1Error correction/detection using convolutional codesError preventionDigital broadcastingData link layer

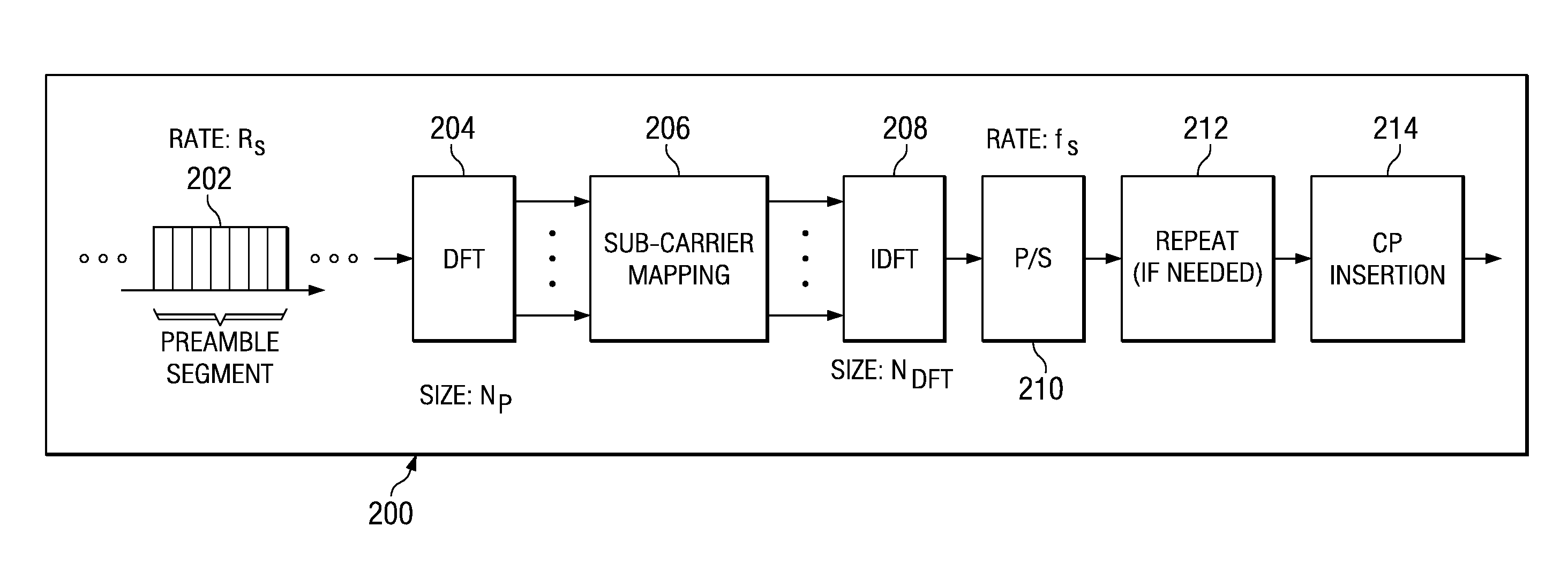

Embodiments are directed to transmitting L1 pre-signaling information with predetermined modulation and code rate such that L1 pre-signaling information can be received without preliminary knowledge on the network. L1 pre-signaling information makes it possible to receive the L1 signaling information, data link layer information, and notification data that may have configurable code rates and modulation. Therefore, L1 pre-signaling information can be thought of as signaling metadata (i.e., information about other signaling information). L1 signaling is divided into pre-signaling and signaling parts. The pre-signaling part includes parameters used for receiving the L1 signaling information. L1 pre-signaling signaling enables the receiver to receive the signaling itself (L1 signaling and data link layer information) by informing the receiver about the type of modulation, coding, and the like, used to transmit the L1 signaling, data link layer, and notification information.

Owner:SAMSUNG ELECTRONICS CO LTD

Method and system for providing low density parity check (LDPC) encoding

ActiveUS7191378B2Readily apparentInterconnection arrangementsError correction/detection using LDPC codesAlgorithmParity-check matrix

An approach is provided for a method of encoding structure Low Density Parity Check (LDPC) codes. Memory storing information representing a structured parity check matrix of Low Density Parity Check (LDPC) codes is accessed during the encoding process. The information is organized in tabular form, wherein each row represents occurrences of one values within a first column of a group of columns of the parity check matrix. The rows correspond to groups of columns of the parity check matrix, wherein subsequent columns within each of the groups are derived according to a predetermined operation. An LDPC coded signal is output based on the stored information representing the parity check matrix.

Owner:DTVG LICENSING INC

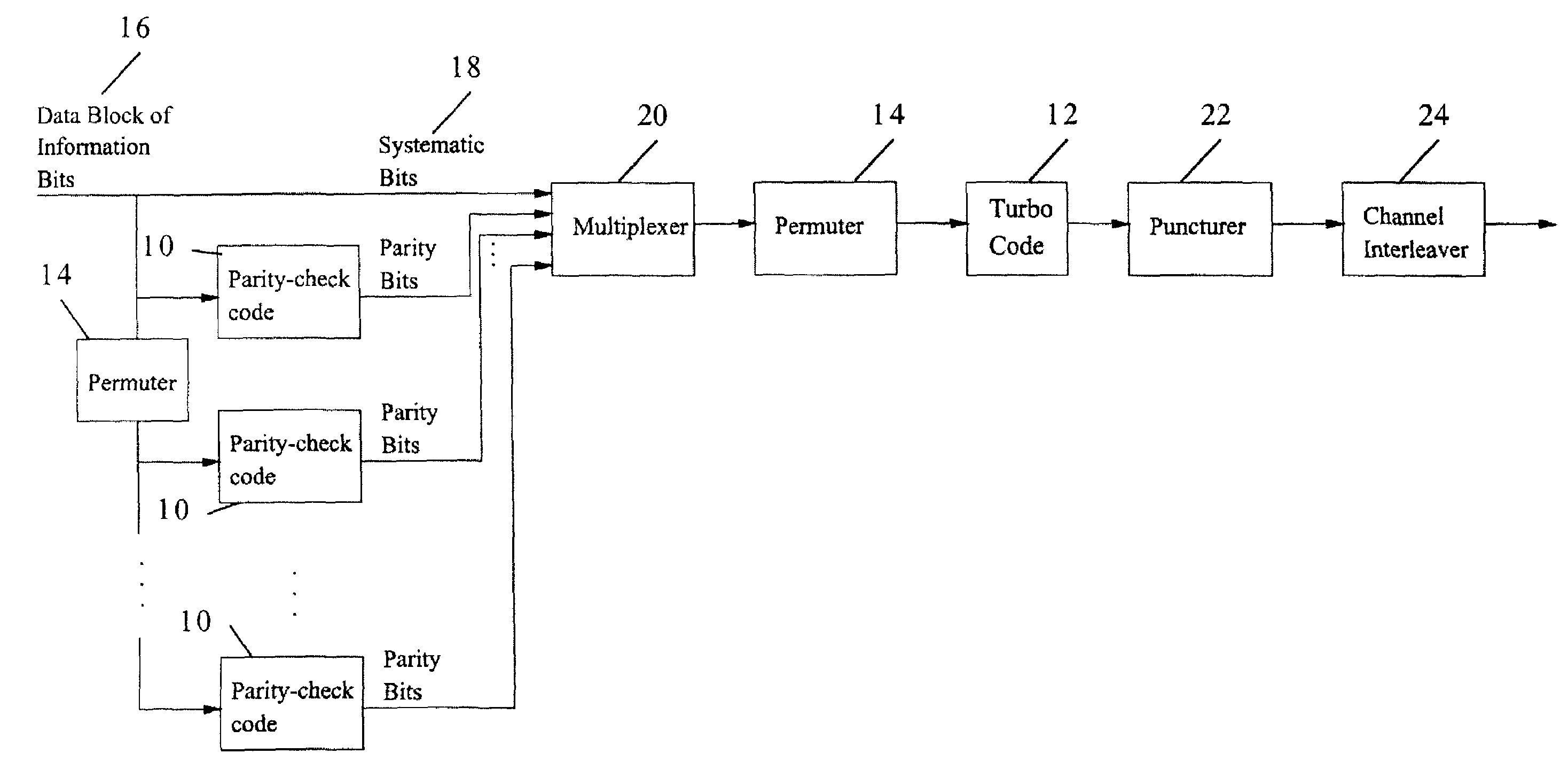

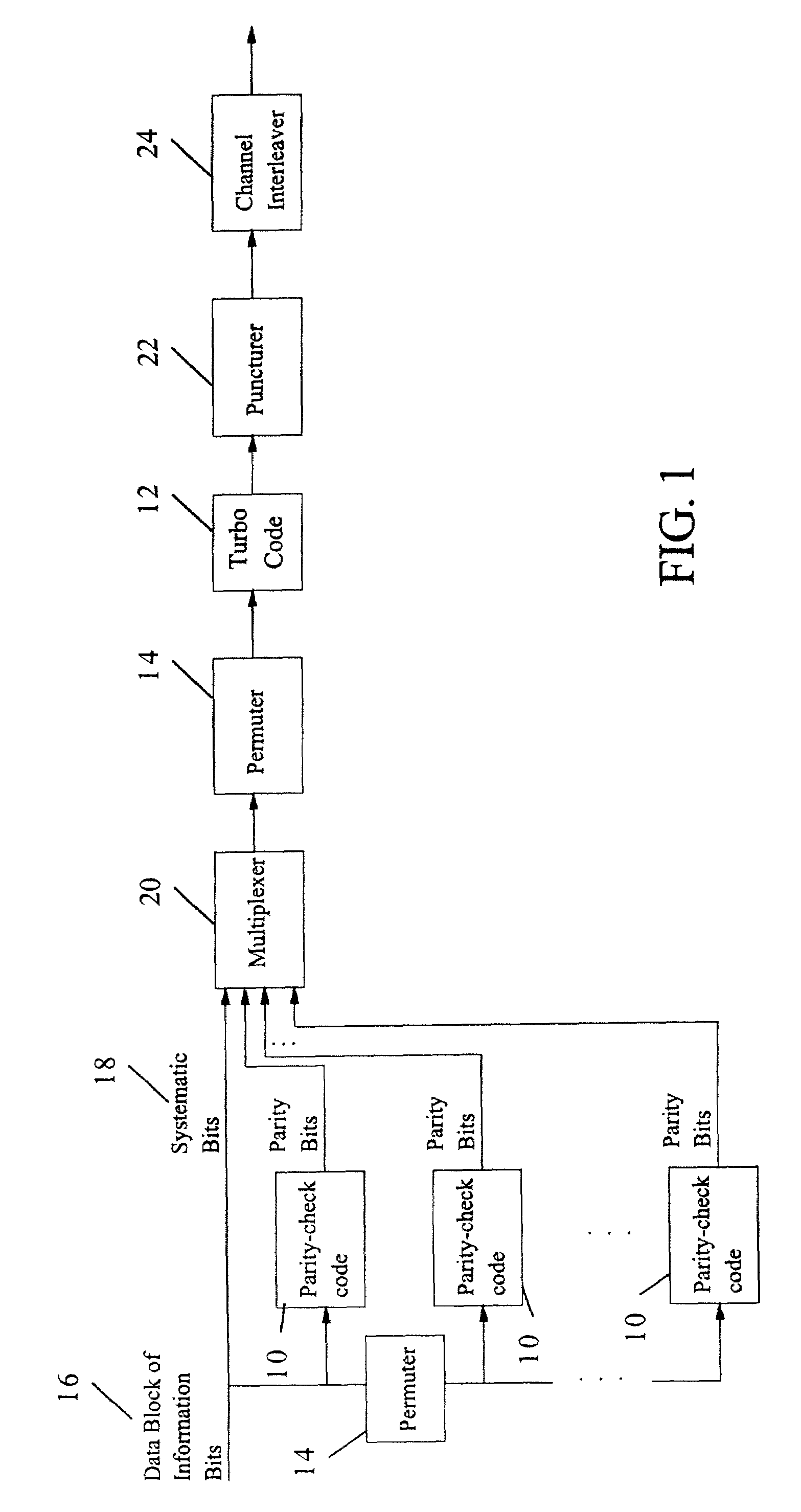

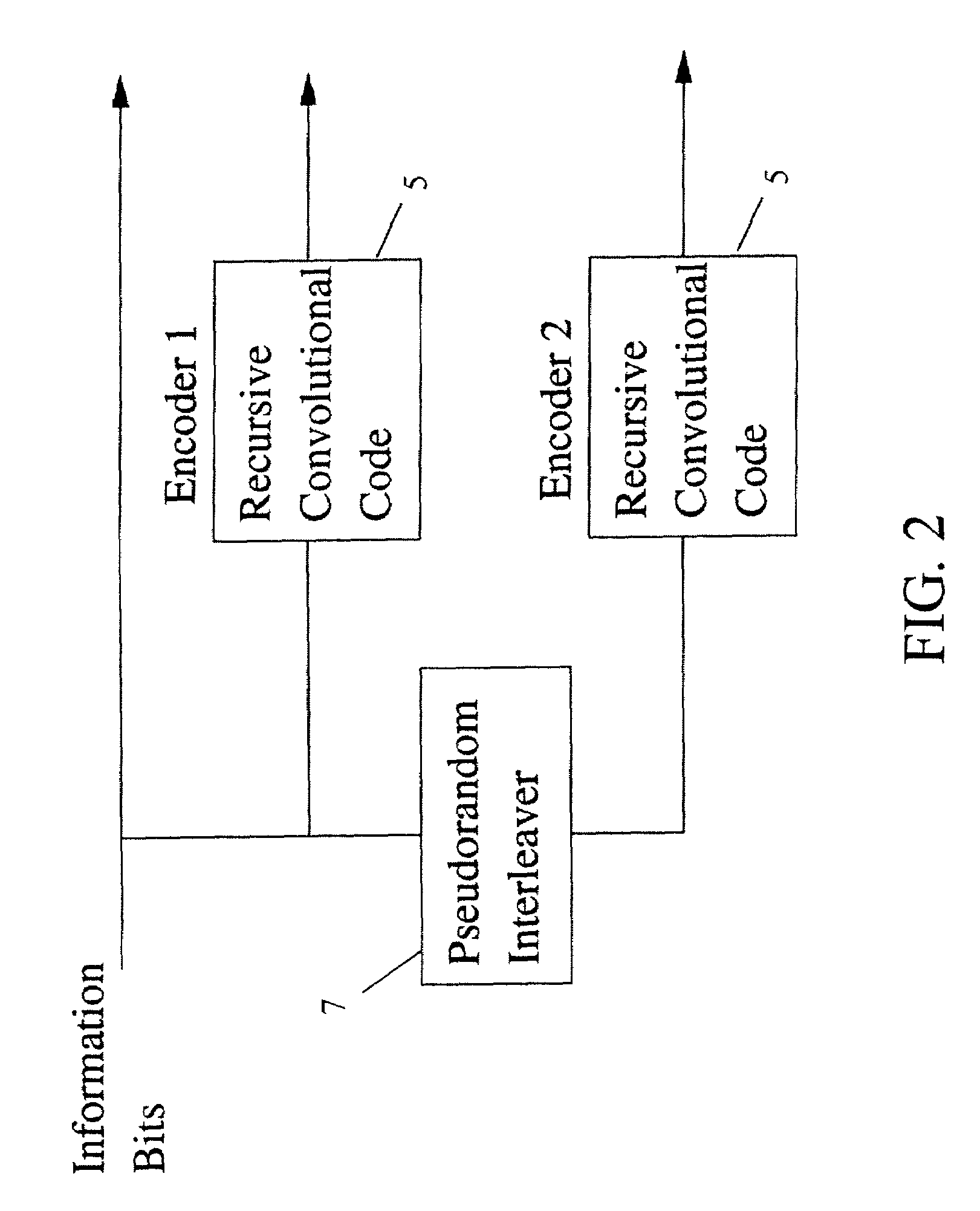

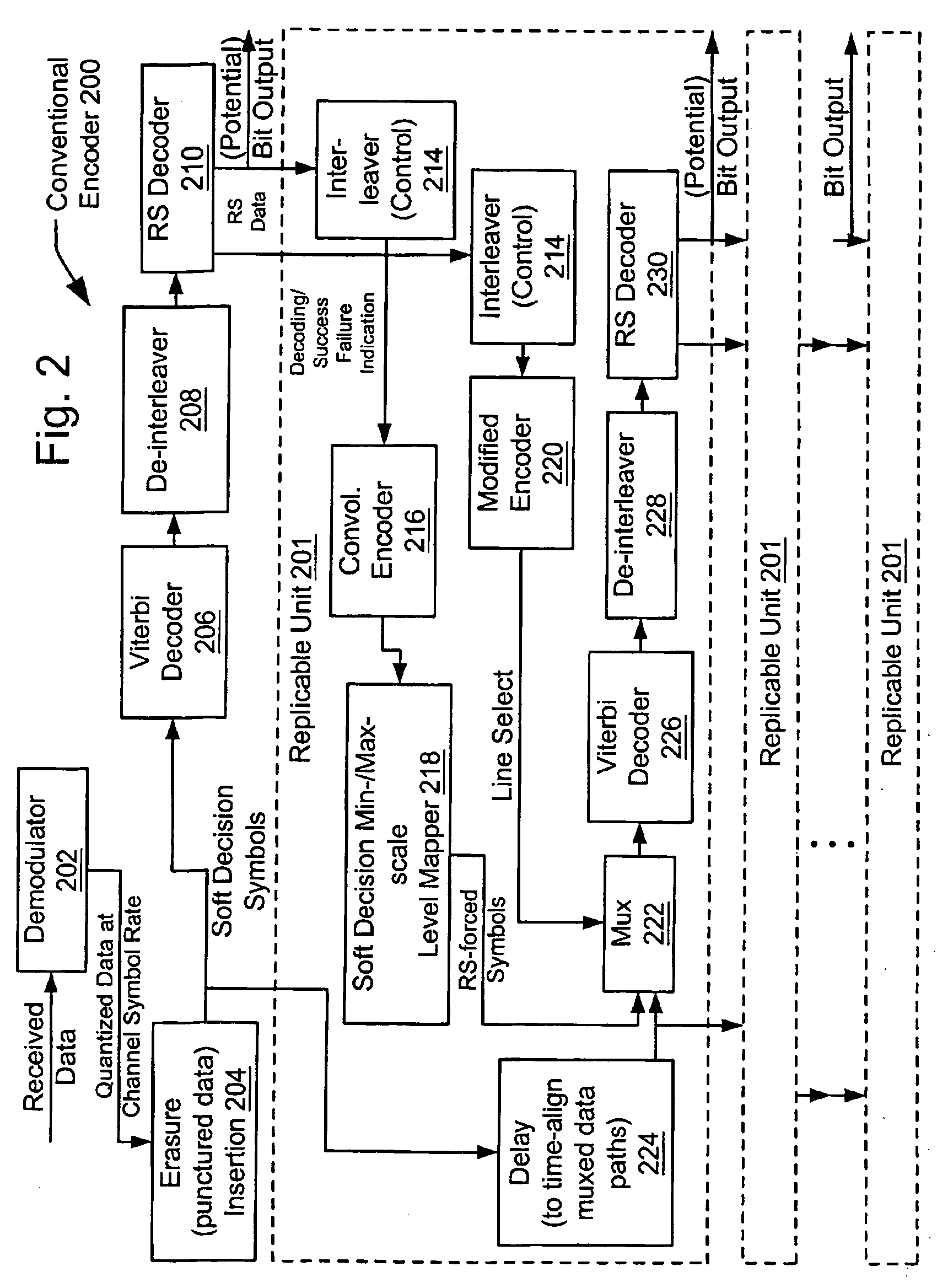

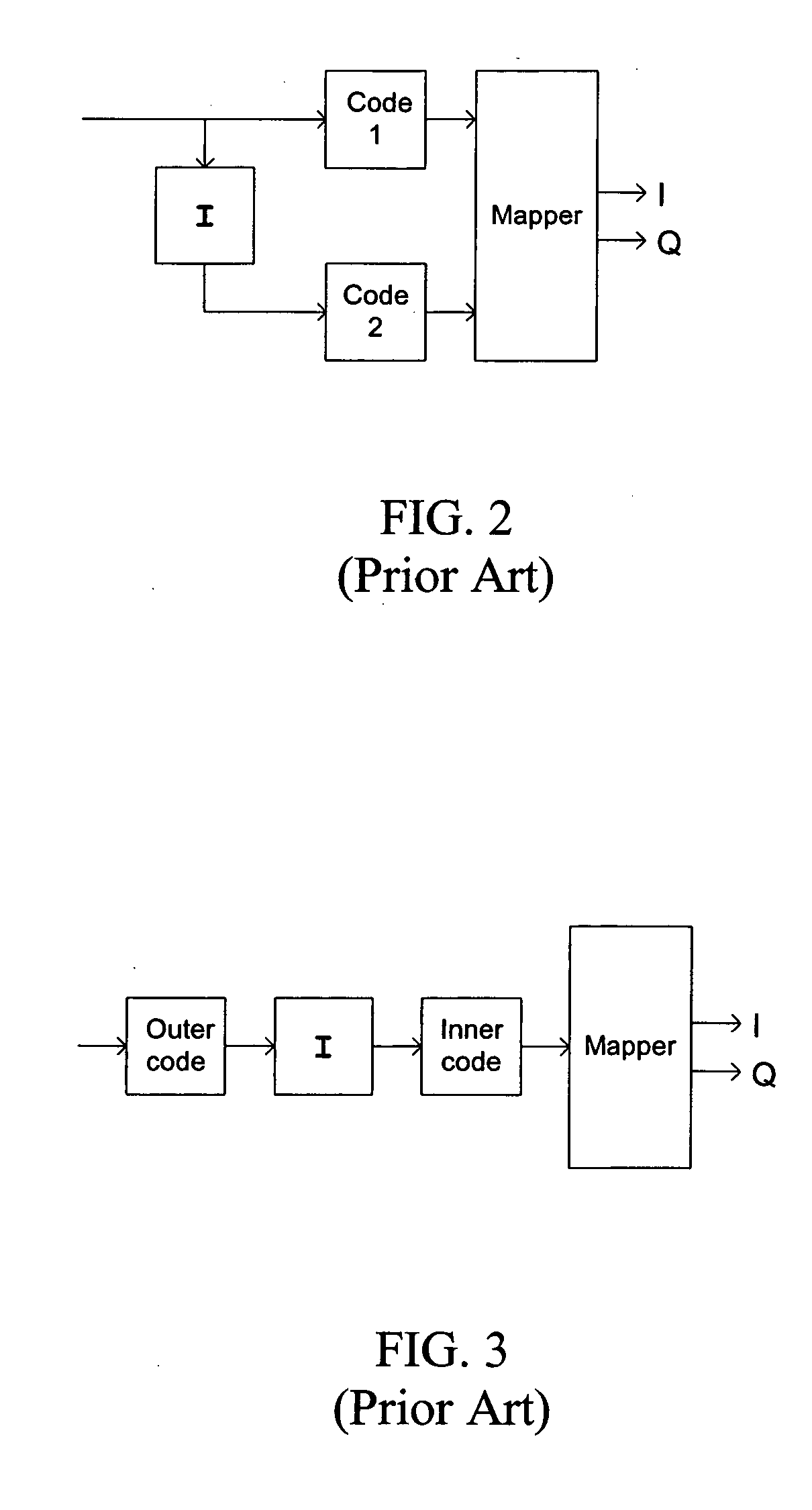

Method and coding means for error-correction utilizing concatenated parity and turbo codes

InactiveUS7093179B2Reduction in rateImprove overall utilizationError preventionError detection/correctionParallel computingTurbo coded

A method and apparatus for encoding and decoding data using an overall code comprising an outer parity-check and an inner parallel concatenated convolutional, or turbo code. The overall code provides error probabilities that are significantly lower than can be achieved by using turbo codes alone. The output of the inner code can be punctured to maintain the same turbo code rate as the turbo code encoding without the outer code. Multiple parity-check codes can be concatanated either serially or in parallel as outer codes. Decoding can be performed with iterative a posteriori probability (APP) decoders or with other decoders, depending on the requirements of the system. The parity-check code can be applied to a subset of the bits to achieve unequal error protection. Moreover, the techniques presented can be mapped to higher order modulation schemes to achieve improved power and bandwidth efficiency.

Owner:FLORIDA UNIV OF A FLORIDA +1

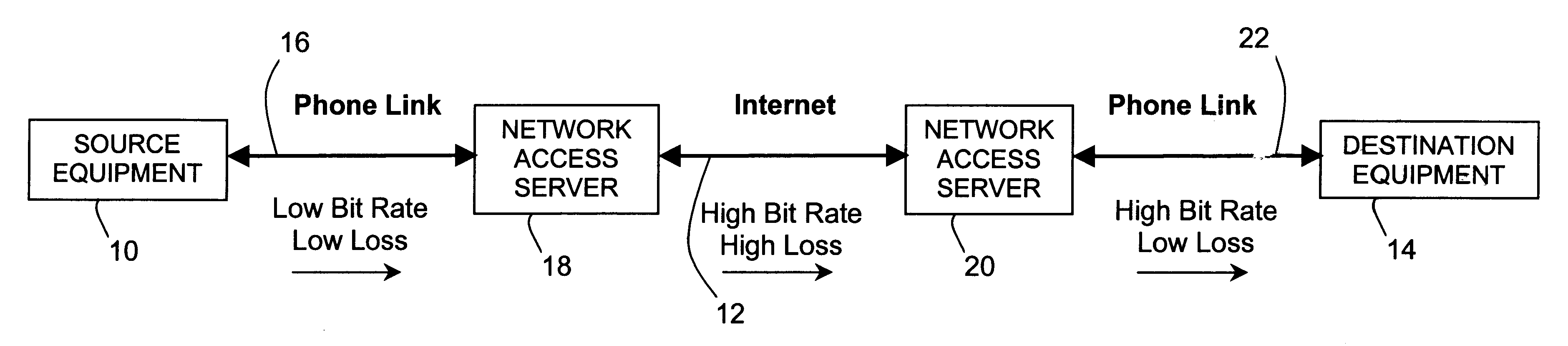

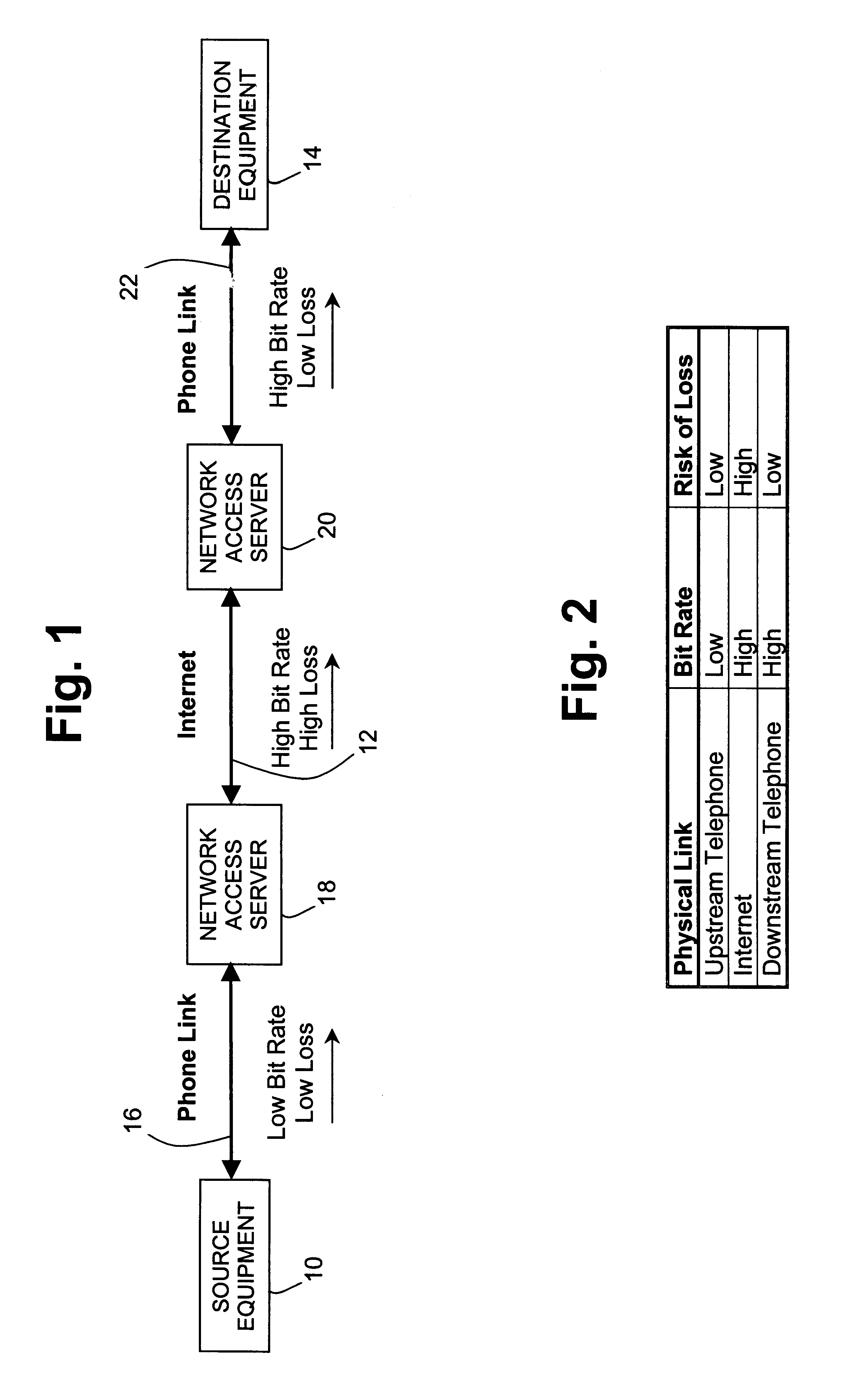

Data and real-time media communication over a lossy network

A method and apparatus for improving the speed and quality of end-to-end data or real-time media transmissions over an internet is disclosed. A media stream being transmitted to the internet is channel coded at the edge of the internet in order to free upstream bit rate for use in source coding the media. The channel coded media stream may then be decoded at a remote edge of the internet to recover lost packets.

Owner:UTSTARCOM INC

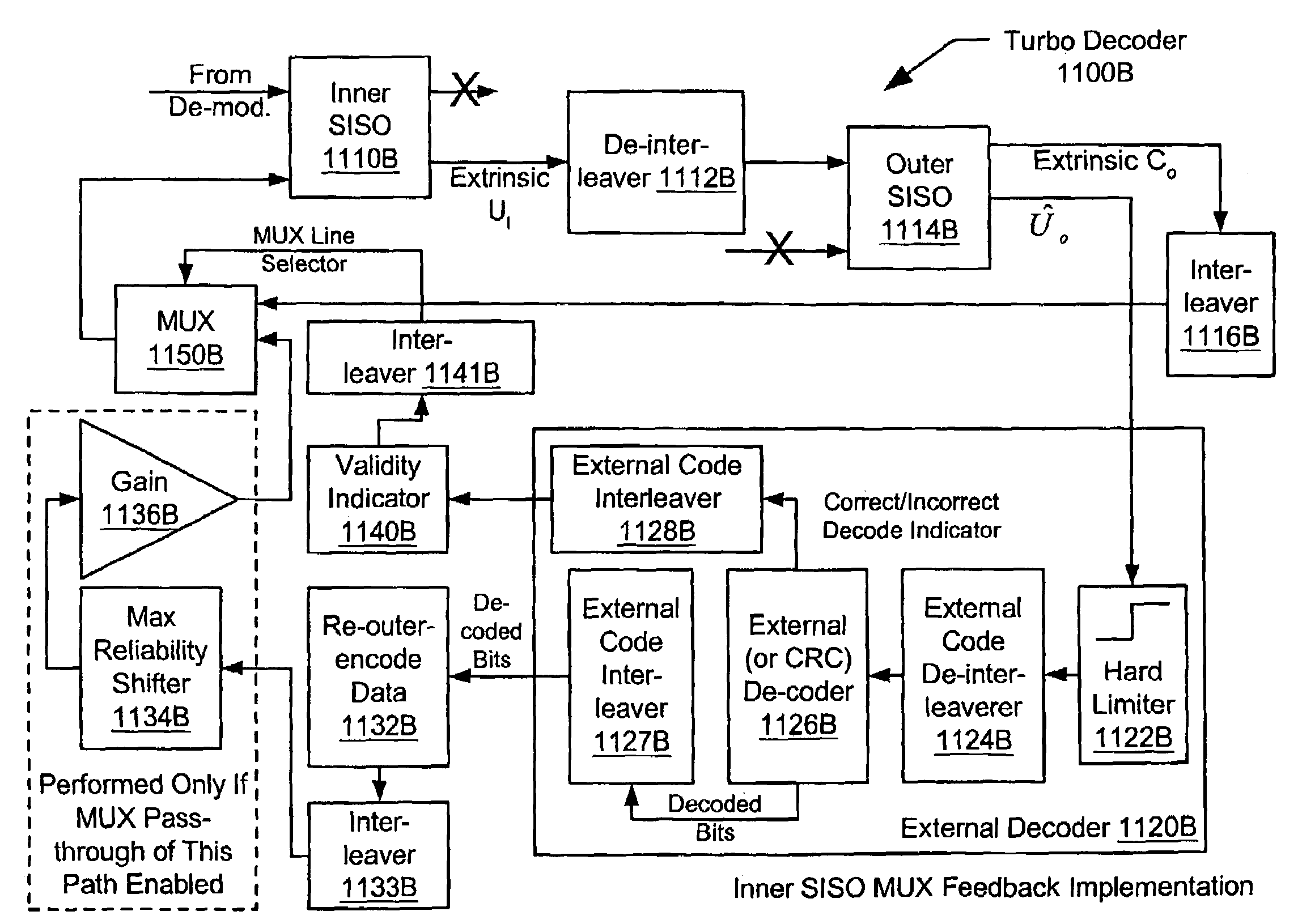

Iterative decoder employing multiple external code error checks to lower the error floor

InactiveUS7310768B2Code conversionError correction/detection by combining multiple code structuresError checkDegree of certainty

Owner:ENTROPIC COMM INC

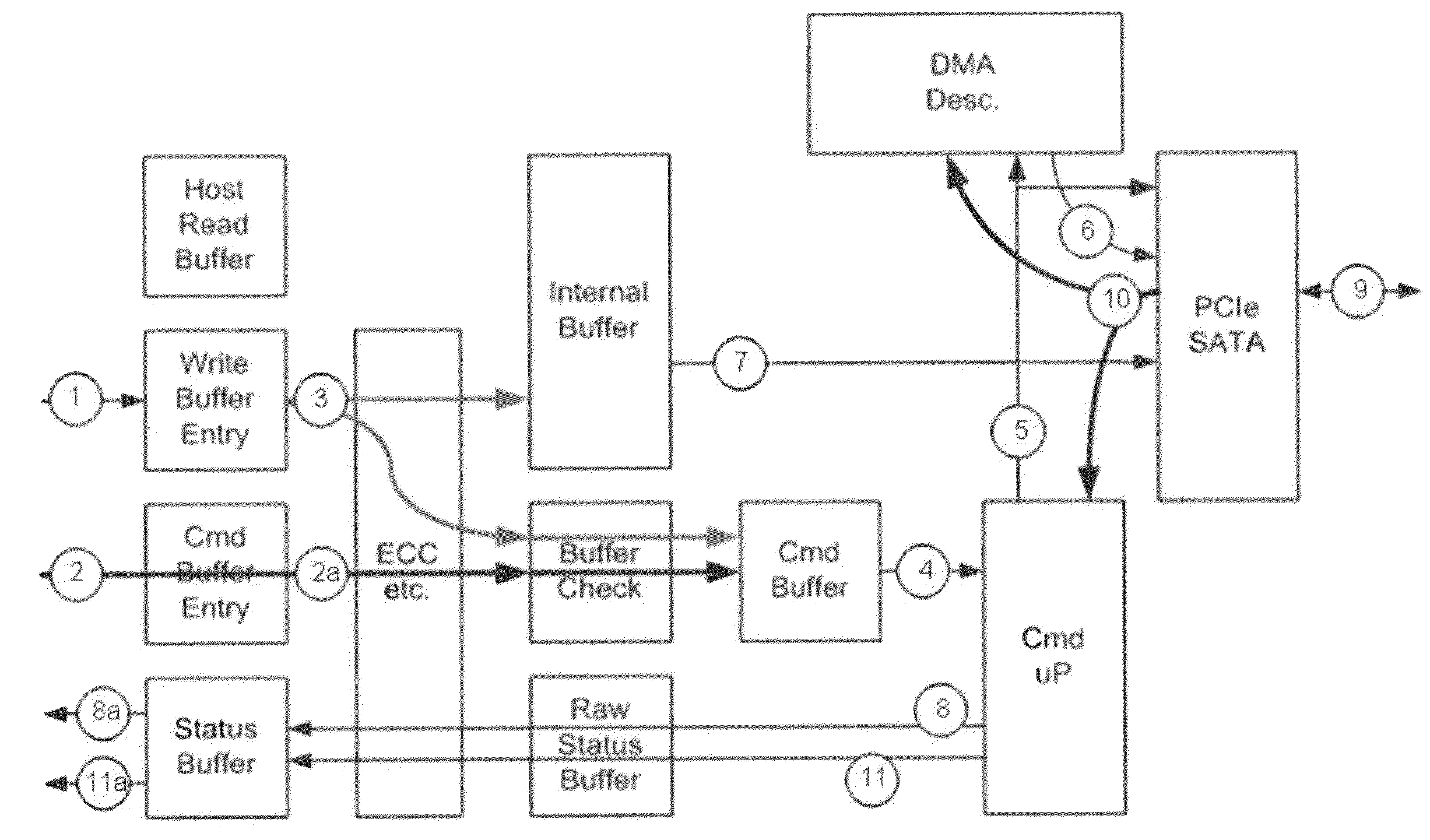

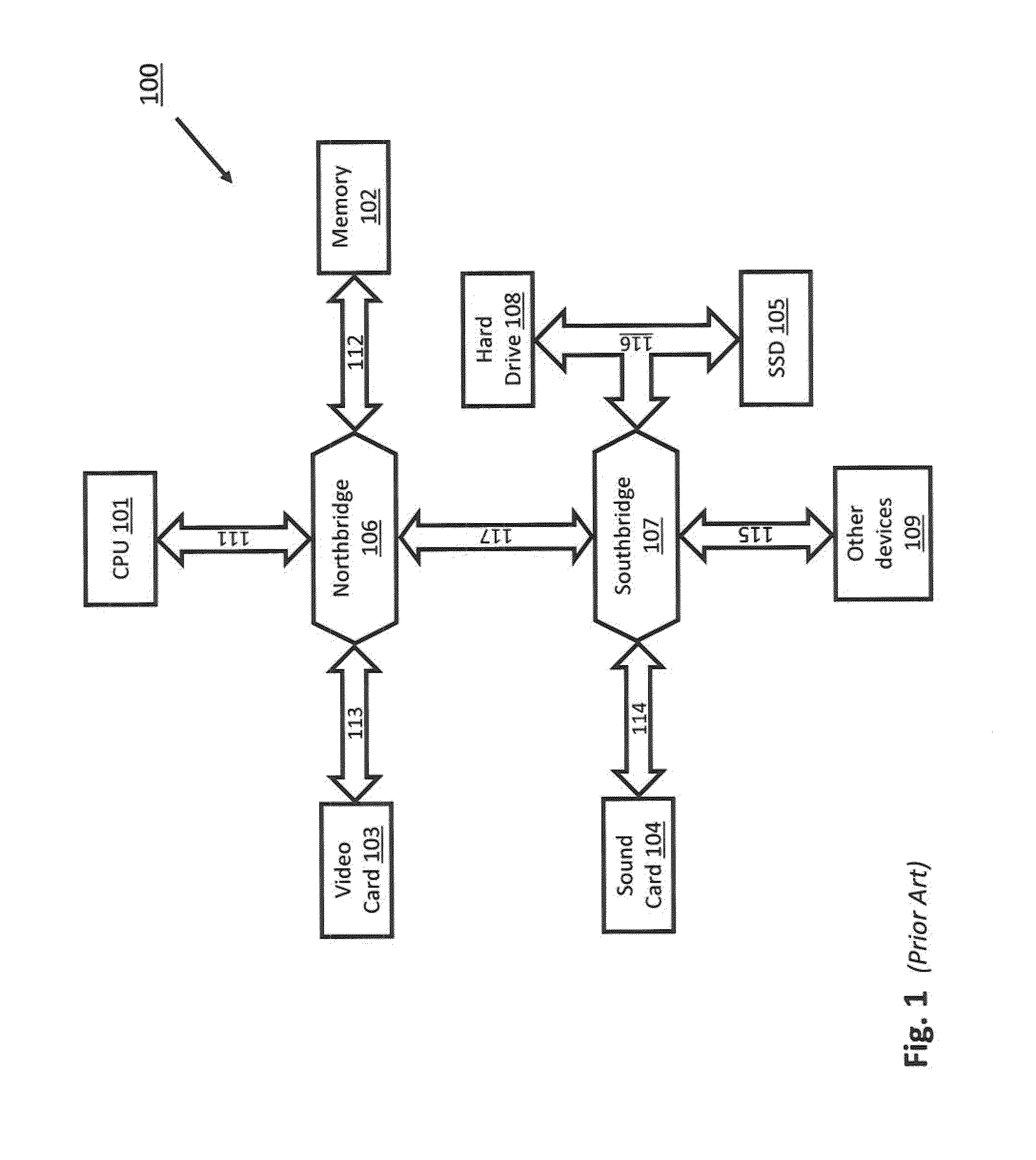

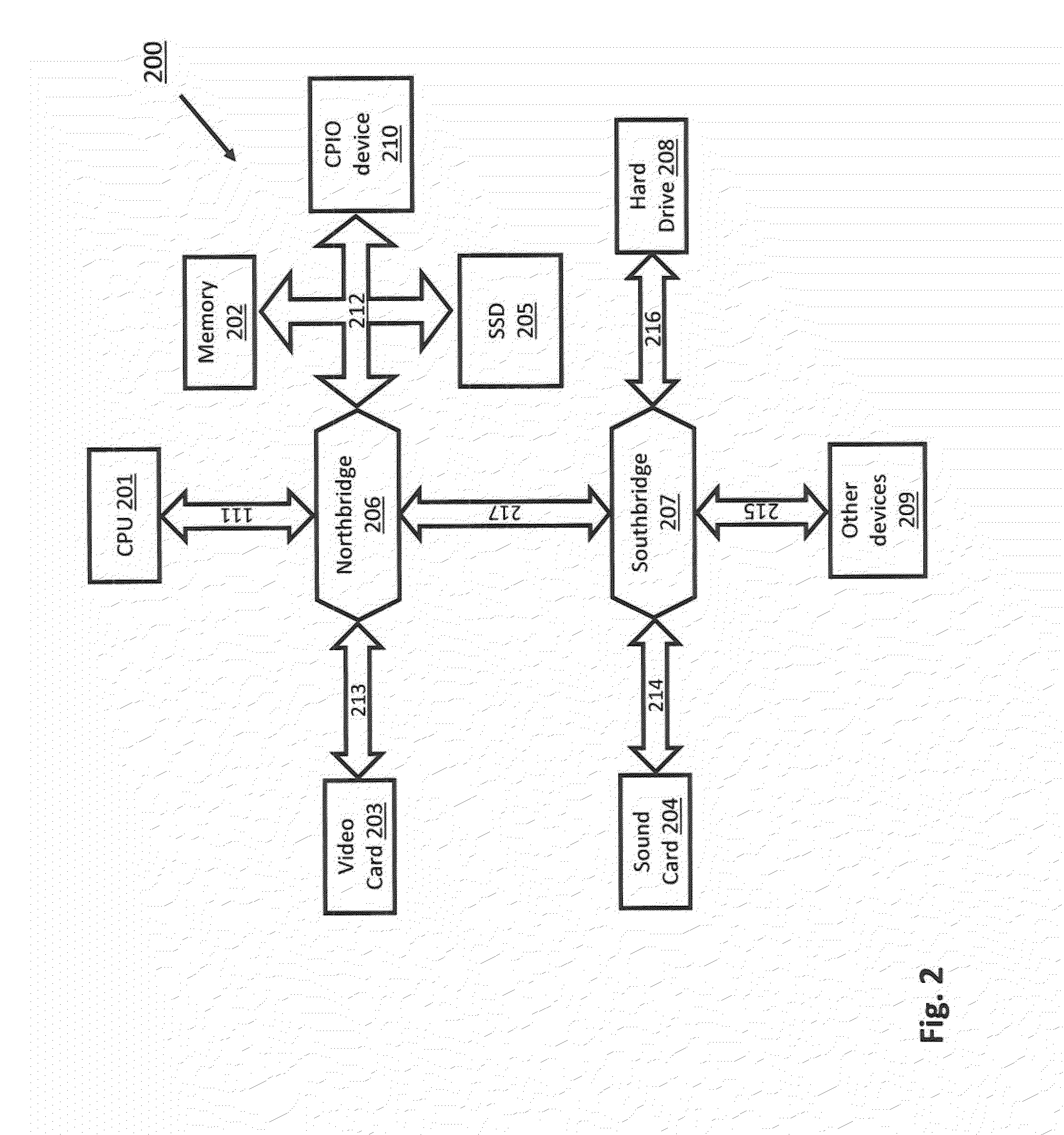

System and method of interfacing co-processors and input/output devices via a main memory system

ActiveUS20120204079A1Memory architecture accessing/allocationError detection/correctionComputer moduleMemory bus

A system for interfacing with a co-processor or input / output device is disclosed. According to one embodiment, the system includes a computer processing unit, a memory module, a memory bus that connects the computer processing unit and the memory module, and a co-processing unit or input / output device, wherein the memory bus also connects the co-processing unit or input / output device to the computer processing unit.

Owner:RAMBUS INC

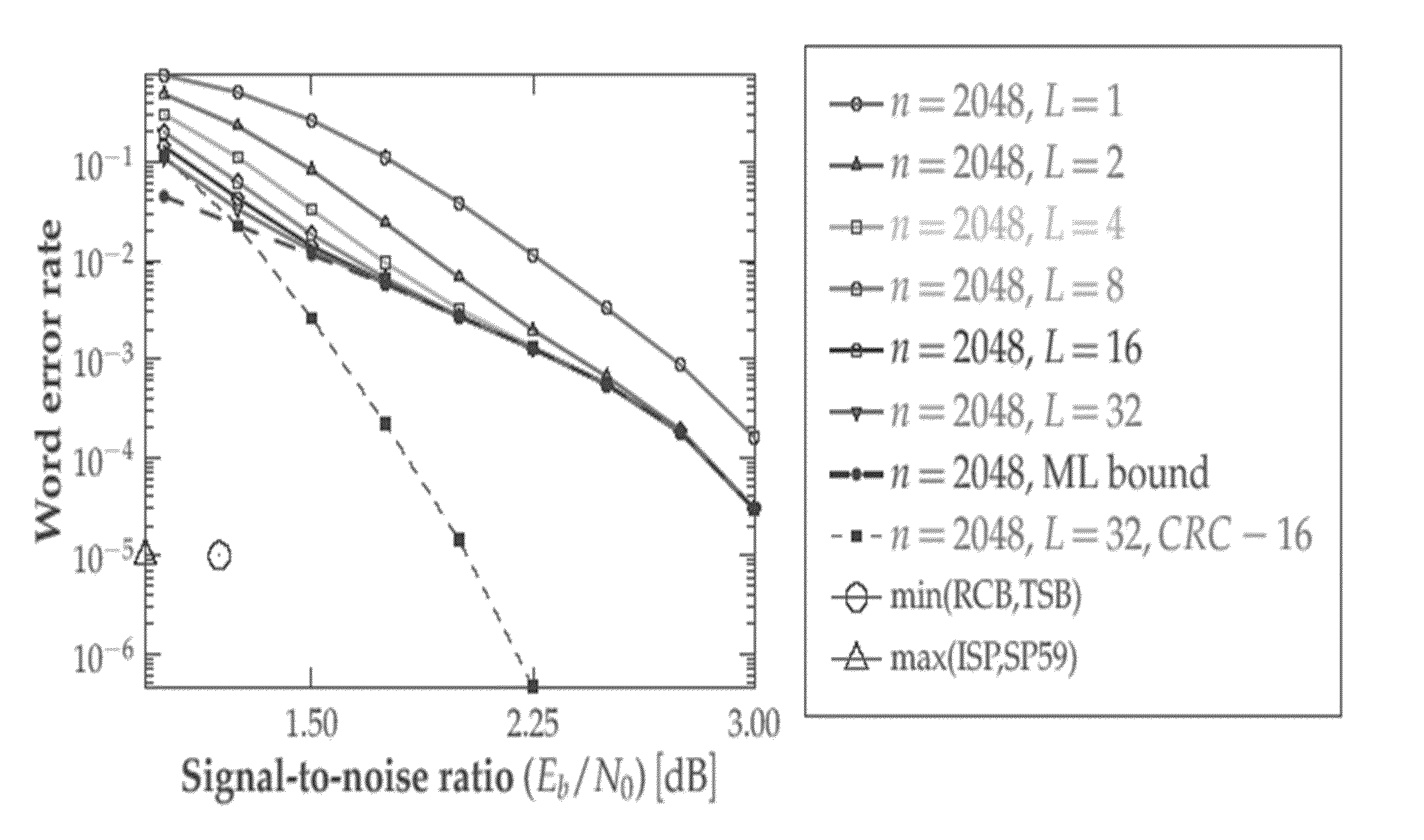

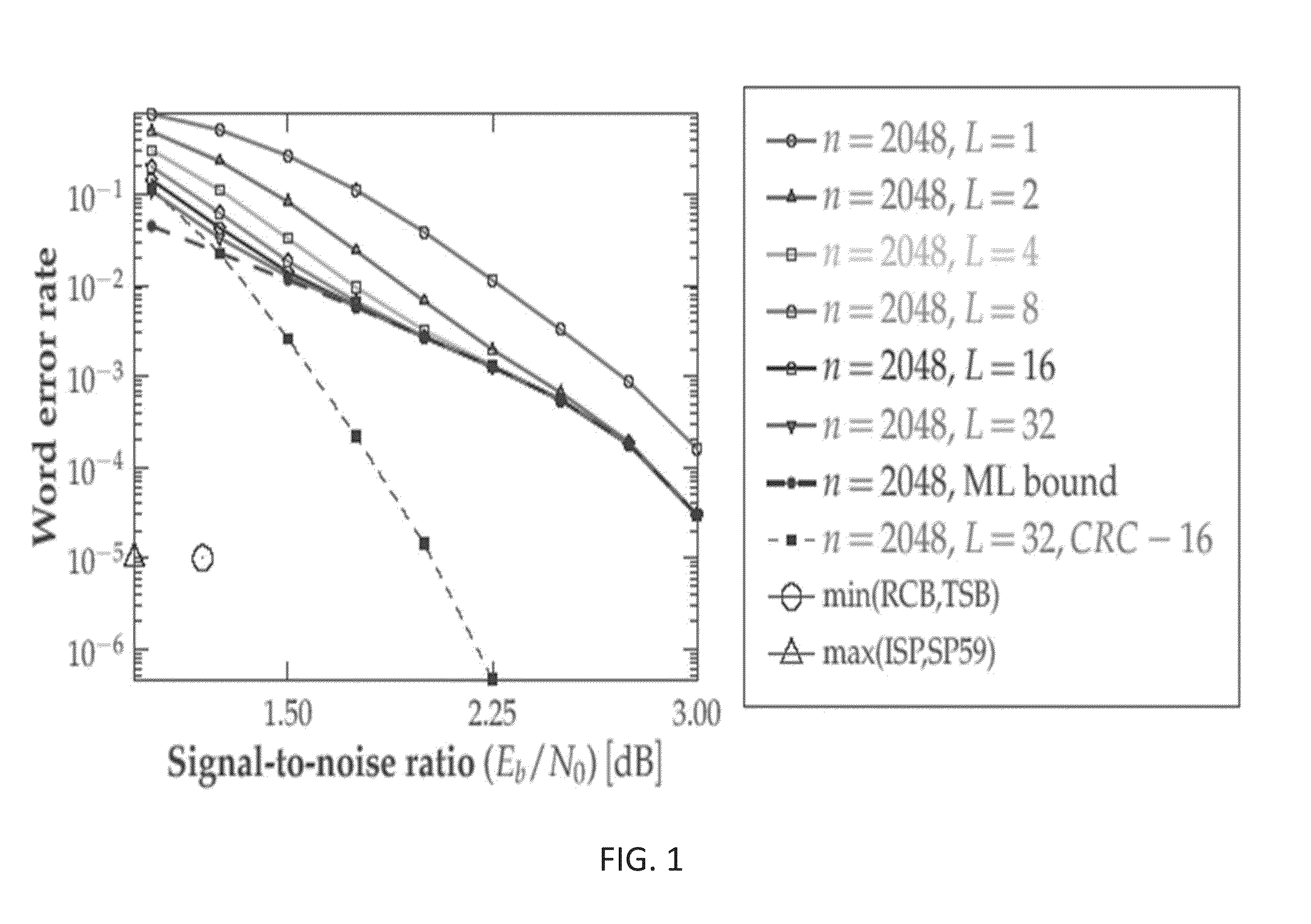

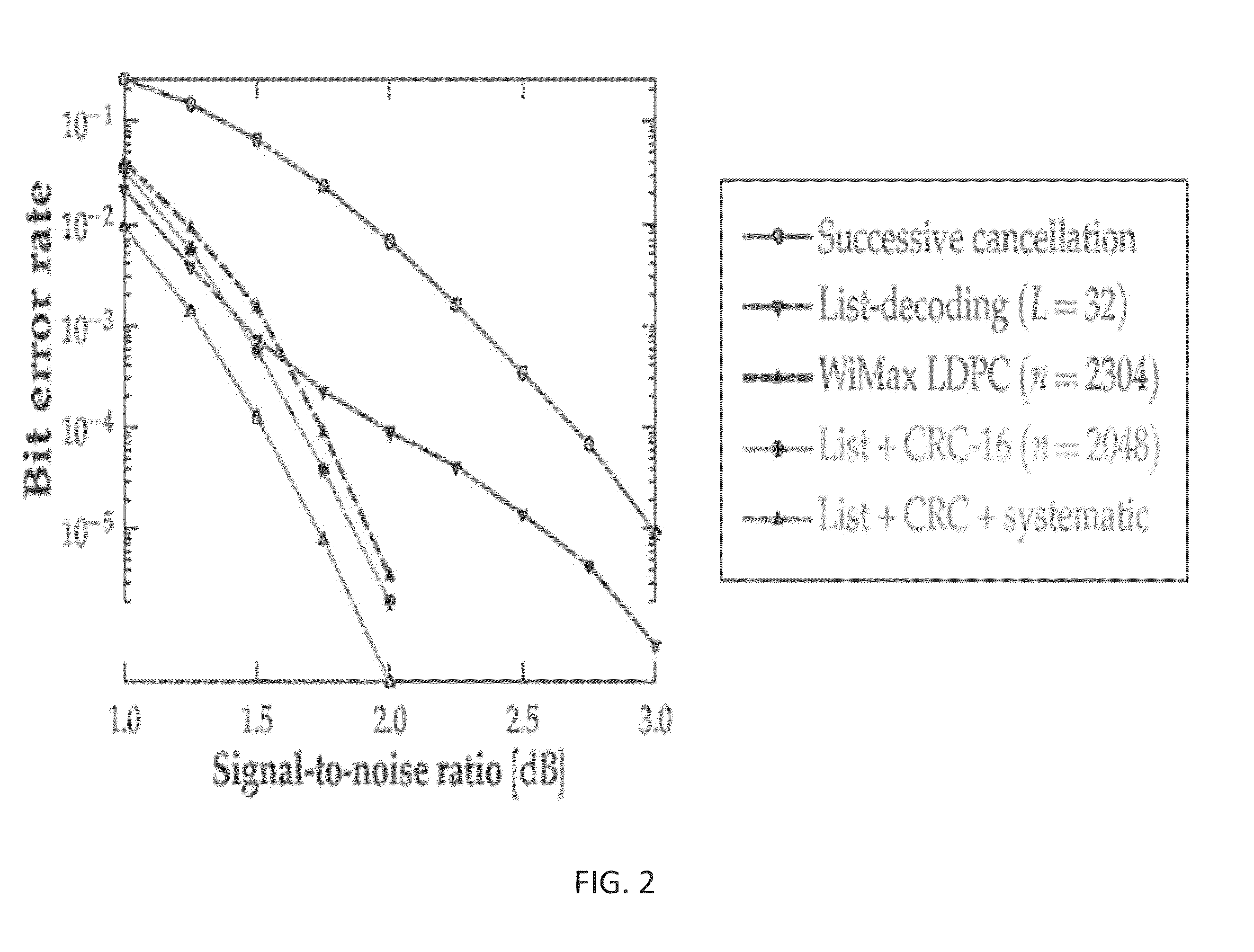

Ecc polar coding and list decoding methods and codecs

A method of decoding data encoded with a polar code and devices that encode data with a polar code. A received word of polar encoded data is decoded following several distinct decoding paths to generate a list of codeword candidates. The decoding paths are successively duplicated and selectively pruned to generate a list of potential decoding paths. A single decoding path among the list of potential decoding paths is selected as the output and a single candidate codeword is thereby identified. In another preferred embodiment, the polar encoded data includes redundancy values in its unfrozen bits. The redundancy values aid the selection of the single decoding path. A preferred device of the invention is a cellular network device, (e.g., a handset) that conducts decoding in accordance with the methods of the invention.

Owner:RGT UNIV OF CALIFORNIA

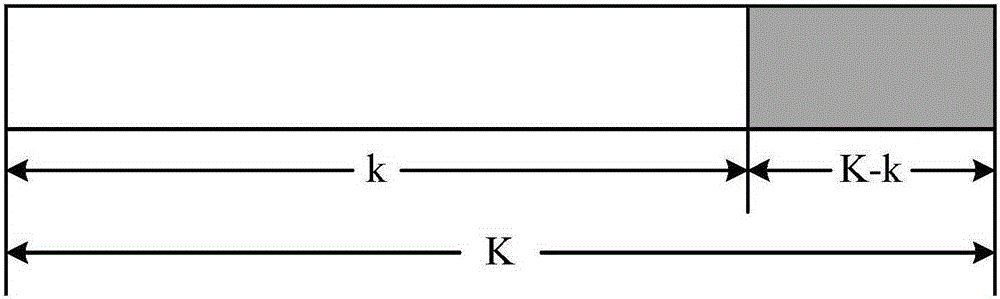

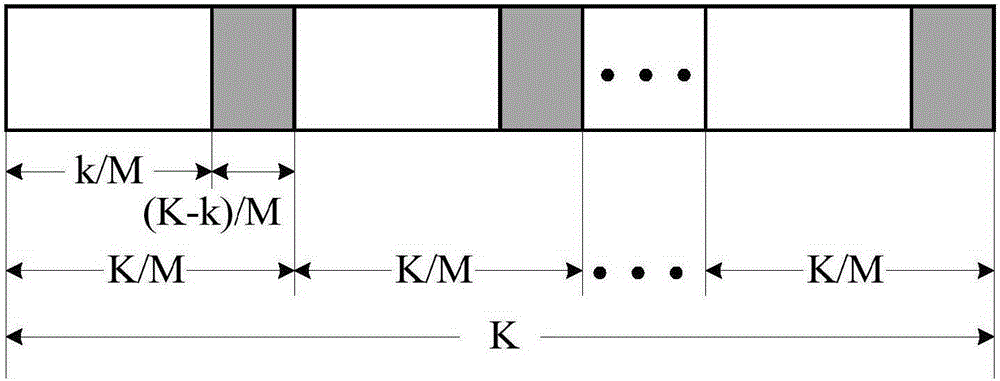

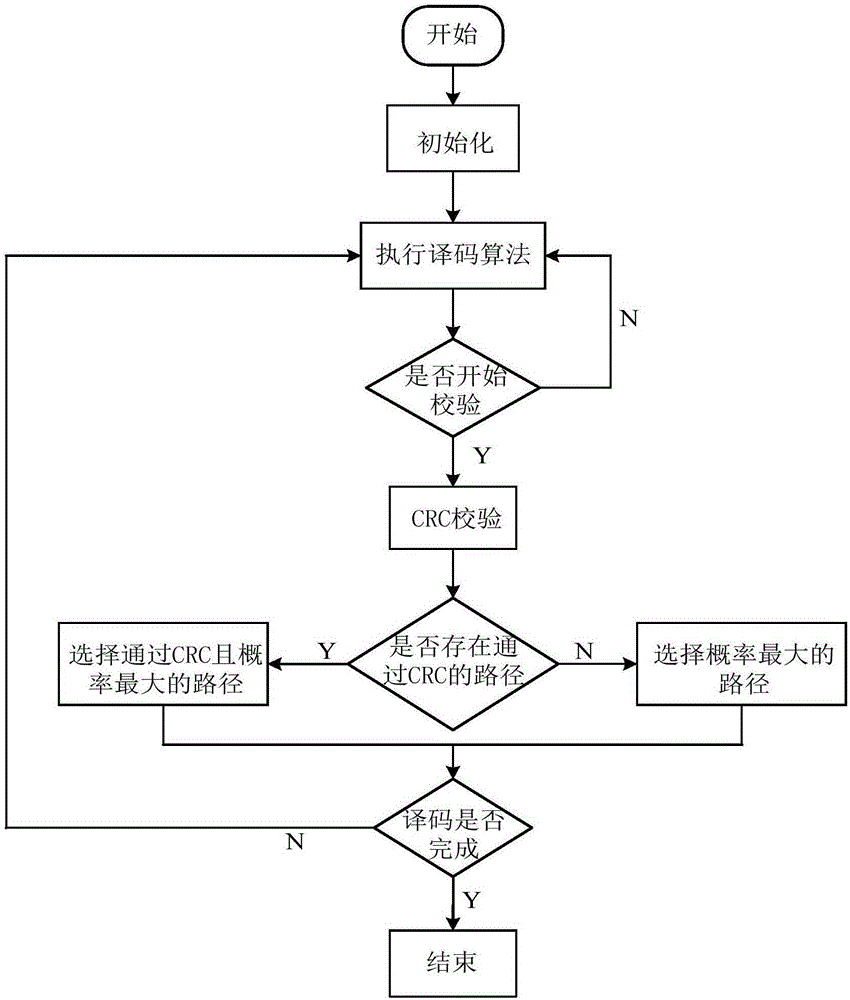

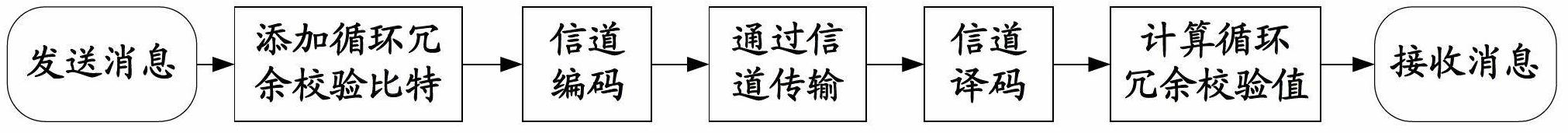

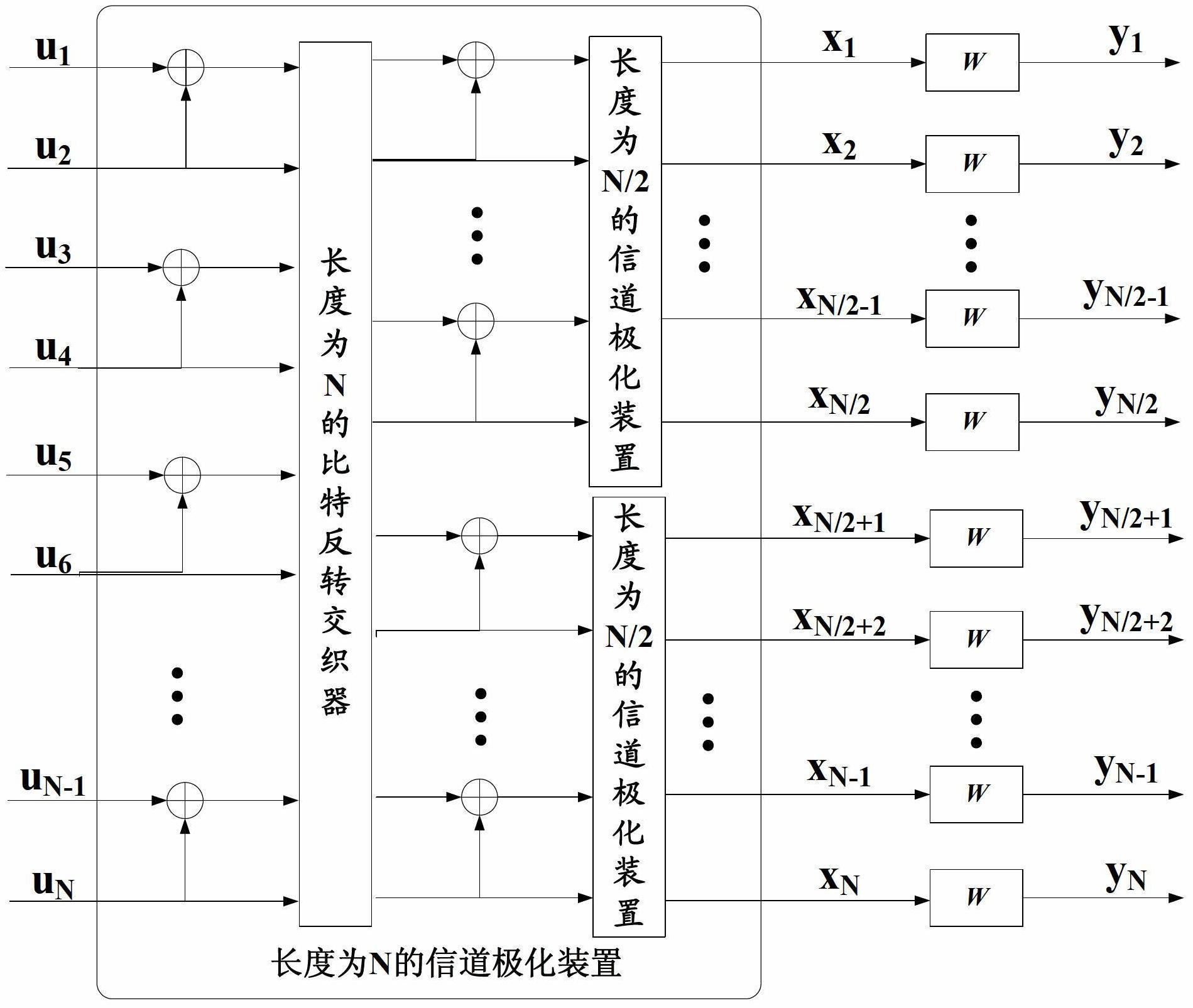

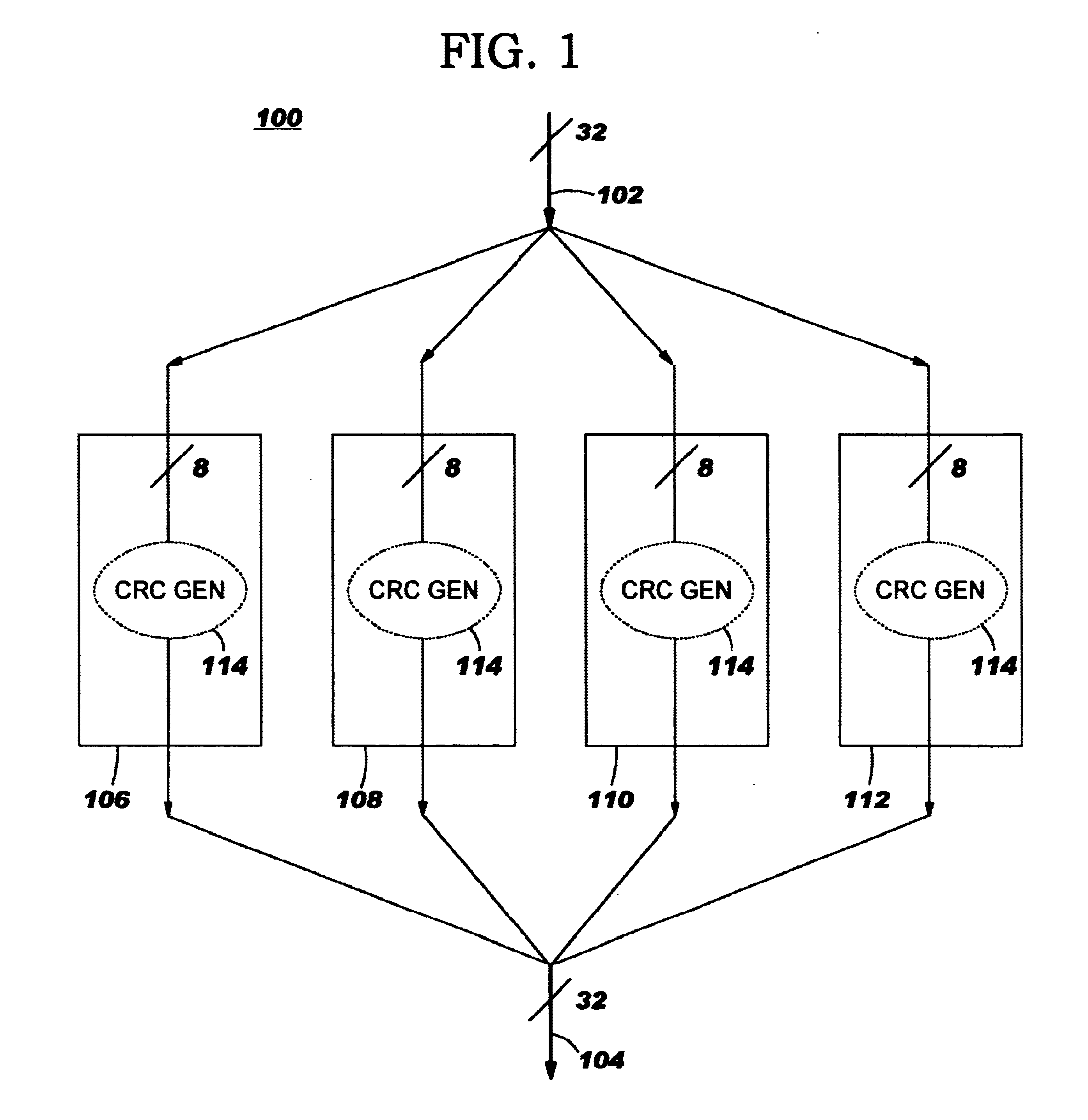

Segmented CRC assisted polar code encoding and decoding method

ActiveCN105227189ASave storage spaceFacilitate real-time communicationError preventionError detection onlyComputer architectureProcessor register

The invention belongs to the field of channel encoding, and particularly relates to a polar code coding and decoding method with segmented cyclic redundancy check (Cyclic Redundancy Check, CRC) auxiliary check. According to the polar code coding and decoding method provided by the invention, certain information bits are sacrificed to check polar codes to improve the decoding performance, and assuming that the length of used CRC is K-k bits, the information is averagely divided into M segments by segmented CRC check, k / M bits of information and (K-k) / M bits of CRC check information constitute an information structure of each segment, as shown in Fig.2. The information bits are encoded and transmitted by a channel, finally, SCL decoding and check are carried out on the information received by a receiving end, and L maximum storage paths are available. The polar code coding and decoding method provided by the invention can be used for shortening the time delay, bringing great convenience for real-time communication, saving the memory space of a register and providing great convenience for hardware realization.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Method and apparatus for low density parity check encoding of data

InactiveUS20030037298A1Improve performanceError preventionError detection/correctionParity-check matrixTheoretical computer science

A method for low-density parity-check (LDPC) encoding of data comprises defining a first MxN parity check matrix; generating, based on the first parity check matrix, a second parity check matrix having an MxM triangular sub-matrix; and, mapping the data into an LDPC code word based on the second parity check matrix. The method is particularly useful for data communications applications, but may also be employed in other applications such as, for example, data storage.

Owner:GLOBALFOUNDRIES US INC

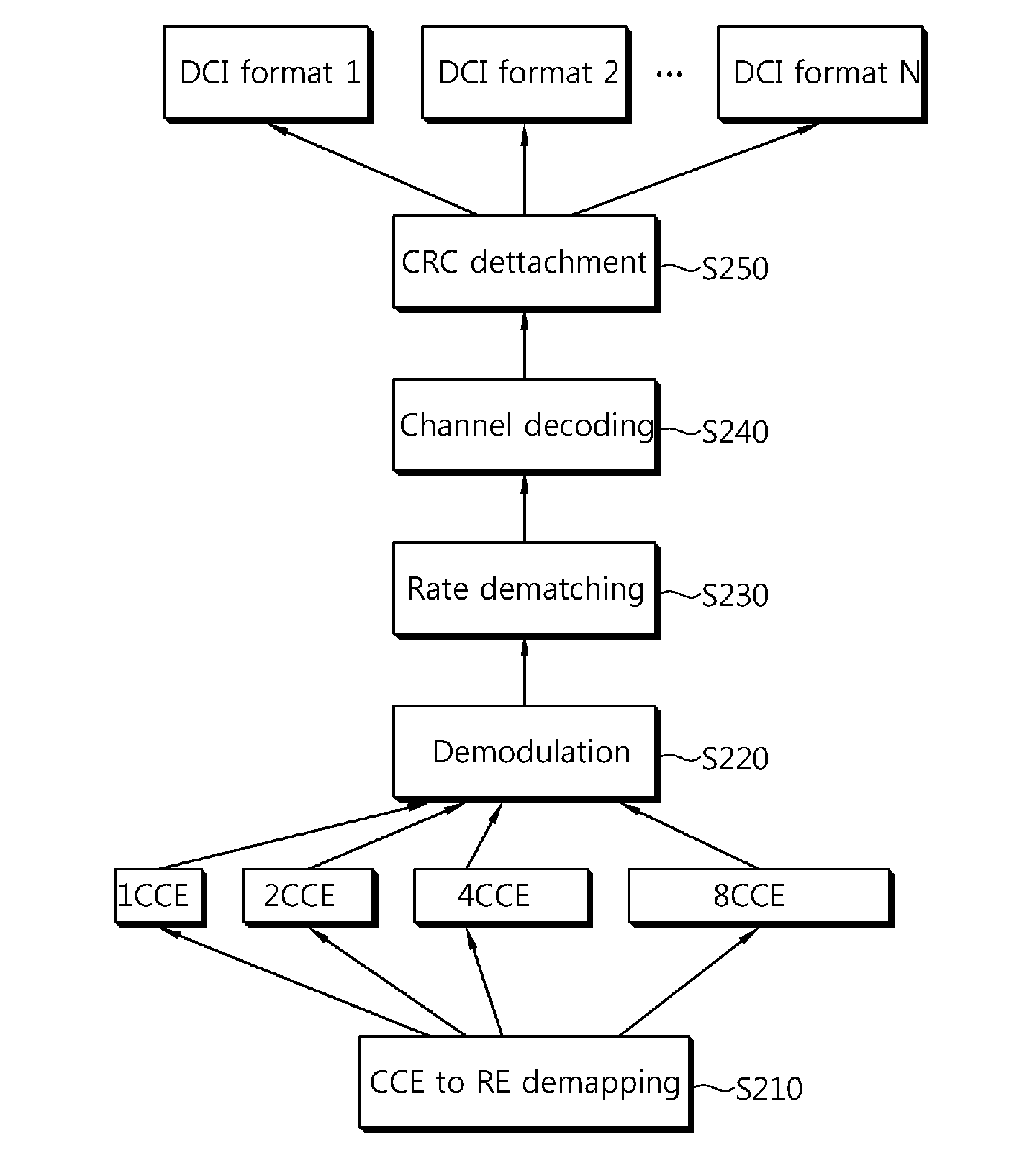

Method for detecting control information in wireless communication system

ActiveUS20110083066A1Improve accuracyAccurate detectionCode conversionSignal allocationError checkCommunications system

A method for detecting control information in a wireless communication system is provided. The method includes checking a cyclic redundancy check (CRC) error by monitoring control channels, determining whether a value of an error check field is equal to a specific value, and, if the value of the error check field is equal to the specific value, detecting the control information on the control channel.

Owner:LG ELECTRONICS INC

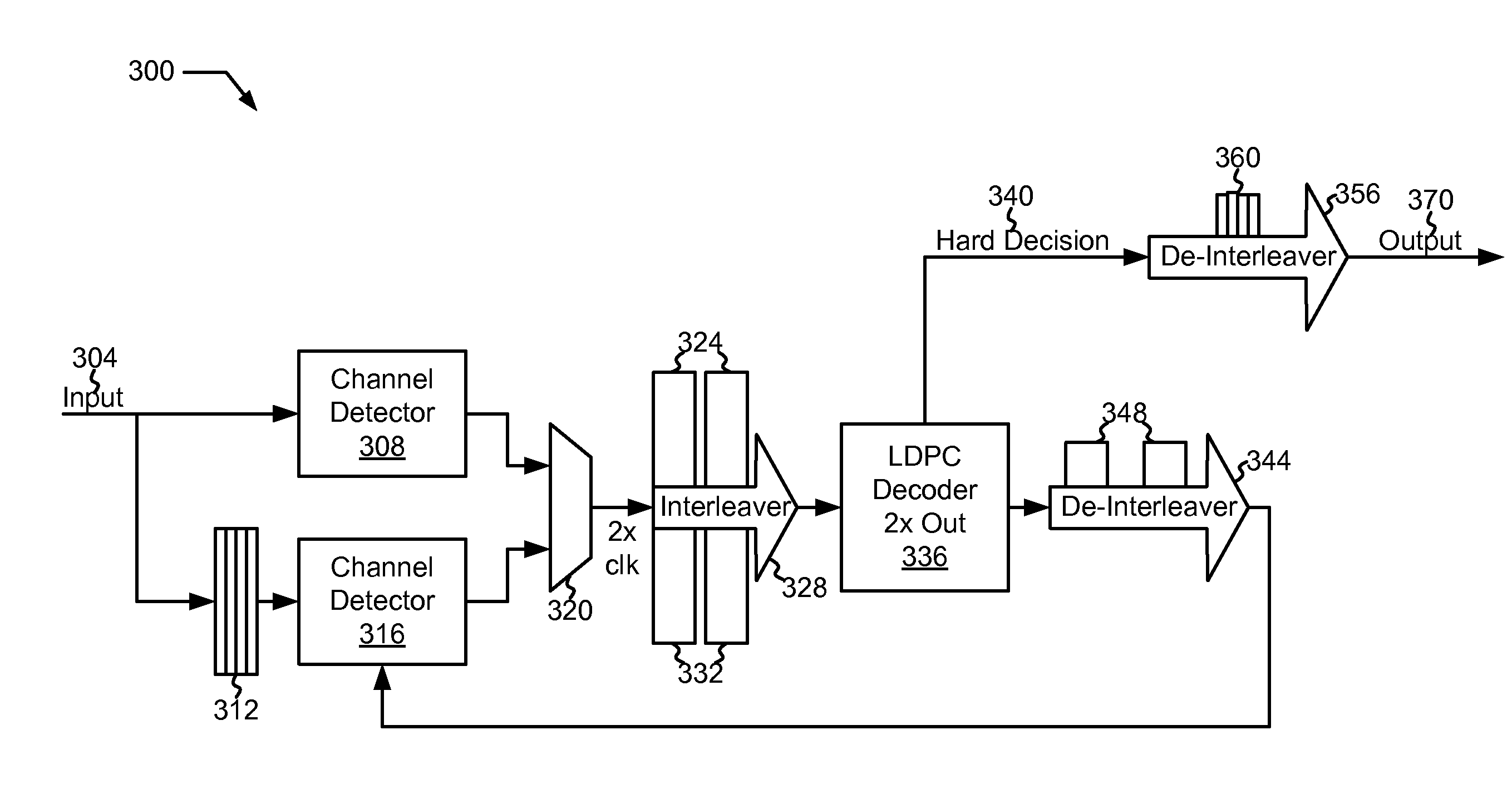

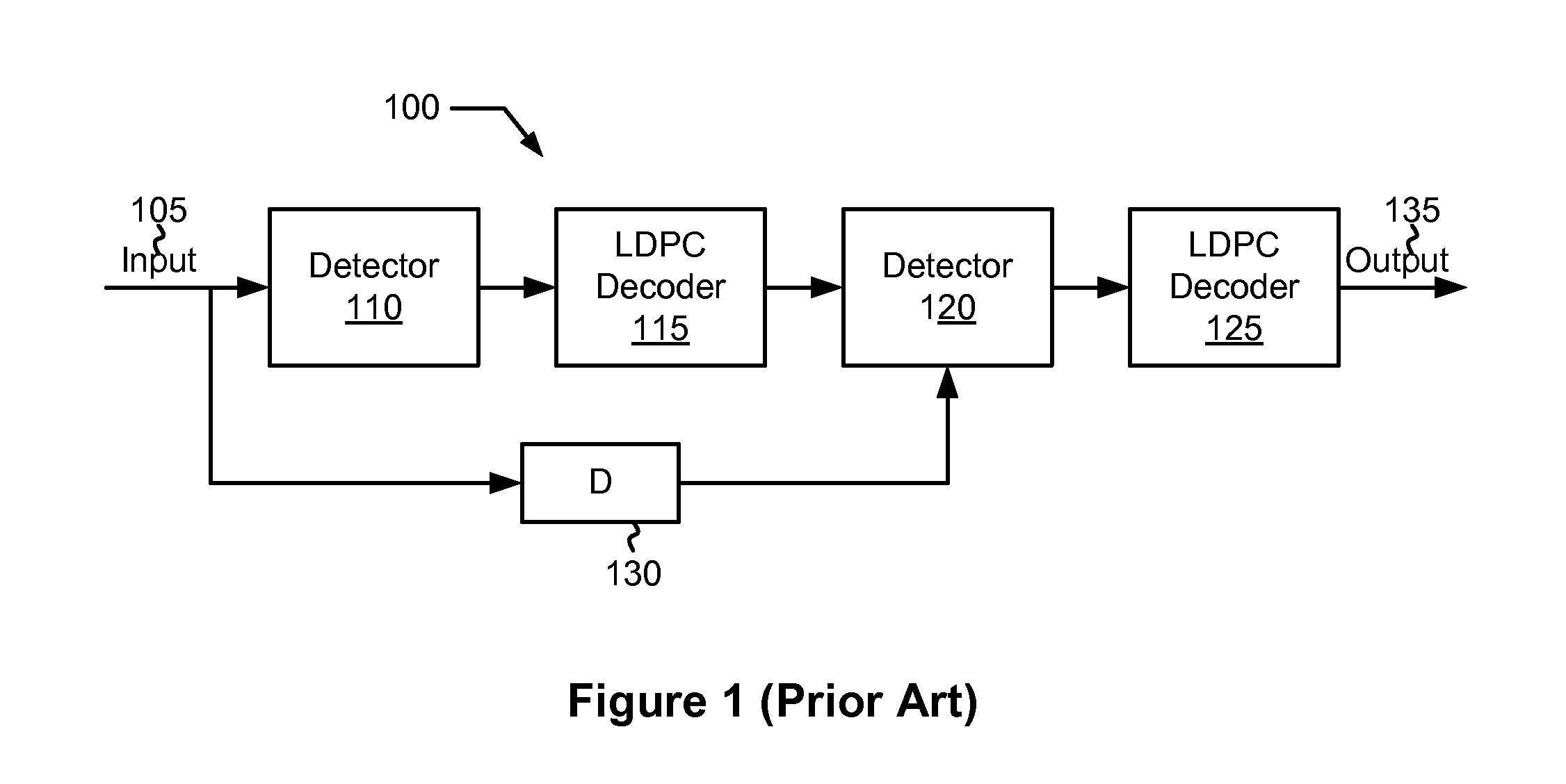

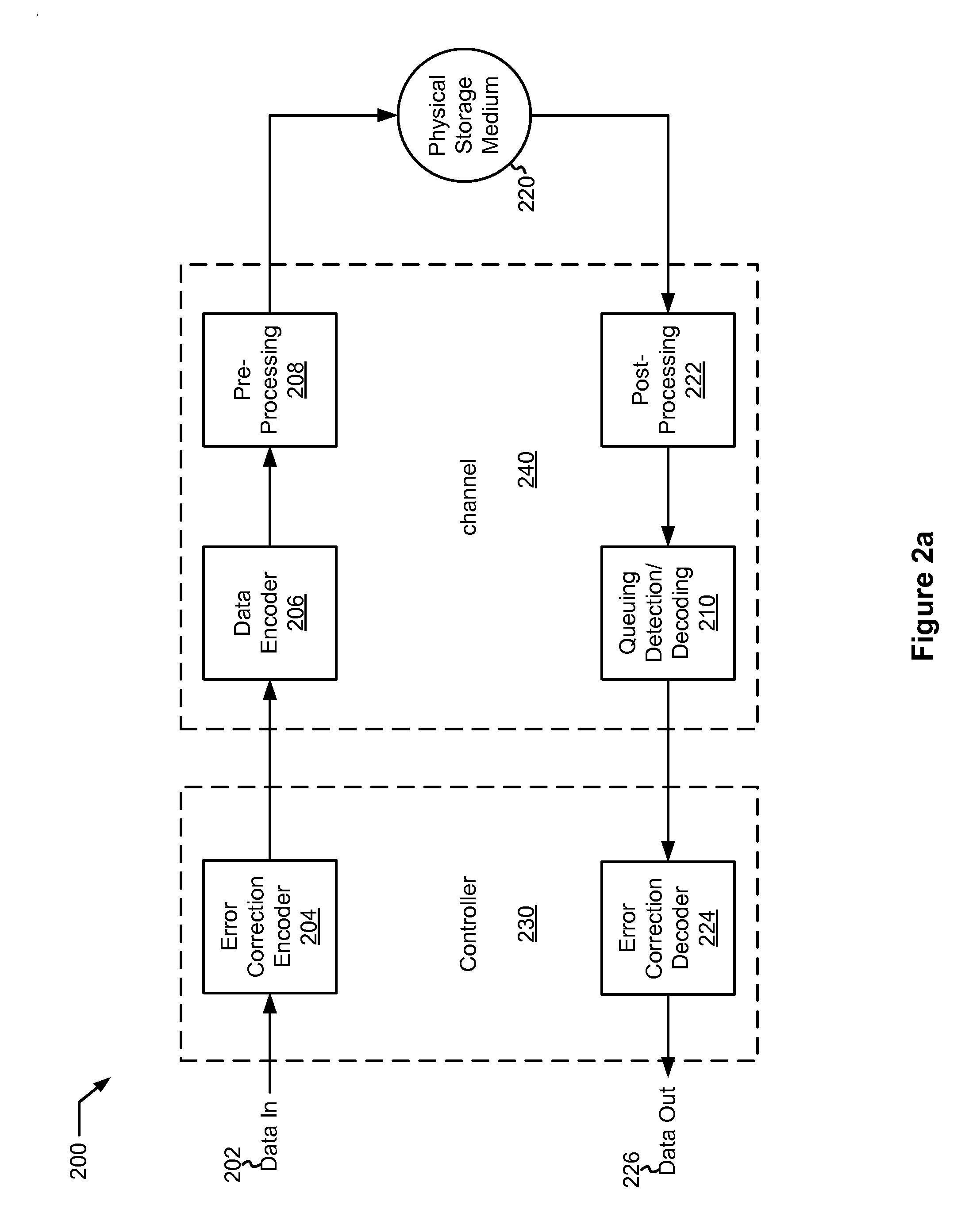

Systems and Methods for Queue Based Data Detection and Decoding

Various embodiments of the present invention provide systems and methods for data processing. For example, a variable iteration data processing system is disclosed that includes at least a first detector, a second detector, a decoder, and a queuing buffer. The first detector is operable to perform a data detection on an input data set at a first time. The decoder receives a derivation of an output from the first detector and performs a decoding process. Where the decoding process fails to converge, the decoder output is passed to the second detector for a subsequent detection and decoding process at a second time.

Owner:AVAGO TECH INT SALES PTE LTD

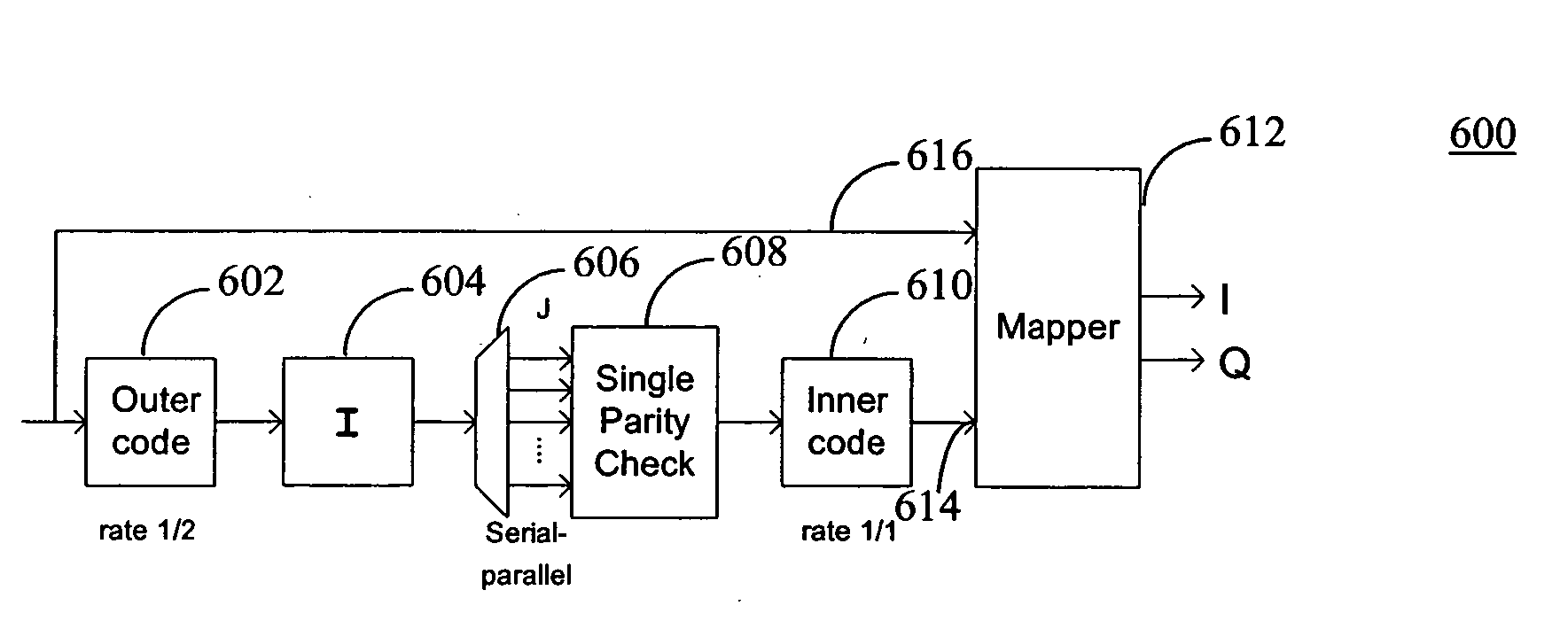

Method and apparatus for communications using turbo like codes

The present invention relates to methods, apparatuses, and systems for performing data encoding involving encoding data bits according to an outer convolutional code to produce outer encoded bits processing the outer encoded bits using an interleaver and a logical unit to produce intermediate bits, wherein the logical unit receives a first number of input bits and produces a second number of corresponding output bits, the second number being less than the first number, and wherein the logical unit takes each of the first number of input bits into account in producing the second number of output bits, encoding the intermediate bits according to an inner convolutional code to produce inner encoded bits, wherein the inner convolutional code is characterized by at least two states, and combining the data bits and the inner encoded bits to produce encoded outputs.

Owner:TRELLIS WARE TECH

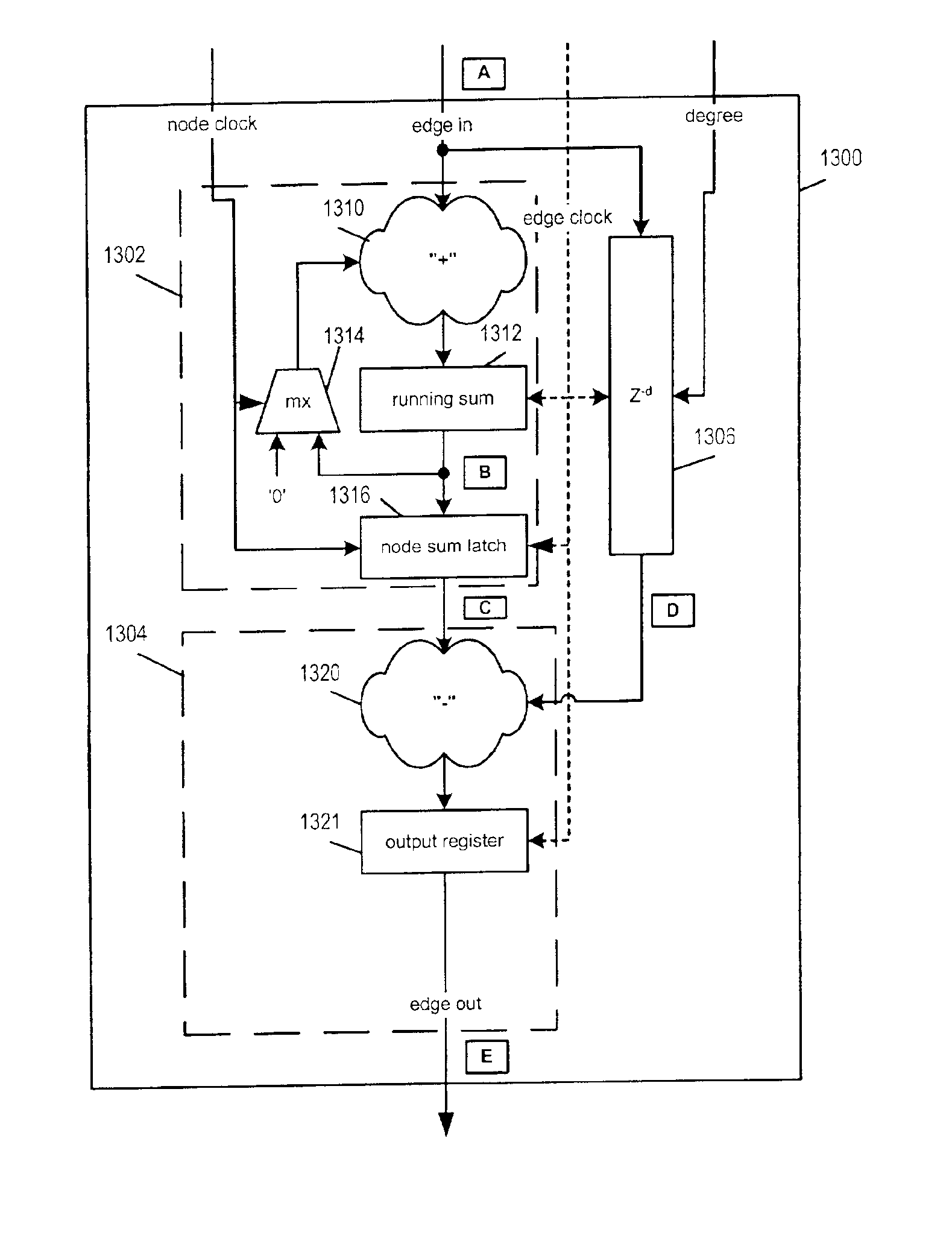

Node processors for use in parity check decoders

InactiveUS6938196B2Big errorCompensating for such errorError prevention/detection by using return channelOther decoding techniquesComputer moduleMessage processing

Techniques for implementing message passing decoders, e.g., LDPC decoders, are described. To facilitate hardware implementation messages are quantized to integer multiples of ½ ln2. Messages are transformed between more compact variable and less compact constraint node message representation formats. The variable node message format allows variable node message operations to be performed through simple additions and subtractions while the constraint node representation allows constraint node message processing to be performed through simple additions and subtractions. Variable and constraint nodes are implemented using an accumulator module, subtractor module and delay pipeline. The accumulator module generates an accumulated message sum. The accumulated message sum for a node is stored and then delayed input messages from the delay pipeline are subtracted there from to generate output messages. The delay pipeline includes a variable delay element making it possible to sequentially perform processing operations corresponding to nodes of different degrees.

Owner:QUALCOMM INC

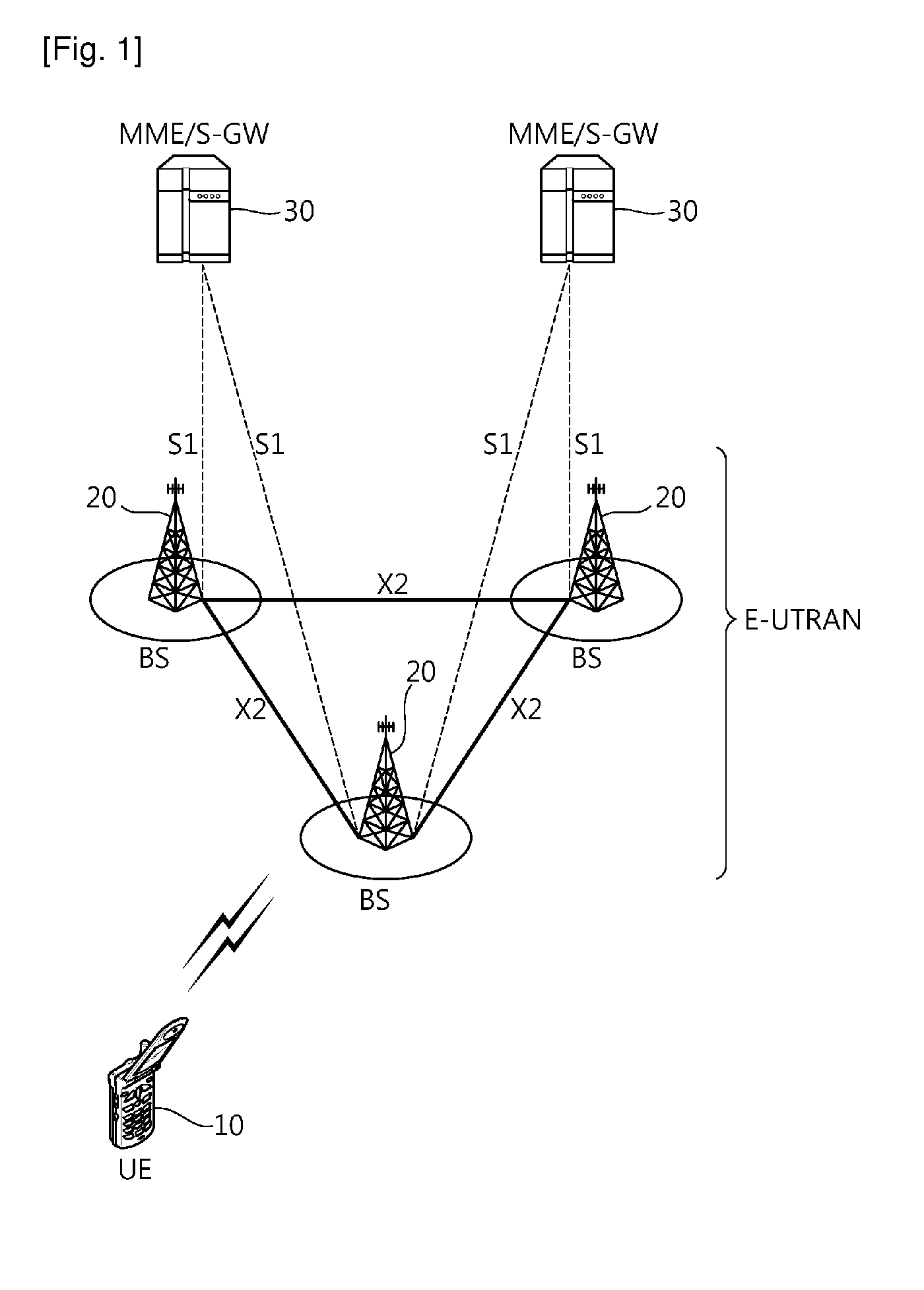

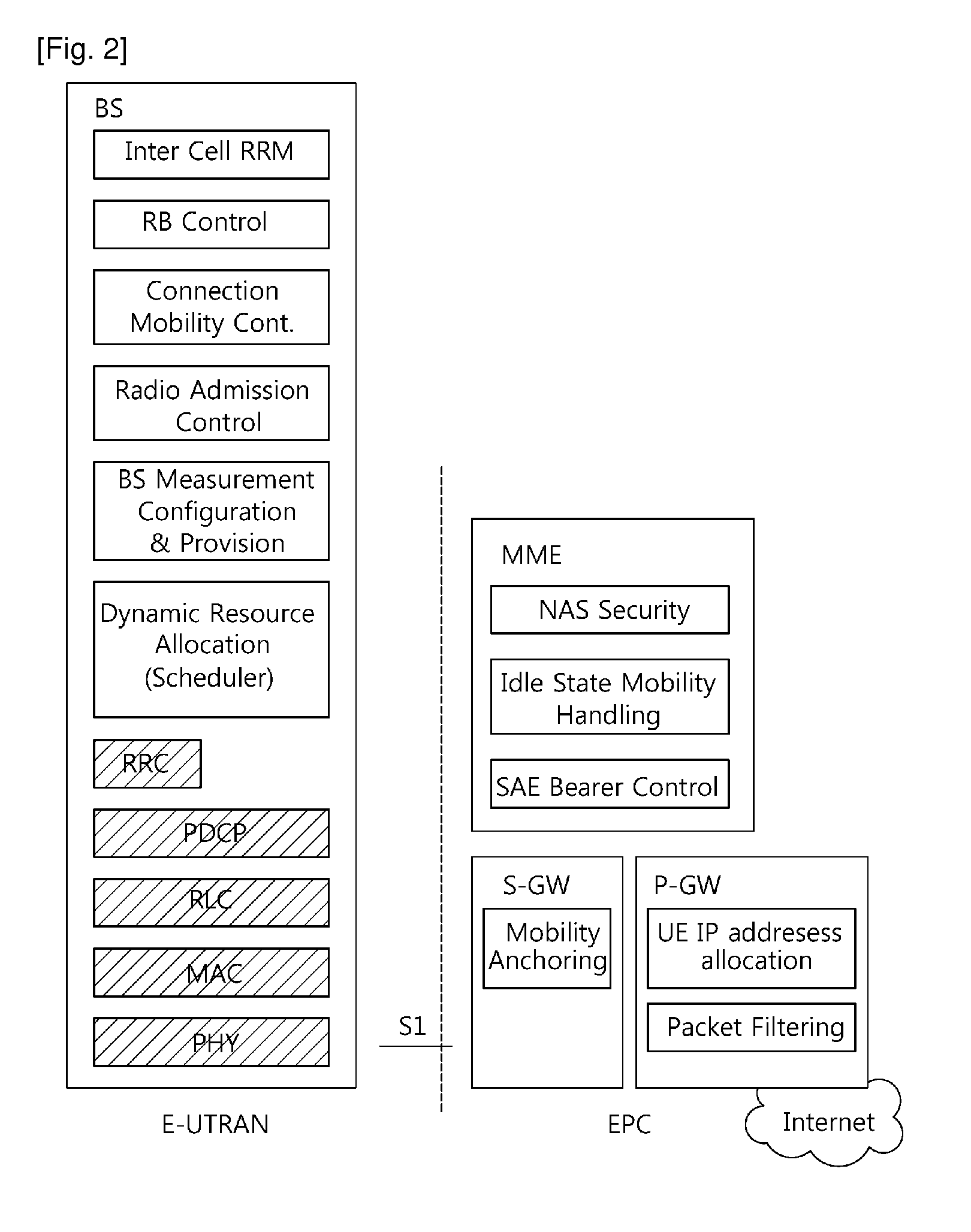

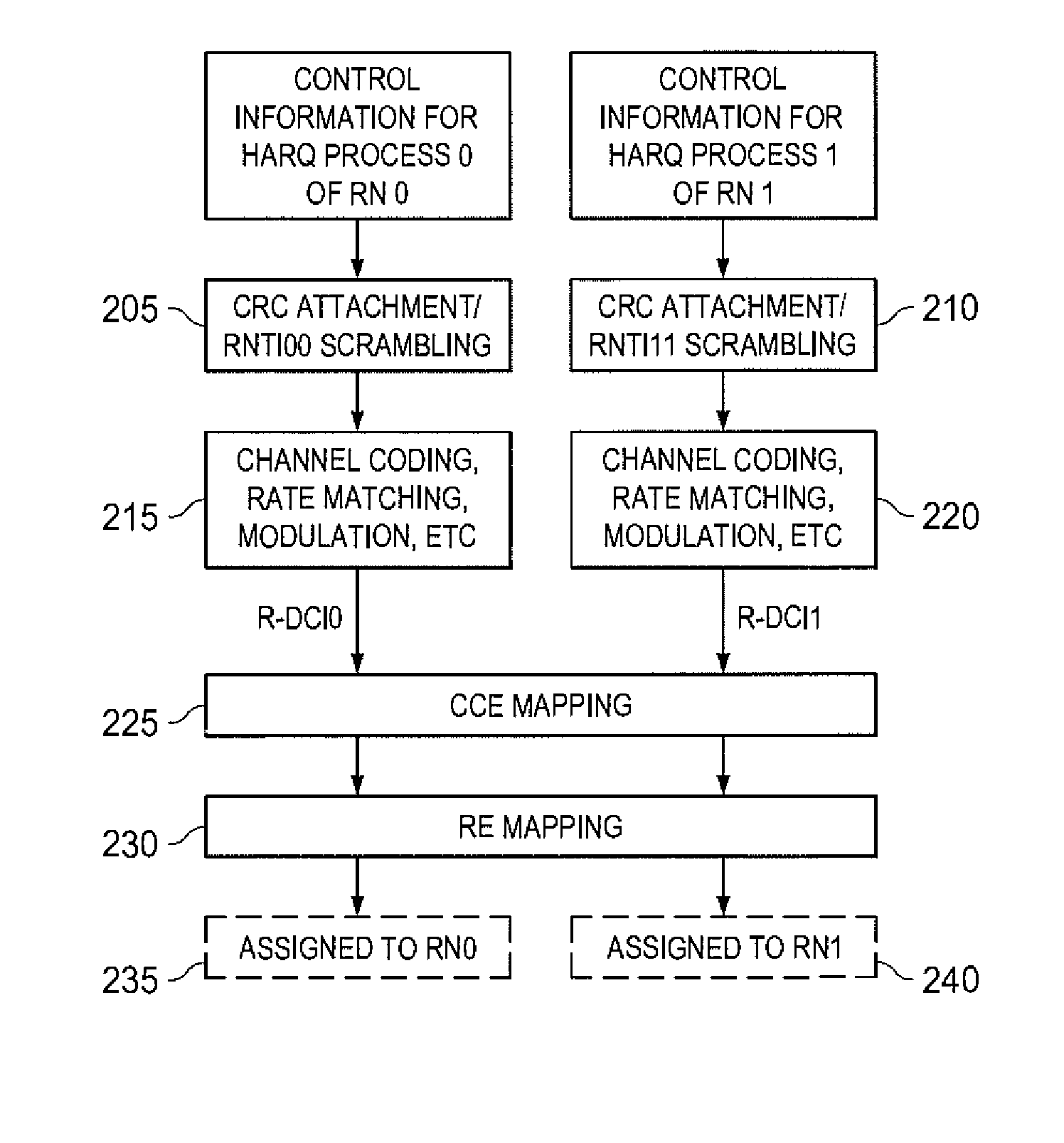

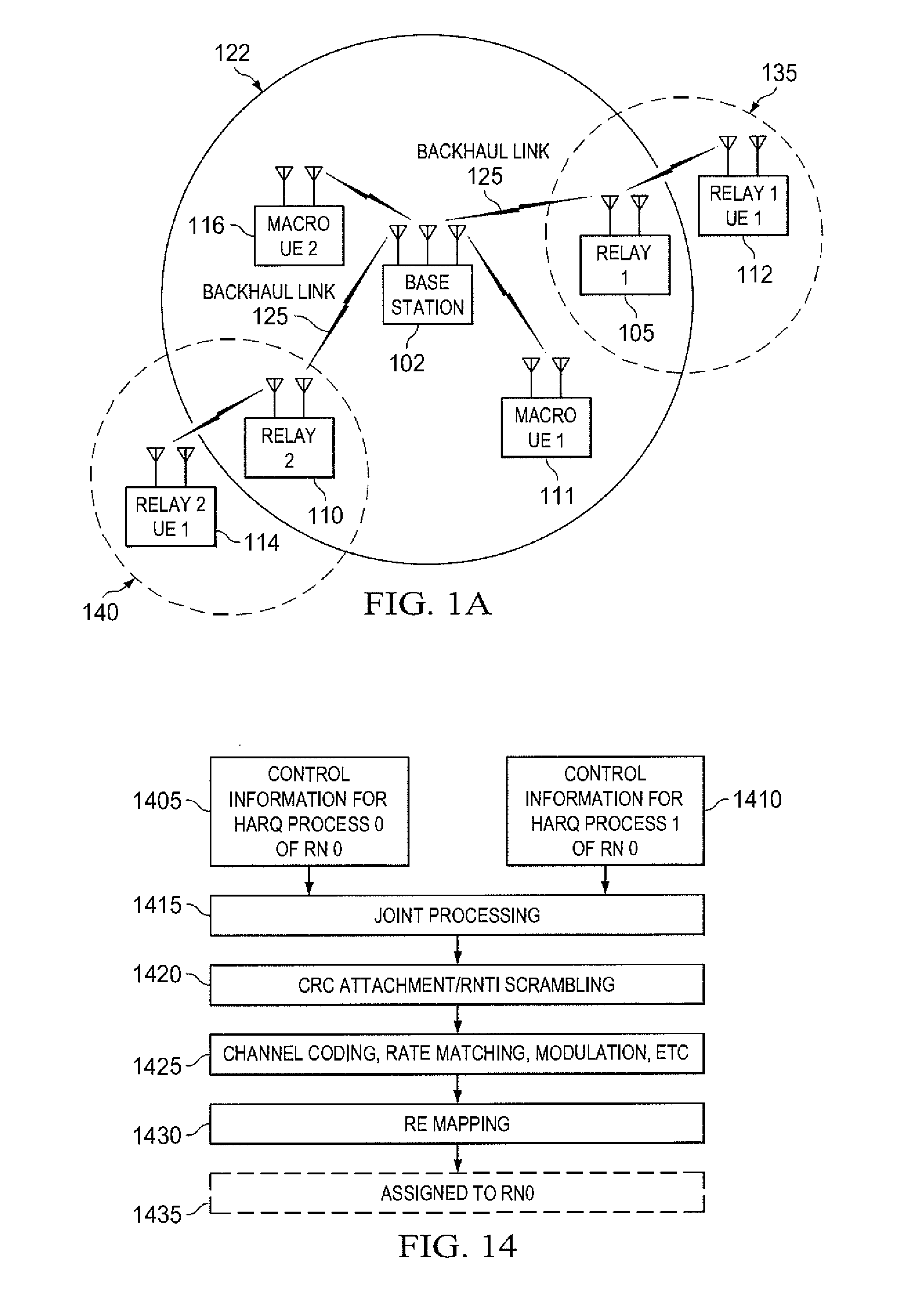

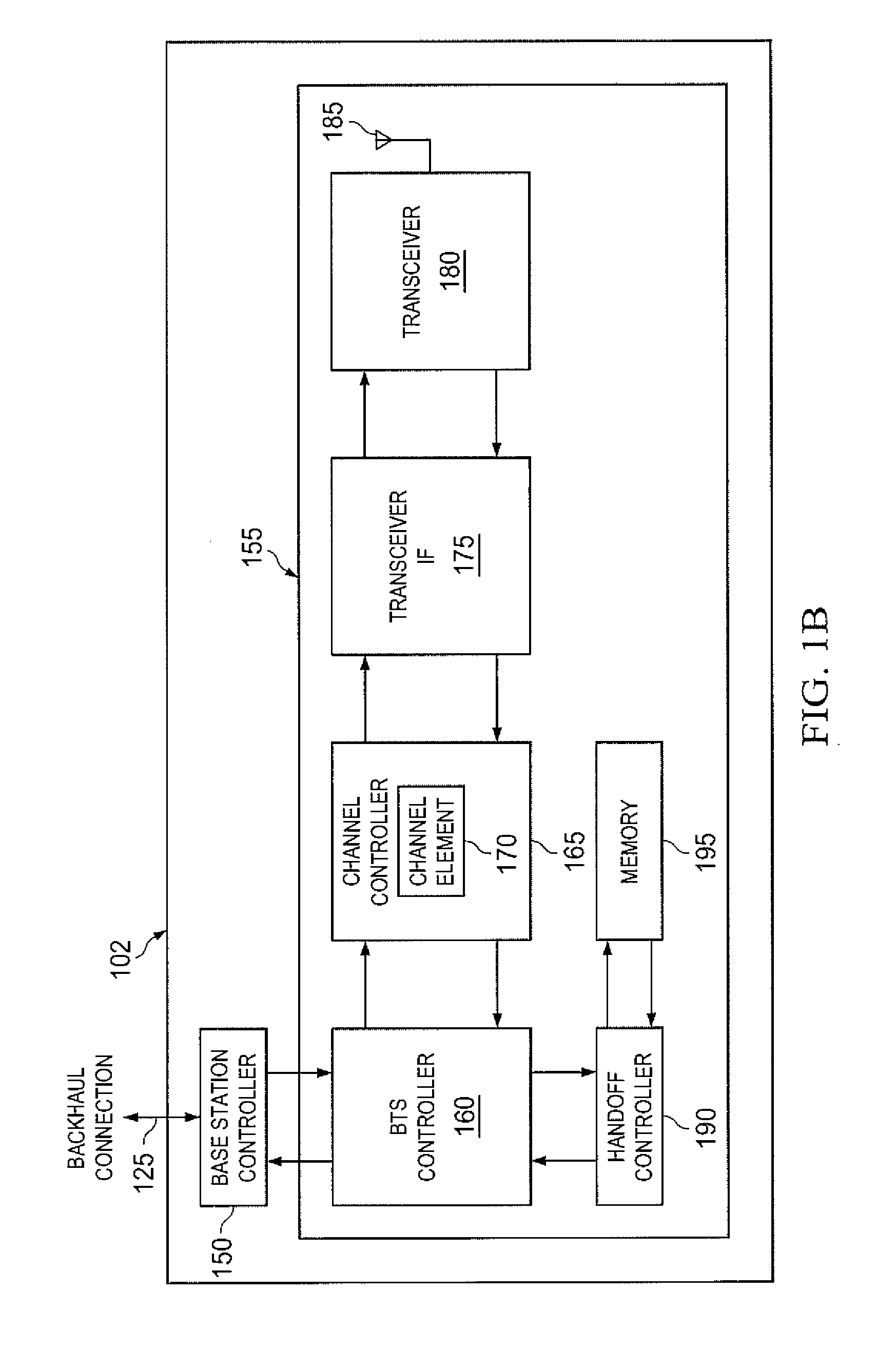

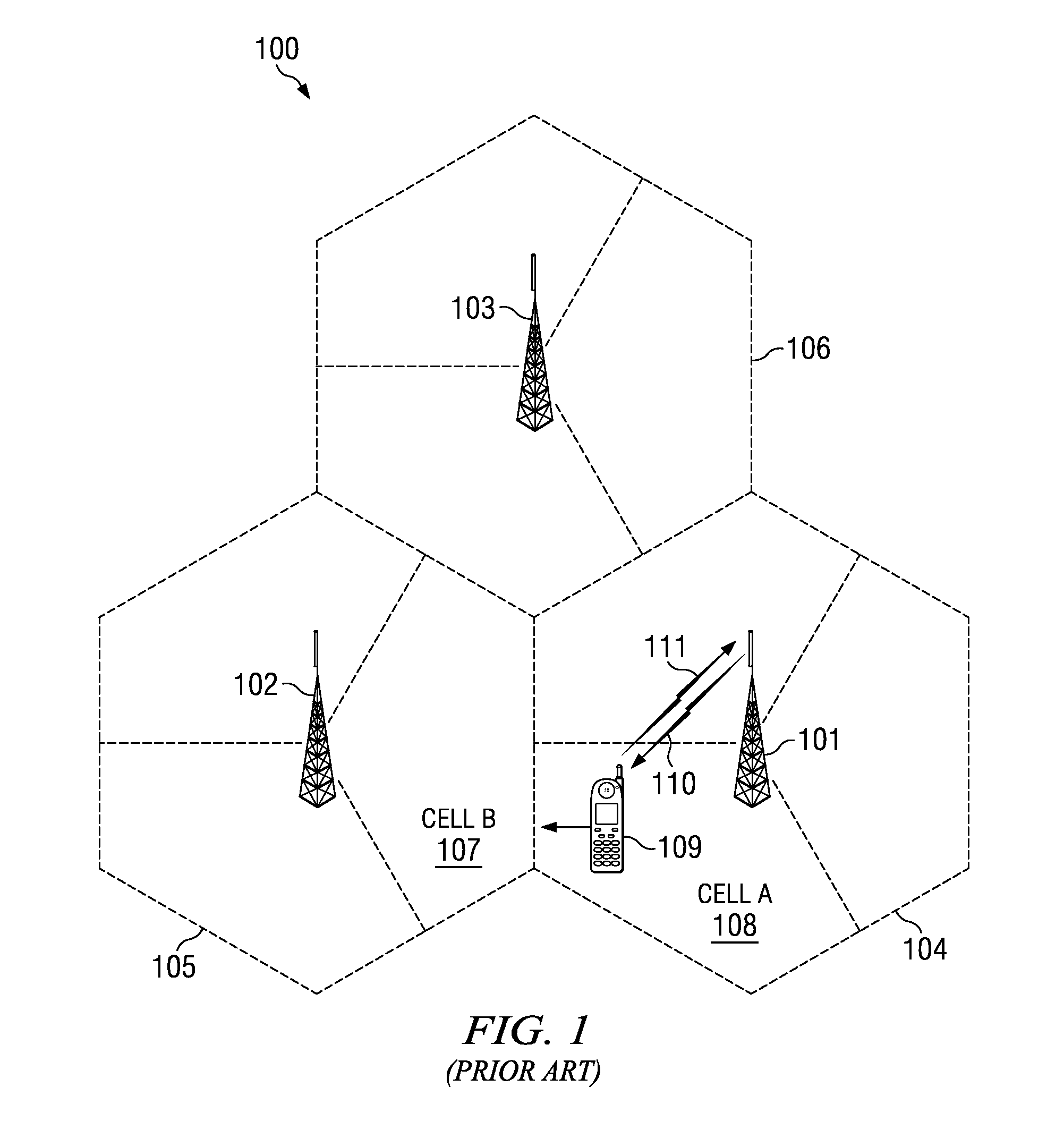

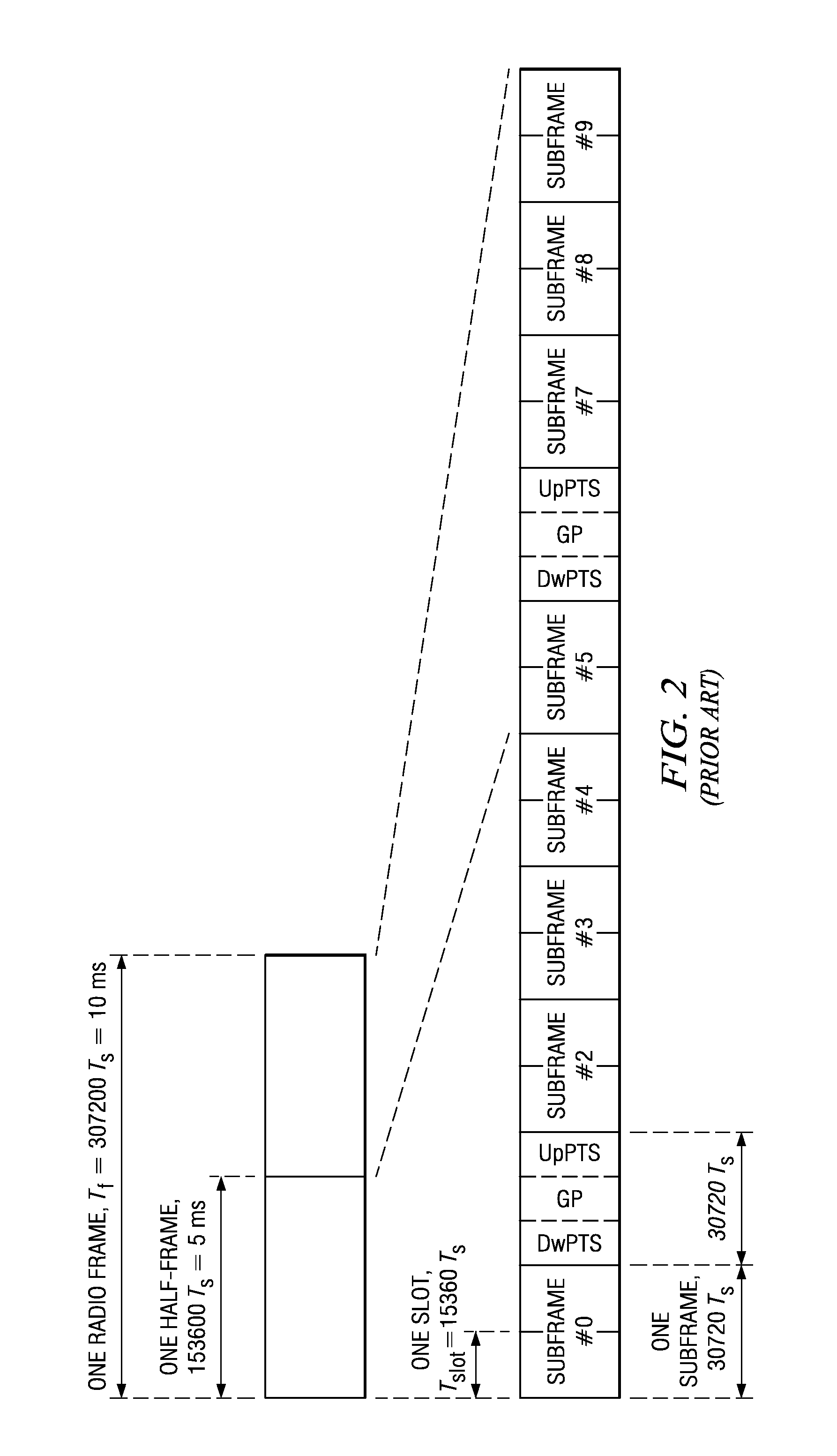

Control design for backhaul relay to support multiple HARQ processes

ActiveUS20100275083A1Error prevention/detection by using return channelError correction/detection using convolutional codesHybrid automatic repeat requestBase station

A wireless communication network includes a base station and a relay station. The relay station is configured to relay communications between the base station and at least one subscriber station. The base station is configured to communicate with the subscriber station via the relay station. The base station further is configured to transmit, in a subframe, a plurality of transport blocks for a plurality of Hybrid Automatic Repeat Request (HARQ) processes to the relay station. Each transport block corresponds to a different HARQ process.

Owner:SAMSUNG ELECTRONICS CO LTD

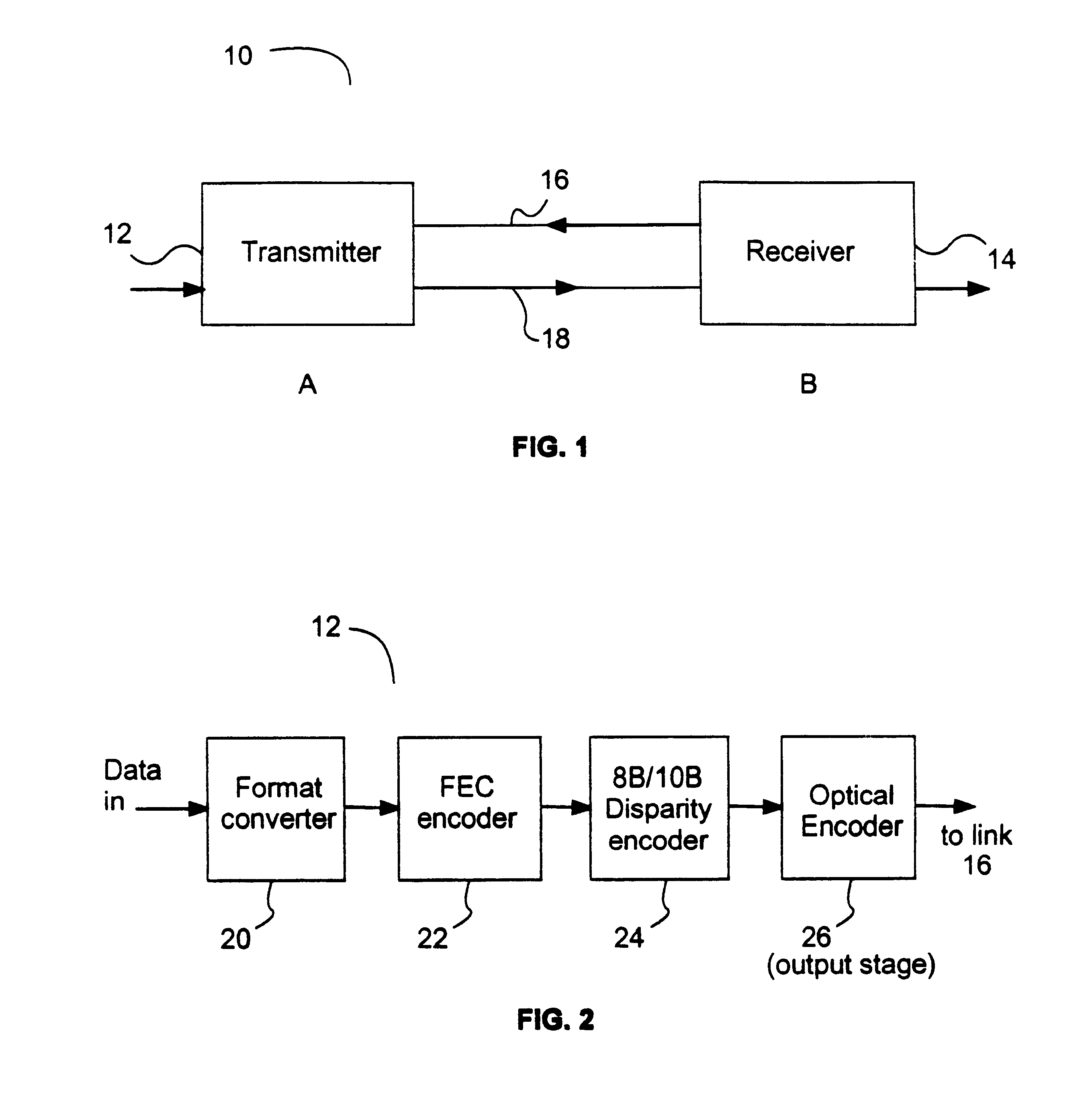

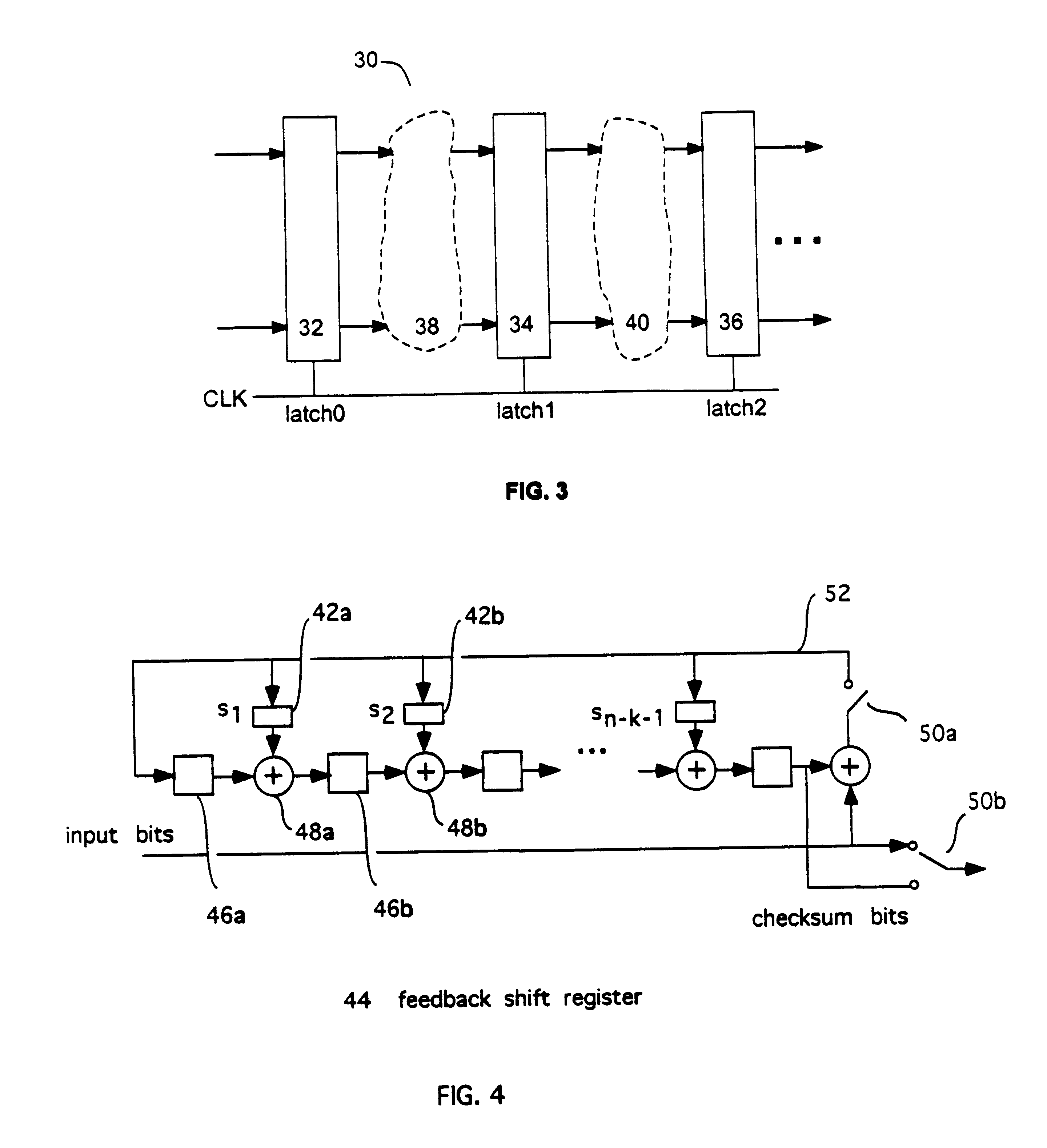

Transmitter, receiver, and coding scheme to increase data rate and decrease bit error rate of an optical data link

InactiveUS6851086B2Increase capacityIncrease bitrateError prevention/detection by using return channelError detection/correctionData packData rate

Transmitters, receivers, and coding schemes to increase data rate and decrease bit error rate of an optical data link are disclosed. Data is transmitted across the link with a less than nominal bit error rate (BER), by encoding the data using a forward error correction (FEC) code or by requesting retransmission of transmitted packets in error. Data is transmitted at a speed that introduces errors at a rate that is in excess of the nominal BER but that may be corrected using the FEC code or retransmission so that the data may be received with less than the nominal BER. The data rate is increased as the link operating speed is increased beyond the overhead required by the FEC codes or retransmission. High speed FEC encoders and decoders facilitating such transmission are disclosed.

Owner:SZYMANSKI TED

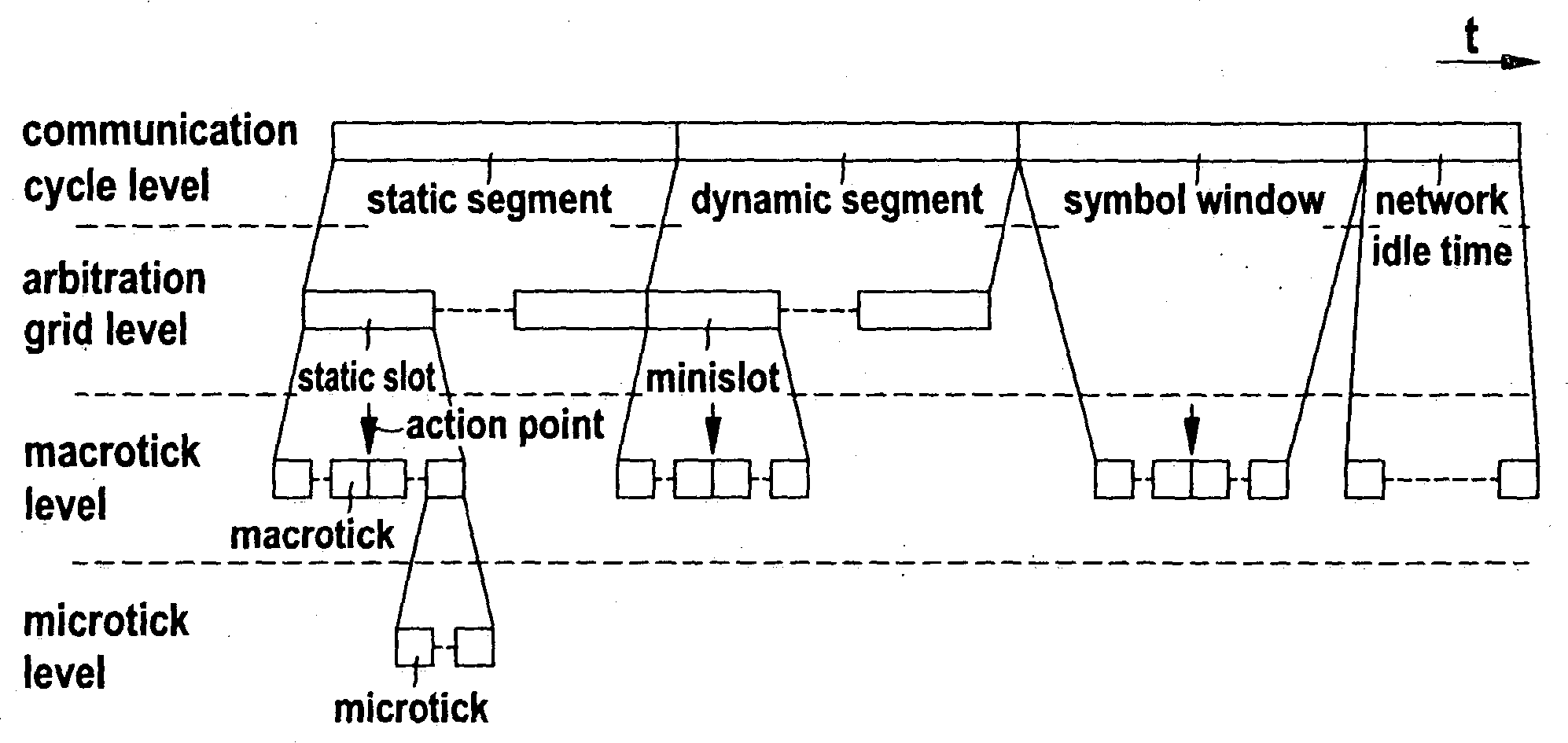

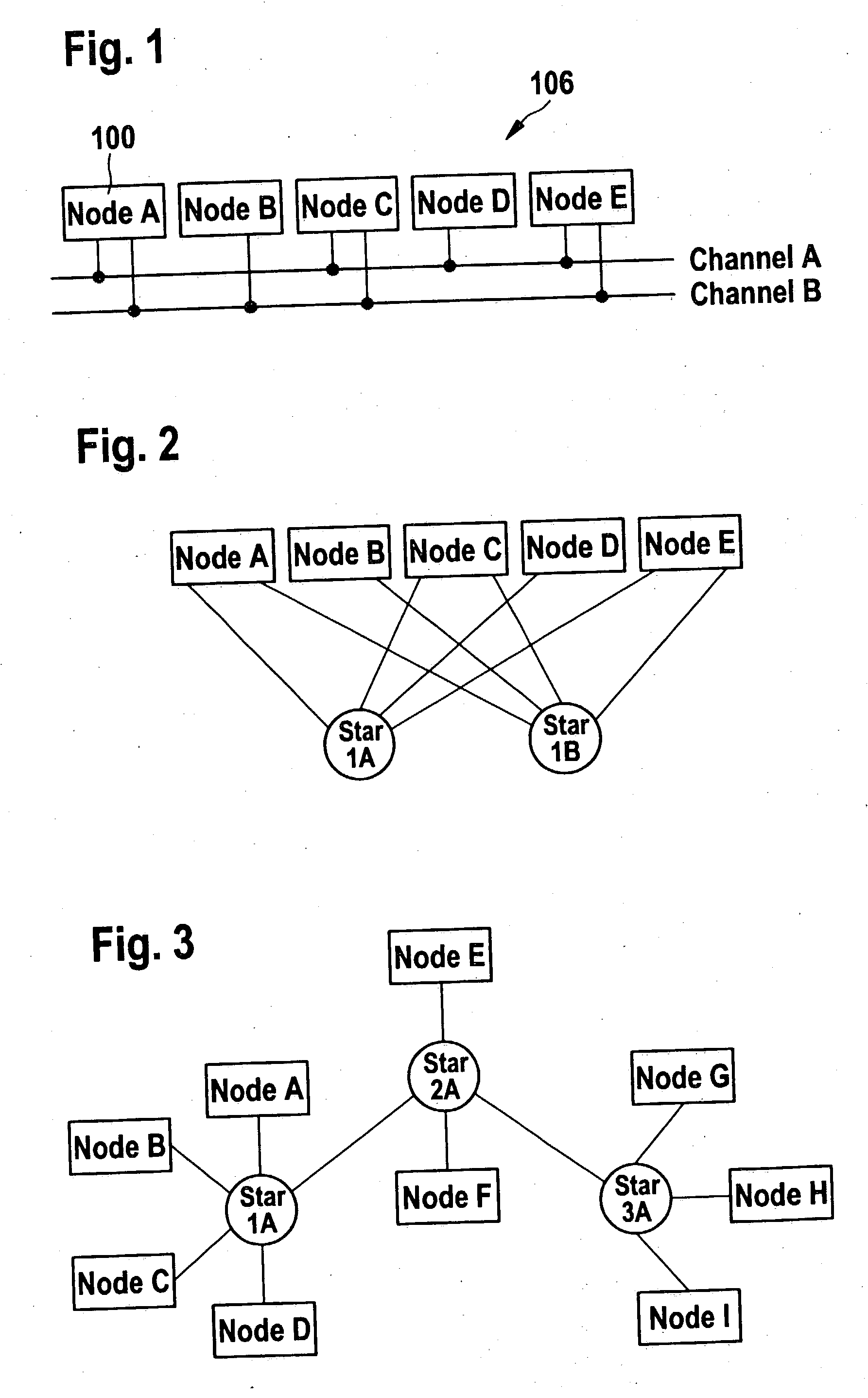

Method for synchronizing clocks in a distributed communication system

InactiveUS20050141565A1Achievable accuracyImprove accuracyOther decoding techniquesTime-division multiplexControl communicationsCommunication control

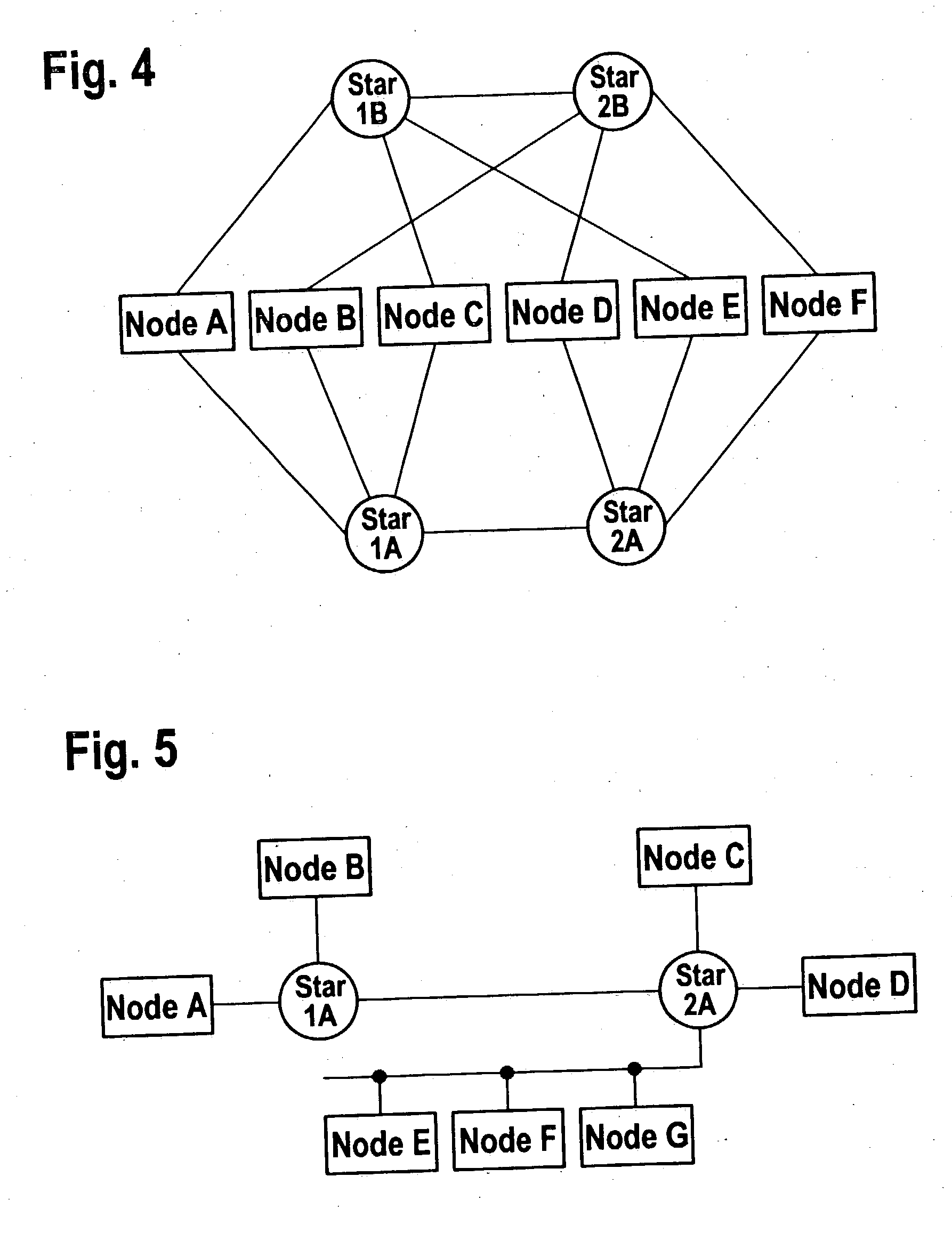

The invention refers to one of a number of nodes of a communication system. The nodes are connected to a communication media for transmitting data among the nodes. Said one node comprises a communication controller, across which the node is connected to the communication media, and a bus guardian for controlling access of the communication controller to the communication media. In order to provide a cheap but nevertheless reliable way for monitoring the synchronized clock signal of a node of a communication system and in particular for detecting deviations of the synchronized clock signal it is suggested that a synchronized clock signal from the communication controller is made available to the bus guardian, and that the bus guardian comprises means for monitoring the synchronized clock signal using a bus guardian internal clock signal, which is generated by means of an electronic circuit and which is less accurate than the synchronized clock signal to be monitored.

Owner:MOTOROLA INC +5

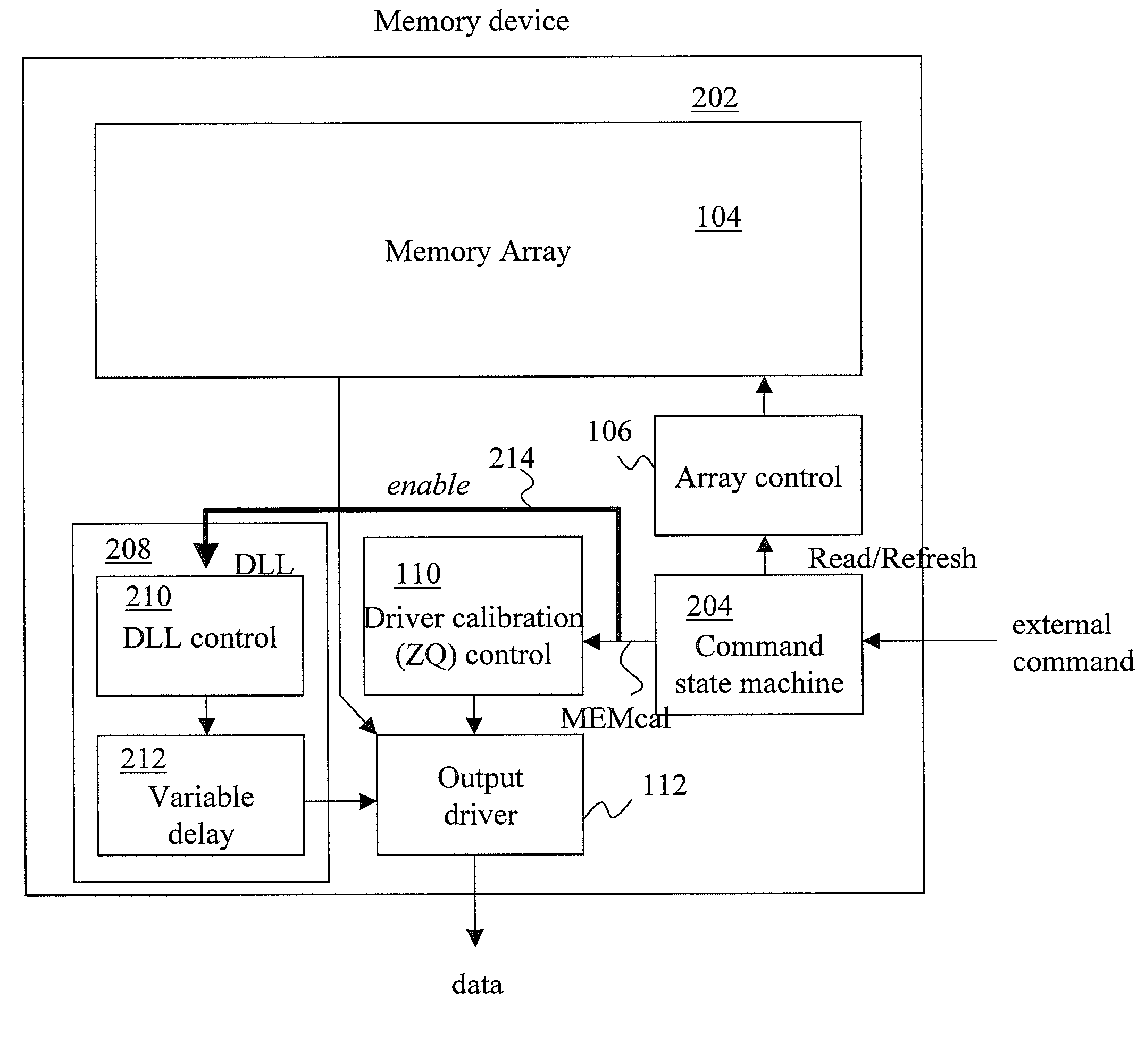

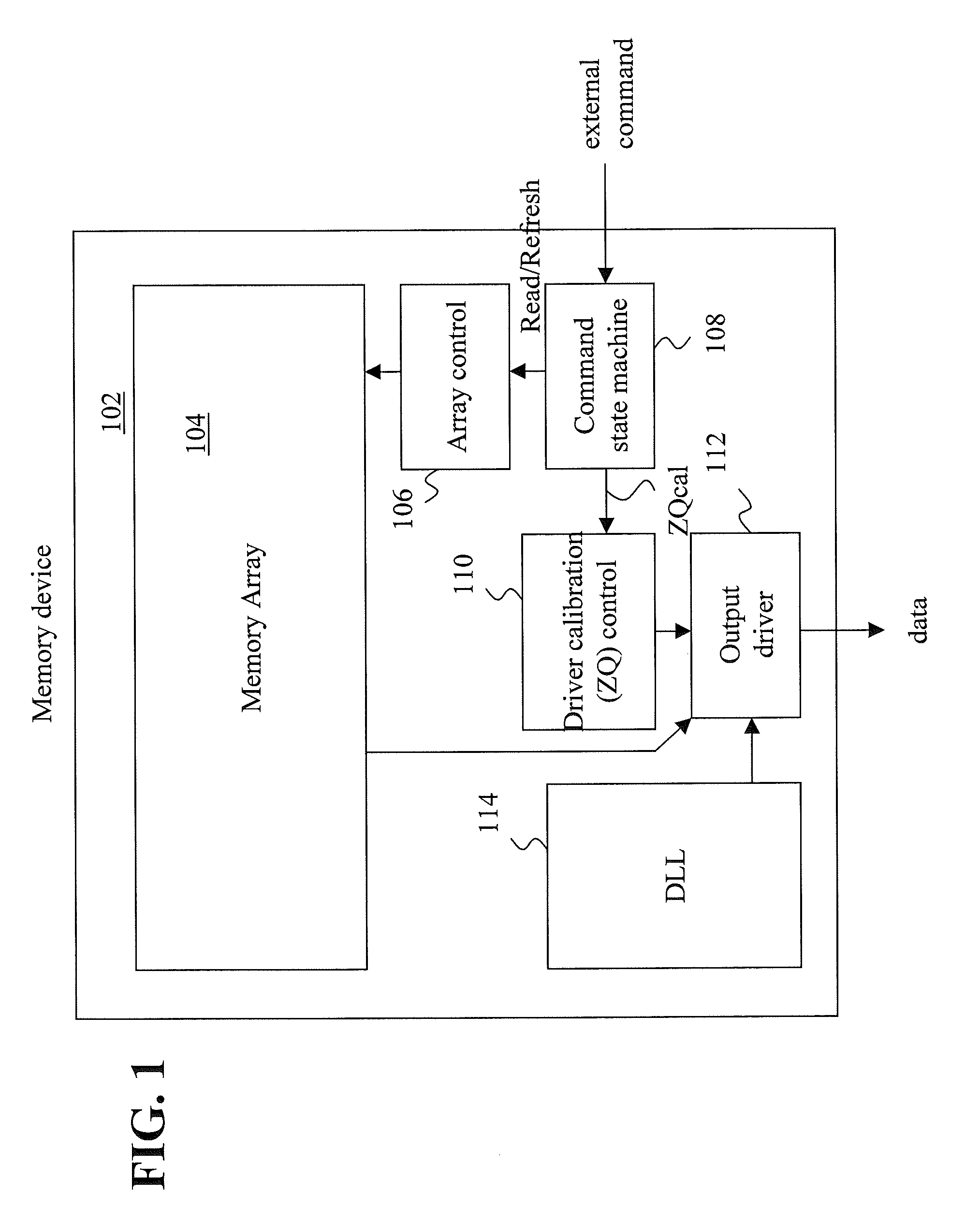

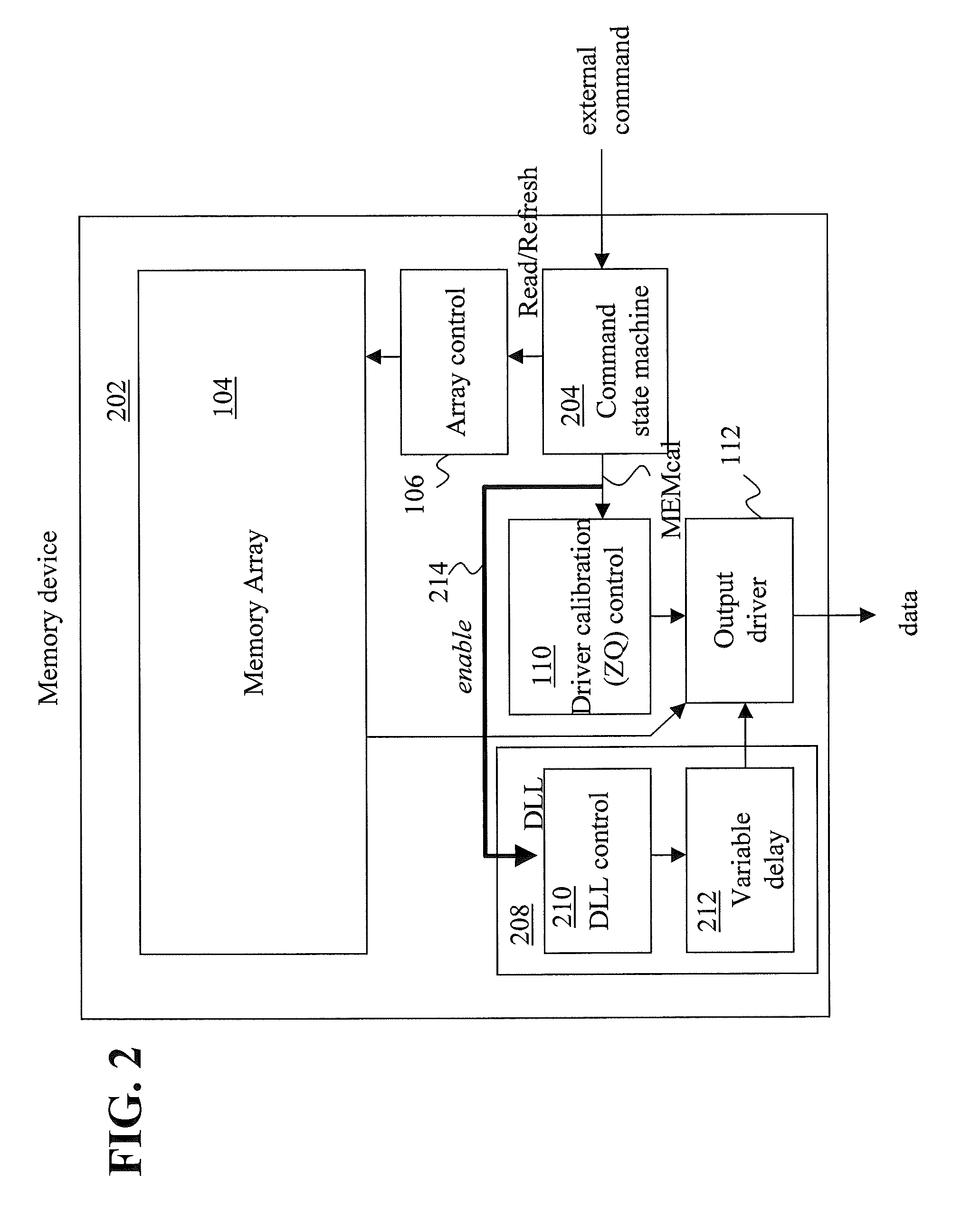

Advanced memory device having improved performance, reduced power and increased reliability

An advanced memory having improved performance, reduced power and increased reliability. A memory device includes a memory array, a receiver for receiving a command and associated data, error control coding circuitry for performing error control checking on the received command, and data masking circuitry for preventing the associated data from being written to the memory array in response to the error control coding circuitry detecting an error in the received command. Another memory device includes a programmable preamble. Another memory device includes a fast exit self-refresh mode. Another memory device includes auto refresh function that is controlled by the characteristic device. Another memory device includes an auto refresh function that is controlled by a characteristic of the memory device.

Owner:GLOBALFOUNDRIES US INC

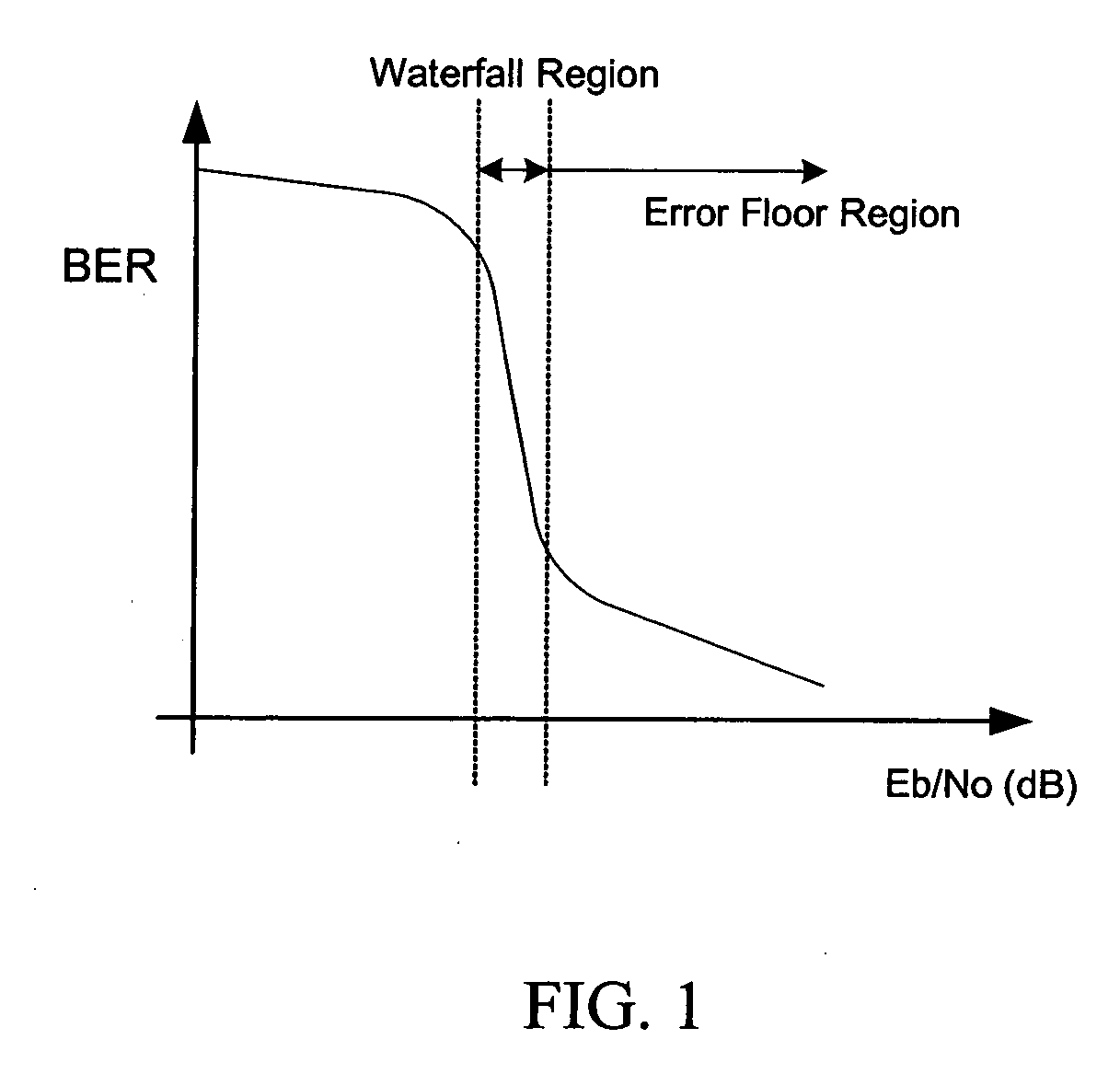

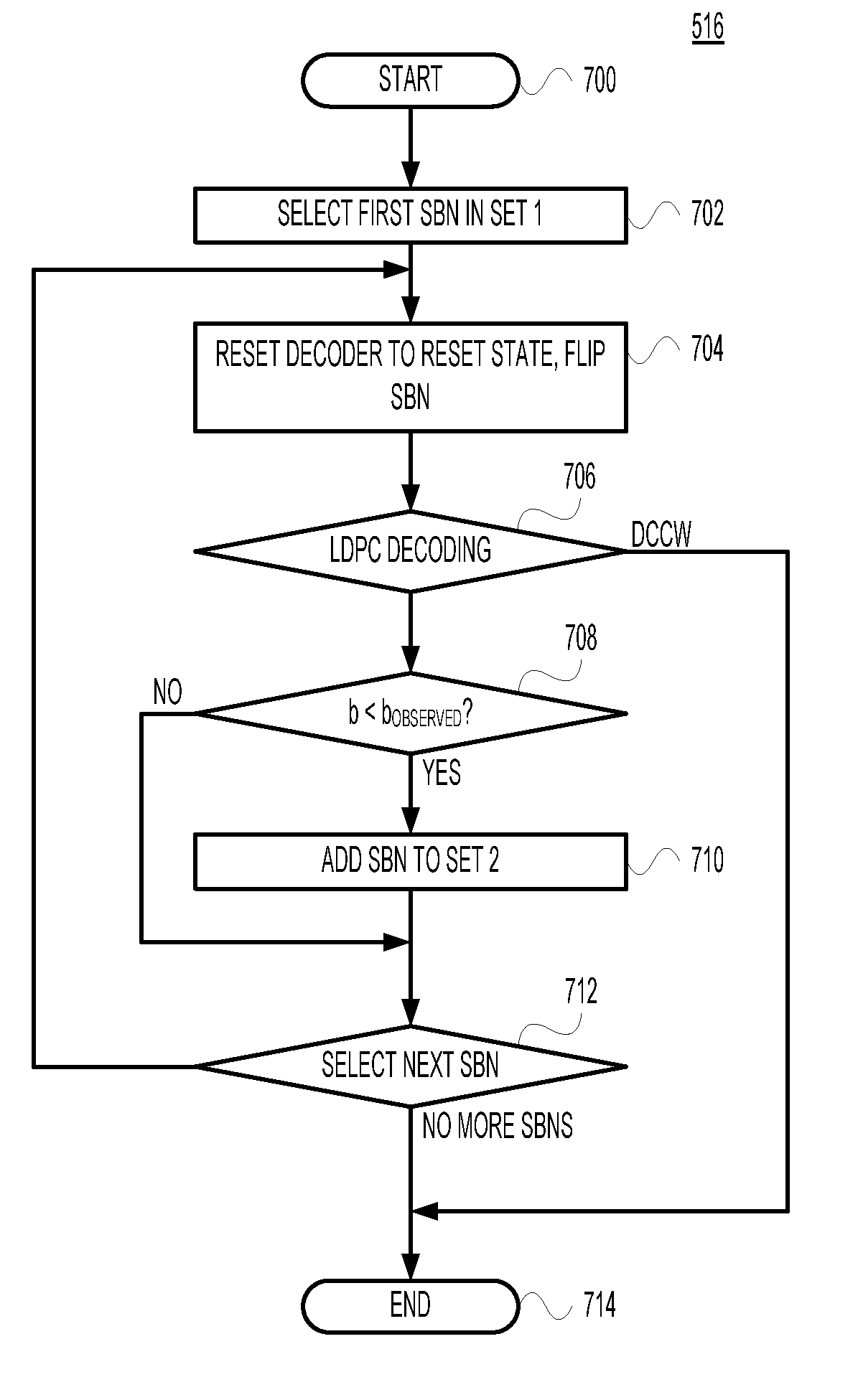

Error-floor mitigation of LDPC codes using targeted bit adjustments

Embodiments of the present invention are methods for breaking one or more trapping sets in a near codeword of a failed graph-based decoder, e.g., an LDPC decoder. The methods determine, from among all bit nodes associated with one or more unsatisfied check nodes in the near codeword, which bit nodes, i.e., the suspicious bit nodes or SBNs, are most likely to be erroneous bit nodes. The methods then perform a trial in which the values of one or more SBNs are altered and decoding is re-performed. If the trial does not converge on the decoded correct codeword (DCCW), then other trials are performed until either (i) the decoder converges on the DCCW or (ii) all permitted combinations of SBNs are exhausted. The starting state of a particular trial, and the set of SBNs available to that trial may change depending on the results of previous trials.

Owner:AVAGO TECH INT SALES PTE LTD

Polarization code decoding method for cyclic redundancy check assistance

InactiveCN102694625AStrong error correction abilityReduce operational complexityError preventionError correction/detection using linear codesCommunications systemCode division multiple access

The invention relates to a polarization code decoding method for cyclic redundancy check assistance. When a polarization code is decoded, in all the routes with cyclic redundancy check values of corresponding bit estimation sequences of being zero from a root node to leaf nodes on a code tree corresponding to the polarization code, one route with maximum reliability metric value is searched by taking a list or stack as assistance for route search, and the bit estimation sequence corresponding to the route is output as a decoding result. The method comprises the following operation steps of: determining parameters according to a search assistance method, constructing an auxiliary structure of the decoding method, searching a candidate bit estimation sequence and executing cyclic redundancy check. By adopting the method disclosed by the invention, error correcting capability of a communication system which adopts the polarization code as channel coding is greatly improved, operation steps are simpler, and operation complexity is equivalent to or even lower than that of a Turbo code coding and decoding method used in a WCDMA (wideband code division multiple access) system, thus the method disclosed by the invention has a good practical prospect.

Owner:BEIJING UNIV OF POSTS & TELECOMM

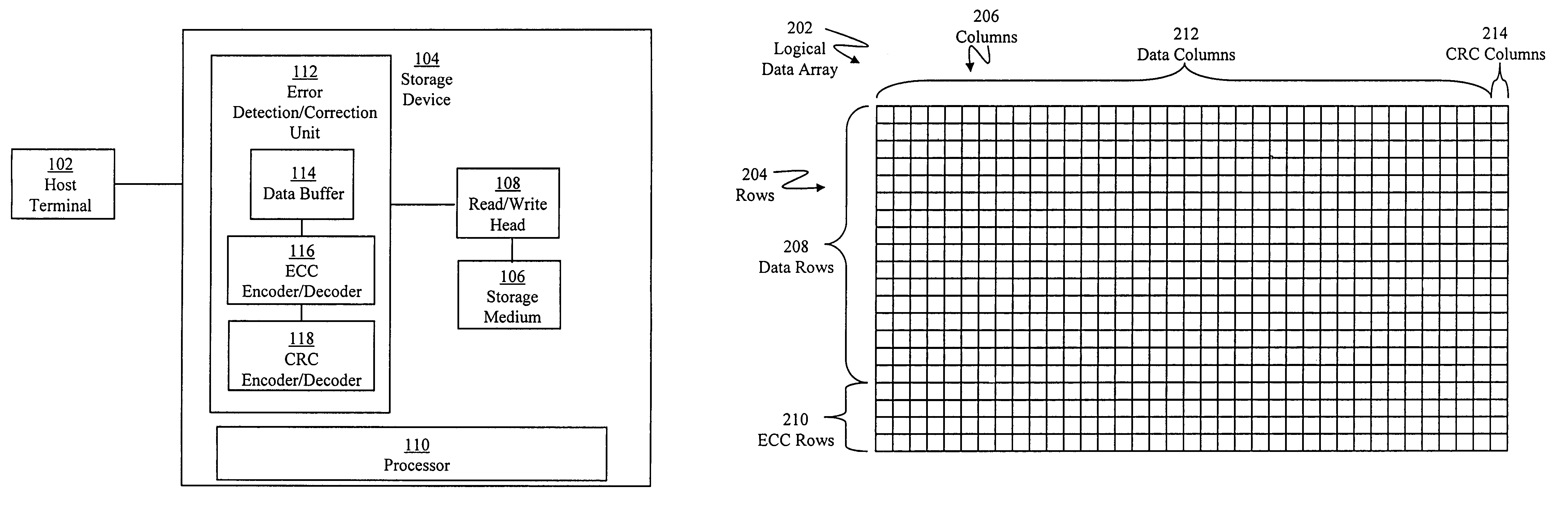

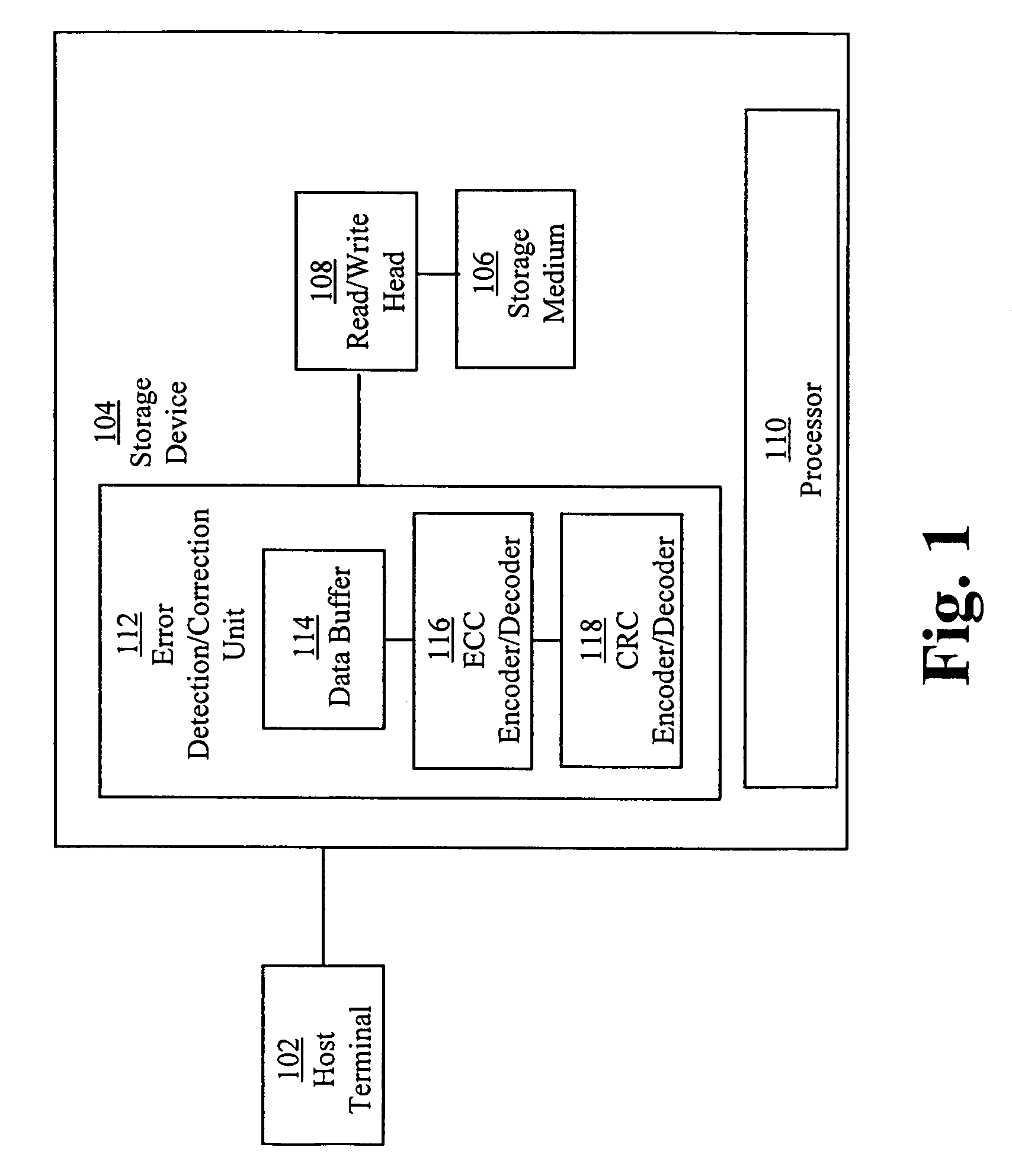

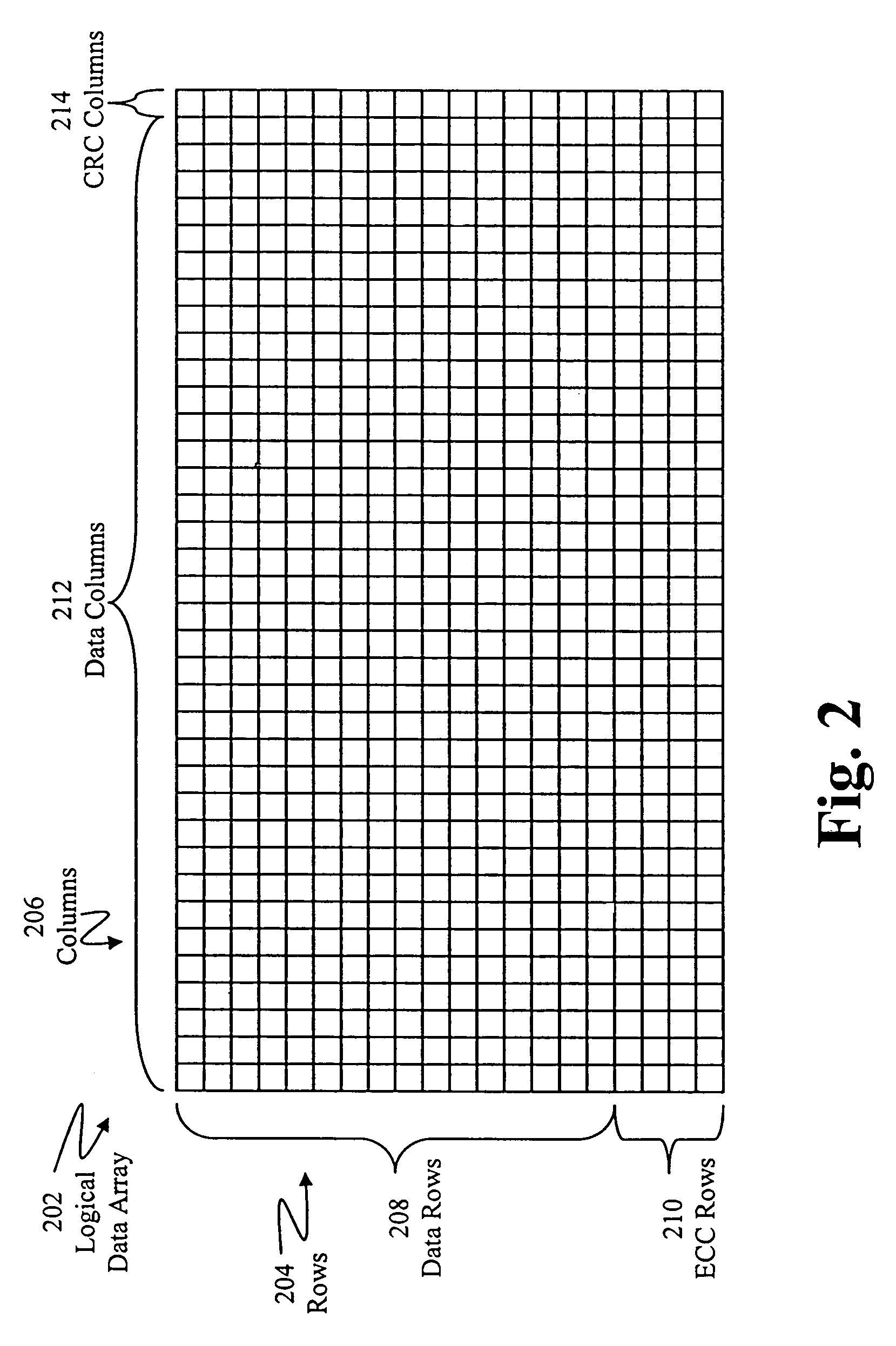

Extended error correction codes

Errors in data retrieved from a storage medium are verified by retrieving a plurality of data blocks from the storage medium. A data set having data from multiple data blocks is selected, where the data set includes a plurality of rows corresponding to the data bocks and a row has data from a data block corresponding to the row. One or more error correction codes (ECCs) are retrieved from the storage medium, where the one or more ECCs correspond to the data set. A plurality of check sums are retrieved from the storage medium, where a check sum corresponds to a data block. Data blocks retrieved from the storage medium having errors are identified using the check sums corresponding to the data blocks. When the number of data blocks identified as having errors is greater than the number of ECCs for the data set, a first set of rows in the data set corresponding to the data blocks identified as having errors is selected, where the number of rows in the first set of rows is equal to the number of ECCs for the data set and less than the number of data blocks identified as having errors. Data for the first set of rows are generated using the ECCs for the data set, and the rows corresponding to the data blocks identified as having errors are verified based on the generated data for the first set of rows.

Owner:QUANTUM CORP

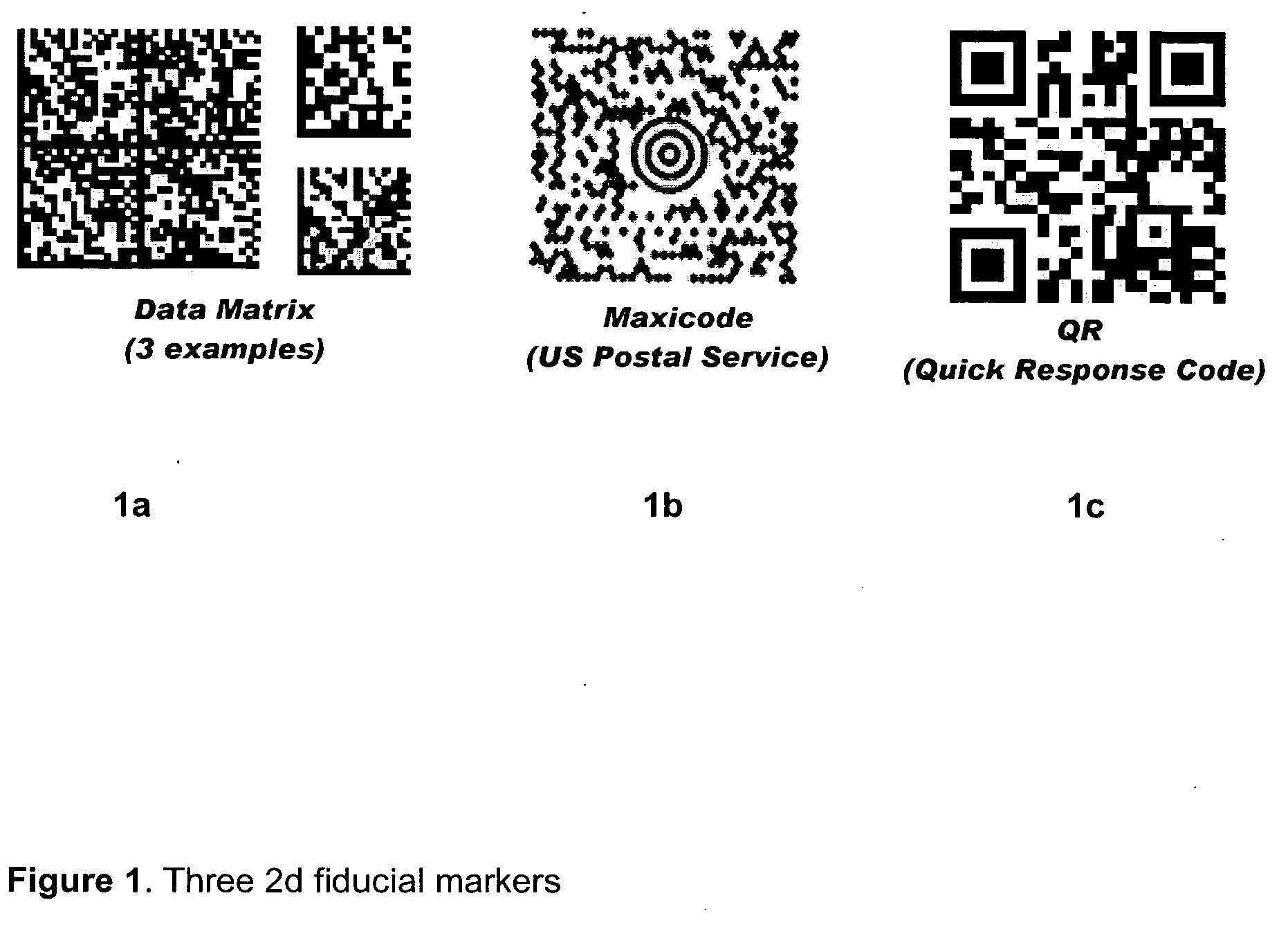

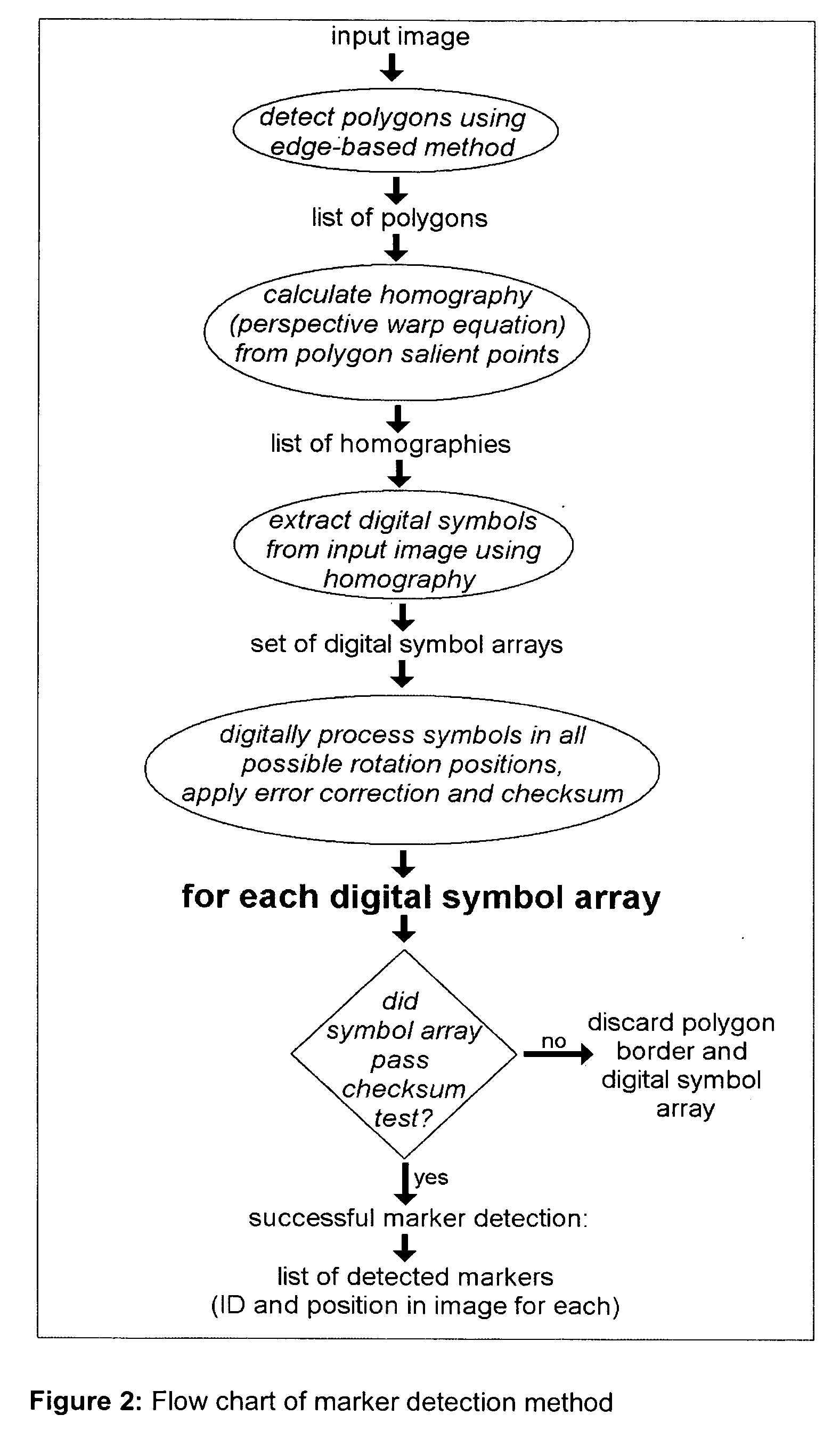

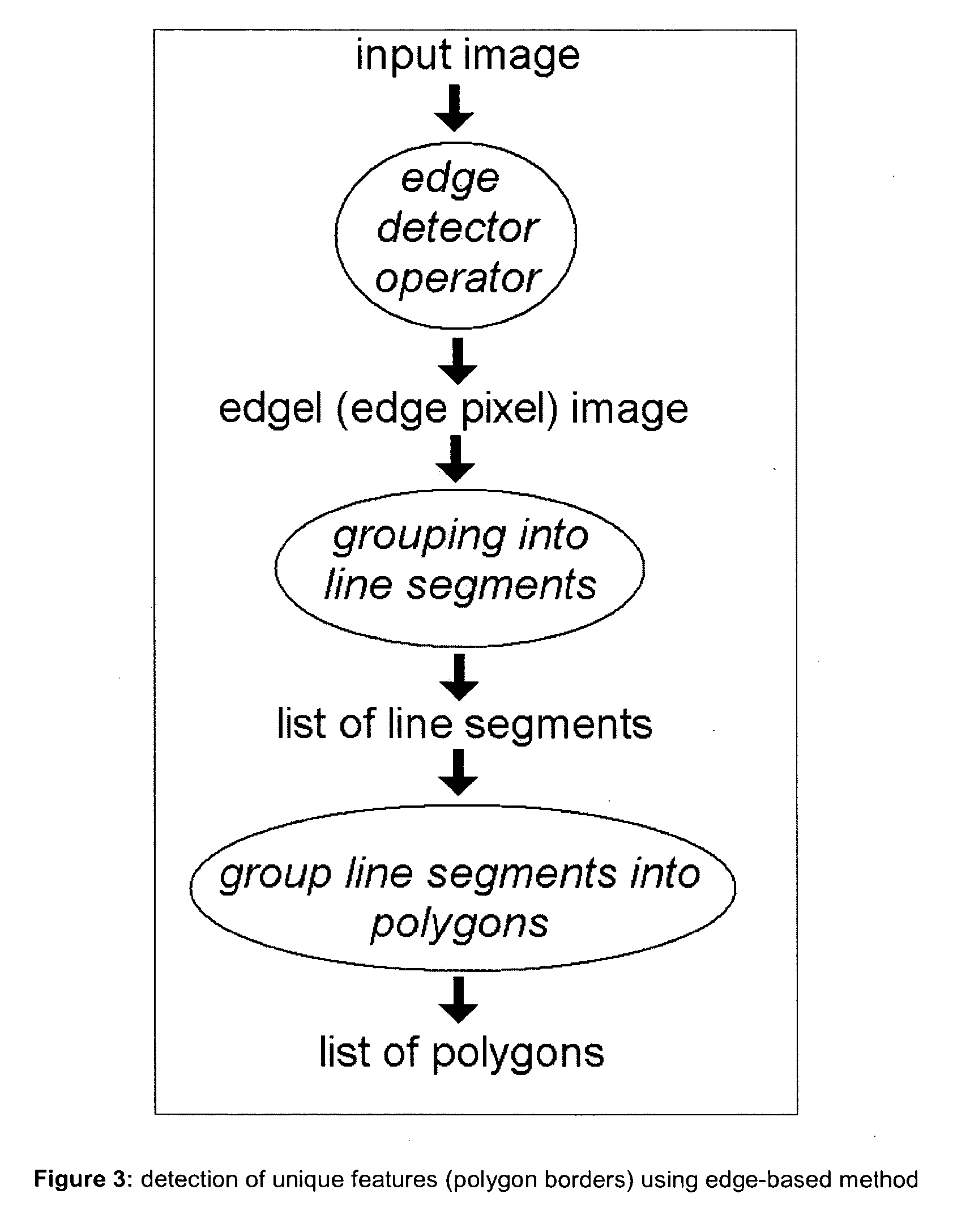

Marker and method for detecting said marker

This invention discloses marker detectable by visual means comprising; a polygonal border having of at least four non collinear salient points. The marker has on it a pattern in binary digital code. The binary code data contains information data, checksum and error correction. The binary code data is on two levels; a first level of binary code readable at a first given distance, a second level of binary code readable at a second given distance, where the second given distance is less than the first given distance and the second level binary code is smaller in size than the first level binary code. The second level of binary code does not interfere with the reading of the first level binary code. It also discloses a method for detecting a marker comprising the steps of detecting an image, using an edge detector to detect an edge in said image, grouping more than one edge into a polygon having salient points, calculating homography from polygon salient points, generating a list of homographies, extracting binary data from input image having homographies, identifying and verifying binary data.

Owner:MILLENNIUM THREE TECH

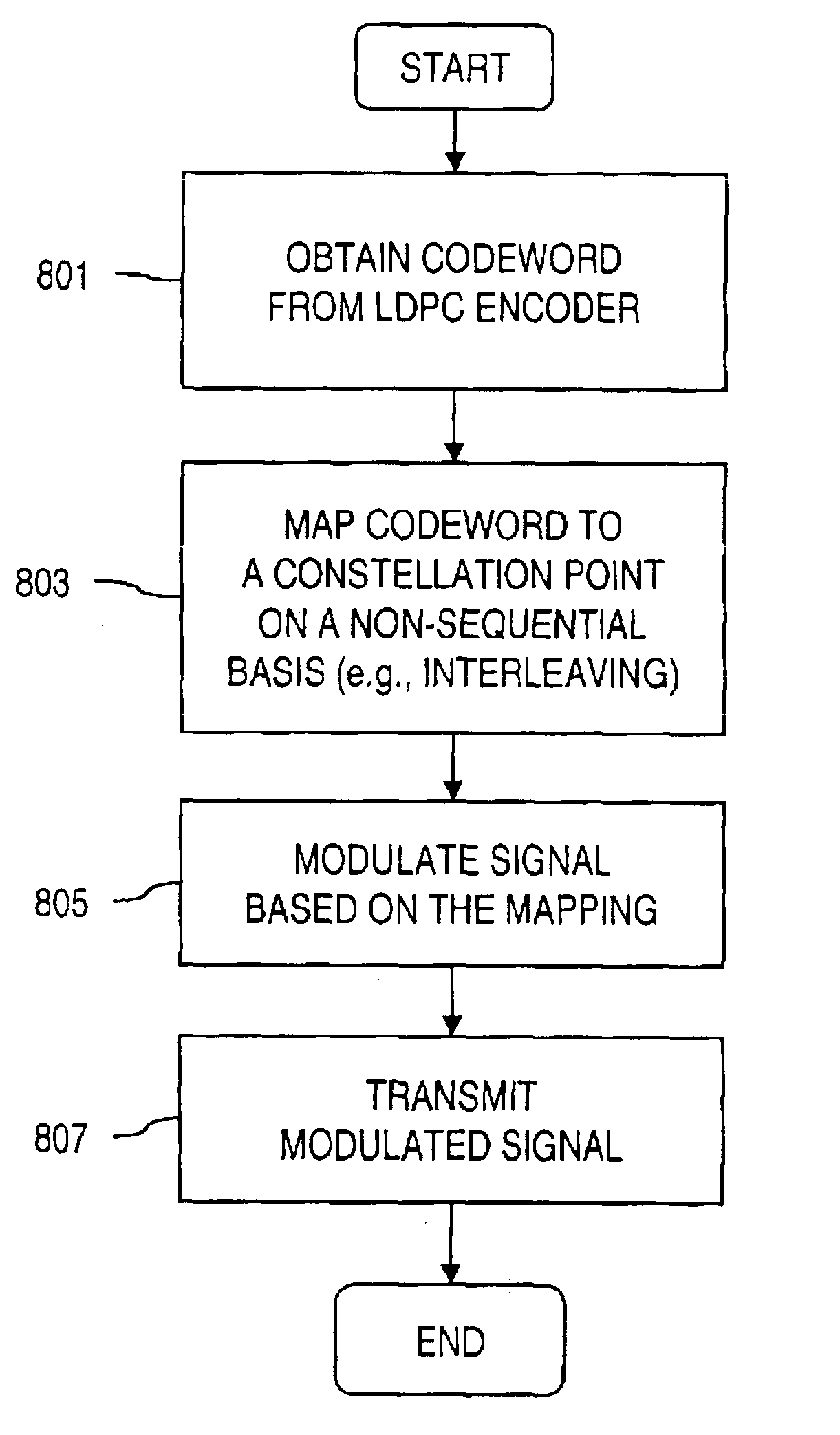

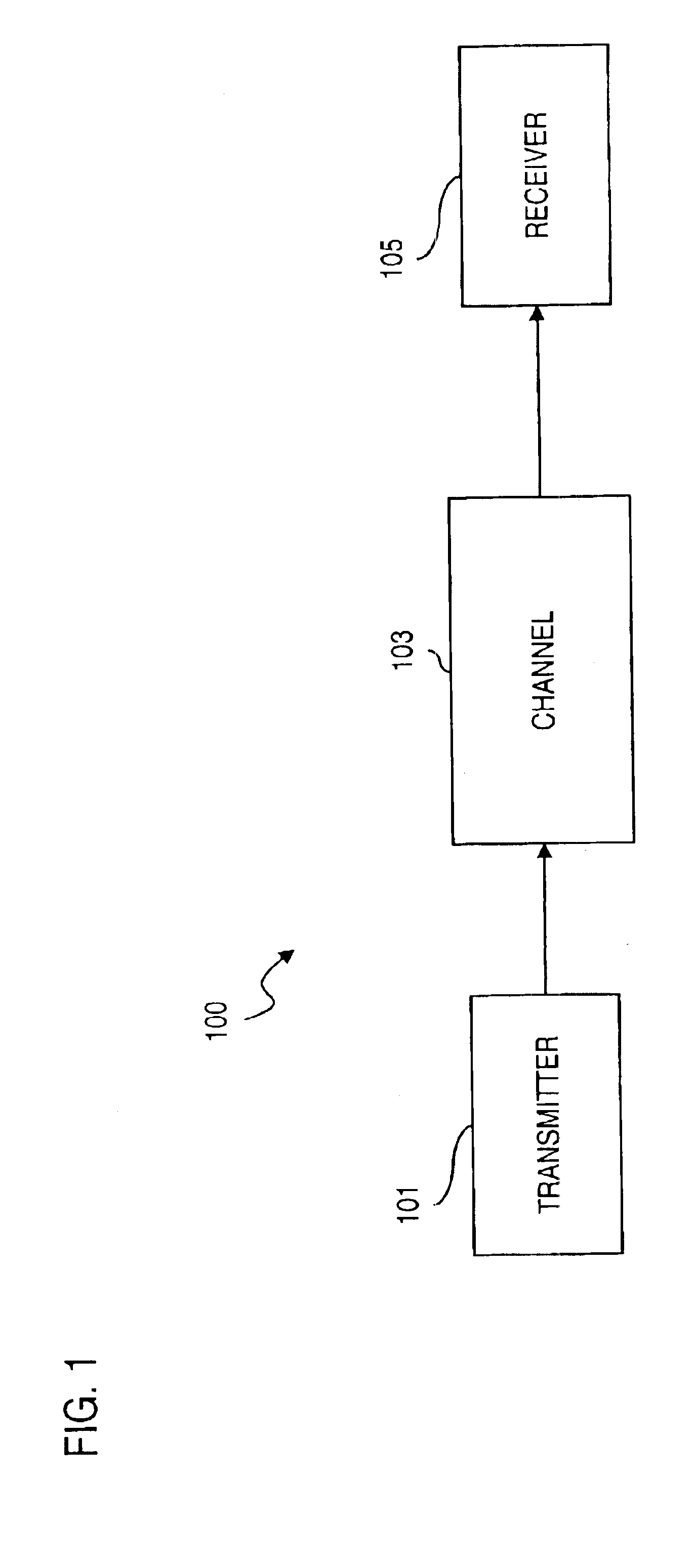

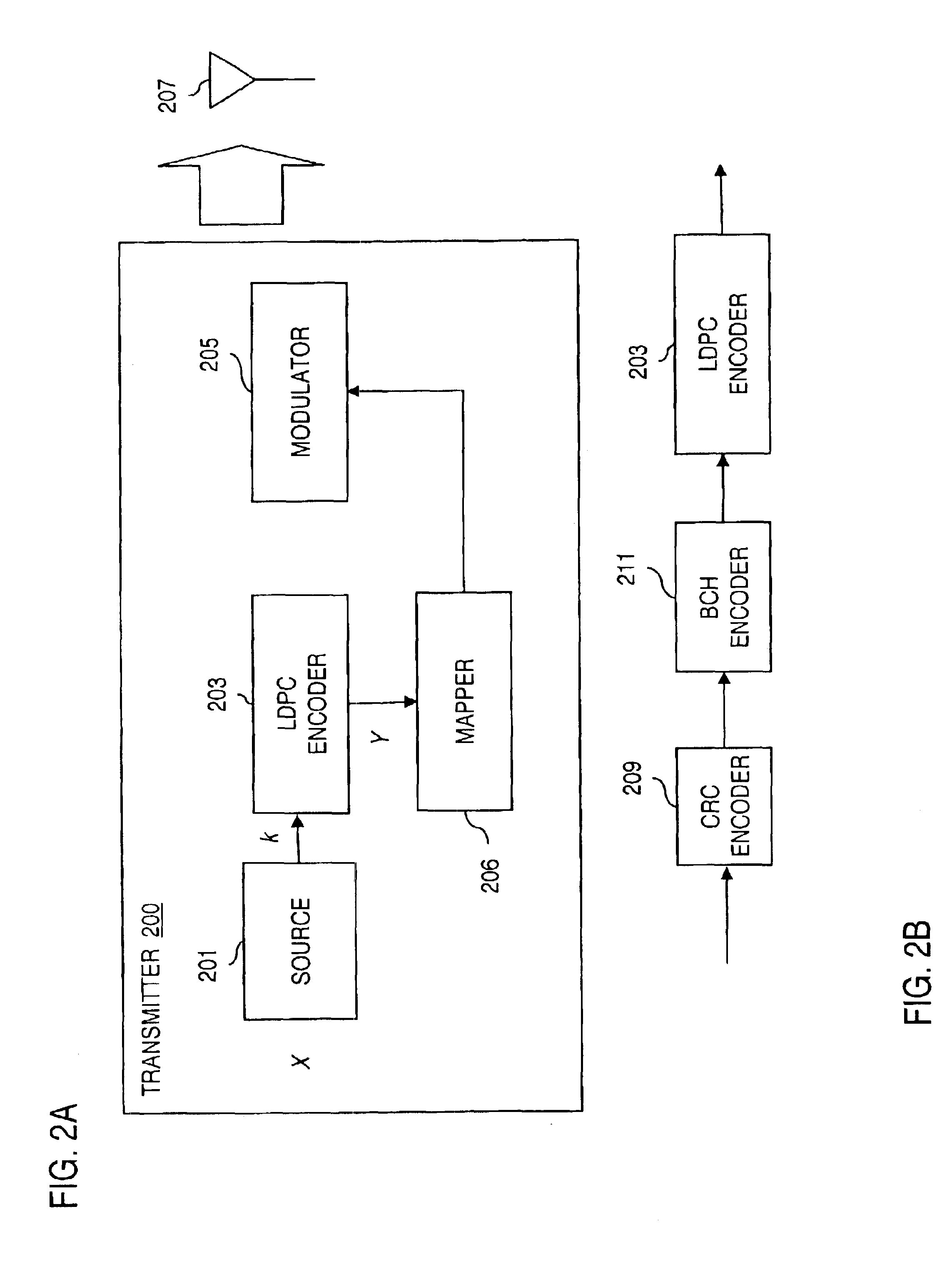

Bit labeling for amplitude phase shift constellation used with low density parity check (LDPC) codes

InactiveUS6963622B2Improve performanceError correction/detection using LDPC codesCode conversionParity-check matrixEngineering

An approach is provided for bit labeling of a signal constellation. A transmitter generates encoded signals using, according to one embodiment, a structured parity check matrix of a Low Density Parity Check (LDPC) code. The transmitter includes an encoder for transforming an input message into a codeword represented by a plurality of set of bits. The transmitter includes logic for mapping non-sequentially (e.g., interleaving) one set of bits into a higher order constellation (Quadrature Phase Shift Keying (QPSK), 8-PSK, 16-APSK (Amplitude Phase Shift Keying), 32-APSK, etc.), wherein a symbol of the higher order constellation corresponding to the one set of bits is output based on the mapping.

Owner:DTVG LICENSING INC

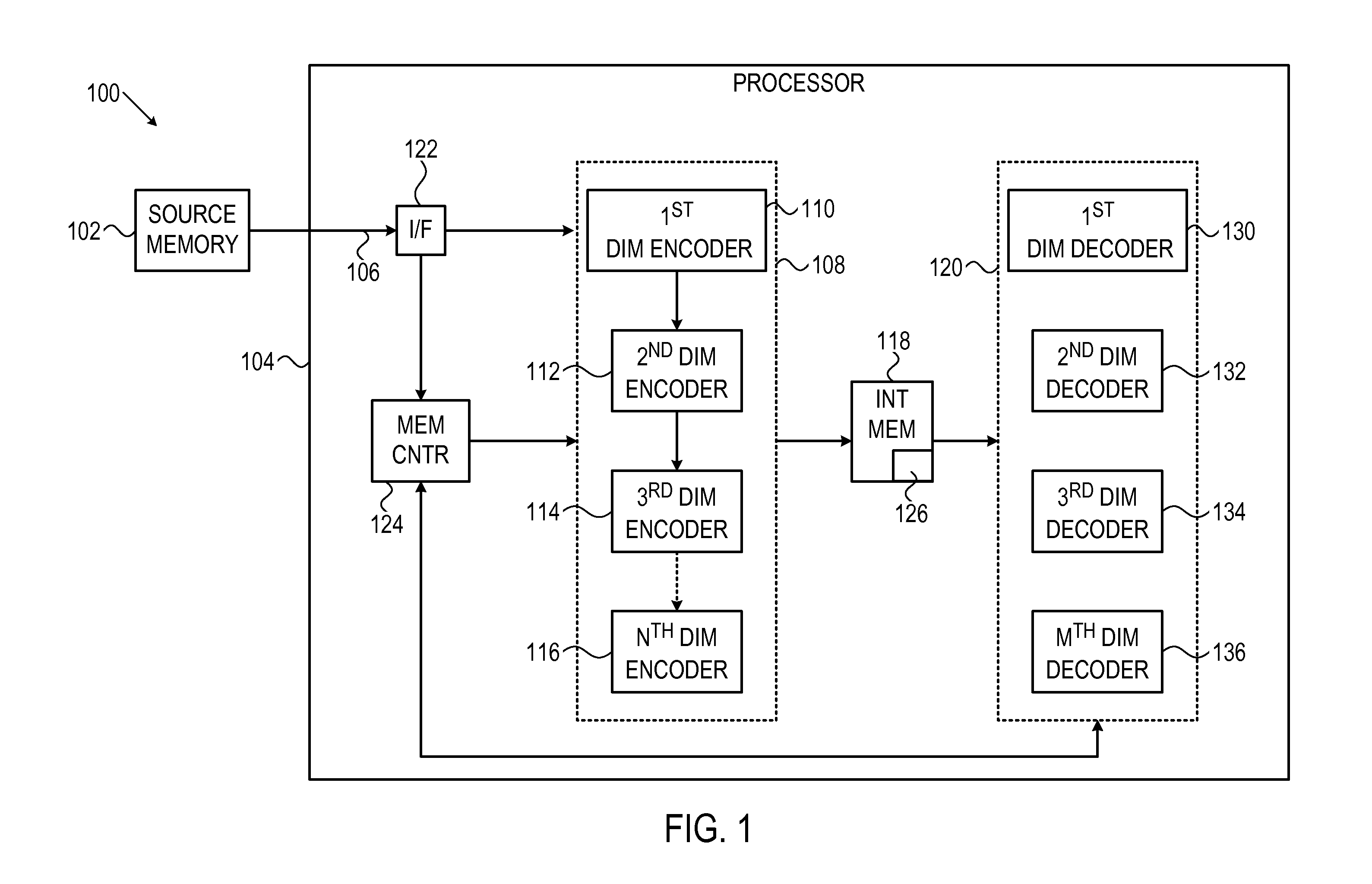

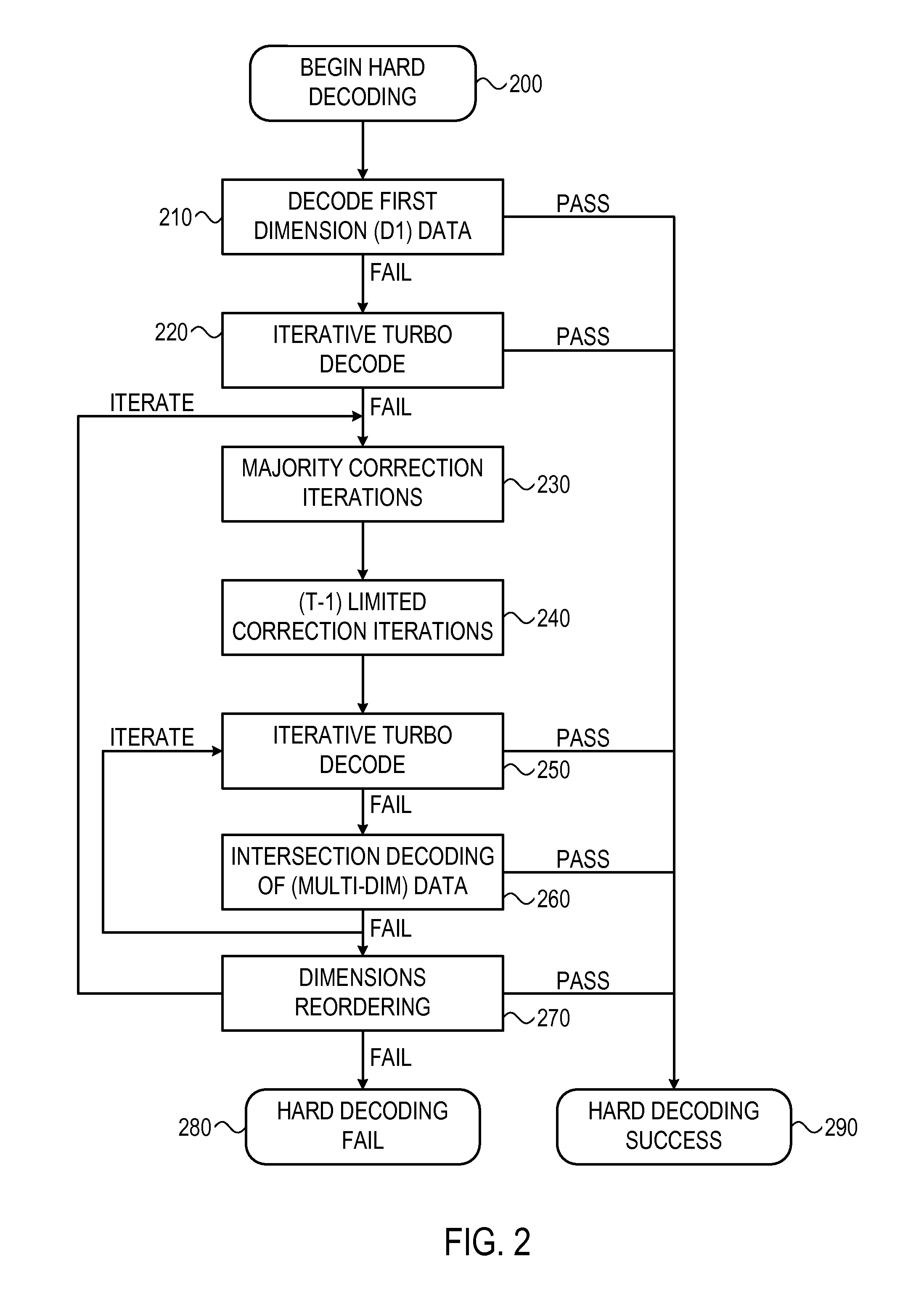

System and method for multi-dimensional encoding and decoding

ActiveUS20120005560A1Error correction/detection using convolutional codesOther decoding techniquesHypothesisDependability

A system and method is provided for decoding a set of bits using a plurality of hypotheses, for example, each independently tested on-the-fly. Initial bit states and associated reliability metrics may be received for the set of bits. A current hypothesis may be decoded for correcting the set of bits, wherein the current hypothesis defines different bit states and associated reliability metrics for the set of bits. If decoding the current hypothesis is not successful, a subsequently ordered hypothesis may be decoded, wherein the hypotheses are ordered such that their associated reliability metric is a monotonically non-decreasing sequence. Decoding may proceed iteratively until the current hypothesis is successful.

Owner:AVAGO TECH INT SALES PTE LTD

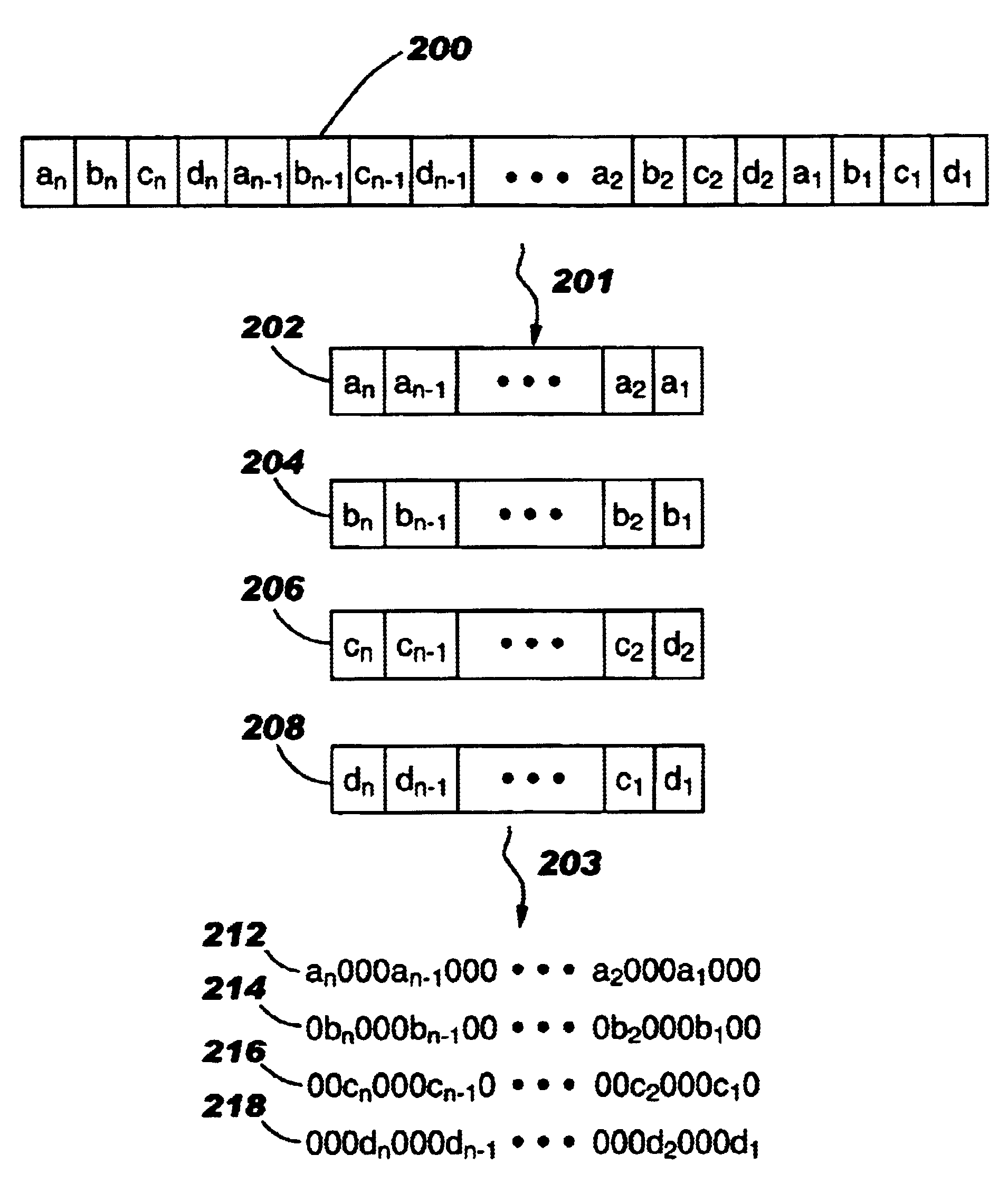

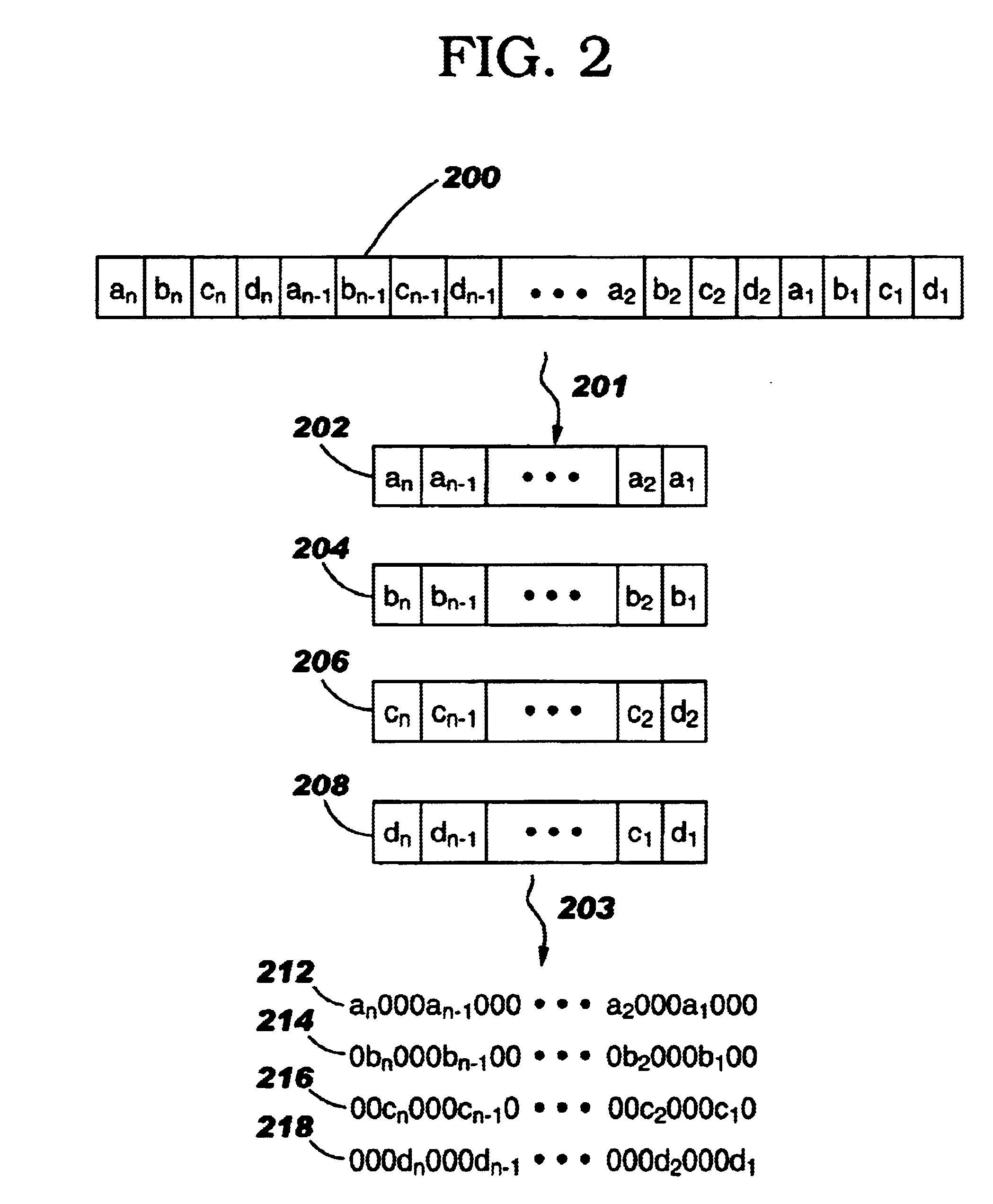

Cyclic redundancy check for partitioned frames

InactiveUS6681364B1Increase flexibilityCode conversionError detection onlyTheoretical computer scienceImproved method

An improved method and system for generating a frame check sequence. A multiple-bit data string, M, is received in which M is of the form:M is thereafter parsed into multiple subframes of the form:andThe subframes are padded with zeros resulting in subframes of the form:andA partial check sum is then generated for each of the multiple subframes. Finally, each of the partial check sums are added together such that a frame check sequence for M is obtained.

Owner:IBM CORP

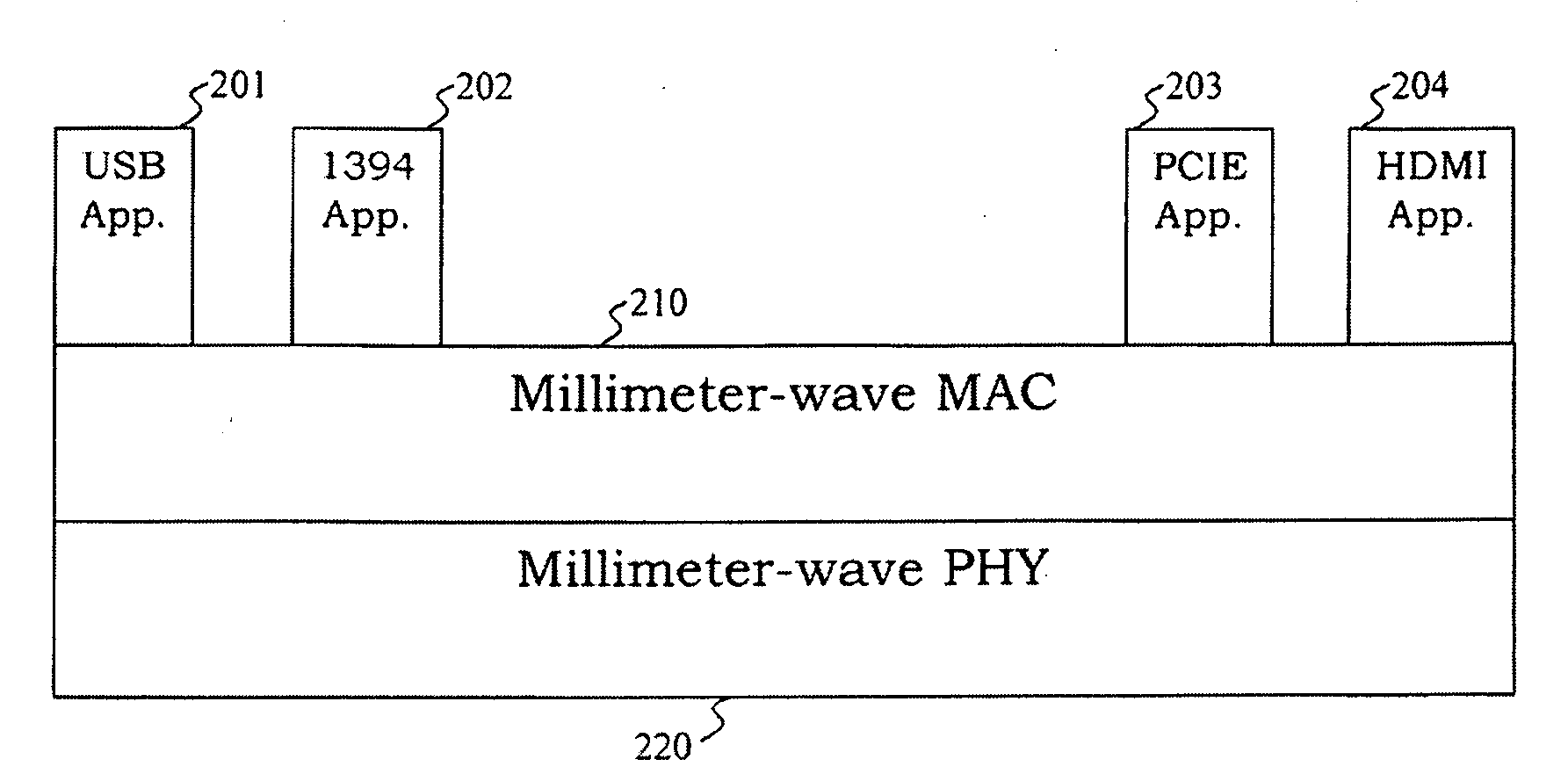

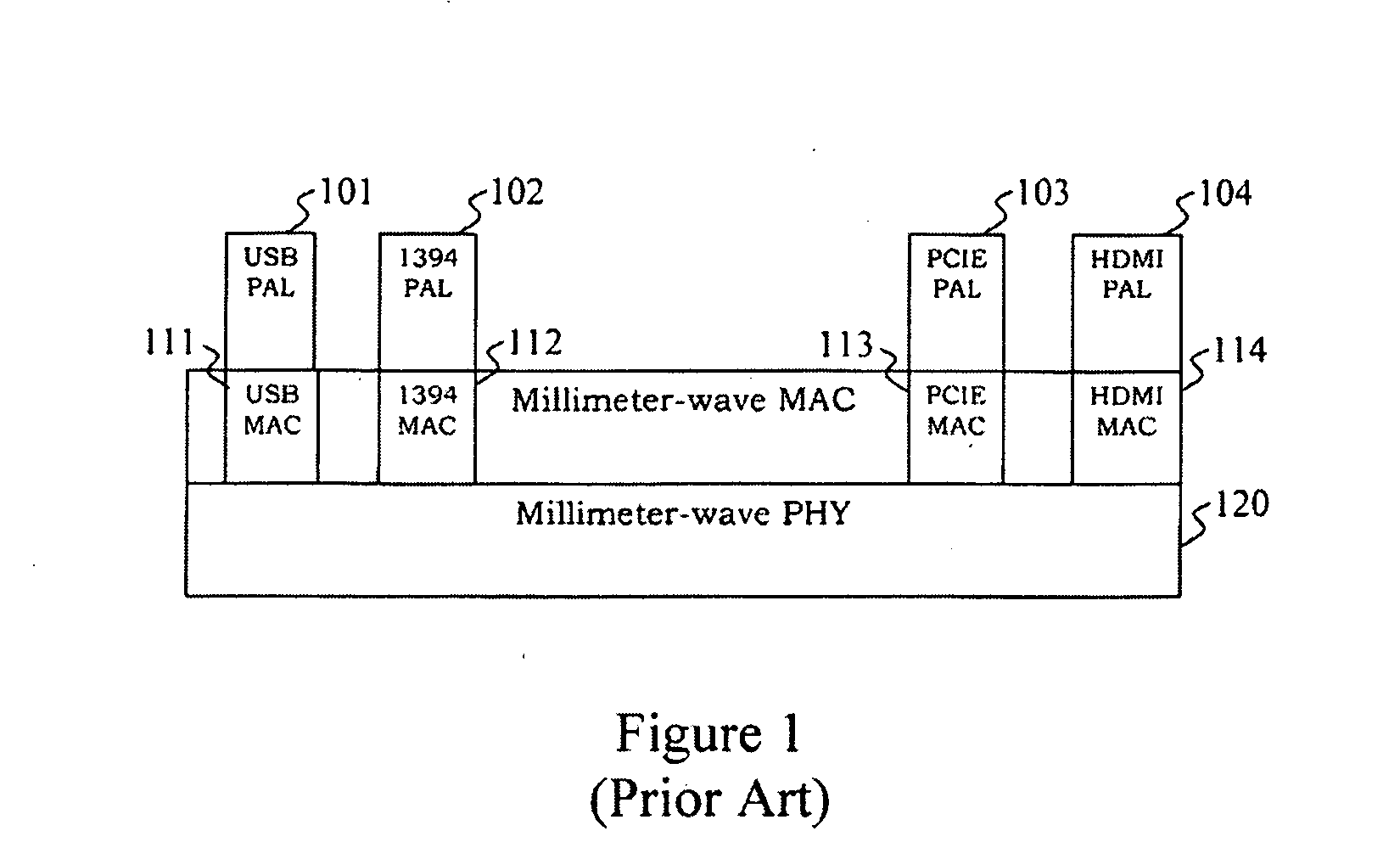

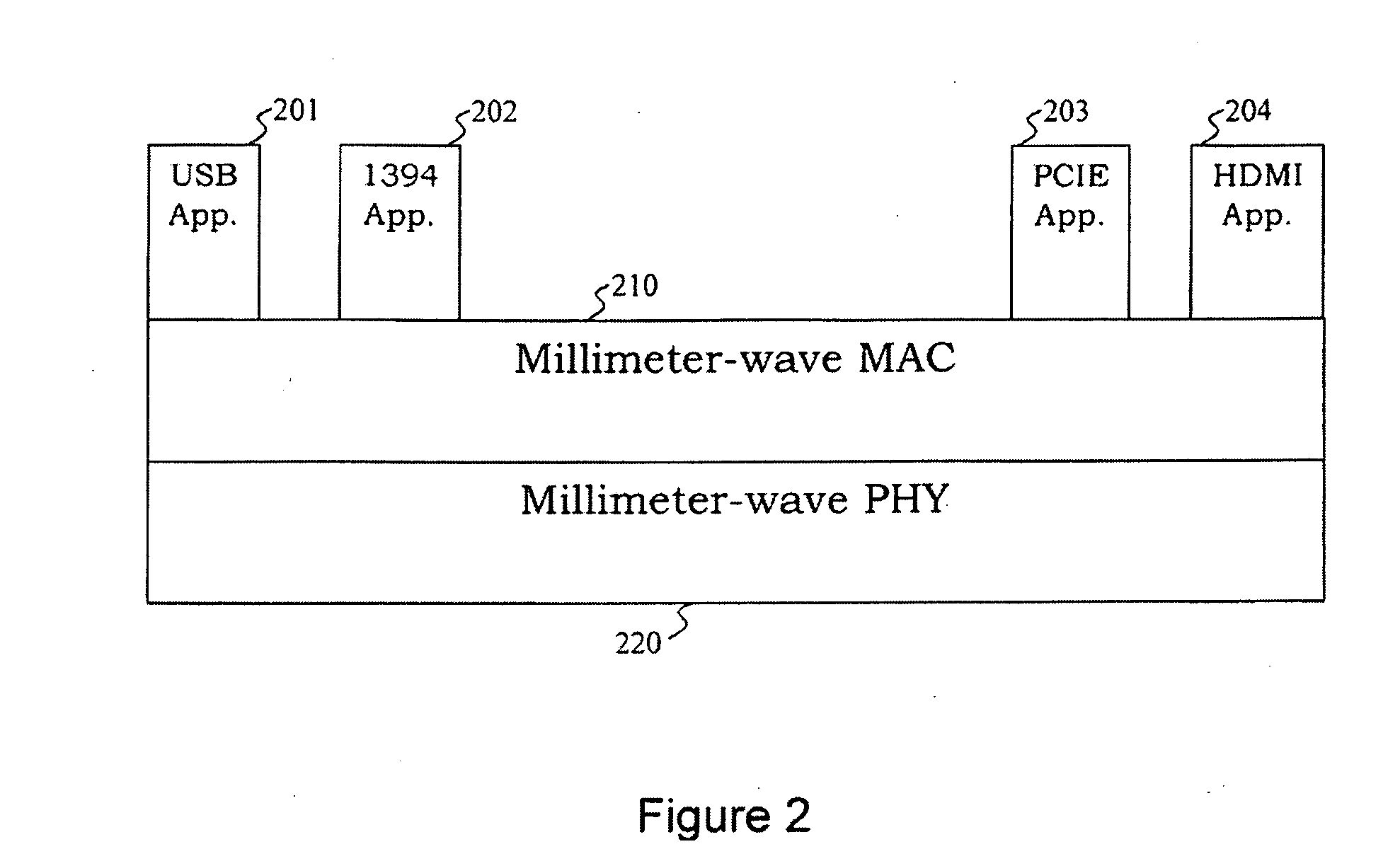

Millimeter-wave communications for peripheral devices

A wireless device couples an electronic device employing a wired-link protocol to, for example, a wireless personal area network (WPAN). The wireless device comprises a wired interface configured for coupling to the electronic device, a wired transceiver coupled to the wired interface, the at least one wired transceiver configured for functioning as a terminus of a wired link coupled to the electronic device, and a wireless transmitter or transceiver coupled to the wired transceiver and configured for functioning as a terminus of a wireless link in the WPAN. The wireless device may be configured for coupling a plurality of dissimilar wired devices together via a wireless link.

Owner:QUALCOMM INC

HARQ rate-compatible polar codes for wireless channels

ActiveUS20160285479A1Error prevention/detection by using return channelCode conversionTelecommunicationsChipset

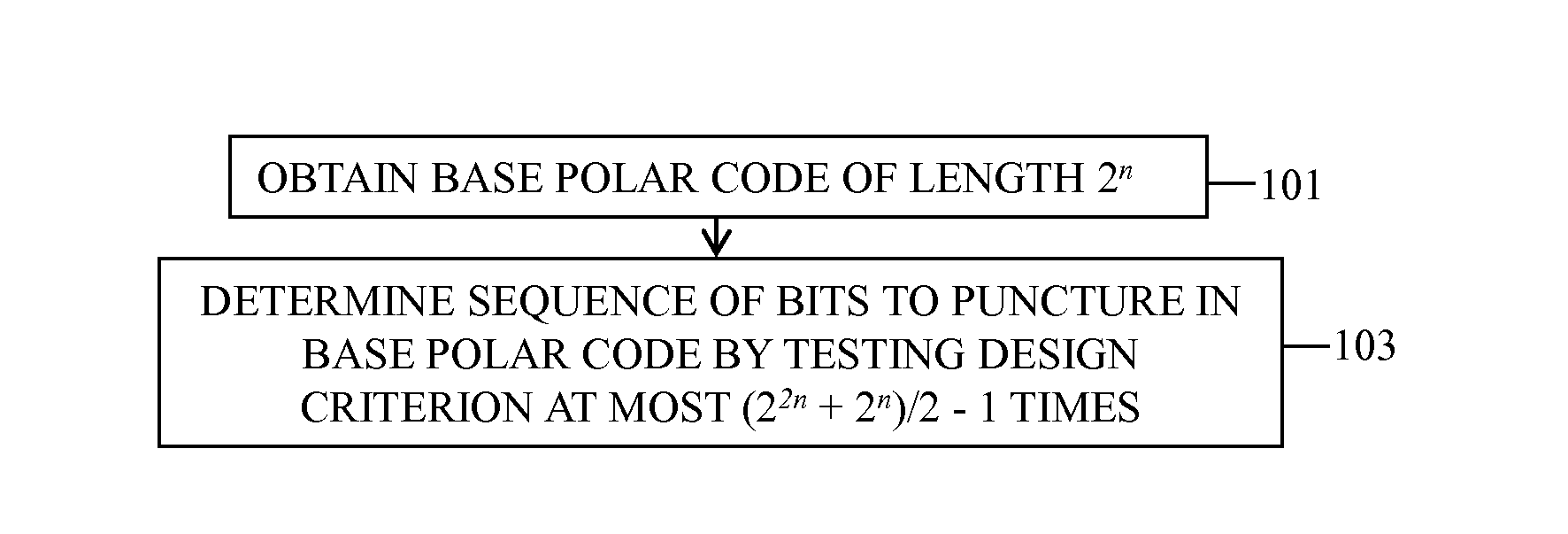

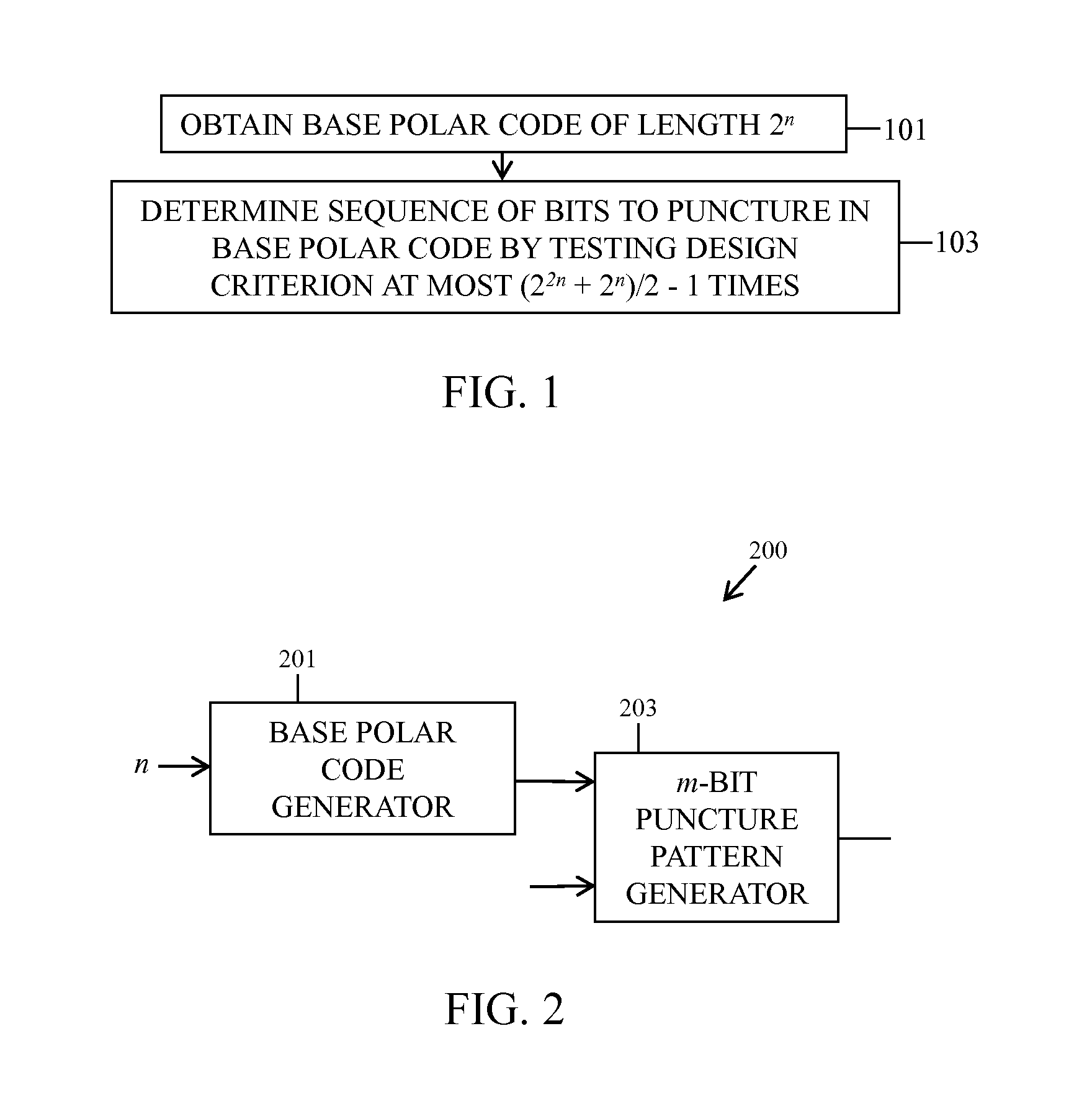

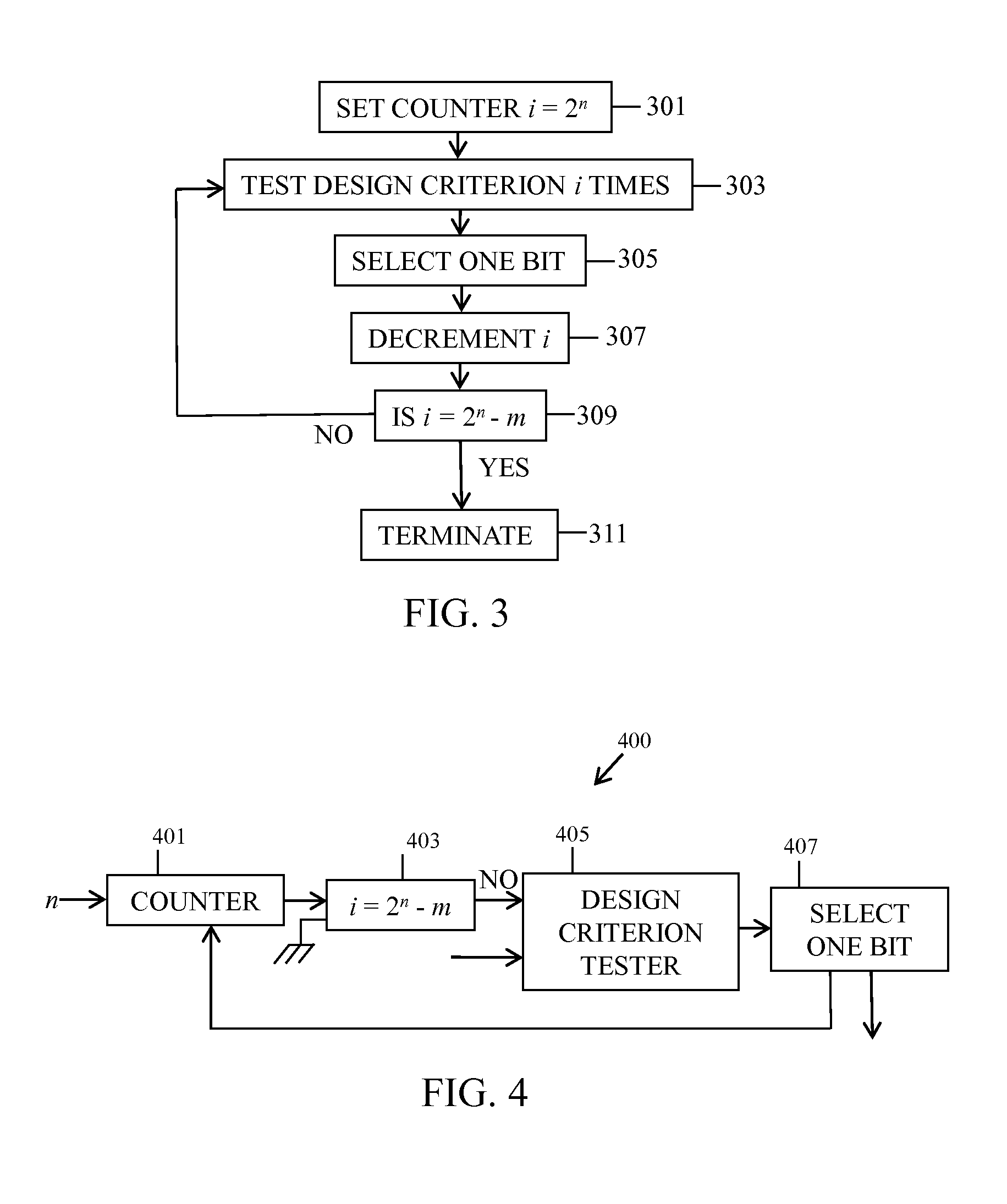

A method, apparatus, and chipset are provided for constructing hybrid automatic repeat request (HARQ) rate-compatible polar codes for communication channels. The method includes constructing, in a terminal, a base polar code of length 2n; and determining a sequence of m<2n bits to puncture in the base polar code by testing a predetermined criterion at most (22n+2n) / 2−1 times.

Owner:SAMSUNG ELECTRONICS CO LTD

Hybrid automatic repeat request acknowledge resource allocation for enhanced physical downlink control channel

ActiveUS20120320848A1Accurate receptionNetwork traffic/resource managementSignal allocationHybrid automatic repeat request harqSignal on

A method and apparatus of wireless communication between a base station and at least one user equipment. The method includes: transmitting an enhanced physical downlink control channel from the base station to the at least one user equipment using a demodulation reference signal antenna port; transmitting message from the base station to the at least one user equipment which is scheduled by the enhanced physical downlink control channel; receiving the message at the at least one user equipment; determining at the at least one user equipment whether the message was correctly received; and transmitting an ACK / NAK signal on an ACK / NAK resource determined from the enhanced physical downlink control channel from the at least one user equipment to the base station indicating whether the message was correctly received by the at least one user.

Owner:TEXAS INSTR INC

Popular searches

Subscribers indirect connection Error correction/detection using multiple parity bits Single error correction Digital signal error detection/correction Frequency-division multiplex details Transmission path division Data switching by path configuration Pilot signal allocation Orthogonal multiplex Multiple modulation transmitter/receiver arrangements