Patents

Literature

132 results about "Error control coding" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

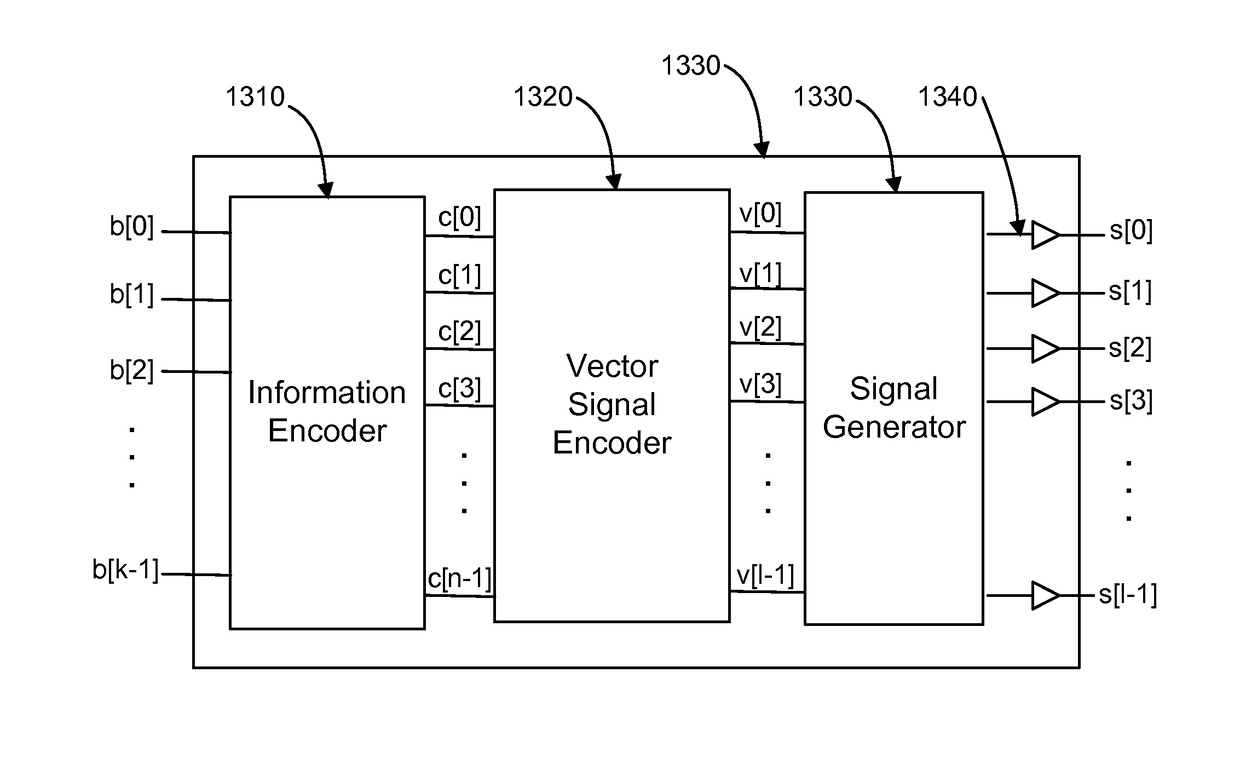

Error control coding for orthogonal differential vector signaling

ActiveUS20110299555A1Error preventionTime-division multiplexForward error correctionComputer science

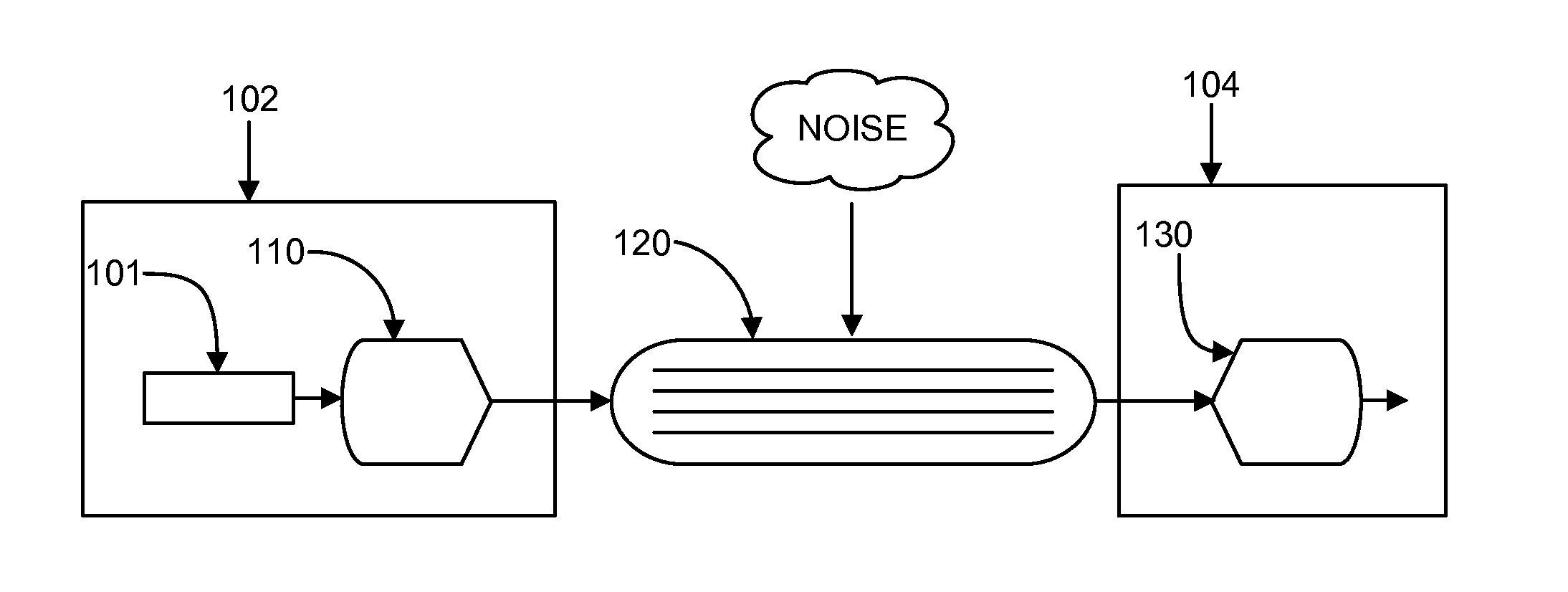

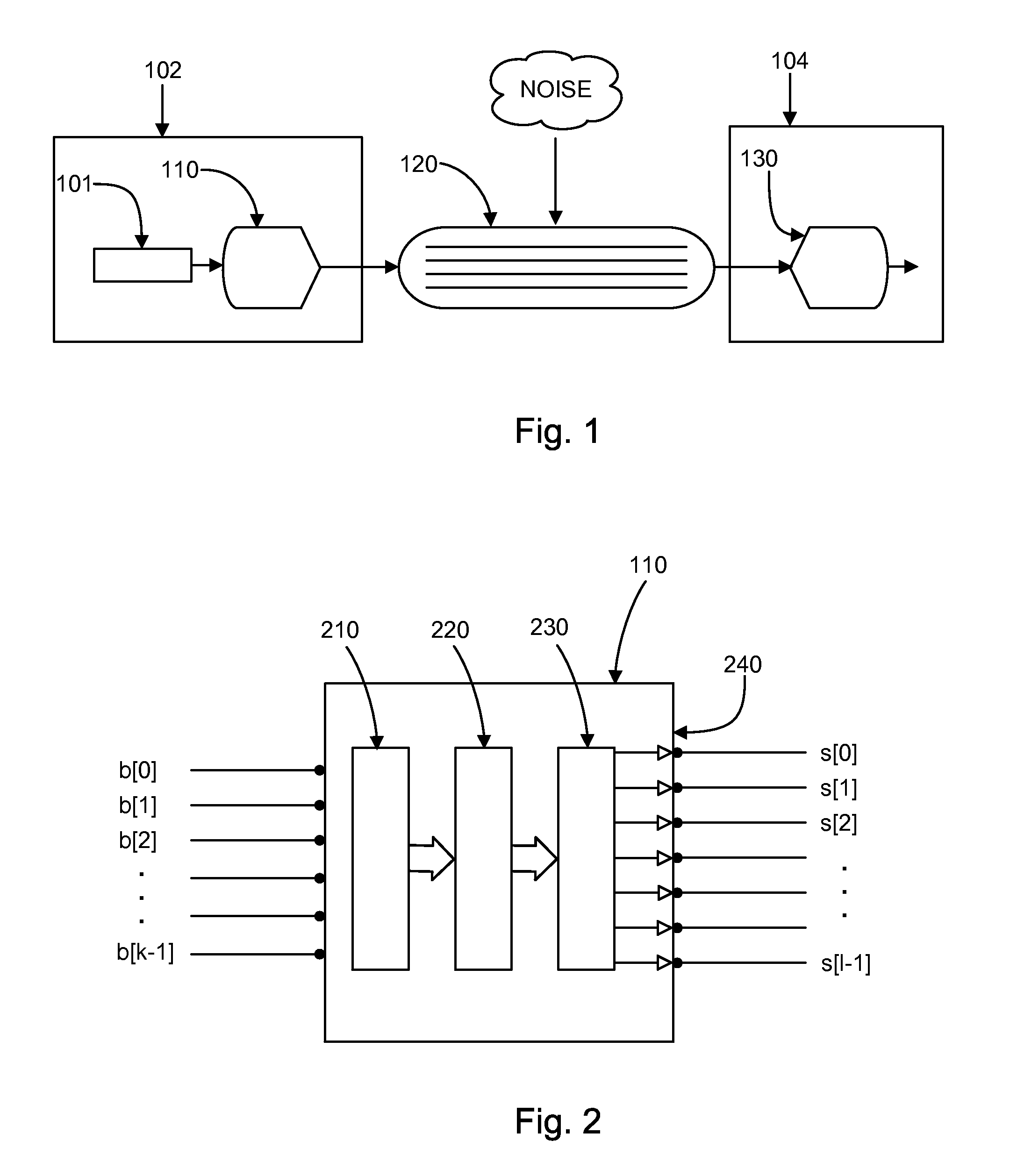

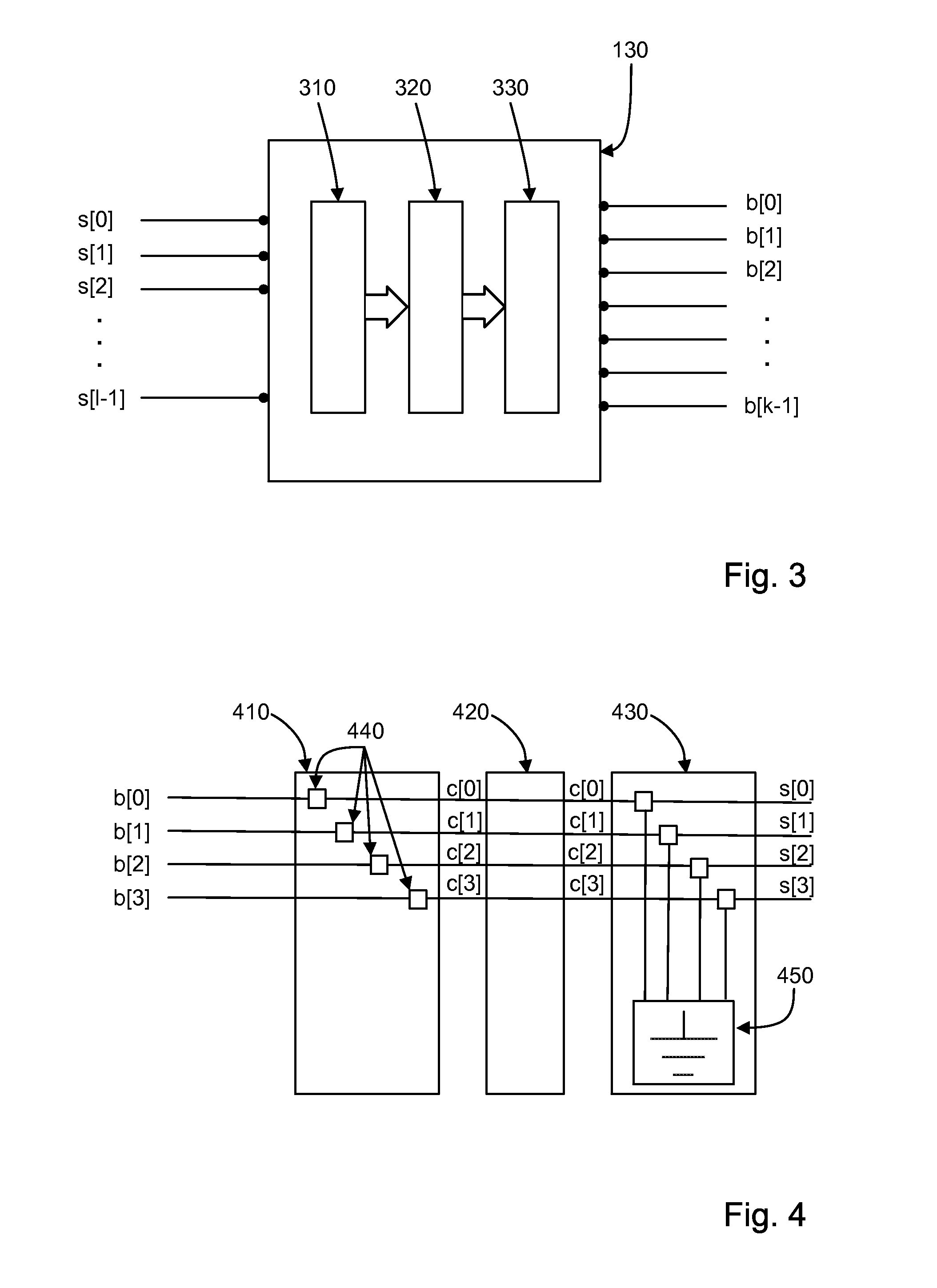

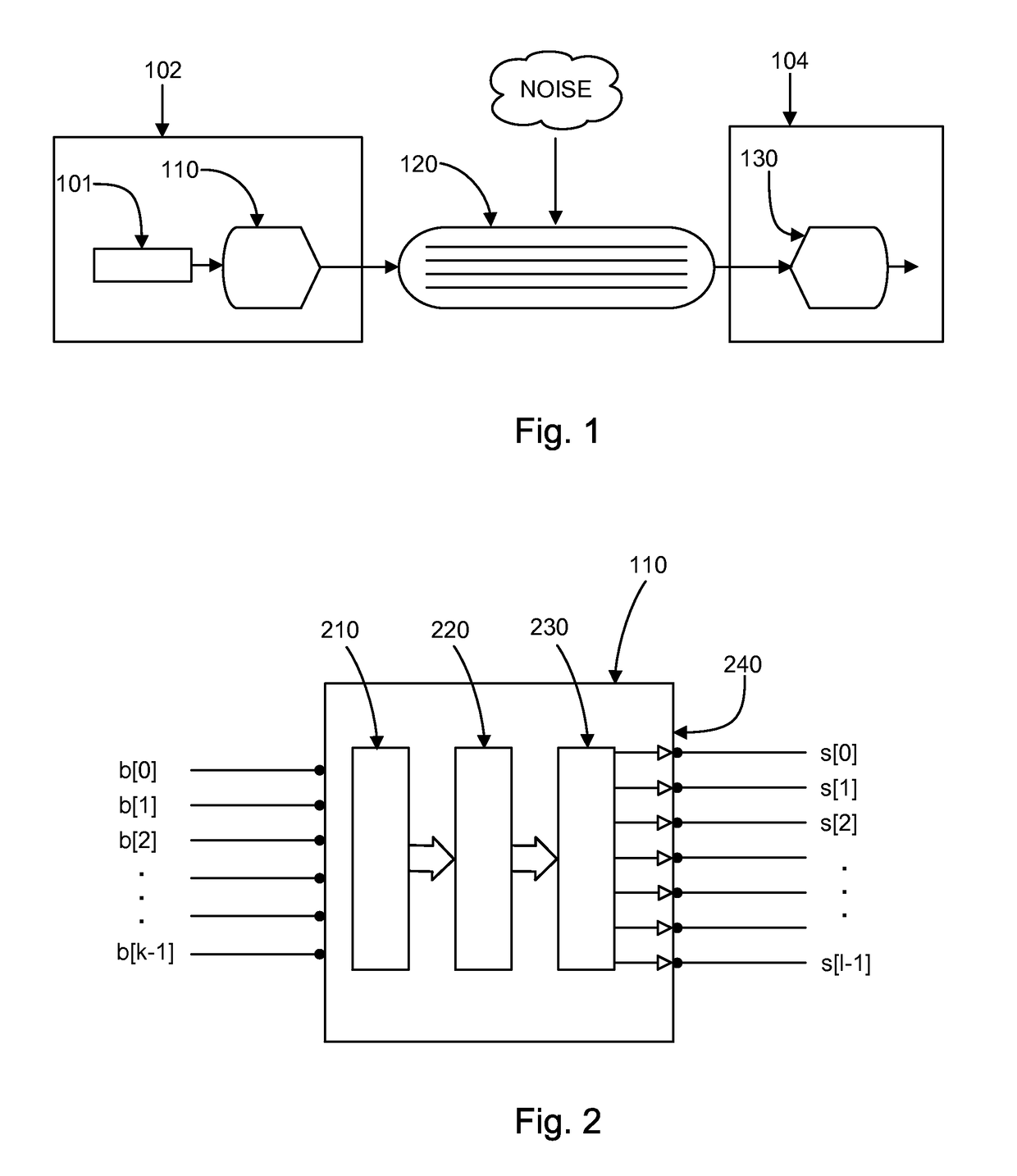

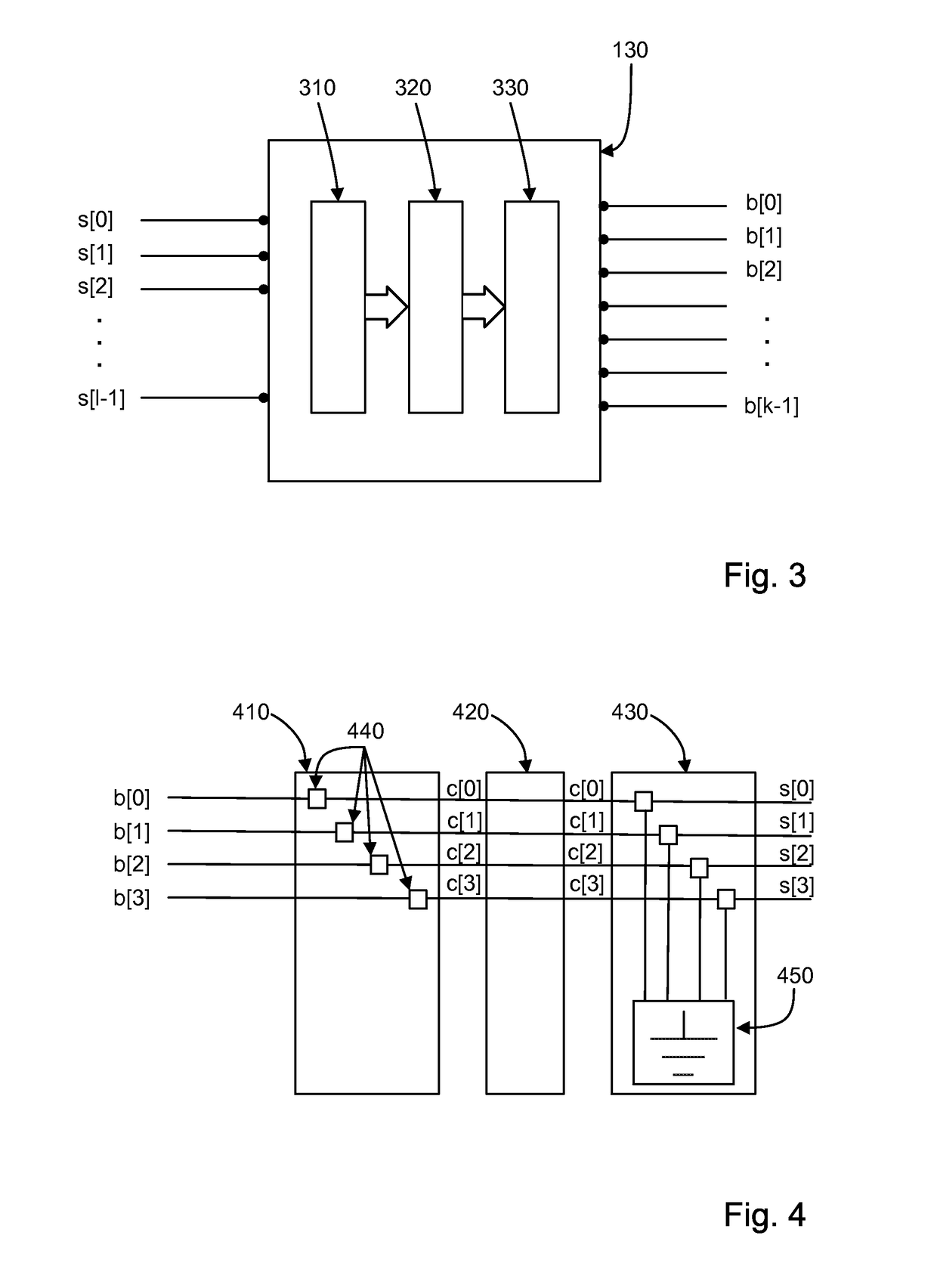

Using a transformation based, at least in part, on a non-simple orthogonal matrix, data may be transmitted over a data bus in a manner that is resilient to one or more types of signal noise, that does not require a common reference at the transmission and acquisition points, and / or that has a pin-efficiency that is greater than 50% and may approach that of single-ended signaling. Such transformations may be implemented in hardware in an efficient manner. The transformation may be combined with methods from forward error correction to lower the required transmission power.

Owner:ECOLE POLYTECHNIQUE FEDERALE DE LAUSANNE (EPFL)

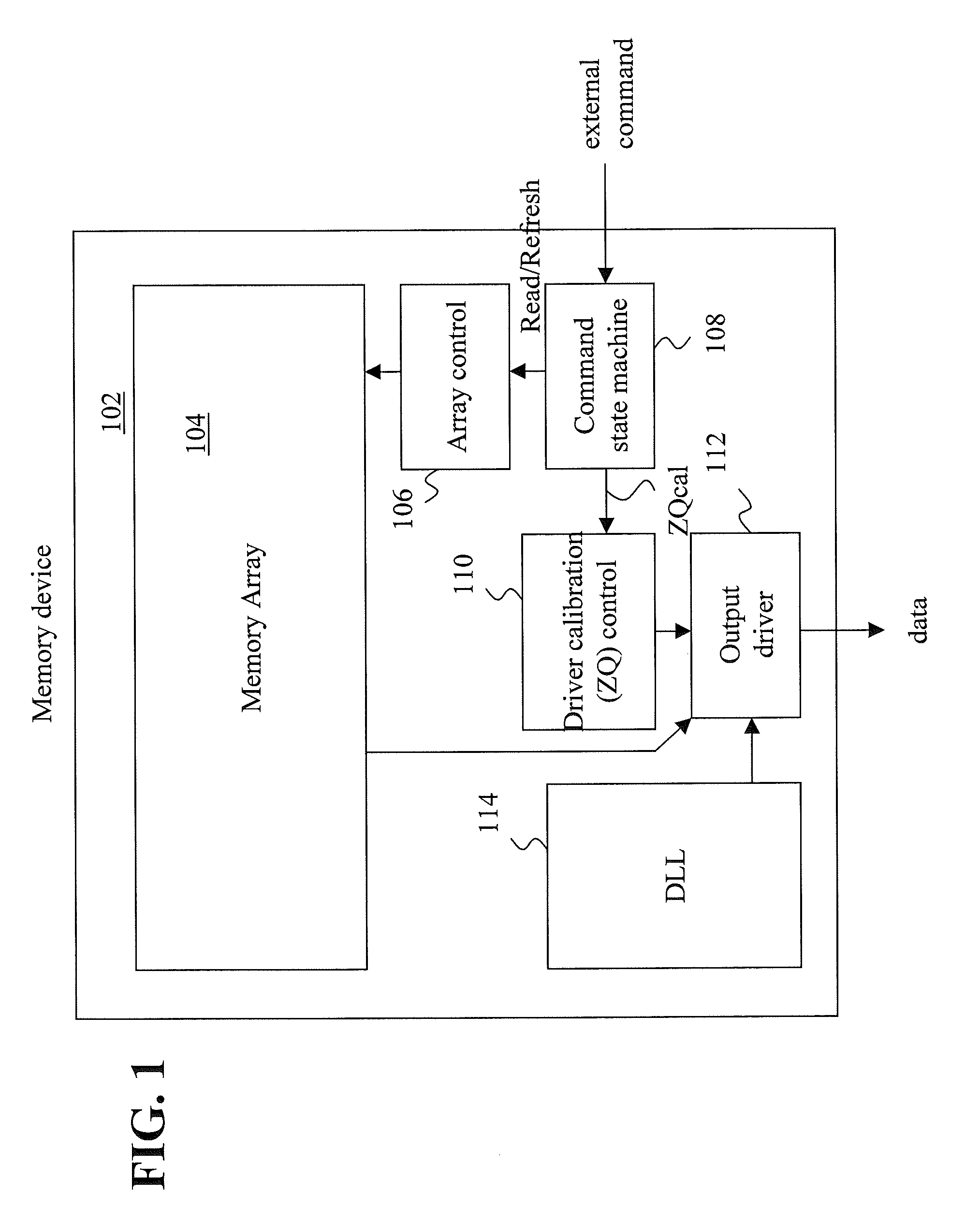

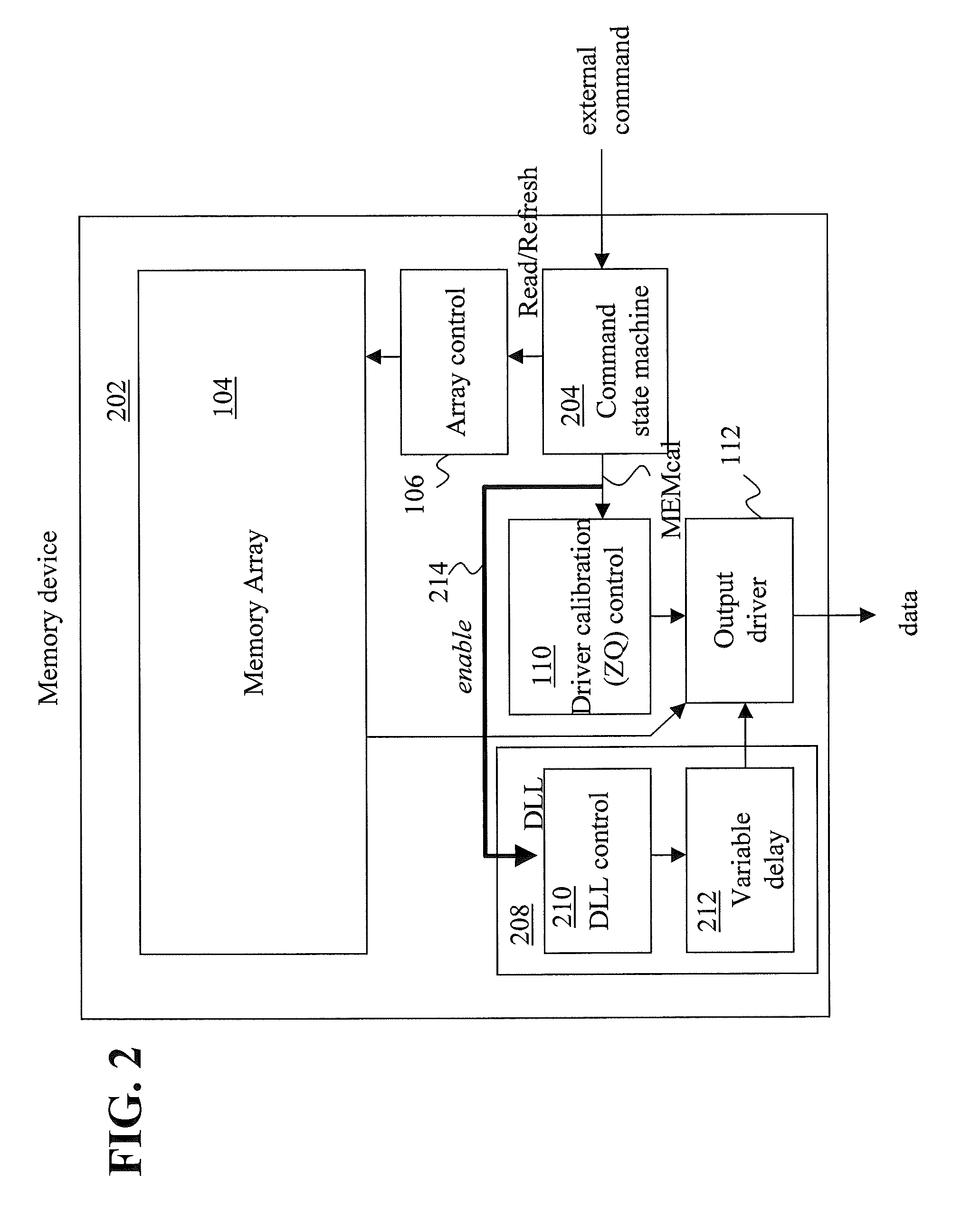

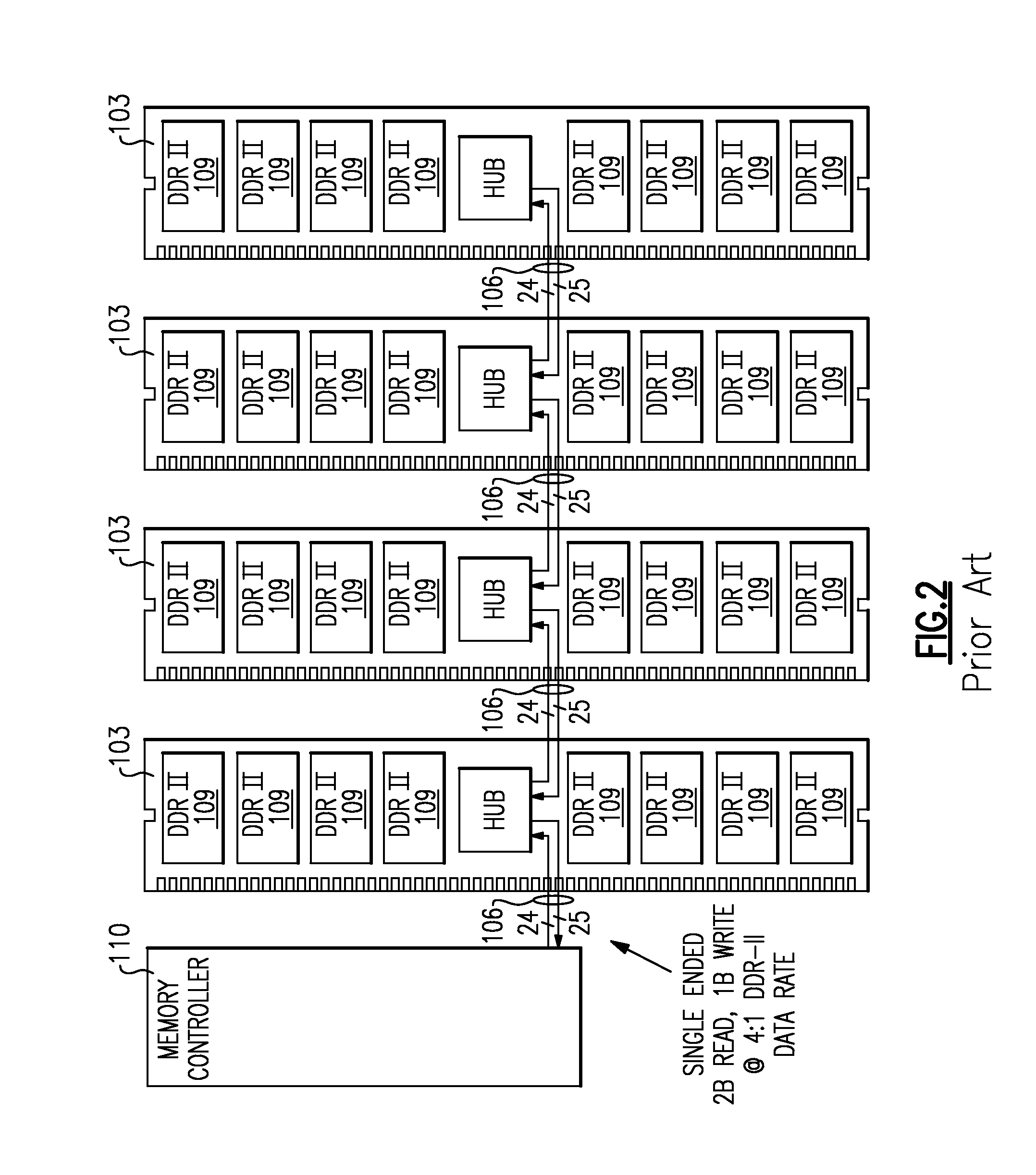

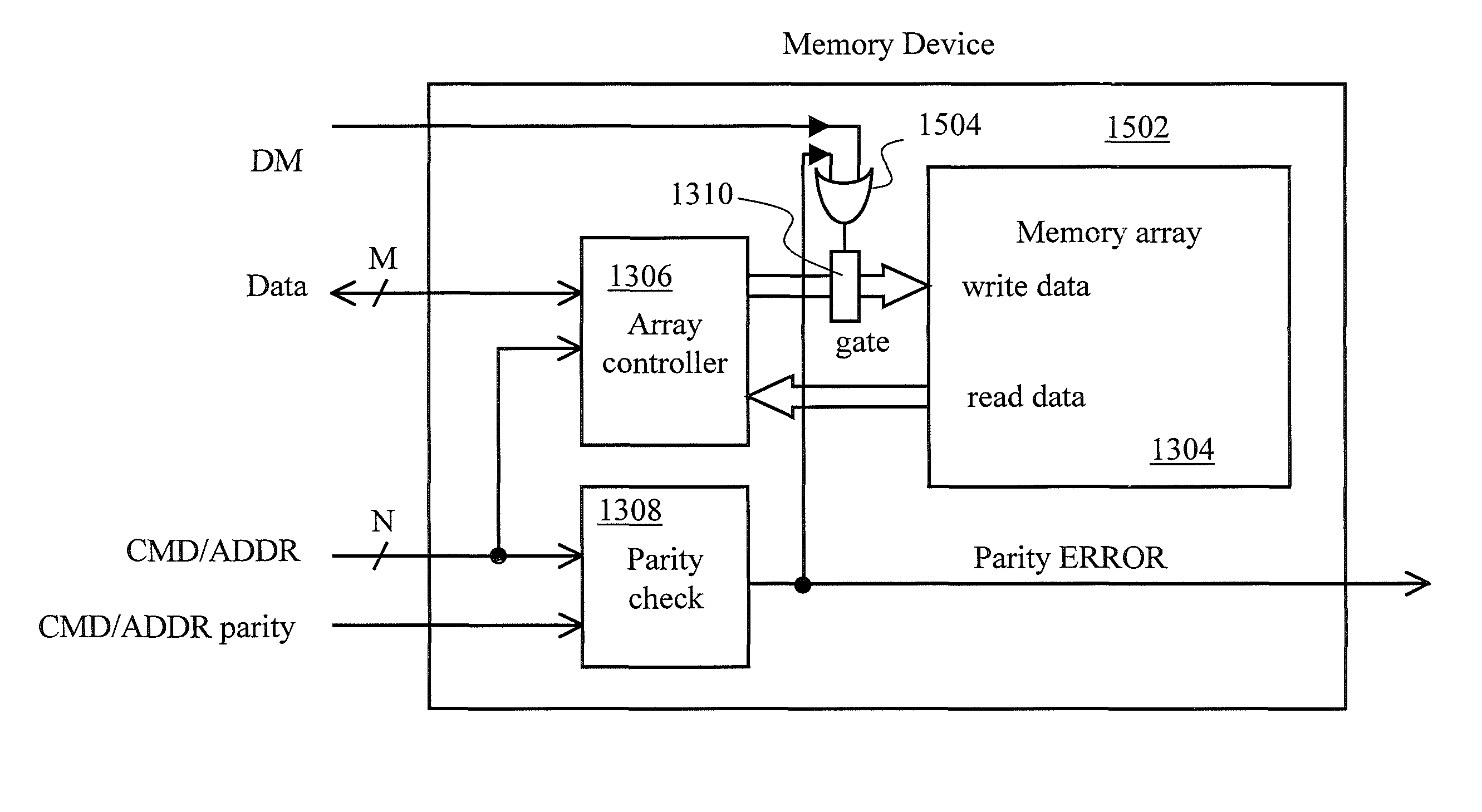

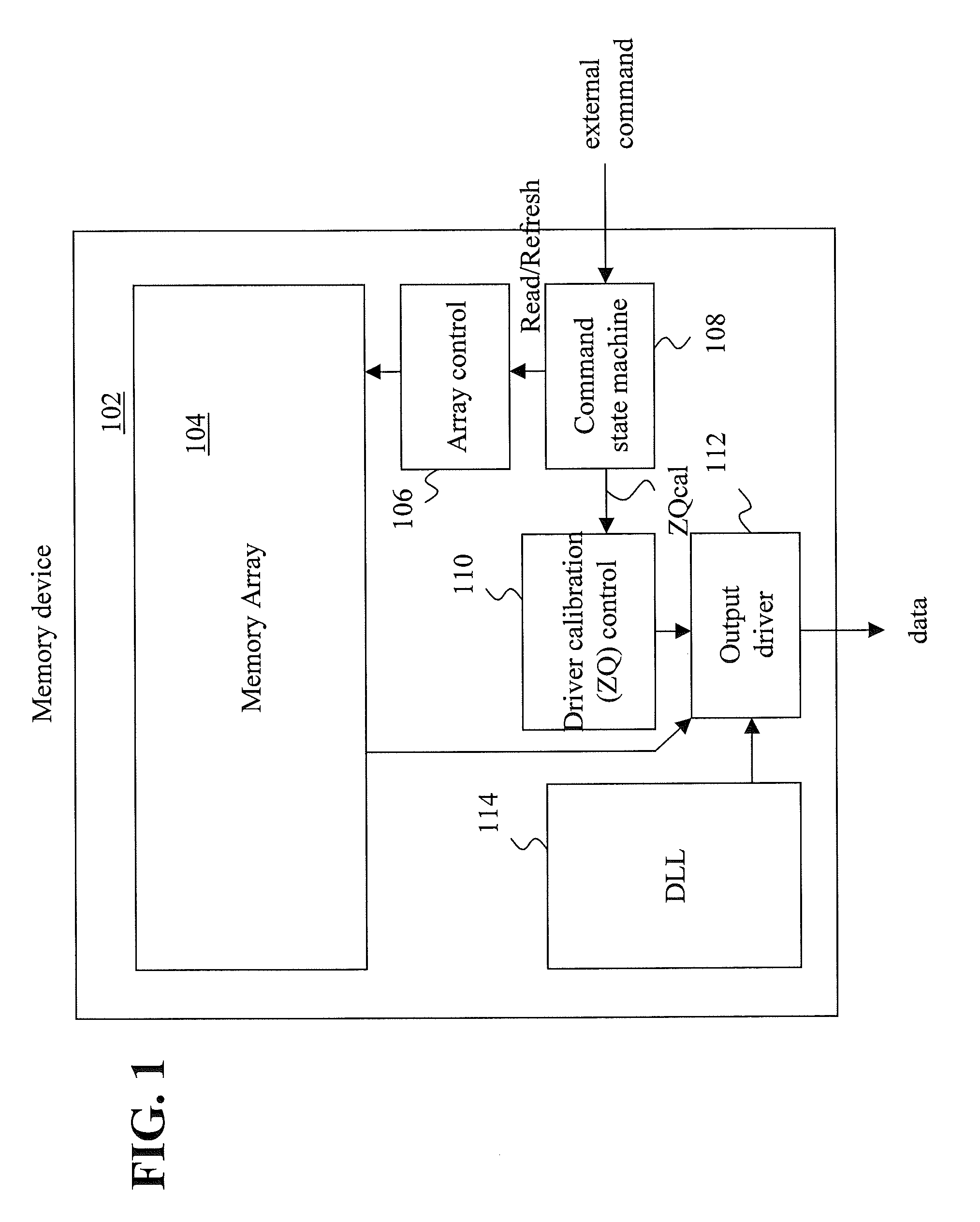

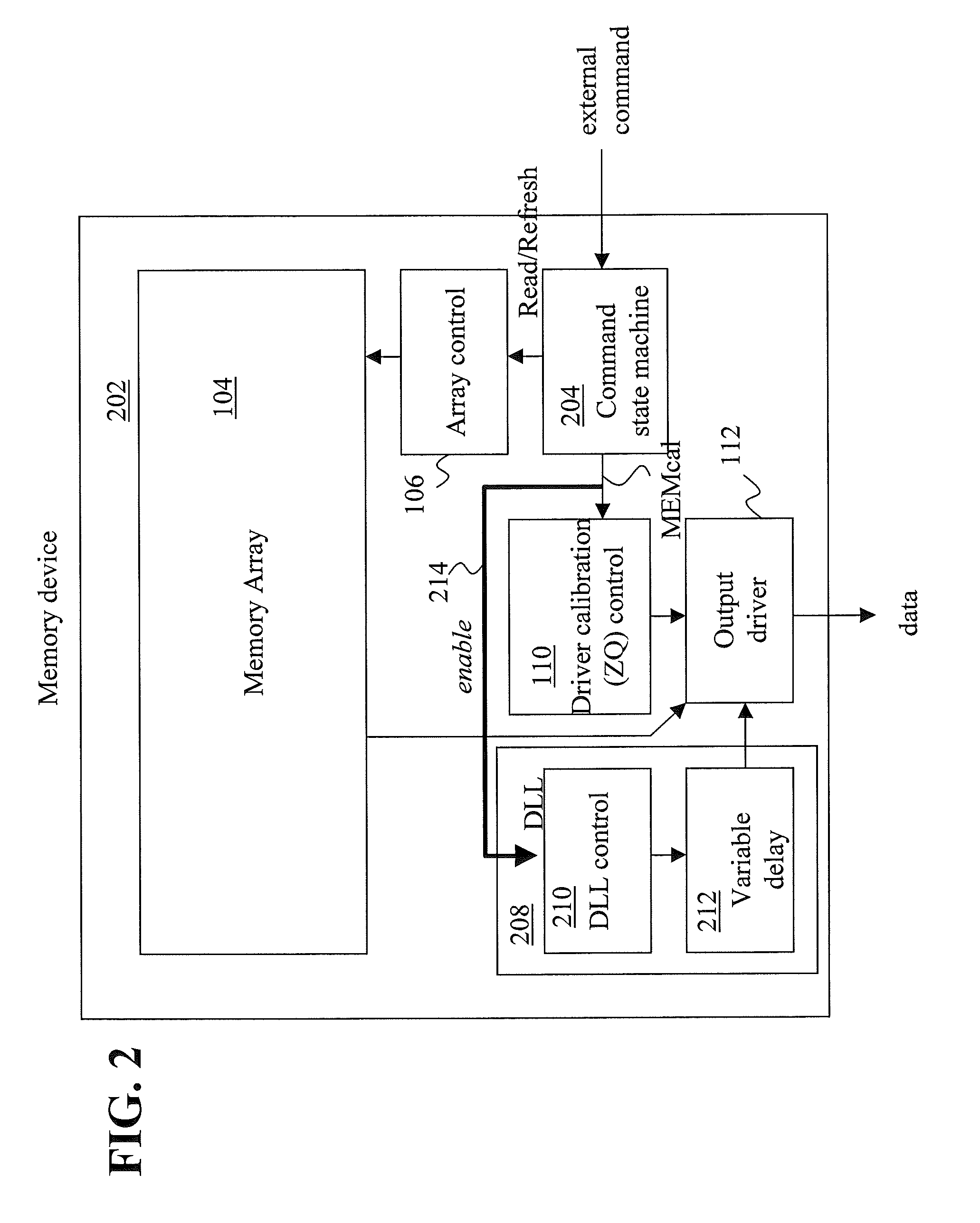

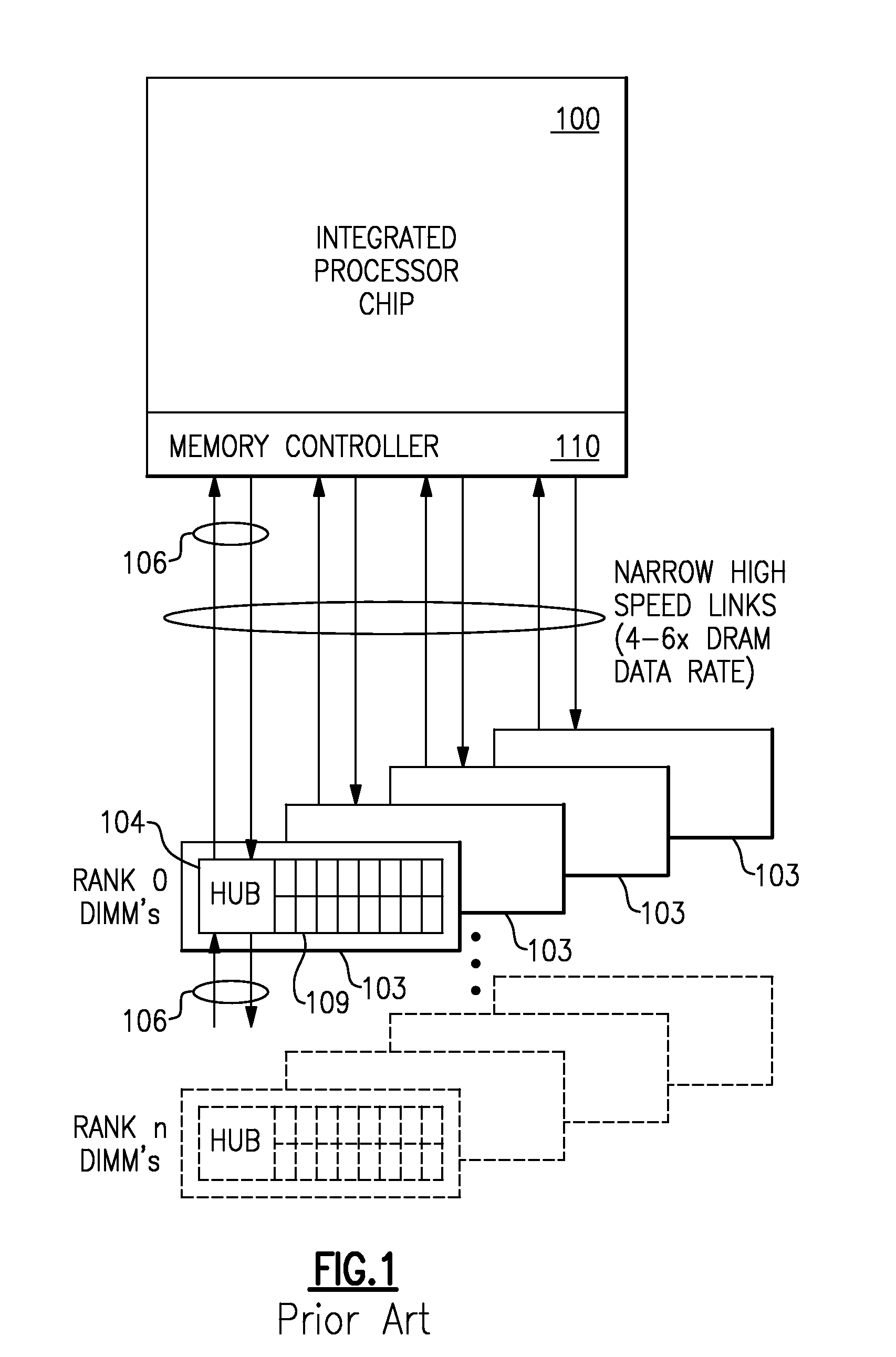

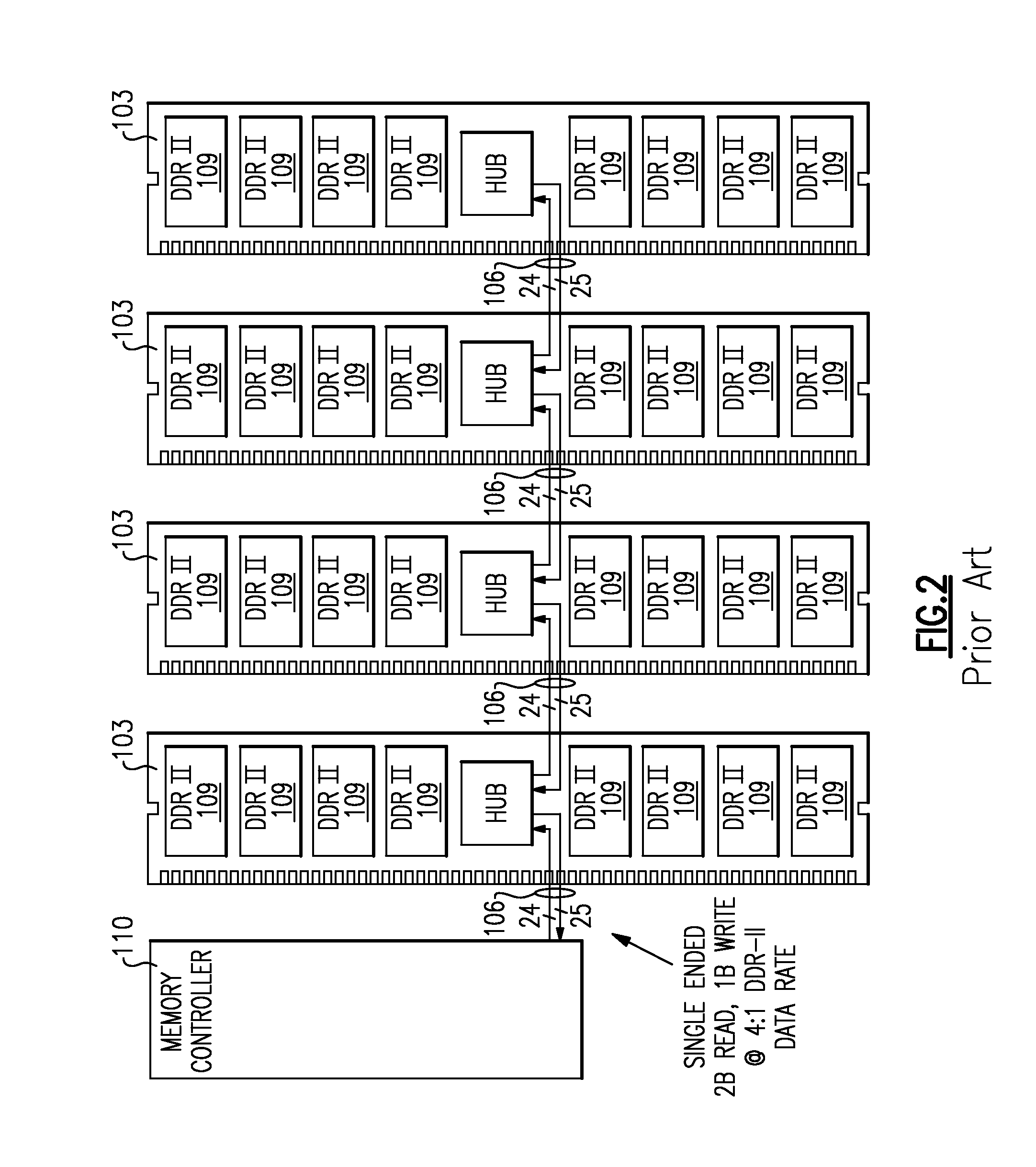

Advanced memory device having improved performance, reduced power and increased reliability

An advanced memory having improved performance, reduced power and increased reliability. A memory device includes a memory array, a receiver for receiving a command and associated data, error control coding circuitry for performing error control checking on the received command, and data masking circuitry for preventing the associated data from being written to the memory array in response to the error control coding circuitry detecting an error in the received command. Another memory device includes a programmable preamble. Another memory device includes a fast exit self-refresh mode. Another memory device includes auto refresh function that is controlled by the characteristic device. Another memory device includes an auto refresh function that is controlled by a characteristic of the memory device.

Owner:GLOBALFOUNDRIES US INC

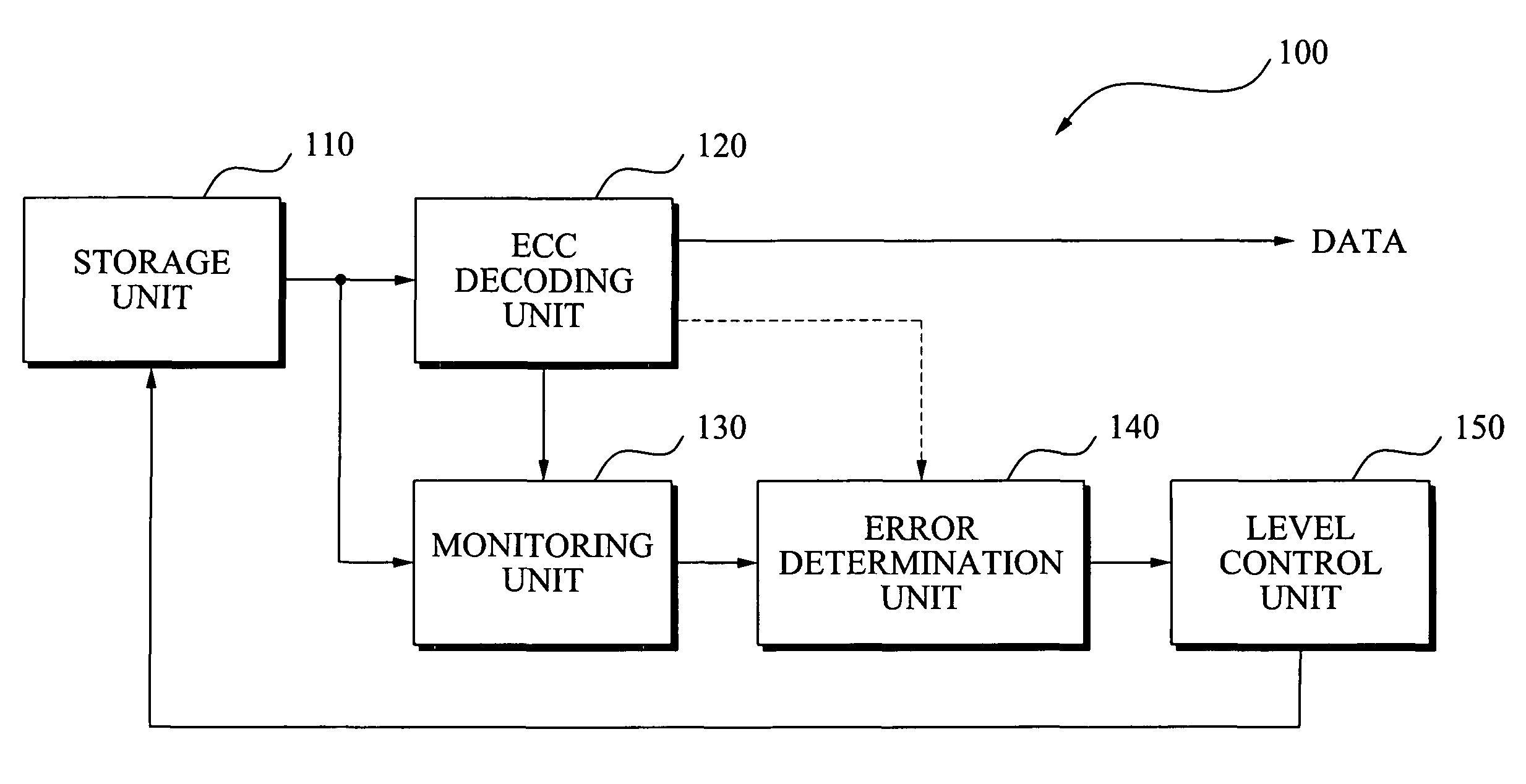

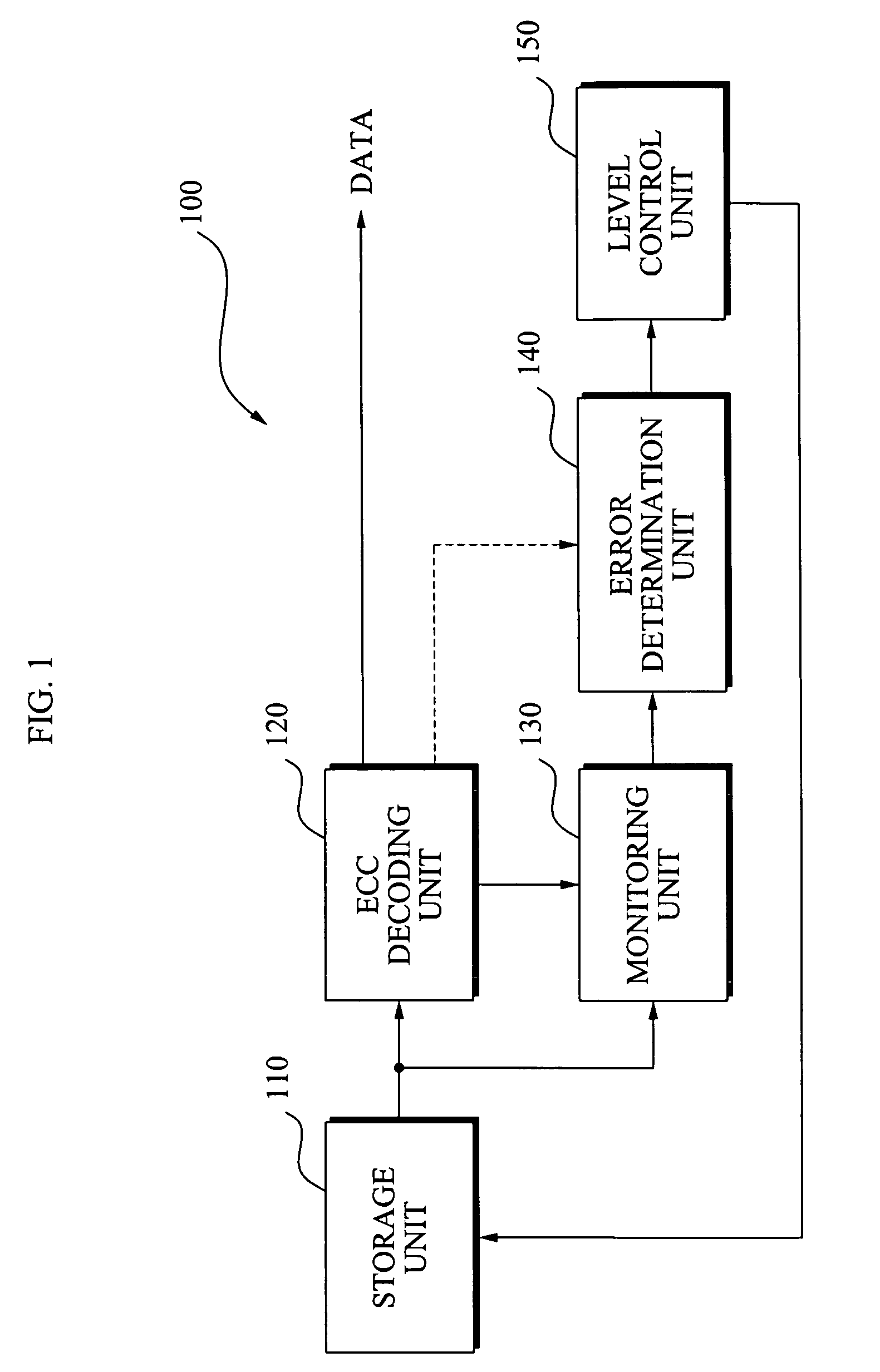

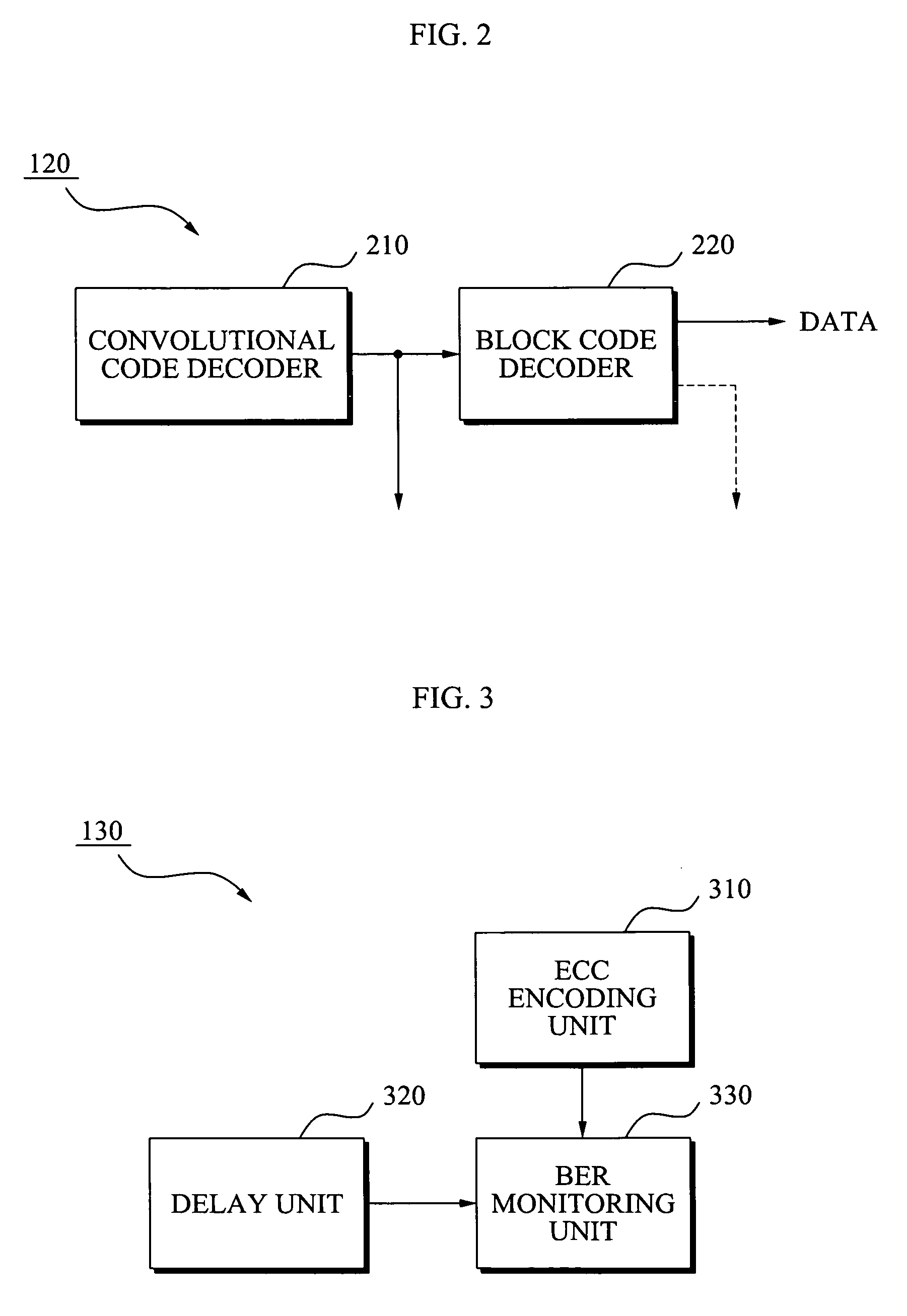

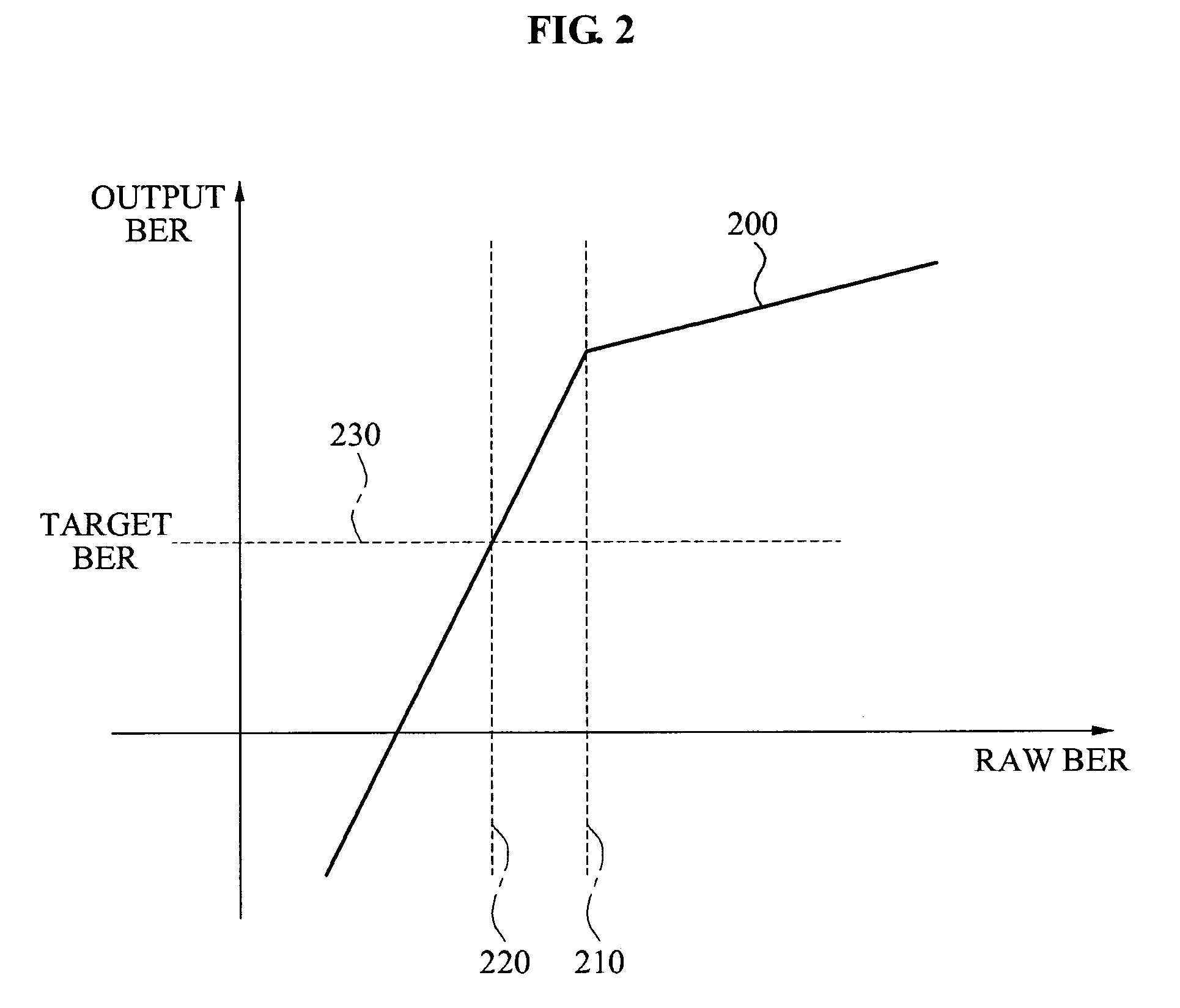

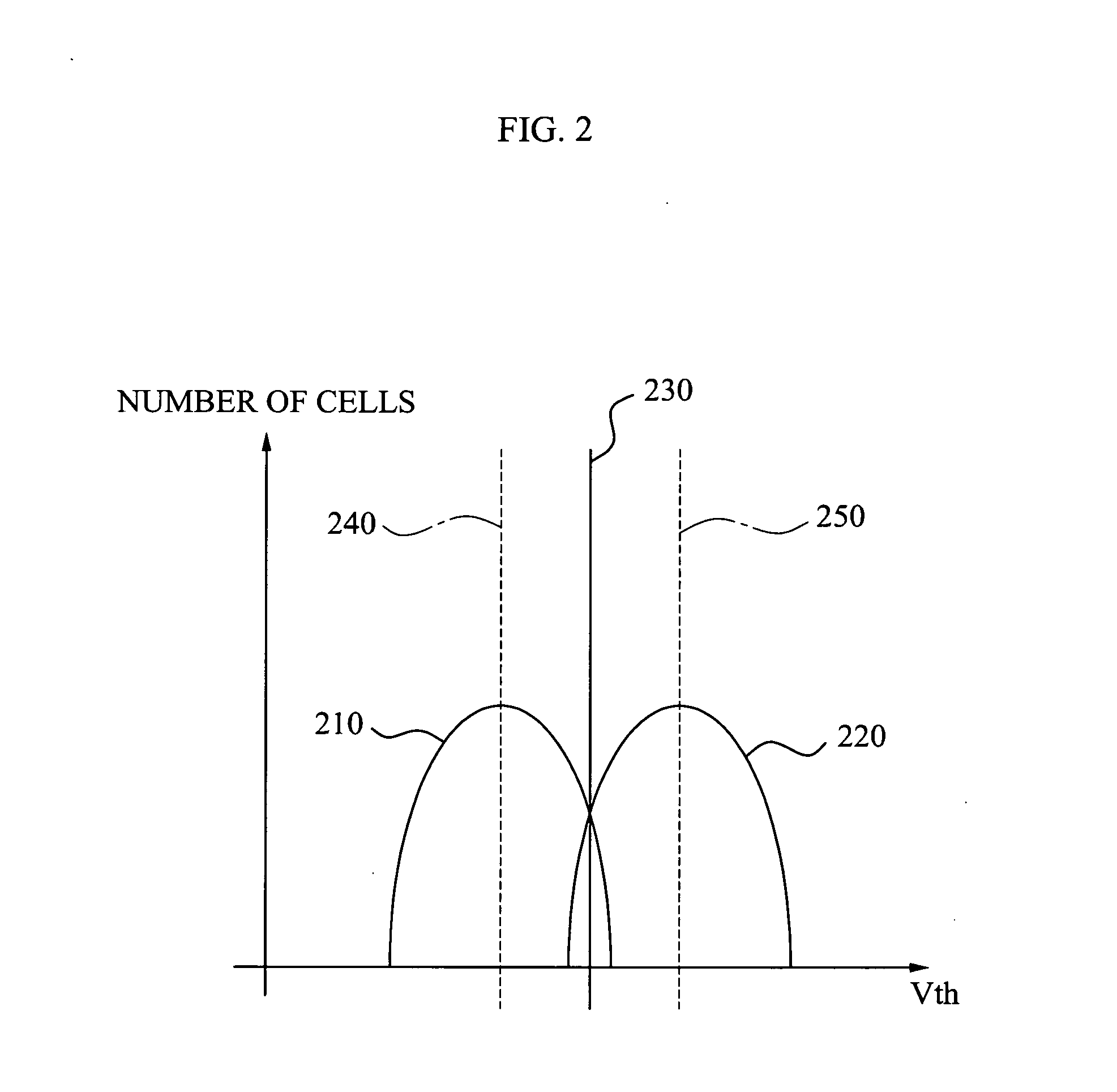

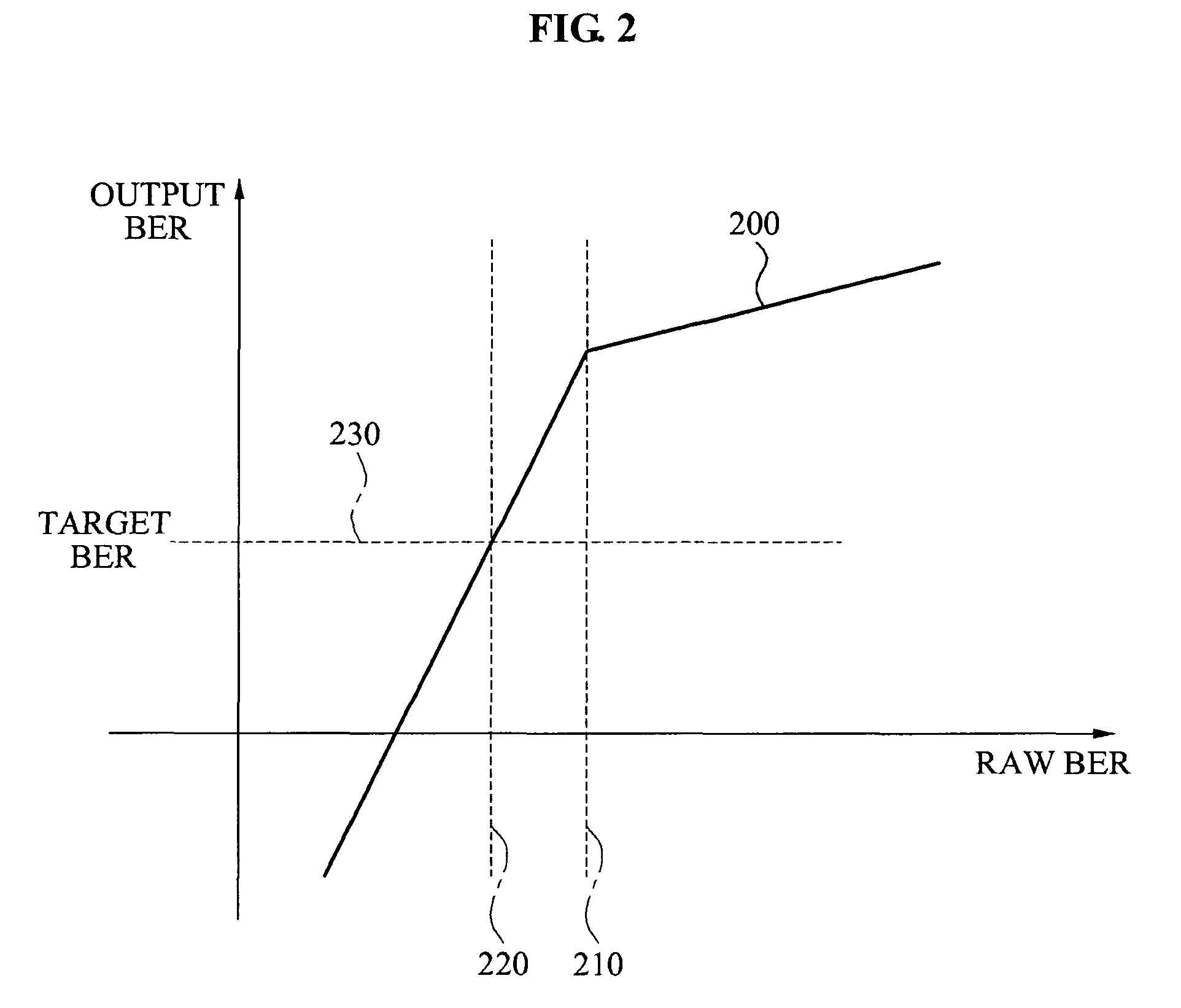

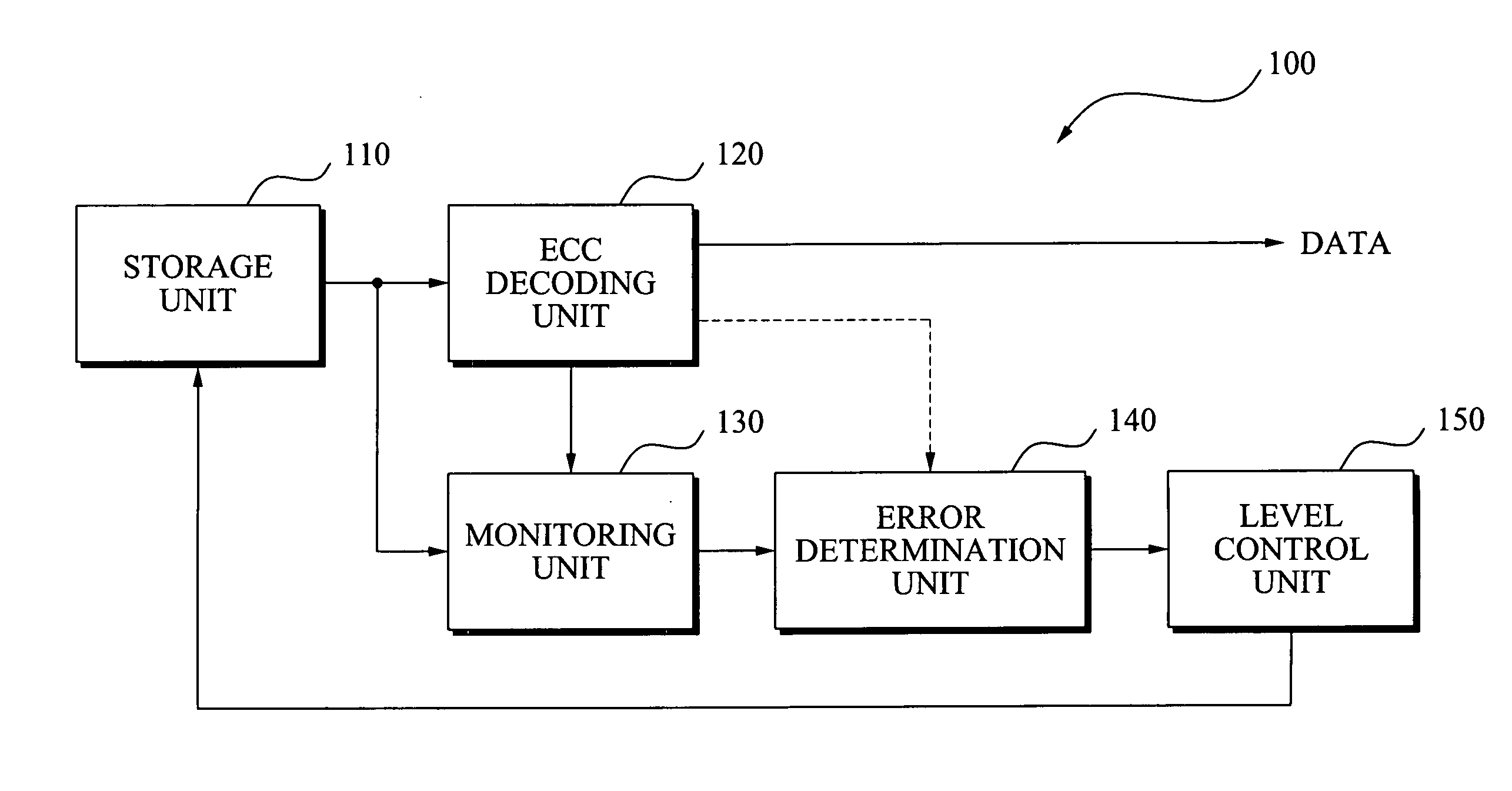

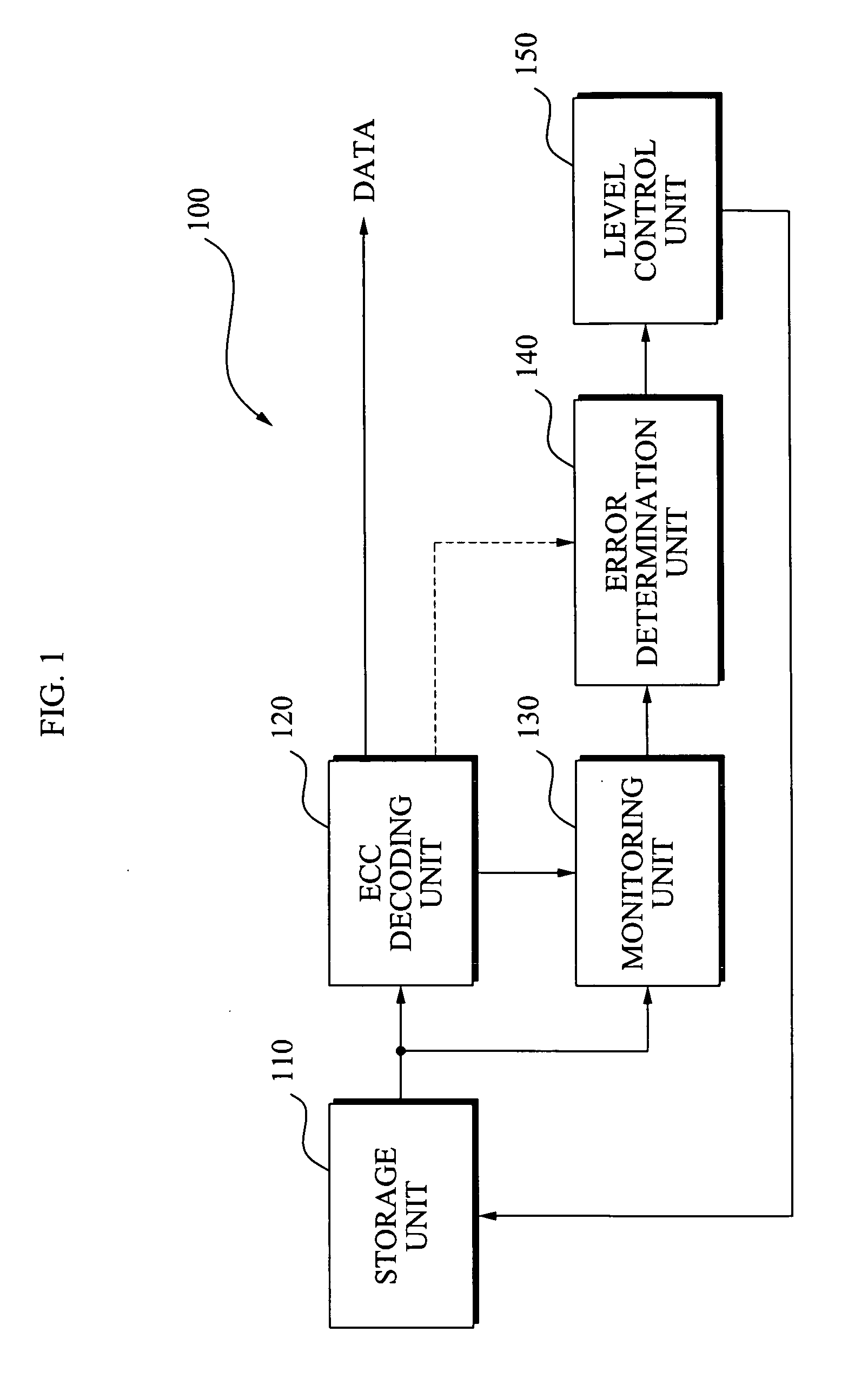

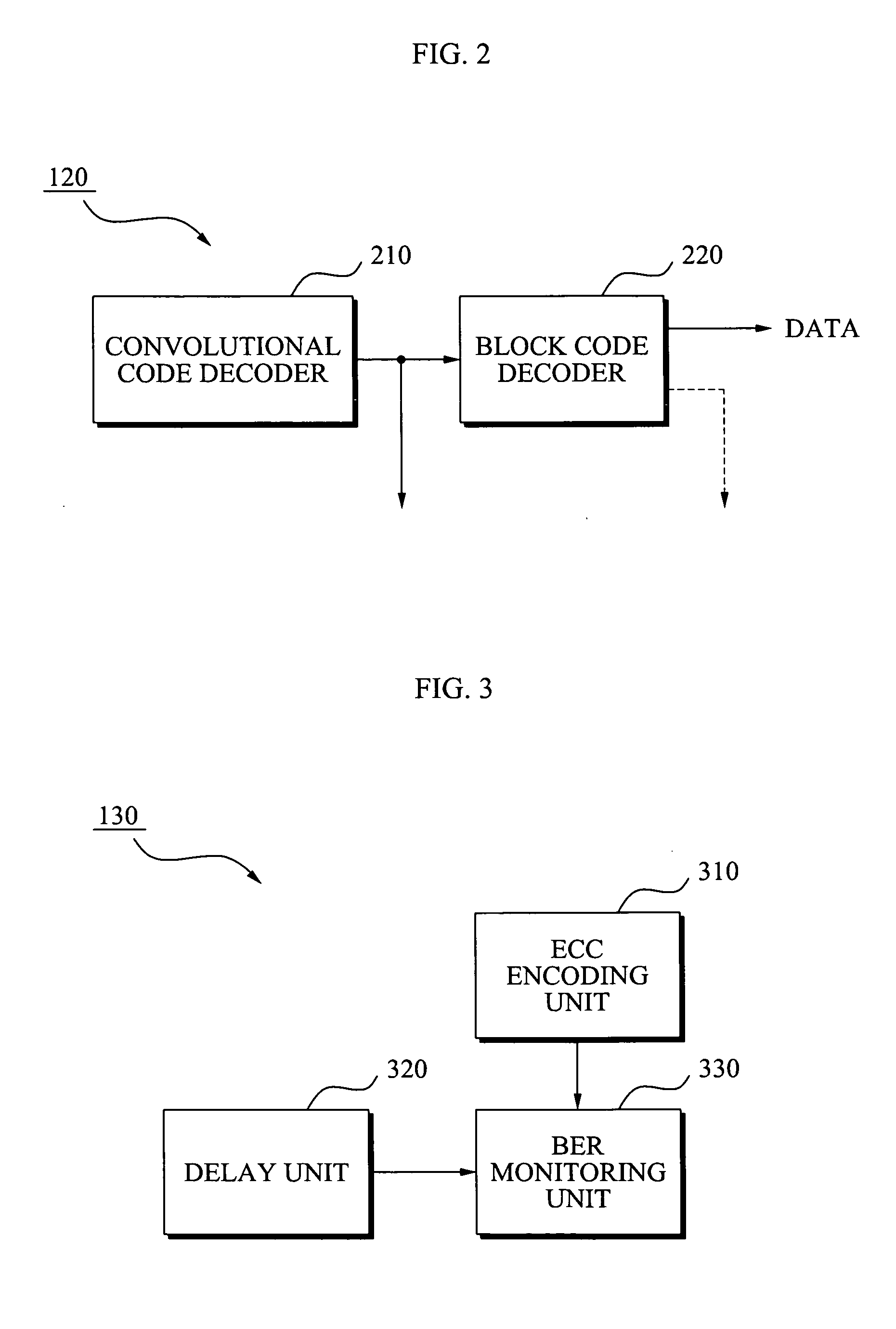

Read level control apparatuses and methods

Various read level control apparatuses and methods are provided. In various embodiments, the read level control apparatuses may include an error control code (ECC) decoding unit for ECC decoding data read from a storage unit, and a monitoring unit for monitoring a bit error rate (BER) based on the ECC decoded data and the read data. The apparatus may additionally include an error determination unit for determining an error rate of the read data based on the monitored BER, and a level control unit for controlling a read level of the storage unit based on the error rate.

Owner:SAMSUNG ELECTRONICS CO LTD

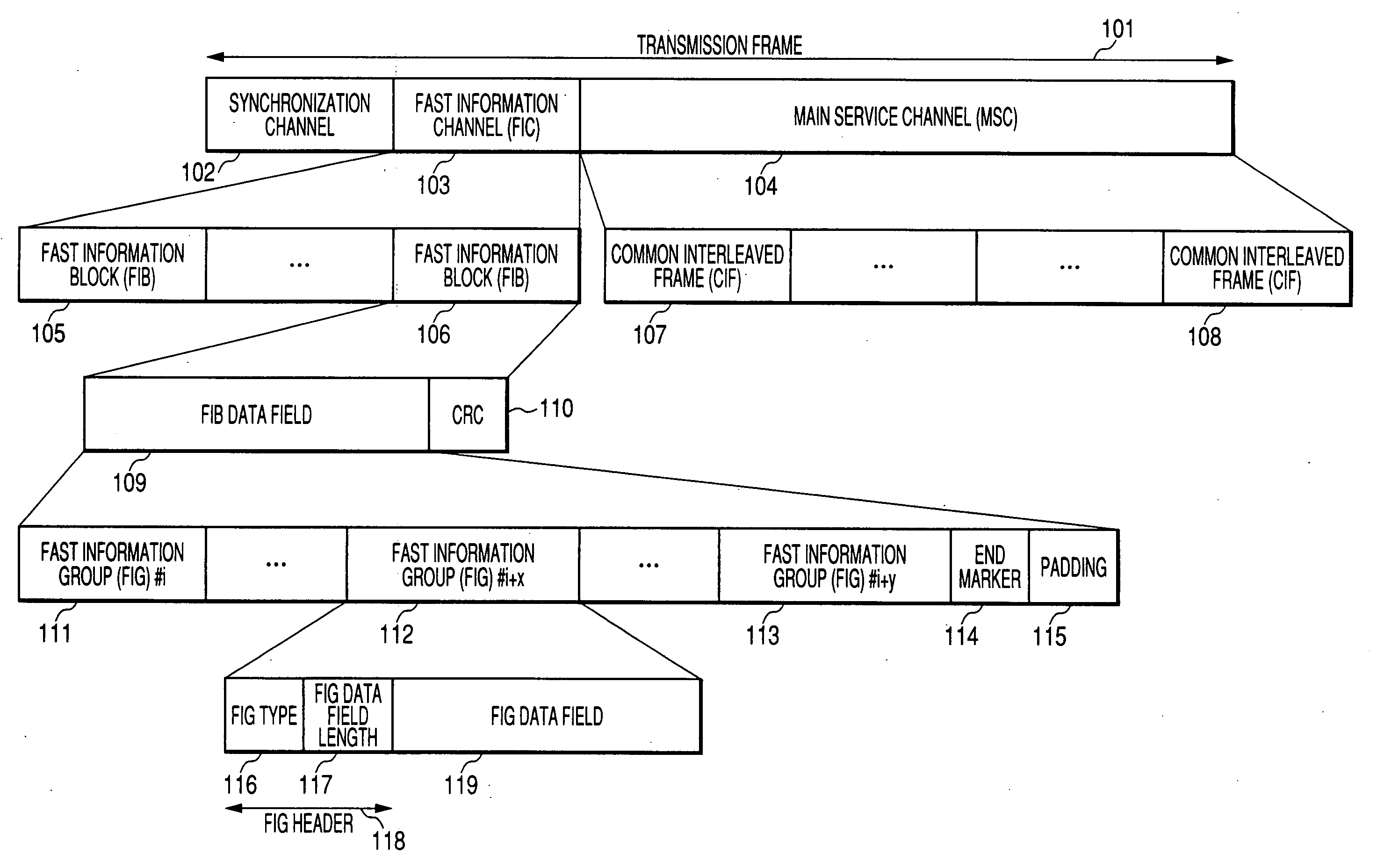

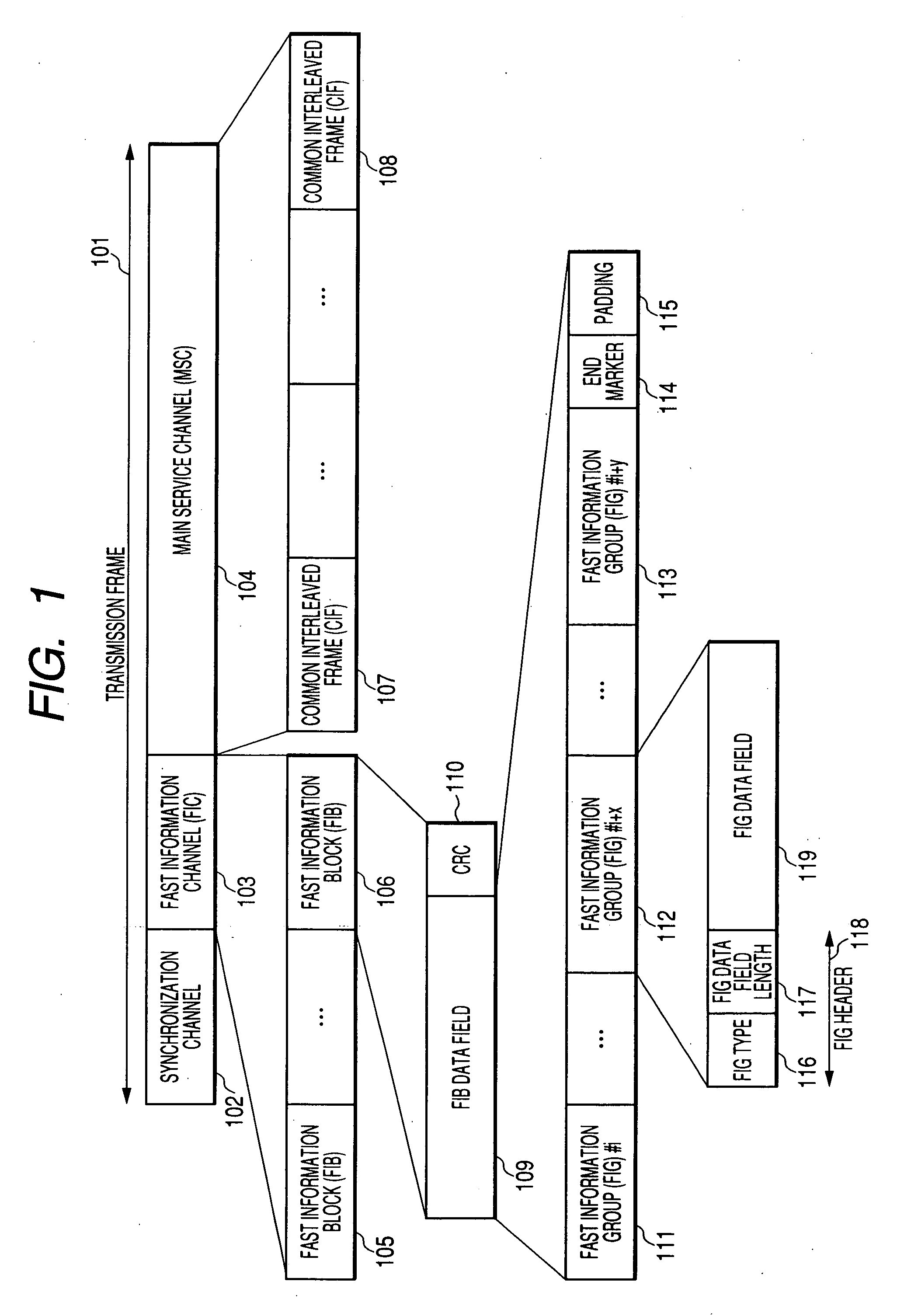

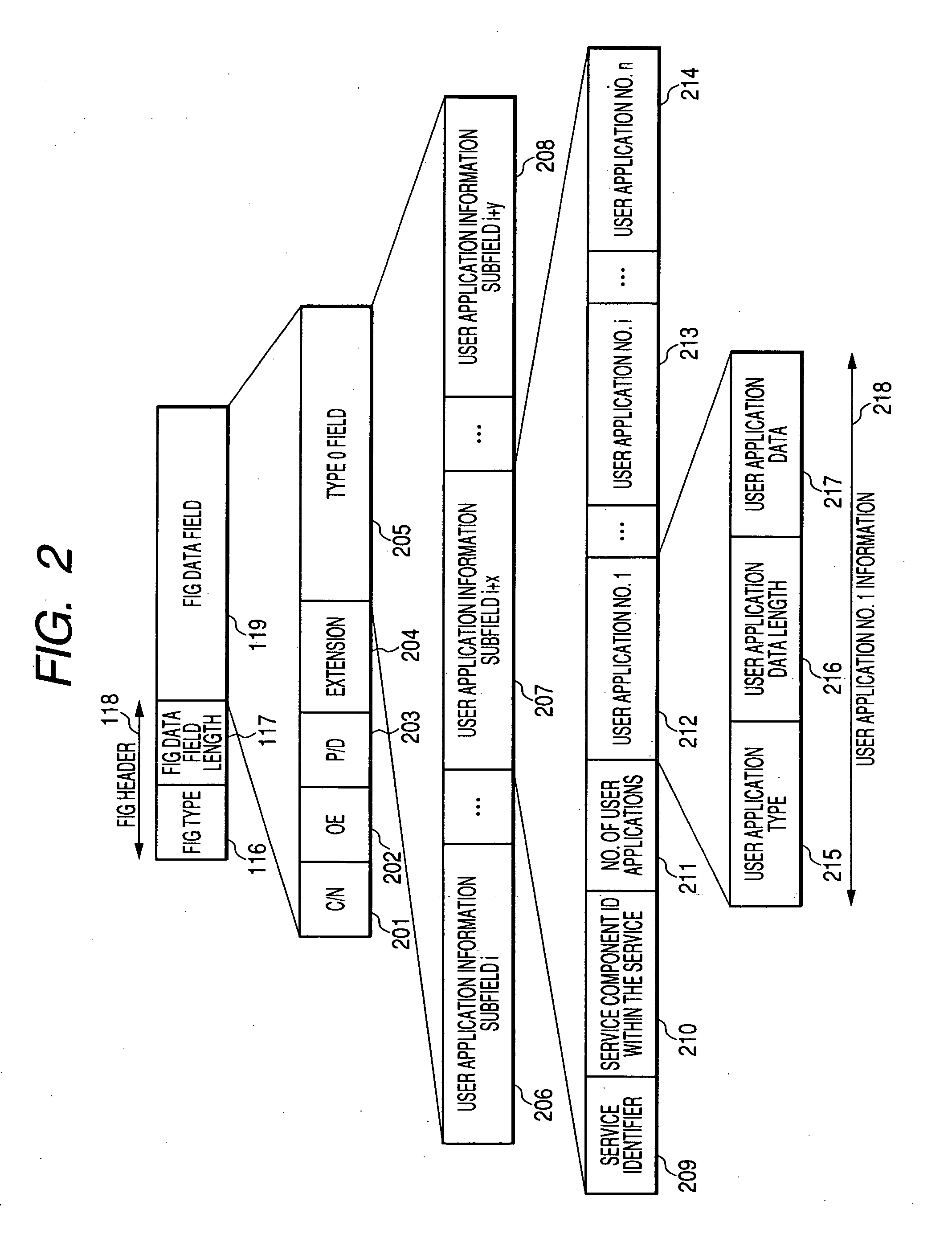

Superframe error coding in digital audio broadcasting systems

InactiveUS20050262419A1Increase the number ofSpecial service provision for substationError prevention/detection by using return channelComputer hardwareData field

The present invention relates to a subchannel structure within a main service channel for transmitting data of at least one application in a digital audio broadcasting system, such as DAB or DRM. Further methods for transmitting and receiving application data using the subchannel structure, as well as a corresponding broadcasting station and receiving terminal are provided. To increase the number of data packets of which undamaged data can be derived under identical reception conditions in a backward-compatible way the present invention provides a subchannel structure comprising a predetermined number of data packets and a predetermined number of error control packets, wherein each of the error control packets comprises an error control code field the data of which is generated based on at least a part of the packet data field and / or at least a part of the packet header of the data packets and a CRC field preceding the error control code field for protecting same.

Owner:PANASONIC CORP

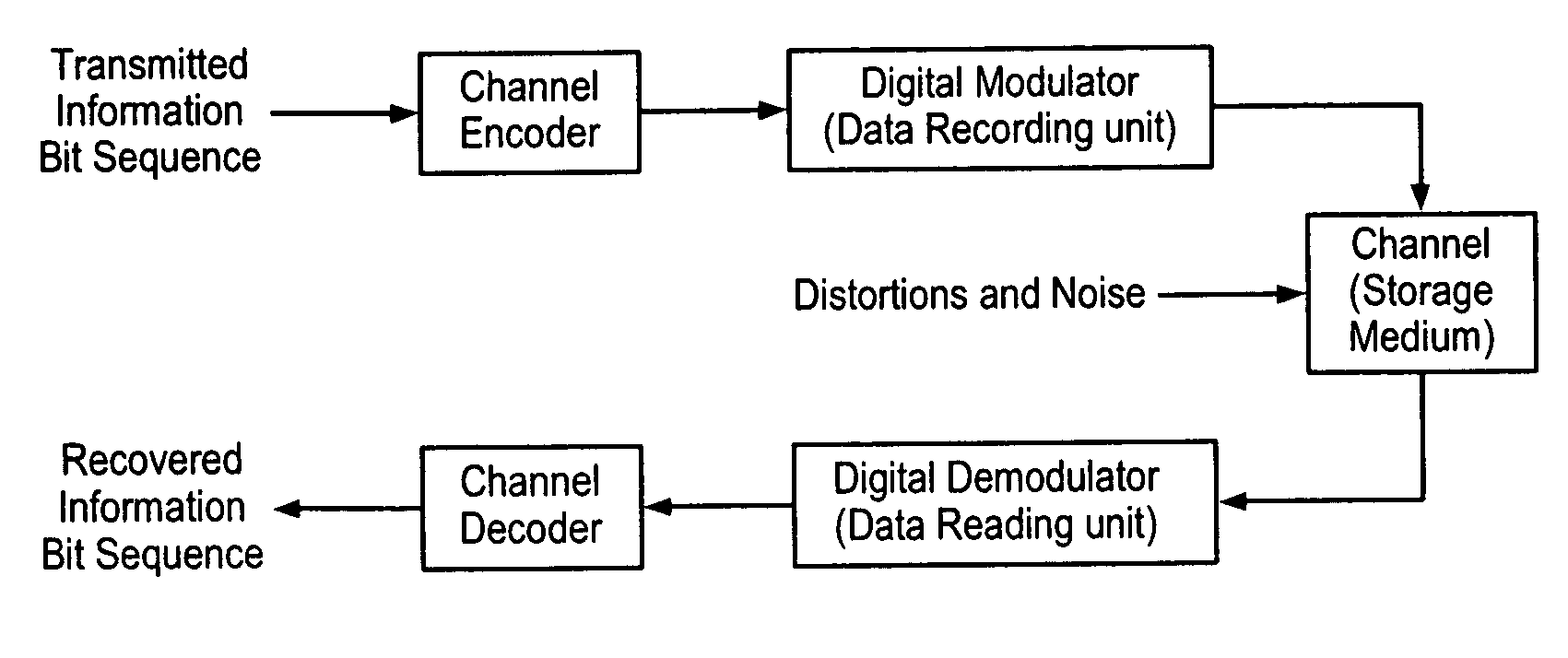

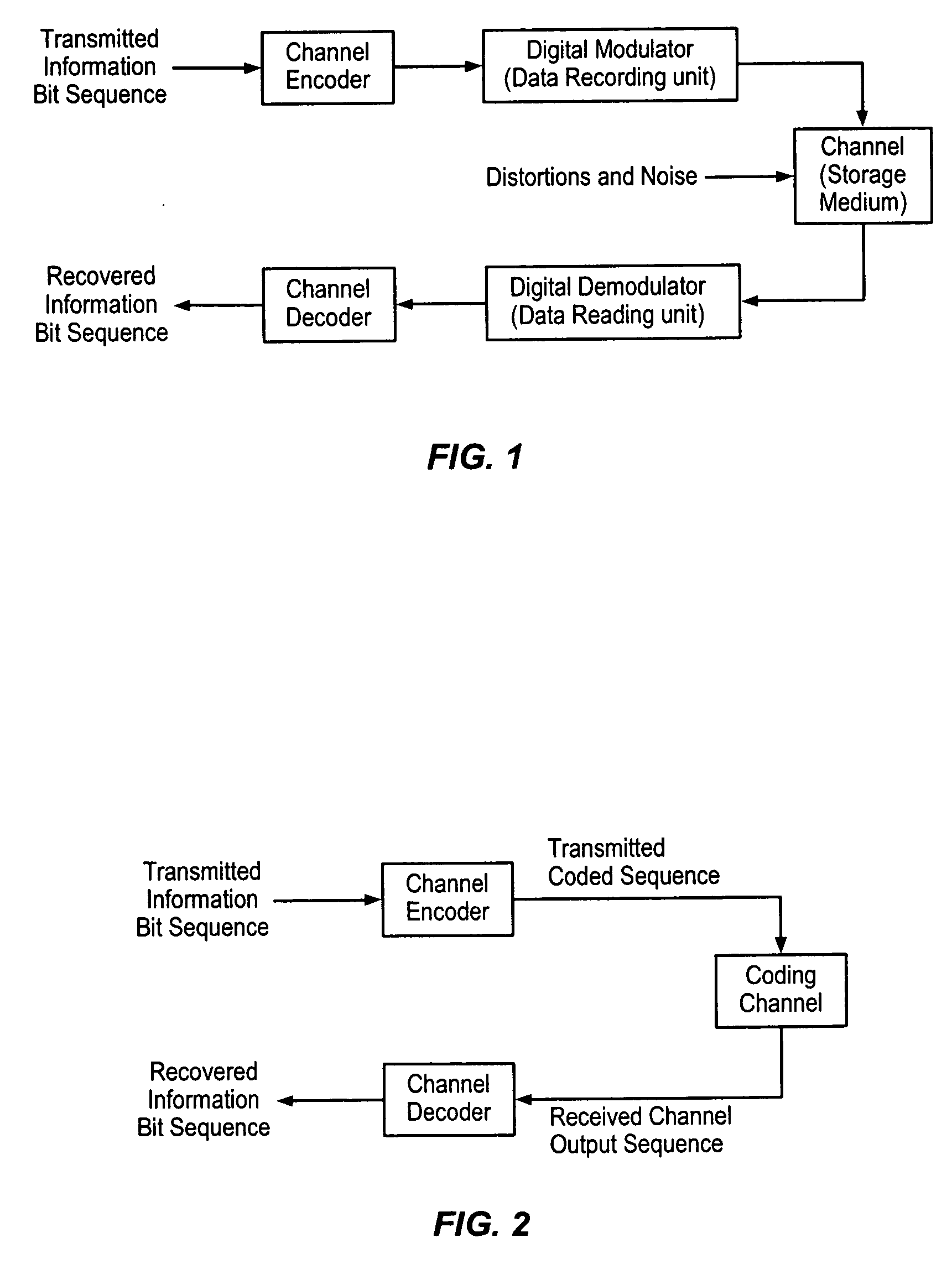

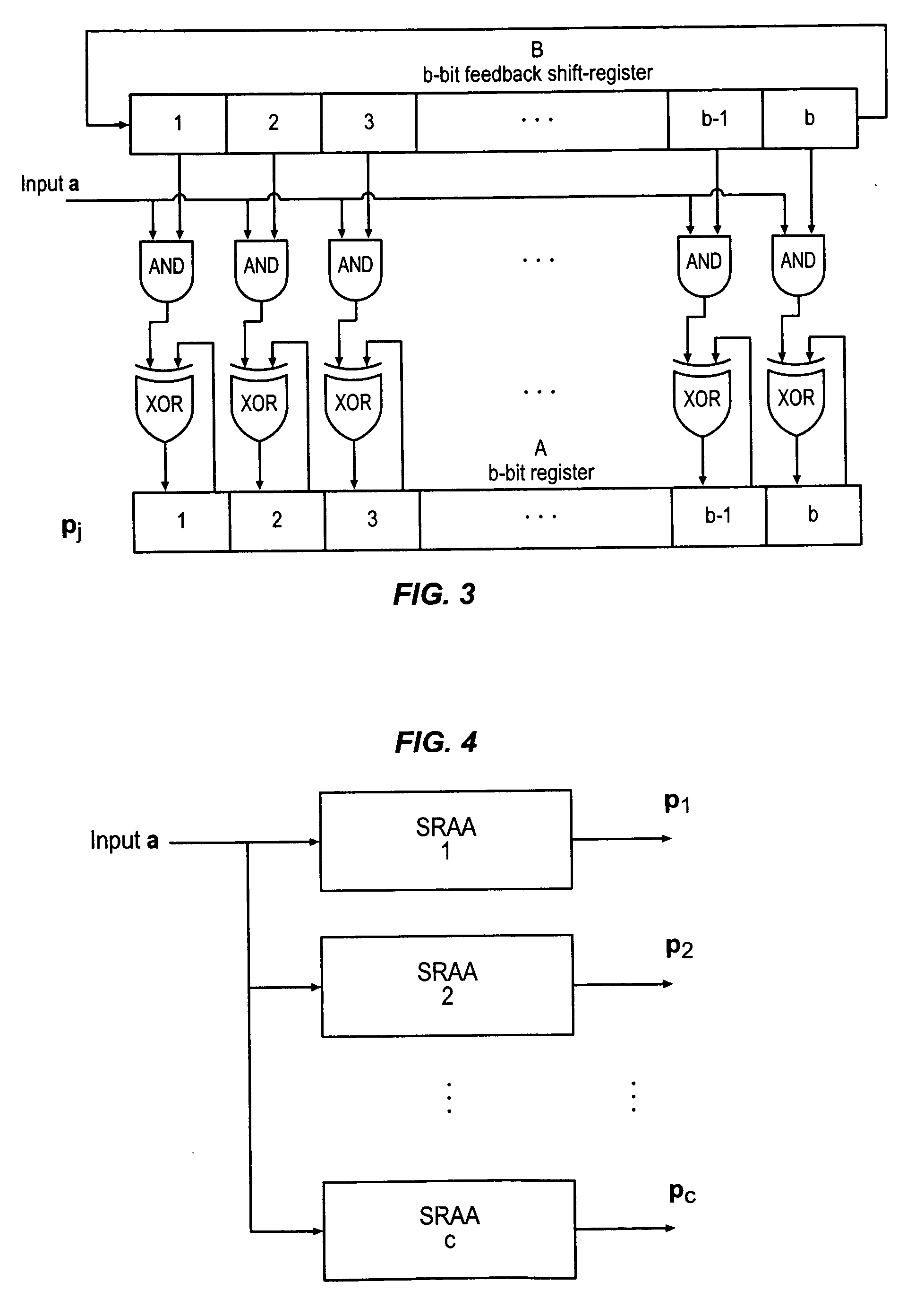

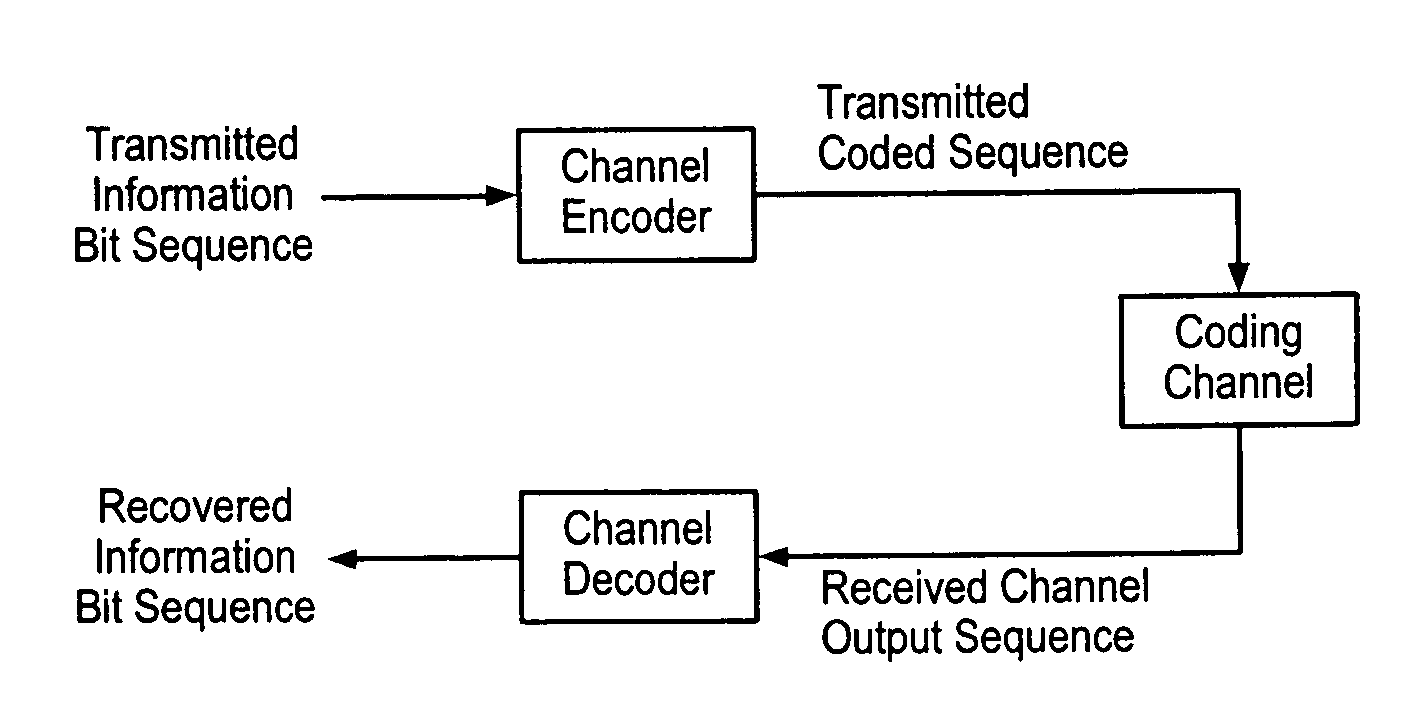

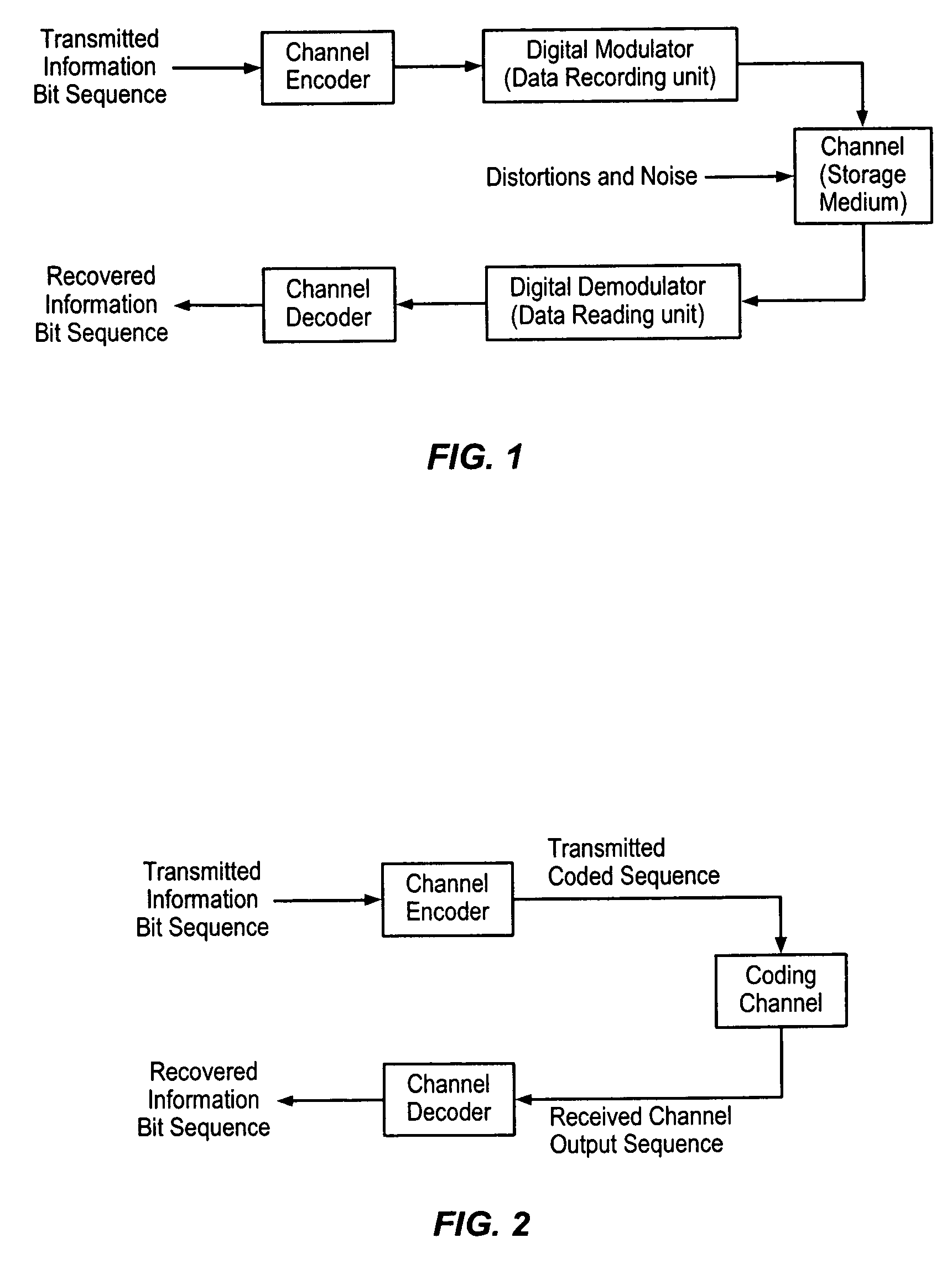

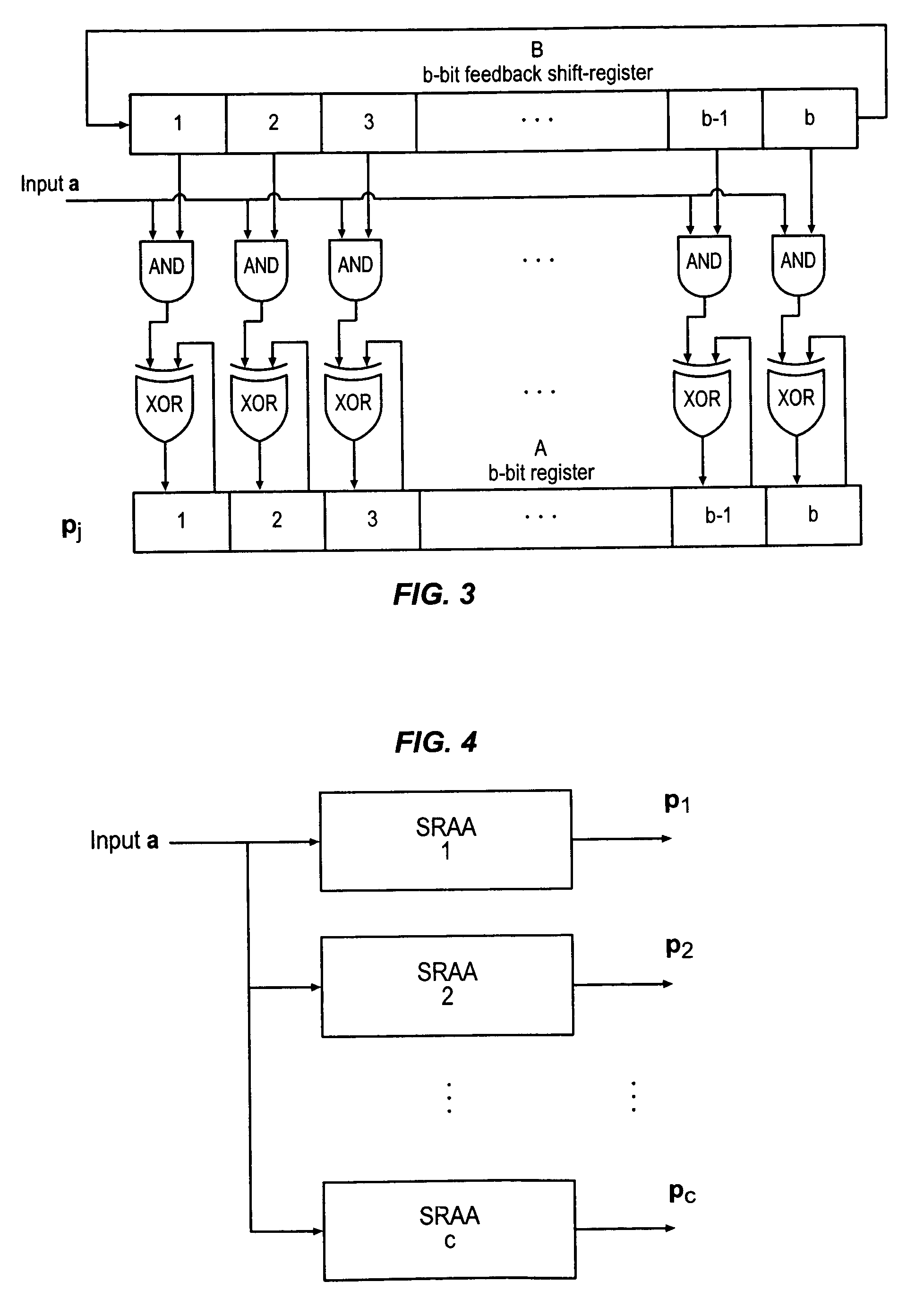

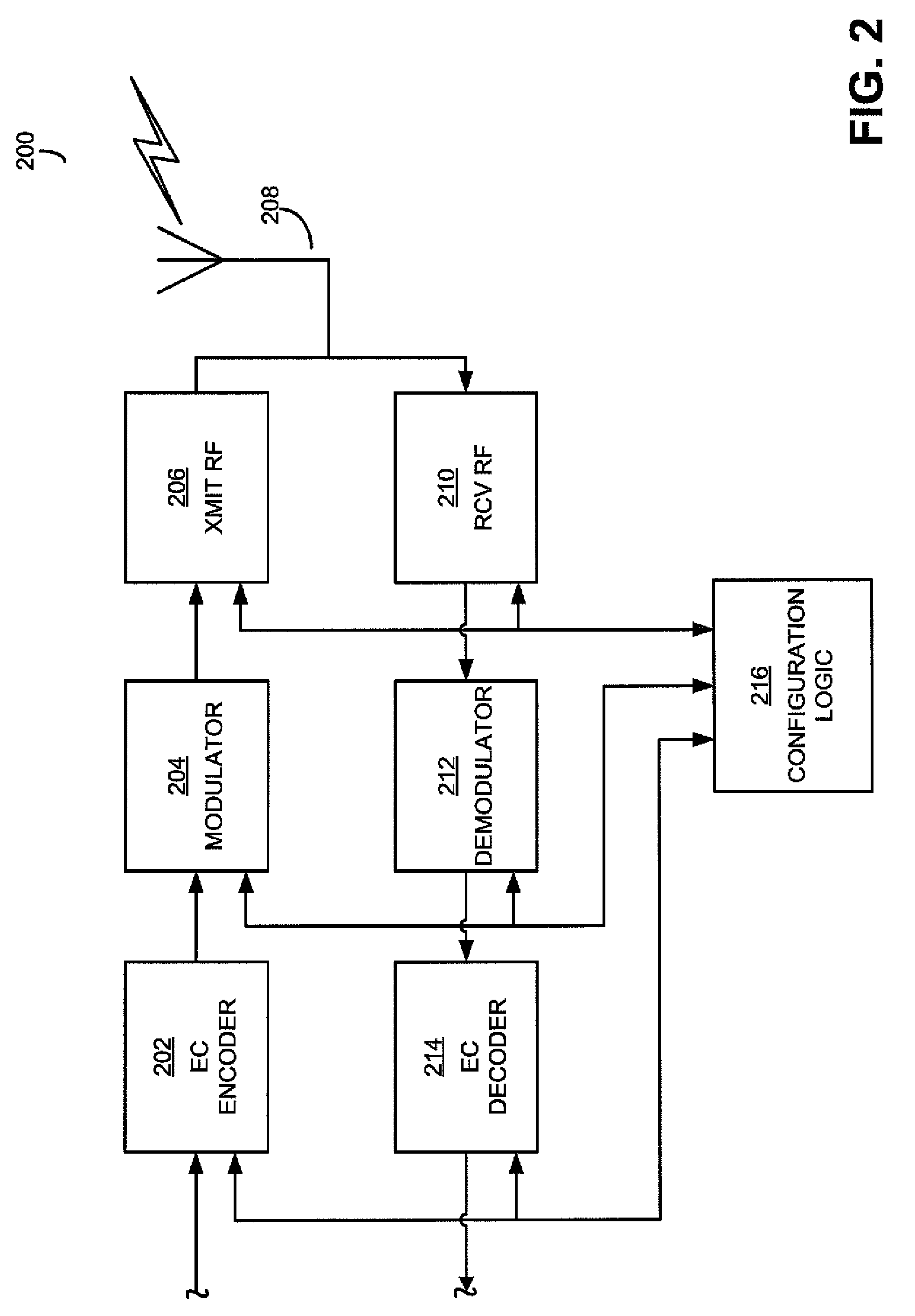

Universal error control coding system for digital communication and data storage systems

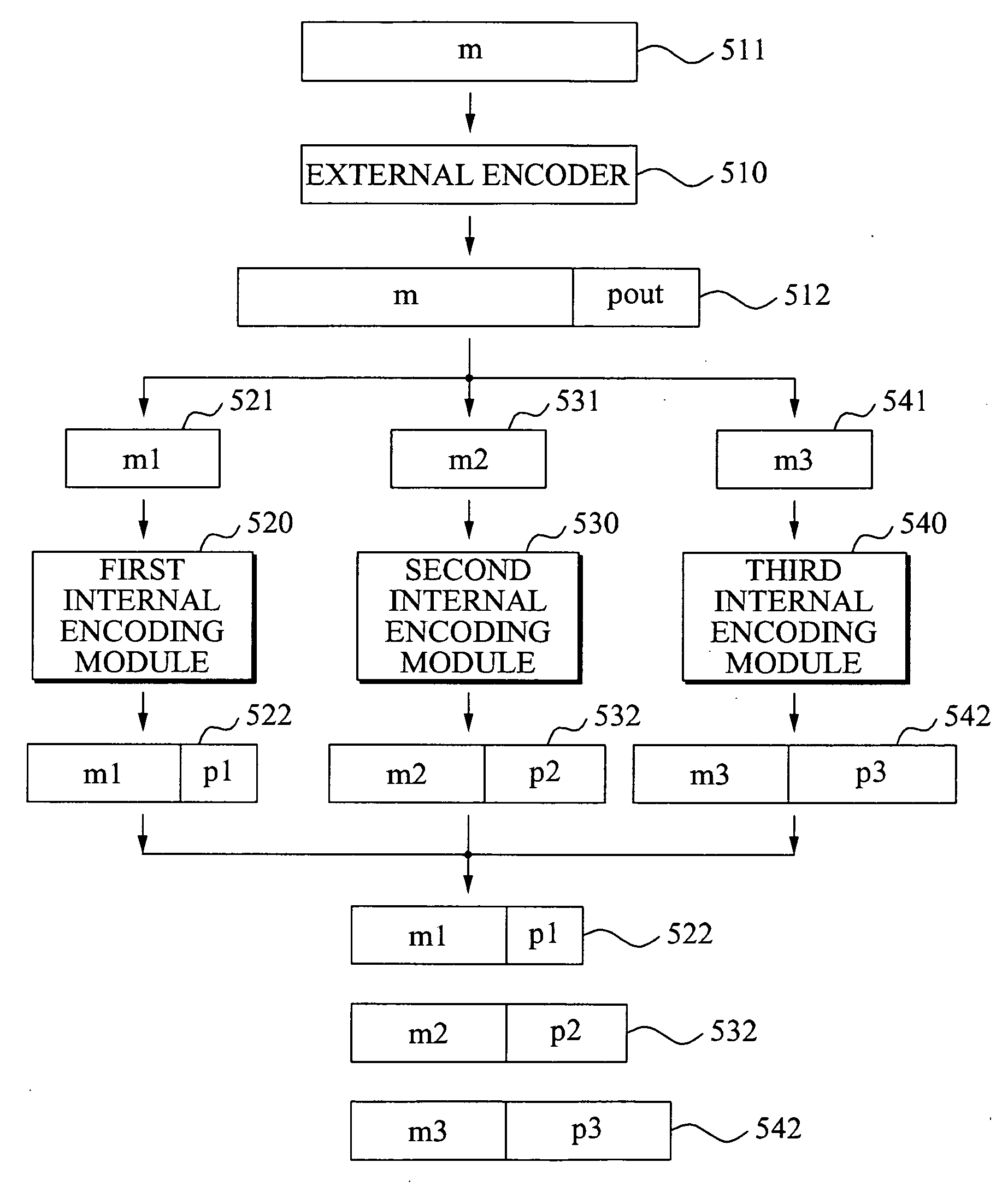

InactiveUS20080126908A1Reduce complexityReduce chip areaError detection/correctionCode conversionComputer architectureRound complexity

The universal forward error-correction coding system provides adjustable code rates and coding gains to greatly benefit the design of many modern digital communications (data storage) systems. The channel encoding and decoding methods are universal such that a single encoder and a single decoder can be used to implement all the forward error-correction codes of different code rates. This universal forward error-correction coding system also includes a novel systematic code generation procedure that has the capability of generating many classes of codes that provide the best balance between coding gain performance and implementation complexity.

Owner:COMM CODING

Error control coding for orthogonal differential vector signaling

Owner:ECOLE POLYTECHNIQUE FEDERALE DE LAUSANNE (EPFL)

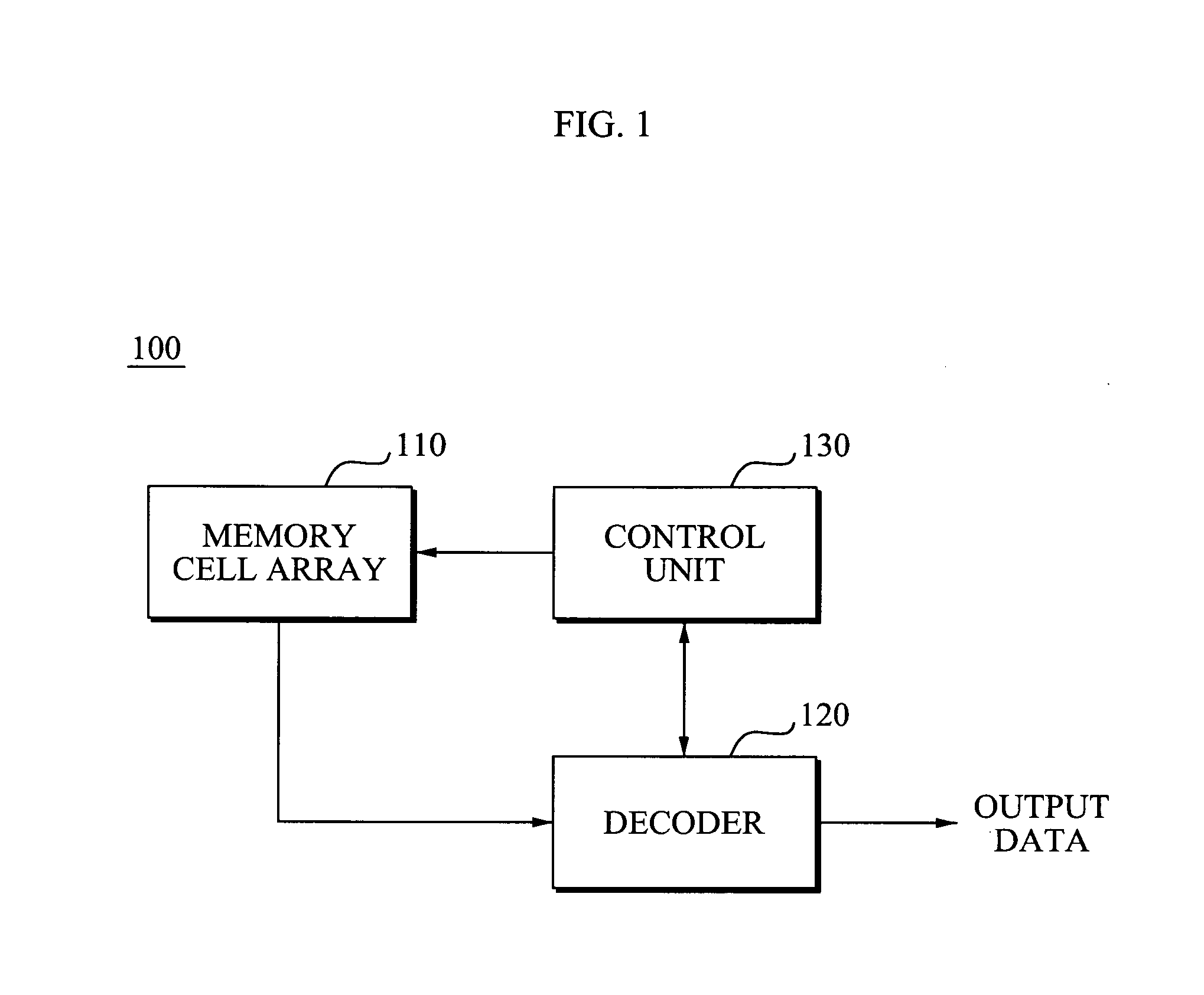

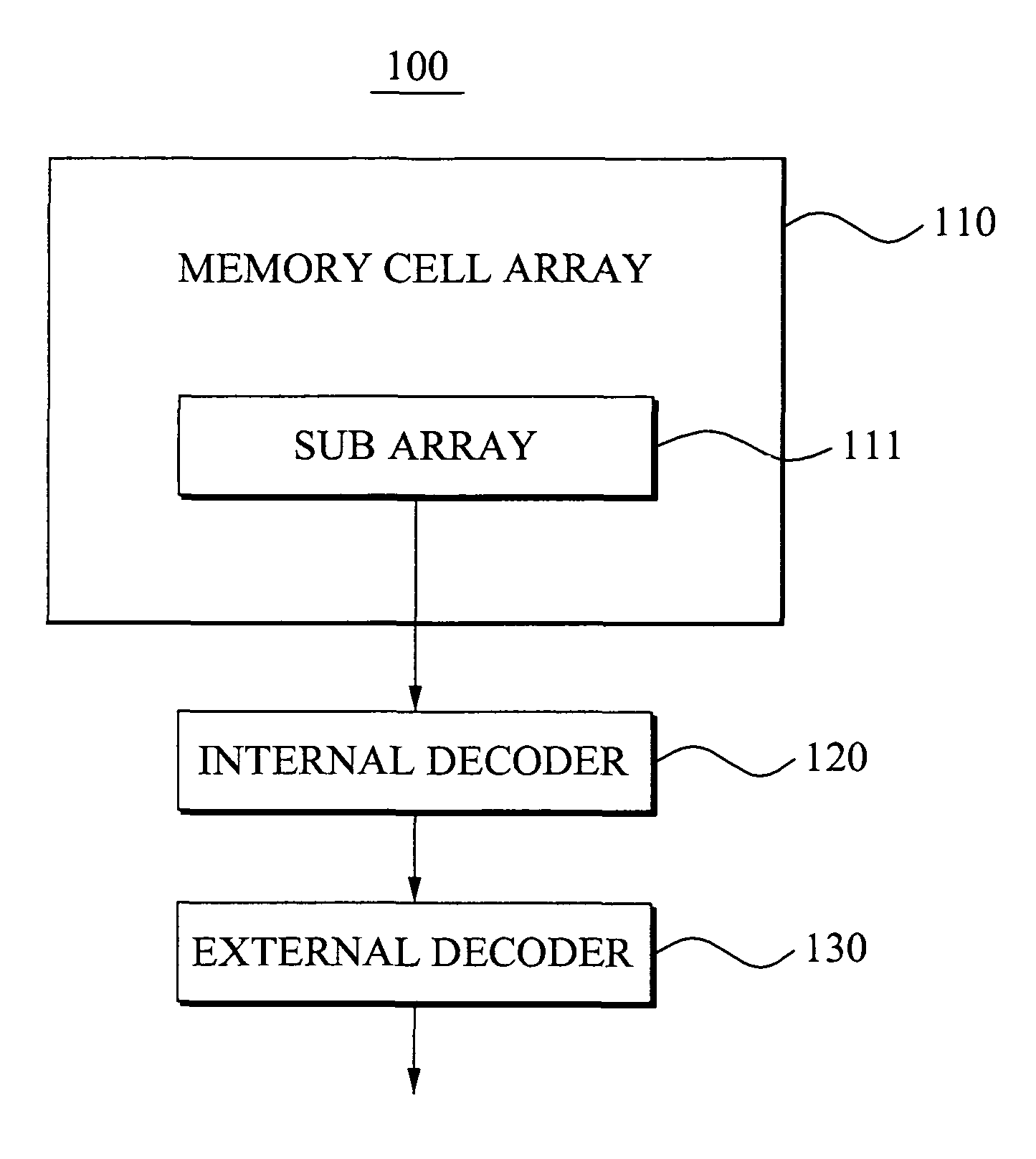

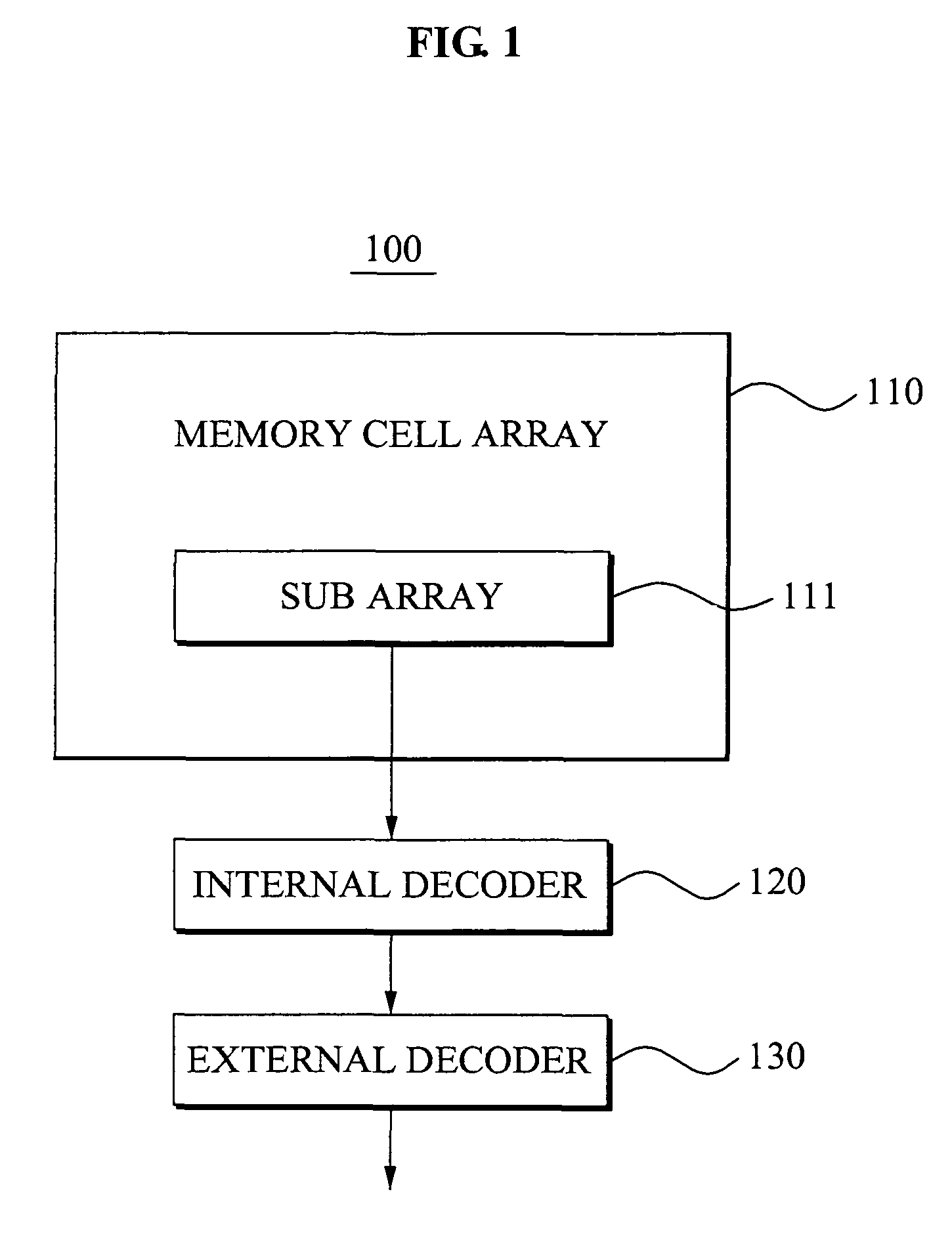

Memory devices and encoding and/or decoding methods

ActiveUS20090241008A1Reduce errorsError rateData representation error detection/correctionCode conversionComputer hardwareError control coding

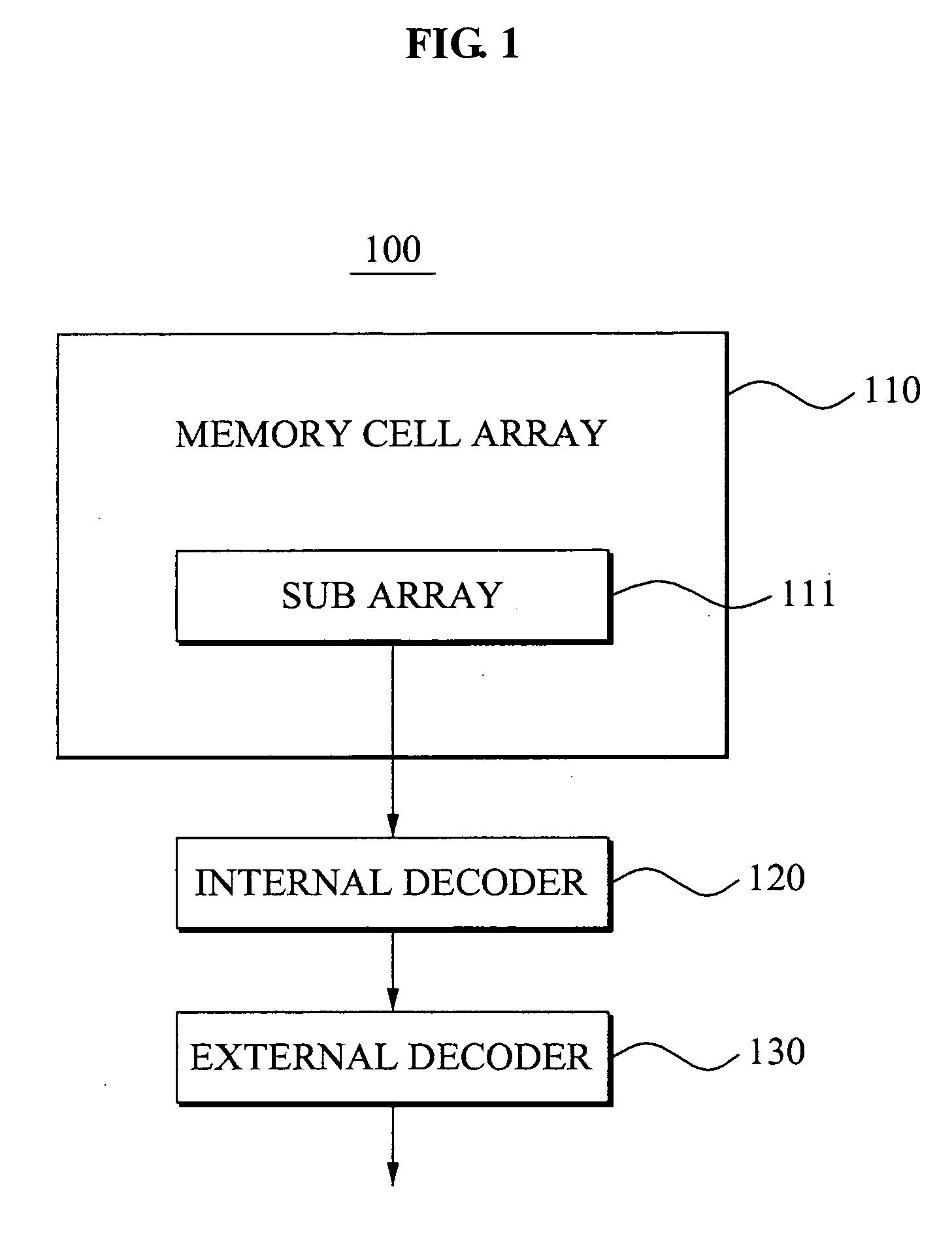

Memory devices and / or encoding / decoding methods are provided. A memory device may include: a memory cell array; an internal decoder configured to apply, to a first codeword read from the memory cell array, a first decoding scheme selected based on a characteristic of a first channel in which the first codeword is read to perform error control codes (ECC) decoding of the first codeword, and apply, to a second codeword read from the memory cell array, a second decoding scheme selected based on a characteristic of a second channel in which the second codeword is read to perform the ECC decoding of the second codeword; and an external decoder configured to apply an external decoding scheme to the ECC-decoded first codeword and the ECC-decoded second codeword to perform the ECC decoding of the first codeword and the second codeword.

Owner:SAMSUNG ELECTRONICS CO LTD

Code calculating device

A code computing apparatus with an error detection code (CRC) generating function and an elliptic curve cryptography (ECC) function, comprising a matrix element computation part 30 for generating matrix elements from parameter values set in first and second registers 201 and 202, a matrix element register 51 for holding the matrix elements generated by the matrix element computation part, and an inner product calculation part 40 for executing inner product calculation between the matrix elements held by the matrix element register and data set in a third register. The matrix element computation part selectively generates matrix elements for error detection and matrix elements for encryption by changing the parameters to be set in the first and second registers, and the inner product calculation part is shared to error control code generation and data encryption by altering the matrix elements to be held in the matrix element register.

Owner:HITACHI LTD

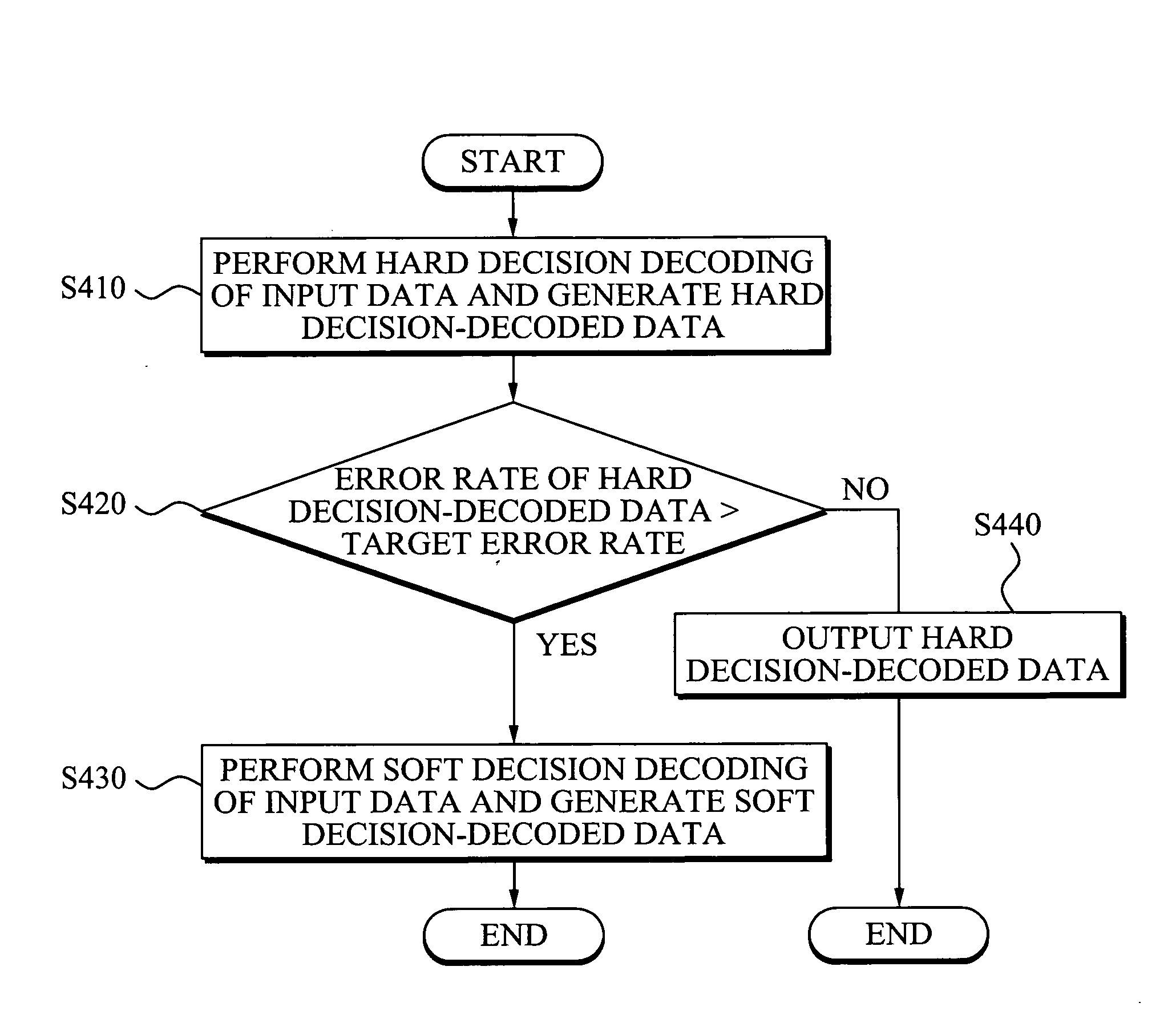

Memory device and error control codes decoding method

ActiveUS20090177931A1Reduce decoding timeImprove decoding performanceError preventionTransmission systemsComputer hardwareStorage cell

Memory devices and / or error control codes (ECC) decoding methods may be provided. A memory device may include a memory cell array, and a decoder to perform hard decision decoding of first data read from the memory cell array by a first read scheme, and to generate output data and error information of the output data. The memory device may also include and a control unit to determine an error rate of the output data based on the error information, and to determine whether to transmit an additional read command for soft decision decoding to the memory cell array based on the error rate. An ECC decoding time may be reduced through such a memory device.

Owner:SAMSUNG ELECTRONICS CO LTD

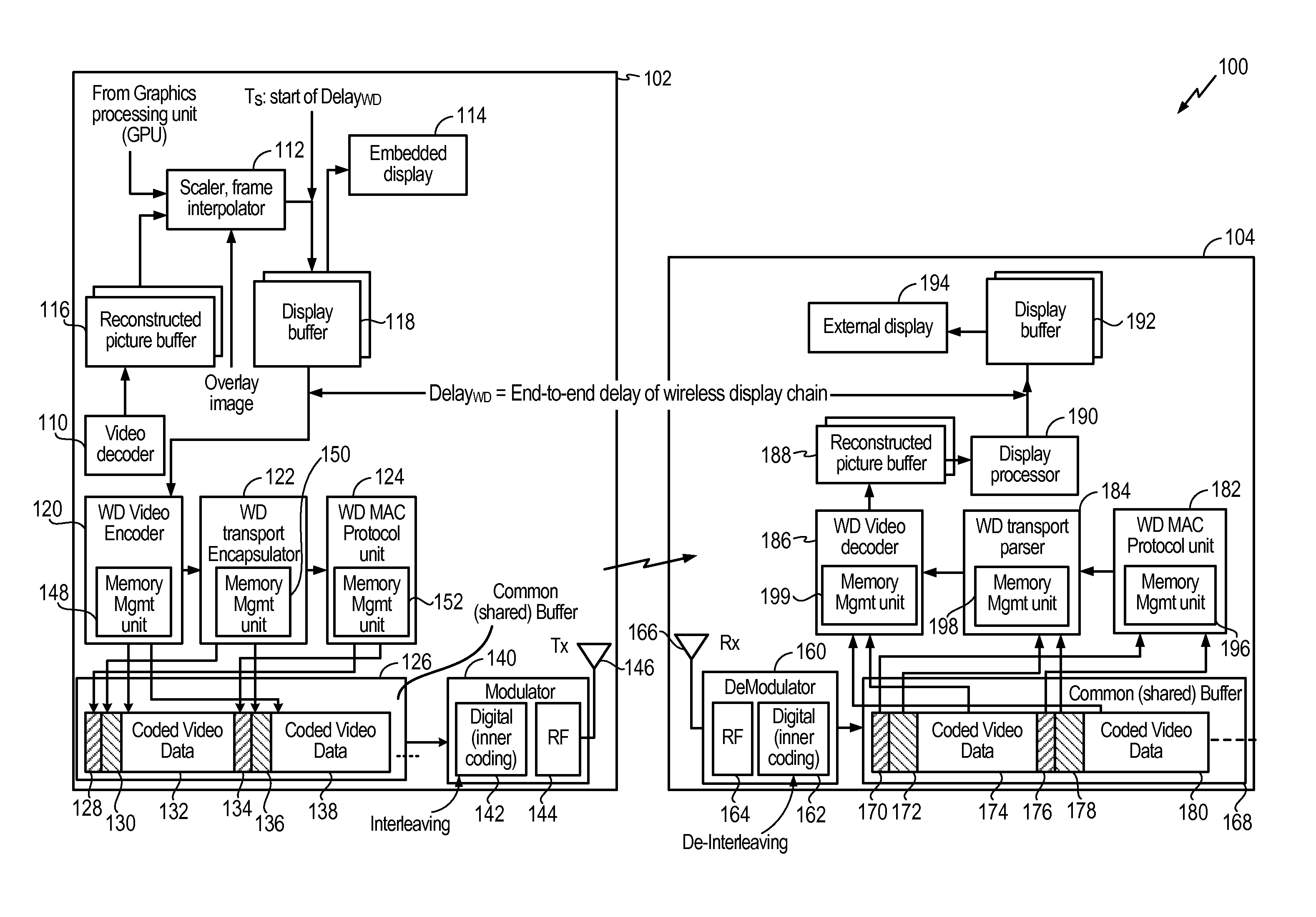

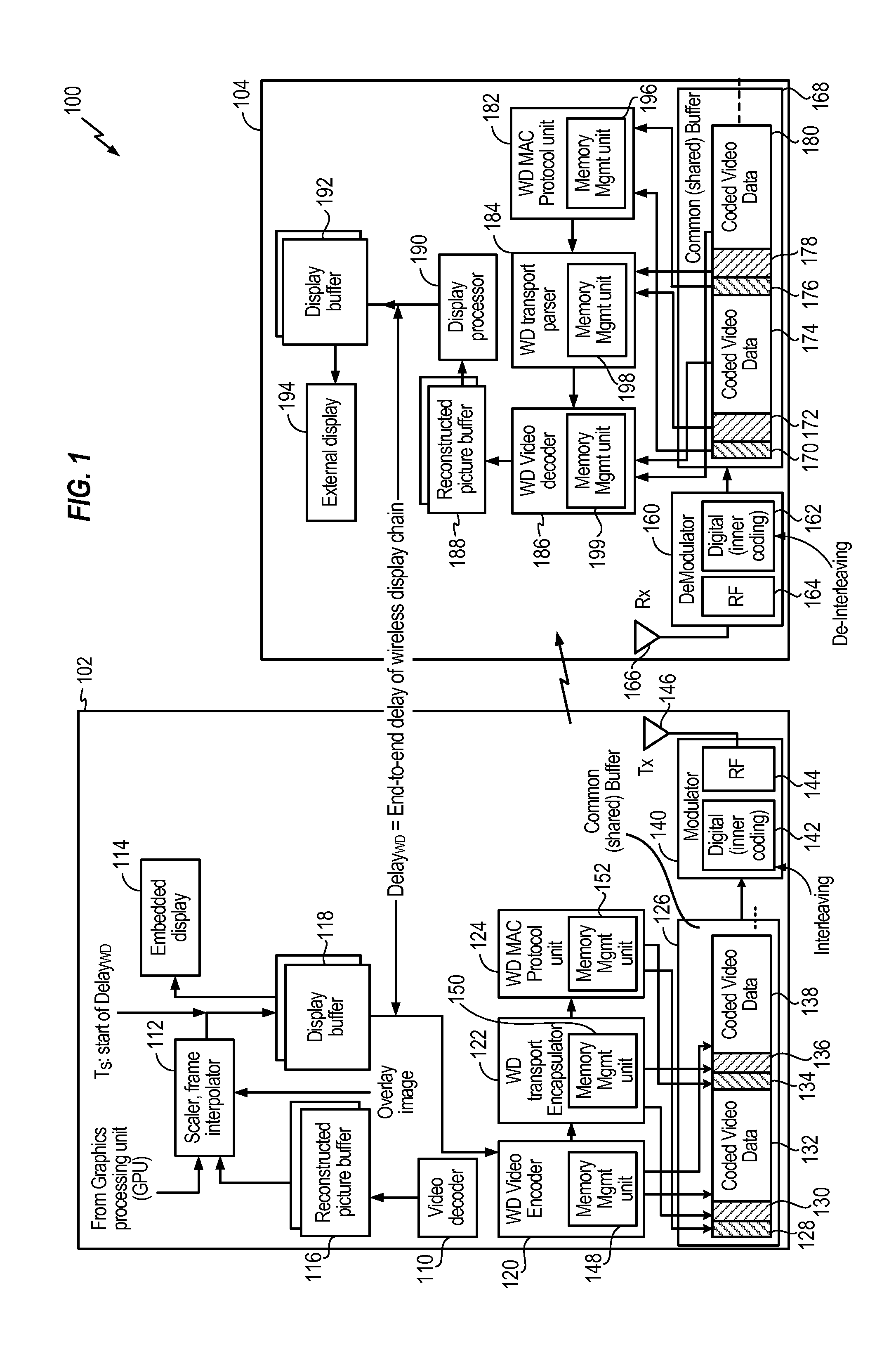

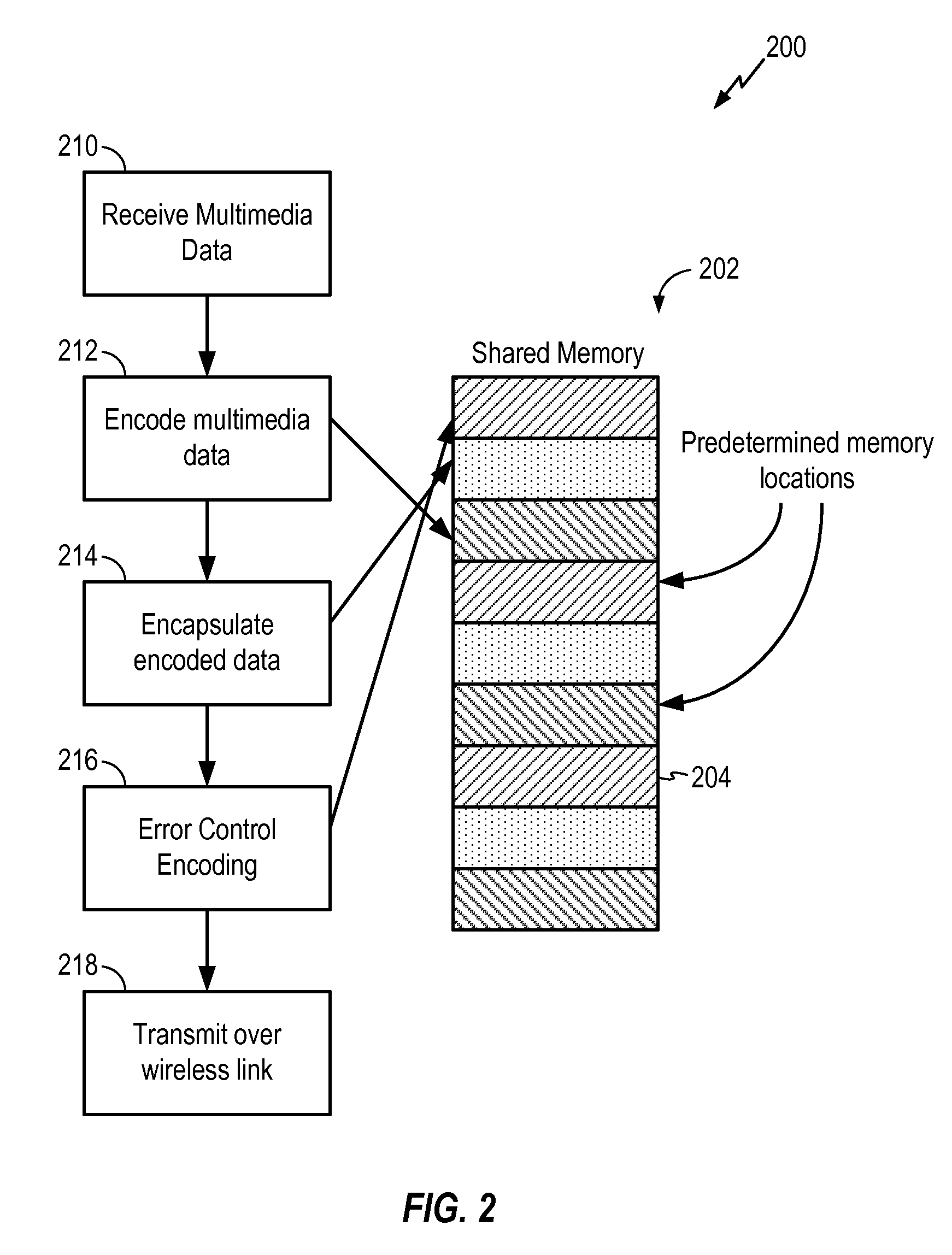

System and method of transmitting content from a mobile device to a wireless display

ActiveUS20110010607A1Special service provision for substationPulse modulation television signal transmissionEncapsulated dataDisplay device

A method of transmitting content to a wireless display device is disclosed. The method may include receiving multimedia data, encoding the multimedia data, and writing encoded multimedia data into a first predetermined memory location of a shared memory. Further, the method may include encapsulating the encoded multimedia data and writing encapsulation data into a second predetermined memory location of the shared memory. The method may also include calculating error control encoding and writing the error control encoding into a third predetermined memory location of the shared memory. Further, the method may include transmitting the encoded multimedia data, the encapsulation data, and the error control encoding to the wireless display device.

Owner:QUALCOMM INC

Universal error control coding system for digital communication and data storage systems

InactiveUS7831895B2Reduce complexity and chip area and chip power consumptionReduce complexityError detection/correctionCode conversionComputer architectureForward error correction

The universal forward error-correction coding system provides adjustable code rates and coding gains to greatly benefit the design of many modern digital communications (data storage) systems. The channel encoding and decoding methods are universal such that a single encoder and a single decoder can be used to implement all the forward error-correction codes of different code rates. This universal forward error-correction coding system also includes a novel systematic code generation procedure that has the capability of generating many classes of codes that provide the best balance between coding gain performance and implementation complexity.

Owner:COMM CODING

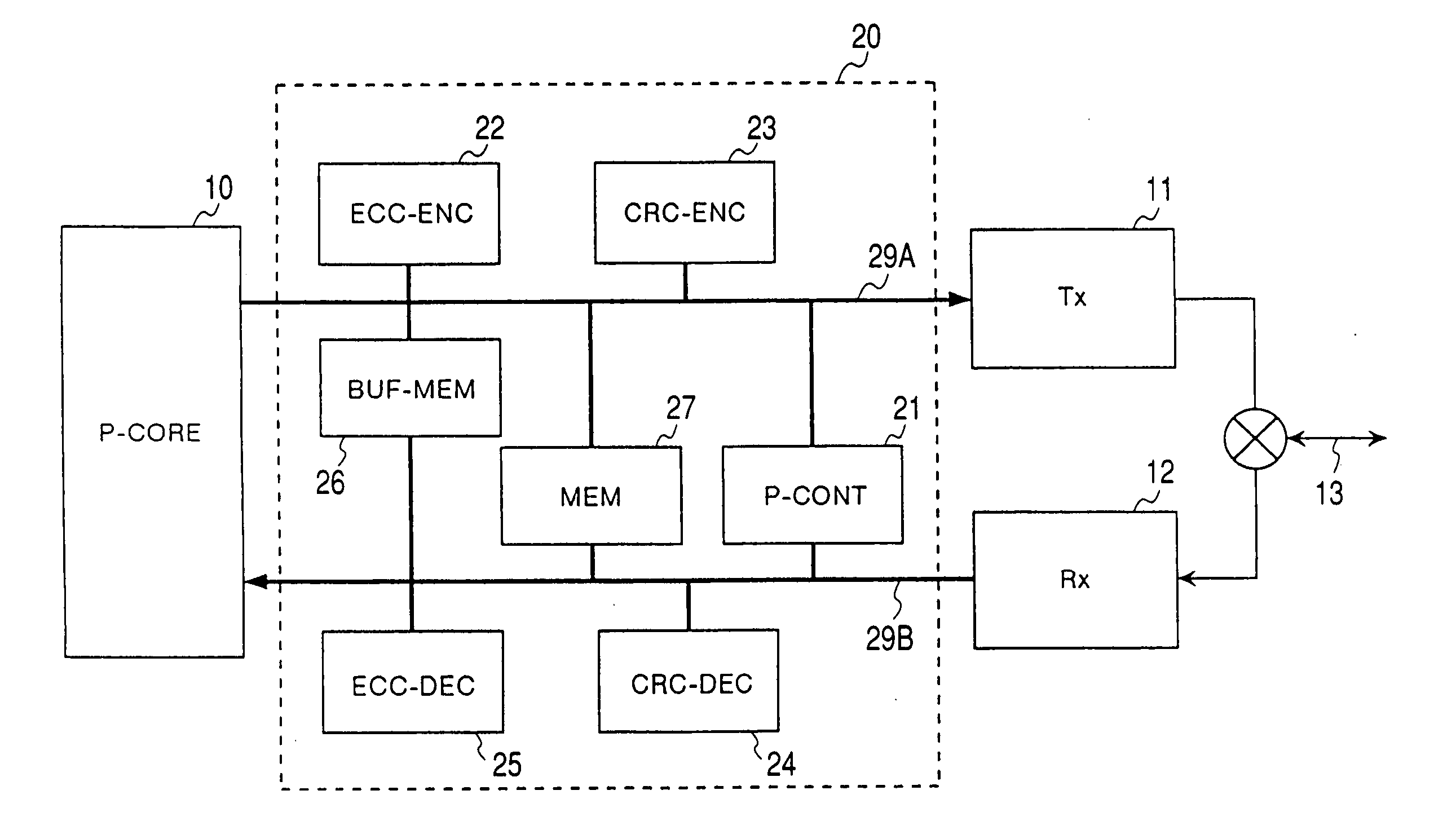

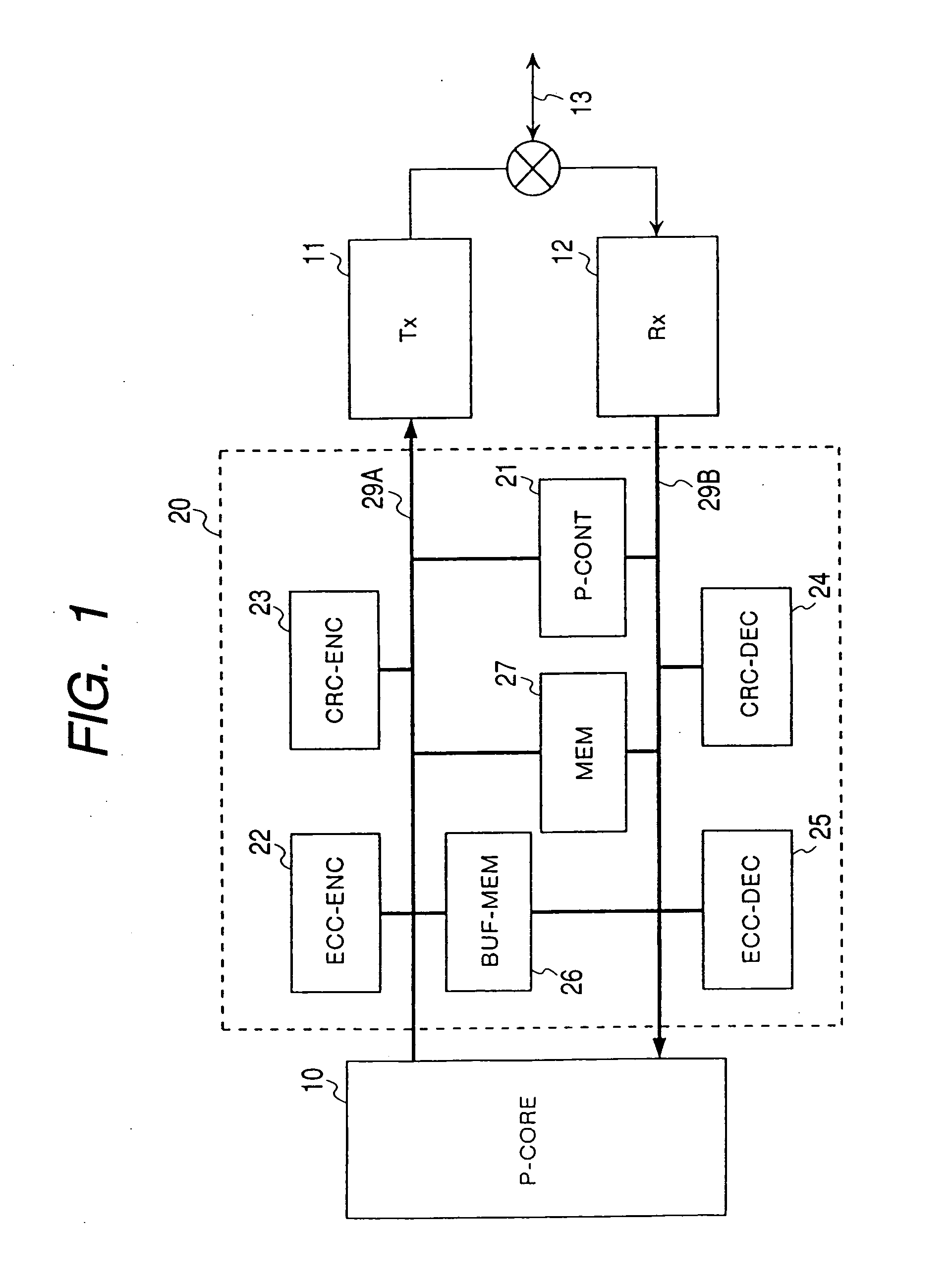

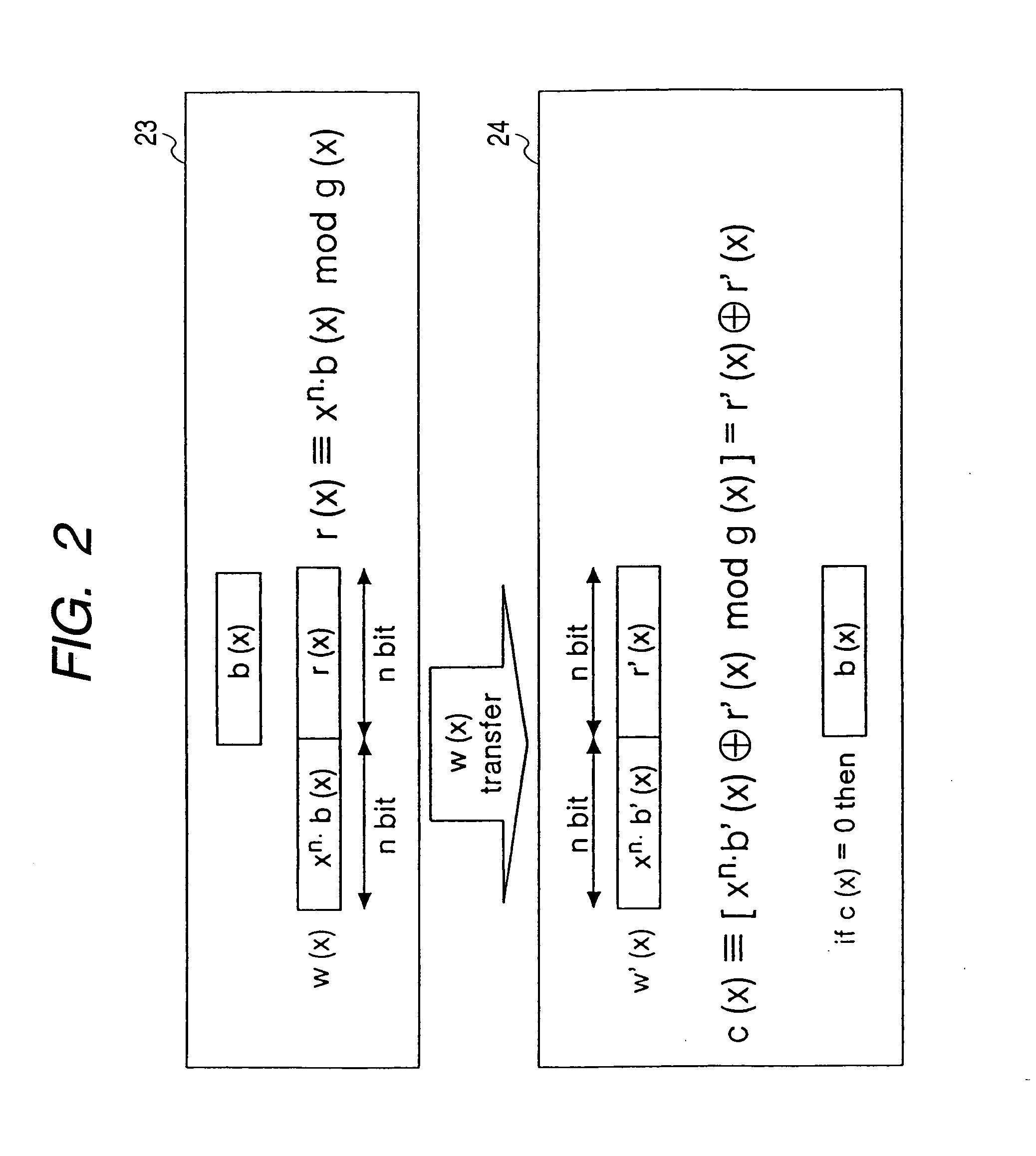

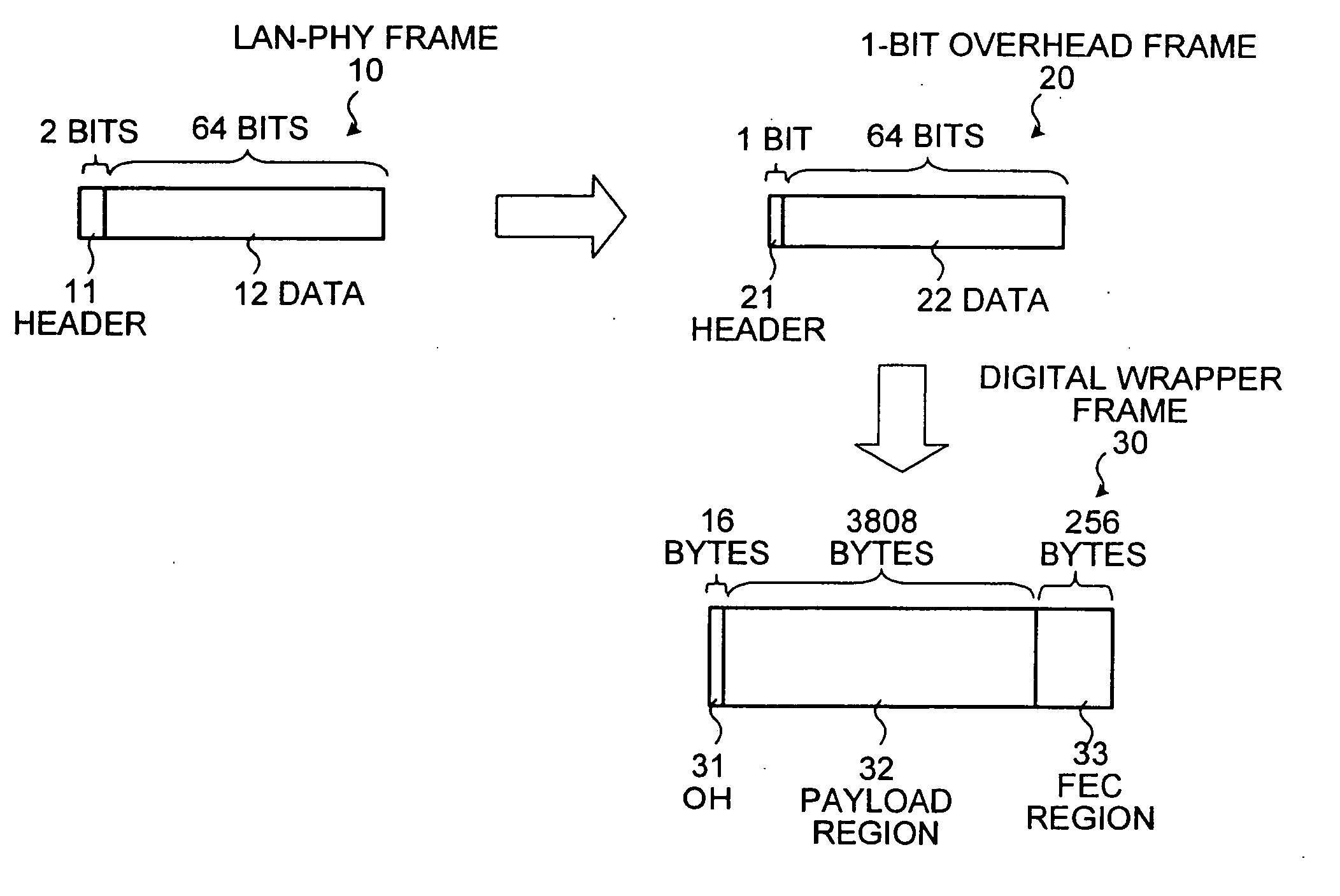

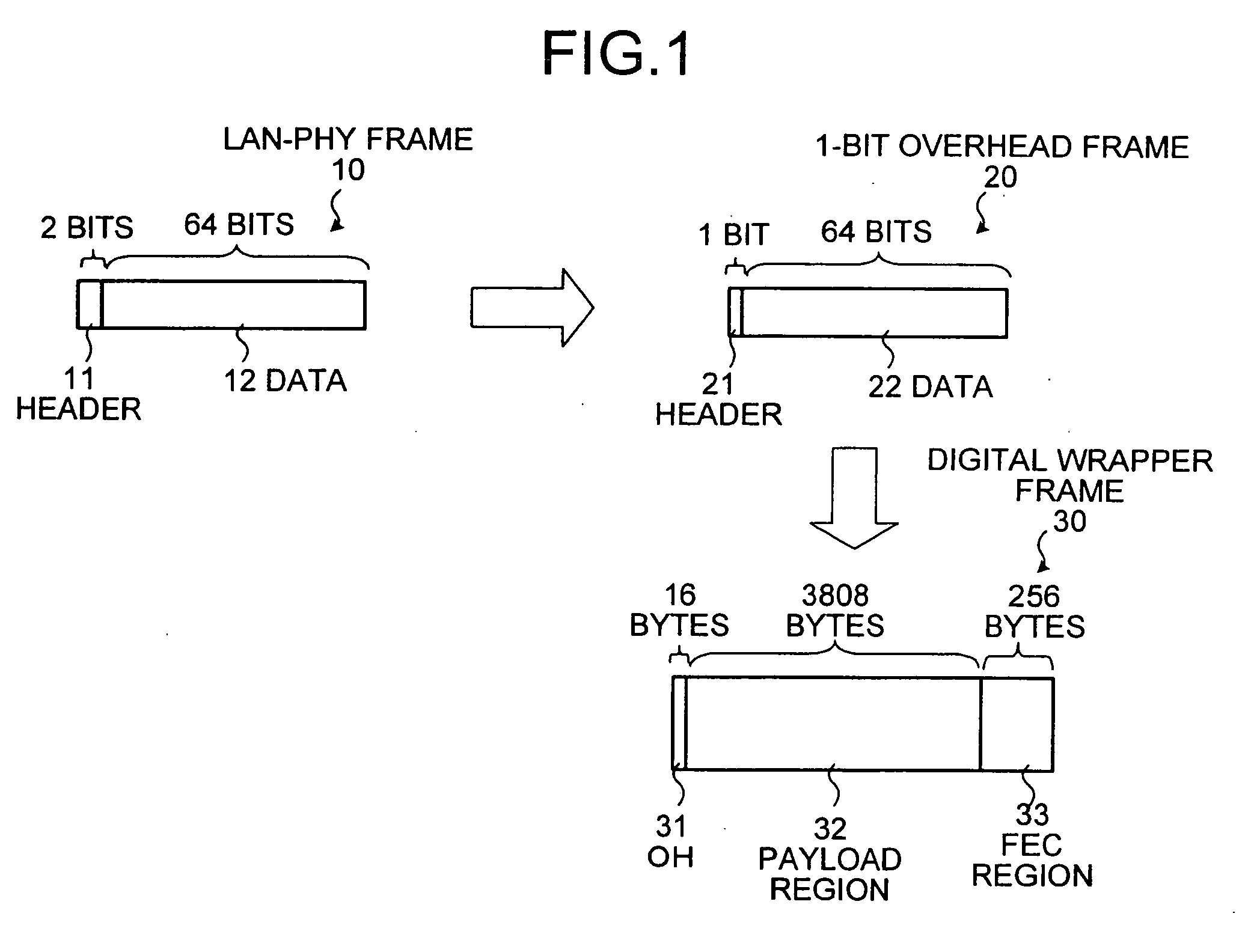

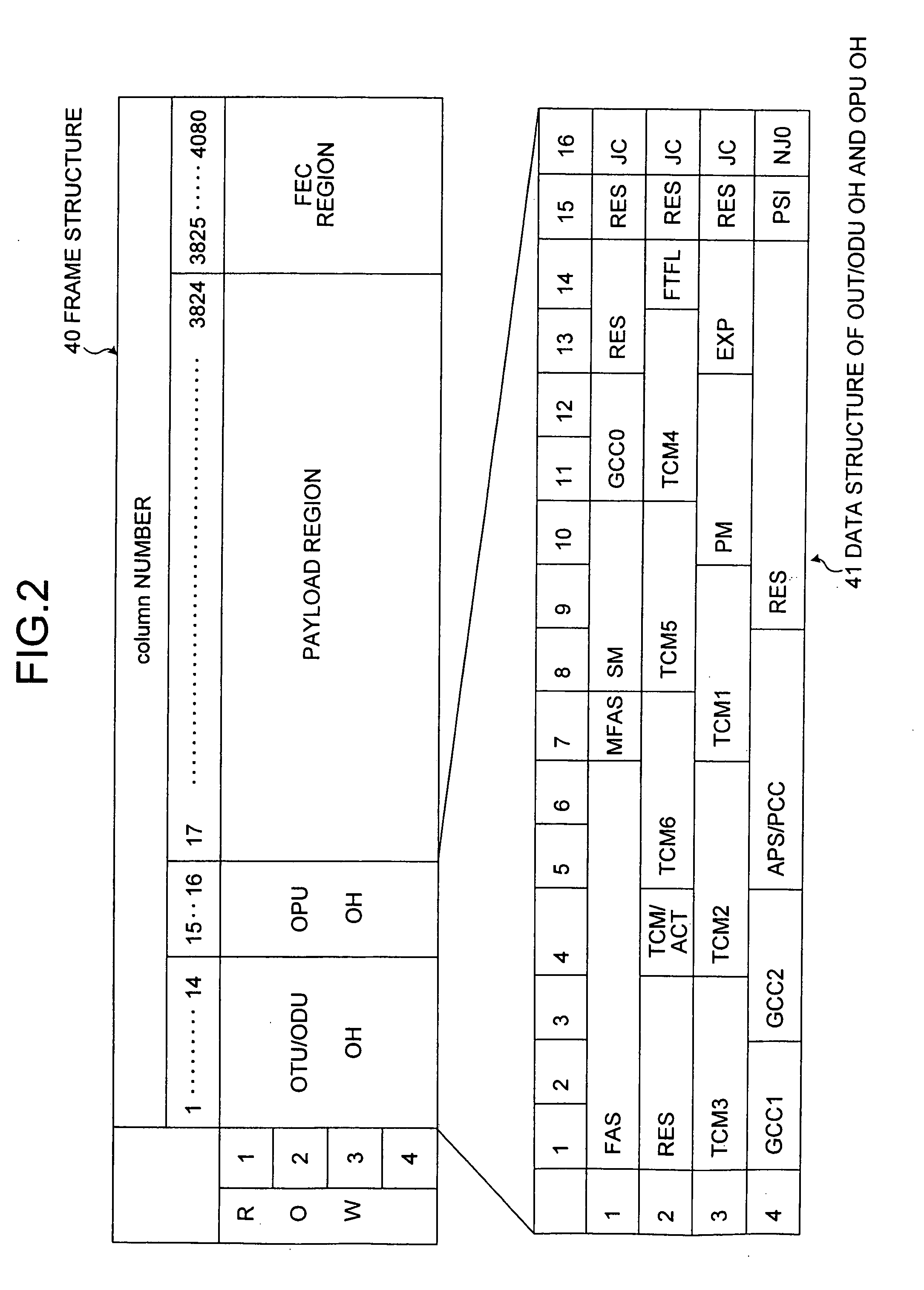

Frame transmitting apparatus and frame receiving apparatus

A frame transmitting apparatus that transmits a frame including data to be transmitted or a frame including control data for a data-transmission control via a network includes a frame generating unit that generates a frame including identification-information-added data to which 1-bit identification information indicating whether a block obtained by dividing data into every n bits includes the control data is added, where n is a positive integer, and an error control code for a data-transmission error control; and a frame transmitting unit that transmits the frame generated.

Owner:FUJITSU LTD

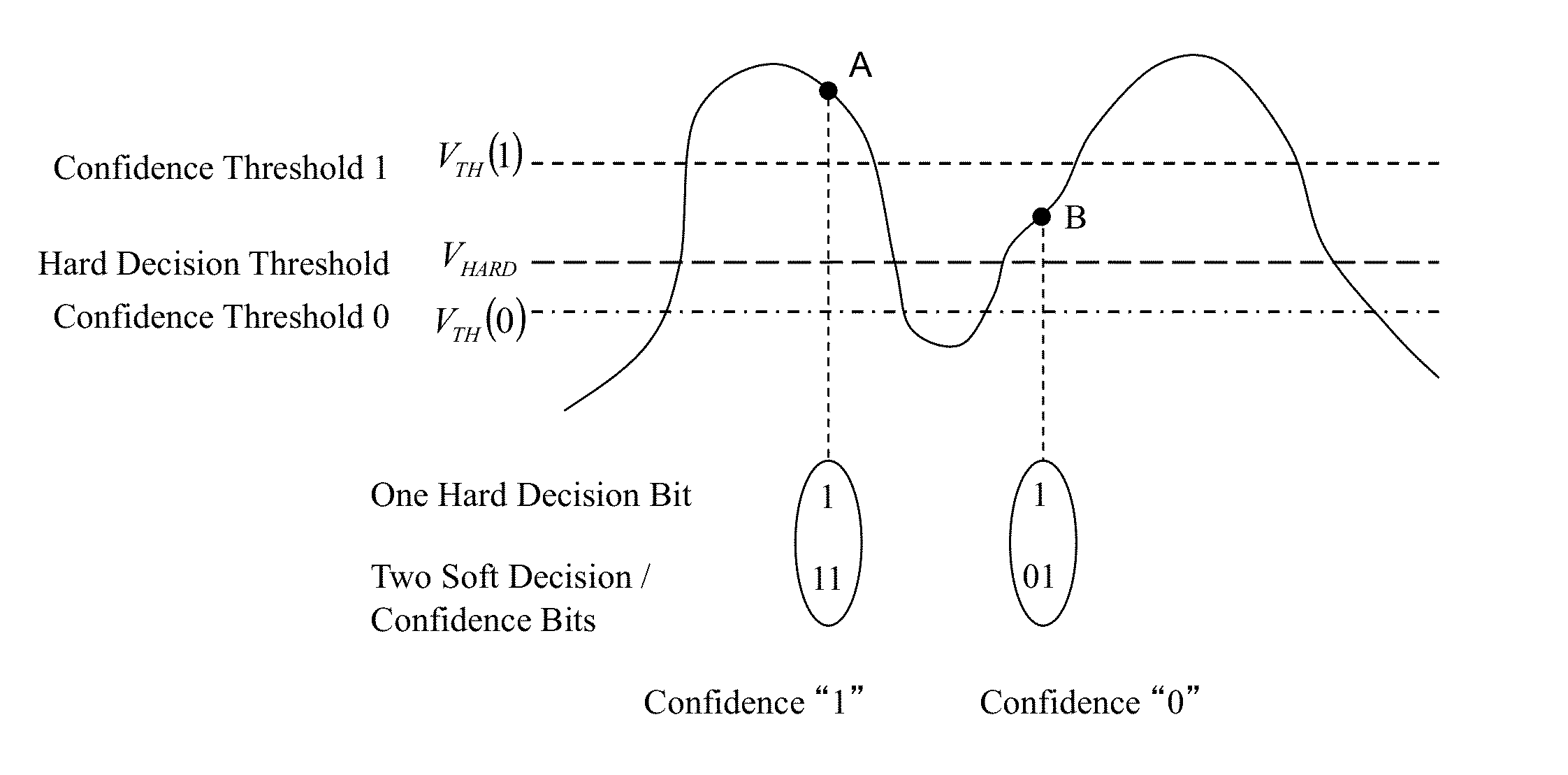

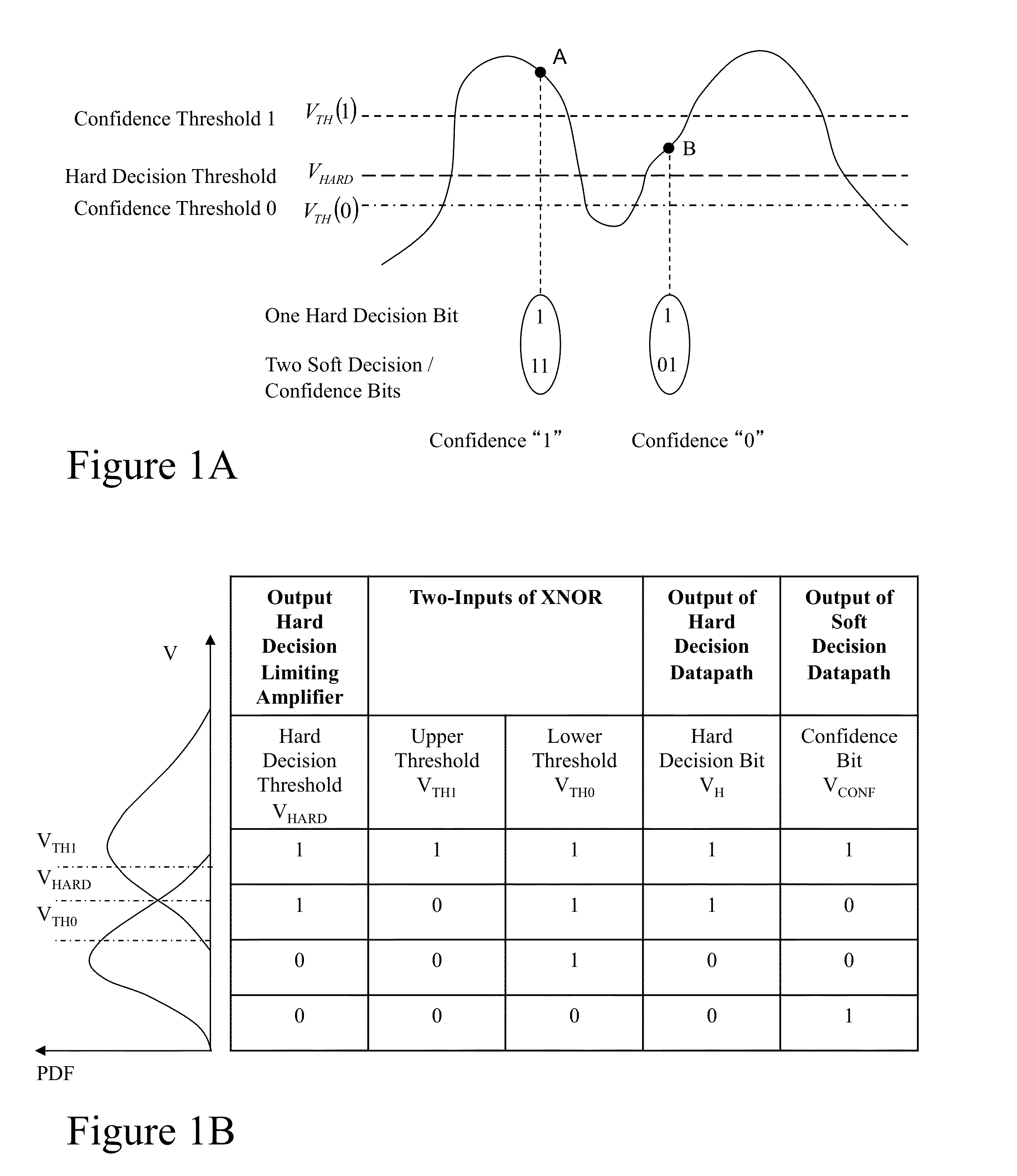

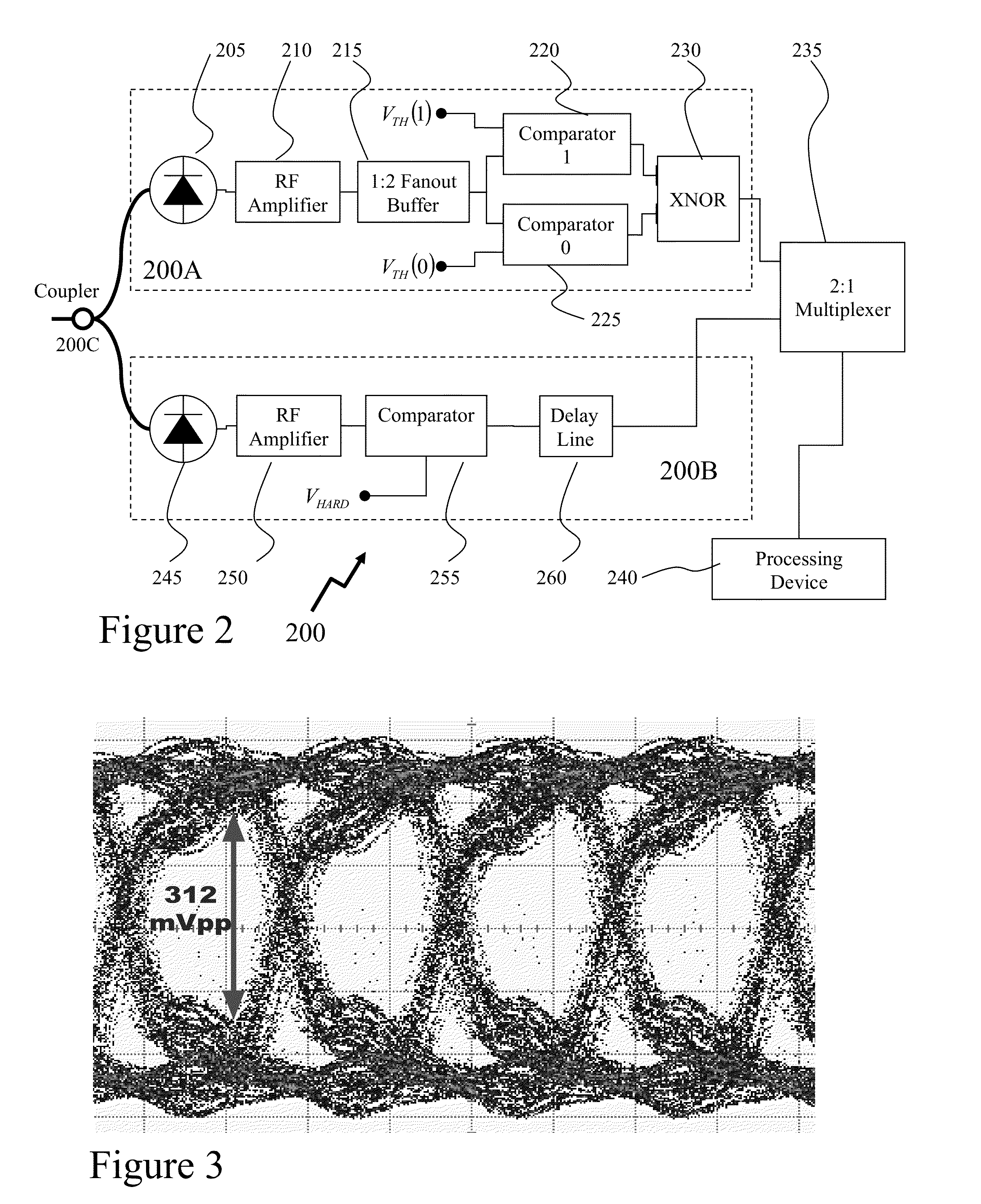

Methods and Systems for Optical Receivers

ActiveUS20130294782A1Reduce complexityOther decoding techniquesCode conversionQuality of serviceFiber

Broadband access networks are driving the upgrade of DWDM networks from 10 Gb / s per channel to more spectrally-efficient 40 Gb / s or 100 Gb / s. Signal quality degradation due to linear and non-linear impairments are significant and error control coding and signal processing solutions play increasingly key roles in meeting increasing demand, providing improved quality of service, and reduced cost. It would be beneficial to reduce the power consumption of optical receivers for optical links exploiting for example LPDC encoding. Accordingly, the inventors have established a low complexity soft-decision front-end compatible with deployable LDPC codes in next-generation optical transmission systems. Beneficially the optical receiver design can be retro-fitted into deployed hard-decision based optical systems and replaces the 3-to-2 encoder of the prior art in the electrical portion of the receiver with a single gate design. Further, the design may act as a 2-bit Flash ADC in multimode fiber based optical receivers.

Owner:MCGILL UNIV

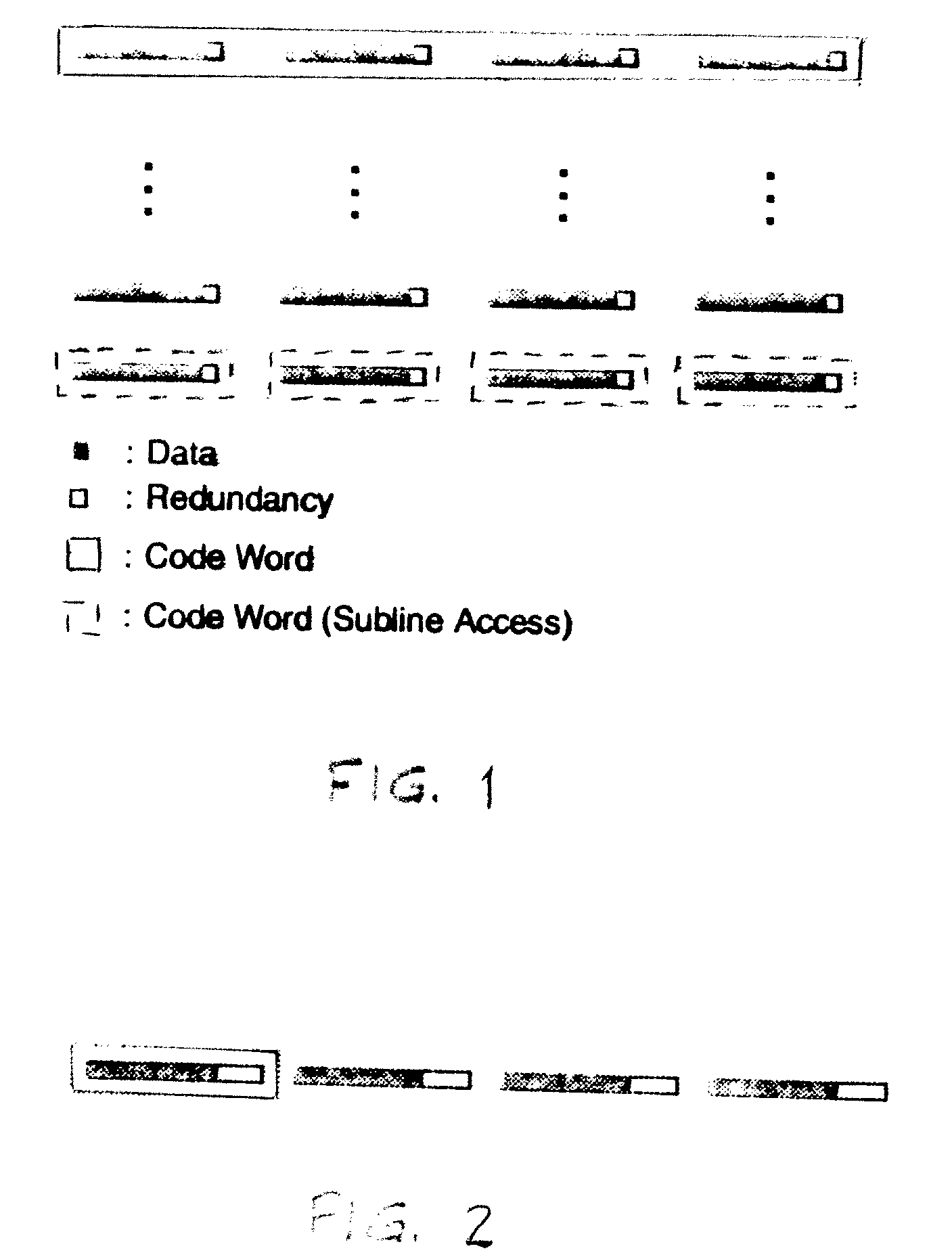

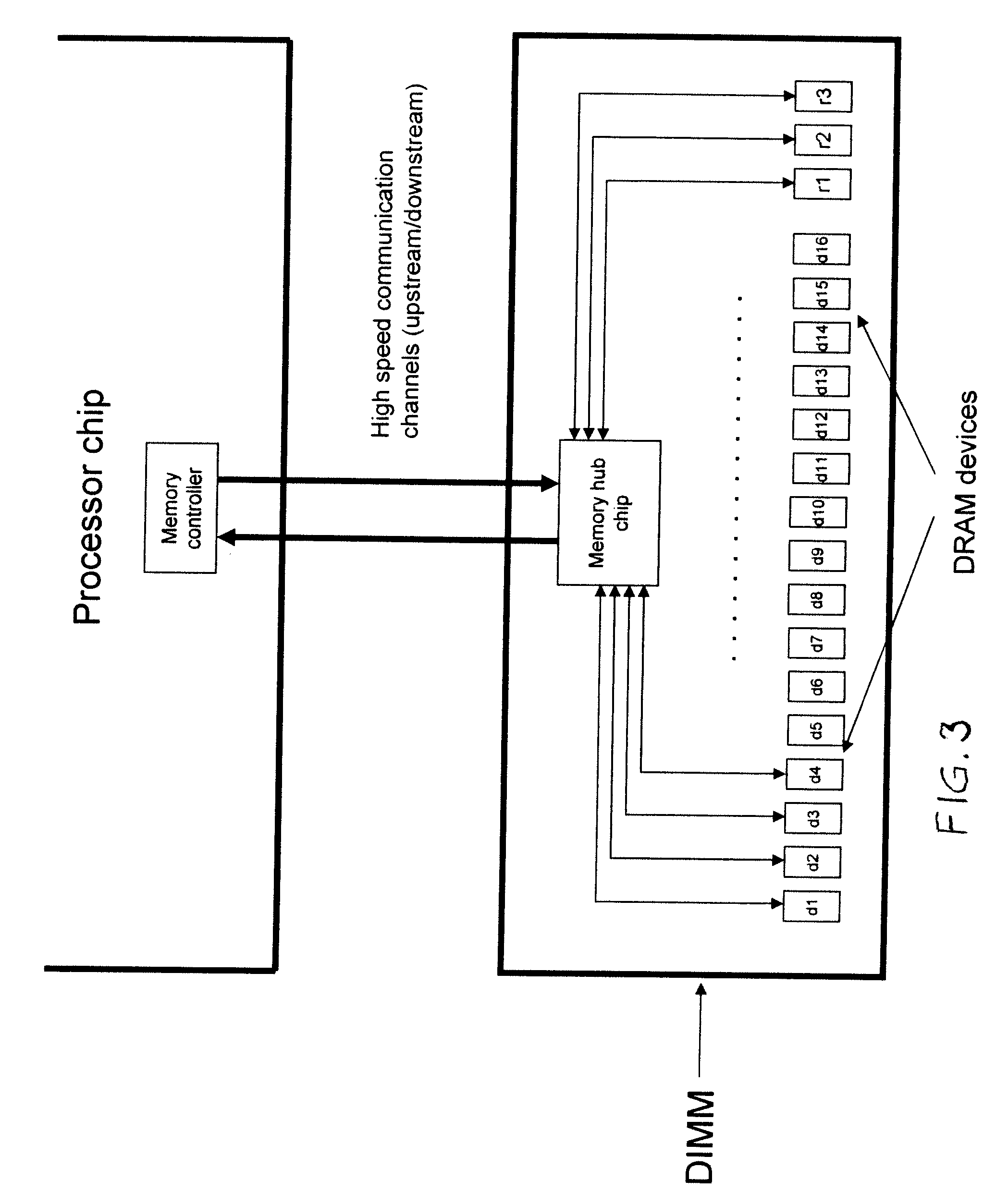

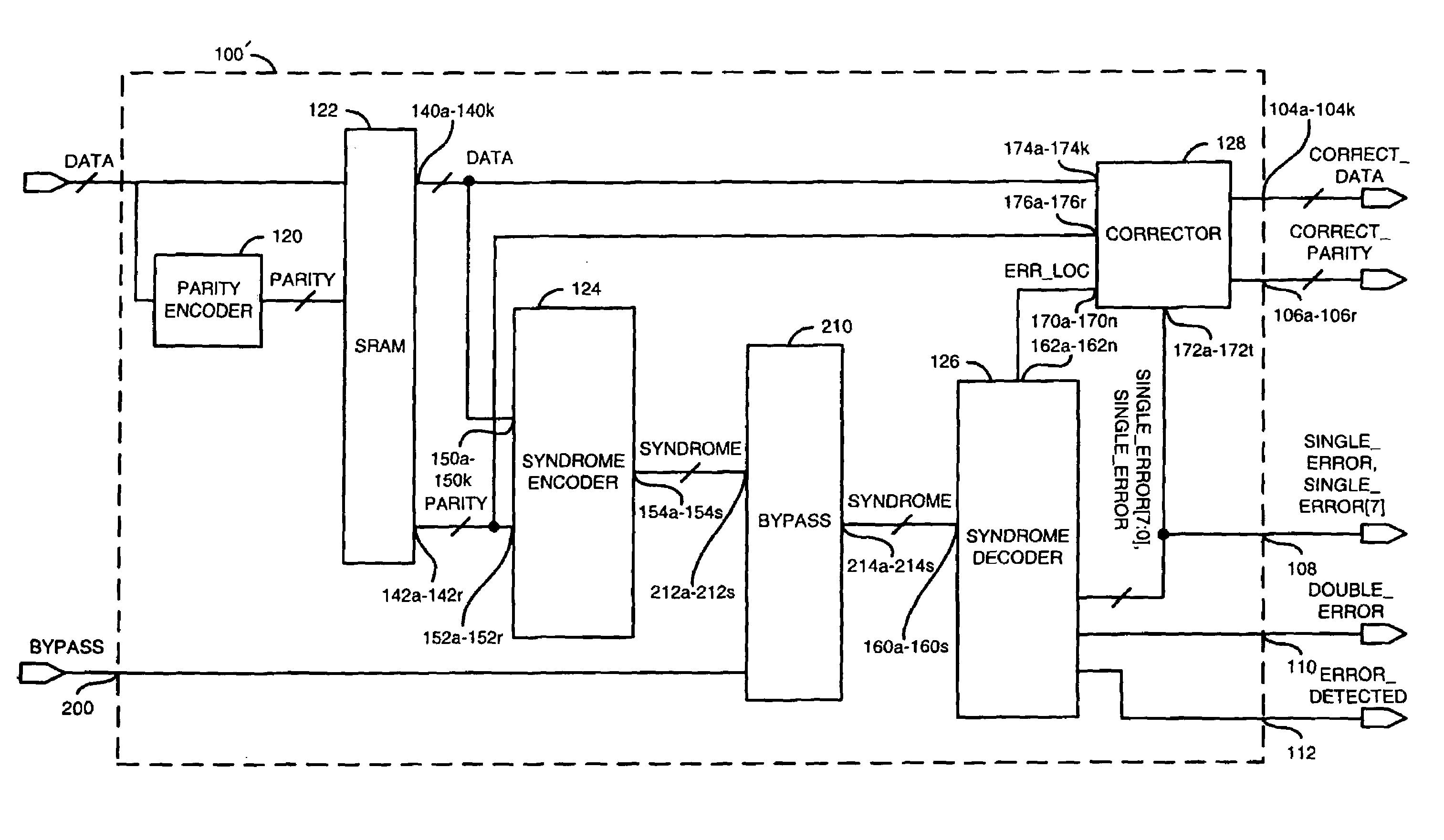

Error control coding methods for memories with subline accesses

InactiveUS20080168329A1Long latencyError detection/correctionCode conversionComputer scienceReal-time computing

A two-level error control protocol detects errors on the subline level and corrects errors using the codeword for the entire line. This enables a system to read small pieces of coded data and check for errors before accepting them, and in case errors are detected, the whole codeword is read for error correction.

Owner:IBM CORP

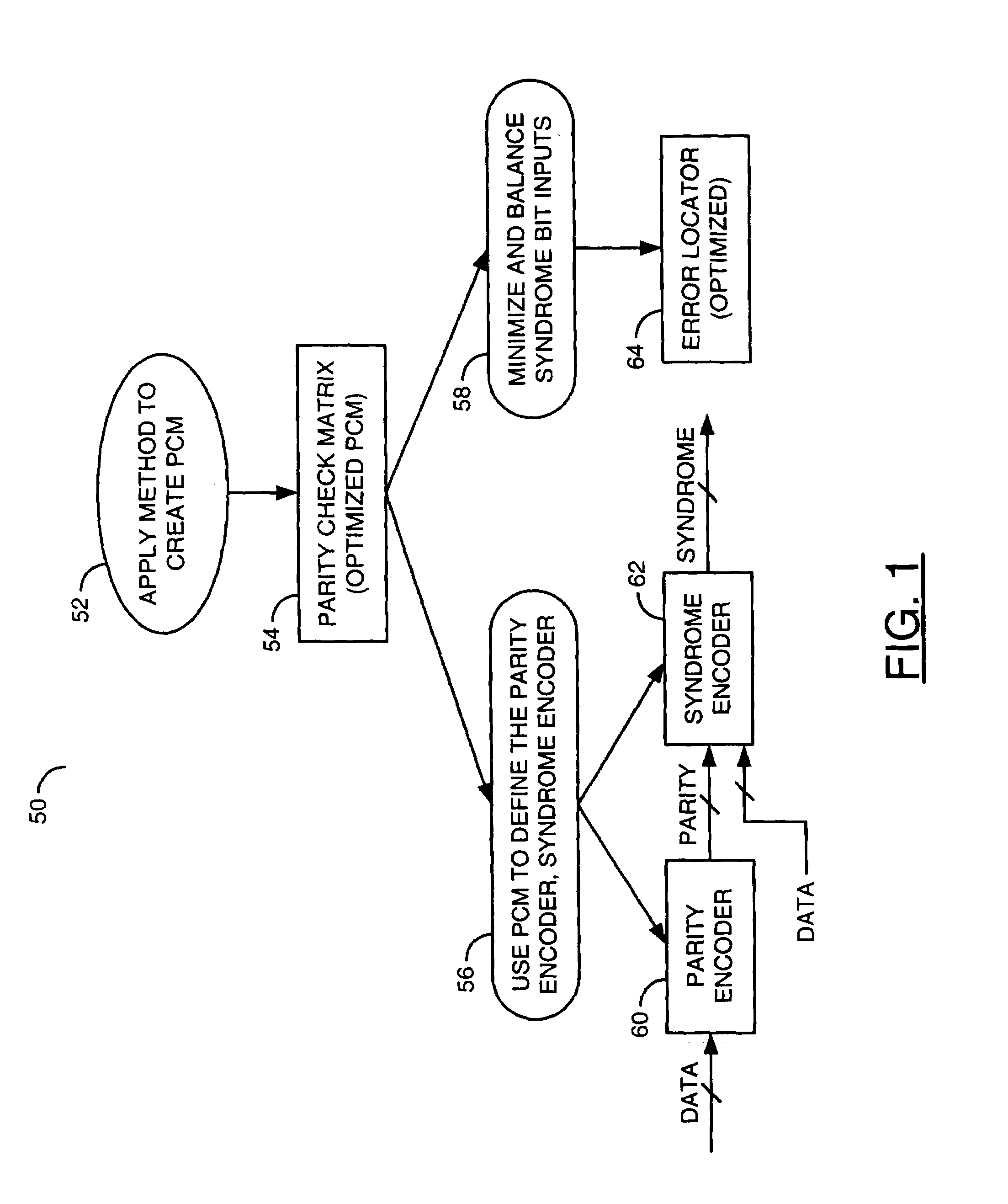

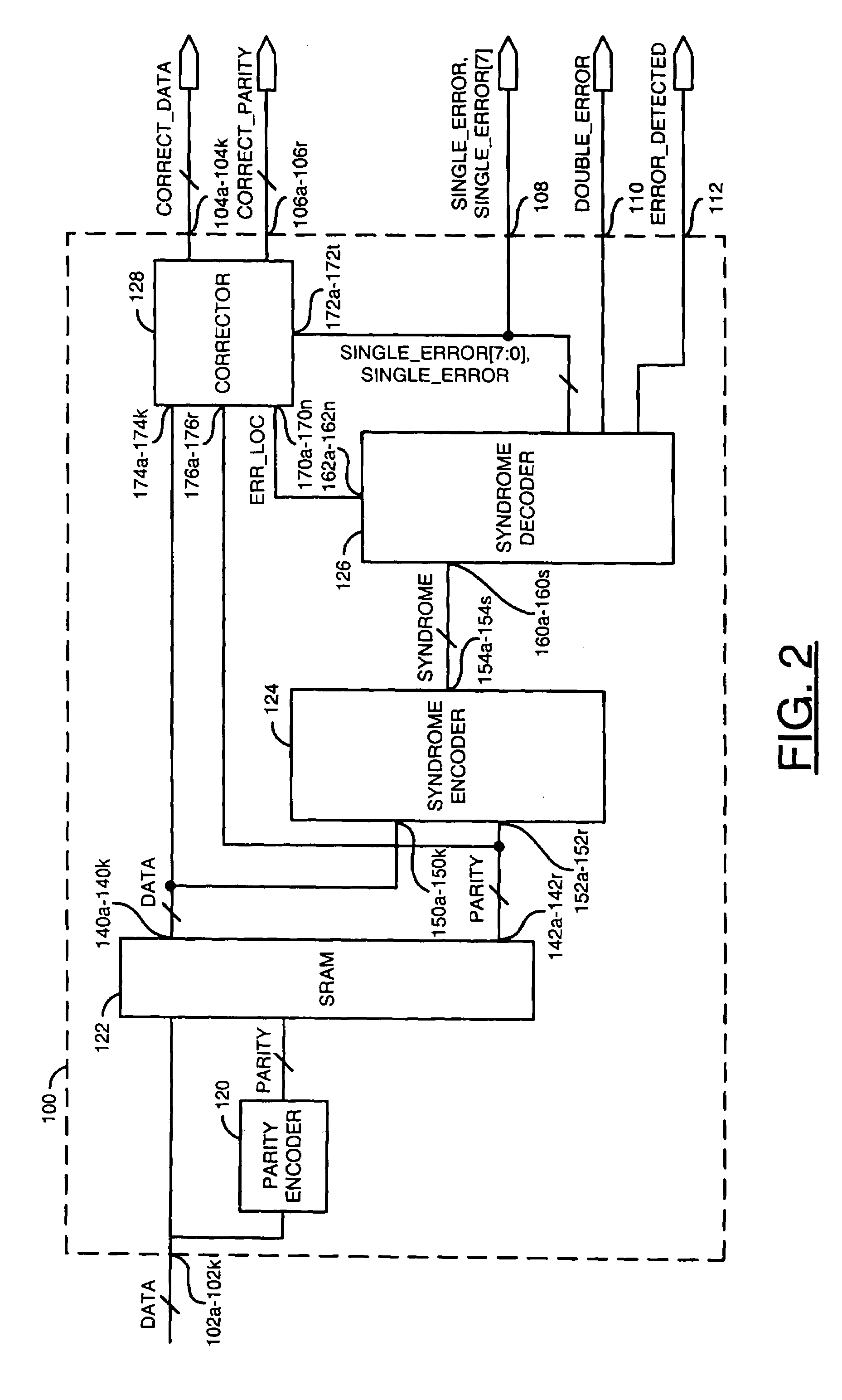

Construction of an optimized SEC-DED code and logic for soft errors in semiconductor memories

InactiveUS7117420B1Reduce soft errorsMinimizes circuit areaCode conversionCoding detailsError control codingSignal production

An apparatus for memory error control coding comprising a first circuit and a second circuit. The first circuit may be configured to generate a multi-bit digital syndrome signal in response to a read data signal and a read parity signal. The second circuit may be configured to (i) detect an error when the bits of the syndrome signal are not all the same state and (ii) generate an error location signal in response the syndrome signal. The error location signal may be generated in response to fewer than all of the bits of the syndrome signal.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

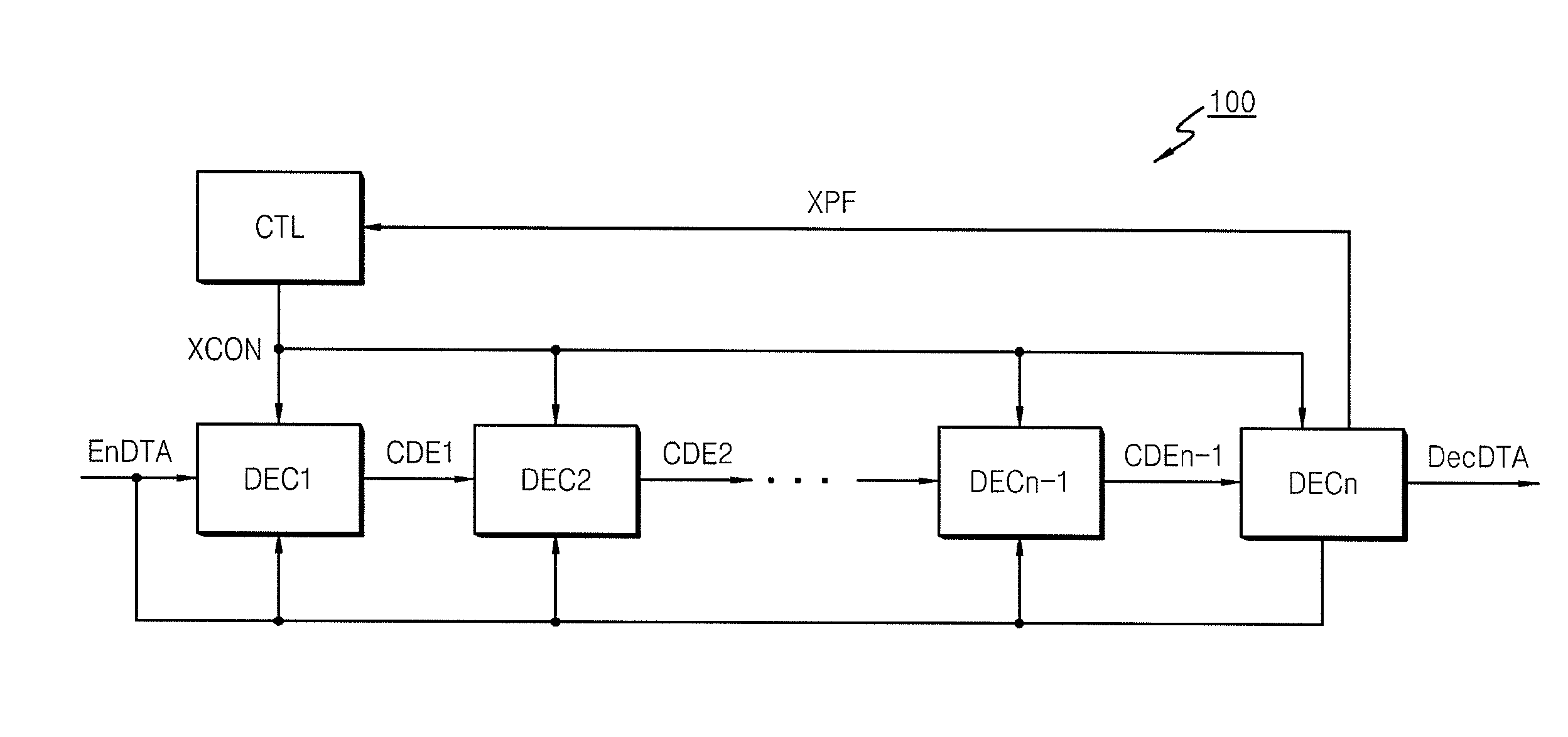

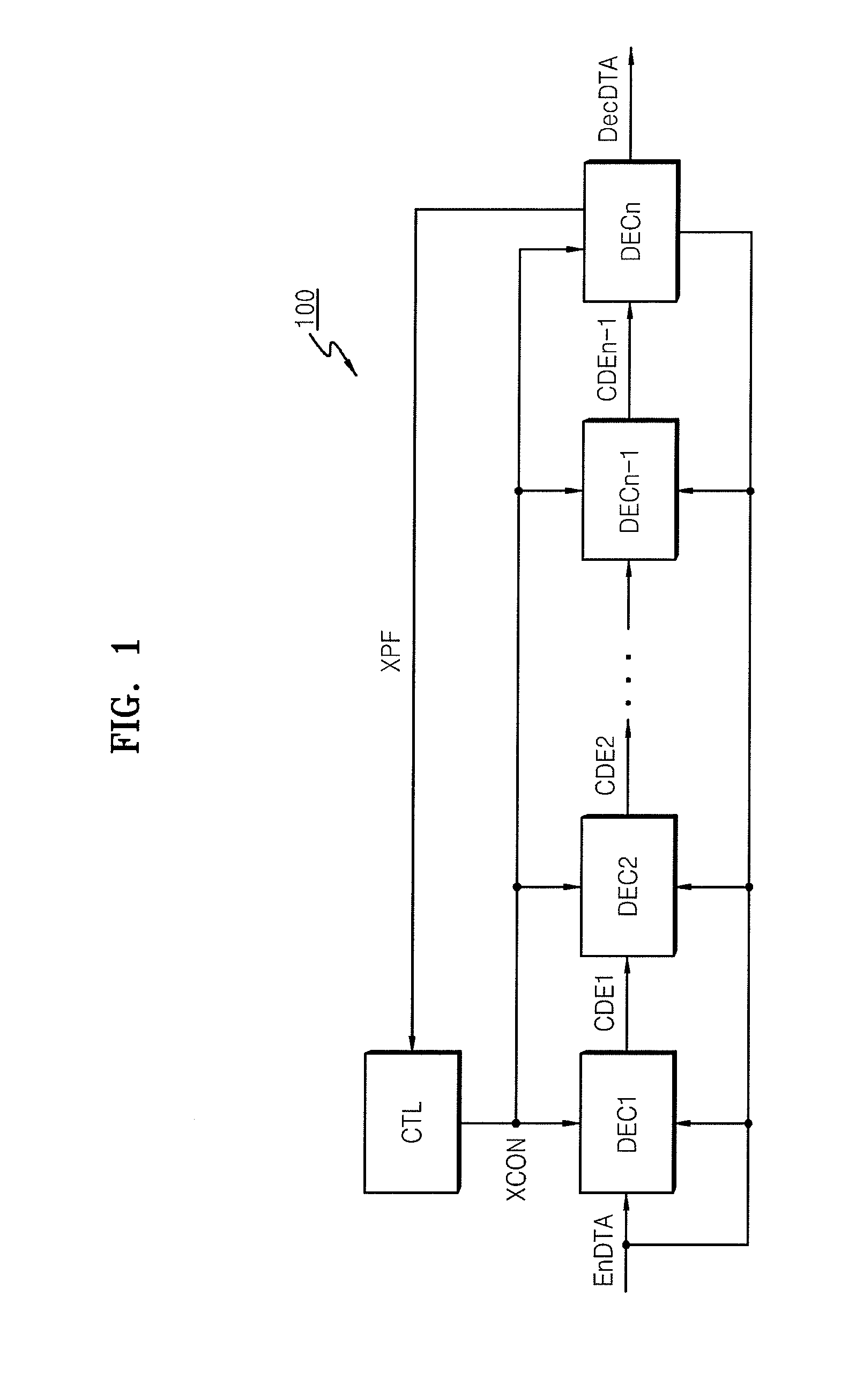

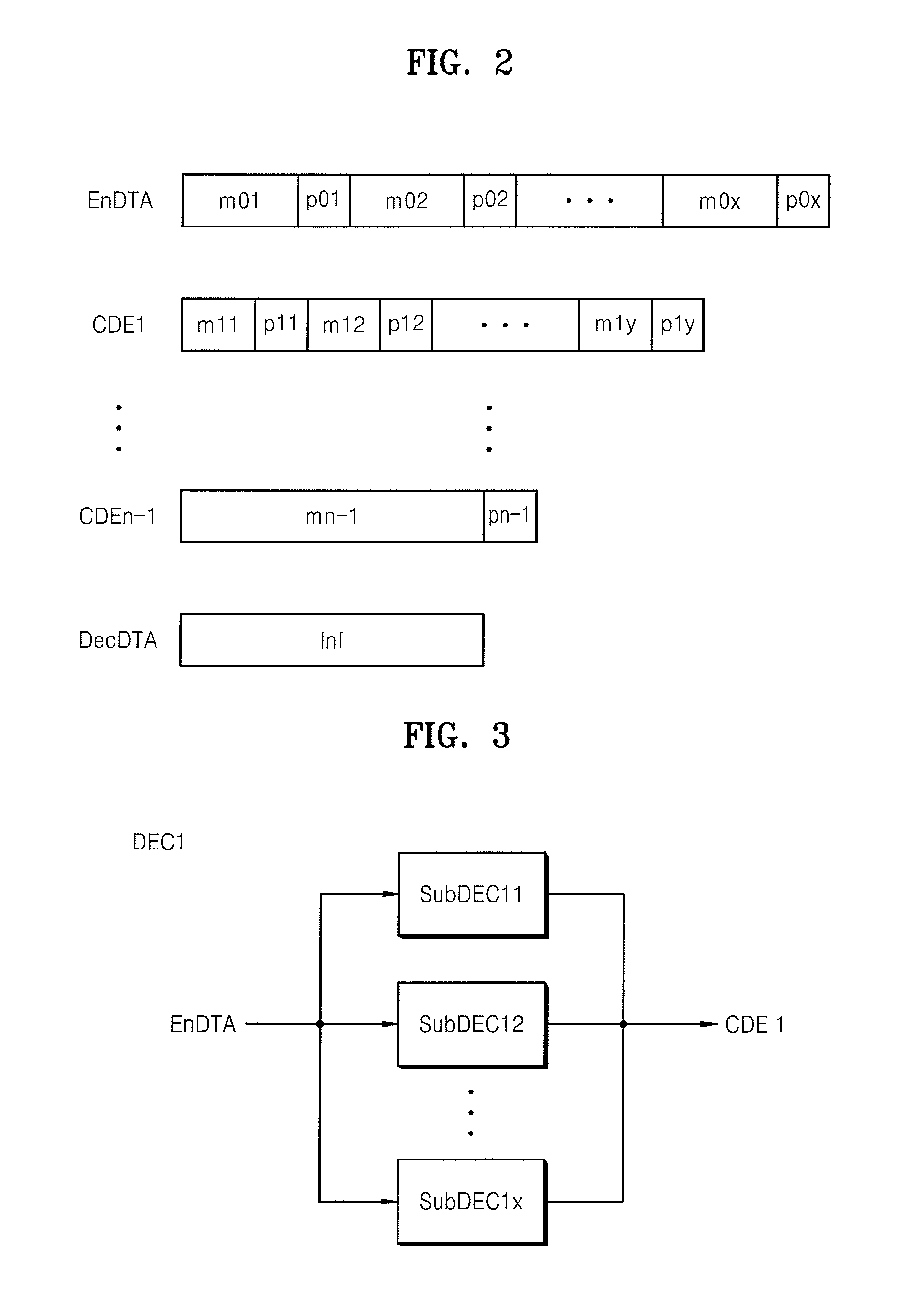

Semiconductor device and decoding method thereof

ActiveUS20110246853A1Correction can not be performedReduce power consumptionCode conversionAmplitude-modulated carrier systemsComputer hardwareControl signal

An error control coding (ECC) circuit includes a first decoder, a second decoder, and a controller. The first decoder receives encoded data comprising a first parity and a second parity. The first decoder decodes the encoded data to a first code by using the first parity. The second decoder is connected to the first decoder. The second decoder is configured to decode the encoded data when the first decoder is deactivated and decode the first code using the second parity when the first decoder is deactivated. The controller transmits a control signal to the first decoder and the second decoder to control the first decoder and the second decoder.

Owner:SAMSUNG ELECTRONICS CO LTD

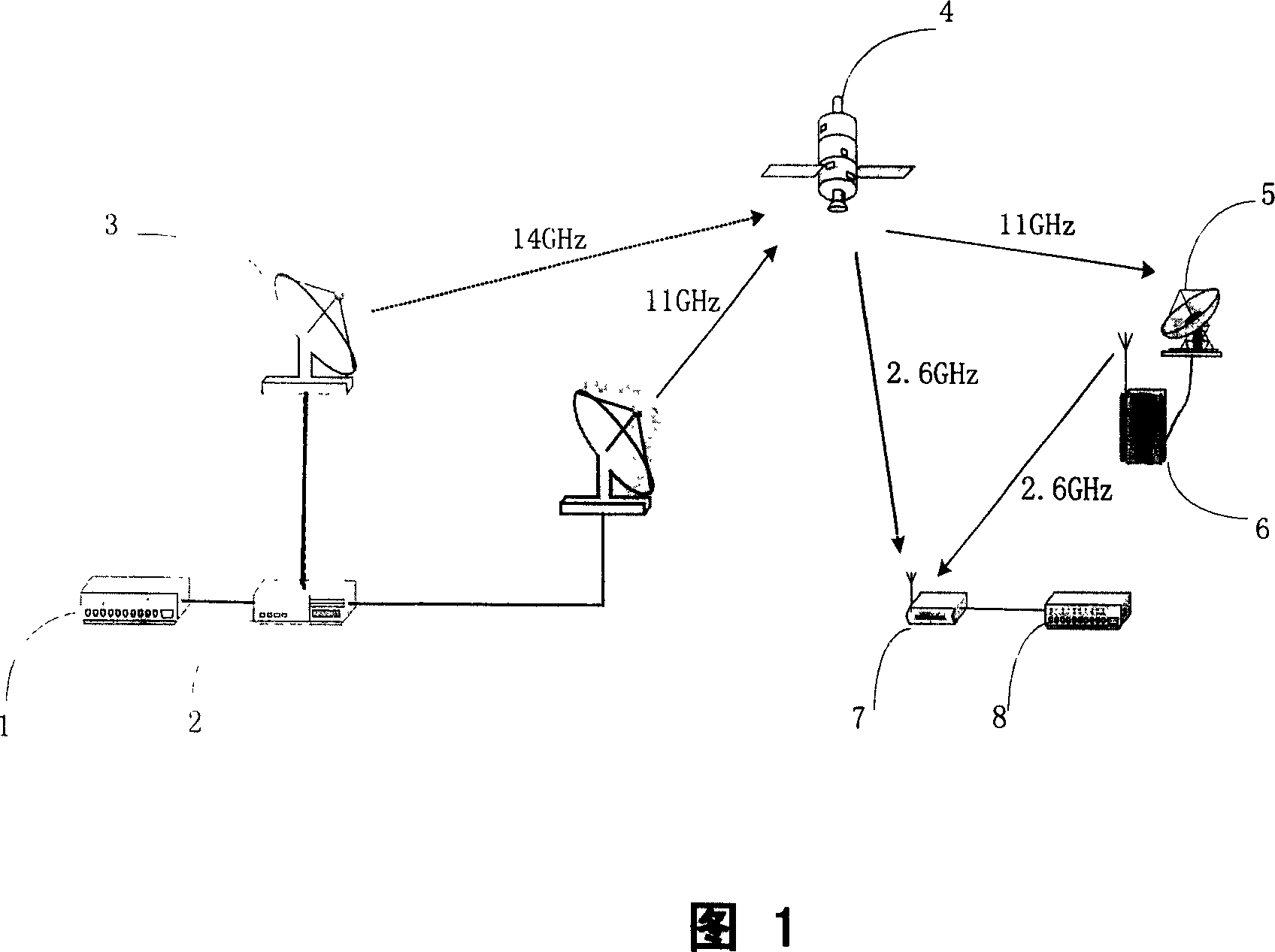

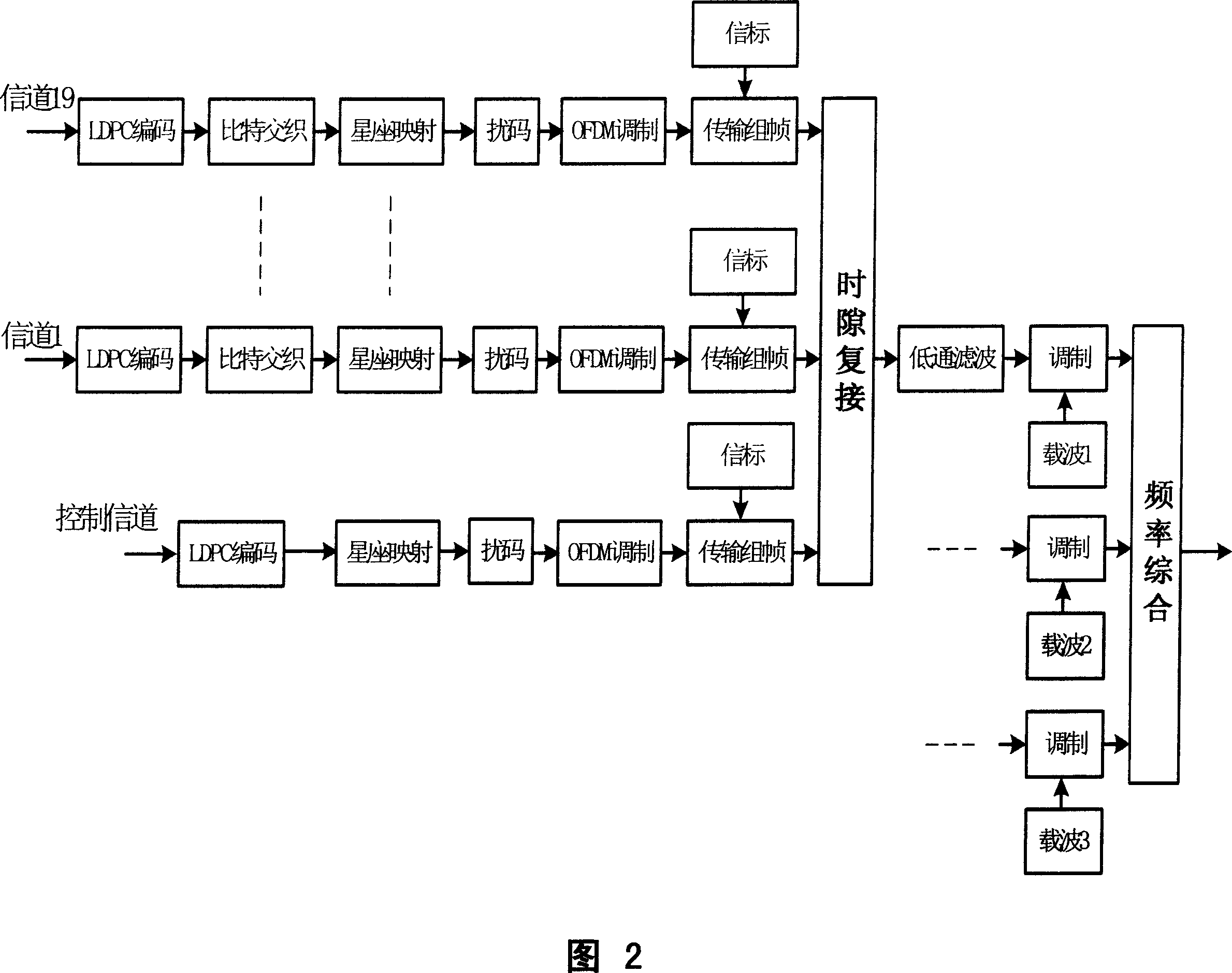

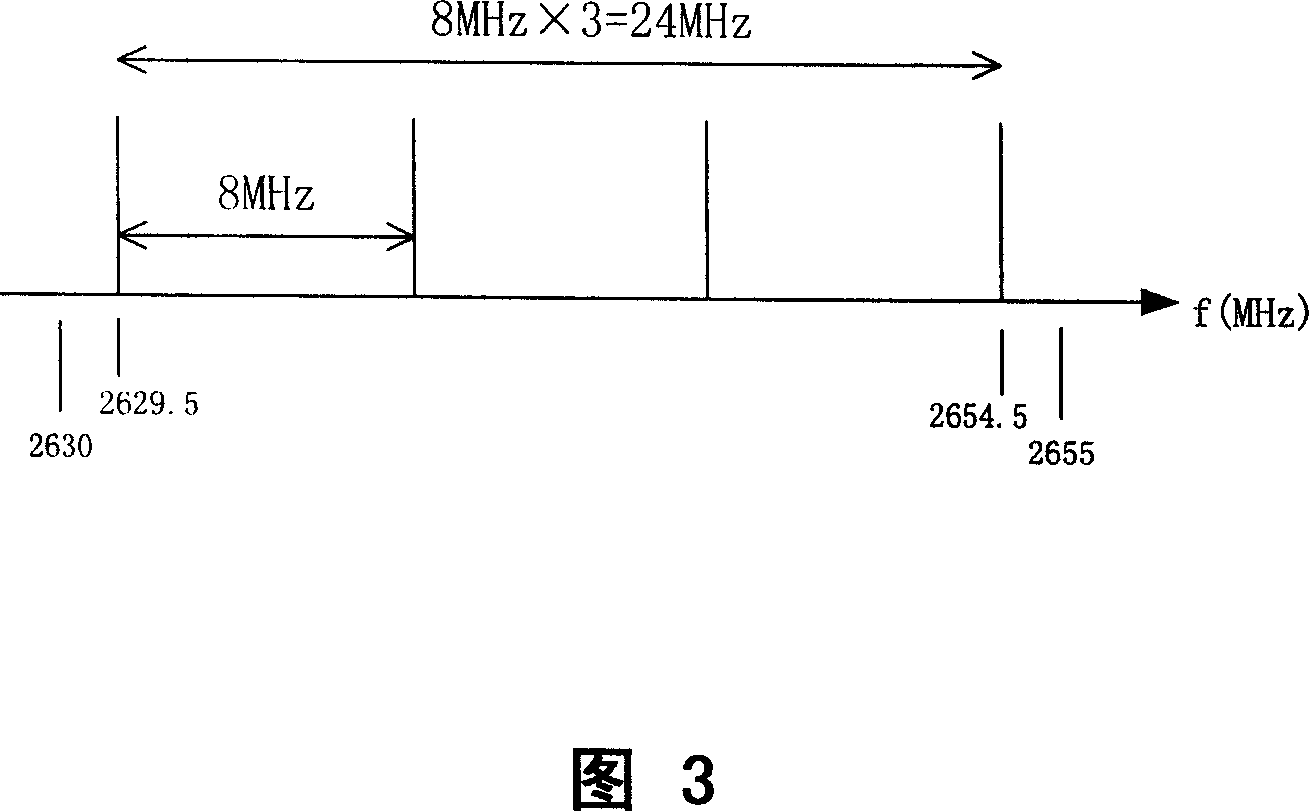

Multi-carrier digital satellite broadcasting system and digital information transmission method thereof

InactiveCN1949692ARealize flexible reuseMeet mobile receptionSatellite broadcast receivingGHz frequency transmissionData streamSatellite broadcasting

The invention relates to a multicarrier digital satellite broadcasting system and the digital information transmitting method thereof, comprising signal source coder, code modulator, transmitter, satellite, user demodulator and signal source decoder, where the signal source coder encodes analog signal into digital signal, which is transmitted to the code modulator for error control coding, constellation mapping, scrambling, OFDM modulation and signal mark addition to obtain transmitted frame group; the transmitted frame group is processed by time gap multiplexing, low-pass filtering, carrier high frequency modulation and synthesizing of various frequency data and finally transmitted to the transmitter; the transmitter transmits the high frequency signal to the satellite and is received by the user demodulator by satellite broadcast; the user demodulator detects signal and demodulates the signal into data stream and transmits the data stream to the signal source decoder to be decoded into analog signal to be outputted to terminals. And it implements flexible multiplexing of multicast services and improves system flexibility.

Owner:TIMI TECH

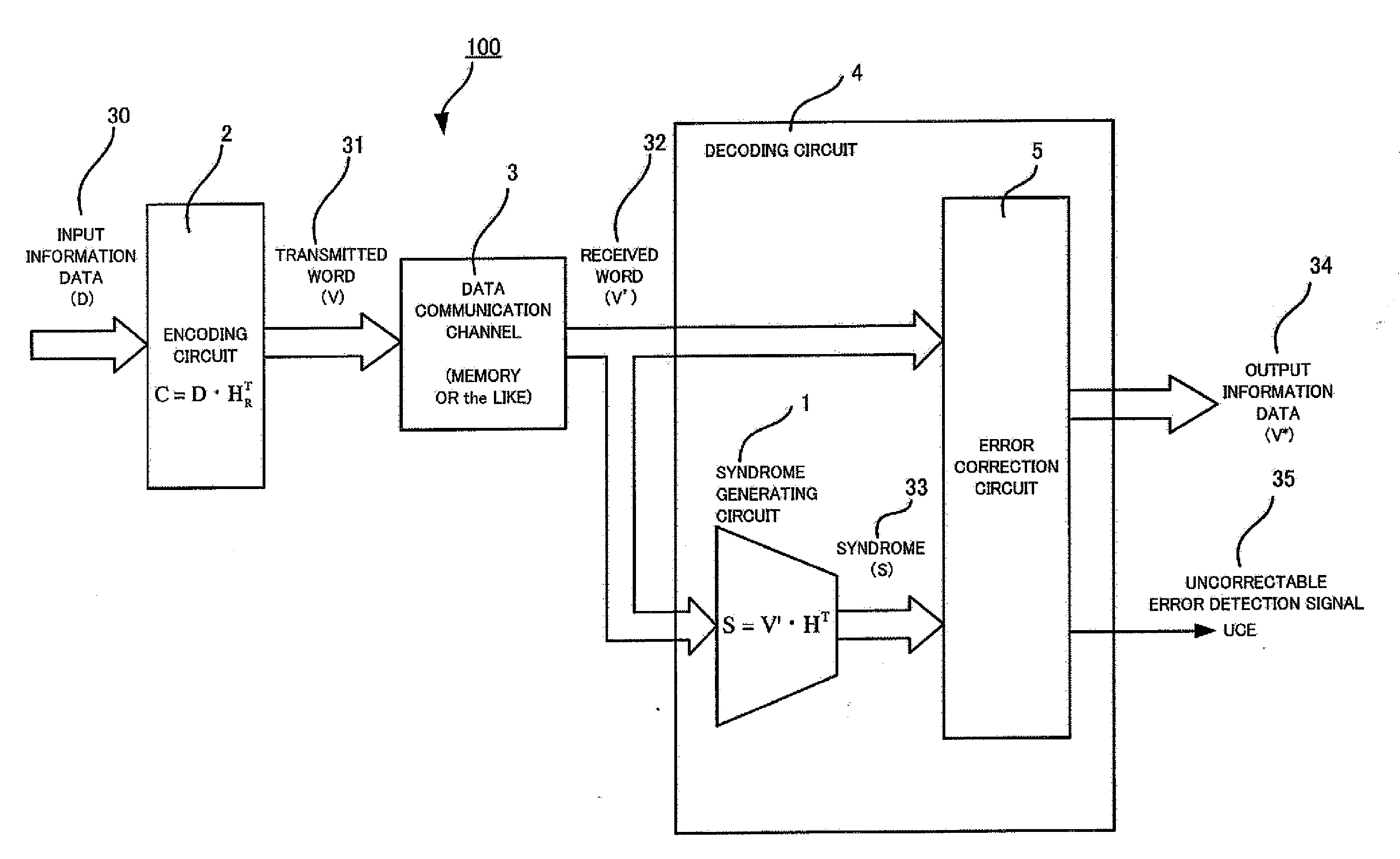

Method and apparatus for correcting and detecting multiple spotty-byte errors within a byte occurred in a limited number of bytes

InactiveUS20090106633A1Efficient implementationMemory loss protectionCode conversionInformation transmissionAlgorithm

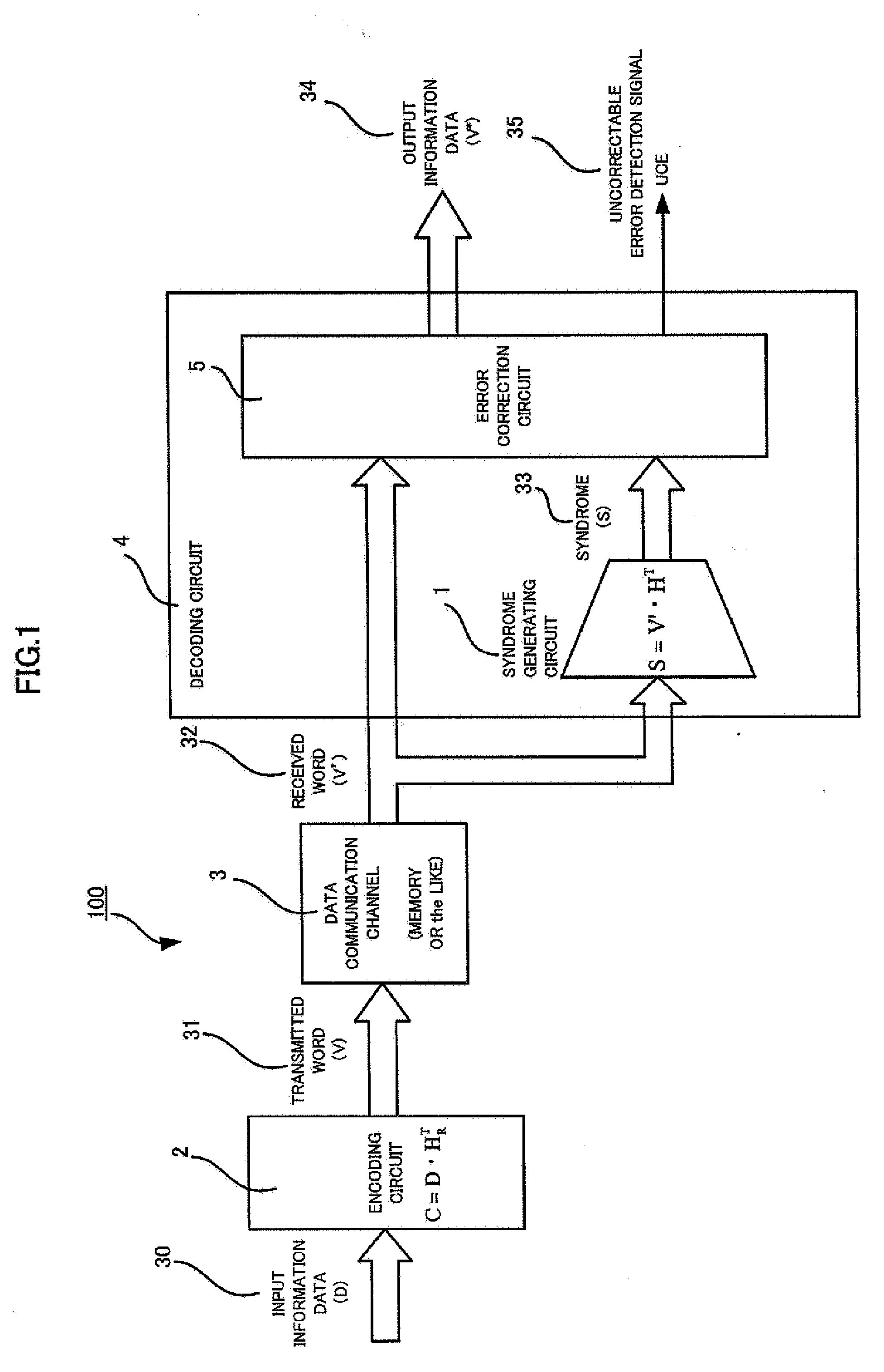

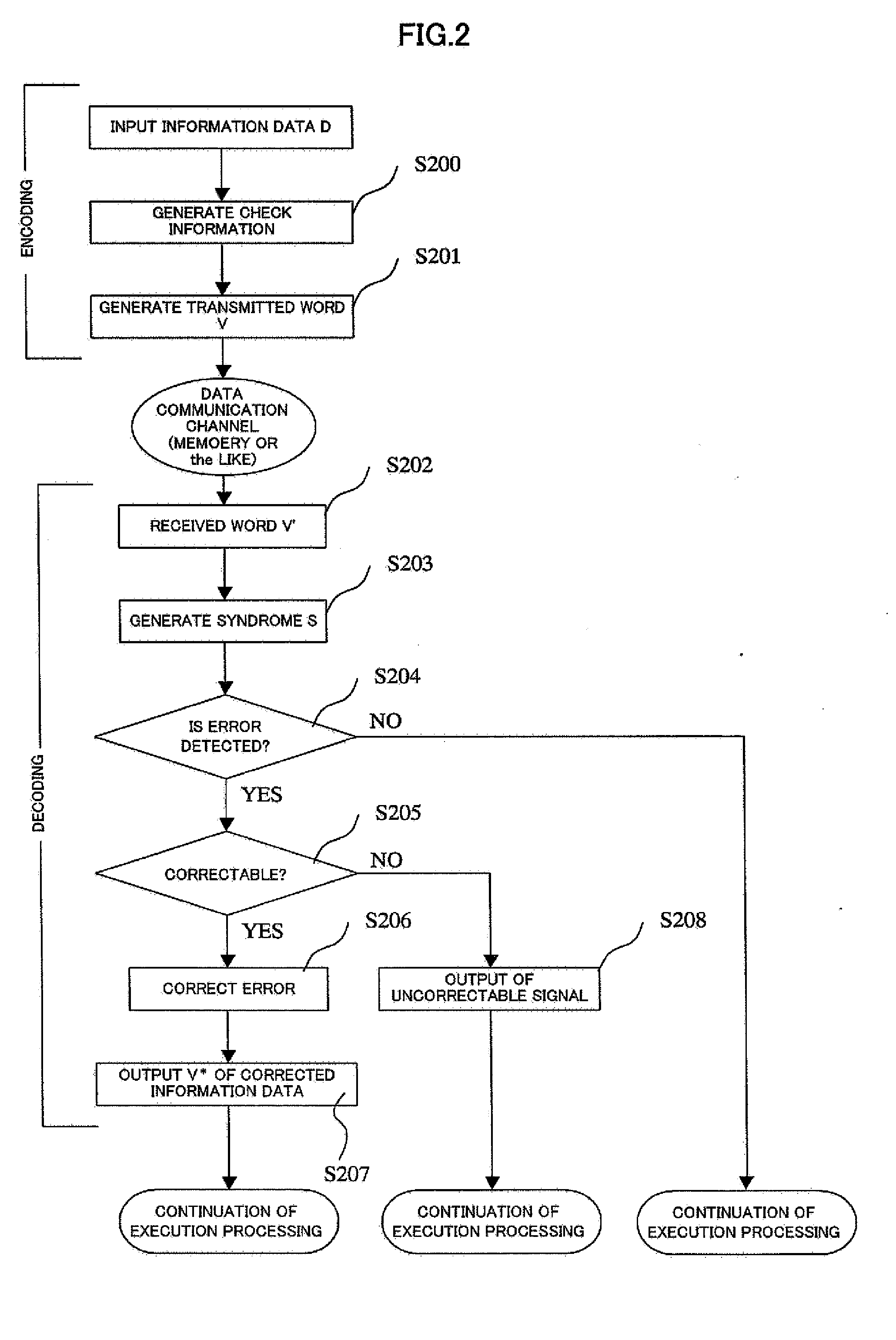

An apparatus for correcting and detecting multiple spotty-byte errors within a byte occurred in a limited number of bytes and which has a function capable of controlling multiple spotty-byte errors within a byte occurred in the limited number of bytes, is provided.The apparatus for correcting and detecting multiple spotty-byte errors within a byte occurred in a limited number of bytes, comprises an encoding means for generating a transmitted word based on input information data; and a decoding means for inputting the transmitted word where errors occurred in an information transmission channel as a received word and correcting and detecting the errors. The encoding means generates the transmitted word by adding check information generated based on a parity check matrix expressing a spotty-byte error control code and the input information data to the input information data. The decoding means comprises a syndrome generating means for generating a syndrome of the received word based on the parity check matrix; and an error correction means for correcting and detecting the errors in the received word based on the syndrome generated by the syndrome generating means.

Owner:TOKYO INST OF TECH +1

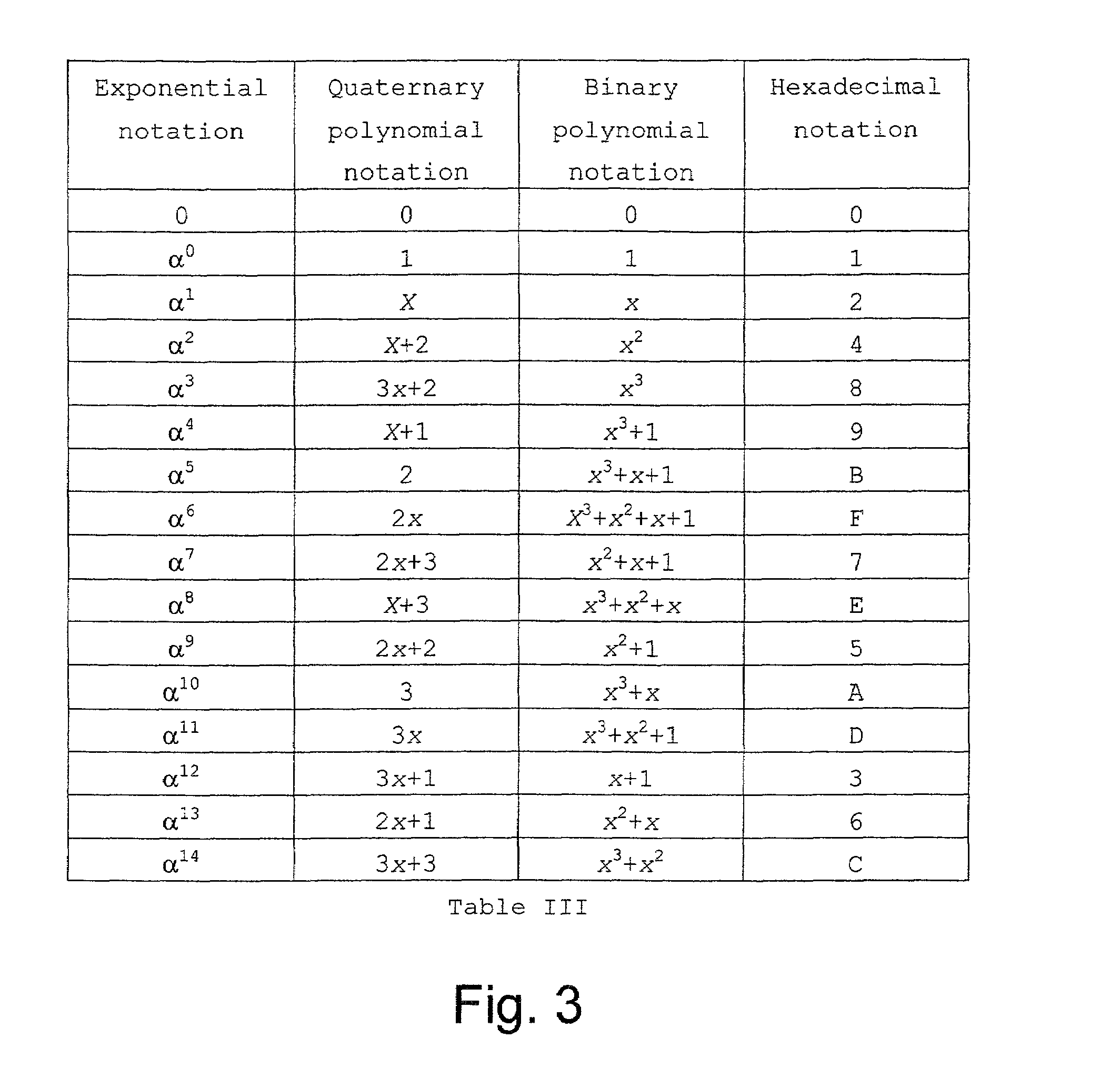

Multipurpose method for constructing an error-control code for multilevel memory cells operating with a variable number of storage levels, and multipurpose error-control method using said error-control code

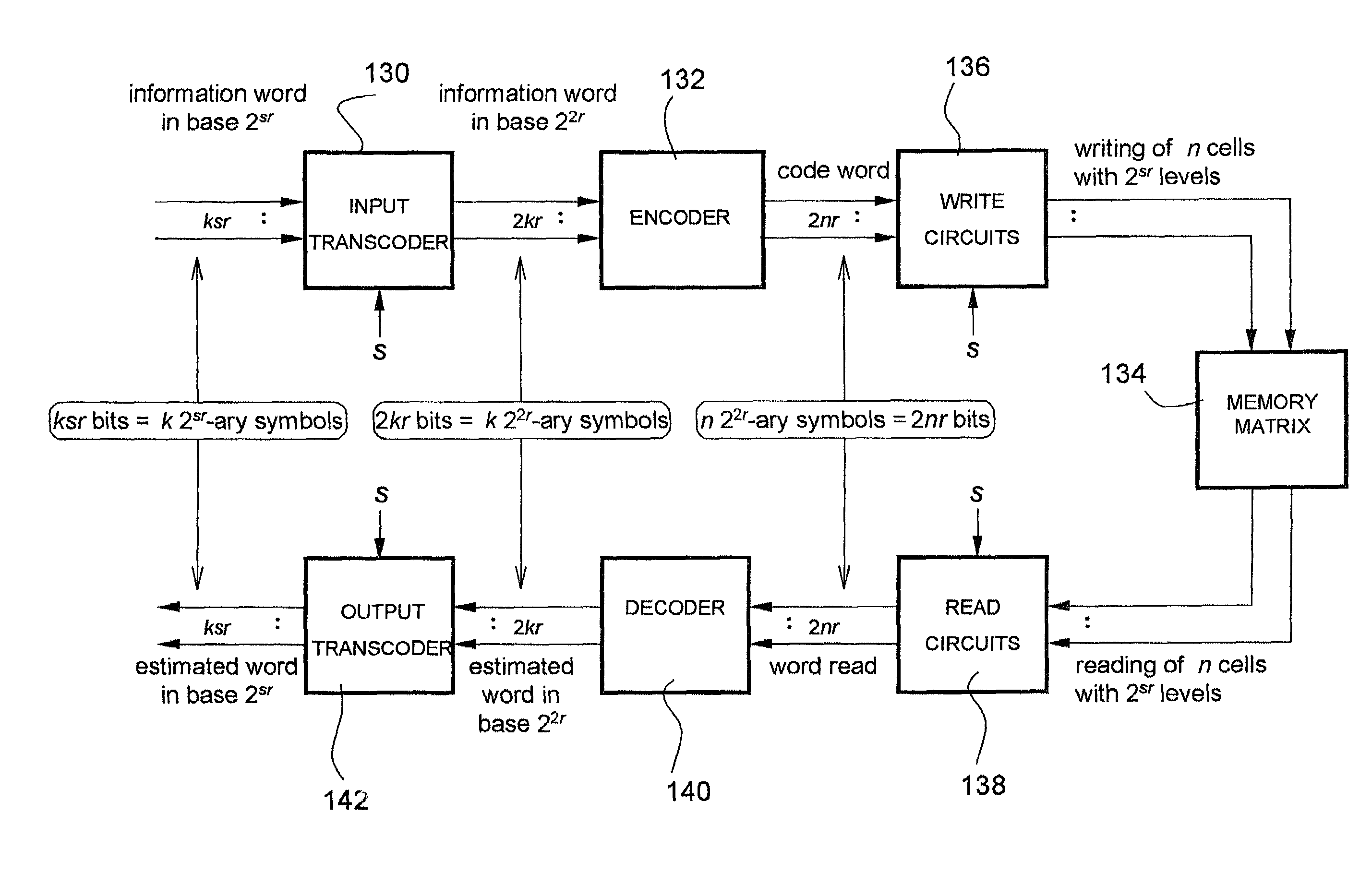

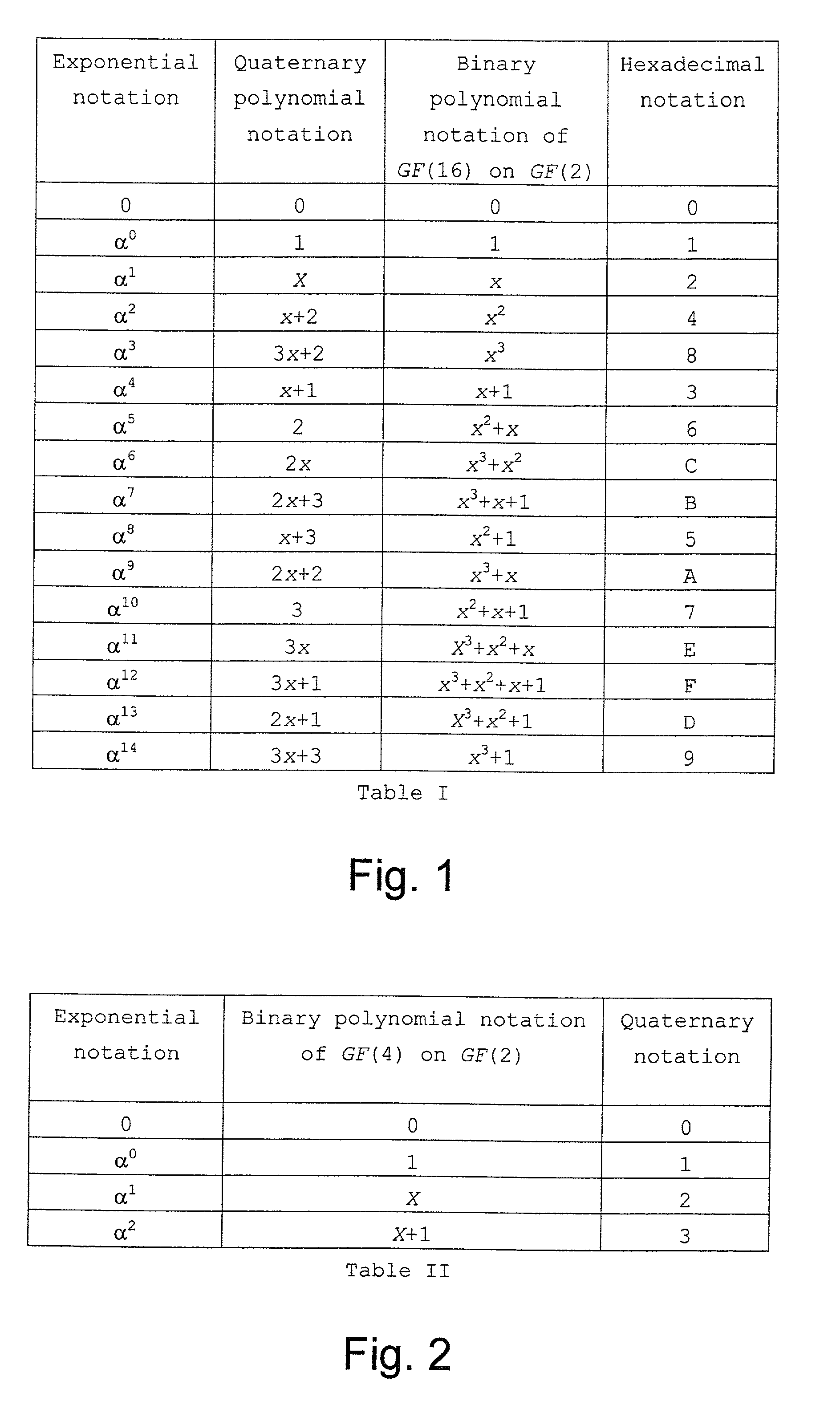

Described is an error control method for multilevel memory cells operating with a variable number of storage levels. The method includes: receiving a first information word having k input symbols each in a first base; converting the first information word into a second base by converting the input symbols into input symbols in the second base; encoding the converted first information word into a first codeword having k+n coded symbols in the second base; and writing the first codeword into the multilevel memory cells. The encoding step may include generating a generating matrix and multiplying the first information word by the generating matrix to produce the first codeword.

Owner:STMICROELECTRONICS SRL

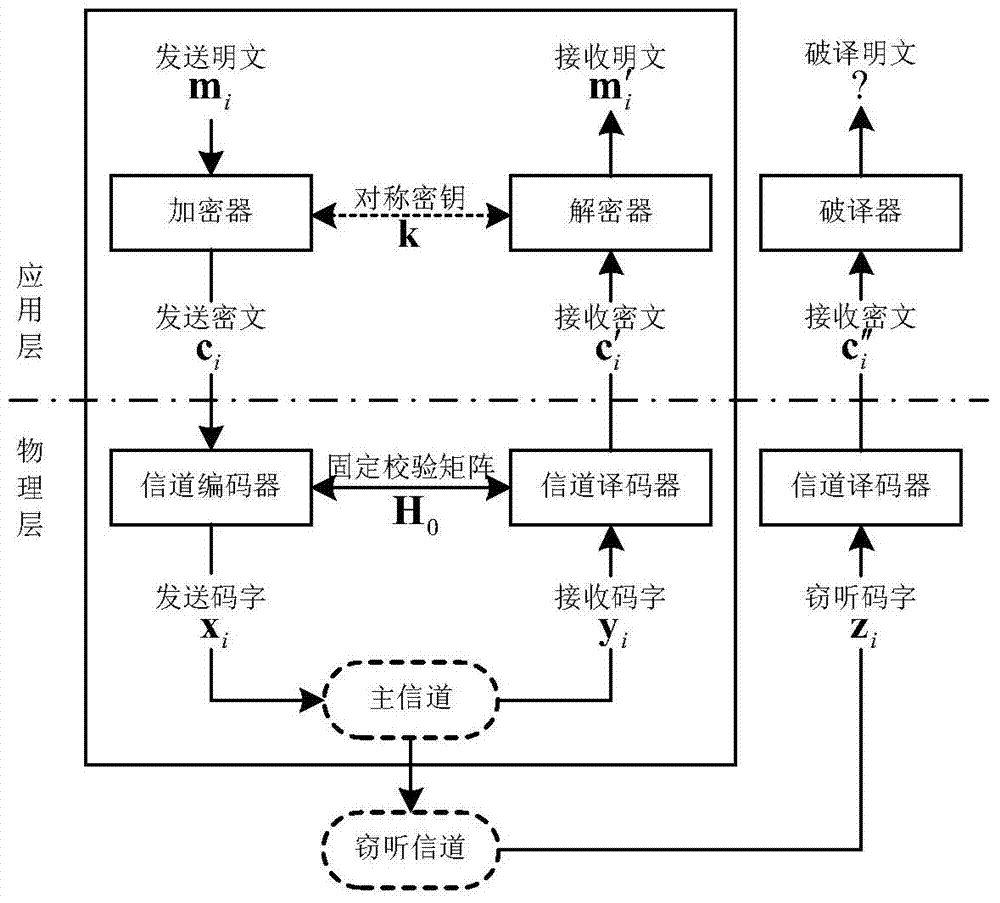

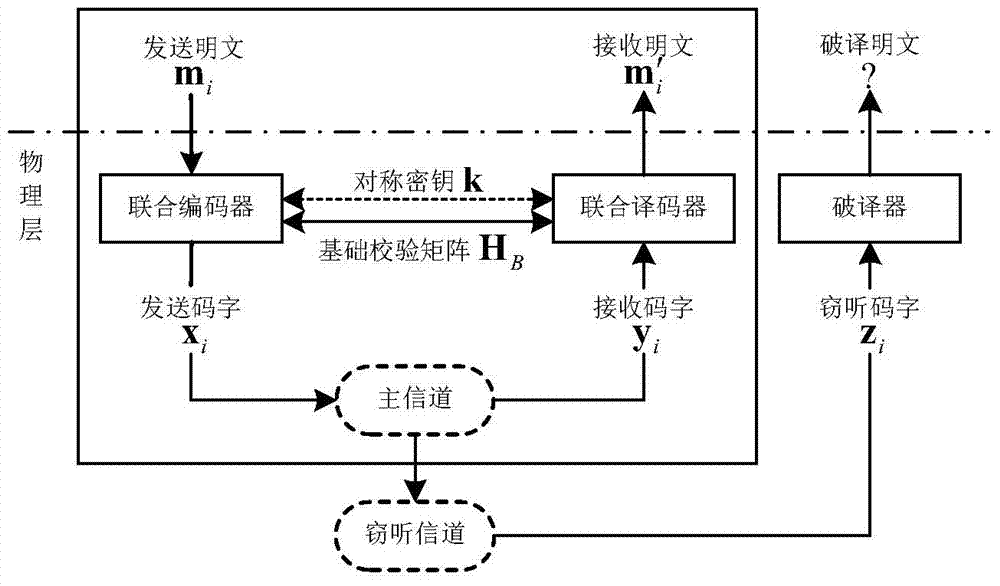

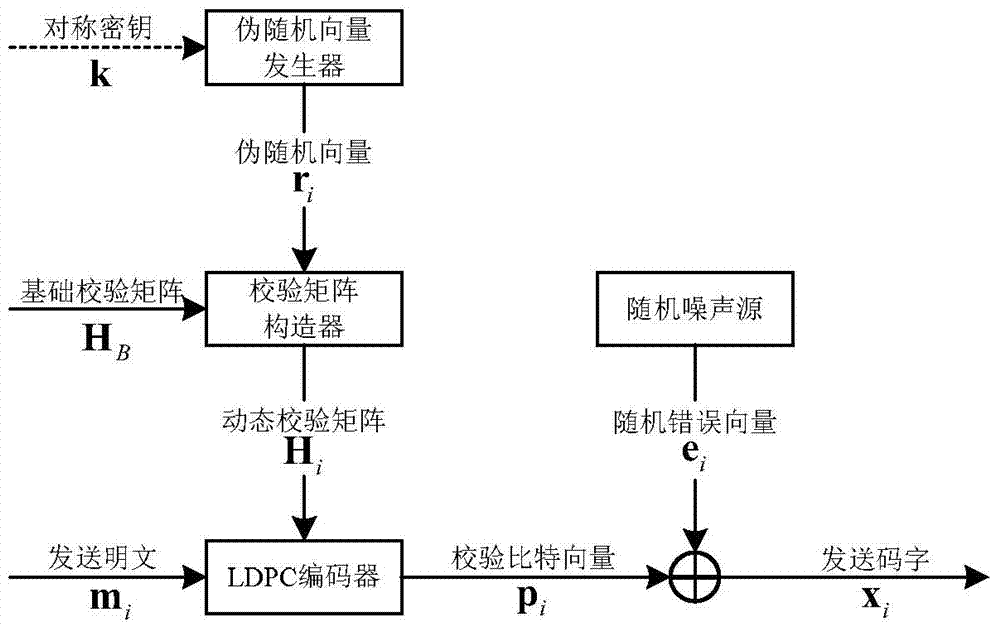

Physical layer secure transmission method and system based on dynamic change of channel encoding matrix

ActiveCN104780022AAddress reliabilityFix security issuesKey distribution for secure communicationError preventionComputer hardwarePlaintext

The invention relates to a physical layer secure transmission method and system based on dynamic change of a channel encoding matrix, and belongs to the field of communication information security. The system comprises a joint encoder arranged on a physical layer of a transmitting end and a joint decoder arranged on a physical layer of a receiving end, and the transmitting end and the receiving end are communicated through a main channel. The method comprises steps as follows: a symmetric key obtained through key agreement is shared between the joint encoder at the transmitting end and the joint decoder at the receiving end on the basis of an existing key exchange protocol; a basic check matrix generated through optimized construction as well as a matrix extension factor is agreed publicly; joint encryption and error-control coding is performed on each transmitted plain text by the joint encoder, and corresponding code words in bit are obtained; the joint decoder decodes received code words into received plain texts at the receiving end. The method and the system can be used for realizing physical layer information transmission with high secrecy performance and high reliability.

Owner:TSINGHUA UNIV

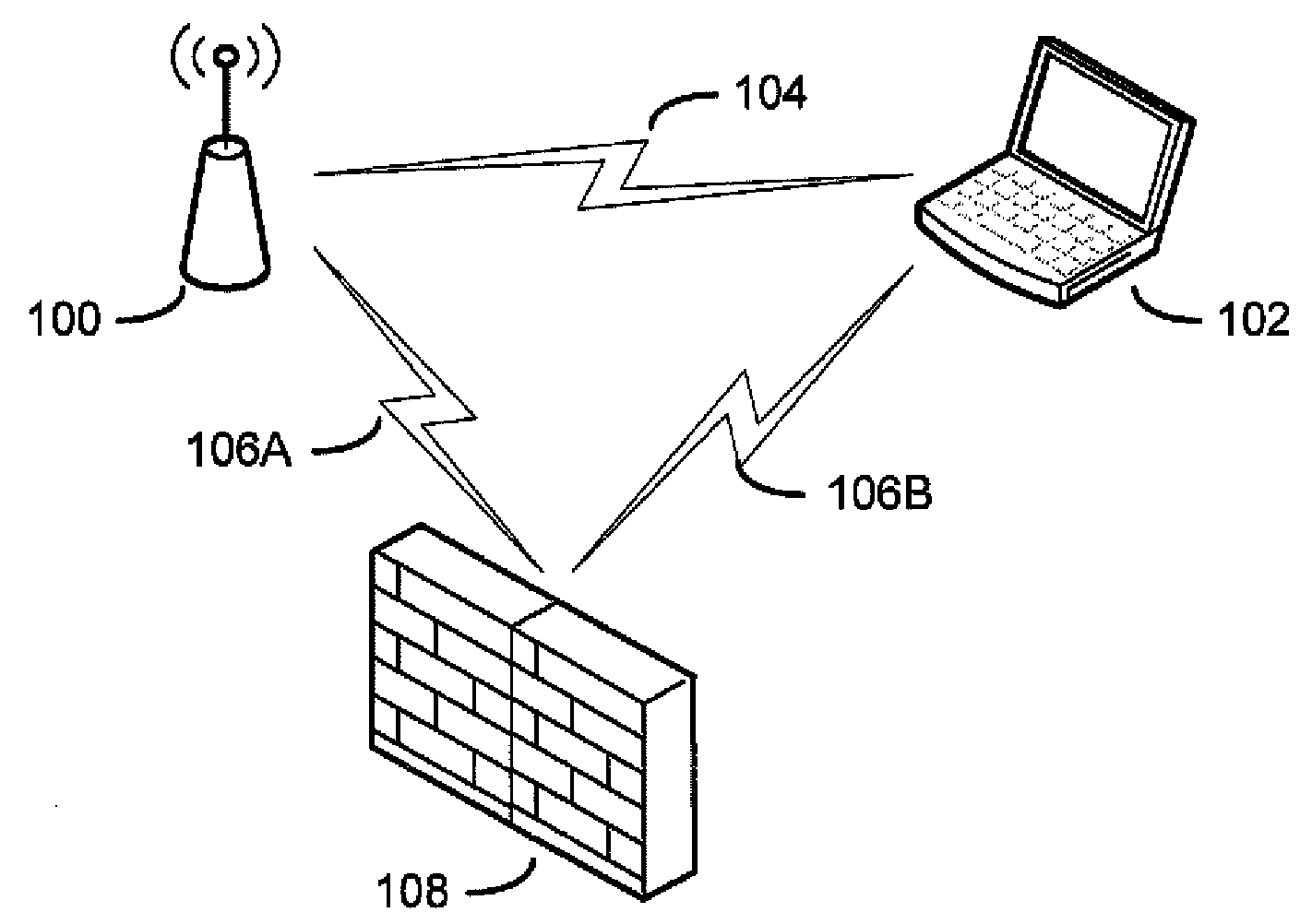

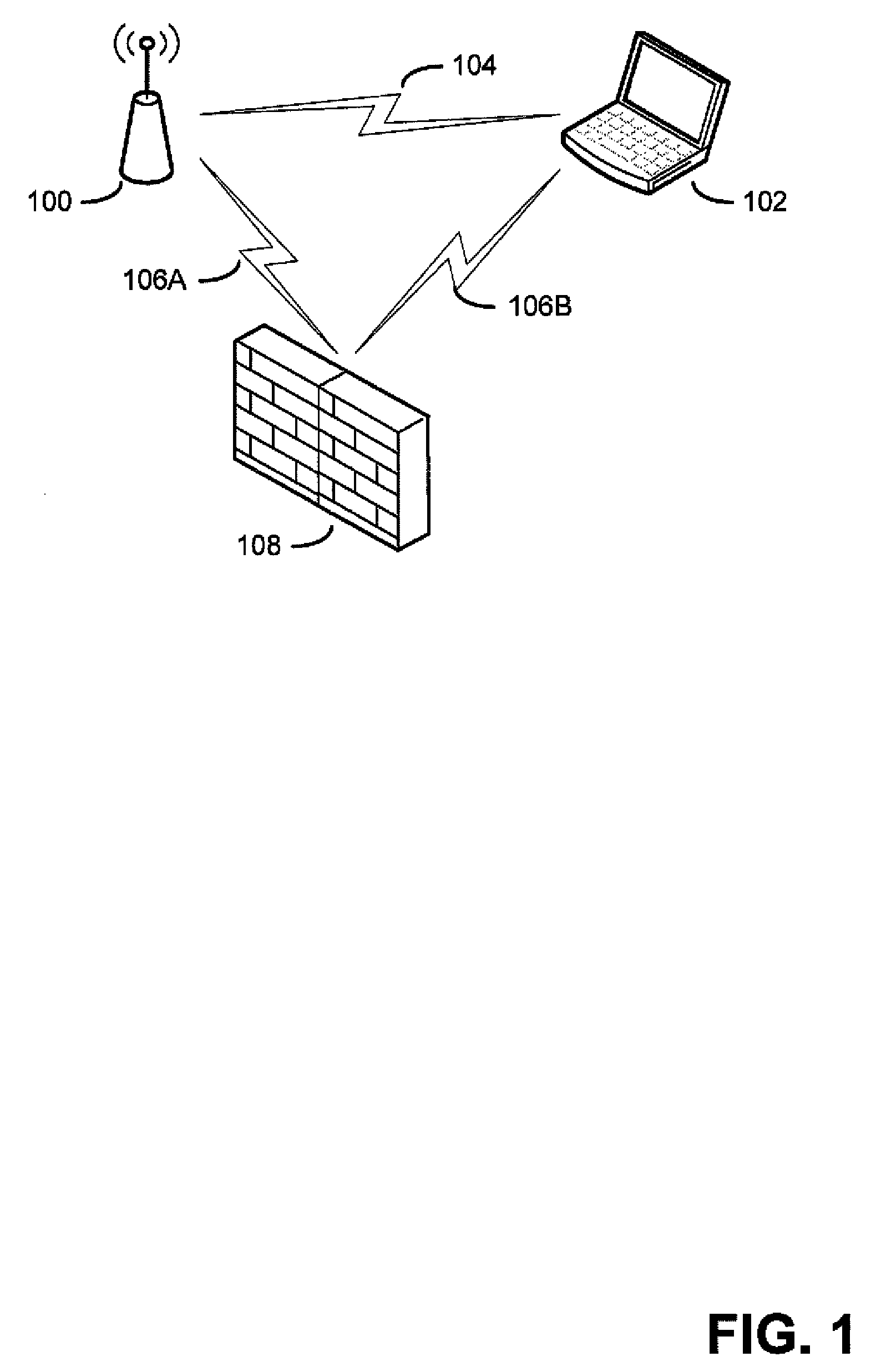

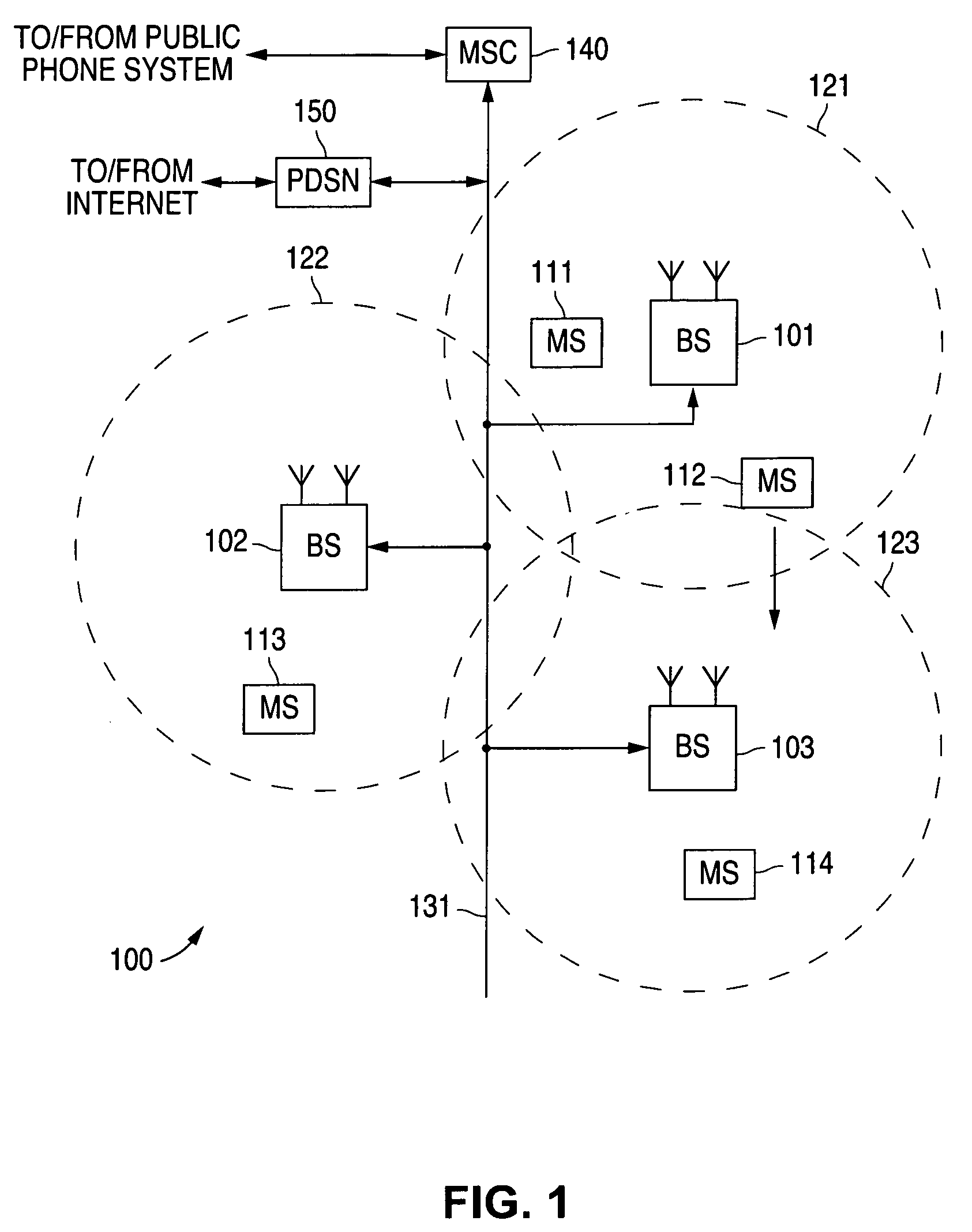

Cognitive error control coding for channels with memory

InactiveUS20100118795A1Increase probabilityHigh control rateChannel coding adaptationWireless commuication servicesComputer hardwareCommunications system

Techniques for adapting error control codes (ECCs) based on memory conditions in a channel. A wireless communication system may be adapted to detect and quantify memory in a channel, such as memory resulting from multipath fading, and adjust an ECC to reduce the possibility of errors impacting communication in the channel. In some implementations, adjusting the ECC may comprise determining a probability that a channel in an error-prone state will remain in an error-prone state, and selecting an ECC based on that probability. In other implementations, a concatenated code may be used, and the relative size of an inner and outer code may be adjusted, and / or an interleaver between the inner and outer code may be adjusted, based on the parameter quantifying the memory in the channel.

Owner:MICROSOFT TECH LICENSING LLC

Memory devices and encoding and/or decoding methods

ActiveUS8281217B2Reduce errorsError rateData representation error detection/correctionError detection/correctionComputer hardwareError control coding

Memory devices and / or encoding / decoding methods are provided. A memory device may include: a memory cell array; an internal decoder configured to apply, to a first codeword read from the memory cell array, a first decoding scheme selected based on a characteristic of a first channel in which the first codeword is read to perform error control codes (ECC) decoding of the first codeword, and apply, to a second codeword read from the memory cell array, a second decoding scheme selected based on a characteristic of a second channel in which the second codeword is read to perform the ECC decoding of the second codeword; and an external decoder configured to apply an external decoding scheme to the ECC-decoded first codeword and the ECC-decoded second codeword to perform the ECC decoding of the first codeword and the second codeword.

Owner:SAMSUNG ELECTRONICS CO LTD

System to Improve Miscorrection Rates in Error Control Code Through Buffering and Associated Methods

InactiveUS20100299576A1Improve miscorrection rateImproves miscorrection rateCode conversionError correction/detection using block codesReal-time computingError signal

A system to improve miscorrection rates in error control code may include an error control decoder with a safe decoding mode that processes at least two data packets. The system may also include a buffer to receive the processed at least two data packets from the error control decoder. The error control decoder may apply a logic OR operation to the uncorrectable error signal related to the processing of the at least two data packets to produce a global uncorrectable error signal. The system may further include a recipient to receive the at least two data packets and the global uncorrectable error signal.

Owner:IBM CORP

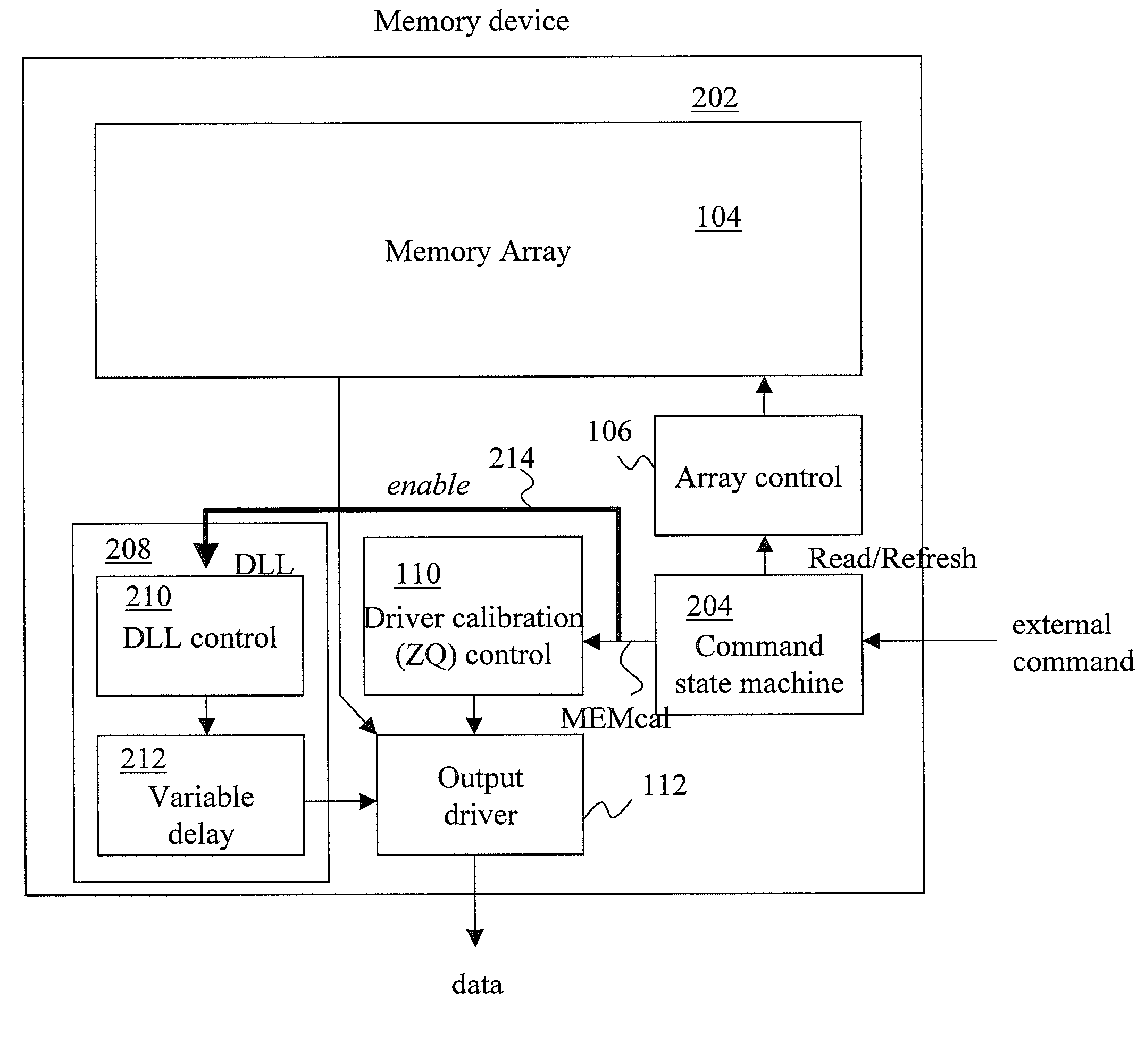

Advanced memory device having improved performance, reduced power and increased reliability

An advanced memory having improved performance, reduced power and increased reliability. A memory device includes a memory array, a receiver for receiving a command and associated data, error control coding circuitry for performing error control checking on the received command, and data masking circuitry for preventing the associated data from being written to the memory array in response to the error control coding circuitry detecting an error in the received command. Another memory device includes a programmable preamble. Another memory device includes a fast exit self-refresh mode. Another memory device includes auto refresh function that is controlled by the characteristic device. Another memory device includes an auto refresh function that is controlled by a characteristic of the memory device.

Owner:GLOBALFOUNDRIES US INC

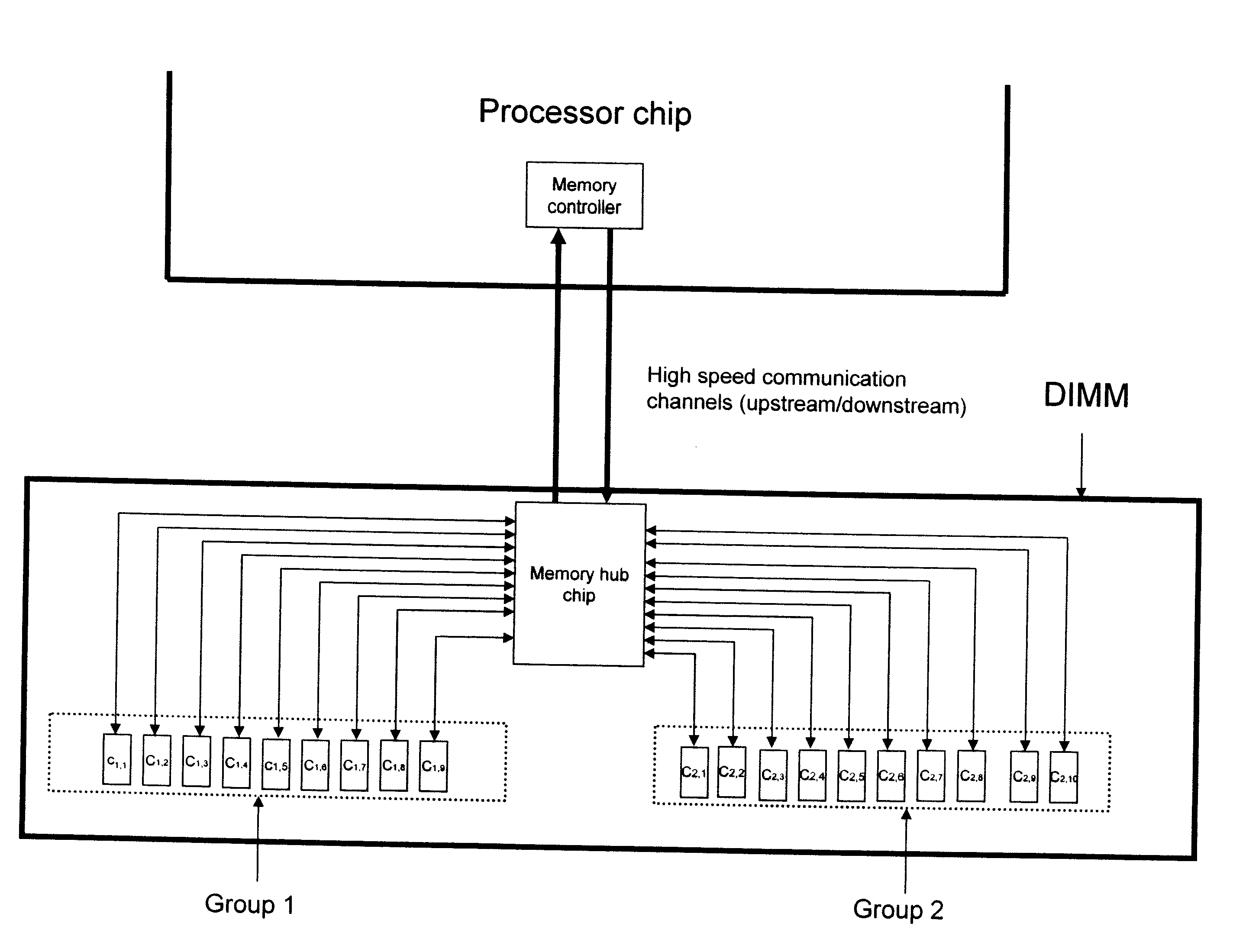

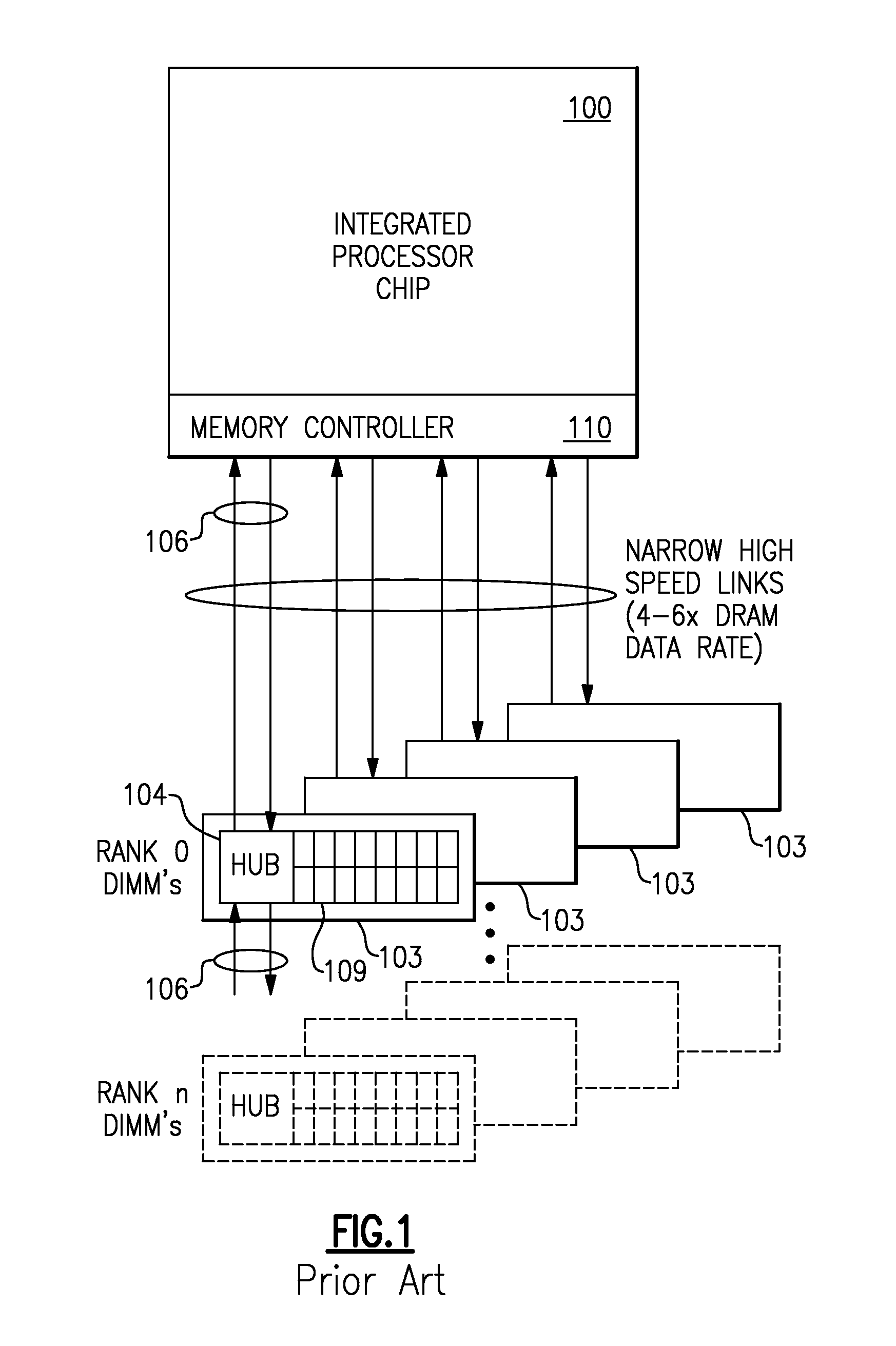

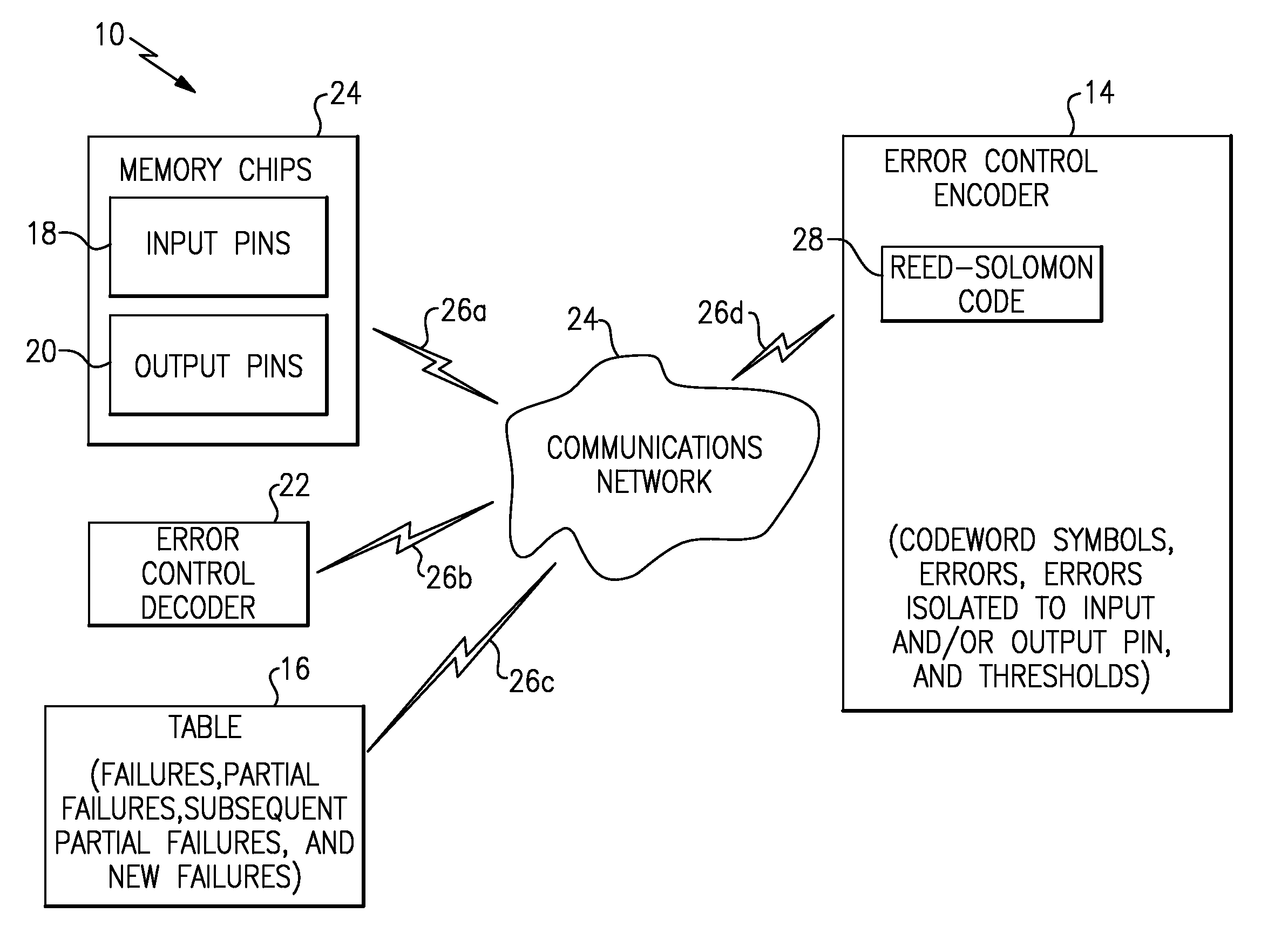

System to Improve Memory Reliability and Associated Methods

ActiveUS20100287445A1Improves memory reliabilityImprove memory reliabilityCode conversionStatic storageMemory chipComputerized system

A system to improve memory reliability in computer systems that may include memory chips, and may rely on a error control encoder to send codeword symbols for storage in each of the memory chips. At least two symbols from a codeword are assigned to each memory chip and therefore failure of any of the memory chips could affect two symbols or more. The system may also include a table to record failures and partial failures of the codeword symbols for each of the memory chips so the error control encoder can correct subsequent partial failures based upon the previous partial failures. The error control coder is capable of correcting and / or detecting more errors if only a fraction of a chip is noted in the table as having a failure as opposed to a full chip noted as having a failure.

Owner:IBM CORP

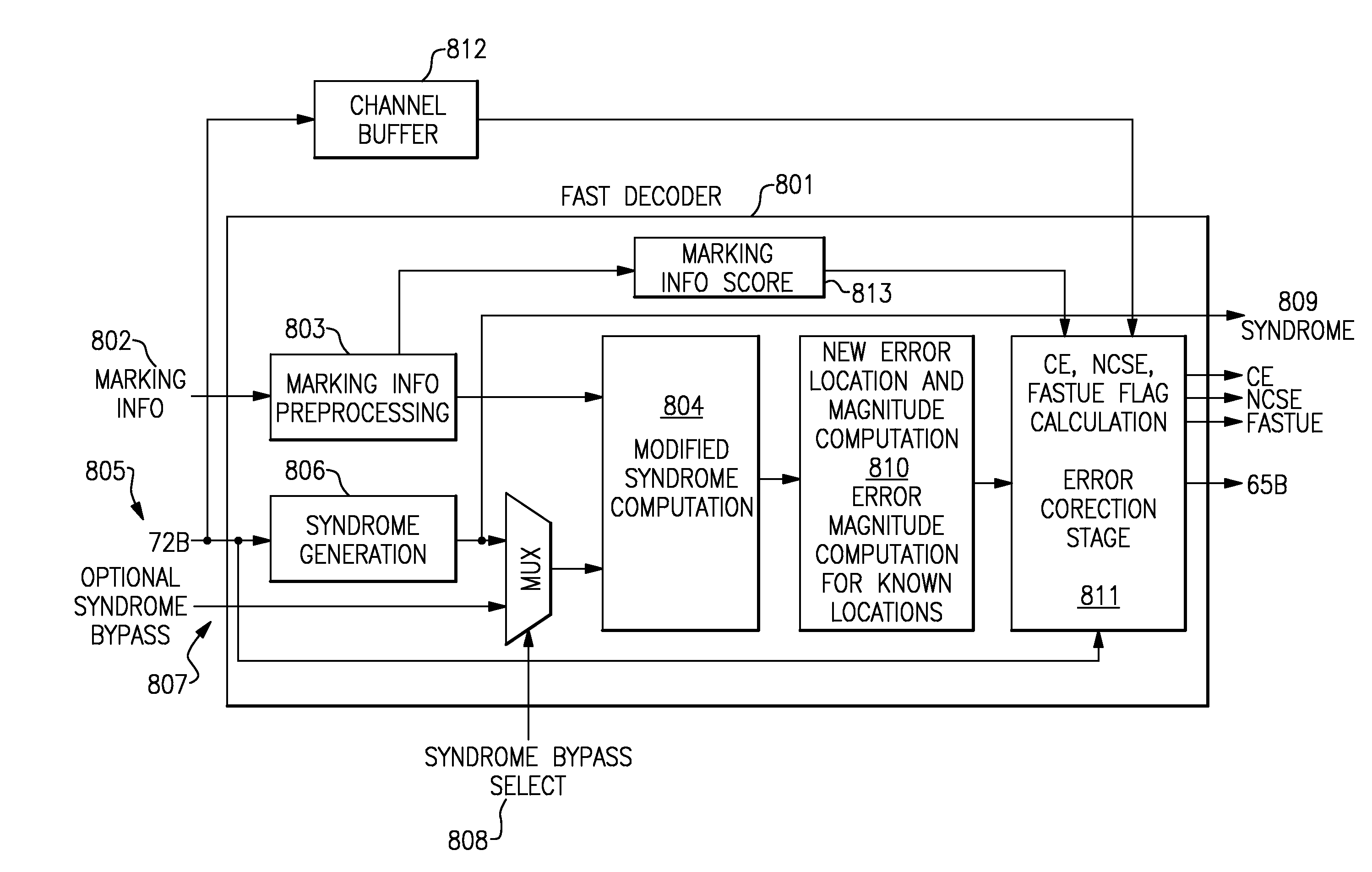

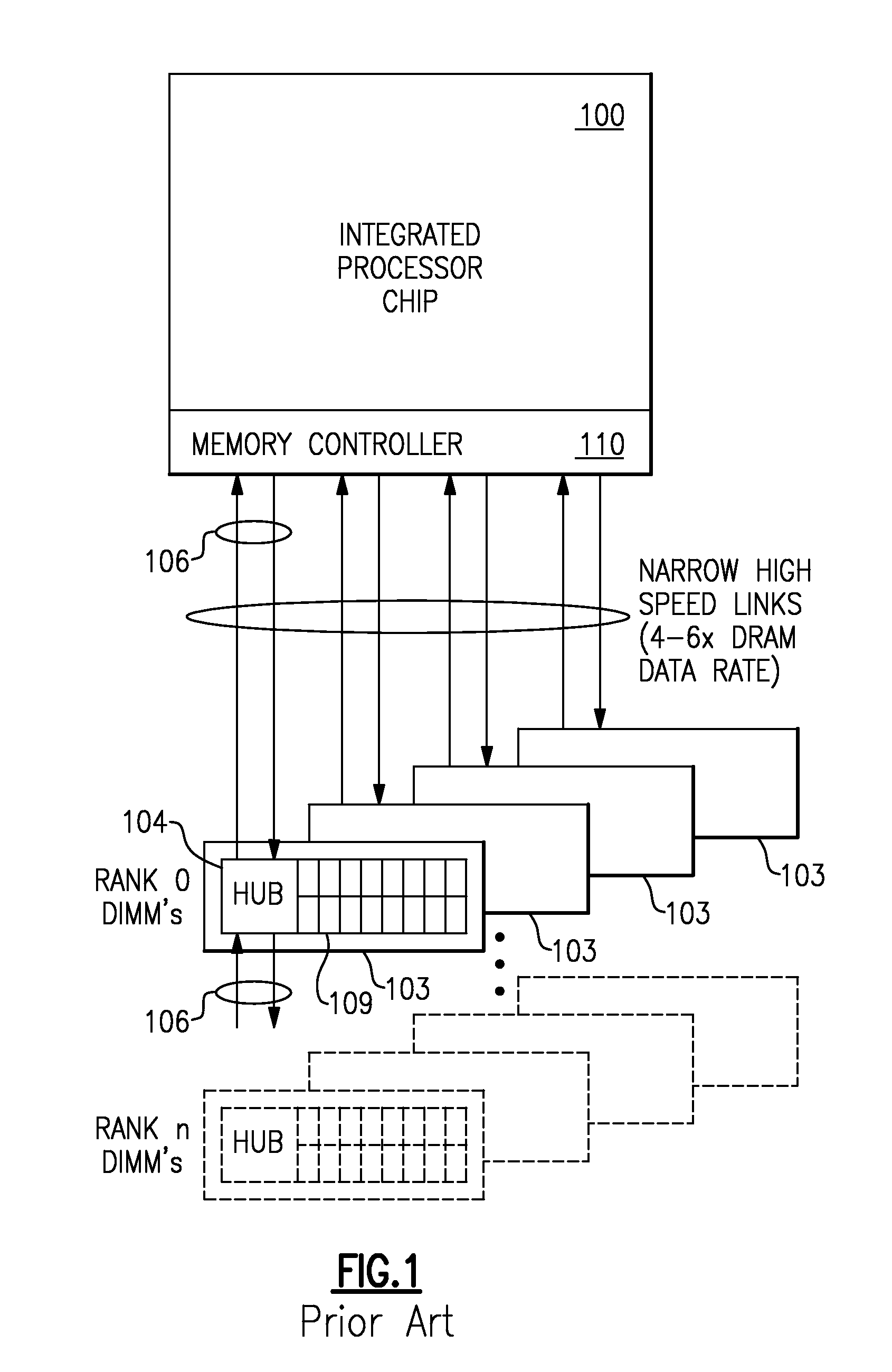

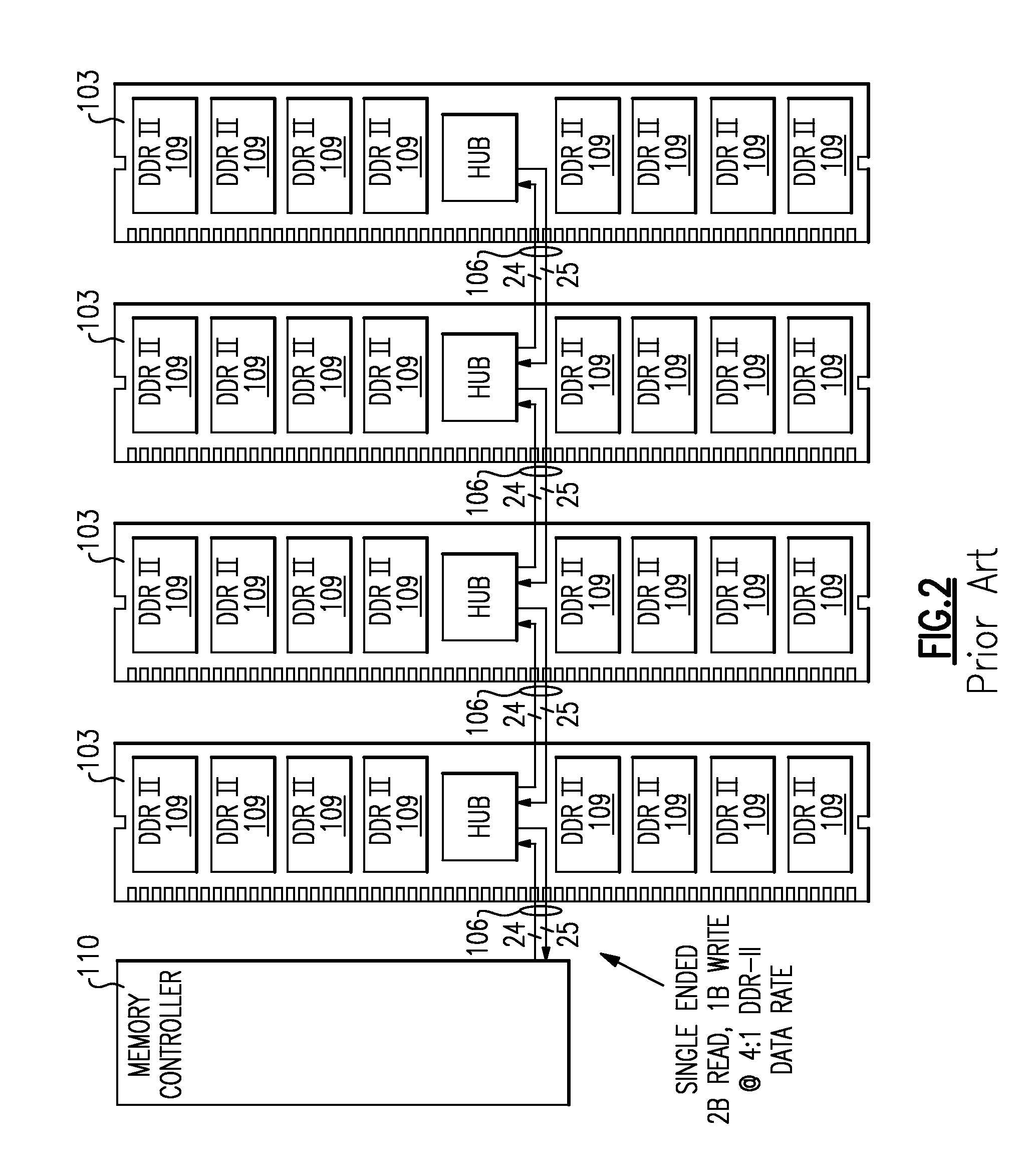

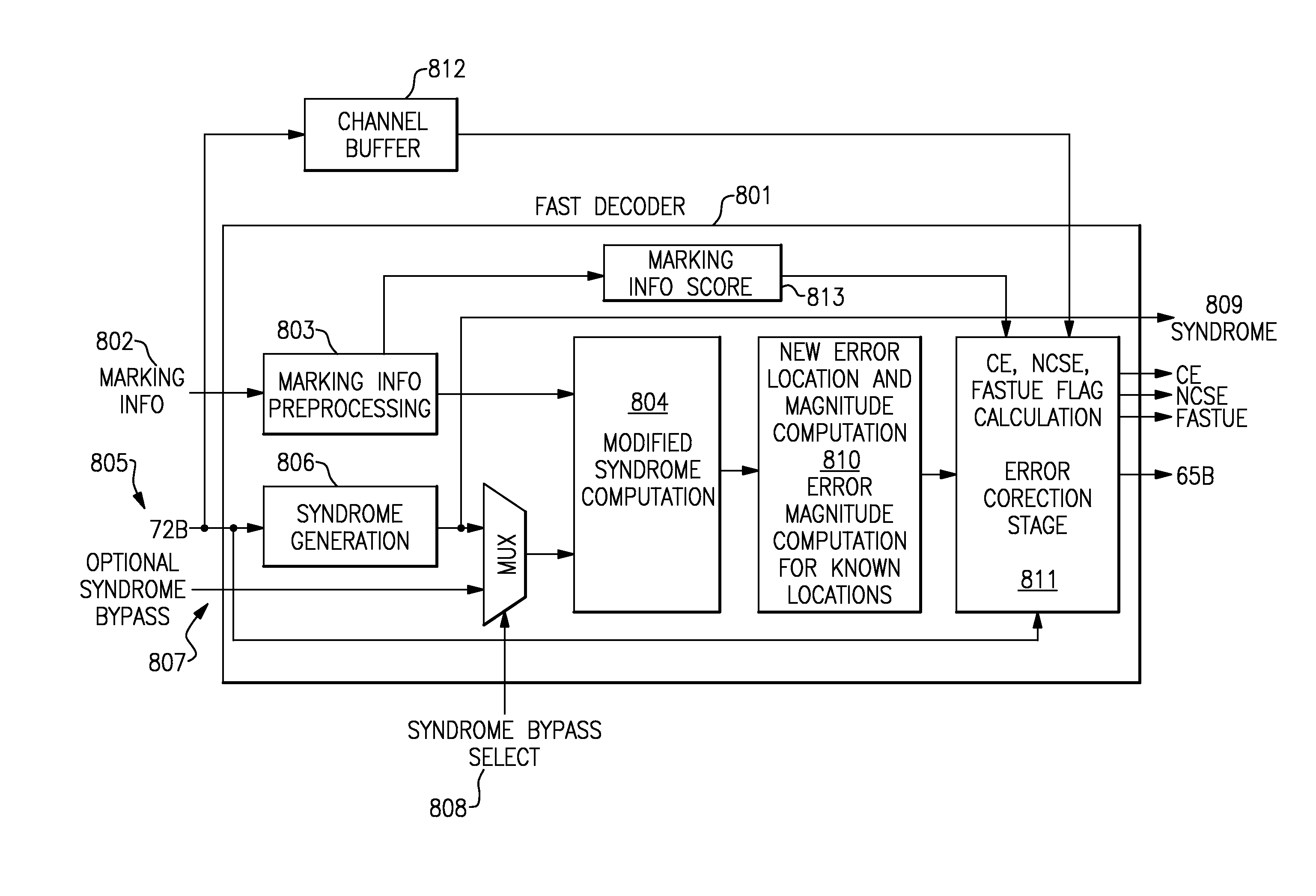

System for Error Control Coding for Memories of Different Types and Associated Methods

ActiveUS20100293436A1Improves error control codingCode conversionUnequal/adaptive error protectionMemory chipEmbedded system

A system to improve error control coding may include memory chips of at least two different kinds. The system may also include error control encoder circuitry to substantially encode data for storage in any memory rank. The system may further include error control decoder circuitry to substantially decode encoded data received from any memory rank. The error decoder circuitry is comprised of a slow decoder and a fast decoder.

Owner:IBM CORP

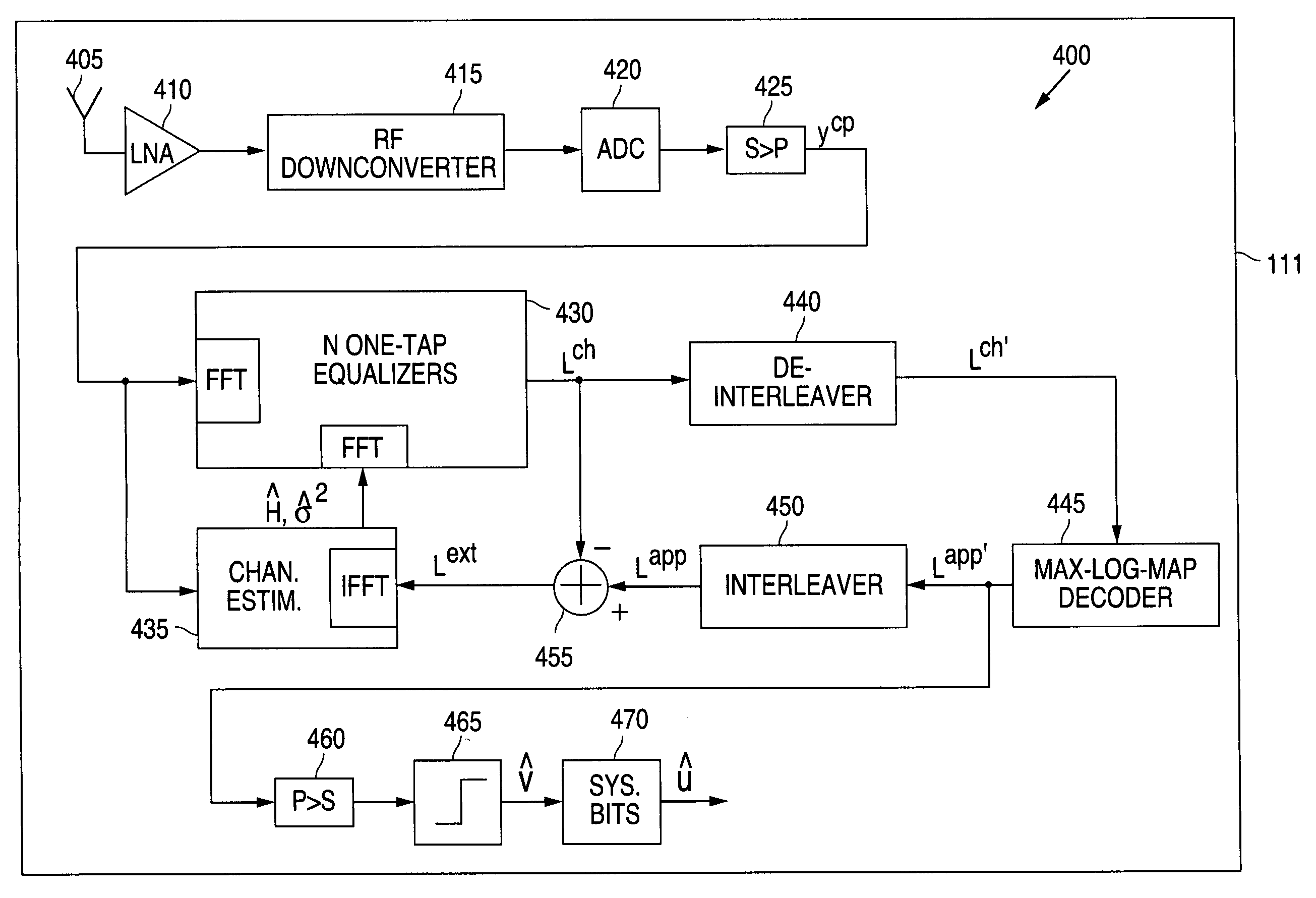

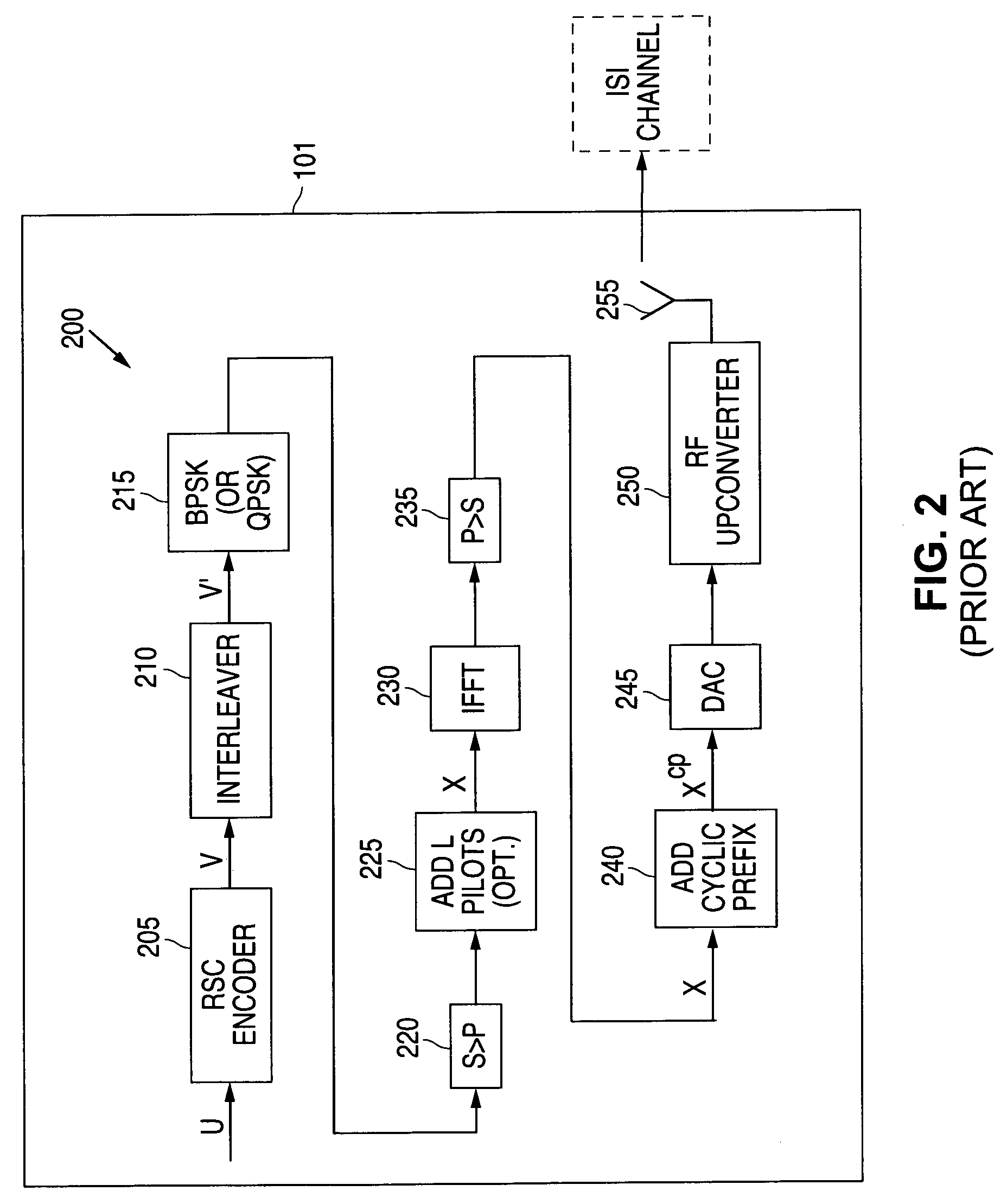

Coded OFDM system using error control coding and cyclic prefix for channel estimation

ActiveUS7633849B1Minimum training overheadImprove robustnessData switching by path configurationOrthogonal multiplexCyclic prefixComputer science

An apparatus for demodulating a coded orthogonal frequency division multiplexing (OFDM) signal in a coded OFDM receiver. The coded OFDM signal comprises systematic bits, error control bits, and a cyclic prefix. The apparatus performs channel estimation quickly and accurately using the error control bits, the channel spread constraint, and the cyclic prefix portion of the received coded OFDM signal.

Owner:THE BOARD OF TRUSTEES OF THE LELAND STANFORD JUNIOR UNIV

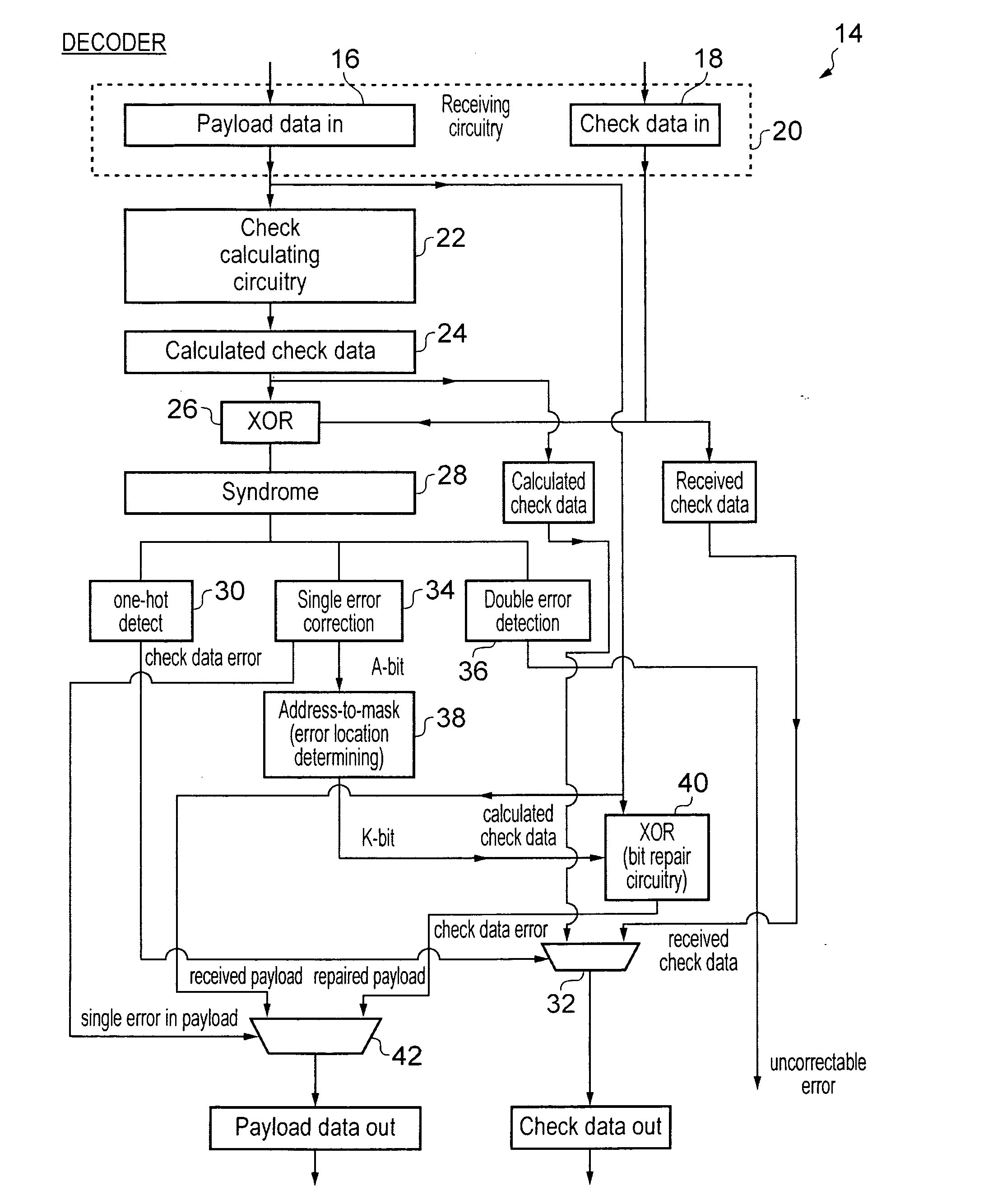

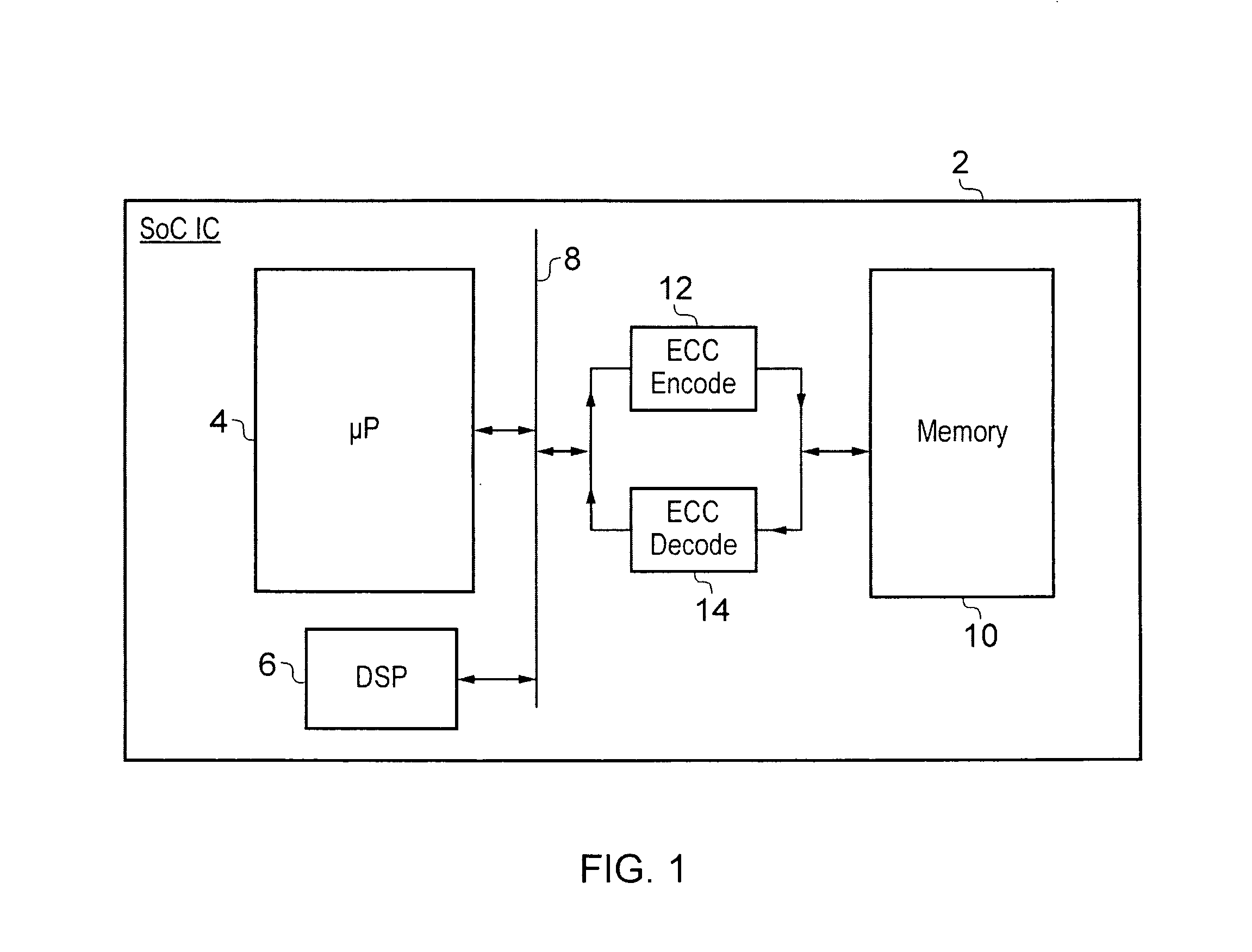

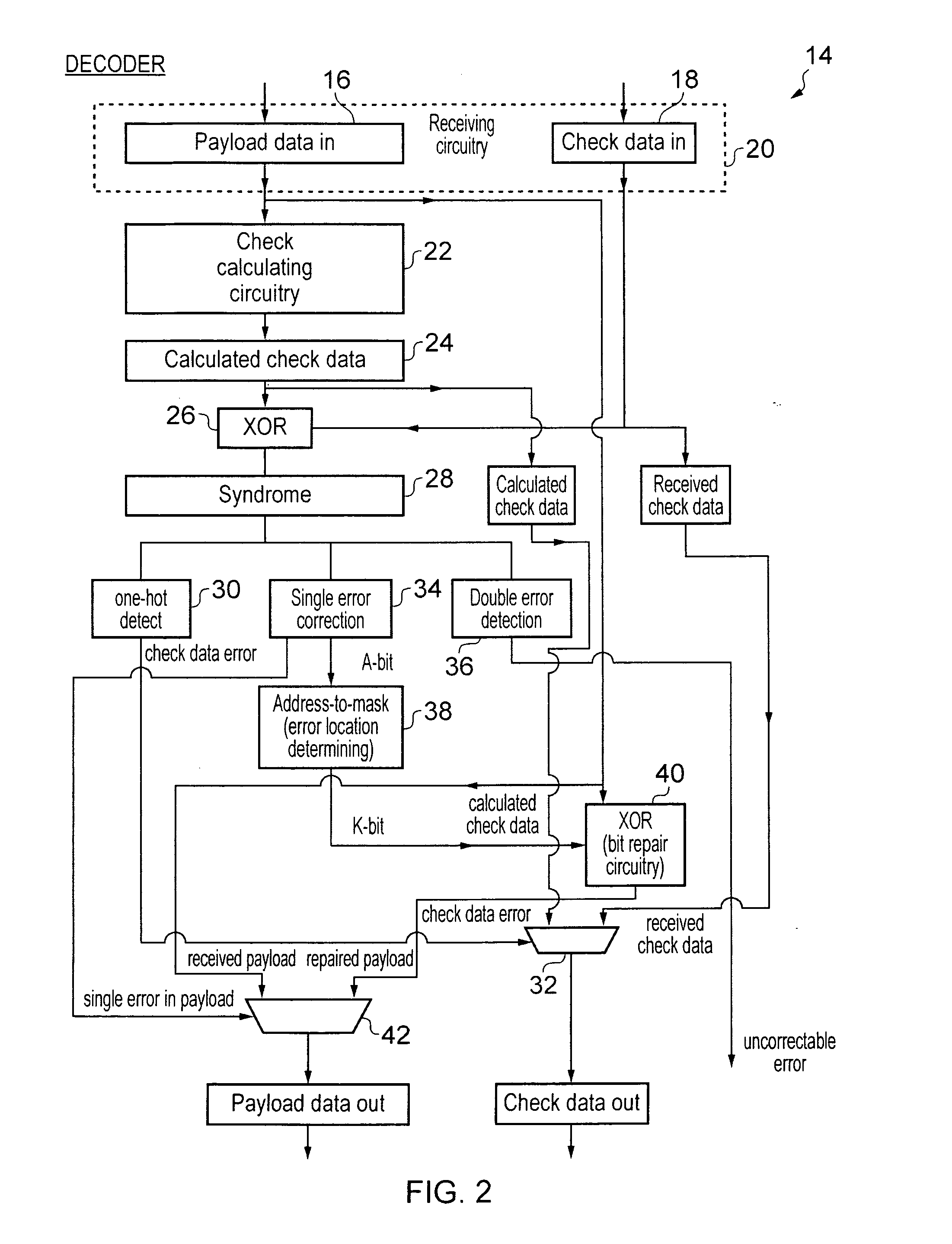

Error control coding for single error correction and double error detection

ActiveUS20110099451A1Good error correction/detectionLow overhead implementationReed-muller codesChecking code calculationsComputer hardwareChecksum

An error correction coding is provided that generates P bits of check data from K M-bit words of payload data. The P bits of check data include an address field A, a bit error indicating field E and an auxiliary field P−(E+A). The address field encodes a set of error addresses which has a cardinality equal to the bit size K of the payload data and providing a one-to-one mapping between values of the address field and the locations of a single bit error within the payload data. The bit error indicating field indicates if a bit error is present. The auxiliary field is a minimum size bit vector such that together with the address field and the bit area indicating field it provides a checksum for a systematic code for the payload data with a minimum Hamming distance serving to provide either single error correction capability or single error correction and double error detection capability.

Owner:ARM LTD

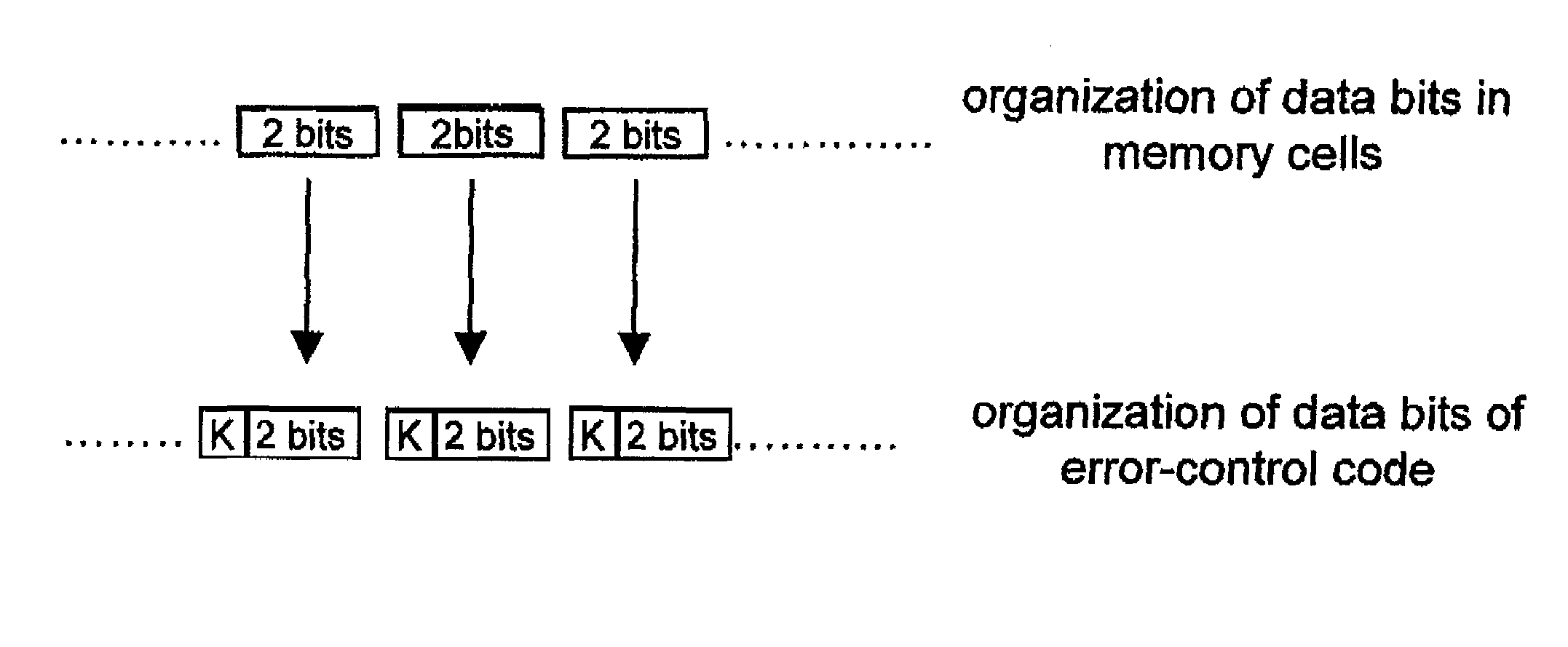

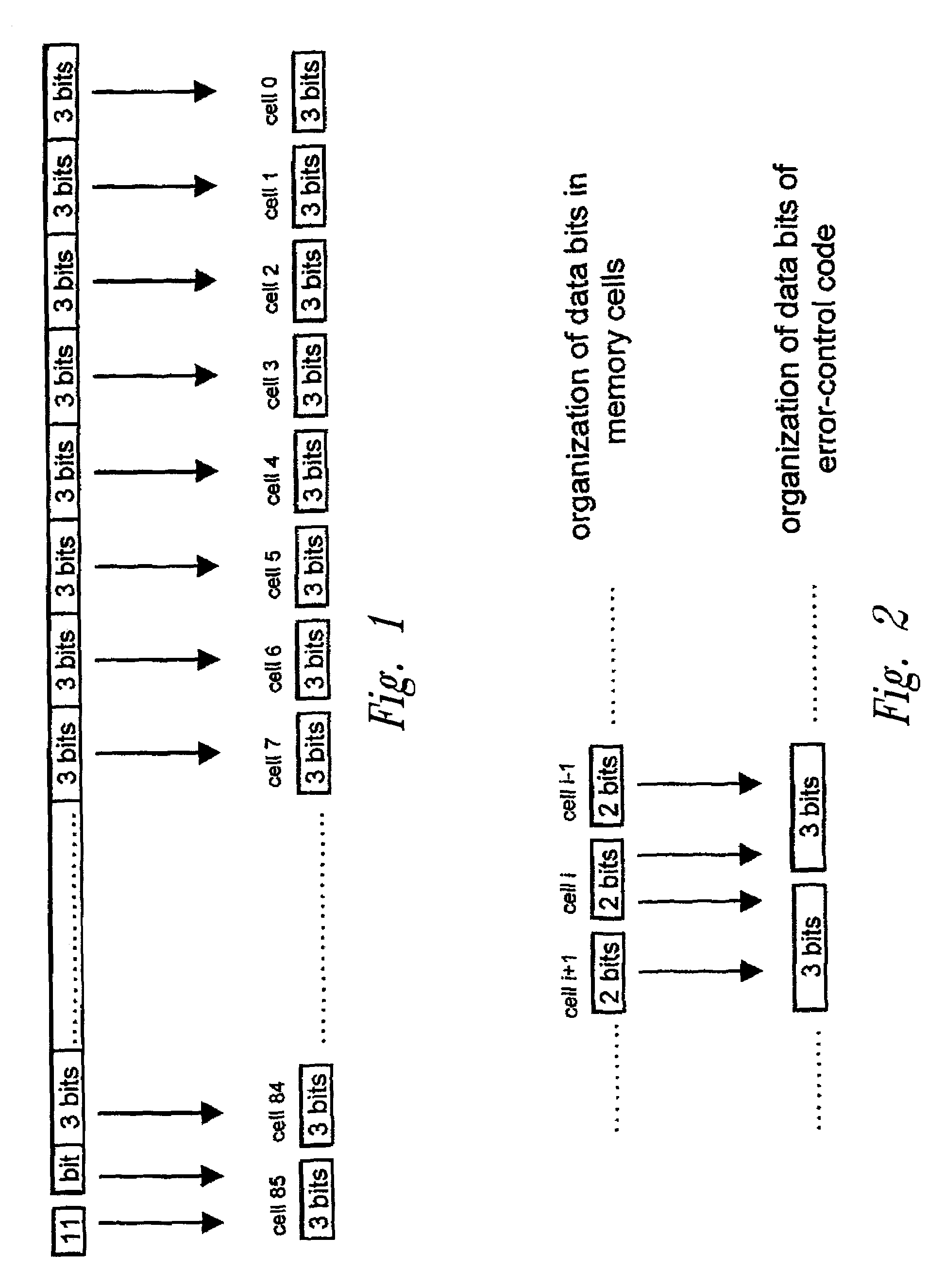

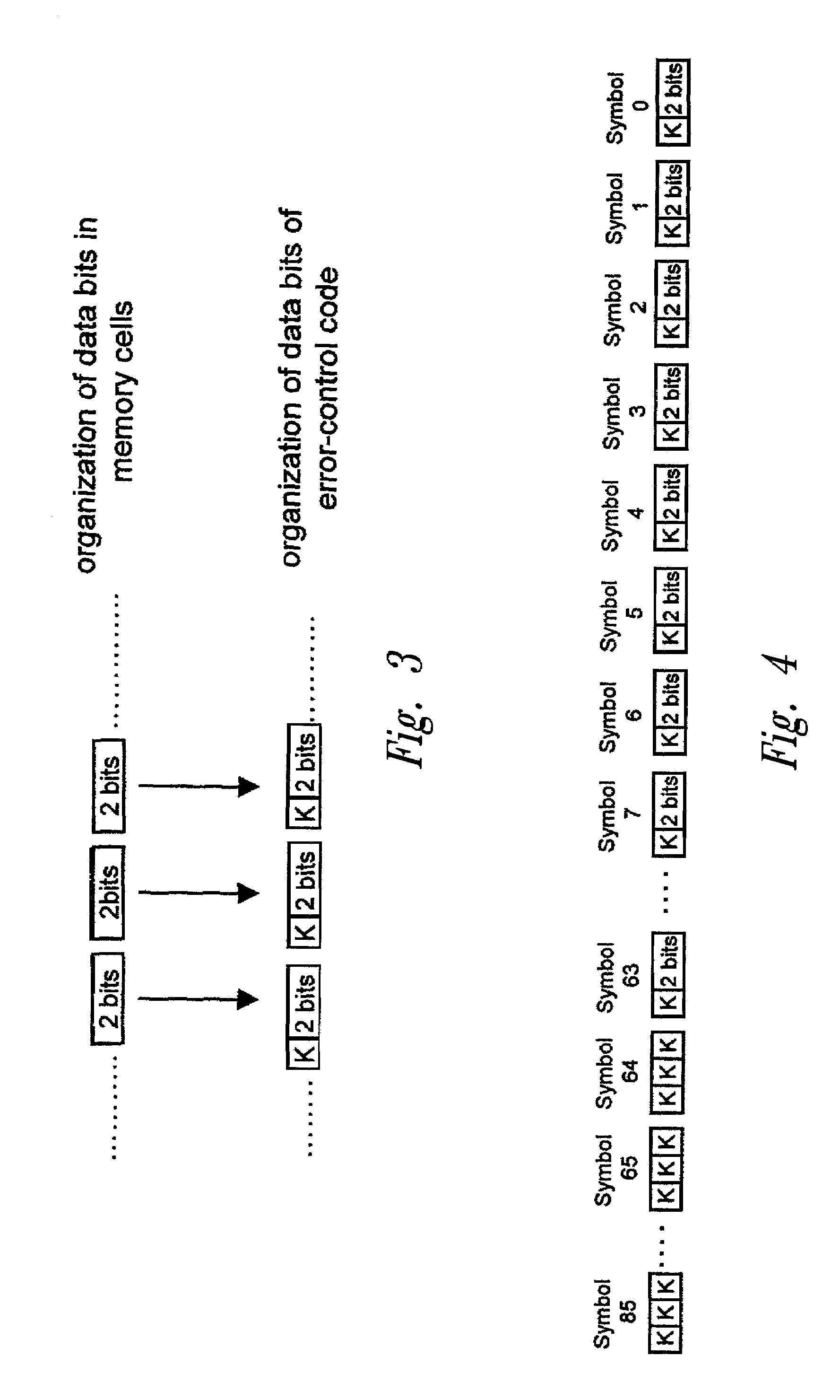

Method for error control in multilevel cells with configurable number of stored bits

A method for error control in multilevel memory cells storing a configurable number of bits. The error control is performed using an error-control code which operates, in the encoding phase, on b-bit binary strings made up of k symbols of r-bit data. When the memory cells store a number r of bits, a data symbol is formed only with the data bits stored in a memory cell. When the memory cells store a number s of bits smaller than r, a data symbol is formed with the data bits stored in a memory cell and with r-s bits having a pre-determined logic value, in which the data bits stored in the memory cell are arranged in the least significant part of the data symbol, and the r-s bits having a pre-determined logic value are arranged in the most significant part of the data symbol.

Owner:MICRON TECH INC

Read level control apparatuses and methods

Various read level control apparatuses and methods are provided. In various embodiments, the read level control apparatuses may include an error control code (ECC) decoding unit for ECC decoding data read from a storage unit, and a monitoring unit for monitoring a bit error rate (BER) based on the ECC decoded data and the read data. The apparatus may additionally include an error determination unit for determining an error rate of the read data based on the monitored BER, and a level control unit for controlling a read level of the storage unit based on the error rate.

Owner:SAMSUNG ELECTRONICS CO LTD