Patents

Literature

239 results about "Systematic code" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In coding theory, a systematic code is any error-correcting code in which the input data is embedded in the encoded output. Conversely, in a non-systematic code the output does not contain the input symbols.

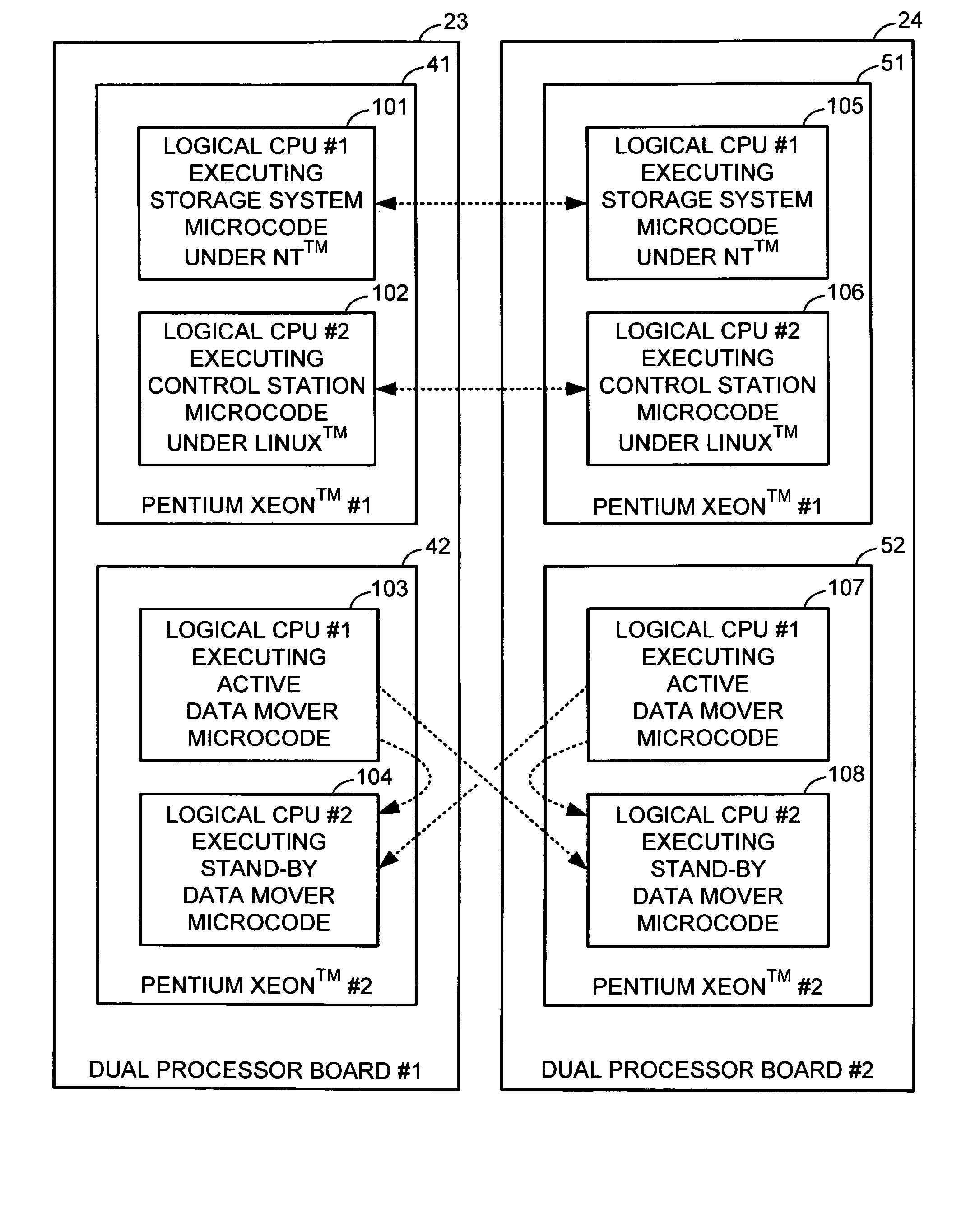

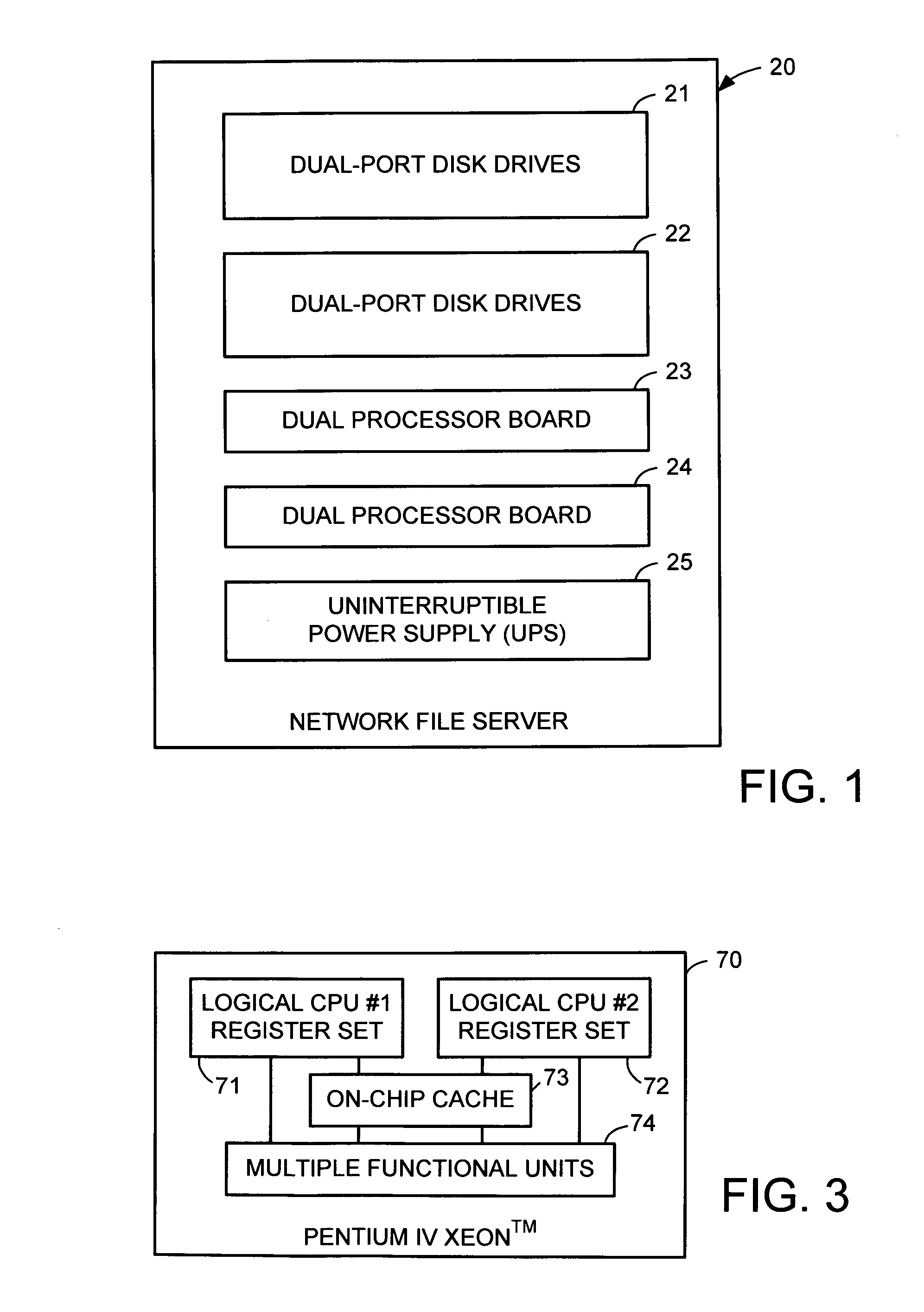

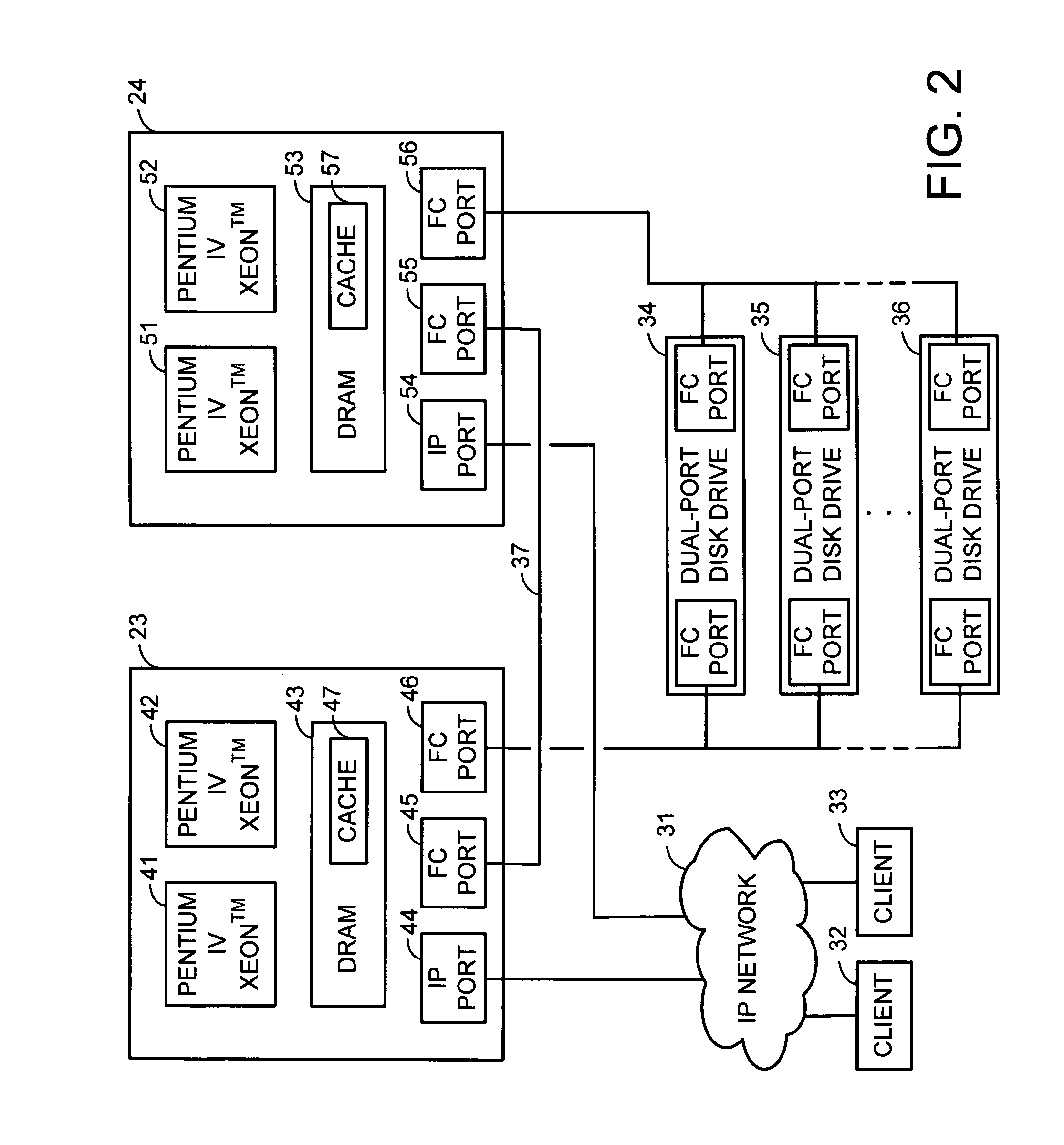

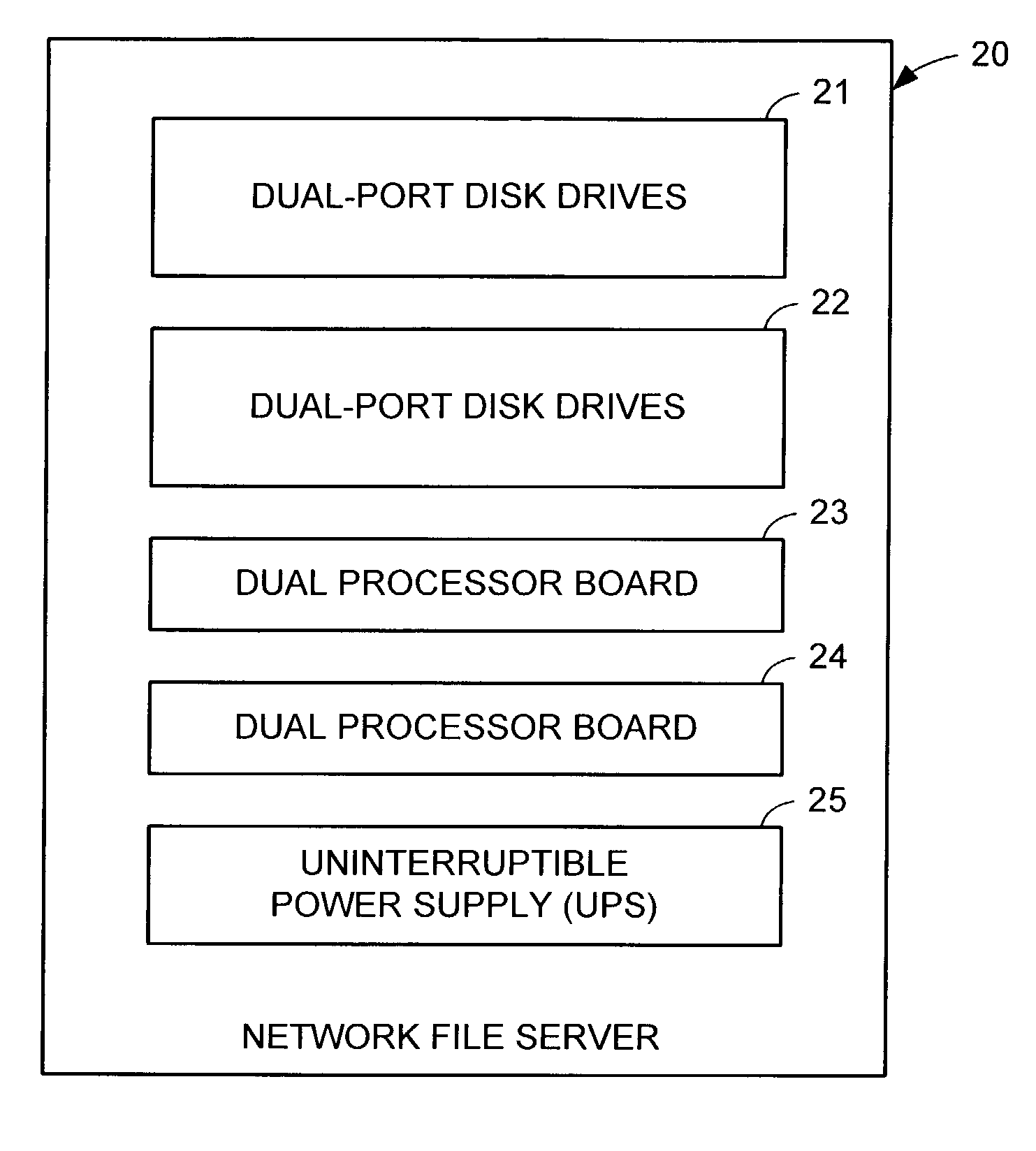

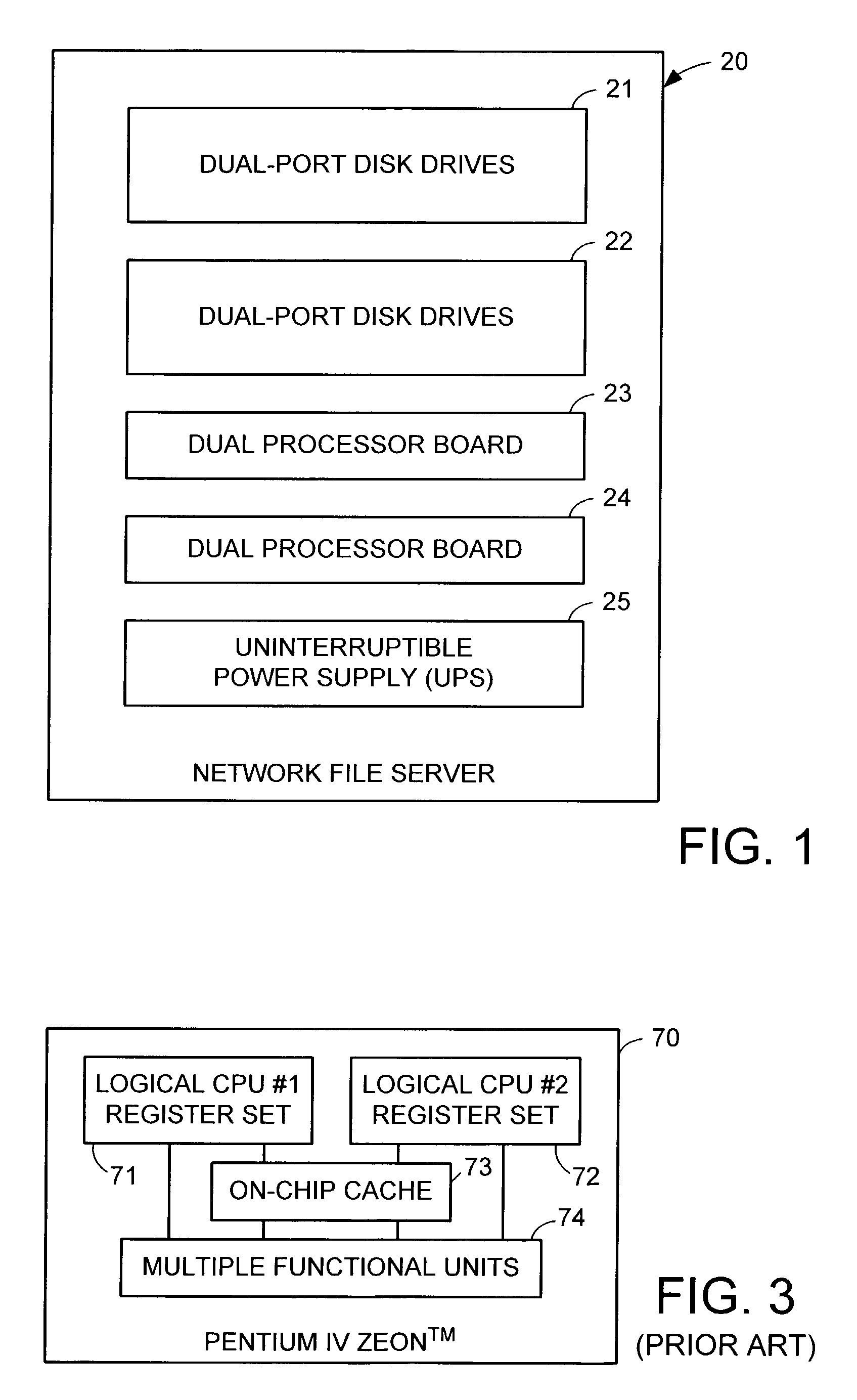

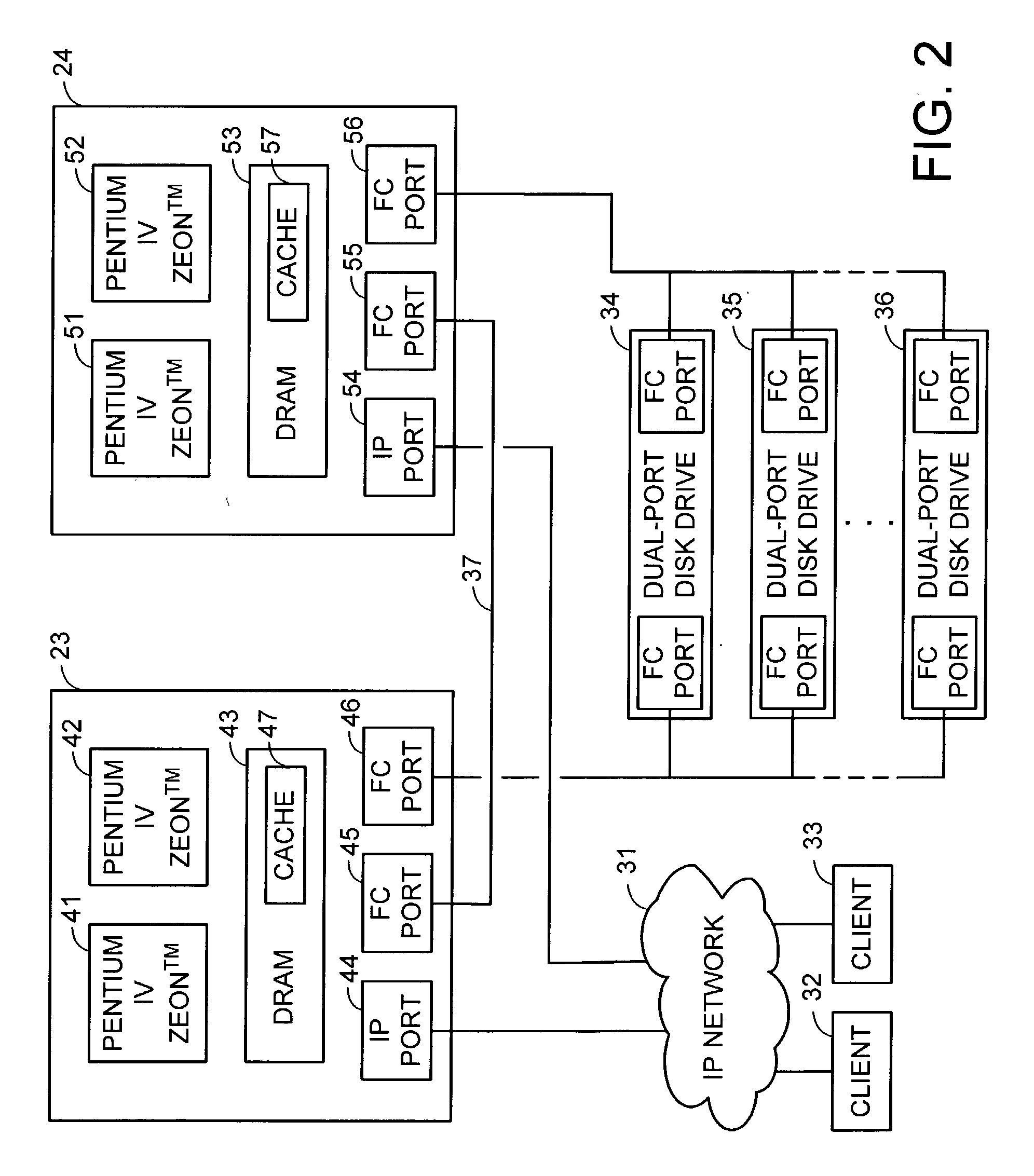

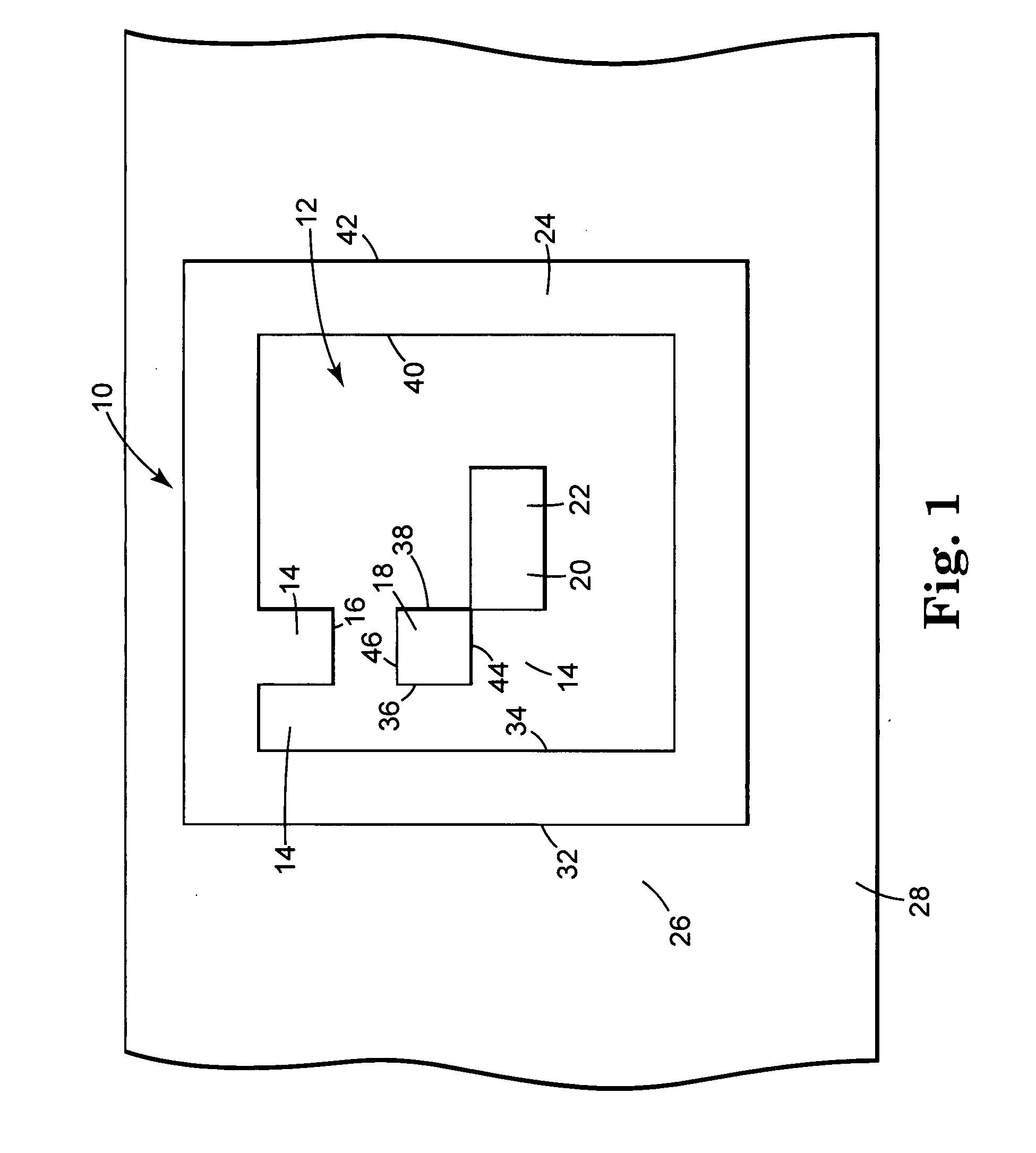

Redundant multi-processor and logical processor configuration for a file server

A redundant file server includes at least two dual processor boards. Each physical processor has two logical processors. The first logical processor of the first physical processor of each board executes storage system code under the Microsoft NT™ operating system. The second logical processor of the first physical processor of each board executes control station code under the Linux operating system. The first logical processor of the second physical processor of each board executes data mover code. The second logical processor of the second physical processor of each board is kept in a stand-by mode for assuming data mover functions upon failure of the first logical processor of the second physical processor on the first or second board.

Owner:EMC IP HLDG CO LLC

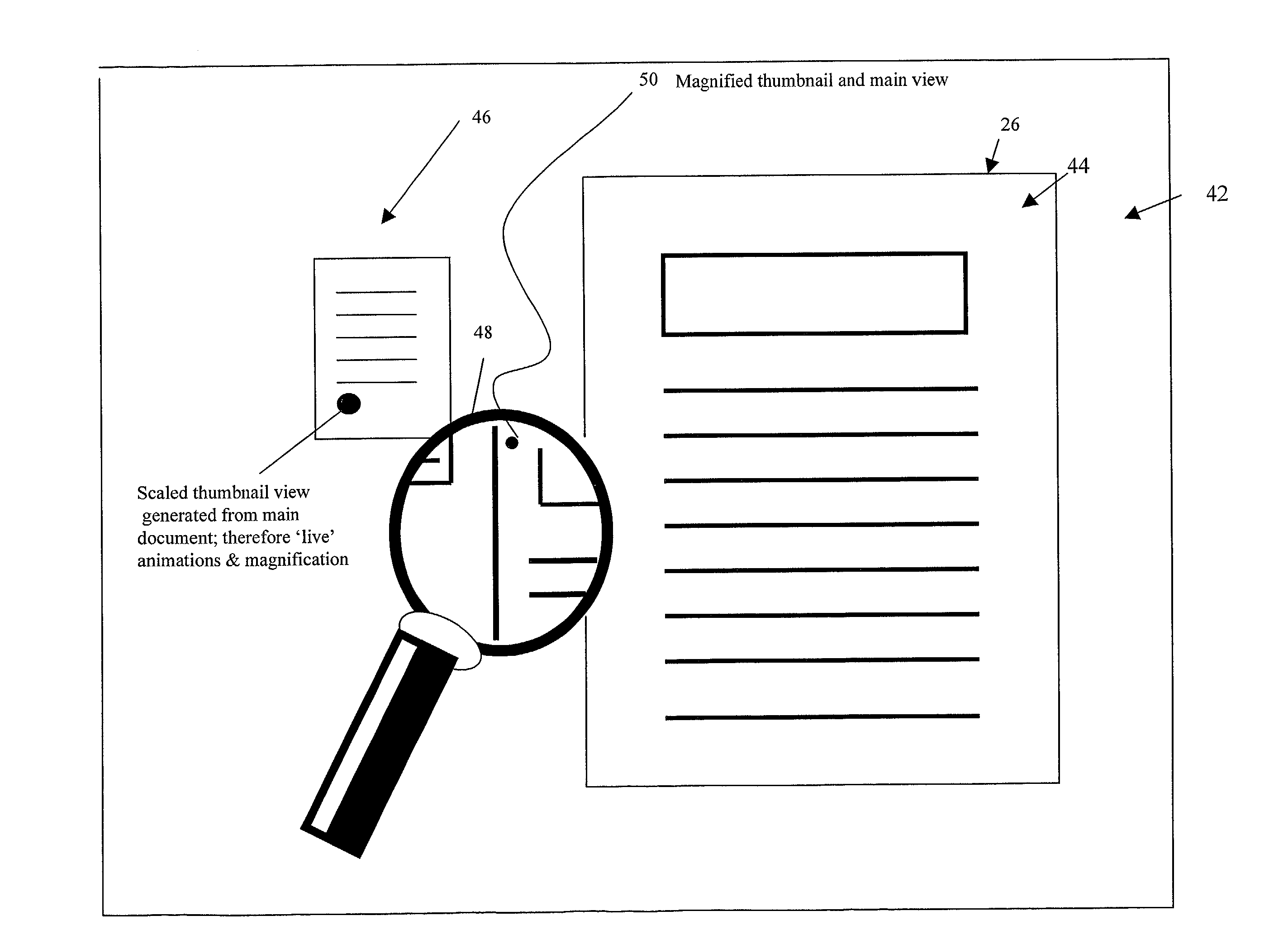

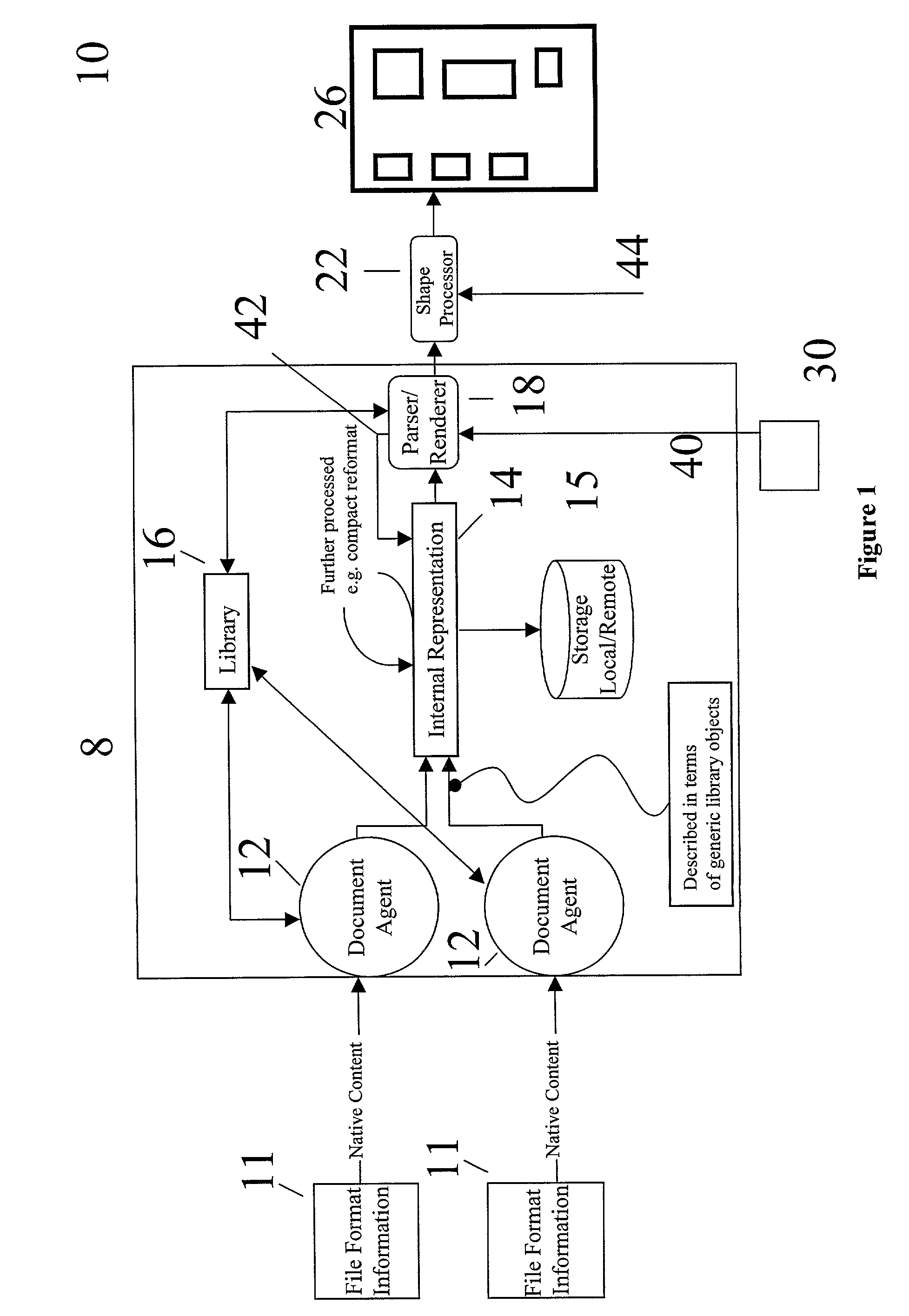

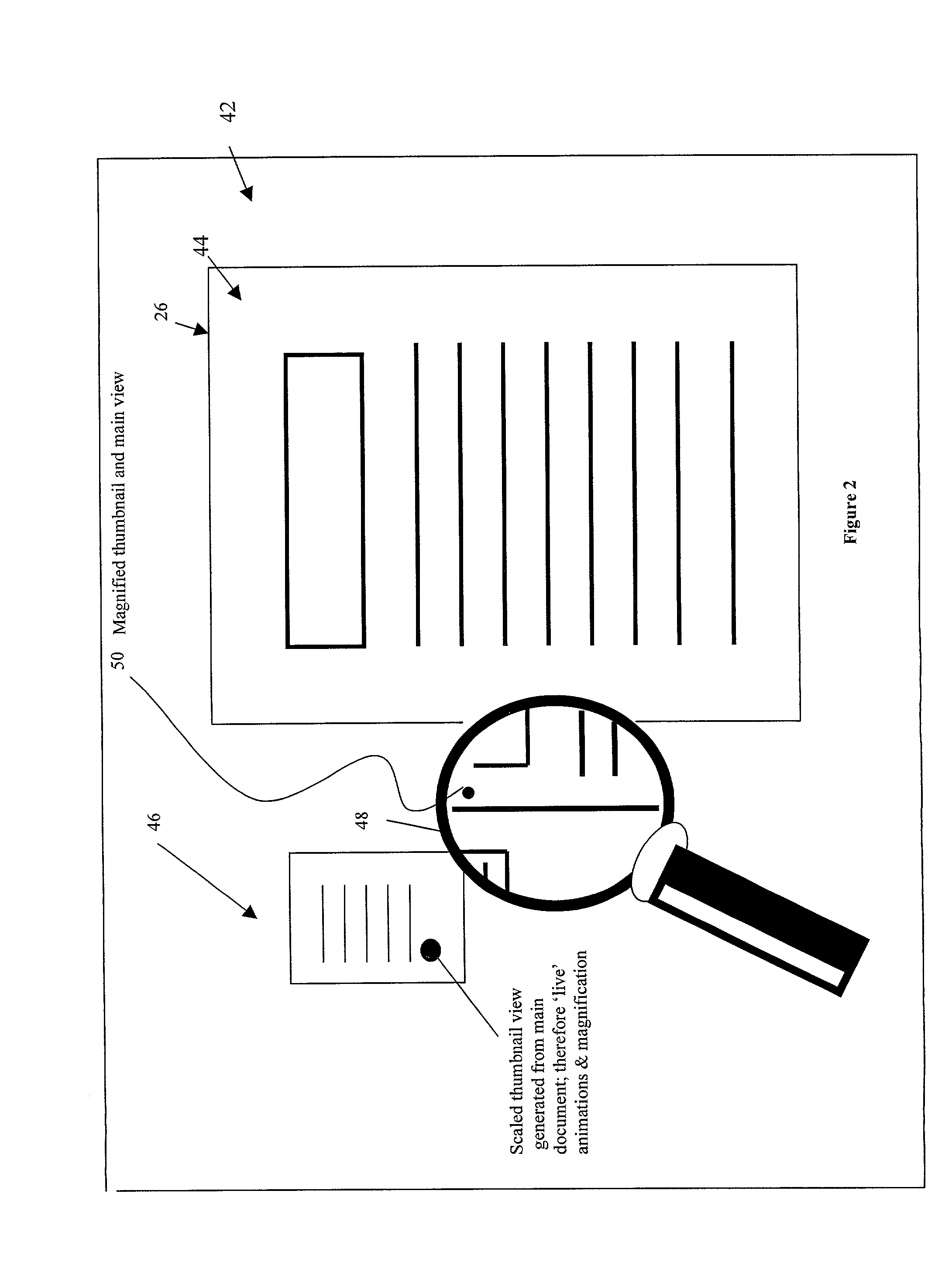

User interface systems and methods for manipulating and viewing digital documents

InactiveUS7450114B2Easily manipulateEasy to viewStatic indicating devicesDigital data processing detailsGraphicsDisplay device

Systems, including handheld computing devices that include system code stored within the memory and adapted to be executed by the processor. The system code can process an input byte stream that is representative of contents to be displayed on the touch sensitive display and can generate a content document file representative of an internal representation of the content. A tool document file may also be stored in the memory and may provide an internal representation of a document providing an image that is representative of a graphical tool. Associated with a tool document can be tool code that is capable of processing the content document file to create an internal representation of the contents that presents the content in a manner that achieves a display effect associated with the tool. The device will also include parsing code that processes the content document file, the tool document file, and the processed internal representation to generate a screen document for display on the touch sensitive display in a manner that portrays the display effect.

Owner:SAMSUNG ELECTRONICS CO LTD

Redundant multi-processor and logical processor configuration for a file server

A redundant file server includes at least two dual processor boards. Each physical processor has two logical processors. The first logical processor of the first physical processor of each board executes storage system code under the Microsoft NT(TM) operating system. The second logical processor of the first physical processor of each board executes control station code under the Linux operating system. The first logical processor of the second physical processor of each board executes data mover code. The second logical processor of the second physical processor of each board is kept in a stand-by mode for assuming data mover functions upon failure of the first logical processor of the second physical processor on the first or second board.

Owner:EMC IP HLDG CO LLC

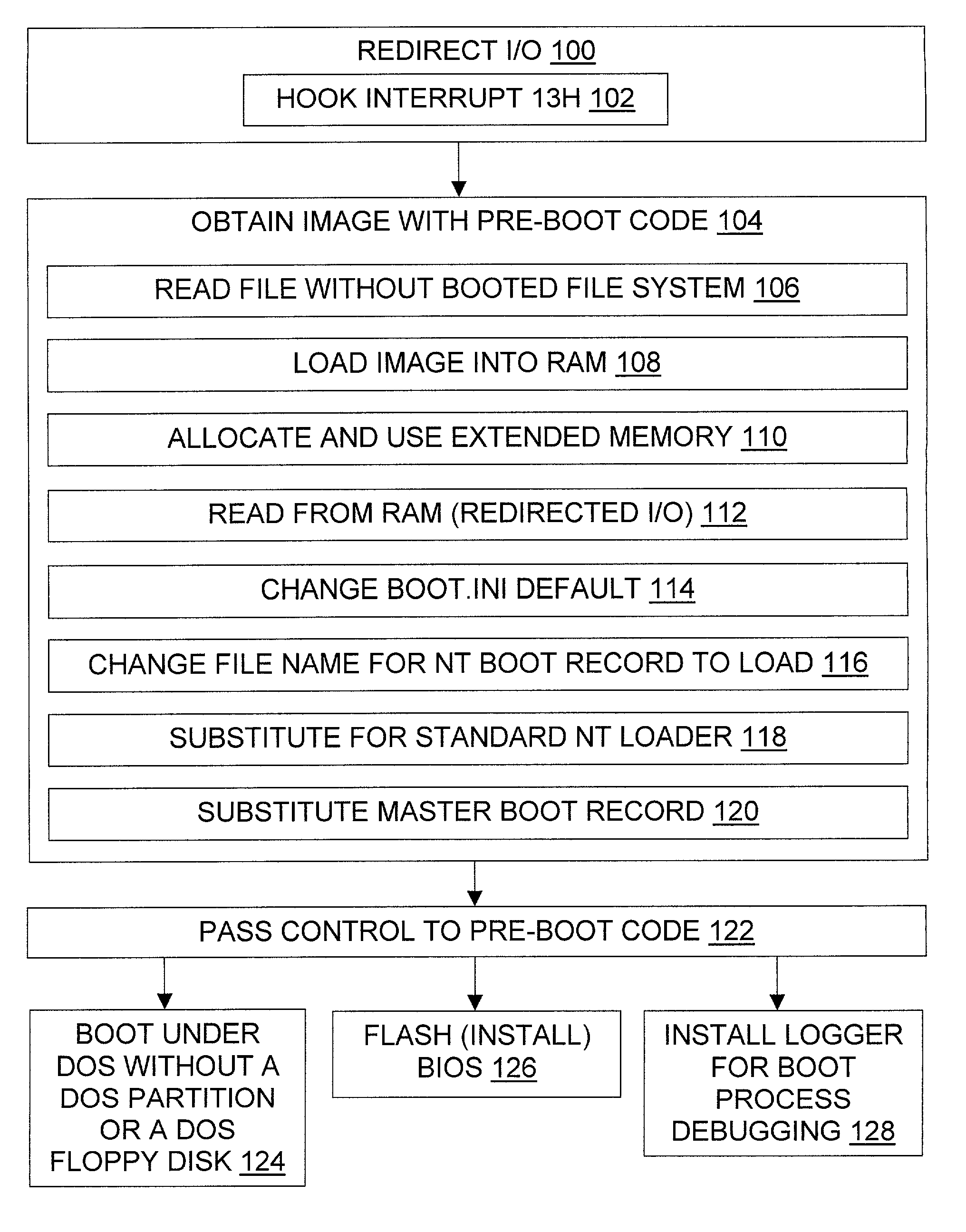

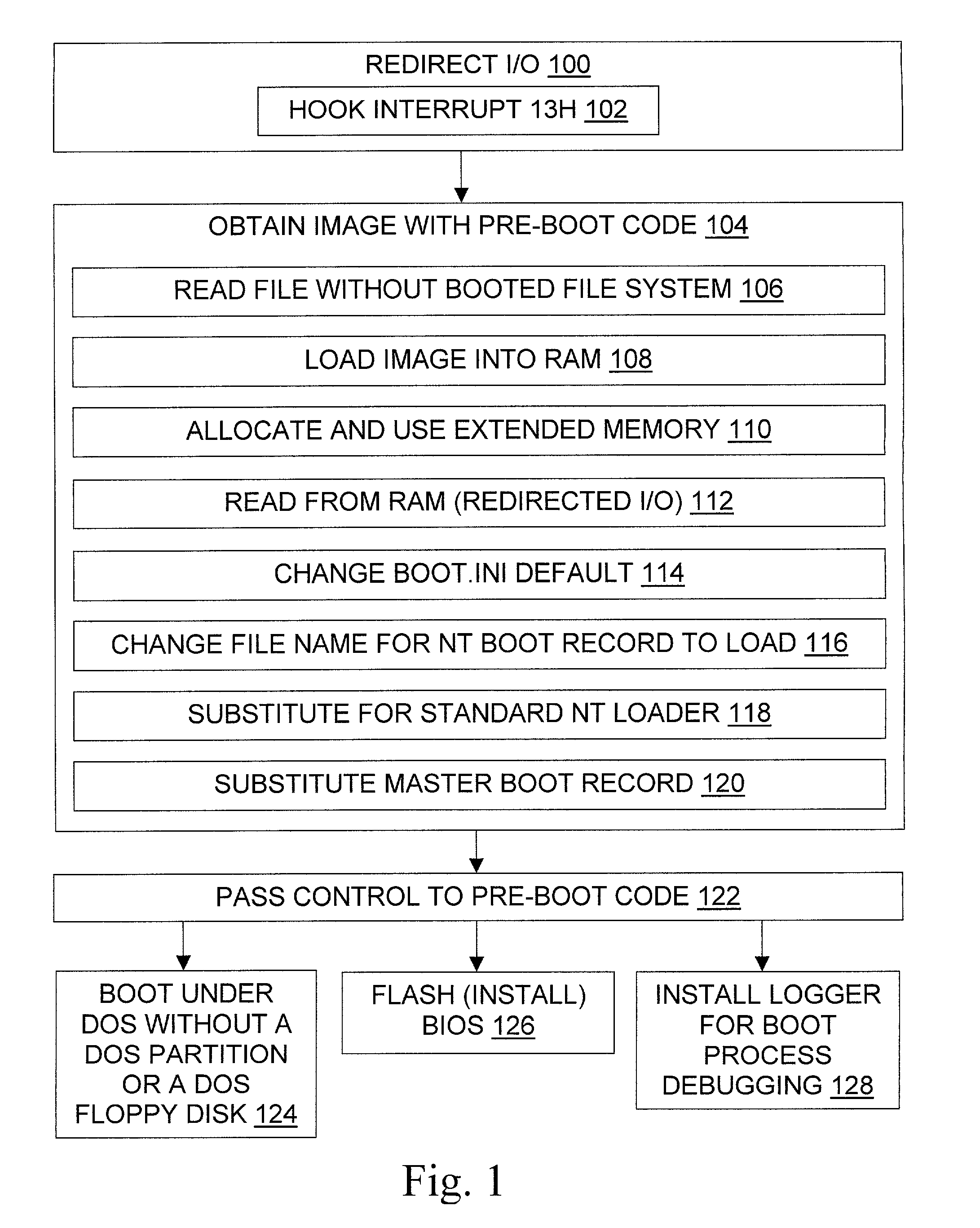

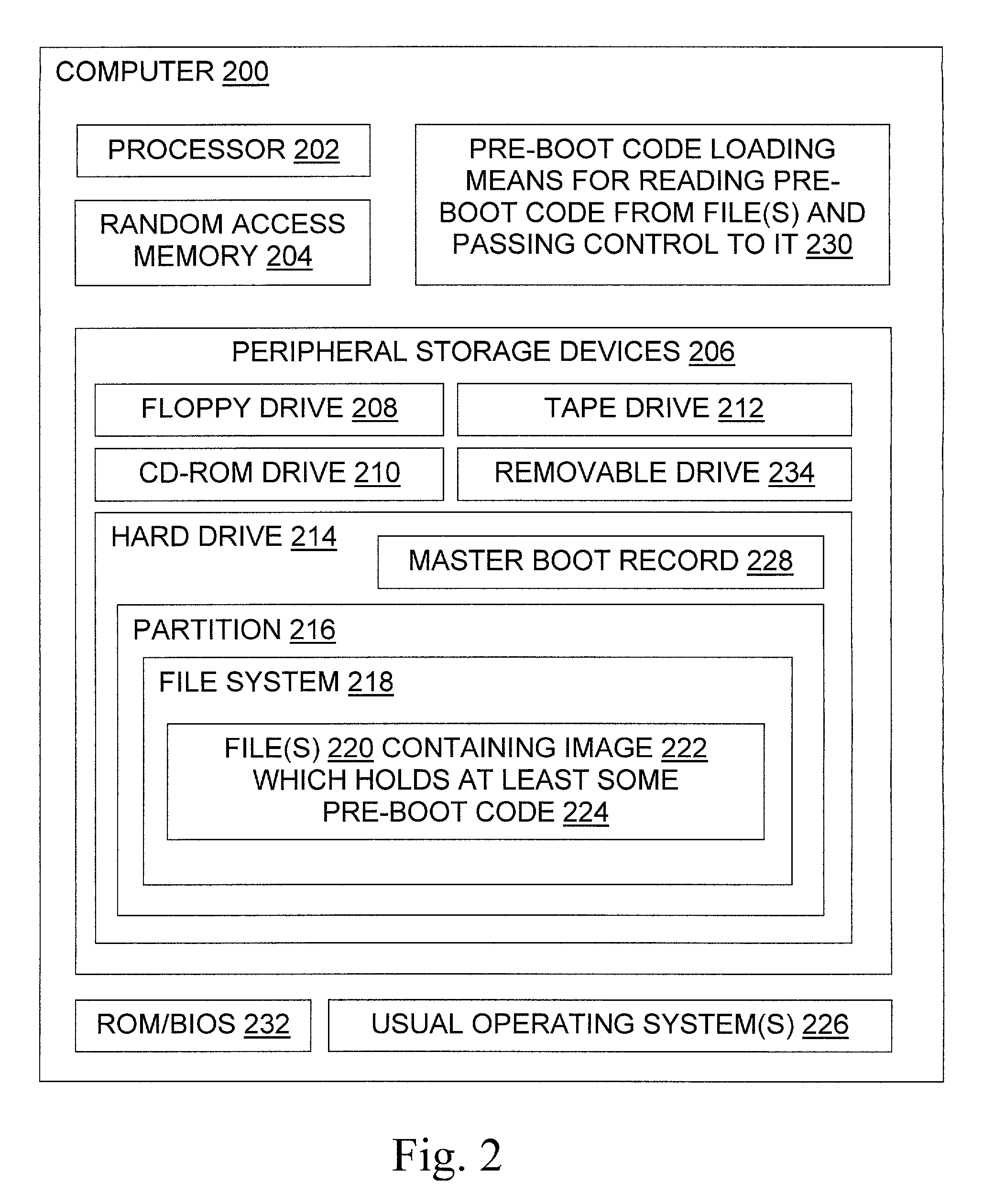

Booting an operating system or running other pre-boot code from a file stored under a different operating system

InactiveUS6996706B1Increase flexibilityWithout usingDigital computer detailsBootstrappingOperational systemFile system

The invention provides tools and techniques for running pre-boot code on a computer from a file stored in a file system on the computer. The pre-boot code may include an operating system which is not otherwise installed on the system. For instance, the pre-boot code may be used to boot a DOS operating system on a computer which lacks a DOS hard disk partition. The pre-boot code may contain code to perform operations that are difficult to perform after the operating system is booted, such as code for monitoring the boot process to help debug it. The pre-boot code is obtained from the file without using booted file system code, and is then executed. The code may be obtained by redirecting floppy drive I / O to read the pre-boot code from a copy in memory, or to read it as needed from one or more files on the hard disk.

Owner:GEN DIGITAL INC

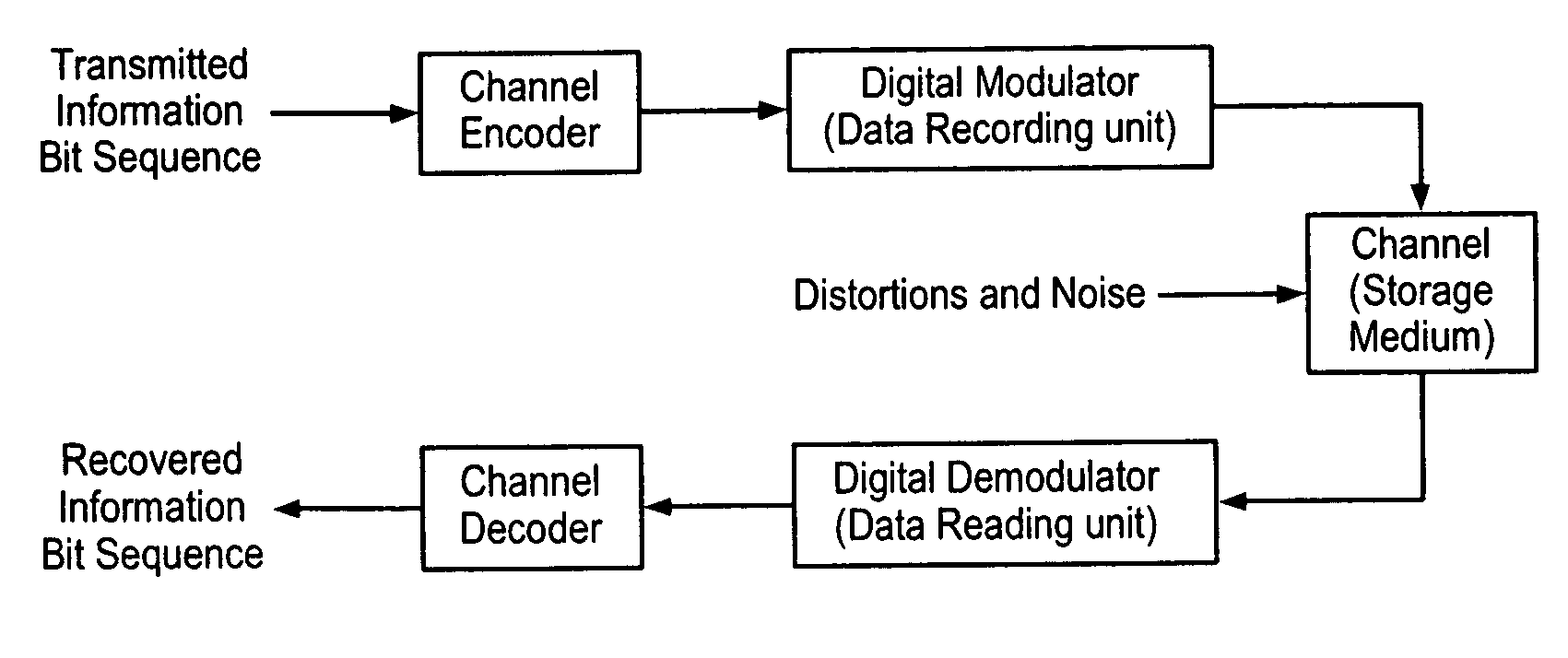

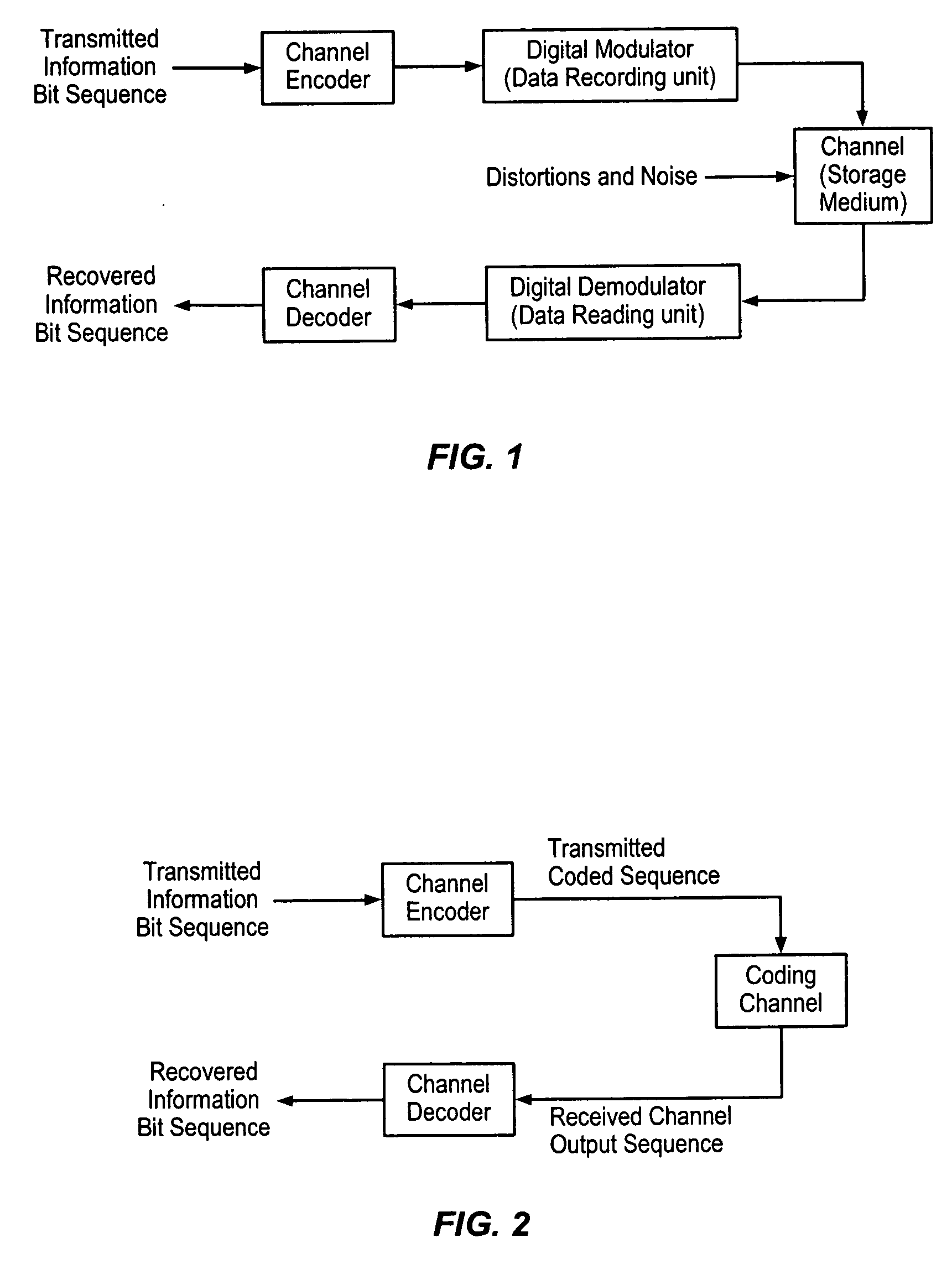

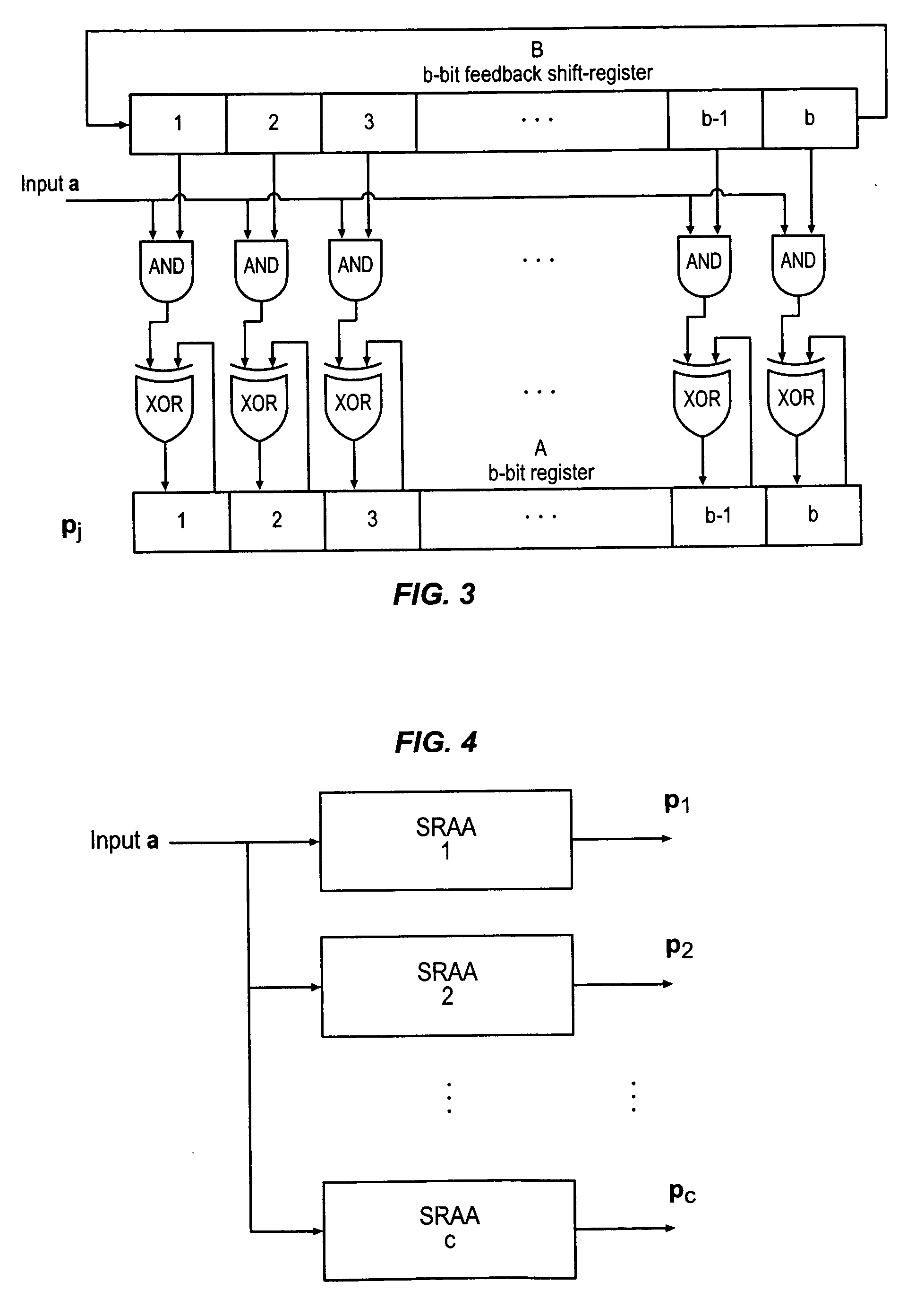

Universal error control coding system for digital communication and data storage systems

InactiveUS20080126908A1Reduce complexityReduce chip areaError detection/correctionCode conversionComputer architectureRound complexity

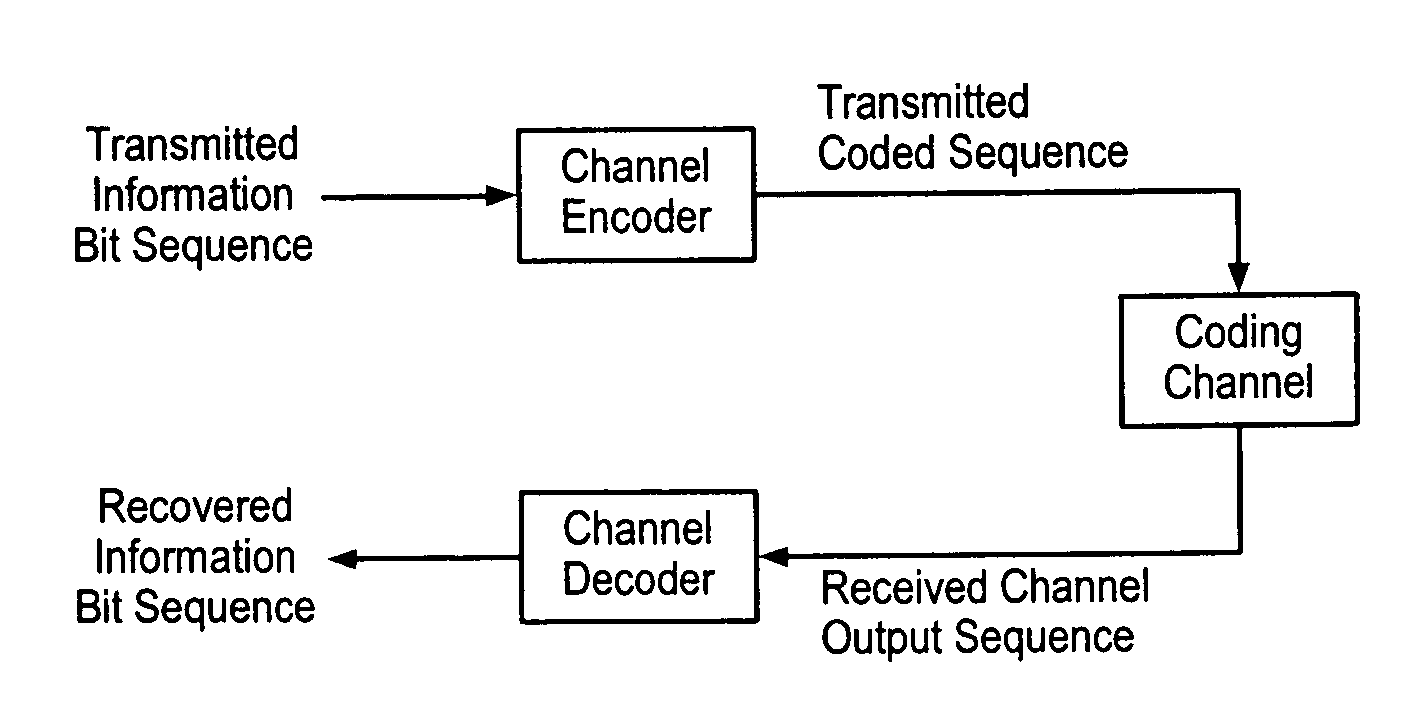

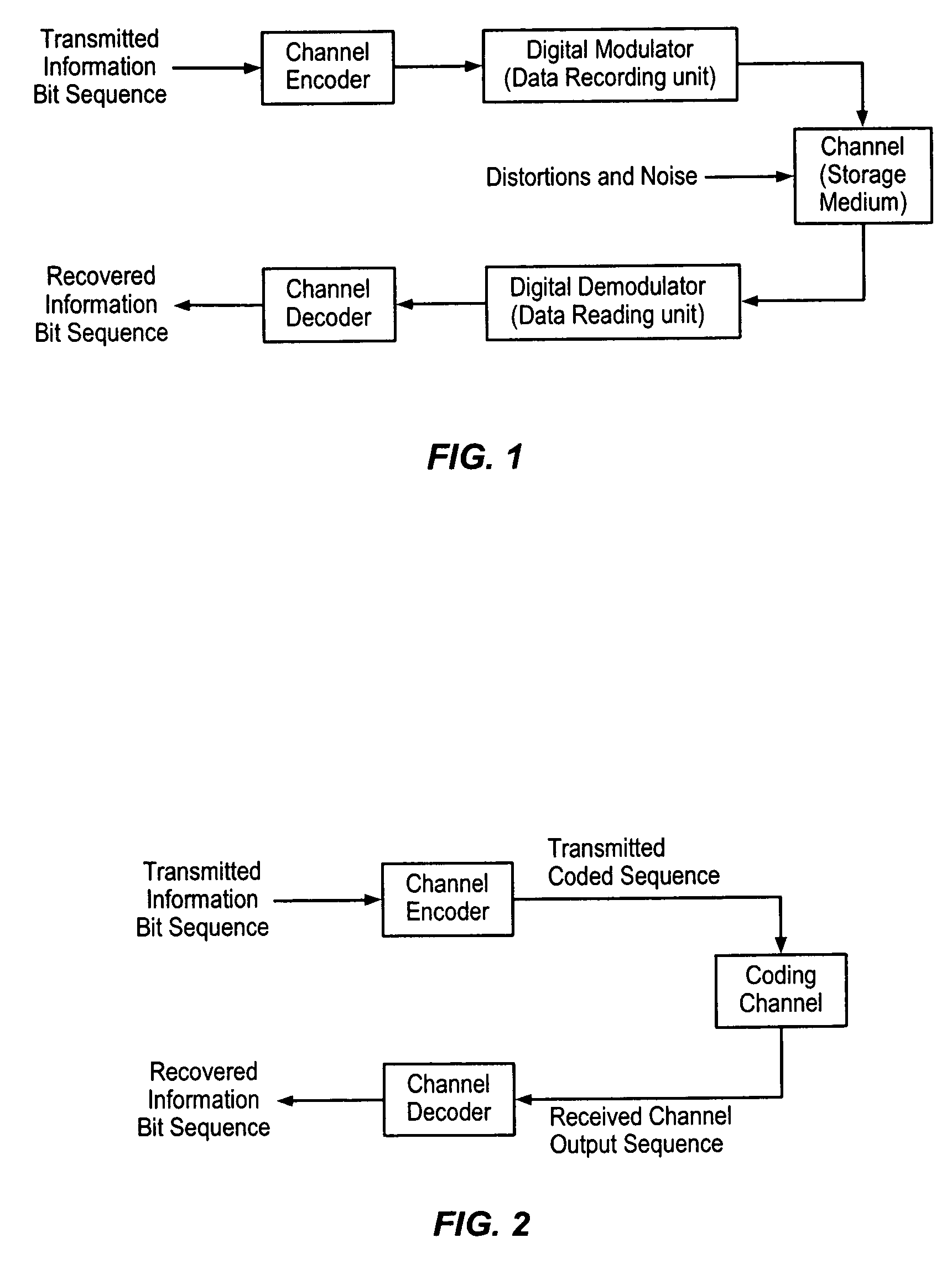

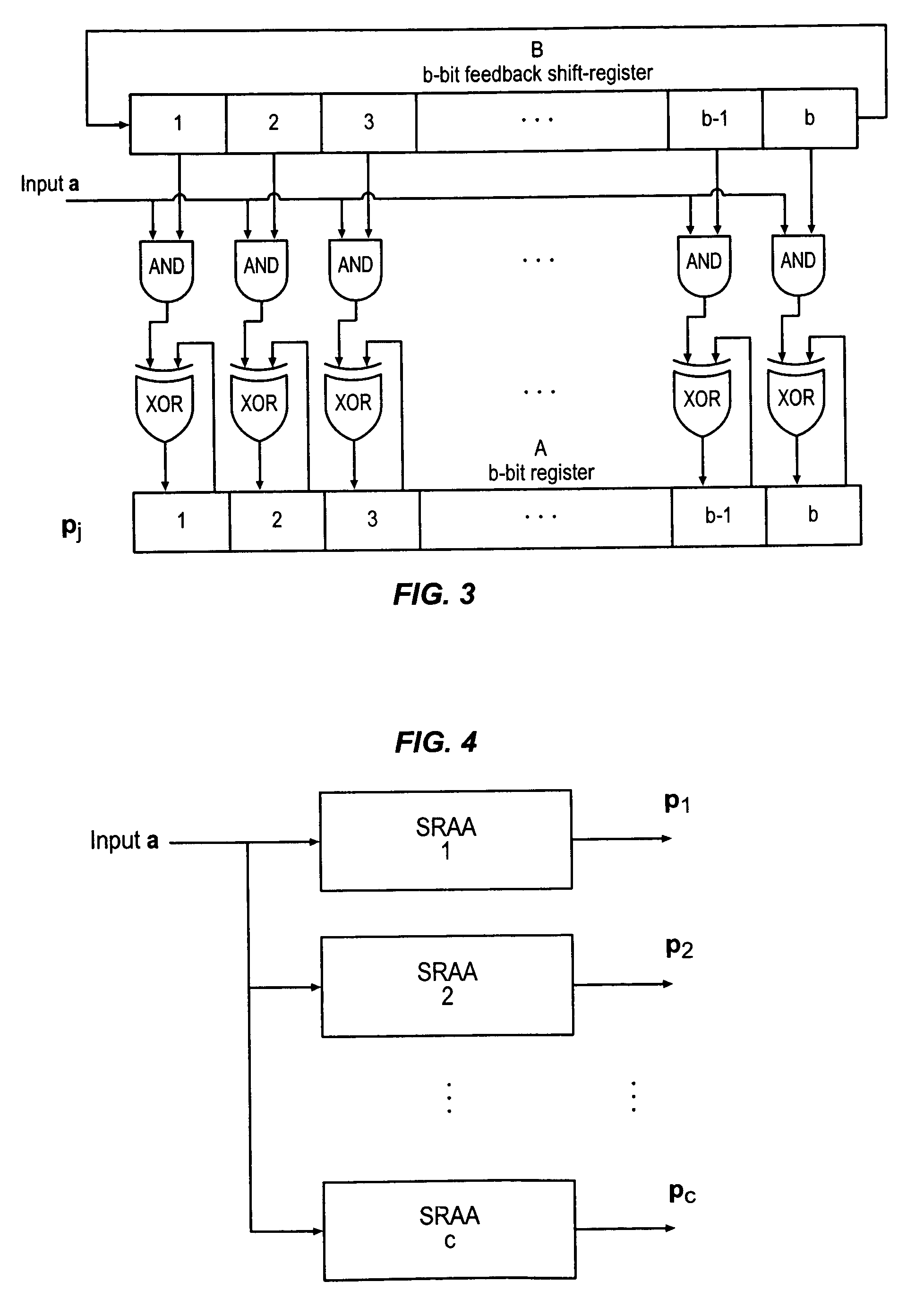

The universal forward error-correction coding system provides adjustable code rates and coding gains to greatly benefit the design of many modern digital communications (data storage) systems. The channel encoding and decoding methods are universal such that a single encoder and a single decoder can be used to implement all the forward error-correction codes of different code rates. This universal forward error-correction coding system also includes a novel systematic code generation procedure that has the capability of generating many classes of codes that provide the best balance between coding gain performance and implementation complexity.

Owner:COMM CODING

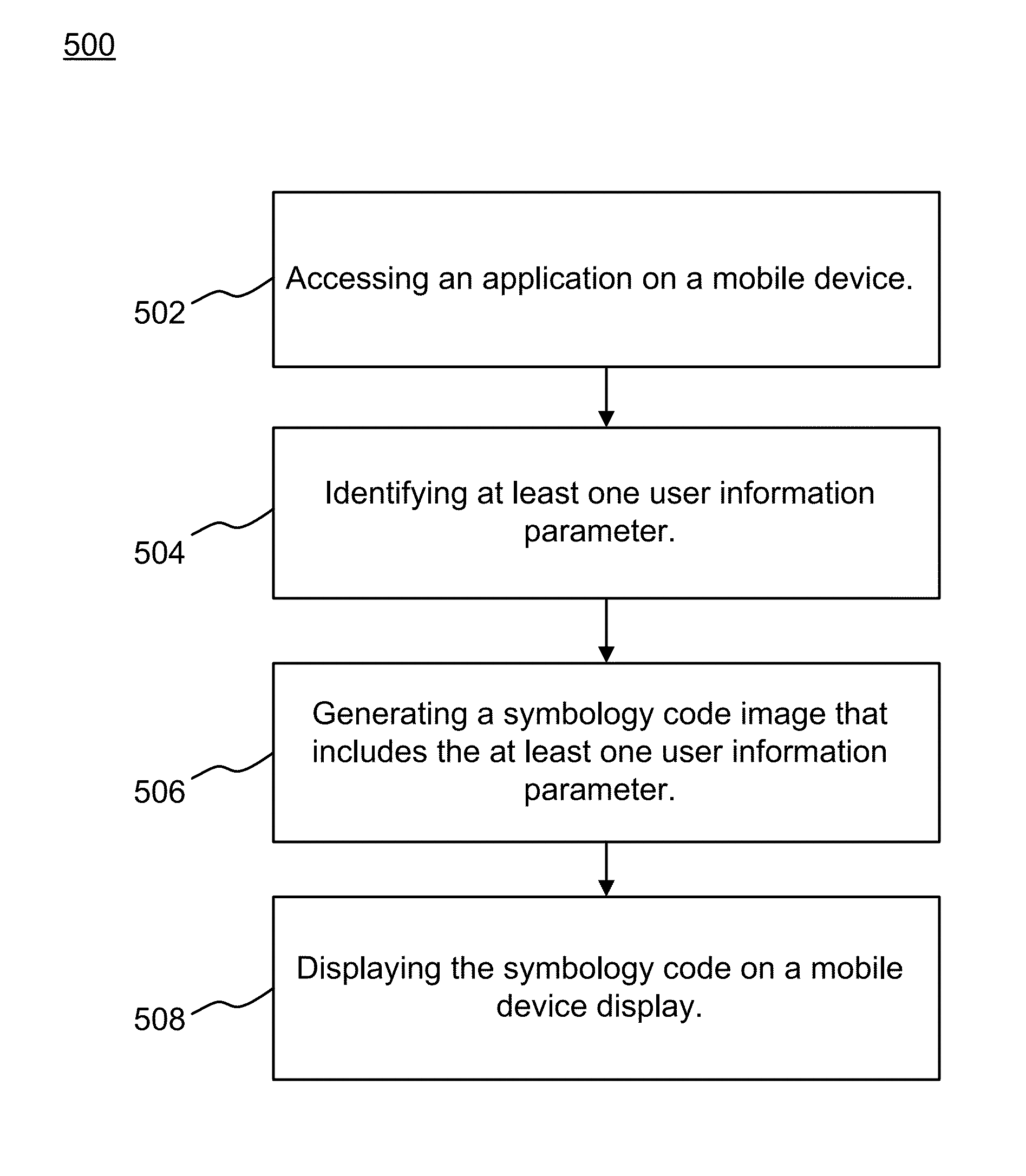

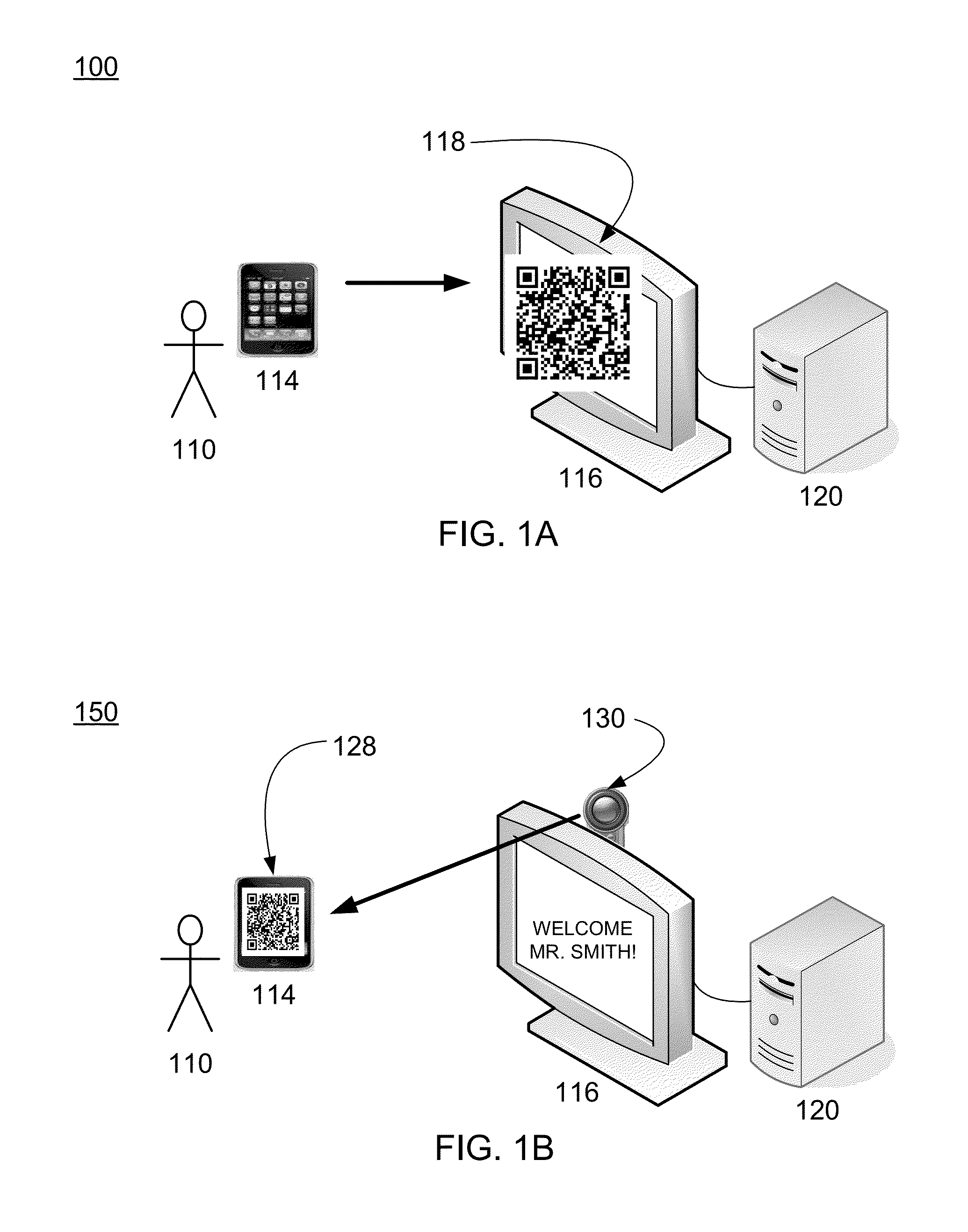

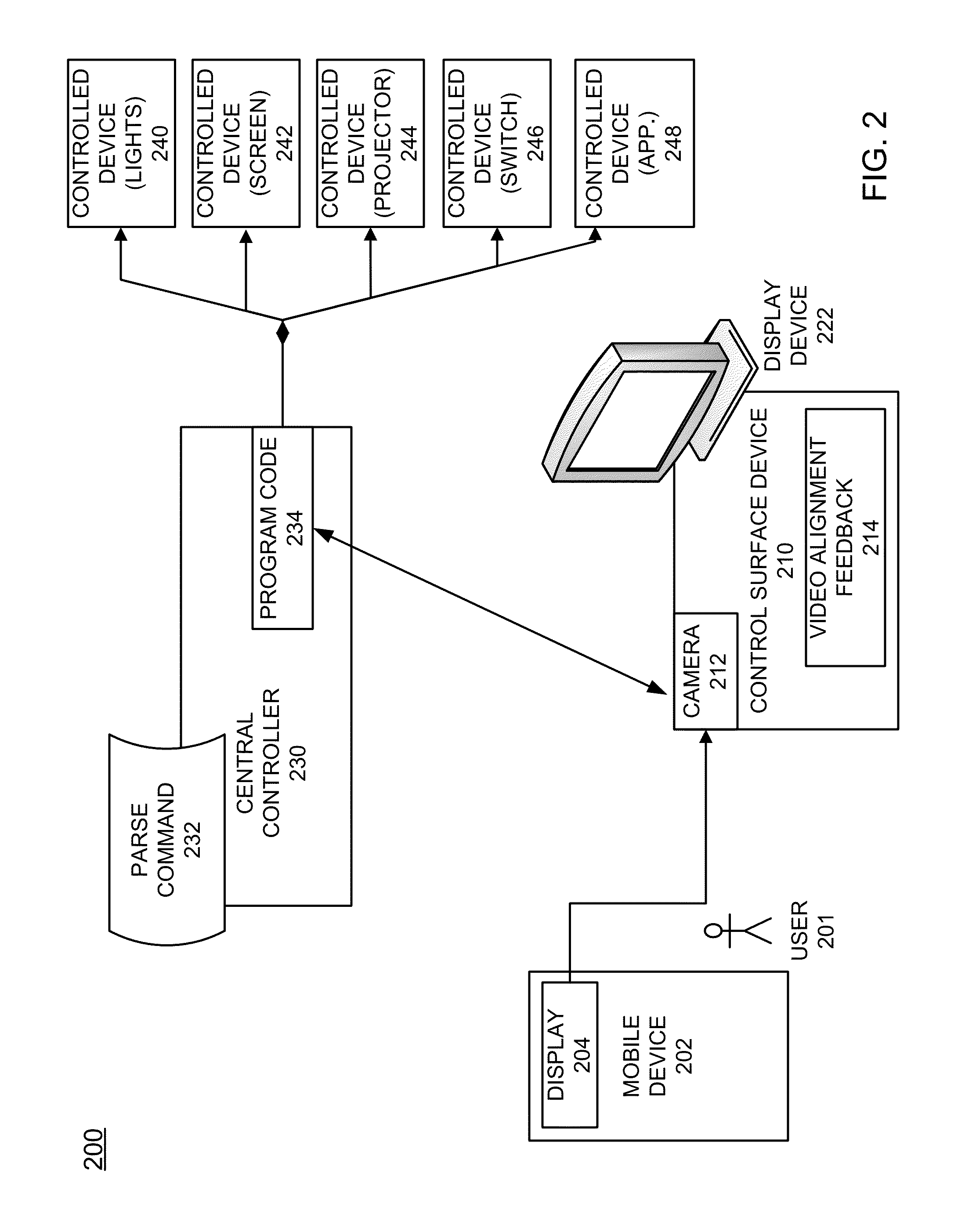

Method and apparatus of processing symbology interactions between mobile stations and a control system

ActiveUS20140001253A1Payment architectureRecord carriers used with machinesSymbolic SystemsControl system

Disclosed are an apparatus and method of creating, displaying and utilizing quick response (QR) codes to perform processing an application on a mobile device and a control system network. One example method of operation may include identifying a user information parameter and generating a symbology code image that includes the user information parameter and displaying the symbology code on a mobile device display.

Owner:HARMAN PROFESSIONAL INC

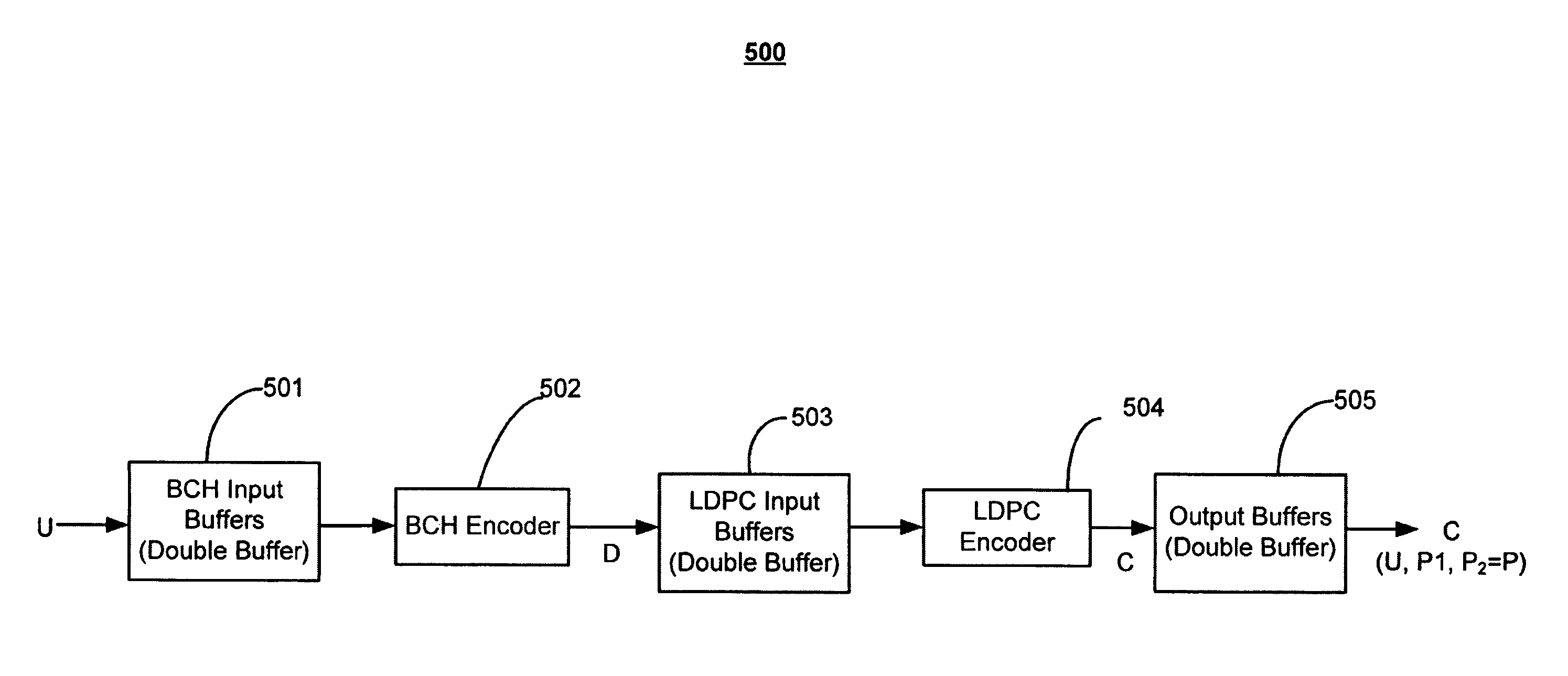

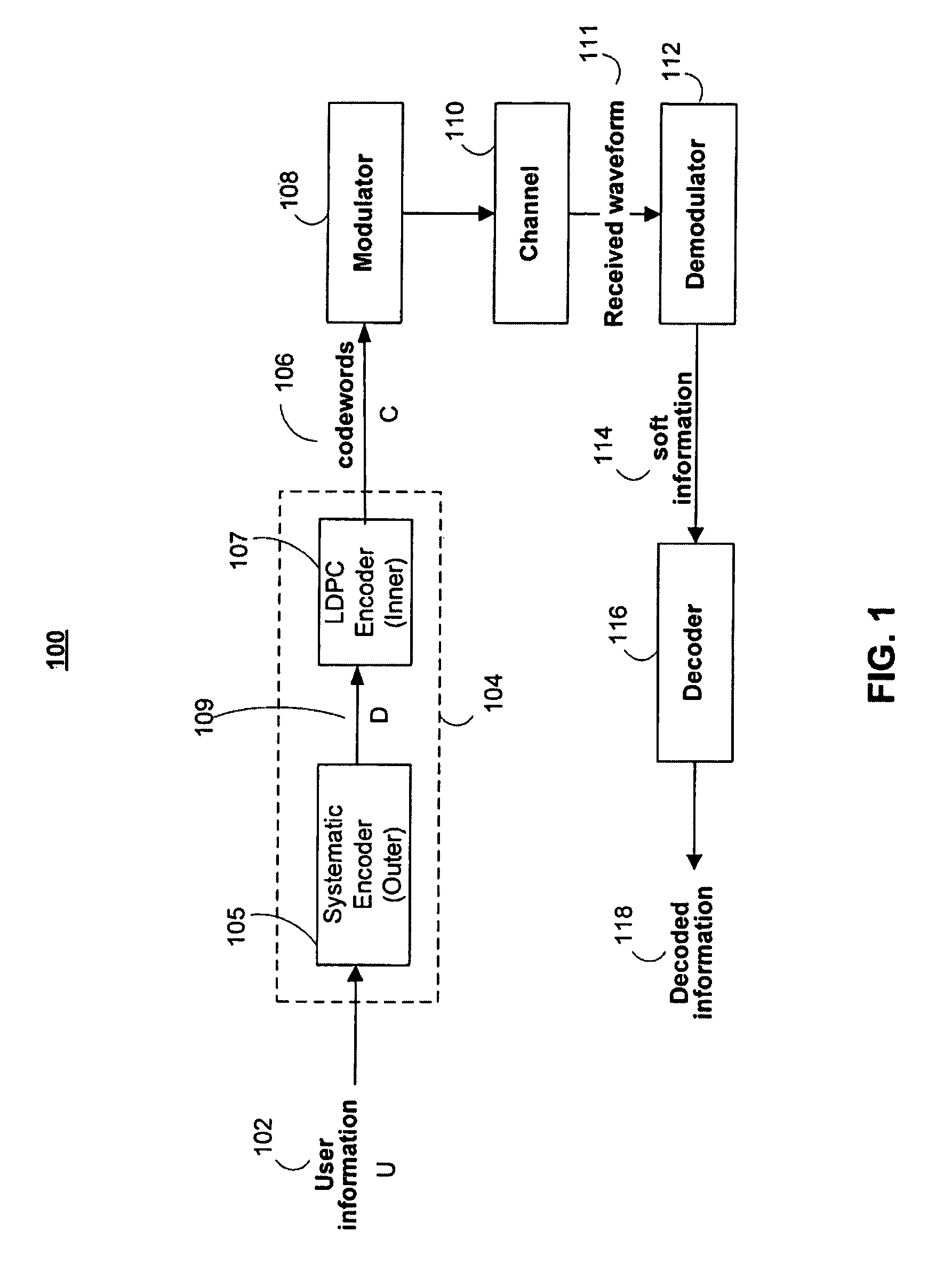

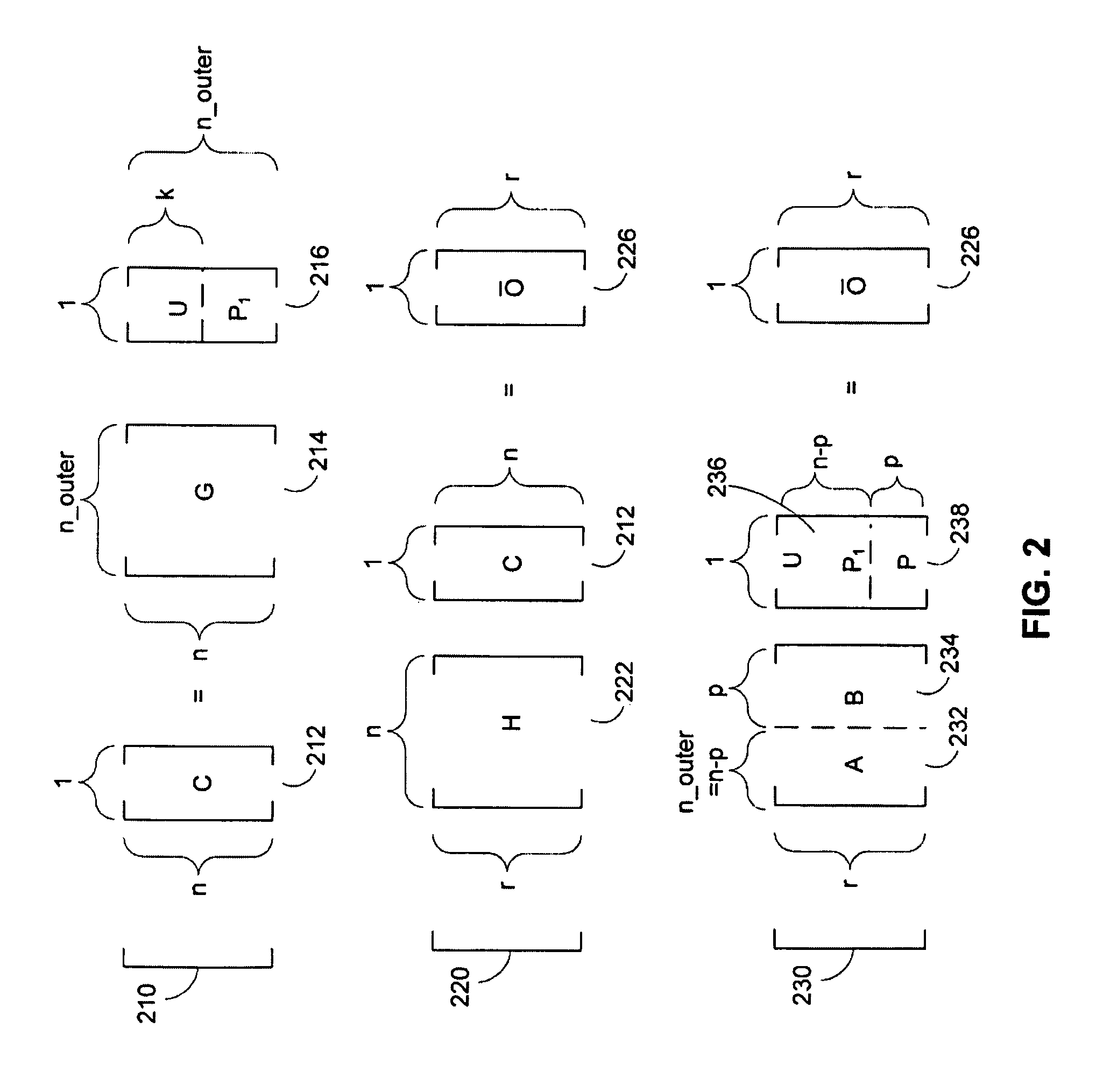

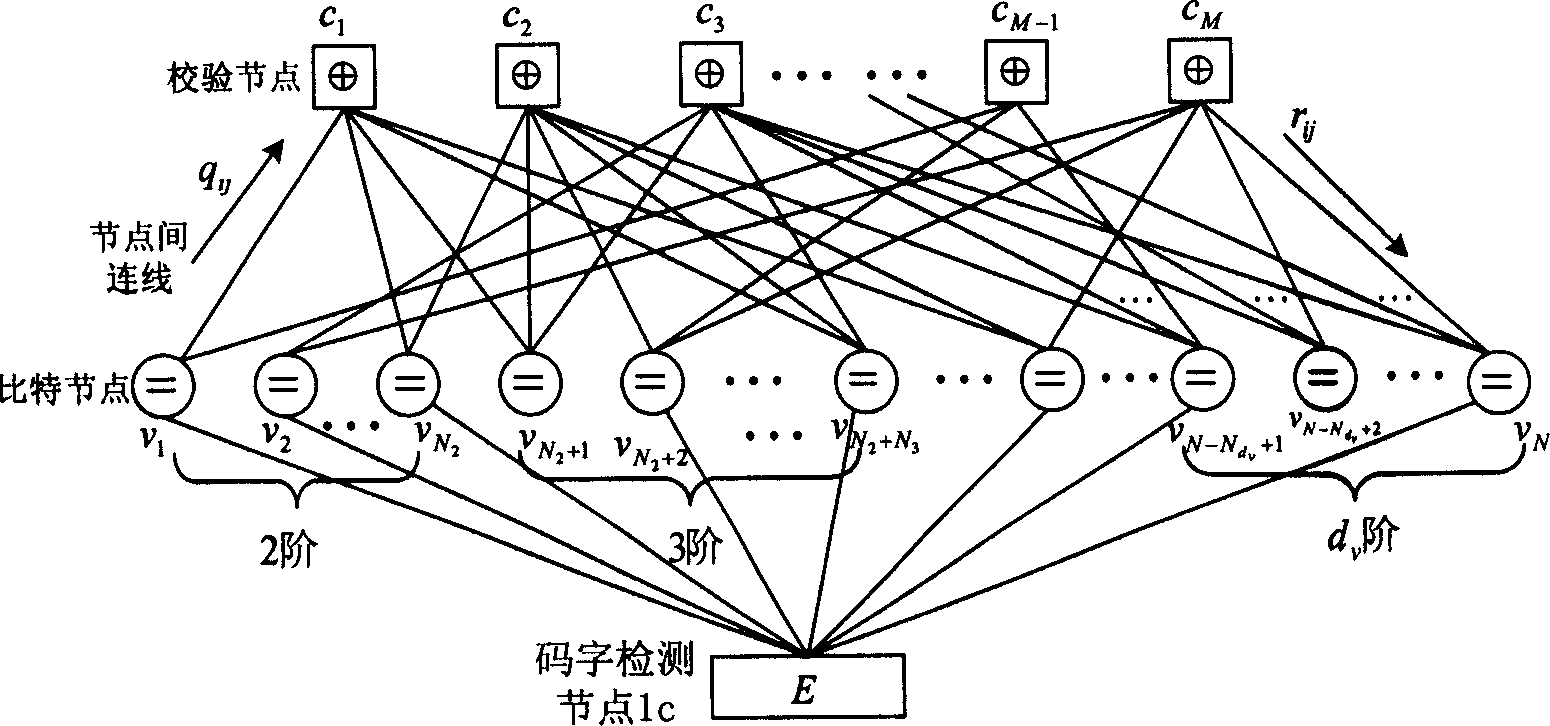

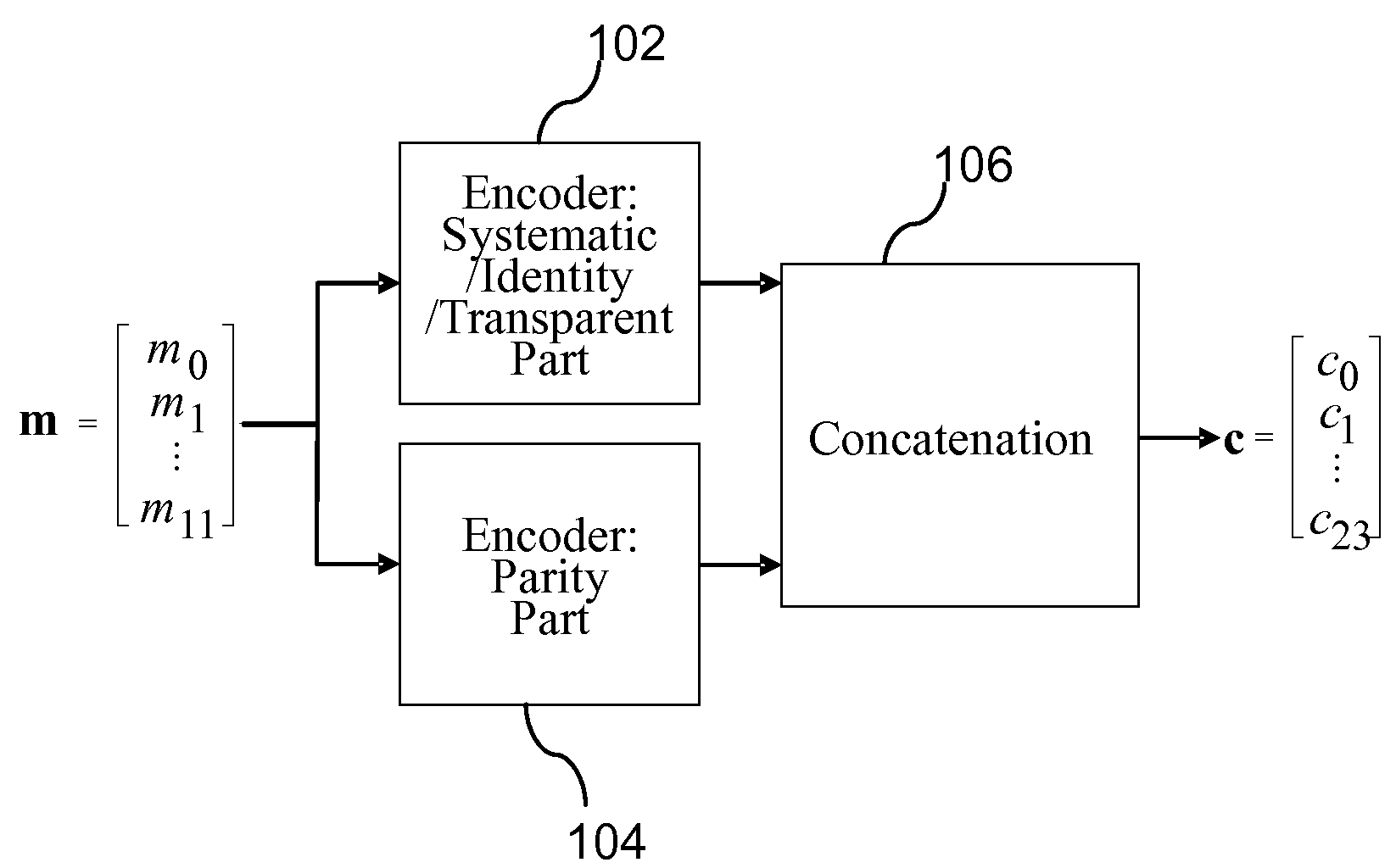

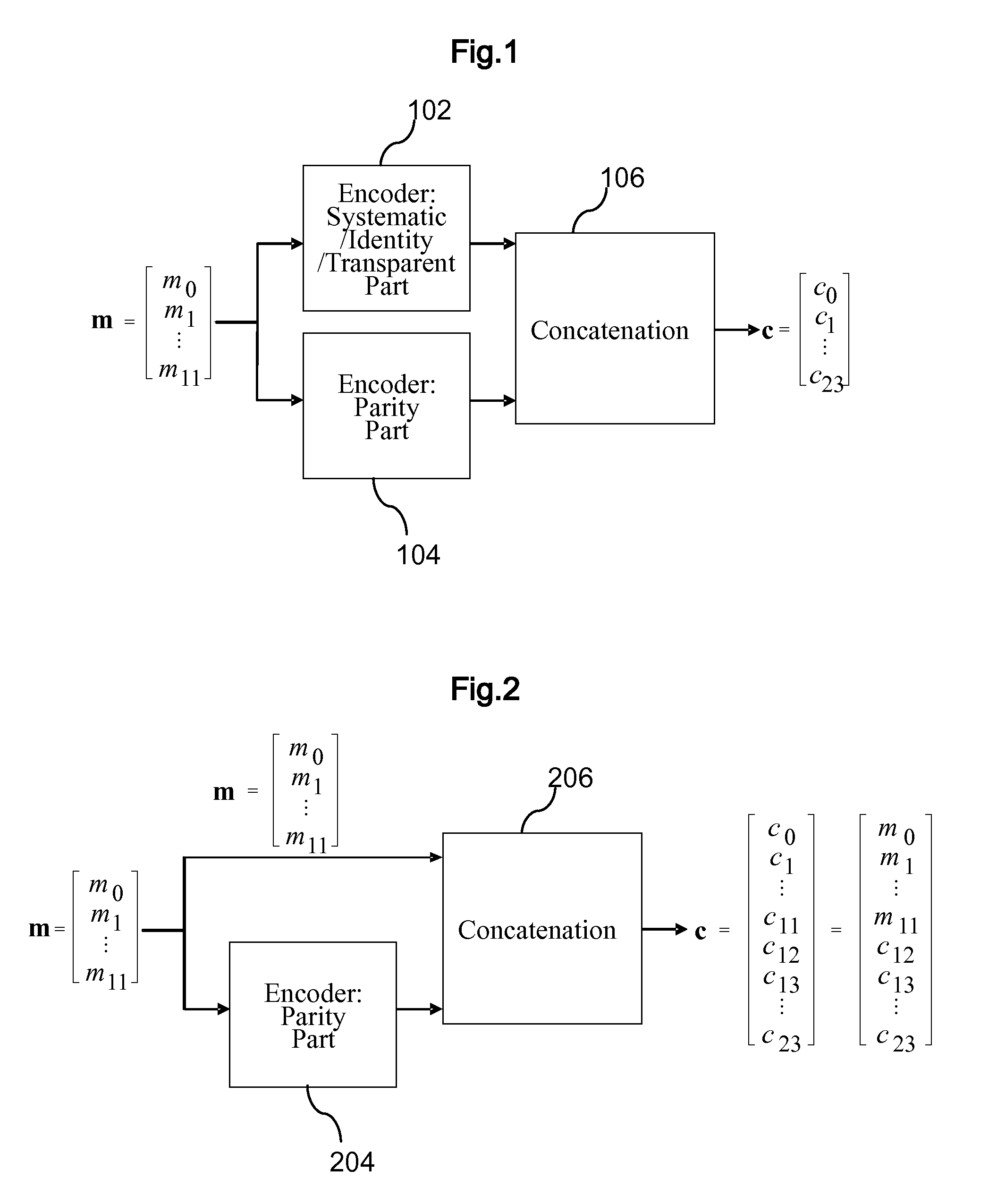

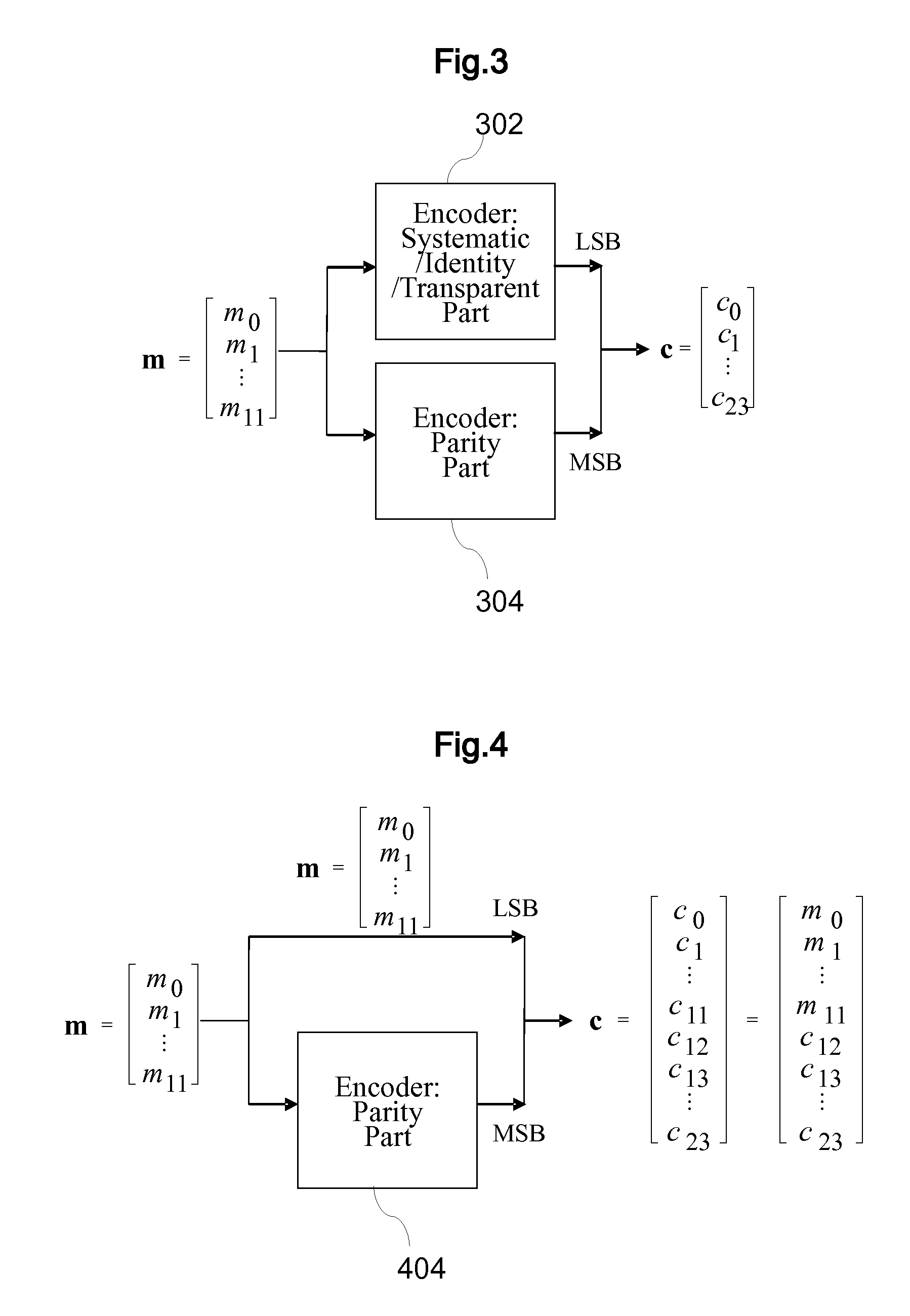

Low latency programmable encoder with outer systematic code and low-density parity-check code

ActiveUS8065598B1Reduce memoryReduce latency requirementError detection/correctionCode conversionLatency (engineering)Parallel computing

Low-latency programmable encoders, and more particularly, low-latency programmable encoders which use low-density parity check (LDPC) codes in combination with an outer systematic code. The LDPC encoder is programmable for any irregular circulant-based LDPC code. The code profile, block length, number of block rows, and number of block columns can vary. The LDPC encoding and the outer systematic code encoding can proceed in a parallel manner (e.g., simultaneously) instead of in a serial manner.

Owner:MARVELL ASIA PTE LTD

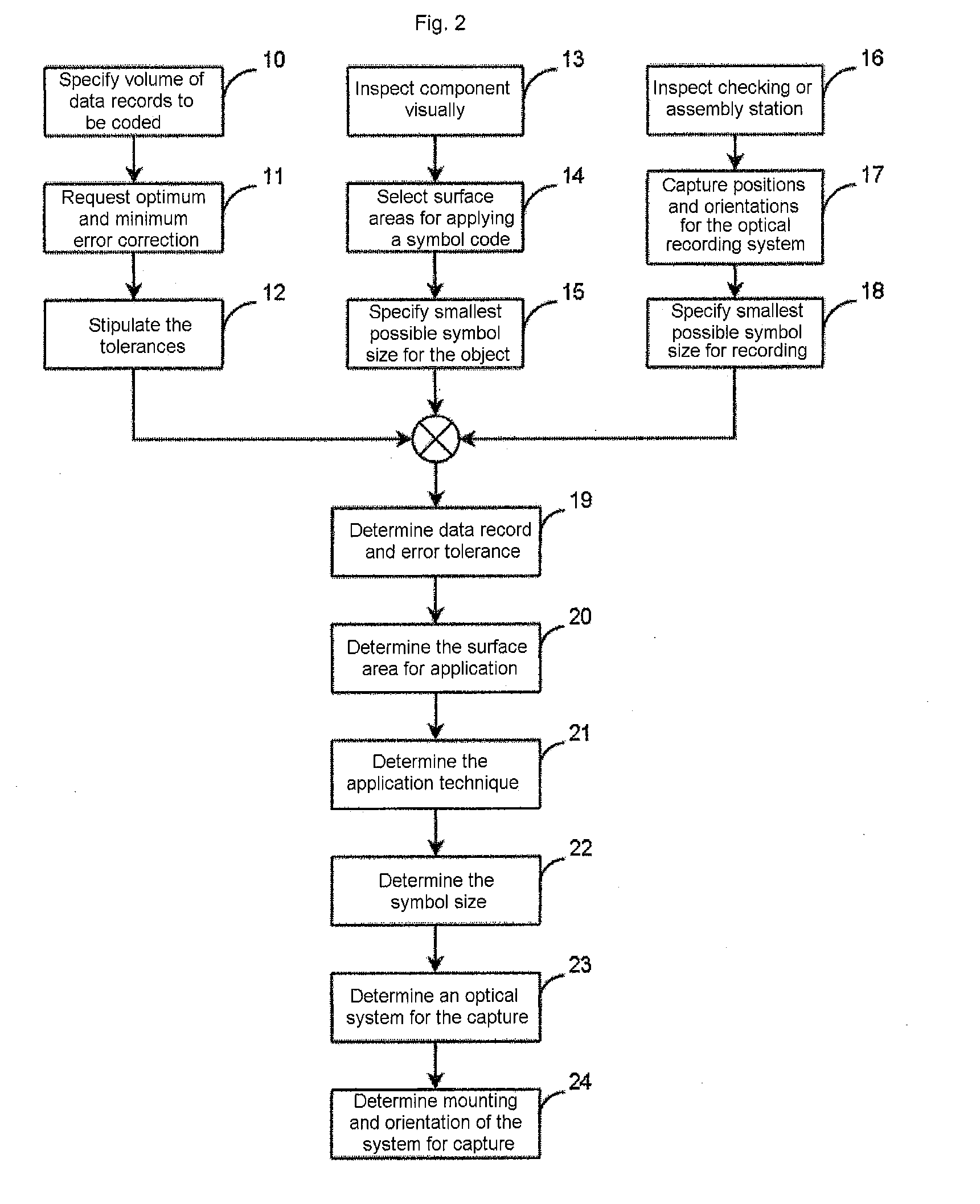

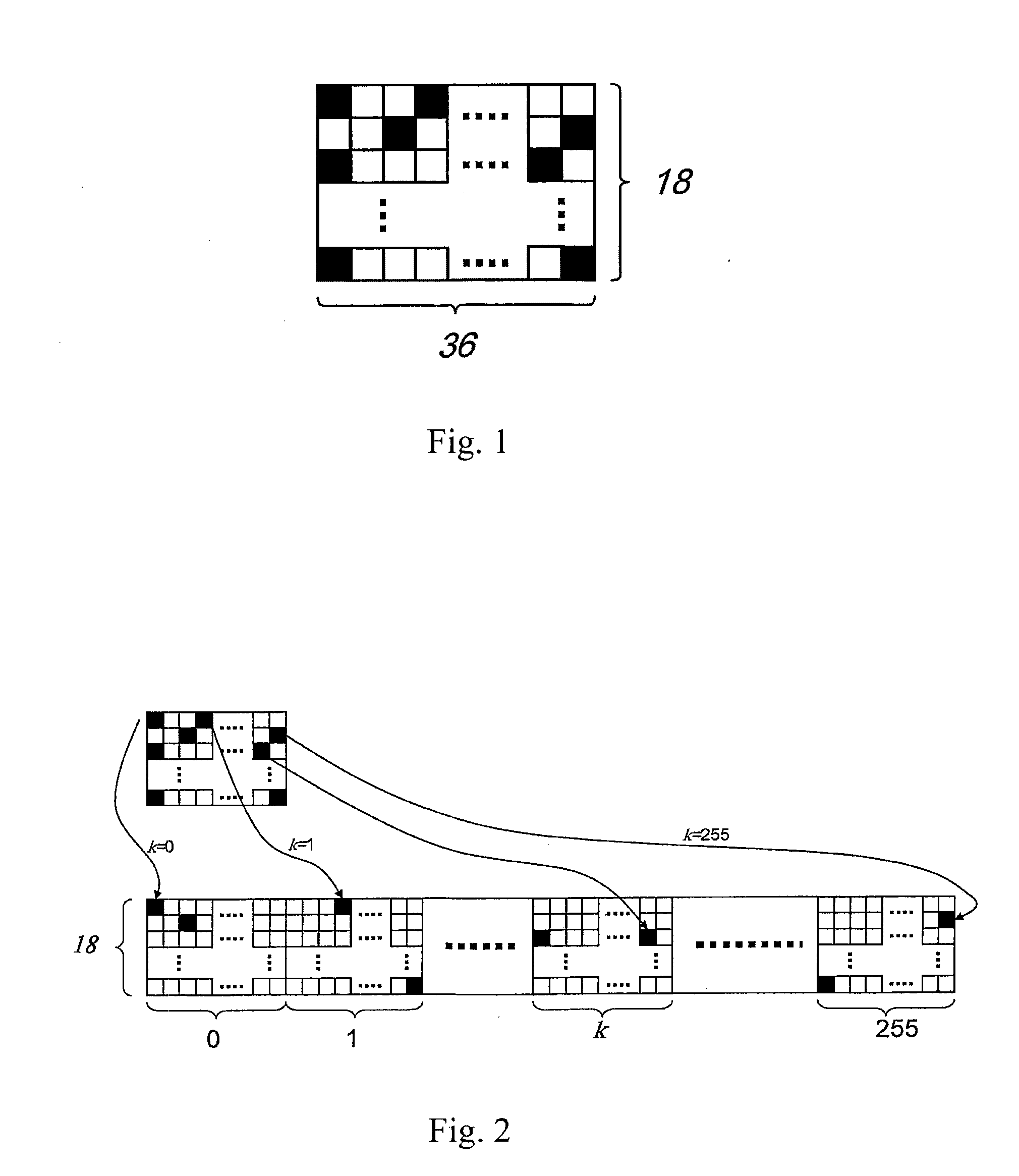

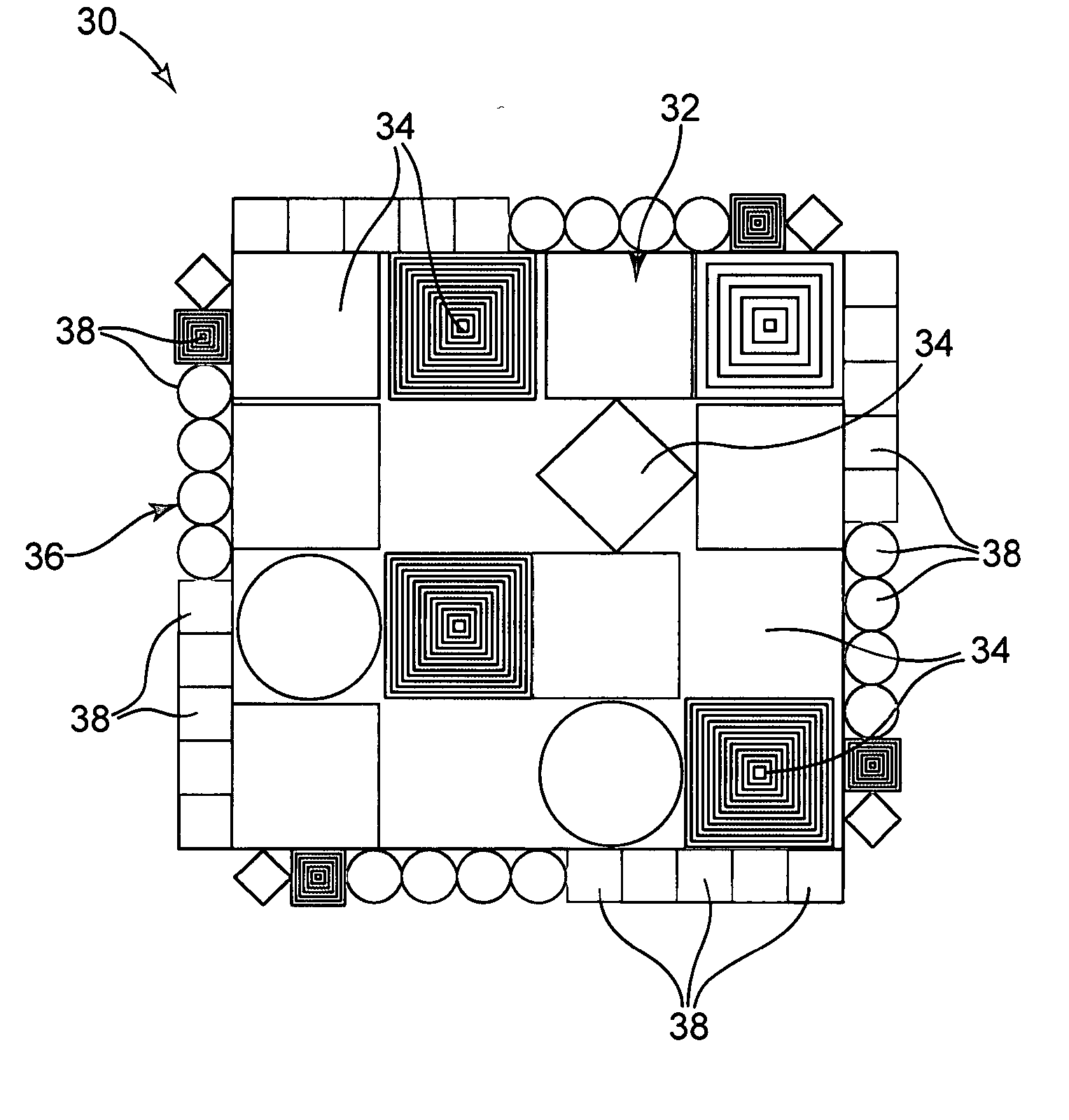

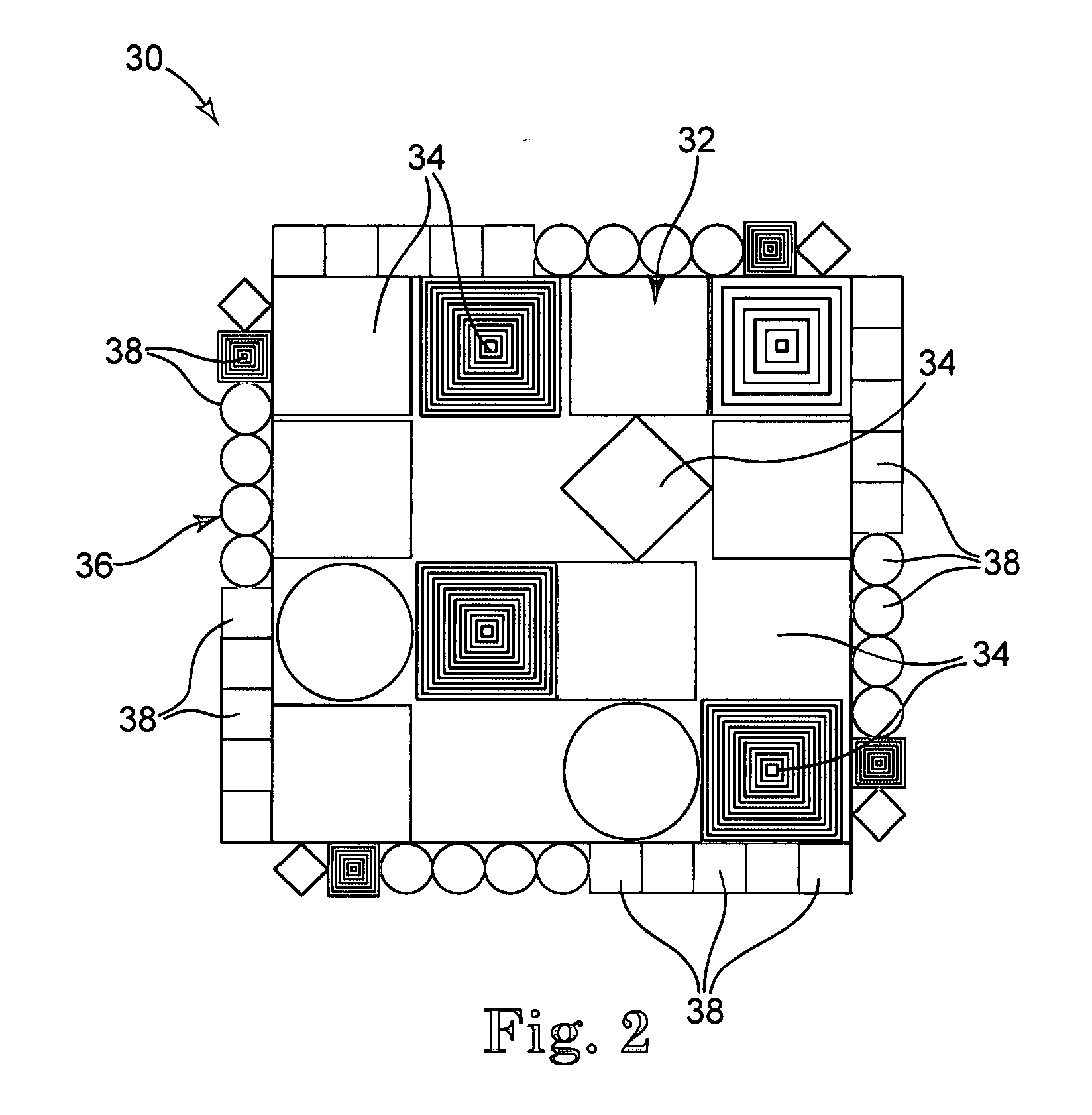

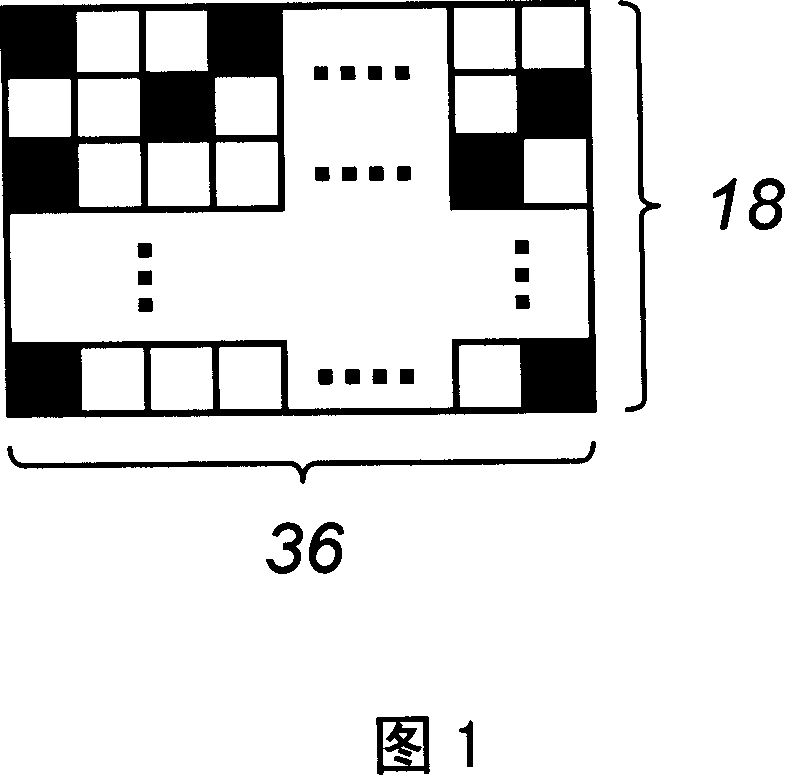

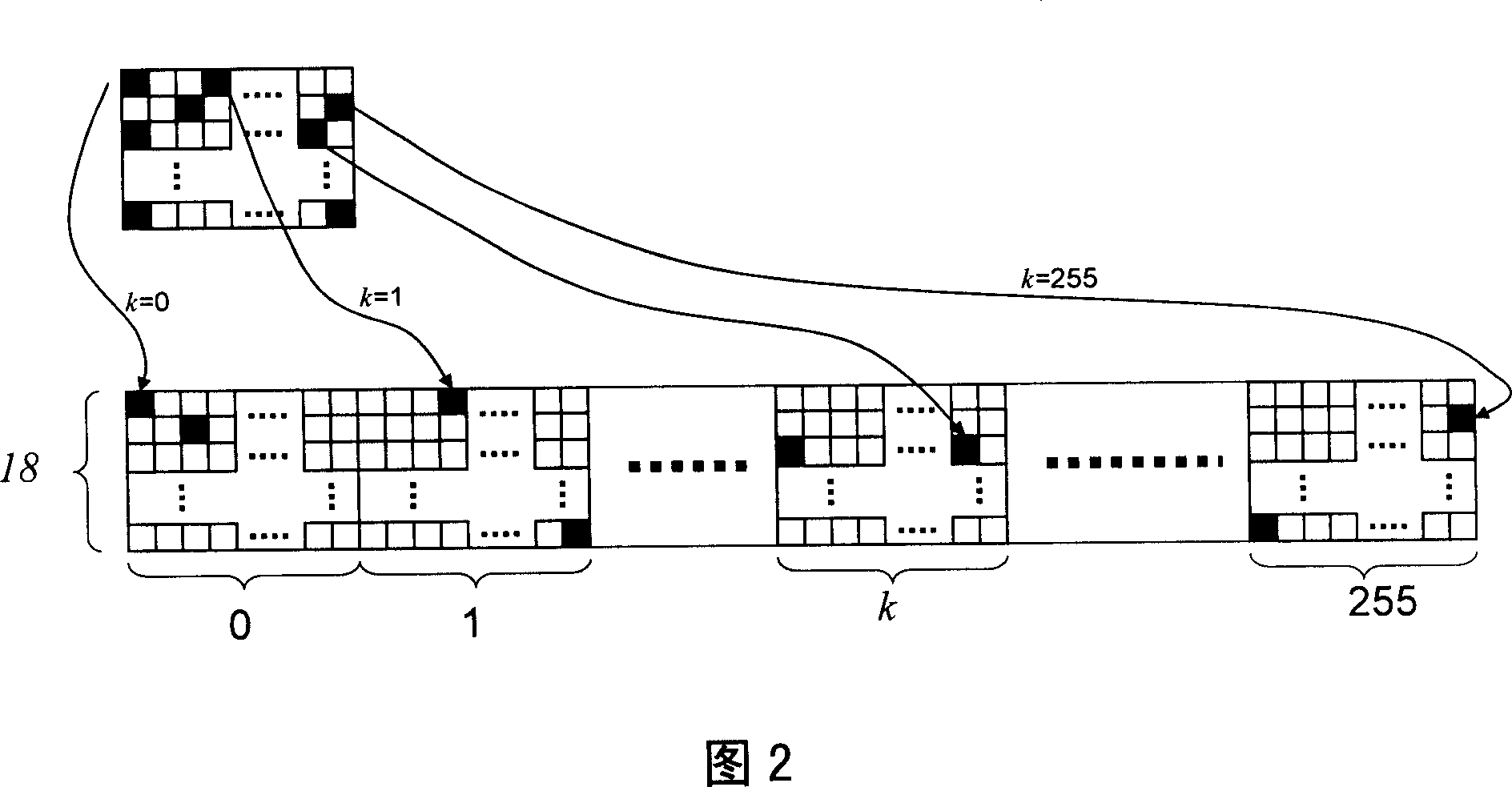

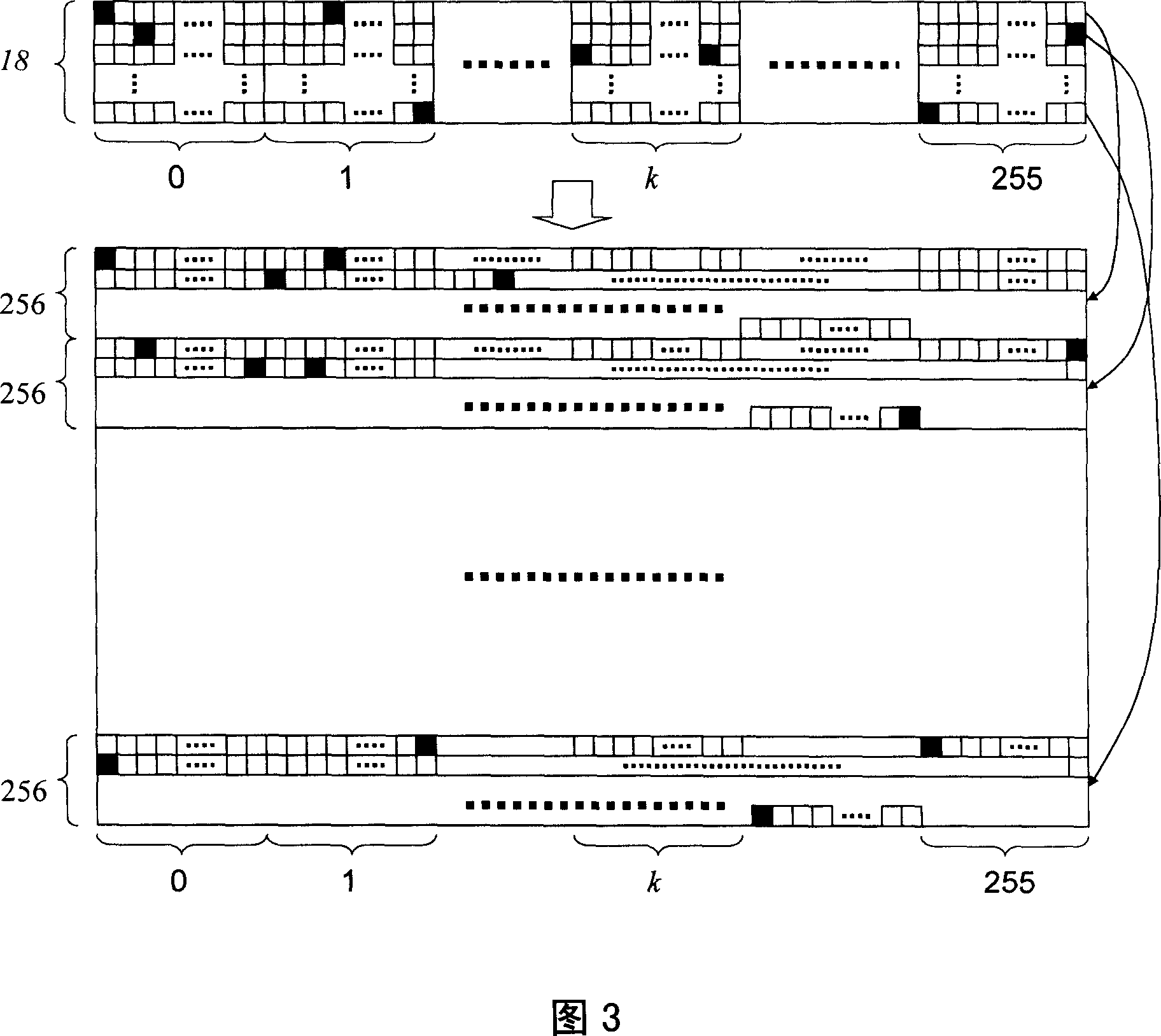

Two-dimensional symbol code and method for reading the symbol code

InactiveUS20120145779A1Shorter clock timeLine area be quicklyCharacter and pattern recognitionRecord carriers used with machinesProgramming languageGraphics

The specification describes a two-dimensional symbol code for representing binary data, which symbol code is constructed from a plurality of graphical symbols arranged next to one another, wherein the symbol code is formed from precisely two different symbols having the same surface area which differ in their areal brightness distribution and each code a value from a binary data word. The symbols have a complementary brightness distribution. In a method for reading this two-dimensional system code, the system code has a filter applied to it which matches the brightness distribution of one of the two complementary symbols, wherein in the event of a match one symbol is recognized and in the event of no match the other symbol is recognized.

Owner:CONTINENTAL TEVES AG & CO OHG

Universal error control coding system for digital communication and data storage systems

InactiveUS7831895B2Reduce complexity and chip area and chip power consumptionReduce complexityError detection/correctionCode conversionComputer architectureForward error correction

The universal forward error-correction coding system provides adjustable code rates and coding gains to greatly benefit the design of many modern digital communications (data storage) systems. The channel encoding and decoding methods are universal such that a single encoder and a single decoder can be used to implement all the forward error-correction codes of different code rates. This universal forward error-correction coding system also includes a novel systematic code generation procedure that has the capability of generating many classes of codes that provide the best balance between coding gain performance and implementation complexity.

Owner:COMM CODING

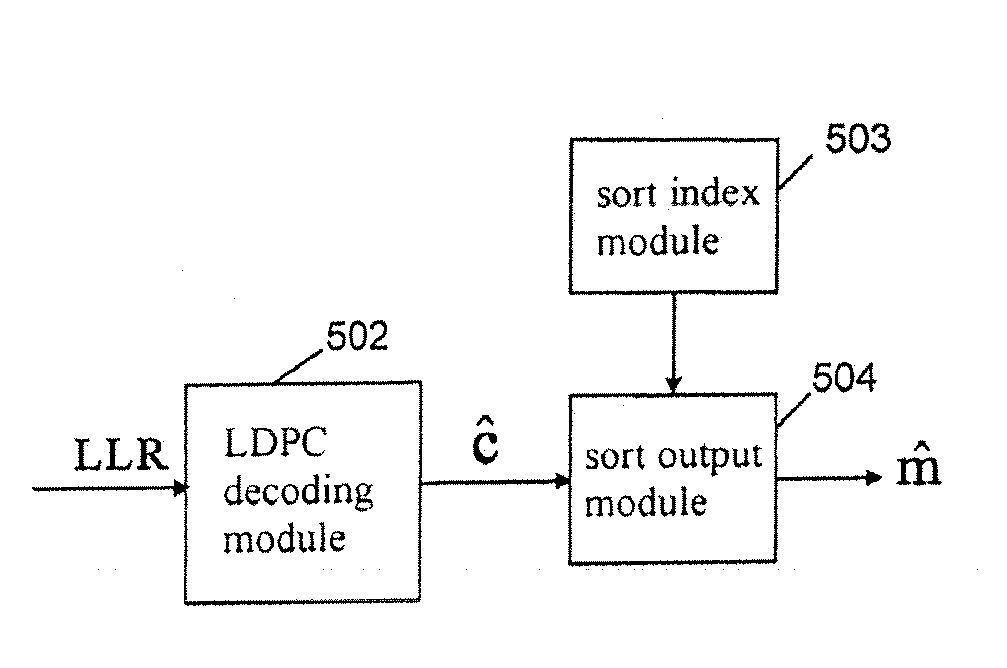

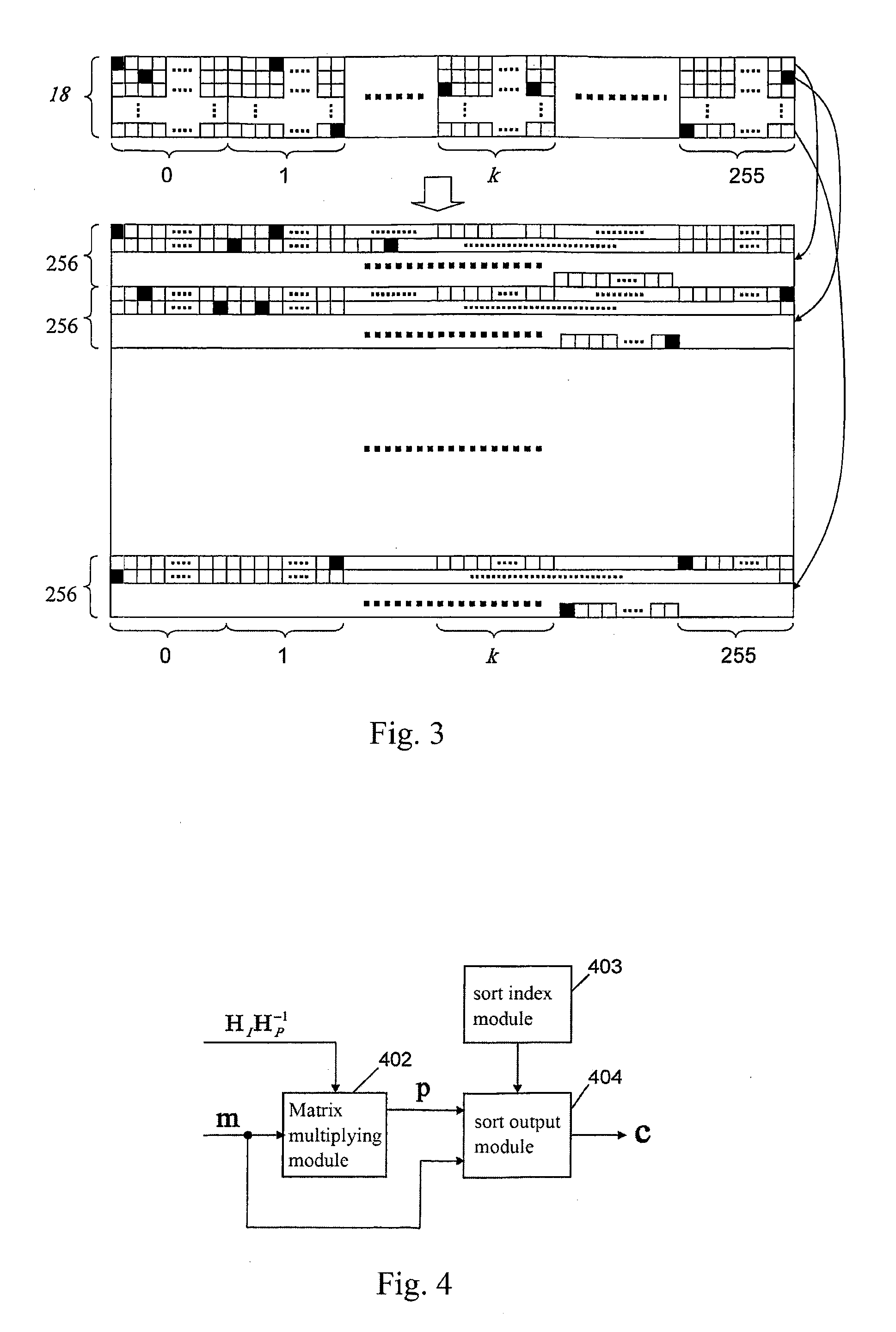

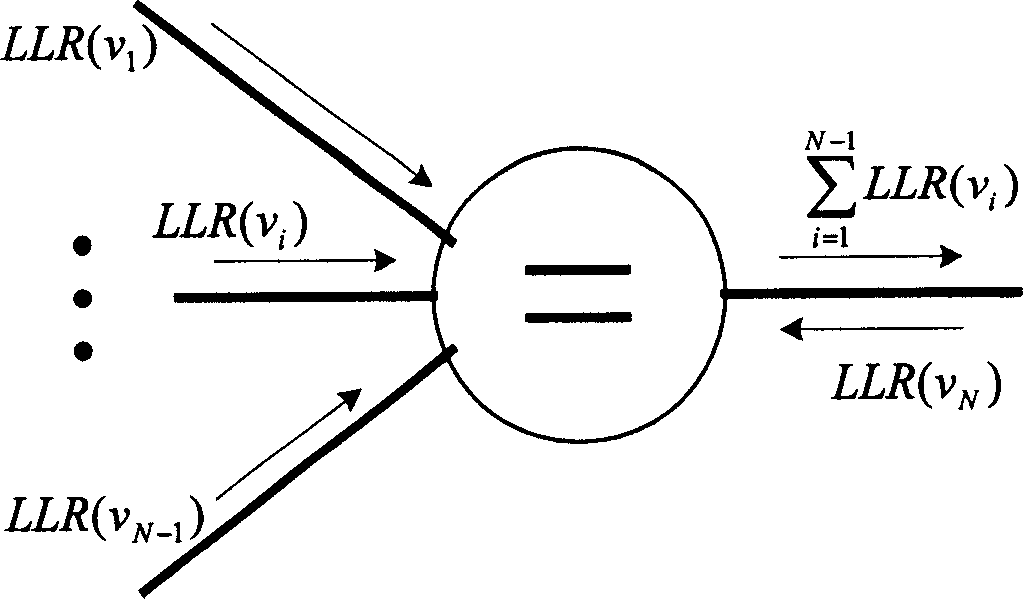

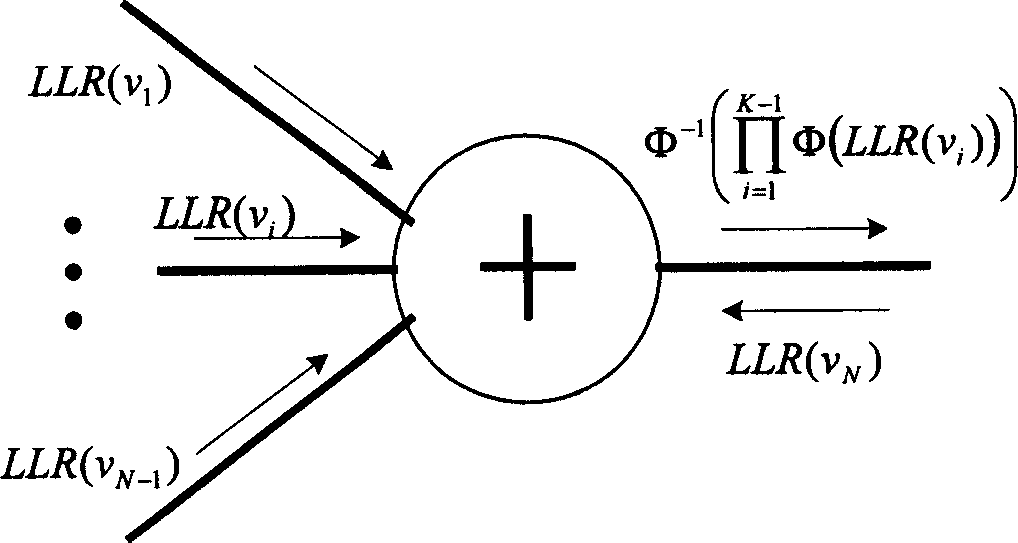

Method for constructing checking matrix of LDPC code and coding and decoding apparatus utilizing the method

InactiveUS20110239077A1Improve performanceLess occupiedError preventionCode conversionAlgorithmEngineering

The present invention relates to a method for constructing LPDC code check matrix and encoding and decoding devices using the same. The encoding device encodes the inputted binary information and outputs the encoded system code sequence of position transformation. The encoding device comprises: a matrix multiplication module outputting a check sequence p which is obtained through the binary information sequence m multiplied with a matrix; a sorting index module having N memory units storing index values of a sorting table IDX in turn; and a sorting output module for sorting the m and p and outputting a code word c based on the index value stored in the sorting index table. The present invention constructs the LDPC code check matrix using an algebraic structure, obtaining the LDPC code with stable performance. In addition, the encoding and decoding devices of the present invention occupy less memory, which is preferable for optimization of the devices.

Owner:TIMI TECH

Systematic code design method for irregular low density parity check code and communication system thereof

InactiveCN1558556ASimple structureEasy to implementError correction/detection using interleaving techniquesError detection onlyCommunications systemTheoretical computer science

The invention relates to a method for designing systematic codes of an irregular low density parity check code and communication system thereof, wherein a semi-random generation method is employed to obtain a base check matrix, then each element of the basis matrix is expanded to a window pane sub-matrix, thus irregular LDPC code check matrix can be obtained, which first conducts pre-transformation to row / line weight distribution pattern when producing the Hb, and a specific matrix whose non-zero row / line element number is greater than 1 to create a systematic code to simplify the encoder arrangement.

Owner:TSINGHUA UNIV

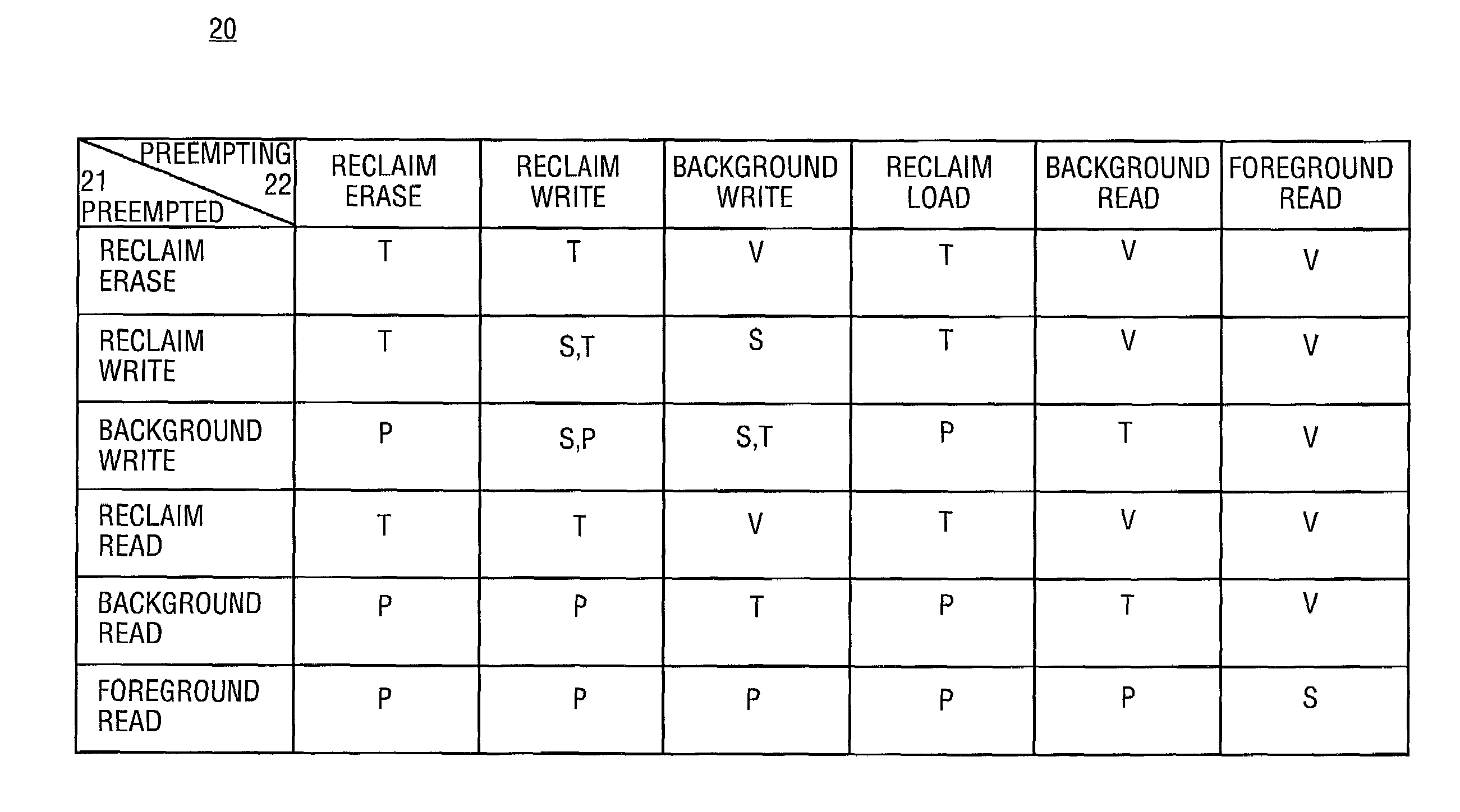

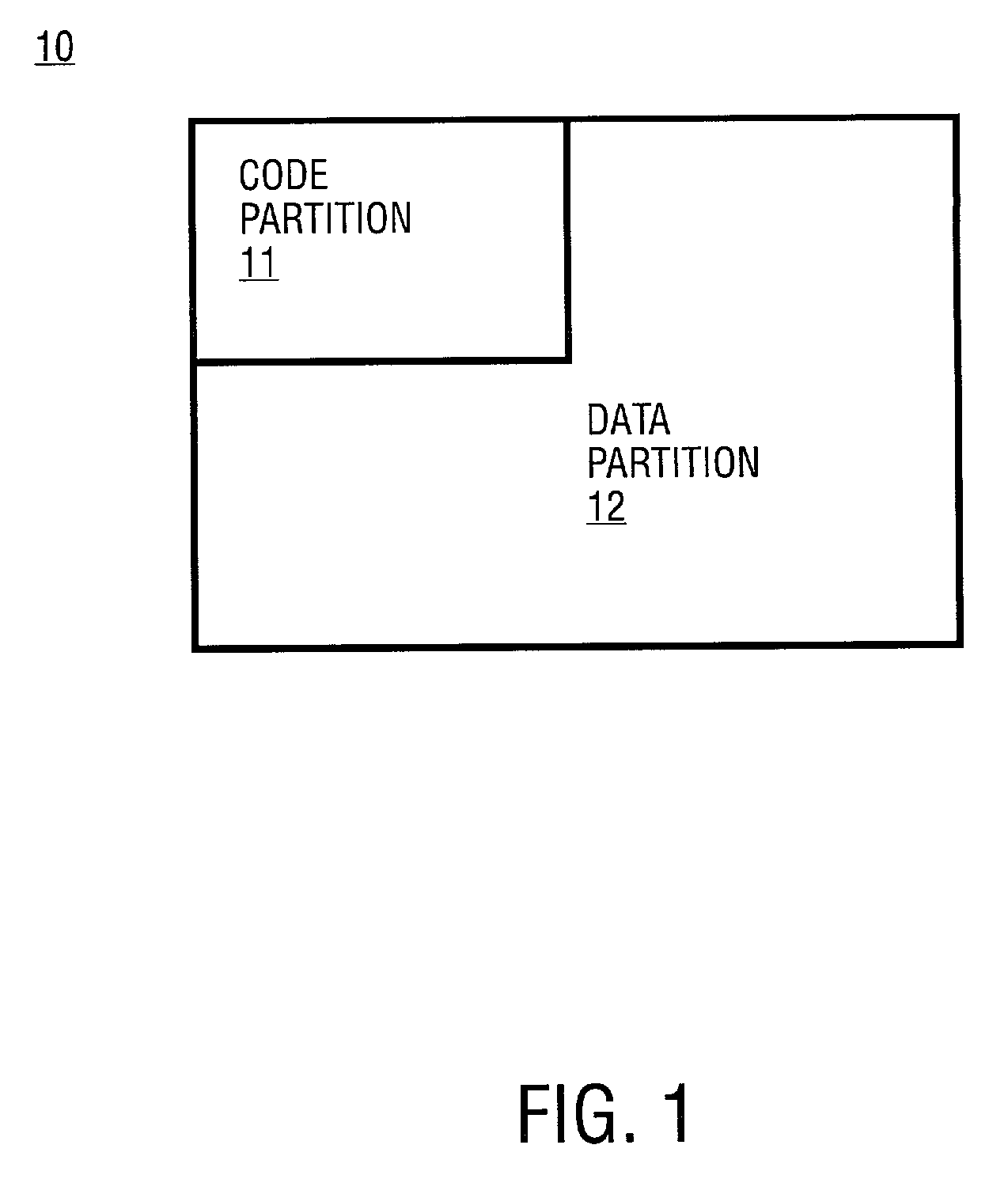

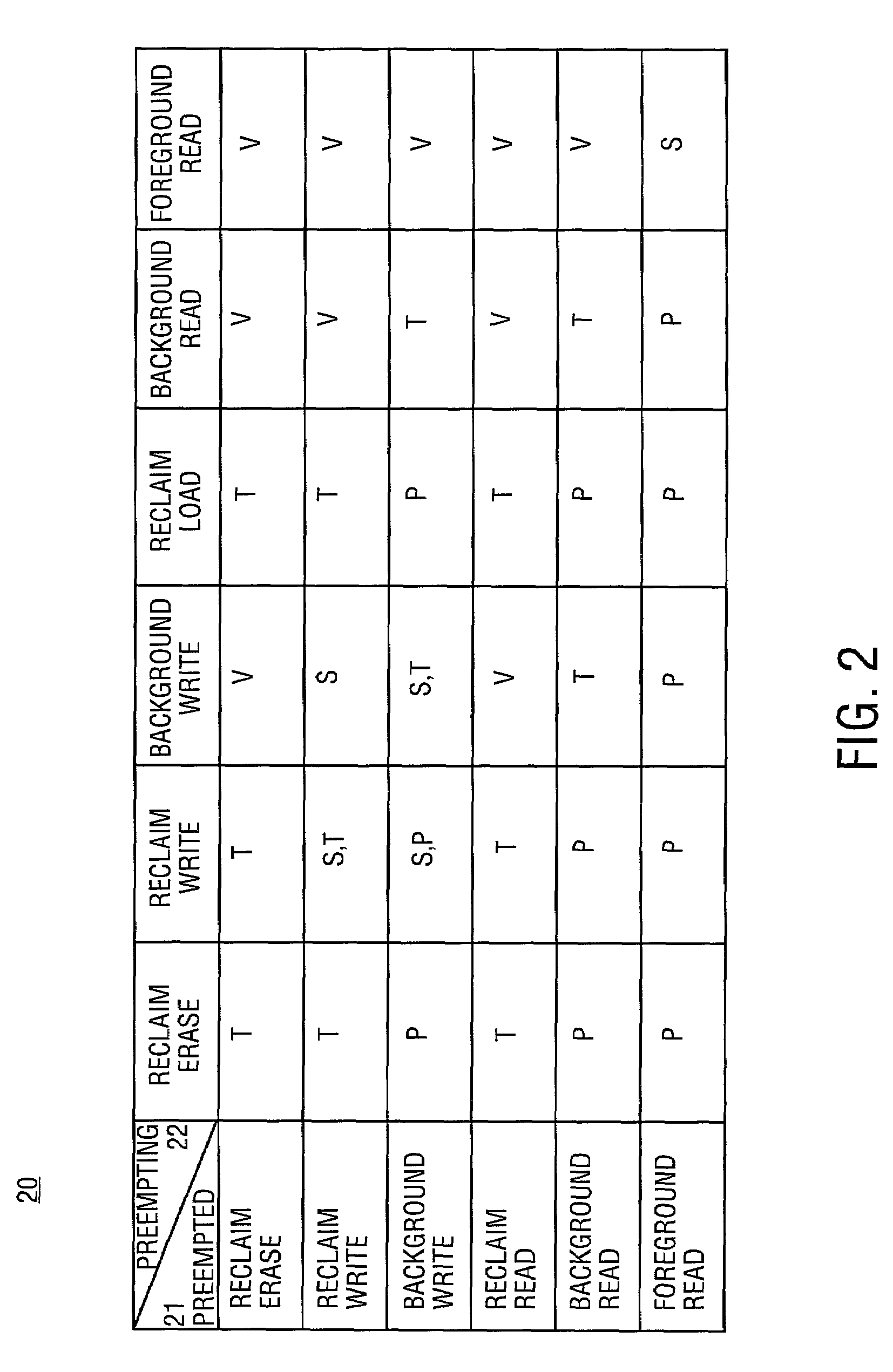

Implementing a dual partition flash with suspend/resume capabilities

A method of performing multiple operations on a flash memory device is described. This is made possible through the implementation of multiple partitions within the flash memory. The partitions are used to store data, application code, and system code. Low level functions within the system code process the data and handle preemption functions within the flash memory.

Owner:INTEL CORP

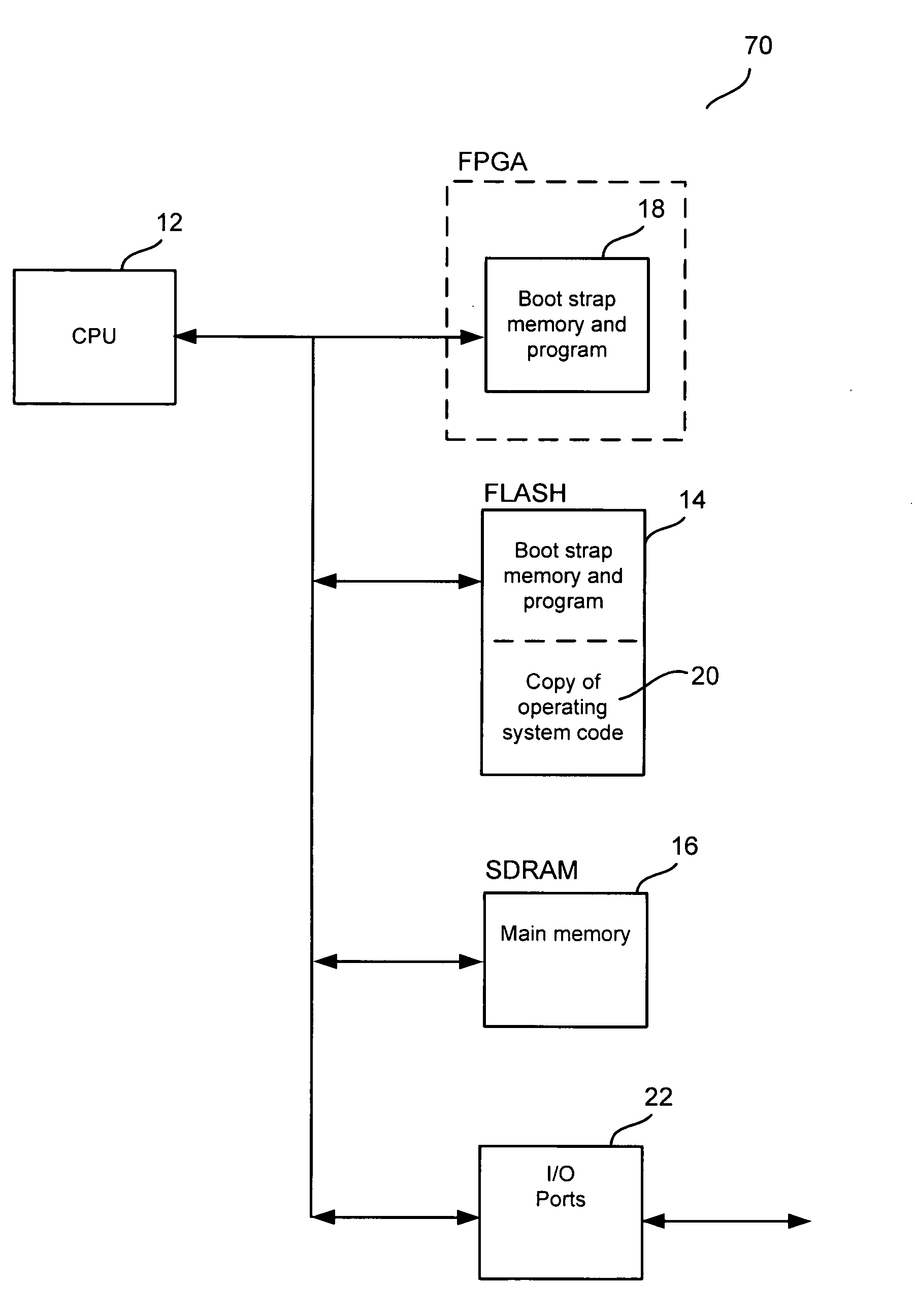

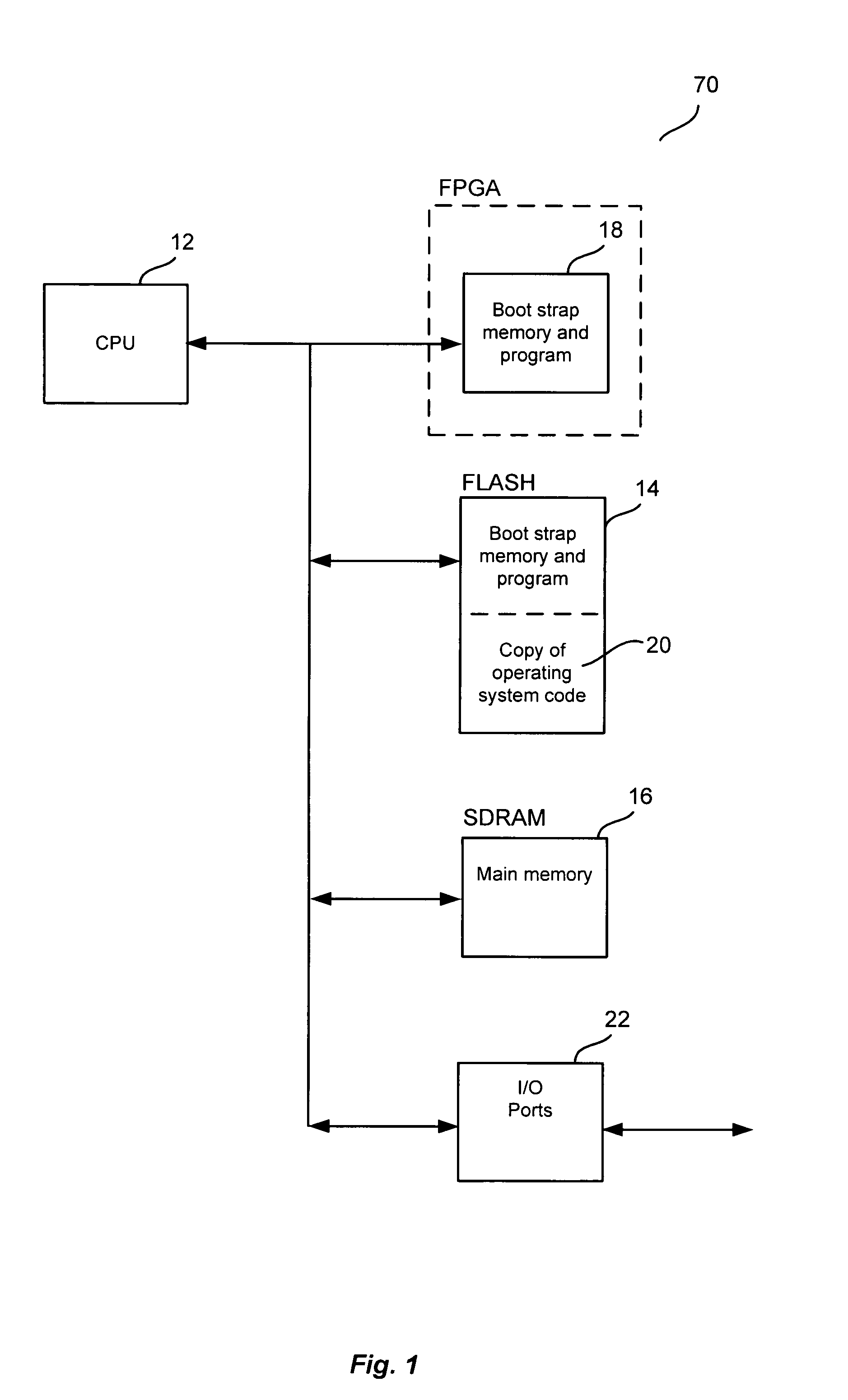

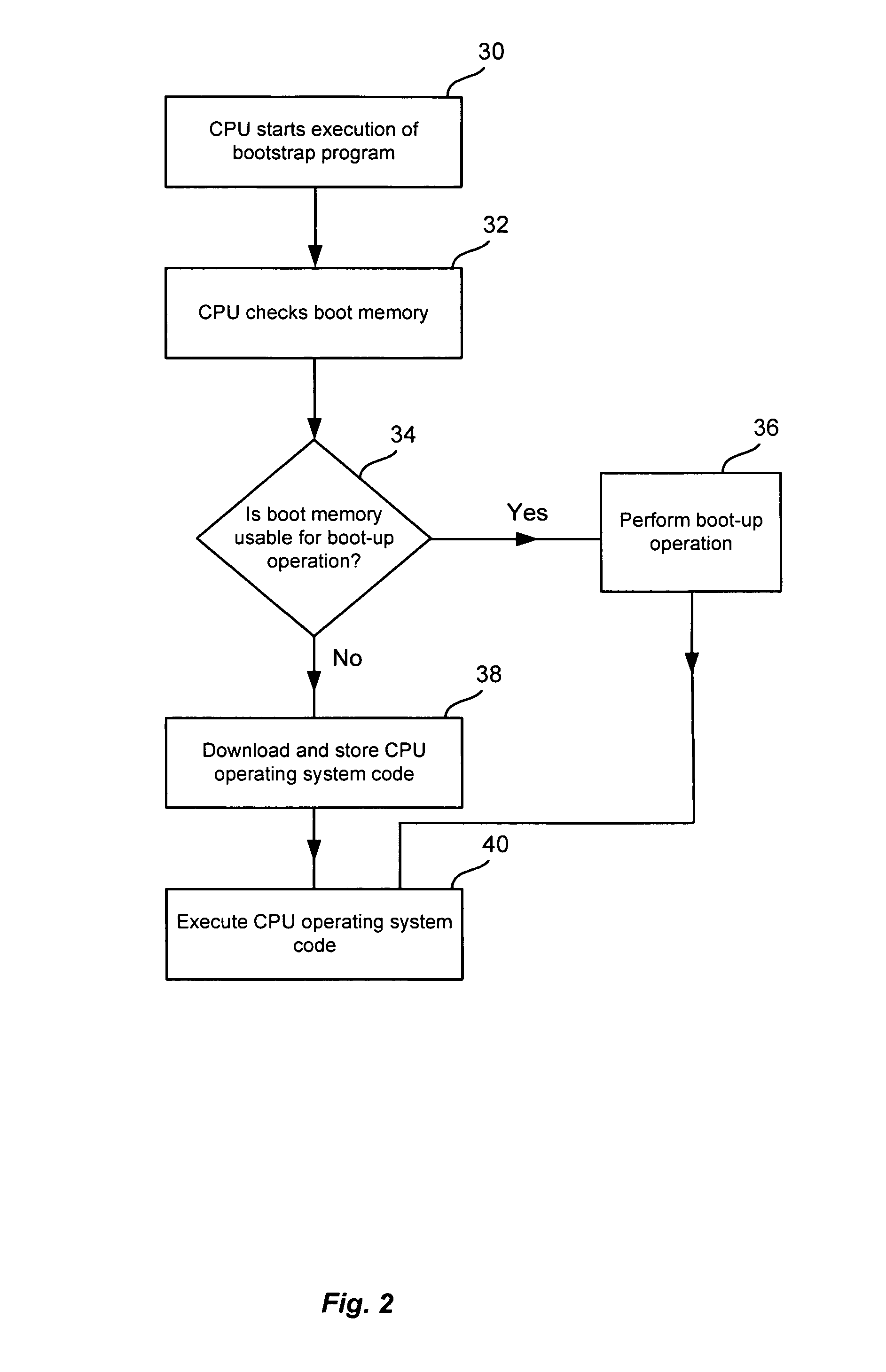

Method and system to provide first boot to a CPU system

ActiveUS7017038B1Minimizes problemError detection/correctionDigital computer detailsOperational systemSystematic code

A boot-up operation system is provided. In one exemplary embodiment, the system includes a CPU, a bootstrap memory, a boot memory, a main memory, an I / O port and CPU operating system code. When the system is turned on, the CPU executes the bootstrap program which directs it to determine whether the boot memory contains the necessary code to perform the boot-up operation. If the boot memory contents are usable for boot-up operation, the CPU starts executing a boot program that is stored in the boot memory. If the boot memory contents are not usable for boot-up operation, the bootstrap program directs the CPU to download a copy of the CPU operating system code from outside the system using the I / O port. After the download, the CPU stores a copy of the downloaded operating system code and the boot program into the boot memory for future use.

Owner:RIBBON COMM OPERATING CO INC

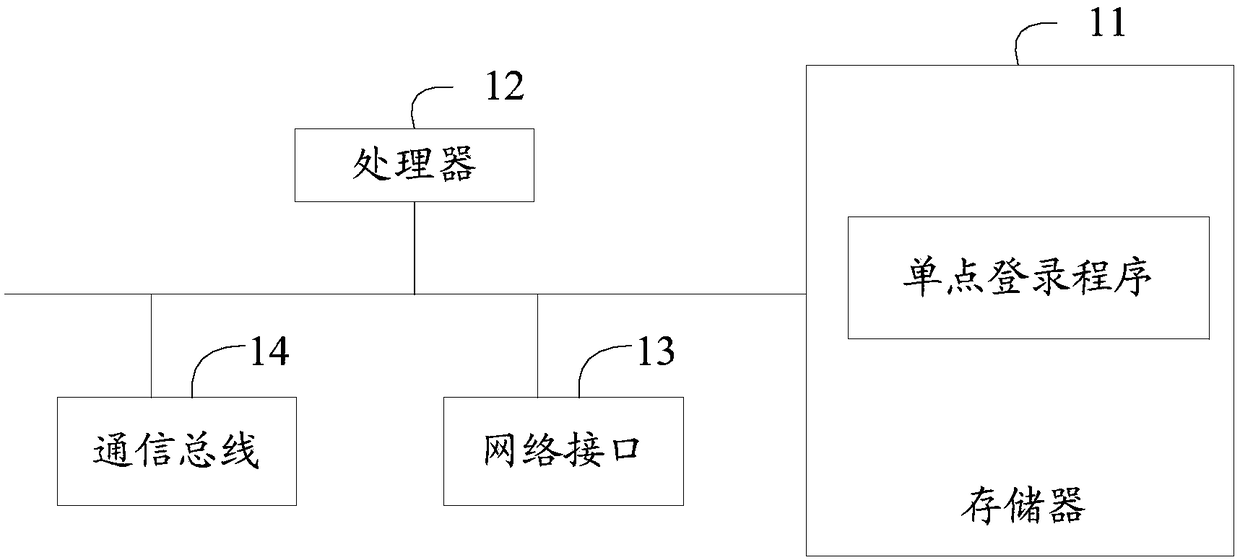

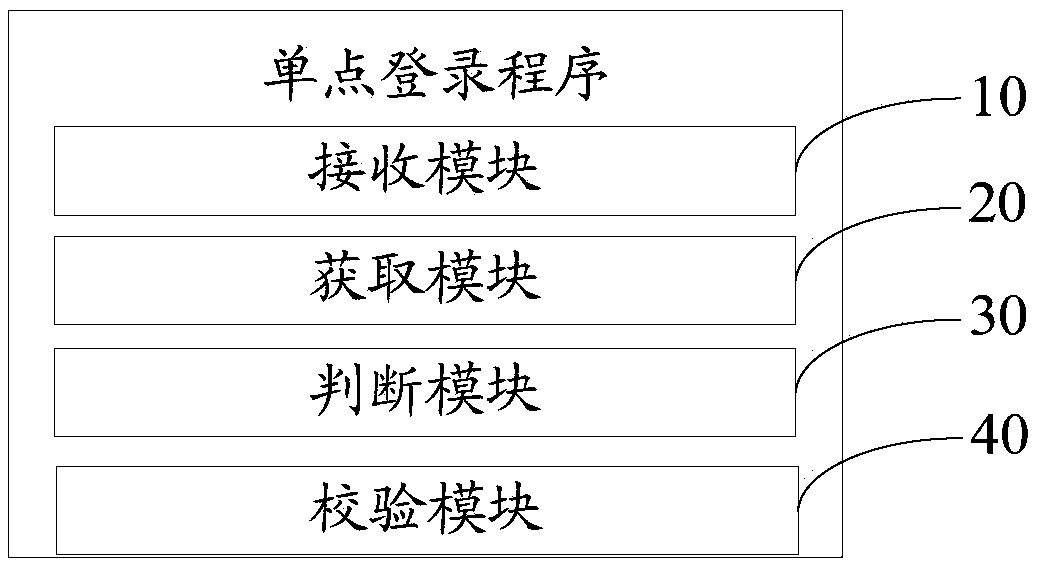

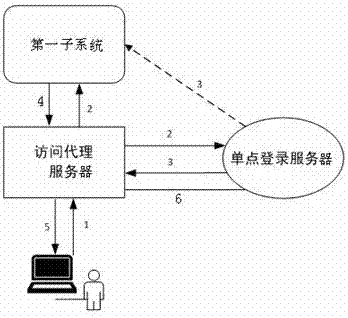

Single sign-on server, single sign-on method and computer readable storage medium

The invention discloses a single sign-on server. The single sign-on server comprises a memory and a processor; a single sign-on program which can be run in the processor is stored in the memory. Whenthe program is carried out by the processor, steps below are realized: obtaining a sign-on request sent from a client to the server based on a reorientation information sent by a service system; obtaining account information from the sign-on request, obtaining a system identifier of the service system and an associated white list from the reorientation information and judging whether account information exists in the white list; if so, verifying the account information and a password in the sign-on request; if the verification passes, returning token information to the client for storage and storing the token information after the token information is associated with the account information of the client. The invention also provides a single sign-on method and a computer readable storage medium. According to the single sign-on server, the single sign-on method and the computer readable storage medium, a system code amount is reduced, the system reusability is improved, and centralizedmanagement of each service system authority in the single sign-on system is realized.

Owner:重庆金融资产交易所有限责任公司

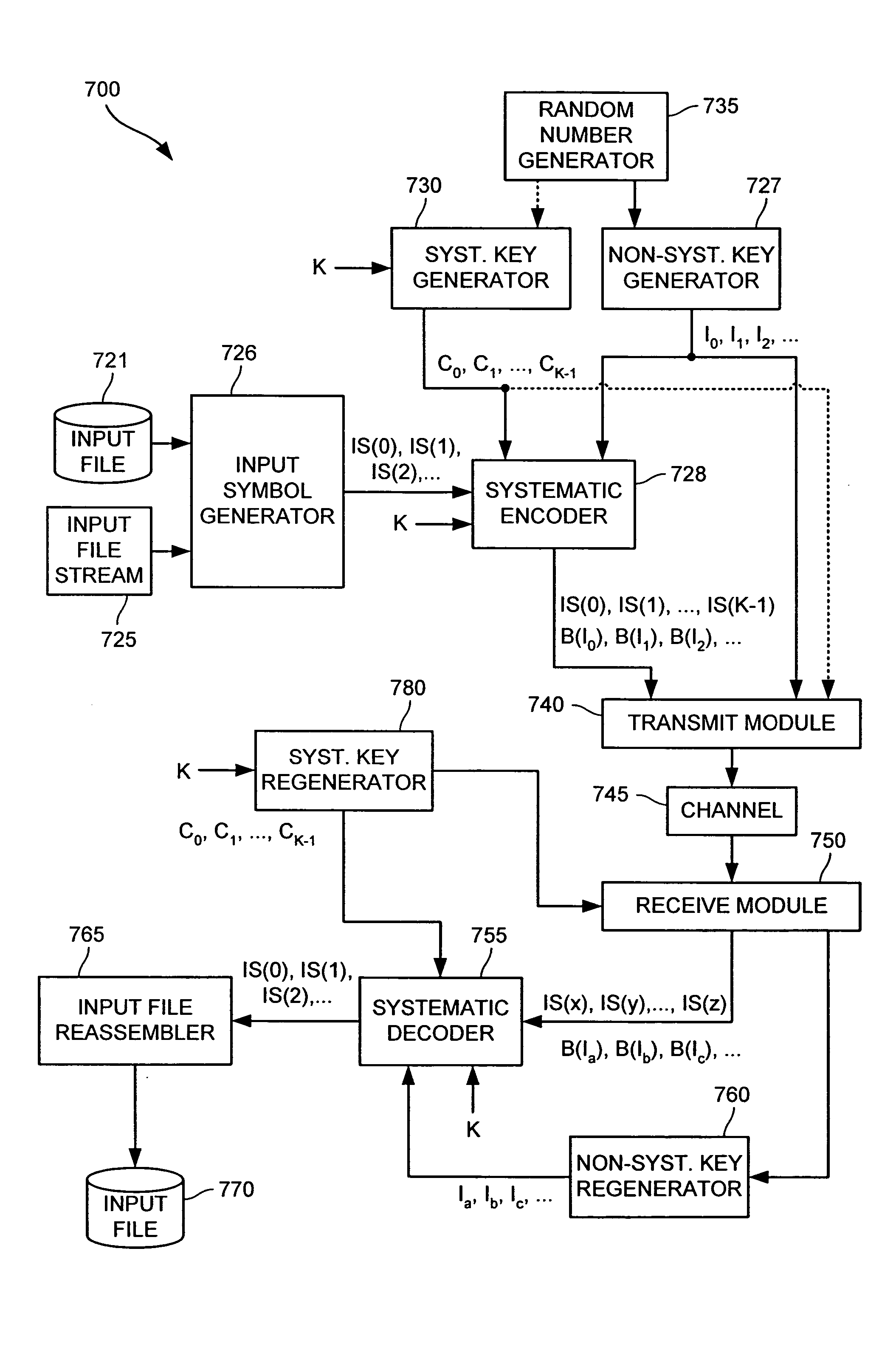

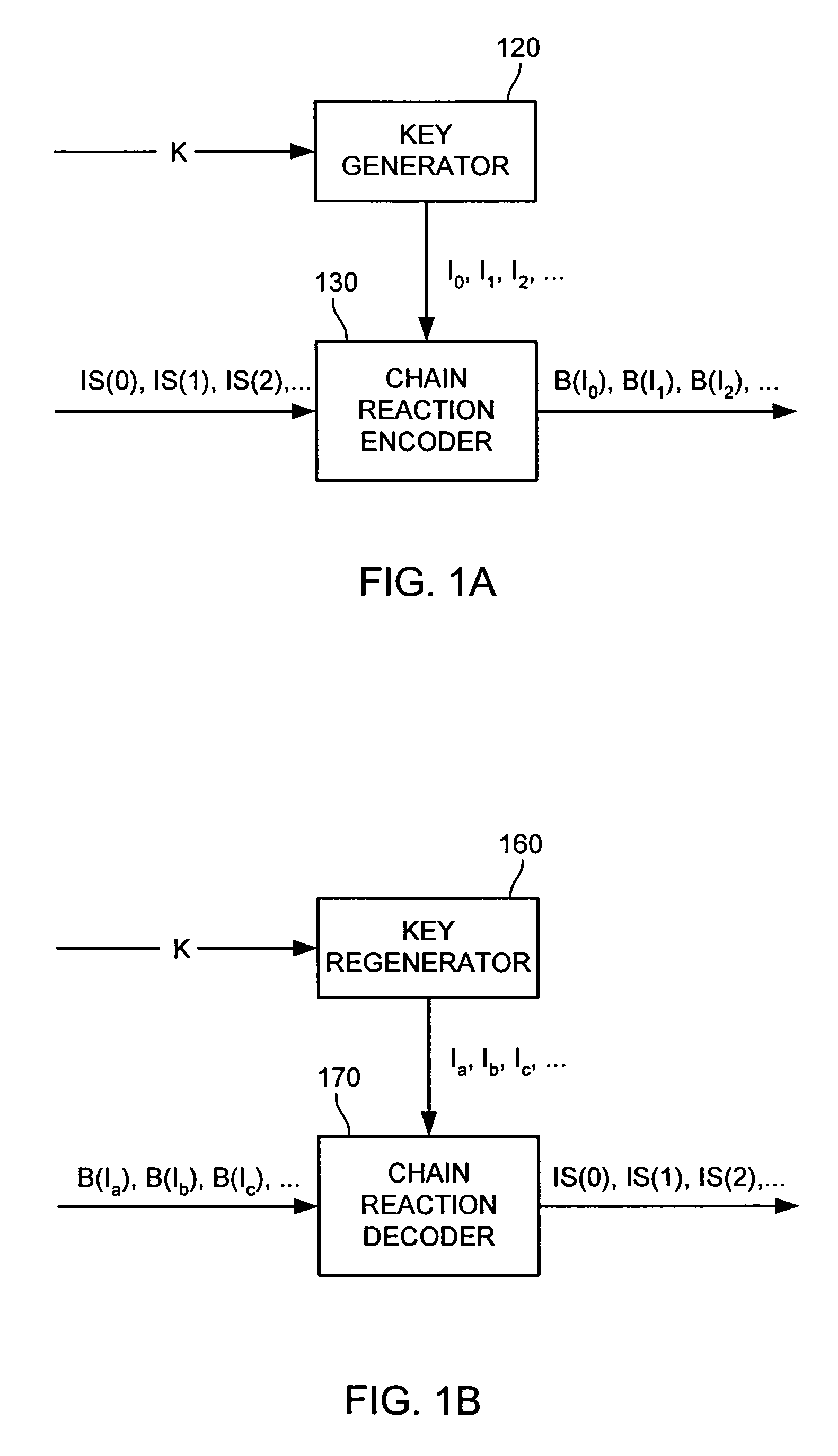

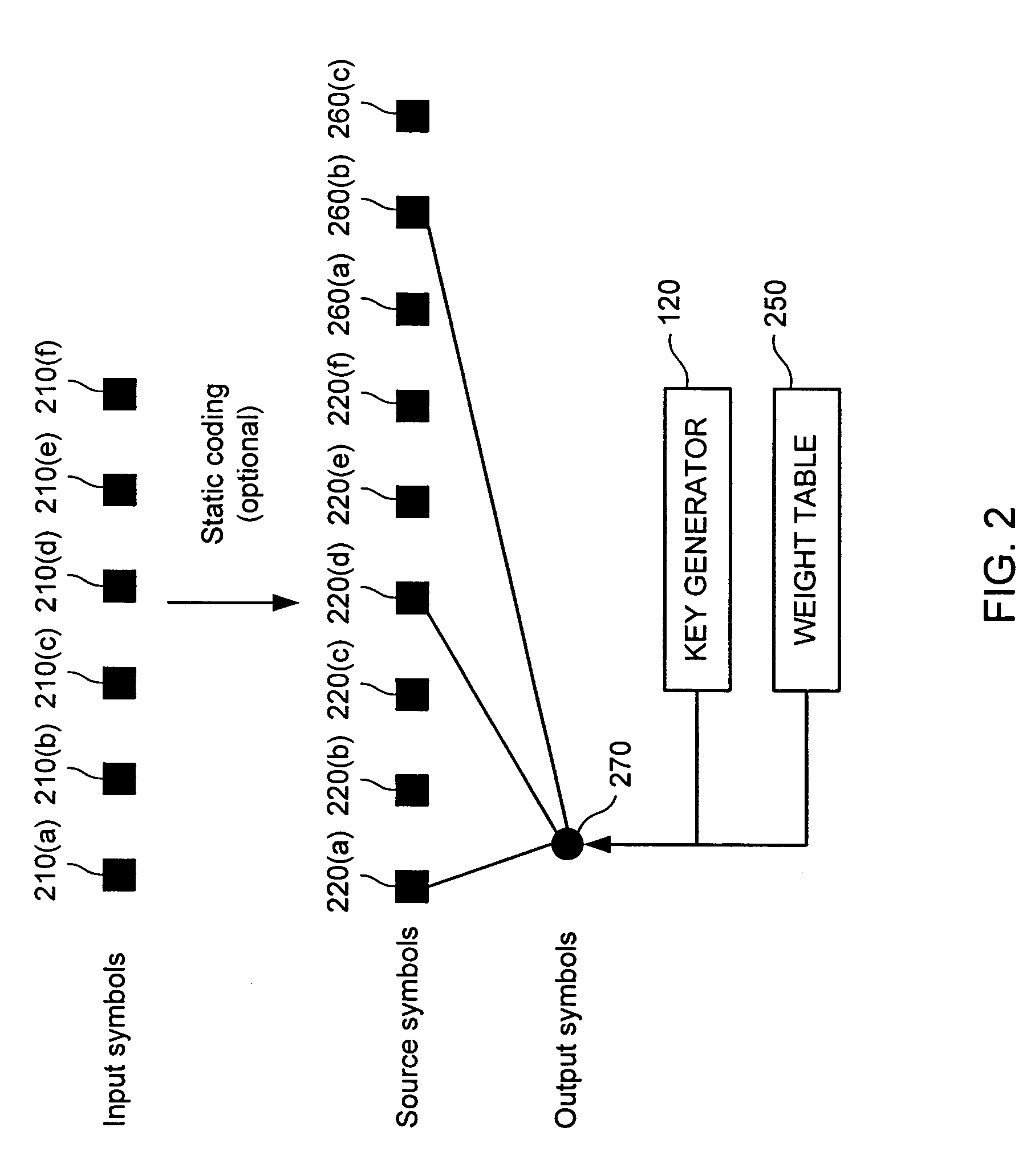

Systematic encoding and decoding of chain reaction codes

InactiveUS7394407B2Communicated faster, more reliablyLess computational expenseError preventionError correction/detection using multiple parity bitsTheoretical computer scienceData encoding

A method of encoding data into a chain reaction code includes generating a set of input symbols from input data. Subsequently, one or more non-systematic output symbols is generated from the set of input symbols, each of the one or more non-systematic output symbols being selected from an alphabet of non-systematic output symbols, and each non-systematic output symbol generated as a function of one or more of the input symbols. As a result of this encoding process, any subset of the set of input symbols is recoverable from (i) a predetermined number of non-systematic output symbols, or (ii) a combination of (a) input symbols which are not included in the subset of input symbols that are to be recovered, and (b) one or more of the non-systematic output symbols.

Owner:QUALCOMM INC

Generation of golay-based systematic block code supporting various sizes

ActiveUS20090217139A1Strong resistanceEffectively generating codesError preventionModulated-carrier systemsComputer hardwareBlock code

A method for generating block codes from Golay code and a method and apparatus for encoding data are provided. The method can effectively generate codes having various lengths, various dimensions, and superior hamming weight distribution, and encodes data such as control information having various lengths into codes having strong resistance to channel errors, resulting in an increase of error correction performance.

Owner:LG ELECTRONICS INC

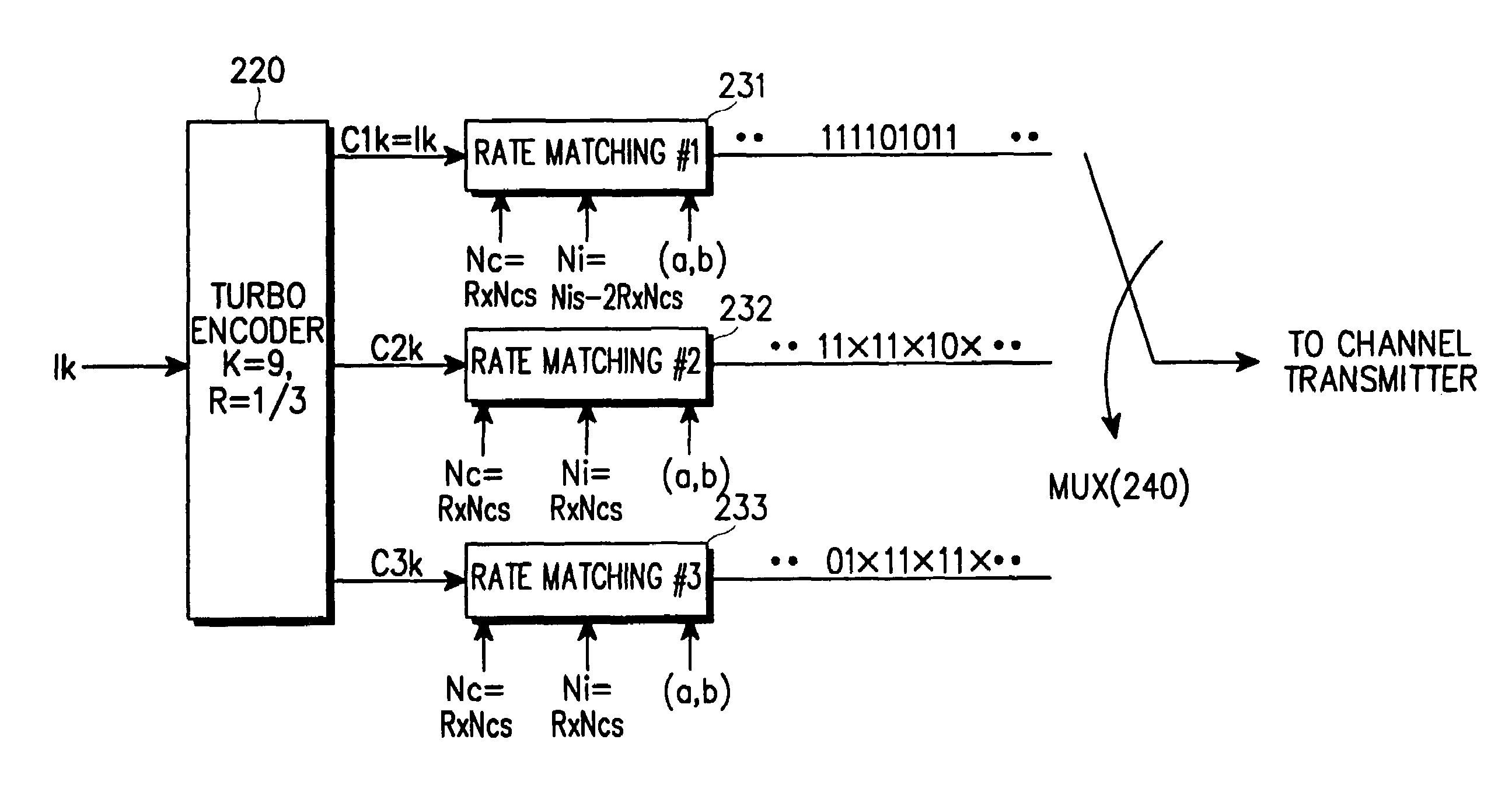

Rate matching device and method for a data communication system

InactiveUS7451383B2Improve data transfer efficiencyImprove system performanceError correction/detection using convolutional codesCode conversionCommunications systemBlock code

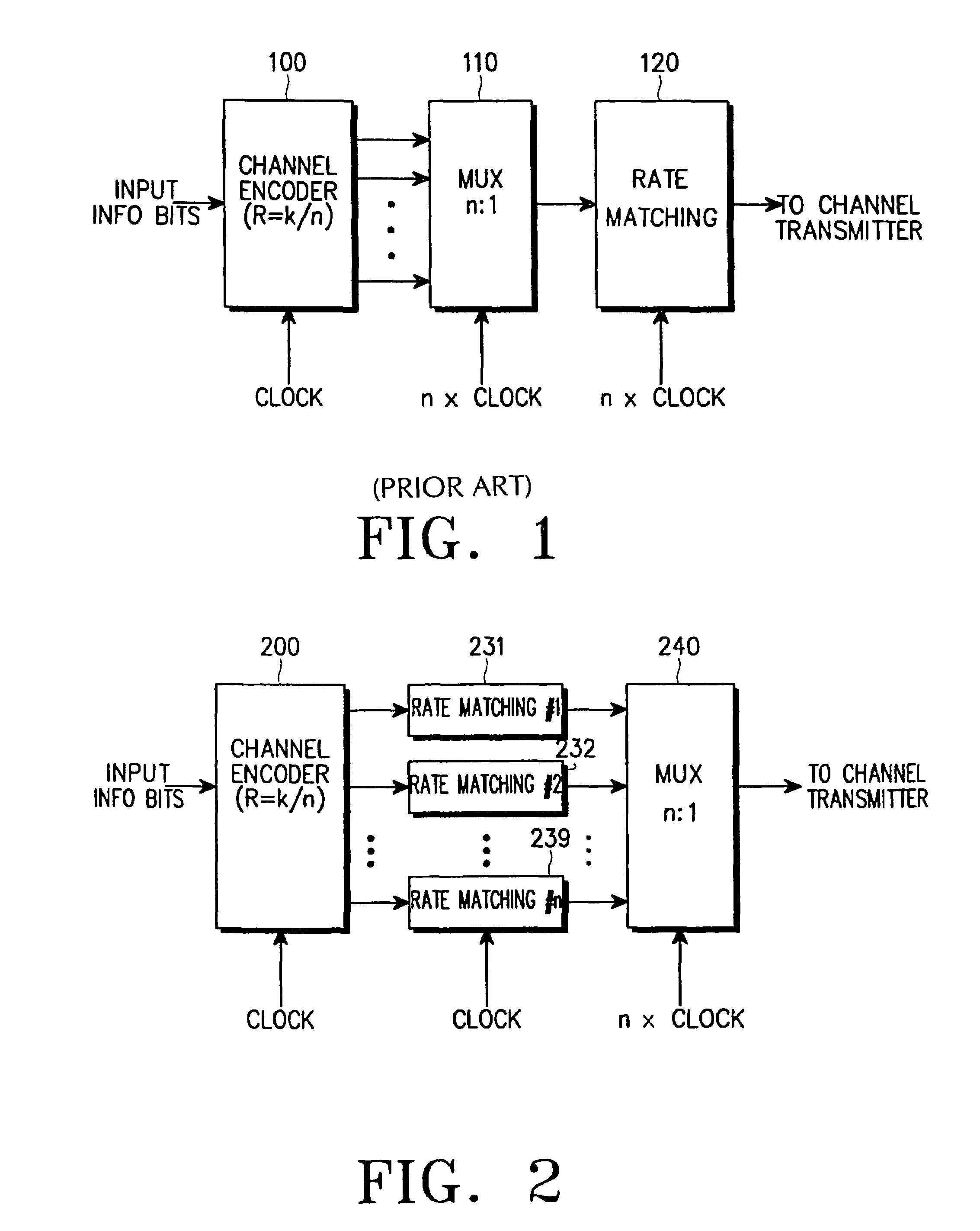

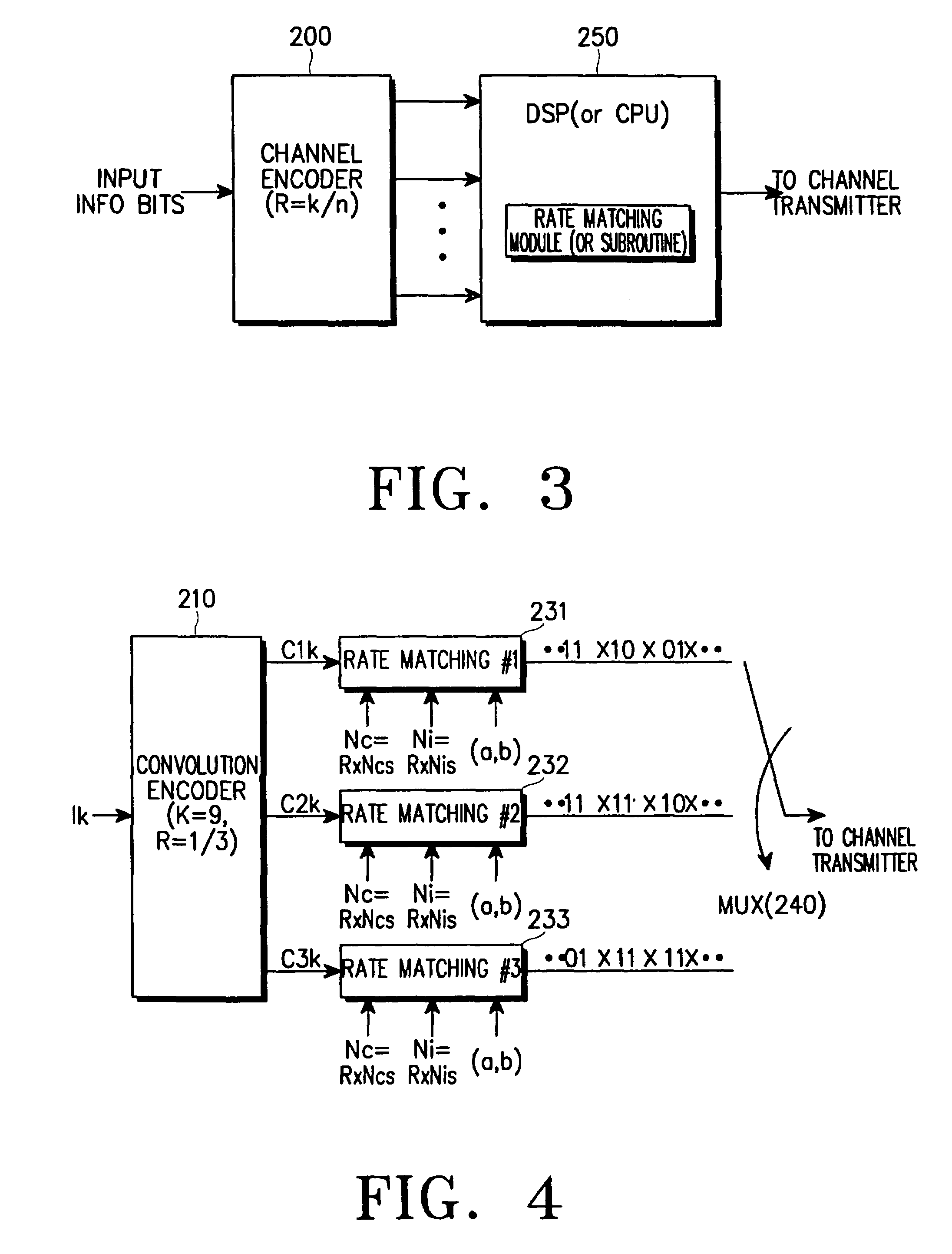

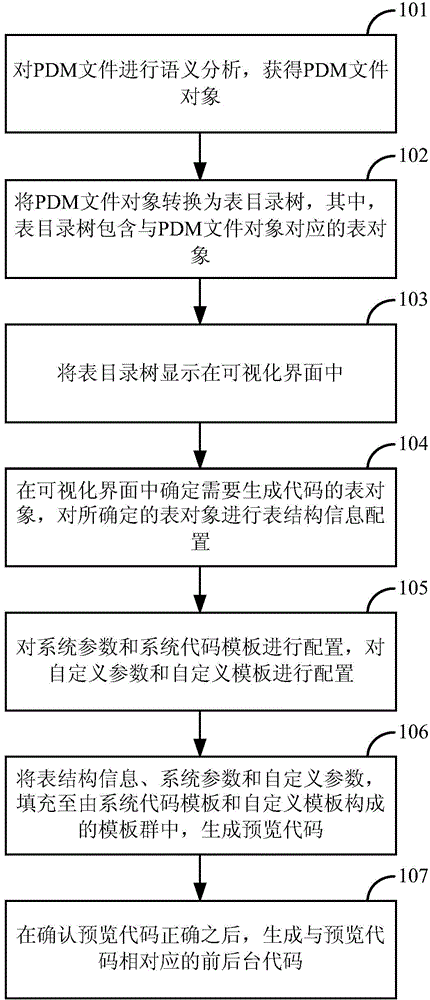

A device and method for rate matching channel-encoded symbols in a data communication system. The rate matching device and method can be applied to a data communication system which uses one or both of a non-systematic code (such as a convolutional code or a linear block code) and a systematic code (such as a turbo code). In one aspect, the rate matching device includes a plurality of rate matching blocks, the number of the rate matching blocks being equal to a reciprocal of a coding rate of a channel encoder. The rate matching device can rate match the symbols encoded with a non-systematic code or the symbols encoded with a systematic code, by changing initial parameters including the number of input symbols, the number of output symbols, and the puncturing or repetition pattern determining parameters.

Owner:SAMSUNG ELECTRONICS CO LTD

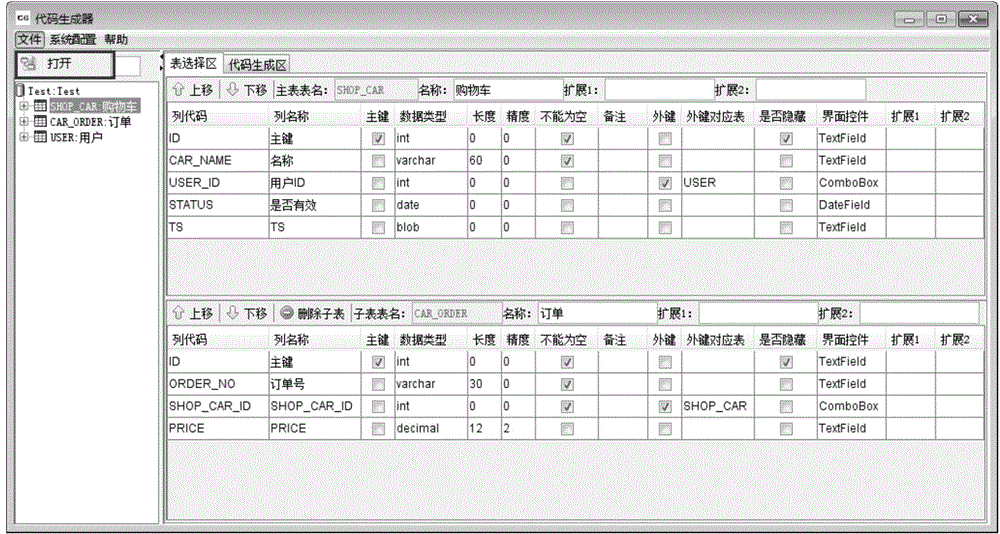

Code generation method and apparatus

InactiveCN106293664AAddressing the lack of versatilitySolve the problem that the generation process cannot be visualizedSpecific program execution arrangementsSystematic codeSystem parameters

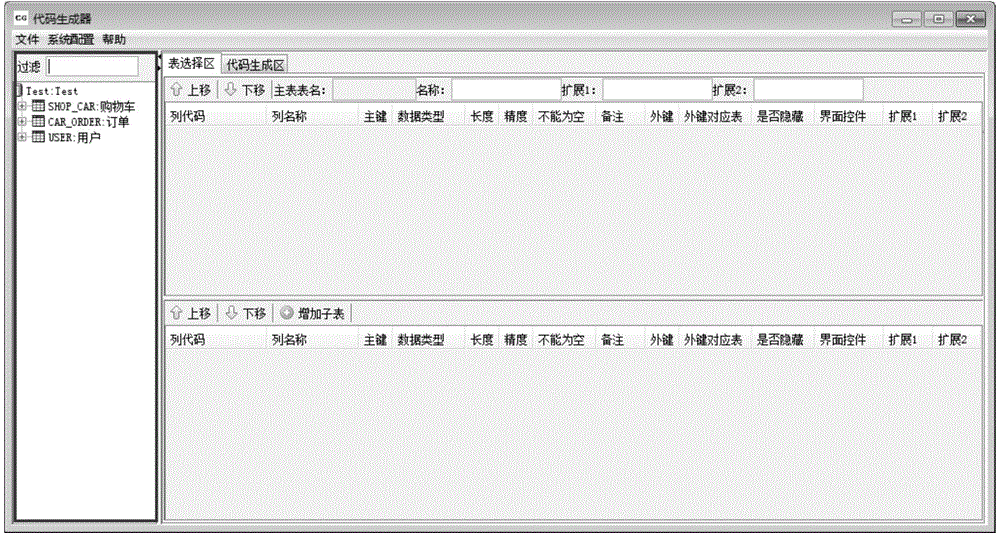

The invention discloses a code generation method and apparatus. The method comprises the steps of performing semantic analysis on a physical data model (PDM) file to obtain a PDM file object; converting the PDM file object into a table directory tree, wherein the table directory tree comprises a table object corresponding to the PDM file object; displaying the table directory tree in a visual interface; determining a table object needed to be subjected to code generation in the visual interface, and performing table structure information configuration on the determined table object; configuring system parameters and system code templates, and configuring self-defined parameters and self-defined templates; filling a template group composed of the system code templates and the self-defined templates with the table structure information, the system parameters and the self-defined parameters to generate a preview code; and after the preview code is confirmed to be correct, generating foreground and background codes corresponding to the preview code. According to the code generation method and apparatus, the software program development efficiency can be improved, the development cost can be reduced, and the development cycle can be shortened.

Owner:BANK OF COMMUNICATIONS

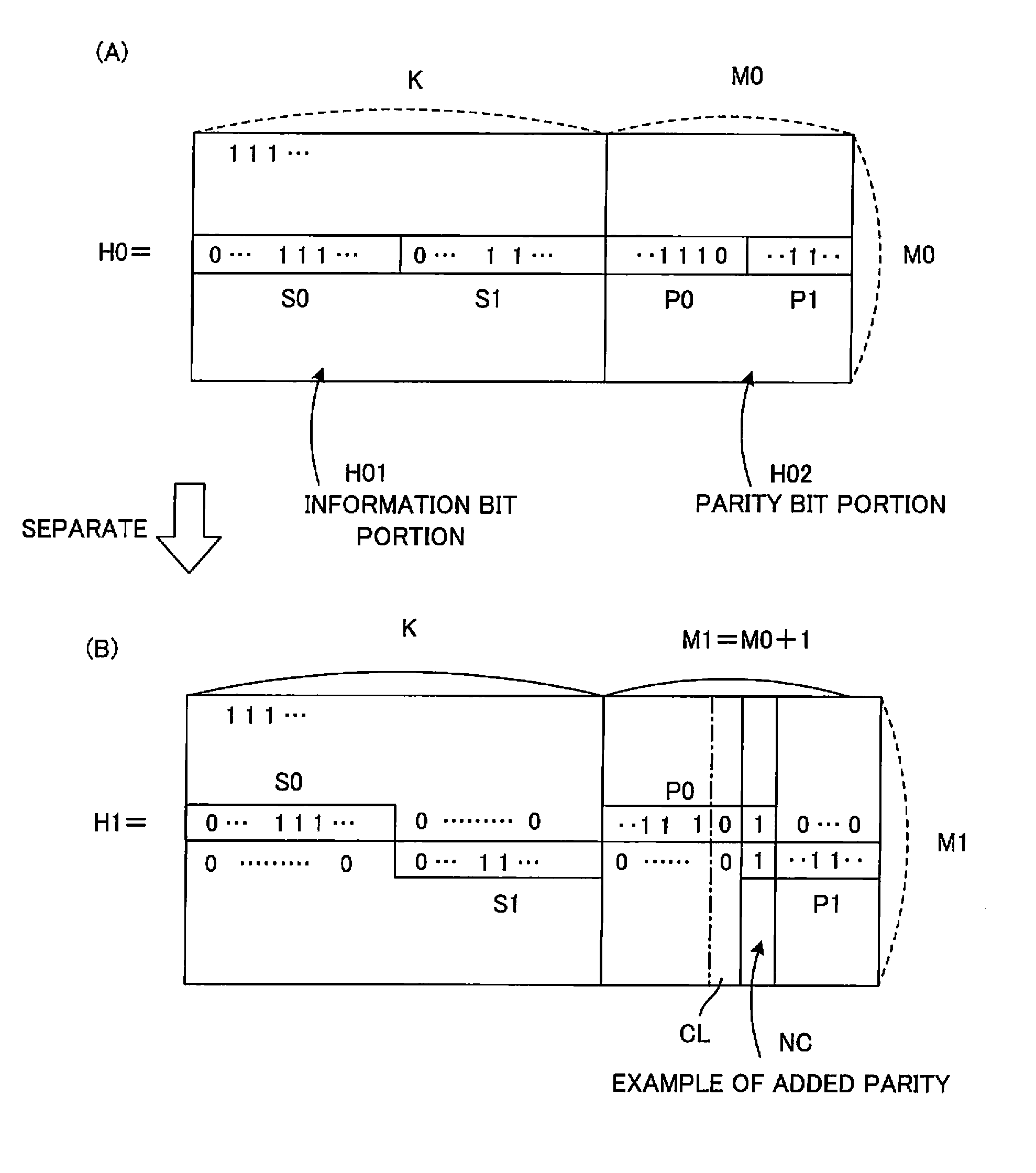

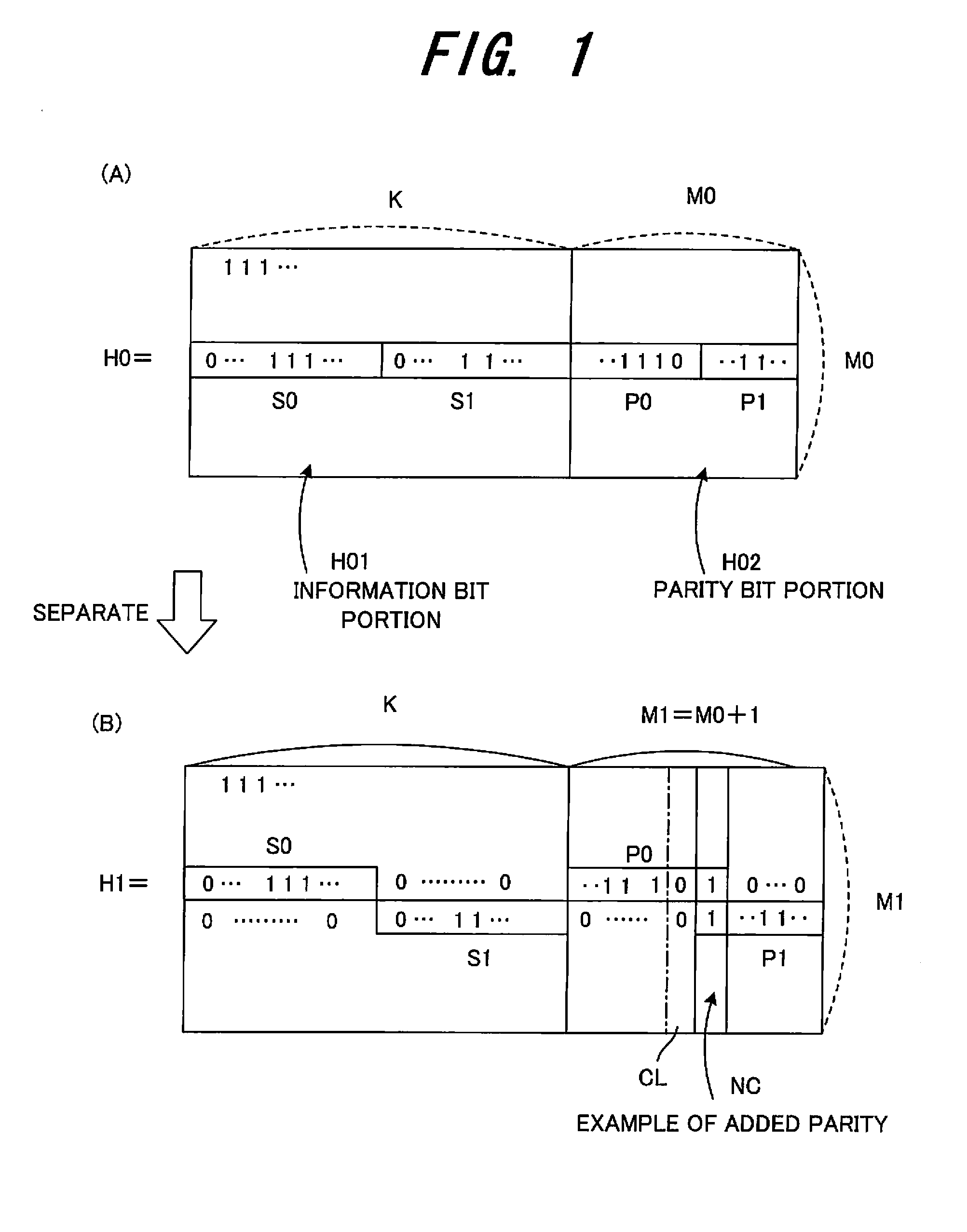

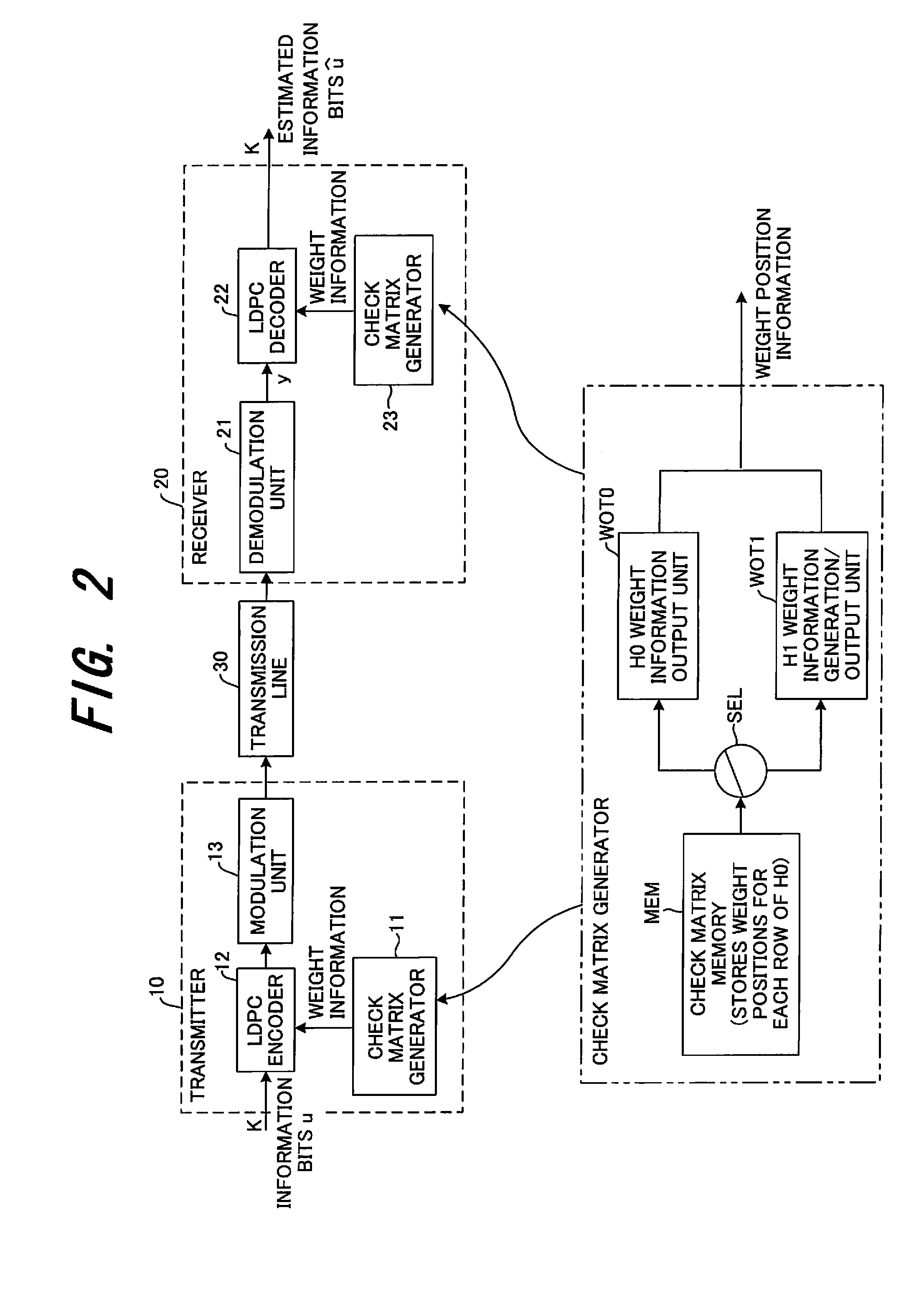

LDPC Check Matrix Generation Method, Check Matrix Generator, and Code Retransmission Method

ActiveUS20080301518A1Improve distributionError preventionCode conversionTheoretical computer sciencePorting

A check matrix generation method for generating a check matrix H1 of a code H1 from a check matrix H0 of a code C0, where codes C0 and C1 are LDPC systematic codes having different encoding ratios in a rate-compatible relationship and information bit sizes of the systematic codes C0 and C1 are K, and parity bit sizes thereof are M0 and M1 (M1−M0=L) respectively. The method comprising steps of: selecting L number of rows out of the check matrix H0; separating an information bit portion and a parity bit portion constituting each of the selected rows into two respectively, such that each of the separated information bit portions includes one or more non-zero elements which are “elements different from 0”; creating a new first row by coupling one separated information bit porting and one separated parity bit portion and creating a new second row by coupling another separated information bit portion and another separated parity portion; and generating the check matrix H1 of the systematic code C1 by placing the new first and second rows in place of each of the selected L number of rows in the check matrix H0.

Owner:FUJITSU LTD

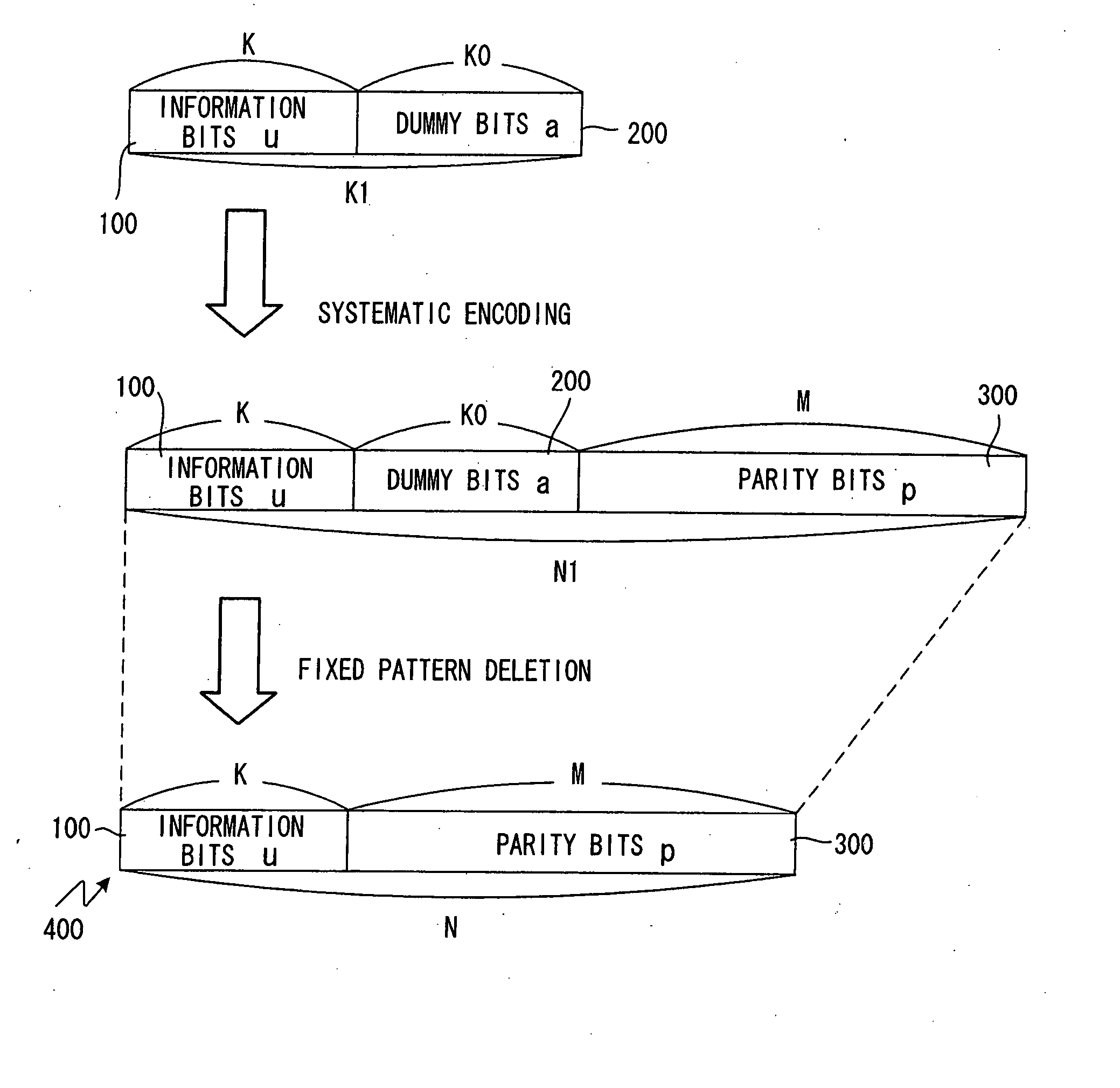

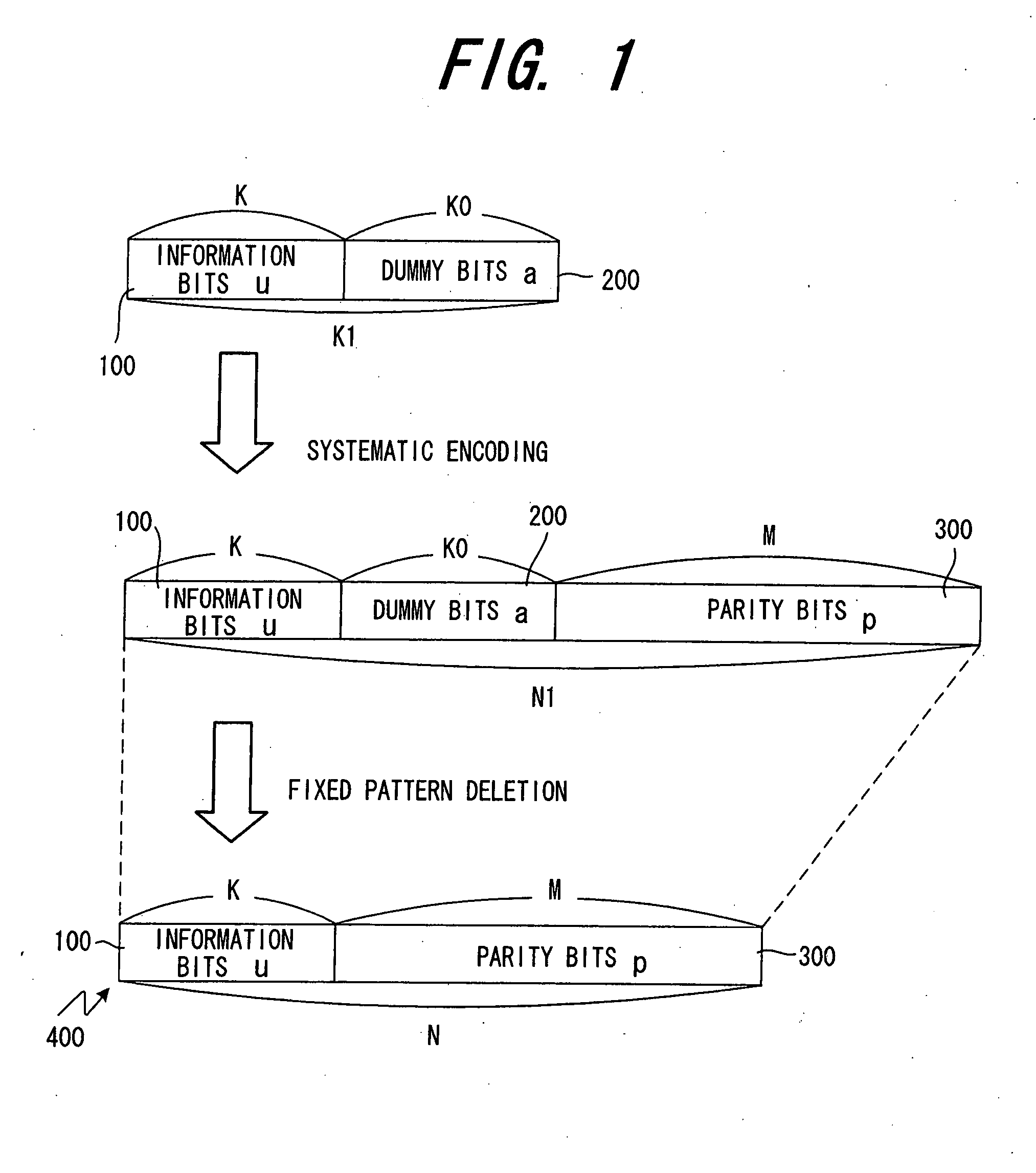

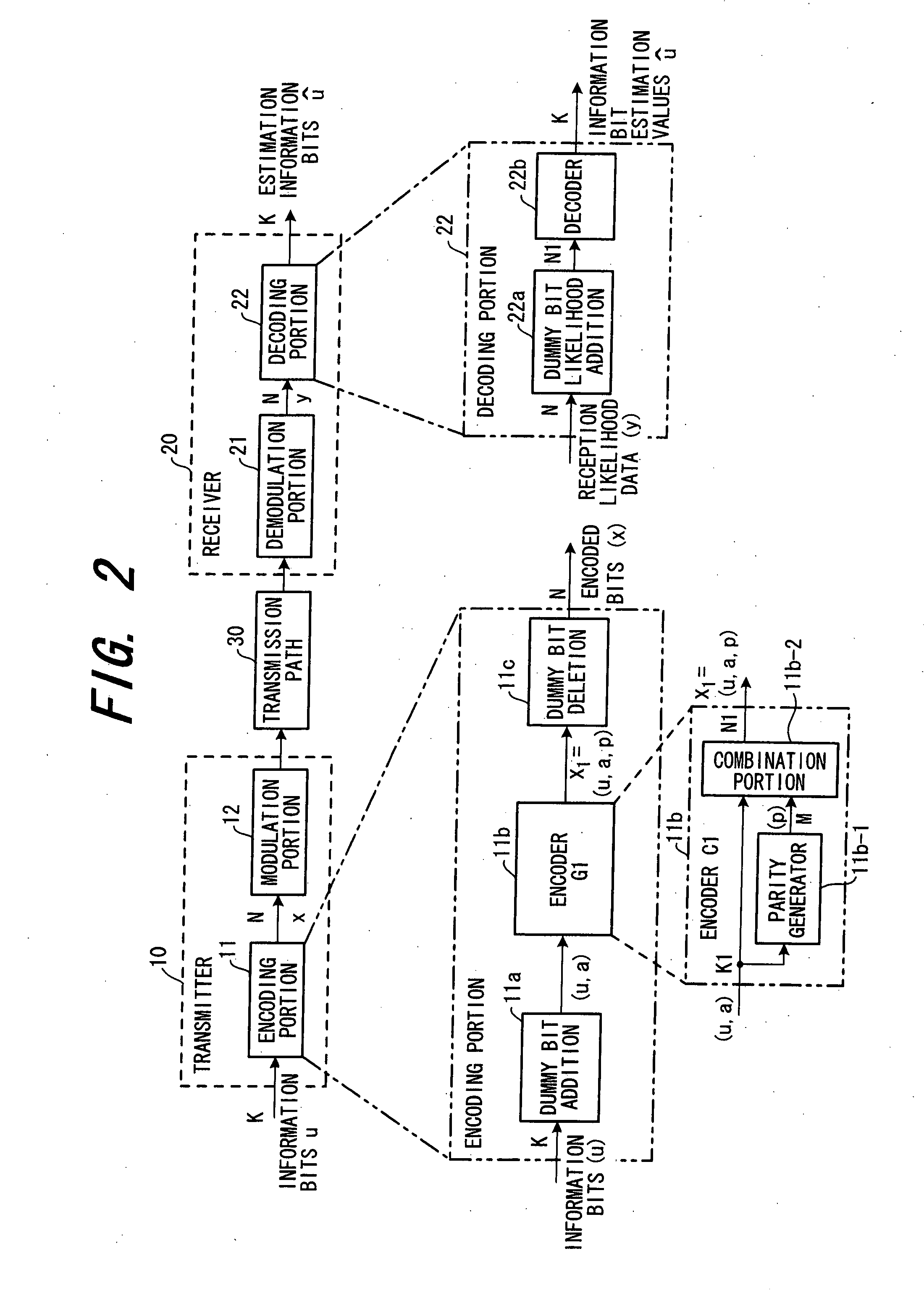

Encoding method, decoding method, and devices for same

InactiveUS20080028281A1Error rateIncrease freedomCode conversionCoding detailsSystematic codeTheoretical computer science

In a system in which systematic code, comprising information alphabet elements to which parity alphabet elements have been added, is transmitted and received, (1) K0 dummy alphabet elements are added to K information alphabet elements to generate first code of K1 (=K+K0) information alphabet elements; (2) M parity alphabet elements, created from the first-code of K1 information alphabet elements, are added to this first code of K1 information alphabet elements, and the K0 dummy alphabet elements are deleted to generate systematic code of N (=K+M) alphabet elements; and (3) the systematic code is received on the receiving side, the K0 dummy alphabet elements are added to the received systematic code, and decoding of the code of N1 alphabet elements obtained by adding the K0 dummy alphabet elements, is performed.

Owner:FUJITSU LTD

Multi-dimensional symbologies and related methods

ActiveUS20080035730A1Increasing data bitImprove abilitiesTransmission systemsSensing detailsMulti dimensionalData mining

Multi-dimensional symbology codes that use plural characteristic features encoded in a data cell and related methods. Such methods include methods of encoding, methods of creating and methods of reading multi-dimensional symbology codes that use such plural characteristic features. The features, for example, include colors, grey scale levels, cell shape, patterns within a cell or any grouping discernable by an area array camera or similar device.

Owner:VERITEC INCORPORATED

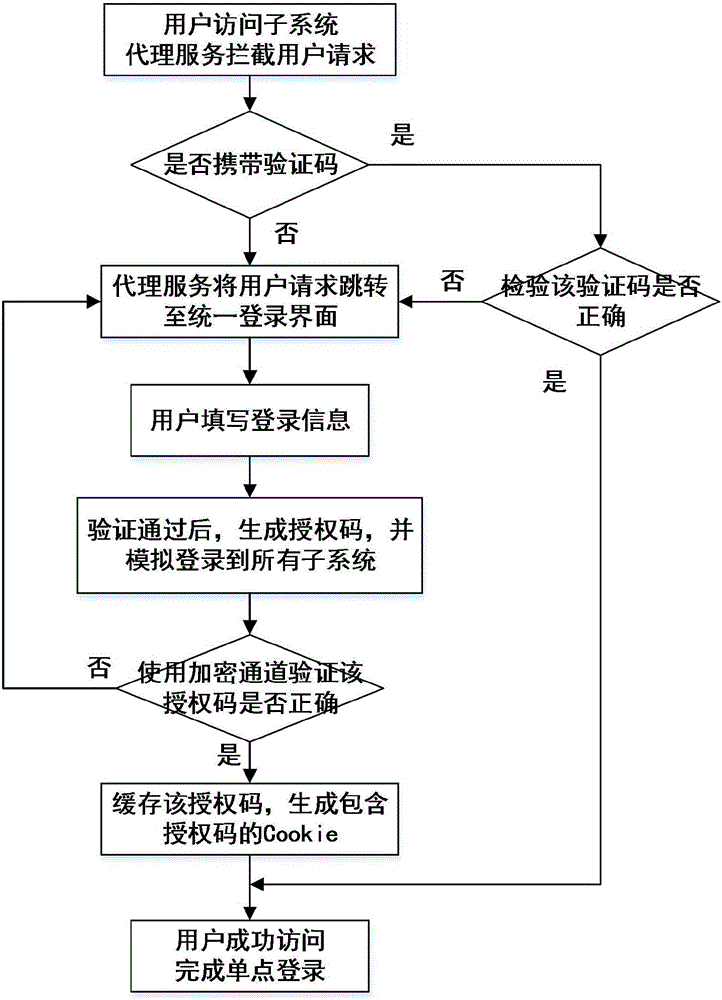

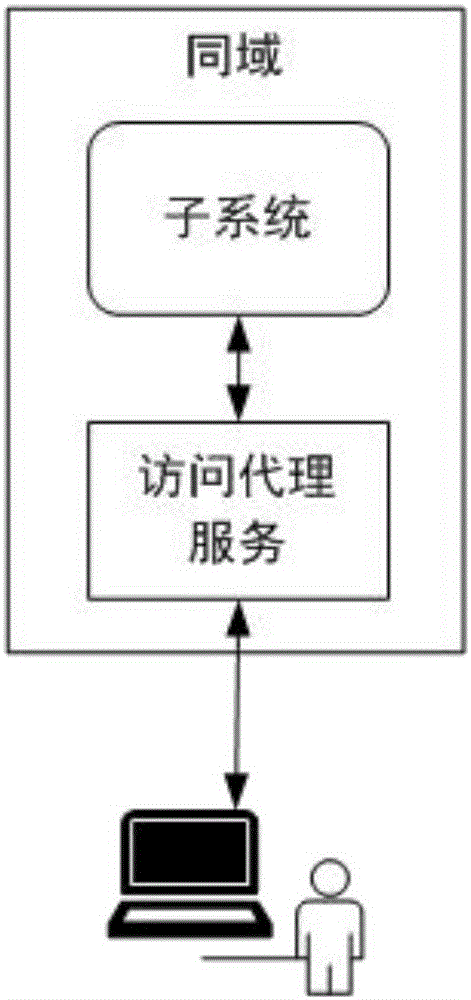

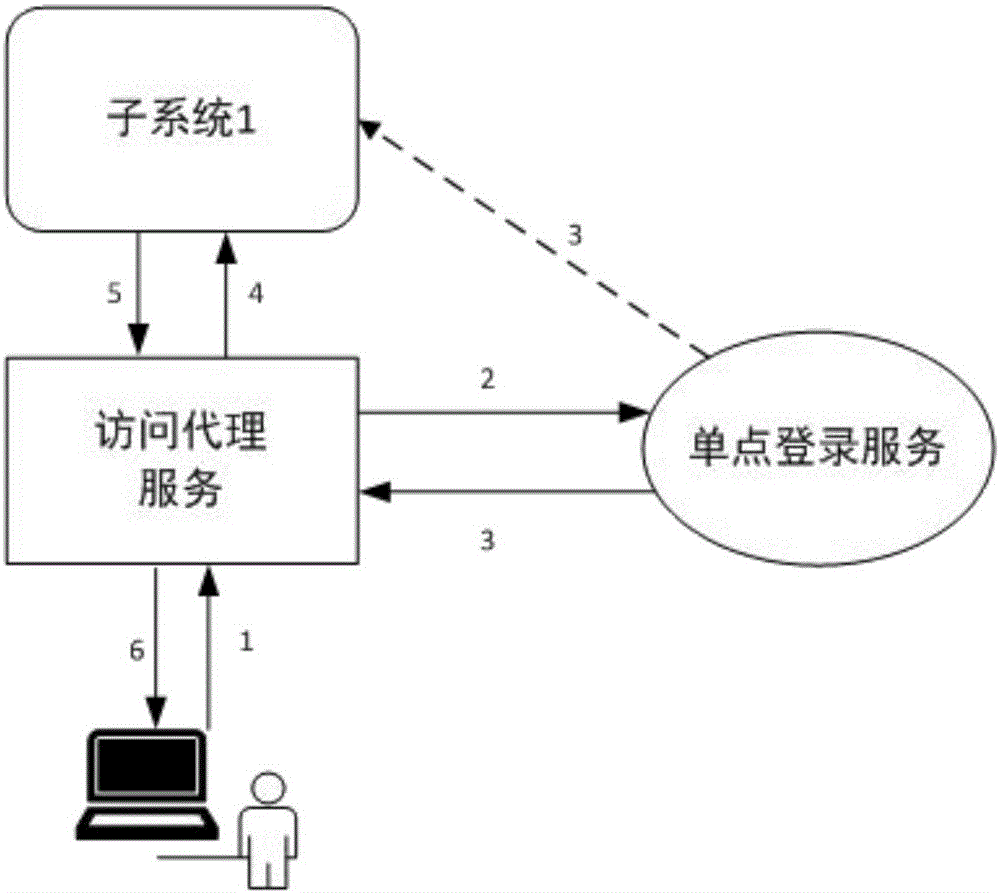

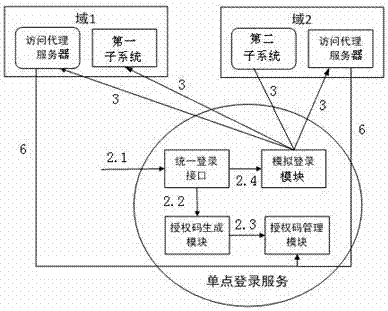

Cross-domain single sign-on method for system integration

The invention discloses a cross-domain single sign-on method for system integration. The method comprises steps: 1) when a user firstly accesses a subsystem, proxy service intercepts the request and jumping to a unified sign-on interface is carried out; 2) the user fills information such as the username and the password in the sign-on interface; 3) a single sign-on server verifies the user information, and a unique authorization code is generated; 4) a simulated sign-on mode is used to send the authorization code and the sign-on information to all systems; and 5) when the user uses the authorization code to access the system or other systems again, sign-on again is not needed. The cross-domain single sign-on method for system integration has the advantages that the configuration is simple; the original system code is not invaded; seamless access to systems crossing domains and distributed under multiple domain names can be realized, and the method is applicable to a high-concurrency scene, and supports a time-limiting sign-on-free feature.

Owner:HOHAI UNIV

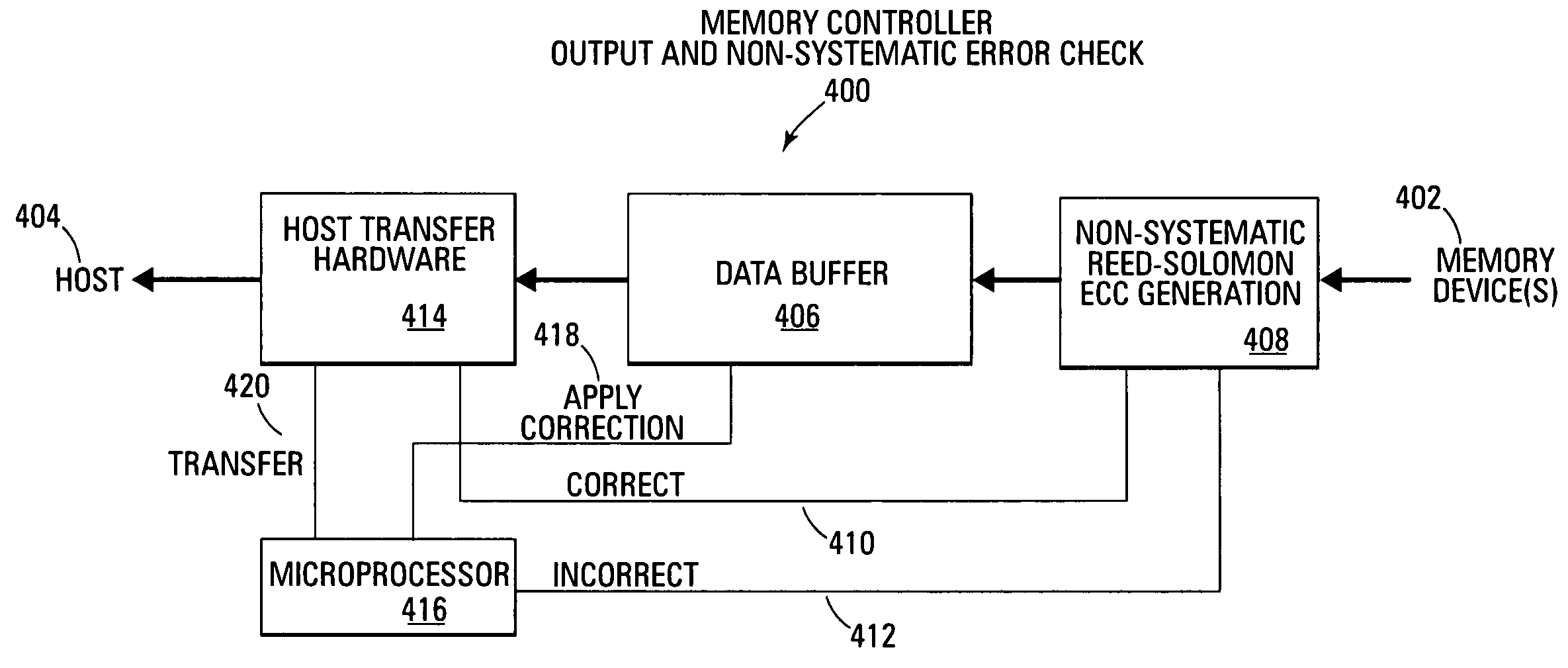

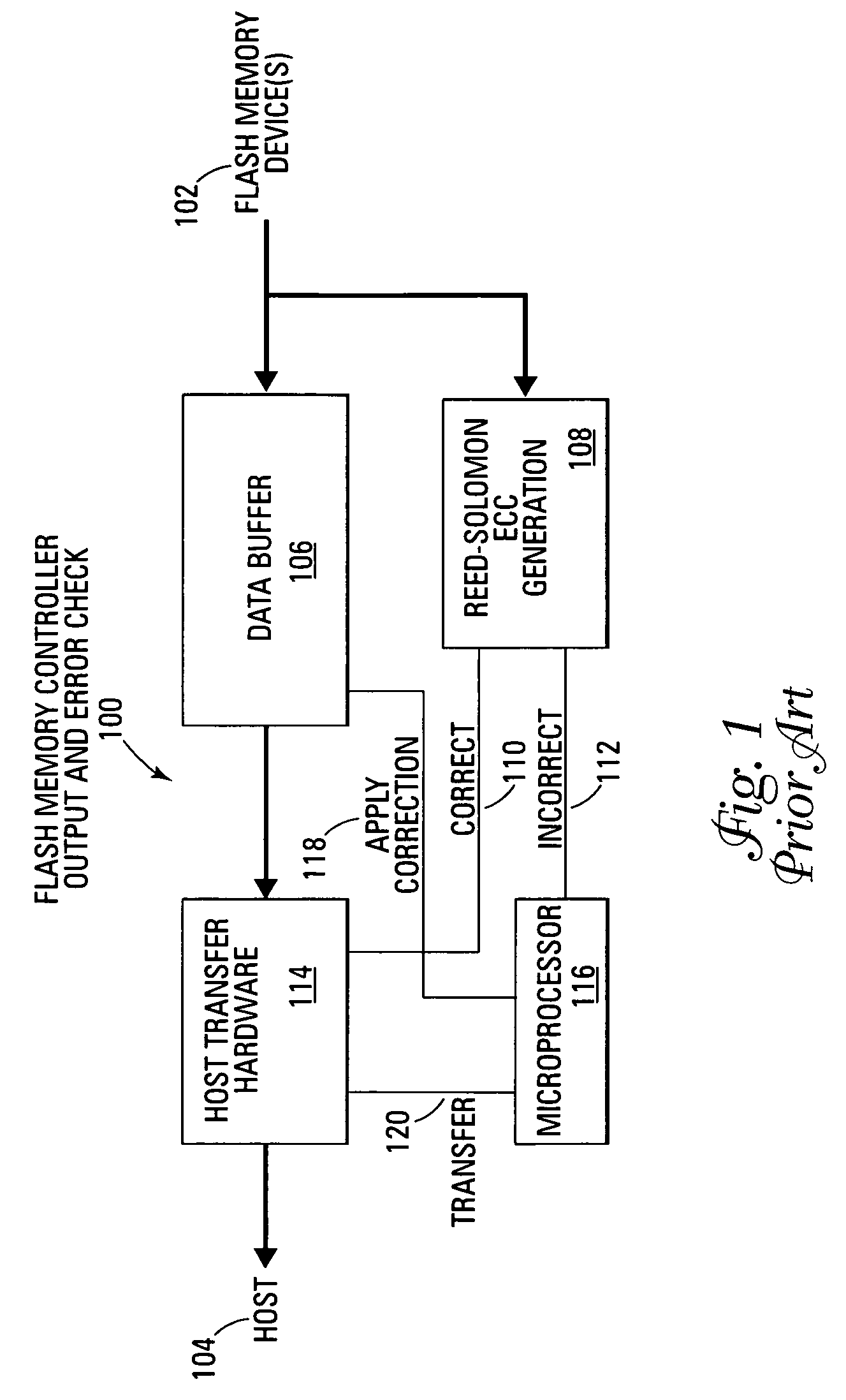

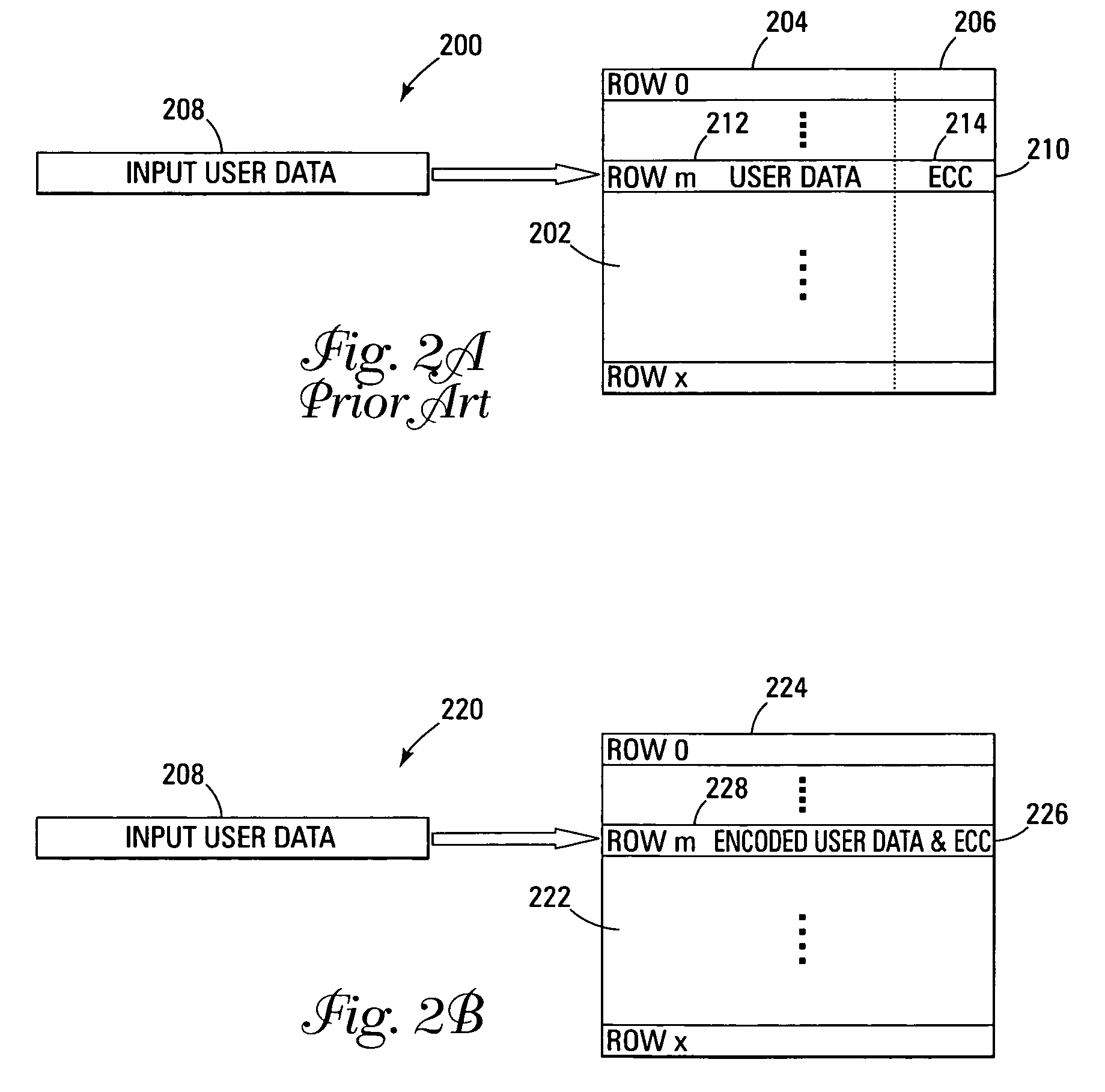

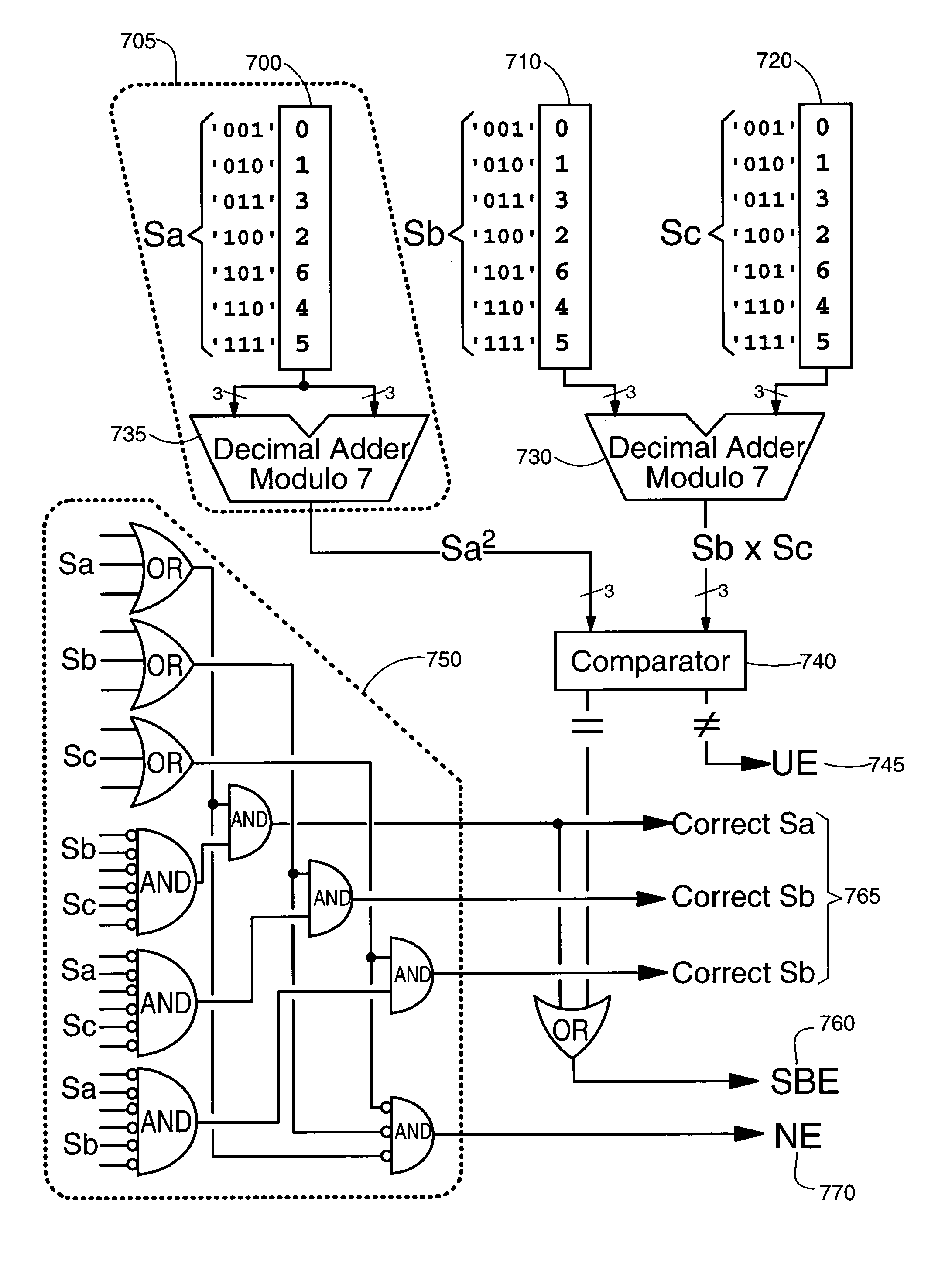

Non-systematic coded error correction

ActiveUS7444579B2Facilitate detection and correctionEasily damagedStatic storageRedundant data error correctionPlaintextData Corruption

Improved memory devices, circuitry, and data methods are described that facilitate the detection and correction of data in memory systems or devices by encoding the data bits of a memory row or block in a non-systematic ECC code. This allows memory embodiments of the present invention to utilize reduced complexity error detection and correction hardware and / or routines to efficiently detect and correct corrupted user data in a segment of memory, such as a sector, word line row, or erase block. Additionally, in embodiments of the present invention user data is not stored in a plaintext format in the memory array, allowing for an increased level of data security. Further, in embodiments of the present invention, the ECC code is distributed throughout the stored data in the memory segment, increasing the robustness of the ECC code and its resistance to damage or data corruption.

Owner:OVONYX MEMORY TECH LLC

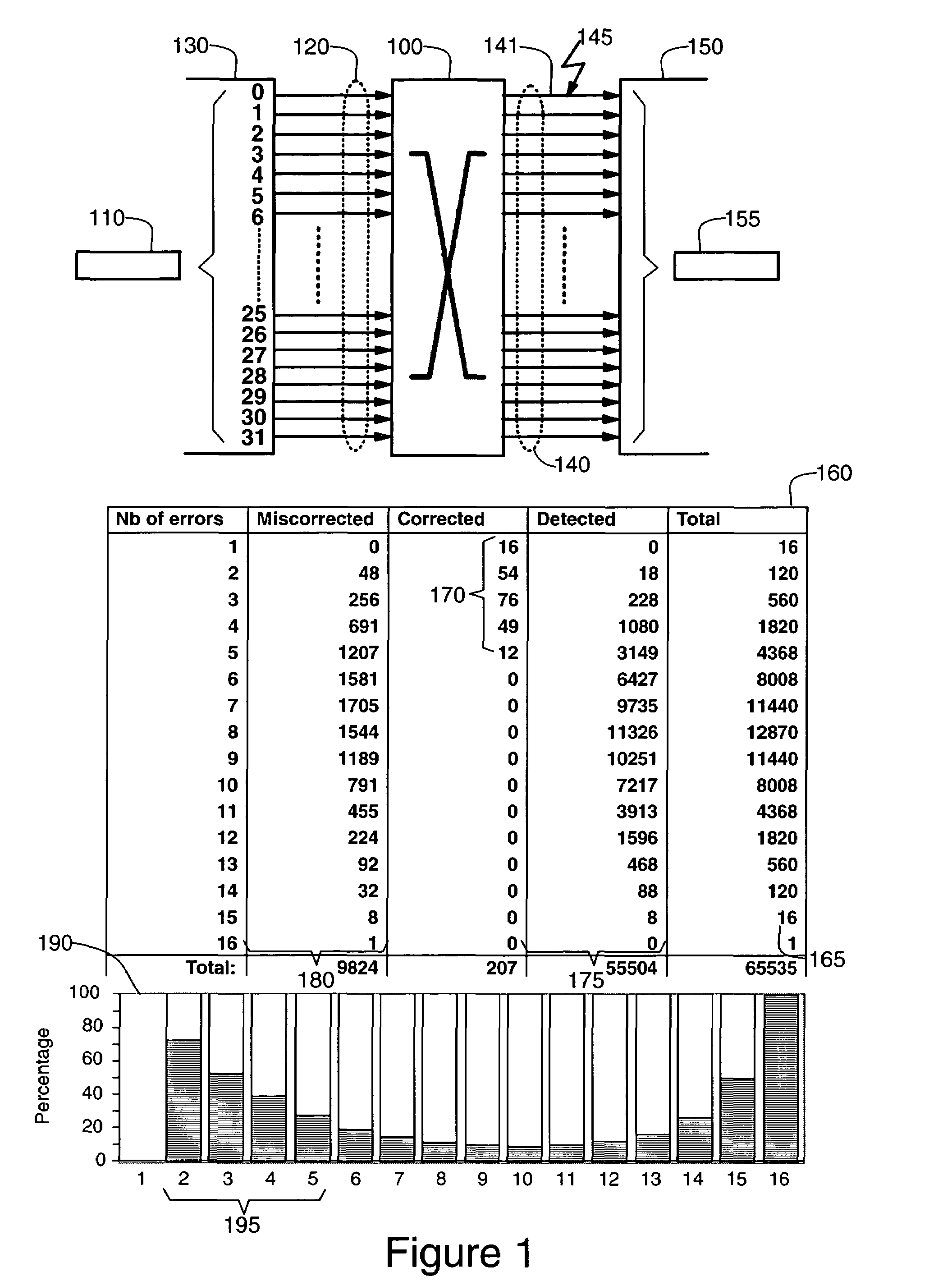

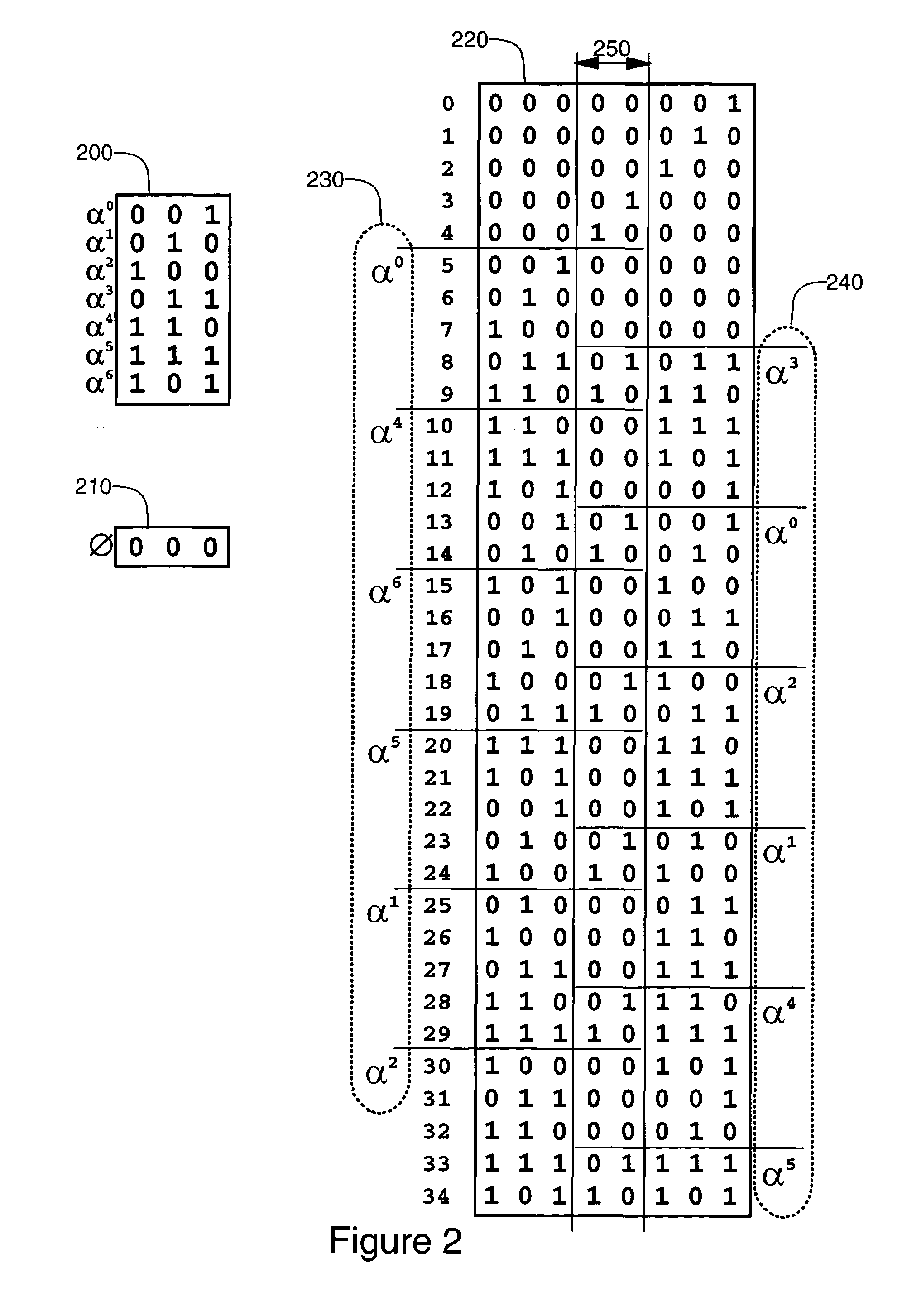

Single-burst-correction / double-burst-detection error code

InactiveUS7249309B2Improve decoding performanceImprove performanceBurst error correctionIndividual digits conversionComputer hardwareP-matrix

A method and apparatus for performing encoding and decoding of bit chain data packets conveying errors which do not spread on more than n bits, at very high speed. In one embodiment, a matrix of the corresponding Systematic code is built using p×p matrix blocks comprising elements of a galois field, generated by an irreducible generator polynomial of degree p, p being greater or equal to n.

Owner:IBM CORP

Cross-domain single-point registration system and method facing system integration

ActiveCN106936853AImplement single sign-onSupport free loginTransmissionSystem integrationProxy server

The invention discloses a cross-domain single-point registration system and method facing system integration. The system comprises a terminal, access proxy servers and a single-point registration server. Each access proxy server is disposed in front of a subsystem, positioned in the same top level domain with the subsystem, and used to process and forward all requests to the subsystem in full authority; and the single-point registration server comprises a unified registration interface, an authorization code generation module, an authorization code management module and a simulated registration module. Under the condition that codes of the system are not invaded and system setting is not changed, cross-domain cross-development-platform single-point registration is realized, and the system is suitable for a high concurrent scene and supports a registration-free condition. When a user access the subsystem, the corresponding access proxy server redirects a request to a unified registration interface, and a unique authorization code is generated after that the user succeeds in registration. A simulated registration manner is used to send the authorization code and registration information to the subsystem. The user can use the authorization code to access the system or other systems directly needless of registration again.

Owner:HOHAI UNIV +1

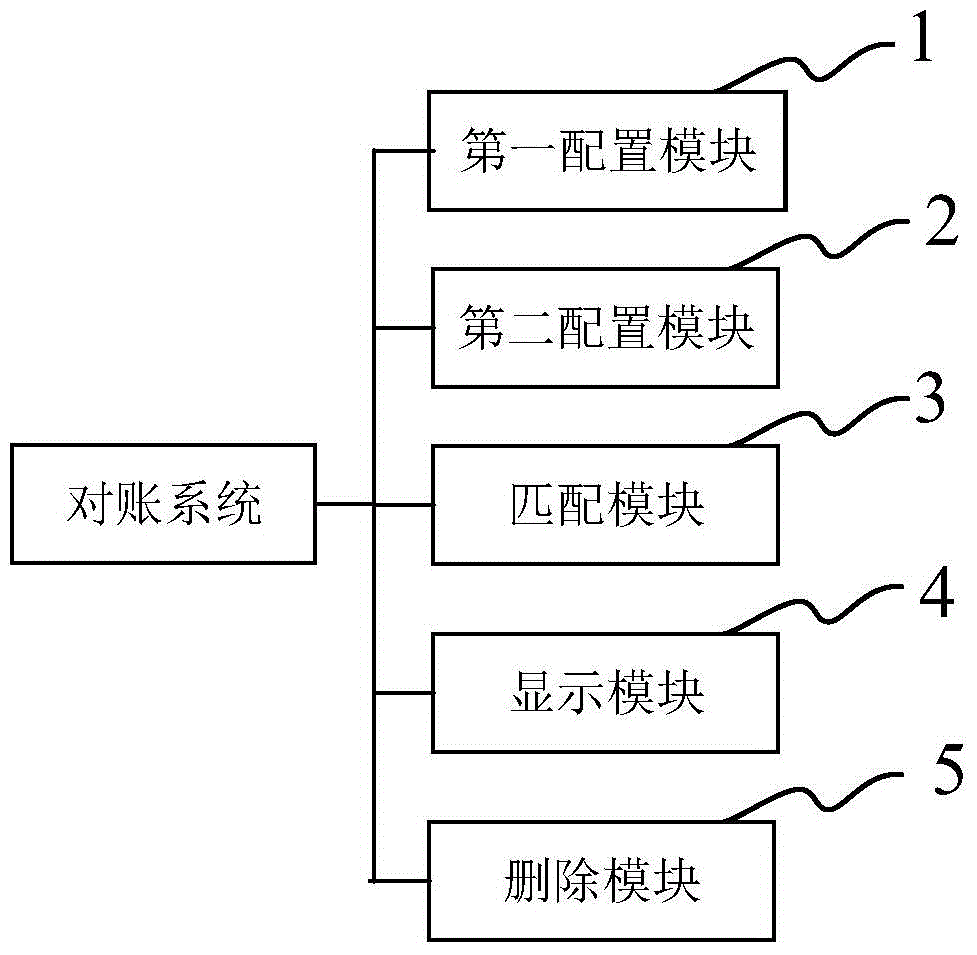

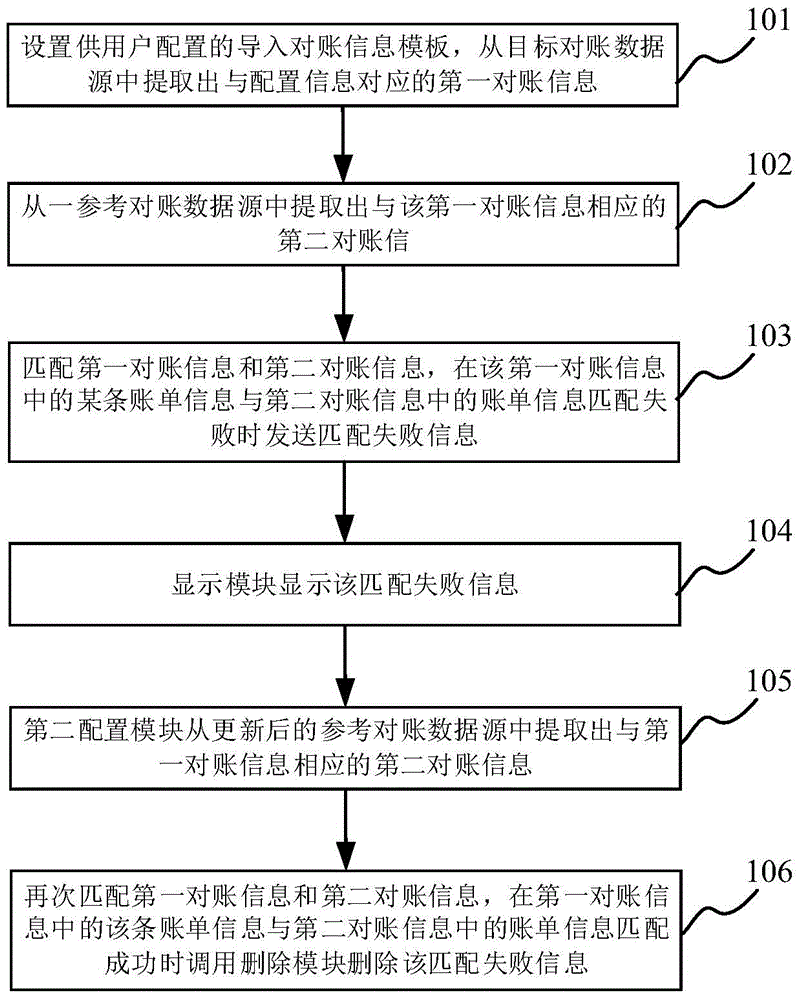

Account checking system and method

InactiveCN105761139AReduce the burden onReduce maintenance costsFinanceSpecial data processing applicationsPaymentData source

The invention provides an account checking system and method. A first configuration module sets an account checking information import template for configuration of a user and extracts first account checking information corresponding to configuration information from a target account checking data source according to the input configuration information, the first account checking information includes multiple pieces of bill information, and each piece of bill information includes payment serial number information, order information, transaction amount information, transaction date information and a transaction company. A second configuration module is used for extracting second account checking information corresponding to the first account checking information from a reference account checking data source. A matching module is used for matching of the first account checking information and the second account checking information and transmitting matching failure information to a display module to display the matching failure information when matching of a certain piece of bill information in the first account checking information and the bill information in the second account checking information fails, and the matching failure information includes the payment serial number information of the bill information. Real-time configuration and real-time application can be realized without modifying the system code level.

Owner:SHANGHAI CTRIP COMMERCE CO LTD

Method of constructing check matrix for LDPC code, and encoding and decoding device of using the method

InactiveCN1960190AImprove performanceReduce occupancyError preventionError correction/detection using multiple parity bitsParallel computingTheoretical computer science

The coder codes the input binary info and outputs the coded position-change system code queue. The coder consists of the matrix multiply module (MM), the compositor index module (CI) and the compositor output module (CO). MM outputs verification queue p obtained via multiplying the binary info queue m with a matrix. CI possesses N storage units and stores orderly the index value of the compositor table IDX. According to the stored index value in IDX, CO compositors against m and p, then outputs code character c. This invention uses the algebra structure to build the verification matrix of LDPC code to obtain a stable LDPC code. Besides, the coder and decoder in this invention occupy less memory units. This benefits the device optimization.

Owner:TIMI TECH

COMMUNICATION TECHNIQUES WITH SELF-DECODABLE REDUNDANCY VERSIONS (RVs) USING SYSTEMATIC CODES

InactiveUS20180367245A1Facilitate communicationLow costError prevention/detection by using return channelError correction/detection using multiple parity bitsAntenna elementSystematic code

The present disclosure provides self-decodable redundancy versions for a systematic code. An apparatus for wireless communications includes at least one processor coupled with a memory and comprising encoder circuitry configured to encode a set of information bits using a systematic code to generate an encoded bit stream with information bits and parity bits, and bit ordering circuitry configured to re-order bits in the encoded bit stream to distribute the information bits and the parity bits. The apparatus includes a transmitter configured to transmit the re-ordered bits in accordance with a radio technology via one or more antenna elements situated proximate the receiver.

Owner:QUALCOMM INC

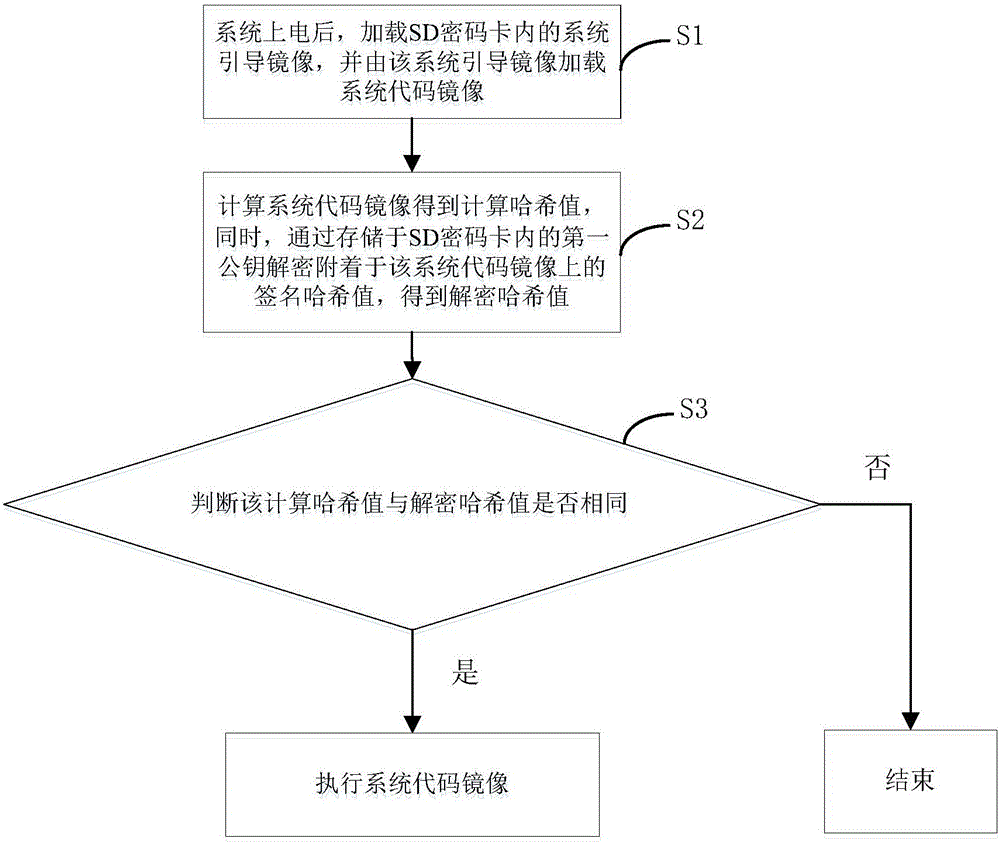

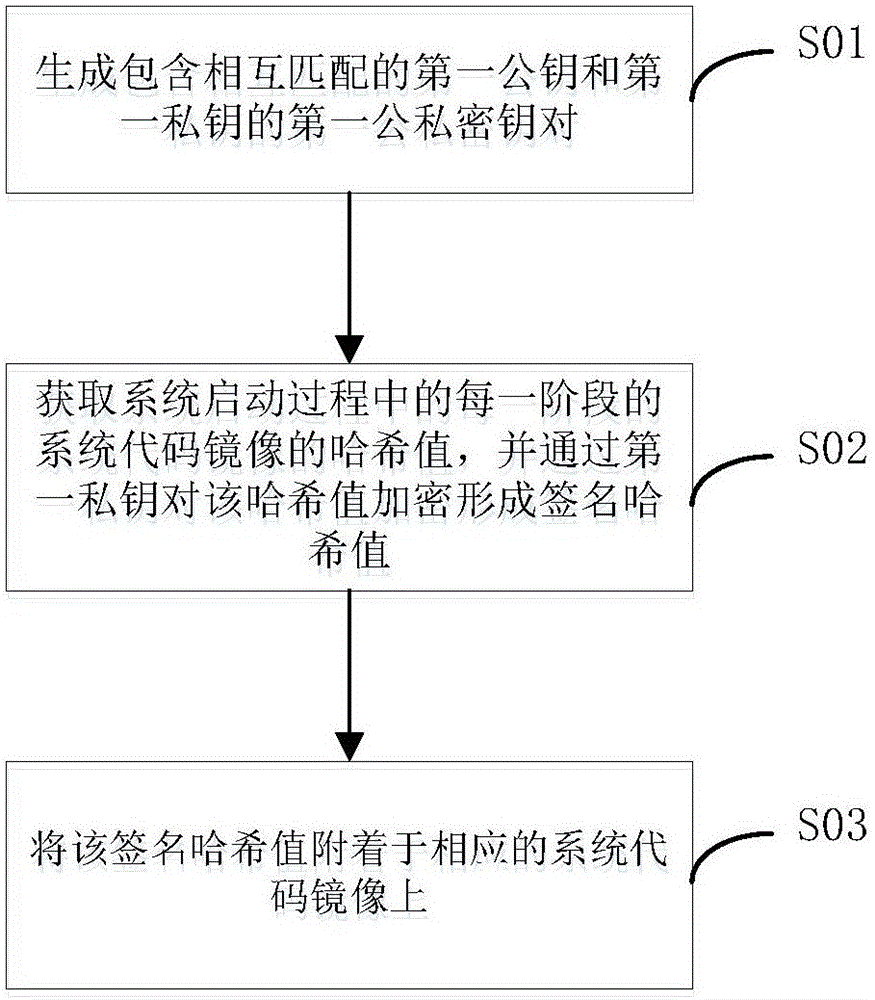

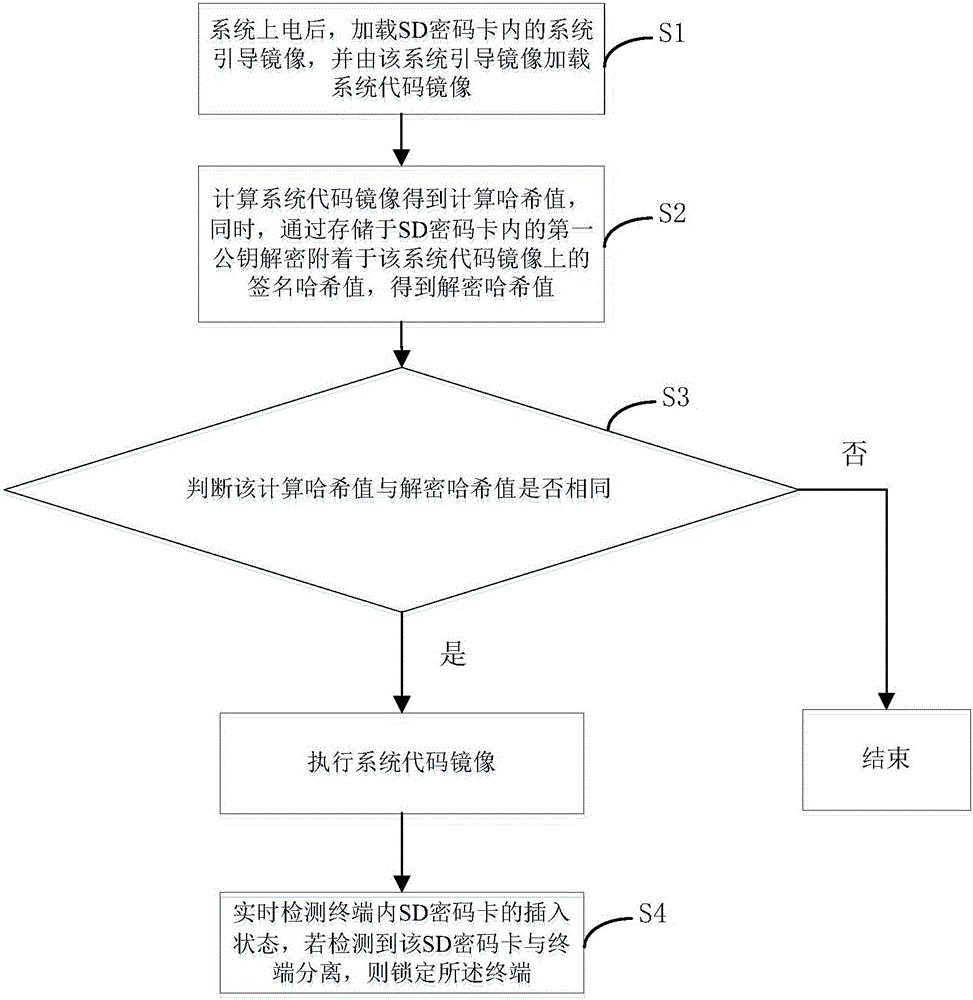

System boot method and apparatus

InactiveCN106295318AImprove securityPlay the role of security verificationComputer security arrangementsComputer hardwarePassword

The invention discloses a system boot method and apparatus. The method comprises the steps of loading a system boot mirror image in an SD password card after a system is powered on, and loading a system code mirror image according to the system boot mirror image; calculating the system code mirror image to obtain a calculated hash value, and meanwhile, decrypting a signed hash value attached to the system code mirror image through a first public key stored in the SD password card to obtain a decrypted hash value; and judging whether the calculated hash value is the same as the decrypted hash value or not, and if yes, executing the system code mirror image. By implementing the system boot method and apparatus, the verification of the system code mirror image of each stage in a terminal is realized, the effect of preventing the tampered system code mirror image from being executed is achieved, and the effect of security verification is achieved in a system boot process, so that the security of the terminal and data information stored in the terminal is improved.

Owner:BEIJING ERENEBEN INFORMATION TECH

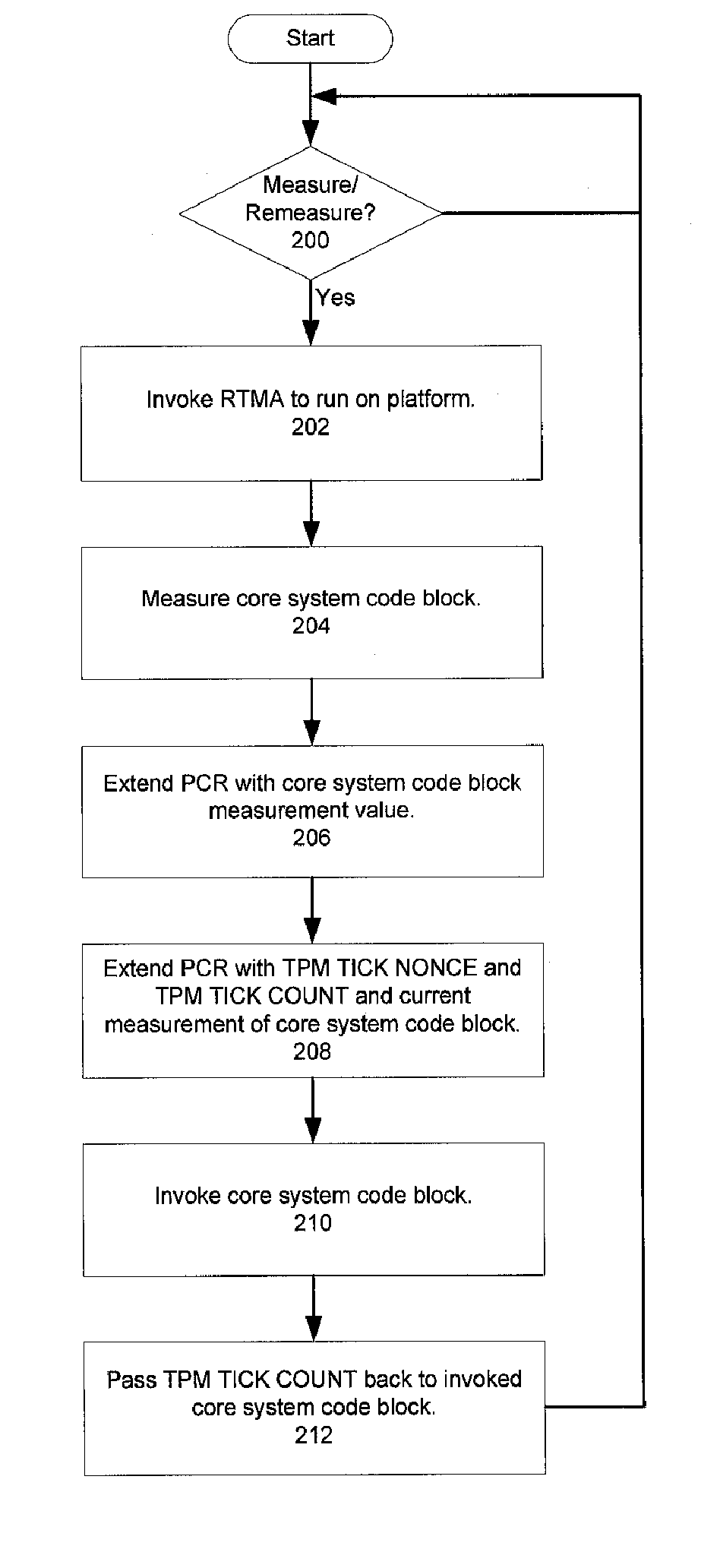

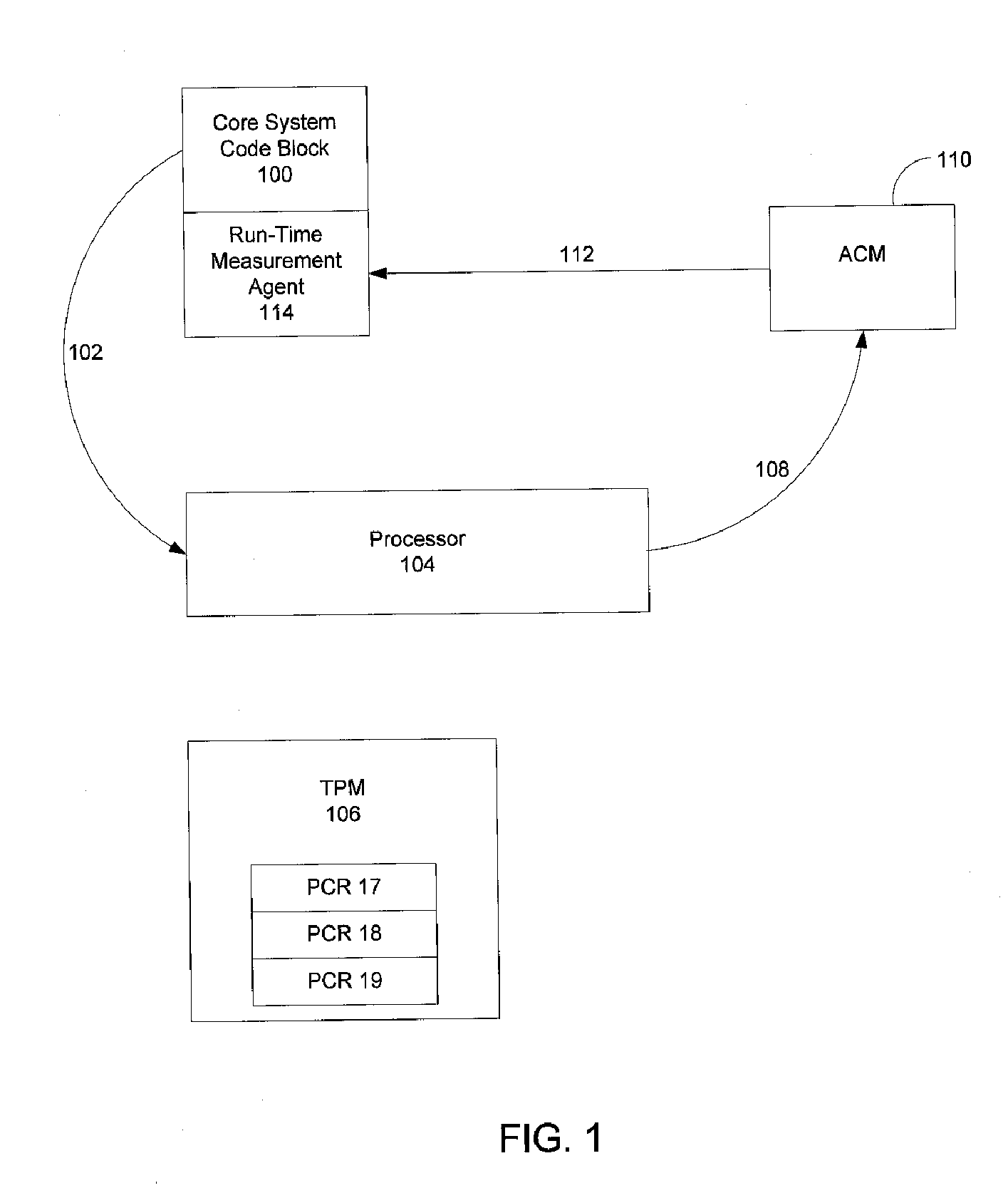

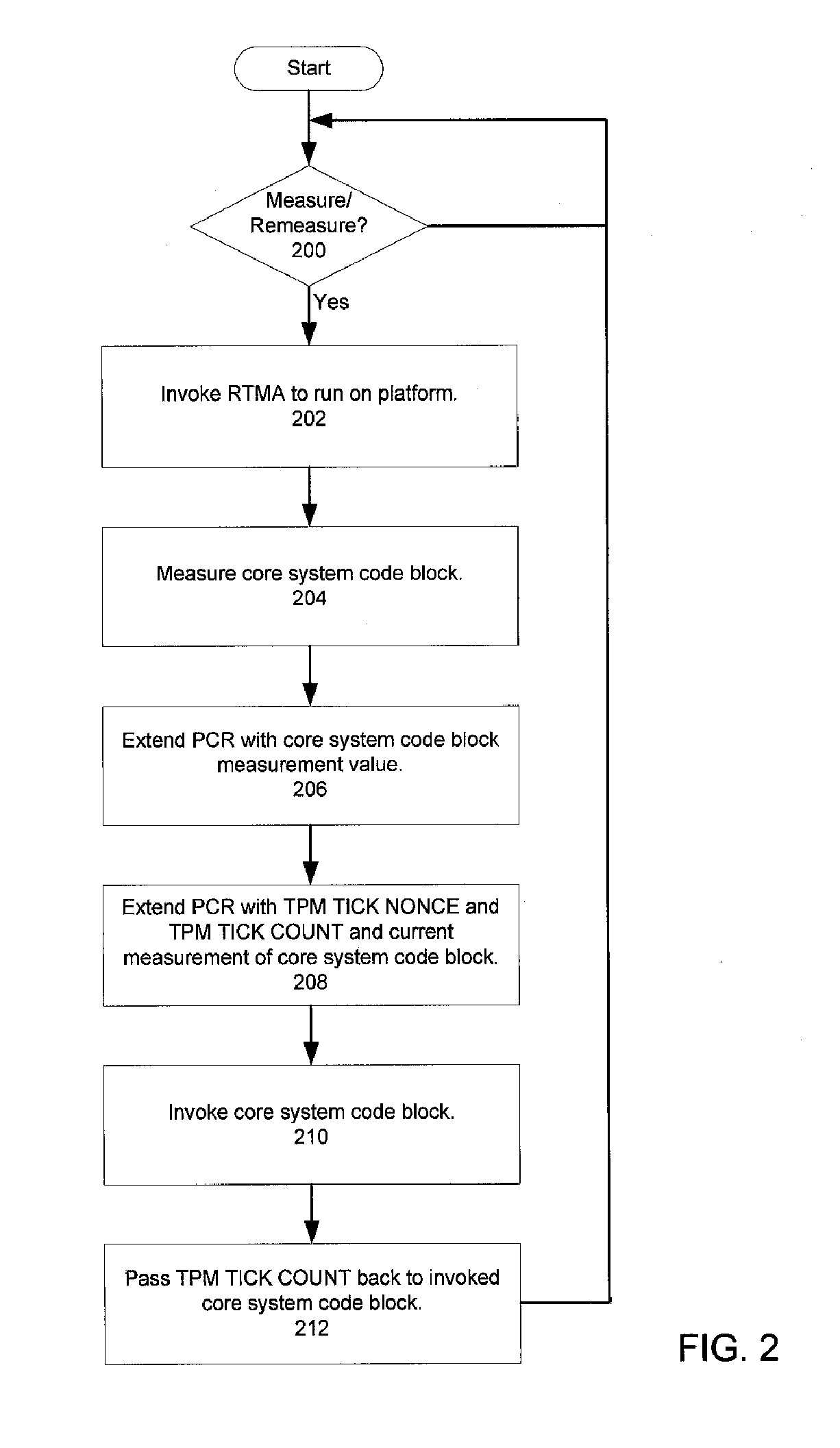

Run-time remeasurement on a trusted platform

InactiveUS20080244746A1Memory loss protectionError detection/correctionCoding blockComputer hardware

A method and system are disclosed. In one embodiment, the method includes invoking a run-time measurement agent (RTMA) to run on a trusted platform, the RTMA measuring a core system code block multiple times after a single boot on the trusted platform; and a trusted platform module storing these multiple measurements.

Owner:ROZAS CARLOS V +3