Patents

Literature

81 results about "Error detection and correction" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In information theory and coding theory with applications in computer science and telecommunication, error detection and correction or error control are techniques that enable reliable delivery of digital data over unreliable communication channels. Many communication channels are subject to channel noise, and thus errors may be introduced during transmission from the source to a receiver. Error detection techniques allow detecting such errors, while error correction enables reconstruction of the original data in many cases.

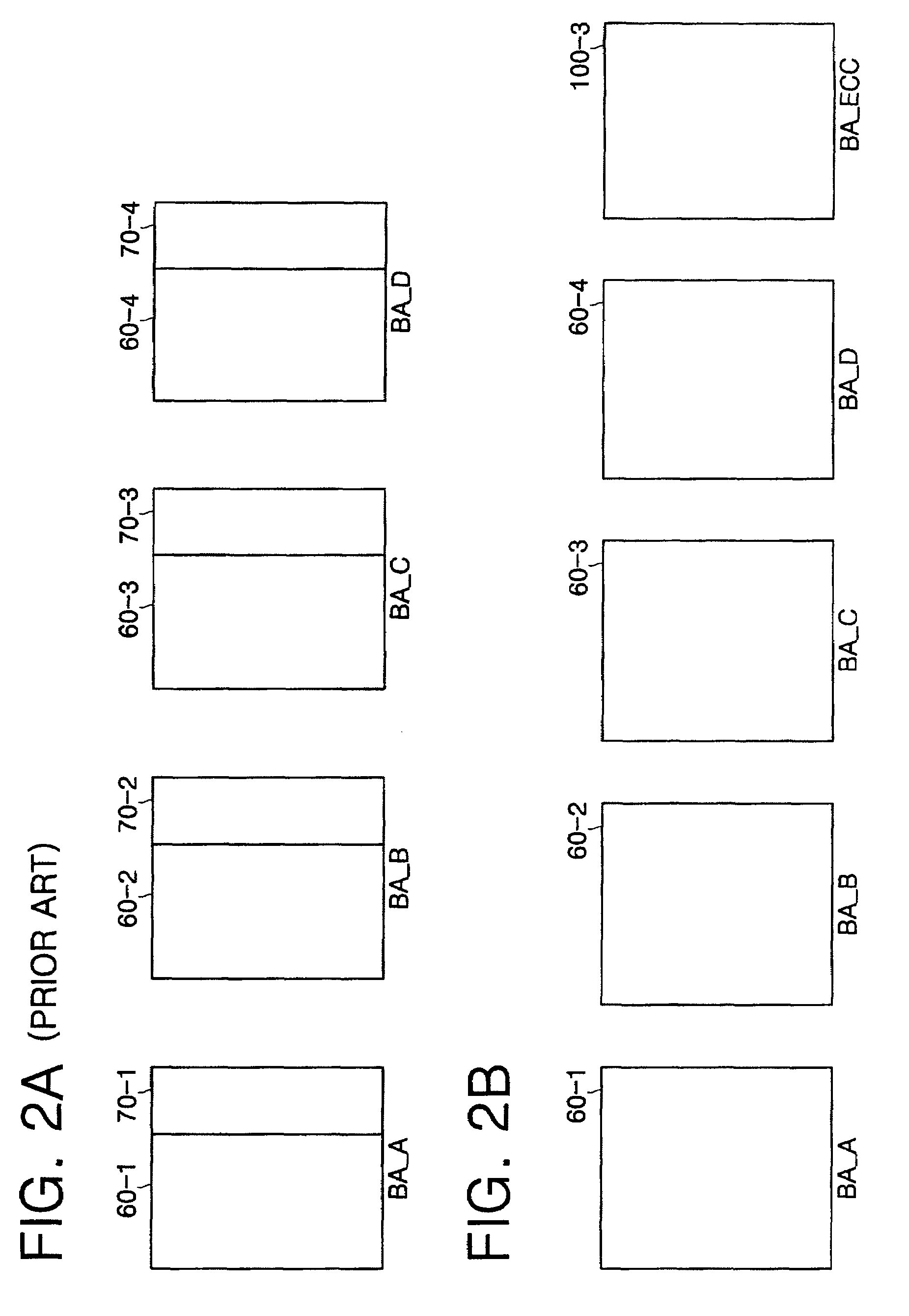

Method for substituting defective recording of discoid recording medium and discoid recording medium recording and reproducing device

InactiveUS6134214AEasy to useSmall sizeFilamentary/web record carriersOptical discsSubstitution methodError detection and correction

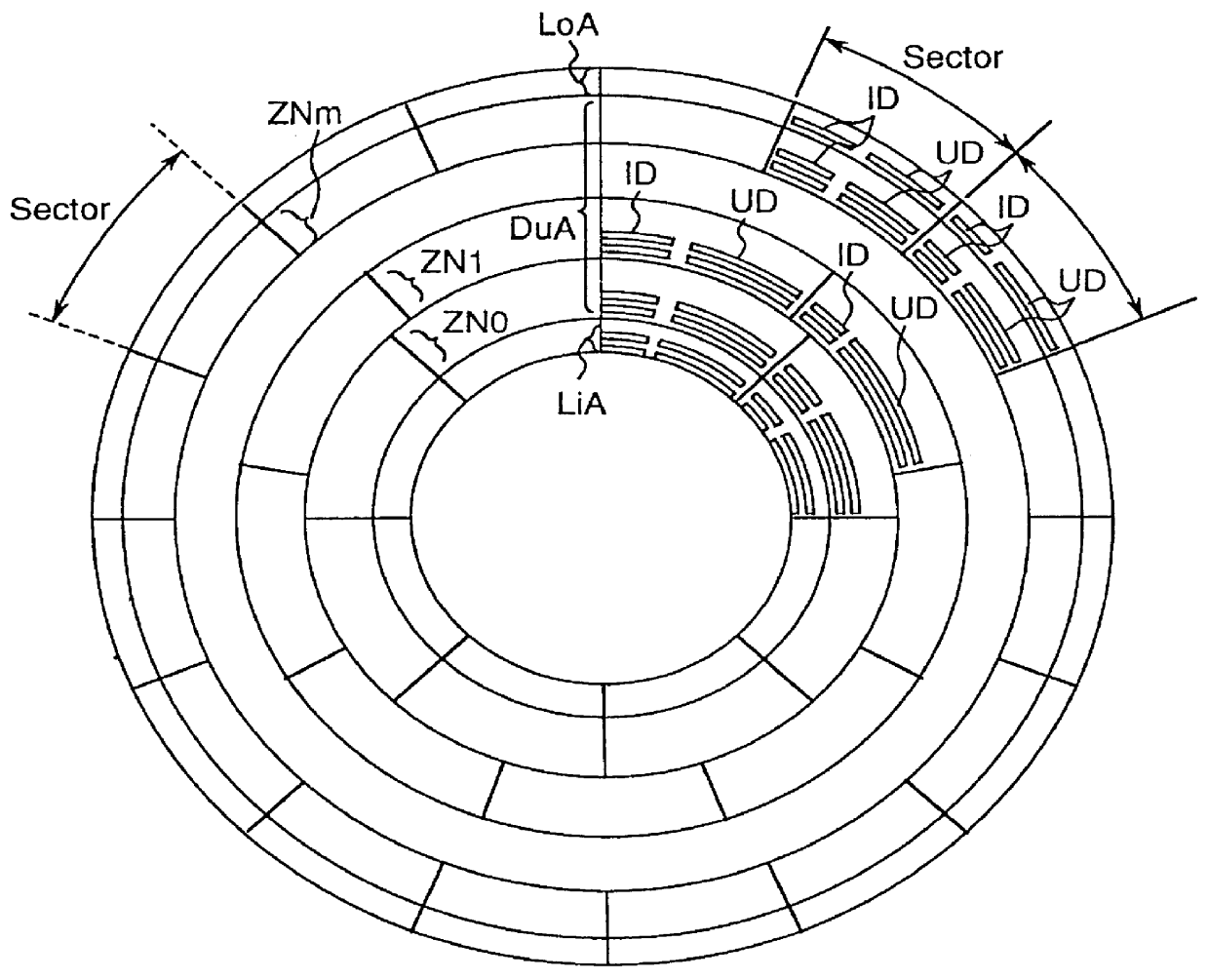

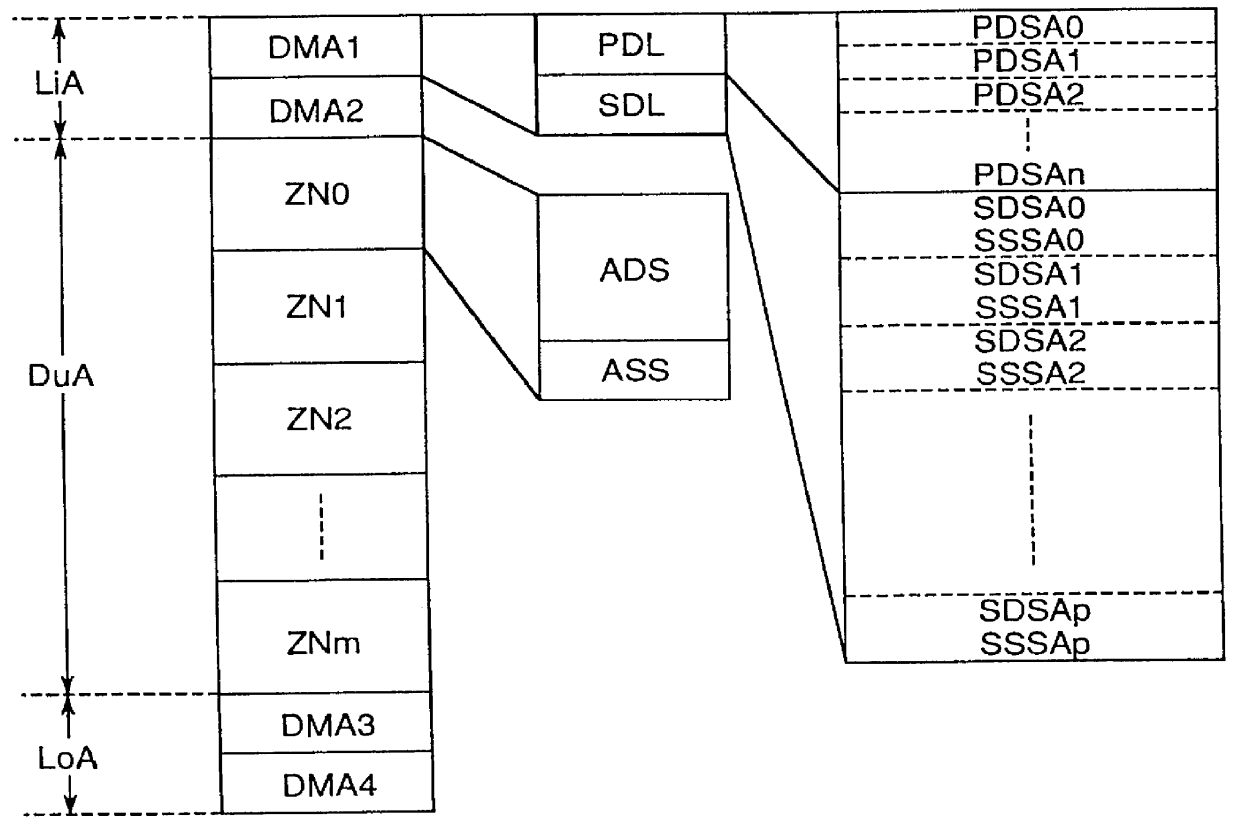

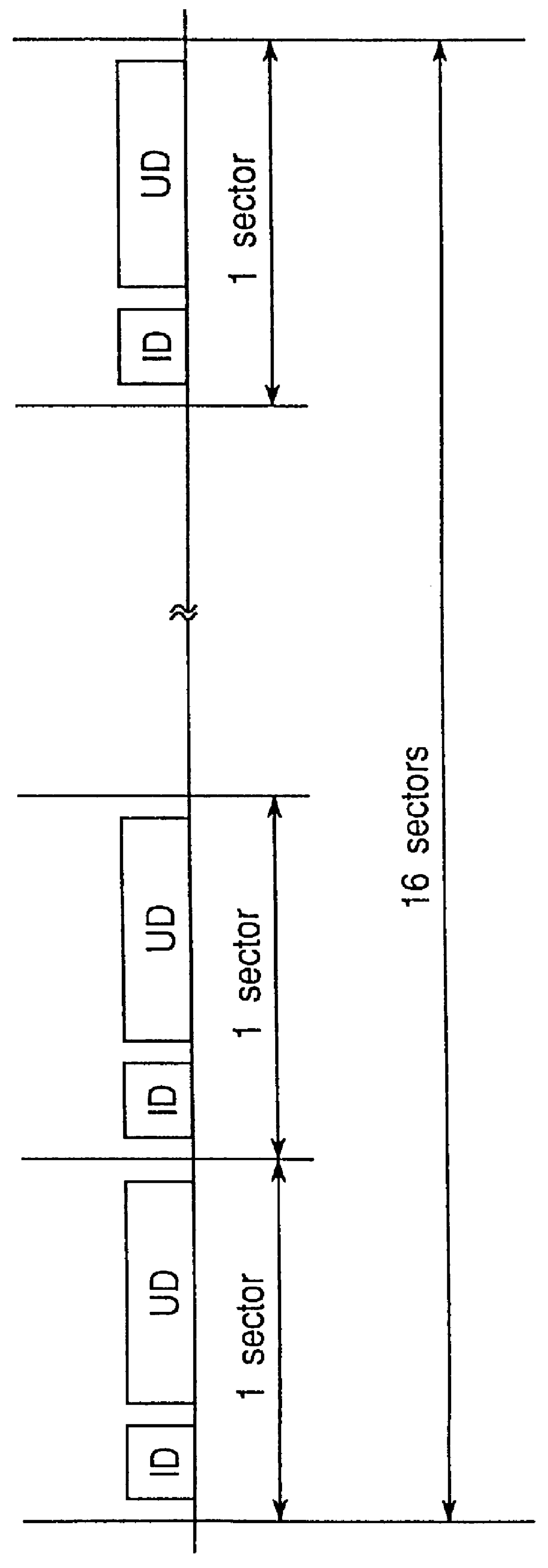

PCT No. PCT / JP97 / 00865 Sec. 371 Date Sep. 18, 1998 Sec. 102(e) Date Sep. 18, 1998 PCT Filed Mar. 18, 1997 PCT Pub. No. WO97 / 35309 PCT Pub. Date Sep. 25, 1997In a recording and reproducing apparatus for a disc-shaped recording medium, and a defect substitution method for a disc-shaped recording medium, whether reproduction of recorded data is good is determined by sector unit and not by product code unit, defective sector discrimination is performed by sector unit, and only sectors determined defective are alternately recorded, when using a recording format in which data that is error detection and correction coded with a product code is segmented and recorded to a plurality of sectors.

Owner:PANASONIC CORP

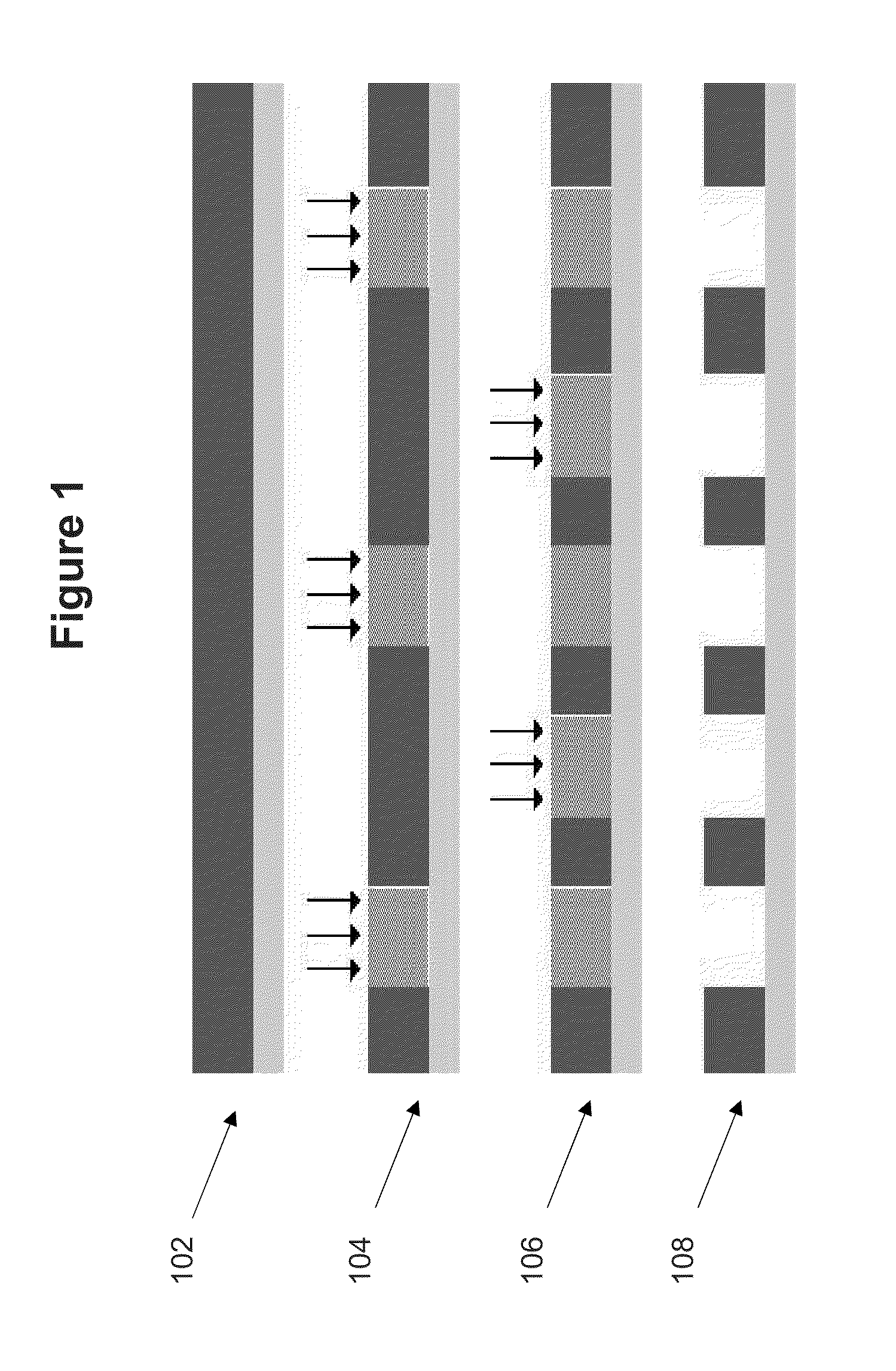

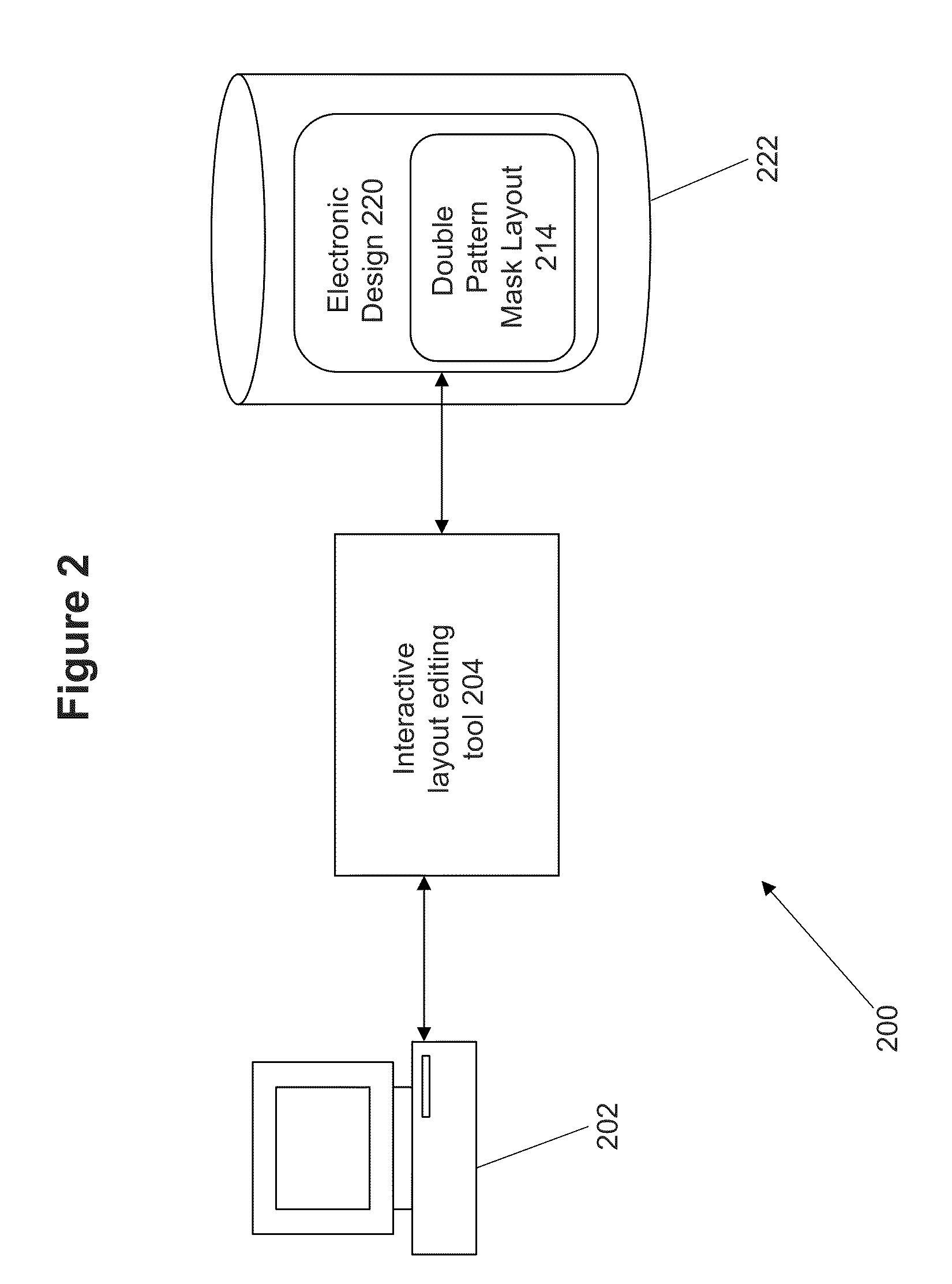

Method, system, and program product for interactive checking for double pattern lithography violations

ActiveUS20110219341A1CAD circuit designOriginals for photomechanical treatmentLithographic artistElectronic design

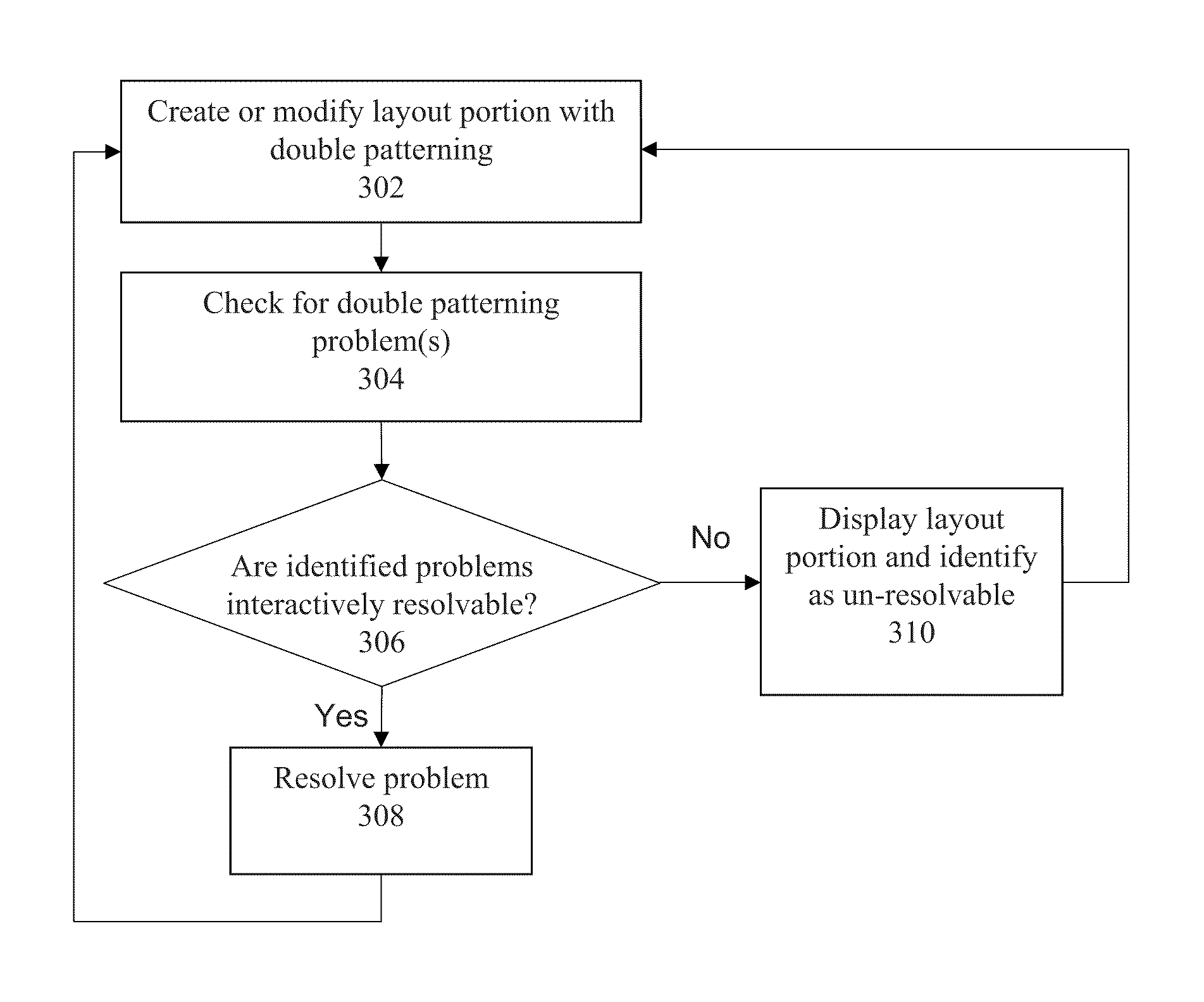

Disclosed are a method, apparatus, and computer program product for performing interactive layout editing to address double patterning approaches to implement lithography of electronic designs. A spatial query is performed around the shape(s) being created during editing with the distance of allowed spacing in a single mask. If a design error is encountered, corrective editing may occur to correct the error. Checking may occur to make sure that the error detection and corrective actions can be performed interactively.

Owner:CADENCE DESIGN SYST INC

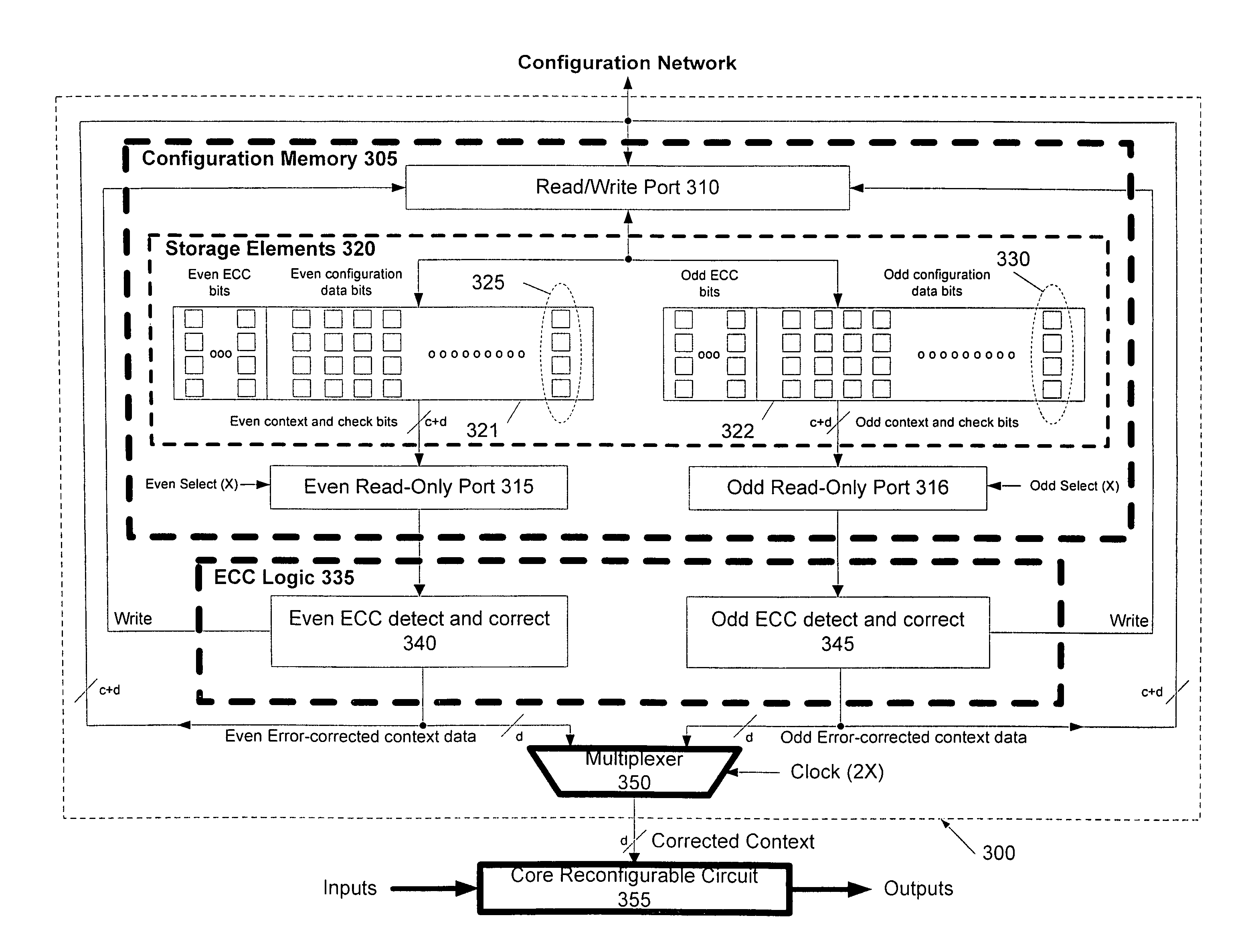

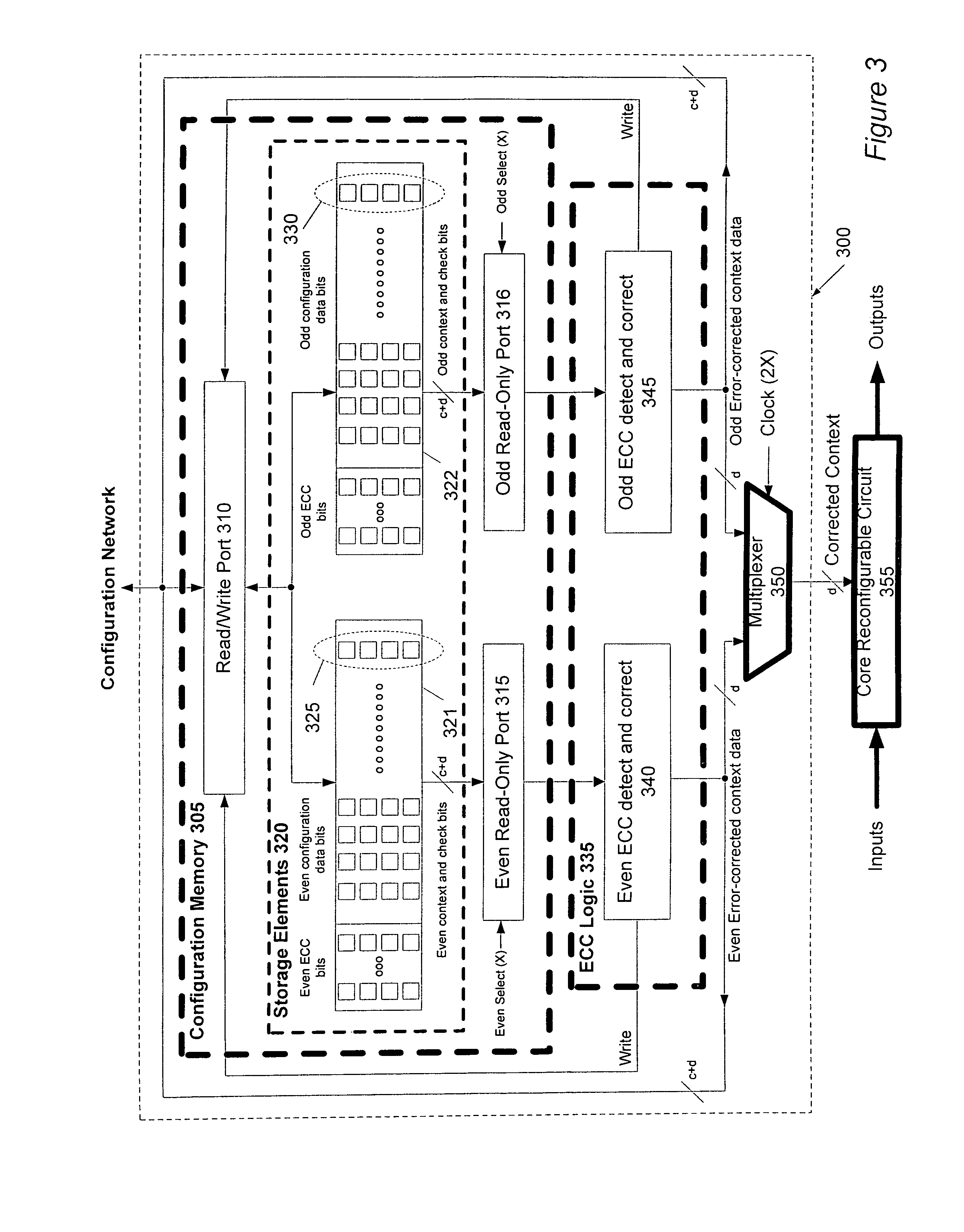

Configurable IC with error detection and correction circuitry

A configurable integrated circuit (IC) performs error detection and correction on configuration data. The IC includes a configuration memory for storing configuration data, an error detection circuitry for detecting an error and a circuit that outputs from the IC an uncorrectable error signal indicating the detection of an error. The configurable IC has a circuit inside of the IC that causes the IC to reset when the error circuitry detects an uncorrectable error. In another embodiment, the circuit that causes the IC to reset is located outside of the IC.

Owner:ALTERA CORP

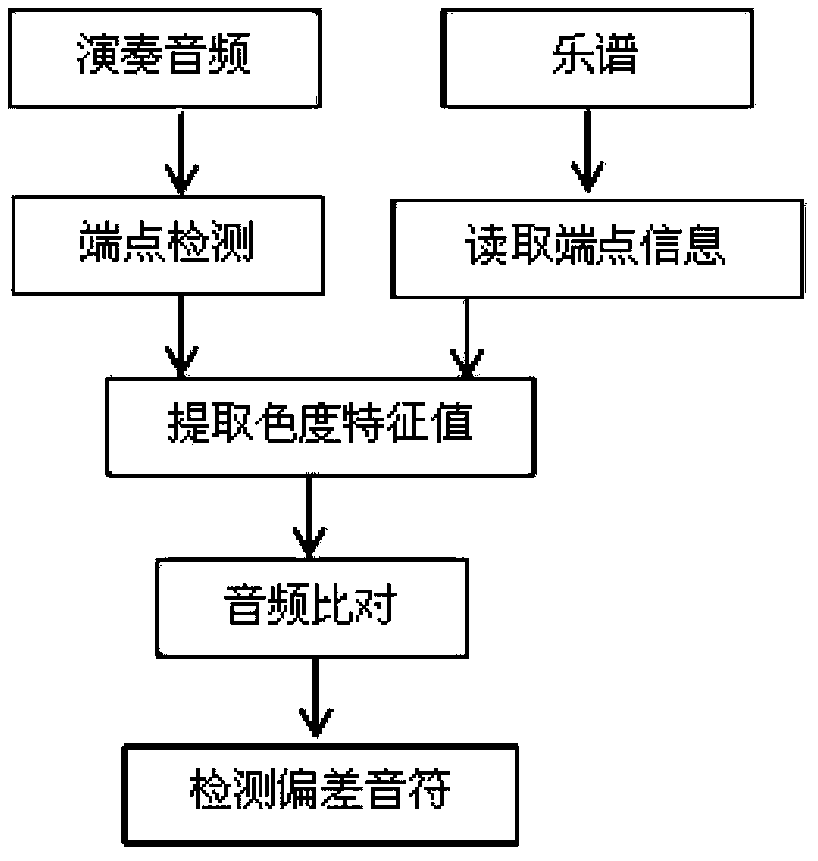

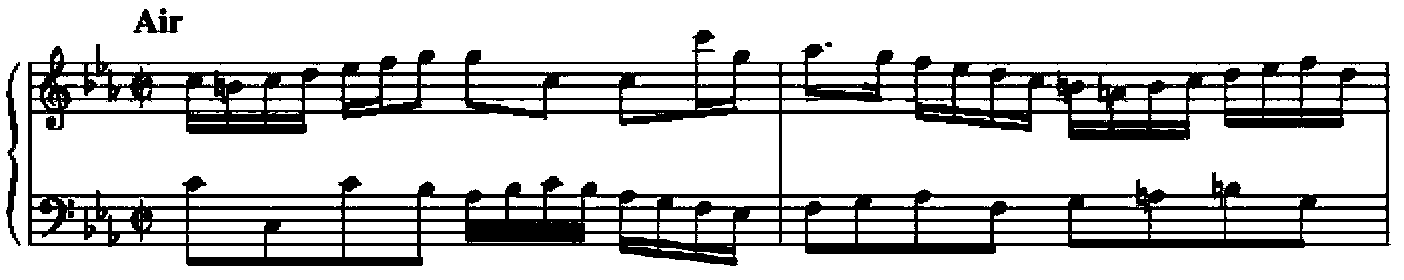

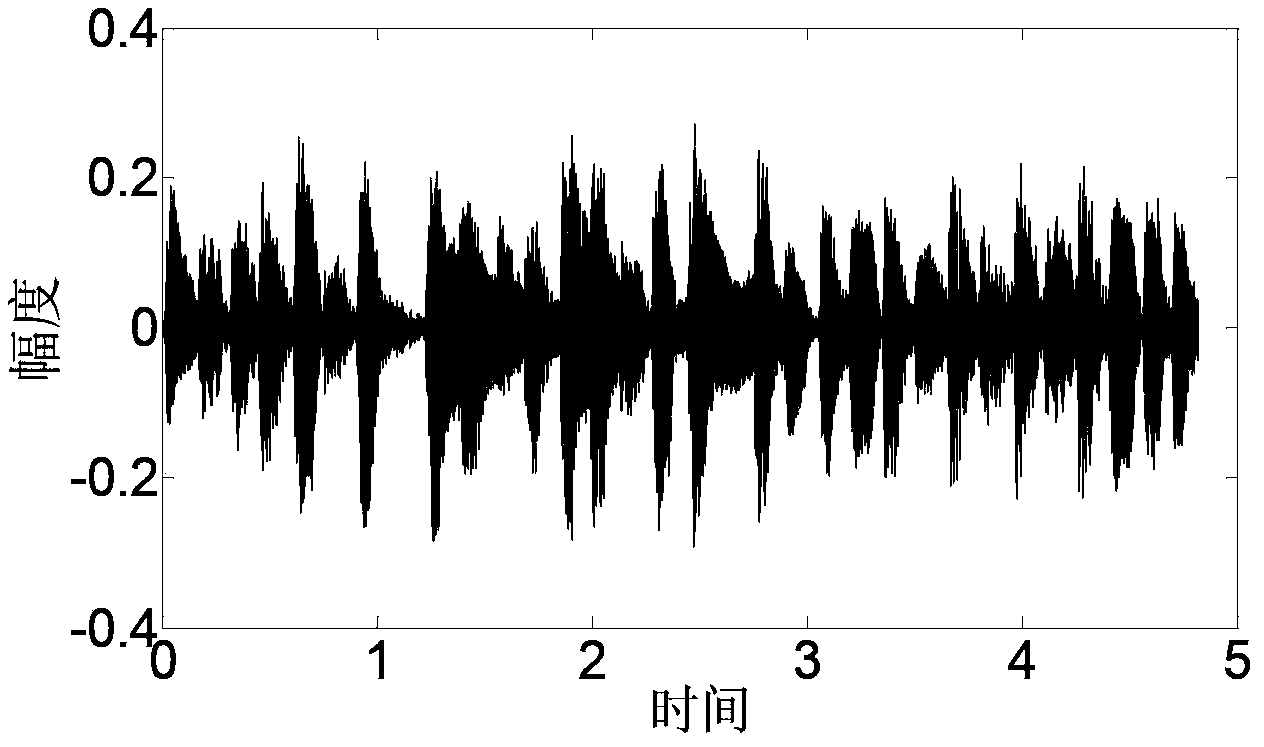

Audio music-score comparison method with error detection function

ActiveCN103354092AHigh precisionImprove execution efficiencyElectrophonic musical instrumentsSpeech analysisTemporal informationStart time

The invention discloses an audio music-score comparison method with an error detection function. The audio music-score comparison method comprises extracting starting time information of every note in a MIDI file, converting the MIDI file to an audio WAV file, carrying out endpoint detection to performance audio frequency P in order to determine starting time of every single-tone or chord, extracting eigenvalues of music score audio frequency S and the performance audio frequency P to obtain a 12-dimension chrominance vector of every single-tone or chord, calculating Euclidean distance matrices of the characteristic vectors of the performance audio frequency P and the music score audio frequency S, comparing the two matrices of the eigenvalues, utilizing a DTW algorithm and finally realizing an aligning function of the performance audio frequency and the music score audio frequency, so that the comparison method can detect whether conditions of redundant playing, missing playing and wrong playing appear in the performance audio frequency. According to the audio music-score comparison method provided by the invention, on-site music performance can be listened to by a computer, positions of performance notes in music score are finally tracked and determined, aligning time is relatively accurate without affecting by beat change and the audio music-score comparison method with the error detection function can detect whether error notes appear in the performance audio frequency.

Owner:天津画国人动漫创意有限公司

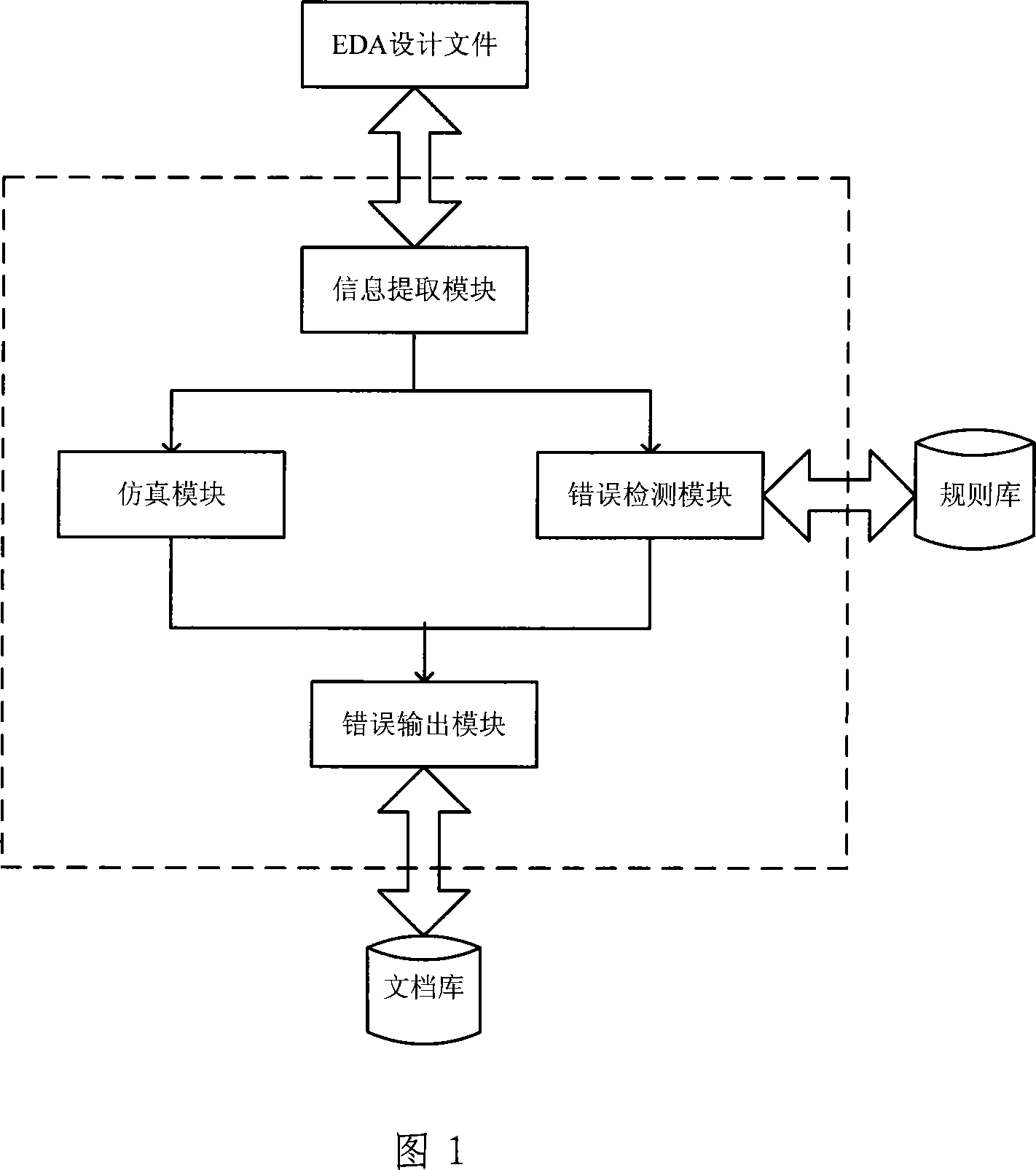

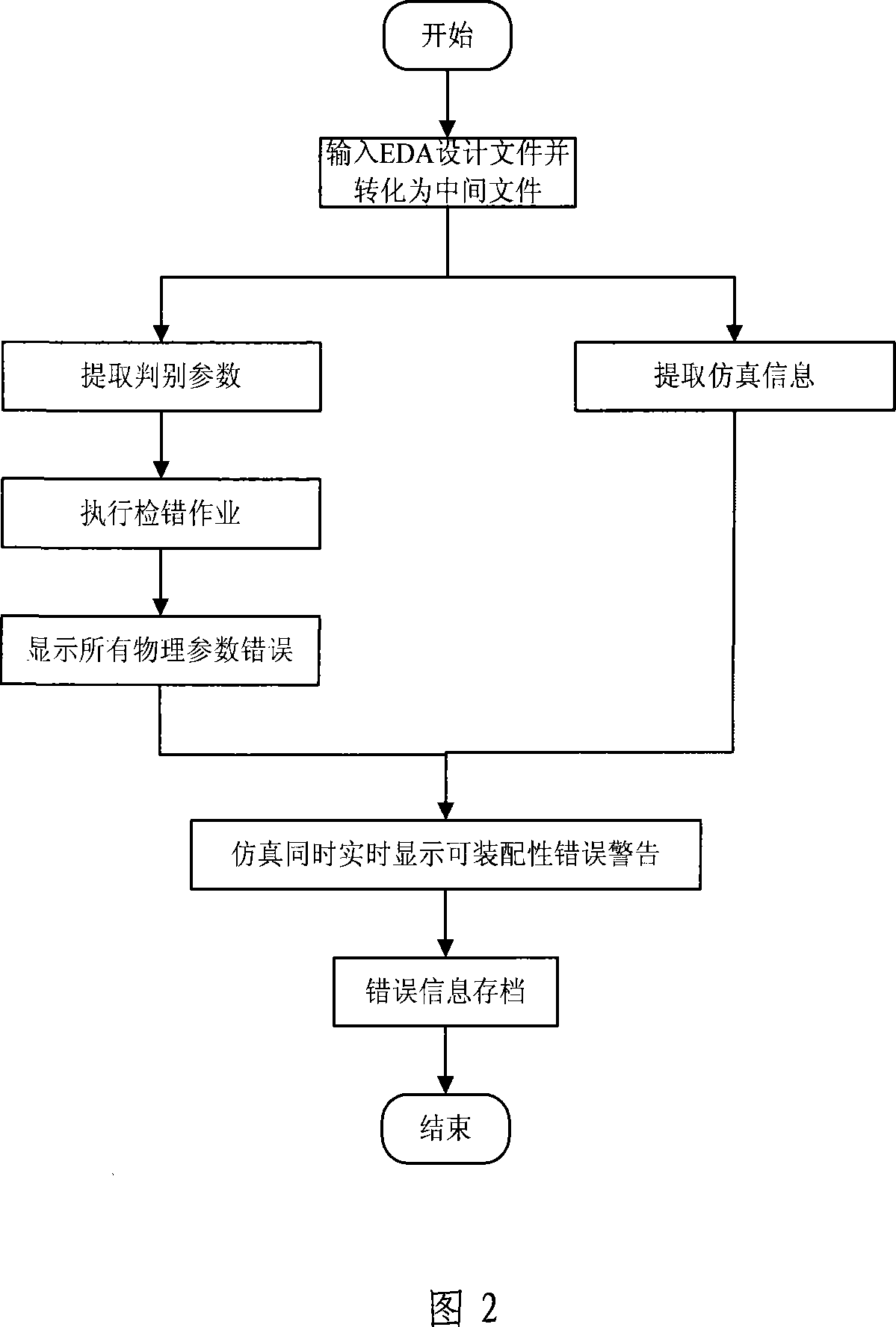

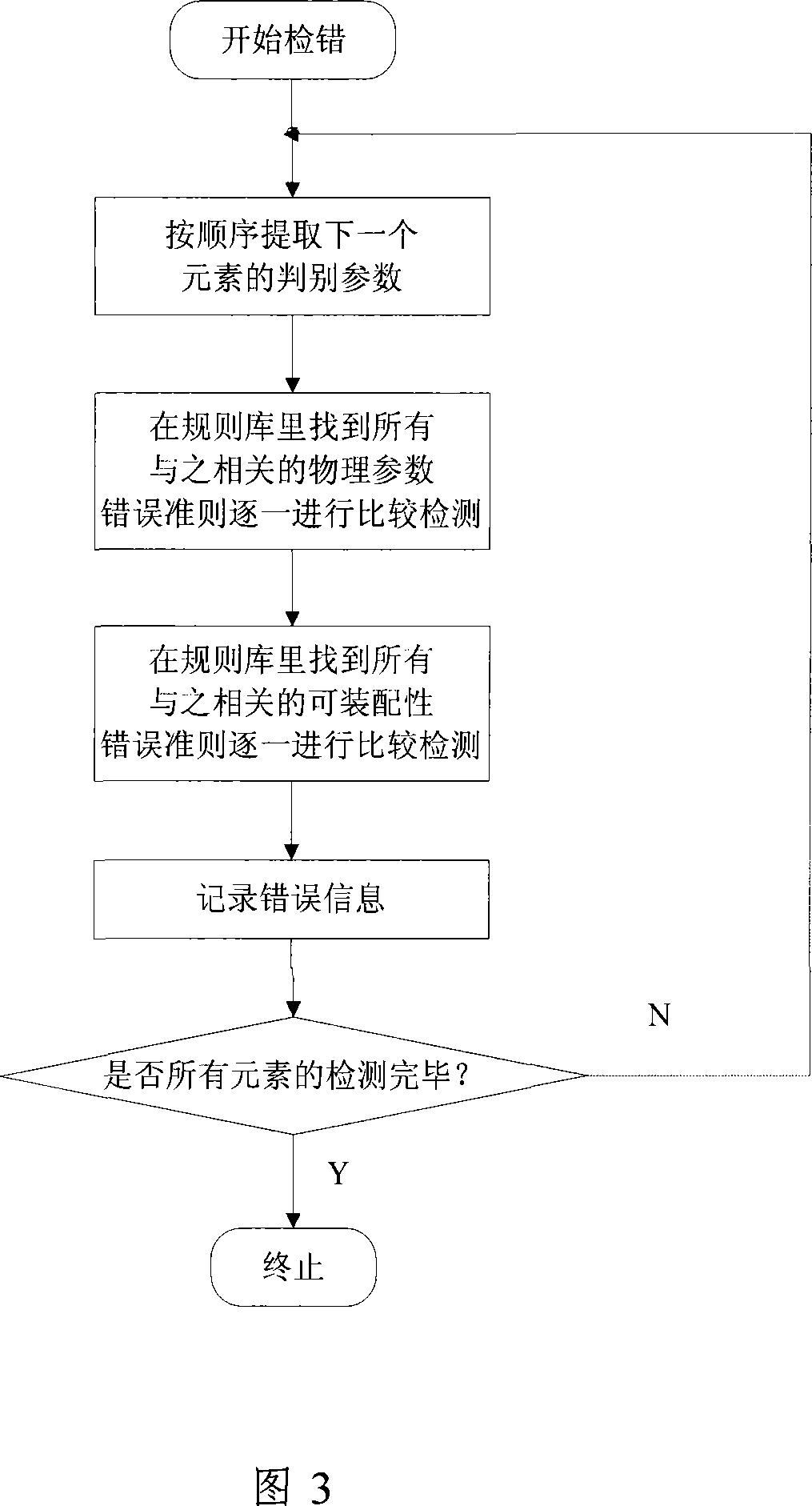

PCB emulation system have error detection function and realization method thereof

InactiveCN101178750ASave time and costSave production costSpecial data processing applicationsError detection and correctionInformation extraction

Owner:来新泉

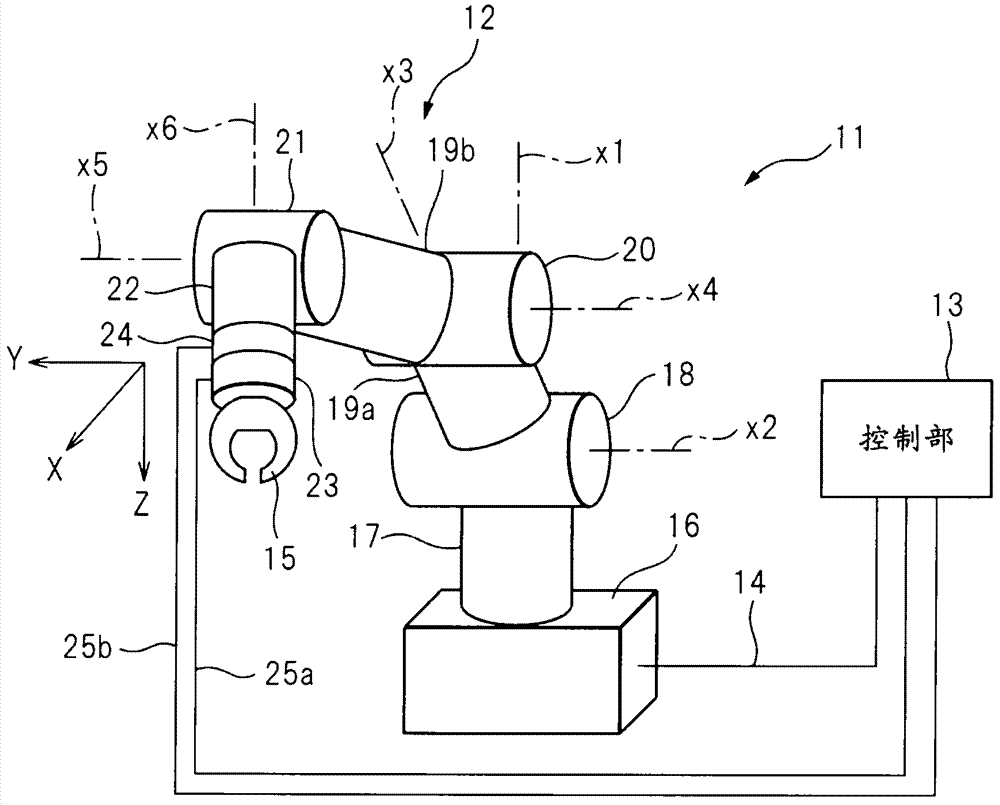

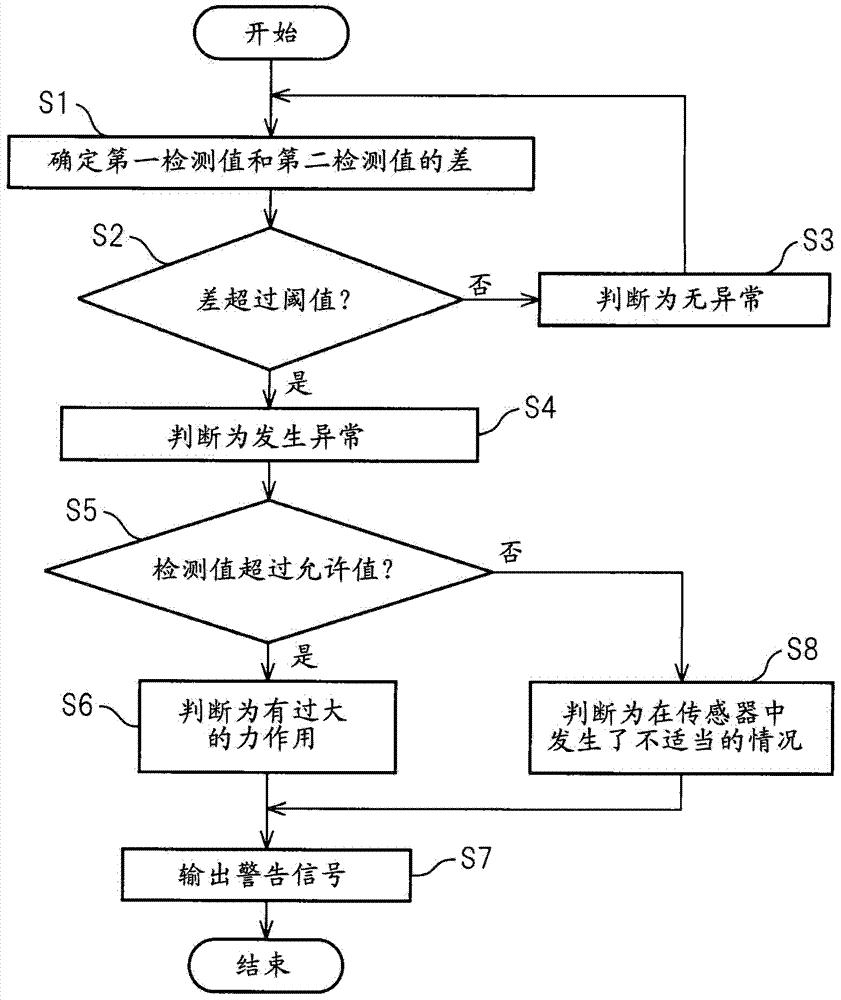

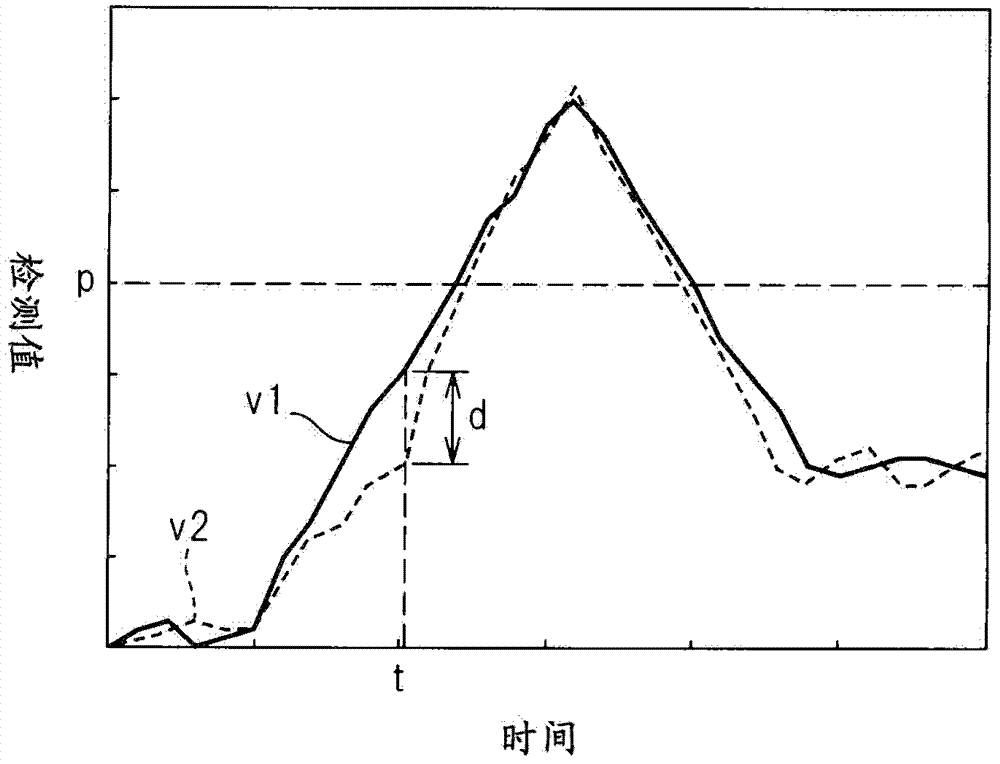

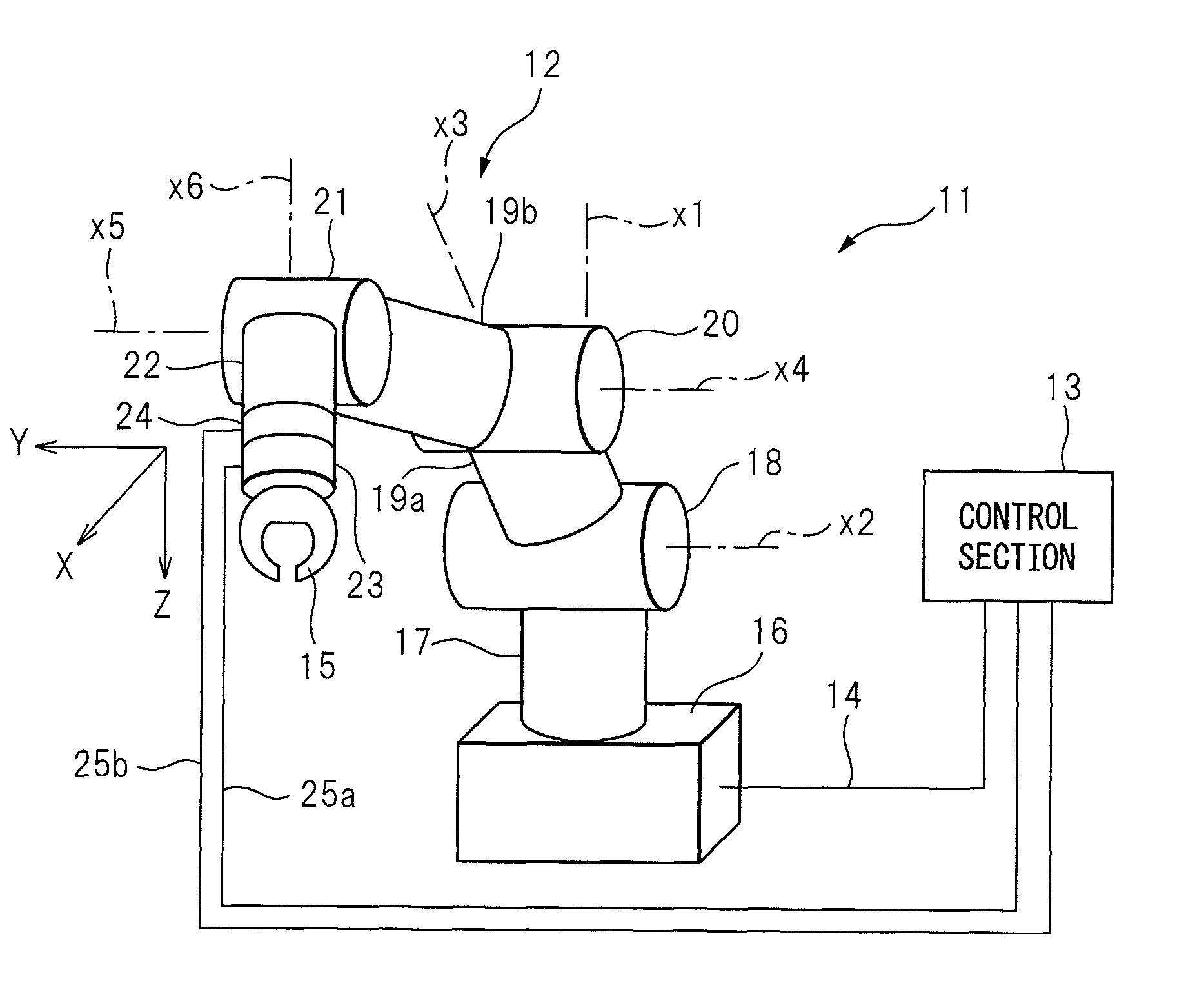

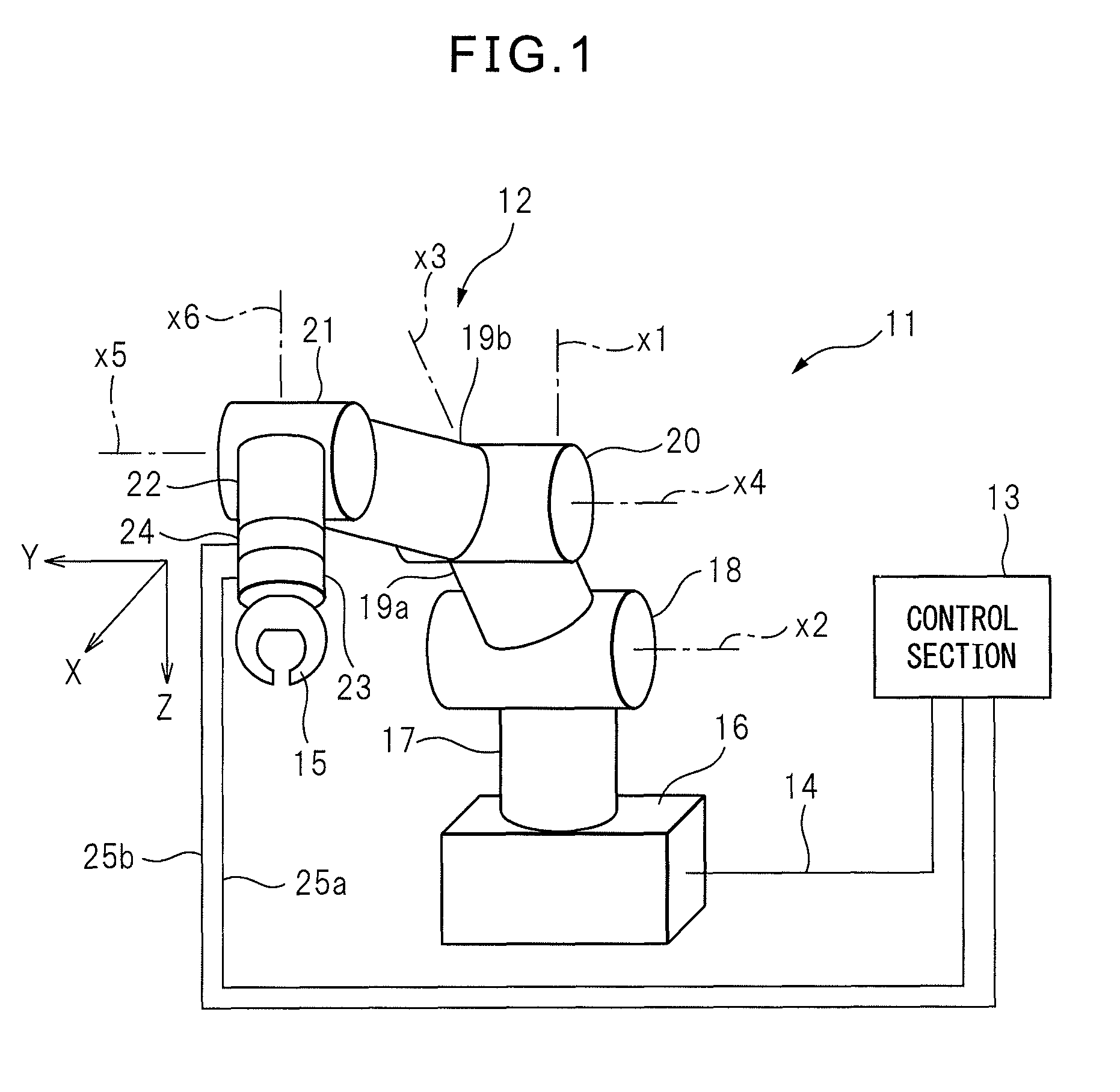

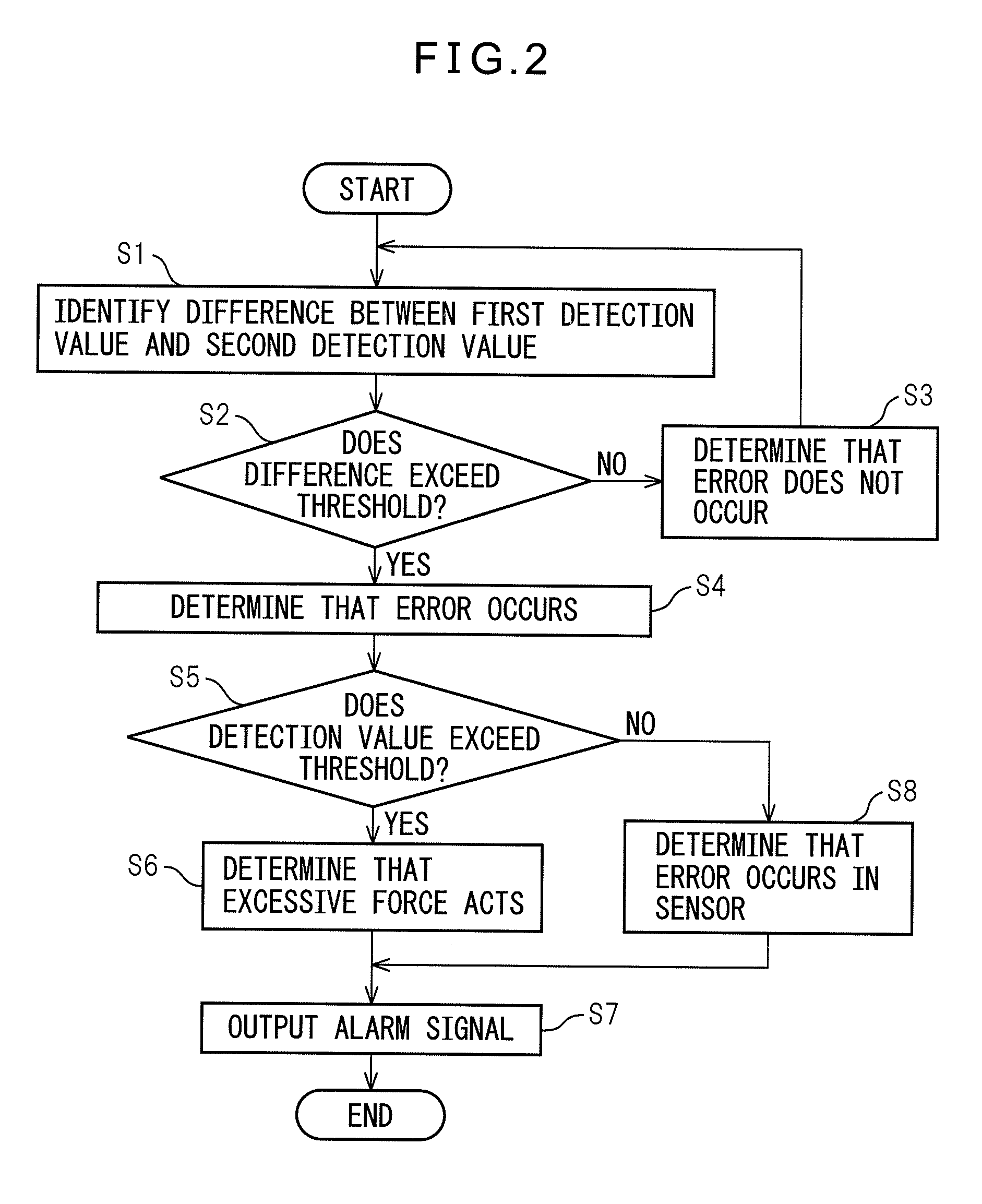

Robot system having error detection function of robot and control method thereof

When an error occurs in robot system, a difference between first and second detection values of two sensors or first and second sensors occurs due to differences in position and responsibility. When this difference exceeds a predetermined threshold, control section detects that a difference has occurred in robot system. The first and second detection values of two sensors or first and second sensors are compared, and therefore, reliability of the detection values can be secured. Further, the abnormal state can be determined through the difference between the first and second detection values, and therefore, errors resulting from problems such as variations in gears and speed reducers due to temperature changes of the operational state and disposition environment of the robot can be avoided. The threshold value of the difference of the detection value can be reduced. The robot can detect the difference with high sensitivity.

Owner:FANUC LTD

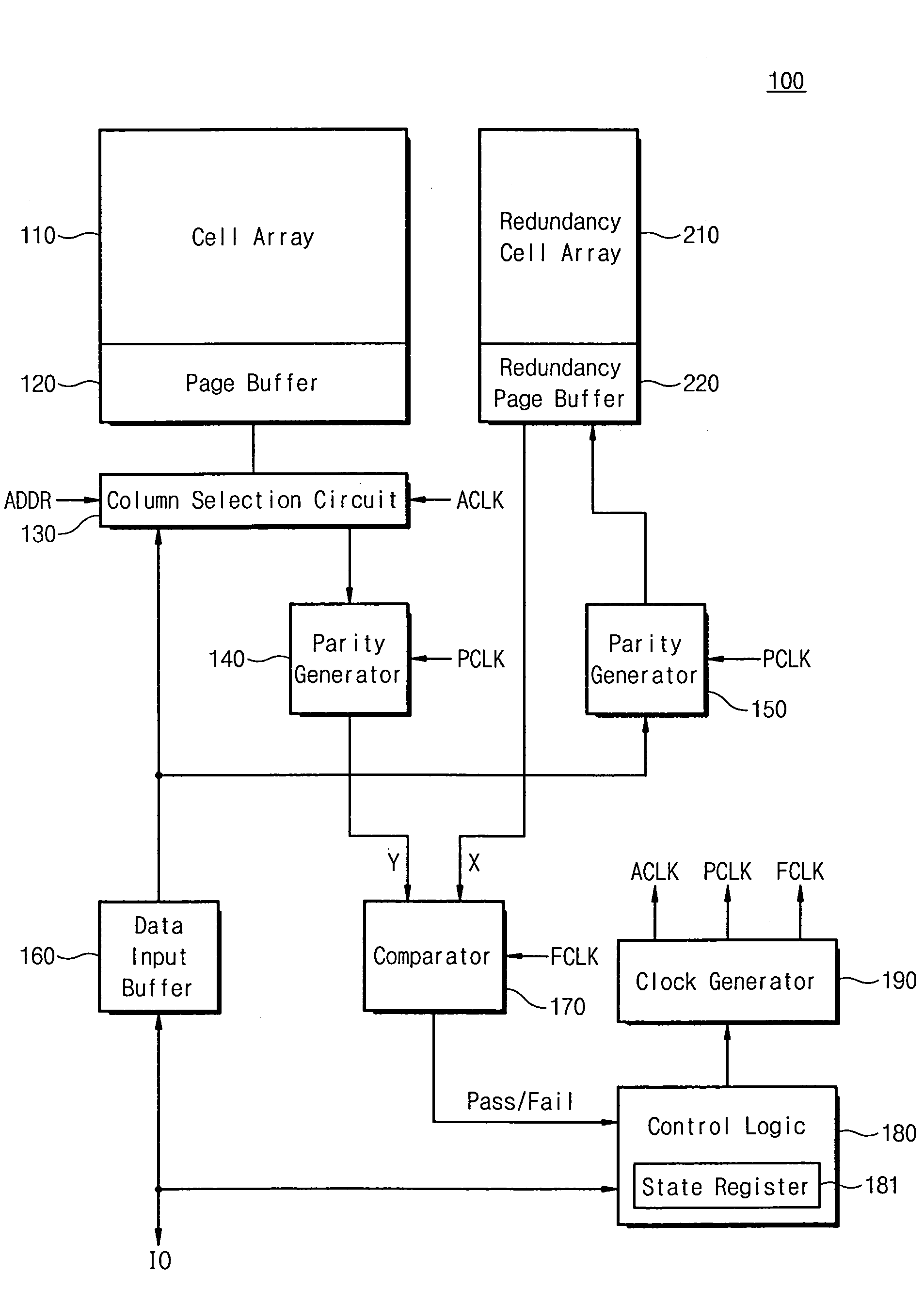

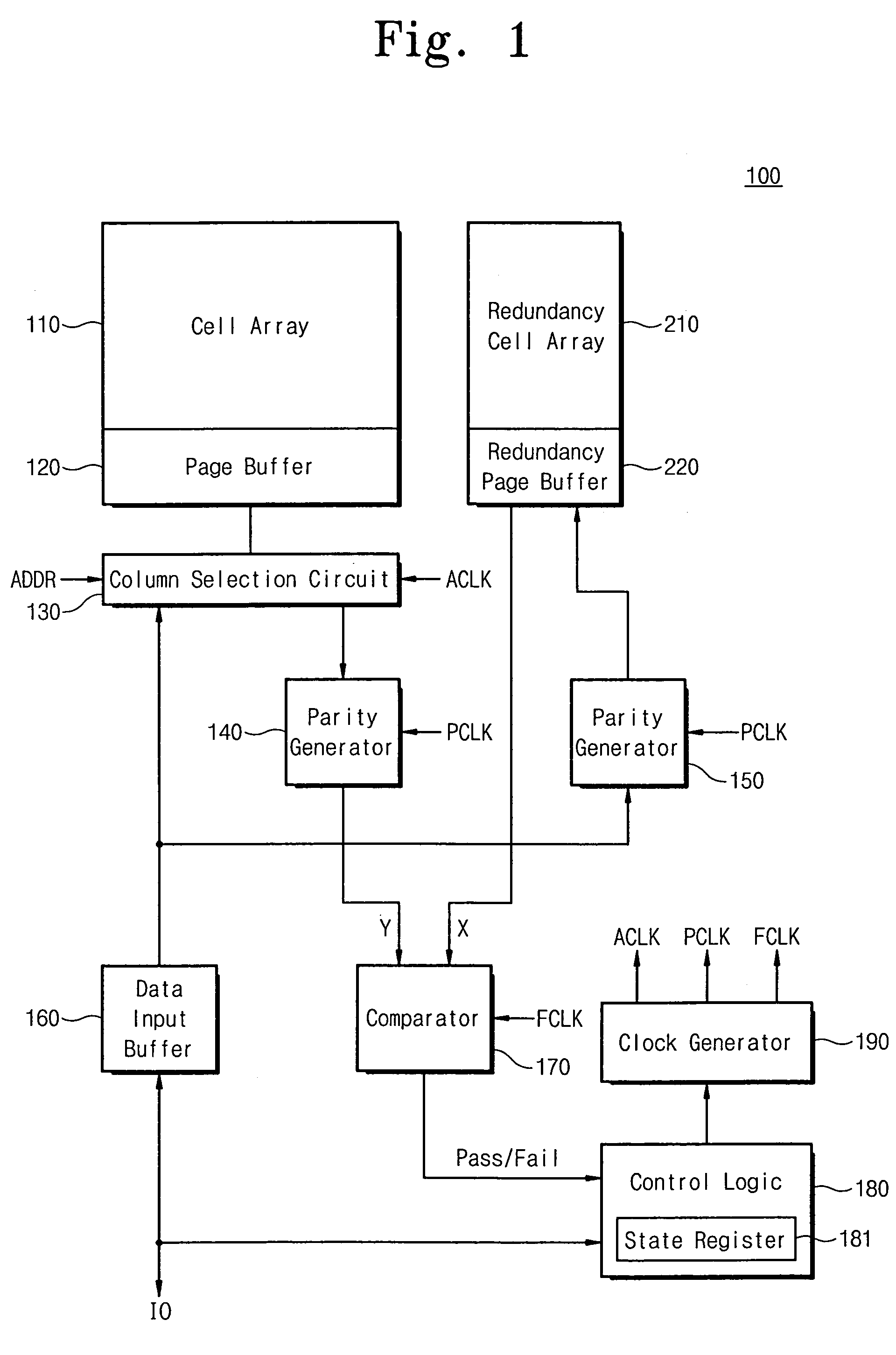

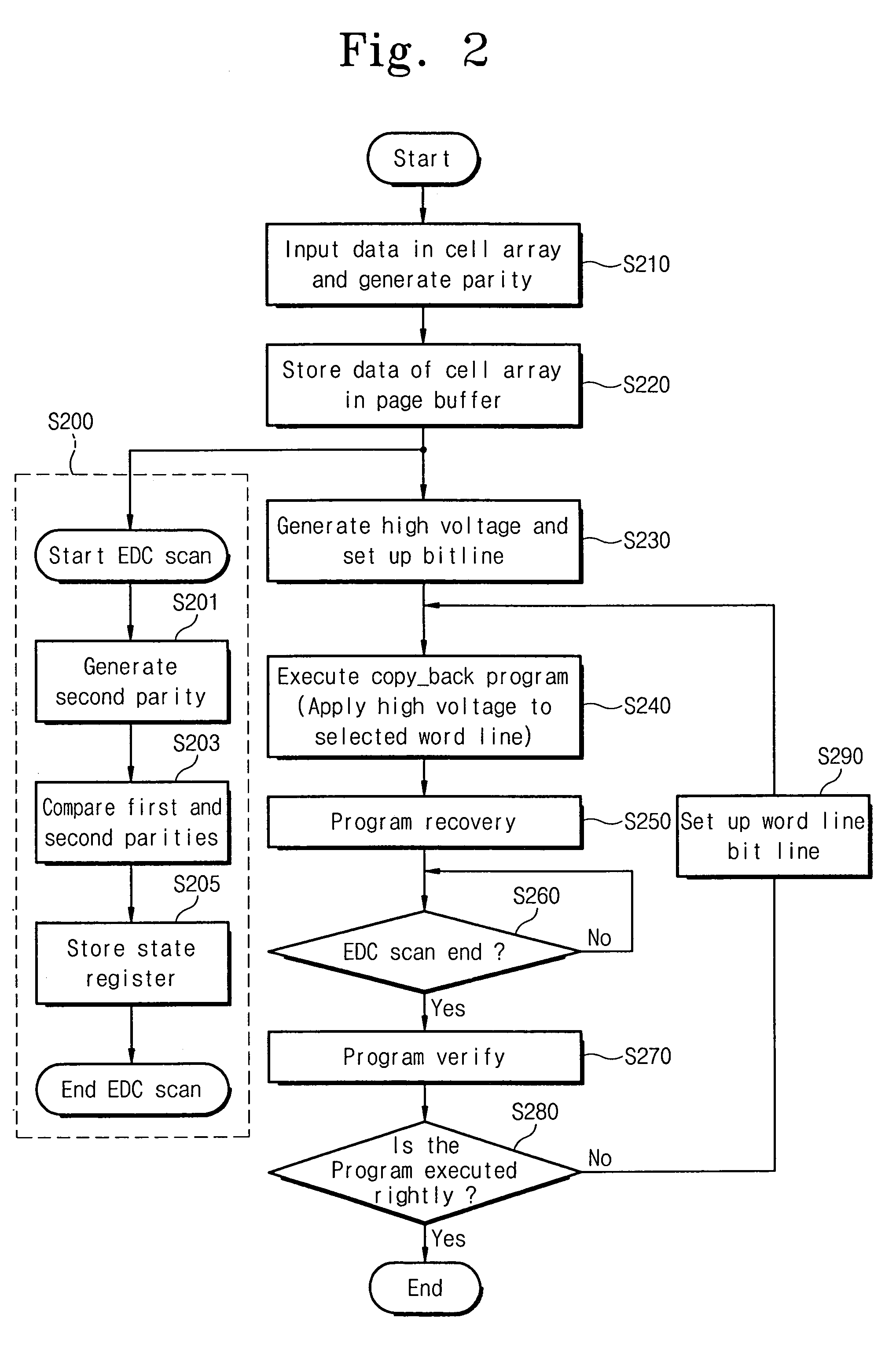

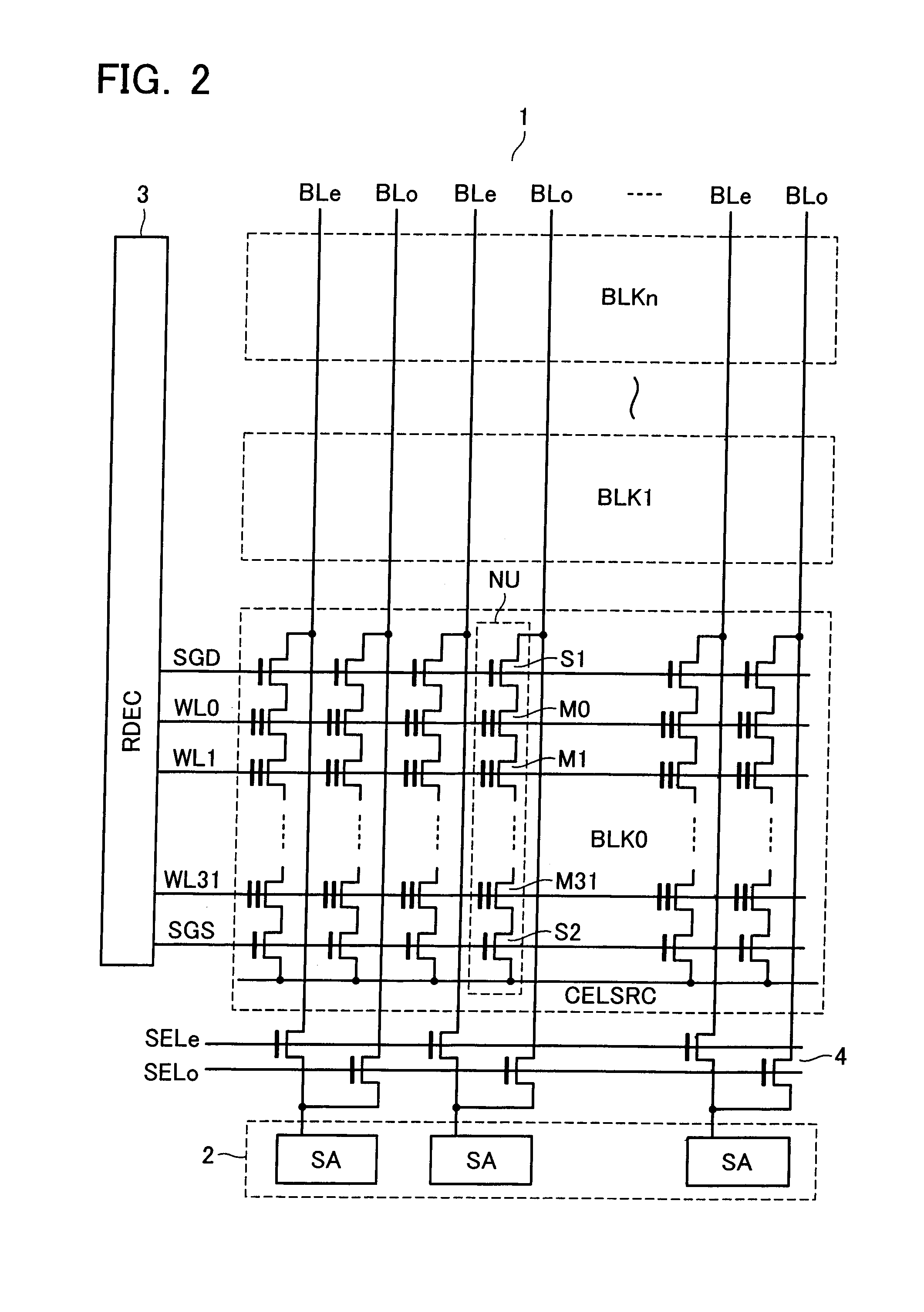

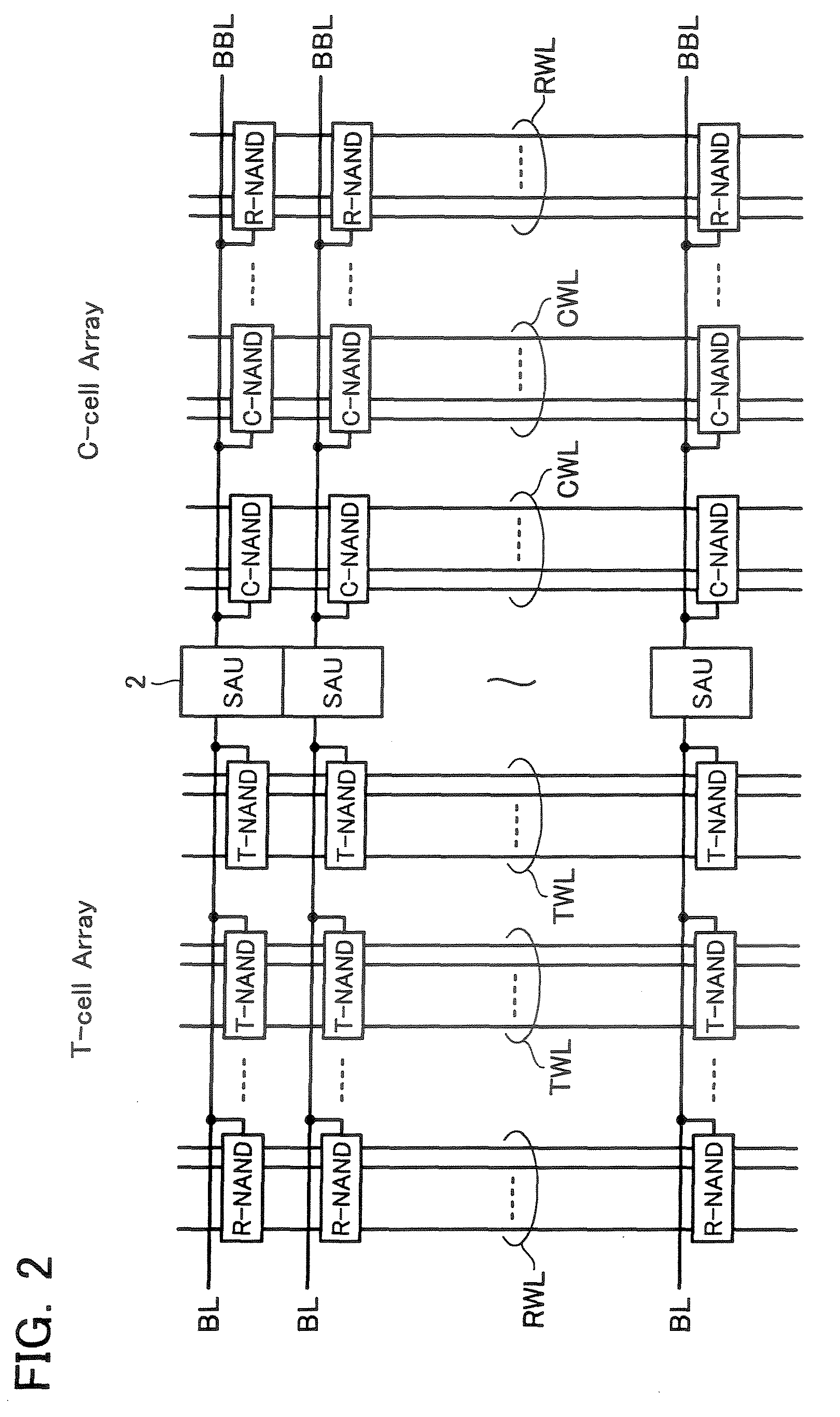

NAND flash memory device and copyback program method for same

A NAND flash memory device according to some embodiments includes a cell array, a page buffer configured to copyback read the data in the cell array, and an error detector for detecting errors that occur during the copyback reading and for generating a detection signal. Detecting errors is performed concurrently with a copyback program operation and completes before finishing a copyback program verify operation. The data stored in the page buffer may be copyback programmed when the detection signal is a pass signal. The copyback operation may end without executing the copyback program operation when the detection signal is a fail signal. Since the copyback program operation and the error detection operation are performed concurrently, the errors occurring during the copyback operation may be detected without additional time delay. Additionally, occurrence of two-bit error may be prevented because the copyback program is not executed when the fail signal is generated.

Owner:SAMSUNG ELECTRONICS CO LTD

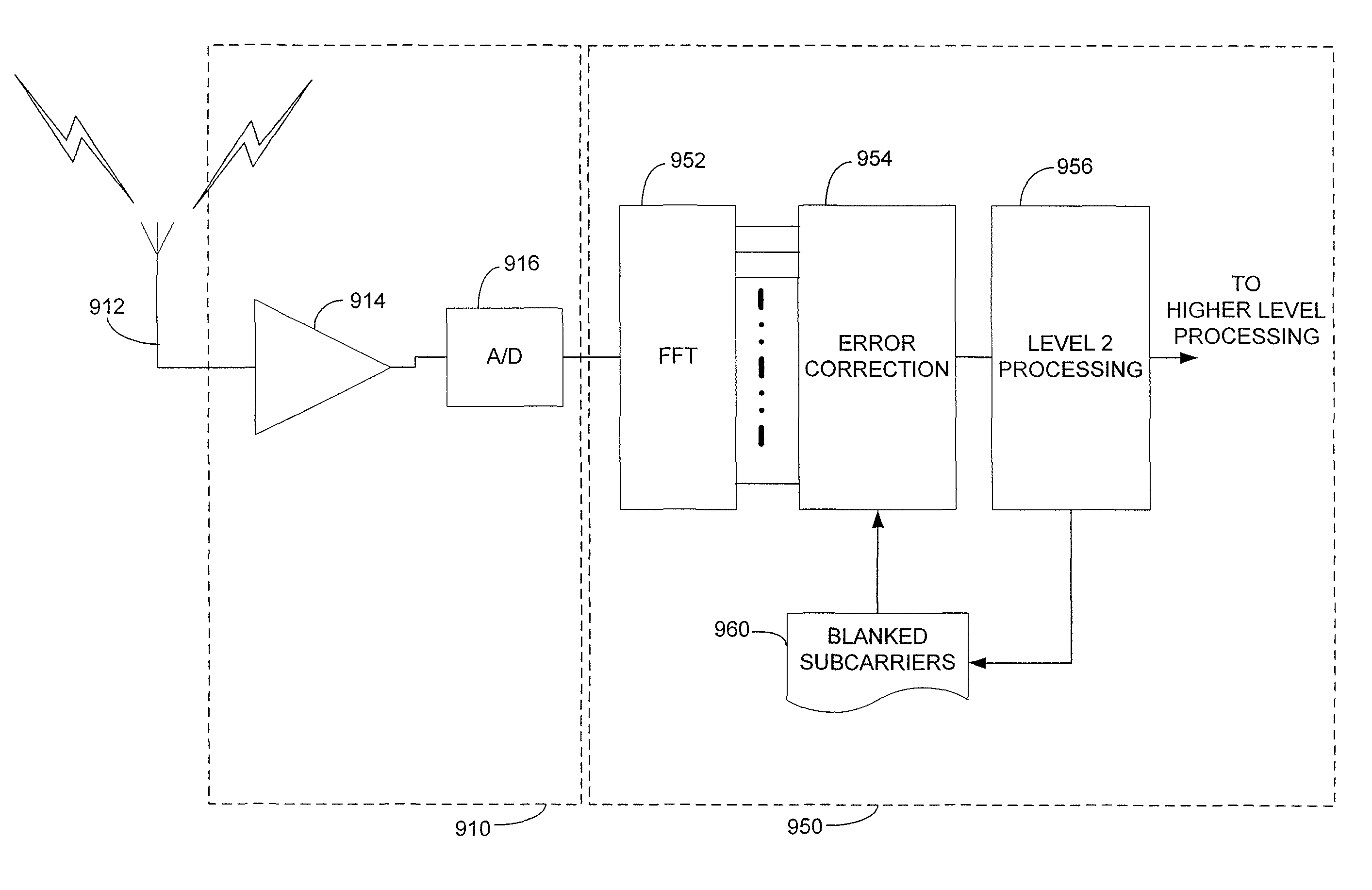

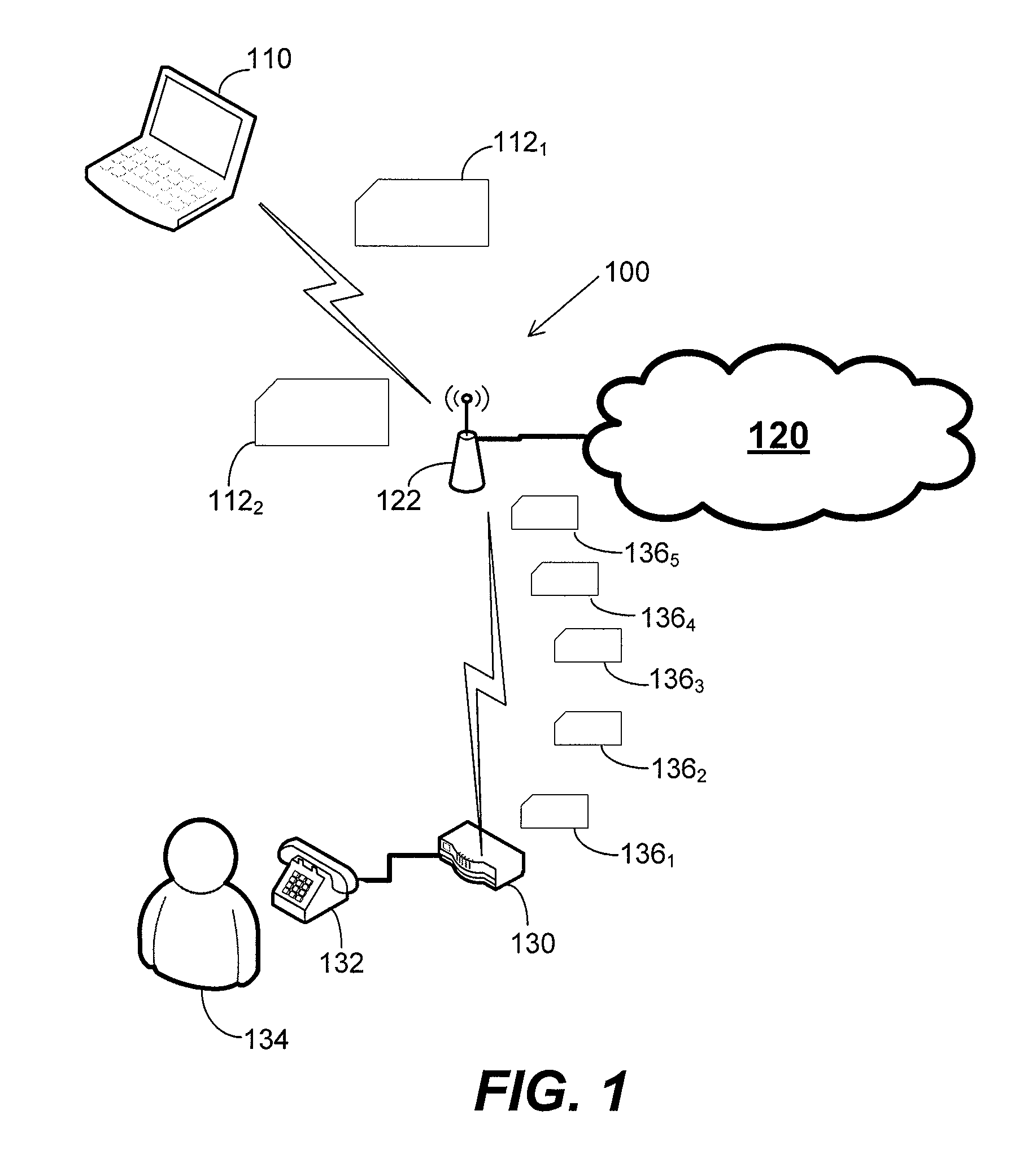

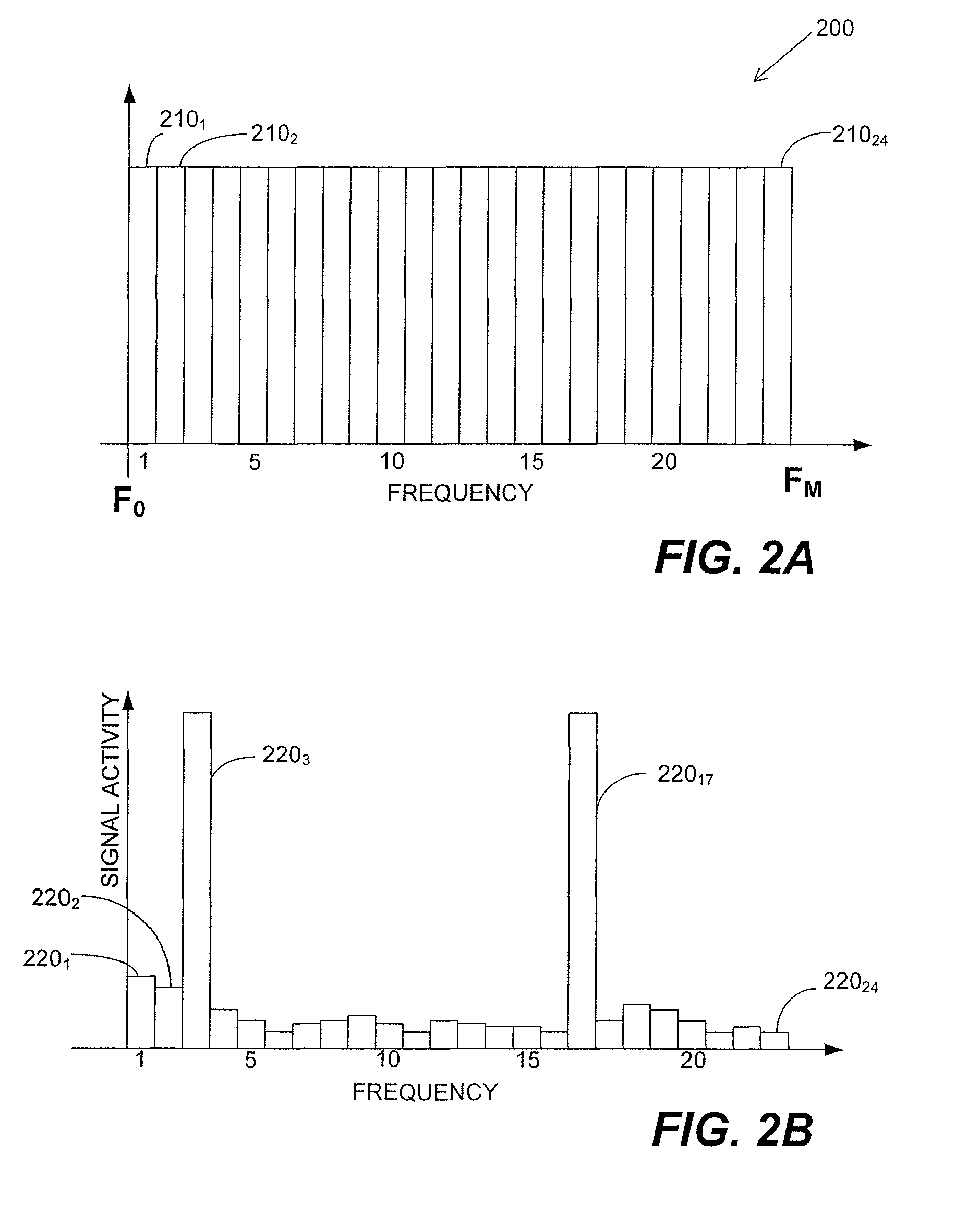

Orthogonal frequency division multiple access with carrier sense

ActiveUS8374130B2Spectral gaps assessmentTransmission path divisionCommunications systemCarrier signal

Owner:MICROSOFT TECH LICENSING LLC

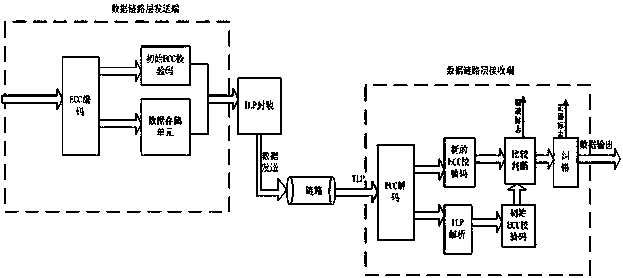

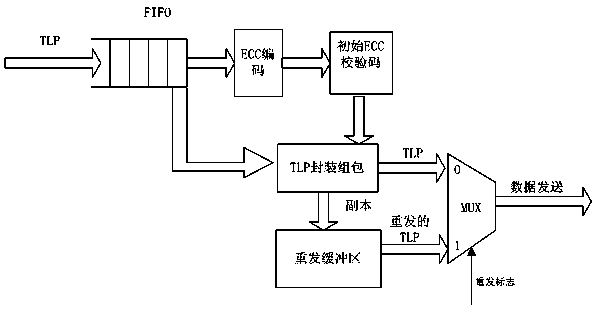

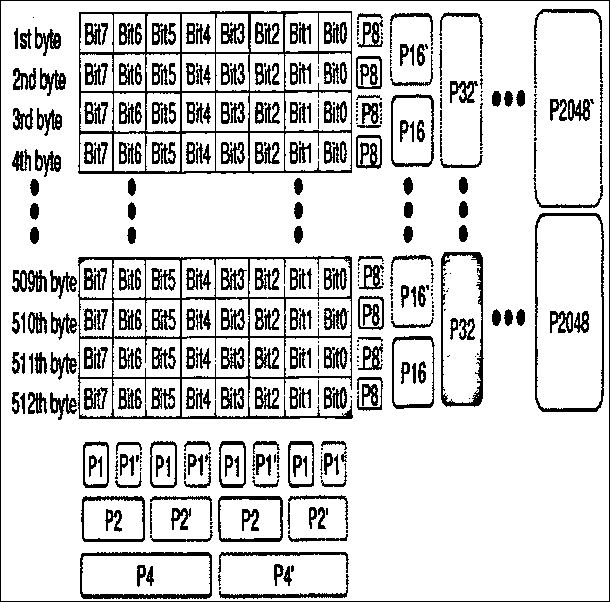

Method for high-performance fault tolerance of PCIE (Peripheral Component Interface Express) data link layer

ActiveCN103533045AImprove fault toleranceImplement error correctionData switching networksElectric digital data processingError checkingFault tolerance

The invention relates to a method for high-performance fault tolerance of a PCIE (Peripheral Component Interface Express) data link layer. On the basis of original CRC (Cyclic Redundancy Check) error checking of PCIE, error checking and correcting (ECC) codes are added to realize real-time error correction and self-repair functions; the error can be corrected while the error is checked; the calculation speed is extremely high. An error packet which can be corrected is not required to be retransmitted, so that the error tolerance of the link is increased, meanwhile, the bandwidth and the time can be saved, and the link transmission efficiency is improved.

Owner:丁贤根

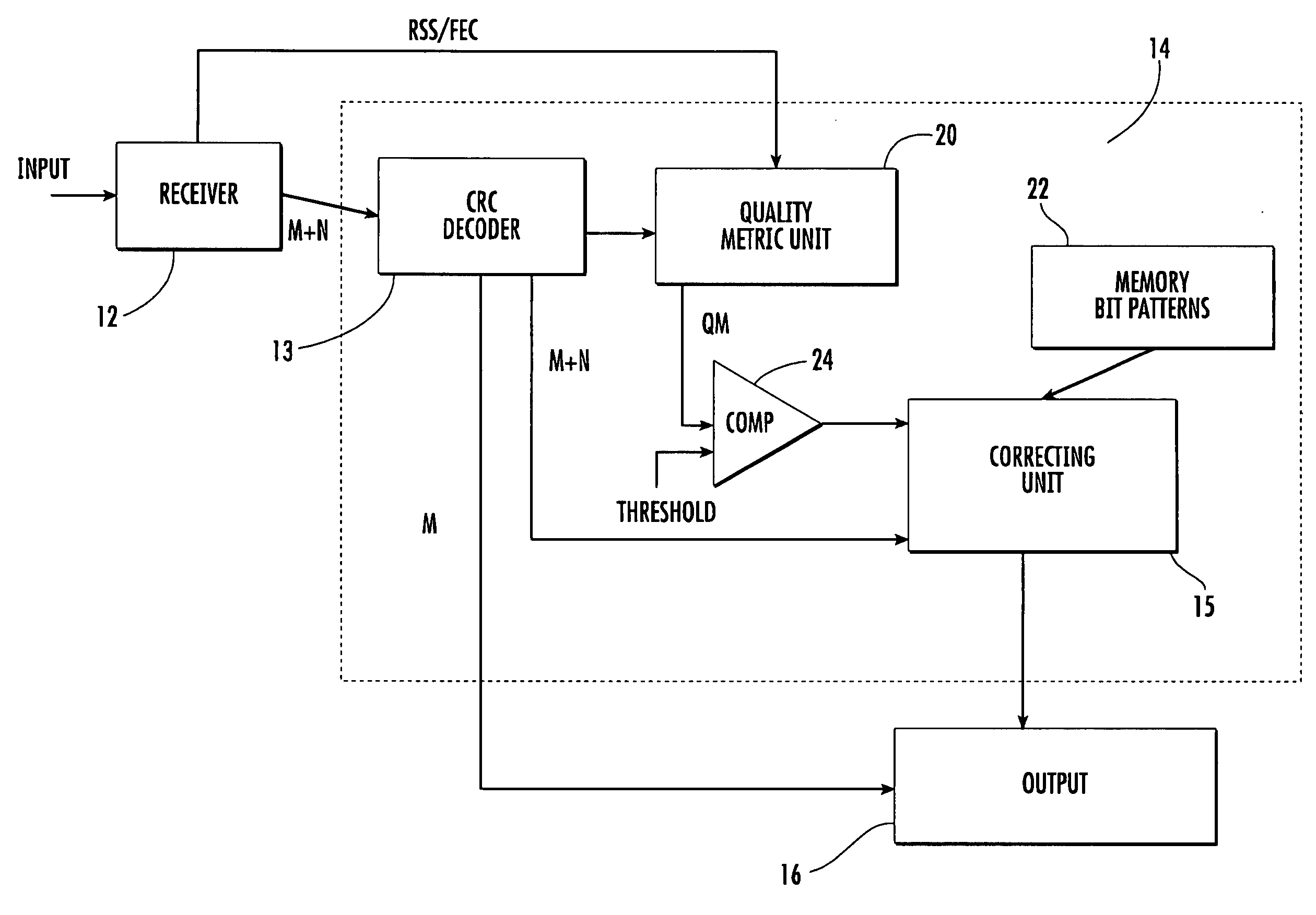

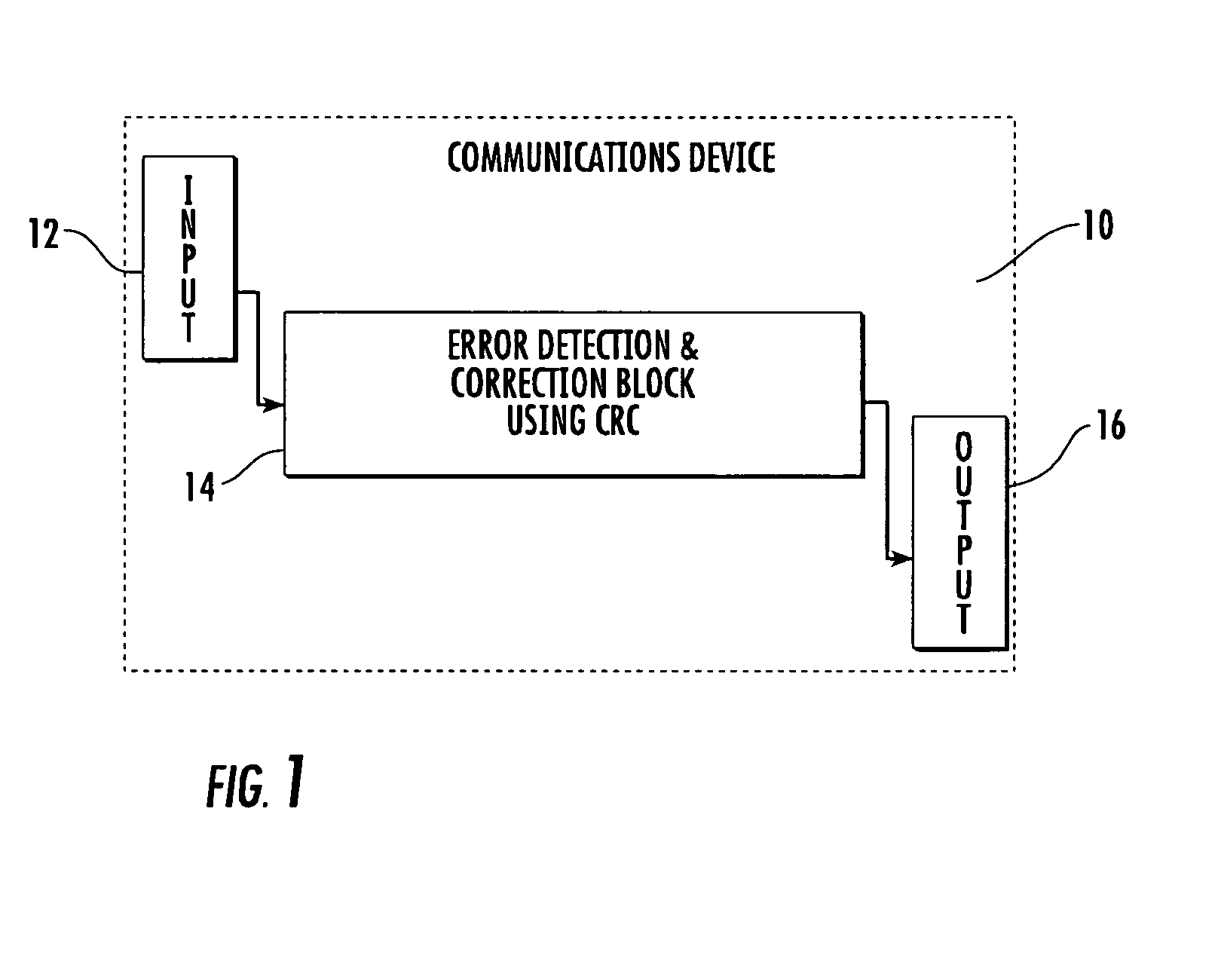

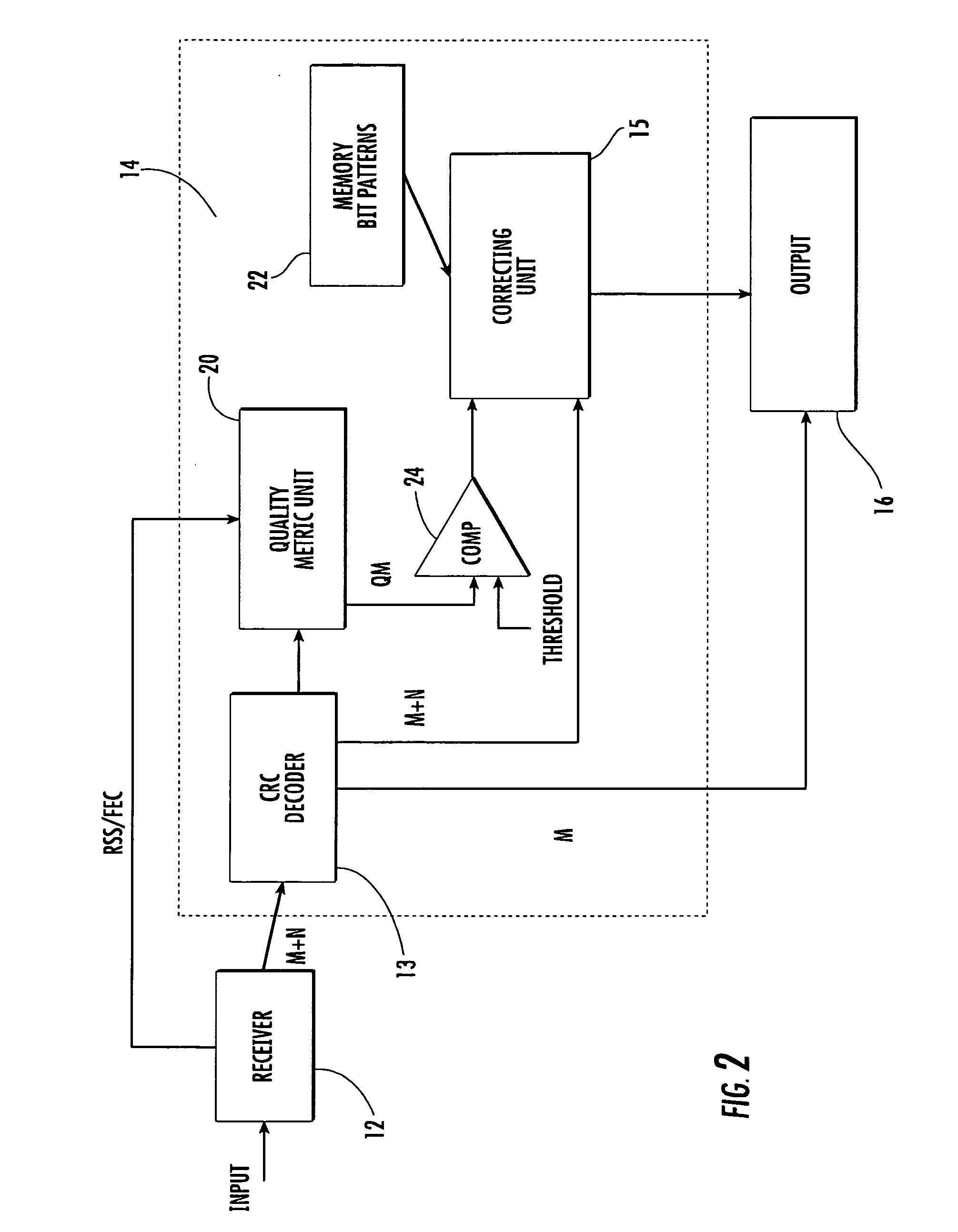

Cyclic redundancy check (CRC) based error correction method and device

InactiveUS20070192667A1Increase the number ofCompromising error detection capabilityOther decoding techniquesCode conversionComputer scienceCorrection method

The communication method includes the use of CRC codes for additional error correaction in addition to the error detection capability. The method is for error detection and correaction in a received message that includes N message bits and M Cyclic Redundancy Check (CRC) bits appended thereto. It is determined whether at least one bit error has occurred in the N message bits and M CRC bits of the received message based upon the M CRC bits, and when at least one bit error is determined, then K bits with a lowest quality metric are selected from the N message bits and M CRC bits. The bit error is corrected based upon possible bit error patterns and the selected K bits. Multiple bit errors may also be corrected.

Owner:HARRIS CORP

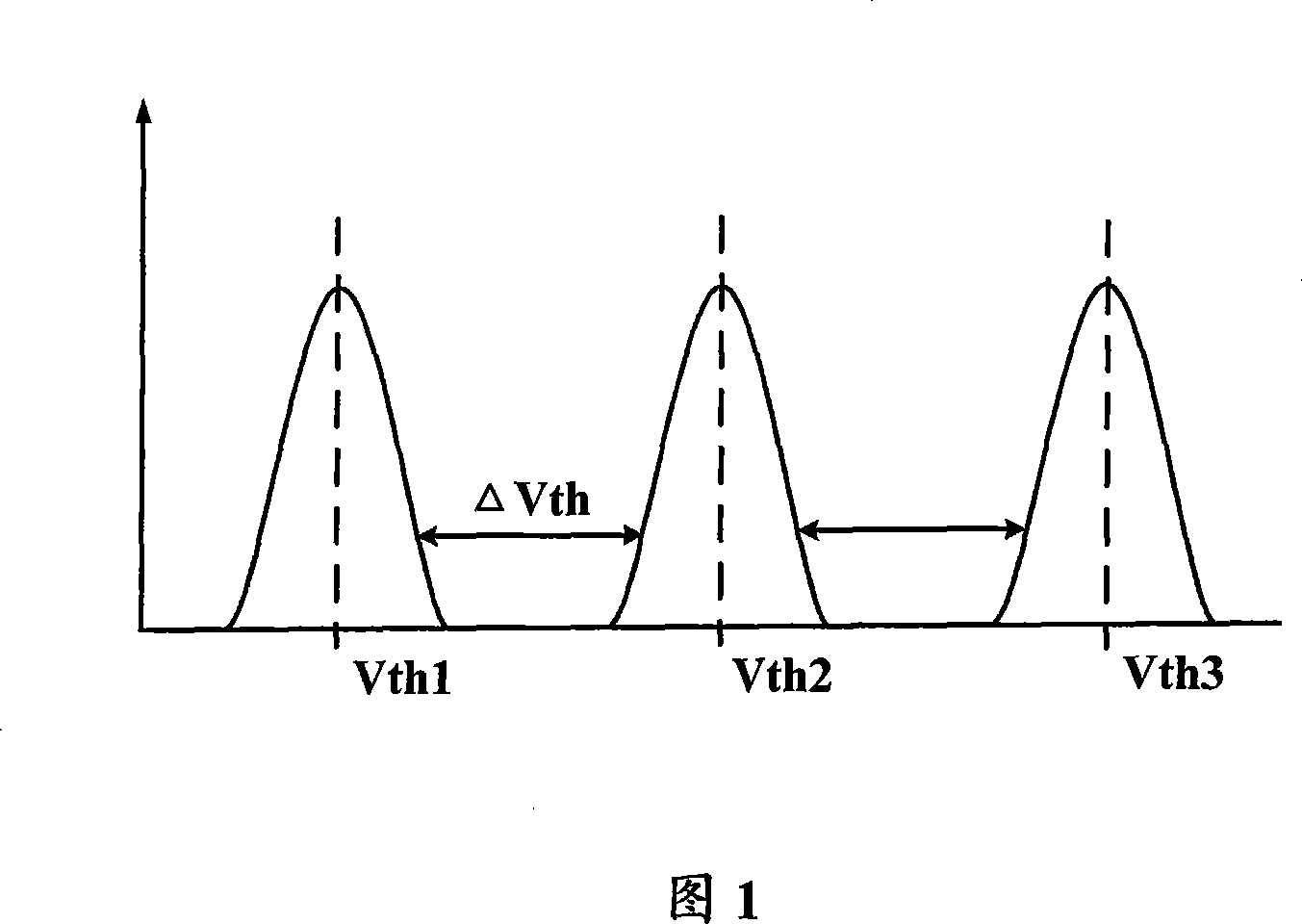

A multi-bit flash memory and its error detection and remedy method

InactiveCN101060015ASolve the problem of difficult signal recognitionGuaranteed reliabilityStatic storageError checkComputer module

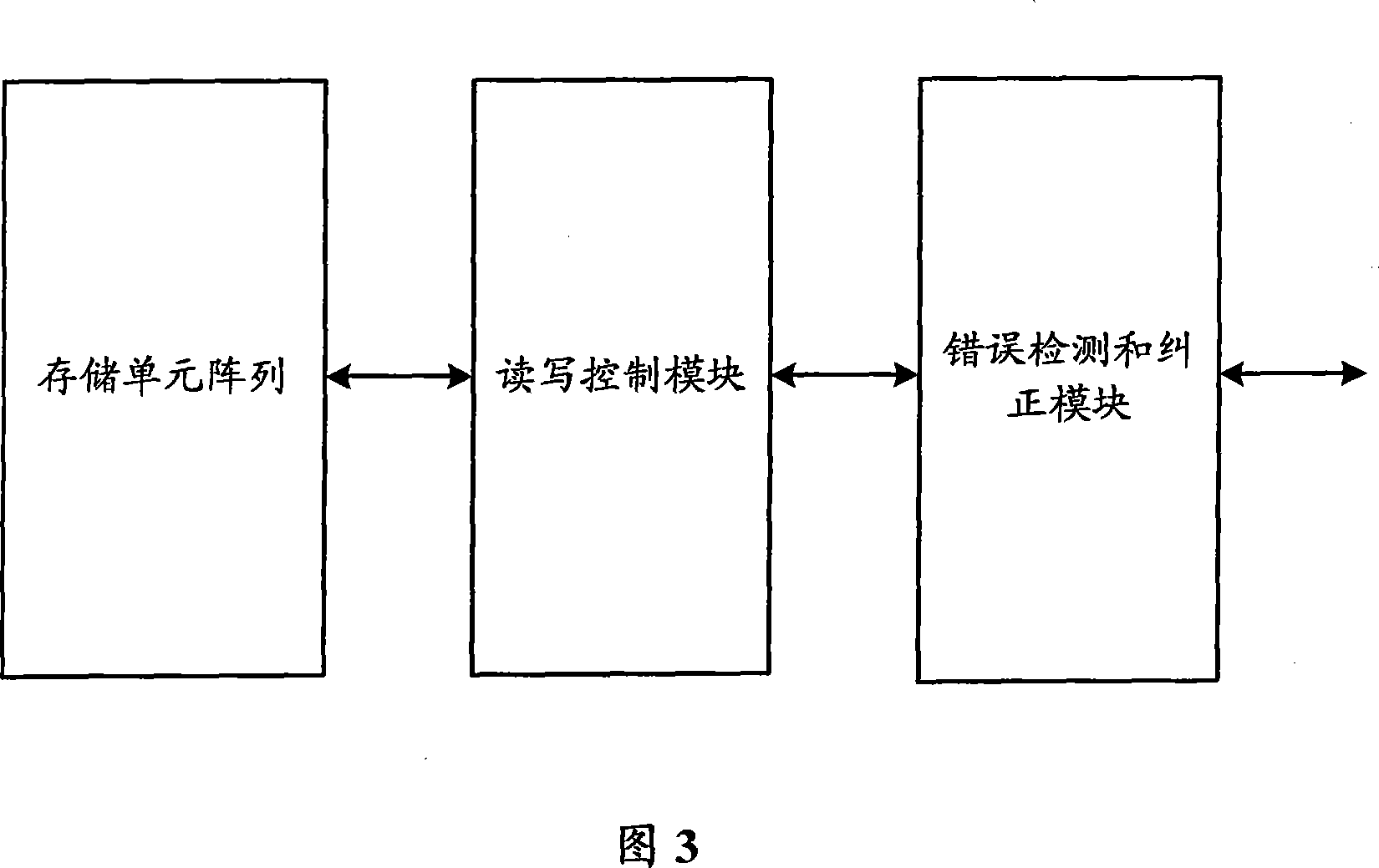

The invention provides a method for checking and correcting the error of a multi-bit flash and a relative multi-bit flash, wherein the multi-bit flash comprises a memory unit array composed of a plurality of memory units, a read / write control module and an error check and correct module with one-bit correct function. The memory unit array is used to store the first data and relative correct data, the nearby memory states of the memory unit are differential with one bit data, the error check and correct module can obtain the first data and relative correct data from the read / write control module, to use the correct data to correct and output the first data. The inventive method and device can recognize signal of multi-bit flash easily, with reliability of data stored in multi-bit flash, to improve density and yield of memory and save cost.

Owner:GIGADEVICE SEMICON (BEIJING) INC

Discrete multi-tone (DMT) system and method that communicates a data pump data stream between a general purpose CPU and a DSP via a buffering scheme

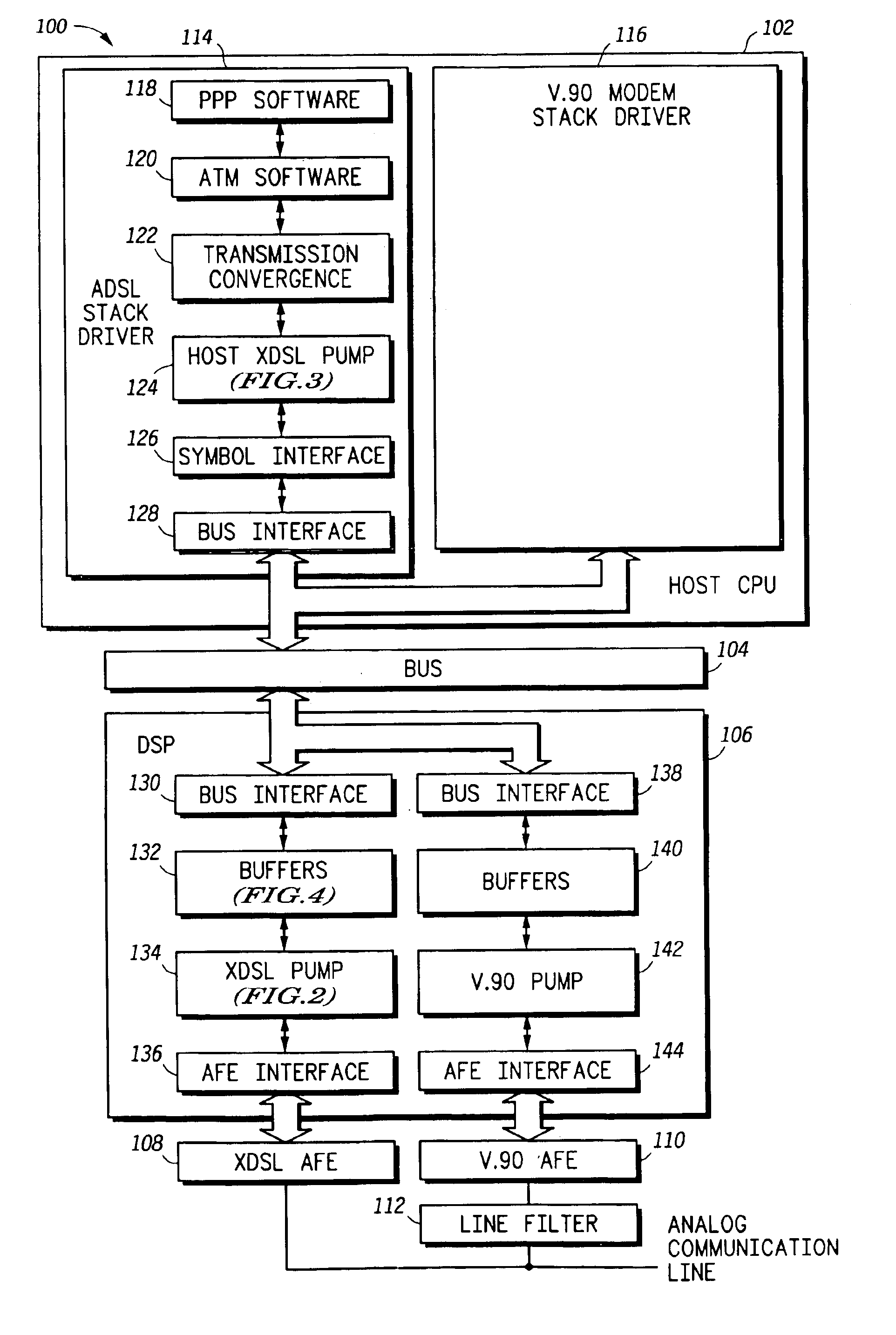

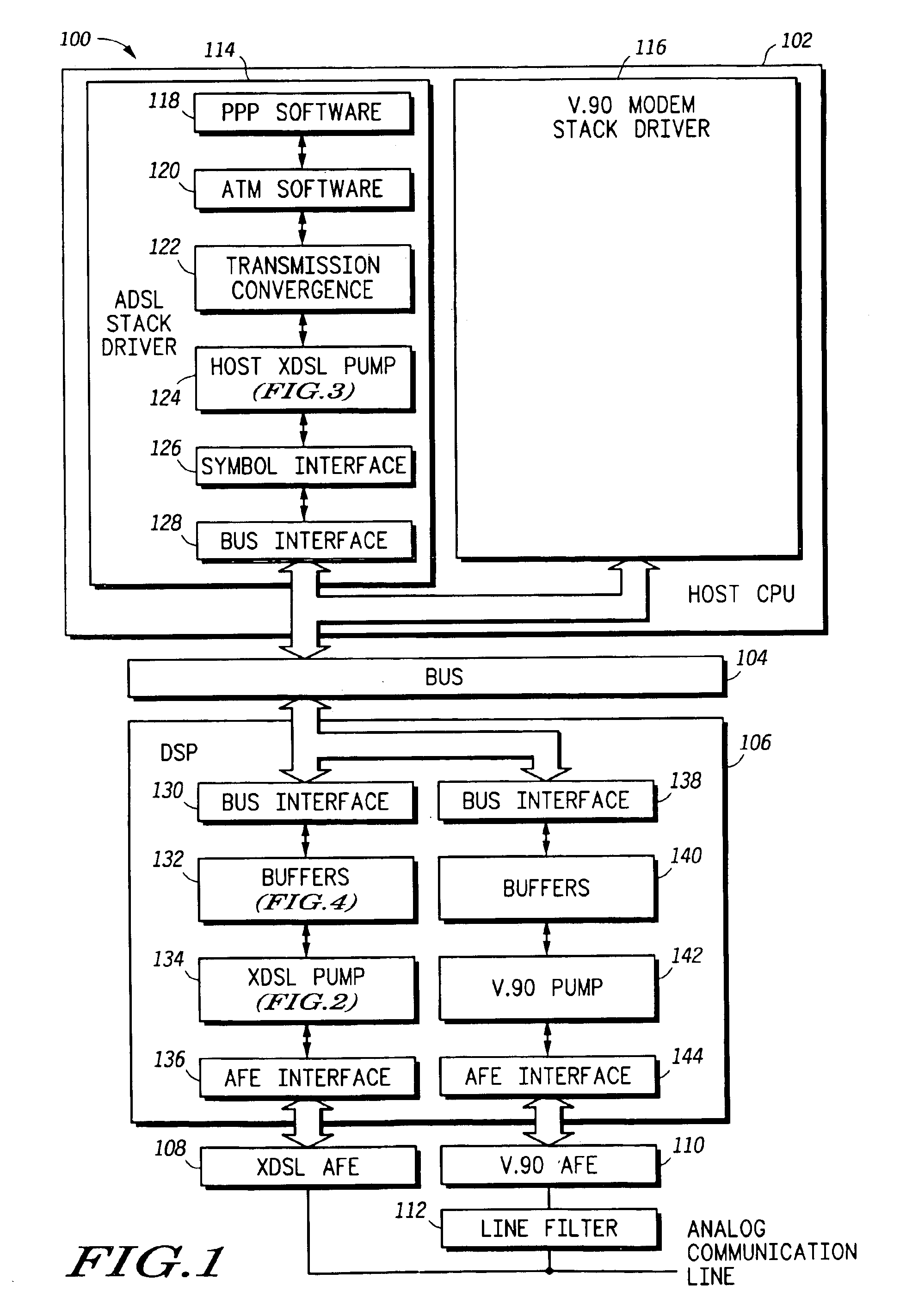

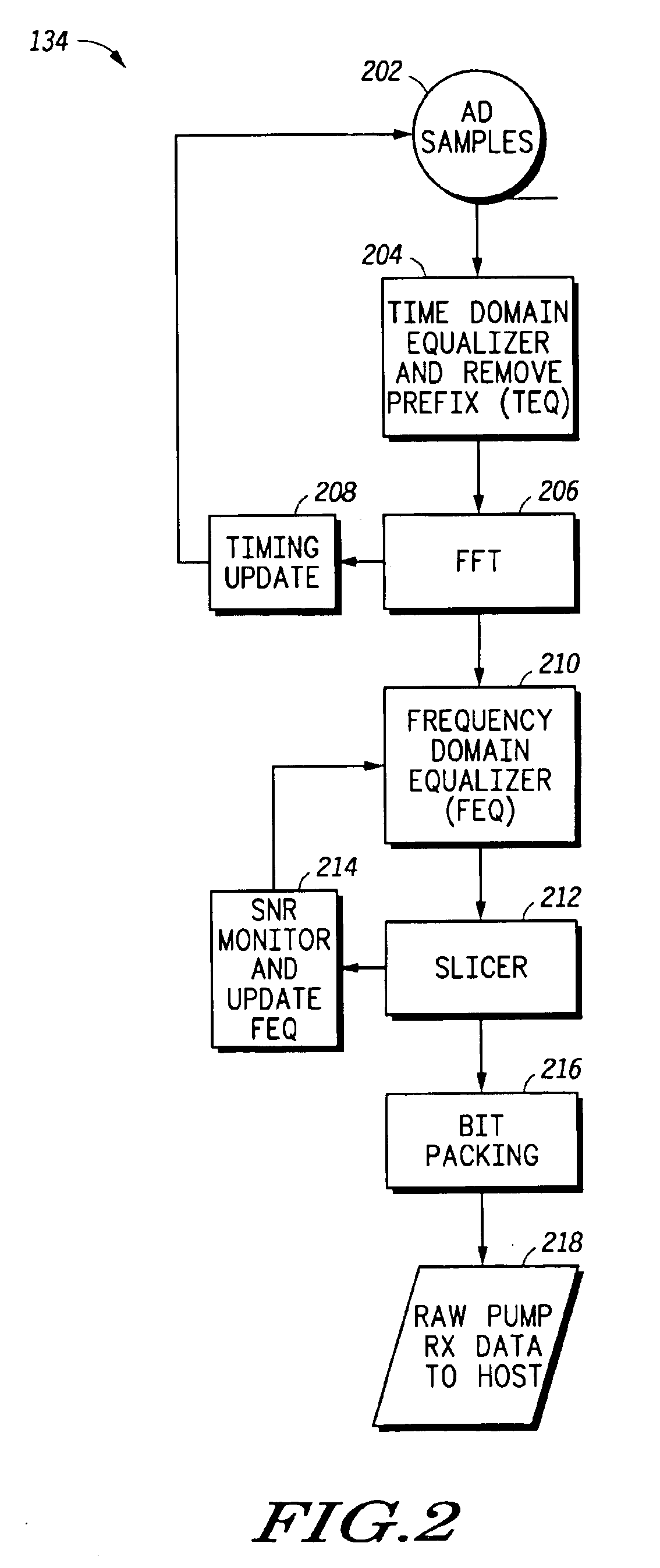

The apparatus and method herein splits the function of a digital subscriber line (DSL) modem data pump between a digital signal processor (DSP 106) and a general purpose host central processing unit (CPU 102). The DSP (106) handles all front end data pump processing such as interface to an analog front end (108 and 110), FFT processing, FEQ processing, QAM decoding, and bit formatting. The host CPU (102) handles all back end data pump processing such as DMT tone deordering, data deinterleaving, error detection and correcting, bit descrambling, CRC processing, and the like. In order to enable the DSP (106) and the CPU (102) to communicate with each other effectively, buffers (132) under the control of specialized buffer management methodology (FIG. 4) are used.

Owner:APPLE INC

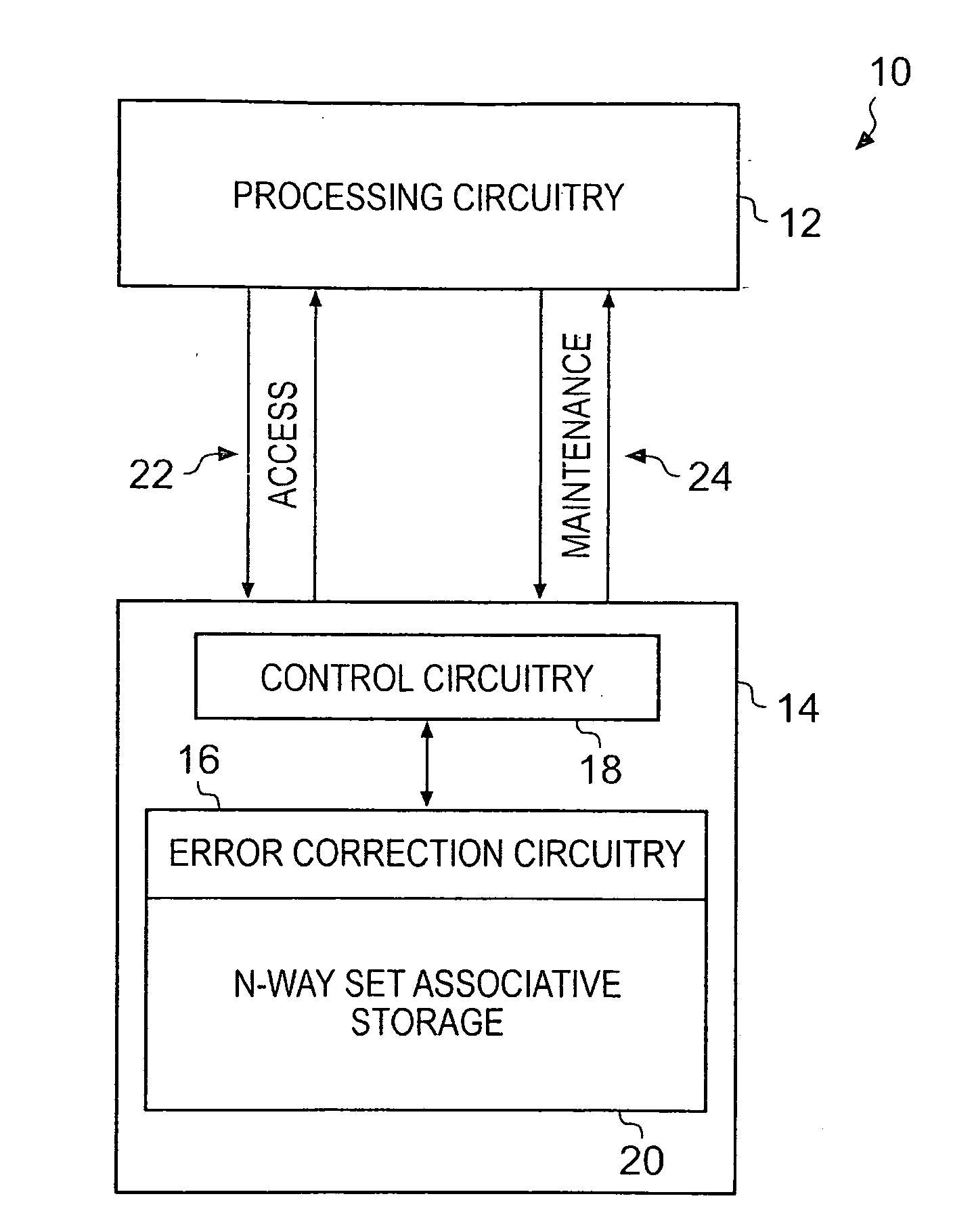

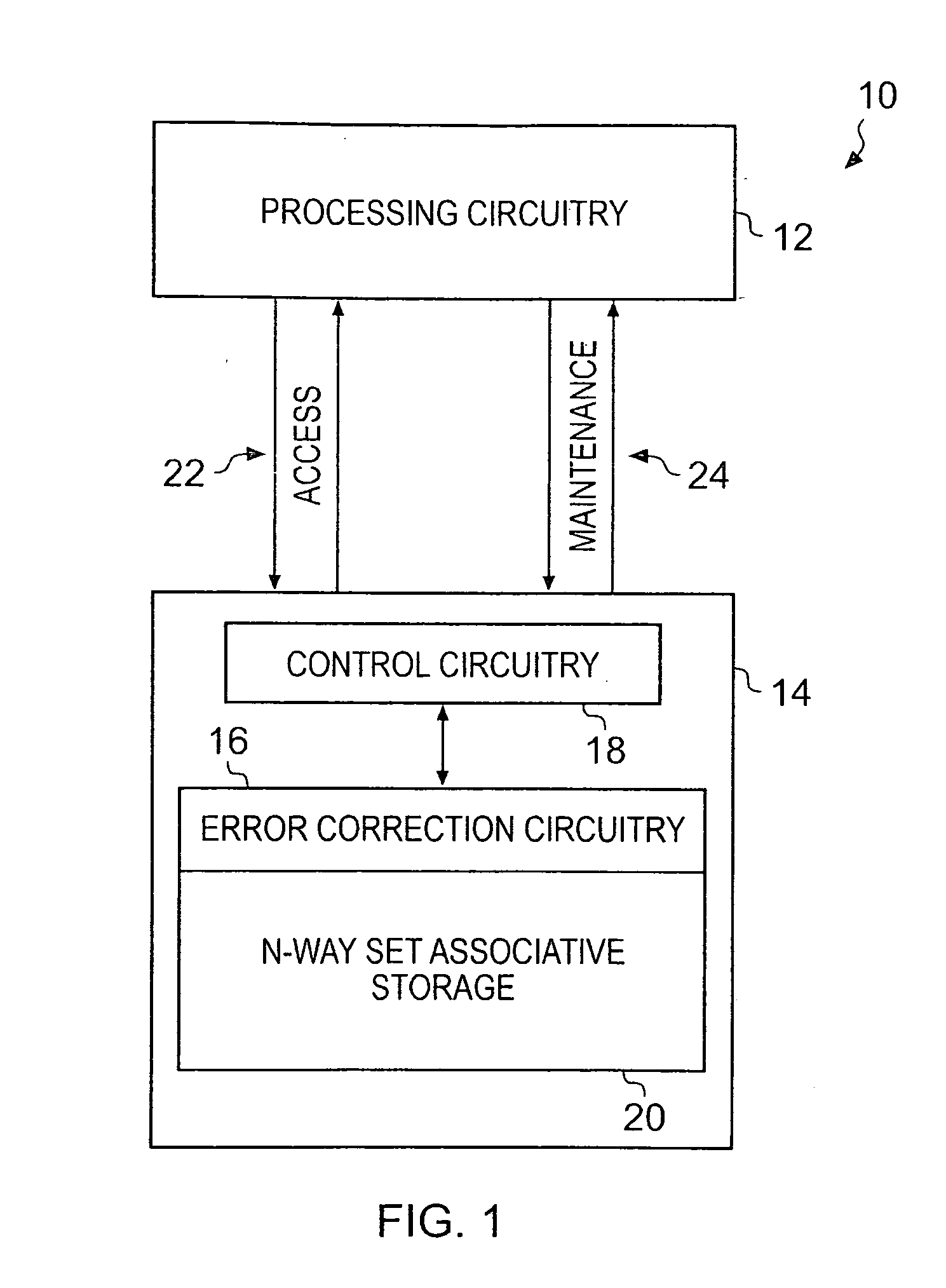

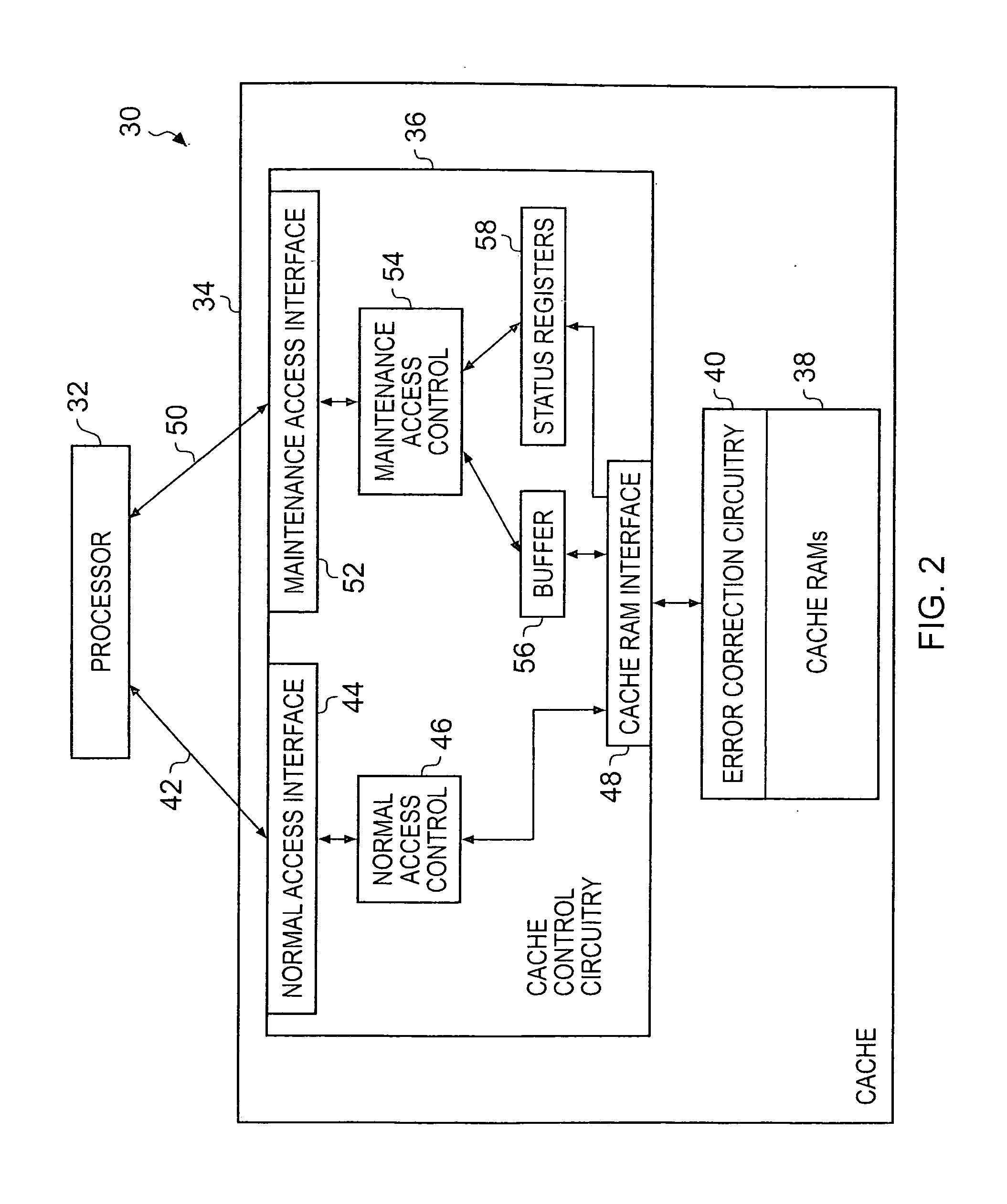

Error correction in a set associative storage device

A data processing apparatus is provided comprising processing circuitry for performing data processing operations, a set associative storage device for storing data values for access by the processing circuitry when performing data processing operations, error detection circuitry for performing, for each access to the storage device, an error detection operation on the data value accessed, and maintenance circuitry associated with the storage device for performing one or more maintenance operations. The processing circuitry is arranged to issue an error detection maintenance request to the maintenance circuitry specifying at least one specific physical location within the storage device, and the maintenance circuitry is responsive to the error detection maintenance request to perform at least one dummy access to the at least one specific physical location within the storage device and to provide the processing circuitry with error status information derived from the error detection operation performed by the error detection circuitry in respect of said at least one dummy access.

Owner:ARM LTD

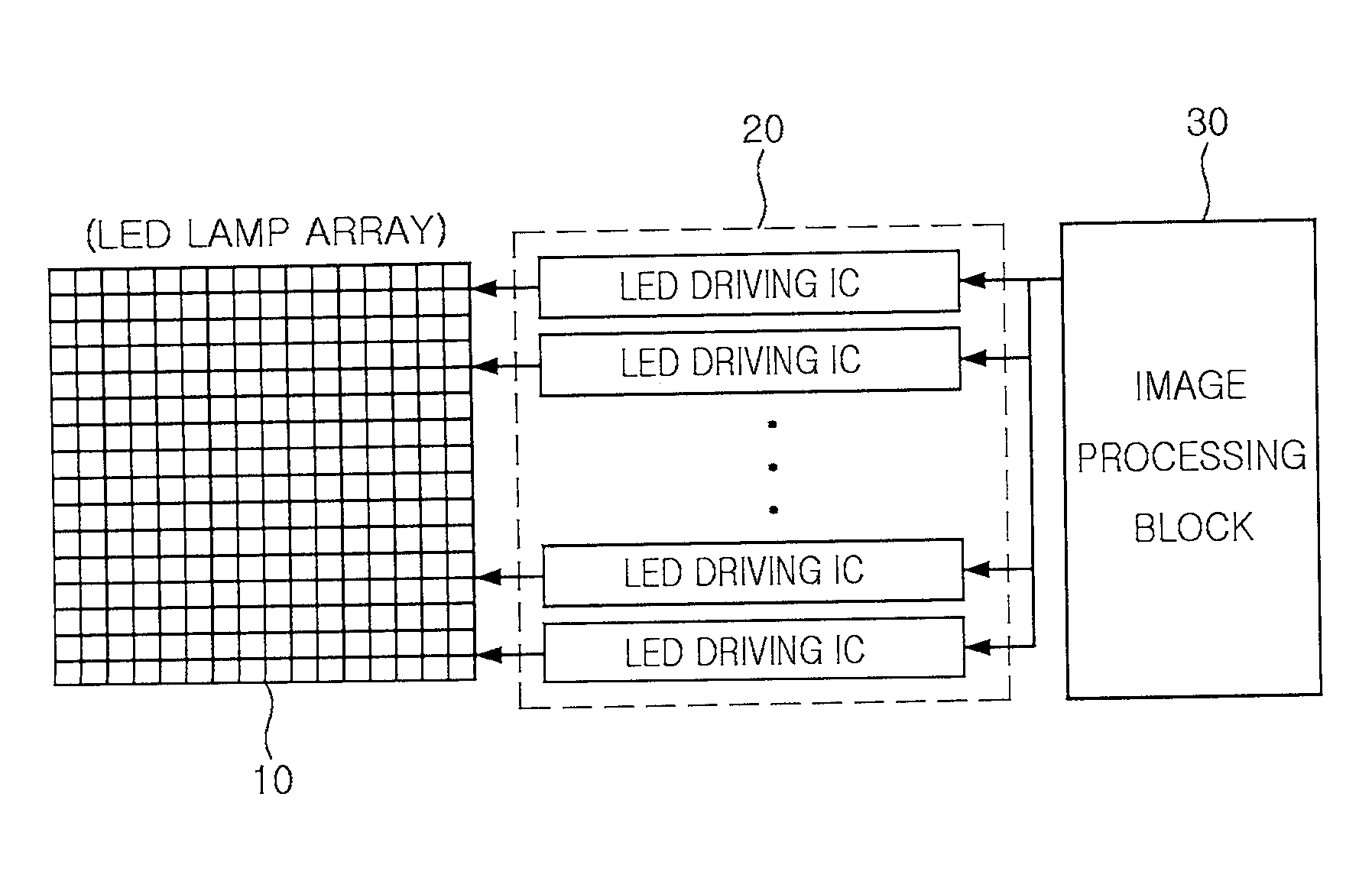

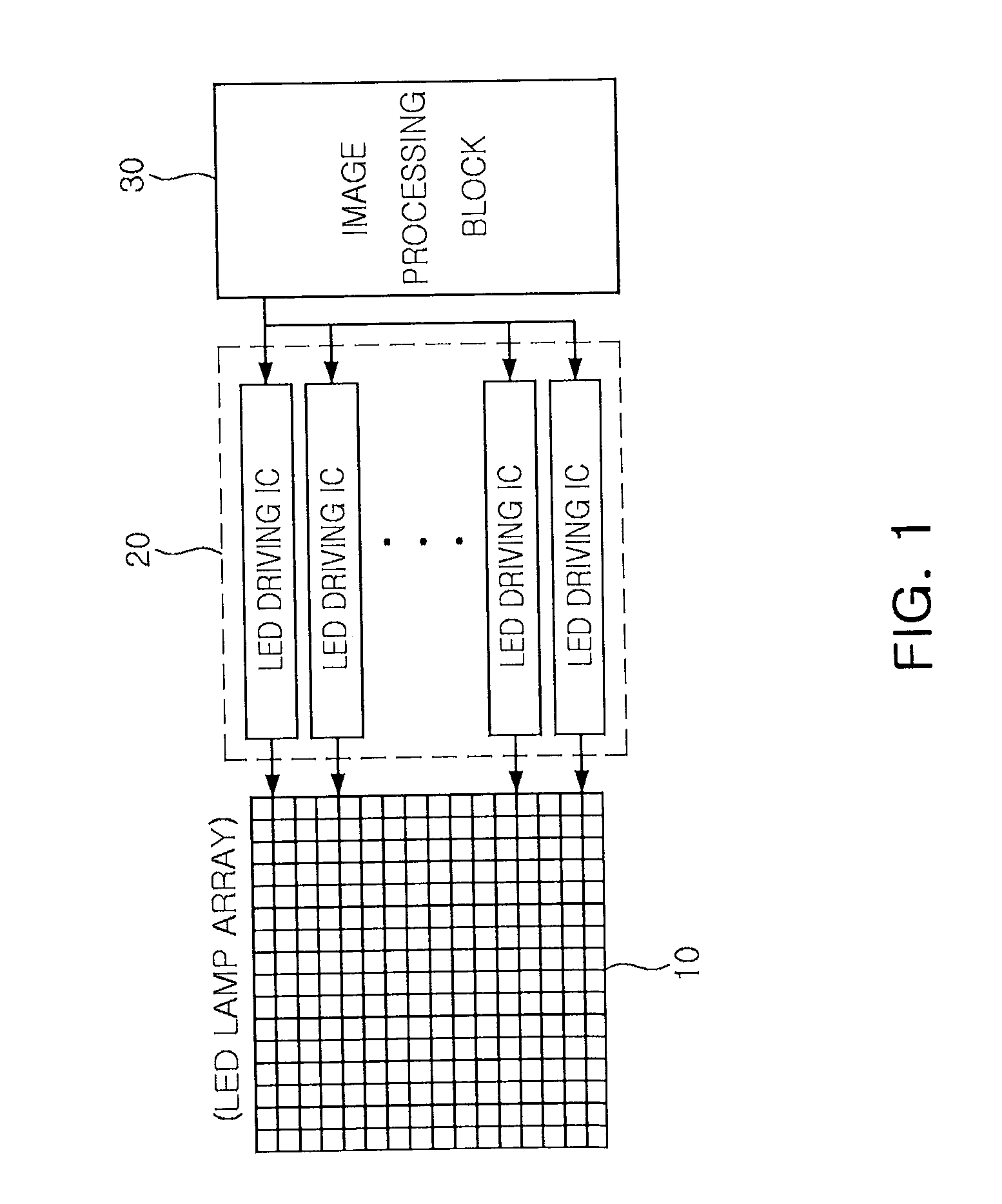

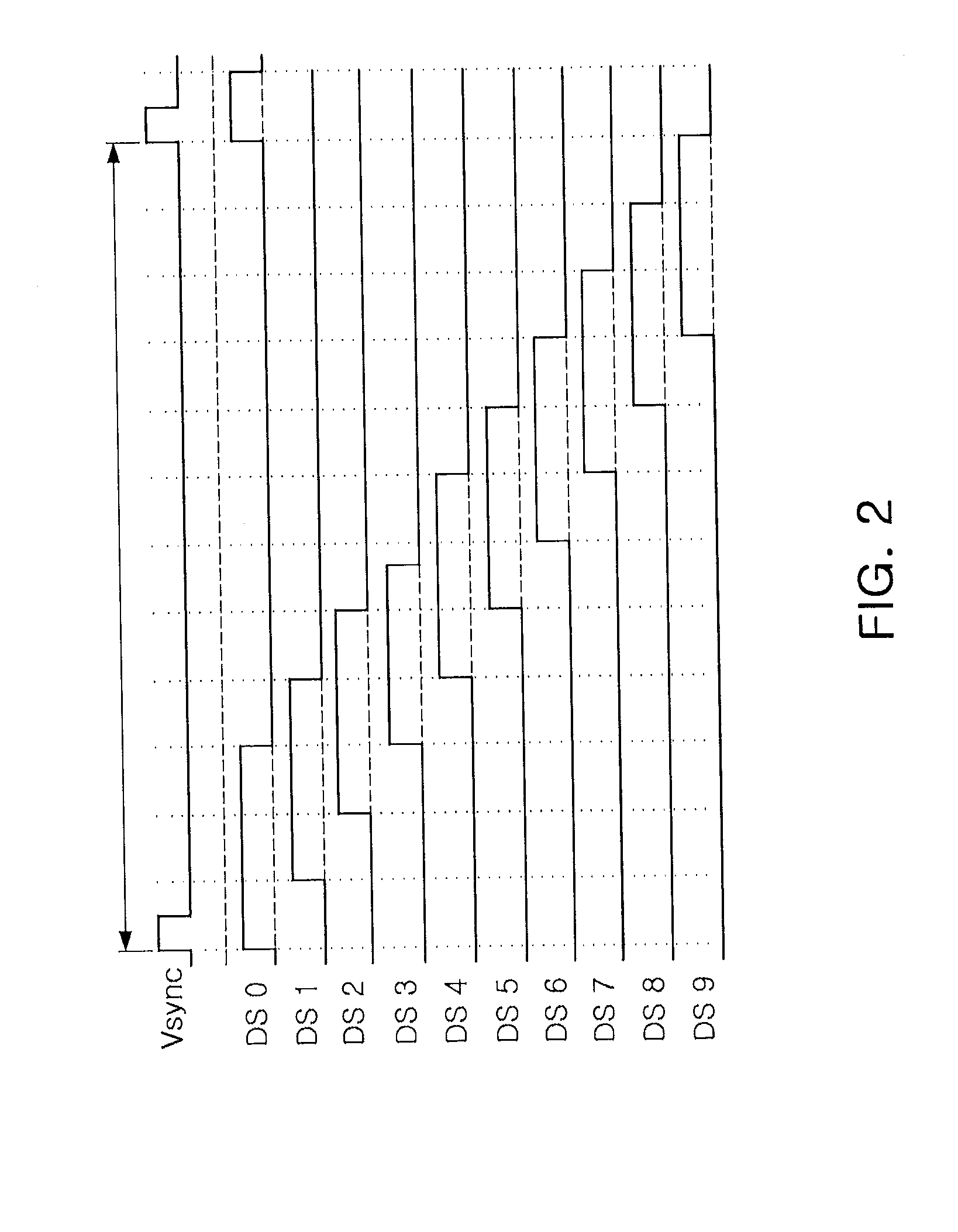

LED driving circuit having error detection function

InactiveUS20110133673A1Detecting errorElectrical apparatusStatic indicating devicesShift registerProcessor register

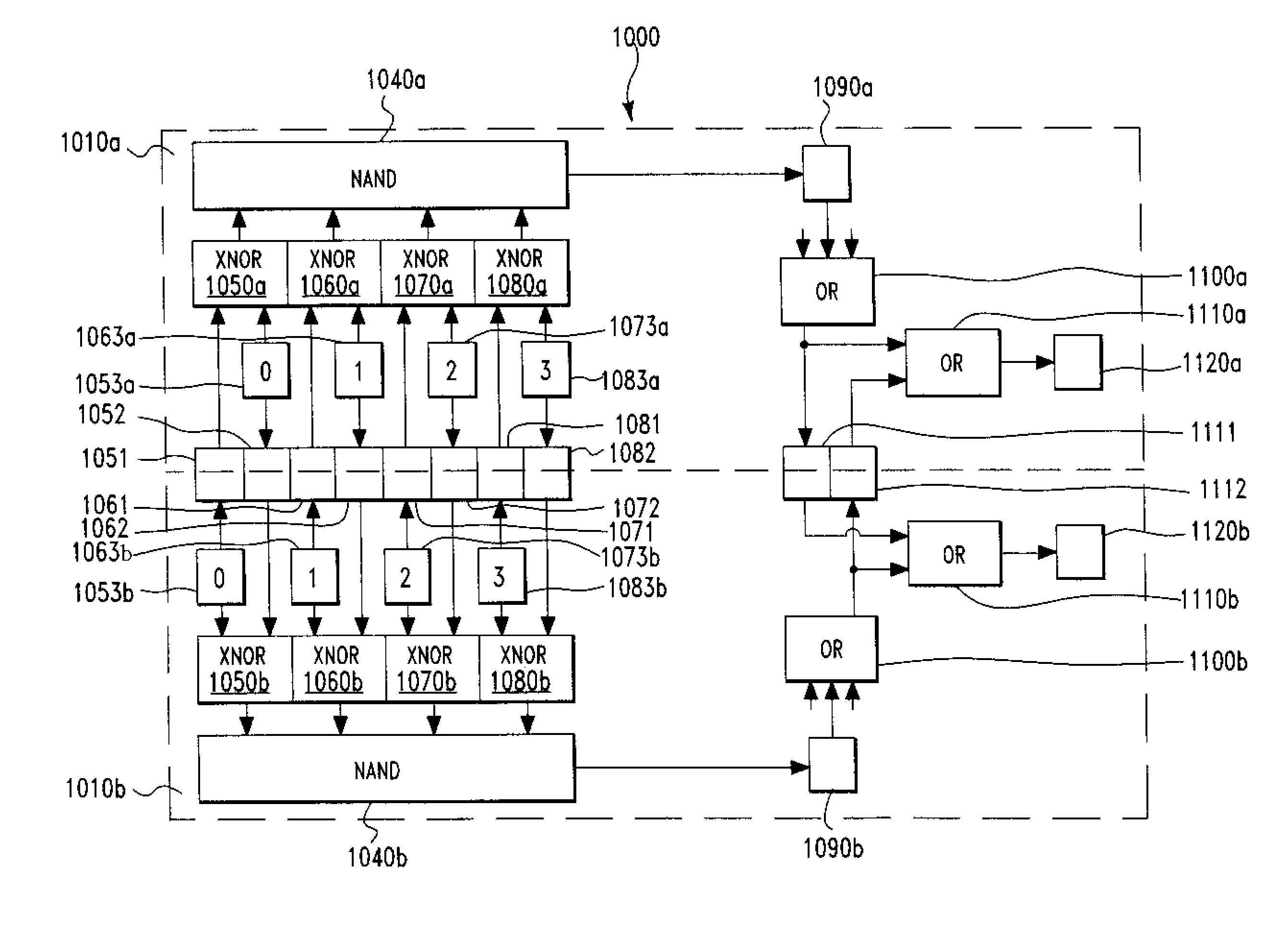

There is provided an LED driving circuit. An LED driving circuit according to an aspect of the invention may include: a shift register separating dimming data and control data from serial peripheral interface (SPI) data and outputting the dimming data and the control data in predetermine data units; a scan register generating scan data according to the control data from the shift register; a first error detection unit detecting an error in the dimming data from the shift register; a second error detection unit detecting an error in the scan data from the scan register; and a logic operation unit performing an OR operation on an output signal from the first error detection unit and an output signal from the second error detection unit.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

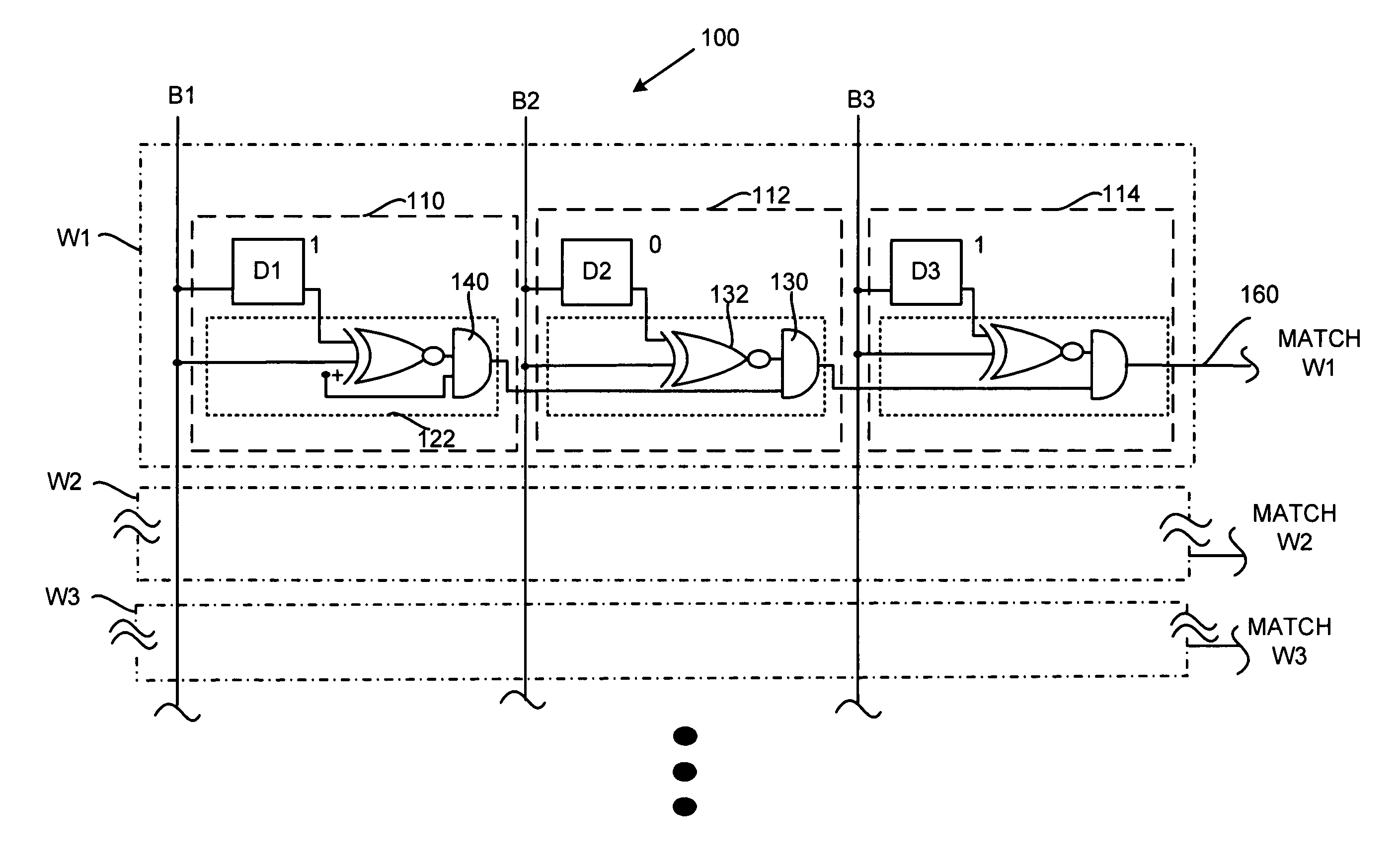

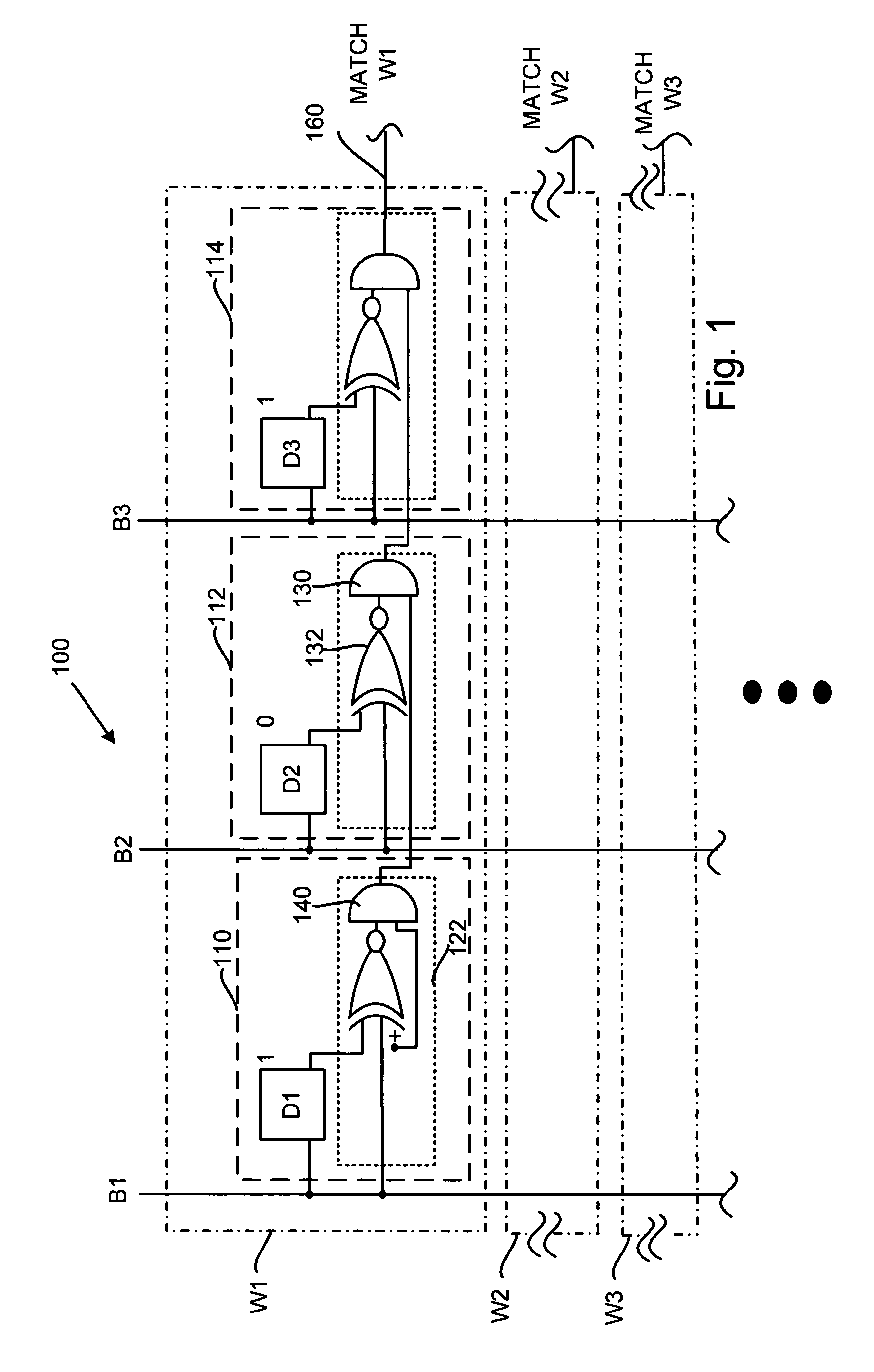

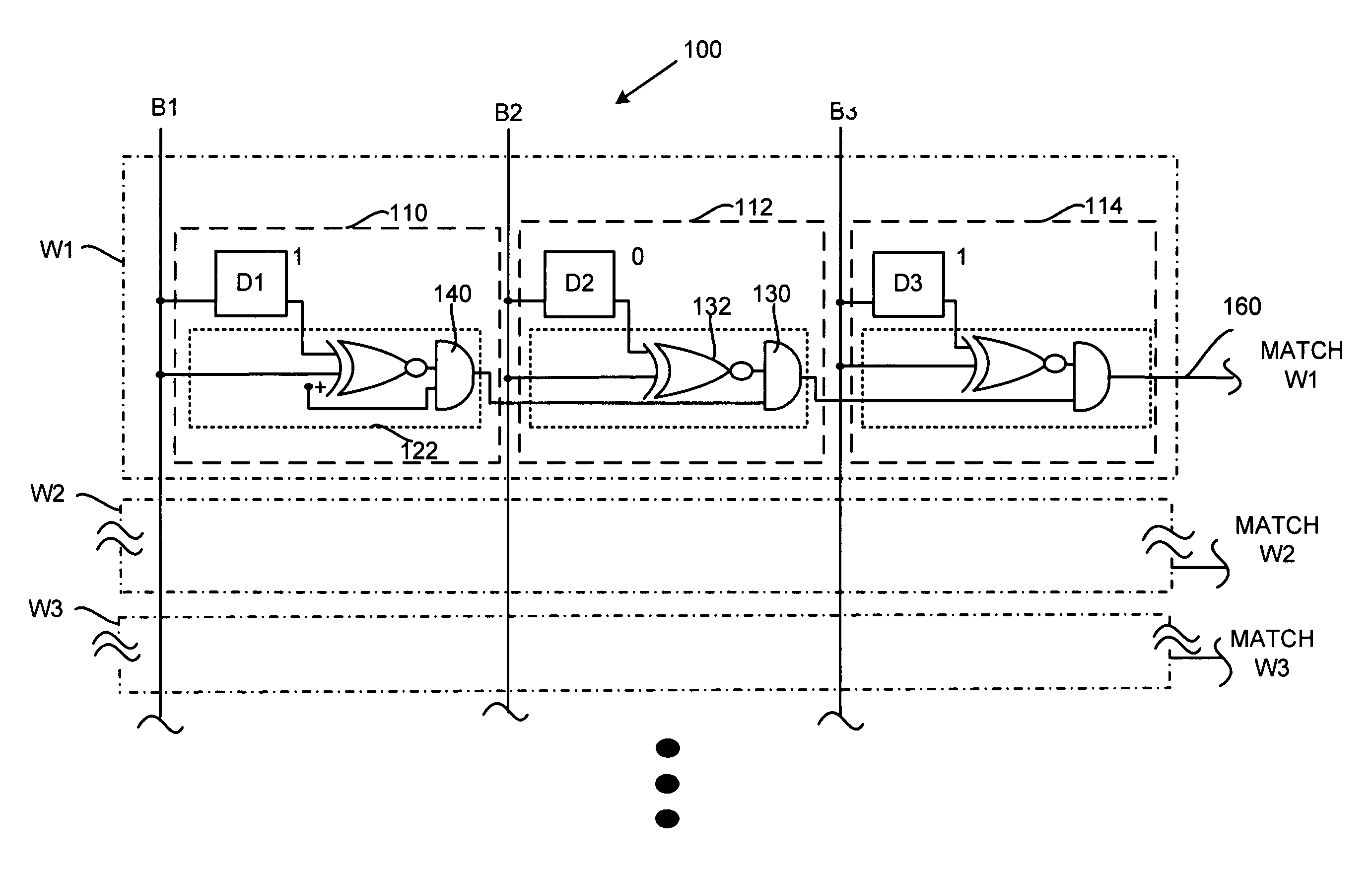

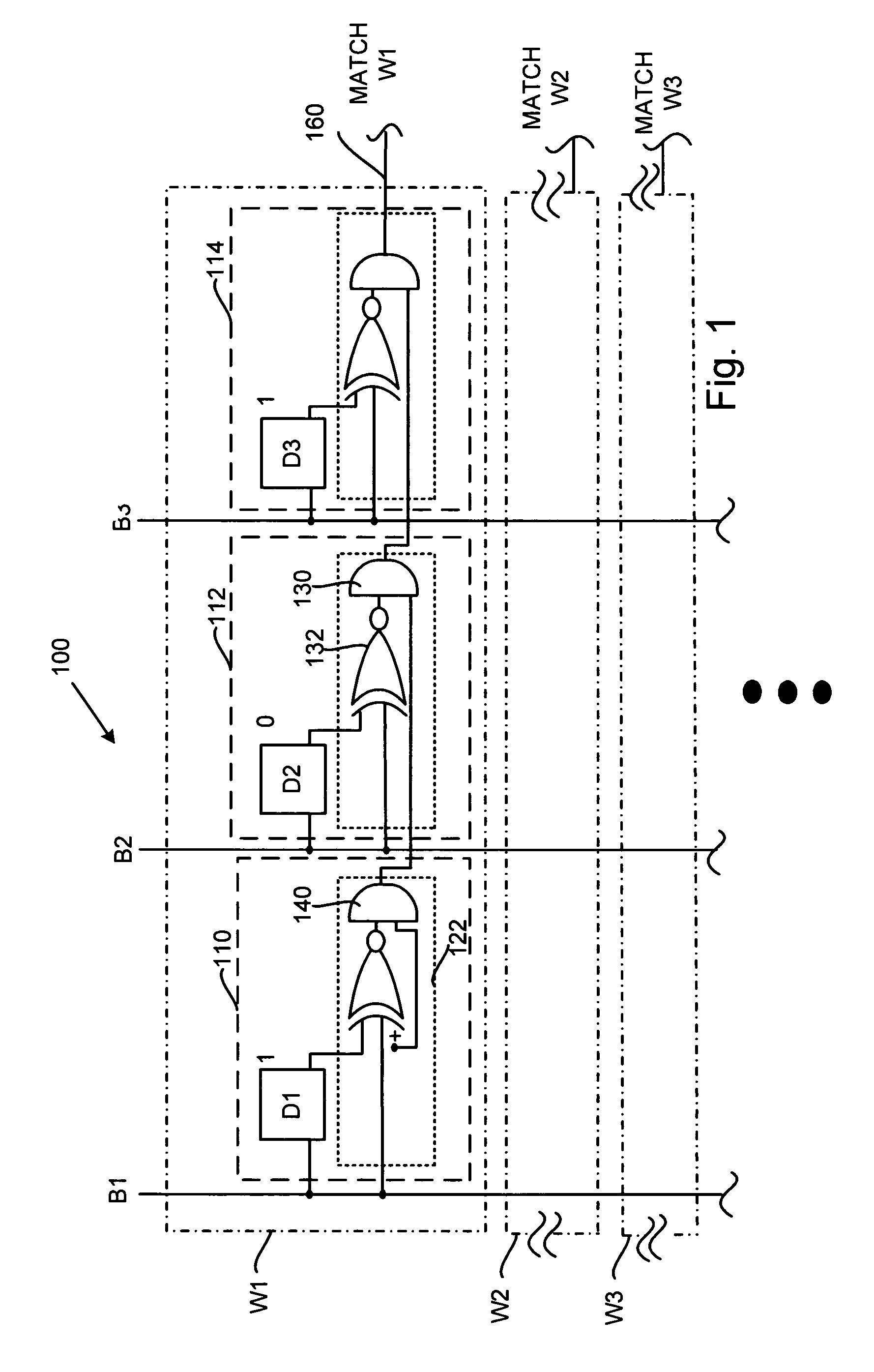

Data corruption scrubbing for content addressable memory and ternary content addressable memory

ActiveUS20070061668A1Error detection/correctionCode conversionData CorruptionTernary content addressable memory

A method for remedying data corruption in a first circuit, which may be a CAM or a TCAM. The method includes providing a RAM circuit external to the first circuit, the RAM circuit being configured for storing error detection information for data stored in the first circuit. The method also includes scrubbing the data stored in the first circuit during scrubbing cycles of the first circuit. The scrubbing corrects stored bit patterns read from the first circuit that fail an error detection test using error detection information corresponding to individual ones of the stored bit patterns. In an embodiment, ECC may be employed for the error detection test and also to correct any single bit error found.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

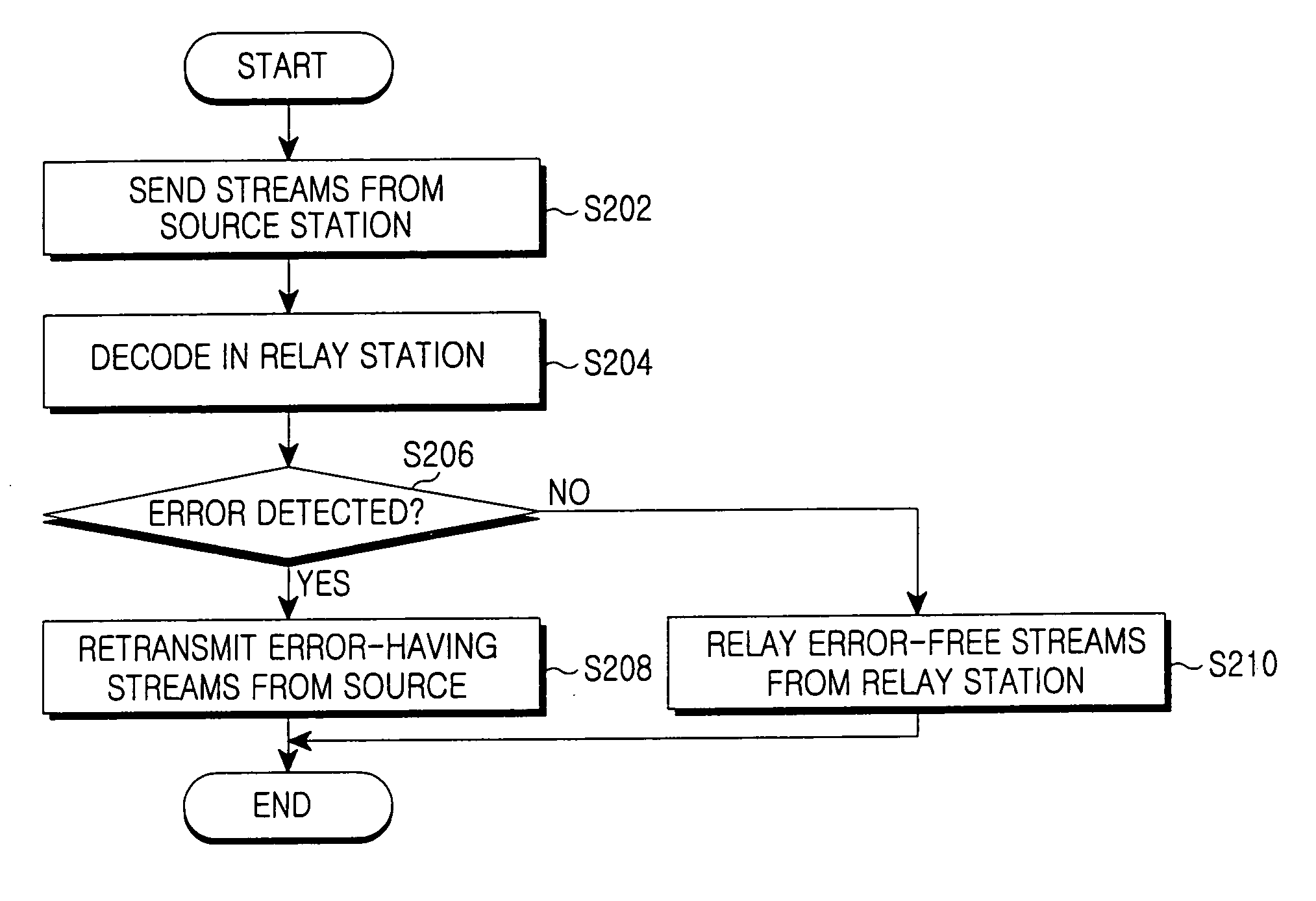

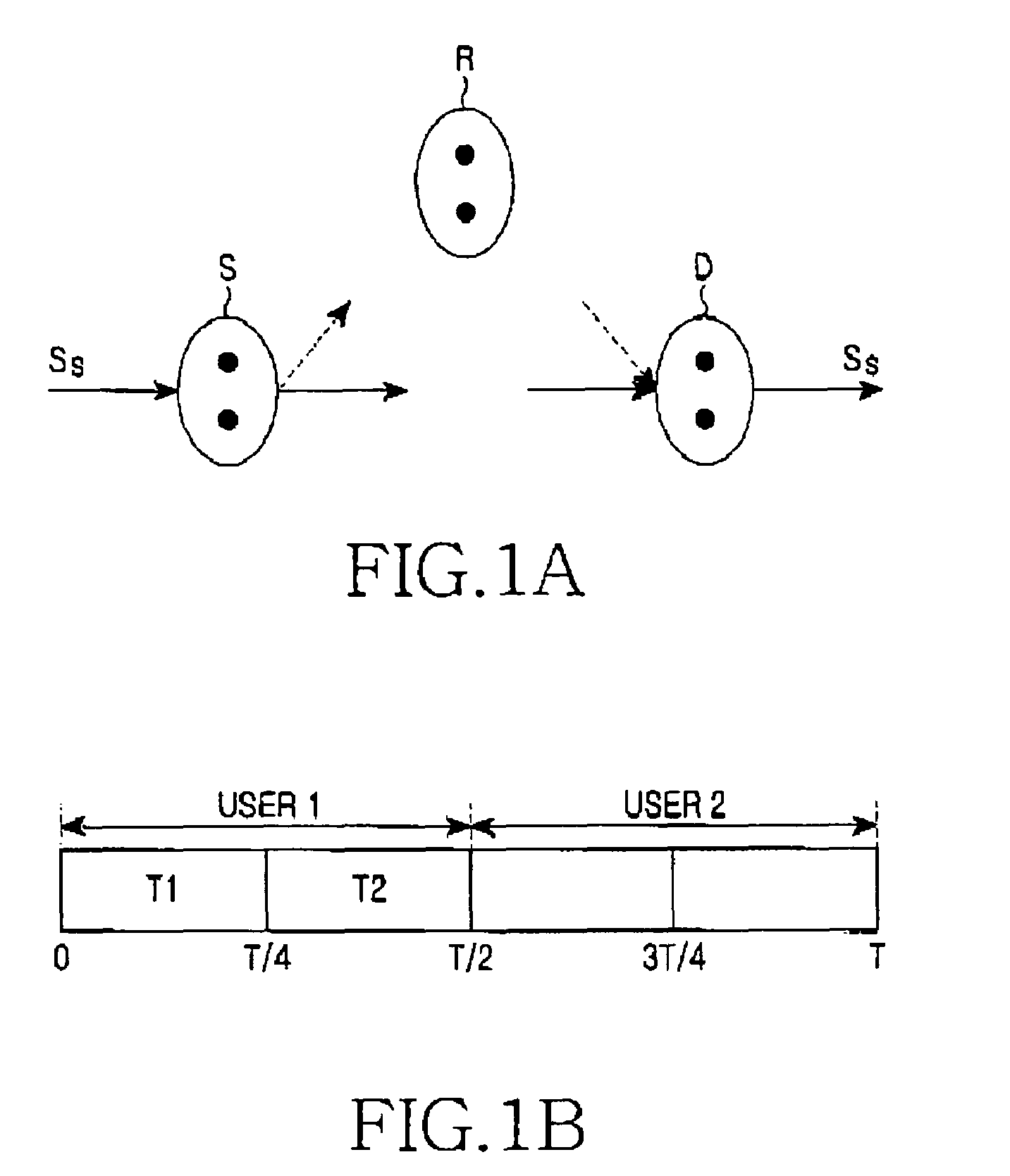

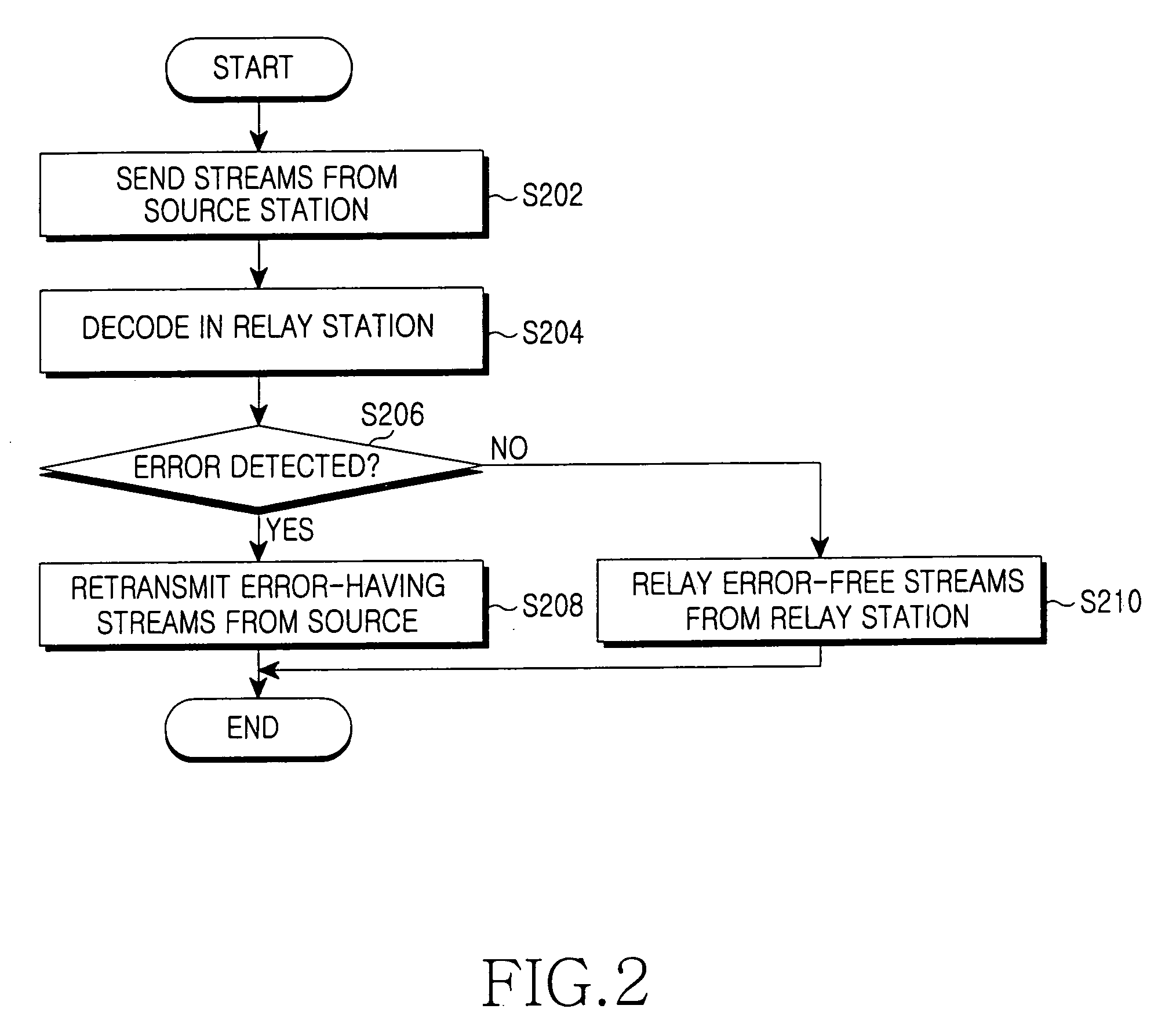

Method of providing cooperative diversity in a MIMO wireless network

ActiveUS7697484B2Error prevention/detection by using return channelSite diversityTelecommunicationsDiversity scheme

Disclosed is a method of providing cooperative diversity in a Multiple Input Multiple-Output (MIMO) wireless network including a source station, a relay station, and a destination station each for transmitting a plurality of streams through multiple antennas, the method including: decoding, by a relay station, a plurality of streams received from the source station, checking for errors in the individual decoded streams, and transmitting error detection information to the source station and thereafter relaying streams having no errors to the destination station and retransmitting, by a source station, streams corresponding to streams which were previously found to include errors to the destination station based on the error detection information.

Owner:SAMSUNG ELECTRONICS CO LTD

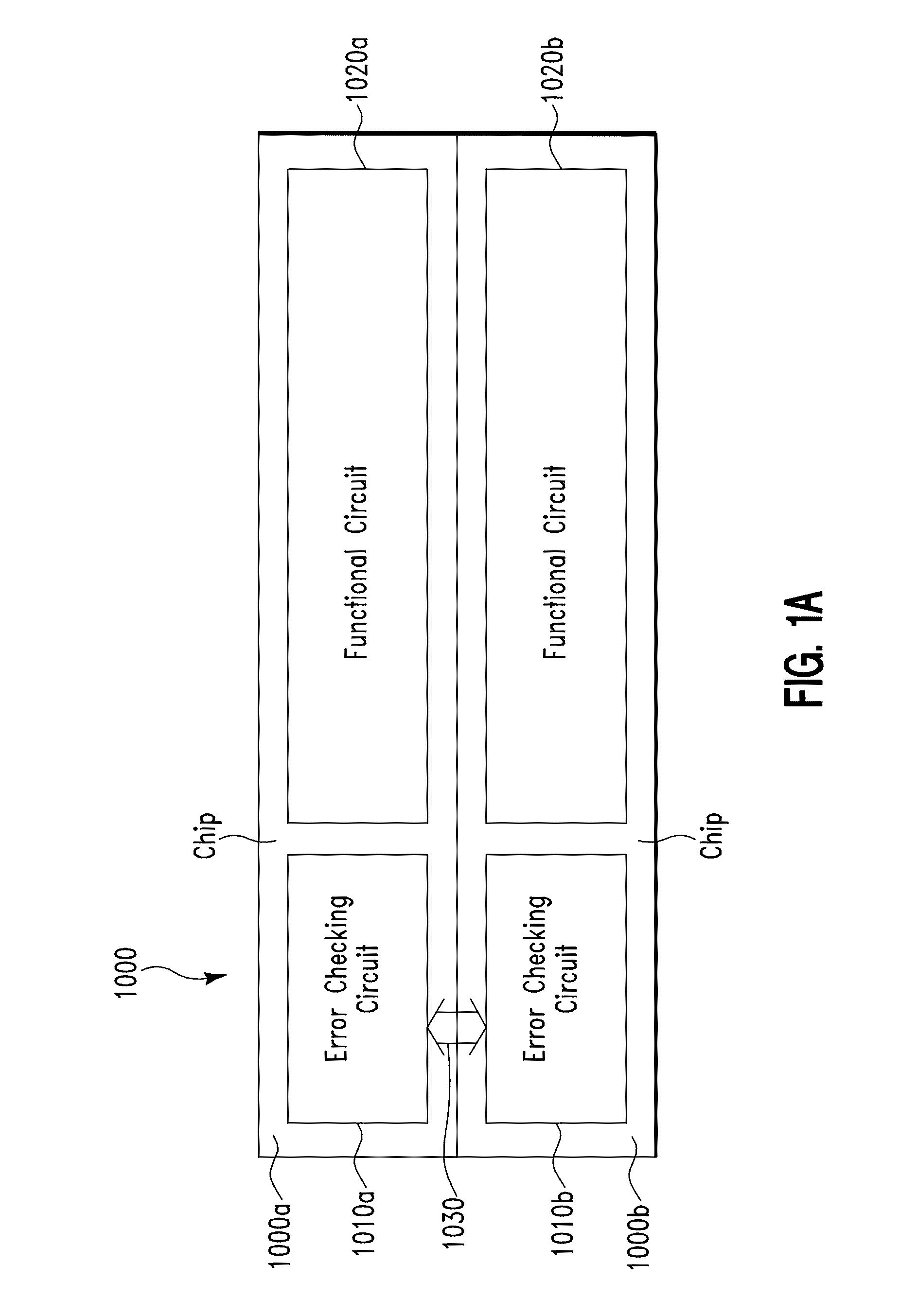

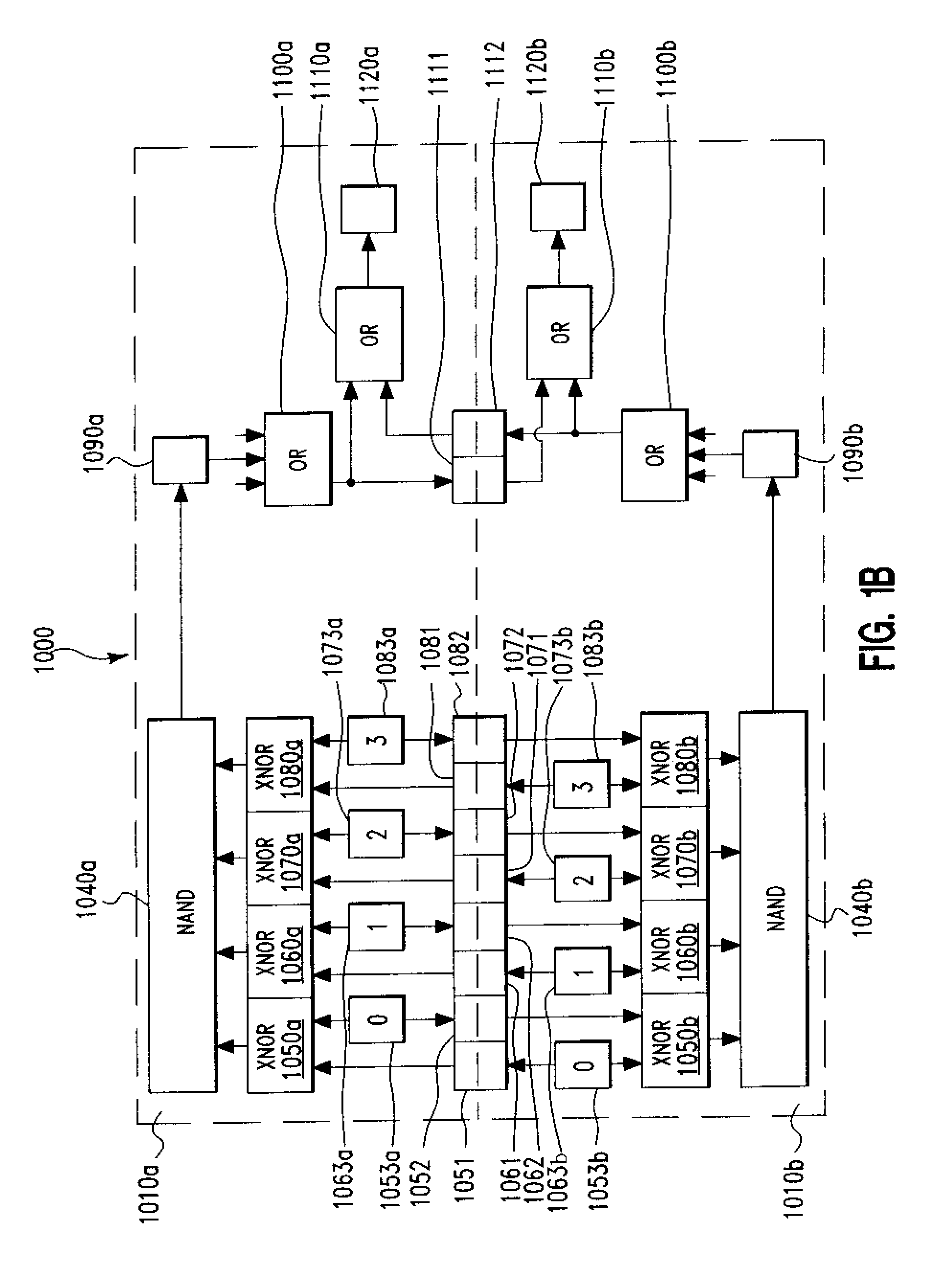

Error detection and correction in semiconductor structures

A semiconductor structure and a method for operating the same. The semiconductor structure includes a first semiconductor chip and a second semiconductor chip. The first semiconductor chip is on top of and bonded to the second semiconductor chip. The first and second semiconductor chips include a first and a second electric nodes. The second semiconductor chip further includes a first comparing circuit. The semiconductor structure further includes a first coupling via electrically connecting the first electric node of the first semiconductor chip to the first comparing circuit of the second semiconductor chip. The first comparing circuit is capable of (i) receiving an input signal from the second electric node directly, (ii) receiving an input signal from the first electric node indirectly through the first coupling via, and (iii) asserting a first mismatch signal in response to the input signals from the first and second electric nodes being different.

Owner:TAIWAN SEMICON MFG CO LTD

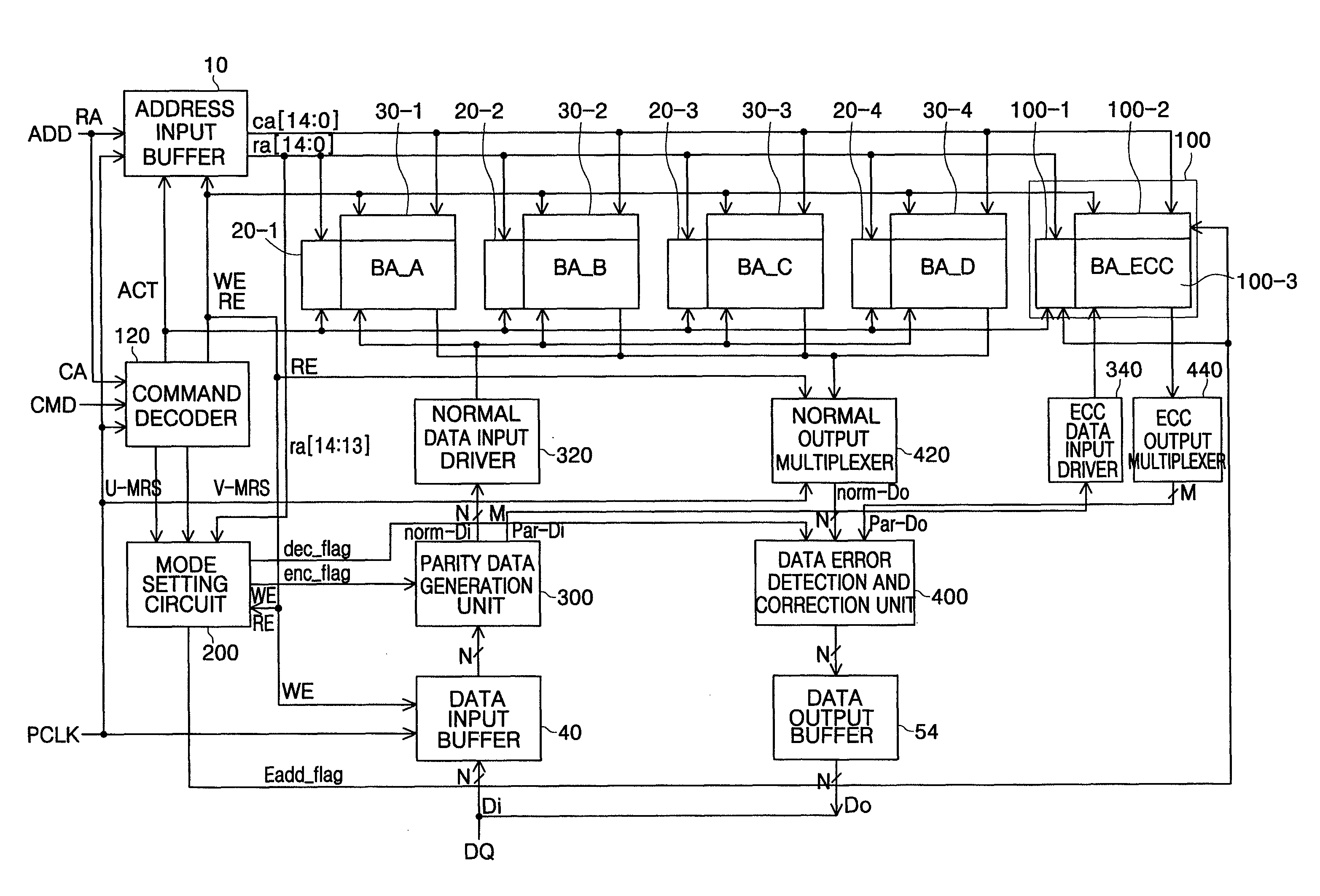

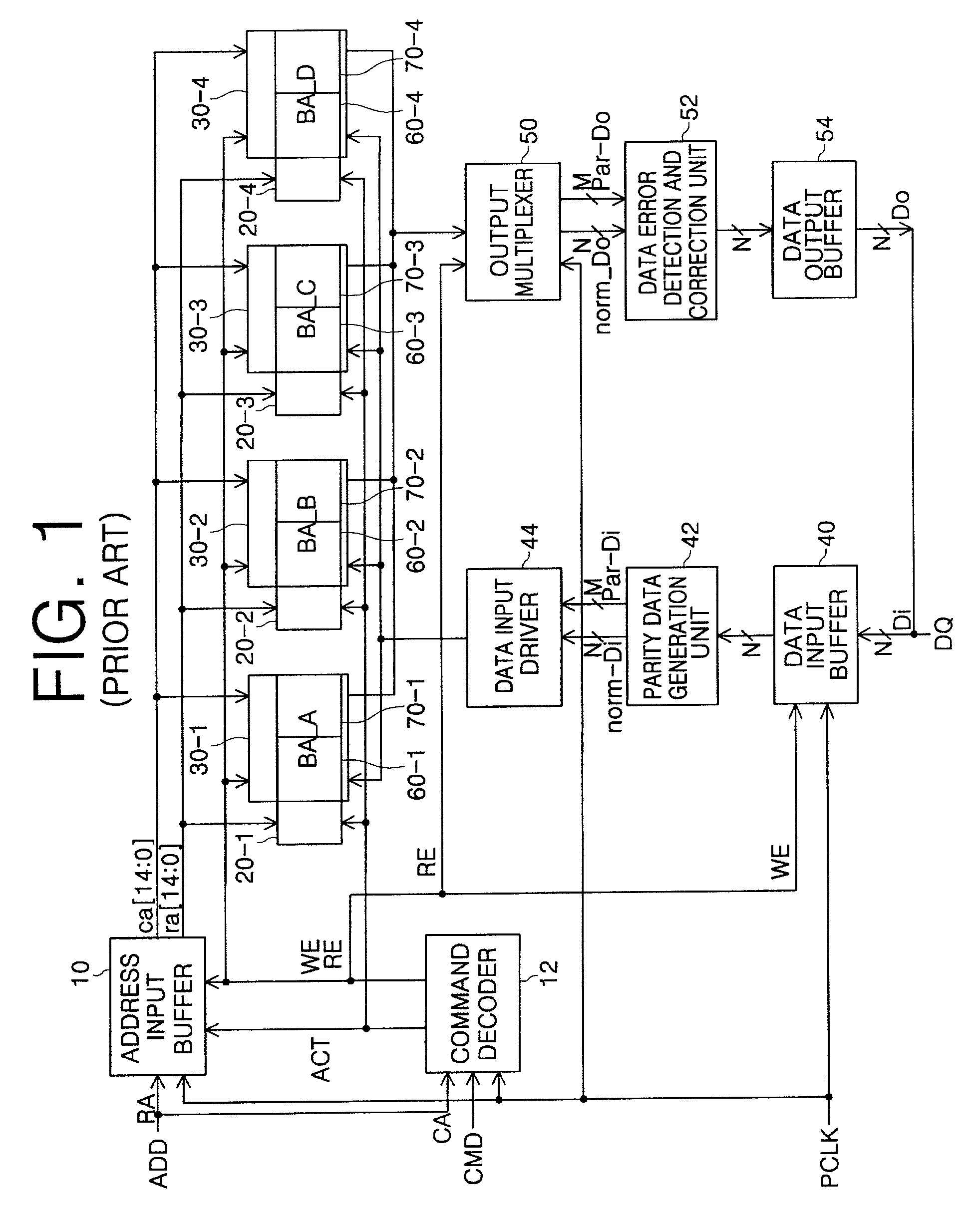

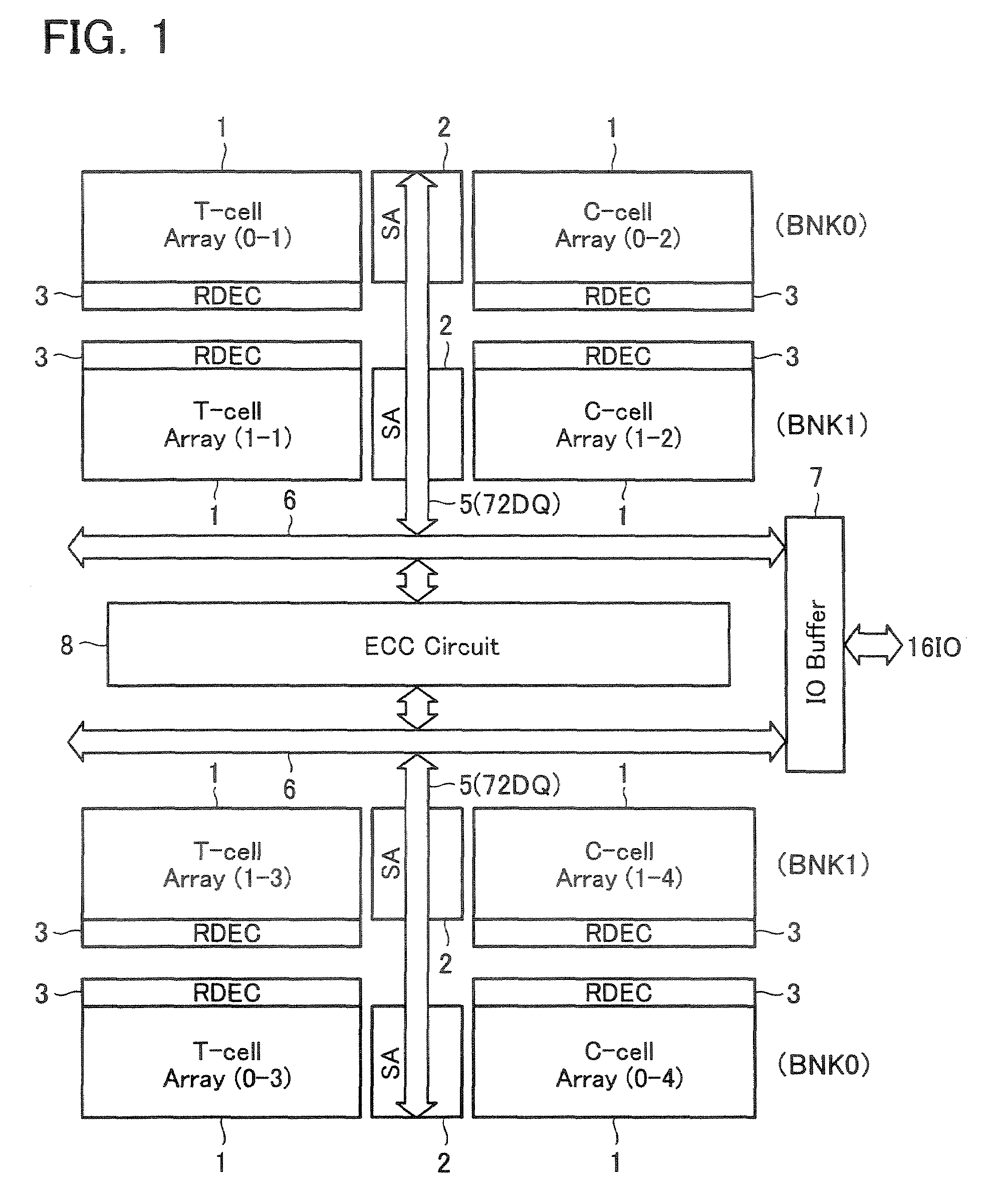

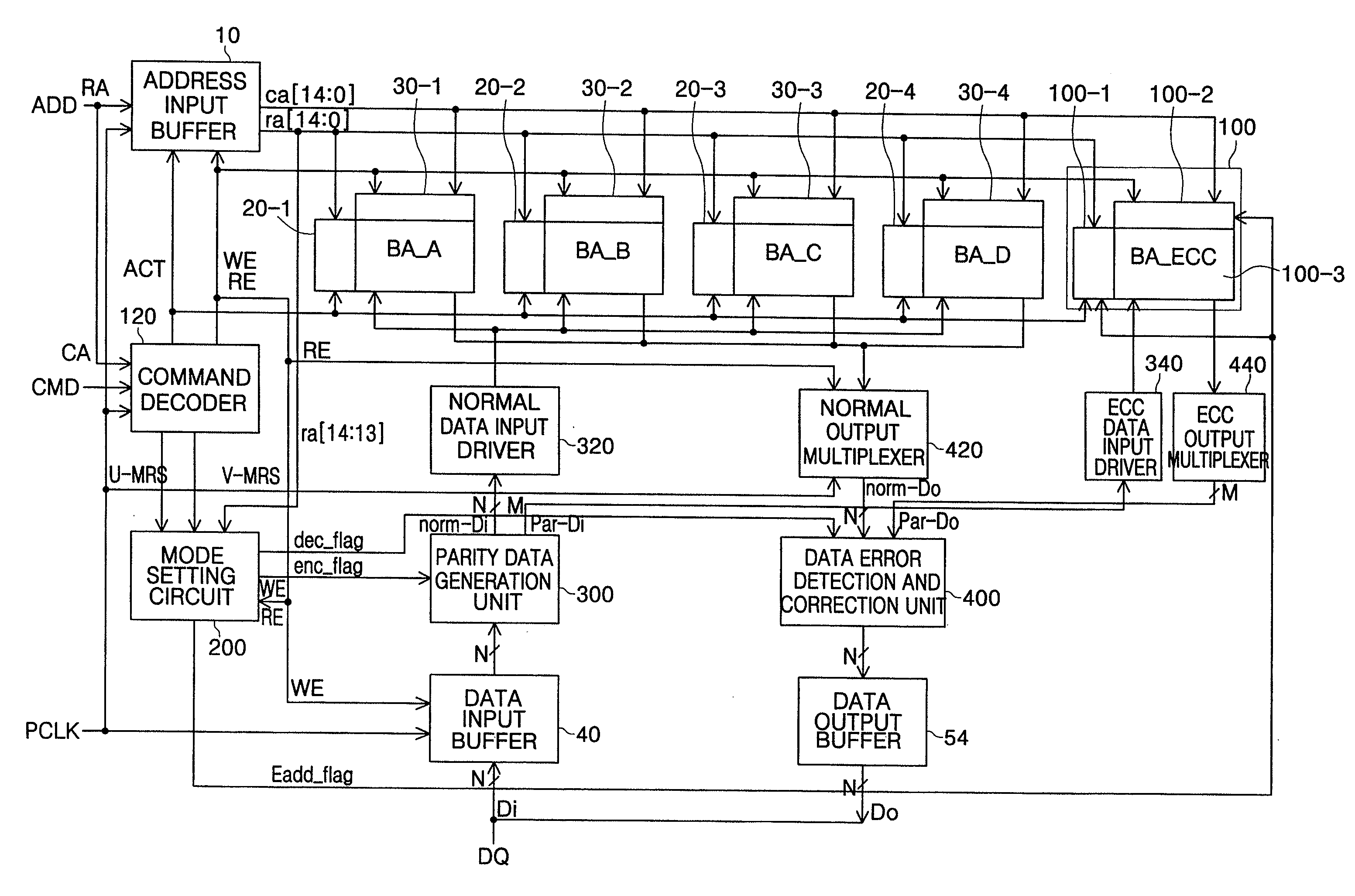

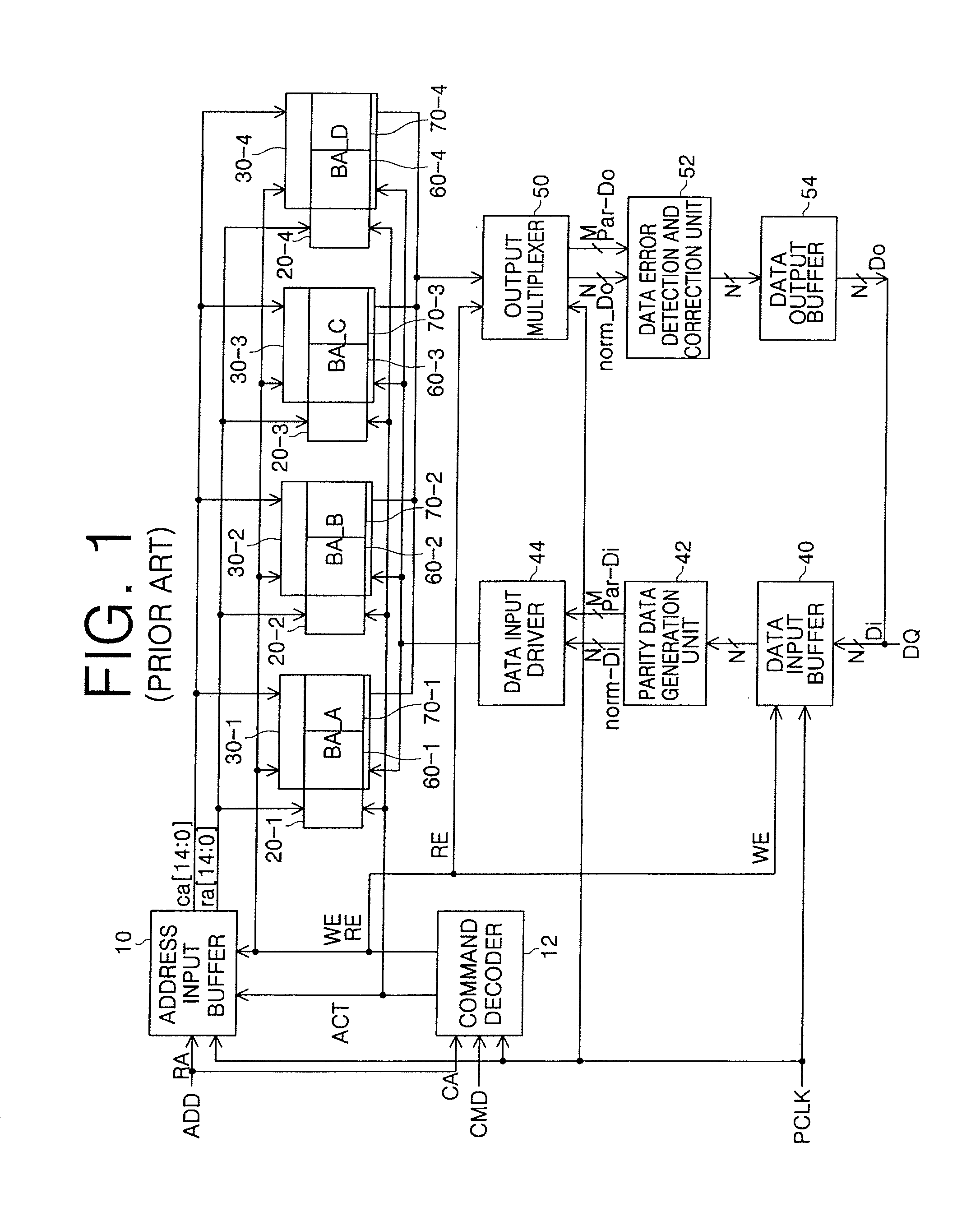

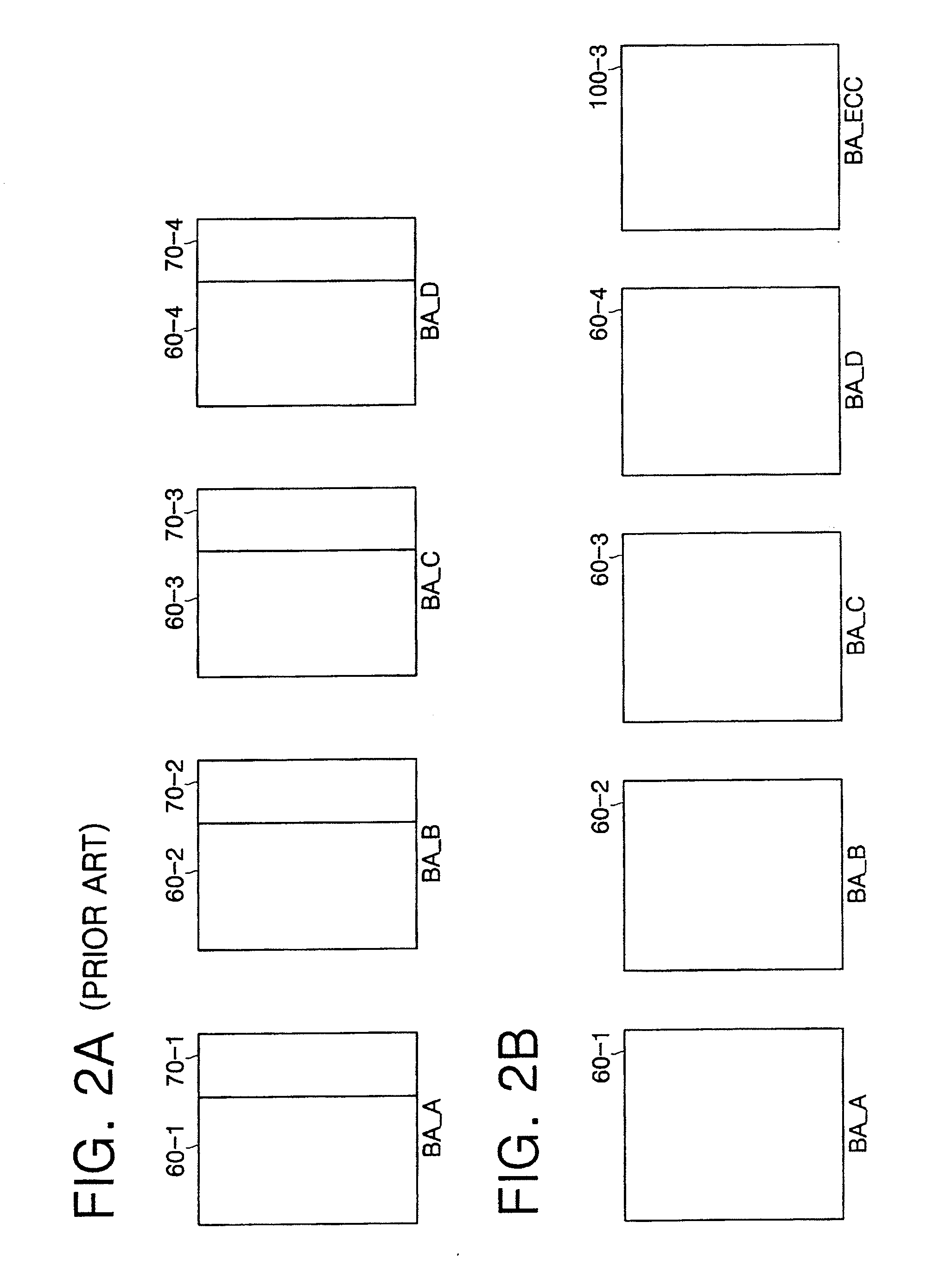

Semiconductor memory device and data error detection and correction method of the same

A semiconductor memory device includes a memory cell array, a mode setting circuit, a parity data generation unit, and a data error detection and correction unit. The memory cell array has a plurality of first memory banks for storing normal data, and a predetermined number of second memory banks less than the number of the first memory banks for storing parity data according to control of a first flag signal. The mode setting circuit sets the first flag signal and a second flag signal controlling based on whether a separate memory bank is used to store the parity data in the second memory banks. The parity data generation unit receives normal write data during a write operation, generates parity data with respect to the normal write data in response to the second flag signal, and outputs the normal data and the parity data. The data error detection and correction unit receives normal read data and parity read data read from the memory cell array during a read operation, detects errors of the normal read data in response to the second flag signal, corrects the normal read data when the errors are detected, and outputs the corrected read data.

Owner:SAMSUNG ELECTRONICS CO LTD

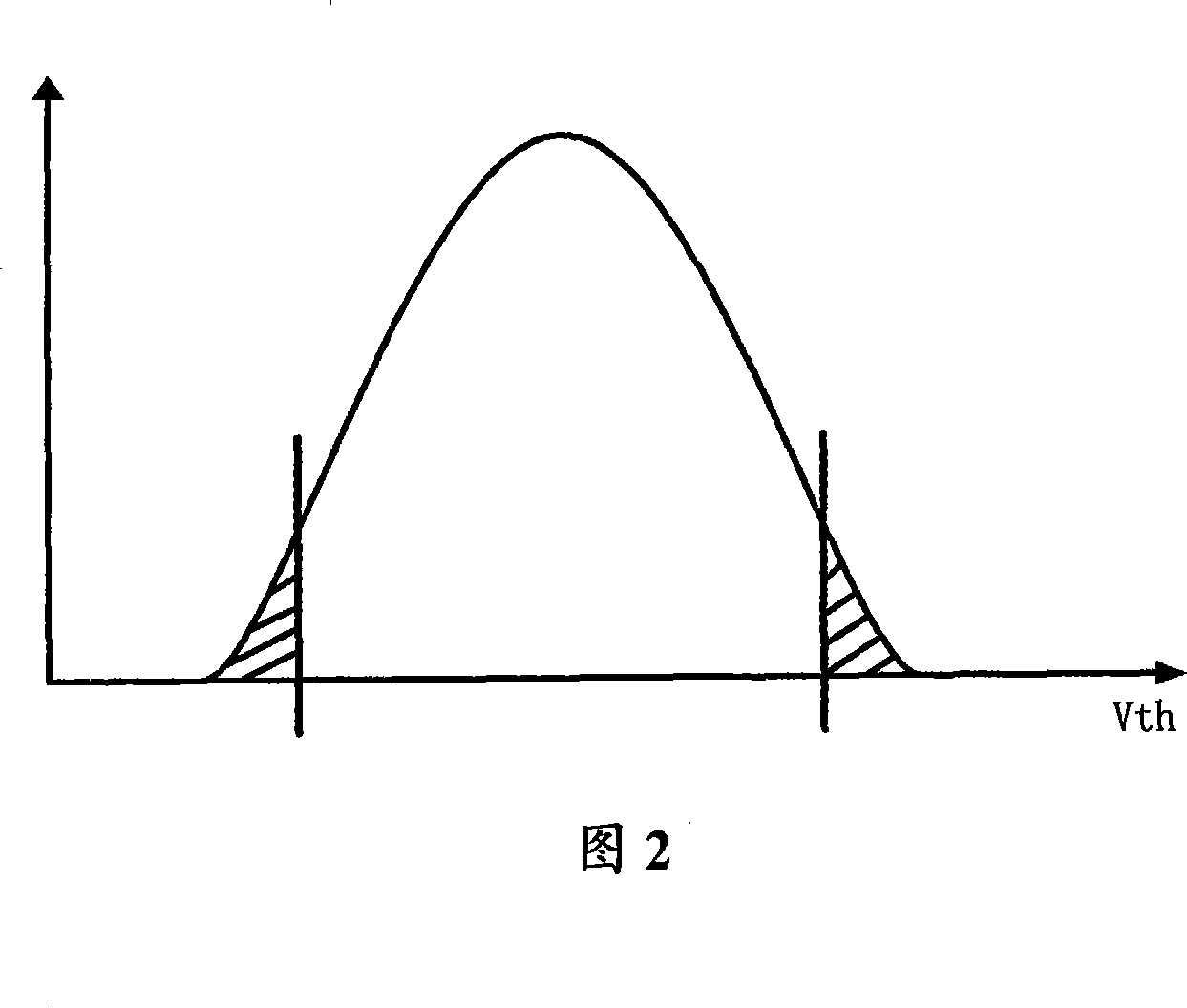

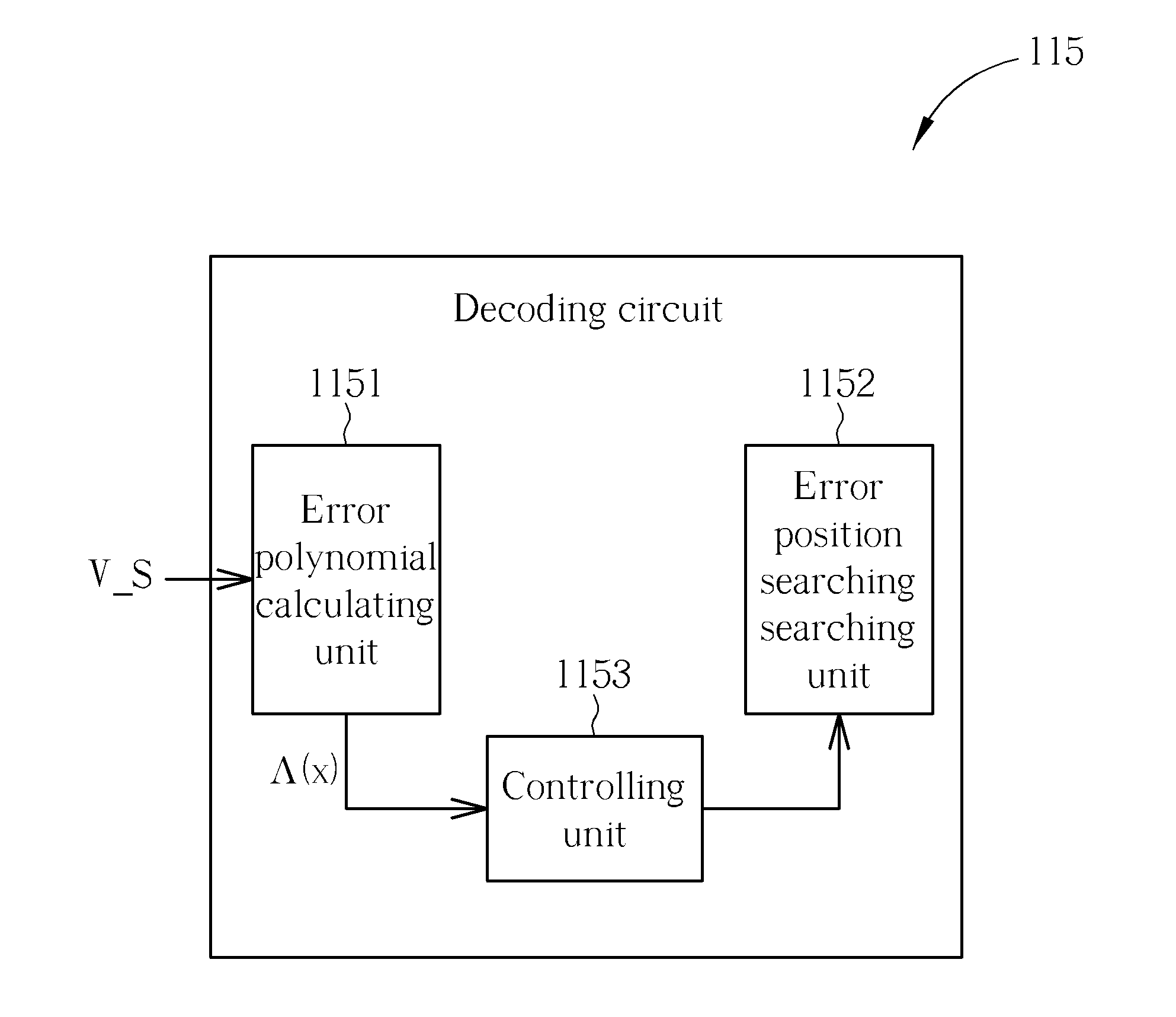

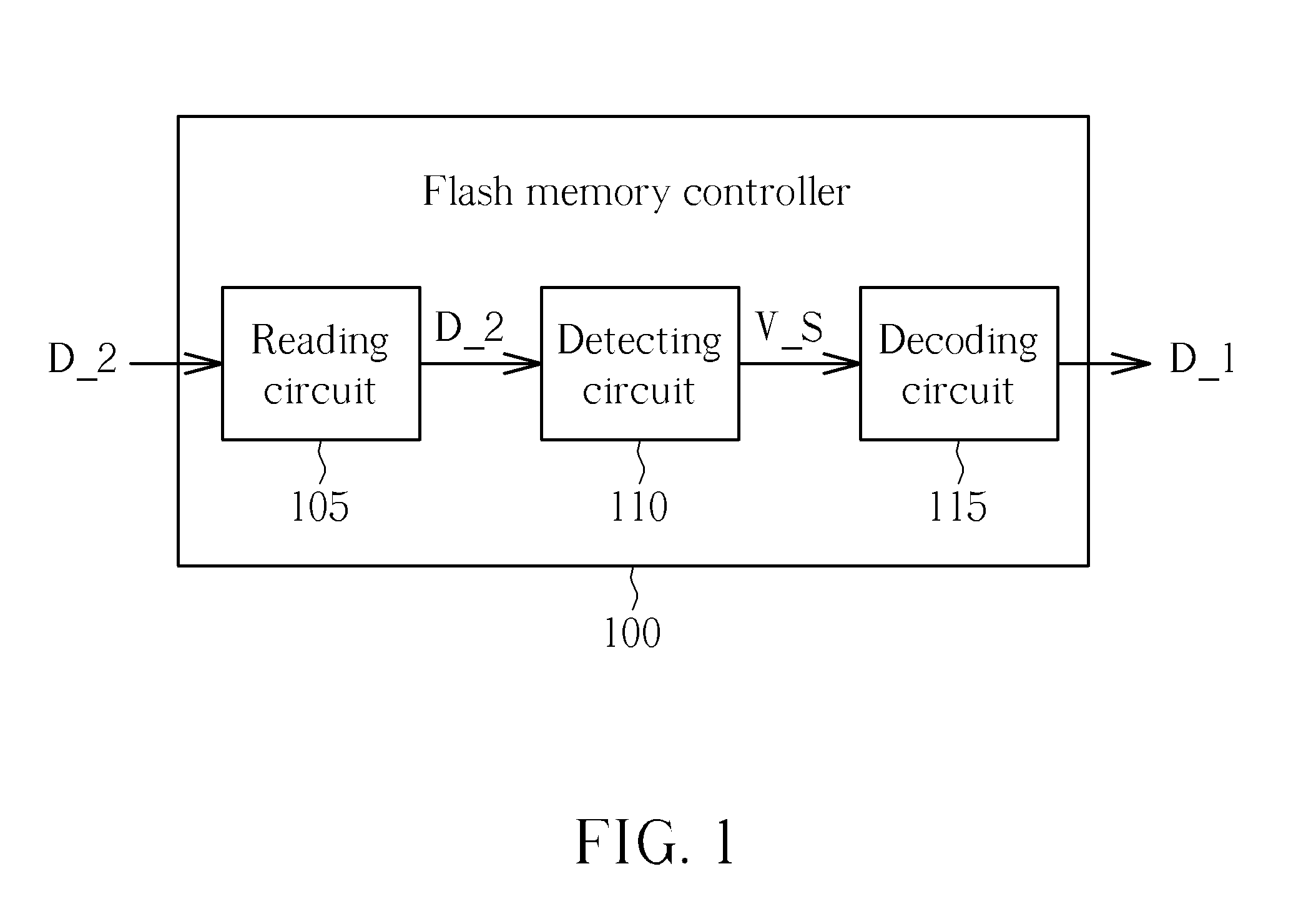

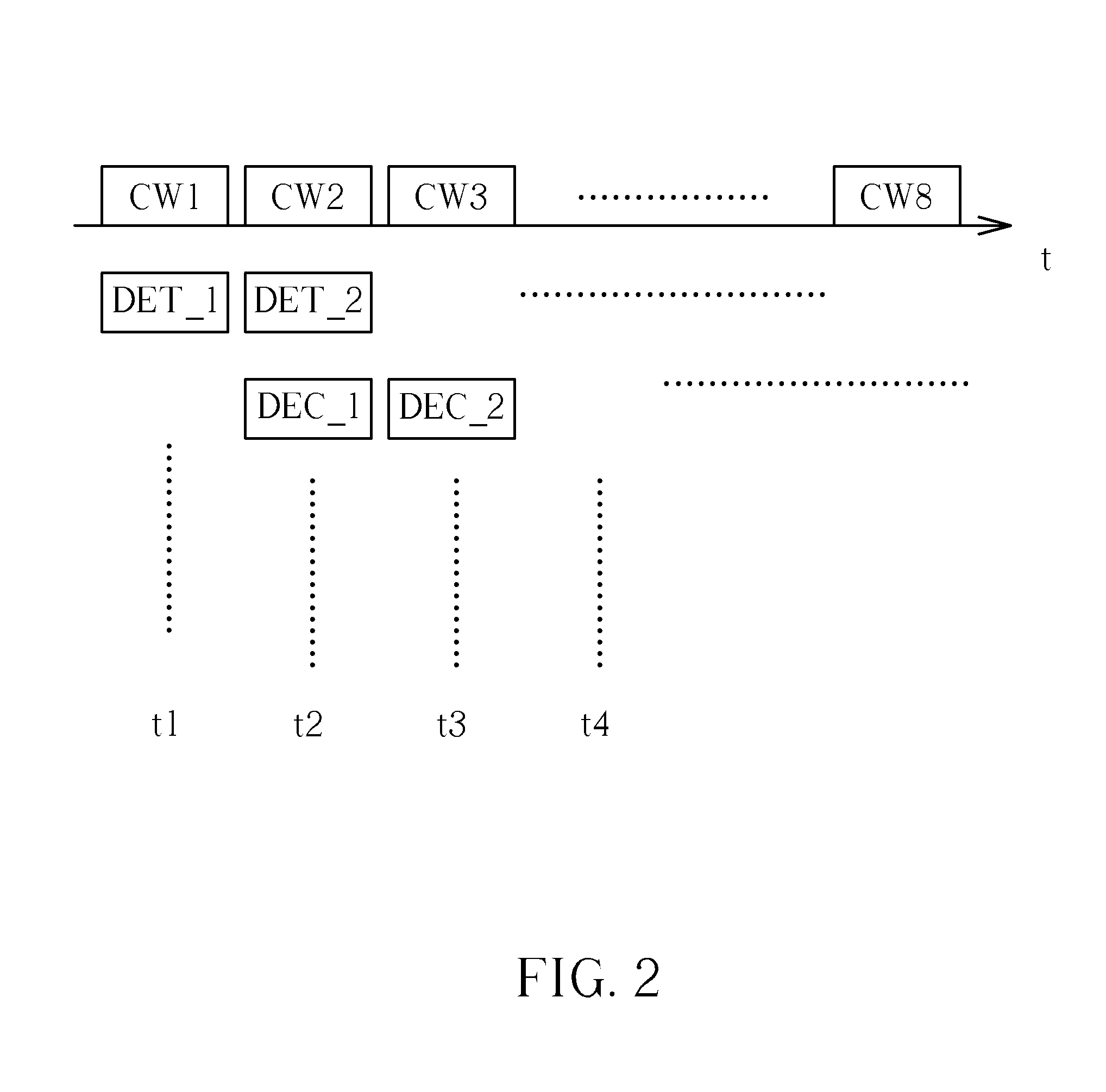

Flash memory controller and data reading method

ActiveUS20130024751A1Short access timeImprove performanceCode conversionError correction/detection using block codesFlash memory controllerMemory controller

A data reading method is provided. The data reading method includes: utilizing a first sense voltage to read a data unit from a flash memory block; performing an error detection operation on the data unit and calculating an error polynomial according to a detection result; and determining whether the error polynomial conforms to a predetermined condition and deciding whether to perform read retry on the data unit according to a determining result.

Owner:SILICON MOTION INC (TW)

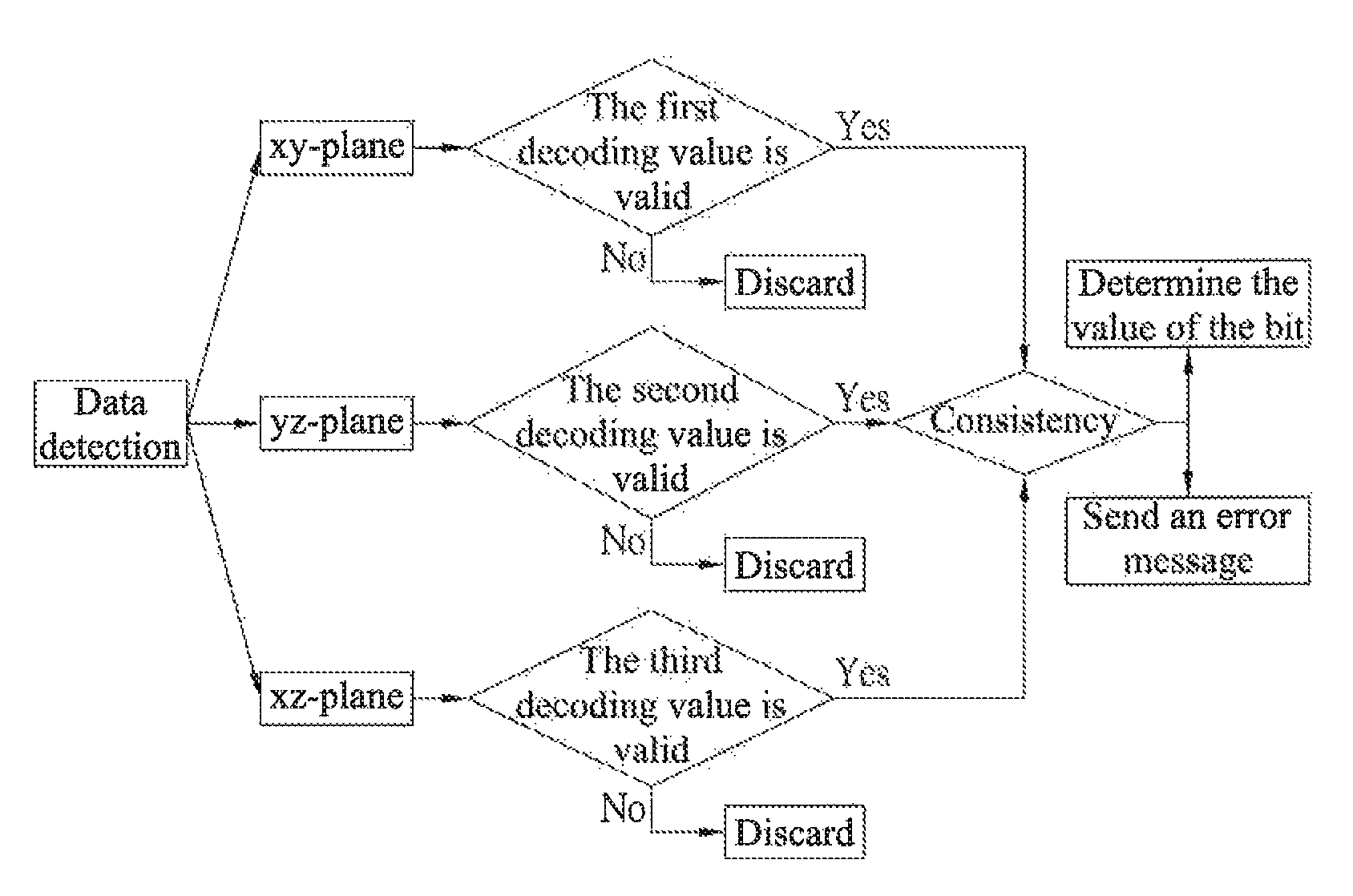

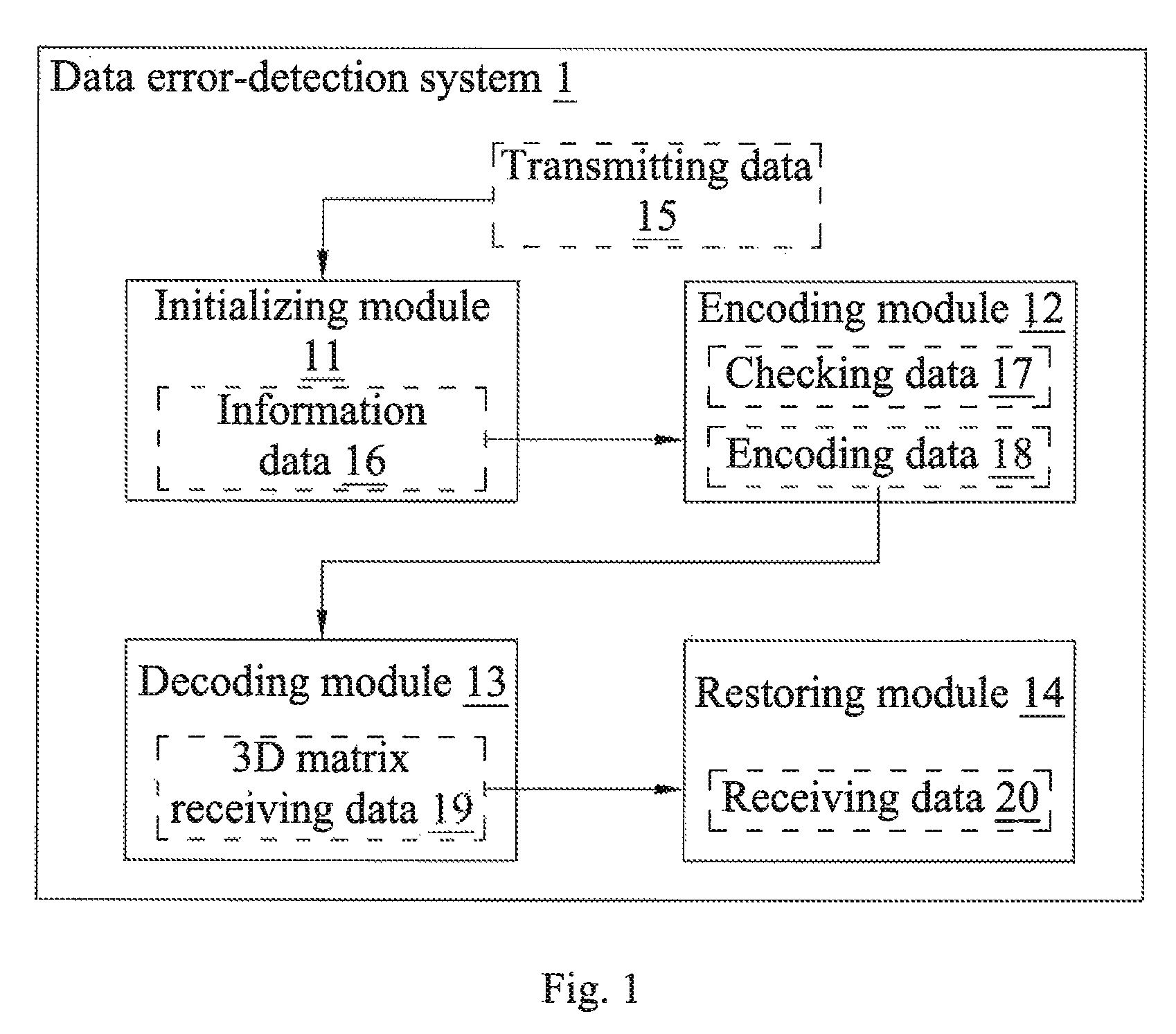

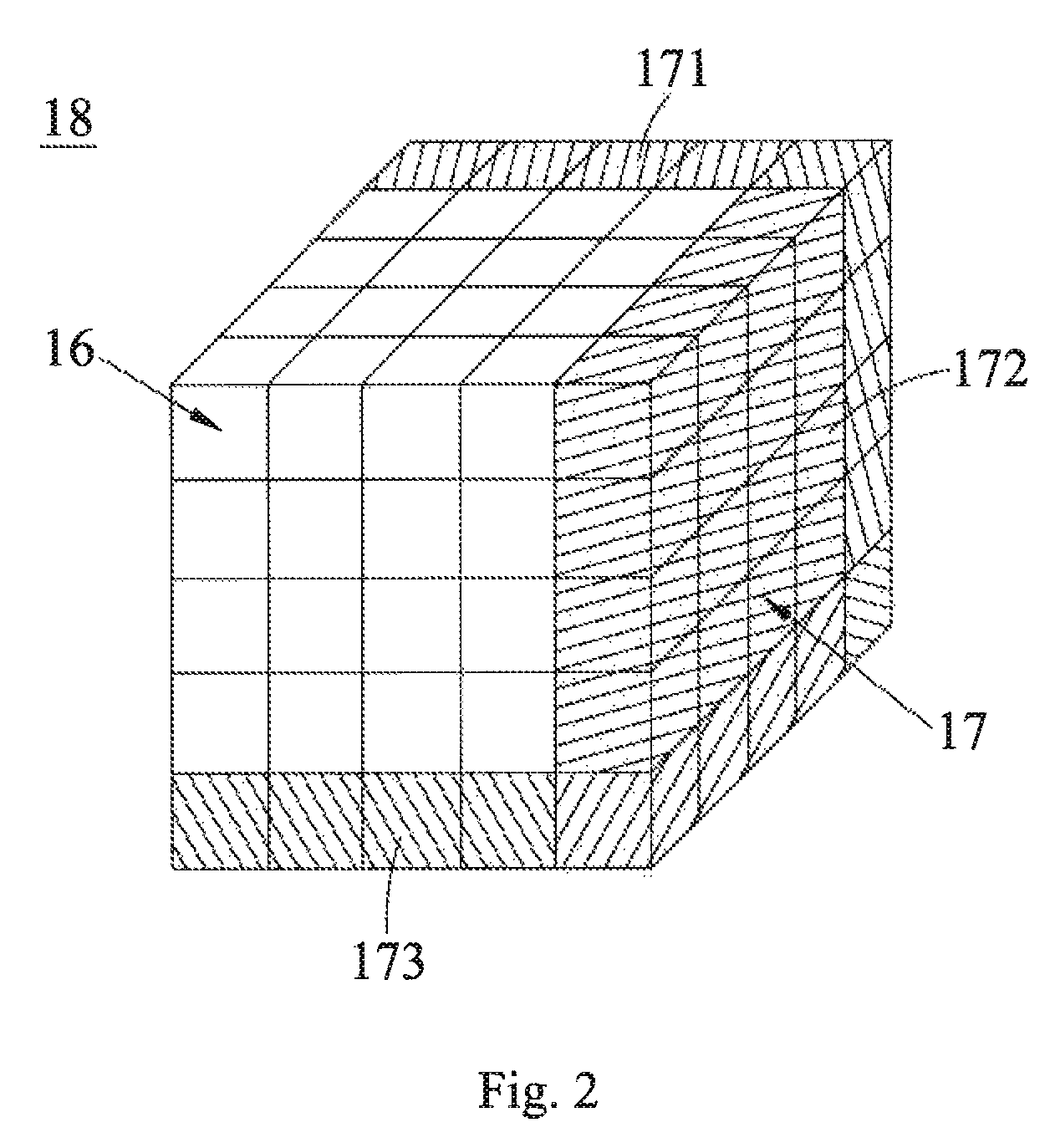

Data error-detection system and data error-detection method thereof

ActiveUS8977942B2Overcome deficienciesError preventionTransmission systemsData errorError detection and correction

Owner:NATIONAL TSING HUA UNIVERSITY

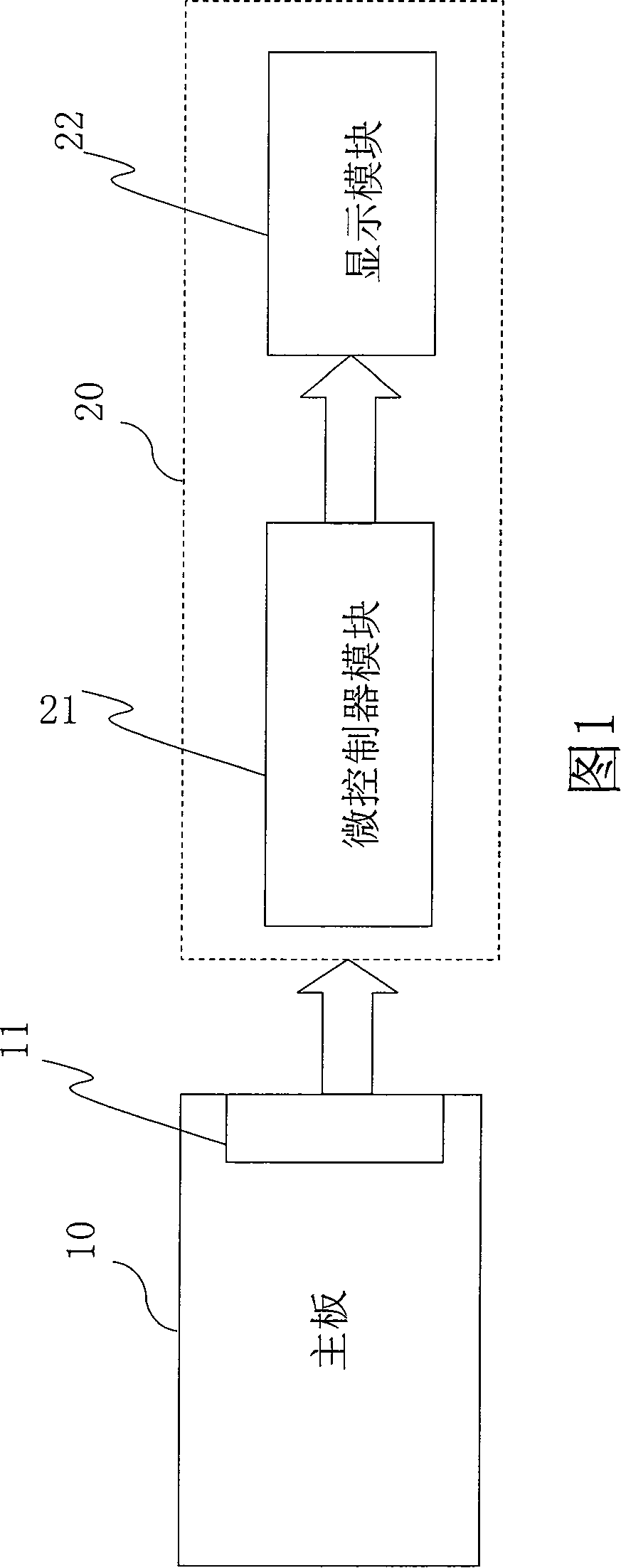

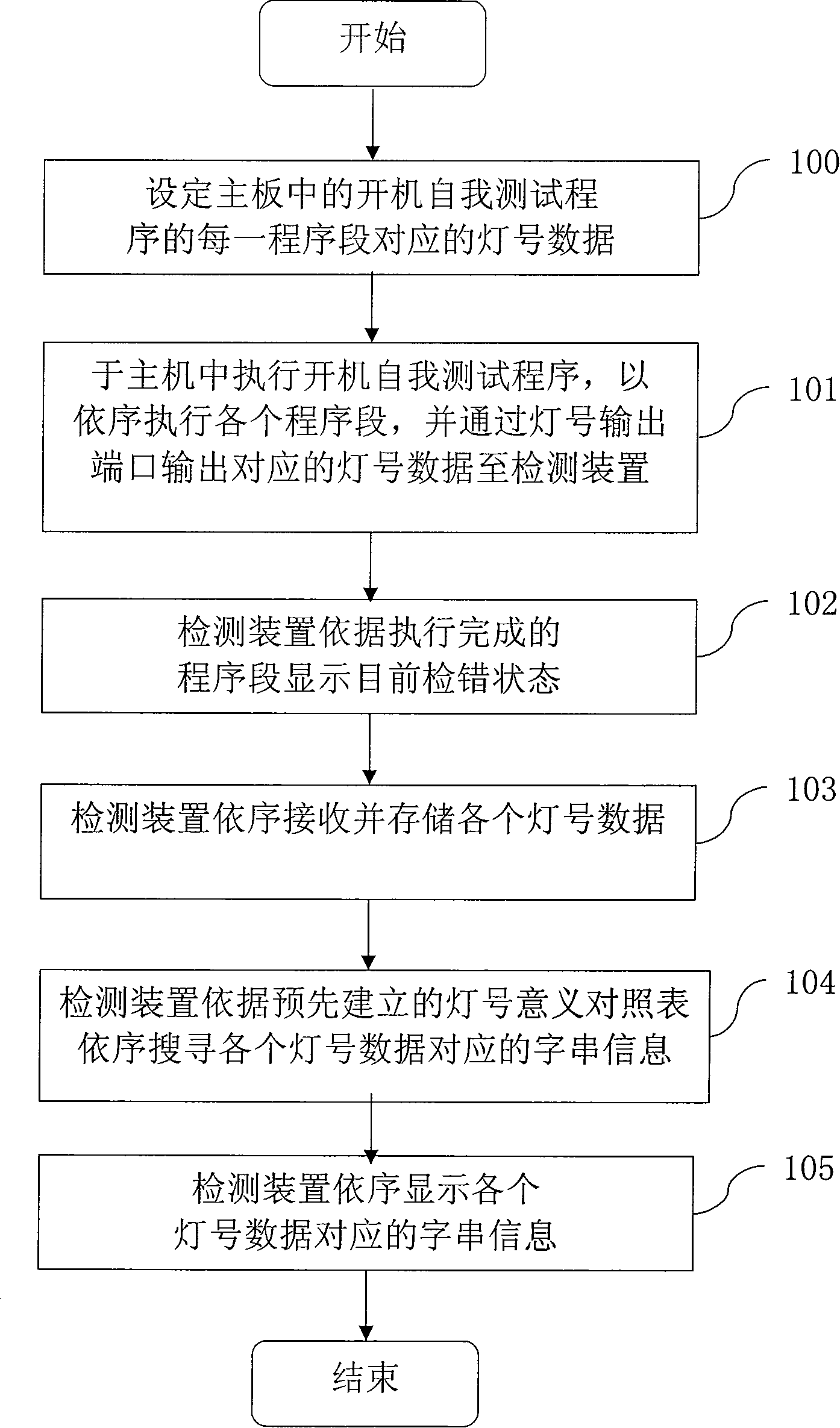

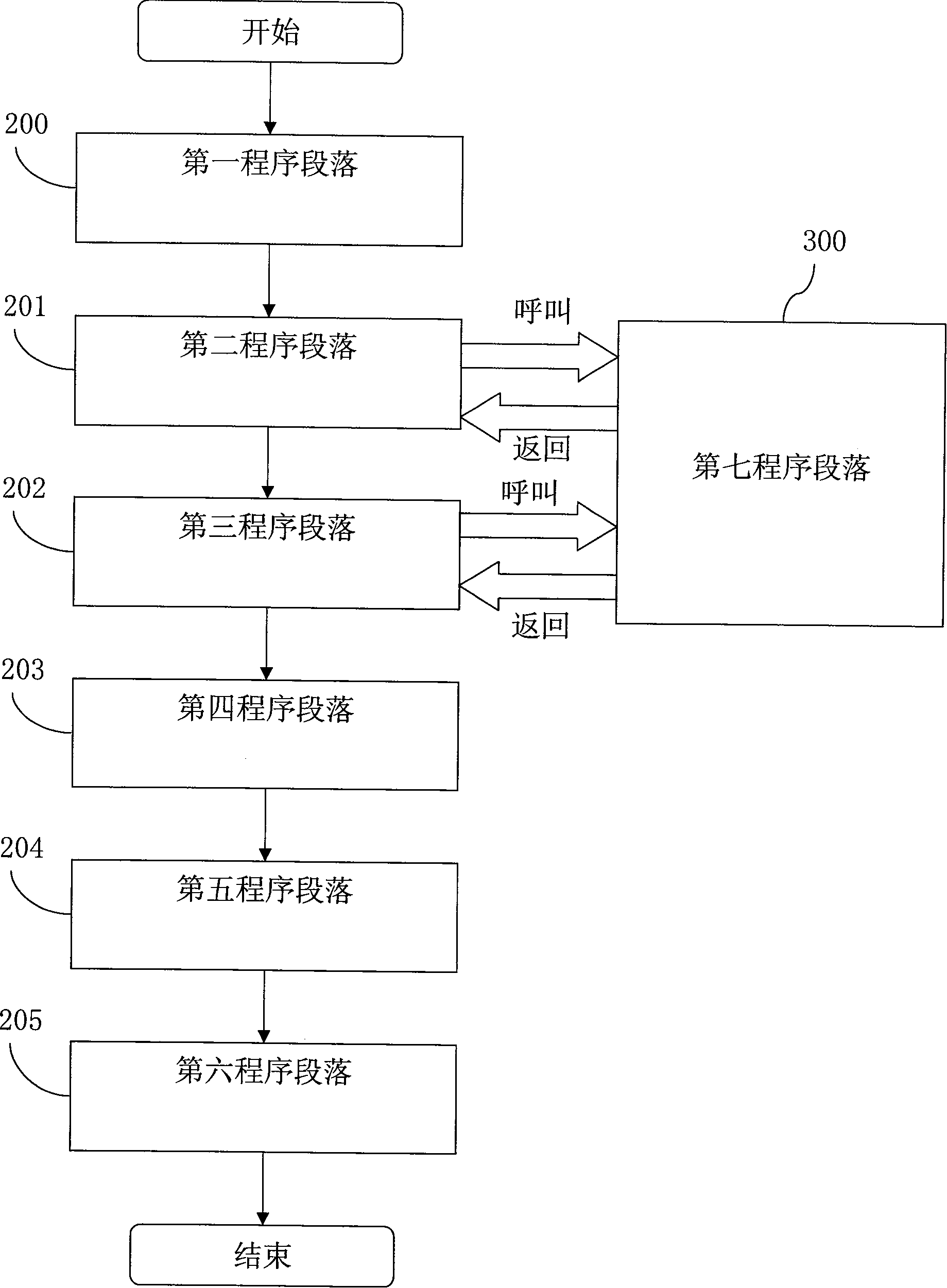

Mainboard error detection method

InactiveCN101174234AImprove detection efficiencyDetecting faulty computer hardwareHardware monitoringProgram segmentComputerized system

The invention discloses a motherboard error detection method. A detection device is connected to a signal output port to obtain related error detection information. The method comprises the steps that corresponding signal data of each program segment of a starting up self test program in the motherboard is set; the starting up self test program is executed in the motherboard, the program segments are executed in sequence, and the corresponding signal data is output to the detection device through the signal output port; the detection device receives and stores the signal data in sequence; the detection device searches the corresponding character string information of the signal data in sequence according to a pre-established signal meaning cross reference list; the detection device displays the corresponding character string information of the signal data in sequence. The invention ensures that maintenance personnel can be aware of the content of an error detecting code without checking an error detecting code technical manual, and provides complete error detection information to facilitate the maintenance personnel to judge the cause of the error of a computer system, thereby improving the motherboard detection efficiency.

Owner:INVENTEC CORP

Data corruption scrubbing for content addressable memory and ternary content addressable memory

ActiveUS7757152B2Error detection/correctionCode conversionData CorruptionTernary content addressable memory

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

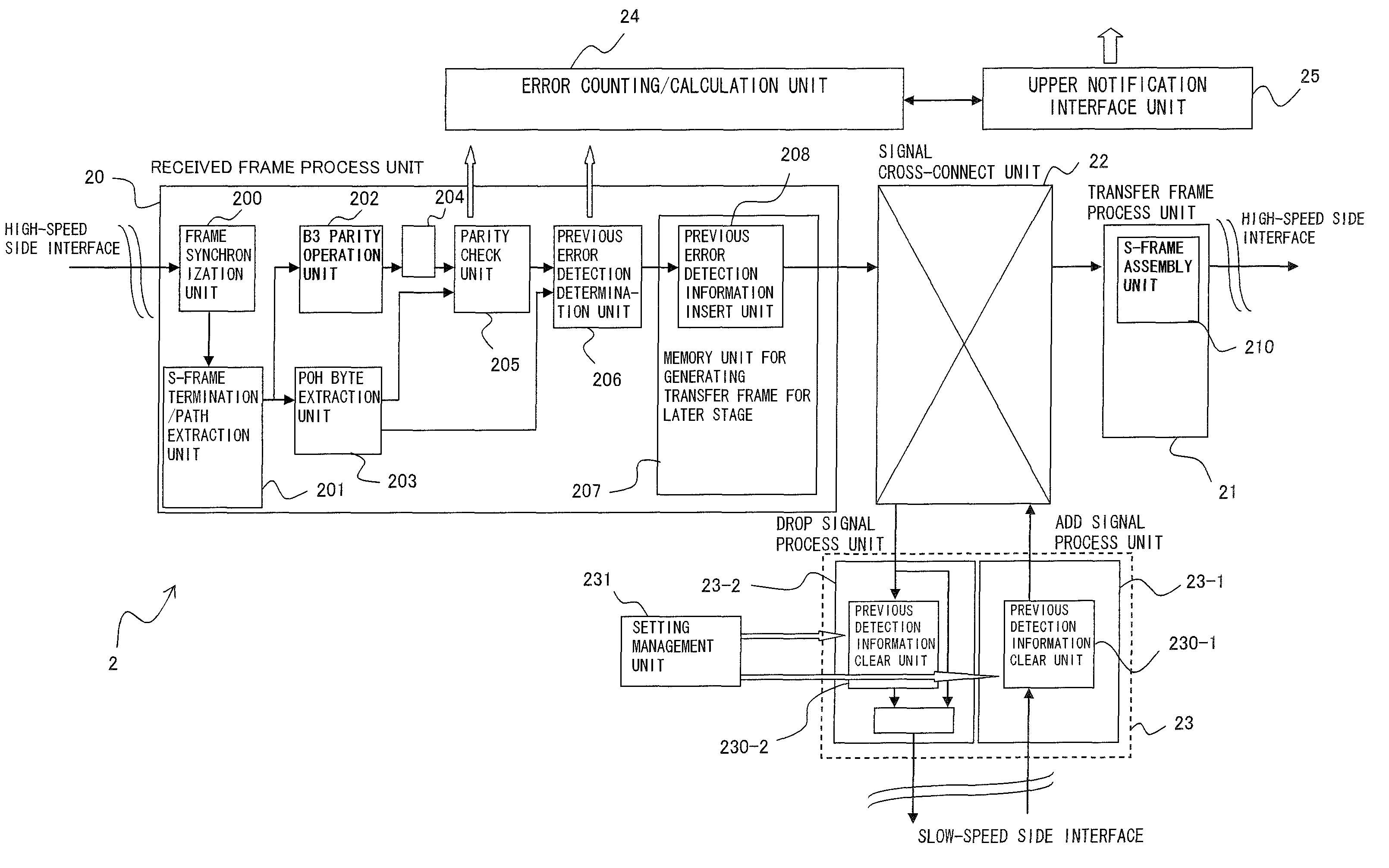

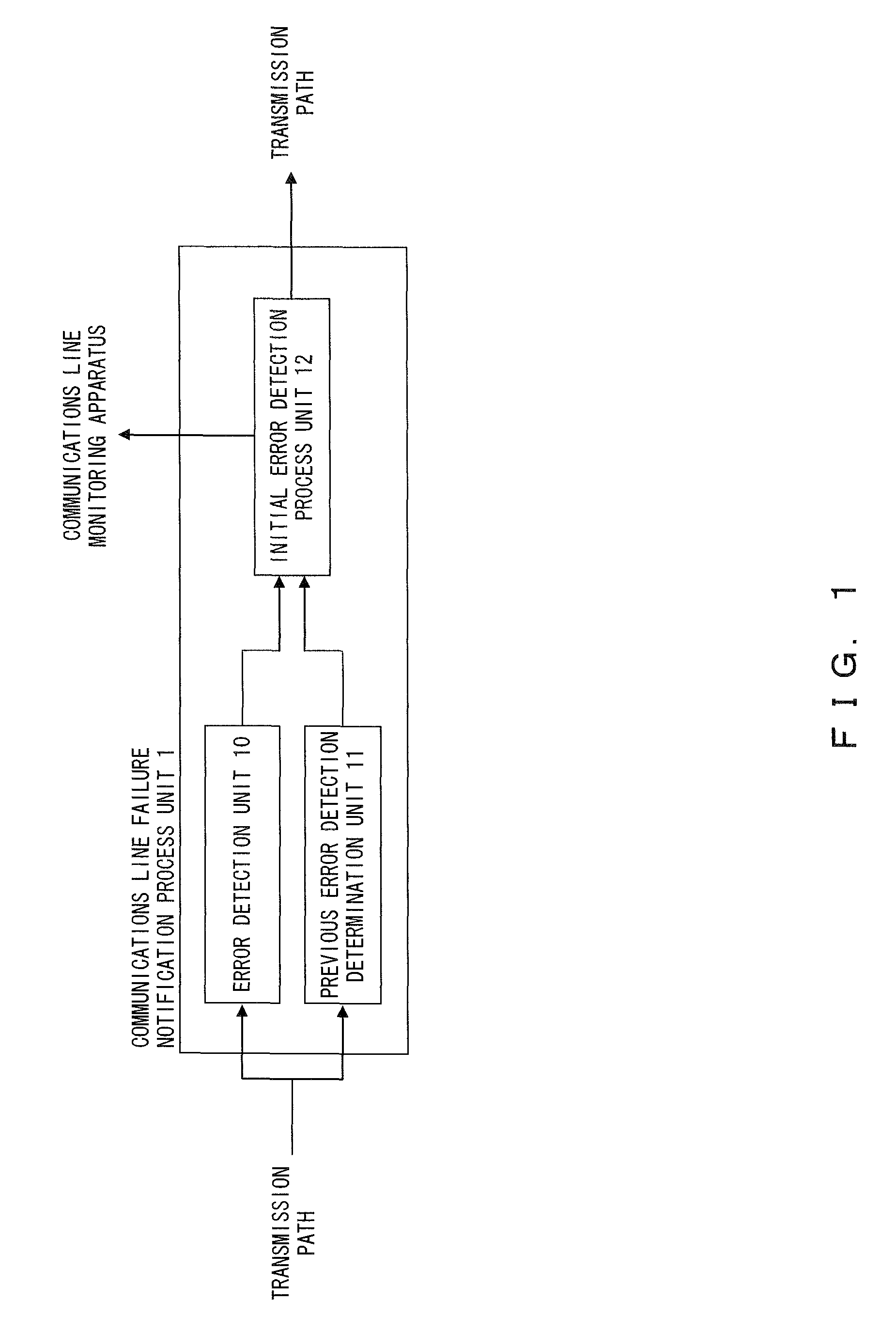

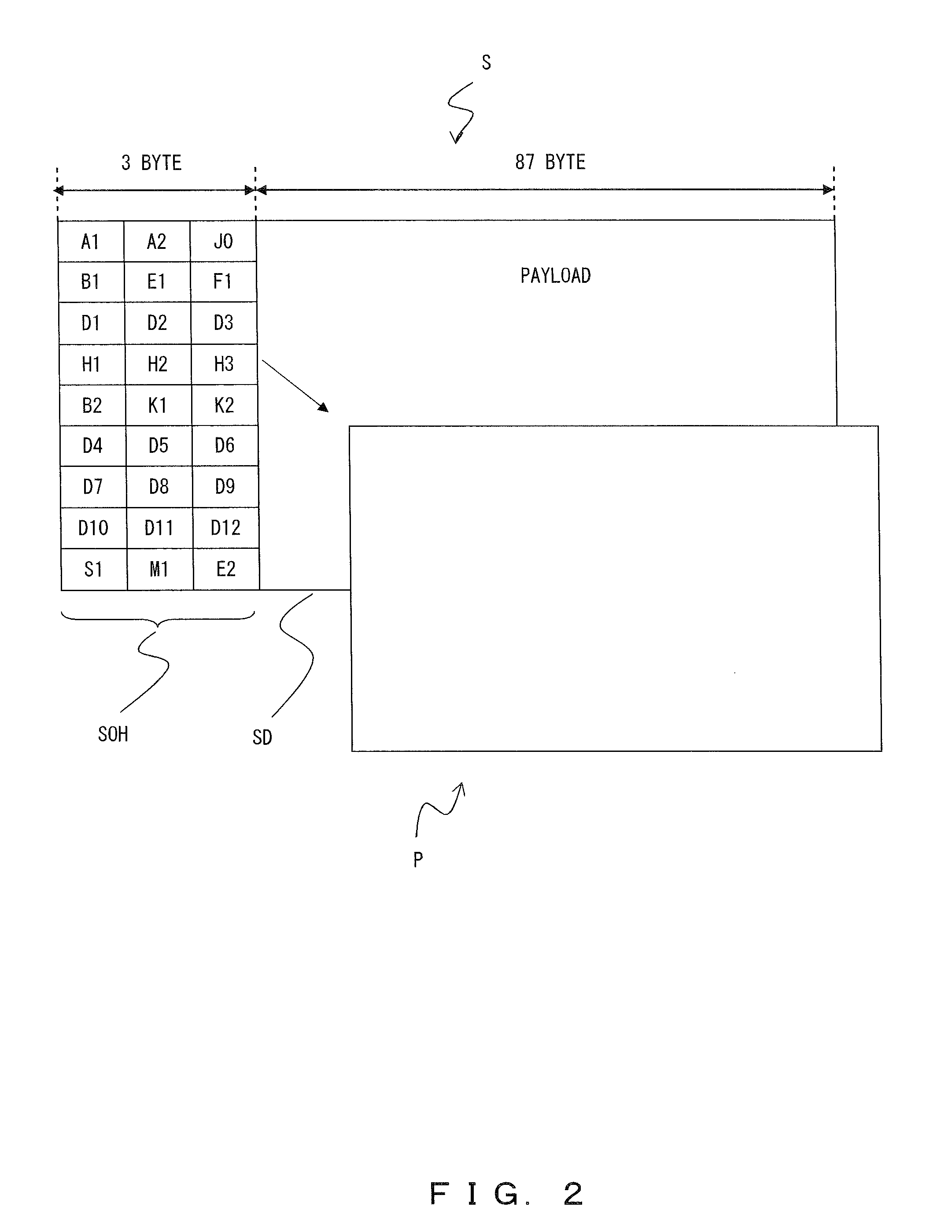

Communications line monitoring system, relay apparatus, and communications line monitoring method

InactiveUS7882419B2Error detection/correctionCode conversionMonitoring systemError detection and correction

A communications line monitoring system of the present invention comprises a plurality of relay apparatus and a communications line monitoring apparatus for monitoring a line quality of a communications line of relayed data, and each of the relay apparatus comprises error detecting unit for detecting errors in received data, previous error detection determination unit for determining whether or not error detection has already been performed in other apparatus based on previous error detection information of the received data, and initial error detection process unit for, only when an error is detected and the error was undetected in other apparatus, autonomously notifying error detection information to the communications line monitoring apparatus, and for adding previous error detection information to data for transmission.

Owner:FUJITSU LTD

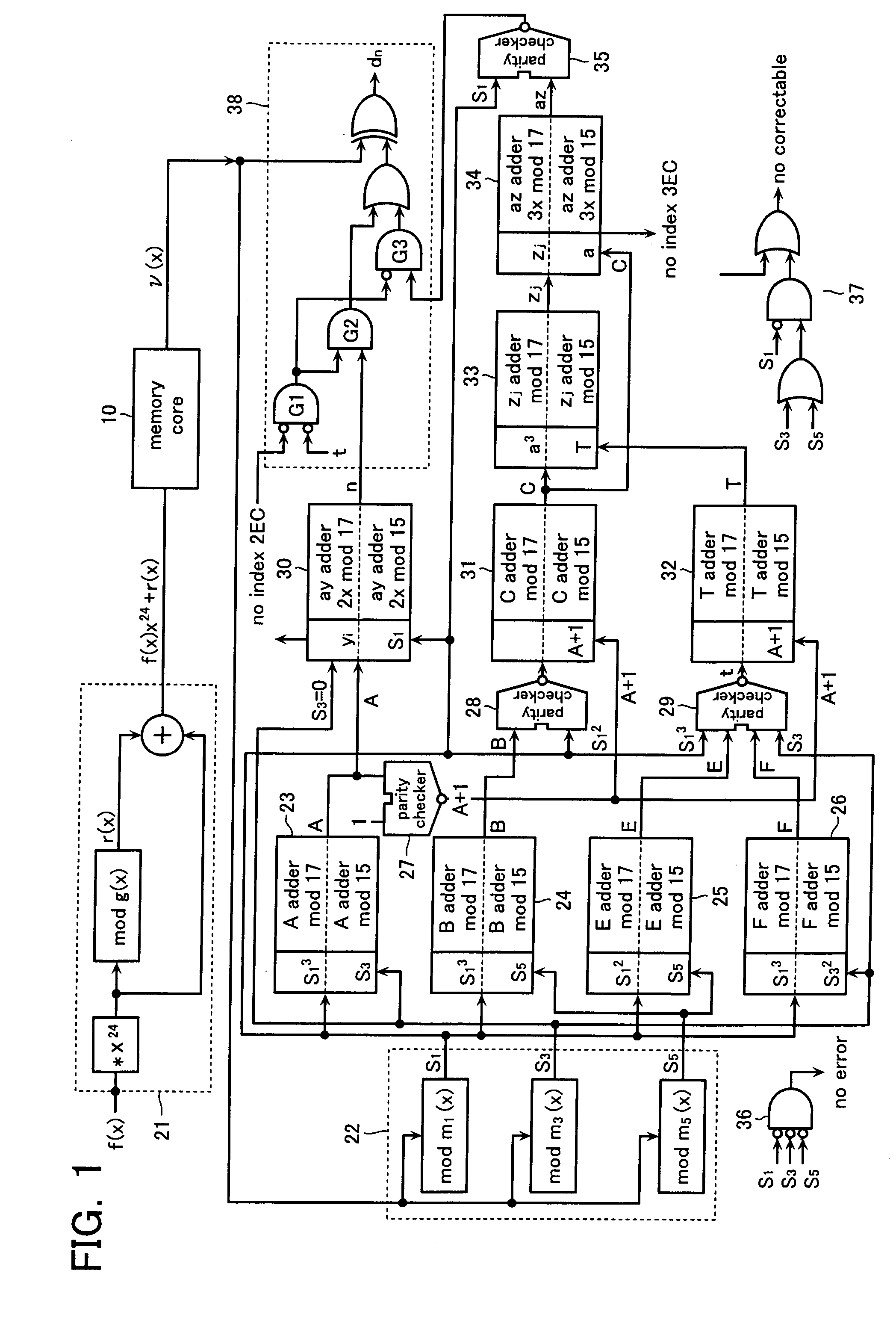

Semiconductor memory device

A semiconductor memory device including an error detecting and correcting system, wherein the error detecting and correcting system includes a 3EC system configured to be able to detect and correct 3-bit errors, and wherein the 3EC system is configured to search errors in such a manner that 3-degree error searching equation is divided into a first part containing only unknown numbers and a second part calculative with syndromes via variable transformation by use of two or more parameters, and previously nominated solution indexes collected in a table and syndrome indexes are compared to each other.

Owner:KK TOSHIBA

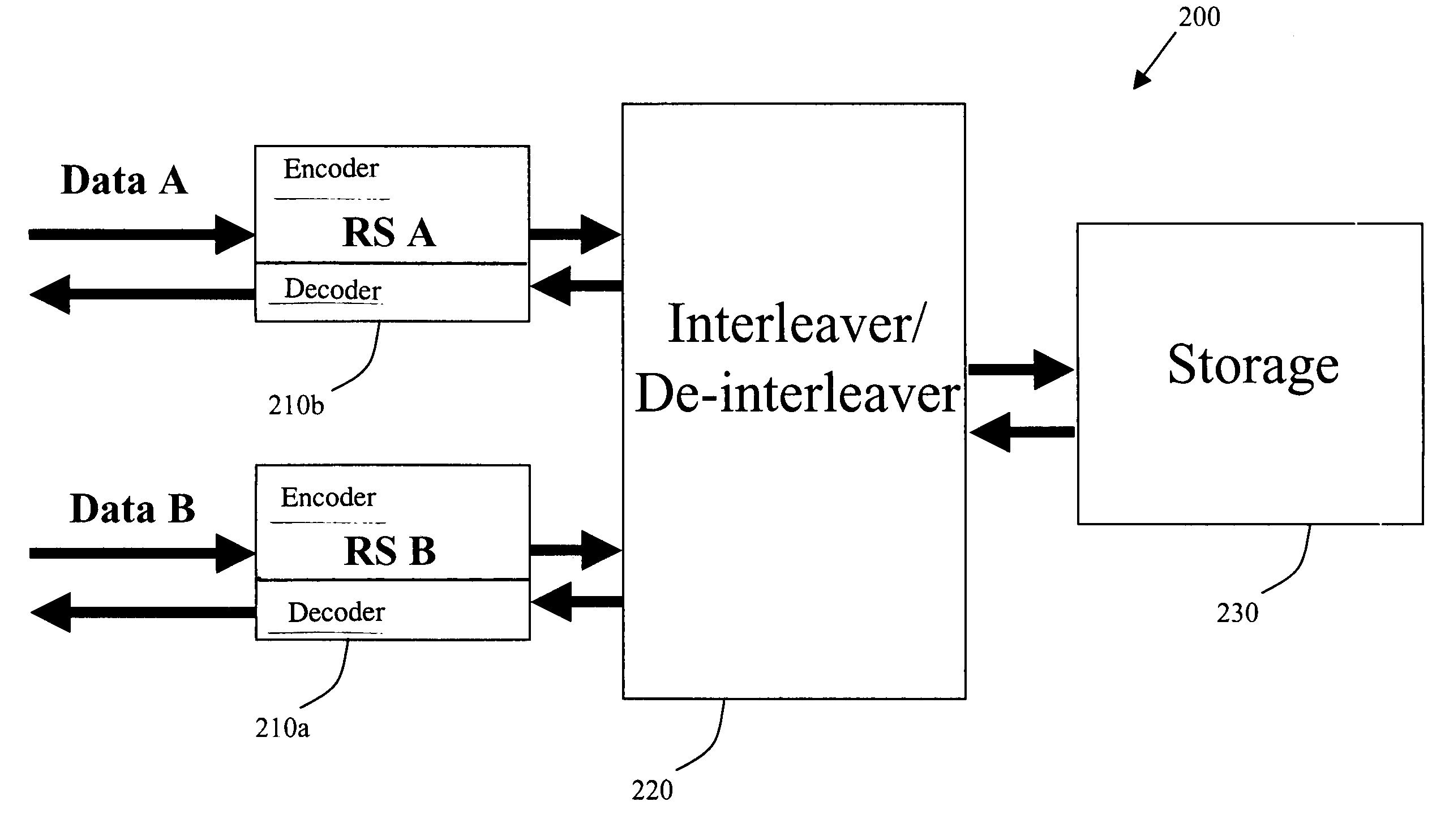

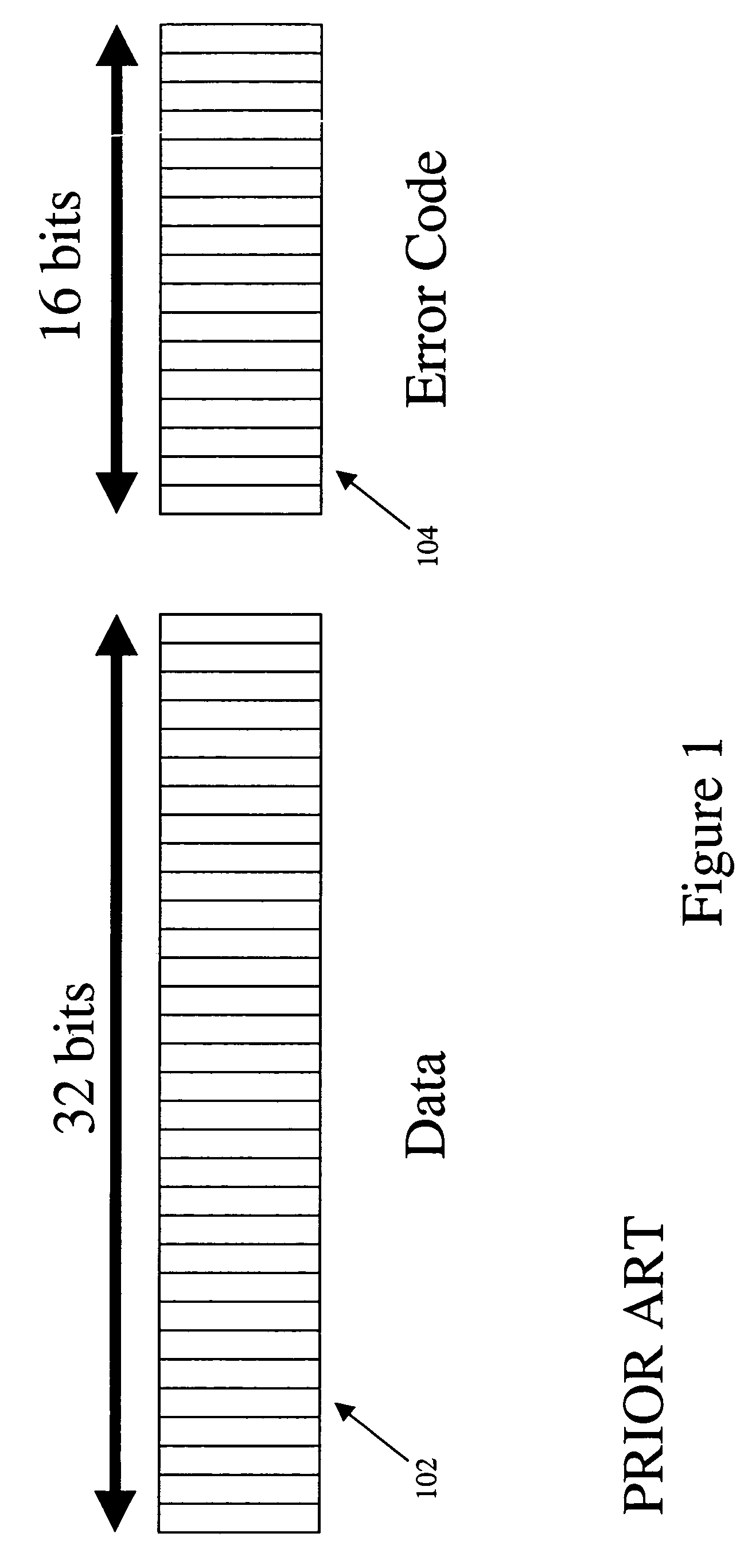

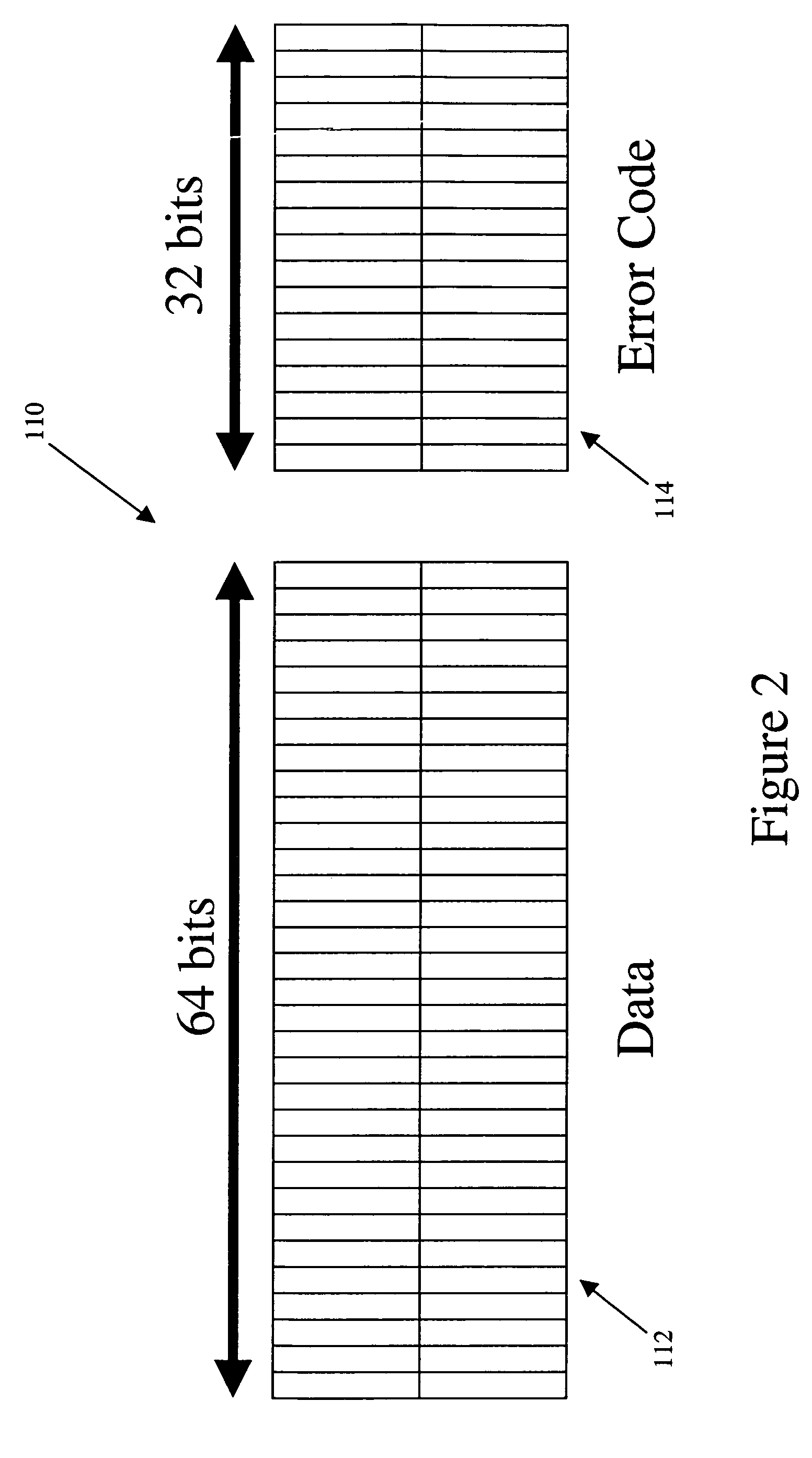

Error detection and correction method and system for memory devices

ActiveUS7475326B2Increasing costIncrease the number ofError detection/correctionStatic storageComputer hardwareData set

A method and a system for the detection and correction of errors in memory systems is disclosed. In one embodiment, a method of error detection in a memory system having a plurality (m>1) of memory devices includes generating check bits for each of a plurality of data sets, dividing each memory device into a plurality (n>1) of segments. The plurality of data sets are interleaved to form a plurality (p>1) of words. Each word includes at least one segment from two or more of the memory devices. Detection and correction may utilize oneor more parallel Reed-Solomon decoder and encoder. The system and method allow for the efficient detection and / or correction of memory device errors and bit errors in one or more memory devices.

Owner:DATA DEVICE CORP

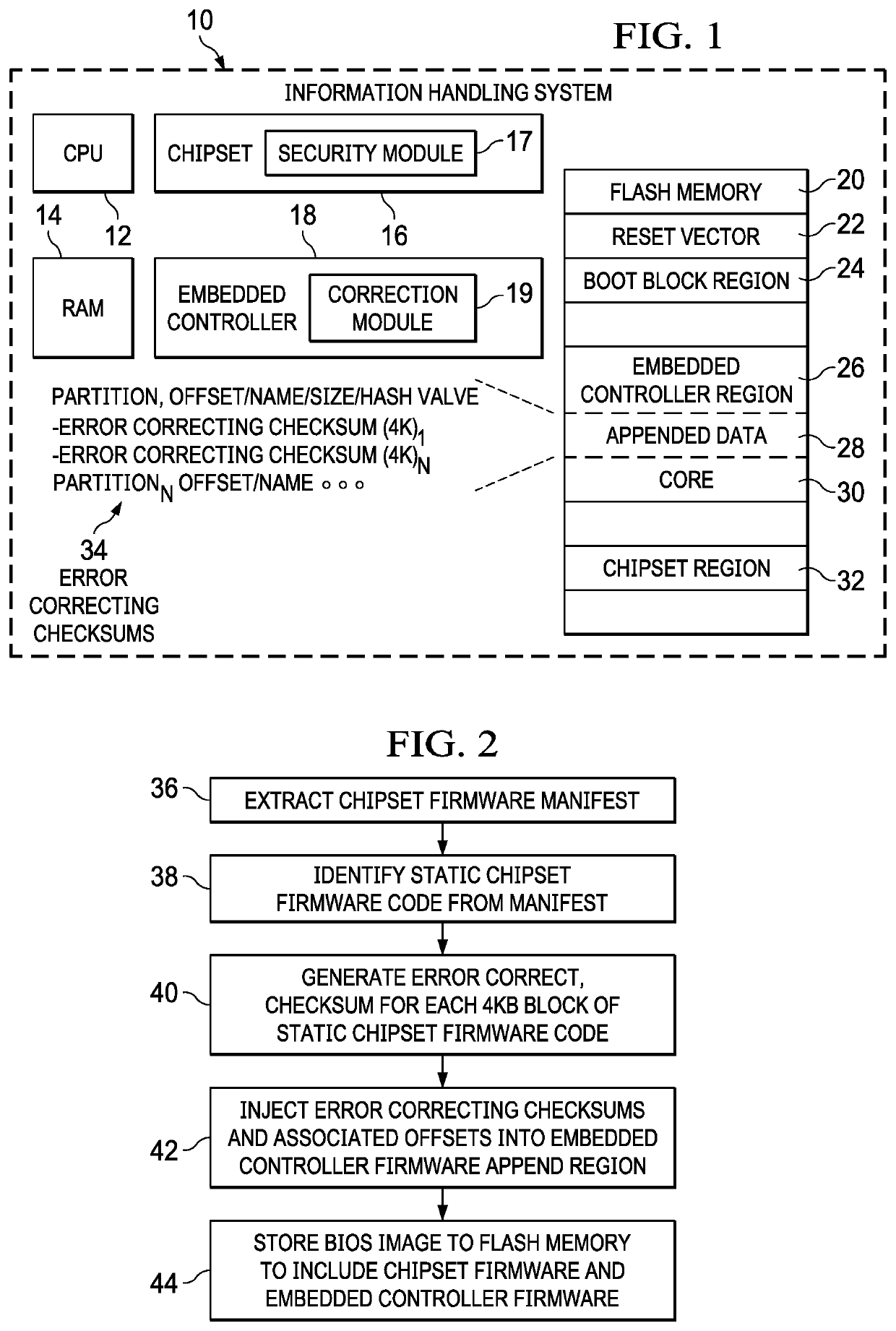

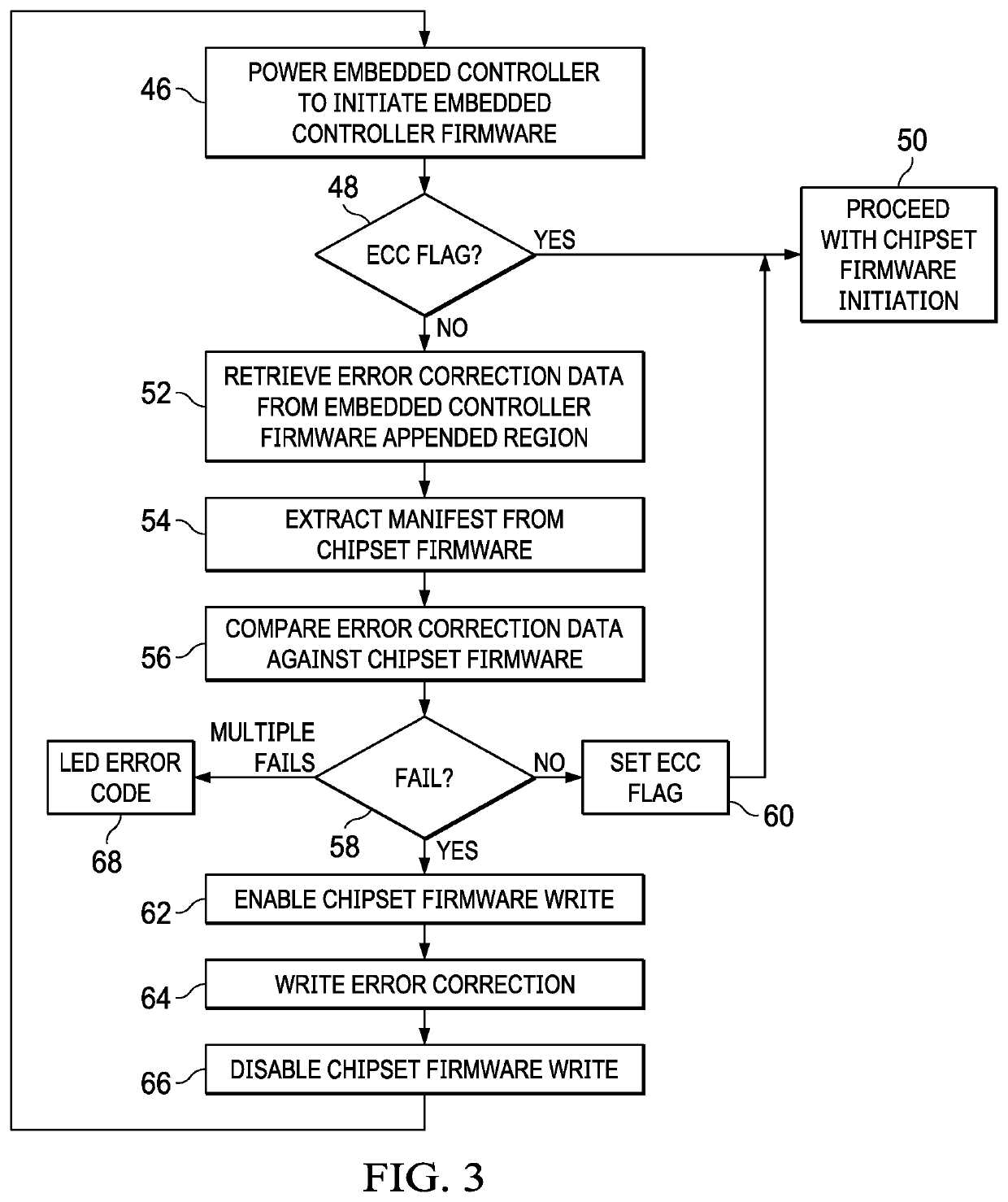

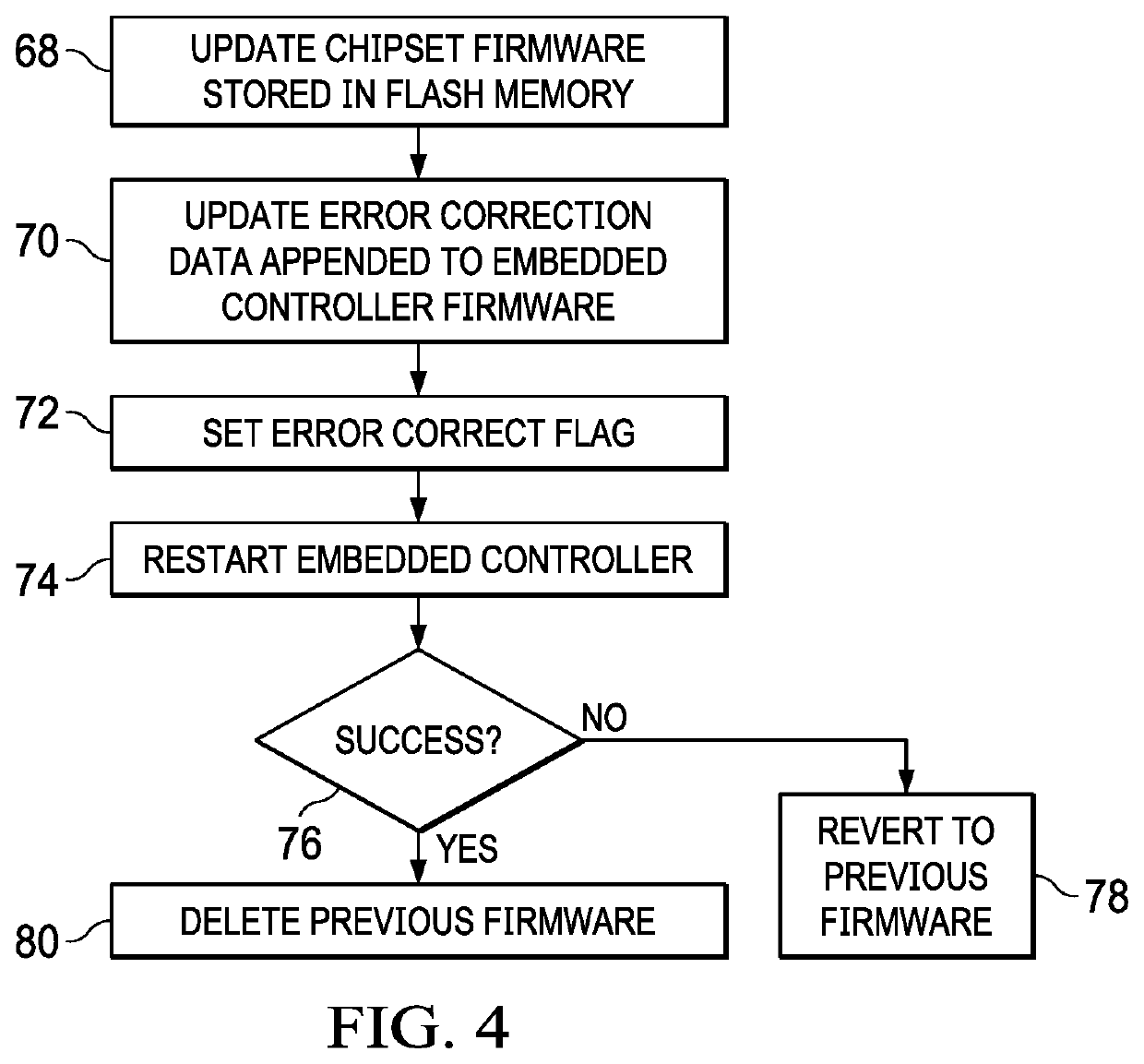

Information handling system firmware bit error detection and correction

ActiveUS20200104504A1Avoiding replacement of partAvoid replacementDigital data protectionPower supply for data processingChecksumChipset

An information handling system embedded controller does not initiate a chipset having secure execution of chipset firmware unless the chipset firmware validates against error correcting checksums inserted into the embedded controller firmware. Comparing checksums calculated from chipset firmware against expected checksum values for the chipset firmware prevents secure chipset initiation failure due to bit errors associated with chipset firmware storage in flash memory.

Owner:DELL PROD LP

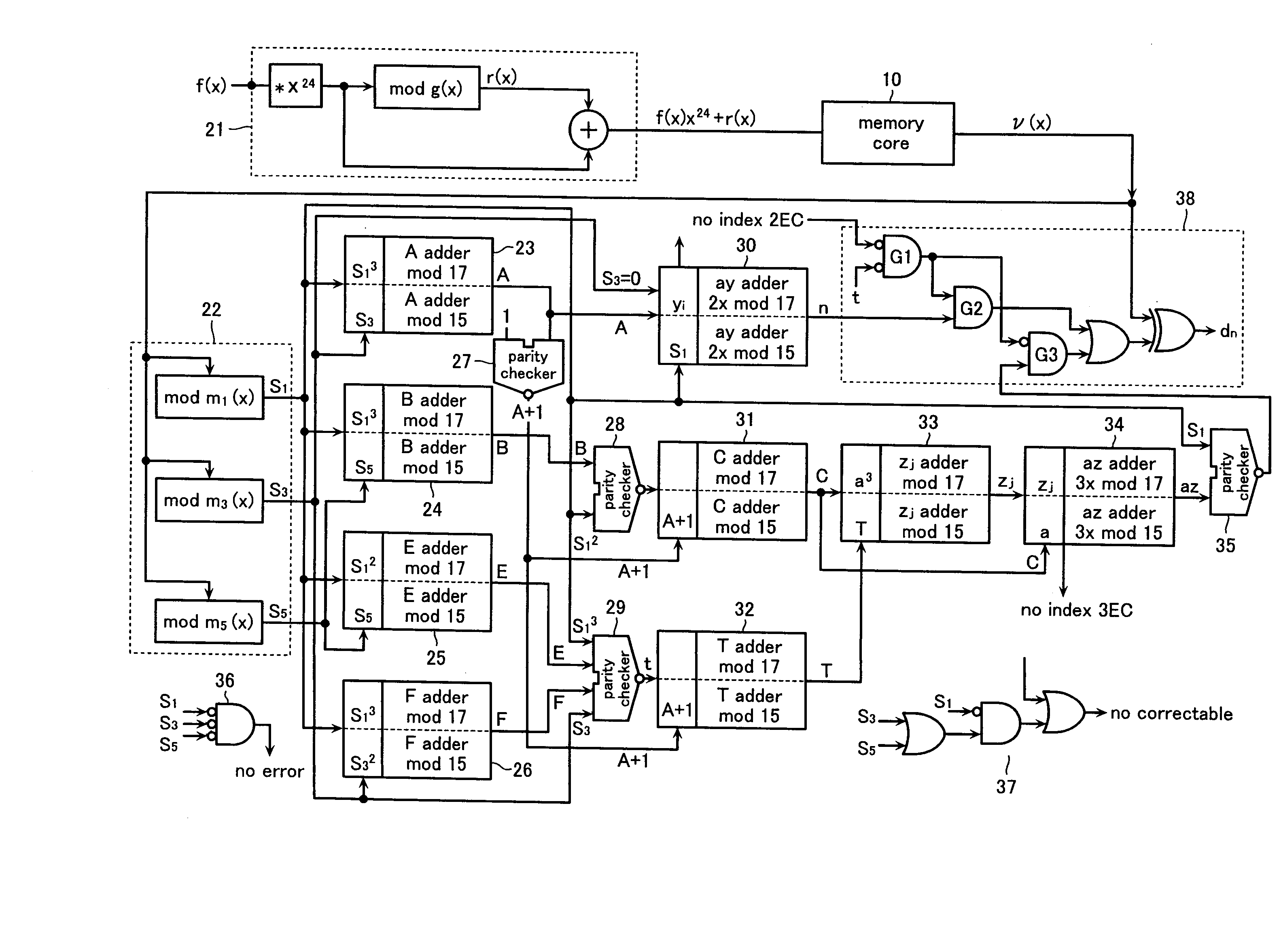

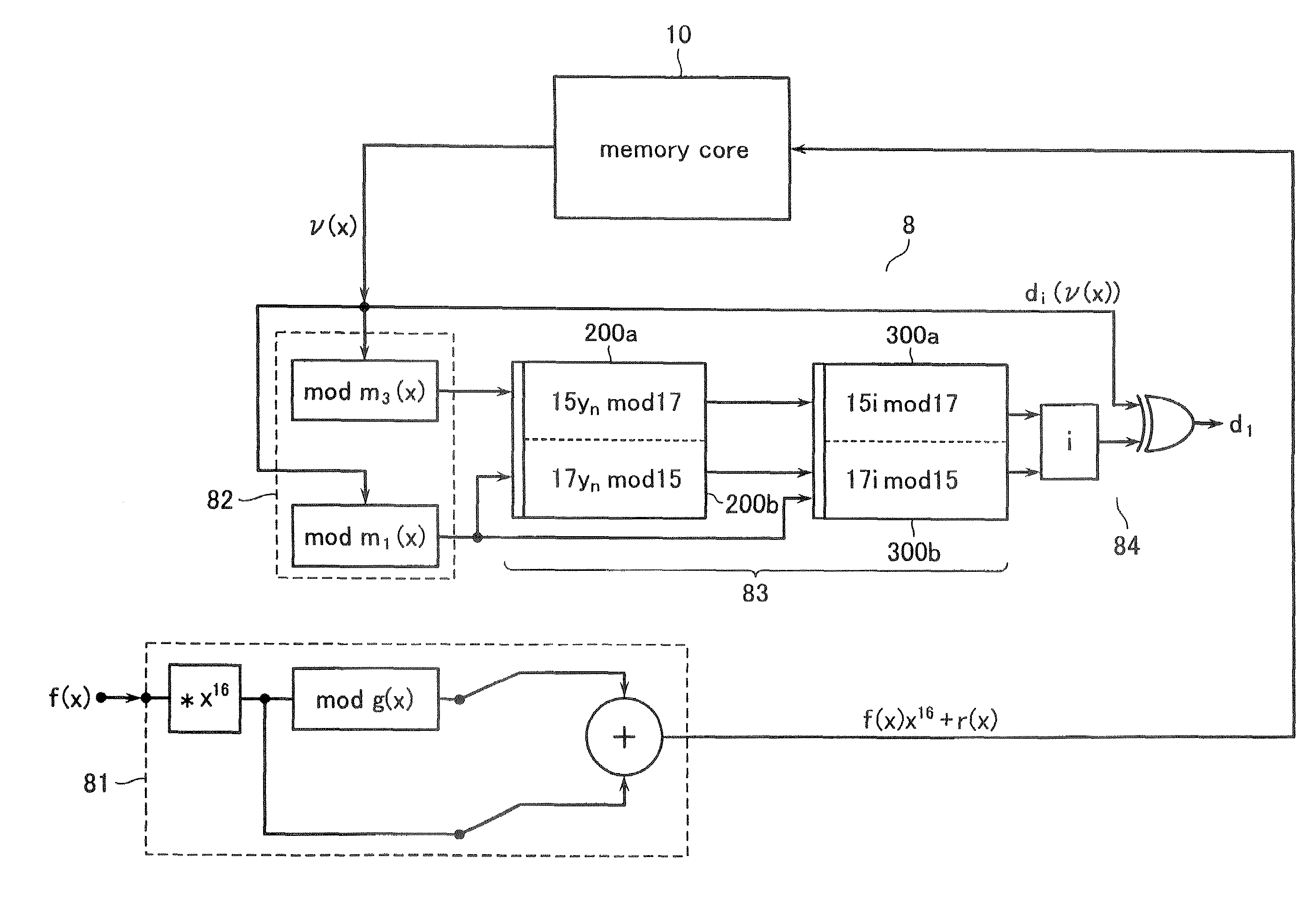

Semiconductor memory device

InactiveUS7941733B2Digital data processing detailsError detection/correctionError detection and correctionSemiconductor memory

A memory device includes an error detection and correction system with an error correcting code over GF(2n) wherein the system has an operation circuit configured to execute addition / subtraction with modulo 2n−1, and wherein the operation circuit has a first operation part for performing addition / subtraction with modulo M and a second operation part for performing addition / subtraction with modulo N (where, M and N are integers which are prime with each other as being obtained by factorizing 2n−1), and wherein the first and second operation parts perform addition / subtraction in parallel to output an operation result of the addition / subtraction with modulo 2n−1.

Owner:KK TOSHIBA

Robot system having error detection function of robot and control method thereof

When an error occurs in robot system, a difference between first and second detection values of two sensors or first and second sensors occurs due to differences in position and responsibility. When this difference exceeds a predetermined threshold, control section detects that a difference has occurred in robot system. The first and second detection values of two sensors or first and second sensors are compared, and therefore, reliability of the detection values can be secured. Further, the abnormal state can be determined through the difference between the first and second detection values, and therefore, errors resulting from problems such as variations in gears and speed reducers due to temperature changes of the operational state and disposition environment of the robot can be avoided.

Owner:FANUC LTD

Semiconductor memory device and data error detection and correction method of the same

ActiveUS20110209030A1Code conversionError correction/detection using block codesMemory bankData error

A semiconductor memory device includes a memory cell array, a mode setting circuit, a parity data generation unit, and a data error detection and correction unit. The memory cell array has a plurality of first memory banks for storing normal data, and a predetermined number of second memory banks less than the number of the first memory banks for storing parity data according to control of a first flag signal. The mode setting circuit sets the first flag signal and a second flag signal controlling based on whether a separate memory bank is used to store the parity data in the second memory banks. The parity data generation unit receives normal write data during a write operation, generates parity data with respect to the normal write data in response to the second flag signal, and outputs the normal data and the parity data. The data error detection and correction unit receives normal read data and parity read data read from the memory cell array during a read operation, detects errors of the normal read data in response to the second flag signal, corrects the normal read data when the errors are detected, and outputs the corrected read data.

Owner:SAMSUNG ELECTRONICS CO LTD

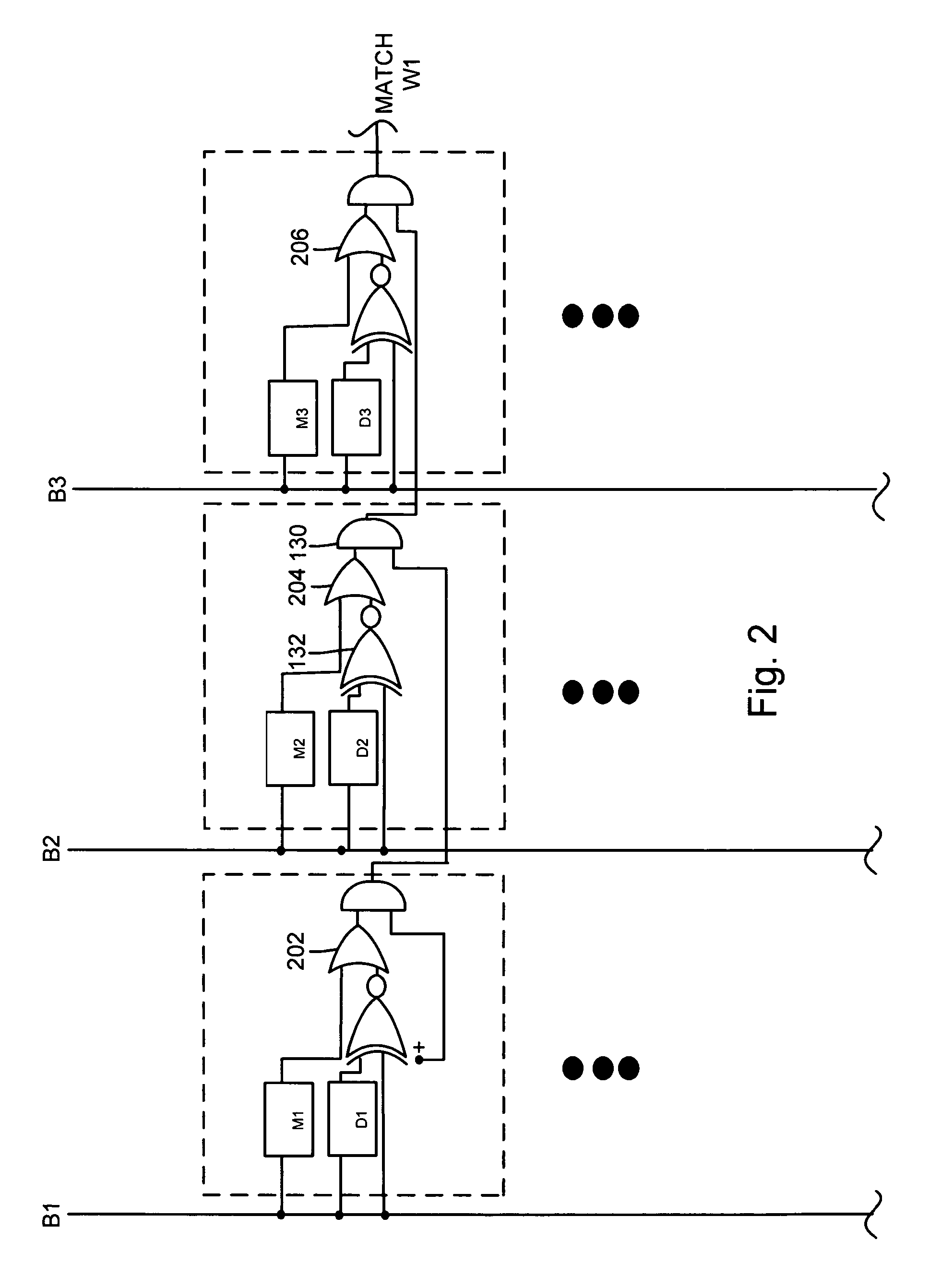

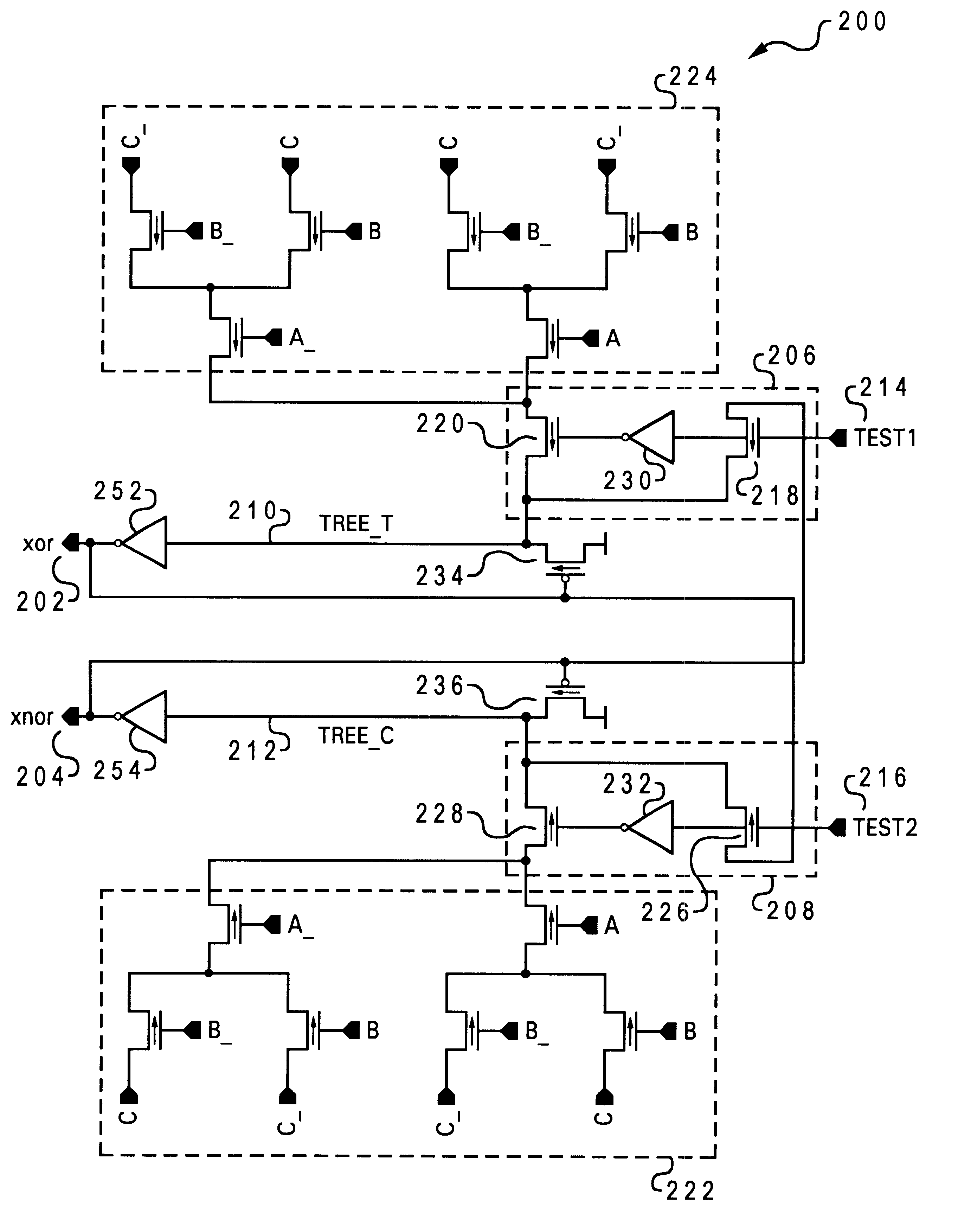

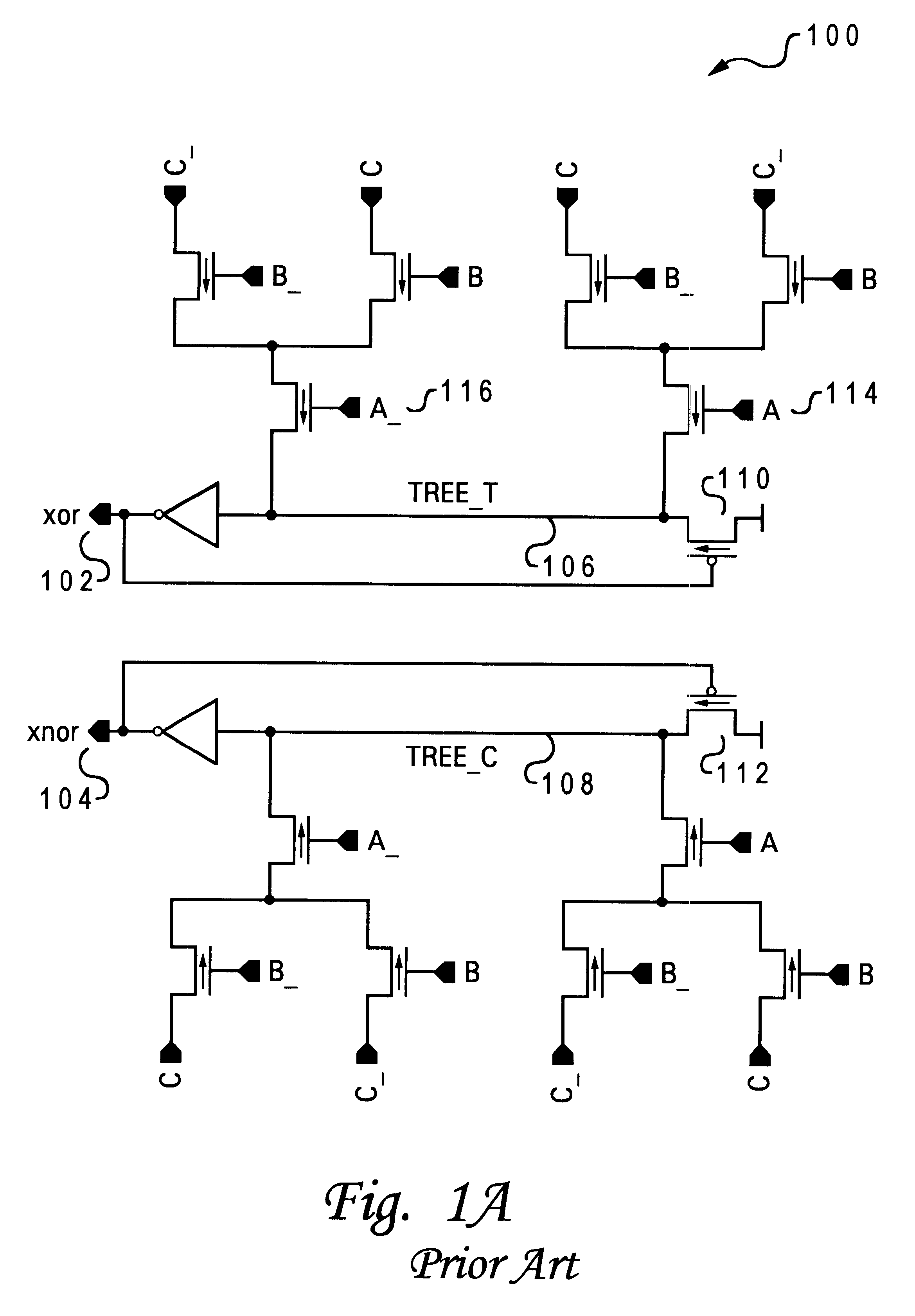

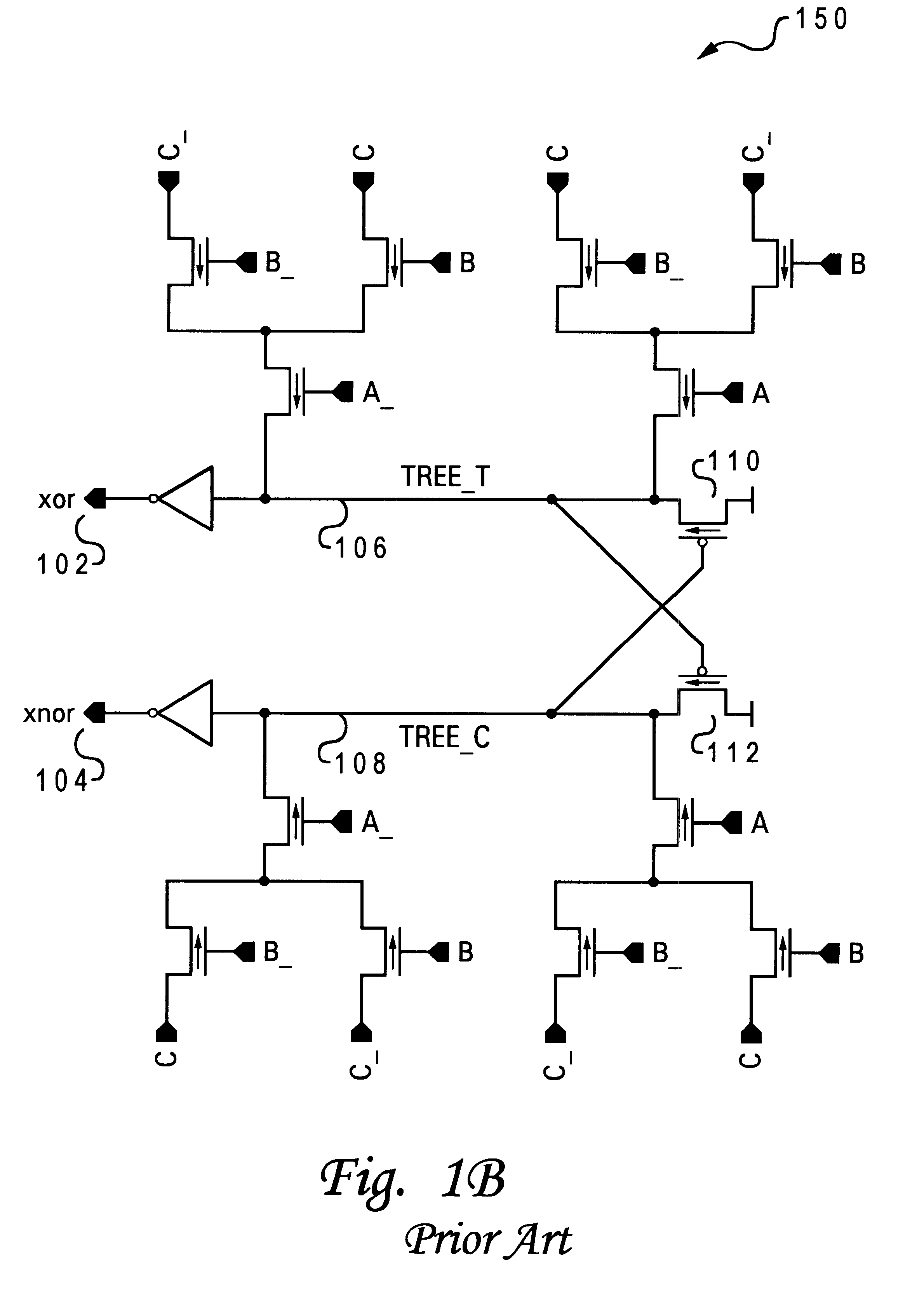

Complementary logic error detection and correction

InactiveUS6502220B1Logic circuits characterised by logic functionError prevention/detection by transmission repeatMultiplexingTheoretical computer science

A system and method for detecting and rectifying a proscribed non-complementary output from a complementary logic circuit. A complementary logic circuit having a true tree and a complement tree is provided. The true tree produces a true signal utilized to generate a true output signal from the complementary logic circuit. The complement tree produces a complement signal utilized to generate a complement output signal from the complementary logic circuit. Logic means coupled to the output of the complementary logic circuit detect an occurrence of a non-complementary output from the complementary logic circuit. Multiplexing means within the true tree is utilized to selectively replace the true signal with the complement signal within the true tree in response to detection by the logic means of a non-complementary output, such that a non-complementary output is seamlessly detected and rectified.

Owner:IBM CORP