Semiconductor memory device

a semiconductor memory and memory device technology, applied in the field of semiconductor memory devices, can solve the problems of increasing the error rate of data rewrite operations, the error rate of flash memories, and the error rate of non-volatile semiconductor memory devices,

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

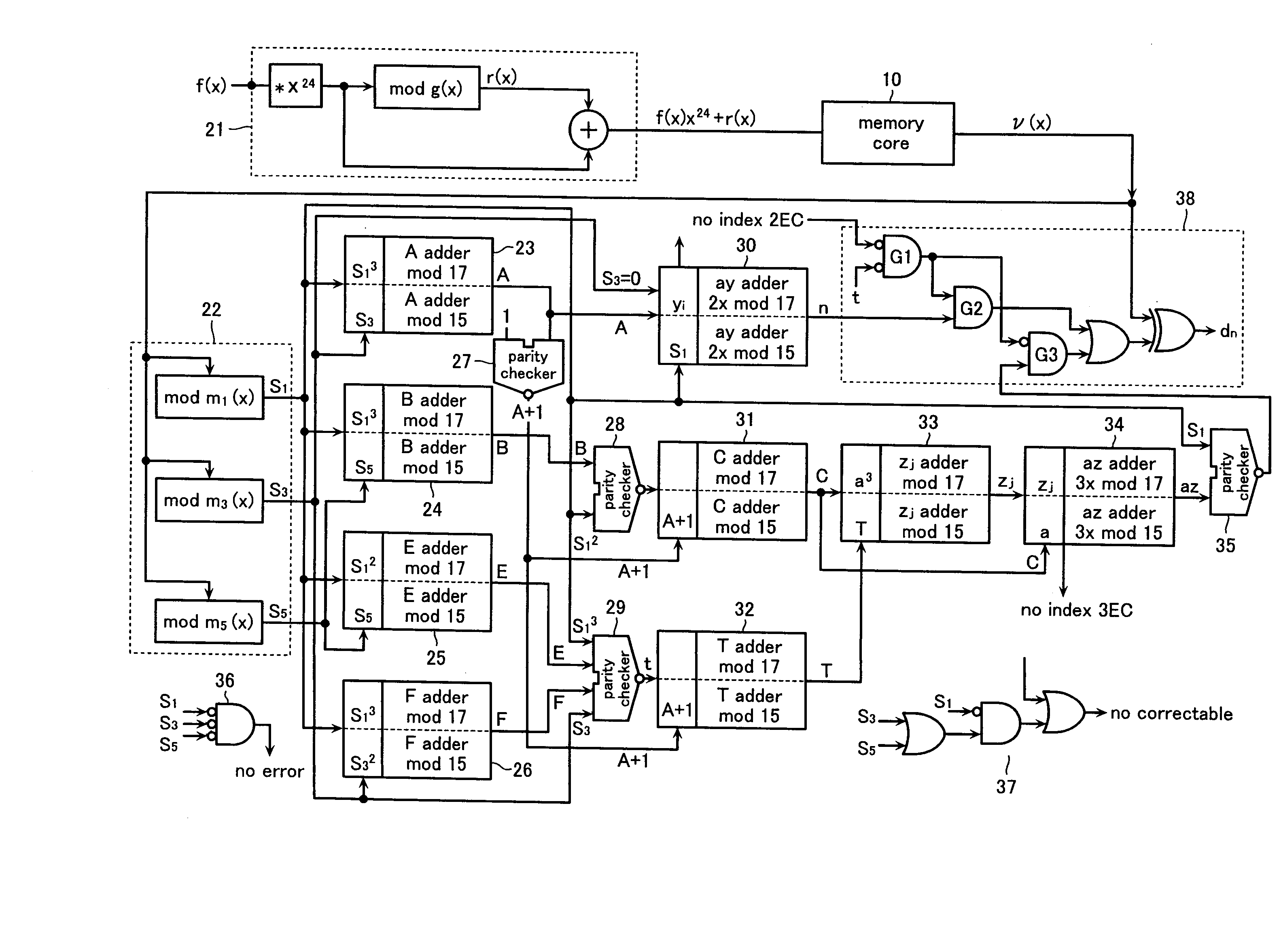

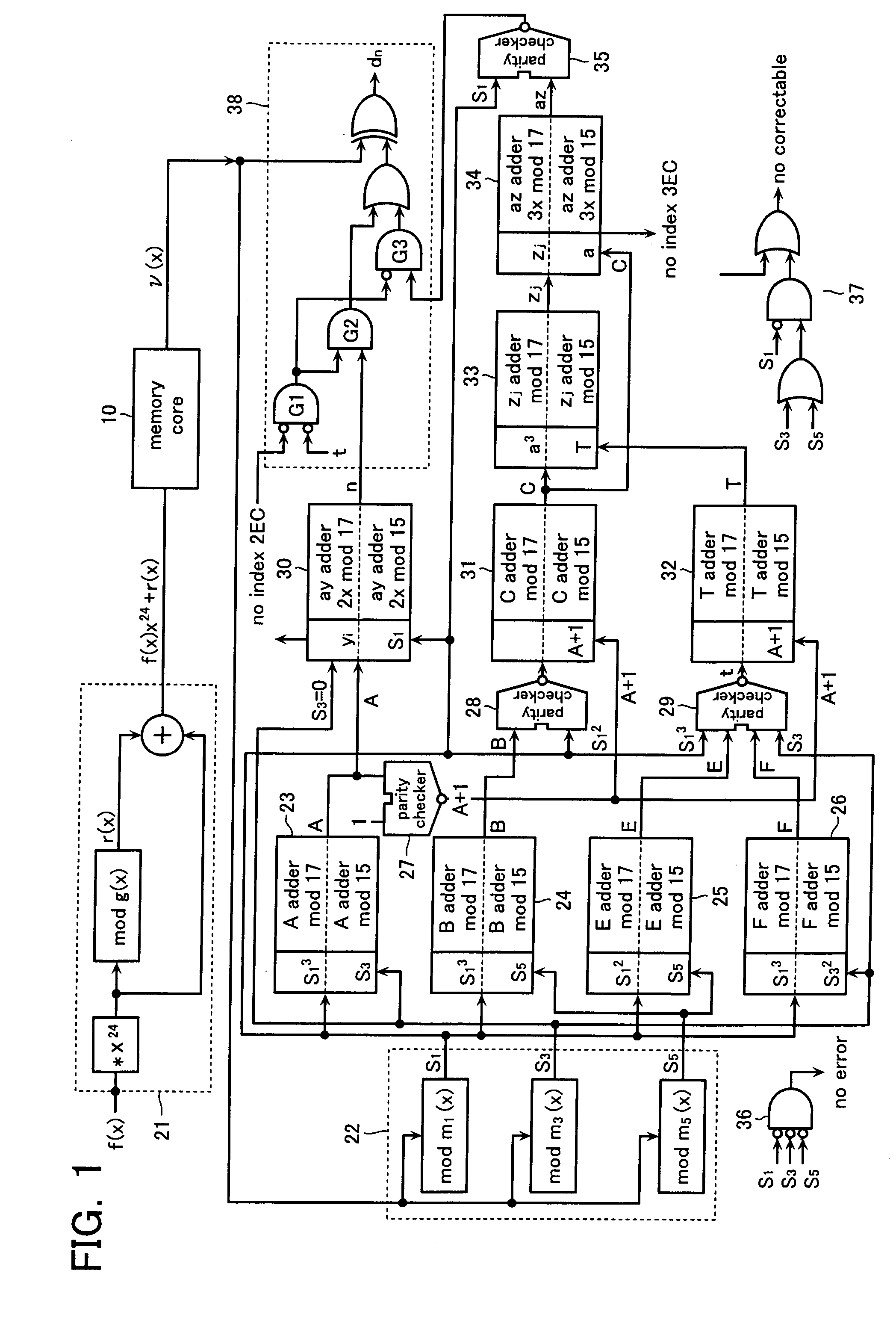

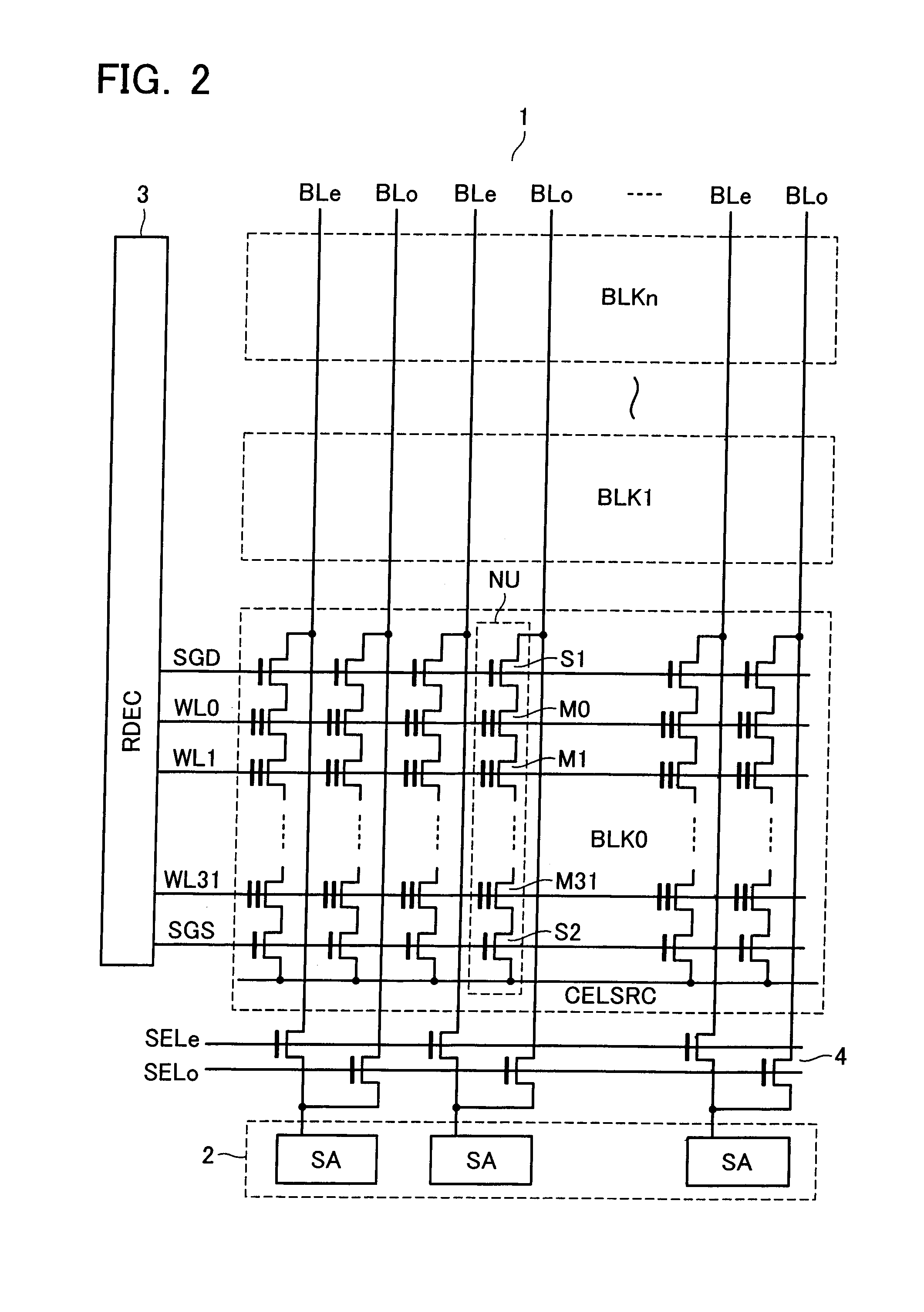

[0084] Illustrative embodiments of this invention will be explained with reference to the accompanying drawings below.

[0085] There has already been provided by this inventor such a method that 2-bit error correction may be performed with a high-speed operation in place of the conventional method, in which finite elements are sequential substituted in the error searching equation to solve it.

[0086] That is, to perform error location search at a high rate with BCH code on GF(256), form a table for designating solution candidacy, and compare syndrome indexes calculated from read out data of a memory with the table to obtain a solution. In detail, an error searching equation including syndromes calculated from the read data is solved. In this case, the error searching equation is divided into a part including only unknown numbers (refer to as a variable part, hereinafter) and another part to be calculated by syndromes (refer to as a syndrome part) by use of variable transformation, so...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More