Patents

Literature

44 results about "BCH code" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In coding theory, the BCH codes or Bose–Chaudhuri–Hocquenghem codes form a class of cyclic error-correcting codes that are constructed using polynomials over a finite field (also called Galois field). BCH codes were invented in 1959 by French mathematician Alexis Hocquenghem, and independently in 1960 by Raj Bose and D. K. Ray-Chaudhuri. The name Bose–Chaudhuri–Hocquenghem (and the acronym BCH) arises from the initials of the inventors' surnames (mistakenly, in the case of Ray-Chaudhuri).

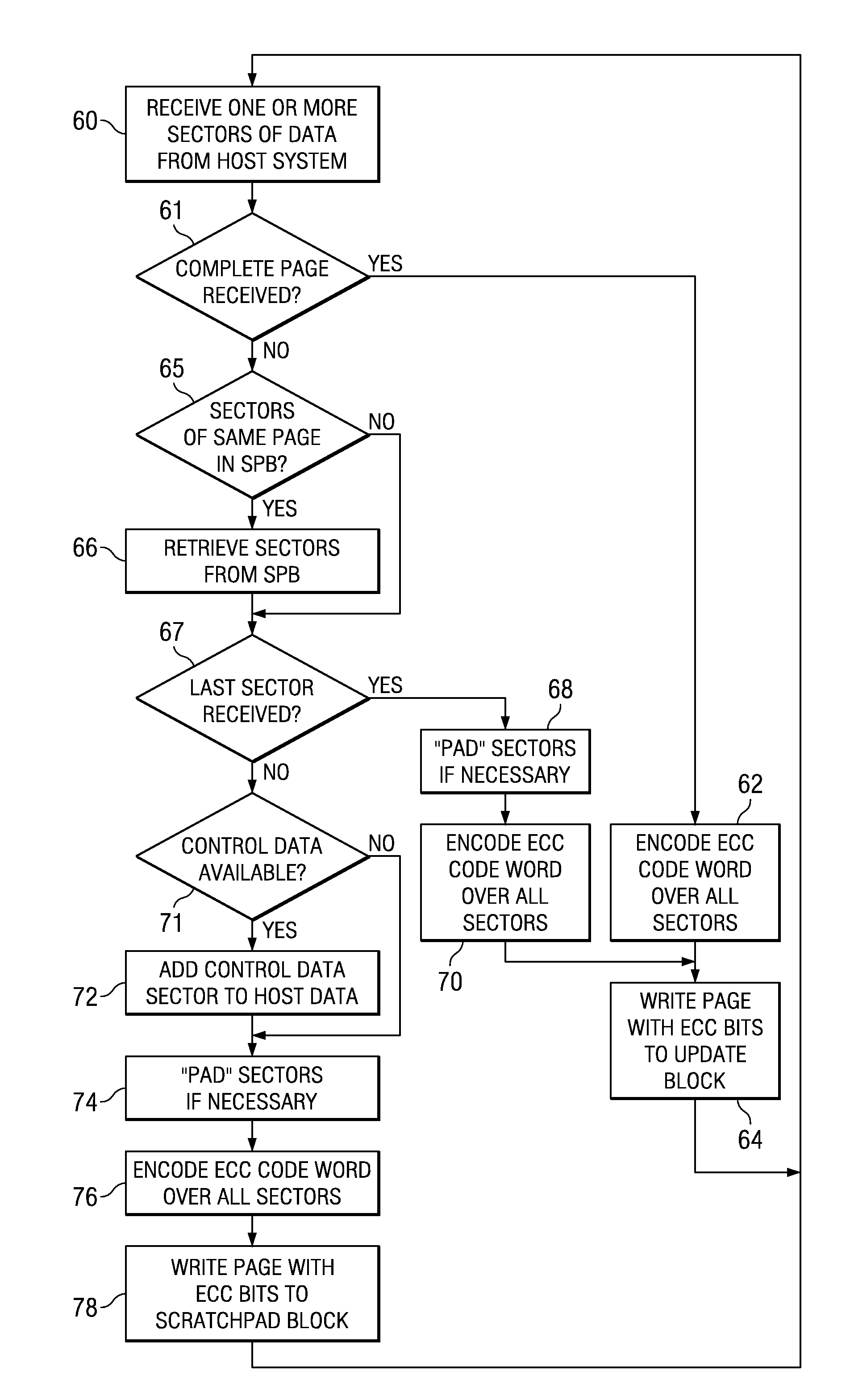

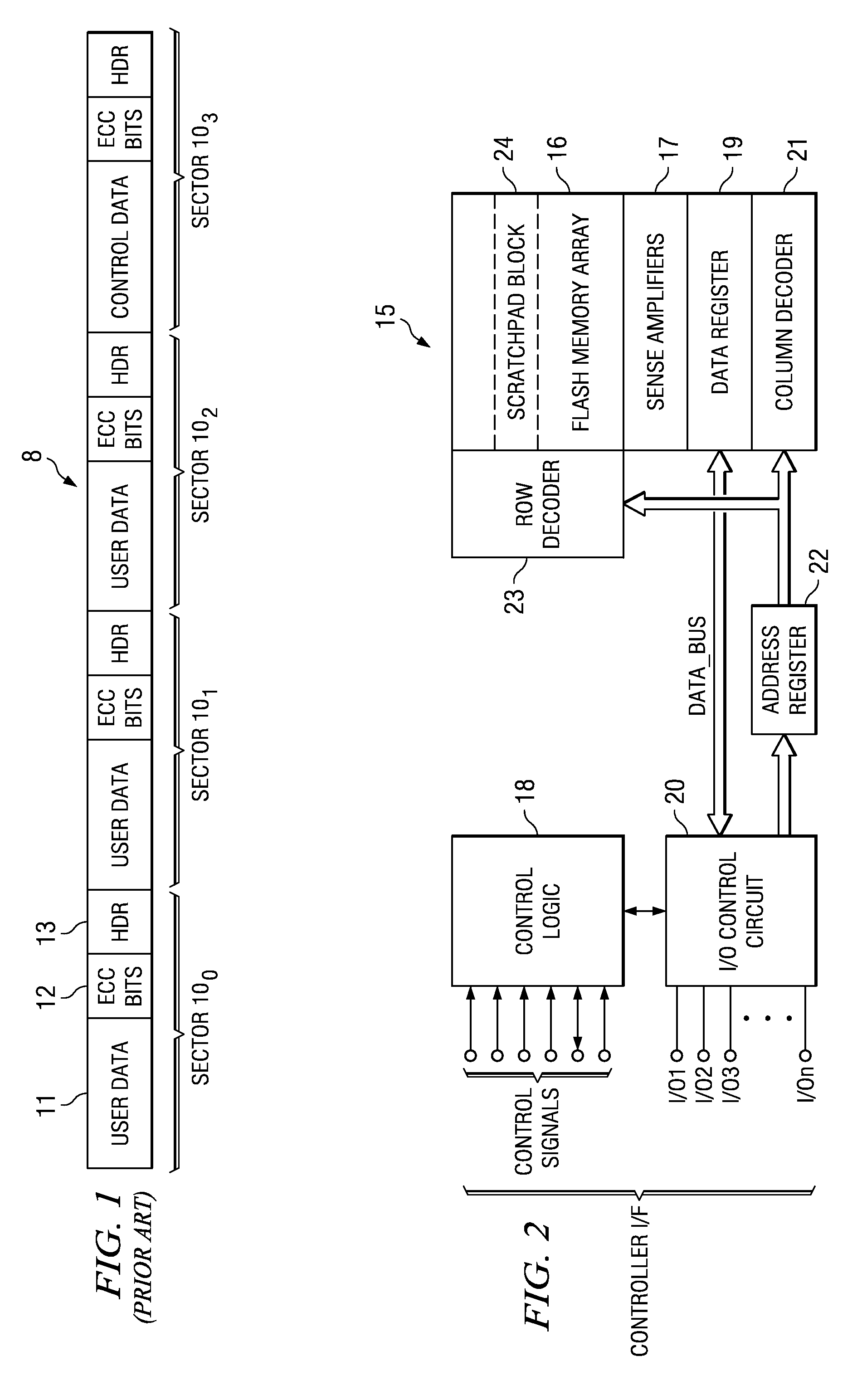

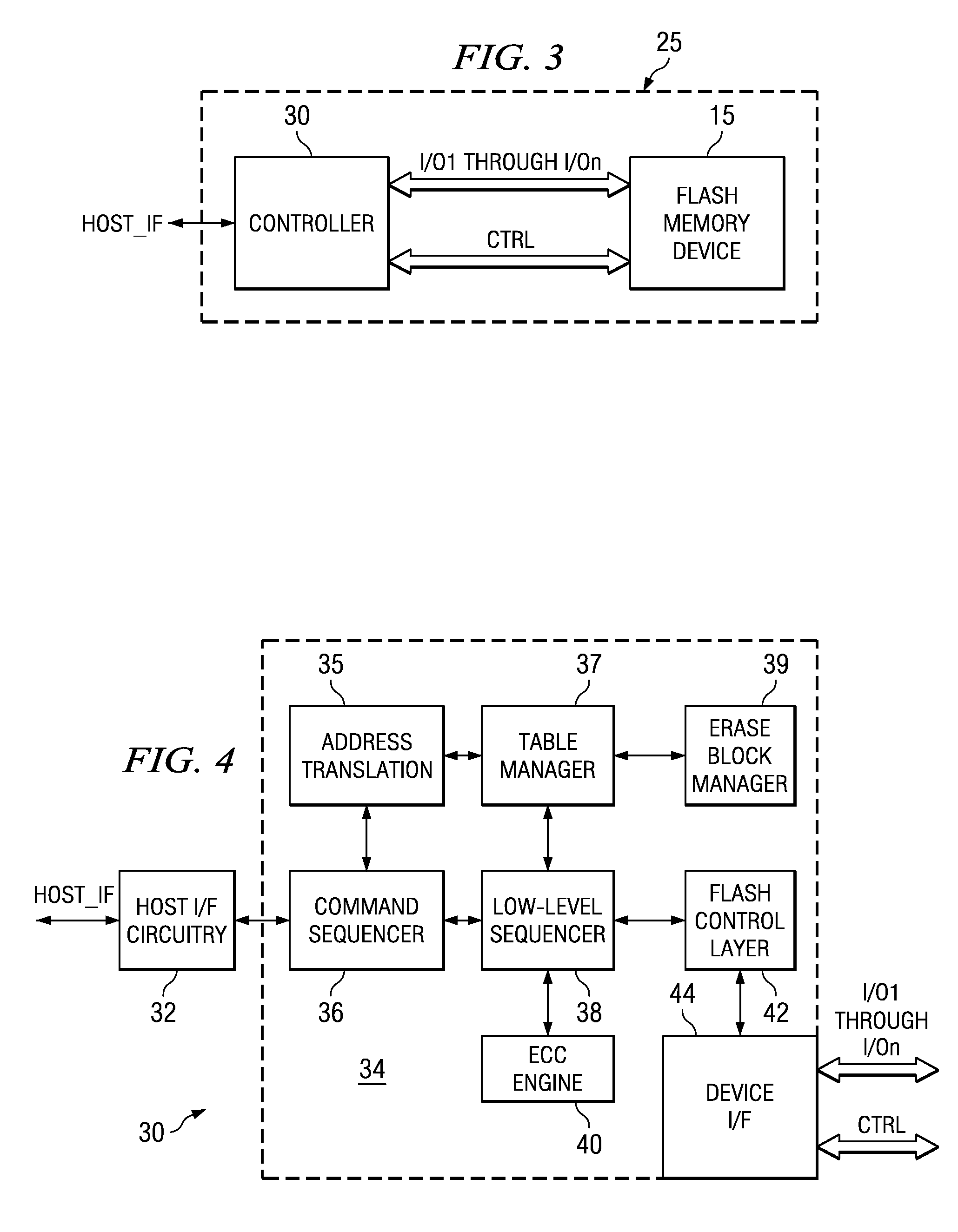

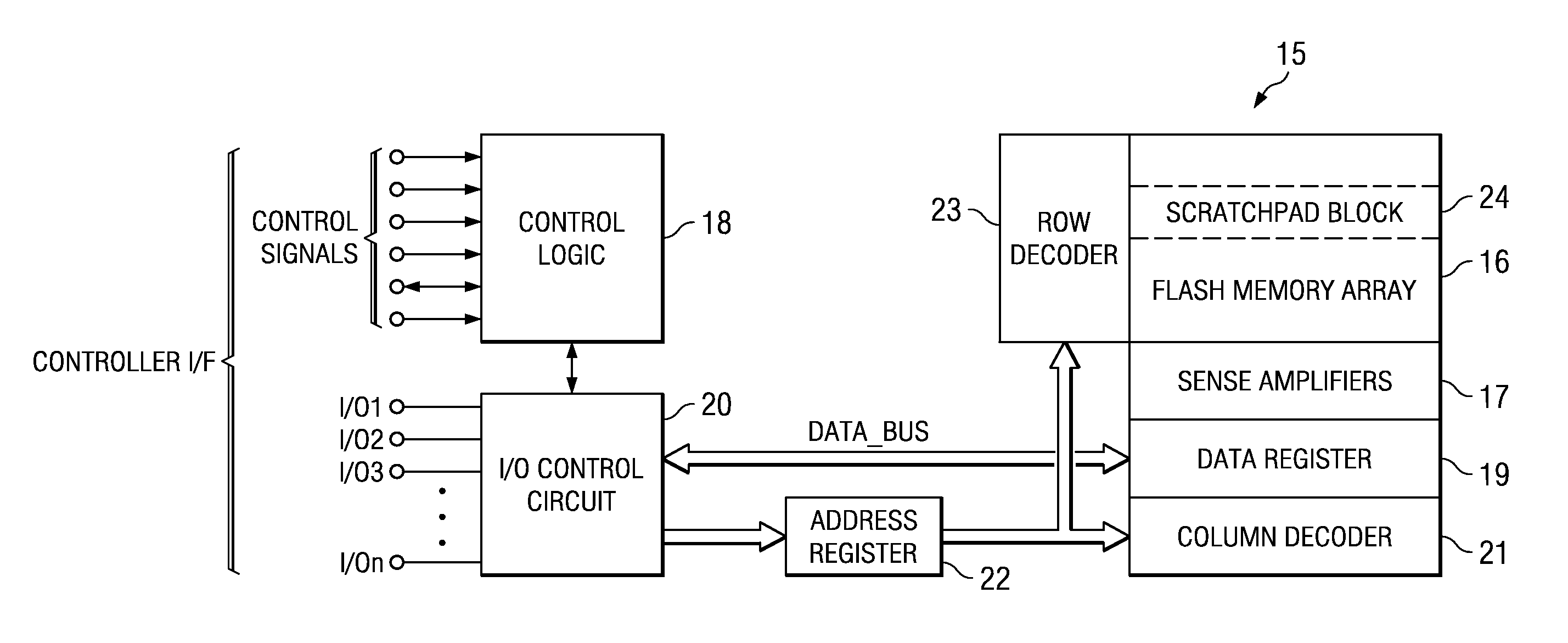

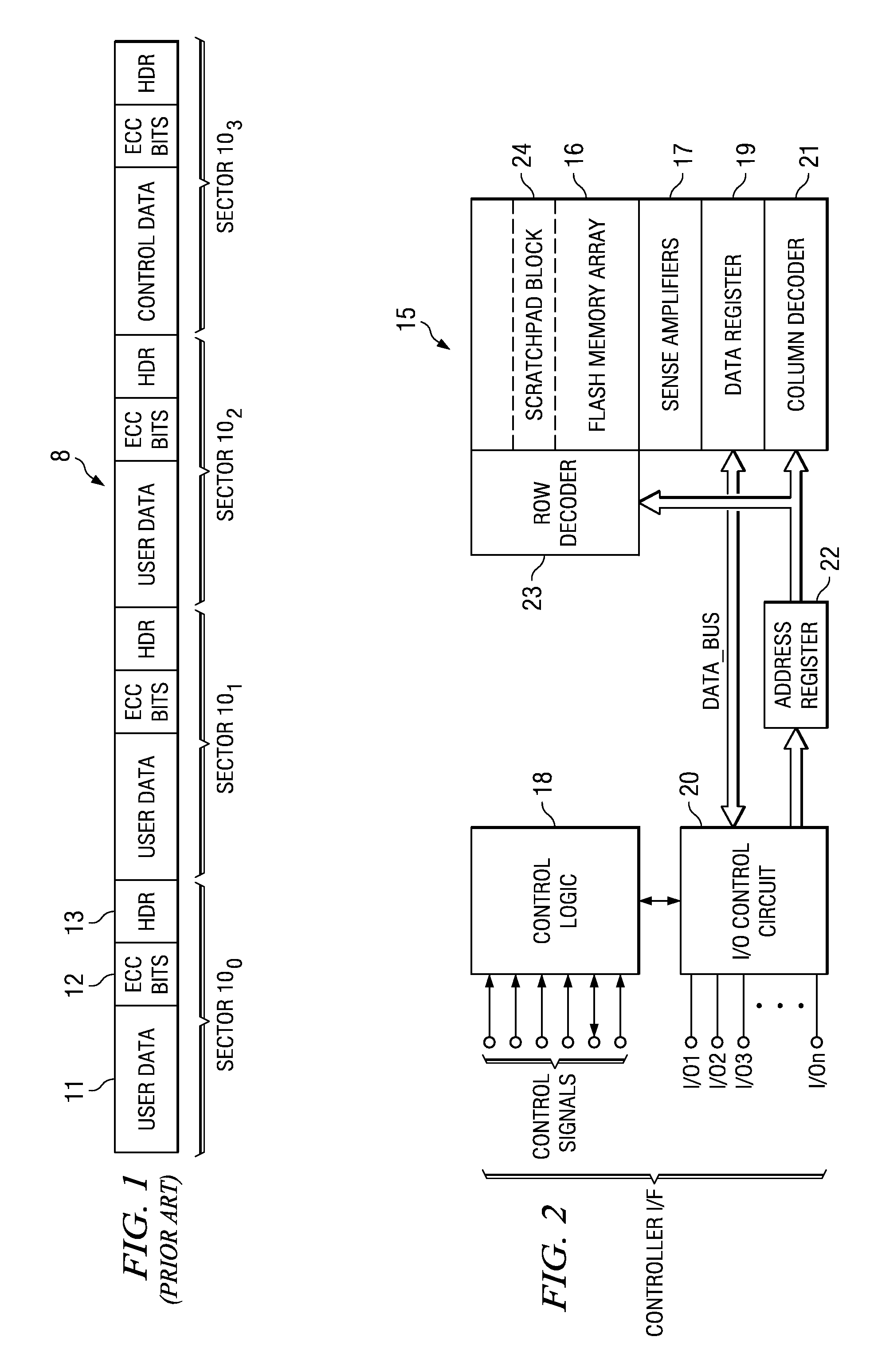

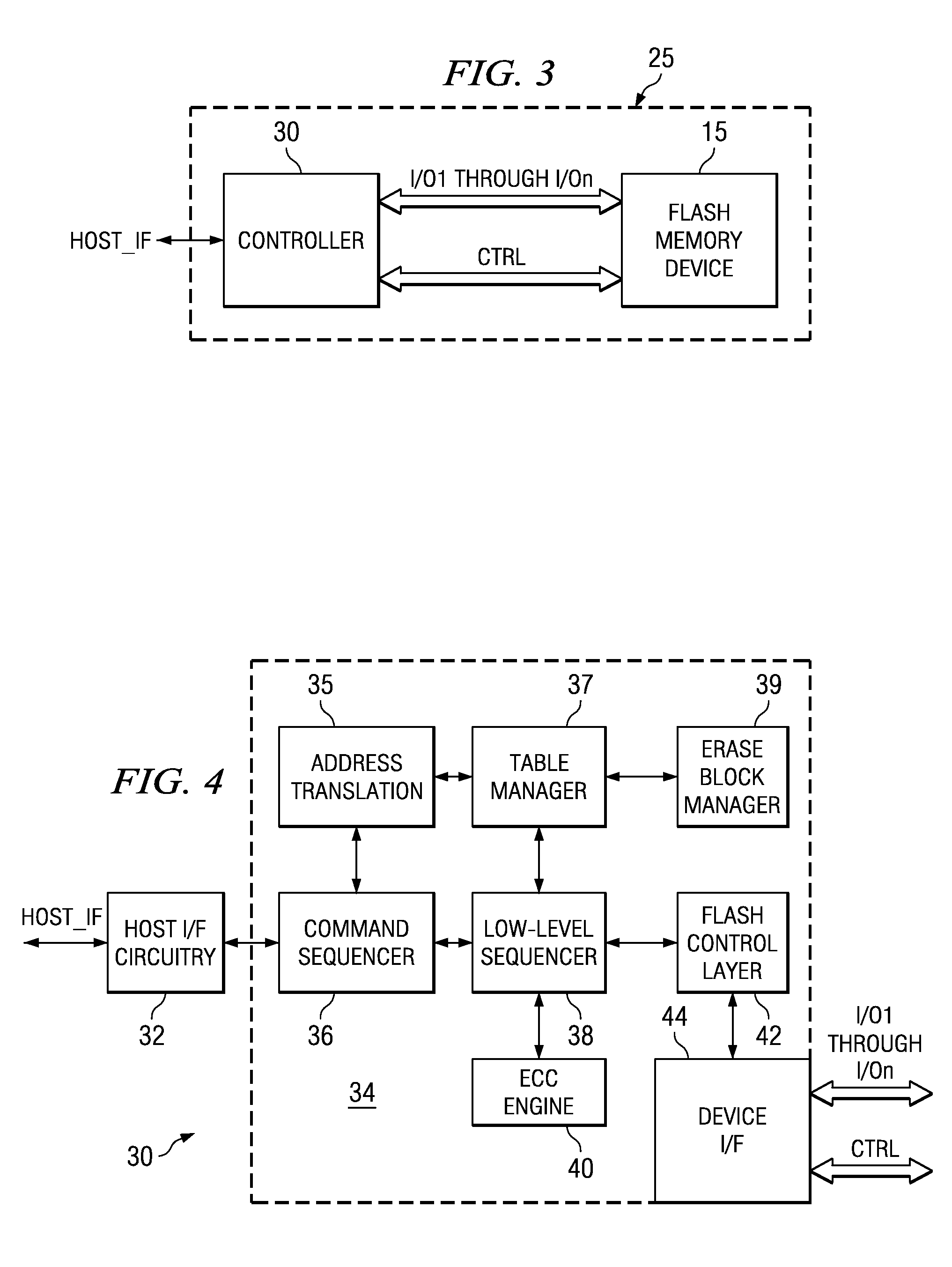

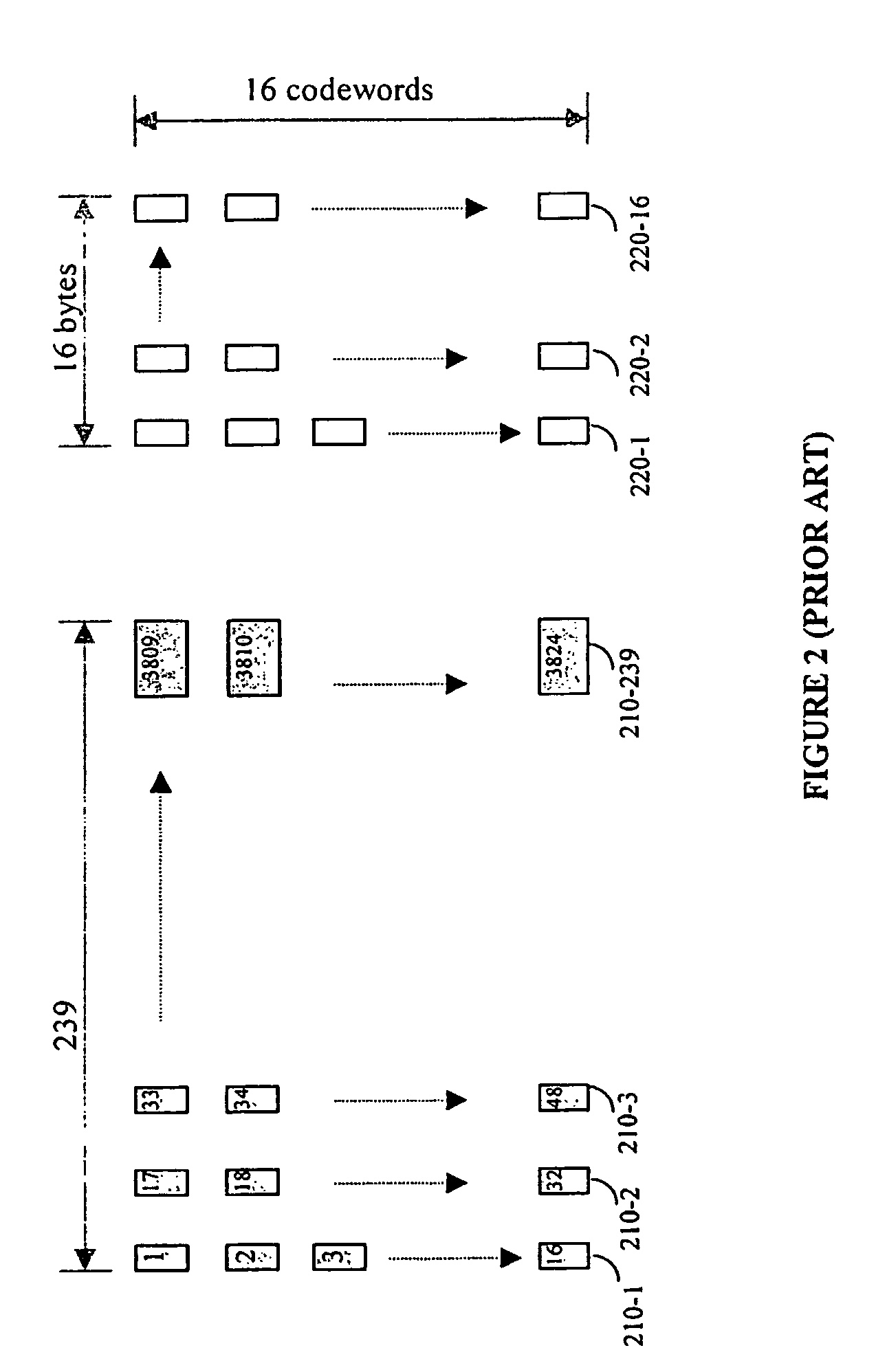

Method of Error Correction Coding for Multiple-Sector Pages in Flash Memory Devices

InactiveUS20070300130A1Efficient error correctionError detection/correctionRead-only memoriesControl dataDependability

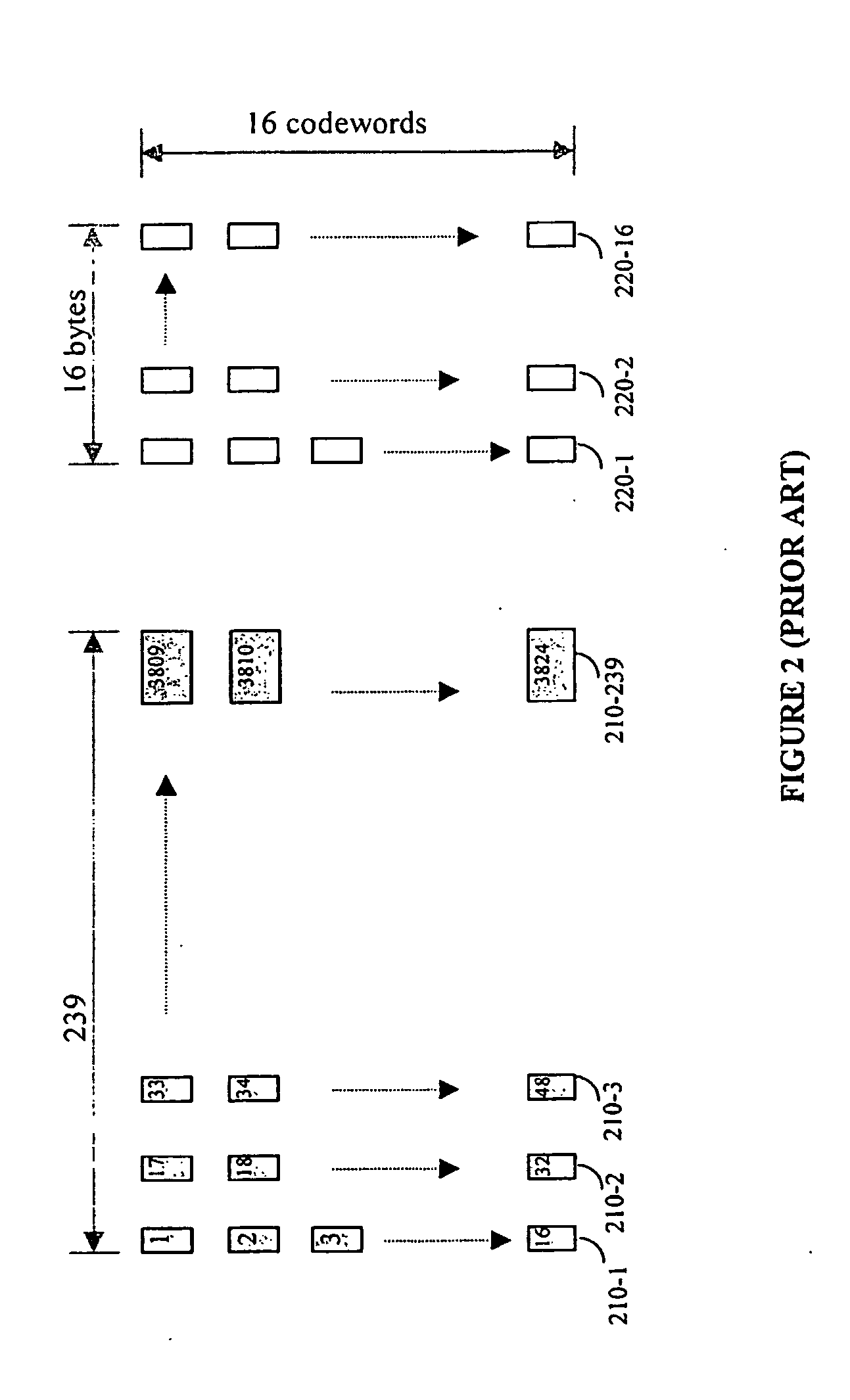

A flash memory system, including a flash memory device and a controller, and having improved efficiency error correction coding (ECC), is disclosed. Each page in the flash memory device has the capacity to store multiple sectors' worth of data. However, partial page programming (i.e., followed by a later write to fill the page) is prohibited for reliability reasons. A scratchpad block within the flash memory device is designed, and stores both user data and control data. ECC efficiency is improved by encoding the ECC, or parity, bits over the entire data block corresponding to the user and control data in the page. Retrieval of a particular sector of data requires reading and decoding of the entire page. Especially for codes such as Reed-Solomon and BCH codes, the larger data block including multiple sectors' data improves the error correction capability, and thus enables either fewer redundant memory cells in each page or improved error correction.

Owner:SANDISK TECH LLC

Error Correction Coding for Multiple-Sector Pages in Flash Memory Devices

ActiveUS20070271494A1Memory architecture accessing/allocationError detection/correctionControl dataDependability

A flash memory system, including a flash memory device and a controller, and having improved efficiency error correction coding (ECC), is disclosed. Each page in the flash memory device has the capacity to store multiple sectors' worth of data. However, partial page programming (i.e., followed by a later write to fill the page) is prohibited for reliability reasons. A scratchpad block within the flash memory device is designed, and stores both user data and control data. ECC efficiency is improved by encoding the ECC, or parity, bits over the entire data block corresponding to the user and control data in the page. Retrieval of a particular sector of data requires reading and decoding of the entire page. Especially for codes such as Reed-Solomon and BCH codes, the larger data block including multiple sectors' data improves the error correction capability, and thus enables either fewer redundant memory cells in each page or improved error correction.

Owner:SANDISK TECH LLC

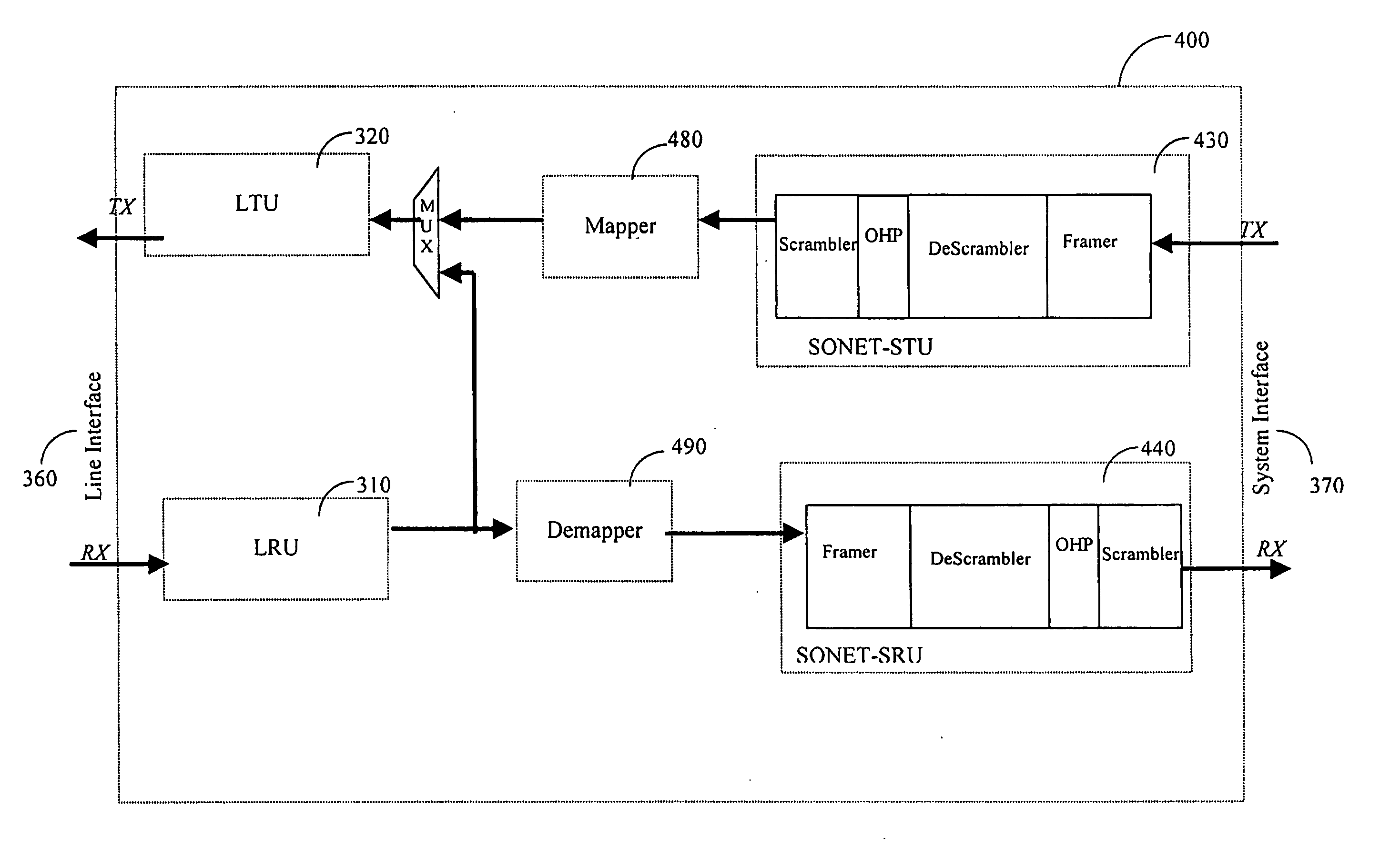

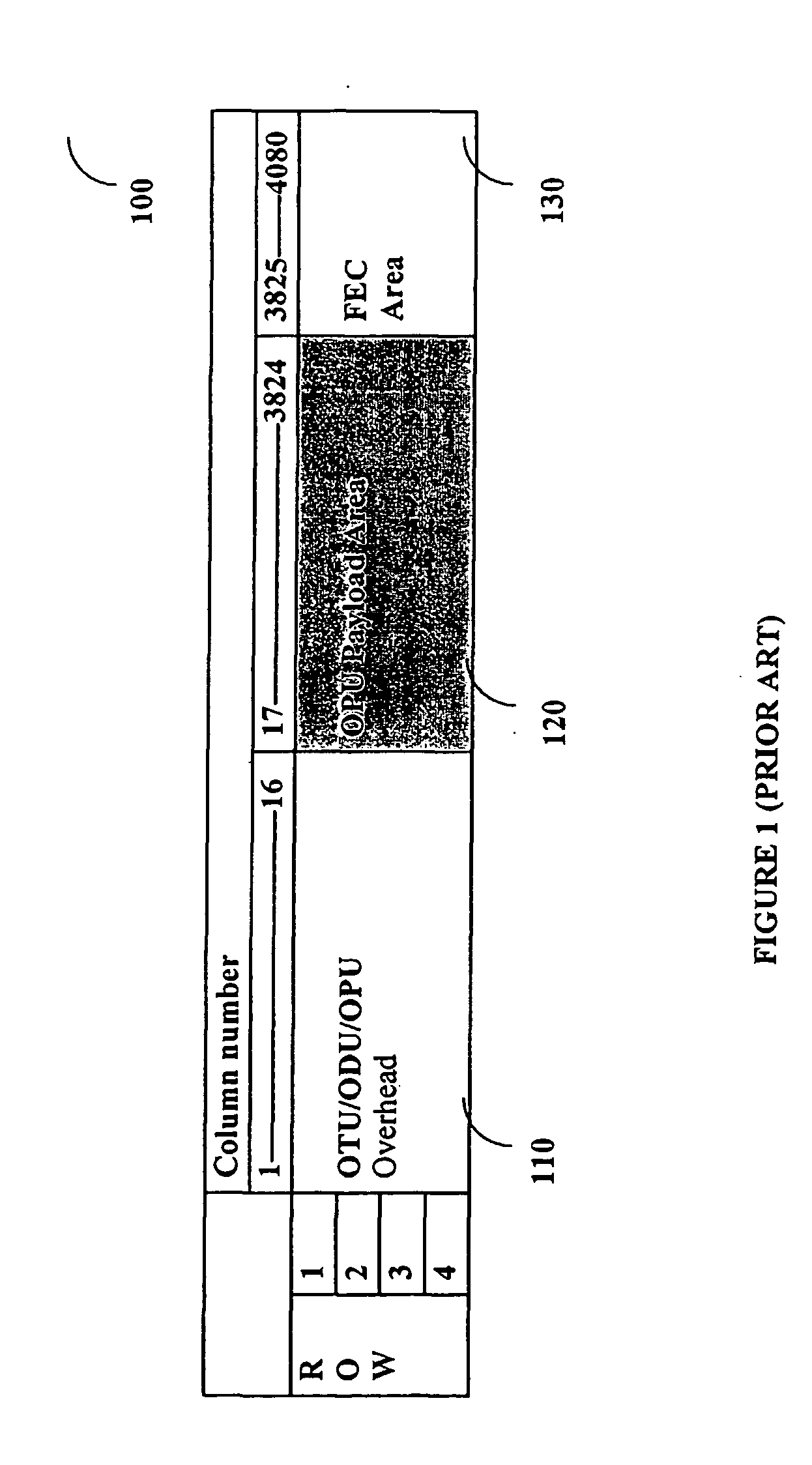

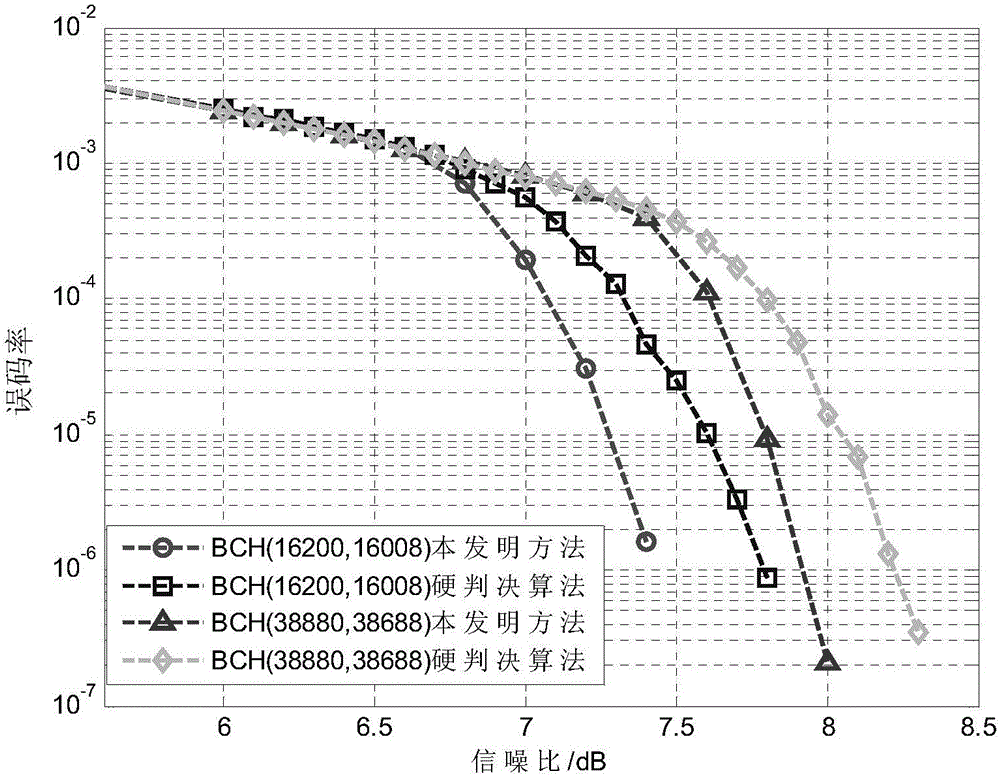

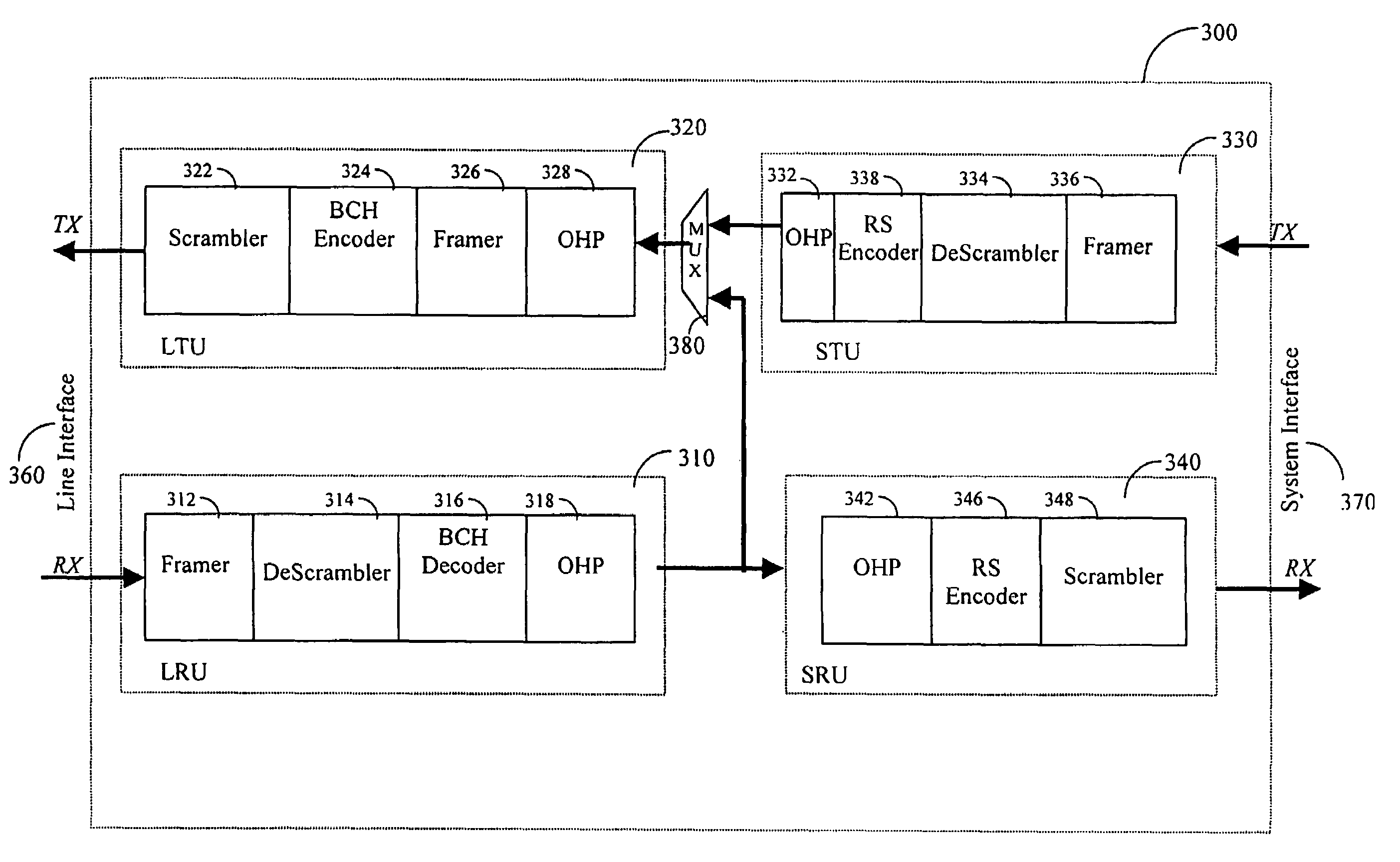

Apparatus for processing otn frames utilizing an efficient forward error correction

InactiveUS20050068995A1Efficient forward error correctionImprove performanceTime-division multiplexData switching by path configurationAlgorithmForward error correction

An apparatus and method utilizing an efficient forward error correction (FEC), targeted for processing optical transport network (CTN) signals having transmission rates in excess of 10 Gbps. The FEC uses an advanced implementation of the Bose Chaudhuri Hocquenghem (BCH) code. The use of the BCH code for the FEC improves the performance over prior art solutions for both error correction and detection.

Owner:OPTIX NETWORKS

Correction coding method for ground digital television broadcast

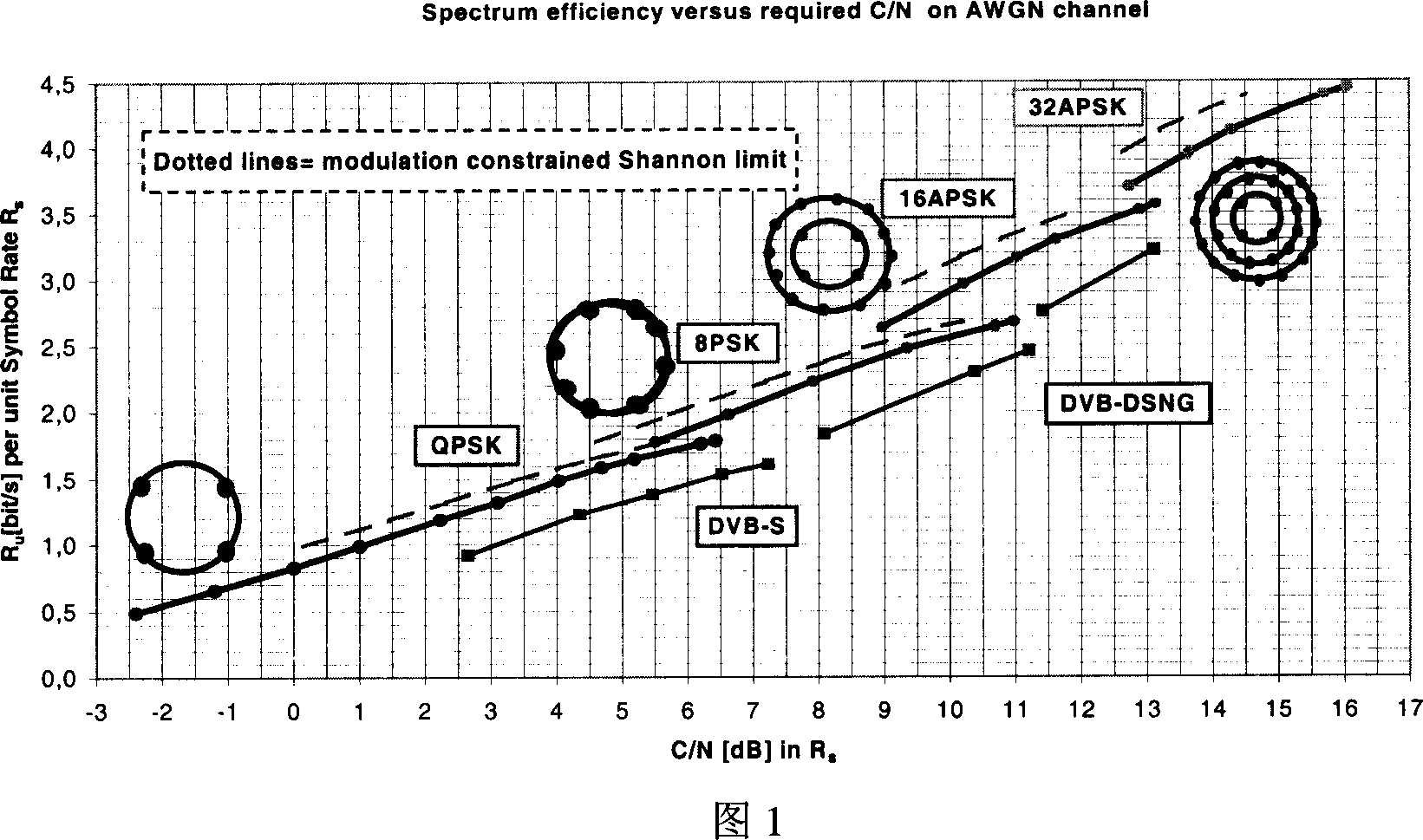

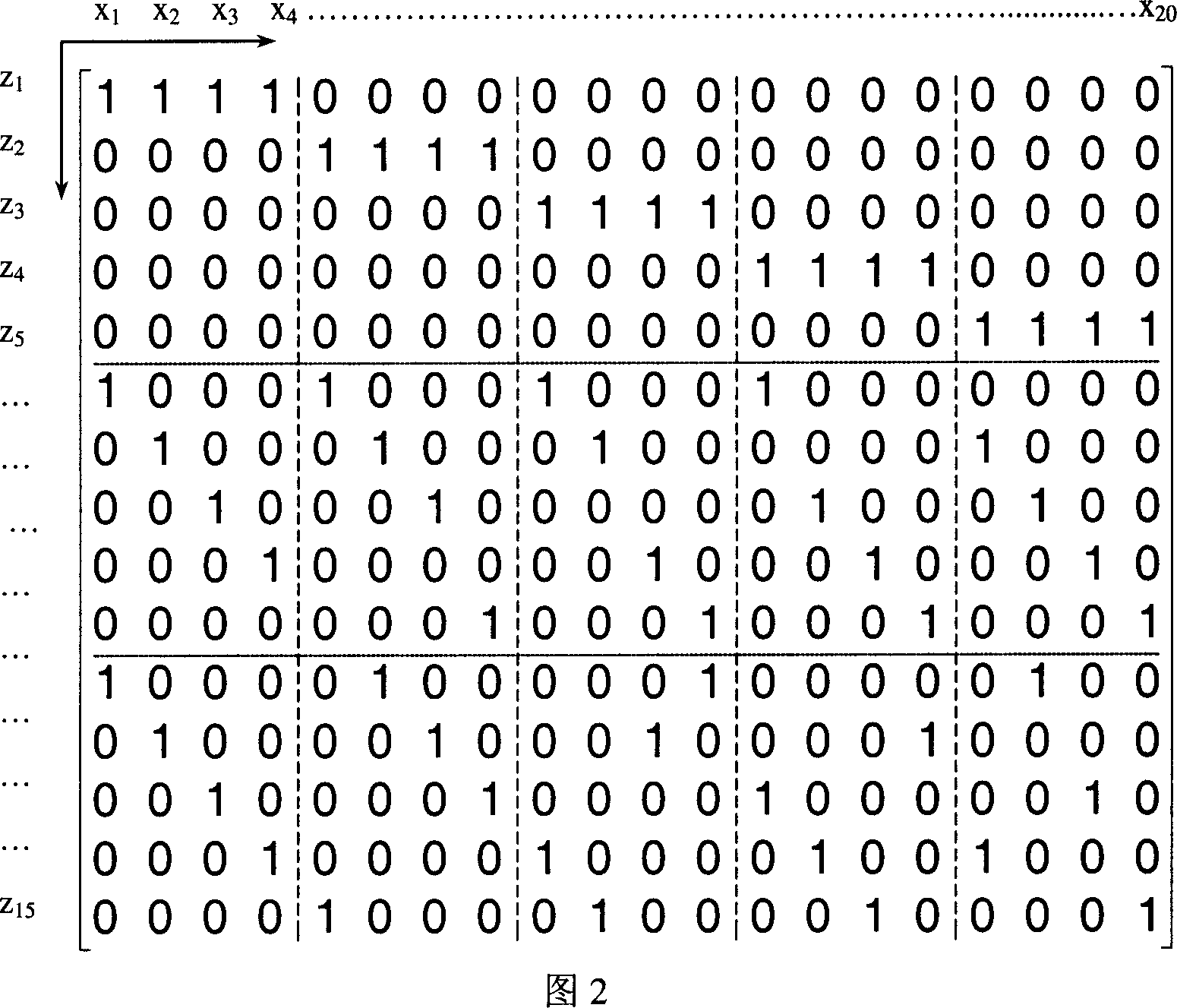

ActiveCN1925615AImprove performanceSimple structureTelevision systemsDigital video signal modificationComputer hardwareInformation transmission

This invention relates to earth digital television broadcast coding method in digital information transmission technique field, which comprises the following steps: diving transmission flow into 752 bit set and adding 261 zeros to get 1013 bit for BCH coding and removing front 261 bit to get BCH(762,752); forming one set of BCH(762,752) with certain number to generate matrix of LDPC(7493,3048),LDPC(7493,4572) or LDPC(7493,6096); deleting output 7493 bit front five correction bit to get final 7488 output bit.

Owner:TSINGHUA UNIV

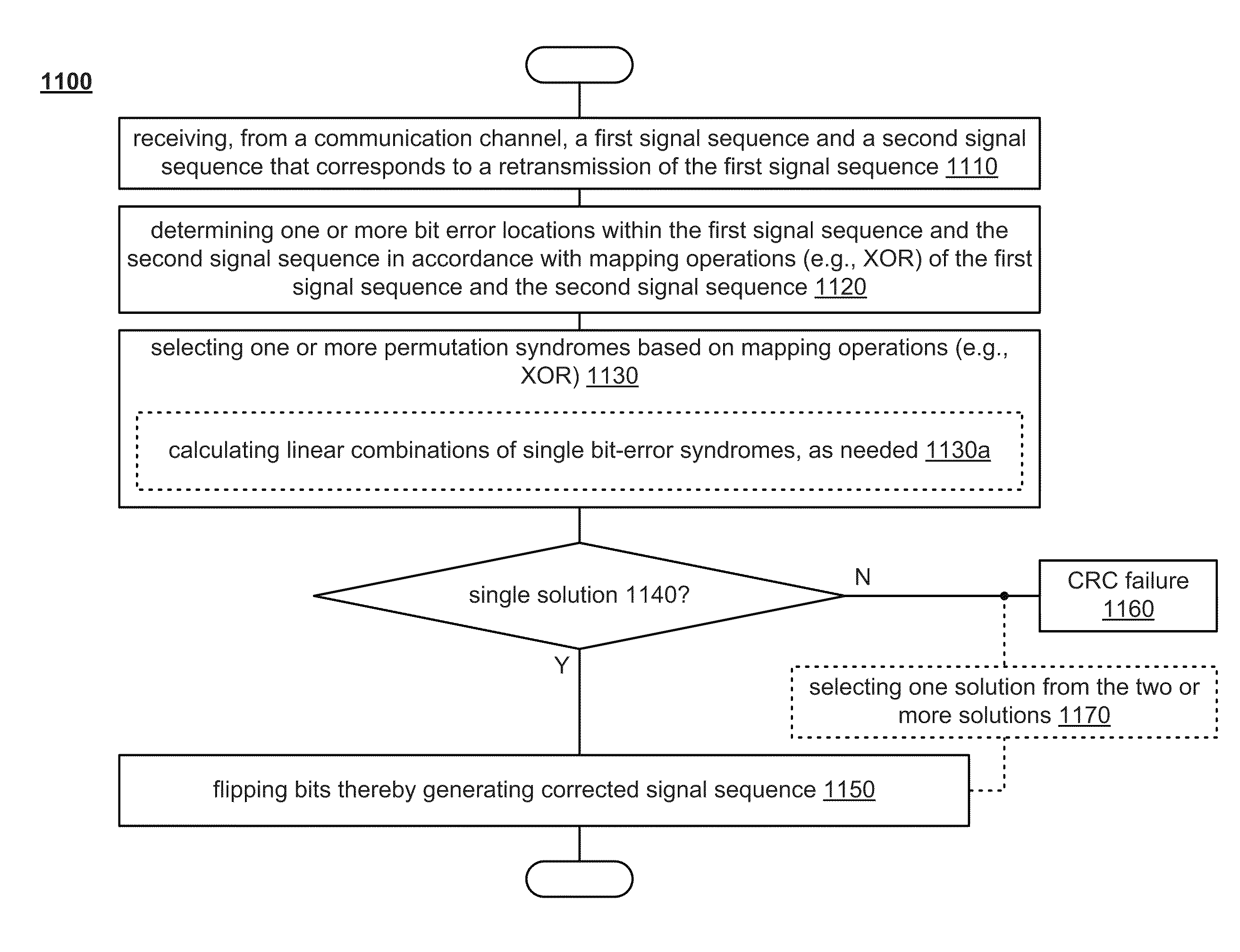

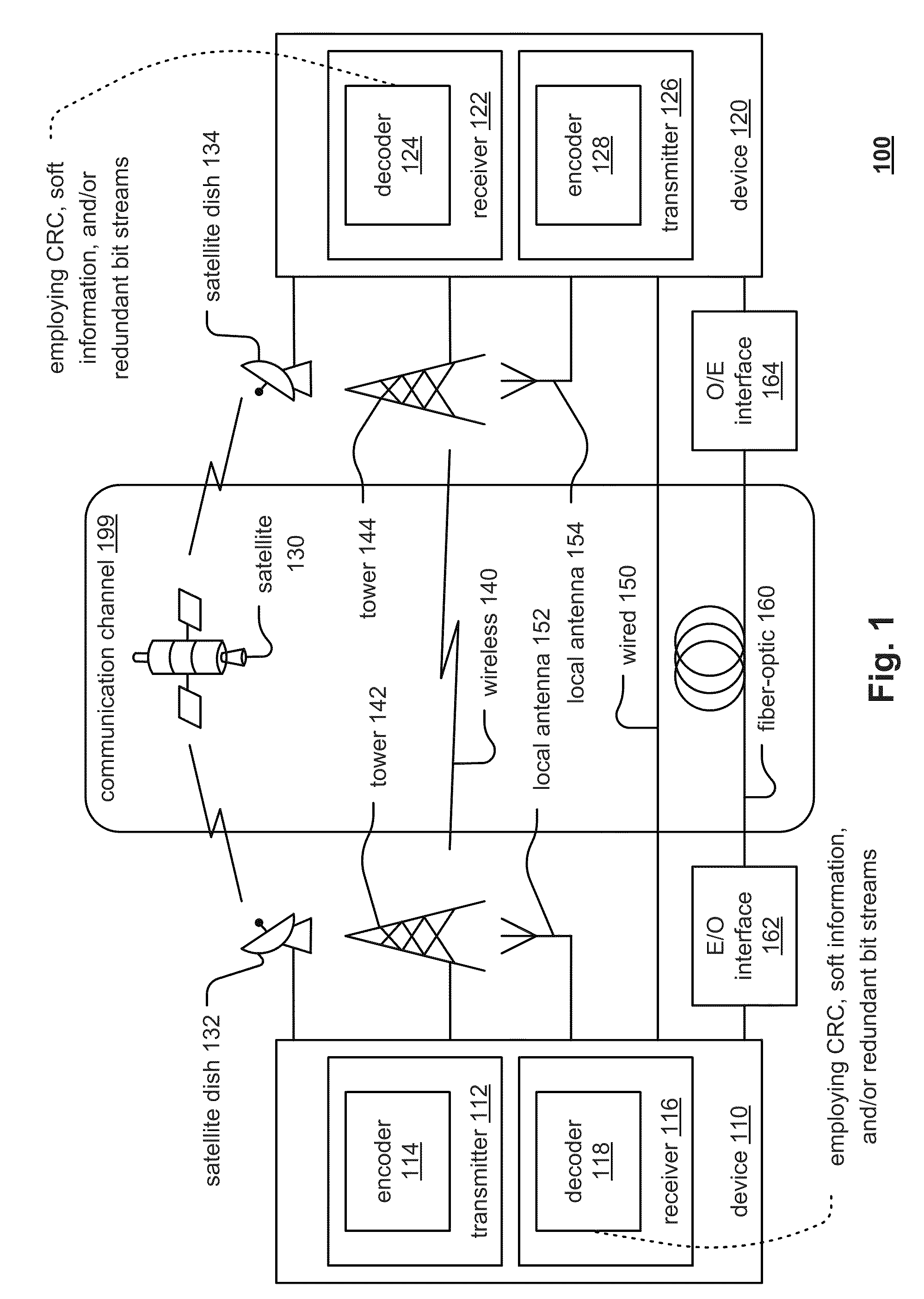

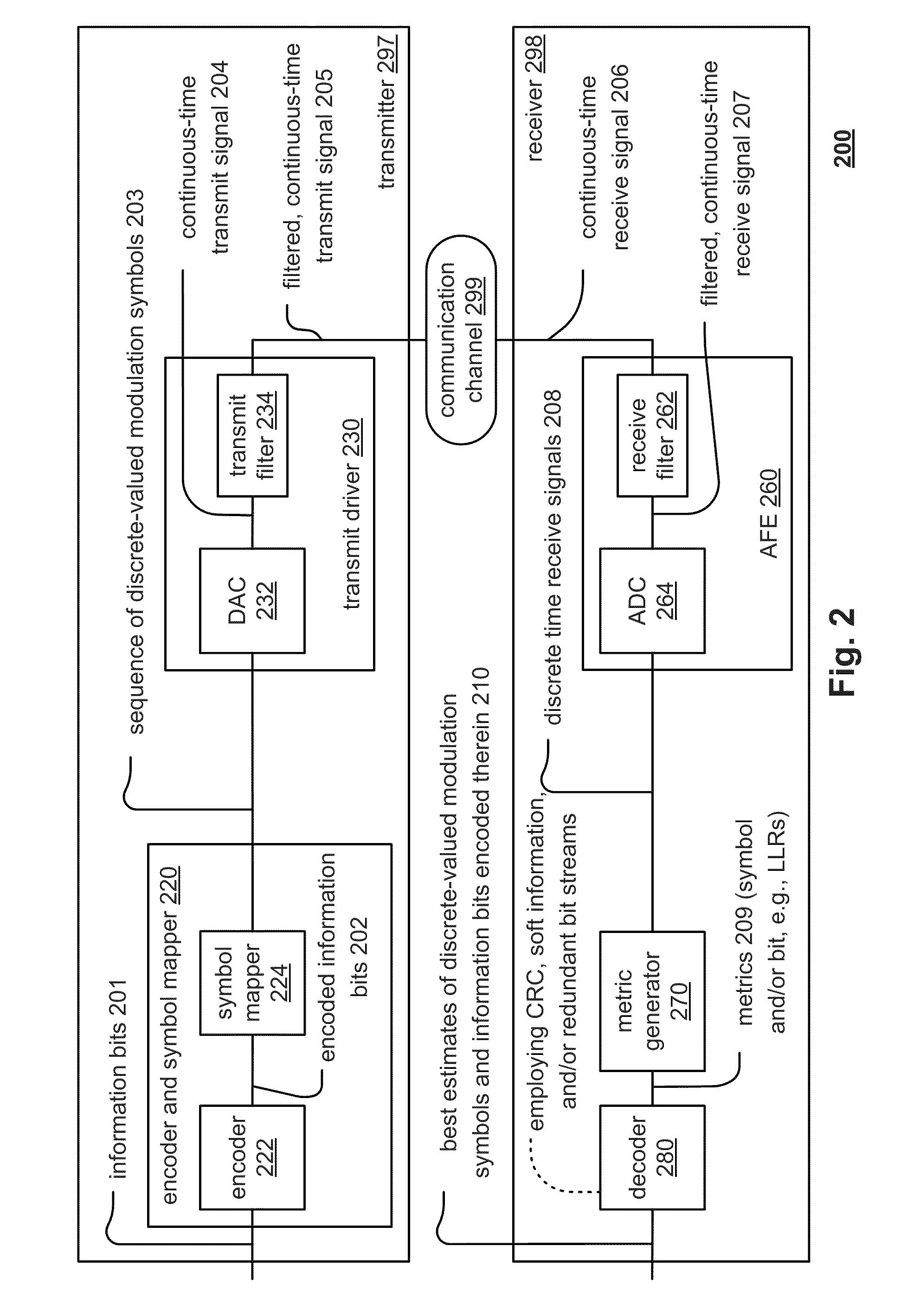

Low complexity error correction using cyclic redundancy check (CRC)

Low complexity error correction using cyclic redundancy check (CRC). Communications between at communication devices, sometimes including at least one redundant transmission from a transmitter to a receiver, undergo low complexity error correction. CRC may be employed in conjunction with using any desired type of ECC or using uncoded modulation. Based on CRC determined bit-errors, as few as a singular syndrome associated with a singular bit-error or a linear combination of syndromes associated with two or more singular bit-errors within two or more received signal sequences are employed to perform error correction of the received signal. Real time combinations of multiple syndromes associated with respective single bit-errors (that may themselves be calculated off-line) are employed in accordance with error correction. In addition to CRC, any ECC may be employed including convolutional code, RS code, turbo code, TCM code, TTCM code, LDPC code, or BCH code.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

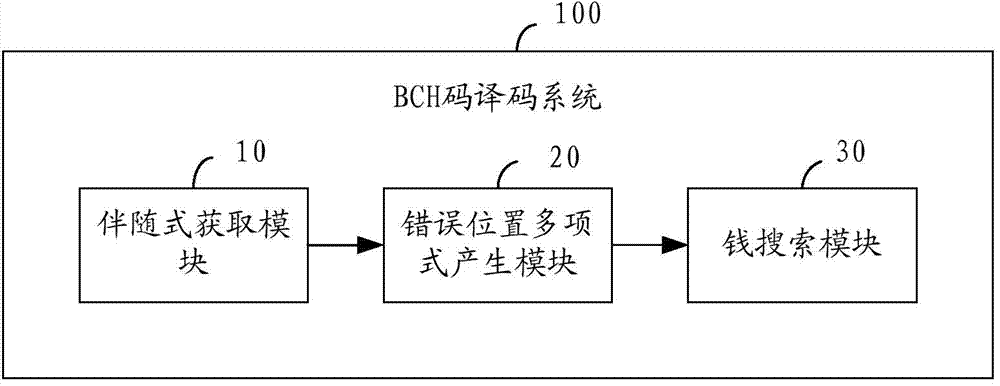

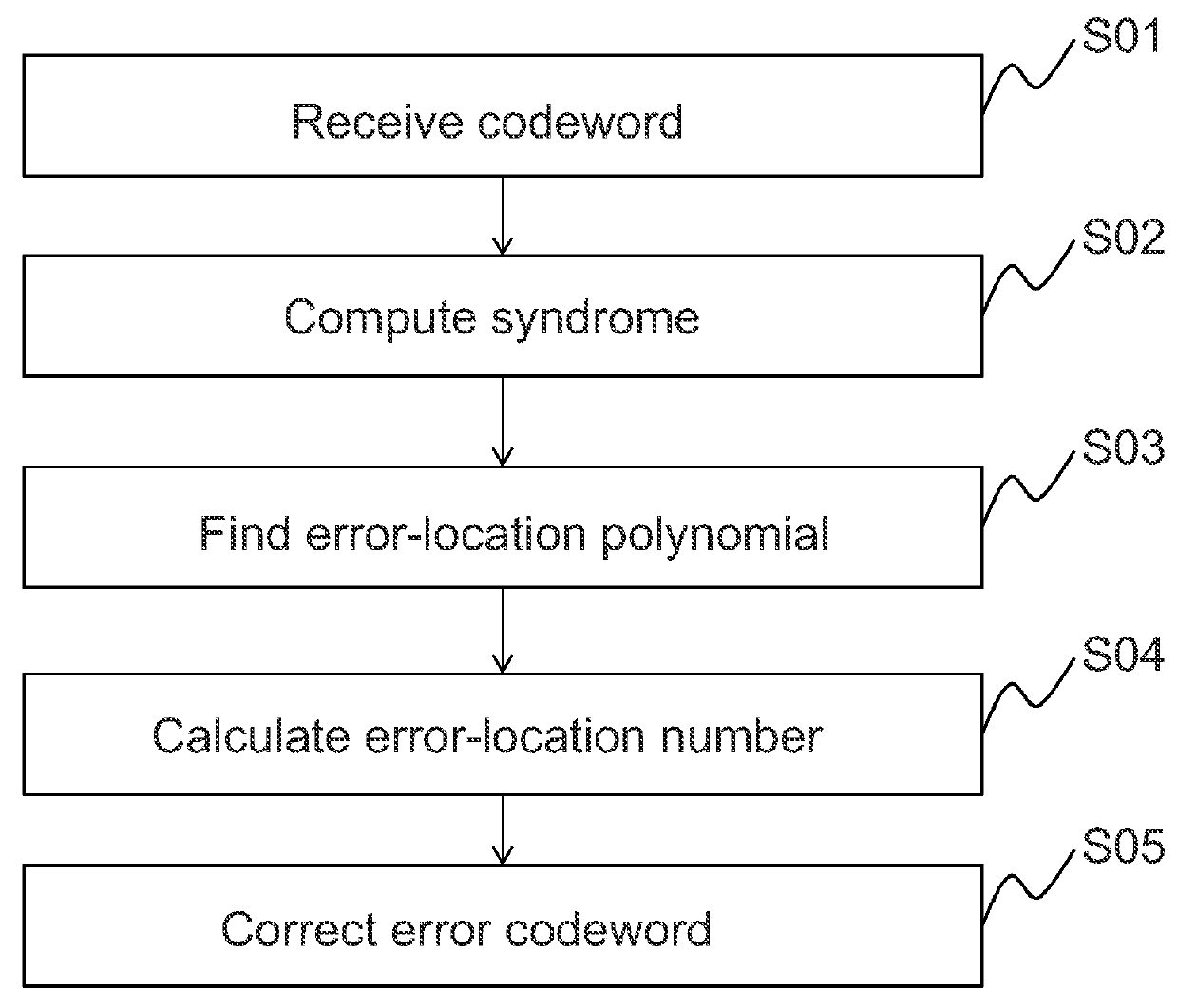

Decoding method and system of BCH codes

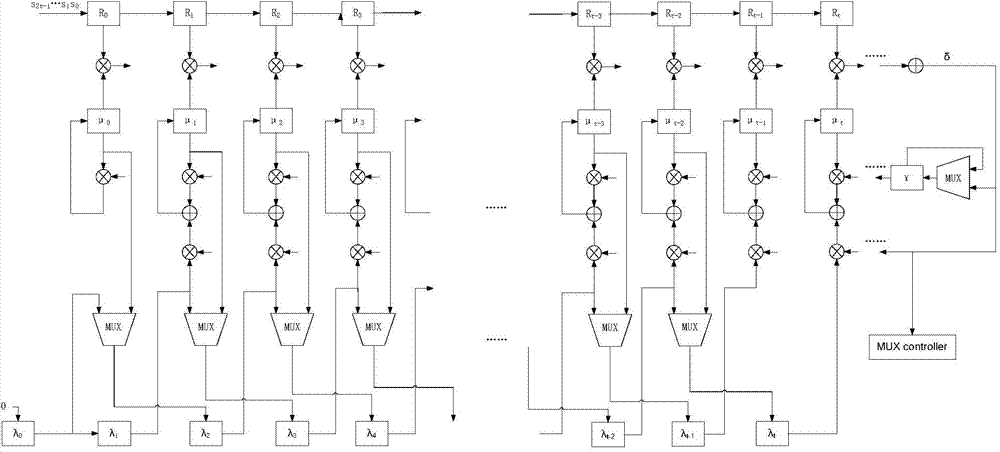

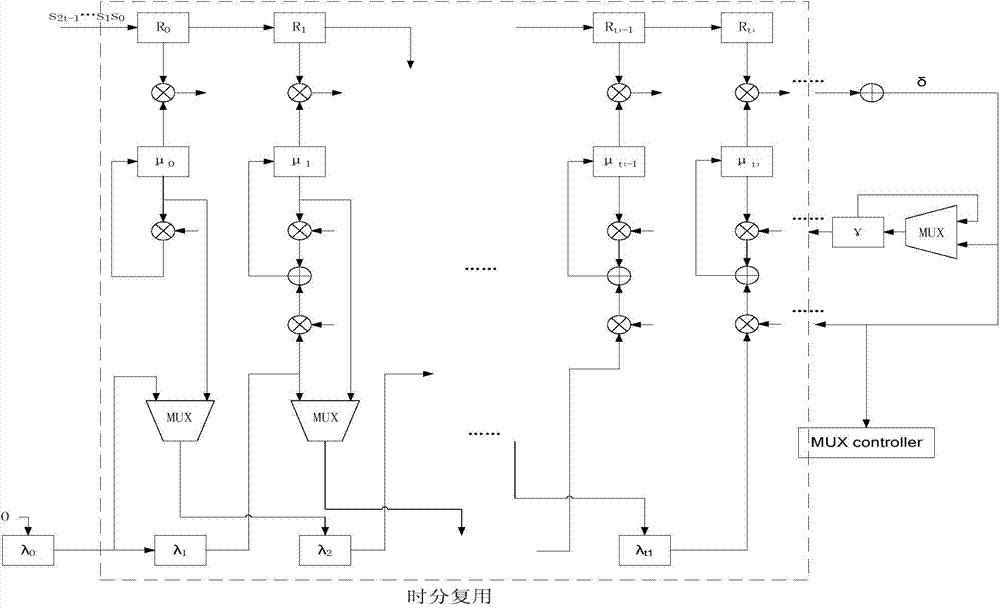

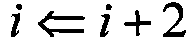

The invention belongs to the field of error correction decoding, and provides a decoding method and system of BCH codes. The decoding method of the BCH codes comprises the steps that syndrome operation is carried out on the received BCH codes to obtain a syndrome polynomial, values of the syndrome polynomial are calculated successively through a parallel iterative decoding circuit on the basis of a BM algorithm without inverse operation so that error location polynomial coefficients and an error location polynomial can be obtained, the root of the error location polynomial is calculated through a Chien search method, and the error location is obtained through calculation. According to the step that the error location polynomial coefficients and the error location polynomial can be obtained through successive calculation of the parallel iterative decoding circuit, the iteration time of the parallel iterative decoding circuit and the calculation time of the Chien search method are matched, and multiplexing is carried out on the parallel iterative decoding circuit according to the iteration time. Therefore, according to the decoding method and system of the BCH codes, the number of adders, the number of multipliers and the number of registers for hardware implementation can be effectively reduced, complexity of combinational logic is reduced, and the size of a chip can be effectively reduced.

Owner:SHENZHEN YILIAN INFORMATION SYST CO LTD

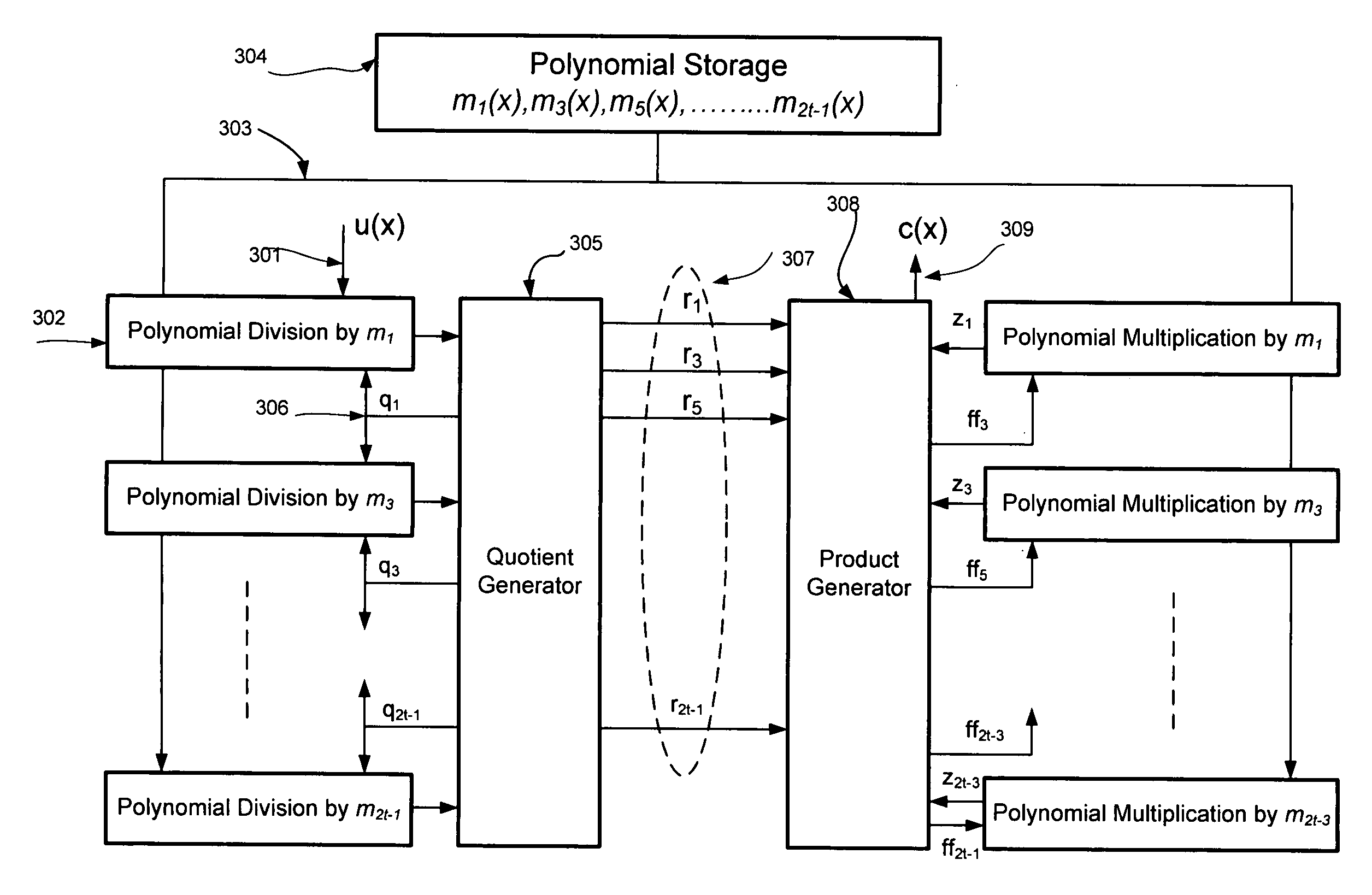

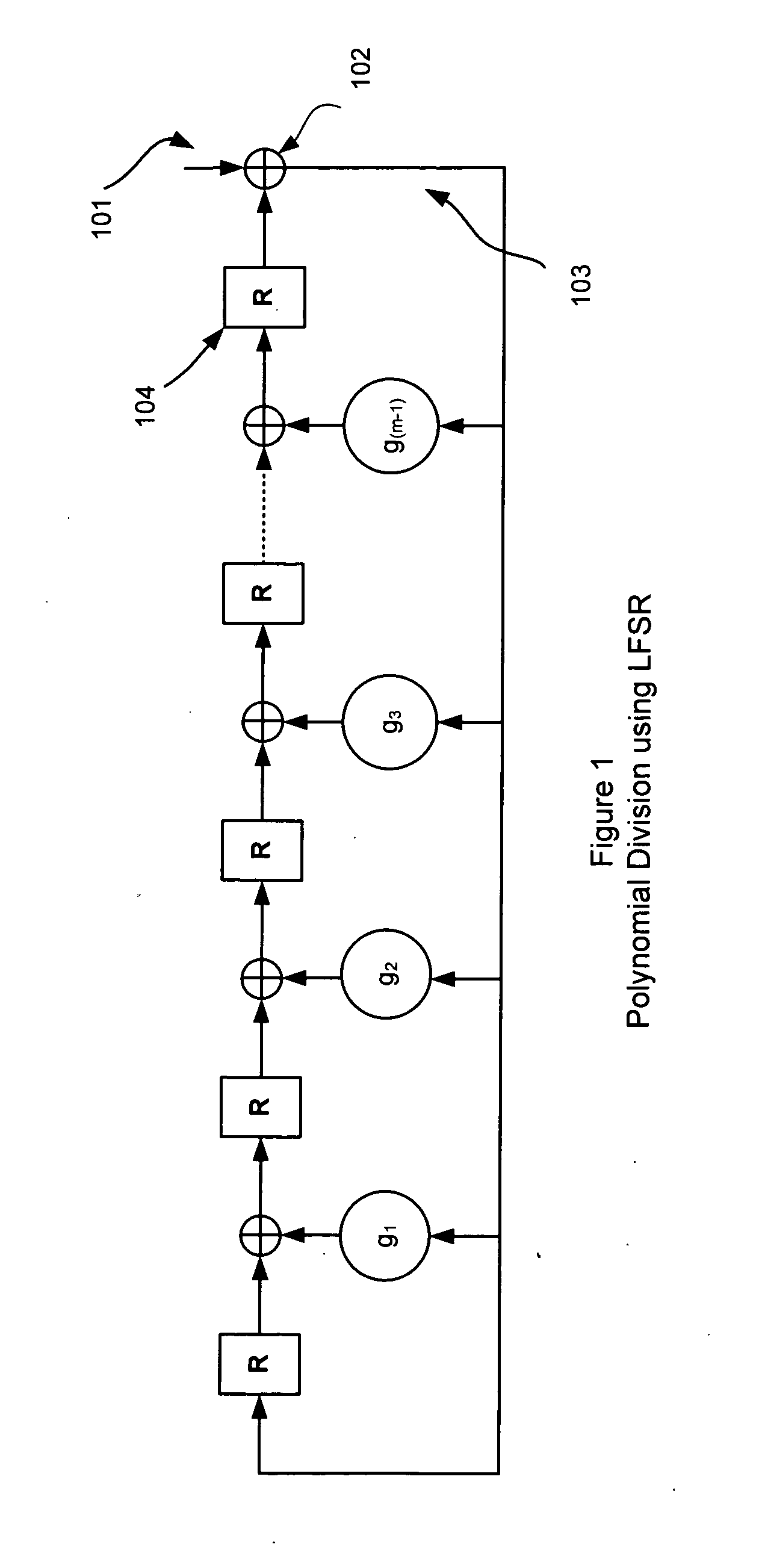

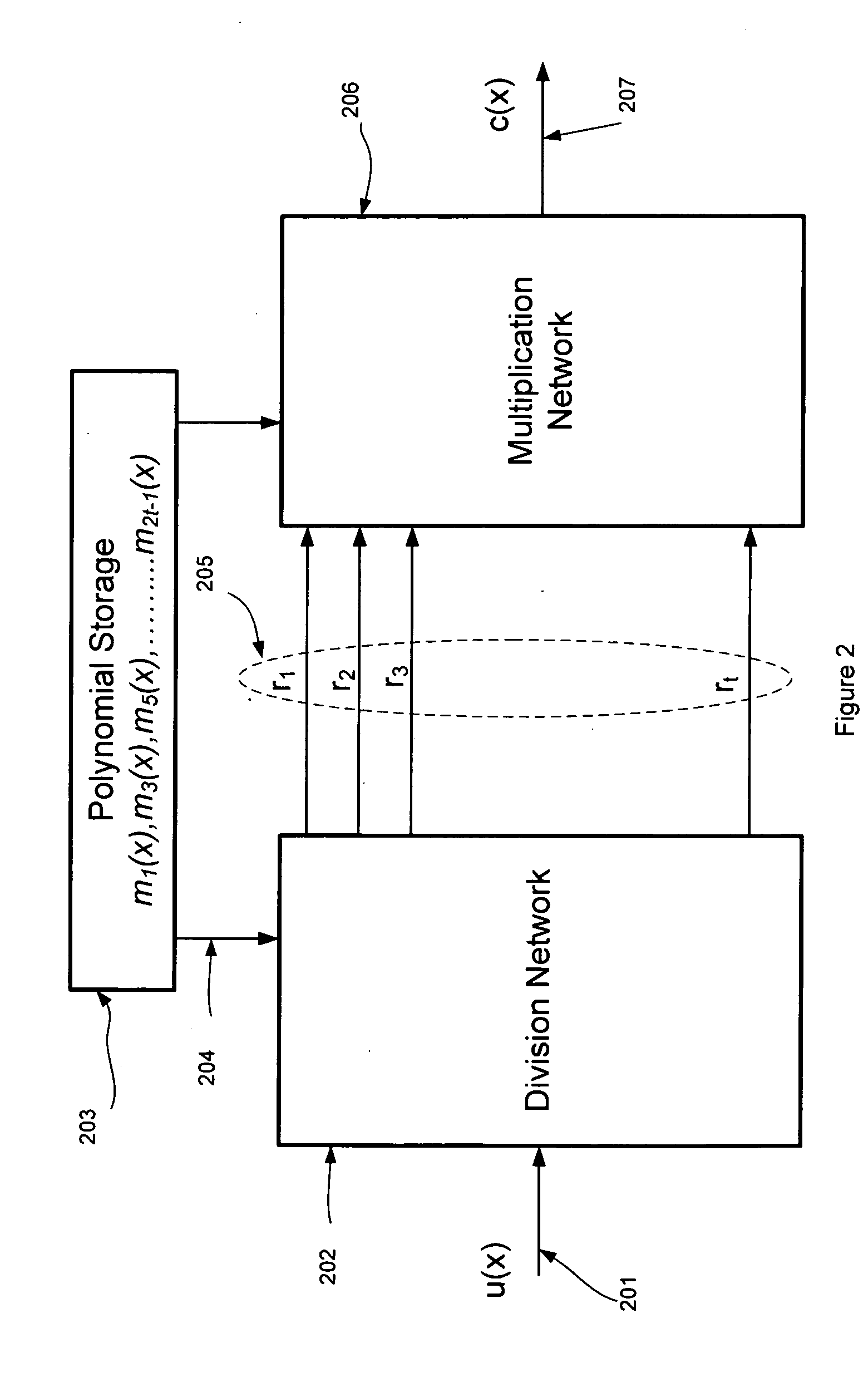

High-speed and agile encoder for variable strength long BCH codes

InactiveUS20110185265A1No additional costMinimal costCode conversionCyclic codesTheoretical computer scienceTrade offs

Agile BCH encoders are useful when the noise characteristics of the channel change which demands that the strength of the error correcting BCH code to be a variable. An agile encoder for encoding a linear cyclic code such as a BCH code, is a code that switches code strength (depth) relatively quickly in unit increments. The generator polynomial for the BCH code is provided in the factored form. The number of factored polynomials (minimal polynomials) chosen by the system determines the strength of the BCH code. The strength can vary from a weak code to a strong code in unit increments without a penalty on storage requirements for storing the factored polynomials. The BCH codeword is formed by a dividing network and a combining network. Special method is described that provides a trade off mechanism between latency and throughput while simultaneously optimizing the delay in the critical path which is in the forward path. Speed enhancements at minimal polynomial level are also provided by retiming, loop unfolding, loop unrolling, and special mathematical transformations. The presented invention can be implemented as an apparatus using software or hardware or in integrated circuit form.

Owner:CHERUKURI RAGHUNATH

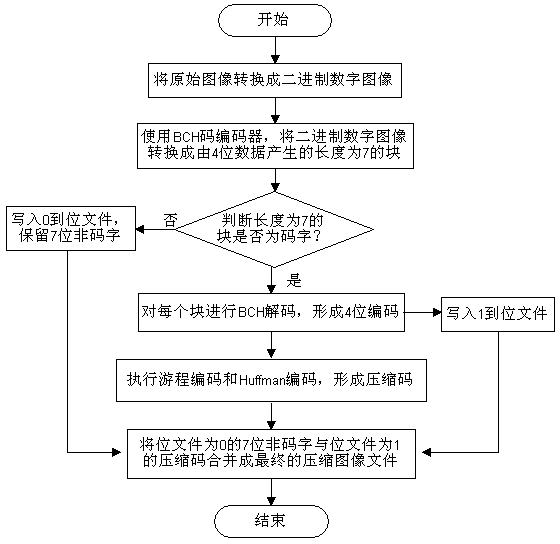

Lossless image compression system

The invention discloses a new binary (bit level) lossless image compression system. An error correction BCH (Broadcast Channel) code is introduced into an image compression algorithm; a four-bit binary of each image adds a 3-bit check code to compose a code word in a size of 7; these blocks enter into a BCH decoder, so that the size of the original blocks is reduced to 4 bits after the check bits are removed. The experiment result shows that the compression algorithm is effective, and a very well compression ratio is given without data loss. The use of the BCH code is better than the use of single Huffman compression in the aspect of improving the compression ratio.

Owner:JIANGSU XINRUIFENG INFORMATION TECH

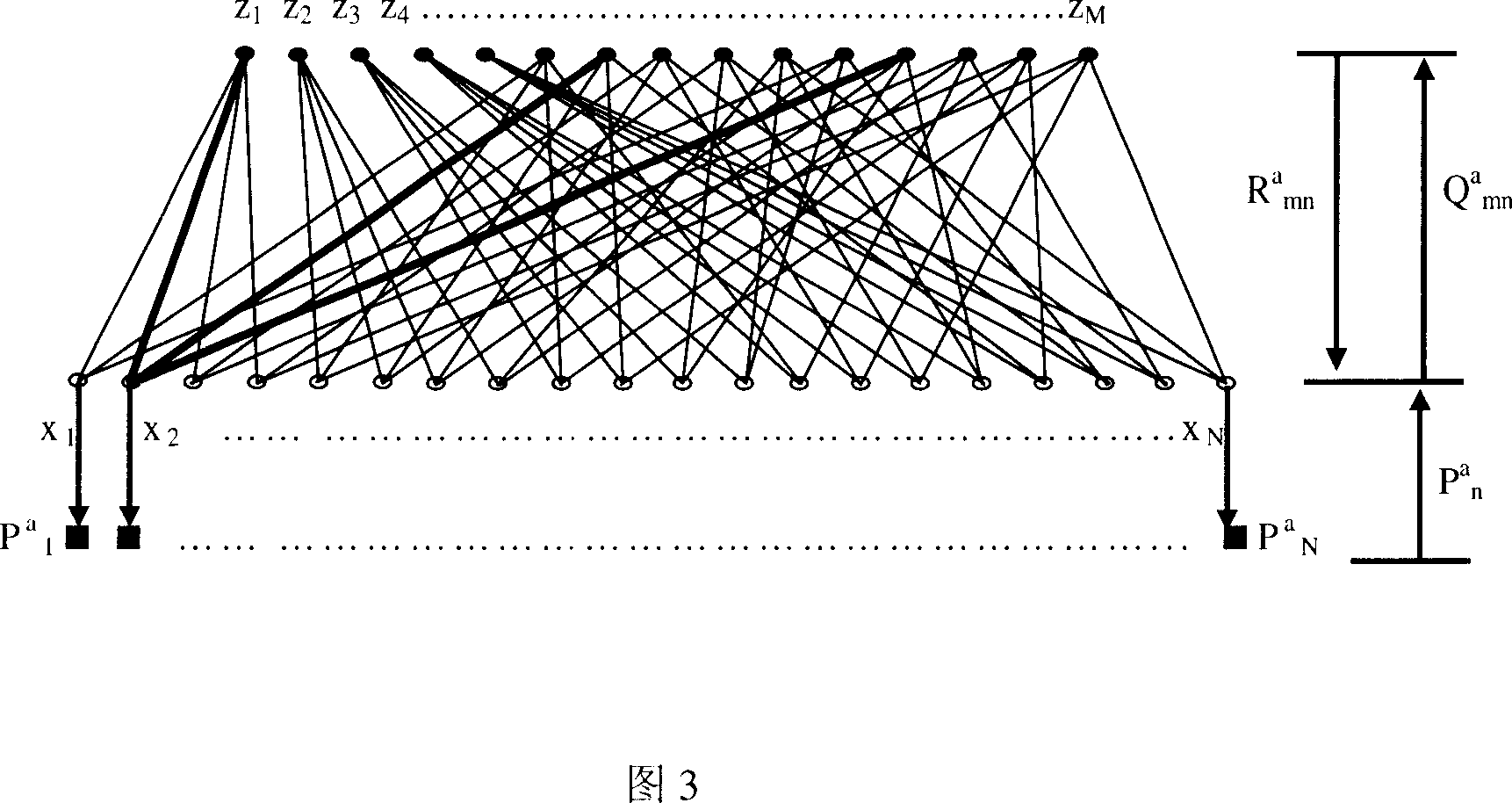

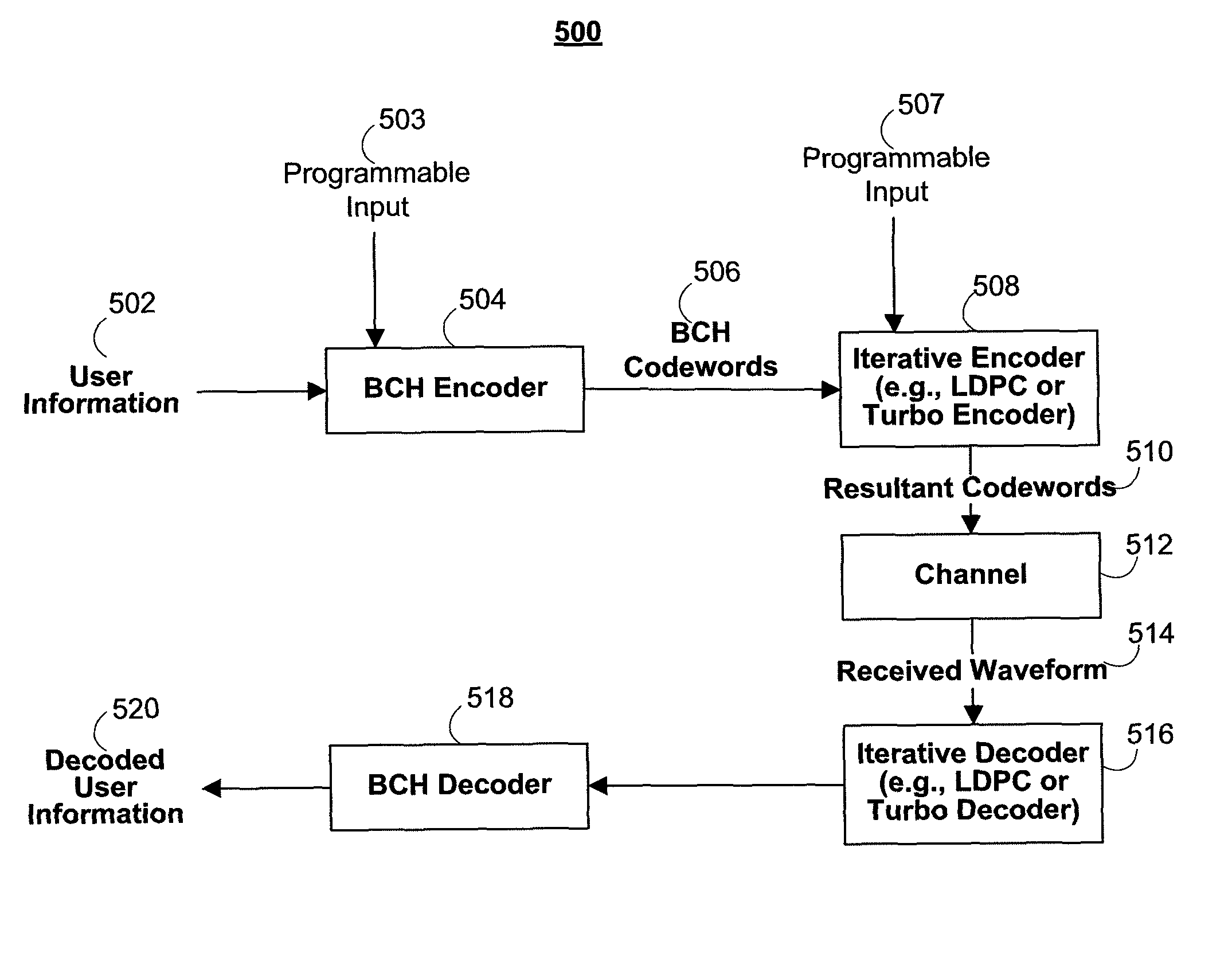

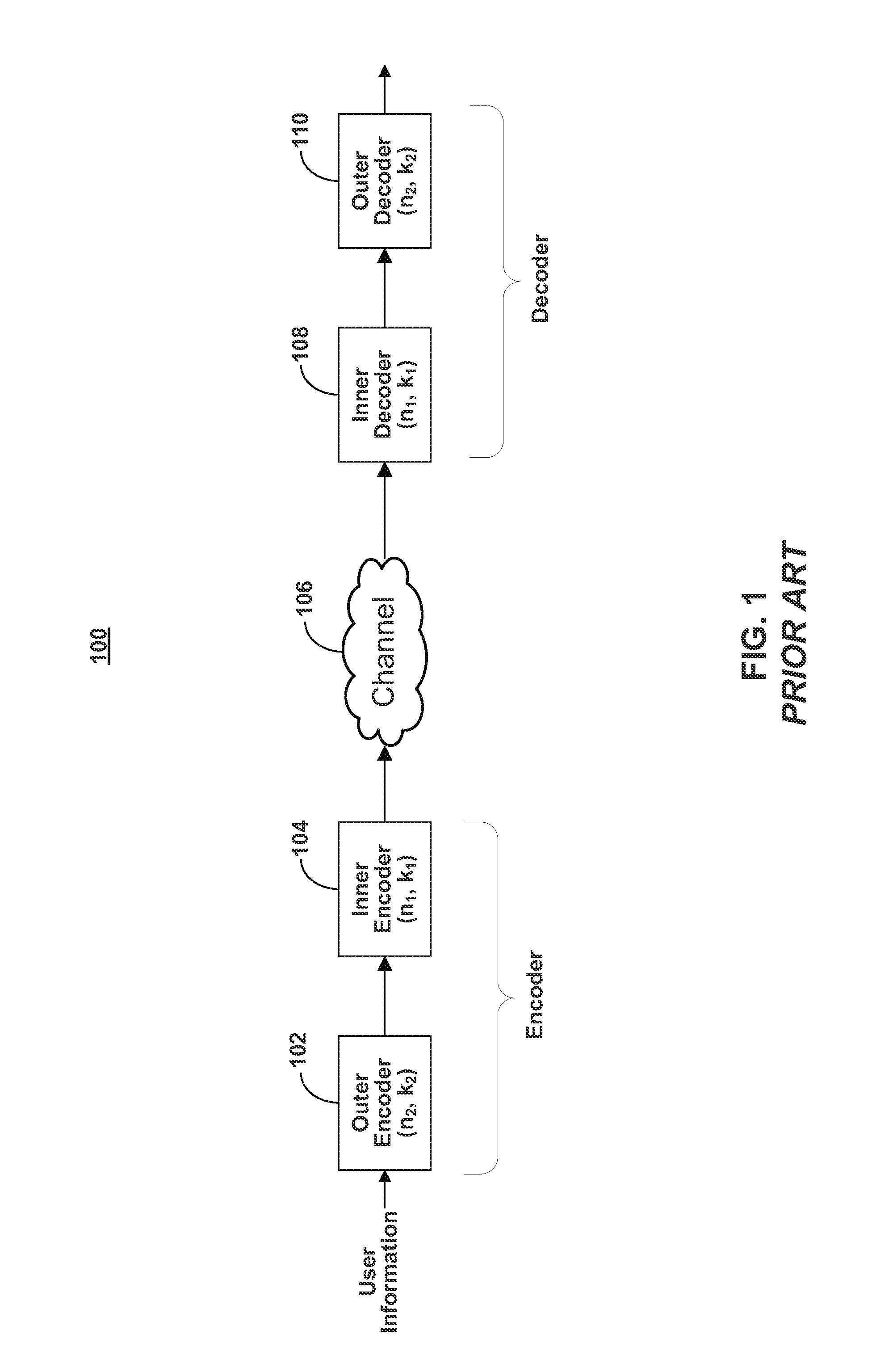

Concatenated codes for holographic storage

ActiveUS8583981B2Robust implementationGood flexibilityError preventionTransmission systemsHolographic storageComputer hardware

Systems and methods for constructing concatenated codes for data storage channels, such as holographic storage channels, are provided. The concatenated codes include an outer BCH code and an inner iteratively decodable code, such as an LDPC code or turbo code. The correction power and coding rate of one or both of the codes may be programmable based on the channel characteristics and the desired SNR coding gain. The correction power and / or coding rate of the inner and / or outer code may also be dynamically adjusted in real-time to compensate for time-varying error conditions on the channel.

Owner:MARVELL ASIA PTE LTD

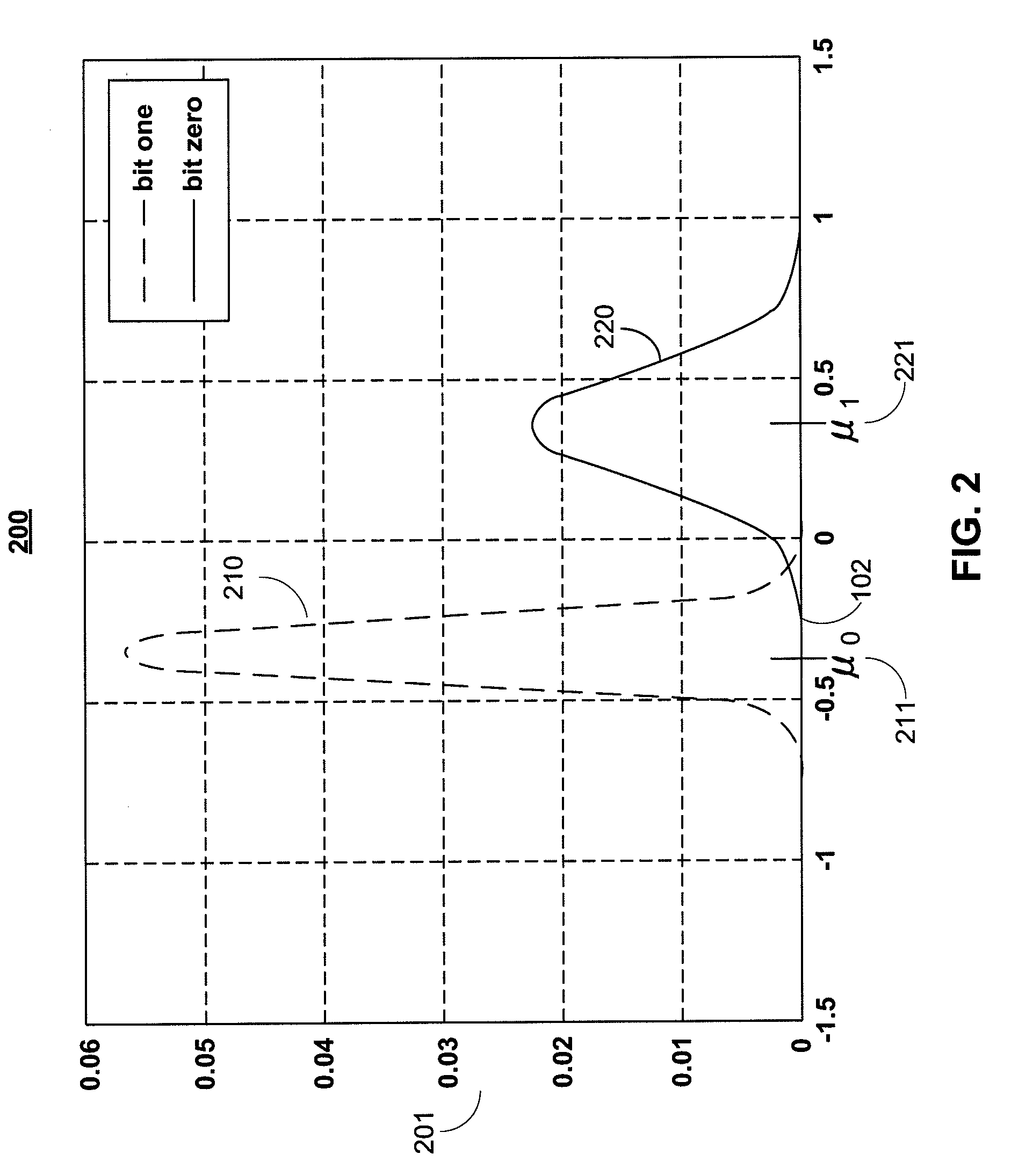

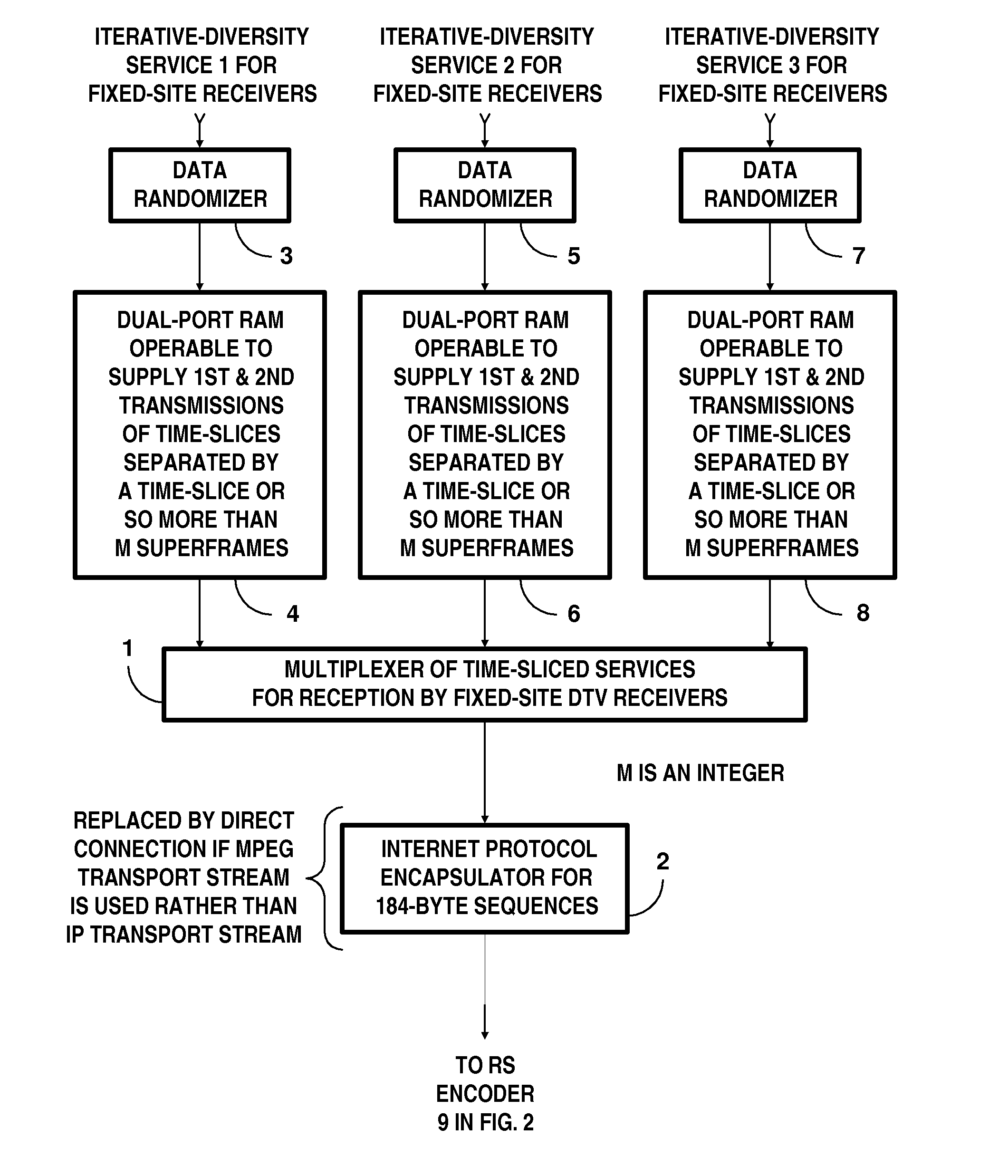

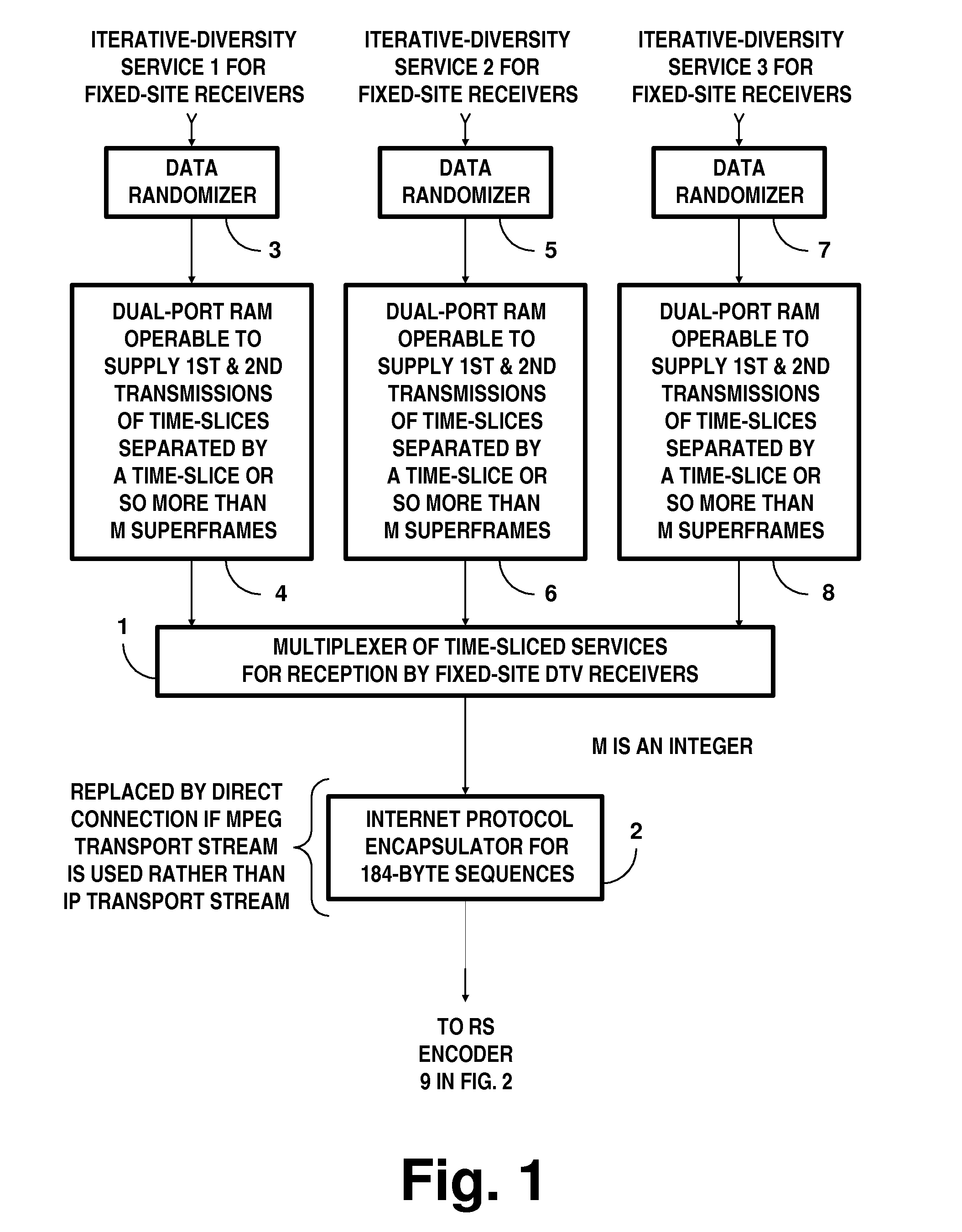

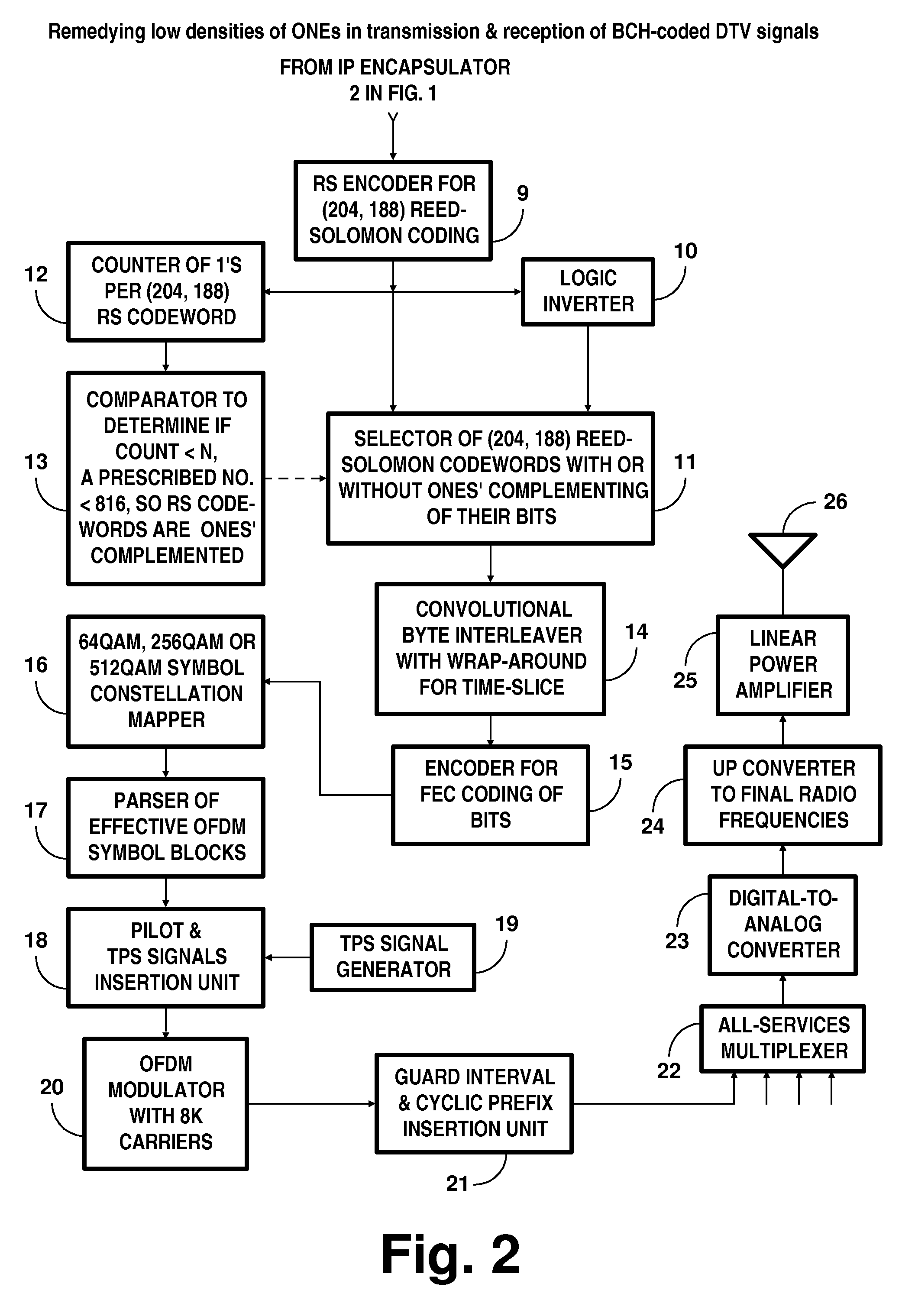

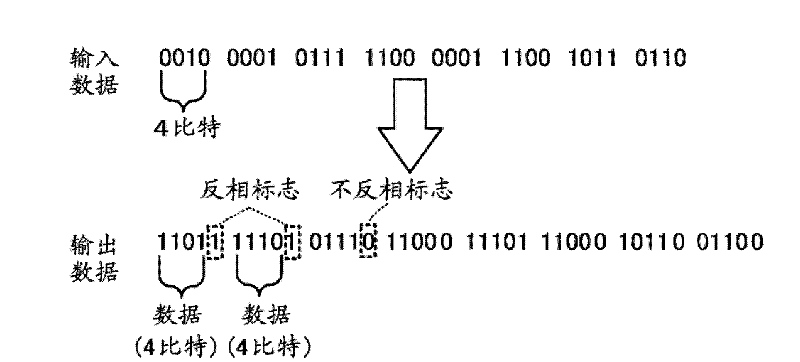

Remedying low densities of ONEs in transmission and reception of digital television signals

InactiveUS20140177731A1Reduce payloadHigh densityPicture reproducers using cathode ray tubesCode conversionCarrier signalDTV receiver

In a DTV transmitter the bits of shortened BCH codewords that exhibit undesirably low densities of ONEs are ONEs' complemented before being further coded, and used to modulate carrier waves. In a DTV receiver the further coding is decoded after demodulation. The results of such decoding are processed to recover successive shortened BCH codewords, some of which are in TRUE form and others of which have had their bits ONEs' complemented. Each shortened BCH codeword is extended to full length with ZEROs, and decoding is attempted. Successful decoding confirms that the shortened BCH codeword was received in TRUE form. If decoding is unsuccessful, the bits of the shortened BCH codeword as received are ONEs' complemented, extended to full length with ZEROs, and decoding is attempted. Successful decoding confirms that the shortened BCH codeword was received in ONEs' complemented form and has subsequently been converted to TRUE form.

Owner:LIMBERG ALLEN LEROY

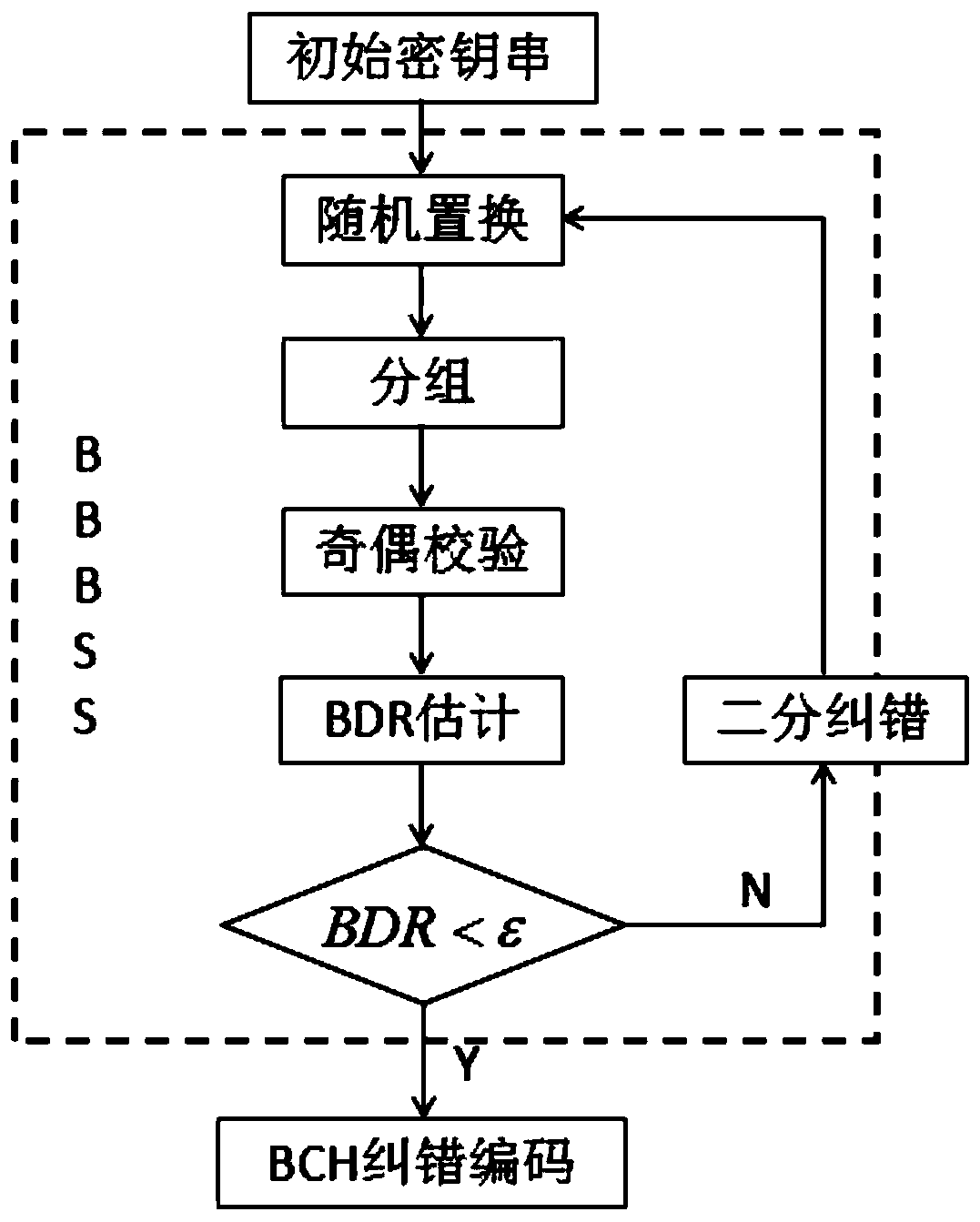

Method and device for computing error location polynomial in decoding through binary BCH (Bose-Chaudhuri-Hocquenghem) code

InactiveCN101951265AReduce decoding delayReduce power consumptionCyclic codesError locationComputer engineering

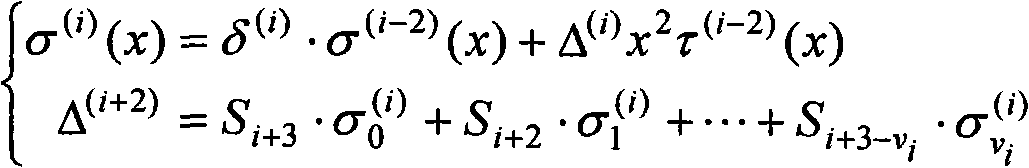

The invention discloses a method and a device for computing an error location polynomial in decoding through a binary BCH (Bose-Chaudhuri-Hocquenghem) code. The method comprises the following steps of: (1) starting iteration from an even number according to a computed syndrome, initializing a step-length initial value i and computing the initial parameter of the error location polynomial; (2) computing the ith iterated error location polynomial and an i+2nd iterated correction term; (3) judging and computing the parameter of the next iterative computation; (4) setting the step length of value buil-up constant of i to be 2, i.e. i<=i+2; (5) comparing the value of iteration times with 2t-1, selecting to continue iteration according to a comparison result, and turning to the step (2), or ending the iteration and turning to a step (6) for processing; and (6) outputting the i-2nd iterated error location polynomial, and finishing the computation. The invention also greatly reduces the power consumption of a decoding circuit while reducing the binary BCH decoding delay.

Owner:ALLWINNER TECH CO LTD

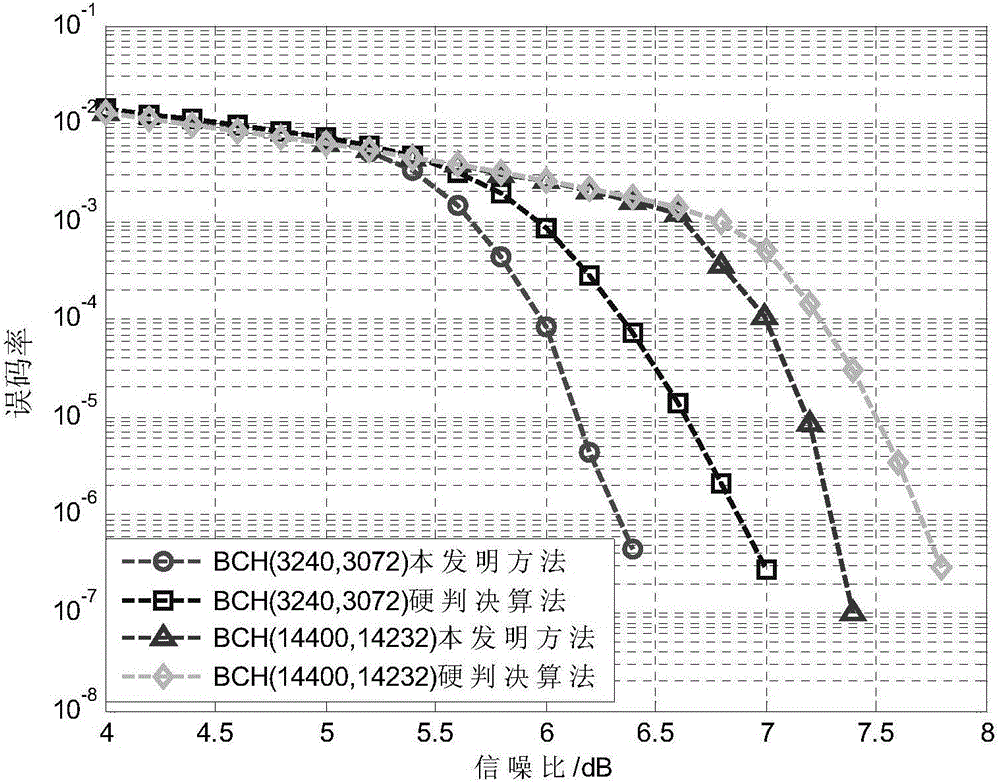

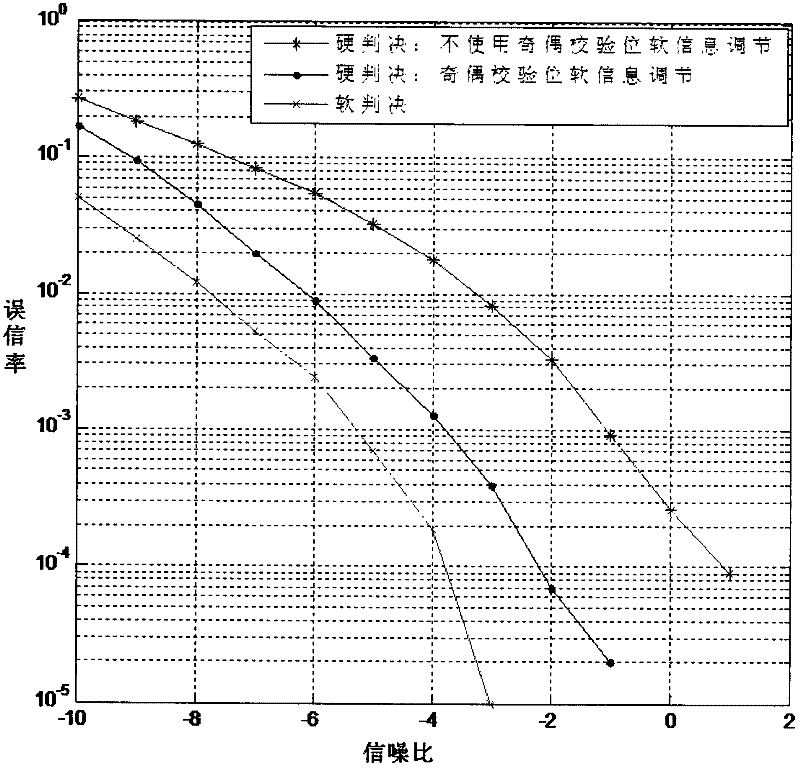

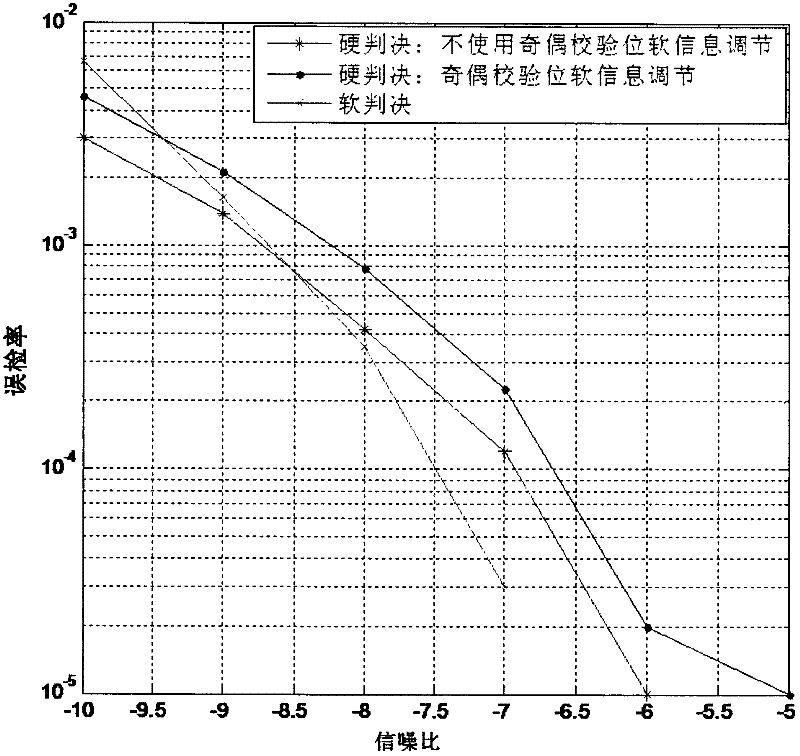

Improved BCH soft-decision decoding algorithm

ActiveCN105812000AReduce Decoding LatencyImprove error correction performanceCode conversionCyclic codesRound complexityImproved algorithm

The invention discloses an improved BCH soft-decision decoding algorithm with the object of resolving the problem in the prior art that a current BCH soft-decision decoding algorithm is complex to perform and decoders are often too much delayed. The improved algorithm is performed through the following steps: firstly, choosing t positions of code symbols with least credibility, according to inputted soft information, as estimated error positions and seeking the numbers of error positions in their corresponding finite fields; conducting hard decision to the inputted soft information for binary BCH codes and seeking an initial adjoint polynomial; fourthly, seeking a polynomial for error positions based on the updated adjoint polynomial; if the supreme power from the polynomial for error positions is less than the maximally correctable number t of a BCH decoder, then seek the error image patterns; otherwise, go back to the third step; and completing decoding by correcting the codes obtained by hard decision to the error image patterns. According to the invention, the soft decision decoding algorithm is made less complex and delay of decoders is shortened, and the algorithm can be applied in error control coding.

Owner:XIDIAN UNIV

Apparatus for processing OTN frames utilizing an efficient forward error correction

InactiveUS7573871B2Improve performanceEfficient forward error correctionTime-division multiplexData switching by path configurationAlgorithmFX.25 Forward Error Correction

An apparatus and method utilizing an efficient forward error correction (FEC), targeted for processing optical transport network (OTN) signals having transmission rates in excess of 10 Gbps. The FEC uses an advanced implementation of the Bose Chaudhuri Hocquenghem (BCH) code. The use of the BCH code for the FEC improves the performance over prior art solutions for both error correction and detection.

Owner:OPTIX NETWORKS

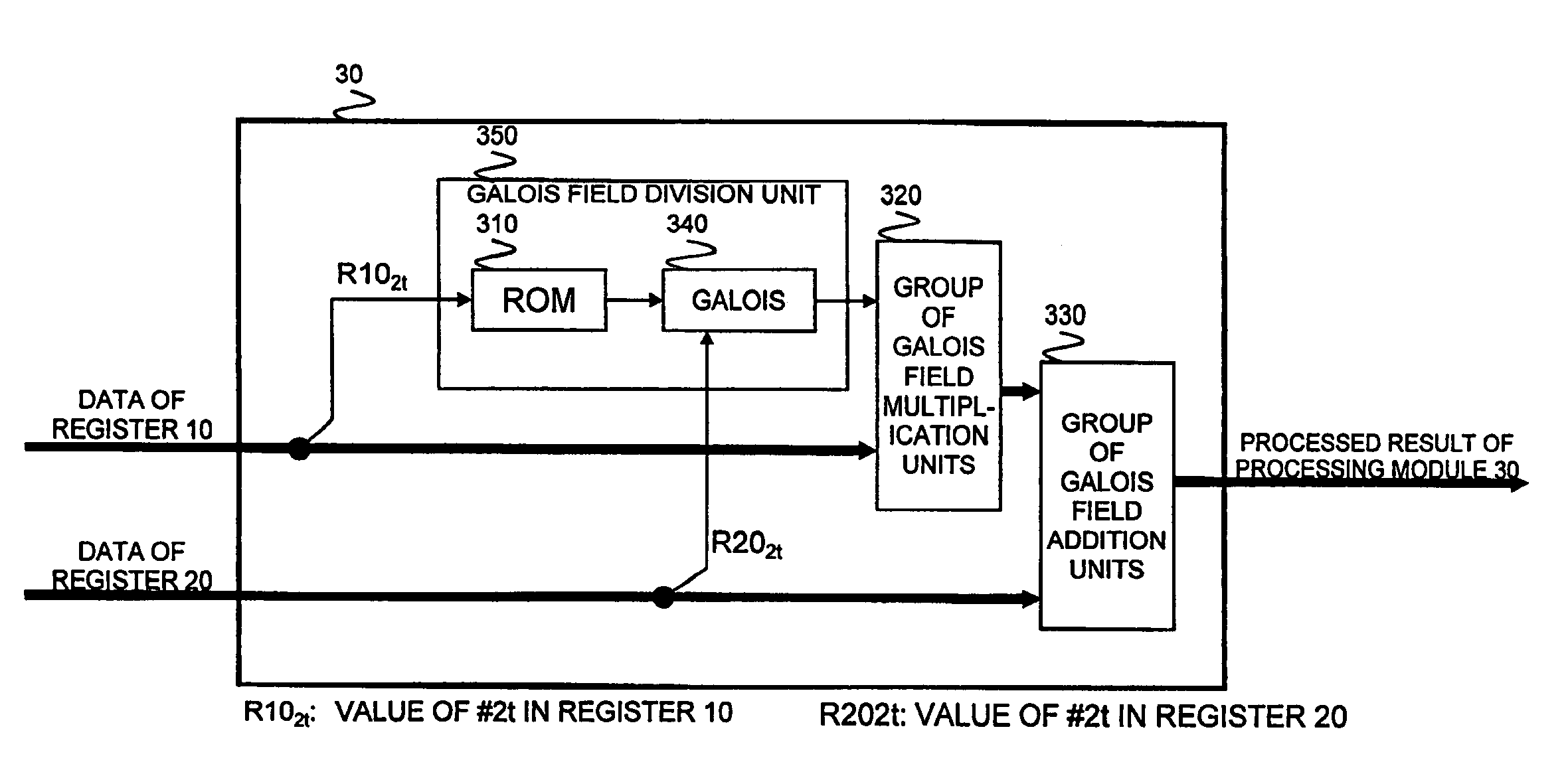

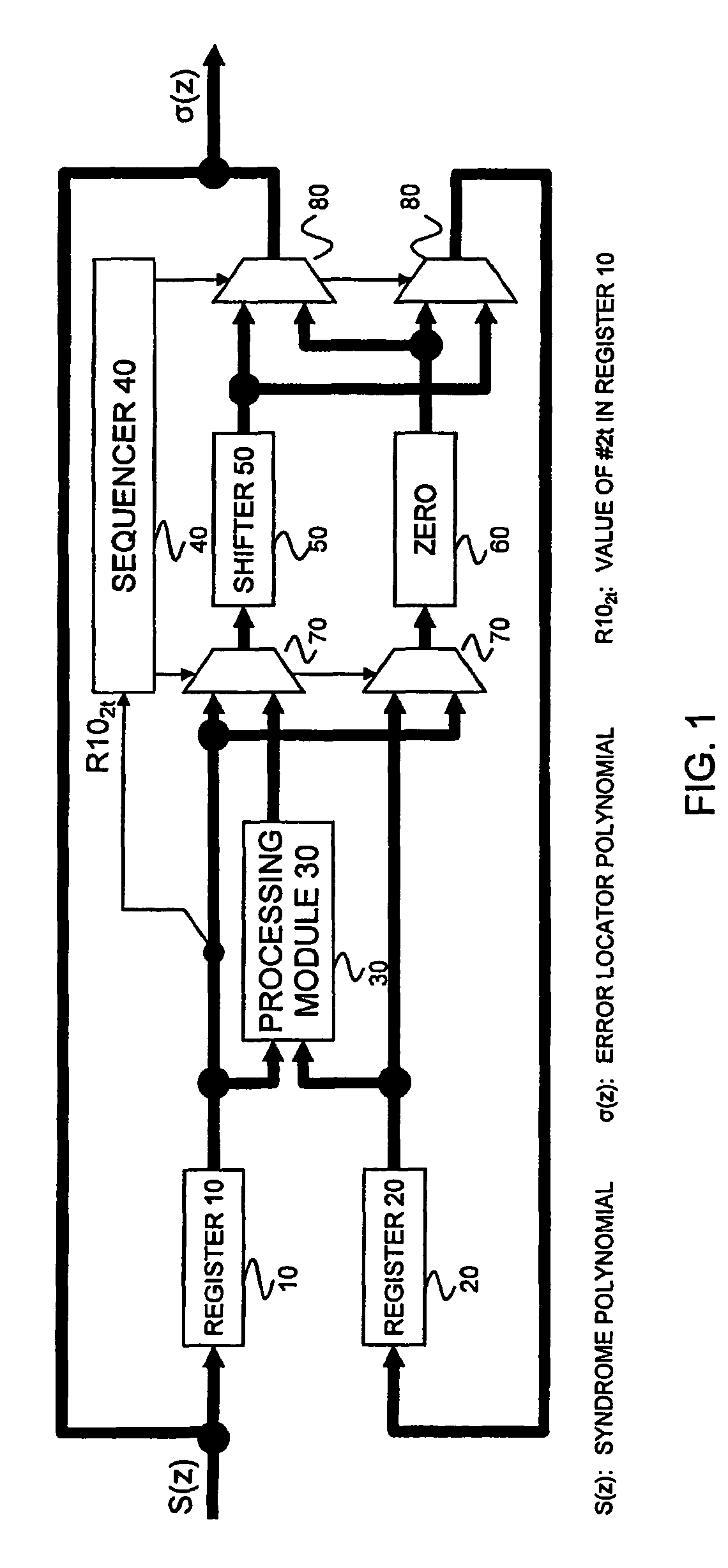

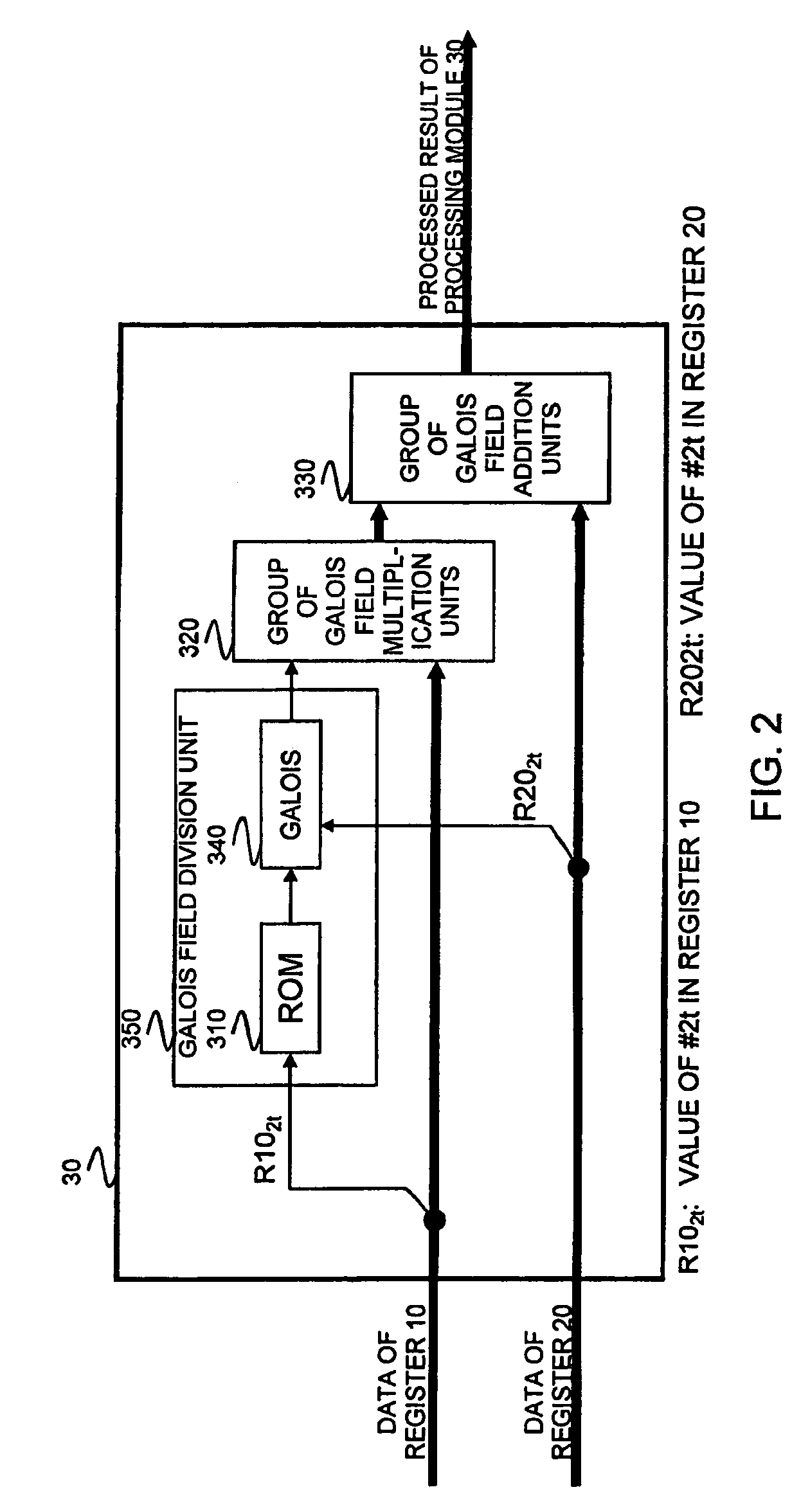

Processing module, error correction decoding circuit, and processing method for error locator polynomial

InactiveUS8335973B2Simple circuit configurationReduce in quantityCode conversionCyclic codesProcessor registerComputer module

A Euclid processing module for obtaining an error locator polynomial of a binary BCH code in an error correction decoding circuit, in which error corrections of words are performed, includes registers, a shifter, a zero insertion unit, selectors and a sequencer. Coefficients of polynomials Ri (z) and Bi (z) stored in the registers are subjected to Galois field calculations by the processing module. Results of the calculations and the data of the registers are shifted by the shifter. Some of the coefficients are erased by the zero insertion unit and stored in registers by controlling the selectors with the sequencer. A necessary polynomial σ (z) is calculated by repeated processing of the processing module. The Euclid processing module decreases a logic scale and simplifies controlling logic in a state of small latency and high operating frequency.

Owner:HITACHI LTD

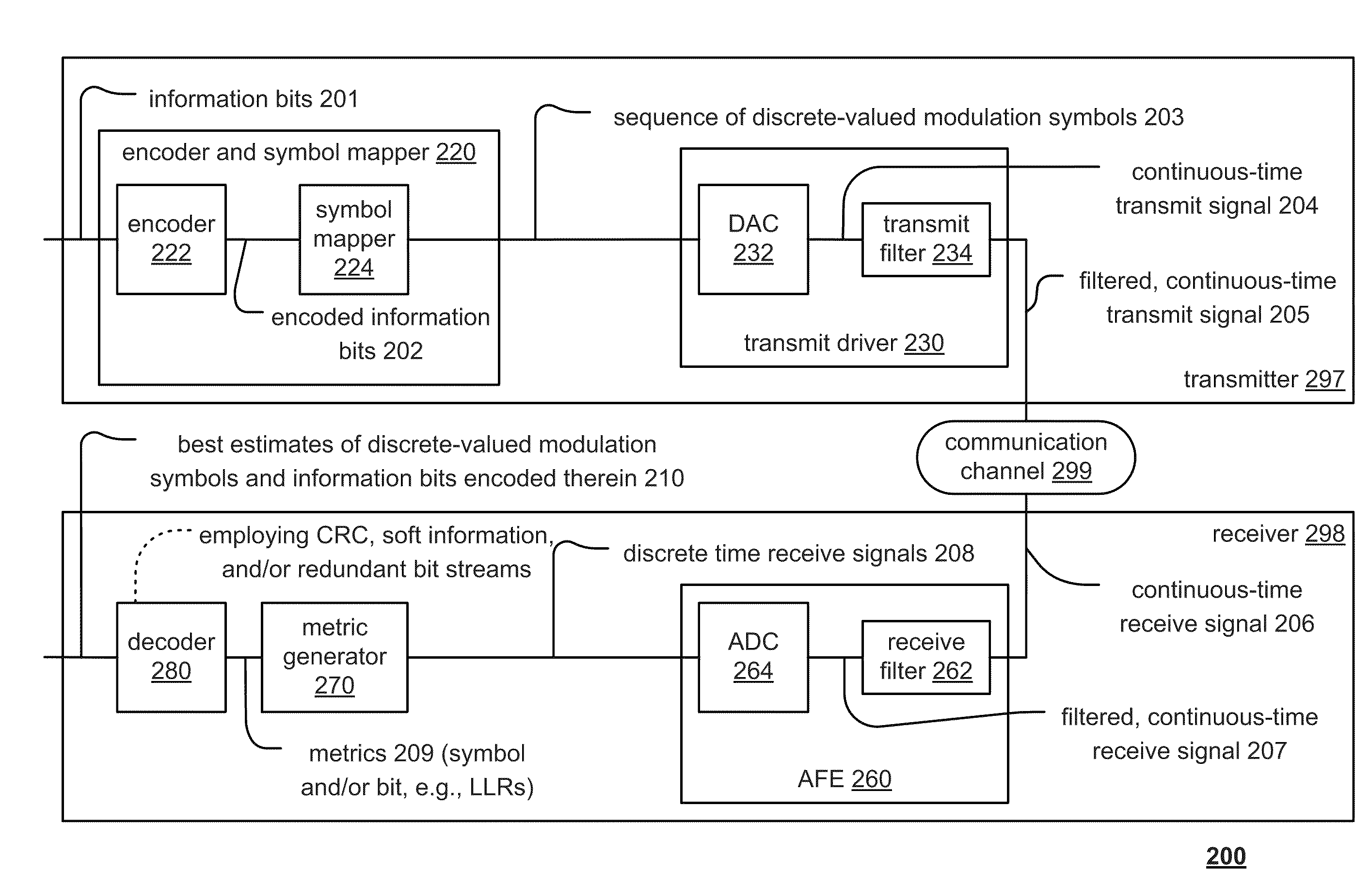

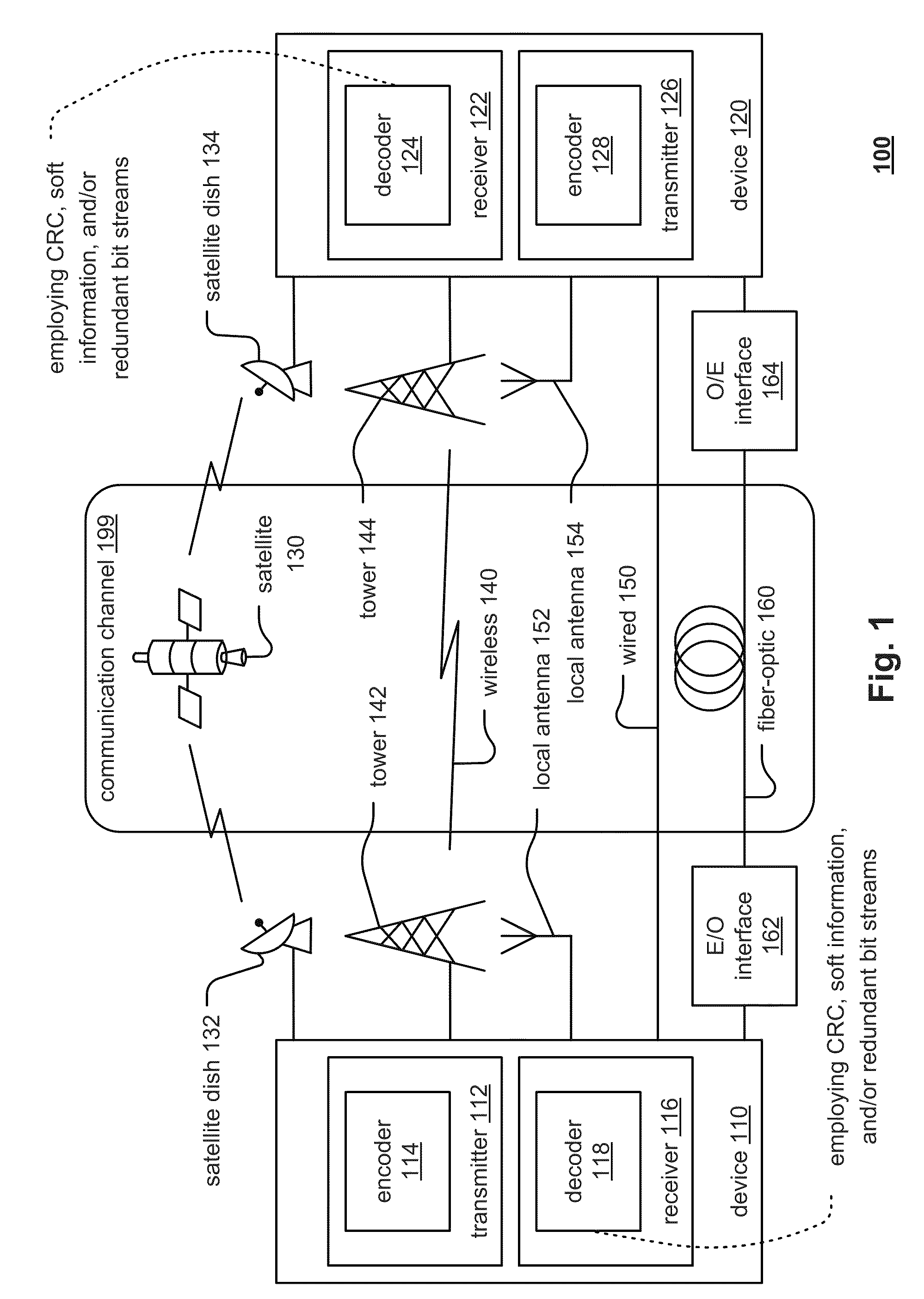

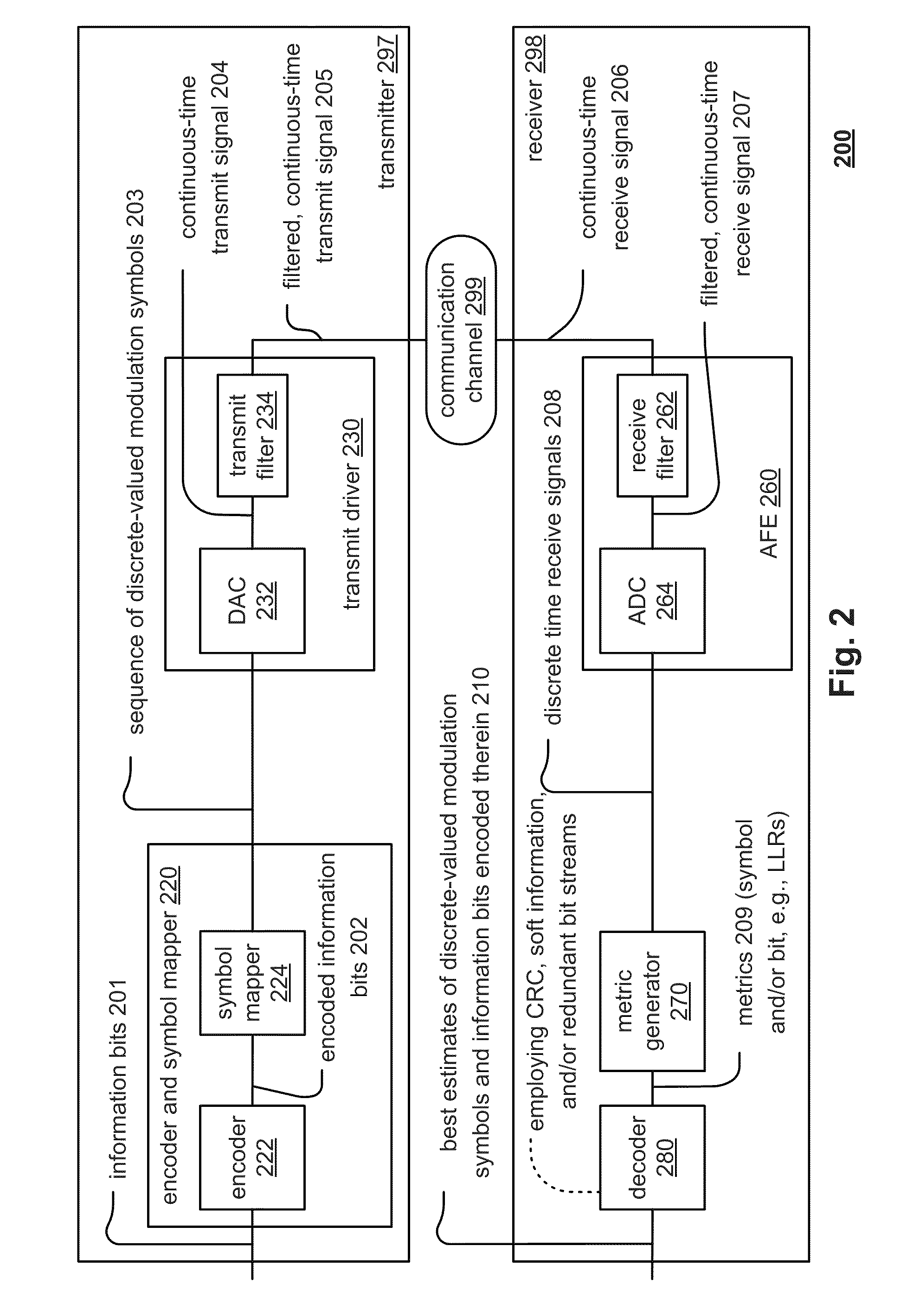

Low complexity error correction using cyclic redundancy check (CRC)

Communications between at communication devices, sometimes including at least one redundant transmission from a transmitter to a receiver, undergo low complexity error correction. CRC may be employed in conjunction with using any desired type of ECC or using uncoded modulation. Based on CRC determined bit-errors, as few as a singular syndrome associated with a singular bit-error or a linear combination of syndromes associated with two or more singular bit-errors within two or more received signal sequences are employed to perform error correction of the received signal. Real time combinations of multiple syndromes associated with respective single bit-errors (that may themselves be calculated off-line) are employed in accordance with error correction. In addition to CRC, any ECC may be employed including convolutional code, RS code, turbo code, TCM code, TTCM code, LDPC code, or BCH code.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Correction coding method for ground digital television broadcast

ActiveCN100584011CImprove error correction performanceImprove bit error resistance performanceTelevision systemsDigital video signal modificationComputer hardwareInformation transmission

Owner:TSINGHUA UNIV

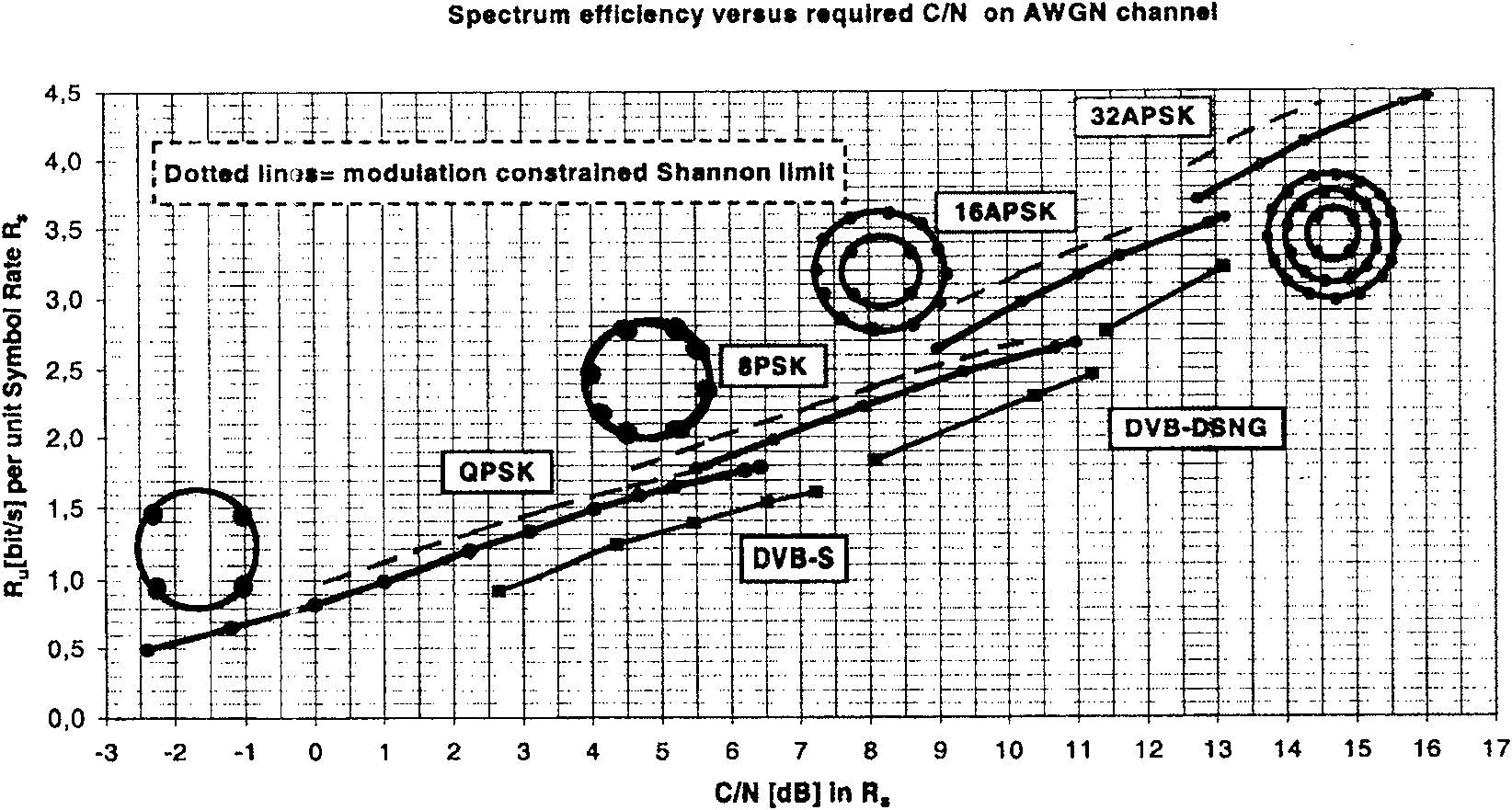

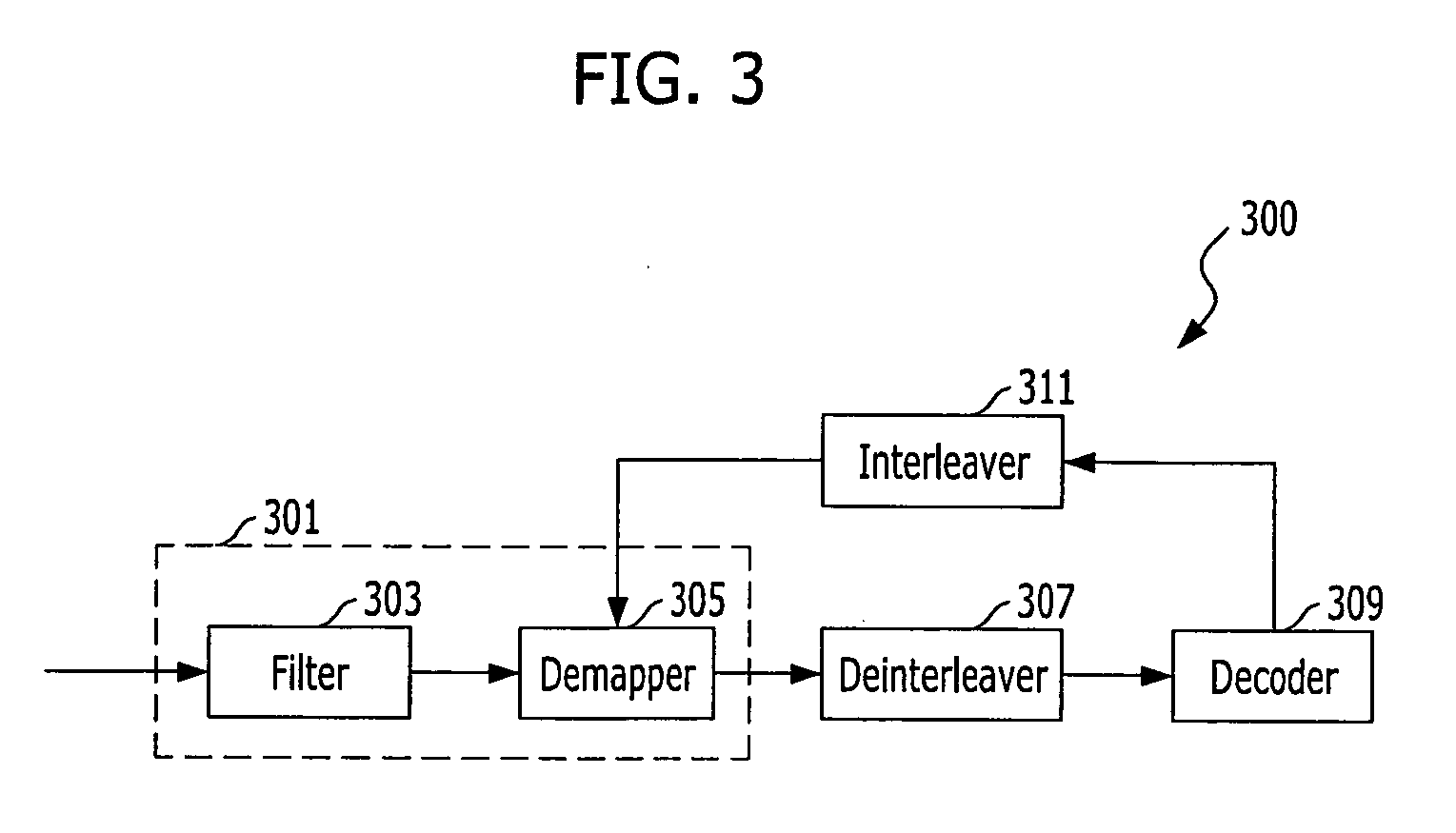

Method and apparatus for transmitting/receiving data using satellite channel

InactiveUS20100316161A1Improve performanceEconomically manufactureAmplitude-modulated carrier systemsRadio transmissionComputer hardwareChannel encoding

A method for transmitting data using a satellite channel includes: channel-encoding bit data using an e-BCH code; interleaving the encoded data; modulating the interleaved data according to a CPM scheme using four symbols; and transmitting the modulated data to a hub station.

Owner:ELECTRONICS & TELECOMM RES INST

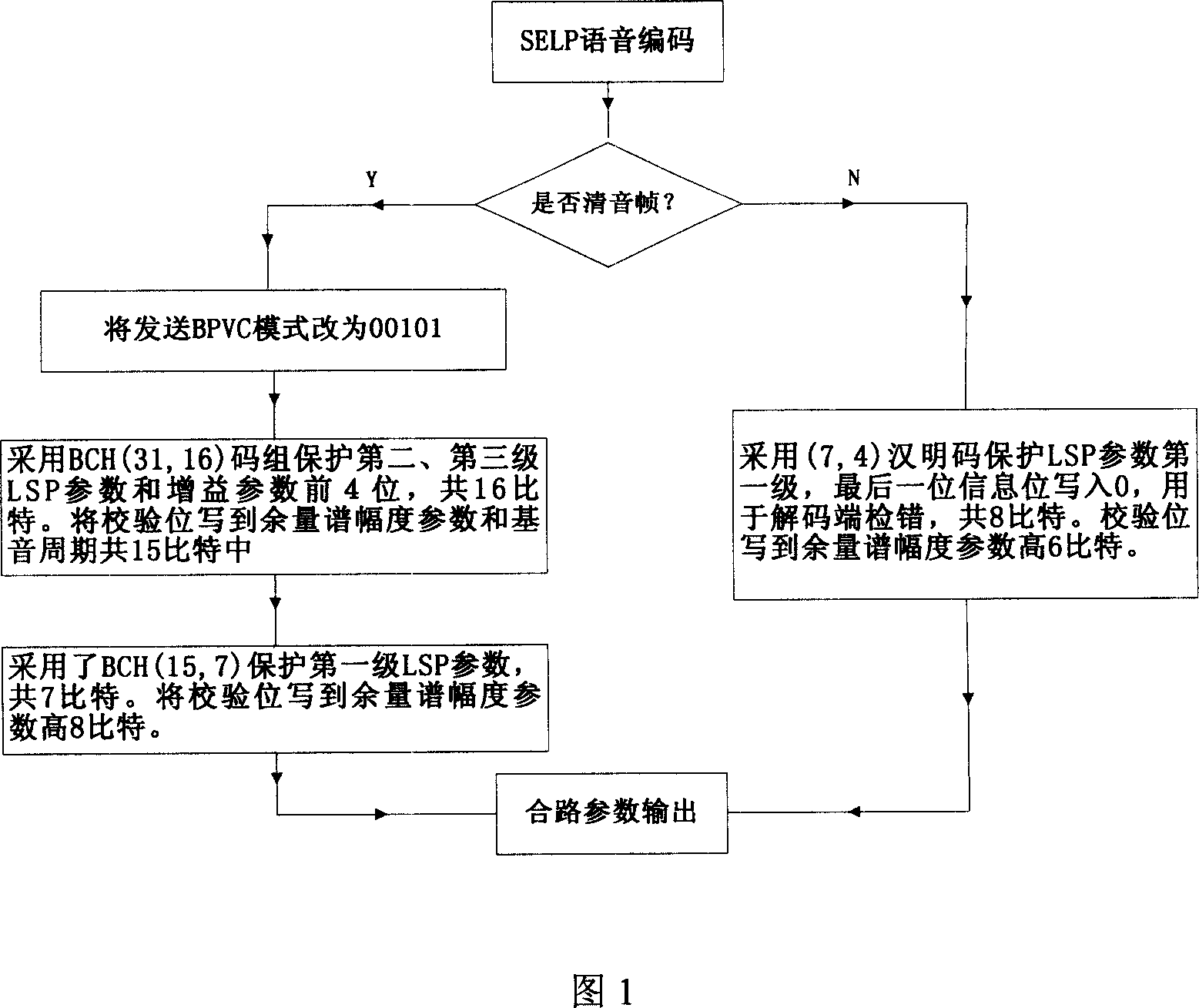

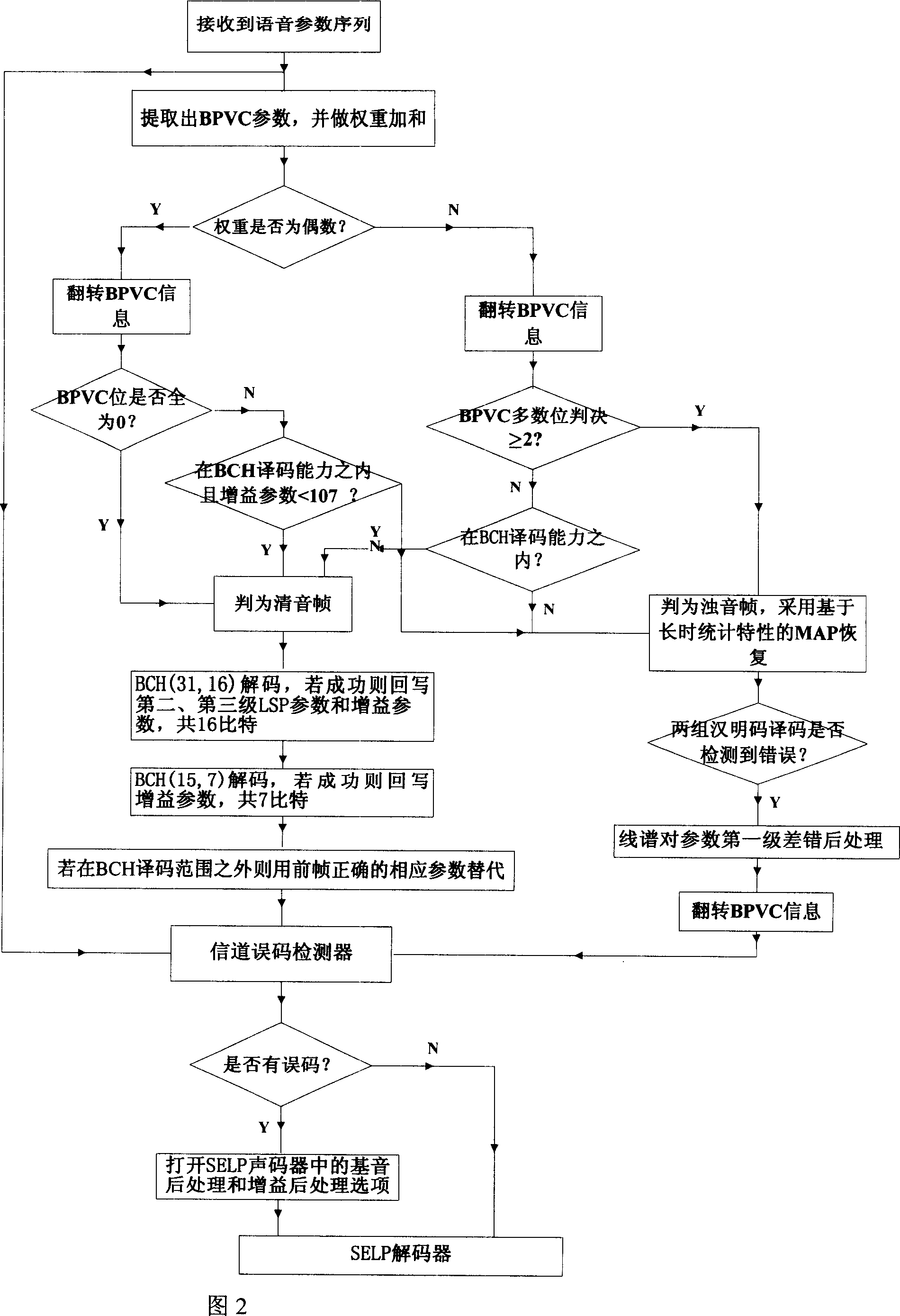

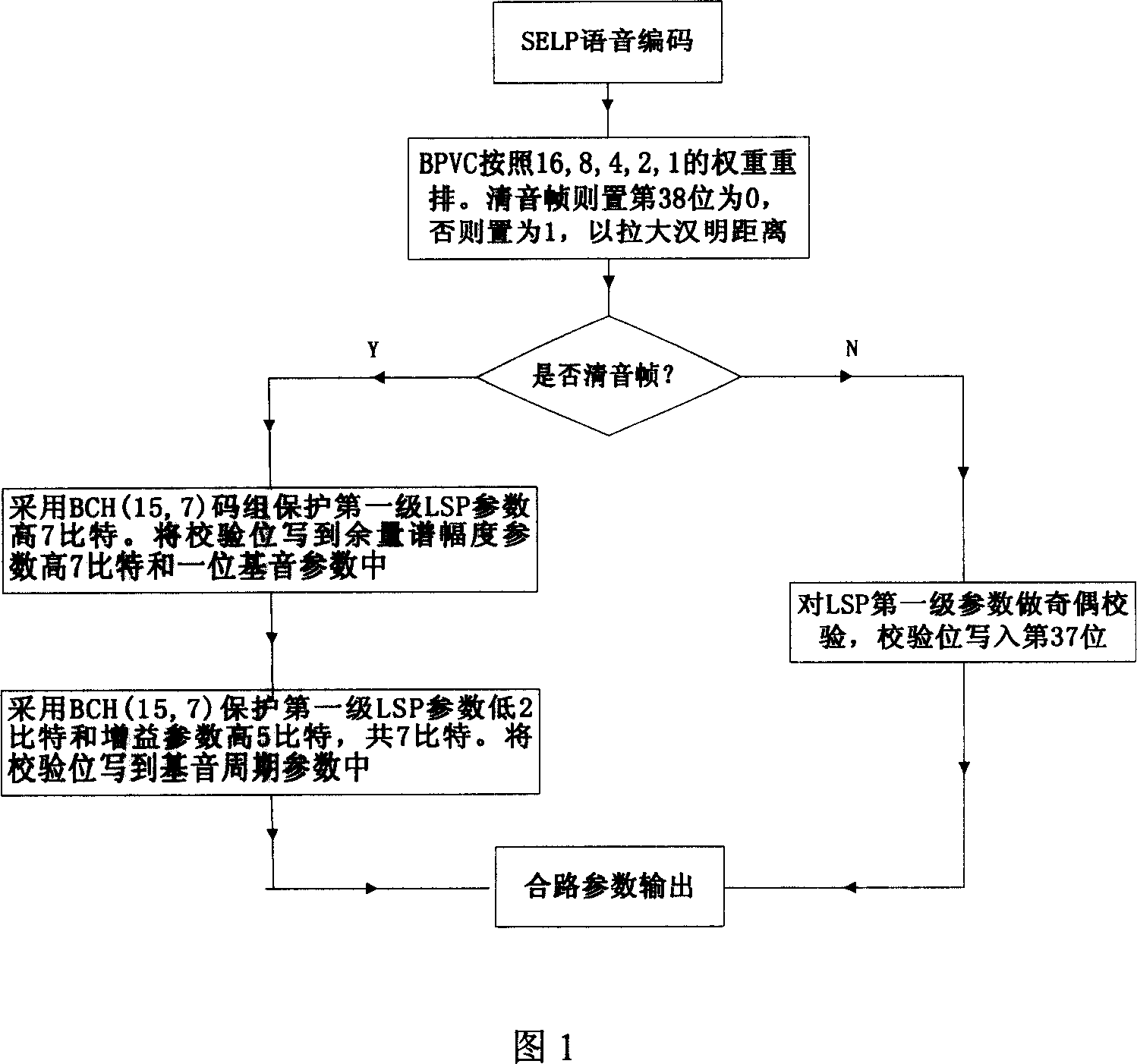

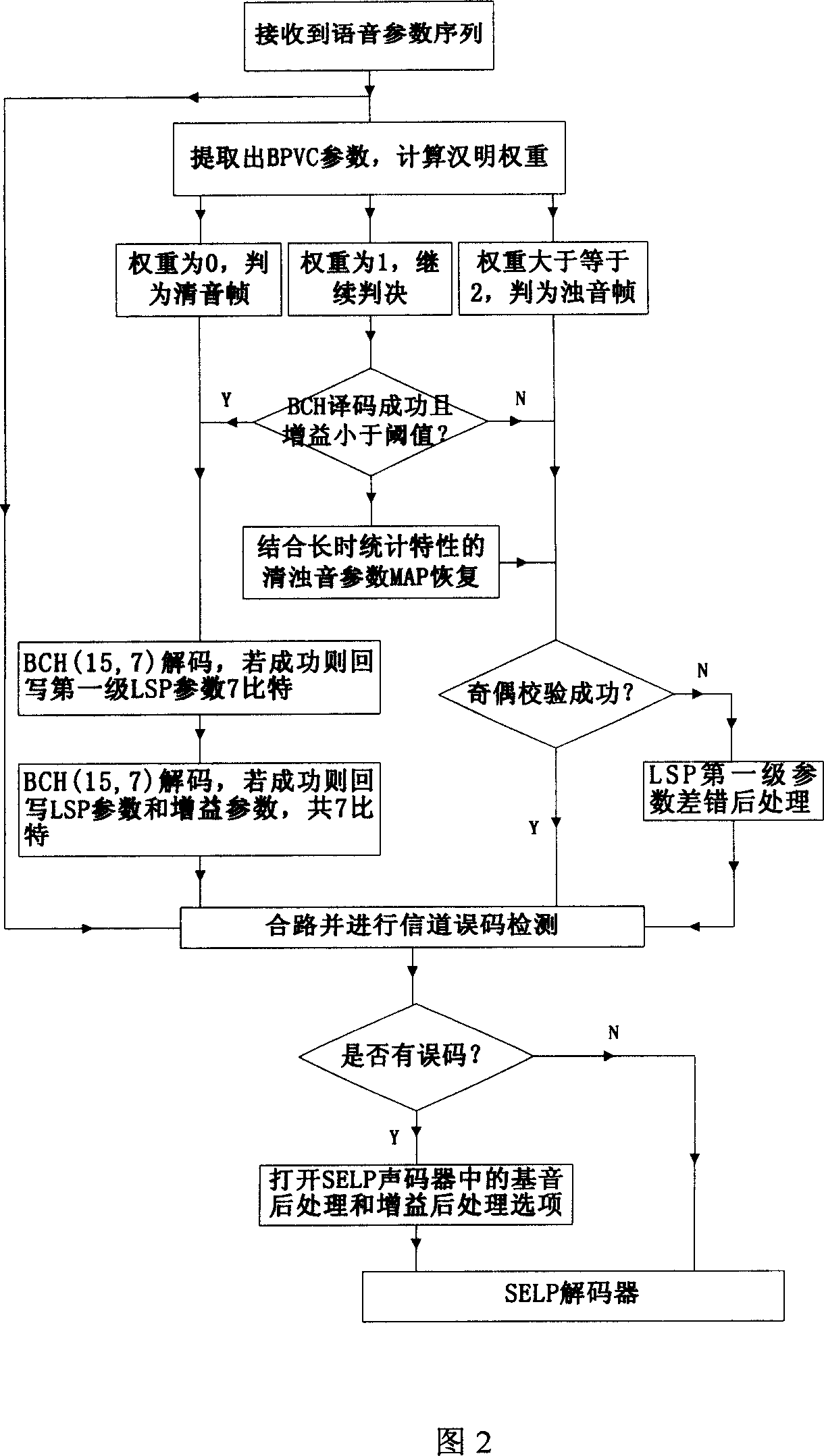

Protection method for anti channel error code of voice coder in 2.4kb/s SELP low speed

InactiveCN101004915AImprove accuracySynthesized speech quality degradesSpeech synthesisHamming codeComputer hardware

A method for protecting channel error code resistance ability of low speed vocoder includes applying improved Chinese plain code and BCH code to separately protect voice parameter in voiceless and voiced sound frames at coding end, using BCH code to recover relevant parameters of voiceless sound frame and using maximum post verification probability rule to recover parameter of voiceless sound accurately for voiced sound frame then using line spectrum to parameter anti-error code algorithm to recover line spectrum to parameter at decoding end.

Owner:TSINGHUA UNIV

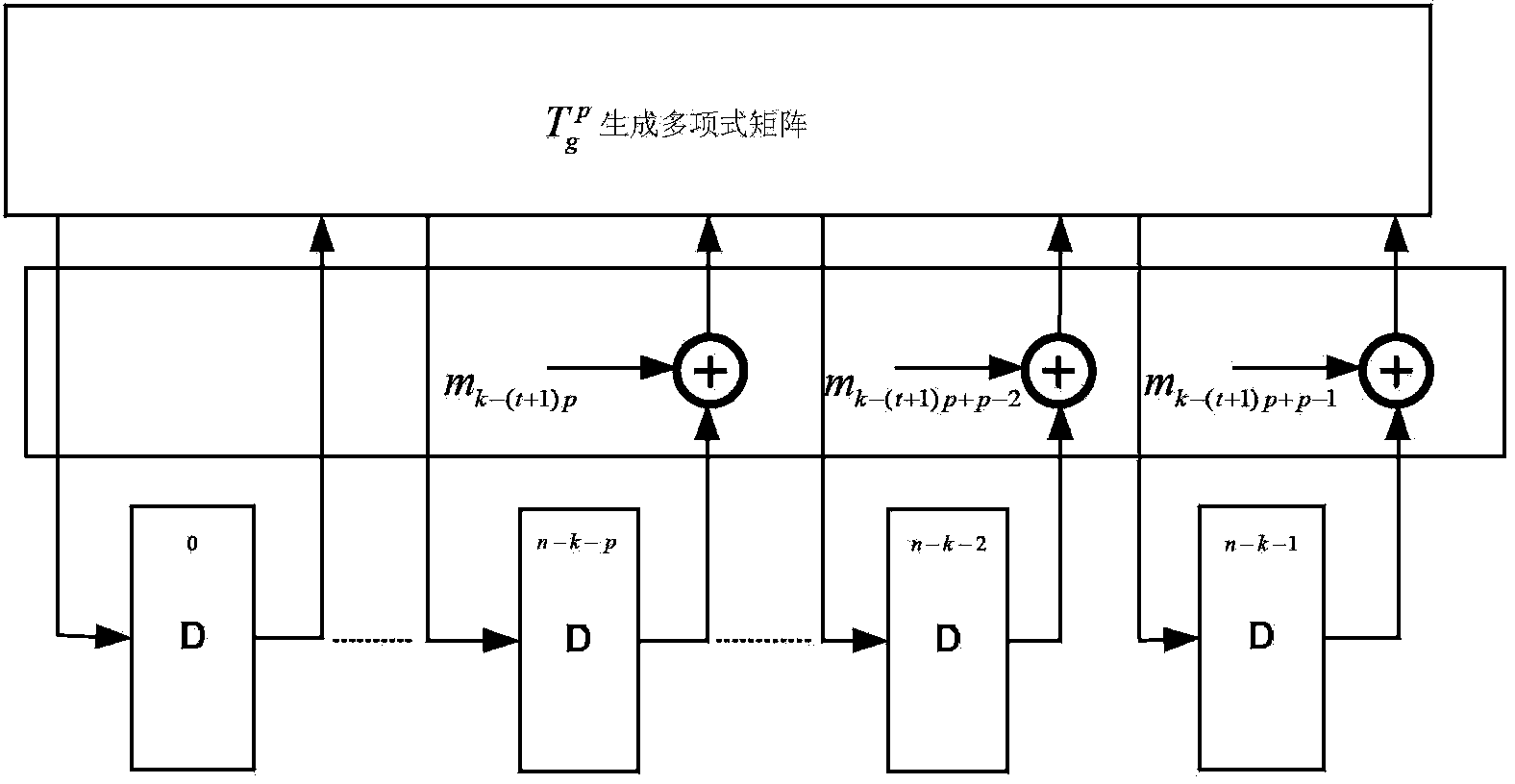

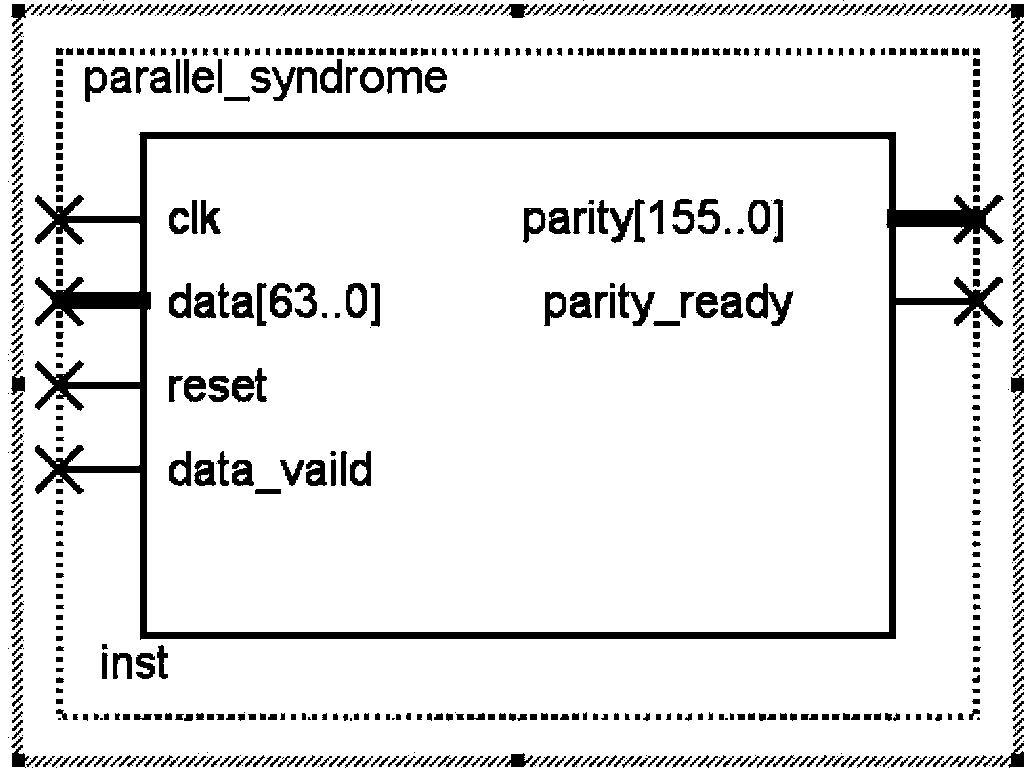

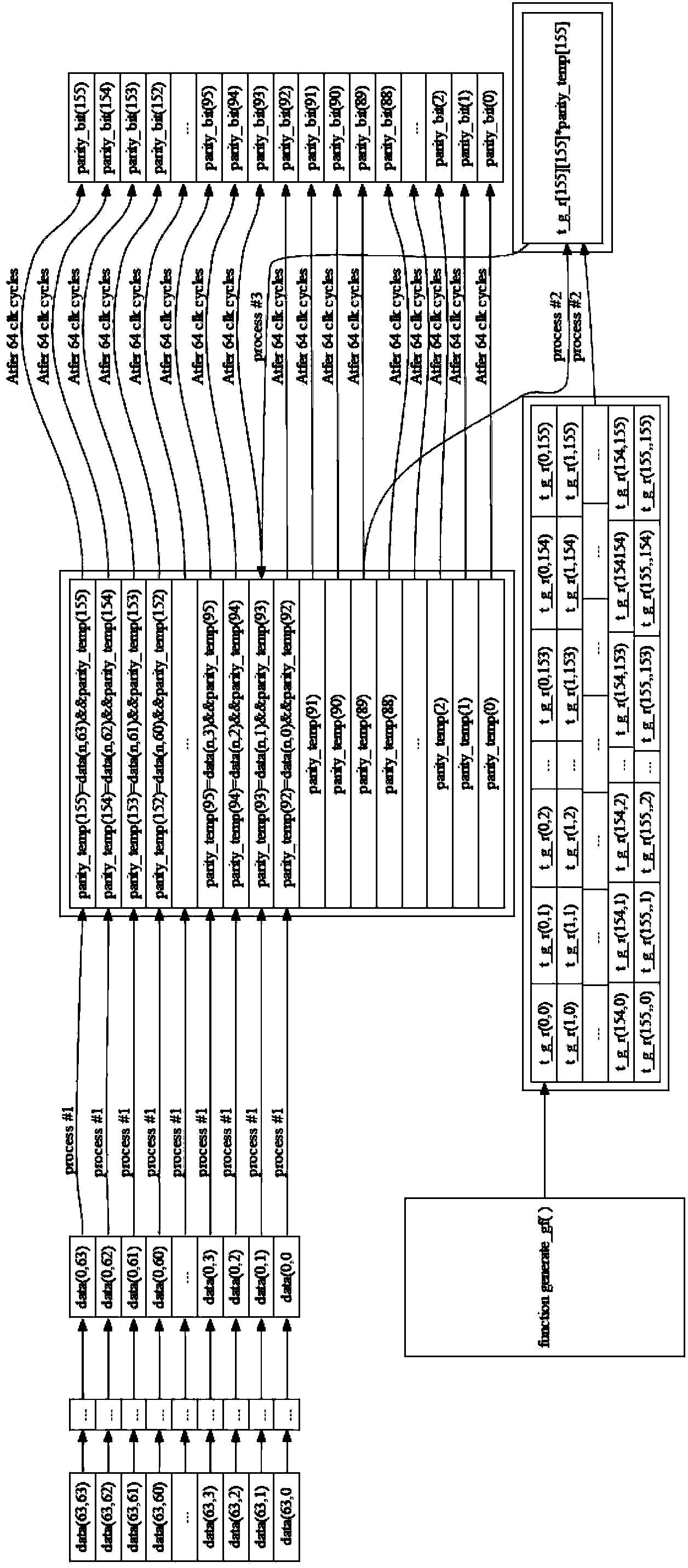

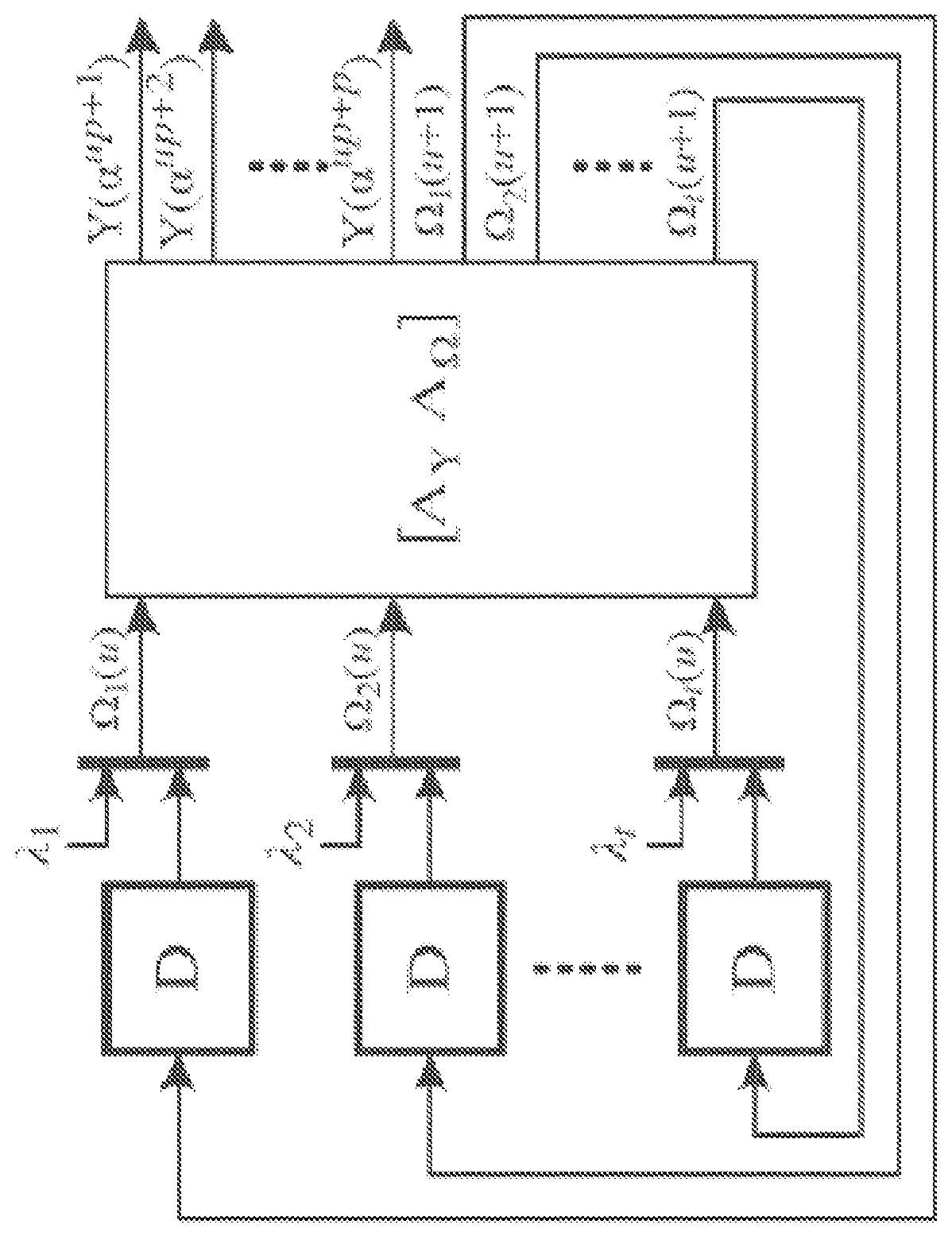

Parameterization BCH (broadcast channel) error-correcting code parallel encoding method and device

InactiveCN103401566AImprove encoding speedFast encodingCyclic codesBroadcast channelsTemporary variable

The invention discloses a parameterization BCH (broadcast channel) error-correcting code parallel encoding method and device. The method comprises the following steps of determining three variable parameters such as the error-correctable bits t, bit width p of the parallel encoding and length k of data information bit, solving a generation polynomial matrix, wherein the number of times of the generation polynomial matrix g(X) is (n-k); carrying out the logic operation for a temporary variable of a check bit and the generation polynomial matrix, and finally outputting a complete encoding module described through a verilog HDL (hardware description language) language. The generated encoding module is high in encoding speed and less in occupied resource. The encoding module utilizes one generation matrix to realize the parallel encoding function and is finally solved through a series of operation according to the generation polynomial of the BCH code. The method and the device are applicable to the application with long code word, high encoding speed and capability for continuously enhancing the error correcting capacity of the error-correcting code.

Owner:HOHAI UNIV

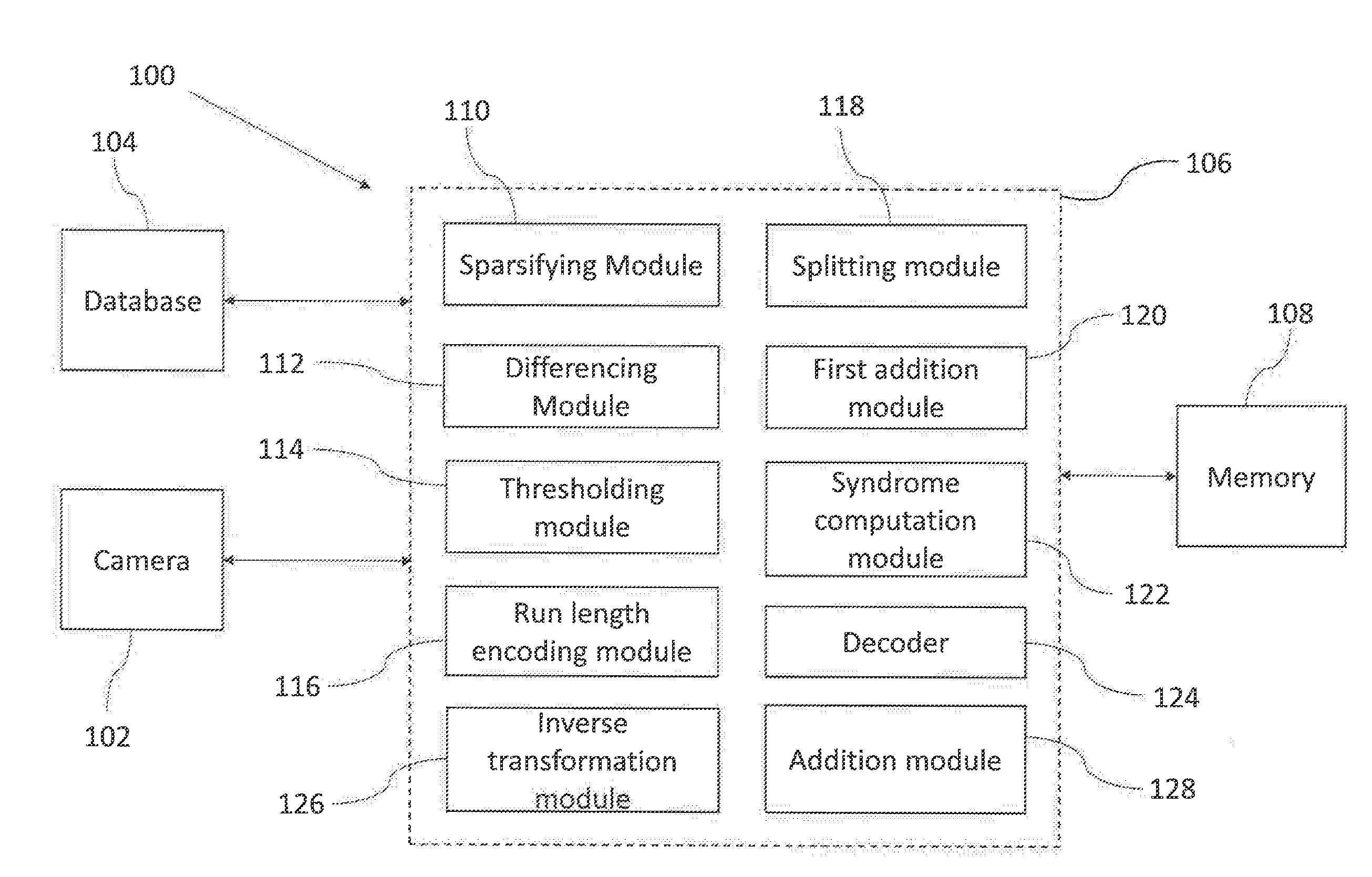

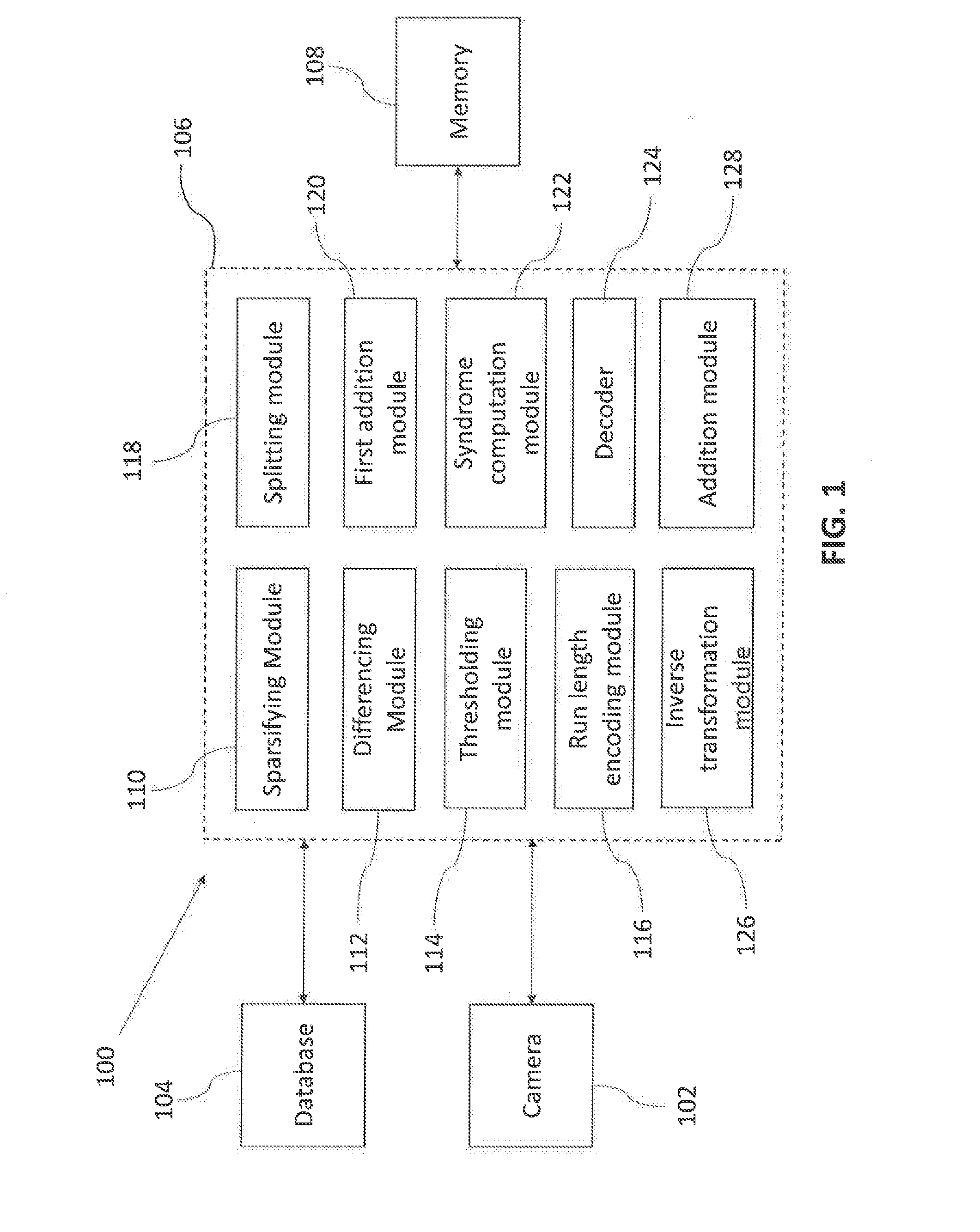

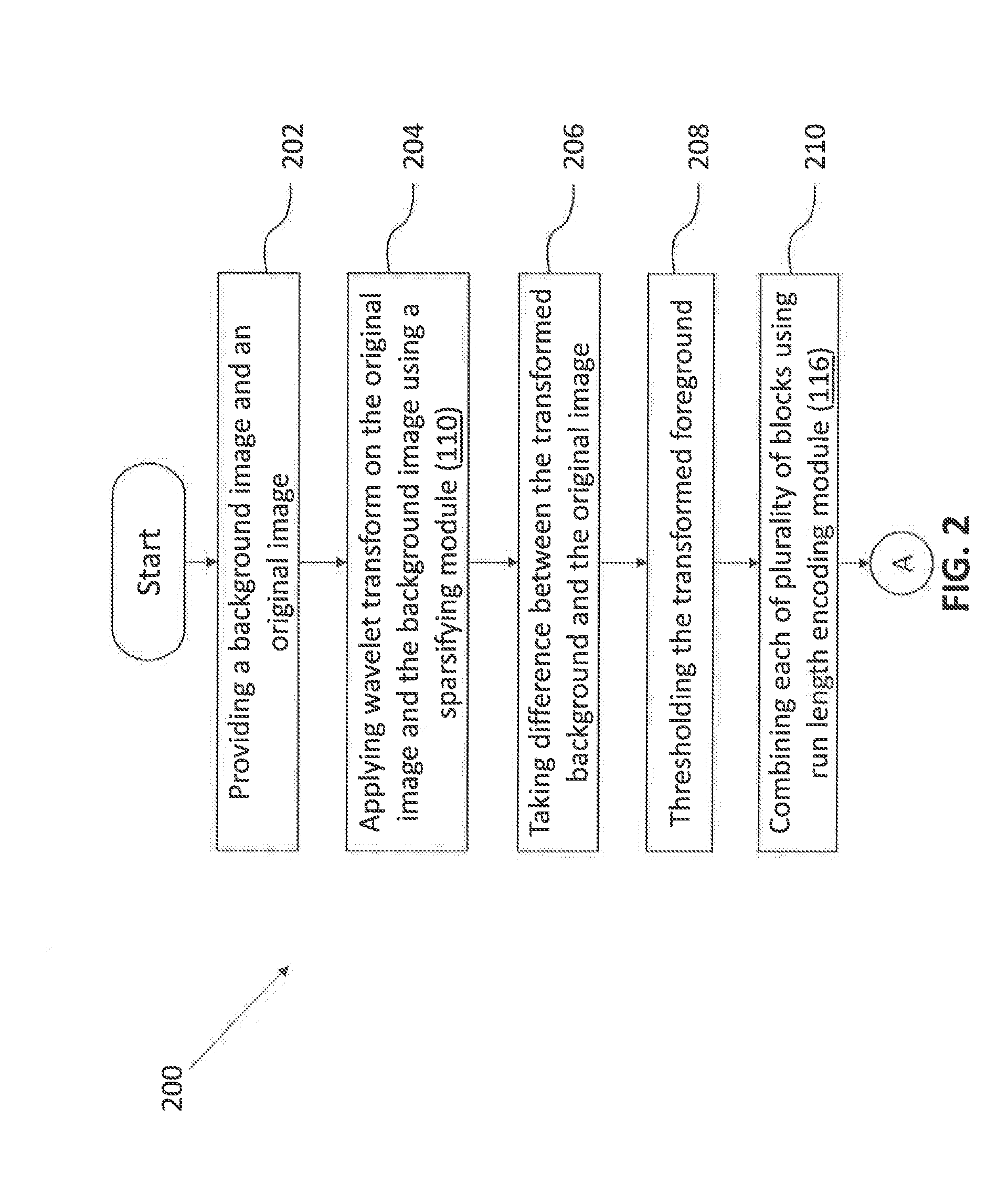

Method and system for compressing a video using background subtraction and change detection in videos

A method and system is provided for the compression of a video captured from a static camera. A background image and an original image is captured from the static camera. A foreground object is extracted by taking the difference between the transformed original image and the transformed background image. The foreground object is represented as a sparse vector using wavelets. The method revolves around the compressive sensing framework by ingeniously using the complex field BCH codes and the syndrome as measurements to achieve robust background subtraction using reduced number of measurements. The reconstruction is carried out by a Complex-field BCH decoder coupled with block based implementation. According to another embodiment, an adaptive techniques has also been proposed for acquiring the measurements required for recovering the images.

Owner:TATA CONSULTANCY SERVICES LTD

Method for decoding broadcast channel (BCH) codes

Owner:NEOLINK COMM TECH HANGZHOU

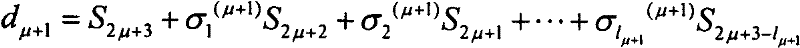

Method for realizing system authentication of intelligent mobile terminal of power grid based on PUF

InactiveCN109525399AAvoid Physical AttacksImprove reliabilityKey distribution for secure communicationError preventionFault tolerancePower grid

The invention provides a method for realizing system authentication of an intelligent mobile terminal of a power grid based on a PUF. The method comprises a registering phase and an authenticating phase. The registering phase comprises: generating a seed value S having a fault tolerance function; generating a standard BCH codeword; generating an identification code ID of the slice SRAM; generatinghelp data HD; completing system registration, and starting normal operation of the system. The authenticating phase comprises: reading an identification code NID with noise; reading help data HD; obtaining a BCH code with errors; performing BCH decoding operation on the BCH code with errors; if the actual error is not larger than the designed error correcting tolerance t, generating a BCH code ofn bits standard, and the system authentication is successful; otherwise, the BCH decoding fails, and the program operation ends; if the decoding is successful, recovering the identification code ID used in the registering phase of the system, and completing the authenticating phase of the system, and then starting the normal operation of the system. According to the method for realizing system authentication of an intelligent mobile terminal of a power grid based on a PUF, the PUF is applied to the intelligent mobile terminal of the power grid, so that the safe and reliable system authentication result is achieved.

Owner:STATE GRID CORP OF CHINA +1

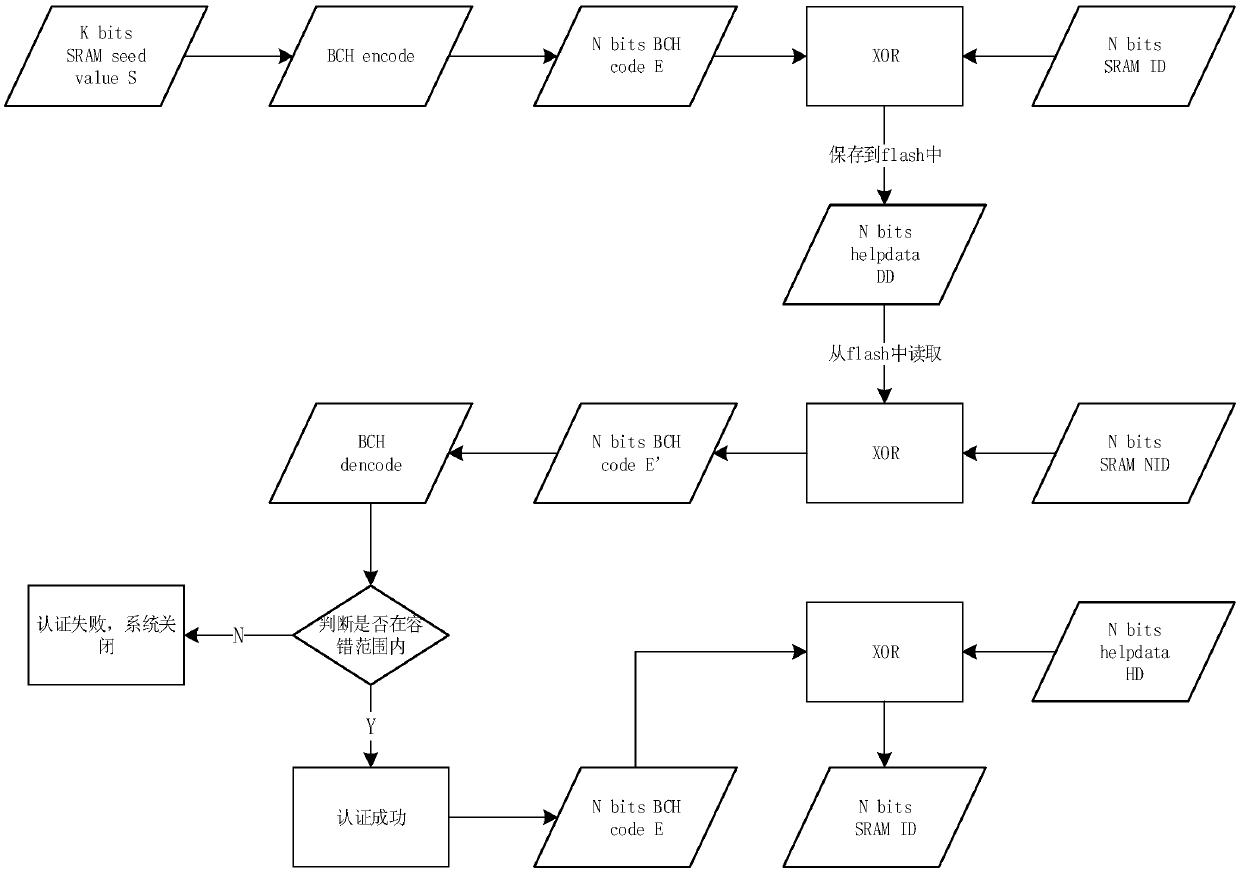

BBBSS protocol and BCH code combined secret key generation part reconciliation method

ActiveCN110071801AAvoid reconciliation defectsReduce computing loadKey distribution for secure communicationChannel state informationInteraction time

The invention discloses a BBBSS protocol and BCH code combined secret key generation part reconciliation method, which comprises the following steps: (1) two communication parties mutually sending known pilot signals on the same frequency band, and obtaining channel state information at the same moment through channel estimation; (2) the two communication parties pre-processing and quantifying the channel state information respectively, and a result being used as an initial secret key; (3) the two communication parties estimating the inconsistency rate of the initial keys according to the received pilot signals, and performing information reconciliation and grouping; (4) the two communication parties adopting a BBSS protocol to carry out partial reconciliation on the initial secret key based on the grouping condition in the step (3) to obtain a partial reconciliation secret key; (5) the communication party using the BCH code to carry out error correction coding on the part of the harmonic key, sending the BCH syndrome to the other party, and the other party carrying out error correction on the part of the harmonic key through the BCH syndrome; and (6) the two communication partiesperforming privacy amplification on the error-corrected harmonic key, and then performing consistency verification to obtain a shared key. The method is low in calculation complexity and fewer in interaction times.

Owner:SOUTHEAST UNIV

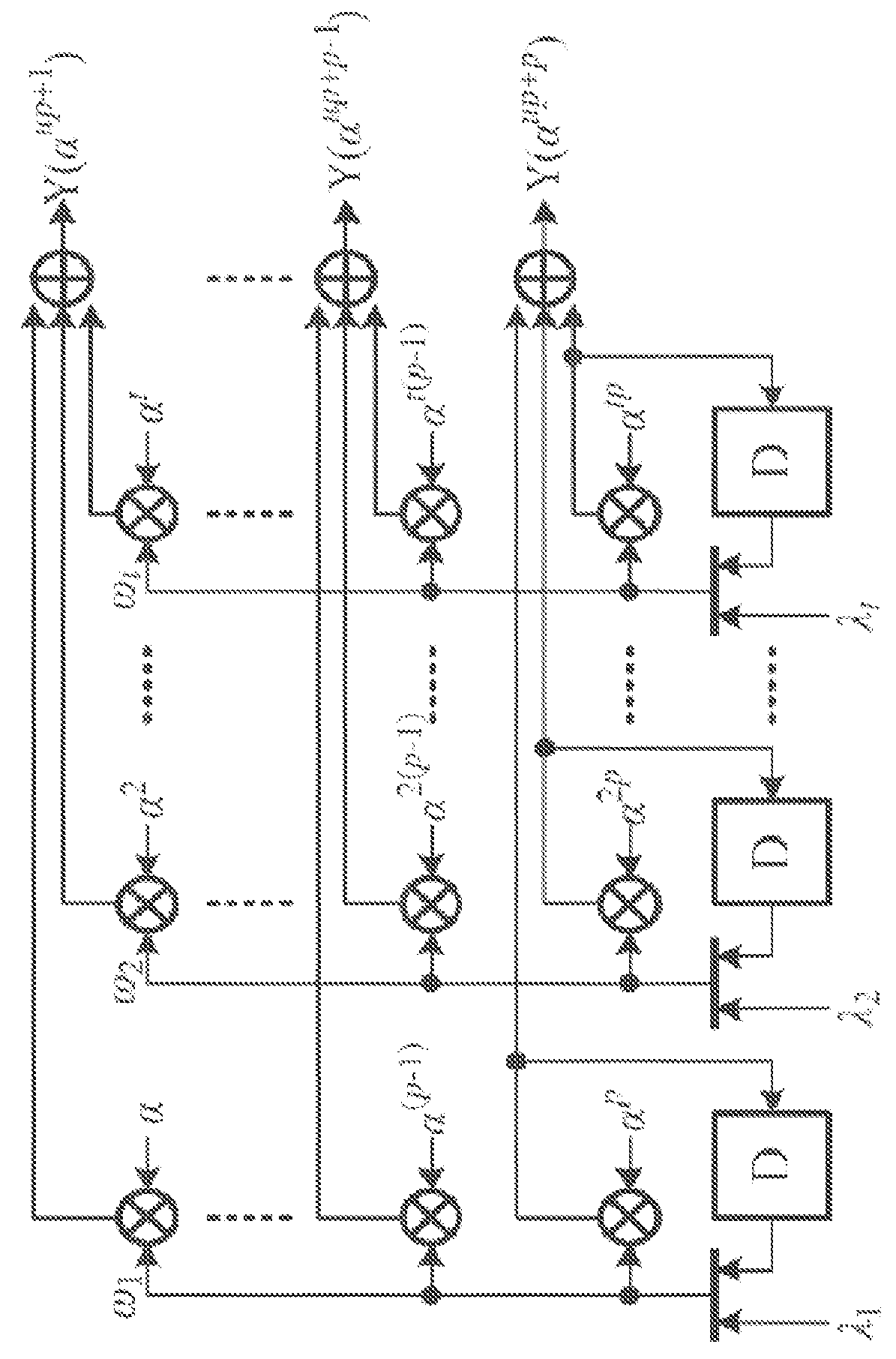

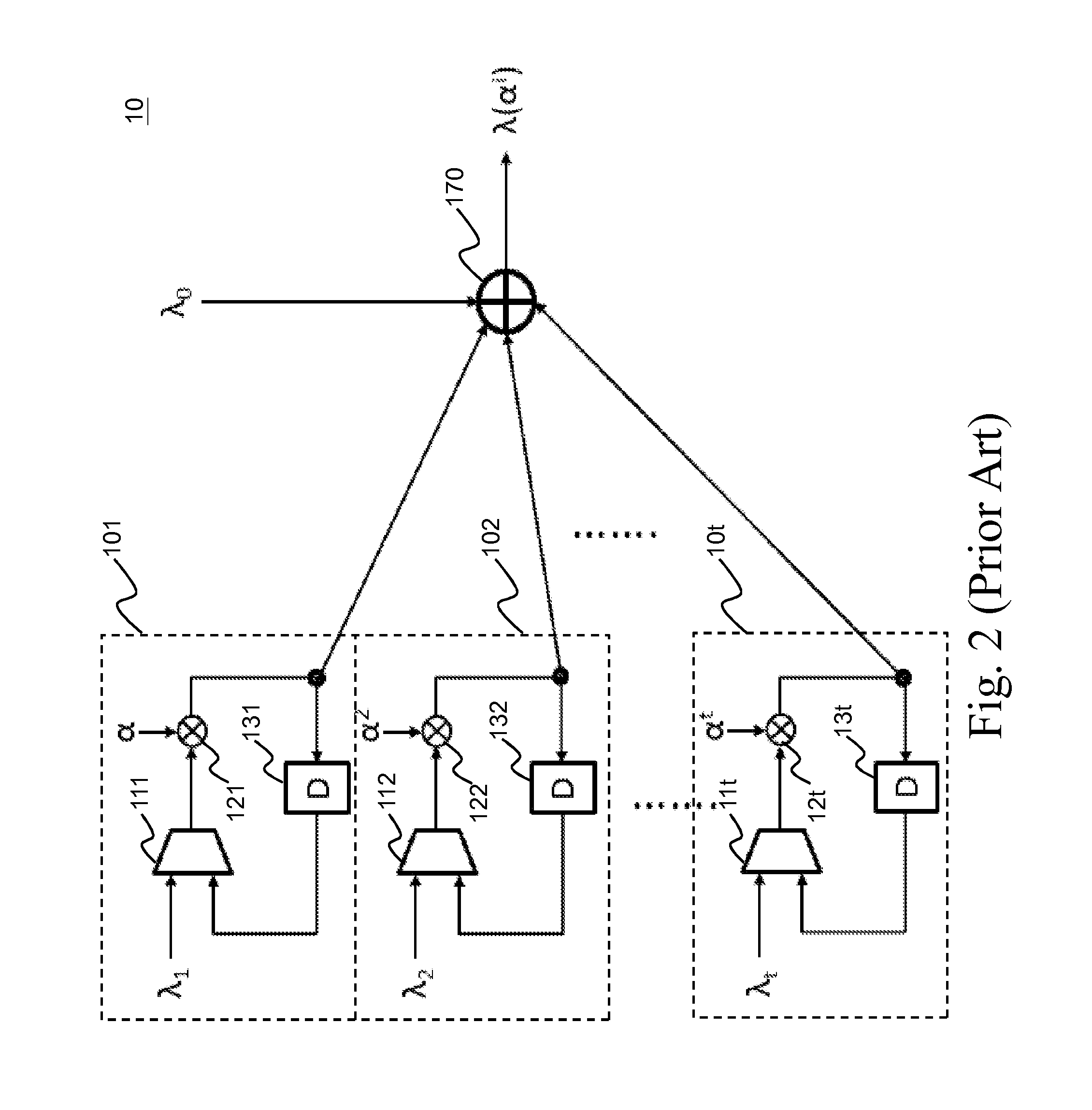

Multi-Code Chien's Search Circuit for BCH Codes with Various Values of m in GF(2m)

ActiveUS20160036464A1Reduce hardware complexityReduce complexityCode conversionError correction/detection by combining multiple code structuresMultiplexerProcessor register

The present invention discloses a multi-code Chien's search circuit for BCH codes with various values of m in GF(2m). The circuit includes: a combined matrix unit, a number of first multiplexers, a number of registers and a number of second multiplexers. By designing the Chien's search circuit having several Chien's search matrices, with peripheral components, it is able to achieve applications for different code rates, different code lengths and even different m in GF(2m).

Owner:STORART TECHSHENZHEN CO LTD

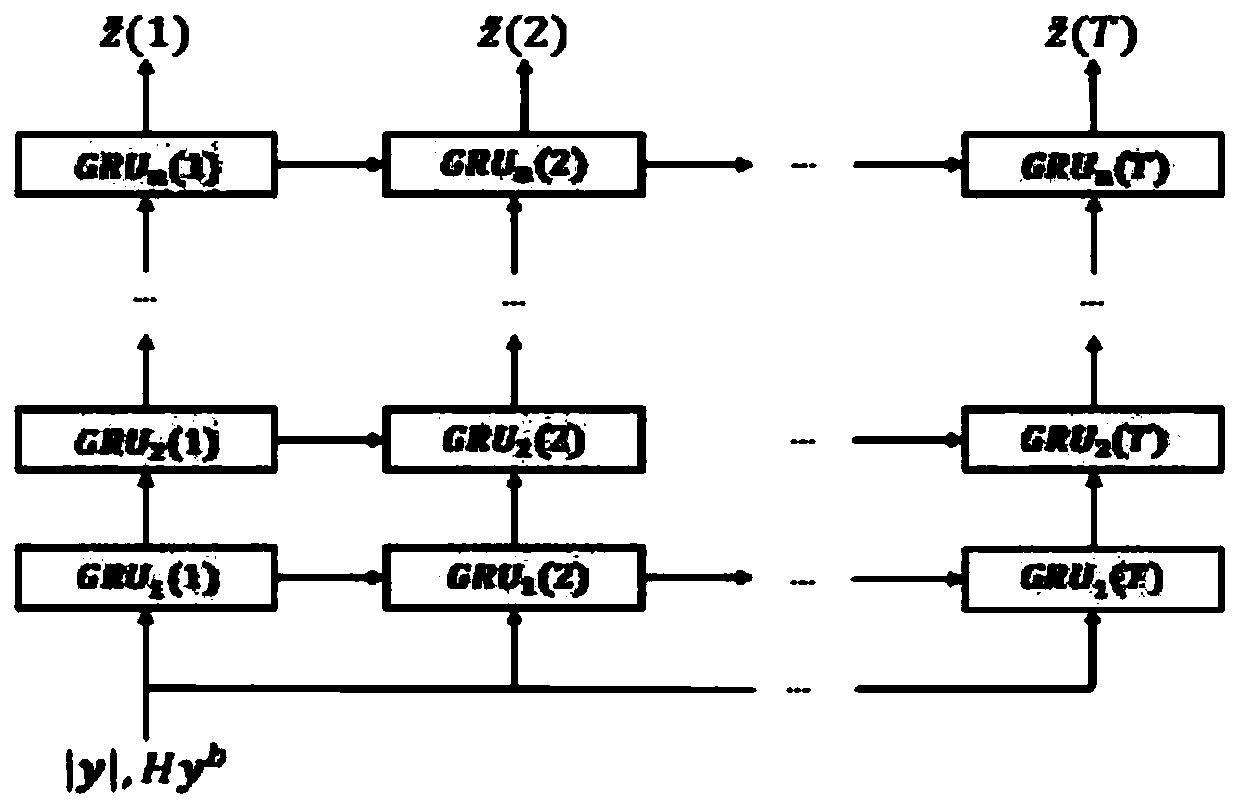

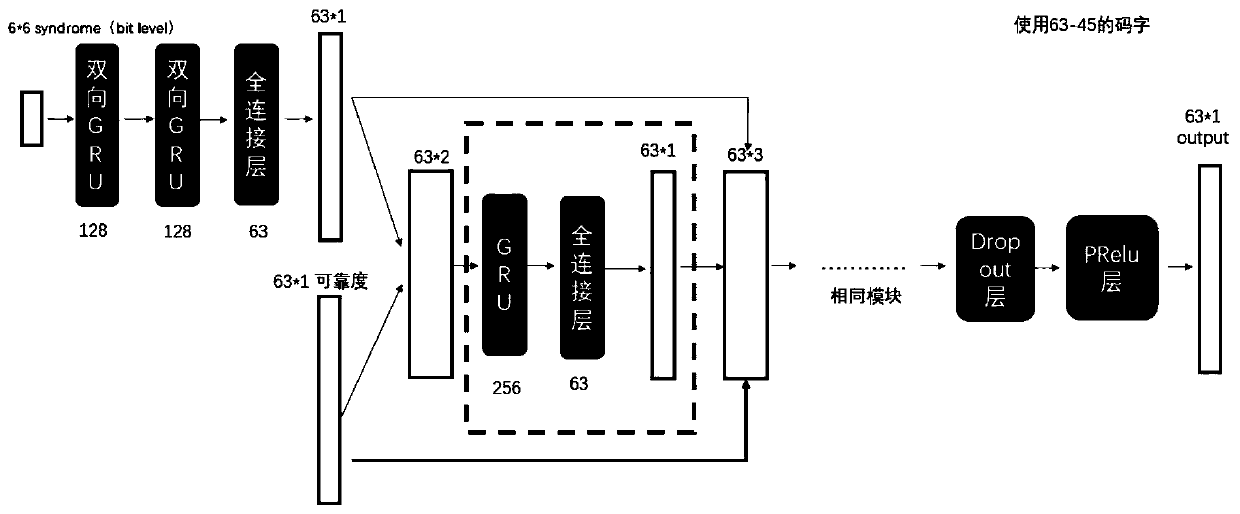

BCH code decoding method based on deep learning

ActiveCN110572166AImprove decoding performanceCyclic codesNeural architecturesInfluence factorTime step

The invention relates to a BCH code decoding method based on deep learning. The method comprises the following steps: receiving and extracting quantization level information from a channel of a BCH code to serve as reliability information, then performing hard decision on a code word, calculating the obtained code word information by using a check matrix to obtain a syndrome of the BCH code, and converting the syndrome into a binary form; gradually inputting binary syndrome information into two bidirectional GRUs connected in series of the neural network at one input end in a time step manner;at the other input end, inputting bit-level quantization level information as reliability into the auxiliary syndrome information for decoding; merging the information output by the MLP and the reliability into new two-dimensional matrix information, inputting the new two-dimensional matrix information into another GRU in the next step to enable the neural network to find part of error positionsfrom two influence factors of reliability and a syndrome, and connecting a full connection layer to the output end of the GRU to flatten the data; and obtaining neural network decoder.

Owner:TIANJIN UNIV

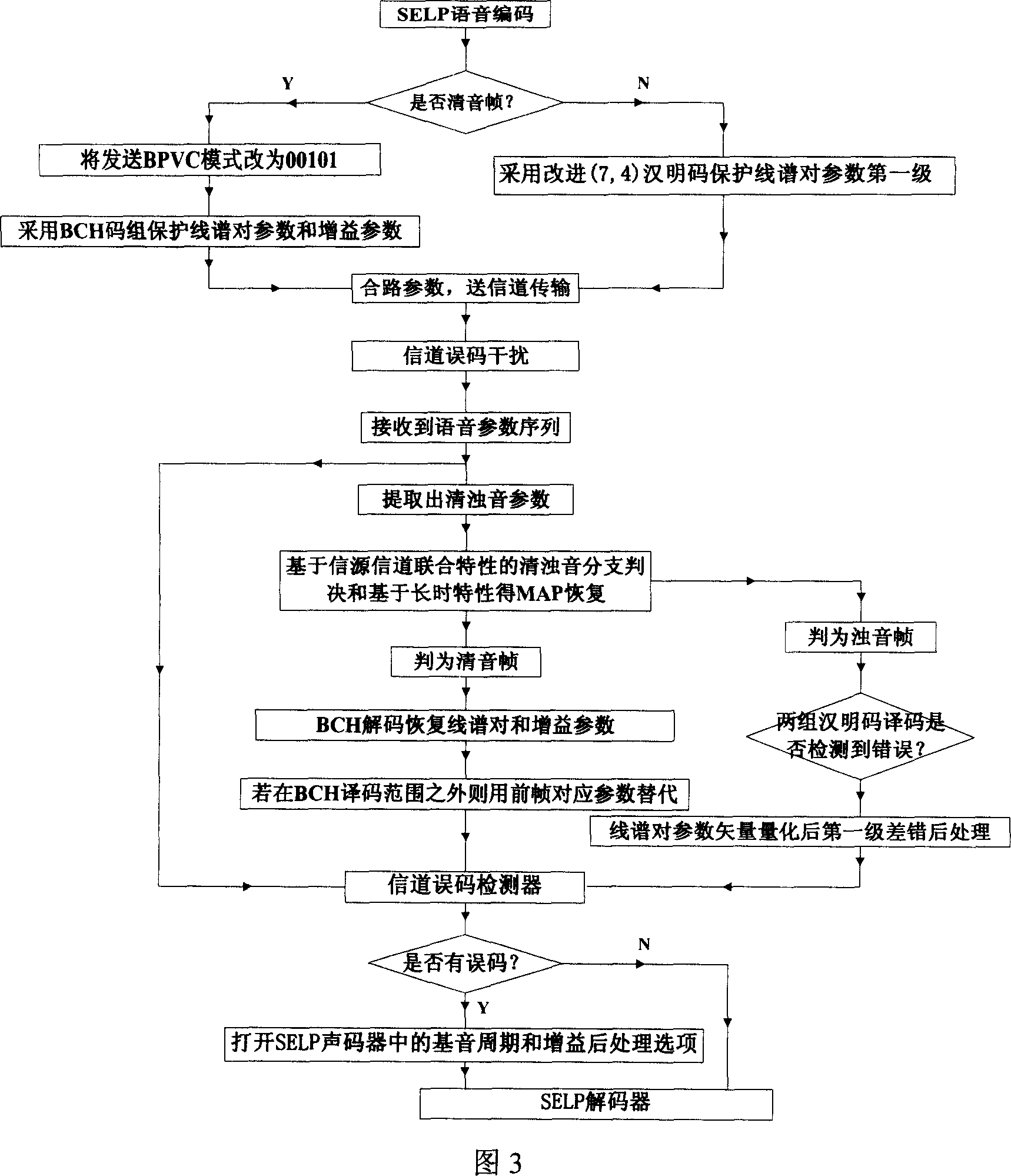

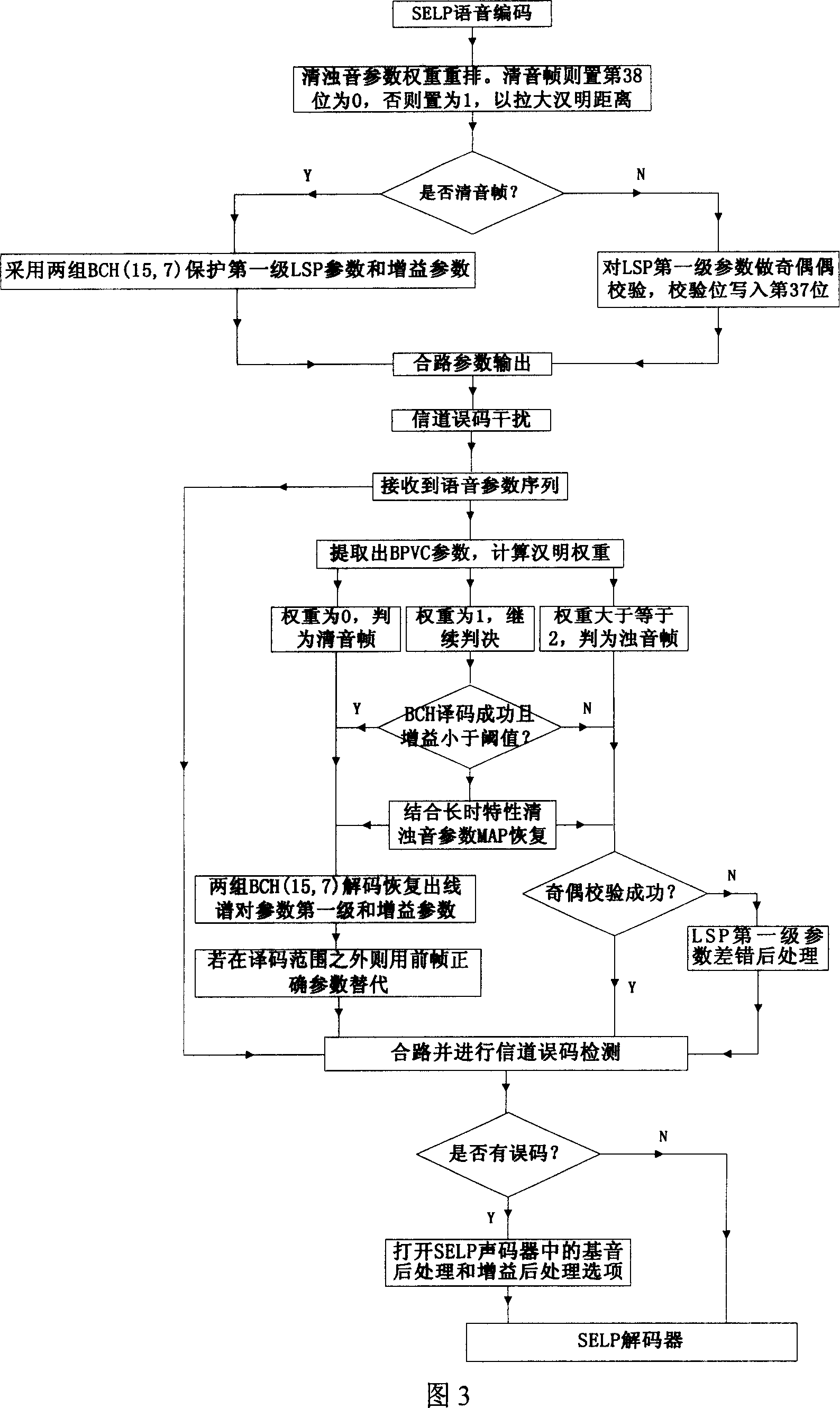

Anti-channel error code protection method for 1.2kb/s SELP low-speed sound coder

InactiveCN101009097AQuality improvementImprove intelligibilitySpeech synthesisLow speedMaximum a posteriori estimation

This invention relates to low speed rate sound anti-error coding technique, which is characterized by the following steps: re-aligning weight and labeling distance on blur parameters on coding on edit end; adopting two sets of BCH codes and odd and even test to protect blur sound and its parameters; on decode end according to signal channel property by use of branch to determine blur sound by use of maximum test possibility; for clear sound by use of BCH codes to restore relative parameters to decode out spectrum to restore anti-error code formula.

Owner:TSINGHUA UNIV

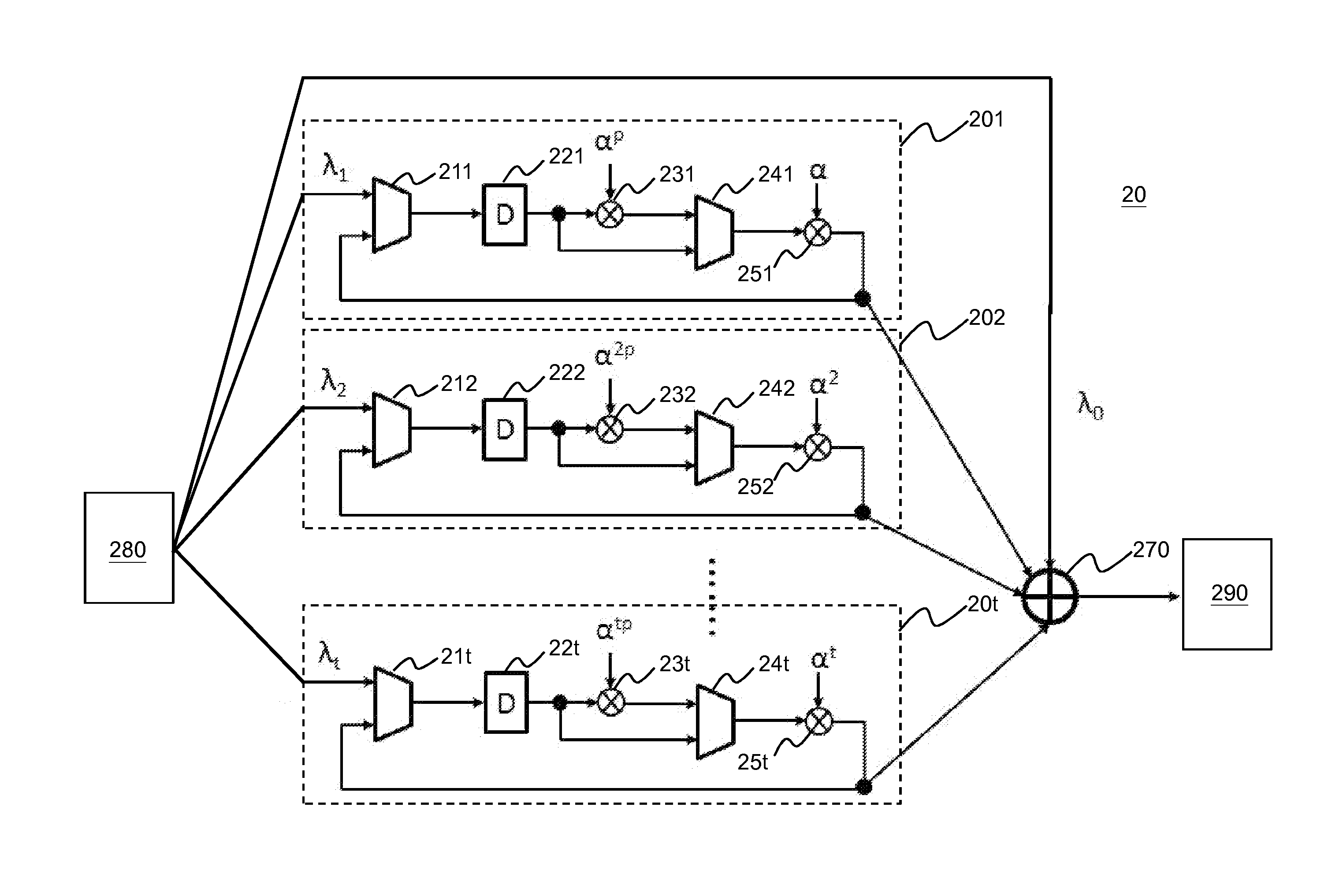

Method and circuit for shortening latency of chien's search algorithm for bch codewords

ActiveUS20150256200A1Lower latencyCode conversionCyclic codesError locationTheoretical computer science

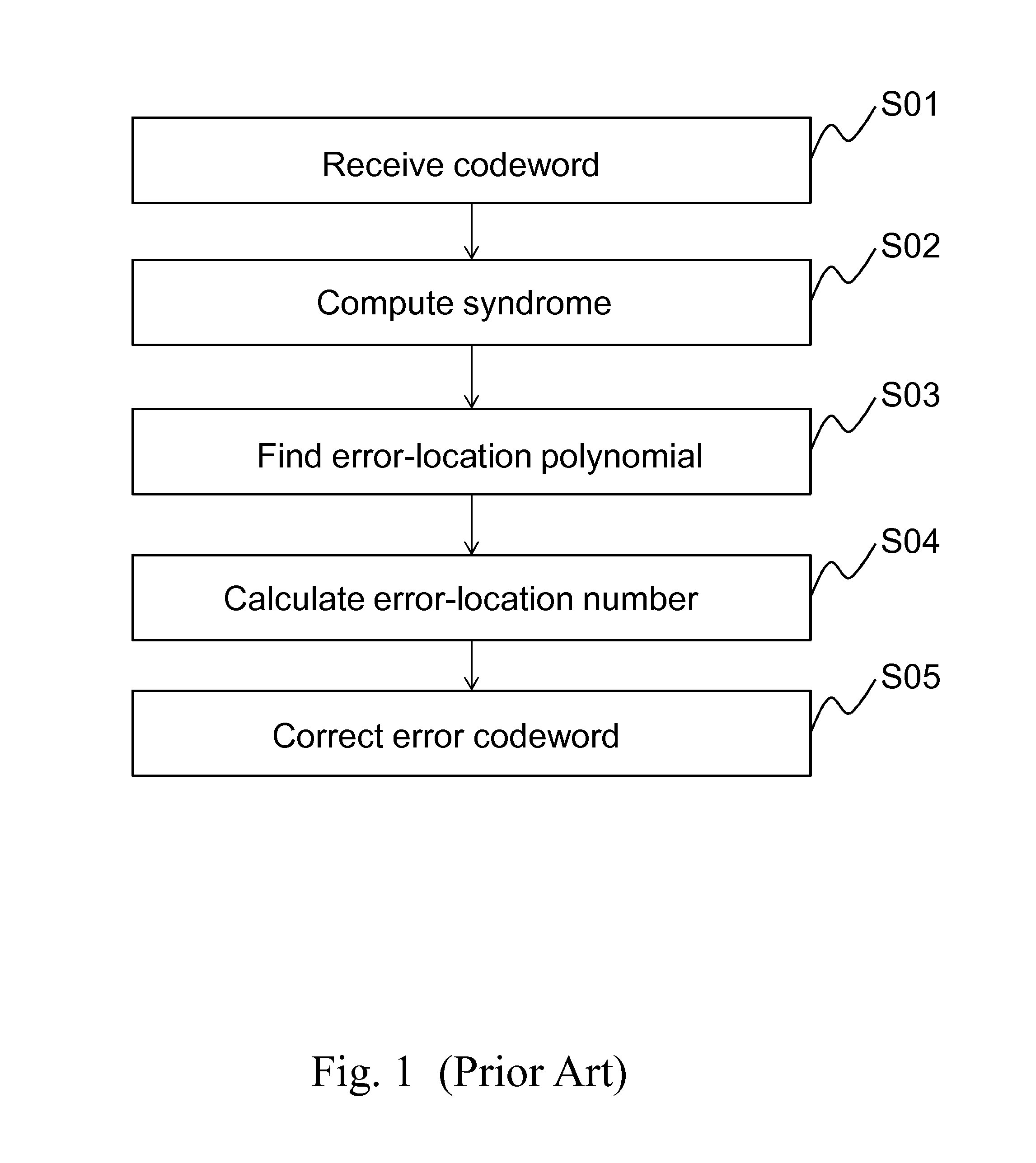

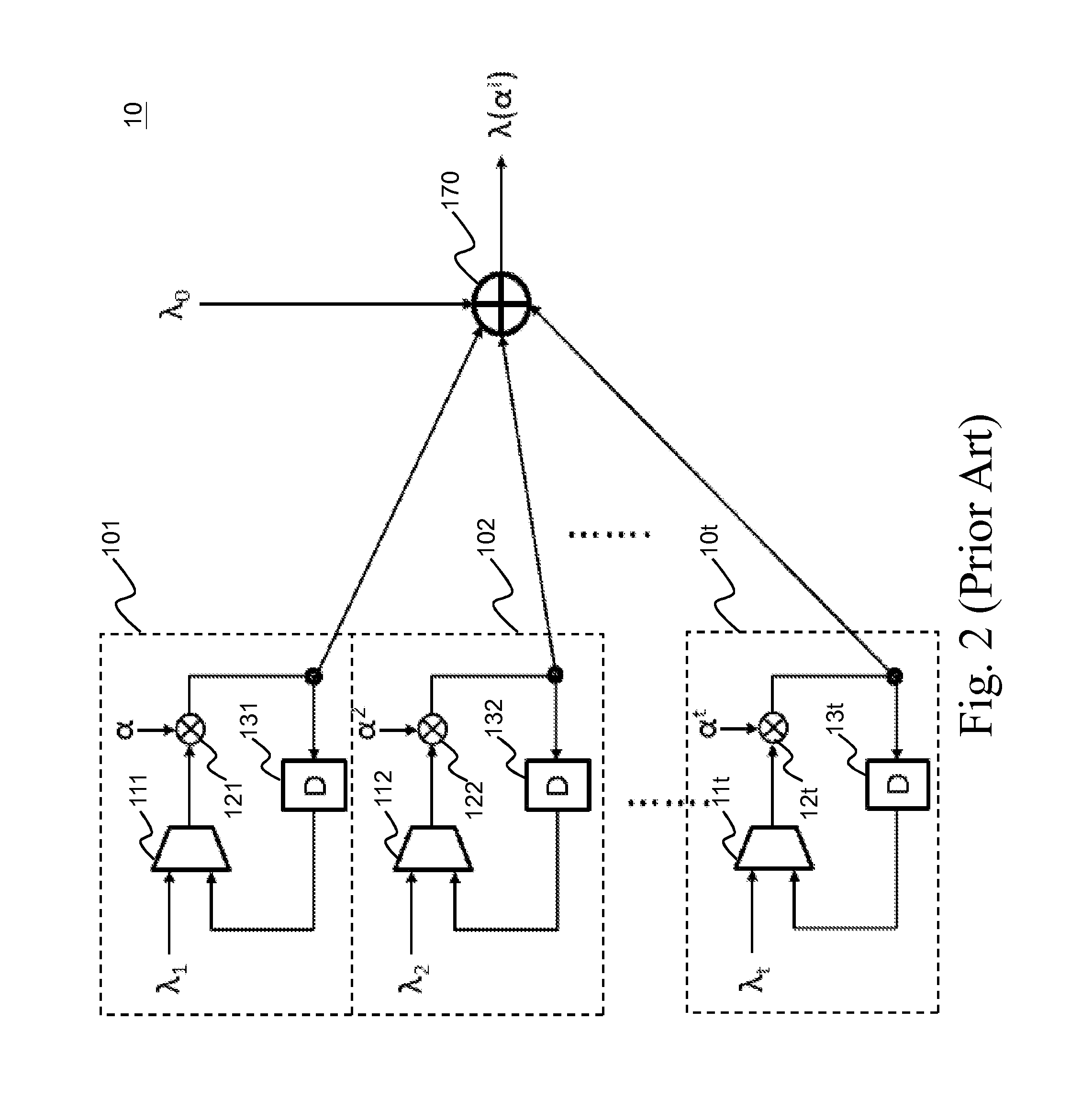

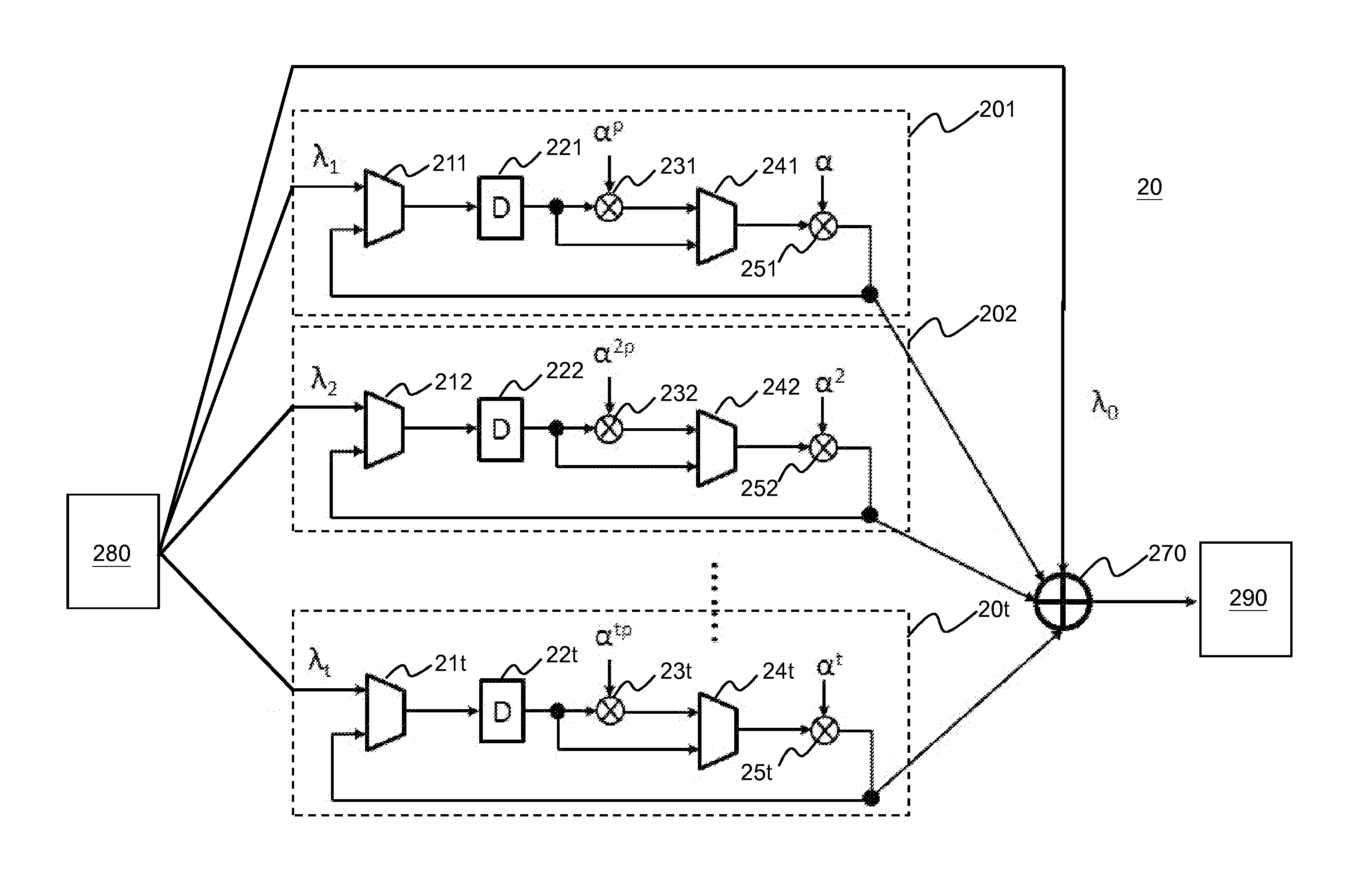

A method for shortening latency of Chien's search and related circuit are disclosed. The method includes the steps of: determining a shifted factor, p; receiving a BCH codeword; computing a syndrome from the BCH codeword; finding an error-location polynomial based on the syndrome; and processing Chien's search for the error-location polynomial to find out roots thereof. p is a number of successive zeroes from the first bit of the BCH codeword, the Chien's search starts iterative calculations by substituting a variable of the error-location polynomial with a nonzero element in Galois Field, GF(2m), and the nonzero element ranges from αp+1 to αn, wherein n is a codelength of the BCH codeword and equals 2m−1, and m is a positive integer.

Owner:STORART TECHSHENZHEN CO LTD

Method and circuit for shortening latency of Chien'S search algorithm for BCH codewords

ActiveUS9287898B2Lower latencyOther error detection/correction/protectionCode conversionError locationShift factor

A method for shortening latency of Chien's search and related circuit are disclosed. The method includes the steps of: determining a shifted factor, p; receiving a BCH codeword; computing a syndrome from the BCH codeword; finding an error-location polynomial based on the syndrome; and processing Chien's search for the error-location polynomial to find out roots thereof. p is a number of successive zeroes from the first bit of the BCH codeword, the Chien's search starts iterative calculations by substituting a variable of the error-location polynomial with a nonzero element in Galois Field, GF(2m), and the nonzero element ranges from αp+1 to αn, wherein n is a codelength of the BCH codeword and equals 2m−1, and m is a positive integer.

Owner:STORART TECHSHENZHEN CO LTD

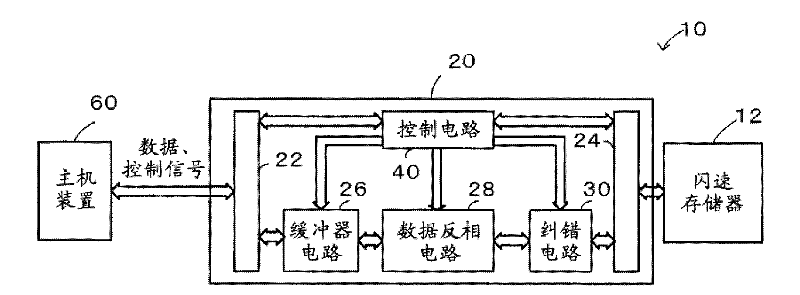

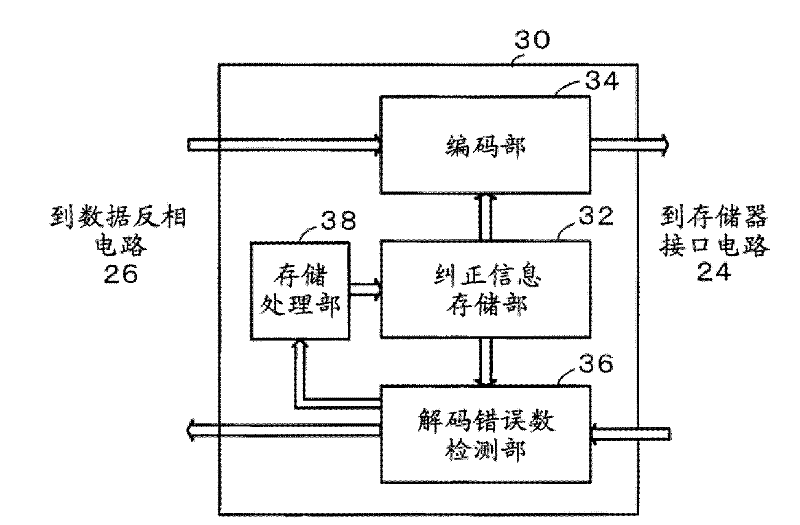

Data input and output control device and semiconductor storage device system

InactiveCN102289394ADigital storageRedundant data error correctionControl storeSemiconductor storage devices

The invention provides a data input / output control device and a semiconductor memory device system. When detected number of errors data Nerror exceeds the upper limit number of errors Nmax, an error correction circuit of a memory controller stores twice as long data length as stored data length for execution Sdata as the data length for execution Sdata in a correction information memory unit, and code length Scref longer than the data length for execution Sdata and detectable more errors than the upper limit number of errors as the code length for execution Scode in the correction information memory unit 32 (step S100 and S110). The error correction circuit encodes input data using BCH code having the stored code length for execution Scode, stored encoded data in a semiconductor memory device, is input data stored in the semiconductor memory device, performs error correction for input data using BCH code, and decode error corrected data.

Owner:THE UNIV OF TOKYO

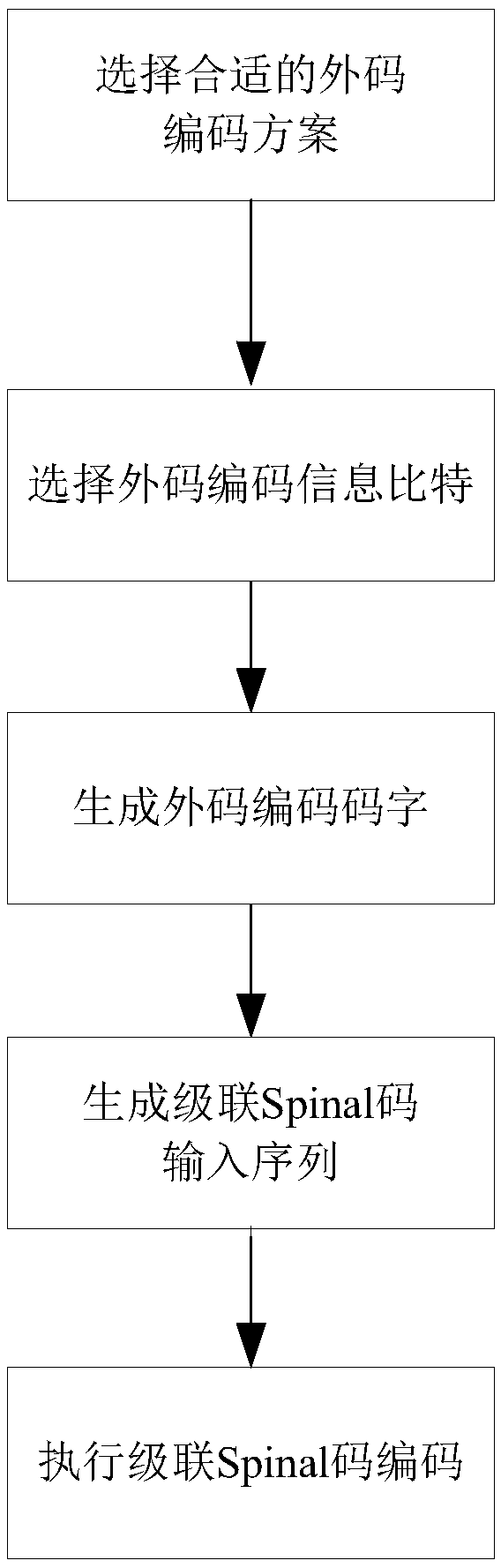

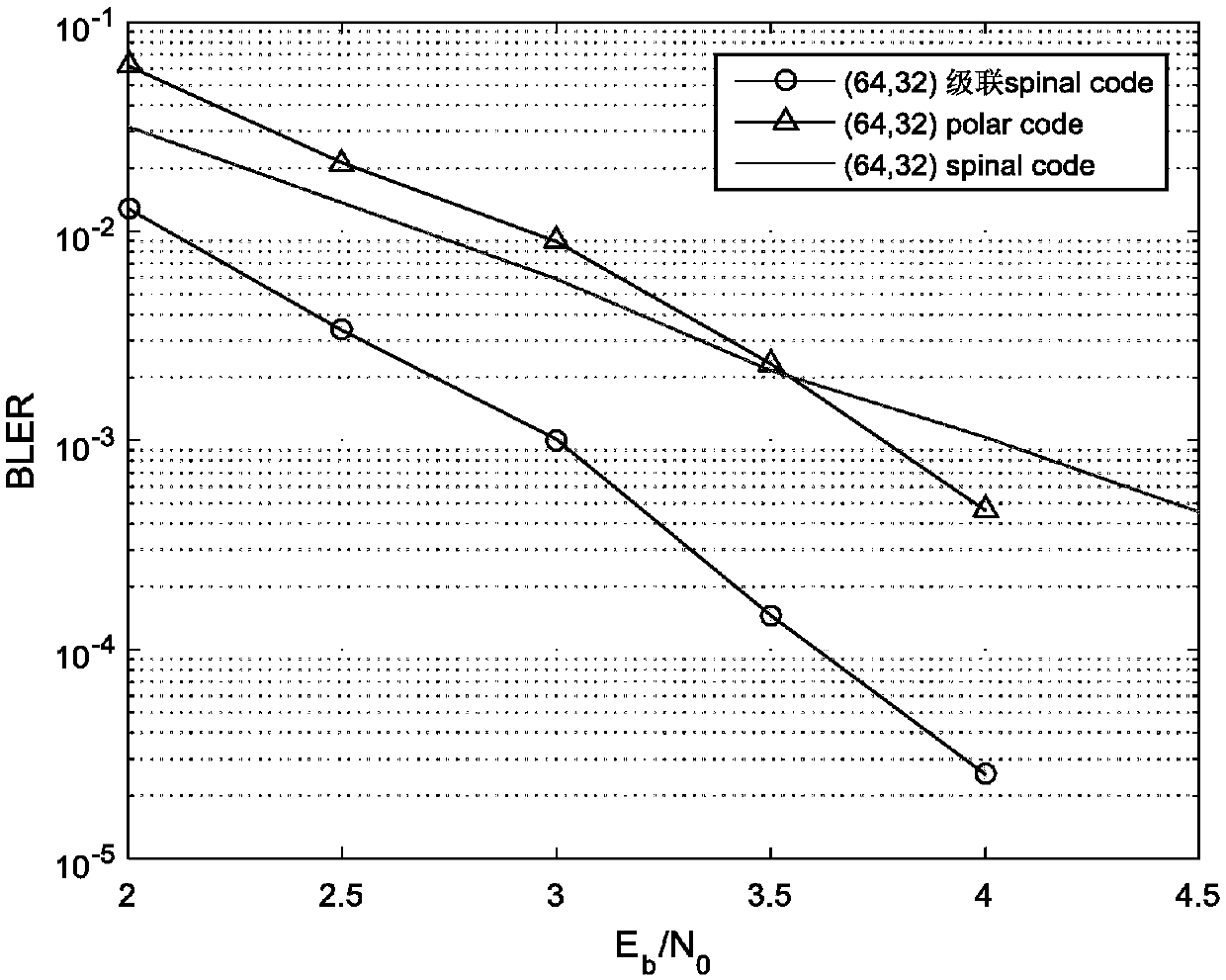

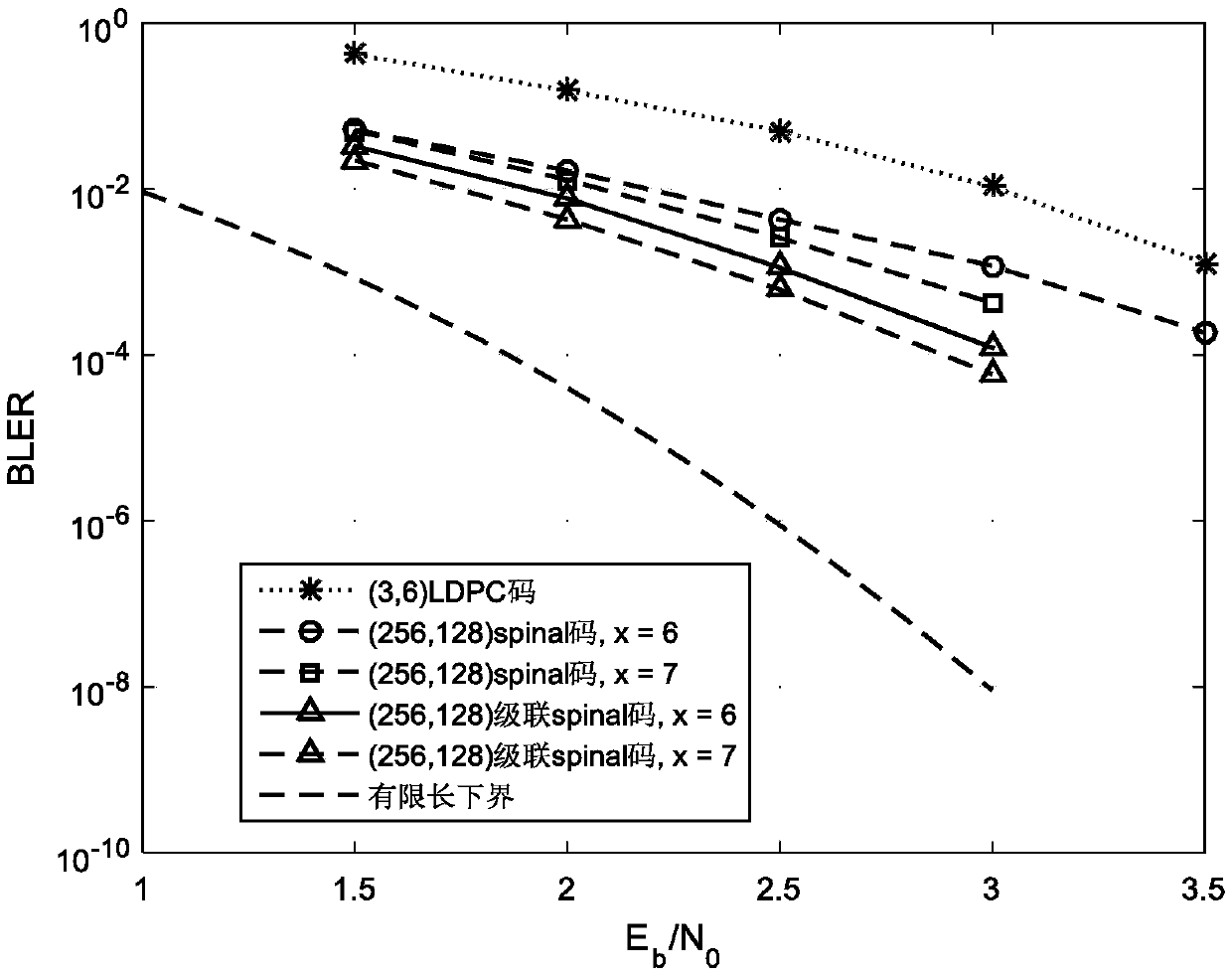

Cascaded Spinal code construction method for reducing error performance

ActiveCN108809518ADoes not affect rate performanceReduce error rateError preventionComputer hardwareCommunications system

The invention discloses a cascaded Spinal code construction method for reducing error performance for mainly solving the problem of poor transmission reliability due to high error performance of codesin the prior art. The implementation scheme is as follows: 1. selecting a BCH code with strong error correction capability to serve as an outer code according to the burst error correction capabilityB; 2. determining an outer code information bit according to an outer code parameter and an original Spinal code parameter in a selected outer code encoding scheme; 3. generating a segmentation checksequence p according to an encoded outer code information bit y; 4. merging an original information bit m with the segmentation check sequence p to generate an input sequence of a cascaded Spinal code; and 5. performing cascaded Spinal encoding to generate a channel input symbol. By adoption of the cascaded Spinal code construction method disclosed by the invention, the error probability of the tail bit of the Spinal code information sequence and the error performance of the Spinal code are reduced, thereby improving the transmission reliability of the communication system, and the cascaded Spinal code construction method can be applied to cellular communication, satellite communication and Internet of Things systems.

Owner:XIDIAN UNIV