Patents

Literature

104 results about "Chien search" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

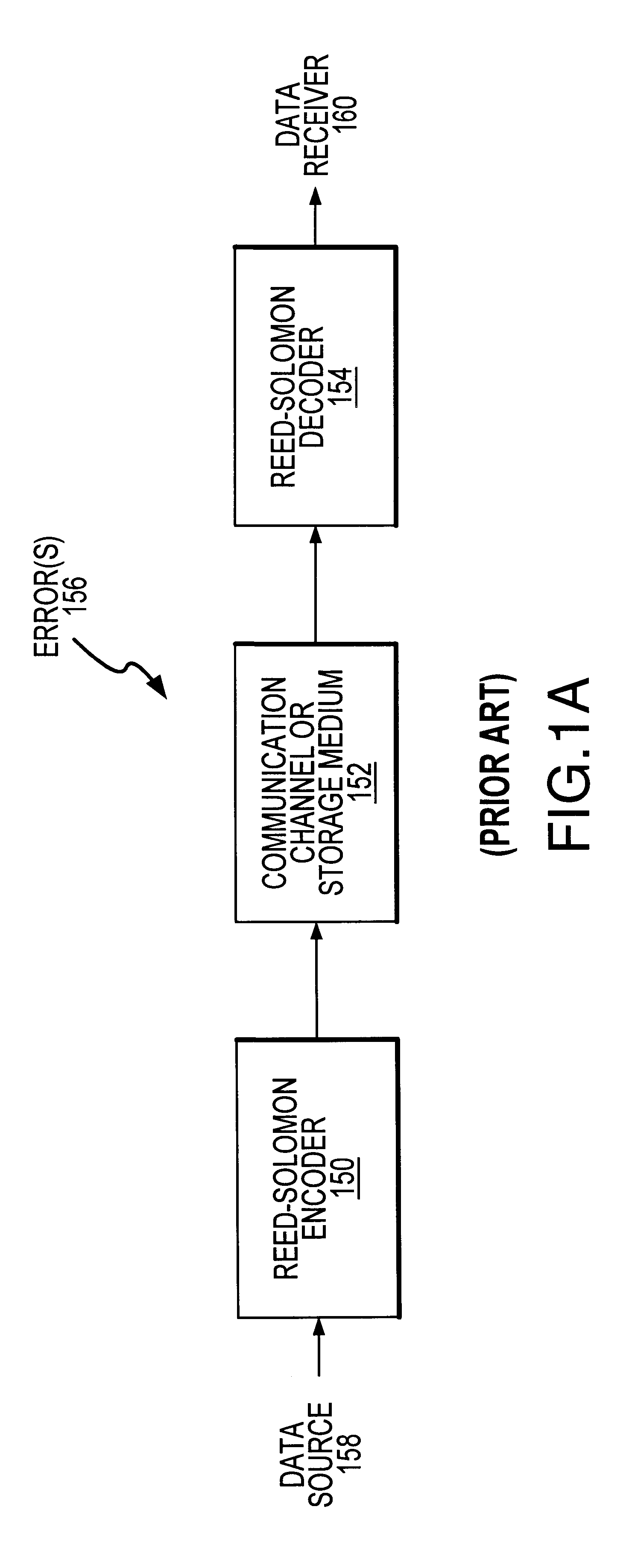

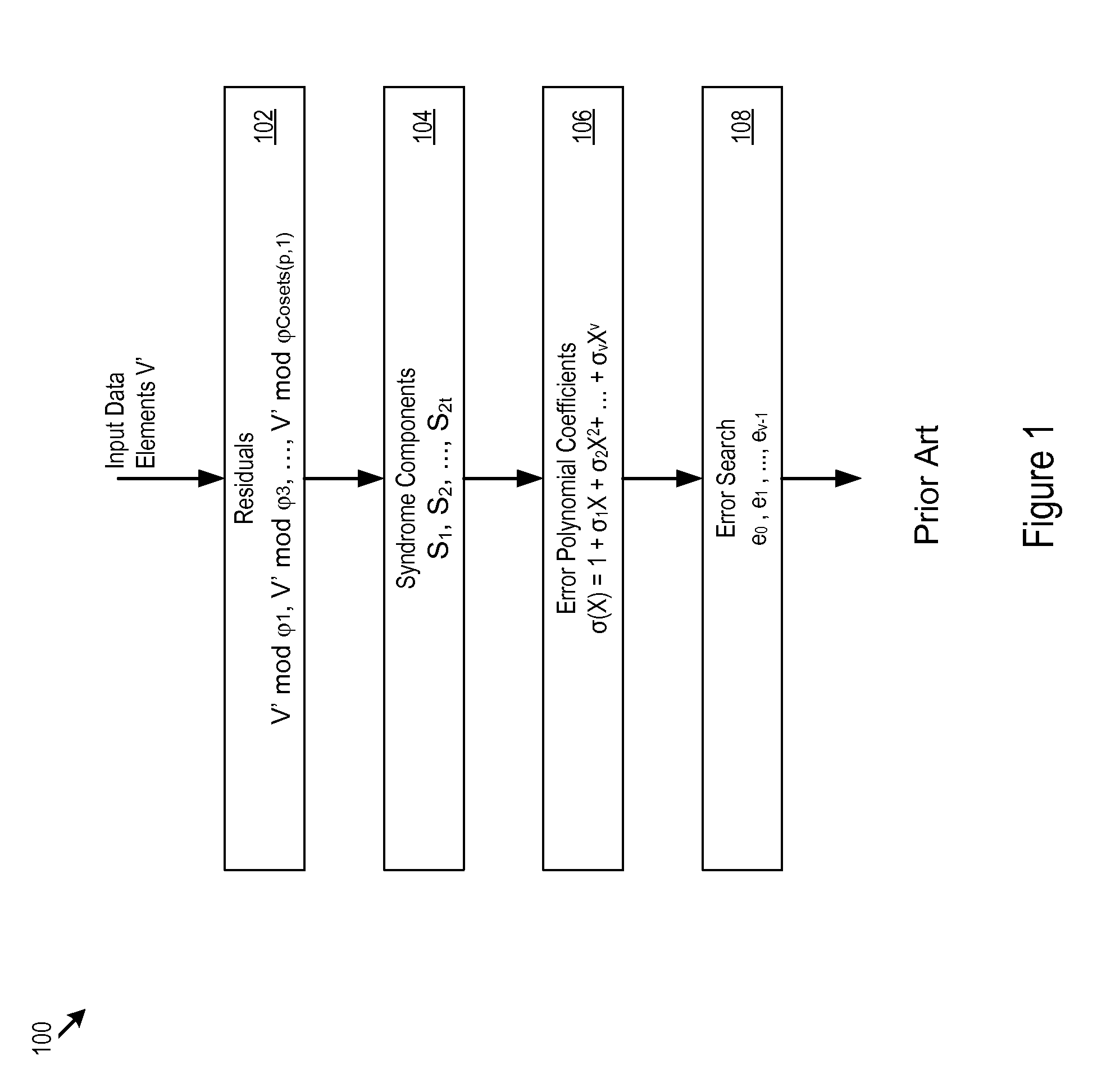

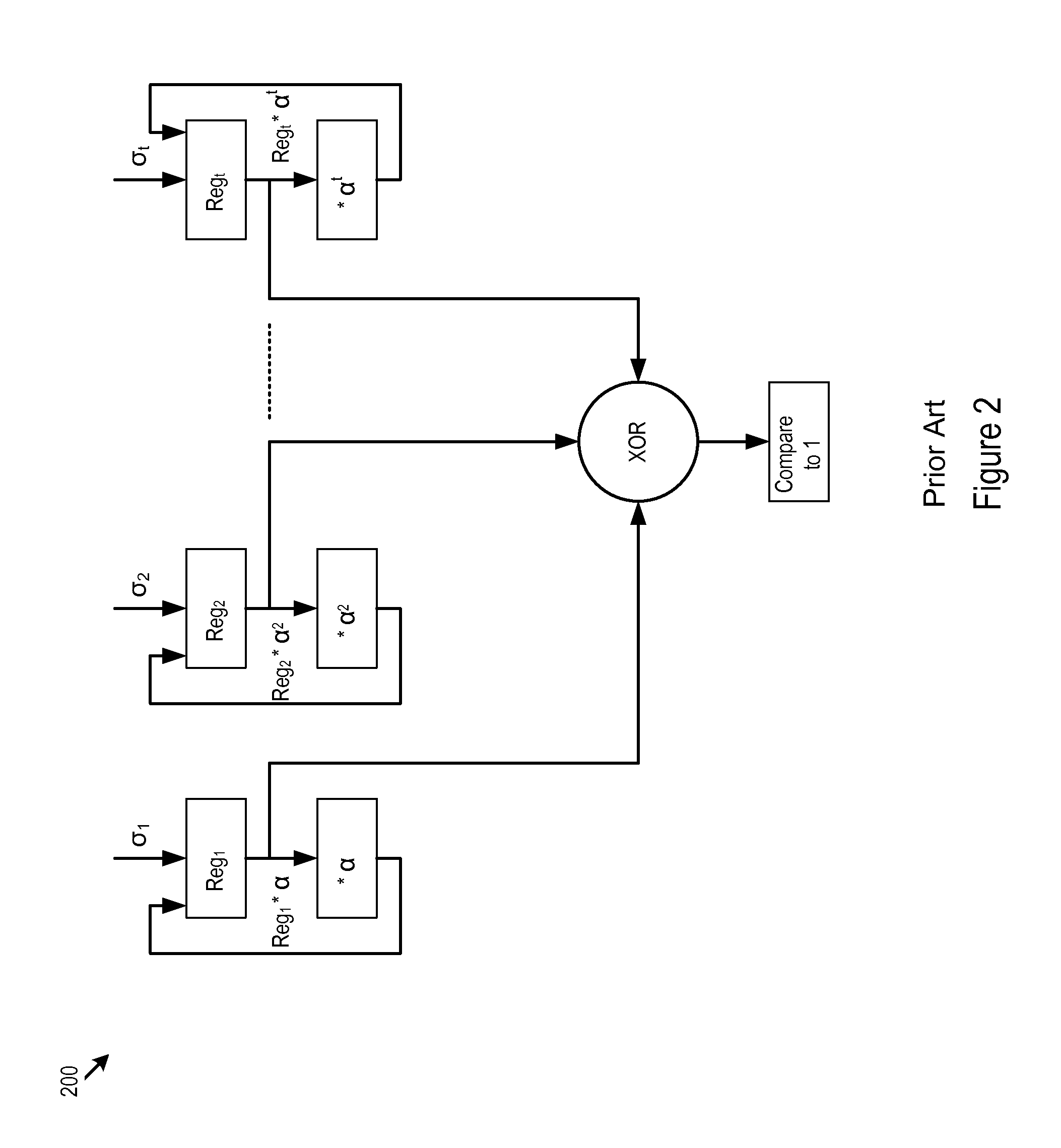

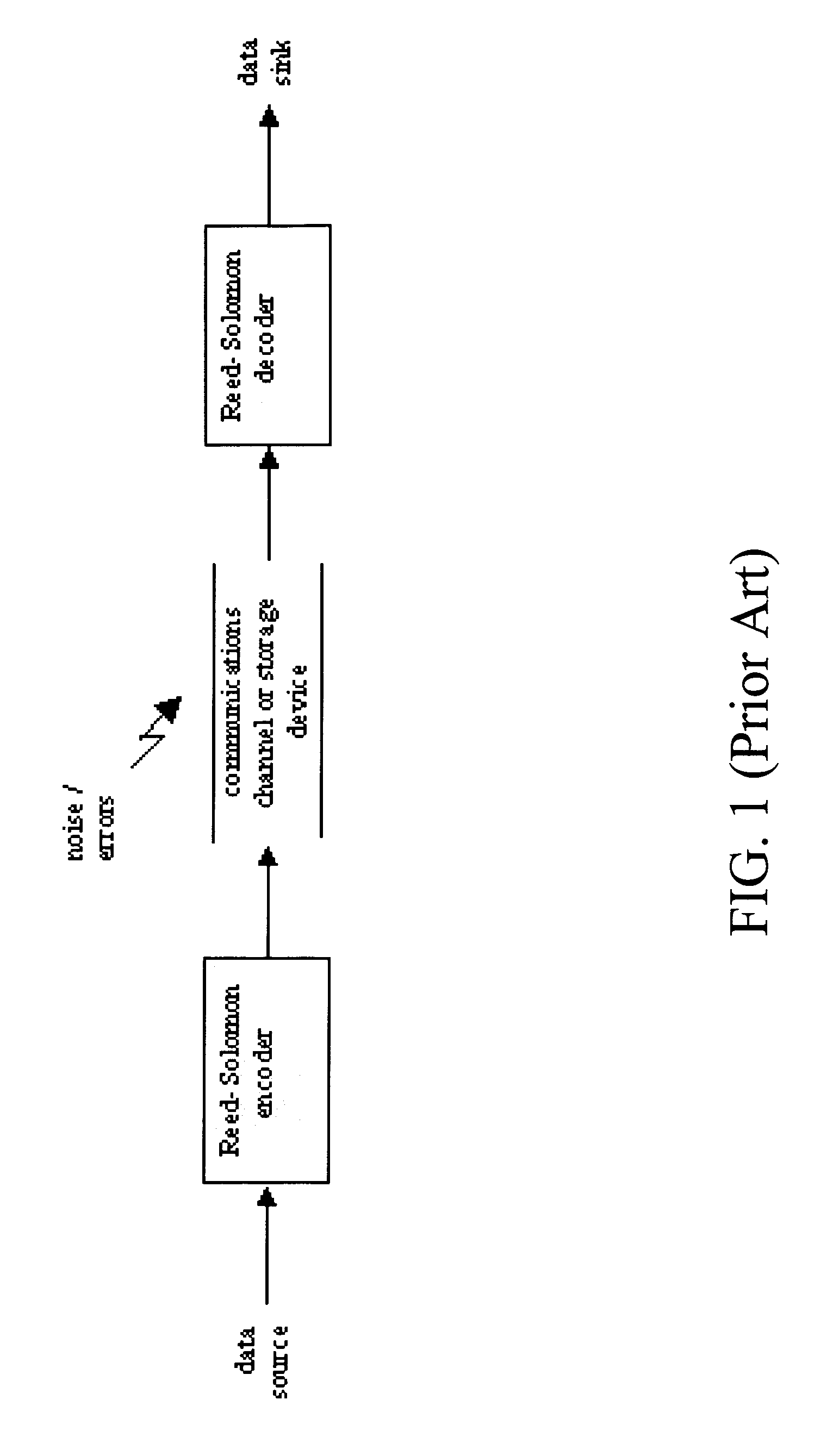

In abstract algebra, the Chien search, named after Robert Tienwen Chien, is a fast algorithm for determining roots of polynomials defined over a finite field. Chien search is commonly used to find the roots of error-locator polynomials encountered in decoding Reed-Solomon codes and BCH codes.

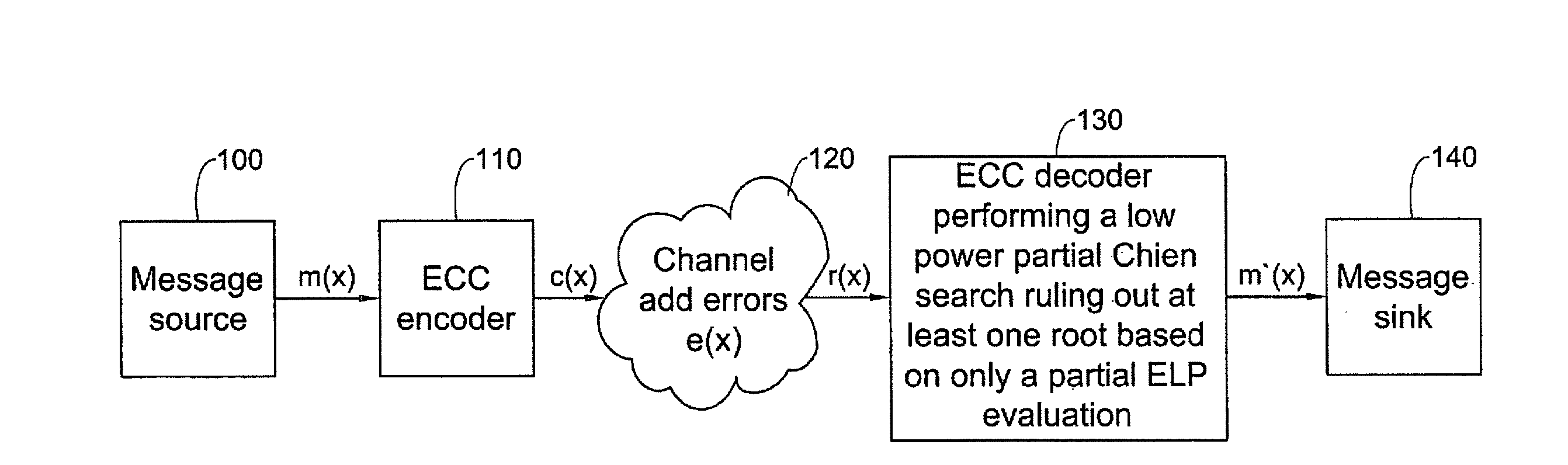

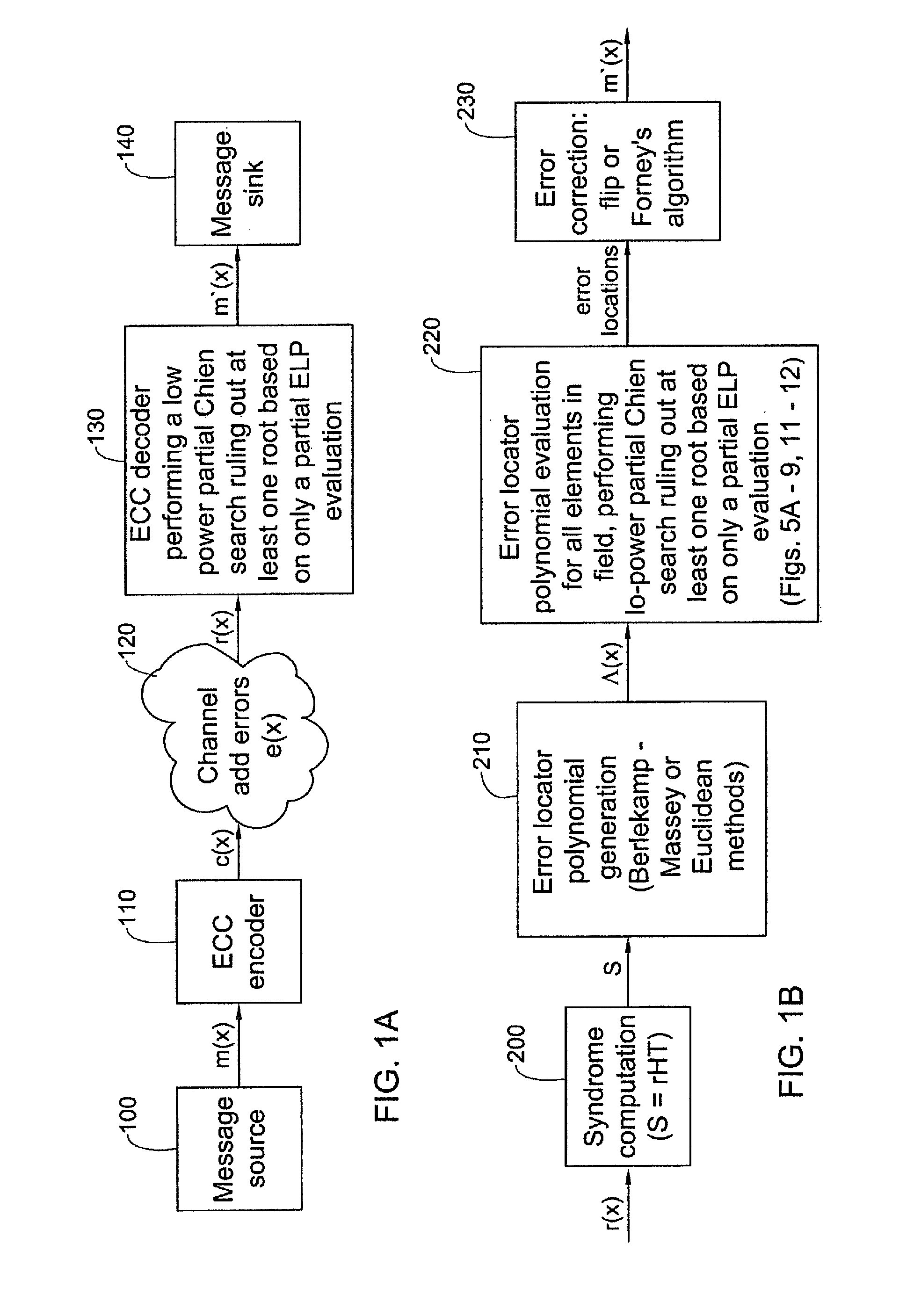

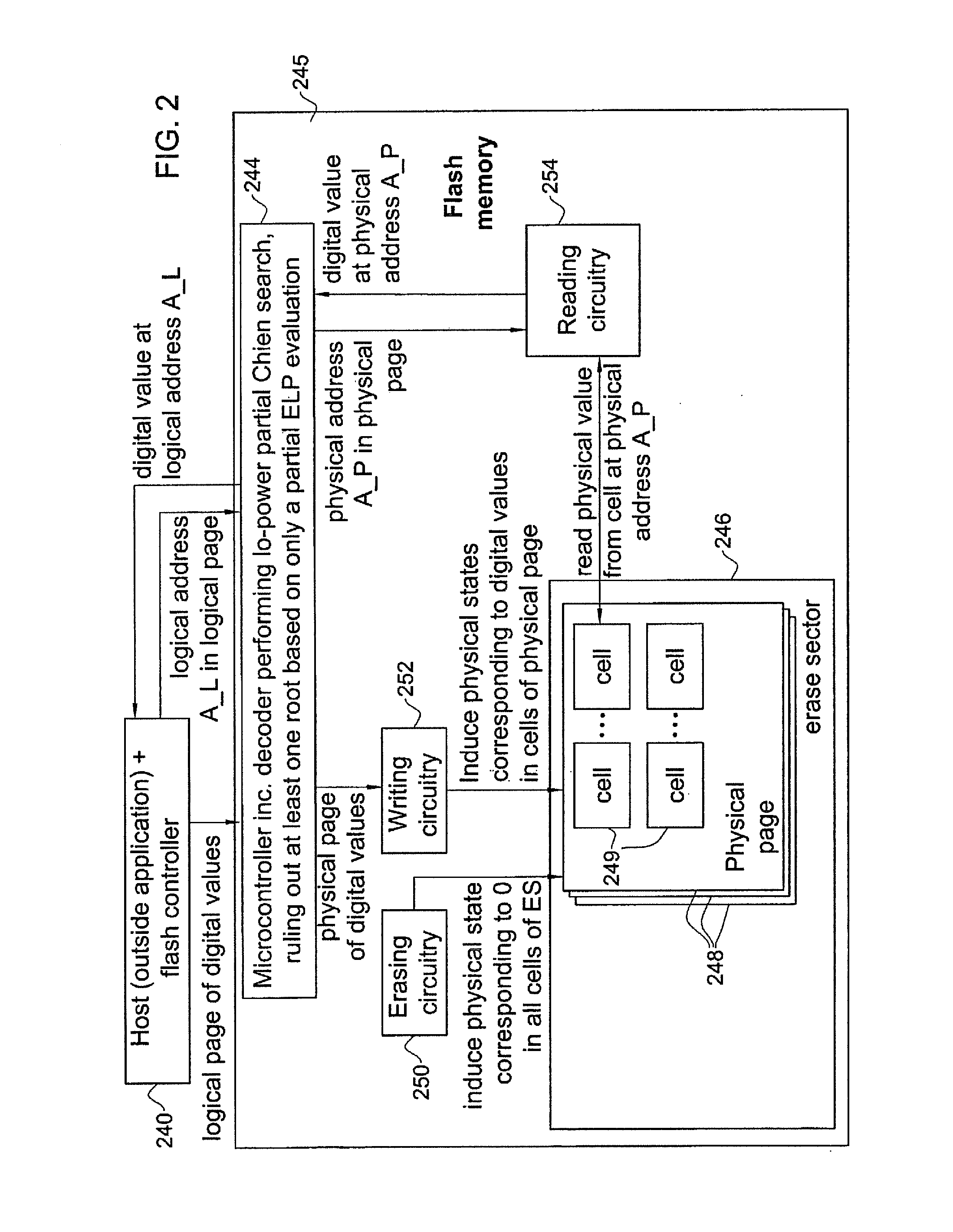

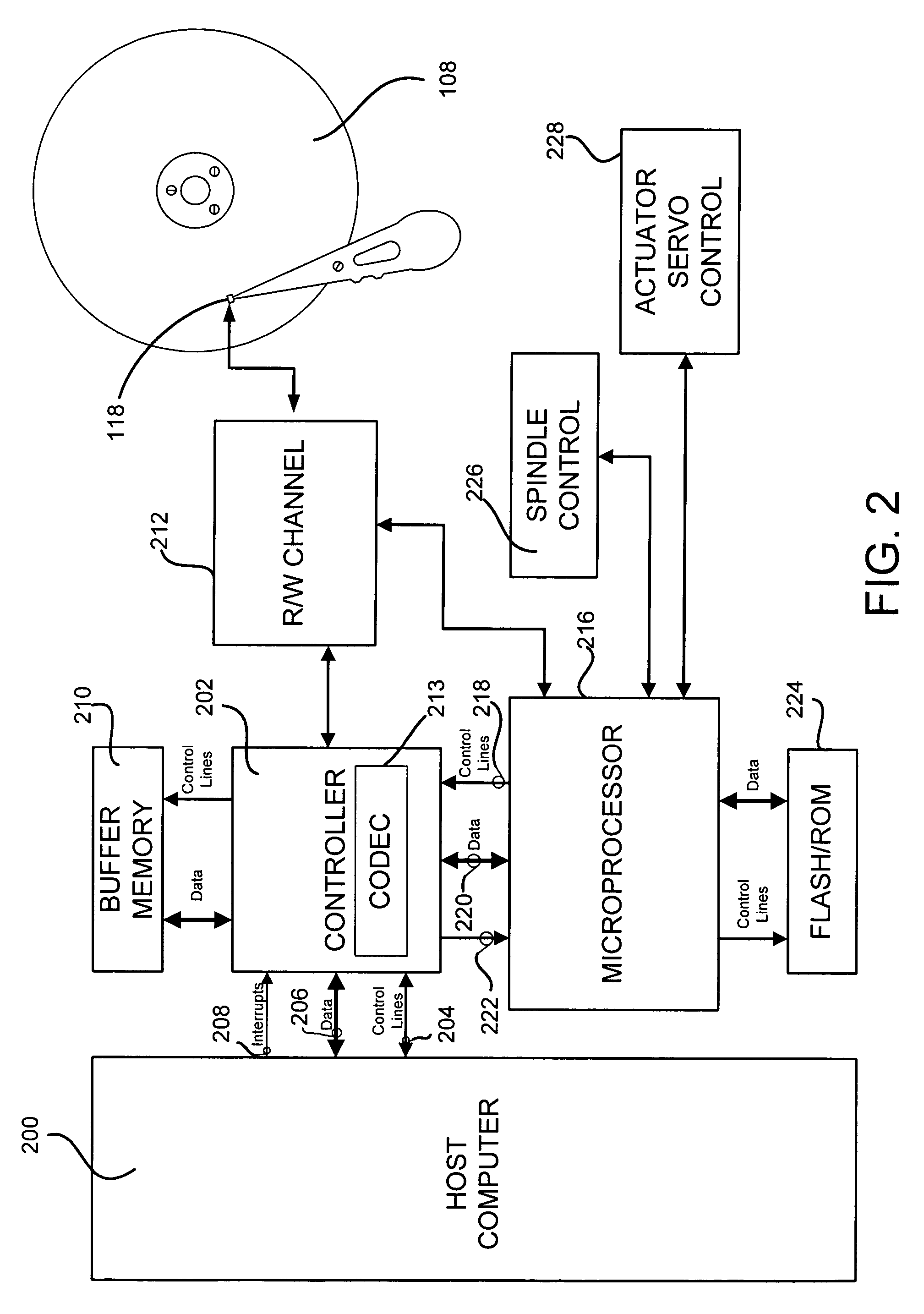

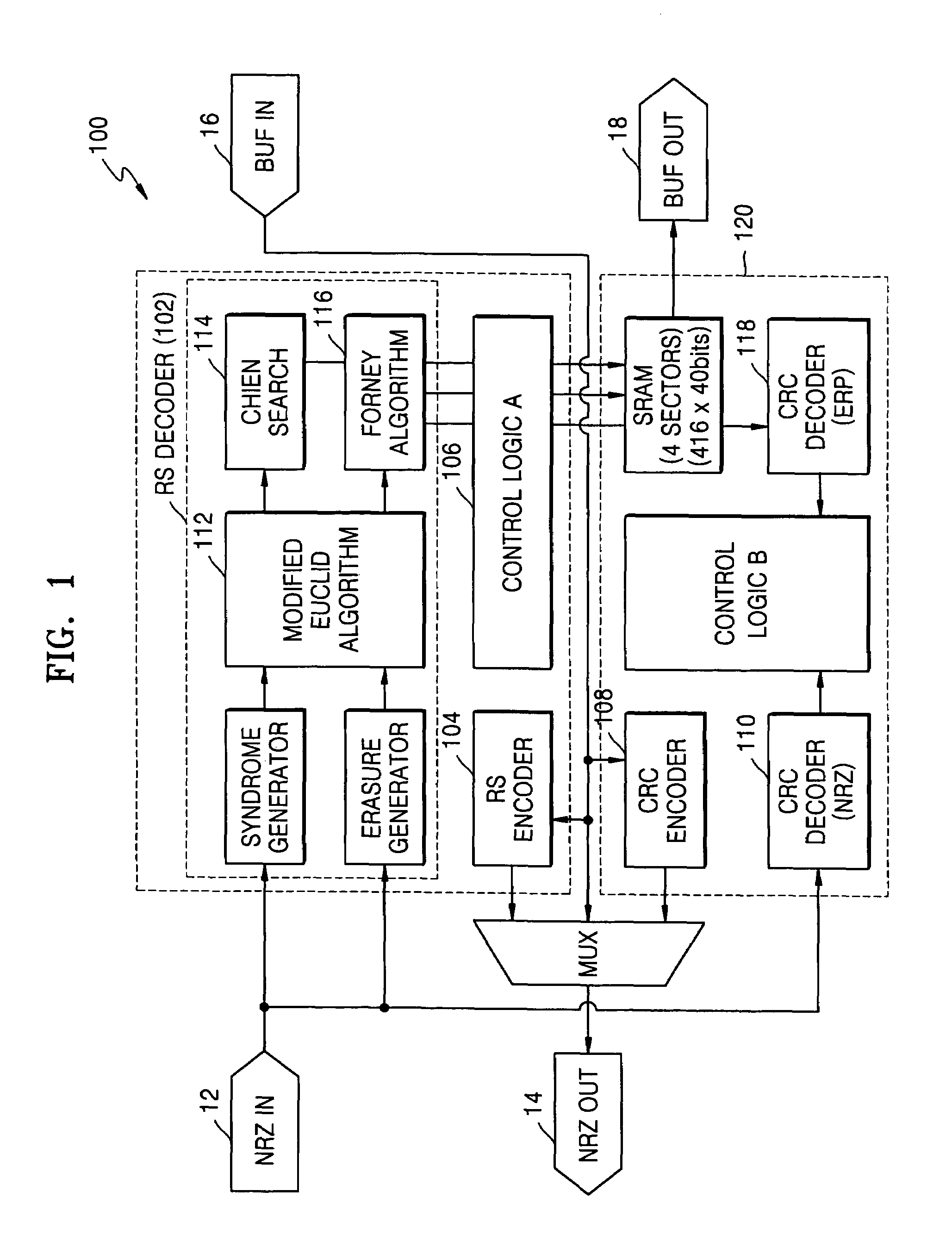

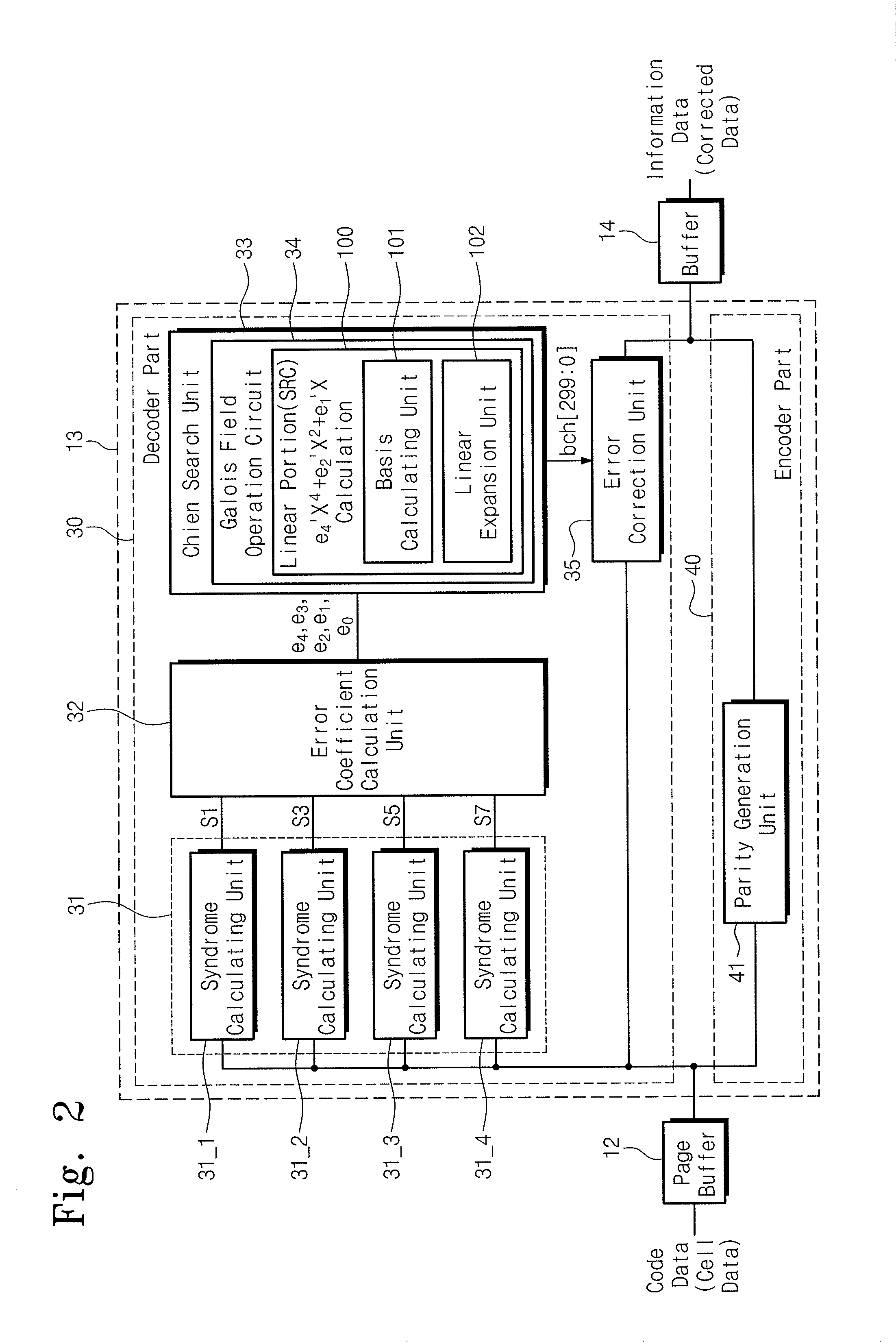

Low power chien-search based bch/rs decoding system for flash memory, mobile communications devices and other applications

ActiveUS20100131831A1Minimizing power useSaving in power consumptionCode conversionStatic storageCommunication deviceChien search

A low power Chien searching method employing Chien search circuitry comprising at least two hardware components that compute at least two corresponding bits comprising a Chien search output, the method comprising activating only a subset of the hardware components thereby to compute only a subset of the bits of the Chien search output; and activating hardware components other than those in the subset of hardware components, to compute additional bits of the Chien search output other than the bits in the subset of bits, only if a criterion on the subset of the bits of the Chien search output is satisfied.

Owner:AVAGO TECH INT SALES PTE LTD

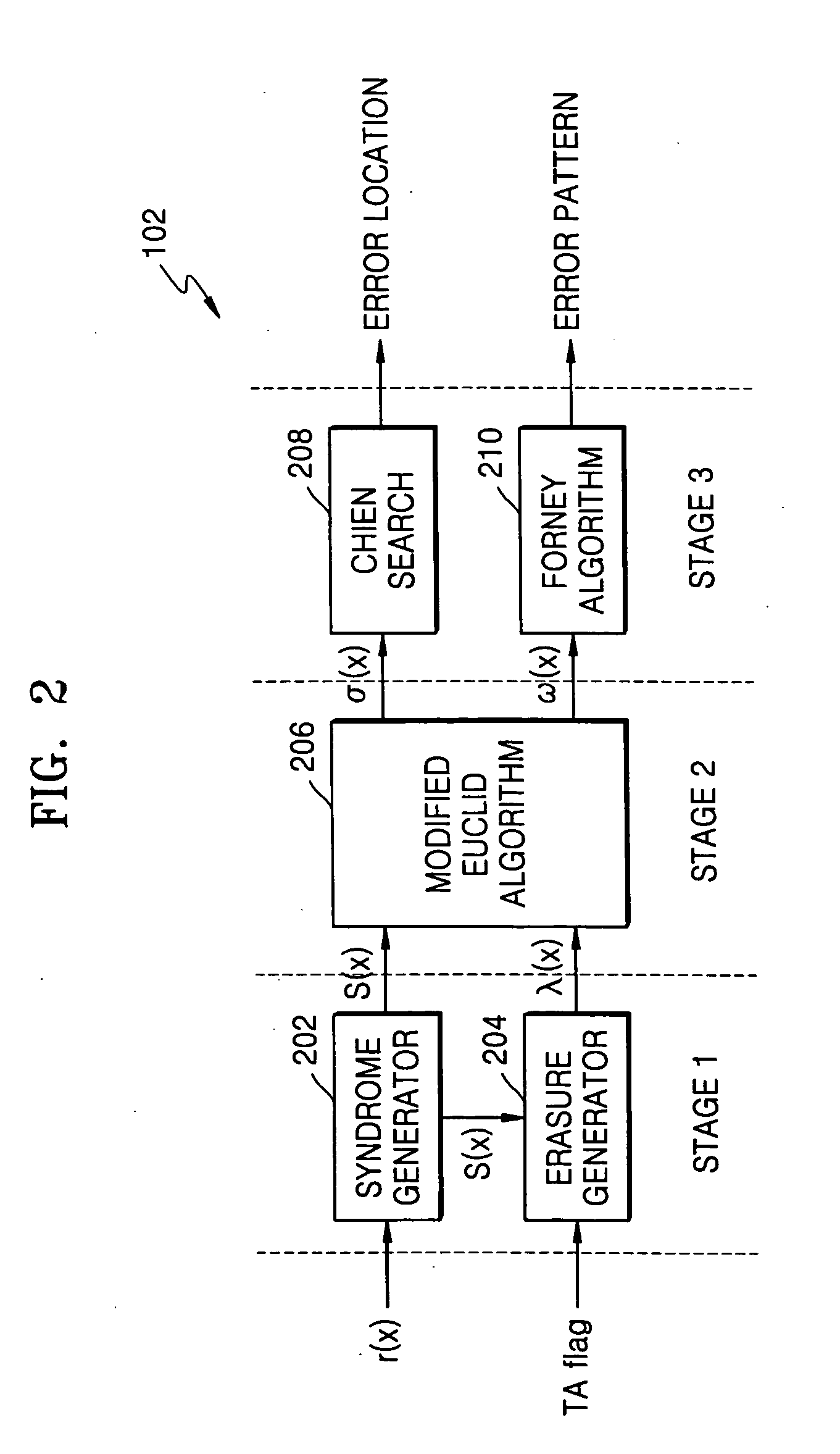

Forward Chien search type Reed-Solomon decoder circuit

ActiveUS20050172208A1Reduce aggregation timeShorten the timeCode conversionCyclic codesError locationReed solomon decoder

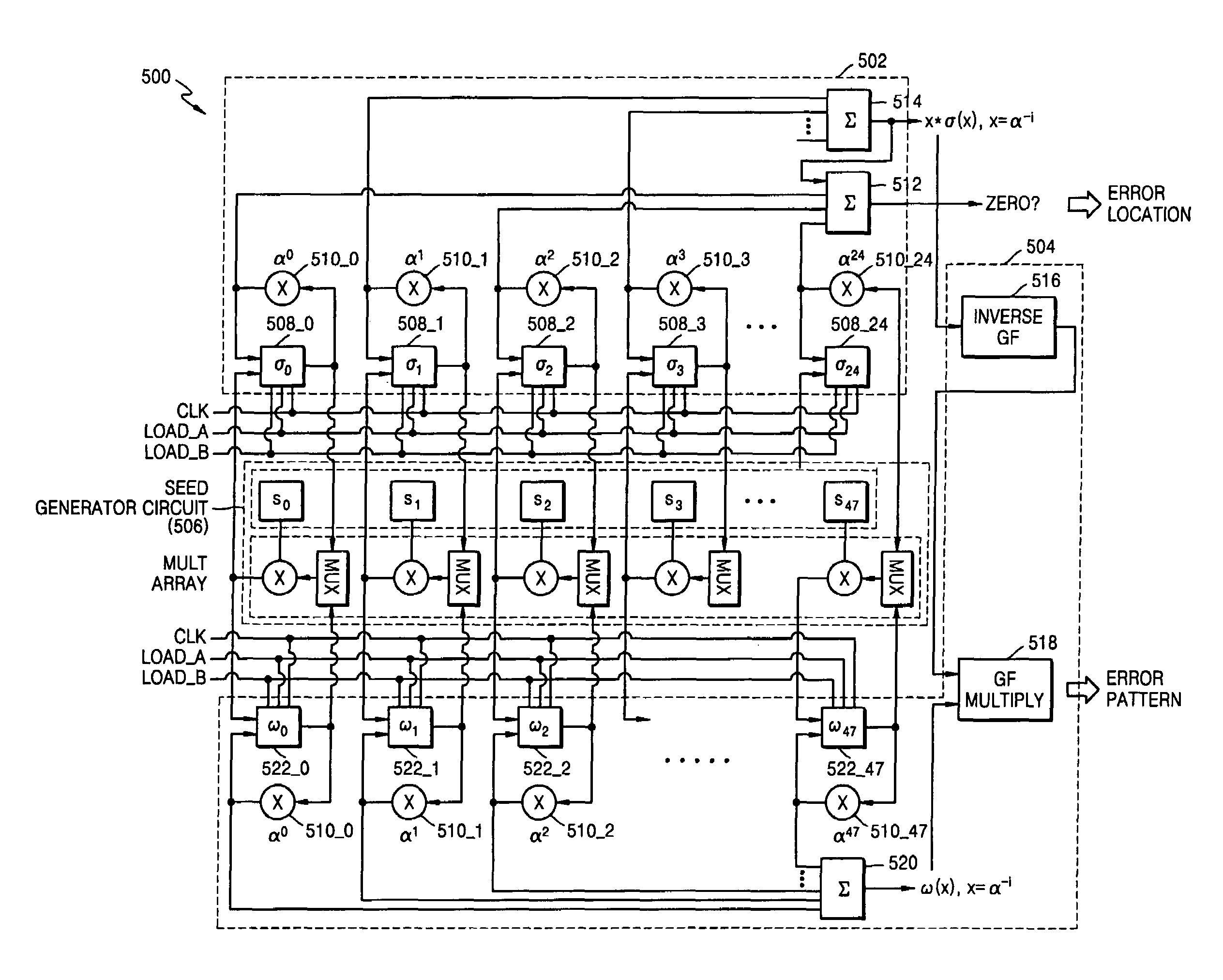

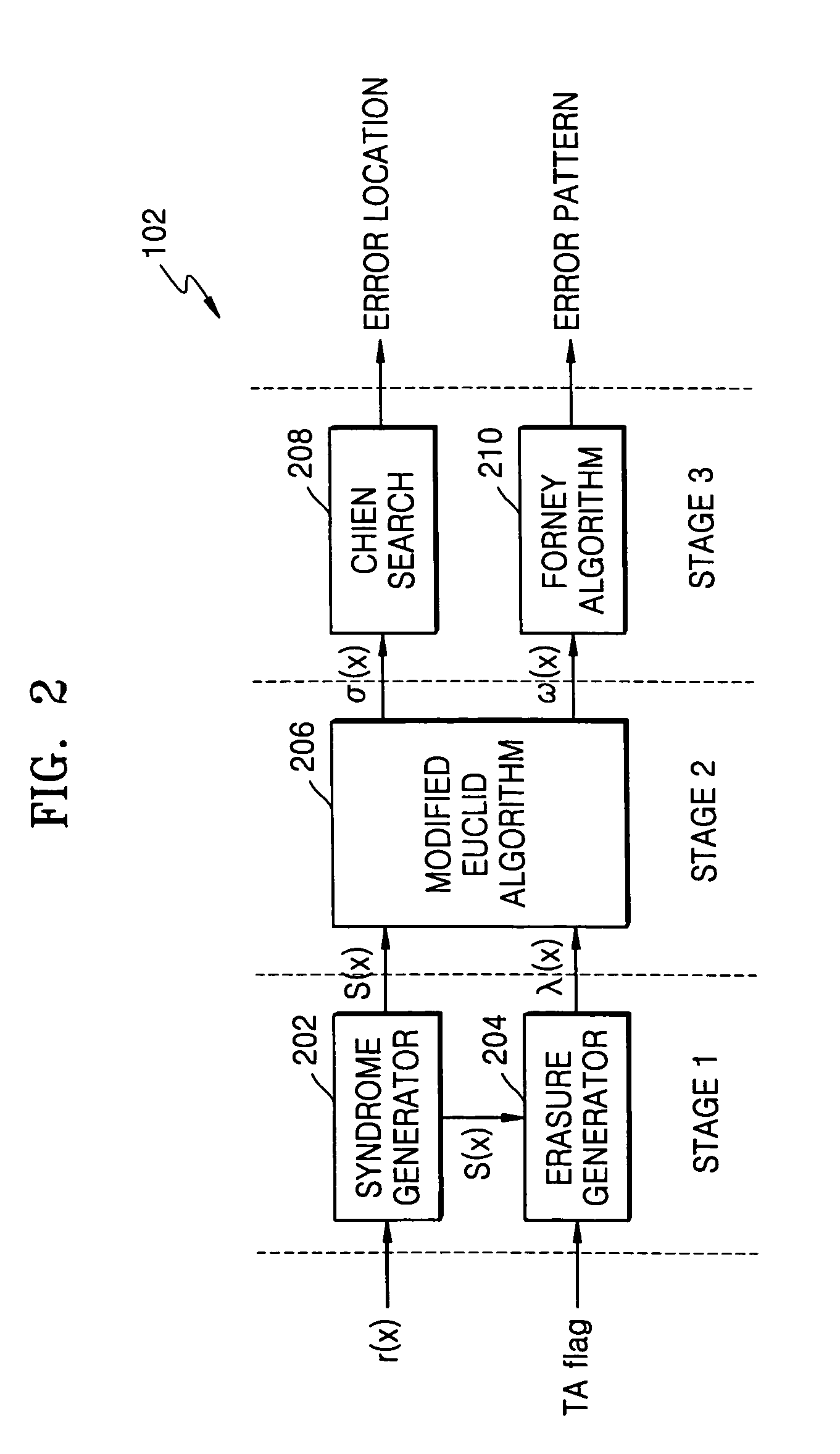

A Reed-Solomon decoder includes a Chien search circuit to receive an error location polynomial function, performs Chien search, and finds an error location; a Forney algorithm circuit to receives an error pattern polynomial function and find an error pattern; and, a seed generator circuit to indicates a seed value corresponding to a codeword length for the input data. A Chien search is performed to obtain and outputs exponential terms related to variables for the polynomials, wherein the Chien search is performed in the same computational direction as an order for the input data.

Owner:SAMSUNG ELECTRONICS CO LTD

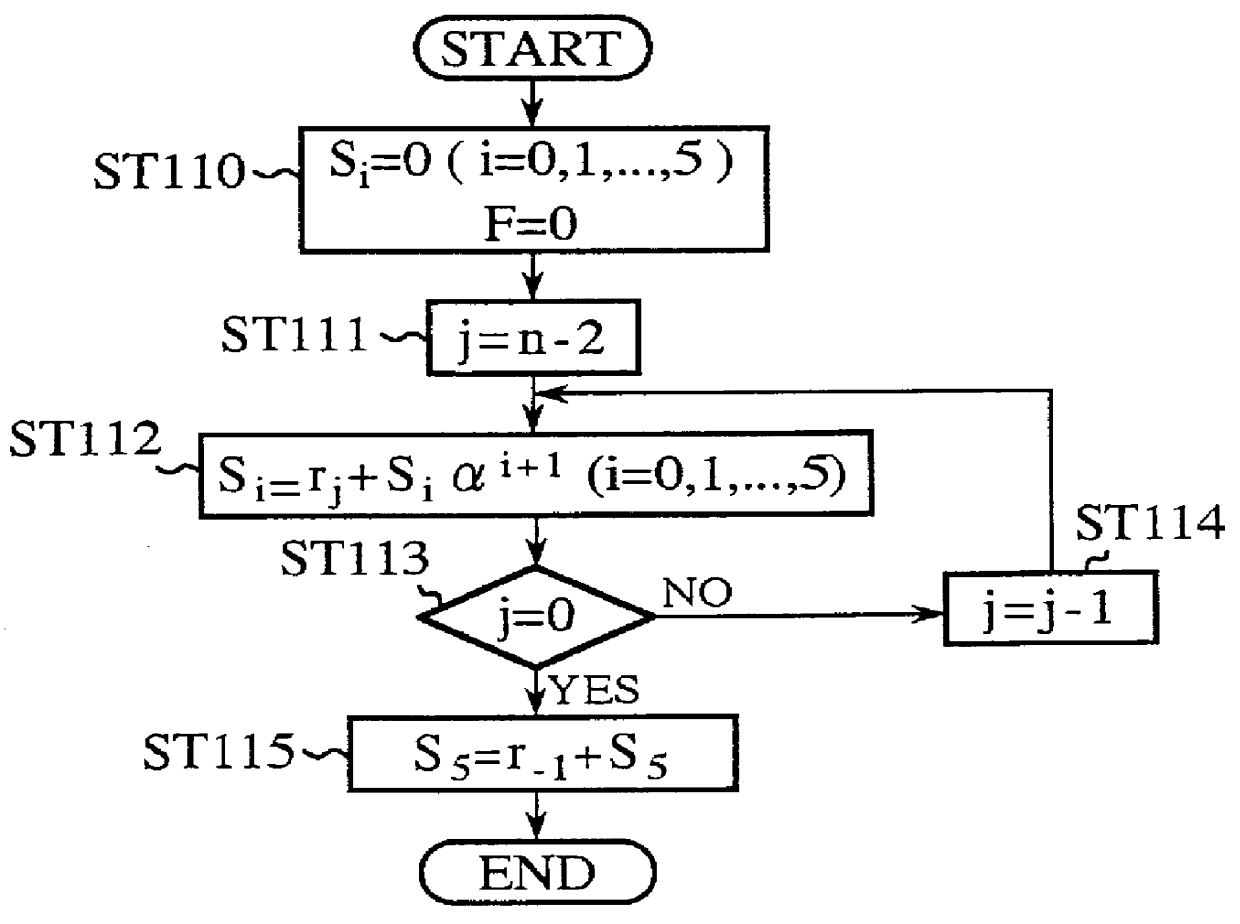

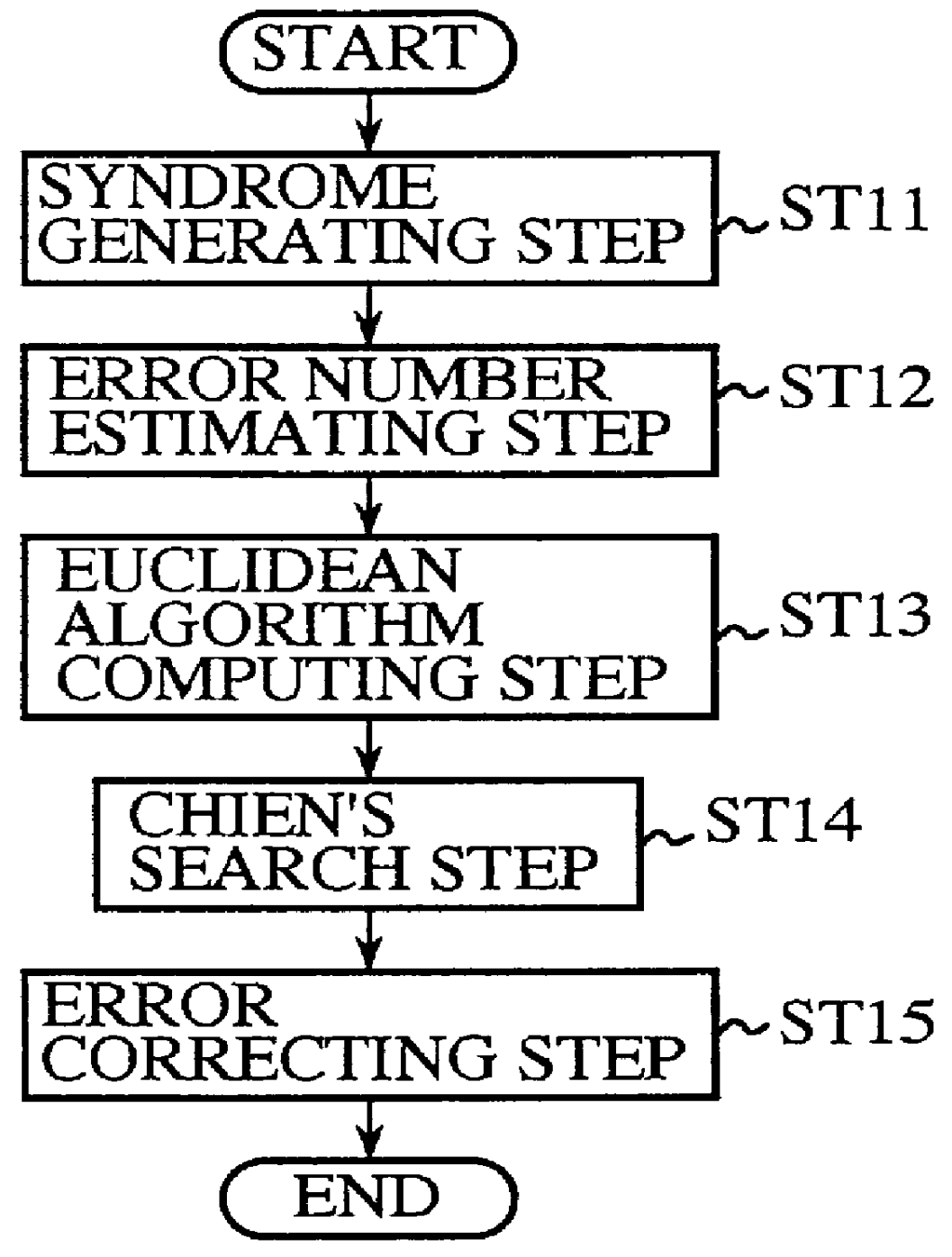

Error correcting decoding apparatus of extended Reed-Solomon code, and error correcting apparatus of singly or doubly extended Reed-Solomon codes

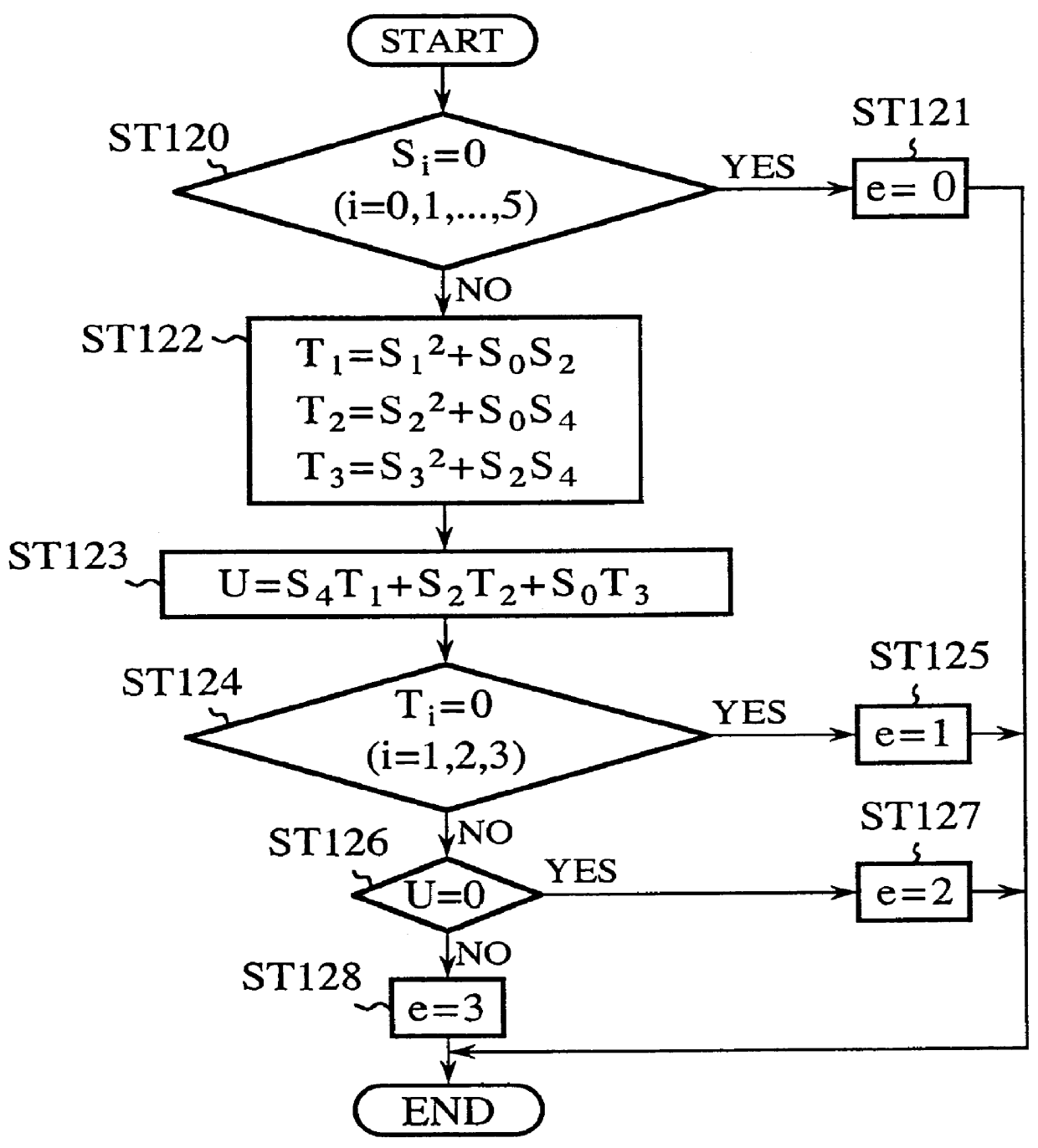

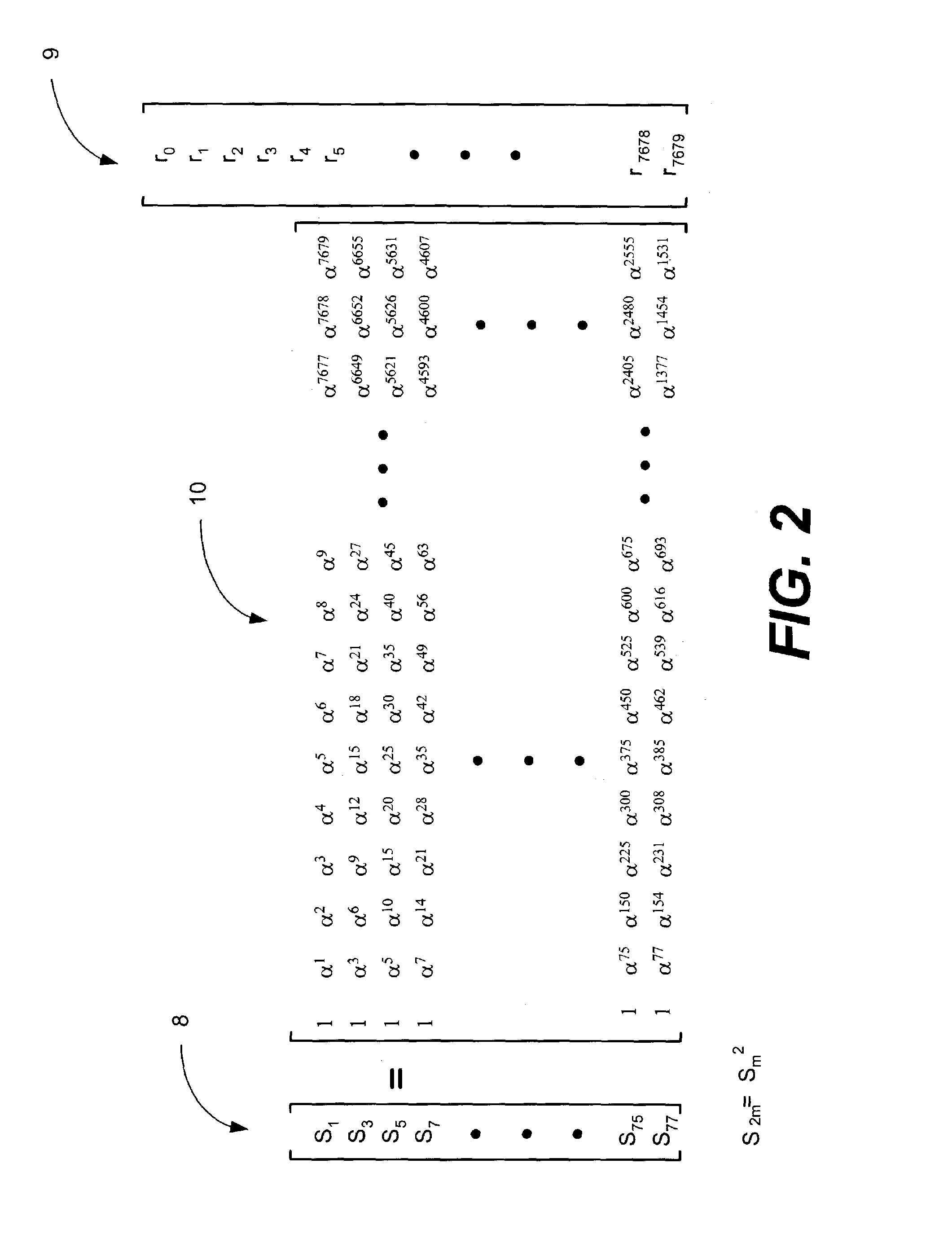

An error correcting decoding apparatus of an extended RS code capable of solving a problem of a conventional method in that Euclidean algorithm or Berlekamp-Massey algorithms must be performed twice in the worst case because of complicated algorithm, and this results in a delay of decoding. The present apparatus generates a syndrome from a received word, estimates the number of errors having occurred in the received word, computes error-locator polynomials and error-value polynomials while changing the initial values and ending condition of the Euclidean algorithm computation in accordance with the number of errors estimated, computes error locations and error values by performing Chien's search on these polynomials, and carries out the error correction on the basis of the error locations and error values. This makes it possible to achieve decoding by performing the Euclidean algorithm computation only once.

Owner:MITSUBISHI ELECTRIC CORP

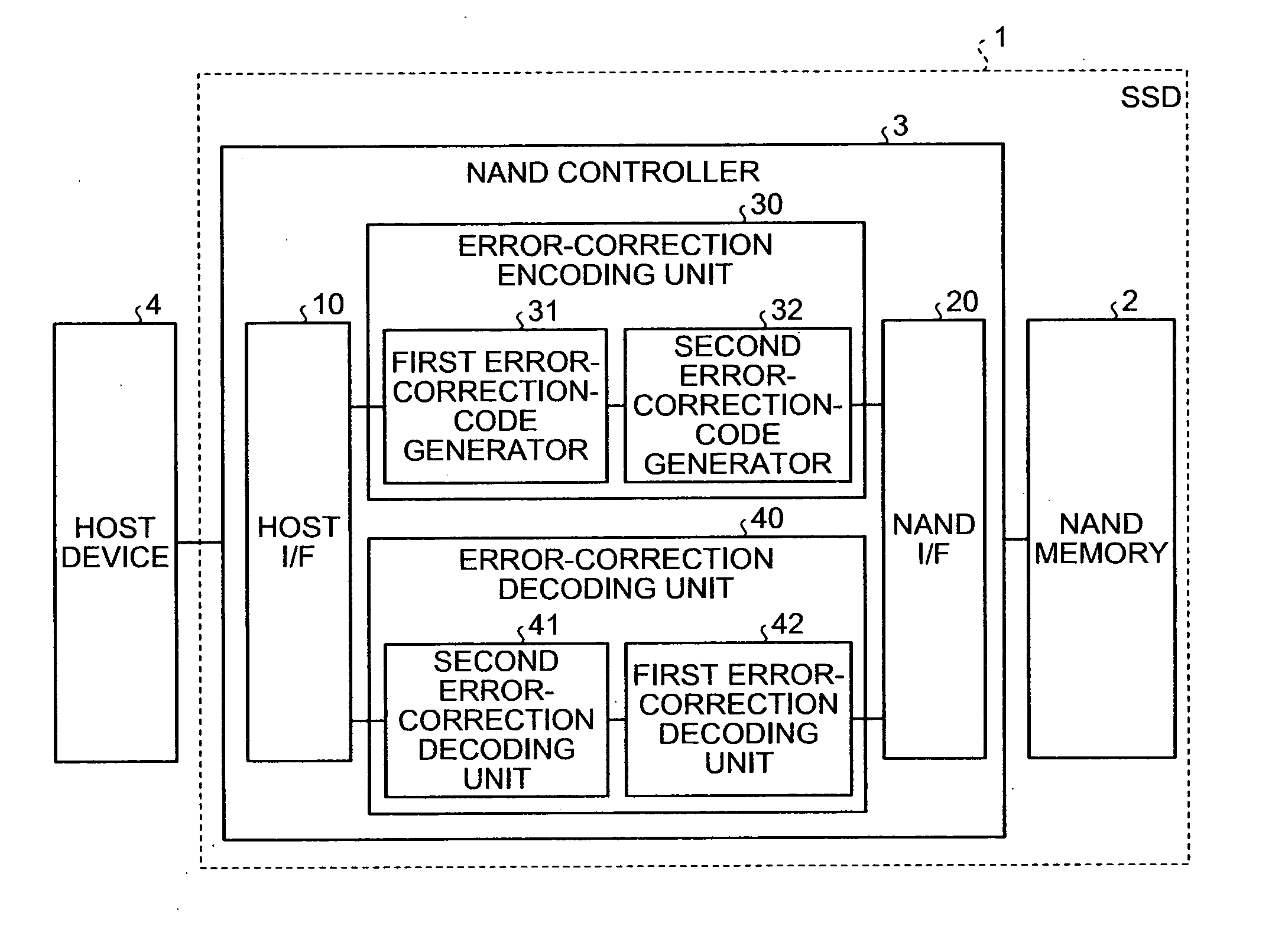

Memory controller and operating method of memory controller

ActiveUS20120290901A1Reduce consumptionEnergy efficient ICTDigital data processing detailsError locationControl memory

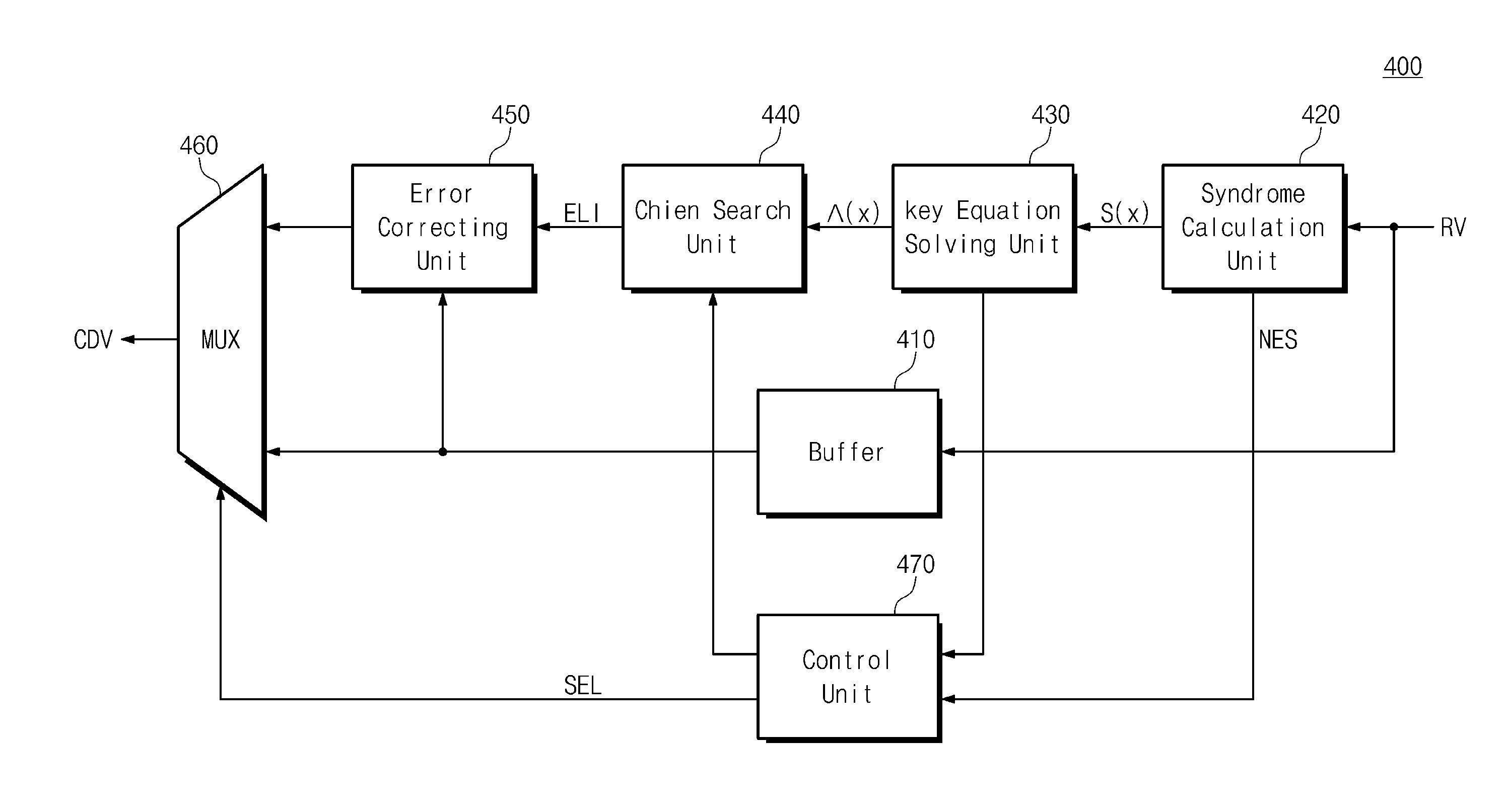

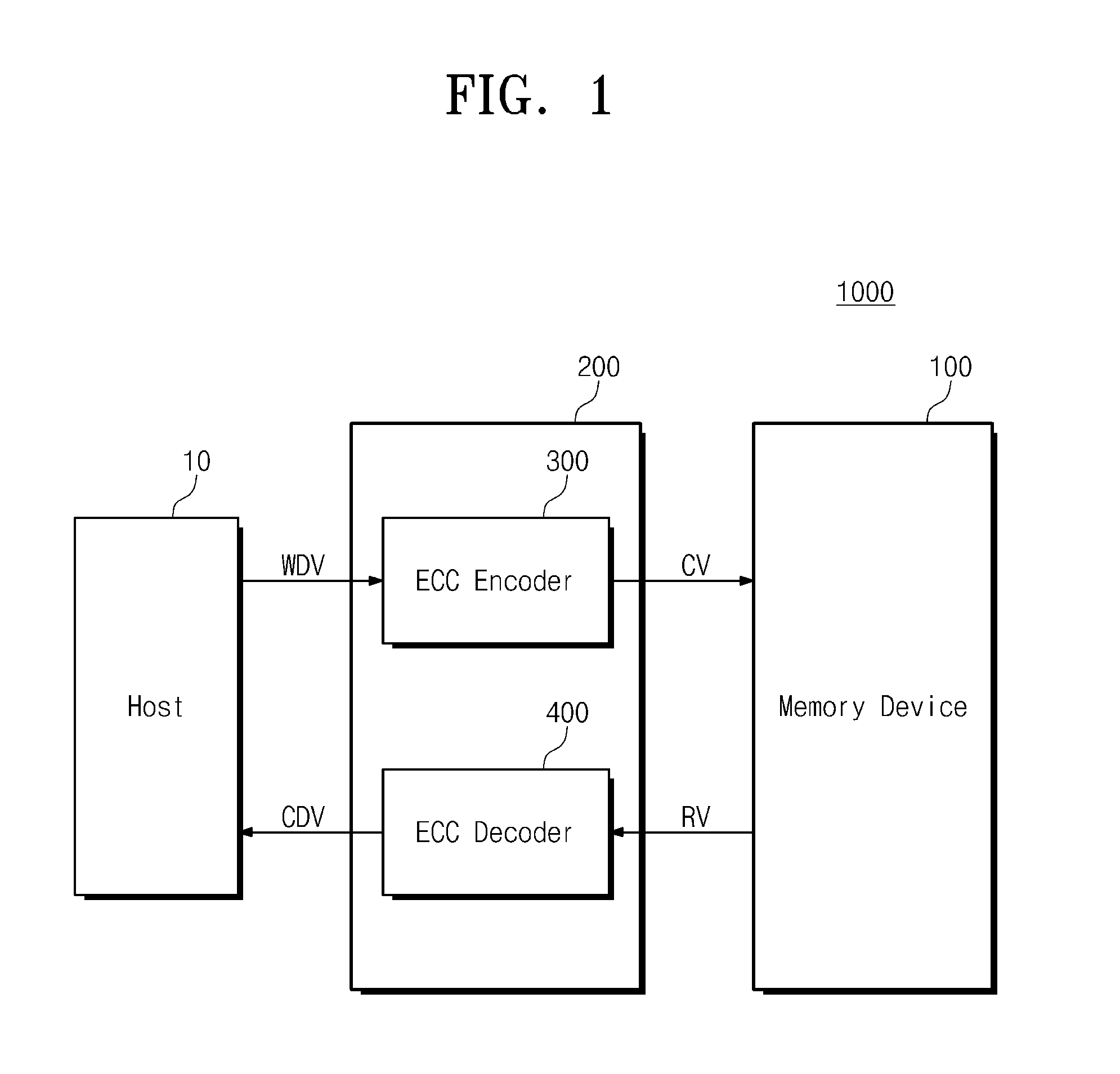

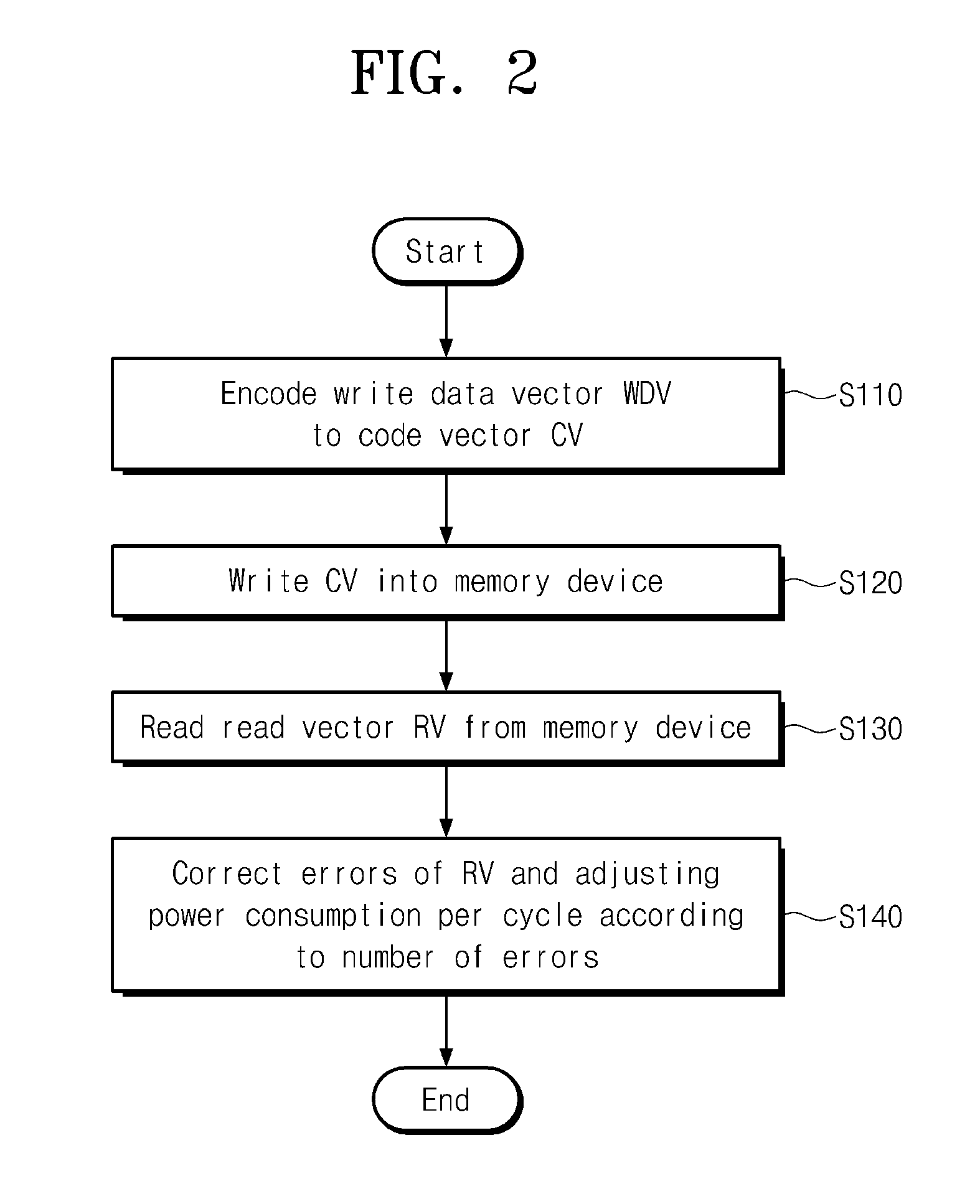

A controller to control a memory system including a memory device. The controlling the memory system may include calculating an error location polynomial in a received read vector with a key equation solving unit of the memory system to read data from the memory device, estimating the number of errors in the received read vector with a control unit of the memory system according to at least one of the calculated error location polynomial and information on the error location polynomial, searching error locations of the received read vector according to the calculated error location polynomial with a chien search unit of the memory system with the control unit. A cycle-per power consumption of the chien search unit may be adjusted with the control unit. A maximum correction time may be adjusted according to the number of errors of the read vector.

Owner:SAMSUNG ELECTRONICS CO LTD

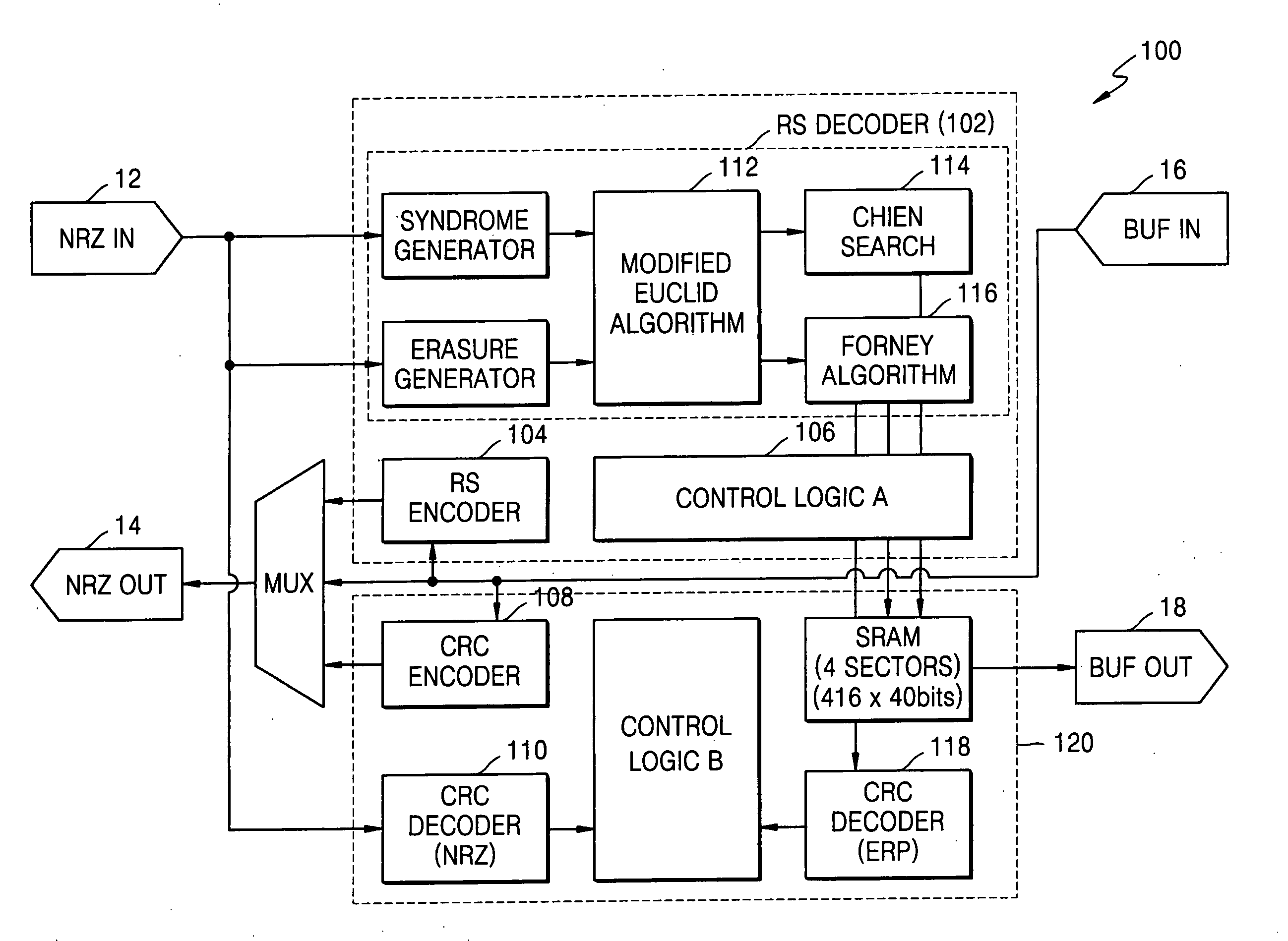

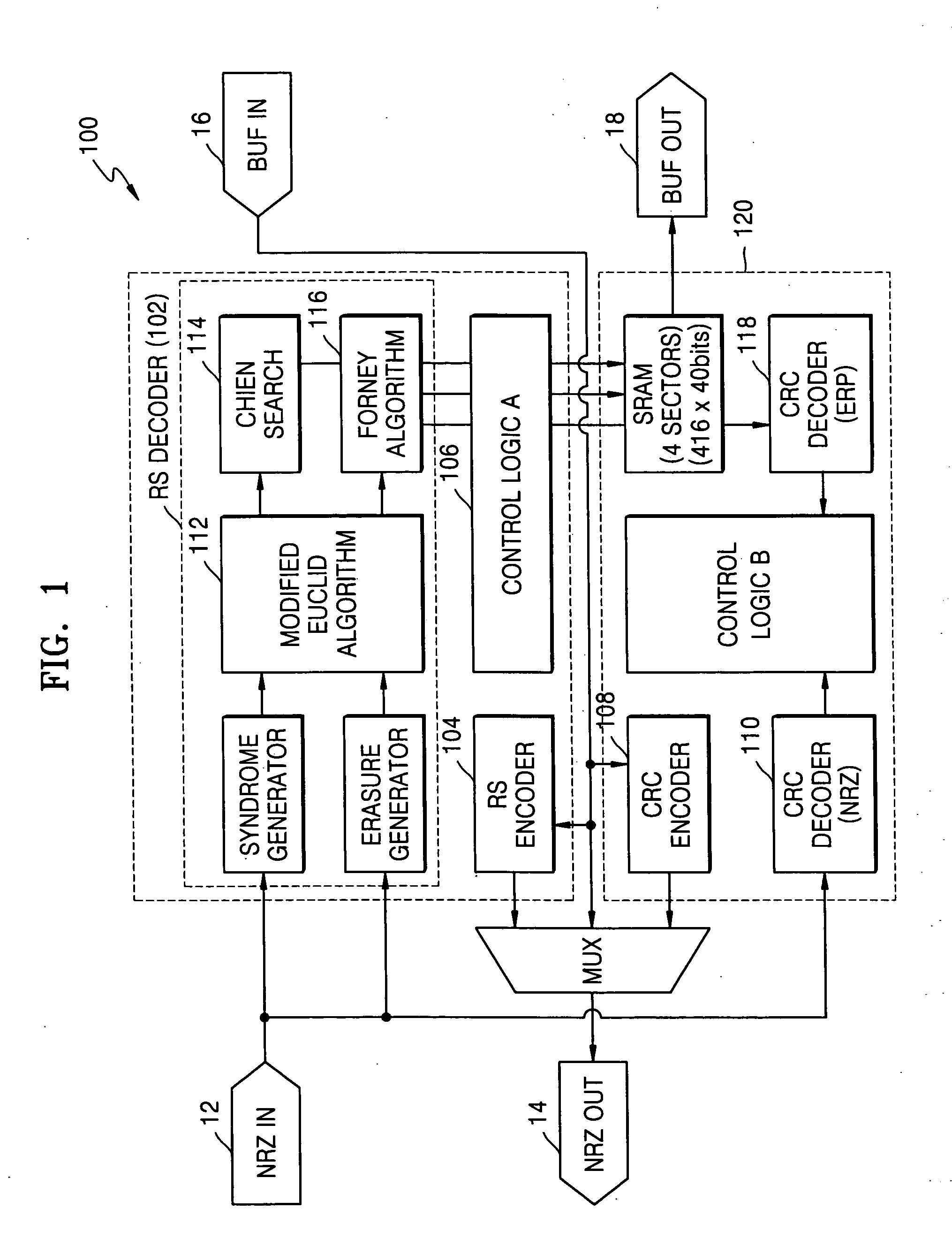

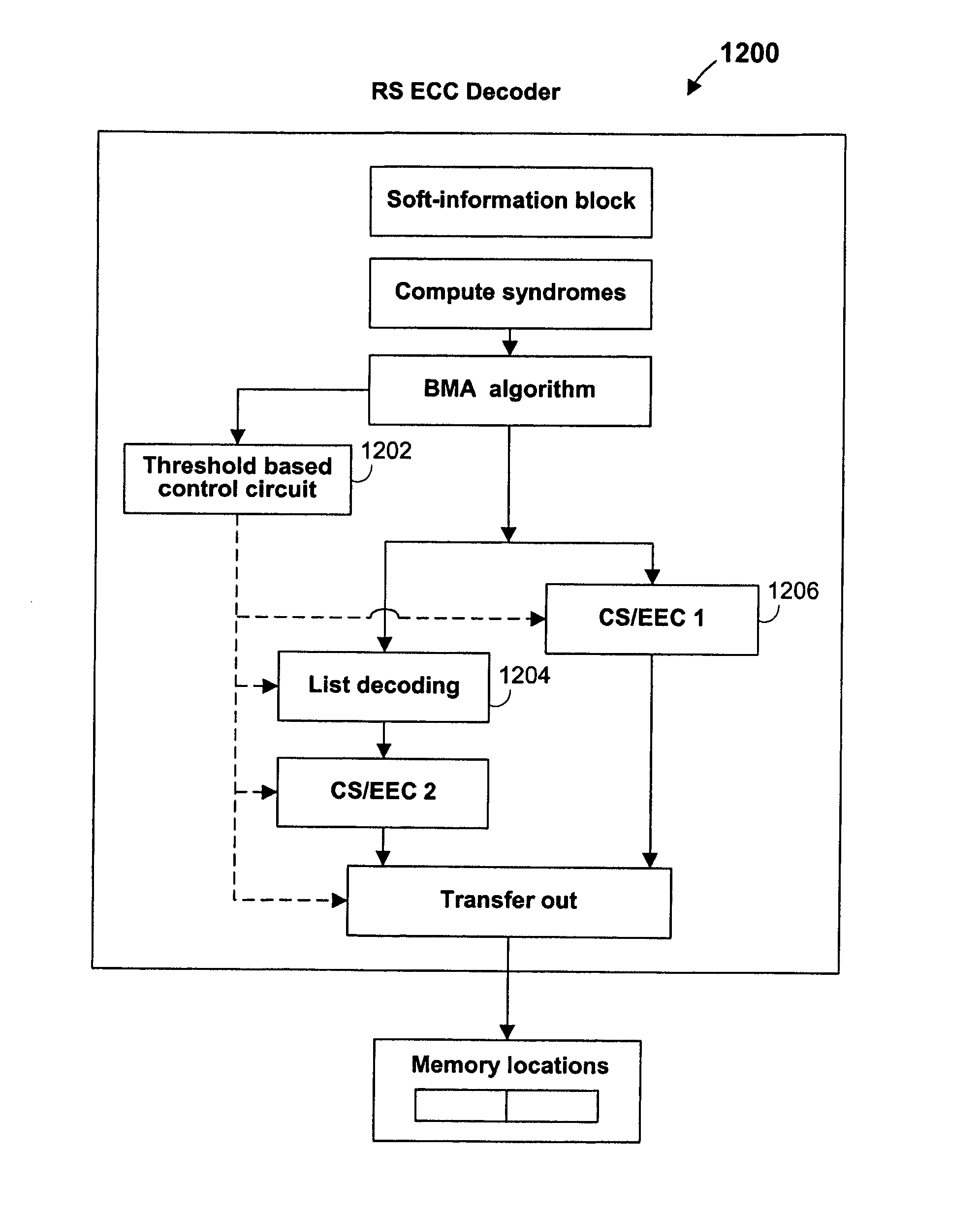

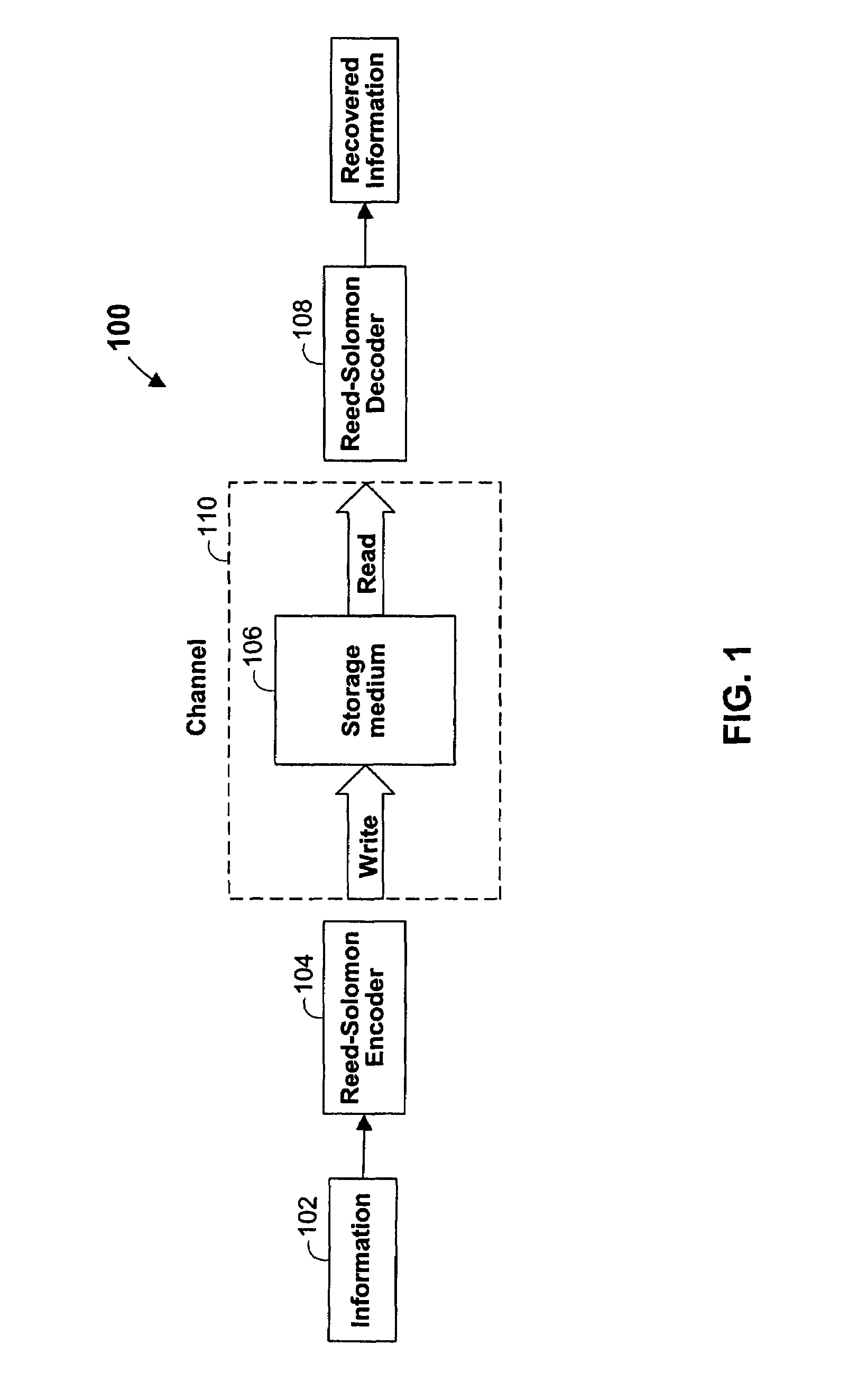

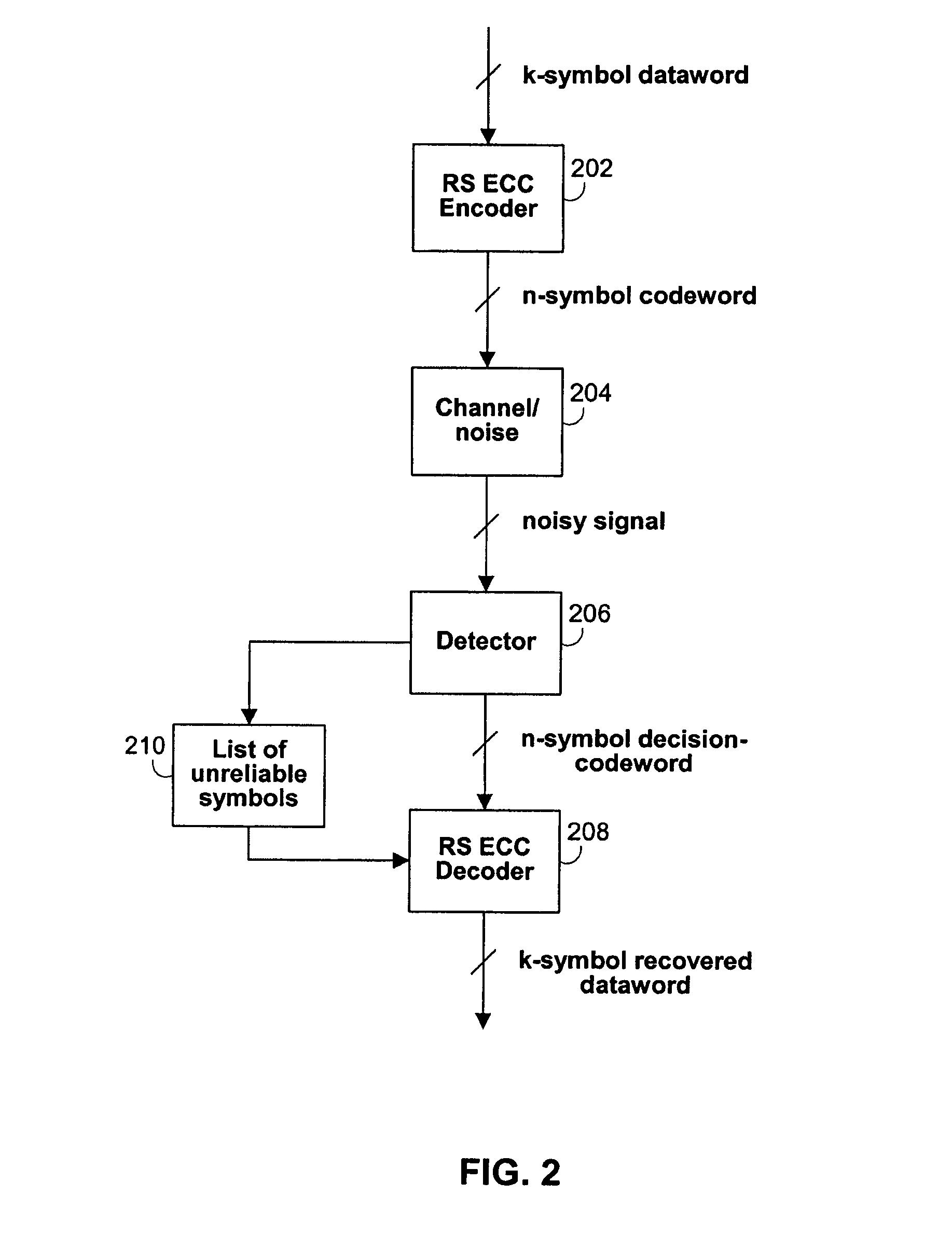

Architecture and control of reed-solomon error-correction decoding

ActiveUS7444582B1Joint error correctionOther decoding techniquesComputer architectureBerlekamp–Massey algorithm

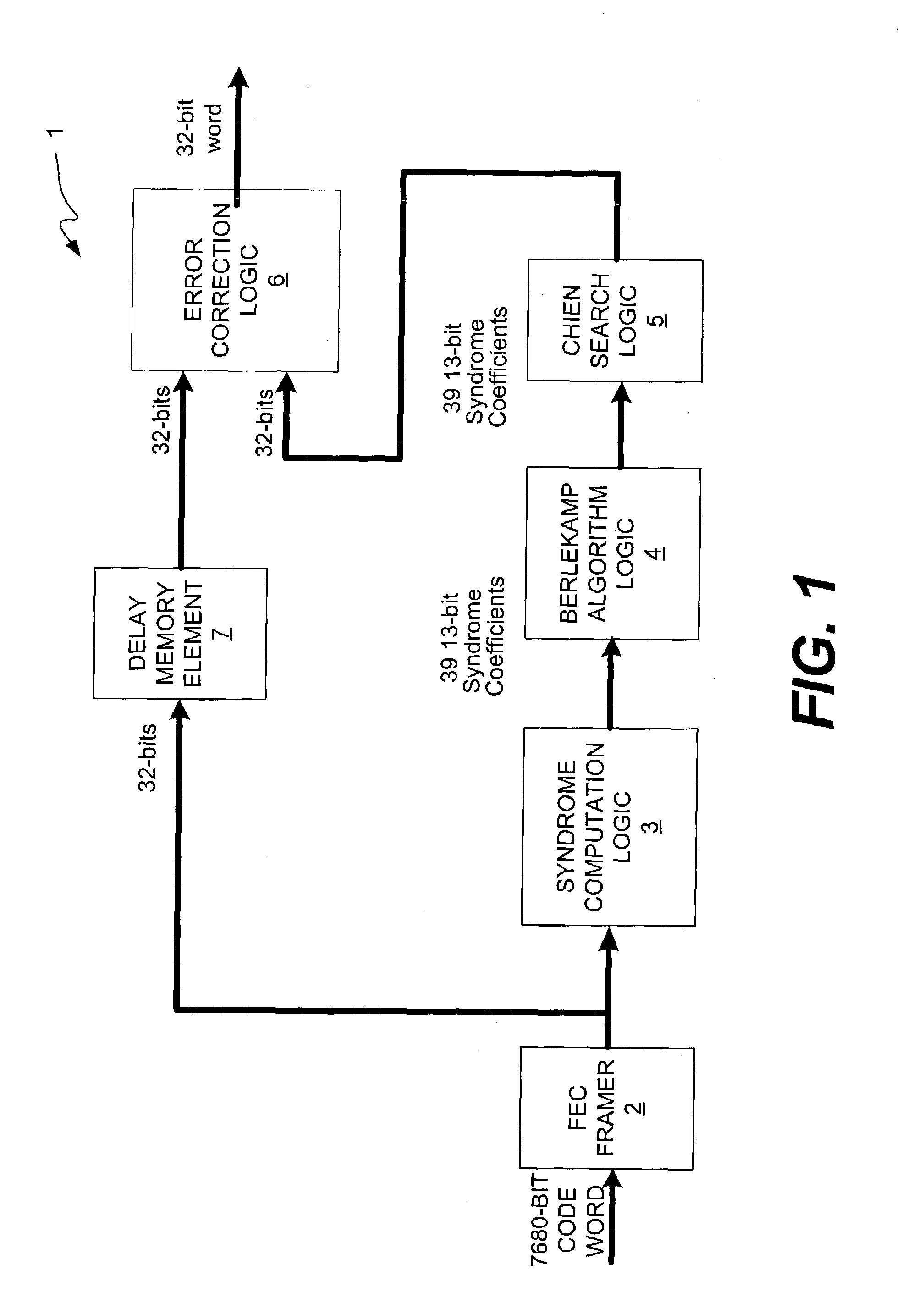

Systems and methods are provided for implementing various aspects of a Reed-Solomon (RS) error-correction system. A detector can provide a decision-codeword from a channel and can also provide soft-information for the decision-codeword. If the decision-codeword corresponds to an inner code and an RS code is the outer code, a soft-information map can process the soft-information for the decision-codeword to produce soft-information for a RS decision-codeword. A RS decoder can employ the Berlekamp-Massey algorithm (BMA), list decoding, and a Chien search, and can include a pipelined architecture. A threshold-based control circuit can be used to predict whether list decoding will be needed and can suspend the list decoding operation if it predicts that list decoding is not needed.

Owner:MARVELL ASIA PTE LTD

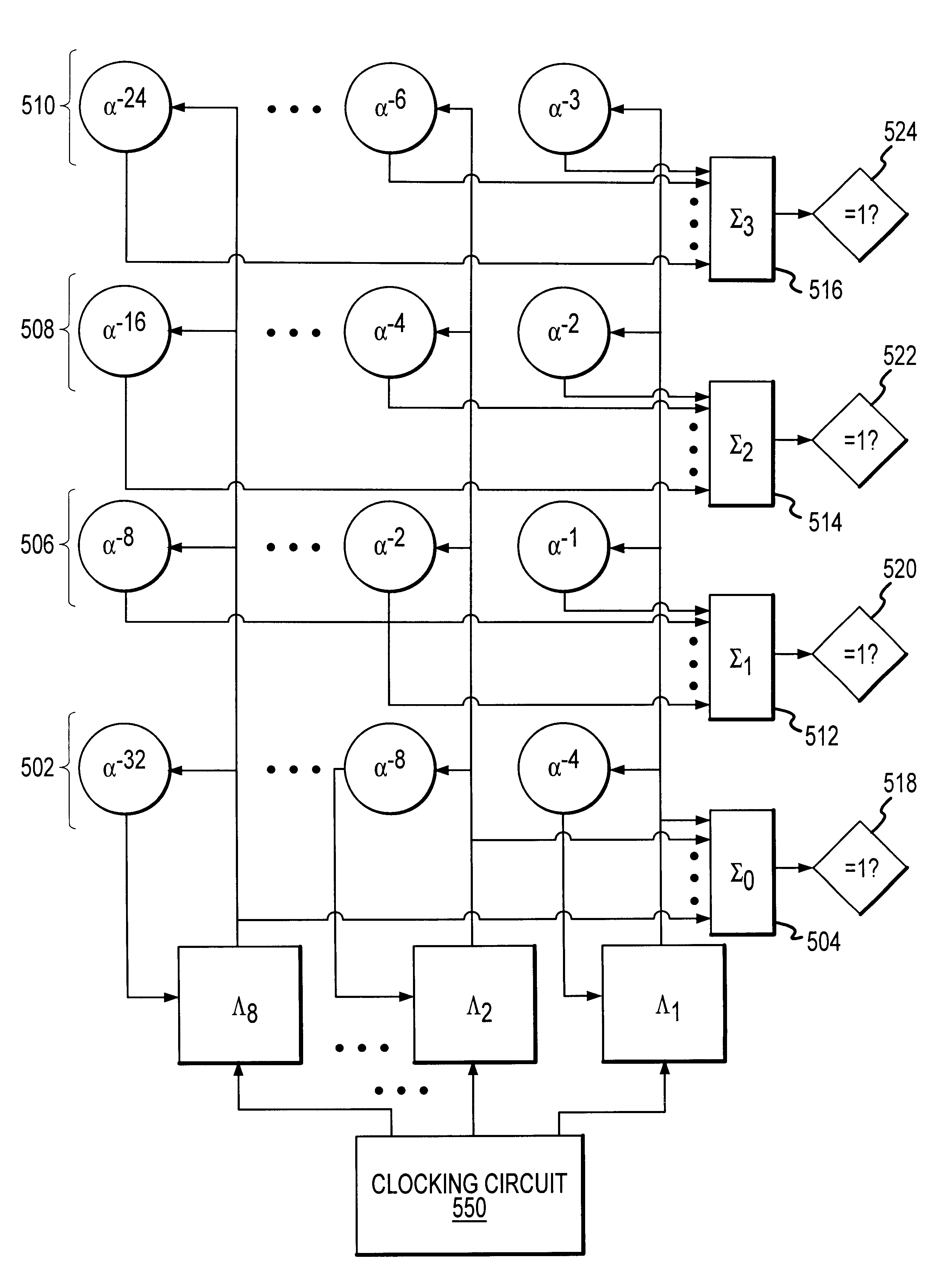

System and method for a storage-efficient parallel Chien Search

A system determines the root of a polynomial by employing a parallel structure that implements a Chien Search and minimizes the amount of storage required. The location of an error in a codeword can be derived from the root of an error locator polynomial. The performance of the Chien Search is enhanced by the parallel structure, and the location of the error can be easily determined using a simple calculation that preferably includes the cycle count, the parallelism, and the index of the multiplier / summer rank that indicates a root. Multiple ranks of multipliers receive data stored in a single array of data storage units. Multiplier values of each multiplier are based on the elements of a Galois Field. A method configures data storage units, multipliers, summers, and comparators, and performs a Chien Search. The location of an error in a codeword is determined using a simple calculation based on a determined root of an error locator polynomial.

Owner:AVAGO TECH INT SALES PTE LTD

Low complexity chien search in chase-type decoding of reed-solomon codes

Data is processed by obtaining a length of an error locator polynomial. It is determined whether the length of the error locator polynomial is greater than a threshold. In the event the length of the error locator polynomial is greater than the threshold, performance of a Chien search on the error locator polynomial is skipped. In the event the length of the error locator polynomial is less than or equal to than the threshold, the Chien search is performed on the error locator polynomial to determine one or more roots of the error locator polynomial, where the roots correspond to one or more error locations.

Owner:SK HYNIX MEMORY SOLUTIONS

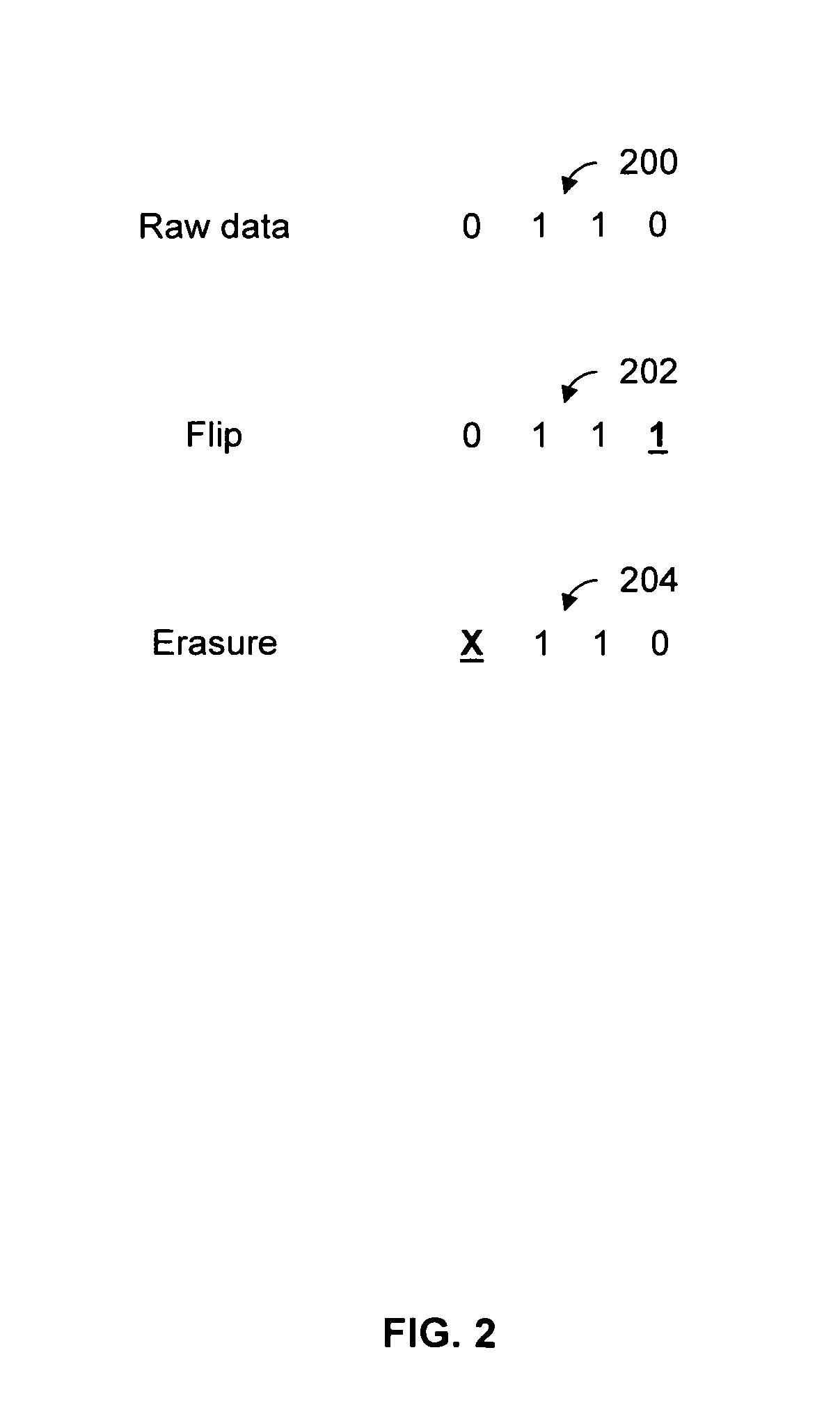

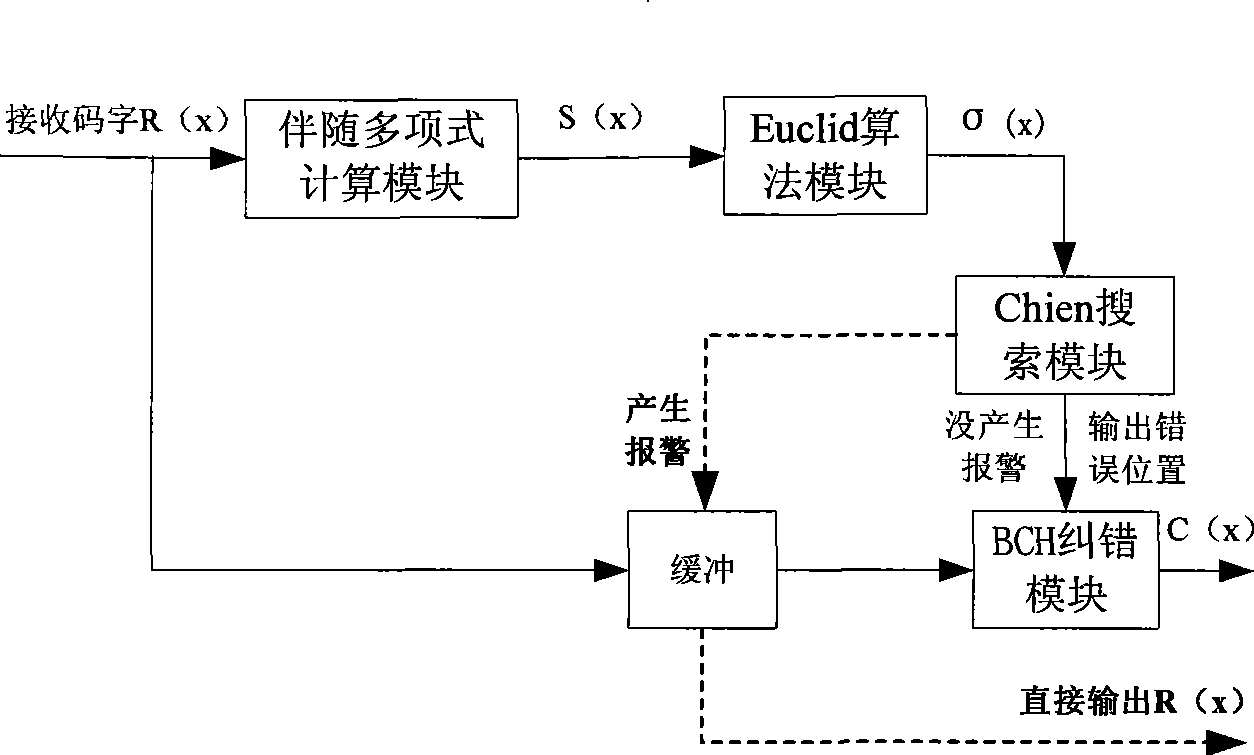

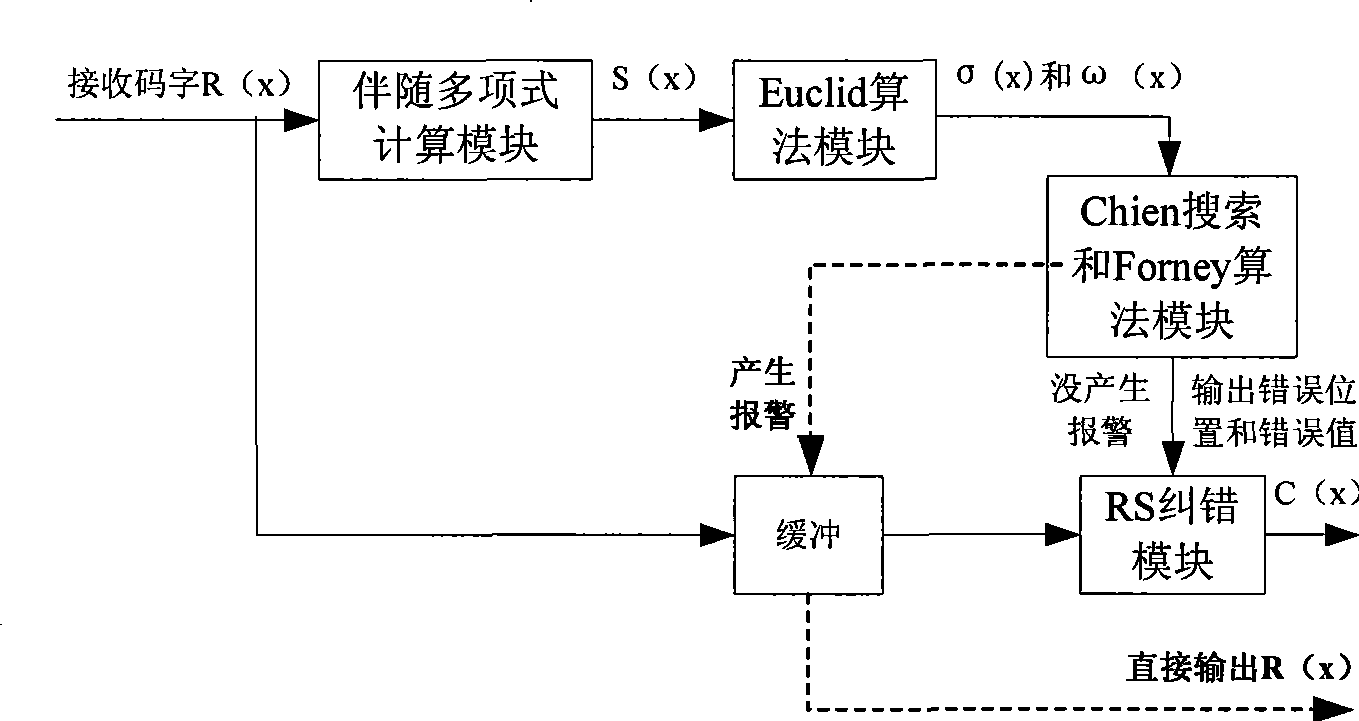

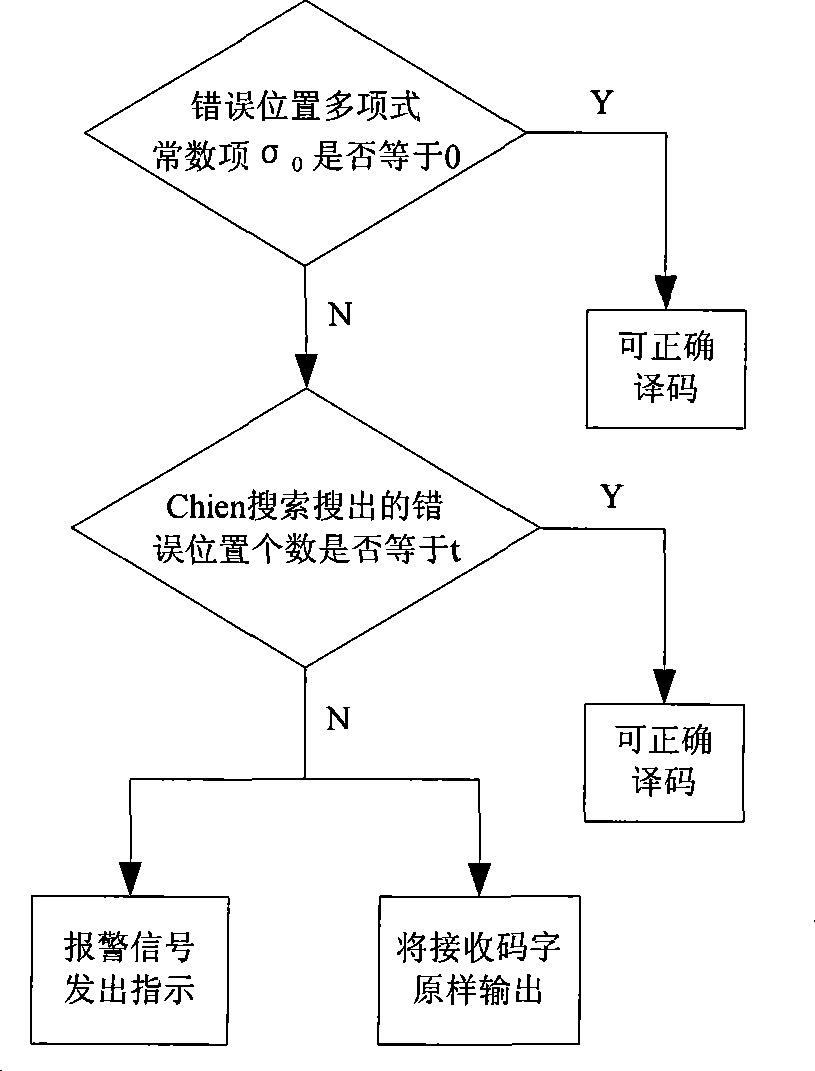

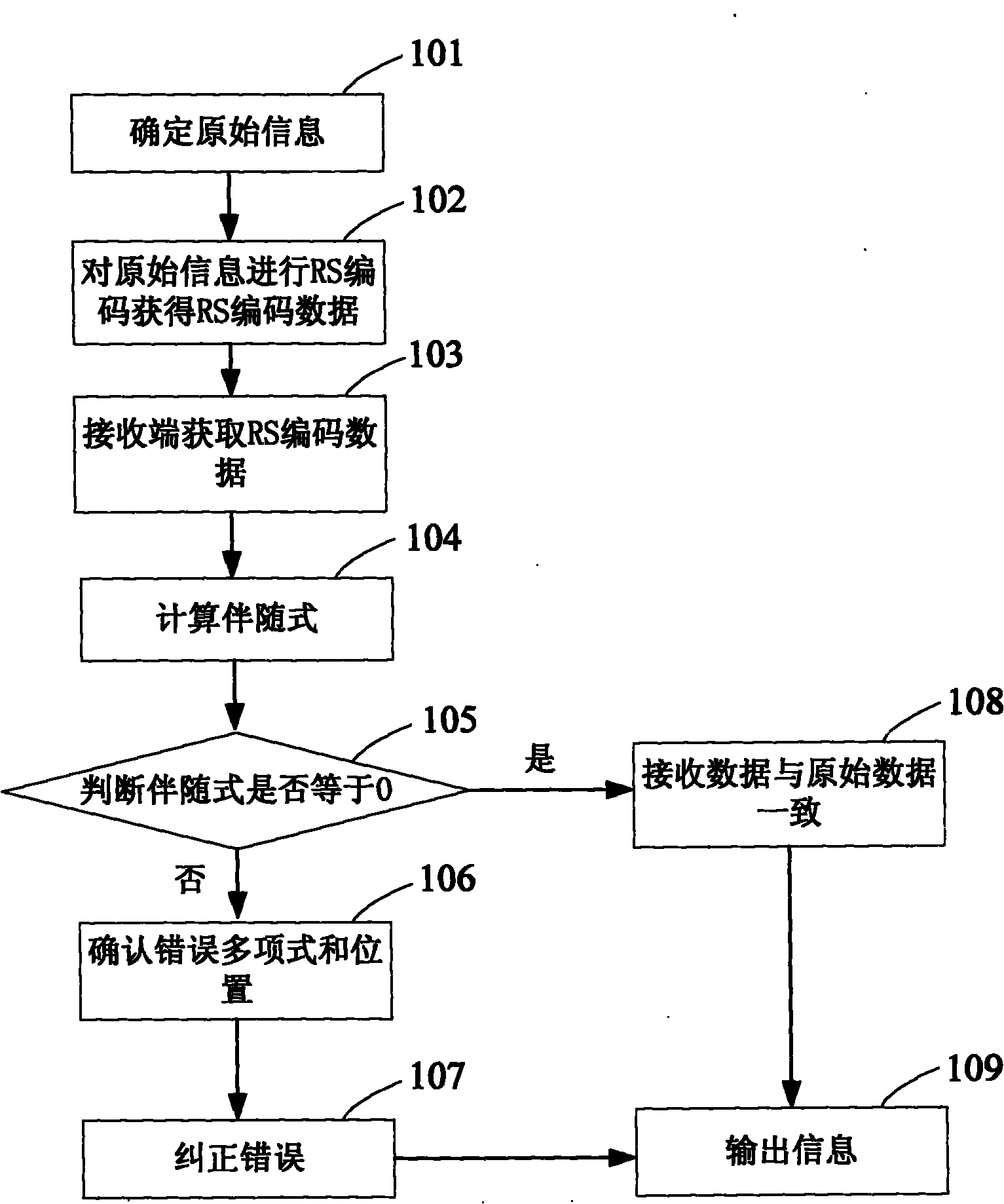

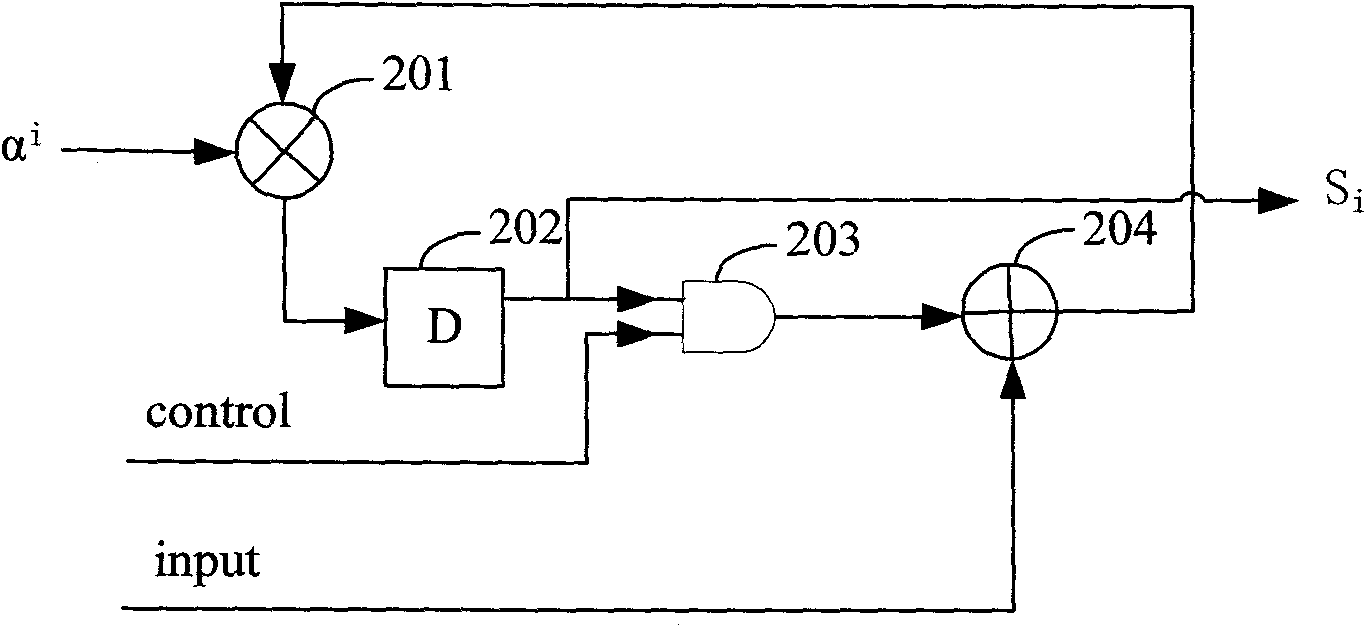

Decoding method for channel error correcting BCH code and RS code

ActiveCN101459431AReduce bit error rateAvoid the situation of "more correction and more error"Error preventionCyclic codesComputer hardwareCommunications system

The invention discloses an encoding method of a channel error correcting code BCH code and an RS code, belonging to the digital communication field, which comprises calculating an adjoint polynomial S(x) through a received code R(x), solving the Berlekamp key equation through the Euclid algorithm to obtain an error location polynomial sigma (x), and correctly encoding if the constant term sigma 0 in the error location polynomial sigma (x) is zero, or calculating the error locations and the relative error values through the Chien search if the constant term sigma 0 in the error location polynomial sigma (x) is not equal to 0, and being able to correctly encode if the number of searched error locations is equal to the largest error correcting capability thereof, or sending a warning indication signal whose error number of receiving signals exceeds the largest error correcting capability, and outputting original receiving codes. The encoding method avoids the condition that the more errors are corrected, the more errors existing when the receiving code error number exceeds the largest error correcting capability of the channel error correcting code, thereby reducing the error code rate of the whole communication system.

Owner:PEKING UNIV +1

Method and apparatus for use in a decoder of a forward error correction (FEC) system for locating bit errors in a error locator polynomial

ActiveUS7058876B1Quickly and efficiently processingLimit amount of neededDigital data processing detailsCode conversionAlgorithmForward error correction

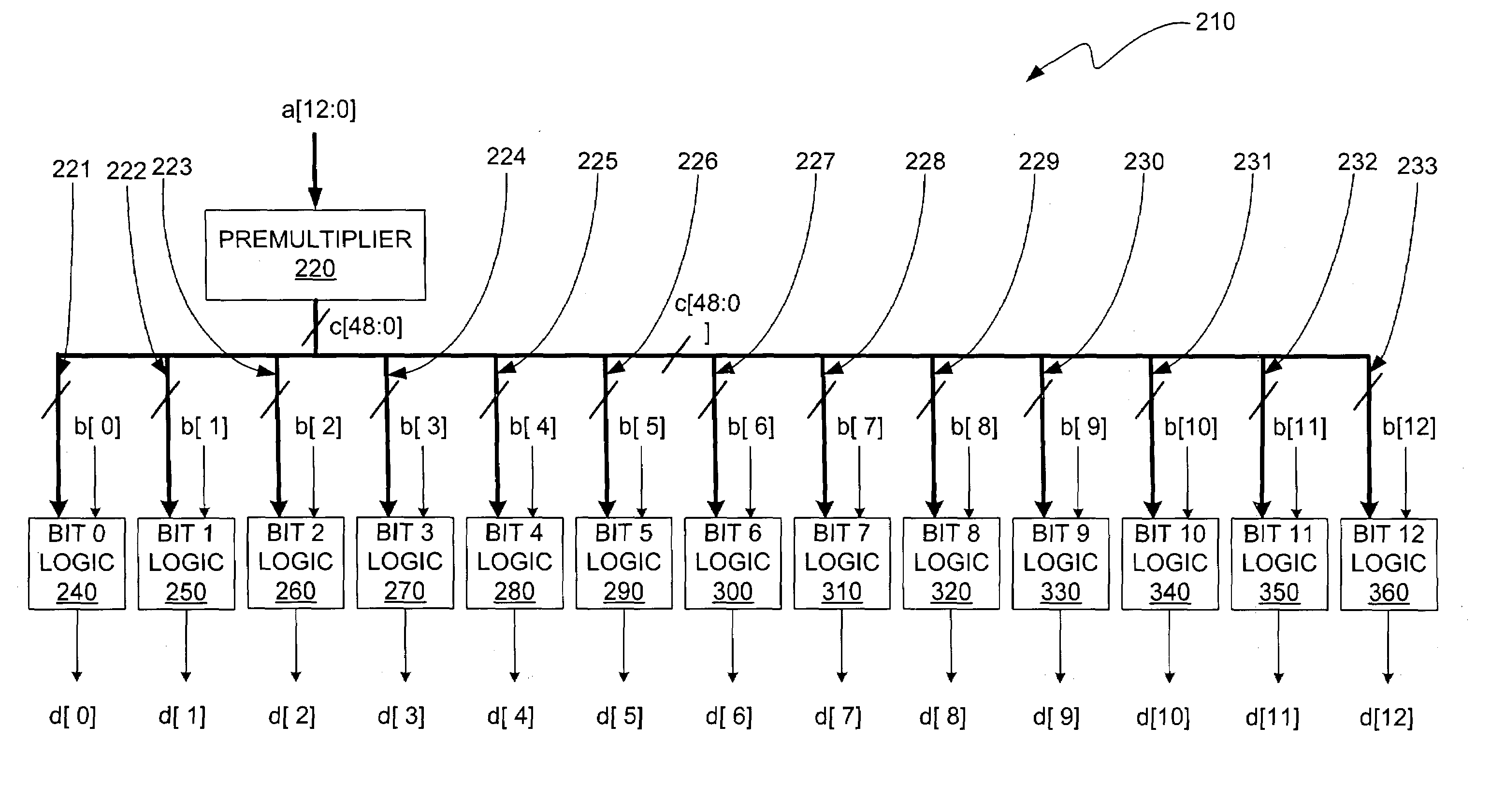

The present invention provides a method and apparatus for quickly and efficiently processing an error correction polynomial to locate bit errors using a Chien search algorithm. In accordance with the present invention, it has been determined that multiplying the Λ coefficients of the error locator polynomial by a scaling vector prior to performing the Chien search algorithm matrix operations, it possible to use constant coefficients in the matrix multiply logic. This enables a relatively small amount of logic to be used to perform the matrix multiplication operations of the Chien search algorithm. The Chien search algorithm logic of the present invention is configured to perform many matrix multiply operations in parallel, which enables the Chien search algorithm to be executed very quickly to locate the bit errors in the error locator polynomial. Such a large number of matrix multiply operations would normally require a very large number of gates. However, the constant coefficient matrix multiply logic configuration of the present invention that is made possible by the aforementioned scaling significantly limits the amount of logic needed to perform the matrix multiply operations. Therefore, the present invention enables very high-speed throughput with respect to error correction, and does so using a relatively small amount of logic. This renders the decoder of the present invention suitable for use in high data rate systems. Furthermore, the use of a relatively small amount of logic limits area and power consumption requirements.

Owner:CIENA

Chien search device and chien search method

To provide a Chien search device and a Chien search method capable of performing a Chien search process at a high speed. The Chien search device calculates an error position at the time of correcting an error included in data read from a nonvolatile memory, and includes a first processing unit that performs a search process of an error position in at least one-bit unit to an error-correction area of input data, and a second processing unit that processes at one time plural bits in an non-error-correction-target area of the input data.

Owner:KK TOSHIBA

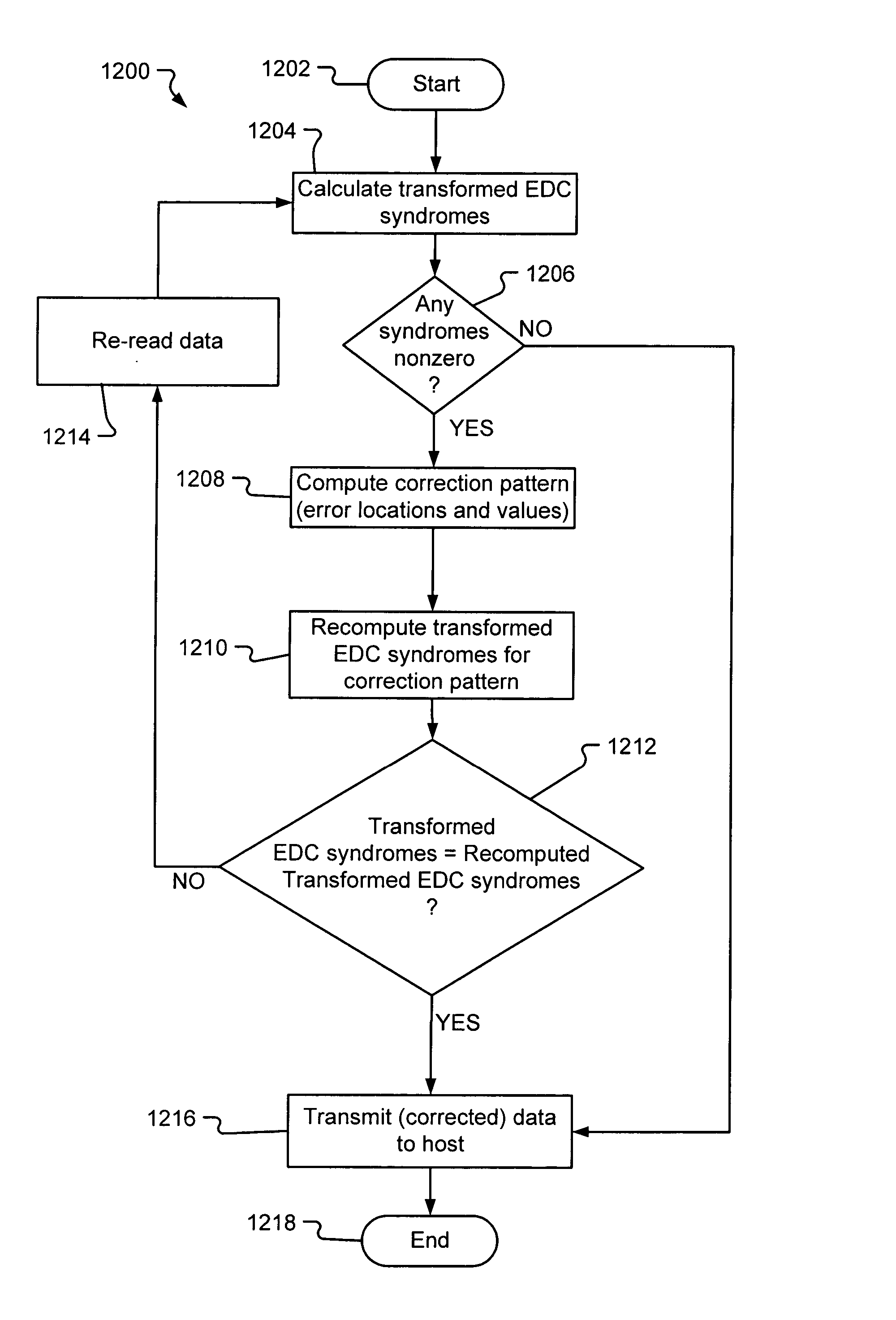

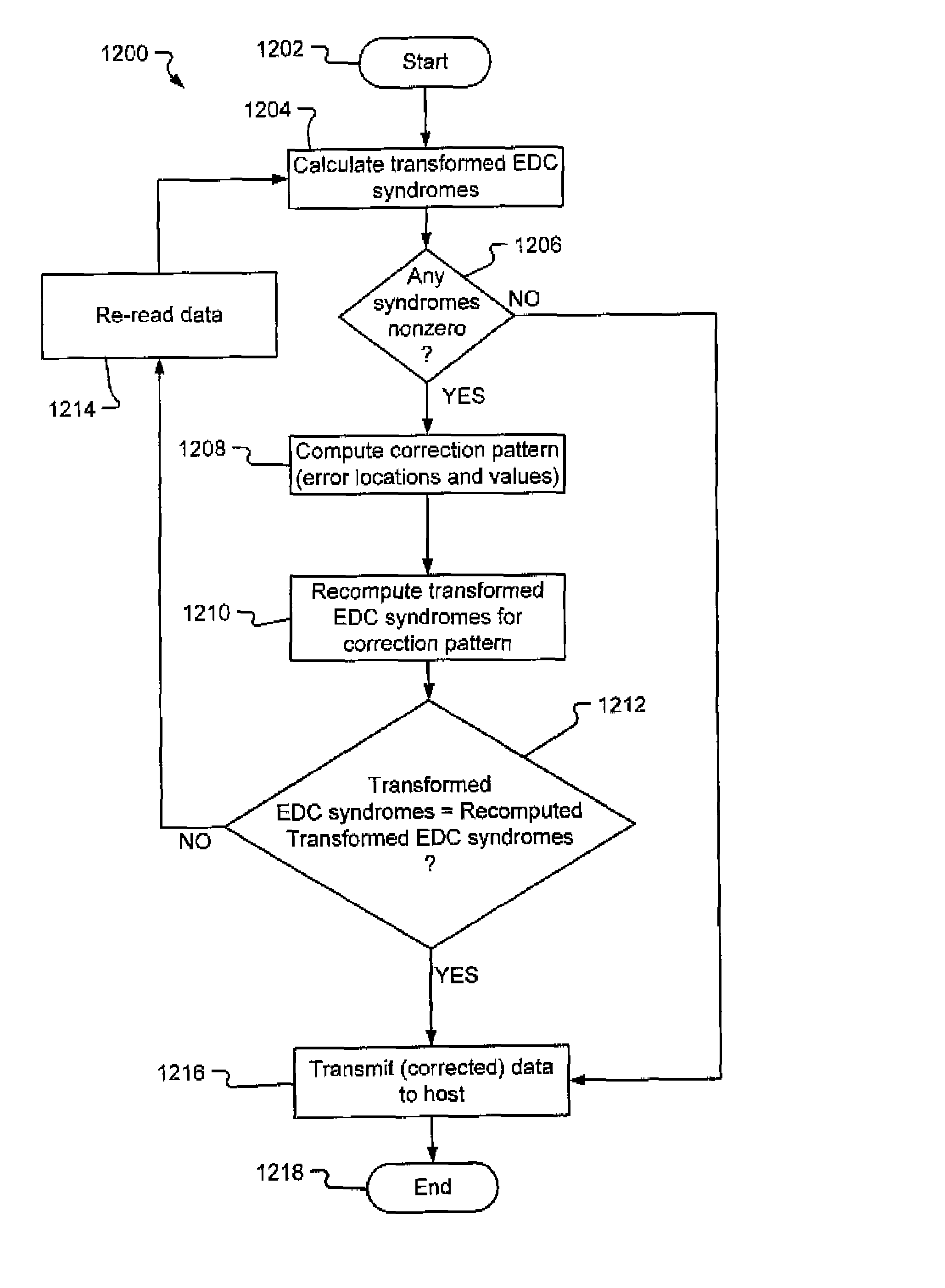

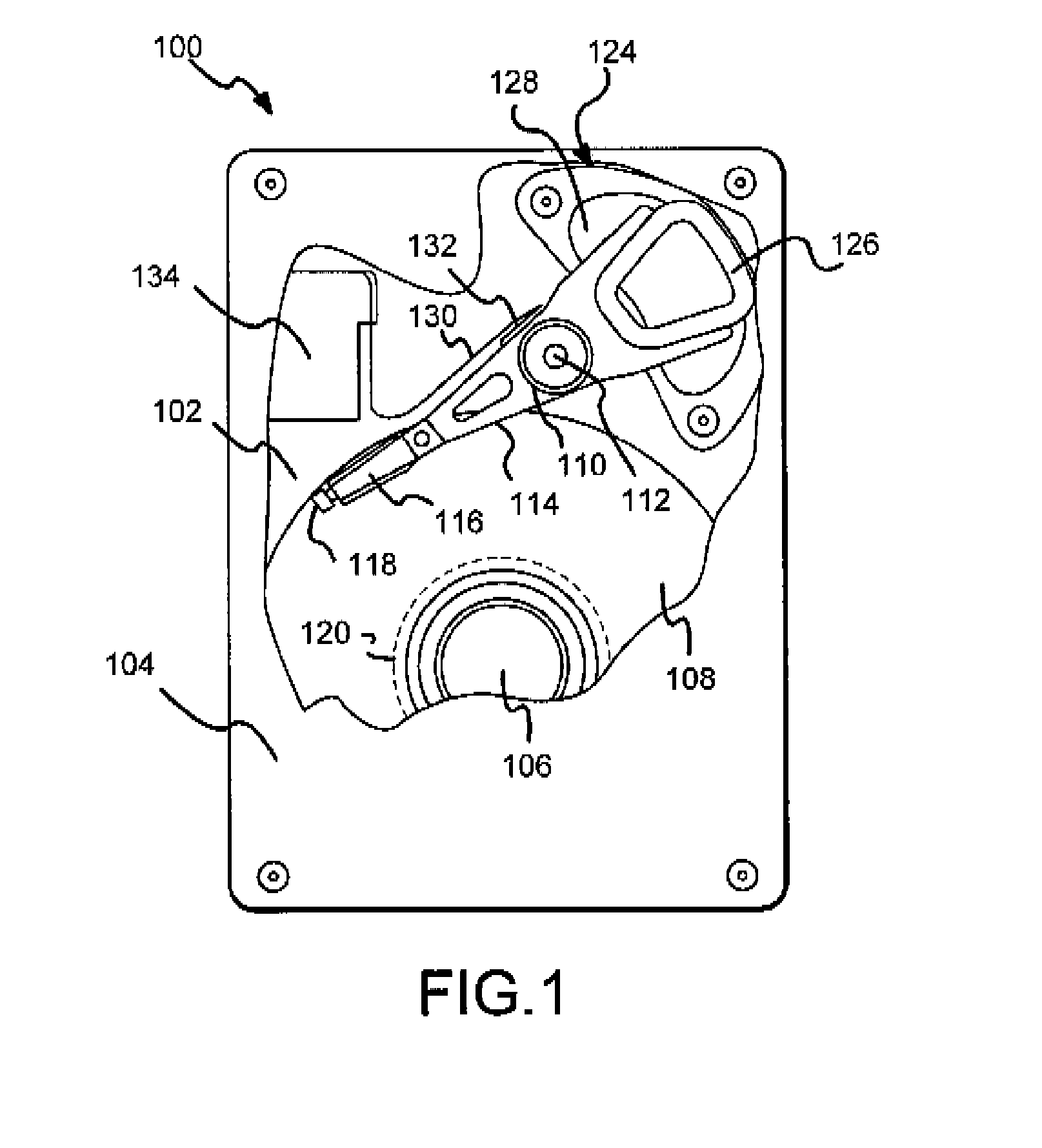

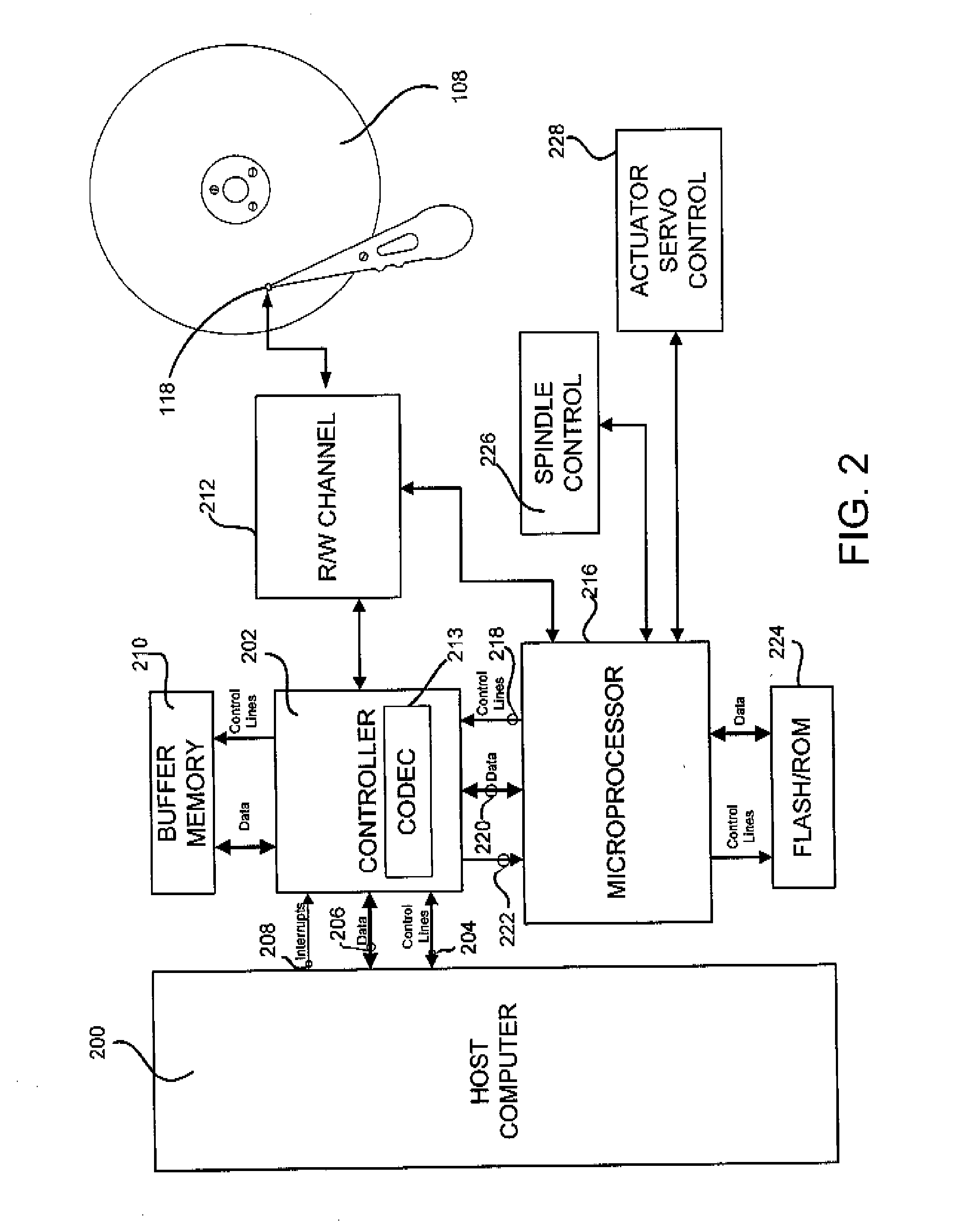

Method and apparatus for error detection

The present invention is an error detection and correction scheme that enables the use of Horner's algorithm for the computation of EDC syndromes from the computed error pattern. Specifically, “transformed” EDC syndromes are computed during the read back of data and parity from the medium. The transformed syndromes are values of the polynomial whose coefficients occur in reverse order from that of the EDC codeword polynomial. In essence, by reversing the order of the coefficients, the Chien search processes the terms in descending order which is the right direction for Horner evaluation.

Owner:SEAGATE TECH LLC

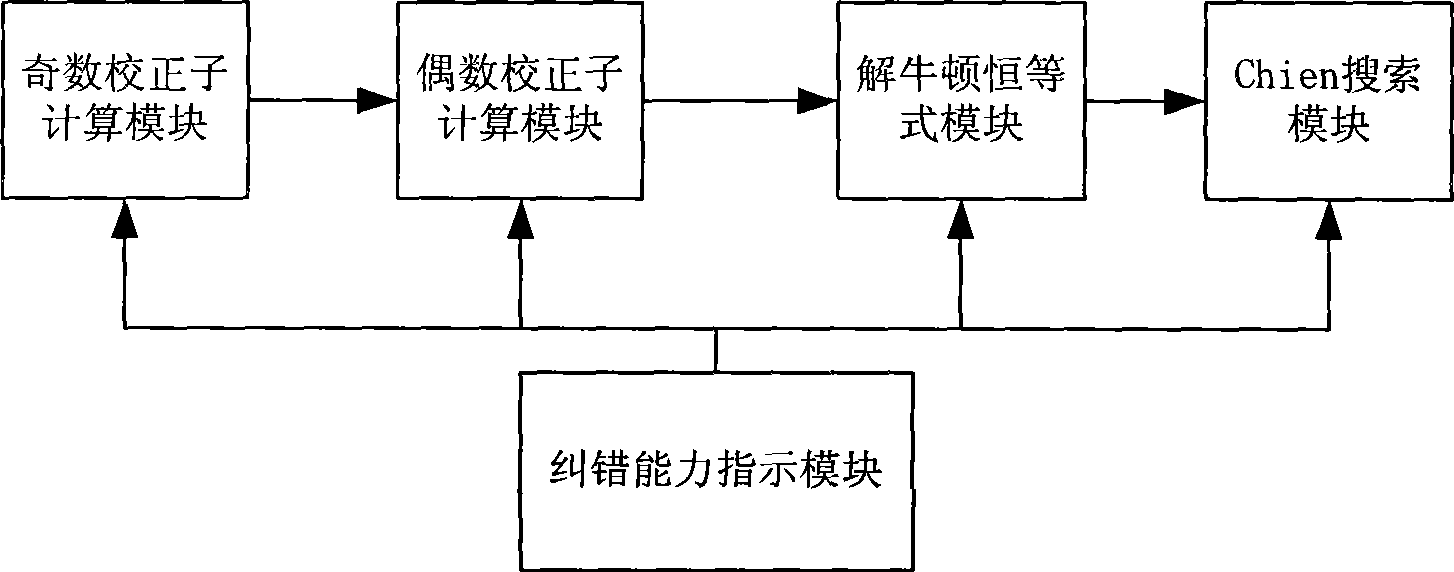

BCH decoder for configuring error correcting capability according to Nand Flash extra space

A BCH decoder which configures error correcting capability according to the spare space of Nand Flash comprises the following components: an error correcting capability indicating module which is used for collocating the error correcting bit number of decoder according to the spare space of Nand Flash; an odd syndrome calculating module which adopts an iterative method for parallel calculating the syndrome of corresponding odd number according to the configured error correcting bit number and the input code word; an even syndrome calculating module which is used for serially calculating the syndrome of oven number according to the calculated syndrome of odd number; a Newton's identity solving module which is used for iteratively solving each coefficient and error code word number of error position equation with the non-inverse simplified BMA algorithm according to the calculated syndrome of odd number and even number; and a chien searching module which is used for searching out the position of error bit according to each solved coefficient and the number of error code for further realizing decoding. The BCH decoder of the invention has the advantages of small decoding delay, excellent compatibility and high multiplexing rate of hardware.

Owner:VERISILICON MICROELECTRONICS SHANGHAI +2

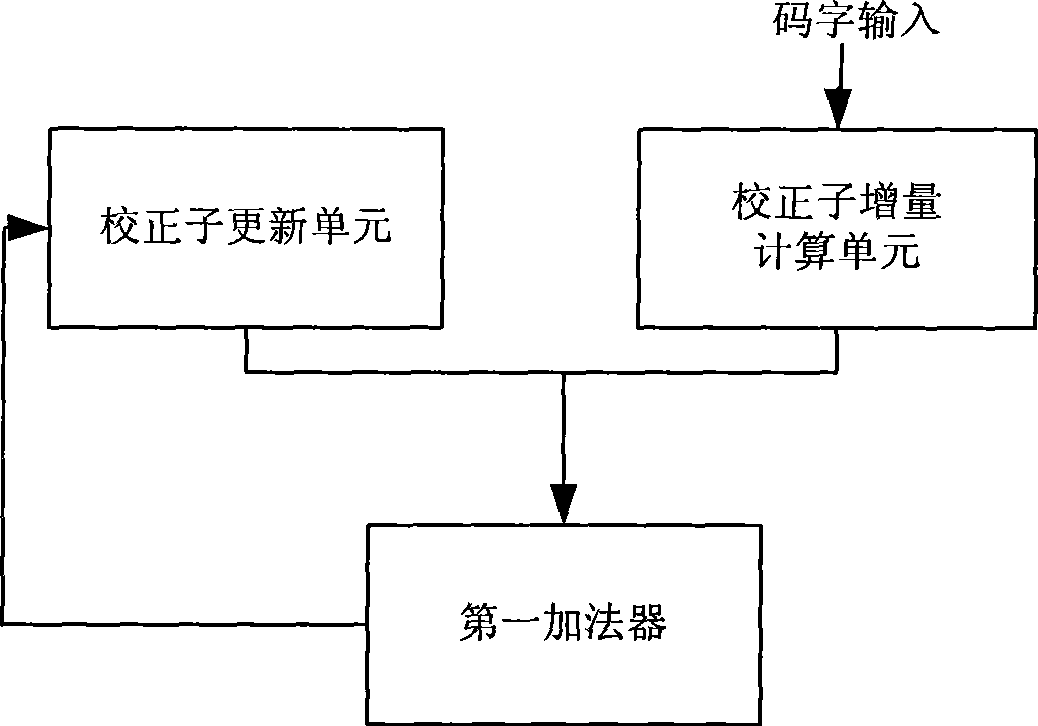

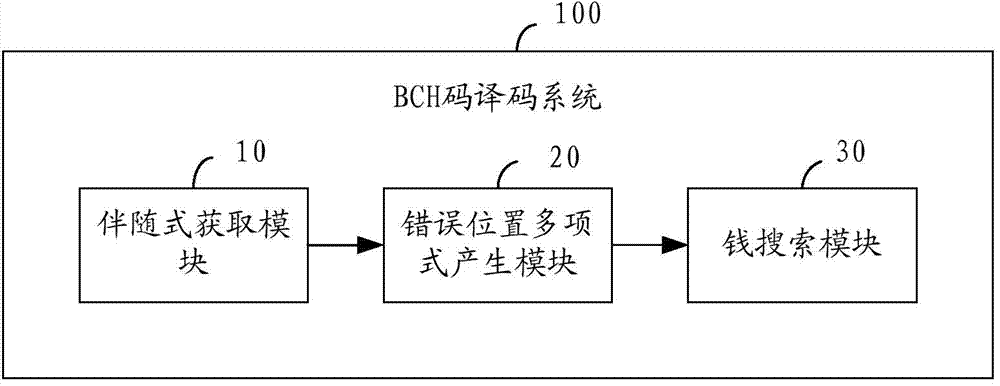

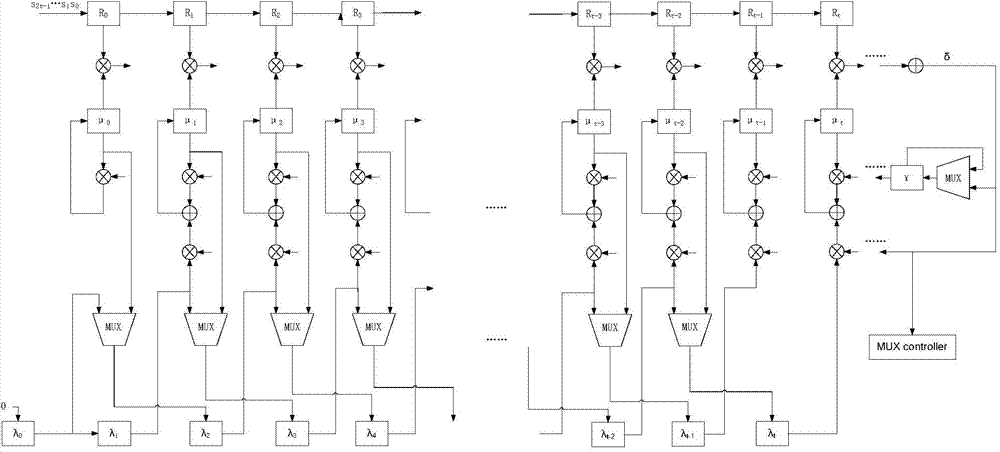

Decoding method and system of BCH codes

The invention belongs to the field of error correction decoding, and provides a decoding method and system of BCH codes. The decoding method of the BCH codes comprises the steps that syndrome operation is carried out on the received BCH codes to obtain a syndrome polynomial, values of the syndrome polynomial are calculated successively through a parallel iterative decoding circuit on the basis of a BM algorithm without inverse operation so that error location polynomial coefficients and an error location polynomial can be obtained, the root of the error location polynomial is calculated through a Chien search method, and the error location is obtained through calculation. According to the step that the error location polynomial coefficients and the error location polynomial can be obtained through successive calculation of the parallel iterative decoding circuit, the iteration time of the parallel iterative decoding circuit and the calculation time of the Chien search method are matched, and multiplexing is carried out on the parallel iterative decoding circuit according to the iteration time. Therefore, according to the decoding method and system of the BCH codes, the number of adders, the number of multipliers and the number of registers for hardware implementation can be effectively reduced, complexity of combinational logic is reduced, and the size of a chip can be effectively reduced.

Owner:SHENZHEN YILIAN INFORMATION SYST CO LTD

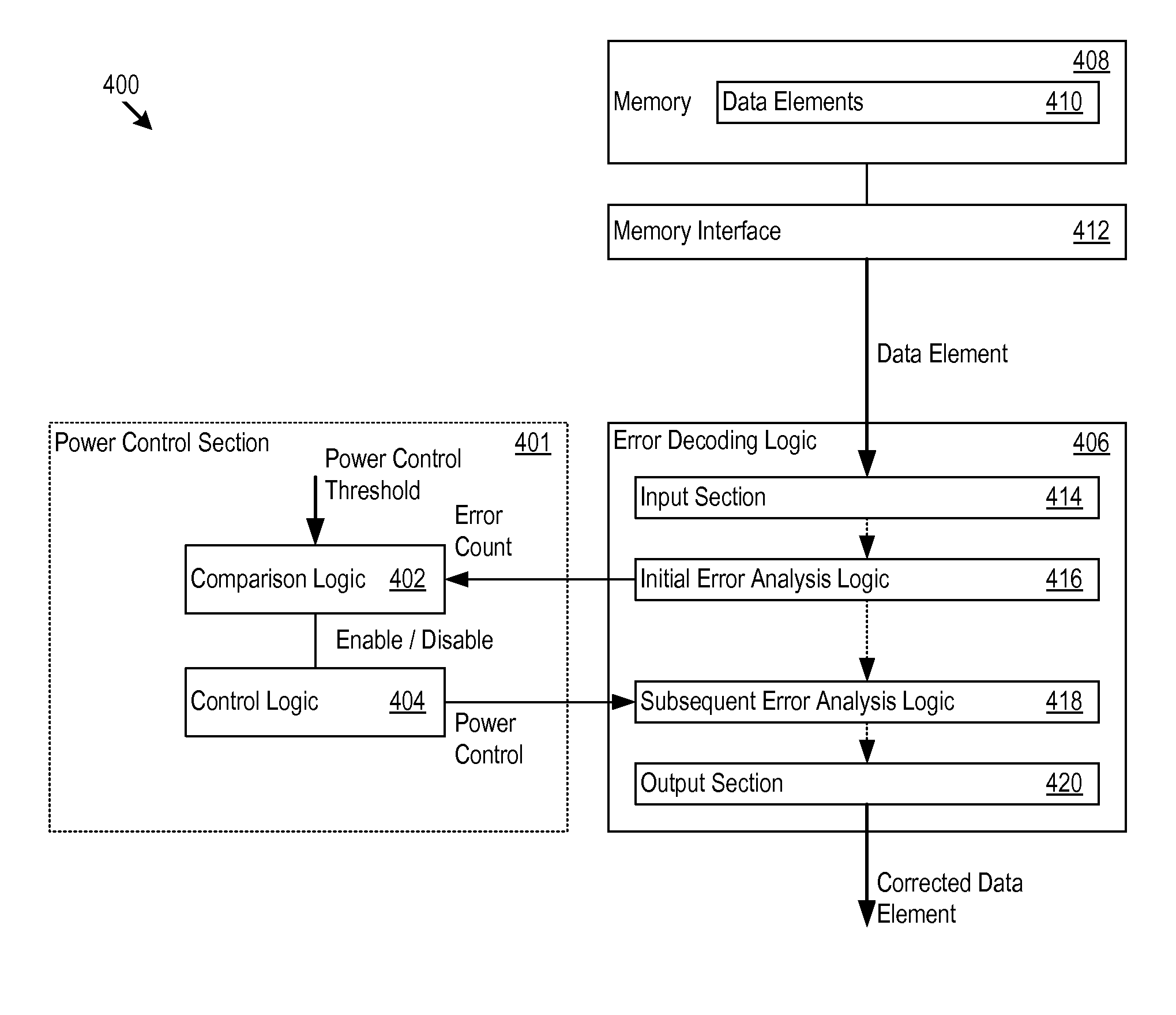

Reduction of power consumption for data error analysis

InactiveUS20120137152A1Reduce operating speedShorten speedEnergy efficient ICTError detection/correctionData elementMemory controller

A controller (e.g., a memory controller) includes initial error analysis logic (e.g., a section of a Reed Solomon or BCH codeword decoder) that determines an error count for a data element. The data element may be data stored in the memory of a memory device (e.g., a flash memory device) that incorporates the controller. Comparison logic in the controller determines when the error count exceeds a power control threshold. When the error count exceeds the power control threshold, control logic in the controller reduces the operational speed of subsequent error analysis logic (e.g., a different section of the Reed Solomon or BCH codeword decoder) for the data element. For example, the subsequent error analysis logic may be error locator logic, such as Chien search logic, that determines where the errors exist in the data element.

Owner:DROR ITAI +3

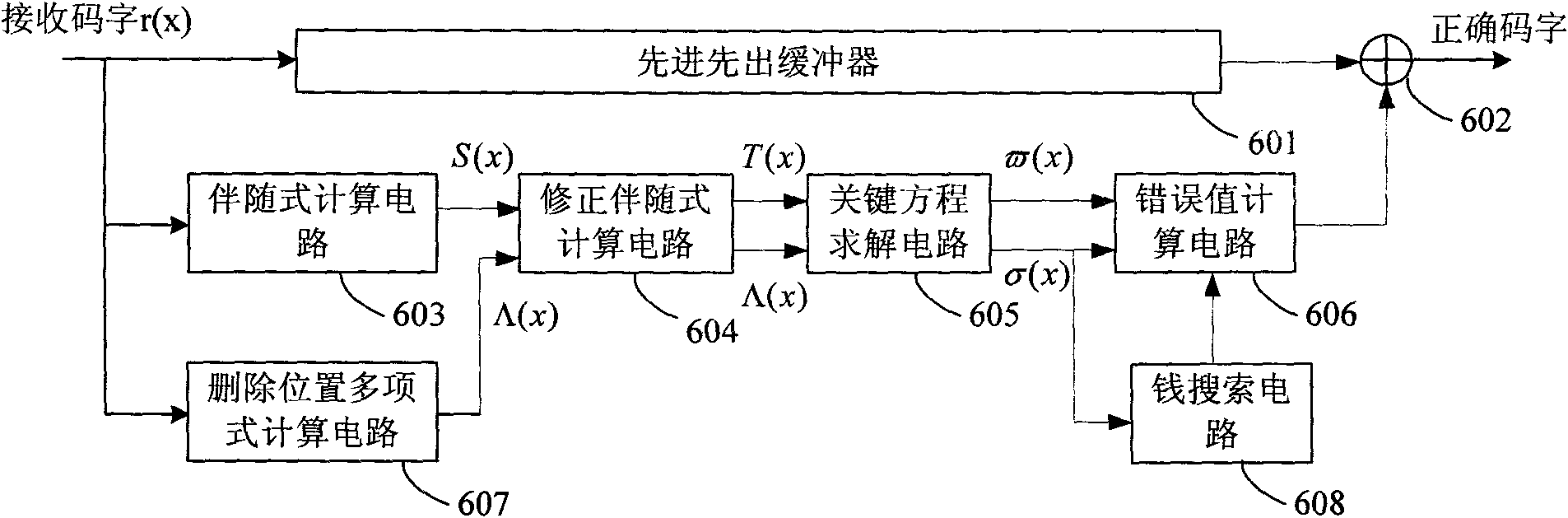

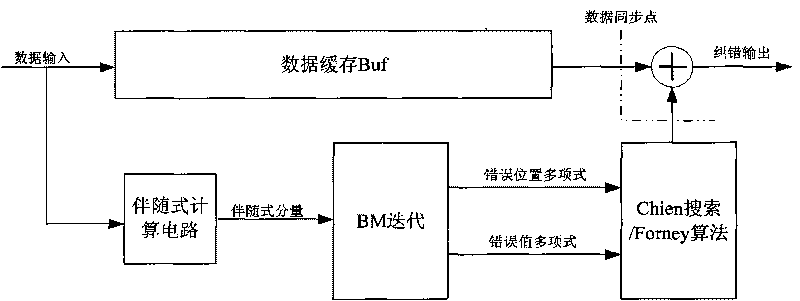

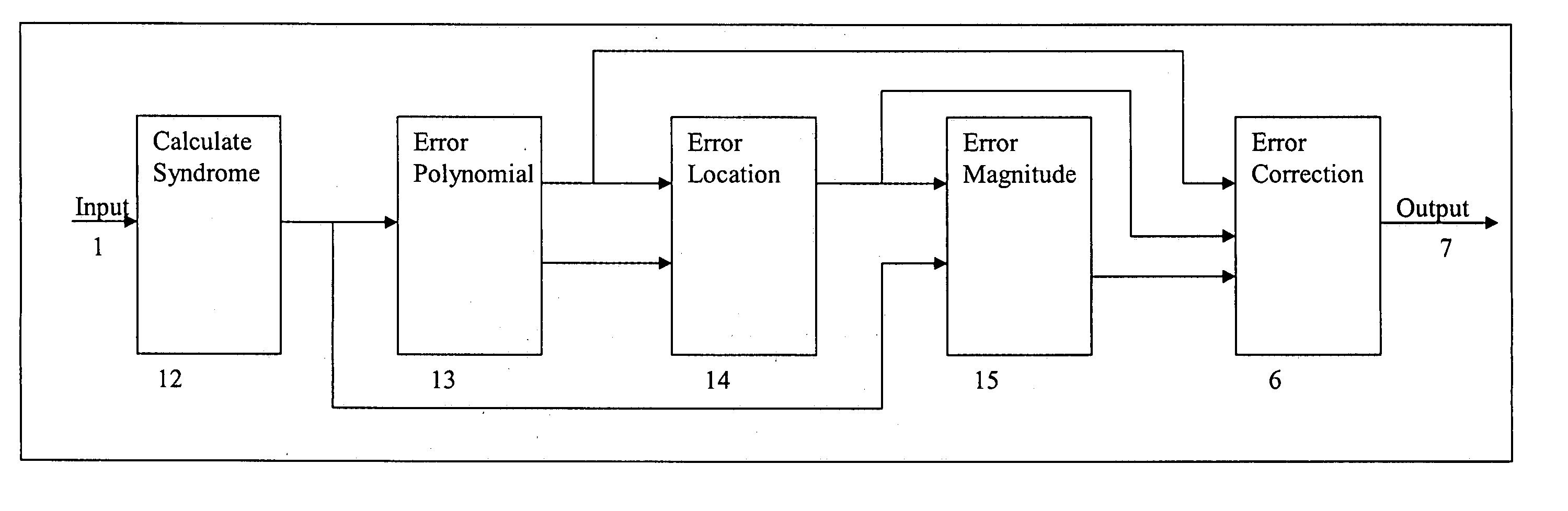

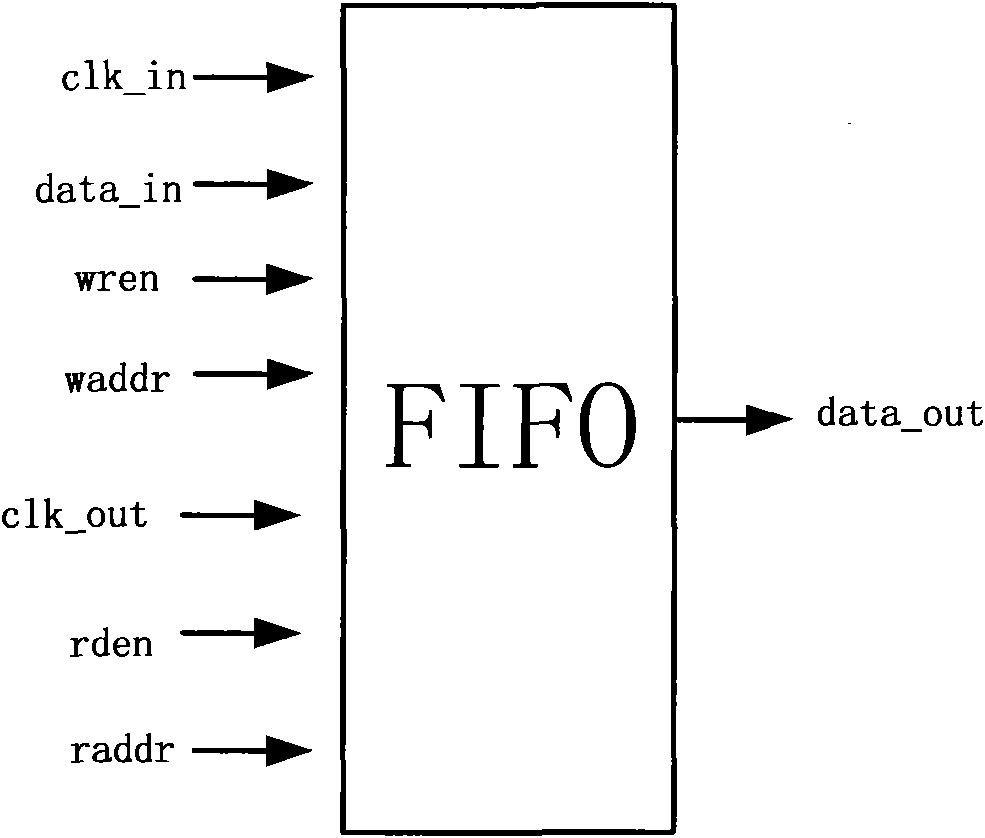

RS (Reed-Solomon) error correction decoder

The invention provides an RS (Reed-Solomon) error correction decoder which comprises an first-in first-out (FIFO) buffer, an adjoint computing circuit, a deleted location polynomial computing circuit, a correction adjoint computing circuit, a key equation solution circuit, a Chien search circuit, an error value computing circuit and a summator, wherein the deleted location polynomial computing circuit and the adjoint computing circuit are arranged in parallel. Through the arrangement, the RS error correction decoder can carry out adjoint computation and deleted location polynomial computationsynchronously, thereby increasing the decoding speed.

Owner:NEWLAND DIGITAL TECH CO LTD

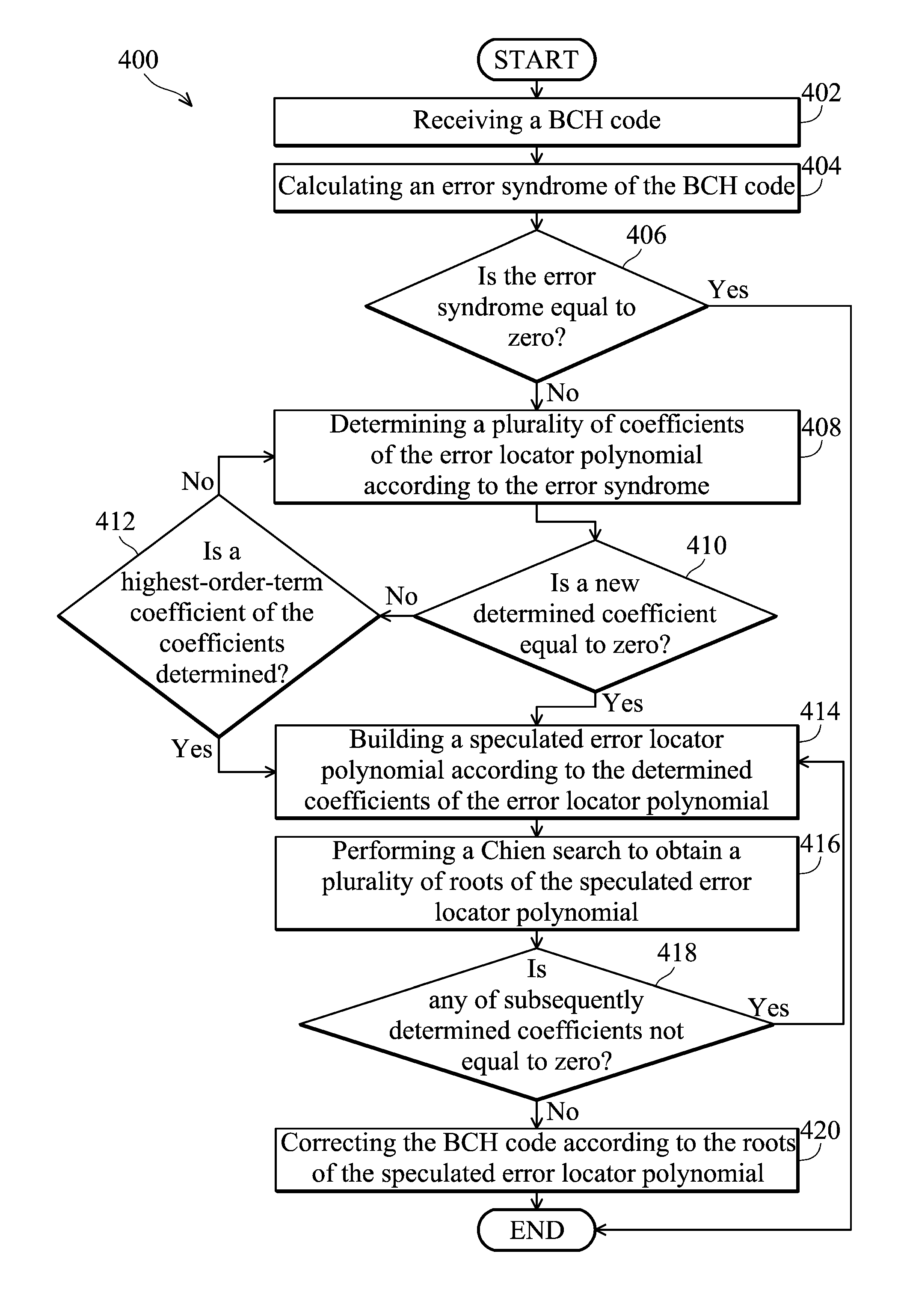

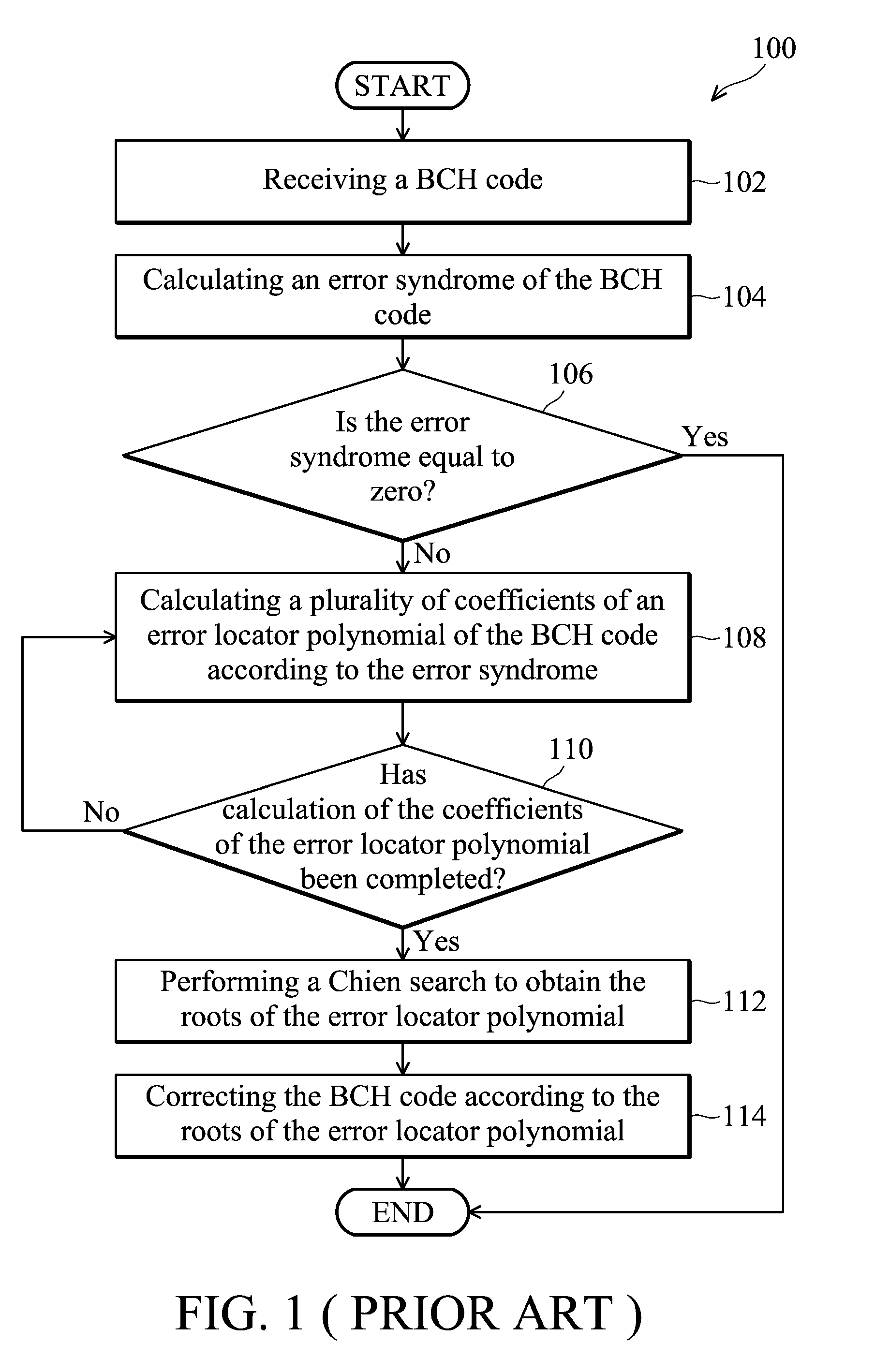

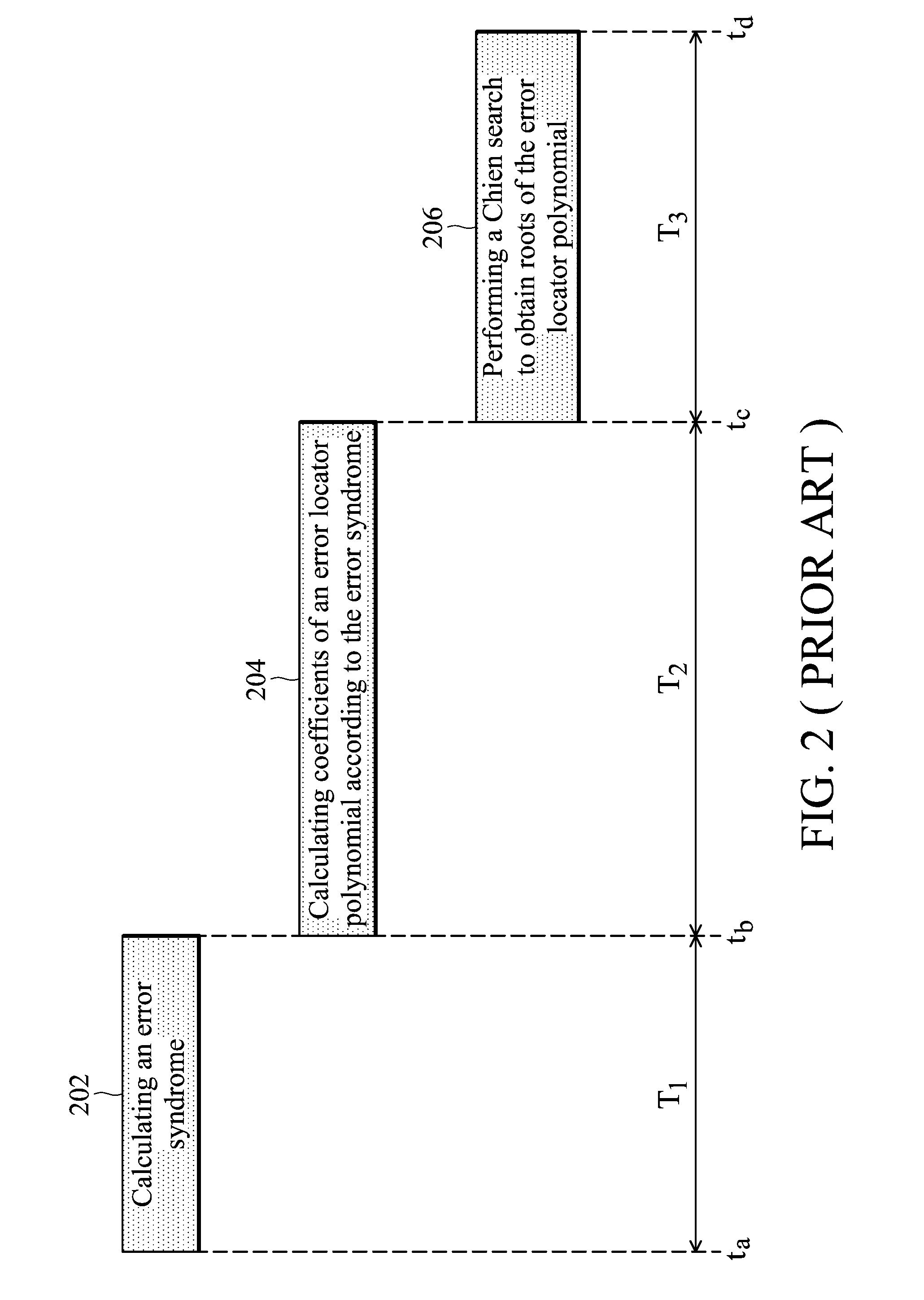

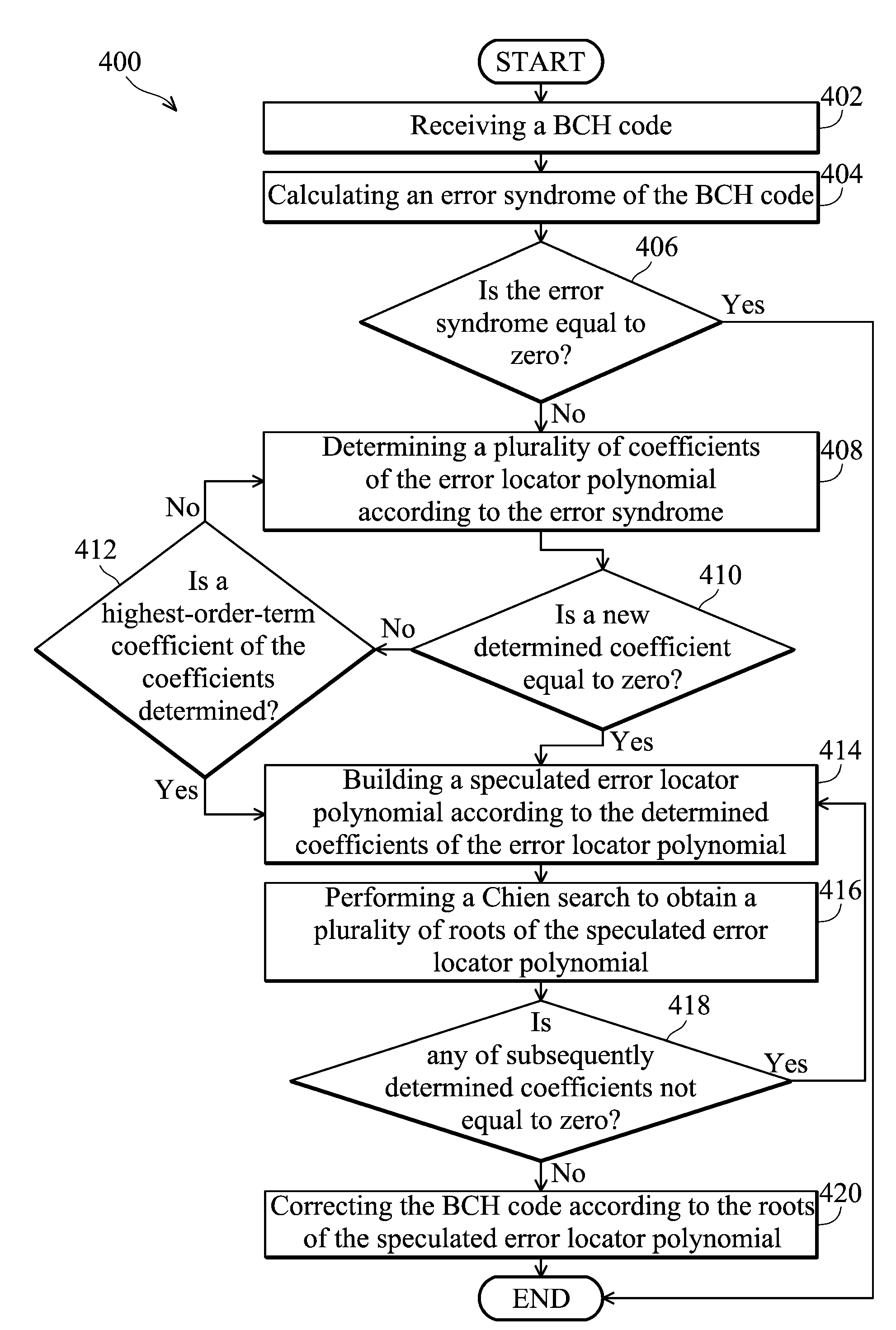

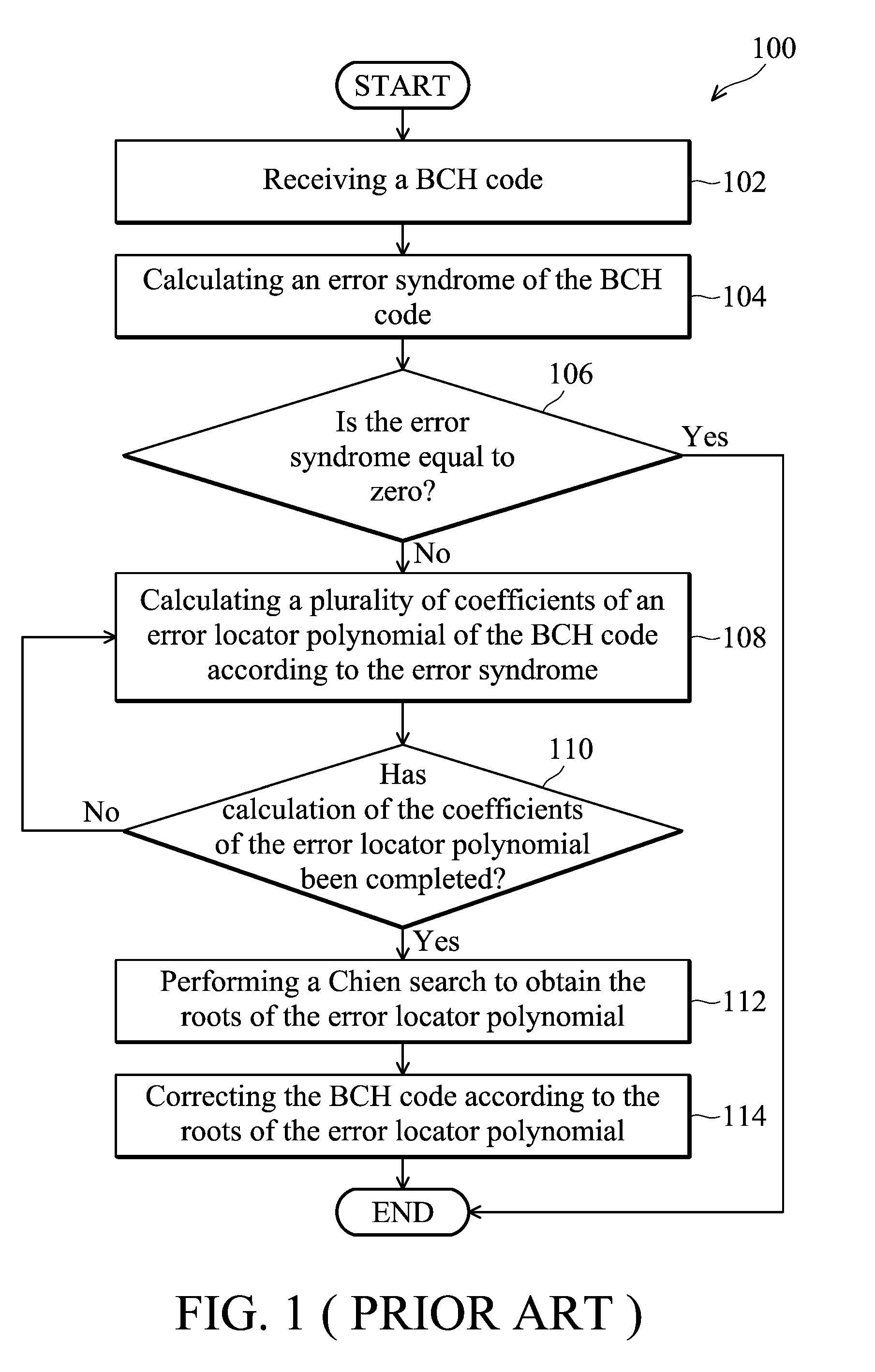

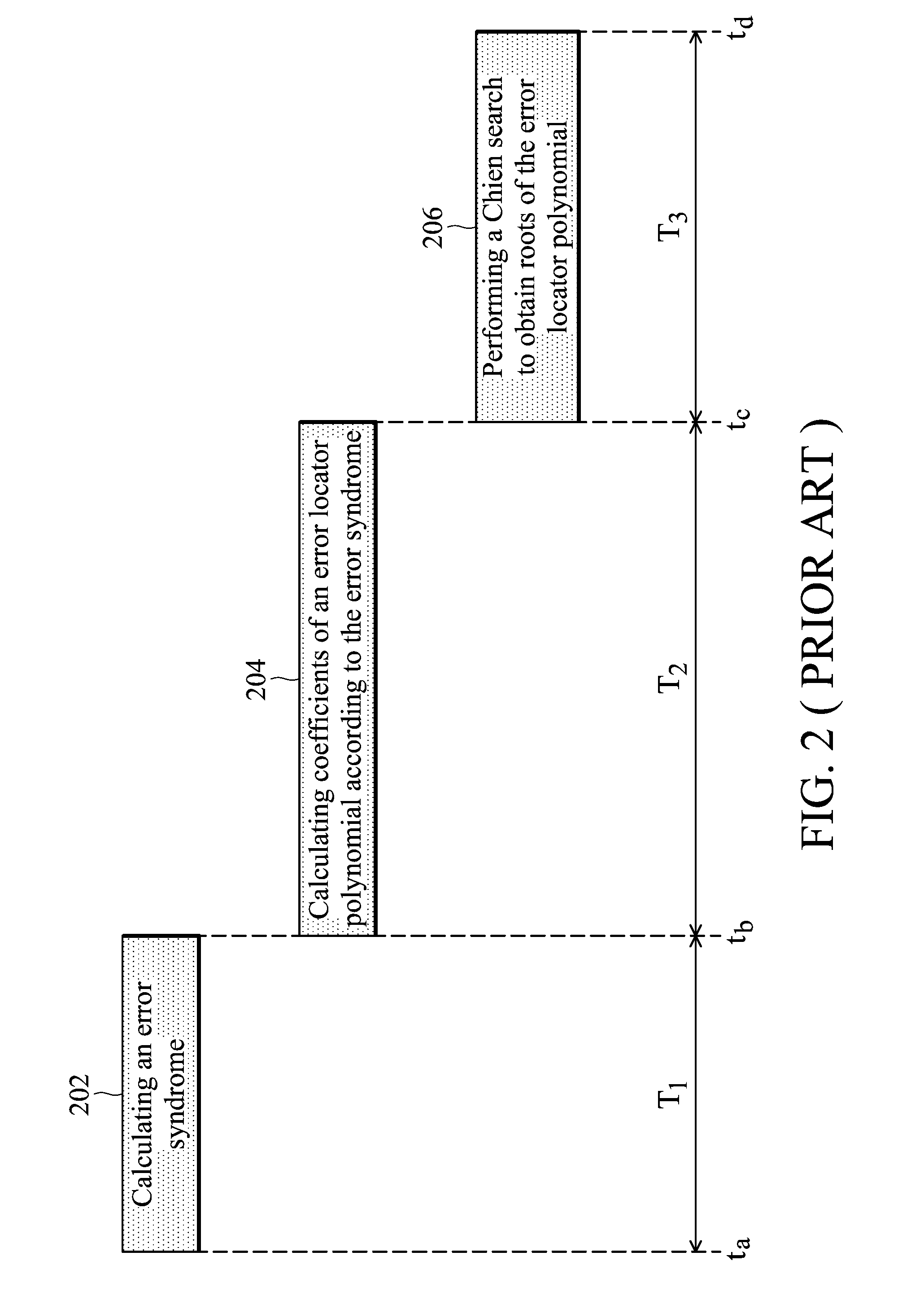

Method and circuit for decoding an error correction code

The invention provides a method for decoding an error correction code. First, an error syndrome of the error correction code is calculated. A plurality of coefficients of an error locator polynomial of the error correction code is then sequentially determined according to the error syndrome. When a new coefficient of the error locator polynomial is determined, it is also determined whether the new determined coefficient is equal to zero. When the new determined coefficient is equal to zero, a speculated error locator polynomial is built according to a plurality of low-order-term coefficients of the error locator polynomial, wherein the orders of the low-order-term coefficients are lower than that of the new determined coefficient. A Chien search is then performed to determine a plurality of roots of the speculated error locator polynomial. The error correction code is then corrected according to the roots of the speculated error locator polynomial.

Owner:SILICON MOTION INC (TW)

Forward Chien search type Reed-Solomon decoder circuit

A Reed-Solomon decoder includes a Chien search circuit to receive an error location polynomial function, performs Chien search, and finds an error location; a Forney algorithm circuit to receives an error pattern polynomial function and find an error pattern; and, a seed generator circuit to indicates a seed value corresponding to a codeword length for the input data. A Chien search is performed to obtain and outputs exponential terms related to variables for the polynomials, wherein the Chien search is performed in the same computational direction as an order for the input data.

Owner:SAMSUNG ELECTRONICS CO LTD

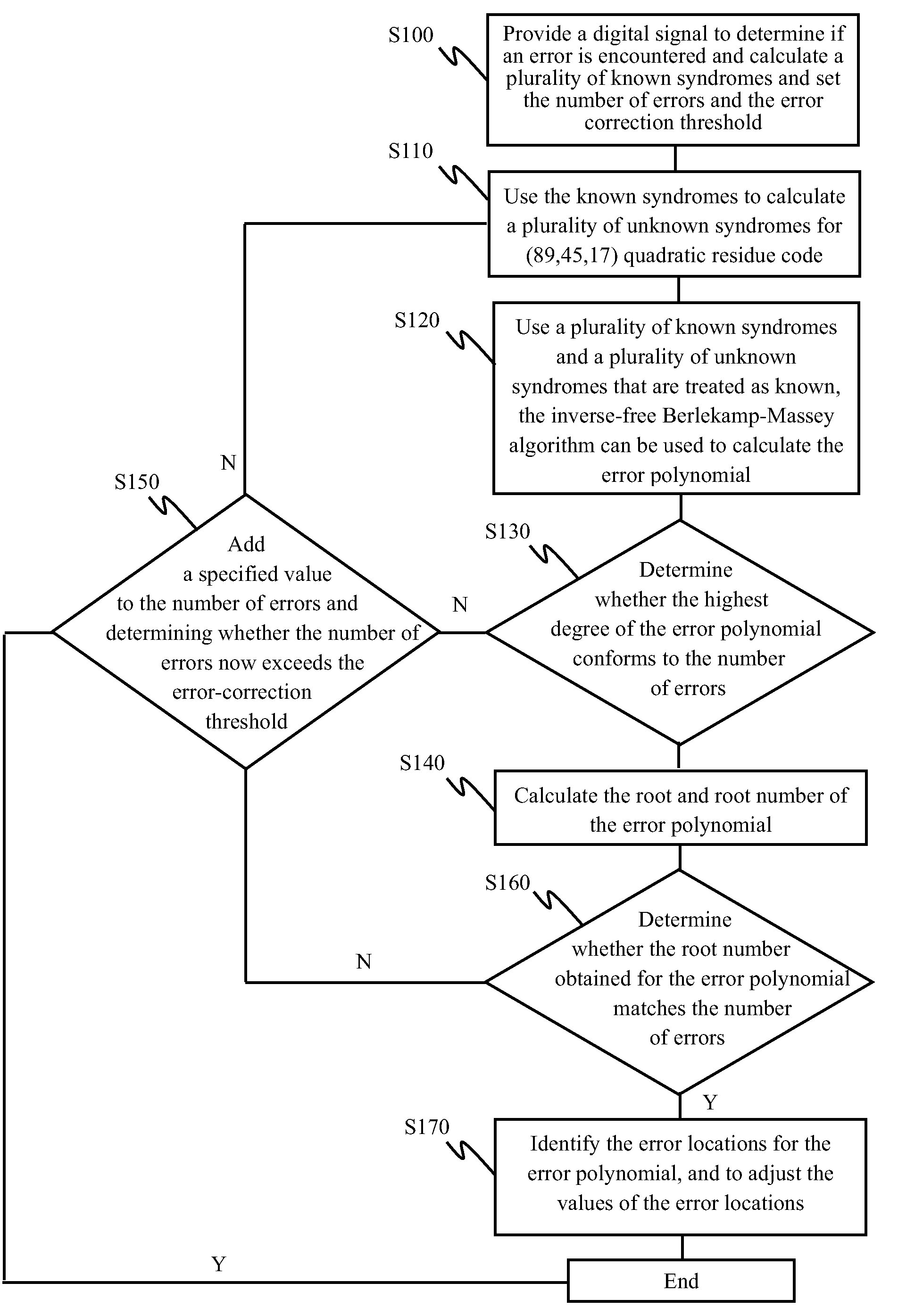

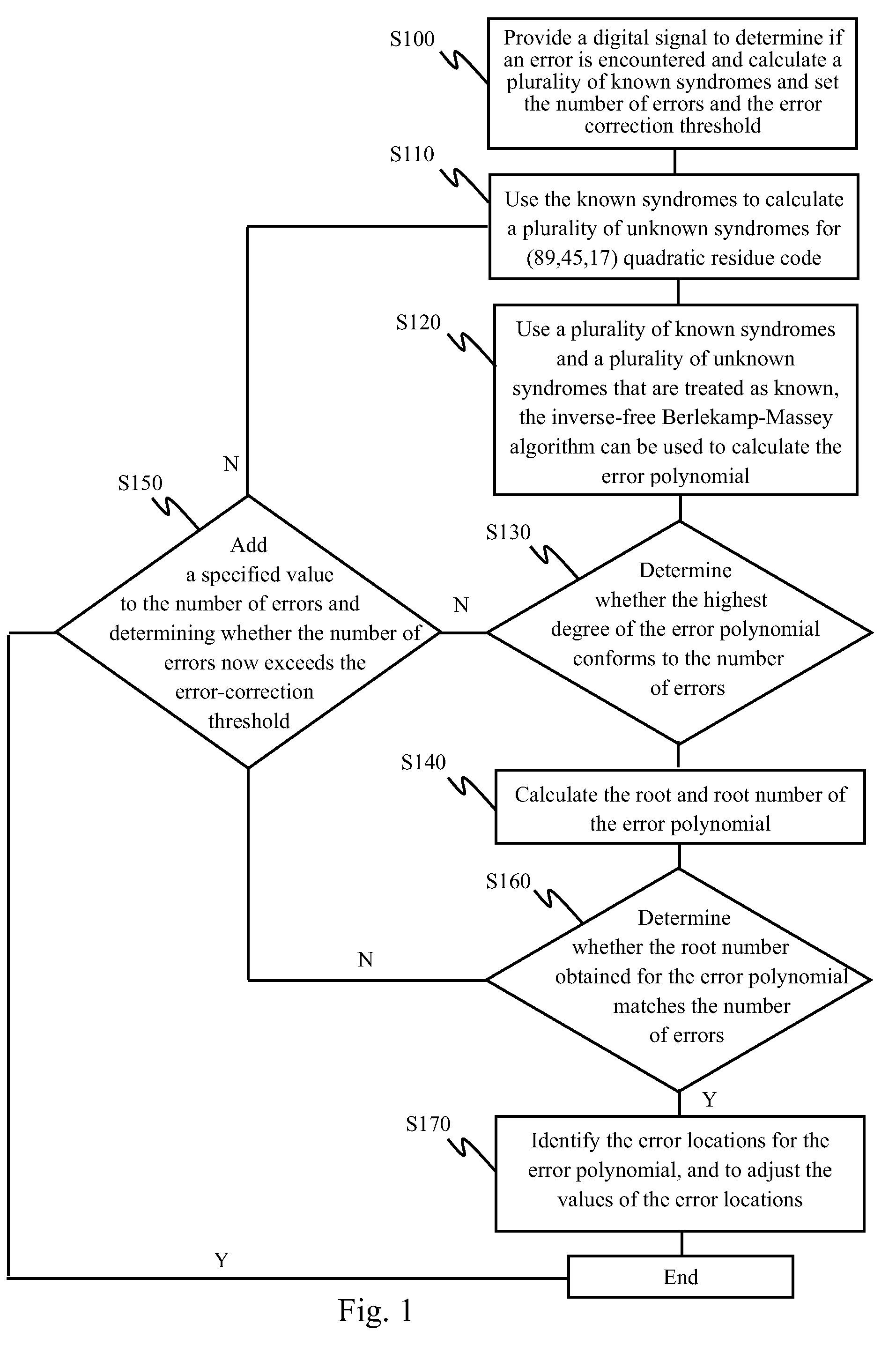

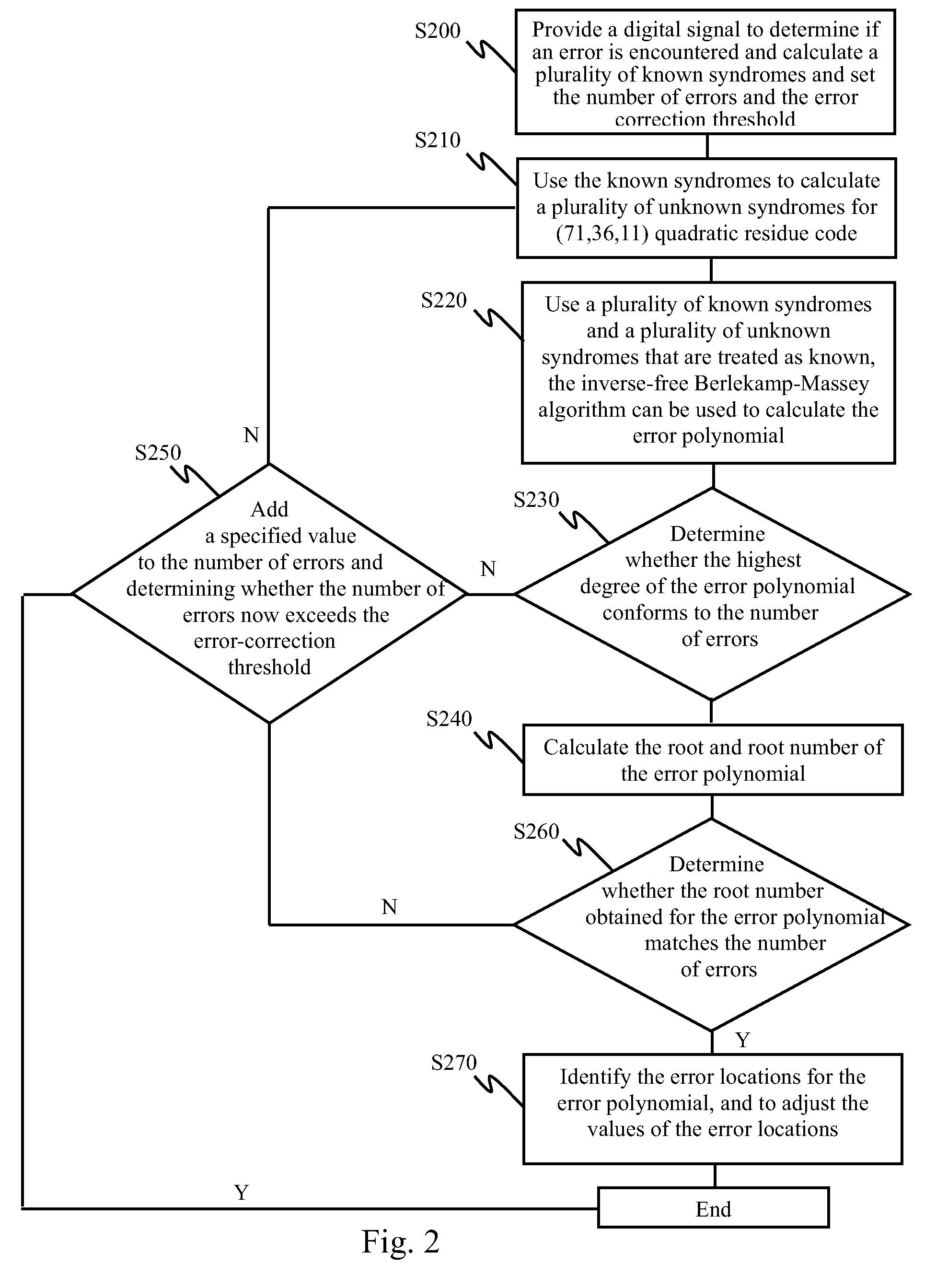

Decoding algorithm for quadratic residue codes

A decoding algorithm for quadratic residue codes applicable to the decoding of all quadratic residue codes is provided. The decoding algorithm employs digital signals to obtain a plurality of known syndromes. These known syndromes are used to calculate a plurality of unknown syndromes. The inverse-free Berlekamp-Massey algorithm is then used to calculate the error polynomial, after which the Chien search algorithm is used to determine the error locations. Adjustments can then be made to the digital signal bits corresponding to the error locations to obtain the correct code.

Owner:I-SHOU UNIVERSITY

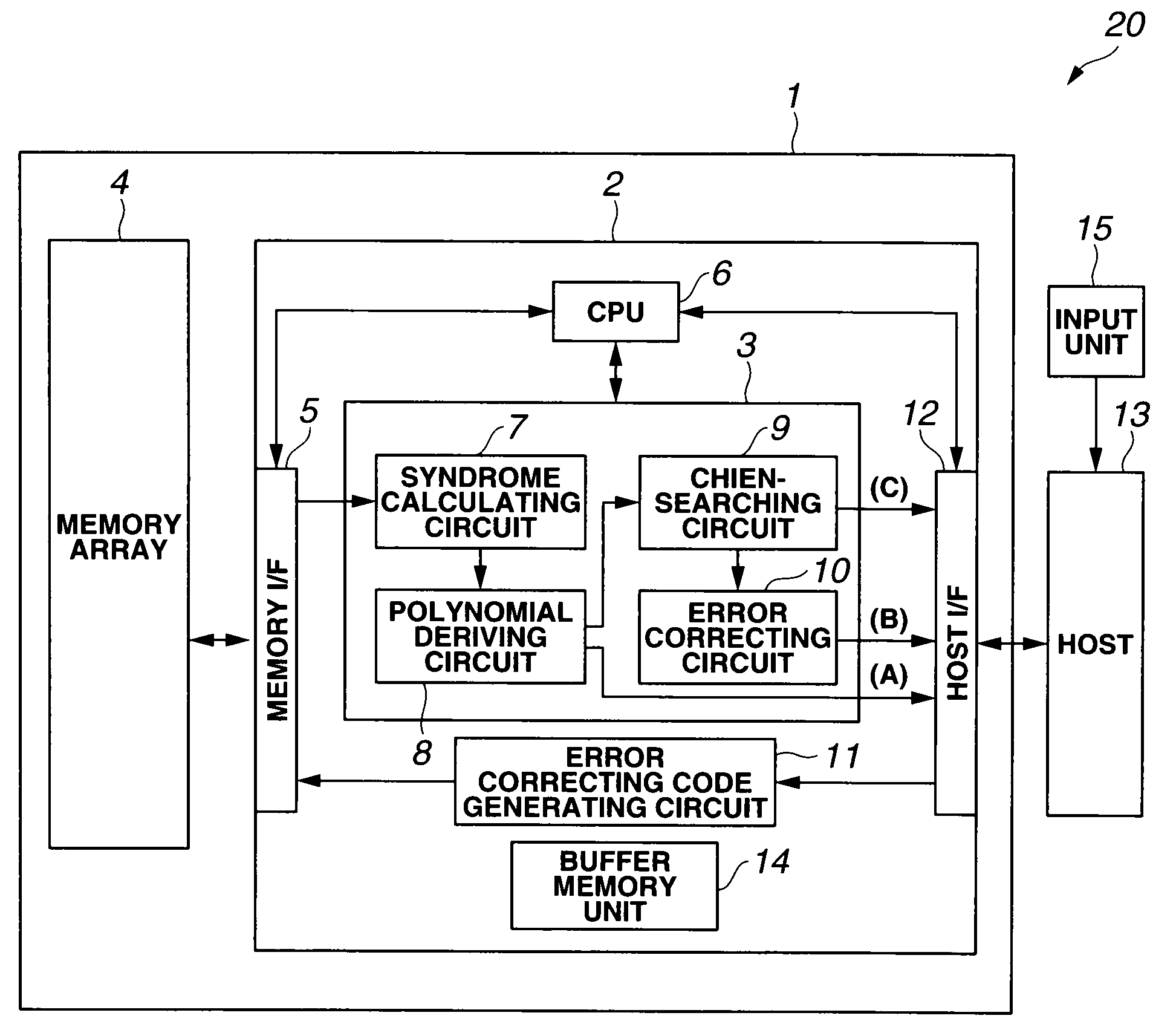

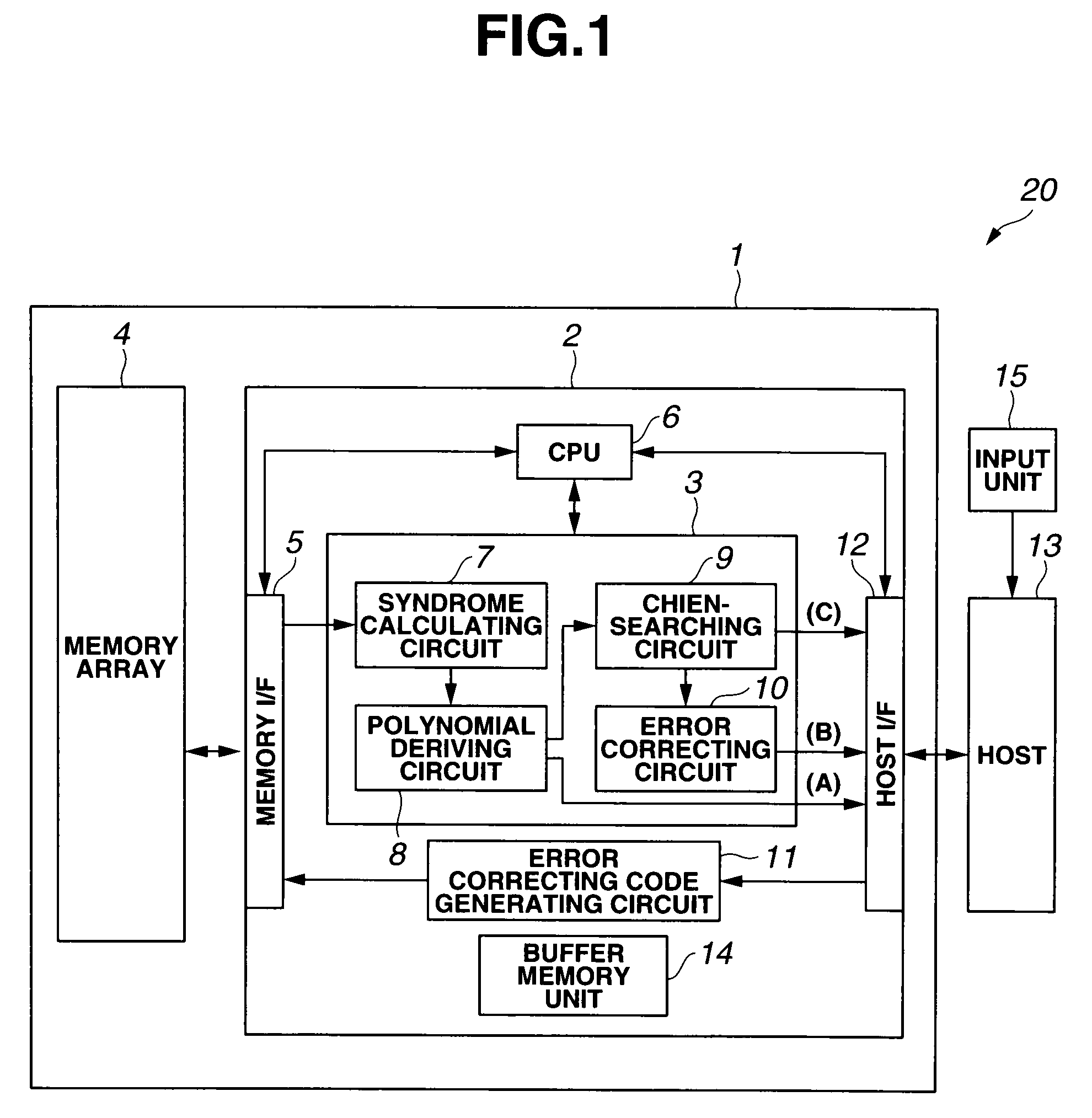

Error detecting and correcting circuit using chien search, semiconductor memory controller including error detecting and correcting circuit, semiconductor memory system including error detecting and correcting circuit, and error detecting and correcting method using chien search

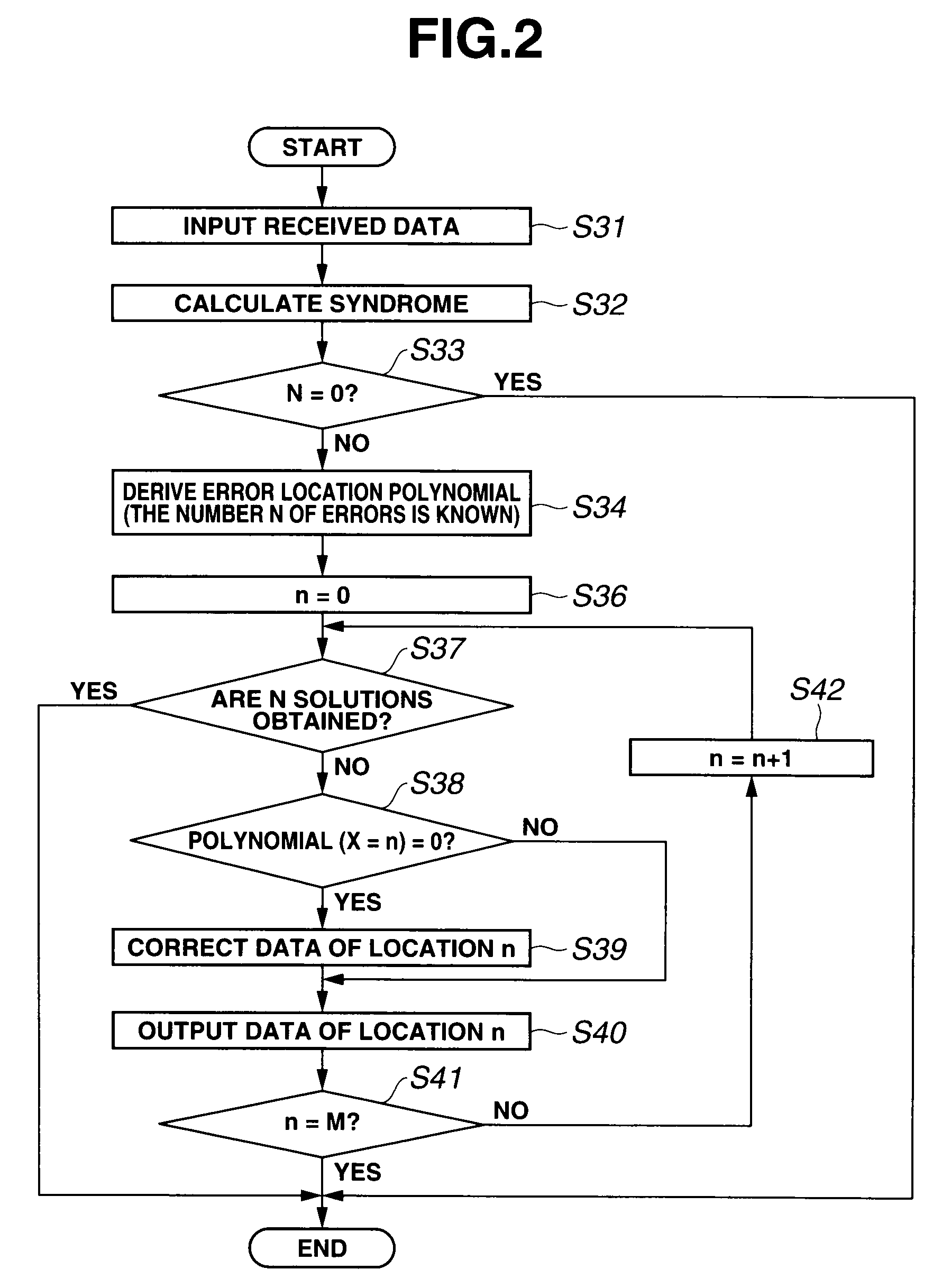

An error detecting and correcting circuit is provided with a syndrome calculating circuit calculating a syndrome of an inputted data sequence including an error correcting code, a polynomial deriving circuit deriving an error location polynomial, a Chien searching circuit obtaining a location of error data of the data sequence, and an error correcting circuit correcting an error of the data, and every time the Chien searching circuit specifies the location of error data, the error correcting circuit immediately corrects the error of the data at the error location, and outputs the corrected data to an external circuit, thereby the error can be efficiently detected and corrected.

Owner:KK TOSHIBA

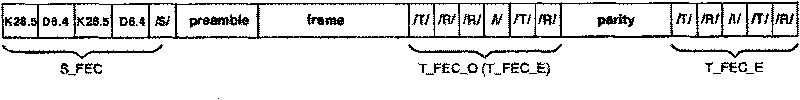

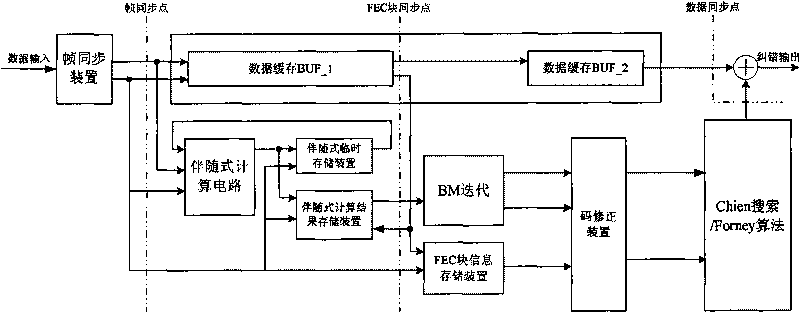

RS decoder and decoding method for EPON system

ActiveCN101695015AThe FEC sublayer function is successfully implementedMultiplex system selection arrangementsError preventionDecoding methodsError correcting

Disclosed are an RS encoder and an encoding method for an EPON system. Data are transmitted by a frame synchronization device to a data buffer BUF-1, a syndrome calculating circuit, an FEC block information storage device, a syndrome temporary storage device and a syndrome calculating result storage device; the data buffer BUF-1 provides data for a data buffer BUF-2, the FEC block information storage device and the syndrome calculating result storage device; the data buffer BUF-2 finishes error correcting output with a Chien search / Forney algorithm module; the syndrome calculating result storage device provides data for the Chien search / Forney algorithm module via a BM iterative circuit and a code correction device. The method transforms a common RS (255, 339, and 8) encoder by combining characteristics of an EPON system FEC frame structure and special requirements of the EPON system, thereby enabling the FEC sub-layer function of the EPON system to be realized smoothly.

Owner:FENGHUO COMM SCI & TECH CO LTD +1

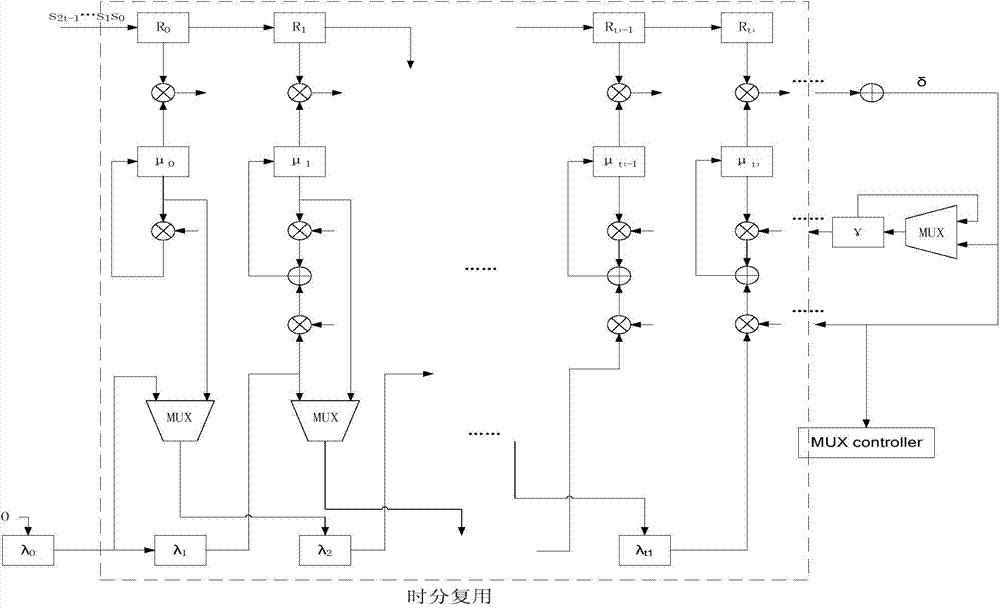

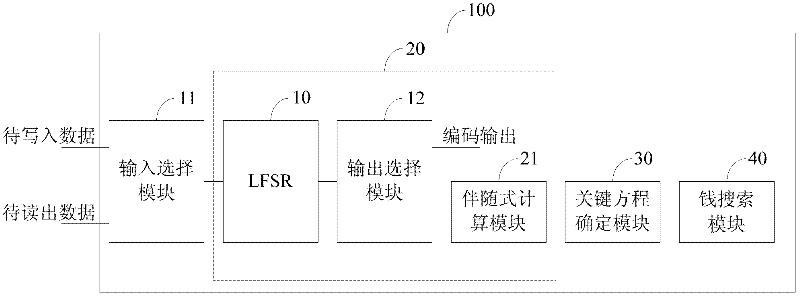

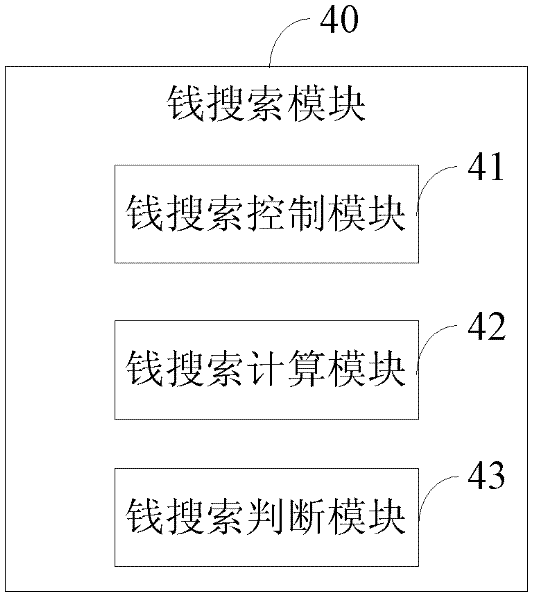

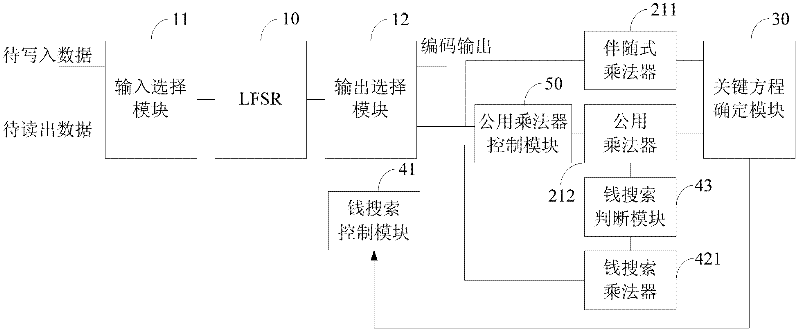

Logical unit multiplexing system

The invention discloses a logical unit multiplexing system which is applicable to an error correction technology of a solid-state hard disk. The logical unit multiplexing system comprises a coding circuit and a decoding circuit. The logical unit multiplexing system is characterized in that: the coding circuit comprises a linear feedback shifting register which is used for complementing a coded / decoded information polynomial; the decoding circuit comprises a syndrome calculating module, a key equation determining module and a Chien search module; the syndrome calculating module is used for calculating to acquire a syndrome and comprises a syndrome calculating module and the linear feedback shifting register; the coding circuit and the decoding circuit multiplex the linear feedback shifting register in a time sharing mode; the key equation determining module is used for determining a key equation according to the syndrome; and the Chien search module is used for judging to acquire a root of the key equation and outputting error position information according to the root of the key equation. Therefore, a logical unit can be multiplexed in the time sharing mode, the area of an error correction code (ECC) chip can be effectively reduced, the power consumption of the ECC chip is reduced, and cost is saved.

Owner:RAMAXEL TECH SHENZHEN

Chien search device and Chien search method

To provide a Chien search device and a Chien search method capable of performing a Chien search process at a high speed. The Chien search device calculates an error position at the time of correcting an error included in data read from a nonvolatile memory, and includes a first processing unit that performs a search process of an error position in at least one-bit unit to an error-correction area of input data, and a second processing unit that processes at one time plural bits in an non-error-correction-target area of the input data.

Owner:KK TOSHIBA

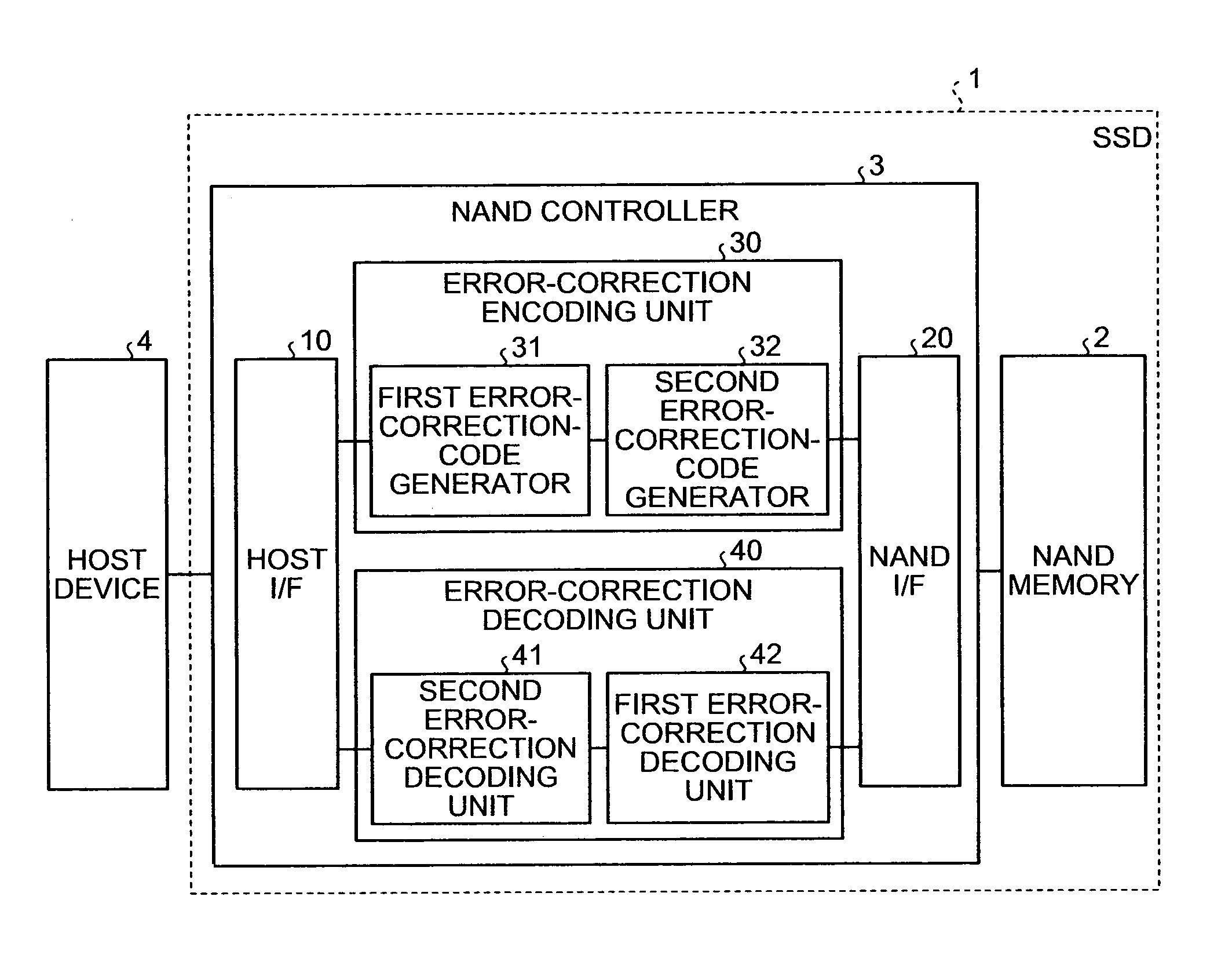

Error correction code circuit and memory device including the same

The ECC circuit includes a Chien search unit configured to determine whether there is an error in each bit of a data sequence. The Chien search unit selects a coefficient of a nonlinear term from among terms of an error locator polynomial as a nonlinear coefficient, separates the error locator polynomial into a first location equation including only linear terms and a second location equation including only nonlinear terms, determines a third location equation by dividing the first location equation by the nonlinear coefficient, determines a fourth location equation by dividing the second location equation by the nonlinear coefficient, and determines whether there is an error for each of the bits by performing an XOR operation on a result of the third location equation using the substitution value and a result of the fourth location equation using an arbitrary element of the error locator polynomial as a substitution value.

Owner:SAMSUNG ELECTRONICS CO LTD

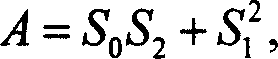

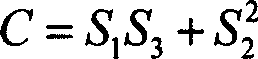

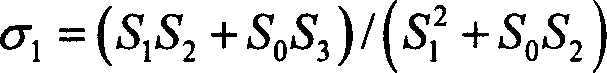

Quick double-error correction BCH code decoder

InactiveCN1561005AReduce complexityDecoding speed is fastError detection/correctionCode conversionControl signalError location

This invention discloses a BCH decoder for correcting double errors quickly working on GF(25) composed of an ad-joint computing circuit, an error number judgment circuit and an error location computing circuit connected sequently. The BCH code is BCH (N, N-10), code length N is any integer in 11-31. This method utilizes the feature of BCH code of correcting double mistakes to present a search method to compute the error location from the ad-joint result without the help of Chien method or ROM.

Owner:汇智系统股份有限公司 +1

Computing an error detection code syndrome based on a correction pattern

The present invention is all error detection and correction scheme that enables the use of Horner's algorithm for the computation of EDC syndromes from the computed error pattern. Specifically, “transformed” EDC syndromes are computed during the read back of data and parity from the medium. The transformed syndromes are values of the polynomial whose coefficients occur in reverse order from that of the EDC codeword polynomial. In essence, by reversing the order of the coefficients, the Chien search processes the terms in descending order which is the right direction for Horner evaluation.

Owner:SEAGATE TECH HDD HLDG +3

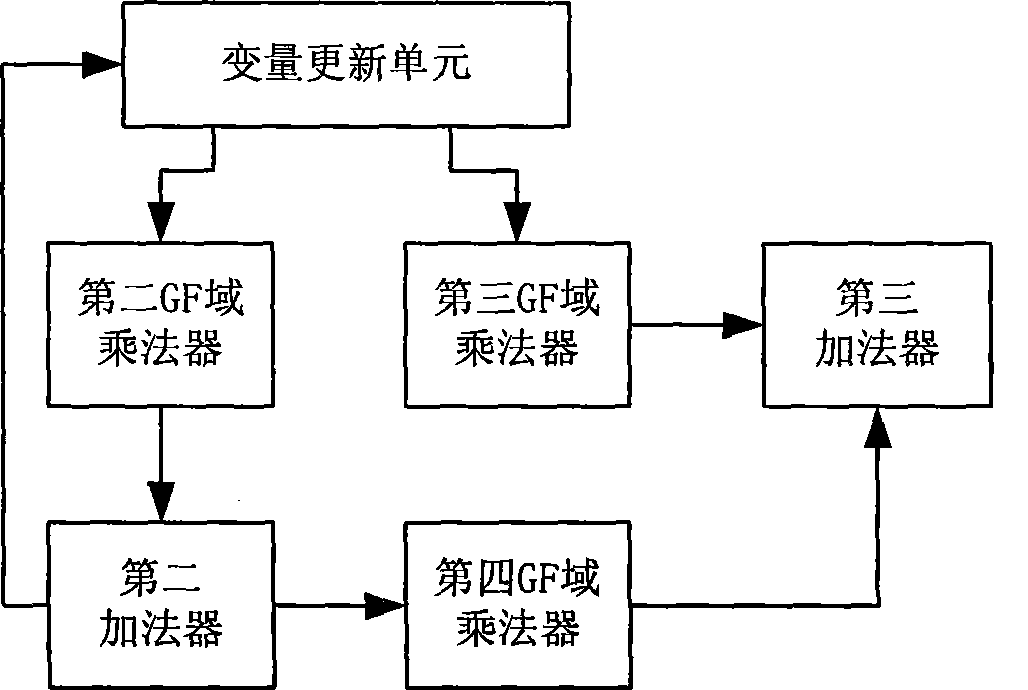

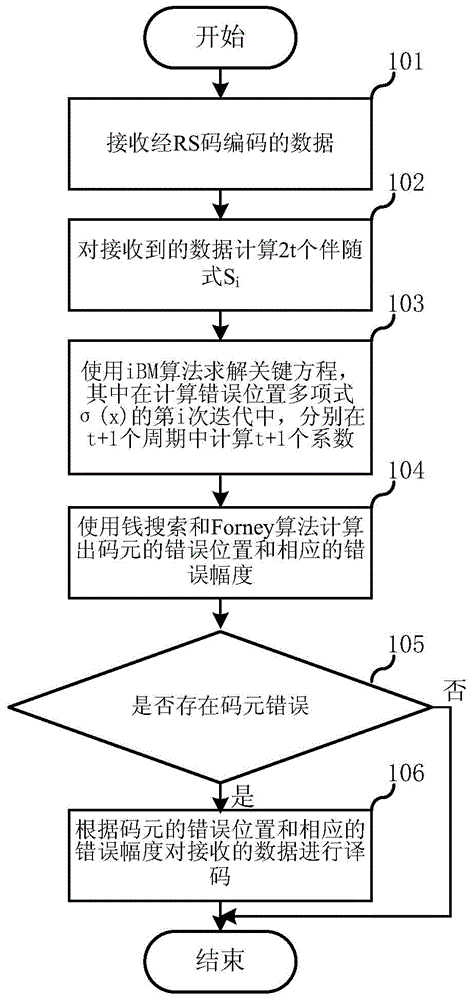

RS (reed Solomon) decoding method and device thereof in communication system

ActiveCN104639282ASave hardware resourcesLow costError preventionDecoding methodsCommunications system

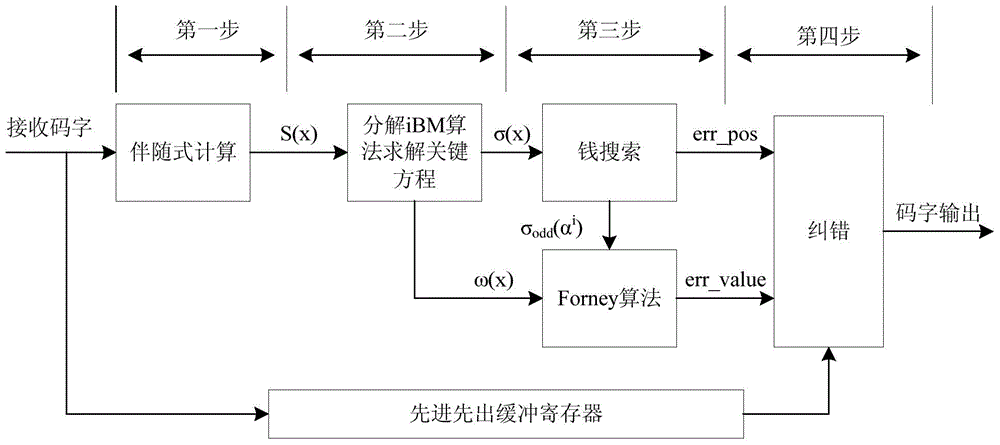

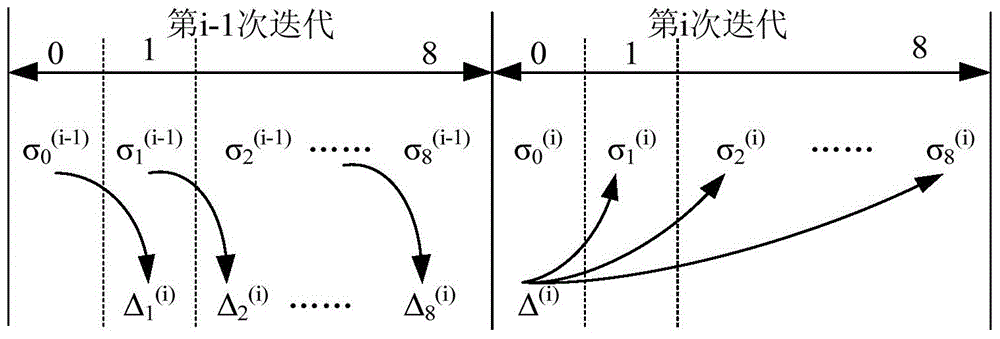

The invention relates to the communication technology and discloses an RS (reed Solomon) decoding method and device thereof in the communication system. By serial decomposition calculation of common parallel iBM algorithm, hardware resource required for solving key equations is greatly reduced and path delay is reduced under the condition of no influence on continuous decoding. Also, by combining and optimizing Chien search and Forney algorithm process, that is, odd-even terms in error position polynomial terminals and error value polynomial terms are split, and control logic and repeated calculation is reduced. Therefore, consumption of the hardware resource is only 1 / 2 to 1 / 3 of that of the common iBM algorithm, the maximum clock frequency and effective data bandwidth are improved by about 30%, high-speed channel error technology can be applied on a low-density chip, and cost is reduced.

Owner:HANGZHOU HIKVISION DIGITAL TECH

Even-load software reed-solomon decoder

A software implementation of a Reed-Solomon decoder placing a constant load on the processor of a computer. A Berlekamp-Massey Algorithm is used to calculate the coefficients of the error locator polynomial, a Chien Search is used to determine the roots of the error locator polynomial, and a Forney Algorithm is used to determine the magnitude of the errors in the received digital code word. Each step is divided into m small tasks where m is the number of computational blocks it takes to read in a code word and the processor can pipeline or parallel process one task from each step each time a block is read.

Owner:GULA CONSULTING LLC

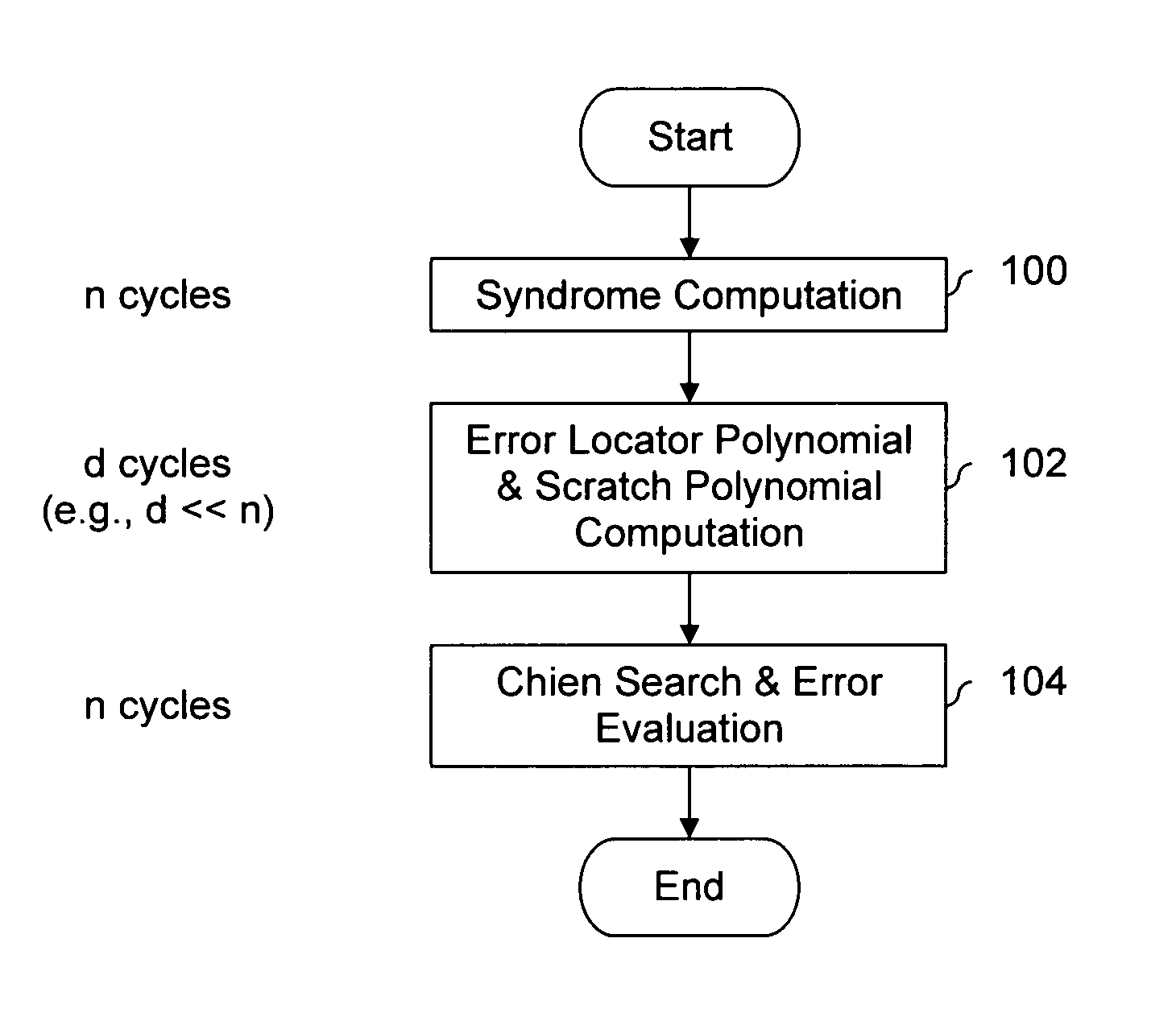

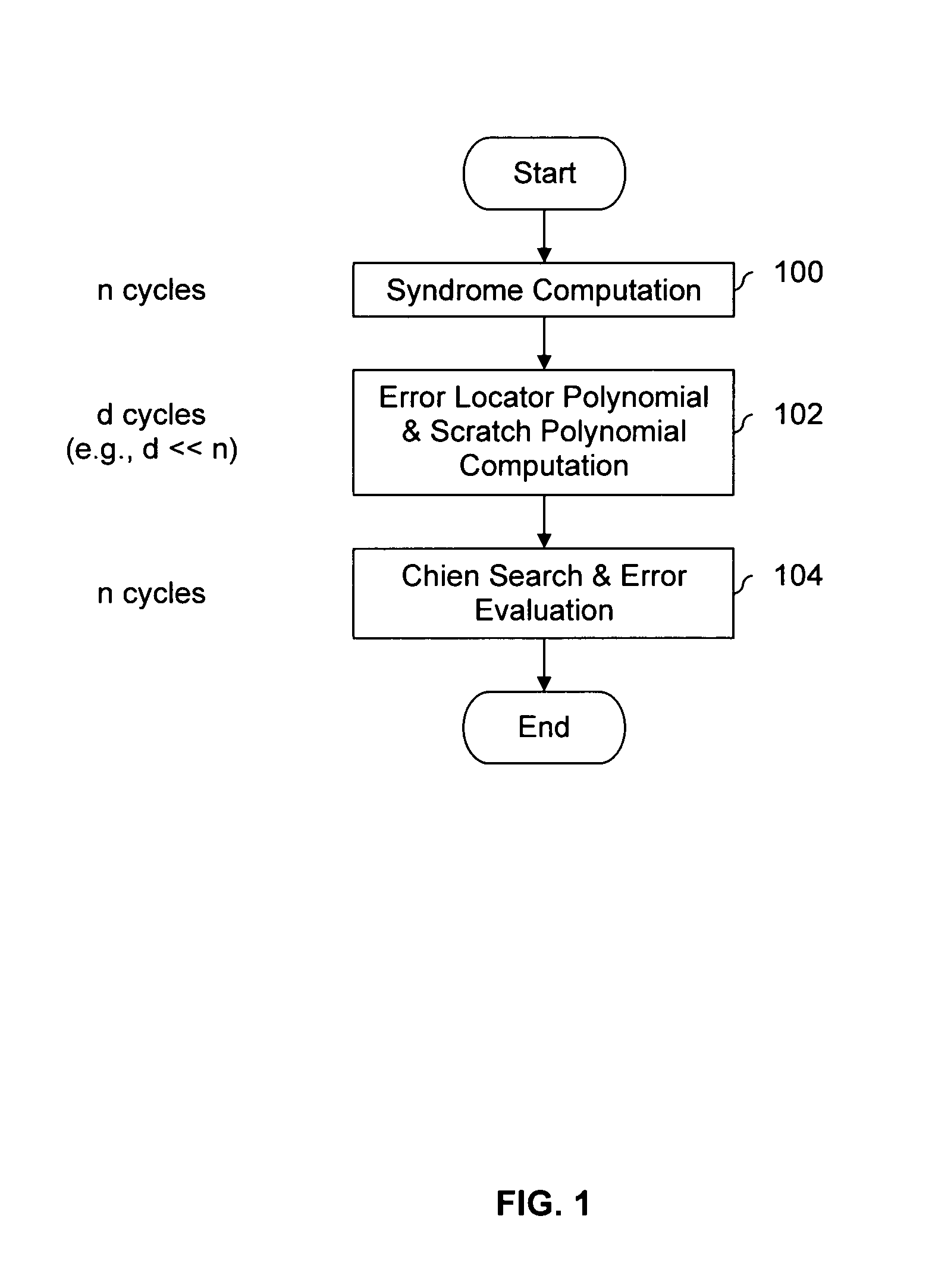

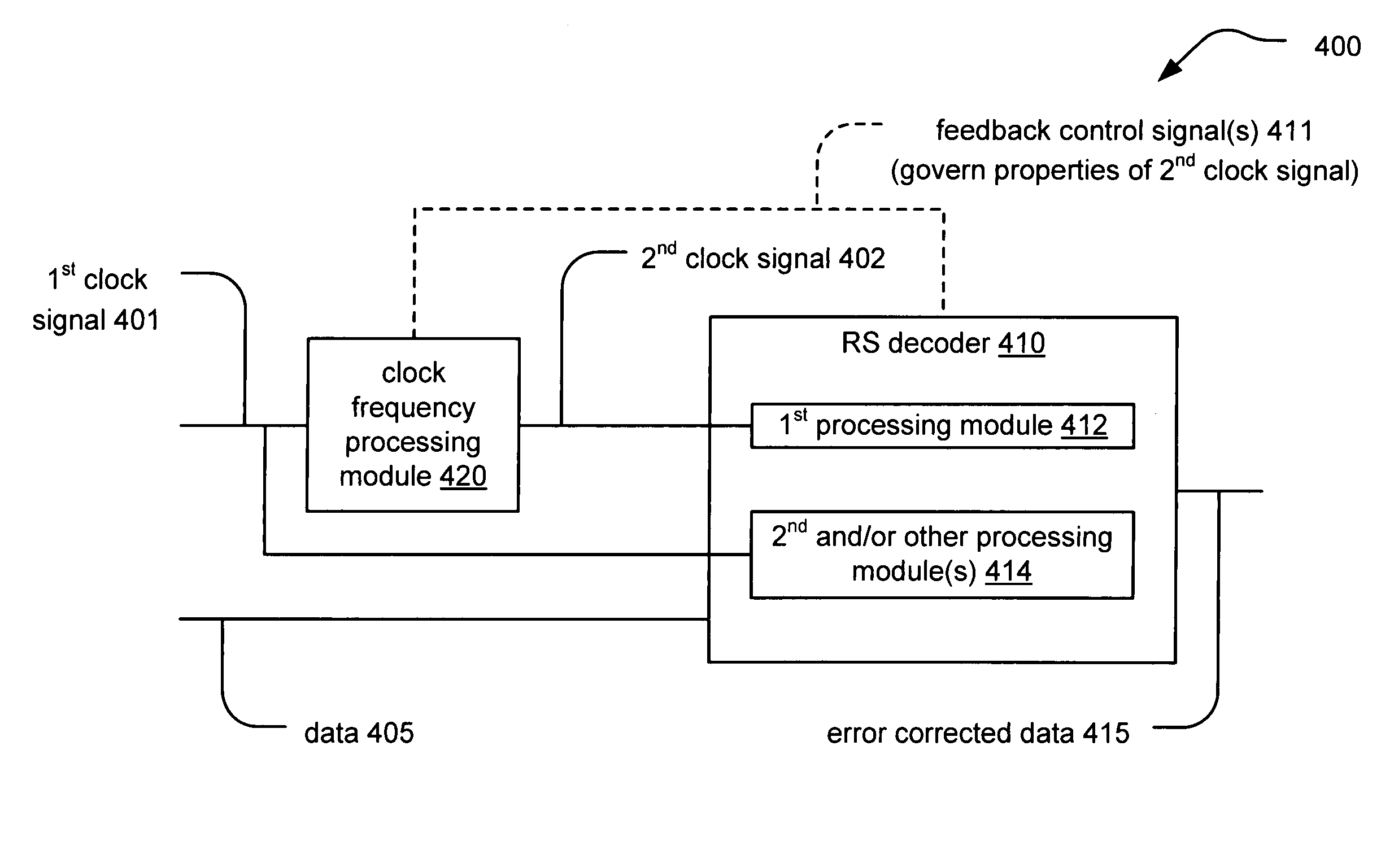

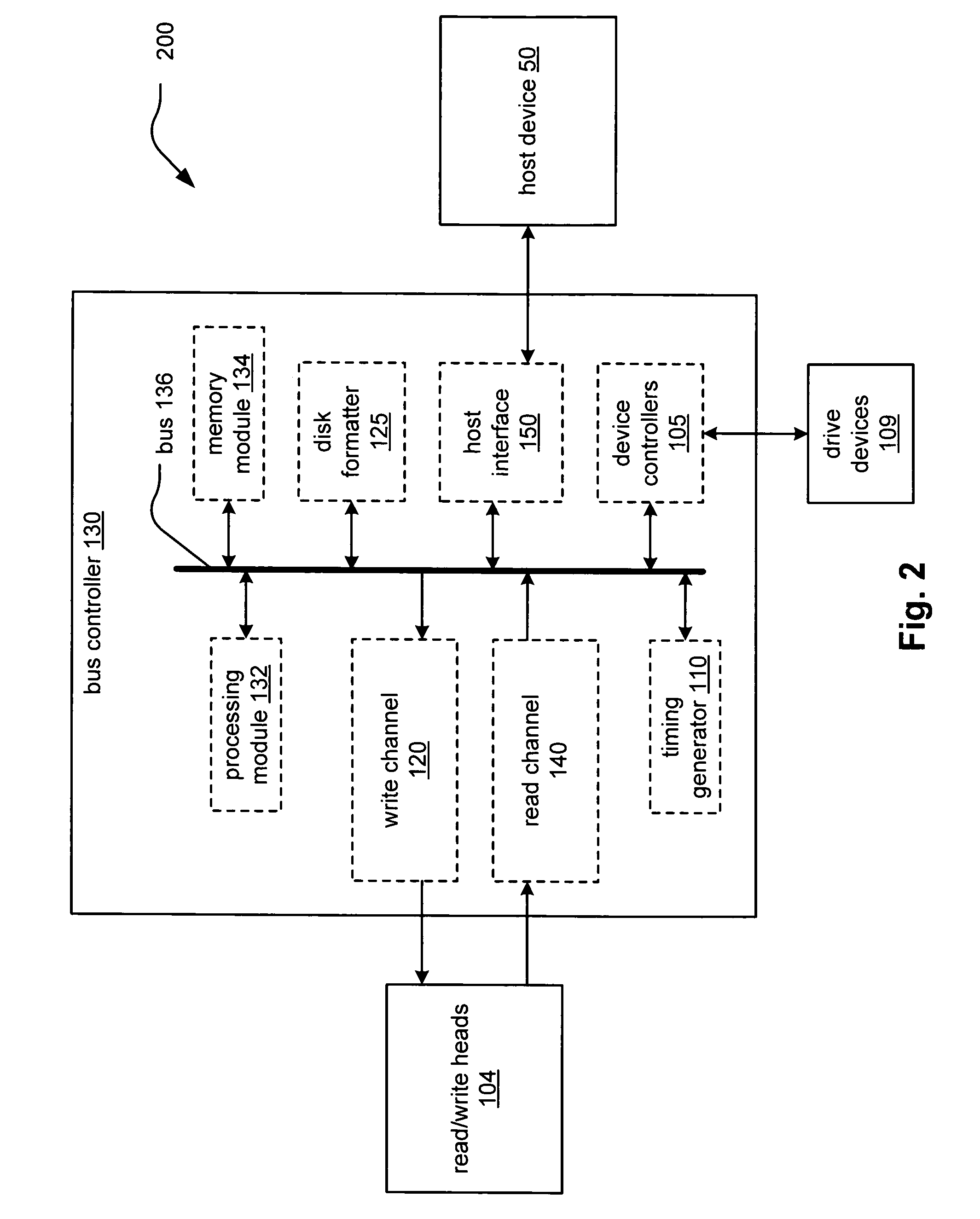

Clocking Chien searching at different frequency than other Reed-Solomon (RS) ECC decoding functions

Clocking Chien searching at different frequency than other Reed-Solomon (RS) ECC decoding functions. An efficient implementation allows for a fast clock signal to govern the operation of the more computationally and time-intensive portions of the error correction code (ECC) time budget. For example, at least one module and / or decoding function within the ECC decoding is governed by using a first clock signal, and at least one other module and / or decoding function (or all the other modules and / or decoding functions) is / are governed by using a second clock signal. In one implementation of Reed-Solomon (RS) decoding, the Chien searching function is operated using a faster clock signal than at least one other RS error correction decoding function thereby allowing for a significant reduction in area and power than other architectural trade-offs.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Method And Circuit For Encoding An Error Correction Code

The invention provides a method for decoding an error correction code. First, an error syndrome of the error correction code is calculated. A plurality of coefficients of an error locator polynomial of the error correction code is then sequentially determined according to the error syndrome. When a new coefficient of the error locator polynomial is determined, it is also determined whether the new determined coefficient is equal to zero. When the new determined coefficient is equal to zero, a speculated error locator polynomial is built according to a plurality of low-order-term coefficients of the error locator polynomial, wherein the orders of the low-order-term coefficients are lower than that of the new determined coefficient. A Chien search is then performed to determine a plurality of roots of the speculated error locator polynomial. The error correction code is then corrected according to the roots of the speculated error locator polynomial.

Owner:SILICON MOTION INC (TW)

16-bit FEC decoding realization method for gpon

InactiveCN101674090AMeet the requirements of downlink decoding speedReasonable useCyclic codes16-bitAsynchronous fifo

The invention relates to a 16-bit FEC decoding realization method for GPON. The prior art can not realize the 16-bit FEC decoding. The 16-bit FEC decoding realization method comprises the following steps: firstly, receiving a RS code and conducing asynchronous FIFO speed acceleration on the RS code; secondly, solving a syndrome of the RS code after the speed acceleration, and then applying the solved syndrome to an improved Euclidean algorithm to solve a polynomial of an error position and an error value; and finally using a Chien search algorithm for searching the error position, using a Forney algorithm for computing the error value, and obtaining a correct value through conducing XOR on the error value and a value received on the error position, thus completing decoding error-correctionprocess. The decoding realization method respectively adopts three paths for parallel computing when using an MEA algorithm, thus shortening the time of the MEA computing; and simultaneously, two Chien search and Forney algorithm are respectively used, thus resolving the problems existing in the 16-bit RS decoding when only one Chien search and Forney algorithm module is used.

Owner:HANGZHOU DIANZI UNIV +1