16-bit FEC decoding realization method for gpon

An implementation method and codeword technology, applied in the direction of using linear codes for error correction/detection, using block codes for error correction/detection, cyclic codes, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] A 16-bit FEC decoding implementation method applied to GPON, comprising the steps:

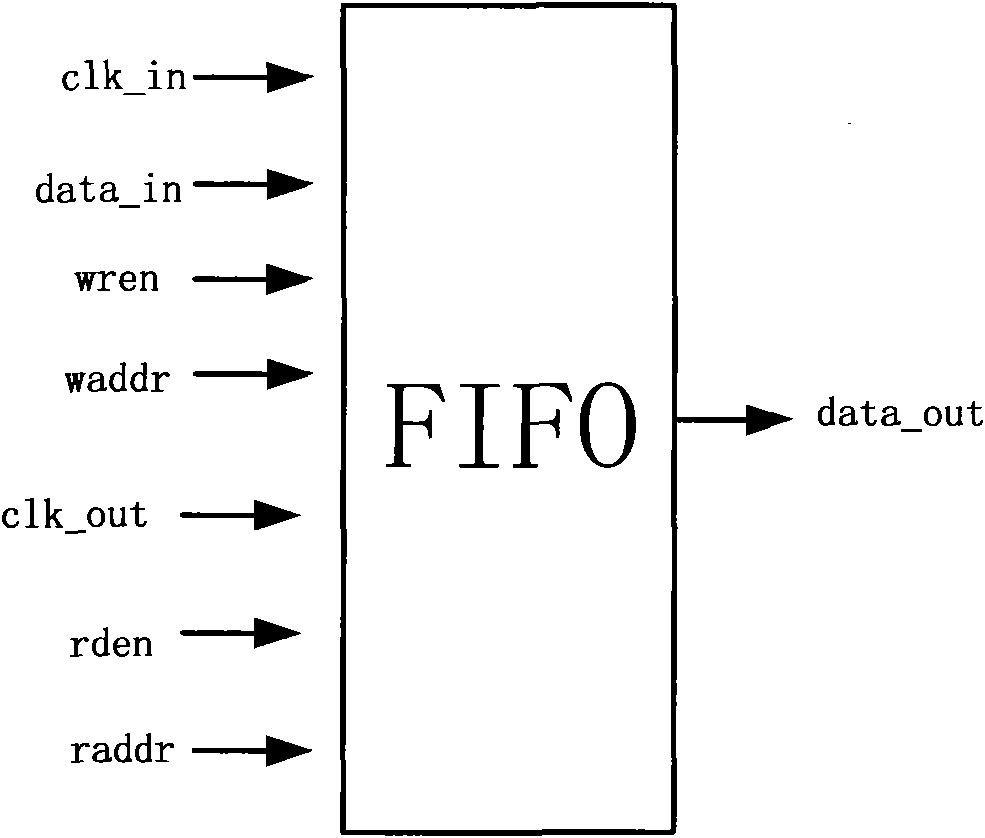

[0046] Step (1). Receive the RS code, and let the RS code speed up through the asynchronous FIFO;

[0047] The present invention uses an asynchronous FIFO to temporarily store the incoming 120-byte valid data. Because GPON downlink frames are continuously transmitted, that is, each downlink frame will encounter this short byte problem when decoding FEC, so in order to avoid the accumulation of data in this FIFO, the output clock of FIFO must be increased. If the input system clock adopts x megahertz, then the output clock must be greater than or equal to y=(135x / 120) megahertz, then a clock of y megahertz must be used for subsequent FEC decoding. After such a speed-up, the insertion time of 135 zeros can be less than or equal to the time for storing 120 bytes into the FIFO, that is, the data stored in the FIFO will not exceed 120 bytes. After the data is restored to normal reading, th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More