Patents

Literature

887 results about "16-bit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In computer architecture, 16-bit integers, memory addresses, or other data units are those that are 16 bits (2 octets) wide. Also, 16-bit CPU and ALU architectures are those that are based on registers, address buses, or data buses of that size. 16-bit microcomputers are computers in which 16-bit microprocessors were the norm.

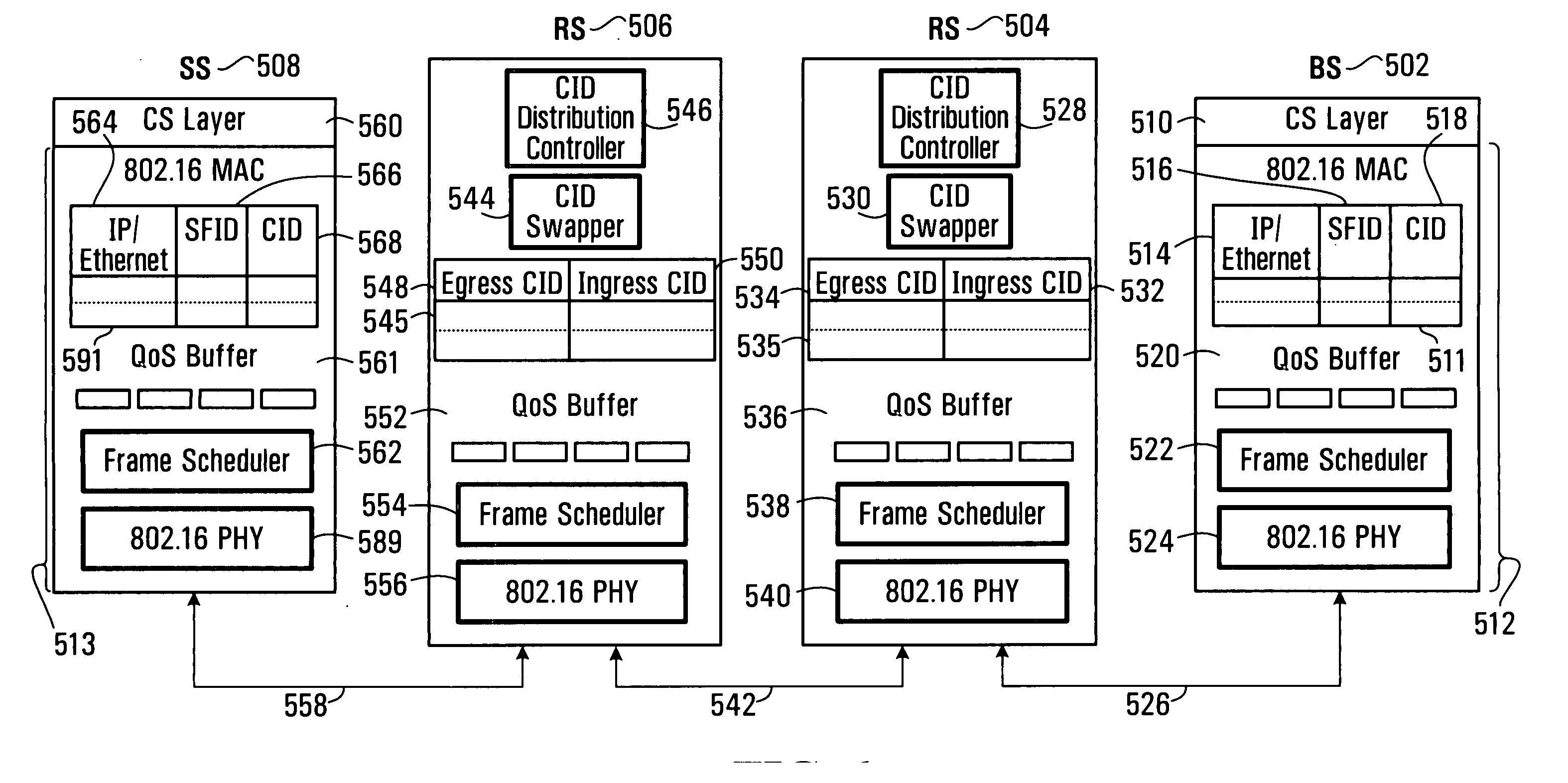

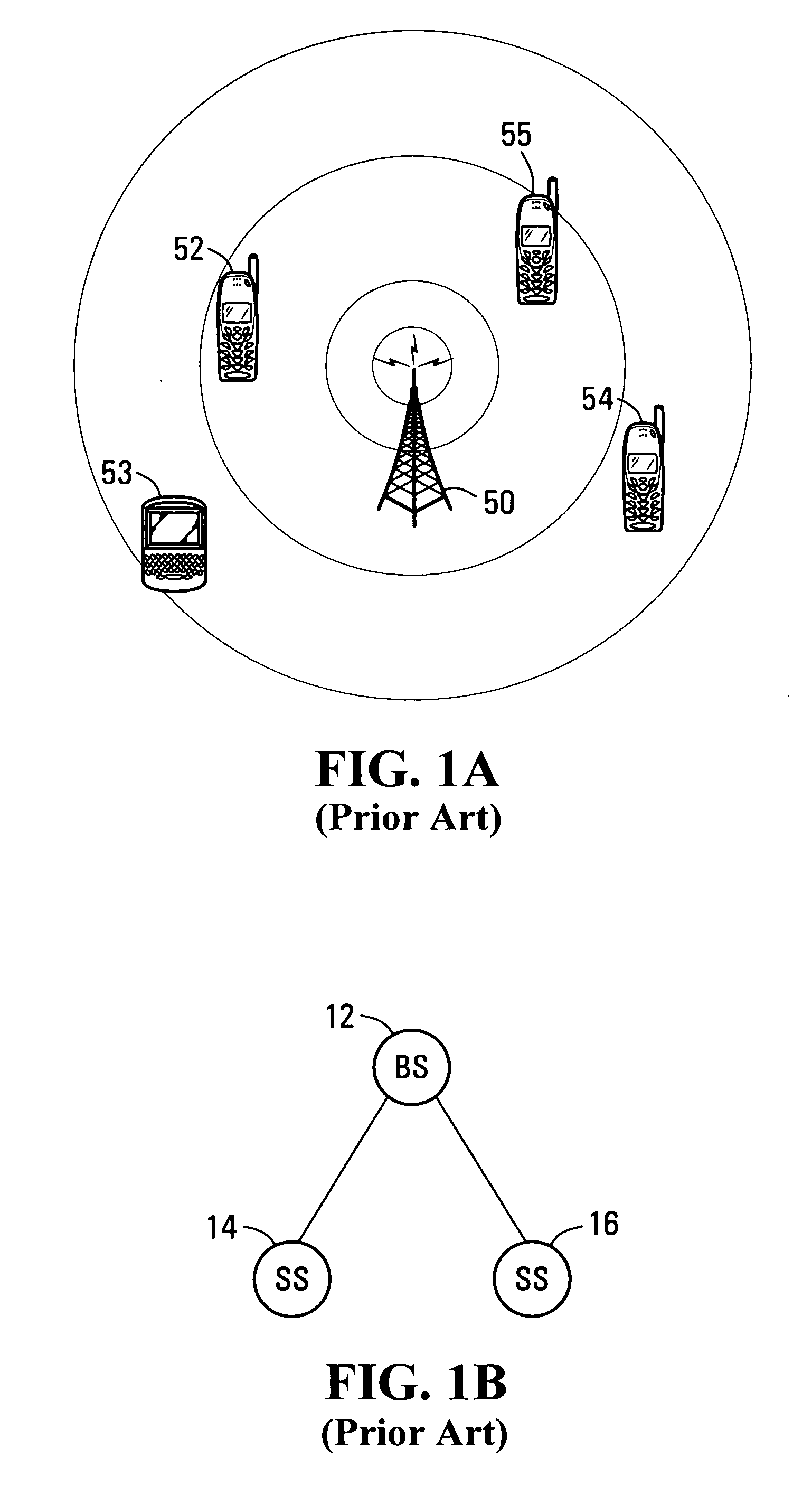

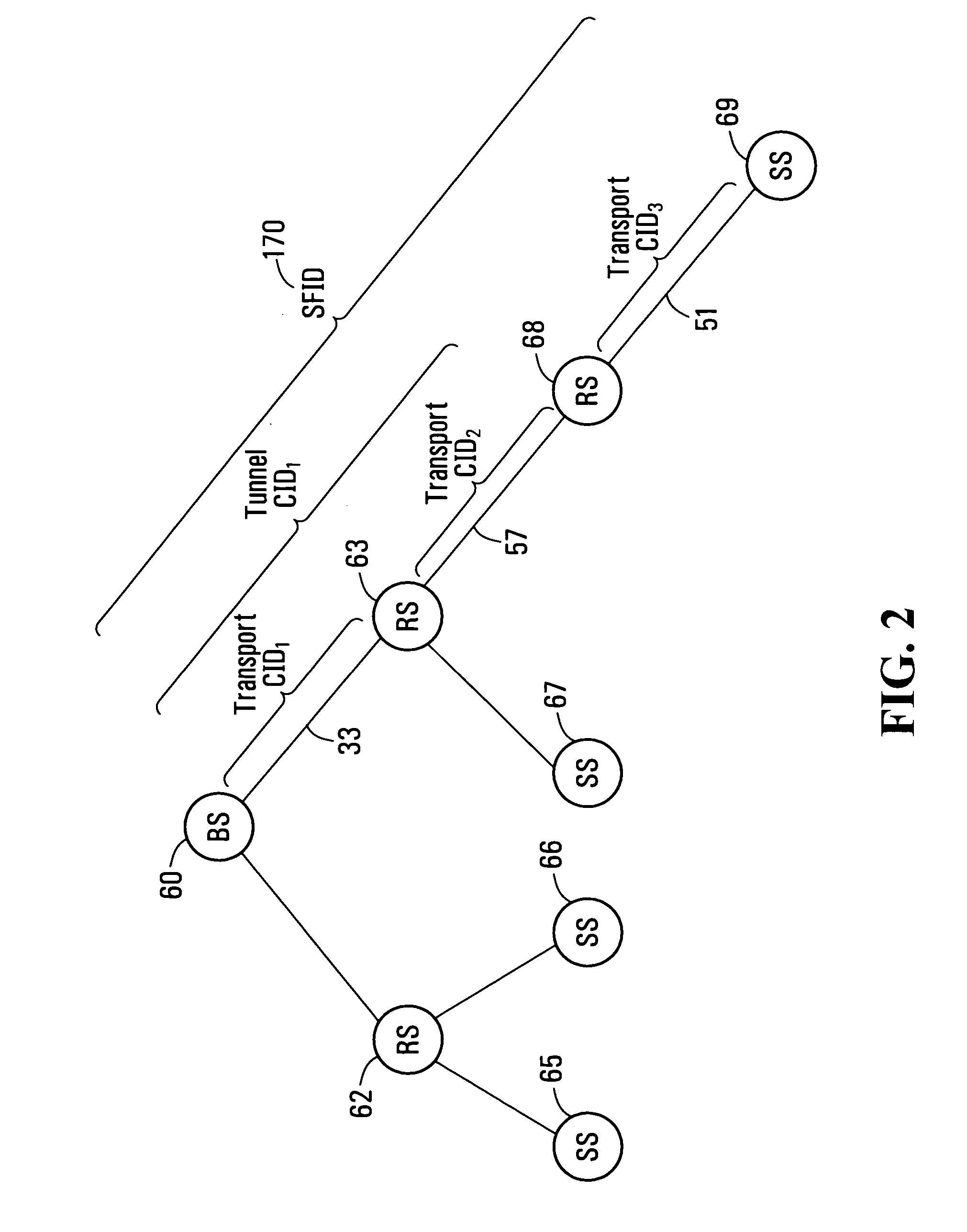

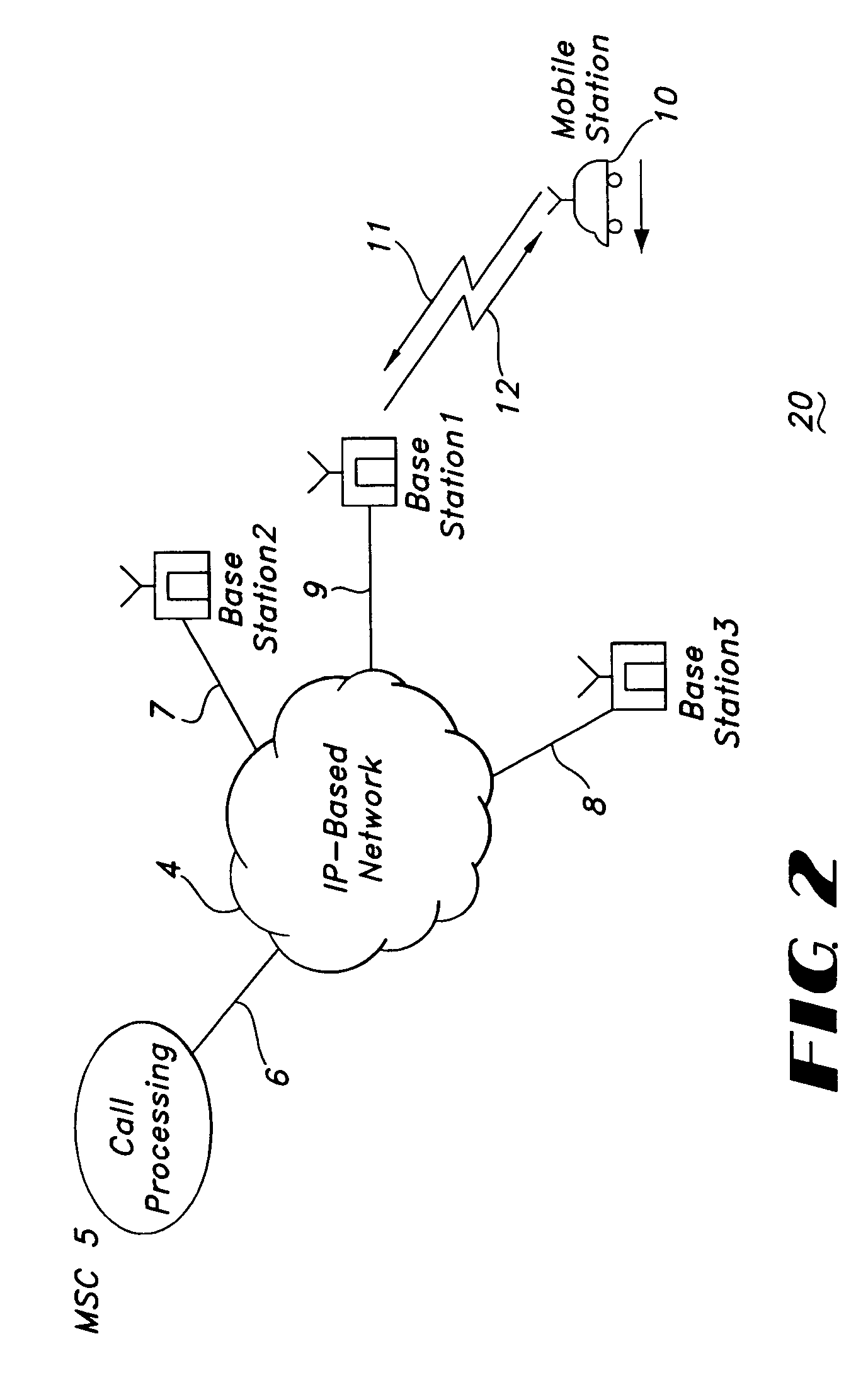

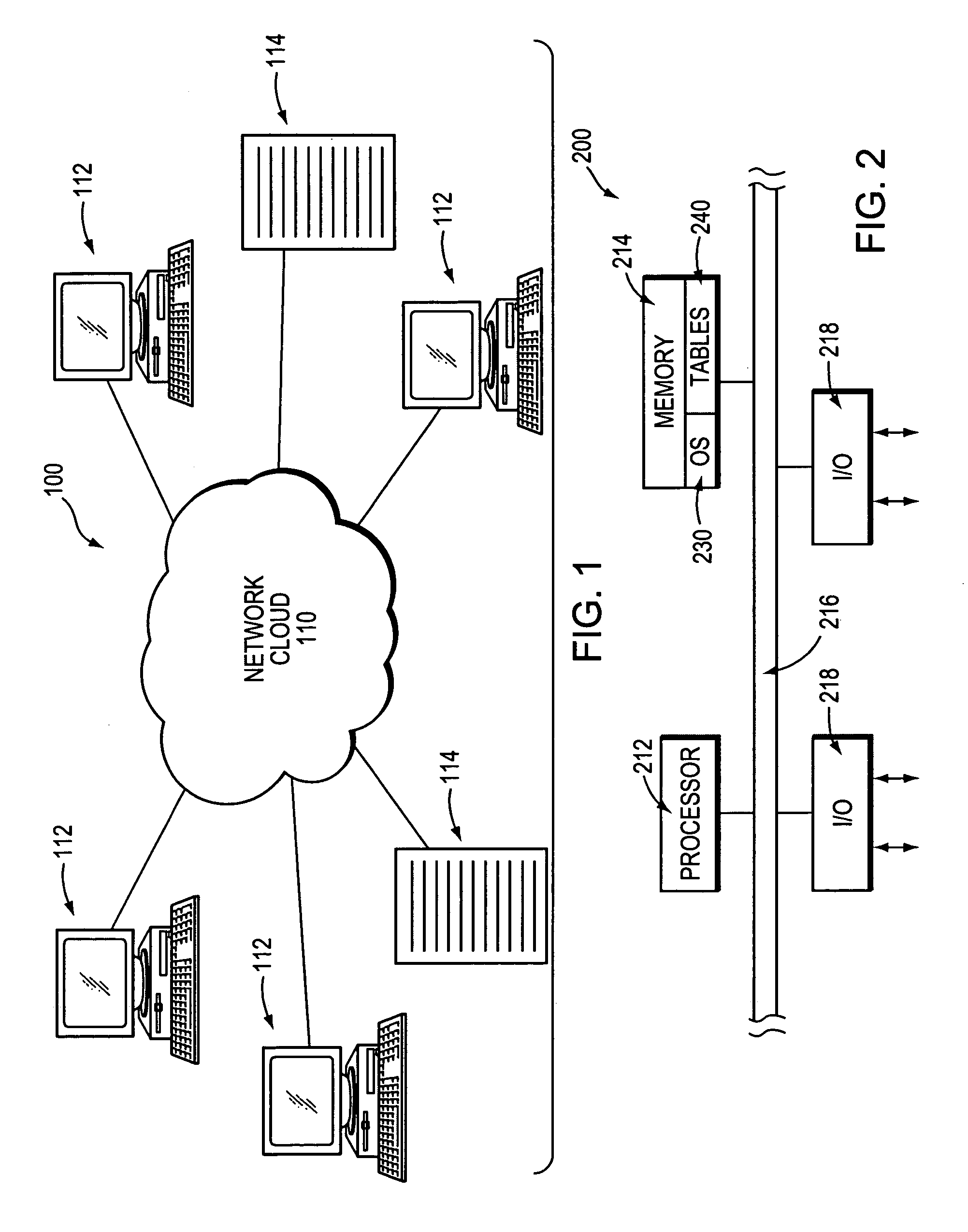

Method and system for a wireless multi-hop relay network

ActiveUS20070072604A1Network traffic/resource managementData switching by path configurationService flowMulti hop relay

A Point to Multipoint (PMP) multi-hop relay network includes a base station, one or more relay stations and one or more subscriber stations. Active service flows in a PMP multi-hop relay network have a 16-bit connection identifier (CID). A CID defines the connection that a packet is servicing. Before traffic can be transmitted, the path through the network, and the association of CIDs with respective hops needs to be established. The CID mapping relationship from the ingress air link to the egress air link at each relay station is first set up, which is then followed by a traffic phase where the CID mapping relationship is used to route traffic from a base station to a subscriber station.

Owner:APPLE INC

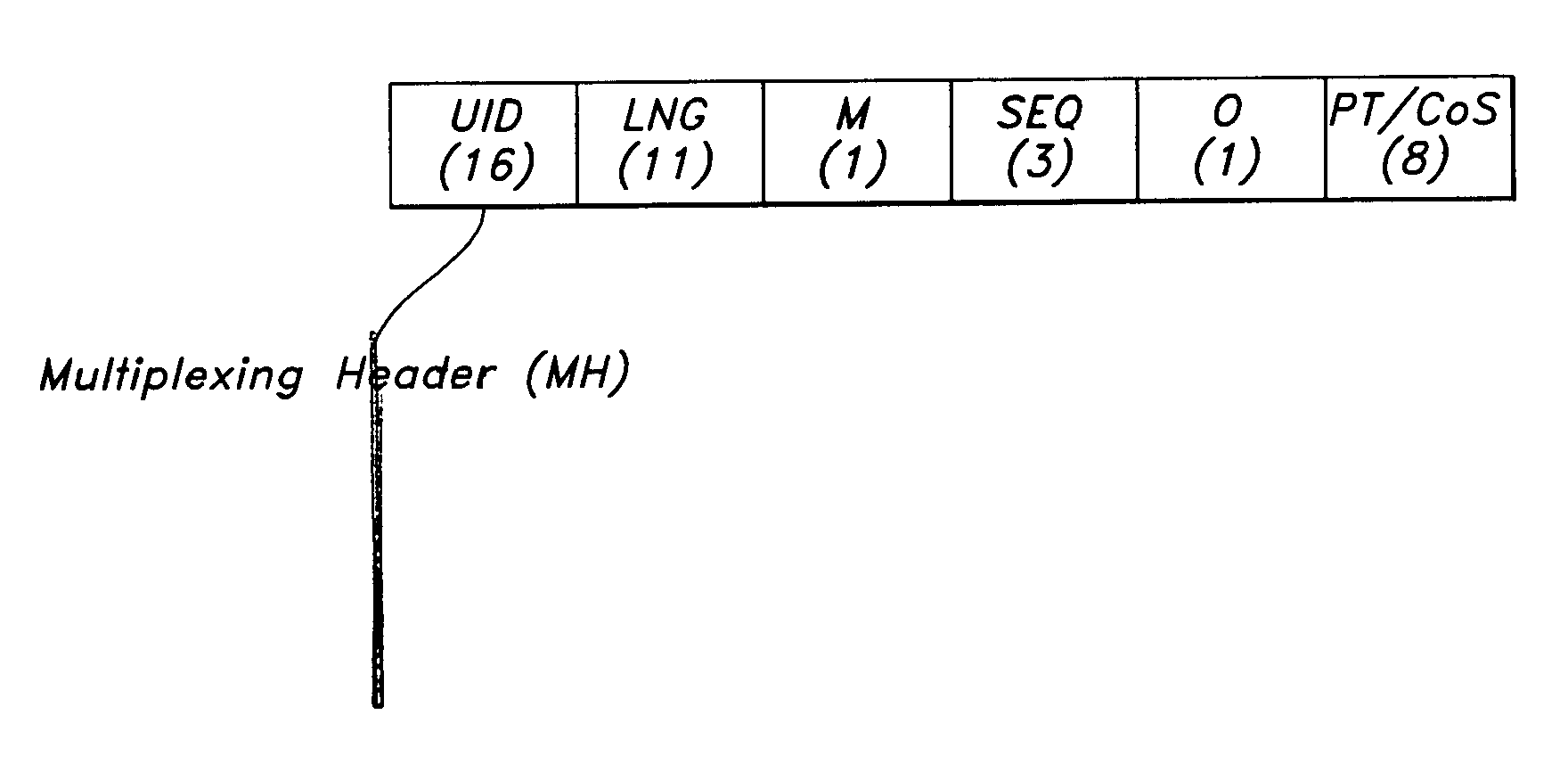

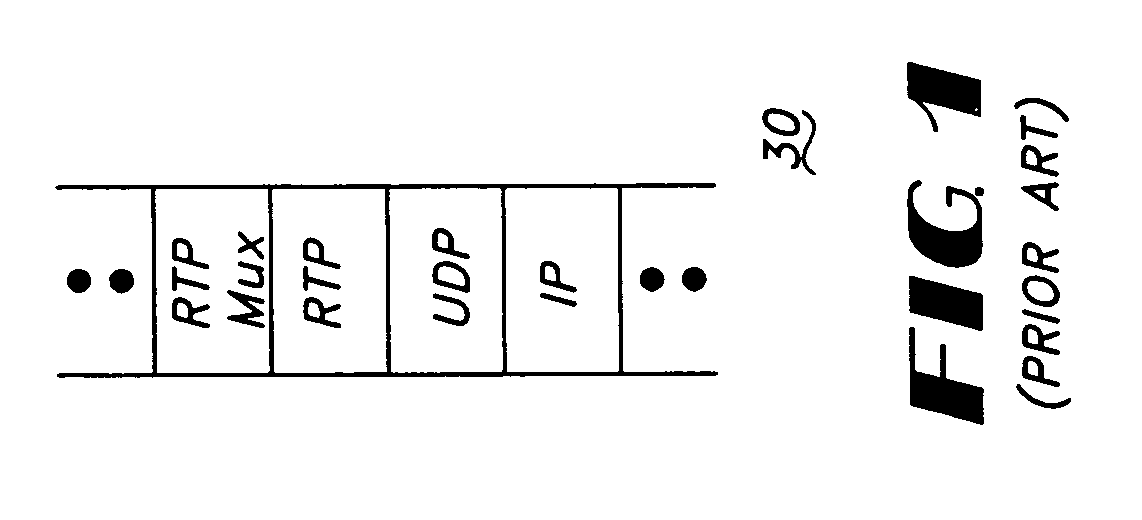

Lightweight internet protocol encapsulation (LIPE) scheme for multimedia traffic transport

InactiveUS6993021B1Increase in sizeTime-division multiplexData switching by path configurationTraffic capacityClass of service

A packet encapsulation scheme for multiplexing application sessions—Lightweight IP Encapsulation (LIPE)—is described. An LIPE packet comprises at least one multiplexing header (NH) and associated multimedia data packet (MDP). The LIPE packet uses UDP / IP as transport. An MH field further comprises a 16-bit a user identifier (UID) field, an 11 bit length indicator (LNG) field, a 1 bit “more” (M) field and an optional payload type / class of service (PT / CoS) field comprising 8 bits.

Owner:ALCATEL-LUCENT USA INC +1

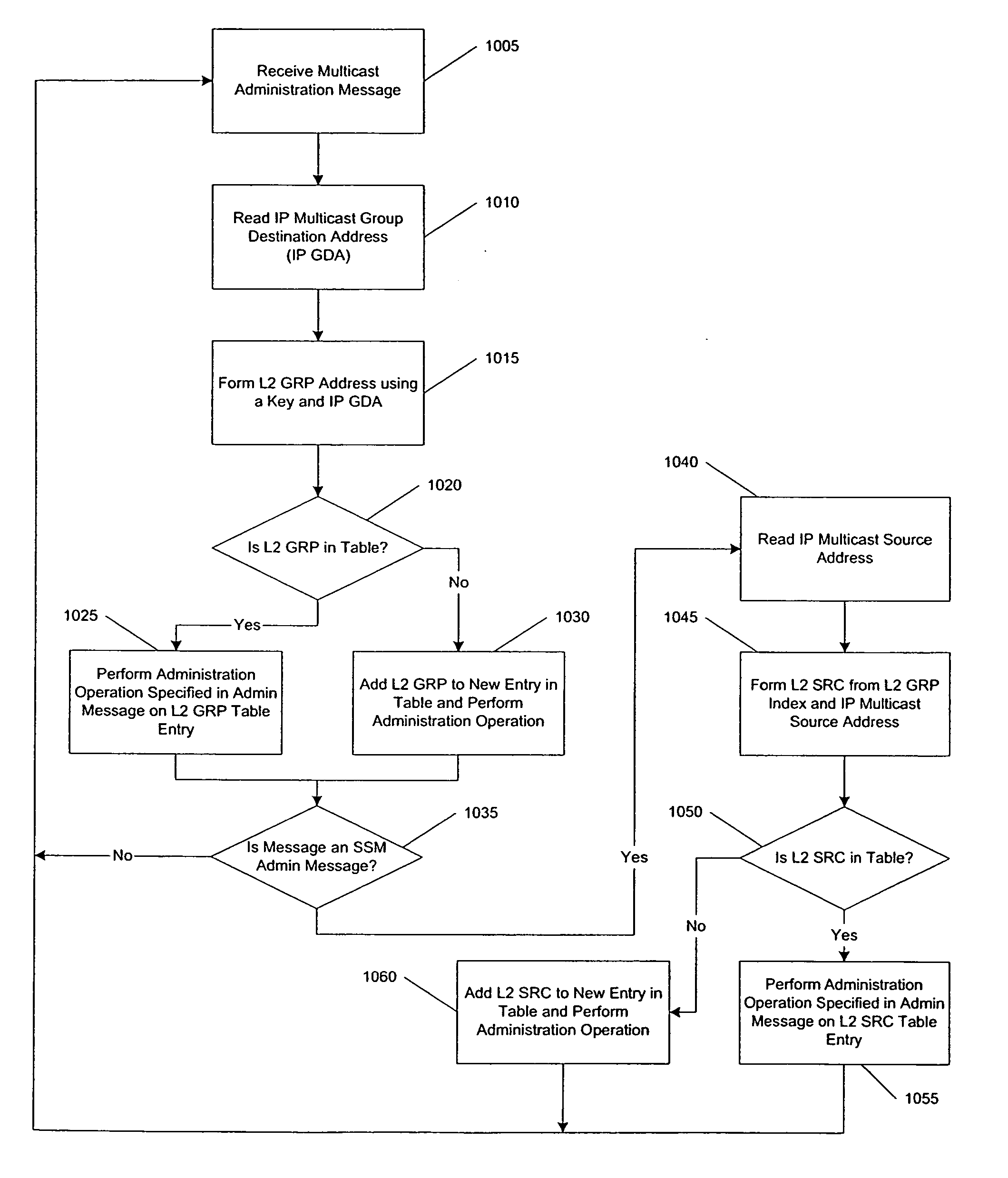

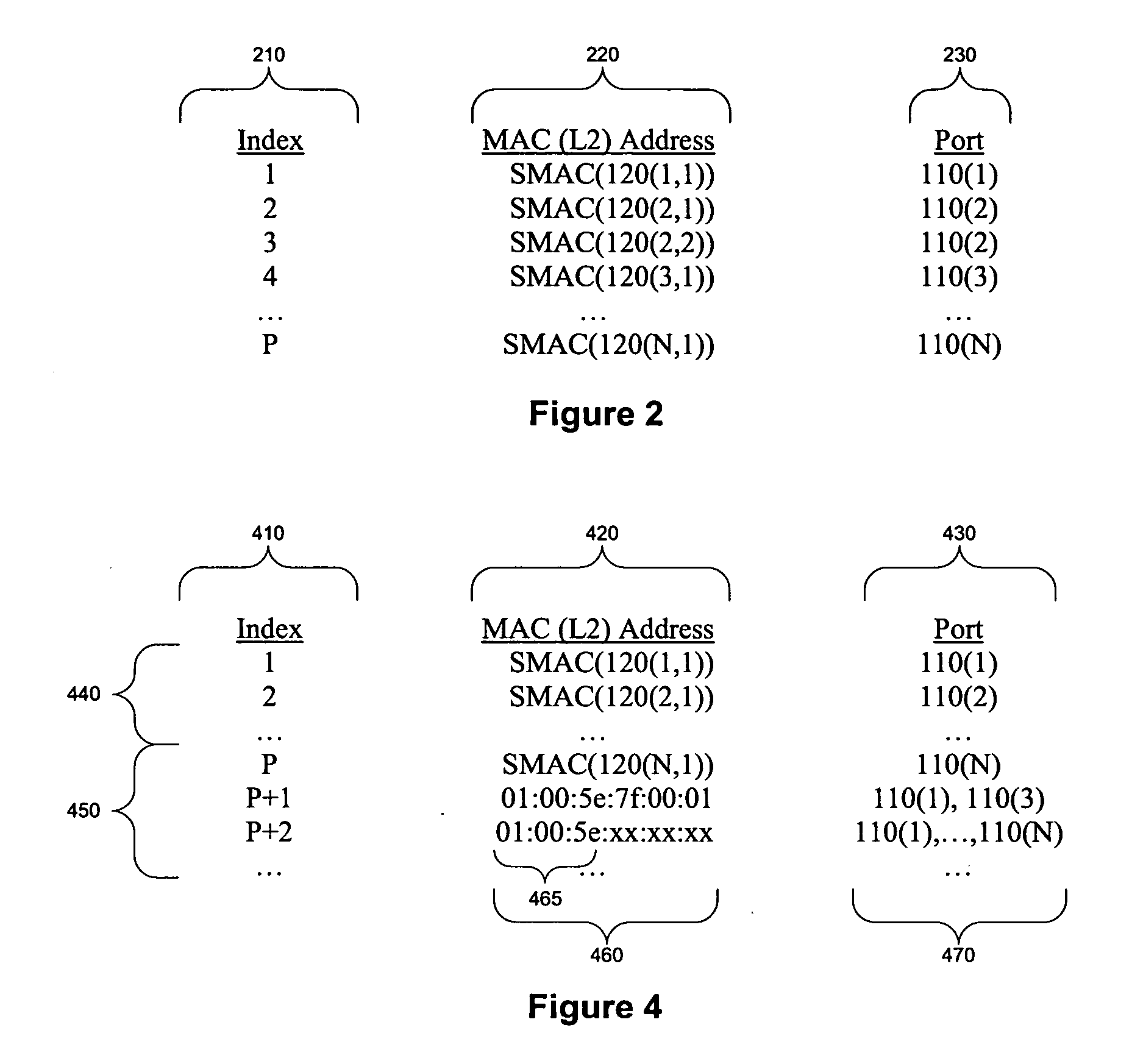

Performing extended lookups on mac-based tables

ActiveUS20060221960A1Special service provision for substationTime-division multiplexInternet trafficIp address

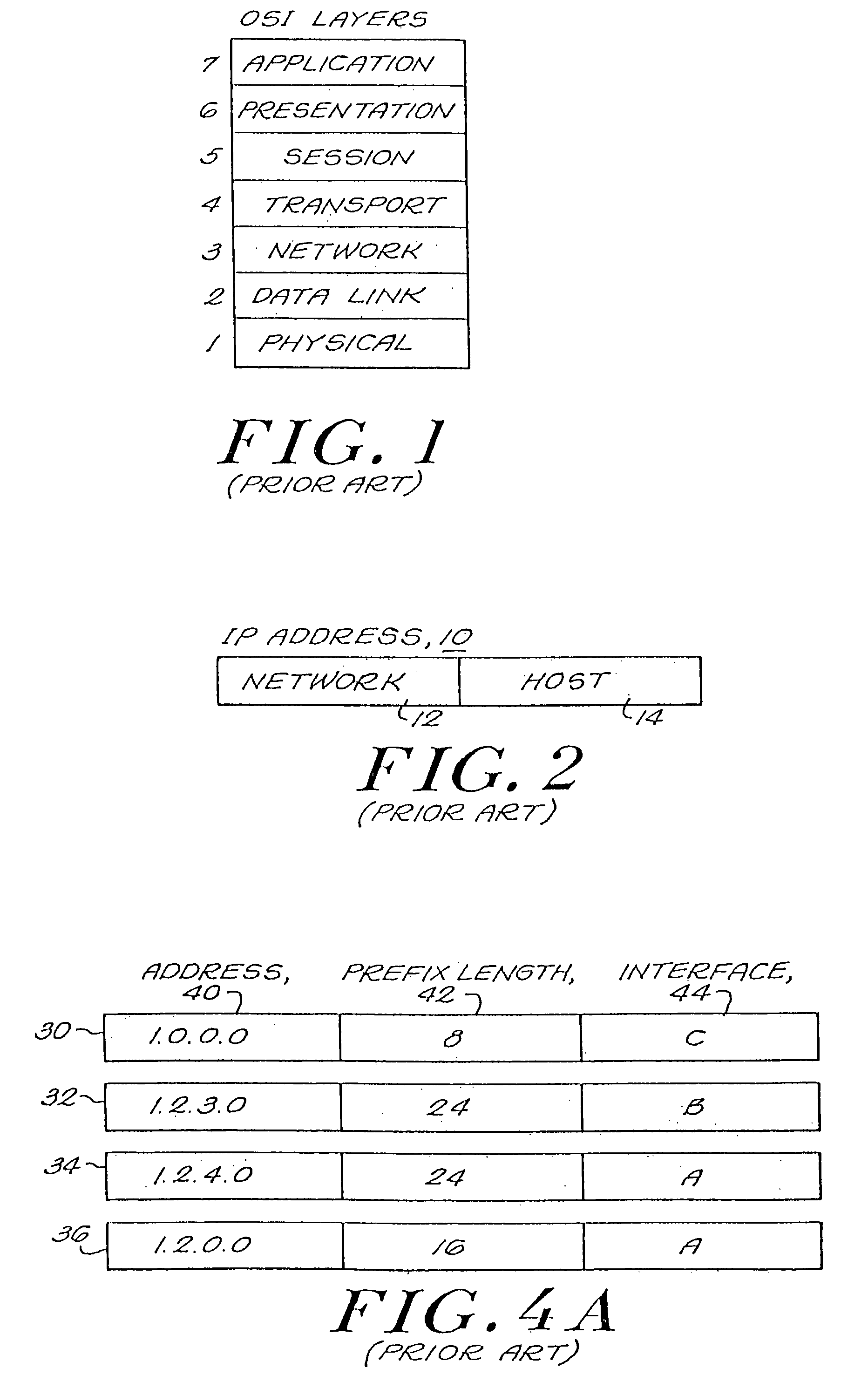

A method, system, and computer program product are presented to optimize OSI Level 2 switch forwarding of frames comprising IP addresses, 802.1 QinQ VLAN identifiers, multi-protocol label switching labels, and any other usable information meaningful to derive an L2 forwarding result on frames. In one embodiment, a 16-bit key is included as a prefix to a 48-bit OSI Level 2 address entry, thereby allowing the inclusion of a 32-bit OSI Level 3 address in the lookup table (e.g., a complete IP version 4 address). Implementations of such a solution are presented to resolve address aliasing issues experienced with multicast group destination addresses, including single source multicast. Solutions to optimizing forwarding of frames in an IEEE 802.1 QinQ environment are also presented. A result of these implementations can be reduction of the amount of unnecessary network traffic generated by a network switch incorporating such an OSI Level 2 address lookup table.

Owner:CISCO TECH INC

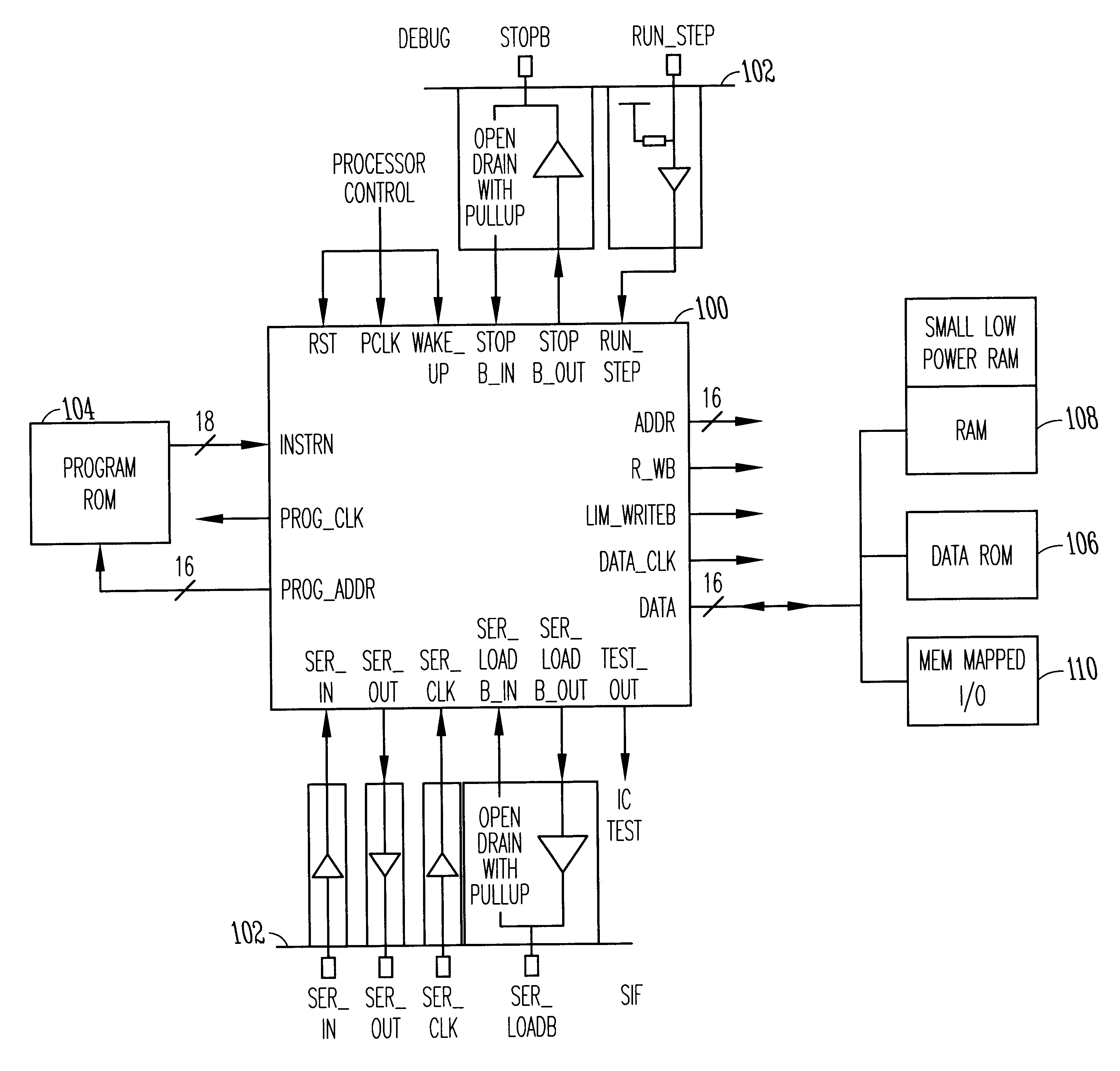

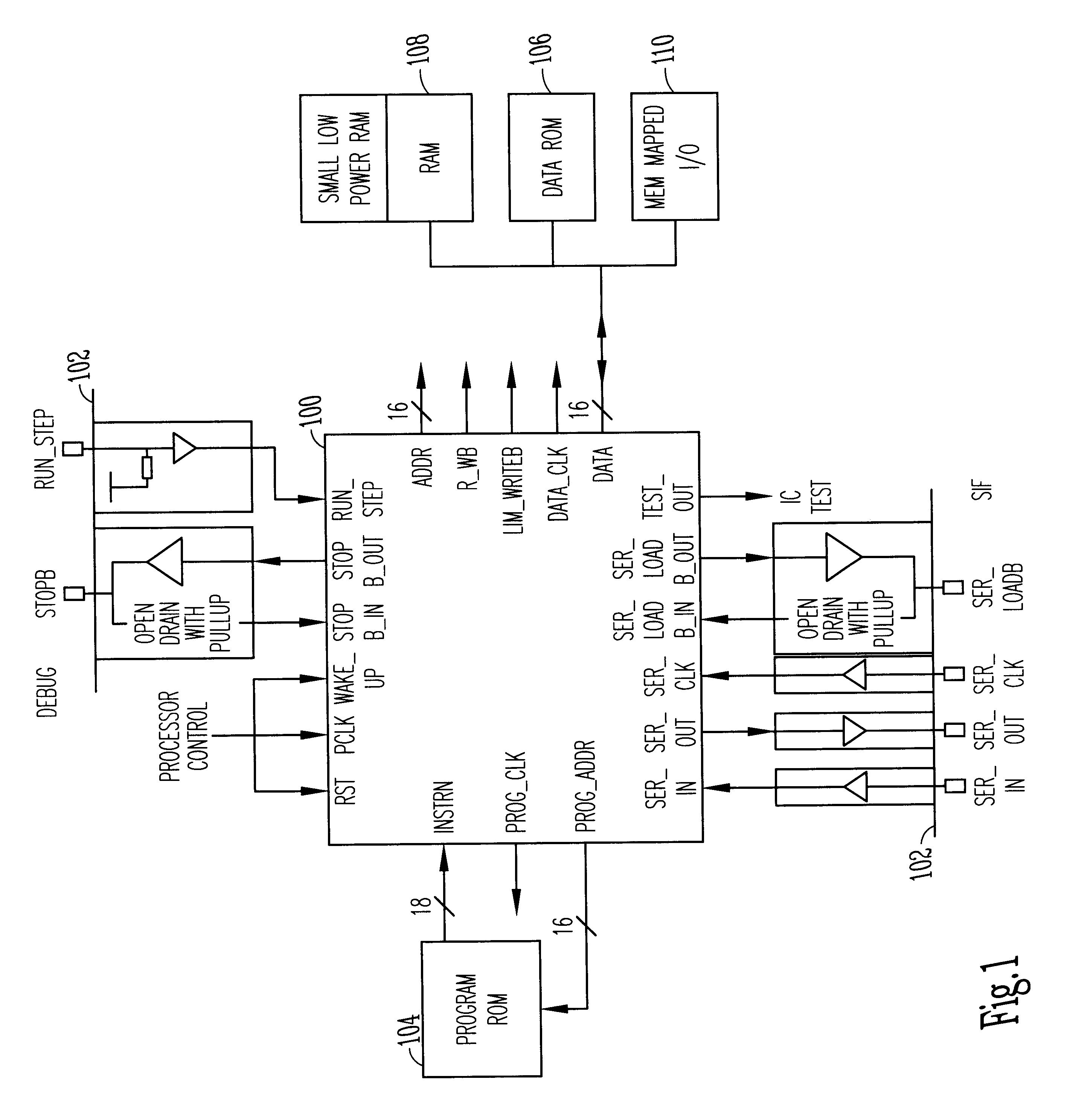

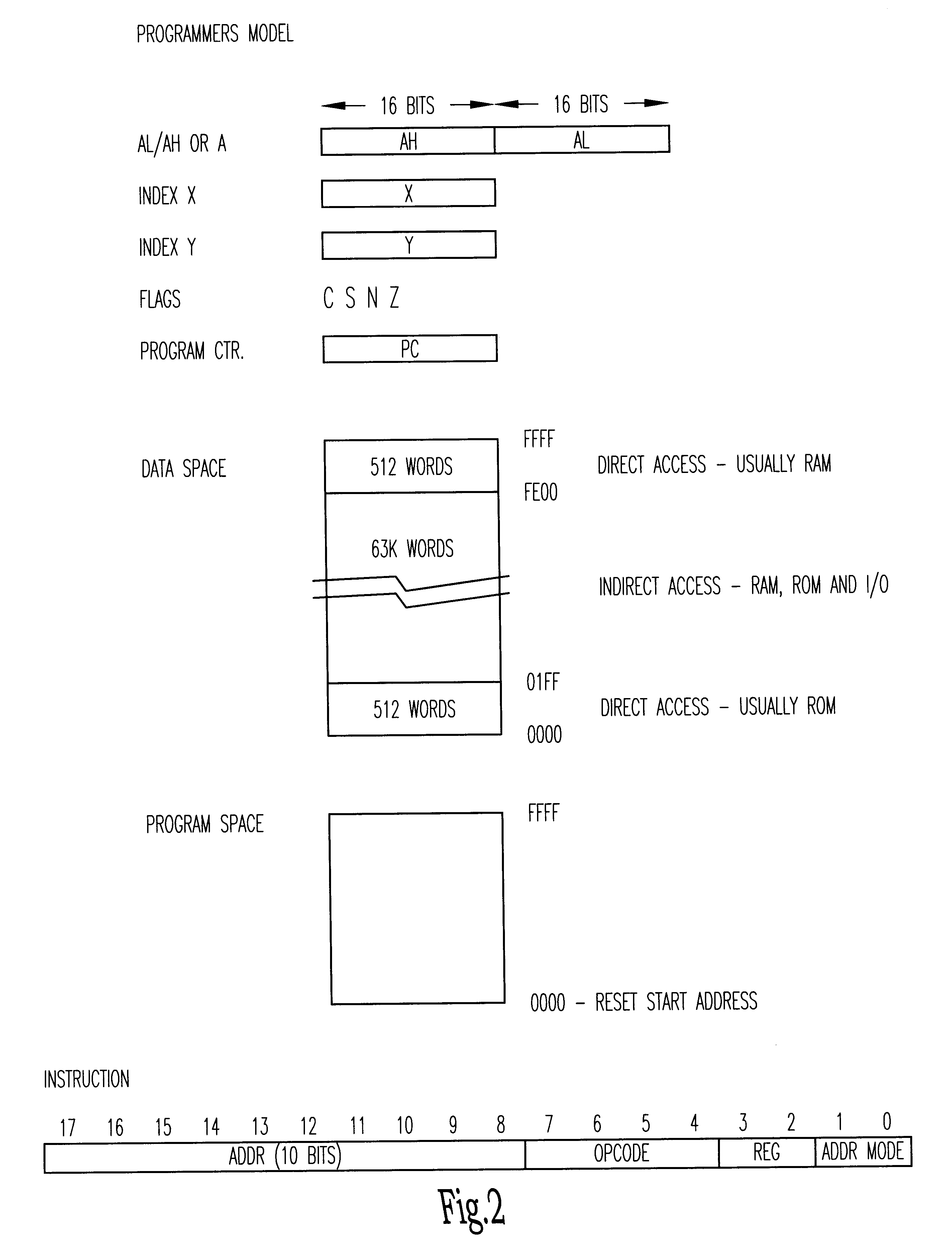

Data processing circuits and interfaces

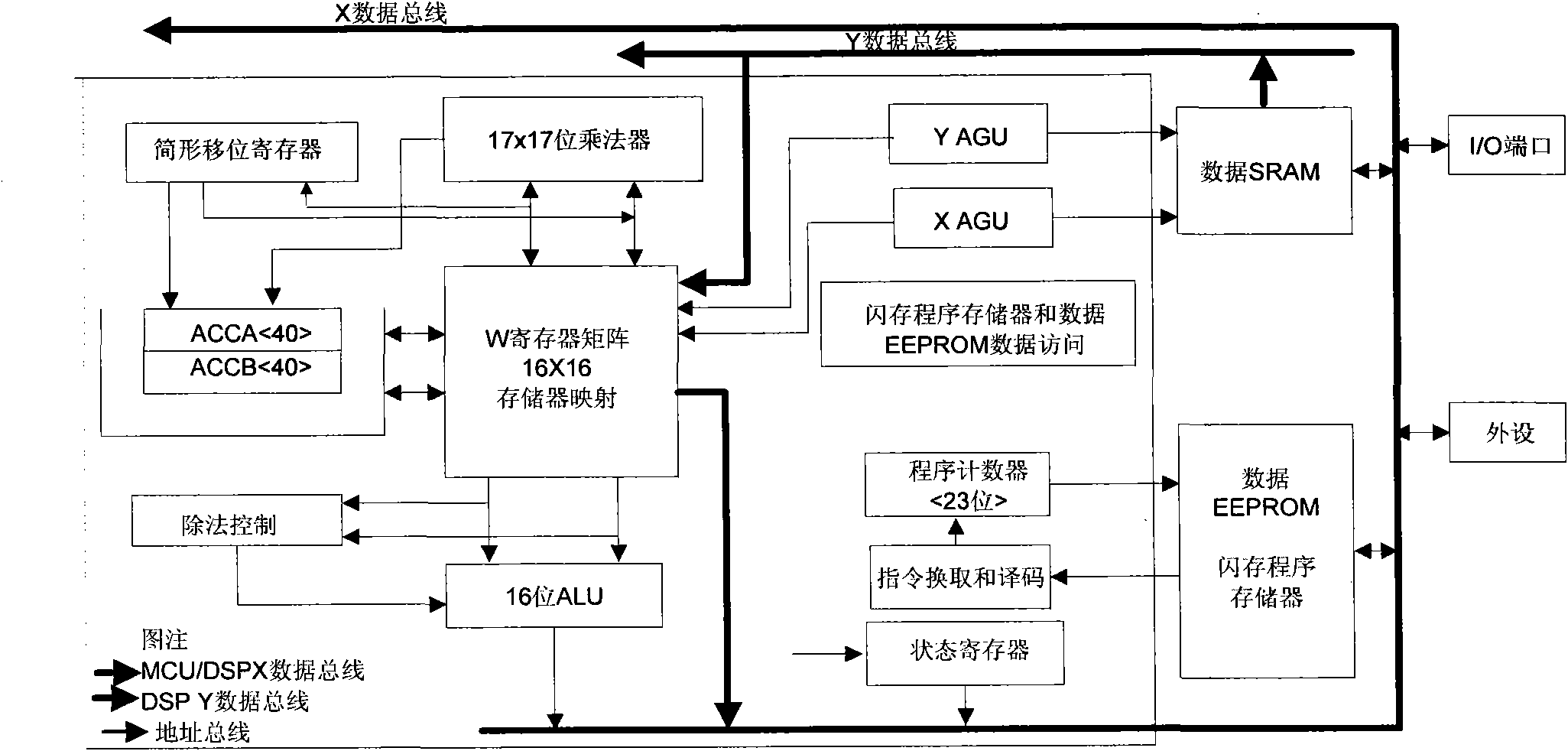

An integrated circuit contains a microprocessor core, program memory and separate data storage, together with analogue and digital signal processing circuitry. The ALU is 16 bits wide, but a 32-bit shift unit is provided, using a pair of 16-bit registers. The processor has a fixed length instruction format, with an instruction set including multiply and divide operations which use the shift unit over several cycles. No interrupts are provided. External pins of the integrated circuit allow for single stepping and other debug operations, and a serial interface (SIF) which allows external communication of test data or working data as necessary. The serial interface has four wires (SERIN, SEROUT, SER-CLK, SERLOADB), allowing handshaking with a master apparatus, and allowing direct access to the memory space of the processor core, without specific program control. Within each processor cycle, the processor circuitry is divided into plural stages, and latches are interposed between the stages to minimize power consumption.

Owner:CAMBRIDGE CONSULTANTS LTD

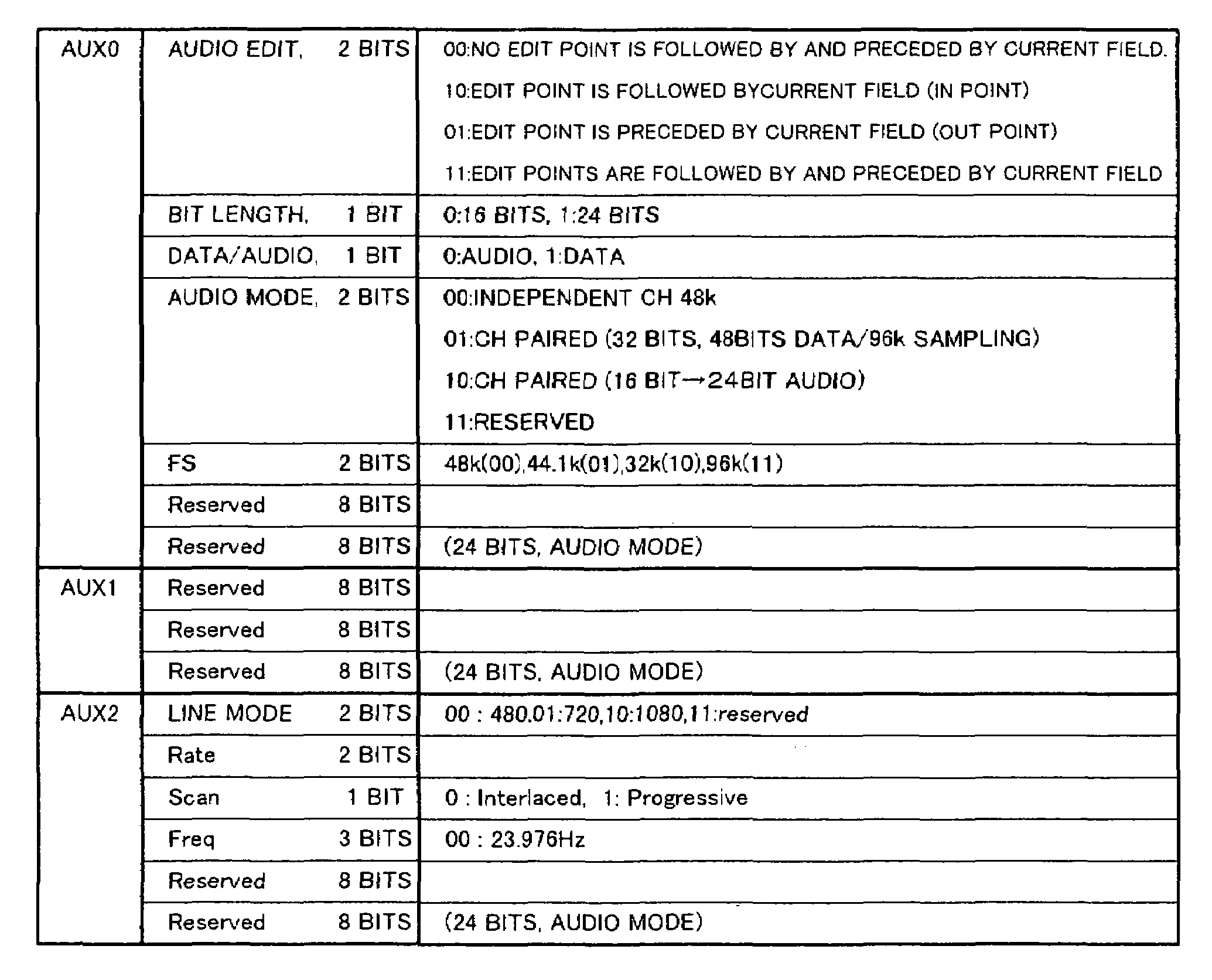

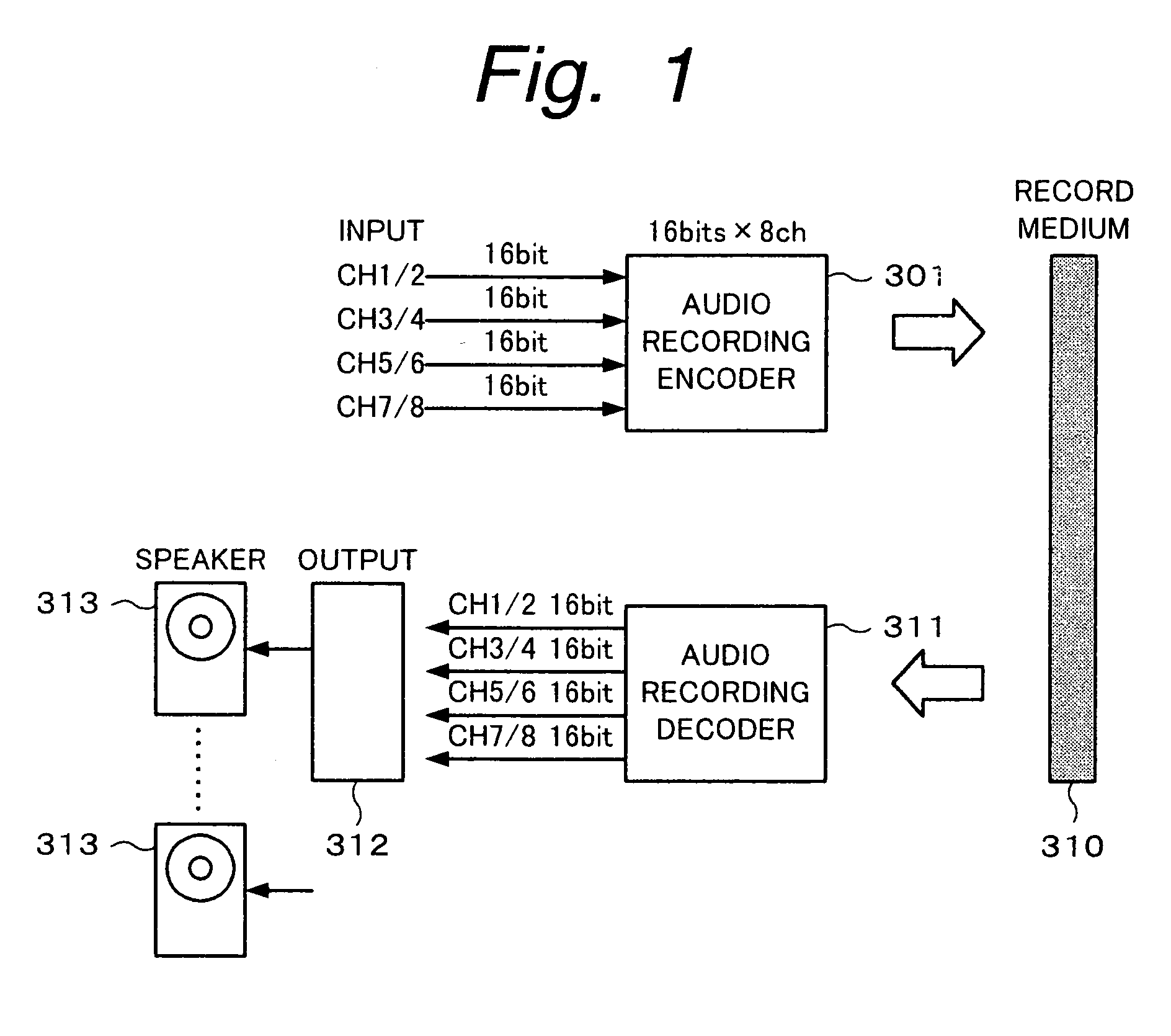

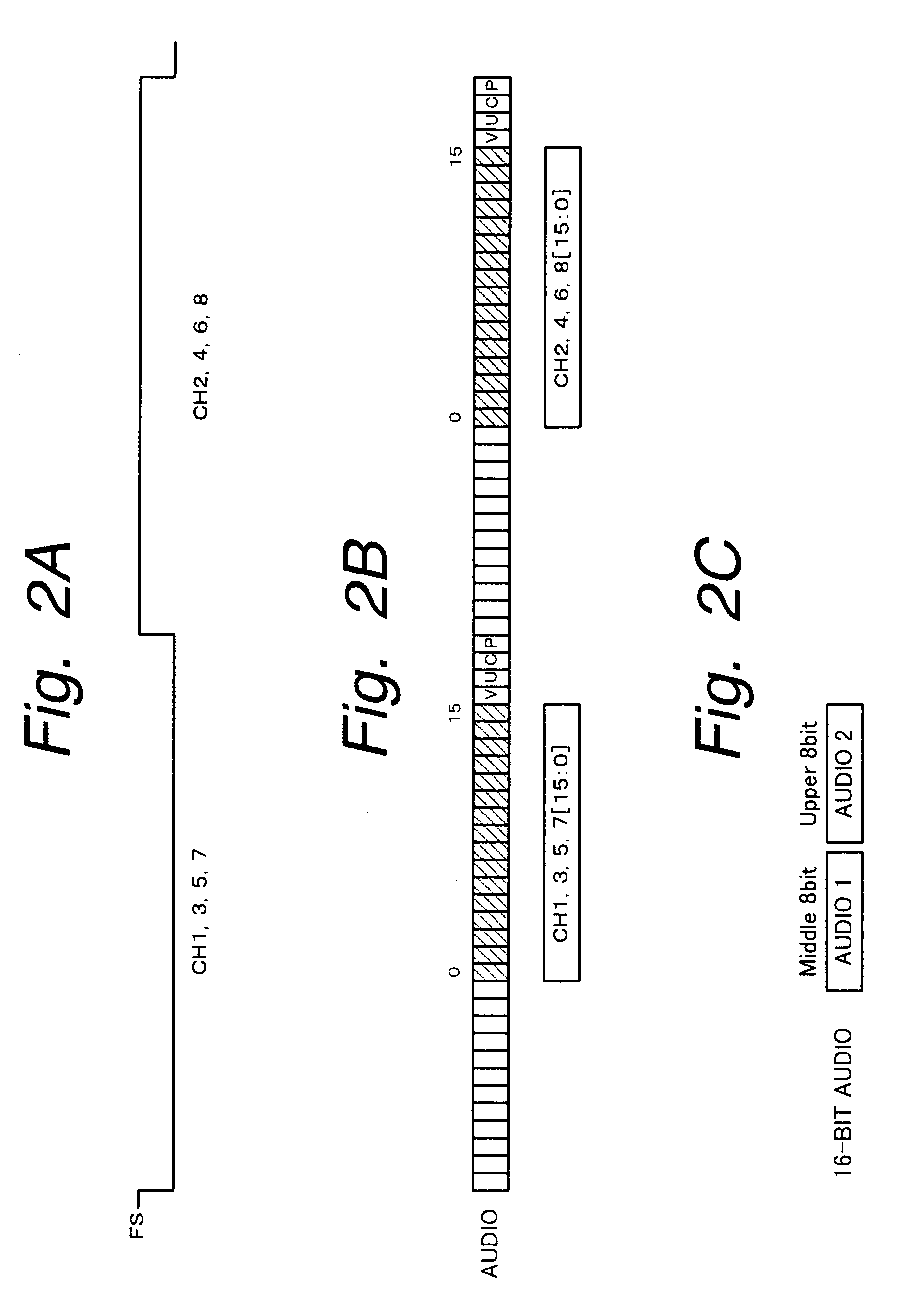

Digital signal, processing apparatus, digital signal processing method, digital signal recording apparatus, digital signal reproducing apparatus, and digital video-audio signal recording and reproducing apparatus

InactiveUS6950603B1Television system detailsColor television signals processingDigital videoDigital signal processing

Owner:SONY CORP

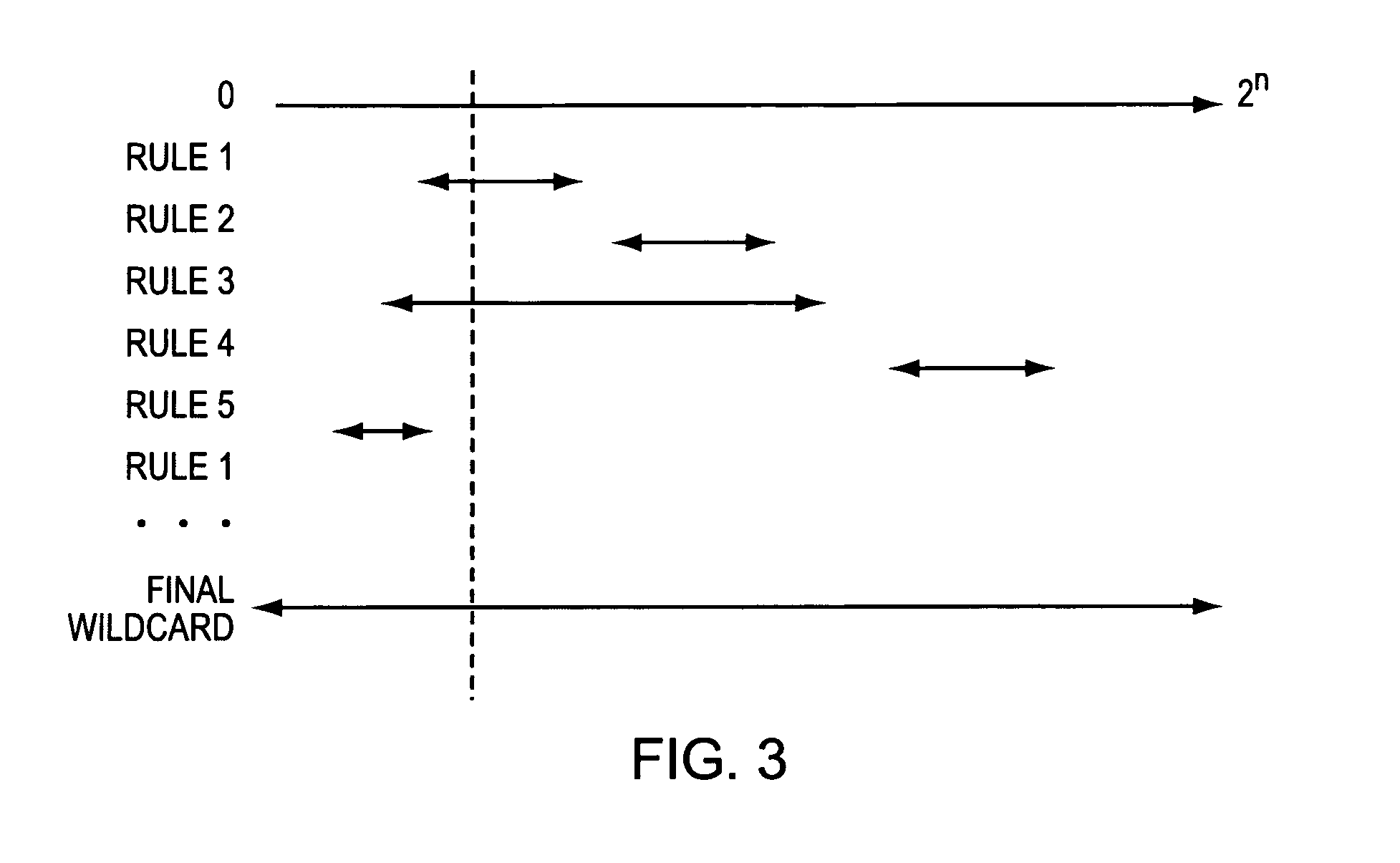

Method for high speed packet classification

Owner:CISCO TECH INC

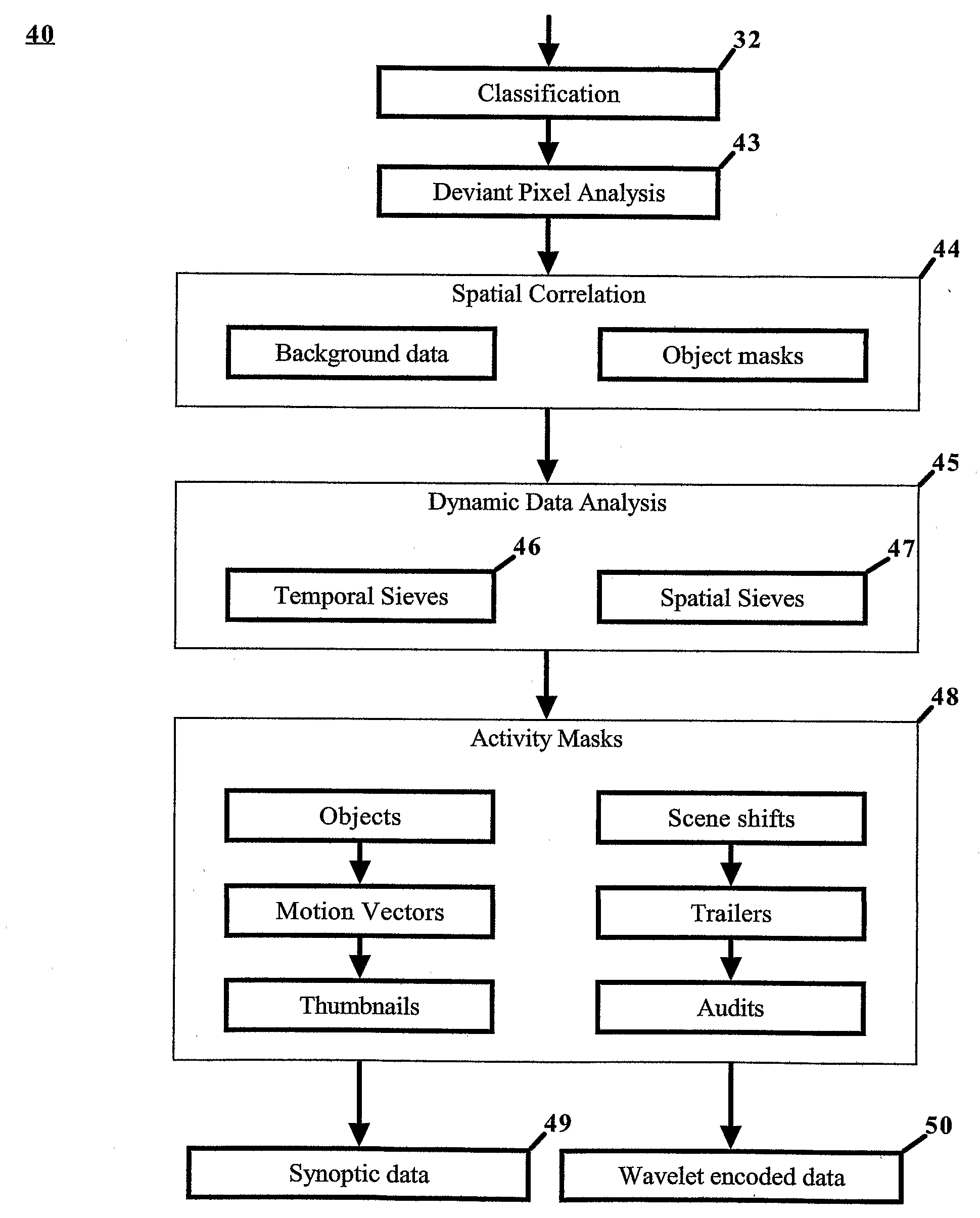

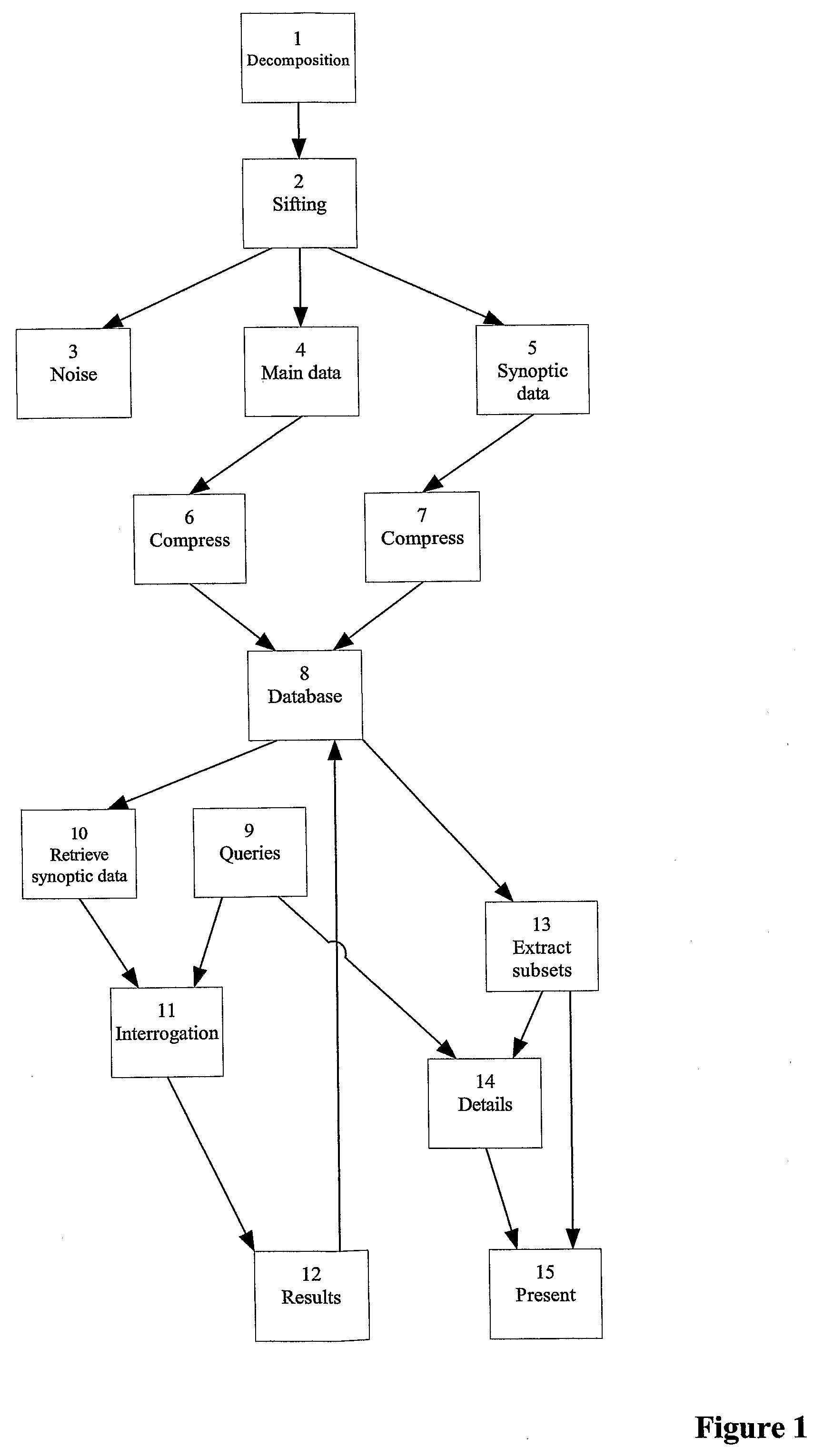

Post-Recording Data Analysis and Retrieval

InactiveUS20080263012A1Digital data information retrievalModulated-carrier systemsDigital dataData compression

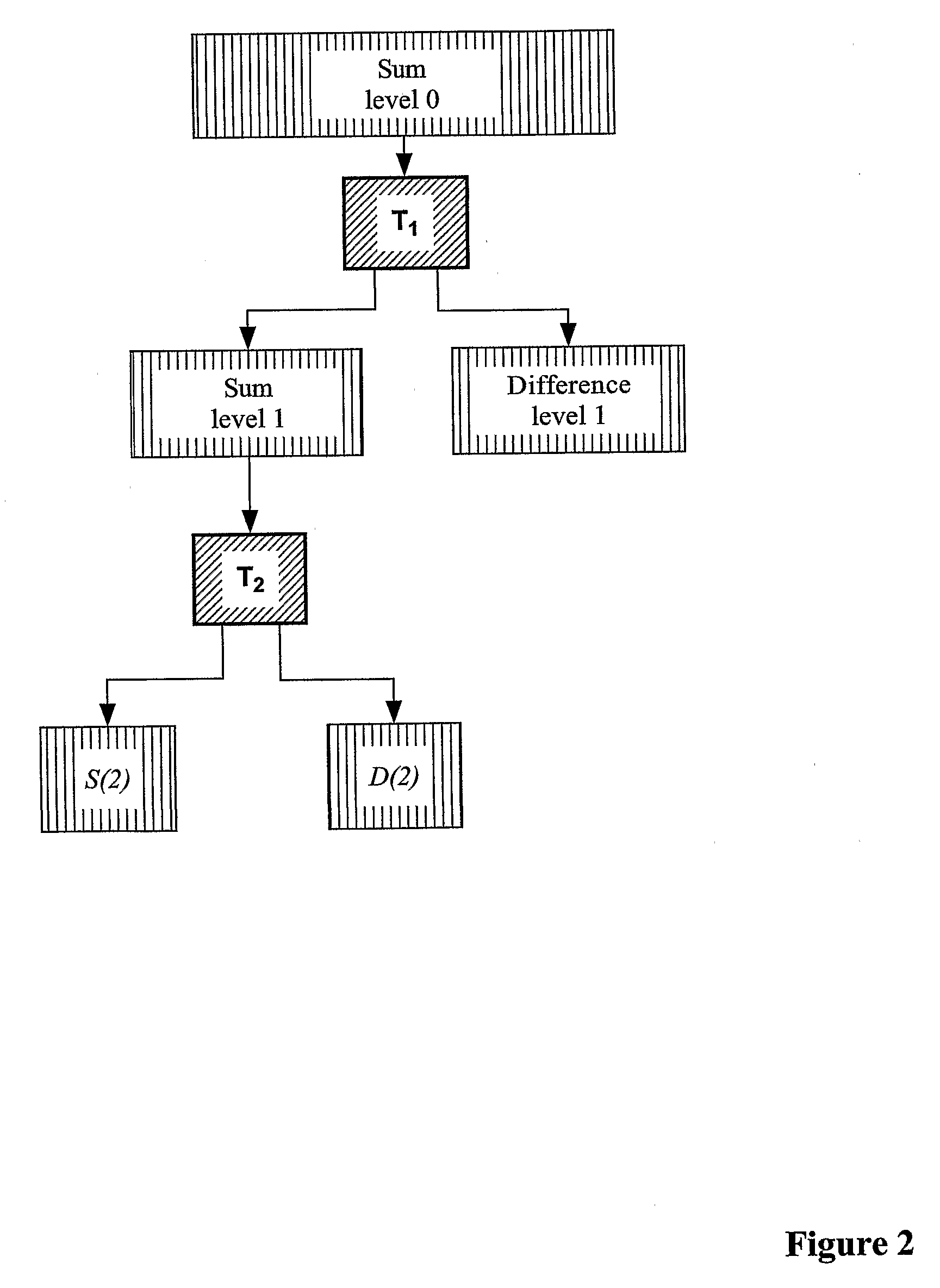

When making digital data recordings using some form of computer or calculator, data is input in a variety of ways and stored on some form of electronic medium. During this process calculations and transformations are performed on the data to optimize it for storage. This invention involves designing the calculations in such a way that they include what is needed for each of many different processes, such as data compression, activity detection and object recognition. As the incoming data is subjected to these calculations and stored, information about each of the processes is extracted at the same time. Calculations for the different processes can be executed either serially on a single processor, or in parallel on multiple distributed processors. We refer to the extraction process as “synoptic decomposition”, and to the extracted information as “synoptic data”. The term “synoptic data” does not normally include the main body of original data. The synoptic data is created without any prior bias to specific interrogations that may be made, so it is unnecessary to input search criteria prior to making the recording. Nor does it depend upon the nature of the algorithms / calculations used to make the synoptic decomposition. The resulting data, comprising the (processed) original data together with the (processed) synoptic data, is then stored in a relational database. Alternatively, synoptic data of a simple form can be stored as part of the main data. After the recording is made, the synoptic data can be analyzed without the need to examine the main body of data. This analysis can be done very quickly because the bulk of the necessary calculations have already been done at the time of the original recording. Analyzing the synoptic data provides markers that can be used to access the relevant data from the main data recording if required. The nett effect of doing an analysis in this way is that a large amount of recorded digital data, that might take days or weeks to analyze by conventional means, can be analyzed in seconds or minutes. This invention also relates to a process for generating continuous parameterised families of wavelets. Many of the wavelets can be expressed exactly within 8-bit or 16-bit representations. This invention also relates to processes for using adaptive wavelets to extract information that is robust to variations in ambient conditions, and for performing data compression using locally adaptive quantisation and thresholding schemes, and for performing post recording analysis.

Owner:ASTRAGROUP AS

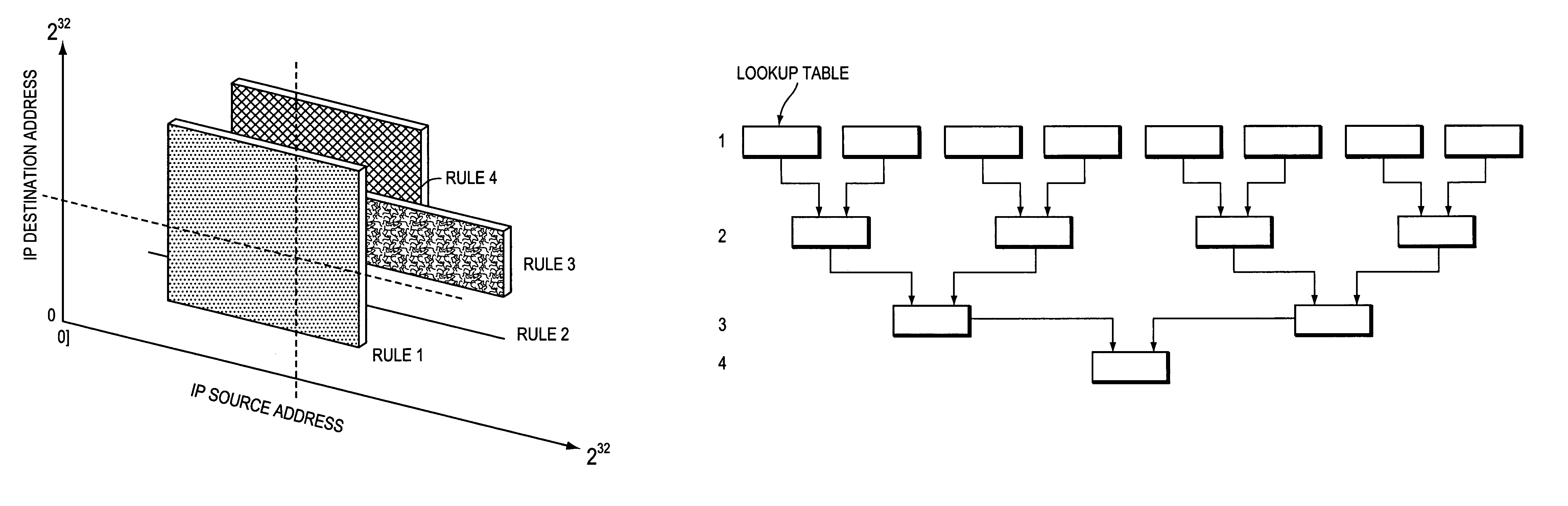

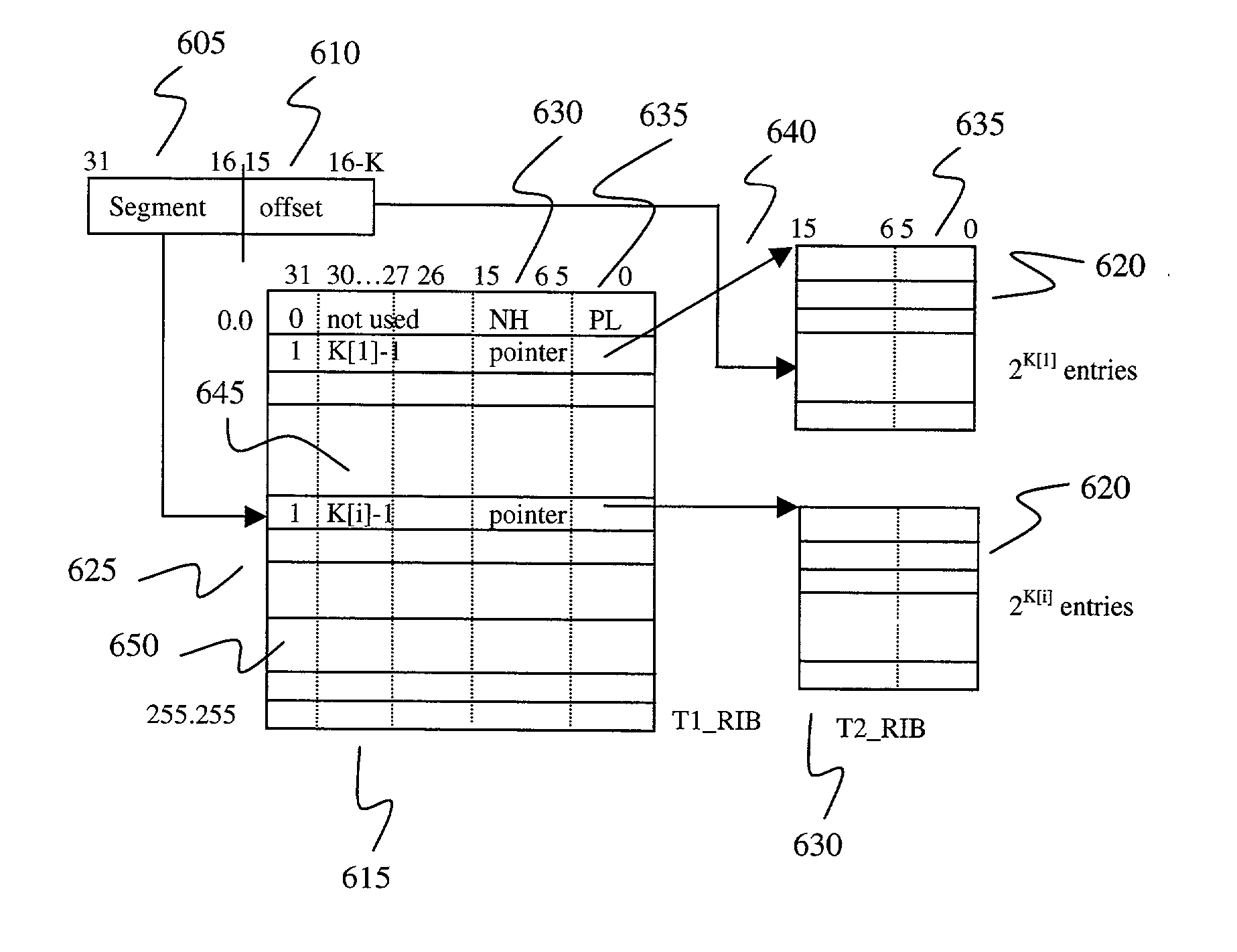

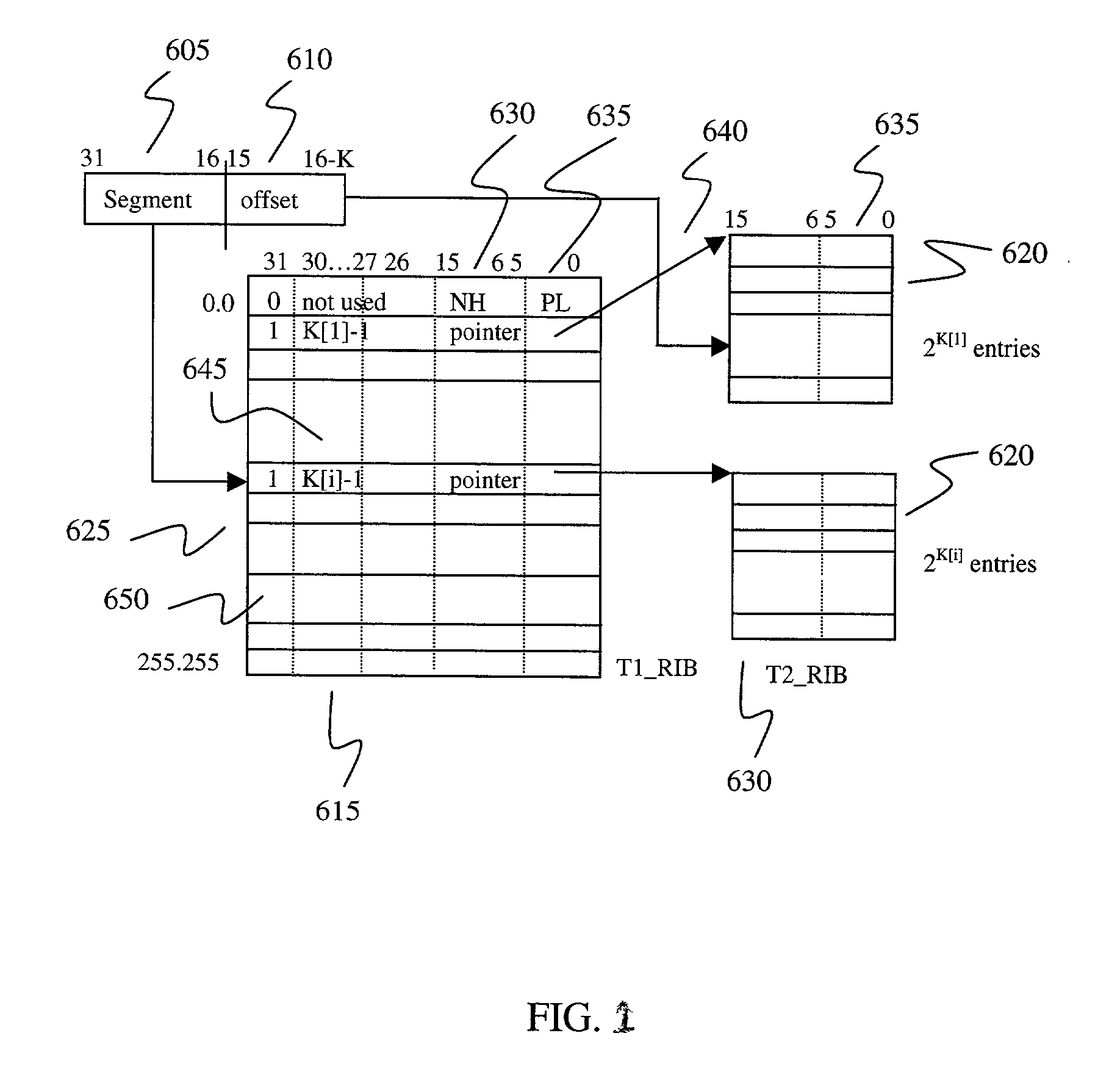

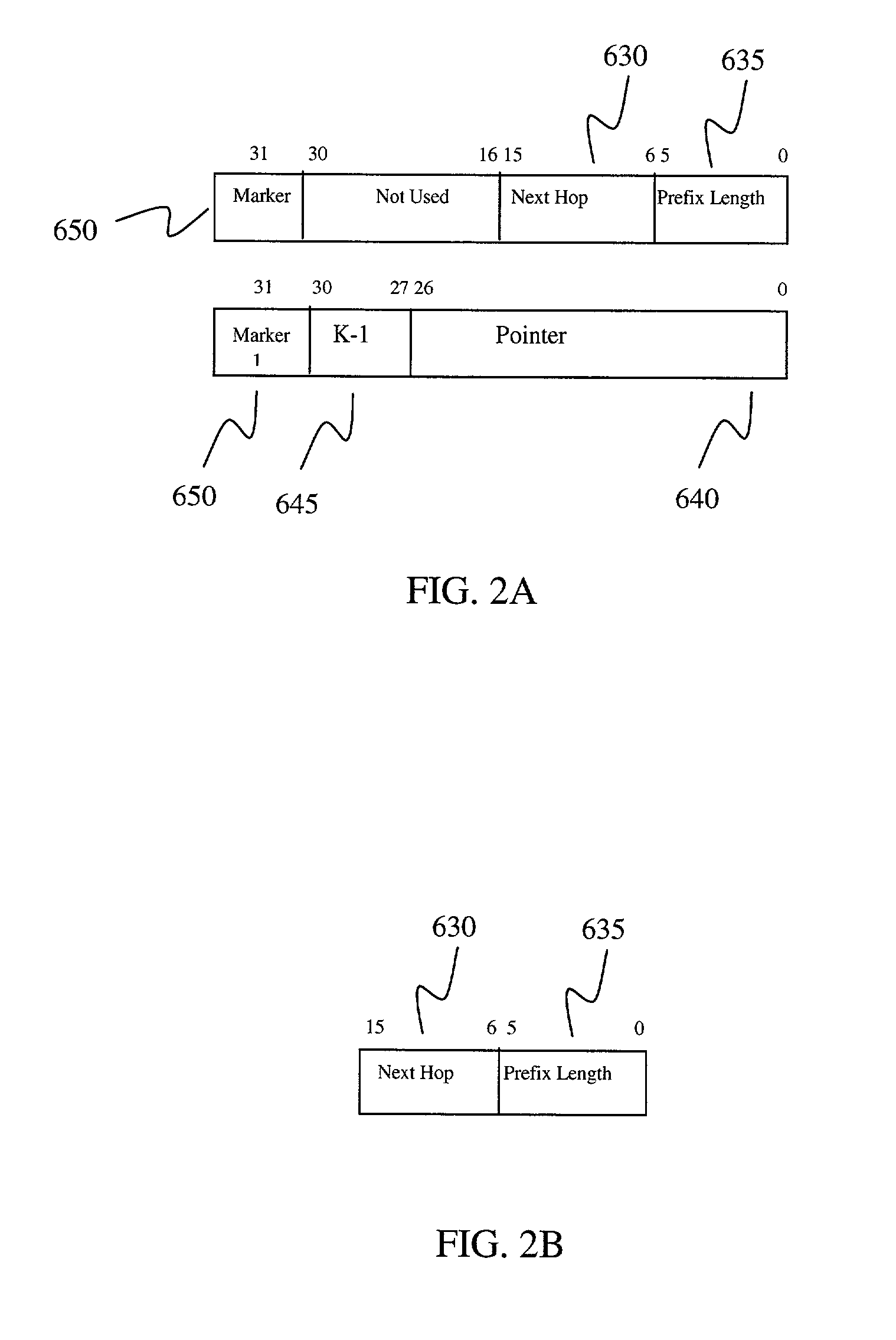

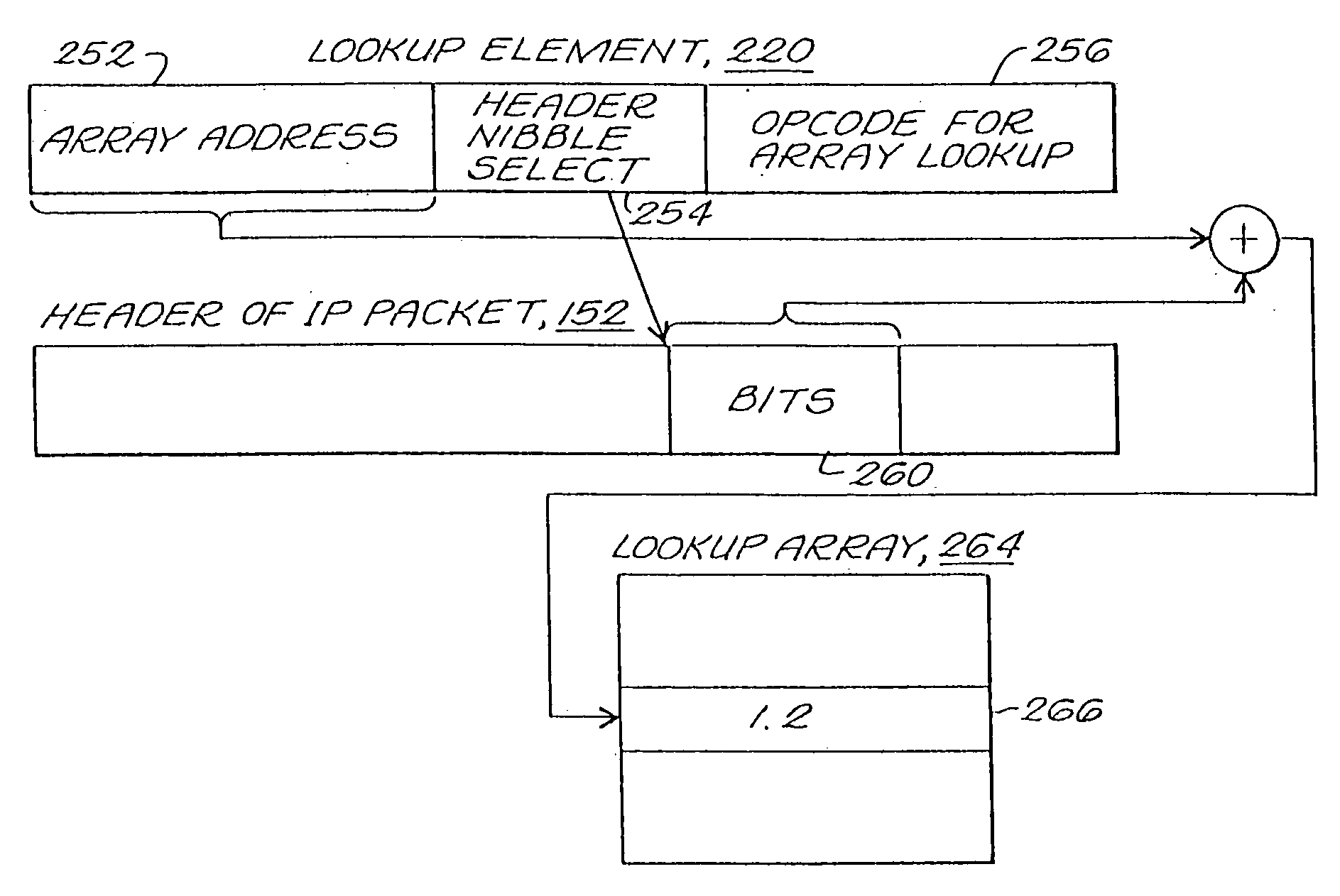

Fast IP route lookup with 16/K and 16/Kc compressed data structures

InactiveUS20020172203A1Data switching by path configurationOther databases indexingPresent dayArray data structure

An advanced data structure allows lookup based upon the most significant 16 bits and the following variable number of K bits of the IP destination address. This 16 / K scheme requires less than 2 MB memory to store the whole routing tables of present day backbone routers. A 16 / Kc version utilizes bitmaps to compress the table to less than 0.5 MB. For the 16 / K data structure each route lookup requires at most 2 memory accesses while the 16 / Kc requires at most 3 memory accesses. By configuring the processor properly and developing a few customized instructions to accelerate route lookup, one can achieve 85 million lookups per second (MLPS) in the typical case with the processor running at 200 MHz. Further, the lookup method can be implemented using pipelining techniques to perform three lookups for three incoming packets simultaneously. Using such techniques, 100 MLPS performance can be achieved.

Owner:TESILICA

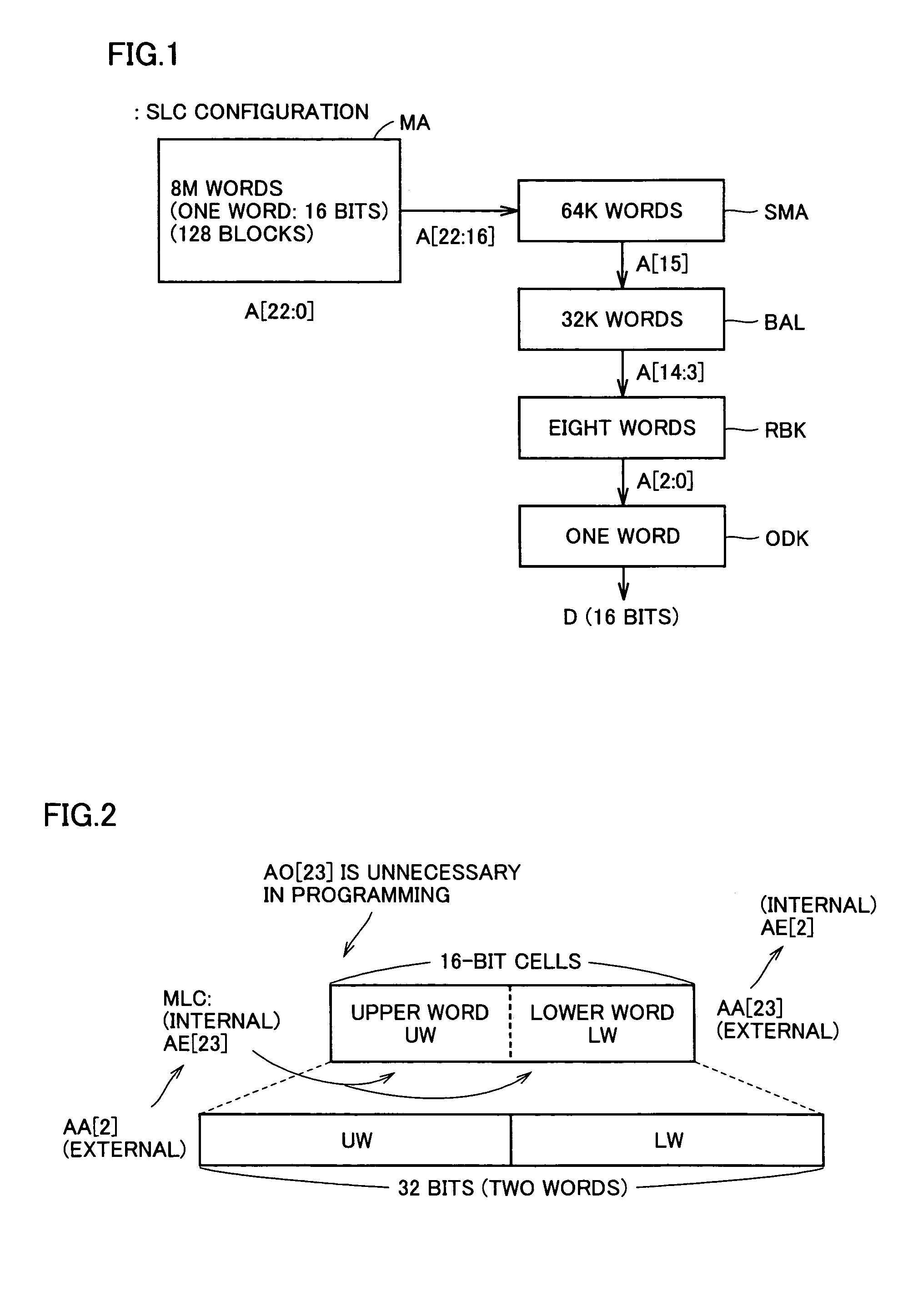

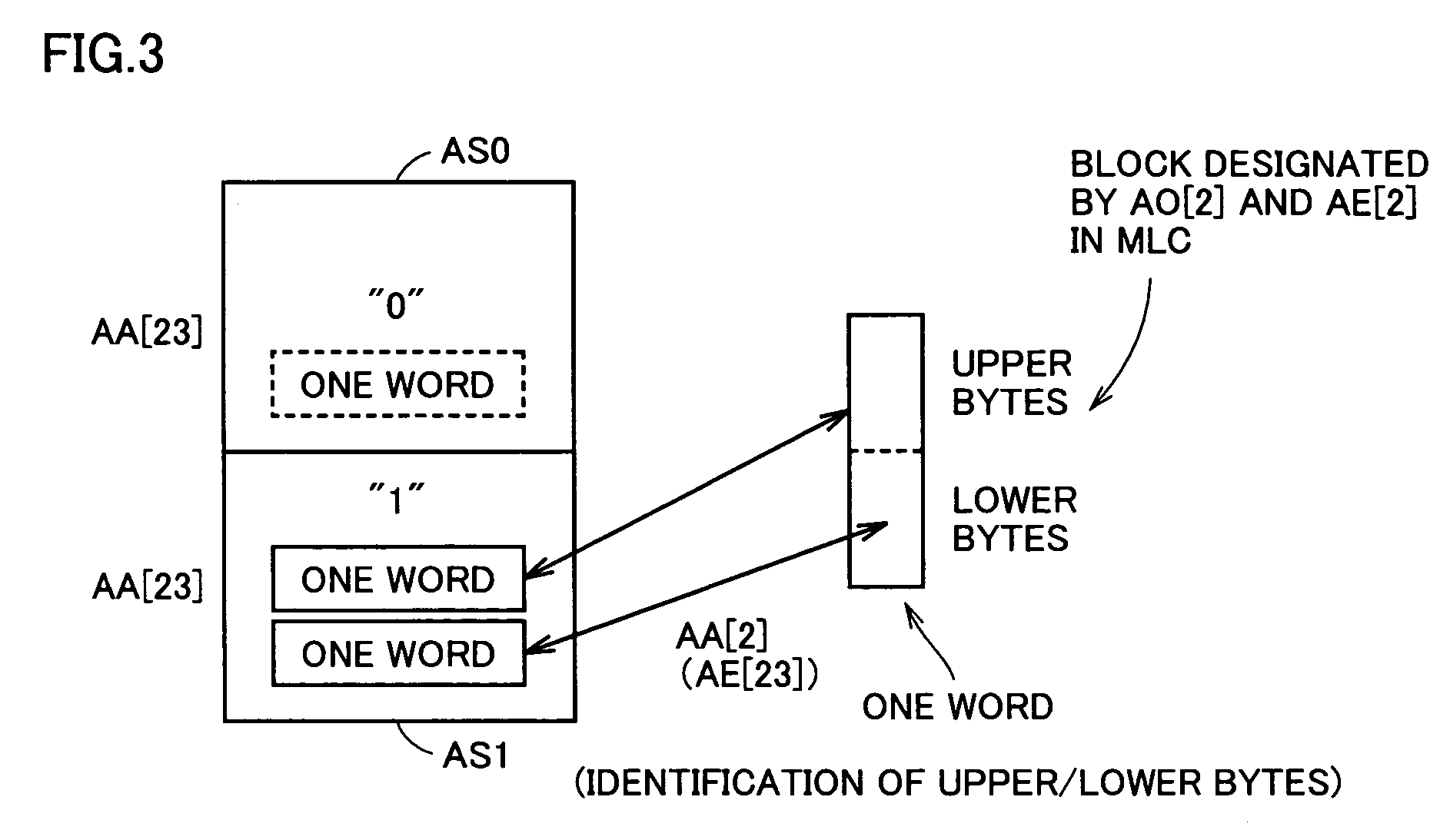

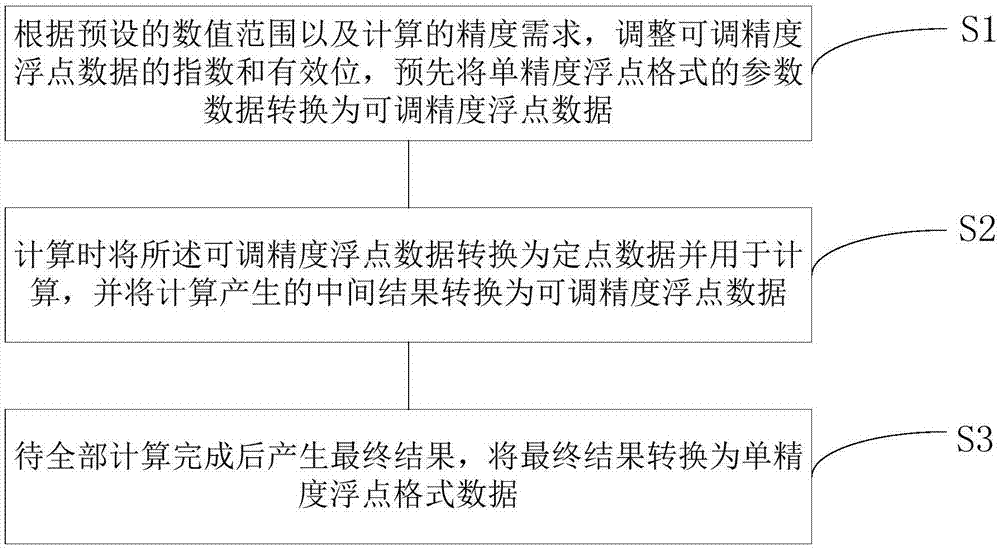

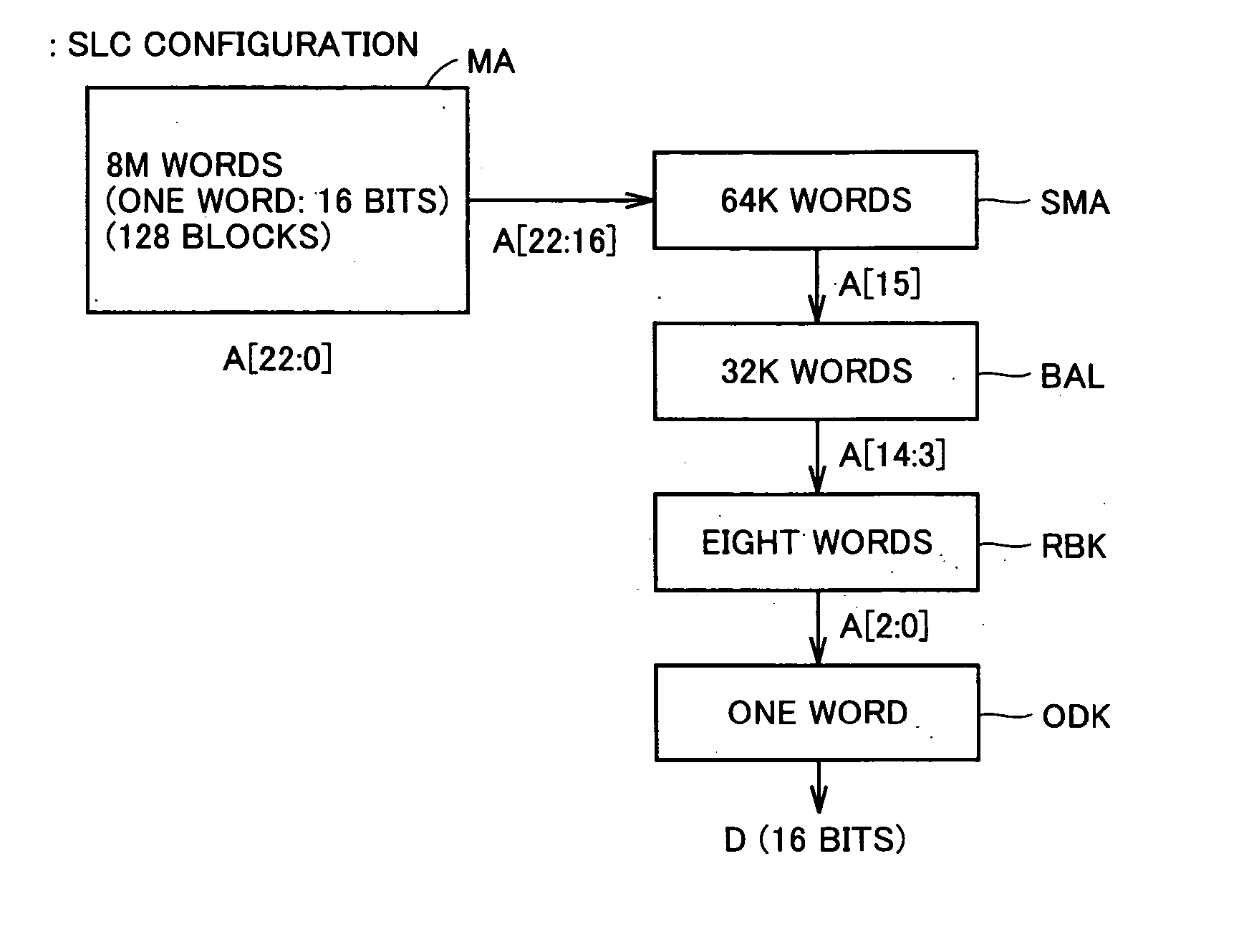

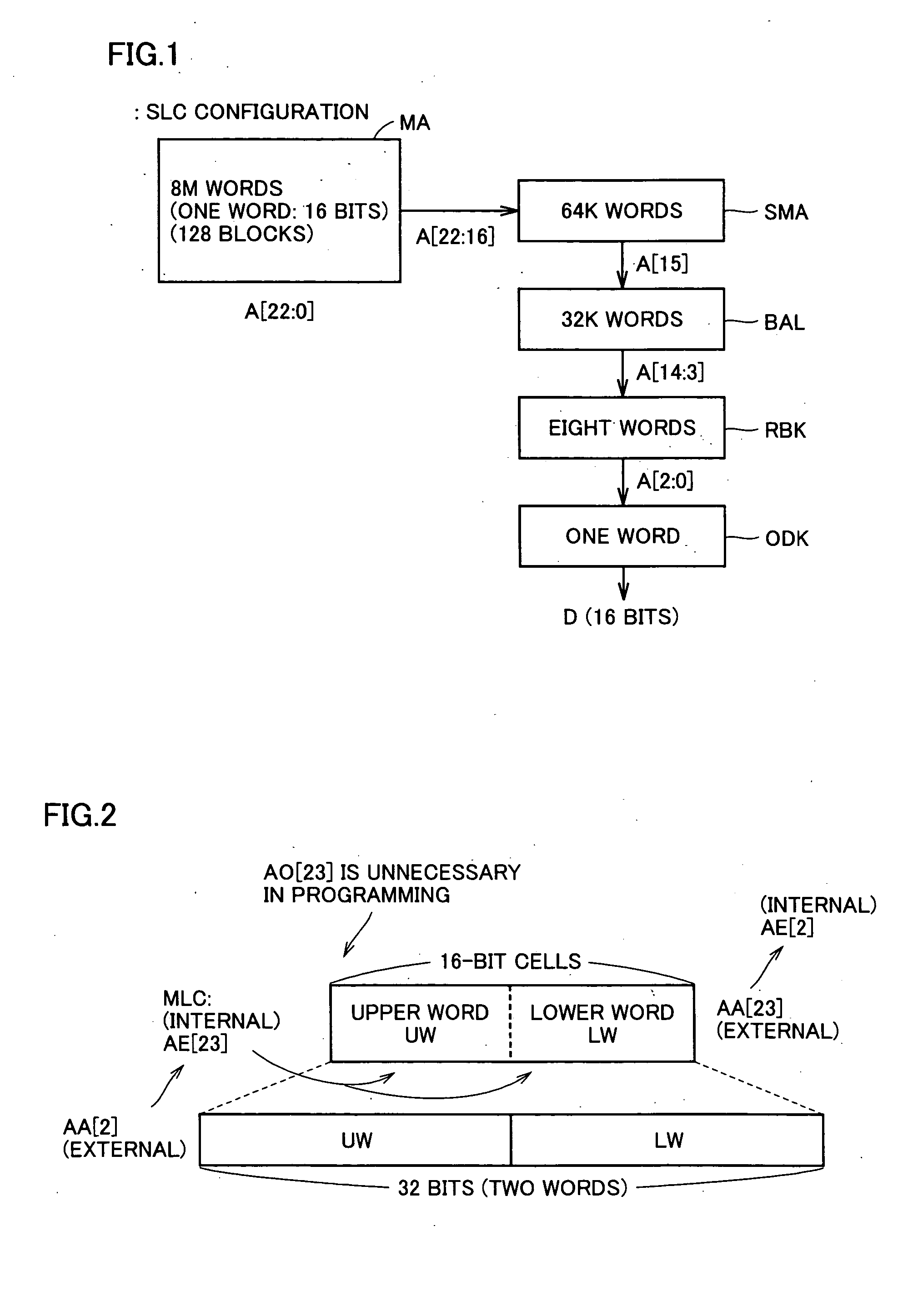

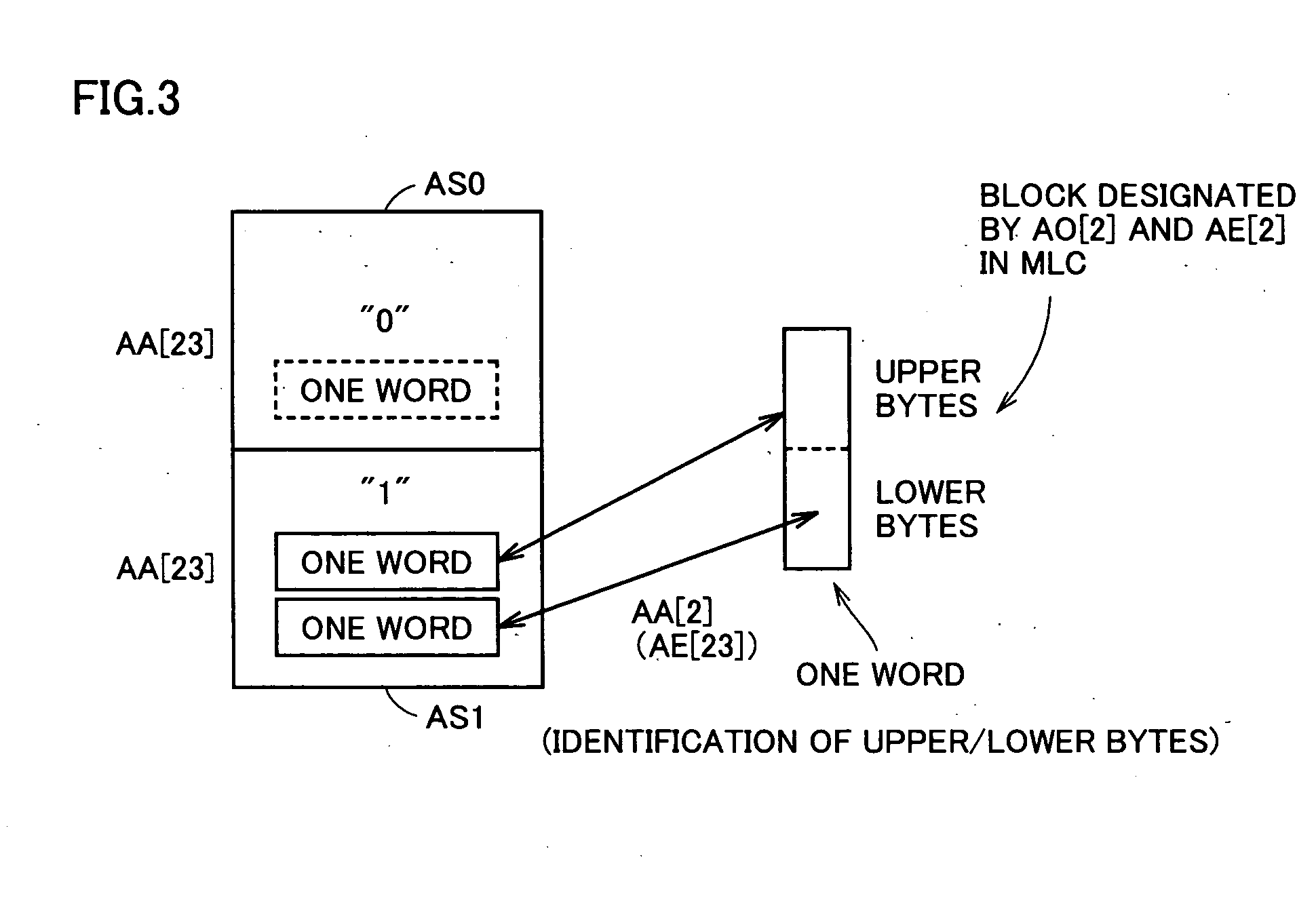

Multi-level nonvolatile semiconductor memory device utilizing a nonvolatile semiconductor memory device for storing binary data

A multi-level semiconductor memory device for storing multi-level data having three or more values is implemented by utilizing a nonvolatile memory device for storing 2-valued data. Identification of successive 16-bit data externally applied is performed with external address bit AA [2], and a storage block is selected with external address bit AA [23]. Upper word data LW and lower word data UW are compressed into byte data of 8 bits, respectively, and stored in a memory cell array.

Owner:RENESAS ELECTRONICS CORP

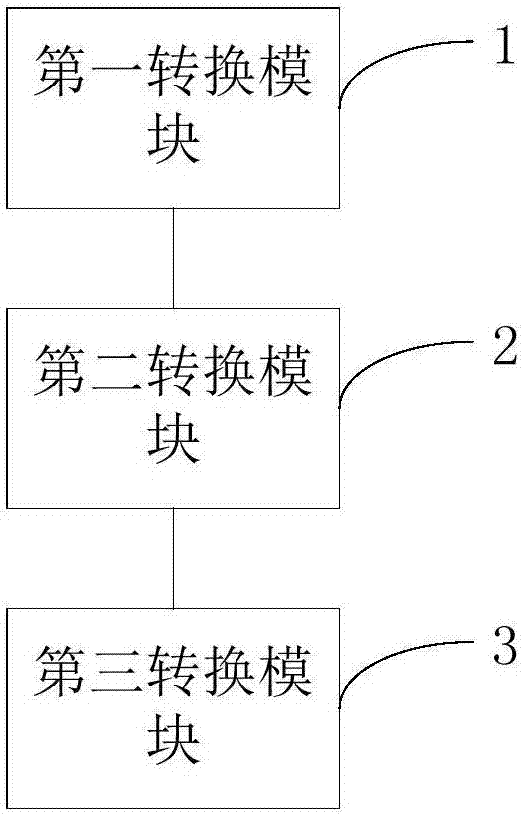

Fixed-point method and system for floating-point operation

ActiveCN107451658AReduce precision lossImprove efficiencyPhysical realisationNeural learning methodsNumerical rangeParallel computing

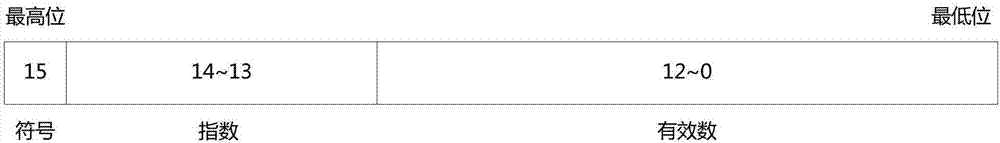

The invention discloses a fixed-point method for a floating-point operation. The method comprises the steps that according to a preset numerical range and the calculation precision requirement, the exponents and significant bits of adjustable-precision floating-point data are adjusted, and the parameter data in a single-precision floating-point format are converted into adjustable-precision floating-point data; when calculating is carried out, the adjustable-precision floating-point data are converted into fixed-point data and used for calculation, and an intermediate result generated by calculation is converted into adjustable-precision floating-point data; a final result is generated after all calculation; and the final result is converted to data in the single-precision floating-point format. According to the invention, standard floating-point data can be represented with a 16-bit bit width or a smaller bit width to realize fixed-point conversion of the floating-point operation; the storage space is saved; the operation performance is improved; and the calculation precision is not influenced.

Owner:HANGZHOU FEISHU TECH CO LTD

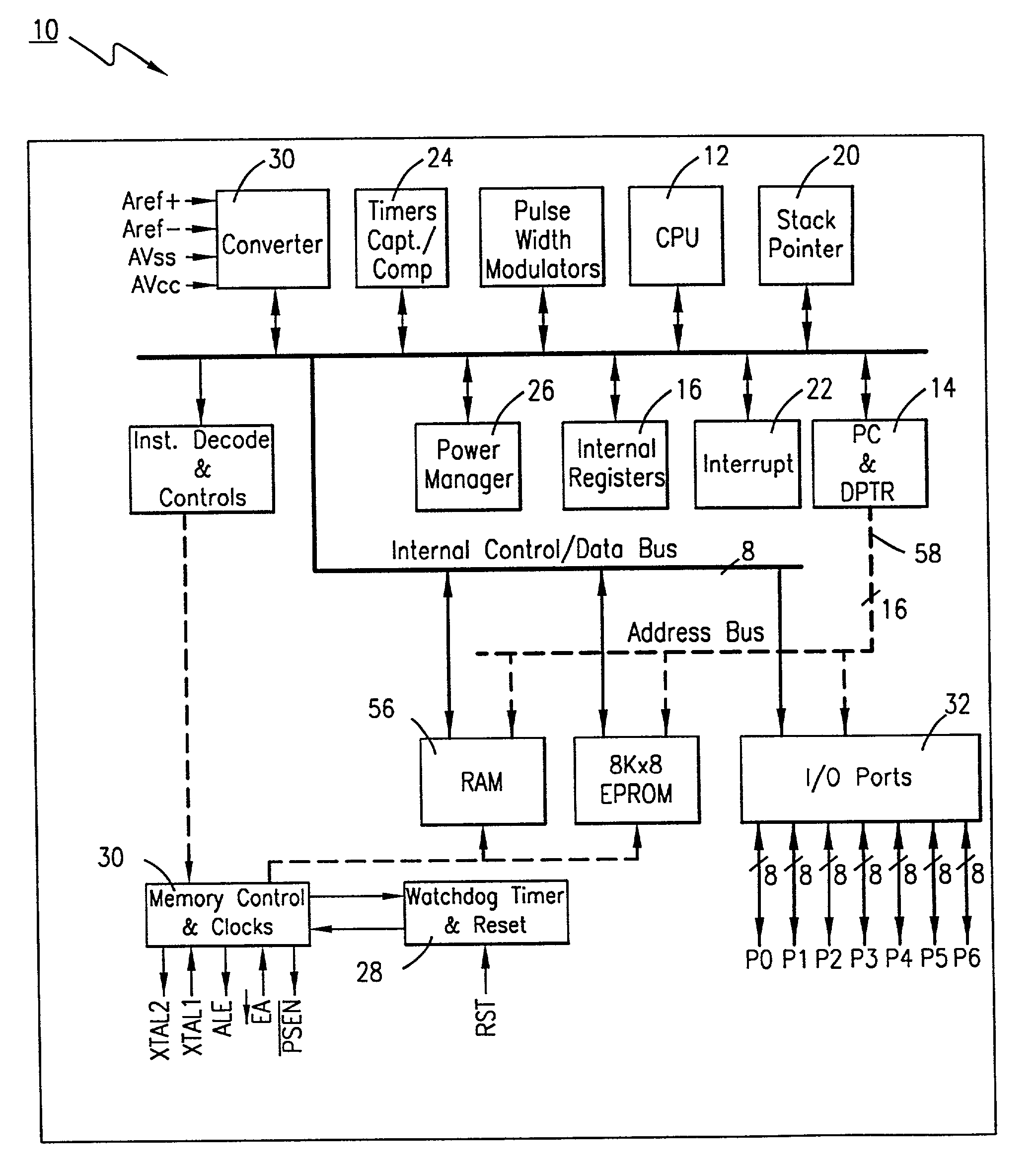

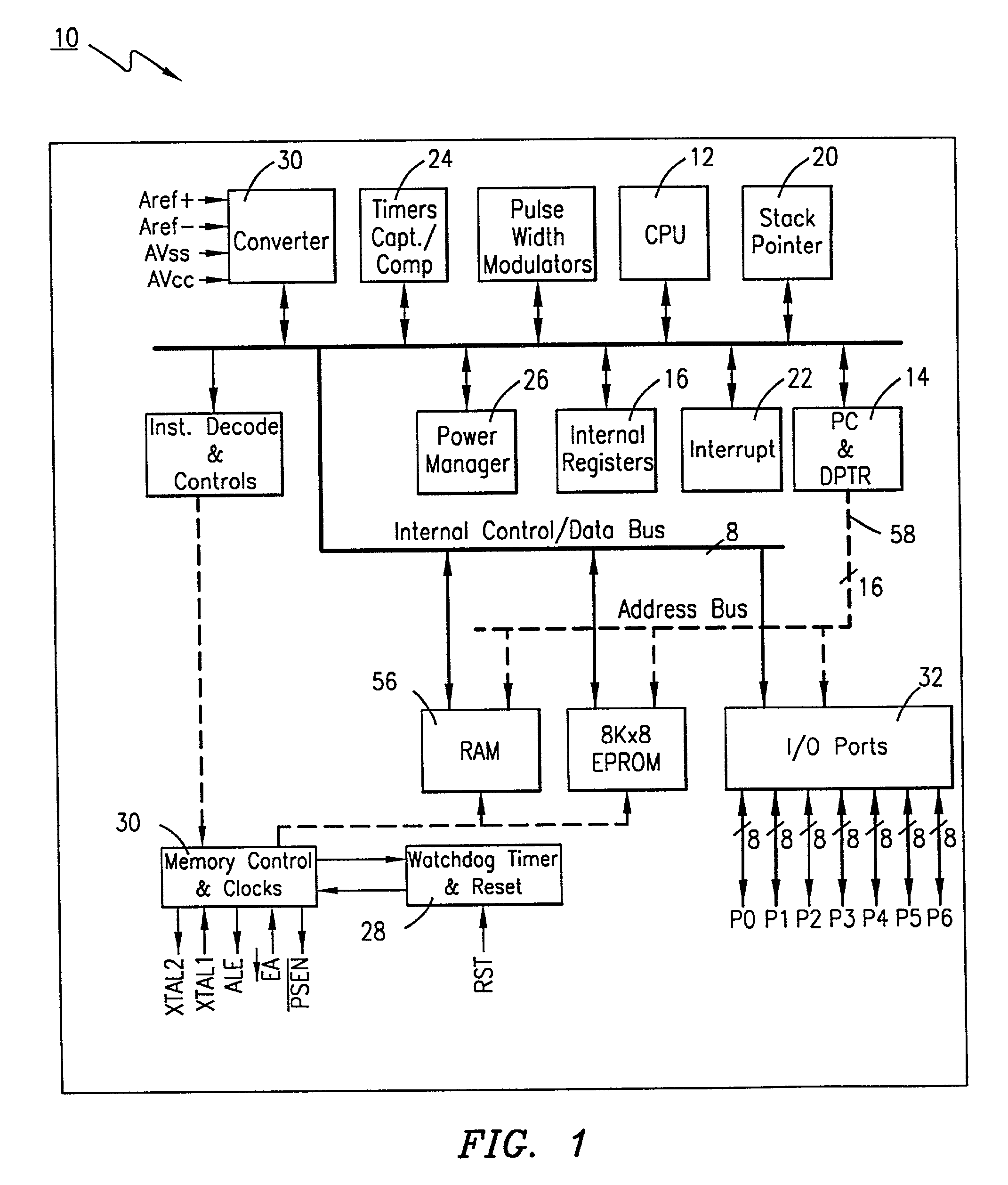

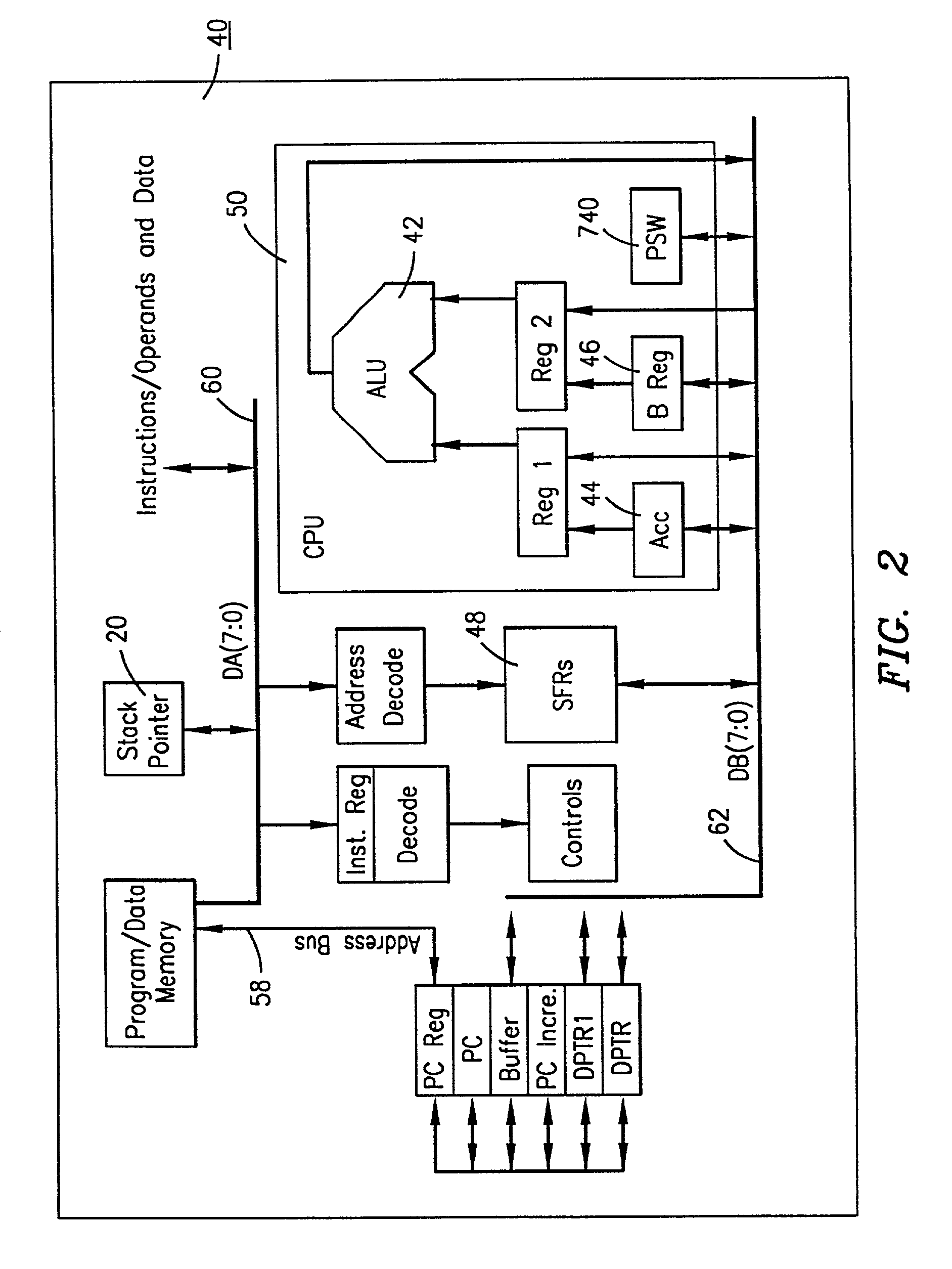

Microcontroller with a user configurable pulse width modulator

A microcontroller integrated circuit incorporating a user configurable pulse width modulator. The pulse width modulator circuitry is configurable to be a single, for example 32-bit pulse width modulator, or a plurality of pulse width modulators each having a bit width that is divisible by the single 32-bit pulse width modulator (e.g., 2, 4, 8 or 16-bit pulse width modulators).

Owner:MA EDWARD TANG KWAI +2

Semiconductor memory device

A multi-level semiconductor memory device for storing multi-level data having three or more values is implemented by utilizing a nonvolatile memory device for storing 2-valued data. Identification of successive 16-bit data externally applied is performed with external address bit AA [2], and a storage block is selected with external address bit AA [23]. Upper word data LW and lower word data UW are compressed into byte data of 8 bits; respectively, and stored in a memory cell array.

Owner:RENESAS ELECTRONICS CORP

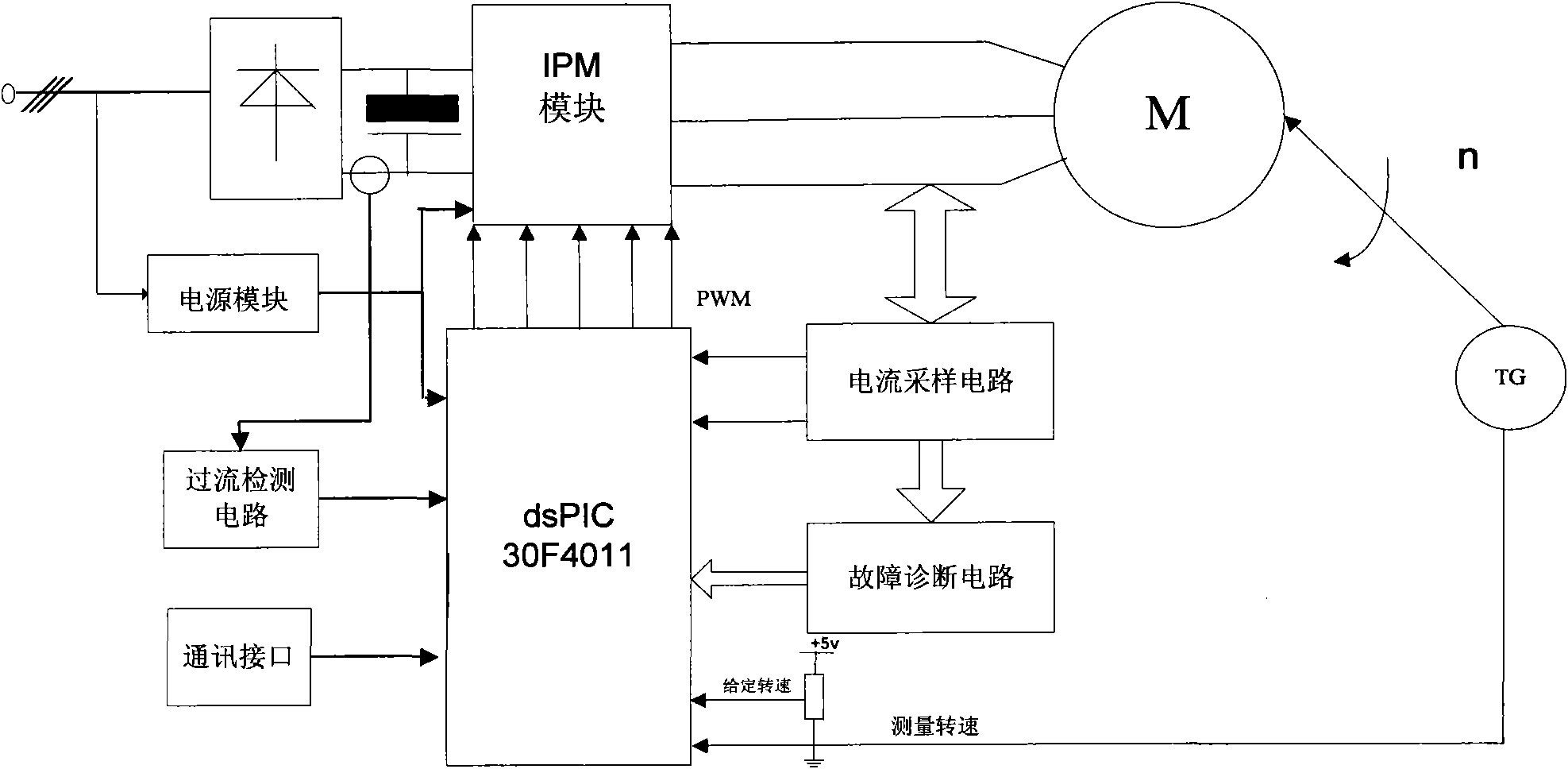

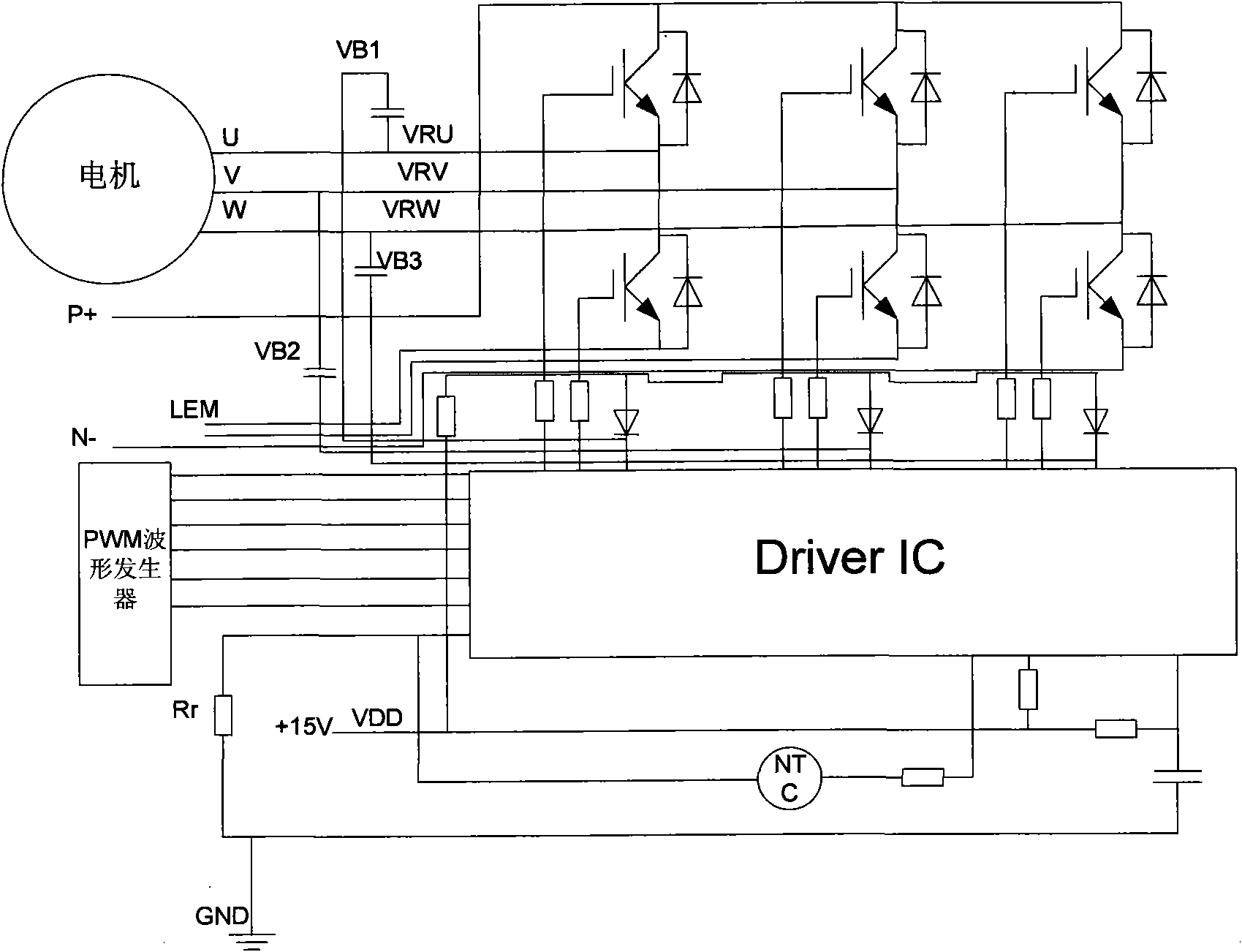

Singlechip-based induction motor variable frequency speed regulation control system

InactiveCN101977016AEfficient and rapid detectionDetect enoughAC motor controlEmergency protective circuit arrangementsMicrocontrollerEngineering

The invention discloses a singlechip-based induction motor variable frequency speed regulation control system. The system comprises a main circuit, an auxiliary power circuit, an inverter circuit, a control part, an over-current protection circuit, a rotation speed detection circuit and other peripheral circuits. A 16-bit high-performance signal controller dsPIC30F4011 which is produced by the Microchip Company is used as a control core by the system to perform speed regulation based on vector control motor excitation. A digital signal controller dsPIC30F4011 of the America Microchip Technology Company is used as a chip special for motor control, a digital signal processor (DSP) inner core is embedded, and the chip has quick data processing capacity and is provided with abundant input and output equipment and interface circuits; an intelligent power module (IPM) IRAMSIOUP 60A of the IR Company is an inverter switching device, so that the variable frequency speed regulation control system of an asynchronous motor is constructed; and the system has the characteristics that the system is simple to drive and easy to realize.

Owner:TIANJIN UNIVERSITY OF TECHNOLOGY

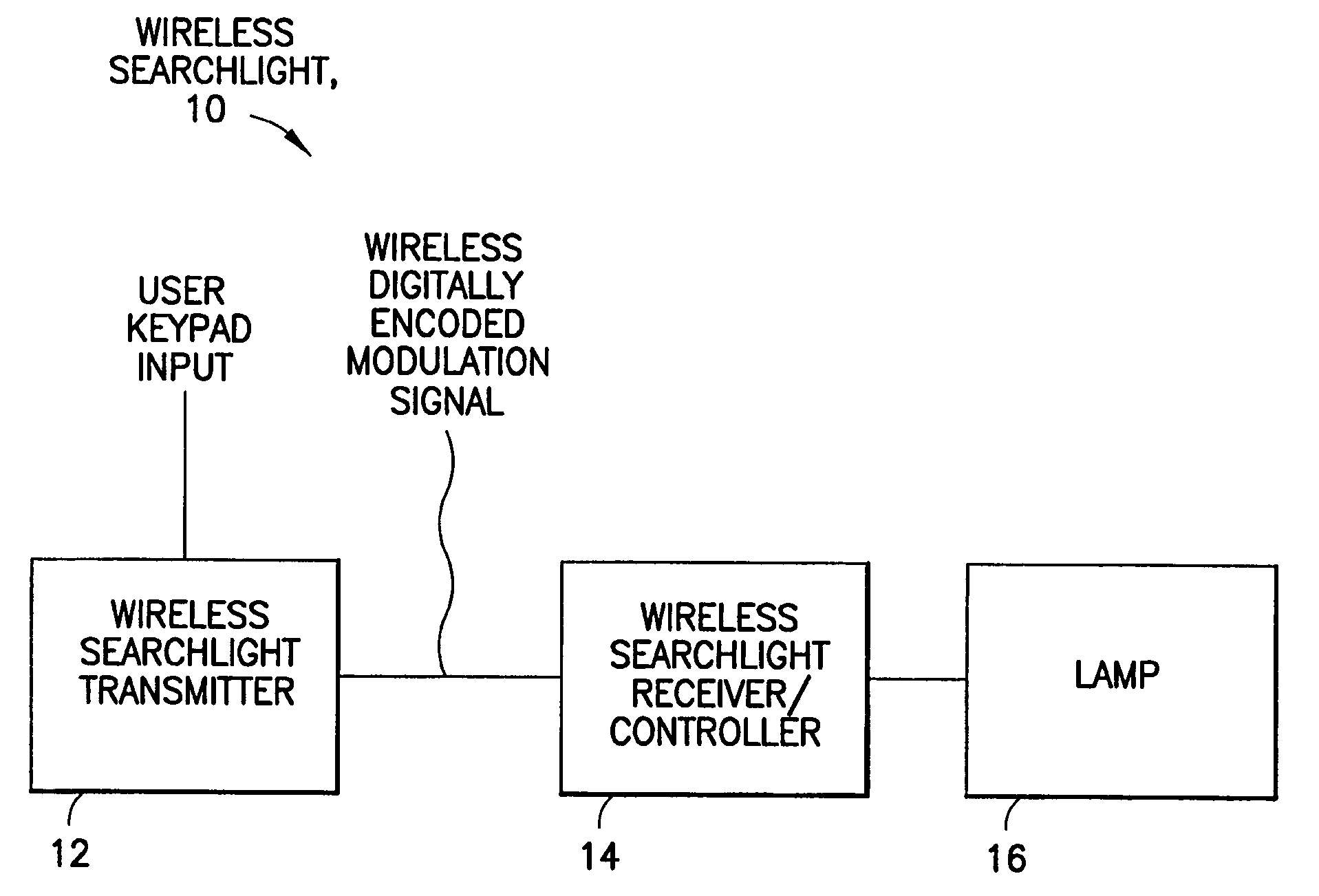

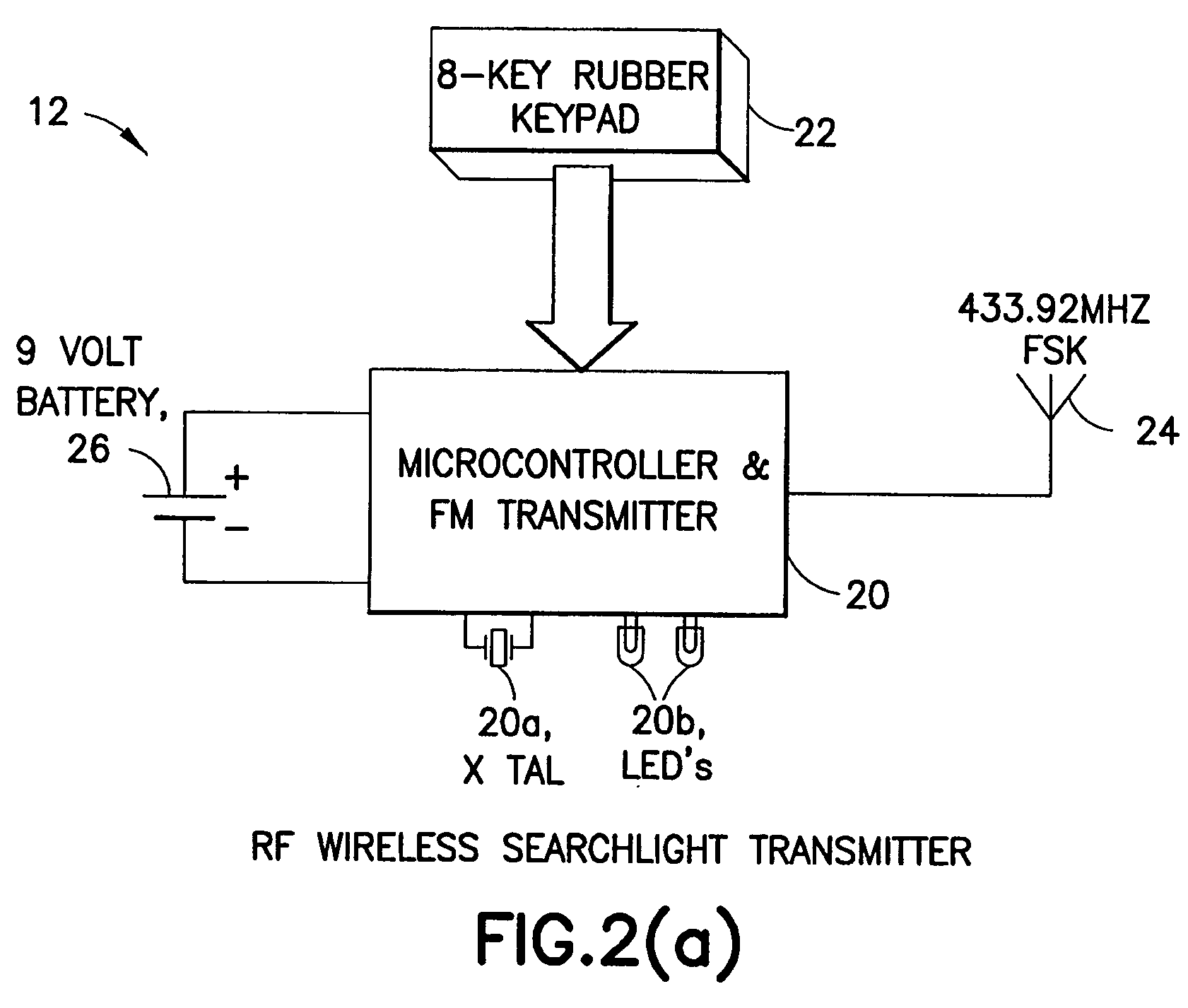

RF wireless permanently mounted searchlight

InactiveUS20050248930A1Eliminate distractionsMinimizes FM interferenceElectric signal transmission systemsElectrical apparatusControl signalUser input

The invention provides apparatus for controlling a search lamp using a wireless transmitter and receiver. The transmitter responds to user inputs by providing a wireless digitally encoded modulation signal containing information indicating at least one operation in a set of operations the search lamp is able to perform. The receiver responds to the wireless digitally encoded modulation signal by providing a control signal for controlling the functionality of the search lamp. The functionality may include, for example, moving the search lamp left / right and / or up / down, a sweep on / off @ ±45 degrees; X / Y / Z movement (Z when motors run simultaneously); Diagonal sweep (motors run simultaneously); Fast / Slow sweep (50% / 100%). The transmitter and receiver are programmable to communicate on a unique 16 bit digital code setting that provides about 65K different code settings, which may also include a random code setting.

Owner:XYLEM IP HLDG

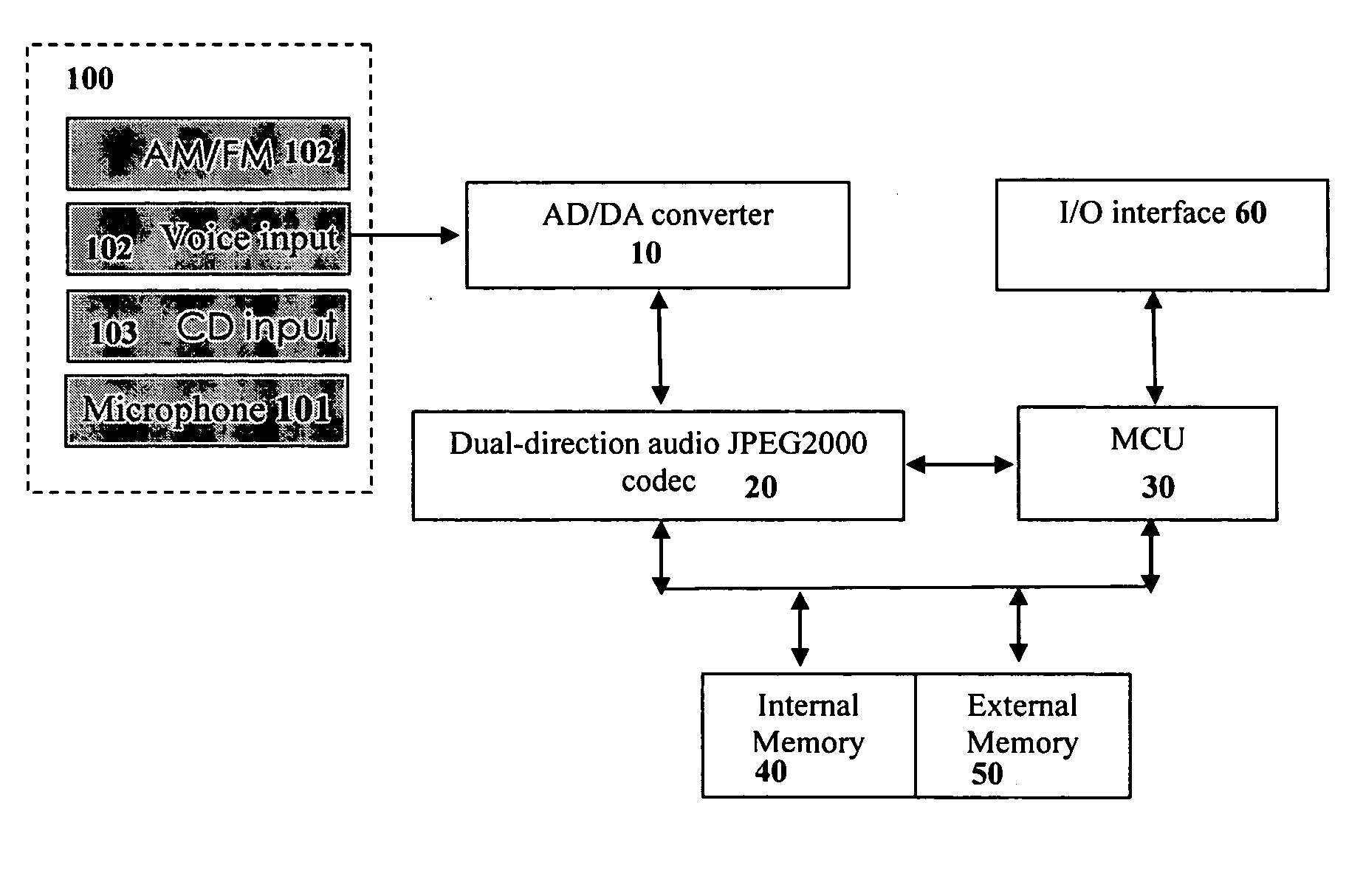

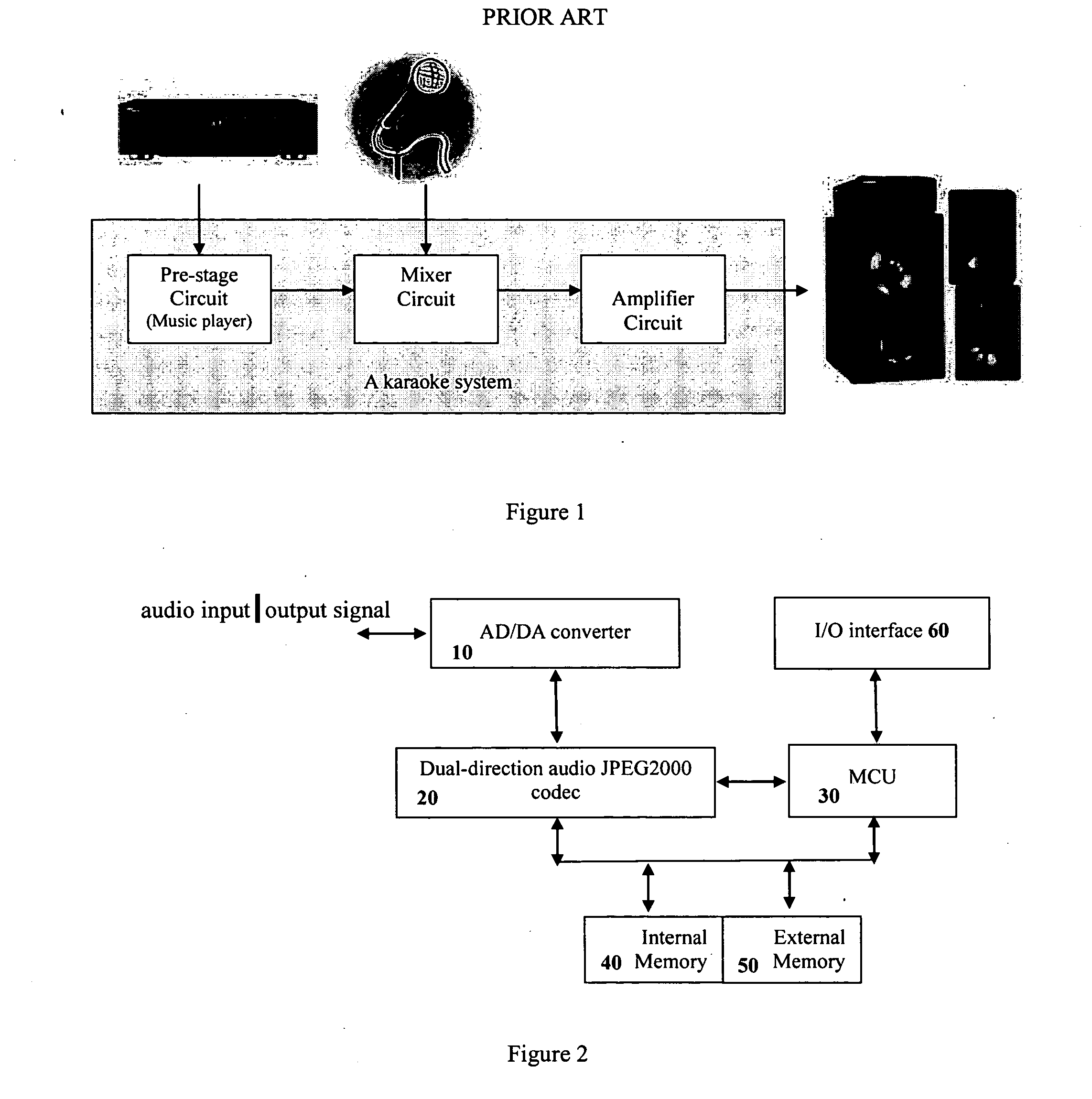

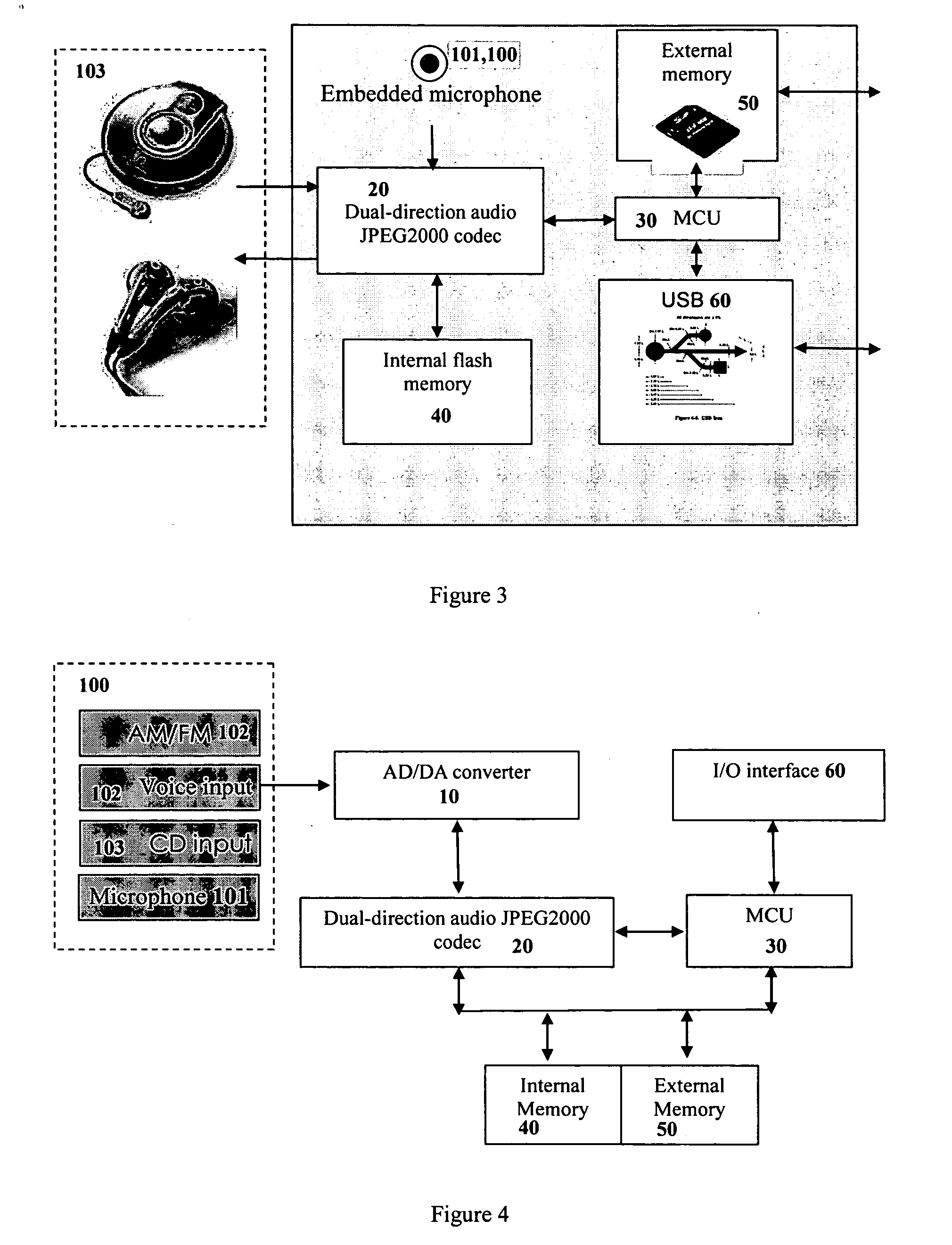

Method, mechanism, implementation, and system of real time listen-sing-record STAR karaoke entertainment (STAR "Sing Through And Record")

InactiveUS20070150082A1Low costIncrease valueElectrophonic musical instrumentsTransmissionUser deviceHand held

A hand-held audio mixing device includes an I / O interface, an AD / DA converter, a dual-direction codec which sample rate is set in 8-48 KHz with a 16-bit resolution, an MCU, a memory, and an operational amplifier. The device executes a first process that the I / O interface receives a first source of analog audio signals, and the amplifier amplifies the received signals thereby playing the amplified signals to a user. The device executes a second process that the I / O interface receives a second source of analog audio signals, the converter mixes the received second source of signals with the amplified first source of signals into an analog mixture, the converter converts the analog mixture into digital mixture signals, the codec compresses the digital mixture signals, and the memory saves the compressed signals. The first and second processes are executed substantially simultaneously such that there is no latency delay perceivable by the user.

Owner:AVERA TECH

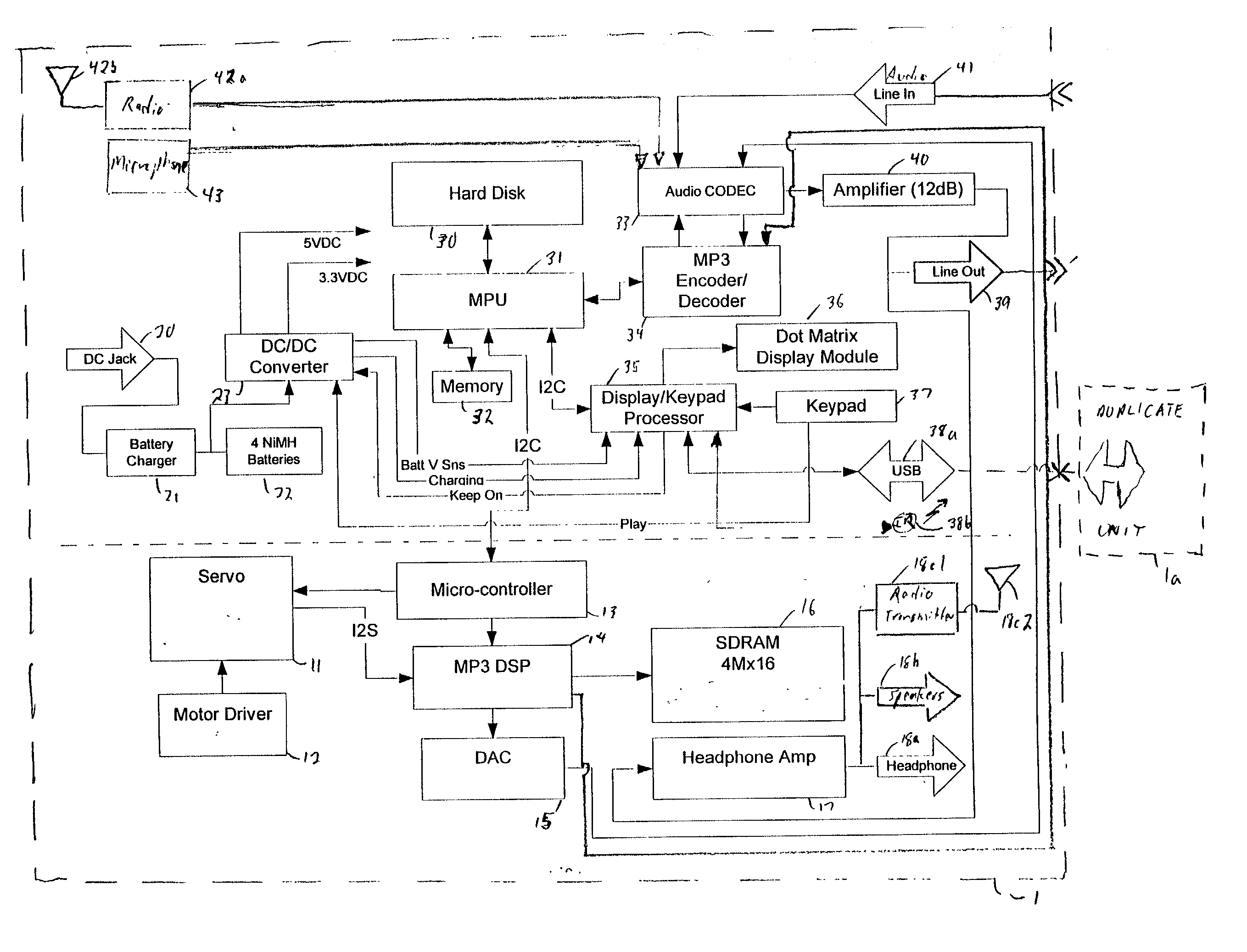

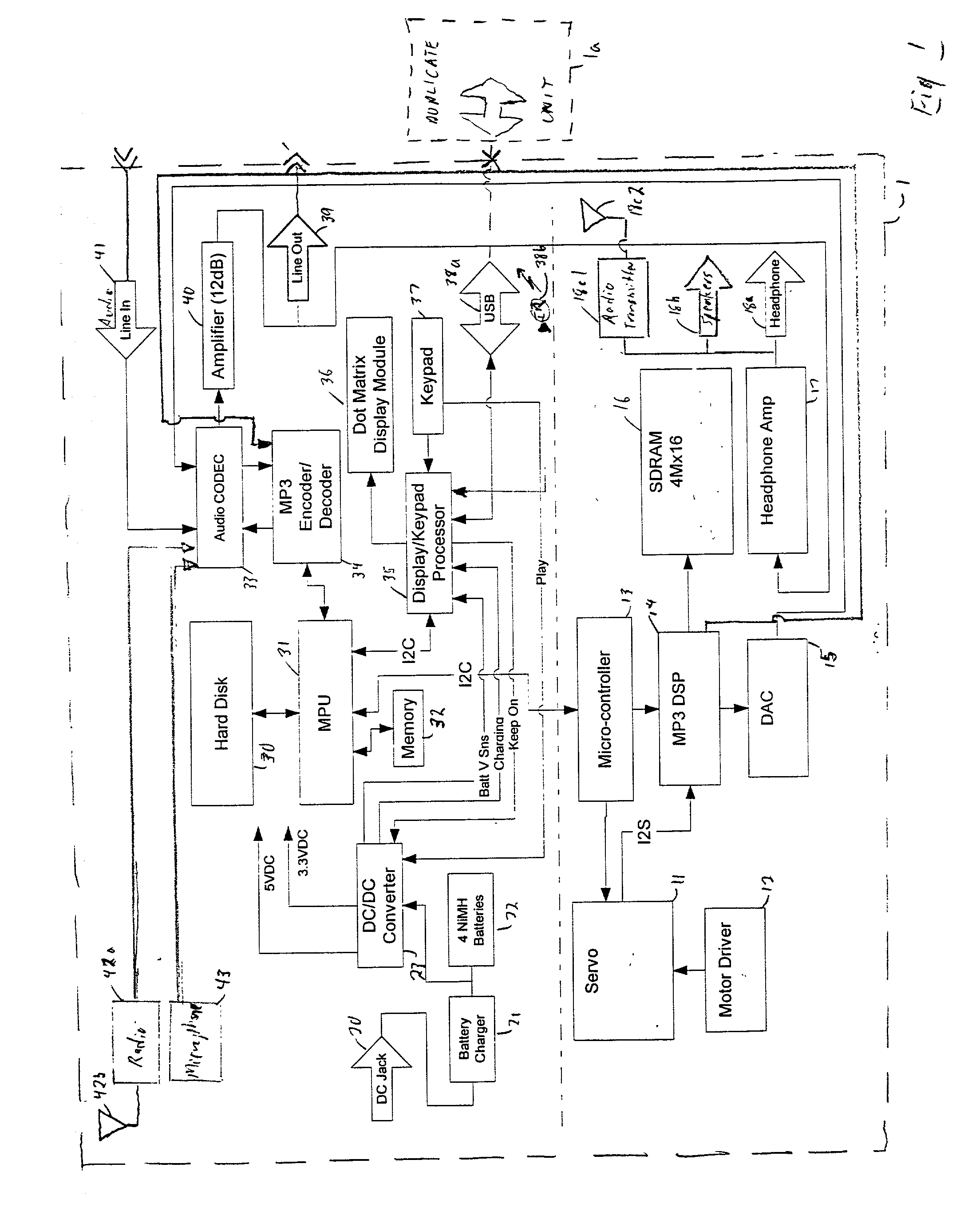

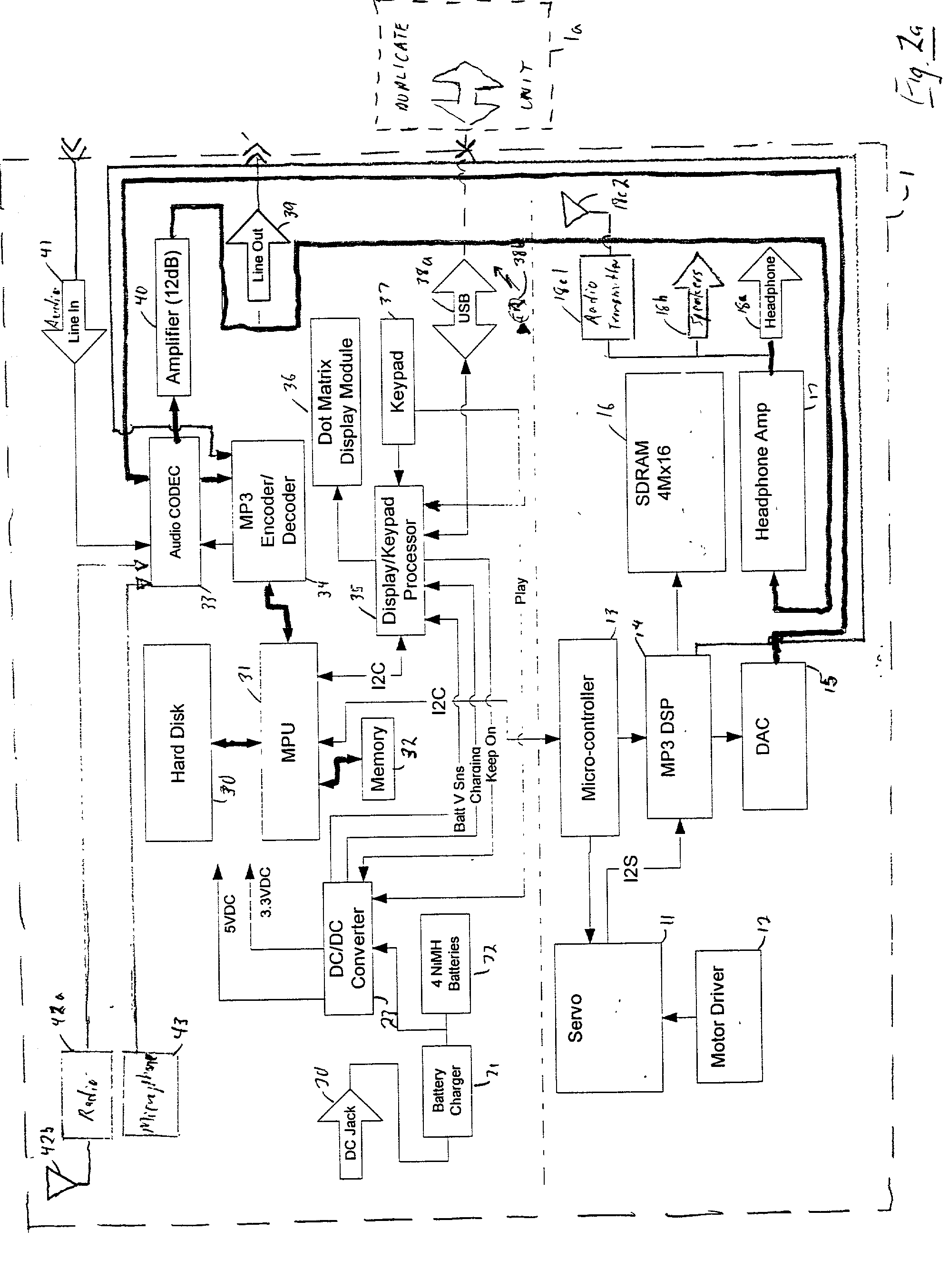

Portable CD-ROM/ISO to HDD/MP3 recorder with simultaneous CD-read/MP3- encode/HDD-write, or HDD-read/MP3-decode, to play, power saving buffer, and enhanced sound output

InactiveUS20020171567A1Reducing, or even eliminating, necessary reference(s)Rid of incredible amountBroadcast with distributionElectronic editing digitised analogue information signalsDigital data24-bit

A combination CD-ROM and MP3 recorder / player playing a CD-ROM decodes 16-bit ISO standard code words into an audio wave form converts this wave form to sound while encoding and digitizing the wave form into 24-bit MP3 format digital data. To conserve power the MP3 data is buffered in a solid state memory, preferably of the FLASH or DRAM type, before being written to a hard disk. Both reading of the CD / ROM and encoding the read contents as MP3 data, and interchange of MP3 data with other recorder / players, can be accomplished at greater than real-time play rates, permitting that, most typically, some 1200+ musical works can transferred expediently.

Owner:HANDAL ANTON +1

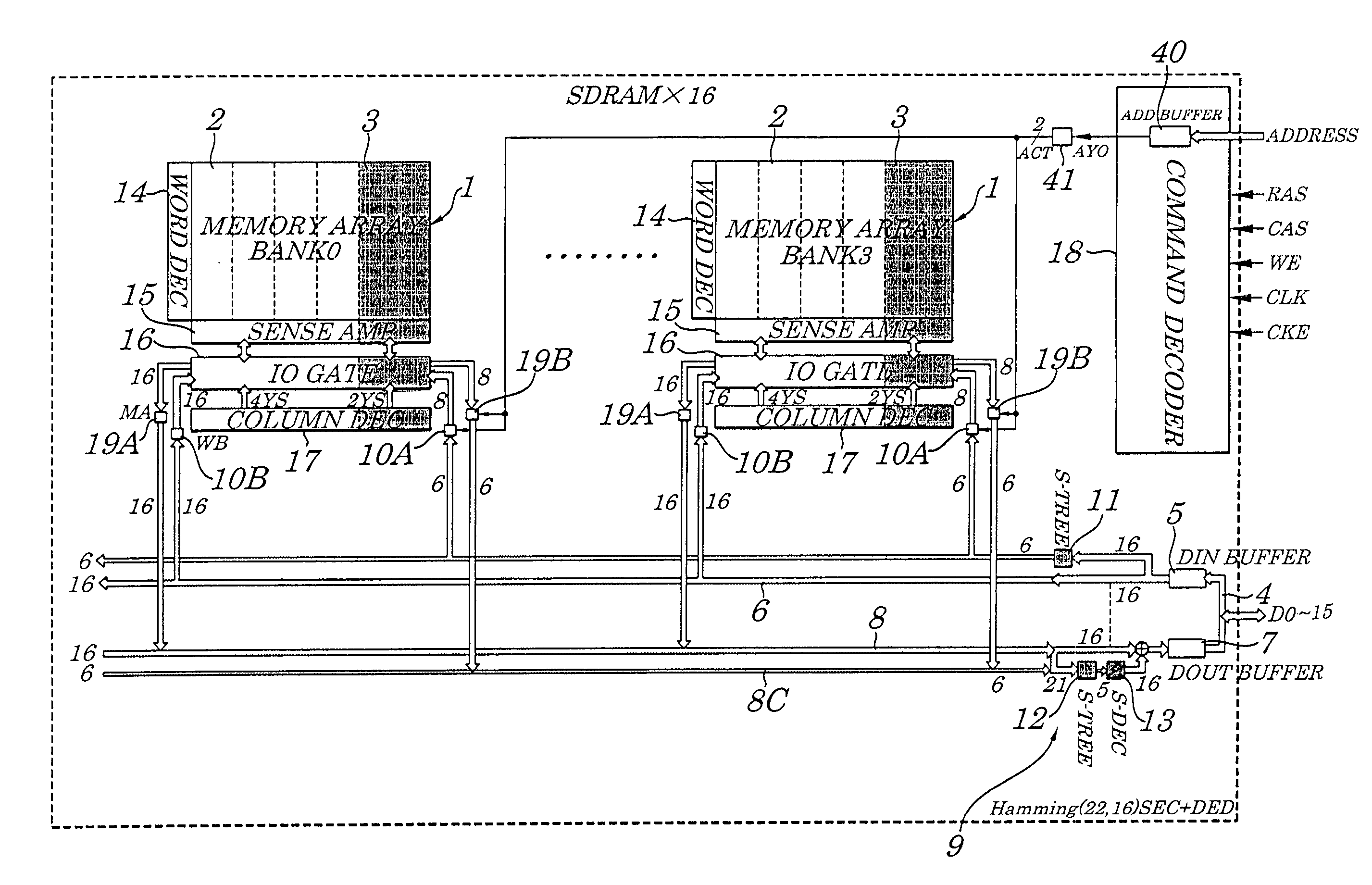

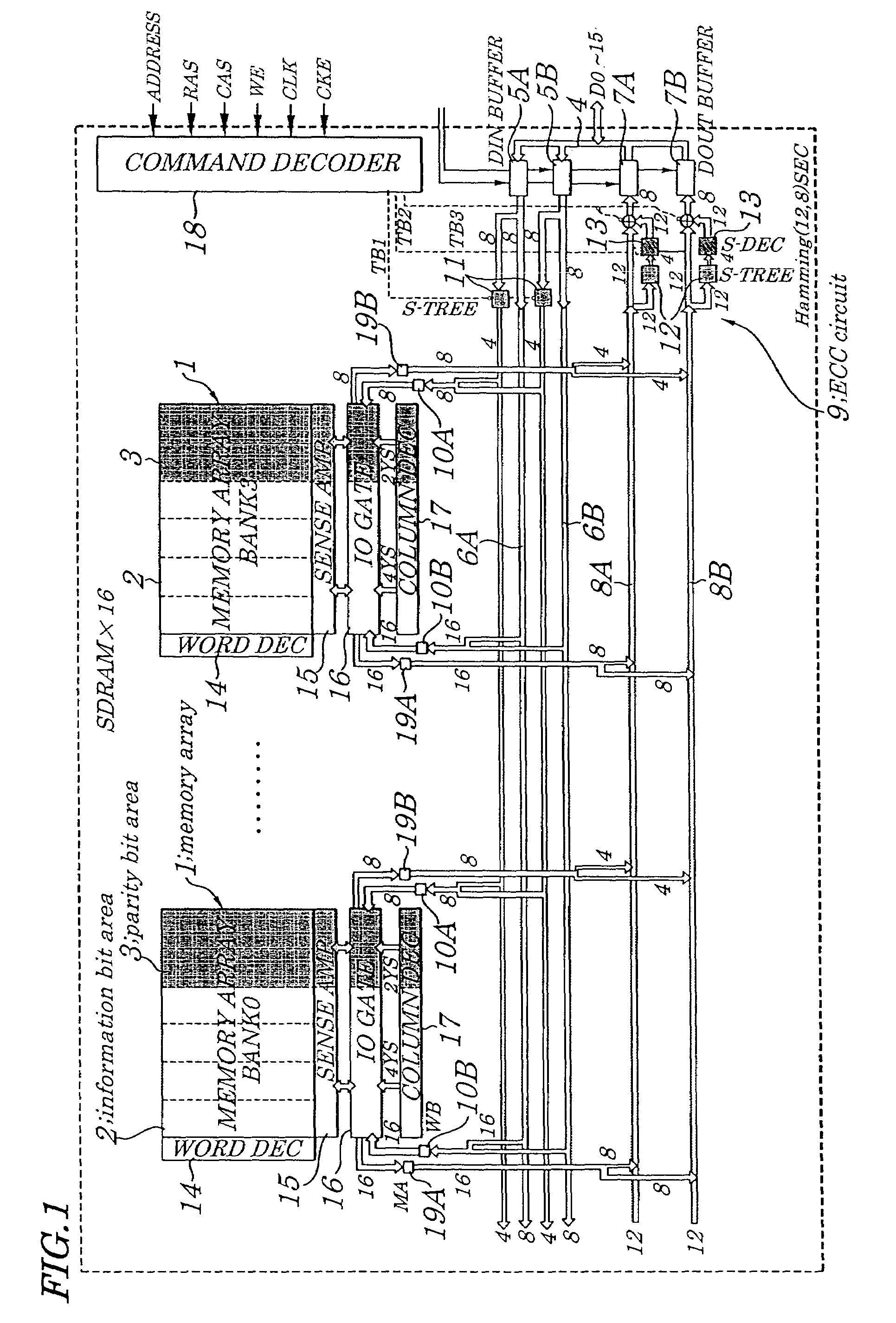

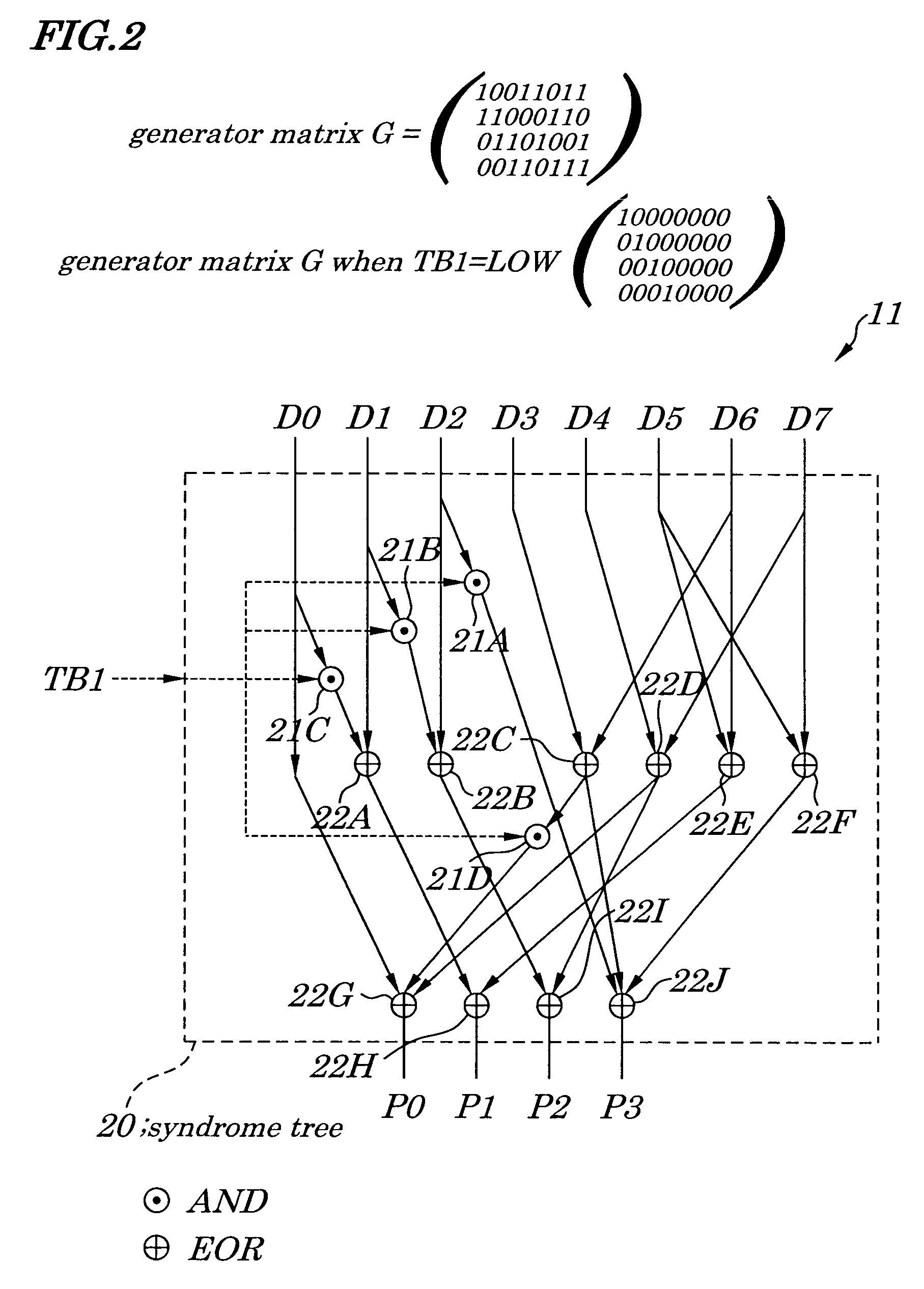

Semiconductor memory device provided with error correcting code circuitry

ActiveUS7225390B2Effective correctionReduce error rateCode conversionDigital storageHamming codeError location

A semiconductor synchronous dynamic random access memory (SDRAM) device capable of correcting bits having a low error rate in a Pause Refresh Tail distribution and of reducing a data holding current by lengthening a refresh period so that the refresh period exceeds a period for a Pause Refresh real power. The semiconductor memory device is made up of a 16-bit SDRAM having a Hamming Code and including an ECC (Error Correcting Code) circuit made up of an encoding circuit controlled by a first test signal to output a parity bit corresponding to an information bit, a decoding circuit controlled by second test signal to output an error location detecting signal indicating an error bit in codeword, and an error correcting circuit controlled by a third test signal to input an error location detecting signal and to output an error bit in a reverse manner.

Owner:LONGITUDE LICENSING LTD

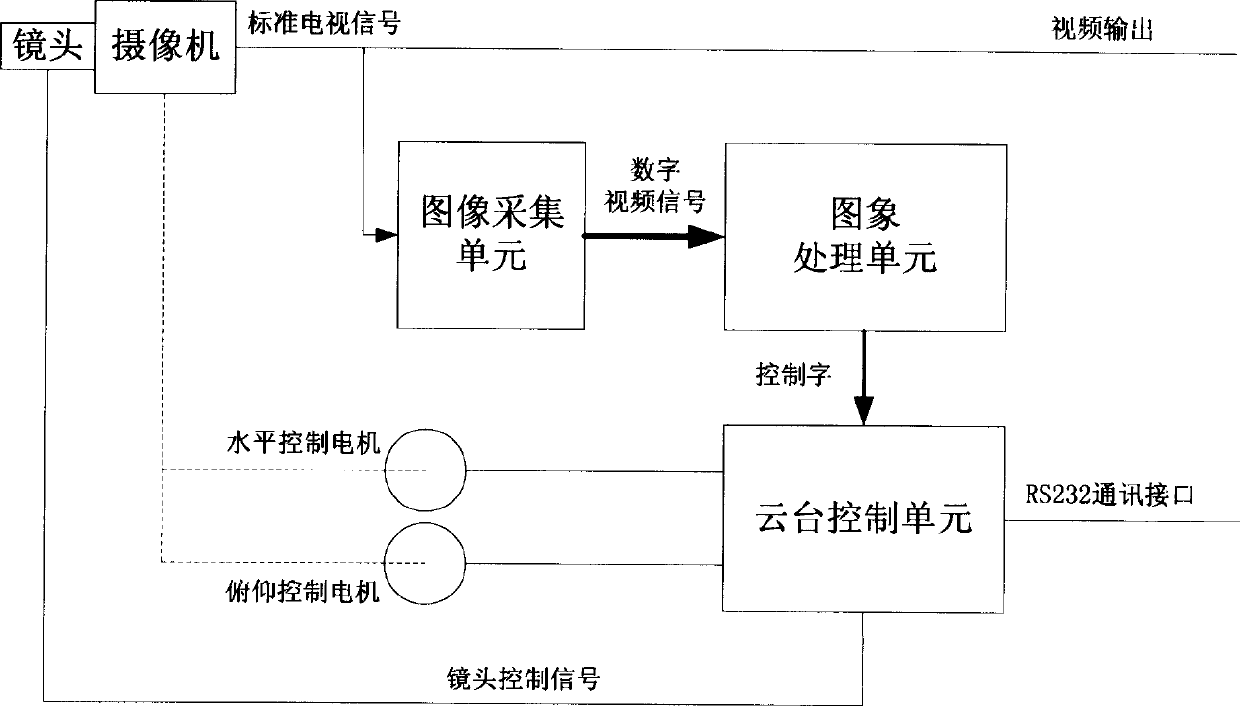

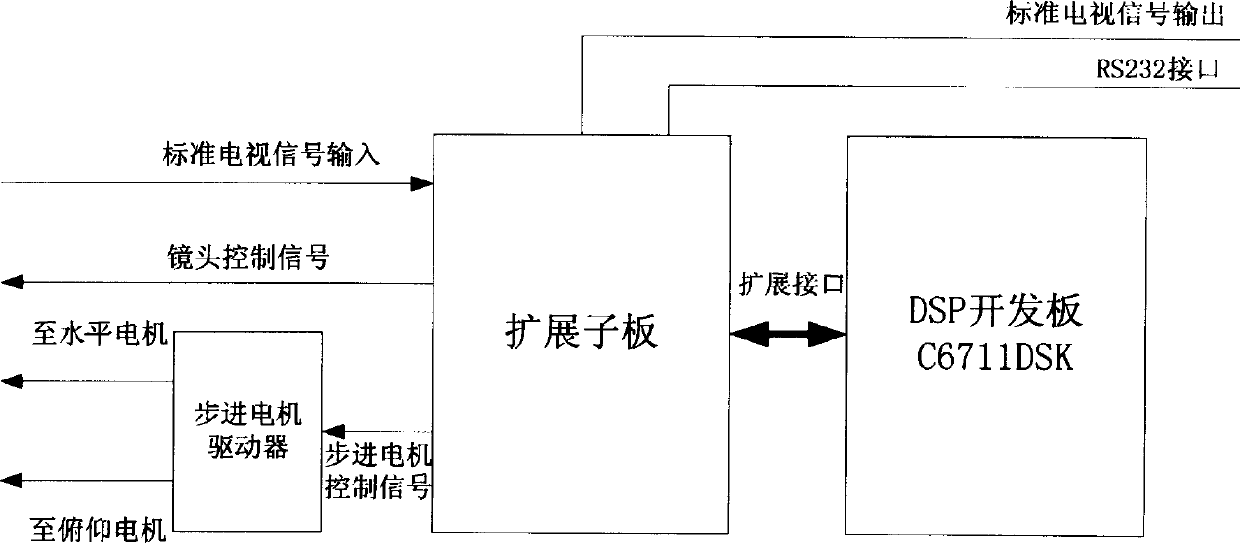

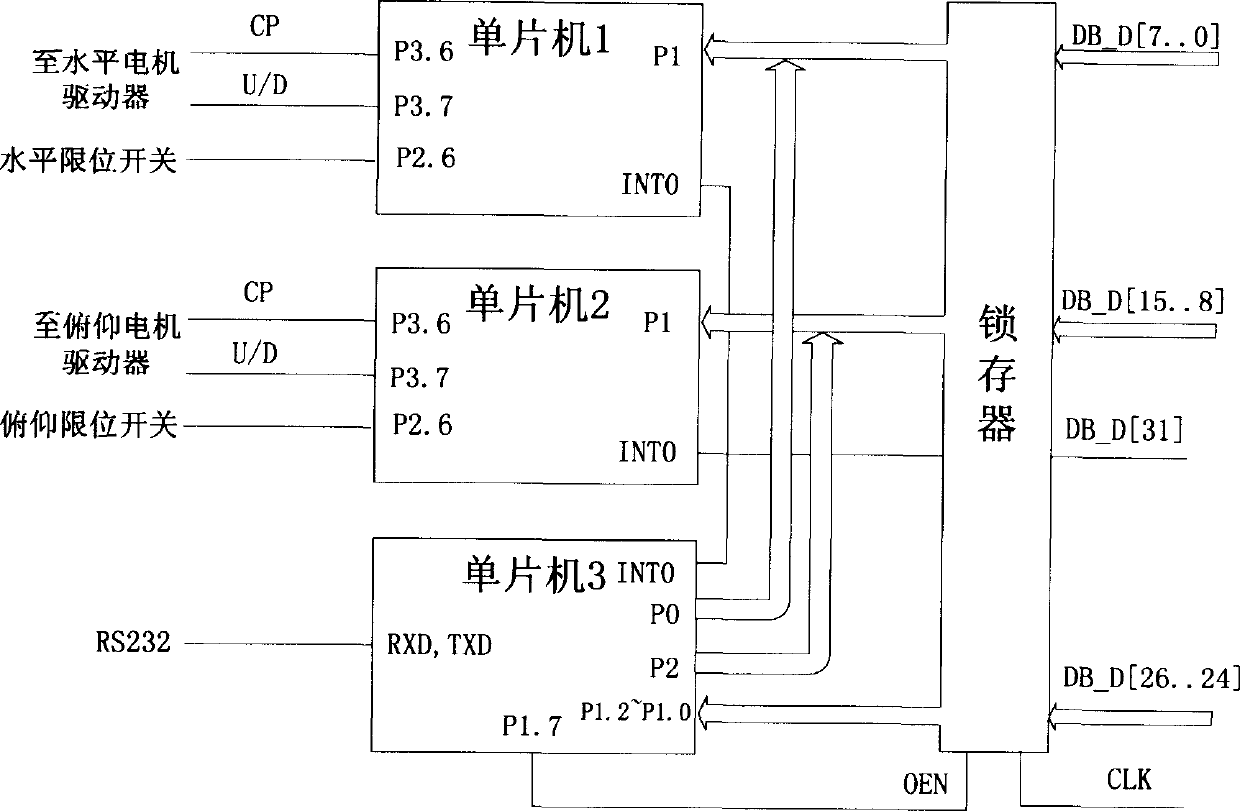

Abnormal object automatic finding and tracking video camera system

InactiveCN1449186AIncrease flexibilityImprove speedTelevision system detailsColor television detailsCamera lensDigital video

The invention relates to a video camera system of discovering and tracking automatically abnormal targets. Camera lens, video camera, image collecting unit, image processing unit, turntable control unit, turntable consist of a closed loop control system. The image collecting unit converts standard television signals output by the camera into 16-bit digital video signals. The image processing unit outputs the center position of the biggest abnormal target after detecting abnormal targets, and outputs the zooming control of lens of the camera according to the size of targets and the position in the visual field. The turntable control unit gives an alarm to the monitoring center, controls rotation of the turntable to make the light axis of the camera installed in the turntable point to the abnormal targets detected, and adjusts automatically the zooming multiple to make the monitoring center obtain clear and intact video image about the abnormal targets. The invention realizes the quick detection and track about invading targets.

Owner:SHANGHAI JIAO TONG UNIV

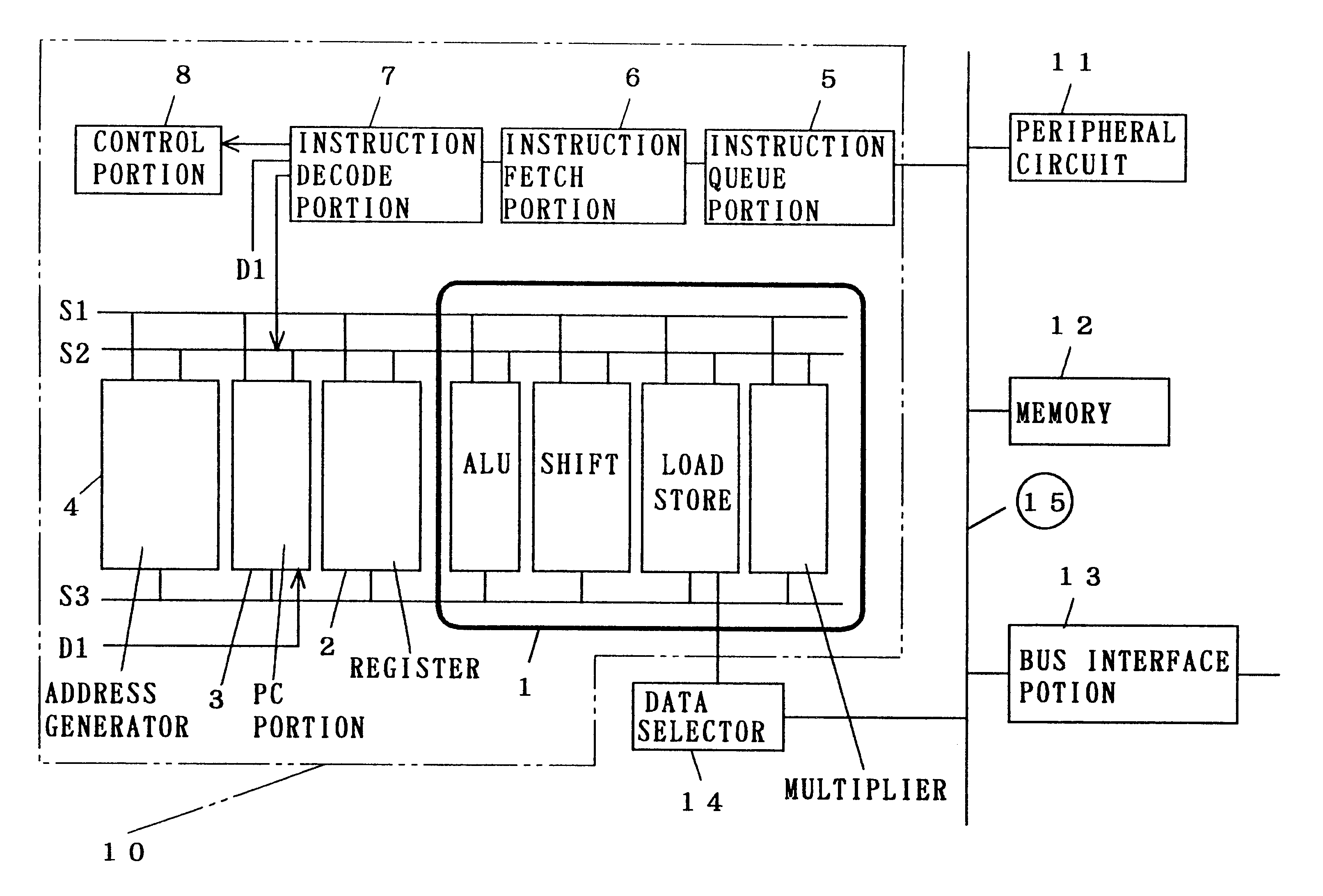

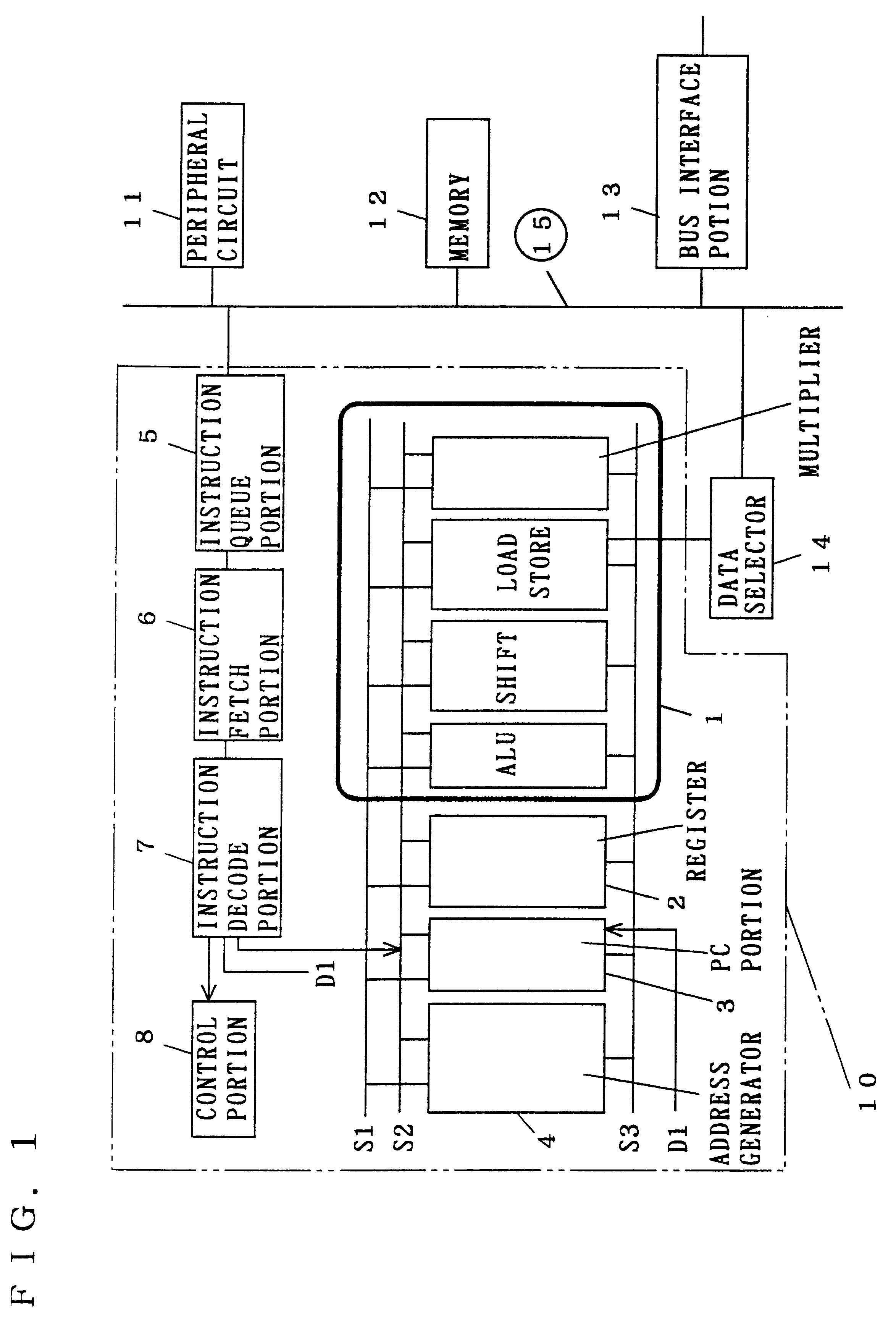

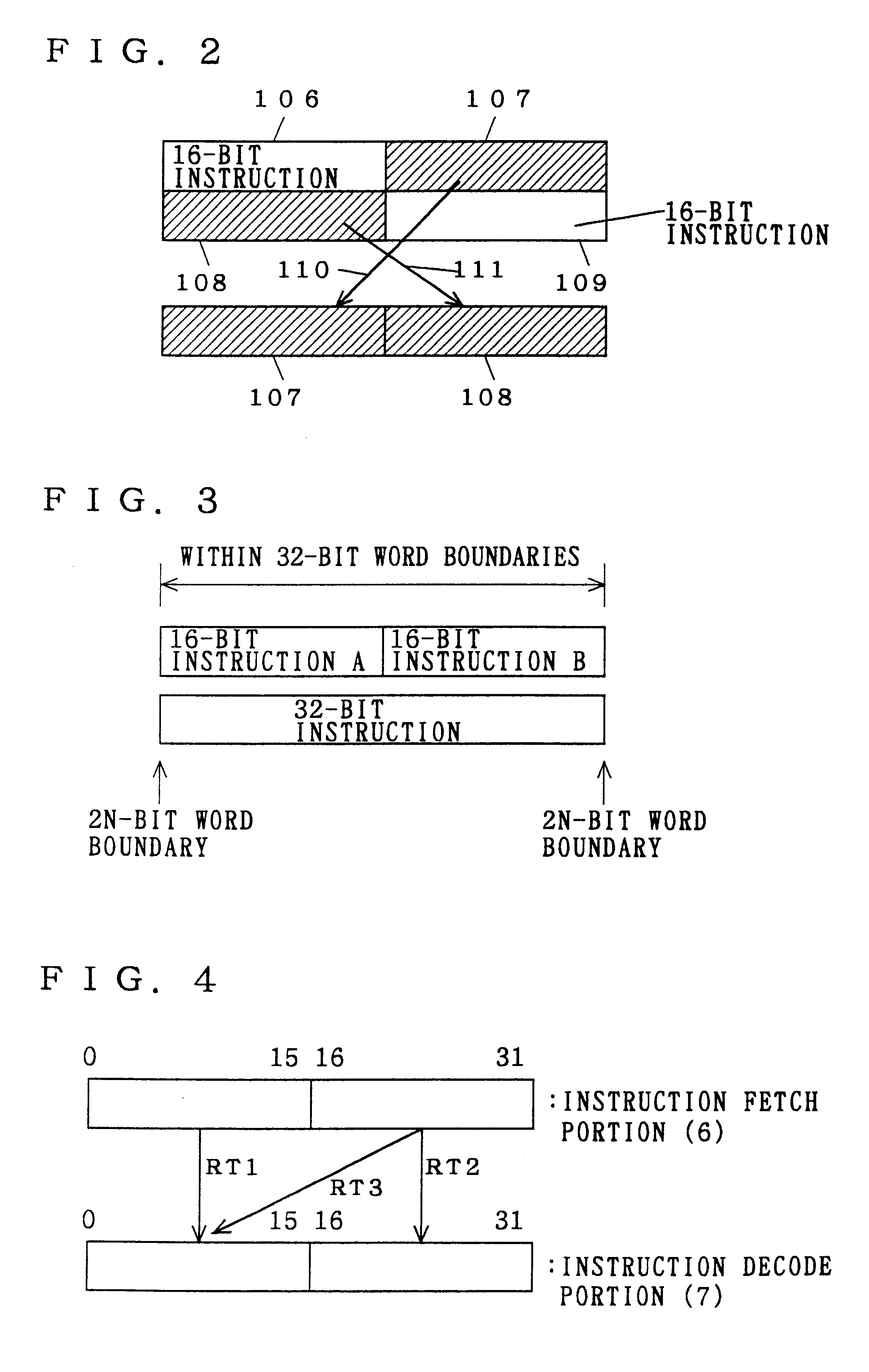

Processor for executing instruction codes of two different lengths and device for inputting the instruction codes

InactiveUS6209079B1Small sizeSmall amountInstruction analysisDigital computer details16-bitParallel computing

For a processor having instruction codes of two instruction lengths (16 bits and 32 bits), methods of locating the instruction codes are limited to two types: (1) two 16-bit instruction codes are stored within 32-bit word boundaries, and (2) a single 32-bit instruction code is stored intactly within the 32-bit word boundaries. A branch destination address is specified only on the 32-bit word boundary. The MSB of each instruction code serves as a 1-bit instruction length identifier for controlling the execution sequence of the instruction codes. This provides two transfer paths from an instruction fetch portion to an instruction decode portion within the processor, achieving reduction in code side and in the amount of hardware and, accordingly, the increase in operating speed.

Owner:RENESAS ELECTRONICS CORP

Apparatus, method and program product to generate and use CRC in communications network

The CRC for the CPS Header of an ATM AAL2 cell is generated by a CRC generator which uses the 8 bits of the CID field to generate partial 5 bits CRCs which are loaded in a first table. The 6 bits LI field and 5 bits UUI field are added to the partial 5 bits CRC to form 16 bits. The CRC generator uses the 2<16 >bits to generate a second CRC table. The CRC for a particular CPS header is generated by correlating bits in the CID field, Li field and UUI field with the two tables.

Owner:META PLATFORMS INC

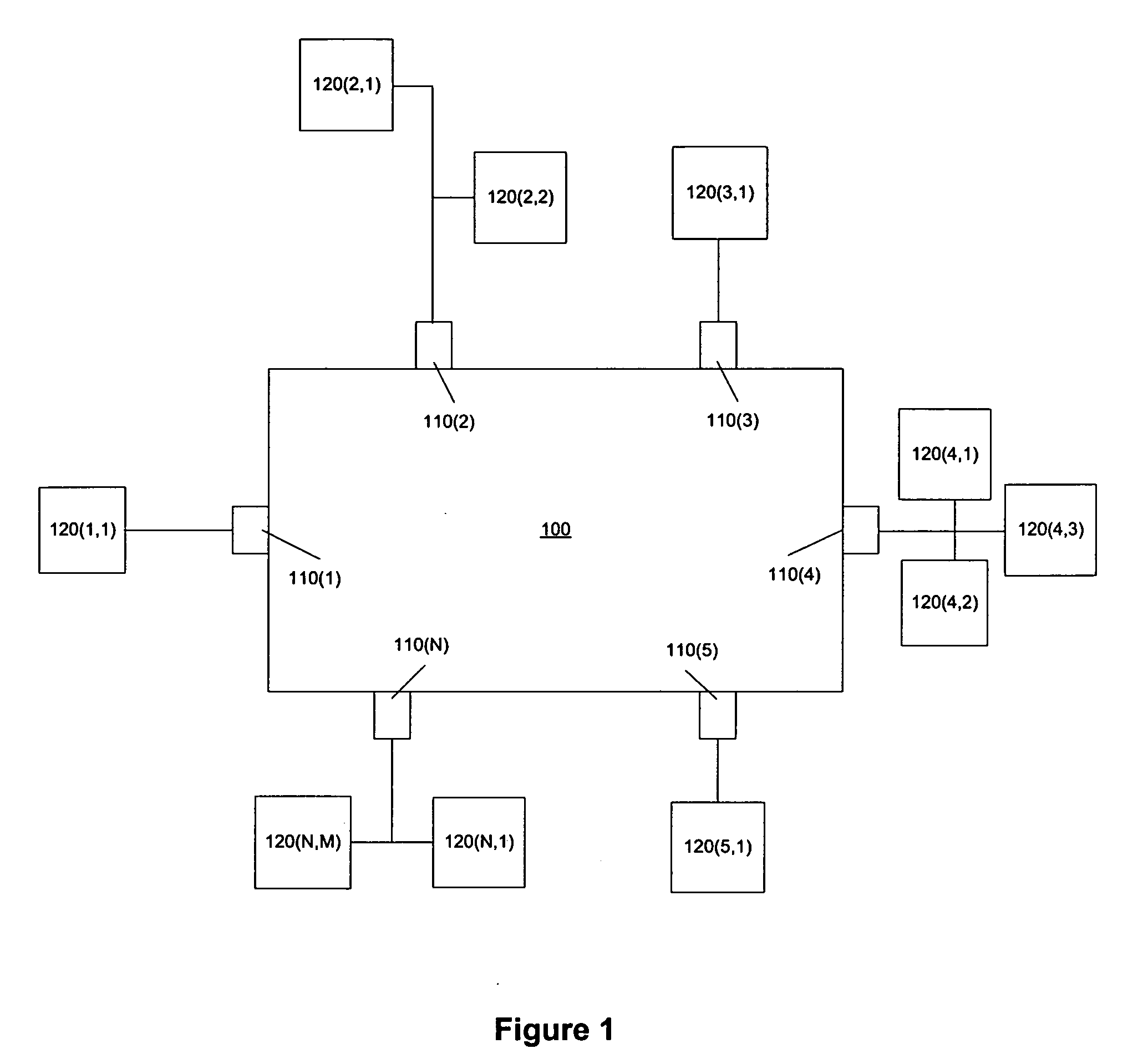

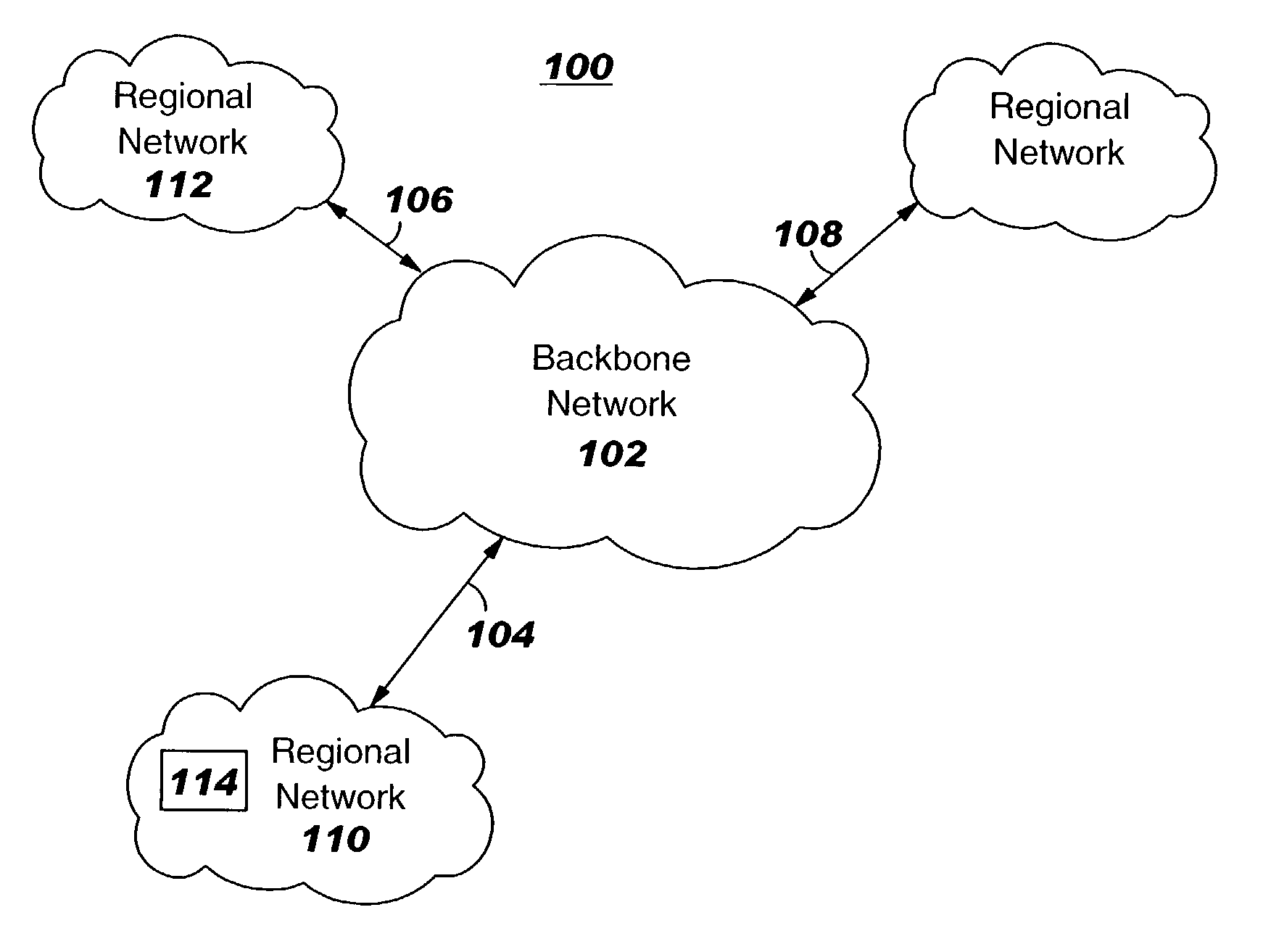

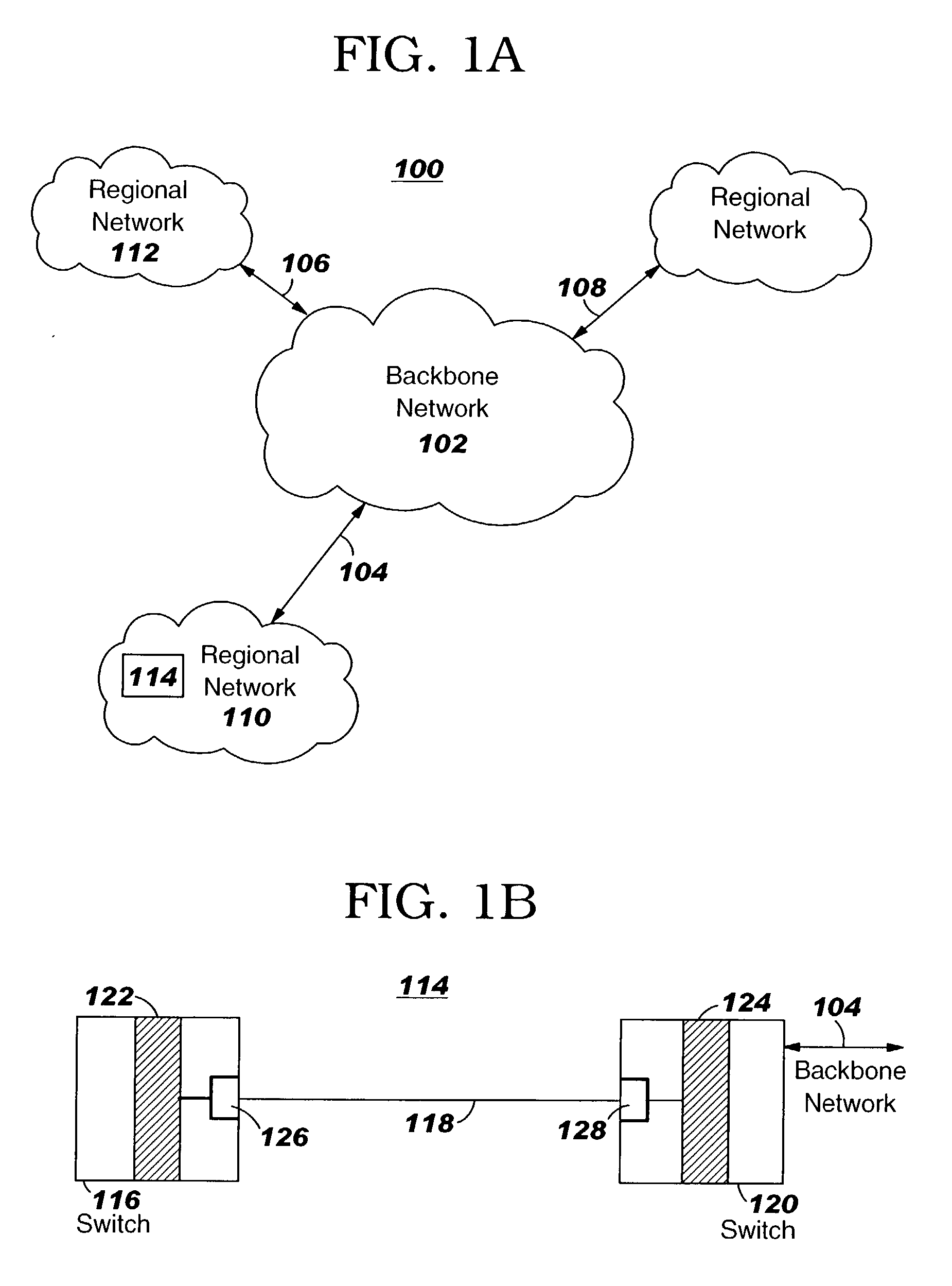

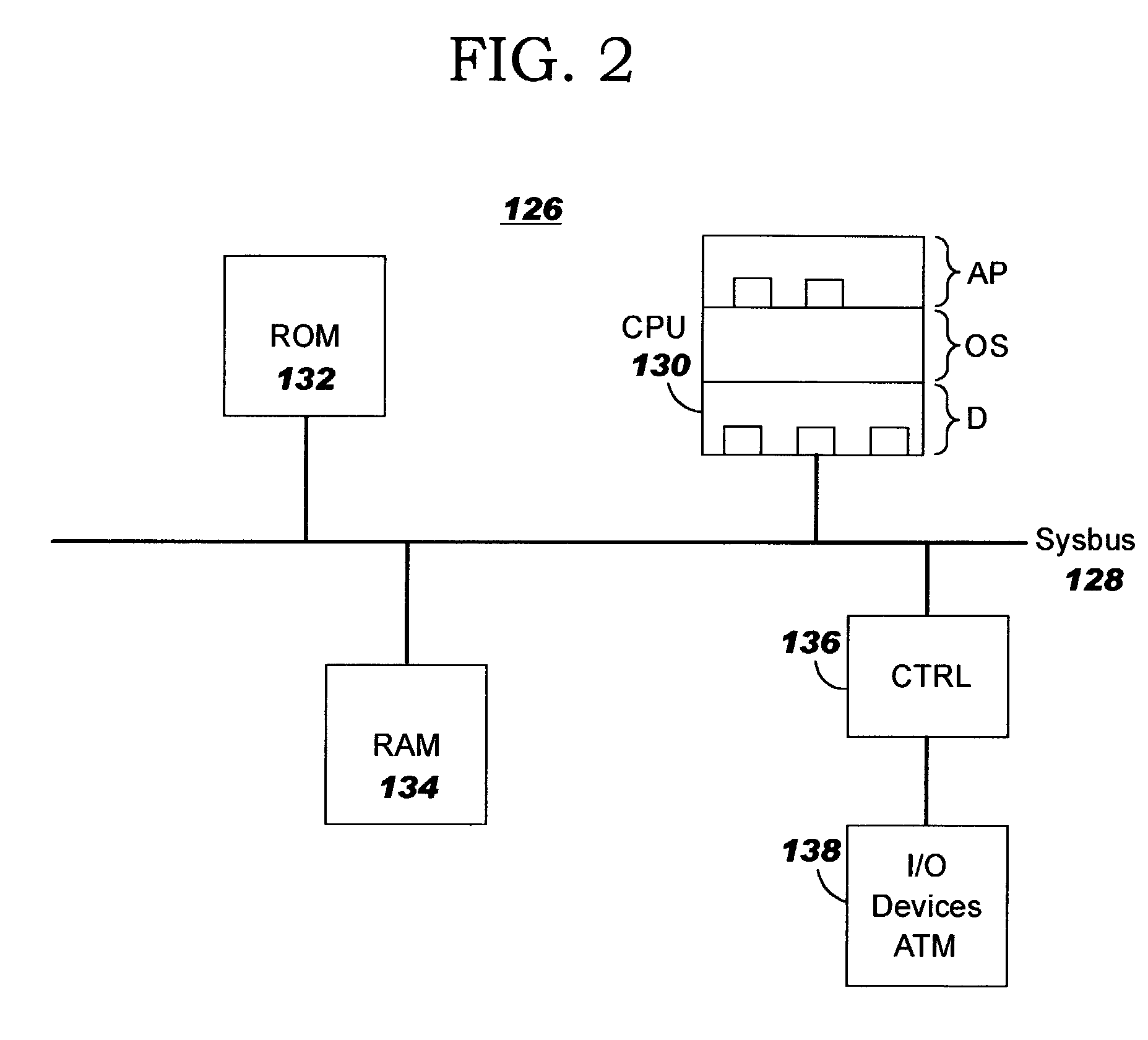

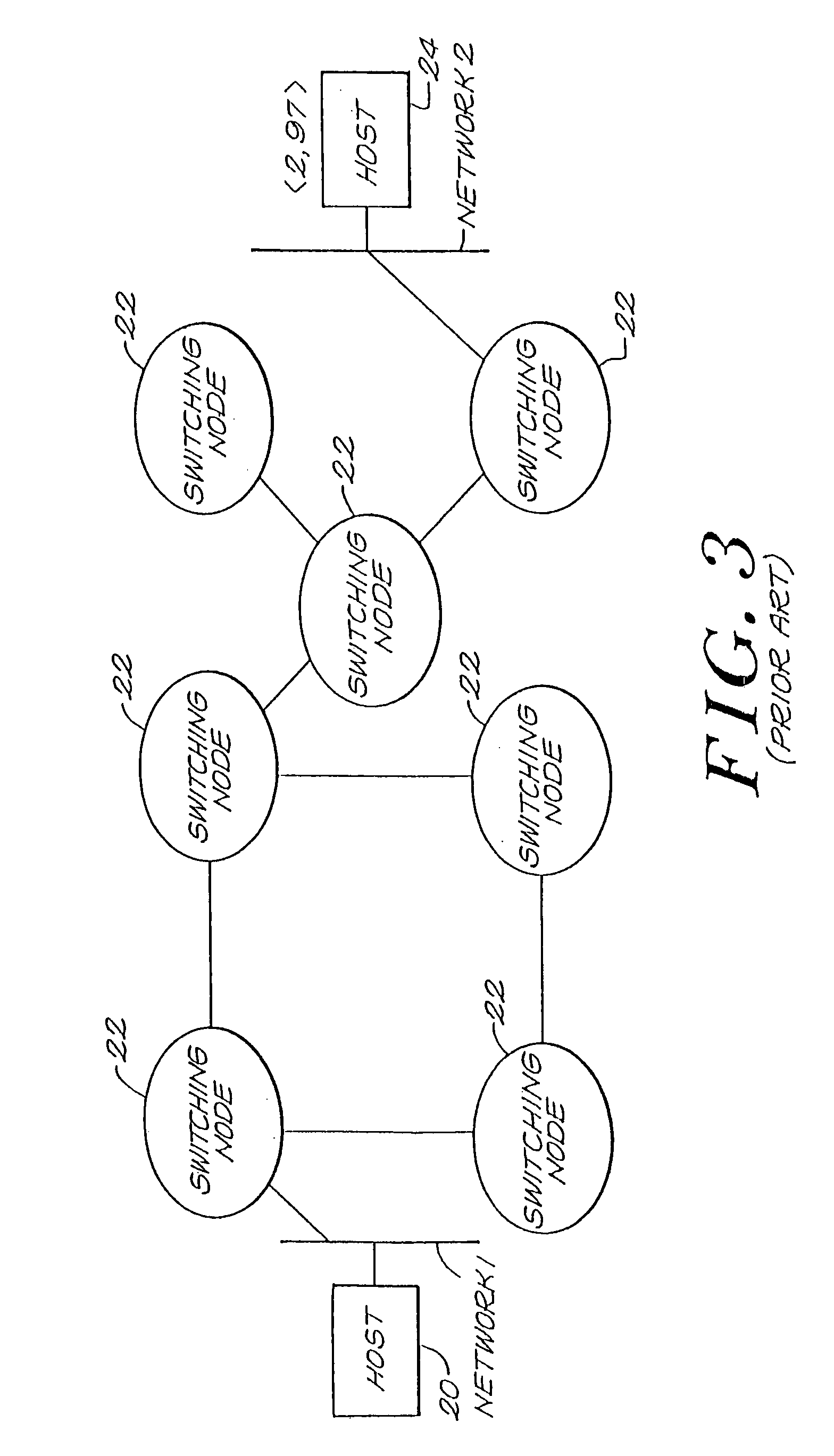

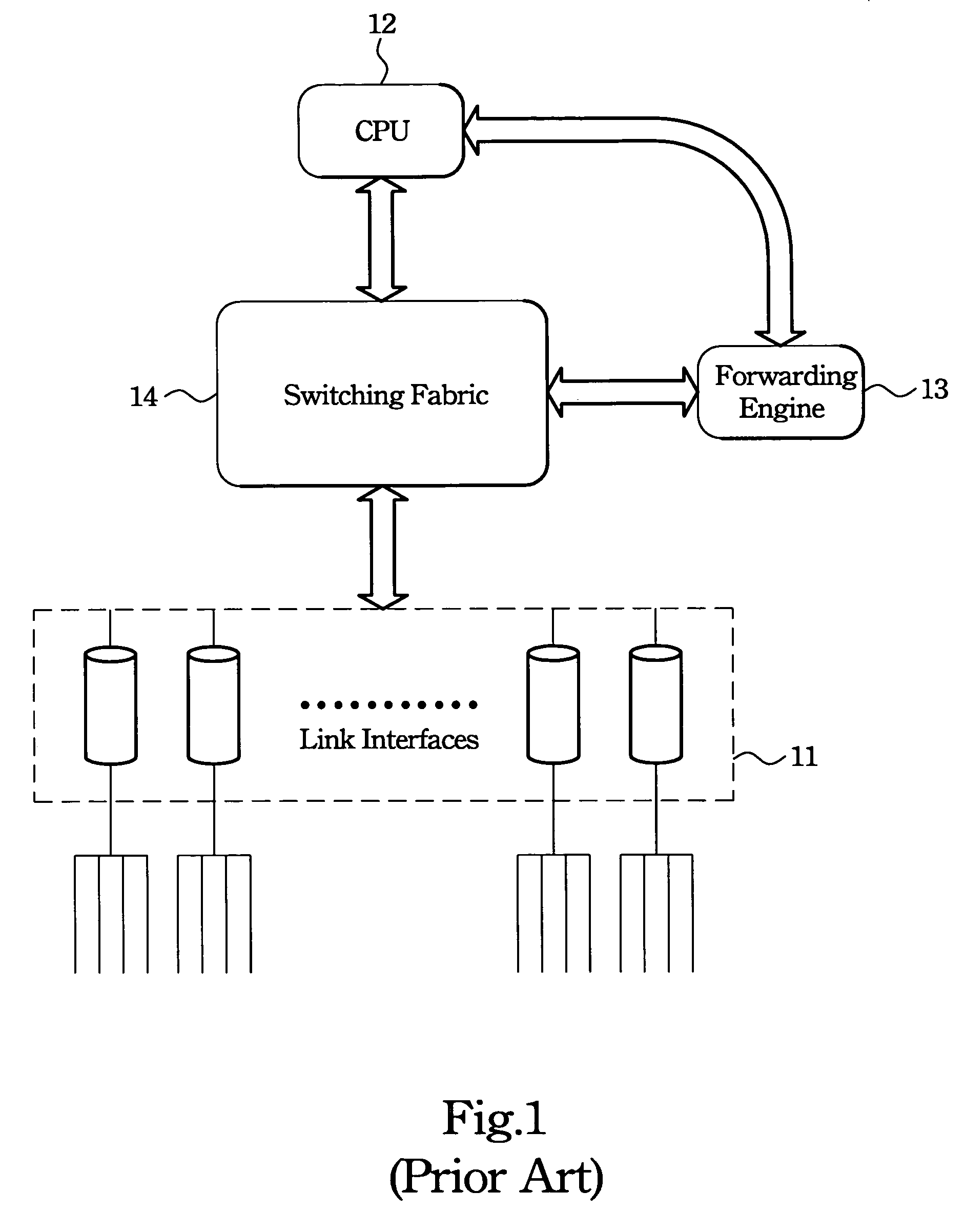

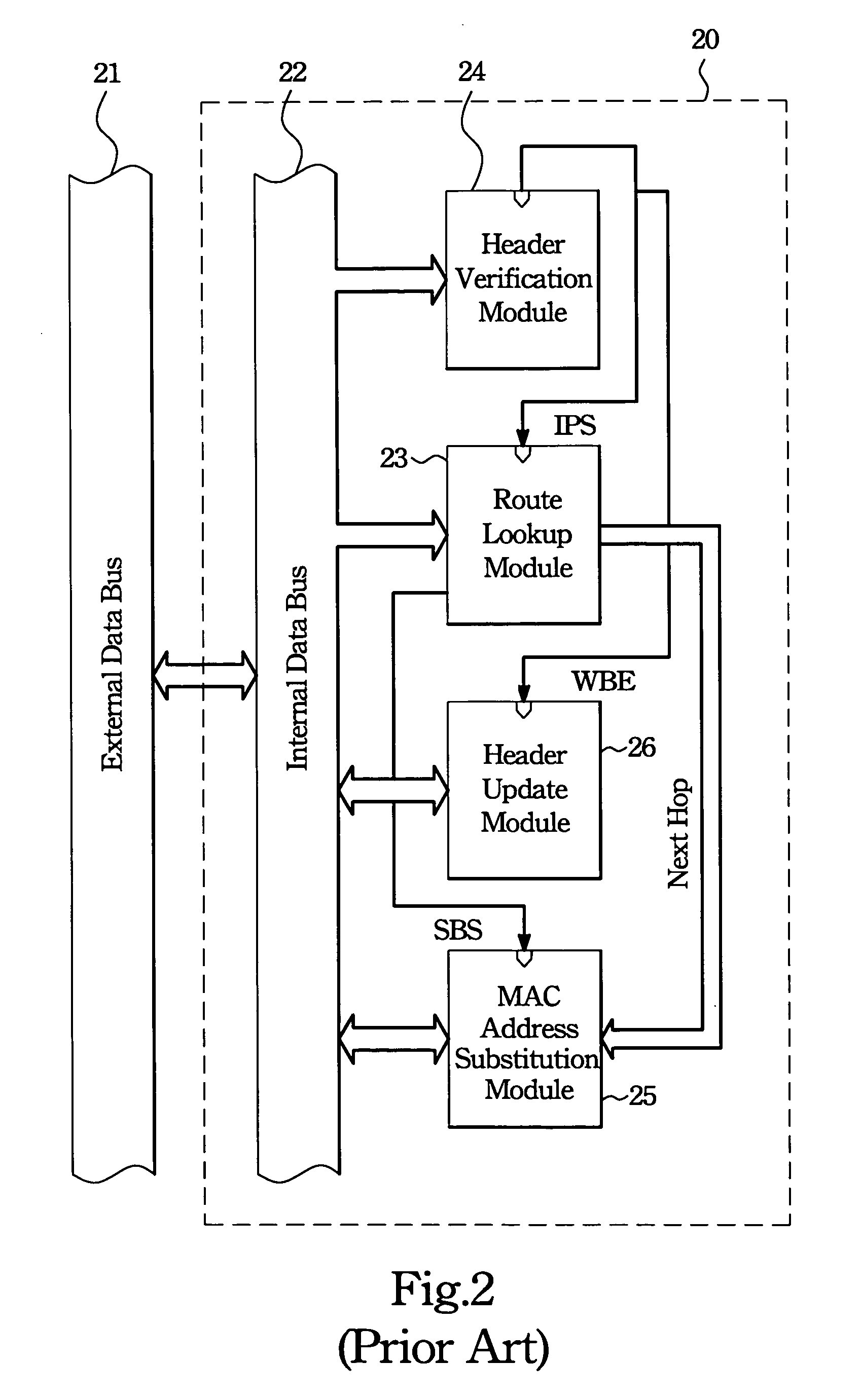

Network packet forwarding lookup with a reduced number of memory accesses

InactiveUS6975631B1Reduce overheadShorten the timeData switching by path configurationMemory addressNetwork packet

A switch / router contains intelligence for more quickly determining a next hop for an network layer packet. A network forwarding lookup table or array structure is configured so as to minimize the number of memory accesses required. This results in a decrease in time due to memory access and a decrease in computational overhead due to the memory accesses. In one embodiment, a first forwarding lookup is indexed by the first 16 bits of a destination address. A second forwarding lookup is indexed by the subsequent 8 bits of the destination address, and a final third forwarding lookup is indexed by the last 8 bits of the destination address. Each entry within a forwarding lookup contains either direction as to how properly forward the packet or reference to a next subsequent forwarding lookup.

Owner:JUMIPER NETWORKS INC

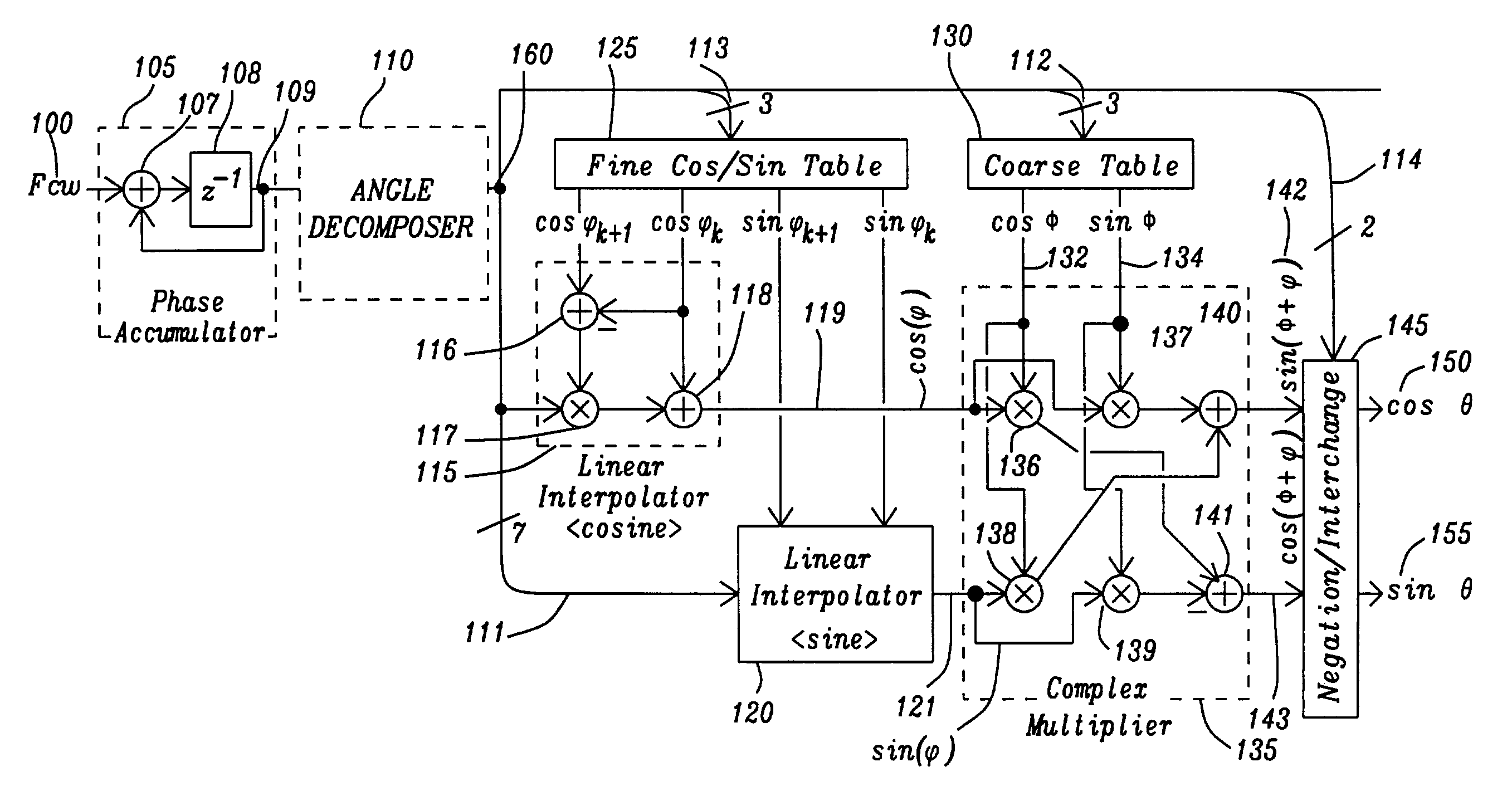

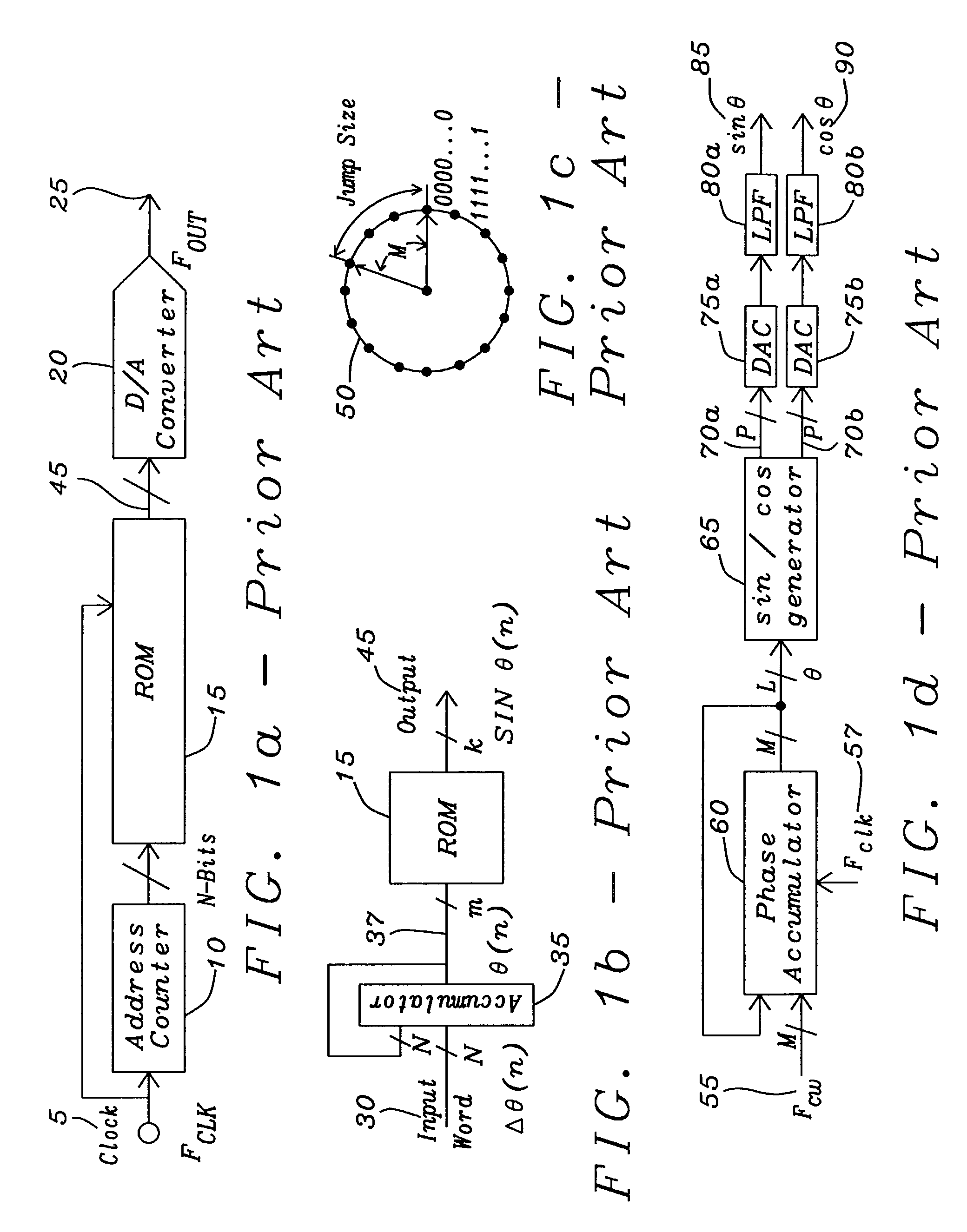

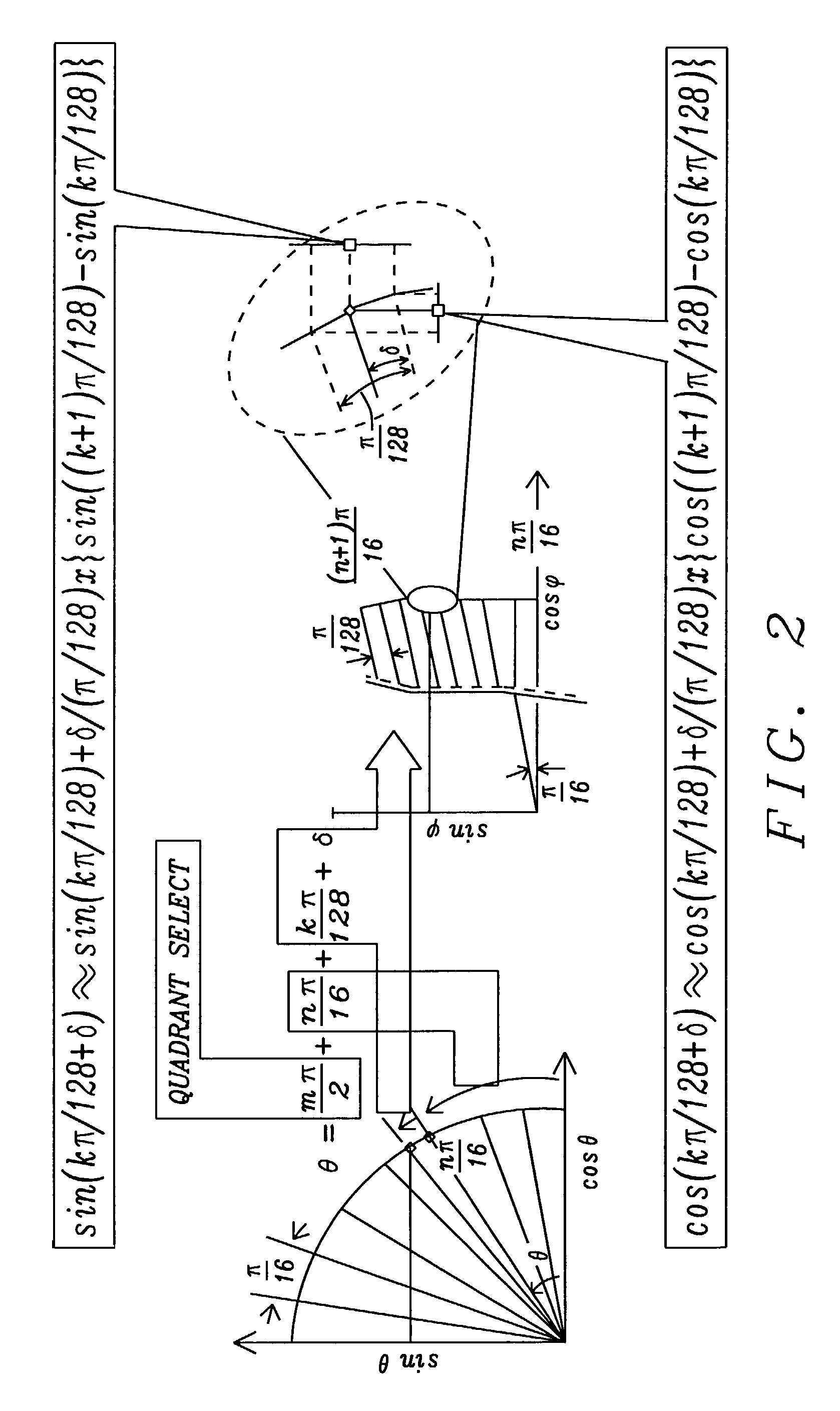

16 bit quadrature direct digital frequency synthesizer using interpolative angle rotation

ActiveUS7440987B1Digital function generatorsComputation using denominational number representation16-bitFunction generator

A direct digital synthesizer employs a trigonometric function generator utilizing decomposition of a larger angle into smaller sub-angles, interpolation of a desired sub-angle between two known angles and calculating the trigonometric function using complex arithmetic. The direct digital synthesizer has a phase accumulator to generate an angular increment signal of the output signal. A trigonometric function generator in communication with the phase accumulator receives the angle signal and from the angle signal creates the trigonometric function signal. An angle decomposing circuit is connected to receive the angle signal to separate the angle signal into sub-angles of the angular increment, a sum of the sub-angles equaling the angular increment. An interpolation circuit receives the smallest of the sub-angles to generate the trigonometric function for the smallest of the sub-angles by interpolating between the trigonometric function of two known angles. The direct digital synthesizer has a first angle trigonometric retaining for retaining the trigonometric functions of the known angles. At least one second angle trigonometric retaining circuit retains the trigonometric functions of for the remaining sub-angles. A complex arithmetic unit combines the interpolated trigonometric function and the second trigonometric function from each of the second angle trigonometric retaining circuits to create the trigonometric function.

Owner:QUALCOMM INC

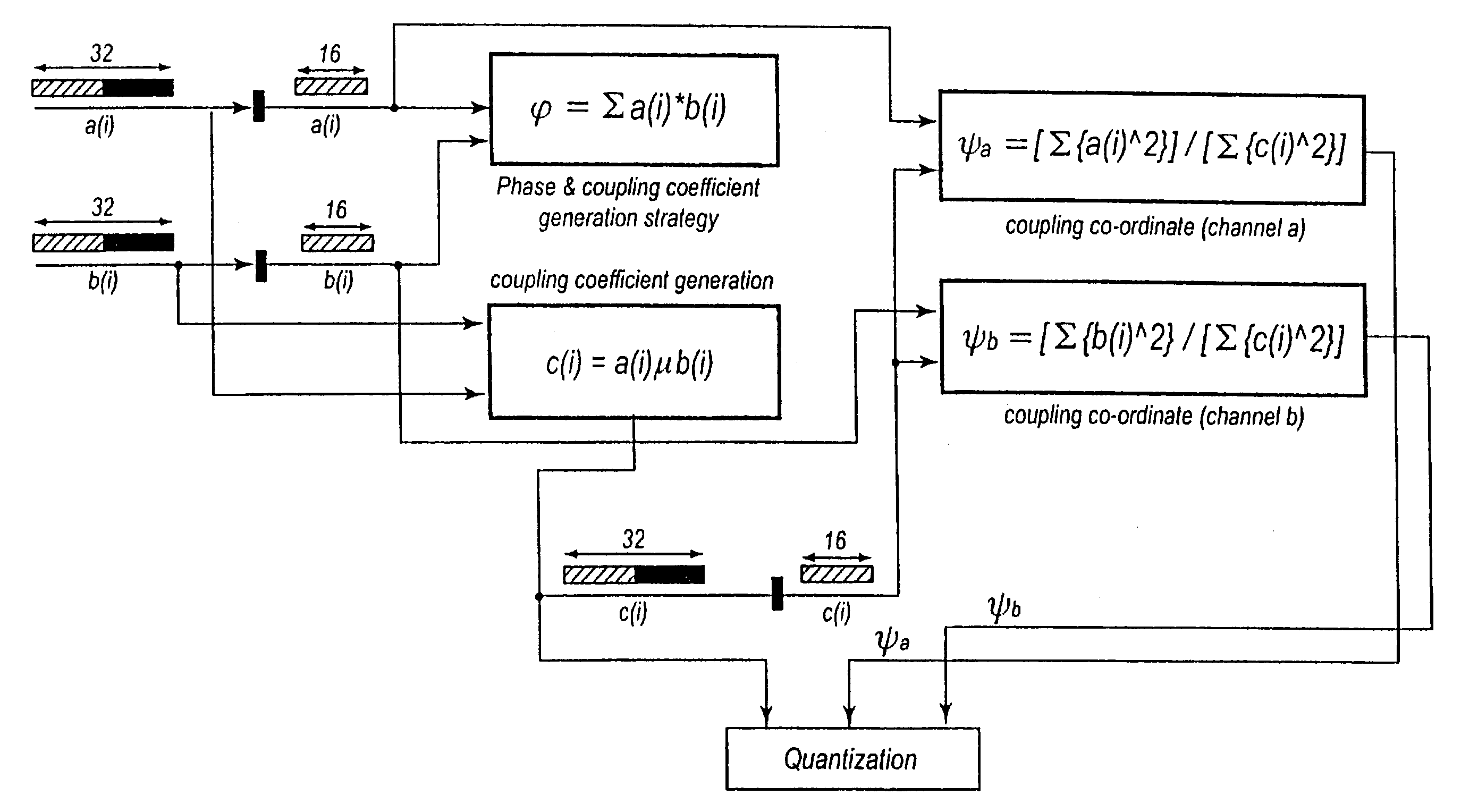

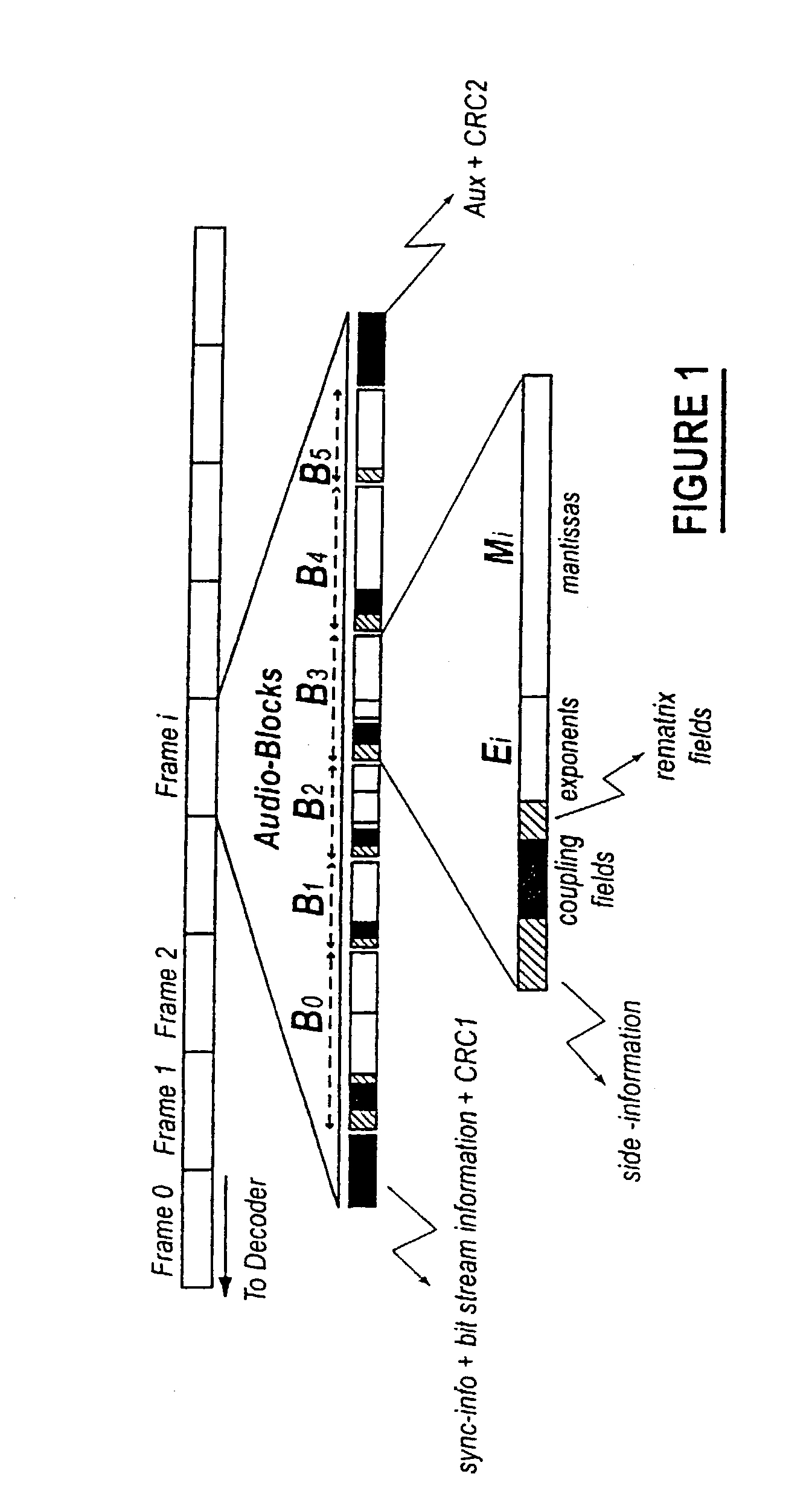

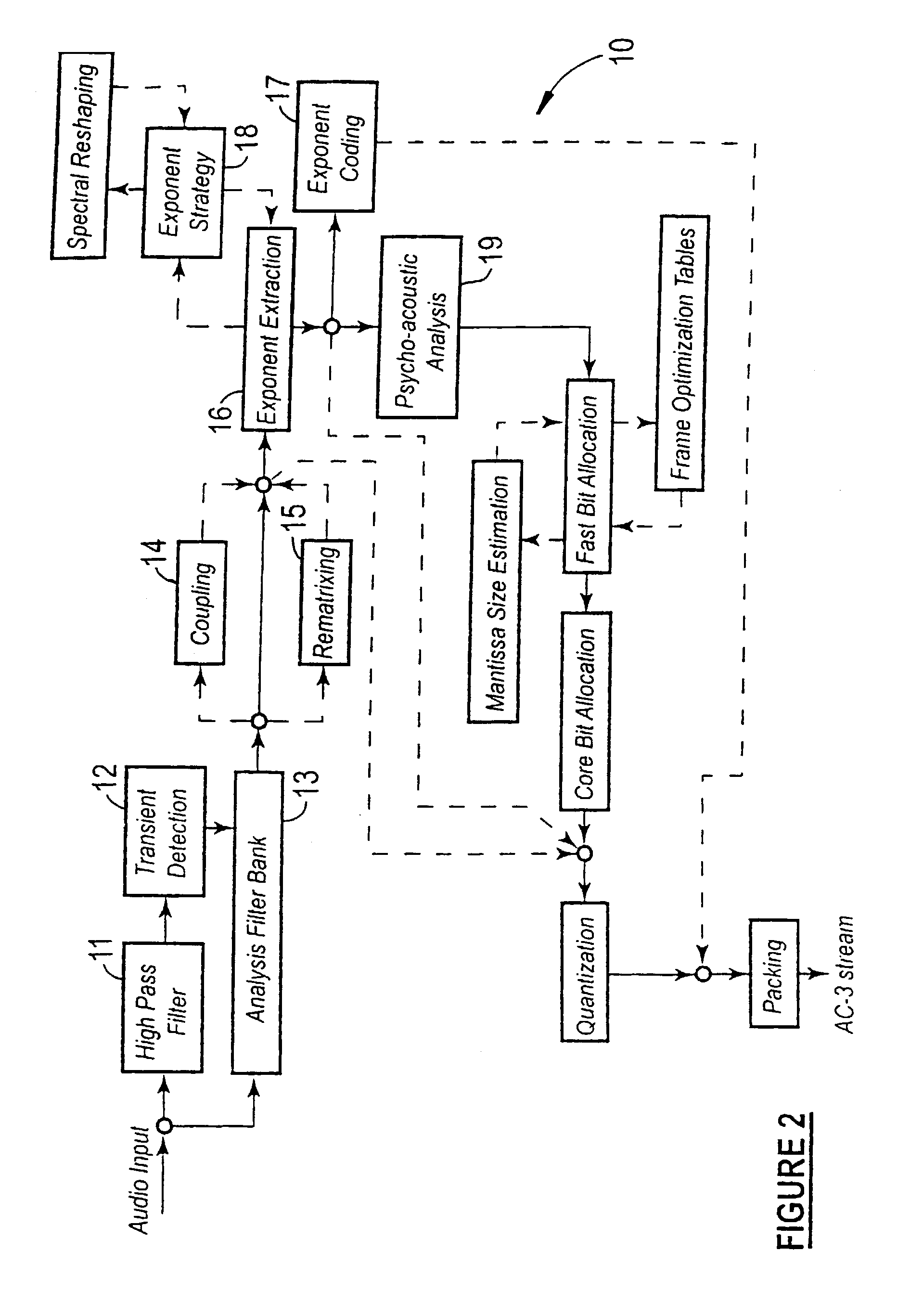

Channel coupling for an AC-3 encoder

InactiveUS7096240B1None is suitable for purposeDigital data processing detailsSpeech analysisChannel coupling16-bit

Channel coupling for an AC-3 encoder, using mixed precision computations and 16-bit coupling coefficient calculations for channels with 32-bit frequency coefficients.

Owner:STMICROELECTRONICS ASIA PACIFIC PTE

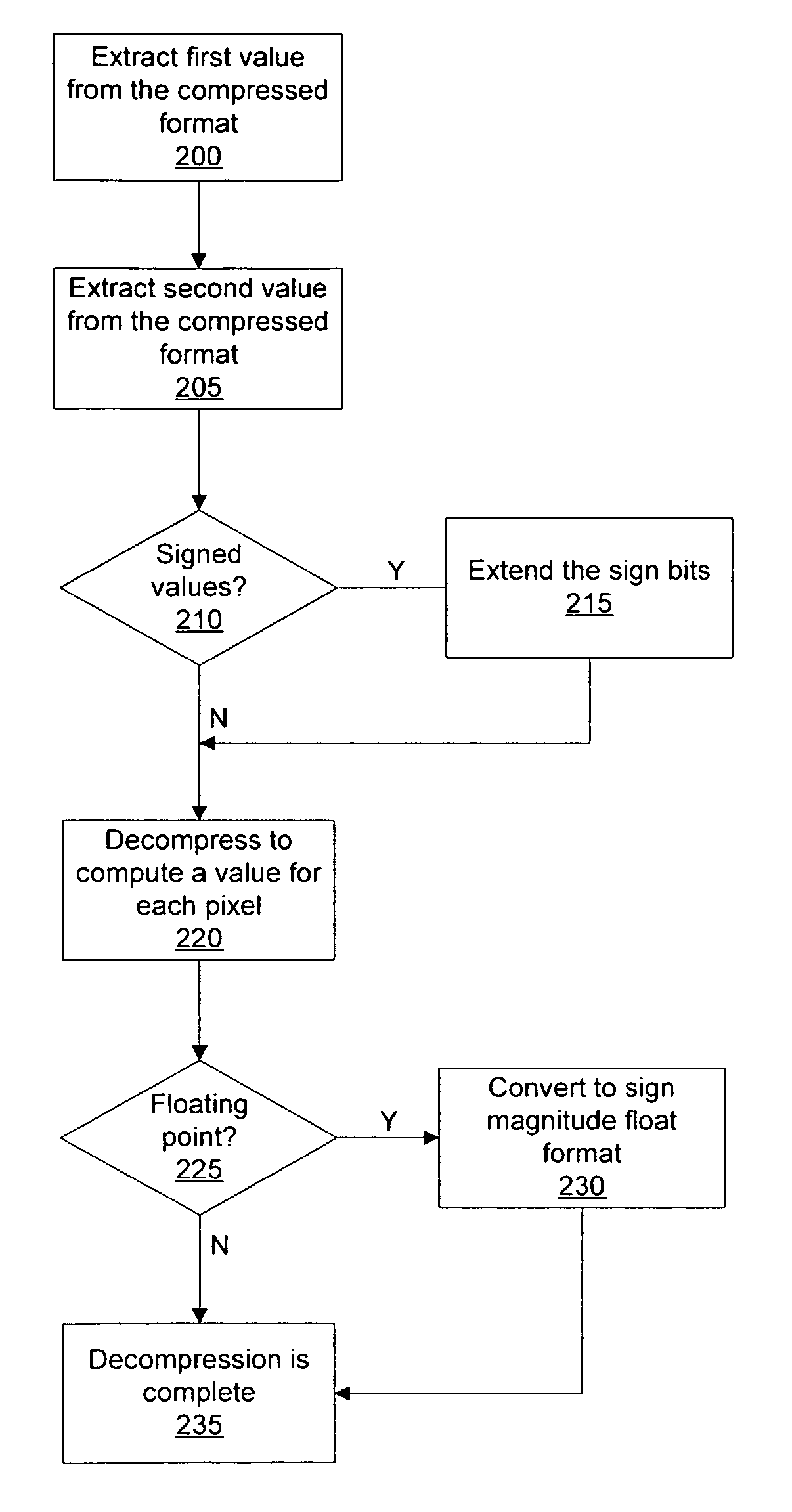

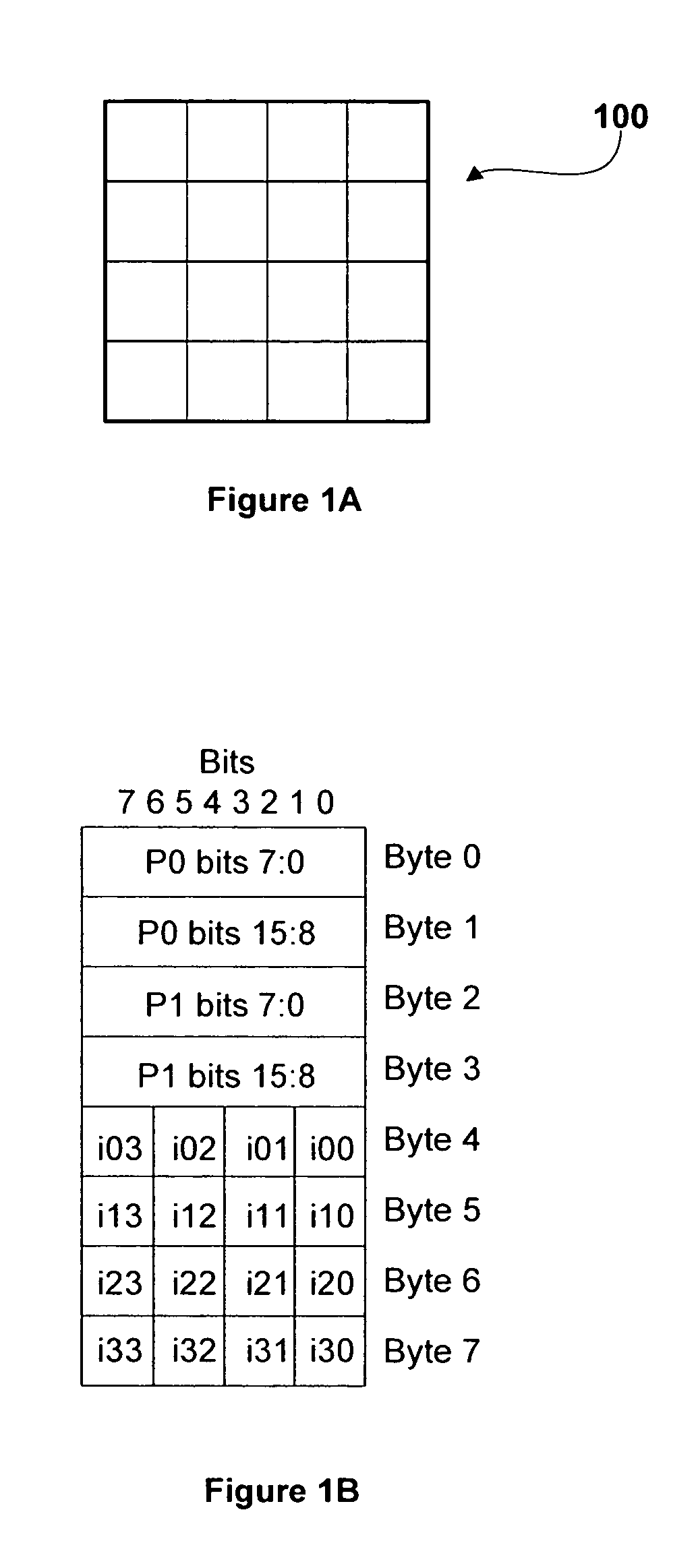

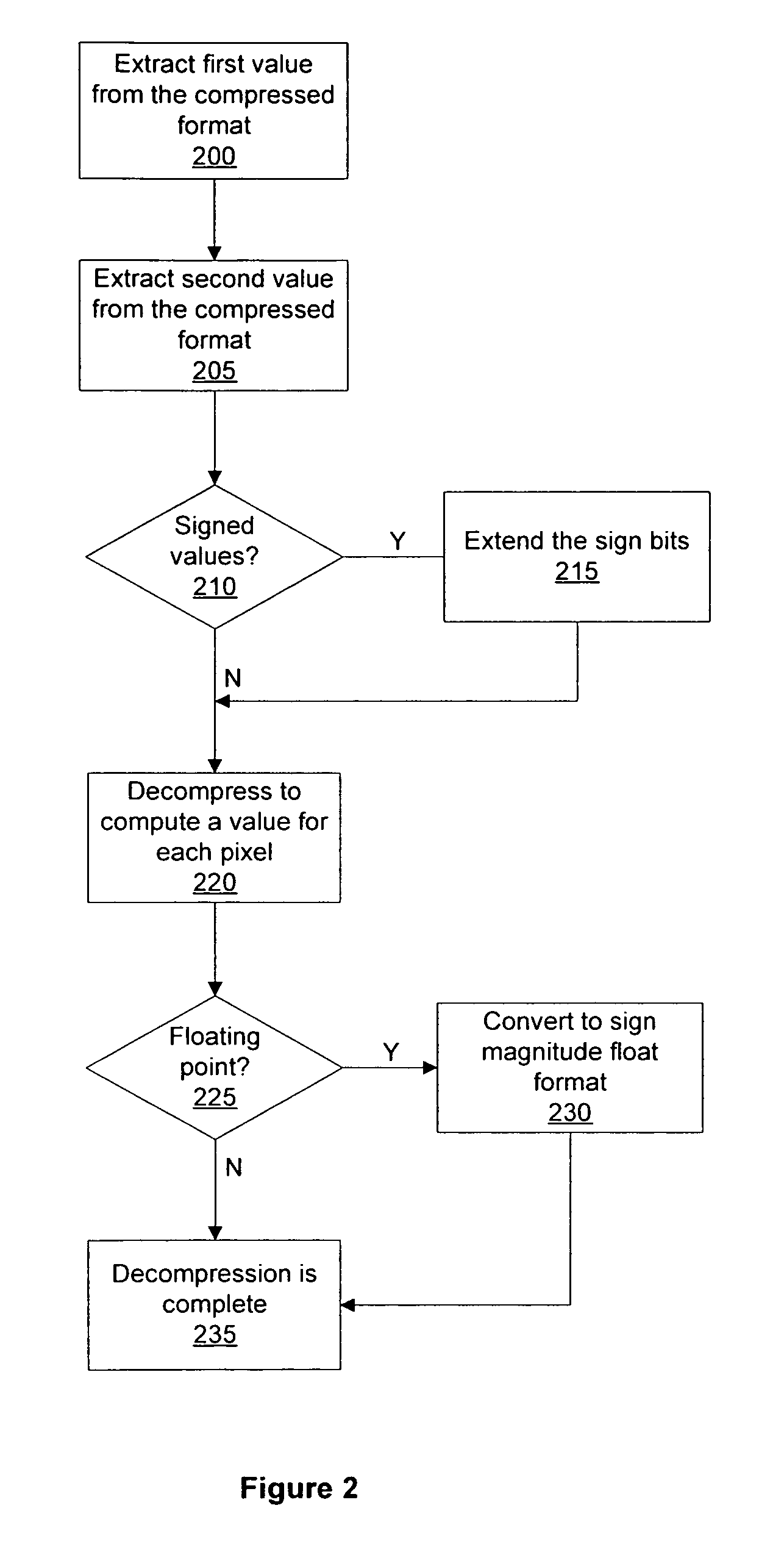

Decompression of compressed 16 bit data

Systems and methods compress and decompress 16 bit data. The 16 bit data may be signed or unsigned and represented in a fixed point or floating point format. A fixed block size of data is compressed into a fixed length format. Data compressed using a medium quality compression scheme may be efficiently decompressed in hardware. Data may be efficiently compressed and decompressed in hardware using a high quality compression scheme. The high quality compression scheme has a lower compression ratio compared with the medium quality compression scheme, but is near lossless in terms of quality.

Owner:NVIDIA CORP

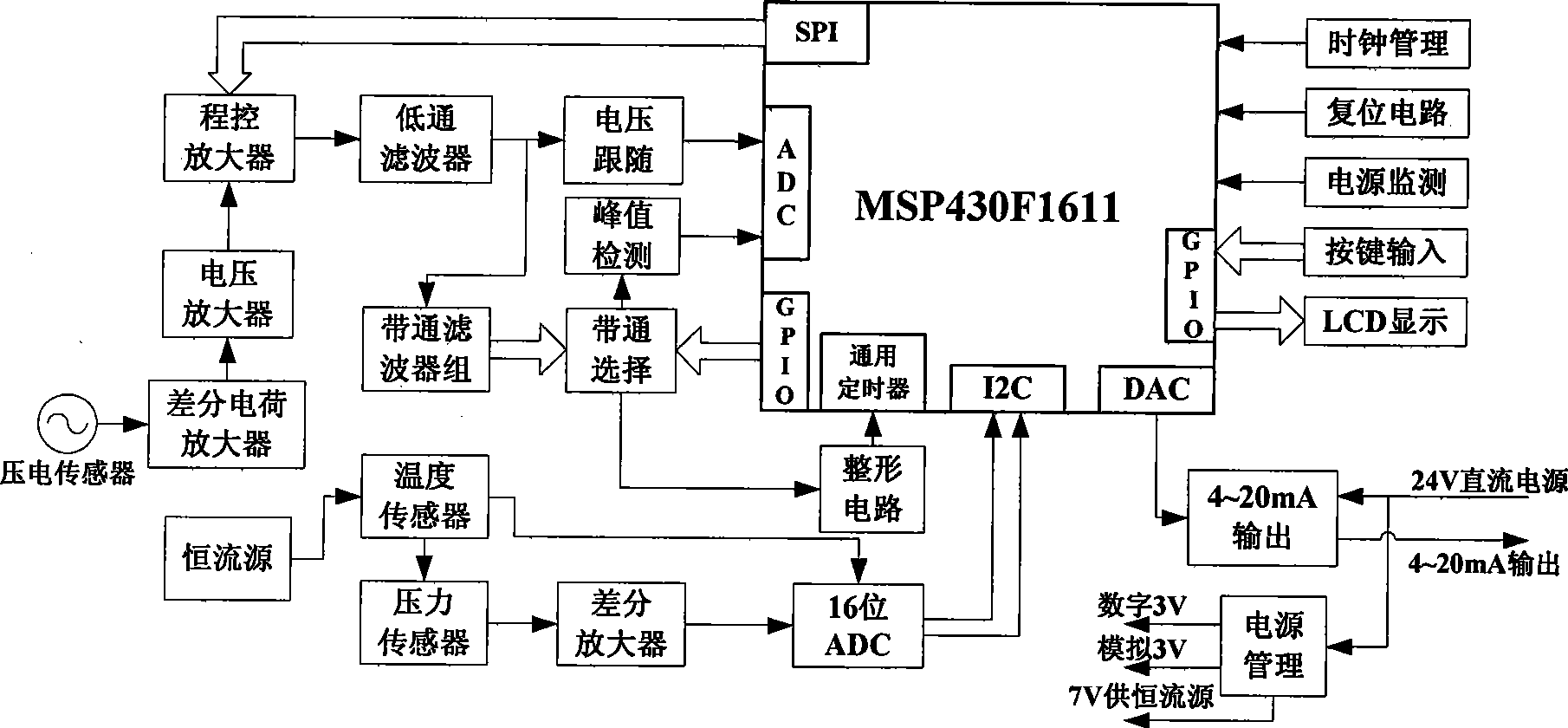

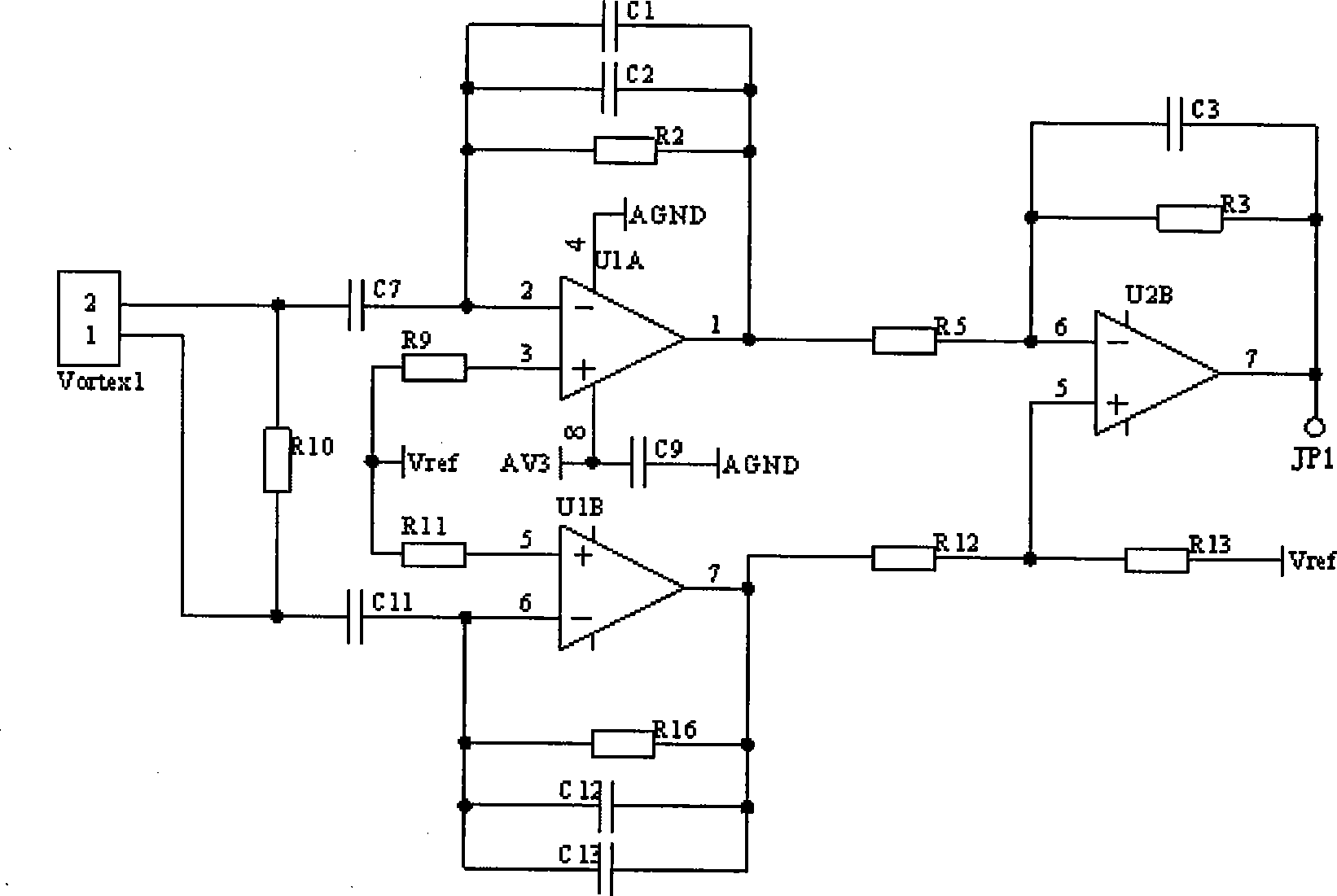

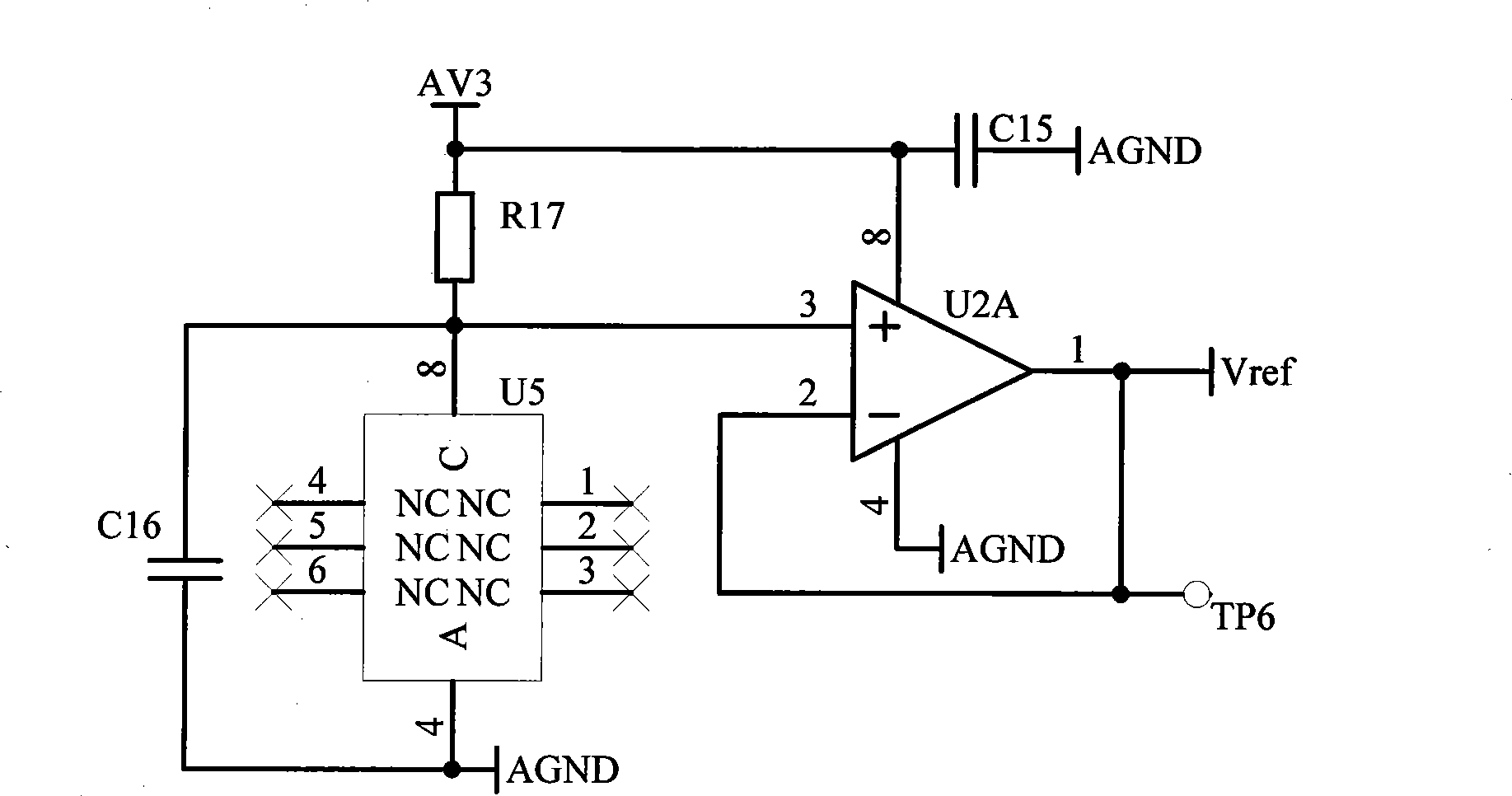

Improved low power consumption two-wire system vortex shedding flowmeter

InactiveCN101451864AImprove the extraction effectHigh precisionCharge amplifiersPulse shapingFrequency spectrumLow-pass filter

The invention relates to the field of flow detection, as an advanced low power consumption two-wire system vortex-shedding meter, comprising a piezo-electric transducer, a differential charge amplifier, a voltage amplifier, a programmable amplifier, a low pass filter, a voltage follower, a band-pass filter set, a band-pass select switch circuit, a peak detection circuit, a wave shaping circuit, asinglechip, a human-computer interface circuit, a 4-20mA output and power management circuit, a constant flow source, a temperature sensor, a pressure sensor, a differential amplifier and a 16-bit analog-to-digital converter. Mini FFT spectral decomposition is used to be combined with the analog band-pass filter set to process signals of a vortex sensor and a multicycle frequency measurement method of precision is used, thereby having temperature and pressure compensating circuit and function, outputting 4-20mA direct current and having two-wire system work. The advanced low power consumptiontwo-wire system vortex-shedding meter has greatly improved measure ratio, measurement precision and capacity of resisting disturbance.

Owner:HEFEI UNIV OF TECH

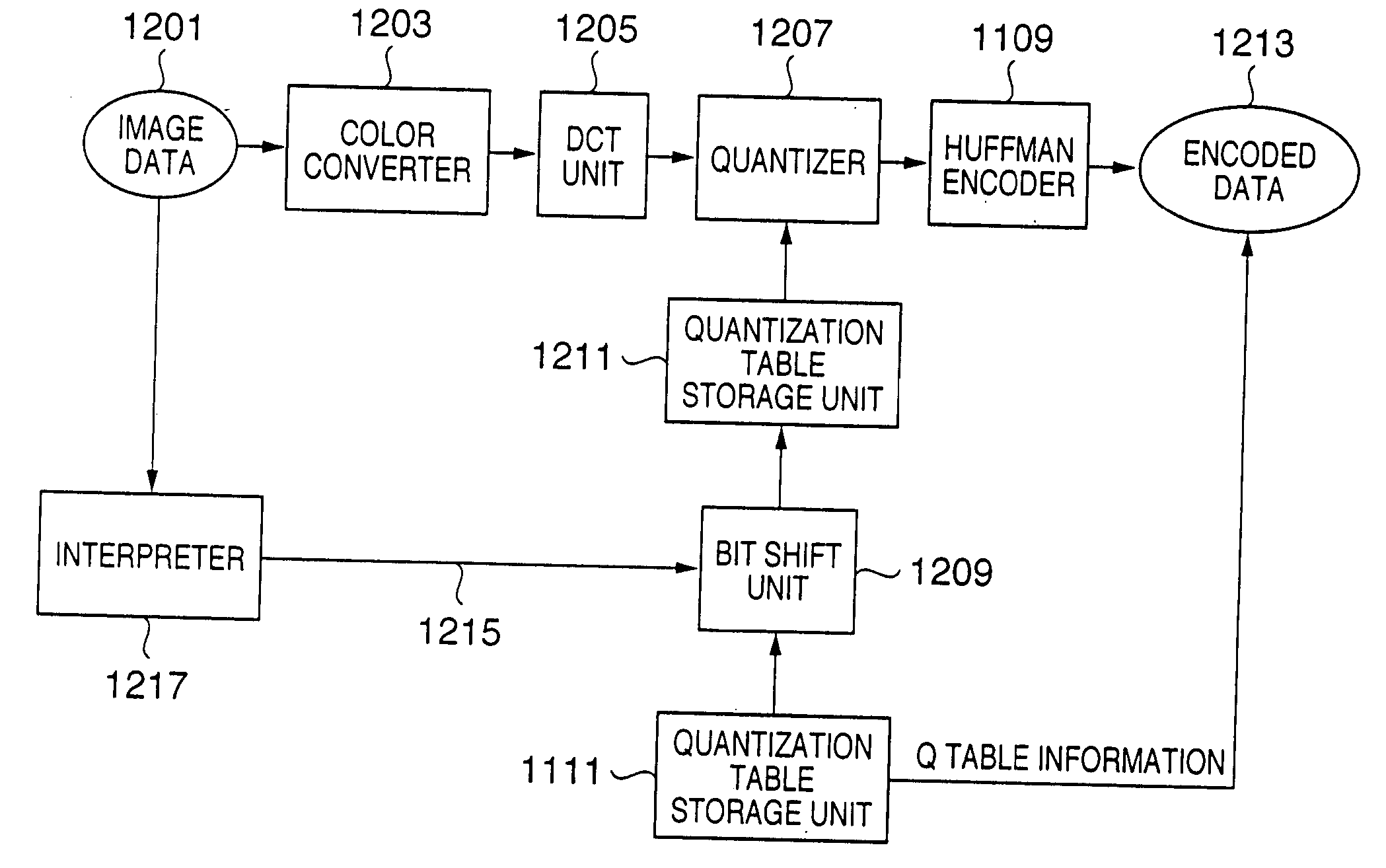

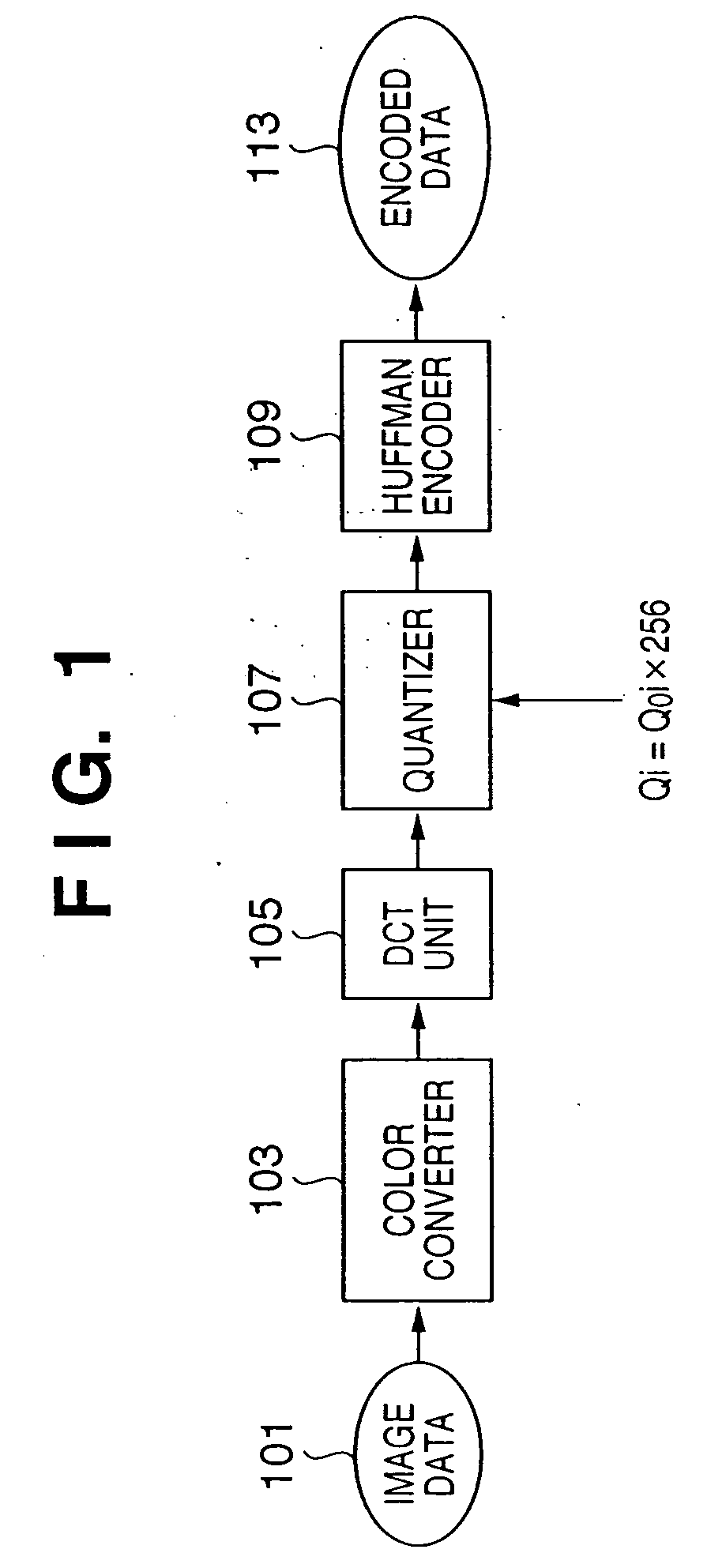

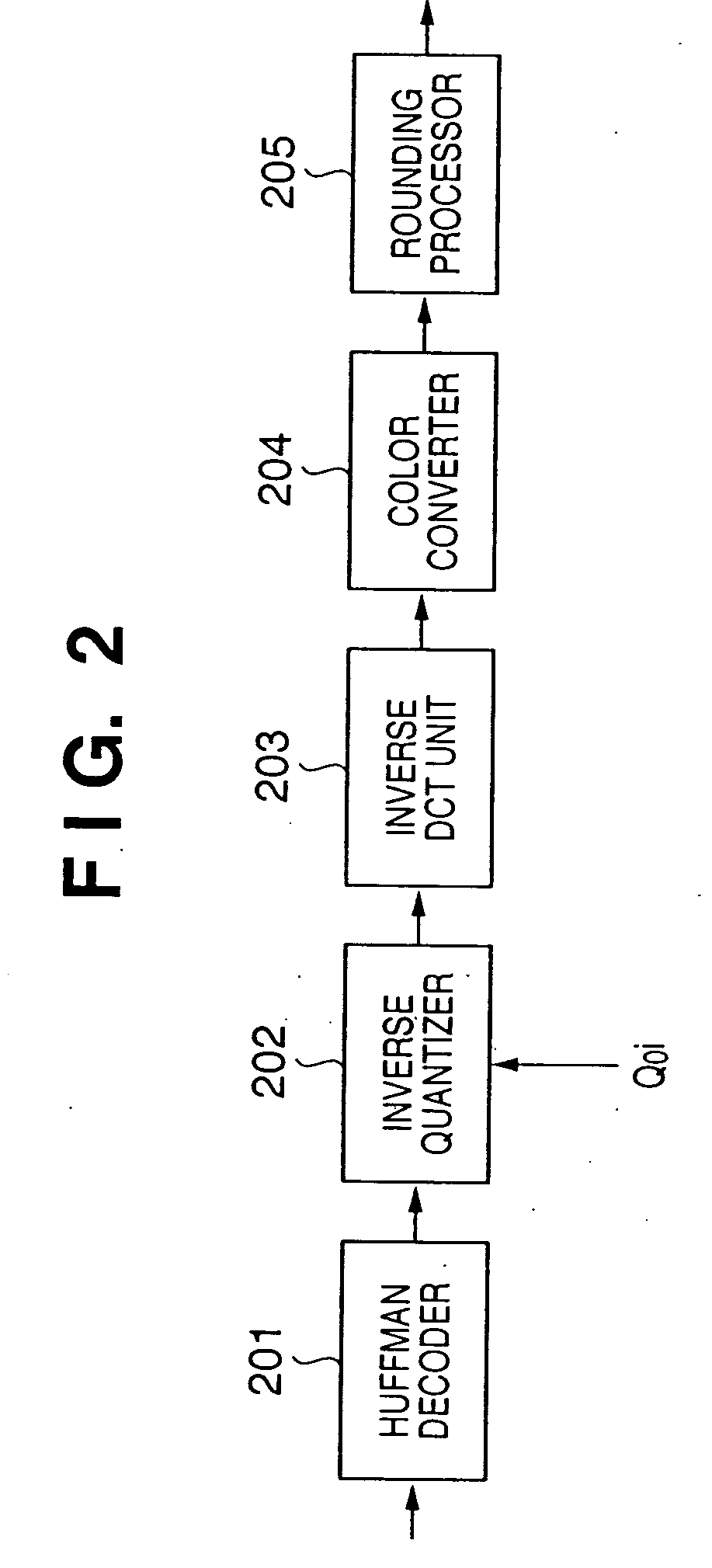

Image encoding apparatus, and image processing apparatus and its control method

InactiveUS20050276500A1Data generationDeterioration of precisionCharacter and pattern recognitionTelevision systemsImaging processingJPEG

This invention generates target encoded data by suppressing an arithmetic precision drop by executing processes such as orthogonal transformation and the like using the number of bits of an input image in place of reducing the number of bits at the time of input upon encoding an image. Upon generating baseline JPEG encoded data, a quantization table for an 8-bit image is stored in a quantization table storage unit. When an interpreter outputs information indicating that each color component per pixel of input image data is 16 bits, a bit shift unit multiplies the quantization table stored in the quantization table storage unit by the 8th power of 2 or {8th power of 2+1}. A quantizer quantizes coefficients output from a DCT unit on the basis of the quantization table stored in the quantization table storage unit, and a Huffman encoder encodes the quantization result to Huffman codes. A header is created by setting information indicating baseline JPEG and the quantization table stored in the quantization table storage unit, thus generating encoded data.

Owner:CANON KK

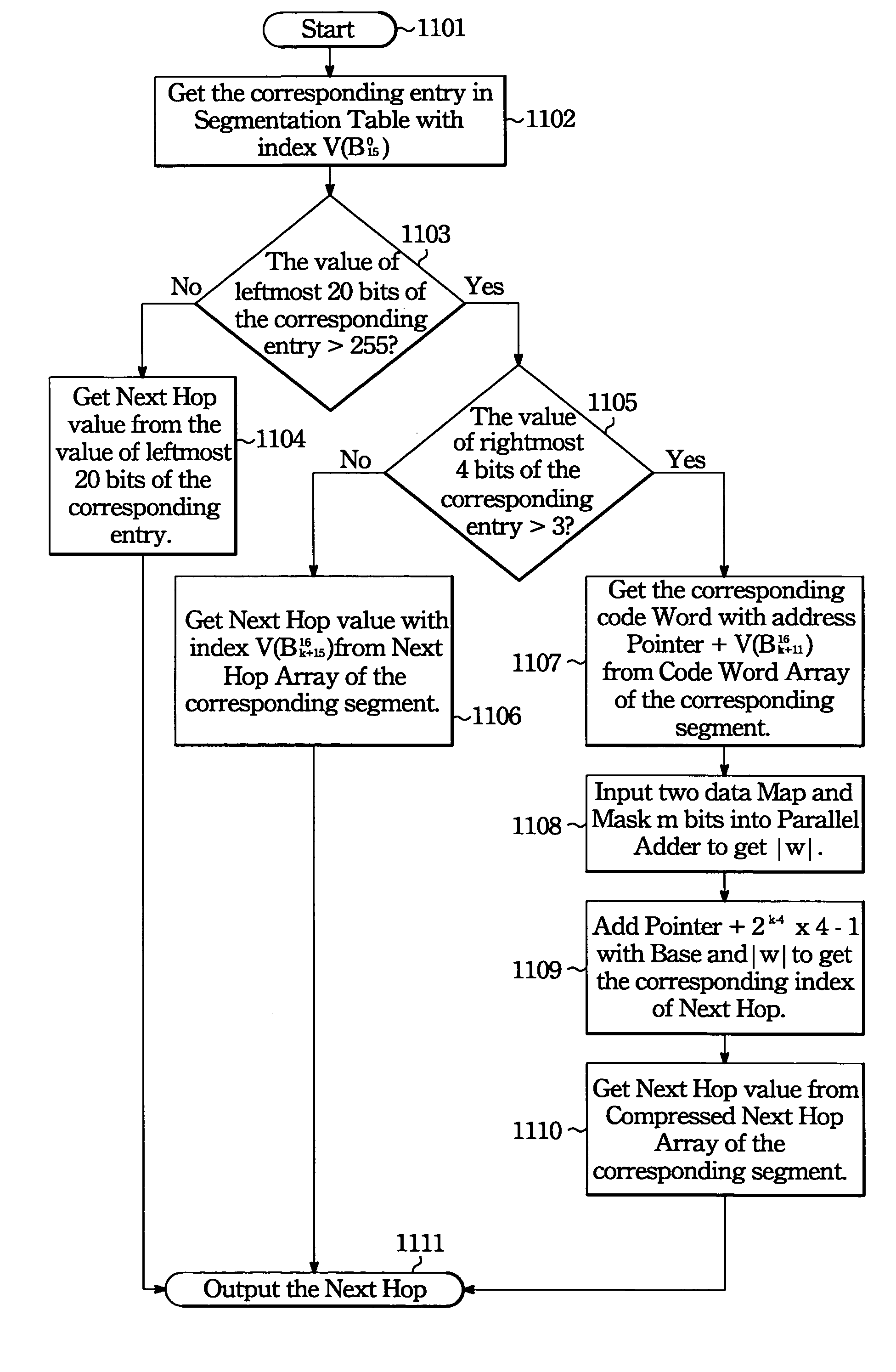

IP routing lookup scheme and system for multi-gigabit switching routers

InactiveUS6963924B1Lookup is very fastLow implementation costData processing applicationsData switching by path configurationRouting table16-bit

An IP routing lookup scheme and system for a multi-gigabit switching router which can reach 3 memory accesses in the worst case using memory size less than 512 KB is disclosed. The invention can compress a routing table with 40,000 routing entries into a forwarding table of 450–470 Kbytes. According to the present invention, a segmentation table storage device stores a next hop or a pointer for looking up a next hop for an incoming packet having prefix length less than or equal to 16 bits. The Next Hop Array storage device is for storing the next hops for a packet having prefix length larger than 16 bits and offset length less than or equal to 3 bits. A Compressed Next Hop Array storage device is encoded and decoded according to a Code Word Array storage device. The Compressed Next Hop Array storage device stores next hops for the incoming packet having prefix length larger than 16 bits and offset length larger than 3 bits. Thus, in the worst case, an output port for a route prefix can be found in 3 memory accesses.

Owner:BROADWEB CORP

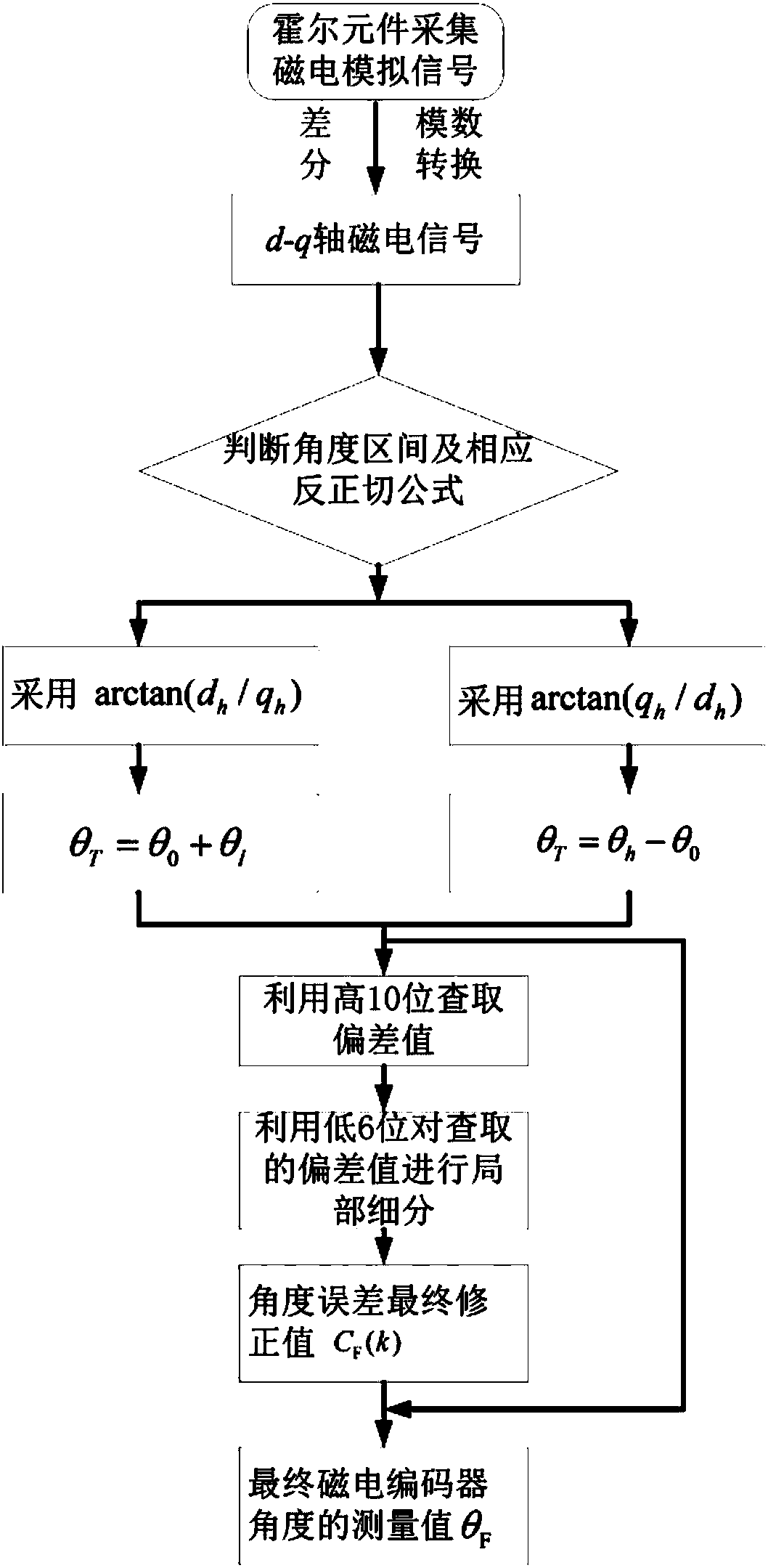

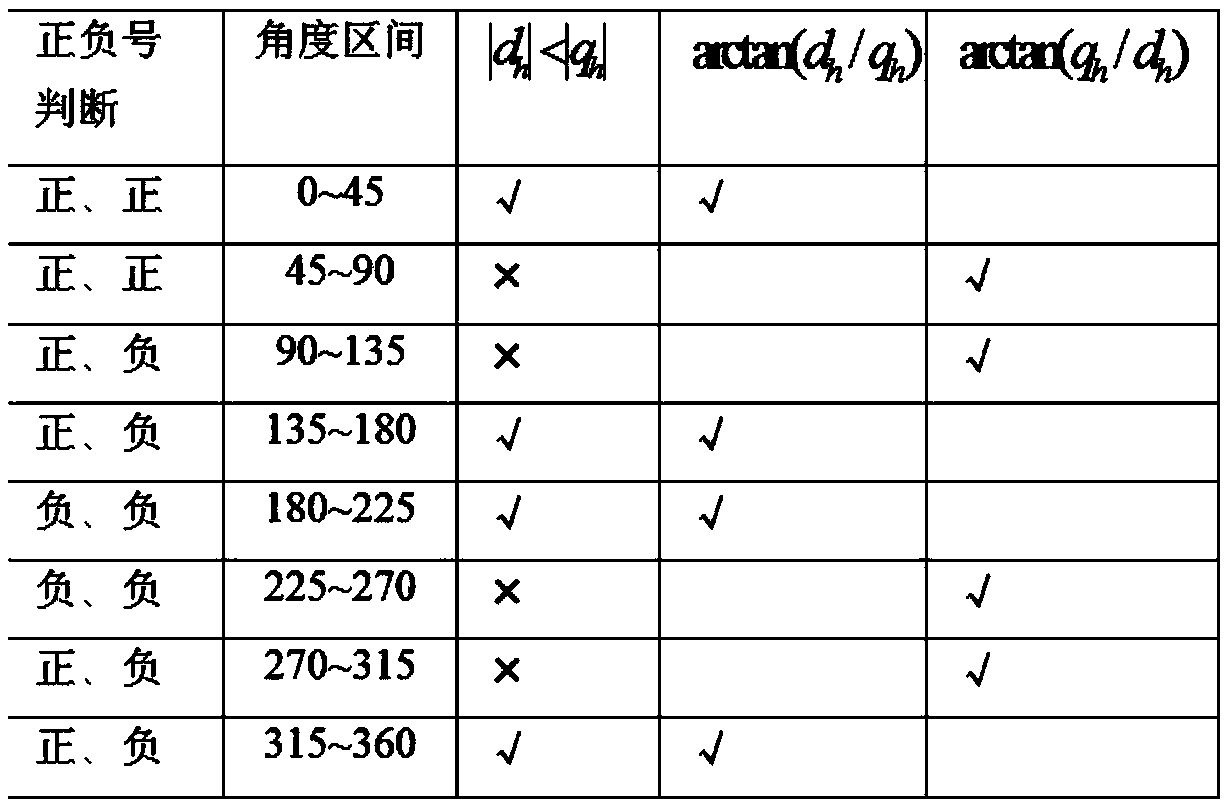

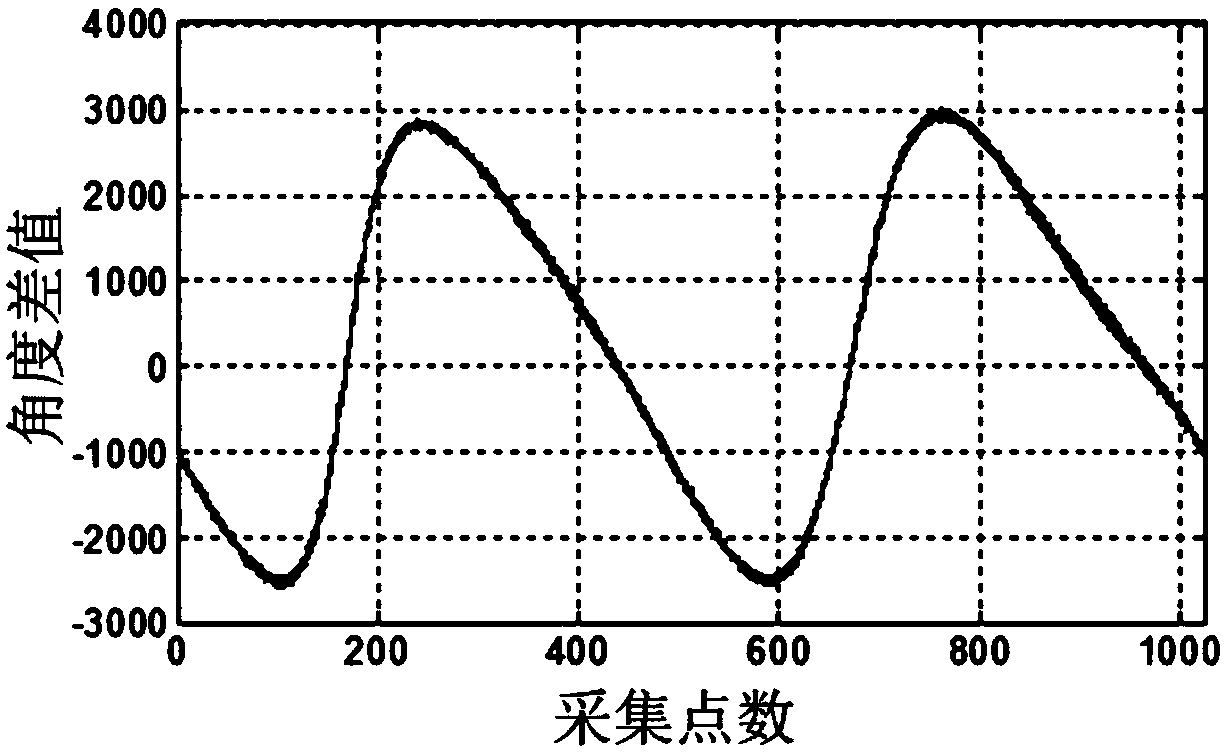

Magneto-electric coder calibration method based on arc tangent crossing interval tabulation method

ActiveCN107607037AImprove stabilityEliminate bad effectsUsing electrical means16-bitComputer science

Owner:上海频控科技有限公司

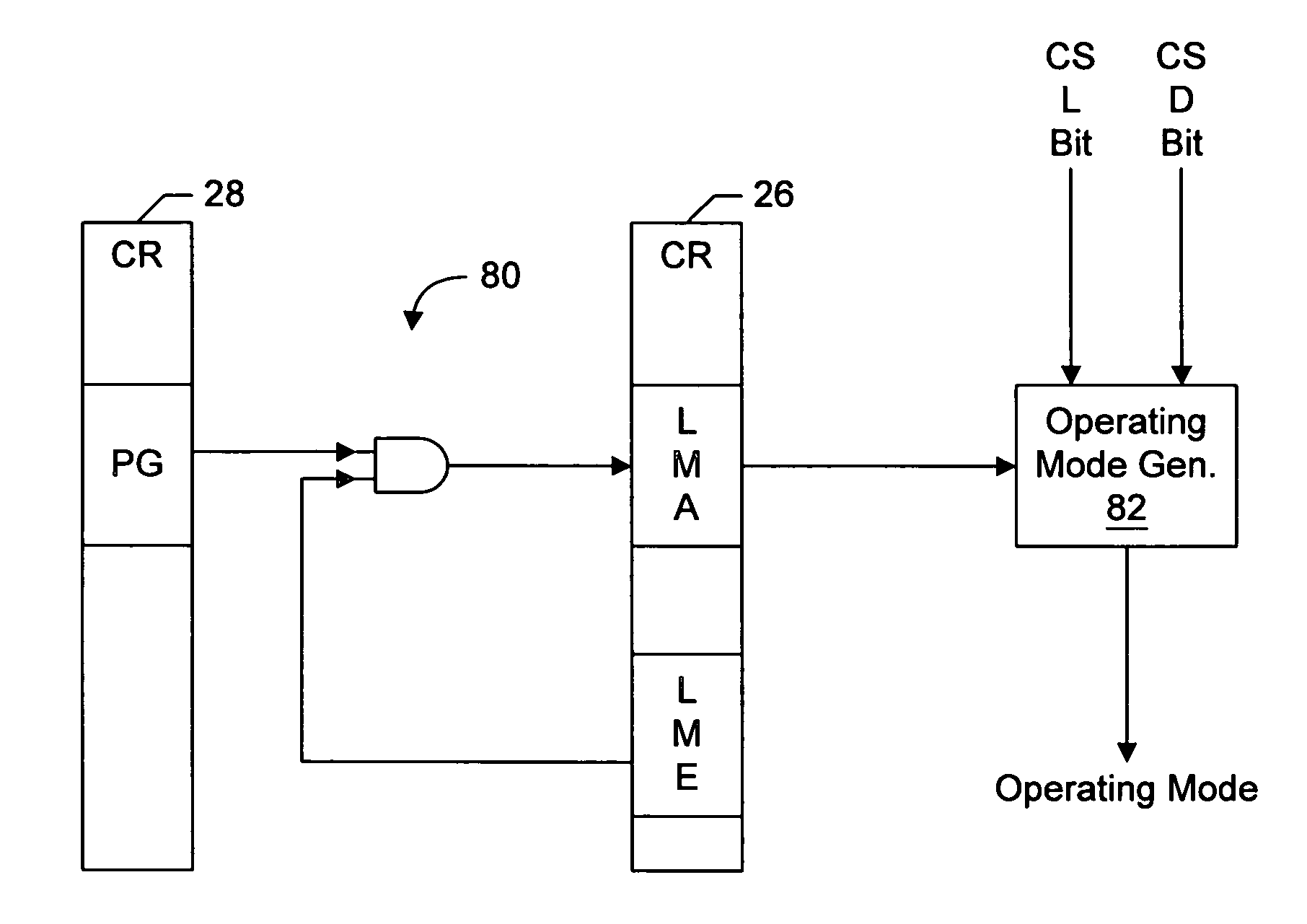

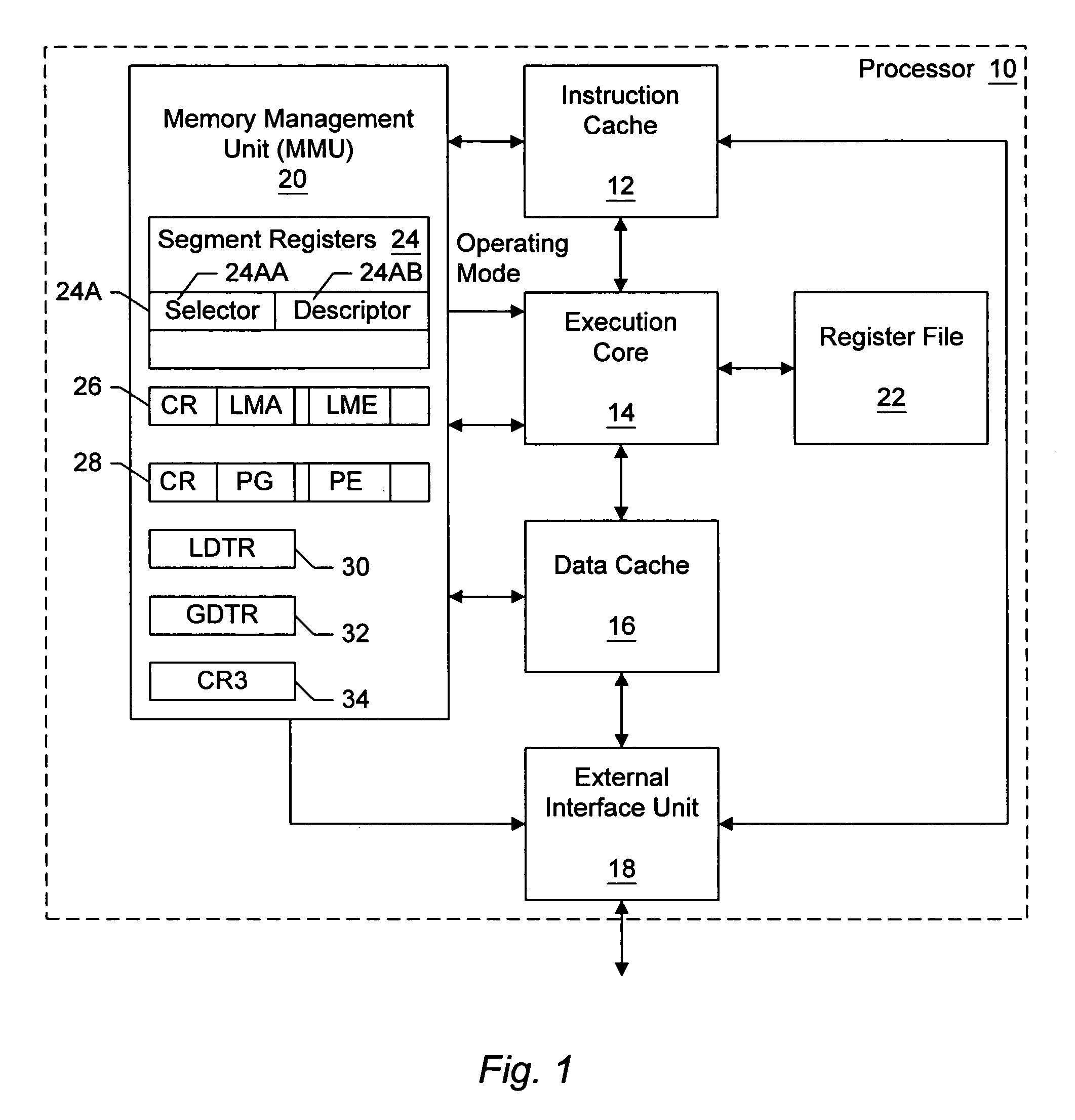

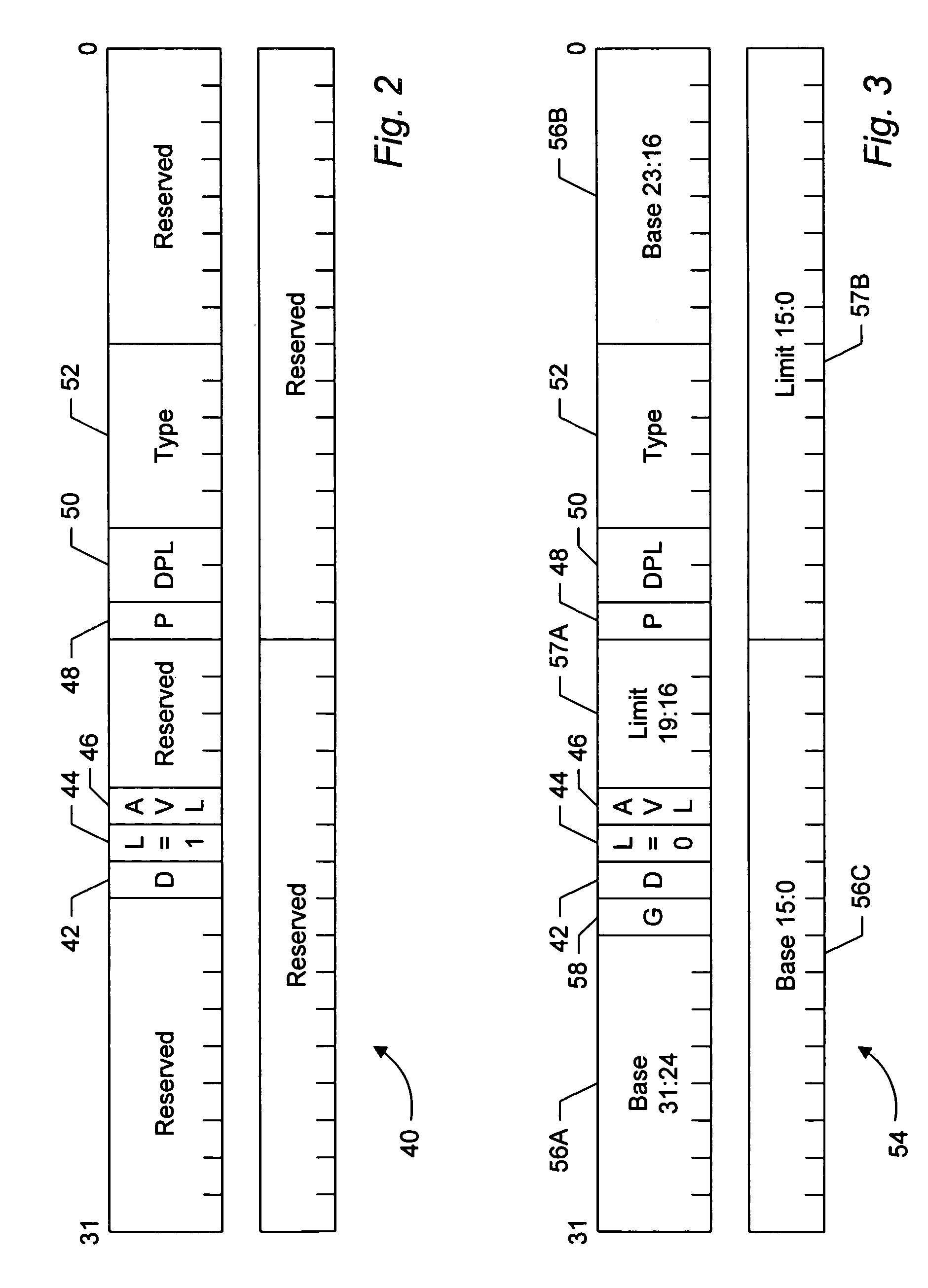

Establishing a mode indication responsive to two or more indications

ActiveUS7058791B1Memory adressing/allocation/relocationGeneral purpose stored program computerLong mode16-bit

A processor generates a mode indication based on two or more other indications. The mode indication is indicative of whether or not a particular mode is active in the processor. Each indication is stored in a storage location which is addressable via a different instruction. In one embodiment, a long mode in which a 64 bit operating mode is selectable in addition to 32 bit and 16 bit modes may be activated via a long mode active indication. The long mode active indication may be generated by the processor, and may indicate that long mode is active if paging is enabled and a long mode enable indication indicates that long mode is enabled. In this manner, long mode may be activated after paging is enabled (with a set of long mode page tables indicated by the page table base address).

Owner:ADVANCED MICRO DEVICES INC

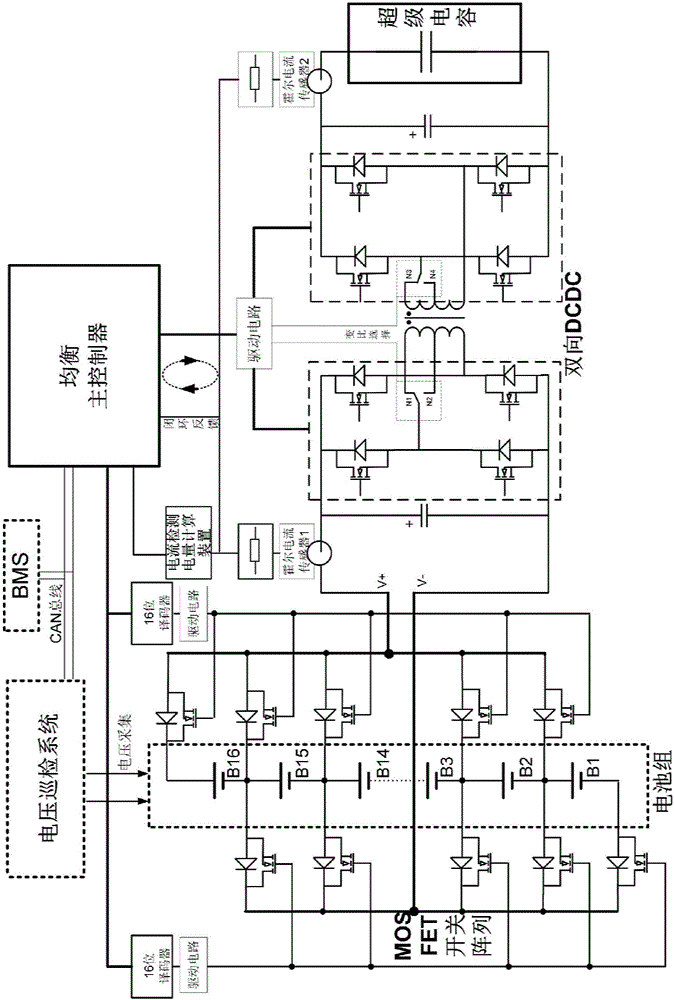

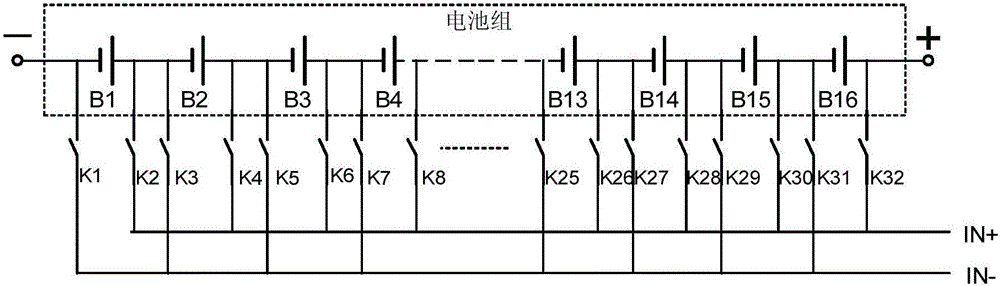

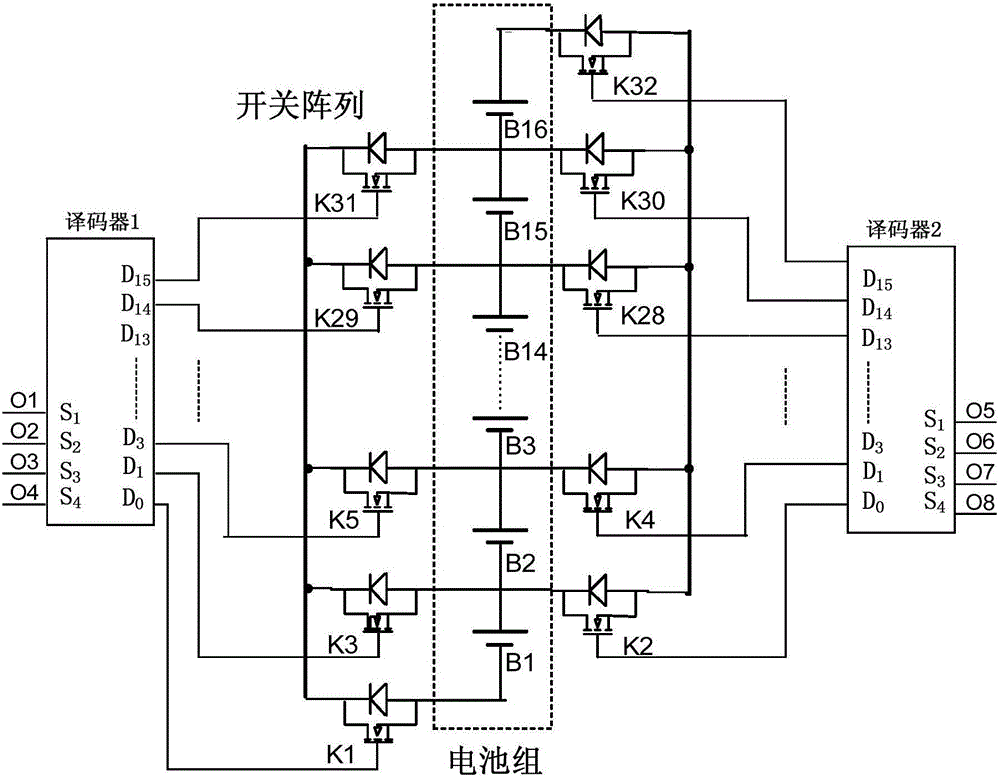

Super-capacitor energy storage and transfer-based active equalization system and method for lithium battery pack

ActiveCN105939034AGuarantee the demand for high power and high currentAchieve interlockCharge equalisation circuitSecondary cells charging/dischargingCapacitanceElectrical battery

The invention provides a super-capacitor energy storage and transfer-based active equalization system and method for a lithium battery pack. The active equalization system comprises an equalization main controller, a switch array, a two-way DC / DC, a super-capacitor, a current detection and power calculation device, a 16-bit decoder and a drive circuit, wherein the equalization main controller obtains a single battery voltage inspection value as an equalization state basis and any to-be-equalized battery is gated by the switch array to be connected to an equalization bus; the preceding stage of the full-bridge two-way DC / DC with an adjustable ratio is connected with the equalization bus and the backward stage is connected with the super-capacitor; the power of the equalization loss is calculated through the current detection and power calculation device; the equalization main controller achieves charging for the super-capacitor by a high-power battery through the two-way DC / DC; and the super-capacitor stores the power and then discharges a low-power battery through the two-way DC / DC until the equalization state. The power is stored and transferred through the super-capacitor; active equalization for the lithium battery pack is achieved; and the super-capacitor energy storage and transfer-based active equalization system has an important significance for prolonging of the lifetime of the lithium battery pack.

Owner:WUHAN UNIV OF TECH