Patents

Literature

548 results about "Holding current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Holding current (electronics) is the minimum current which must pass through the device in order for it to remain in the 'ON' state. Holding voltage (physiology), in electrophysiology, specifically while voltage clamping a cell, the holding current is the current that is passed into the cell in order to hold it at the command potential.

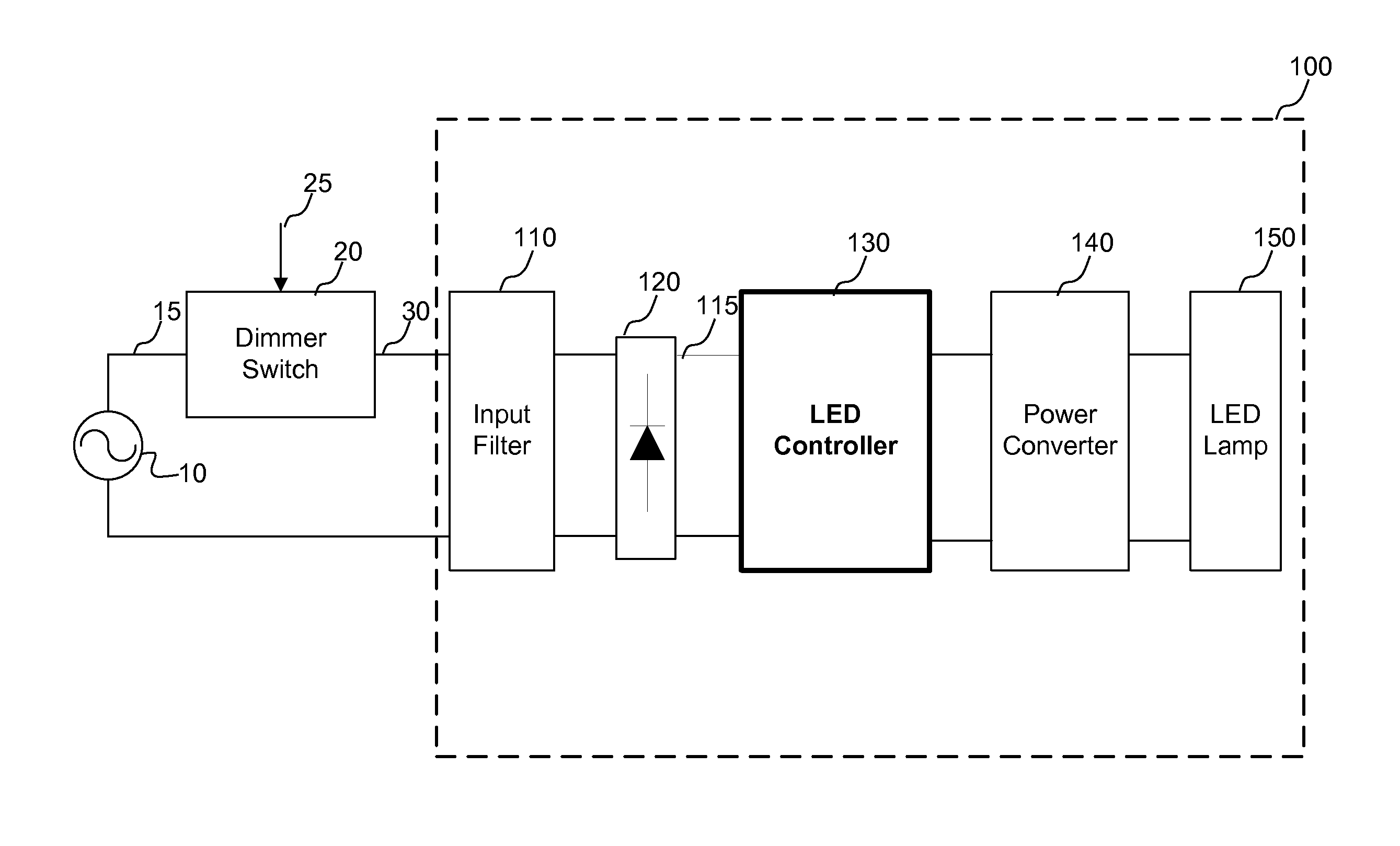

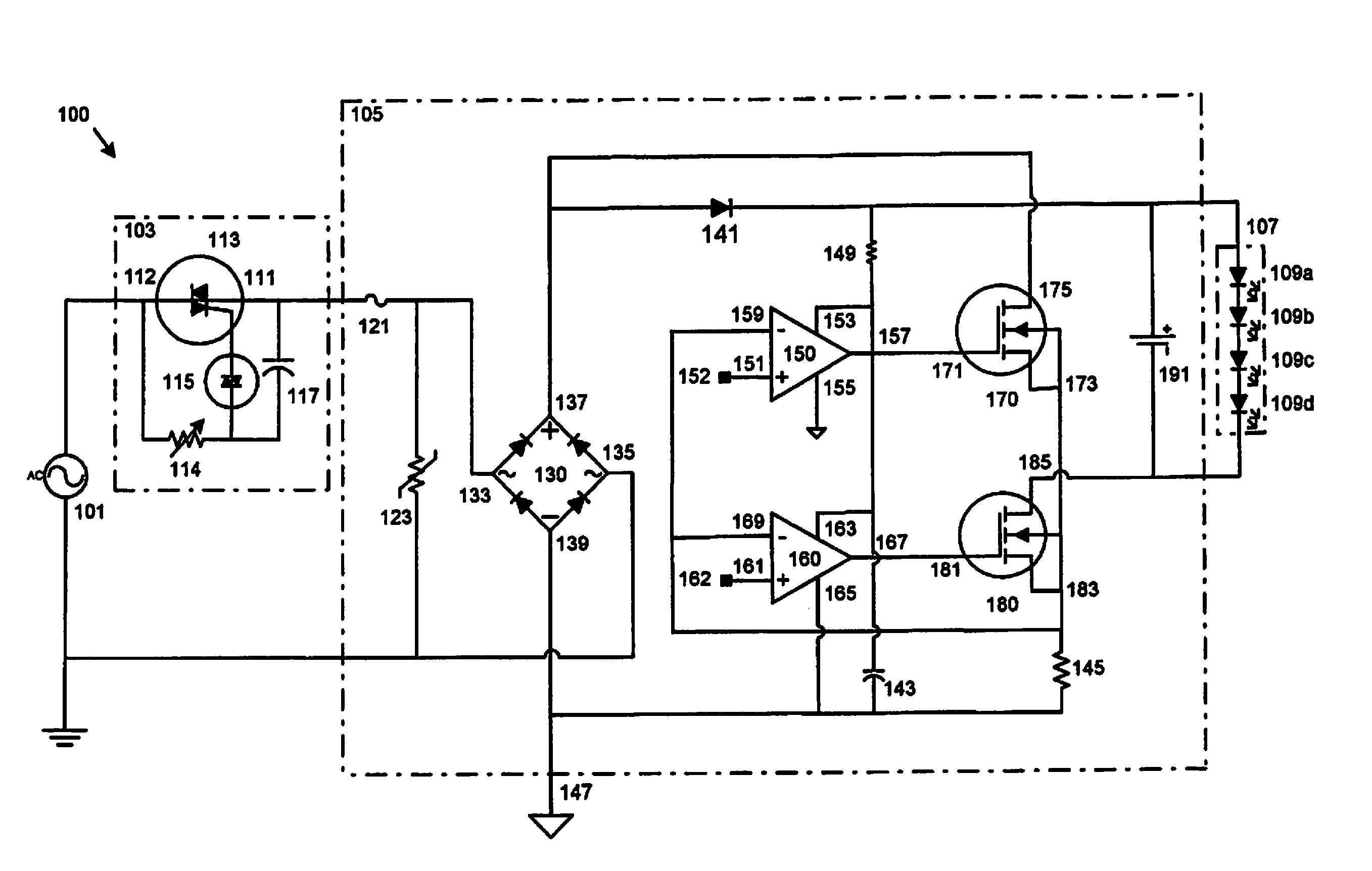

Current regulator for modulating brightness levels of solid state lighting

ActiveUS20070182338A1Low component requirementsElectrical apparatusElectroluminescent light sourcesImpedance matchingRoot mean square

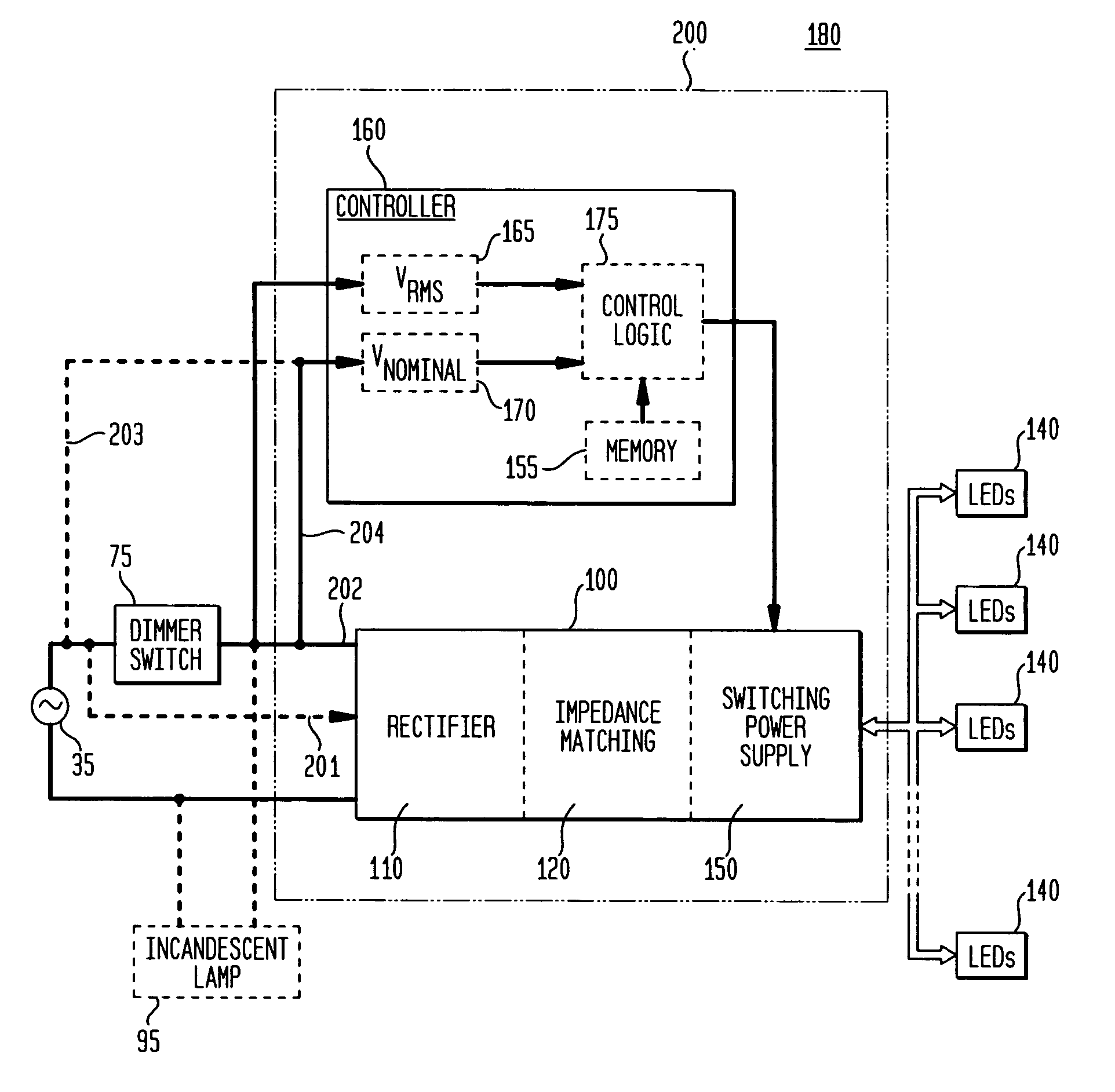

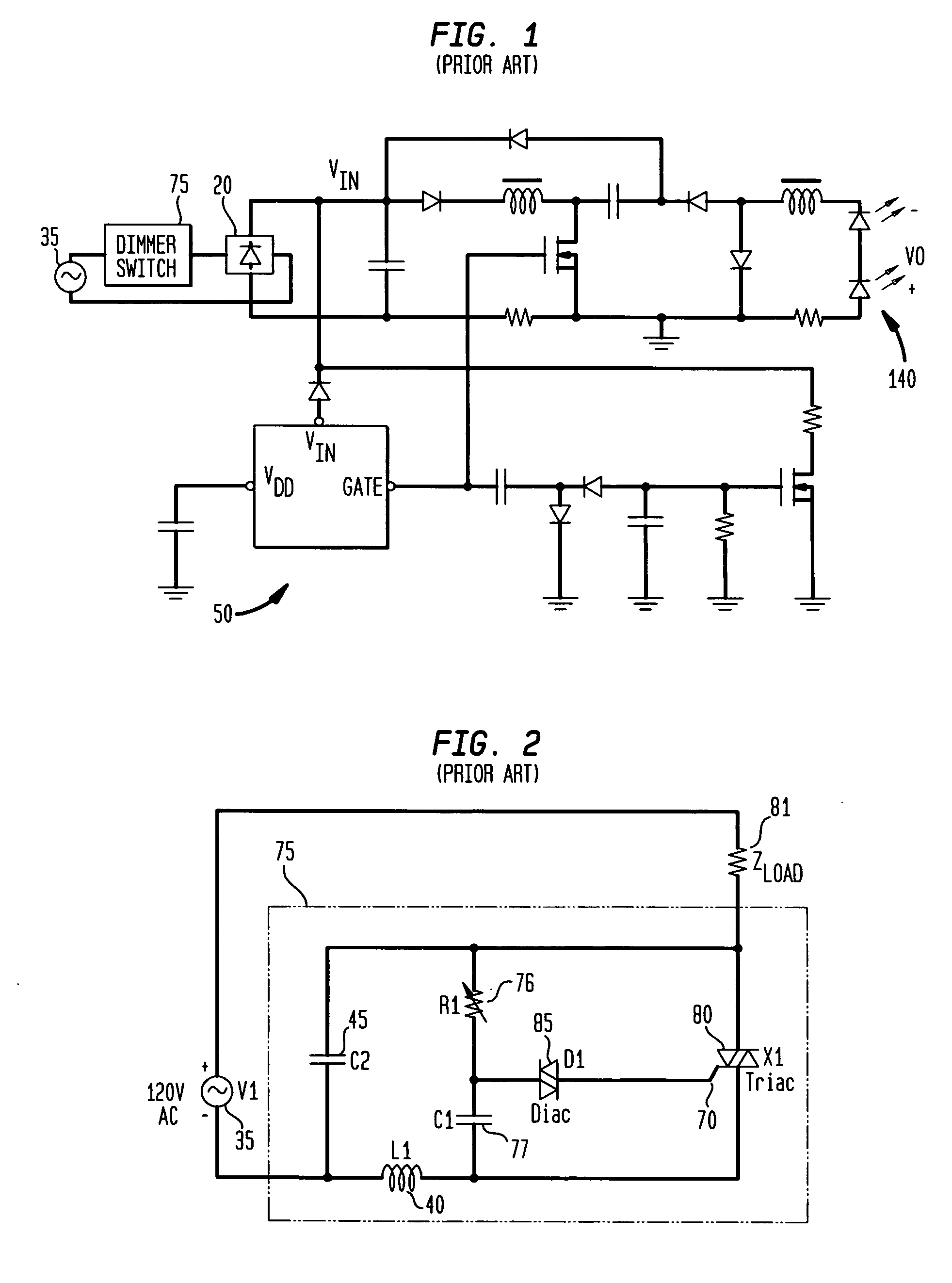

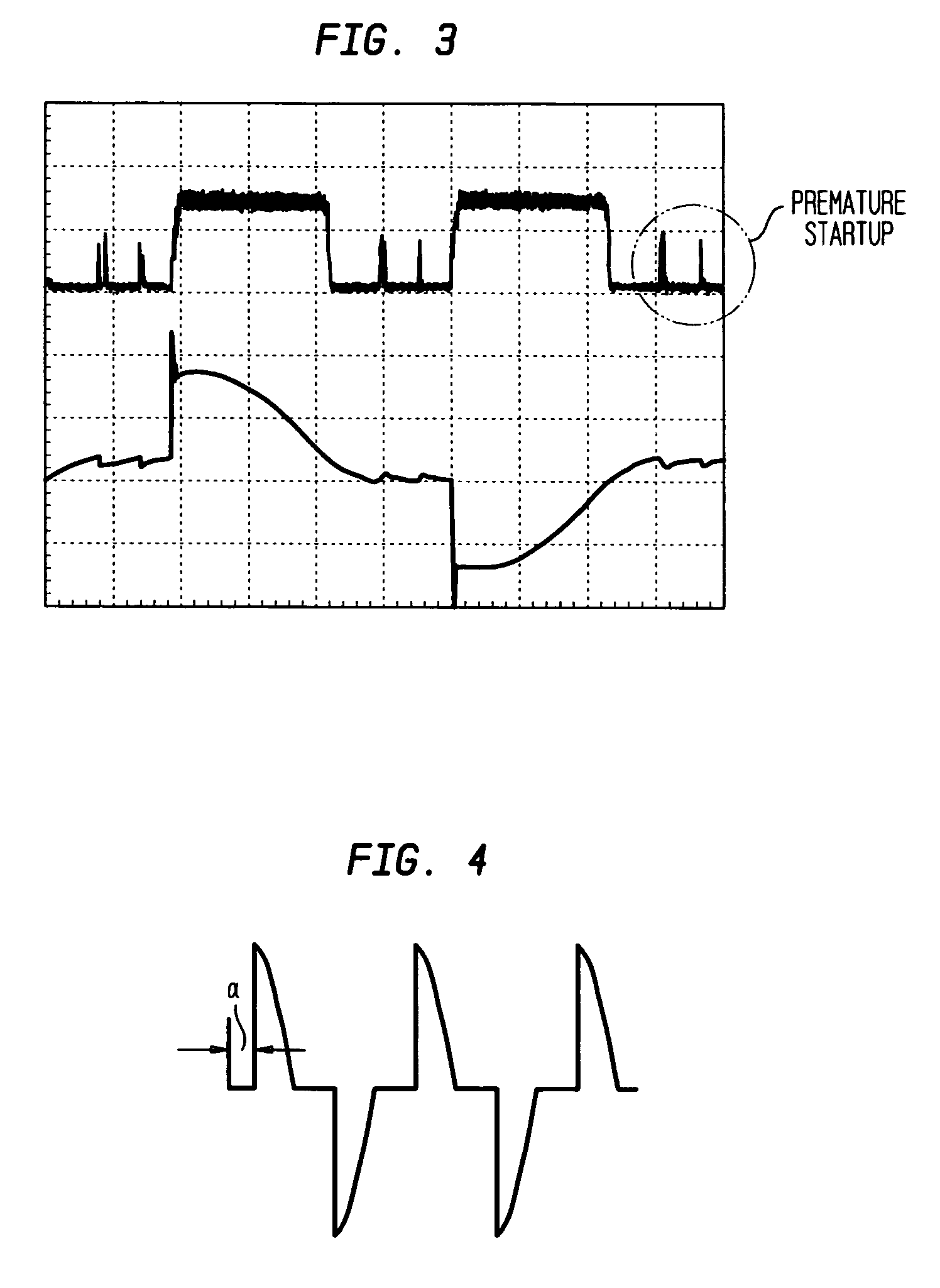

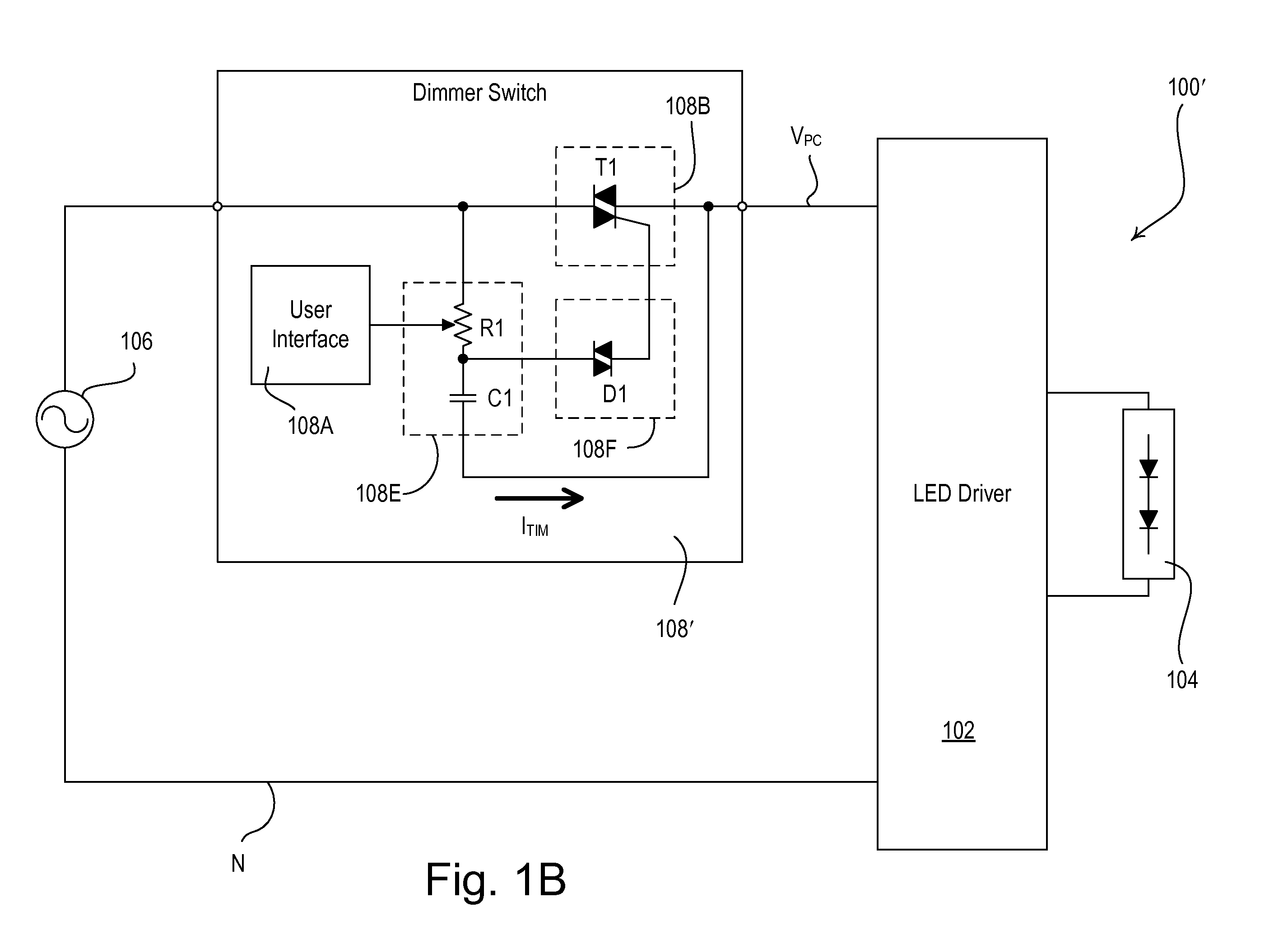

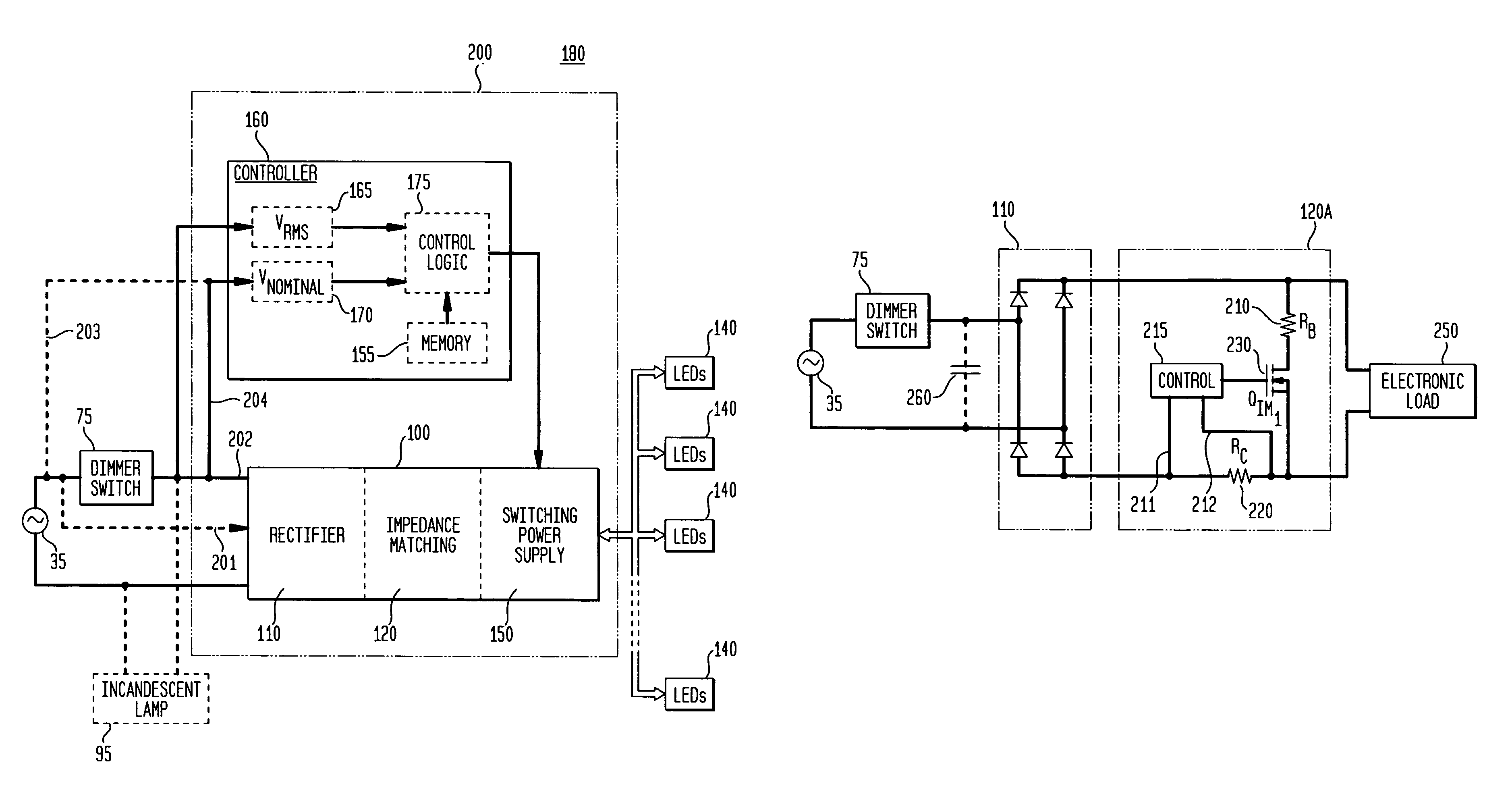

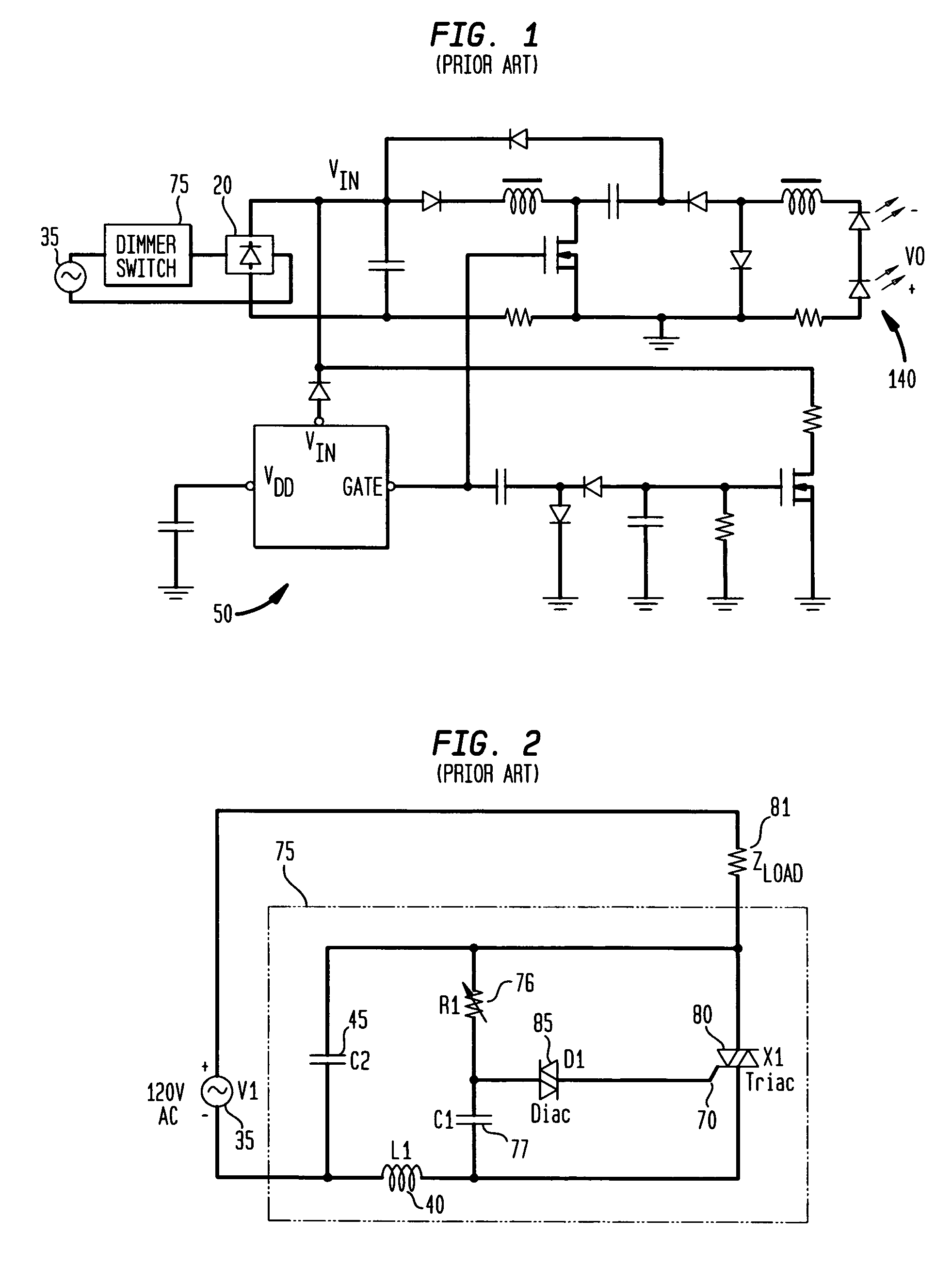

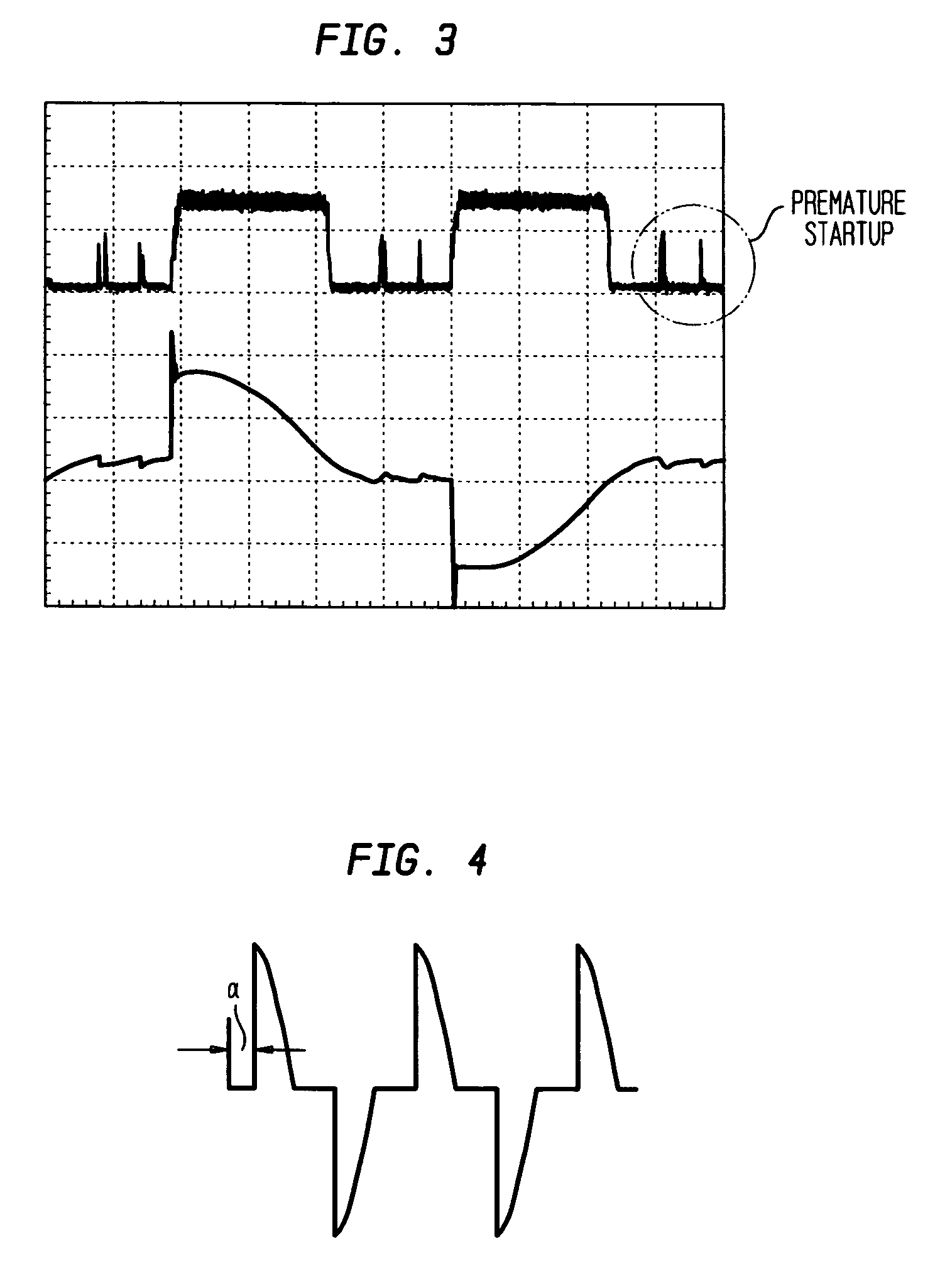

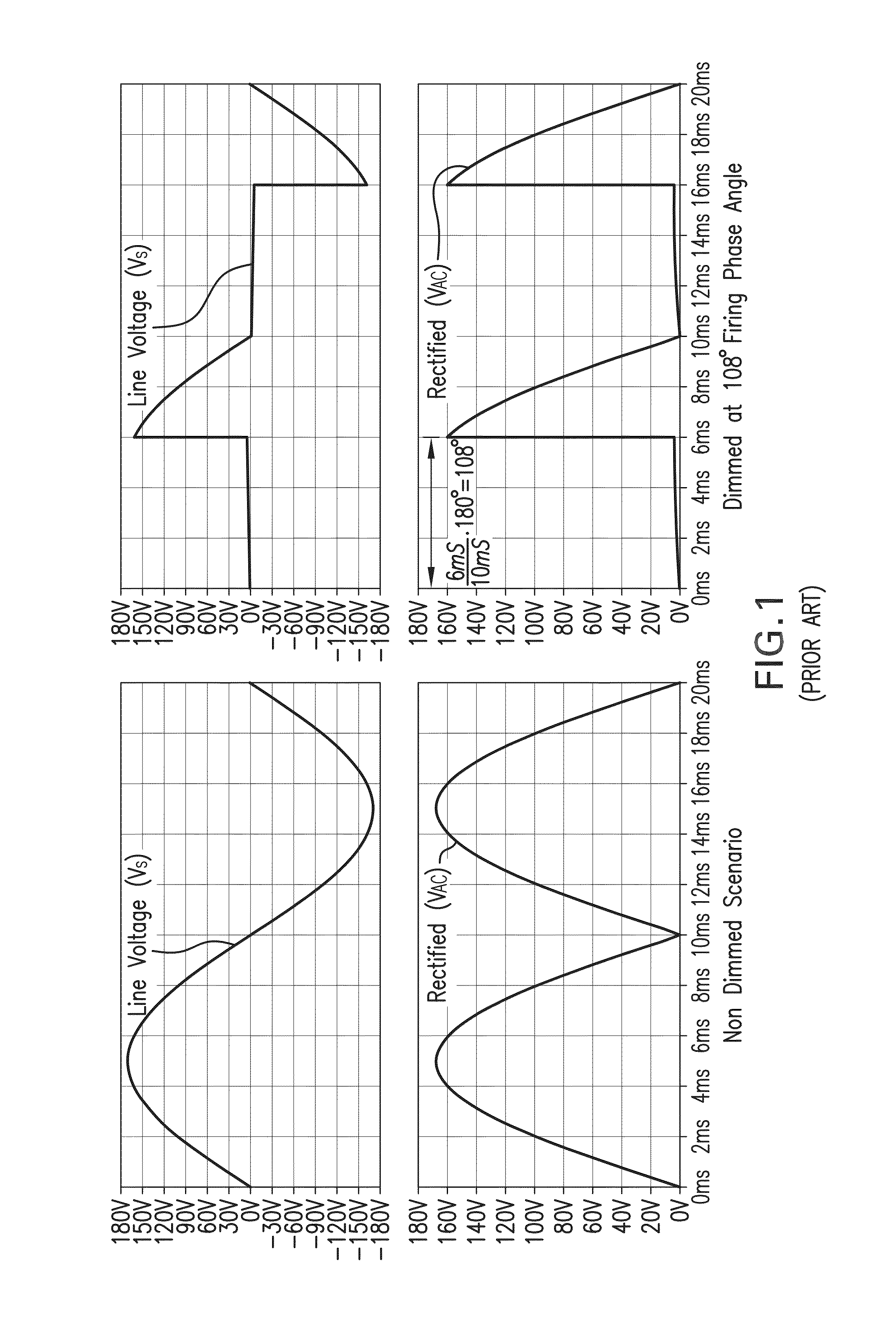

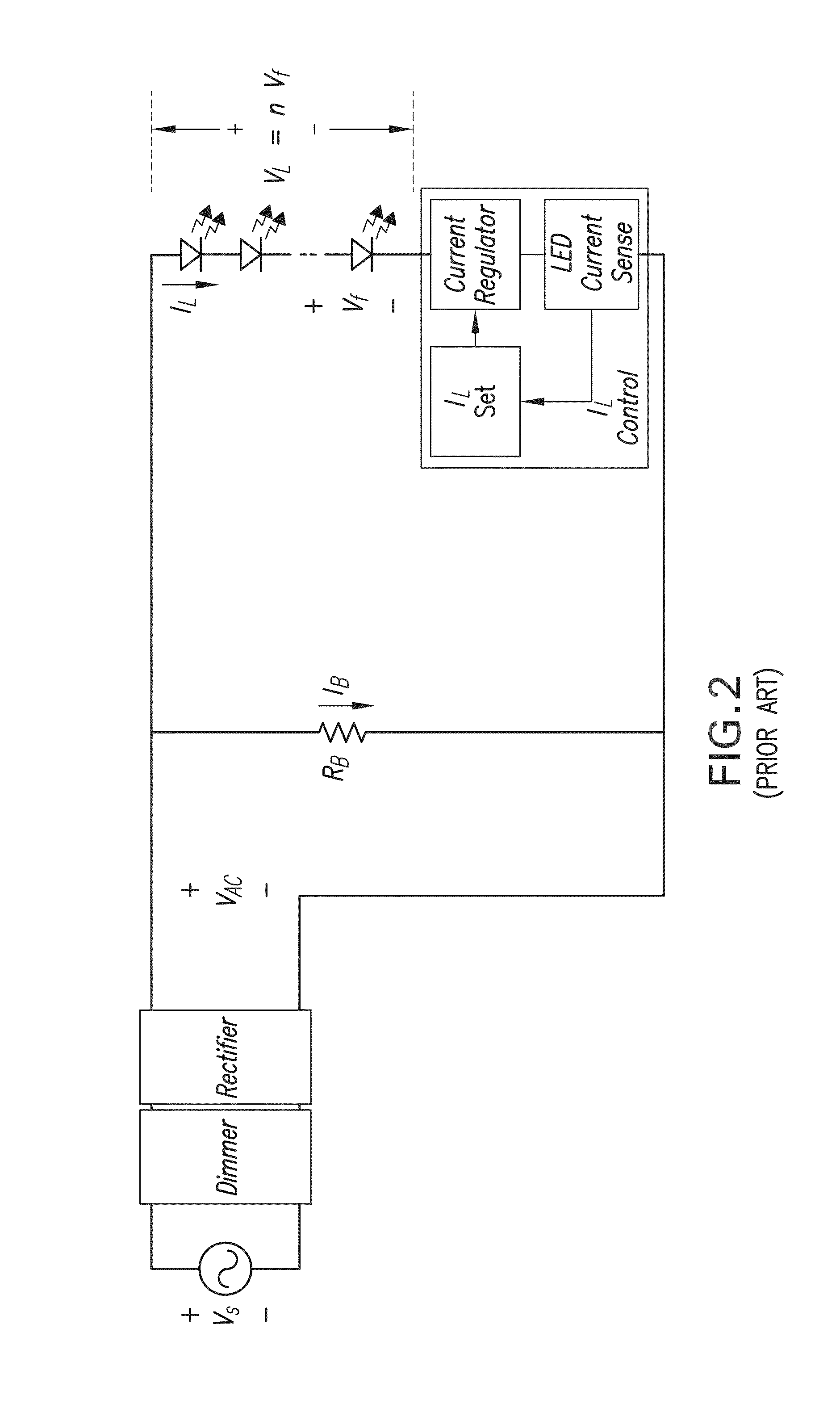

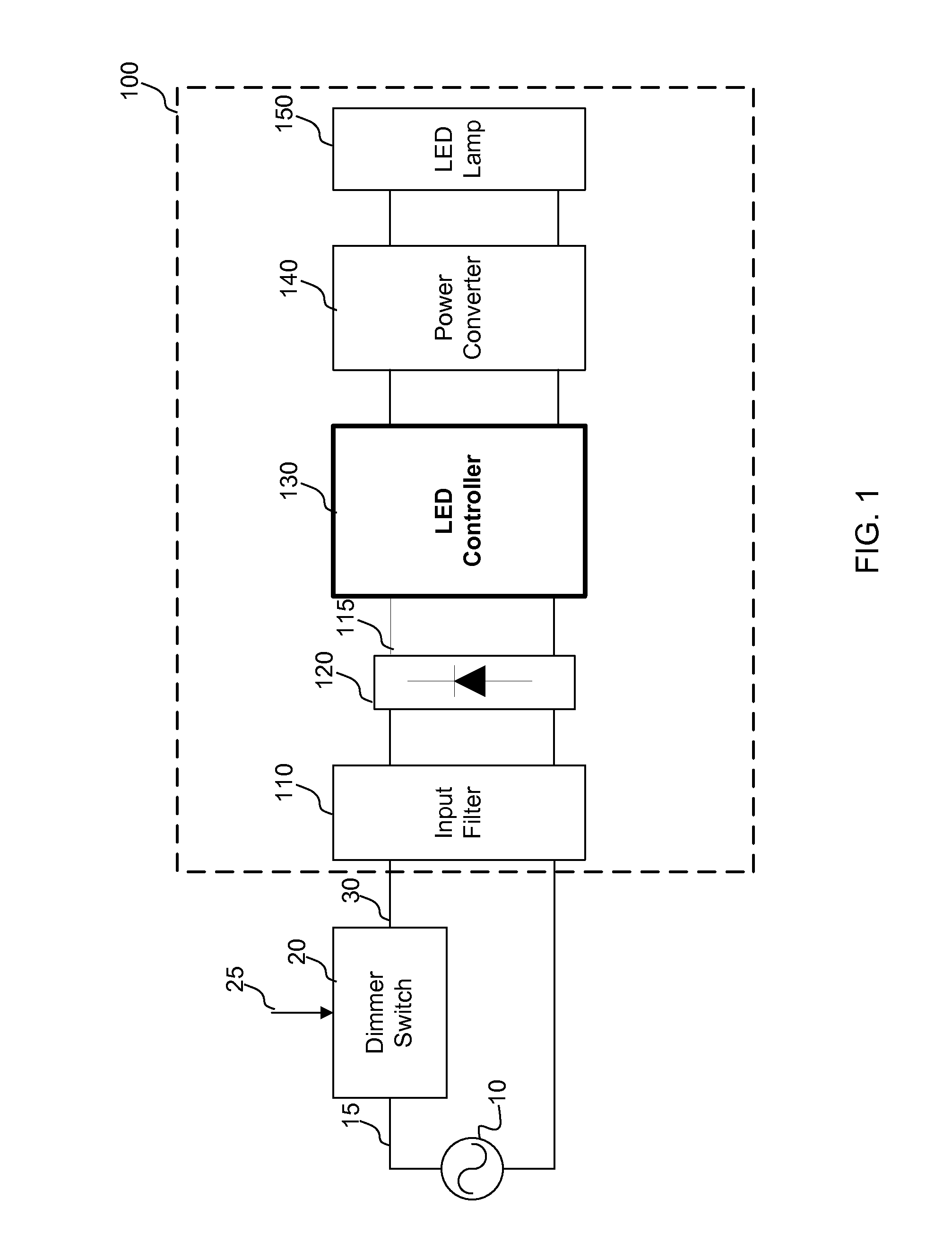

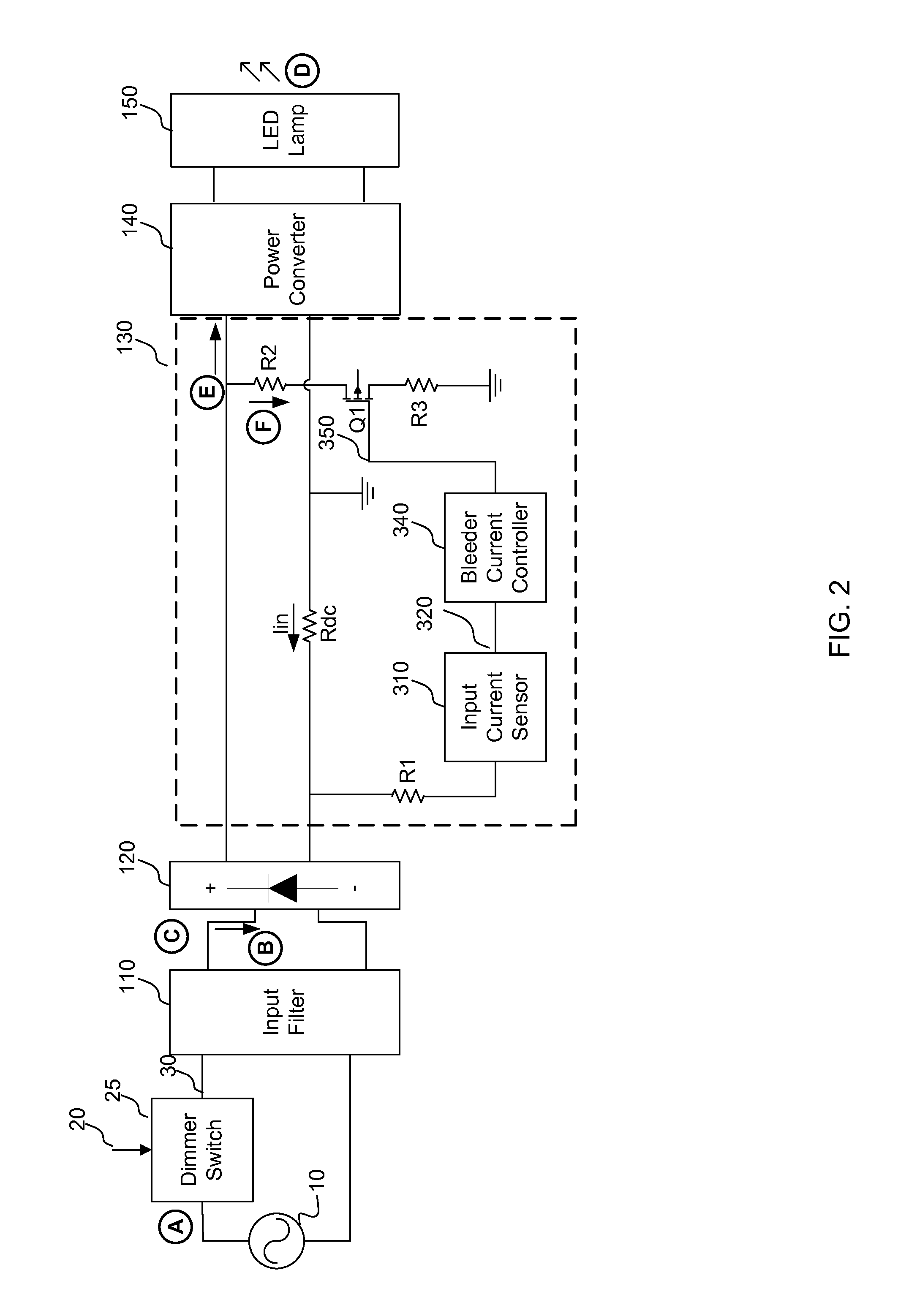

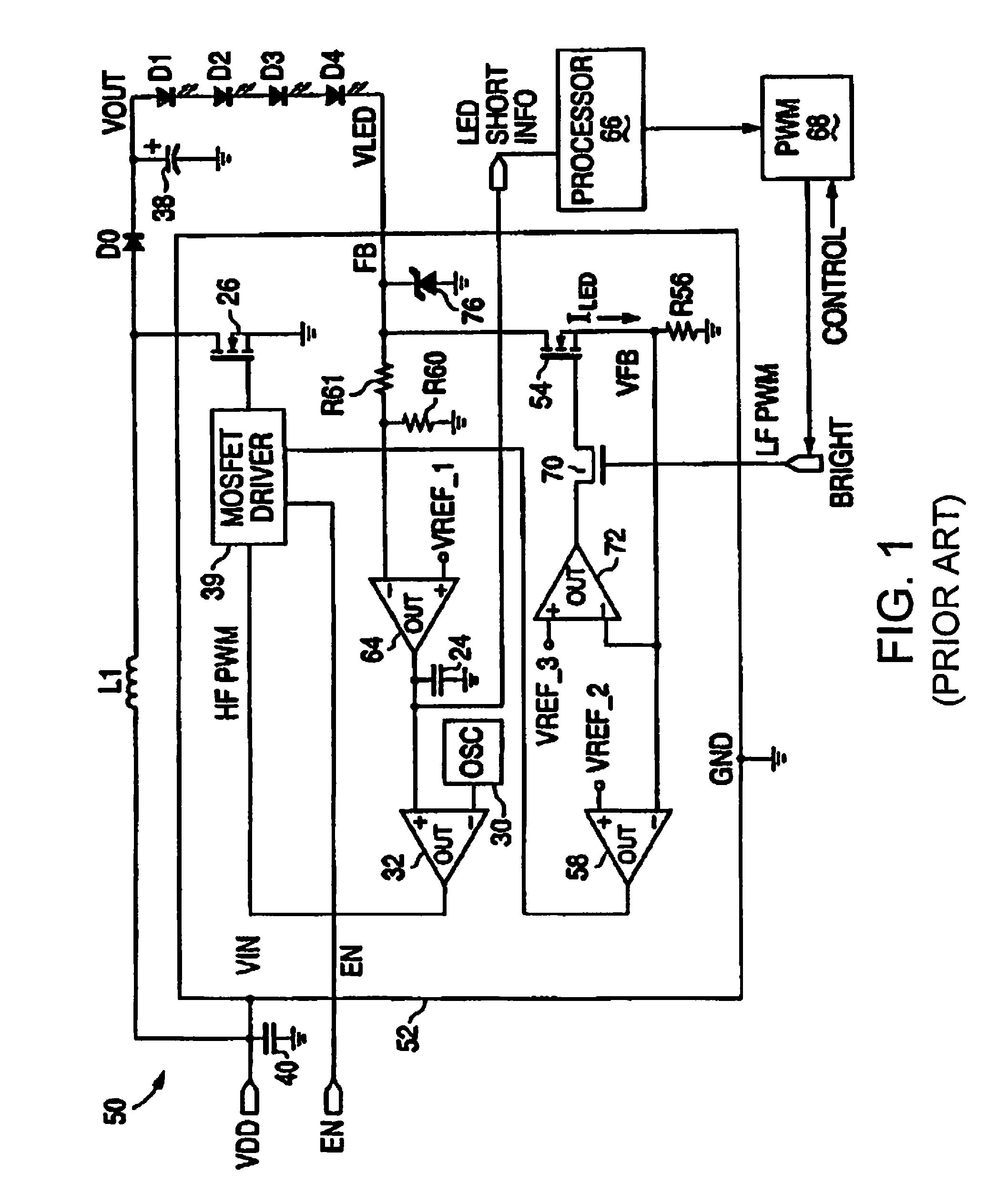

An exemplary embodiment provides a current regulator for controlling variable brightness levels for solid state lighting. The current regulator is couplable to a phase-modulating switch, such as a dimmer switch, which is coupled to an AC line voltage. An exemplary current regulator includes a rectifier; a switching power supply providing a first current; an impedance matching circuit; and a controller. The impedance matching circuit is adapted to provide a second current through the phase-modulating switch when a magnitude of the first current is below a first predetermined threshold, such as a holding current of a triac of the phase-modulating switch. The controller is adapted to determine a root-mean-square (RMS) voltage level provided by the phase-modulating switch from the AC line voltage and to determine a duty cycle for pulse-width current modulation by the switching power supply in response to the comparison of the RMS voltage level to a nominal voltage level.

Owner:CHEMTRON RES

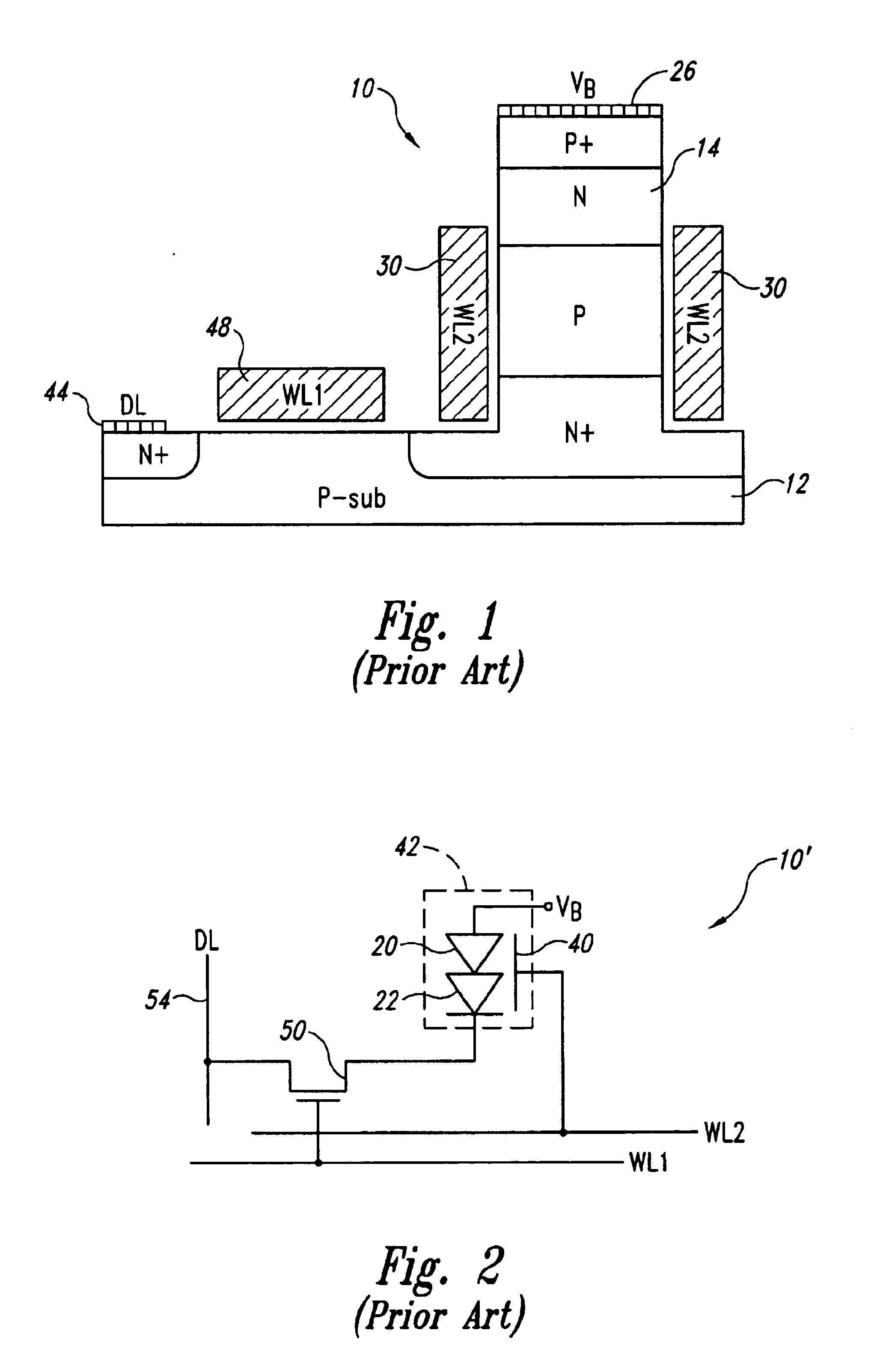

Planar capacitor memory cell and its applications

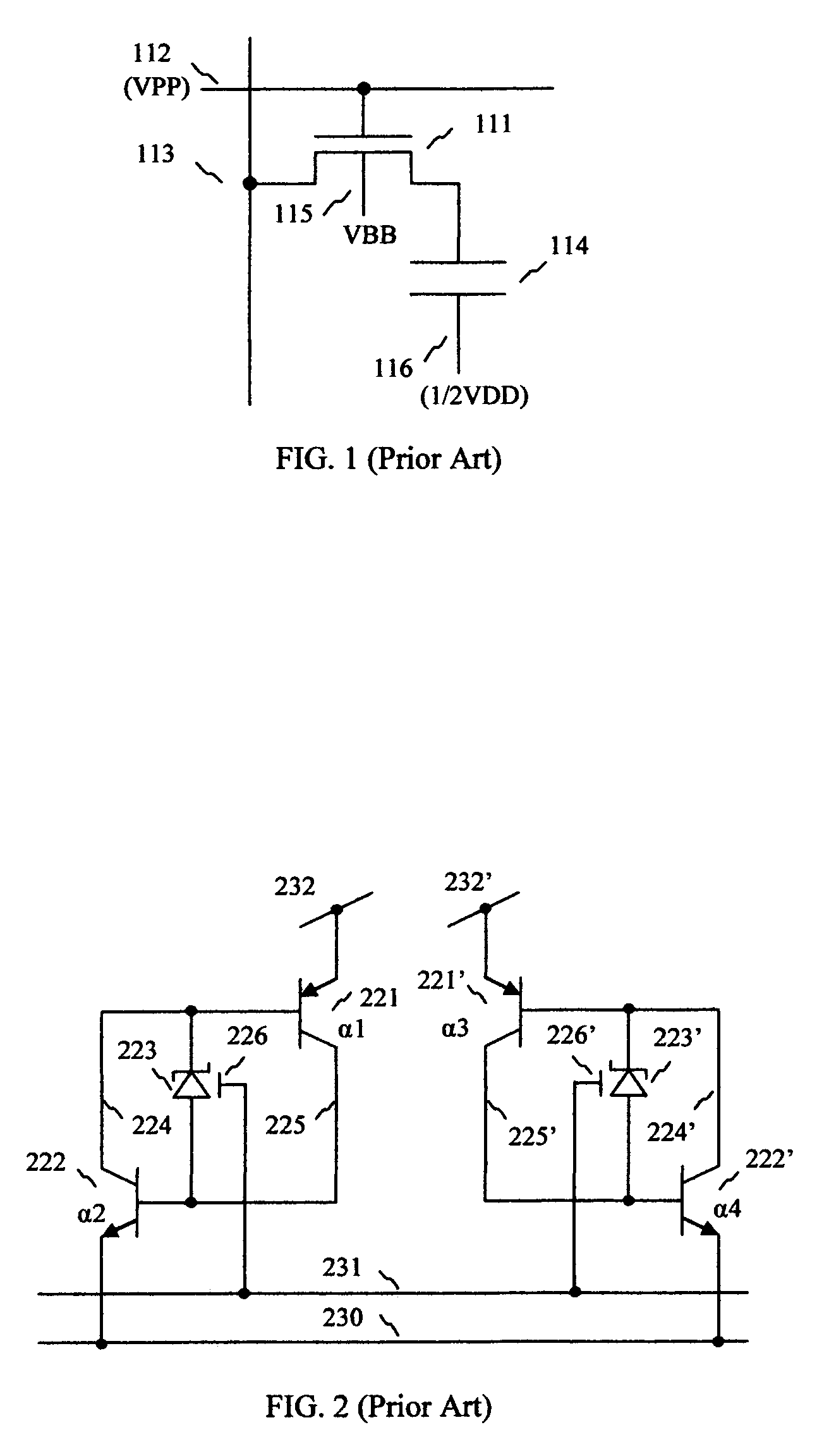

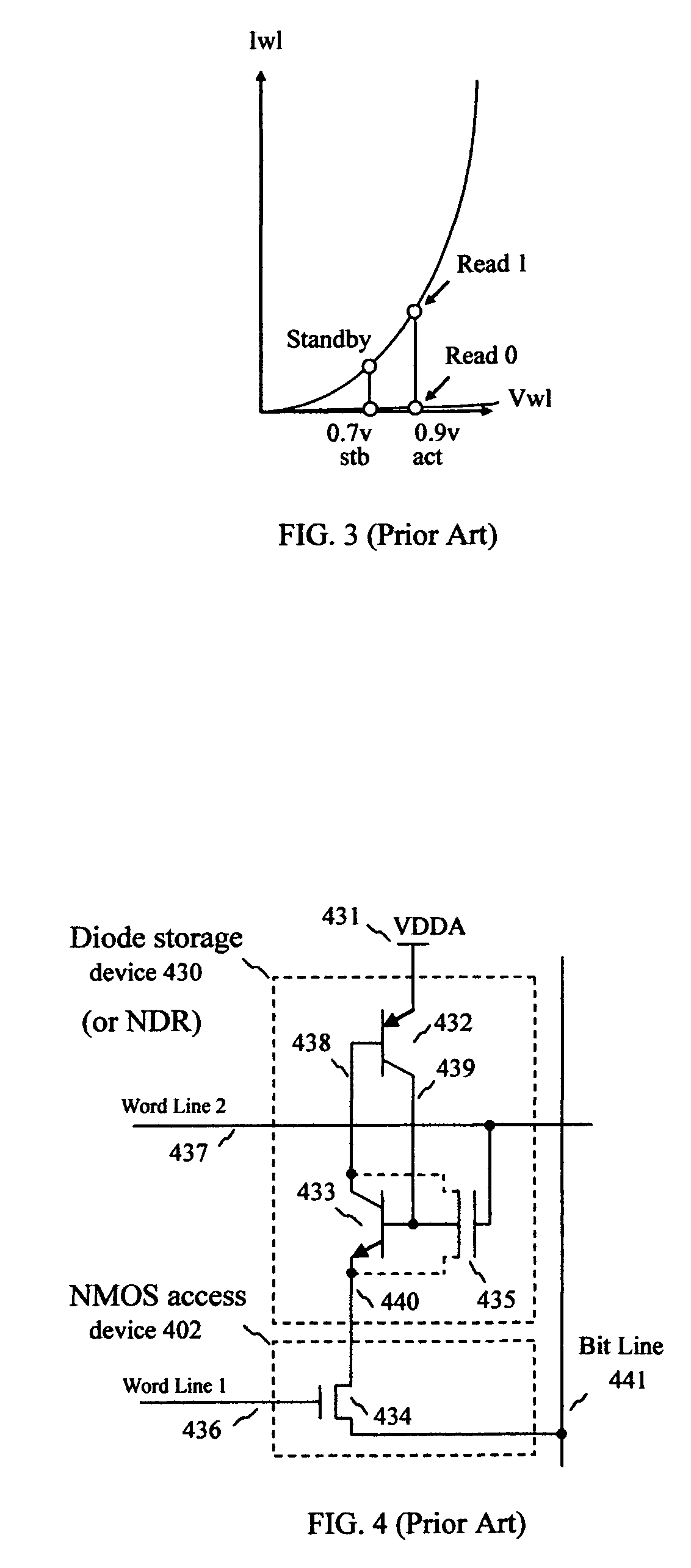

InactiveUS7209384B1Less complicated to fabricateImprove performanceTransistorSolid-state devicesHemt circuitsEngineering

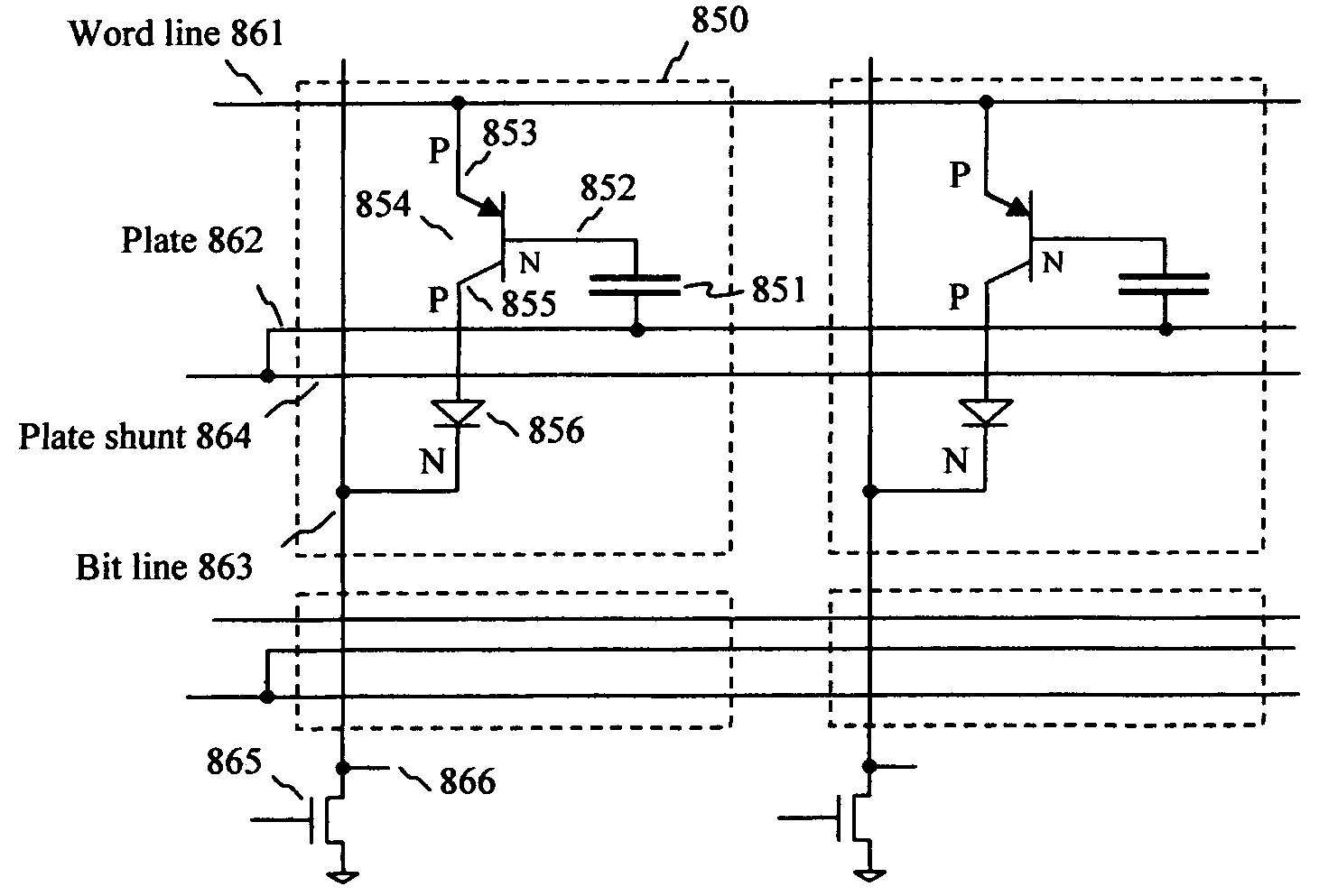

A capacitor memory is realized, wherein a capacitor stores data and a diode controls to store data “1” or “0”. Diode has four terminals wherein first terminal serves as word line, second terminal serves as storage node, third terminal is floating, and fourth terminal serves as bit line, wherein back channel effect is suppressed adding additional ions in the bottom side of third terminal or applying negative voltage in the well or substrate. A capacitor plate couples to second terminal, which plate has no coupling region to first, third and fourth terminal. With no coupling, the inversion layer of plate in the storage node is isolated from the adjacent nodes. In doing so, the plate can swing ground level to positive supply level to write. As a result, no negative generator is required for controlling plate. Word line and bit line keep ground level during standby, and rise to supply level for read or write operation. In this manner, no holding current is required during standby, and operating current is dramatically reduced with no negative generator. Write has a sequence to clear the state of cell before writing to store data regardless of previous state. Refresh cycle is periodically asserted to sustain data. The present invention can be applied for destructive read, or for nondestructive read adding pull-down device to bit line. The height of cell is almost same as control circuit on the bulk or SOI wafer.

Owner:KIM JUHAN

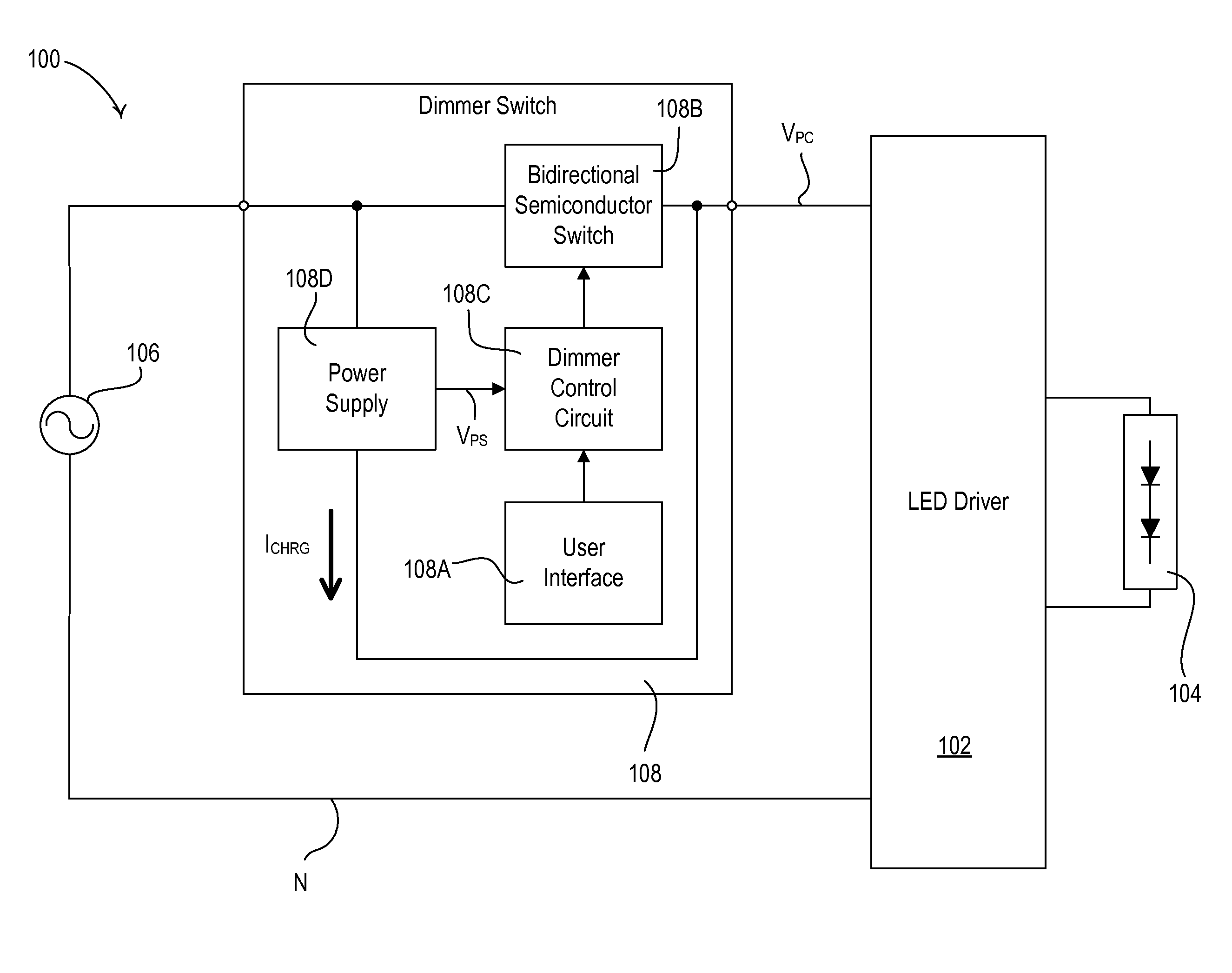

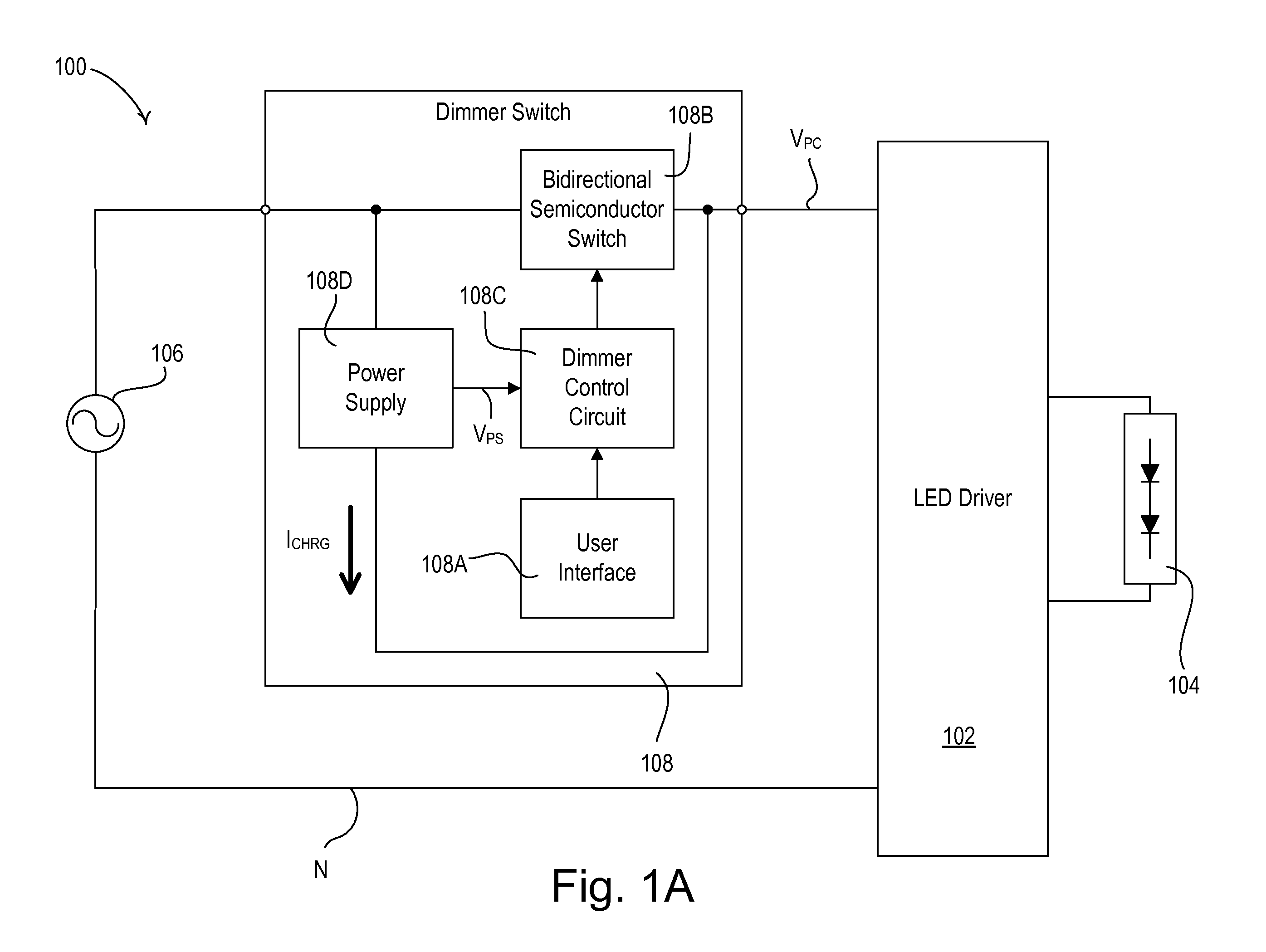

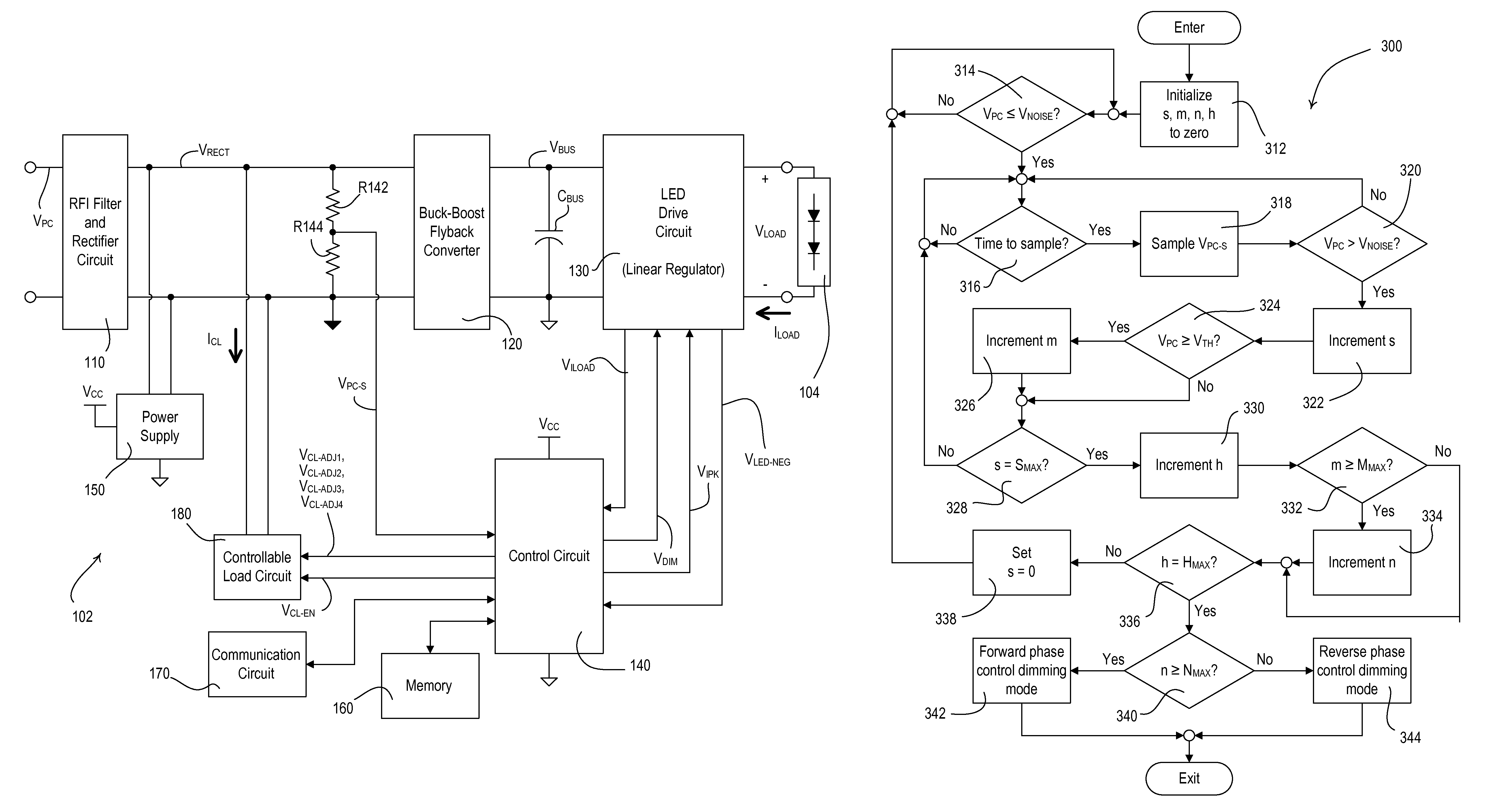

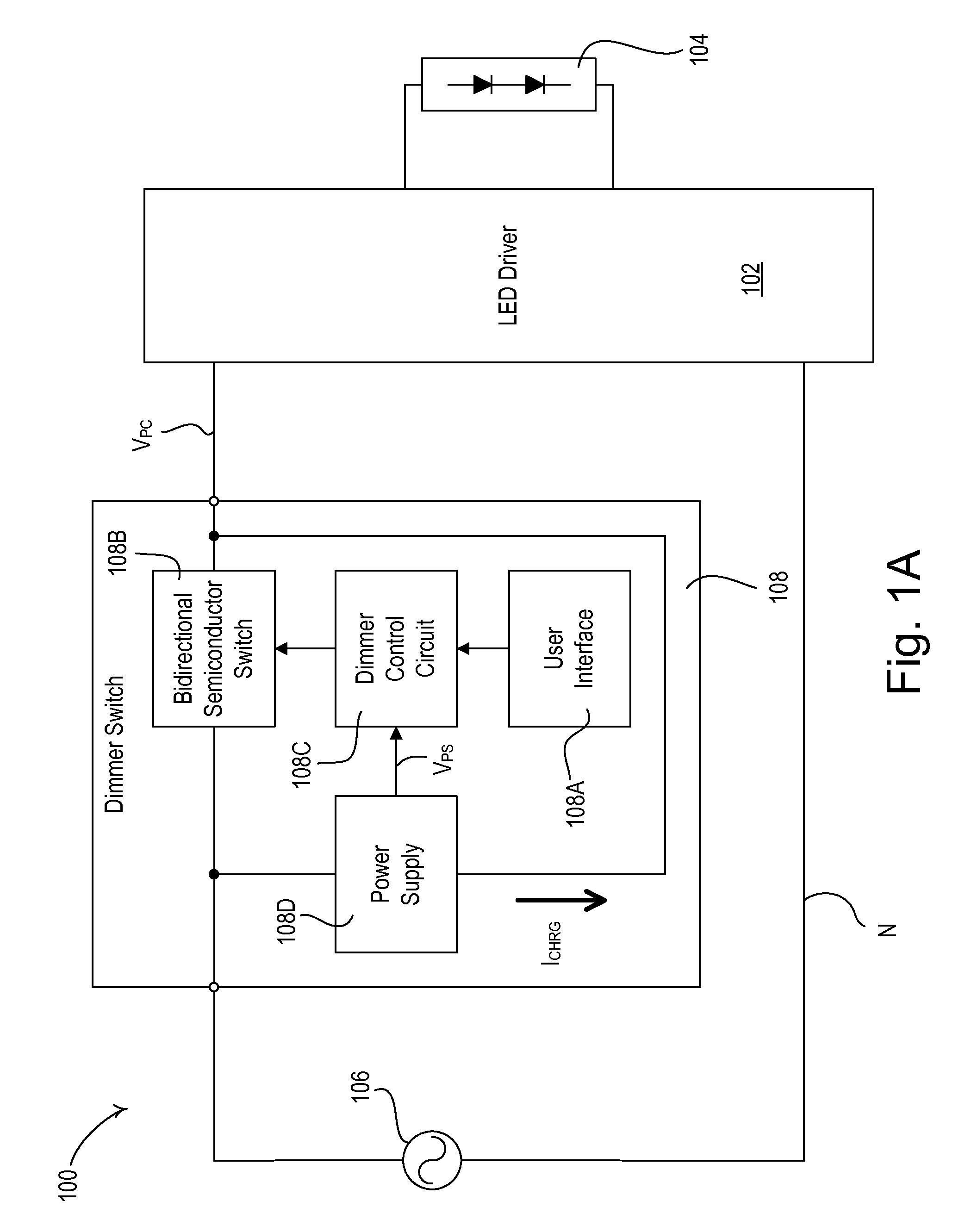

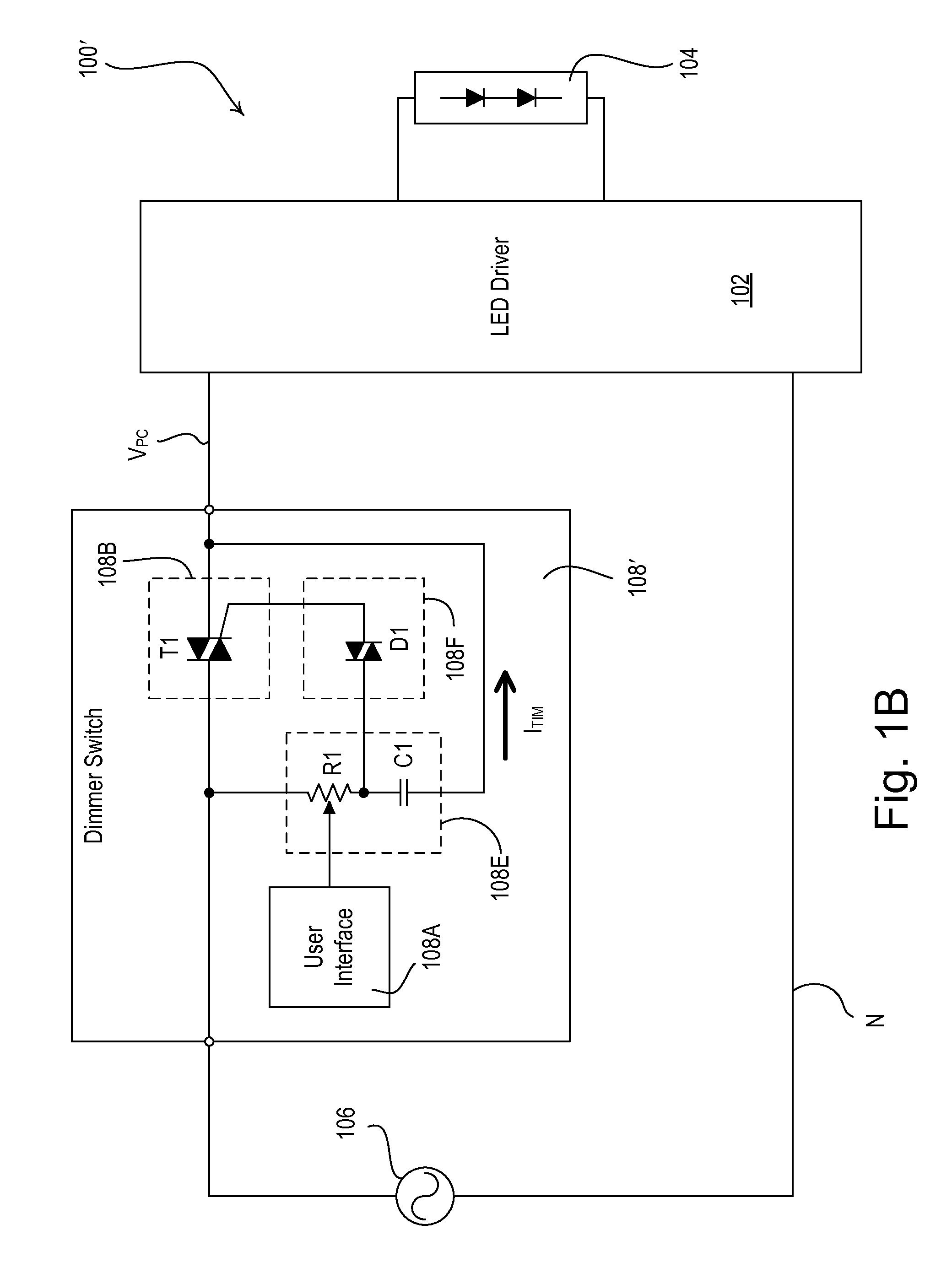

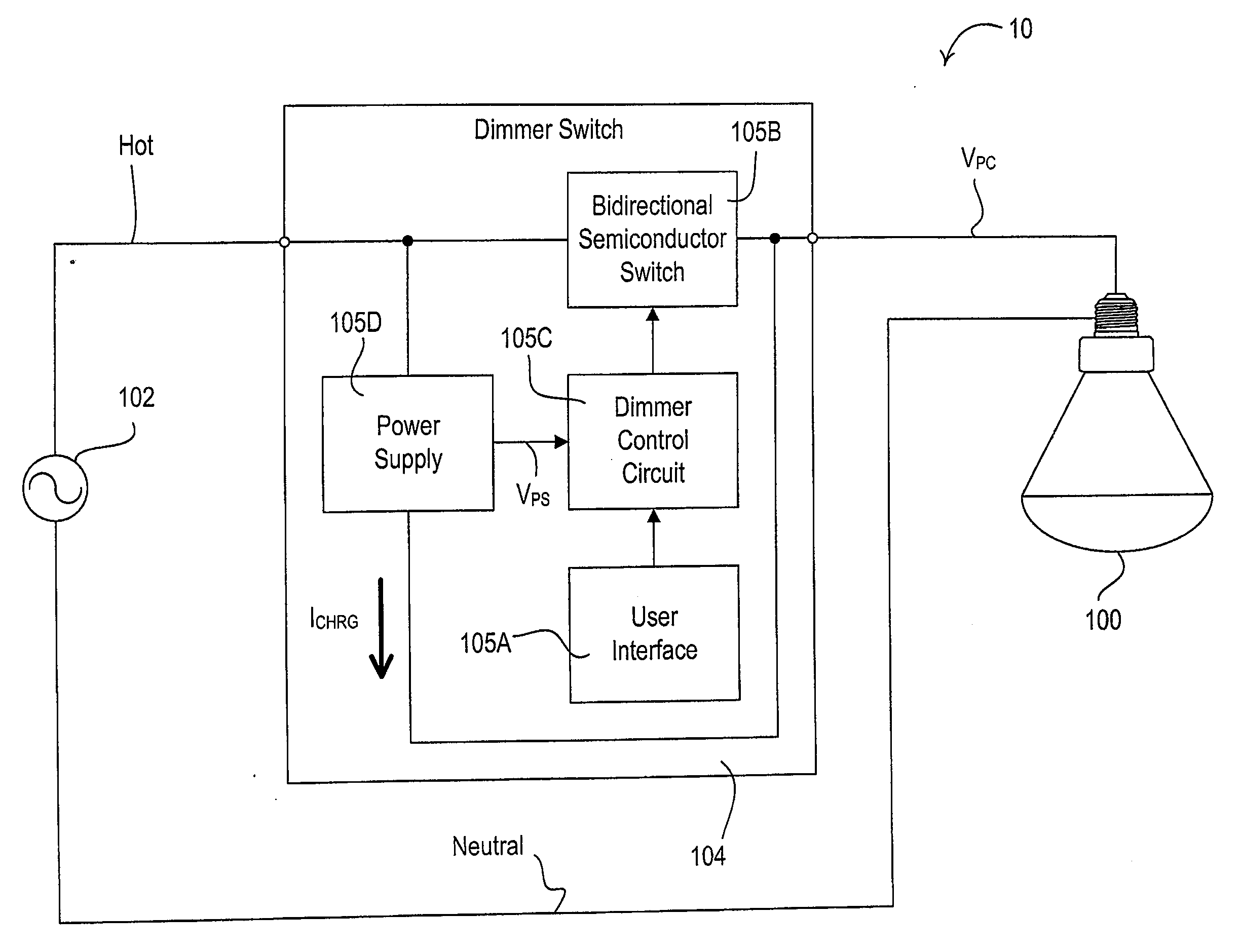

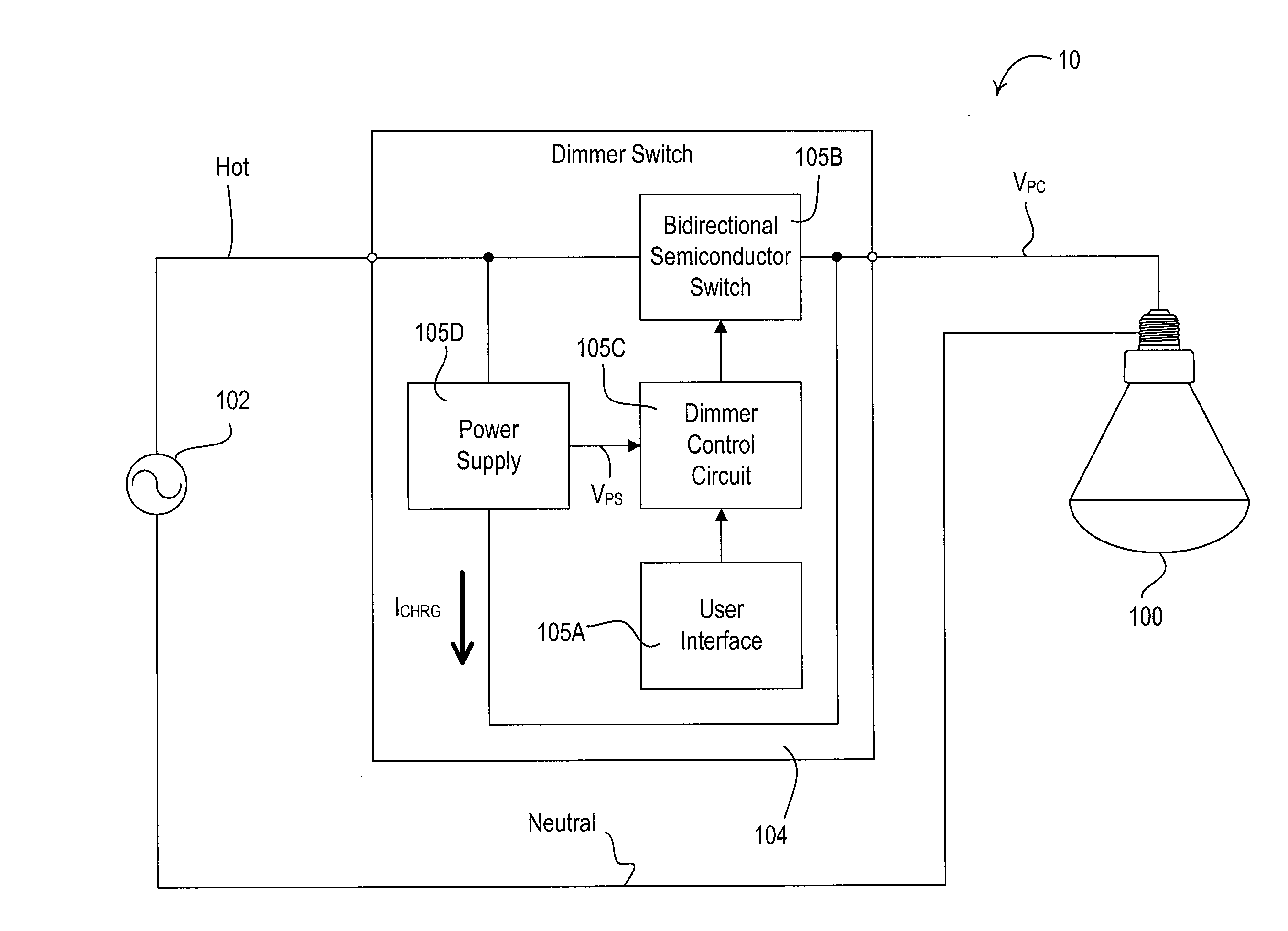

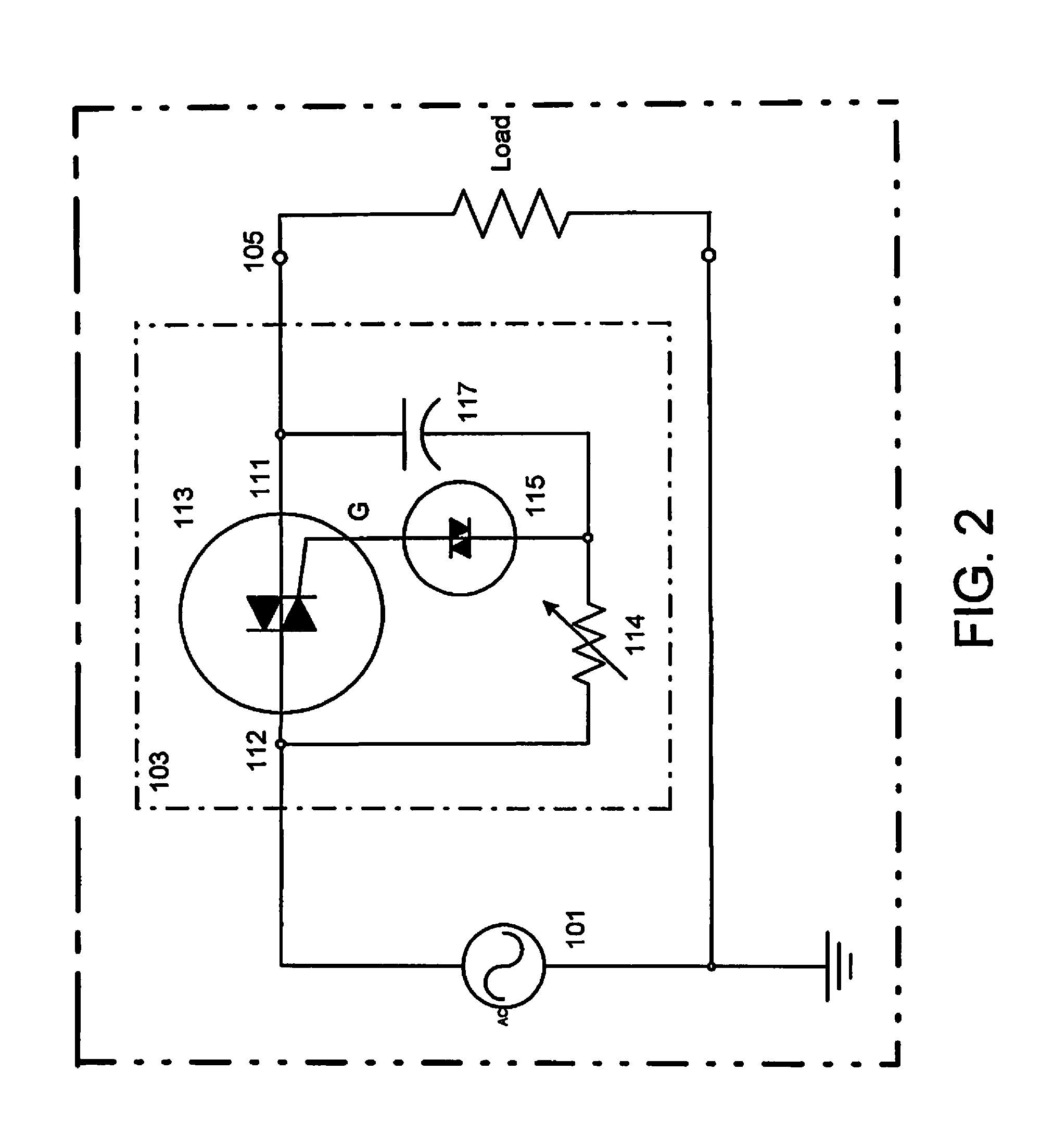

Controllable-load circuit for use with a load control device

ActiveUS20110121744A1Weakening rangeElectroluminescent light sourcesElectric light circuit arrangementLoad circuitElectricity

A load control device for controlling the amount of power delivered from an AC power source to an electrical load is operable to conduct enough current through a thyristor of a connected dimmer switch to exceed rated latching and holding currents of the thyristor. The load control device comprises a controllable-load circuit operable to conduct a controllable-load current through the thyristor of the dimmer switch. The load control device disables the controllable-load circuit when the phase-control voltage received from the dimmer switch is a reverse phase-control waveform. When the phase-control voltage received from the dimmer switch is a forward phase-control waveform, the load control device is operable to decrease the magnitude of the controllable-load current so as to conduct only enough current as is required in order to exceed rated latching and holding currents of the thyristor.

Owner:LUTRON TECH CO LLC

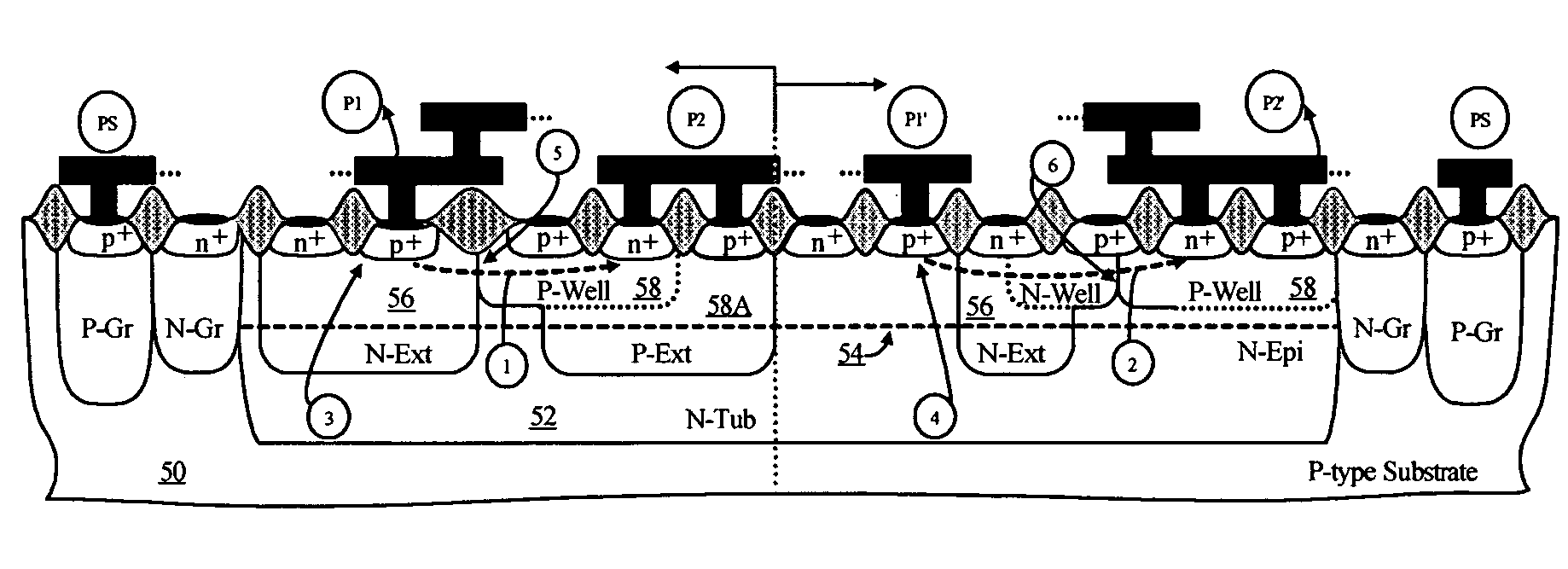

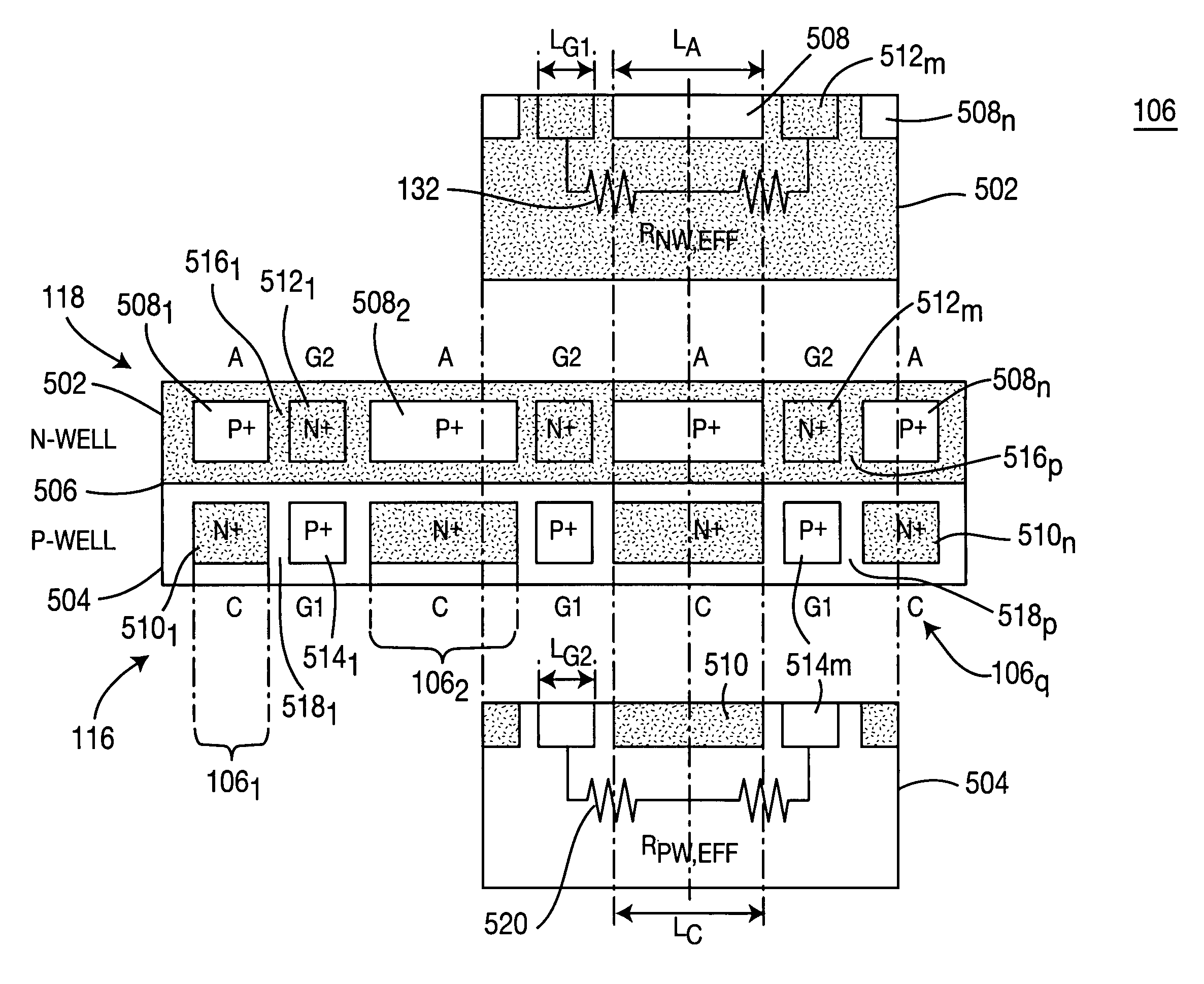

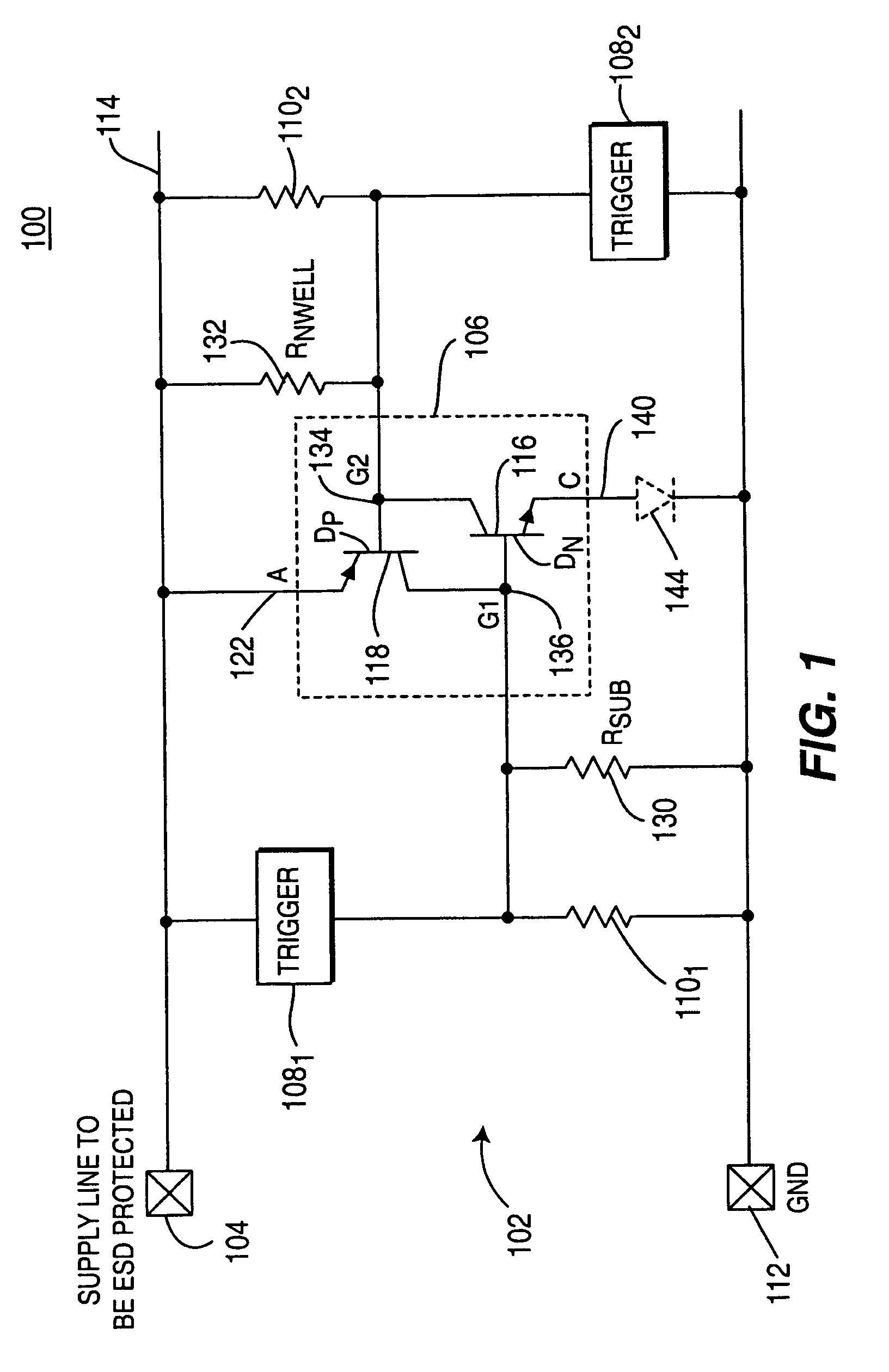

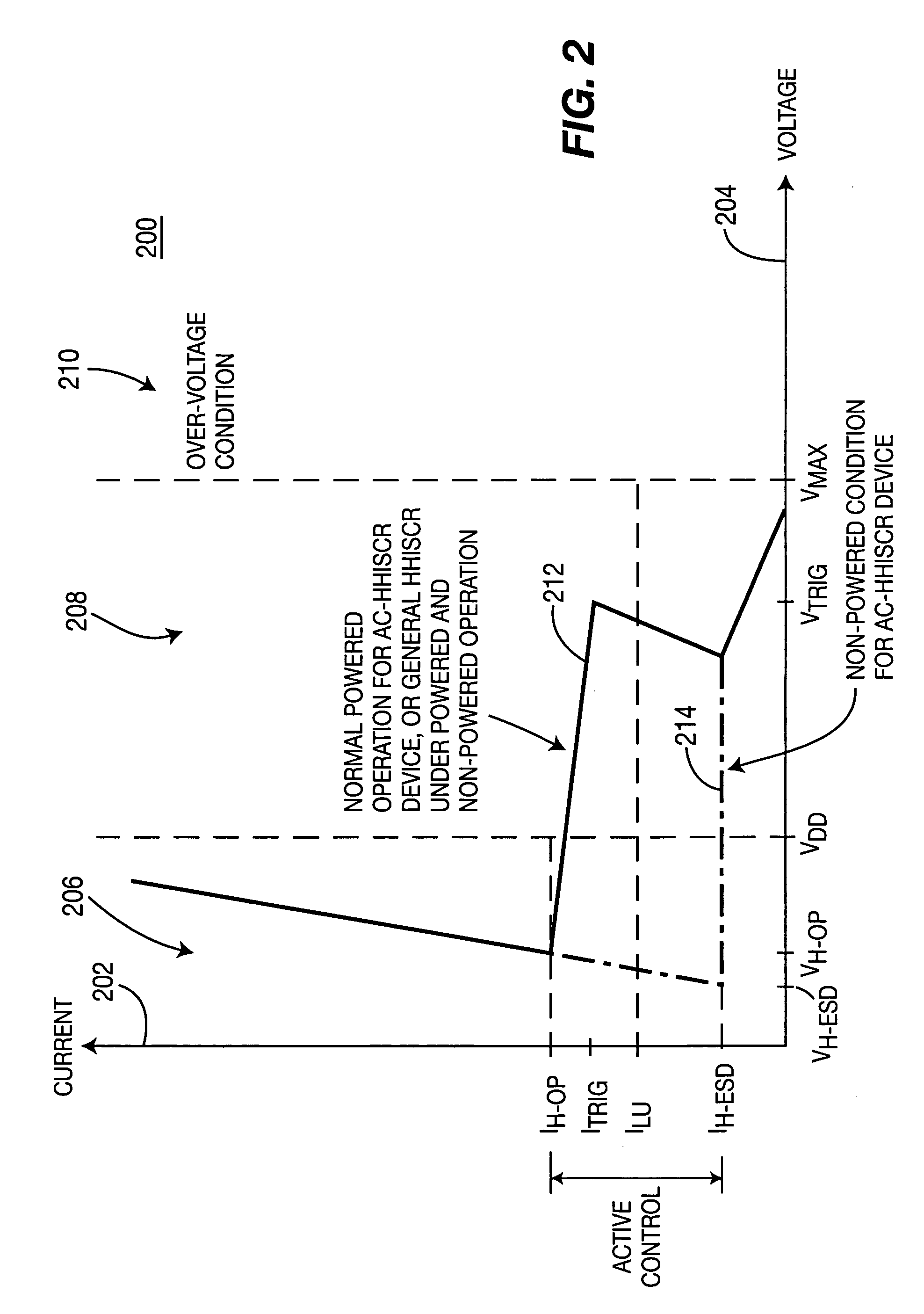

Devices with adjustable dual-polarity trigger- and holding-voltage/current for high level of electrostatic discharge protection in sub-micron mixed signal CMOS/BiCMOS integrated circuits

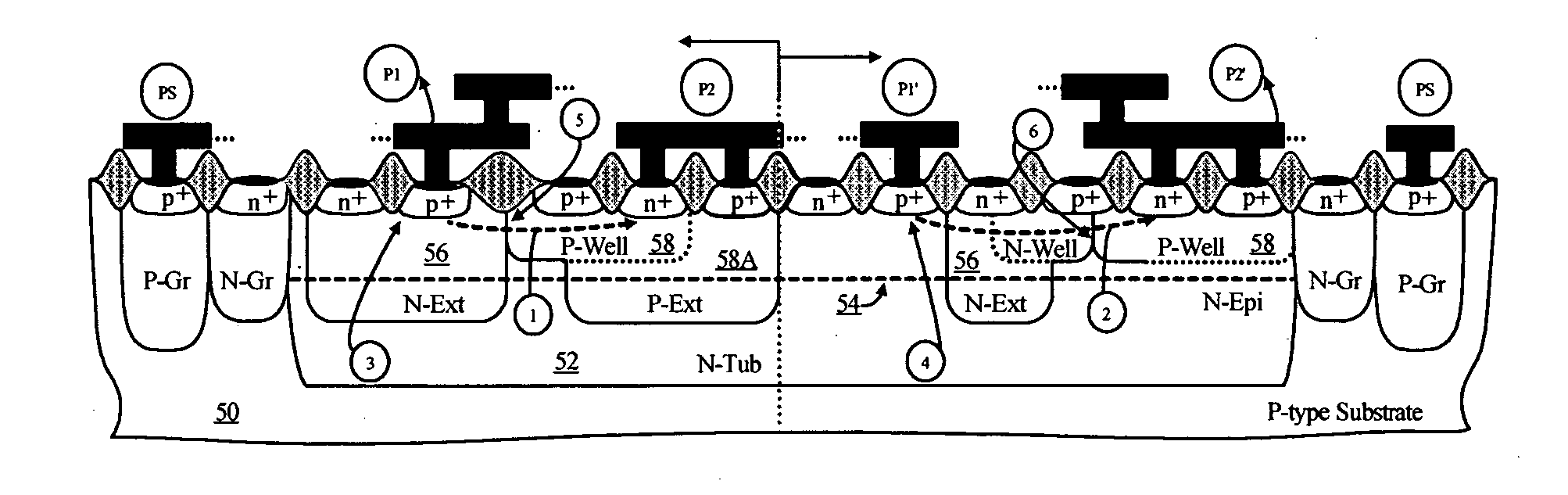

InactiveUS20070007545A1Impaired immunityHigh protection levelTransistorThyristorNon symmetricTransmission-line pulse

Symmetrical / asymmetrical bidirectional S-shaped I-V characteristics with trigger voltages ranging from 10 V to over 40 V and relatively high holding current are obtained for advanced sub-micron silicided CMOS (Complementary Metal Oxide Semiconductor) / BiCMOS (Bipolar CMOS) technologies by custom implementation of P1-N2-P2-N1 / / N1-P3-N3-P1 lateral structures with embedded ballast resistance 58, 58A, 56, 56A and periphery guard-ring isolation 88-86. The bidirectional protection devices render a high level of electrostatic discharge (ESD) immunity for advanced CMOS / BiCMOS processes with no latchup problems. Novel design-adapted multifinger 354 / interdigitated 336 layout schemes of the ESD protection cells allow for scaling-up the ESD performance of the protection structure and custom integration, while the I-V characteristics 480 are adjustable to the operating conditions of the integrated circuit (IC). The ESD protection cells are tested using the TLP (Transmission Line Pulse) technique, and ESD standards including HBM (Human Body Model), MM (Machine Model), and IEC (International Electrotechnical Commission) IEC 1000-4-2 standard for ESD immunity. ESD protection performance is demonstrated also at high temperature (140° C.). The unique high ratio of dual-polarity ESD protection level per unit area, allows for integration of fast-response and compact protection cells optimized for the current tendency of the semiconductor industry toward low cost and high density-oriented IC design. Symmetric / asymmetric dual polarity ESD protection performance is demonstrated for over 15 kV HBM, 2 kV MM, and 16.5 kV IEC for sub-micron technology.

Owner:INTERSIL INC +1

Current regulator for modulating brightness levels of solid state lighting

ActiveUS7902769B2Low component requirementsElectrical apparatusElectroluminescent light sourcesImpedance matchingRoot mean square

An exemplary embodiment provides a current regulator for controlling variable brightness levels for solid state lighting. The current regulator is couplable to a phase-modulating switch, such as a dimmer switch, which is coupled to an AC line voltage. An exemplary current regulator includes a rectifier; a switching power supply providing a first current; an impedance matching circuit; and a controller. The impedance matching circuit is adapted to provide a second current through the phase-modulating switch when a magnitude of the first current is below a first predetermined threshold, such as a holding current of a triac of the phase-modulating switch. The controller is adapted to determine a root-mean-square (RMS) voltage level provided by the phase-modulating switch from the AC line voltage and to determine a duty cycle for pulse-width current modulation by the switching power supply in response to the comparison of the RMS voltage level to a nominal voltage level.

Owner:CHEMTRON RES

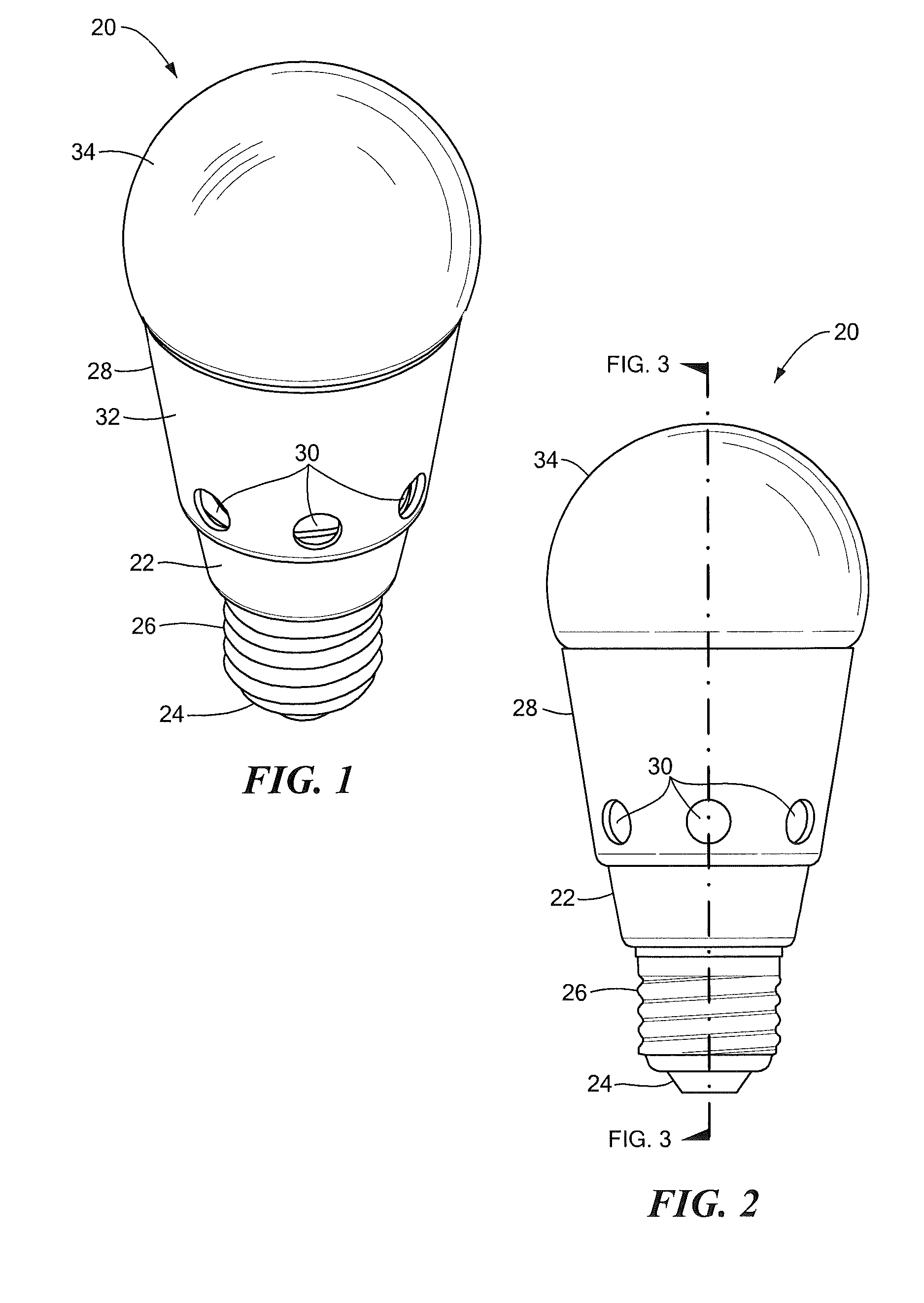

Dimmable LED luminaire

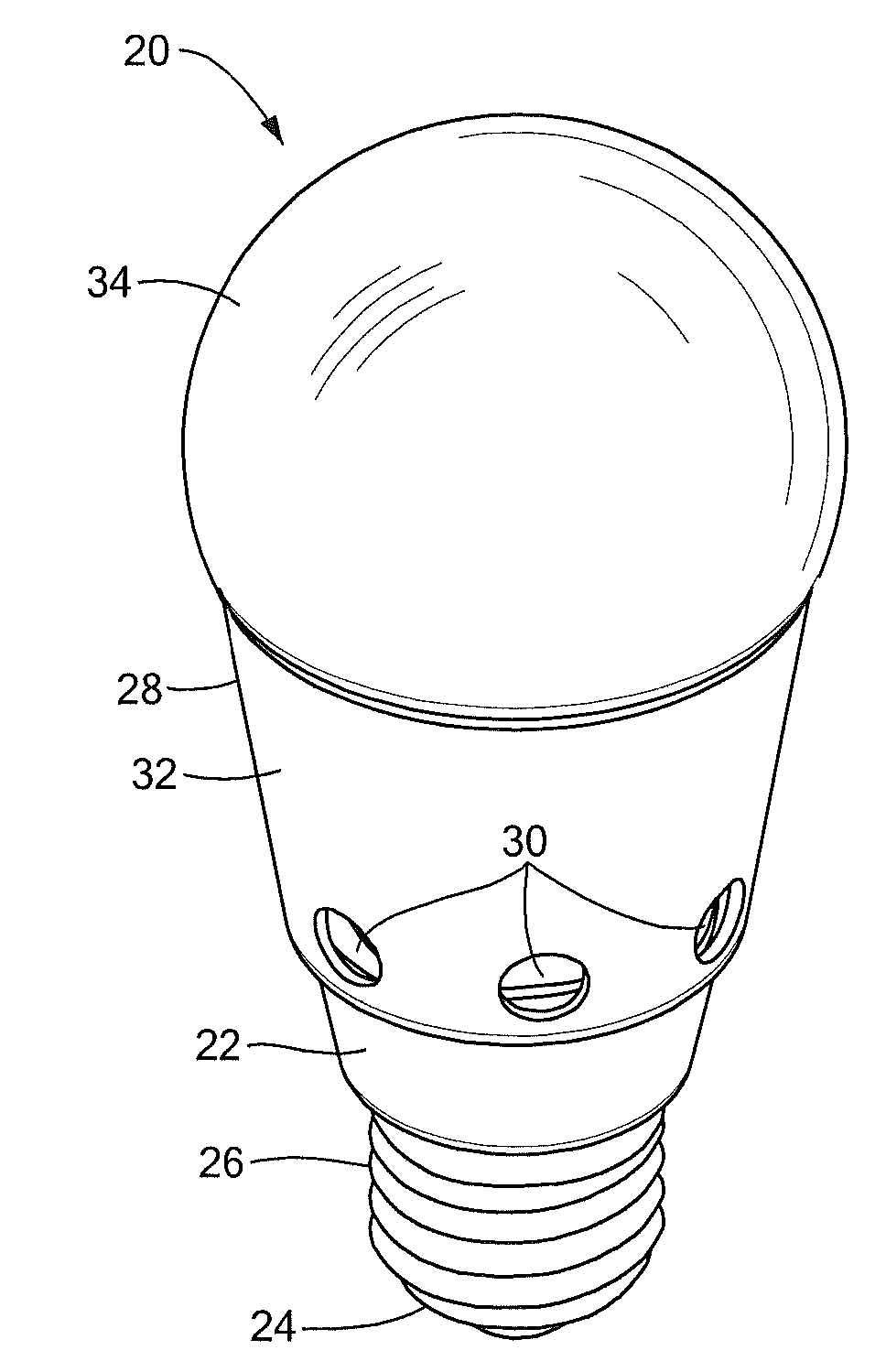

InactiveUS20100277067A1Point-like light sourceElectric circuit arrangementsElectricityDriver circuit

A luminaire includes an Edison type electrical base, an optic, and a heat sink disposed between the base and the optic. An LED driver circuit is disposed at least partially within the heat sink, and is disposed in electrical communication with the base. An LED assembly is disposed in thermal communication with a surface of the heat sink, and in electrical communication with the driver circuit, the LED assembly includes an LED. The driver circuit includes circuitry that converts an AC signal at the base to a DC signal and provides the DC signal to the LED assembly, the circuitry includes holding current circuitry that produces a holding current for an electrical dimmer disposed upstream of the base in response to a current to the LED assembly being reduced for light dimming purposes.

Owner:LIGHTING SCI GROUP

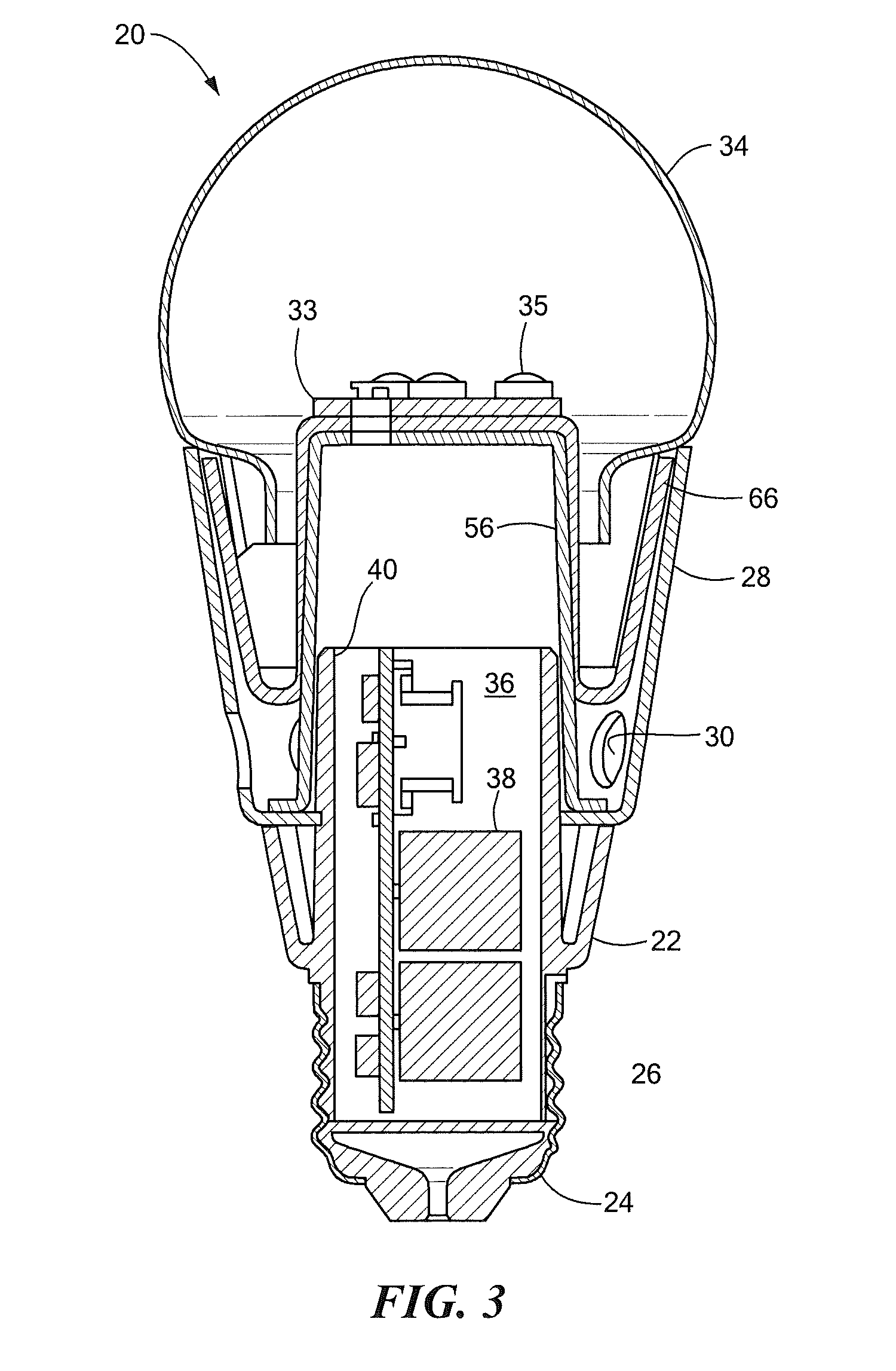

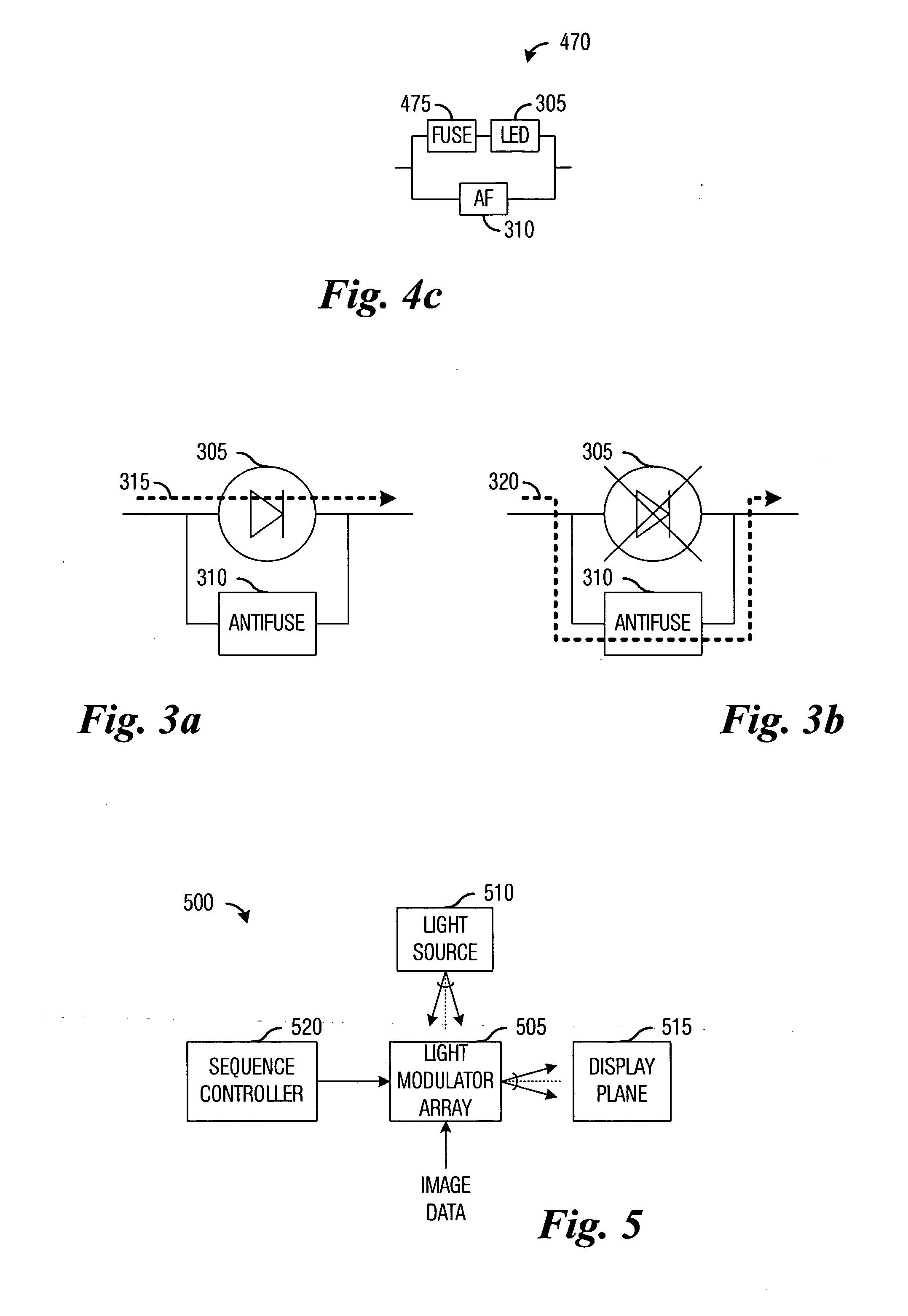

System for improving LED illumination reliability in projection display systems

InactiveUS20080007885A1Improve reliabilityNone of can remain in operationElectroluminescent light sourcesEmergency protective arrangements for automatic disconnectionAntifuseHolding current

System and method for increasing the reliability of LED illumination systems used in projection display systems. A preferred embodiment comprises a light source with one or more serially connected sequences of two or more light elements coupled to a power source. Each light element includes a light emitting diode and an antifuse coupled in parallel to the light emitting diode, wherein the antifuse short circuits if a current flowing through the antifuse exceeds a specified magnitude. The current exceeds the specified magnitude only if an open circuit type failure occurs in the light emitting diode and the short circuit of the antifuse creates a low-resistance current path, thereby preserving current flow through the serially connected sequence and keeping the remaining light elements illuminated.

Owner:TEXAS INSTR INC

Devices with adjustable dual-polarity trigger- and holding-voltage/current for high level of electrostatic discharge protection in sub-micron mixed signal CMOS/BiCMOS integrated circuits

Symmetrical / asymmetrical bidirectional S-shaped I-V characteristics with trigger voltages ranging from 10 V to over 40 V and relatively high holding current are obtained for advanced sub-micron silicided CMOS (Complementary Metal Oxide Semiconductor) / BiCMOS (Bipolar CMOS) technologies by custom implementation of P1-N2-P2-N1 / / N1-P3-N3-P1 lateral structures with embedded ballast resistance 58, 58A, 56, 56A and periphery guard-ring isolation 88-86. The bidirectional protection devices render a high level of electrostatic discharge (ESD) immunity for advanced CMOS / BiCMOS processes with no latchup problems. Novel design-adapted multifinger 354 / interdigitated 336 layout schemes of the ESD protection cells allow for scaling-up the ESD performance of the protection structure and custom integration, while the I-V characteristics 480 are adjustable to the operating conditions of the integrated circuit (IC). The ESD protection cells are tested using the TLP (Transmission Line Pulse) technique, and ESD standards including HBM (Human Body Model), MM (Machine Model), and IEC (International Electrotechnical Commission) IEC 1000-4-2 standard for ESD immunity. ESD protection performance is demonstrated also at high temperature (140° C.). The unique high ratio of dual-polarity ESD protection level per unit area, allows for integration of fast-response and compact protection cells optimized for the current tendency of the semiconductor industry toward low cost and high density-oriented IC design. Symmetric / asymmetric dual polarity ESD protection performance is demonstrated for over 15 kV HBM, 2 kV MM, and 16.5 kV IEC for sub-micron technology.

Owner:INTERSIL INC +1

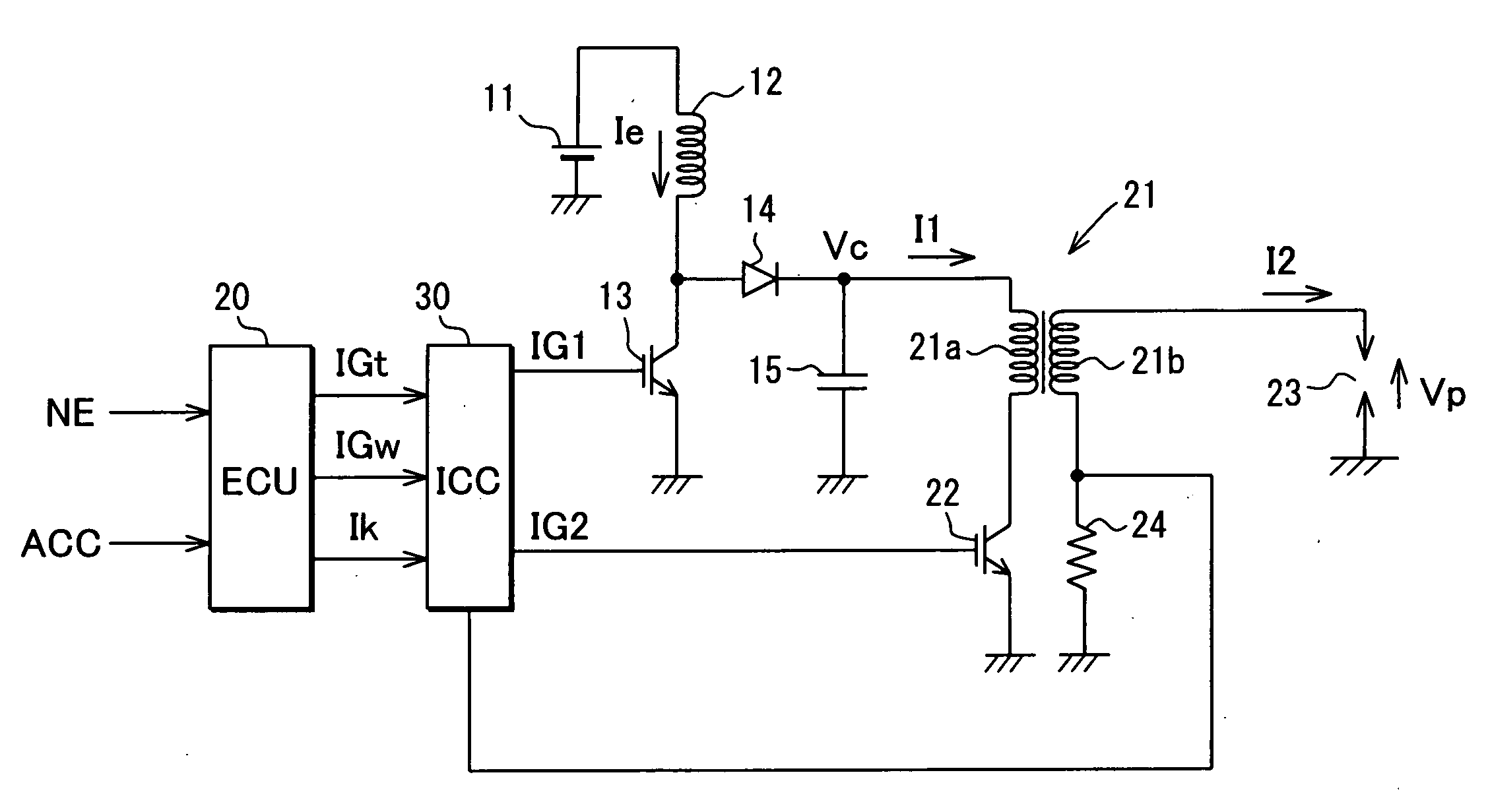

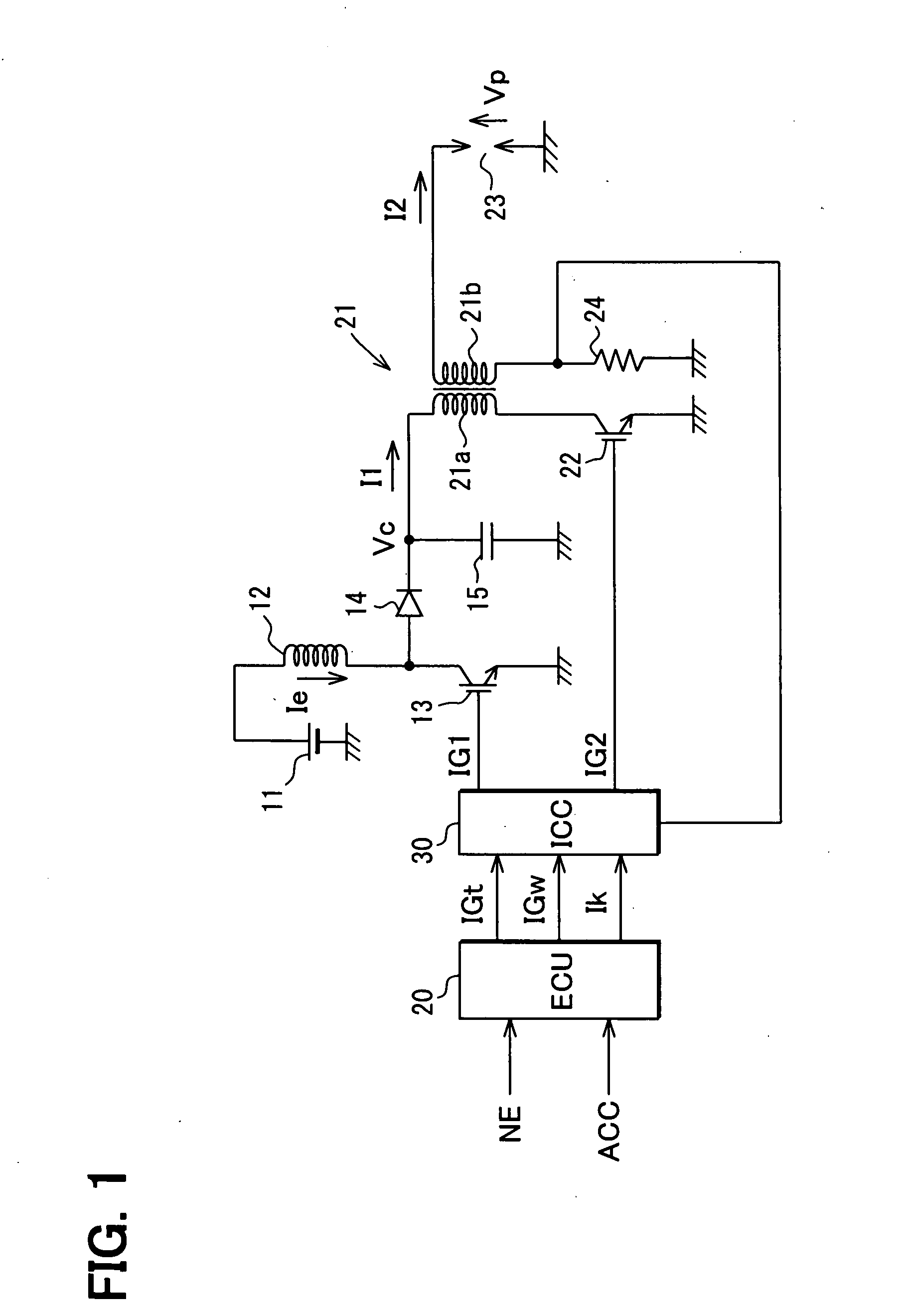

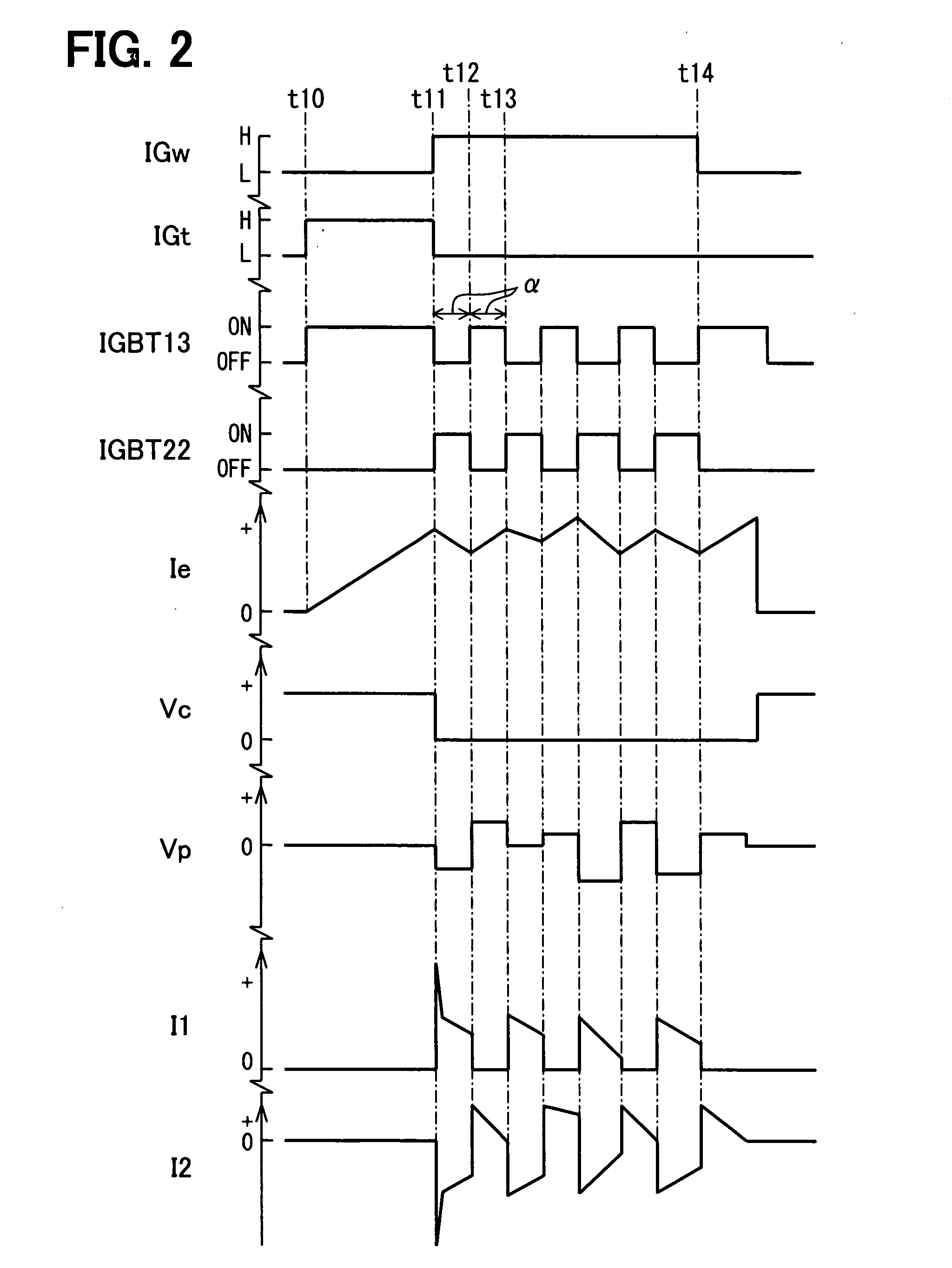

Multiple discharge ignition control apparatus and method for internal combustion engines

InactiveUS20070181110A1Strong enoughMachines/enginesAdvancing/retarding ignitionElectrical batteryEngineering

In a multiple discharge ignition control apparatus, a battery, an energy storage coil and a first IGBT are connected in series. Further, the energy storage coil, a diode, a primary coil and a second IGBT are connected in series. The energy storage coil is connected with a capacitor through the diode, and a secondary coil is connected with a spark plug and a resistor for current detection. An ignition control circuit switches the IGBTs between ON and OFF each time the secondary current detected by the resistor reaches a positive or negative discharge holding current in multiple discharge operation. A booster circuit is provided in addition to the energy storage coil and its output is feedback-controlled.

Owner:DENSO CORP

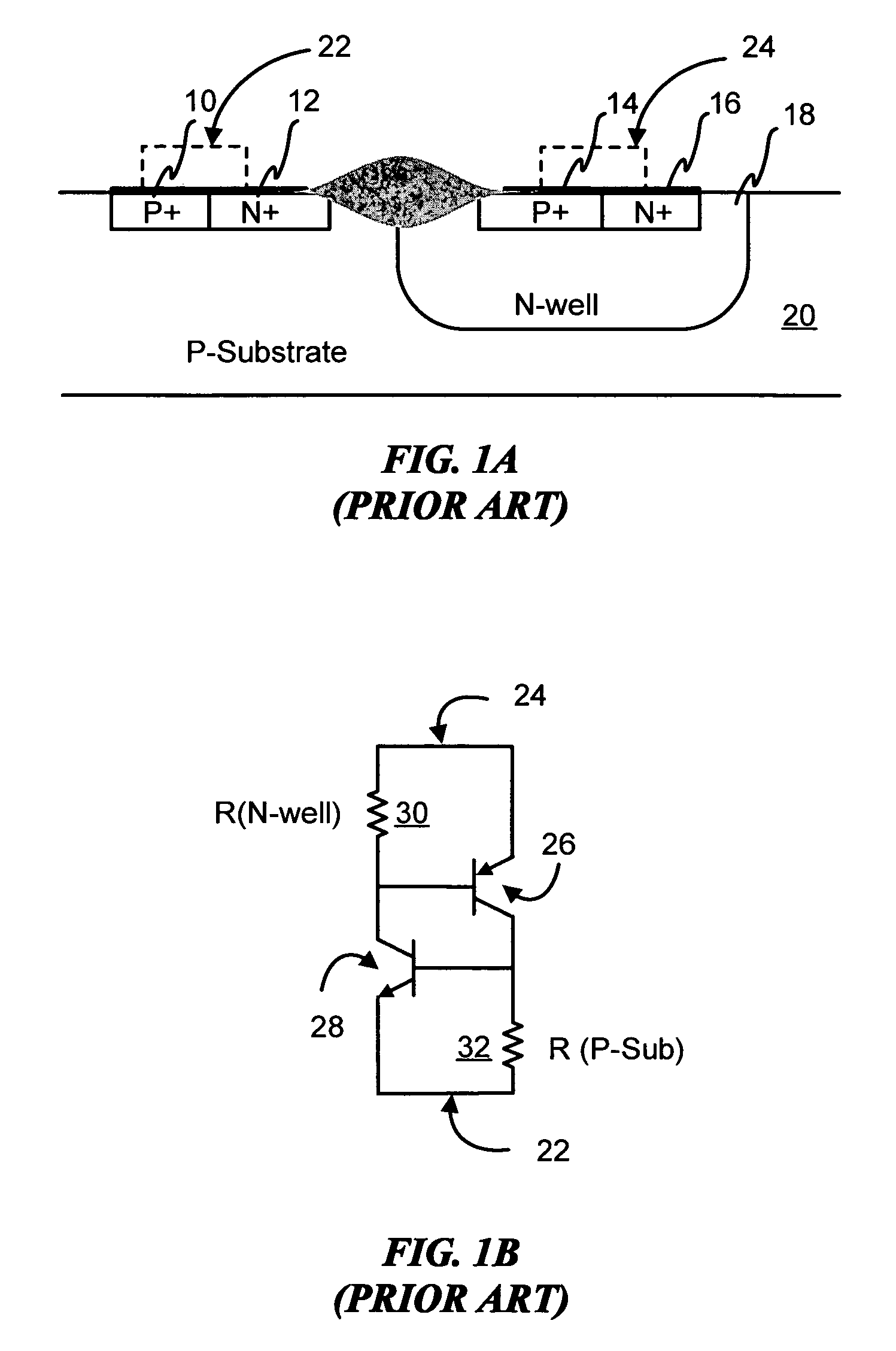

Electrostatic discharge protection structures having high holding current for latch-up immunity

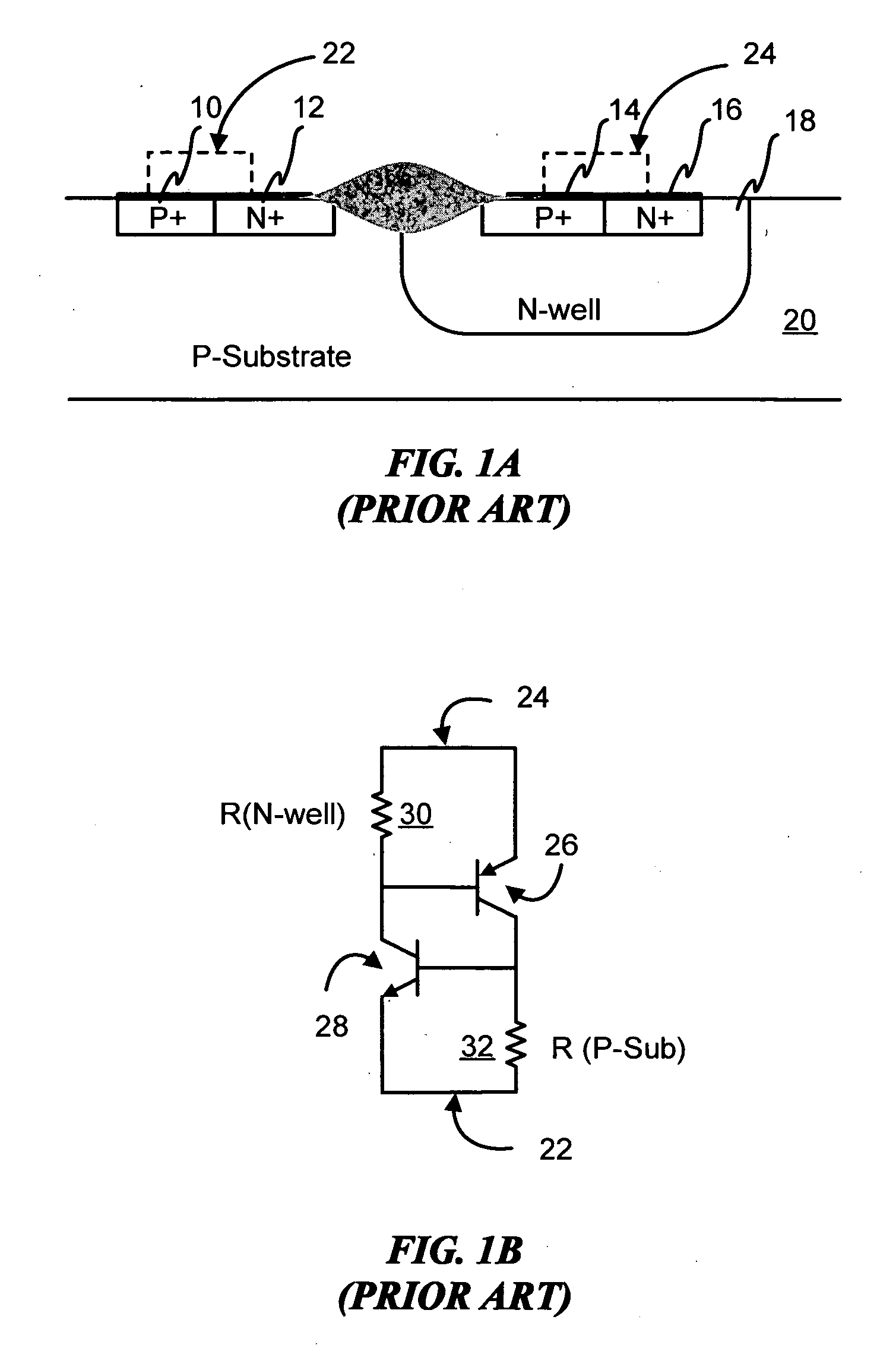

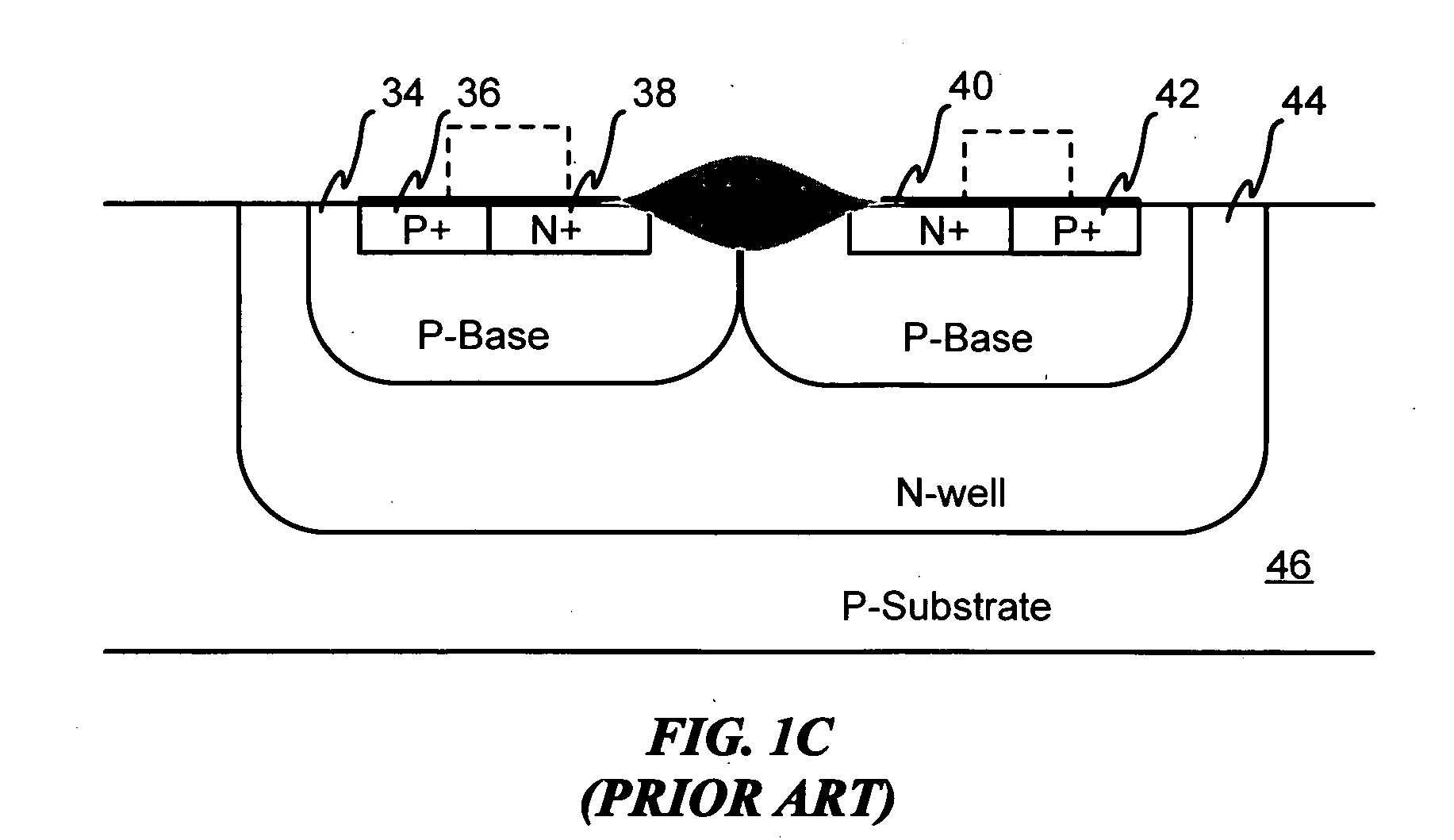

InactiveUS7064393B2High holding currentOvercome disadvantagesTransistorThyristorElectrical resistance and conductanceSilicon-controlled rectifier

An electrostatic discharge (ESD) protection device having high holding current for latch-up immunity. The ESD protection circuit is formed in a semiconductor integrated circuit (IC) having protected circuitry. The ESD protection device includes a silicon controlled rectifier (SCR) coupled between a protected supply line of the IC and ground. A trigger device is coupled from the supply line to a first gate of the SCR, and a first substrate resistor is coupled between the first gate and ground. A first shunt resistor is coupled between the first gate and ground, wherein the shunt resistor has a resistance value lower than the substrate resistor.

Owner:SOFICS BVBA

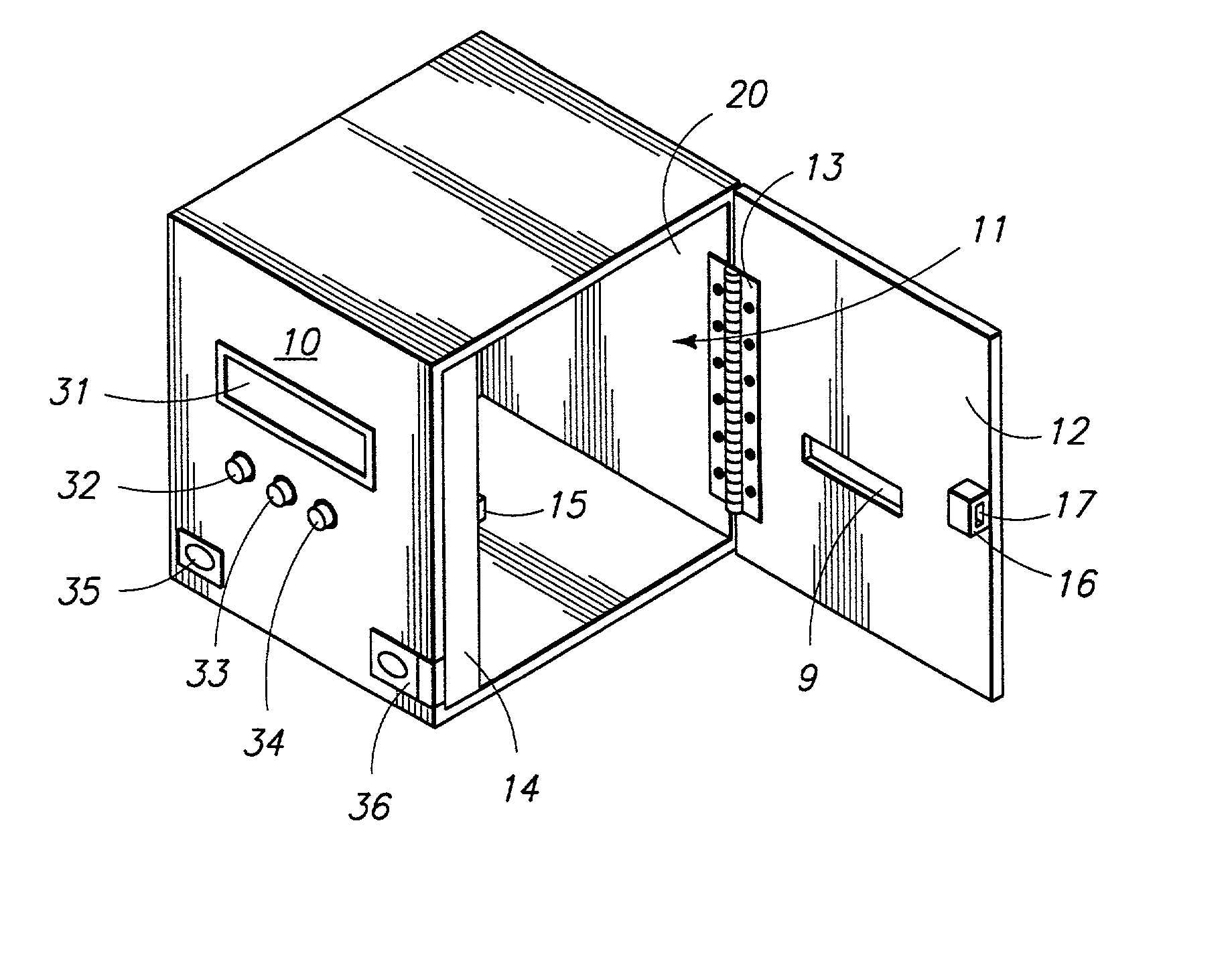

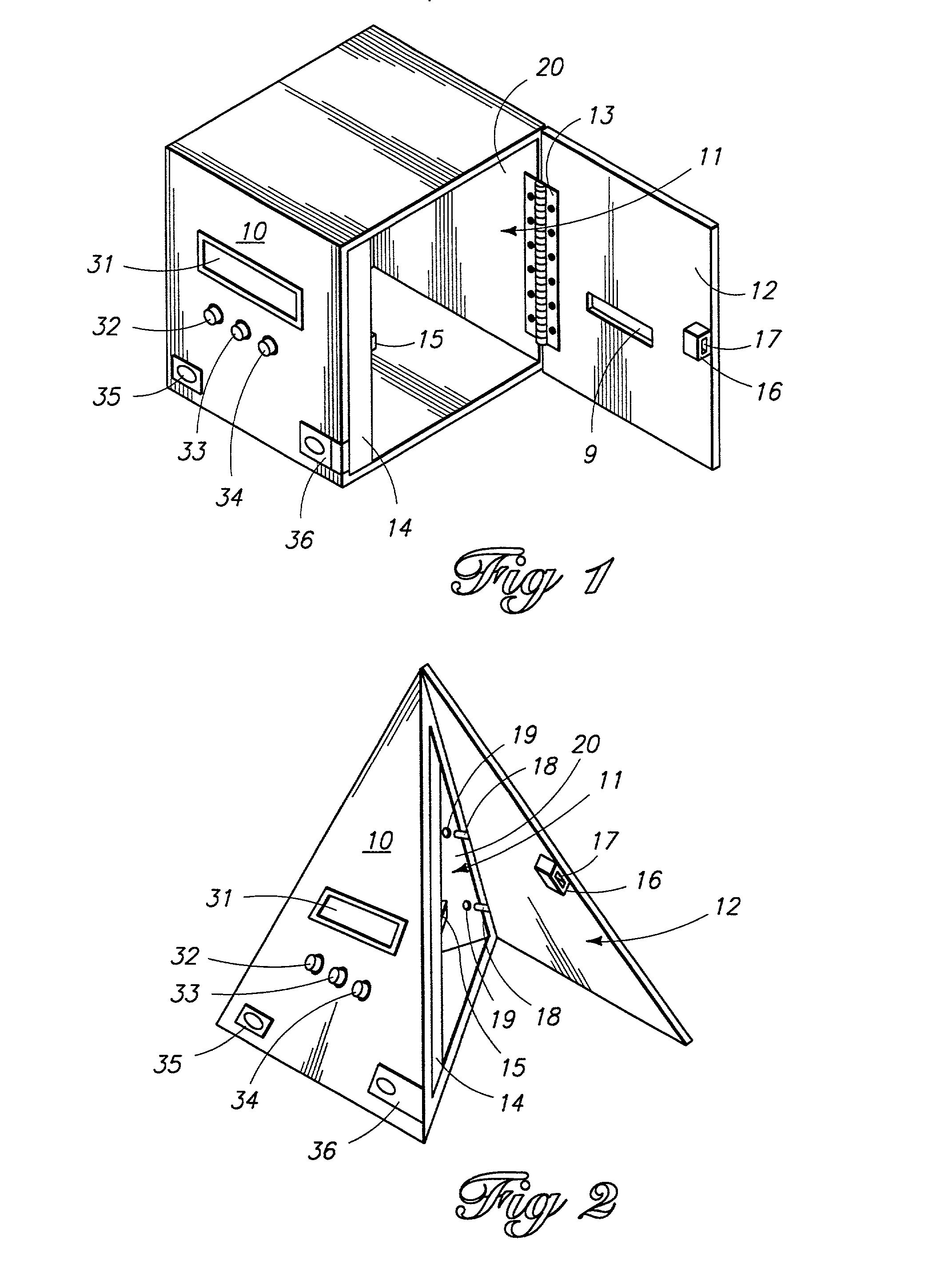

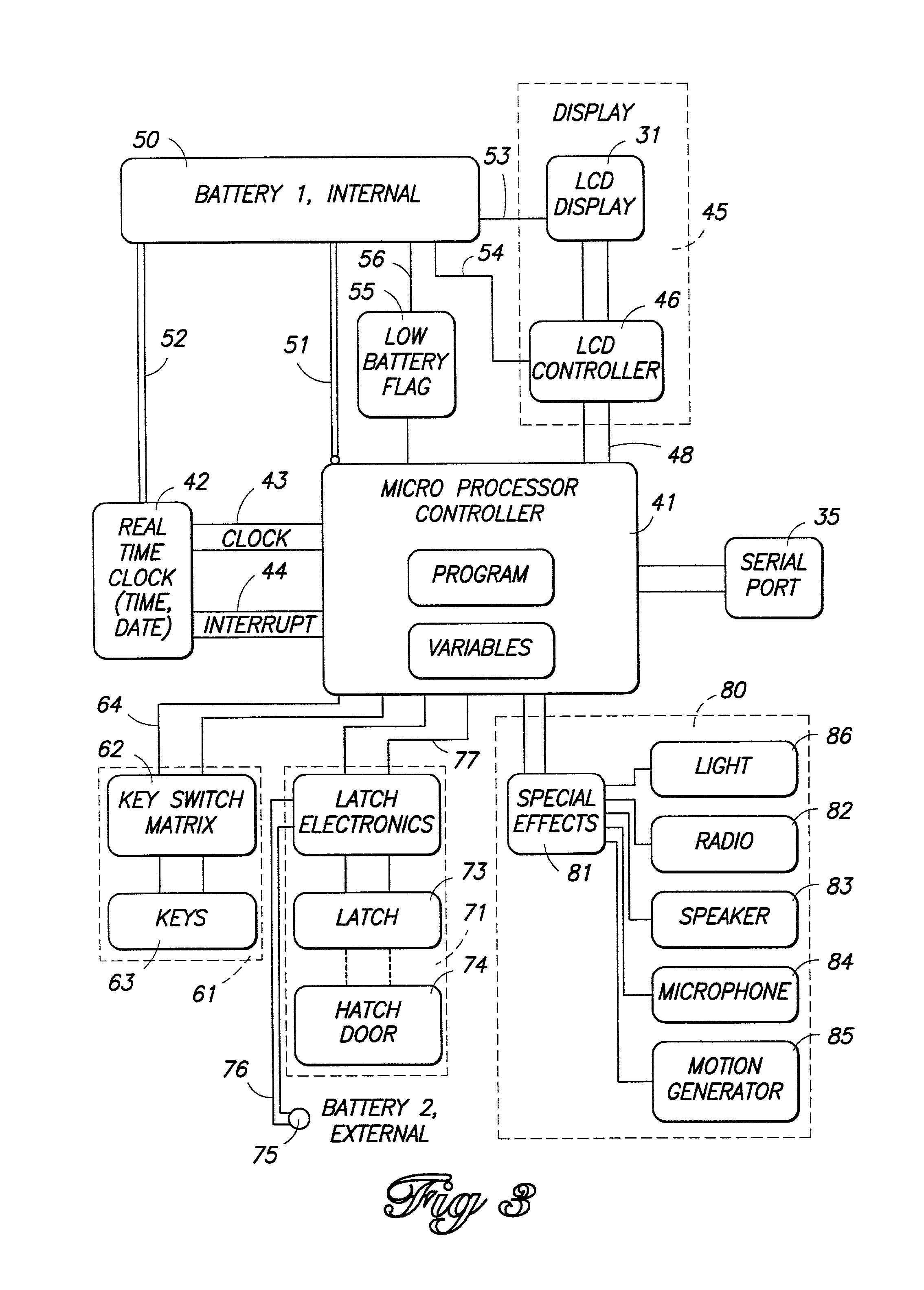

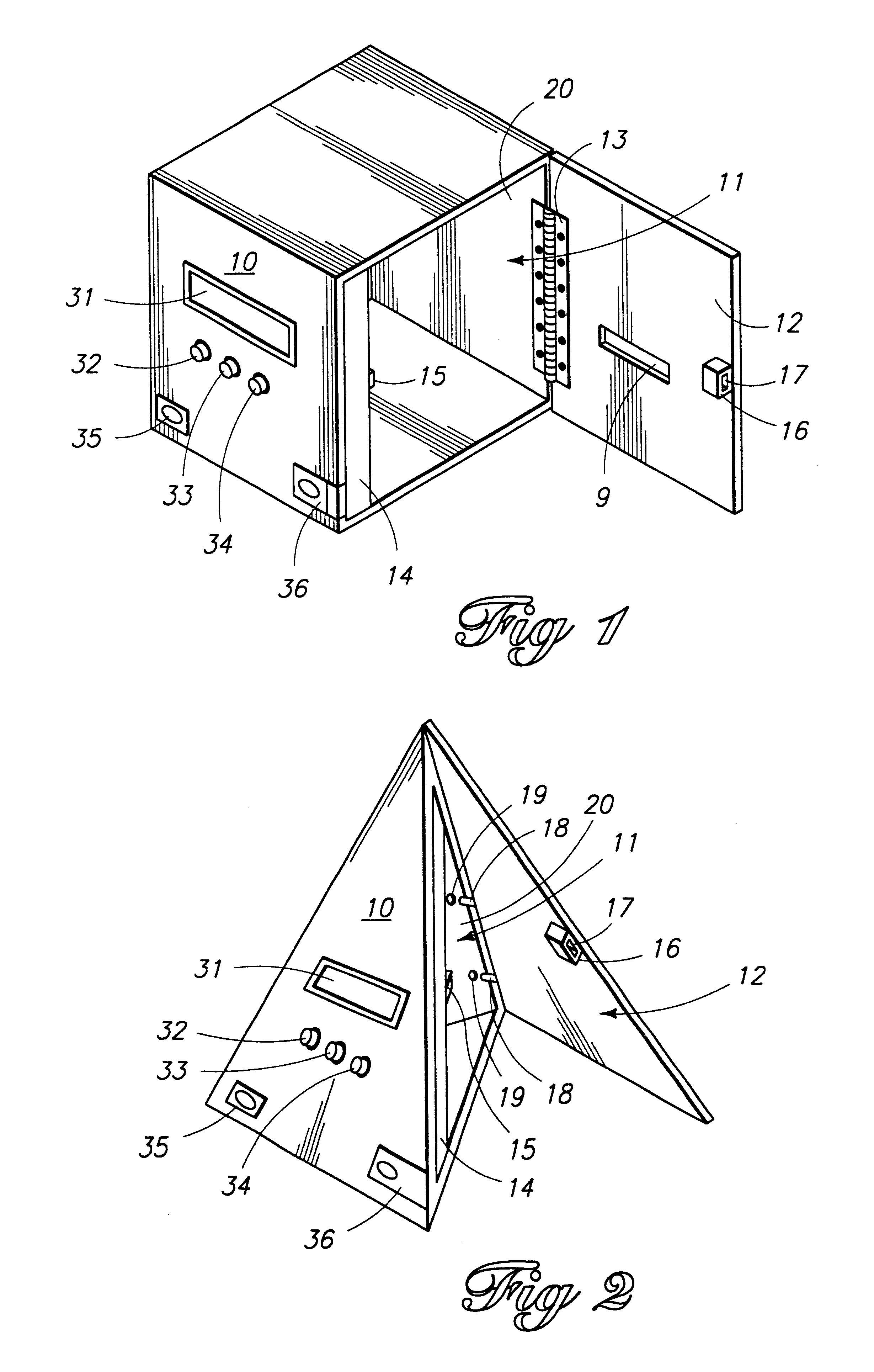

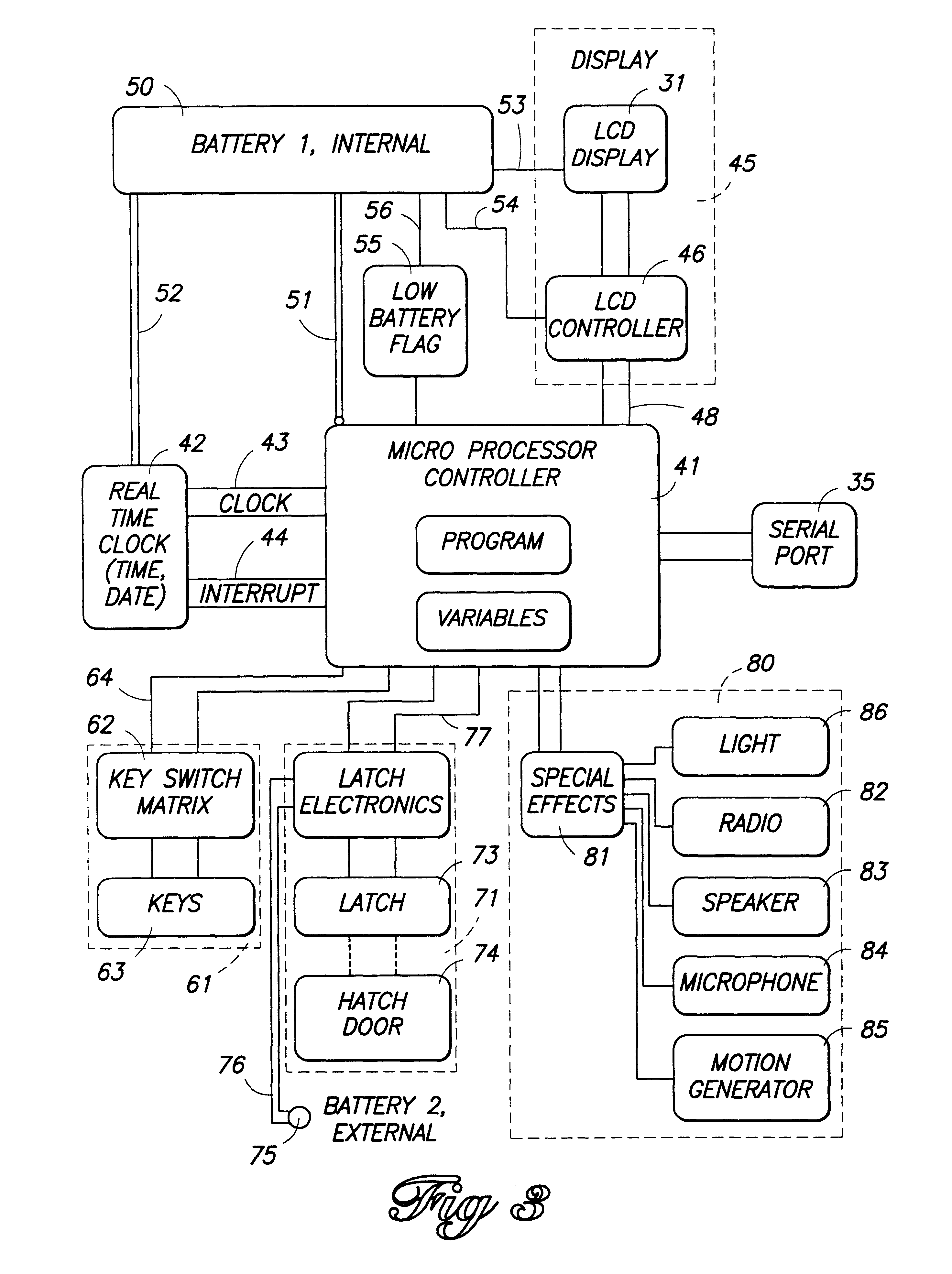

Time-lock box

InactiveUS20030090364A1Electric signal transmission systemsDigital data processing detailsLocking mechanismPassword

A lockable storage assembly, or lockbox container, is disclosed, with programmable opening utility, for providing access to the contents of the storage assembly at a time chosen by a user to suit an occasion. The lockbox includes non-volatile memory for holding current time and date, and opening time and date, and is assembled of integrated circuits and display, requiring very low power, such that the lockbox may retain function over extended periods of time, while locking mechanisms with higher power requirements are powered by a replaceable, externally accessible battery. The lockbox is assembled and programmed so that the interior is accessible only upon reaching a match date, whereupon the lockbox unlocks automatically, or upon entry of a password chosen by the user.

Owner:CARDINALE SALVATORE J

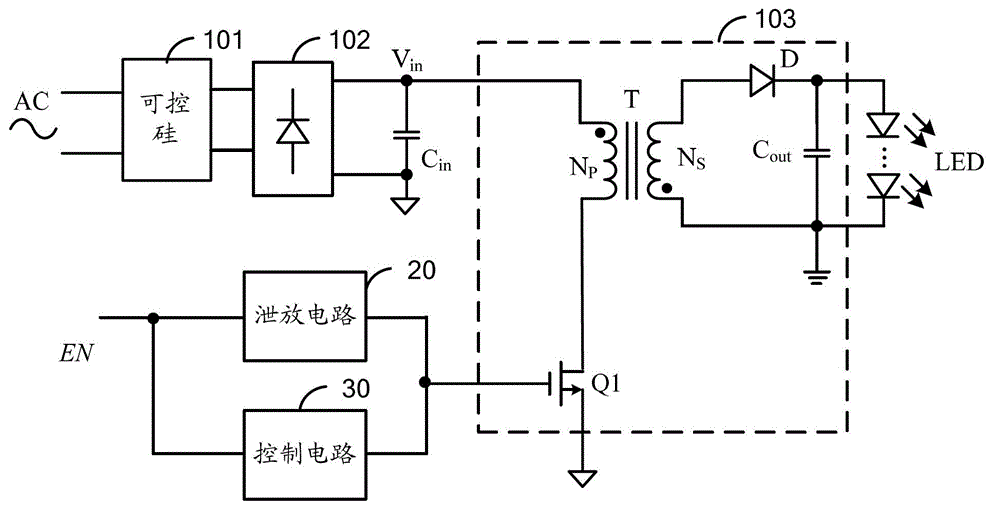

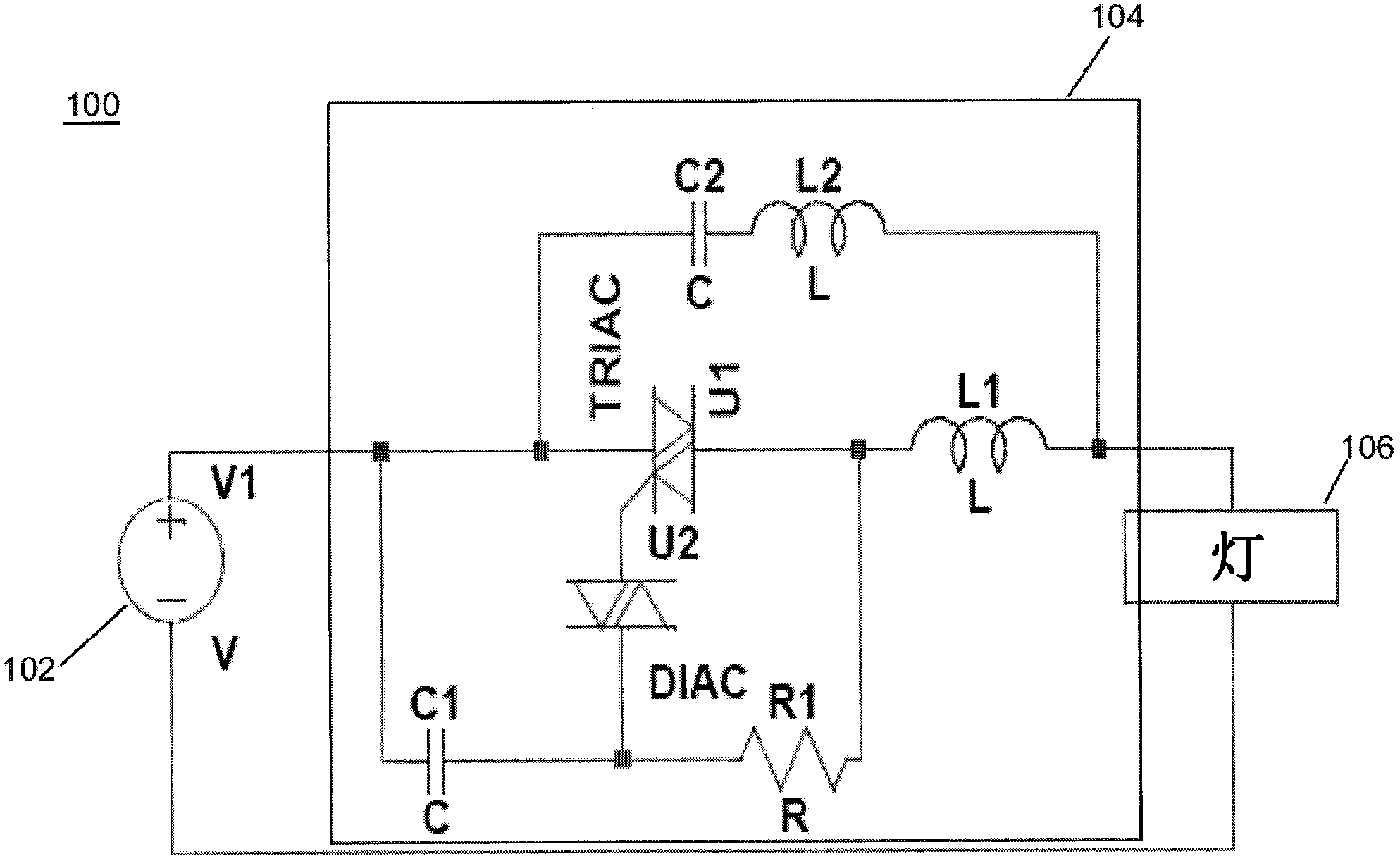

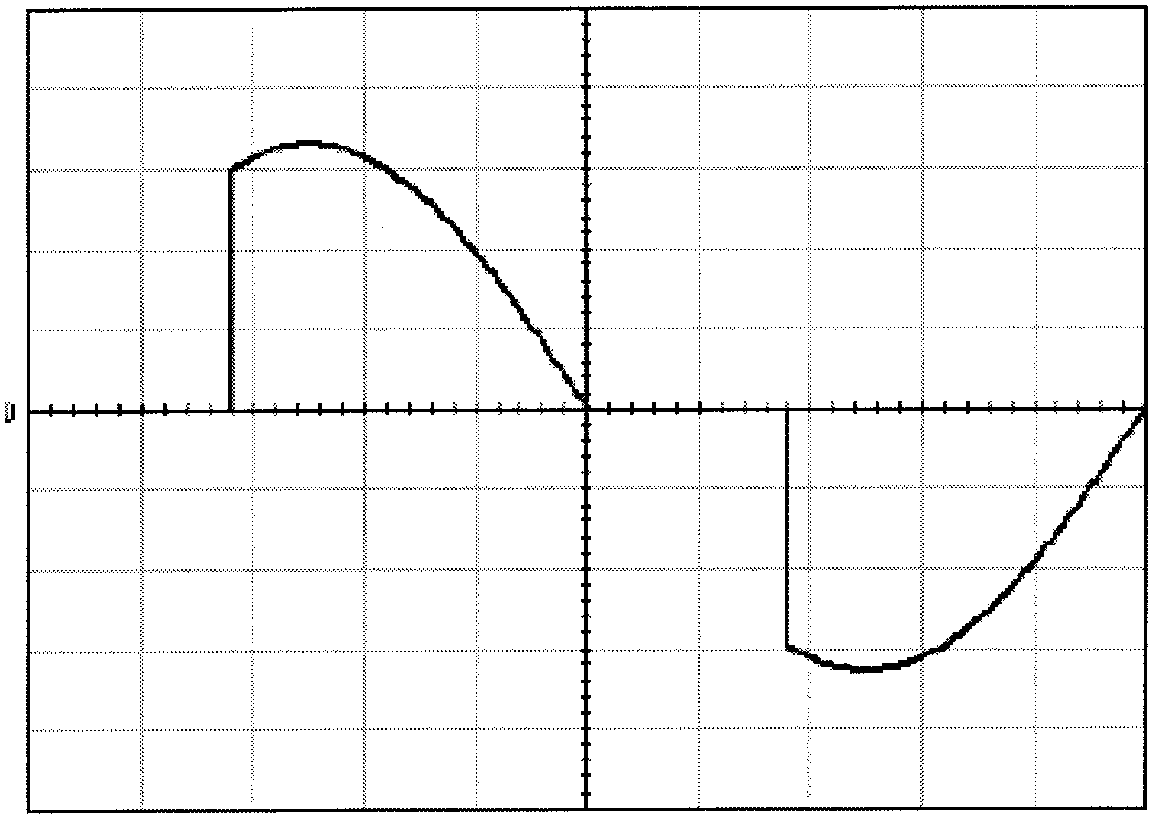

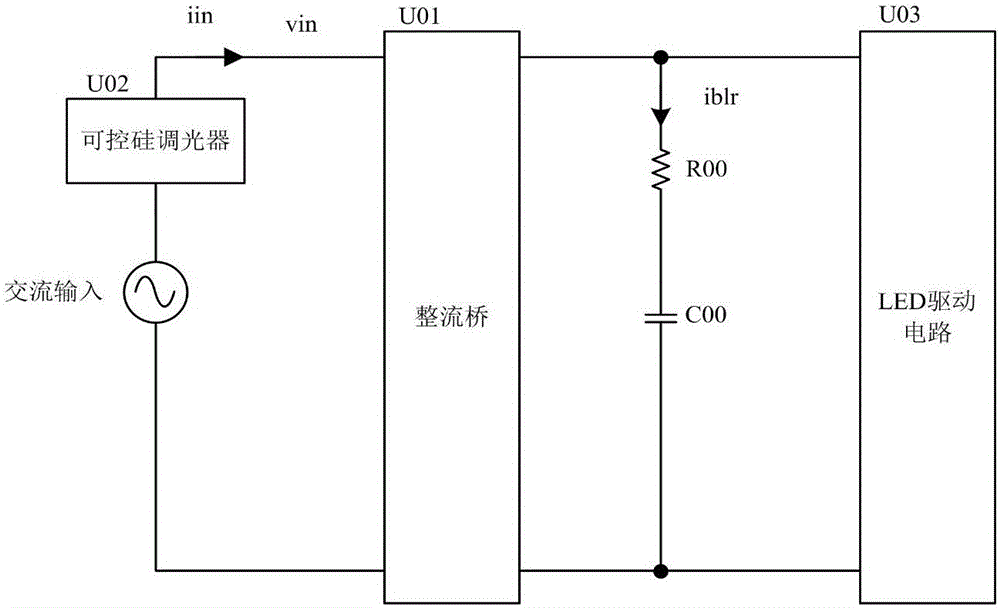

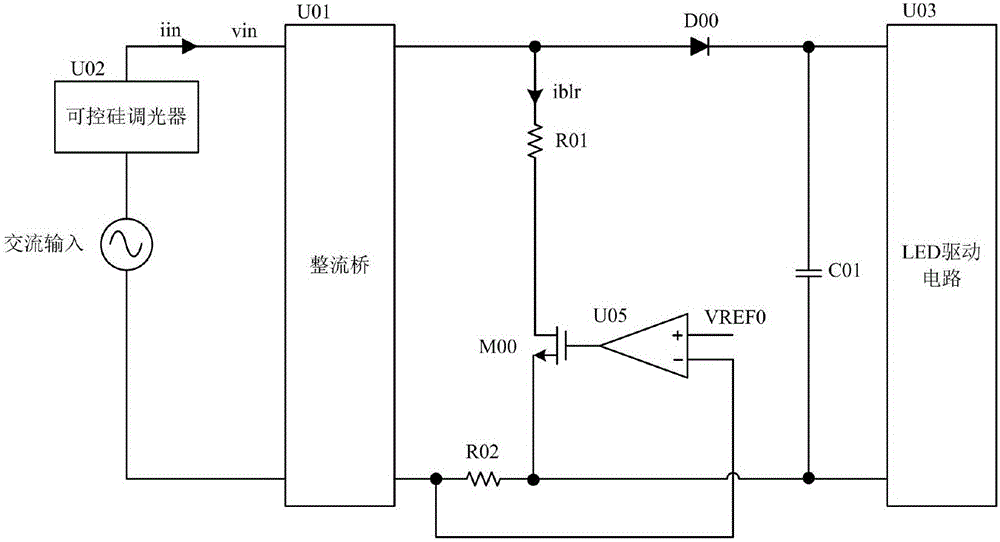

Controllable silicon dimming circuit with nondestructive leakage circuit and method thereof

ActiveCN102946674ASimple structureImprove utilization efficiencyElectroluminescent light sourcesDc-dc conversionEngineeringAlternating current

The invention provides a controllable silicon dimming circuit with a nondestructive leakage circuit. Sine alternating-current voltage received by the controllable silicon dimming circuit is processed by controllable silicon and a rectified bridge to obtain default phase input voltage, and the default phase input voltage is input to a power level circuit to perform electric energy conversion so as to drive light load. The leakage circuit is used for controlling a main switch tube in the power level circuit in a first preset time interval so as to perform opening and closing movement in a specific mode to provide a charging circuit loop for a controllable silicon circuit. The controllable silicon dimming circuit does not need extra leakage switches and related elements, is simple in structure, does not generate extra energy consumption in a leakage process, and improves utilization efficiency of electric energy. In addition, an enable signal controls the power level circuit to stop working before input current is reduced to holding current of the controllable silicon, the state is maintained in a second preset time interval, namely load current in a connection interval of the controllable silicon is guaranteed to be above the holding current of the controllable silicon always, and sparkling of a light-emitting diode (LED) lamp caused by misconnection of the controllable silicon is avoided.

Owner:SILERGY SEMICON TECH (HANGZHOU) CO LTD

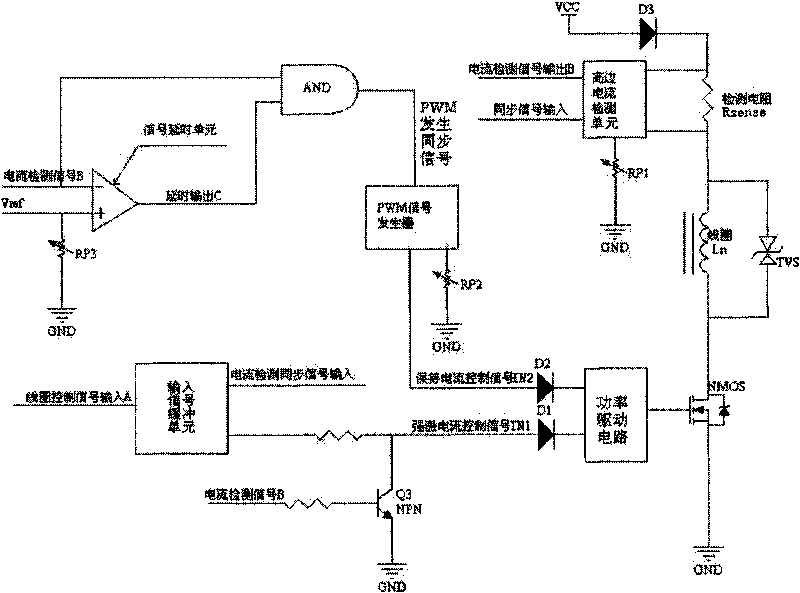

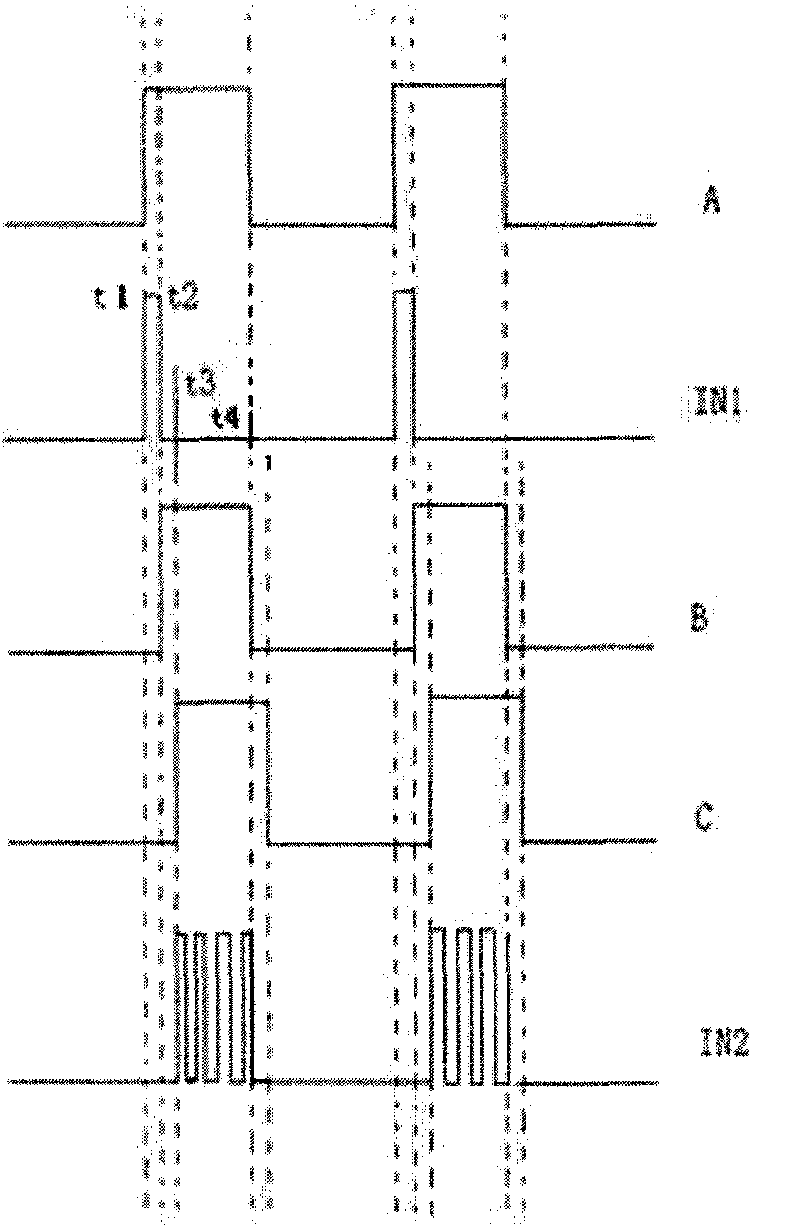

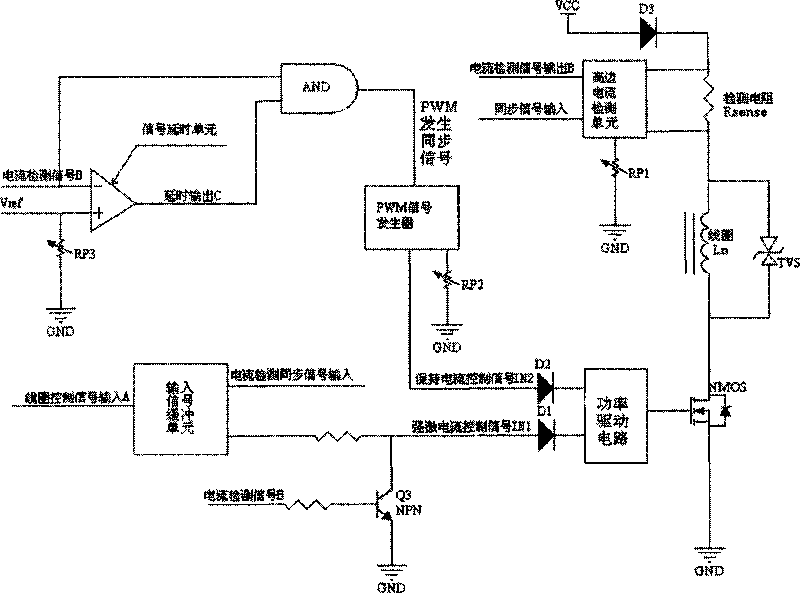

High-speed electromagnetic valve driver circuit

ActiveCN101737551AIncreased complexitySimple structureElectrical controlOperating means/releasing devices for valvesTime delaysDelayed time

The invention relates to a high-speed electromagnetic valve driver circuit. An input signal buffer unit mainly performs buffering shaping on an input signal from an external central control unit and improves the antijamming capacity thereof; a high side current detection unit realizes current detection by detecting differential voltage of one resistor in a load branch circuit; a PWM signal generator mainly generates a PWM wave with fixed frequency, the current is controlled and kept by regulating the duty cycle of the waveform; a power drive unit mainly supplies enough power drive for a power NMOS tube so that the power NMOS tube can fully operate in a switch state and reduce switch loss and heating; a signal time delay unit outputs a time delay for a current detection signal; in the delay time, the power NMOS tube is cut off, so that a coil can have afterflow; a logical gate circuit unit is a coincidence gate and generates a synchronizing signal required by the PWM signal generator after performing phasing on the current detection signal and a time delay signal thereof.

Owner:SICHUAN AEROSPACE FENGHUO SERVO CONTROL TECH CO LTD

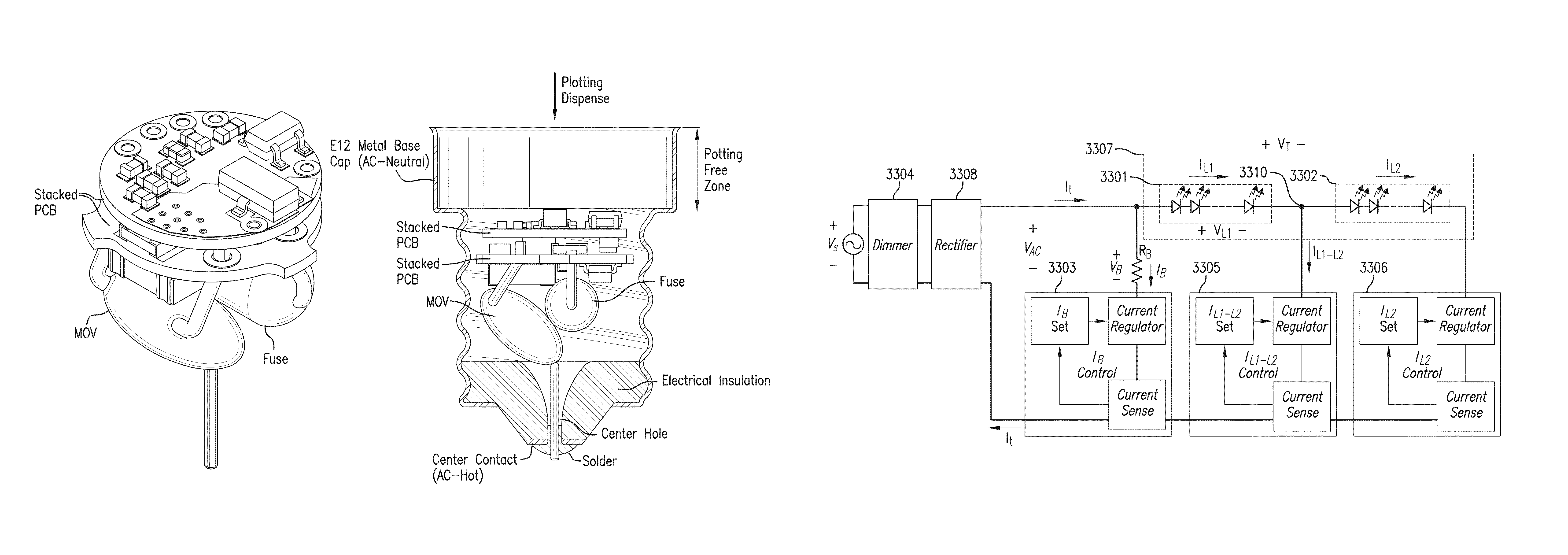

LED lighting

ActiveUS9420644B1Energy efficiency sufficientGuaranteed uptimeElectrical apparatusElectric circuit arrangementsTRIACDimmer

Apparatus and associated methods relate to a diversion driver module that dynamically adds a diversion current to an LED current so that the summed current maintains a predetermined minimum holding current requirement of a phase-controlled dimmer supply. In an illustrative example, the diversion current may be a function of input AC line voltage and / or firing angle of the phase-controlled dimmer supply. The phase controlled device may include, for example, a triac. The triac may supply adjustable pulse-width current to dim the LED according to a phase control signal. The diversion driver module may include one or more heat dissipating components disposed in thermal communication with the lamp base. Some driver modules may be sufficiently compact and energy efficient to provide smooth dim-to-black performance while operating within acceptable temperature limits for reliable operation while contained in the base of a standard form factor lamp, such as an E12 full-glass lamp.

Owner:FILAMENT LIGHTING LLC

Bleeding circuit and related method for preventing improper dimmer operation

Disclosed are a method and apparatus for controlling bleed current, to provide the bleed current until ringing of input current at a dimmer has ceased in order to prevent misfiring of a dimmer and flicker of the light source. The return path current to the dimmer is boosted by the bleed current to be at a level greater than the holding current of the dimmer. As a result, the load current of the dimmer is increased to a sufficient minimum so that the dimmer can operate properly.

Owner:SIGNIFY HLDG BV

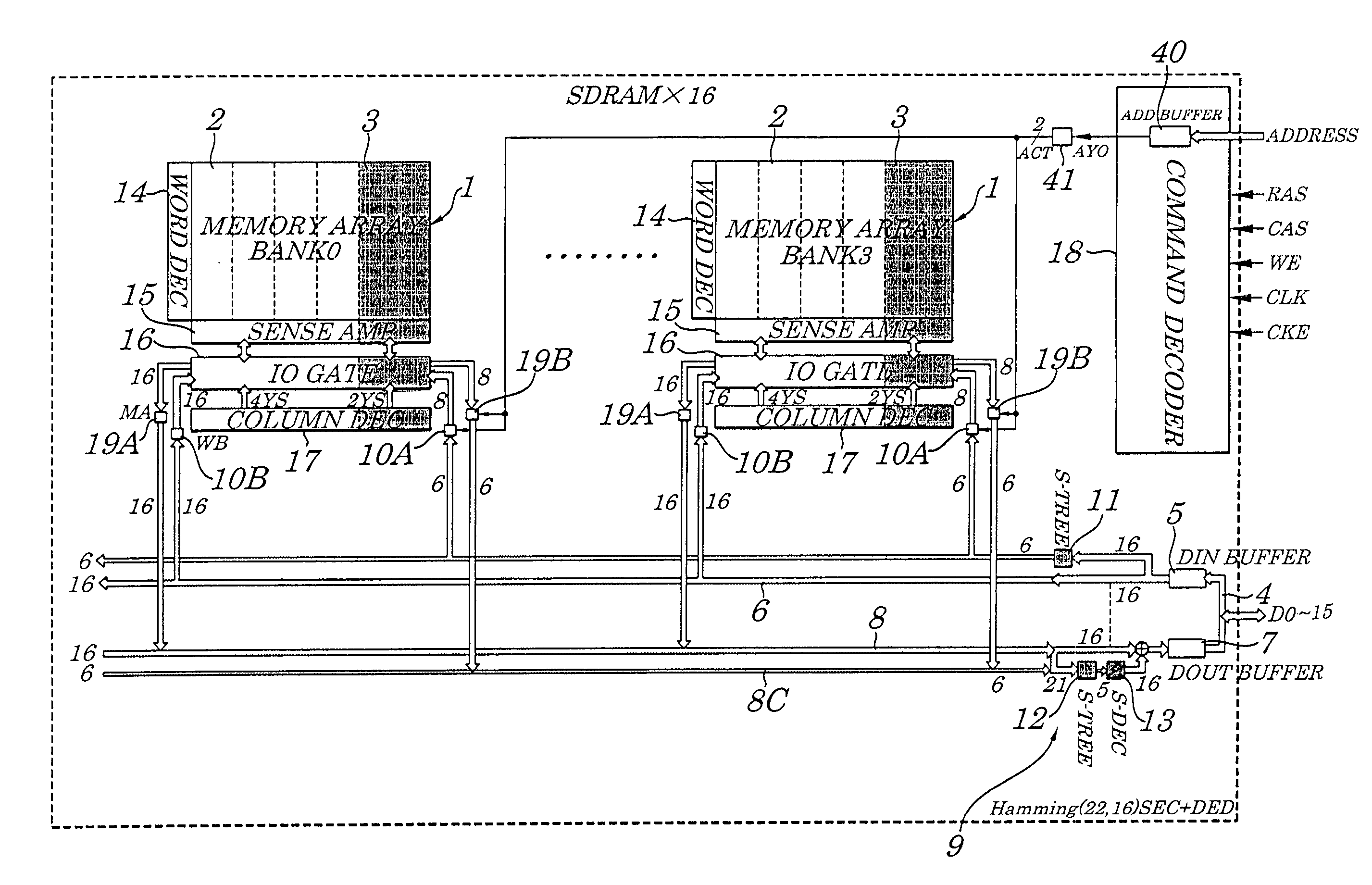

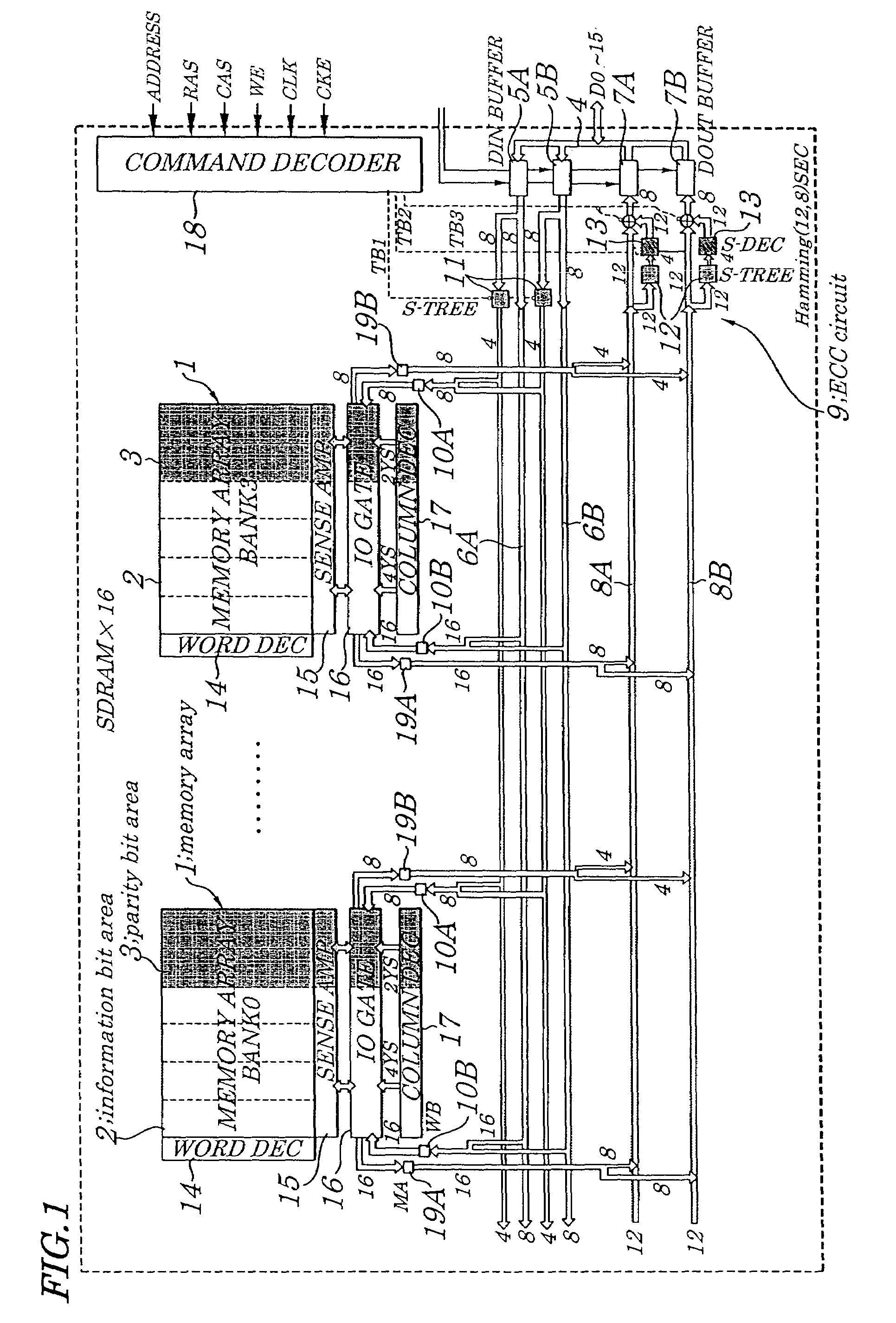

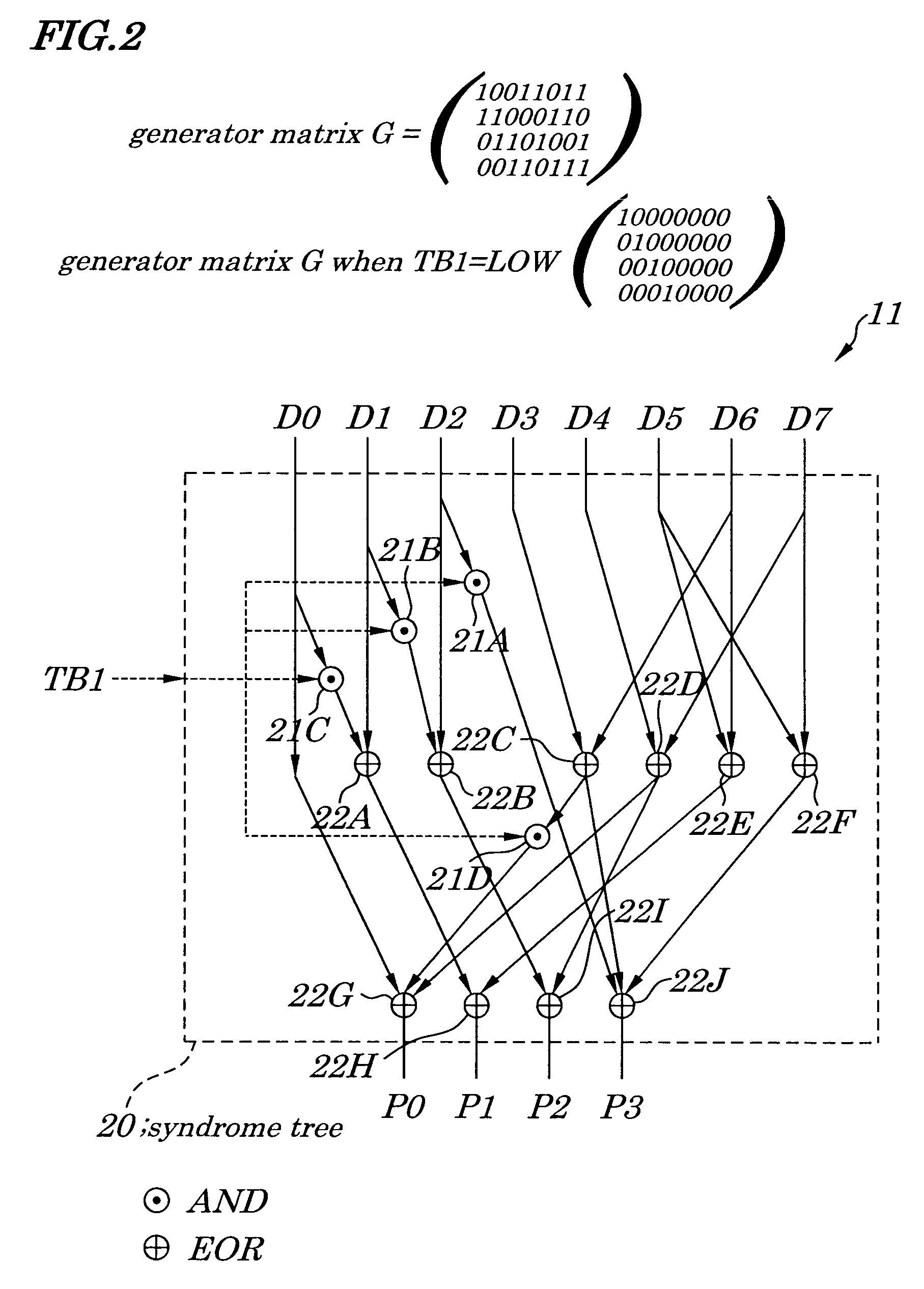

Semiconductor memory device provided with error correcting code circuitry

ActiveUS7225390B2Effective correctionReduce error rateCode conversionDigital storageHamming codeError location

A semiconductor synchronous dynamic random access memory (SDRAM) device capable of correcting bits having a low error rate in a Pause Refresh Tail distribution and of reducing a data holding current by lengthening a refresh period so that the refresh period exceeds a period for a Pause Refresh real power. The semiconductor memory device is made up of a 16-bit SDRAM having a Hamming Code and including an ECC (Error Correcting Code) circuit made up of an encoding circuit controlled by a first test signal to output a parity bit corresponding to an information bit, a decoding circuit controlled by second test signal to output an error location detecting signal indicating an error bit in codeword, and an error correcting circuit controlled by a third test signal to input an error location detecting signal and to output an error bit in a reverse manner.

Owner:LONGITUDE LICENSING LTD

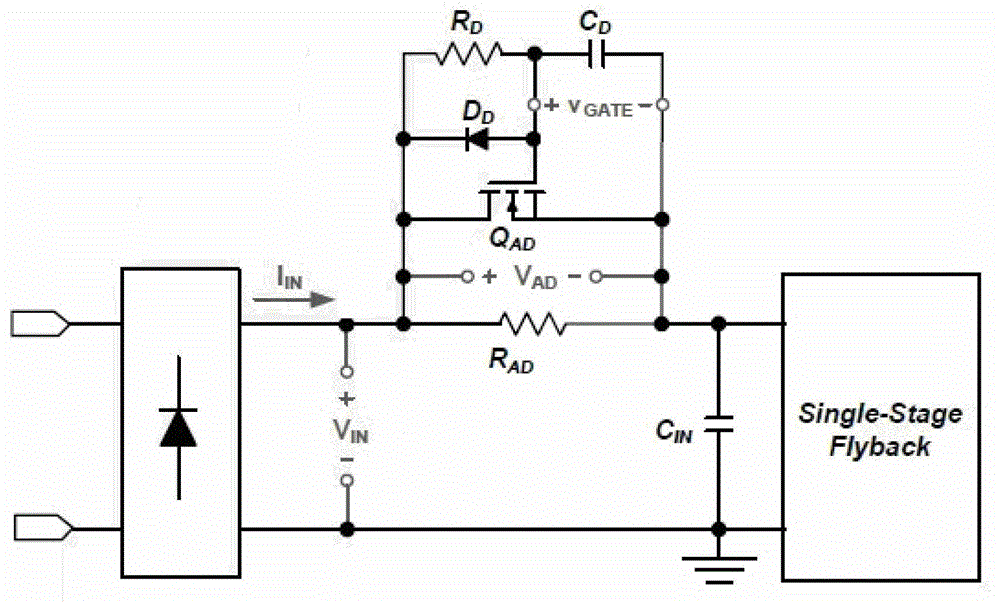

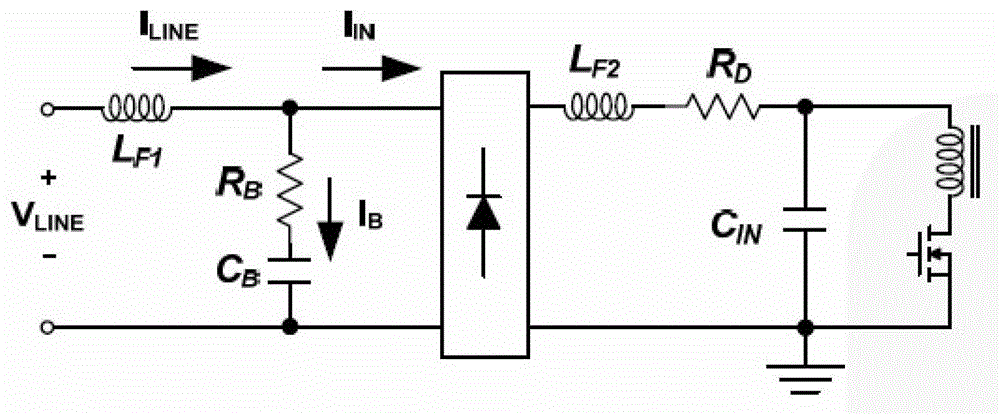

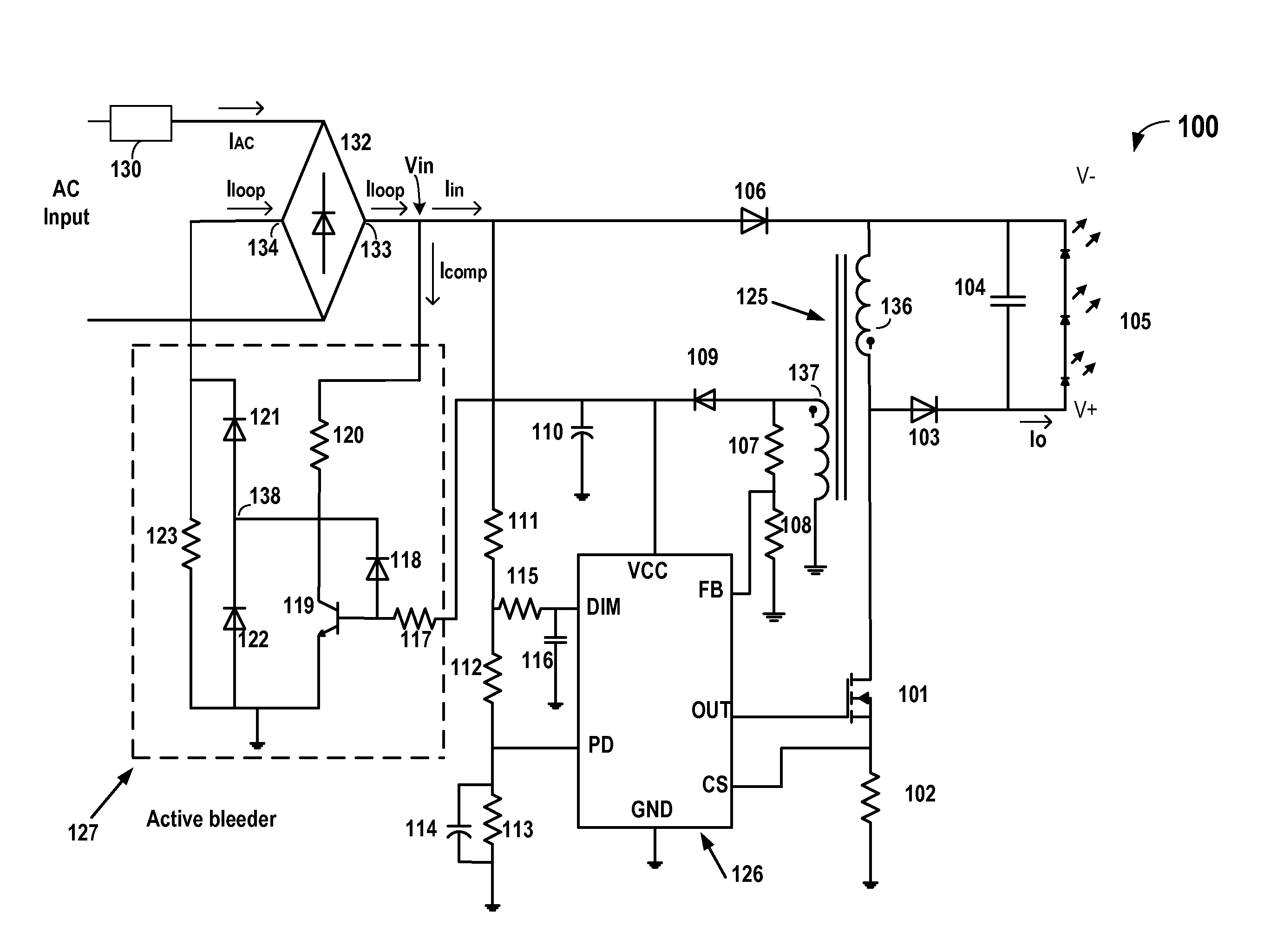

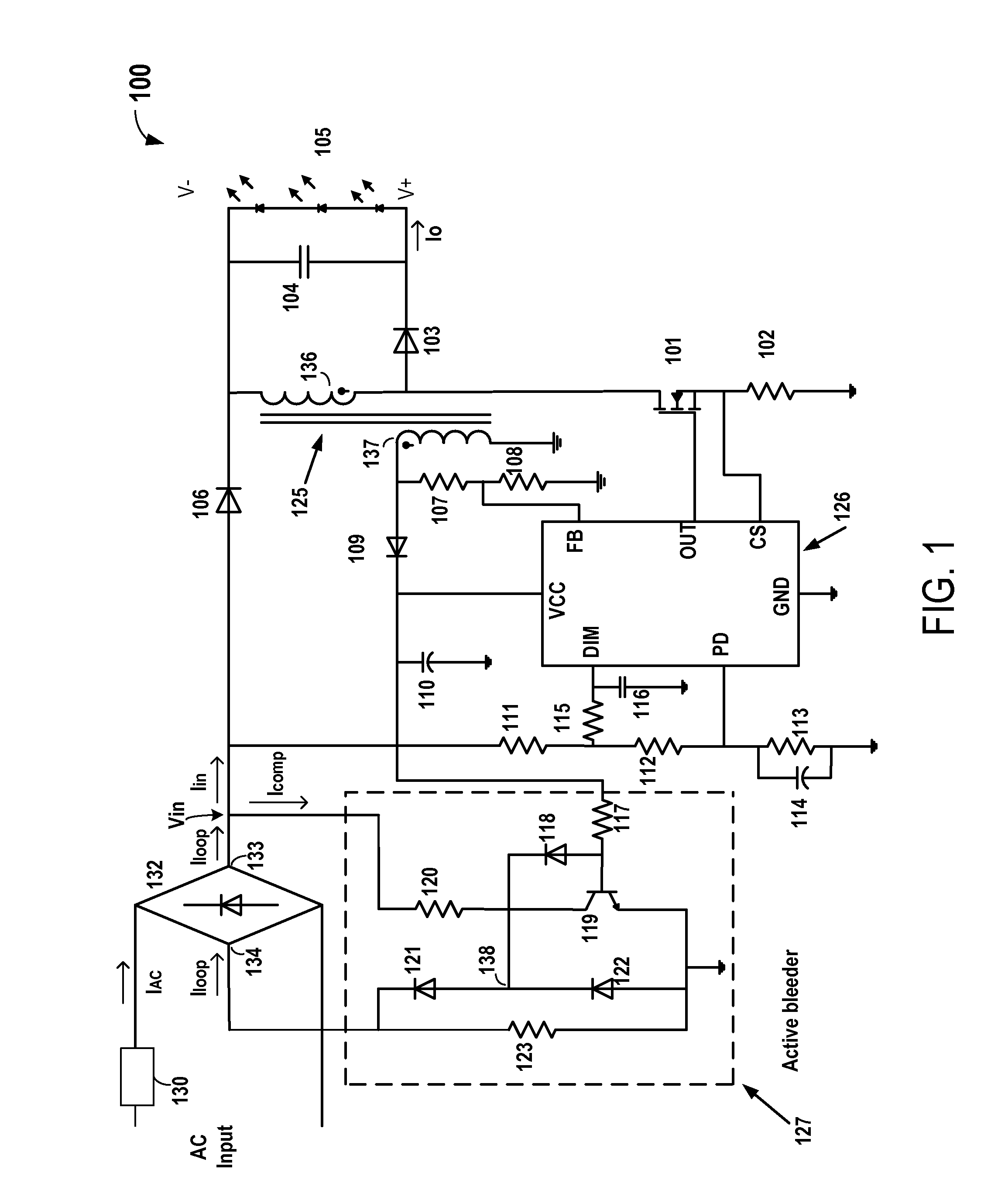

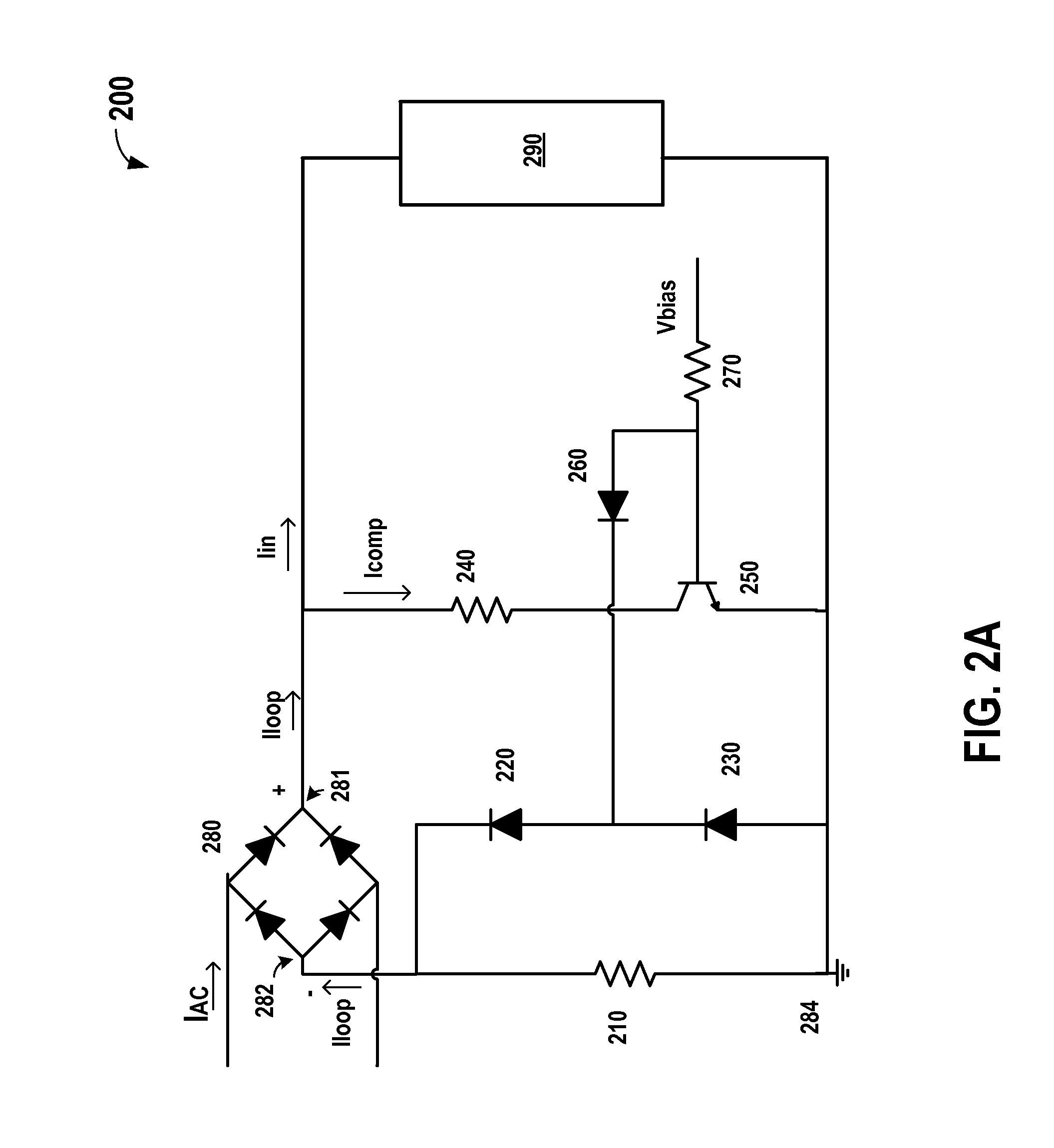

Power supply for LED lamp with triac dimmer

ActiveUS20170027029A1Reducing bleeder current consumptionImprove power factorElectrical apparatusElectroluminescent light sourcesSilicon-controlled rectifierTRIAC

A bleeder circuit is provided in a switched mode power supply (SMPS) that provides a compensation current when the loop current drops below the holding current of the TRIAC to alleviate light flickering problem. Further, automatic power factor correction is also provided in embodiments of the invention, which enables the output current to be in phase with the input voltage. The power factor correction not only improves the efficiency of the power supply, it can also reduce the compensation current and the duration in which compensation current flows, thereby reducing the power loss in the bleeder circuit.

Owner:BCD SHANGHAI MICRO ELECTRONICS CO LTD +1

Adaptive holding current control for LED dimmer

ActiveUS20140159616A1Increase currentReduces perceivable flickeringElectrical apparatusElectroluminescent light sourcesTRIACDimmer

A TRIAC dimmer controller for an LED lamp dynamically adjusts the amount of additional current supplied to the TRIAC dimmer based on the TRIAC dimmer operating mode. A TRIAC dimmer current controller continually senses the TRIAC dimmer current loading and determines a TRIAC dimmer operating mode based on the detected current. The TRIAC dimmer controller compares the detected current with a threshold current value called a TRIAC holding current, and adjusts the amount of bleeder current based on the difference between the detected current and the threshold current value. By continually sensing the TRIAC dimmer current loading, the LED controller regulates the amount of bleeder current supplied to the TRIAC dimmer using a single sink current path to satisfy the TRIAC dimmer current demands of multiple TRIAC dimmer operating modes.

Owner:DIALOG SEMICONDUCTOR INC

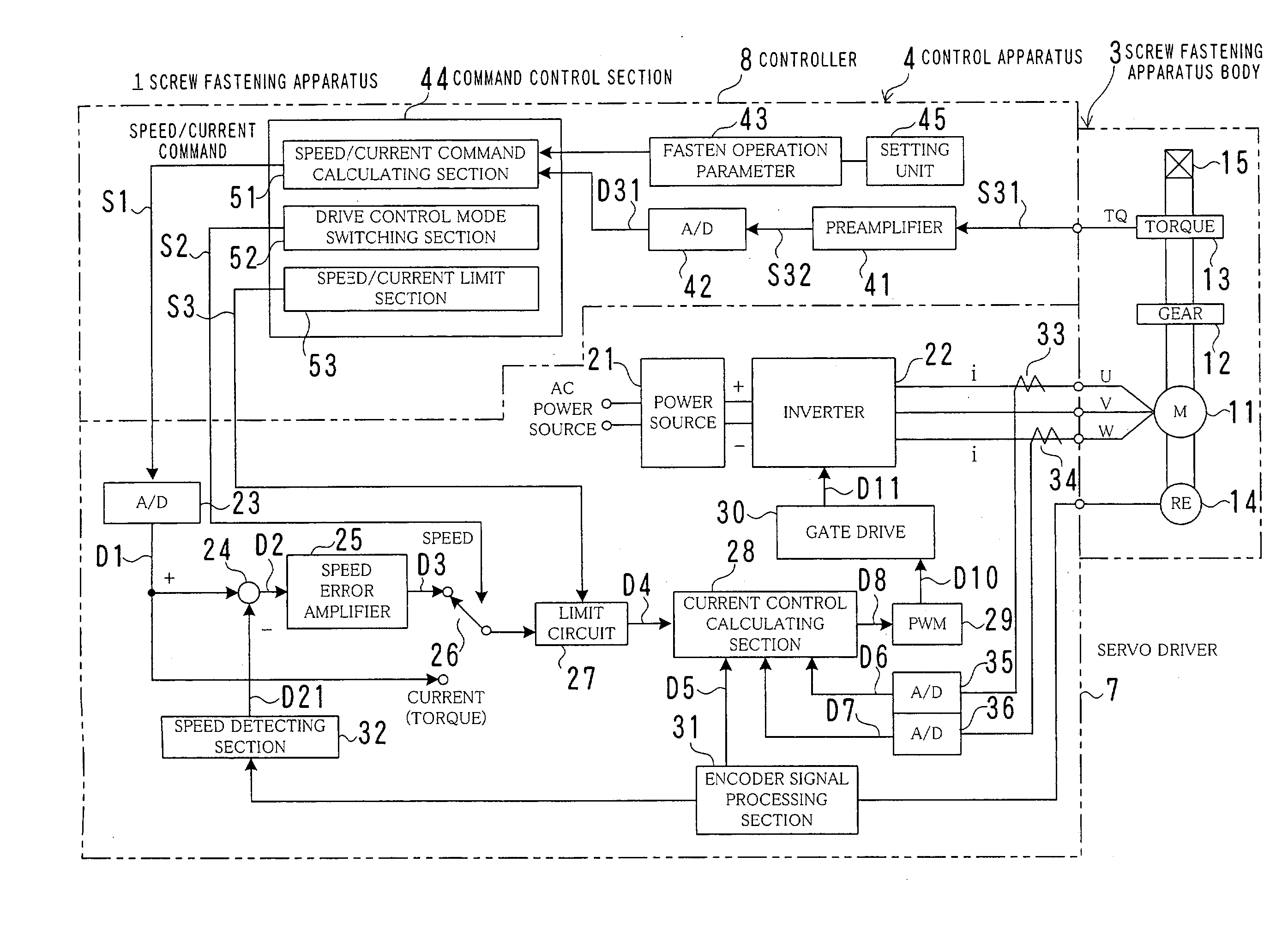

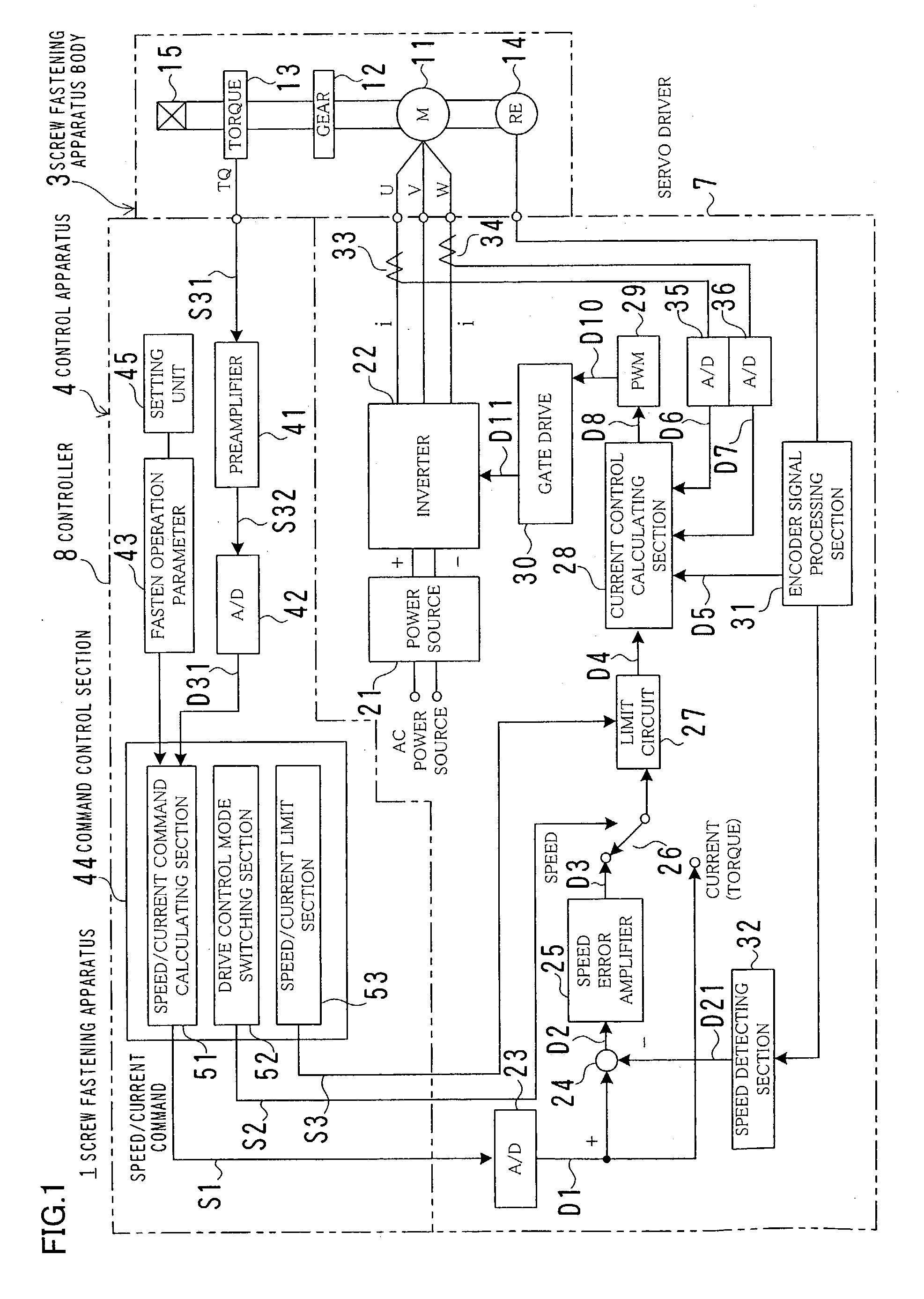

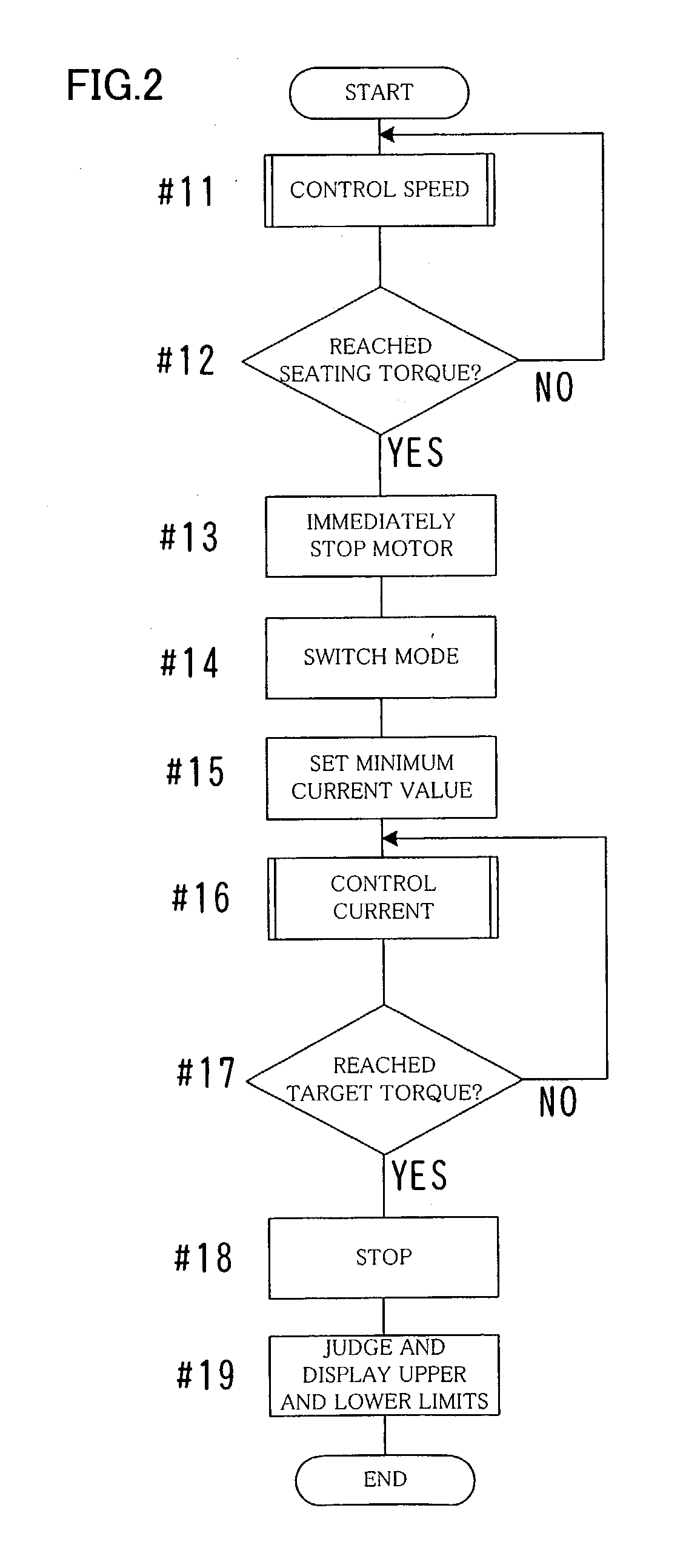

Control method and apparatus of screw fastening apparatus

It is an object of the present invention to overcome various drawbacks of a conventional oil pulse wrench by using an electric motor, to reduce a reaction force and to fasten a screw with high precision. To achieve the object, the invention provides a control method of a screw fastening apparatus using an electric motor as a rotation driving source, the method comprising the steps of; intermittently supplying current pulse DP to the motor, detecting an actual torque at predetermined time intervals, maintaining a current value when a detected torque value does not exceed a maximum value of past detected torques value and increasing the current value by a predetermined amount when the detected torque value exceeds the maximum value of the past detected torque value, and stopping the supply of the current pulse DP when the detected torque value reaches a target value TQJ.

Owner:ESTIC CORP

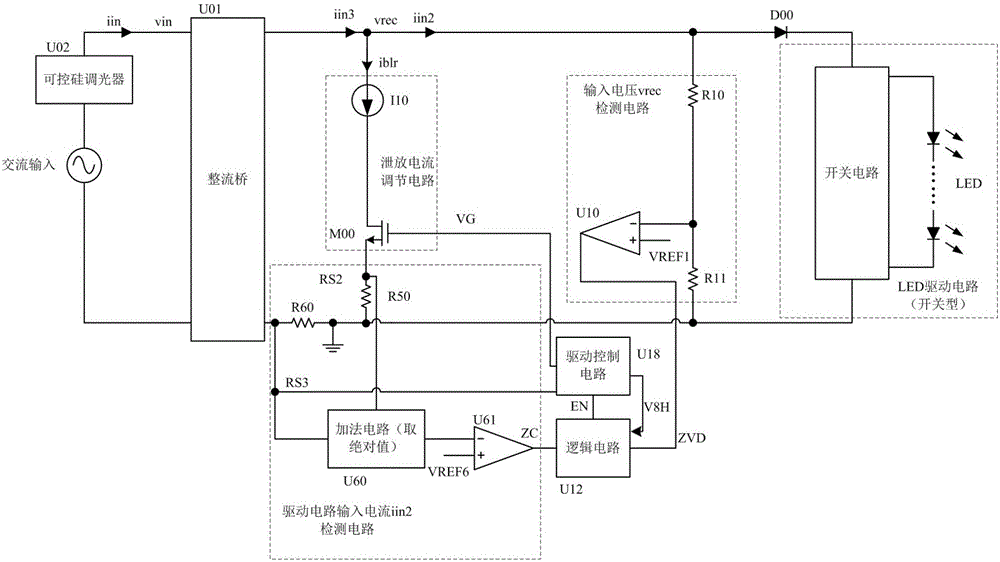

Bleeder circuit and method for controlling bleeder current and LED control circuit

ActiveCN106332374AIncrease the maximum conduction angleGuaranteed dimming effectElectrical apparatusElectroluminescent light sourcesTRIACControl circuit

The invention discloses a bleeder circuit and a method for controlling bleeder current and an LED control circuit. The scheme of the invention can be applied to the switch driving scheme. The threshold voltage is a zero passage value. When input voltage passes zero, bleeder current is generated, so that input current is more than the holding current of silicon controlled. Whether or not the bleeder current regulating circuit is enabled is controlled in accordance with the waveform characteristics of the front and rear half cycles of the sine wave and the input current of the driving circuit. According to the bleeder circuit, on the premise of ensuring the dimming effect, the bleeder circuit is reduced, and the efficiency and reliability of the system are improved. Meanwhile, the TRIAC maximum conduction angle is increased, and thereby easily meeting the requirement of the maximum output current.

Owner:JOULWATT TECH ZHANGJIAGANG INC LTD

Controllable-load circuit for use with a load control device

ActiveUS9220133B2Electroluminescent light sourcesElectric light circuit arrangementLoad circuitElectricity

A load control device for controlling the amount of power delivered from an AC power source to an electrical load is operable to conduct enough current through a thyristor of a connected dimmer switch to exceed rated latching and holding currents of the thyristor. The load control device comprises a controllable-load circuit operable to conduct a controllable-load current through the thyristor of the dimmer switch. The load control device disables the controllable-load circuit when the phase-control voltage received from the dimmer switch is a reverse phase-control waveform. When the phase-control voltage received from the dimmer switch is a forward phase-control waveform, the load control device is operable to decrease the magnitude of the controllable-load current so as to conduct only enough current as is required in order to exceed rated latching and holding currents of the thyristor.

Owner:LUTRON TECH CO LLC

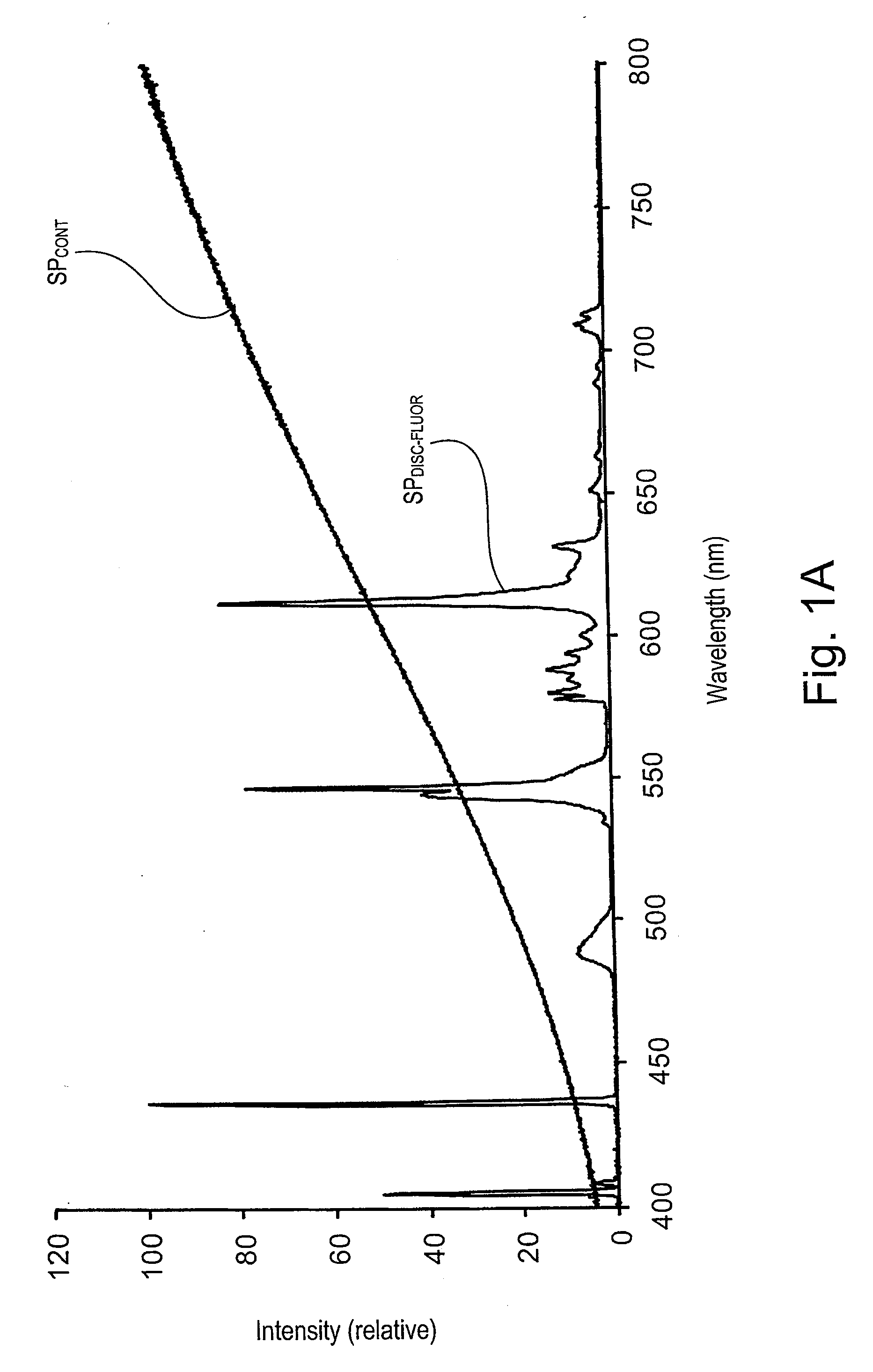

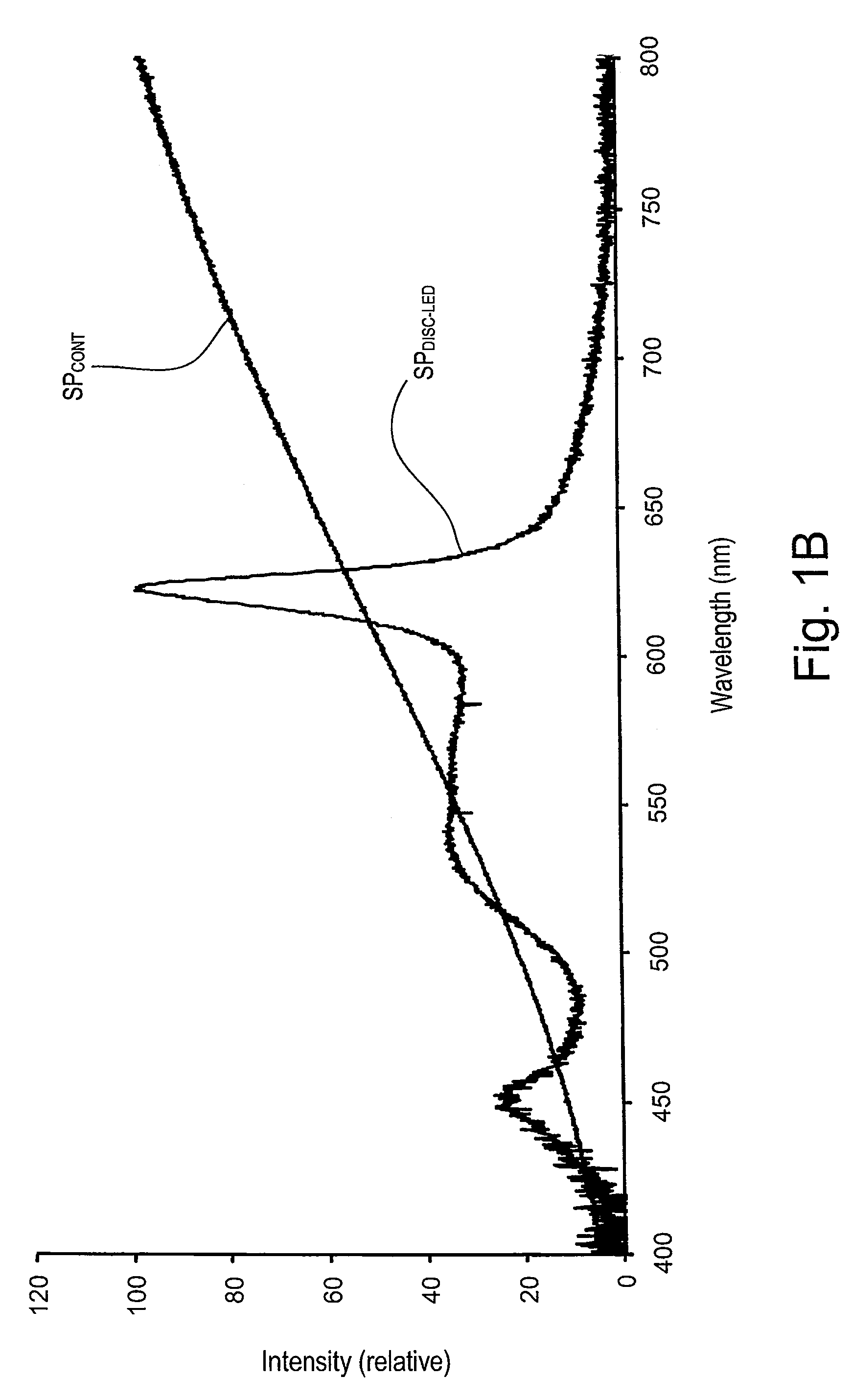

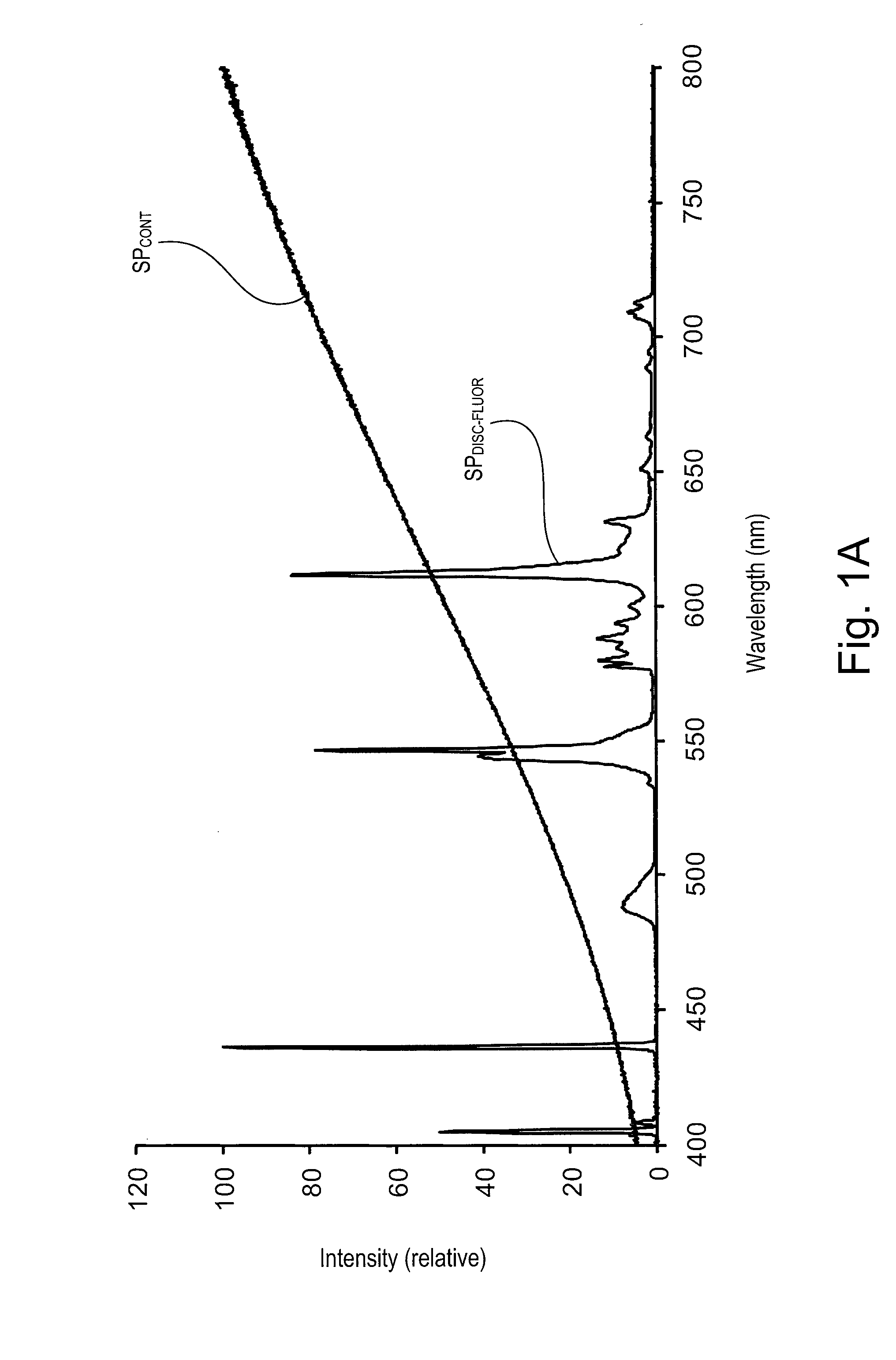

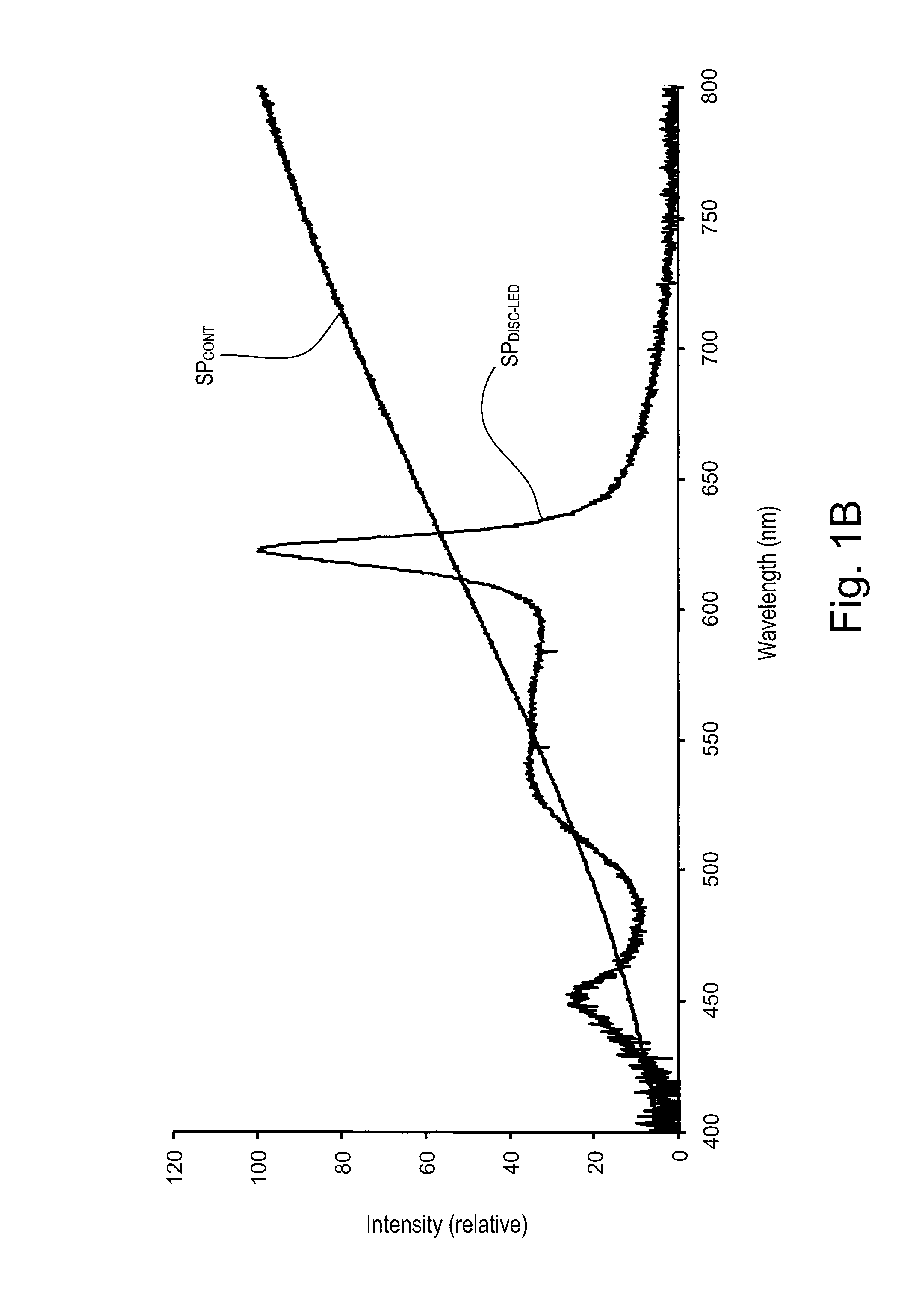

Hybrid light source

InactiveUS20100141158A1Low color temperatureReduce light outputElectrical apparatusElectroluminescent light sourcesEngineeringFluorescent lamp

A hybrid light source comprises a discrete-spectrum lamp (for example, a fluorescent lamp) and a continuous-spectrum lamp (for example, a halogen lamp). A control circuit individually controls the amount of power delivered to the discrete-spectrum lamp and the continuous-spectrum lamp in response to a phase-controlled voltage generated by a connected dimmer switch, such that a total light output of the hybrid light source ranges throughout a dimming range. The discrete-spectrum lamp is turned off and the continuous-spectrum lamp produces all of the total light intensity of the hybrid light source when the total light intensity is below a transition intensity. The continuous-spectrum lamp is driven by a continuous-spectrum lamp drive circuit, which is operable to conduct a charging current of a power supply of the dimmer switch and to provide a path for enough current to flow through the hybrid light source, such that the magnitude of the current exceeds rated latching and holding currents of a thyristor of the dimmer.

Owner:LUTRON TECH CO LLC

Hybrid light source

InactiveUS20100066260A1Electrical apparatusElectroluminescent light sourcesEngineeringFluorescent lamp

A hybrid light source comprises a discrete-spectrum lamp (for example, a fluorescent lamp) and a continuous-spectrum lamp (for example, a halogen lamp). A control circuit individually controls the amount of power delivered to the discrete-spectrum lamp and the continuous-spectrum lamp in response to a phase-controlled voltage generated by a connected dimmer switch, such that a total light output of the hybrid light source ranges throughout a dimming range. The discrete-spectrum lamp is turned off and the continuous-spectrum lamp produces all of the total light intensity of the hybrid light source when the total light intensity is below a transition intensity. The continuous-spectrum lamp is driven by a continuous-spectrum lamp drive circuit, which is operable to conduct a charging current of a power supply of the dimmer switch and to provide a path for enough current to flow through the hybrid light source, such that the magnitude of the current exceeds rated latching and holding currents of a thyristor of the dimmer.

Owner:LUTRON TECH CO LLC

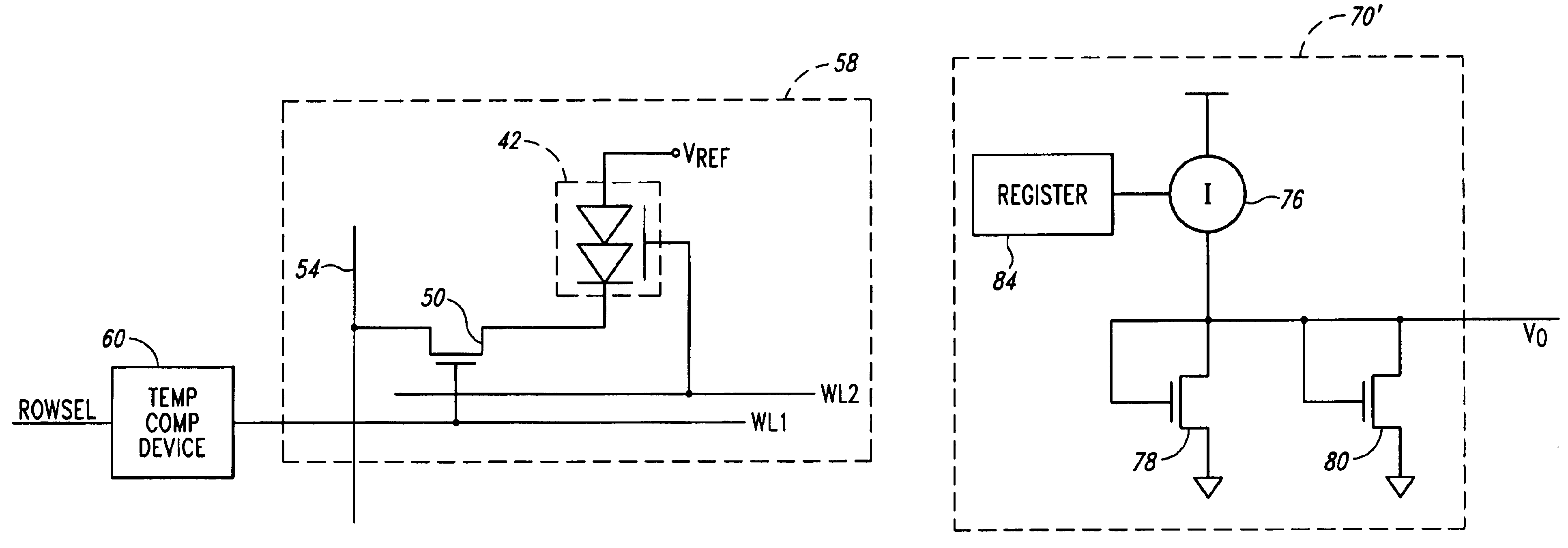

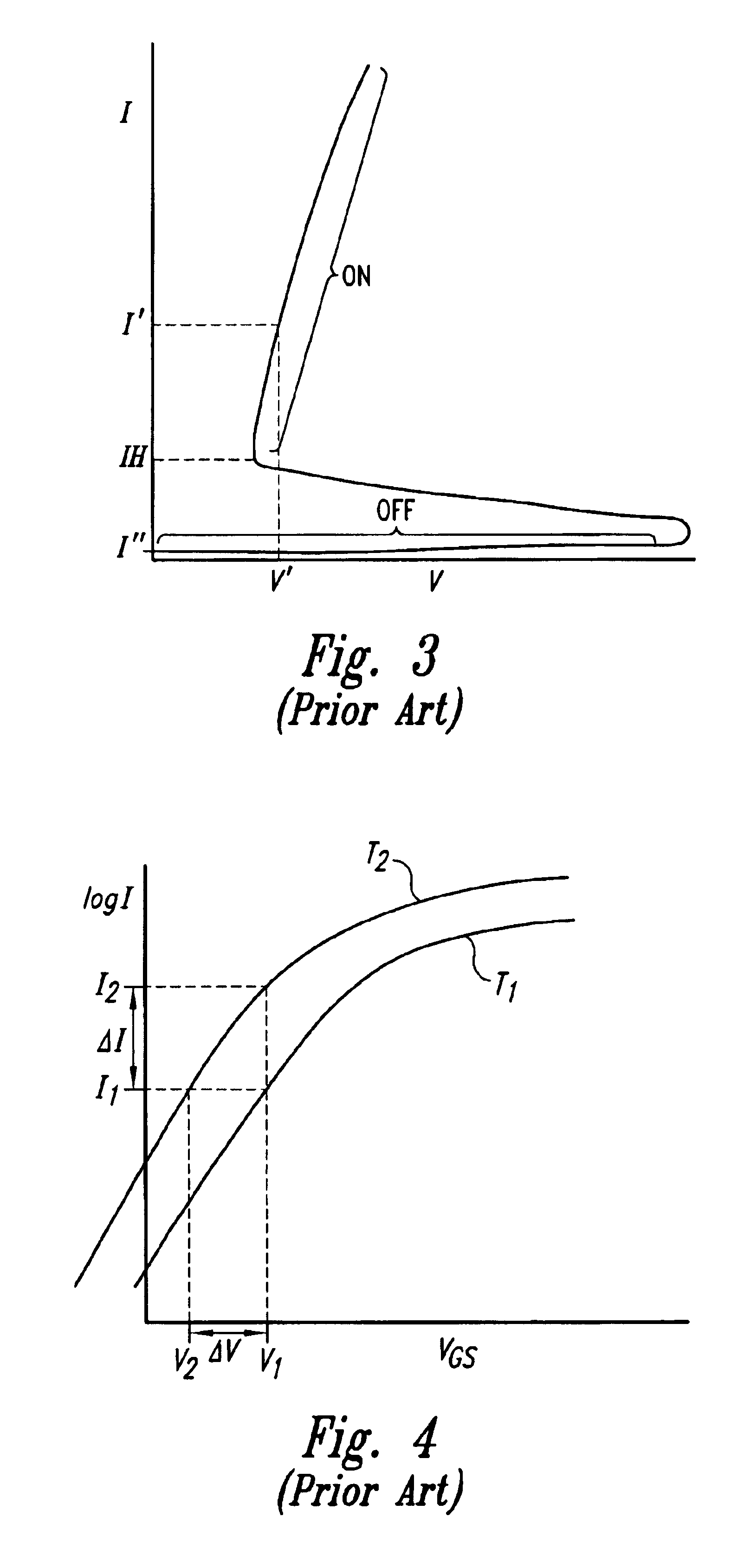

Temperature compensated T-RAM memory device and method

A T-RAM memory cell includes a temperature compensation device to adjust the gate-to-source voltage of an access transistor for the memory cell as a function of temperature so that the sub-threshold current of the transistor is insensitive to temperature variations. As a result, the sub-threshold current can be maintained slightly above the holding current of a thyristor used in the memory cell despite substantial temperature variations. In one embodiment, the temperature compensation device includes a current source directing a fixed current through a diode-connected transistor of the type used as the memory cell access transistor. Temperature induced changes in a reference voltage generated at the junction between the current source and the transistor therefore match the temperature induced changed in the sub-threshold current of the access transistor. As a result, the sub-threshold current of the access transistor can be made insensitive to temperature variations by applying the reference voltage to the gate or source of the access transistor.

Owner:MICRON TECH INC

Thyristor power control circuit

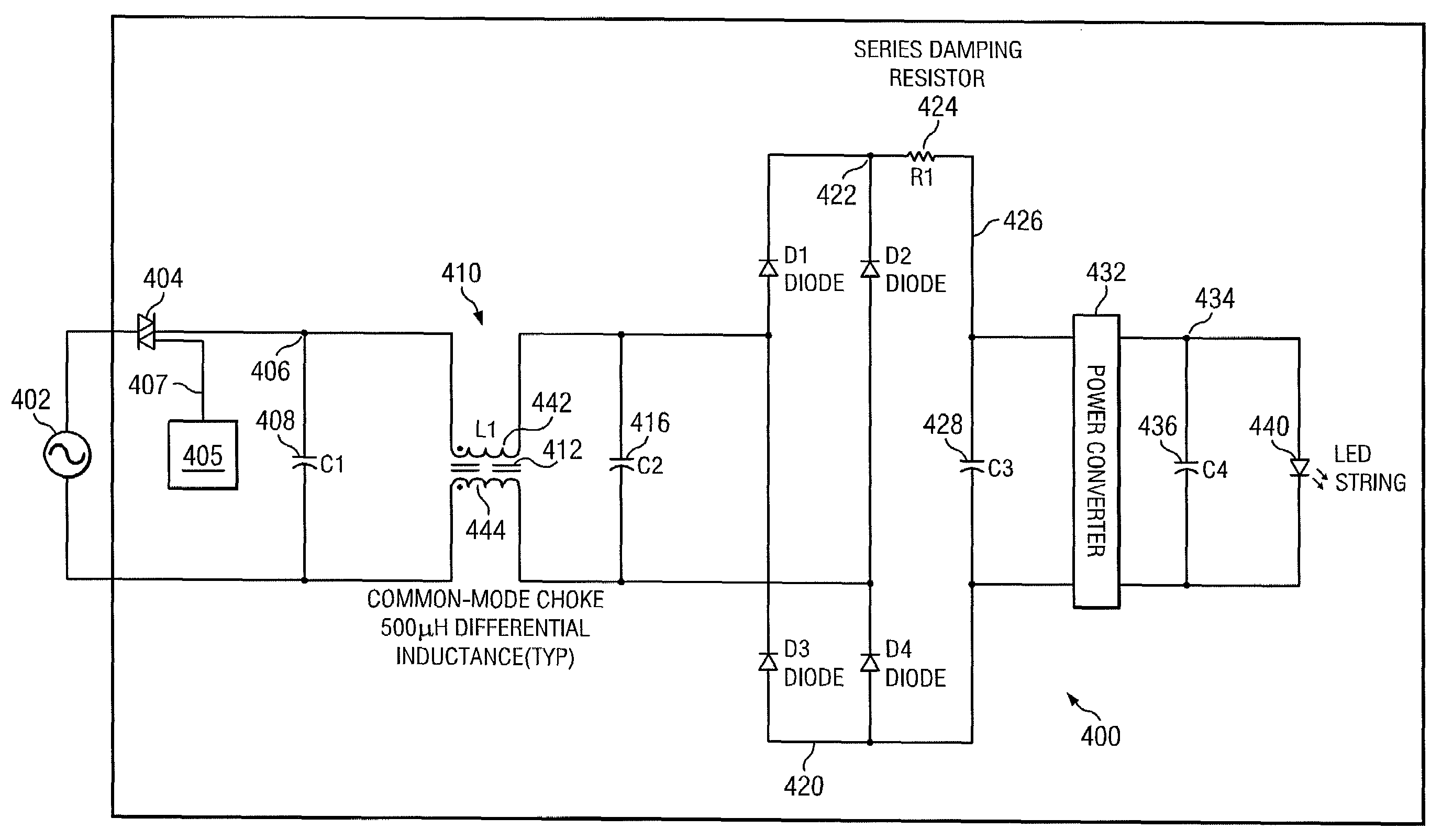

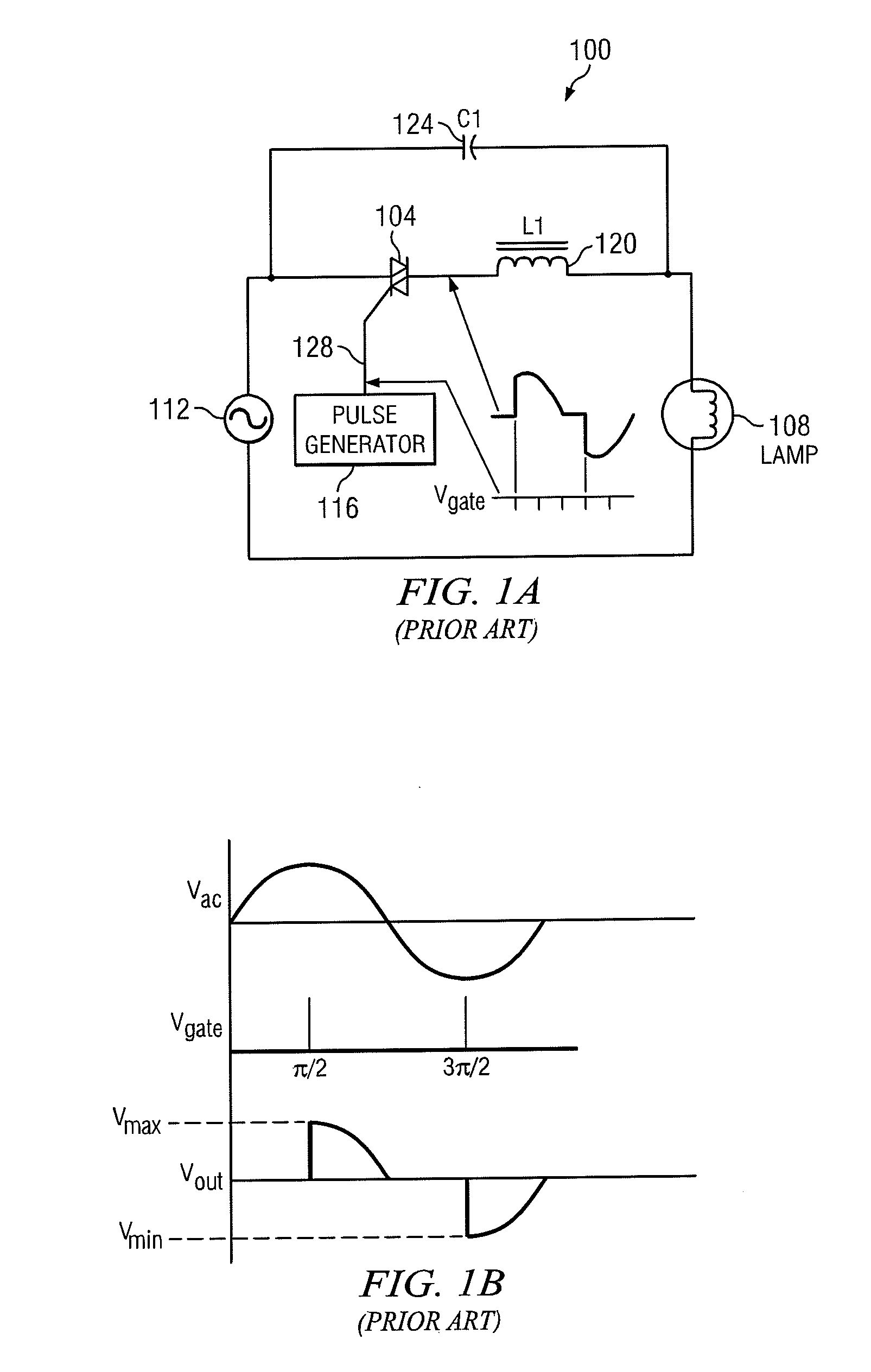

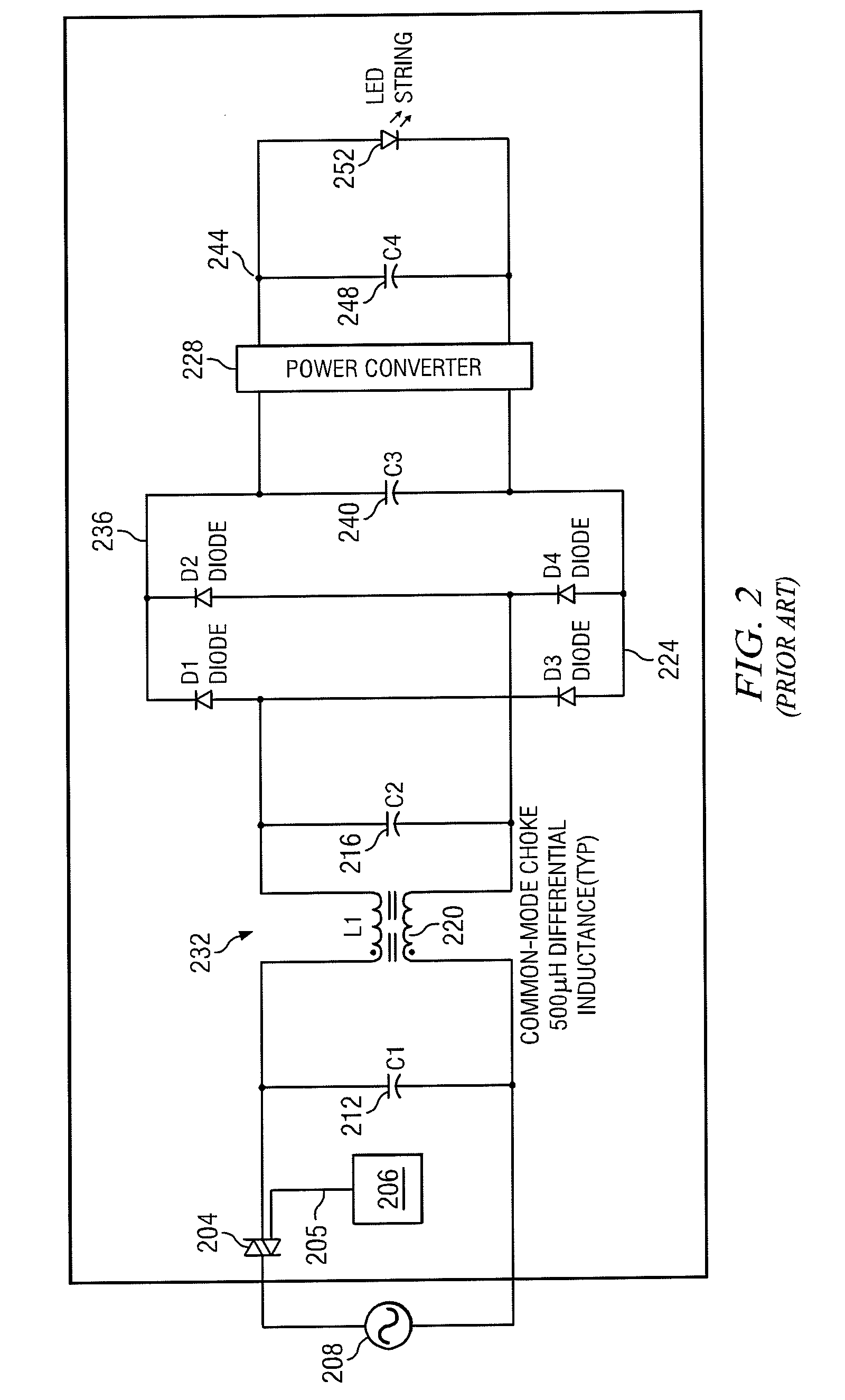

ActiveUS20090122580A1Avoid flickeringAc-dc conversion without reversalConversion with intermediate conversion to dcControl circuitDc voltage

A thyristor power control circuit reduces EMI and maintains a holding current in the thyristor to prevent flickering at a load. The power control circuit includes a thyristor configured to receive an input AC voltage, and responsive to a gate pulse generates a modified AC voltage. A rectifier receives the modified AC voltage and generates a rectified DC voltage. A power converter coupled to the rectifier receives the rectified DC voltage and generates a controlled output current. A damping circuit coupled to an output terminal of the rectifier includes a damping resistor for maintaining the holding current in the thyristor during an ON period of the thyristor. The damping circuit includes a first capacitor coupled in series to the damping resistor and a diode coupled in parallel to the damping resistor. The diode enables the first capacitor to discharge without causing power loss at the damping resistor.

Owner:STMICROELECTRONICS SRL

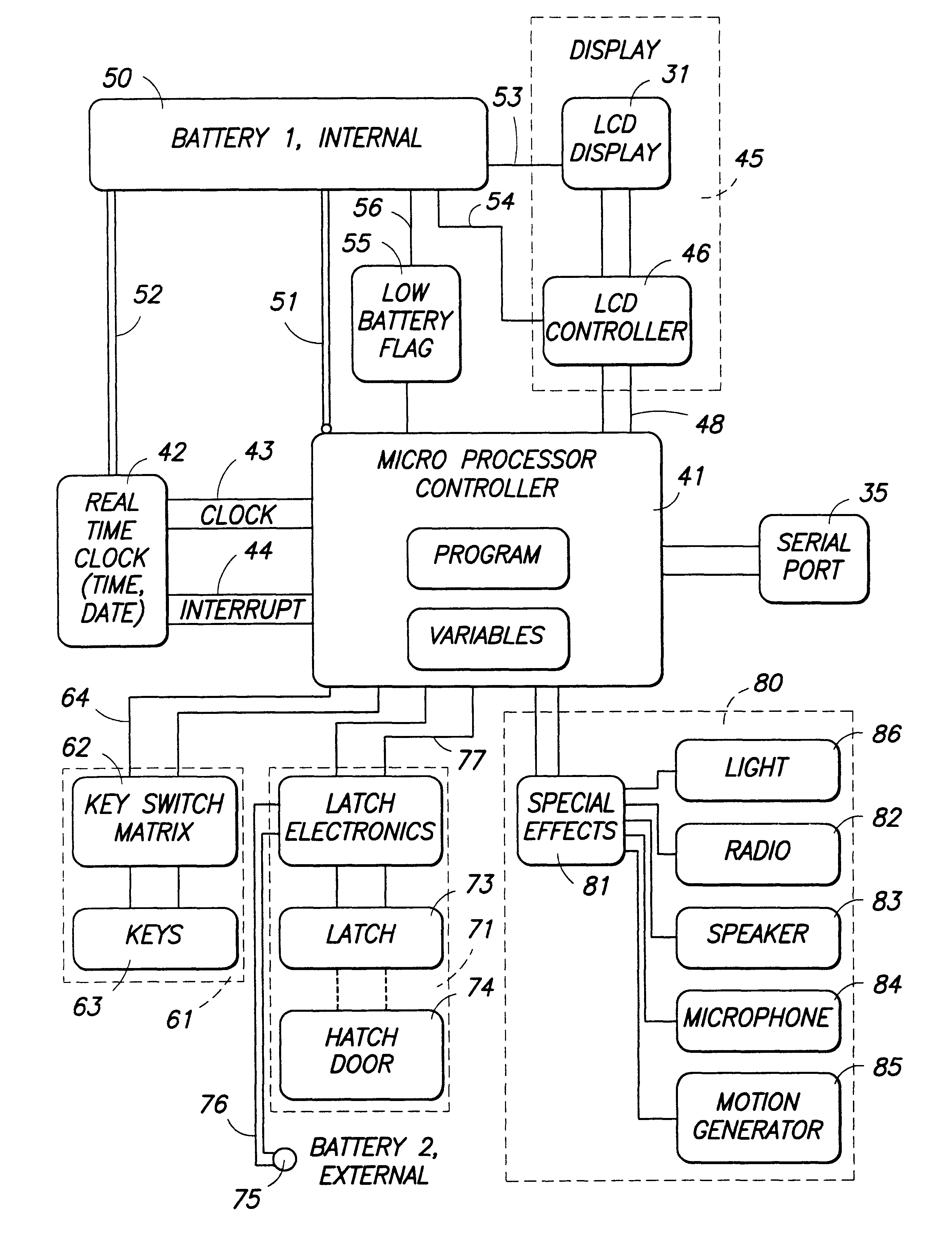

Time-lock box

InactiveUS6825753B2Electric signal transmission systemsDigital data processing detailsPasswordLocking mechanism

A lockable storage assembly, or lockbox container, is disclosed, with programmable opening utility, for providing access to the contents of the storage assembly at a time chosen by a user to suit an occasion. The lockbox includes non-volatile memory for holding current time and date, and opening time and date, and is assembled of integrated circuits and display, requiring very low power, such that the lockbox may retain function over extended periods of time, while locking mechanisms with higher power requirements are powered by a replaceable, externally accessible battery. The lockbox is assembled and programmed so that the interior is accessible only upon reaching a match date, whereupon the lockbox unlocks automatically, or upon entry of a password chosen by the user.

Owner:CARDINALE SALVATORE J

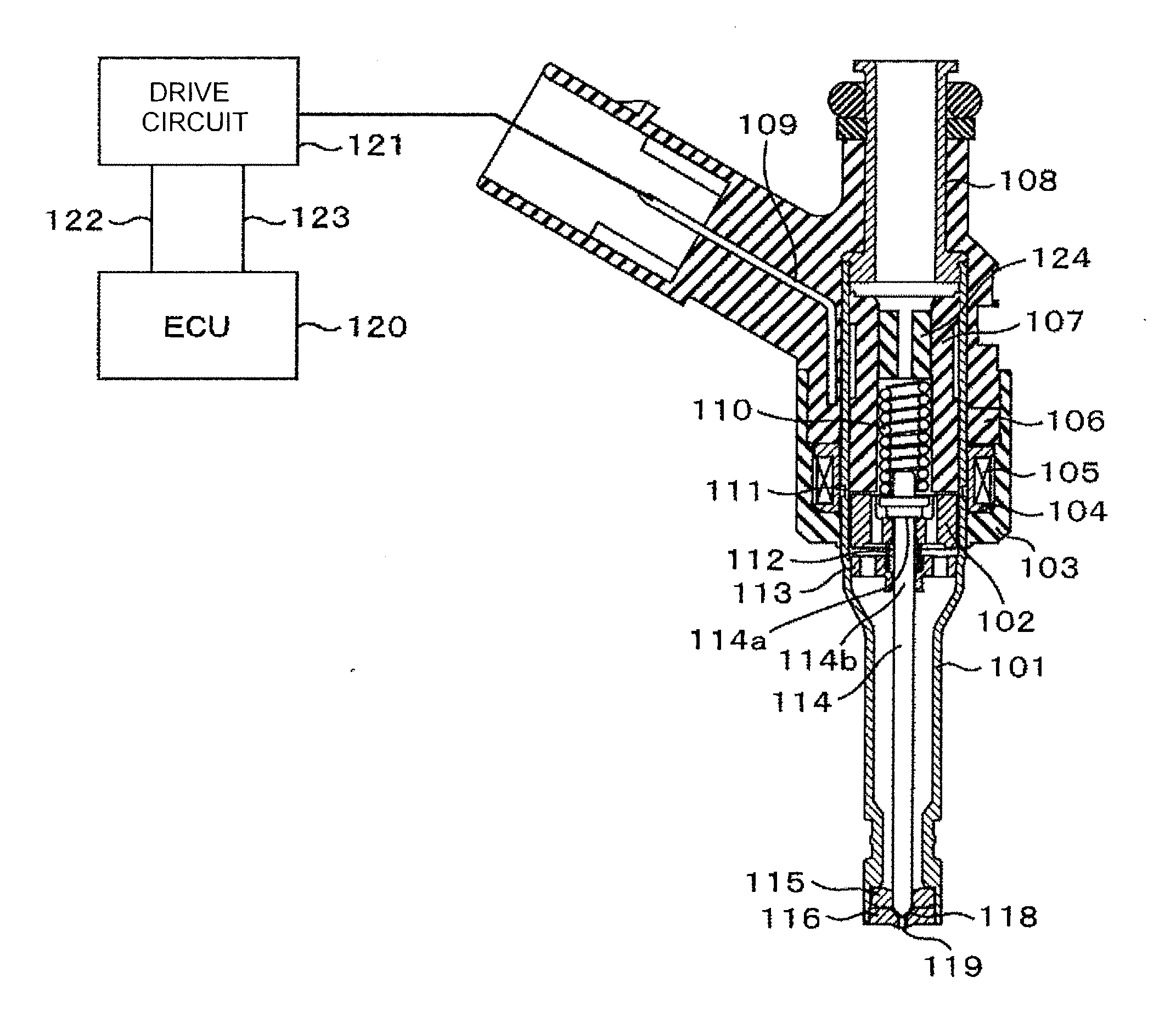

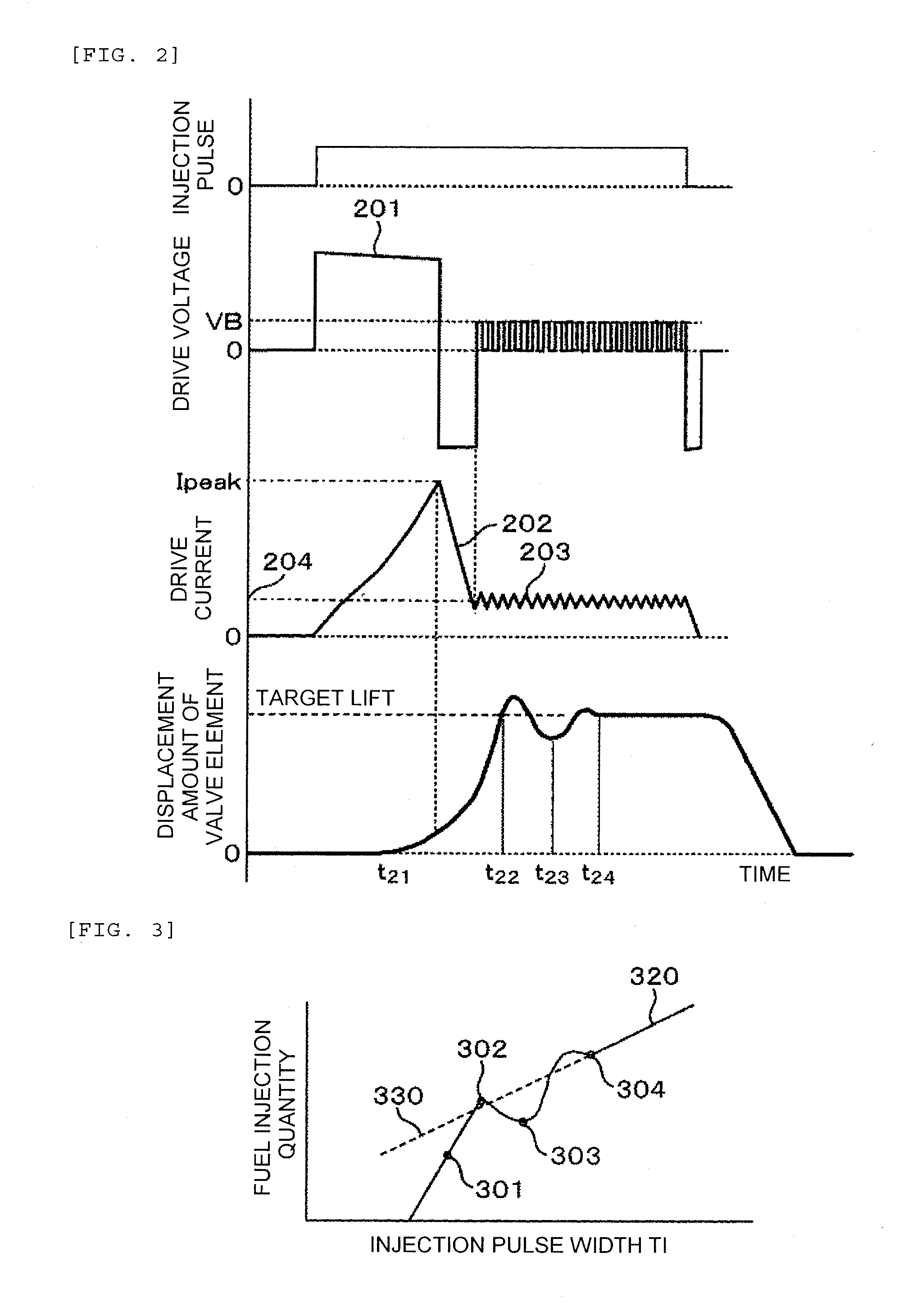

Drive unit of fuel injection device

ActiveUS20130139791A1Unstable behavior of the valve element can beReduce in quantityElectrical controlLow pressure fuel injectionElectrical batteryEngineering

In a drive unit of a fuel injection device, an electric current is supplied to the fuel injection device by applying a high voltage to the fuel injection device from a high voltage source whose voltage is boosted to a voltage higher than a battery voltage at the time of opening a valve of the fuel injection device. Thereafter, the electric current supplied to the fuel injection device is lowered to a current value at which a valve element cannot be held in a valve open state by stopping the applying of the high voltage from the high voltage source. Thereafter, in a stage where a supply current is switched to a hold current, another high voltage is applied to the fuel injection device from the high voltage source.

Owner:HITACHI ASTEMO LTD

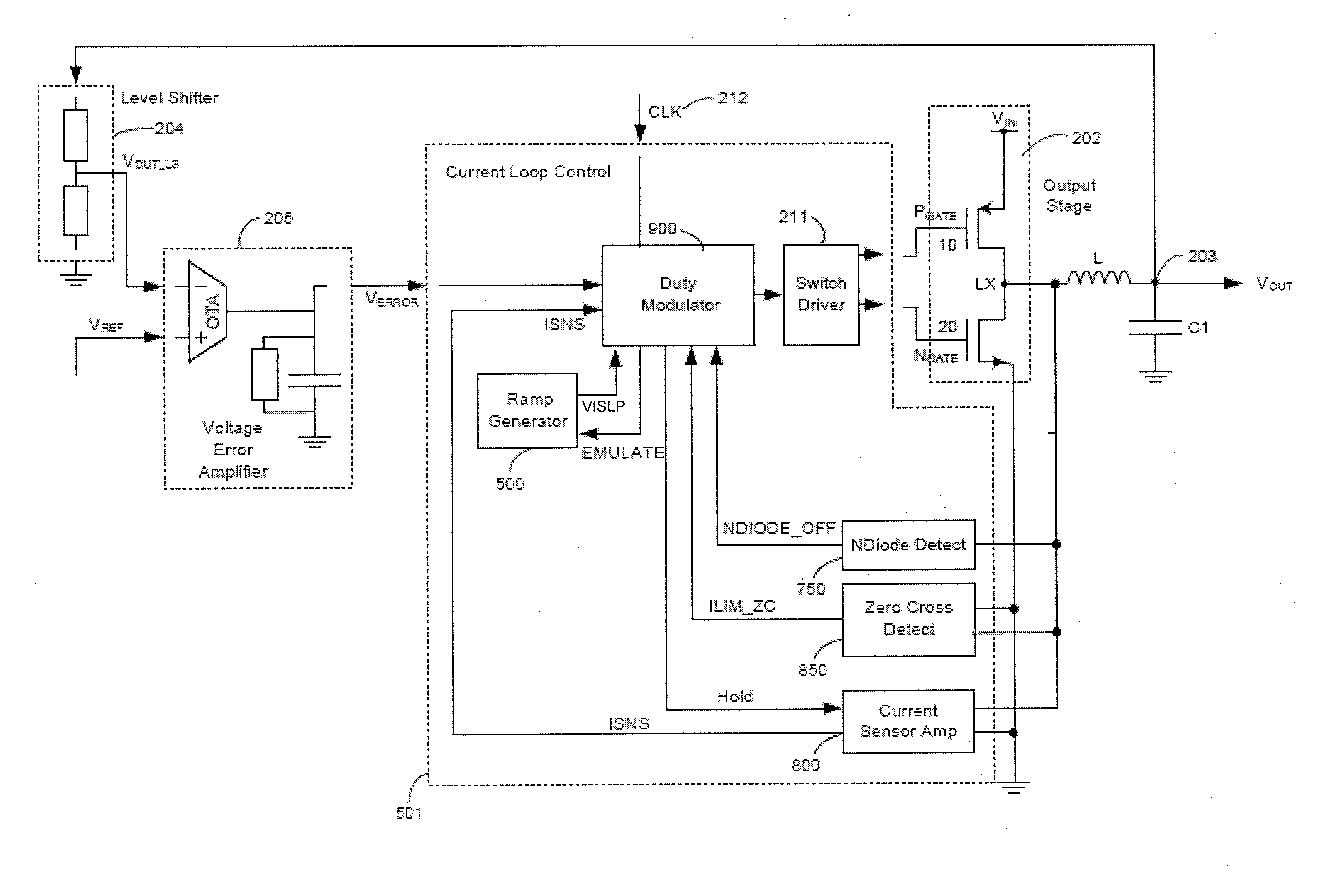

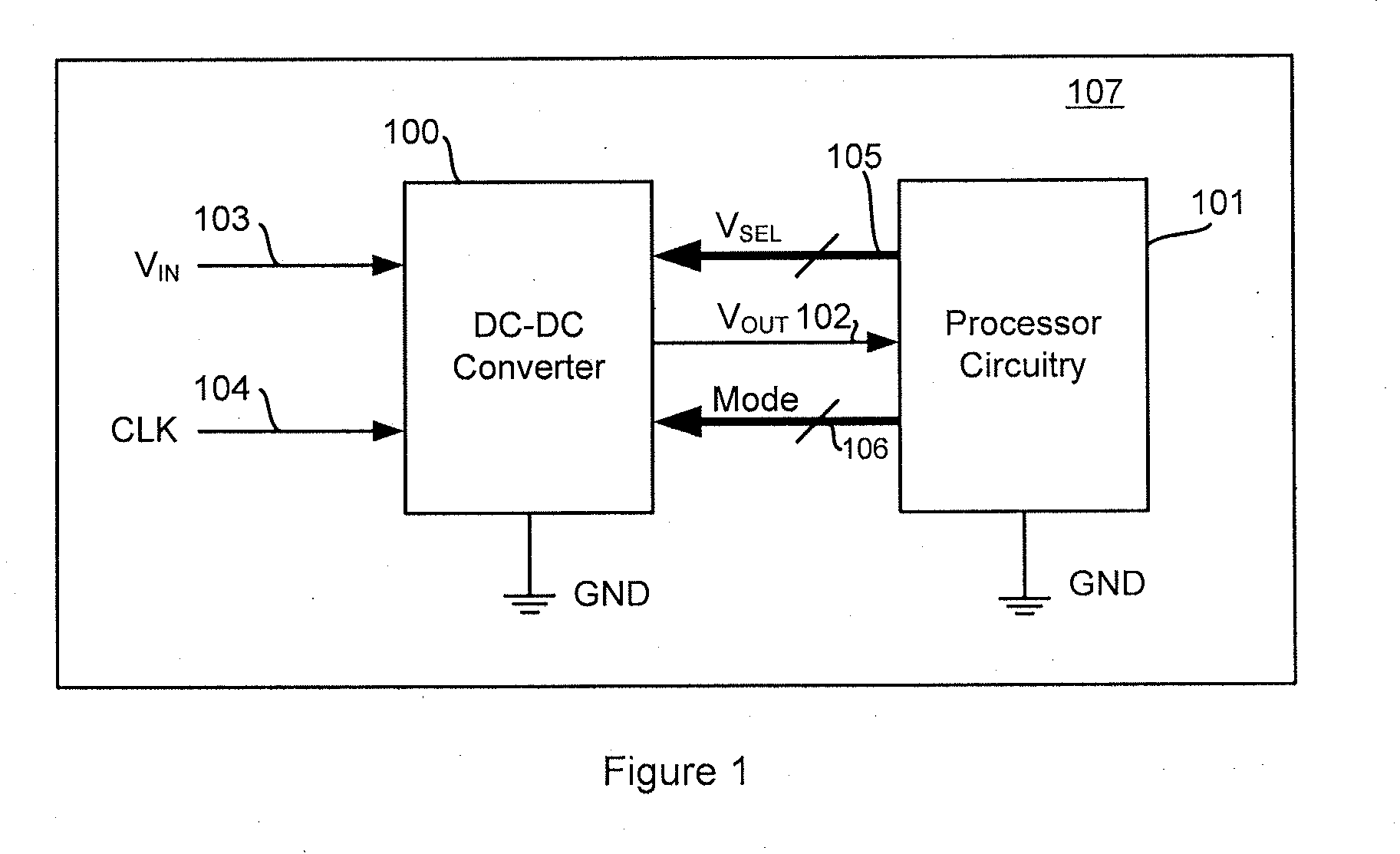

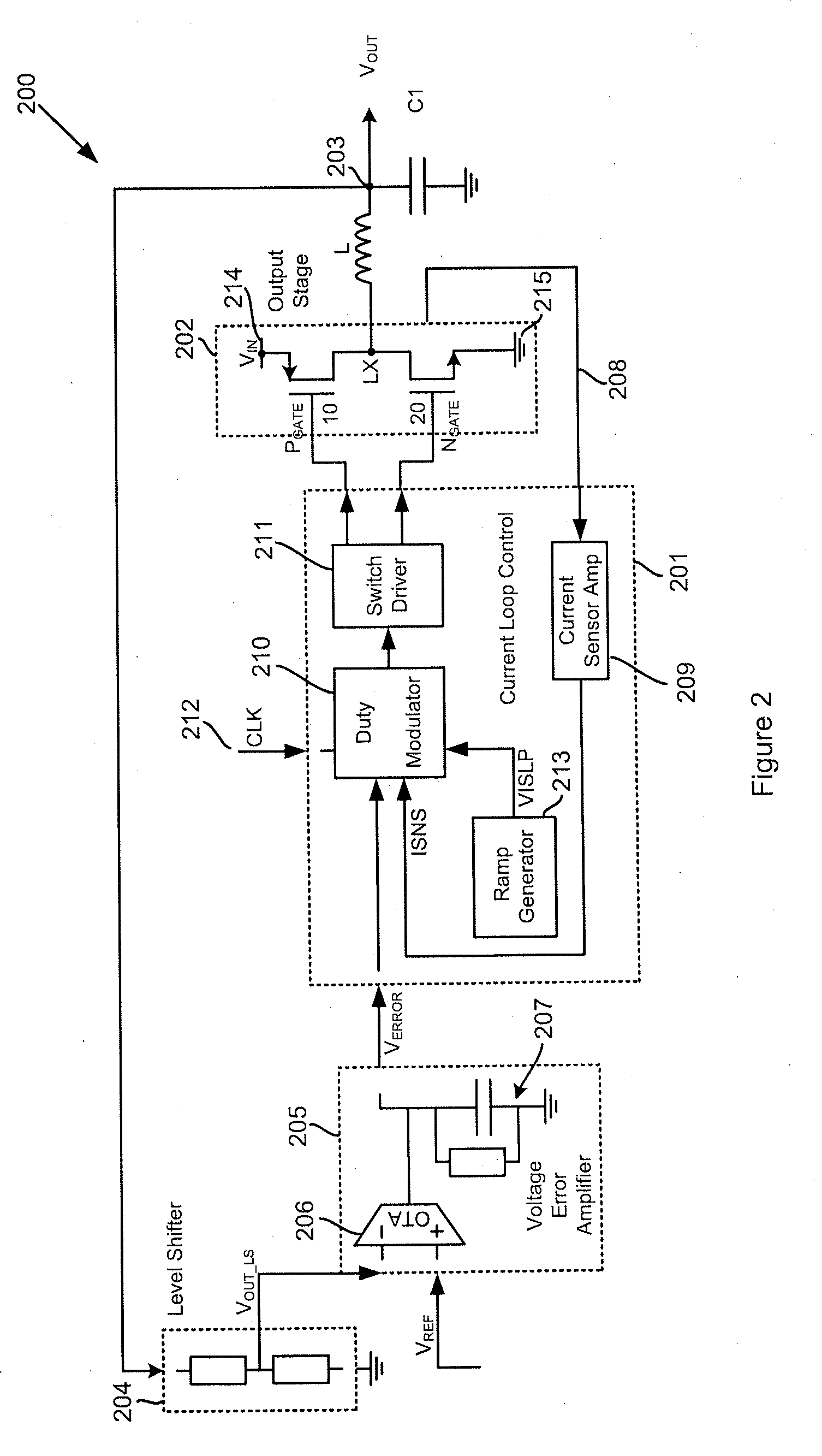

Dc-dc converters

ActiveUS20110050185A1Easy to controlTransistorEfficient power electronics conversionCurrent loadCurrent loop control

Methods and apparatus for control of DC-DC converters, especially in valley current mode. The DC-DC converter is operable so that a low side supply switch may be turned off, before the high side supply switch is turned on. During the period when both switches are off the current loop control remains active and the change in inductor (L) current is emulated. One embodiment uses a current sensor for lossless current sensing and emulates the change in inductor current by holding the value of the output of the current sensor (ISNS) at the time that the low side switch turns off and adding an emulated ramp signal (VISLP) until the inductor current reaches zero. Embodiment employing a pulse-skip mode of operation based on a minimum conduction time are also disclosed. The invention enables a seamless transition from Continuous Conduction Mode the Discontinuous Conduction Mode and Pulse Skipping and provide converters that are efficient at low current loads.

Owner:CIRRUS LOGIC INC

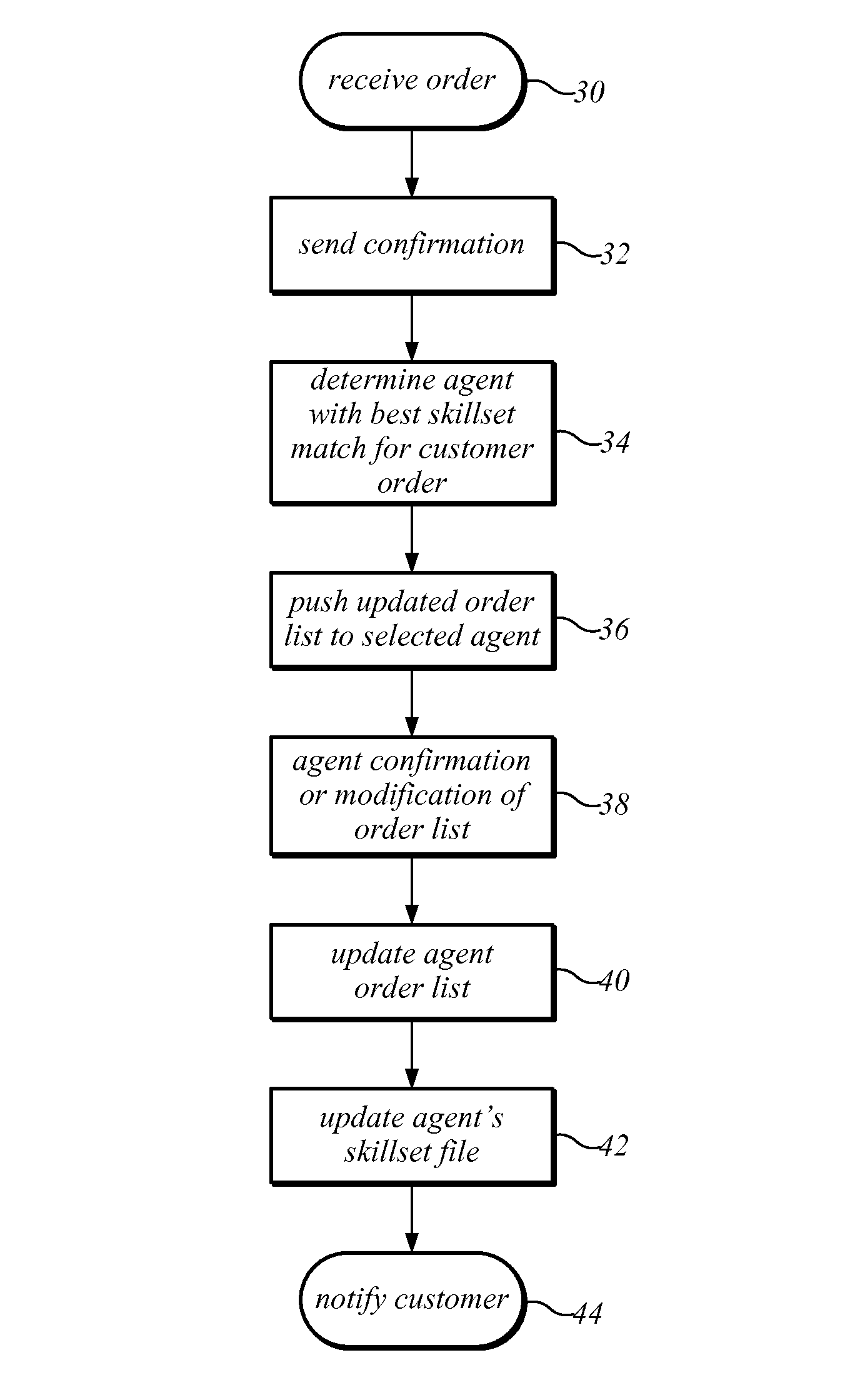

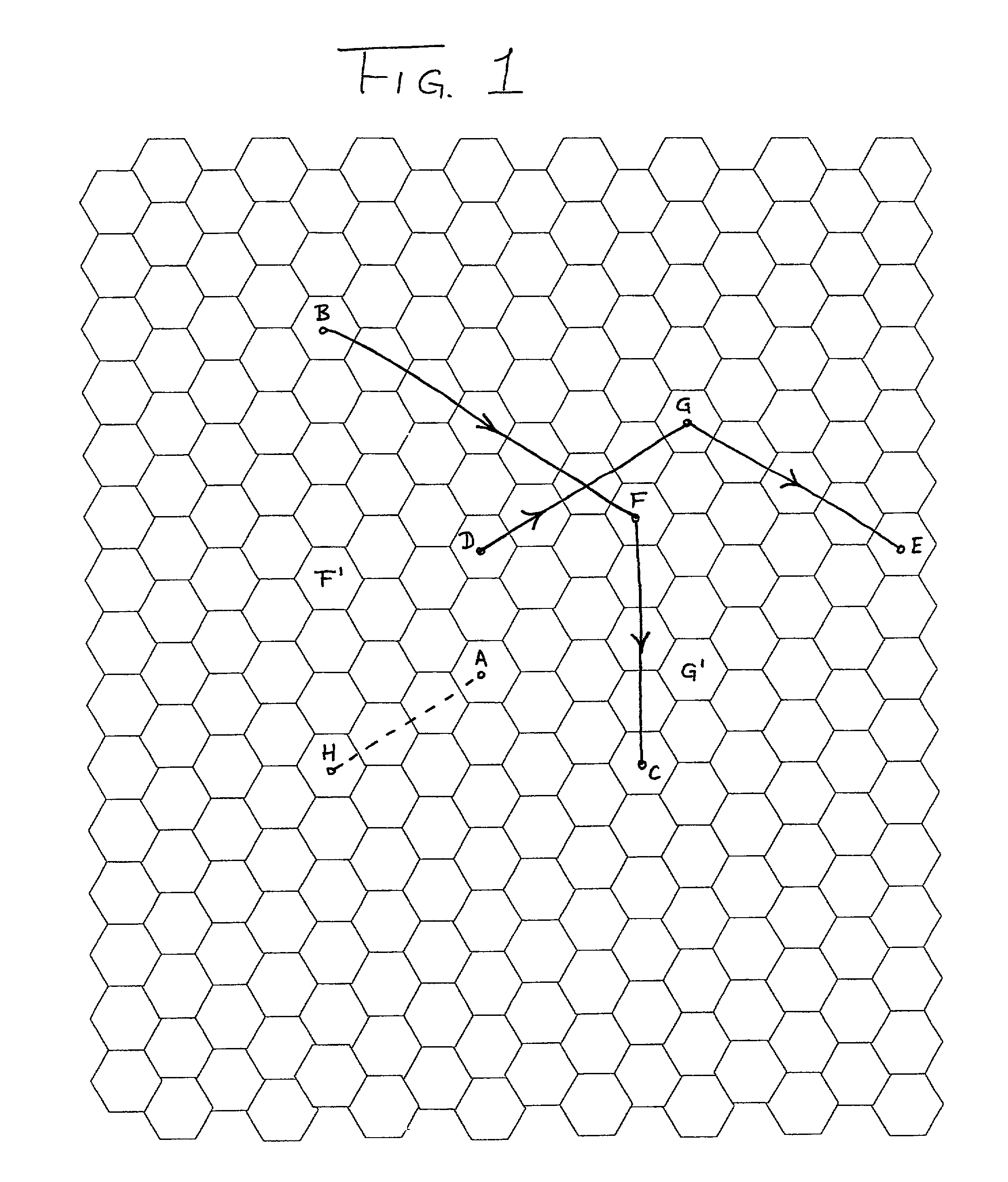

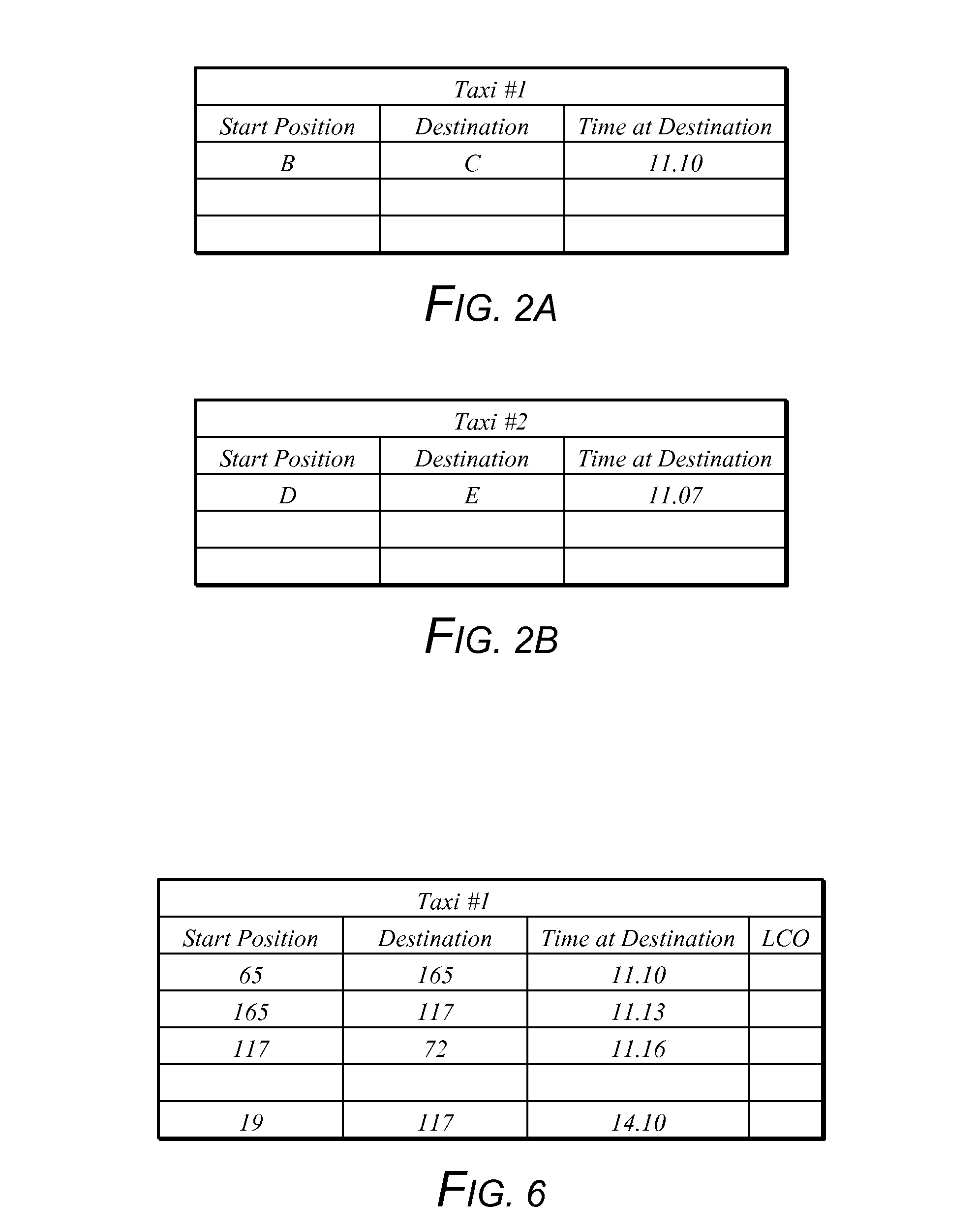

Allocation of location-based orders to mobile agents

ActiveUS8706542B2Easy to processImprove customer service levelsResourcesPosition dependentHolding current

A method of allocating a location-related order to one of a number of mobile agents, such as taxicabs, delivery or repair vehicles. The method involves the following steps:a) holding current order details which identify at least the location and time at which each agent is expected to become free to fulfill new orders;b) keeping a listing of locations, where each location in the listing is prioritised for an agent according to the availability of the agent to reach that location after the agent becomes free;c) receiving a new order and recording the location and time at which this order is to be fulfilled;d) deciding, based on the prioritised listing of locations, which agent(s) are most suitable to take the new order; ande) allocating the new order to the identified agent(s).

Owner:APPLE INC

Highly integrated non-inductive LED driver

ActiveUS8698407B1Eliminate flickeringIncreased energy and manufacturing efficiencyElectrical apparatusElectroluminescent light sourcesSilicon-controlled rectifierFull wave

An inductorless LED driver powers a string of low current LEDs. A phase controlled triac dimmer, serially connected to a full-wave rectifier circuit, performs as an LED current and triac holding current control element. The output of the full-wave rectifier circuit is divided into two circuit paths; the first path provides power to drive a string of serially-connected low-current LEDs, and the second path connects to a dynamic load, which supplies a holding current that flows through the triac dimmer. There are two feedback control systems; the first regulates the luminance of the LEDs; the second regulates the triac holding current to eliminate lamp flicker.

Owner:TECHN CONSUMER PRODS