Logical unit multiplexing system

A logic unit, linear feedback shifting technology, applied in static memory, instruments, etc., can solve inconvenience and other problems, and achieve the effect of reducing chip area, reducing use, and reducing power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

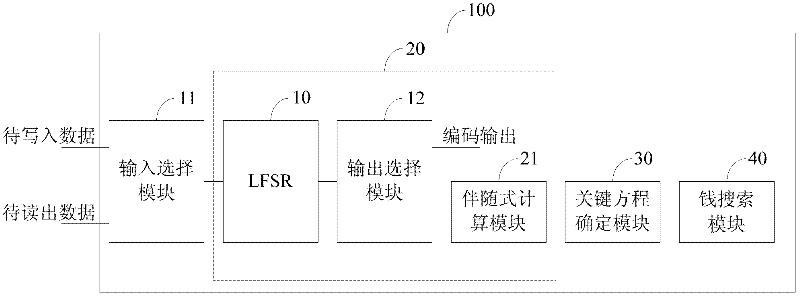

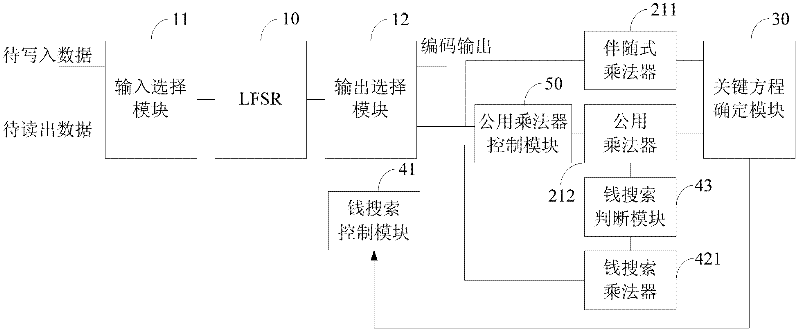

[0026] see figure 1 , the present invention provides a logical unit multiplexing system 100, which is mainly used in error correction technology of solid-state hard disks. Encoded input or decoded output, and BCH error correction can be used.

[0027] Specifically, the encoding circuit includes a linear feedback shift register (LFSR) 10, which is used to calculate the remainder of the polynomial of the information to be encoded / decoded. In fact, the encoding function of the encoding circuit is realized by the linear feedback shift register 10. For the BCH algorithm, the encoding process is the pr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More