Patents

Literature

471 results about "Linear feedback shift register" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

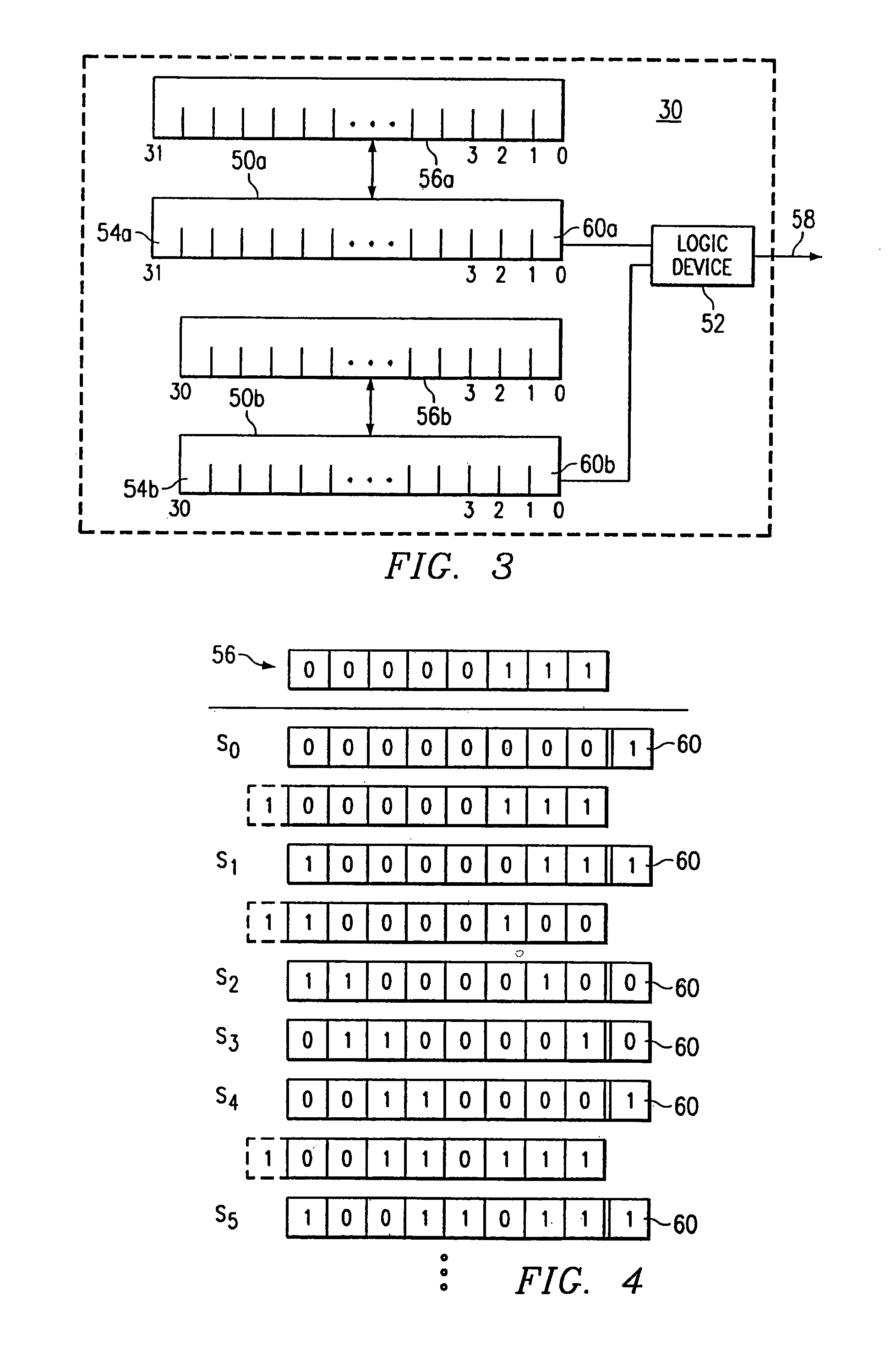

In computing, a linear-feedback shift register (LFSR) is a shift register whose input bit is a linear function of its previous state. The most commonly used linear function of single bits is exclusive-or (XOR). Thus, an LFSR is most often a shift register whose input bit is driven by the XOR of some bits of the overall shift register value.

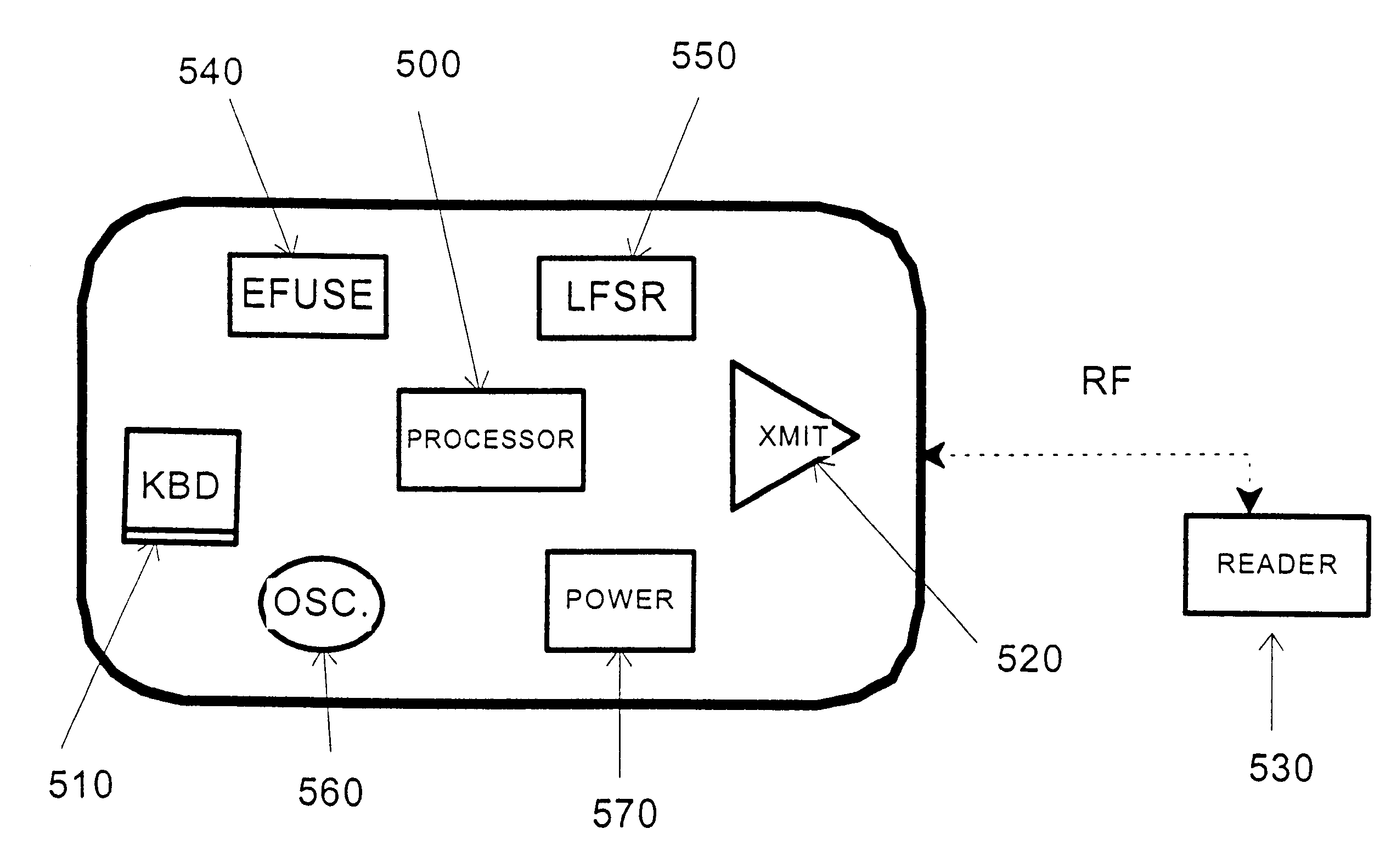

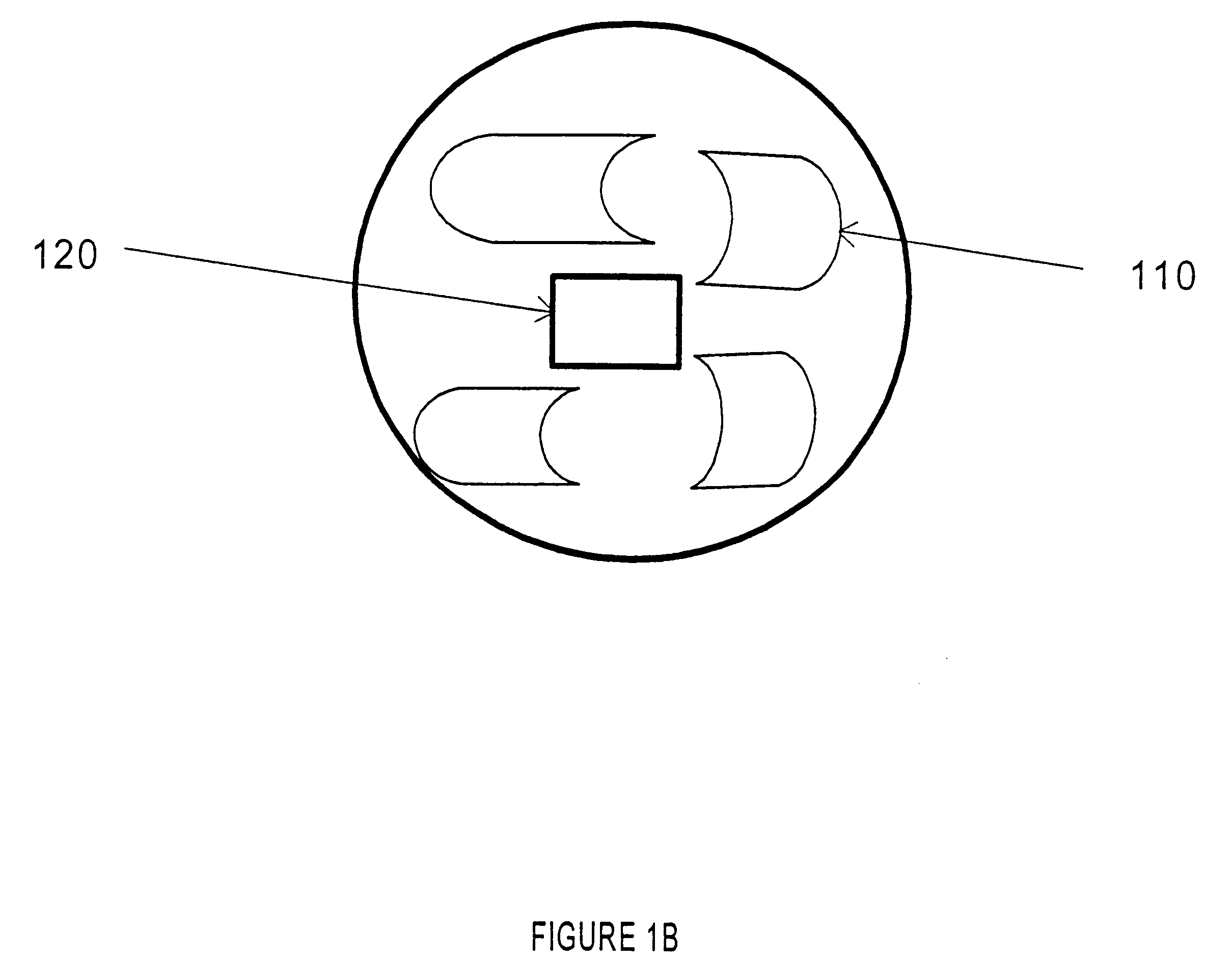

Secure credit card

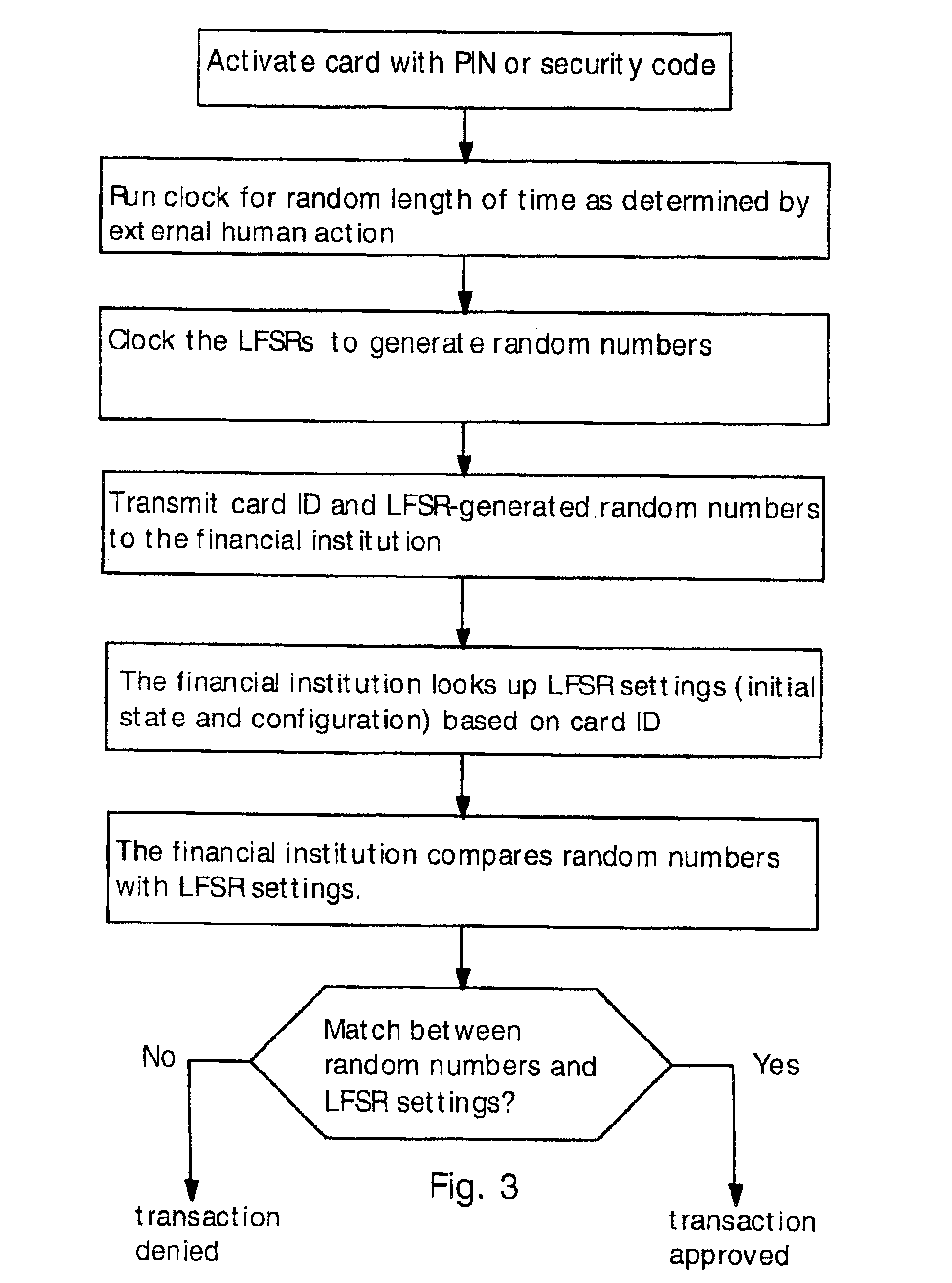

Credit card or portable identification cards containing smart card technology and electronic fuse (e-fuse) technology are combined with an LFSR pseudo random number generator to provide a secured method to prevent fraud and unauthorized use. Secure personalization via e-fuses, a pseudo-random number generator linear feedback shift register, free running clock oscillator, and power source embedded in the card provide a highly secured method to render a lost or stolen card useless. A unique card ID is permanently encoded within the card which requires a specific activation code to activate the card. A PIN number permits the card owner to activate the card for a predetermined length of time while processing a transaction. The card dynamically generates random code sequences and synchronization keys to secure a transaction.

Owner:KYNDRYL INC

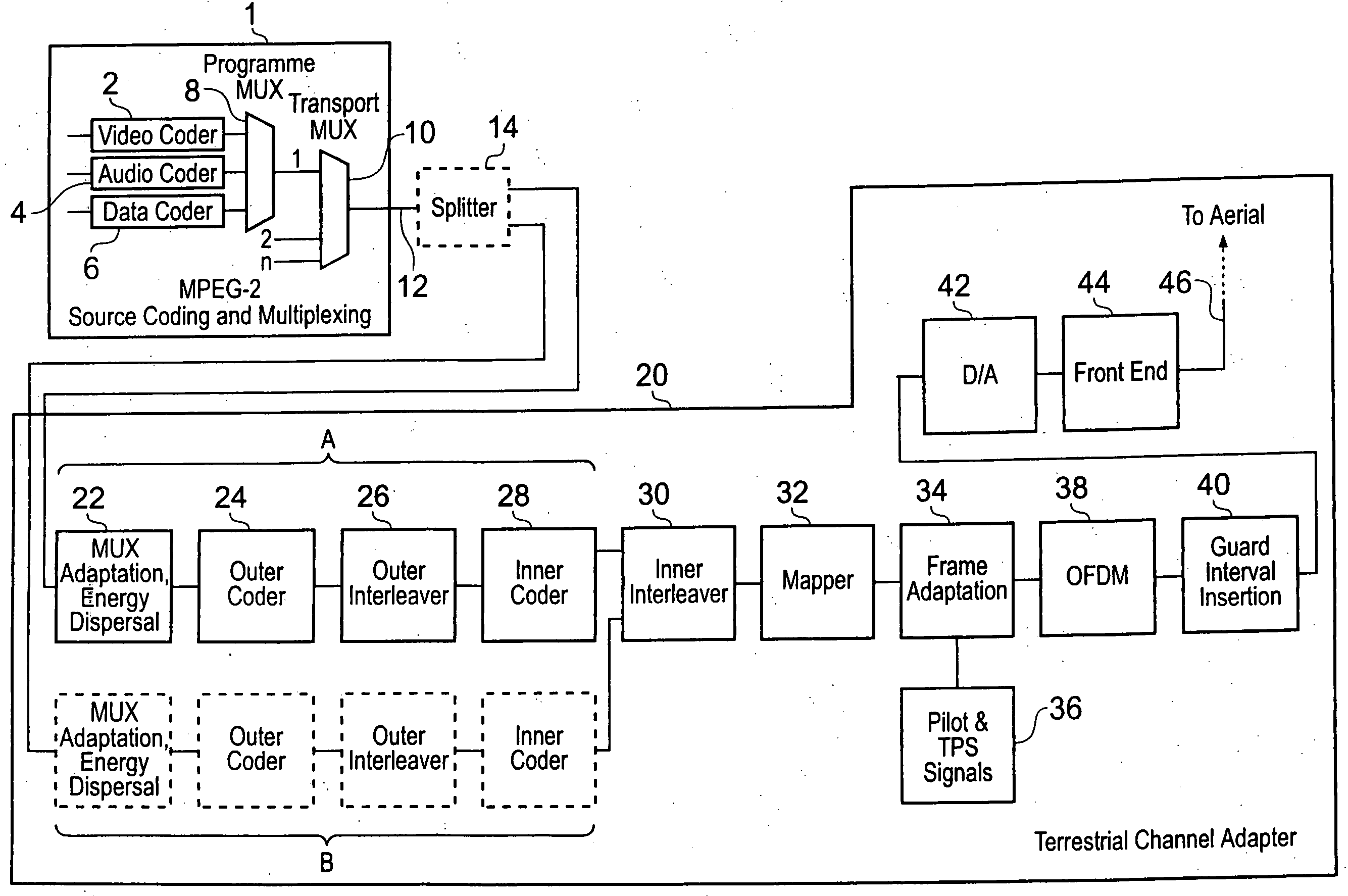

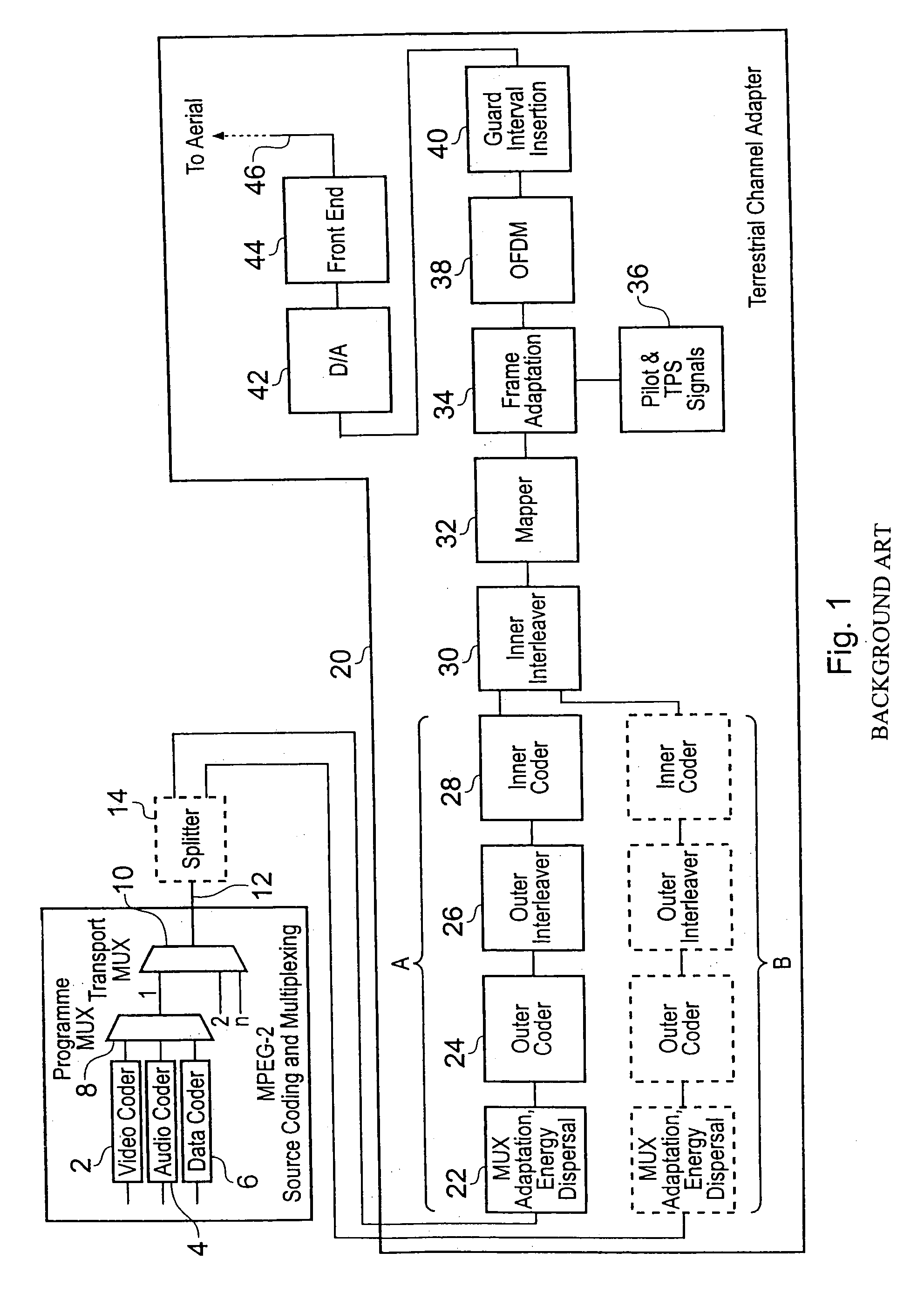

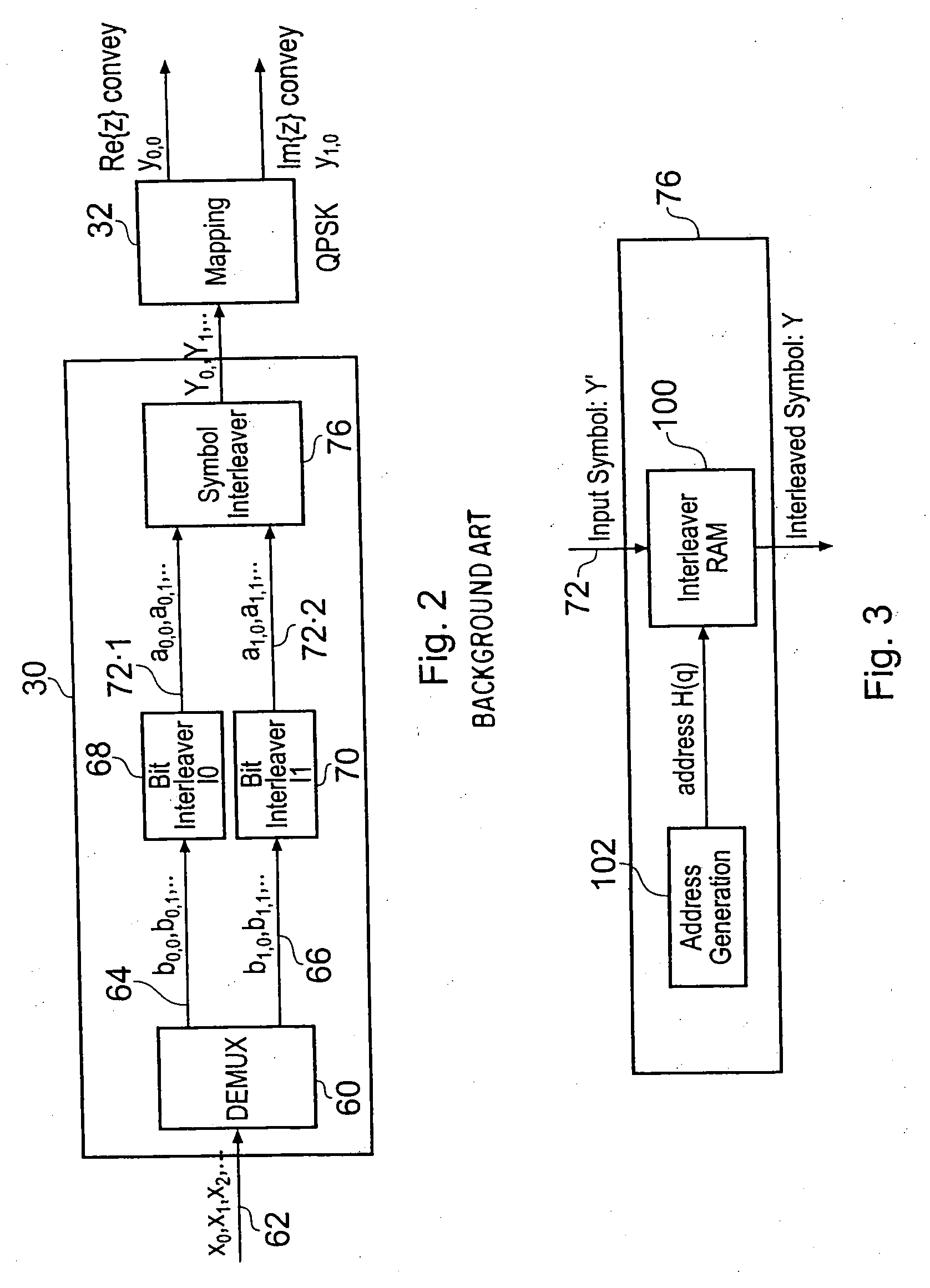

Data processing apparatus and method

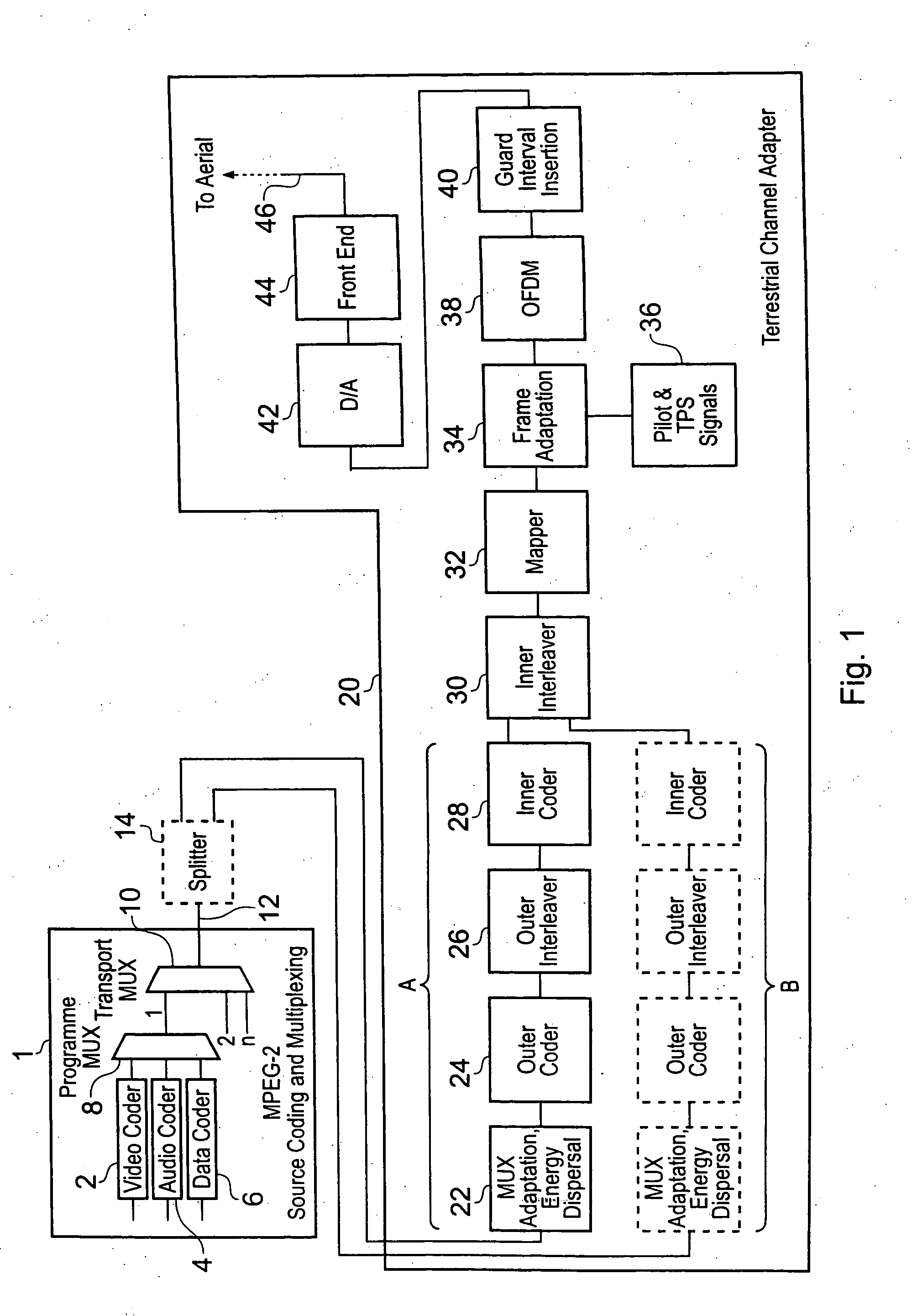

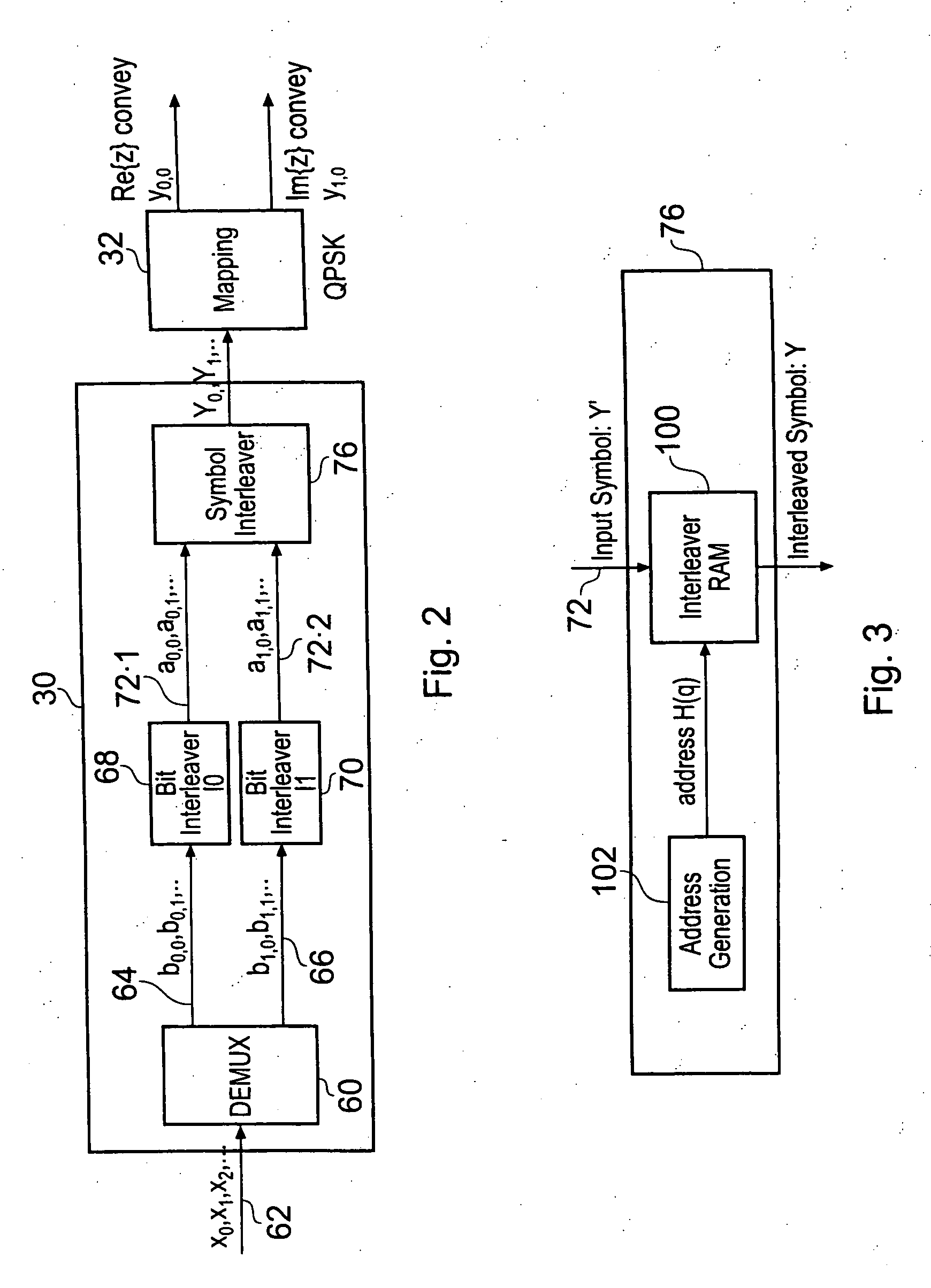

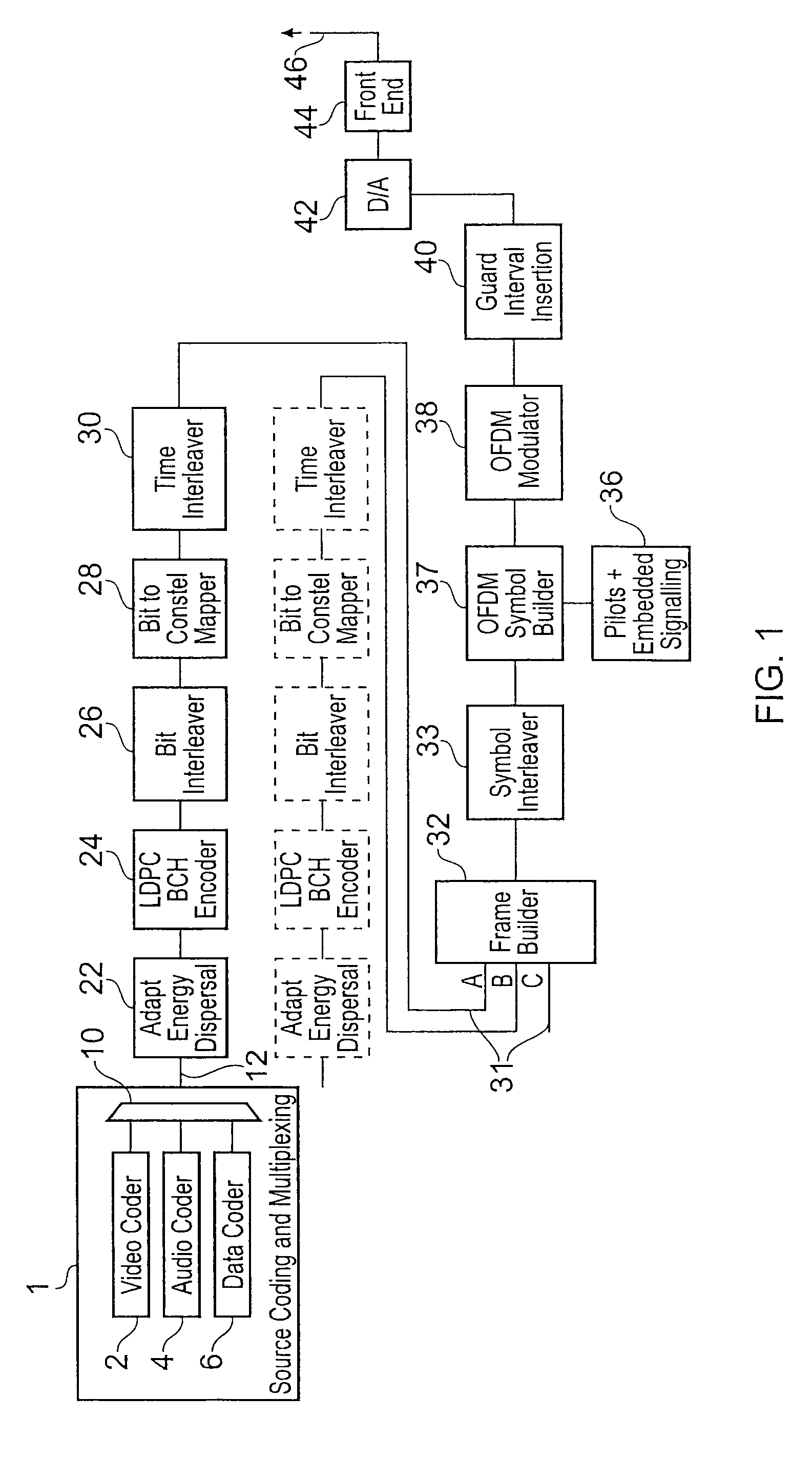

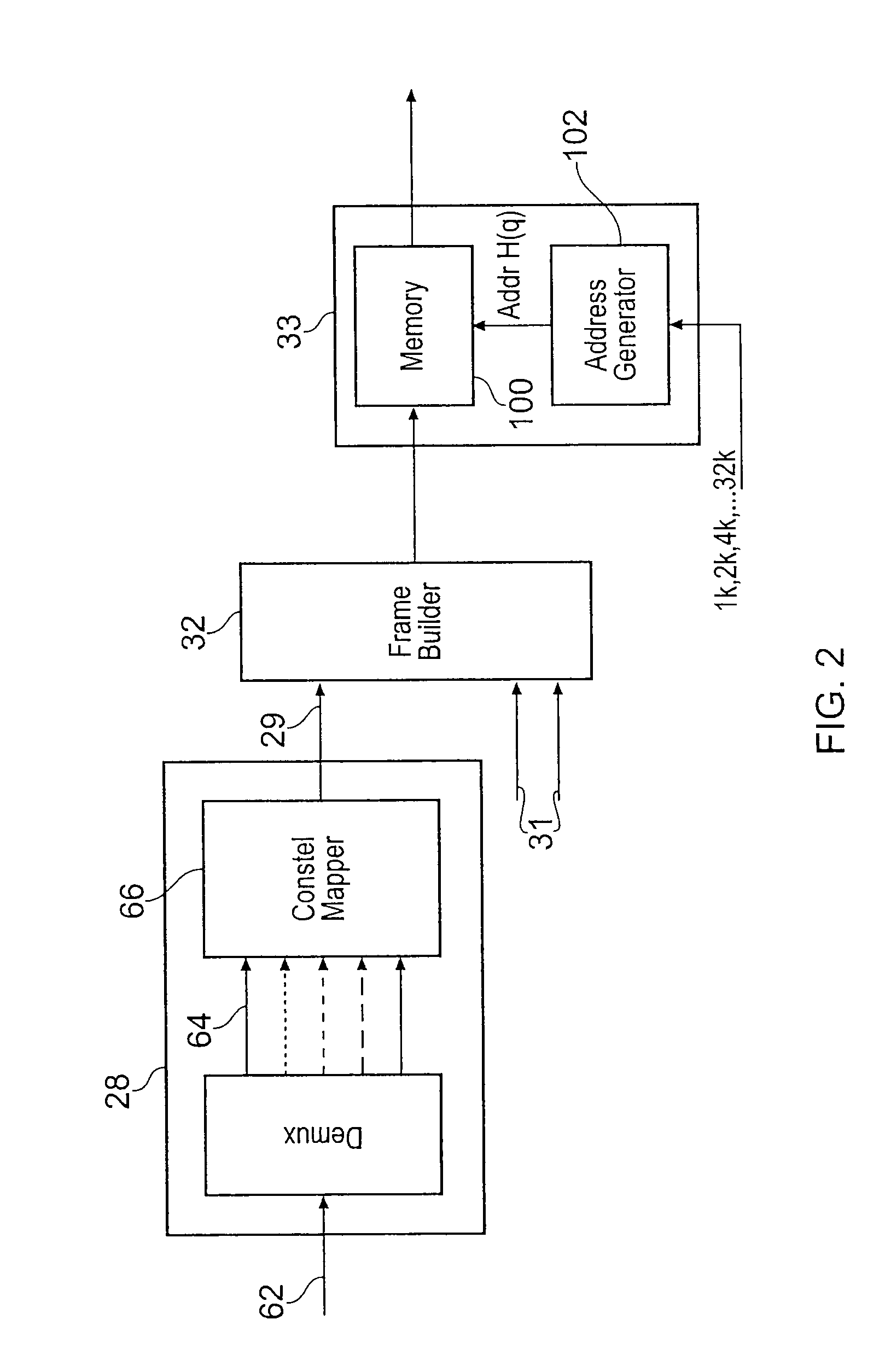

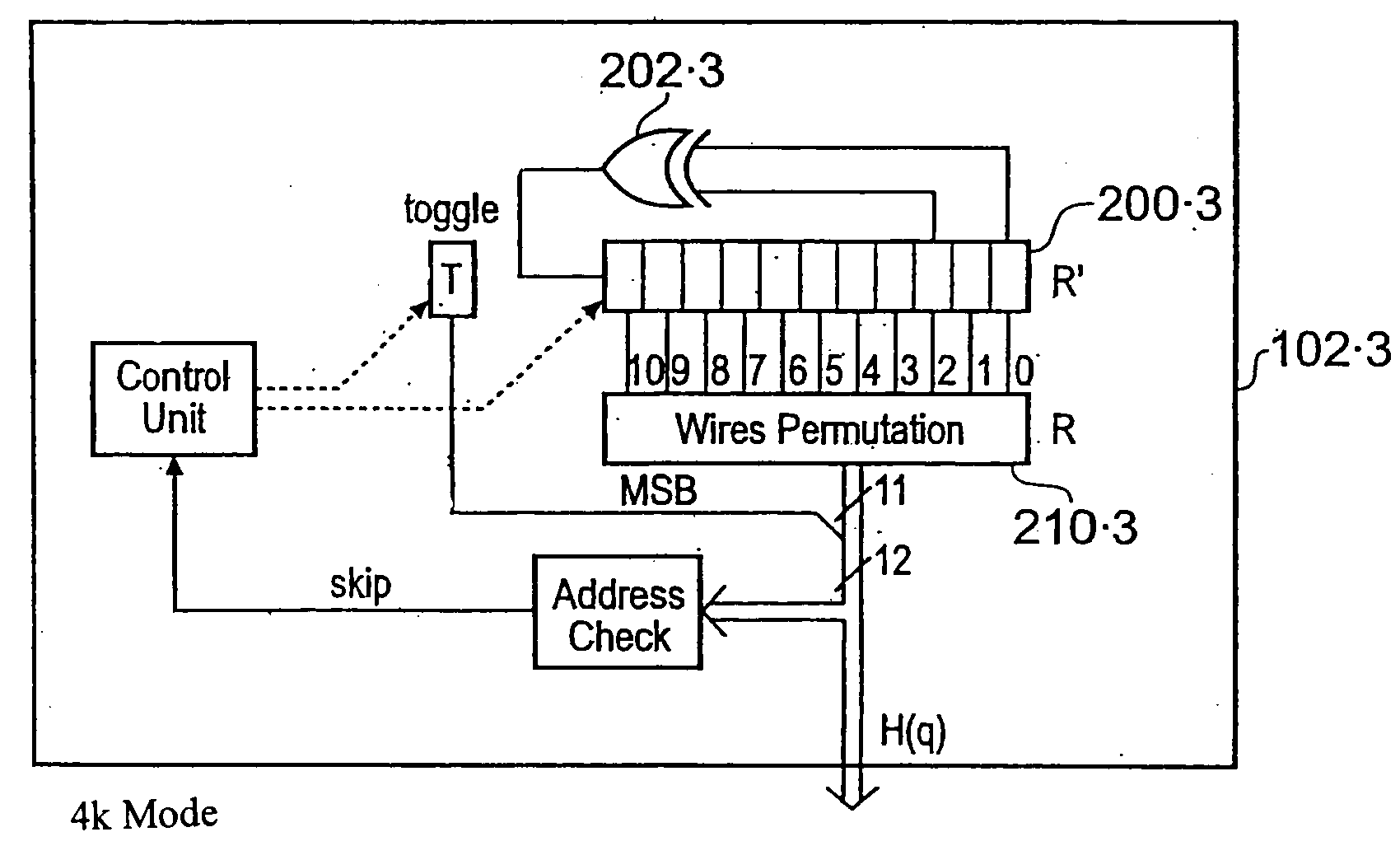

ActiveUS20040246888A1Easy to receiveTrack time variationTelevision system detailsCode conversionCarrier signalAddress generator

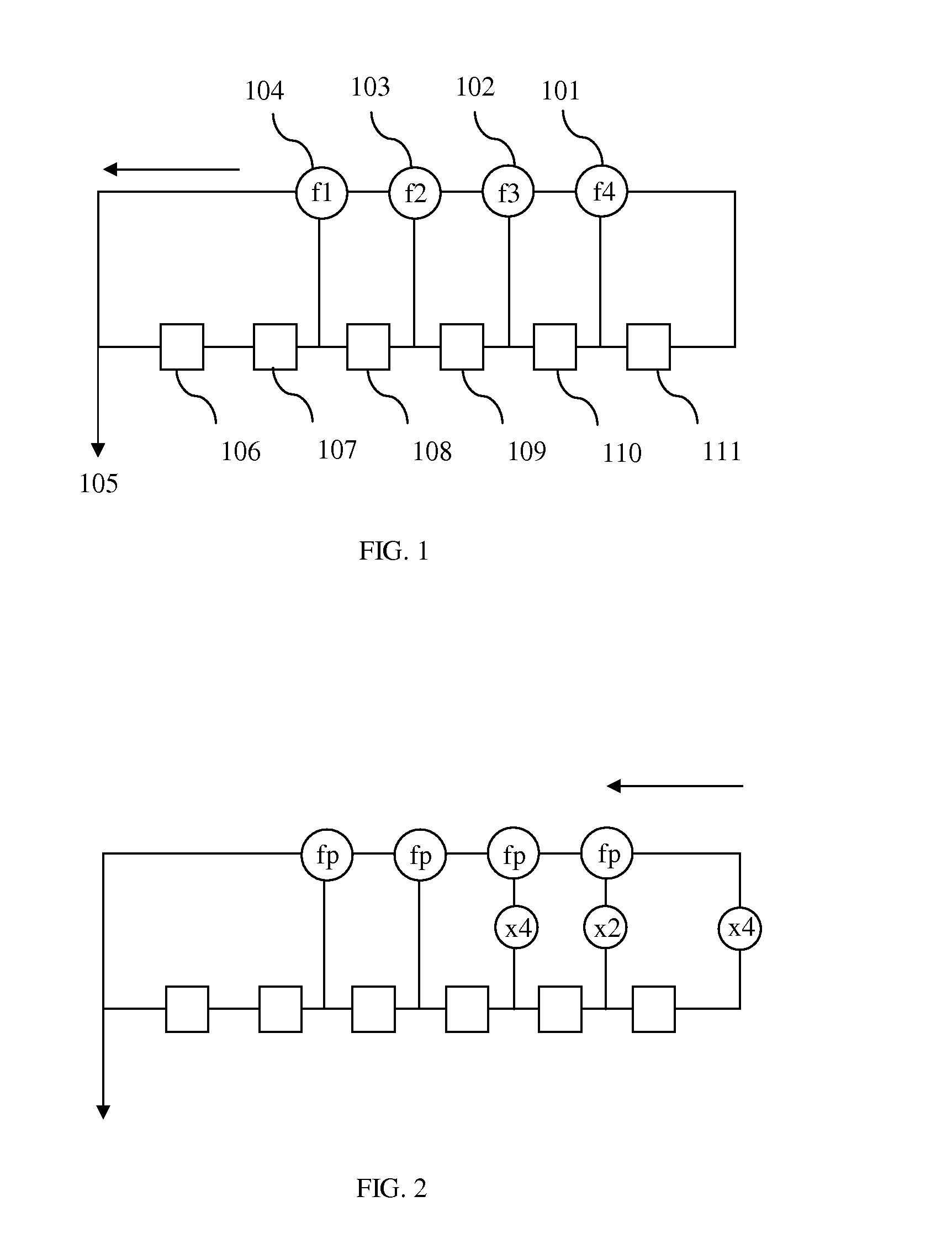

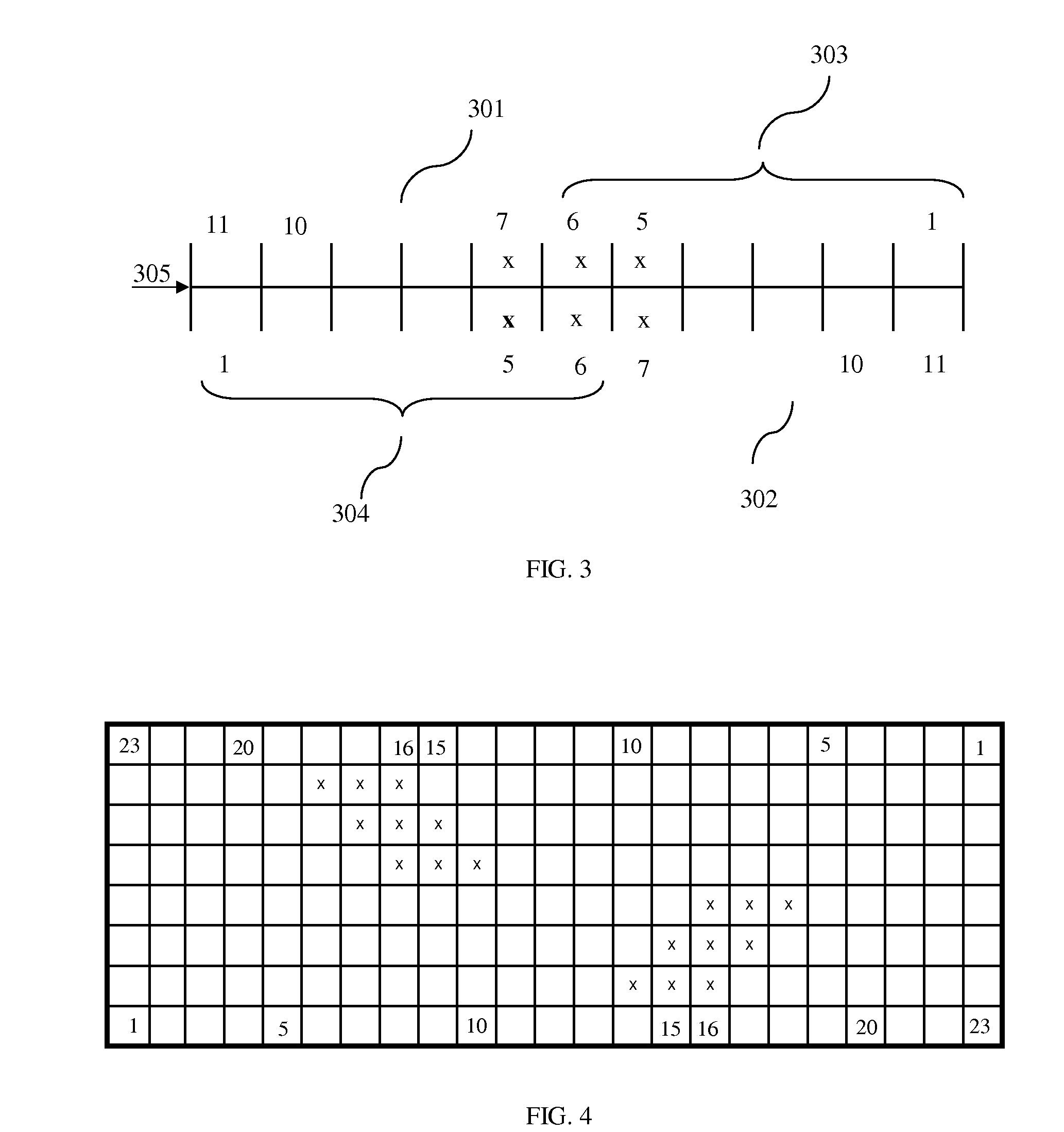

A data processing apparatus maps input symbols to be communicated onto a predetermined number of carrier signals of an Orthogonal Frequency Division Multiplexed (OFDM) symbol. The data processor includes an interleaver memory which reads-in the predetermined number of data symbols for mapping onto the OFDM carrier signals. The interleaver memory reads-out the data symbols on to the OFDM carriers to effect the mapping, the read-out being in a different order than the read-in, the order being determined from a set of addresses, with the effect that the data symbols are interleaved on to the carrier signals. The set of addresses are generated from an address generator which comprises a linear feedback shift register and a permutation circuit. In order to provide a 4 k mode for an OFDM modulated system such as a Digital Video Broadcasting (DVB) standard such as DVB-Terrestrial (DVB-T) or DVB-Handheld (DVB-H) standards, a generator polynomial for the linear feedback shift register of Ri'[10]=Ri-1'[0]⊕Ri-1'[2] is provided with a permutation order which has been established by simulation analysis to optimise communication performance via typical radio channels.

Owner:SONY EUROPE BV

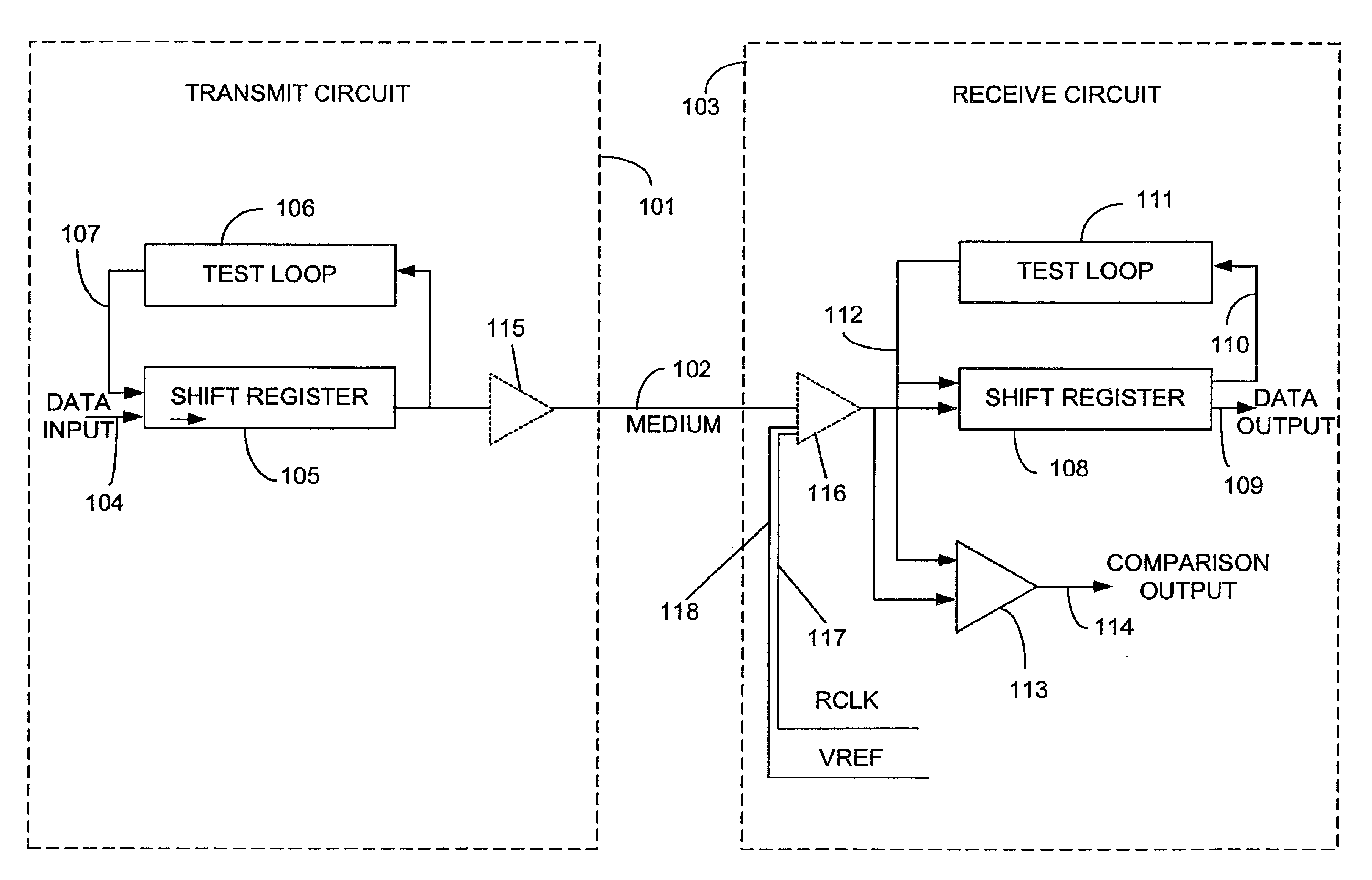

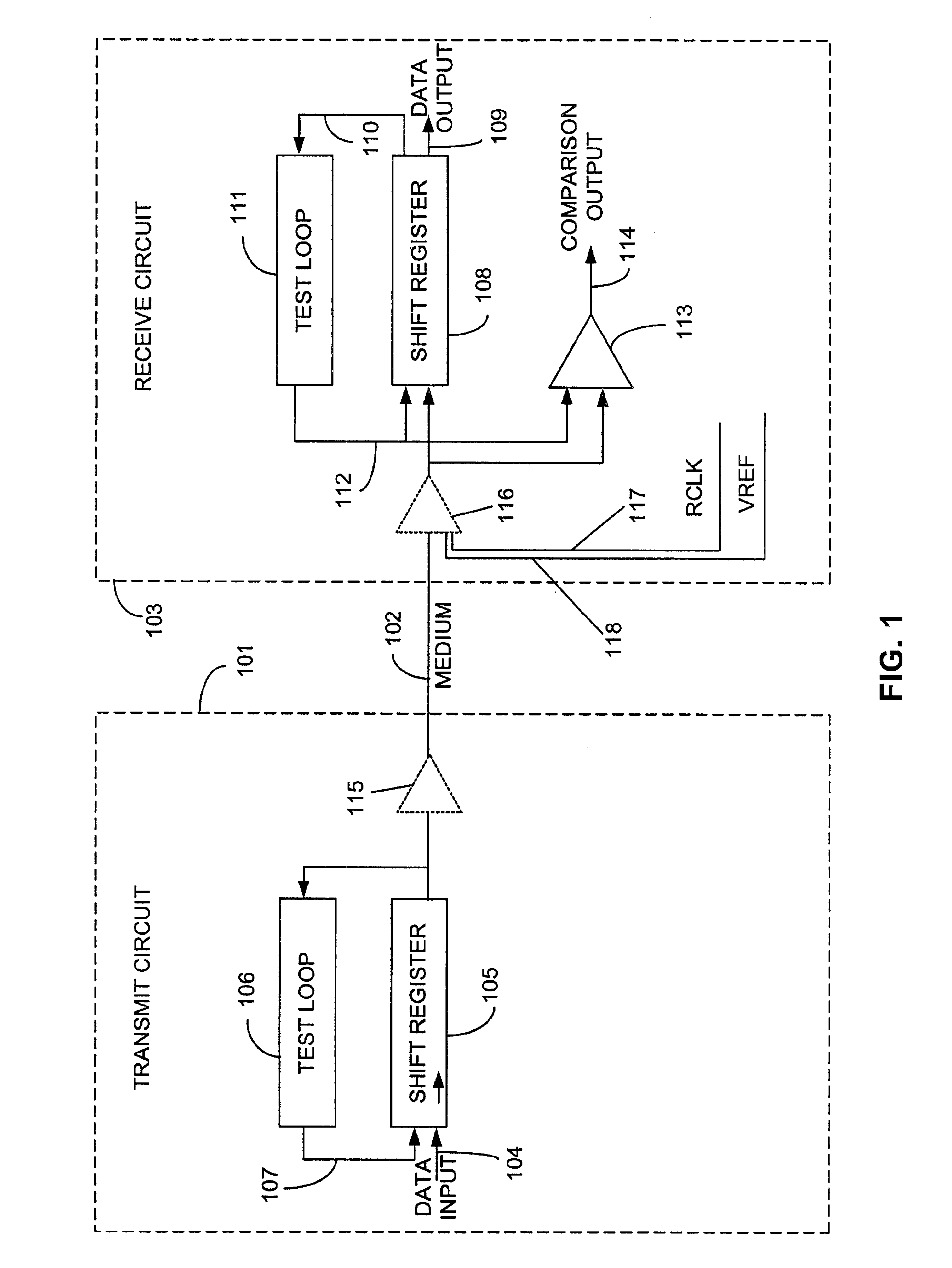

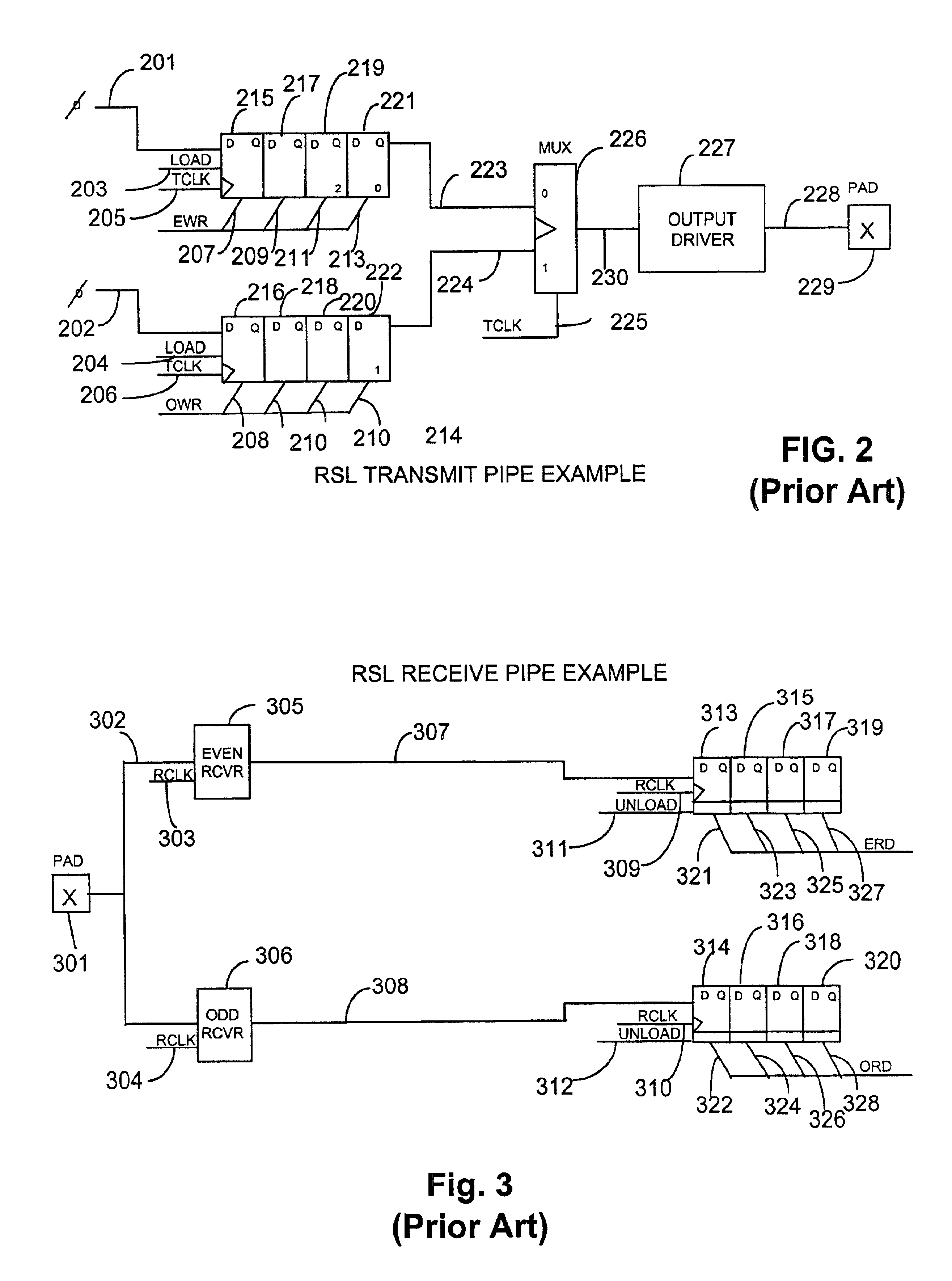

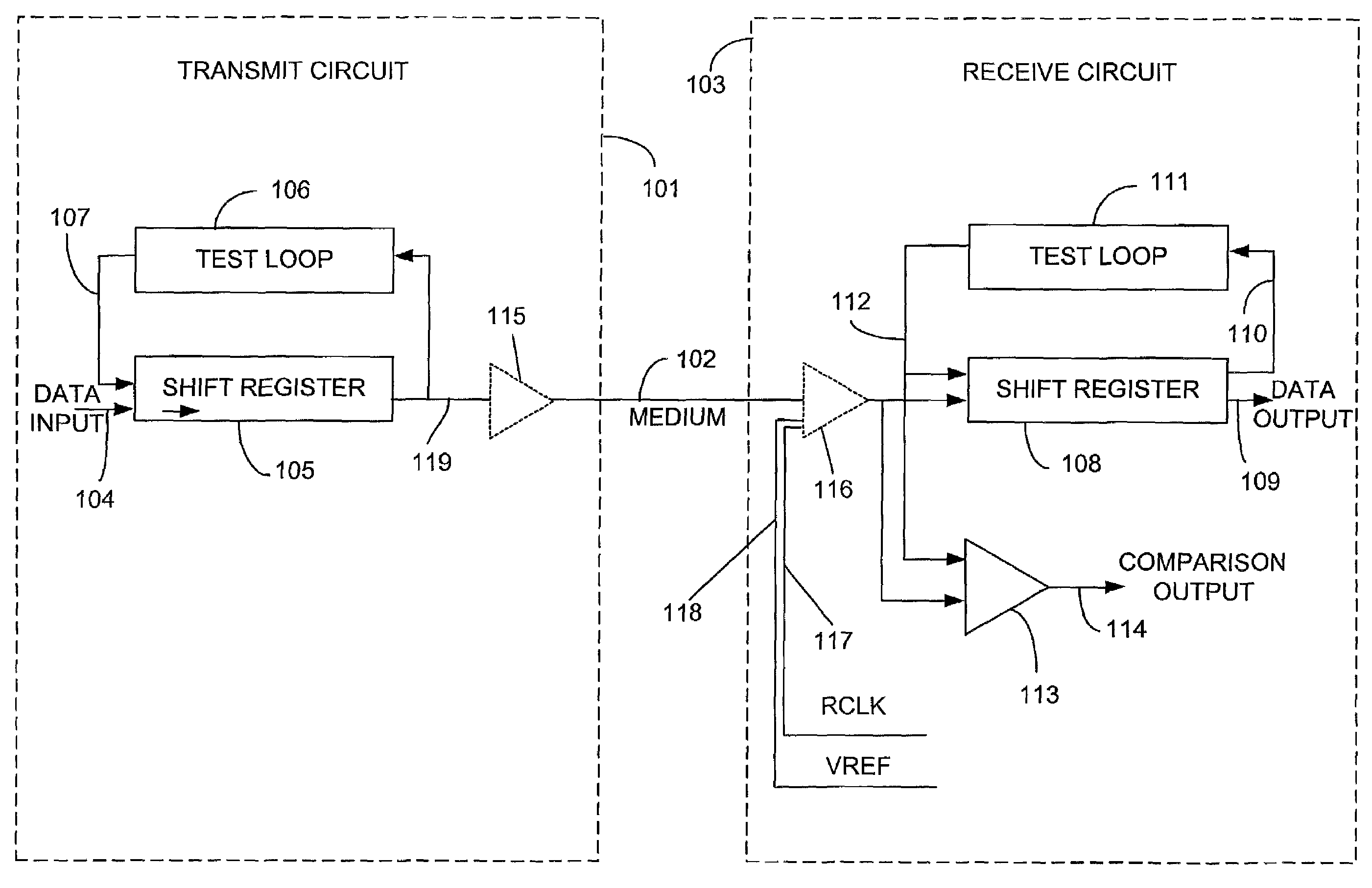

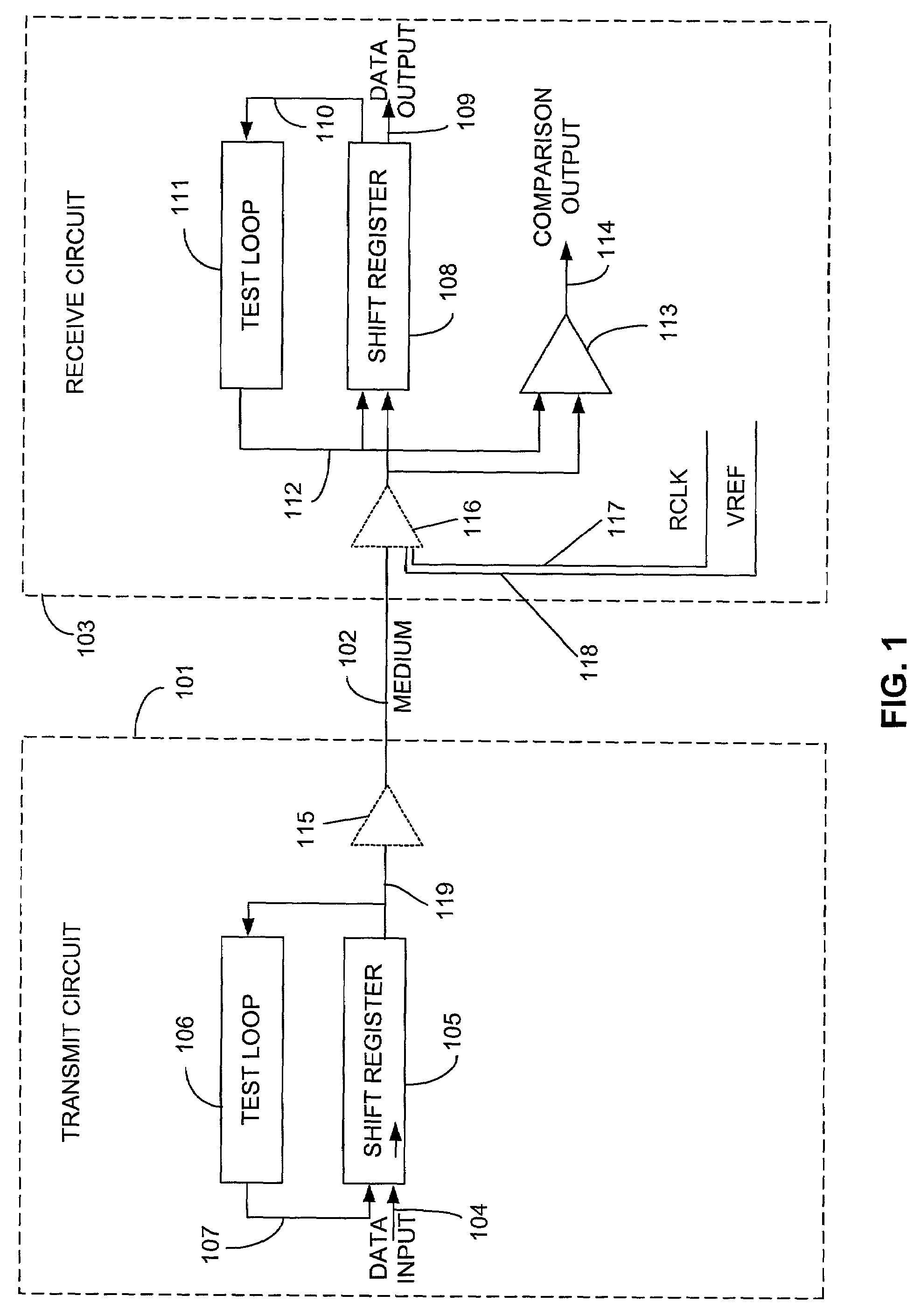

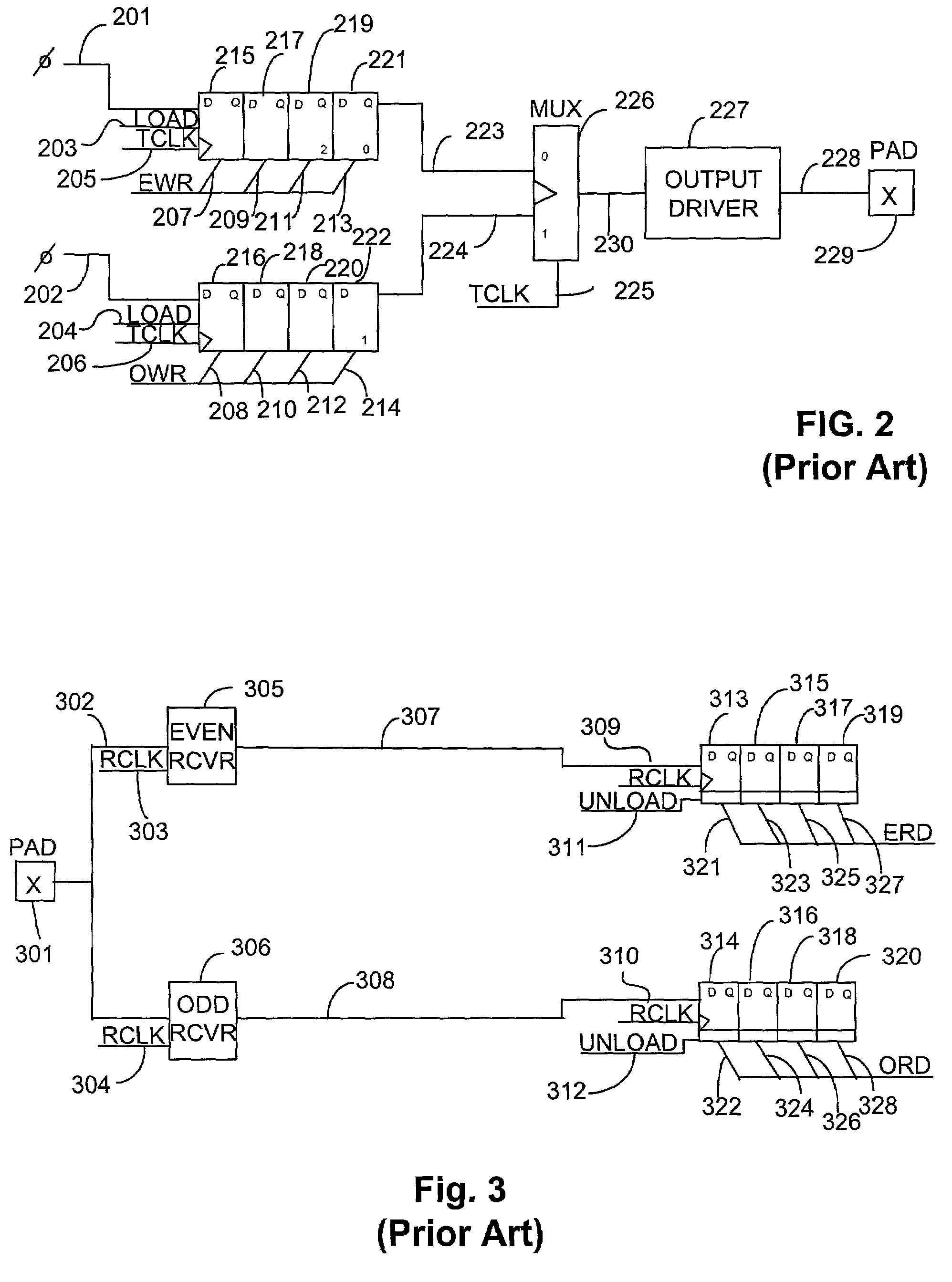

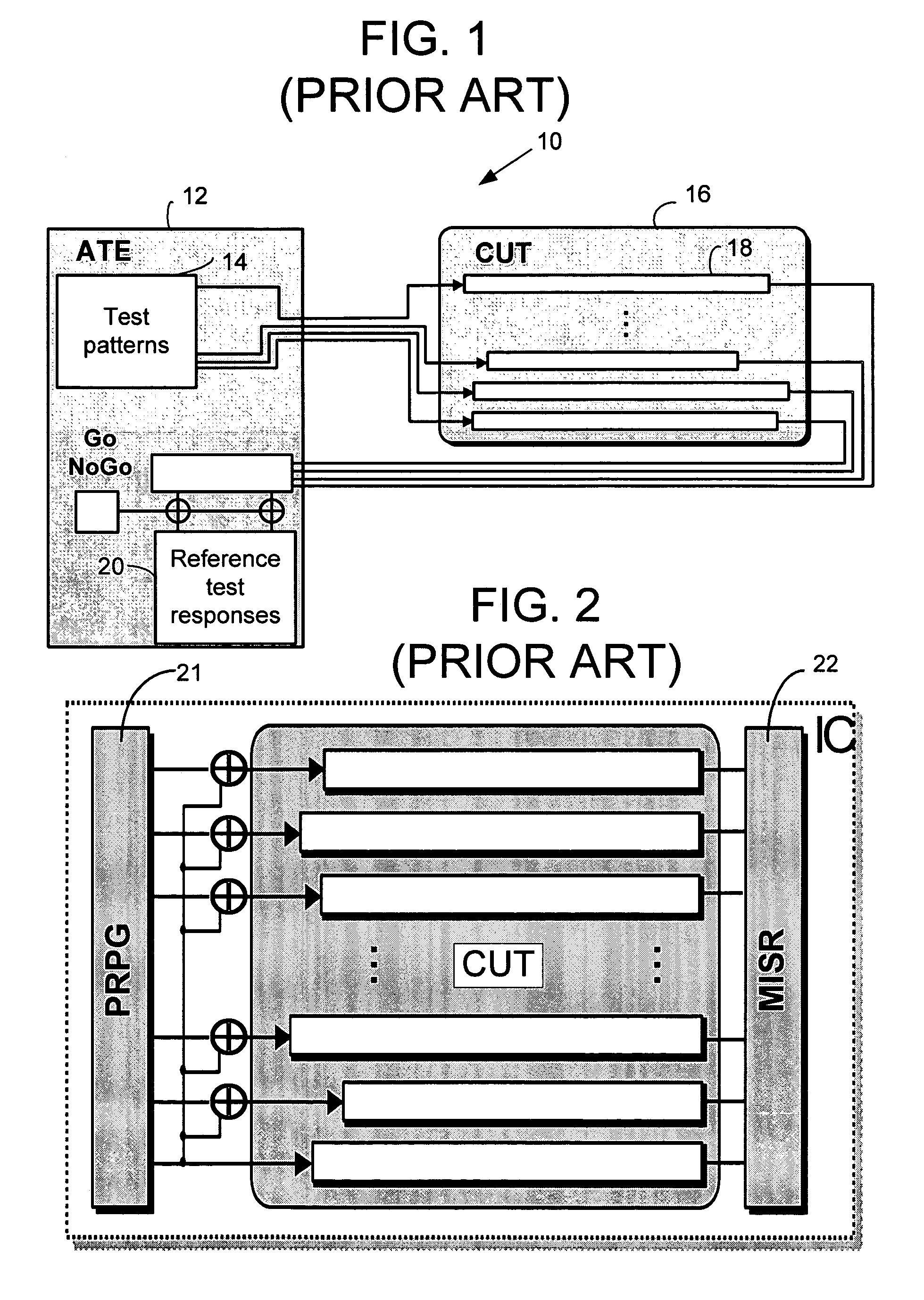

Method and apparatus for evaluating and calibrating a signaling system

InactiveUS6873939B1Amplifier modifications to reduce noise influenceElectronic circuit testingCrosstalk cancellationElectrical conductor

A method and apparatus for evaluating and calibrating a signaling system is described. Evaluation is accomplished using the same circuits actually involved in normal operation of the signaling system. Capability for in-situ testing of a signaling system is provided, and information may be obtained from the actual perspective of a receive circuit in the system. A pattern of test information is generated in a transmit circuit of the system and is transmitted to a receive circuit. A similar pattern of information is generated in the receive circuit and used as a reference. The receive circuit compares the patterns. Any differences between the patterns are observable. Preferably, the patterns are repeating patterns that allow many iterations of testing to be performed. In one embodiment, a linear feedback shift register (LFSR) is implemented to produce patterns. Information obtained from testing may be used to assess the effects of various system parameters, including but not limited to output current, crosstalk cancellation coefficients, and self-equalization coefficients, and system parameters may be adjusted to optimize system performance. An embodiment of the invention may be practiced with various types of signaling systems, including those with single-ended signals and those with differential signals. An embodiment of the invention may be applied to systems communicating a single bit of information on a single conductor at a given time and to systems communicating multiple bits of information on a single conductor simultaneously.

Owner:RAMPART ASSET MANAGEMENT LLC

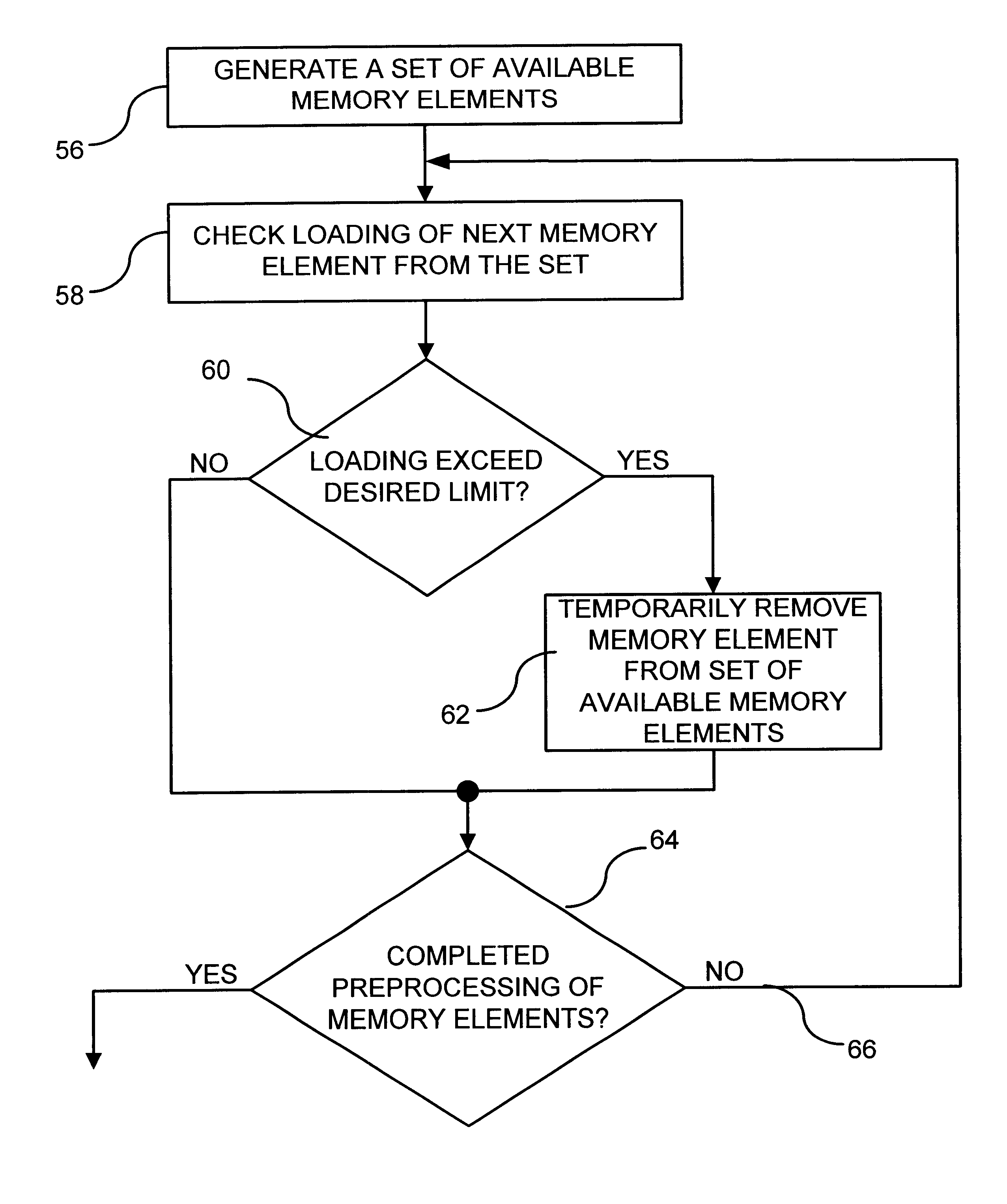

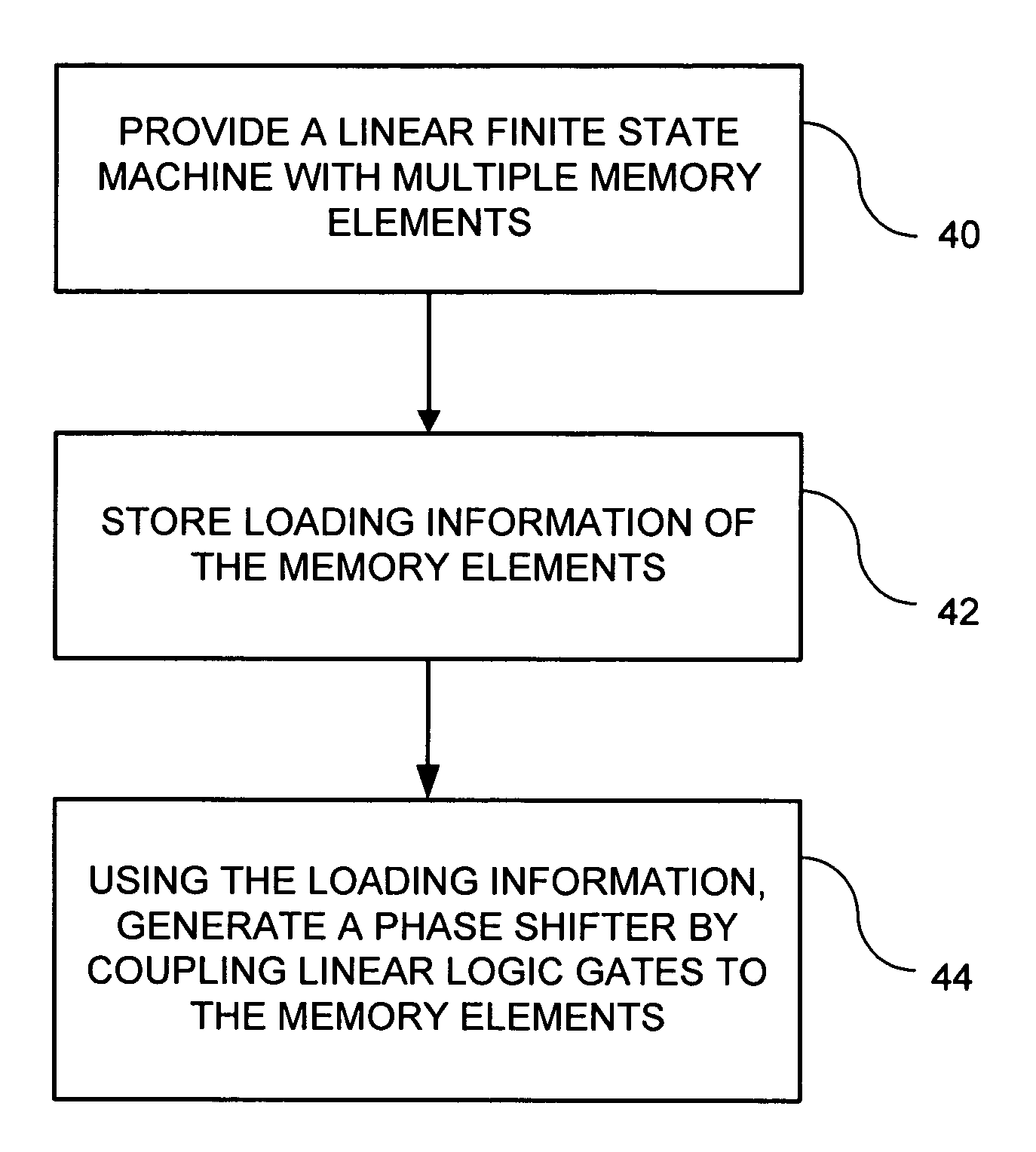

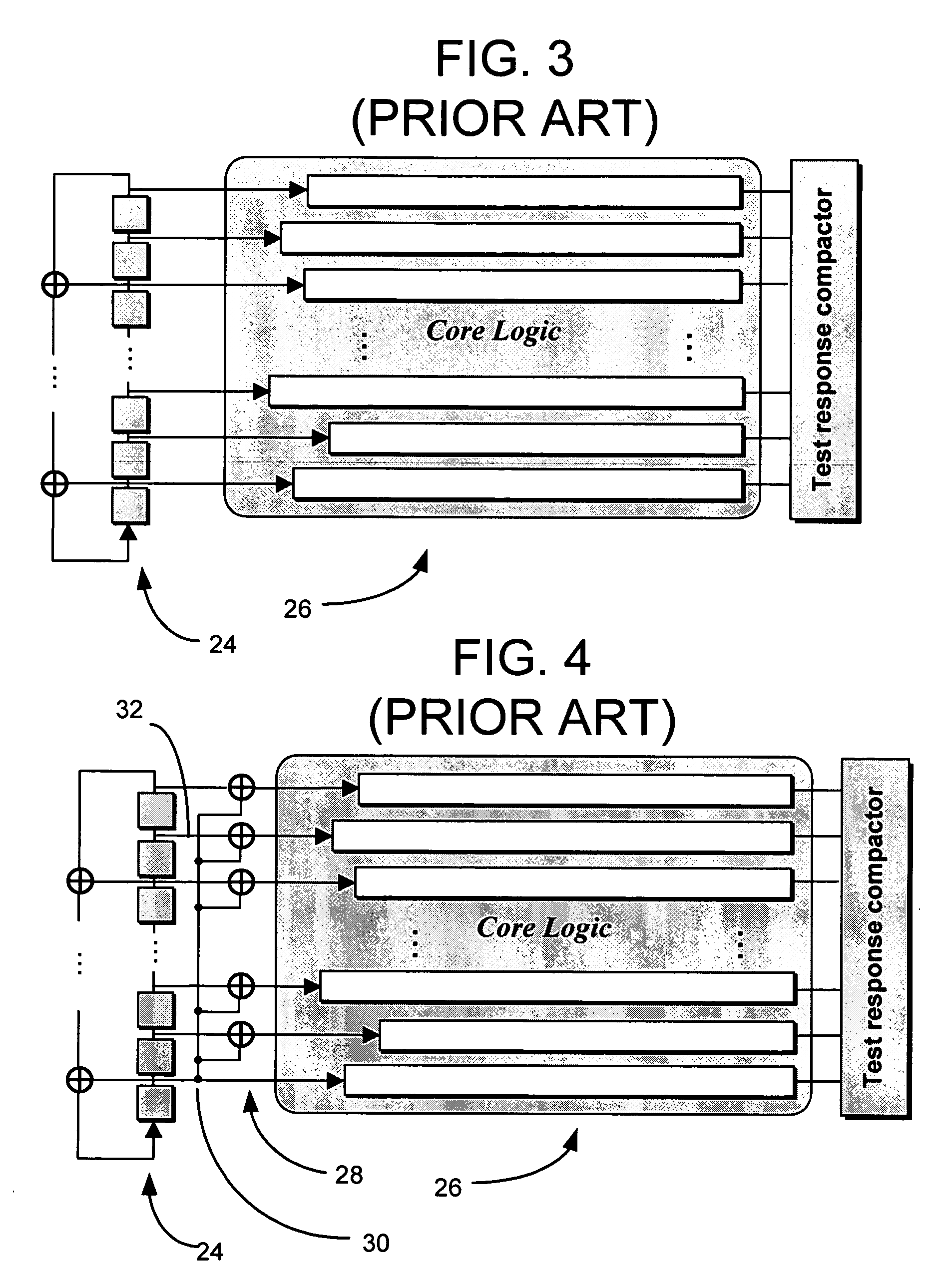

Phase shifter with reduced linear dependency

InactiveUS6874109B1Electronic circuit testingError detection/correctionCircuit complexityLinear dependency

A method is disclosed for the automated synthesis of phase shifters. Phase shifters comprise circuits used to remove effects of structural dependencies featured by pseudo-random test pattern generators driving parallel scan chains. Using a concept of duality, the method relates the logical states of linear feedback shift registers (LFSRs) and circuits spacing their inputs to each of the output channels. The method generates a phase shifter network balancing the loads of successive stages of LFSRs and satisfying criteria of reduced linear dependency, channel separation and circuit complexity.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

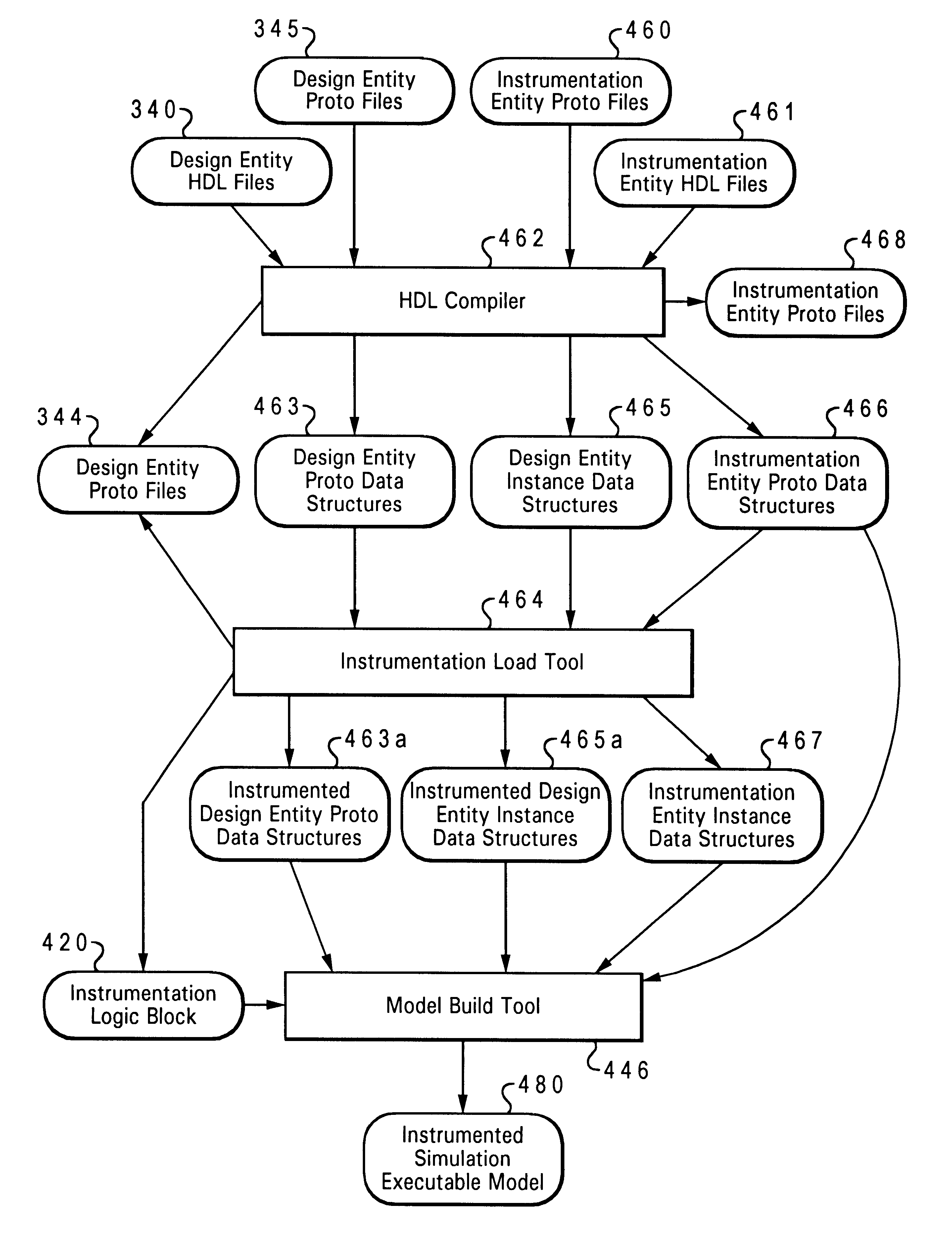

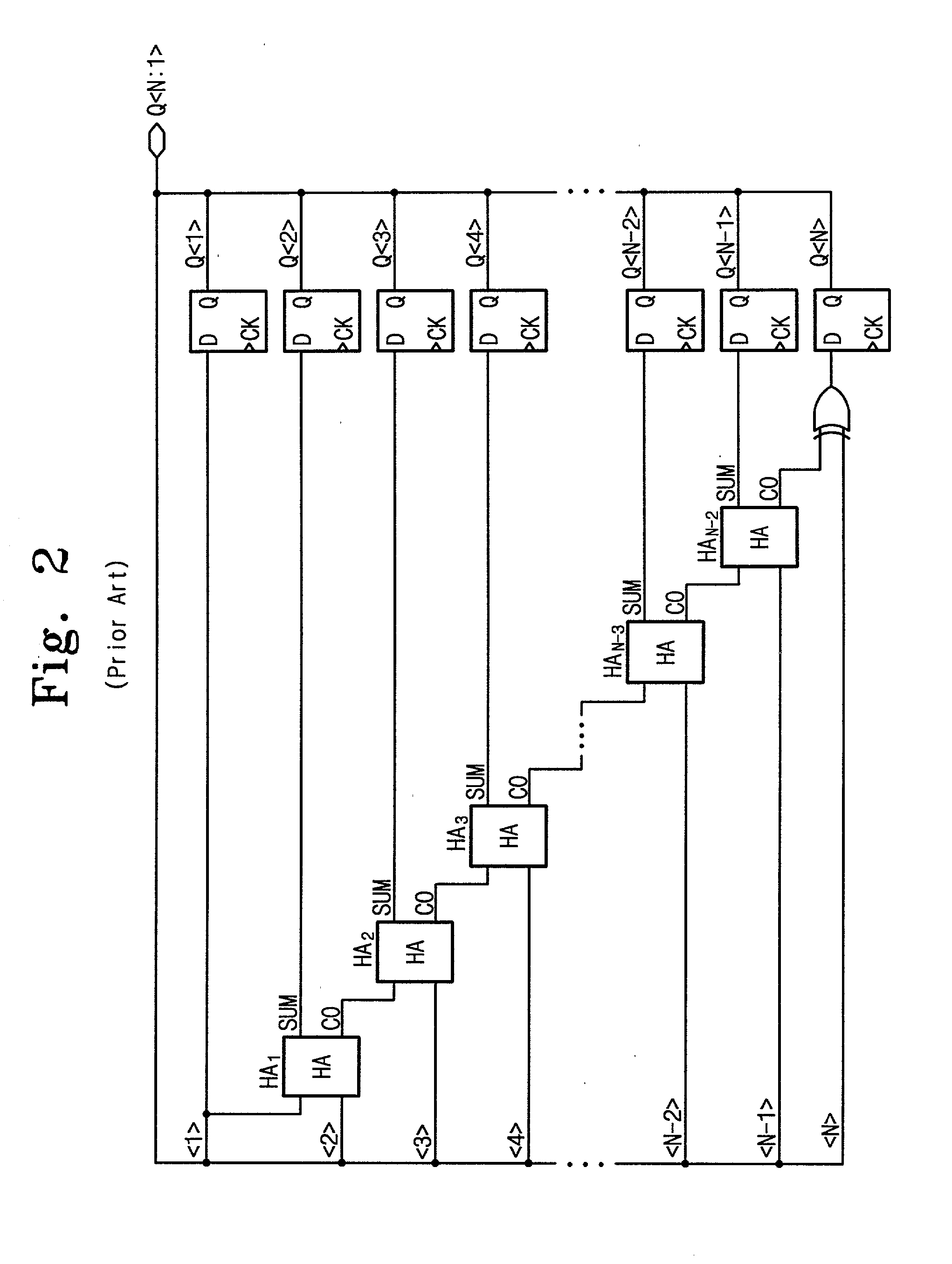

Method and system for counting events within a simulation model

InactiveUS6470478B1Monitor performanceDigital circuit testingDetecting faulty computer hardwareTheoretical computer scienceLinear feedback shift register

A method and system that utilize the expressiveness of hardware description languages for efficiently and comprehensively monitoring performance characteristics of a digital circuit design during simulation. According to the present invention, a design entity that is part of a digital circuit design is first described utilizing a hardware description language. Next, a counting instrument is described utilizing the same hardware description language. The counting instrument is designed to detect occurrences of a count event within the design entity during simulation of the digital circuit design. The counting instrument is associated with the design entity utilizing a non-conventional call, such that the counting instrument may be utilized to monitor each instantiation of the design entity within the simulation model without the instrumentation entity becoming incorporated into the digital circuit design. In association with the counting instrument, a linear feedback shift register is automatically generated for recording the number of occurrences of the count event within the design entity.

Owner:GLOBALFOUNDRIES INC

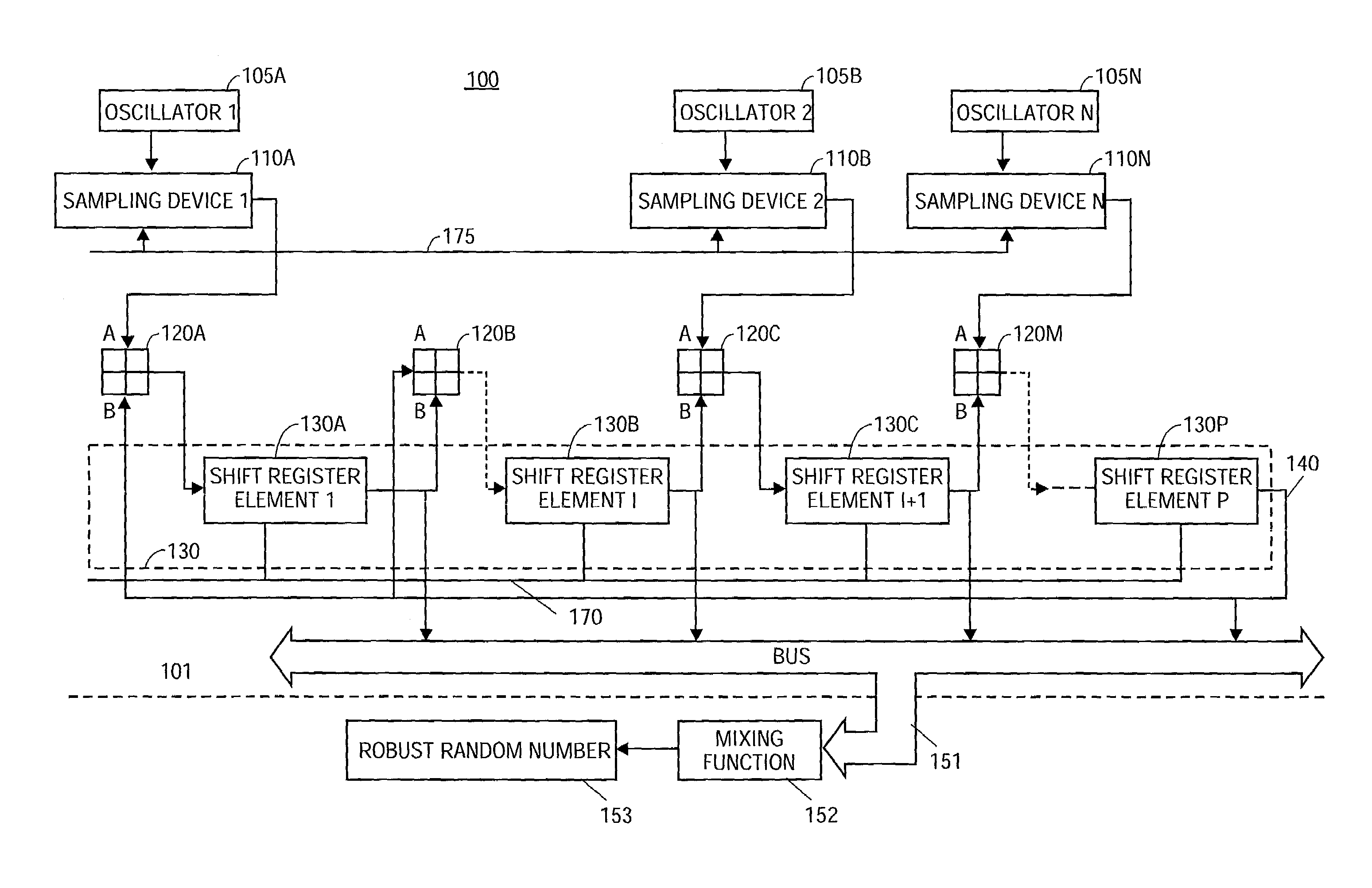

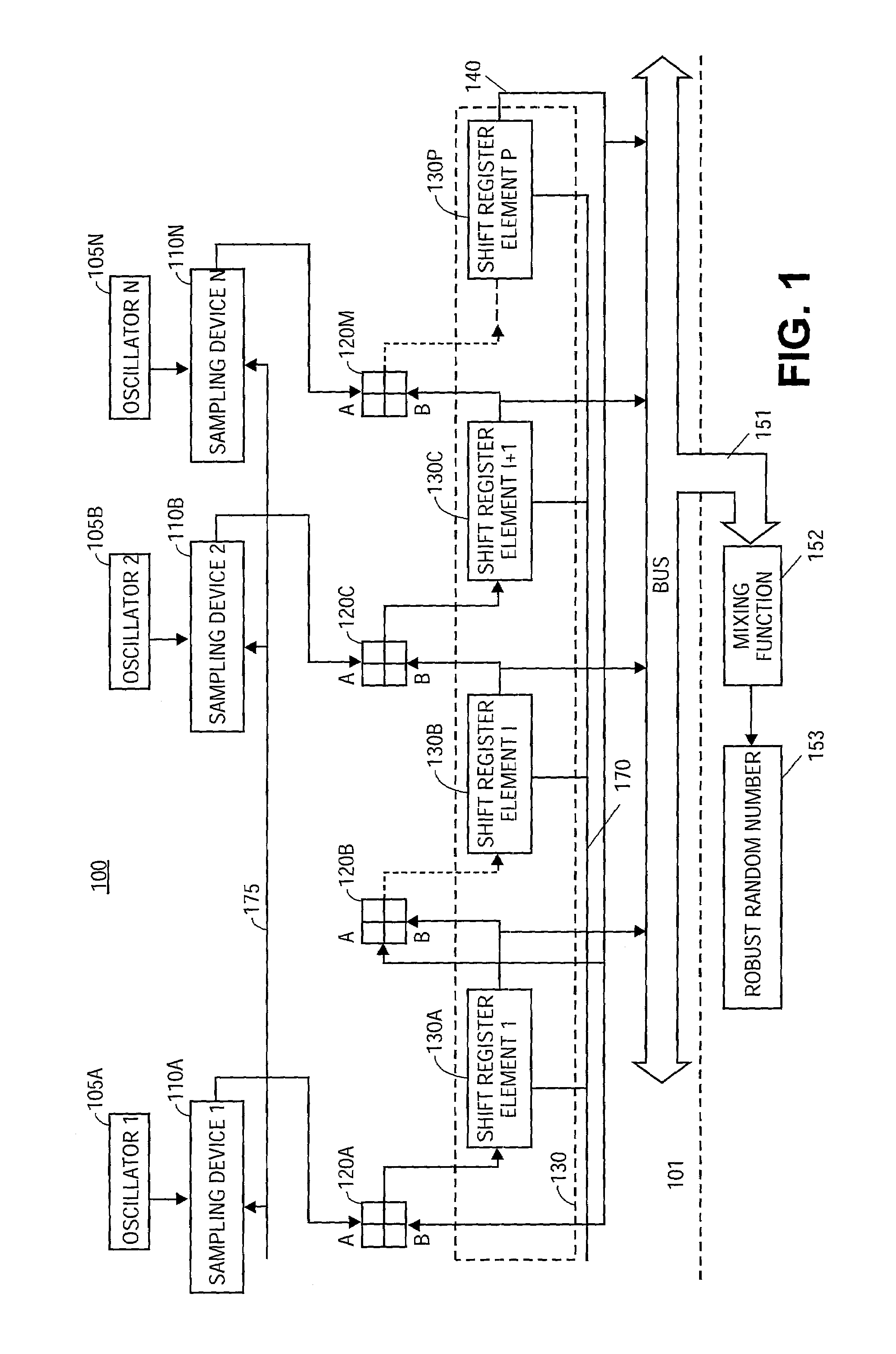

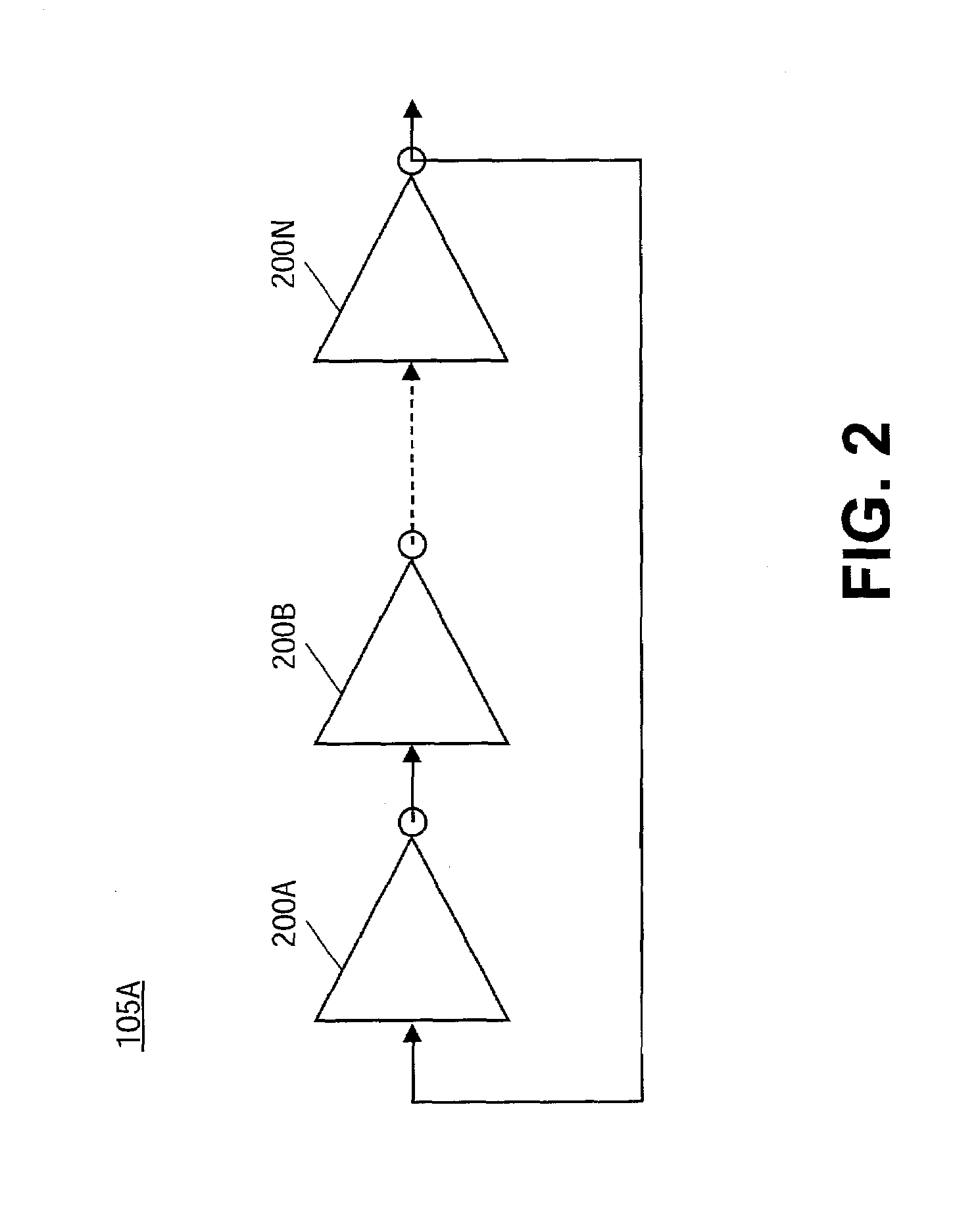

Random number generator

A random number generator comprising an oscillator with an output signal dependant upon a random source, a sampling device to sample the output signal from the oscillator to obtain a sampled oscillator output, and a fixed frequency clock driven linear feedback shift register (LFSR) communicatively coupled to the sampling device via a digital gate to receive the sampled oscillator output, and to provide a random number at an output of the LFSR. Additionally, the random number generator may comprise an optional mixing function communicatively coupled to the LFSR to read the random number, and to insert the random number into an algorithm to obtain a robust random number.

Owner:MARVELL ASIA PTE LTD

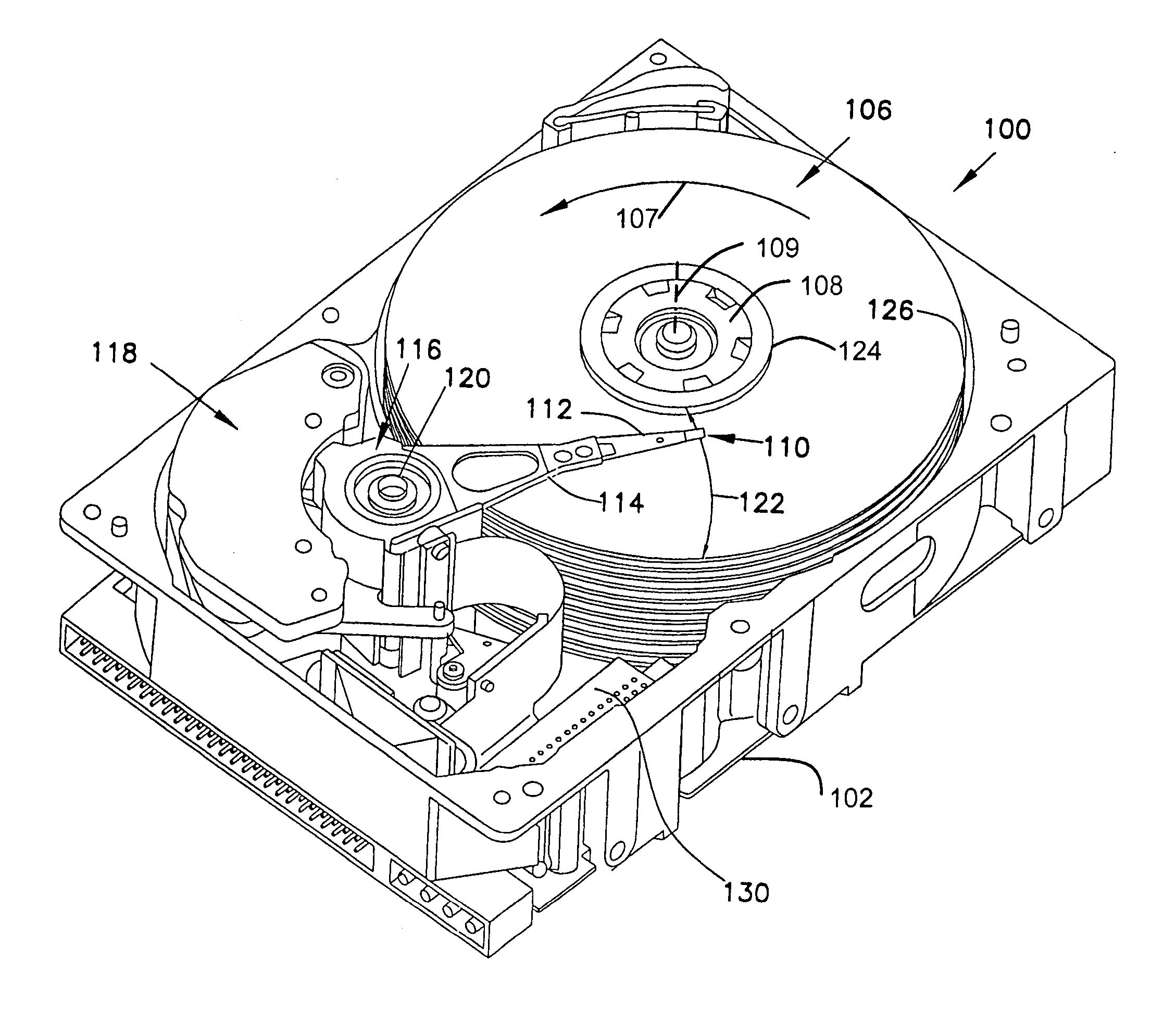

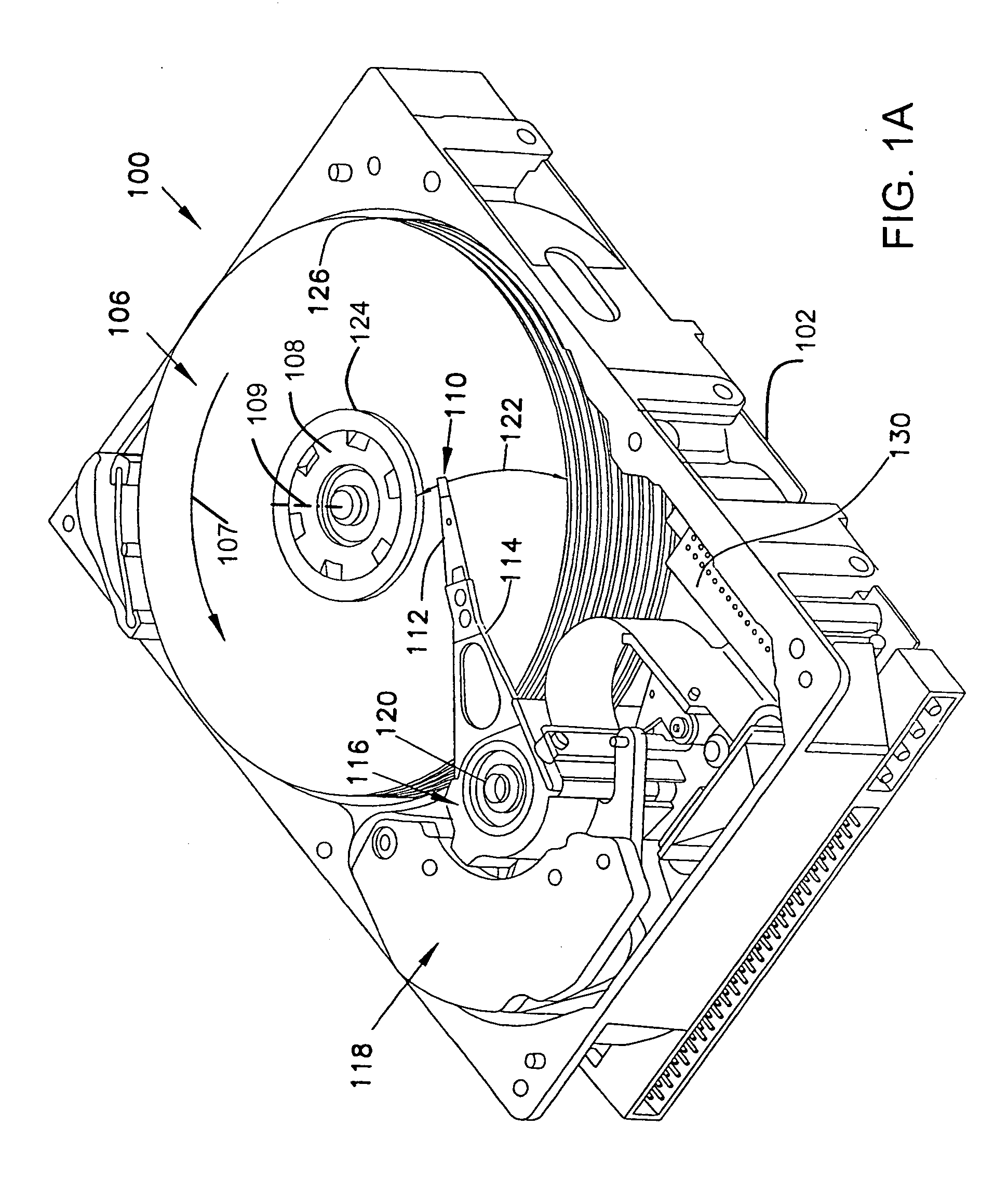

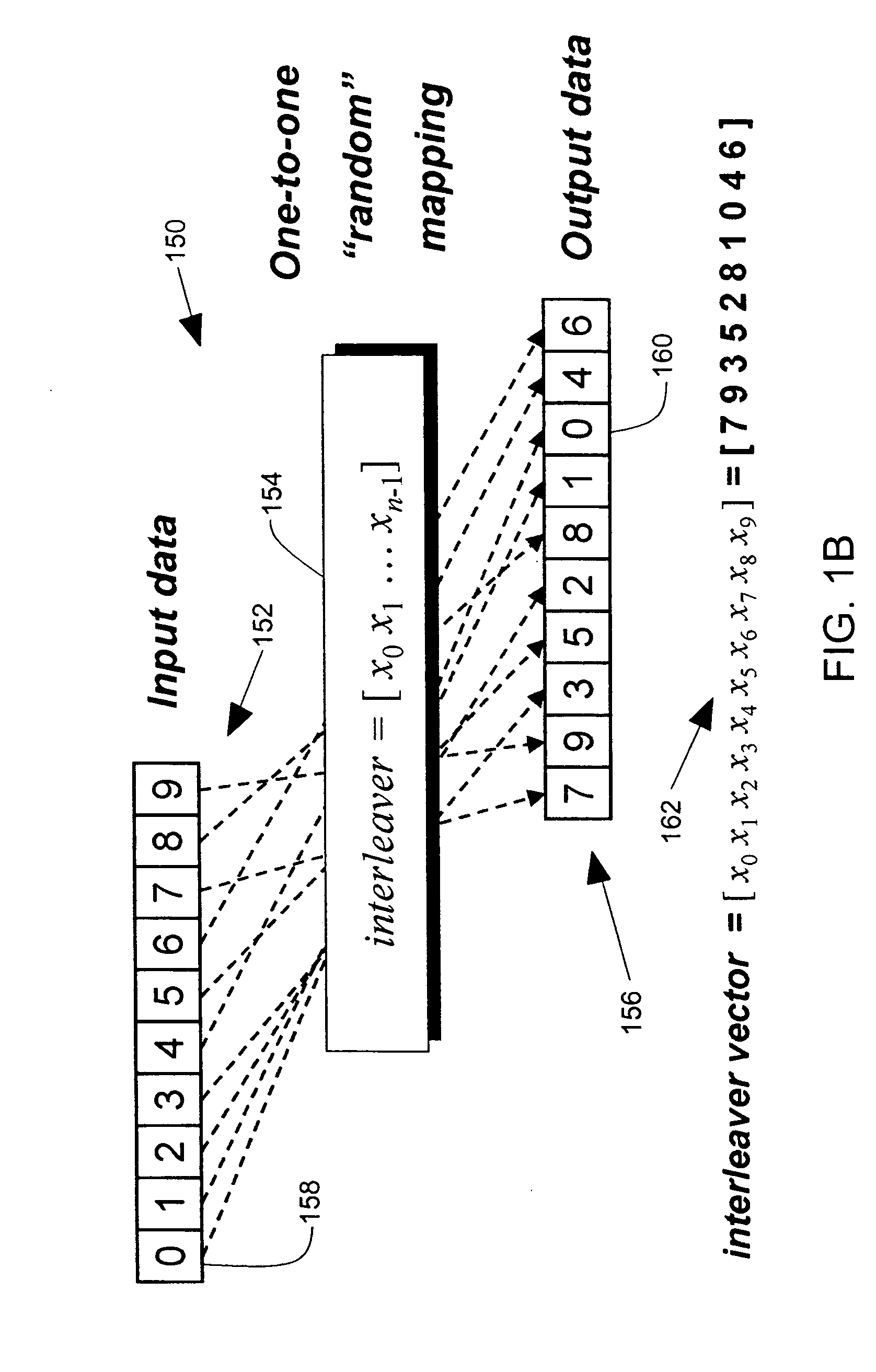

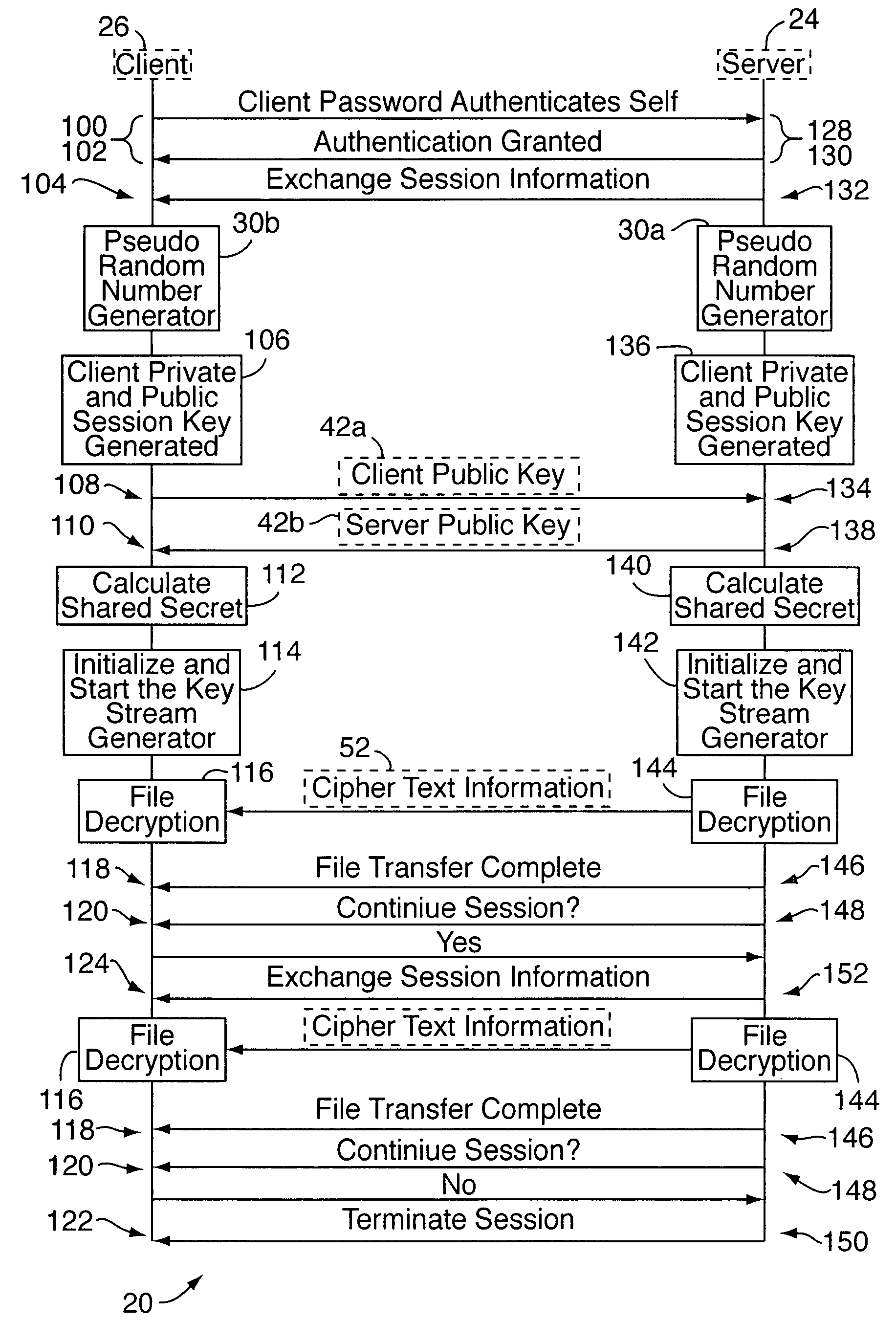

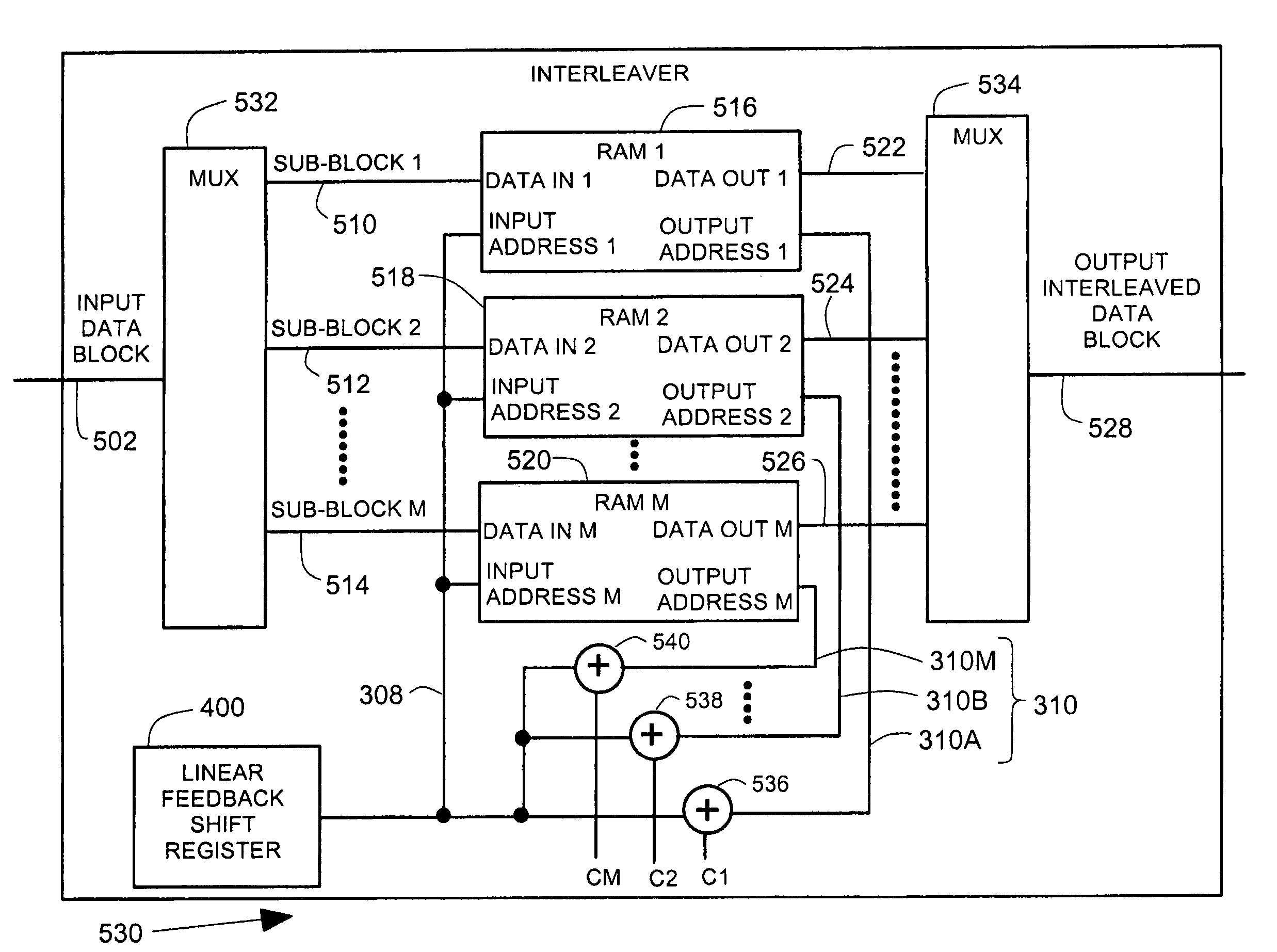

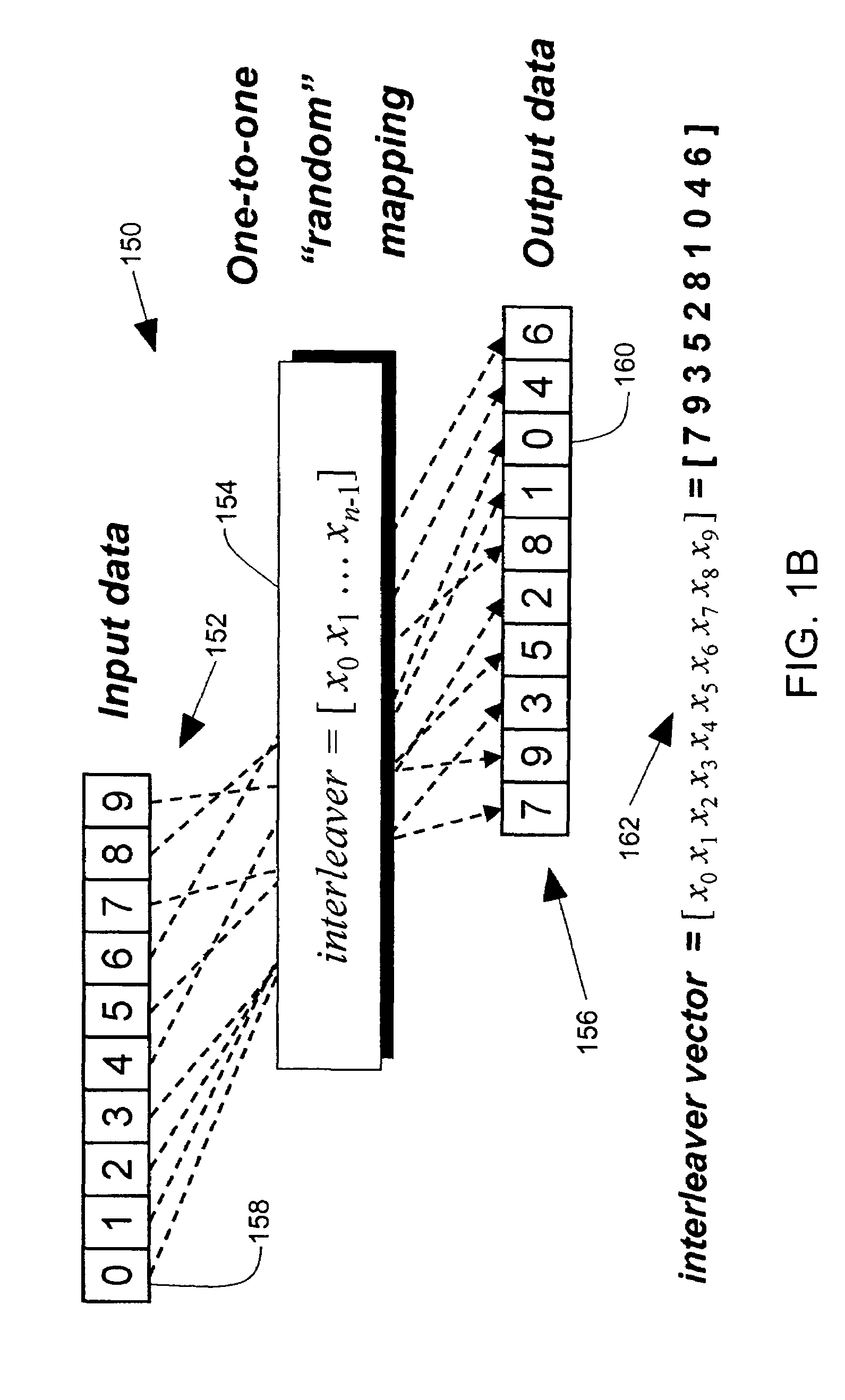

Low complexity pseudo-random interleaver

An interleaver has an input multiplexer that receives a data sequence at an interleaver input and that separates the data sequence into multiple data sub-blocks. The interleaver has a linear feedback shift register that generates an input address sequence. The interleaver has adder circuits that generate output address sequences associated with each data sub-block. The interleaver has memory that stores the data sub-blocks at addresses controlled by the input address sequence. The memory reproduces each data sub-block in an interleaved sequence controlled by the associated output address sequence. The interleaver has an output multiplexer that assembles the interleaved sequences to provide an interleaver output.

Owner:SEAGATE TECH LLC

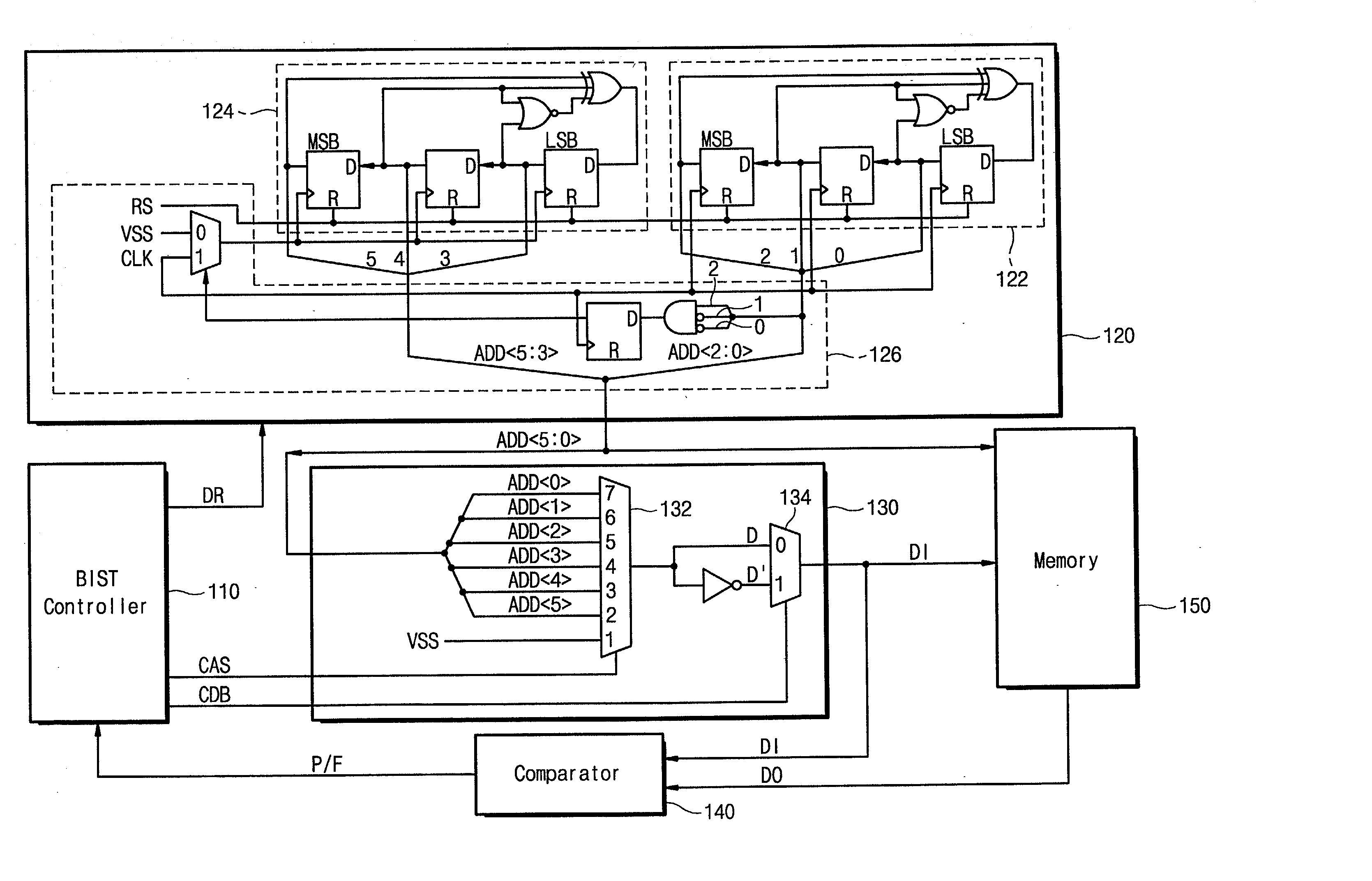

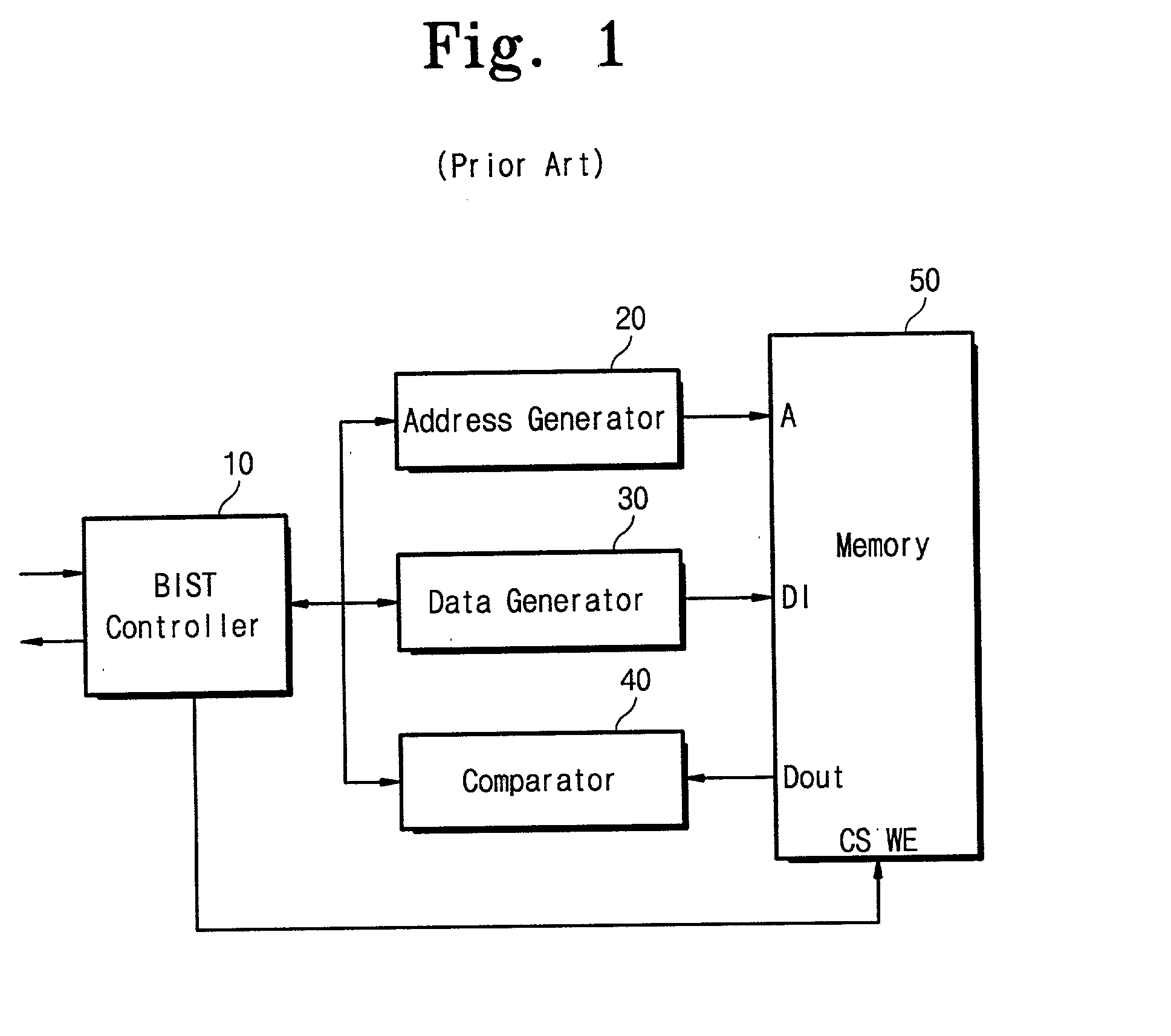

Built-in self test circuit using linear feedback shift register

A built-in self test (BIST) circuit comprising a linear feedback shift register is disclosed. The BIST circuit comprises a controller for controlling a self-testing operation of a memory chip embedded in an integrated circuit, an address generator for generating pseudo-random address patterns under control of the controller, a data generator for producing test data associated with data backgrounds of the address bits under the control of the controller, and a comparator for comparing the test data with memory data output from the memory chip to detect a defect, if any, of the memory chip. The pseudo-random random pattern comprises a single-random pseudo-random address pattern.

Owner:SAMSUNG ELECTRONICS CO LTD

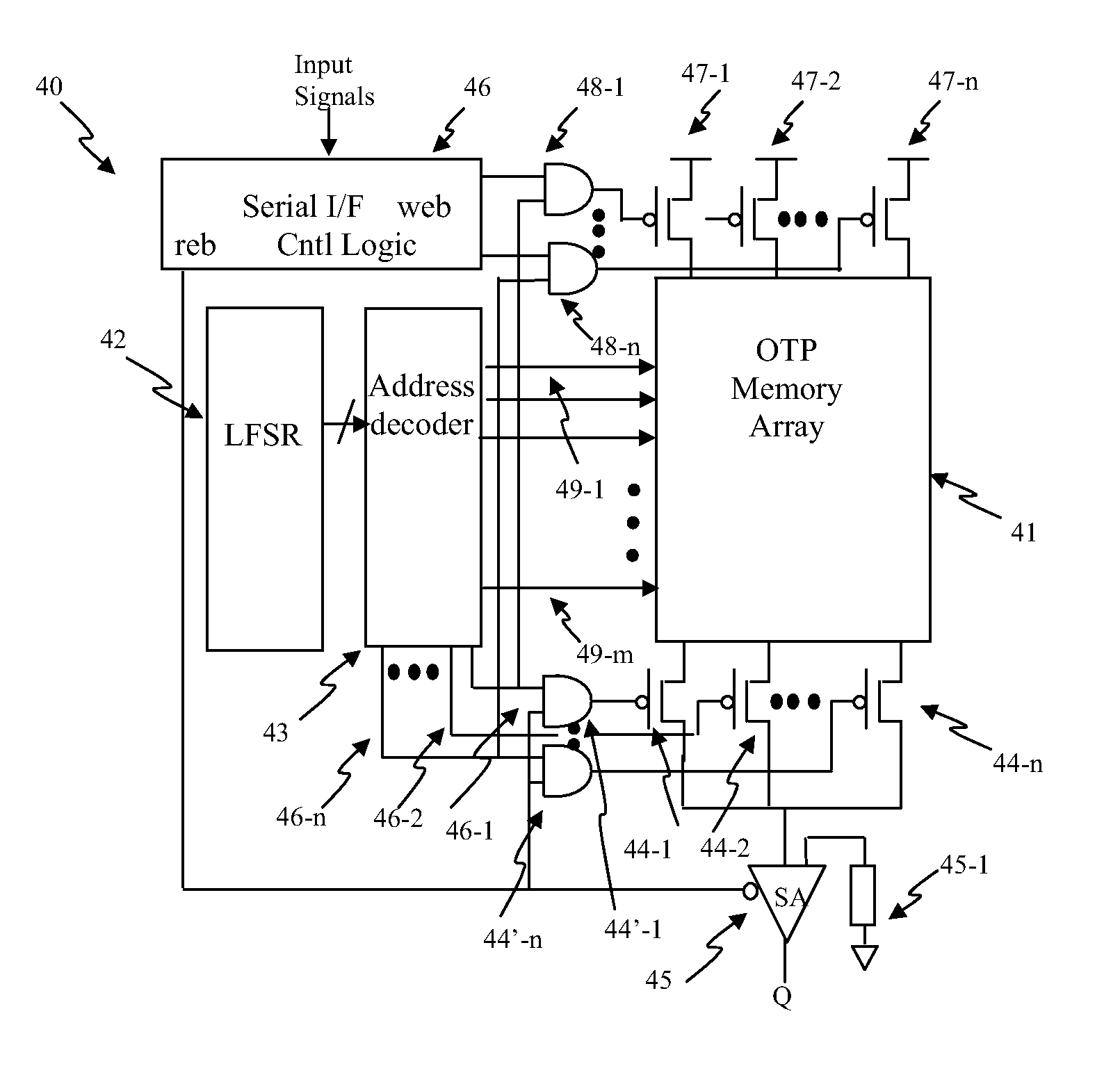

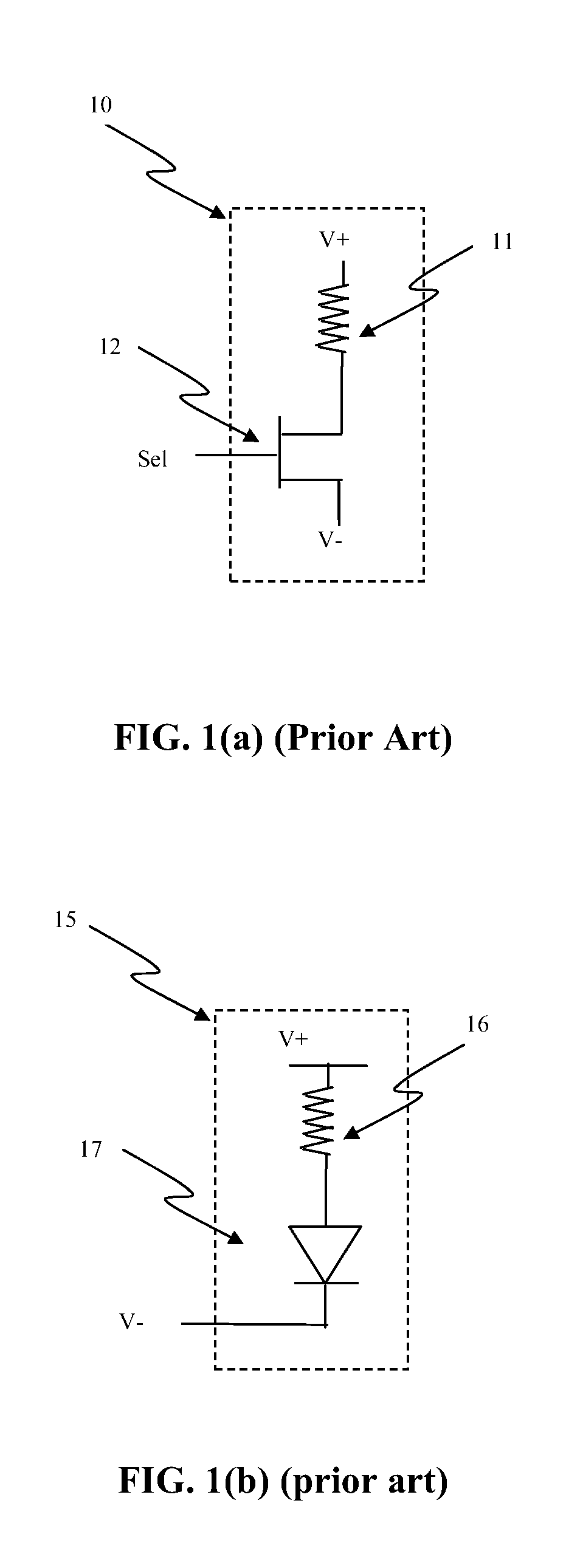

Circuit and System of a Low Density One-Time Programmable Memory

InactiveUS20130201745A1Low density OTPsReduce memory sizeElectric analogue storesRead-only memoriesAddress generatorHemt circuits

A low density One-Time Programmable (OTP) memory is disclosed to achieve low gate count and low overhead in the peripheral circuits to save the cost. A maximum-length Linear Feedback Shift Register (LFSR) can be used to generate 2n−1 address spaces from an n-bit address. The registers used in the address generator can have two latches. Each latch has two cross-coupled inverters with two outputs coupled to the drains of two MOS input devices, respectively. The inputs of the latch are coupled to the gates of the MOS input devices, respectively. The sources of the MOS input devices are coupled to the drains of at least one MOS device(s), whose gate(s) are coupled to a clock signal and whose source(s) are coupled to a supply voltage. The two latches can be constructed in serial with the outputs of the first latch coupled to the inputs of the second latch.

Owner:ATTOPSEMI TECH CO LTD

Error correction by symbol reconstruction in binary and multi-valued cyclic codes

InactiveUS20080016431A1Rapidly detect and correct errorCode conversionCyclic codesAlgorithmSymbol of a differential operator

Methods, apparatus and systems for error correction of n-valued symbols in codewords of p n-valued symbols with n>2 and for n=2 and k information symbols have been disclosed. Coders and decoders using a Linear Feedback Shift Registers (LFSR) are applied to generate codewords and detect the presence of errors. An LFSR can be in Fibonacci or Galois configuration. Errors can be corrected by execution of an n-valued expression in a deterministic non-iterative way. Deterministic error correction methods based on known symbols in error are provided. Corrected codewords can be identified by comparison with received codewords in error. N-valued LFSR based pseudo-noise generators and methods to determine if an LFSR is appropriate for generating error correcting codes are also disclosed. Methods and apparatus applying error free assumed windows and error assumed windows are disclosed. Systems using the error correcting methods, including communication systems and data storage systems are also provided.

Owner:TERNARYLOGIC

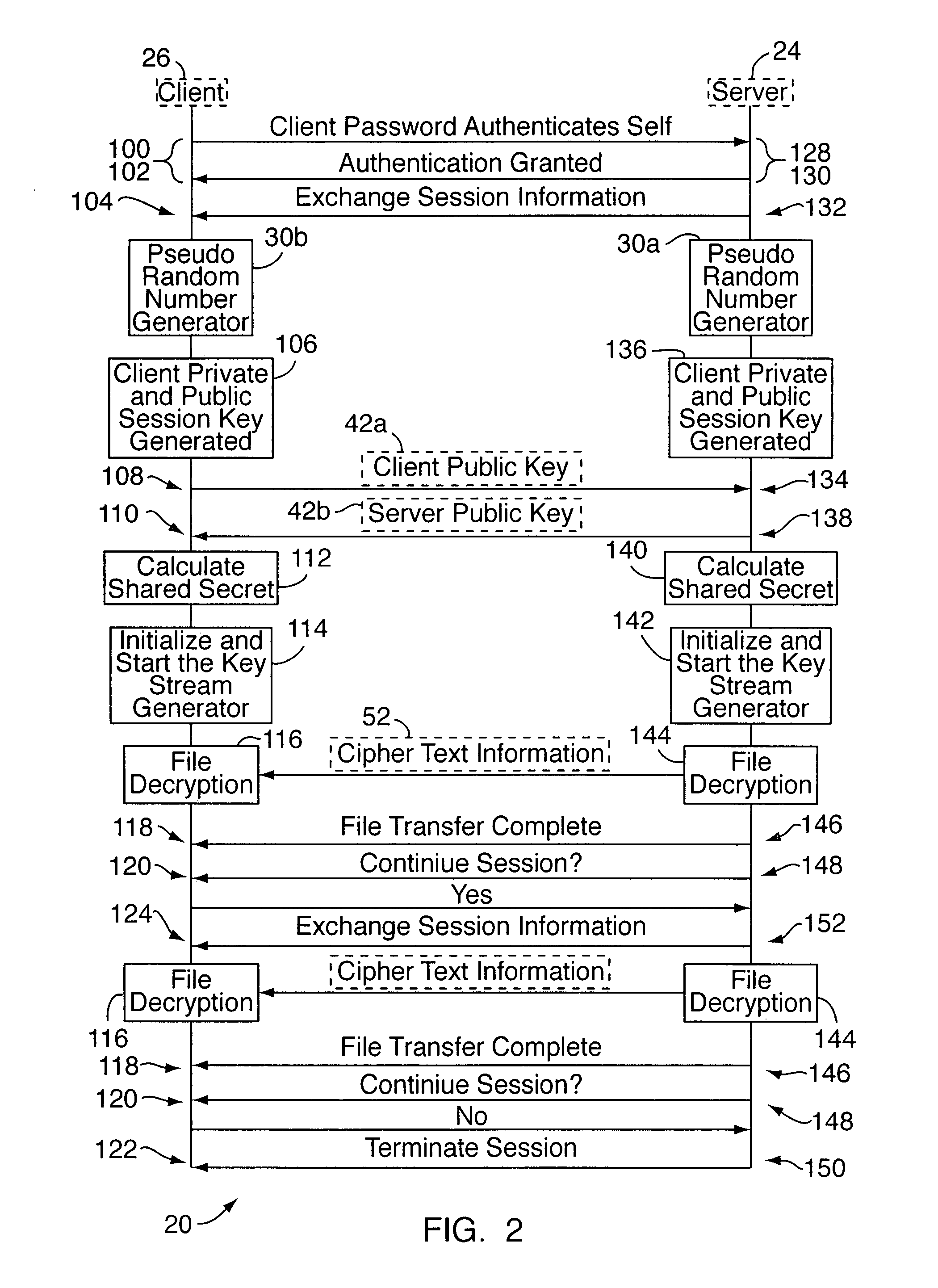

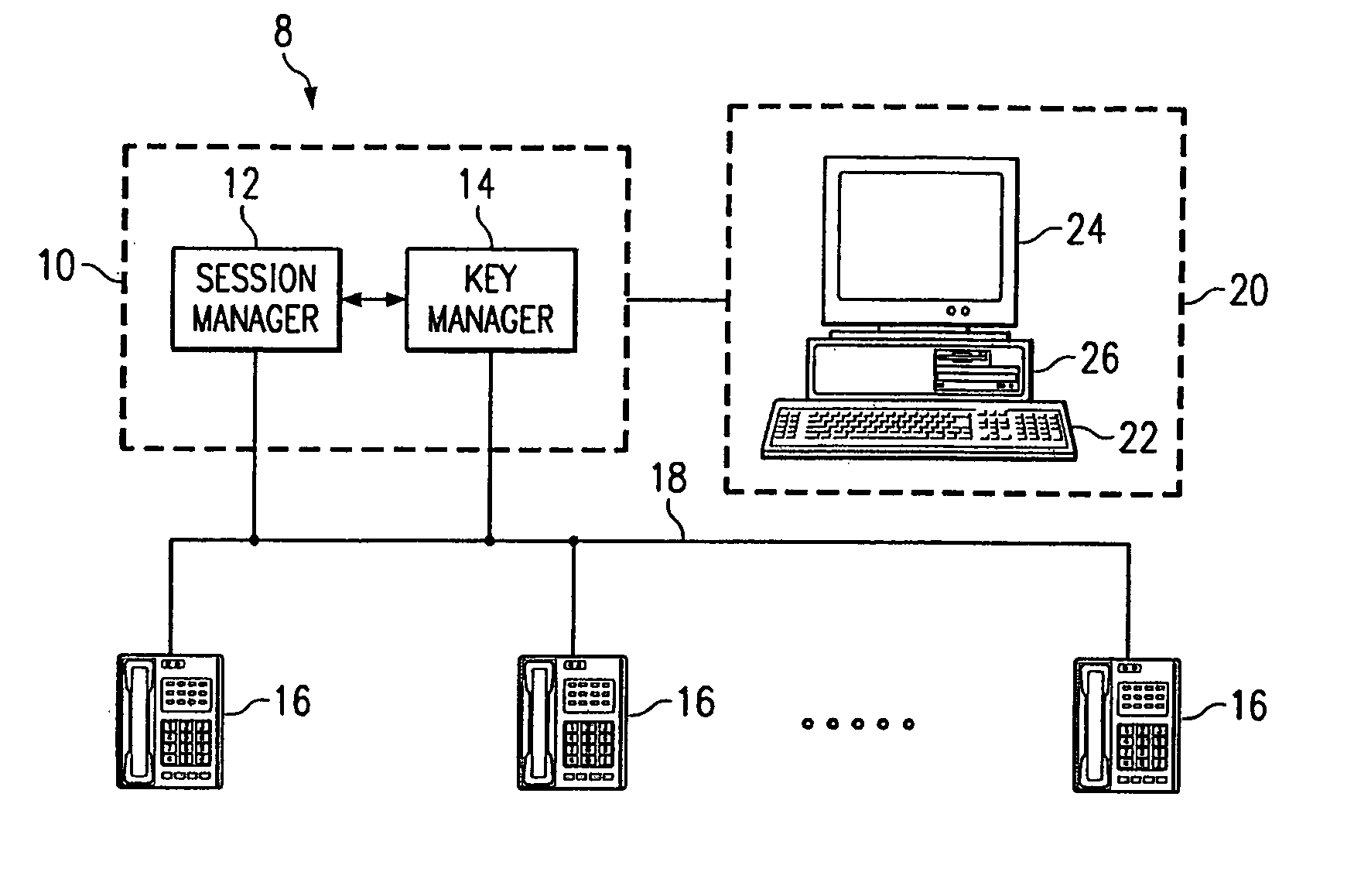

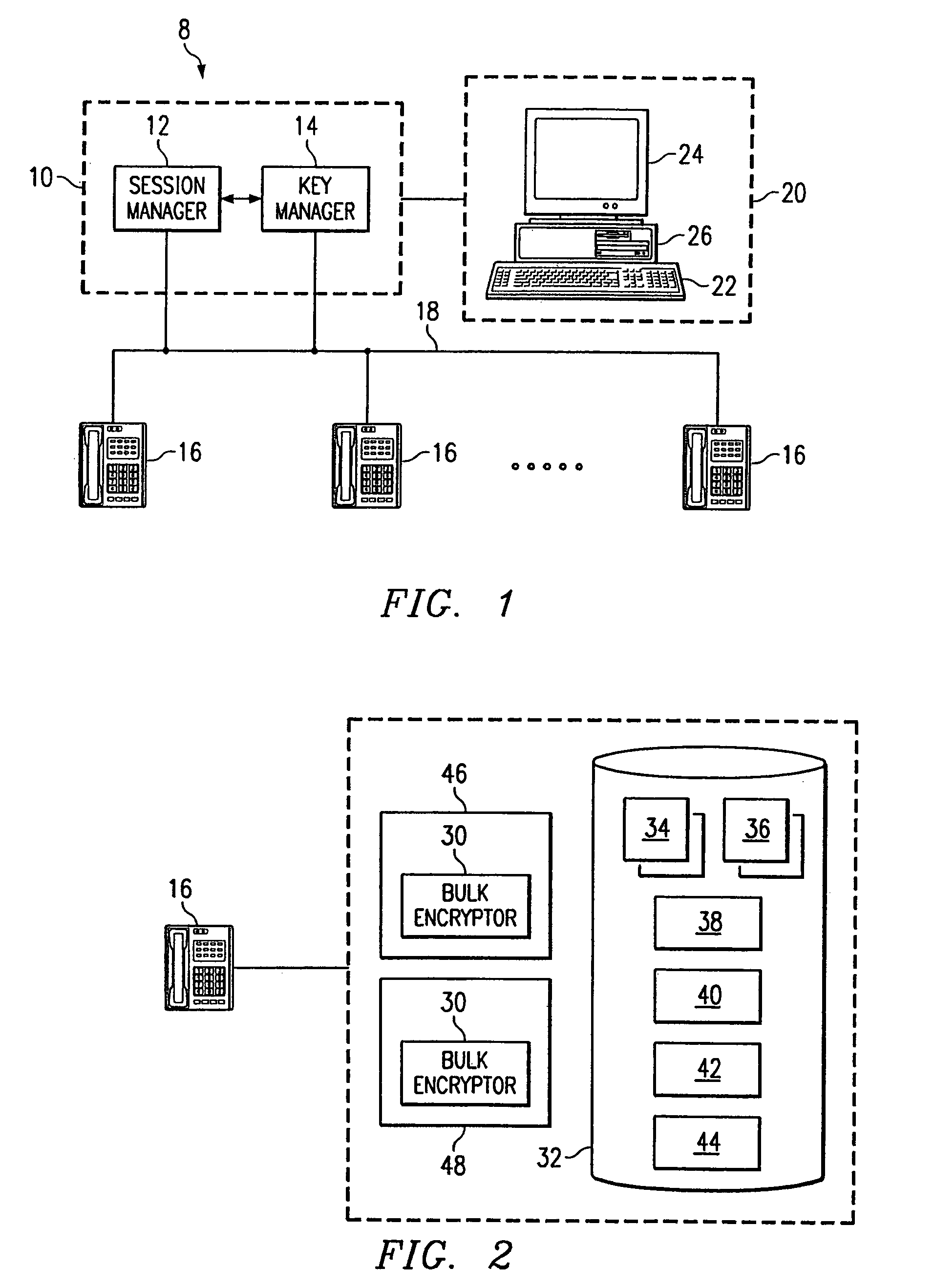

Dual-mode variable key length cryptography system

InactiveUS20090103726A1More robustMore secureSynchronising transmission/receiving encryption devicesKey sizeTime transfer

Owner:LUCENT TECH INC

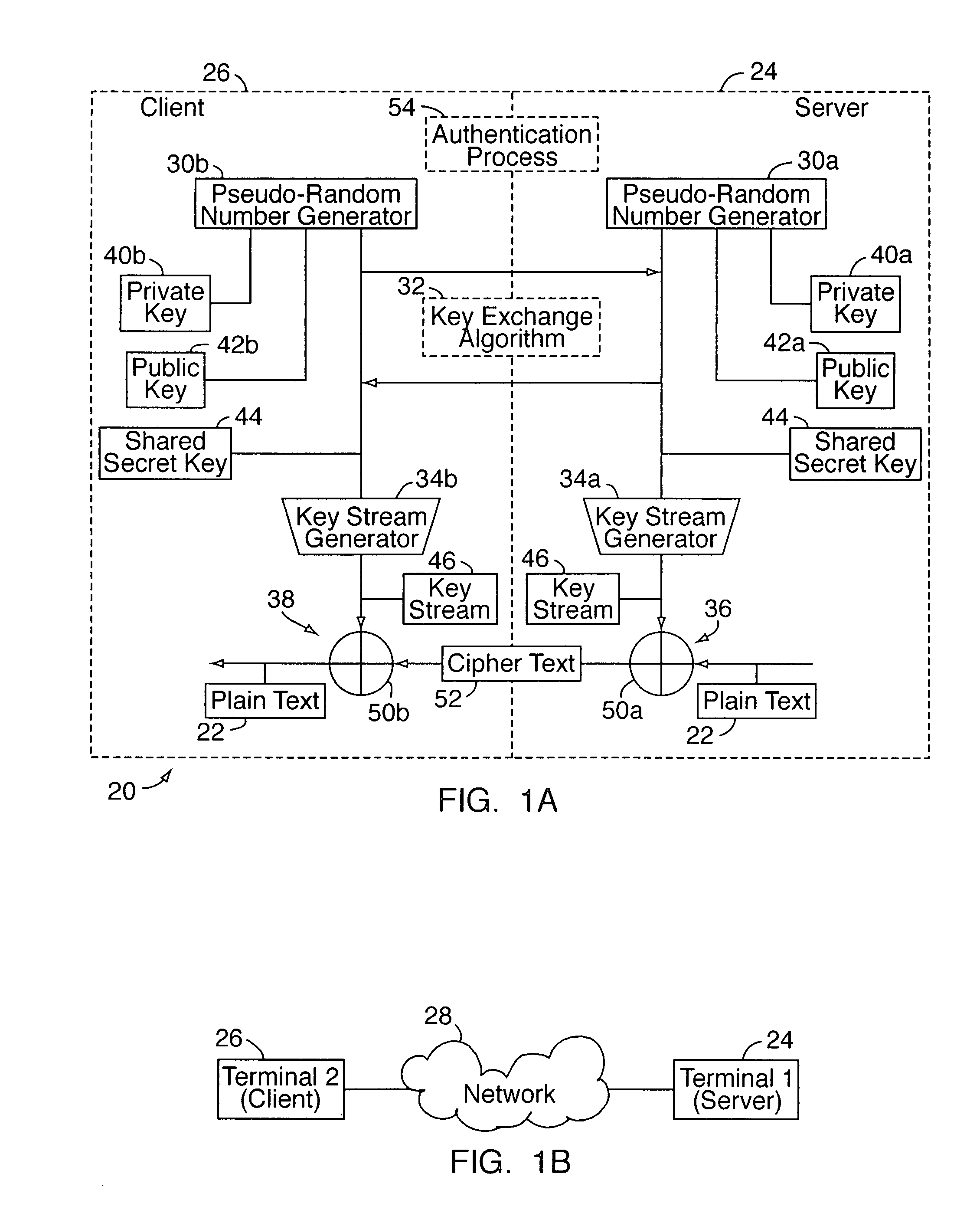

Encrypting information in a communications network

InactiveUS7171552B1Disadvantages can be reduced eliminatedNetwork be reduced eliminatedKey distribution for secure communicationSynchronising transmission/receiving encryption devicesComputer terminalComputer science

According to one embodiment, an end station is provided for coupling to a communications network and participation in a communications session with another end station using the network. The end station includes encryption circuitry including a first linear feedback shift register (LFSR) and an associated first interconnect mask. The encryption circuitry is operable to generate an output sequence using the first LFSR and the first interconnect mask. A first table contains a plurality of polynomials each corresponding to an available interconnect mask. The end station is operable to receive a key specifying the first interconnect mask and to use the output sequence of the encryption circuitry to encrypt an information stream.

Owner:CISCO TECH INC

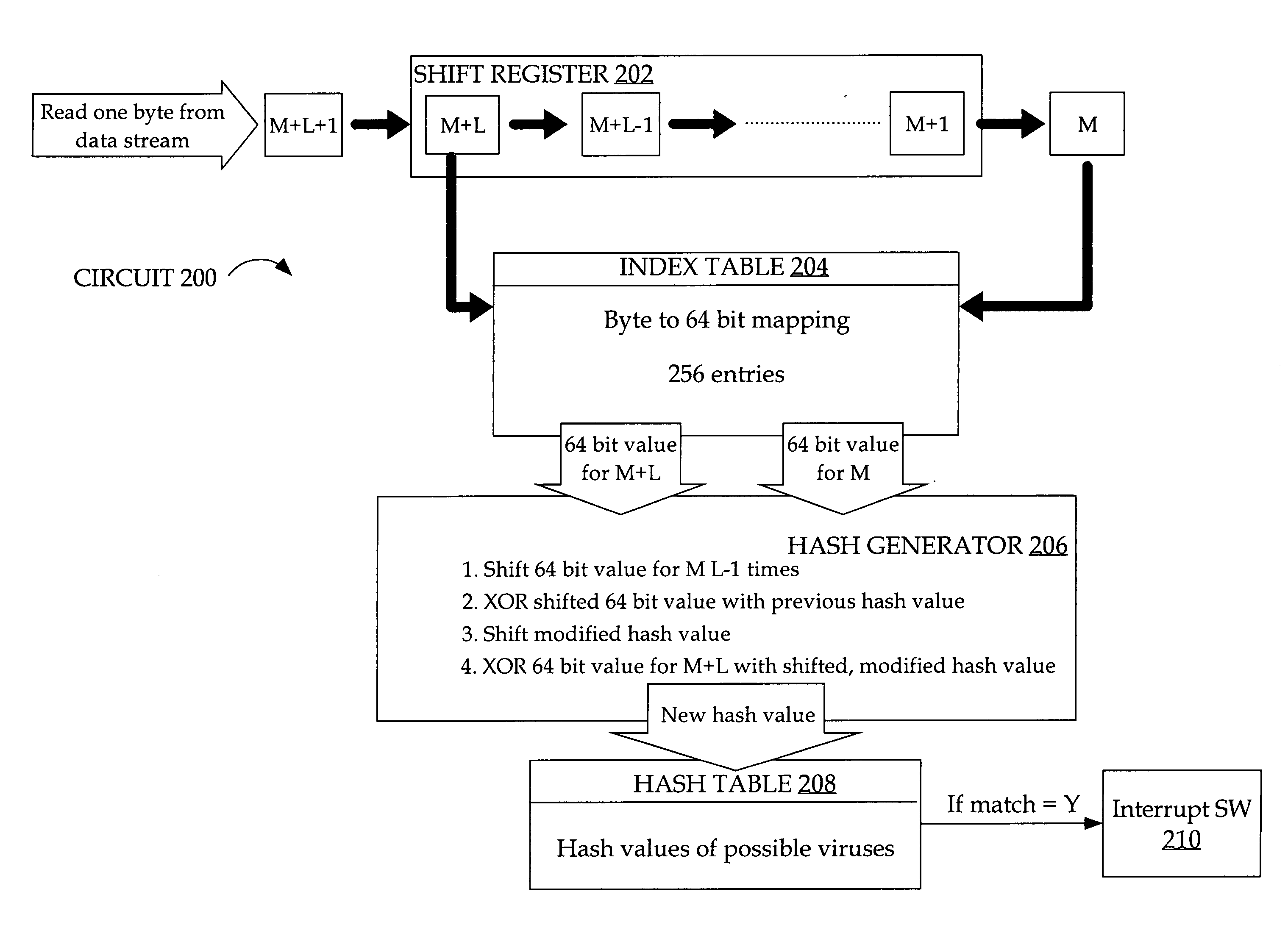

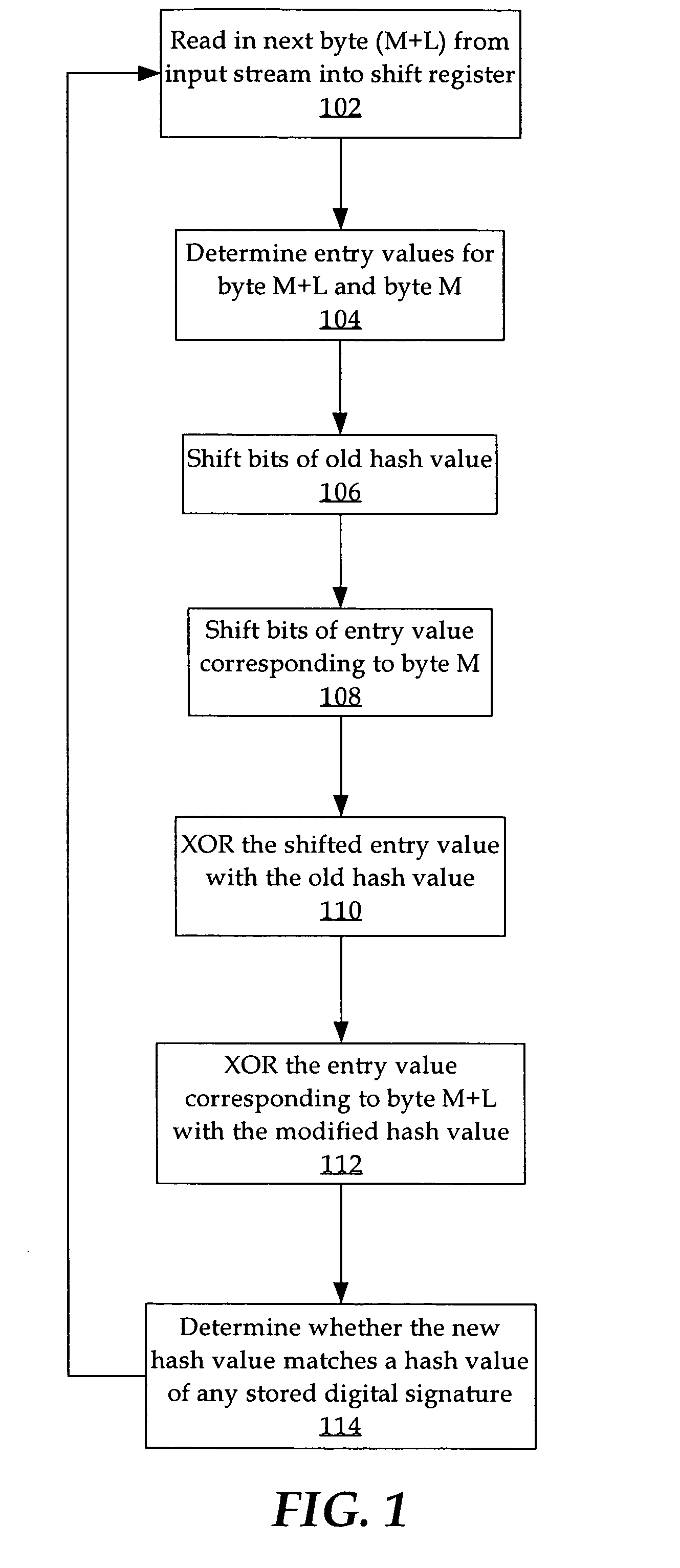

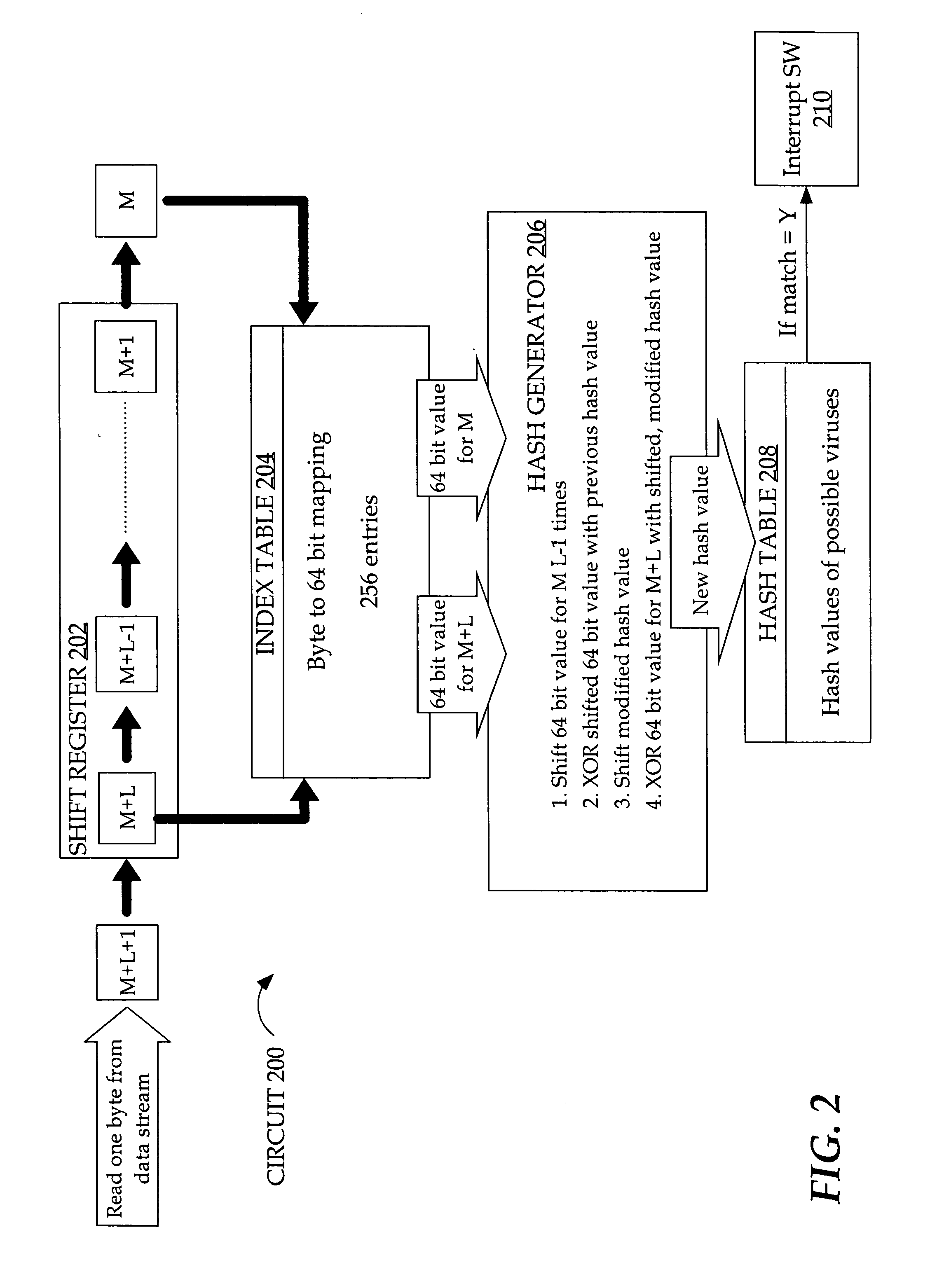

Substring search algorithm optimized for hardware acceleration

ActiveUS20080033942A1Digital data information retrievalRandom number generatorsData streamTheoretical computer science

Techniques are provided for generating a hash value for searching for substrings in a data stream without reading more than one element (e.g. one byte) at a time. According to one technique, a before a next element is added to an old hash value, the old hash value is circularly shifted one or more bits. The first original element is shifted a number of bits and XOR'ed against the old hash value. The next element is added to the old hash value. In one embodiment, an entry value is retrieved for each element from an index table and the XOR and shift operations are performed on the entry values. According to another technique, each Linear Feedback Shift Register (LFSR) of a plurality of LFSRs read in one element at a time beginning at different offsets. Each LFSR uses the same state machine. The result of reading a number of elements into an LFSR is used as the hash value.

Owner:CISCO TECH INC

Method and apparatus for evaluating and optimizing a signaling system

InactiveUS7137048B2Digital circuit testingError detection/correctionElectrical conductorDifferential signaling

A method and apparatus for evaluating and optimizing a signaling system is described. A pattern of test information is generated in a transmit circuit of the system and is transmitted to a receive circuit. A similar pattern of information is generated in the receive circuit and used as a reference. The receive circuit compares the patterns. Any differences between the patterns are observable. In one embodiment, a linear feedback shift register (LFSR) is implemented to produce patterns. An embodiment of the invention may be practiced with various types of signaling systems, including those with single-ended signals and those with differential signals. An embodiment of the invention may be applied to systems communicating a single bit of information on a single conductor at a given time and to systems communicating multiple bits of information on a single conductor simultaneously.

Owner:RAMPART ASSET MANAGEMENT LLC

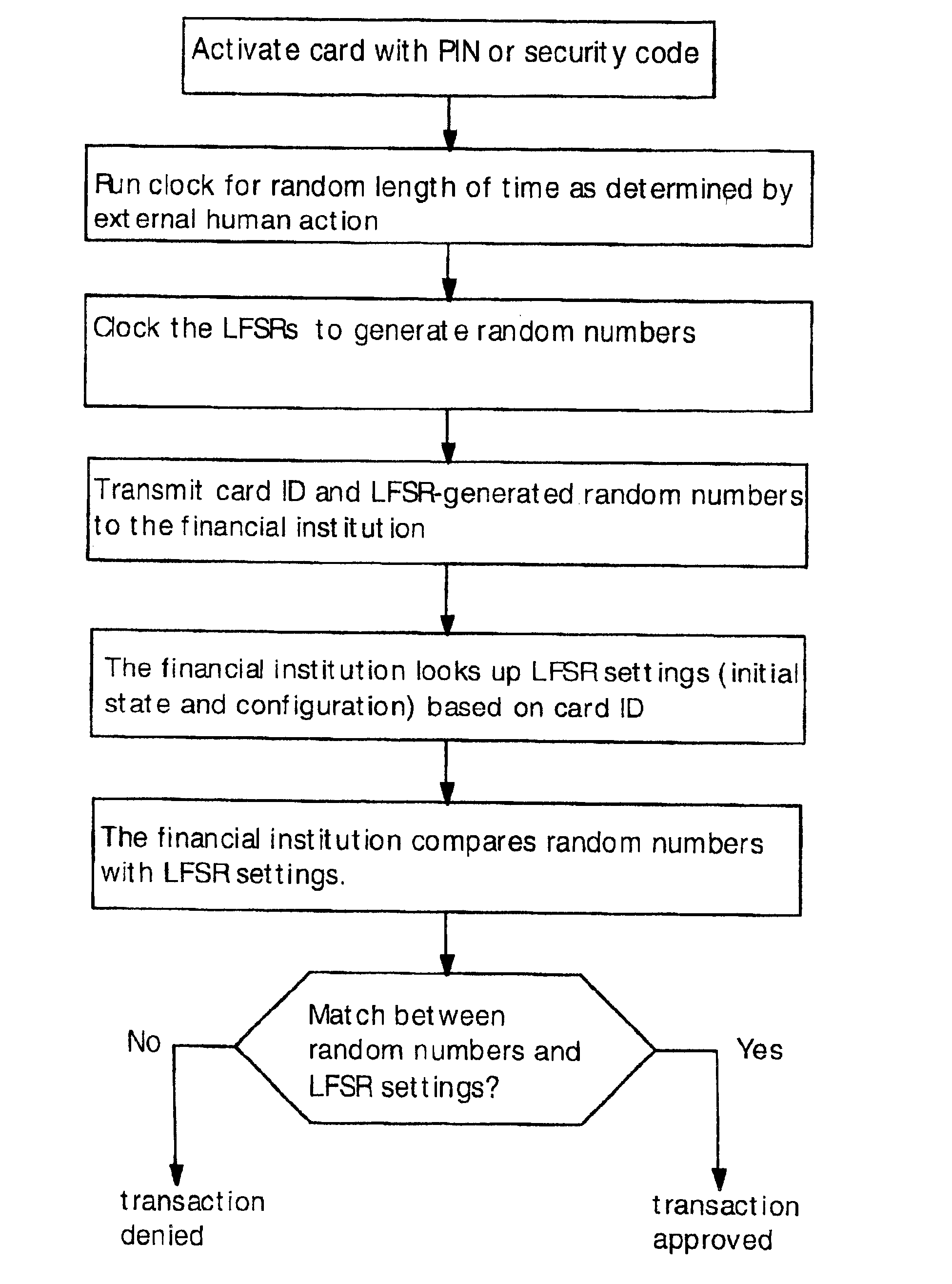

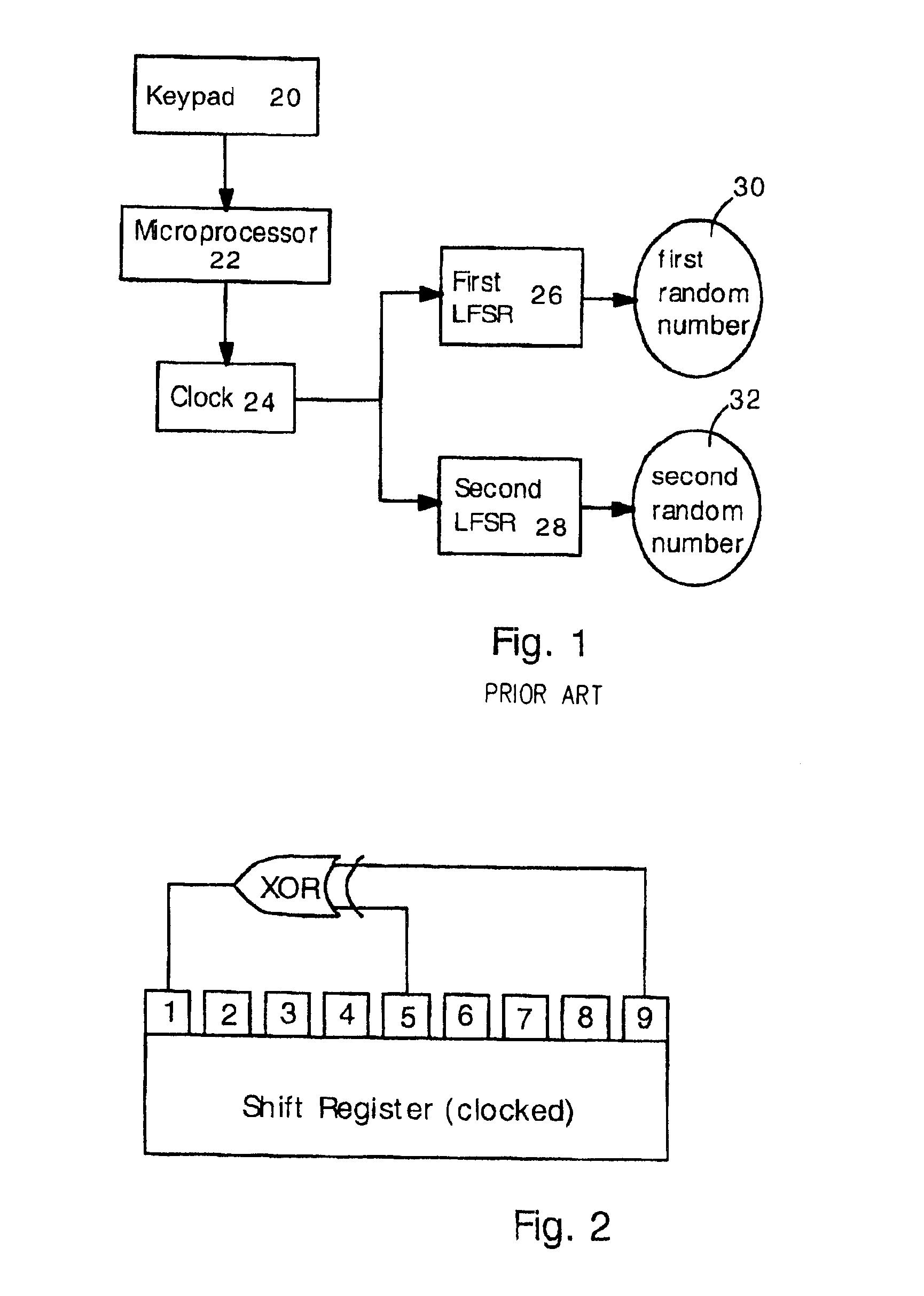

Secure credit card employing pseudo-random bit sequences for authentication

ActiveUS6883717B1Complete banking machinesRandom number generatorsCredit cardTheoretical computer science

A secure credit card has a pair of linear feedback shift registers (LFSRs) for generating a pair of random numbers. The LFSRs each have a unique initial state and feedback tap configuration. Hence, they each produce a unique sequence of numbers. When a financial transaction occurs, the LFSRs are operated for a random number of clock cycles, to create a pair of matched random numbers. Each card issued has unique LFSR settings, and so will produce characteristic random numbers. At a financial institution, the LFSR settings are known, so the financial institution can determine by calculation if the pair of random numbers is authentic. There are many variations, including a credit card with a secret security code for activation, and 2-way “handshake” communication with the financial institution. Also, one of the LFSRs may be replaced with a binary, or similar counter.

Owner:KYNDRYL INC

Phase shifter with reduced linear dependency

InactiveUS20050015688A1Electronic circuit testingRecord information storageCircuit complexityLinear correlation

A method is disclosed for the automated synthesis of phase shifters. Phase shifters comprise circuits used to remove effects of structural dependencies featured by pseudo-random test pattern generators driving parallel scan chains. Using a concept of duality, the method relates the logical states of linear feedback shift registers (LFSRs) and circuits spacing their inputs to each of the output channels. The method generates a phase shifter network balancing the loads of successive stages of LFSRs and satisfying criteria of reduced linear dependency, channel separation and circuit complexity.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

Method for synthesizing linear finite state machines

InactiveUS7260591B2Random number generatorsDigital function generatorsCellular automationVirtual finite-state machine

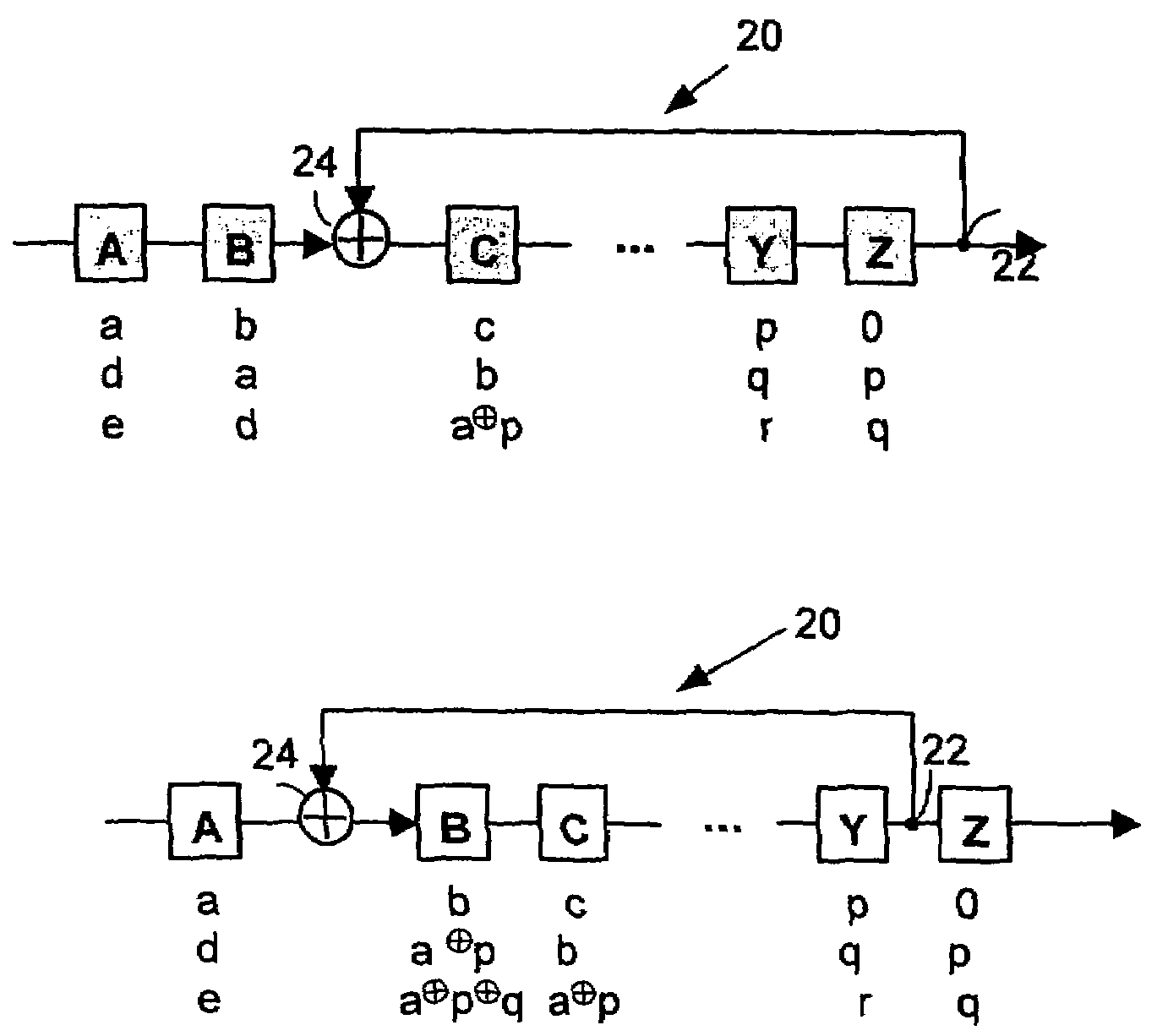

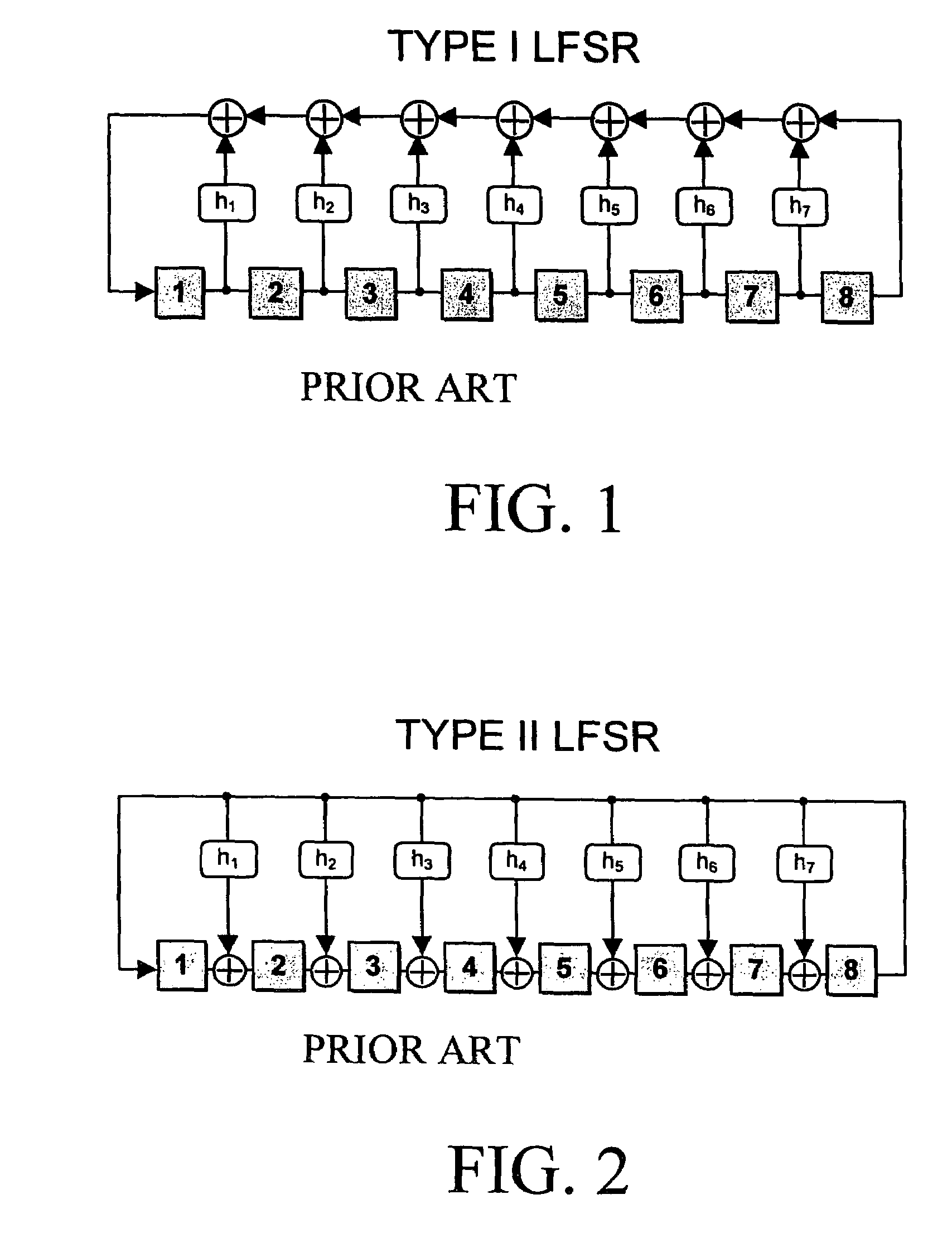

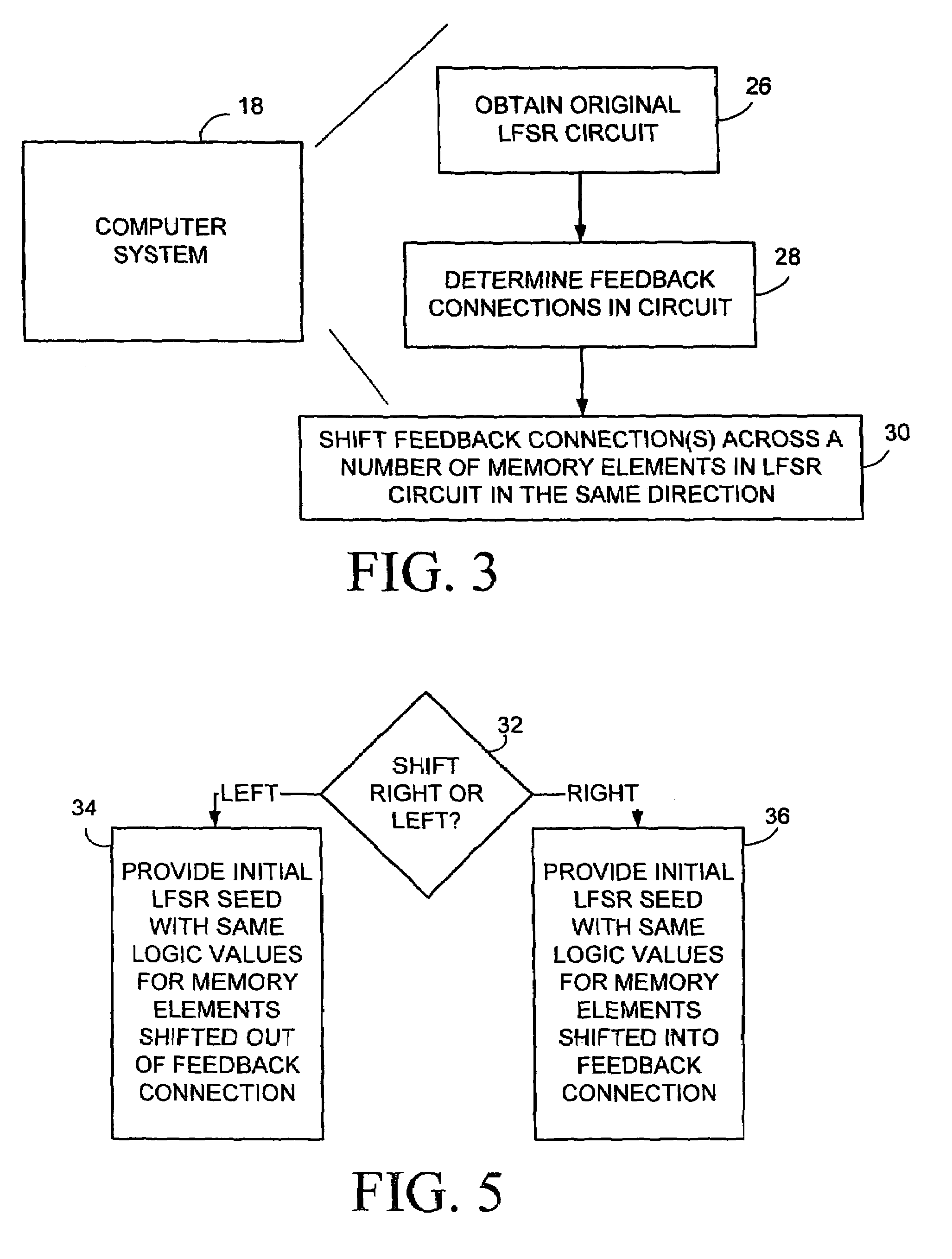

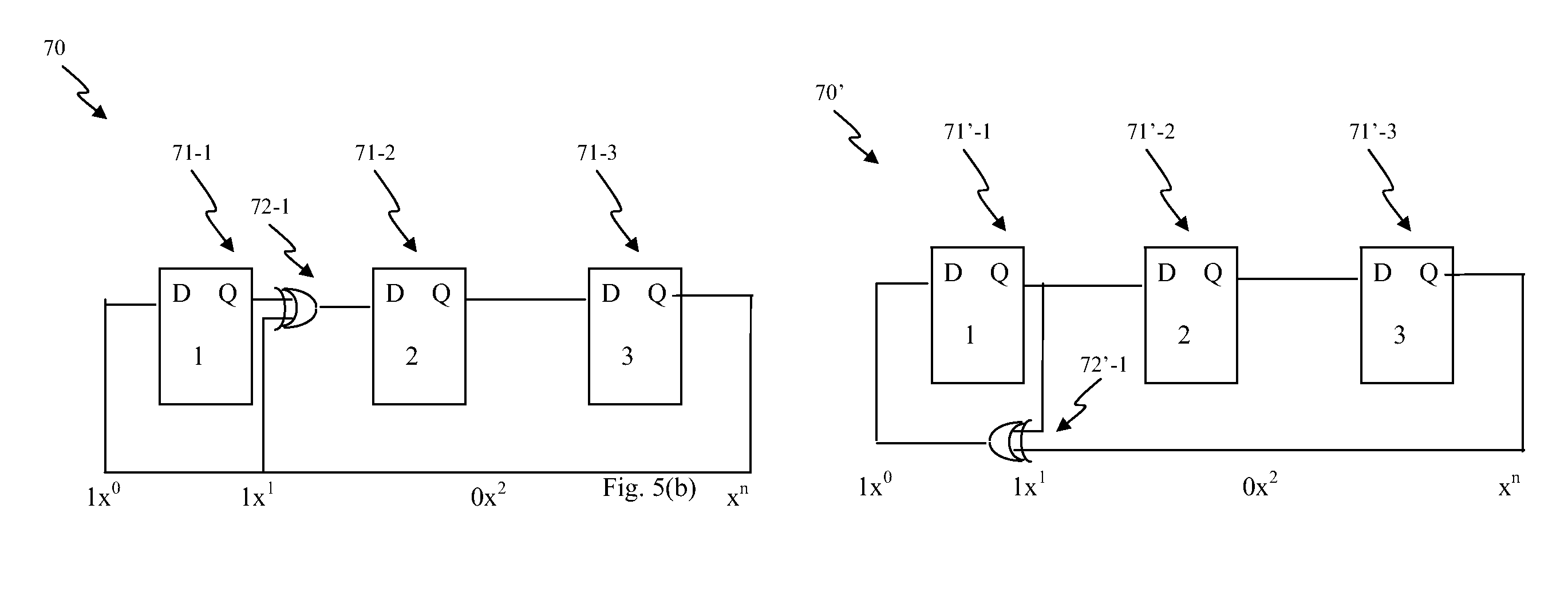

Method and apparatus for synthesizing high-performance linear finite state machines (LFSMs) such as linear feedback shift registers (LFSRs) or cellular automata (CA). Given a characteristic polynomial for the circuit, the method obtains an original LFSM circuit such as a type I or type II LFSR. Feedback connections within the original circuit are then determined. Subsequently, a number of transformations that shift the feedback connections can be applied in such a way that properties of the original circuit are preserved in a modified LFSM circuit. In particular, if the original circuit is represented by a primitive characteristic polynomial, the method preserves the maximum-length property of the original circuit in the modified circuit and enables the modified circuit to produce the same m-sequence as the original circuit. Through the various transformations, a modified LFSM circuit can be created that provides higher performance through shorter feedback connection lines, fewer levels of logic, and lower internal fan-out.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

Circuit and system of a low density one-time programmable memory

InactiveUS8861249B2Low density OTPsReduce memory sizeElectric analogue storesRead-only memoriesIp addressAddress generator

A low density One-Time Programmable (OTP) memory is disclosed to achieve low gate count and low overhead in the peripheral circuits to save the cost. A maximum-length Linear Feedback Shift Register (LFSR) can be used to generate 2n−1 address spaces from an n-bit address. The registers used in the address generator can have two latches. Each latch has two cross-coupled inverters with two outputs coupled to the drains of two MOS input devices, respectively. The inputs of the latch are coupled to the gates of the MOS input devices, respectively. The sources of the MOS input devices are coupled to the drains of at least one MOS device(s), whose gate(s) are coupled to a clock signal and whose source(s) are coupled to a supply voltage. The two latches can be constructed in serial with the outputs of the first latch coupled to the inputs of the second latch.

Owner:ATTOPSEMI TECH CO LTD

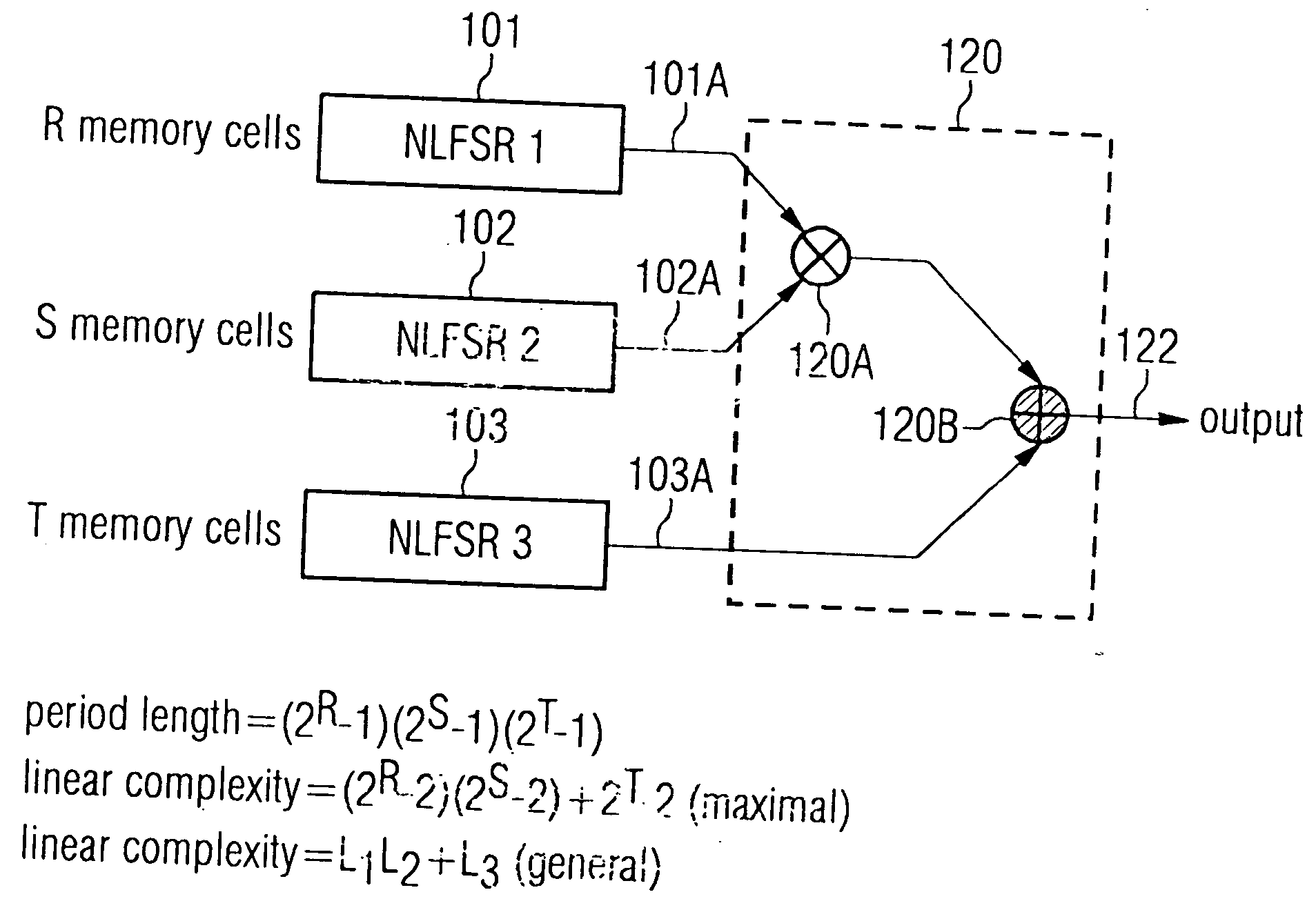

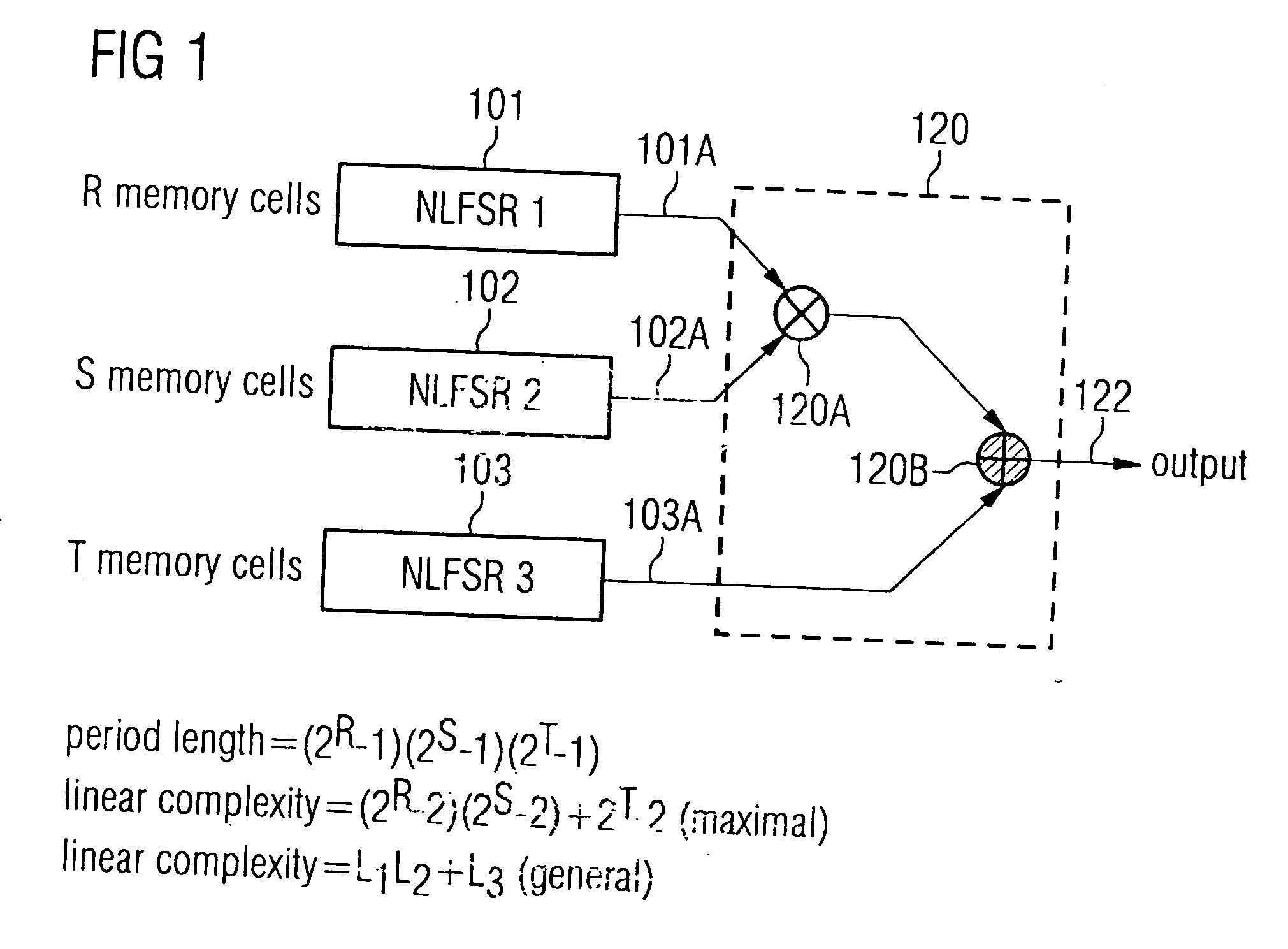

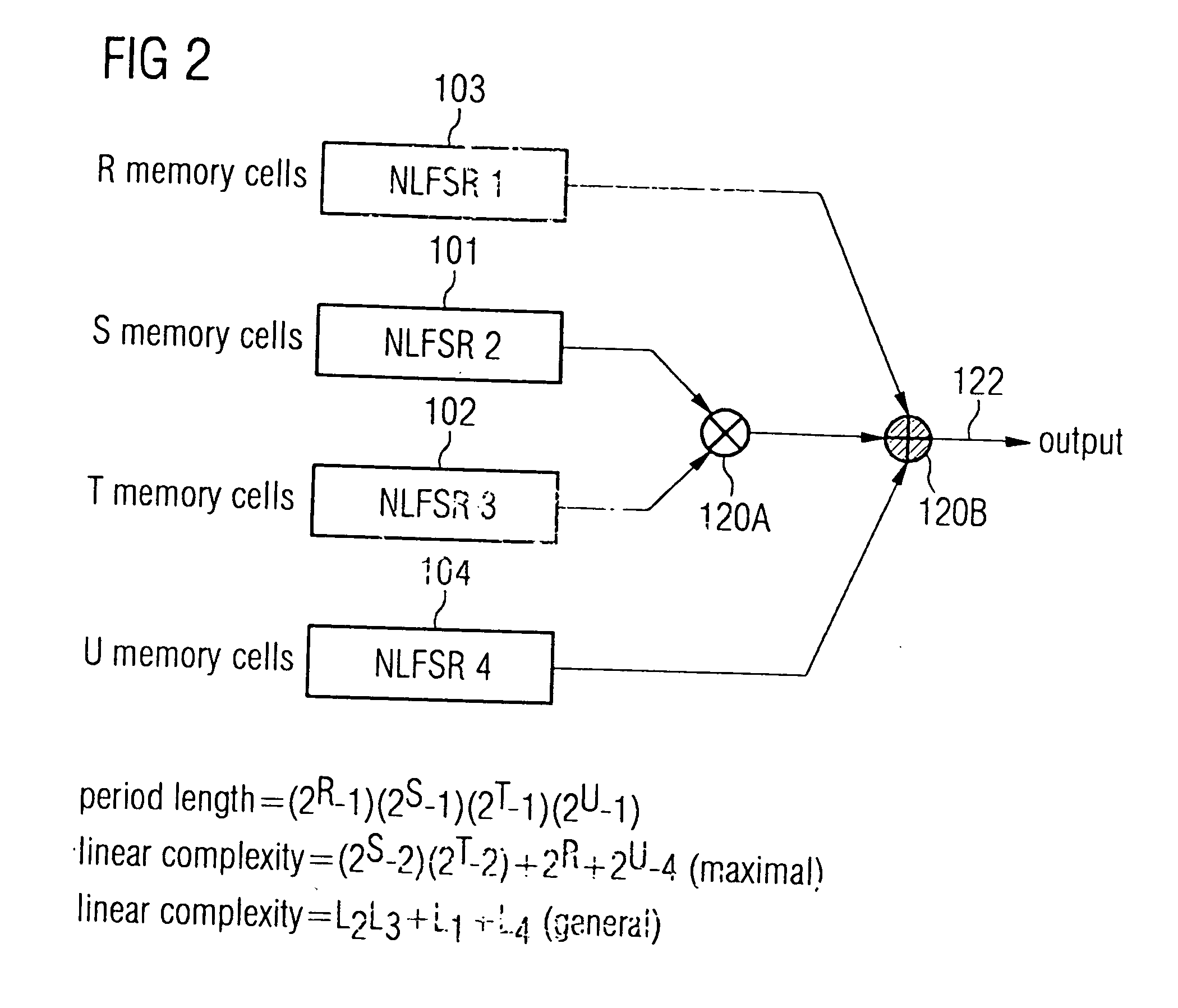

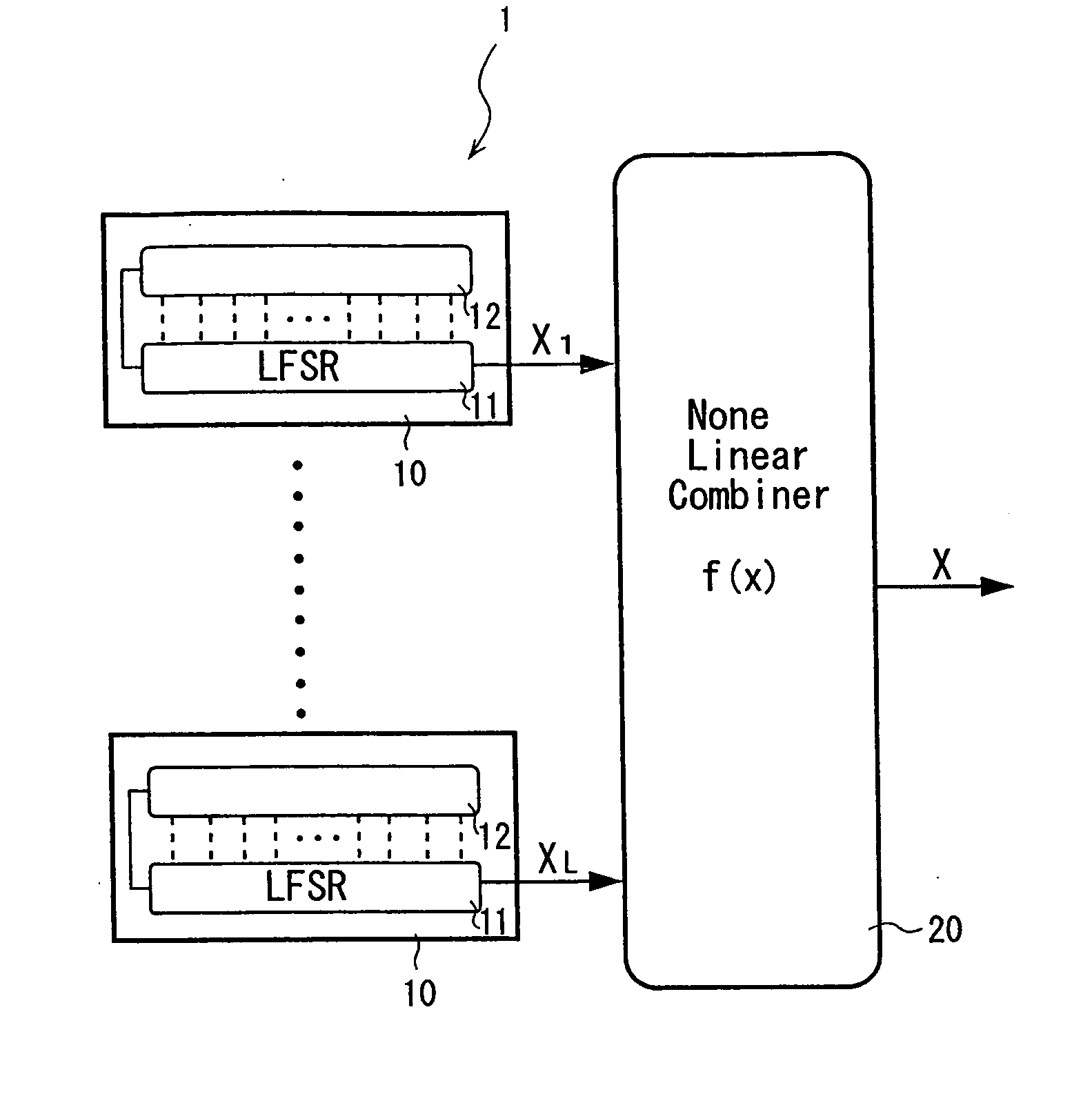

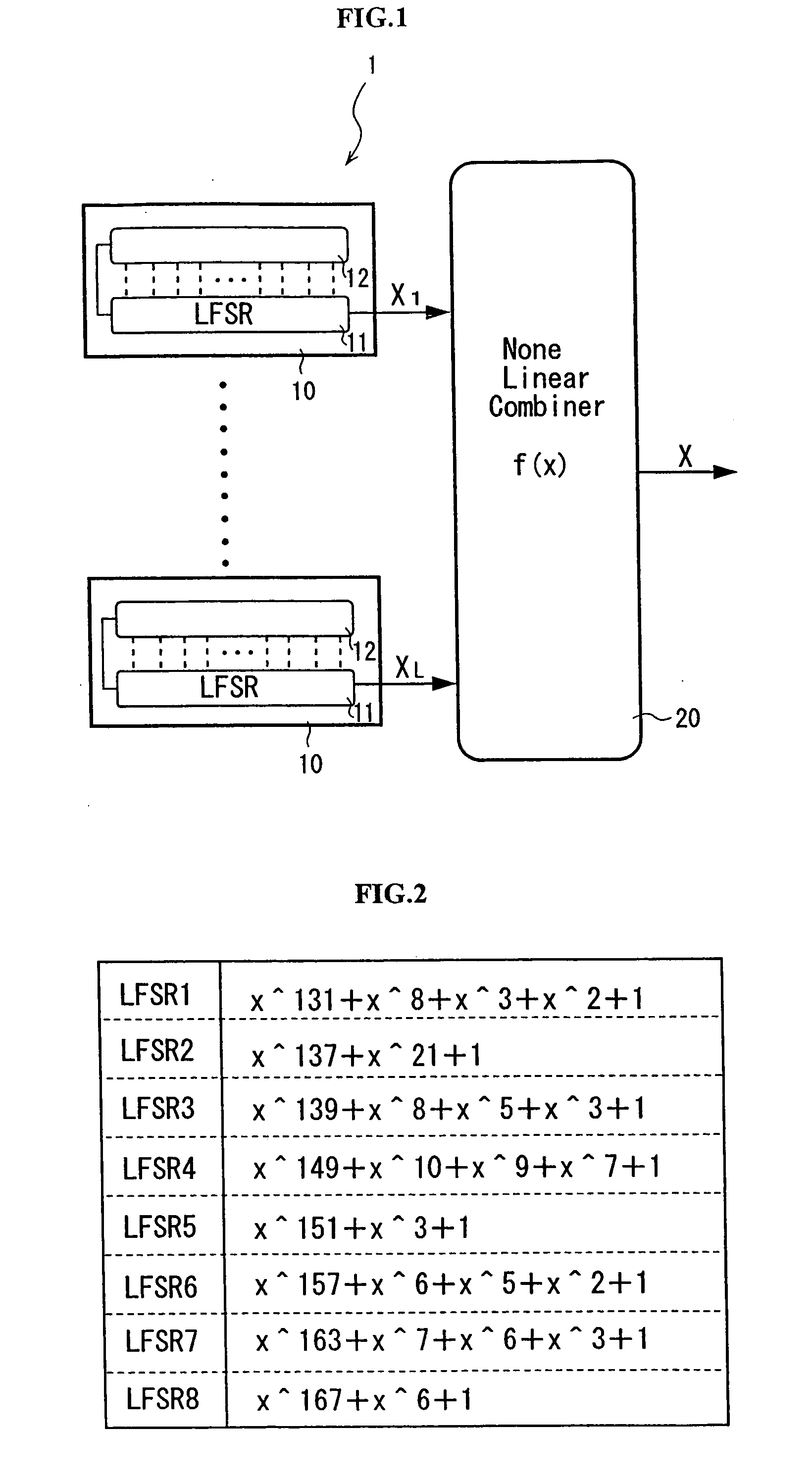

Pseudorandom number generator

InactiveUS20050097153A1Flexible usage of hardware resourceHigh complexityRandom number generatorsDigital function generatorsProcessor registerLinear complexity

A pseudorandom number generator includes a first elemental shift register having a non-linear feedback feature, a second elemental shift register and combiner for combining signals at an output of the first elemental shift register and the second elemental shift register to obtain a combined signal representing a pseudorandom number. The combination of individual non-linear elemental shift registers allows a safe and flexible implementation of random number generators, the output sequences of which include a high linear complexity and a high period length.

Owner:INFINEON TECH AG

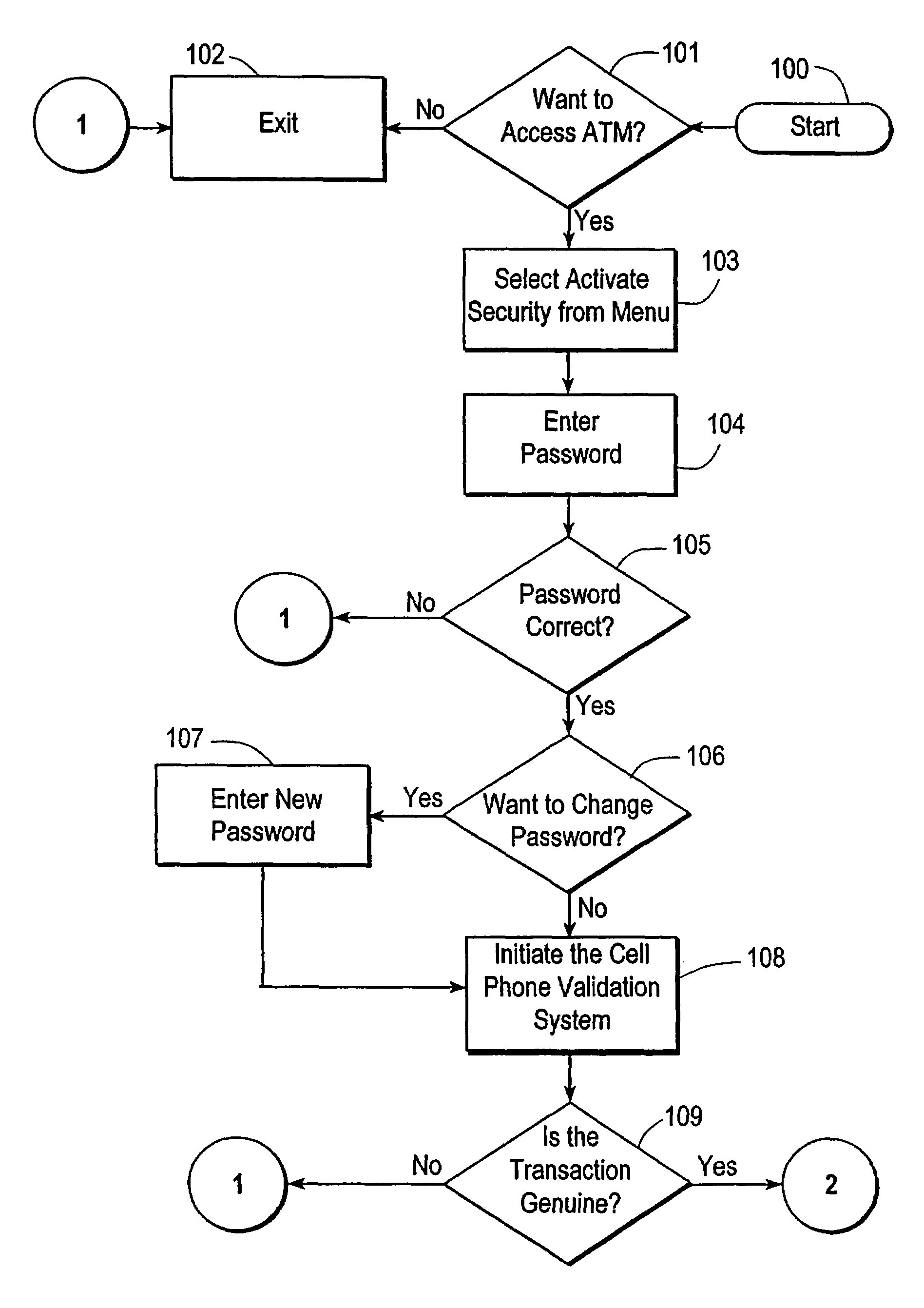

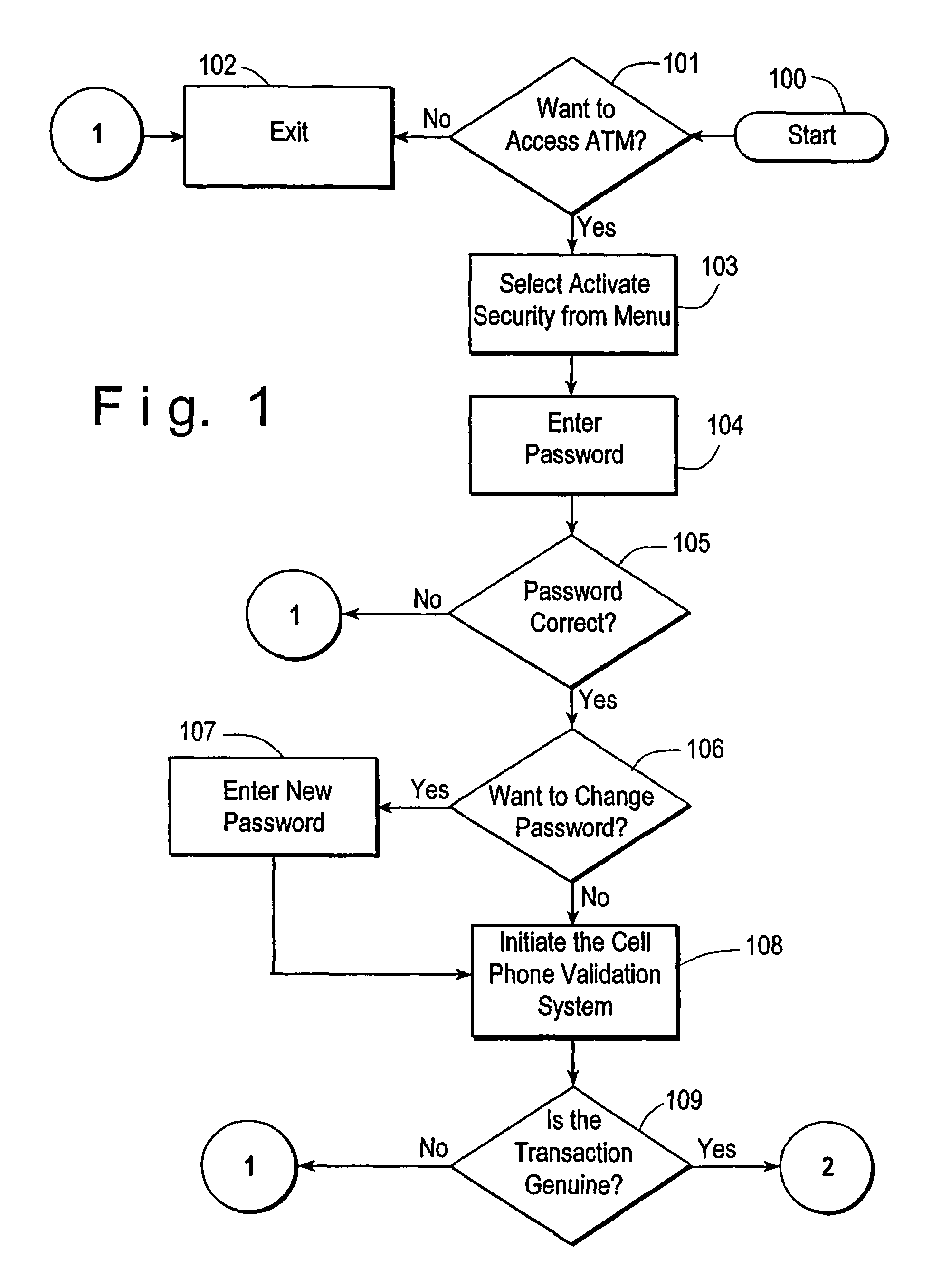

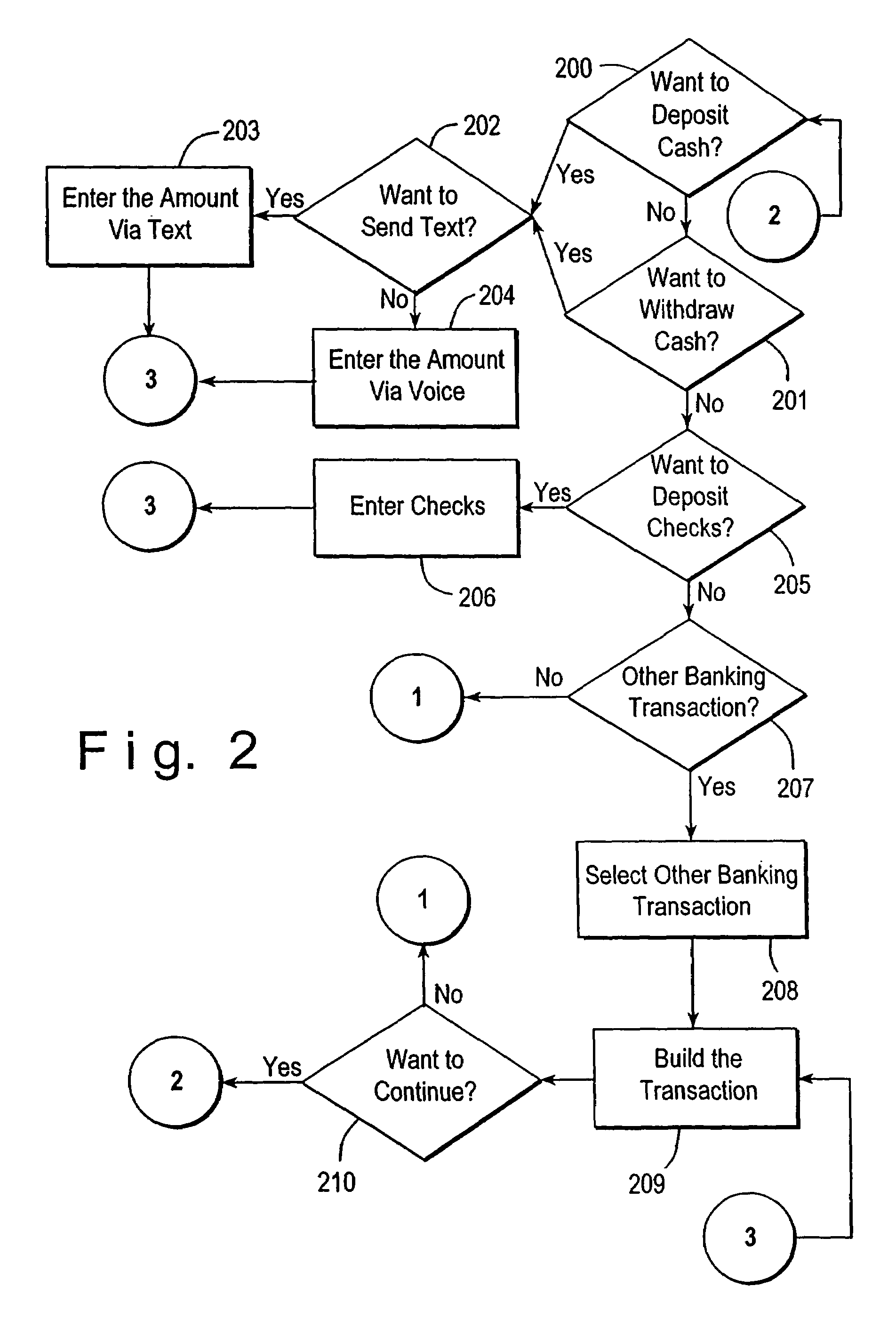

Secure cell phone for ATM transactions

ActiveUS7175073B2Avoid it happening againComplete banking machinesFinanceSoftware emulationLinear feedback shift register

Owner:PAYPAL INC

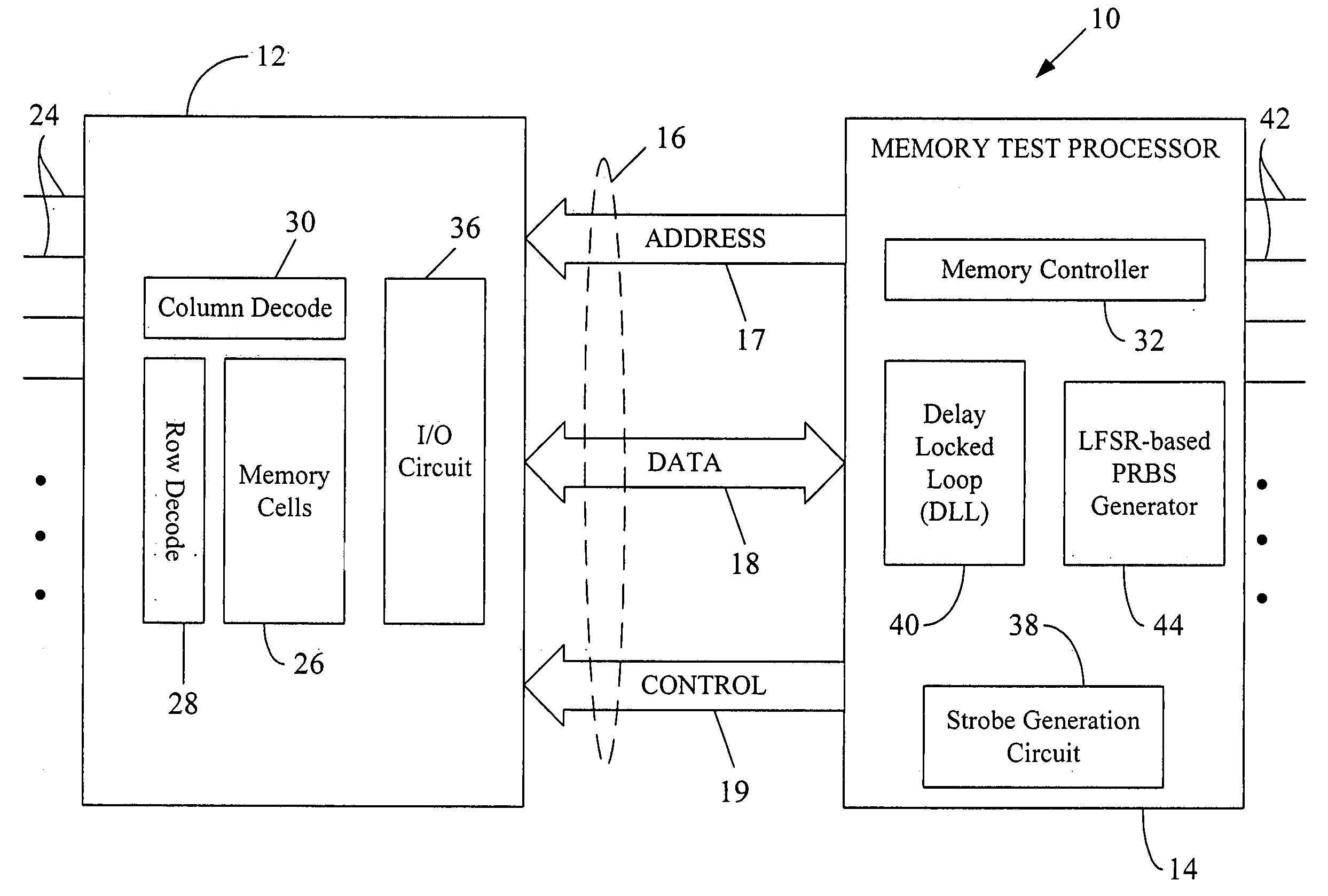

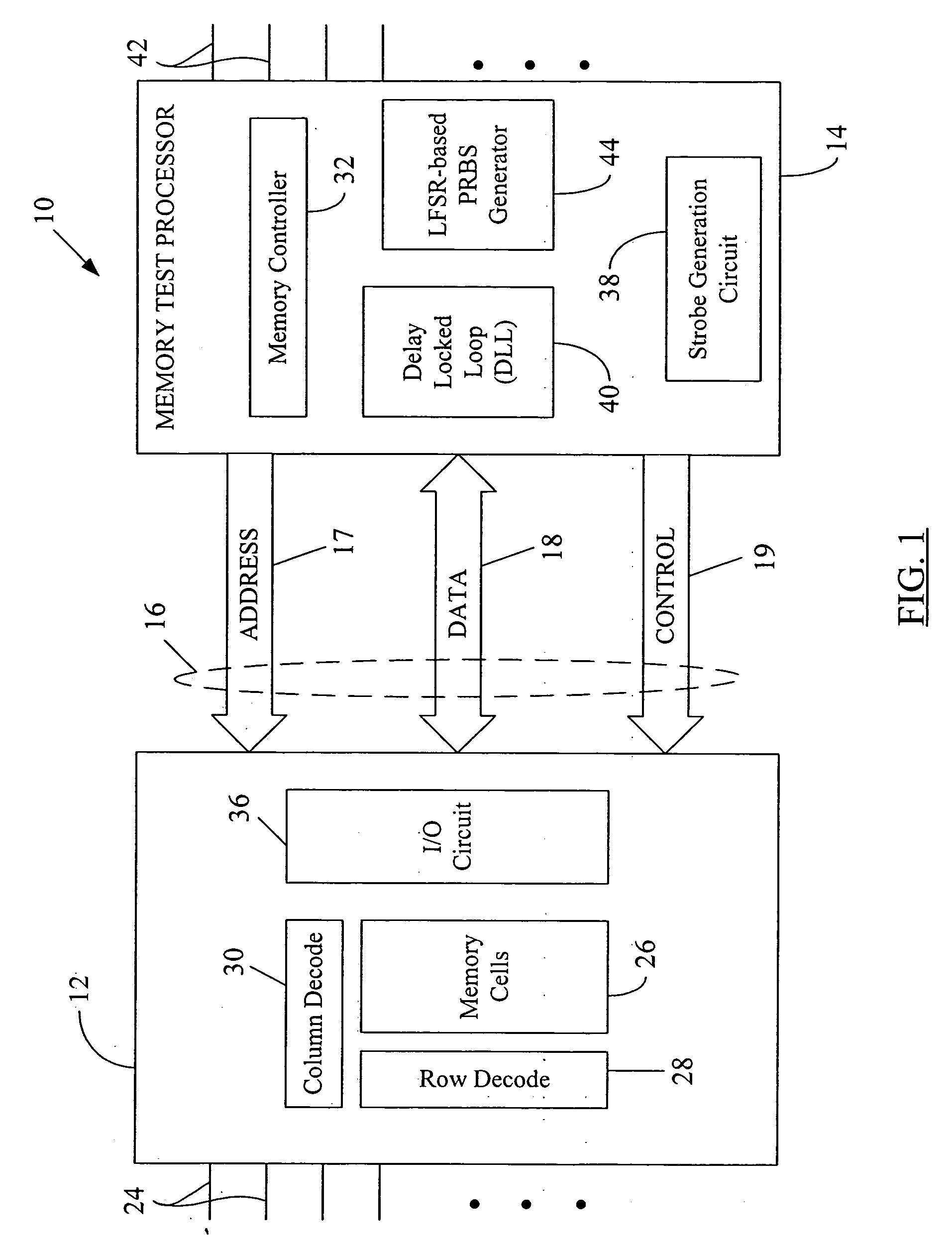

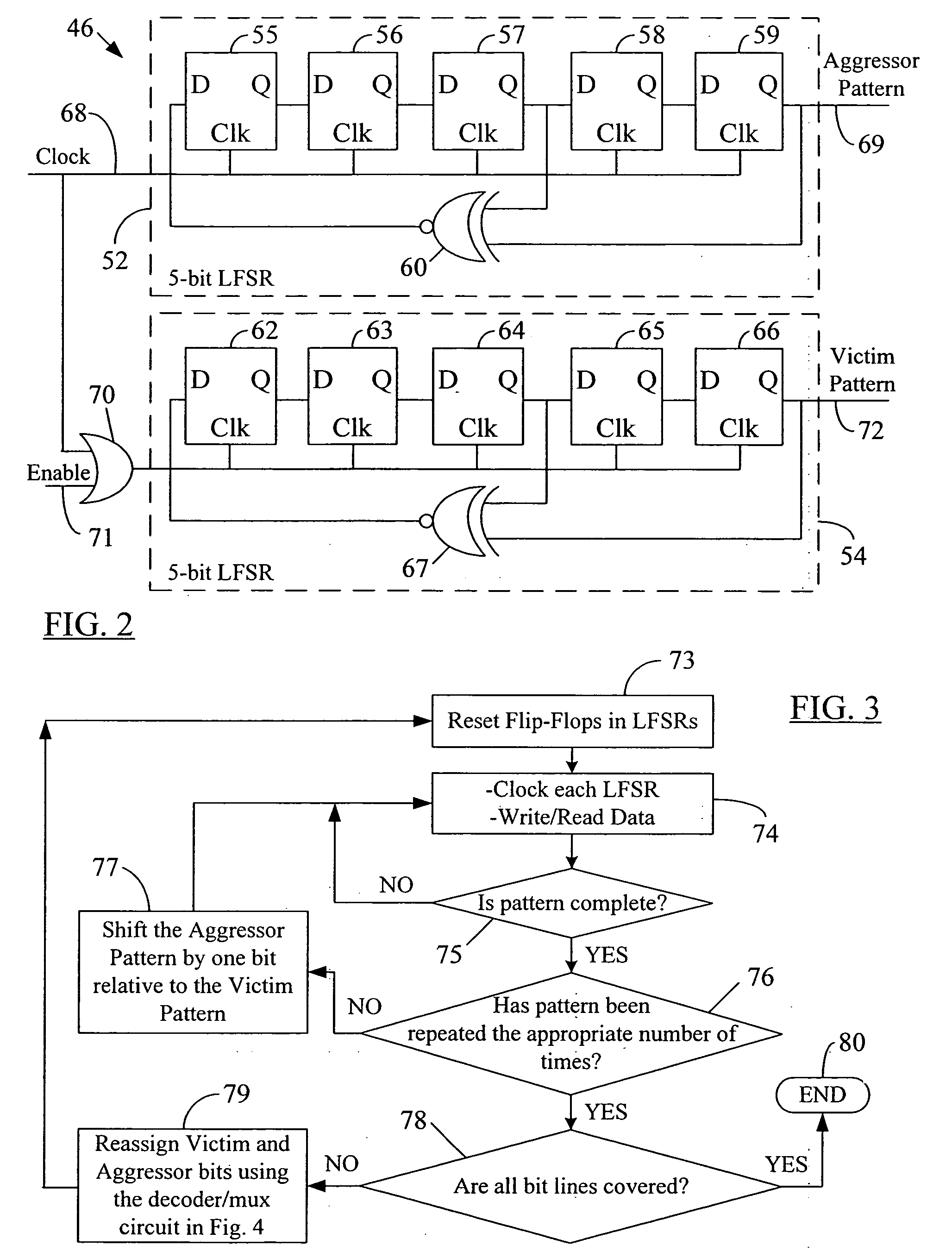

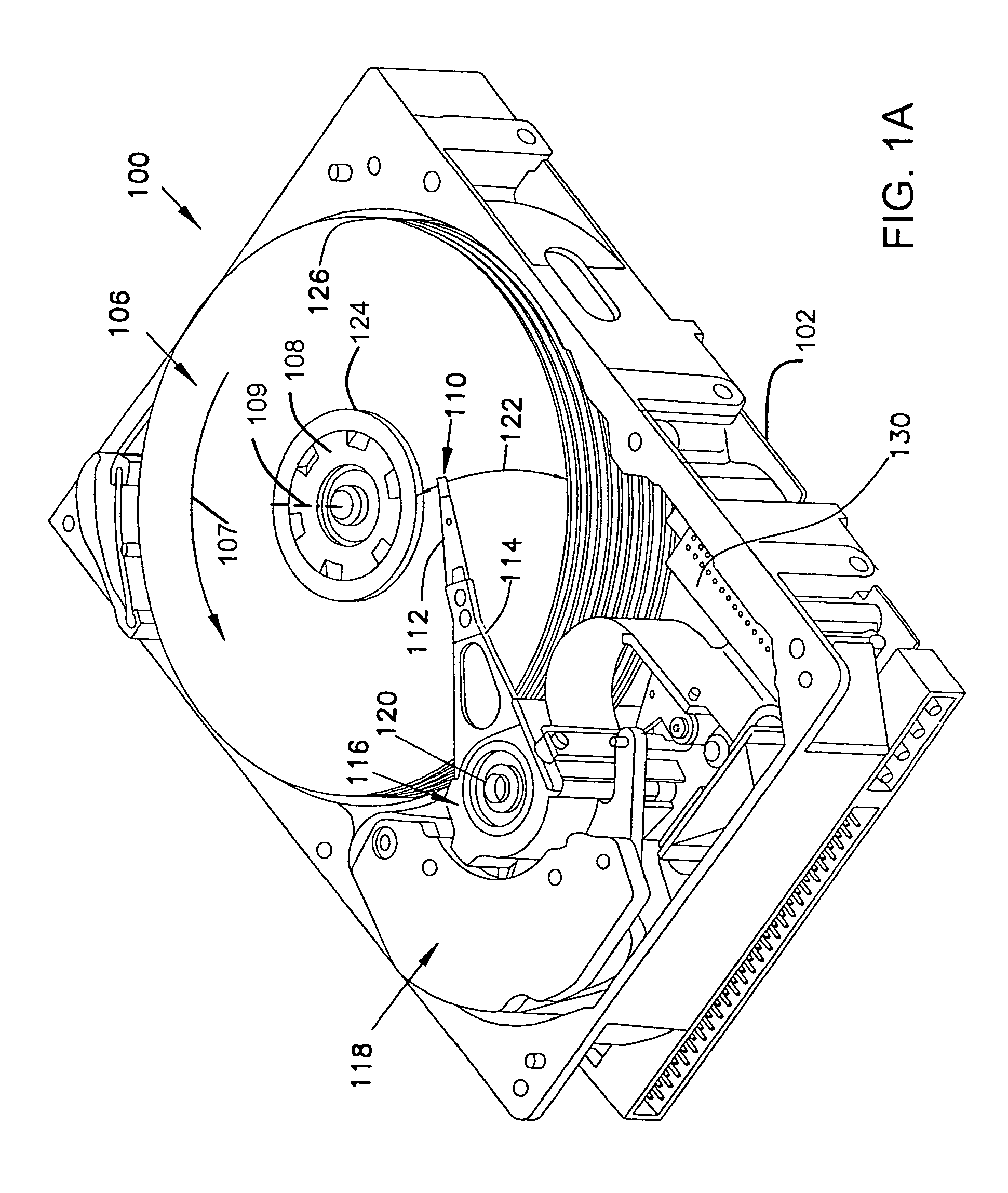

Generation of memory test patterns for DLL calibration

InactiveUS20050166110A1Accurate CalibrationOptimum delay calibrationElectronic circuit testingError detection/correctionMemory chipBit line

A system and method to generate memory test patterns for the calibration of a delay locked loop (DLL) using pseudo random bit sequences (PRBS) generated through a pair of liner feedback shift registers (LFSR). The generated patterns are implemented on the system data bus as test patterns that closely simulate run-time switching conditions on the system bus, so as to allow more accurate calibration of the DLL. Test data write / read operations may be performed while signals for the test patterns are present on various bit lines in the data bus so as to allow for accurate determination or adjustment of the value for the delay to be provided by the DLL to the strobe signals during memory data reading operations at run time. Memory chips may also be tested over an operating range of values using the generated test patterns.

Owner:ROUND ROCK RES LLC

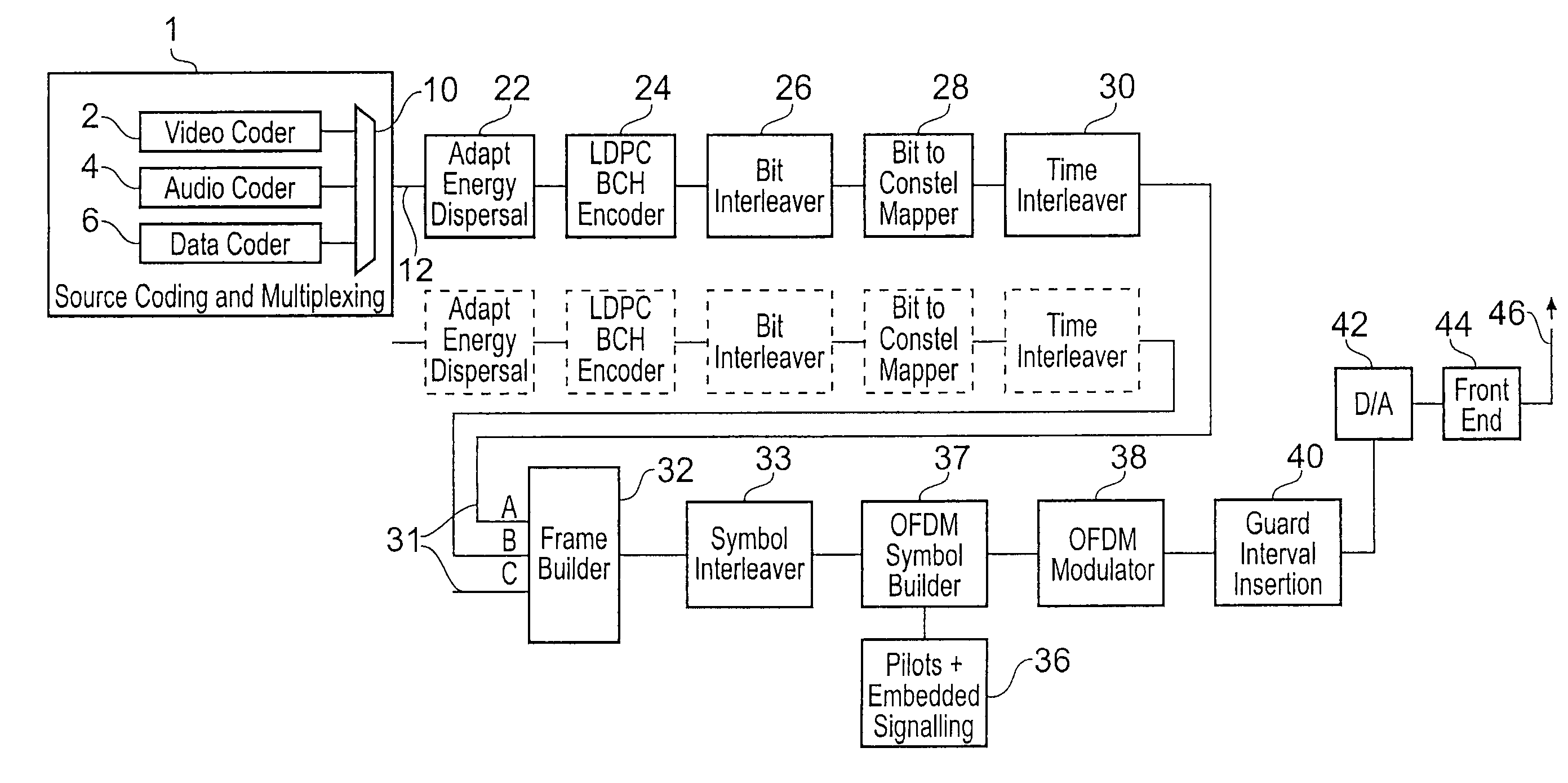

Data processing apparatus and method

ActiveUS20090110094A1Improve integrityGuaranteed to workPulse modulation television signal transmissionDigital data processing detailsData streamCarrier signal

A data processing apparatus maps input symbols to be communicated onto a predetermined number of sub-carrier signals of an Orthogonal Frequency Division Multiplexed (OFDM) symbol. The data processor includes an interleaver memory which reads-in the predetermined number of data symbols for mapping onto the OFDM sub-carrier signals. The interleaver memory reads-out the data symbols on to the OFDM sub-carriers to effect the mapping, the read-out being in a different order than the read-in, the order being determined from a set of addresses, with the effect that the data symbols are interleaved on to the sub-carrier signals. The set of addresses are generated from an address generator which comprises a linear feedback shift register and a permutation circuit. The linear feedback shift register has twelve register stages with a generator polynomial for the linear feedback shift register of R′i[11]=R′i-1[0]R′i-1[1]R′i-1[4]R′i-1[6], and the permutation code forms, with an additional bit, a thirteen bit address. The permutation code is changed from one OFDM symbol to another, thereby providing an improvement in interleaving the data symbols for an 8K operating mode of an OFDM modulated system such as a Digital Video Broadcasting (DVB) standard such as DVB-Terrestrial2 (DVB-T2). This is because there is a reduced likelihood that successive data bits which are close in order in an input data stream are mapped onto the same sub-carrier of an OFDM symbol.

Owner:SONY CORP

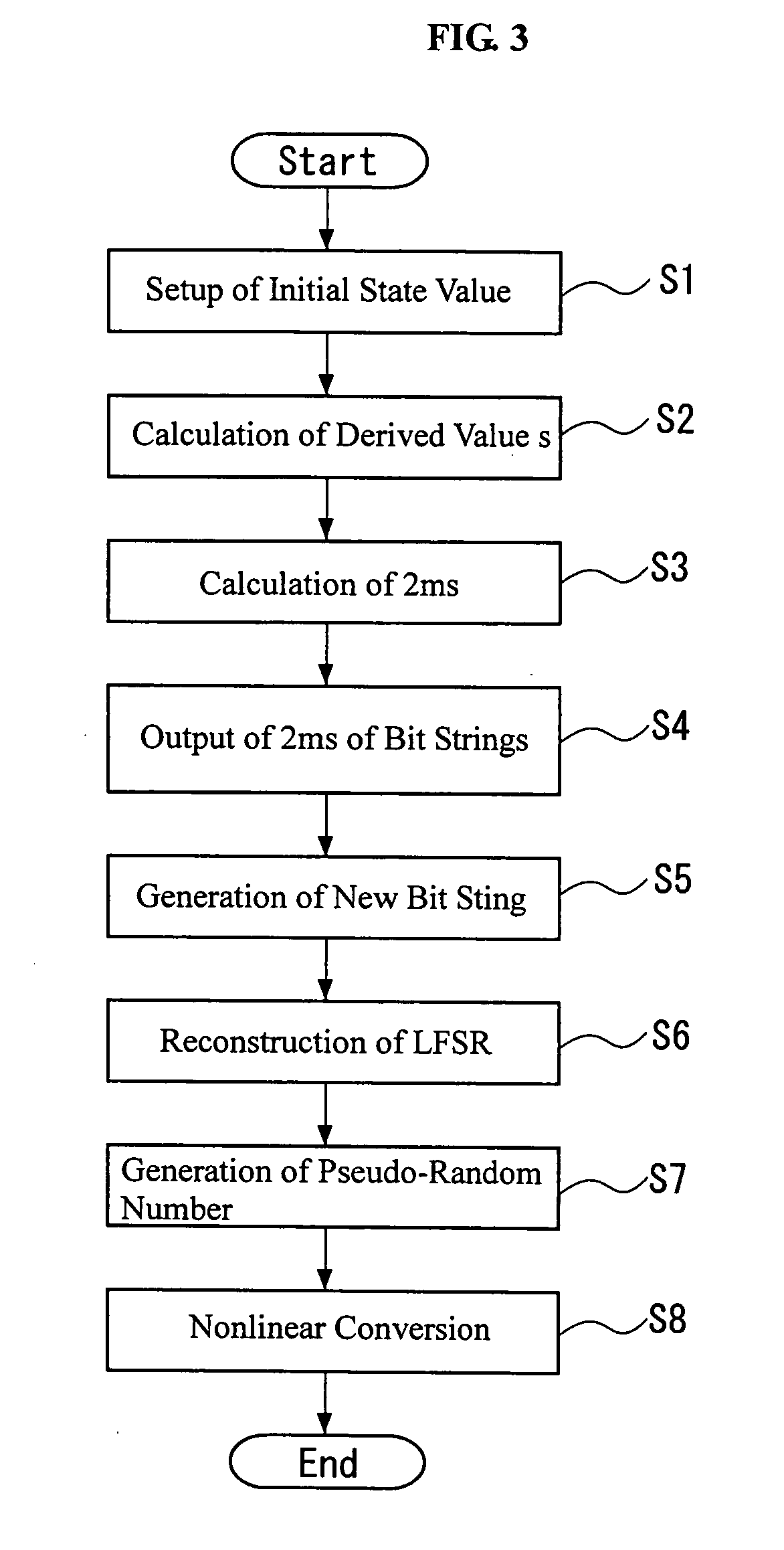

Pseudo-random number generation method and pseudo-random number generator

InactiveUS20060039558A1Easy to changeHigh encryption strengthRandom number generatorsCoding/ciphering apparatusLinearityNumber generator

A bit string obtained by sampling, every the number s, bits of a bit string whose output sequence is M sequence, when the bit number per one cycle of the M sequence is prime to the derived value, constitutes M sequence of a linear feedback shift register having other construction. Further, the linear feedback shift register can be determined from bits corresponding to at least two cycles by Berlekamp-Massay algorithm, whereby the linear feedback shift register 11 can be easily and dynamically reconstructed based on the initial state value.

Owner:KOBAYASHI AKIRA +1

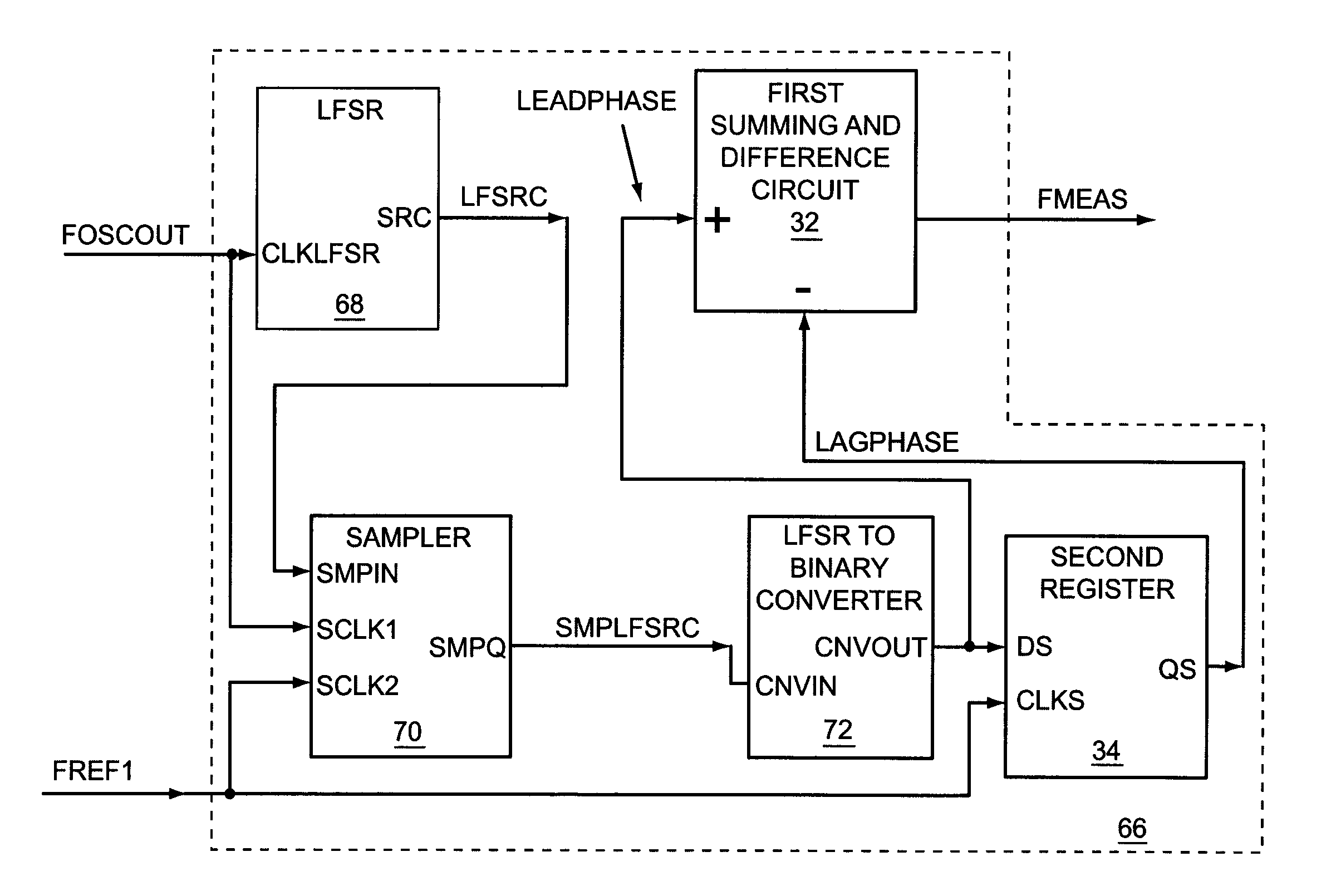

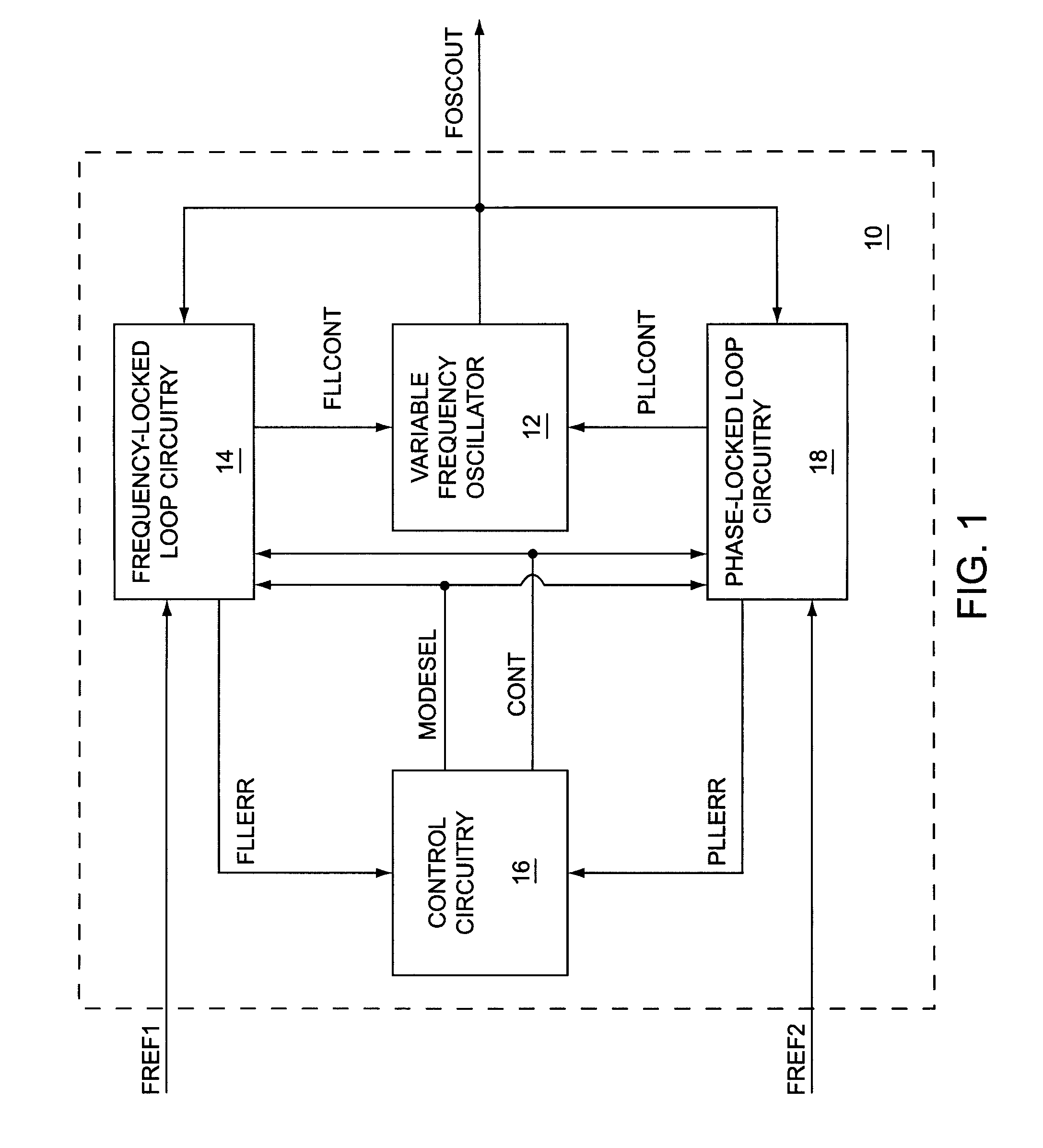

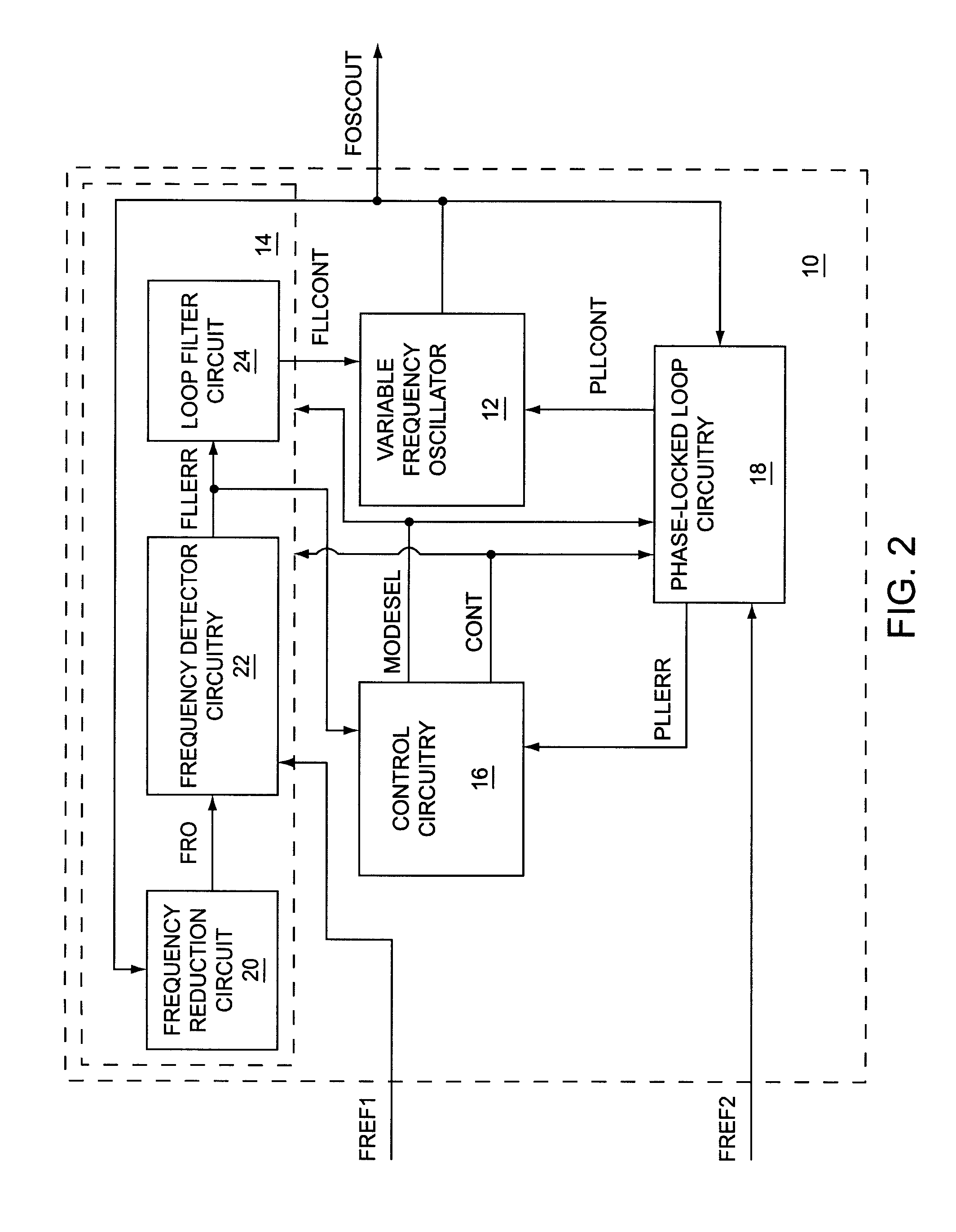

Frequency measurement based frequency locked loop synthesizer

ActiveUS7750685B1Fast settling timeReduce frequencyMultiple input and output pulse circuitsPulse automatic controlFrequency measurementsEngineering

A first embodiment of the present invention relates to a frequency and phase locked loop (FPLL) synthesizer having a frequency-locked loop (FLL) operating mode and a phase-locked loop (PLL) operating mode. The FLL operating mode is used for rapid coarse tuning of the FPLL synthesizer and is followed by the PLL operating mode for fine tuning and stabilization of the frequency of an output signal from the FPLL synthesizer. A second embodiment of the present invention relates to a high resolution frequency measurement circuit that is capable of directly measuring the frequency of a high frequency signal to provide a high resolution frequency measurement using a lower frequency reference signal, and may include linear feedback shift register (LFSR) circuitry and LFSR-to-binary conversion circuitry. A third embodiment of the present invention relates to an FPLL having an FLL that includes the high resolution frequency measurement circuit.

Owner:QORVO US INC

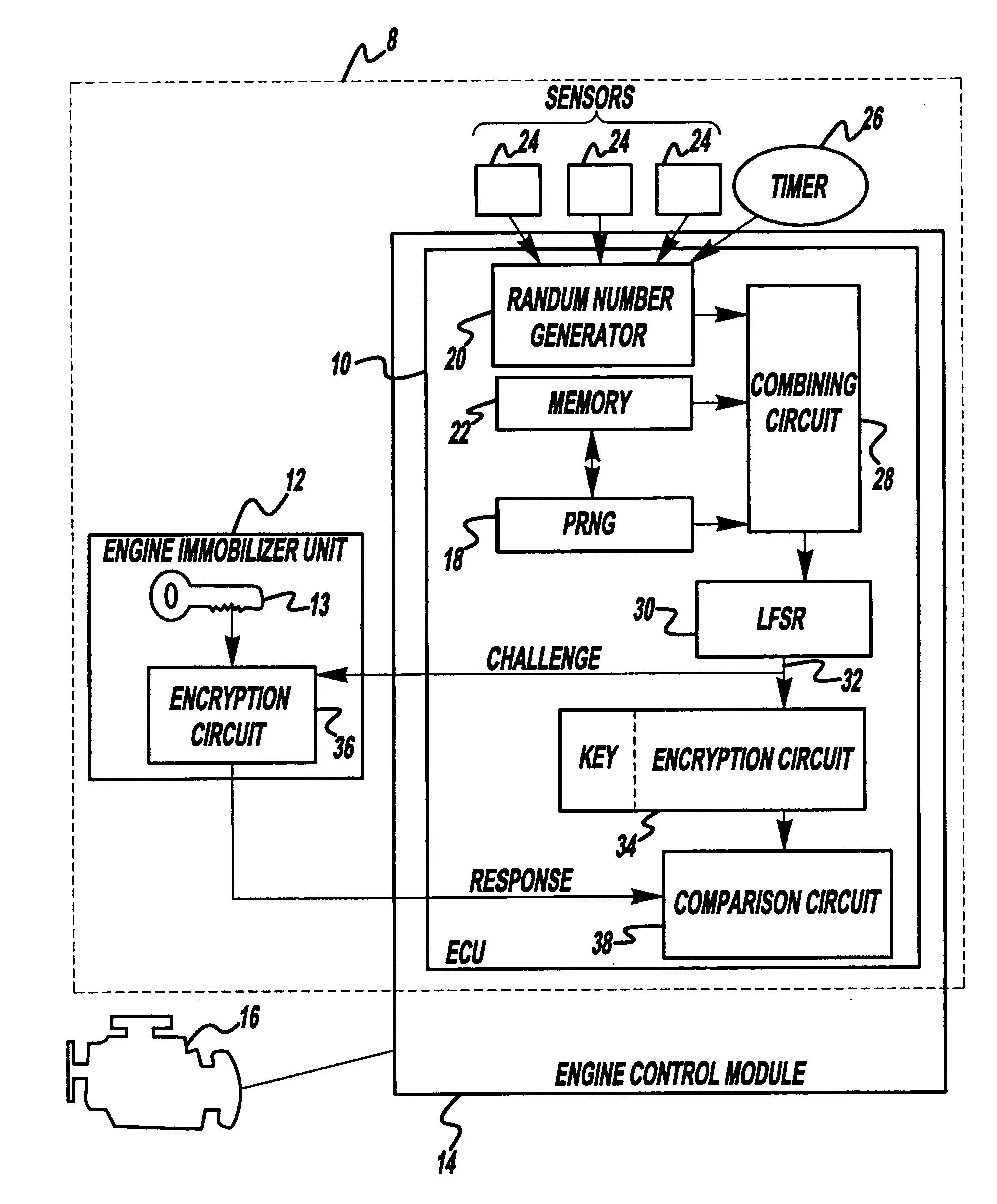

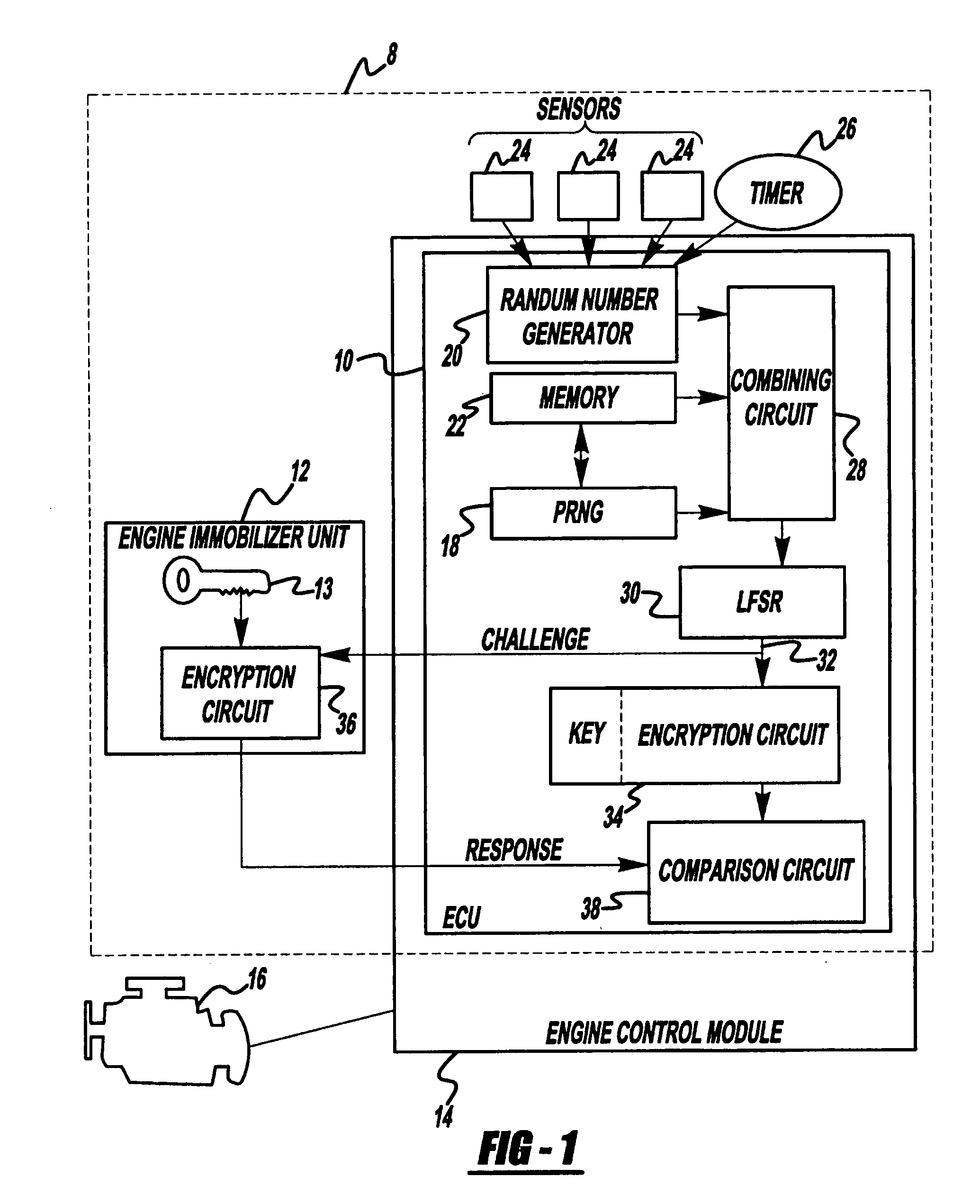

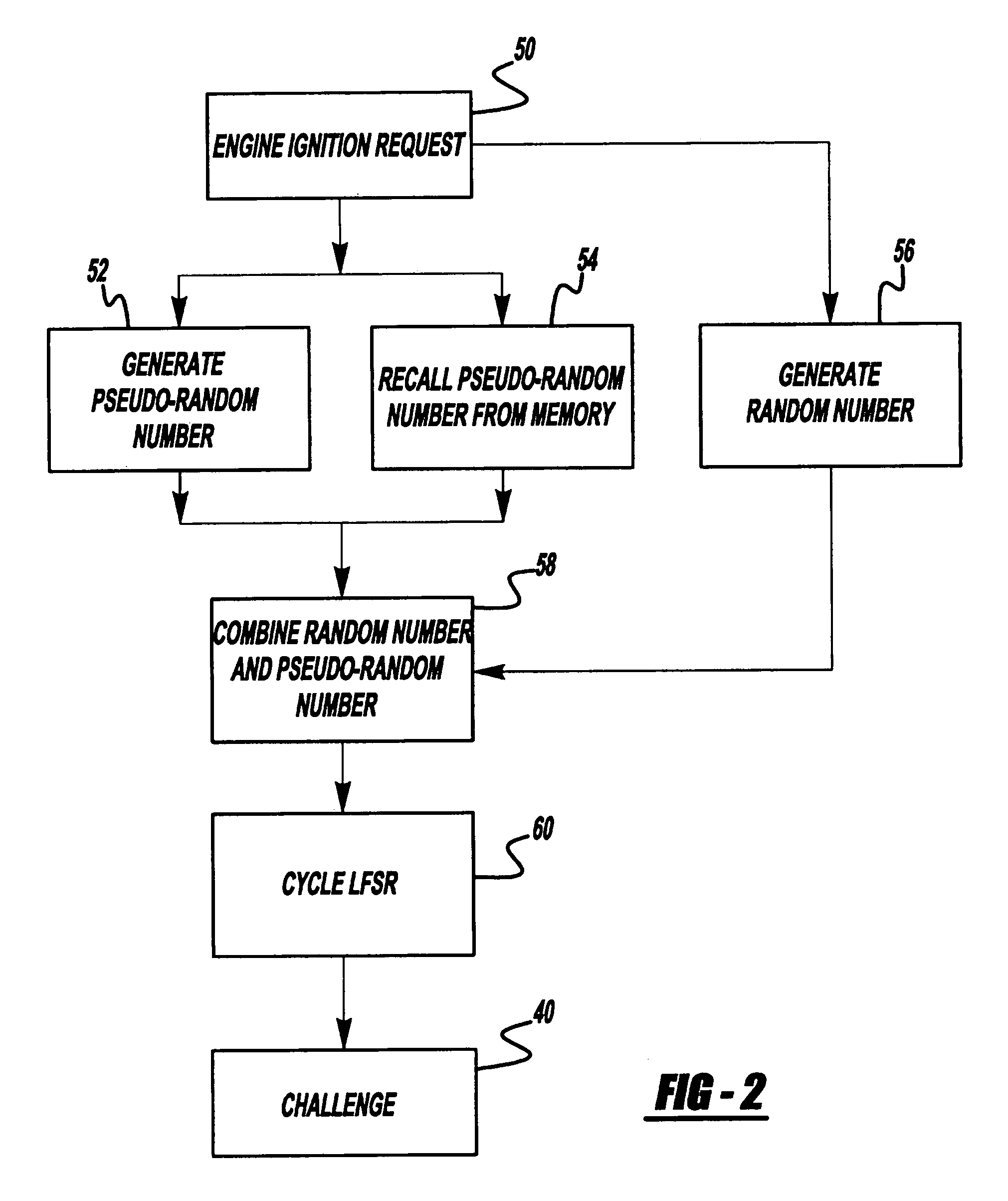

Motor vehicle engine immobilizer security system and method

ActiveUS7034654B2Electric signal transmission systemsRandom number generatorsMobile vehicleEngineering

Methods and apparatus are provided for insuring that a motor vehicle is being operated by an authorized operator. The apparatus includes an electronic control unit (ECU), an engine immobilizer unit, and a shared encryption key. The ECU generates a challenge by combining the output of a pseudo-random number generator and the output of a somewhat random number generator and cycling the combined number through a linear feedback shift register. The ECU sends the challenge to the immobilizer unit where it is encrypted with the shared key and sent back to the ECU as a response. The ECU uses the same key to encrypt the challenge and compares the encrypted challenge to the response. If the response matches the encrypted challenge, engine operation is enabled.

Owner:GM GLOBAL TECH OPERATIONS LLC +1

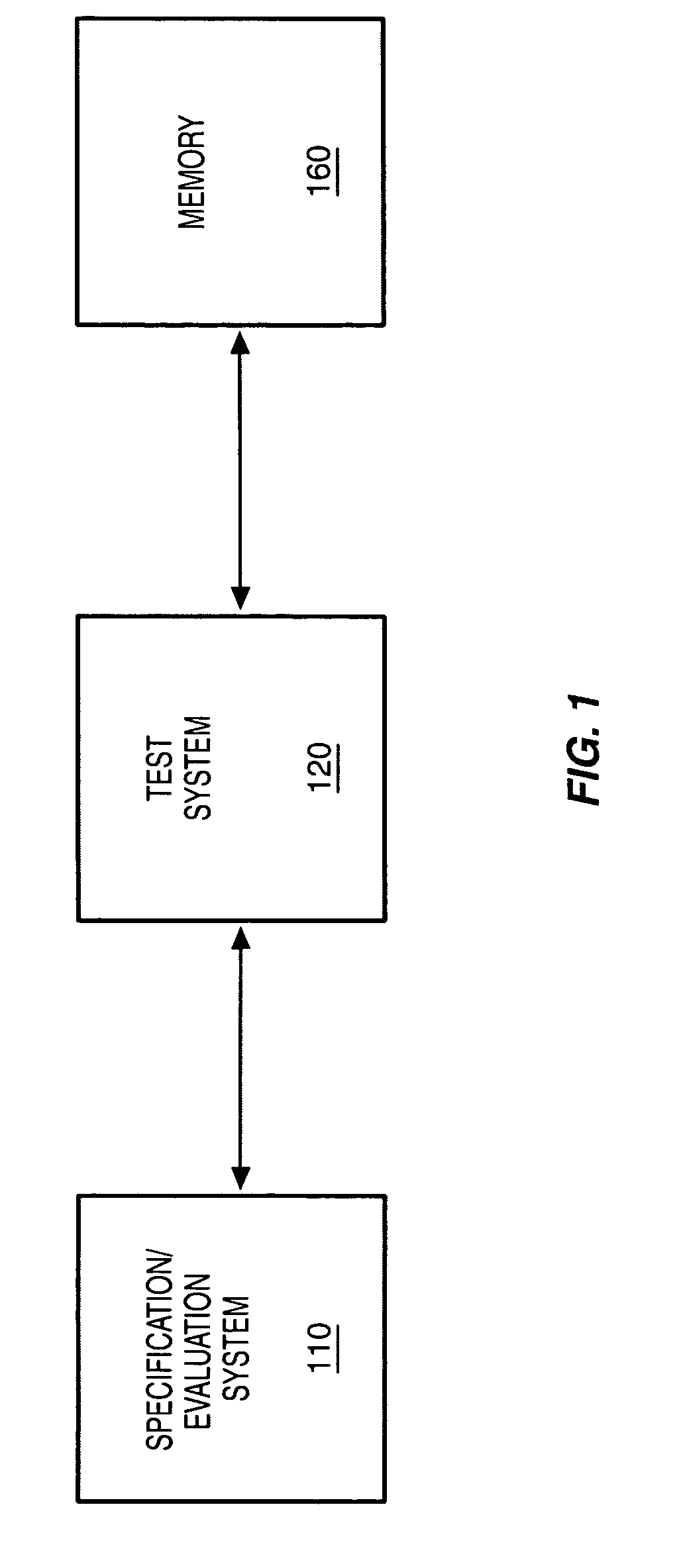

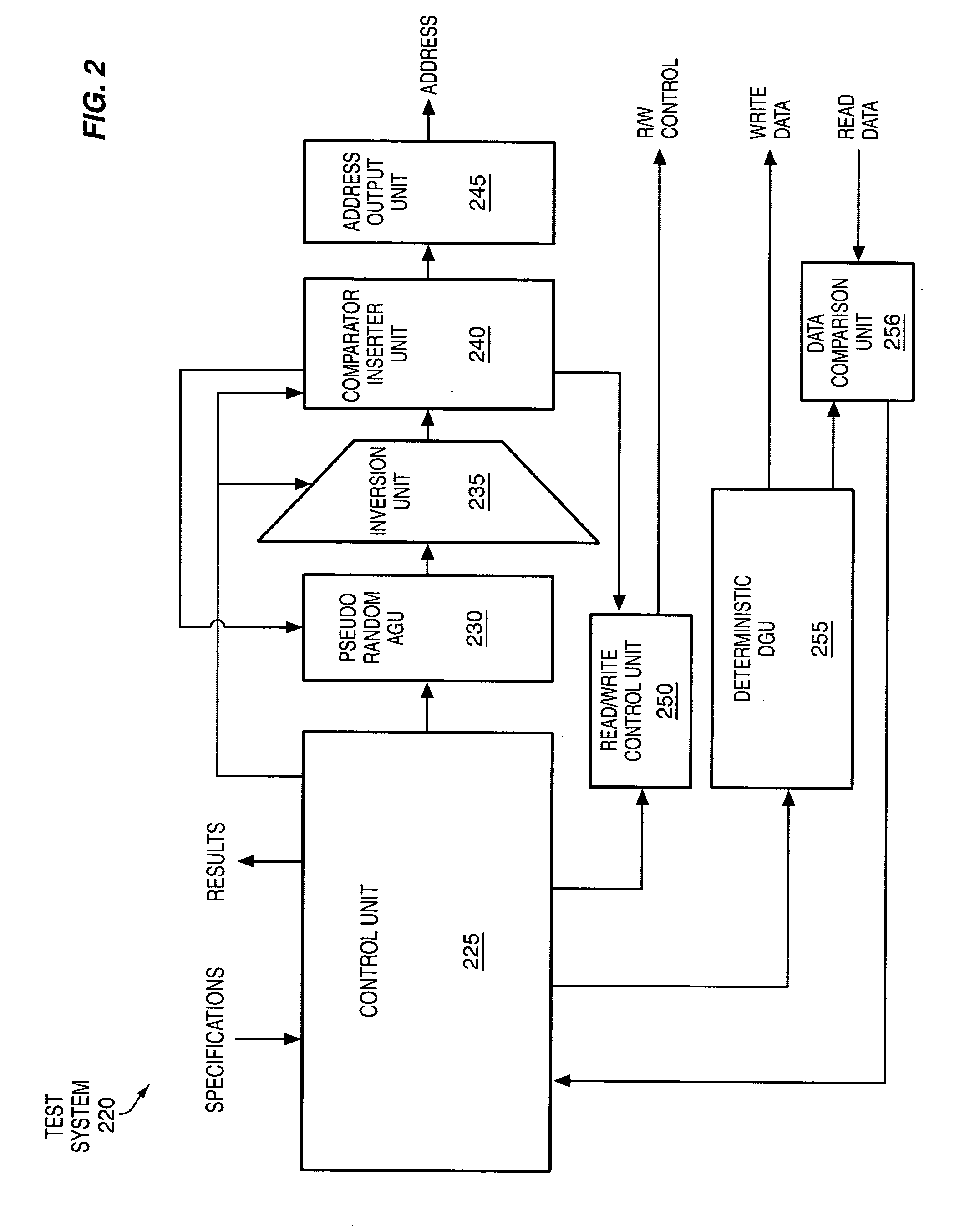

Testing memories

InactiveUS20060085710A1Electronic circuit testingStatic storageMemory addressAddress generation unit

Methods and apparatus to test memories, such as, for example, caches of processors, are disclosed. In one aspect, an apparatus may include a pseudo random address generation unit, such as, for example, including a linear feedback shift register, to generate pseudo random memory addresses, and a deterministic data generation unit, such as, for example, including a state machine, to generate deterministic data to be written to the pseudo random memory addresses. Computer systems and other electronic systems including such apparatus are also disclosed.

Owner:INTEL CORP

Low complexity pseudo-random interleaver

An interleaver has an input multiplexer that receives a data sequence at an interleaver input and that separates the data sequence into multiple data sub-blocks. The interleaver has a linear feedback shift register that generates an input address sequence. The interleaver has adder circuits that generate output address sequences associated with each data sub-block. The interleaver has memory that stores the data sub-blocks at addresses controlled by the input address sequence. The memory reproduces each data sub-block in an interleaved sequence controlled by the associated output address sequence. The interleaver has an output multiplexer that assembles the interleaved sequences to provide an interleaver output.

Owner:SEAGATE TECH LLC

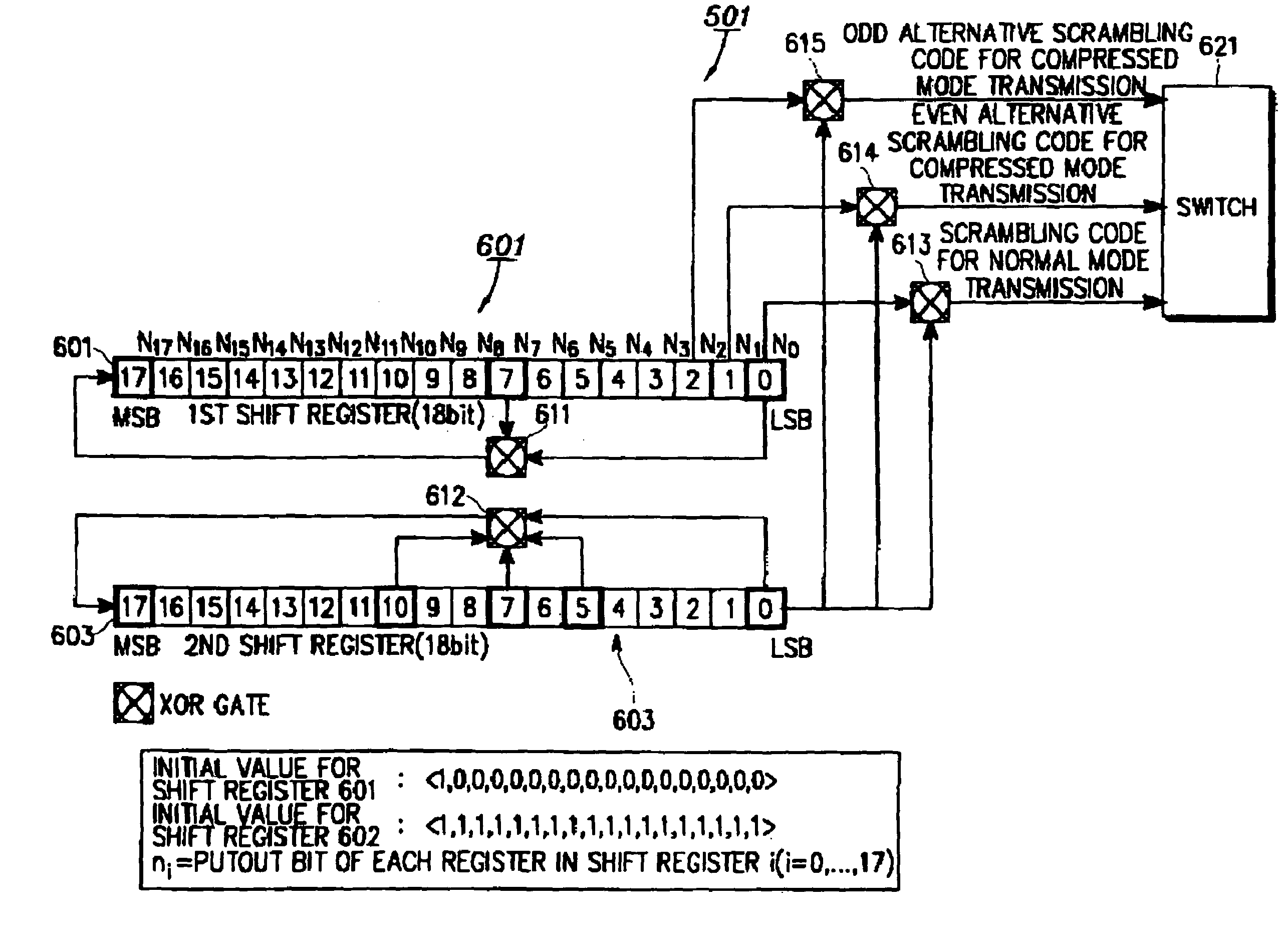

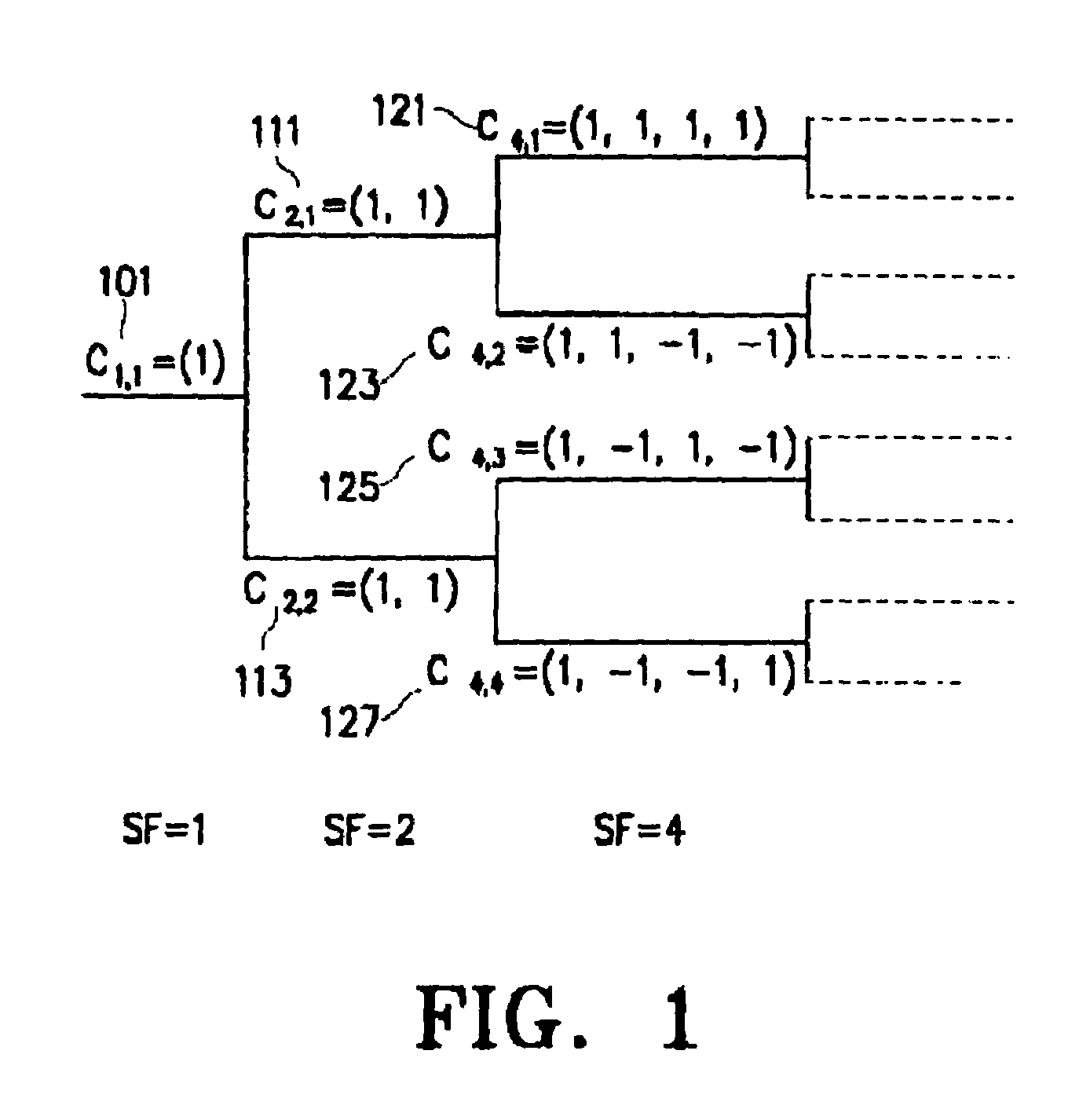

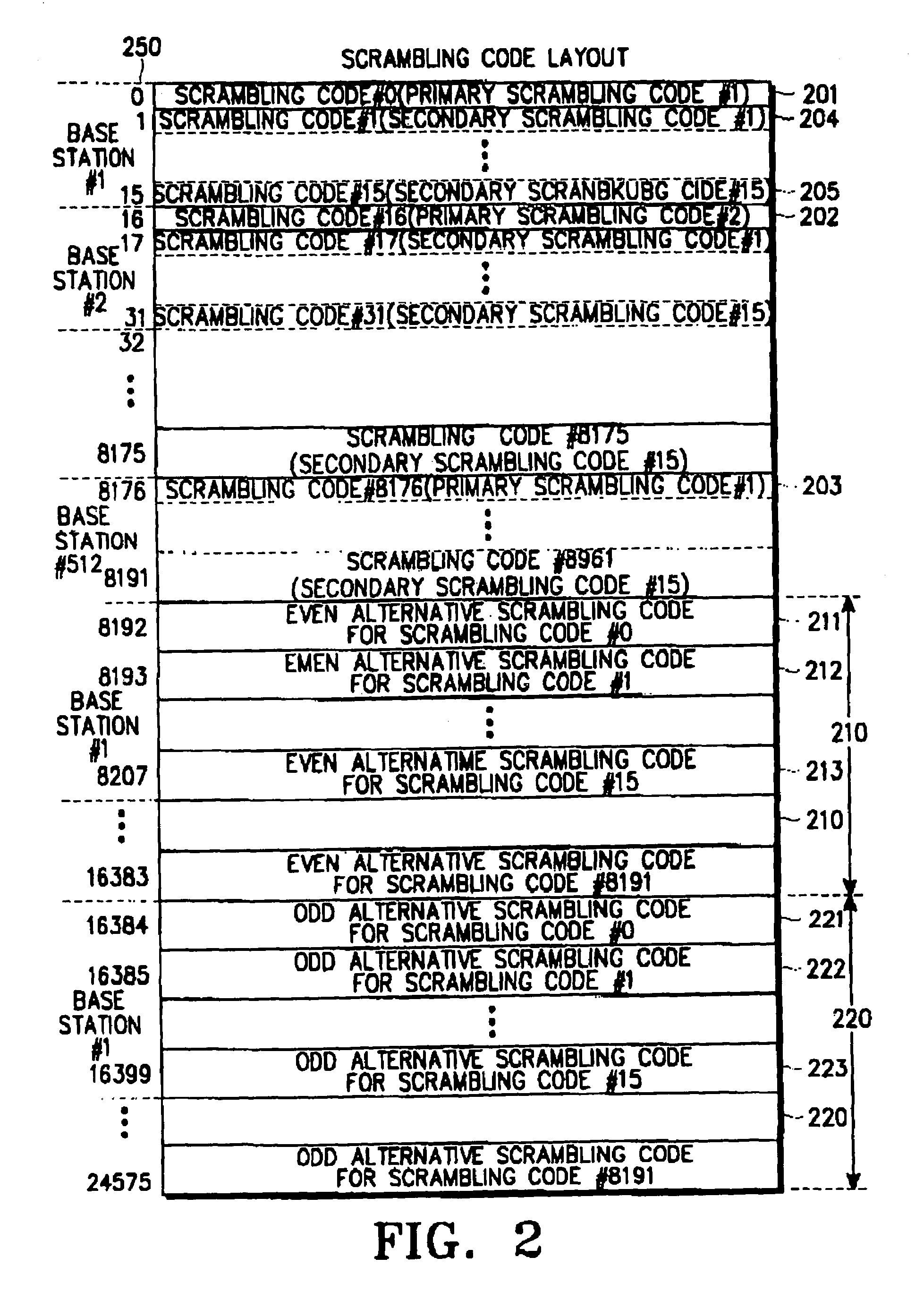

Apparatus and method for generating multiple scrambling codes in asynchronous mobile communication system

An apparatus and method for generating multiple scrambling codes in an asynchronous mobile communication system. In a scrambling code generating apparatus for generating a current scrambling code and a compressed mode scrambling code for compressed mode transmission in a base station device having a spreader for spreading an input data sequence with one of a plurality of OVSF codes and a scrambler for scrambling the spread data sequence with a primary scrambling code used as a default or one of a plurality of secondary scrambling codes according to the number of mobile stations in communication, a first feedback linear shift register generates an m-sequence from first predetermined initial bits, a second feedback linear shift register generates another m-sequence from second predetermined initial bits, a first adder generates the current scrambling code by adding the outputs of the first and second linear feedback shift registers, a second adder adds the output of the second linear feedback register and an m-sequence one bit delayed from the output of the first linear feedback register, and a third adder adds the output of the second linear feedback register and an m-sequence two bits delayed from the output of the first linear feedback register. Here, the compressed mode scrambling code is one of the outputs of the second and third adders and provided to the scrambler to scramble the spread data sequence.

Owner:SAMSUNG ELECTRONICS CO LTD

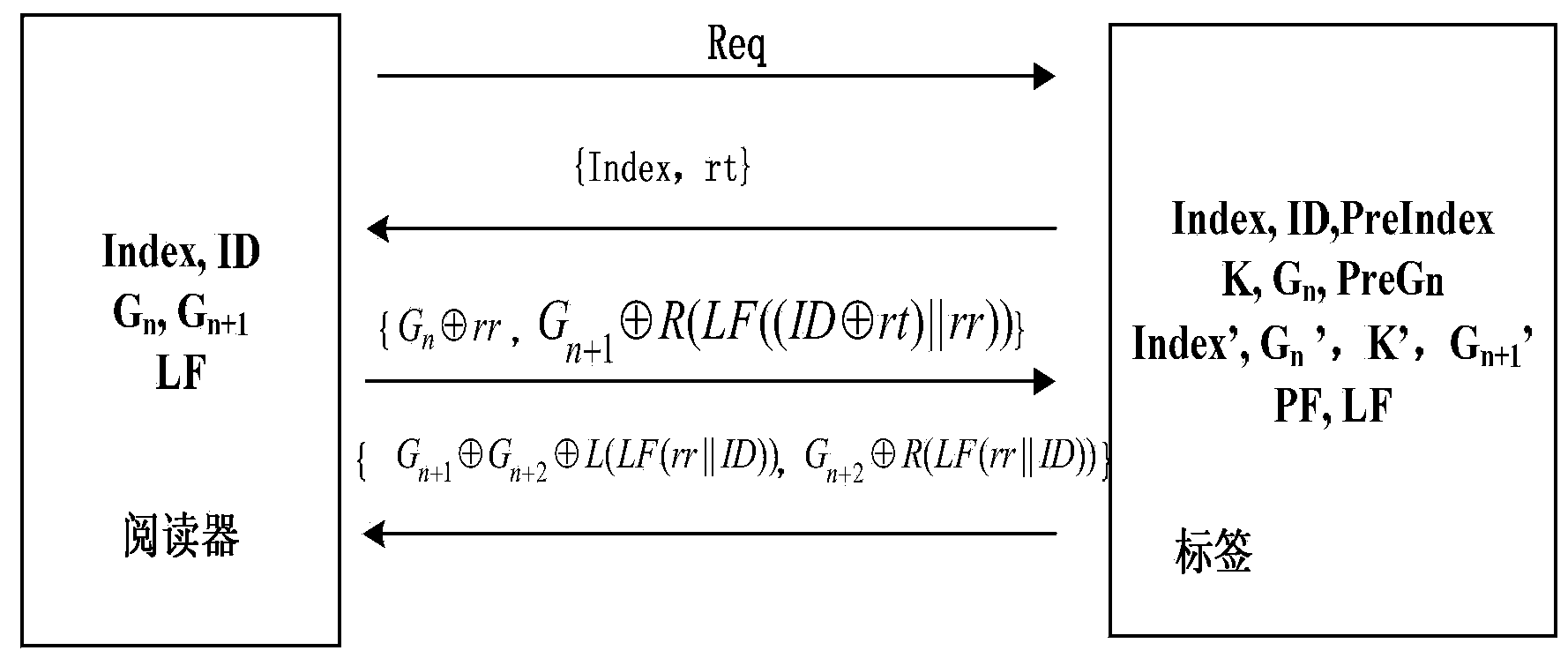

RFID lightweight class bidirectional authentication method based on PUF

InactiveCN103905202AReduce complexityLow costUser identity/authority verificationCo-operative working arrangementsAttackThe Internet

The invention discloses an RFID lightweight class bidirectional authentication method based on a PUF. Information encryption and pseudo random number generation are carried out through a linear feedback shift register protected through a secret key seed, counterfeit attack can be resisted, a pseudo random number generator does not need to be additionally integrated, and complexity and cost of a label are reduced; in the communication process, all communication information is effectively utilized to carry out authentication, the problem of desynchronization attack of out-of-step information between a reader and the label can be effectively solved through falsification and other means, and security is higher. The method can be widely applied to the internet of things and information security authentication fields.

Owner:GUANGDONG UNIV OF TECH

Data processing apparatus and method

InactiveUS20080298487A1Easy to receiveTrack time variationTelevision system detailsCode conversionSymbol mappingSoftware engineering

A data processing apparatus maps input symbols to be communicated onto a predetermined number of carrier signals of an Orthogonal Frequency Division Multiplexed (OFDM) symbol. The data processor includes an interleaver memory which reads-in the predetermined number of data symbols for mapping onto the OFDM carrier signals. The interleaver memory reads-out the data symbols on to the OFDM carriers to effect the mapping, the read-out being in a different order than the read-in, and the order being determined from a set of addresses. The set of addresses are generated from an address generator. The address generator includes a linear feedback shift register and a permutation circuit.

Owner:SONY EUROPE BV