Patents

Literature

778results about How to "Save hardware resources" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

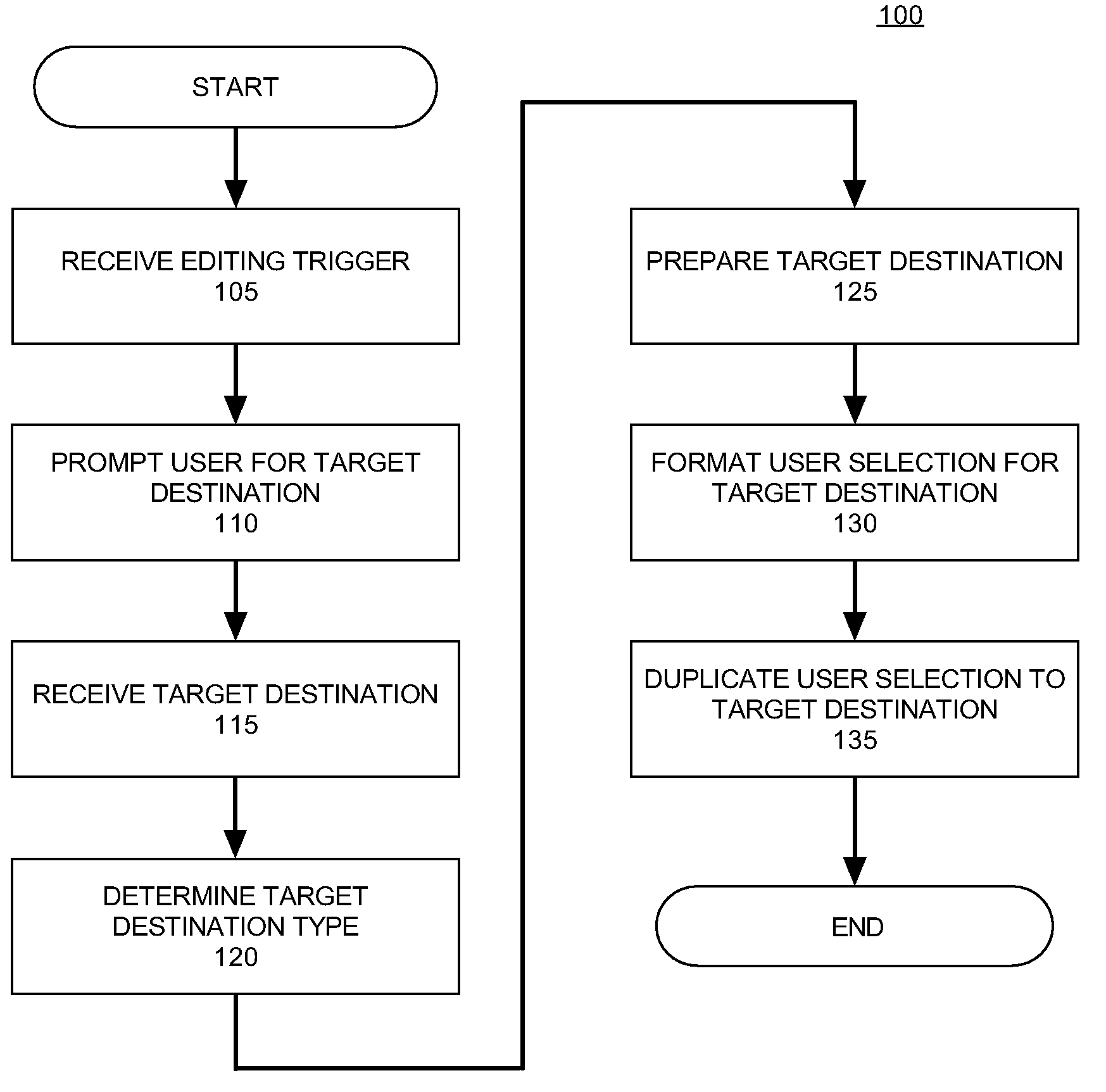

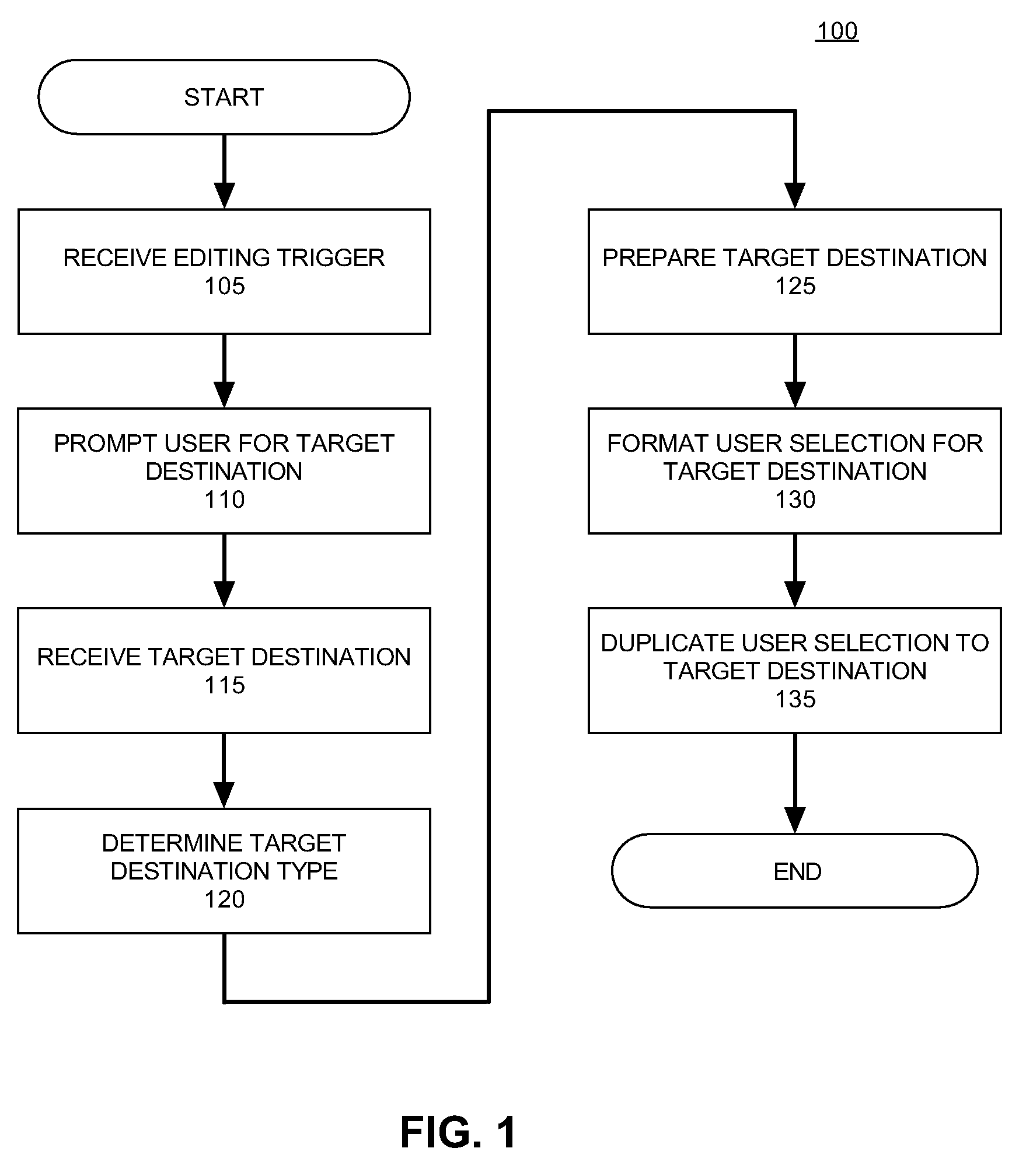

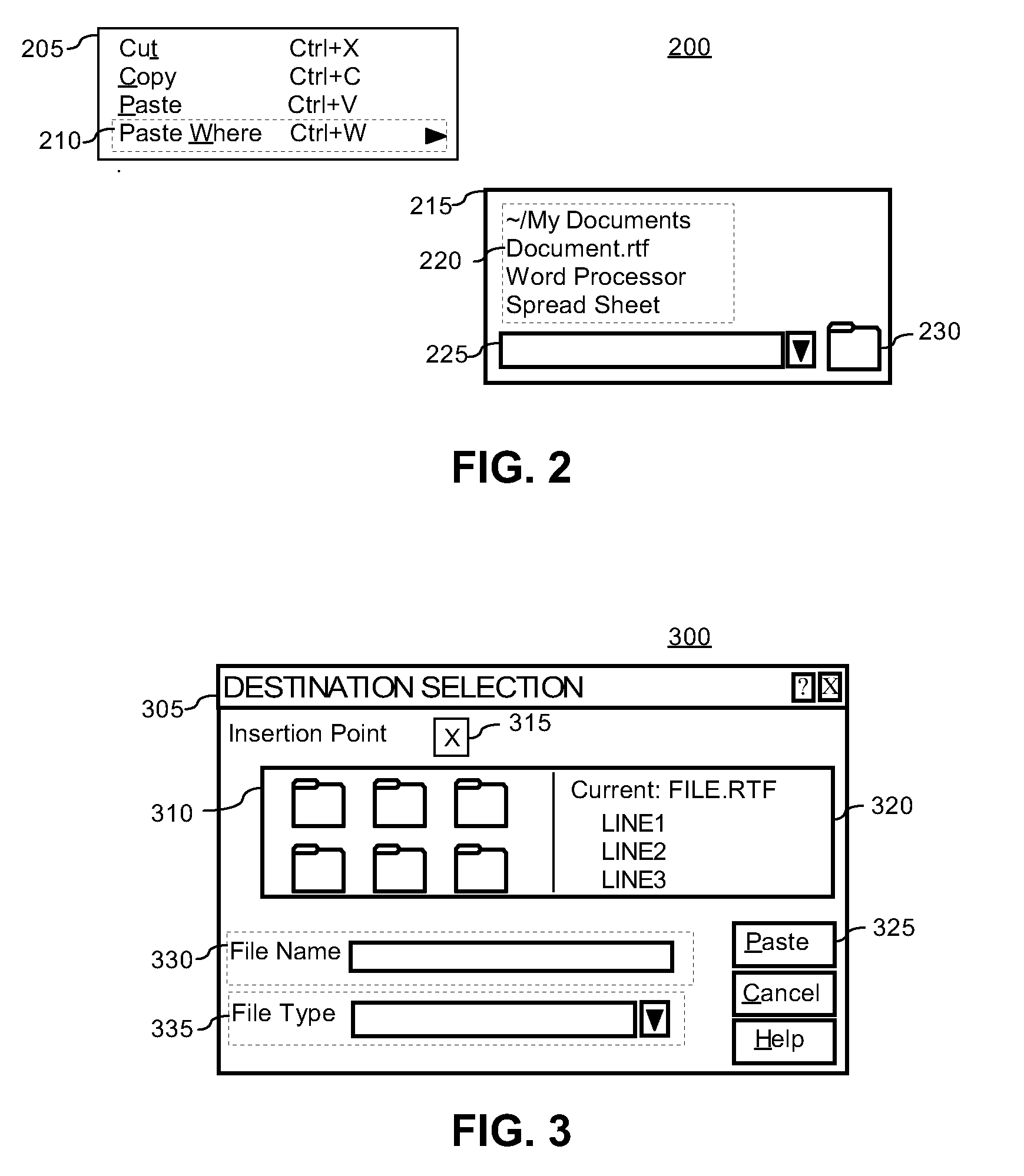

Facilitated source to target object editing functions

InactiveUS20070266333A1Facilitating source to target stepDuplicating user selectionsMultiprogramming arrangementsCathode-ray tube indicatorsElectronic documentUser input

A method for editing software objects can include identifying at least one user selection of at least a portion of an electronic document displayed within an application and prompting a user for a target destination to which the user selection is to be posted. A user input specifying the target destination to which the user selection is to be posted can be received and the user selection can be duplicated to the target destination.

Owner:IBM CORP

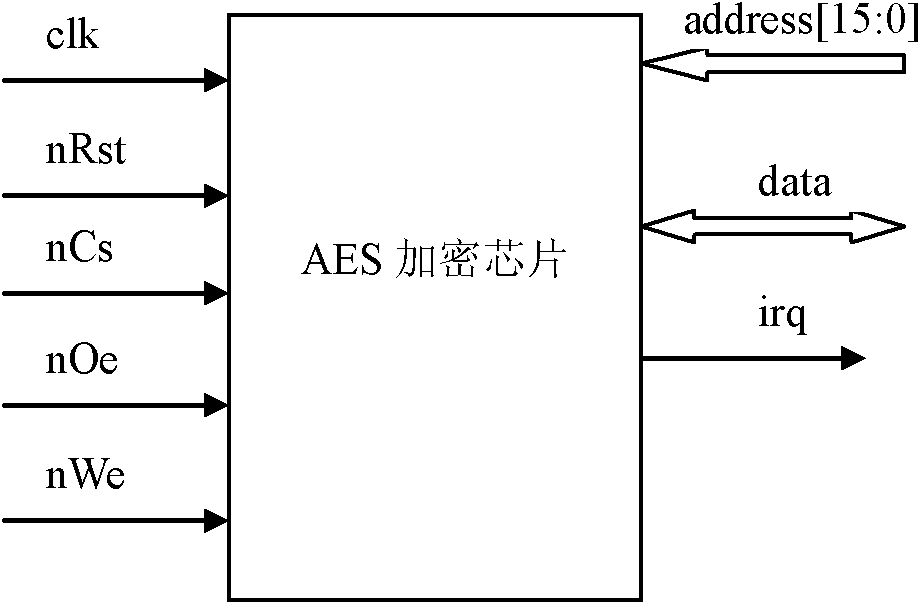

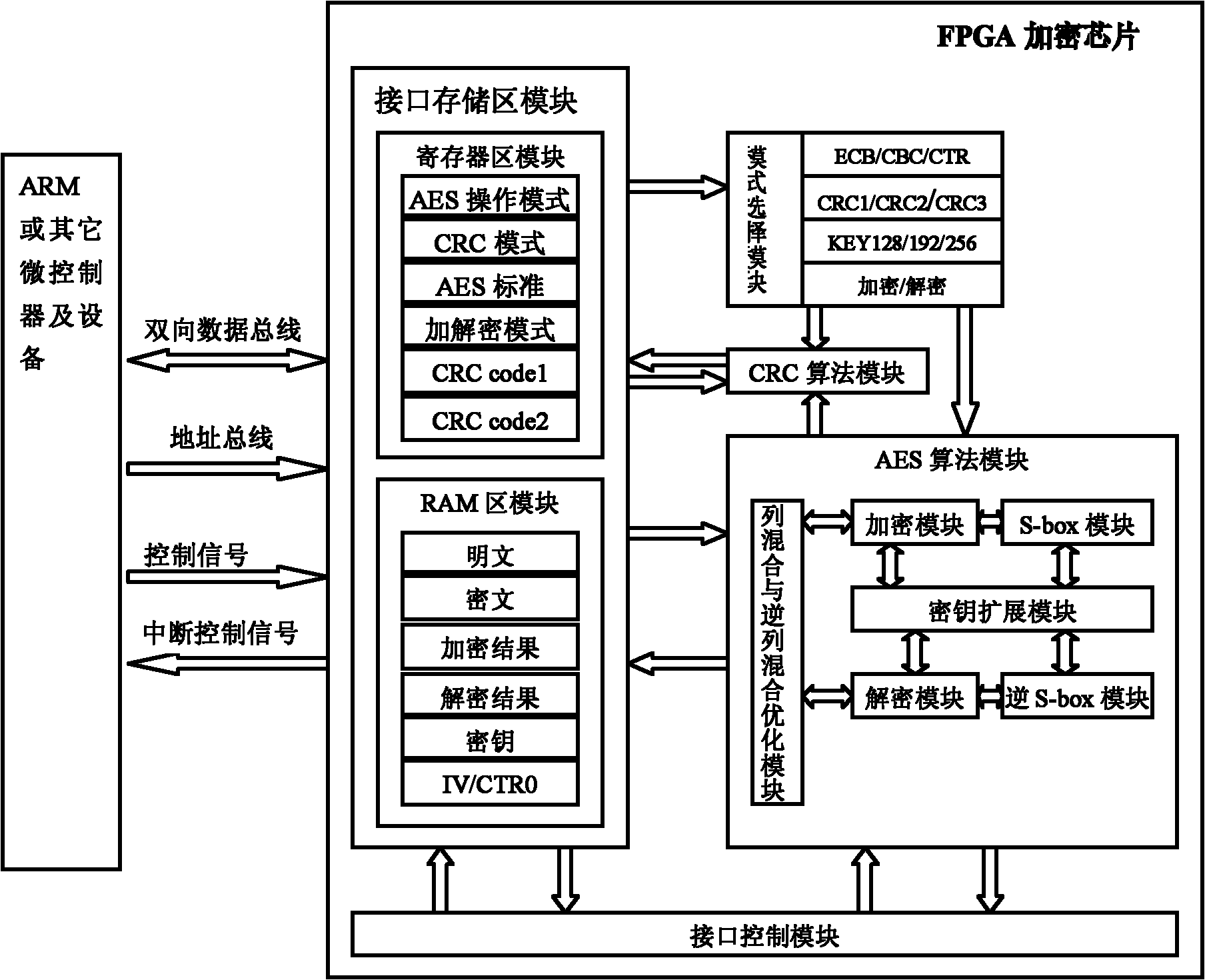

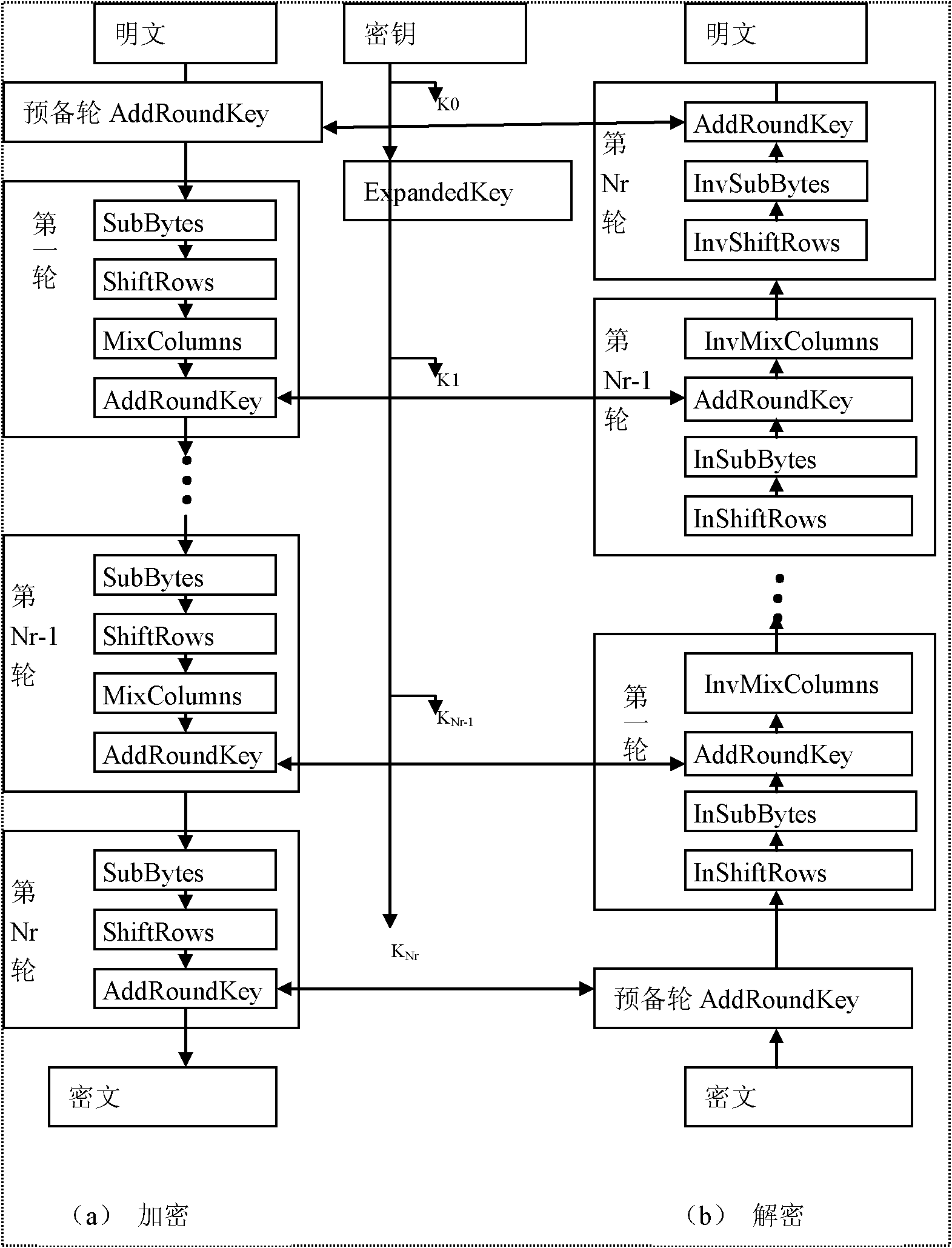

Method for designing AES (Advanced Encryption Standard) encryption chip based on FPGA (Field Programmable Gate Array) and embedded encryption system

InactiveCN102223228AFlexible useReduce areaEncryption apparatus with shift registers/memoriesInformation technologyEncryption system

The invention discloses a method for designing an AES (Advanced Encryption Standard) encryption chip based on an FPGA (Field Programmable Gate Array), which is designed for aiming at the requirement of an embedded system. The AES encryption chip not only can be used in a manner of a solid chip but also used in a manner of a software module. Three operation modes of ECB (Electronic Code Book), CBC (Cipher Block Chaining) and CTR (Counter Technical Requirement) are supported simultaneously. All standards of the AES can be encrypted and decrypted. The byte replacement and the key expansion are carried out by using a look-up table optimization algorithm. A column mixed optimization structure is provided. Device resources are saved while the operation speed is ensured. An RAM (Random-Access Memory) can be configured as a cache of information and a key through double ports of the FPGA. A problem for storing a time sequence and data of other devices or equipment and the FPGA is resolved. Safe and reliable communication with an FPGA interface joins CRC (Cyclic Redundancy Check) error detection in a manner of a memory bus. The AES encryption chip has the advantages of high safety, high encryption and decryption speeds, low device resource requirement, low cost and the like. The AES encryption chip can be widely used in information technology industries of intelligent card systems, ATMs (Automatic Teller Machines), wireless local area networks, wireless sensor networks and the like.

Owner:BEIHANG UNIV

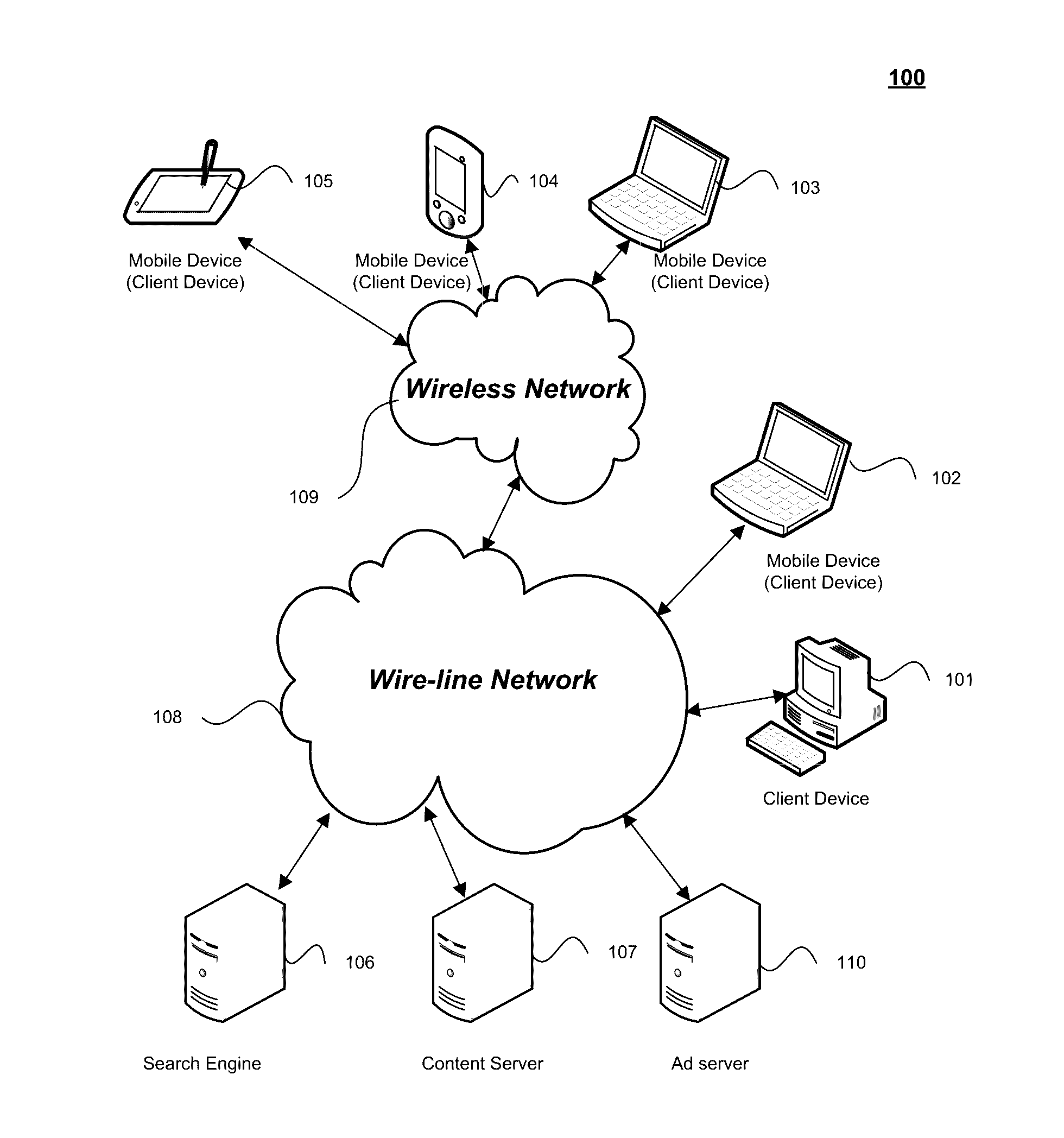

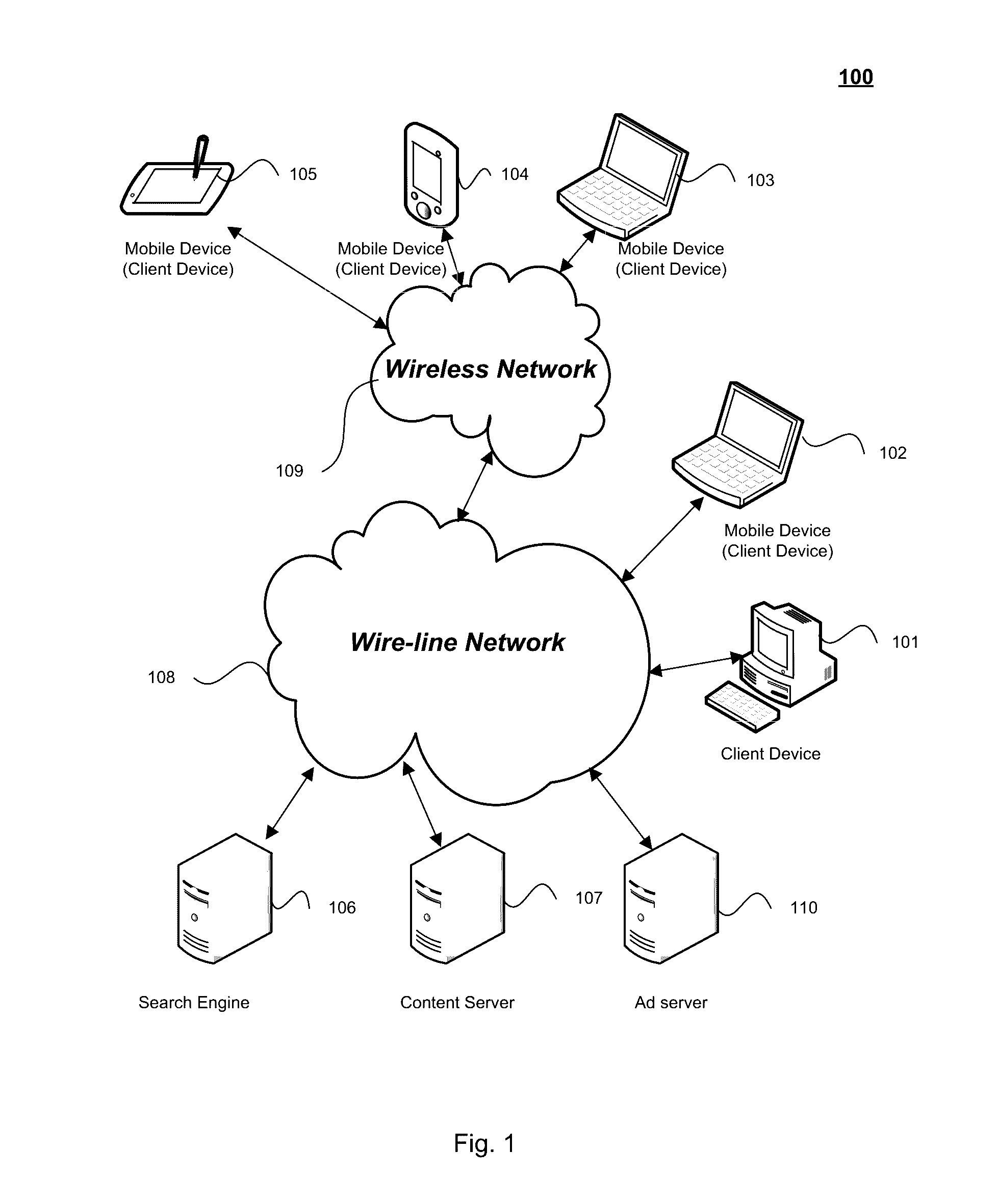

Systems and methods for online content recommendation

ActiveUS20160371589A1Improve technologyEnhance performanceProbabilistic networksMachine learningClient-sidePre-existing

The present disclosure relates to computer systems implementing methods for online content recommendation. The computer systems may be configured to receive a training sample from a first client device corresponding to a predefined feedback interacting with online content displayed on the first client device; update a preexisting training database in real-time based on the received training sample to generate an updated training sample, wherein prior to being updated based on the training sample received from the first client, the training database includes a set of historical training samples; conduct a regression training to a computer learning model in real-time, using the updated training sample, to produce a set of trained parameters for an online content recommendation model; call the set of trained parameters in real-time to determine recommend online content for a second user with the online content recommendation model; and send the recommended online content to a second client device of the second user.

Owner:YAHOO ASSETS LLC

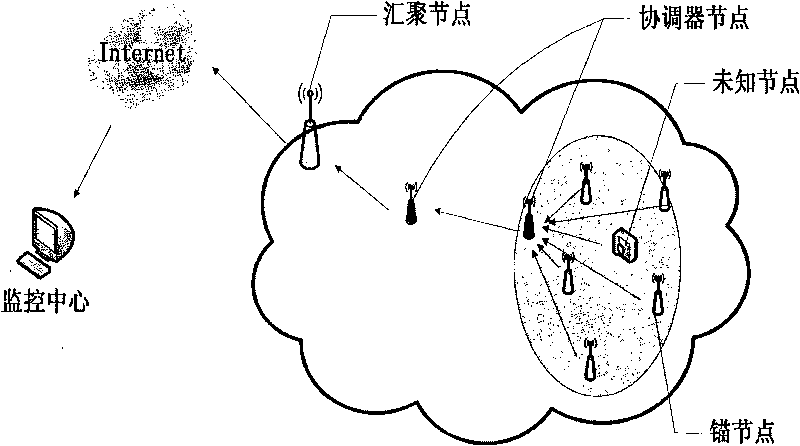

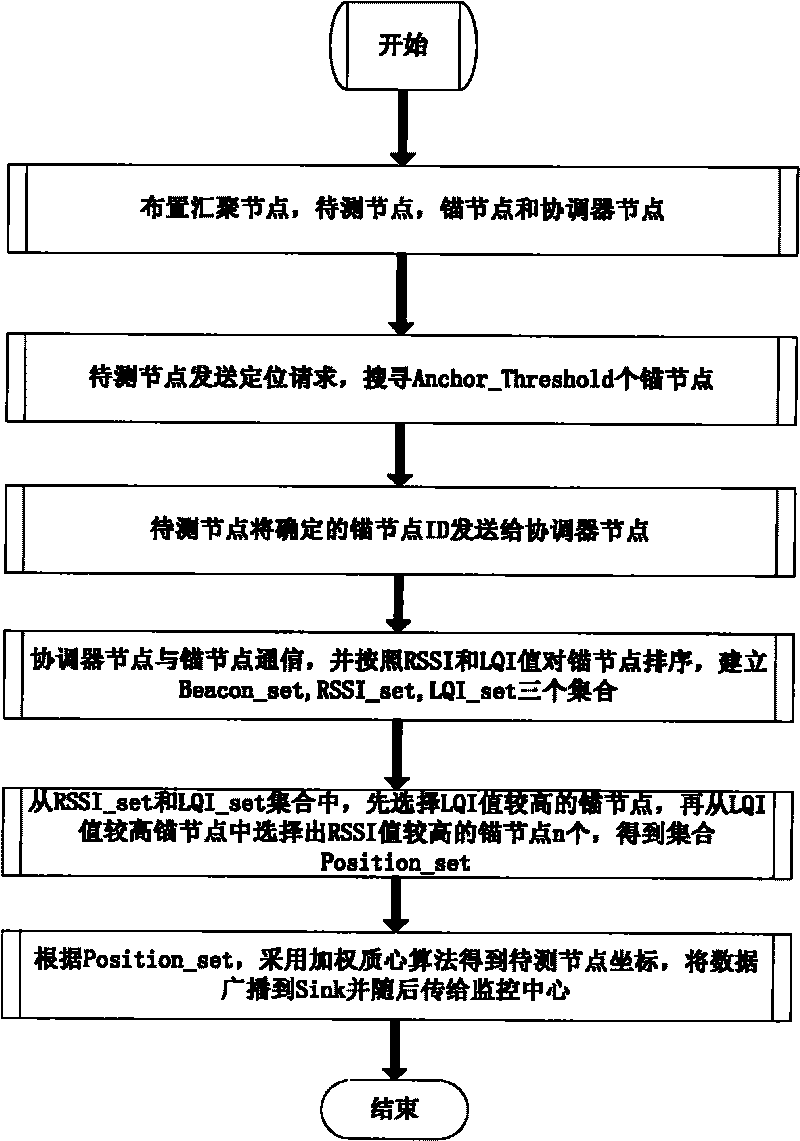

Positioning method of weighted wireless sensor network nodes based on RSSI and LQI

InactiveCN101715232AEasy to implementSave hardware resourcesNetwork topologiesComputation complexityRound complexity

The invention relates to a positioning method of weighted wireless sensor network nodes based on an RSSI and an LQI, which is characterized in that (1) the parameters of the RSSI and the LQI, which can be acquired easily from a hardware register, are used for positioning, thus the method can be realized easily and has few required hardware resources; (2) an LQI ranging model obtained by fitting experimental data is combined with an RSSI ranging model to select anchor nodes; and (3) an RSSI value and an LQI value which pass through an average filter are weighted and combined, an improved weighted centroid algorithm is used for estimating the positions of nodes to be detected, the data is broadcasted to cluster nodes, and then, the data is uploaded to a monitoring centre through a wired network. The positioning method of invention has the advantages of high positioning accuracy without being influenced by the environment easily, easy implementation of hardware, lower cost and smaller computation complexity.

Owner:XIDIAN UNIV

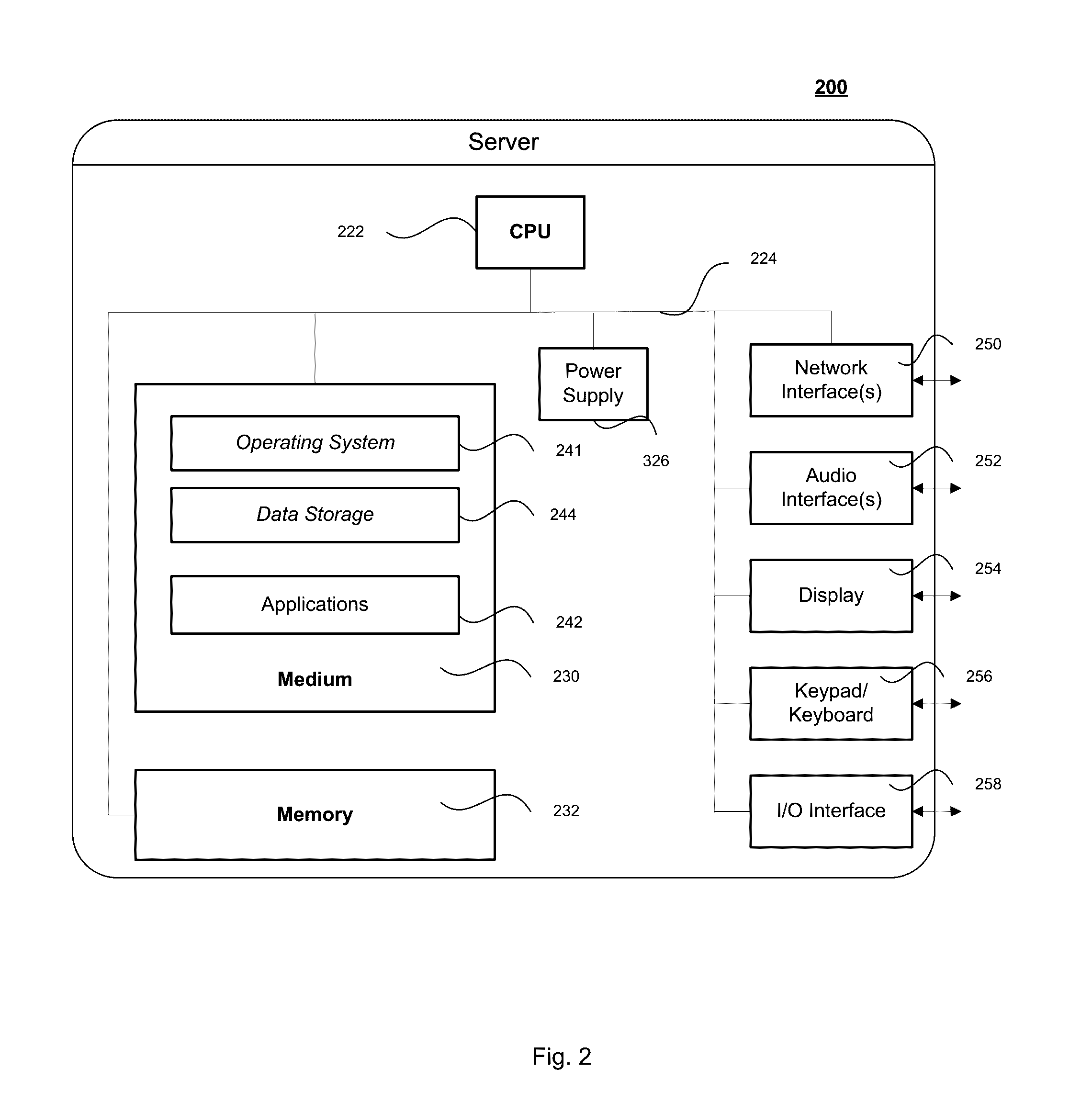

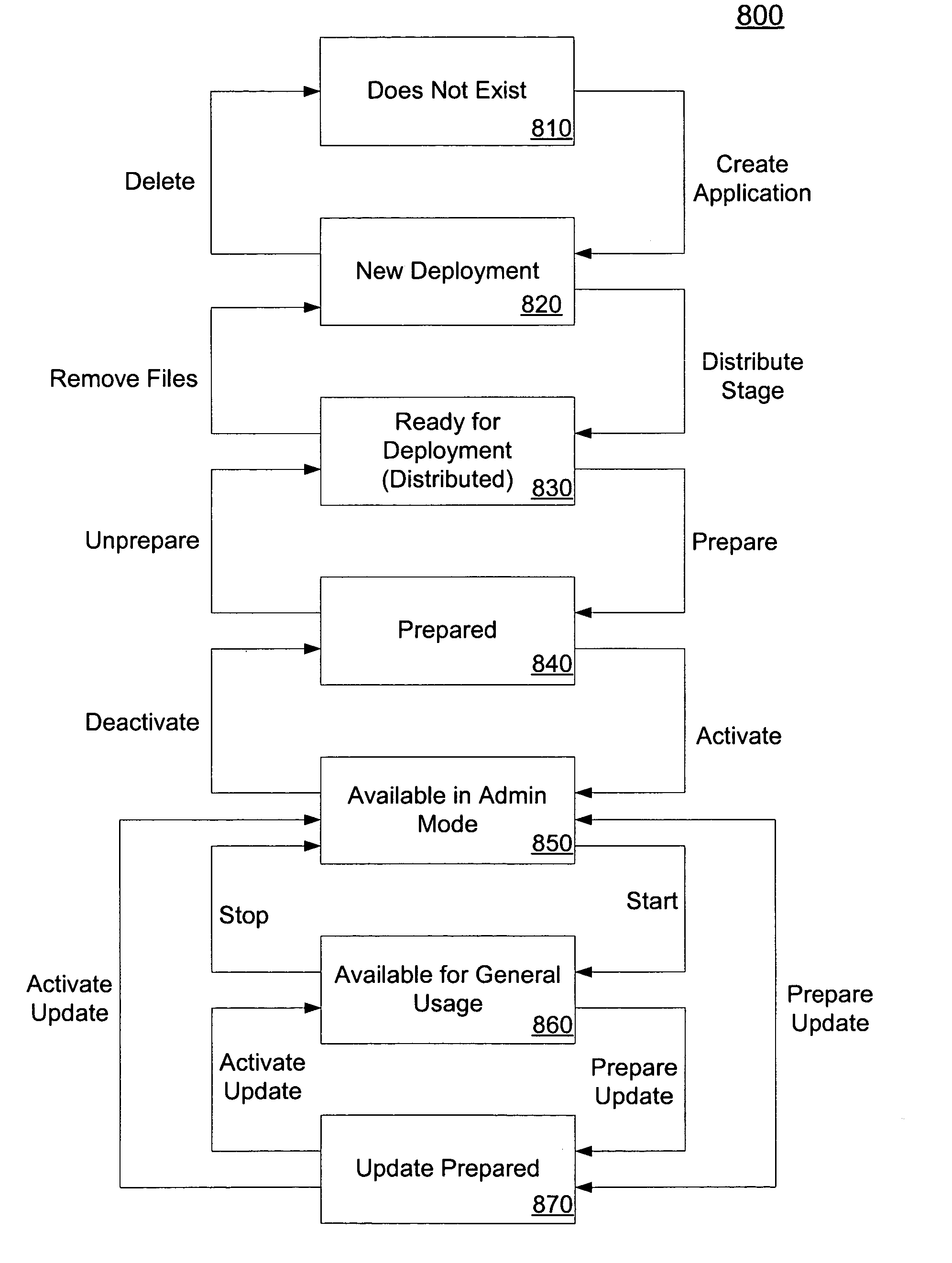

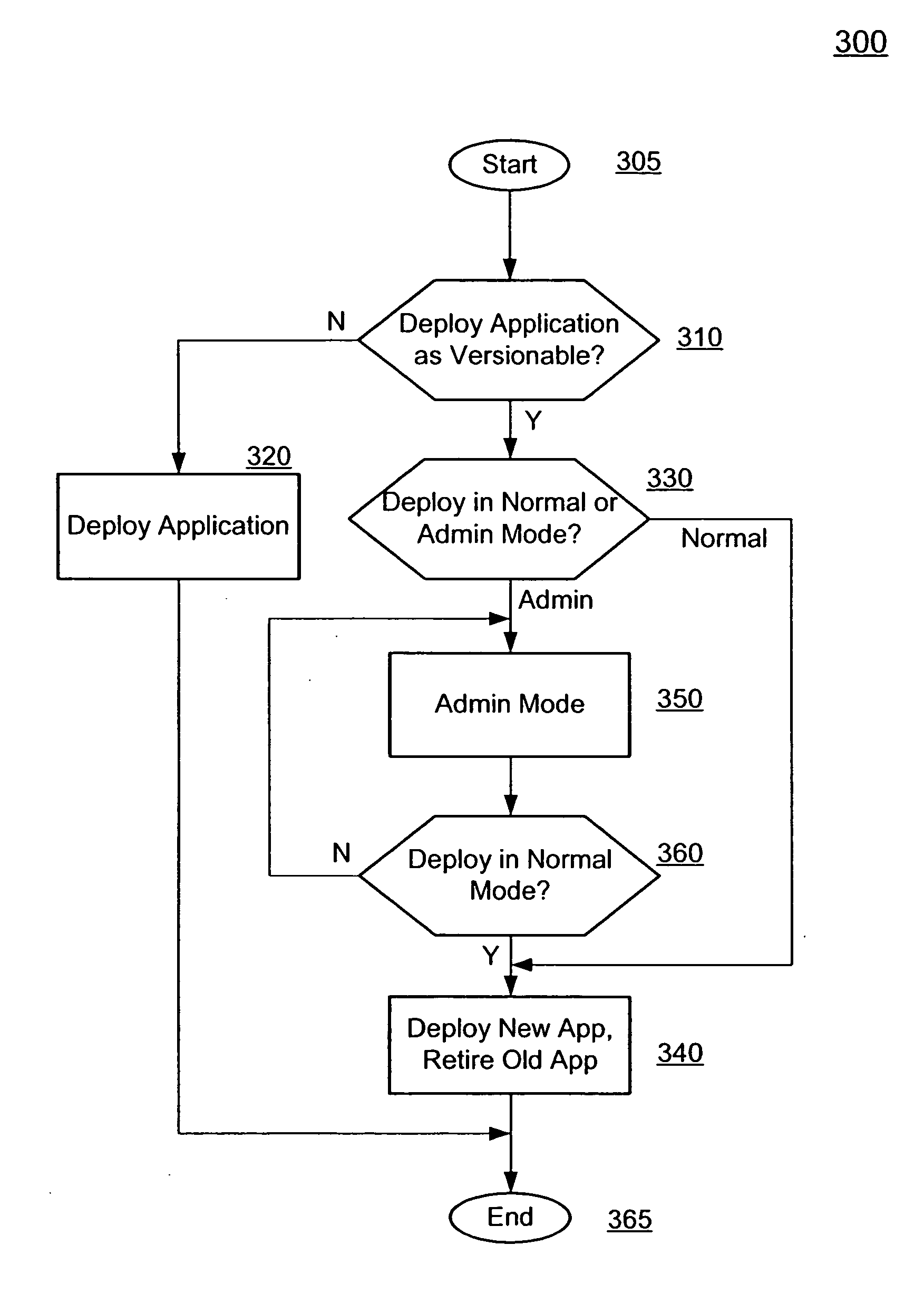

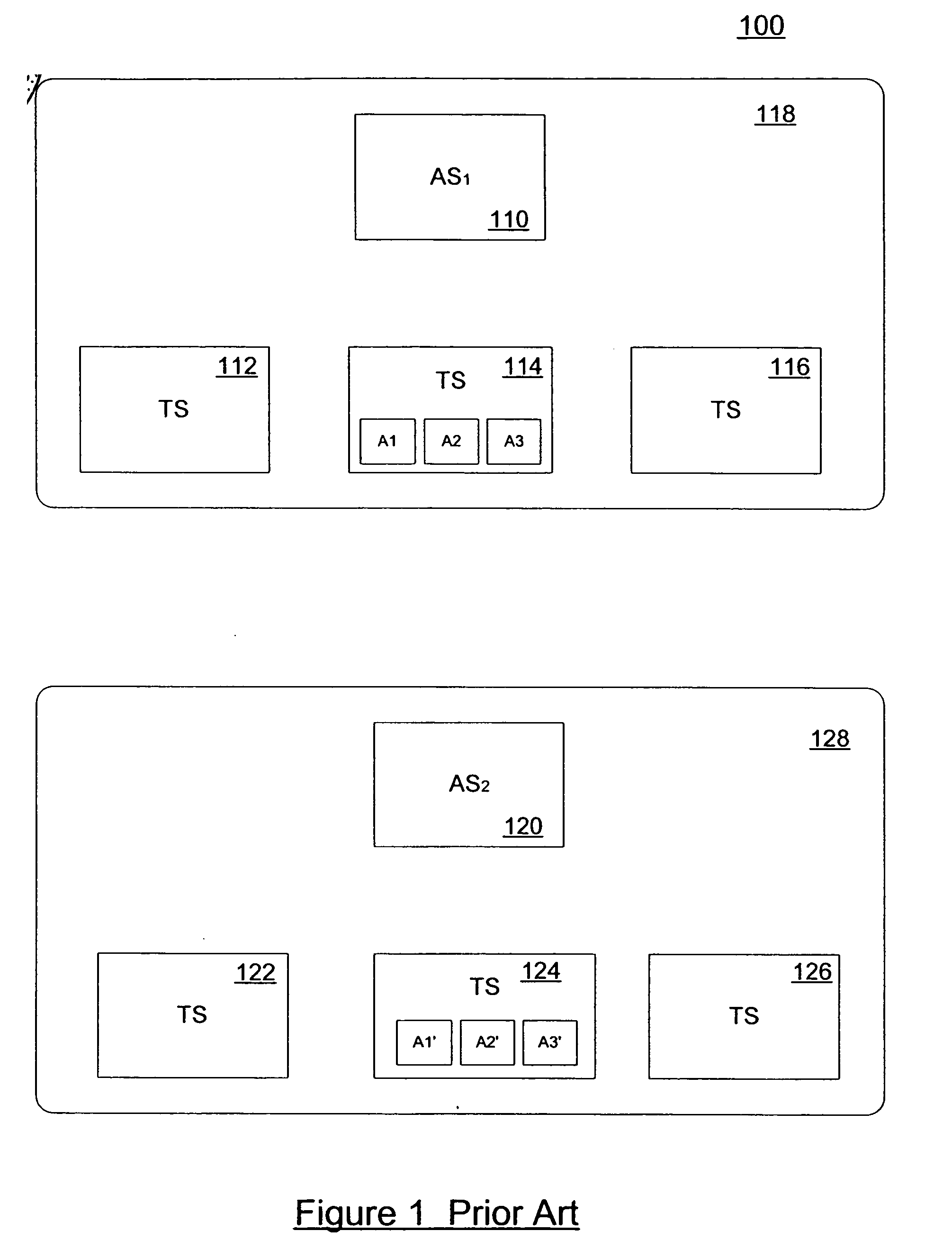

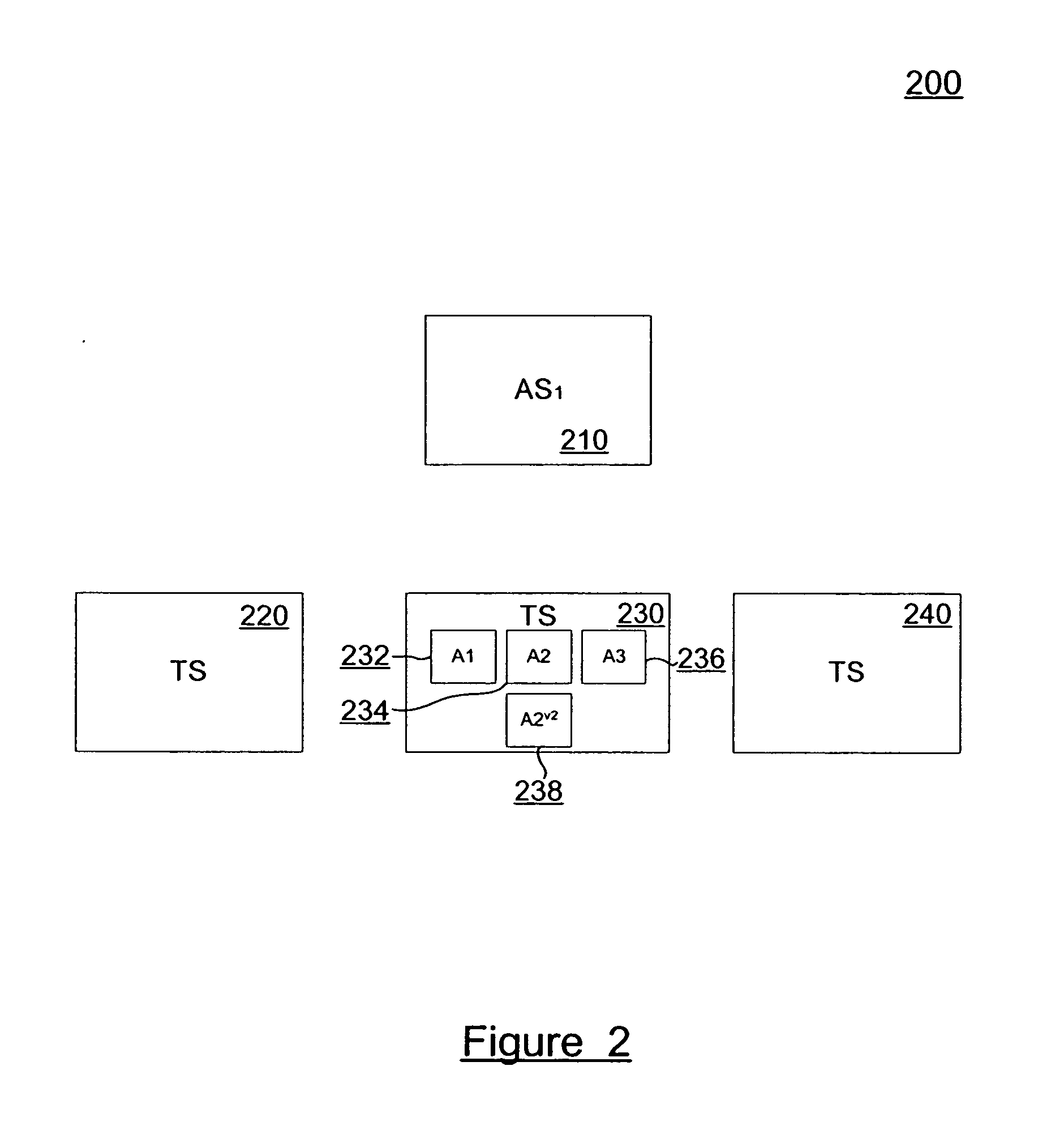

Administration mode for server applications

InactiveUS20050262495A1Save hardware resourceEasily manageProgram loading/initiatingMemory systemsClient-sideMultiple applications

In one embodiment, application versioning and production redeployment support is designed to handle application upgrade needs in mission-critical, production environments. With multiple application versions, application availability to both existing and new clients is not interrupted during the process of application upgrade. It also provides the ability to test a new application version before opening it to general public as well as the ability to roll back to previous safe versions if there are any errors in the currently active version. Clients see consistent application versions, irrespective and transparent of all failure conditions, including admin or managed server restarts and / or failover. Administrators can monitor and manage application versions easily with the management Console. Being a software-based solution, it improves upon traditional application upgrade solution by eliminating the need of hardware load-balancers and duplicate cluster / domain configurations and their associated resource requirements and by providing sophisticated management capabilities.

Owner:BEA SYST INC

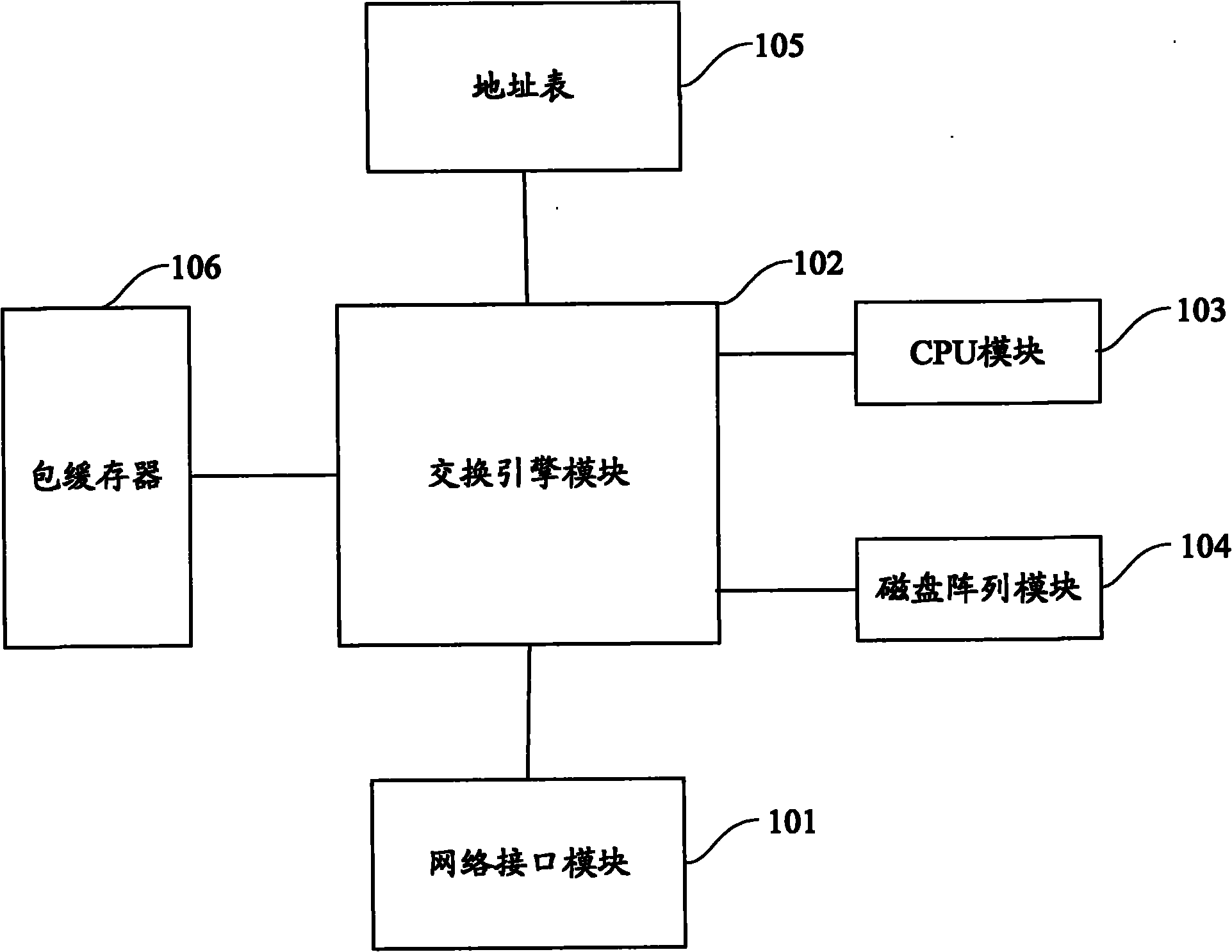

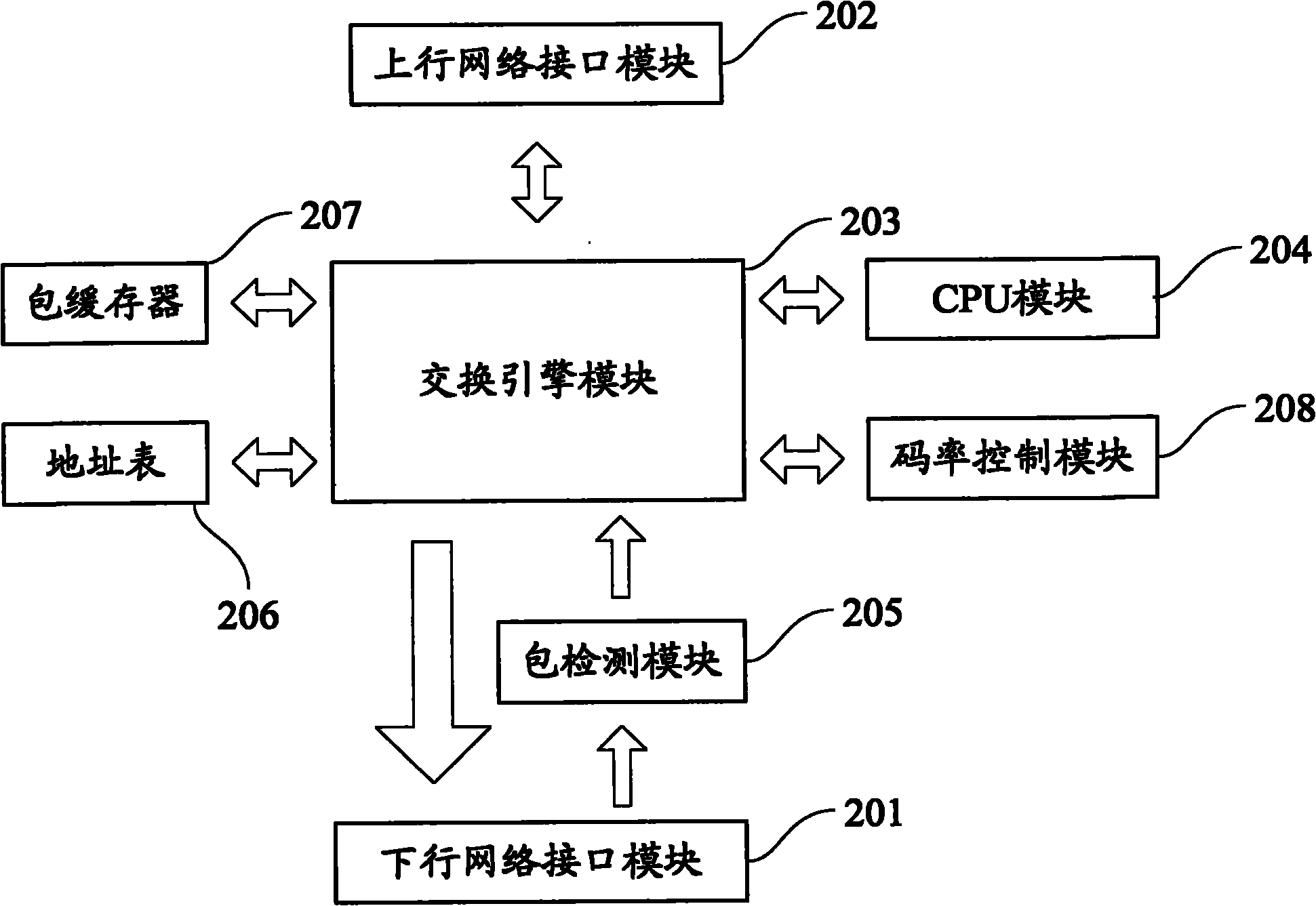

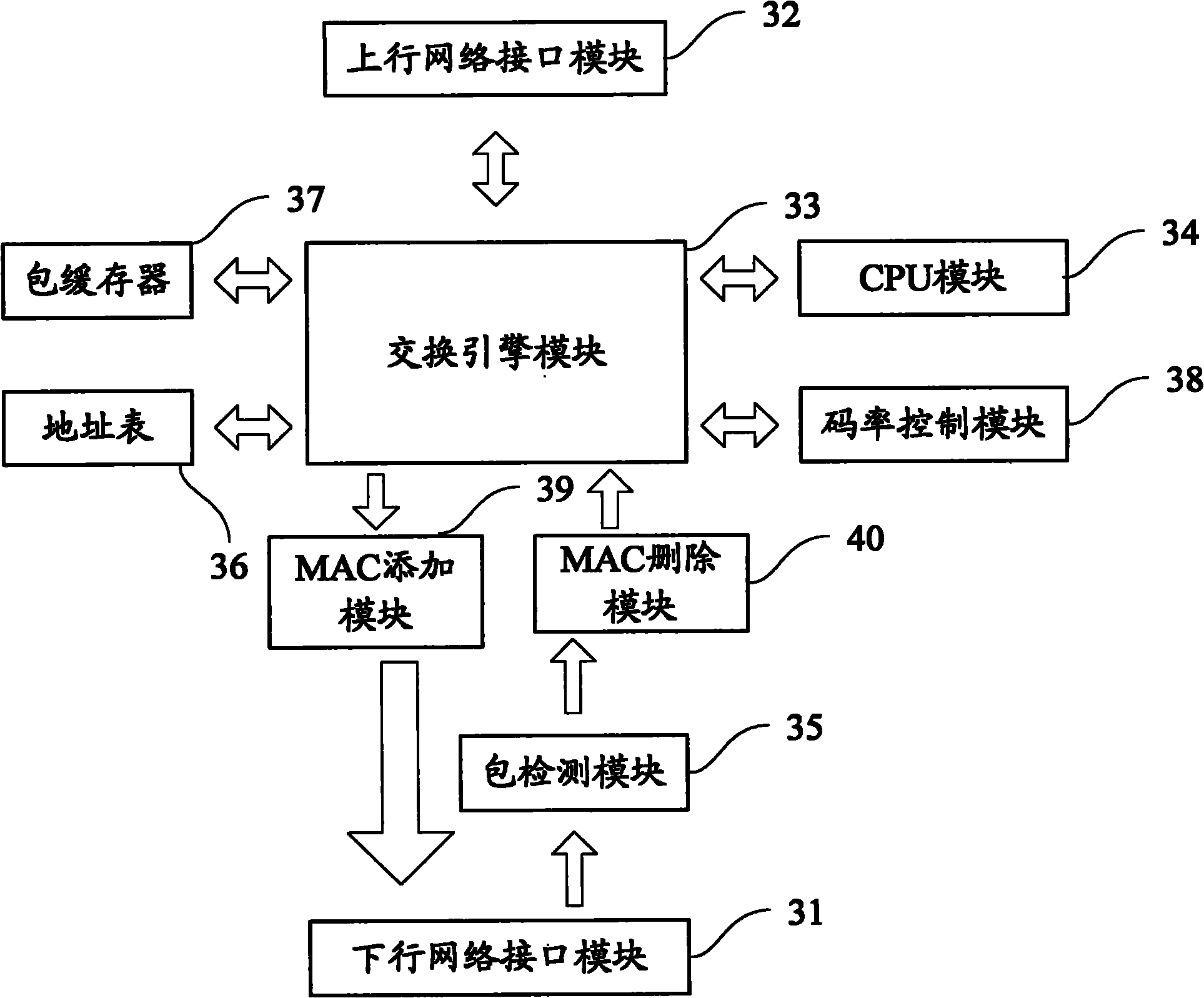

Communication method and communication system of novel network

ActiveCN101917492AAvoid delayMeet security needsSpecial service provision for substationTelecommunications linkCommunications system

The invention discloses a communication method of a novel network. The novel network is a network with a centralized control function and comprises a main control server and subordinate network equipment, and the subordinate network equipment comprises terminals. The method comprises the following steps that: the main control server configures downlink communication link for a current service; and the main control server sends the current service data packet sent by a source terminal to a target terminal according to the downlink communication link. Through the communication method and the communication system, the stability and smoothness of the transmission channel are ensured, the delay of multimedia services is prevented, the requirements for the state information security are met, the hardware resources are saved and the network transmission quality is guaranteed.

Owner:BEIJING QIANTANG NETWORK TECH

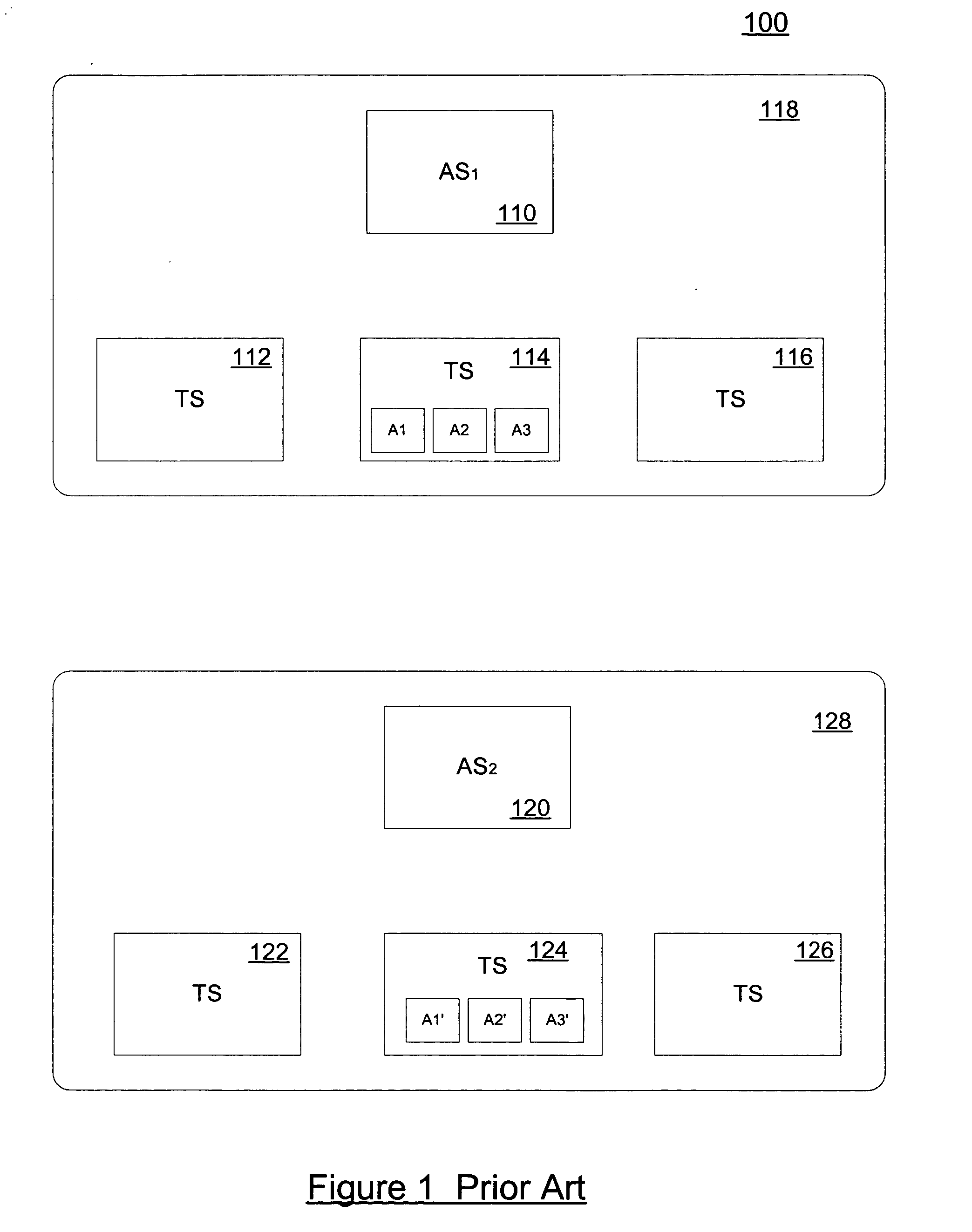

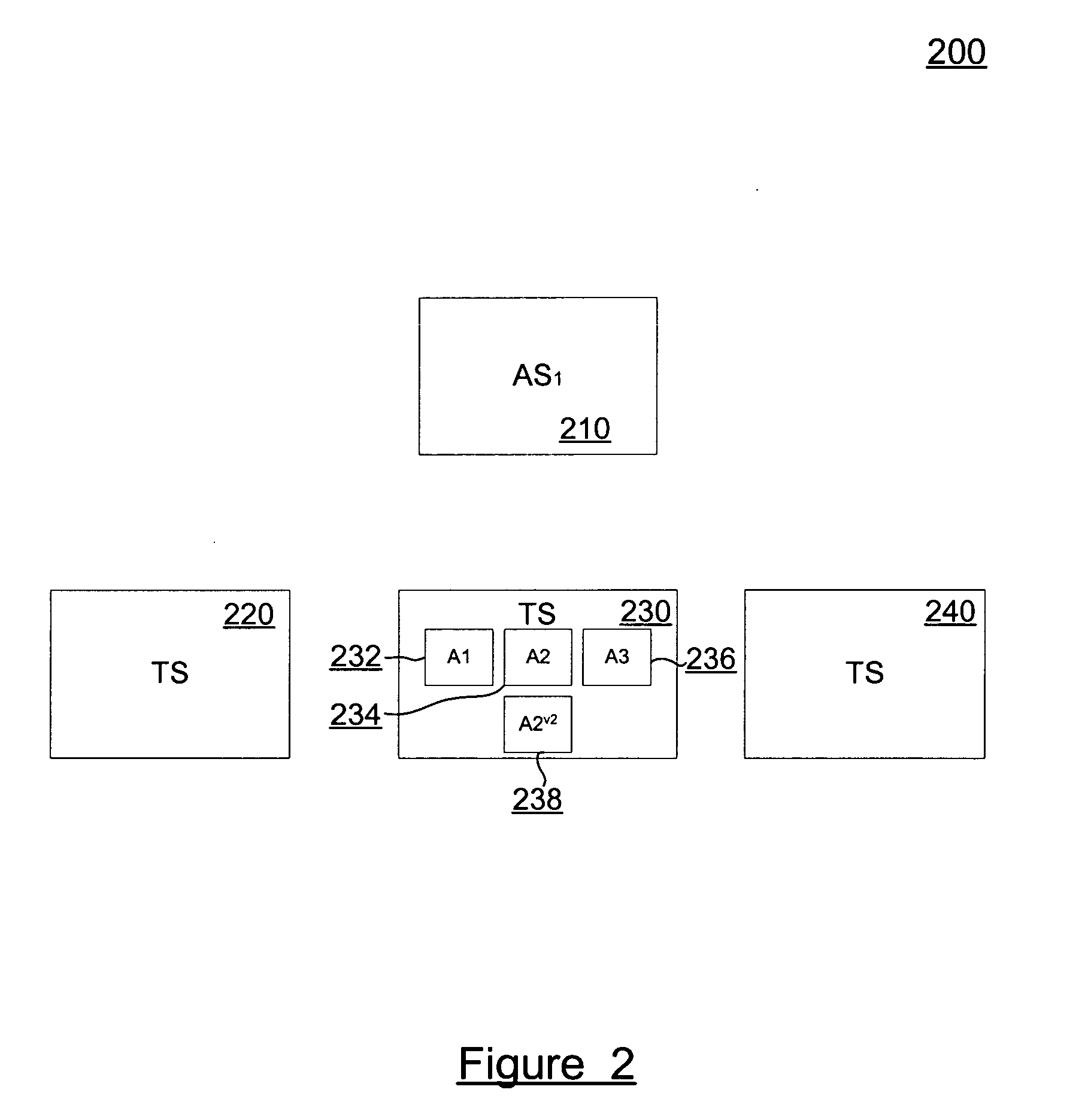

Production redeployment through application versioning

InactiveUS20050262494A1SaveIncrease flexibilitySoftware engineeringProgram loading/initiatingFailoverApplication software

In one embodiment, application versioning and production redeployment support is designed to handle application upgrade needs in mission-critical, production environments. With multiple application versions, application availability to both existing and new clients is not interrupted during the process of application upgrade. It also provides the ability to test a new application version before opening it to general public as well as the ability to roll back to previous safe versions if there are any errors in the currently active version. Clients see consistent application versions, irrespective and transparent of all failure conditions, including admin or managed server restarts and / or failover. Administrators can monitor and manage application versions easily with the management Console. Being a software-based solution, it improves upon traditional application upgrade solution by eliminating the need of hardware load-balancers and duplicate cluster / domain configurations and their associated resource requirements and by providing sophisticated management capabilities.

Owner:BEA SYST INC

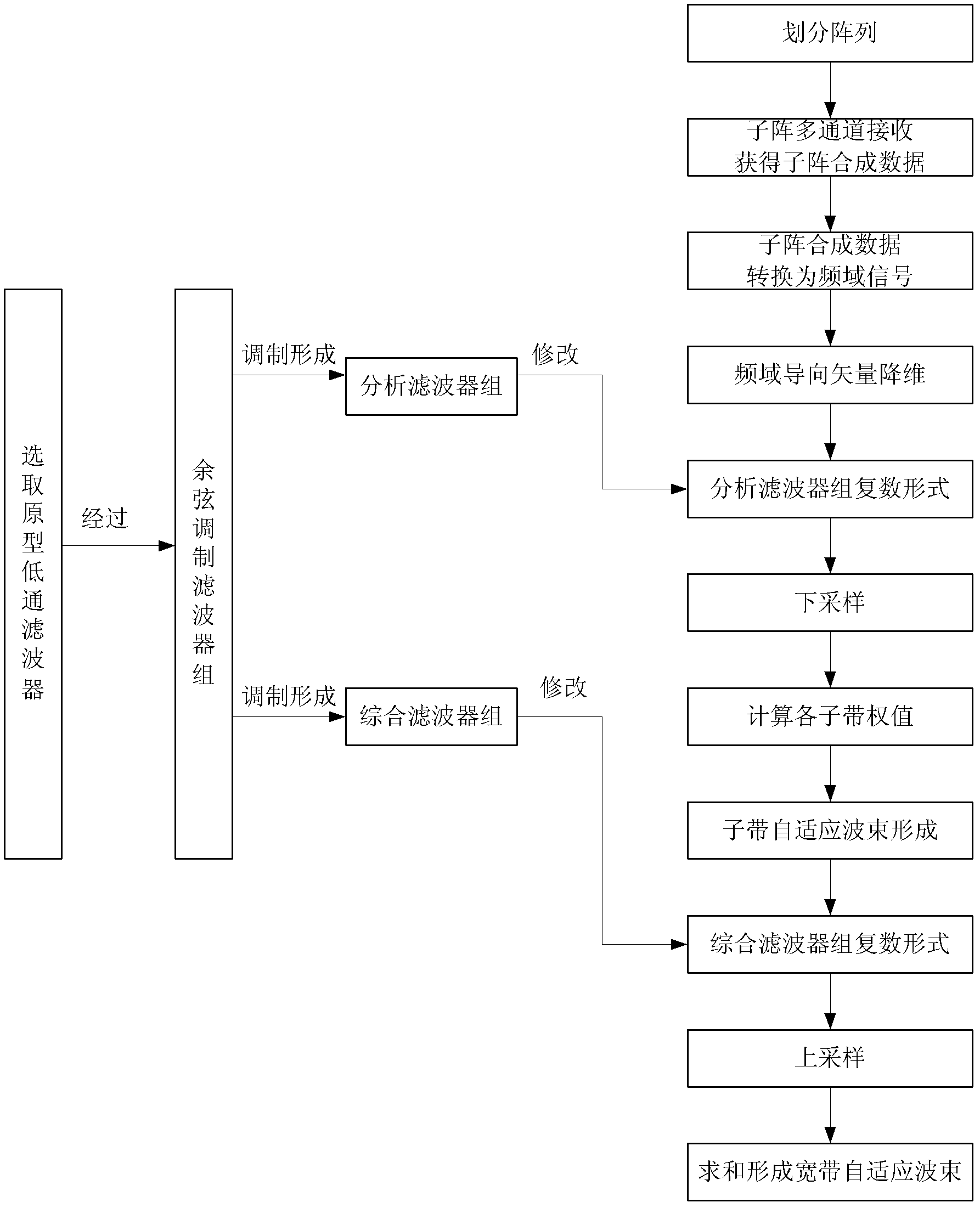

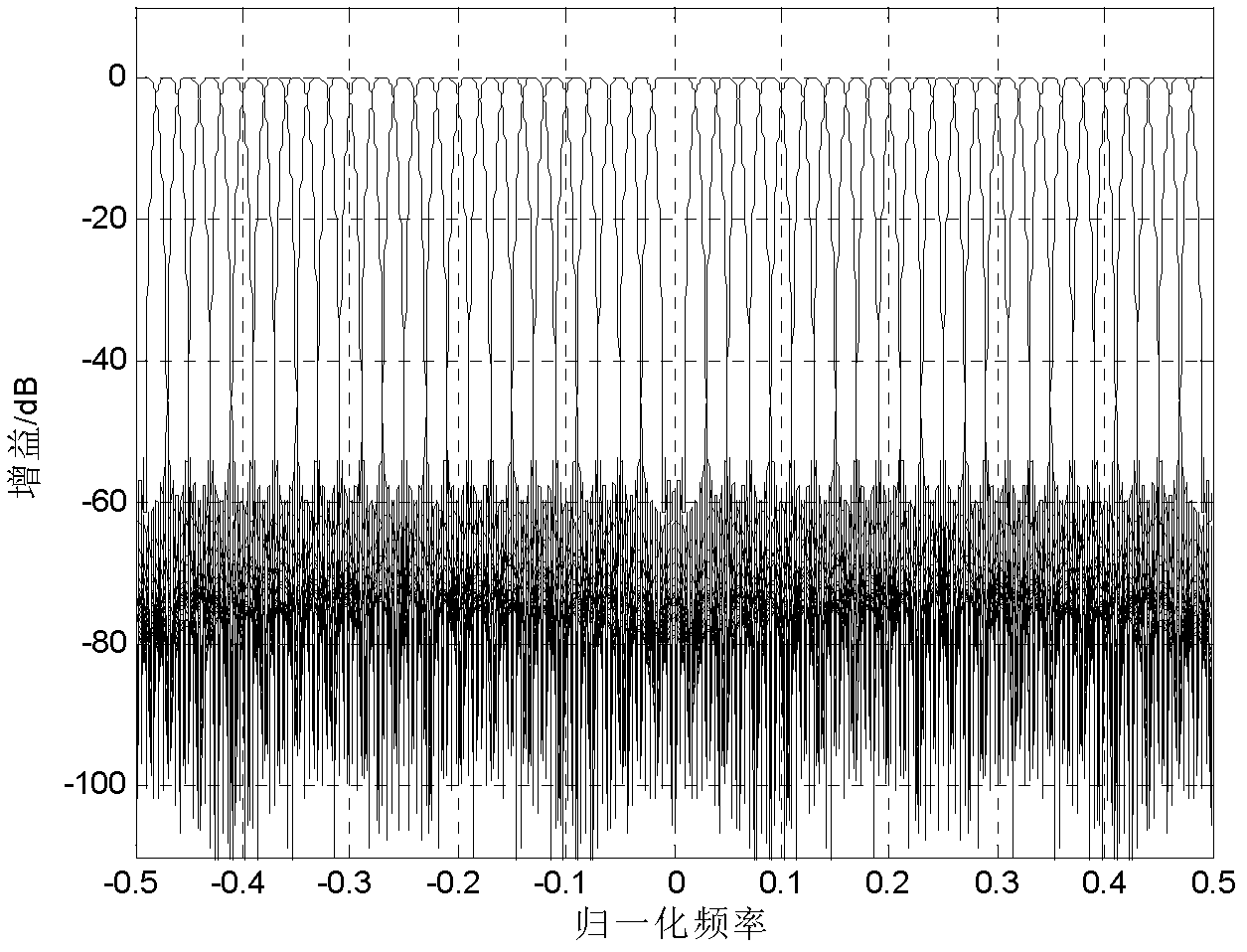

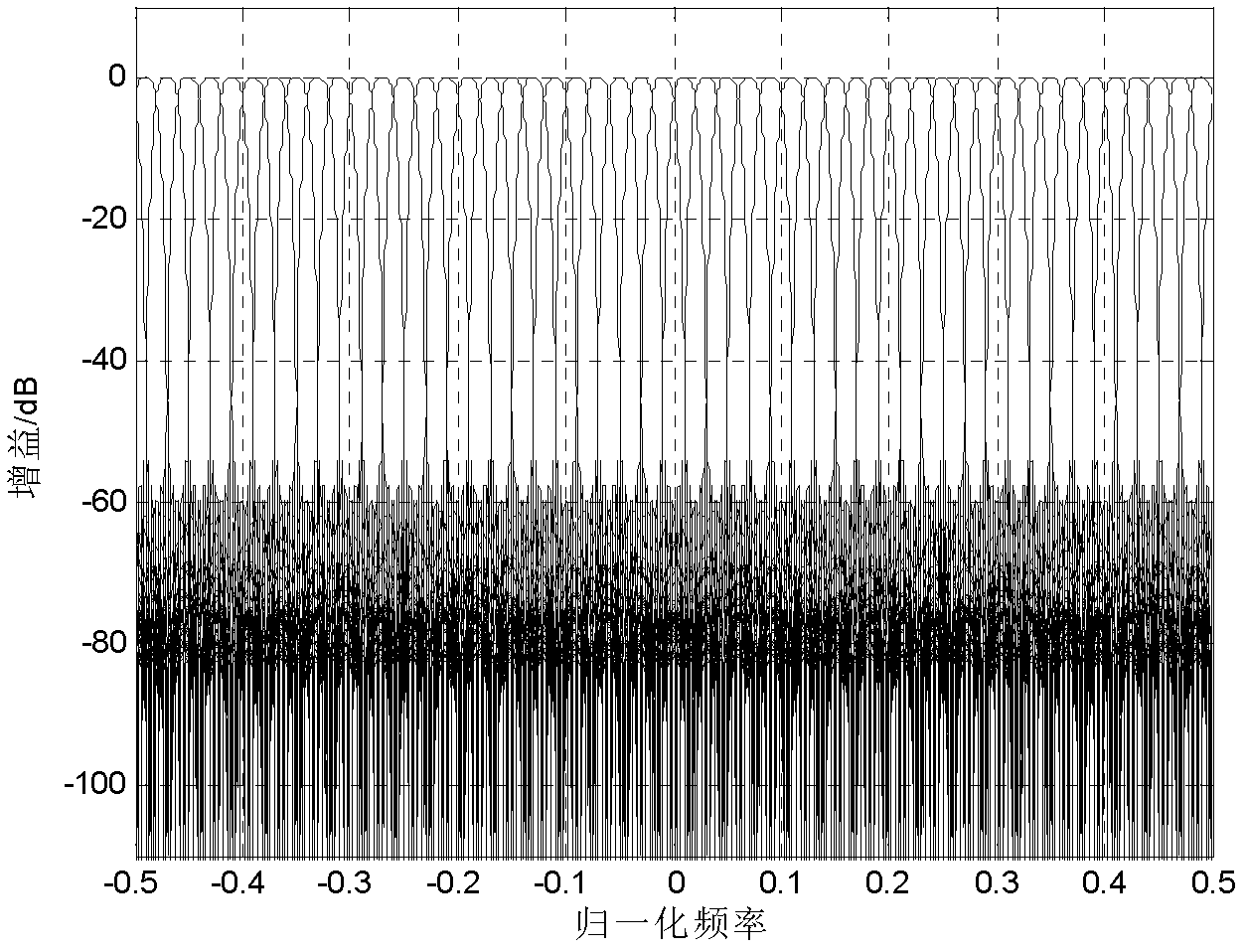

Broadband sub-matrix adaptive beamforming method based on sub-band decomposition

InactiveCN102608588AReduce computationSave hardware resourcesRadio wave reradiation/reflectionDecompositionPhased array

The invention discloses a broadband sub-matrix adaptive beamforming method based on sub-band decomposition, which mainly resolves the problem that computation burden in the prior art is high, and broadband interference signals cannot be processed and suppressed adaptively. The implementation process of the broadband sub-matrix adaptive beamforming method includes steps: 1) dividing a total matrix into a plurality of sub-matrixes, leading the sub-matrixes to be aligned with local beam pointing by the aid of microwave synthesis of a phase shifter, and obtaining sub-matrix synthesis data; 2) selecting a prototype filter and obtaining corrected analyzing and comprehensive filter banks via a cosinusoidal modulation filter bank; 3) under-sampling the sub-matrix synthesis data after the sub-matrix synthesis data pass through the analyzing filter banks, solving an adaptive weight in a narrow band and performing sub-band beamforming in the narrow band; and 4) up-sampling signals after sub-band beamforming, leading the up-sampling signals to pass through the comprehensive filter banks, and summating data of the comprehensive filter banks to obtain data after broadband adaptive beamforming. The broadband sub-matrix adaptive beamforming method has the advantages that the dimension of hardware is small, computation burden is low and broadband interference signals can be suppressed adaptively. In addition, the broadband sub-matrix adaptive beamforming method can be used for adaptive beamforming of a broadband phased array radar.

Owner:XIDIAN UNIV

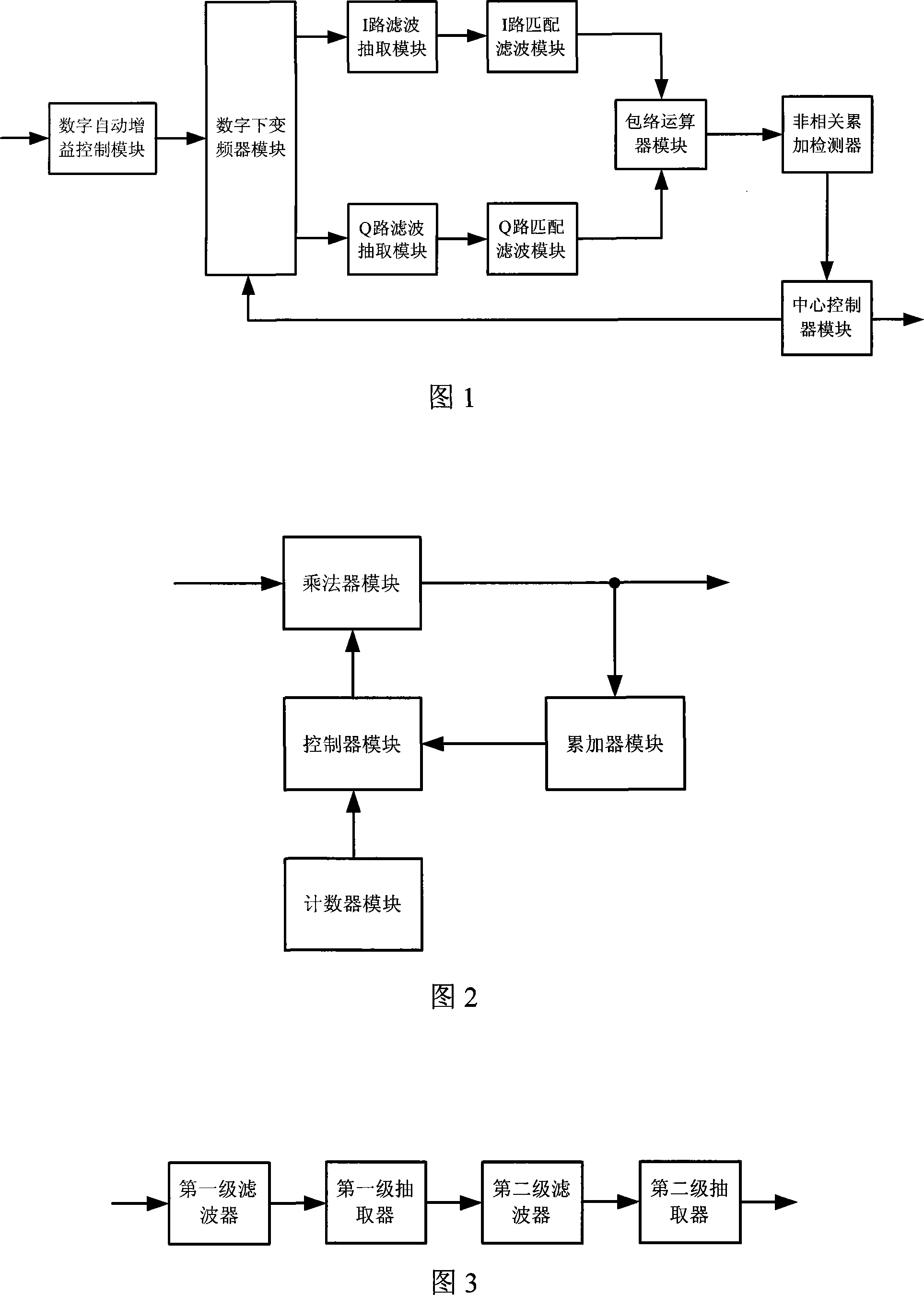

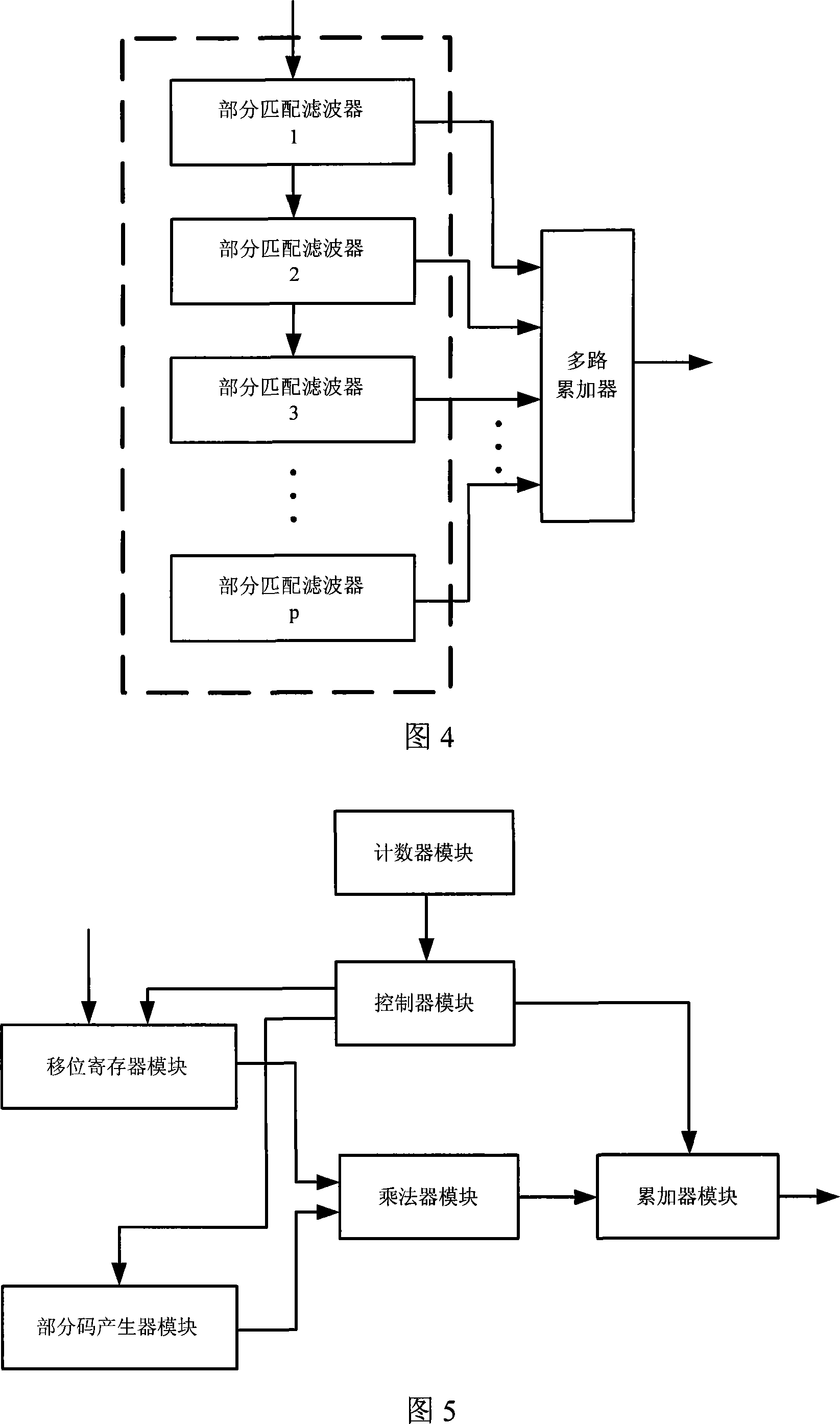

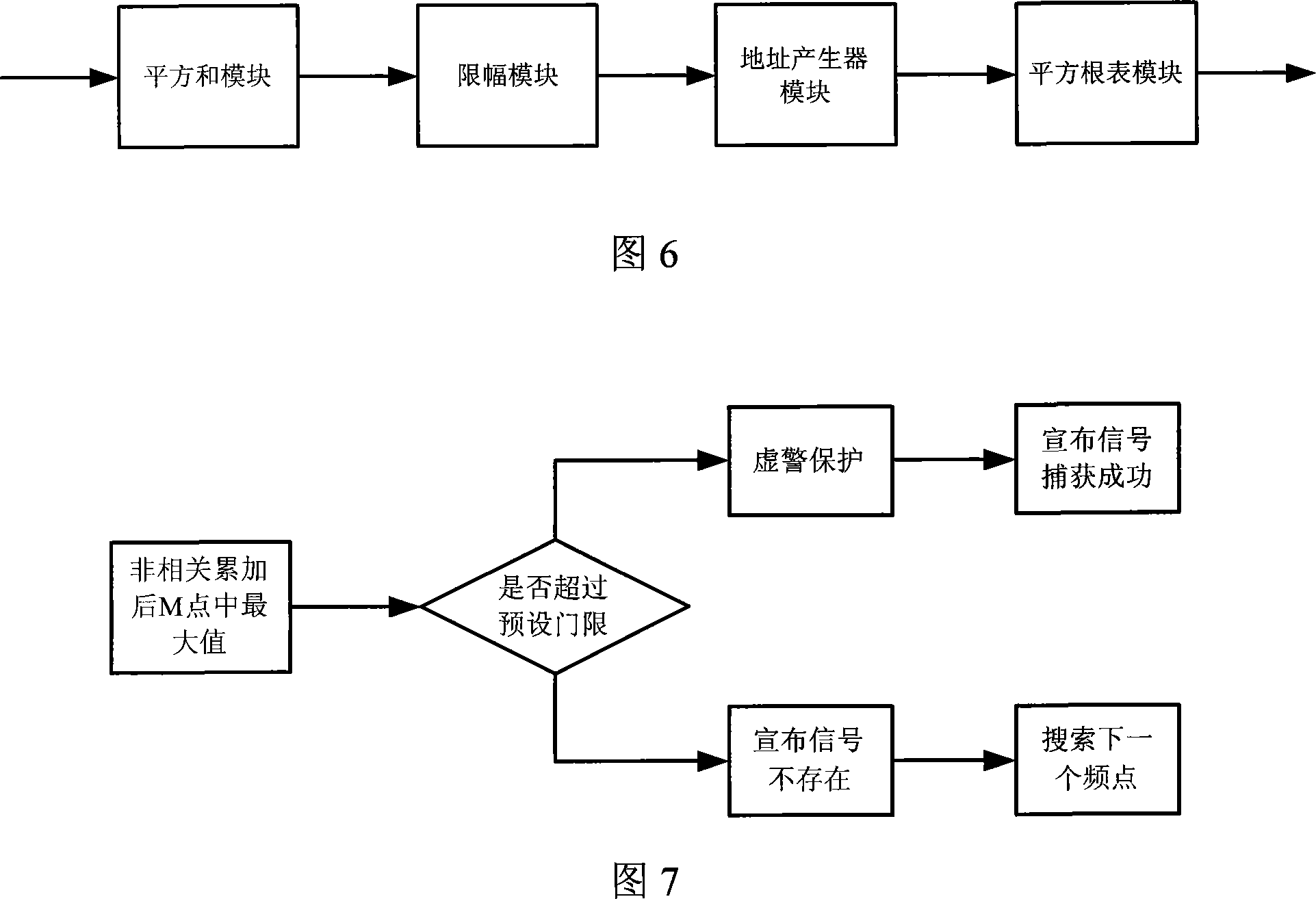

Devices and methods for fast catching signal in high dynamic satellite navigation receiving machine

InactiveCN101082664AReduce complexityGuaranteed stabilityBeacon systems using radio wavesPosition fixationFrequency changerSignal-to-noise ratio (imaging)

The invention discloses a signal rapid-capturing device and method in the high-dynamic satellite navigational receiver based on segmented mated filter, which comprises the following parts: frequency converter, low-pass filter, extractor, segmented mated filter, envelope calculator, incoherent signal accumulated tester and central controller, wherein the mated filter searches the entire code phase within time T in relative to integral, which obtains a relative result of all code phases under one Doppler frequency deviation to improve signal-to-noise ratio through incoherent signal accumulated tester, in order to judge whether the signal exists; the central frequency is changed by frequency converter to do frequency shaft stepping research. The invention can transmit two-dimensional research on the traditional code phase and Doppler frequency deviation into one-dimensional research on the Doppler frequency deviation, which improves the capture speed of signal greatly to save hardware resource through the design of the segmented mated filter.

Owner:ZHEJIANG UNIV

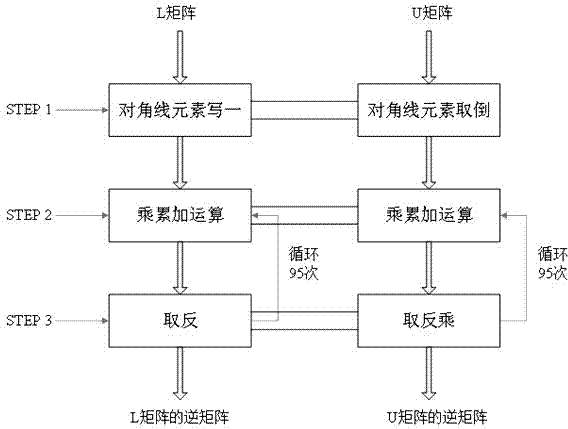

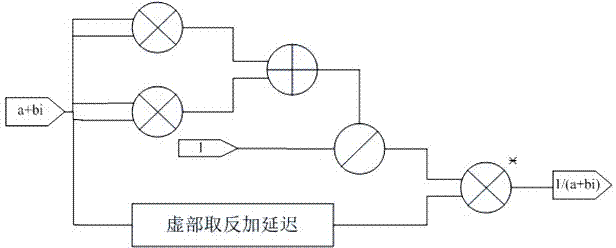

Inverse operation method for lower triangle complex matrix with any order

InactiveCN103927290AImplement the inverse operationSave hardware resourcesComplex mathematical operationsDiagonalComputer science

The invention relates to an inverse operation method for a lower triangle complex matrix with any order. The inverse operation method comprises the following steps that (1) a reciprocal obtaining unit is set, and is used for carrying out reciprocal obtaining operation on a diagonal element of an N-order matrix L, and outputting a matrix obtained after reciprocal obtaining operation is accomplished; (2) a multiplication and accumulation unit is set and is used for receiving the matrix obtained after reciprocal obtaining operation is accomplished, and multiplication and accumulation operation is carried out on the first element to the (i-1)th element in the ith row in the matrix; (3) a reciprocal multiplication obtaining unit is set and is used for receiving the accumulation result corresponding to the elements in the ith row of the matrix, reciprocal obtaining operation is carried out on the accumulation result, and then the accumulation result processed through reciprocal obtaining operation is multiplied by a diagonal element in the ith row so that a matrix element of the ith row of an inverse matrix L-1 can be obtained. In the whole process, a plurality of multiplication and accumulation units are used for carrying out parallel calculation. The inverse operation method for the lower triangle complex matrix with any order has the advantages that the inverse operation of the lower triangle complex matrix with any order can be achieved, and restriction caused by the number of operation units does not exist; only the design of a multiply-accumulator with one plural adder and one plural multiplier is adopted, hardware resources are saved, and operation efficiency is ensured through an effective parallelization mode.

Owner:NANJING UNIV

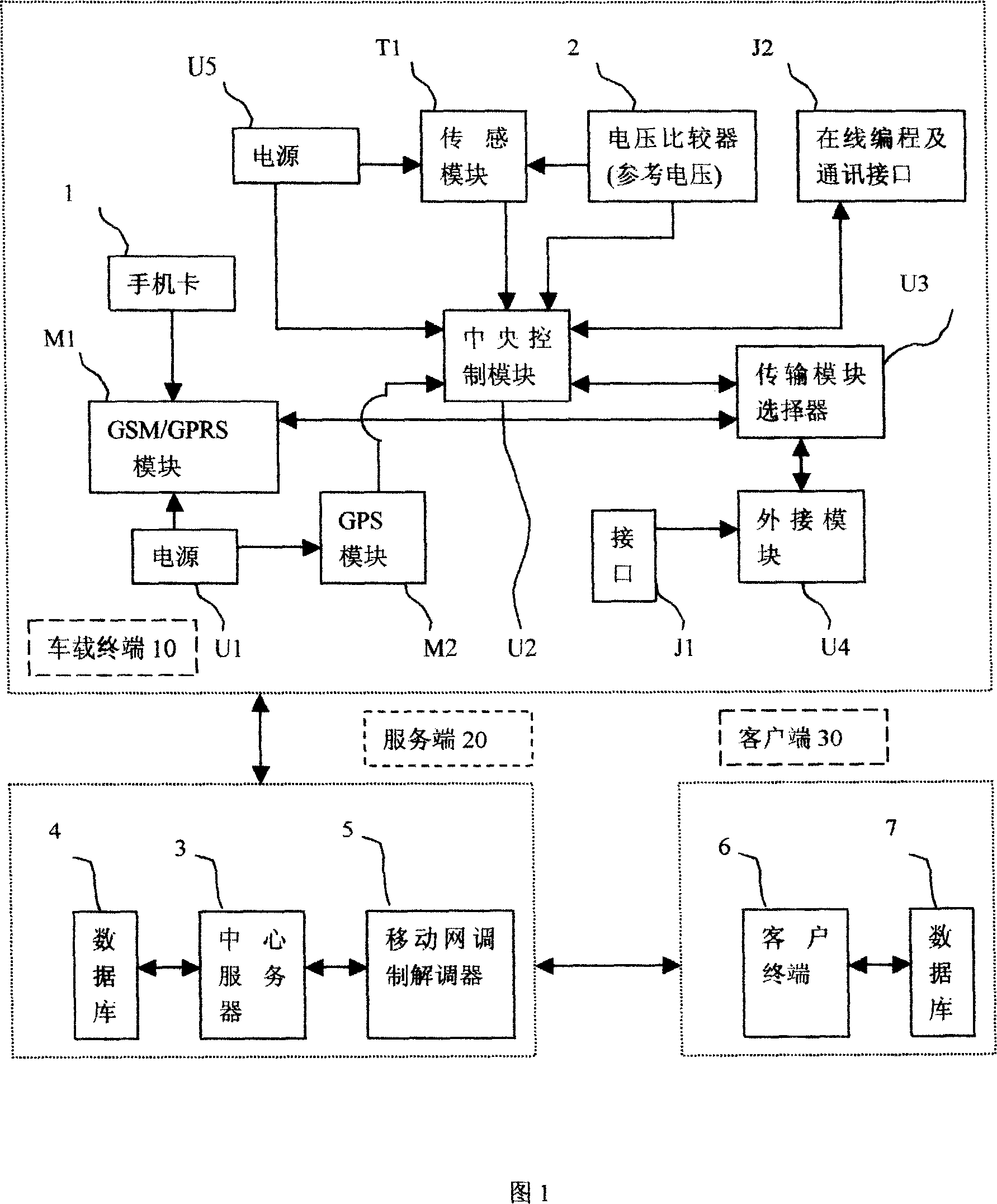

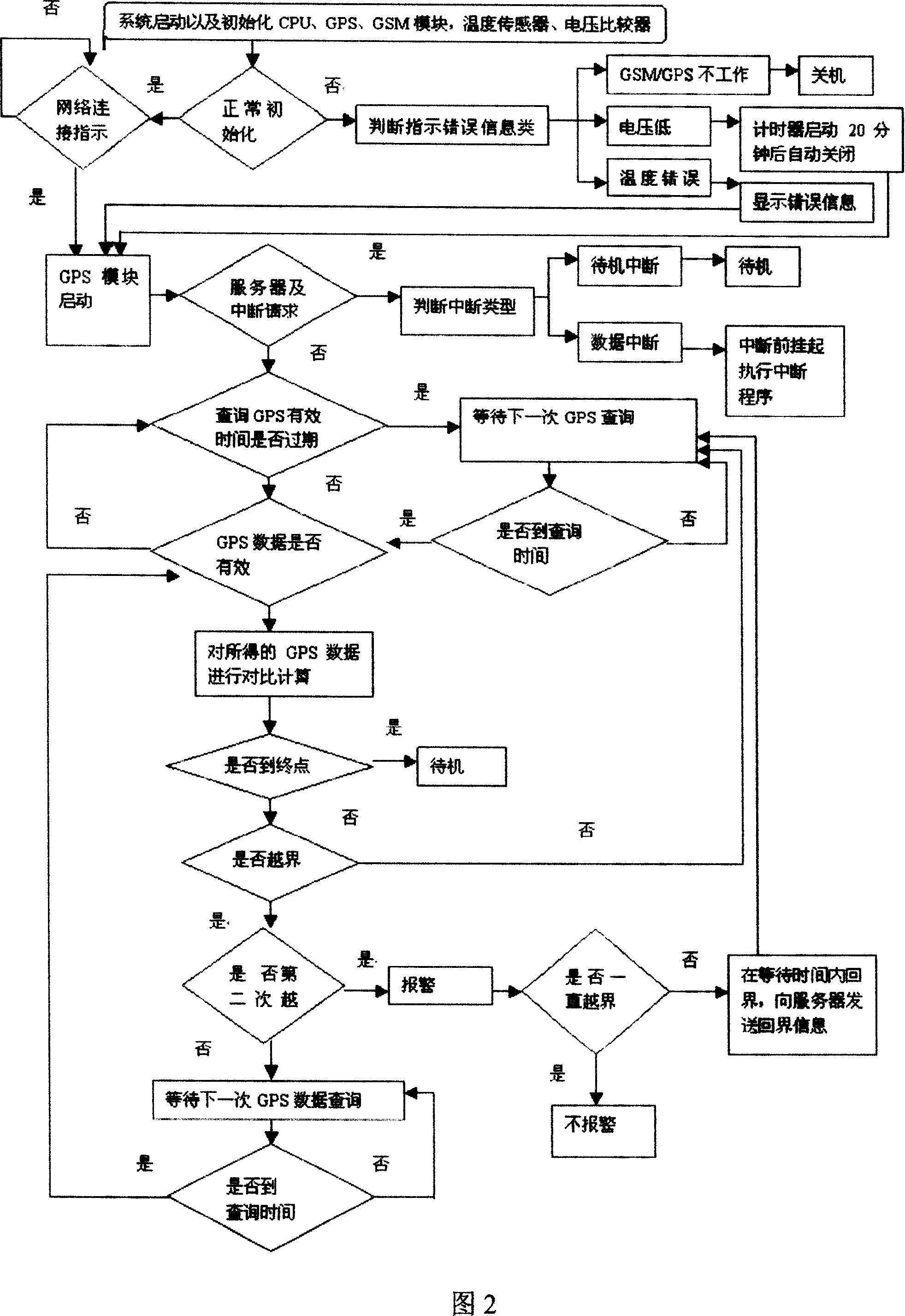

Apparatus for automatically tracking automobile running orbit and its monitoring method

InactiveCN101075375AFast and effective economic monitoringFast and effective economic controlDetection of traffic movementOrbitData transmission

An automatic-tracking device of vehicle movement orbit consists of vehicle terminal, service end and client end. It is featured as selecting position coordinate automatically by vehicle terminal according to preset movement path to set up highway enclosing wall, confirming specific position relative to highway enclosing wall by vehicle terminal according to highway position coordinate and actual position coordinate for judging whether vehicle is in the scope of highway enclosing wall or not.

Owner:包头奥普德电子科技有限公司

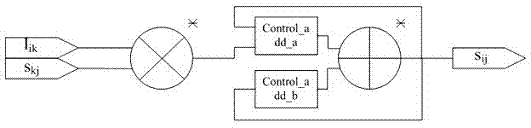

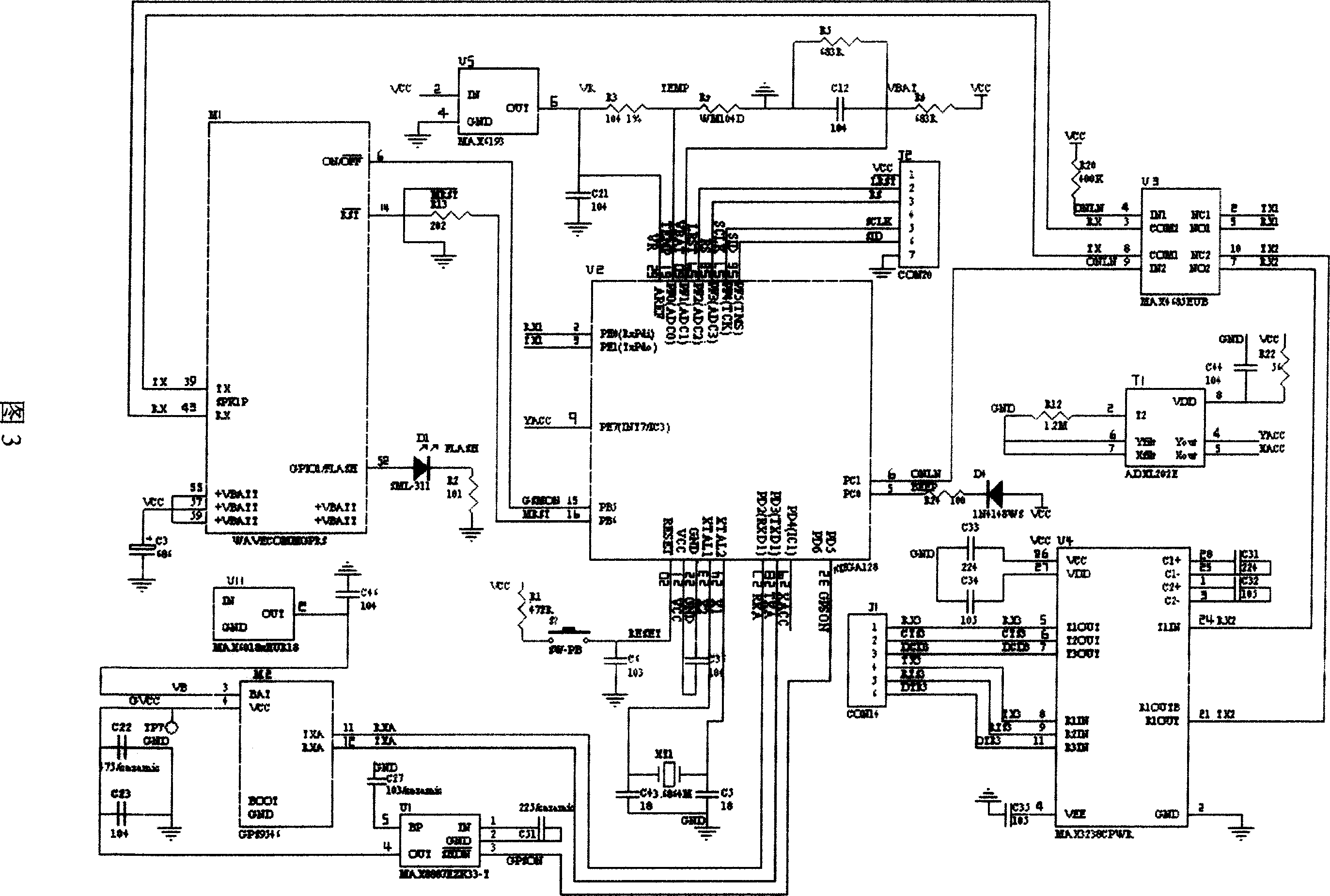

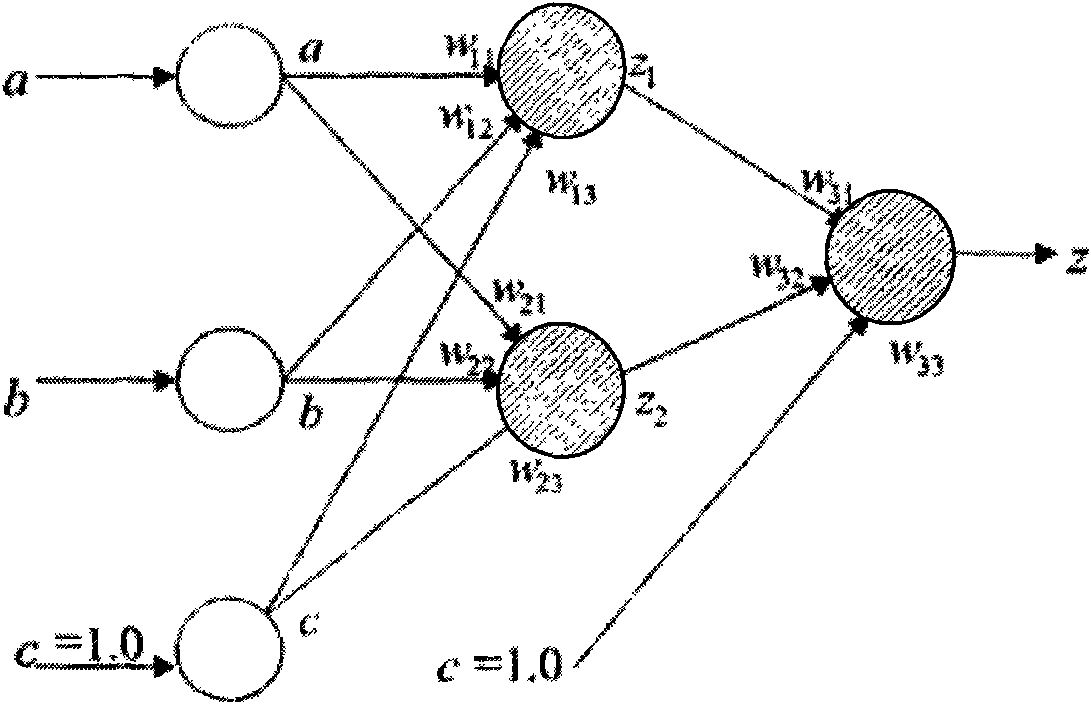

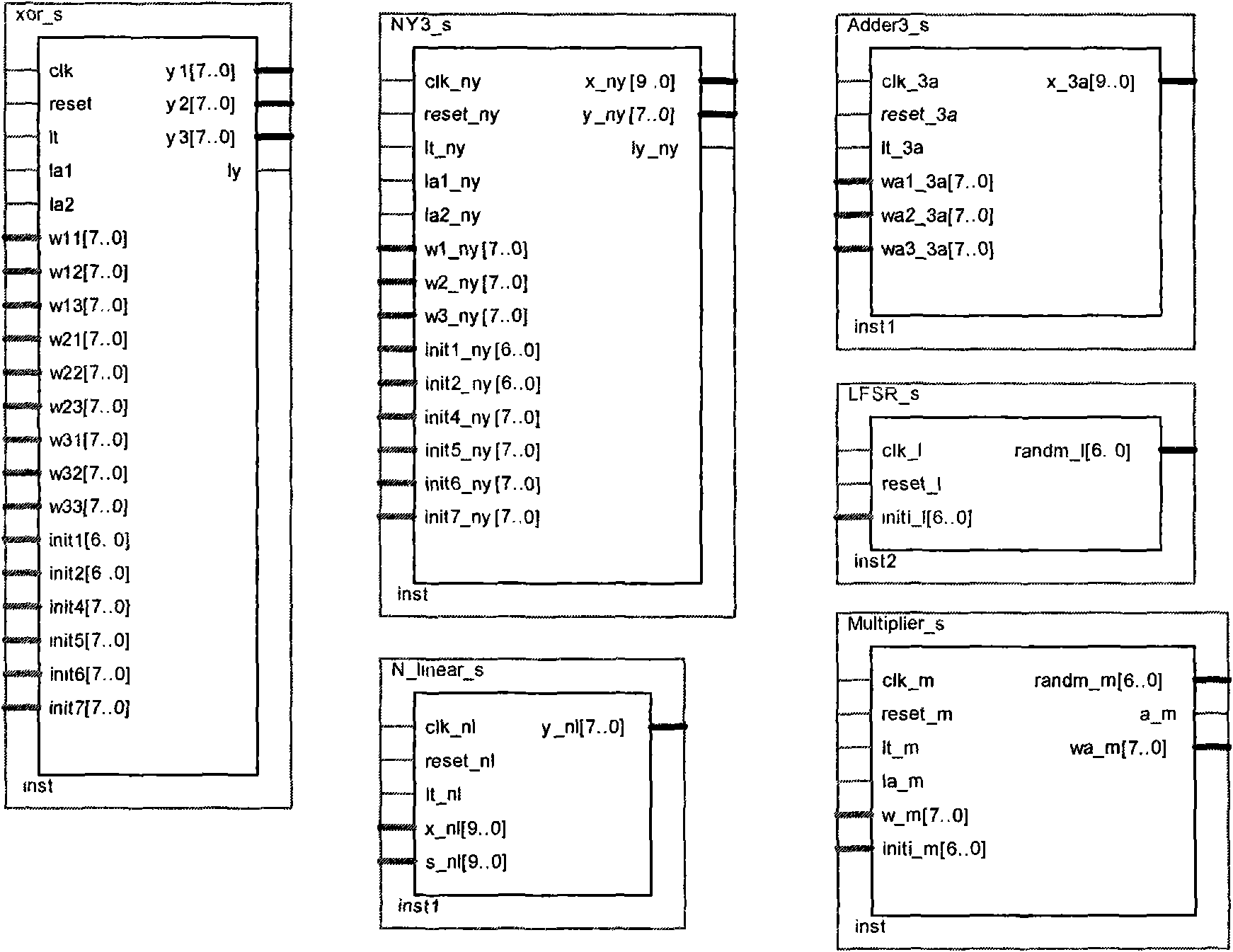

Hardware realization method and system for artificial neural network algorithm

The invention provides a hardware realization method and a system for an artificial neural network algorithm, which overcome the defects of high cost and overlarge occupation of hardware resources of the prior hardware realization technology. The system comprises a top layer module, the top layer module consists of a plurality of neuron modules, pulse input ends of the neuron modules input given weight products, output ends of the neuron modules fit the given weight products into a Sigmoid function of a neutral network through a normal distribution random generator and a nonlinear converter, and then the Sigmoid function is converted into pulse to be output through a pulse converter. Compared with the prior realization technology, the hardware realization method and the system for the neural network algorithm avoid the embarrassment that a serial mode in the prior software realization is used to finish parallel computation, overcome the disadvantages of software realization, save a large amount of hardware resources due to the algorithm optimization, have lower cost due to the realization on an FPGA platform, utilize an optimized algorithm to avoid the difficulty that the Sigmoid function is difficult to realize by a hardware, and also save the hardware resources by using an accumulation mode.

Owner:UNIV OF SHANGHAI FOR SCI & TECH

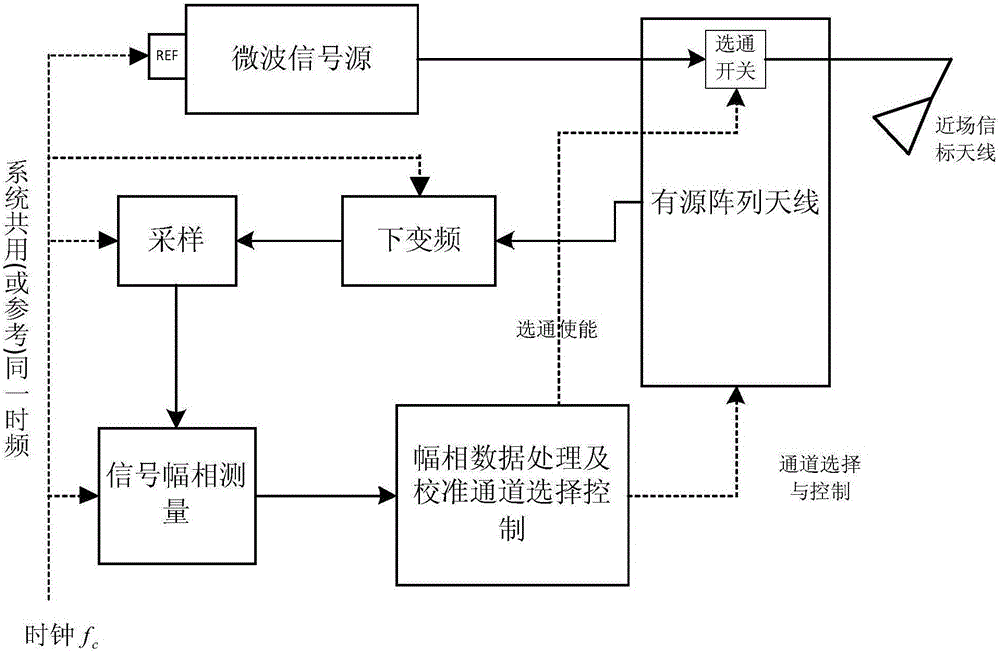

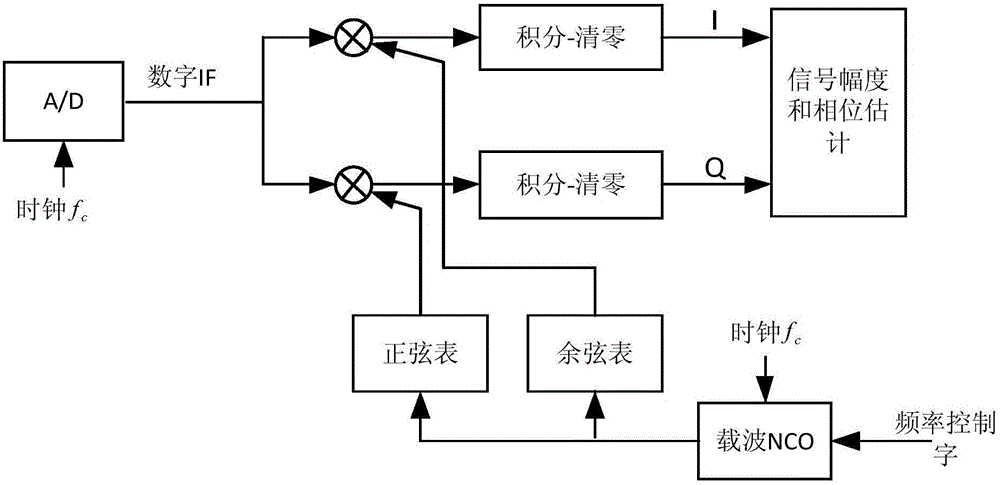

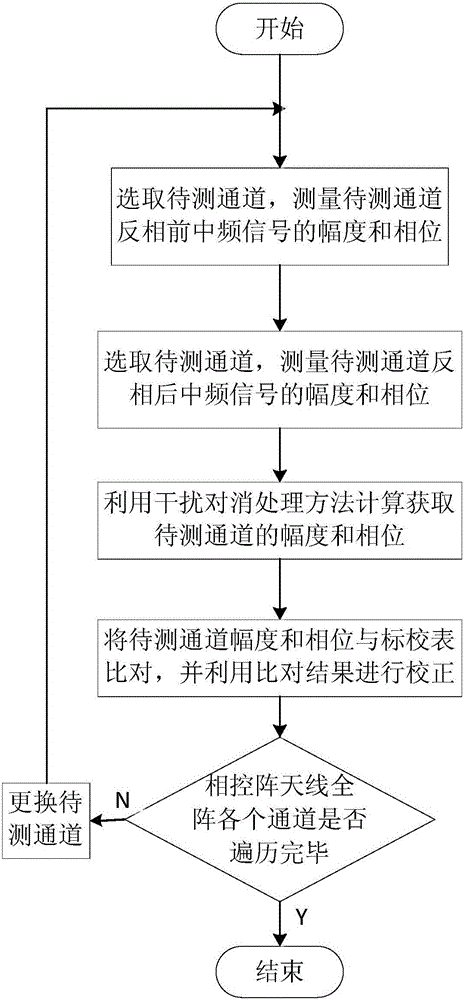

System and method for correcting on-orbit amplitude phase of phased-array antenna

ActiveCN105162536AAchieve gatingSave hardware resourcesPropogation channels monitoringSystem hardwarePhase array antenna

The invention relates to a system and method for correcting an on-orbit amplitude phase of a phased-array antenna. A signal output by a microwave signal source and used for correcting is transmitted through a beacon antenna in a phased-array near field and received by a certain channel to be detected of the phased-array antenna; the output signal is subjected to down-conversion and AD acquisition; amplitude and phase measurement of the signal can be completed through a signal processing module; finally, the measured amplitude and phase of the signal are subjected to data processing; obtaining of the amplitude and the phase of the channel to be detected is completed; and amplitude phase correction is completed. According to the invention, on the basis of the beacon in the phased-array near field, with the help of an interference cancellation principle, the amplitude phase measurement influence to the channel to be detected by leaking (multipath) signals can be eliminated; the accuracy of a measurement result is increased; the implementation principle is simple; system software resources are saved; in the aspect of implementing amplitude phase measurement, a single-channel amplitude phase measurement scheme is selected and used; an auxiliary reference channel is not adopted; and thus, system hardware resources and the cost are saved.

Owner:XIAN INSTITUE OF SPACE RADIO TECH

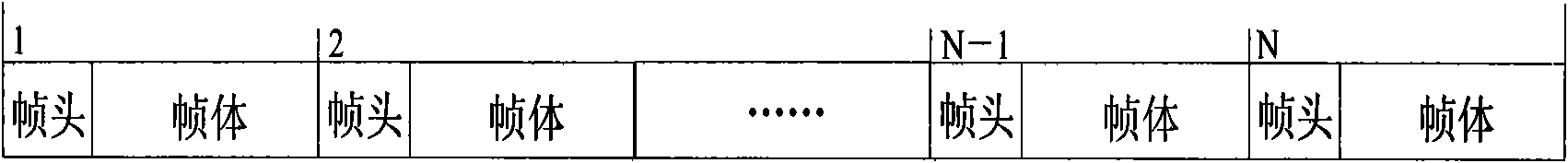

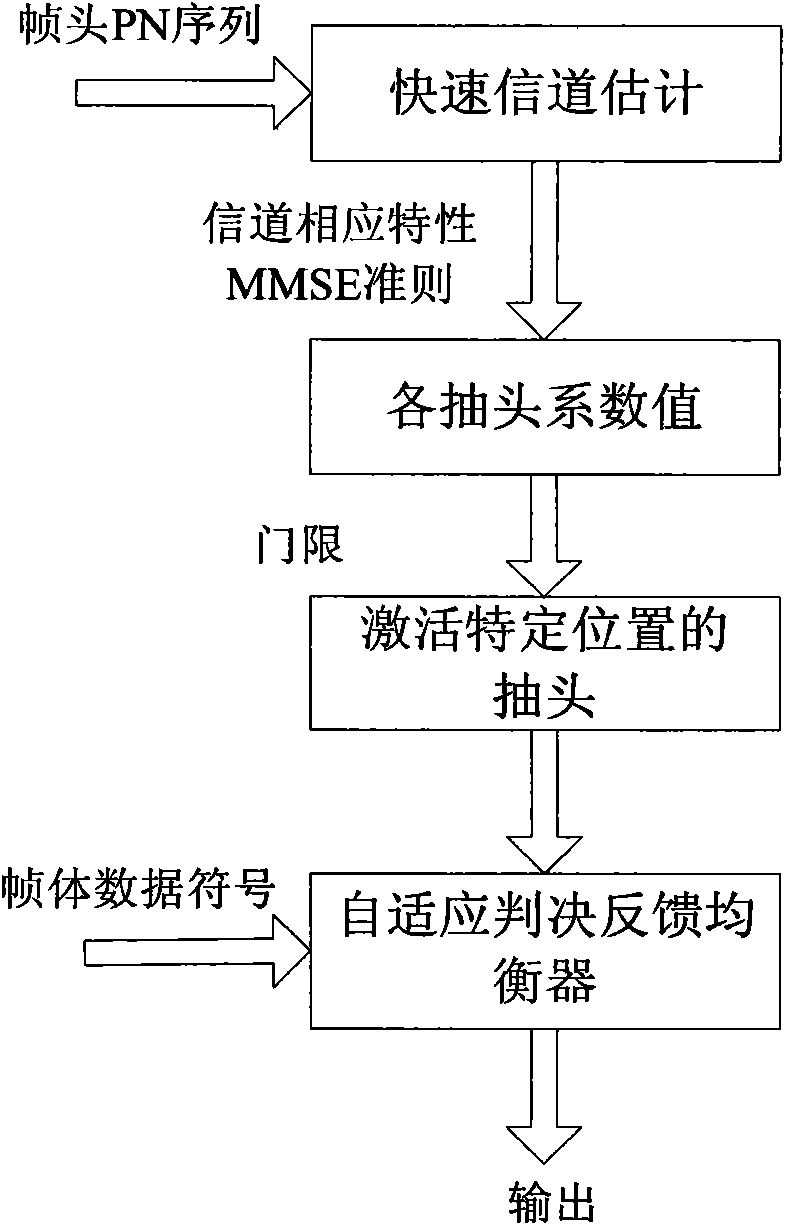

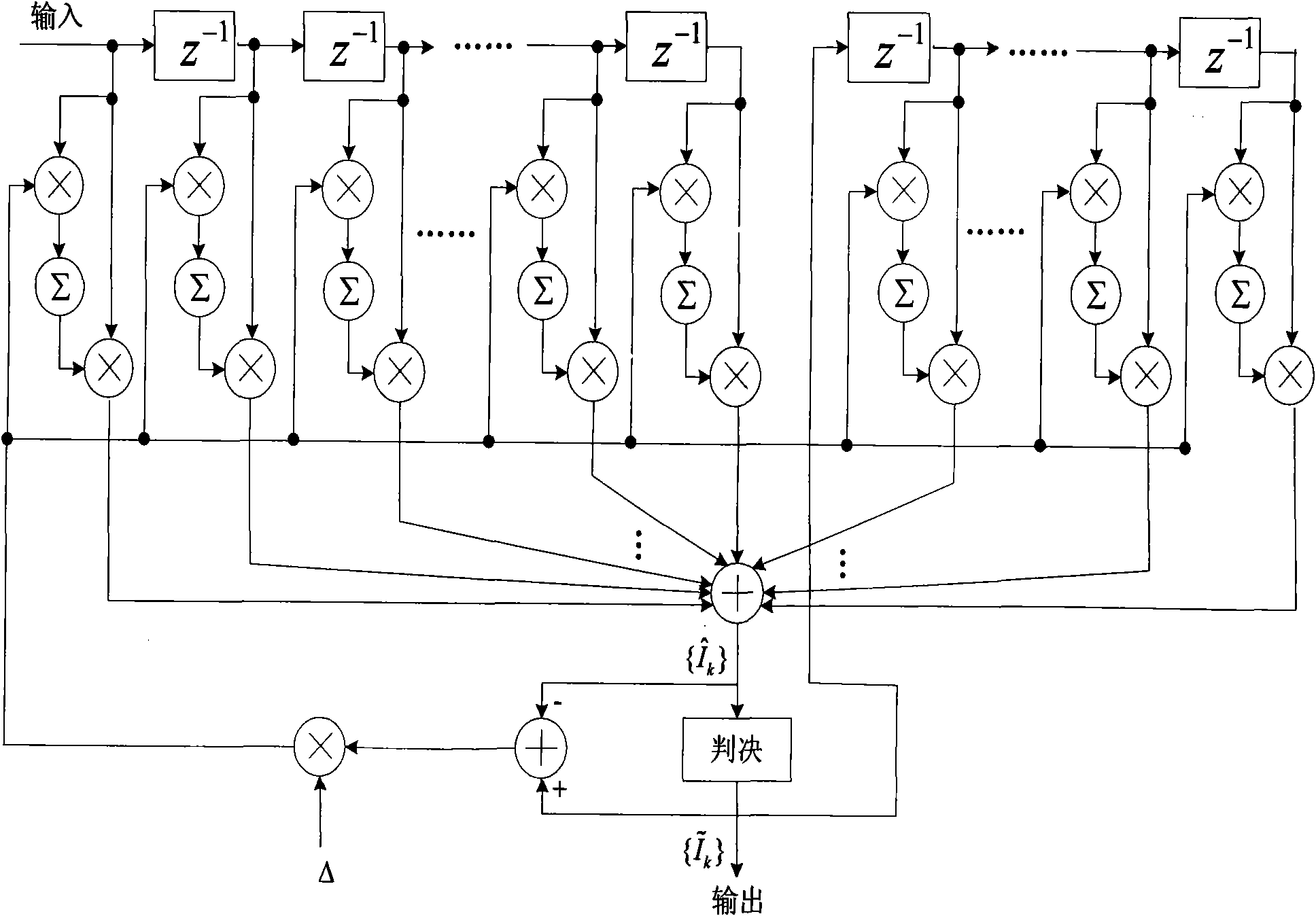

Indirect self-adaptive balancing method of shallow-sea underwater acoustic communication system

InactiveCN101567863ASimple structureGood estimateTransmitter/receiver shaping networksCommunications systemShallow sea

The invention discloses an indirect self-adaptive equalization method of a shallow-sea underwater acoustic communication system to eliminate transmission intersymbol interference brought by a shallow-sea underwater acoustic channel with the time-varying and multi-diameter characteristics. The method comprises the following steps: designing a signal frame structure suitable for transmission in the shallow-sea underwater acoustic channel at a sending terminal; utilizing a frame head PN sequence to carry out rapid channel estimation and the initialization of equalizer tap coefficients at a receiving terminal; selecting a corresponding threshold according to the practical transmission environment to realize the decentralization of equalizer taps; and adopting an LMS algorithm with a variable step size to further reduce errors so as to better equalize frame body data. The invention enables an equalizer in the shallow-sea underwater acoustic communication system to have rapid convergence and lower hardware complexity, has good equalization effect on a sending signal after high-level modulation and can be effectively applied to the shallow-sea high-speed digital communication system.

Owner:魏昕

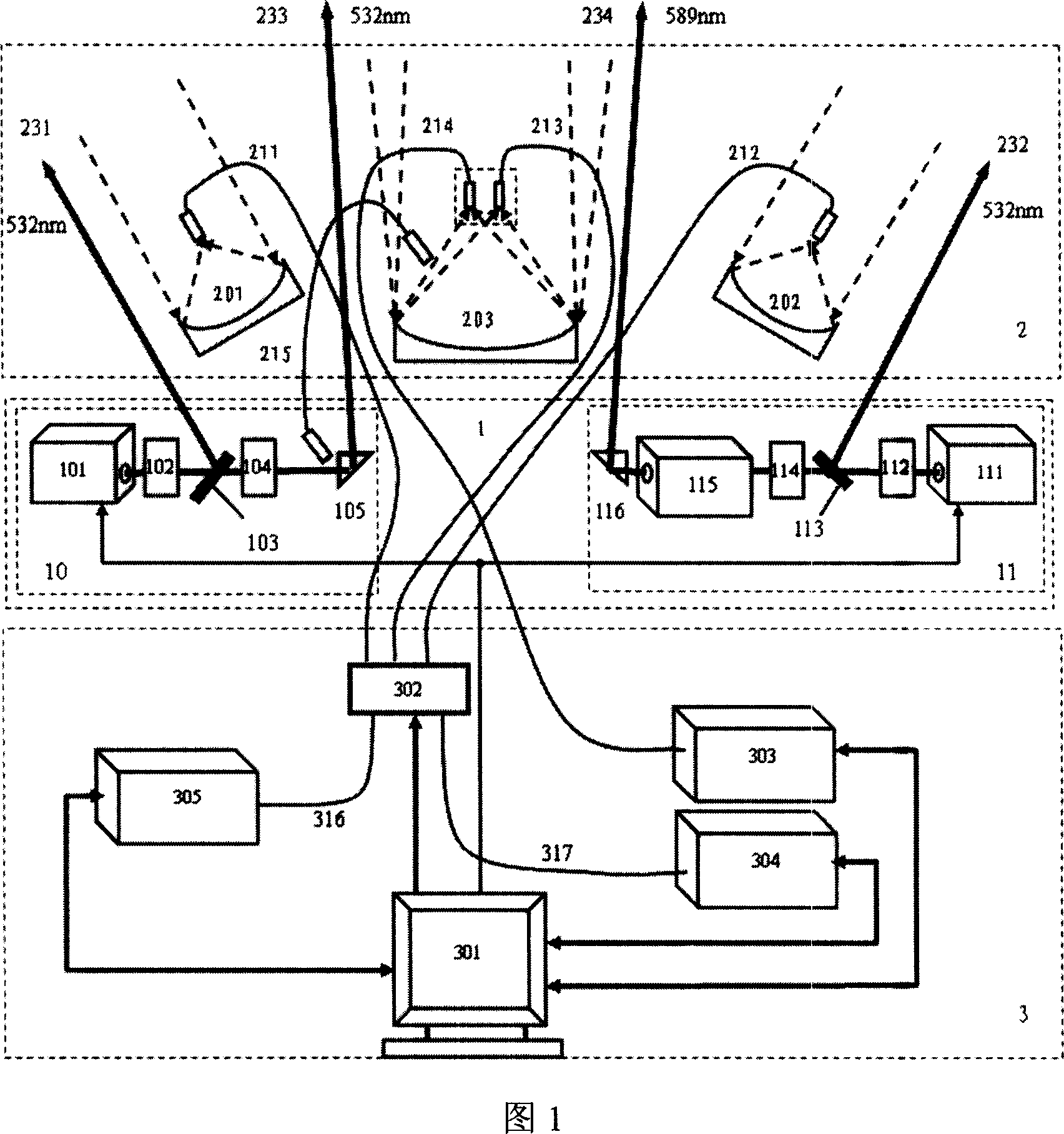

Synthesis multifunctional middle and upper atmosphere exploration laser radar

InactiveCN101034162AHigh measurement accuracyImprove operational reliabilityLaser detailsElectromagnetic wave reradiationRayleigh scatteringFiltration

This invention discloses a synthetic multifunctional middle and upper atmosphere monitoring laser radar, which is made up of laser emission (1), optical receiving (2), signal detecting (3). This radar reasonably mixes together Rayleigh scattering laser radar, natrium fluorescent light laser radar and Rayleigh monitoring wind laser radar. The invention makes hardware be of multiple utilization, implements a laser radar monitors density, temperature, fluctuation and wind field of middle and upper atmosphere all the day. This laser radar utilizes key techniques such as: three direction fixed receiving and dispatching, optical fiber switch, single channel and borderline wind monitoring, launching laser and backward wave frequency discrimination frequency inter locked on molecule transition, atom filtration, complex filtration, twice multiple-frequency remnant light reuse, double optical fiber spectro-surface, square pulse dye laser atom steady frequency. The invention has advantages of stable and reliable working, high detection precision, high automatic, more monitoring parameter and long monitor time.

Owner:WUHAN INST OF PHYSICS & MATHEMATICS CHINESE ACADEMY OF SCI

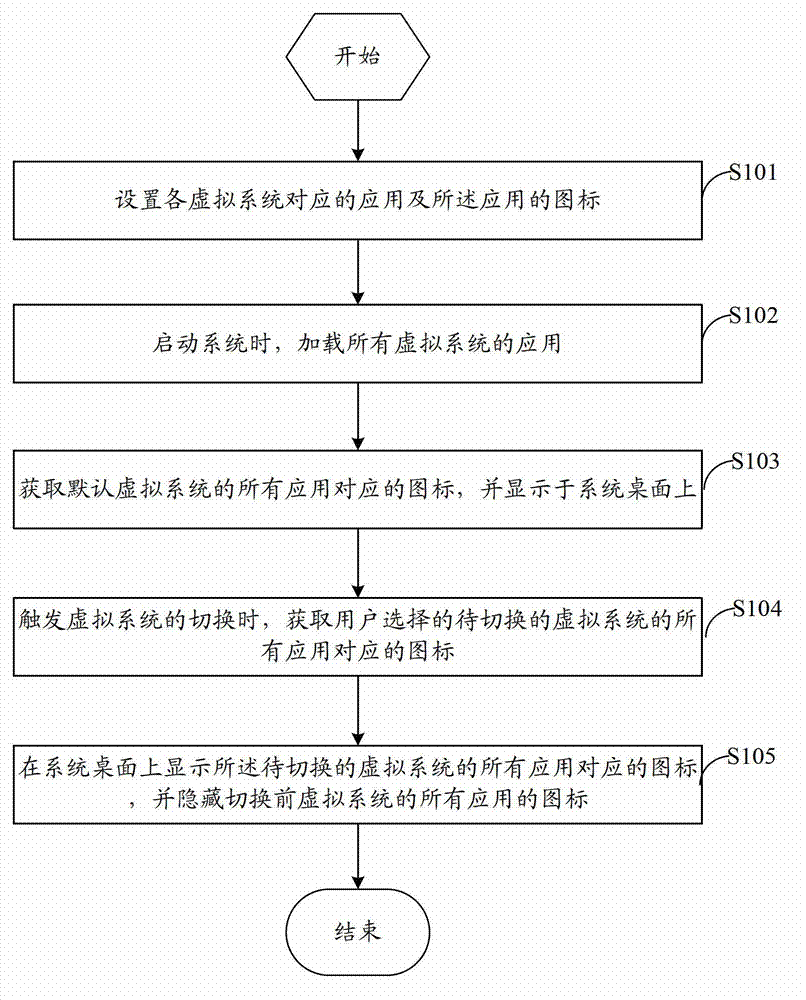

Method and device for achieving virtual multisystem based on Android system

ActiveCN103049289ASave space and hardware resourcesSave resourcesProgram loading/initiatingSoftware simulation/interpretation/emulationEmbedded system

The invention relates to the field of communication and provides a method and device for achieving virtual dual system based on Android system. The method includes the following steps: step1, triggering virtual system switch and acquiring icons which corresponds to all the applications of the virtual system which is chosen by users and waits for being switched, step2, displaying the icons which corresponds to all the applications of the virtual system which waits for being switched, hiding all the icons of all the applications of the virtual system before the virtual system is switched and step3, achieving the virtual system switch. According to the embodiment of the method and device for achieving virtual multisystem based on Android system, needs of different users are satisfied and the cost is saved.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

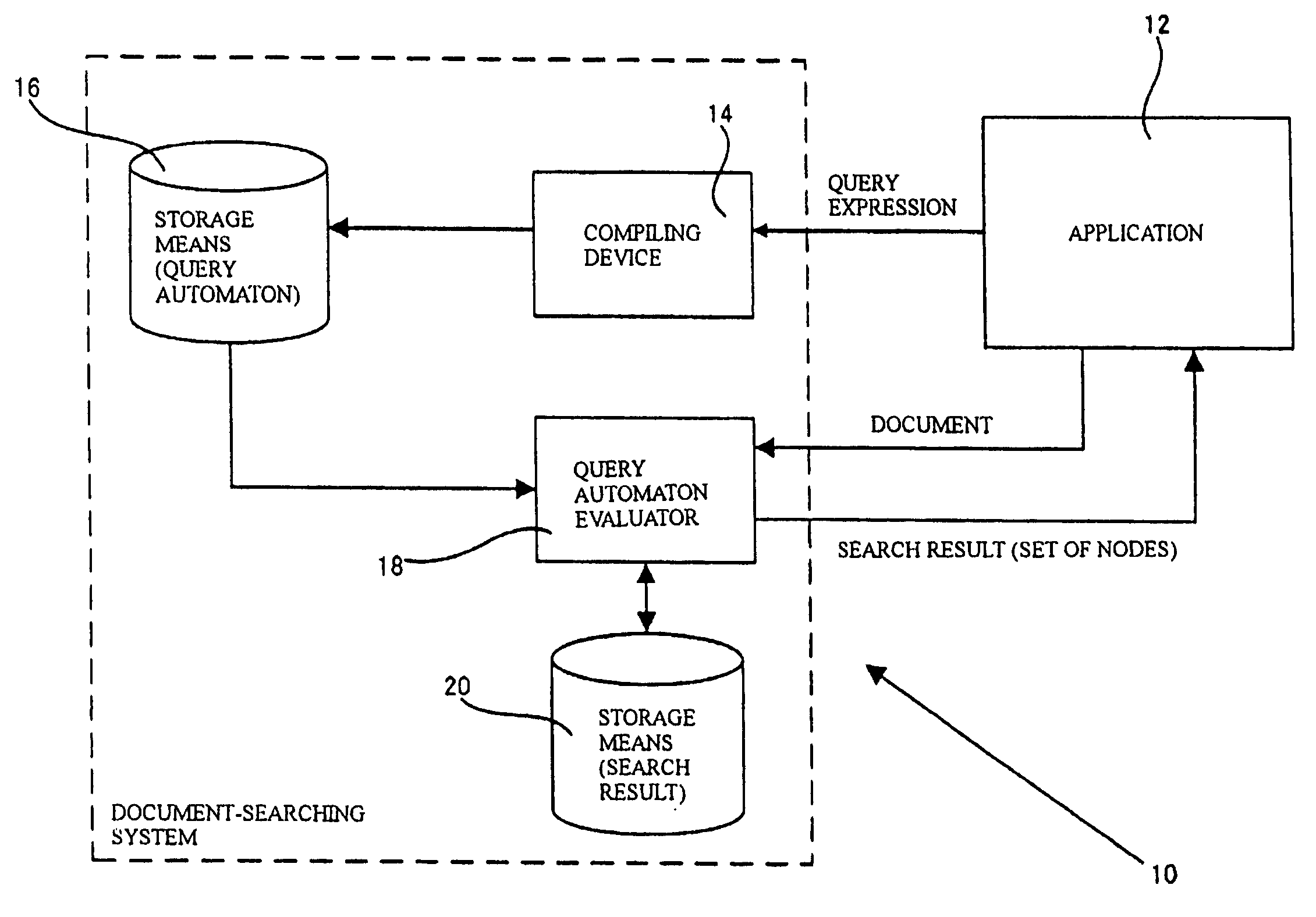

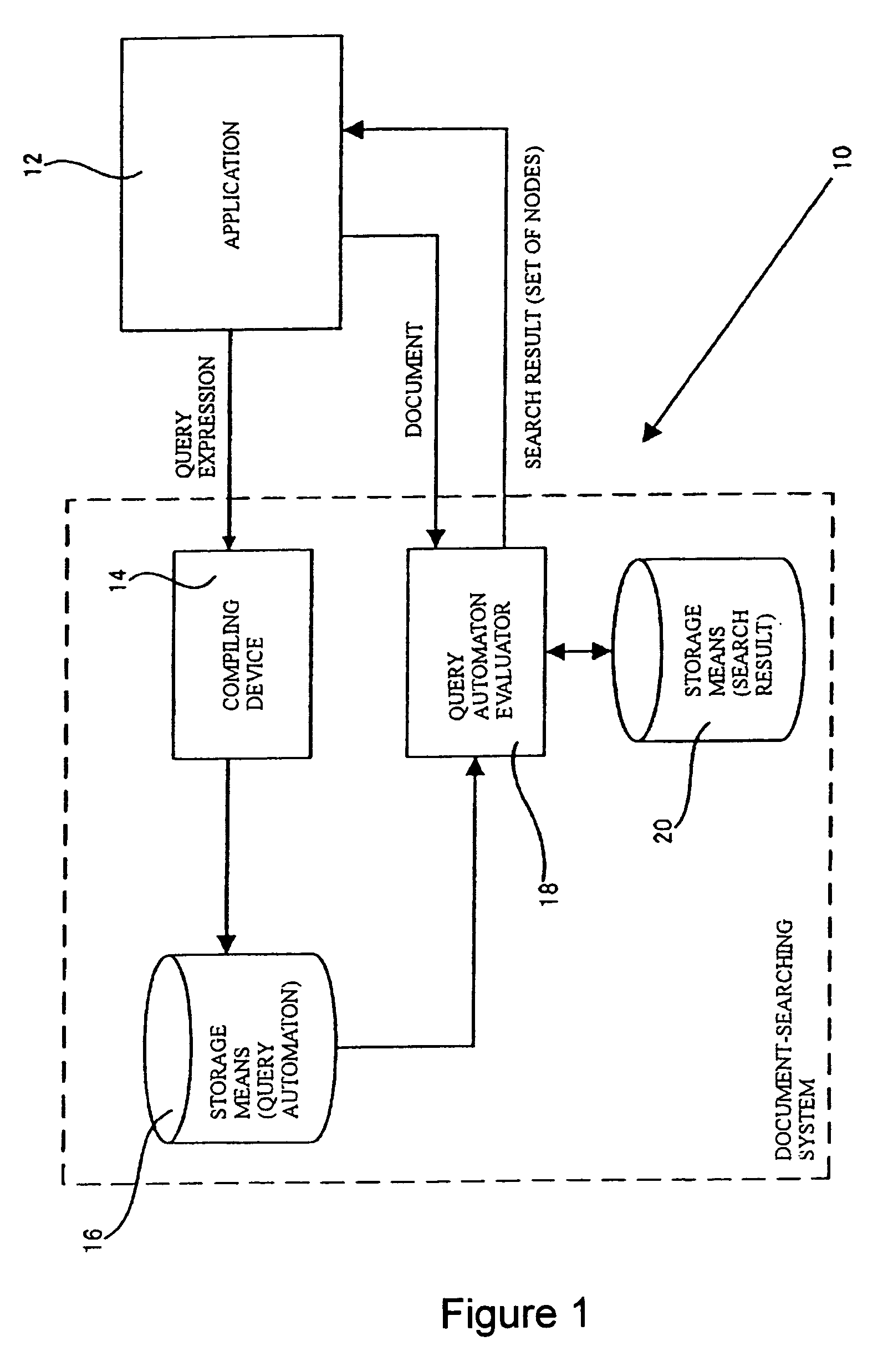

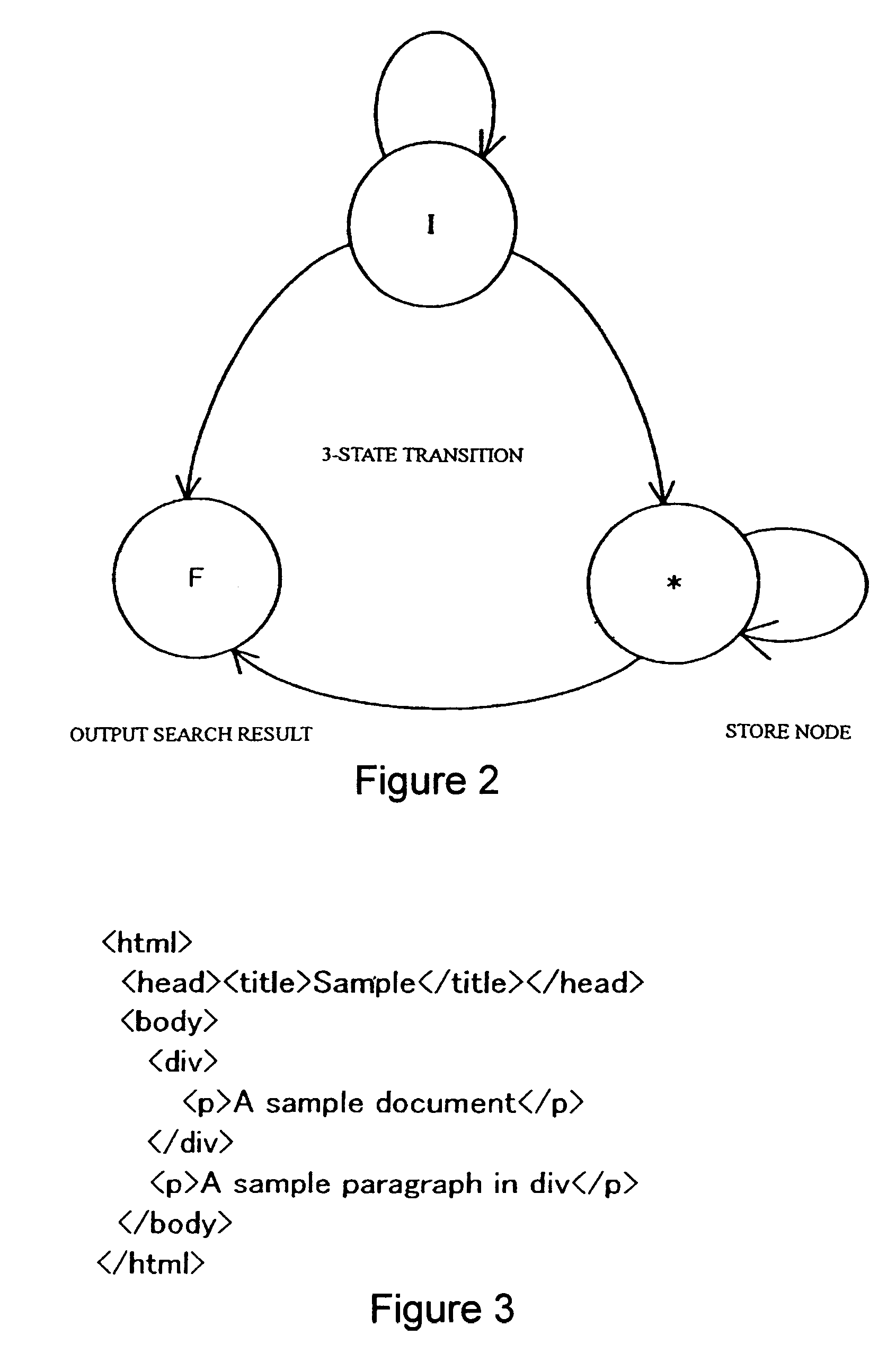

Method for document-searching

InactiveUS7509305B2Improve versatilityImprove efficiencyDigital data processing detailsSemi-structured data retrievalState switchingAutomaton

Document-searching using a compiling device for generating a two-state input automaton for enabling a state transition by storing an input query expression, performing parsing, and reading at least two states from different types of nodes in an element identifier, and a storage device for storing the two-state input automaton. Also included is an automaton-evaluating device for enabling three state transitions by reading out a two-state input automaton from the storage device and storing the automaton, while reading in a document and identifying the input two states.

Owner:IBM CORP

Information processing method of low-density check codes

InactiveCN101820288ASave hardware resourcesReduce power consumptionError correction/detection using multiple parity bitsRound complexityData vector

The invention relates to an information processing method of low-density check codes, which belongs to the field of communication technology. The method comprises the steps of: carrying out swivel adjustment on a check matrix H1 of the low-density check codes by a sending terminal to obtain a processed matrix H2; sending an initial data vector V by using a low-density check code encoder accordingto the matrix H2 to obtain a codeword vector X and sending the codeword vector X through channel; receiving a codeword vector Y by a receiving terminal and storing the codeword vector Y in a decoder buffer directly according to the order of reception; and receiving and processing the codeword vector Y by the receiving terminal by using the present layered low-density check code decoder to obtain a codeword vector Z, and then outputting the codeword vector Z directly according to the order of reception. The invention omits the input and output cyclic shift network for the low-density check code decoder, reduces the area and power consumption of the decoder, does not increase the processing complexity of the sending terminal and does not decrease the error correction of the codeword.

Owner:SHANGHAI JIAO TONG UNIV

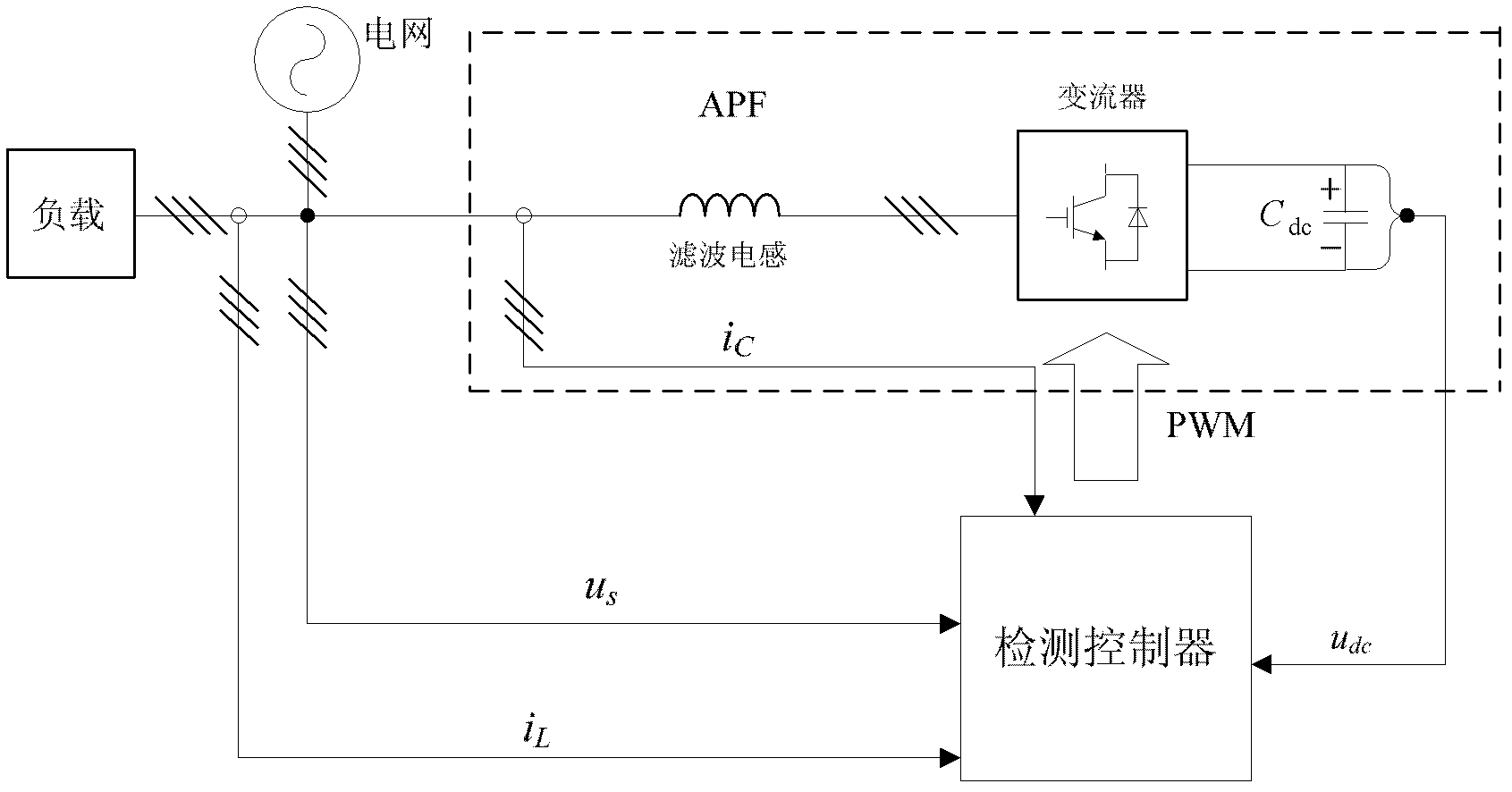

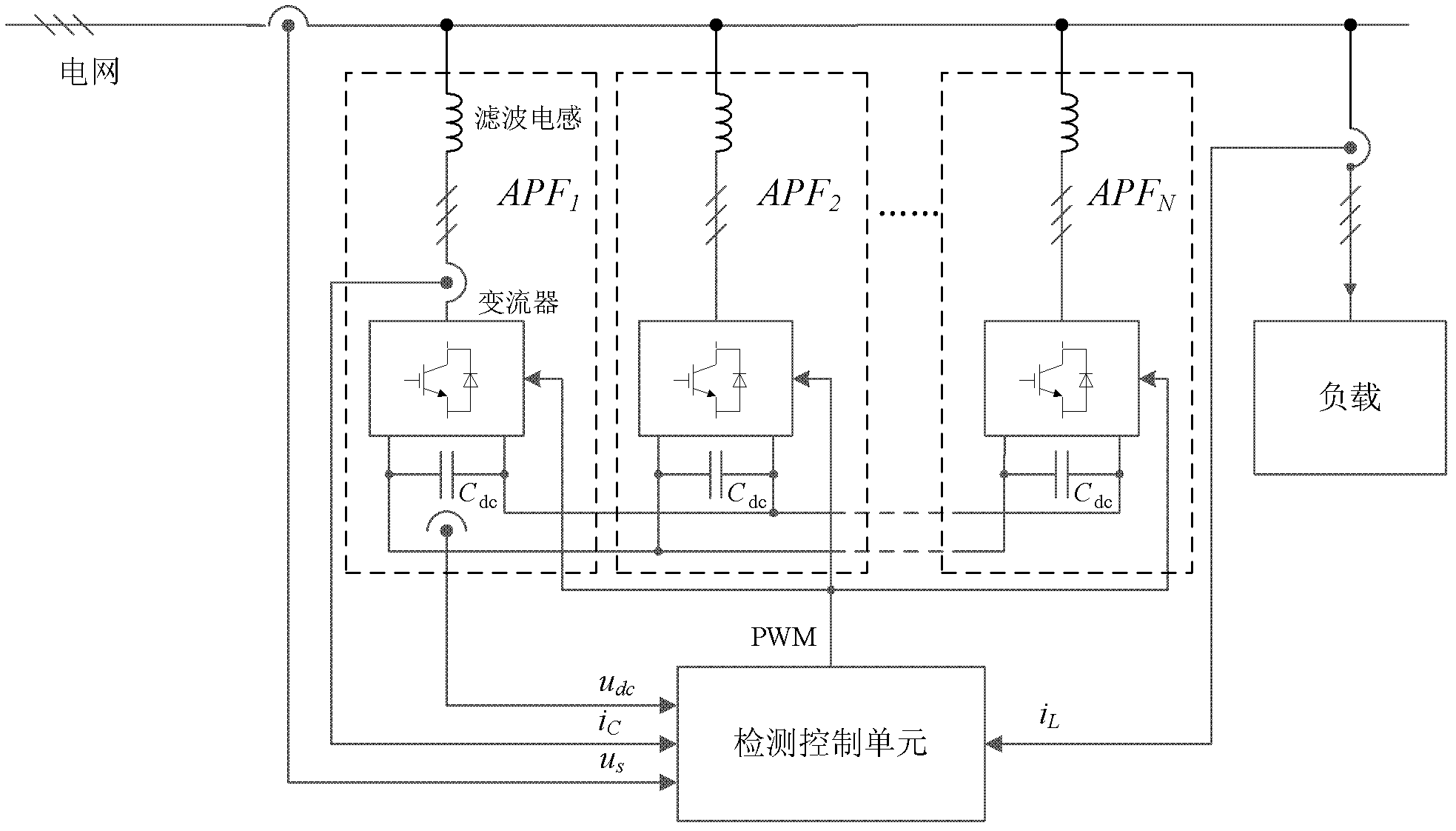

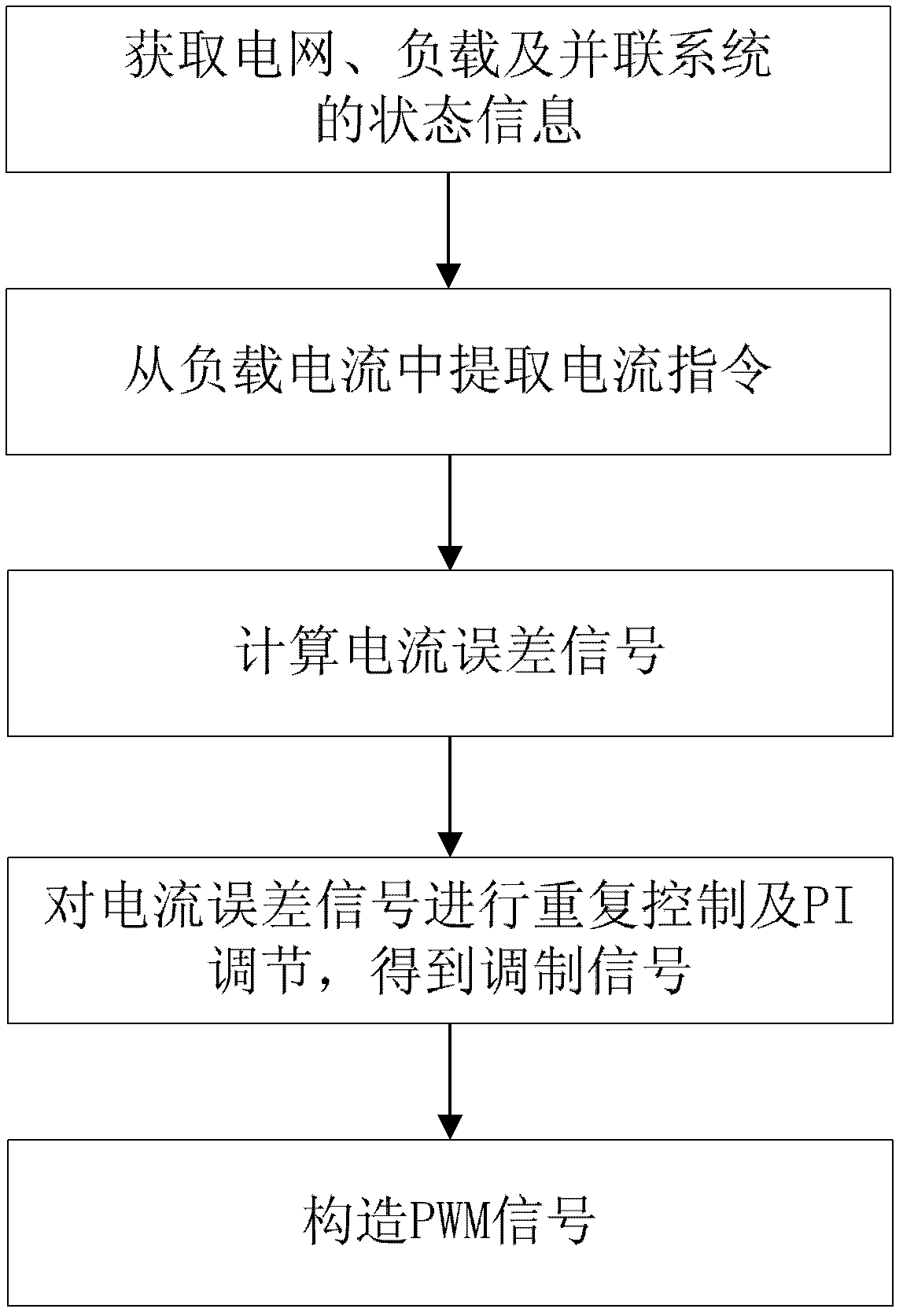

APF (Active Power Filter)parallel system and control method thereof

InactiveCN102638043AAvoid Voltage FluctuationsSave hardware resourcesActive power filteringReactive power adjustment/elimination/compensationCapacitancePower grid

The invention discloses an APF (Active Power Filter) parallel system. The APF parallel system comprises a plurality of APFs connected with a power grid, and a detection control unit. High-voltage ends of direct current support capacitors of all the APFs are commonly connected, and low-voltage ends of the direct current support capacitors of all the APFs are commonly connected. The parallel system provided by the invention only needs a set of detection control equipment to control the plurality of APFs, thus, less hardware resource is occupied. Simultaneously, the invention further discloses a control method of the APF parallel system. The control method comprises the following steps of: (1) obtaining state information of the power grid, the loads and the parallel system; (2) extracting a current instruction from the load current; (3) calculating a current error signal; (4) performing repetitive control and PI (proportional integral) regulation on the current error signal to obtain a modulation signal; (5) forming a PWM (Pulse-Width Modulation) signal. The method provided by the invention has higher reactive compensation precision and harmonic suppression capability, and can effectively suppress system circulating current.

Owner:ZHEJIANG UNIV +1

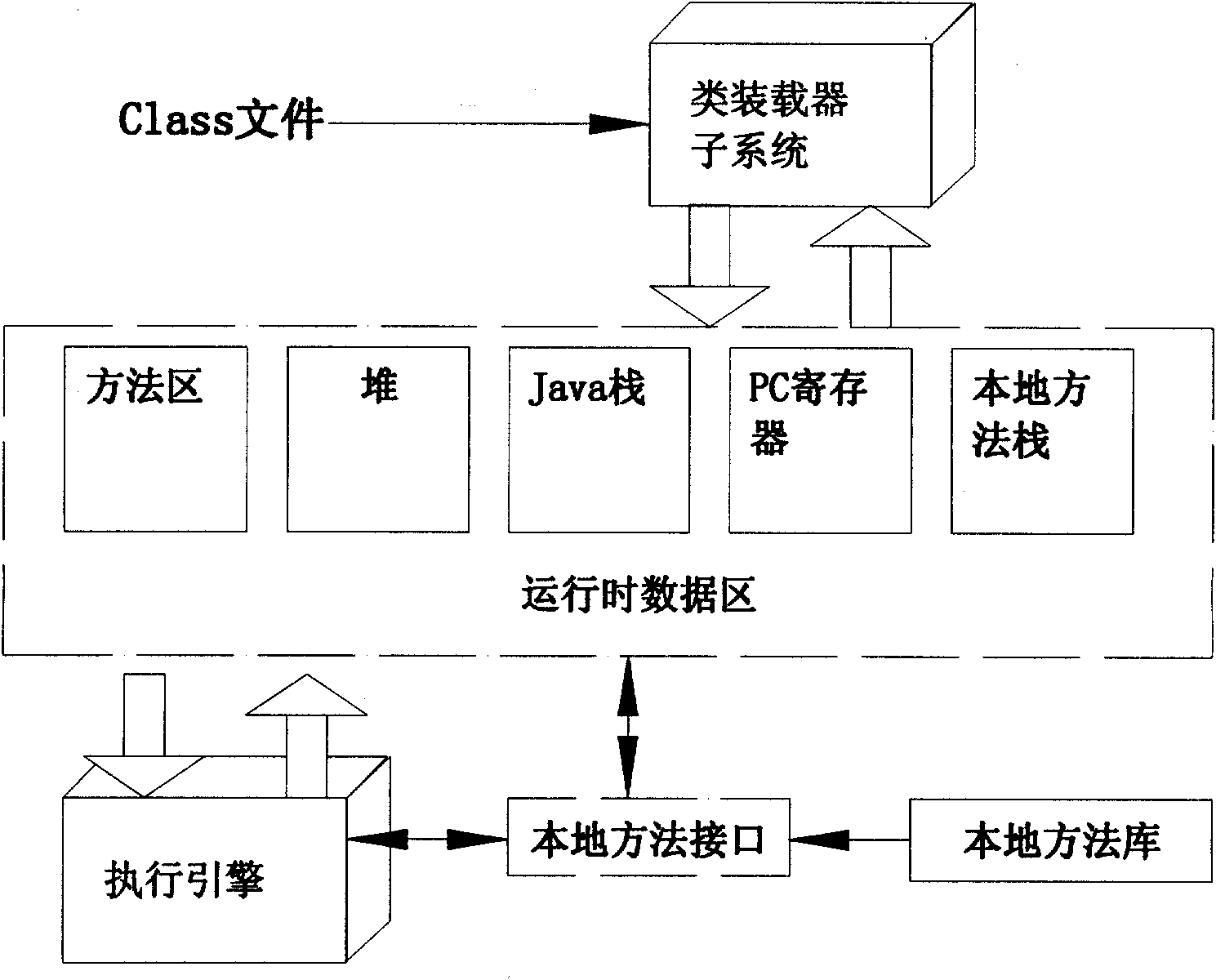

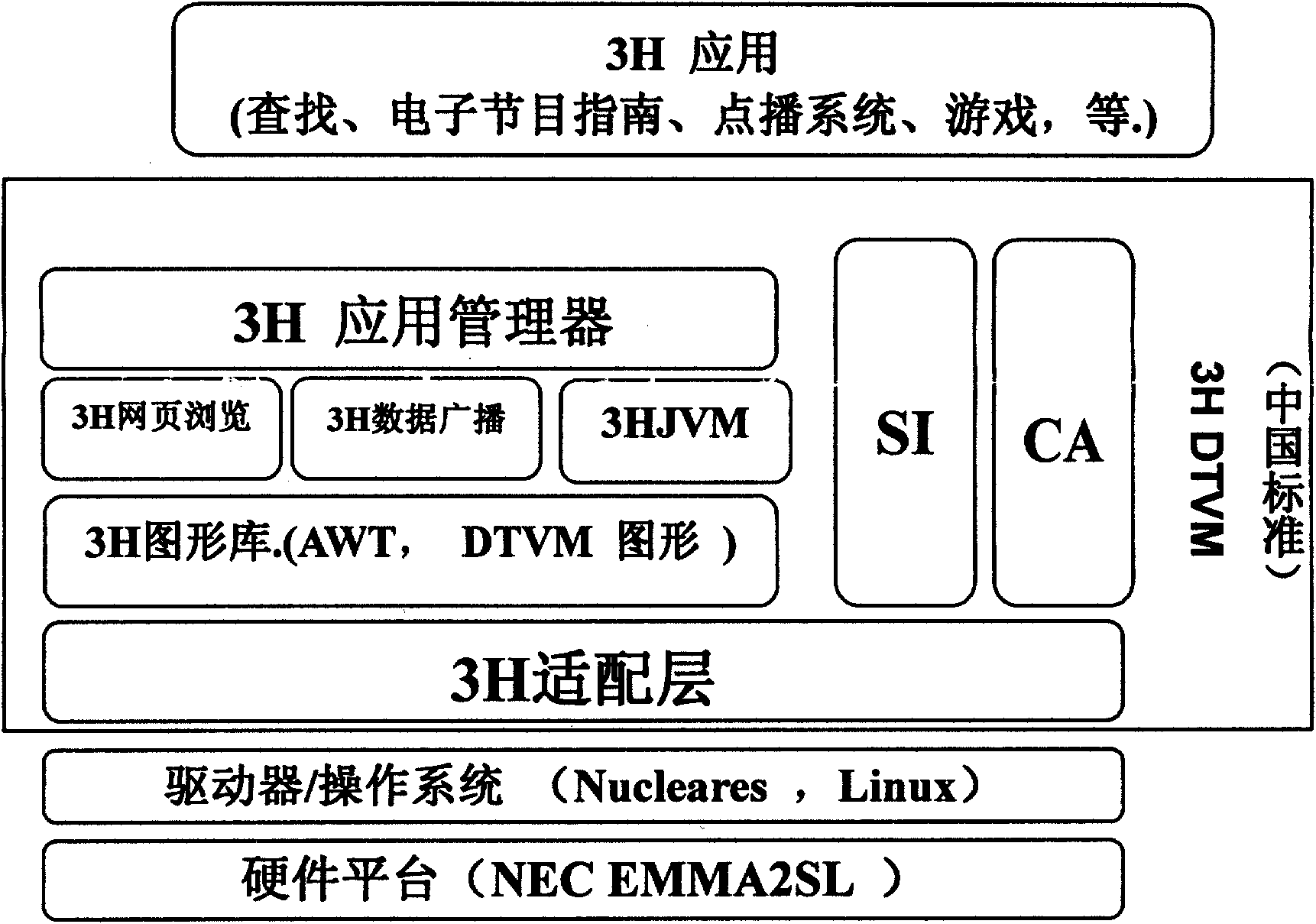

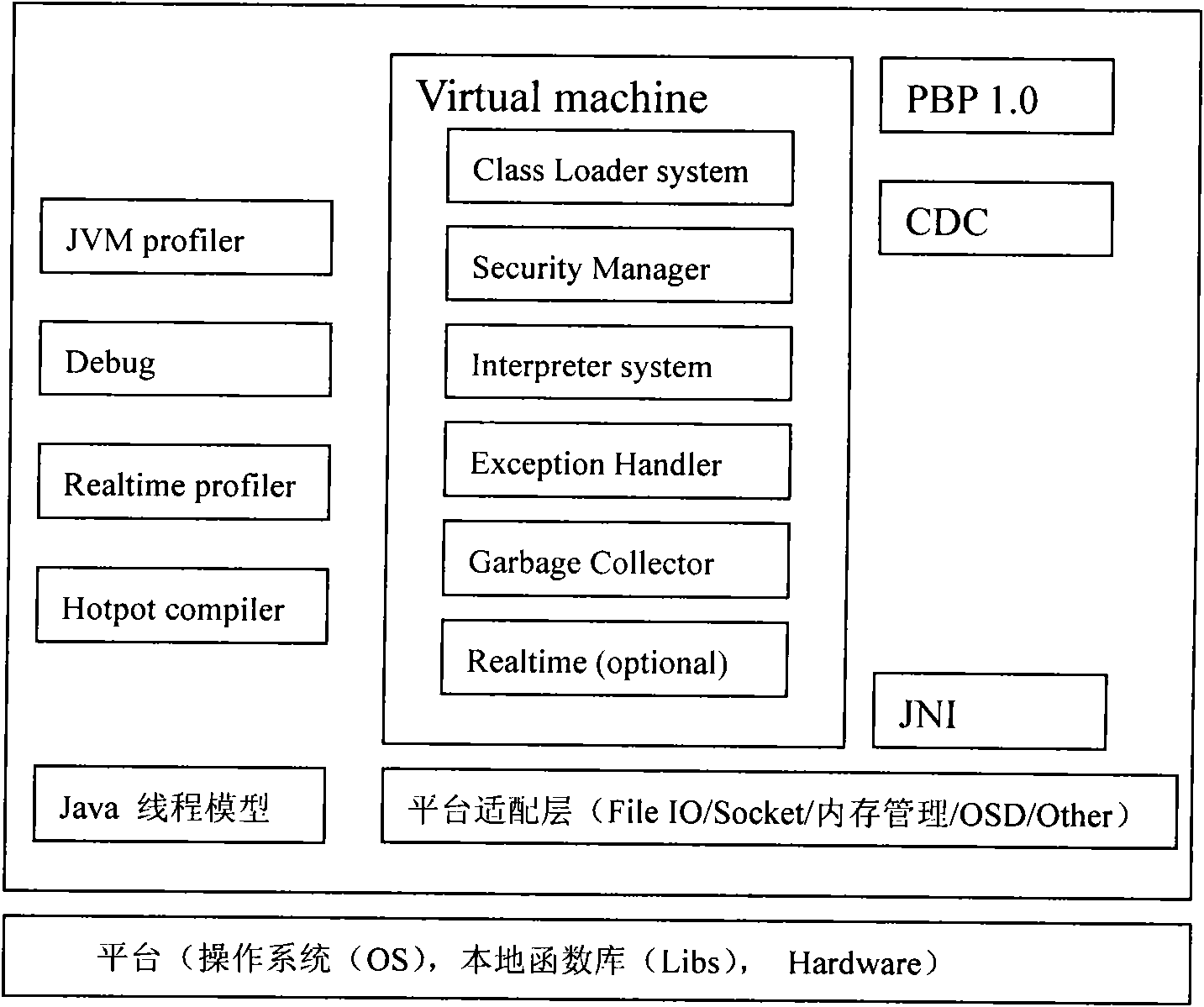

Cross-platform Jave virtual machine of digital television middleware system

InactiveCN101593127AReduce workloadEasy to transplantTelevision system detailsAnalogue secracy/subscription systemsOperational systemMiddleware

The invention discloses a cross-platform Jave virtual machine of a digital television middleware system, belonging to the technical field of communication. The cross-platform Jave virtual machine comprises an operating system and a device drive program based on a hardware platform, wherein a platform adaptation layer is arranged based on the operating system and the device drive program; and a core class library containing a Java virtual machine and a set-top box device installed in the middleware system is utilized based on the platform adaptation layer to build the Jave virtual machine which is at least formed by a class loading sub-system, a security management sub-system, an execution engine and a local method invoking interface sub-system functional module so as to provide an operation platform of the Java application and the service for the digital television middleware. The invention supports the China standard, is easy to transplant to the other standards, and has no relation with the hardware platform, unified resource management, no OS limitation on the quantity of operational Jave threads, more compact system structure, less occupied hardware resource and less limitation on the hardware platform.

Owner:商埃曲网络软件(上海)有限公司

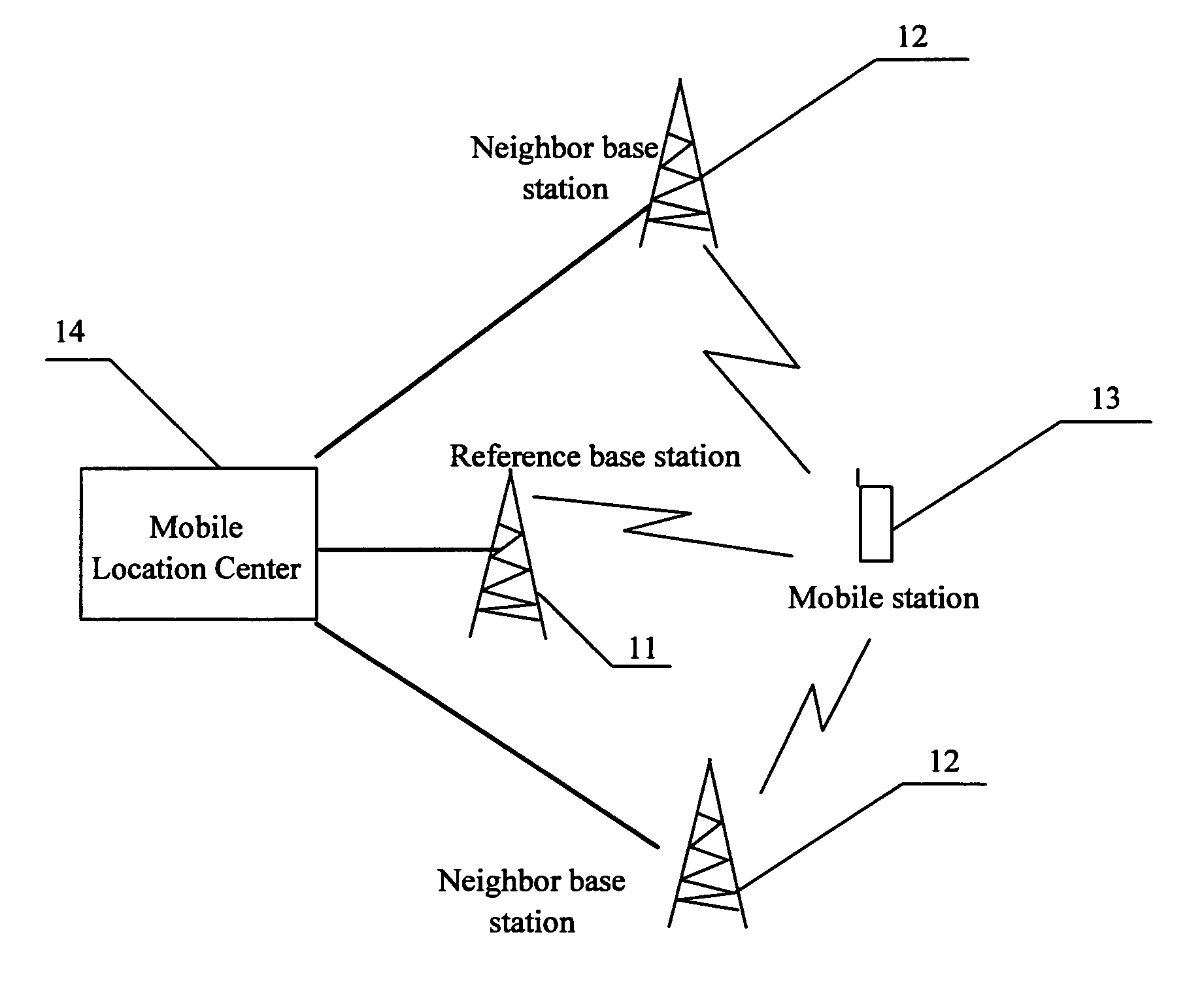

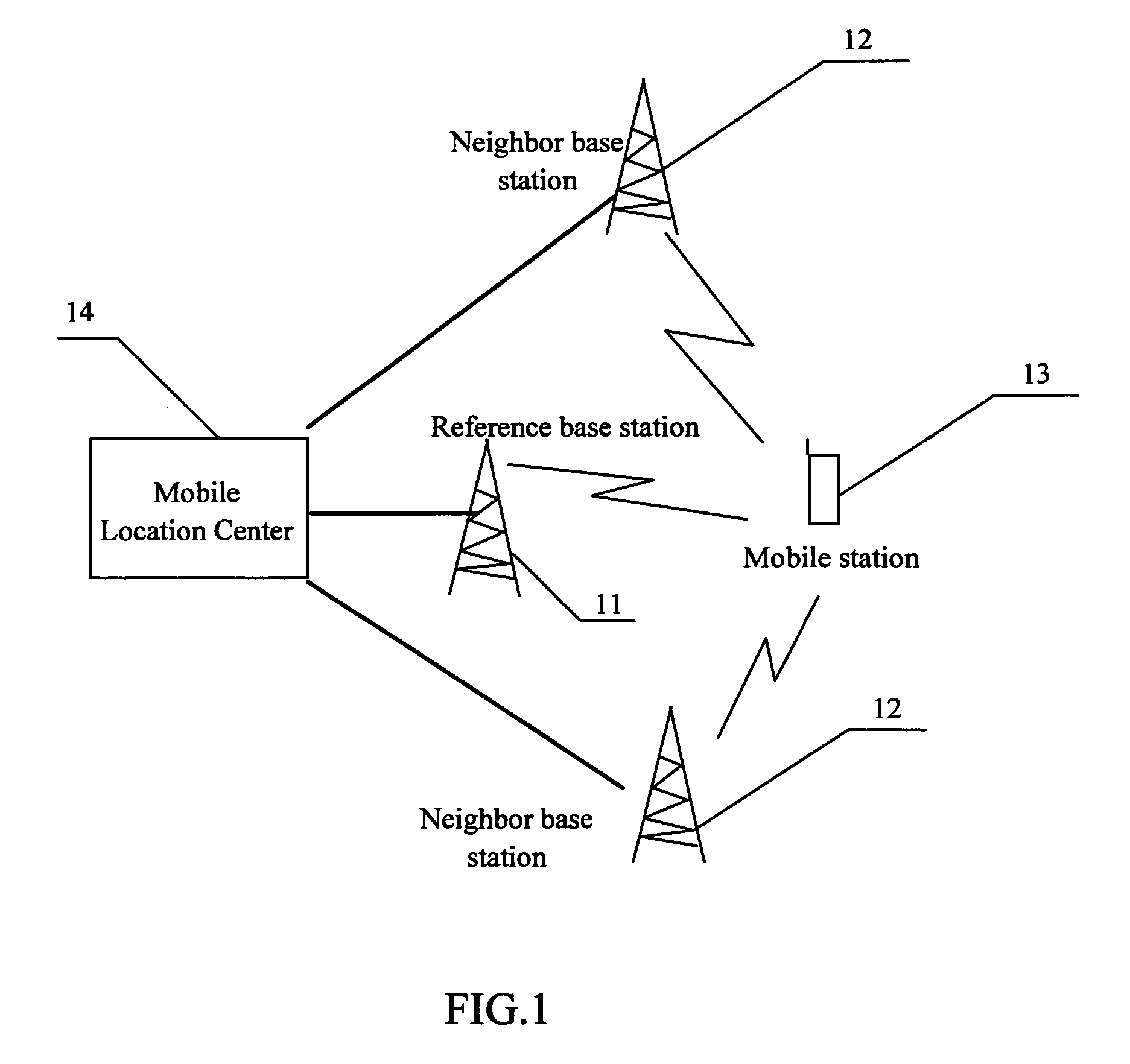

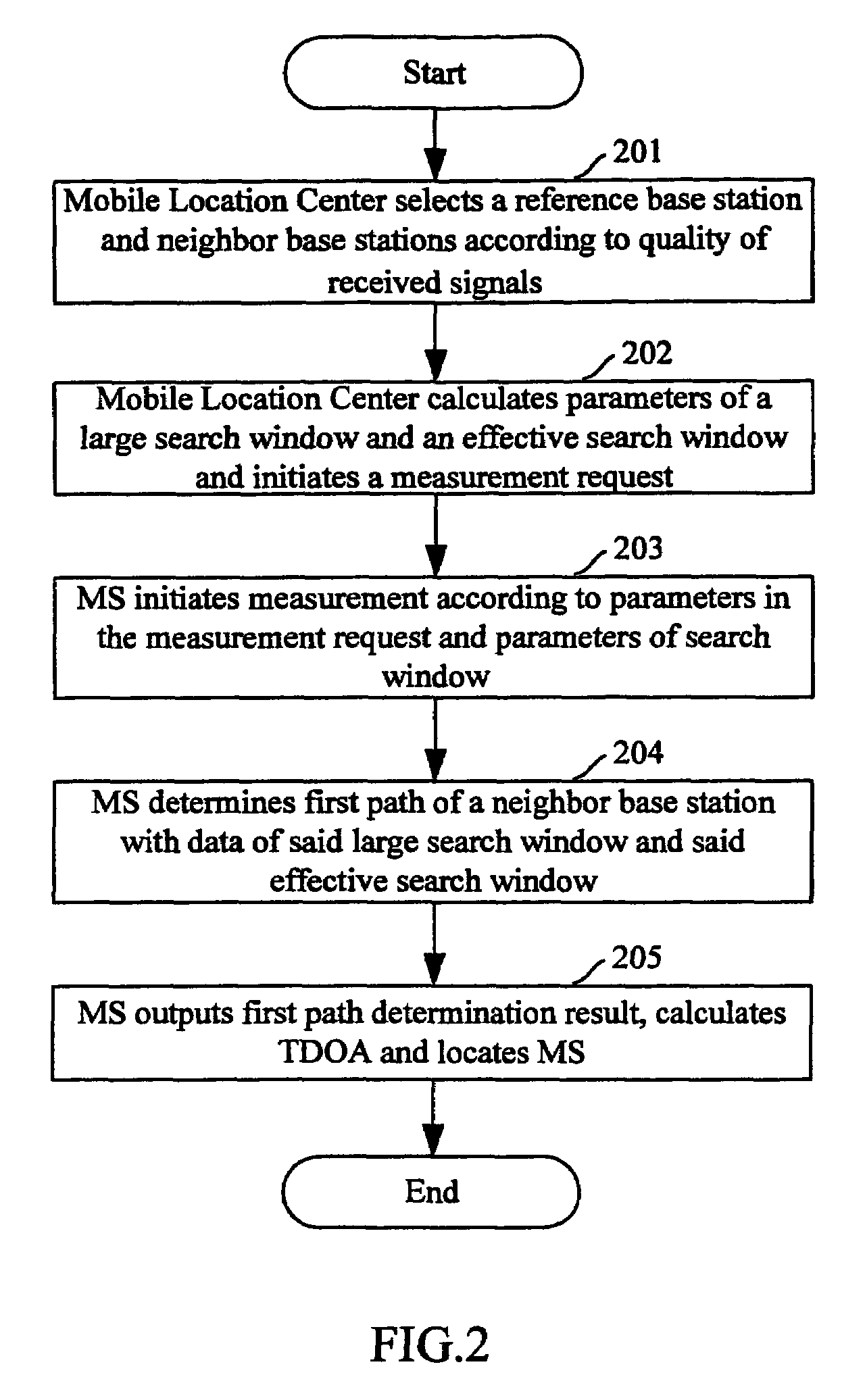

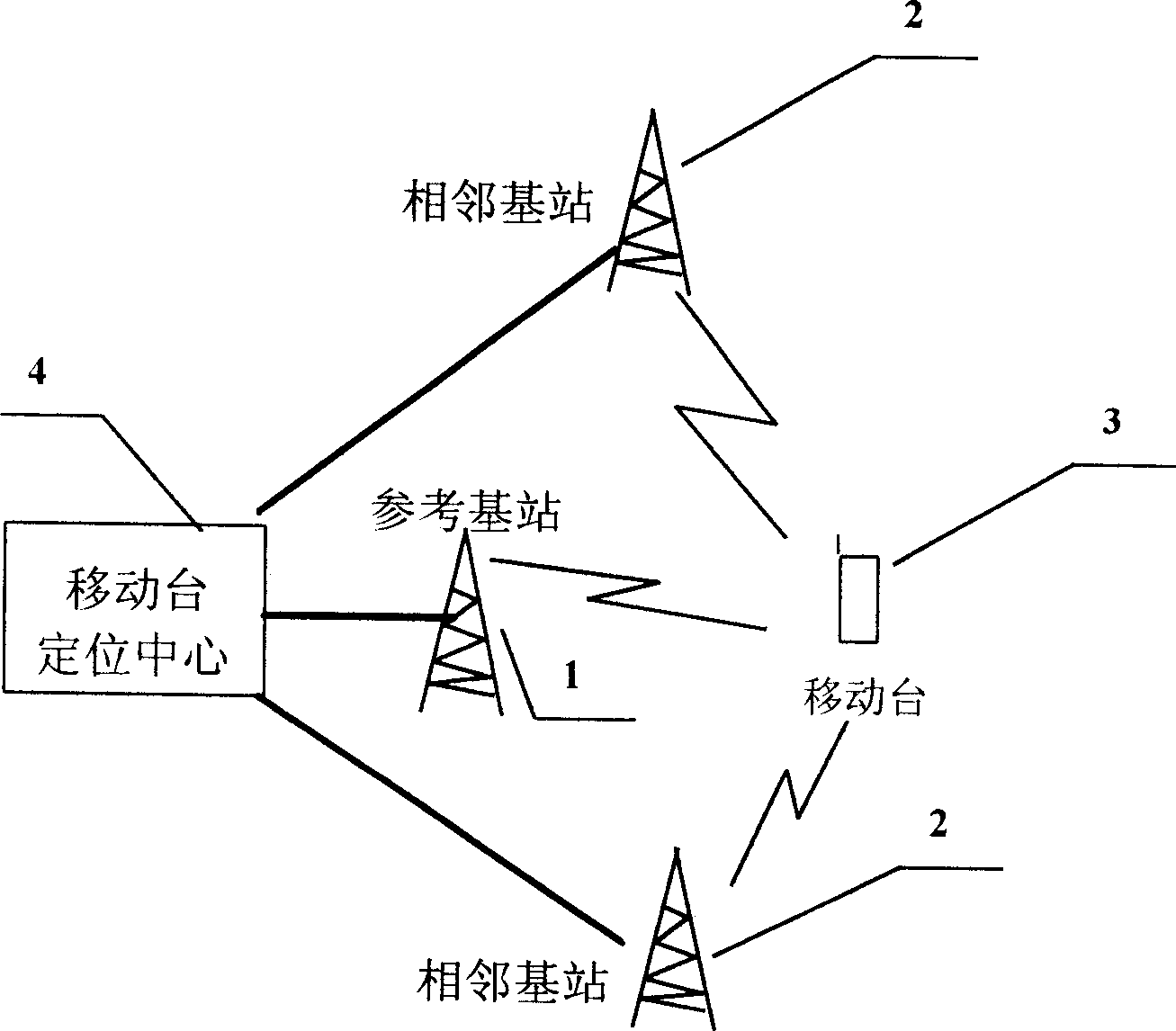

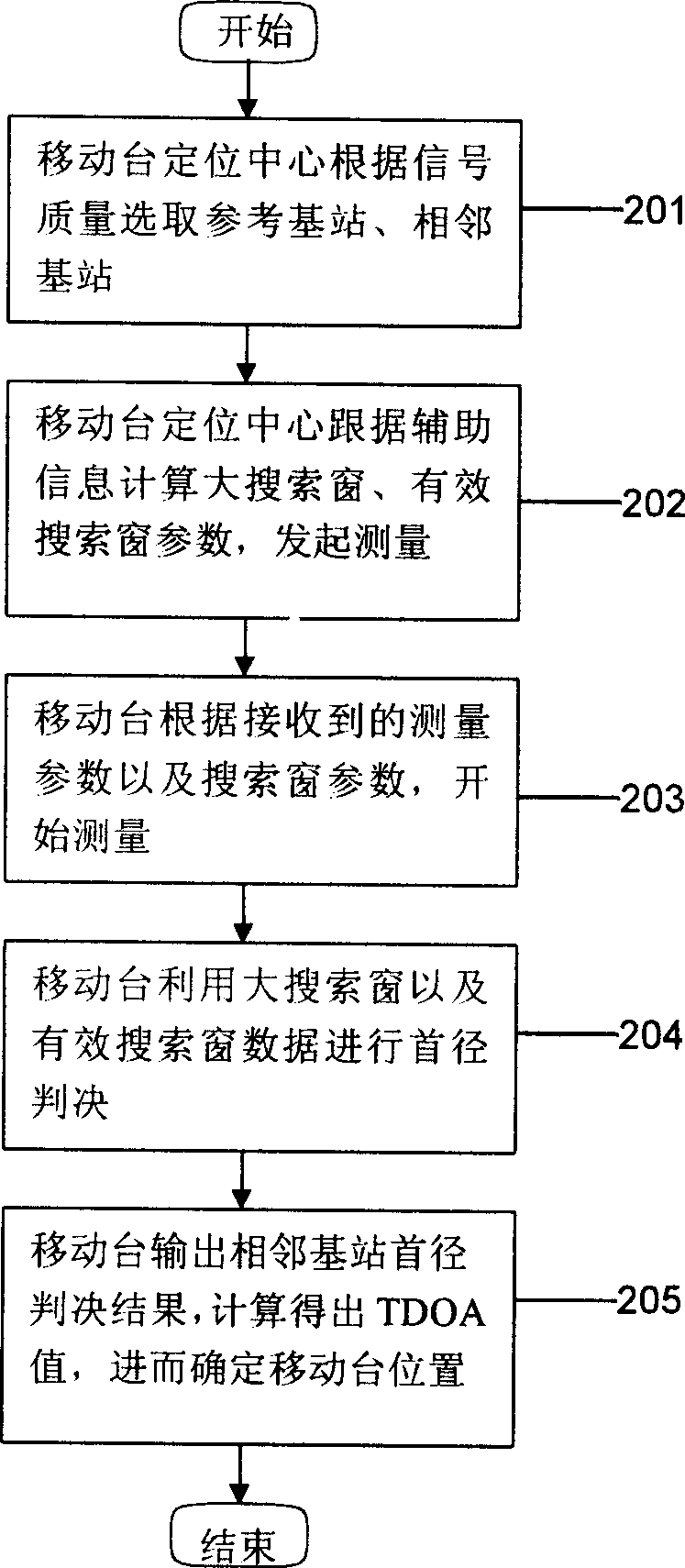

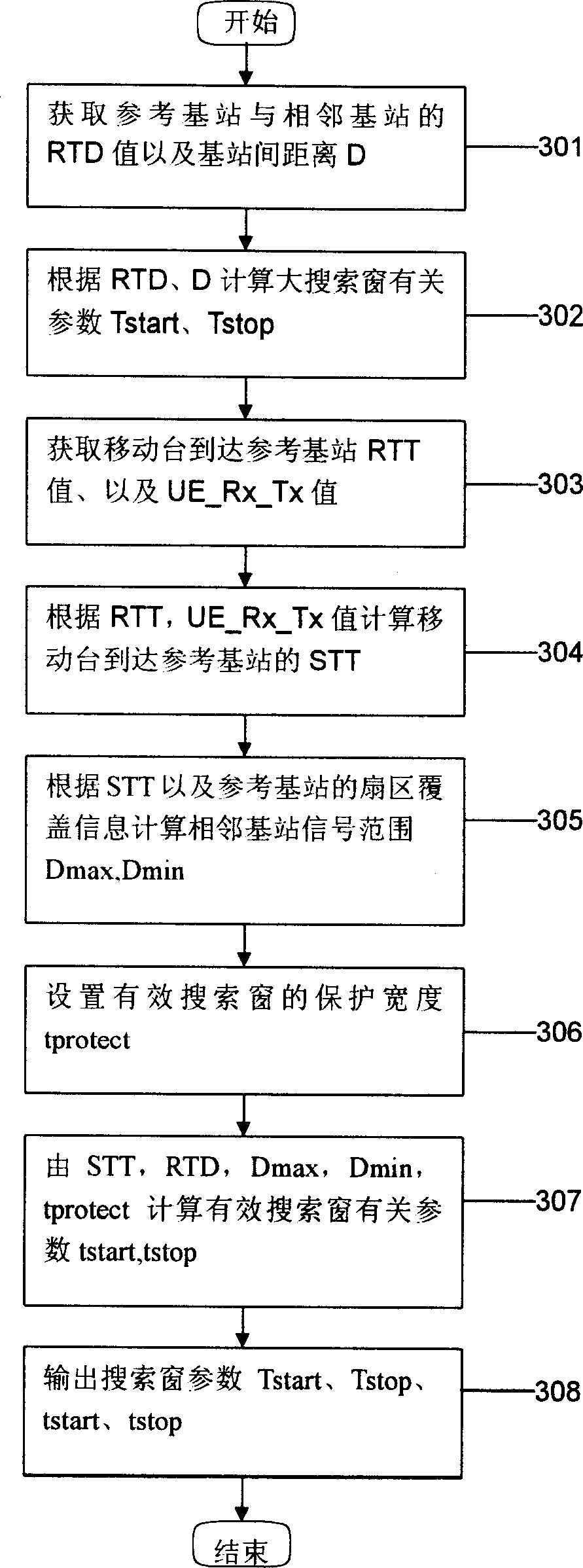

Method of locating and measuring a mobile station

InactiveUS7065369B2High measurement accuracyHigh positioning accuracyError preventionFrequency-division multiplex detailsMobile stationWireless positioning

The invention discloses a method of locating and measuring a mobile station, which relates with the radio locating technique in mobile communication field. Comparing with the conventional radio locating technique, the method improves the first path determination method of a neighbor base station downlink signal as follows: with geometrical relationship such as the distance between a MS to the reference base station and the distance between a neighbor base station to the reference base station, an effective range of the downlink signal first path of the neighbor base station can be calculated; the effective range is an effective search window that is shorter than the original large search window, and the first path determination of the neighbor base station downlink signal is made within the effective search window. The invention raises the first path determination accuracy of a neighbor base station downlink signal, so the mobile station locating accuracy is raised too.

Owner:HUAWEI TECH CO LTD

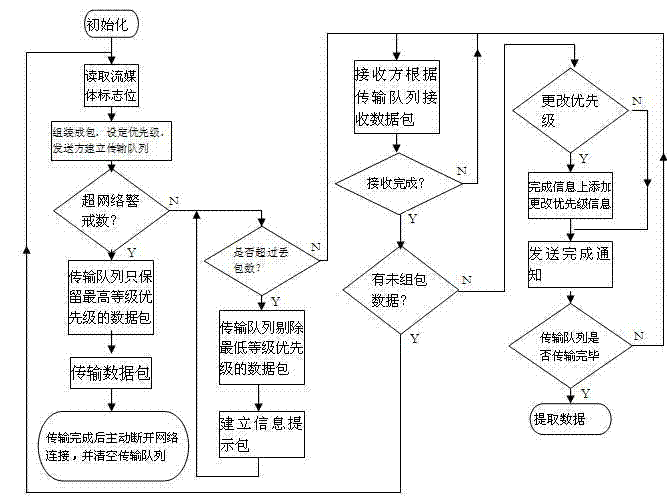

Streaming media content priority-adaptation transmission method

InactiveCN102244608AOn time priority deliverySave hardware resourcesData switching networksPacket lossData information

The invention relates to a streaming media transmission method. The problems that a great amount of data information is easy to accumulate in a transmission queue to cause network congestion, that data is easy to transmit unstably in wireless terminal application and that important information is transmitted incompletely in the prior art can be well solved. Key points of the technical scheme are that: the priority of streaming media is determined by judging streaming media contents, high priority is endowed to the important information to ensure the punctual and preferable service of the important information, and simultaneously, strategic packet loss can be performed under the condition of network congestion to ensure the accurate service of the important information. By the method, the accurate transmission of the important information can be ensured in a relatively poorer network environment.

Owner:杭州斯凯网络科技有限公司

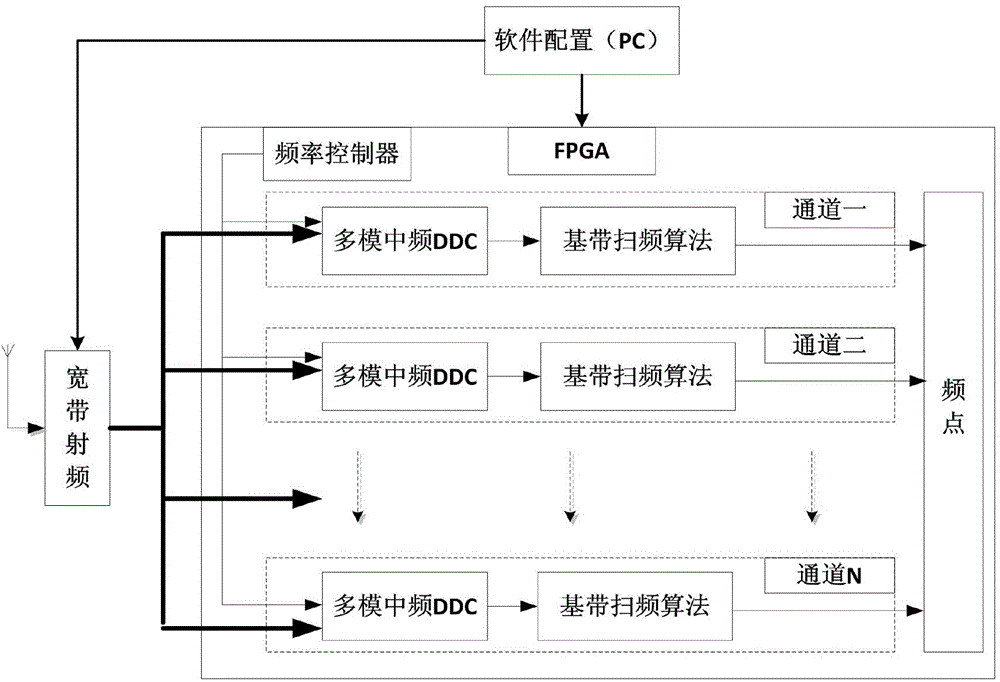

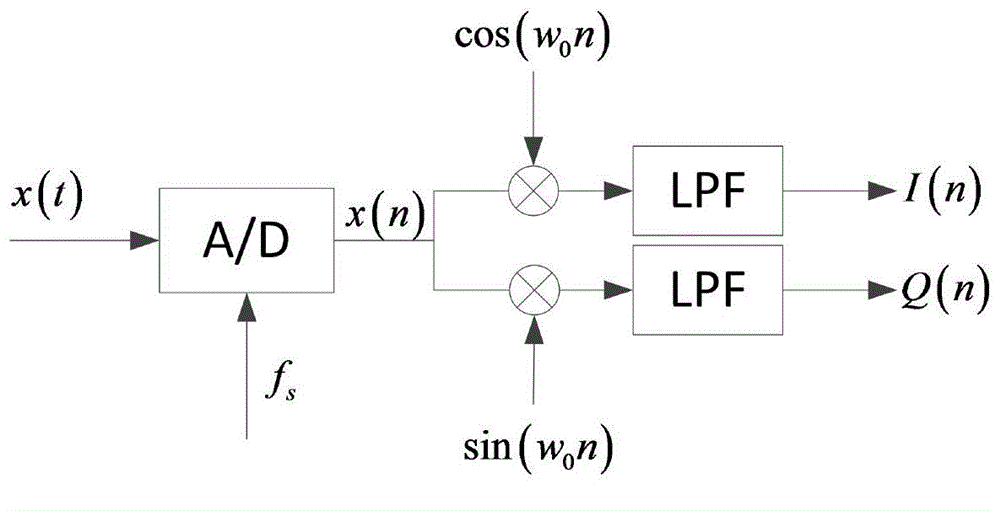

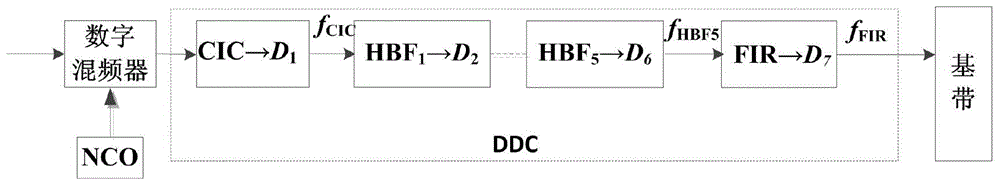

Multimode support parallel multichannel fast frequency sweeping method and multimode support parallel multichannel fast frequency sweeping system

ActiveCN104661287AProcessing speedReduce design difficultyAssess restrictionCode division multiple accessDigital intermediate frequency

The invention relates to a multimode support parallel multichannel fast frequency sweeping method and a multimode support parallel multichannel fast frequency sweeping system. The system consists of four parts including a broadband radio frequency part, a multimode medium frequency part, a baseband frequency sweep algorithm part and a software configuration module, wherein the broadband radio frequency part is mainly used for carrying out analog amplification, filtering, frequency mixing, analog-to-digital (A / D) conversion and the like on the received radio-frequency signals; the multimode medium frequency party is mainly used for carrying out down-conversion treatment on digital intermediate frequency signals, wherein digital frequency mixing is carried out on the signals before down-conversion; the baseband frequency sweep algorithm part mainly comprises a frequency point detection module and a power calculation module; the frequency point detection module is used for rapidly and accurately judging frequency points, and the power calculation module is used for determining a main base station frequency point and a neighbor cell site frequency point; the software configuration module is used for carrying out online configuration on radio frequency and intermediate frequency by an upper computer, so that broadband radio frequency and multimode medium frequency are realized, and multiple communication systems are compatible. The multimode support parallel multichannel fast frequency sweeping system is capable of realizing rapid frequency sweeping of multiple communication modes such as global system for mobile communication (GSM), code division multiple access (CDMA), wideband code division multiple access (WCDMA), line termination equipment (LTE) and the like; the system is high in flexibility, rapid in speed, wide in application scope and cost-saving.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

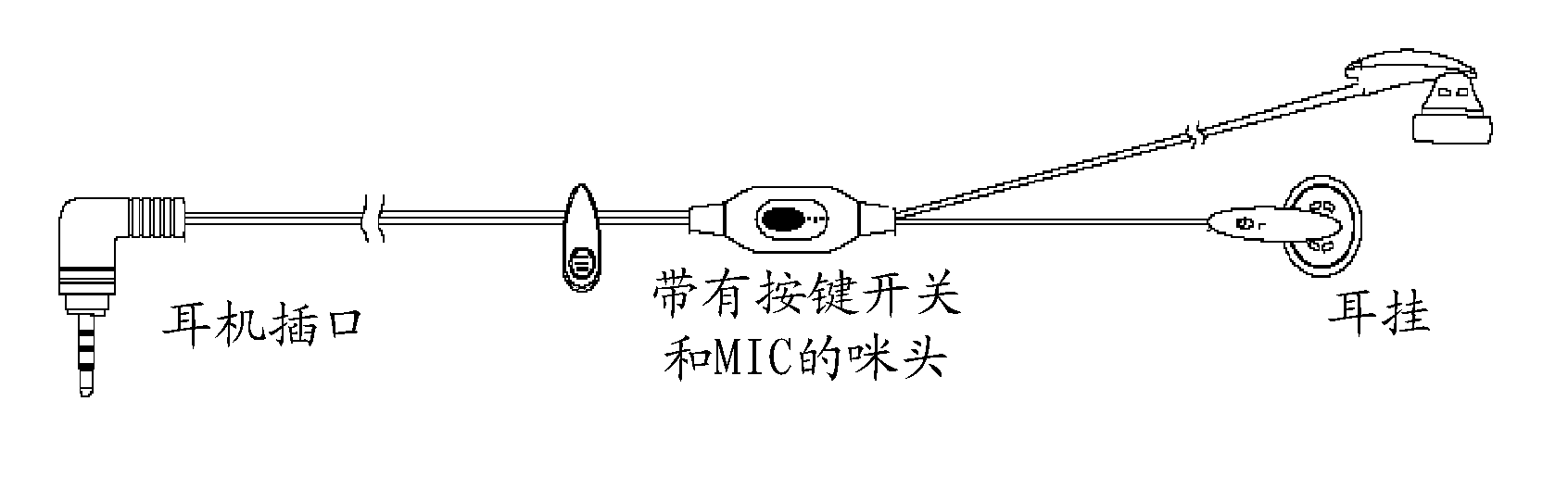

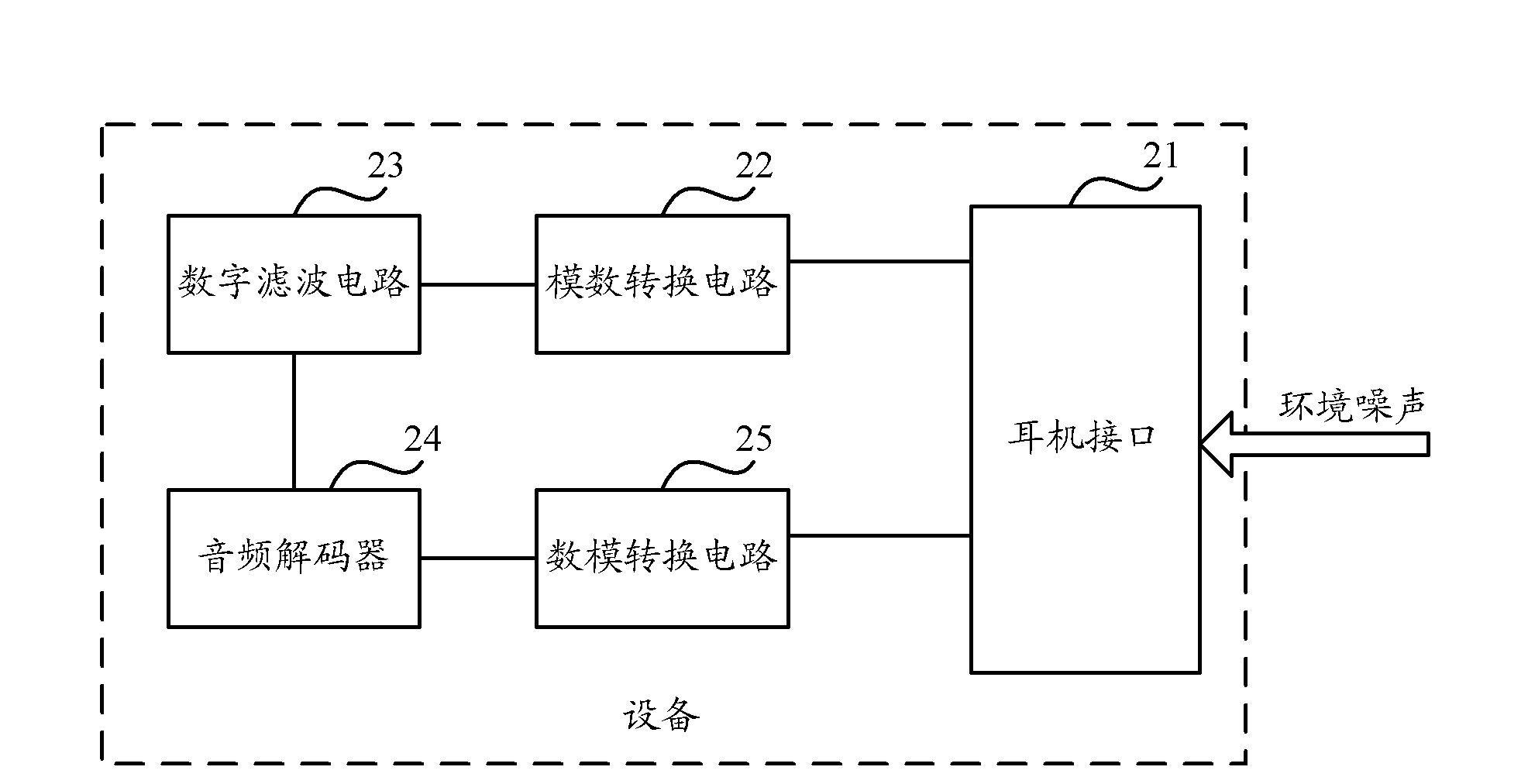

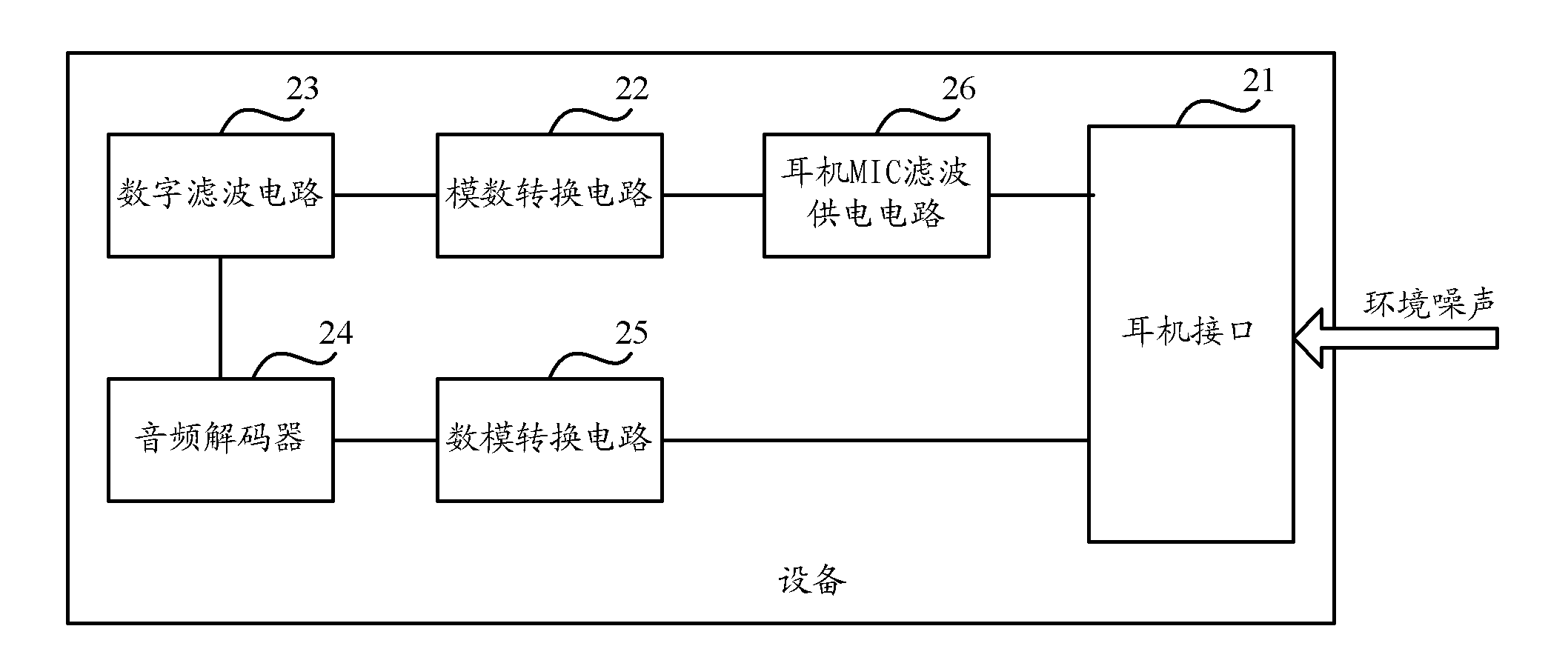

Method, equipment and system for reducing headset noise

InactiveCN102158778AReduced versatilityReduced flexibilityEarpiece/earphone attachmentsTransducer circuitsEnvironmental noisePhase noise

The invention discloses a method, equipment and system for reducing headset noise, aiming at providing a method for reducing the headset noise without addition of hardware equipment and further saving the hardware equipment. The method comprises the following steps of: processing environment noise acquired by an MIC (Microphone) of a headset through a headset interface, an analog / digital conversion circuit, a digital filtering circuit, an audio decoder and a digital / analog conversion circuit of equipment to obtain reverse-phase environment noise corresponding to the environment noise; and overlaying the reverse-phase environment noise into an audio signal and transmitting the reverse-phase environment noise to the headset so that the reverse-phase environment noise and the environment noise heard by human ears can be cancelled out each other to realize noise reduction of the headset. By adopting the technical scheme disclosed by the invention, the headset noise can be reduced without improving the headset, or equipment connected with the headset, the procedure of reducing the headset noise is simplified, the hardware equipment is saved; and the hardware equipment does not need to be improved, thus the commonality and the flexibility of reducing the headset noise are improved.

Owner:QINGDAO HISENSE MOBILE COMM TECH CO LTD

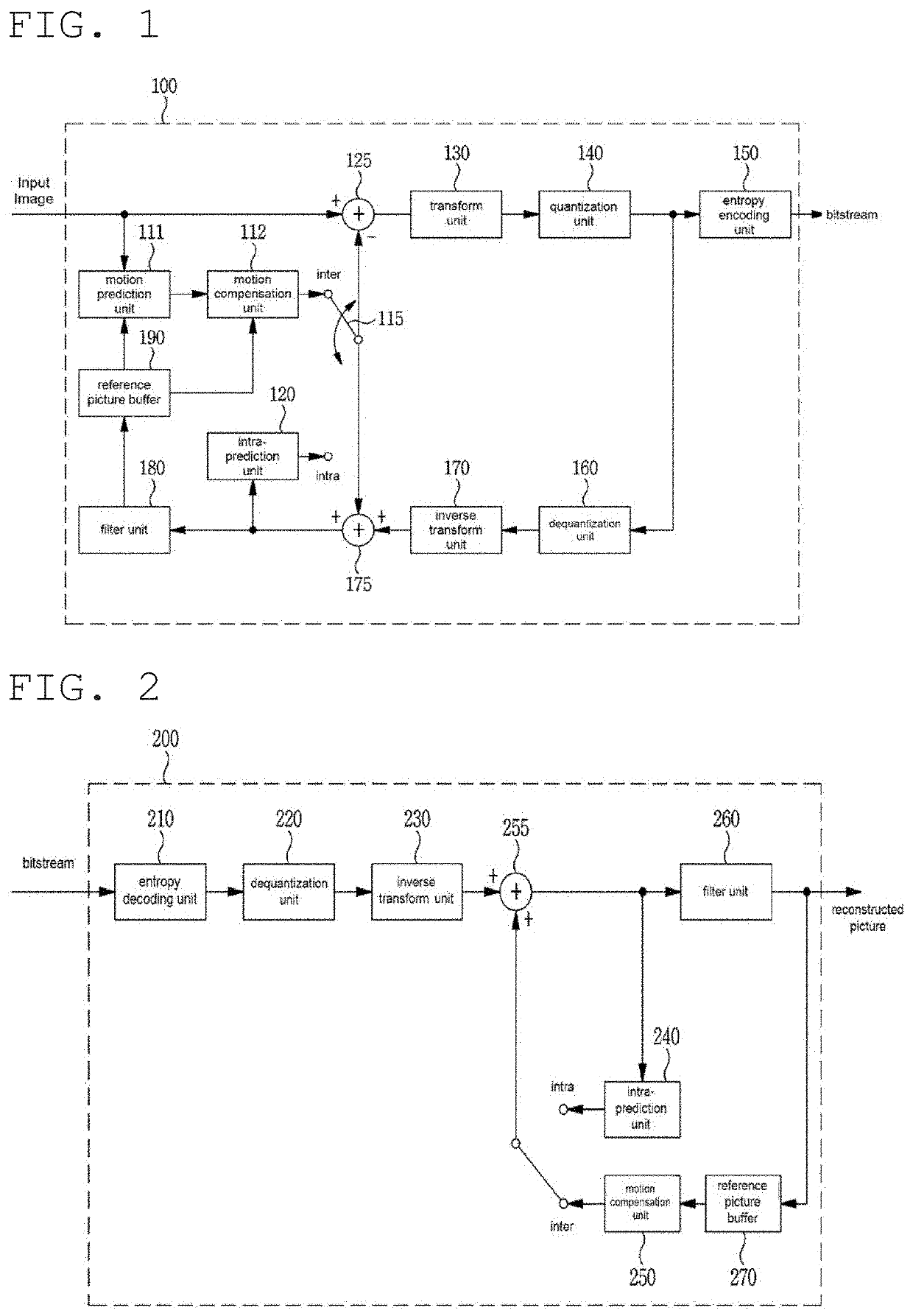

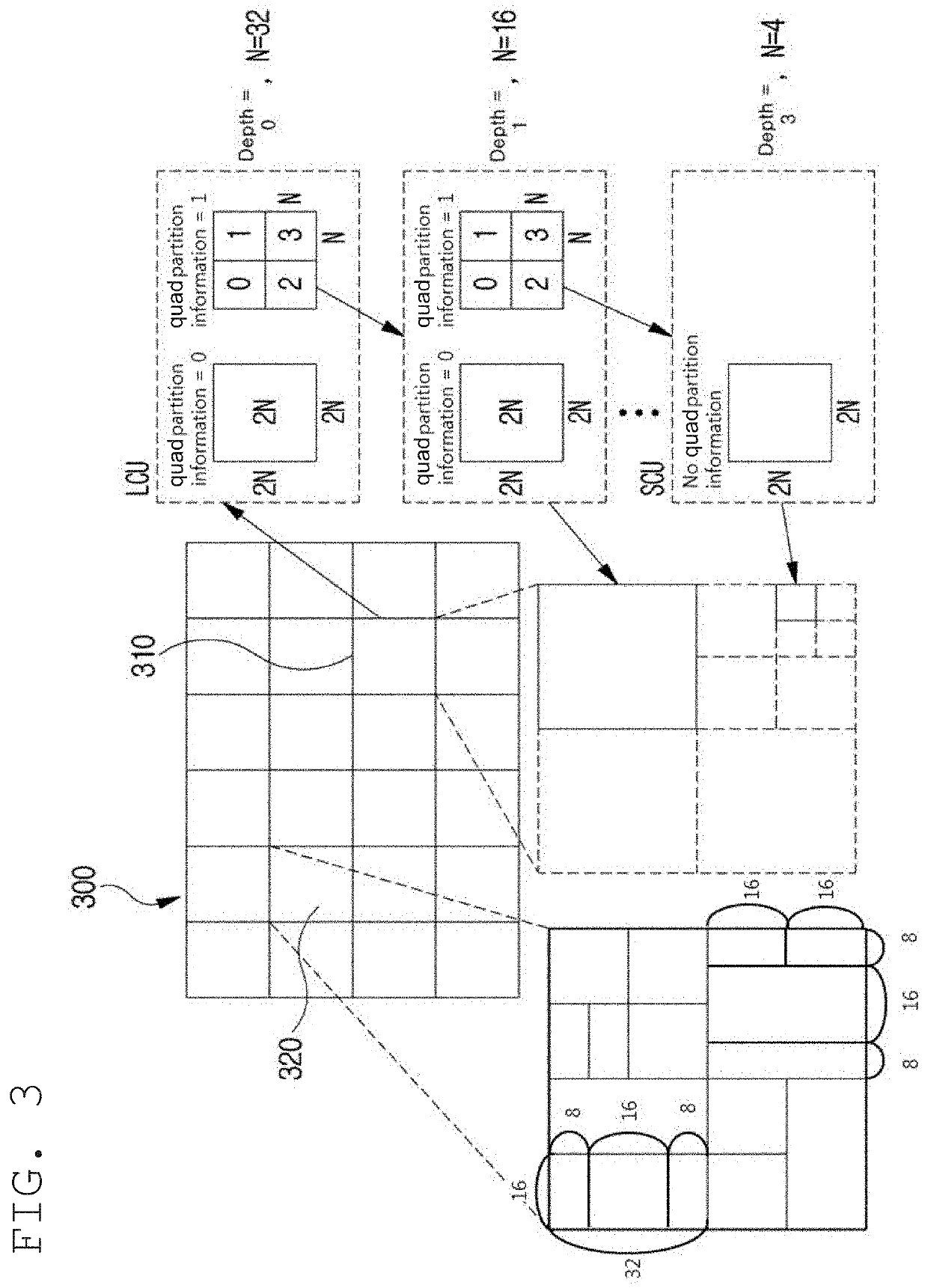

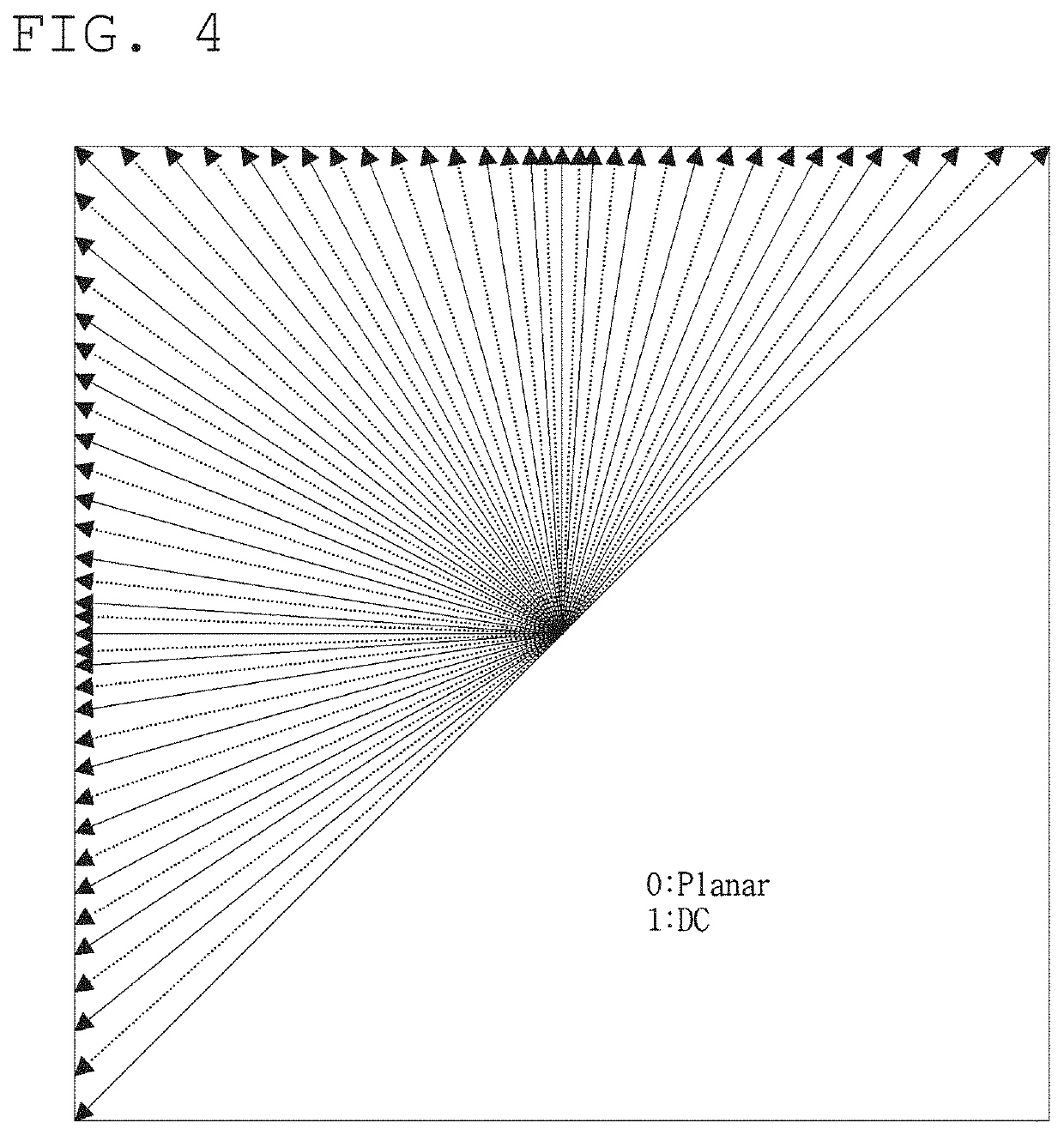

Image encoding/decoding method and device, and recording medium in which bitstream is stored

ActiveUS20210120261A1Improve compression efficiencySave hardware resourcesDigital video signal modificationComputer hardwareBitstream

Owner:LX SEMICON CO LTD

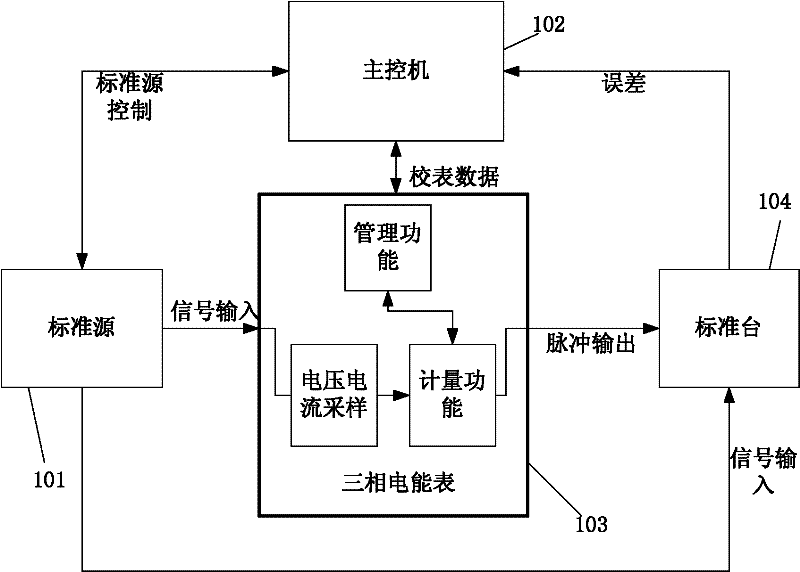

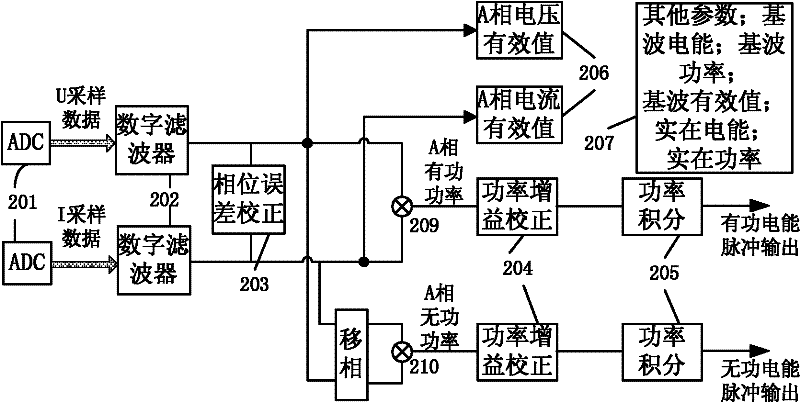

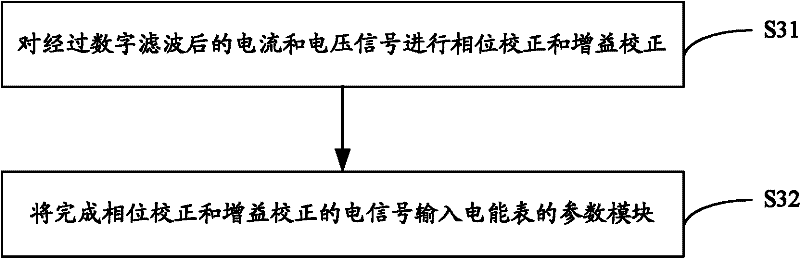

Method and system for calibrating electric energy meter and electric energy meter

InactiveCN102230959AAbundant hardware resourcesFewer correction stepsElectrical measurementsPhase correctionElectric power system

The invention is suitable for the field of electric power, and provides a method and system for calibrating an electric power meter and the electric power meter. The method comprises the following steps of: performing phase calibration and gain calibration on current and voltage signals which are subjected to digital filtration; and inputting electric signals which are subjected to phase calibration and gain calibration into a parameter module of the electric power meter. The technical scheme of the invention has the advantages of reduction in calibrating steps and small quantity of hardware resources.

Owner:SHENZHEN RENERGY TECH

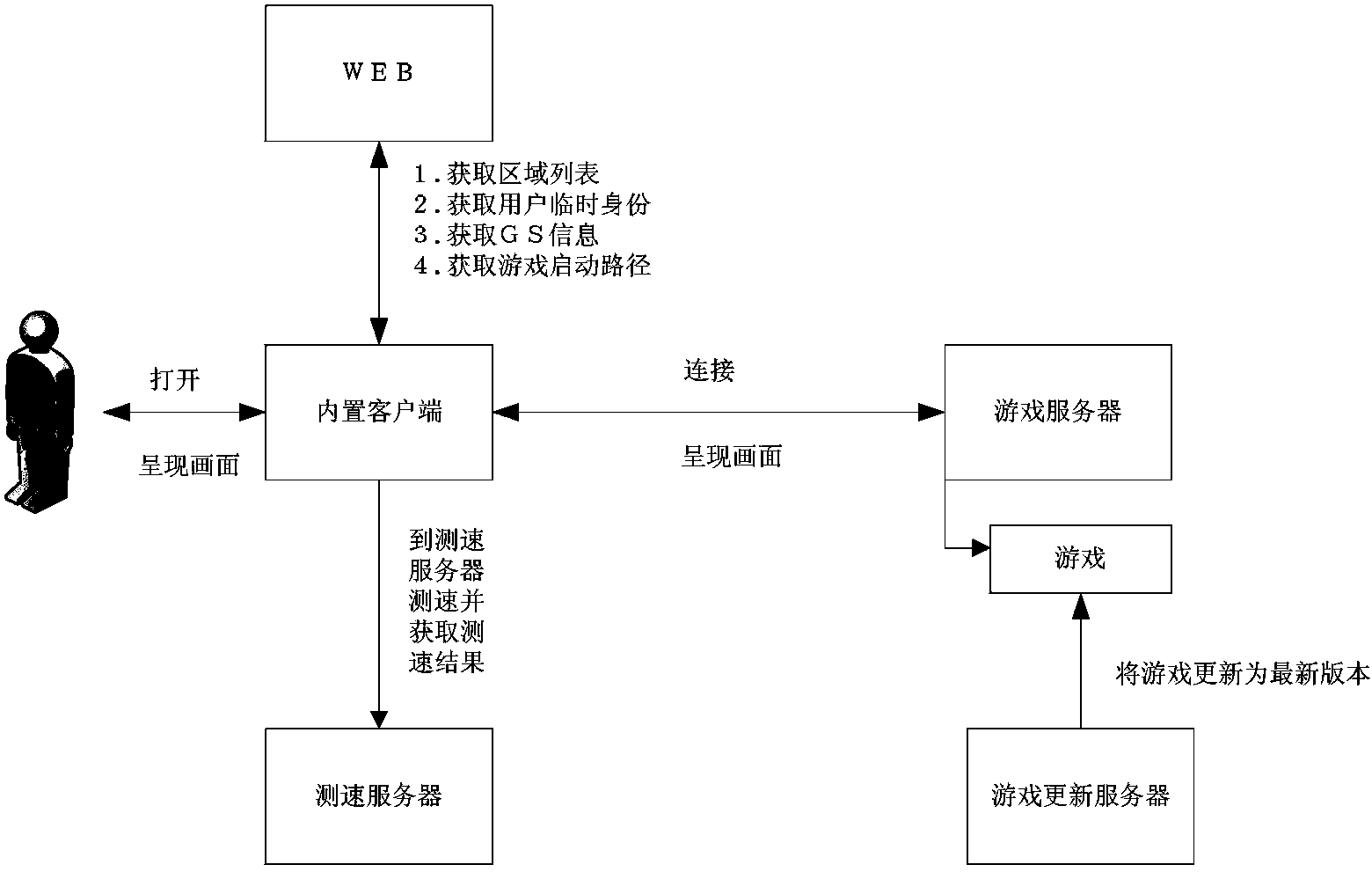

Method for achieving online game operation based on cloud computing

The invention provides a method for achieving online game operation based on cloud computing. The method comprises the following steps: a built-in client of a browser is started on a user terminal to build a request for WEB of a cloud service system to request a list of currently opened zones, and the list is shown for a user; speed measurement is conducted on a selected zone, and temporary identity of the current user is requested; when a speed measurement result meets the requirements, the built-in client carries the speed measurement result to request for the start of a server of a currently available game to the WEB, game image and sound and other information are sent to the built-in client, the built-in client loads the game interface sound and shows the game interface sound for the user, and the user starts the game operation; when the game is played to a pre-set level, a game application program conveys a game-off message to the WEB; a dialog box is popped up to prompt the user to download a game client, and the built-in client of the browser is disconnected with the server at the moment. Through the adoption of the method, the user can be guaranteed to smoothly enter a free-to-try game, so that the user can enter the game once.

Owner:北京千禧光年信息技术有限公司

Localization measurement method of mobile station

InactiveCN1434305AImprove the accuracy of head path judgmentReasonable settingPosition fixationRadio transmission for post communicationMobile stationWireless positioning

The invention provides a position measurement method of mobile station. It advances the judging method of the head diameter of the down signal, uses the geometrical relations such as the distance between the mobile station and the referenced base station and the between the adjacent base station and the referenced one to calculate out the effective range of the head diameter of the down signal ofthe adjacent station, according to the parameter of the effective range, and fractionizes out the effective searching window in which thus it makes the judgement of the head diameter.

Owner:HUAWEI TECH CO LTD

Method and system for updating programme labeling information and set top box

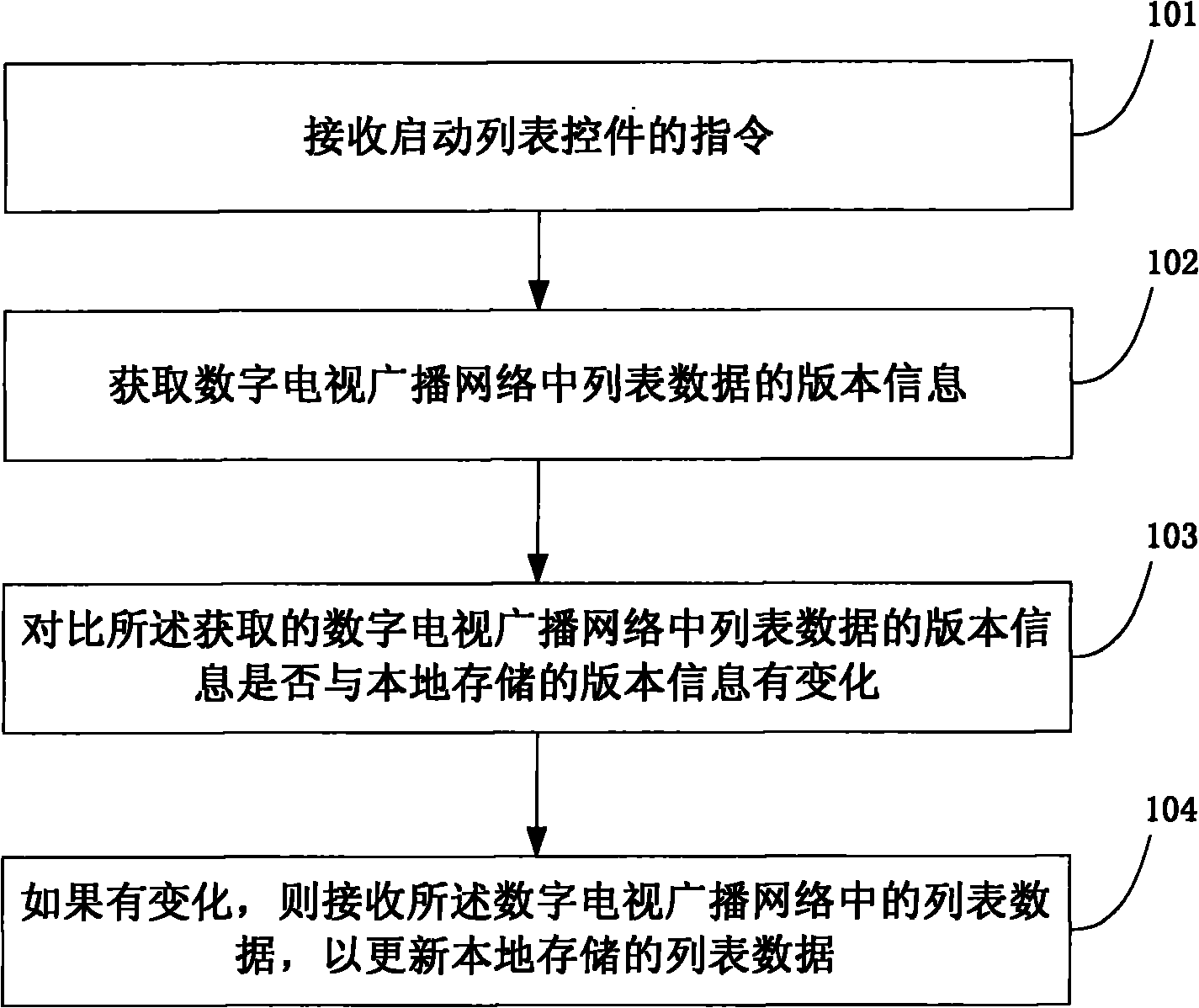

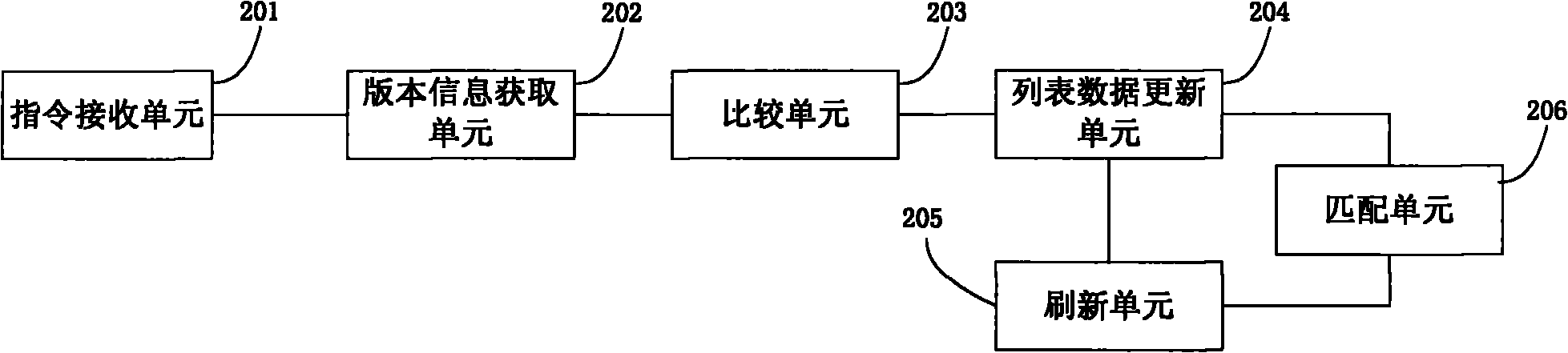

InactiveCN101917569AQuick responseRealize timely updateTelevision system detailsColor television detailsDisplay listComputer science

The invention relates to the field of digital televisions and solves the problems of wasting the network resources and influencing the response speed of a set top box because the set top box in the prior art needs updating a program list when being started every time, and provides a method and a system for updating the programme labeling information and a set top box. The method comprises the steps of: receiving a command of starting a list control, wherein the list control is used for displaying list data including programme labeling and the programme list corresponding to the programme labeling; obtaining edition information of the list data in a digital television broadcast network; comparing whether the obtained edition information of the list data in the digital television broadcast network has a change with the locally stored edition information or not; and if so, receiving list data in the digital television broadcast network to update the locally stored list data. The embodiment of the invention has the advantages of realizing that the list data of the set top box is properly updated and quickening the response speed of the set top box.

Owner:CHINA CABLE TELEVISION NETWORK +1

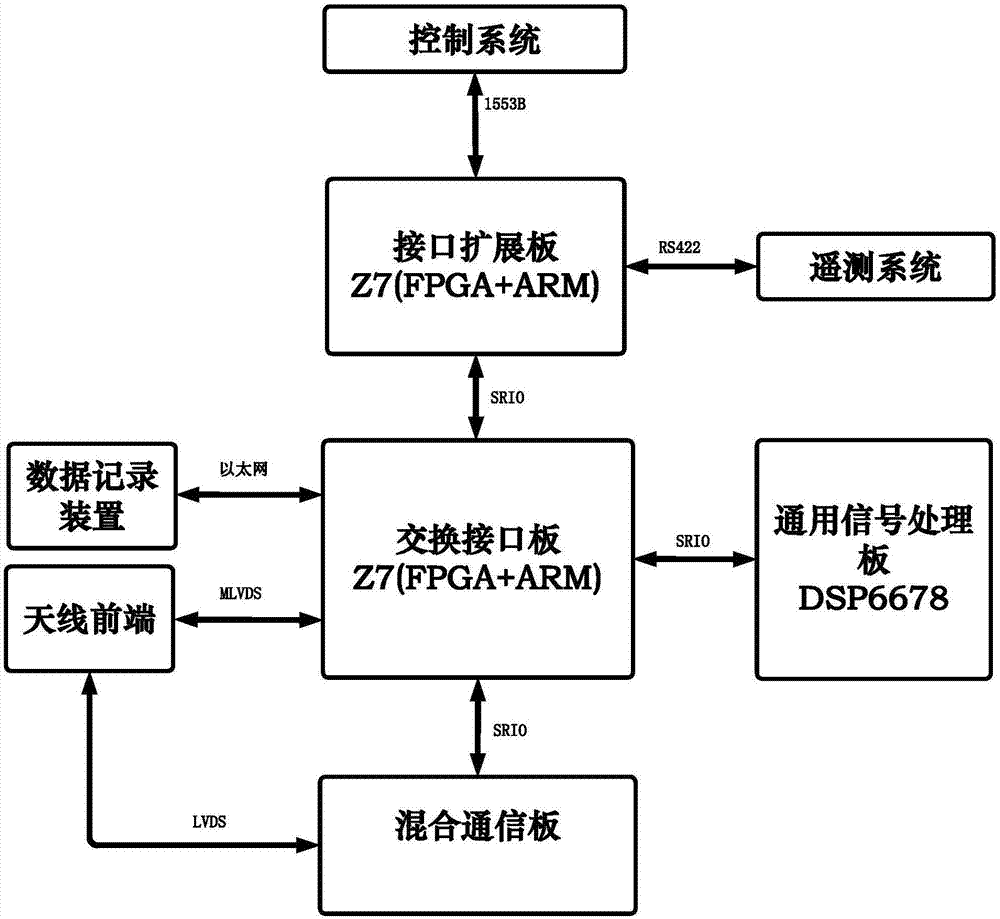

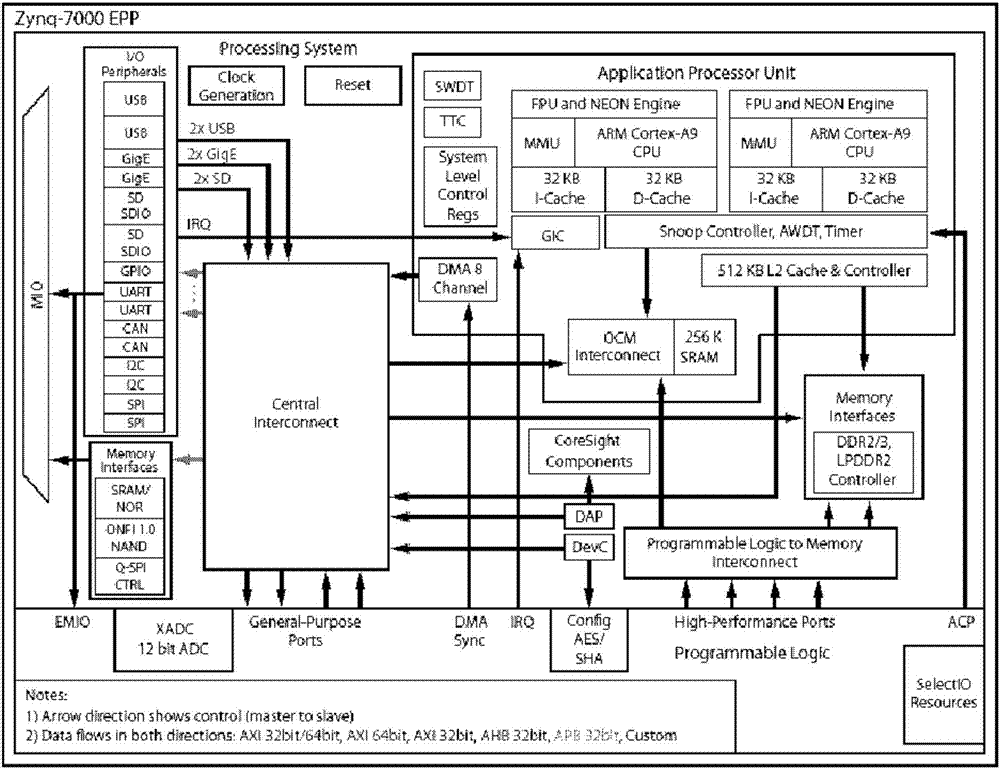

Integrated processing system based on VPX platform and software design method thereof

ActiveCN107202977AImprove portabilityImprove versatilityWave based measurement systemsDual coreSoftware design

The present invention discloses an integrated processing system based on a VPX platform and a software design method thereof. The system comprises a backboard provided with a plurality of slots, the system is mother-daughter board configuration based on a standard VPX bus, the system comprises a motherboard and a daughter board, the motherboard is an exchange interface board, the daughter board is an extension interface board, the motherboard and the daughter board are connected through an XMC connector, and the motherboard and the daughter board are communicated through an X4 SRIO bus; the slots can be inserted into a plurality of other board cards, the backboard can realize the communication of the motherboard, the daughter board and other board cards in the processing system; and a motherboard dual-core ARM Cortex<TM>-A9 processor PS and a daughter board dual-core ARM Cortex<TM>-A9 processor PS perform real-time operation of the system. The integrated processing system has rich extension capability, can satisfy application requirements of different scenes through replacing of daughter boards having different functions, has good, flexibility is wide in application range, can realize shelf performances of modules, and can rapidly build an integrated processing system aiming at a special guidance application background according to the application requirements.

Owner:THE GENERAL DESIGNING INST OF HUBEI SPACE TECH ACAD