Method for designing AES (Advanced Encryption Standard) encryption chip based on FPGA (Field Programmable Gate Array) and embedded encryption system

A technology of encryption chip and design method, which is applied in the direction of encryption device with shift register/memory, etc., can solve the problem of communication error detection without considering the problem of AES operation mode

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0067] The specific embodiment of the present invention will be described in further detail in conjunction with the accompanying drawings.

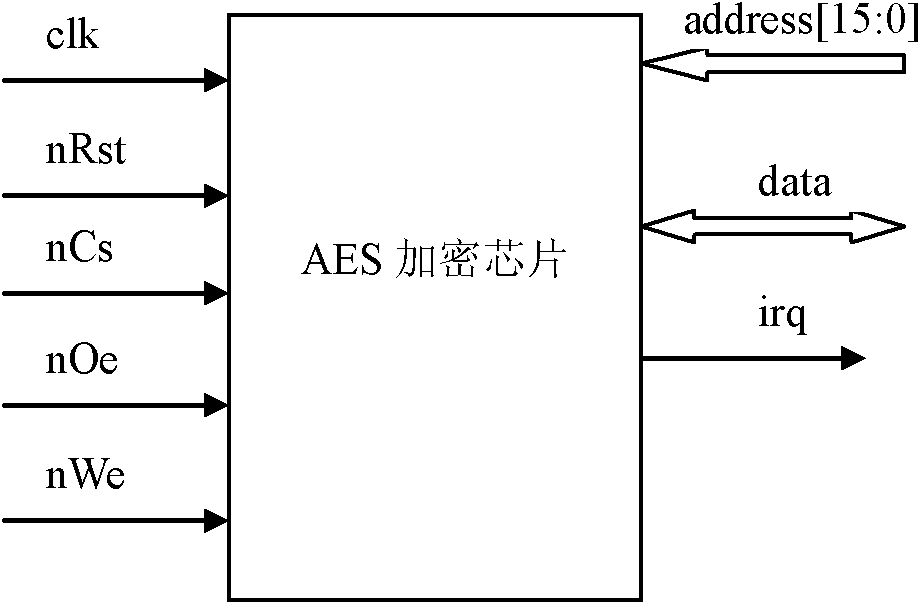

[0068] First, describe the main external signals of the AES encryption chip, see figure 1 and Table 2 below.

[0069]

[0070] Table 2

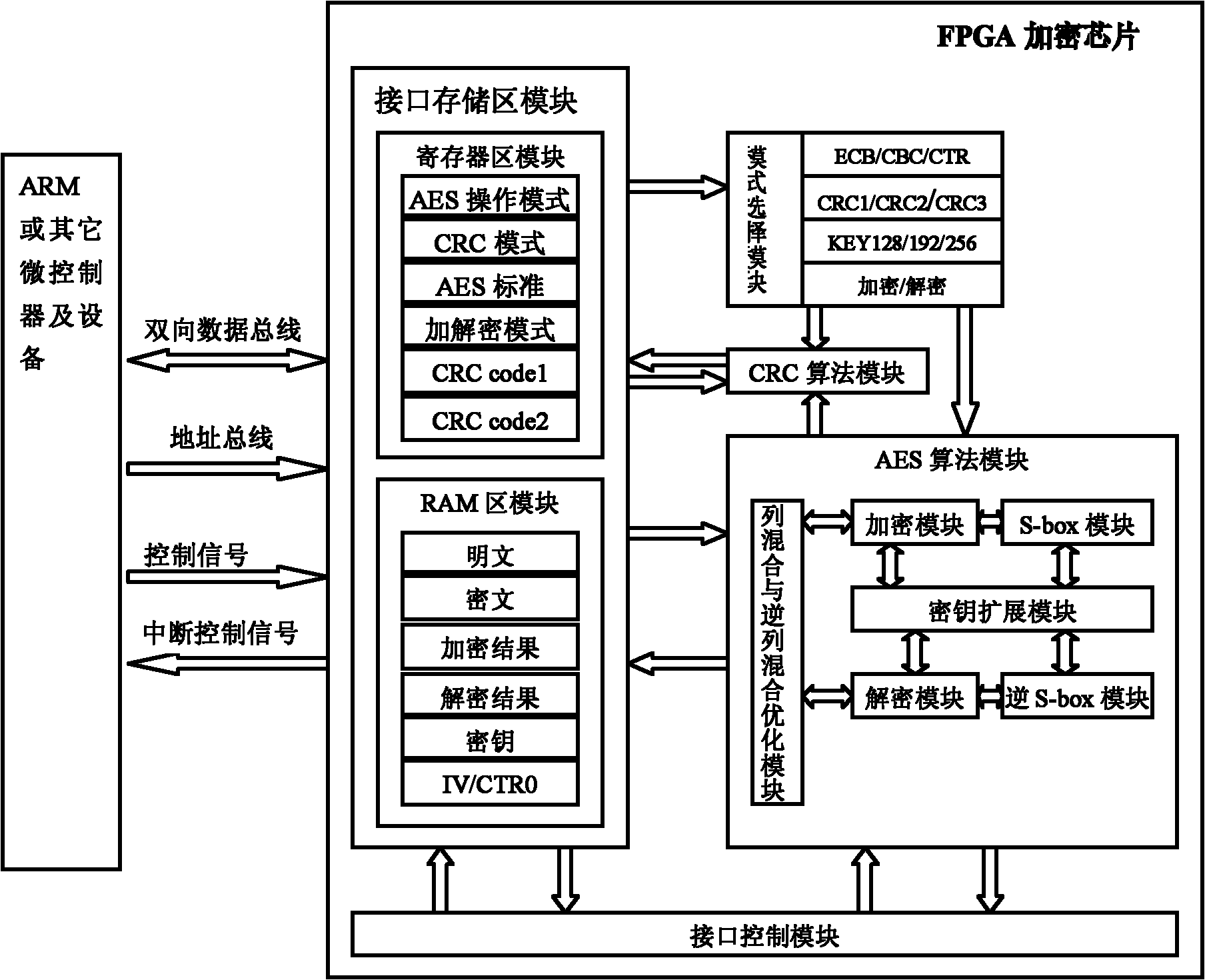

[0071] Secondly, describe the overall structure of the AES encryption chip, see figure 2 shown.

[0072] The hardware architecture design is based on ARM or other microcontrollers and devices as the main controller, and the FPGA encryption chip as the coprocessor, such as figure 2 shown. The main controller completes the management work of the entire encryption system, involving encryption or decryption mode setting, operation mode setting, initial key, initial vector IV (CBC mode) and initial count value CTR0 (CTR mode) setting and CRC (Cyclic Redundancy Check) mode settings. After setting these modes, the FPGA works according to the corresponding requirements.

[0073] The AES encryption c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More