Patents

Literature

2642results about "Other decoding techniques" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

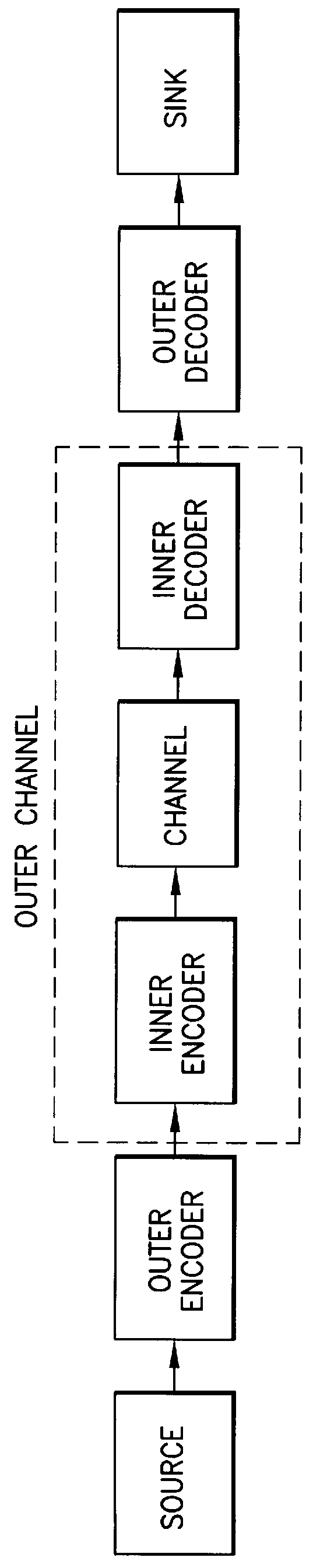

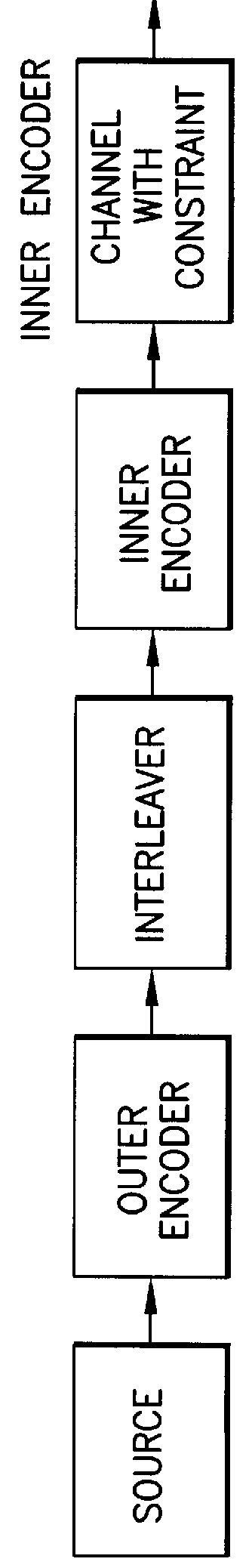

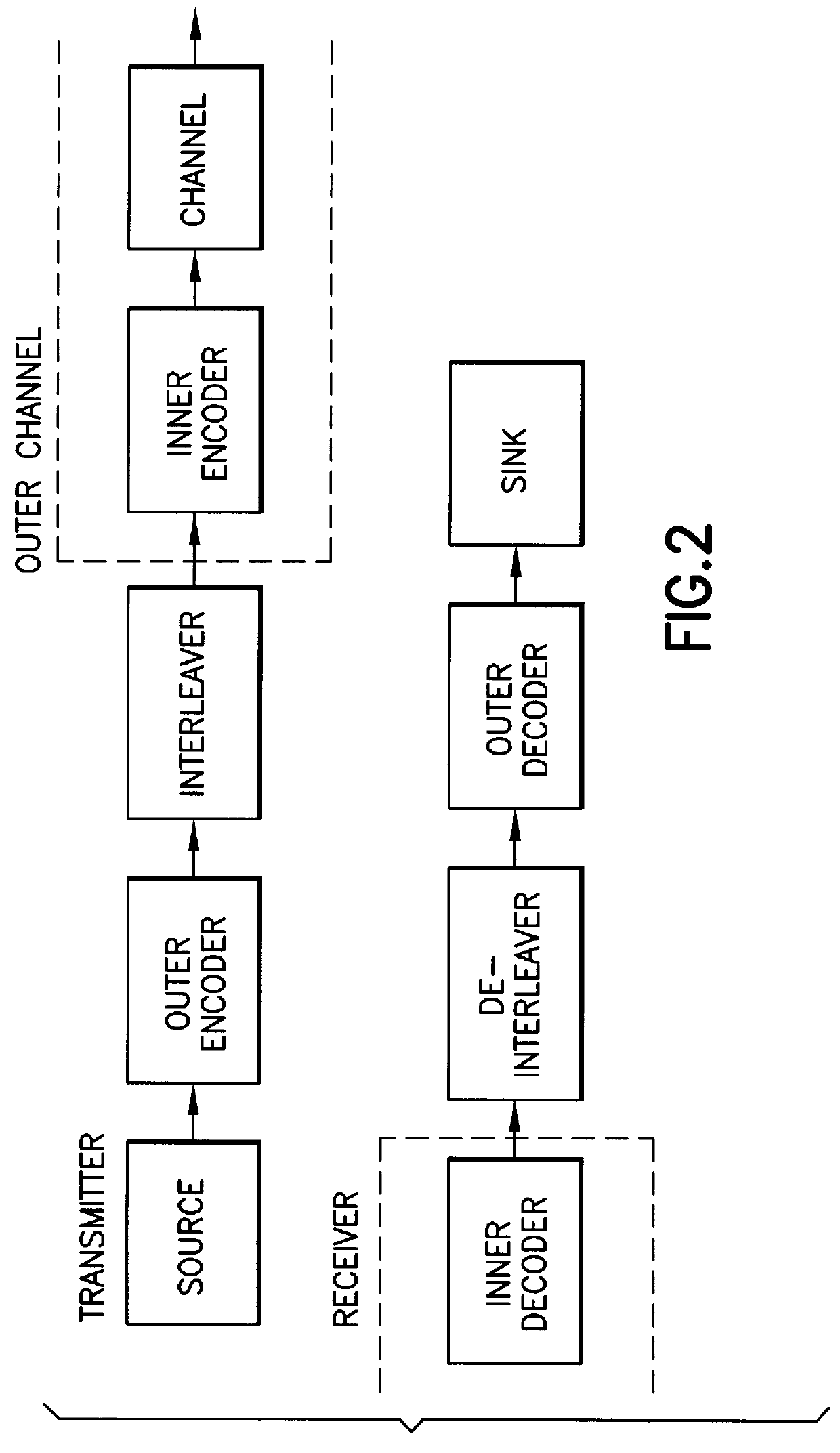

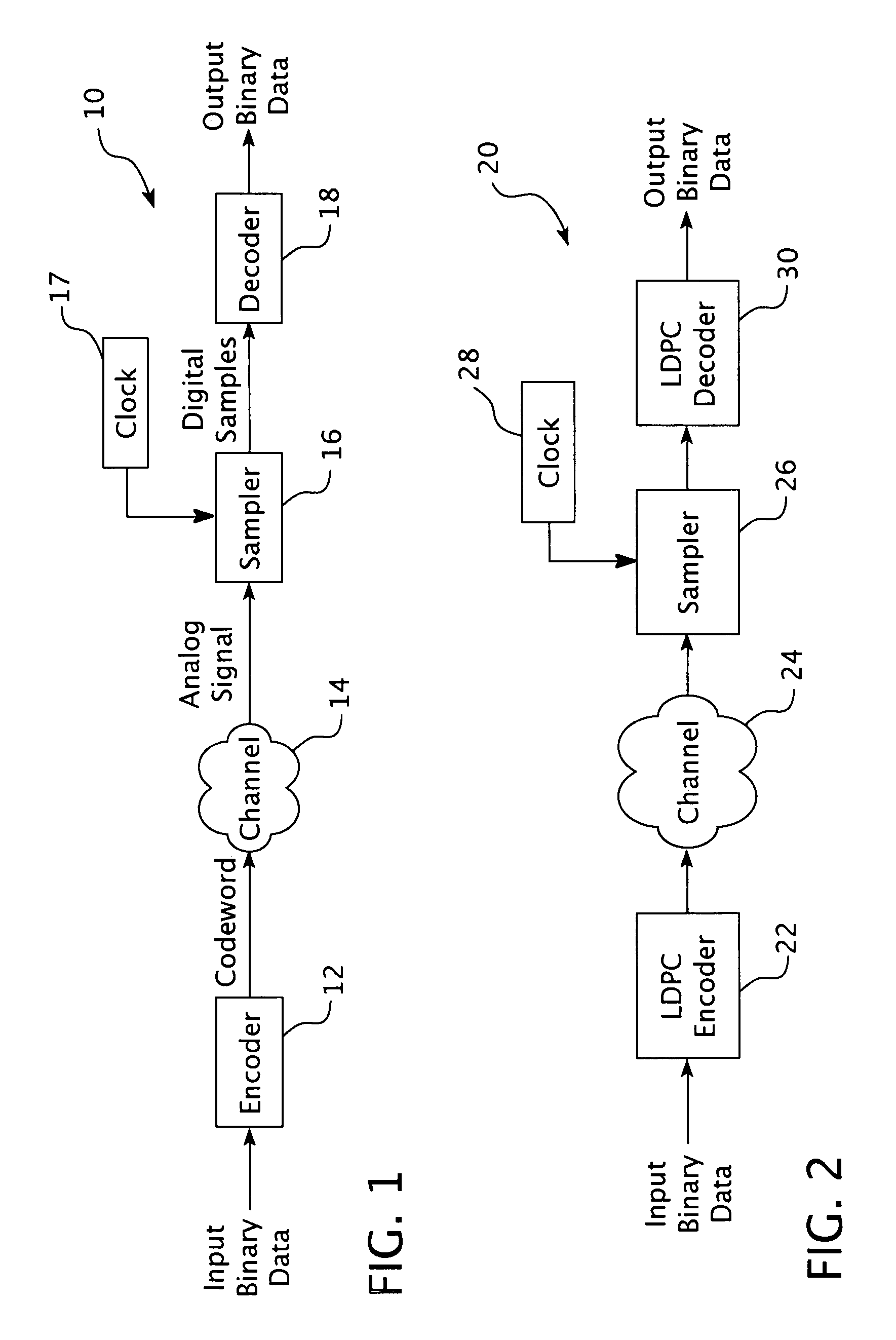

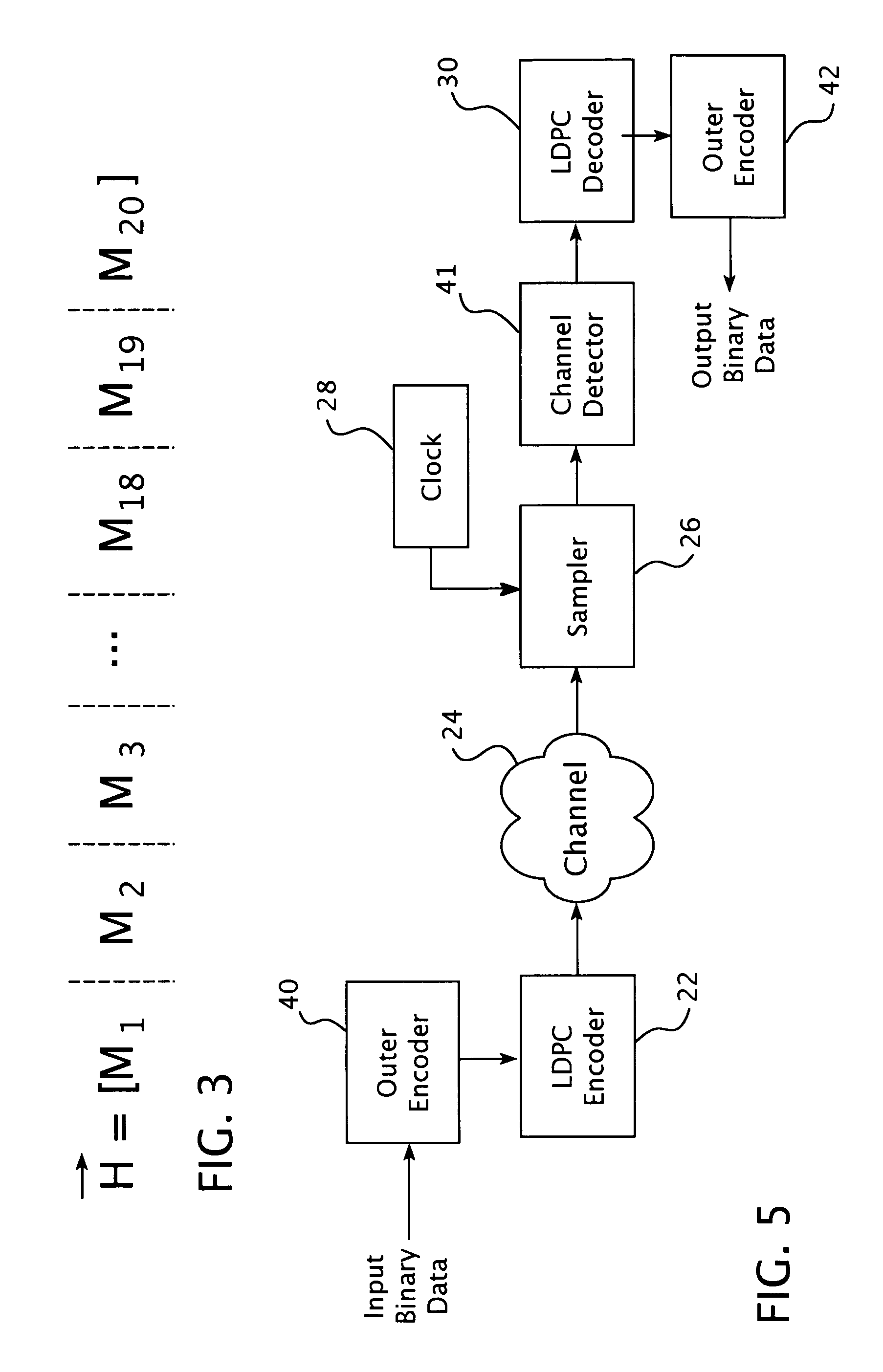

System and method for error correcting a received data stream in a concatenated system

A received signal is first converted into a digital sequence that may contain "erasures" (or ambiguity symbols) as well as errors. Then iterative decoding is applied in order to eliminate or reduce the erasures. This decoding procedure works effectively with the associated transmitter that adopts a concatenation of an outer coder, a permutation and an inner coder. The principal of the invention is also applicable to a system in which the inner coder is replaced by a "digital modulator" that introduces some constraint, or a channel that introduces some memory such as partial response signaling, intersymbol interference or multipath propagation. The invention can be applied to many existing systems while maintaining "backward compatibility" in the sense that the transmitter side need not be modified.

Owner:THE TRUSTEES FOR PRINCETON UNIV

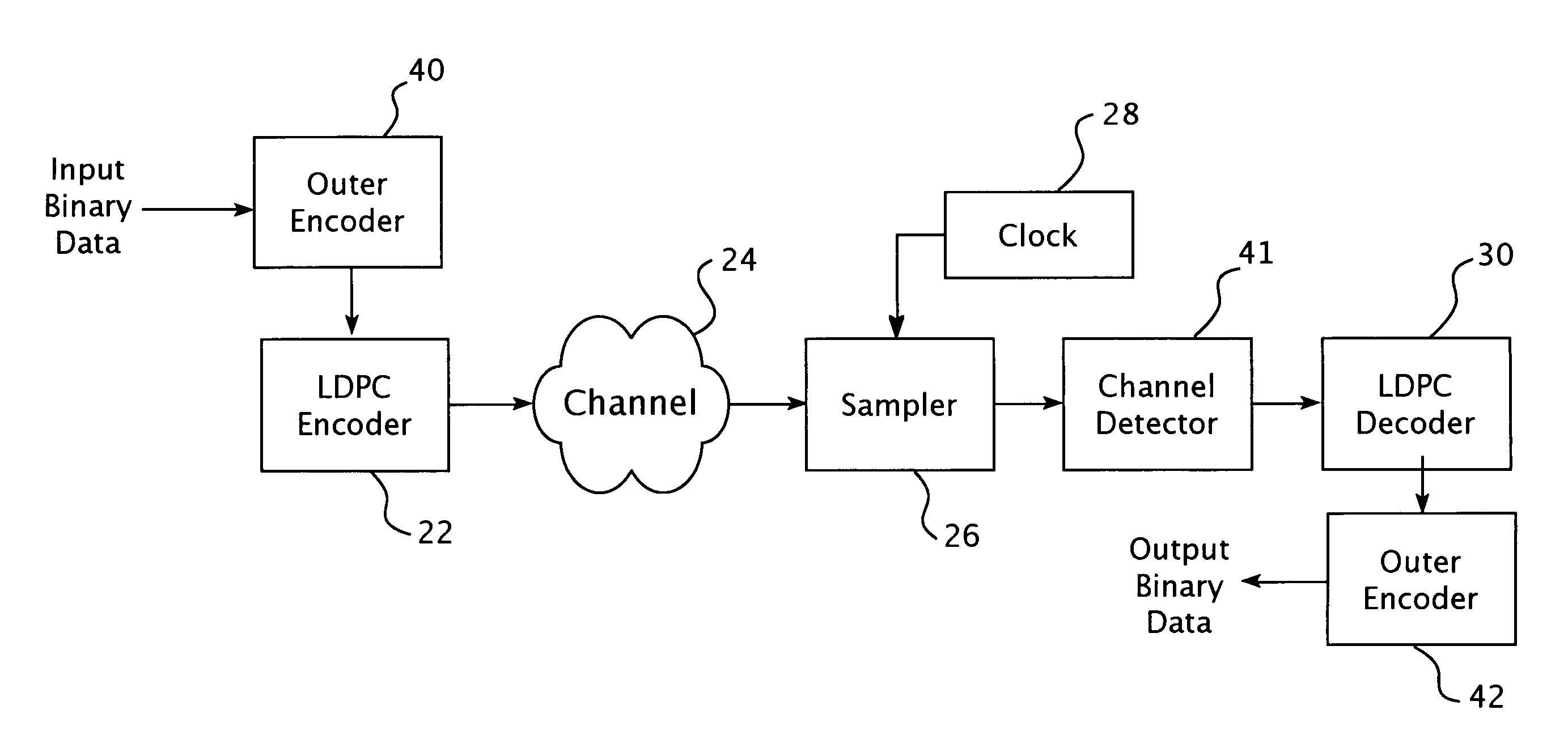

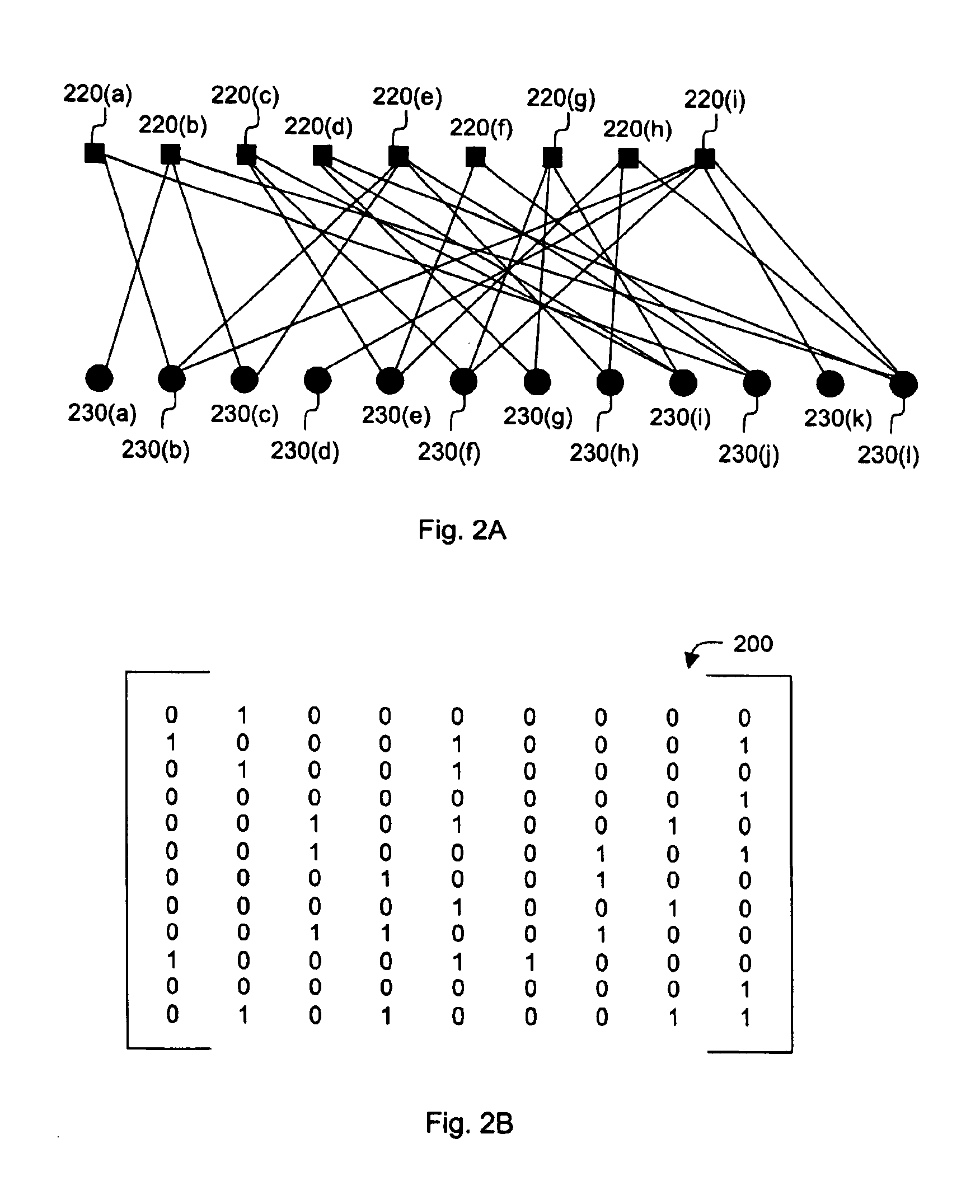

Encoding method using a low density parity check code with a column weight of two

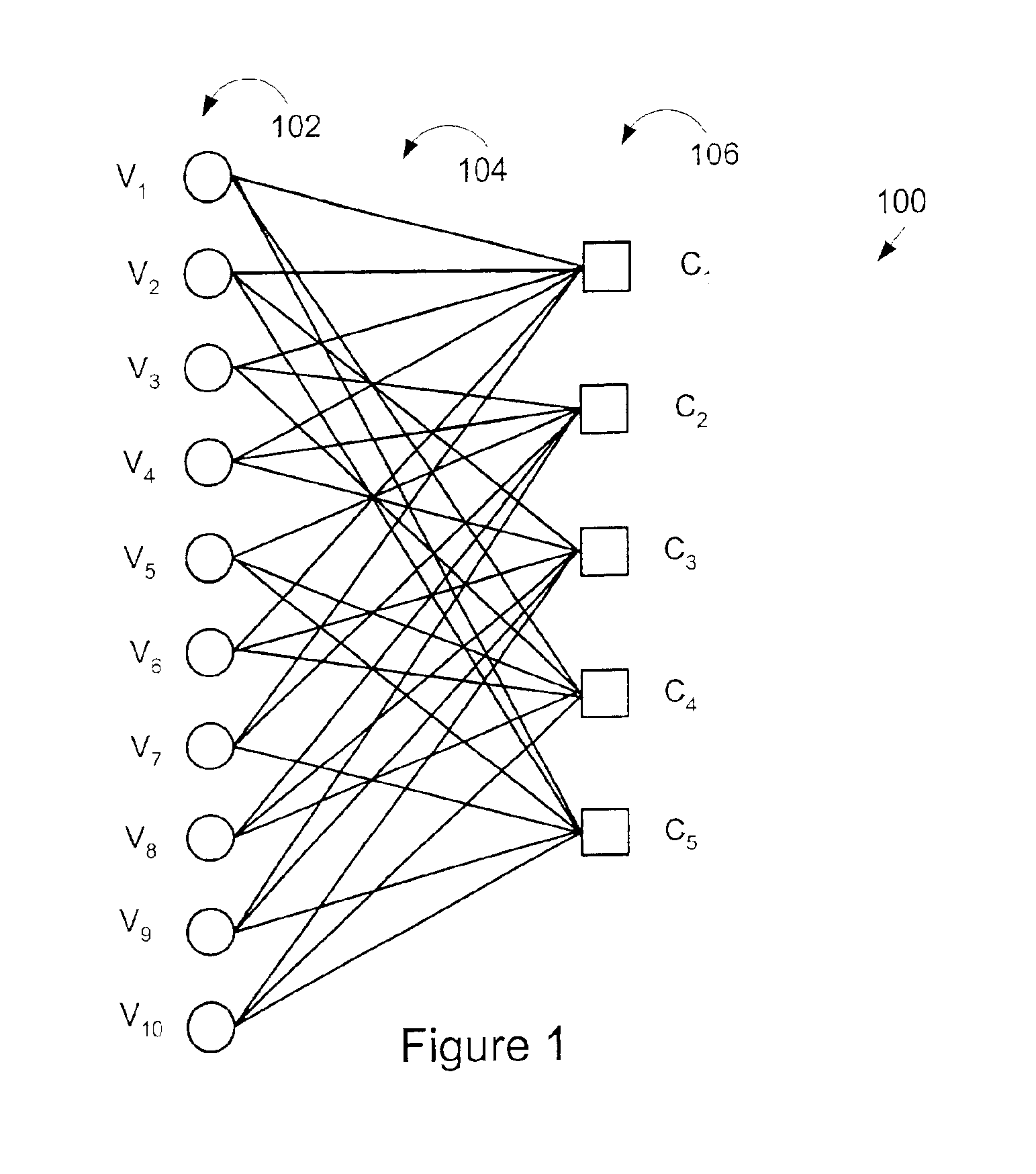

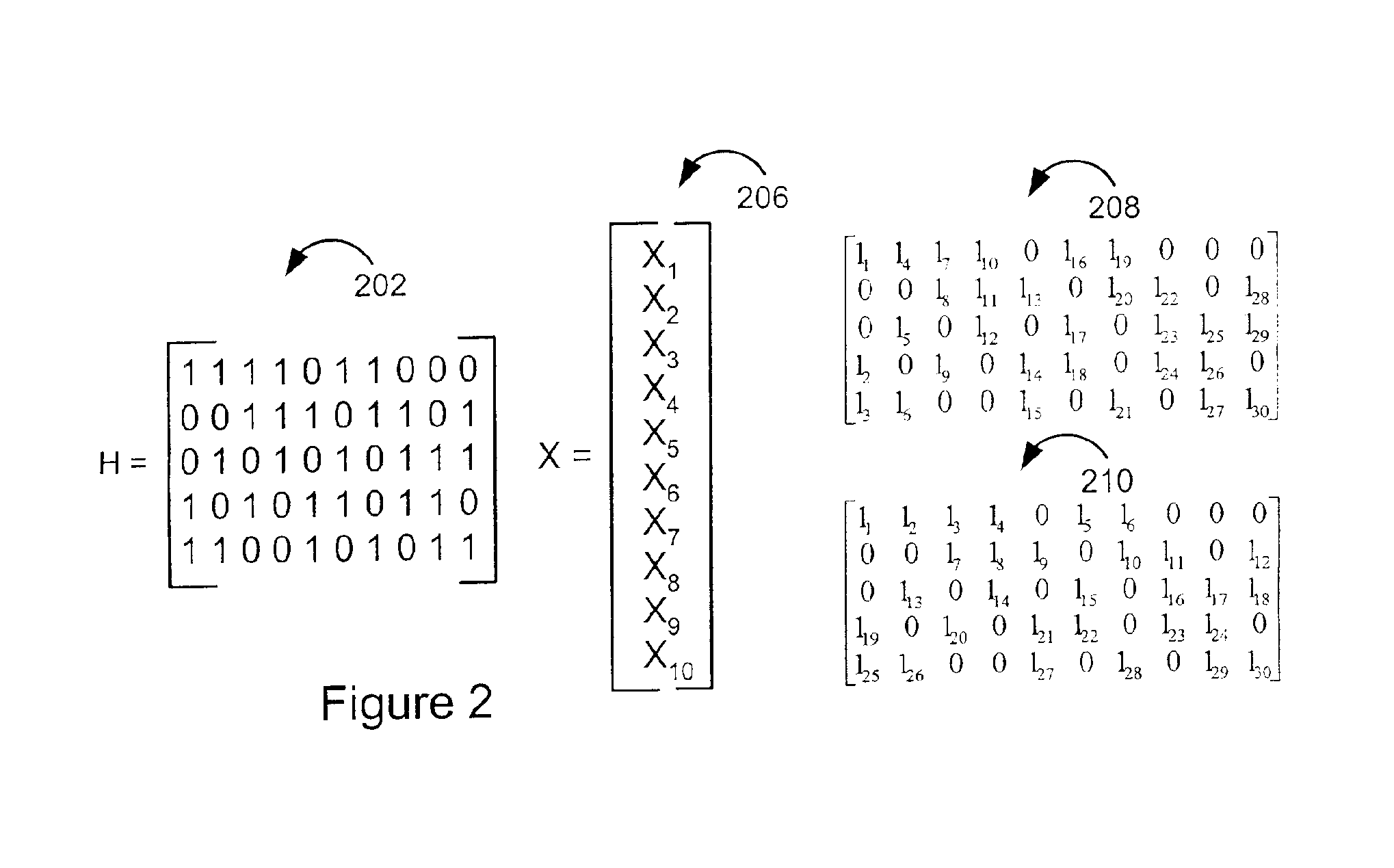

ActiveUS7058873B2Facilitate the processOther decoding techniquesError correction/detection using multiple parity bitsTanner graphCommunications system

A method for communicating binary data and a digital communication system are presented. According to one embodiment, the method includes encoding a message word by multiplying the message word with a generator matrix, wherein the generator matrix multiplied by the transpose of a parity check matrix for a low density parity check code yields a null set, and wherein the parity check matrix has a column weight of two. Additionally disclosed is an encoding scheme based on a three-tier Tanner graph having a girth of twelve.

Owner:CARNEGIE MELLON UNIV

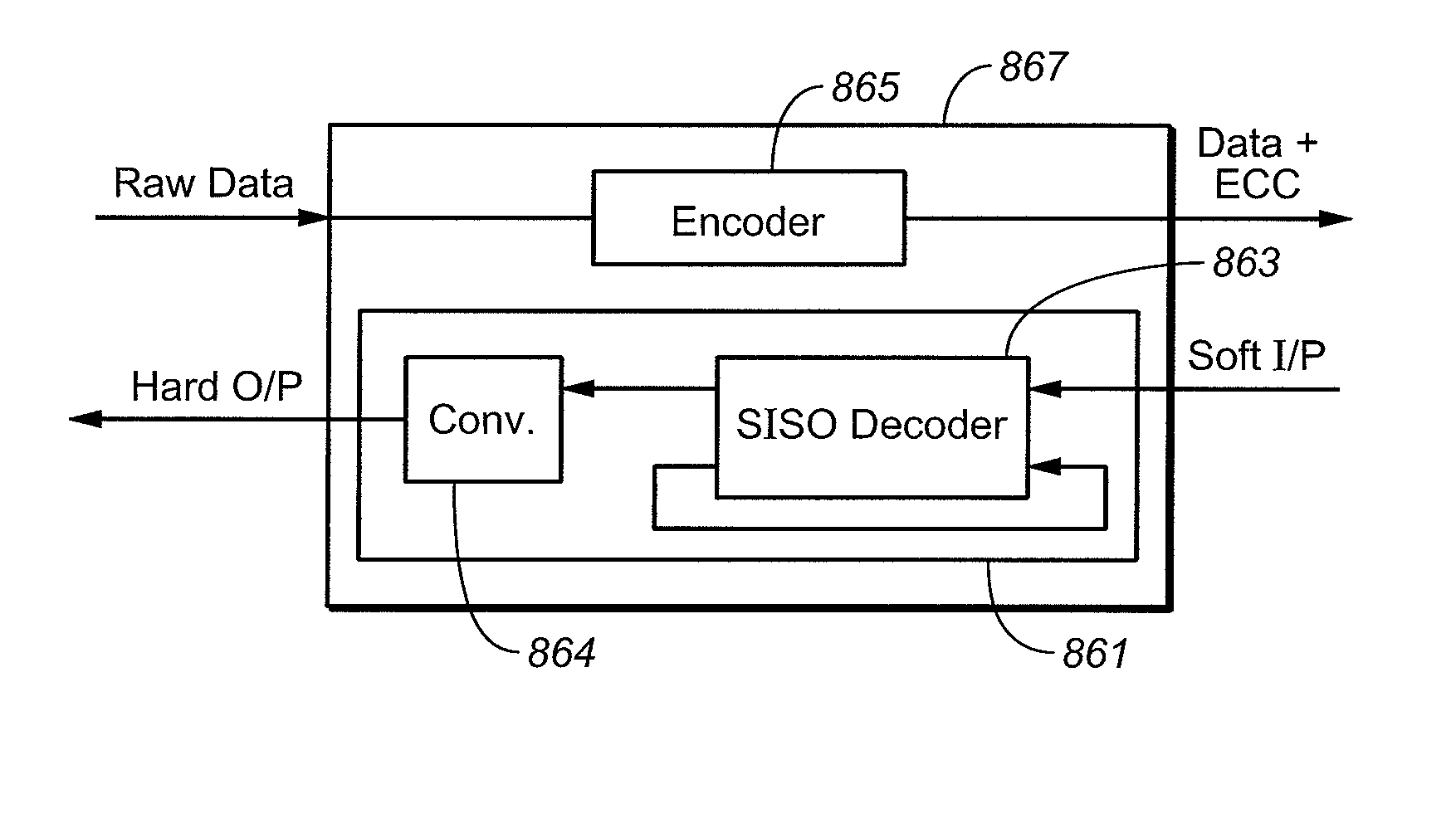

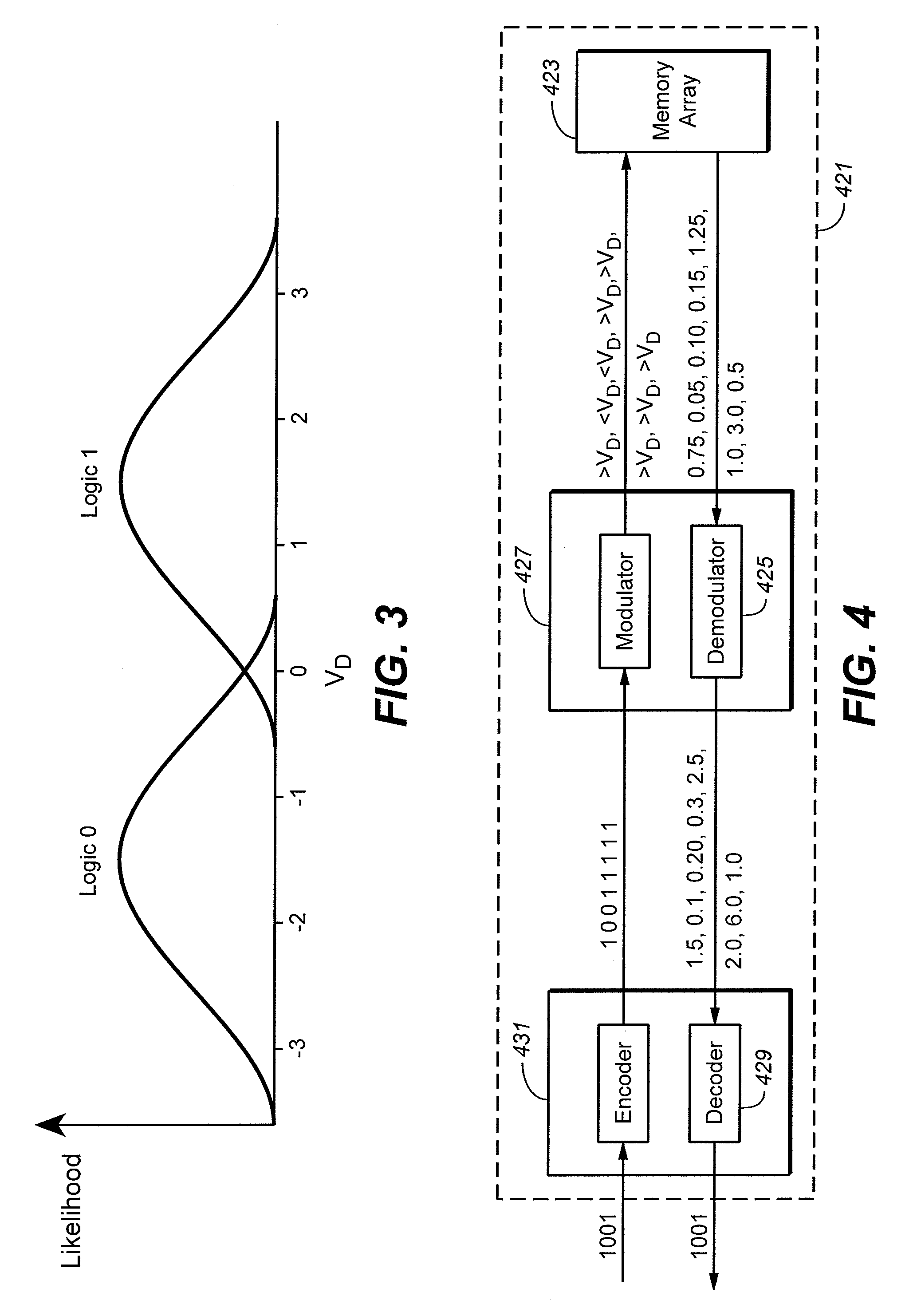

Methods of Soft-Input Soft-Output Decoding for Nonvolatile Memory

ActiveUS20080092026A1Data representation error detection/correctionOther decoding techniquesNon-volatile memoryMemory systems

In a nonvolatile memory system, data is read from a memory array and used to obtain likelihood values, which are then provided to a soft-input soft-output decoder. The soft-input soft-output decoder calculates output likelihood values from input likelihood values and from parity data that was previously added according to an encoding scheme.

Owner:SANDISK TECH LLC

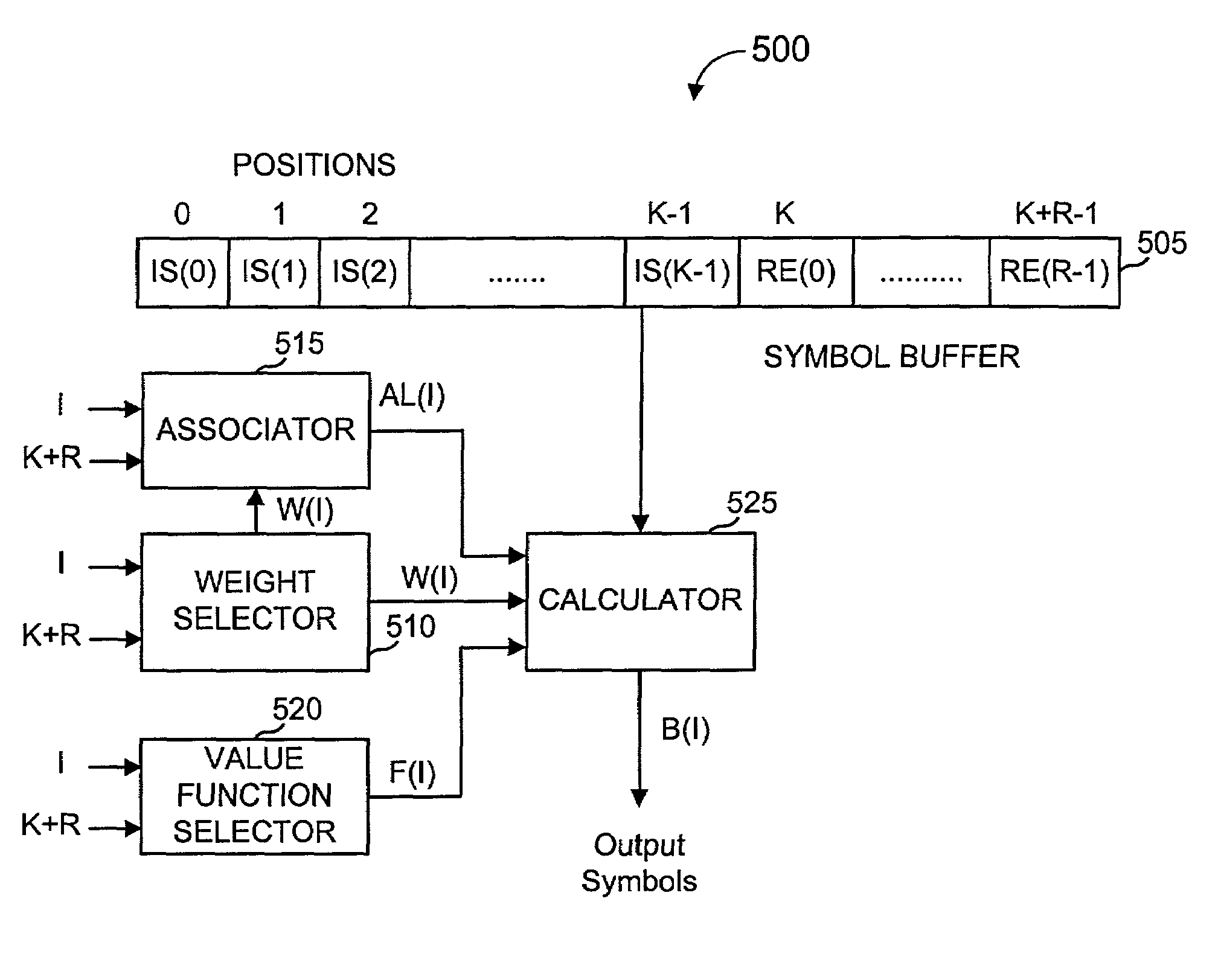

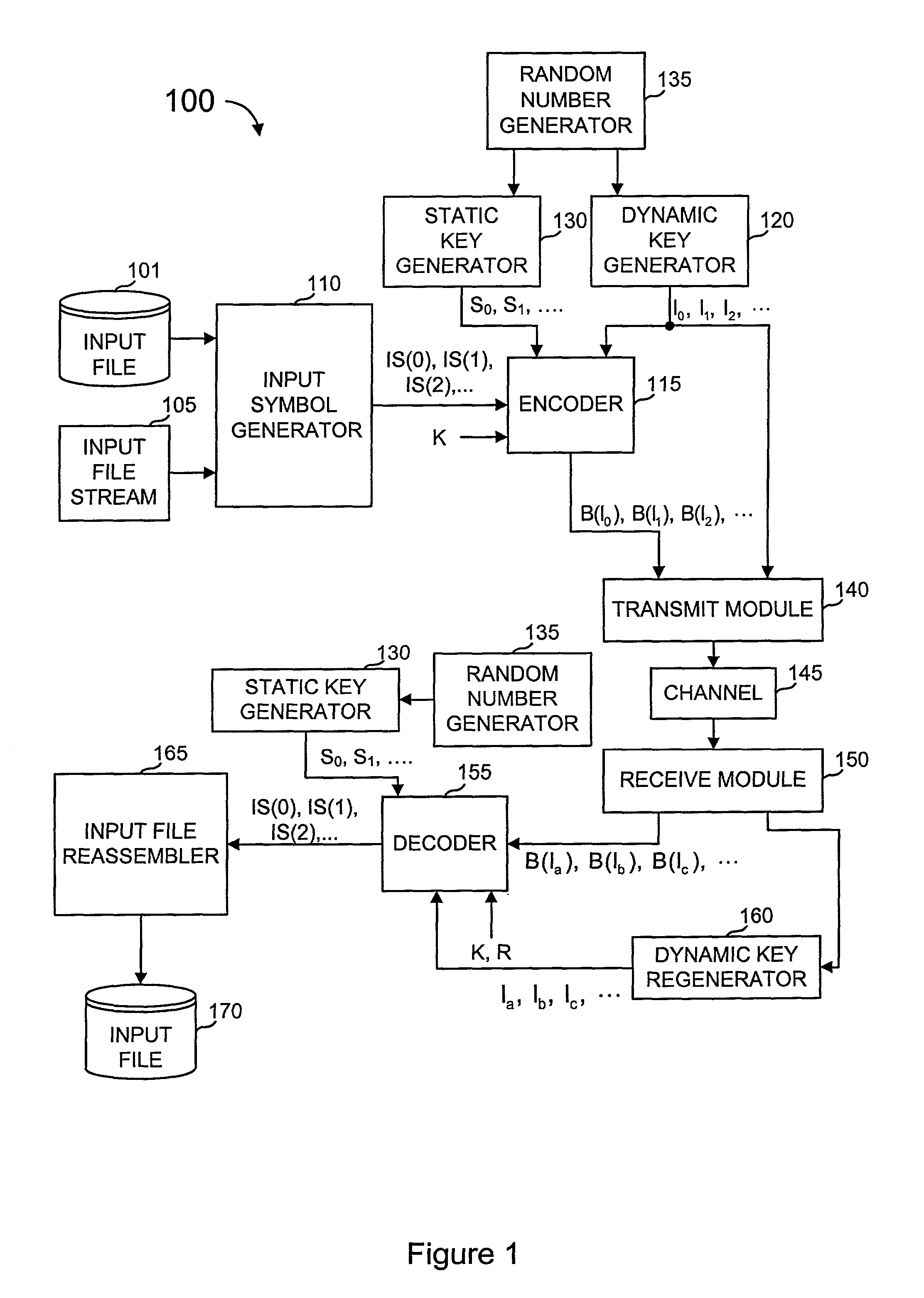

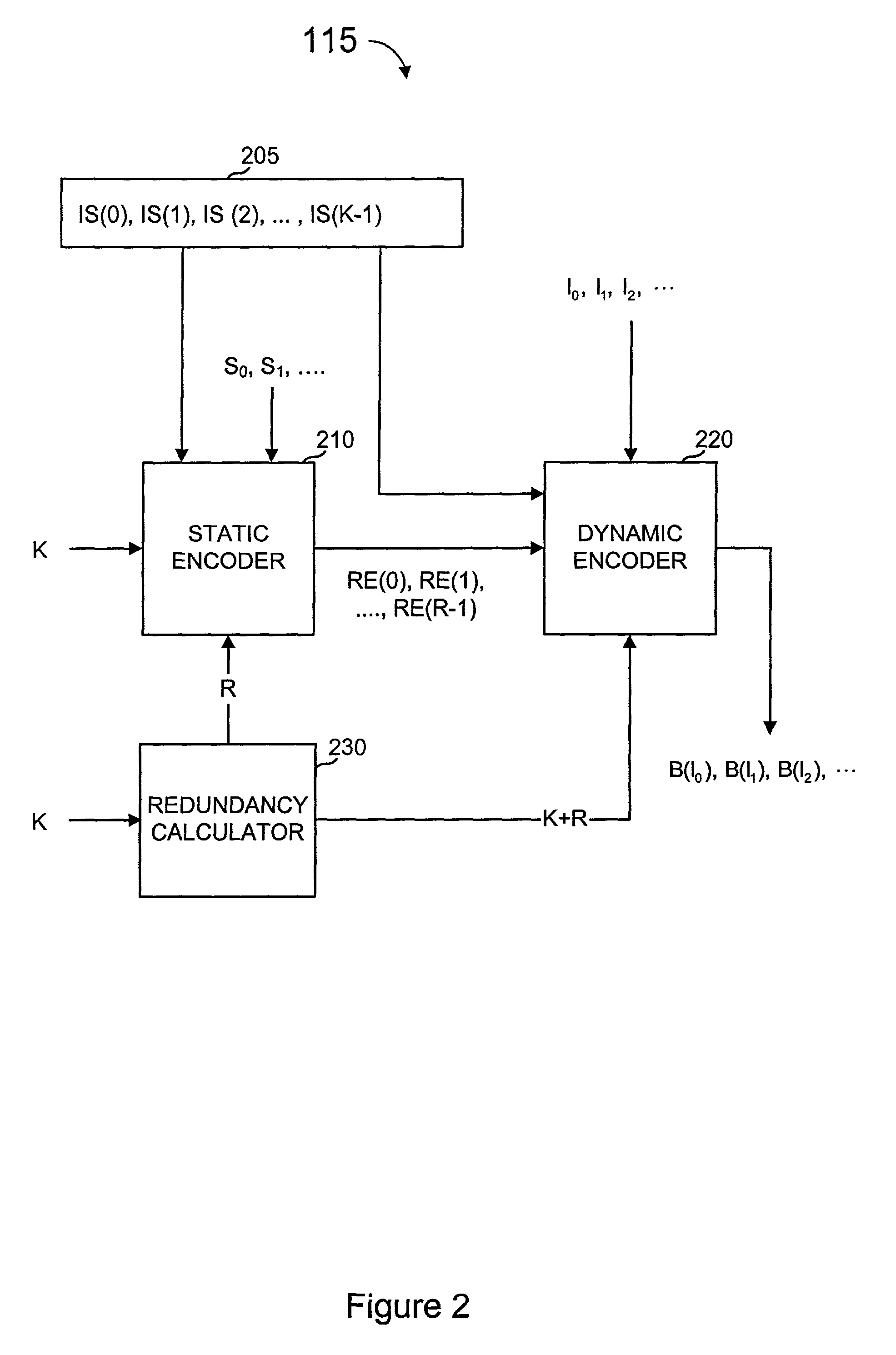

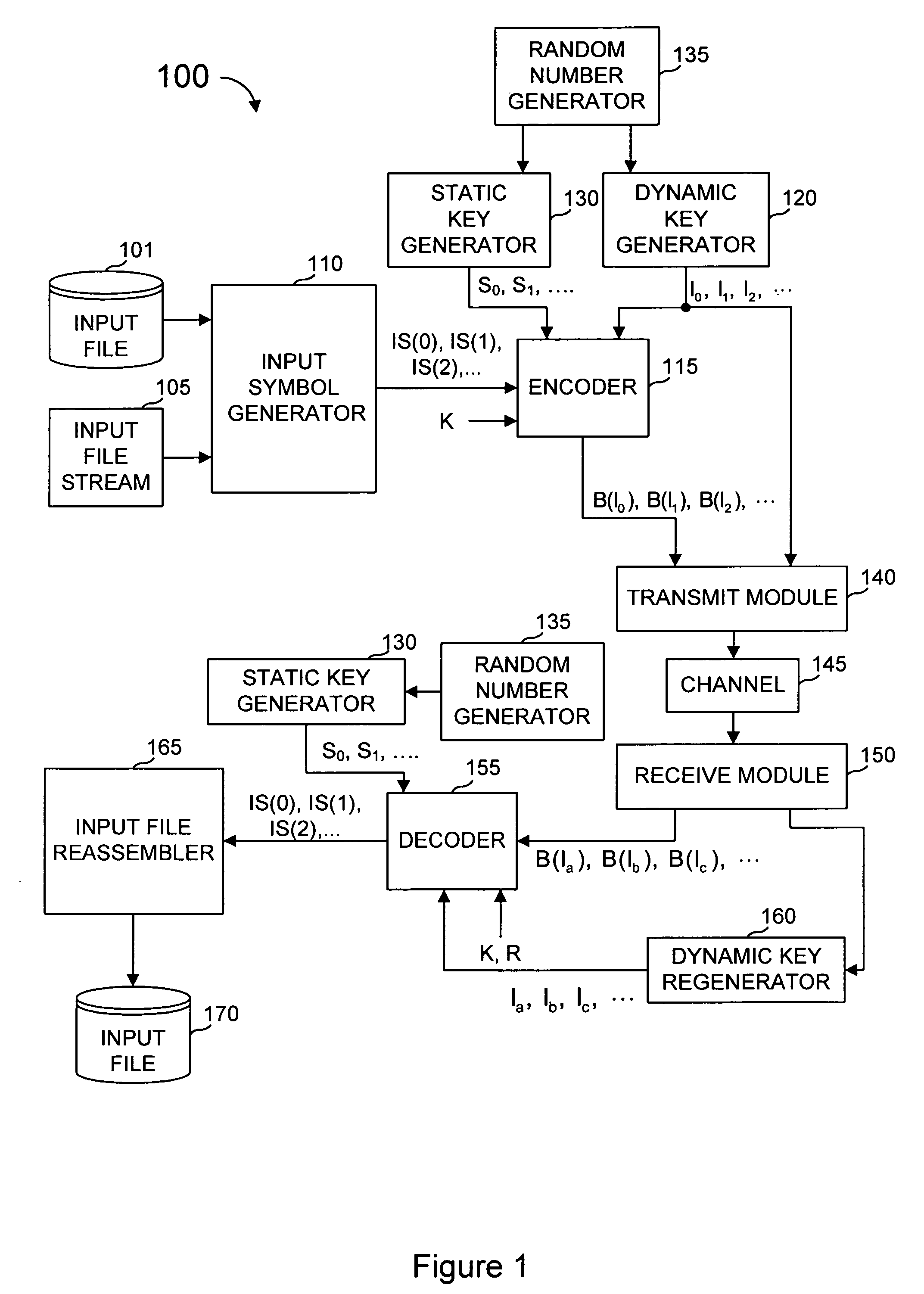

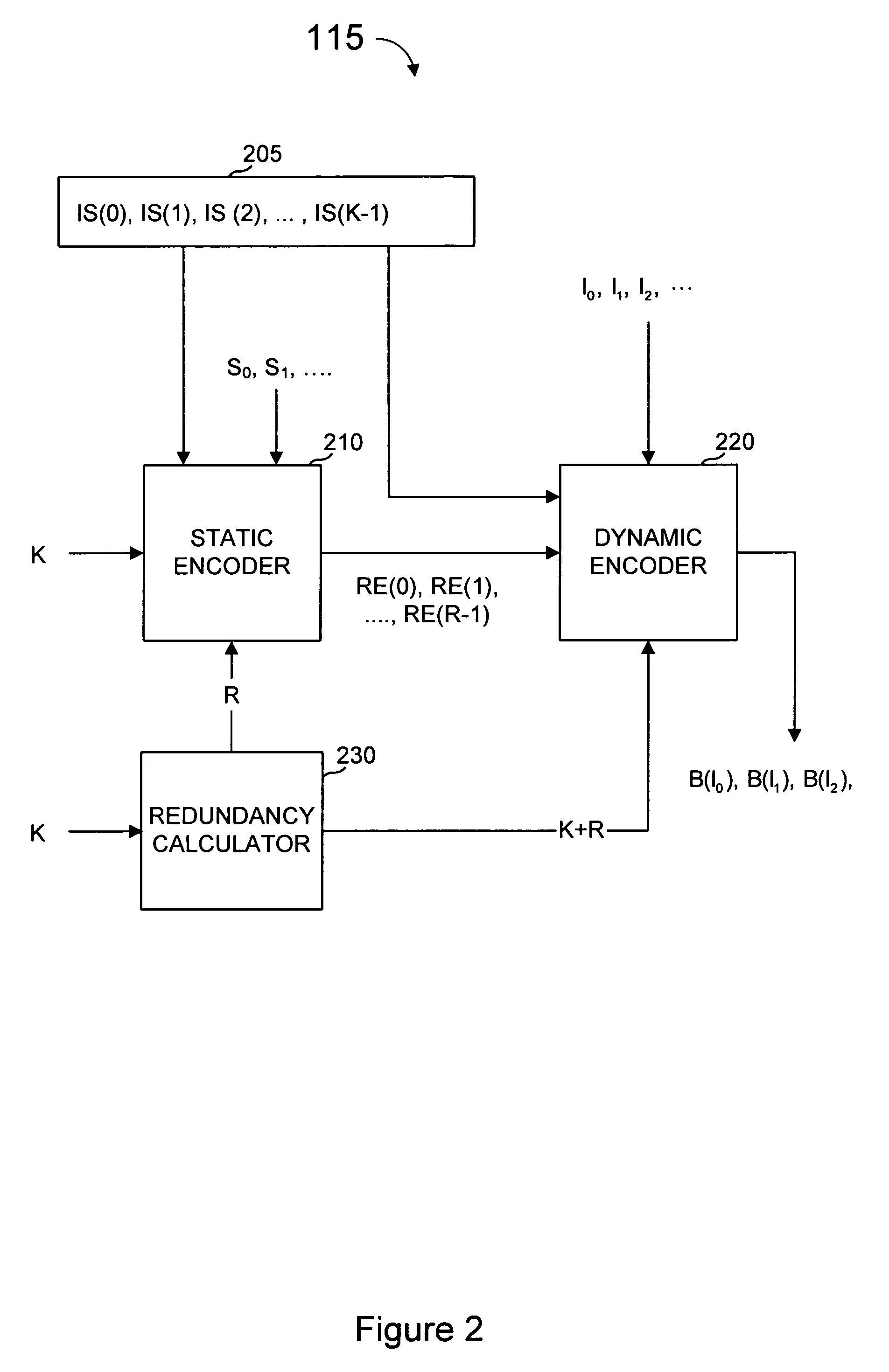

Multi-stage code generator and decoder for communication systems

InactiveUS7068729B2Reduce expensesOther decoding techniquesOther error detection/correction/protectionCommunications systemOrder set

Owner:QUALCOMM INC

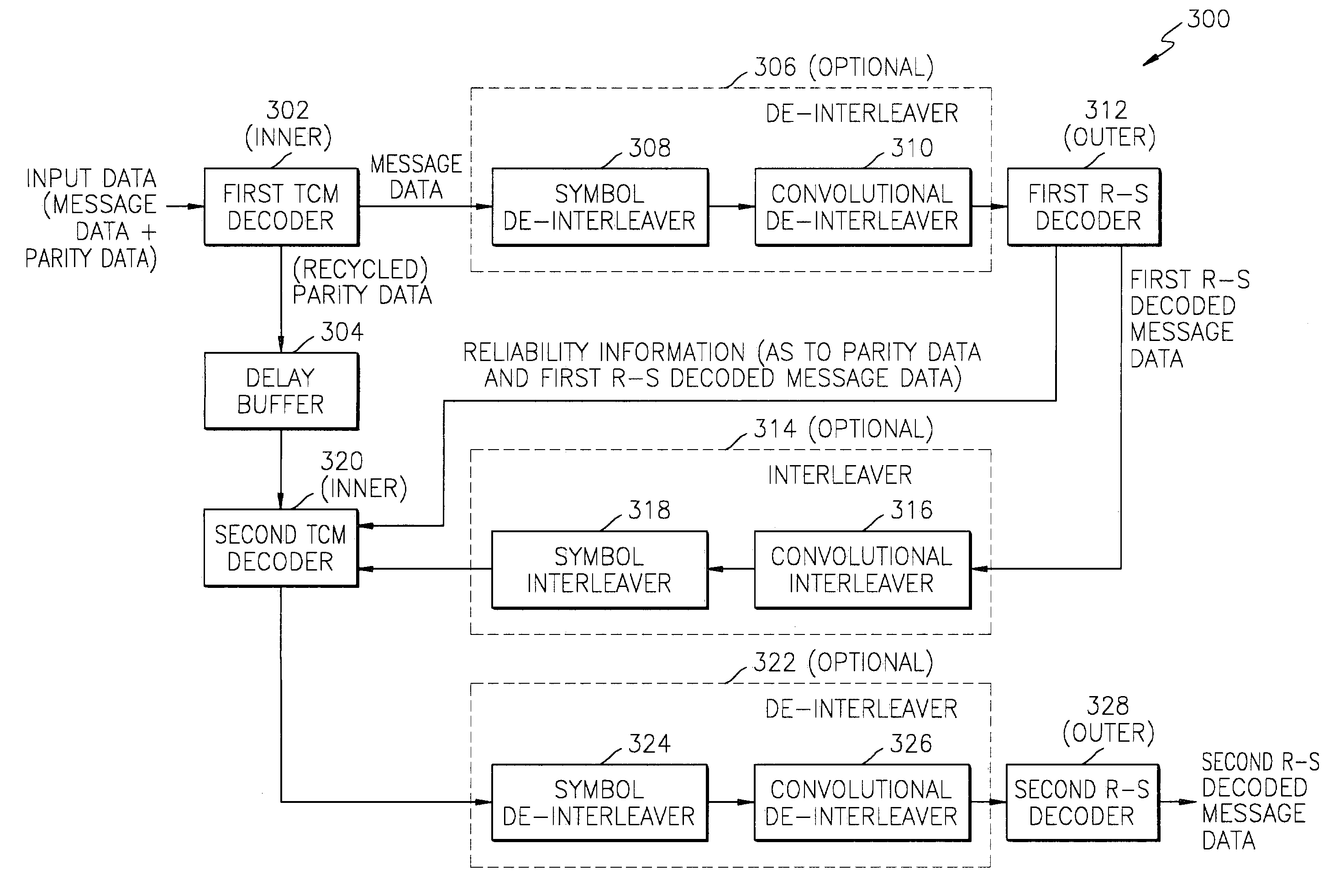

Decoding concatenated codes via parity bit recycling

Owner:SAMSUNG ELECTRONICS CO LTD

Digital communication system for transmitting and receiving robustly encoded data

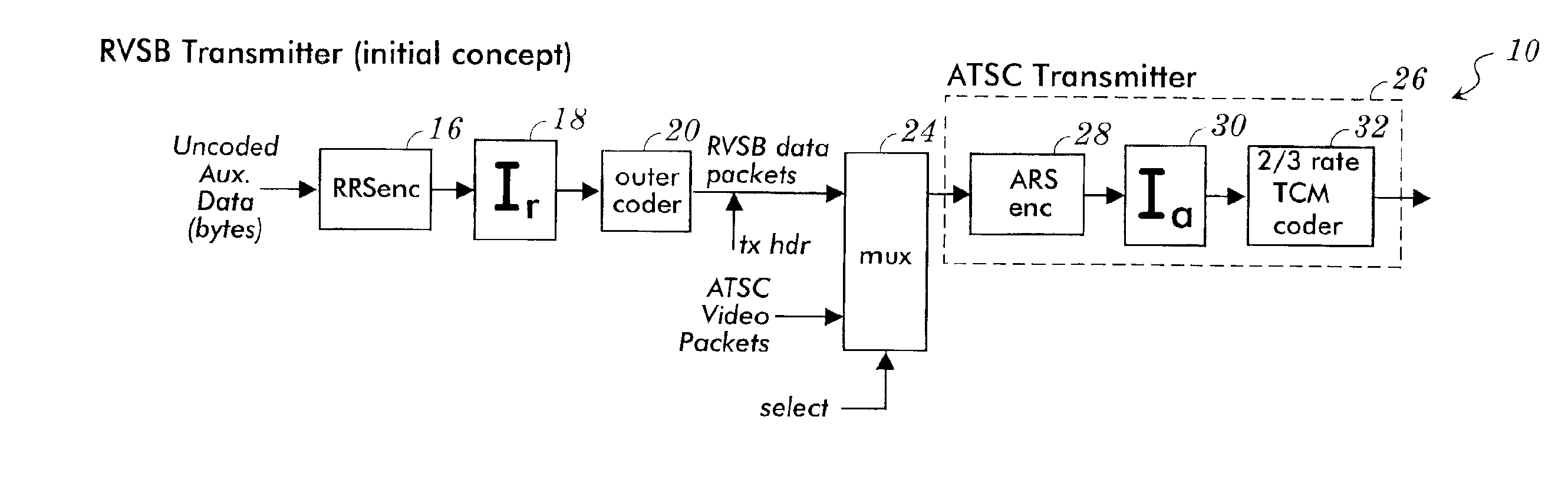

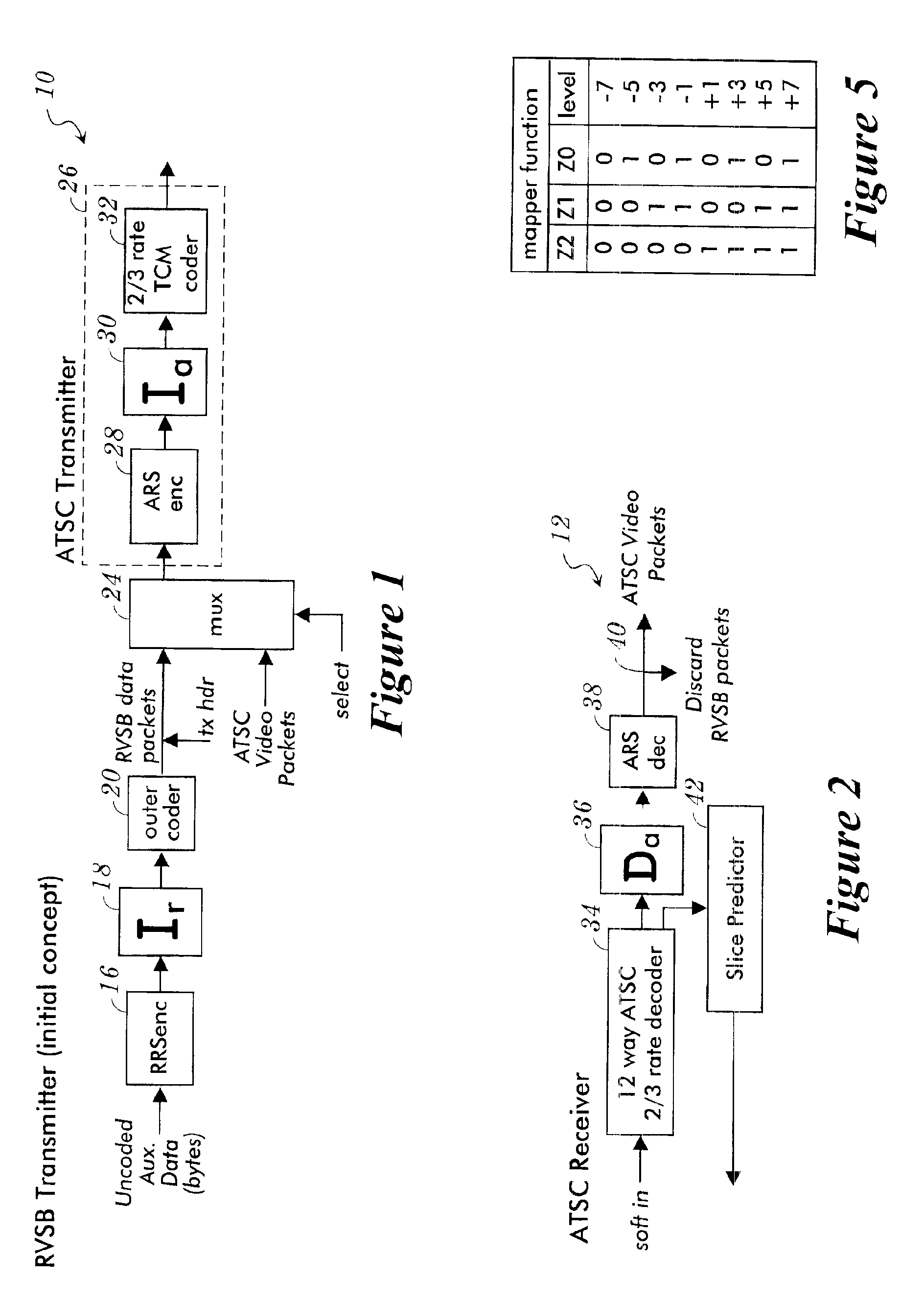

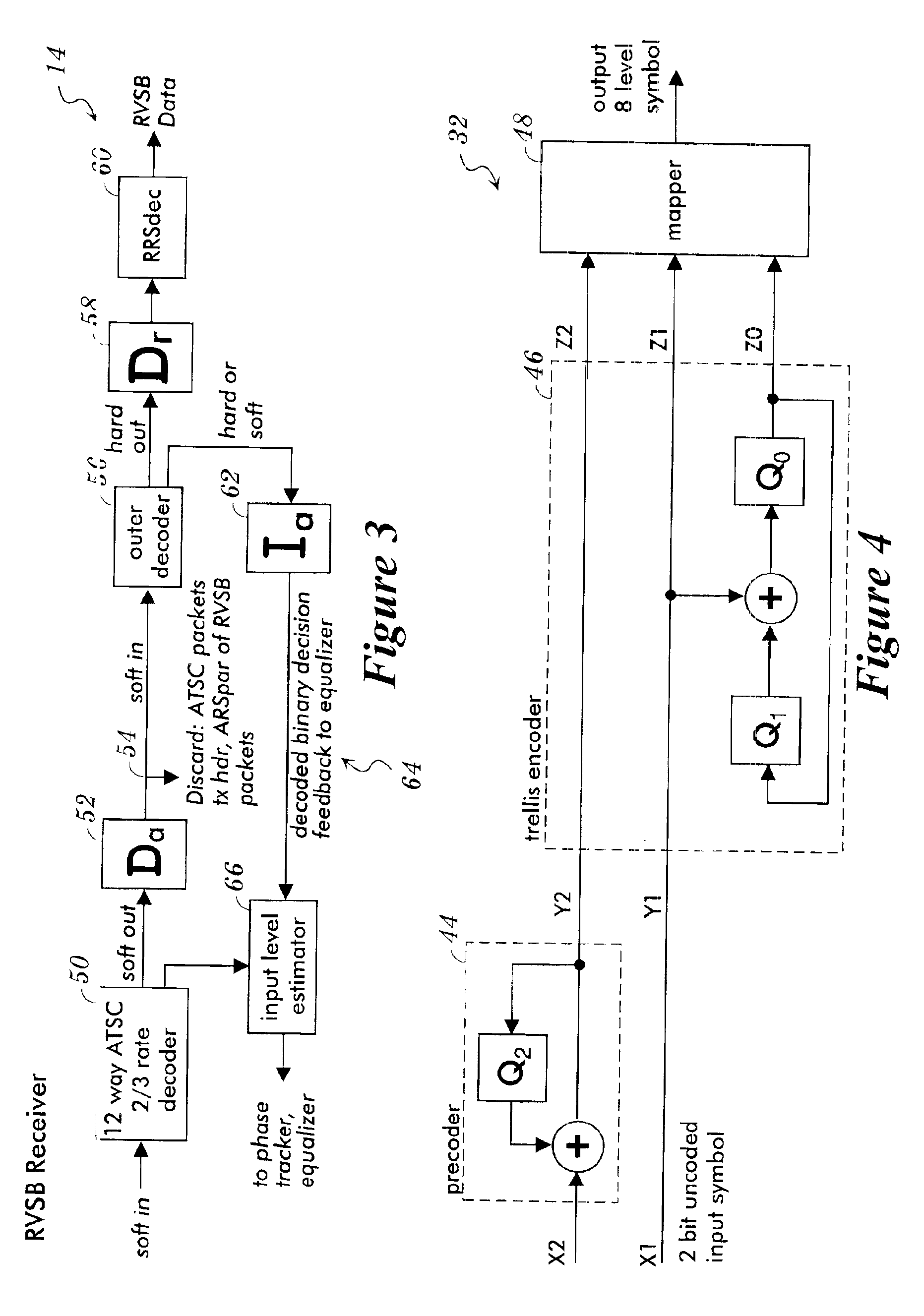

Normally ordered robust VSB data are reordered in accordance with a first interleave to produce reordered robust VSB data, The reordered robust VSB data and ATSC data are reordered in accordance with a second interleave to produce normally ordered robust VSB data and reordered ATSC data. The normally ordered robust VSB data and reordered ATSC data are time multiplexed for transmission to a receiver. The receiver discards the reordered ATSC data or the normally ordered robust VSB data depending upon receiver type or user selection. A robust VSB receiver is able to process the normally ordered robust VSB data upstream of an outer decoder without an interleave thereby avoiding the delay associated with an interleave.

Owner:ZENITH F ECTRONICS LLC

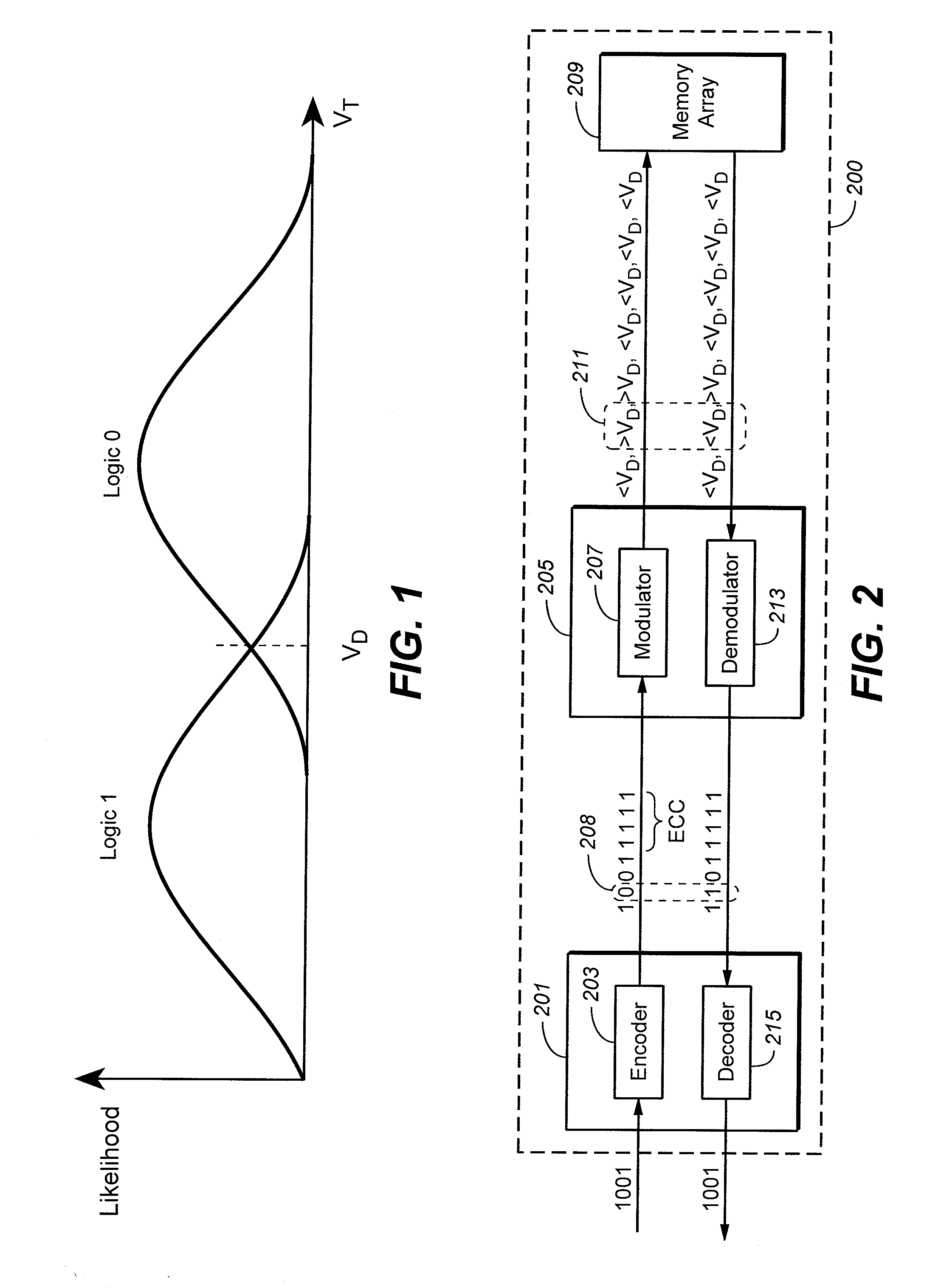

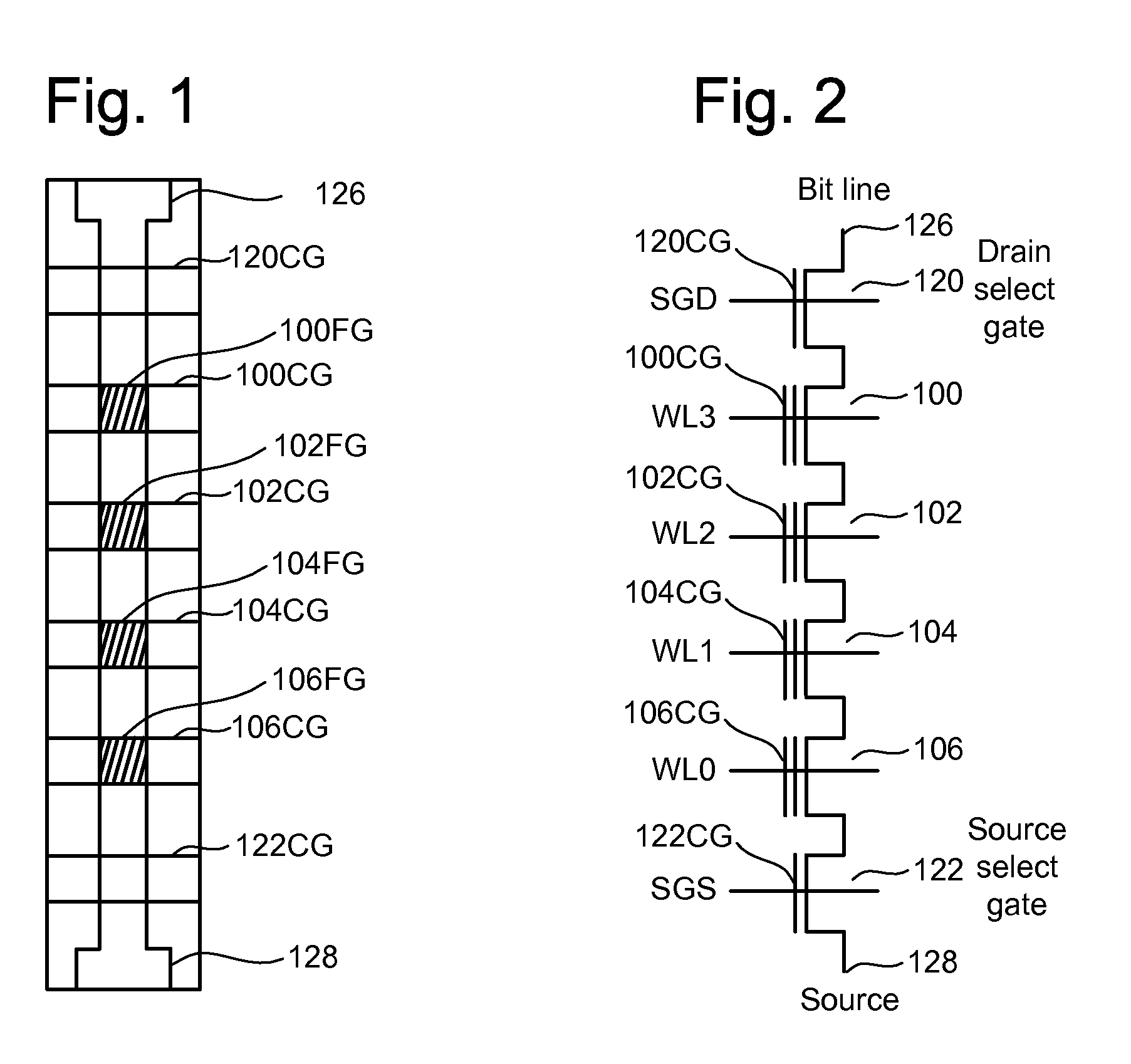

Probabilistic error correction in multi-bit-per-cell flash memory

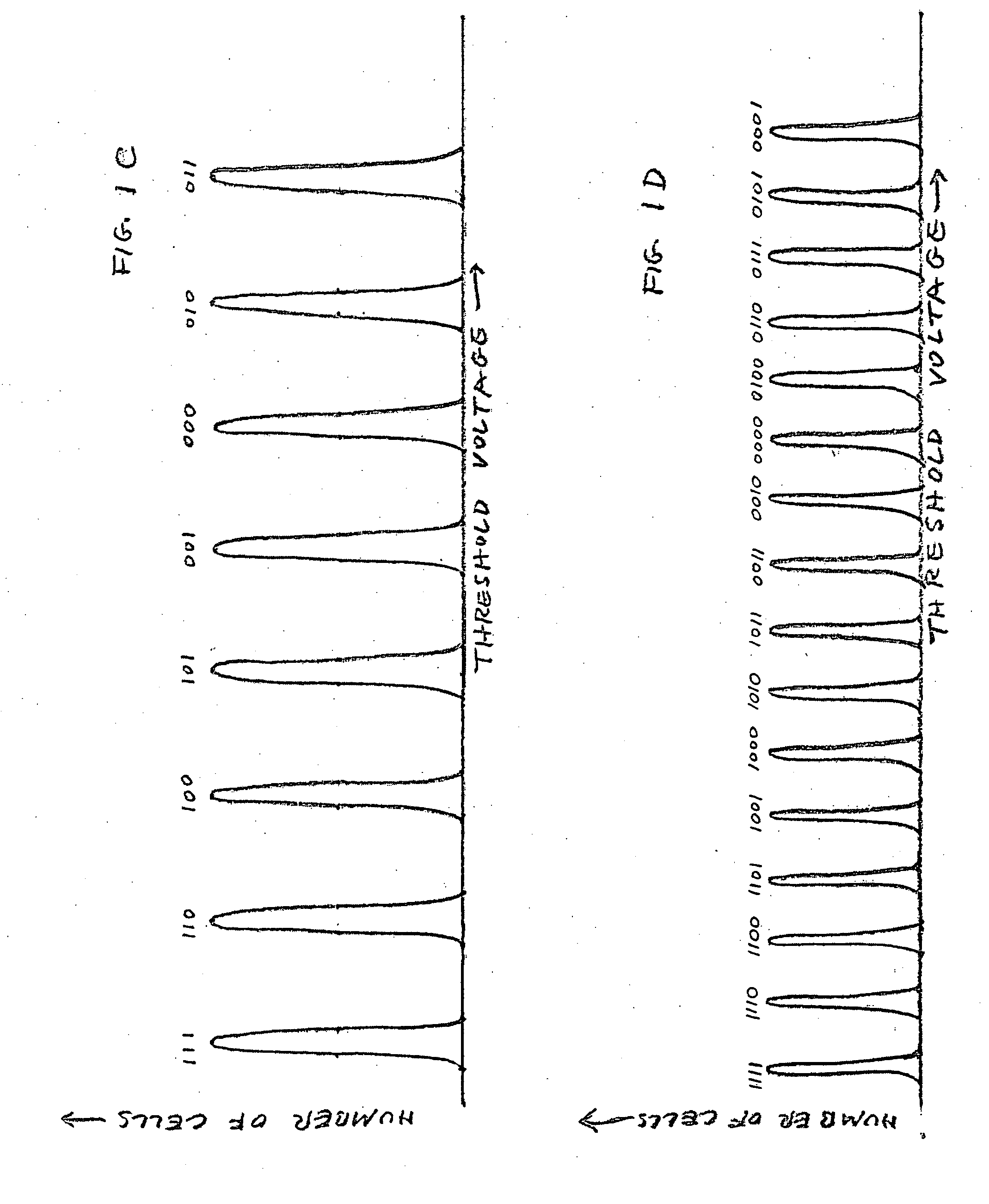

InactiveUS20070086239A1Other decoding techniquesError detection/correctionComputer scienceCell memory

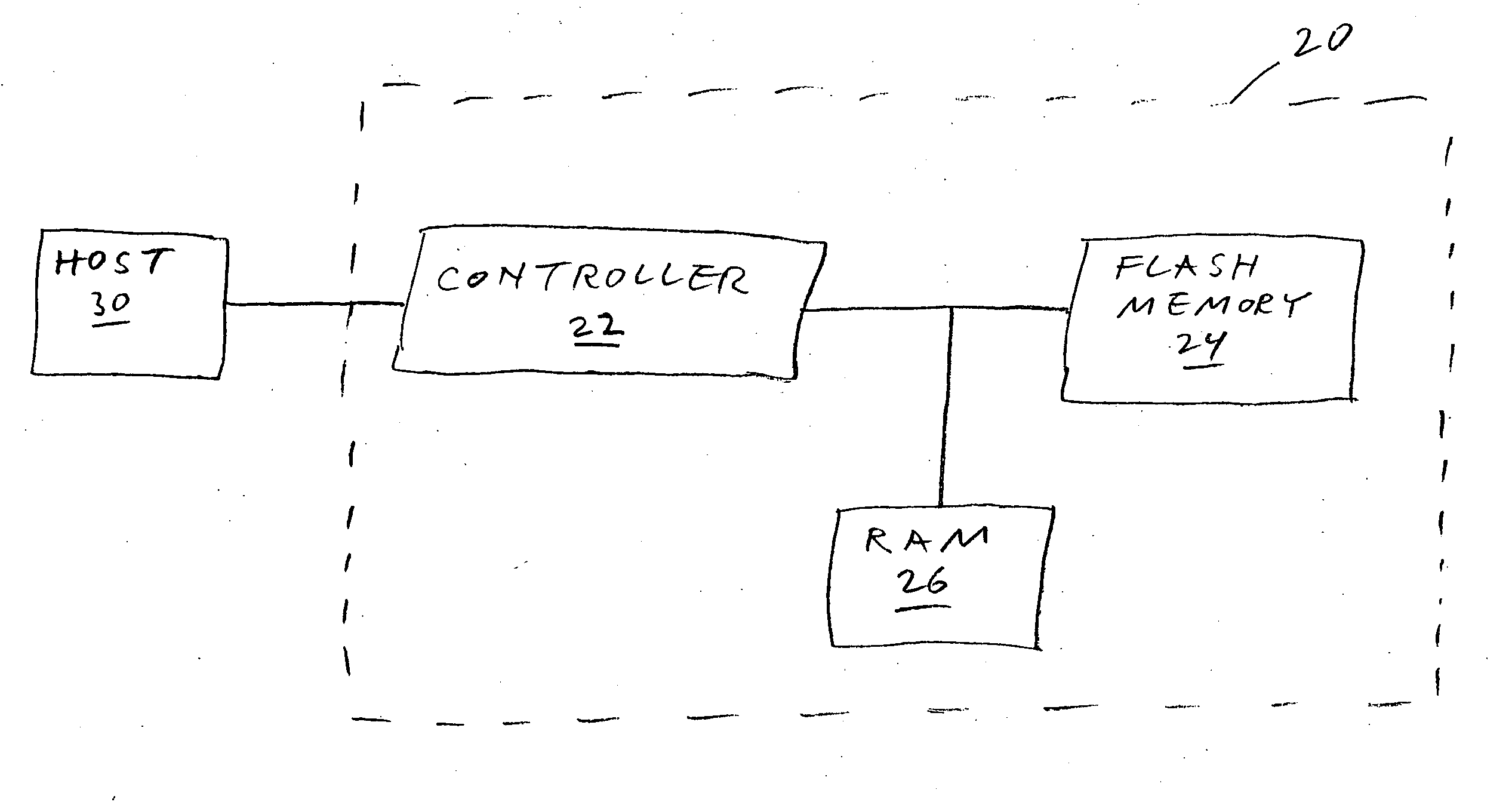

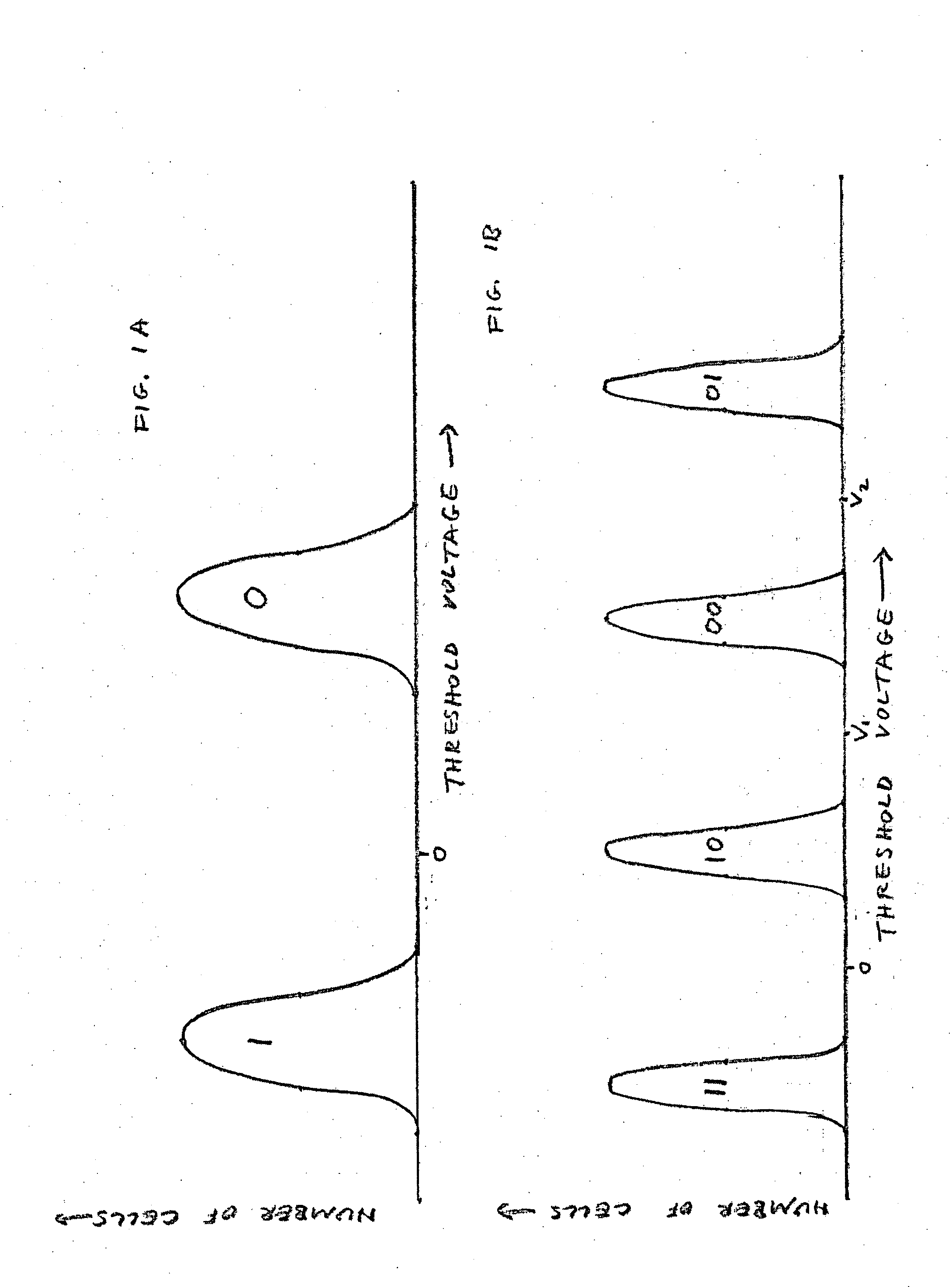

Data that are stored in cells of a multi-bit-per cell memory, according to a systematic or non-systematic ECC, are read and corrected (systematic ECC) or recovered (non-systematic ECC) in accordance with estimated probabilities that one or more of the read bits are erroneous. In one method of the present invention, the estimates are a priori. In another method of the present invention, the estimates are based only on aspects of the read bits that include significances or bit pages of the read bits. In a third method of the present invention, the estimates are based only on values of the read bits. Not all the estimates are equal.

Owner:RAMOT AT TEL AVIV UNIV LTD

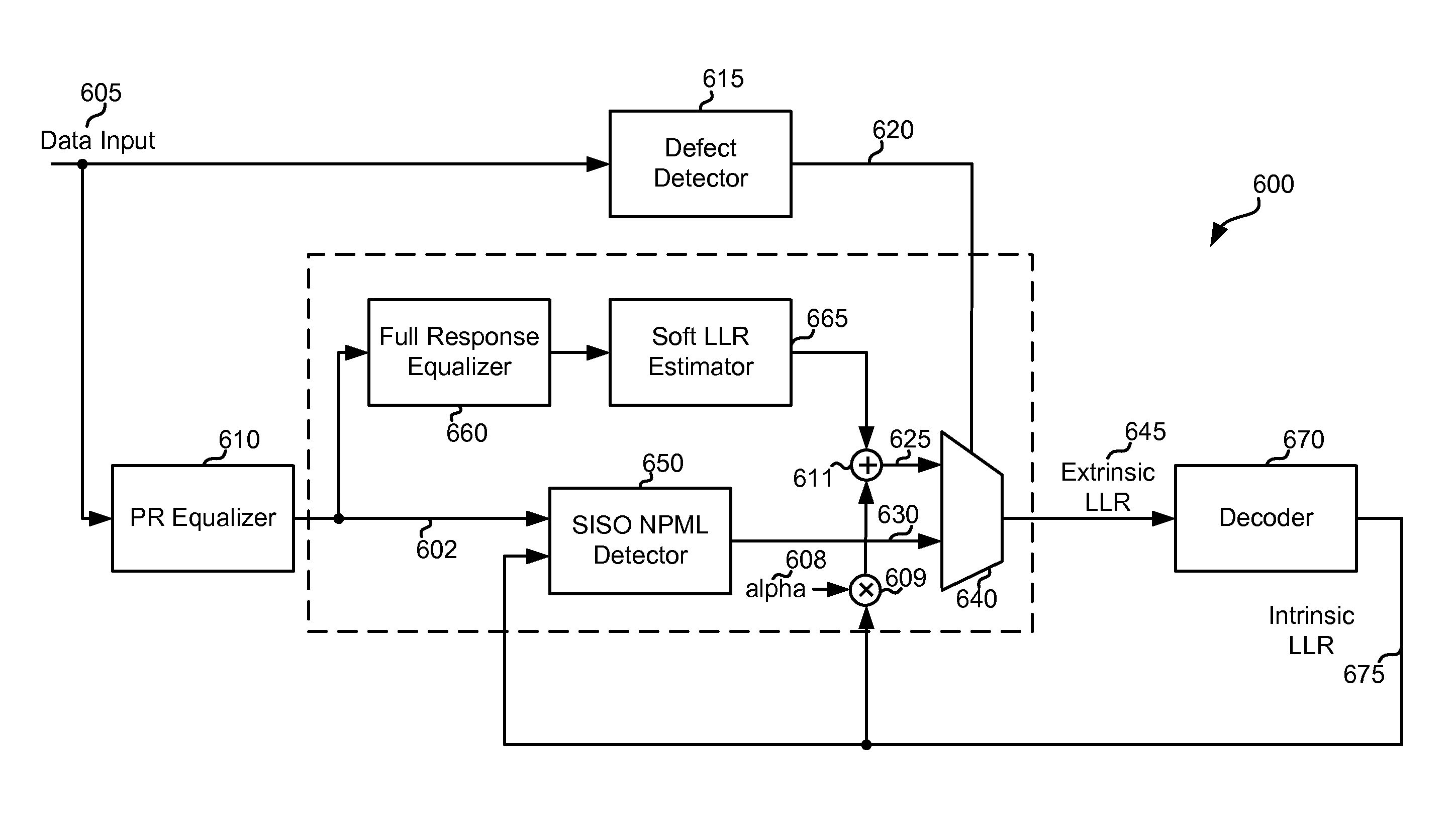

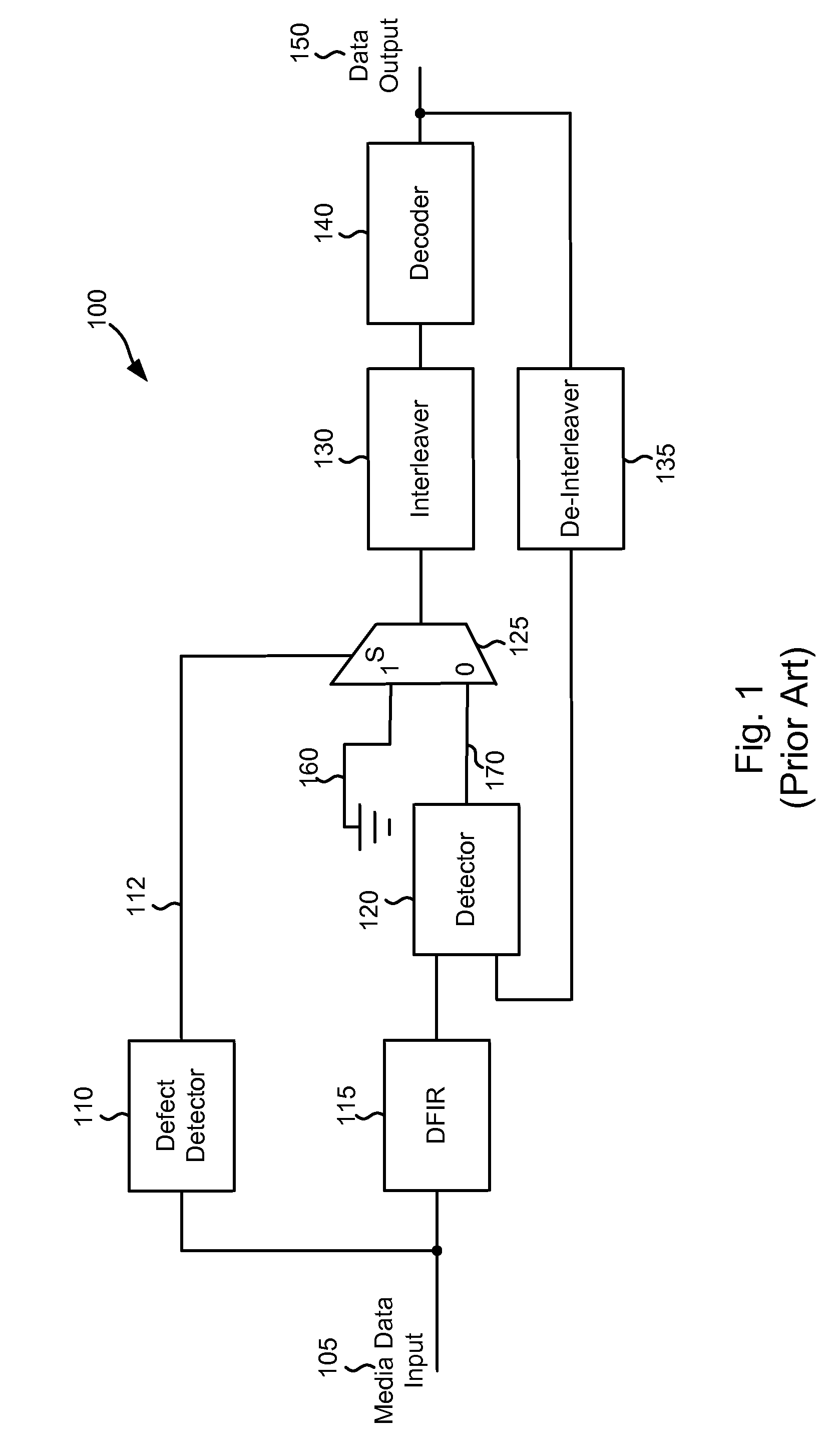

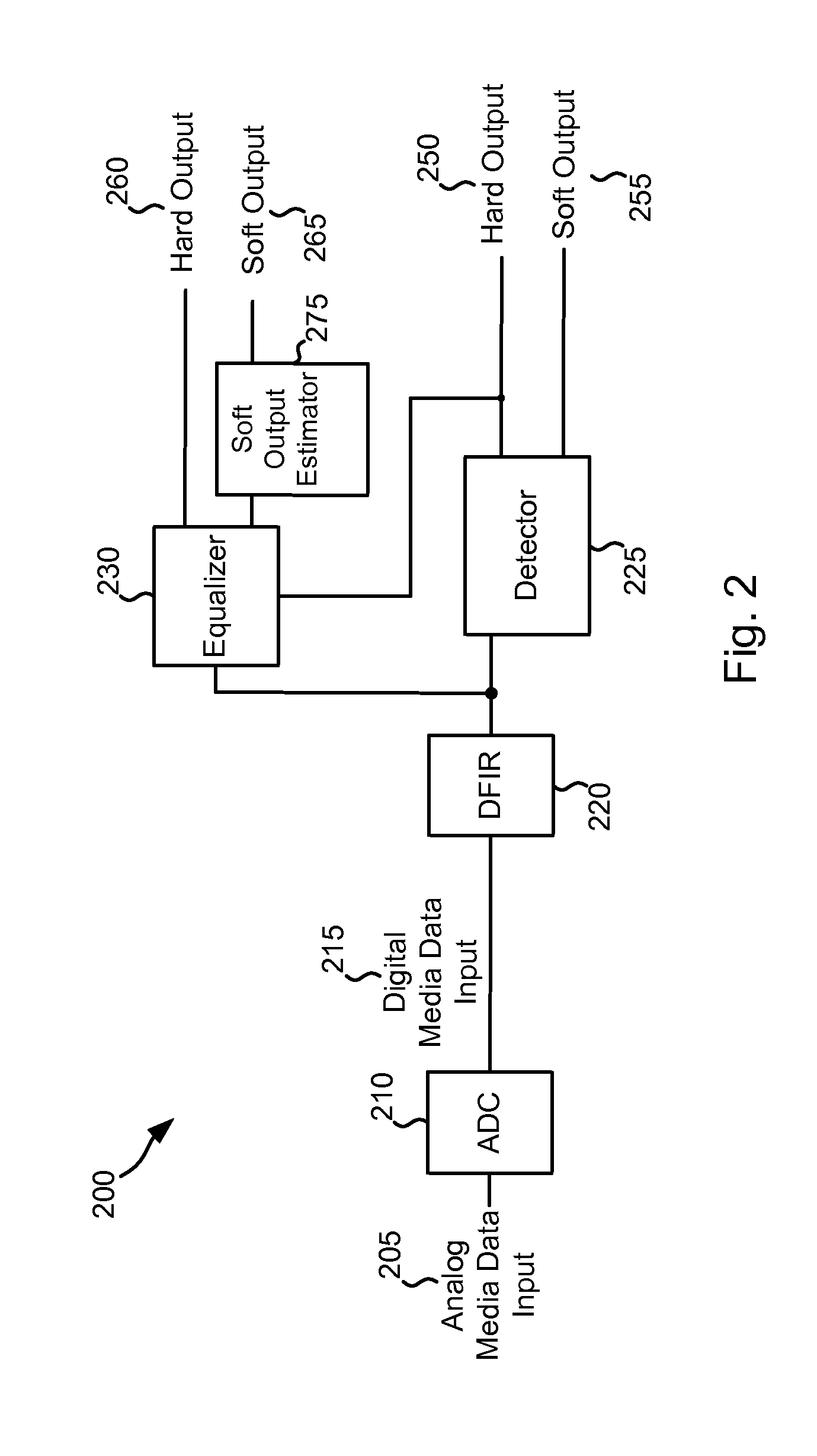

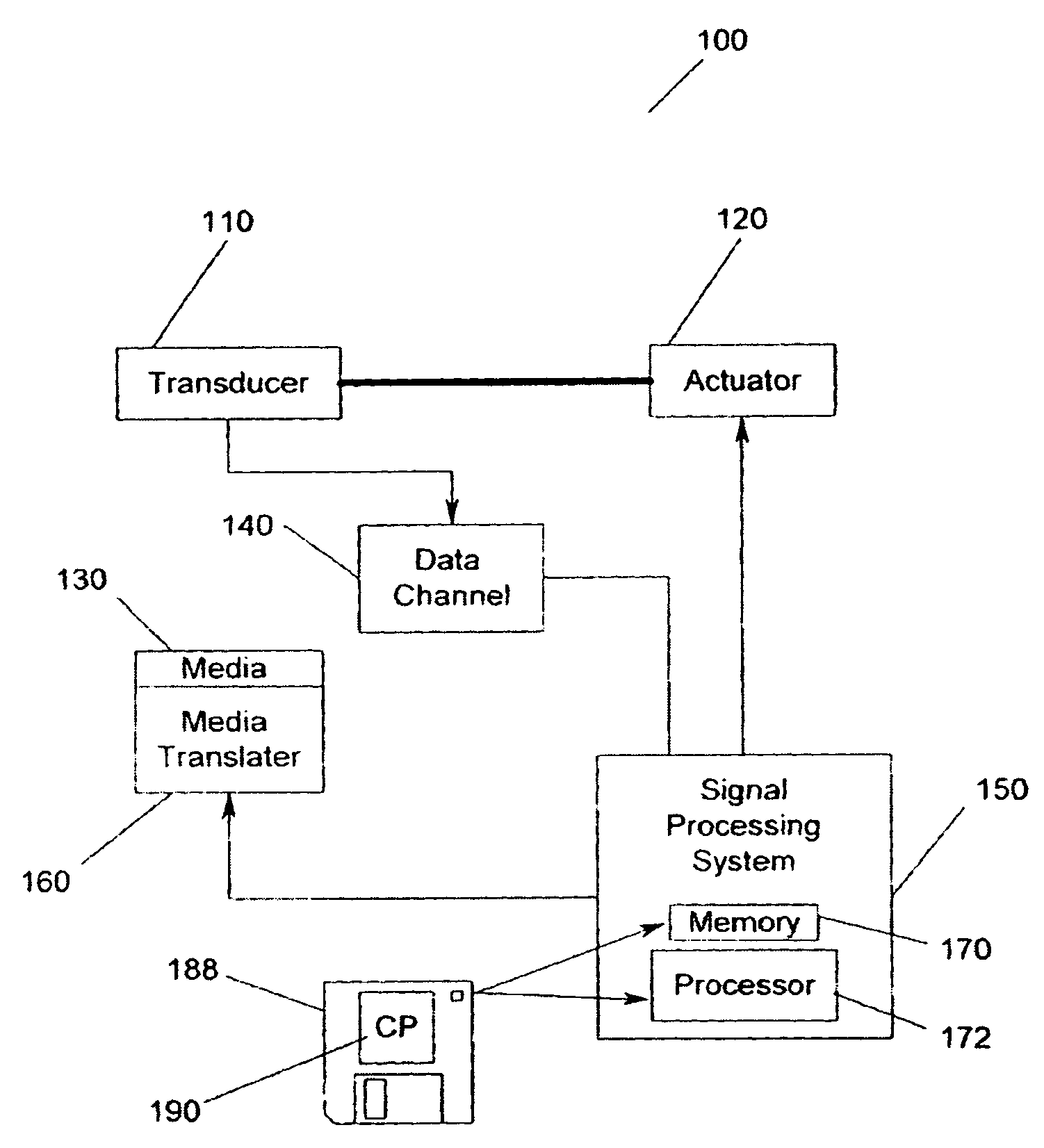

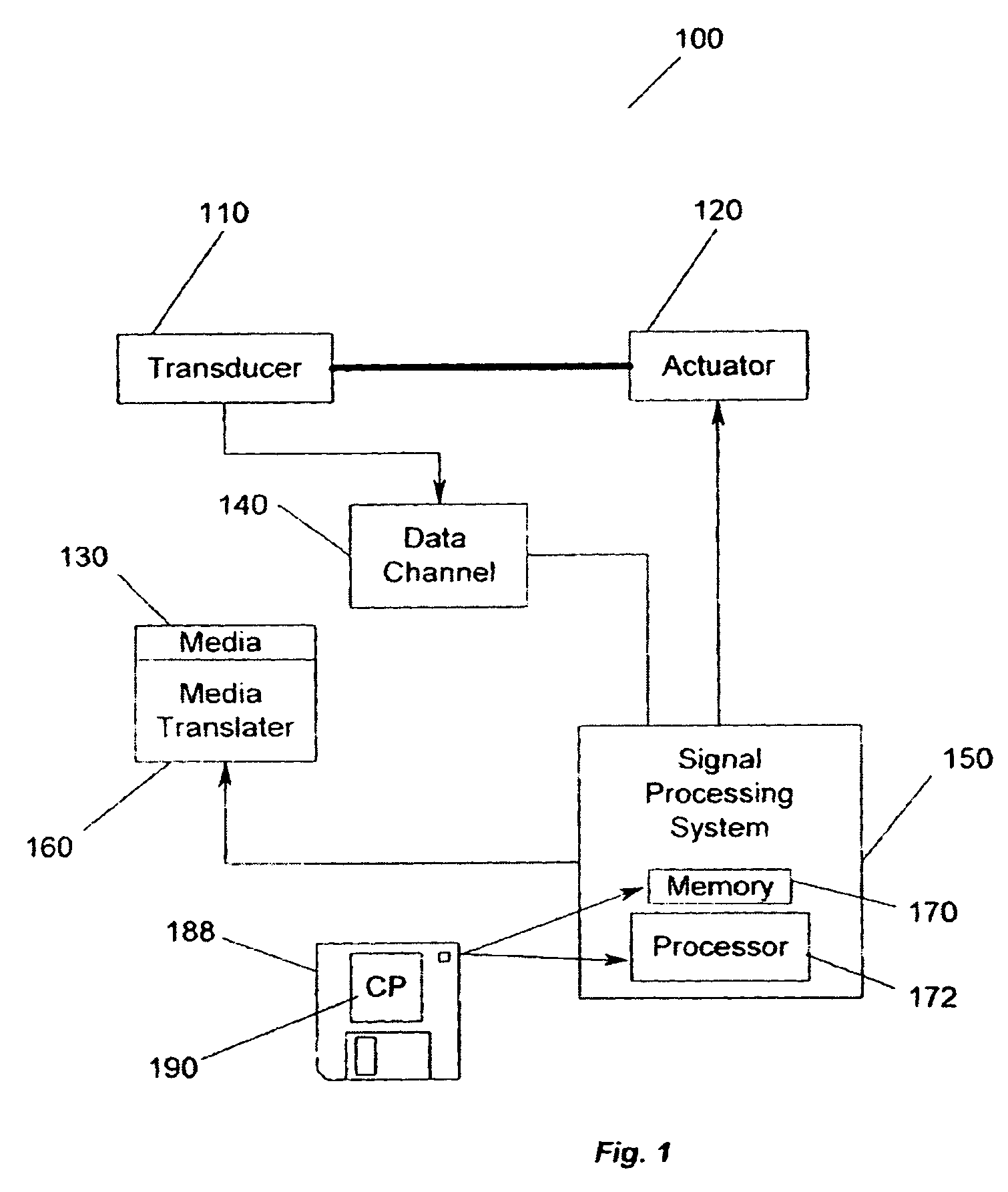

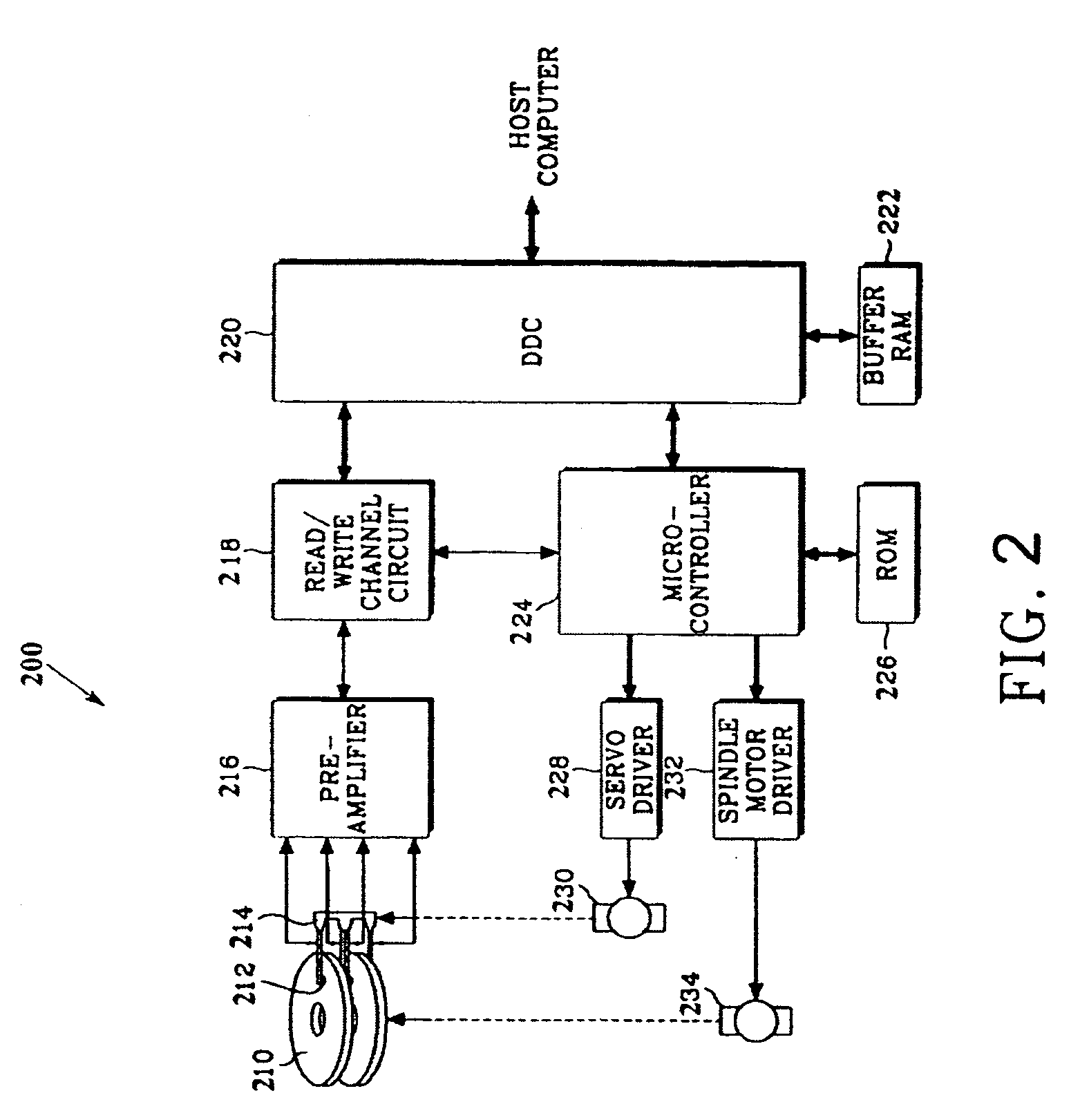

Systems and Methods for Using Intrinsic Data for Regenerating Data from a Defective Medium

ActiveUS20090235146A1Error prevention/detection by using return channelData representation error detection/correctionMultiplexerData recovery

Various embodiments of the present invention provide systems and methods for data regeneration. For example, a system for data regeneration is disclosed that includes a data input derived from the medium. A data detector and a data recovery system receive the data input. The data detector provides a first soft output, and the data recovery system provides a second soft output. The first soft output and the second soft output are provided to a multiplexer. A media defect detector performs a media defect detection process, and provides a defect flag that indicates whether the data input is derived form a defective portion of the medium. The defect flag is provided to the multiplexer where it is used to select whether the first soft output or the second soft output is provides as an extrinsic output.

Owner:AVAGO TECH INT SALES PTE LTD

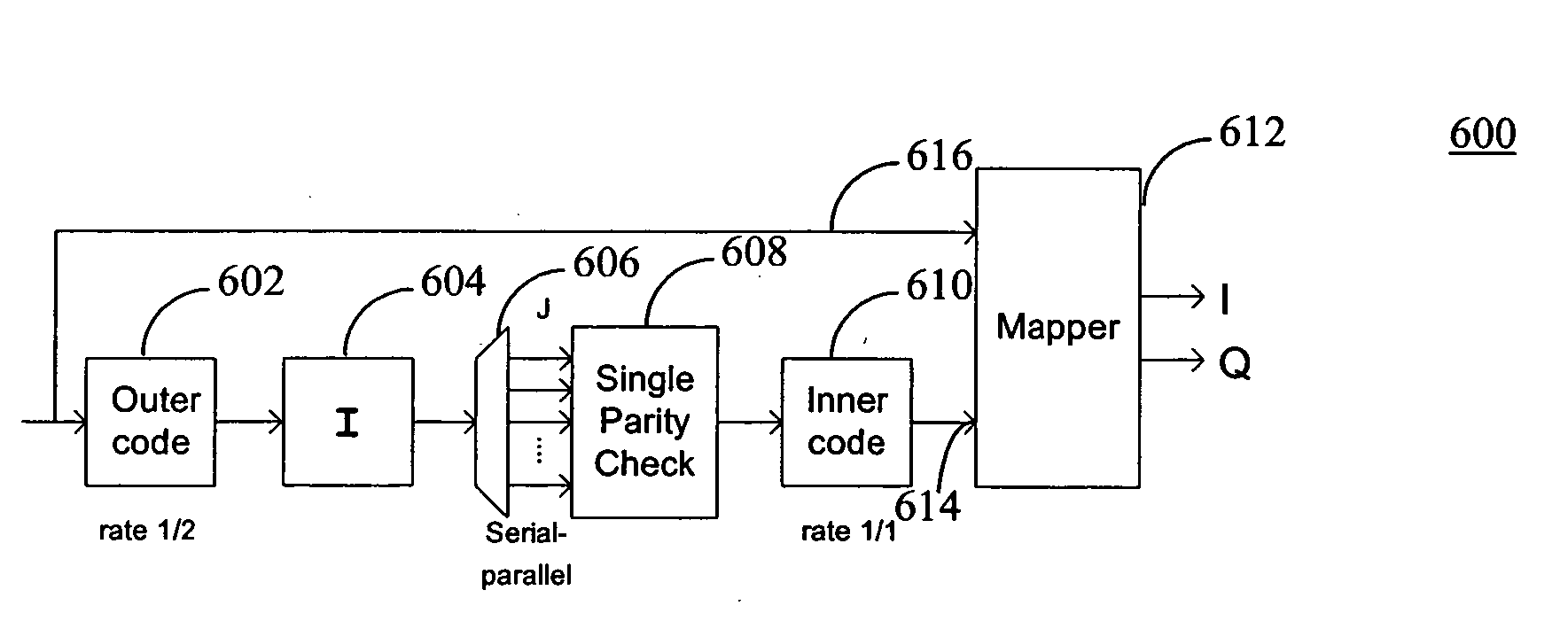

Method and apparatus for communications using turbo like codes

The present invention relates to methods, apparatuses, and systems for performing data encoding involving encoding data bits according to an outer convolutional code to produce outer encoded bits processing the outer encoded bits using an interleaver and a logical unit to produce intermediate bits, wherein the logical unit receives a first number of input bits and produces a second number of corresponding output bits, the second number being less than the first number, and wherein the logical unit takes each of the first number of input bits into account in producing the second number of output bits, encoding the intermediate bits according to an inner convolutional code to produce inner encoded bits, wherein the inner convolutional code is characterized by at least two states, and combining the data bits and the inner encoded bits to produce encoded outputs.

Owner:TRELLIS WARE TECH

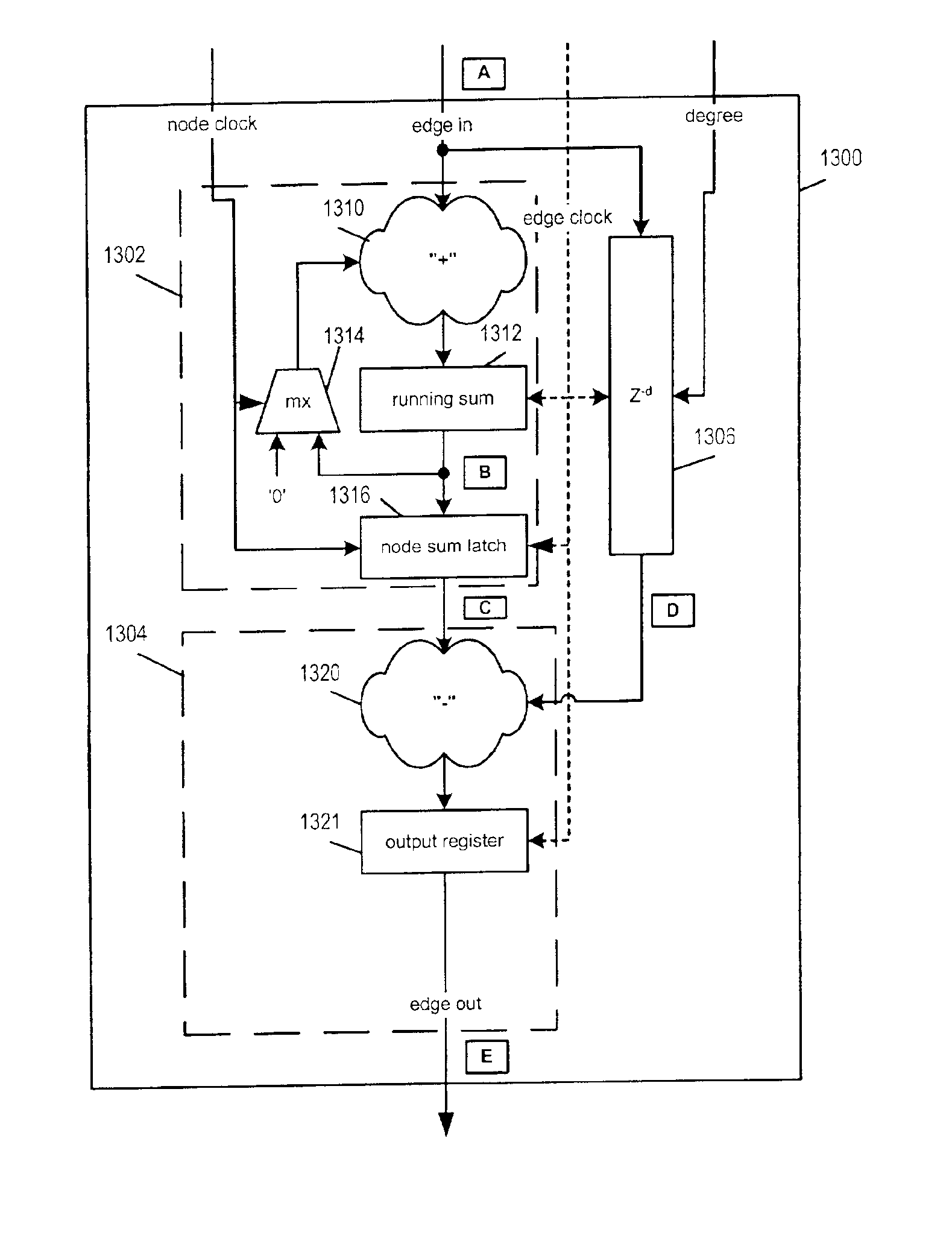

Node processors for use in parity check decoders

InactiveUS6938196B2Big errorCompensating for such errorError prevention/detection by using return channelOther decoding techniquesComputer moduleMessage processing

Techniques for implementing message passing decoders, e.g., LDPC decoders, are described. To facilitate hardware implementation messages are quantized to integer multiples of ½ ln2. Messages are transformed between more compact variable and less compact constraint node message representation formats. The variable node message format allows variable node message operations to be performed through simple additions and subtractions while the constraint node representation allows constraint node message processing to be performed through simple additions and subtractions. Variable and constraint nodes are implemented using an accumulator module, subtractor module and delay pipeline. The accumulator module generates an accumulated message sum. The accumulated message sum for a node is stored and then delayed input messages from the delay pipeline are subtracted there from to generate output messages. The delay pipeline includes a variable delay element making it possible to sequentially perform processing operations corresponding to nodes of different degrees.

Owner:QUALCOMM INC

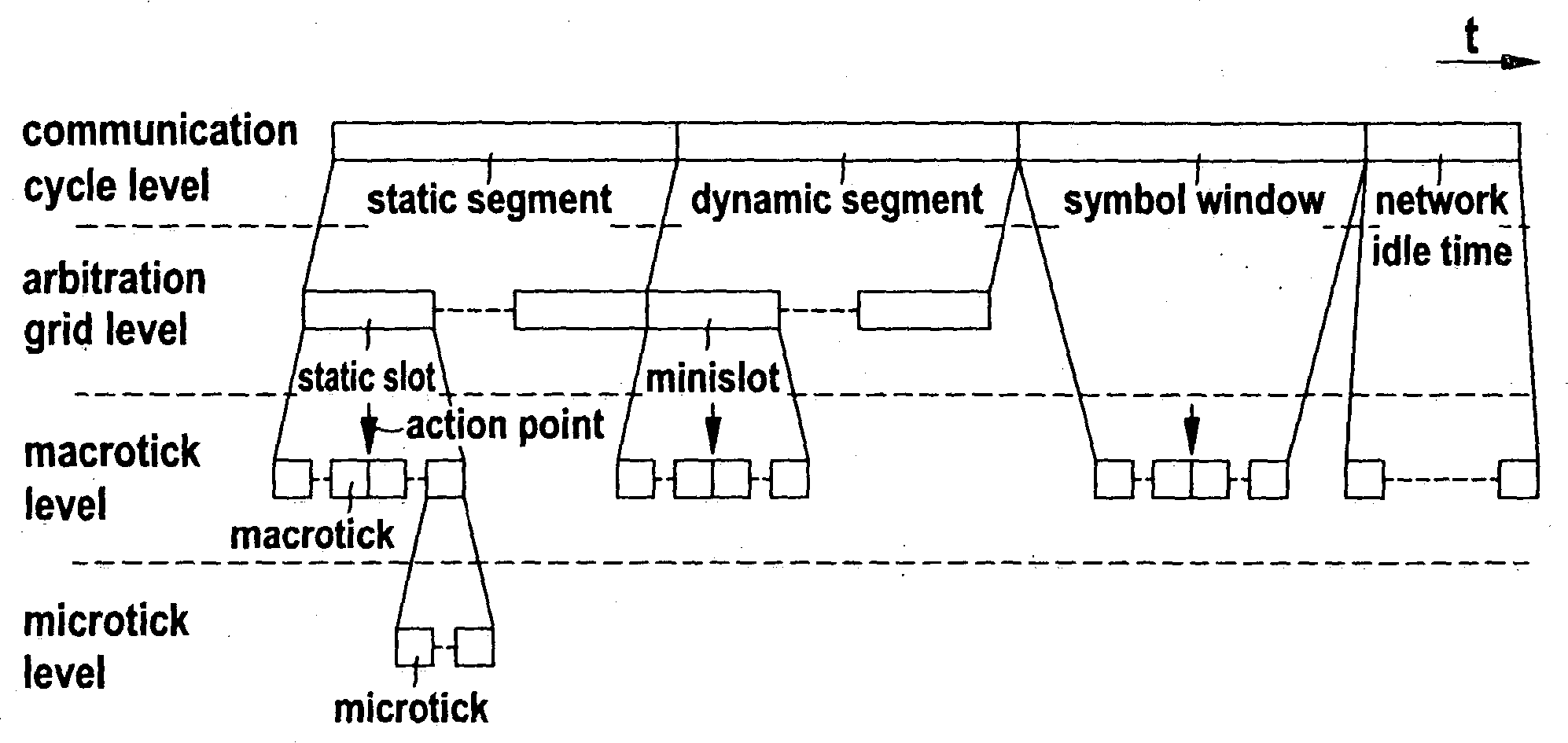

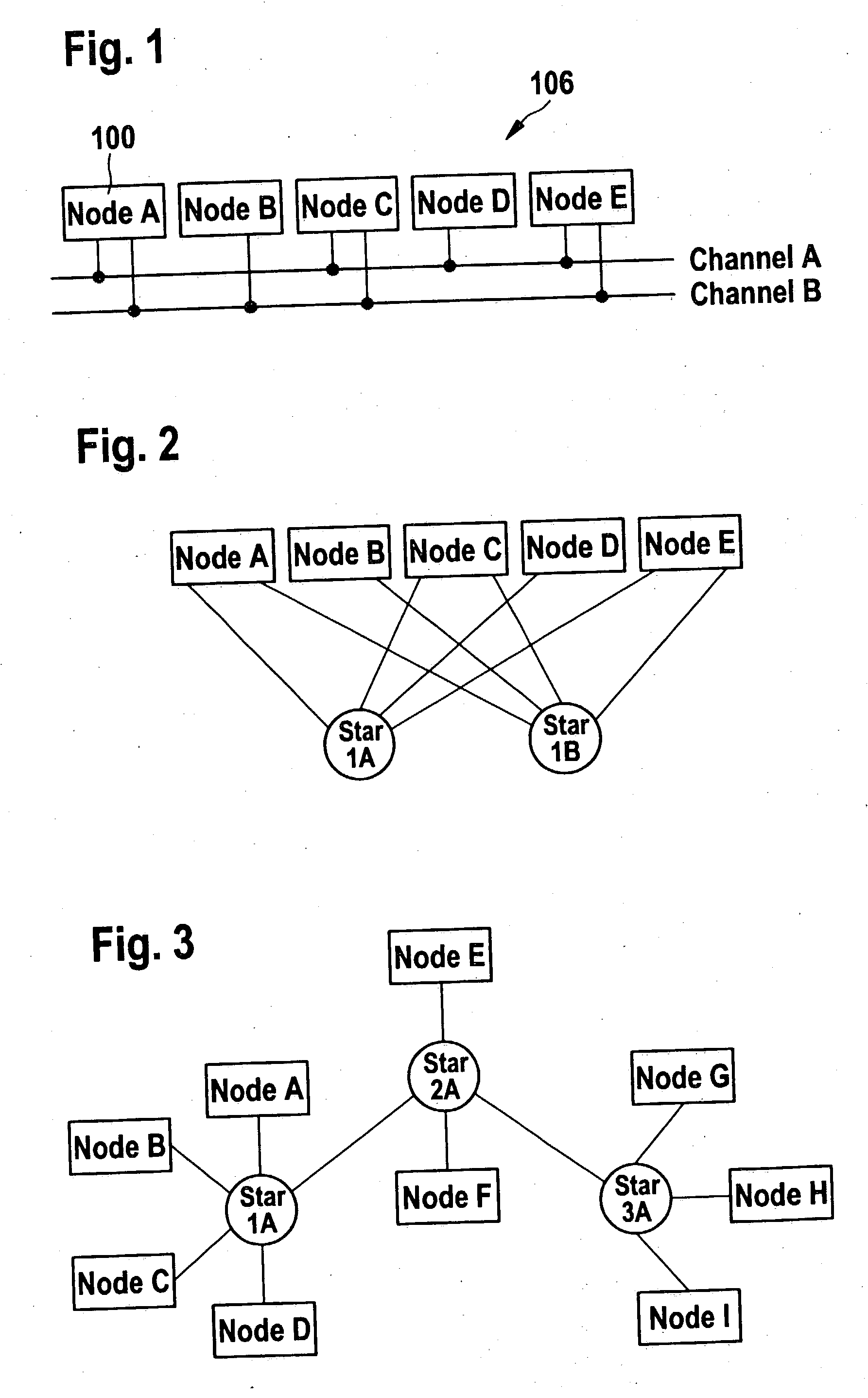

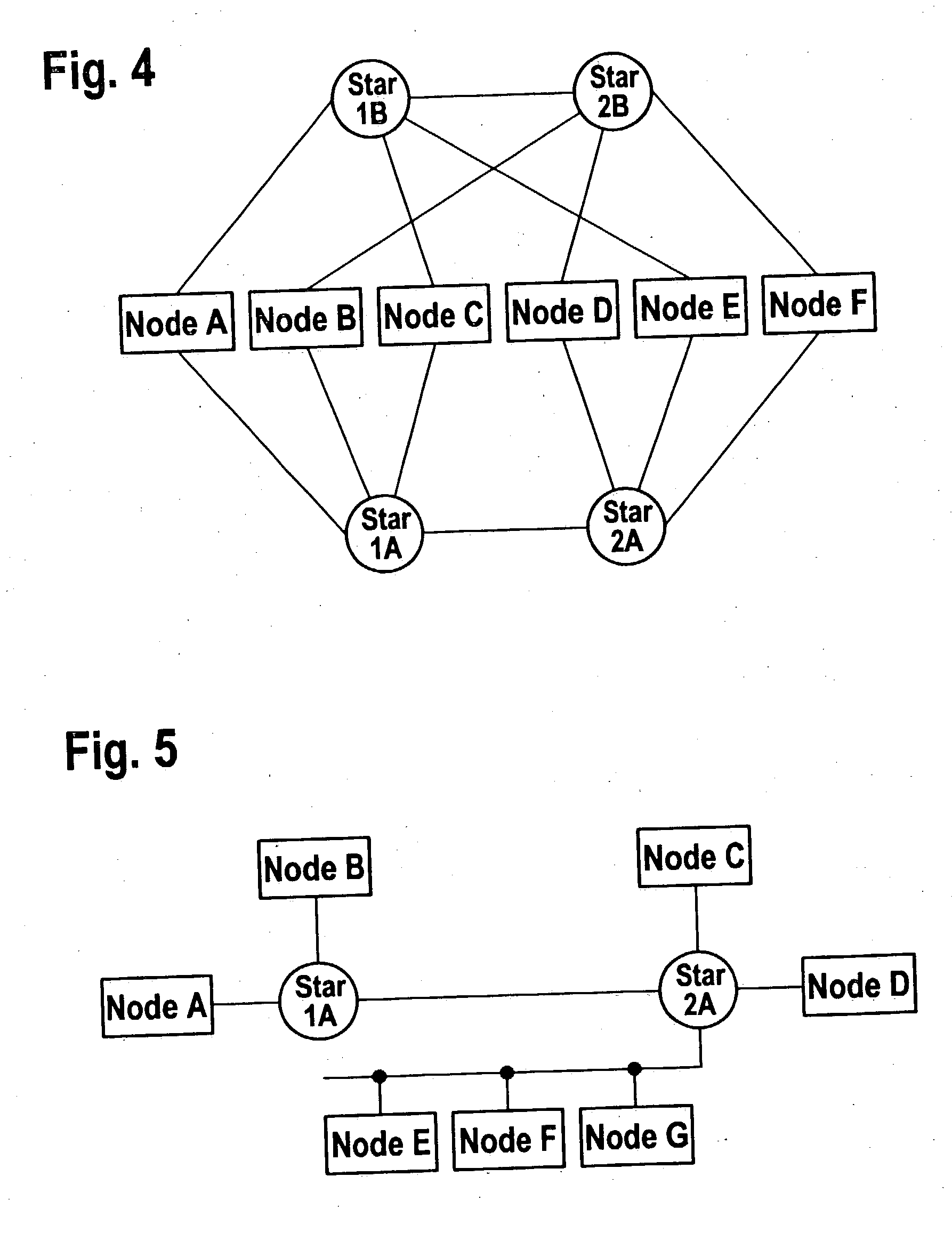

Method for synchronizing clocks in a distributed communication system

InactiveUS20050141565A1Achievable accuracyImprove accuracyOther decoding techniquesTime-division multiplexControl communicationsCommunication control

The invention refers to one of a number of nodes of a communication system. The nodes are connected to a communication media for transmitting data among the nodes. Said one node comprises a communication controller, across which the node is connected to the communication media, and a bus guardian for controlling access of the communication controller to the communication media. In order to provide a cheap but nevertheless reliable way for monitoring the synchronized clock signal of a node of a communication system and in particular for detecting deviations of the synchronized clock signal it is suggested that a synchronized clock signal from the communication controller is made available to the bus guardian, and that the bus guardian comprises means for monitoring the synchronized clock signal using a bus guardian internal clock signal, which is generated by means of an electronic circuit and which is less accurate than the synchronized clock signal to be monitored.

Owner:MOTOROLA INC +5

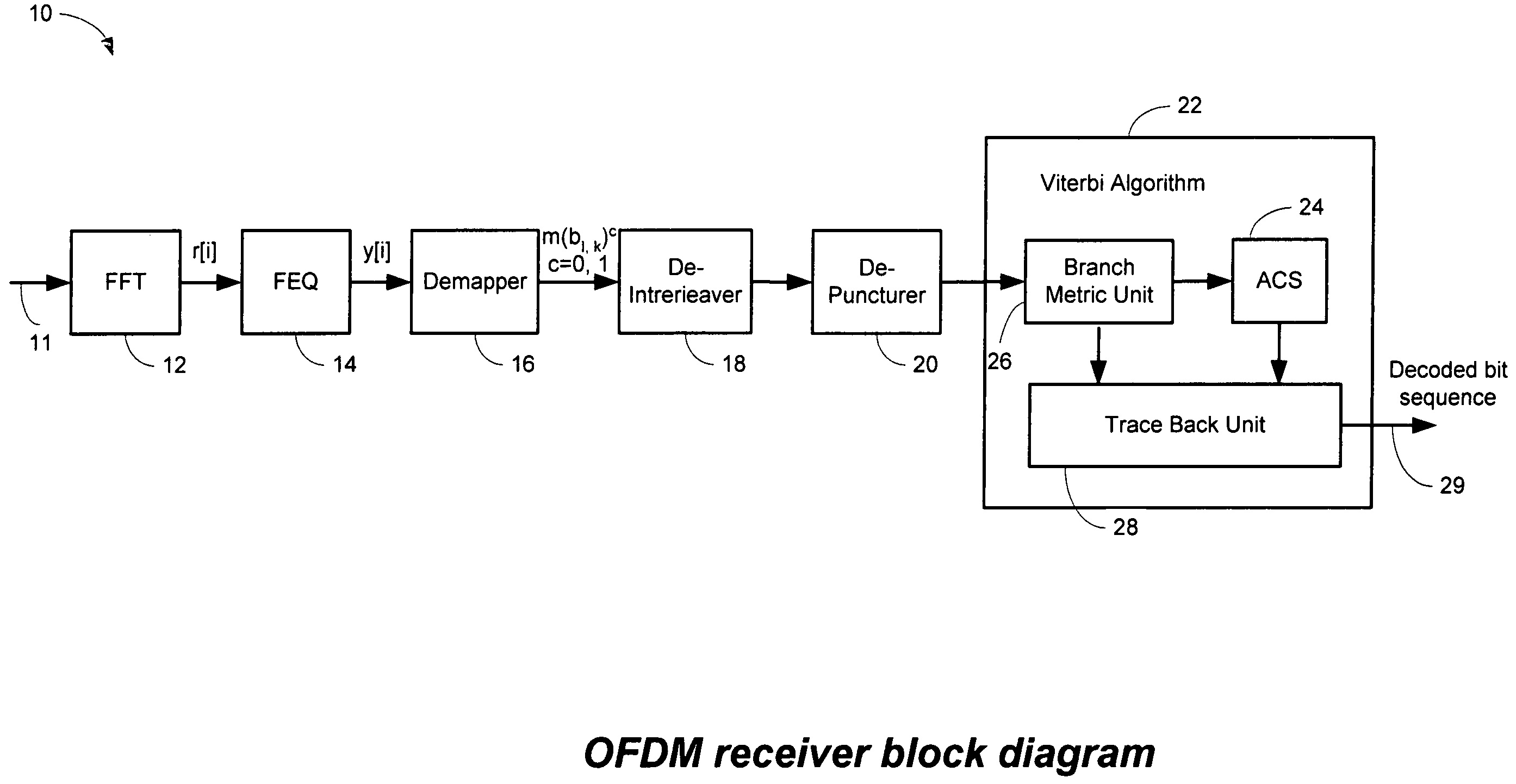

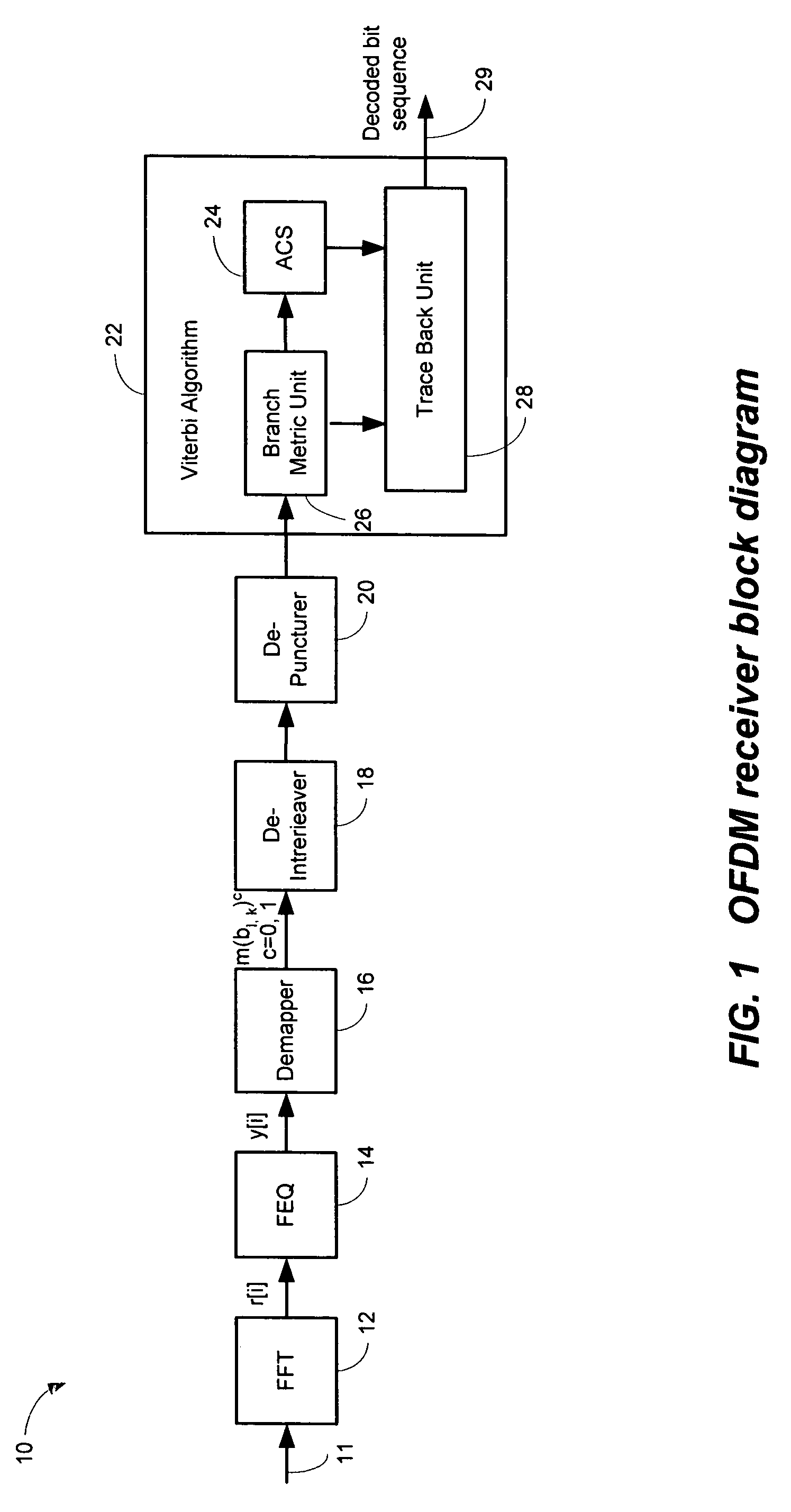

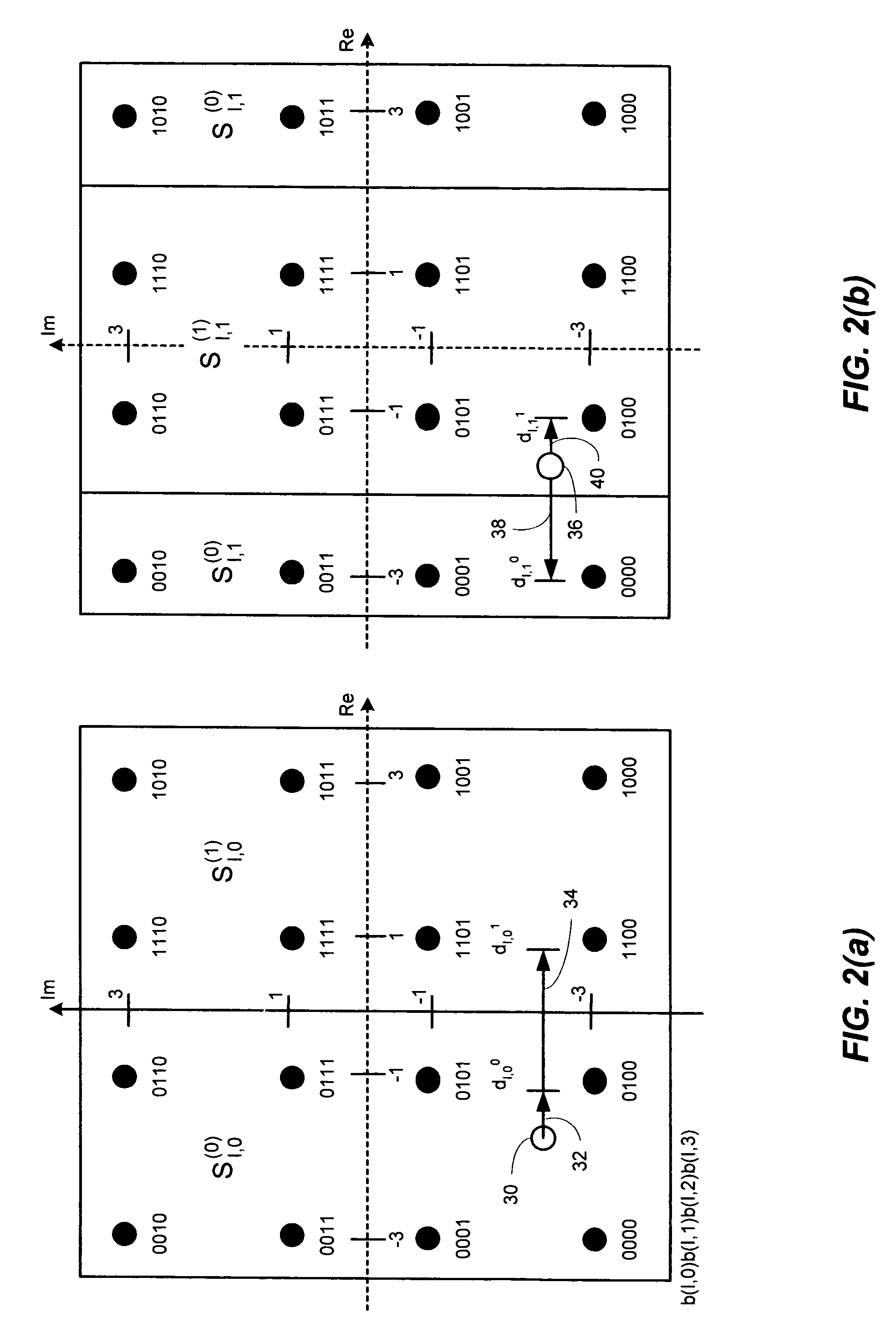

Efficient soft decision demapper to minimize viterbi decoder complexity

InactiveUS7313750B1Improve performanceSmall sizeData representation error detection/correctionOther decoding techniquesViterbi decoderComputer science

A receiver system that receives signals and has a demapper device that is responsive to an equalizer output and generates a demapper output including one or more bit metrics. The receiver system also generates equalizer output, and the demapper uses distance measure to calculate bit metrics. The receiver system uses demapper output to generate a processed output. The receiver system further includes a convolutional decoder which is responsive to the processed output, and subsequently generates a decoded bit sequence, as well as uses the processed output to generate one or more path metrics. The convolutional decoder uses bit metrics and path metrics to the decode processed output, to generate a decoded bit sequence. The receiver system uses the distance measure to reduce the size of the bit metrics and the size of the path metrics to improve the performance of said convolutional decoder.

Owner:MEDIATEK INC

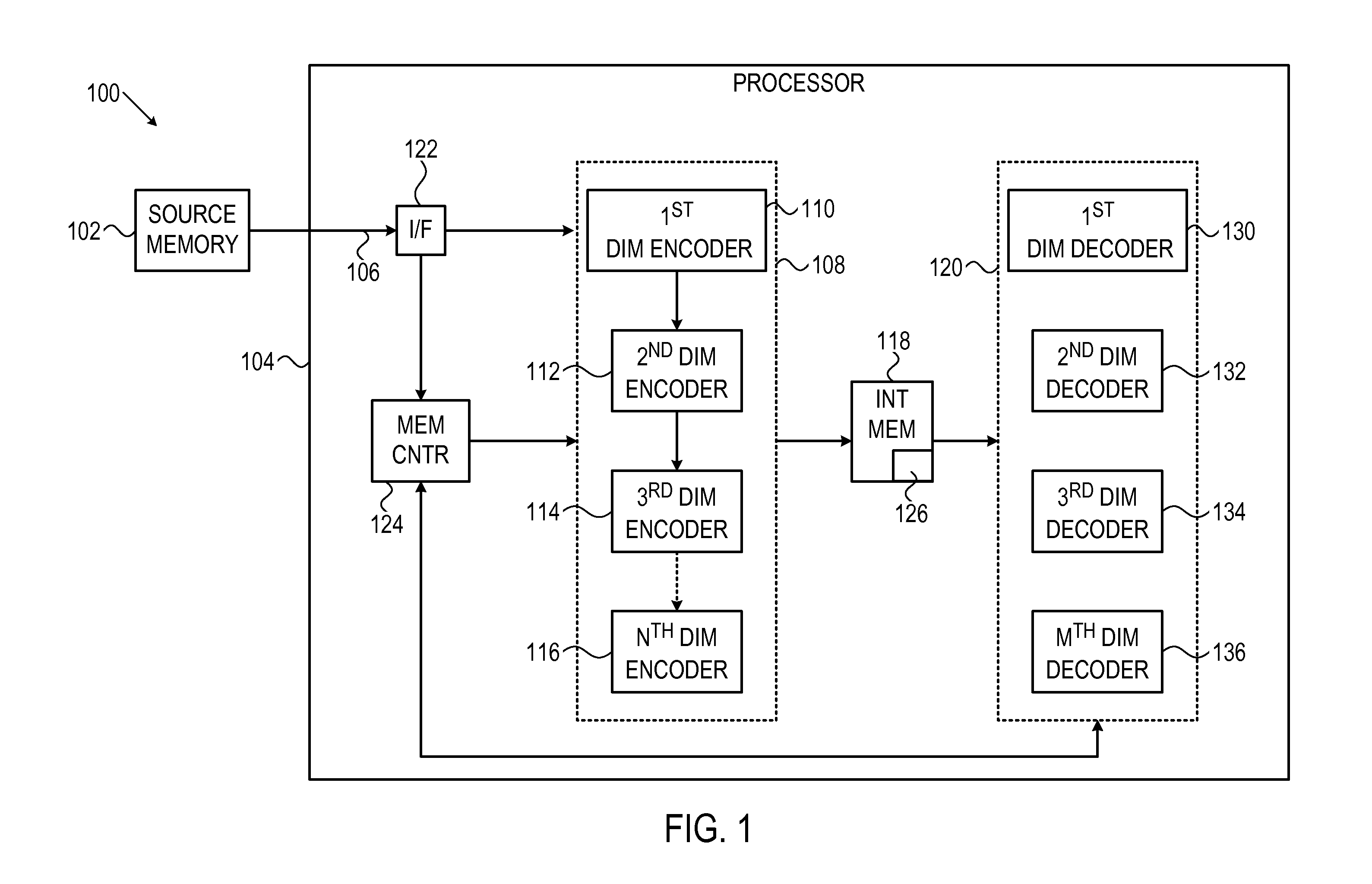

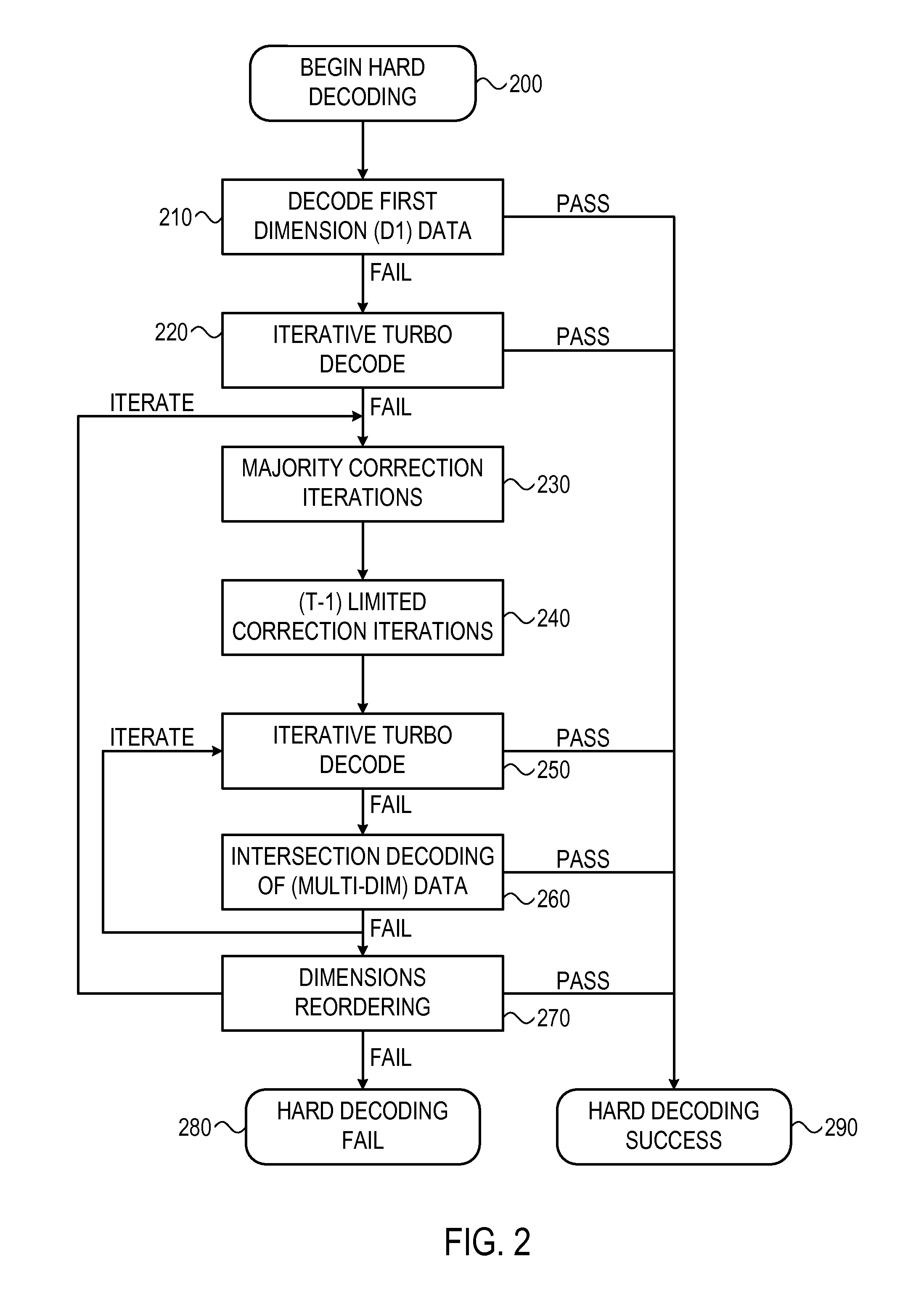

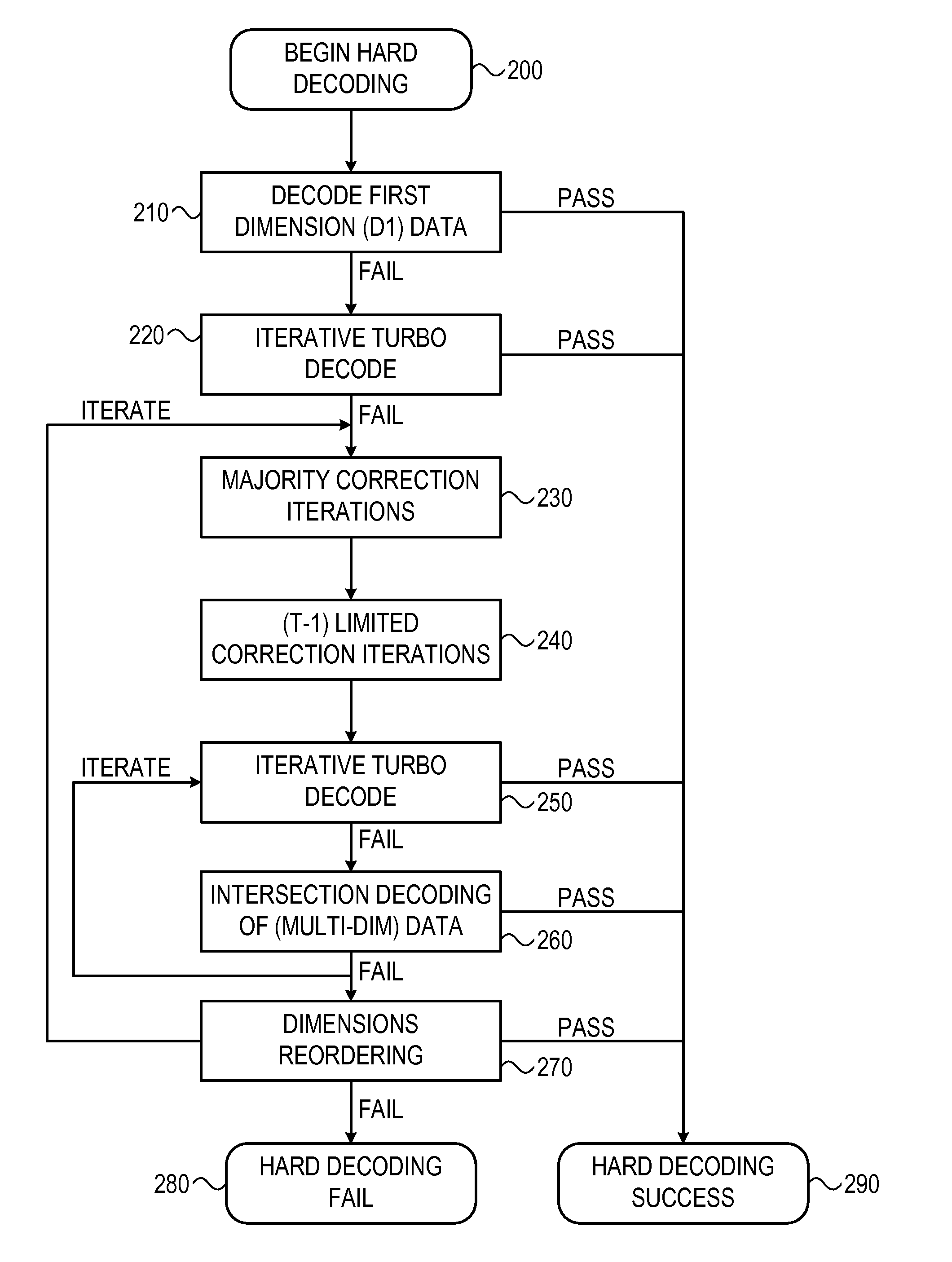

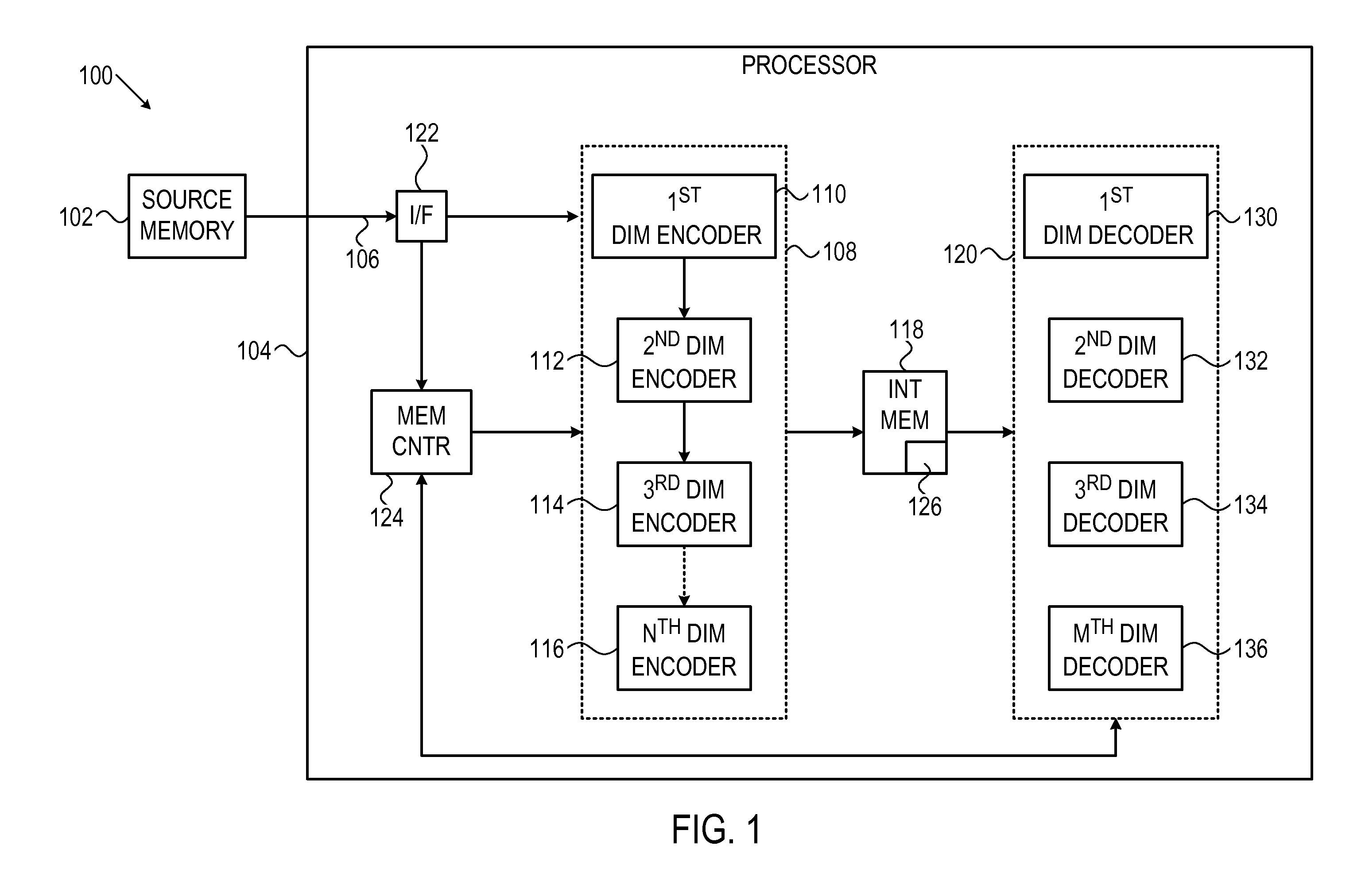

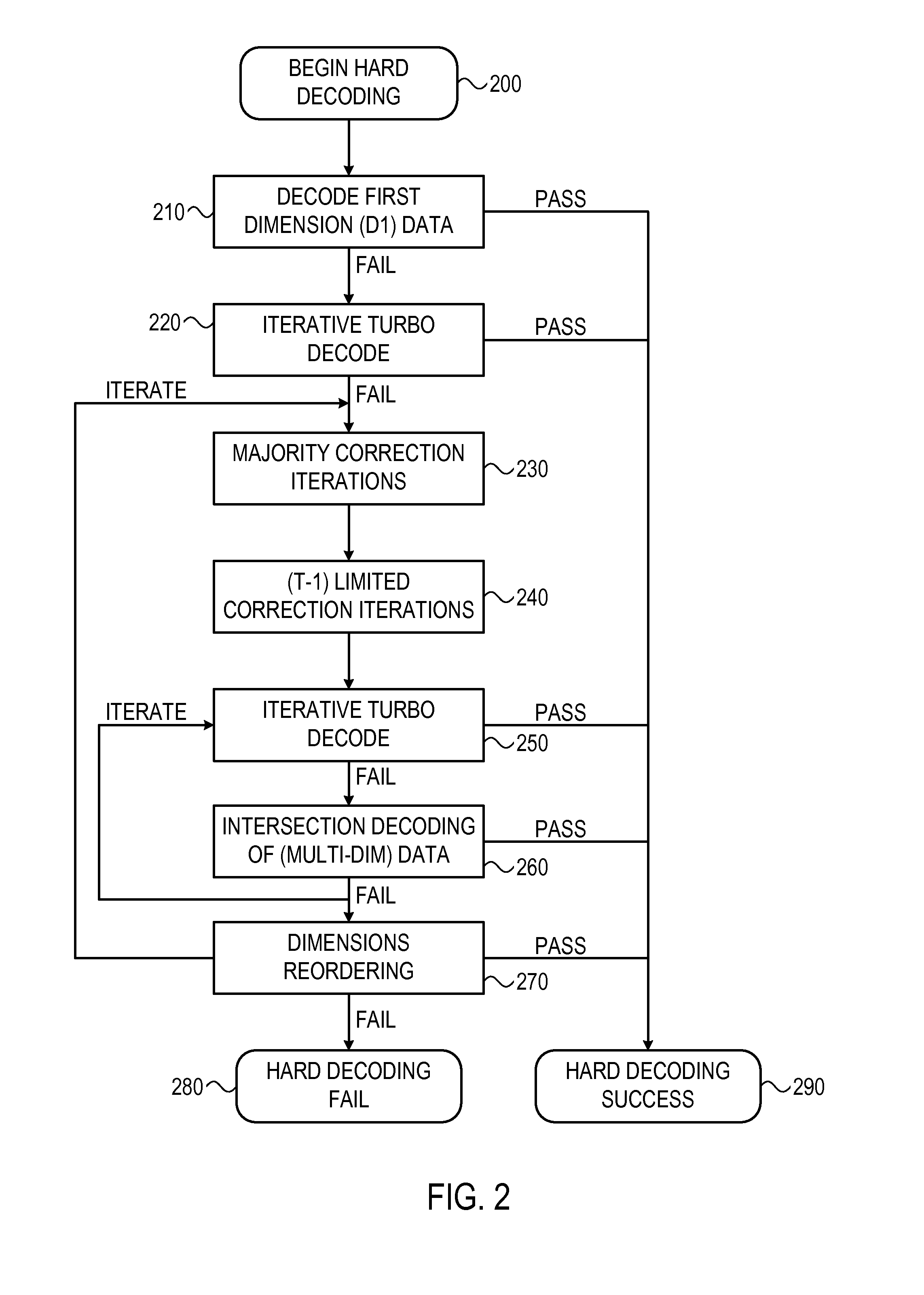

System and method for multi-dimensional encoding and decoding

ActiveUS20120005560A1Error correction/detection using convolutional codesOther decoding techniquesHypothesisDependability

A system and method is provided for decoding a set of bits using a plurality of hypotheses, for example, each independently tested on-the-fly. Initial bit states and associated reliability metrics may be received for the set of bits. A current hypothesis may be decoded for correcting the set of bits, wherein the current hypothesis defines different bit states and associated reliability metrics for the set of bits. If decoding the current hypothesis is not successful, a subsequently ordered hypothesis may be decoded, wherein the hypotheses are ordered such that their associated reliability metric is a monotonically non-decreasing sequence. Decoding may proceed iteratively until the current hypothesis is successful.

Owner:AVAGO TECH INT SALES PTE LTD

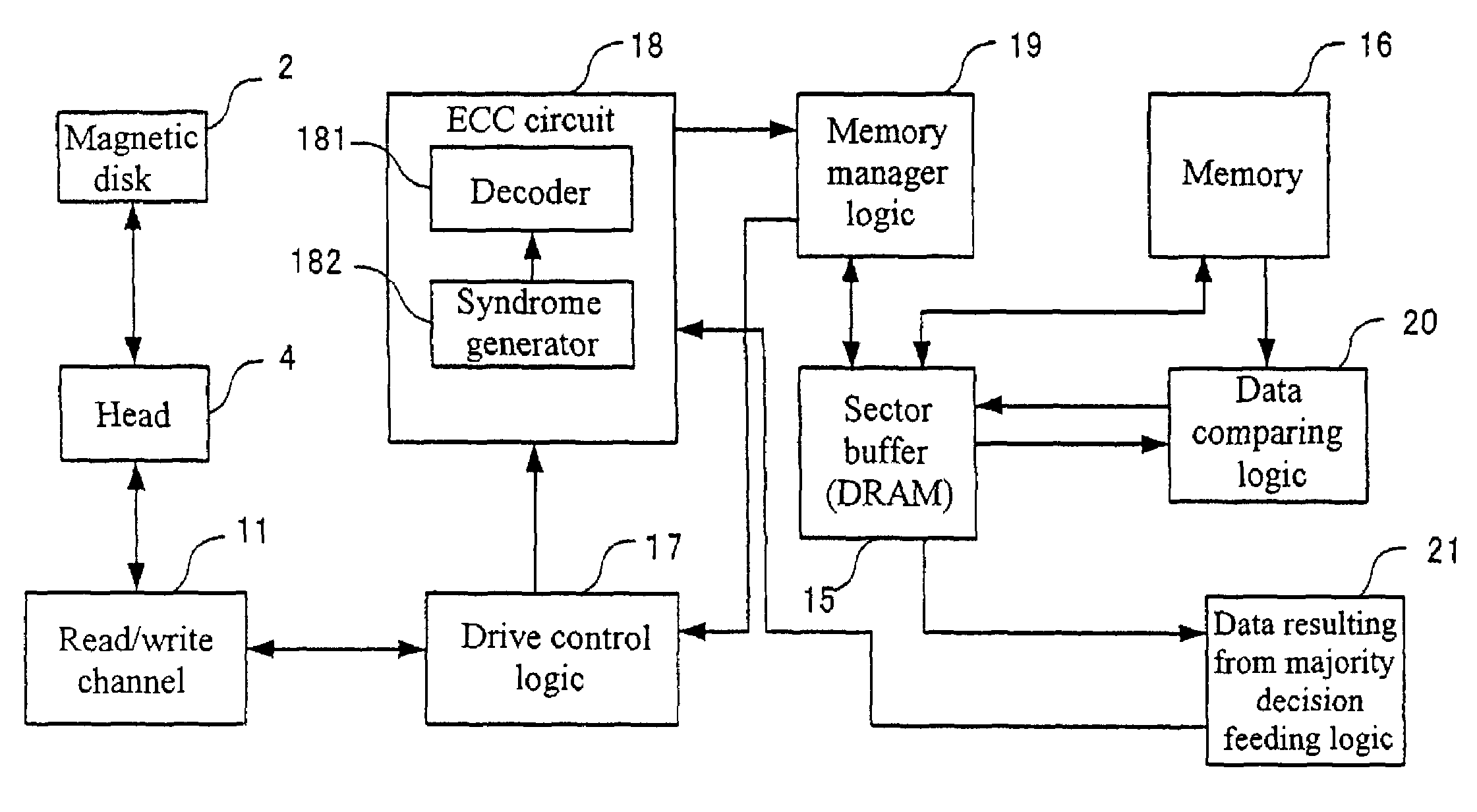

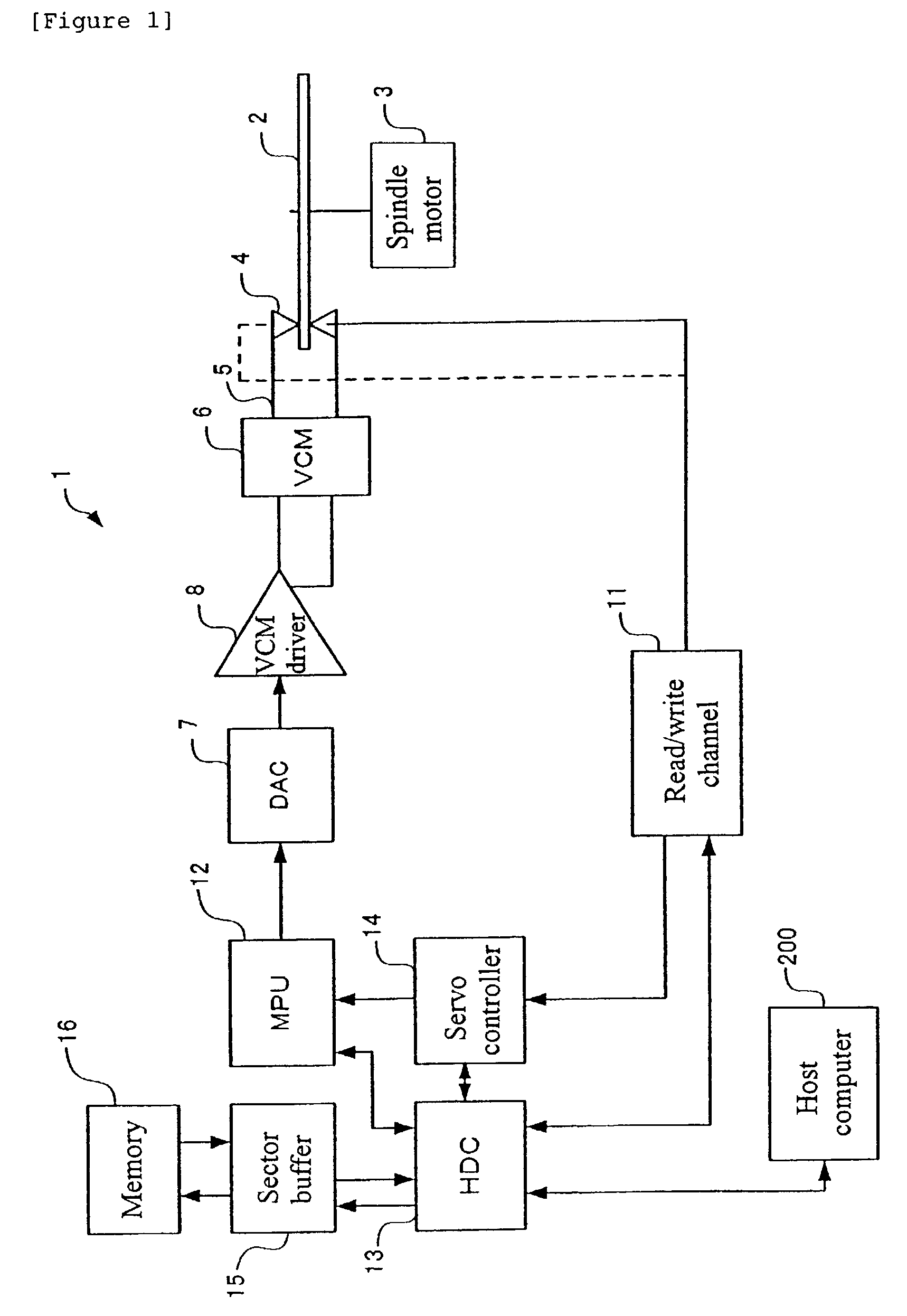

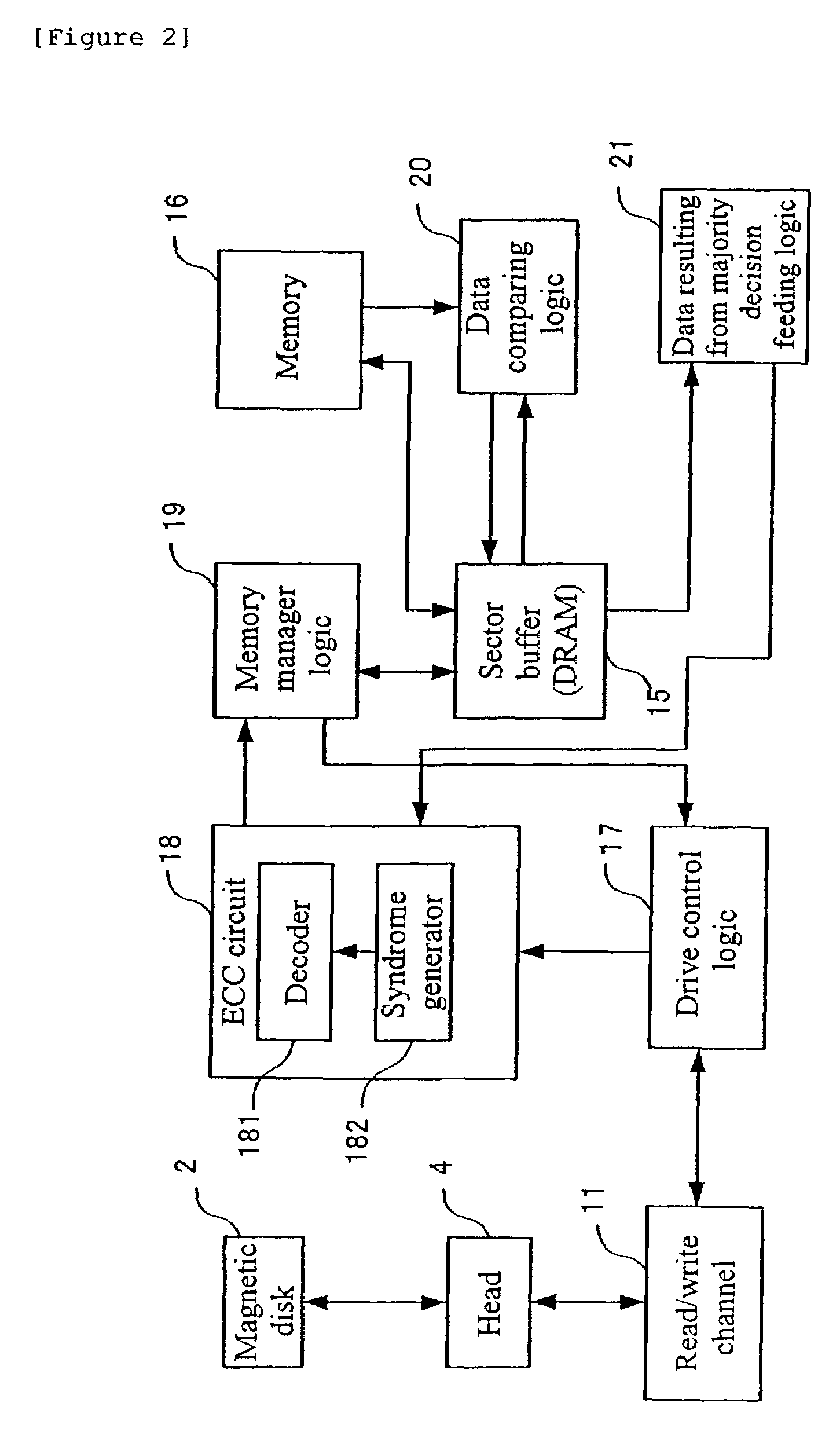

Data storage apparatus, read data processor, and read data processing method

ActiveUS6981205B2Improving error correcting probabilityIncrease probabilityInput/output to record carriersOther decoding techniquesComputer architectureData value

To improve the probability of error correction, thereby generating correct read data. Data is read from the same sector by a number of times and a majority decision is done in the same address, thereby the most frequently read value is regarded as the true data value in the address. For example, for an address 00, “00” is handled as a true data value.

Owner:LENOVO PC INT

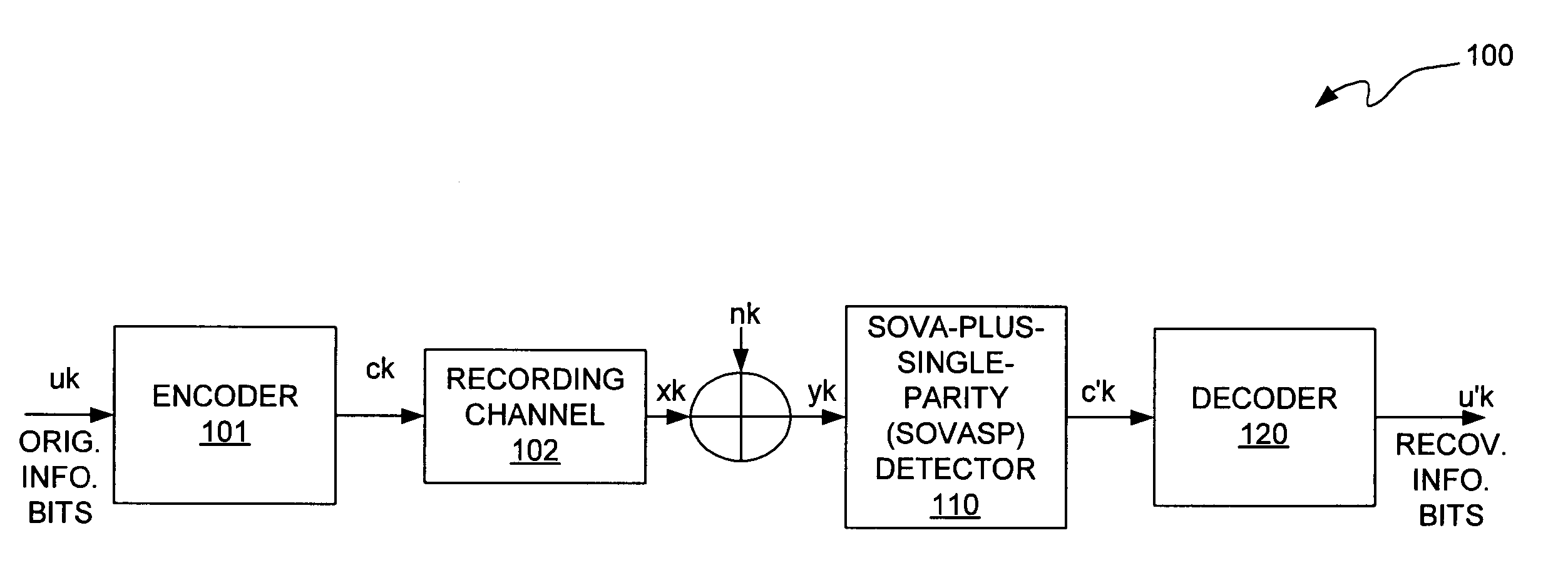

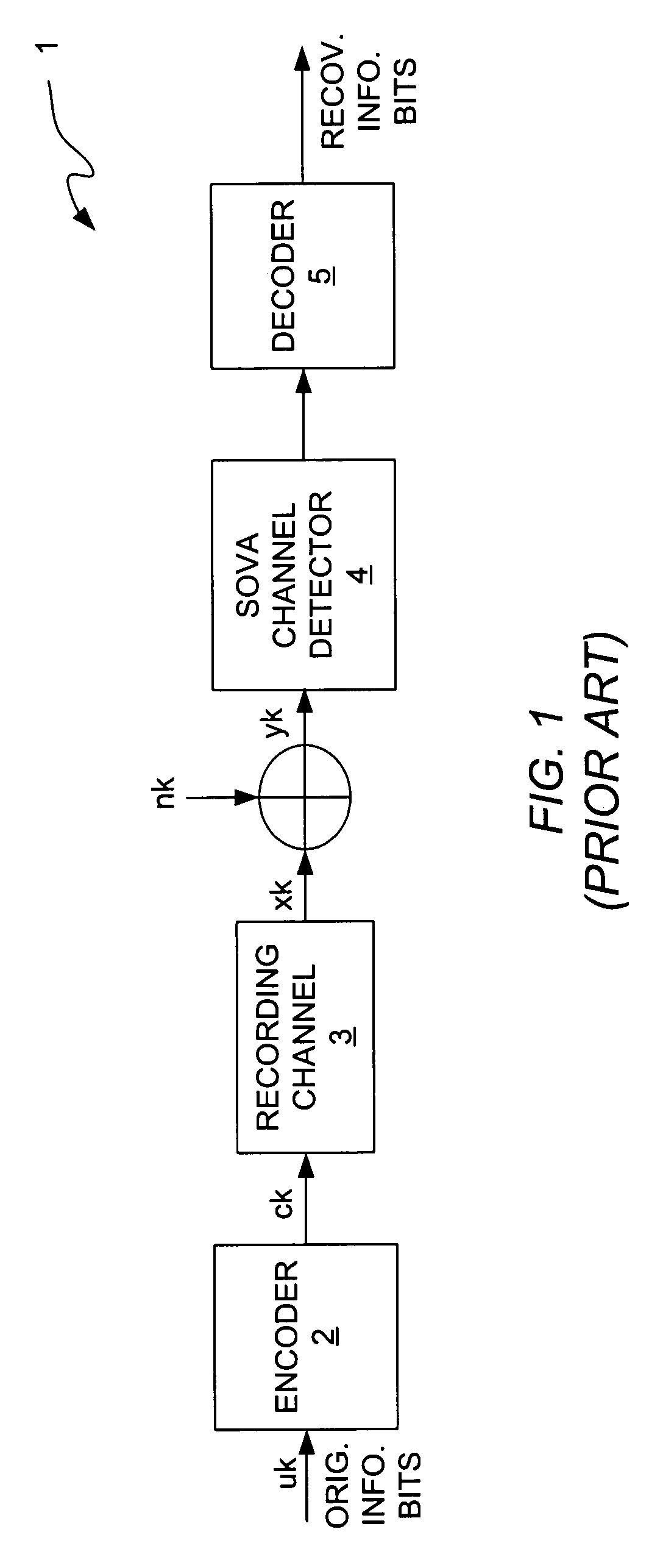

Data detection and decoding system and method

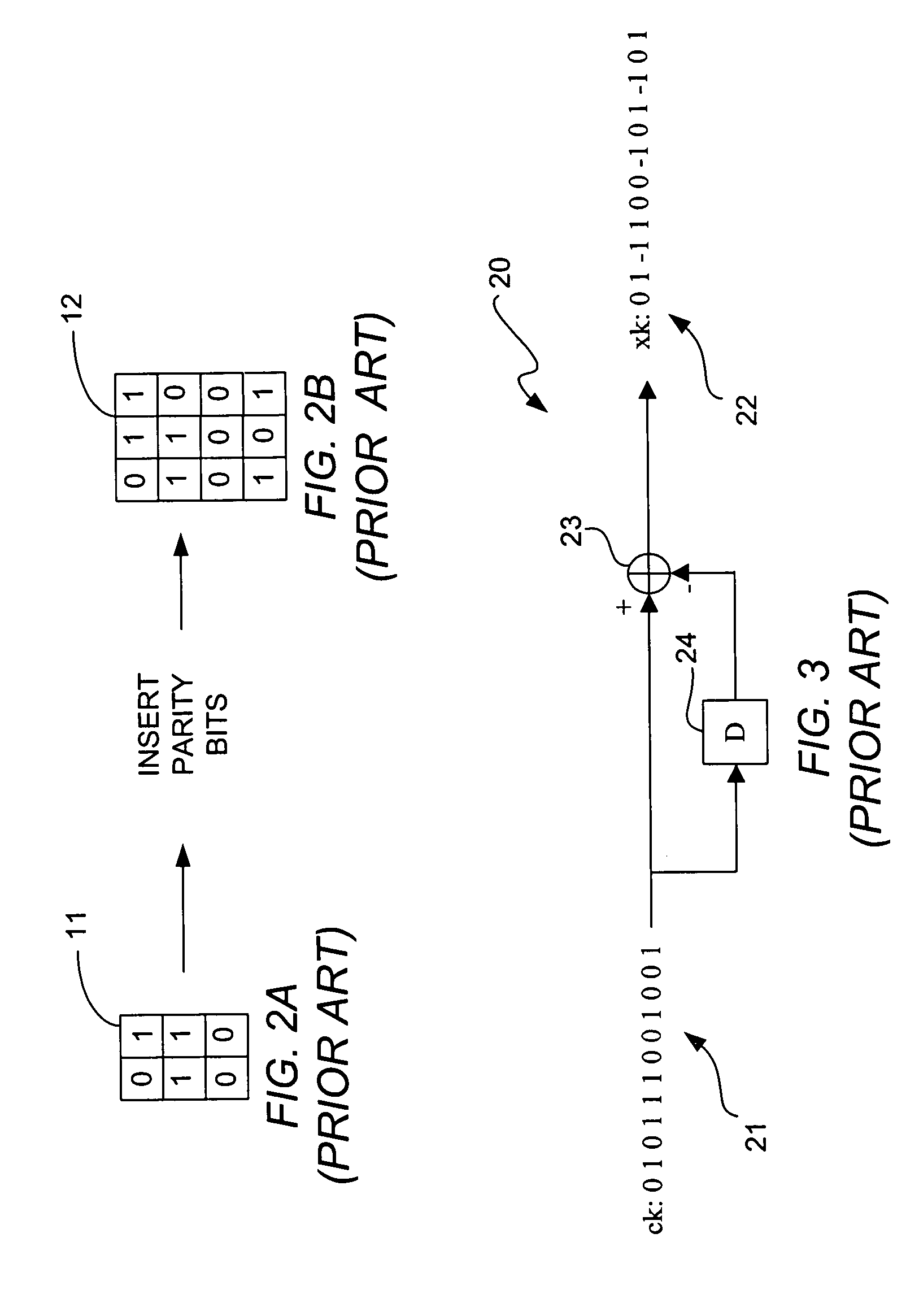

ActiveUS20060168493A1Data representation error detection/correctionOther decoding techniquesSingle parity checkAlgorithm

A data detection and decoding system includes a SOVA channel detector that uses single parity (SOVASP) to improve the accuracy with which the detector estimates bits. Each column or row read back from the read channel constitutes a code word and each code word is encoded to satisfy single parity. Because the SOVASP channel detector detects whether each code word satisfies single parity, it is unnecessary to use both a column decoder and a row decoder in the channel decoder. Either the row decoder or the column decoder can be eliminated depending on whether bits are read back on a column-by-column basis or on a row-by-row basis. This reduction in components reduces hardware complexity and improves system performance. The output of the row or column decoder is received by a second detector that processes the output received from the decoder to recover the original information bits.

Owner:AVAGO TECH INT SALES PTE LTD

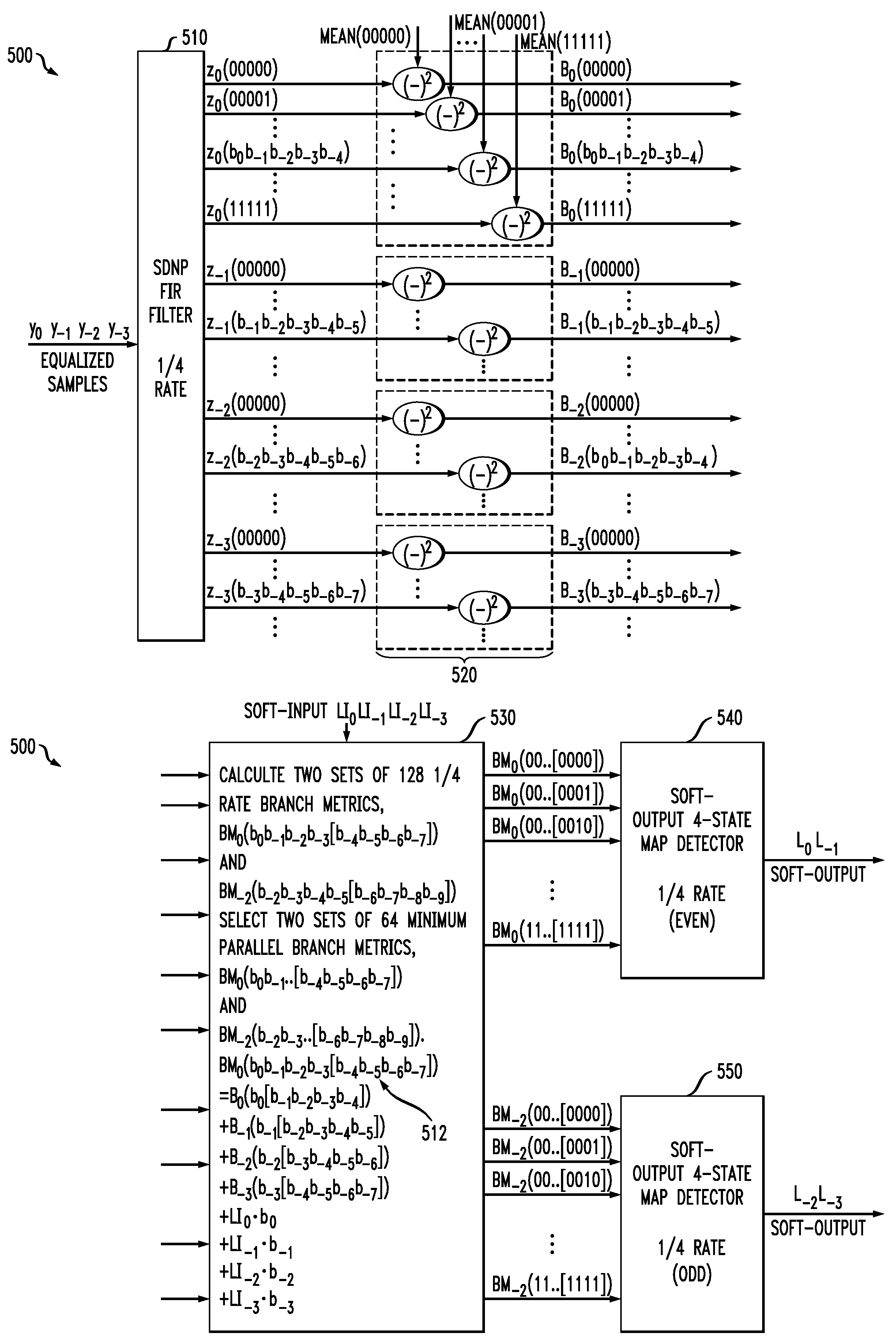

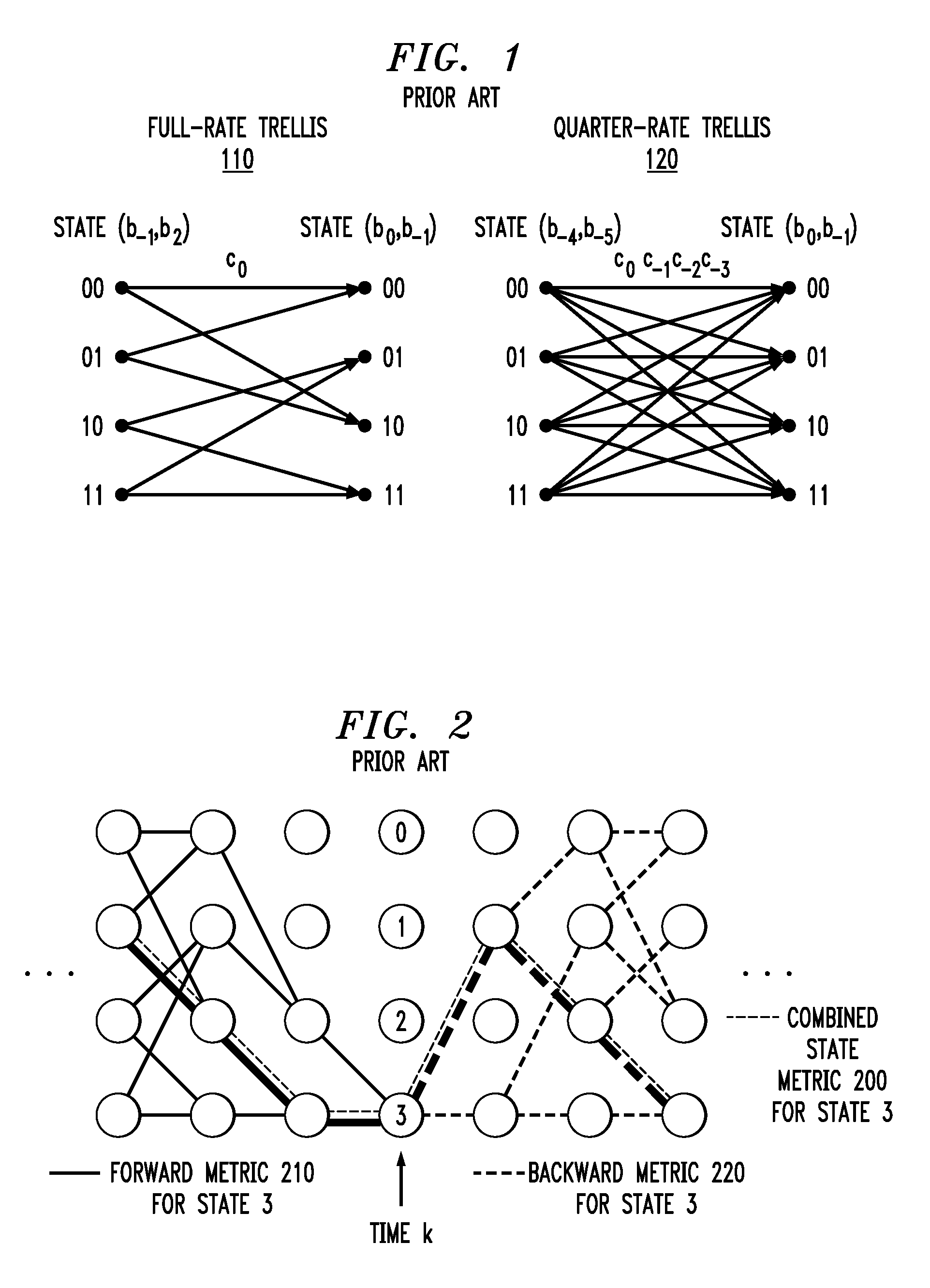

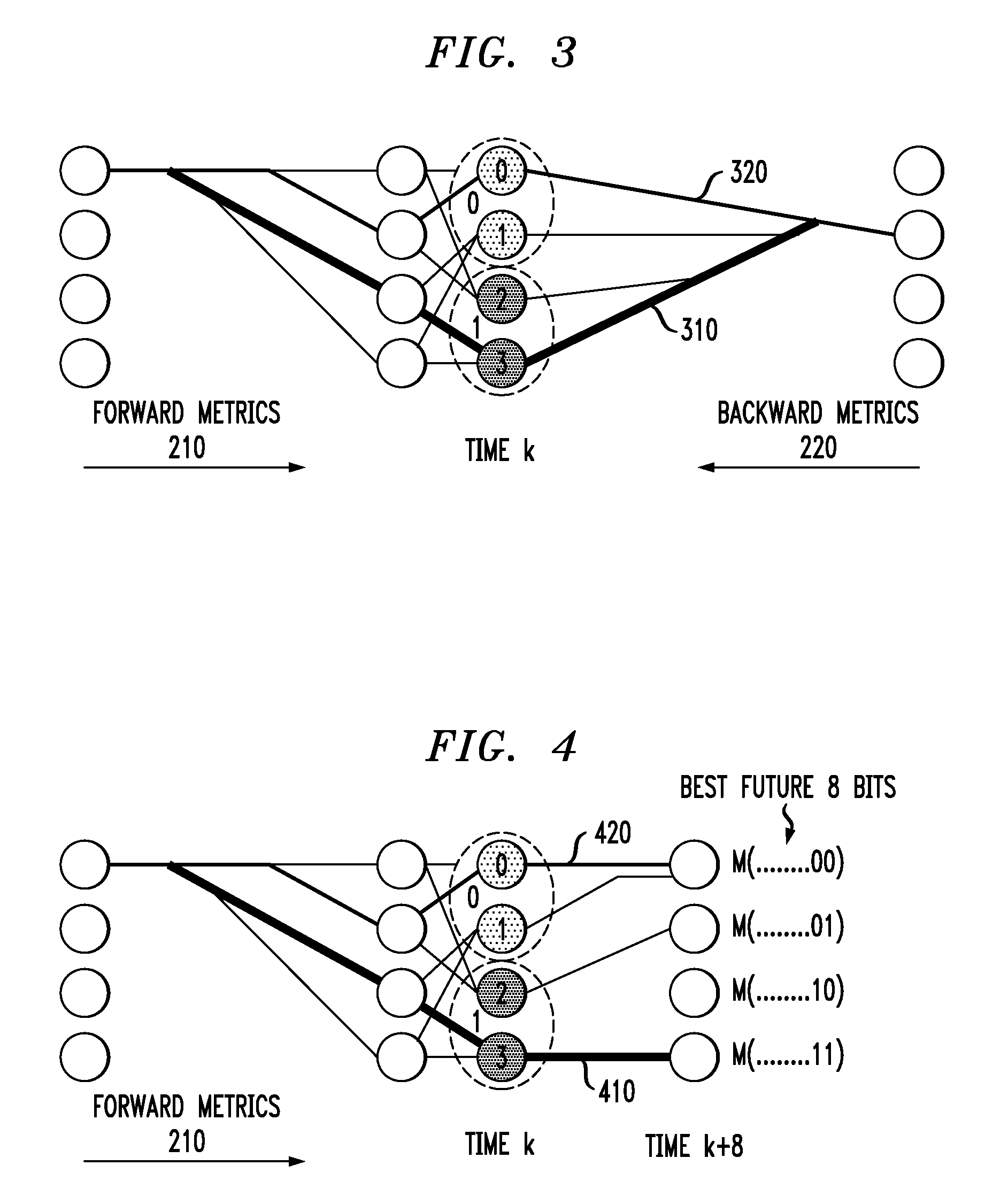

Methods and Apparatus for Map Detection with Reduced Complexity

ActiveUS20090185643A1Reduce complexityDependence moreDriving/moving recording headsError preventionLog likelihoodComputer science

Methods and apparatus are provided for high-speed, low-power, high-performance channel detection. A soft output channel detector is provided that operates at a rate of 1 / N and detects N bits per 1 / N-rate clock cycle. The channel detector comprises a plurality, D, of MAP detectors operating in parallel, wherein each of the MAP detectors generates N / D log-likelihood ratio values per 1 / N-rate clock cycle and wherein at least one of the plurality of MAP detectors constrains each of the bits. The log-likelihood ratio values can be merged to form an output sequence. A single MAP detector is also provided that comprises a forward detector for calculating forward state metrics; a backward detector for calculating backward state metrics; and a current branch detector for calculating a current branch metric, wherein at least two of the forward detector, the backward detector and the current branch detector employ different trellis structures.

Owner:AVAGO TECH INT SALES PTE LTD

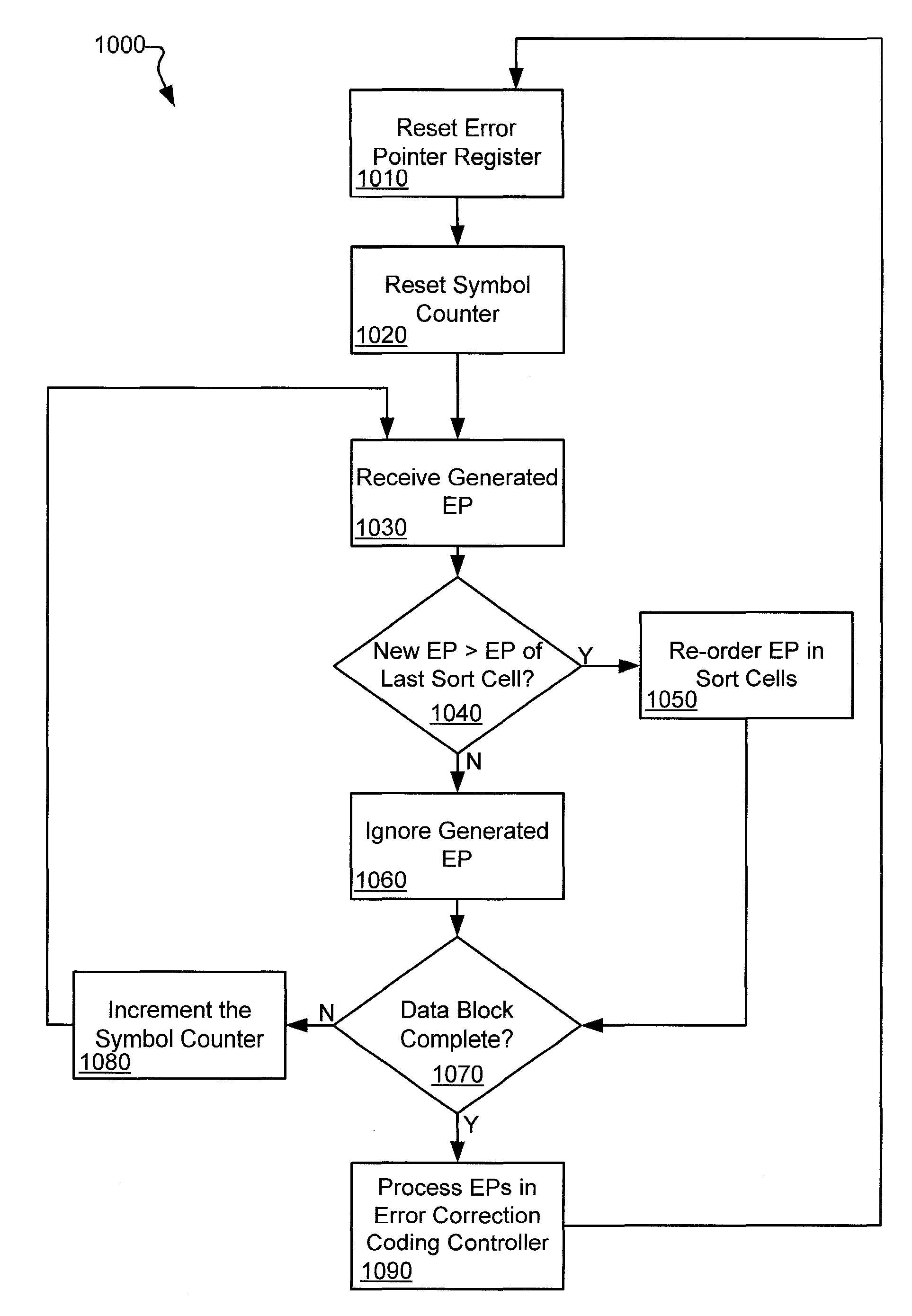

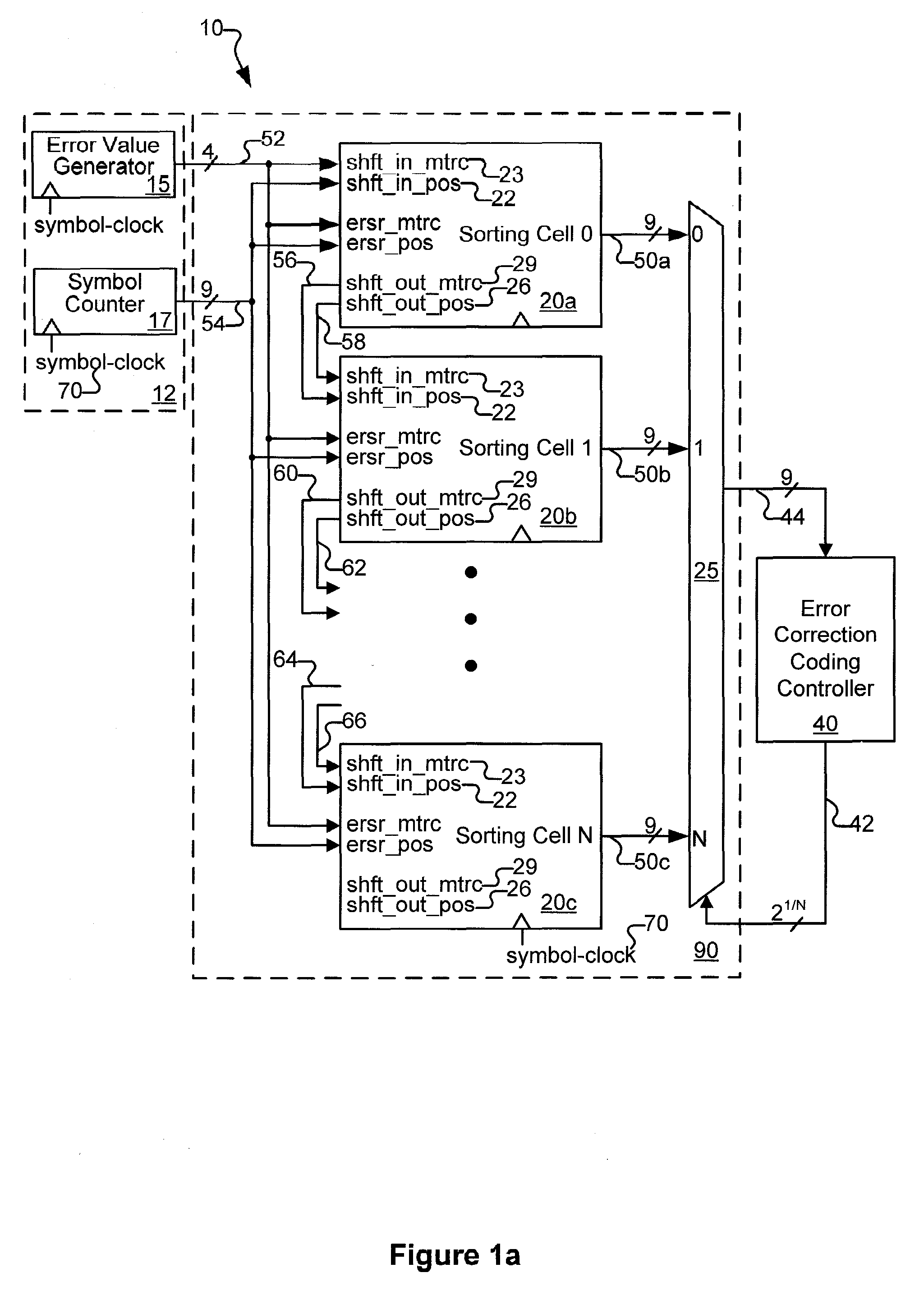

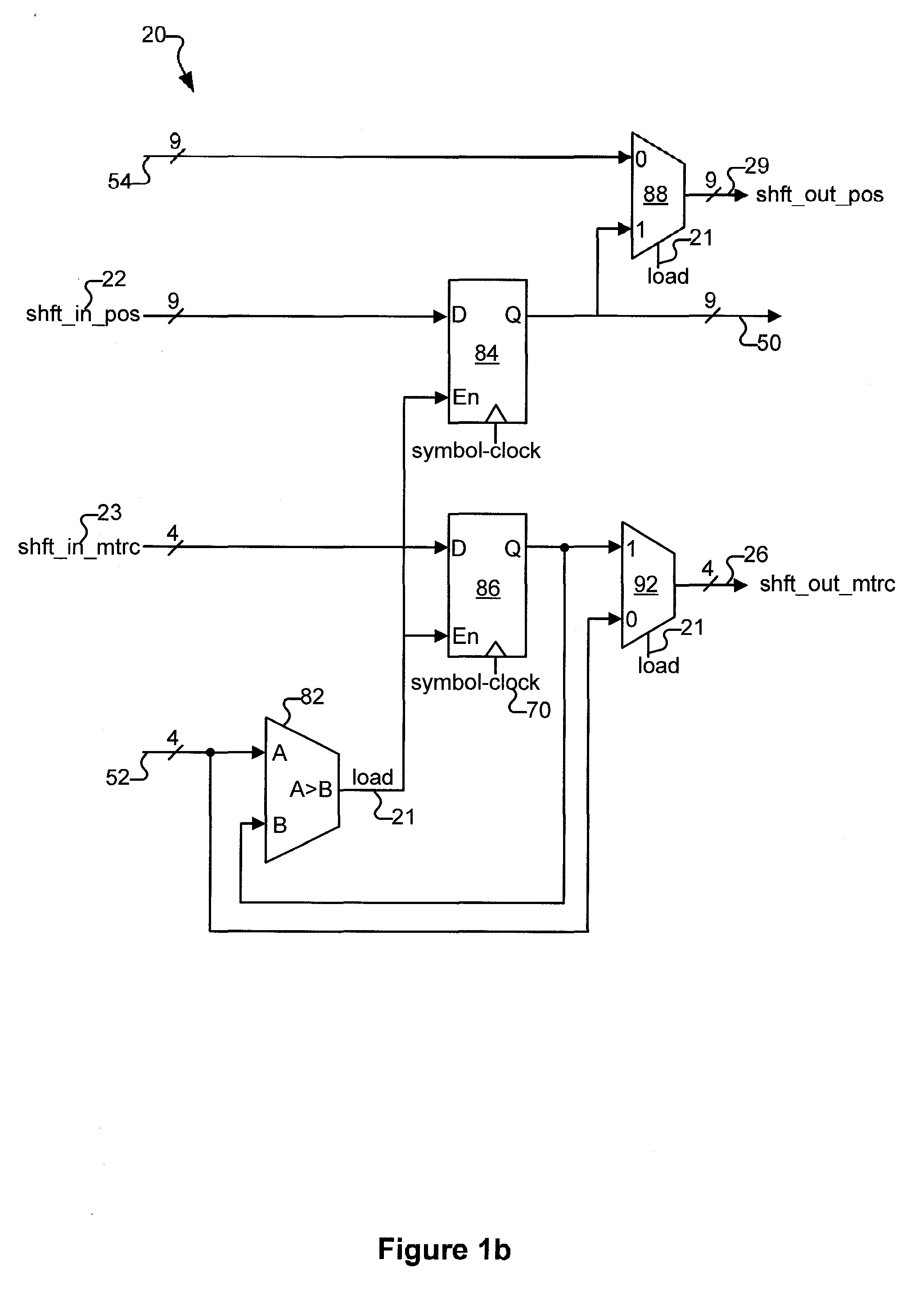

Systems and methods for prioritizing error correction data

ActiveUS20080168330A1Data representation error detection/correctionOther decoding techniquesCell basedReal-time computing

Various systems and methods for generating and / or ordering error indications are disclosed herein. In some cases, the error indication is used as an erasure pointer in a memory access system. As one particular example, a system for ordering erasure pointers is disclosed that includes a group of N sort cells, where N is a whole number. Each of the sort cells is operable to maintain a respective error indication that includes an error value and an associated error pointer. Further, the group of N sort cells is operable to receive an incoming error indication including error value and associated error pointer, and to update the error indication of one or more of the group of N sort cells based in part on the incoming error value. The system also includes a selector circuit that is operable to allow selectable access to each of the respective error pointers maintained in the group of N sort cells.

Owner:AVAGO TECH INT SALES PTE LTD

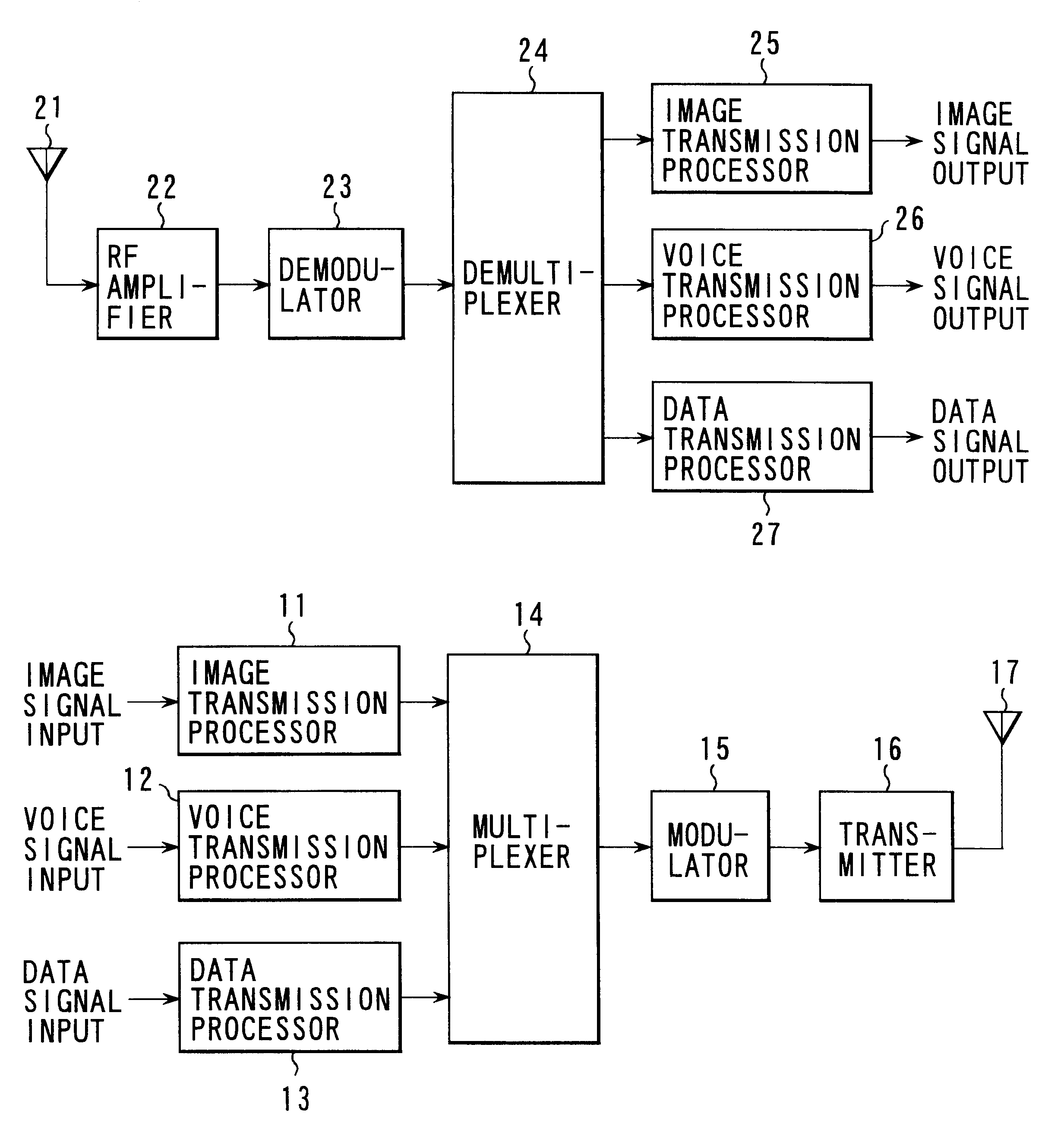

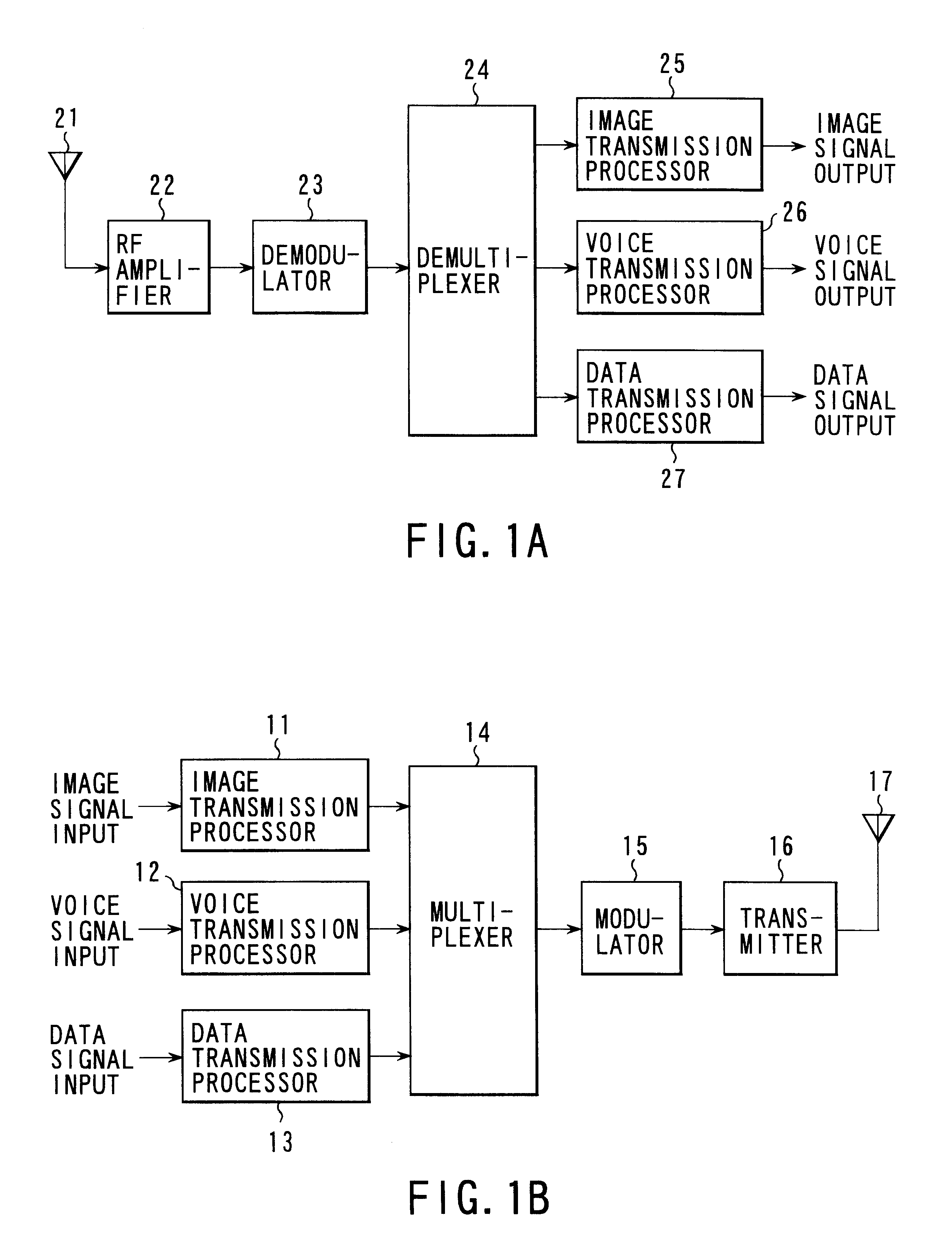

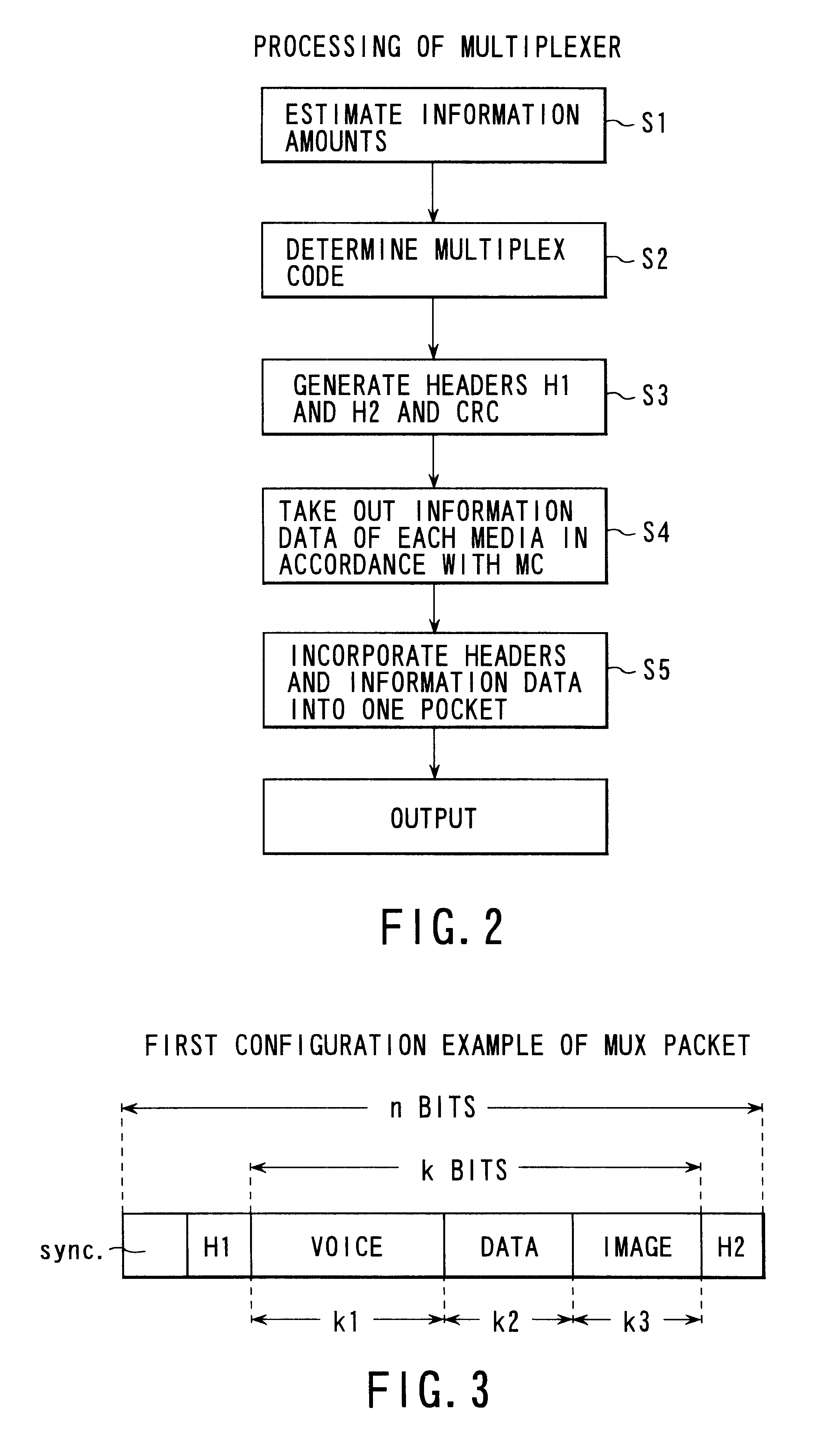

Information data multiplex transmission system, its multiplexer and demultiplexer and error correction encoder and decoder

InactiveUS6490243B1Reduce the probability of packet lossAccurate readingData representation error detection/correctionPulse modulation television signal transmissionMultiplexingMultiplexer

A multiplexing unit on the transmitting side estimates information amounts supplied from respective signal processing units, determines a multiplex code on the basis of respective information amounts, derives a parity of the first determined multiplex code to form a second multiplex code, adds a CRC to each of the multiplex codes to generate two headers H1 and H2, takes out information data of respective media according to the multiplex codes, incorporates the information data into a packet together with the two headers H1 and H2, and outputs the packet. If error correction of H1 is impossible on the receiving side, error correction decoding is conducted by using the header H2. If error correction of H2 is also impossible, error correction decoding is conducted collectively for H1 and H2.

Owner:KK TOSHIBA

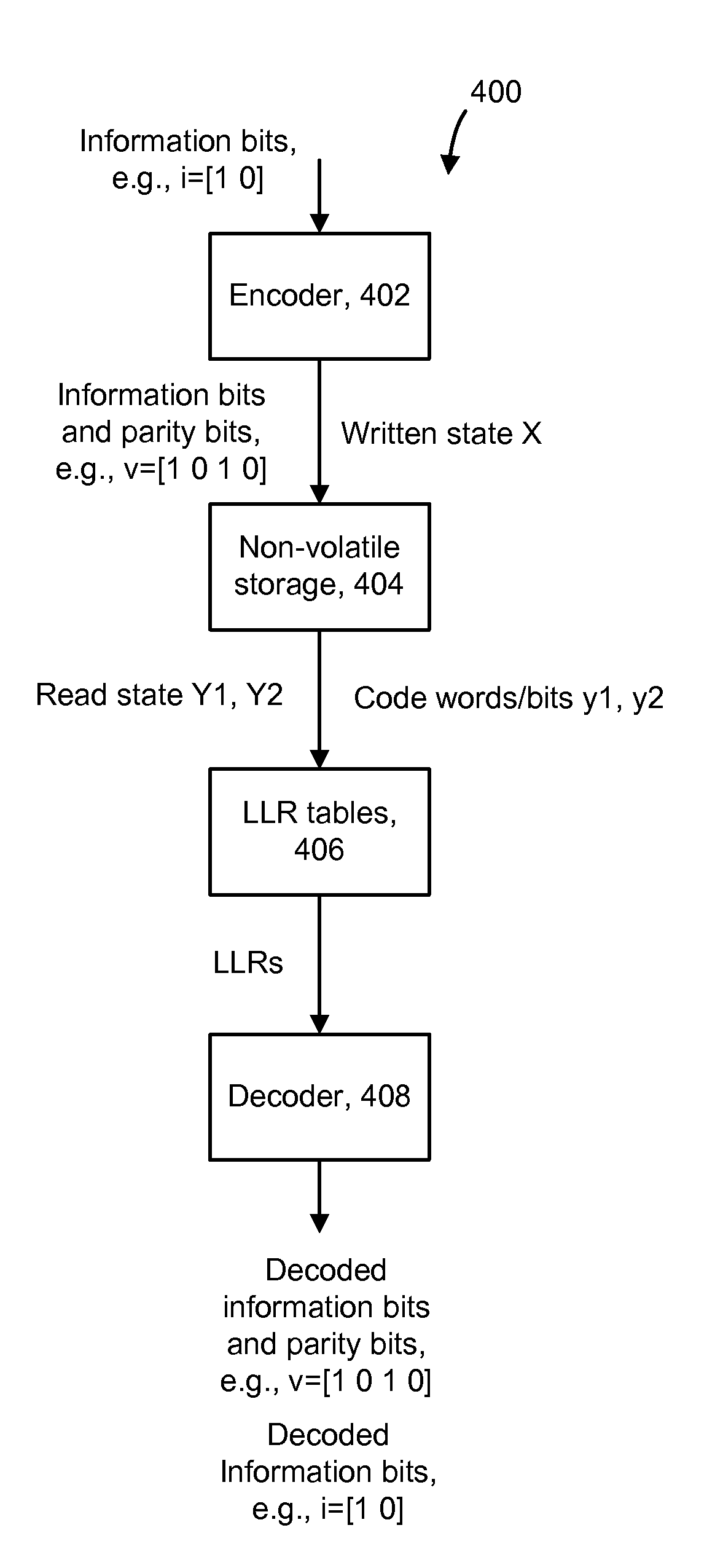

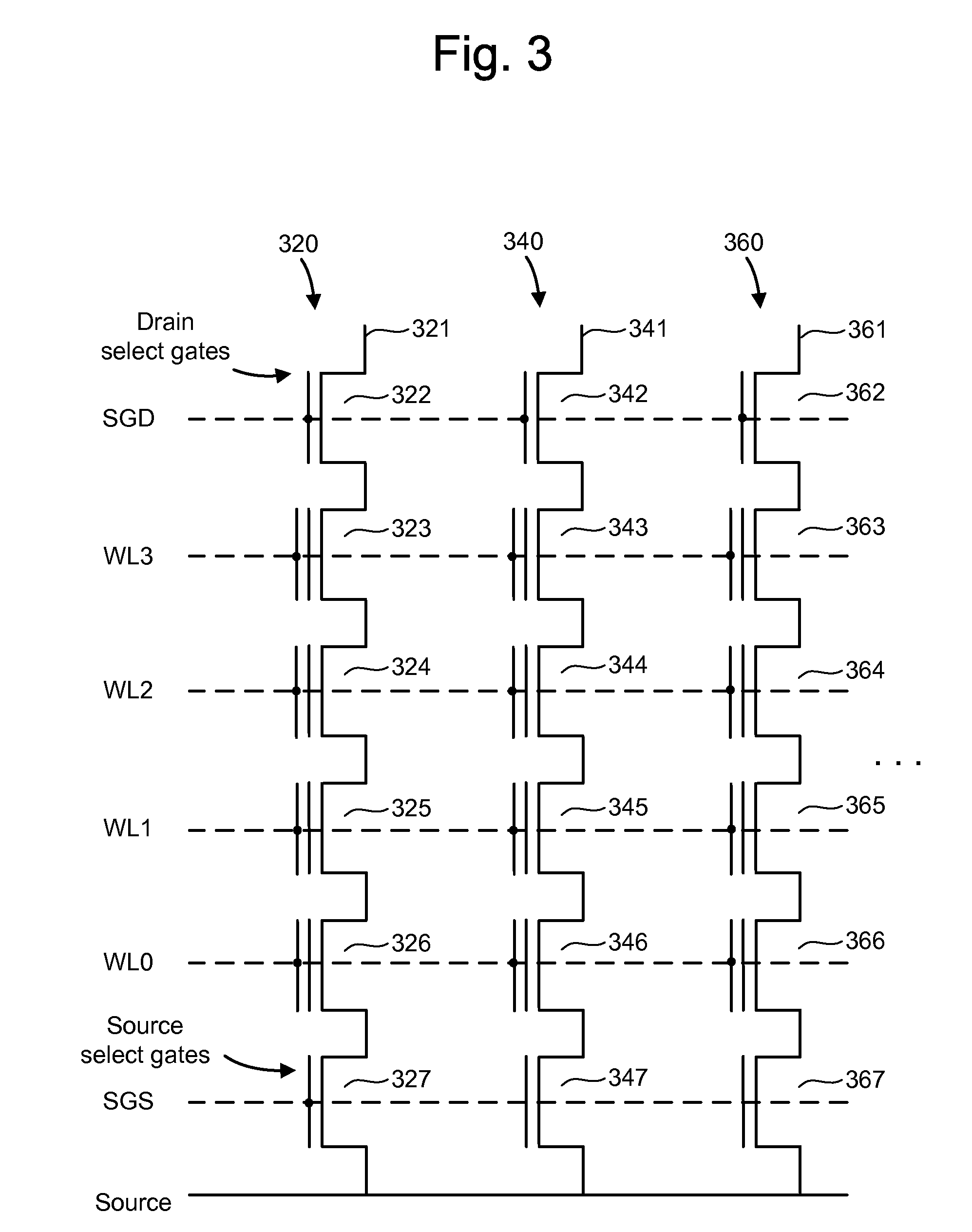

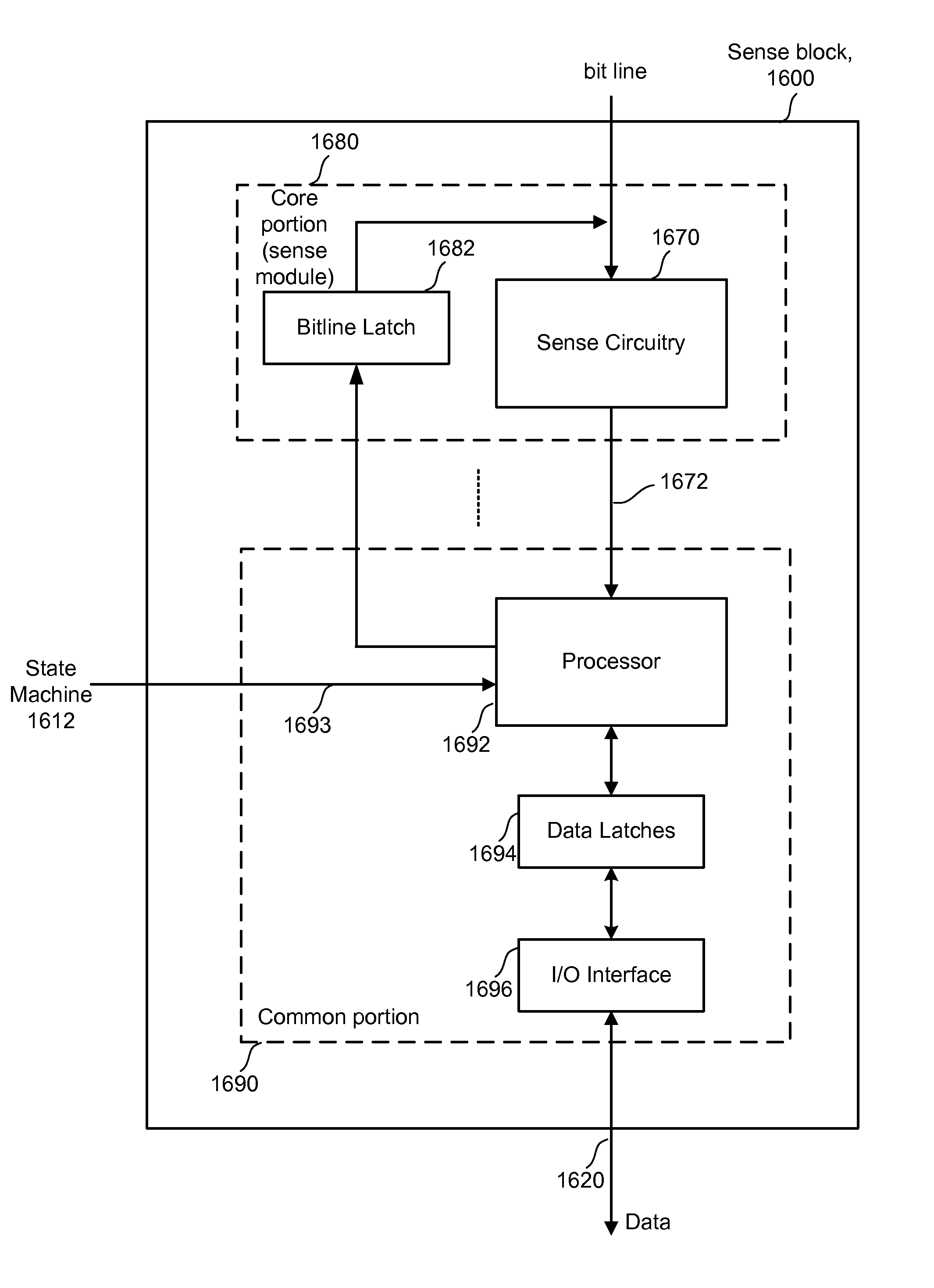

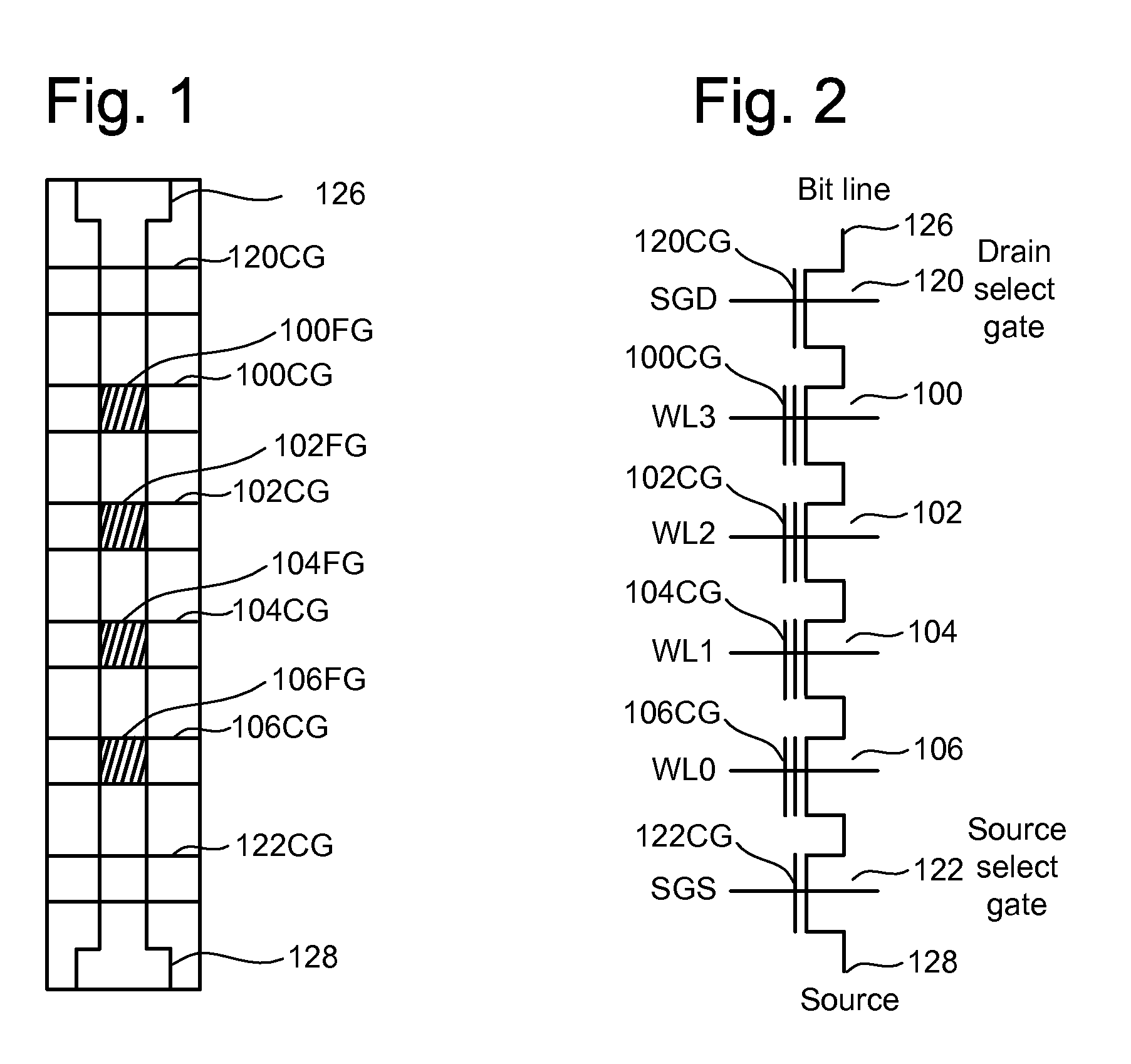

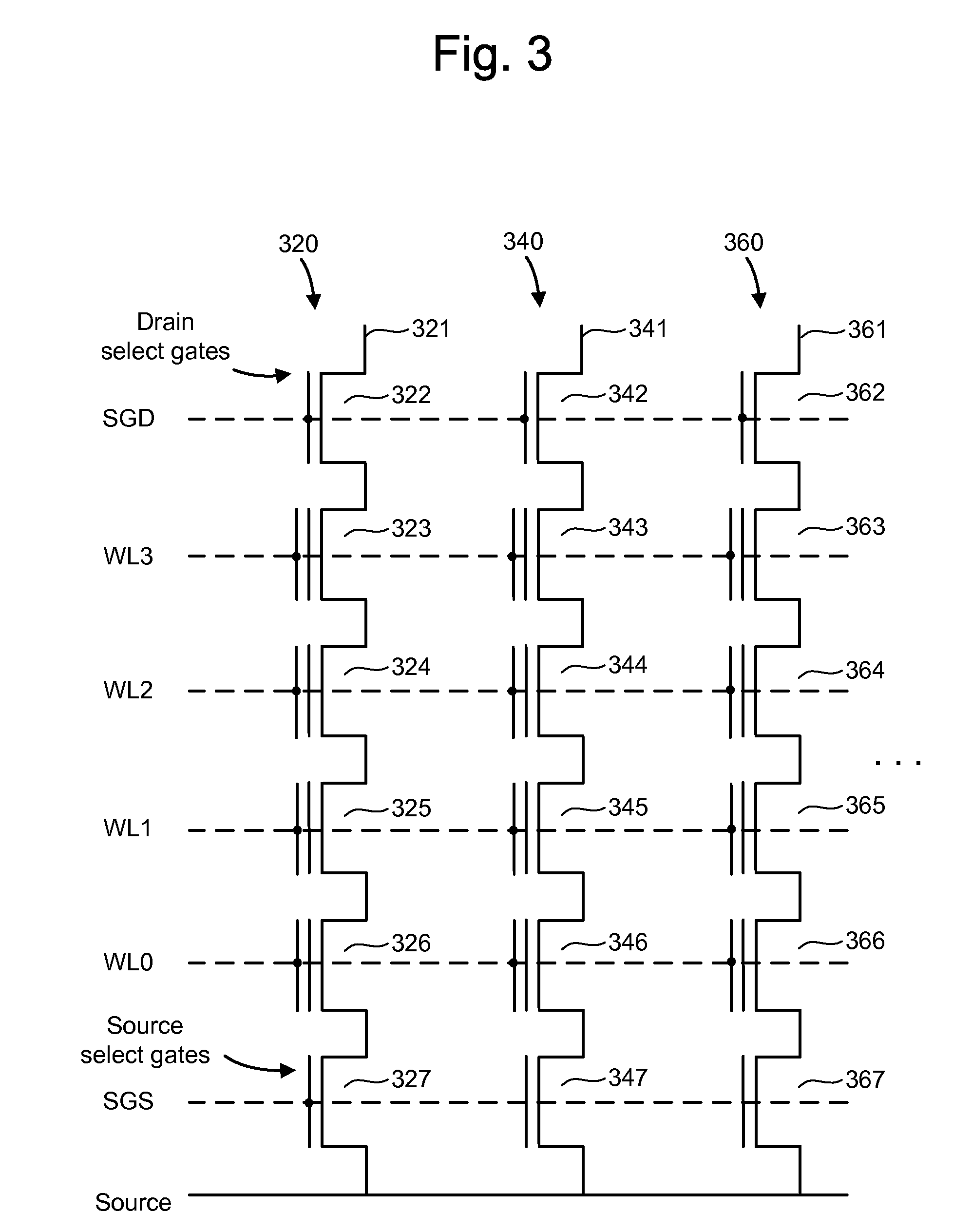

Method for decoding data in non-volatile storage using reliability metrics based on multiple reads

ActiveUS20080250300A1Other decoding techniquesError correction/detection using multiple parity bitsLow-density parity-check codeDependability

Data stored in non-volatile storage is decoded using iterative probabilistic decoding and multiple read operations to achieve greater reliability. An error correcting code such as a low density parity check code may be used. In one approach, initial reliability metrics, such as logarithmic likelihood ratios, are used in decoding read data of a set of non-volatile storage element. The decoding attempts to converge by adjusting the reliability metrics for bits in code words which represent the sensed state. If convergence does not occur, e.g., within a set time period, the state of the non-volatile storage element is sensed again, current values of the reliability metrics in the decoder are adjusted, and the decoding again attempts to converge. In another approach, the initial reliability metrics are based on multiple reads. Tables which store the reliability metrics and adjustments based on the sensed states can be prepared before decoding occurs.

Owner:SANDISK TECH LLC

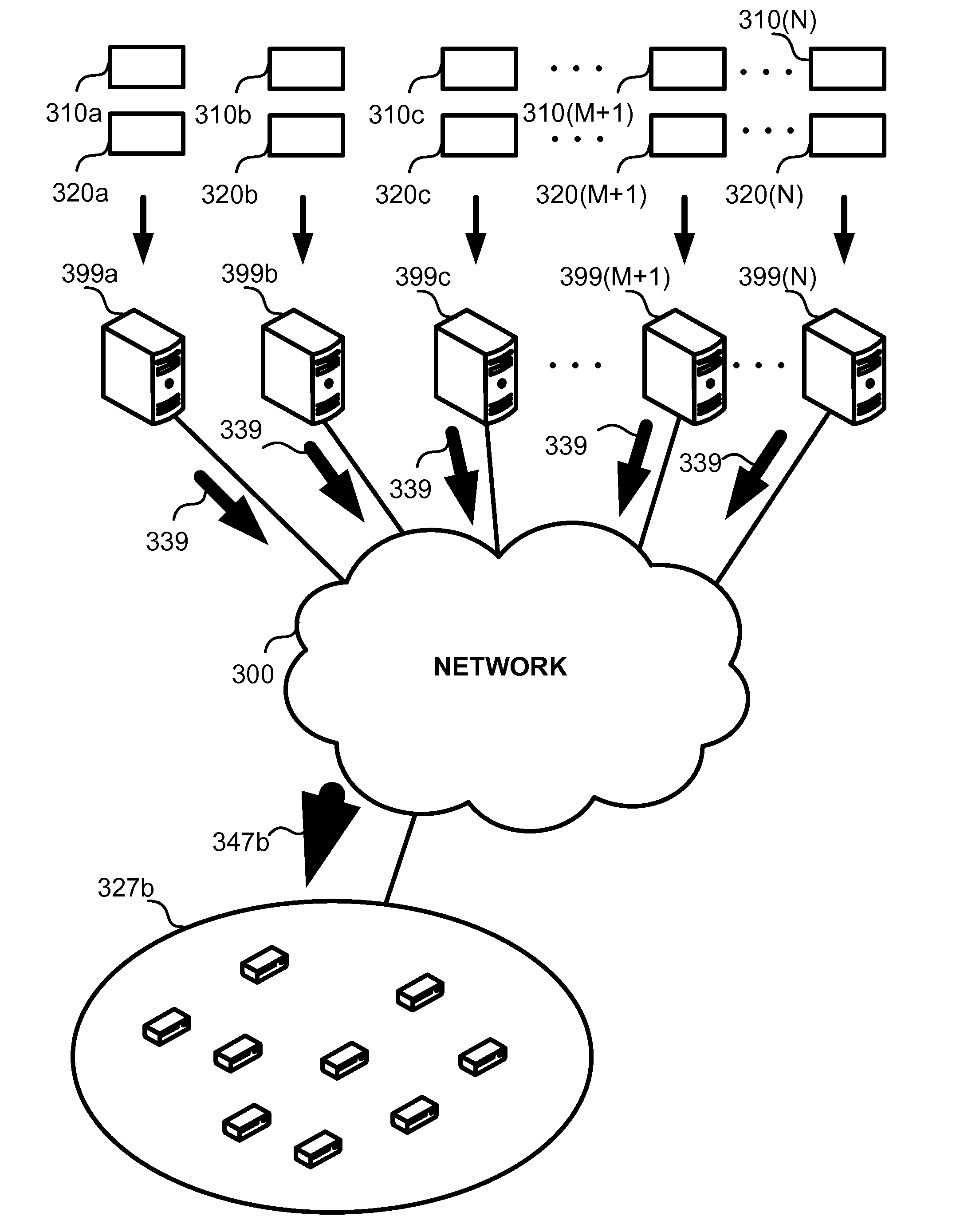

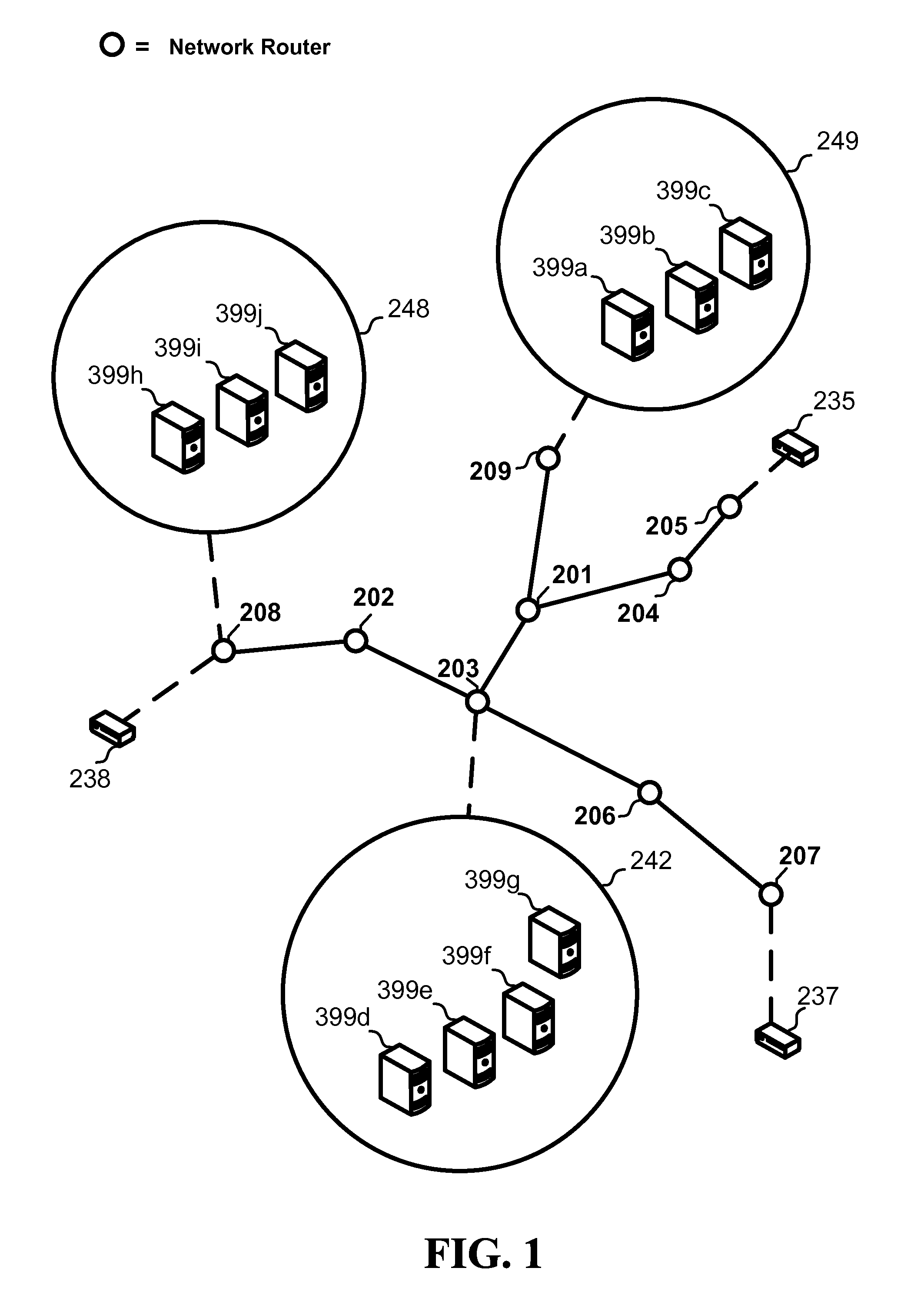

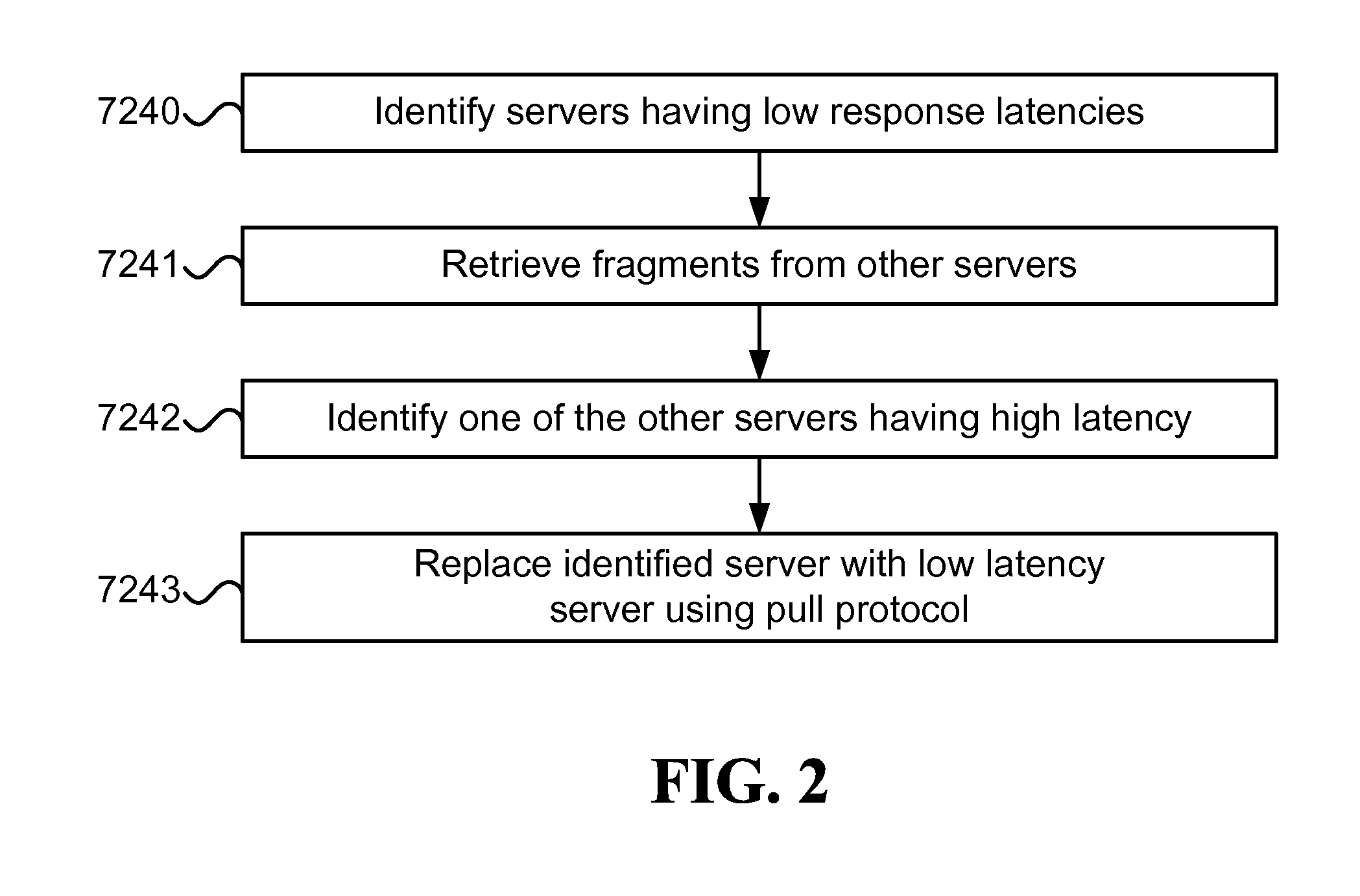

Latency based selection of fractional-storage servers

InactiveUS20100094970A1Reduce response delayOther decoding techniquesCode conversionResponse delayErasure code

Latency based selection of fractional-storage servers, including the steps of identifying a first group of fractional-storage servers estimated to have low response latencies in relation to an assembling device. Retrieving, by the assembling device from a second group of fractional-storage servers, enough erasure-coded fragments for reconstructing approximately sequential segments of streaming content. While retrieving the fragments, identifying at least one server from the second group having latency higher than a certain threshold in response to a fragment pull protocol request. And using the fragment pull protocol to replace the identified server with at least one server selected from the first group.

Owner:PATENTVC

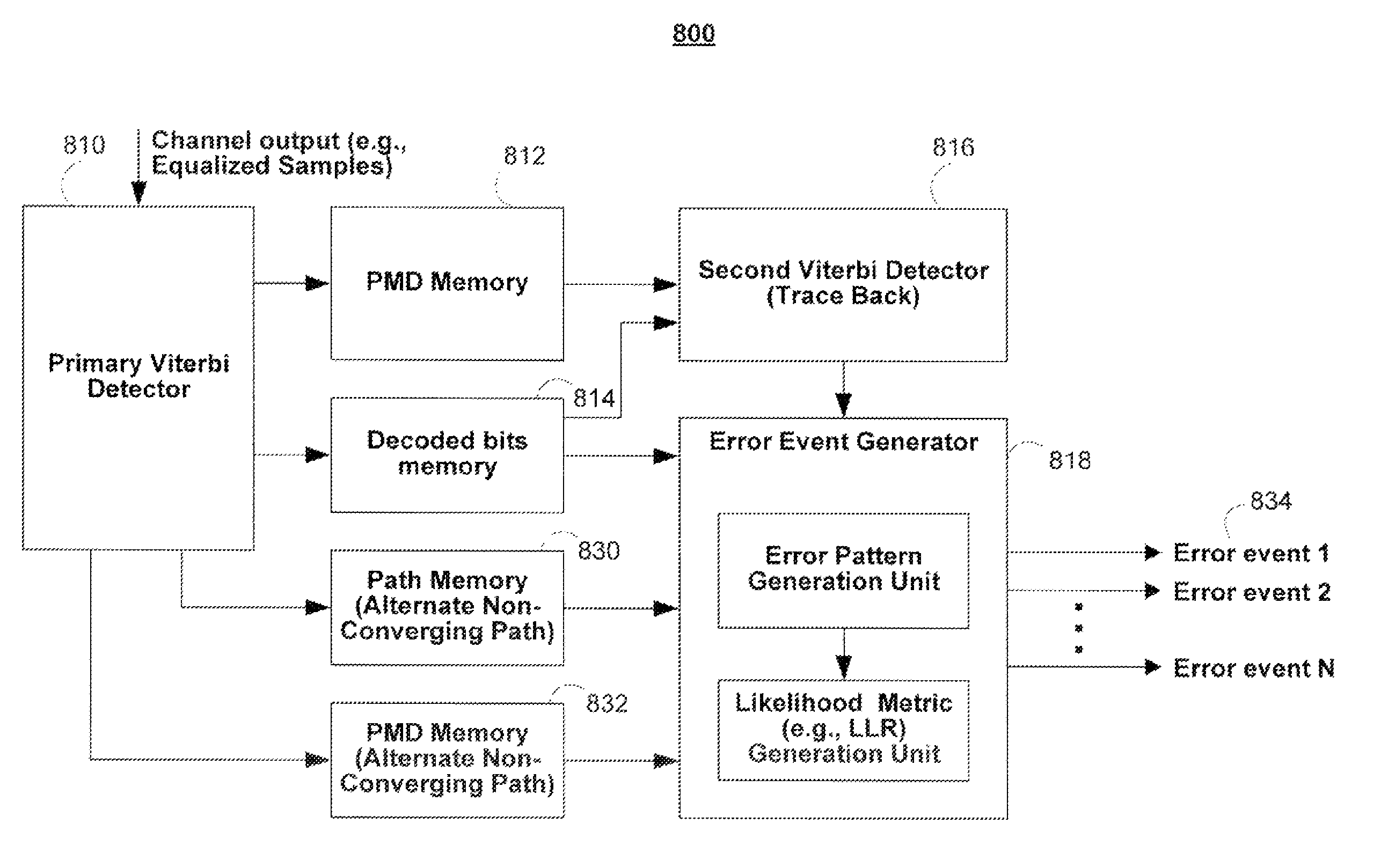

Likelihood metric generation for trellis-based detection and/or decoding

ActiveUS7805664B1Accurate likelihoodAccurately reflect reliability of detectionData representation error detection/correctionOther decoding techniquesReal-time computingAlgorithm

Systems and methods for generating likelihood metrics for trellis-based detection and / or decoding are described. In some embodiments, likelihood metrics for a first subset of bit locations in an error pattern (e.g., bit locations that fall within the error event update window) are updated based on a first metric, such as the path metric difference, associated with an alternate path that converges to the same trellis state as the decoded sequence. In some embodiments, likelihood metrics for a second subset of bit locations in the error patterns (e.g., bit locations that do not fall within the error event update window) are updated based on a second metric, such as a predetermined value of zero, a small metric, or the path metric difference for a path that does not converge into the same winning state as the decoded sequence for the particular error update window of interest.

Owner:MARVELL ASIA PTE LTD

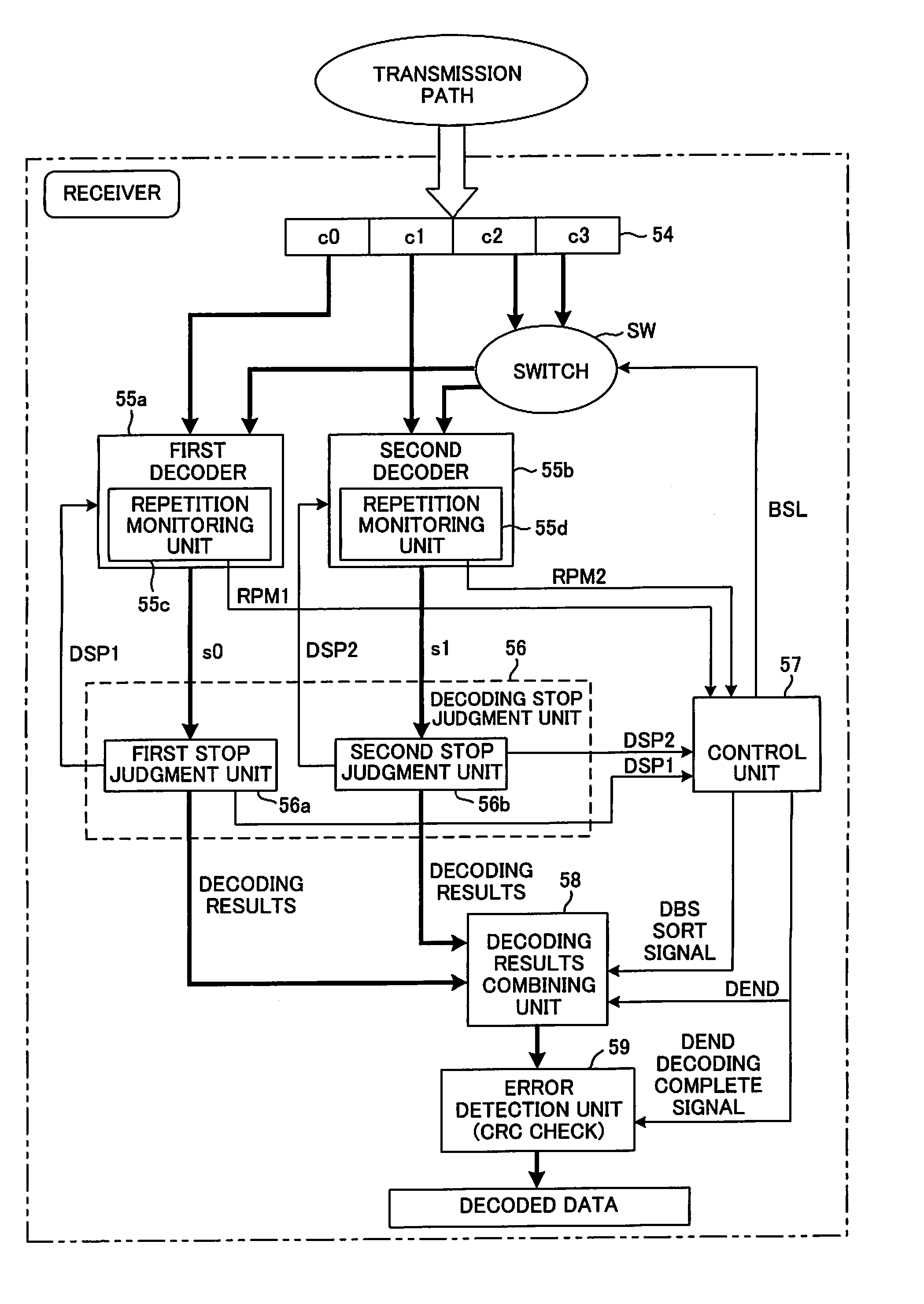

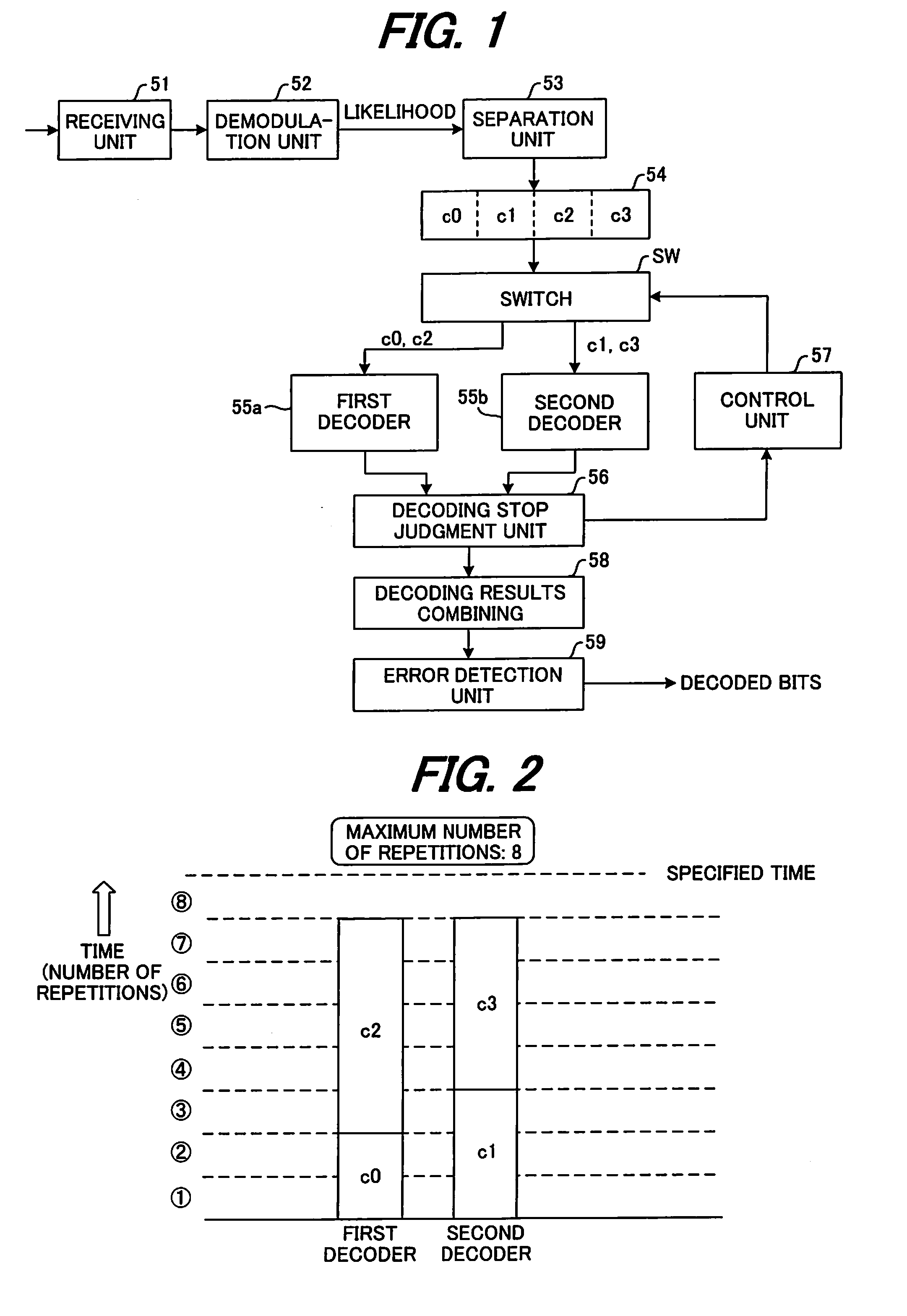

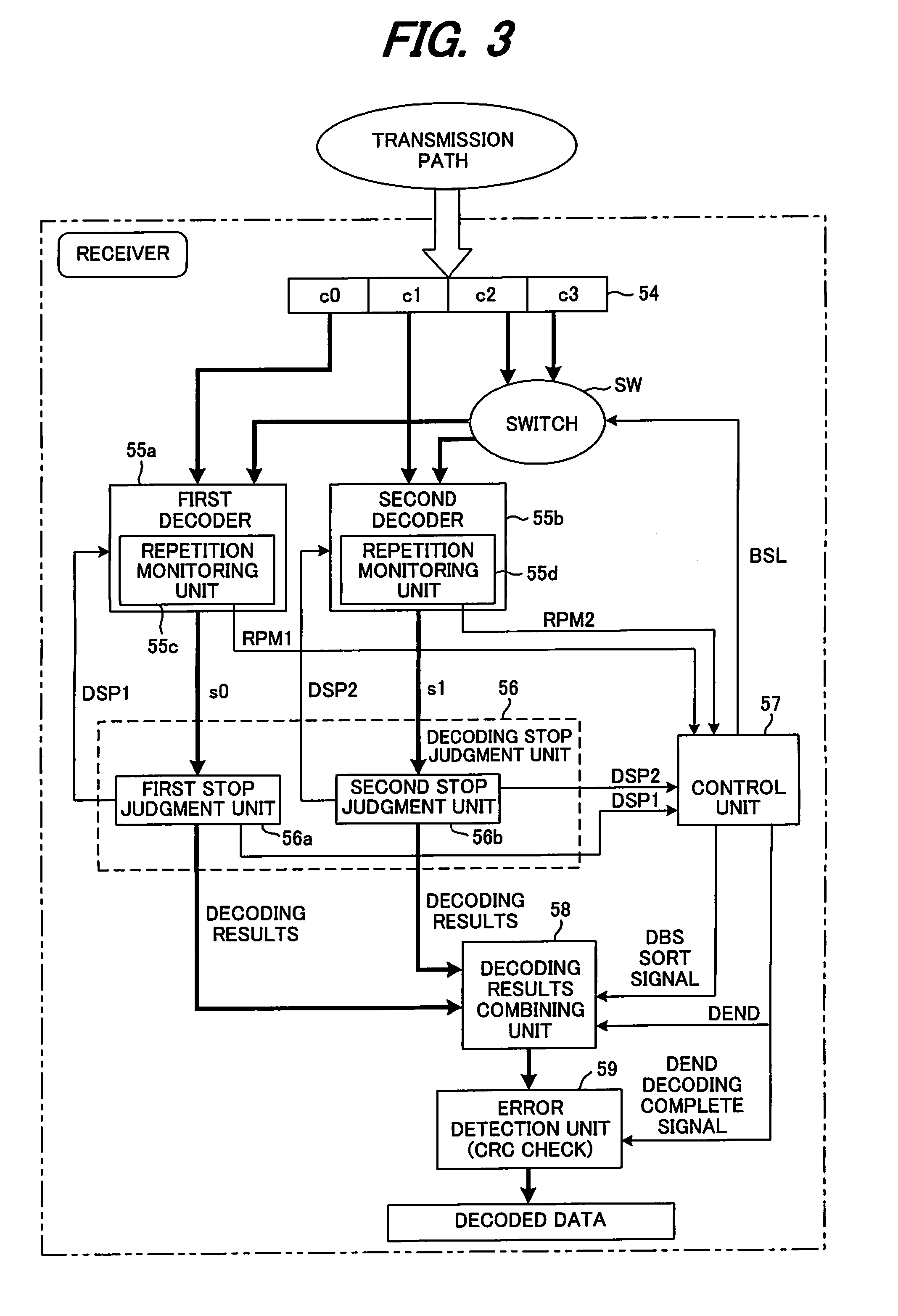

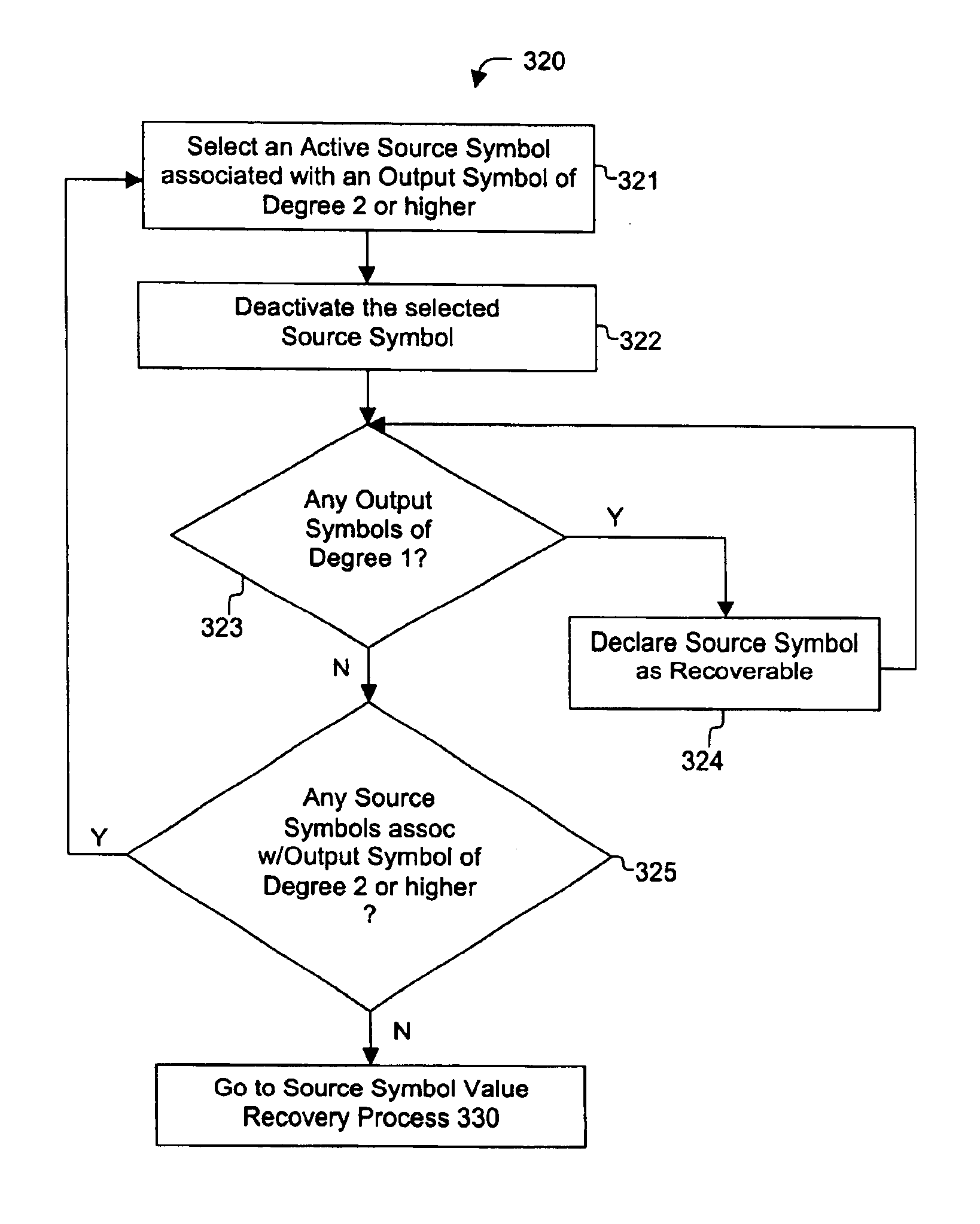

Receiving device and decoding method thereof

InactiveUS20090132893A1Avoid mistakesReduce the numberOther decoding techniquesCode conversionComputer hardwareDecoding methods

A receiving device in a communication system that separates one frame of information bits into plural blocks, performs turbo encoding of the information bits of each block and transmits the result, and decodes the encoded information bits, where the receiving device includes plural decoders number of which is less than the number of blocks per frame. Each decoder performs a decoding process on encoded information bits of each block that have been expressed by likelihood, when a condition for stopping decoding is met, executes the decoding process of encoded information bits of another block for which decoding has not yet been performed. When the condition for stopping decoding has been met for all block before the number of times decoding has been performed for each decoder reaches a preset maximum number of repetitions, the decoding results of all the blocks are serially combined, an error detection process is executed, and when no error is detected, the decoding results are output.

Owner:FUJITSU LTD

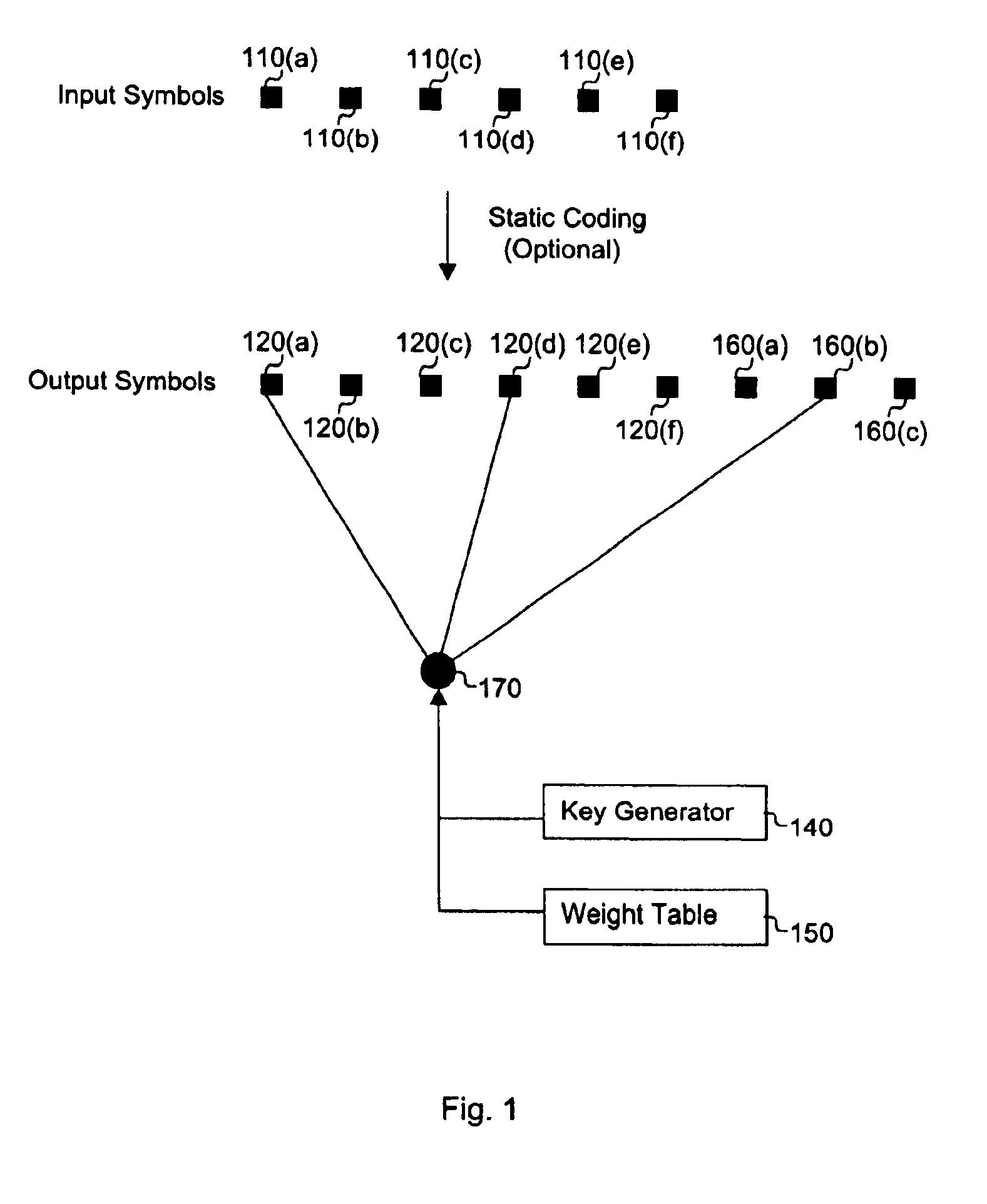

Systems and processes for decoding chain reaction codes through inactivation

InactiveUS6856263B2Error prevention/detection by using return channelOther decoding techniquesAlgorithmChain reaction

A method for processing a chain reaction codes includes first selecting a source symbol which is associated an output symbol of degree two or higher (i.e., an output symbol which is itself associated with two or more input symbols), and subsequently deactivating the selected source symbol in an attempt to produce an output symbol of degree one. The inactivation process can be repeated either successively until an output symbol of degree one is identified, and / or whenever the decoding process is unable to locate an output symbol of degree one.

Owner:QUALCOMM INC

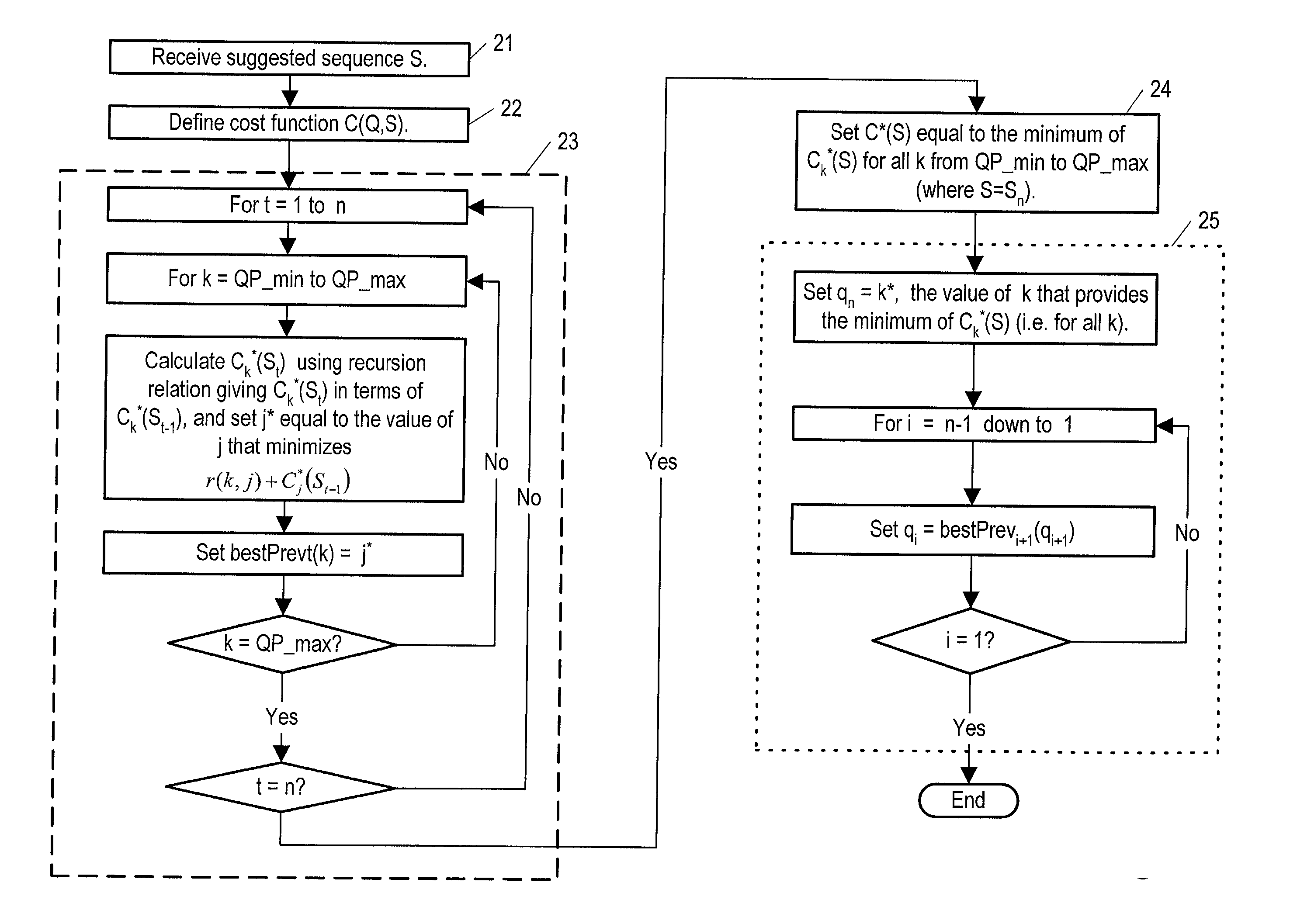

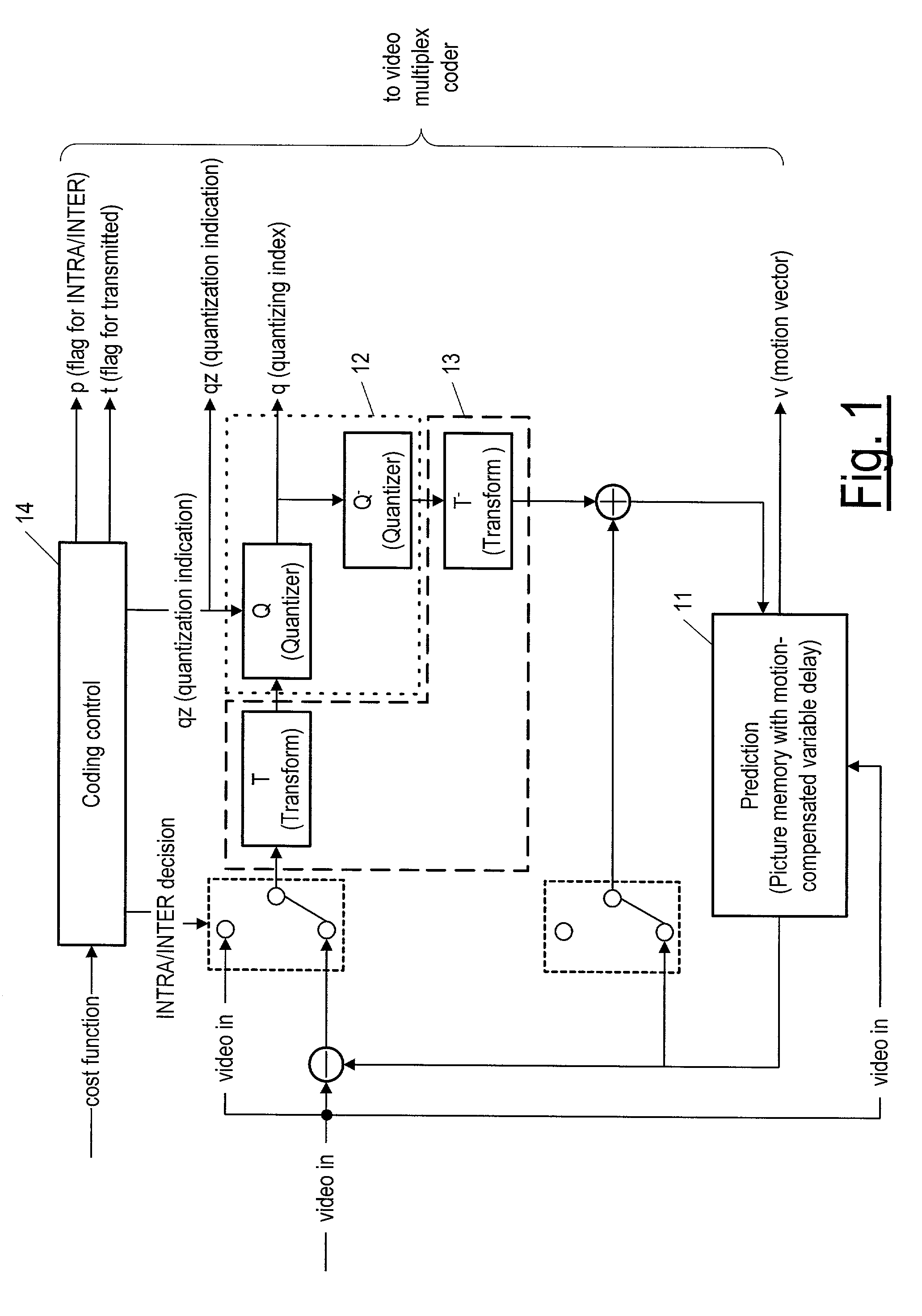

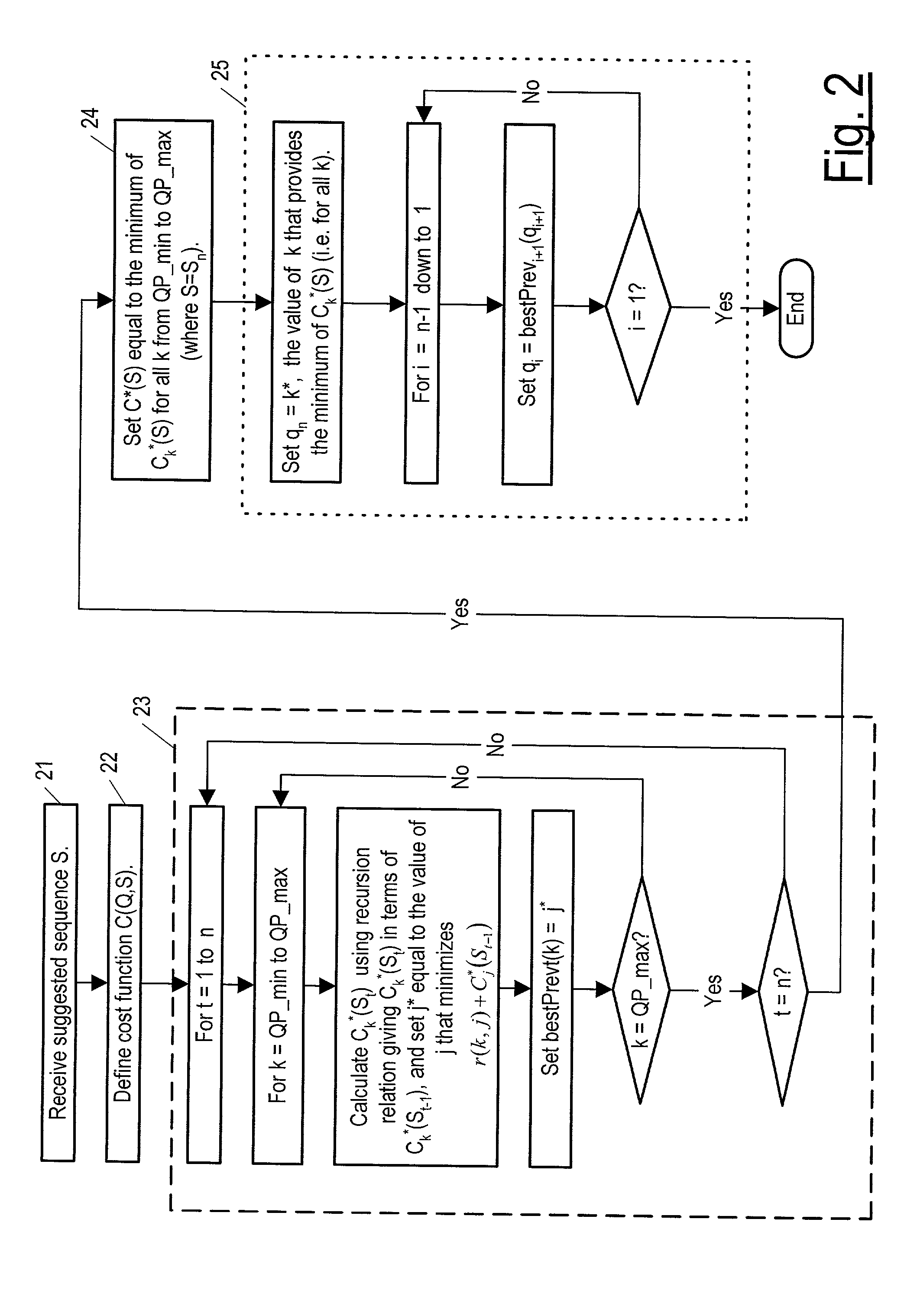

Method and apparatus for selecting macroblock quantization parameters in a video encoder

InactiveUS20030128756A1Other decoding techniquesPicture reproducers using cathode ray tubesVideo encodingAlgorithm

A method and corresponding apparatus for selecting a sequence of quantization parameter values in a video encoder, the video encoder being arranged to encode a video frame as a sequence of n macroblocks and to assign a quantization parameter value for each macroblock of the video frame. The method includes steps (23 24 25) in which quantization parameter values assigned to at least a subset of said sequence of n macroblocks are optimized in such a way as to minimize a cost associated with their encoding.

Owner:WSOU INVESTMENTS LLC

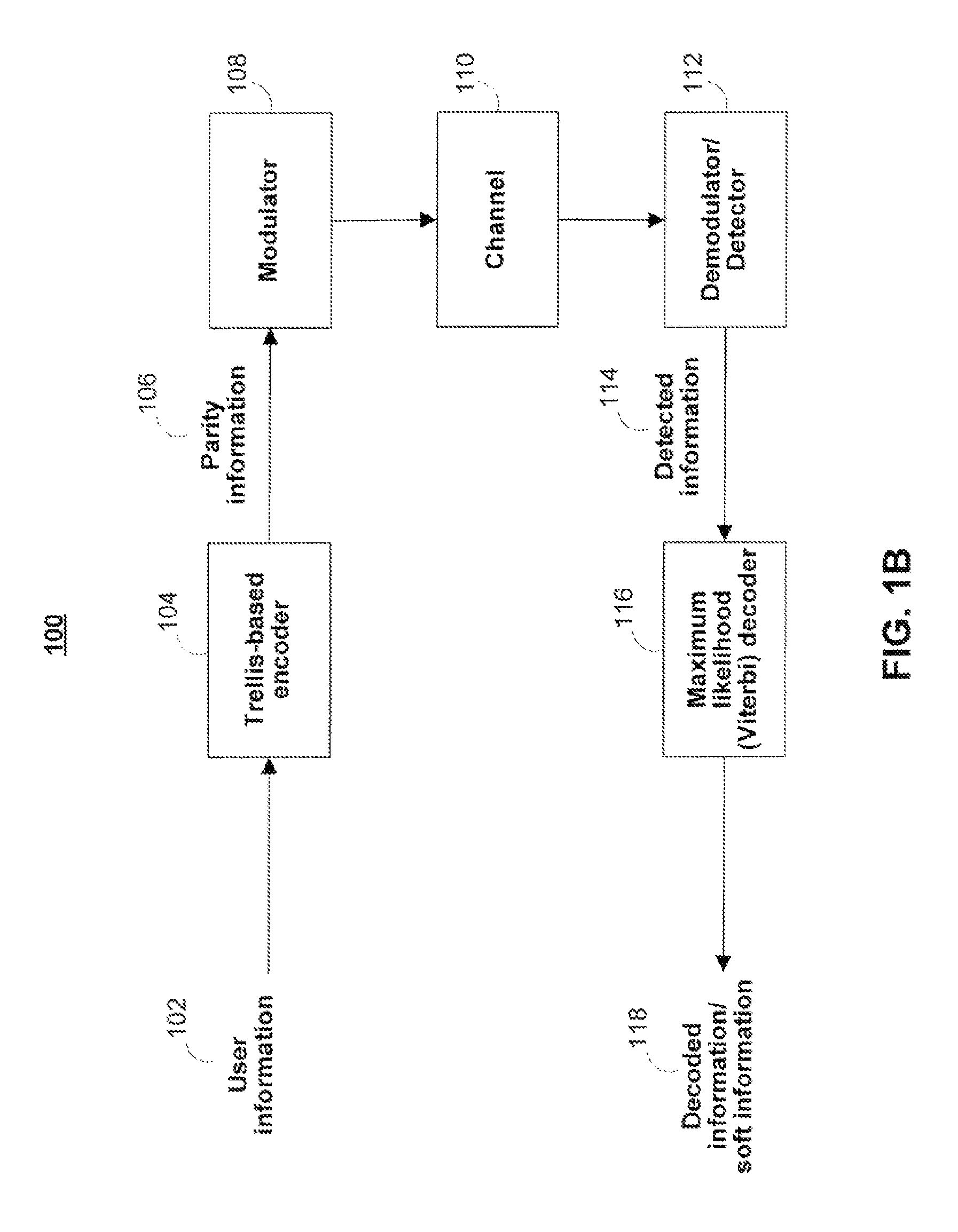

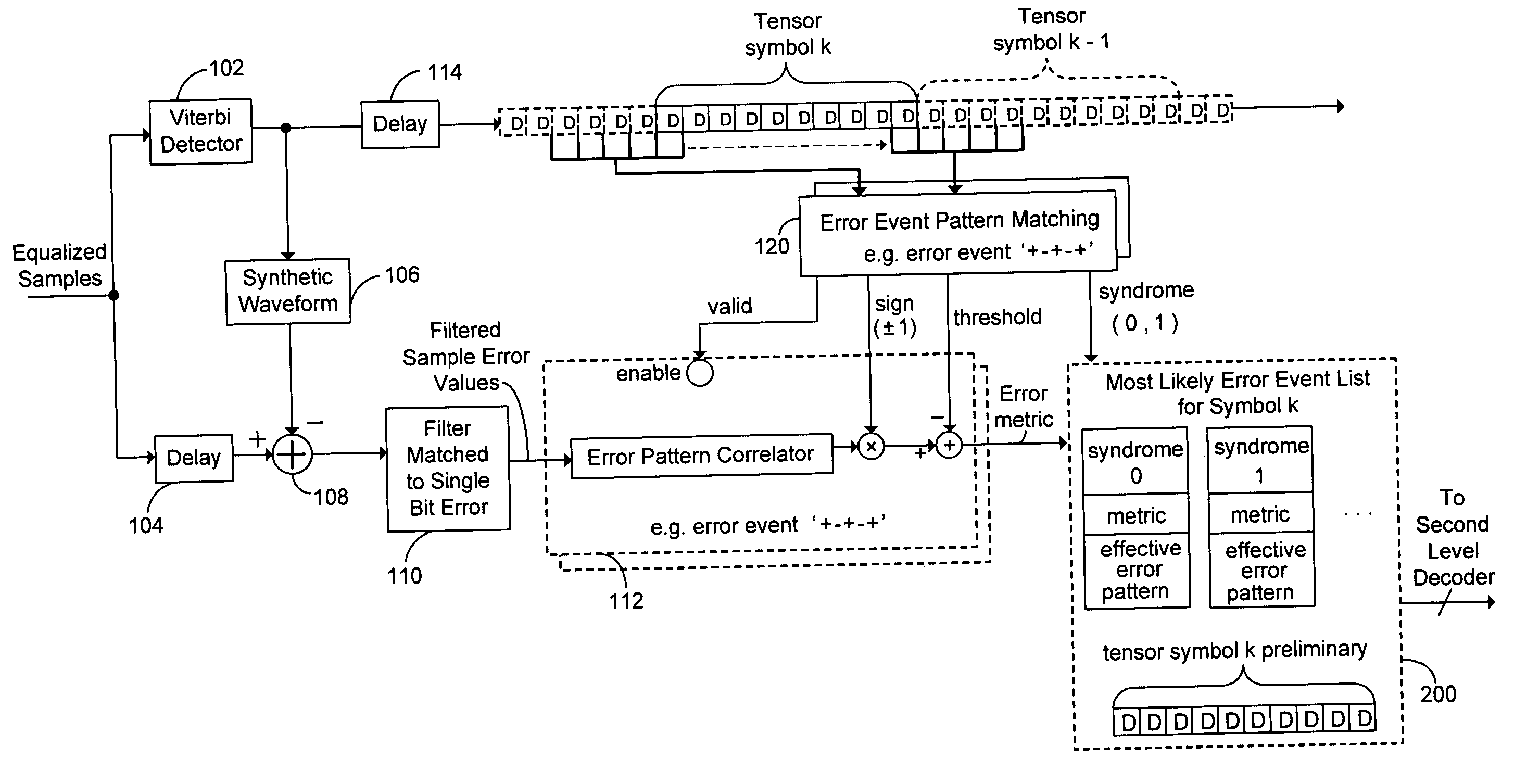

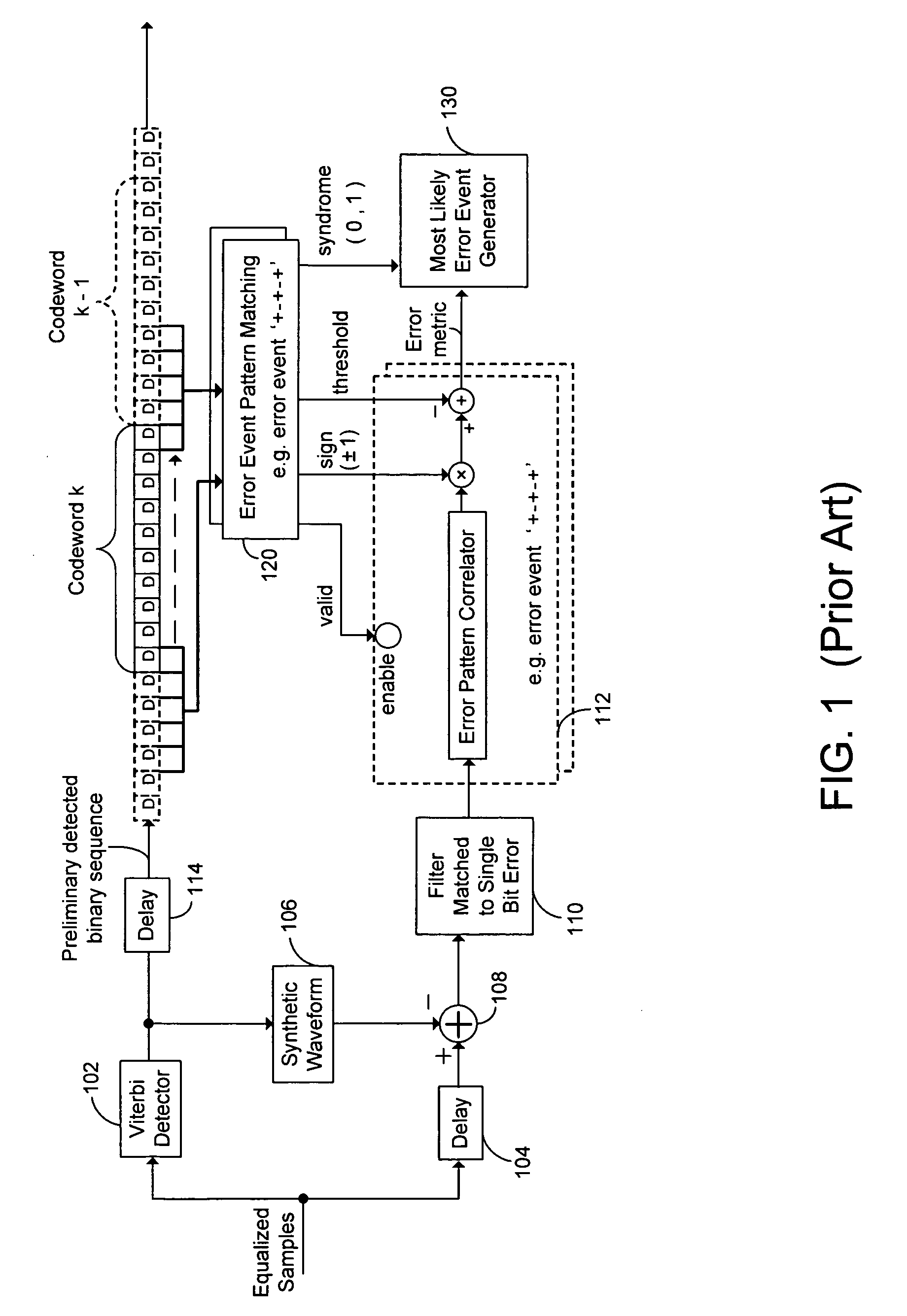

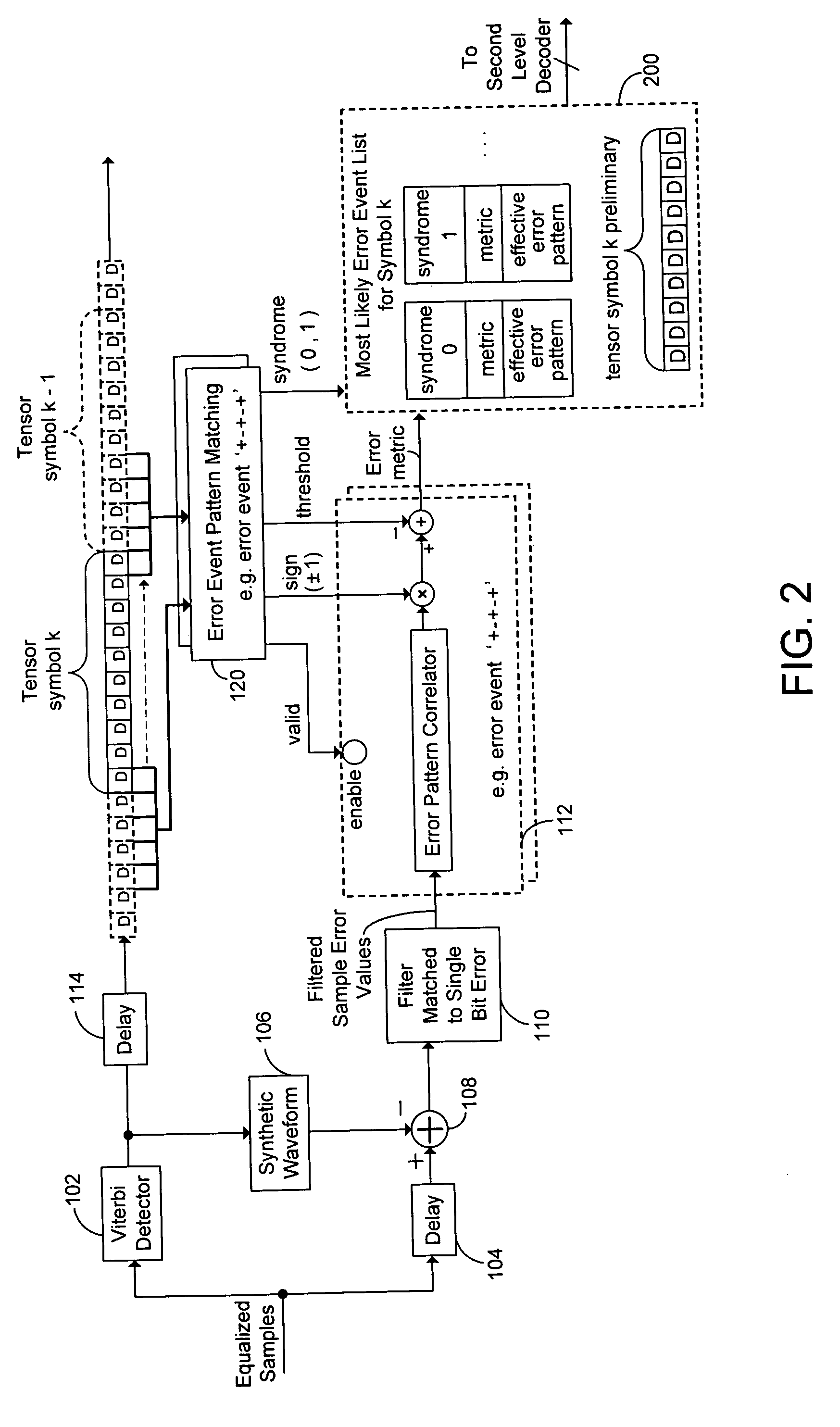

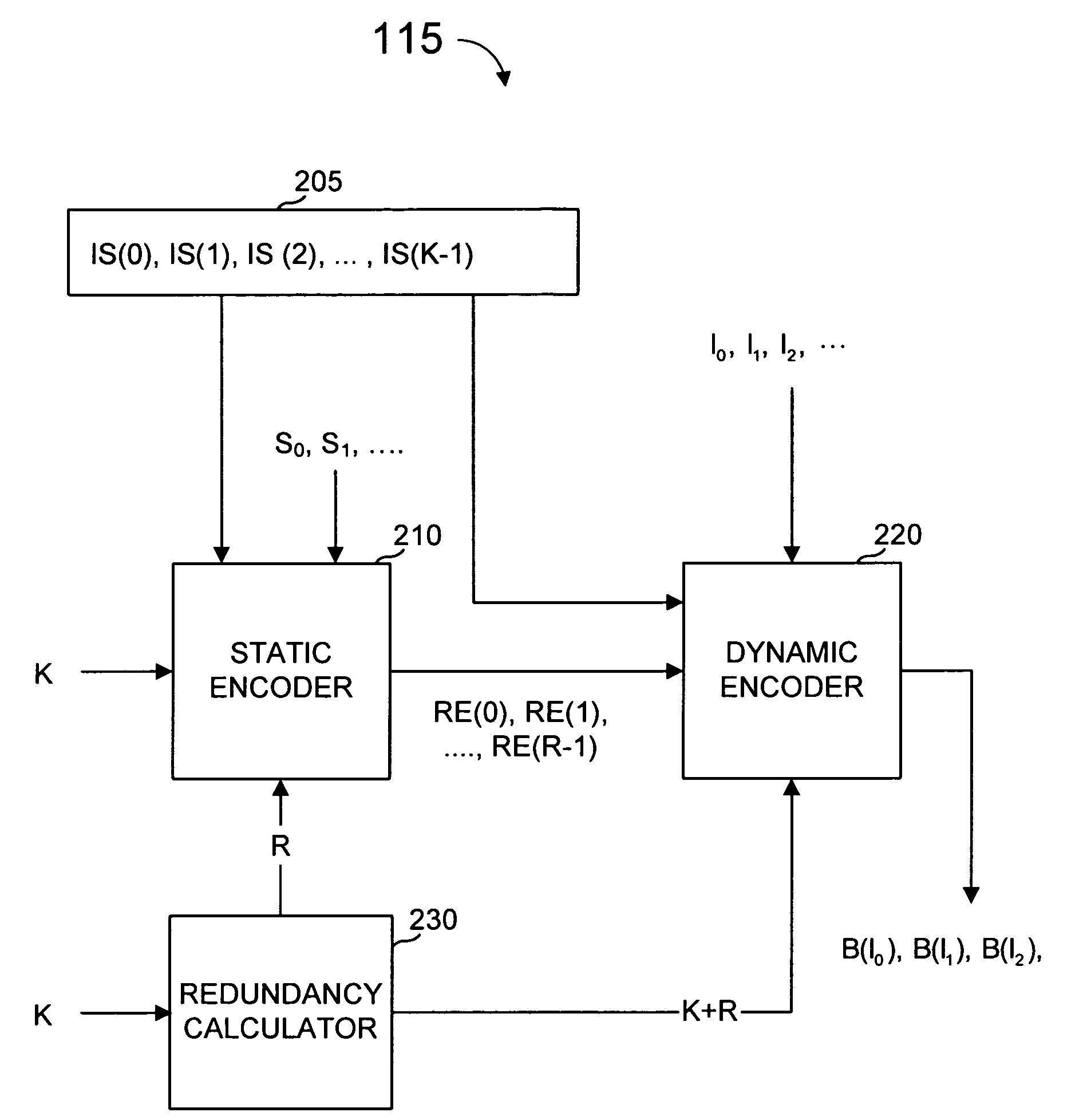

Decoding techniques for correcting errors using soft information

ActiveUS20070044006A1Increase ratingsData representation error detection/correctionOther decoding techniquesComputer hardwareSoft information

Two levels of error correction decoding are performed using first and second level decoders. A composite code formed by combining an inner component code and an outer component code can be used to decode the data and correct any errors. Performing two level decoding using a composite code allows the size of the inner parity block to be reduced to a single Reed-Solomon symbol while keeping a good code rate. The first level decoder generates soft information. The soft information can indicate a most likely error event for each possible syndrome value of the inner component code. The soft information can also include error metric values for each of the most likely error events. The second level decoder generates corrected syndrome values based on the soft information using the outer component code. The most likely trellis path that corresponds to the corrected syndrome values is then selected.

Owner:WESTERN DIGITAL TECH INC

File download and streaming system

Owner:QUALCOMM INC

Detection of synchronization mark from output of matched filter upstream of viterbi detector

InactiveUS20090274247A1Avoid delayAccurate startModification of read/write signalsOther decoding techniquesViterbi detectorMatched filter

Embodiments of the present invention relate to the detection of synchronization marks in data storage and retrieval. According to one embodiment, synchronization marks are detected from the output of a matched filter, upstream of the Viterbi detector. This approach avoids the delay associated with the latency of the Viterbi output, thereby allowing time to align parity framing and to properly start the time-varying trellis. Certain embodiments disclose 34- and 20-bit primary synchronization marks located at the beginning of a data region. Other embodiments disclose 16-, 20-, and 24-bit embedded synchronization marks located within a data region.

Owner:WESTERN DIGITAL TECH INC

Method for decoding data in non-volatile storage using reliability metrics based on multiple reads

ActiveUS7904793B2Other decoding techniquesRead-only memoriesLow-density parity-check codeDependability

Data stored in non-volatile storage is decoded using iterative probabilistic decoding and multiple read operations to achieve greater reliability. An error correcting code such as a low density parity check code may be used. In one approach, initial reliability metrics, such as logarithmic likelihood ratios, are used in decoding read data of a set of non-volatile storage element. The decoding attempts to converge by adjusting the reliability metrics for bits in code words which represent the sensed state. If convergence does not occur, e.g., within a set time period, the state of the non-volatile storage element is sensed again, current values of the reliability metrics in the decoder are adjusted, and the decoding again attempts to converge. In another approach, the initial reliability metrics are based on multiple reads. Tables which store the reliability metrics and adjustments based on the sensed states can be prepared before decoding occurs.

Owner:SANDISK TECH LLC

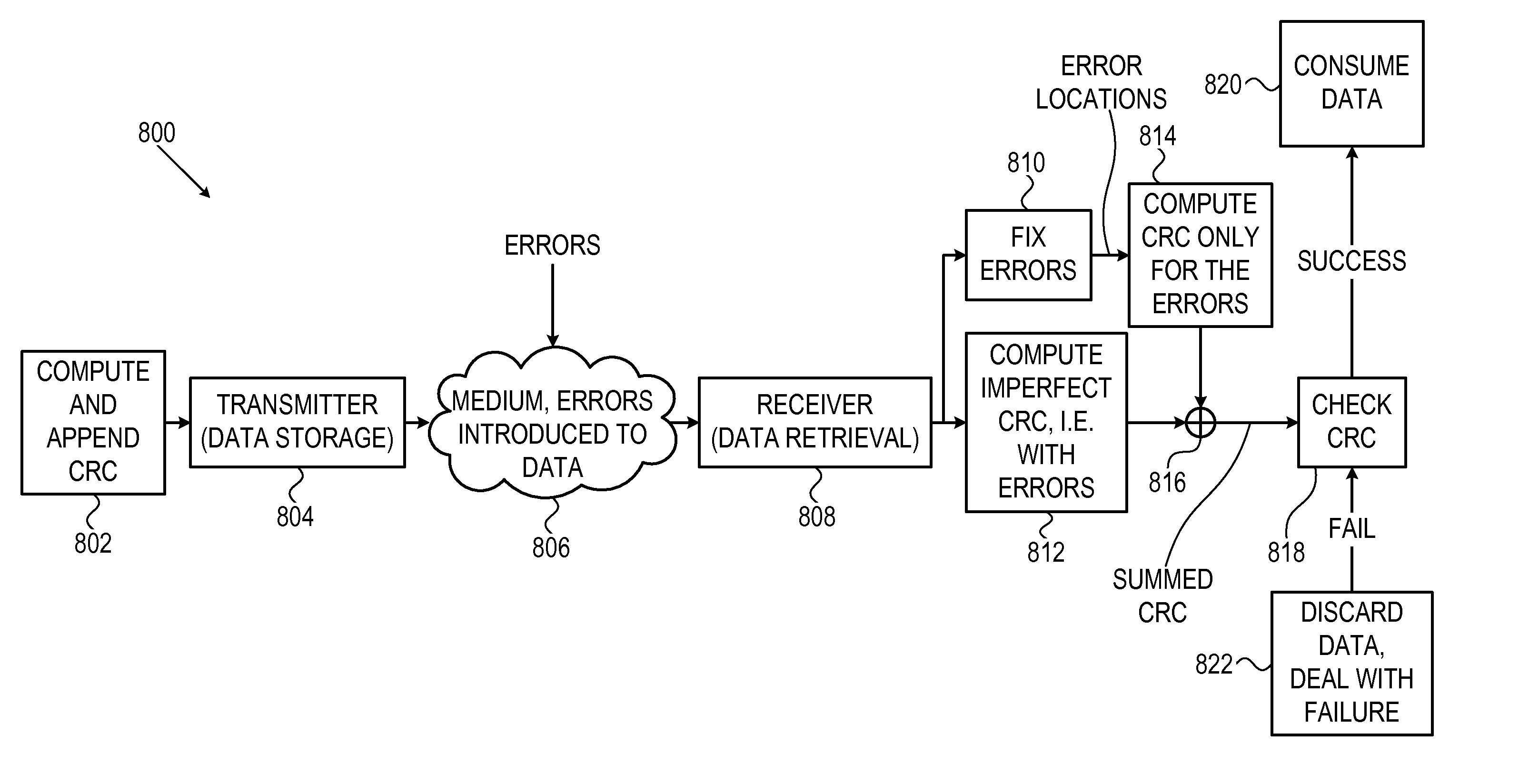

System and method for multi-dimensional encoding and decoding

ActiveUS20120005554A1Correction errorError correction/detection using convolutional codesOther decoding techniquesData setMulti dimensional

A system and method for using a cyclic redundancy check (CRC) to evaluate error corrections. A set of data and initial CRC values associated therewith may be received. The set of data by changing a sub-set of the data may be corrected. Intermediate CRC values may be computed for the entire uncorrected set of data in parallel with said correcting. Supplemental CRC values may be computed for only the sub-set of changed data after said correcting. The intermediate and supplemental CRC values may be combined to generate CRC values for the entire corrected set of data. The validity of the corrected set of data may be evaluated by comparing the combined CRC values with the initial CRC values.

Owner:AVAGO TECH INT SALES PTE LTD

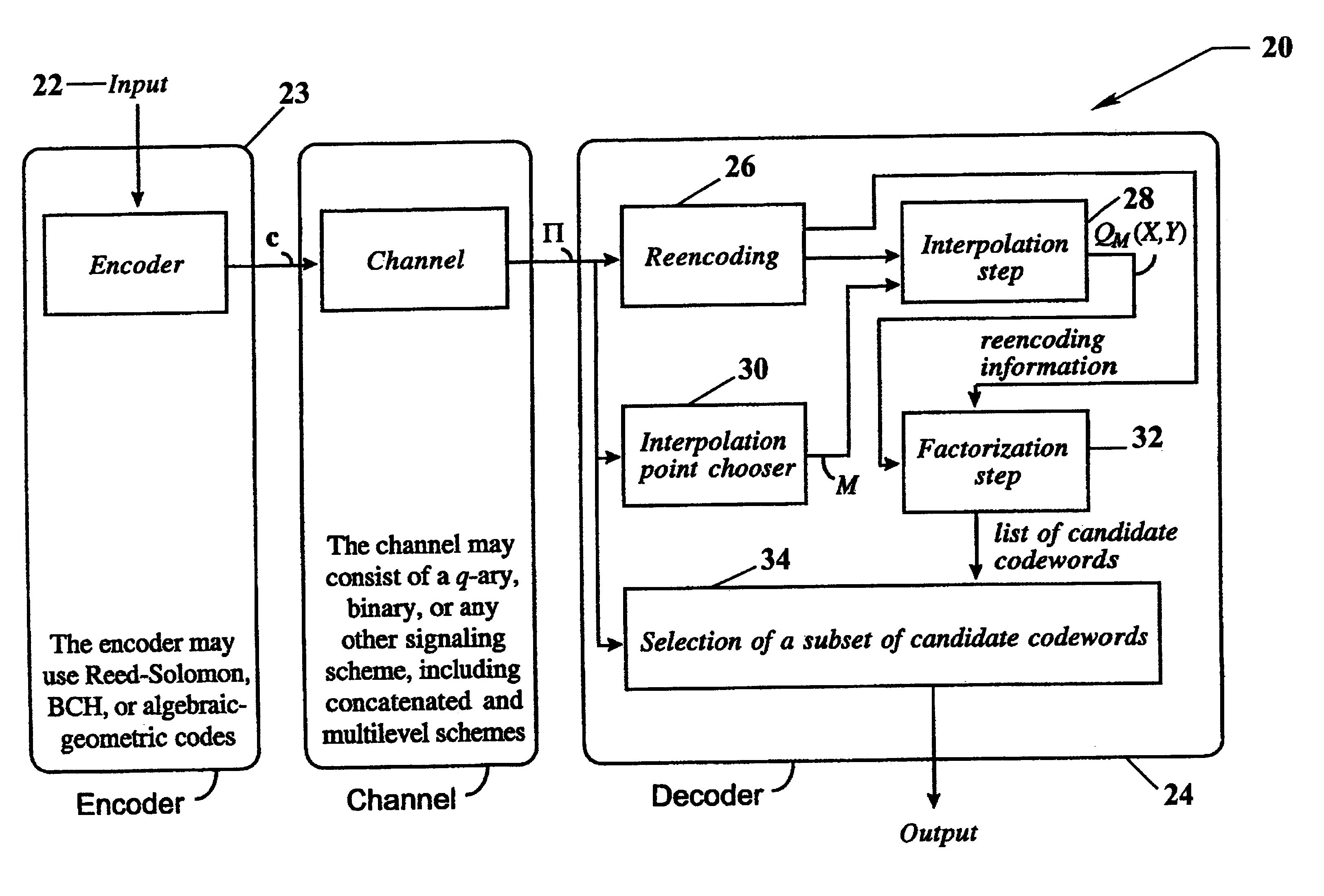

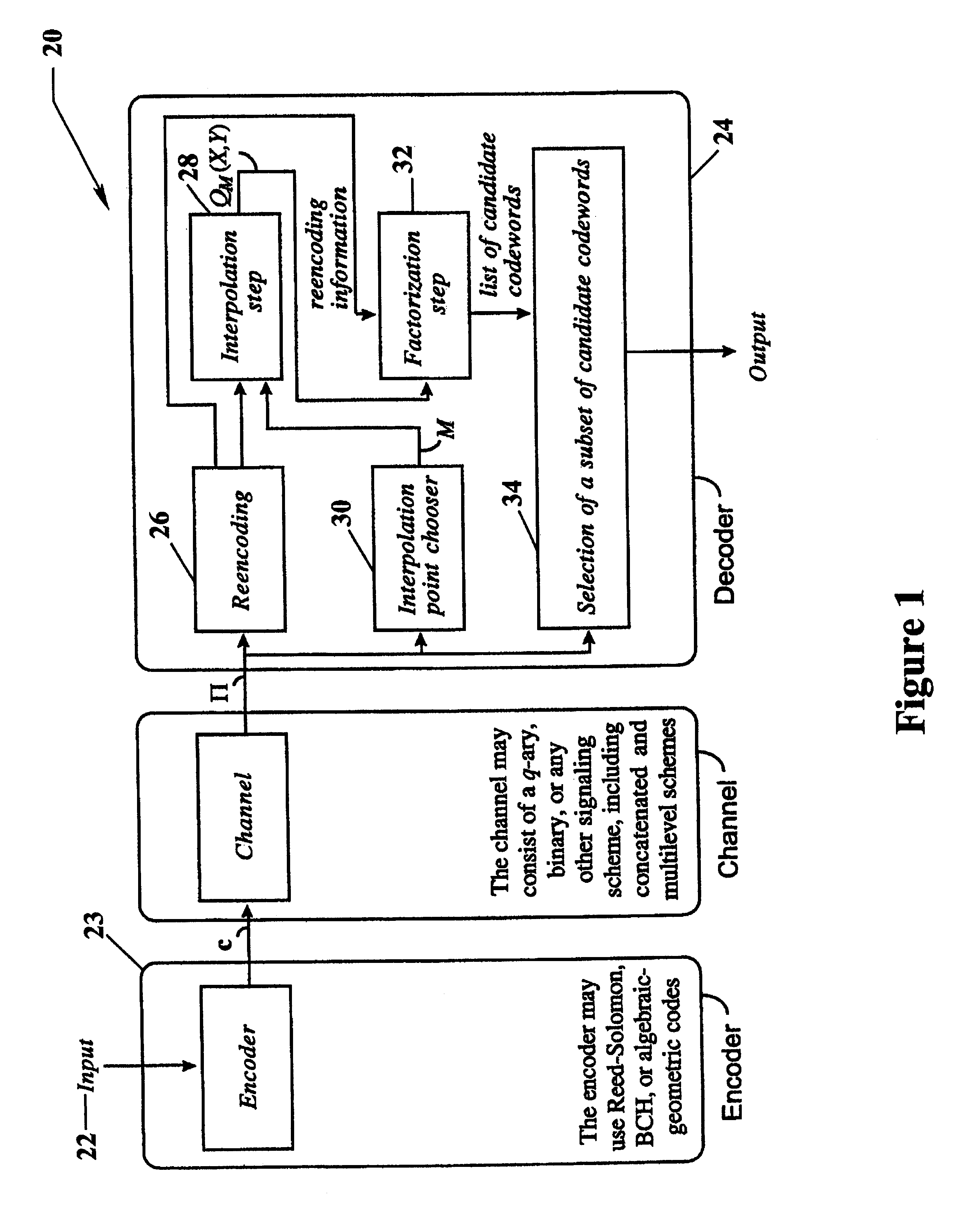

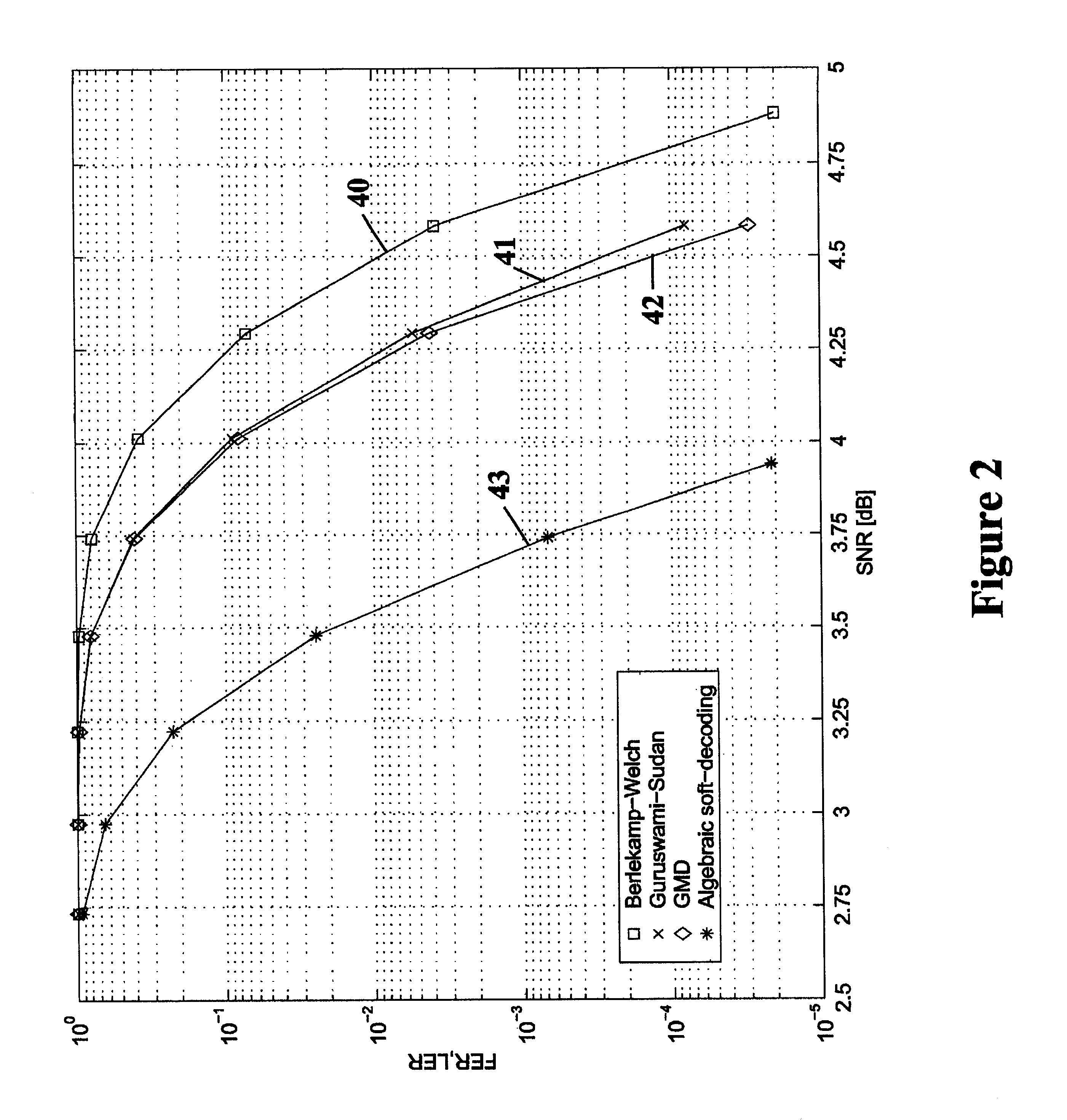

Algebraic soft decoding of reed-solomon codes

InactiveUS6634007B1Maximizes the expected scoreMaximizing the expected scoreOther decoding techniquesAlgebraic geometric codesDecoding methodsRound complexity

An algorithmic soft-decision decoding method for Reed-Solomon codes proceeds as follows. Given the reliability matrix Pi showing the probability that a code symbol of a particular value was transmitted at each position, computing a multiplicity matrix M which determines the interpolation points and their multiplicities. Given this multiplicity matrix M, soft interpolation is performed to find the non-trivial polynomial Q<HIL><PDAT>M< / SB><PDAT>(X,Y) of the lowest (weighted) degree whose zeros and their multiplicities are as specified by the matrix M. Given this non-trivial polynomial Q<HIL><PDAT>M< / SB><PDAT>(X,Y), all factors of Q<HIL><PDAT>M< / SB><PDAT>(X,Y) of type Y-f(X) are found, where f(X) is a polynomial in X whose degree is less than the dimension k of the Reed-Solomon code. Given these polynomials f(X), a codeword is reconstructed from each of them, and the most likely of these codewords selected as the output of the algorithm. The algorithmic method is algebraic, operates in polynomial time, and significantly outperforms conventional hard-decision decoding, generalized minimum distance decoding, and Guruswami-Sudan decoding of Reed-Solomon codes. By varying the total number of interpolation points recorded in the multiplicity matrix M, the complexity of decoding can be adjusted in real time to any feasible level of performance. The algorithmic method extends to algebraic soft-decision decoding of Bose-Chaudhuri-Hocquenghem codes and algebraic-geometry codes.< / PTEXT>

Owner:MIND FUSION LLC

Popular searches

Single error correction Error correction/detection by combining multiple code structures Forward error control use Amplitude-modulated carrier systems Amplitude demodulation Signal channels Local circuits Secret communication Transmitter/receiver shaping networks Transmission link error control system