Patents

Literature

370 results about "Viterbi decoder" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

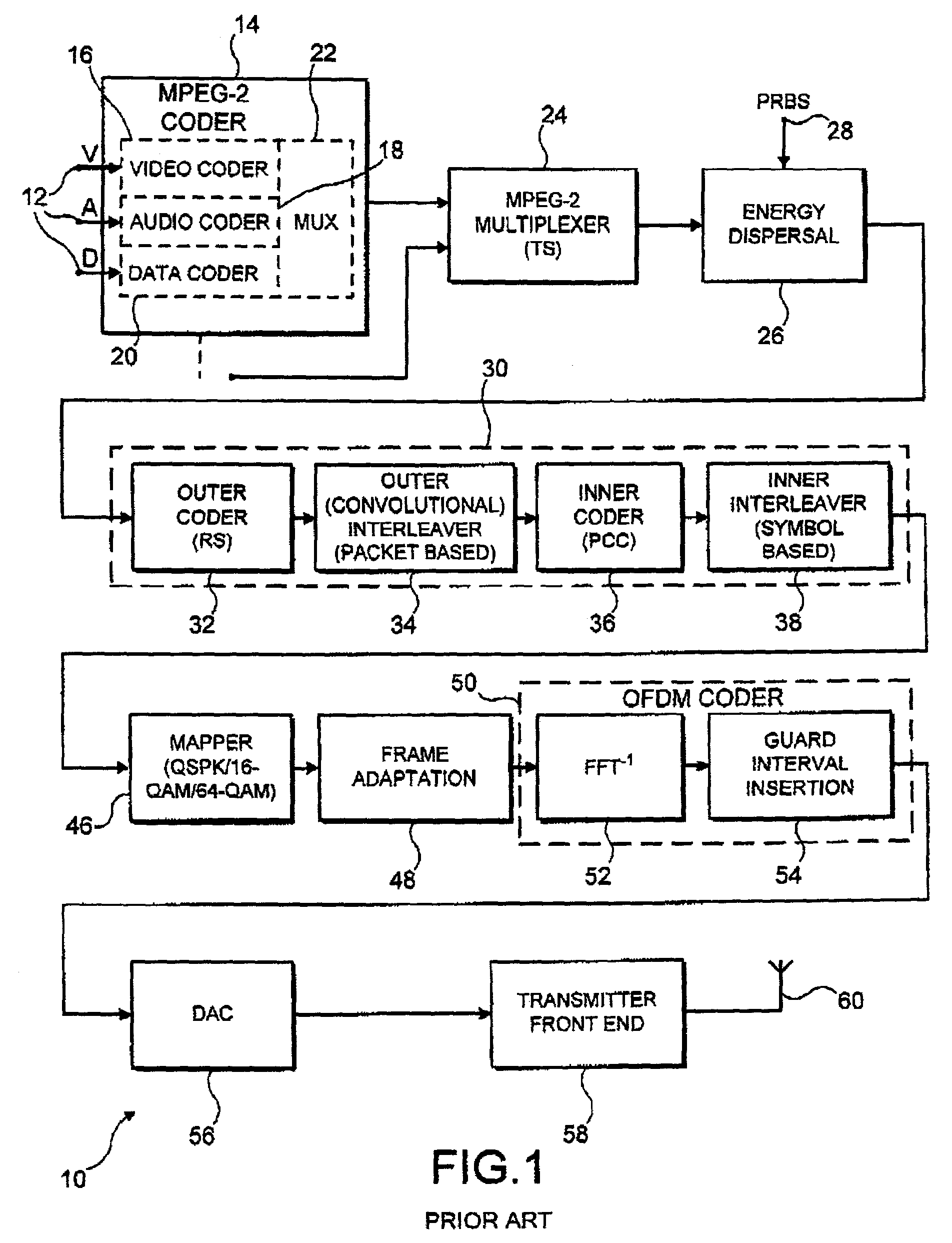

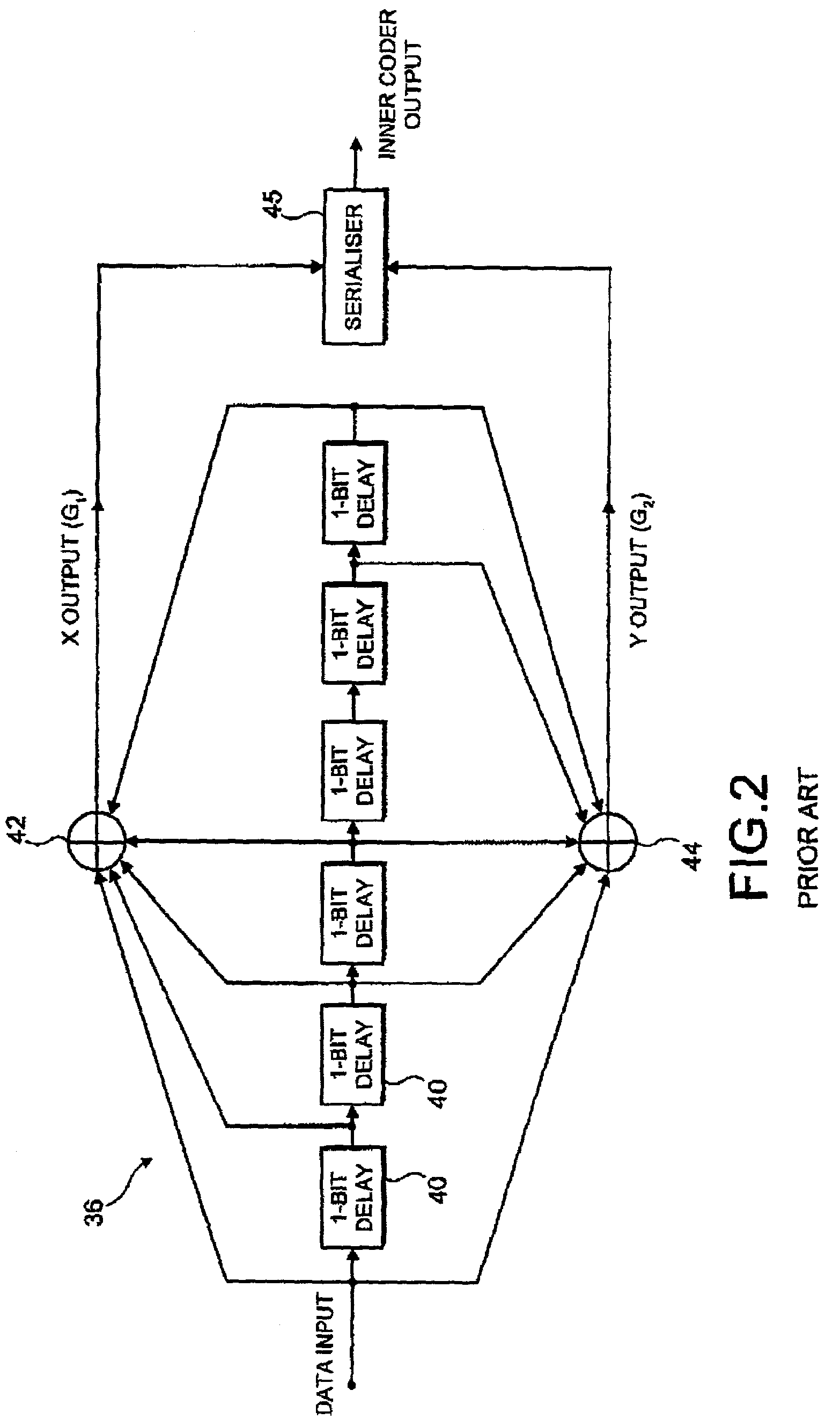

A Viterbi decoder uses the Viterbi algorithm for decoding a bitstream that has been encoded using convolutional code or trellis code. There are other algorithms for decoding a convolutionally encoded stream (for example, the Fano algorithm). The Viterbi algorithm is the most resource-consuming, but it does the maximum likelihood decoding. It is most often used for decoding convolutional codes with constraint lengths k≤3, but values up to k=15 are used in practice.

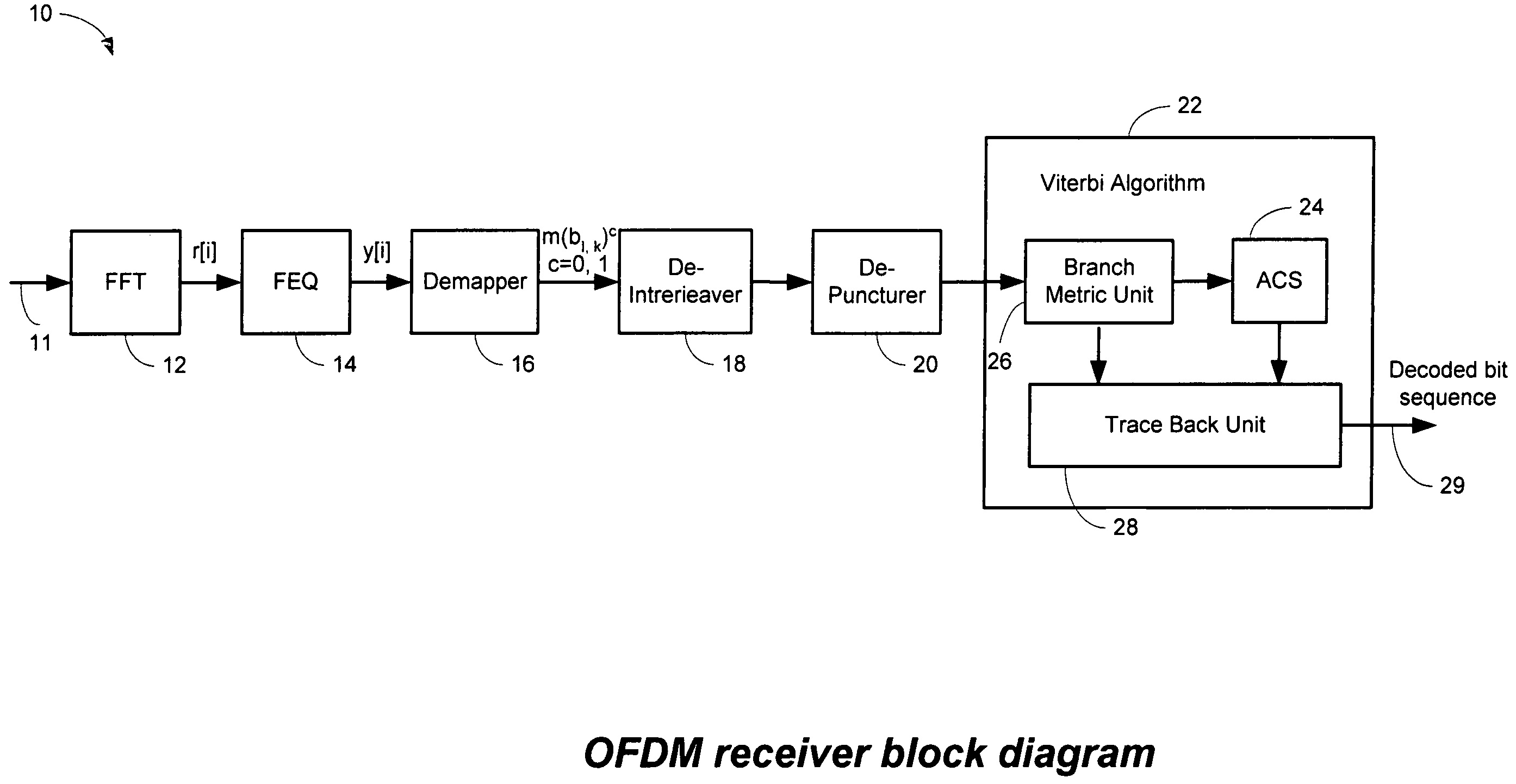

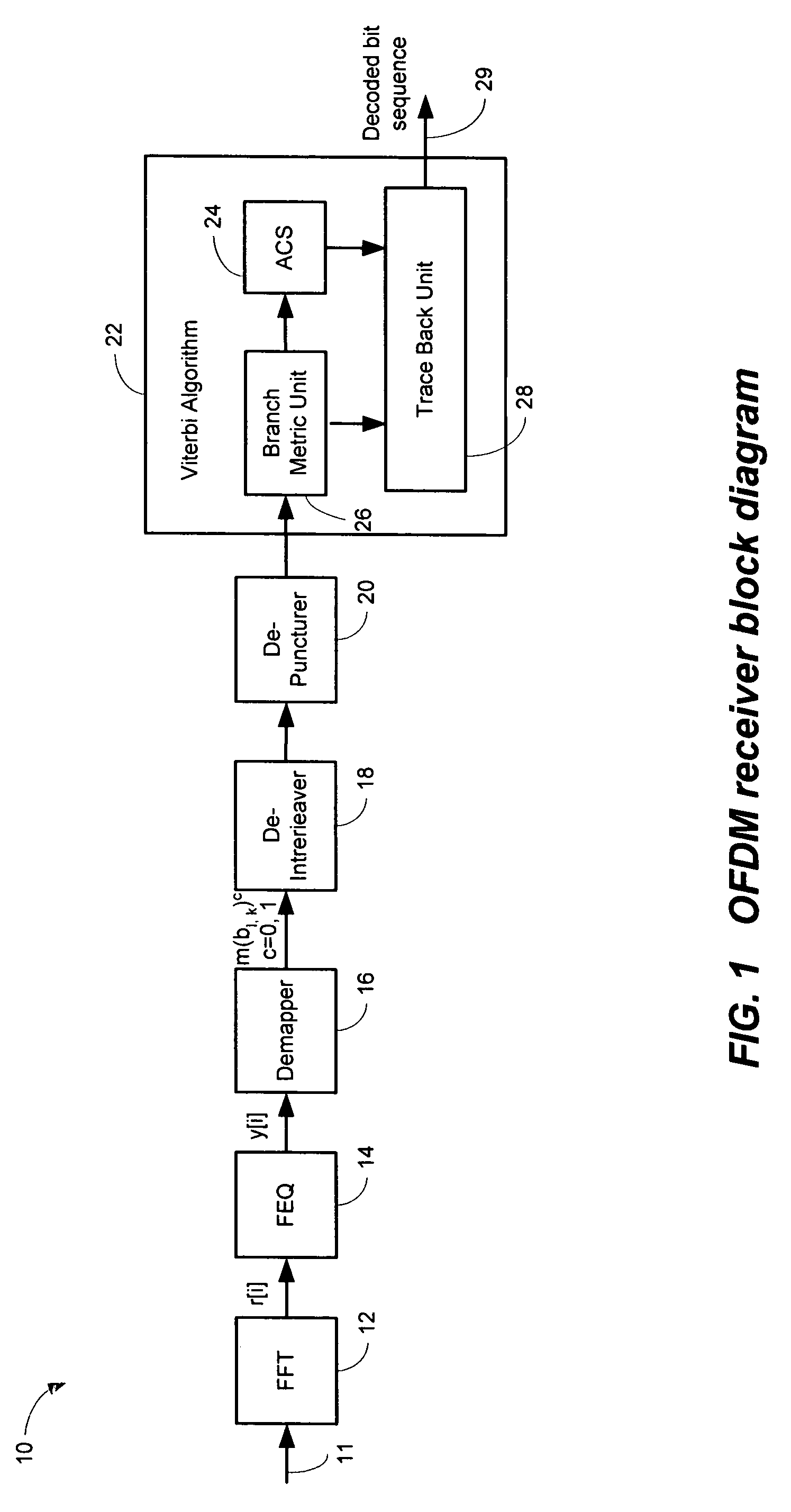

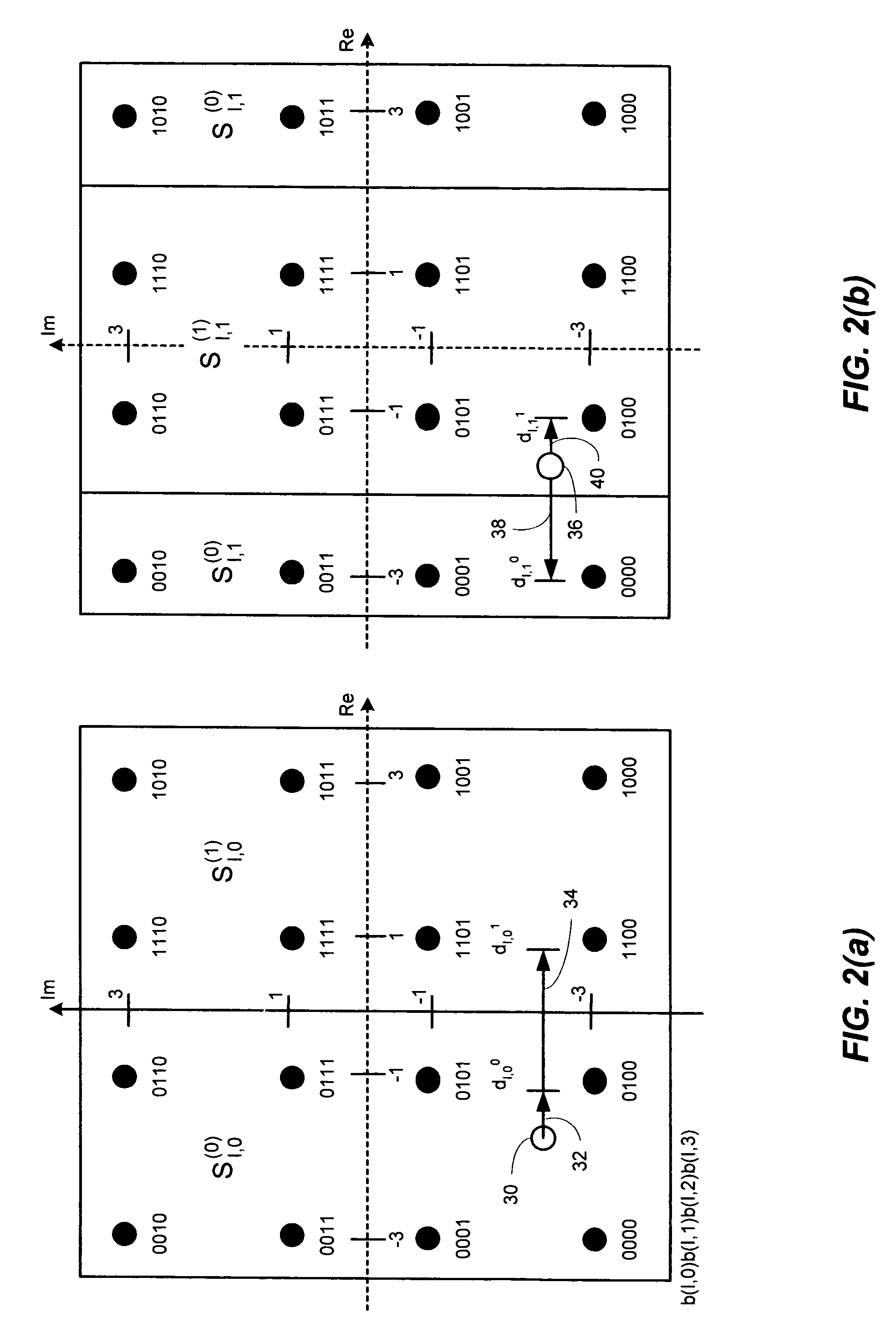

Efficient soft decision demapper to minimize viterbi decoder complexity

InactiveUS7313750B1Improve performanceSmall sizeData representation error detection/correctionOther decoding techniquesViterbi decoderComputer science

A receiver system that receives signals and has a demapper device that is responsive to an equalizer output and generates a demapper output including one or more bit metrics. The receiver system also generates equalizer output, and the demapper uses distance measure to calculate bit metrics. The receiver system uses demapper output to generate a processed output. The receiver system further includes a convolutional decoder which is responsive to the processed output, and subsequently generates a decoded bit sequence, as well as uses the processed output to generate one or more path metrics. The convolutional decoder uses bit metrics and path metrics to the decode processed output, to generate a decoded bit sequence. The receiver system uses the distance measure to reduce the size of the bit metrics and the size of the path metrics to improve the performance of said convolutional decoder.

Owner:MEDIATEK INC

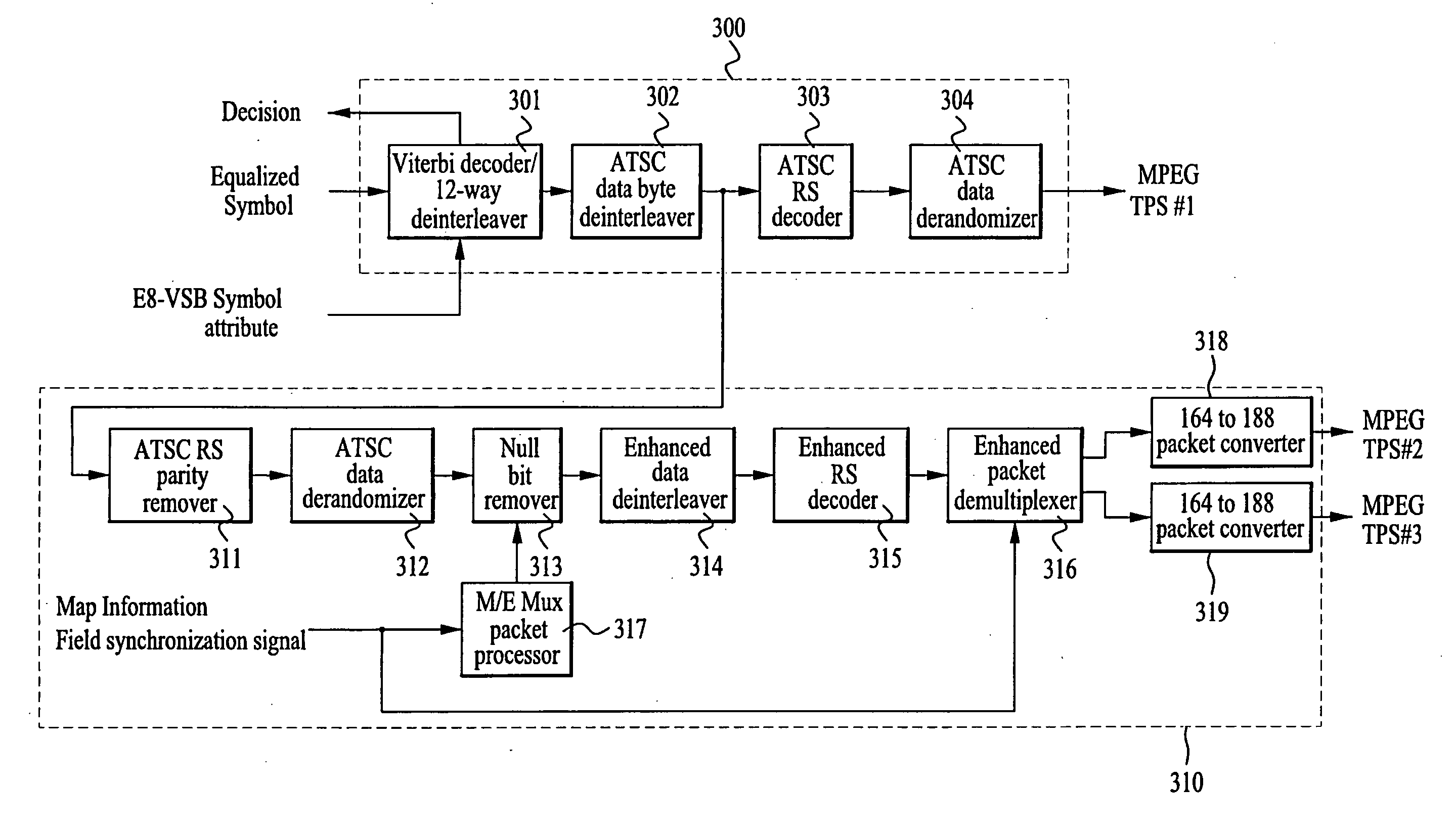

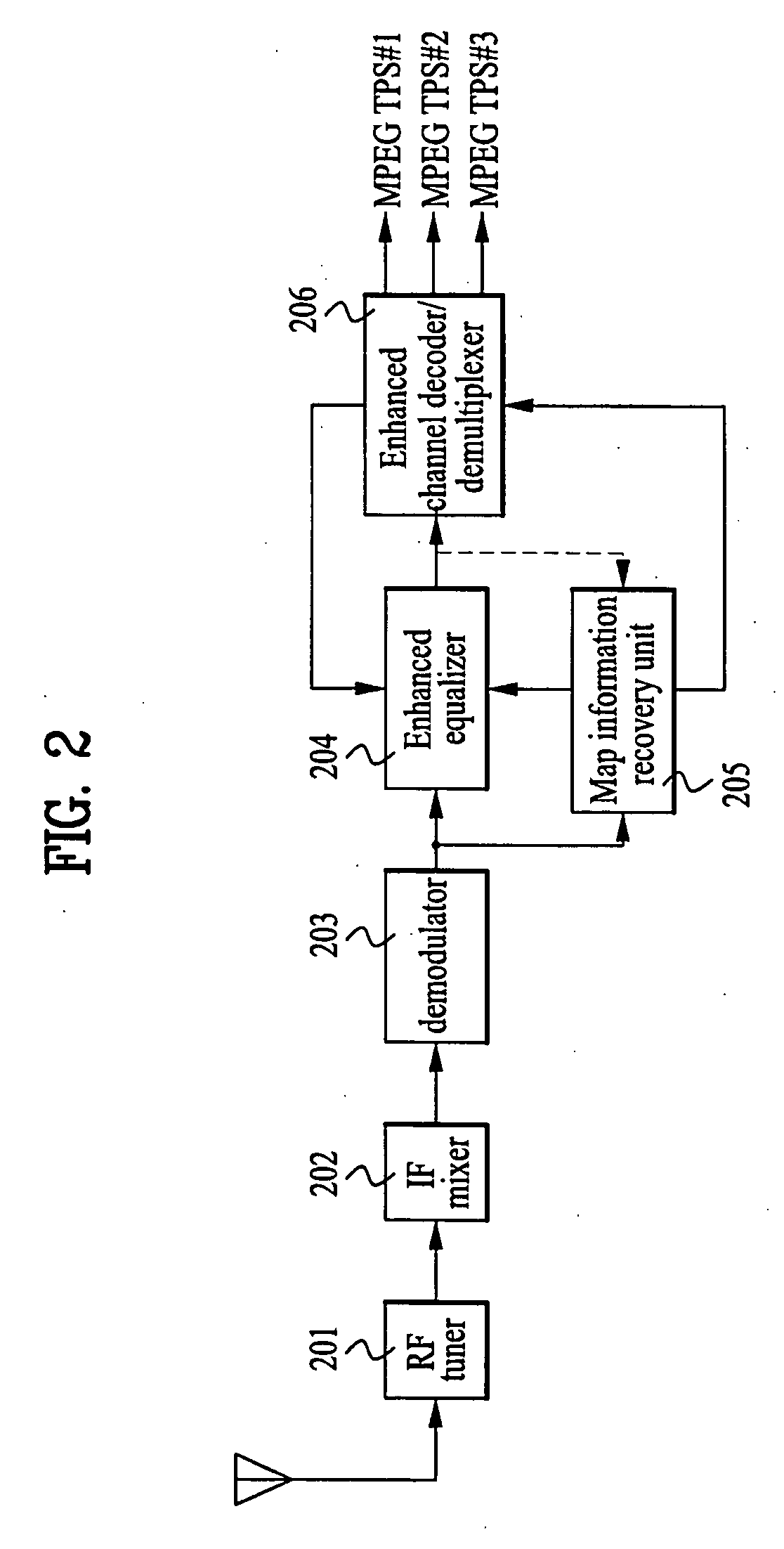

Enhanced VSB viterbi decoder

An enhanced VSB receiver includes a tuner which tunes an RF signal and converts it into an IF signal, an IF mixer which converts the IF signal into a baseband signal, and a demodulator which demodulates the baseband signal signal into a VSB signal. The enhanced VSB receiver further includes a map recovery unit which recovers VSB map information of the VSB signal, an enhanced equalizer for compensating channel distortion of the VSB signal and outputting an equalized symbol, and an enhanced Viterbit decoder for estimating whether polarity inversion occurred during a symbol period of the equalized symbol and Viterbi-decoding the equalized symbol based on the polarity estimation.

Owner:LG ELECTRONICS INC

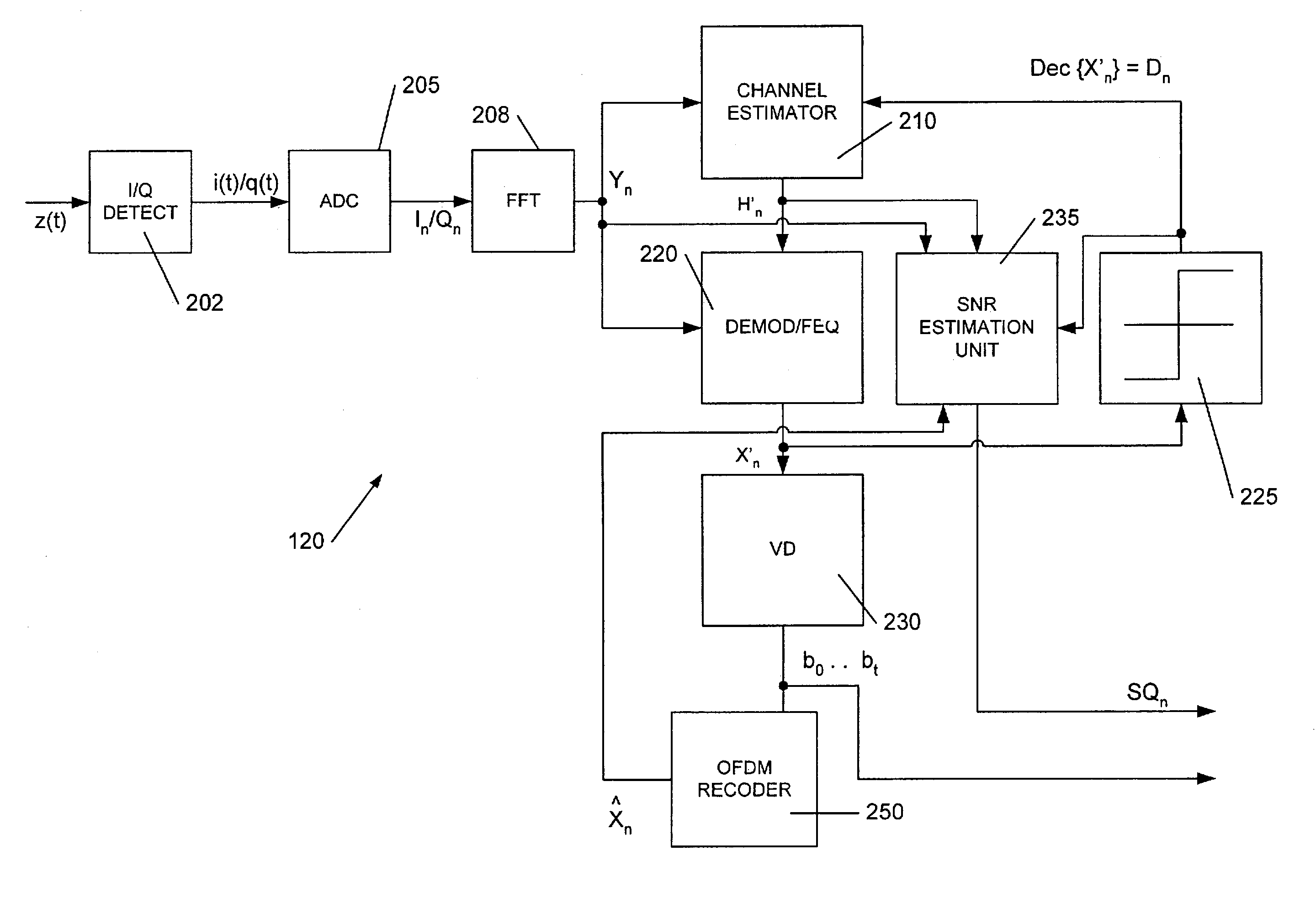

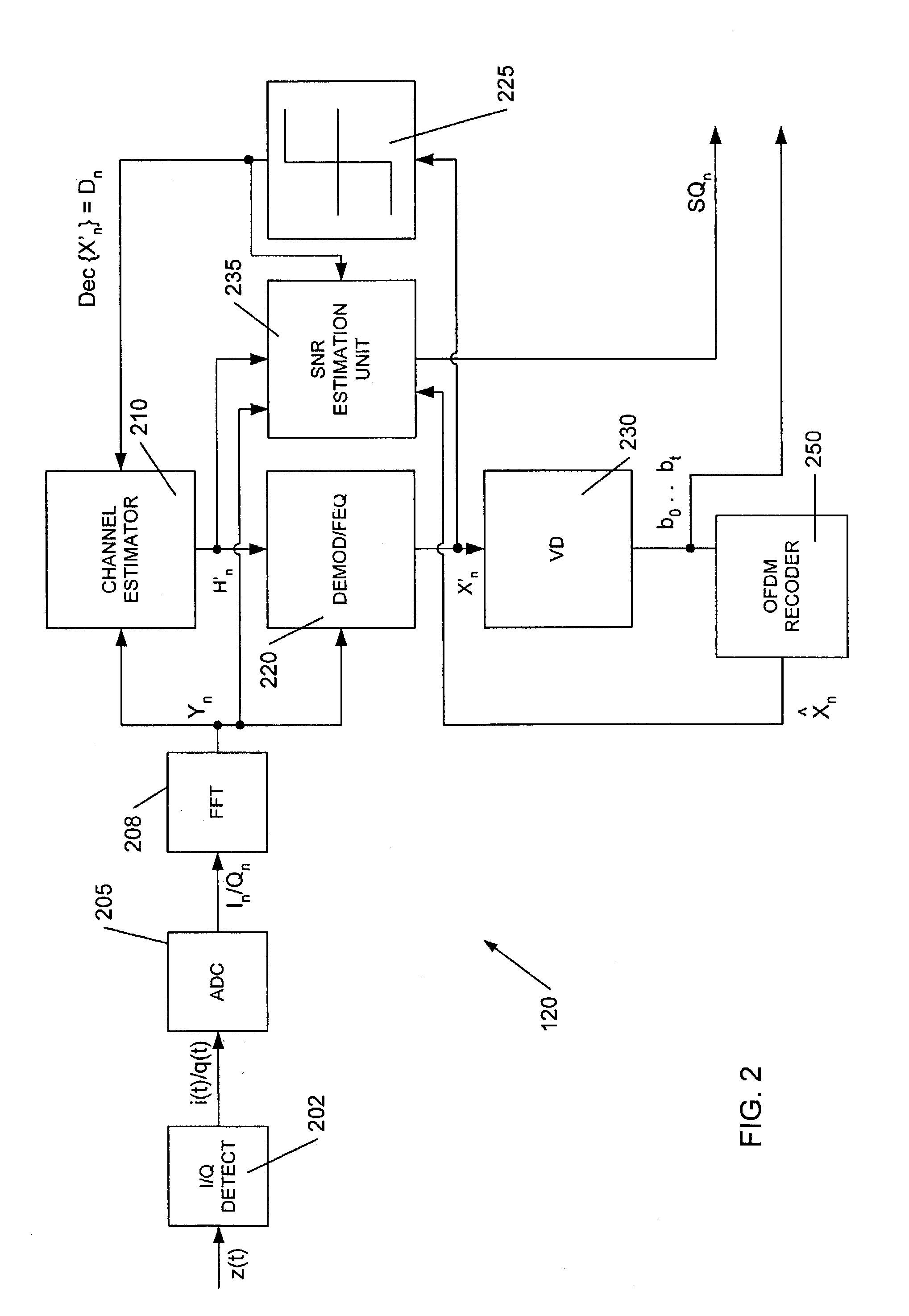

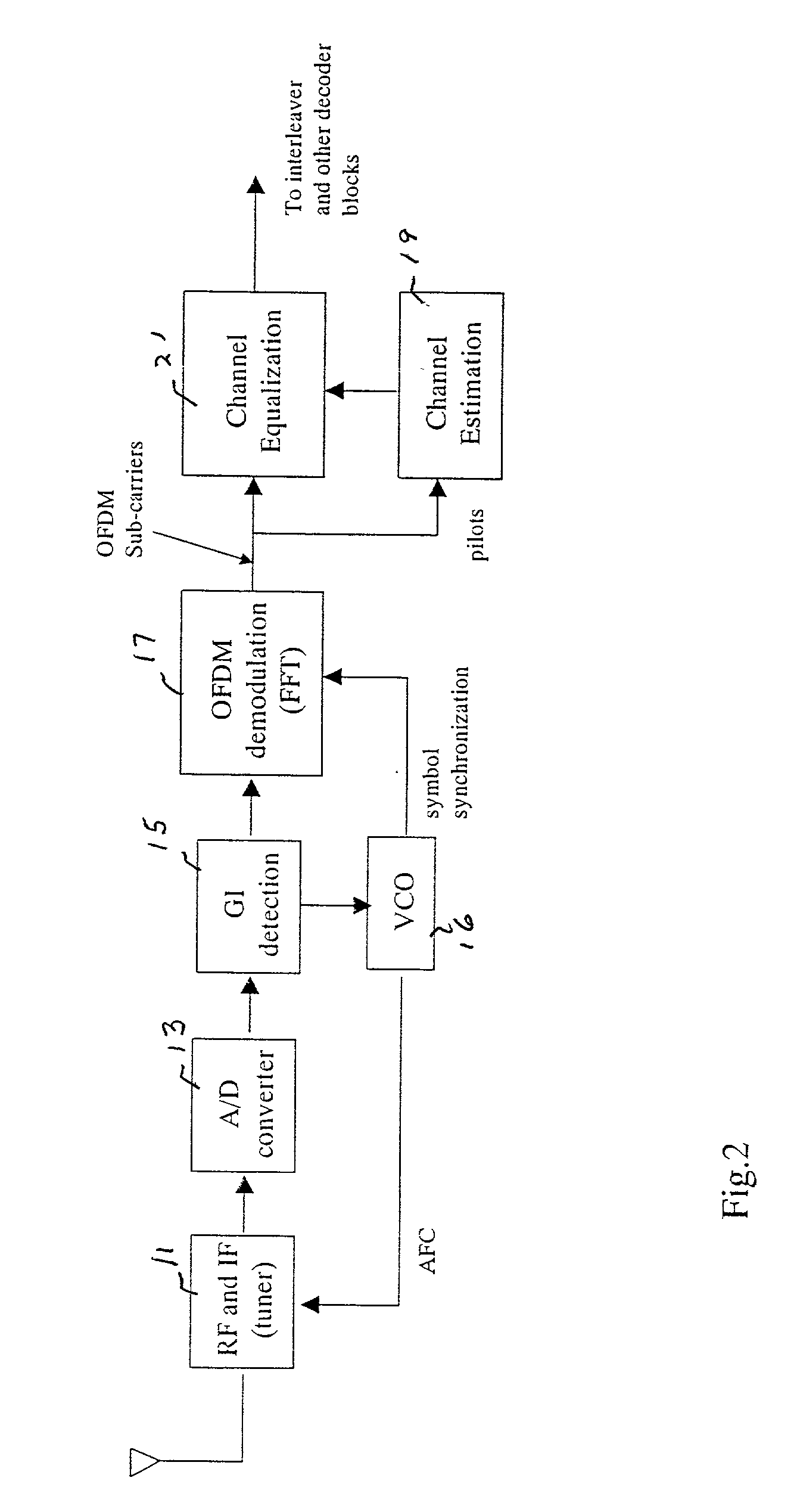

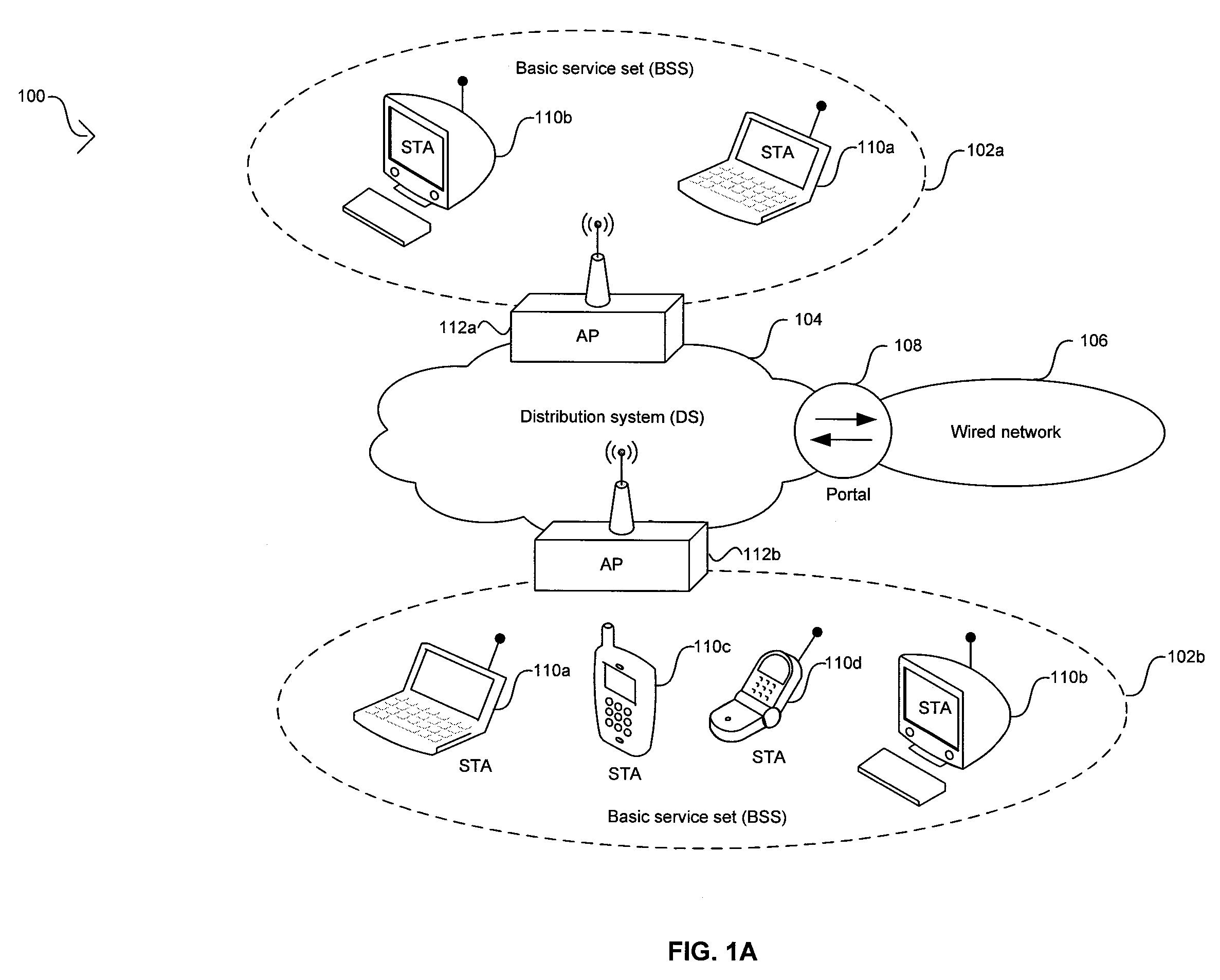

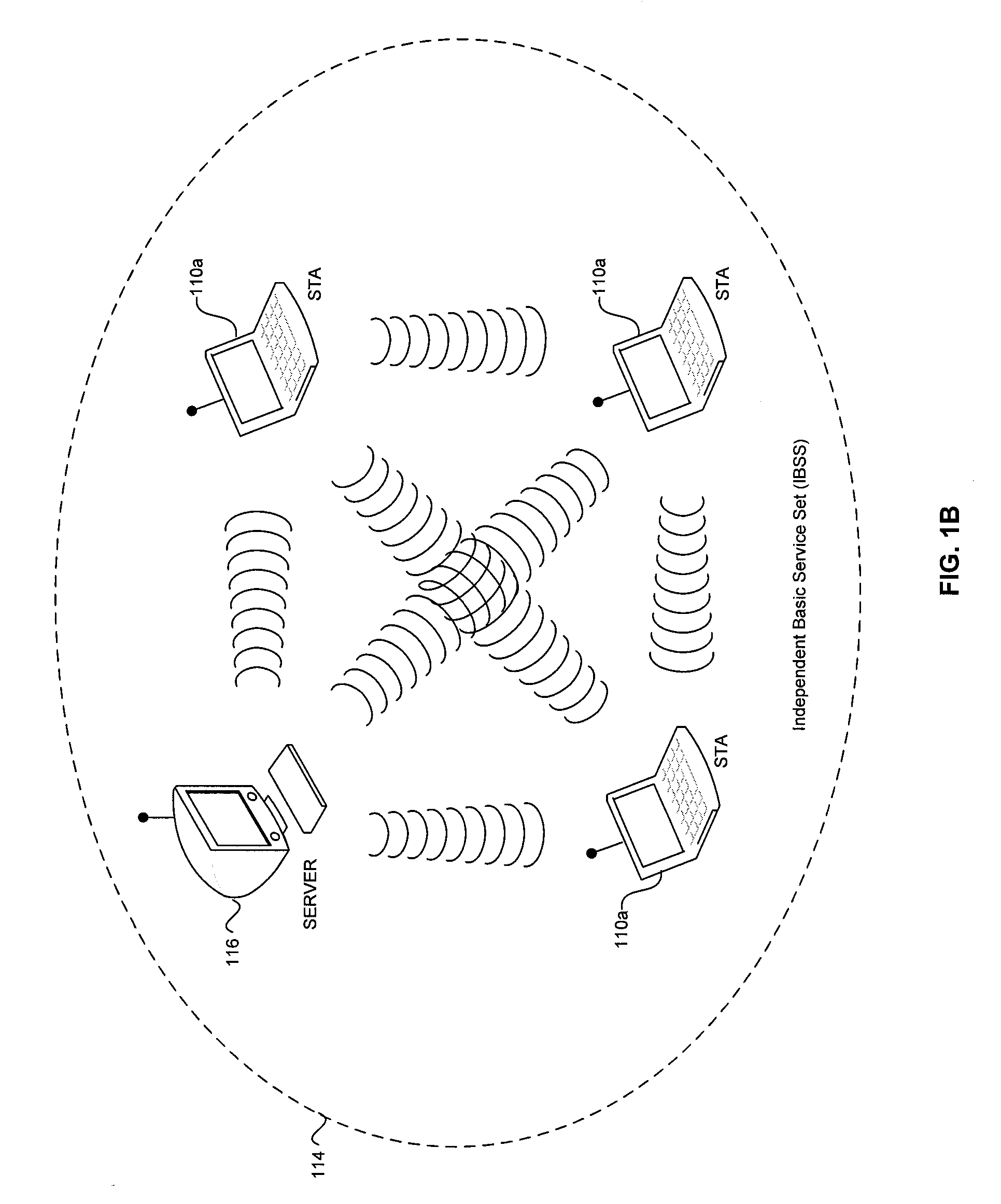

Apparatus and method for measuring signal quality of a wireless communications link

ActiveUS7016651B1Way accurateAccurate geometric SNR estimateResonant long antennasError detection/prevention using signal quality detectorViterbi decoderTelecommunications link

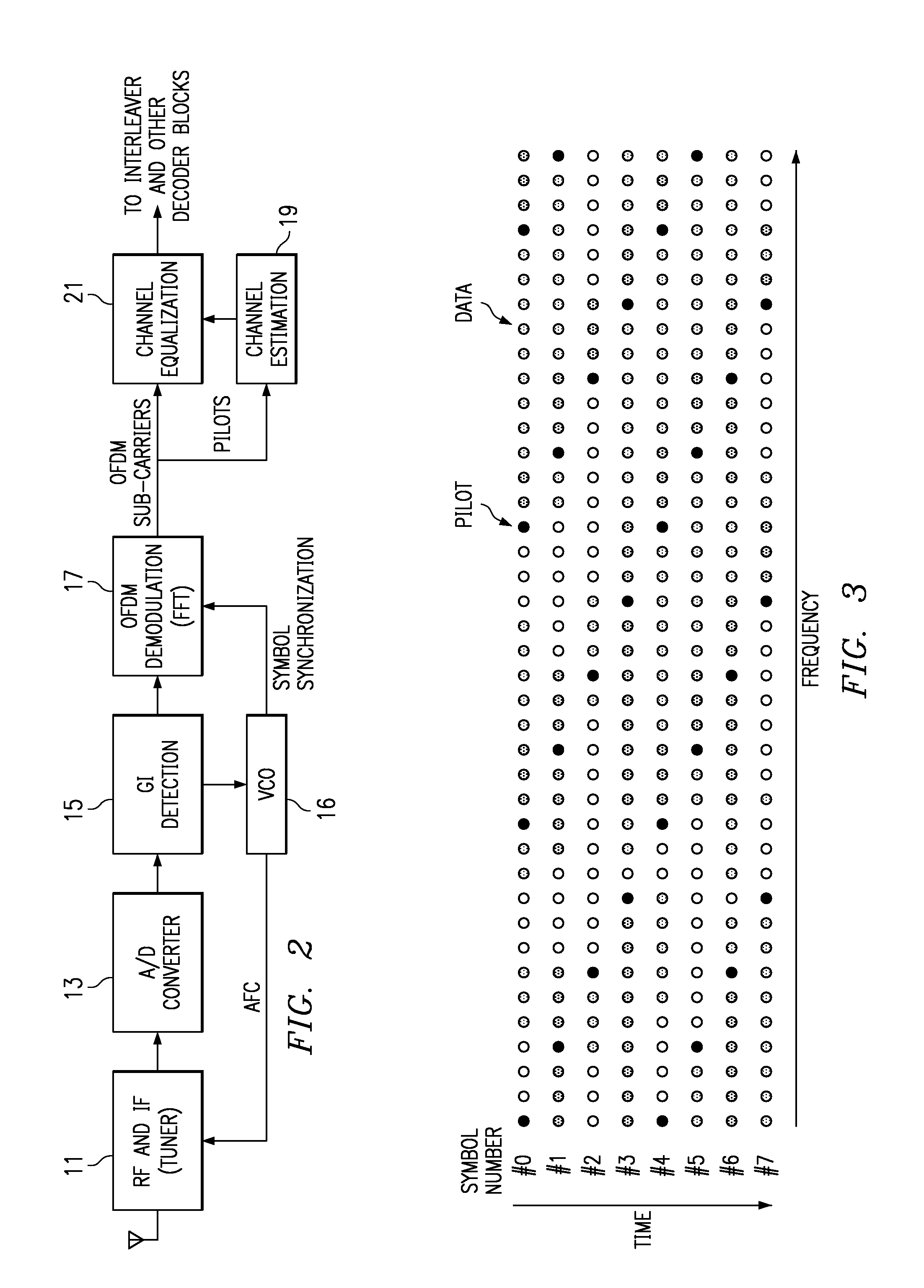

Techniques for measuring signal quality in a communications link supporting OFDM symbol transfer across plural sub-carriers are disclosed. These techniques employ a link interface receiving OFDM symbol(s) from the link, and a signal-to-noise ratio (SNR) estimation unit generating an estimate of a geometric SNR (SNRgeo) for the received symbols based on an average of the logrithmic difference between soft decision and hard decisions for the received symbol. SNRgeo here defines a scalar measure of the link signal quality, which results in a computationally efficient yet accurate link signal quality assessment, and thereby permit selective link characteristic alteration. Only sub-carrier subsets need be used to derive a relatively an accurate SNRgeo estimate. Sharing calculation resources between SNR estimation and soft decision units further reduce implementation complexity. Hard decision generation may use a relatively quick slicer or more accurate viterbi decoder / OFDM re-coder combination, as design goals dictate.

Owner:MARVELL ASIA PTE LTD

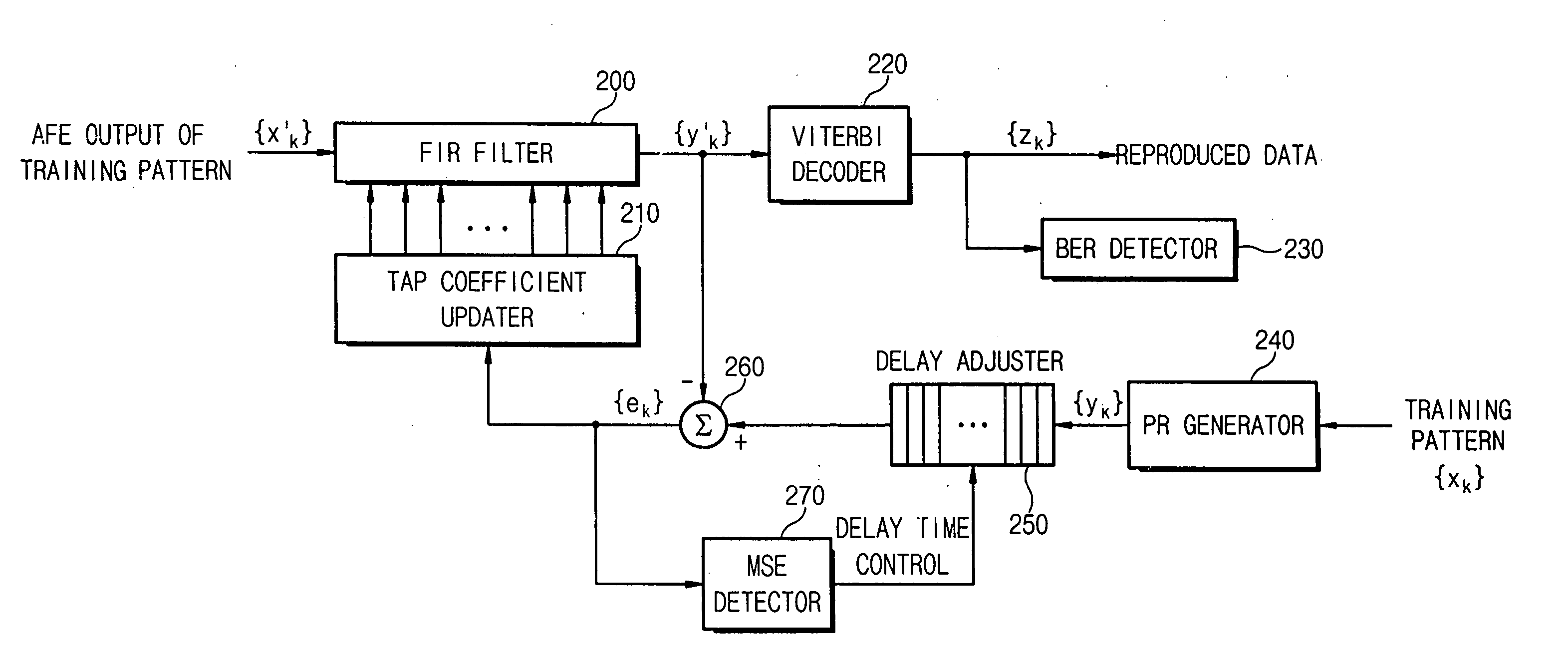

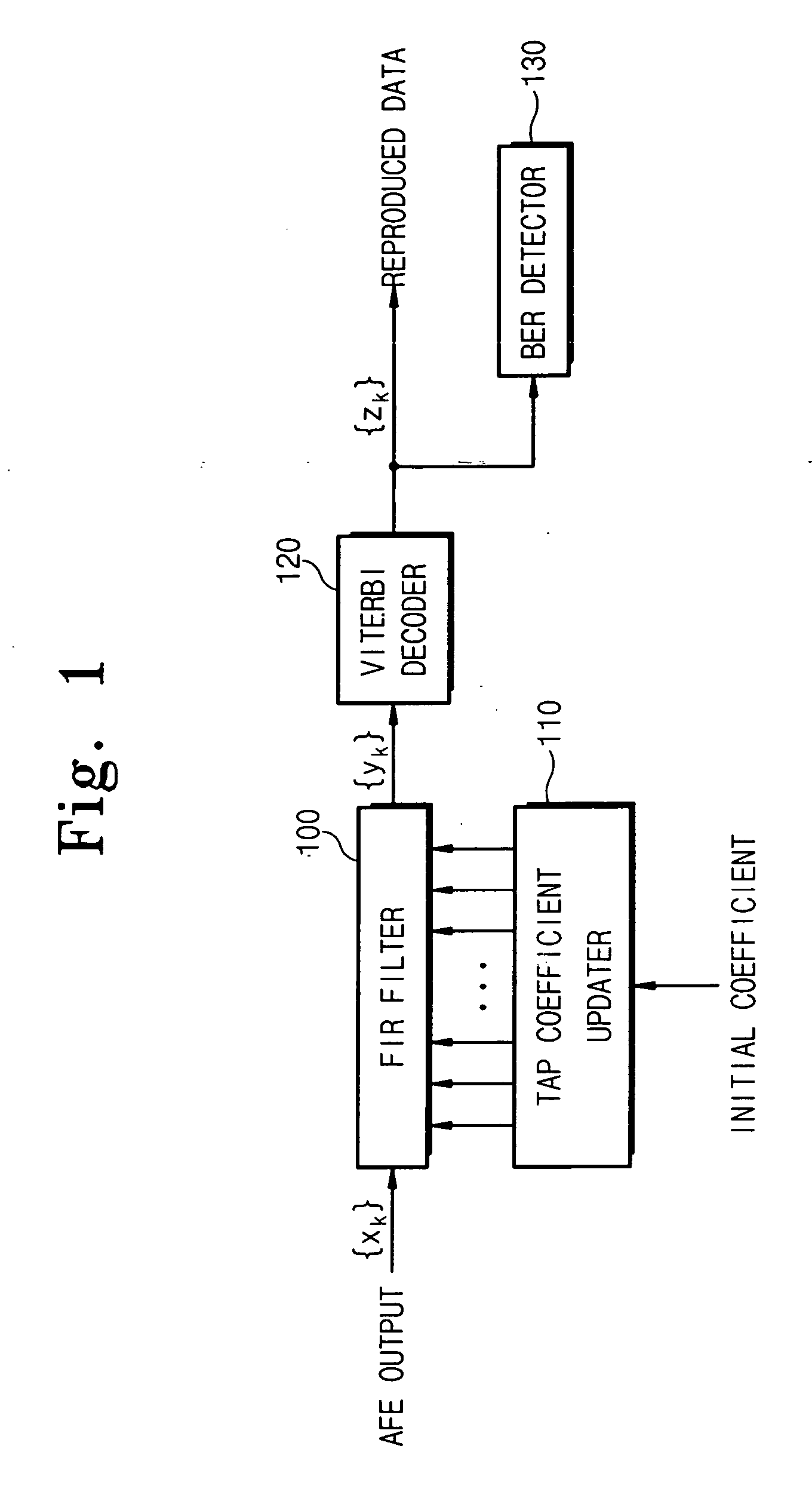

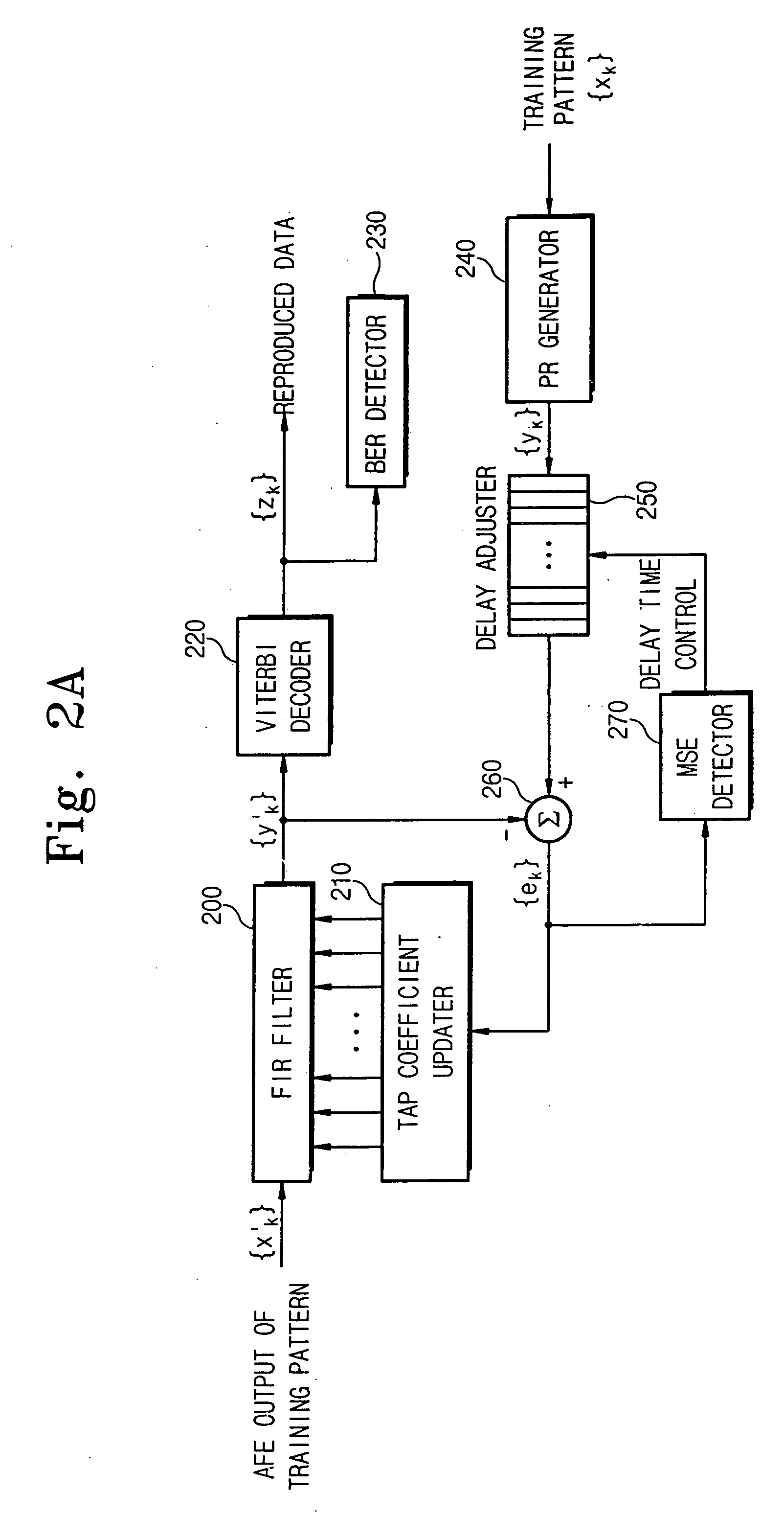

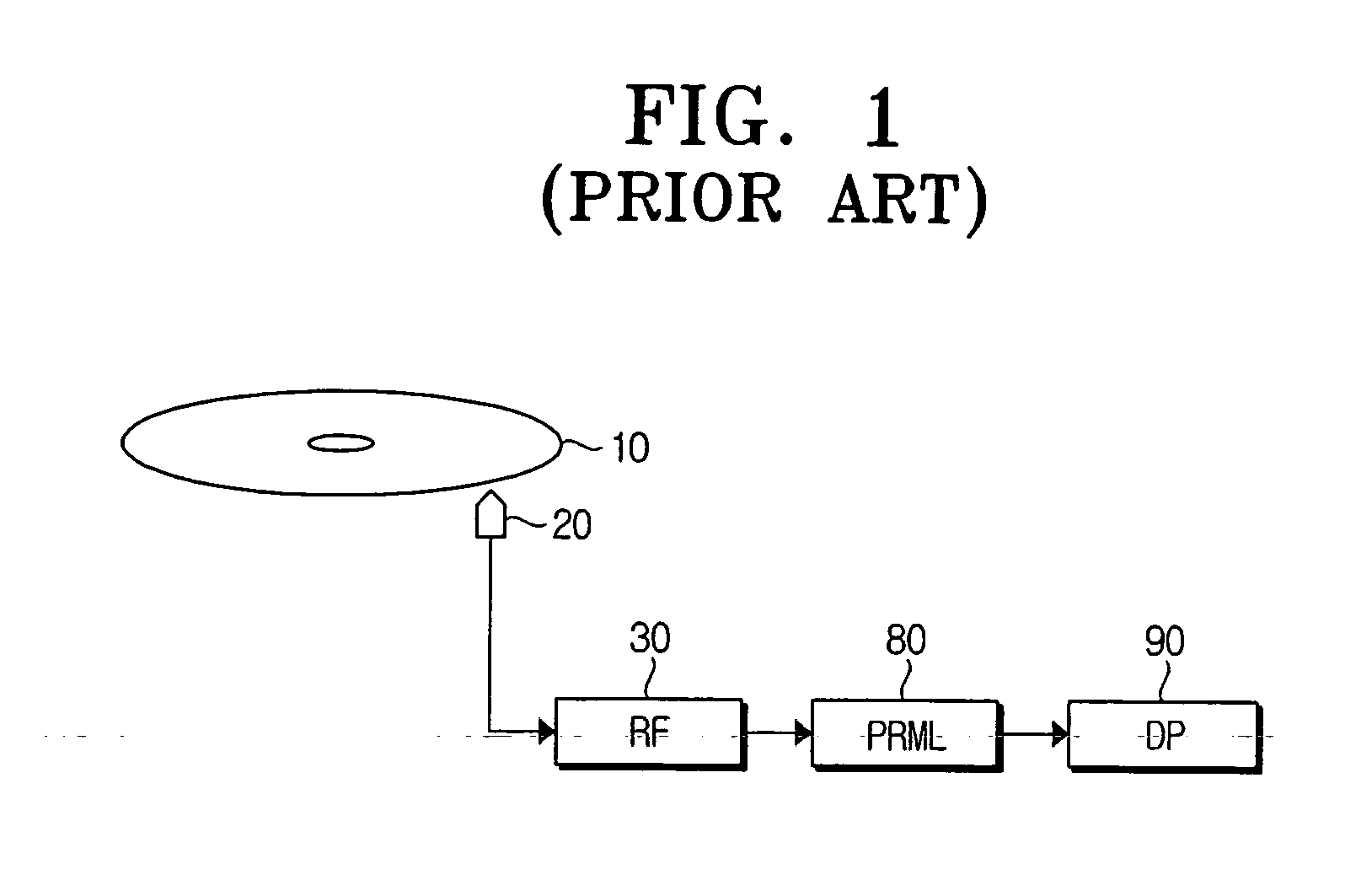

Apparatus and method for setting tap coefficient of adaptive equalizer

InactiveUS20060176947A1Wrong levelStable reproductionMultiple-port networksError preventionViterbi decoderOperation mode

There is provided an apparatus and method for initializing a tap coefficient of an adaptive equalizer constituting a read path for a storage medium, where the apparatus includes an FIR filter, a Viterbi decoder, a level error detector, and a tap coefficient updater, the FIR filter receives a first signal stream and outputs the first signal stream in the form of a second signal stream, the Viterbi decoder corrects a bit error of the second signal stream, the level error detector detects a level error between the second signal stream and a third signal stream that is an ideal output signal corresponding to the second signal stream, the tap coefficient updater selects a tap coefficient minimizing the level error and provides the selected tap coefficient as a tap coefficient of the FIR filter, the tap coefficient minimizing the level error is determined as an initial value in a system initialization mode, and the determined initial value is used as an initial value of the tap coefficient of the FIR filter in a normal operation mode.

Owner:SAMSUNG ELECTRONICS CO LTD

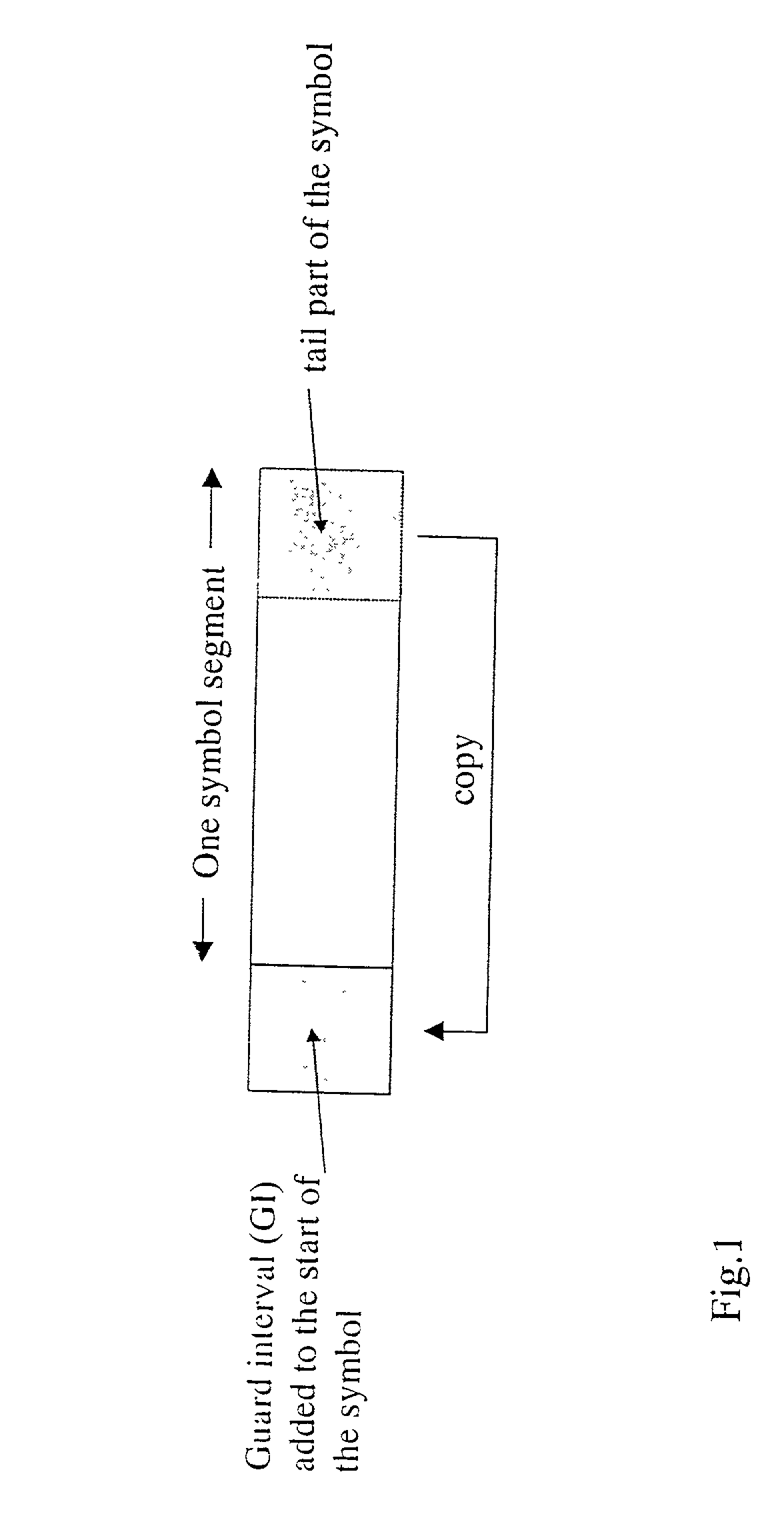

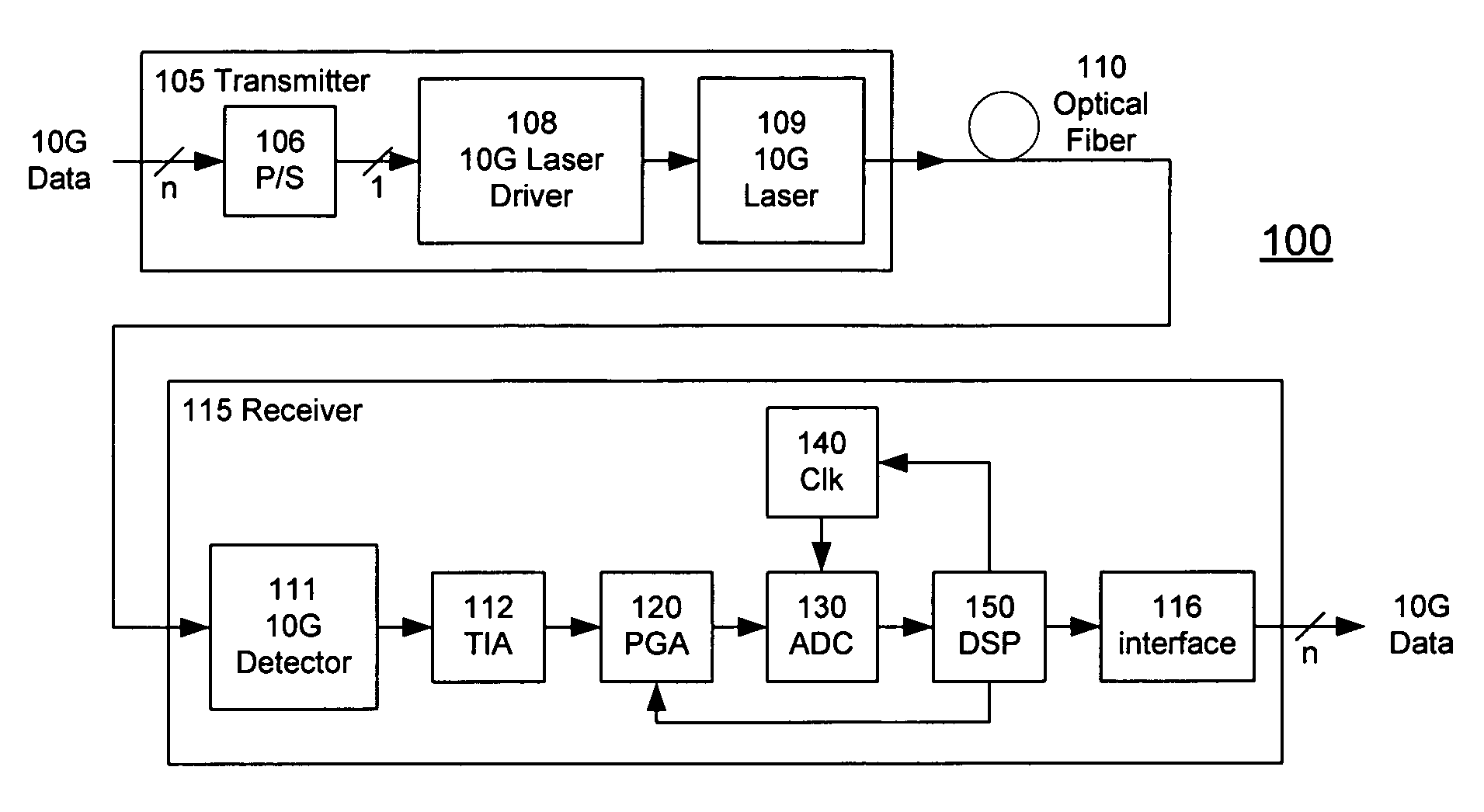

Multi-path equalization for orthogonal frequency division multiplexing communication system

ActiveUS7099270B2Transmission control/equalisingAmplitude-modulated carrier systemsFourier transform on finite groupsEqualization

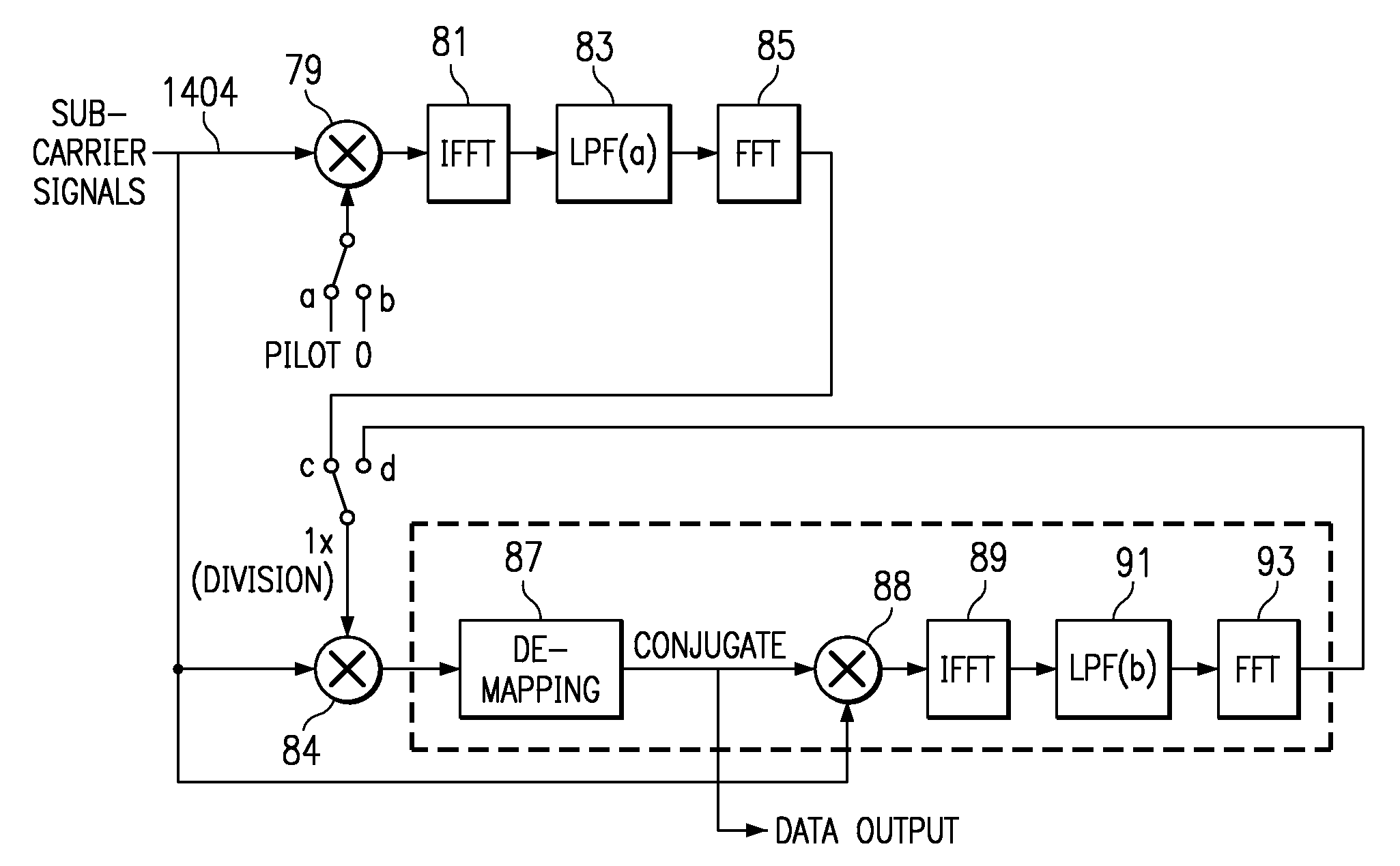

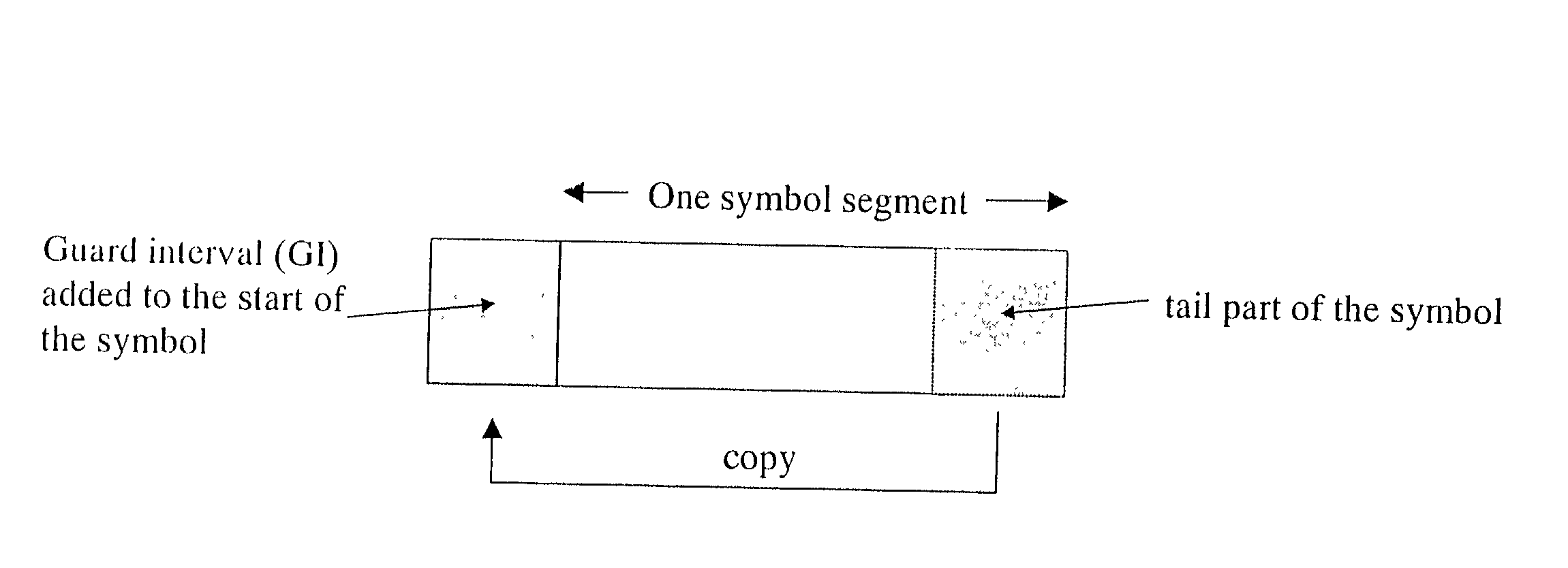

A multi-path equalization system for orthogonal frequency division multiplexing communication (OFDM) system includes a first estimator for estimating the channel characteristic using pilot signal. A divider is coupled to the estimator for dividing each sub-carrier with the channel characteristic to get the equalization to the data signal. A de-mapper uses the phase and amplitude correction of the channel estimate to recover the data signals. An improved channel estimation is provided by a repeat channel estimation feedback loop that includes the de-mapper a multiplier, an inverse fast Fourier transform (IFFT), a low pass filter and a fast Fourier transform (FFT). The improved channel estimation is obtained by multiplying at the multiplier the conjugate of the de-mapped data to the input sub-carriers and applying inverse FFT, low pass filtering and FFT to get the new channel estimate. Each sub-carrier is divided with new channel characteristic to get new equalization to the data signal. The channel estimation is repeated until there is convergence. The output is provided after the de-mapper. In the case of channel decoding to improve performance a Viterbi decoder and convolutional encoder is coupled in loop between the de-mapper and the multiplier.

Owner:TEXAS INSTR INC

Multi-path equalization for orthogonal frequency division multiplexing communication system

ActiveUS20030227866A1Evenly goodTransmission control/equalisingAmplitude-modulated carrier systemsViterbi decoderCommunications system

A multi-path equalization system for orthogonal frequency division multiplexing communication (OFDM) system includes a first estimator for estimating the channel characteristic using pilot signal. A divider is coupled to the estimator for dividing each sub-carrier with the channel characteristic to get the equalization to the data signal. A de-mapper uses the phase and amplitude correction of the channel estimate to recover the data signals. An improved channel estimation is provided by a repeat channel estimation feedback loop that includes the de-mapper a multiplier, an inverse fast Fourier transform (IFFT), a low pass filter and a fast Fourier transform (FFT). The improved channel estimation is obtained by multiplying at the multiplier the conjugate of the de-mapped data to the input sub-carriers and applying inverse FFT, low pass filtering and FFT to get the new channel estimate. Each sub-carrier is divided with new channel characteristic to get new equalization to the data signal. The channel estimation is repeated until there is convergence. The output is provided after the de-mapper. In the case of channel decoding to improve performance a Viterbi decoder and convolutional encoder is coupled in loop between the de-mapper and the multiplier.

Owner:TEXAS INSTR INC

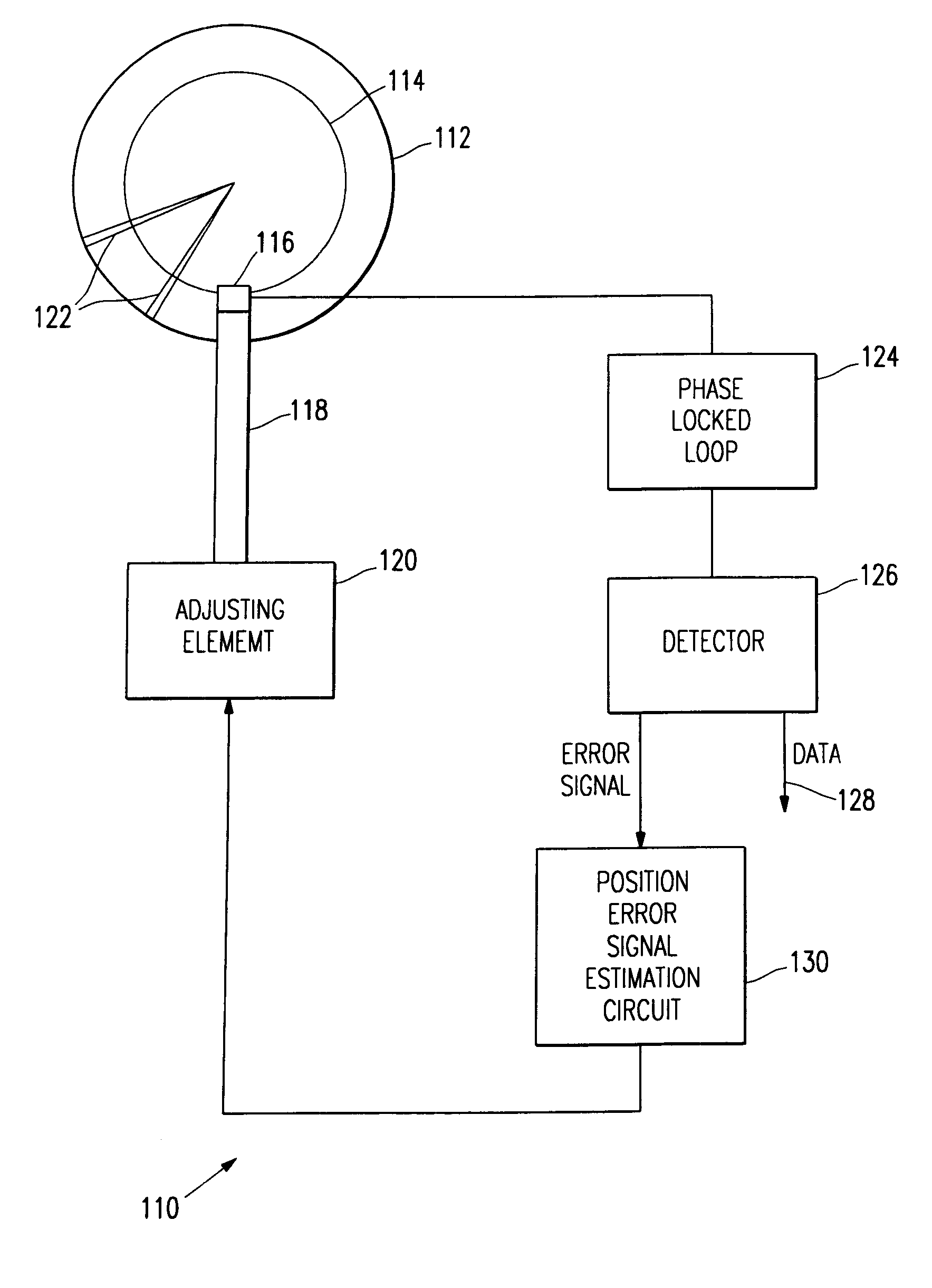

Read channel generating absolute value servo signal

InactiveUS6594103B1Record information storageAlignment for track following on disksHard disc driveMagnetic storage

A servo control system and method controls systems at least partially on the basis of an observable variable that has an absolute value functional relationship with the controlled variable and does not change sign for positive and negative variations from a nominal value. The control system and method find particularly advantageous application in magnetic storage hard disk drive systems because the system allows such hard disk drives to perform servo operations such as track following on the basis of the data signals being read from the track. A particularly useful source of the absolute value observable variable is a read channel chip that performs decoding of data recovered from the disk. Error measures are developed as the data signals from the disk are processed and decoded, including error measures from the slicer used in an adaptive equalization process and from the data decoder, which may be a Viterbi decoder. One or more of these error measures is provided to an output terminal of the read channel chip for use with an absolute value control system and method.

Owner:RATEZE REMOTE MGMT LLC

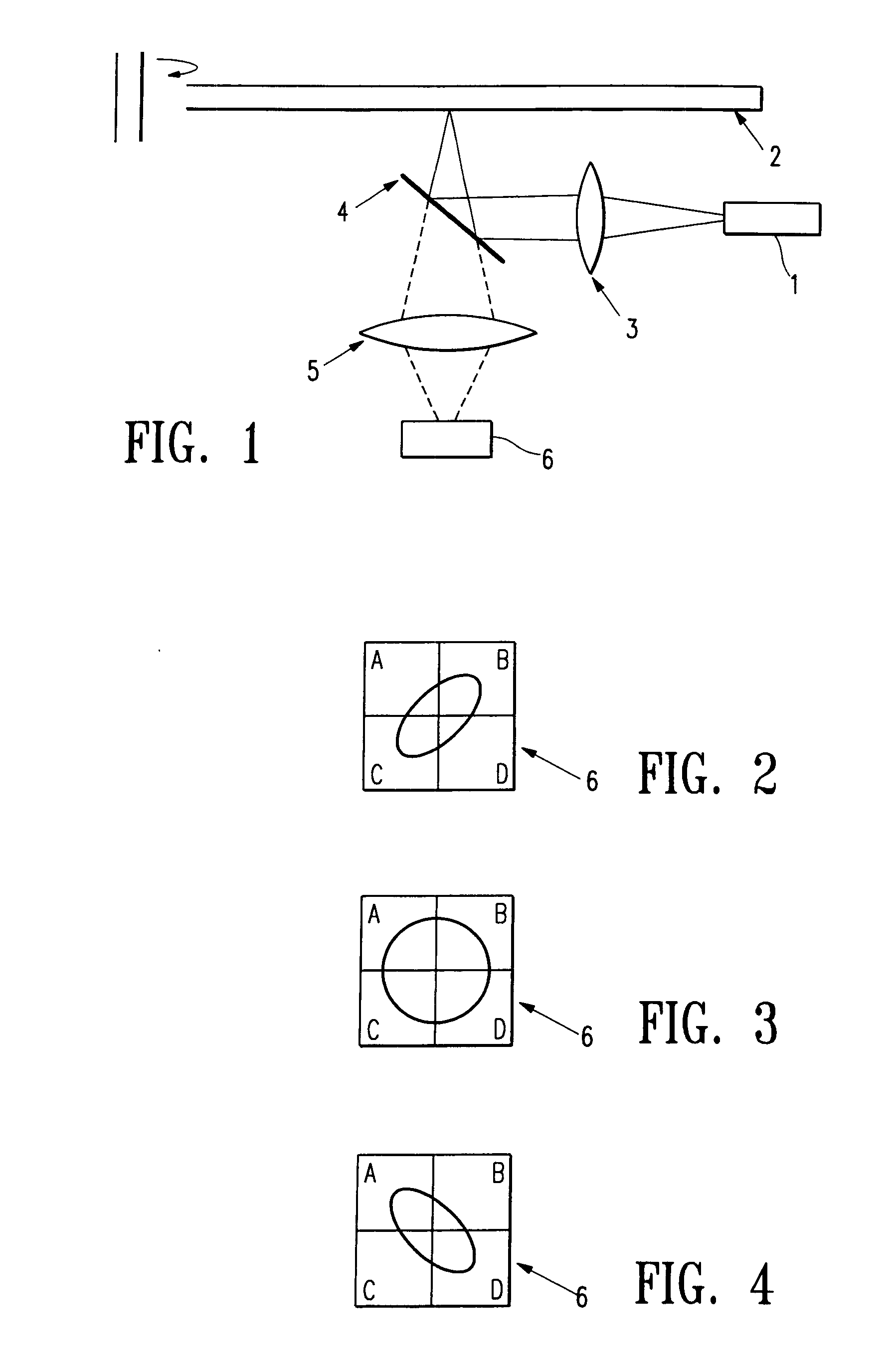

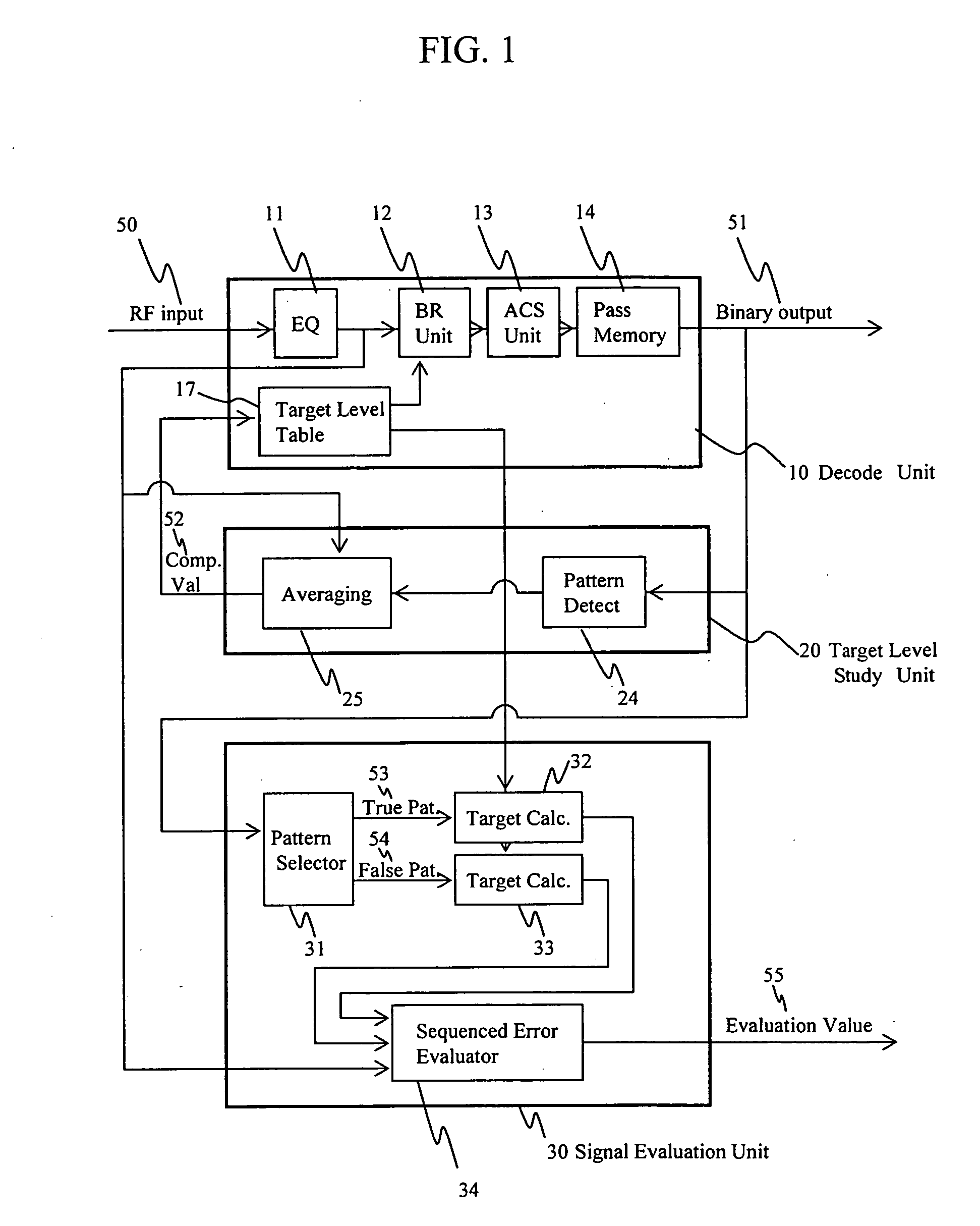

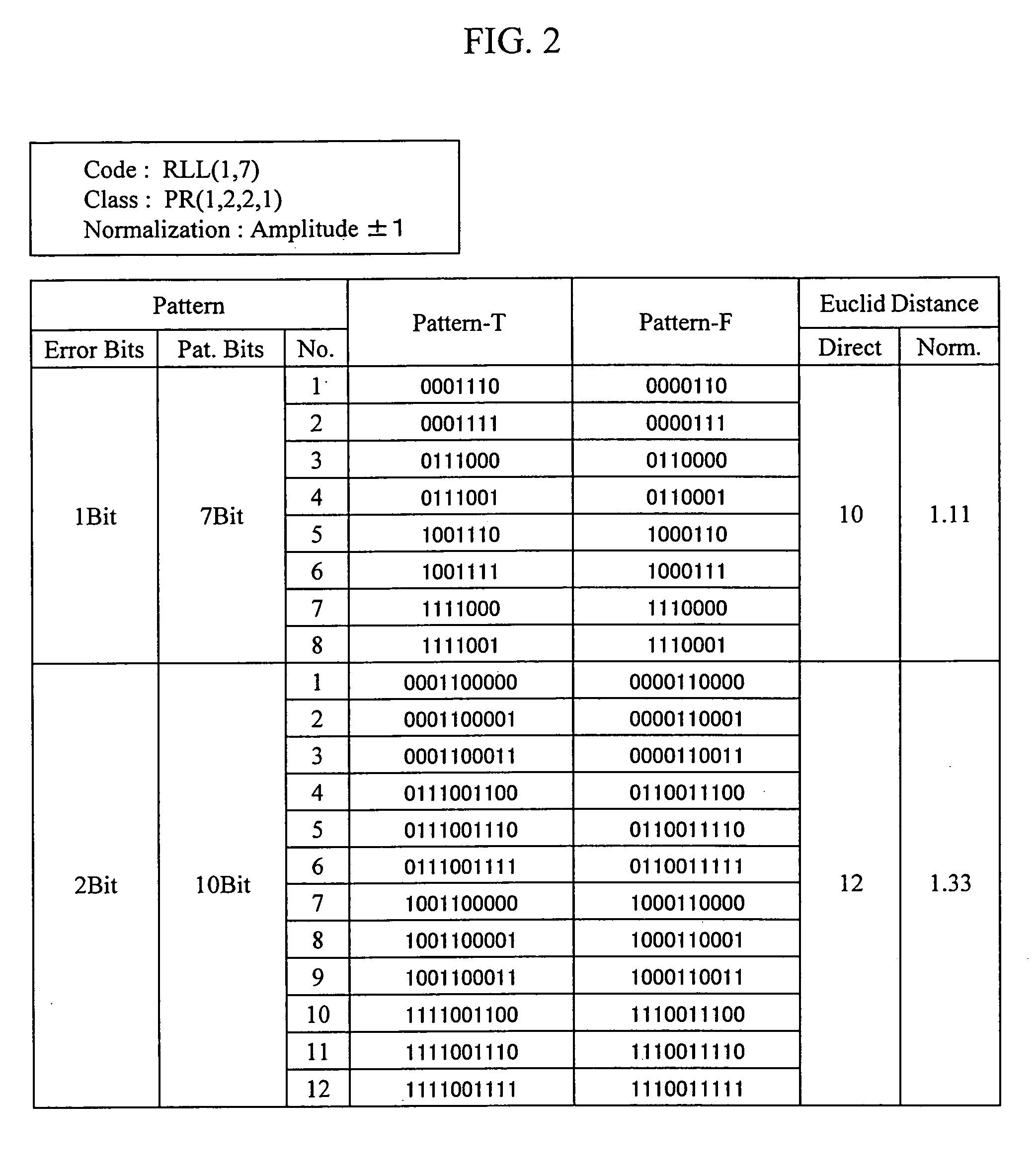

Method of evaluating a readout signal, and optical disc apparatus

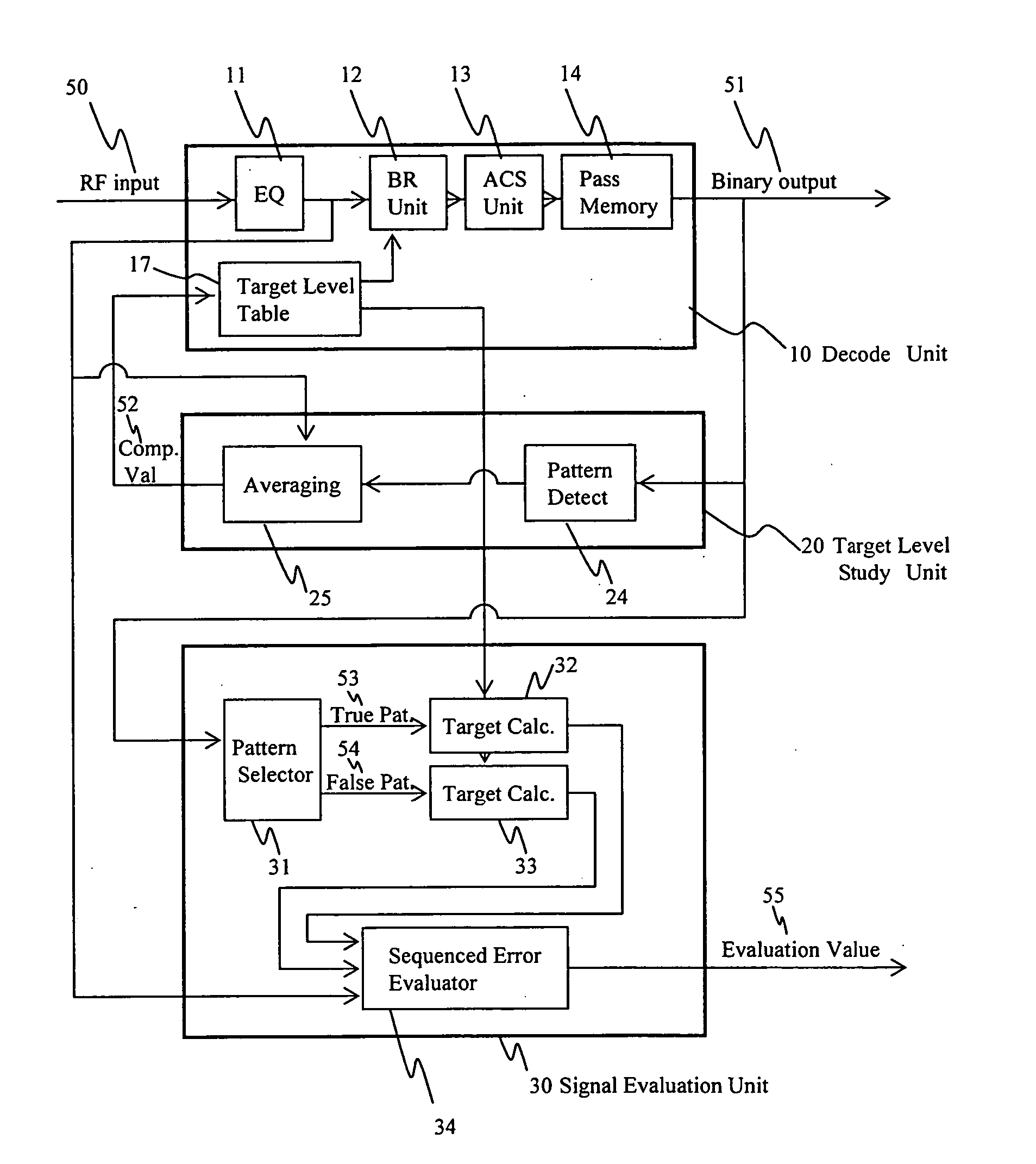

InactiveUS20050249318A1Precise positioningAccurate assessmentModification of read/write signalsOptical beam sourcesViterbi decoderSignal quality

A method of evaluating the quality of a read signal from the viewpoint of the detection margin of a Viterbi decoder in the PRML method in which a target signal level varies depending on the read signal, and an optical disc apparatus implementing the method. A method of evaluating the quality of a signal pattern comprising a combination of minimum run lengths from the viewpoint of edge shift, and an optical disc apparatus implementing the method. From the target signal level that varies depending on the read signal, a target signal is generated based on a decoding result, and an error target signal is generated in which the decoding result is edge-shifted. The signal quality is evaluated by calculating a Euclidean distance between these signals and the read signal. A virtual state that is not included in the Viterbi decoder and that is less than the minimum run length is defined, and a target signal level for the virtual state is generated using a target signal level table inside the Viterbi decoder, based on the concept of convolution. In this way, the signal quality can be evaluated by the same method as mentioned above even in cases where the pattern of a combination of the minimum run lengths has edge-shifted.

Owner:HITACHI-LG DATA STORAGE +1

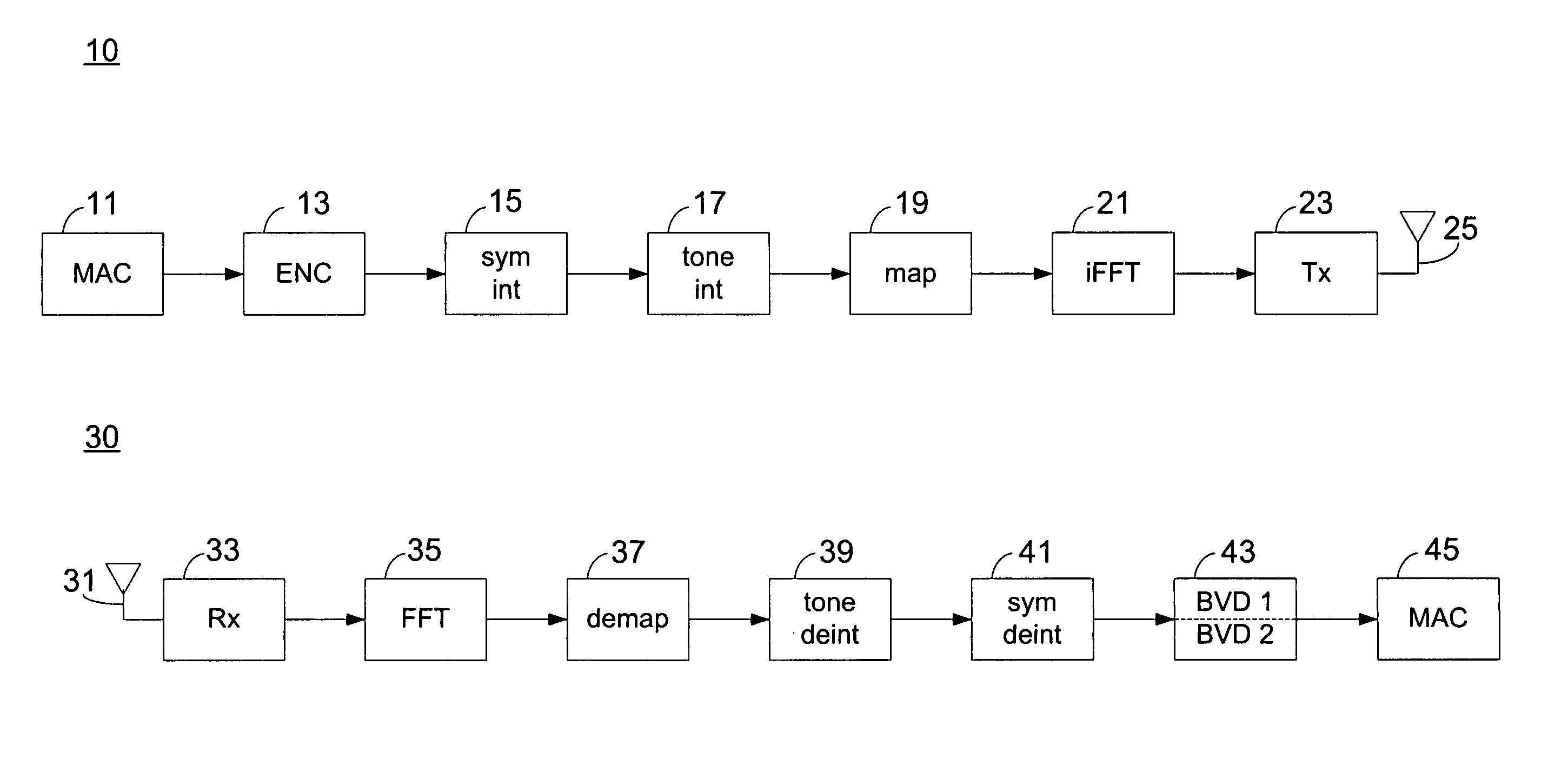

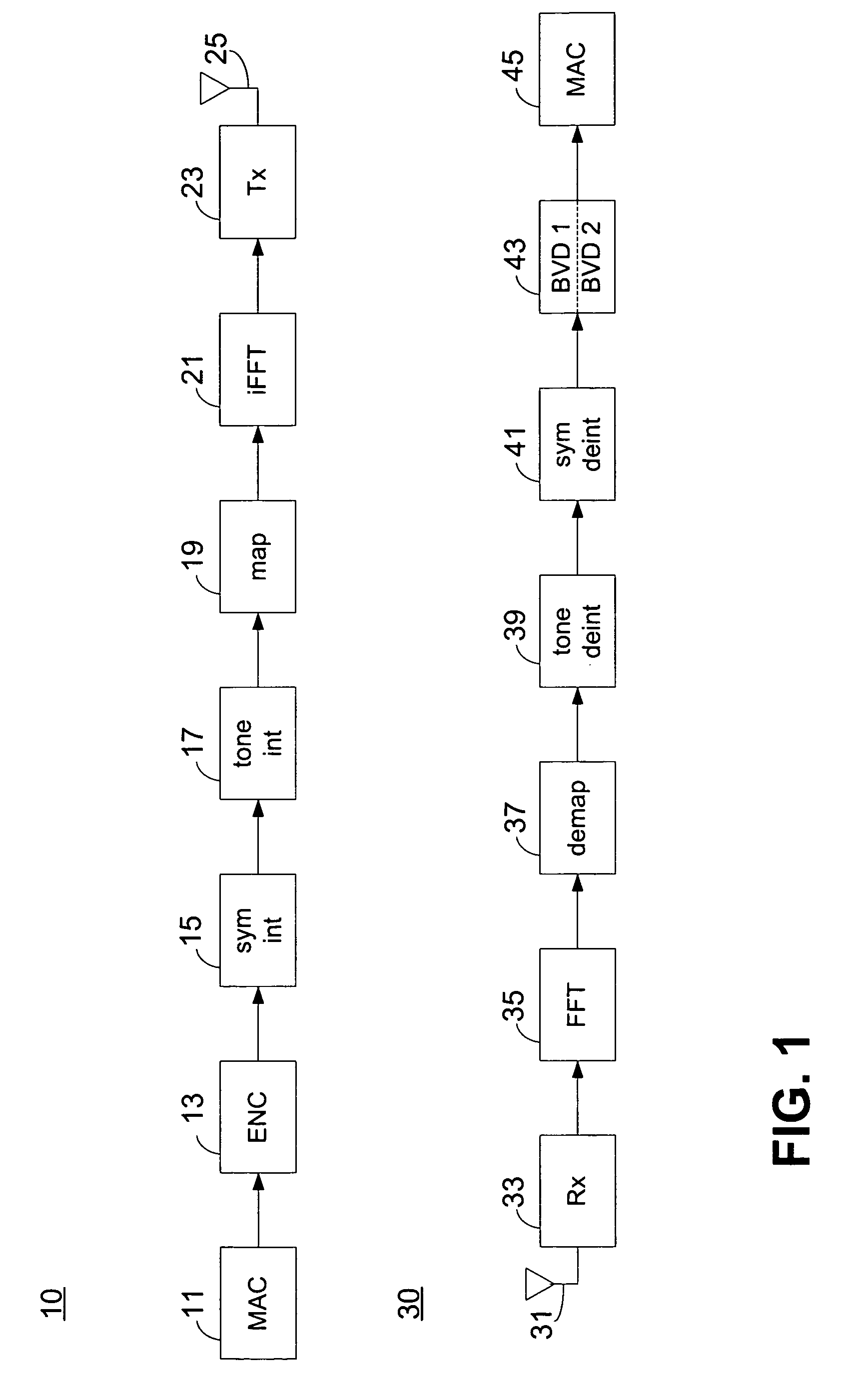

Deinterleaver and dual-viterbi decoder architecture

ActiveUS20070067704A1Fully comprehendedData representation error detection/correctionOther decoding techniquesViterbi decoderMemory bank

Pairs of parallel Viterbi decoders use windowed block data for decoding data at rates above 320 Mbps. Memory banks of the deinterleavers feeding the decoders operate such that some are receiving data while others are sending data to the decoders. Parallel input streams to every pair of decoders overlap for several traceback lengths of the decoder causing data input to a first decoder at the end of an input stream to be the same as the data input to a second decoder of the same pair at the beginning of an input stream. Then, the first decoder is able to post-synchronize its path metric with the second decoder and the second decoder is able to pre-synchronize its path metric with the first. Either, the deinterleaver data length is an integer multiple of the traceback length or the data input to only the first block of the first interleaver is padded.

Owner:REALTEK SEMICON CORP +1

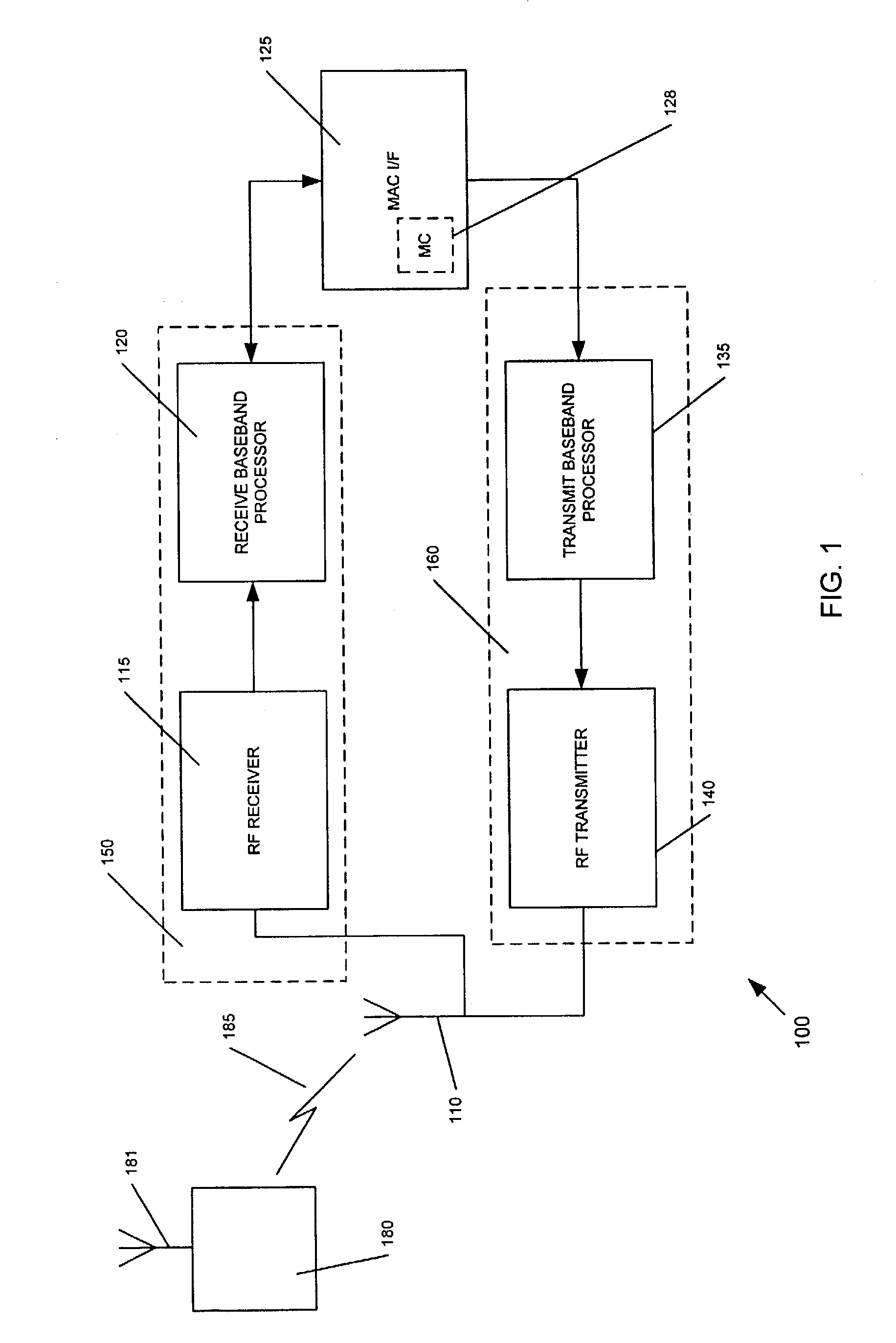

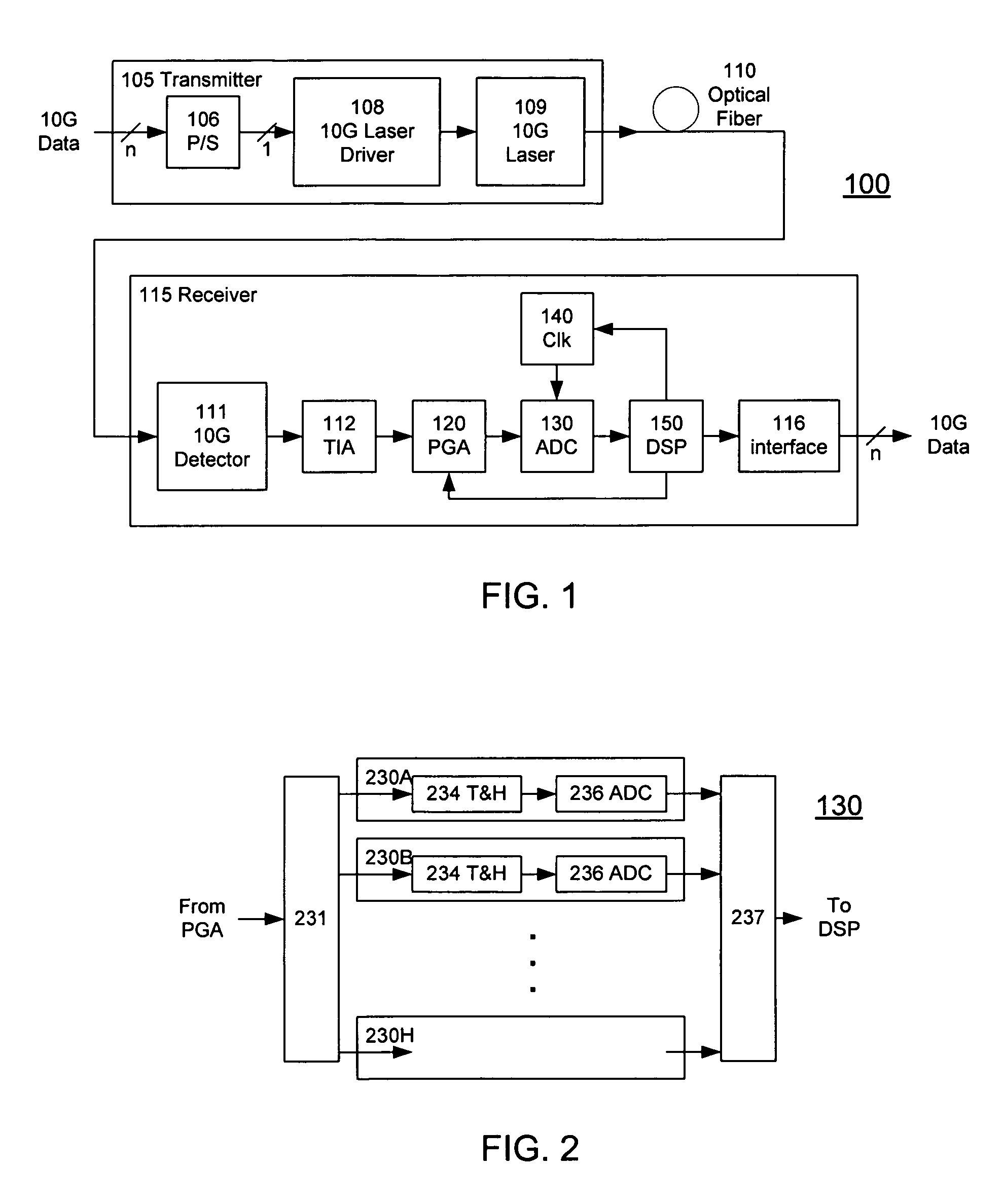

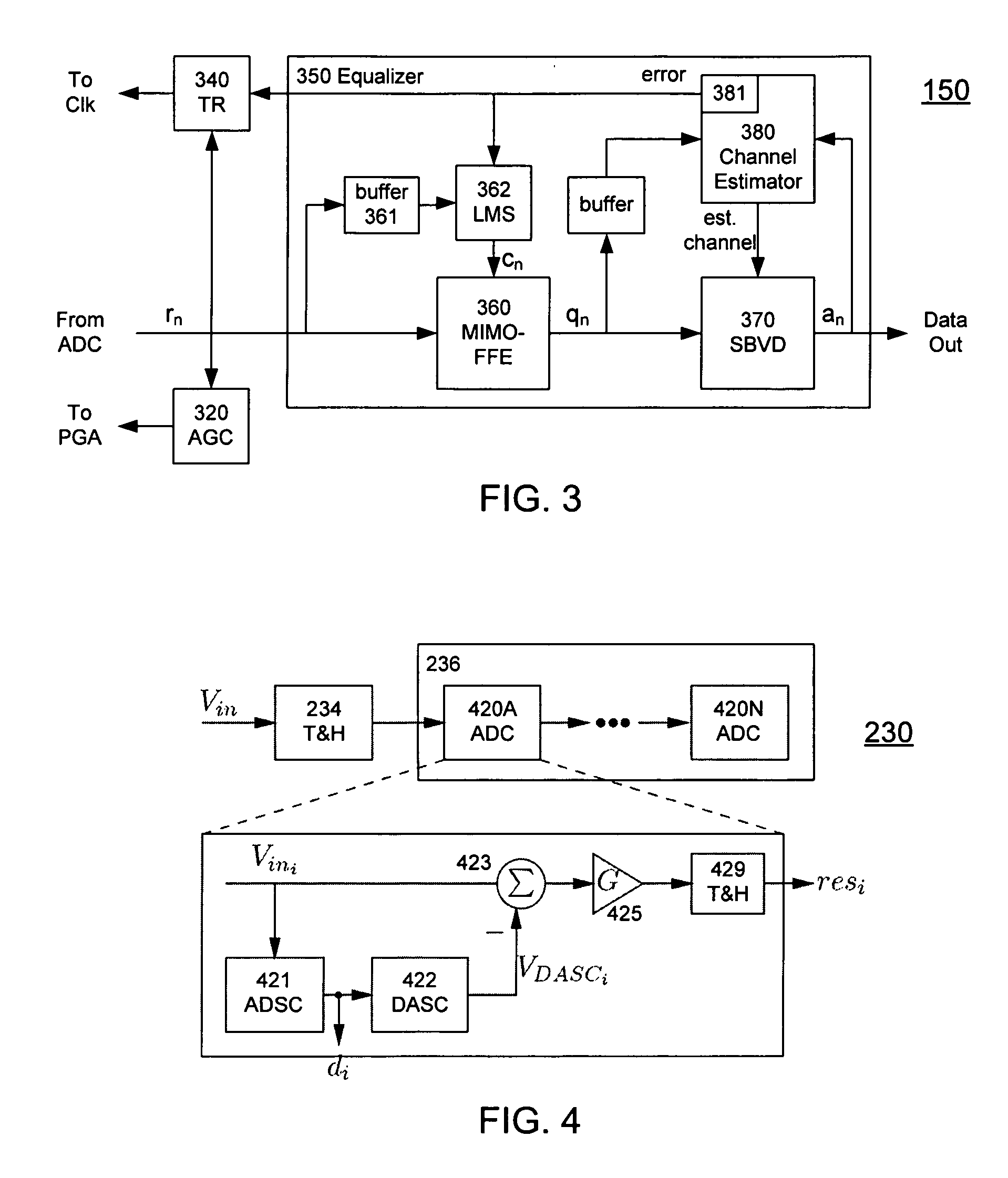

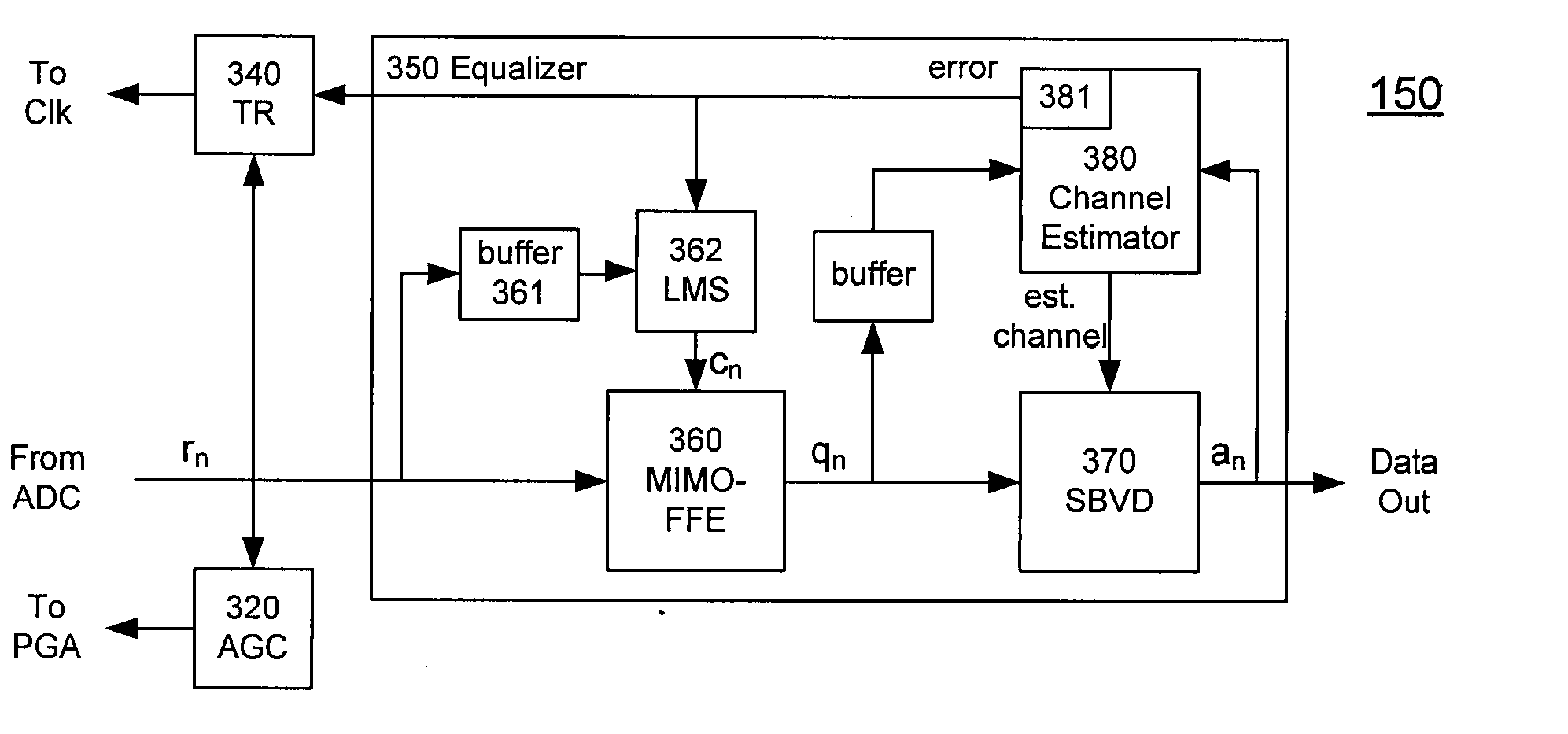

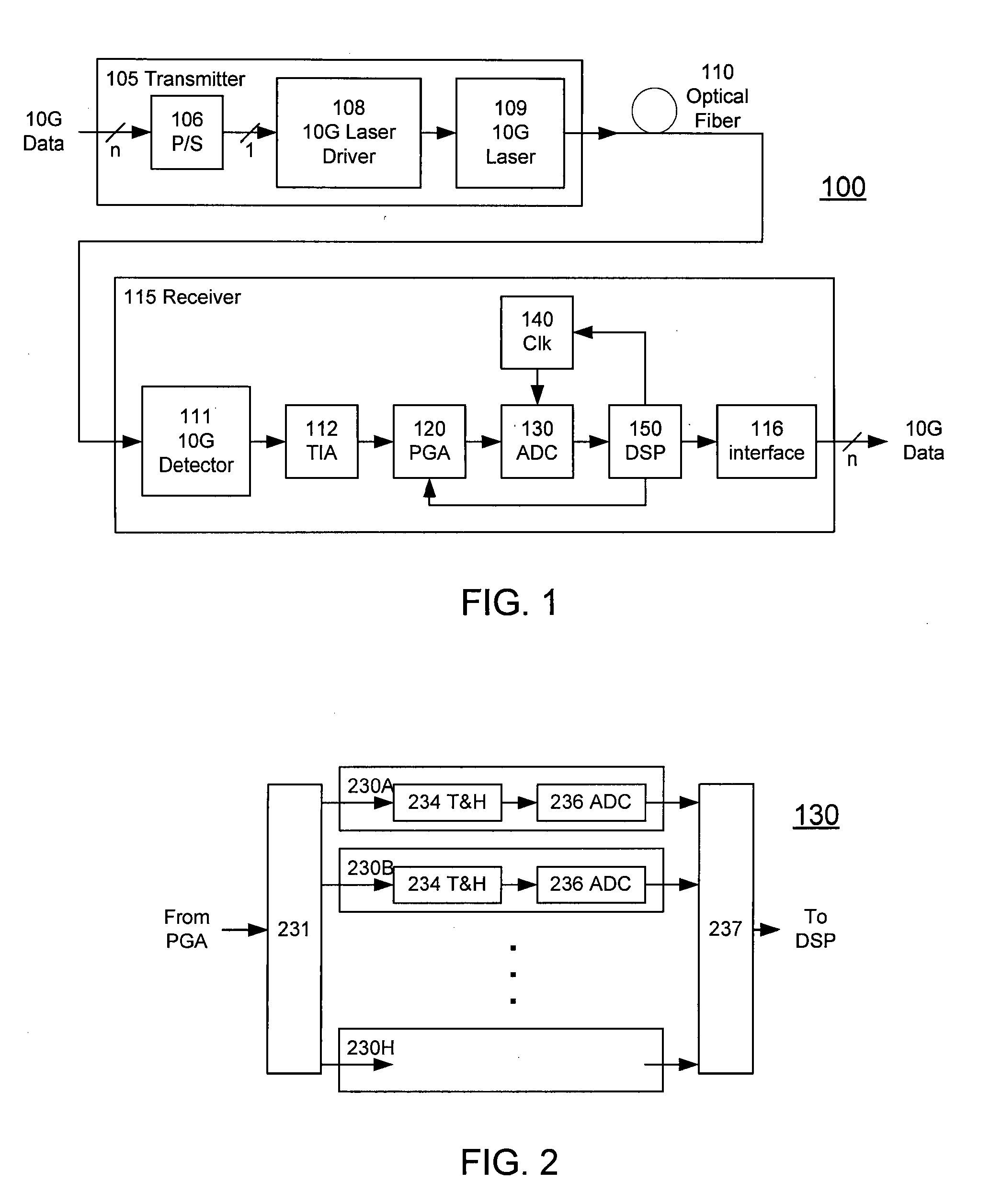

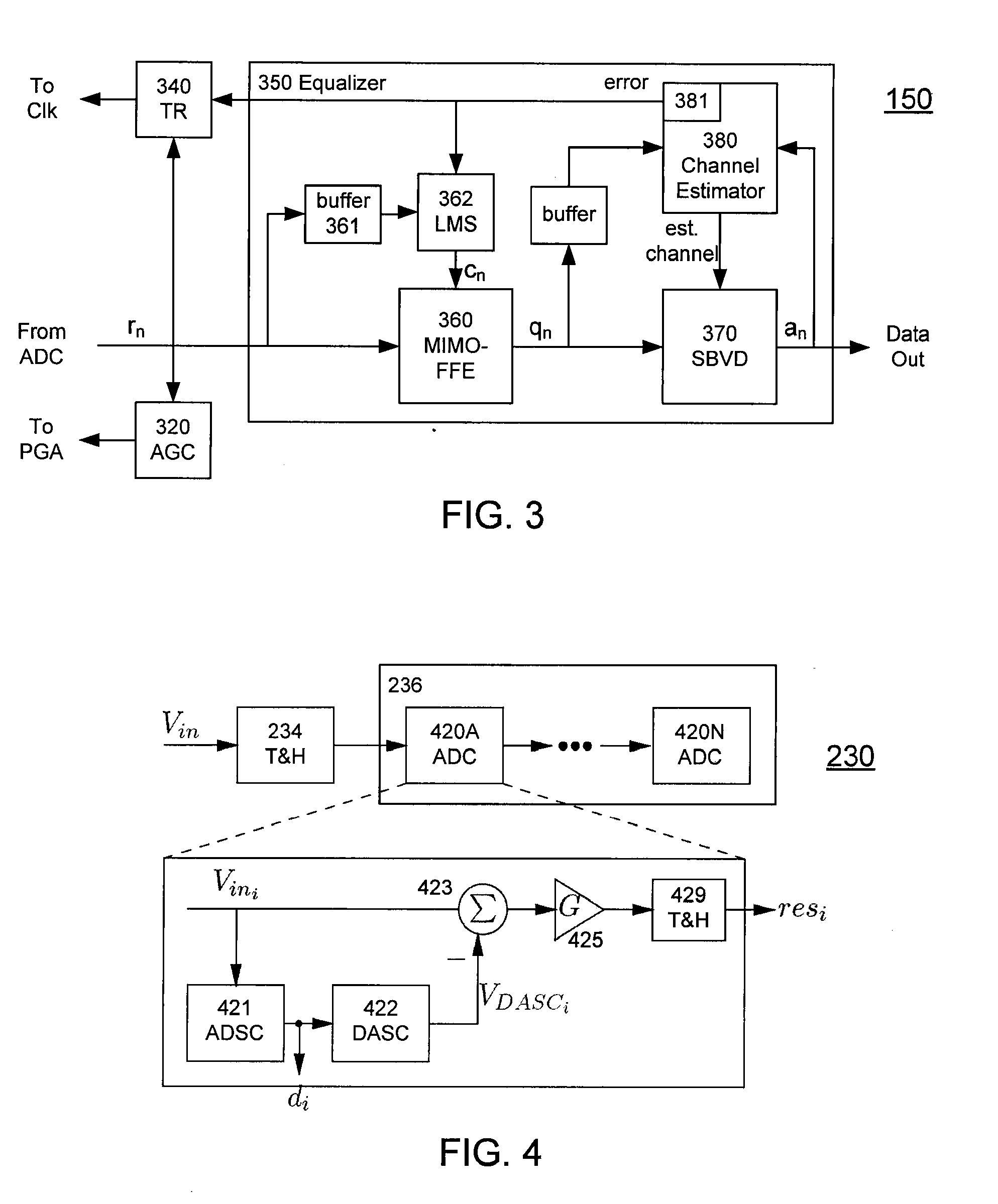

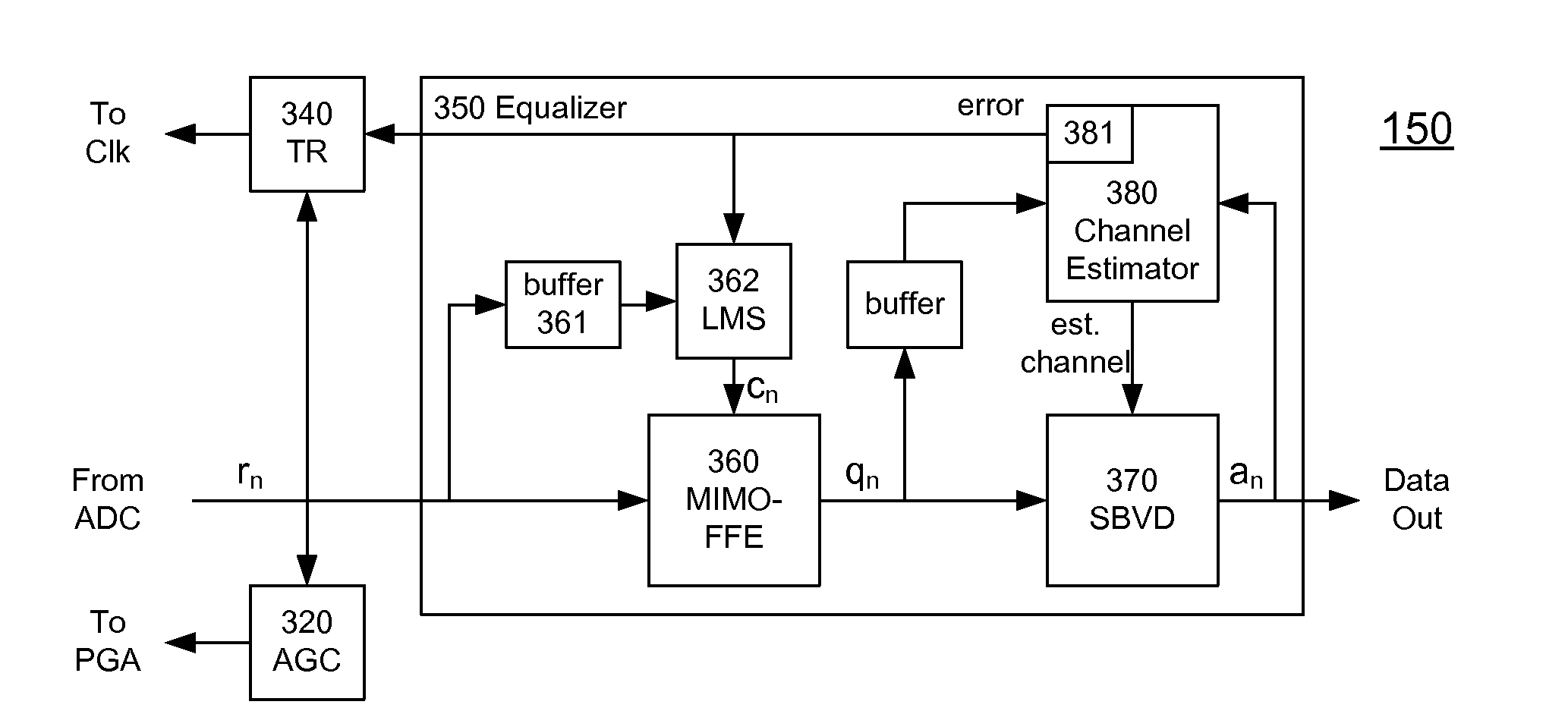

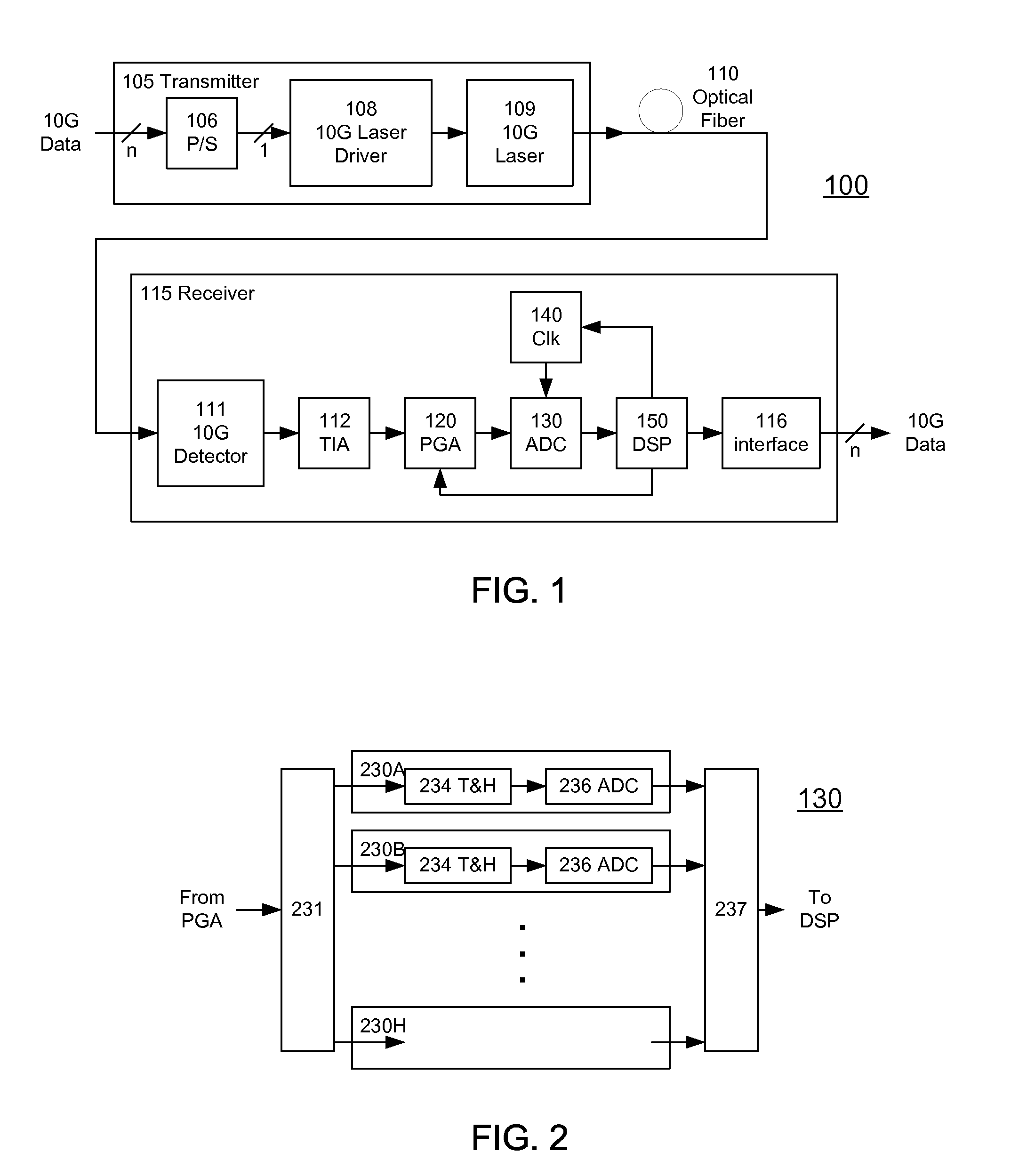

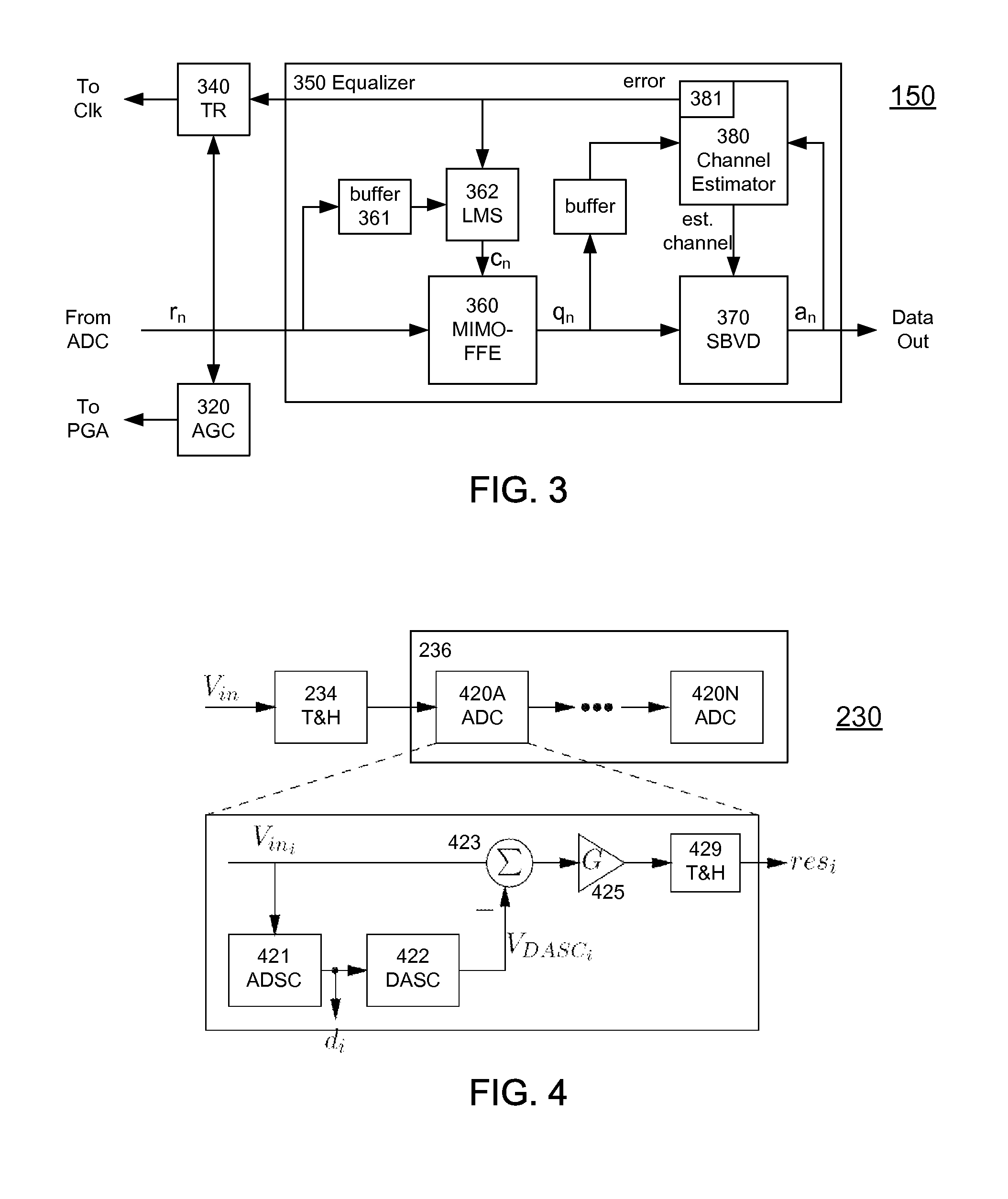

High-Speed Receiver Architecture

ActiveUS20080240325A1Overcome limitationsLower latencyAnalogue/digital conversionReceiver initialisationViterbi decoderTelecommunications link

A receiver (e.g., for a 10 G fiber communications link) includes an interleaved ADC coupled to a multi-channel equalizer that can provide different equalization for different ADC channels within the interleaved ADC. That is, the multi-channel equalizer can compensate for channel-dependent impairments. In one approach, the multi-channel equalizer is a feedforward equalizer (FFE) coupled to a Viterbi decoder, for example a sliding block Viterbi decoder (SBVD); and the FFE and / or the channel estimator for the Viterbi decoder are adapted using the LMS algorithm.

Owner:MARVELL ASIA PTE LTD

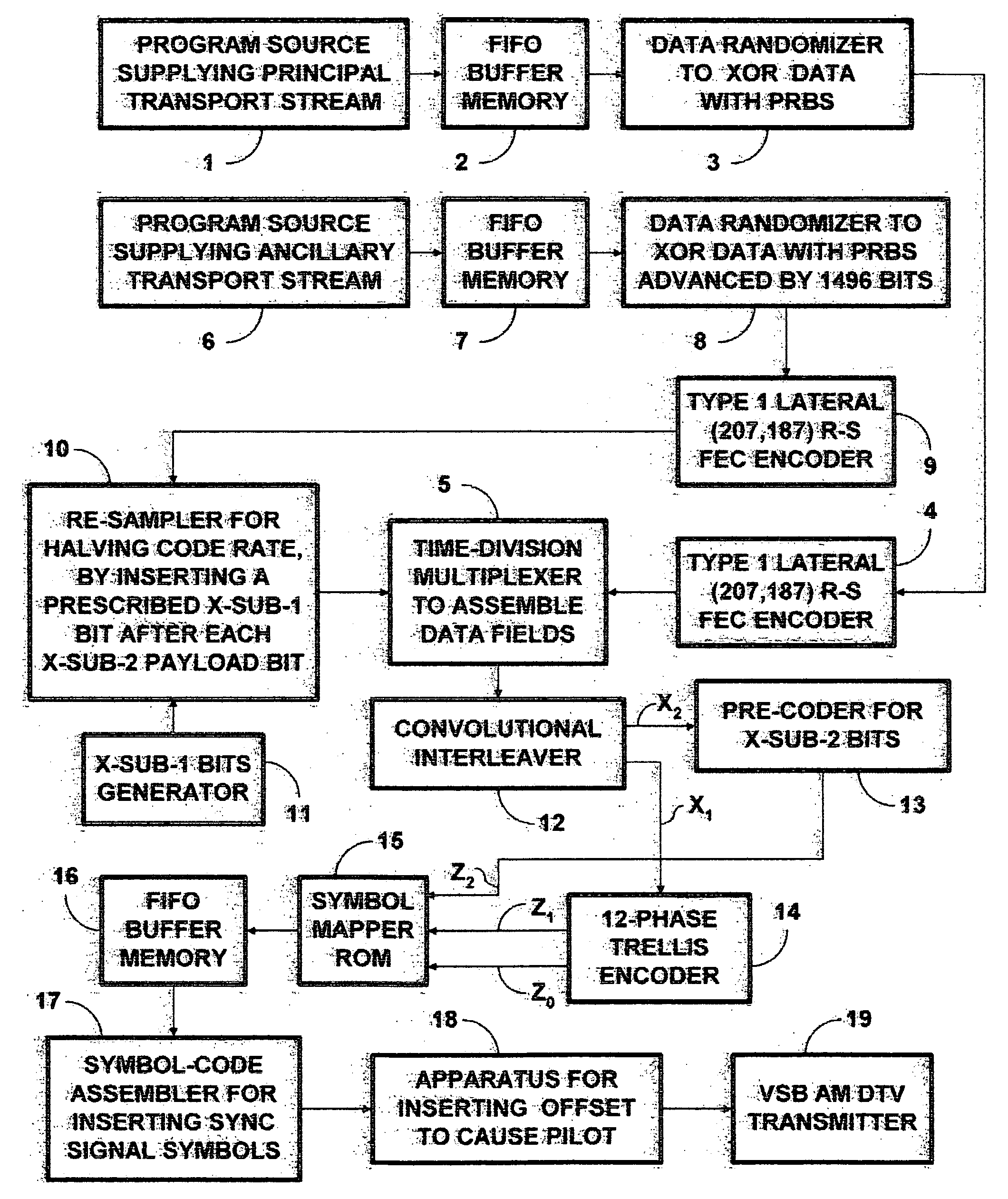

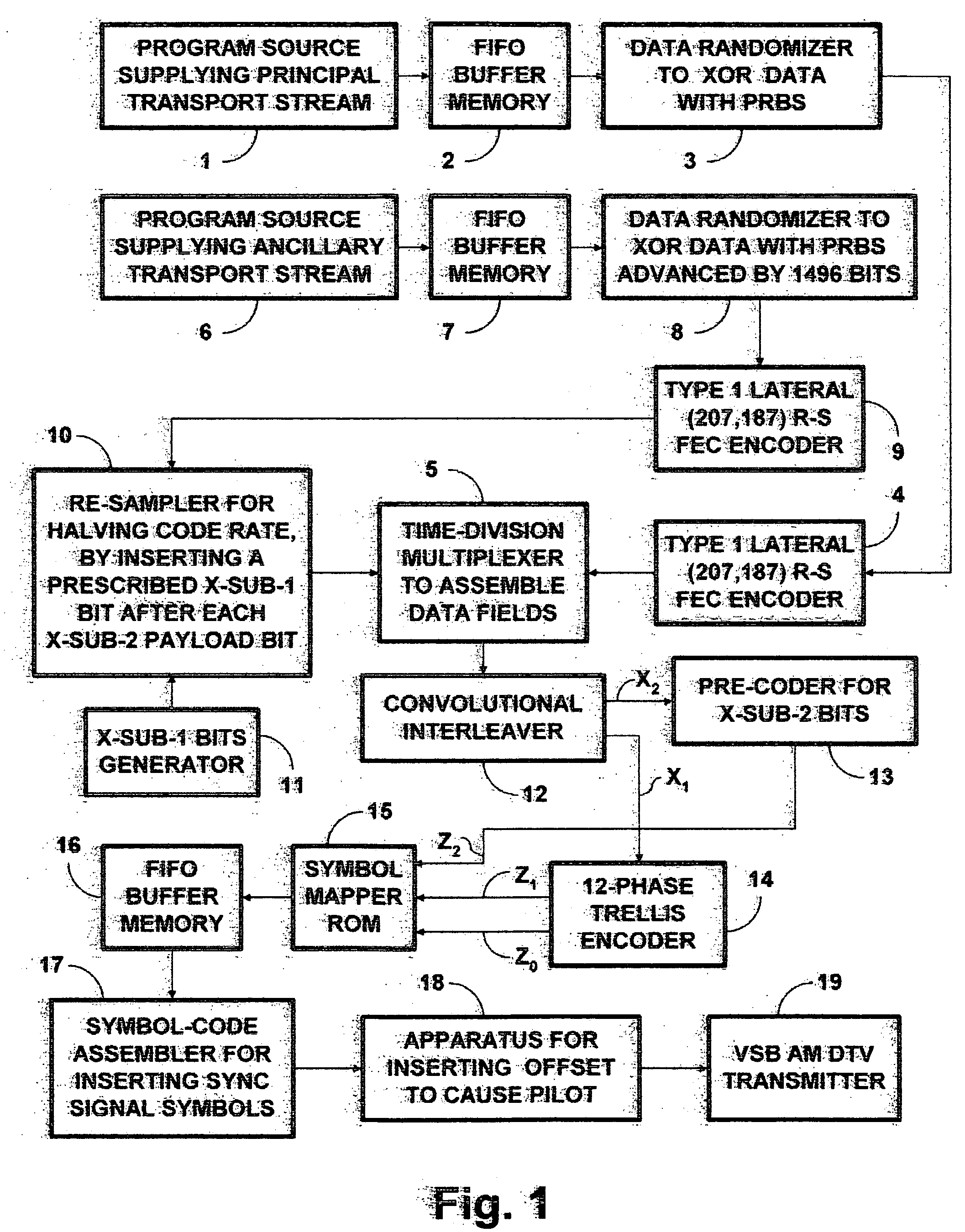

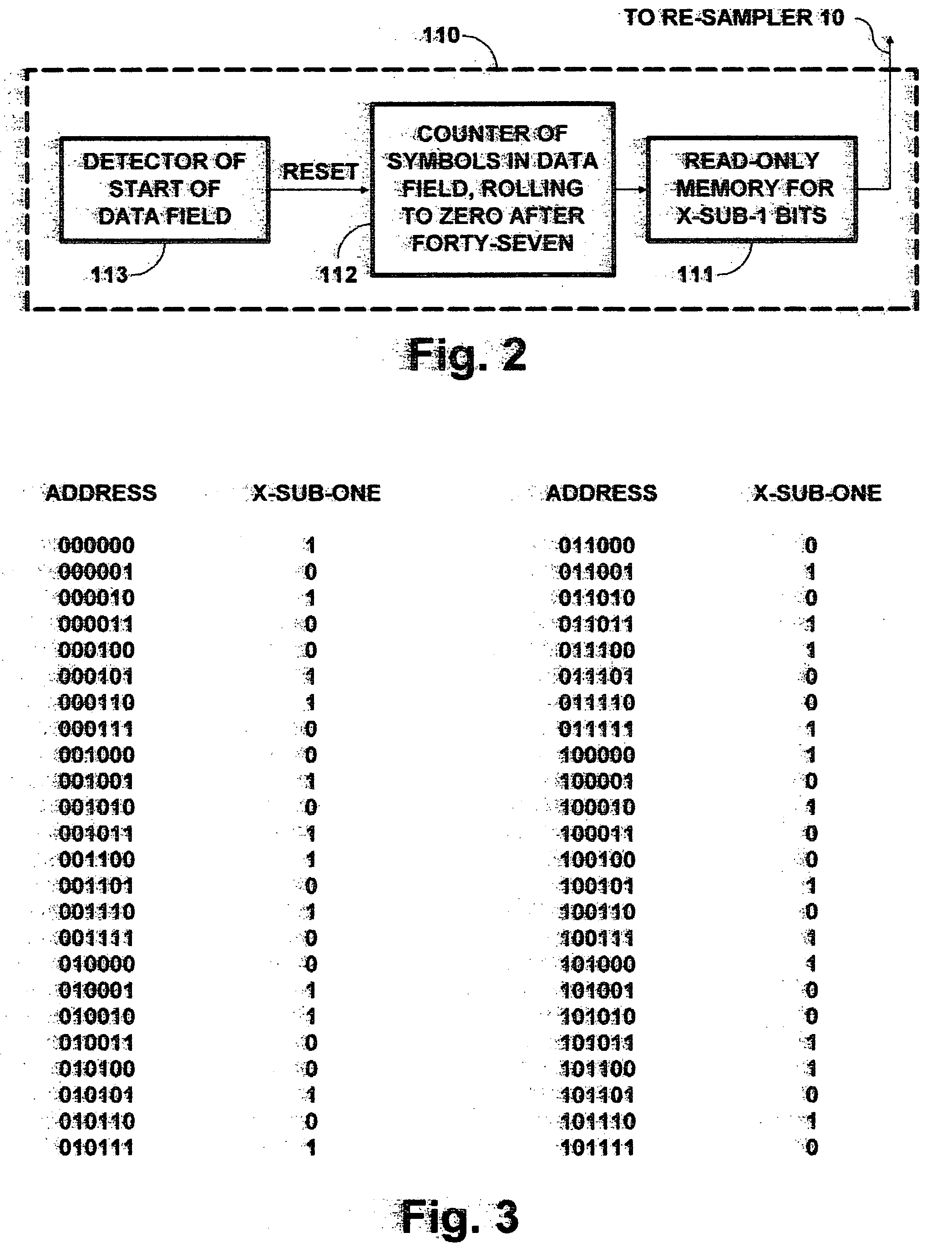

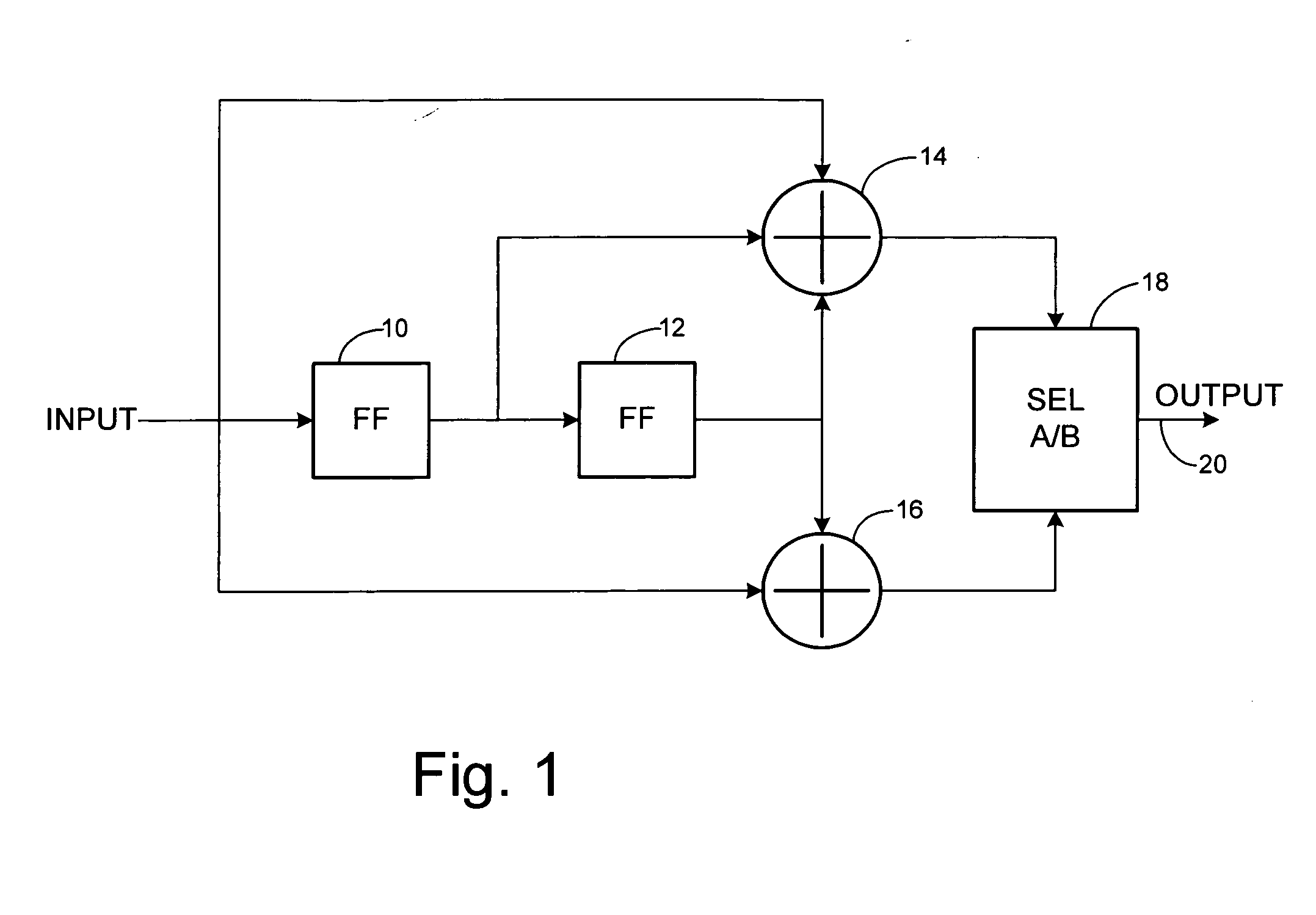

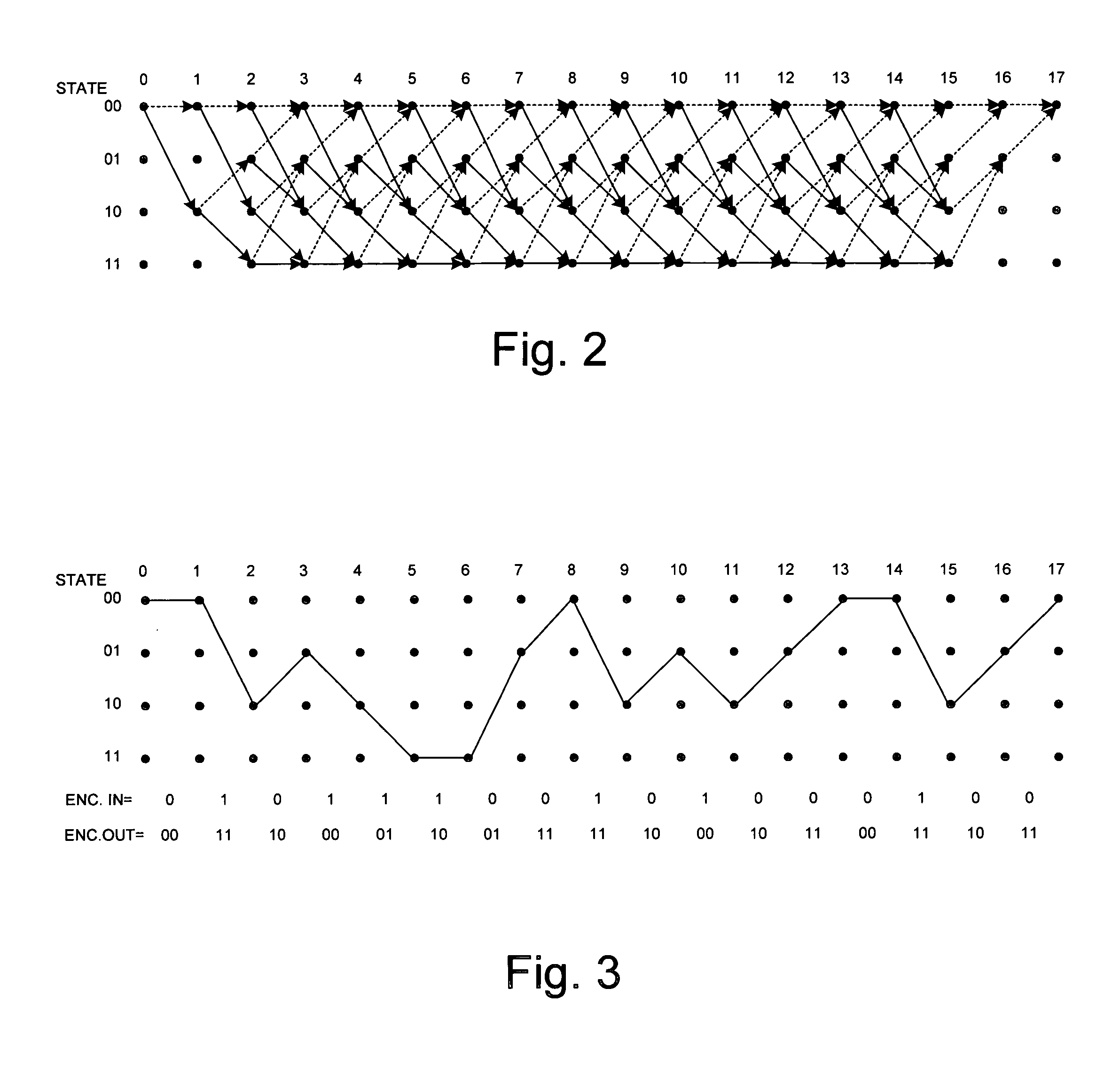

Time-dependent trellis coding for more robust digital television signals

InactiveUS20050074074A1Improve robustnessIncrease distanceLine-faulsts/interference reductionAmplitude demodulation detailsViterbi decoderData transmission

Owner:SAMSUNG ELECTRONICS CO LTD

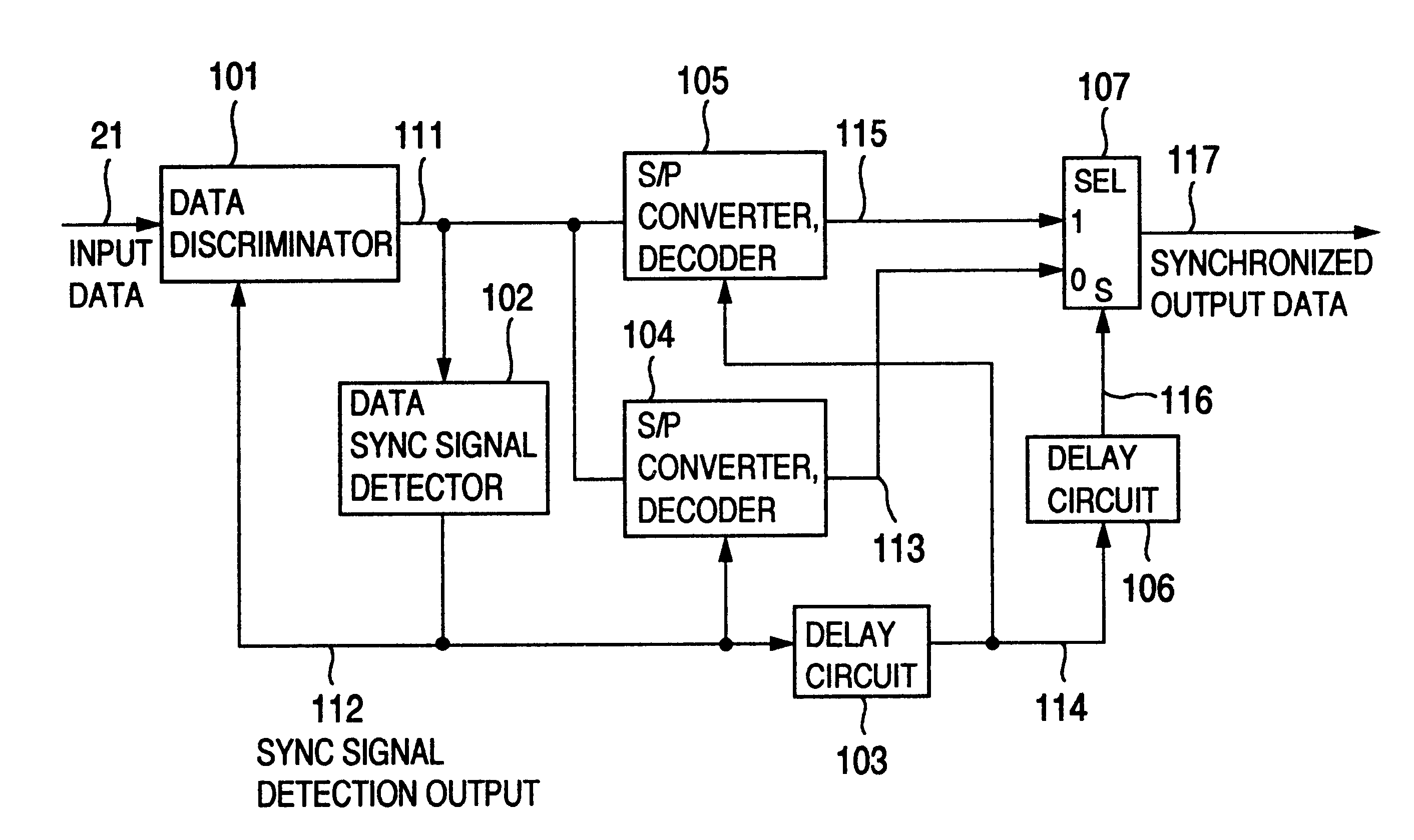

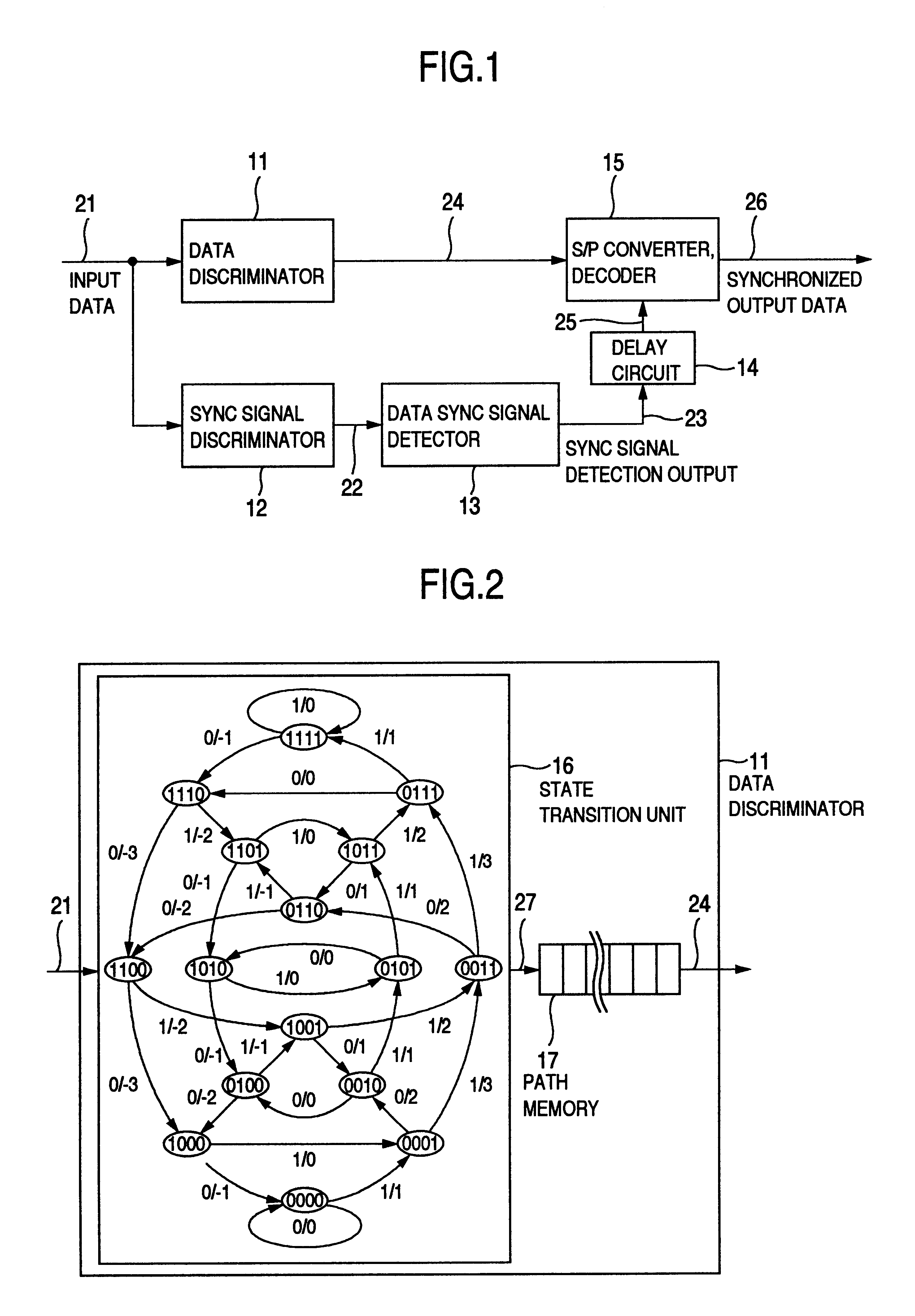

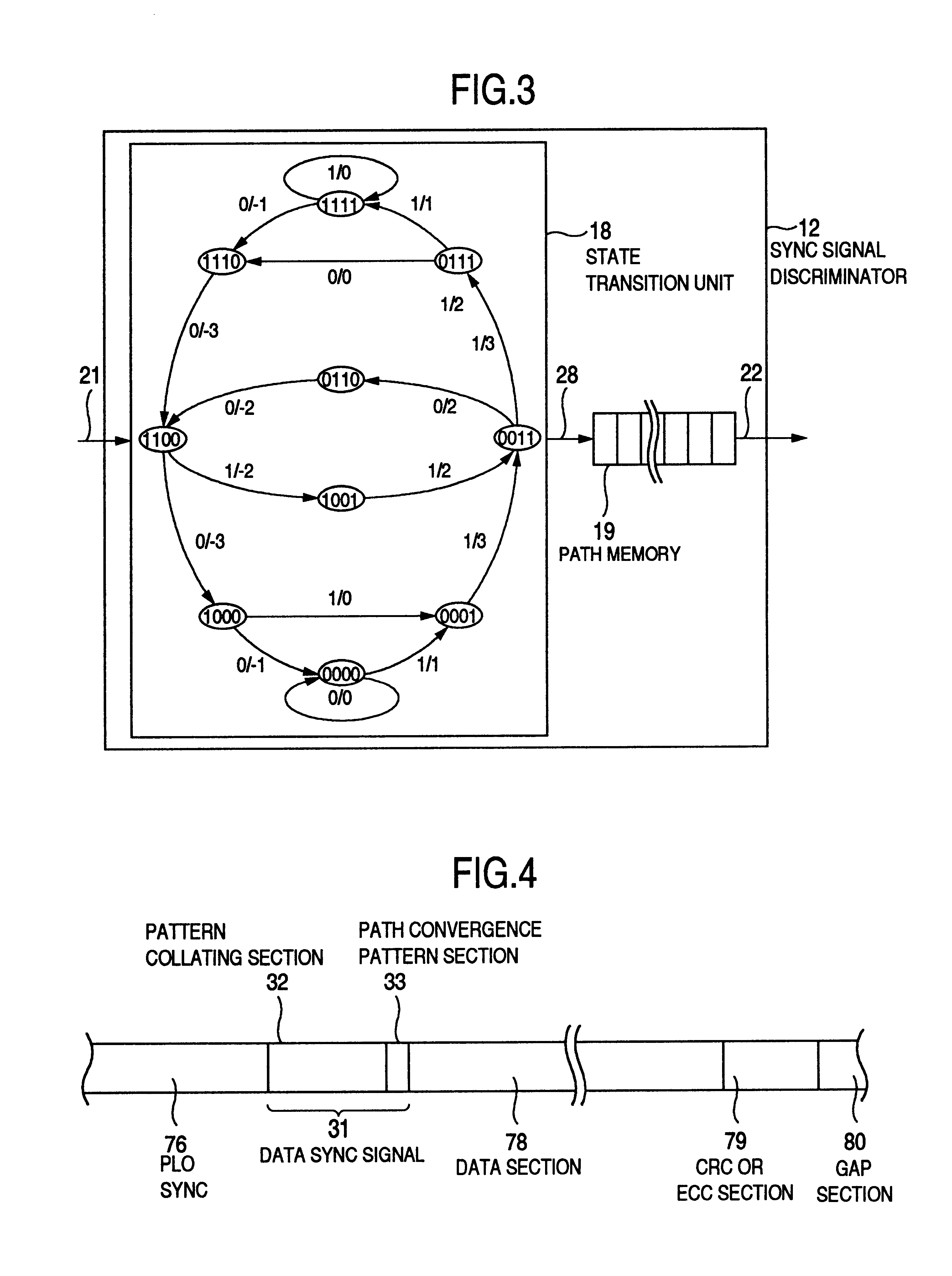

Data synchronizing signal detector, signal processing device using the detector, information recording and reproducing apparatus having the detector and the device, data synchronizing signal detecting method, and information recording medium for using in the method

InactiveUS6791777B2Improve accuracyImprove the detection rateModification of read/write signalsSynchronisation information channelsDiscriminatorData synchronization

A data discriminating unit includes a data discriminator and a sync signal discriminator. A data sync signal is detected for the bit string discriminated from the output of the sync signal discriminator, and the data is demodulated for the bit string discriminated from the output of the data discriminator, thereby optimizing the signal to a form suitable for discrimination and detection of the data sync signal and demodulation for data reproduction. As a result, the detection performance of the data sync signal can be improved while maintaining the data discrimination performance. A Viterbi decoder is used for discrimination by the data discriminator and the sync signal discriminator for the optimization thereby to optimize the number of states, the number of paths for state transition and the path memory length. A signal having no continuous inversions of the recording data is used as the data sync signal.

Owner:HITACHI GLOBAL STORAGE TECH JAPAN LTD +1

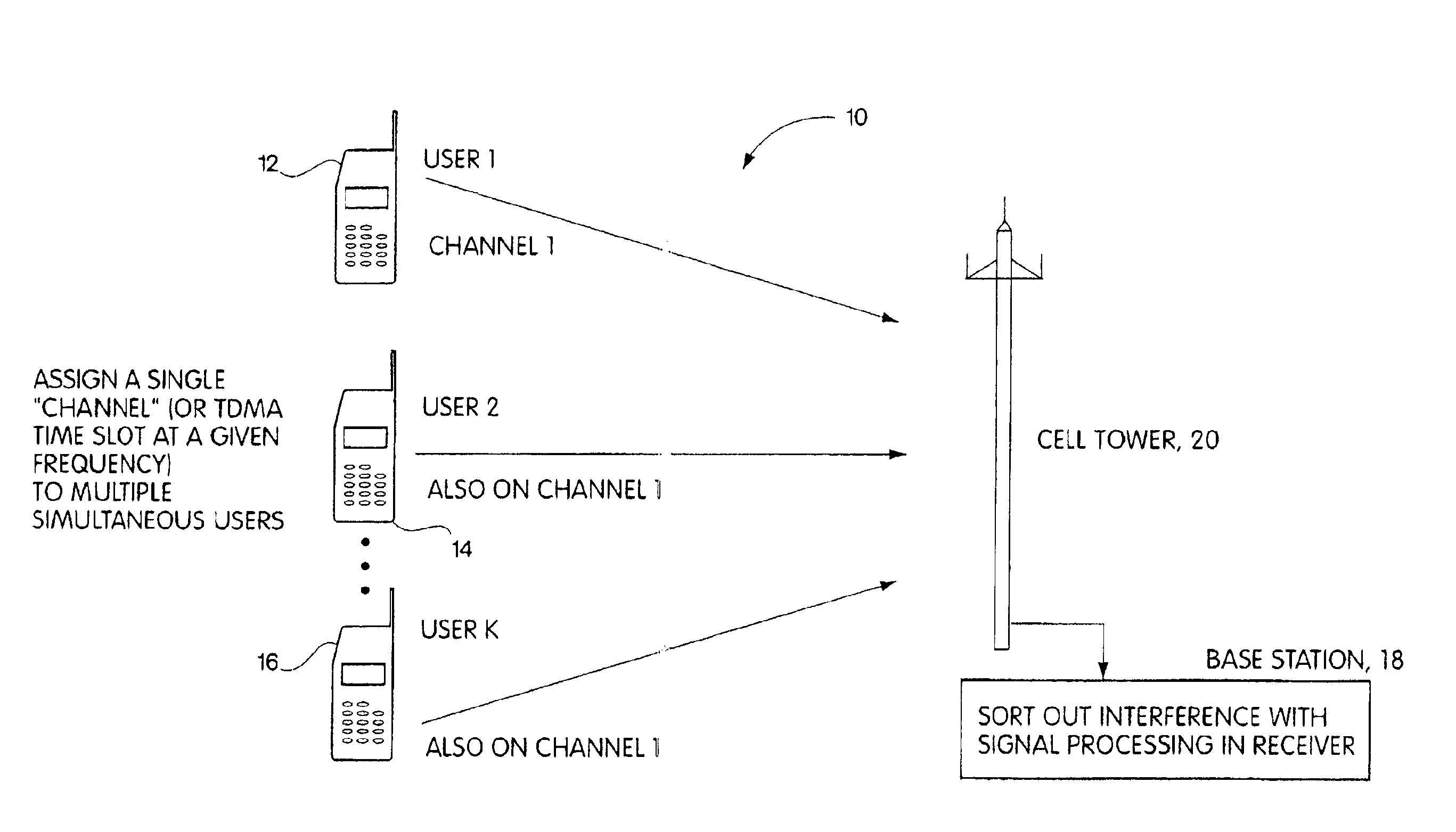

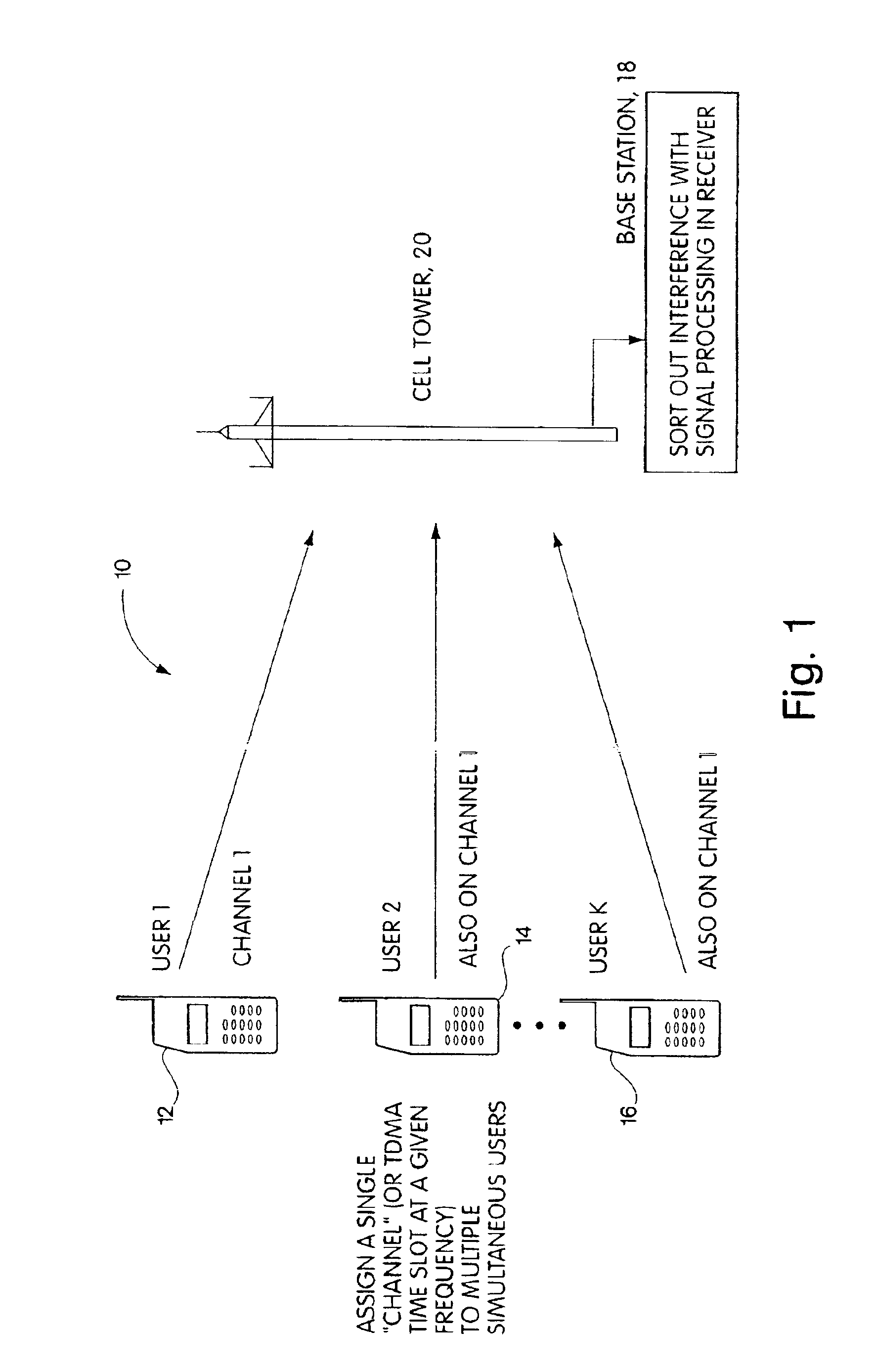

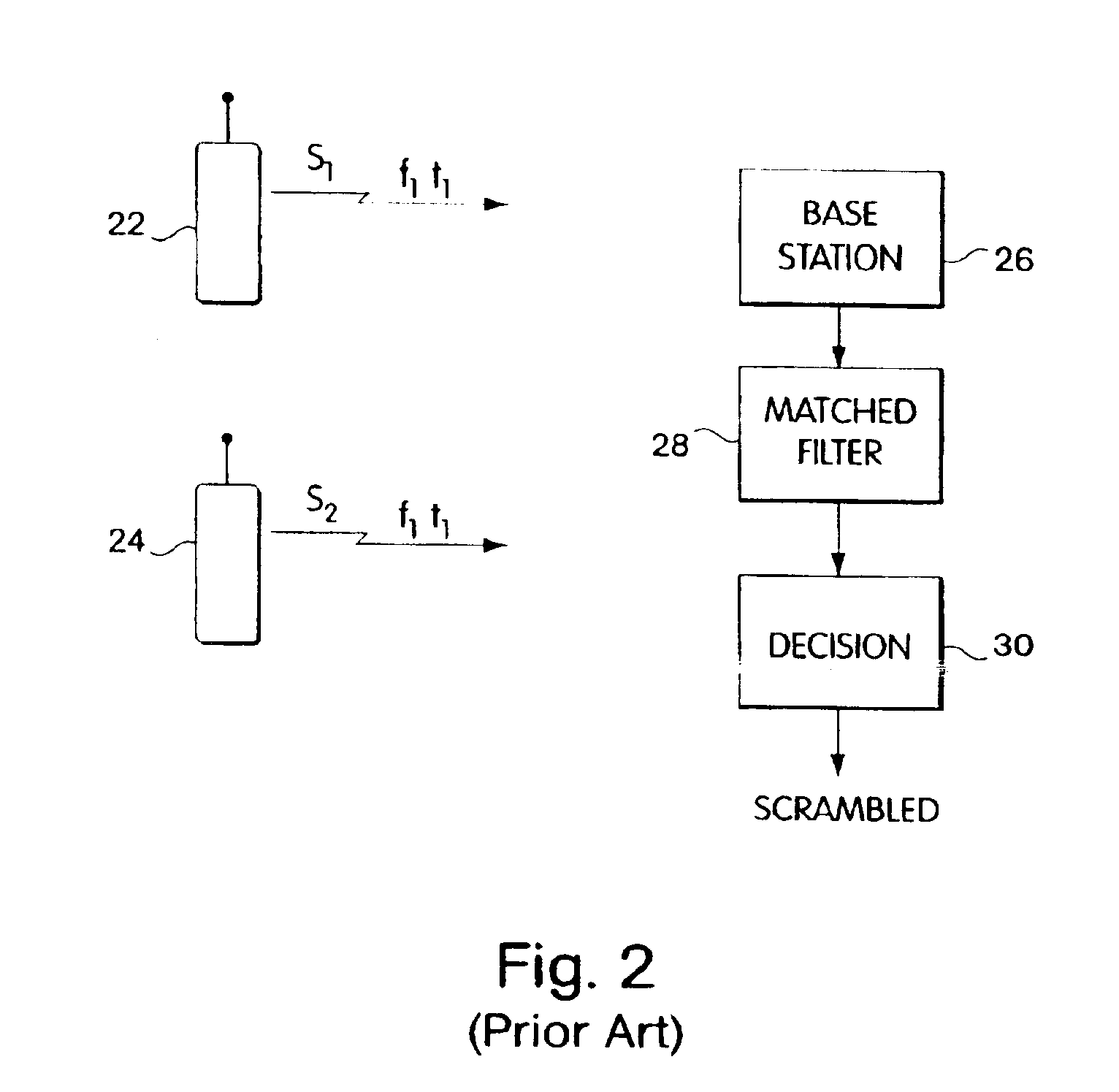

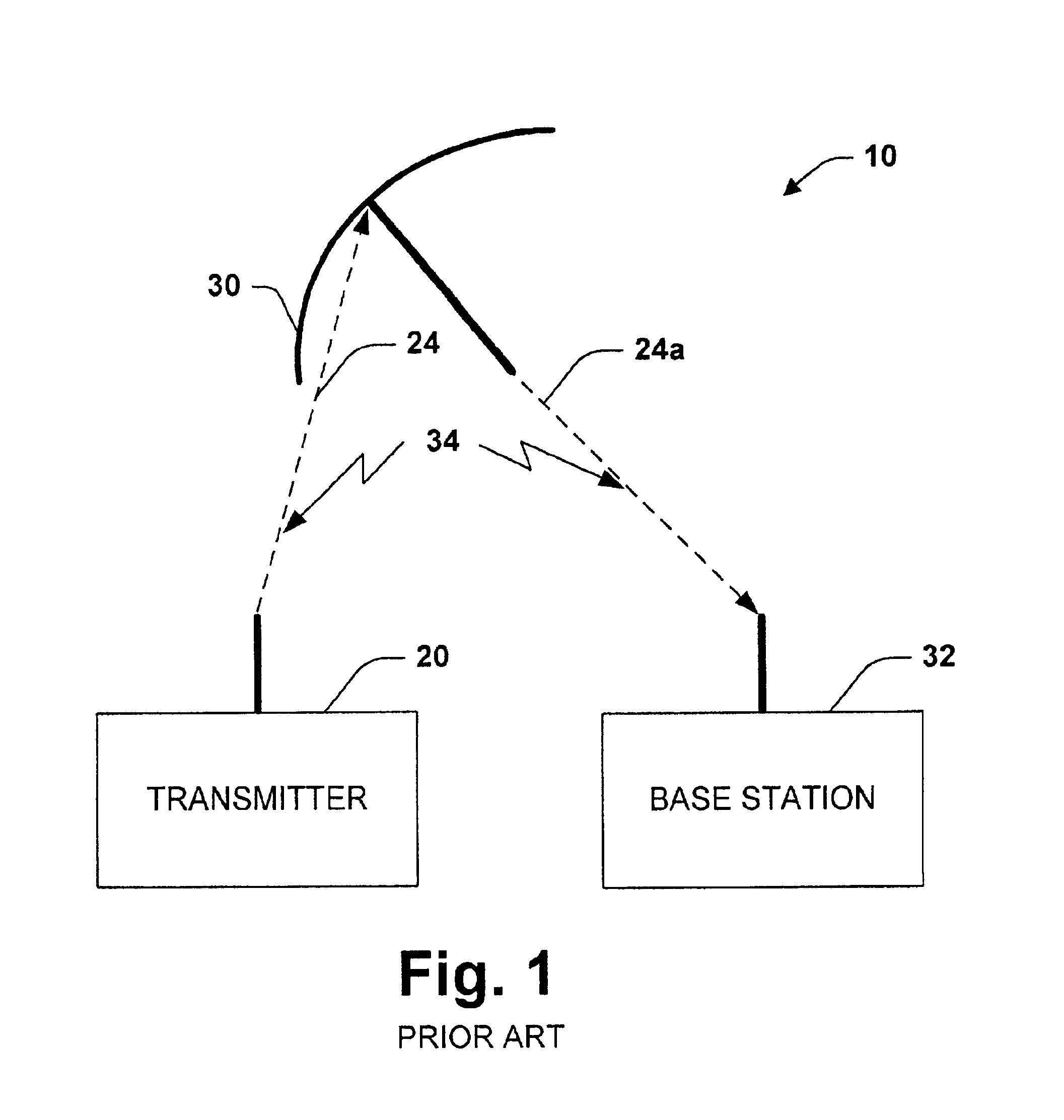

Method for overusing frequencies to permit simultaneous transmission of signals from two or more users on the same frequency and time slot

InactiveUS7058422B2Increase probabilityData representation error detection/correctionSpatial transmit diversityViterbi decoderSignal on

A system is provided for increasing the number of users capable of communicating over a wireless network to permit multiple users to transmit information simultaneously on the same channel or frequency in which a Viterbi decoder-based signal separation system is used to pull apart or uncorrupt the otherwise interfering signals on the channel. In one embodiment, two users are assigned to the same channel, with a joint parameter estimation pre-processor being utilized to provide an estimation of the power, time and frequency offsets and phase of the incoming signals. The joint parameters estimated by the parameter estimation unit are applied to a signal separator which recovers and pulls apart the two signals. The subject system is capable of accommodating more than two simultaneously transmitted signals to provide signal packing over existing channels without requiring new waveforms through the utilization of stripping techniques and tail chopping techniques so as to minimize the computational load involved in separating the signals.

Owner:COLLISION COMM INC

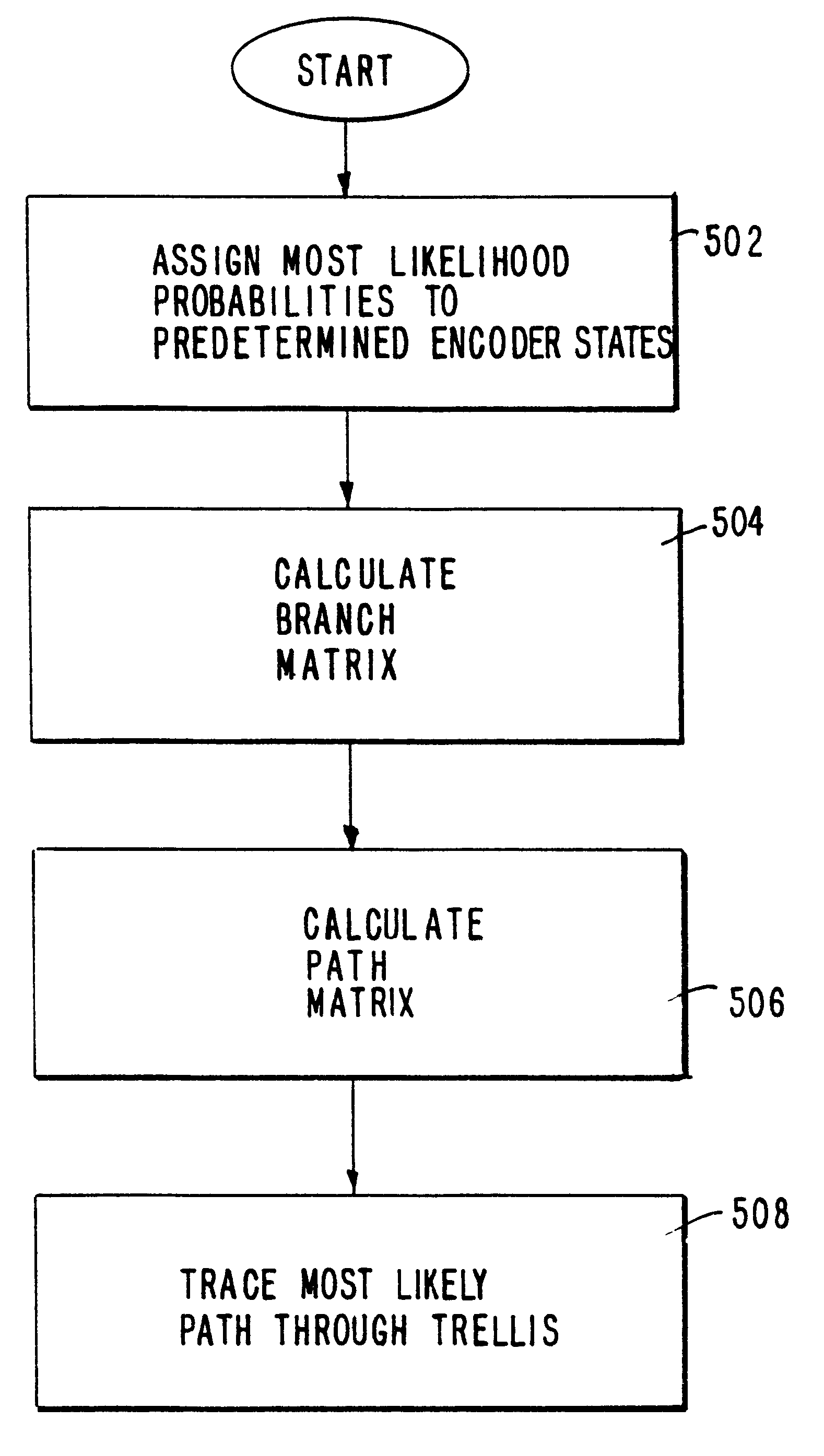

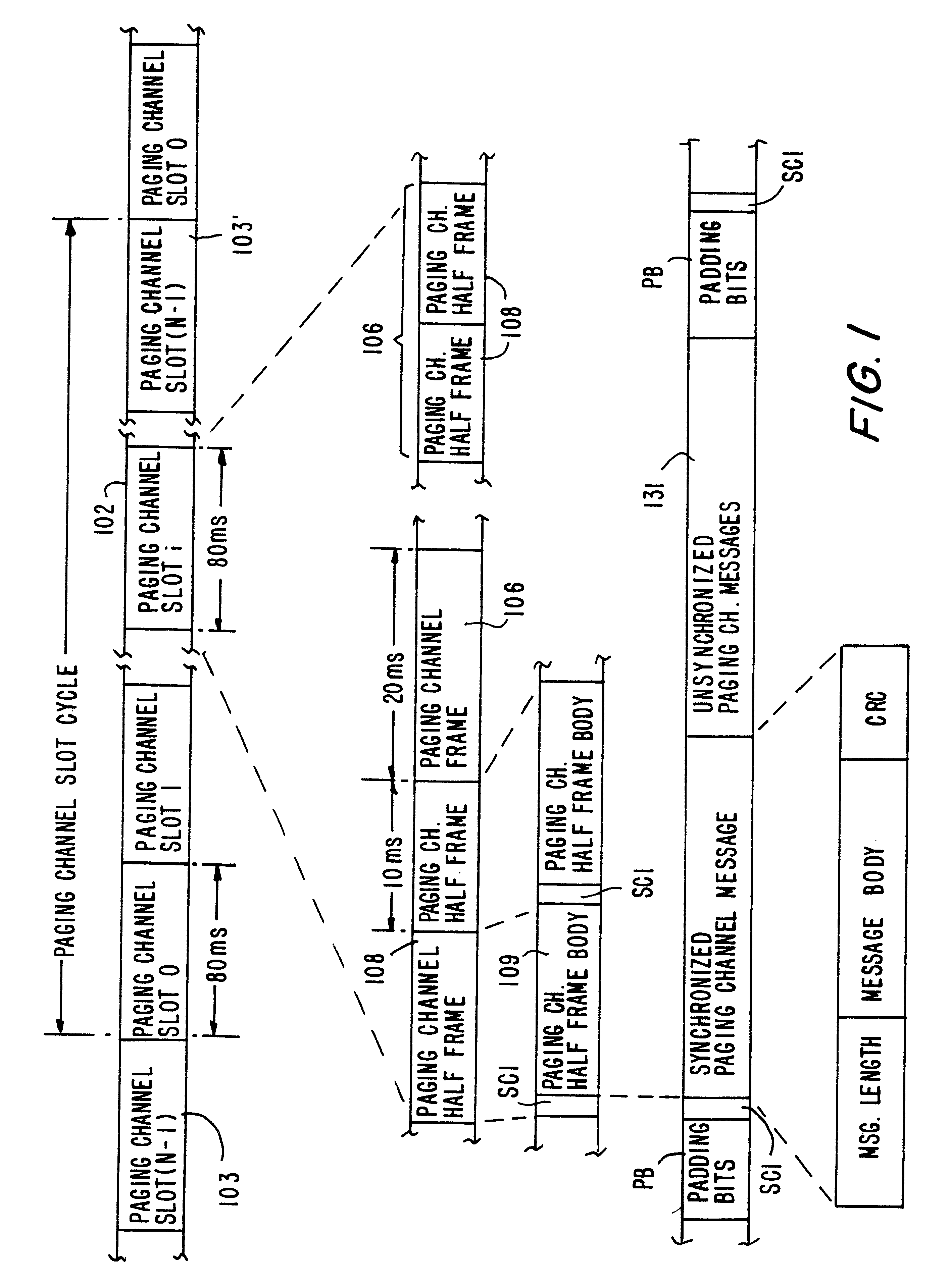

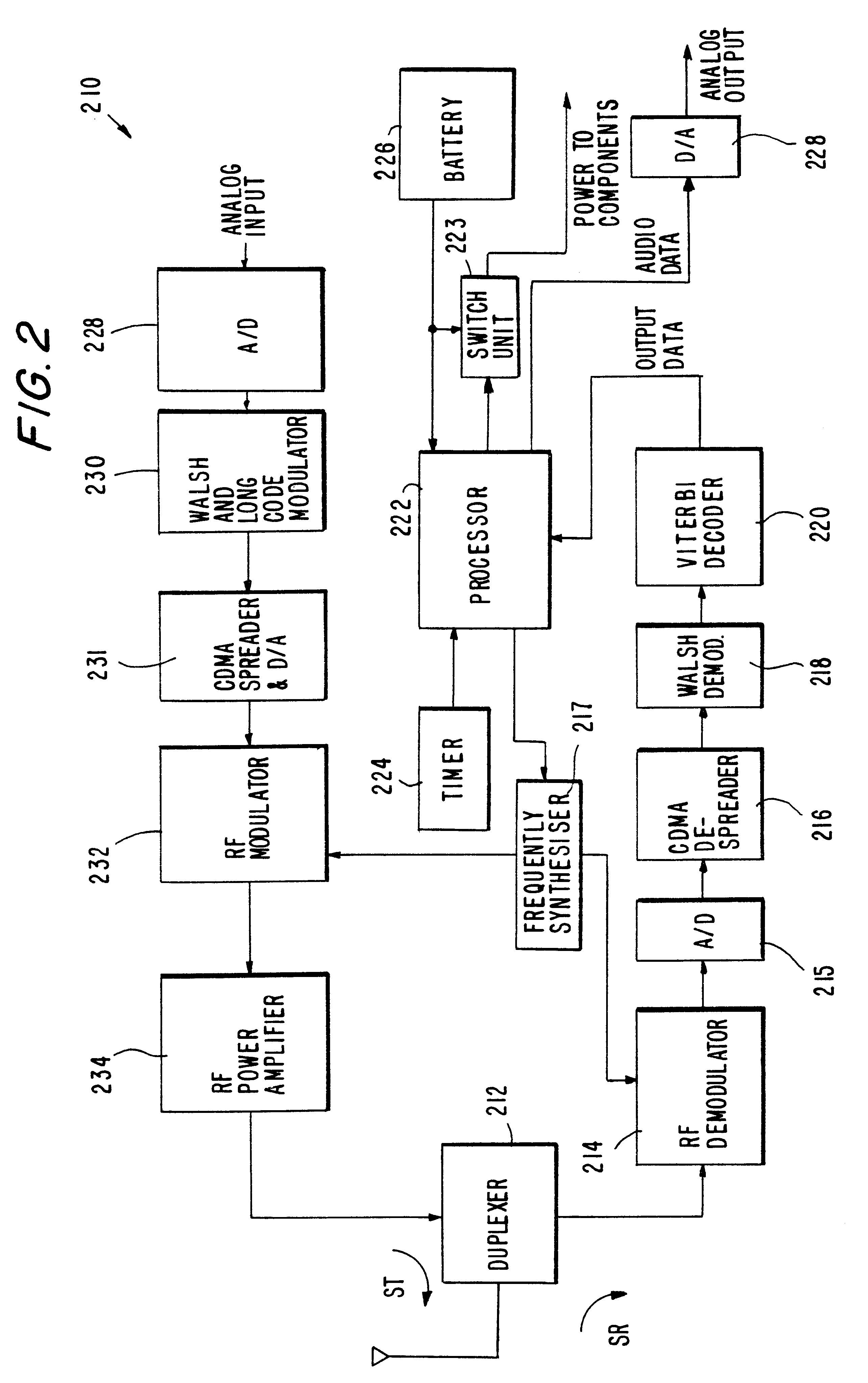

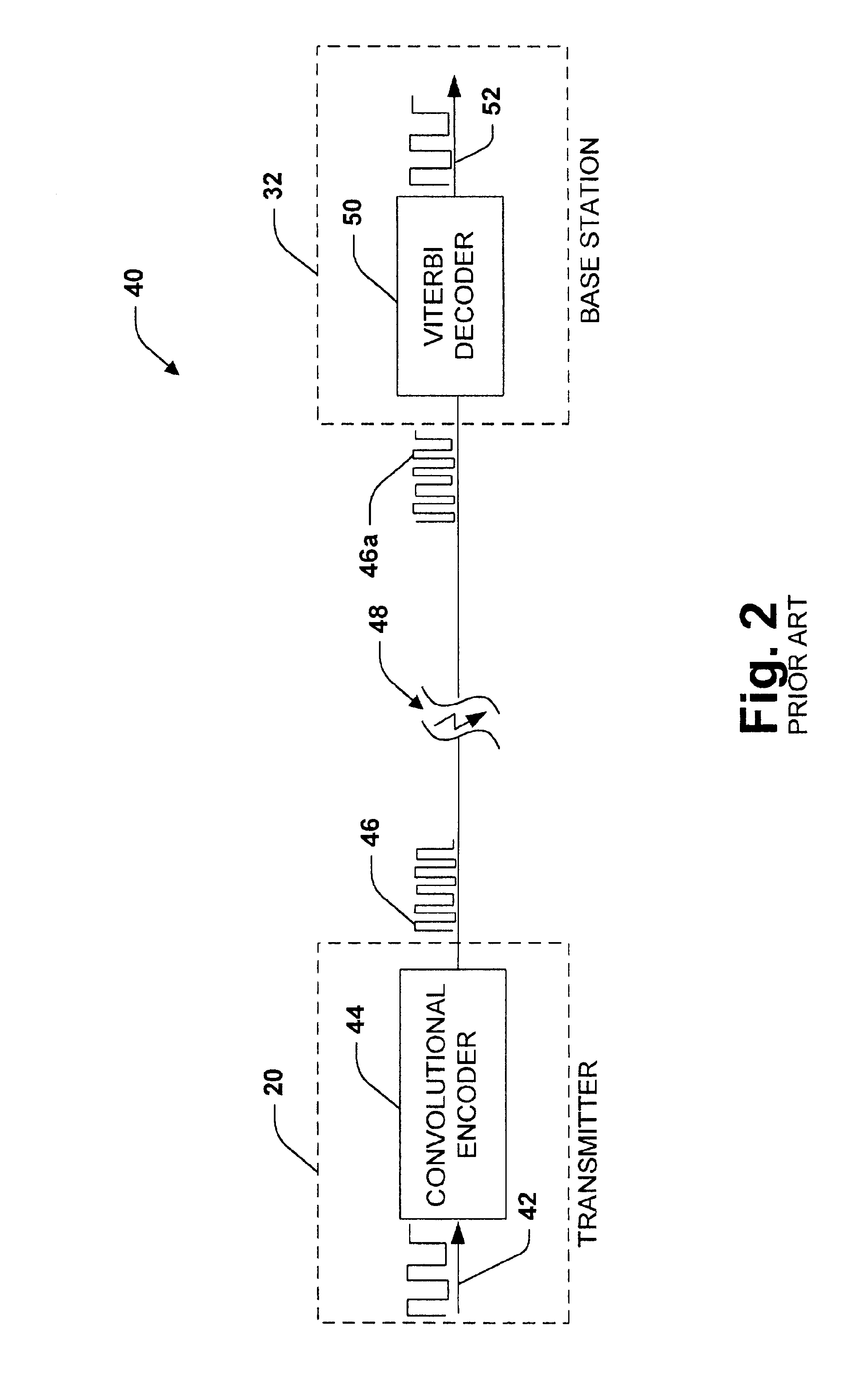

Method and apparatus for decoding continuously coded convolutionally encoded messages

InactiveUS6356595B1Reduce power consumptionReduce error rateData representation error detection/correctionError preventionViterbi decoderCommunications system

A decoding method for use in a communications system employing a communication channel in which a message is convolutionally encoded by a base station encoder and transmitted to a remote terminal during a time slot allocated to at least that remote terminal. The encoder is not completely reset immediately prior to the allocated time slot such the encoder state is unknown at the onset thereof. The decoding method includes assigning a most likelihood probability for an initial encoder state as being one of a number of predetermined encoder states; and, convolutionally decoding ensuing bits of the message based on the assumption of the initial encoder state as one of the predetermined states. The method affords low error rate decoding, and allows for improved power conservation by a mobile station, since the mobile station need not awaken significantly prior to its allocated time slot. Preferably, a Viterbi decoder is used to perform the convolutional decoding. The method has particular utility when used for decoding page messages indicative of call notifications in a paging channel of a code division multiple access (CDMA) wireless telecommunications system.

Owner:SONY ELECTRONICS INC +1

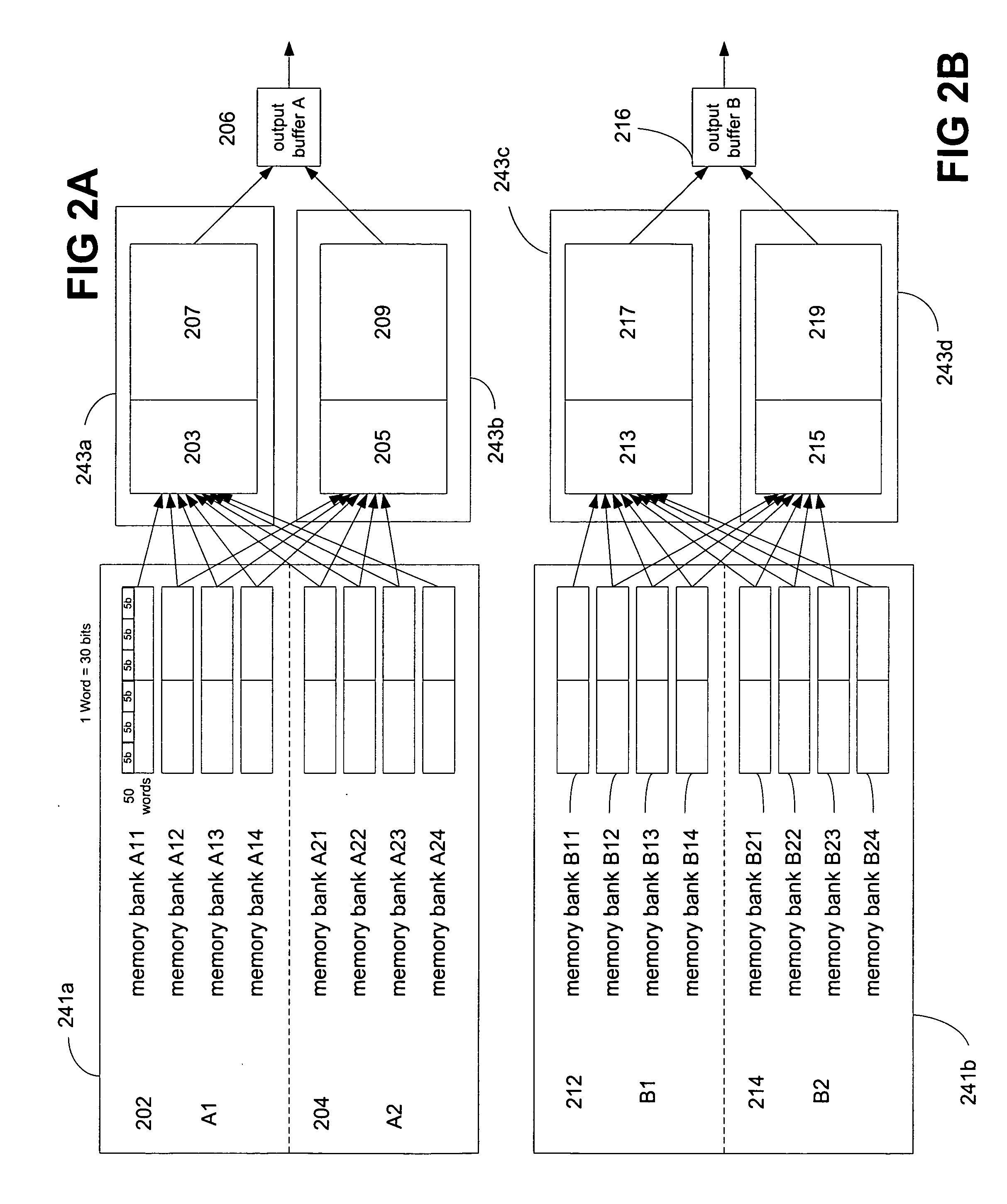

High-speed receiver architecture

ActiveUS20070133719A1Lower latencyIncrease loop bandwidthAnalogue/digital conversionMultiple-port networksViterbi decoderFiber

A receiver (e.g., for a 10 G fiber communications link) includes an interleaved ADC coupled to a multi-channel equalizer that can provide different equalization for different ADC channels within the interleaved ADC. That is, the multi-channel equalizer can compensate for channel-dependent impairments. In one approach, the multi-channel equalizer is a feedforward equalizer (FFE) coupled to a Viterbi decoder, for example a sliding block Viterbi decoder (SBVD); and the FFE and / or the channel estimator for the Viterbi decoder are adapted using the LMS algorithm.

Owner:MARVELL ASIA PTE LTD

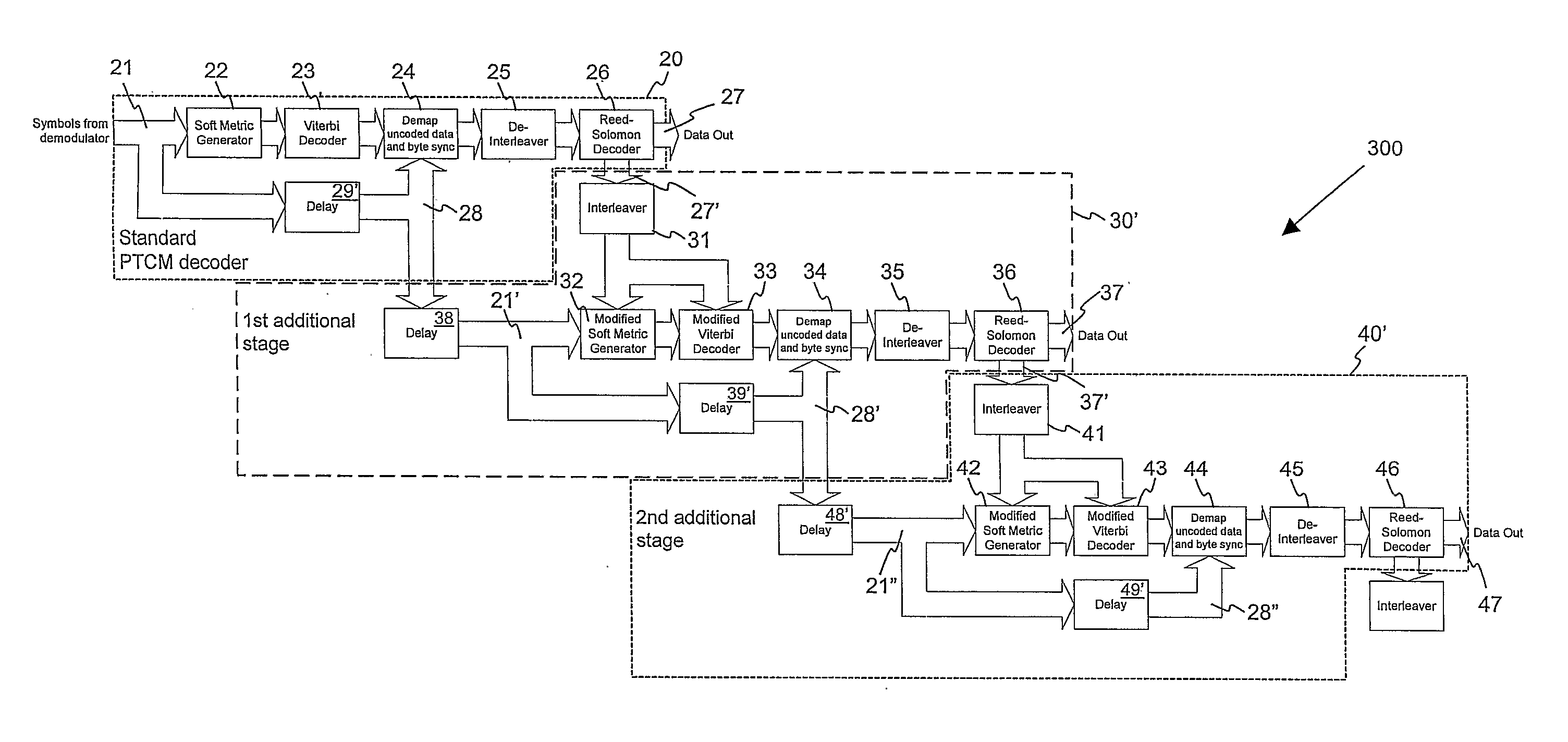

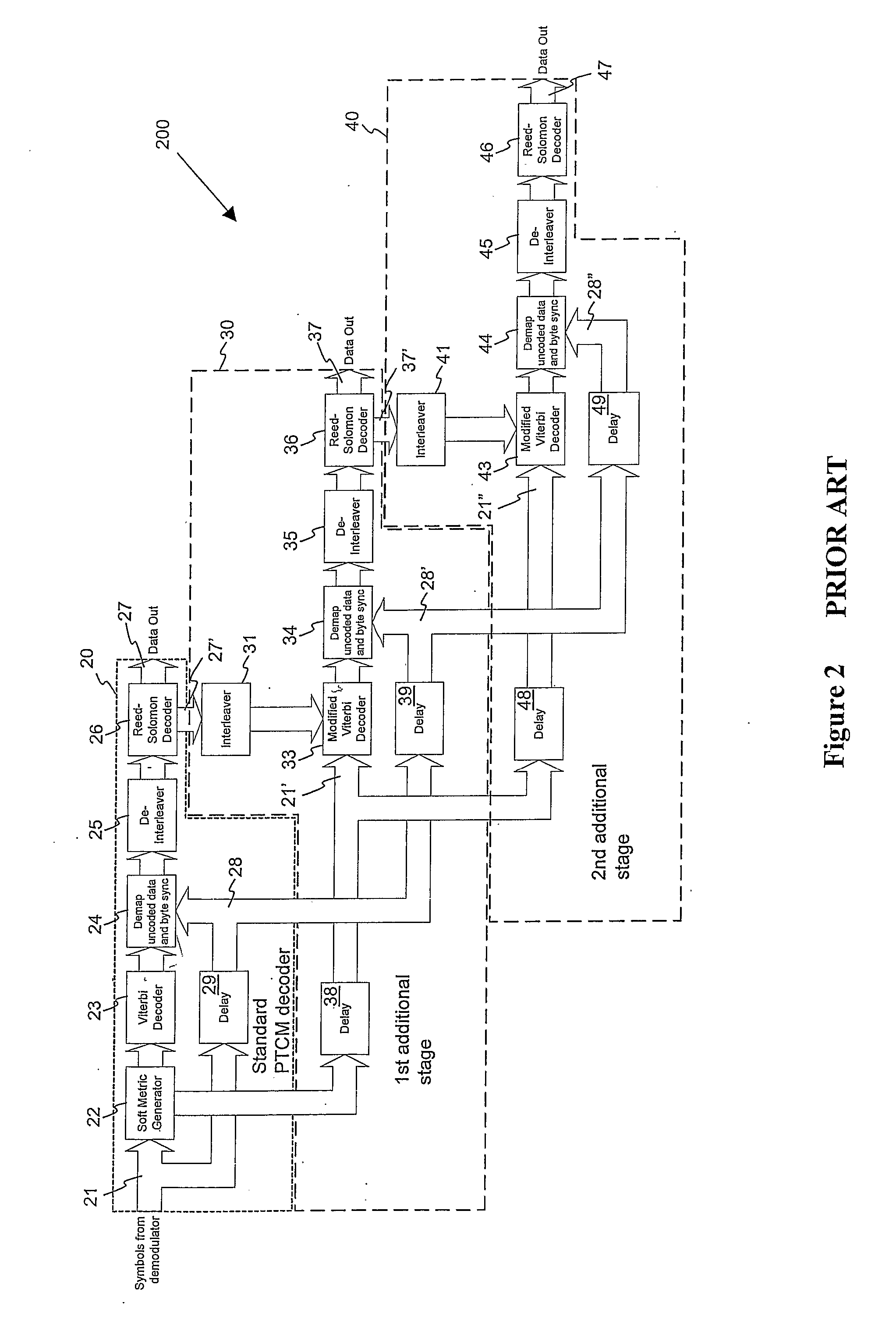

Decoding a Concatenated Convolutional-Encoded and Block Encoded Signal

ActiveUS20070220408A1Improve efficiencySpeed up the decoding processData representation error detection/correctionOther decoding techniquesViterbi decoderReed solomon decoder

Encoded symbols of a concatenated convolutional-encoded and block encoded signal are presented to a conventional first stage of a concatenated decoder, comprising in sequence a soft metric generator, a Viterbi decoder, a first de-interleaver and a first block decoder such as a Reed-Solomon decoder. The encoded symbols are also presented to a delay chain to produce progressively delayed encoded symbols. Where an output block of the conventional decoder is indicated as being a valid codeword by the first block decoder, the bytes in this block are marked as being correct. These bytes that are known to be correct are then used after interleaving and serialisation as known bits input to a second stage of the decoder process operating on the delayed encoded symbols and incorporating a modified soft metric generator constrained by the known bits. This process can be extended to further iterations as required. A modified Viterbi decoder, which is also constrained by the known bits, may also be used in the second and subsequent iterative stages.

Owner:MK SYST USA INC

High-Speed Receiver Architecture

ActiveUS20090185613A1Overcome limitationsLower latencyAnalogue/digital conversionMultiple-port networksViterbi decoderTelecommunications link

A receiver (e.g., for a 10 G fiber communications link) includes an interleaved ADC coupled to a multi-channel equalizer that can provide different equalization for different ADC channels within the interleaved ADC. That is, the multi-channel equalizer can compensate for channel-dependent impairments. In one approach, the multi-channel equalizer is a feedforward equalizer (FFE) coupled to a Viterbi decoder, for example a sliding block Viterbi decoder (SBVD); and the FFE and / or the channel estimator for the Viterbi decoder are adapted using the LMS algorithm.

Owner:MARVELL ASIA PTE LTD

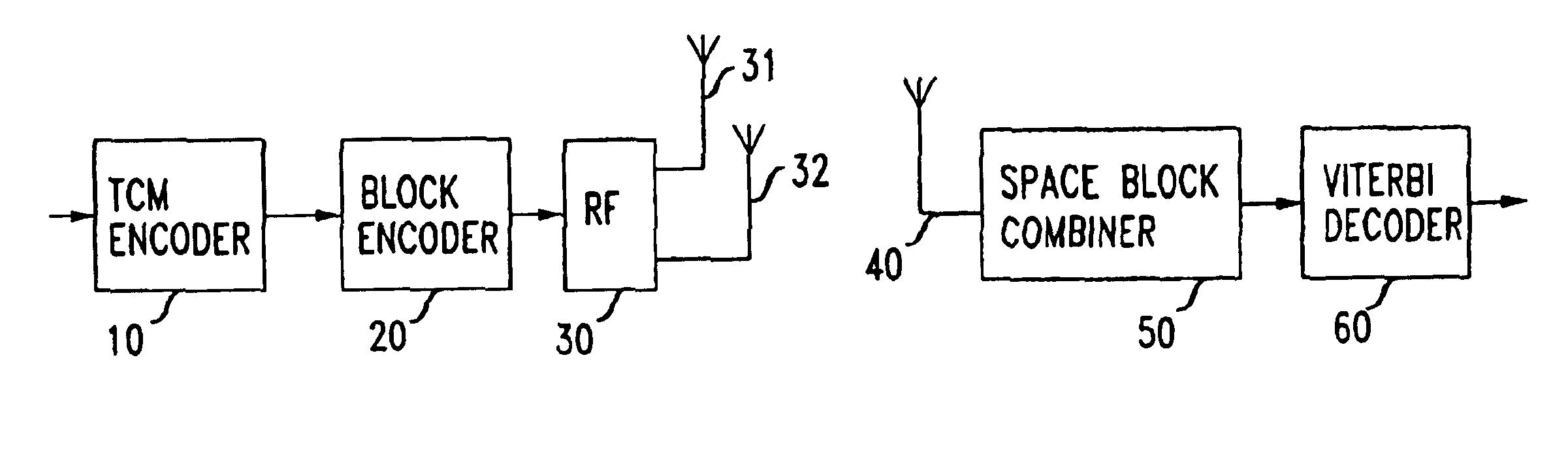

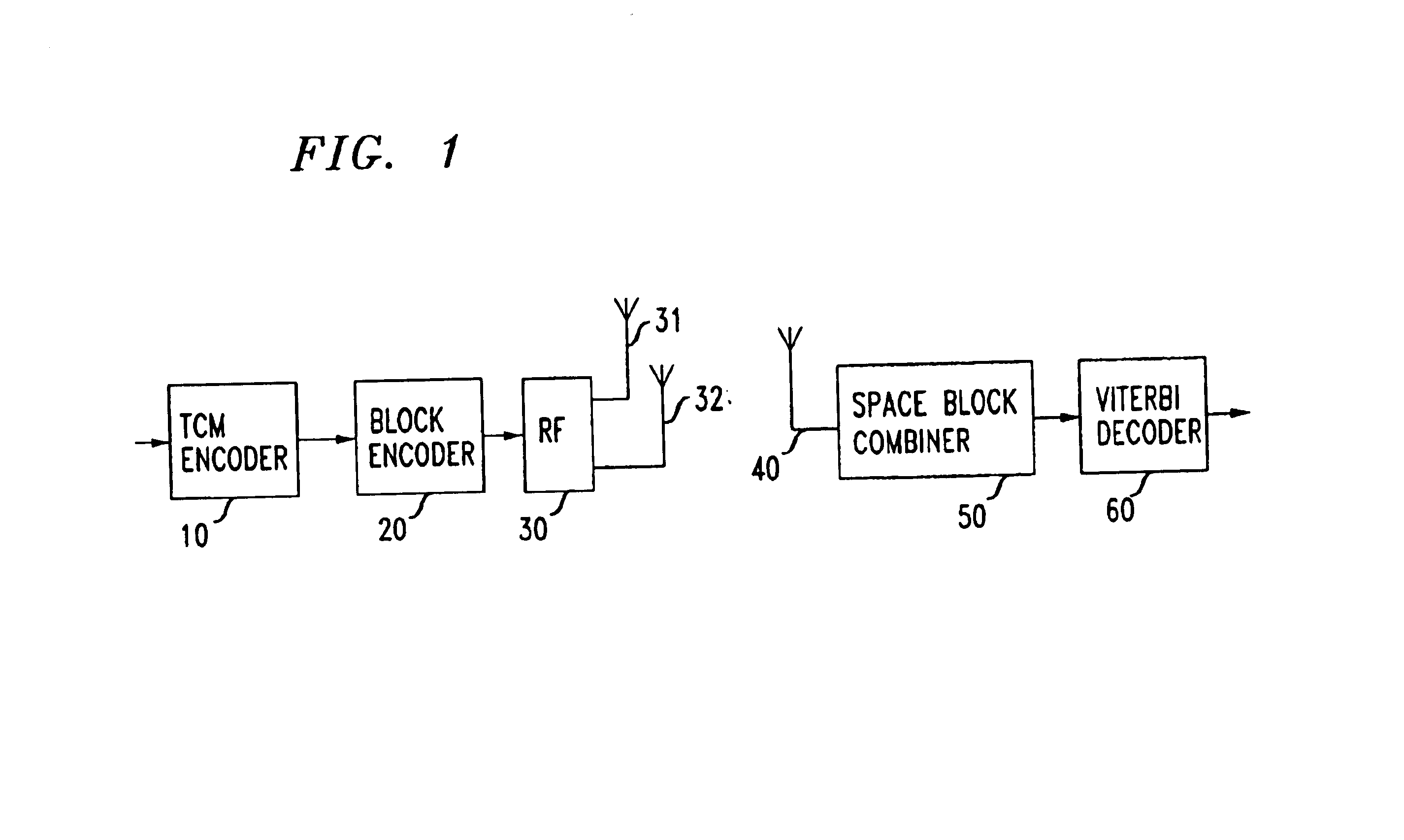

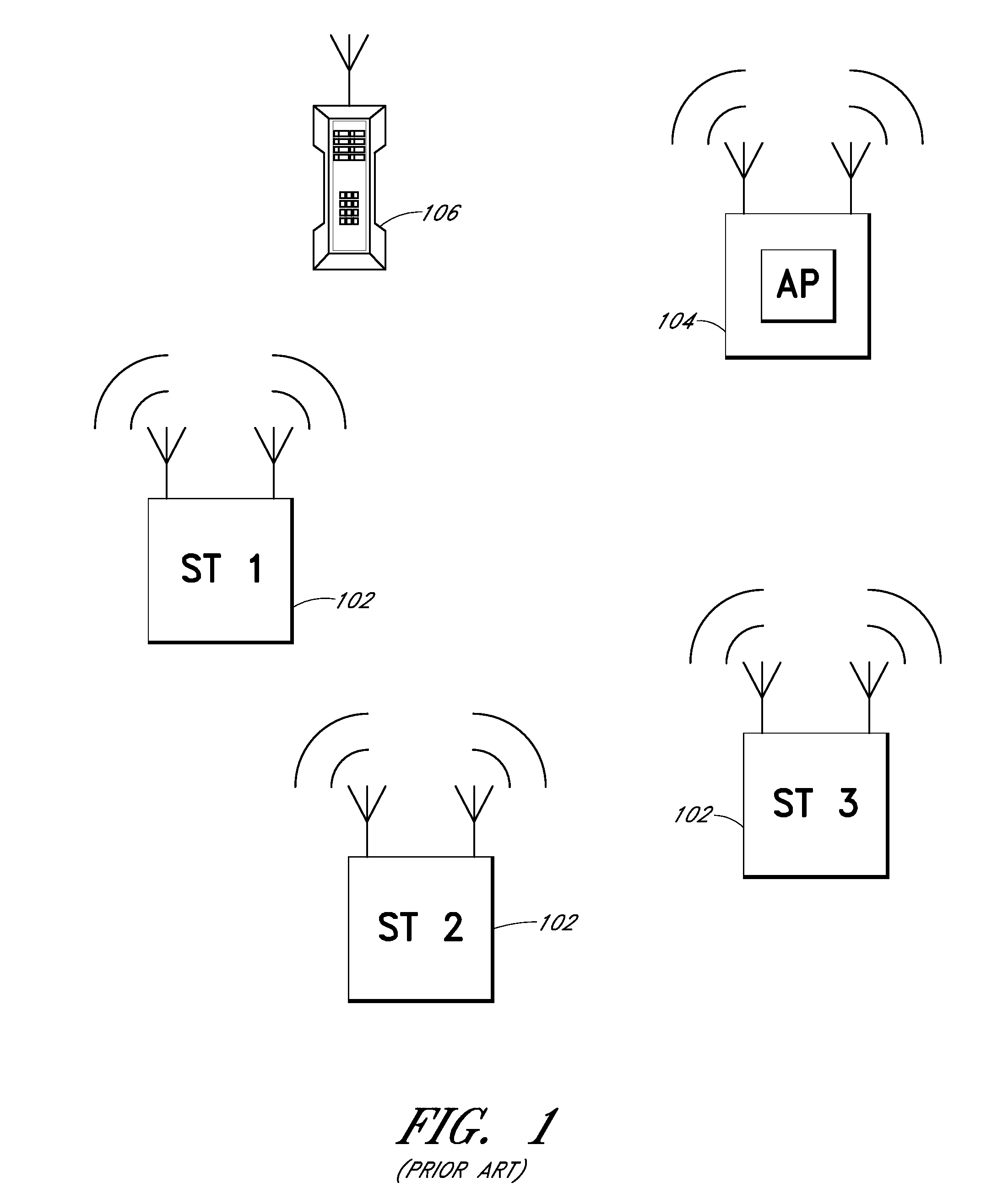

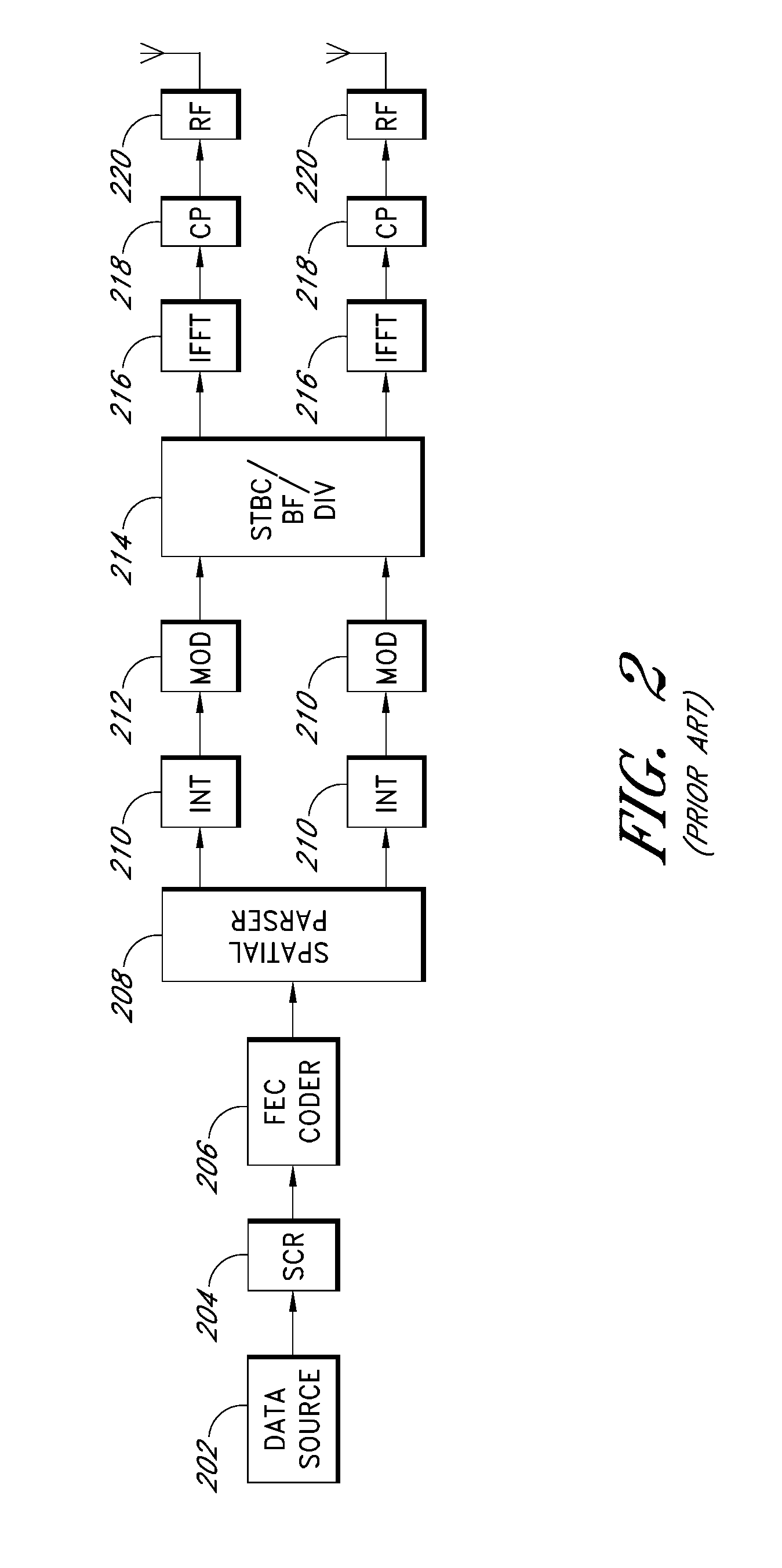

Low complexity maximum likelihood detection of concatenated space codes for wireless applications

InactiveUS6853688B2Data representation error detection/correctionSpatial transmit diversityViterbi decoderSpace time diversity

Good transmission characteristics are achieved in the presence of fading with a transmitter that employs a trellis coder followed by a block coder. Correspondingly, the receiver comprises a Viterbi decoder followed by a block decoder. Advantageously, the block coder and decoder employ time-space diversity coding which, illustratively, employs two transmitter antennas and one receiver antenna.

Owner:AT&T WIRELESS SERVICES

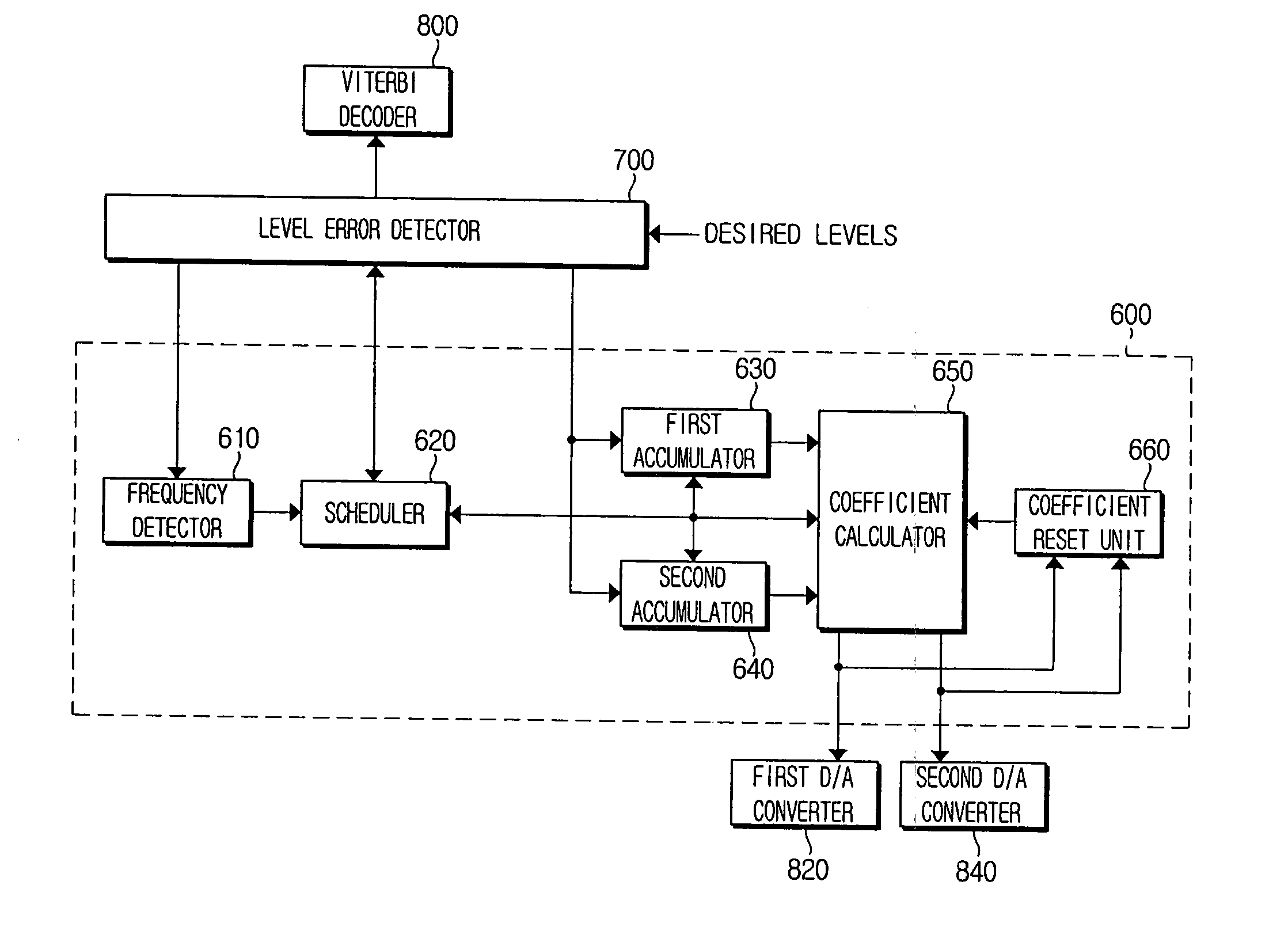

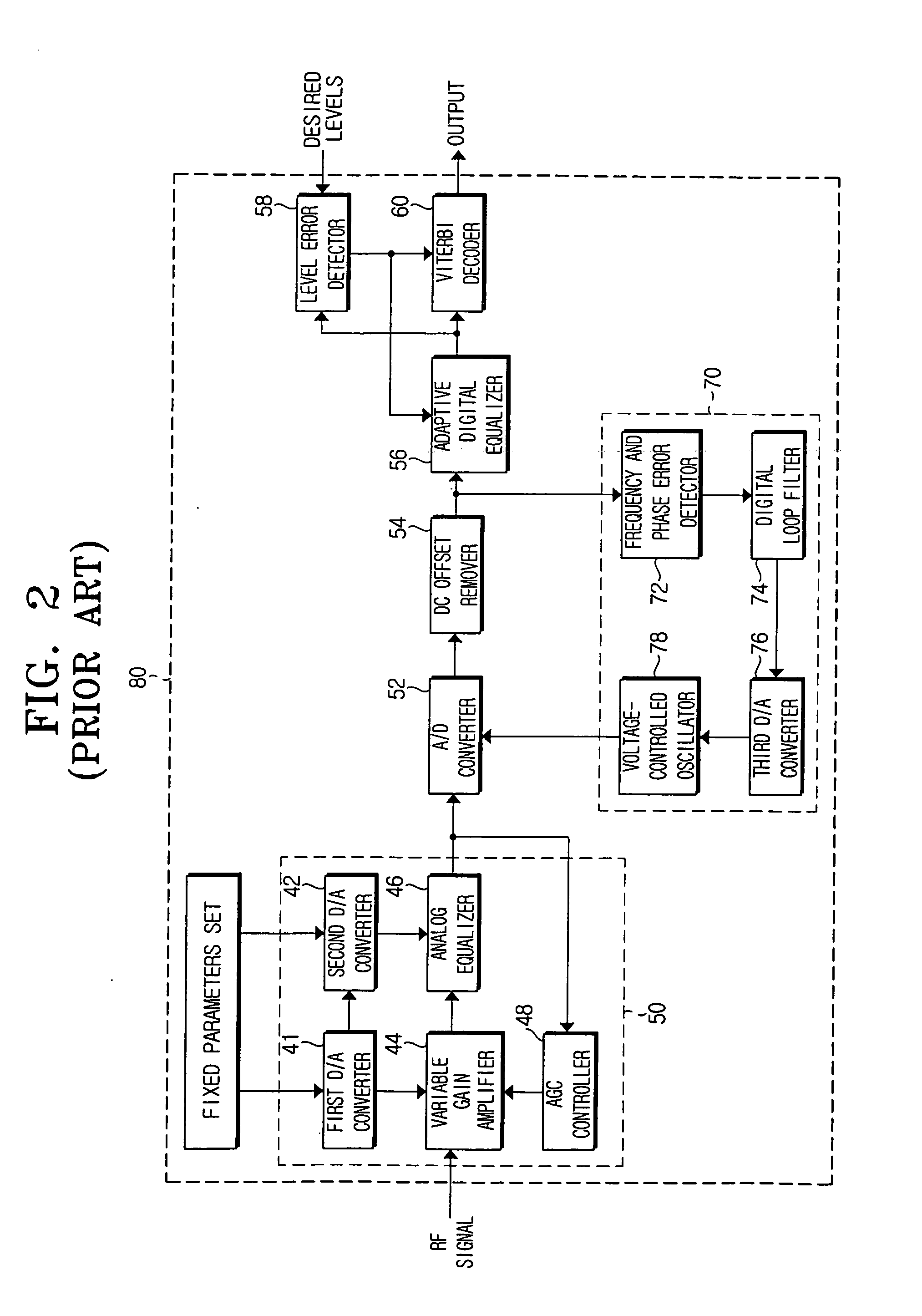

High-speed mixed analog/digital PRML data detection and clock recovery apparatus and method for data storage

InactiveUS20050180287A1Reduce chip areaImprove system speedTelevision system detailsModification of read/write signalsViterbi decoderAudio power amplifier

A high-speed mixed analog / digital PRML data detection and clock recovery apparatus and method. The high-speed mixed analog / digital PRML data detection and clock recovery apparatus includes a variable gain amplifier, an analog equalizer, an analog-to-digital (A / D) converter, a DC offset remover, a level error detector, a Viterbi decoder, and an adaptive digital controller. The adaptive digital controller separately stores the level error values by predetermined frequencies, calculates predetermined coefficient values by each frequency component based on the level error values, and D / A-converts and applies the calculated predetermined coefficient values to the variable gain amplifier and the analog equalizer.

Owner:SAMSUNG ELECTRONICS CO LTD

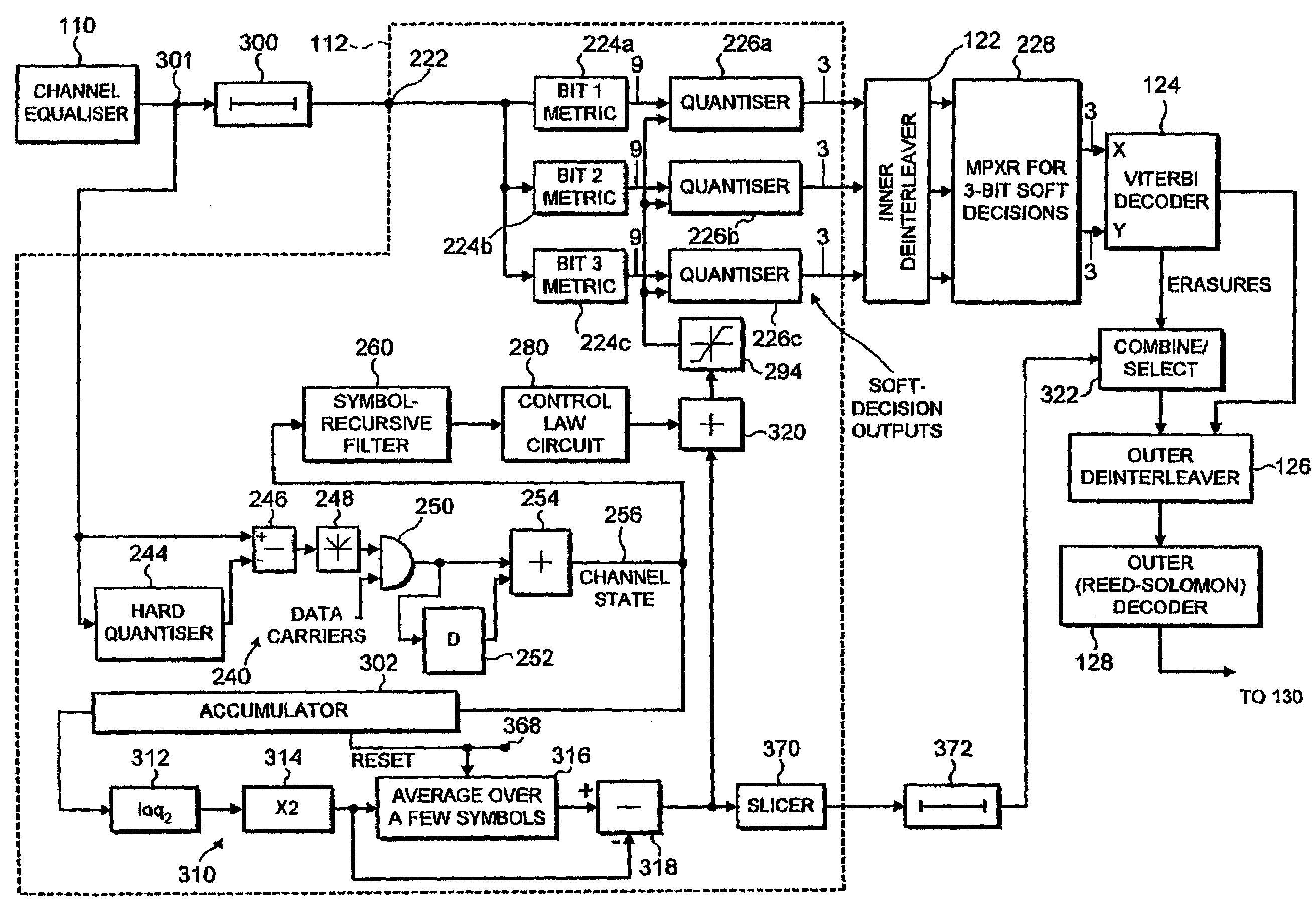

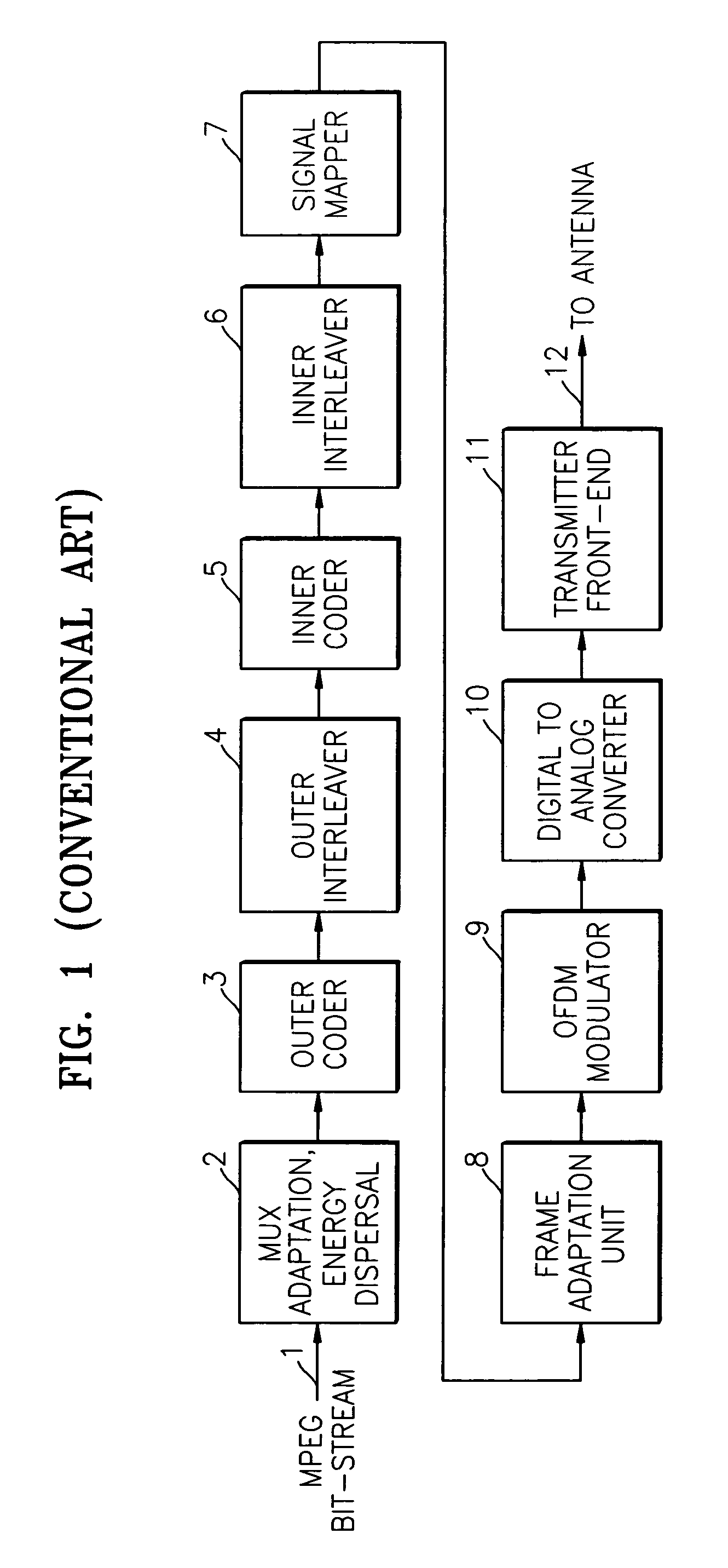

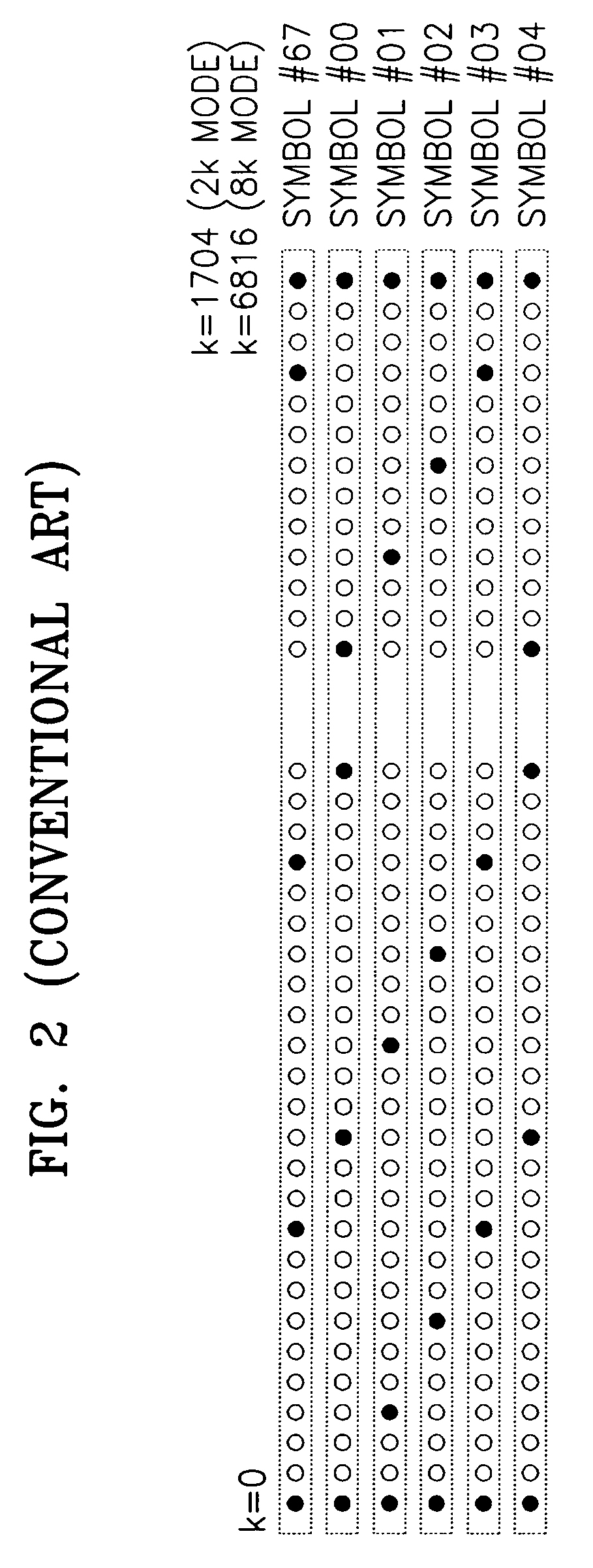

Decoders for many-carrier signals, in particular in DVB-T receivers

InactiveUS7221720B2Large memory requirementIncrease the number ofData representation error detection/correctionPulse modulation television signal transmissionViterbi decoderCarrier signal

A DVB-T receiver includes a channel equalizer, a metric assignment and demapping circuit, a Viterbi decoder and an outer Reed-Solomon decoder. The metric assignment and demapping circuit includes a soft-decision quantising arrangement which provides confidence values for the Viterbi decoder. The quantising arrangement receives a control input from channel state indication (CSI) measurement circuitry.A further channel state indication is obtained on a symbol-by-symbol basis. This is compared an average obtained over a few symbols, to detect impulsive interference, and applied as part of the control for the soft-decision quantiser.A signal derived from the further channel state indication is also applied to the erasures input of the Reed-Solomon decoder.

Owner:BRITISH BROADCASTING CORP

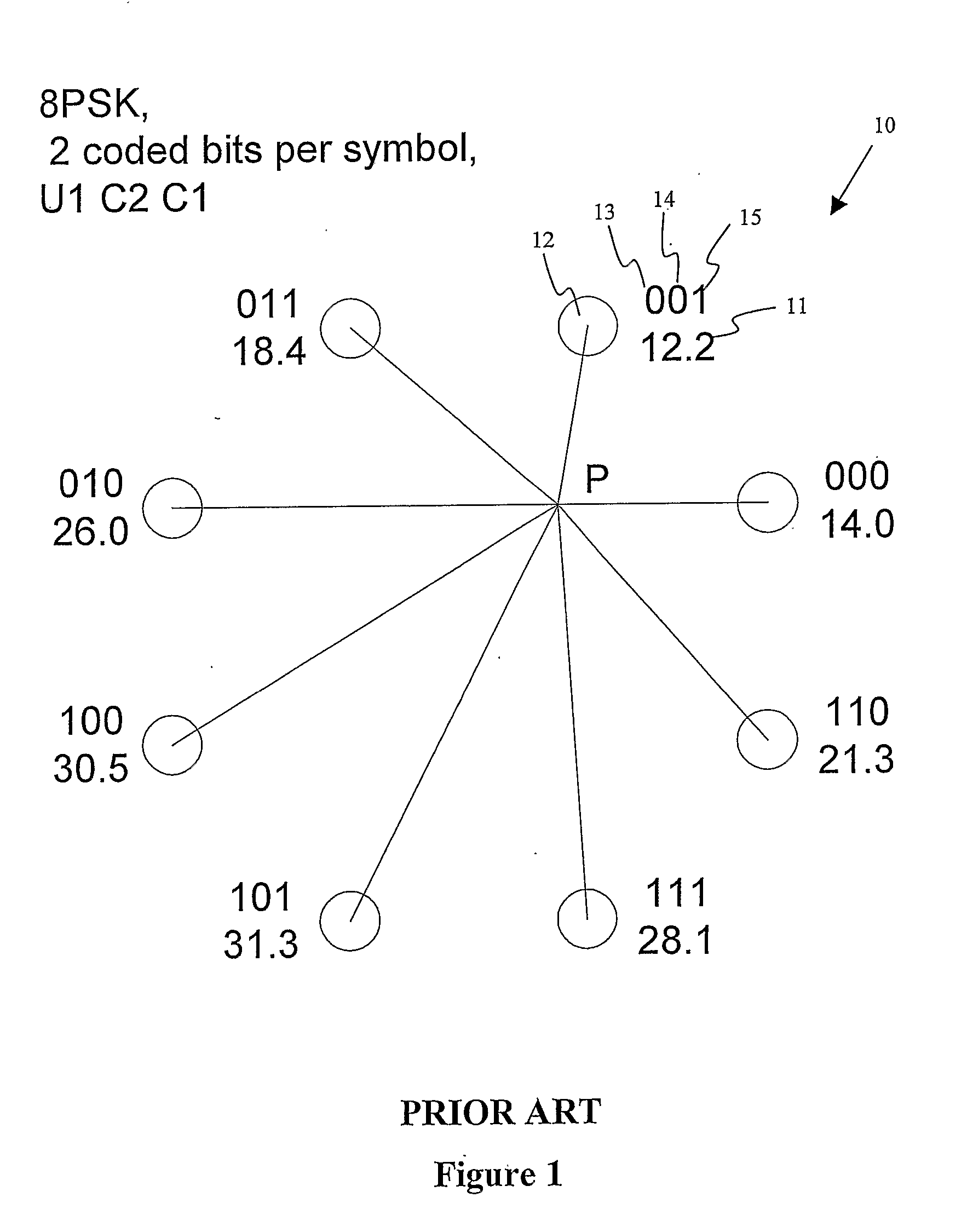

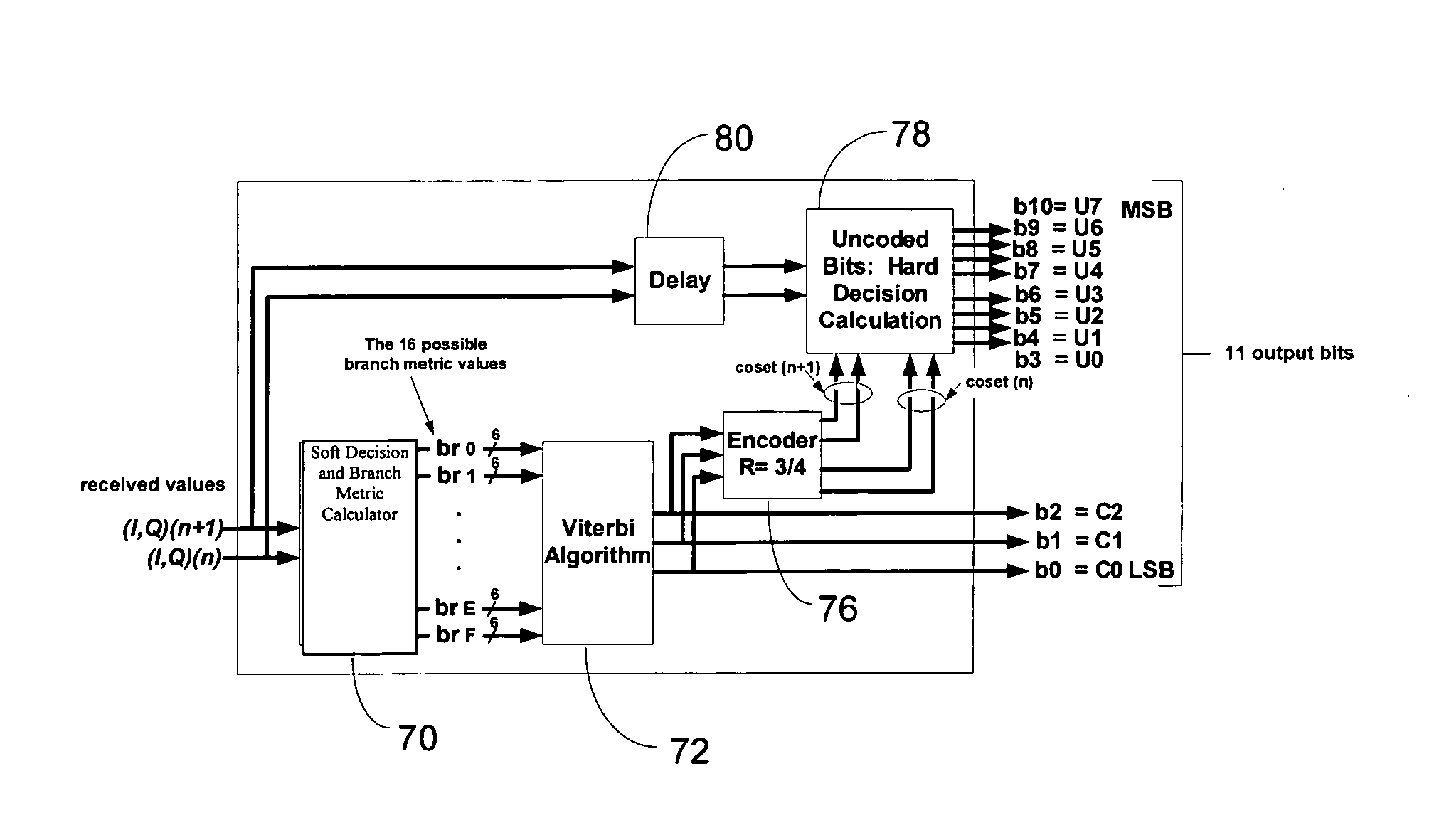

Efficient decoding of trellis coded modulation waveforms

ActiveUS7224743B2Improve performanceData representation error detection/correctionOther decoding techniquesDigital dataViterbi decoder

A method and apparatus for decoding trellis-coded digital data. Digital data samples that have been convolutionally encoded by trellis-coded modulation (TCM) for purposes of forward error correction require a computationally intensive Viterbi decoder for best performance. A technique known as pragmatic trellis-code modulation (PTCM) reduces decoder complexity but at the expense of degraded performance in some situations. This disclosure provides a solution that retains the reduced complexity of PTCM, but uses a full trellis approach that yields significantly better performance in terms of bit error rate (BER).

Owner:NORTHROP GRUMMAN SYST CORP

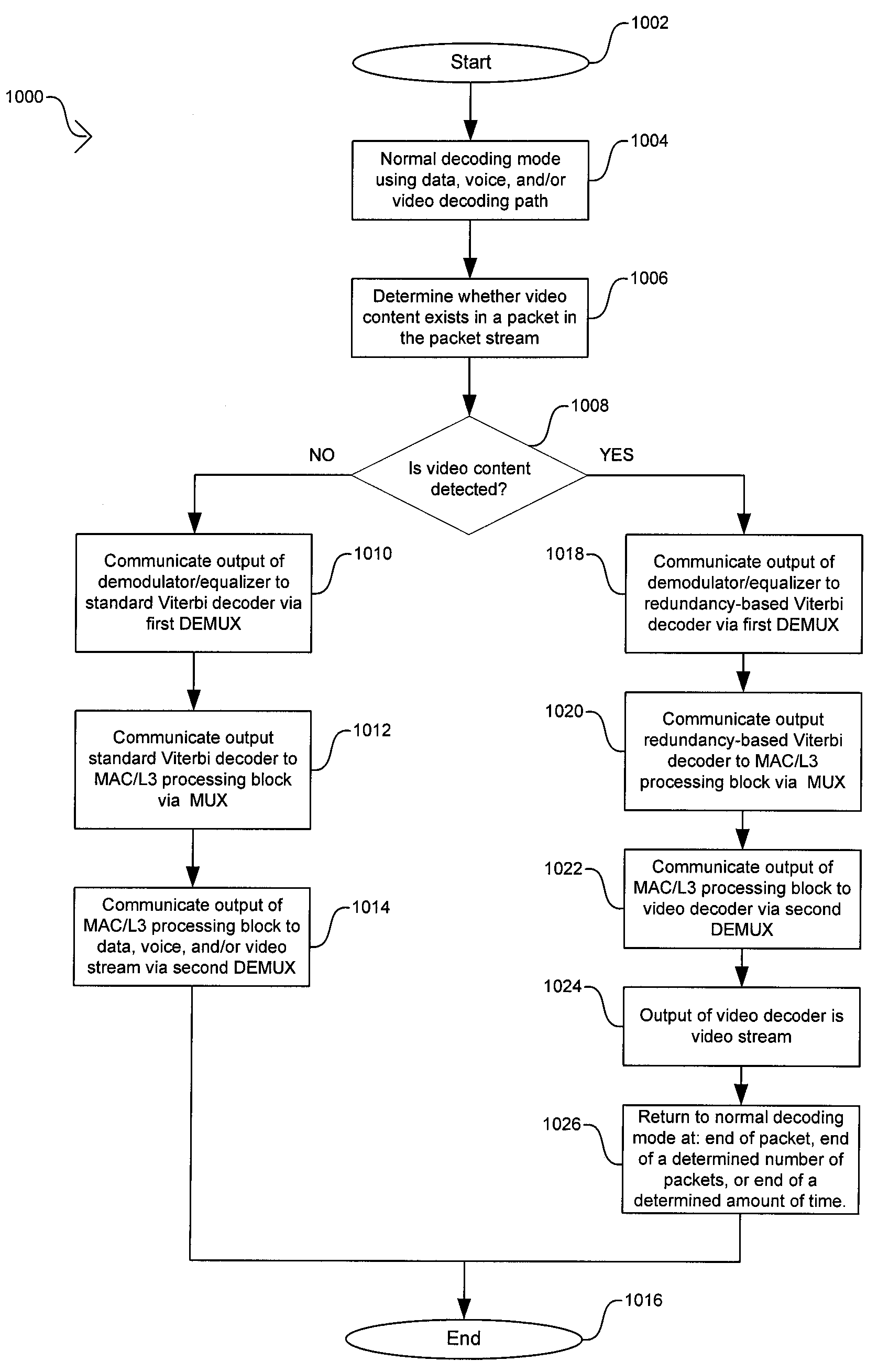

Method and system for redundancy-based decoding of video content in a wireless system

ActiveUS20080219381A1Error preventionModulated-carrier systemsViterbi decoderMultimedia data streams

Aspects of a method and system for redundancy-based decoding of video content in a wireless system are provided. A wireless receiver may determine whether a received multimedia data stream comprises video content and may select a redundancy-based decoder when video content is detected. The wireless receiver may be a WLAN receiver or a cellular receiver. Video content may be indicated by at least one flag in a preamble or a reserved field of the received multimedia data. The redundancy-based decoder may be a Viterbi decoder. The wireless receiver may enable a standard Viterbi decoder to decode portions of the multimedia data that do not comprise video content. The wireless receiver may generate at least one signal to select the redundancy-based decoder or the standard Viterbi decoder.

Owner:AVAGO TECH INT SALES PTE LTD

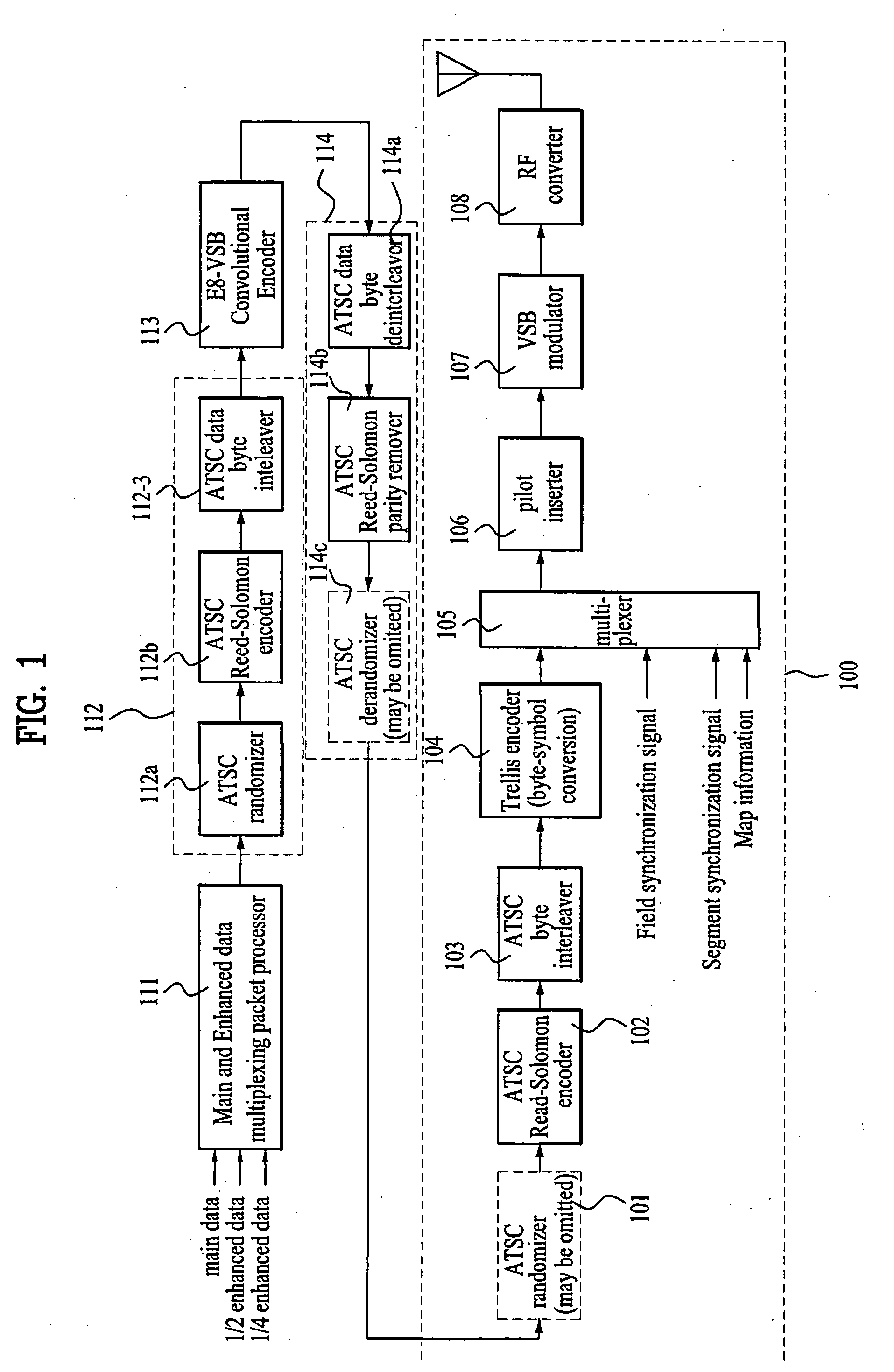

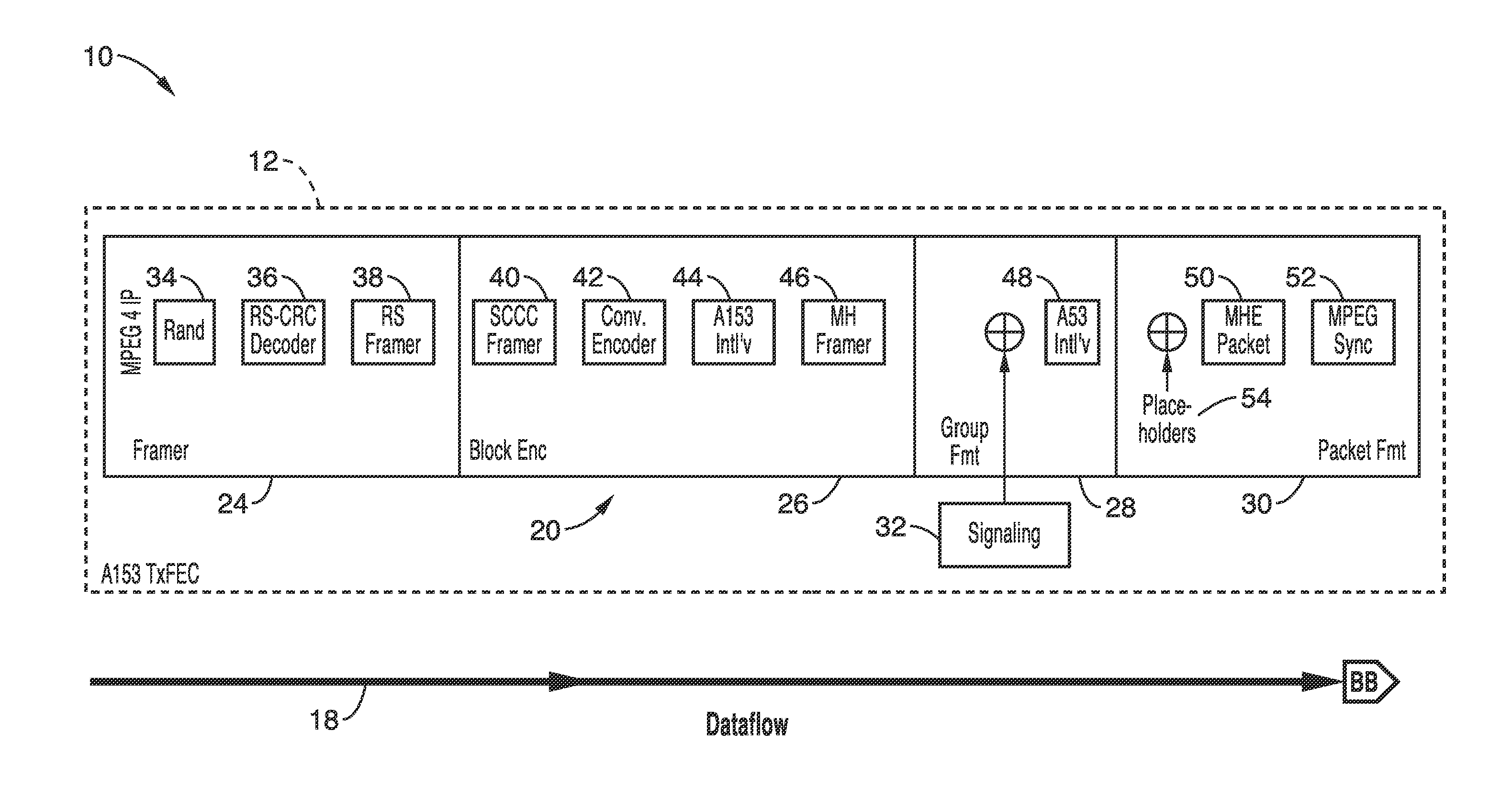

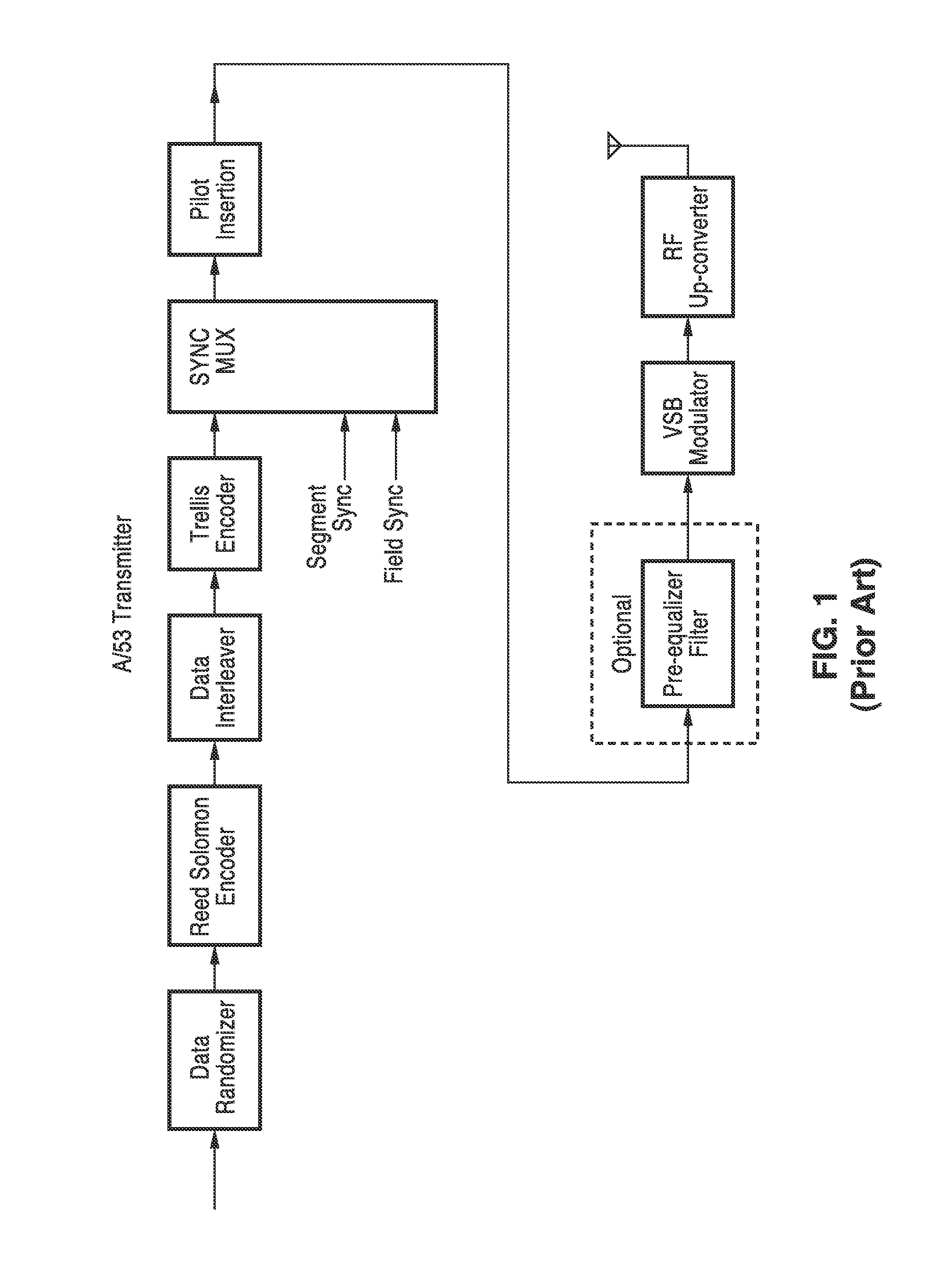

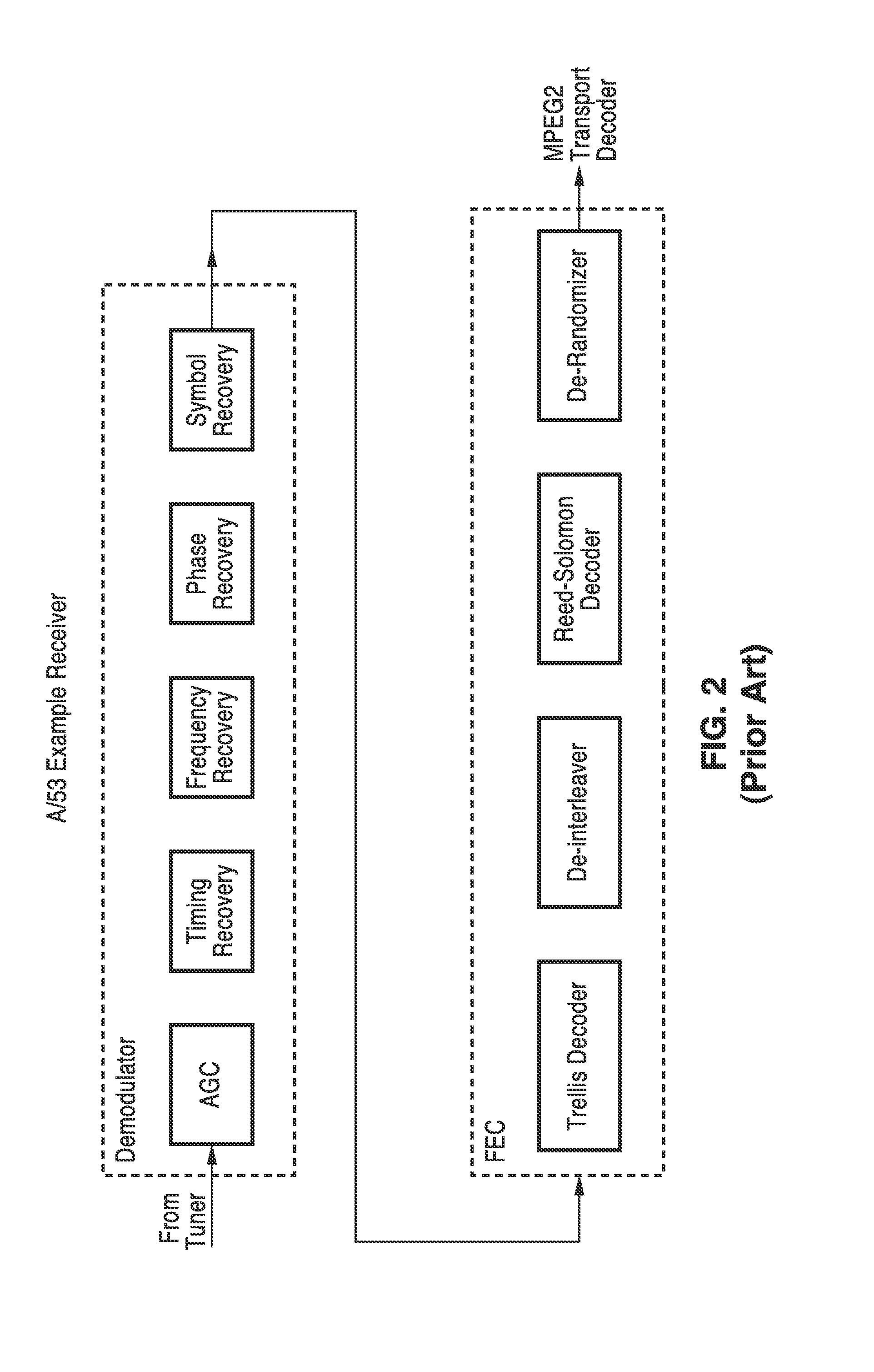

Combination a/53 and a/153 receiver using a hiho viterbi decoder

ActiveUS20140072056A1Bridging the gapLong collection timeOther decoding techniquesPicture reproducers using cathode ray tubesComputer hardwareViterbi decoder

A broadcast and receiver system for performing content from combined A / 53 and A / 153 standard transmissions enabling simultaneous reception of both signal types with one device. A combination HDTV / Mobile DTV chip can be used that does not alter the legacy HDTV forward error correction (FEC) decoder and Mobile DTV standard transmissions may include extra training signals aiding the demodulation of legacy HDTV reception. Two separate Trellis decoders can be used: one for A / 53 legacy HDTV decoding and the other for A / 153 Mobile DTV decoding that uses a Hard Input Hard Output (HIHO) type of architecture. Separate Viterbi decoders are allocated for each block of data with a block Viterbi rotator to parse out / collect results of each Viterbi decoder. Each block has its convolutional encoder reset at the beginning. The second Trellis decoder operates serially so as not to disturb the A / 53 HDTV data but could also be operated in parallel.

Owner:SONY CORP

Kalman-viterbi joint channel equalizer

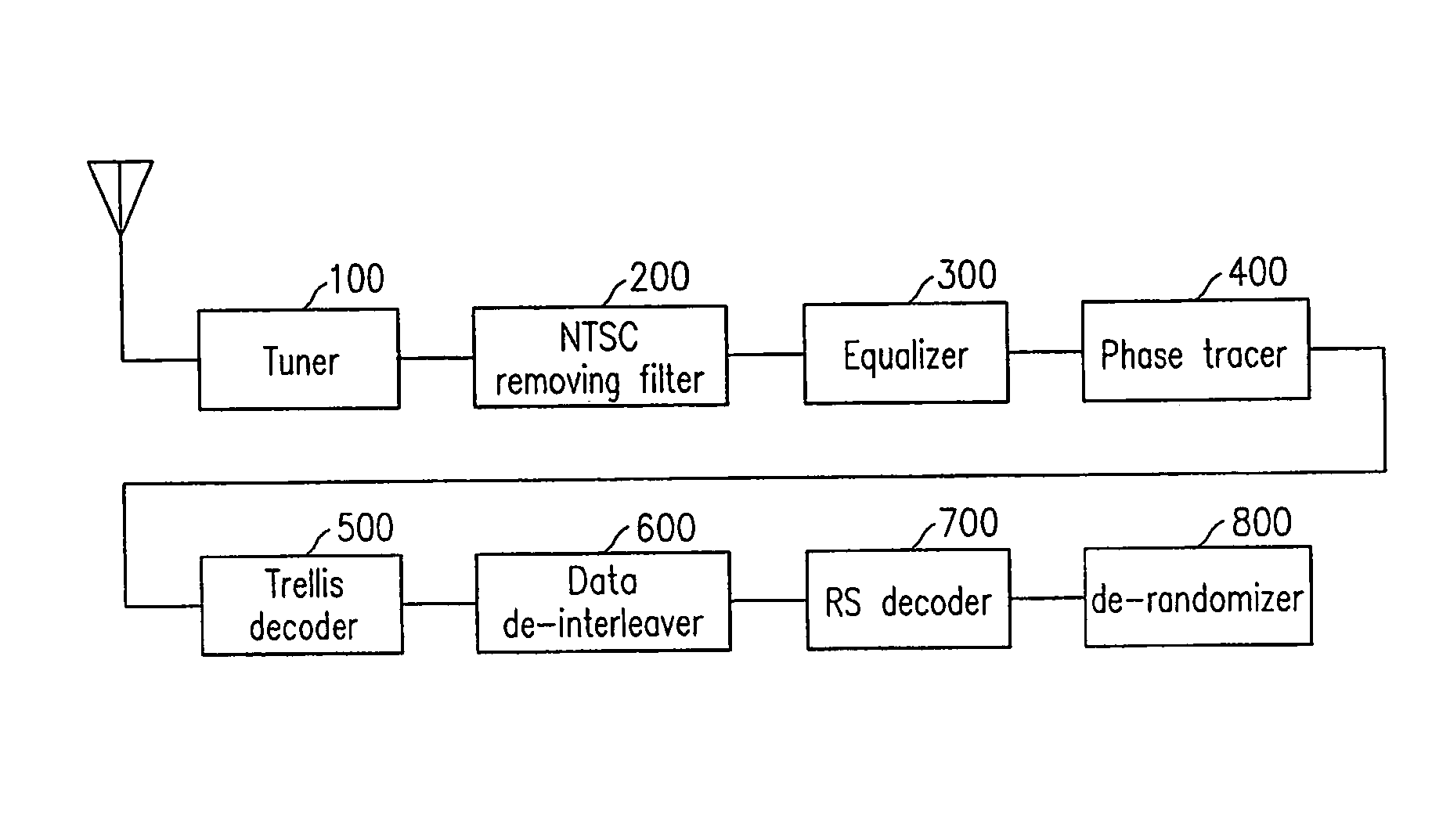

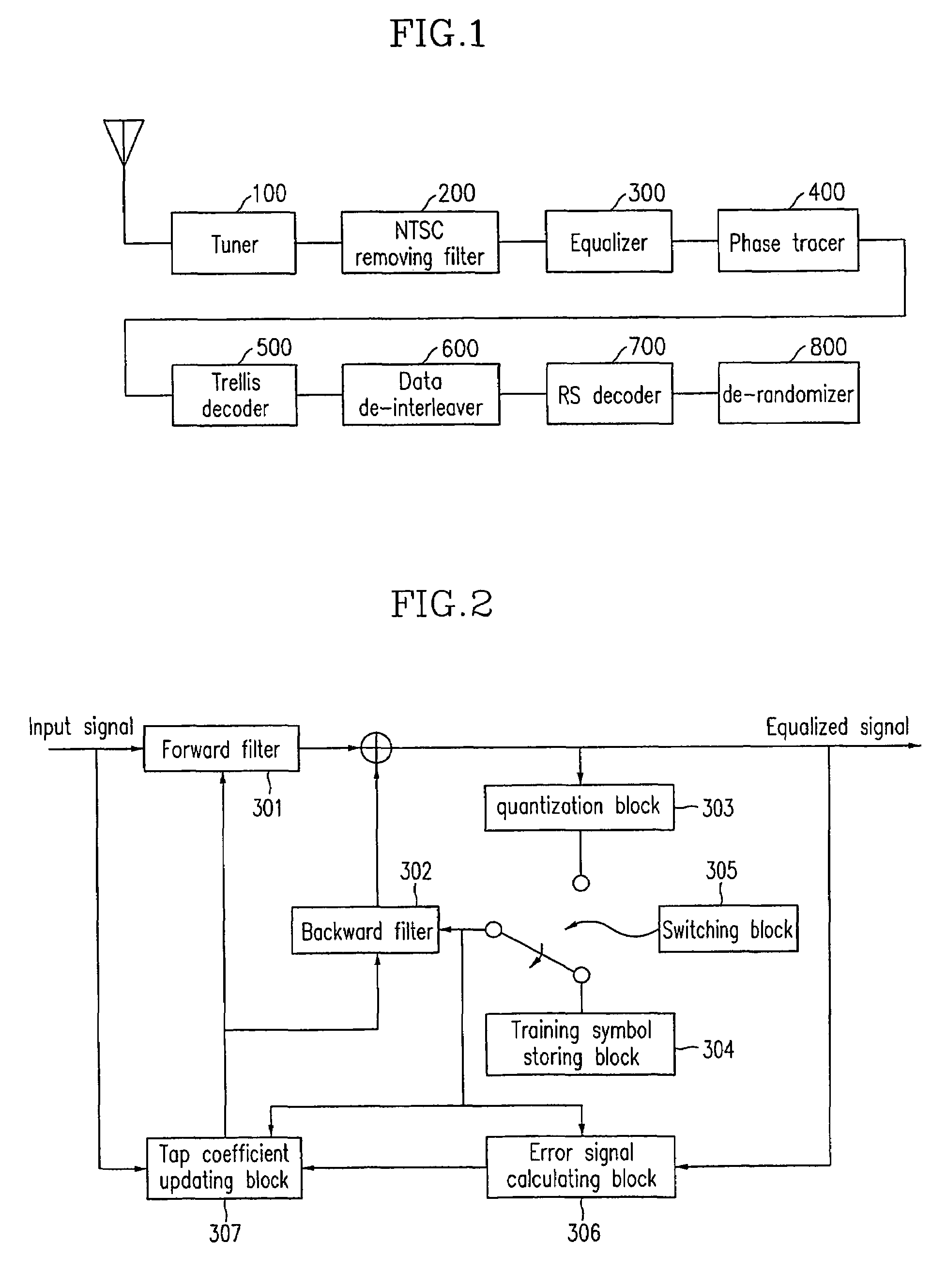

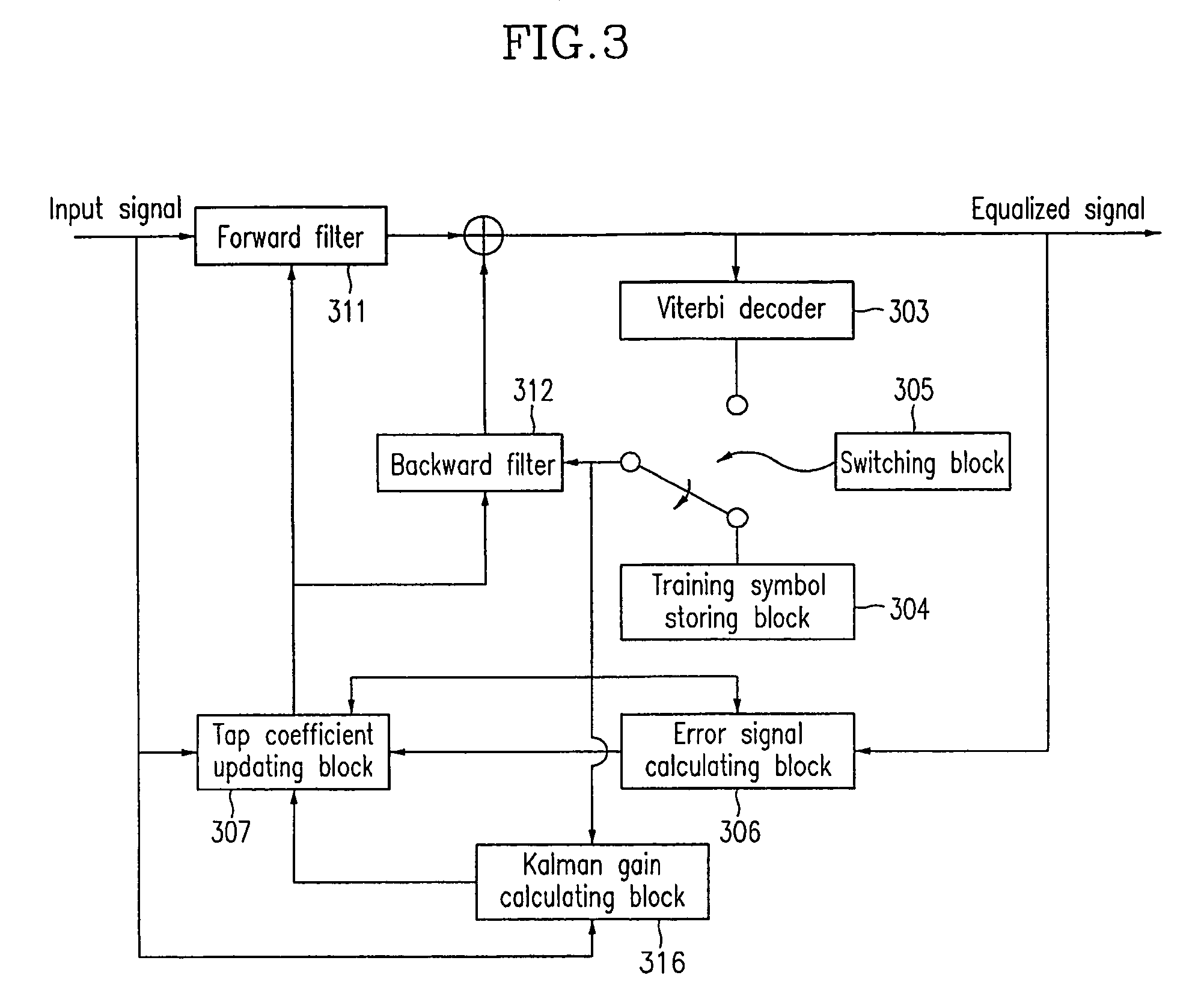

InactiveUS7548582B2Easy to solve distortionEliminate errorsMultiple-port networksTelevision system detailsViterbi decoderChannel equalizer

In a channel equalizer applicable to a digital television receiver, a forward filter and a backward filter perform filtering to an input signal and a predetermined signal. A Viterbi decoder corrects errors during a transmission procedure in a blind mode. A training symbol storing block stores training symbols. An output signal of the Viterbi decoder and symbols are provided to the backward filter in accordance with a blind mode or a training mode. A Kalman gain is calculated in a Kalman gain calculating block and an error signal is calculated by comparing an equalized signal, symbols, and the output signal of the Viterbi decoder with one another. A tap coefficient is updated by using the calculated error signal and the Kalman gain.

Owner:ELECTRONICS & TELECOMM RES INST

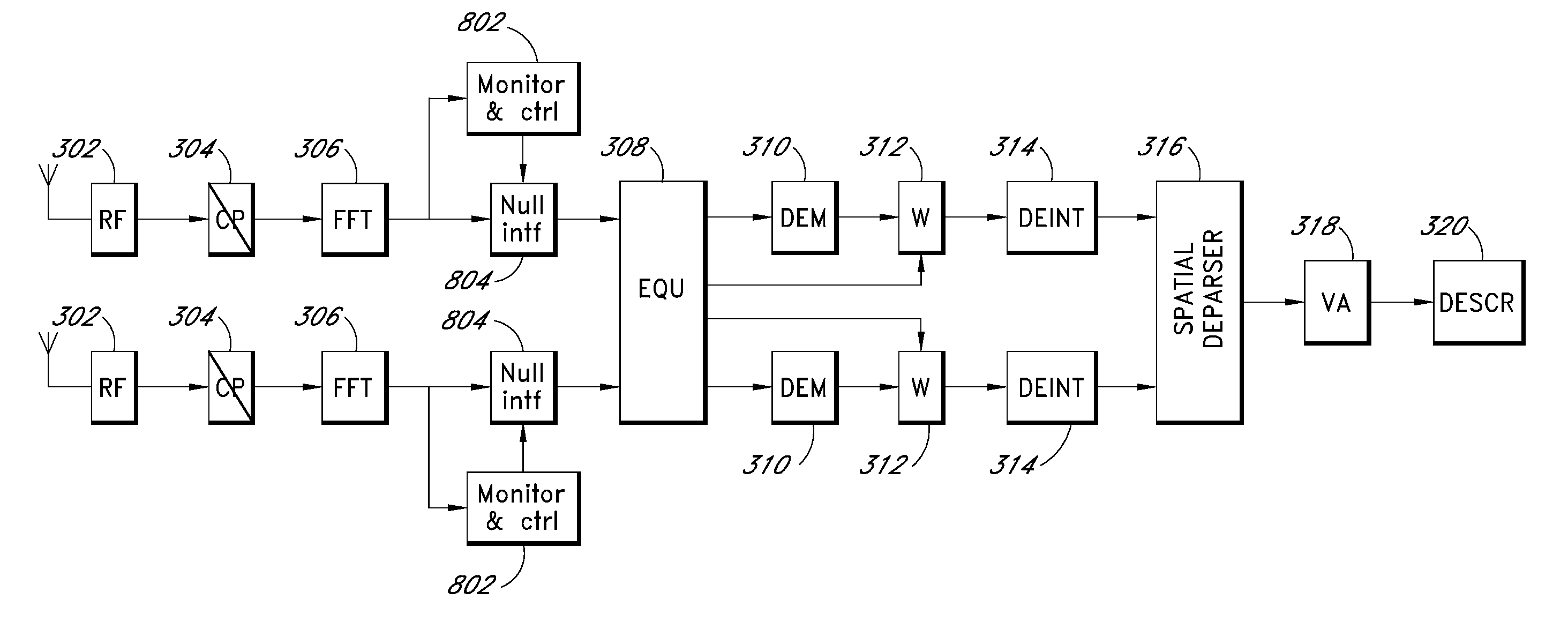

Interference erasure using soft decision weighting of the Viterbi decoder input in OFDM systems

InactiveUS8019029B1Reduce impactLow signal-to-interference-plus-noise ratio (SINR)Error preventionModulated-carrier systemsViterbi decoderSignal quality

Disclosed is a technique for mitigating the effect of an in-band interferer in Orthogonal Frequency Division Multiplexing (OFDM) wireless or wired networks that employ soft decision Viterbi decoder in the physical layer. The technique uses an independent estimation of the signal quality, which is passed to the Viterbi algorithm decoder so that it is able to discard the corrupted subcarriers. This improves the error correction capability of the Viterbi algorithm decoder in a receiver, which leads to fewer retransmissions and into higher information throughput.

Owner:MICROSEMI STORAGE SOLUTIONS

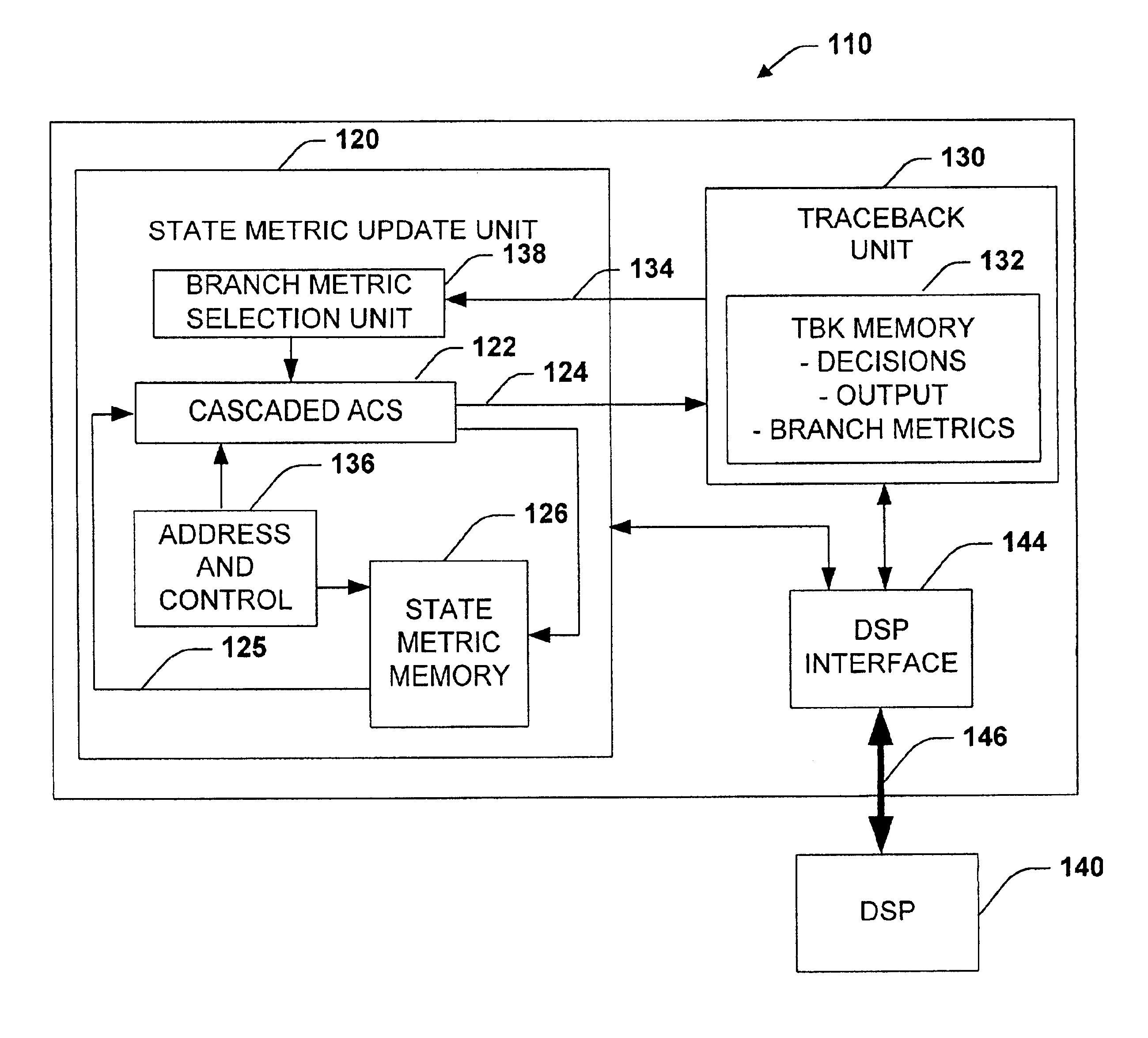

Enhanced viterbi decoder for wireless applications

InactiveUS6901118B2Flexibility and low-power and high data throughput rateCost-effective solutionData representation error detection/correctionOther decoding techniquesViterbi decoderOperating system

A Viterbi decoder system is provided in accordance with the present invention. The decoder system includes a State Metric Update unit including a state metric memory and a cascaded Add / Compare / Select (ACS) unit. The cascaded ACS unit comprises a plurality of serially coupled ACS stages for performing a plurality of ACS operations in conjunction with the state metric memory. An ACS stage is operable to identify a plurality of path decisions and path differences and communicate the identified path decisions and the identified path differences to a next ACS stage coupled thereto. The decoder also includes a Traceback unit for storing a set of accumulated path decisions in a traceback memory associated therewith, and performing a traceback on the set of accumulated path decisions. The path decisions associated with the ACS stage and the next ACS stage are accumulated as a set during the ACS operations before being written to the traceback memory, thereby minimizing accesses to the traceback memory. The path differences associated with the ACS stage and the next ACS stage provide a reliability estimation of the correctness of the path decisions.

Owner:TEXAS INSTR INC

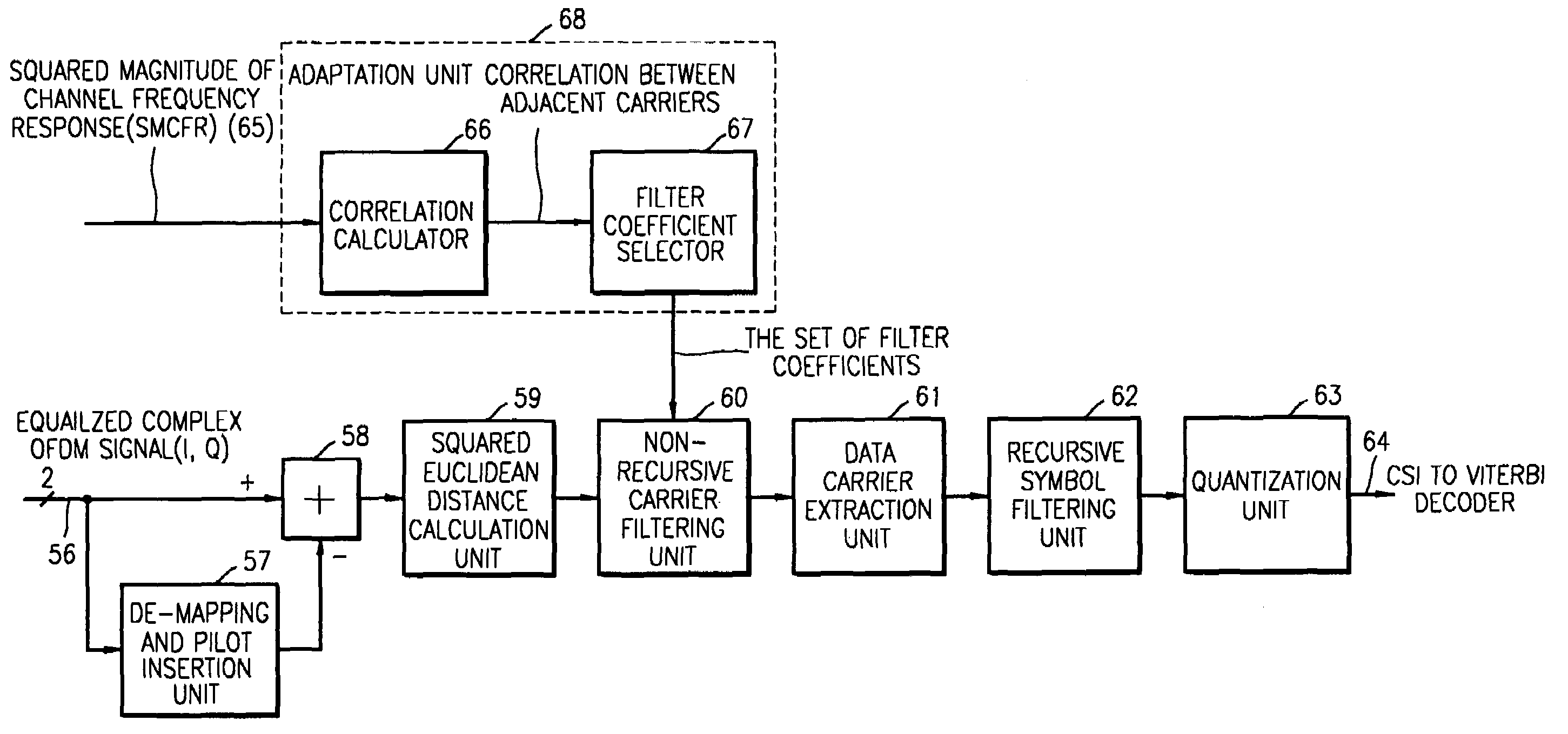

Apparatus and method for direct measurement of channel state for coded orthogonal frequency division multiplexing receiver

InactiveUS7486736B2Increase SNR (Signal-to-Noise Ratio) gainAmplitude-modulated carrier systemsSecret communicationSquared euclidean distanceEngineering

An apparatus and method for direct measurement of the channel state of a receiver, such as an OFDM (Orthogonal Frequency Division Multiplexing) receiver. The apparatus adapts a frequency selective channel using a squared Euclidean distance between a received signal value and a de-mapped value for measurement of the channel state and estimates the CSI (Channel State Information) which is also suitable for signal processing with co-channel interference. The estimated CSI may be used in a bit metric calculation of subsequent error correction decoders, such as a Viterbi decoder, to increase system SNR (Signal-to-Noise Ratio) gain. Because receiving equipment, such as digital televisions, receive clearer DVB-T (Terrestrial Digital Video Broadcasting) signals, clearer pictures with less distortion can be displayed, for example, on the digital television.

Owner:SAMSUNG ELECTRONICS CO LTD

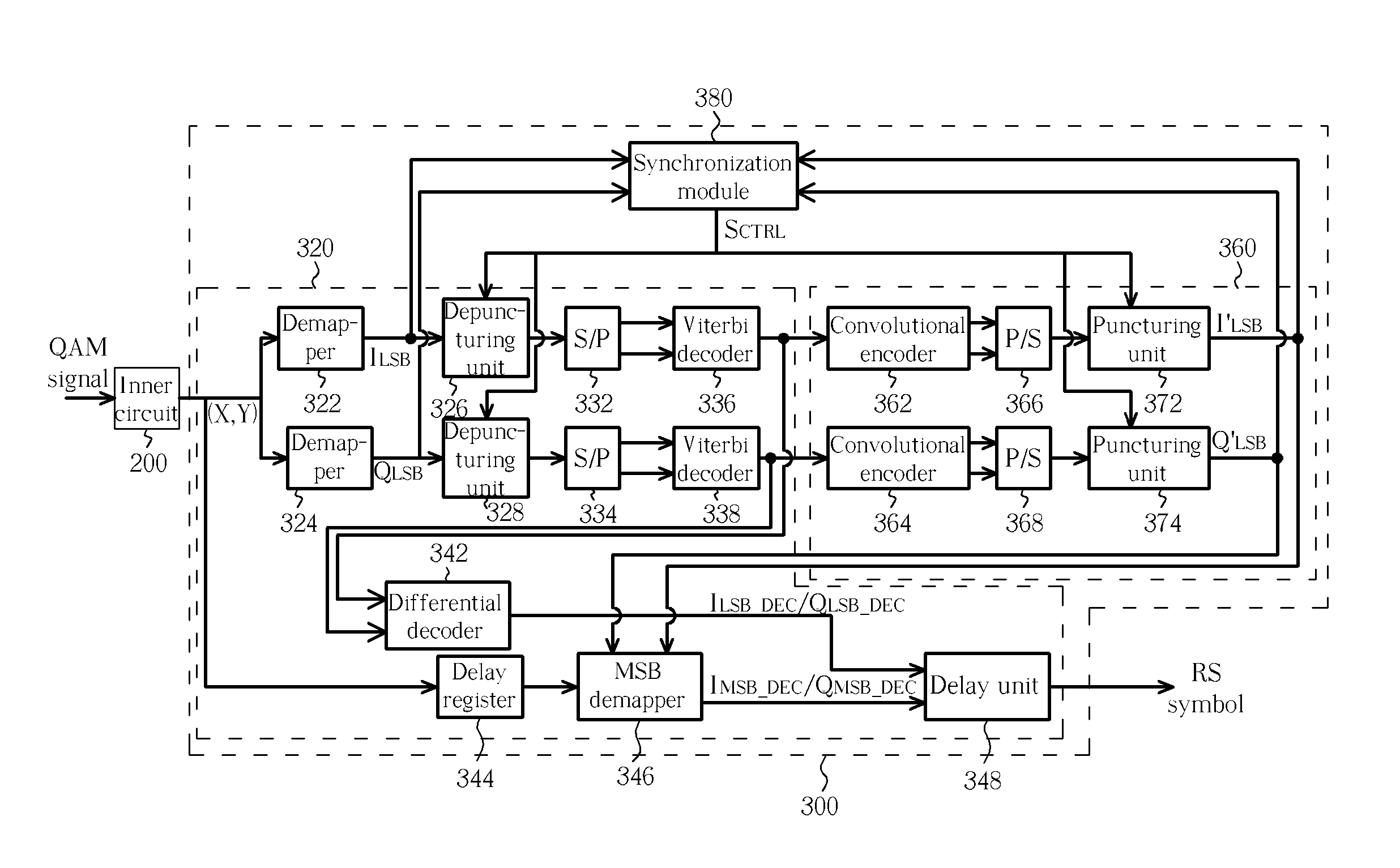

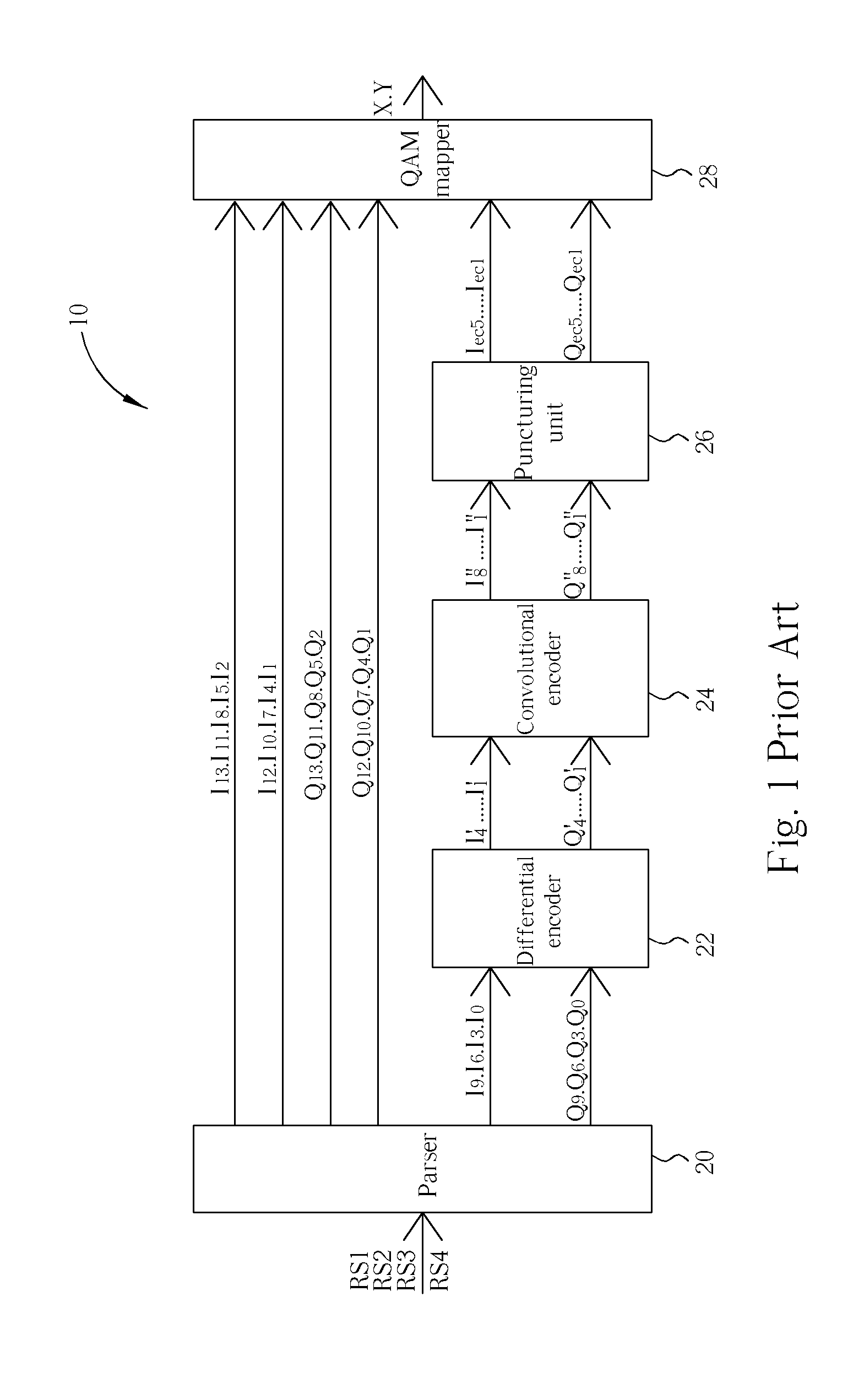

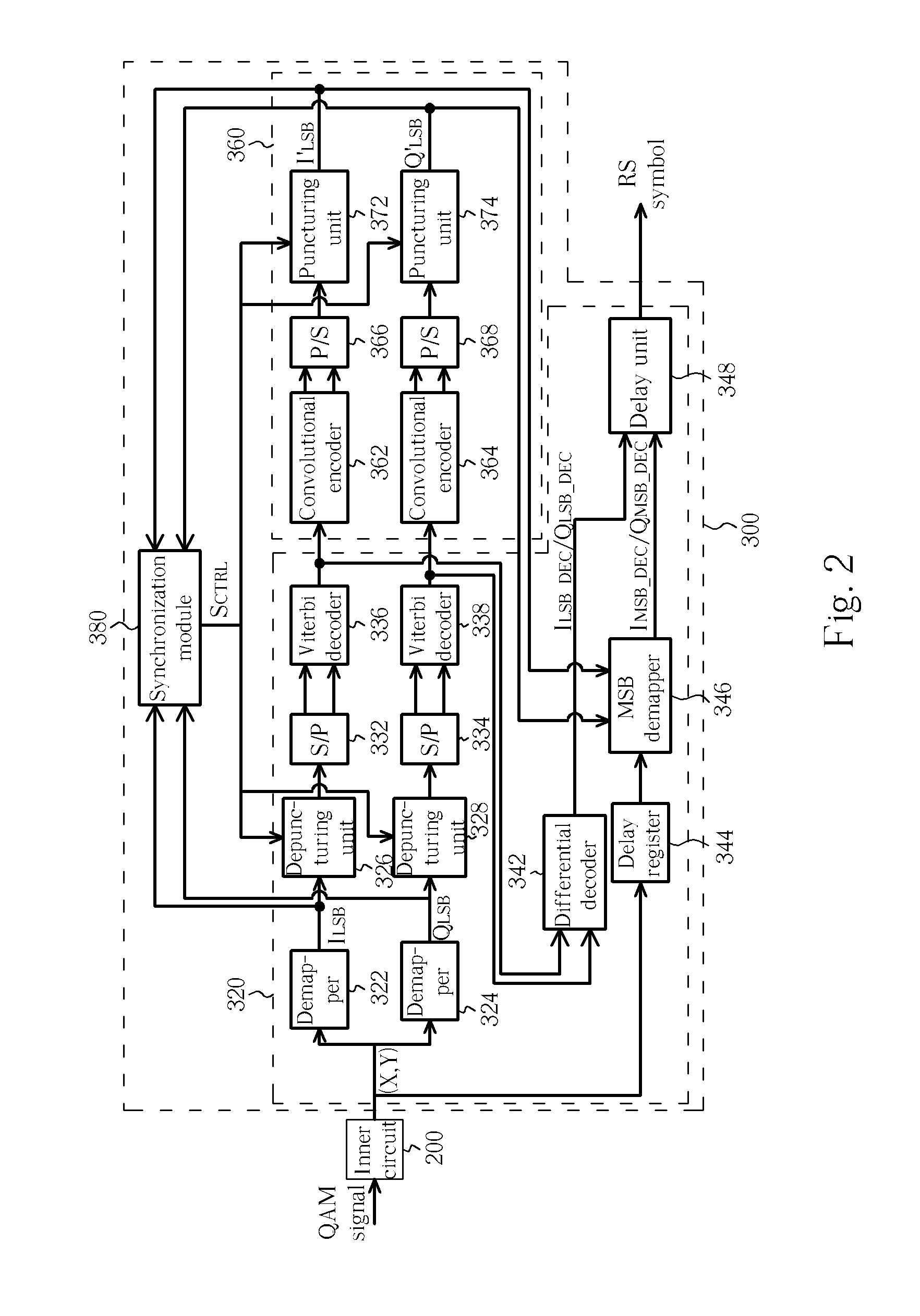

Quadrature Amplitude Modulation Trellis Coded Modulation Decoding Apparatus and Method Thereof

ActiveUS20060274845A1Reduce complexityData representation error detection/correctionCode conversionViterbi decoderLeast significant bit

A quadrature amplitude modulation trellis coded modulation (QAM-TCM) decoding apparatus and the related method that receives and decodes a QAM signal. The QAM-TCM decoding apparatus includes an in-phase least significant bit (LSB) decoding path, which includes a in-phase Viterbi decoder for executing a decoding procedure on at least one LSB corresponding to an in-phase component of the QAM signal, a quadrature-phase LSB decoding path, which includes a quadrature-phase Viterbi decoder for executing a decoding procedure on at least one LSB corresponding to a quadrature-phase component of the QAM signal, and a most significant bit (MSB) decoding path for executing a decoding procedure on MSB portions corresponding to the in-phase or the quadrature-phase of the QAM signal. In doing so, the apparatus and method reduces the complexity of the decoding calculation.

Owner:REALTEK SEMICON CORP

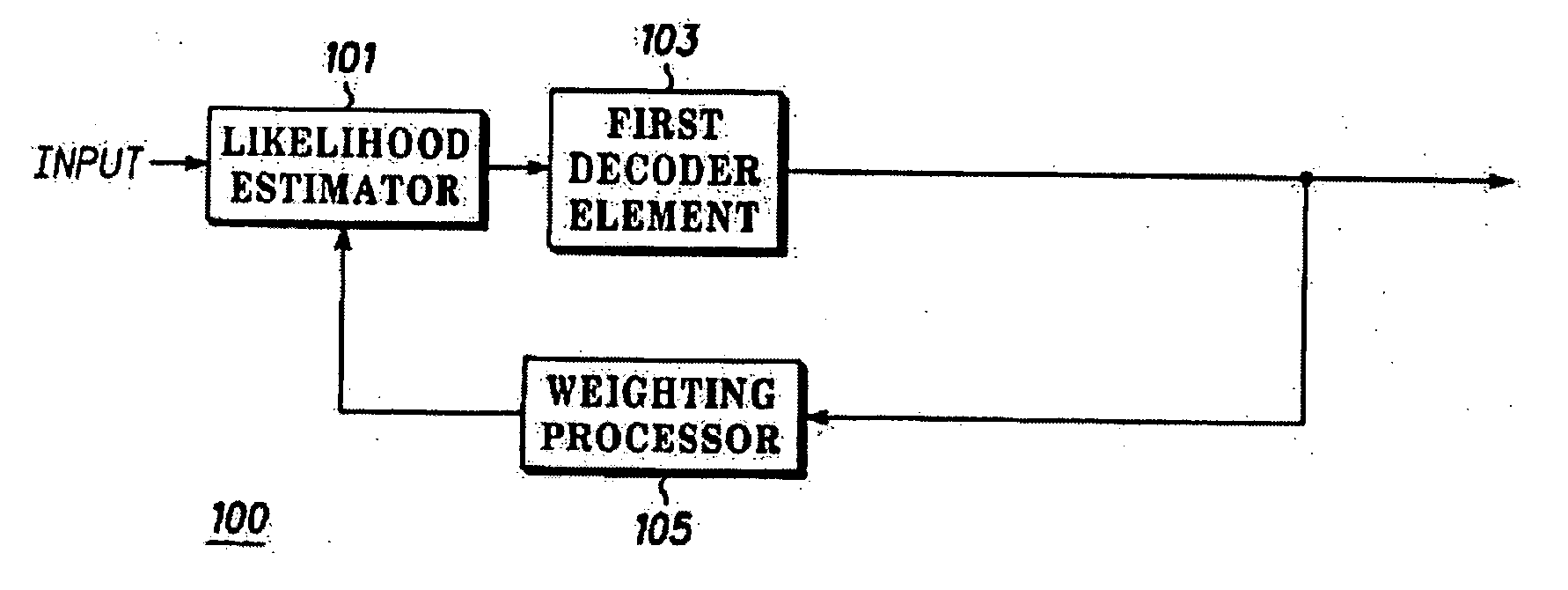

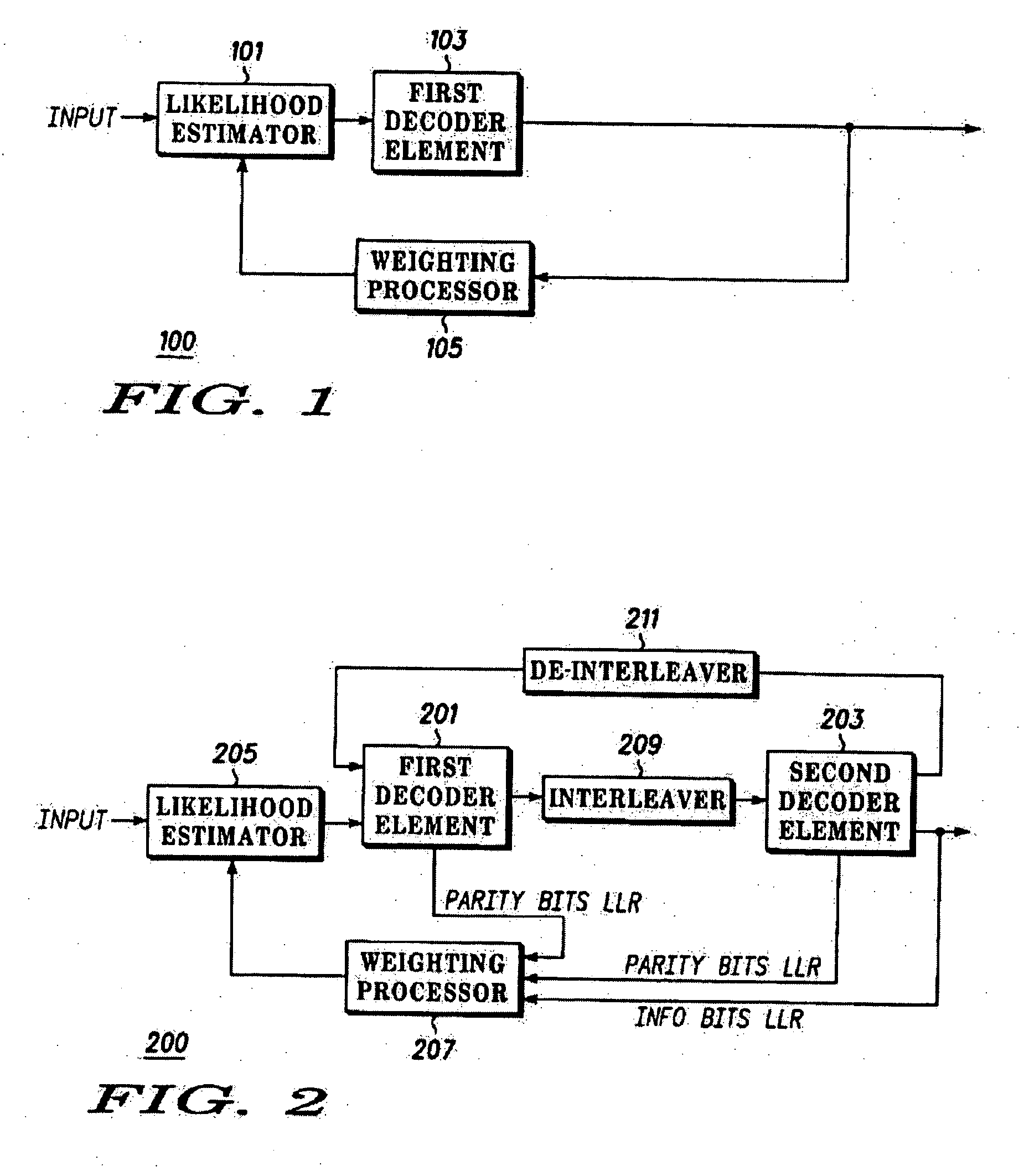

Iterative decoding with likelihood weighting

ActiveUS20060168500A1Mitigate, alleviate or eliminate oneData representation error detection/correctionCode conversionViterbi decoderLogit

The invention relates to an error correcting decoder apparatus (100) and method. The decoder apparatus (100) comprises a likelihood estimator (101) which generates a sequence of bit value likelihood estimates, such as log likelihood ratios, for multi bit symbols of a data sequence. The decoder apparatus (100) further comprises a decoder element (103), such as a Maximum A Priori (MAP) or appropriate Soft Output Viterbi decoder. The decoder element (103) generates a decoded data sequence in response to the bit value likelihood estimates. The decoder apparatus (100) also comprises a weighted processor (105) which generates a weighted compensation data sequence from the decoded data sequence. The weighted compensation data is used to modify the sequence of bit value likelihood estimates. The decoding is subsequently repeated using the improved bit value likelihood estimates whereby improved decoding performance is achieved. The invention may be applied to a two decoder element decoding apparatus (300) and may specifically be applied to turbo decoders.

Owner:GOOGLE TECH HLDG LLC

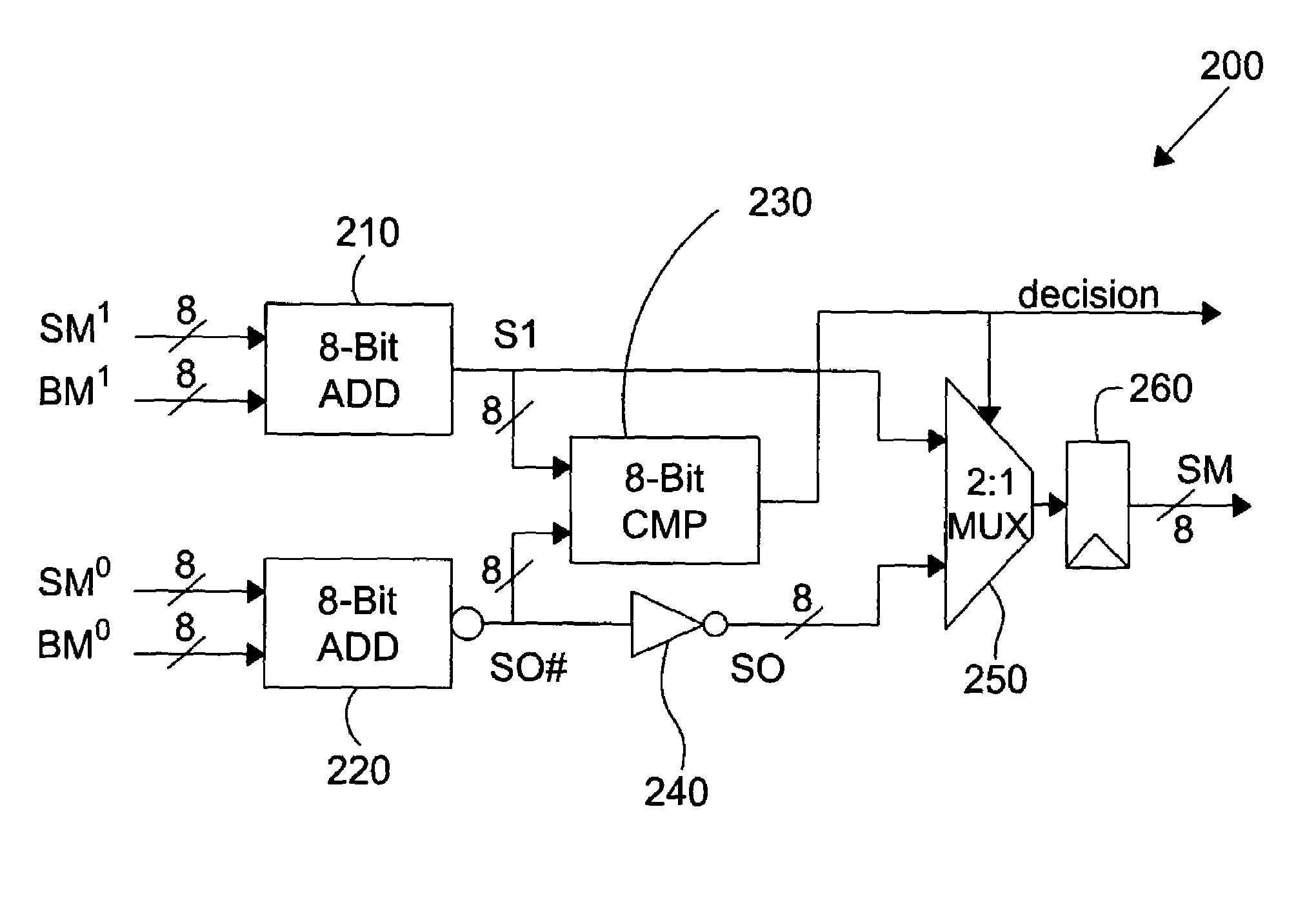

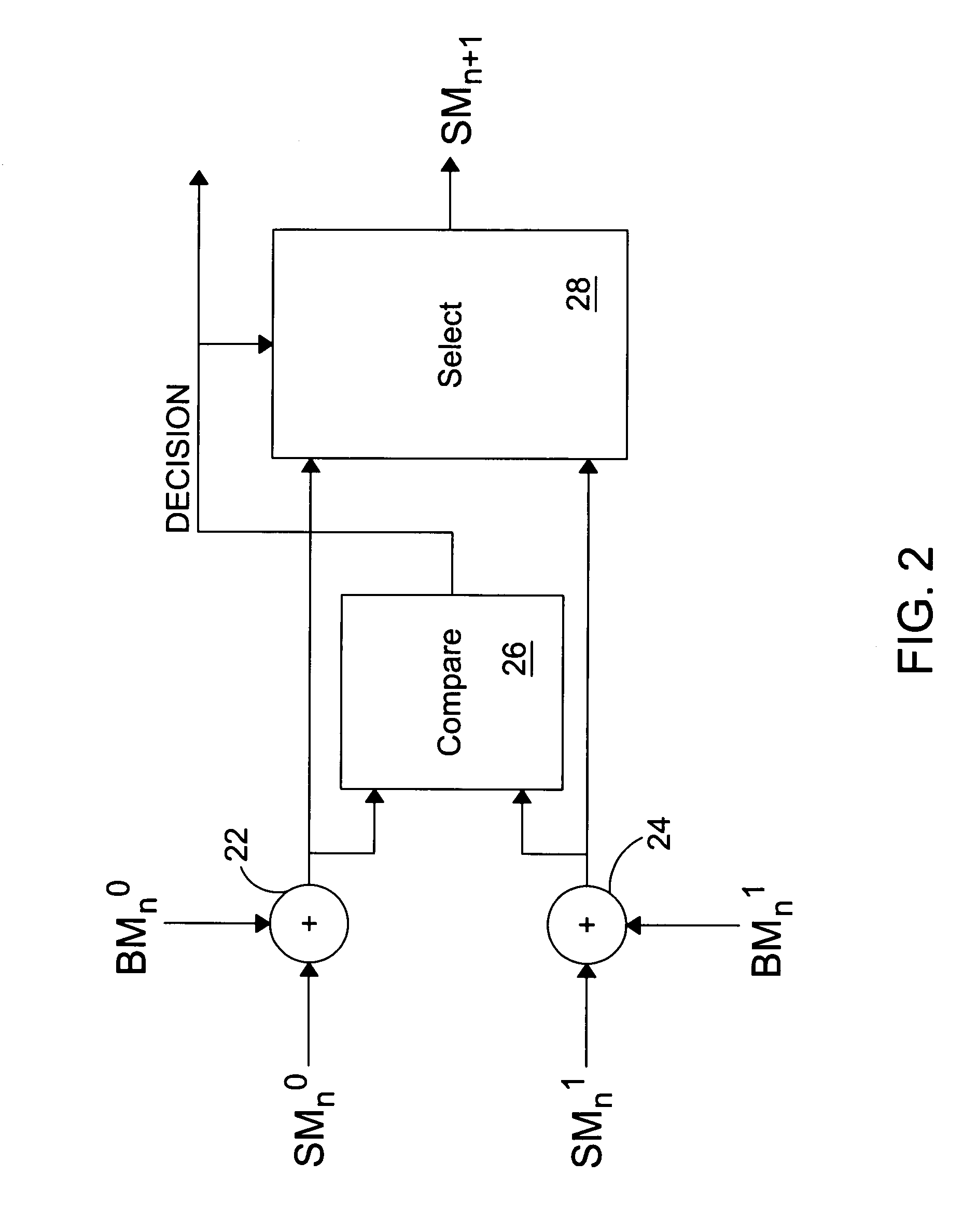

Fast bit-parallel Viterbi decoder add-compare-select circuit

InactiveUS7131055B2Data representation error detection/correctionError preventionViterbi decoderMultiplexer

A Viterbi decoder includes an ACS unit that performs state metric updates for every symbol cycle. State metric updates involve adding the state metrics corresponding to a likely input symbol to the respective branch matrix, comparing the results of the additions to determine which is smaller, and selecting the smaller result for the next state metric. The ACS unit includes two parallel adders followed by a parallel comparator that generates a multiplexer-select signal. The outputs of the parallel adders are input into a multiplexer and the multiplexer-select signal is input into the multiplexer for a decision.

Owner:INTEL CORP