Patents

Literature

468 results about "Cell memory" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

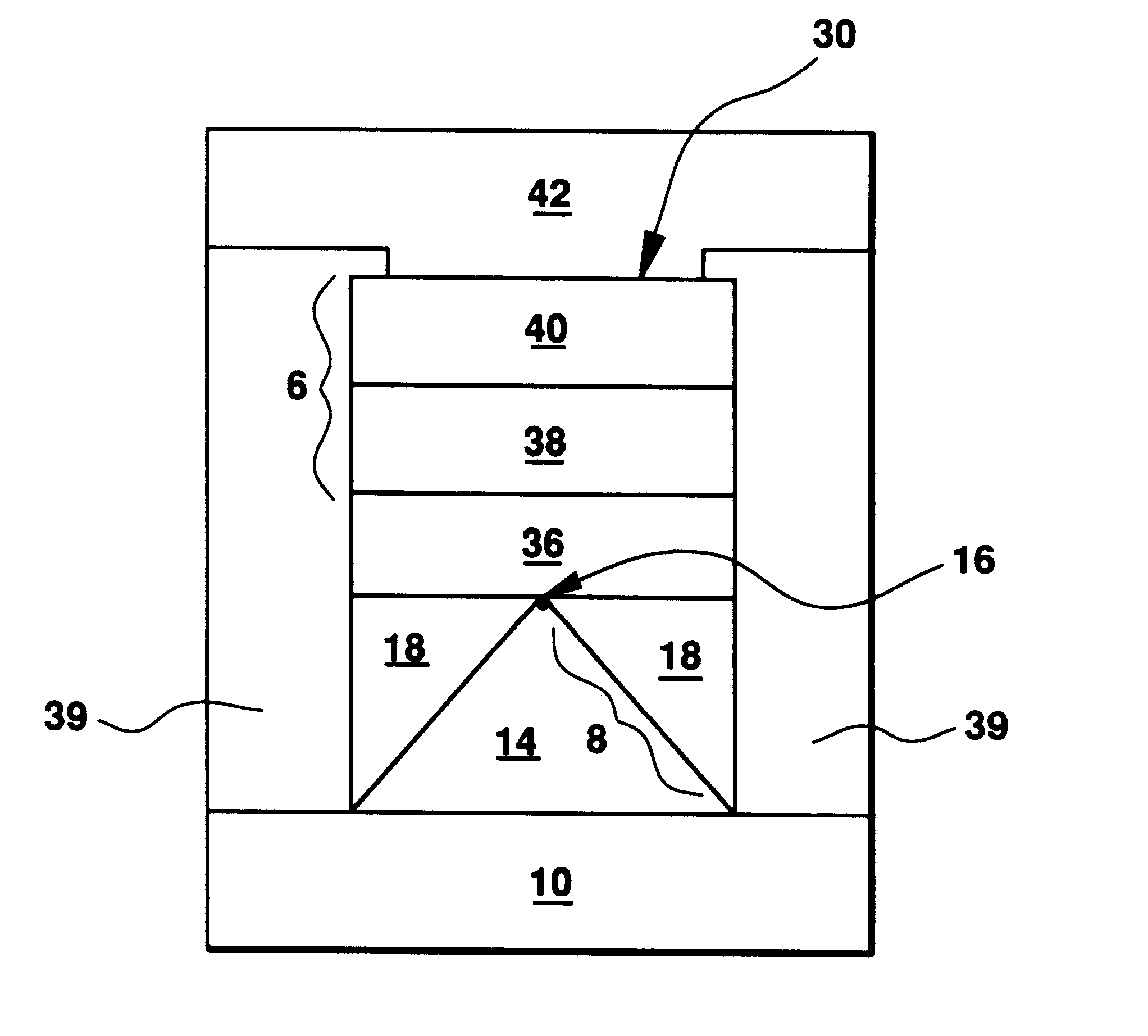

Multibit single cell memory element having tapered contact

InactiveUSRE37259E1Large electric resistance valueSolid-state devicesRead-only memoriesPeak valueEngineering

An electrically operated, directly overwritable, multibit, single-cell chalcogenide memory element with multibit storage capabilities and having at least one contact for supplying electrical input signals to set the memory element to a selected resistance value, the second contact tapering to a peak adjacent to the memory element. In this manner the tapered contact helps define the size and position of a conduction path through the memory element.

Owner:OVONYX MEMORY TECH LLC

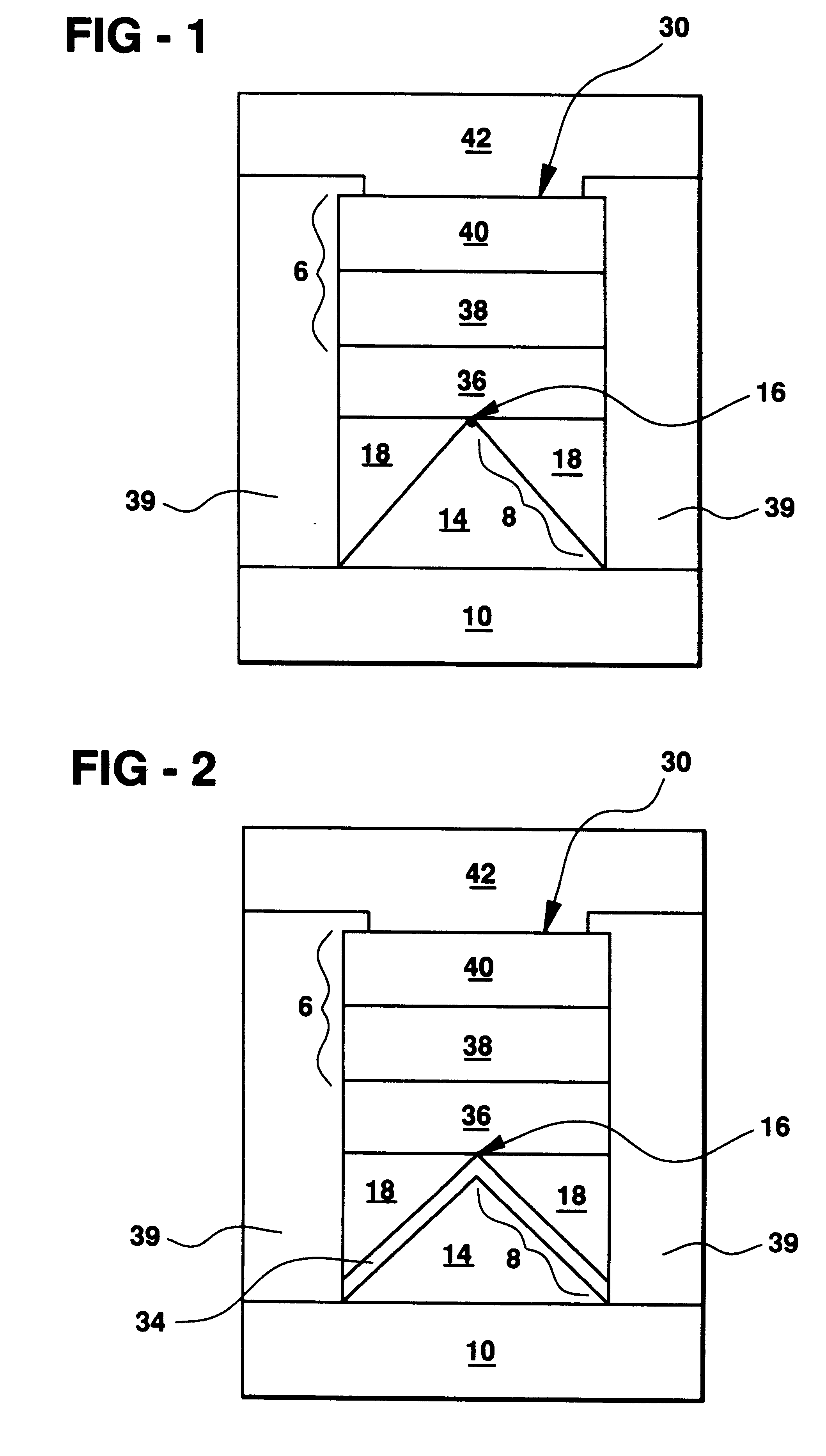

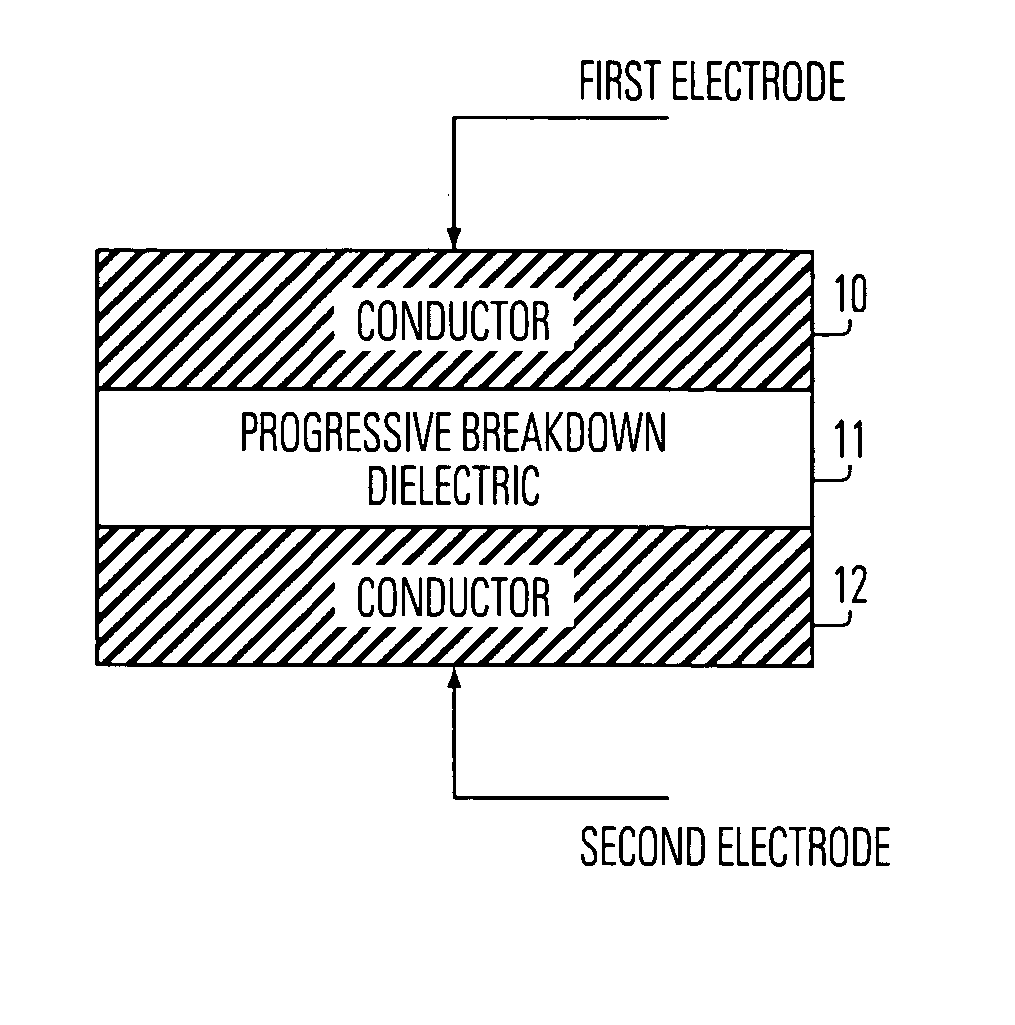

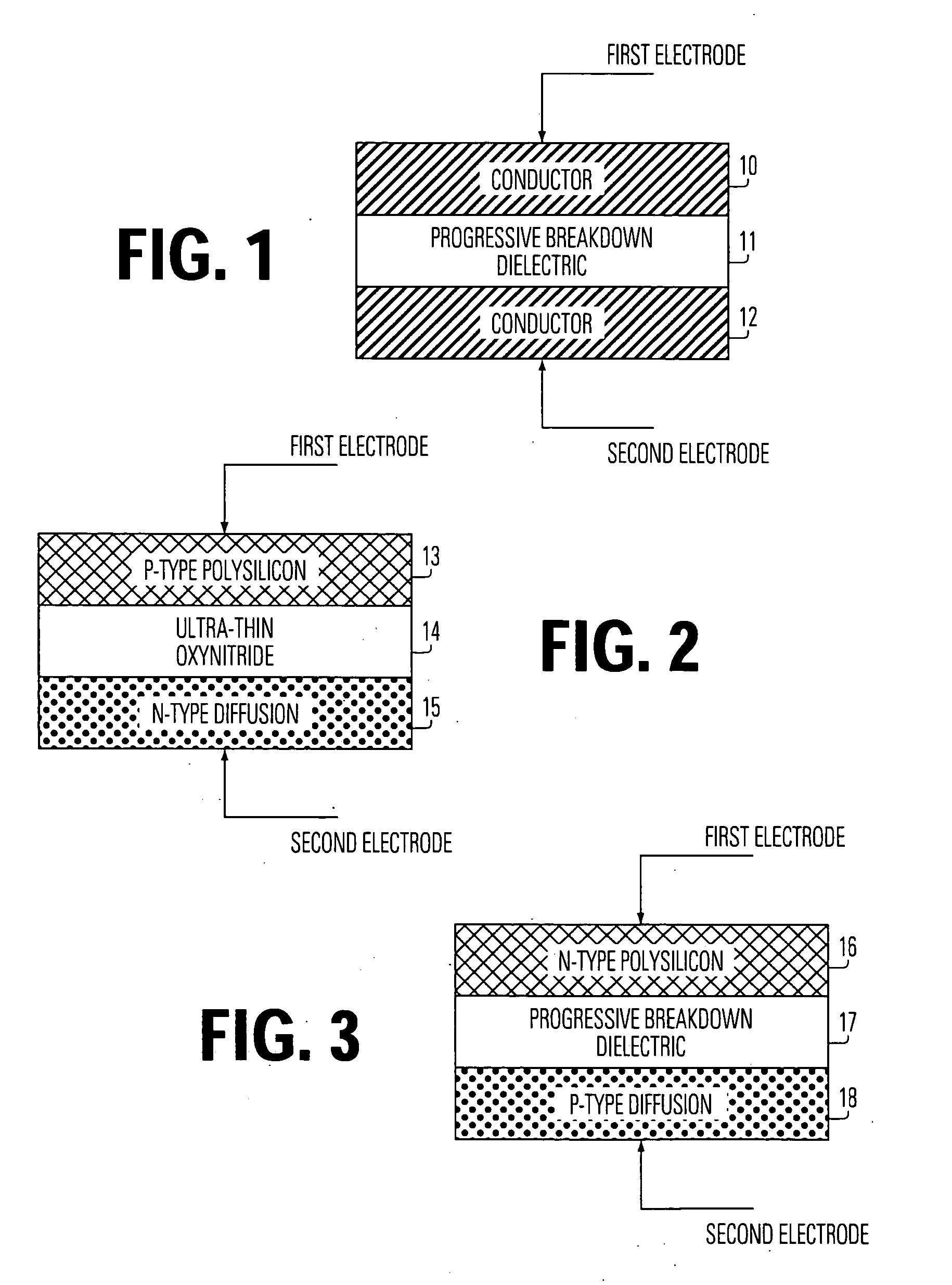

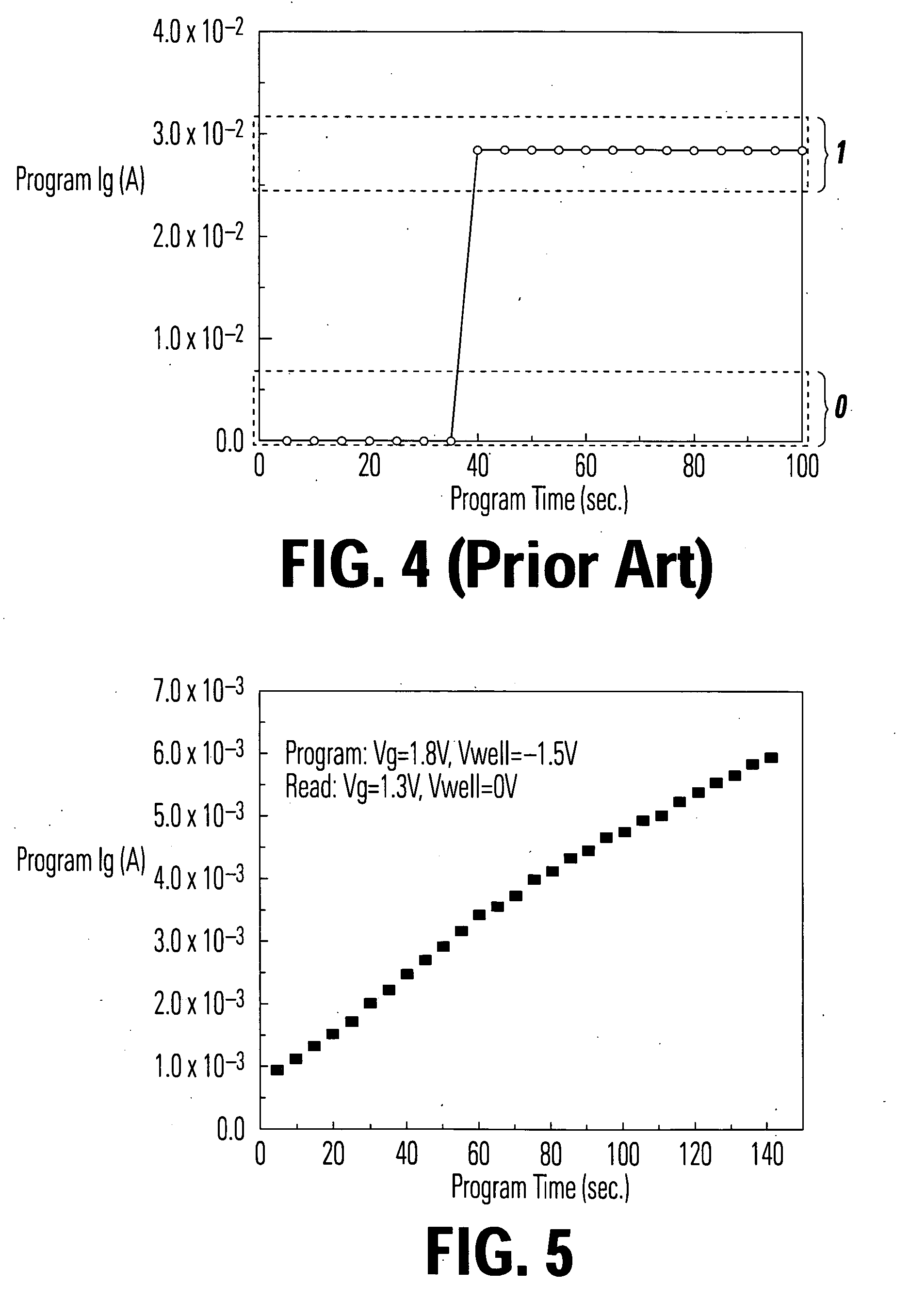

Method for manufacturing a multiple-bit-per-cell memory

ActiveUS20060073642A1Easy to manufactureSolid-state devicesSemiconductor/solid-state device manufacturingThin oxideOptoelectronics

A method for manufacturing an electrically programmable non-volatile memory cell comprises forming a first electrode on a substrate, forming an inter-electrode layer of material on the first electrode having a property which is characterized by progressive change in response to stress, and forming a second electrode over the inter-electrode layer of material. The inter-electrode layer comprises a dielectric layer, such as ultra-thin oxide, between the first and second electrodes. A programmable resistance, or other property, is established by stressing the dielectric layer, representing stored data. Embodiments of the memory cell are adapted to store multiple bits of data per cell and / or adapted for programming more than one time without an erase process.

Owner:MACRONIX INT CO LTD

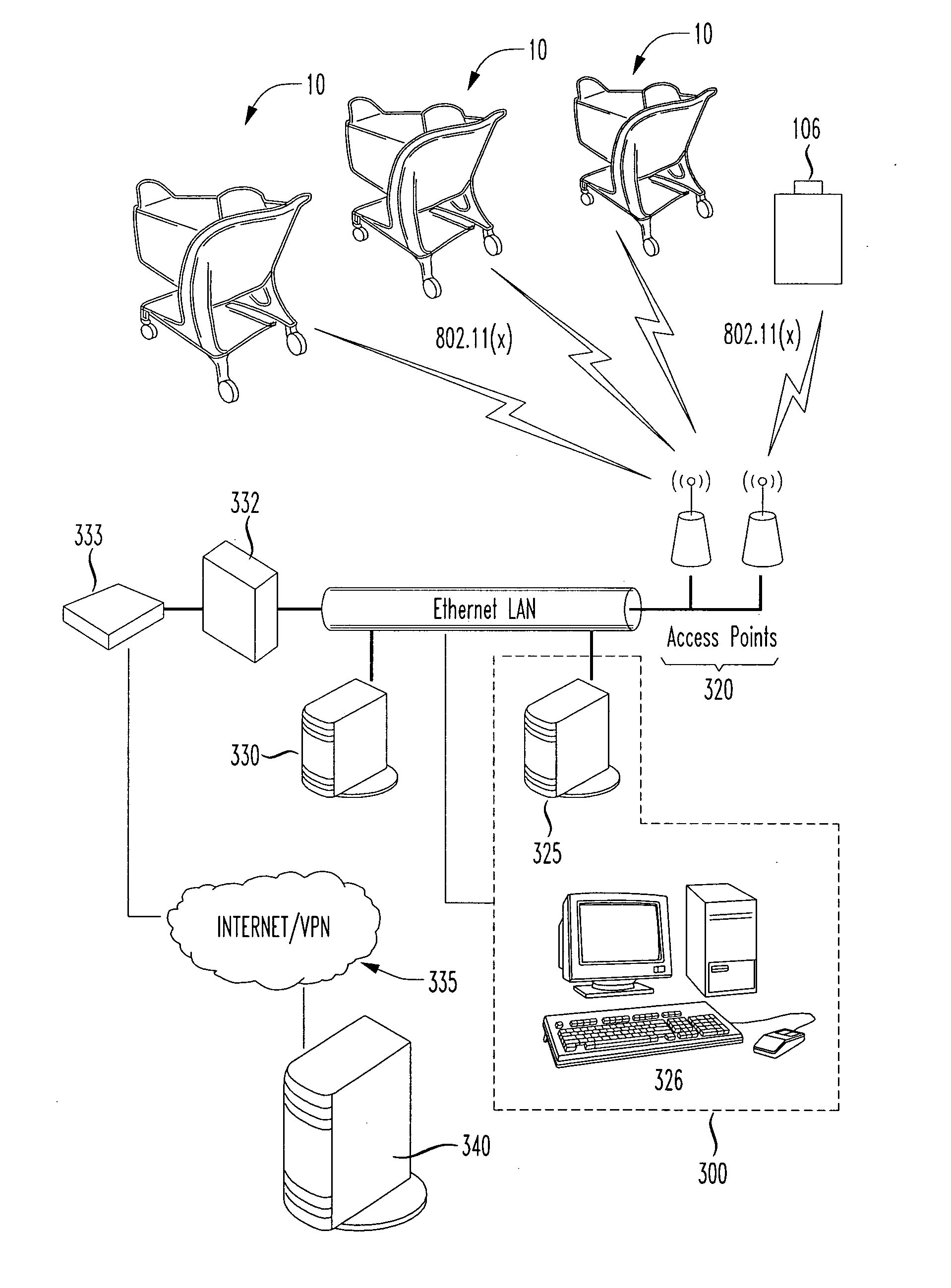

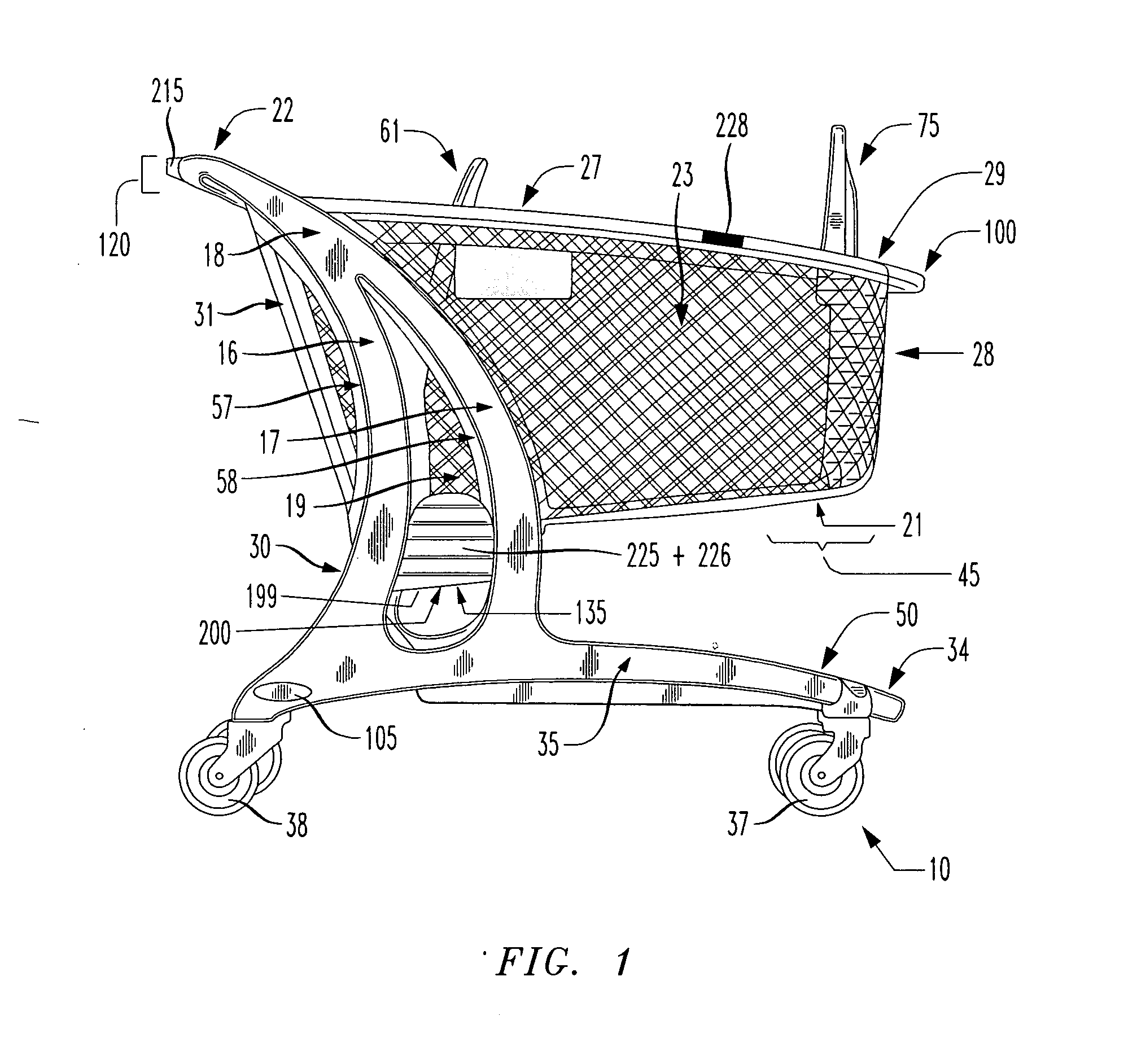

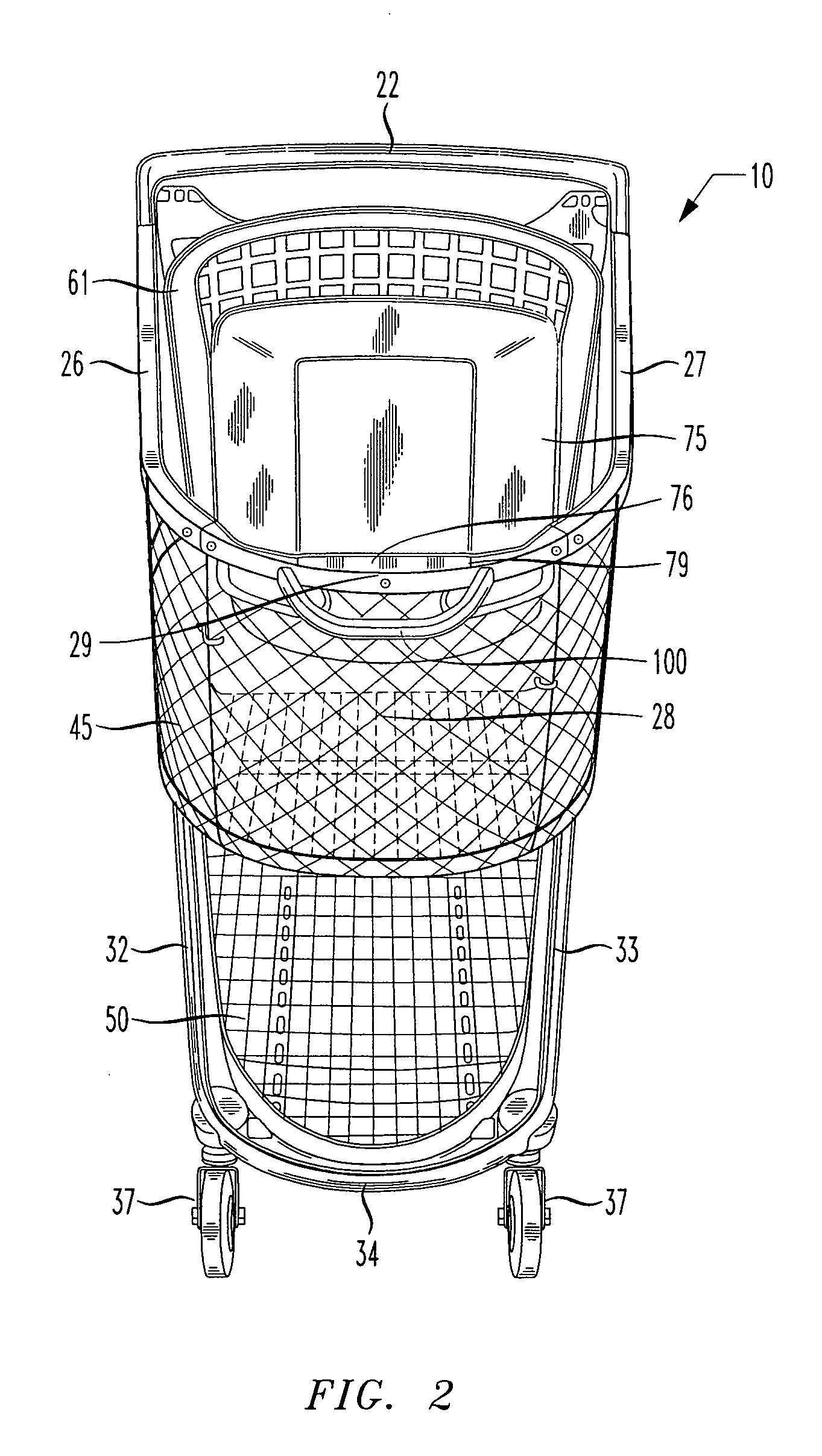

Media enabled shopping cart system with basket inventory

InactiveUS20060289637A1Enhanced shopping cart systemService system furnitureVisual presentationTransceiverModularity

A media enhanced shopping cart system comprises a shopping cart comprising a frame, a basket, a handle, a base tray, and a plurality of wheels, a modular computing device comprising a central processing unit, a memory and a network transceiver configured for wireless communication, the modular computing device being attached to the shopping cart, an inventory component for determining an inventory contained by the shopping cart, a shopping list component for listing one or more products of a consumer shopping list for purchase by a consumer, and a correlation component for correlating data from the inventory component with the shopping list component.

Owner:MEDIA CART HLDG

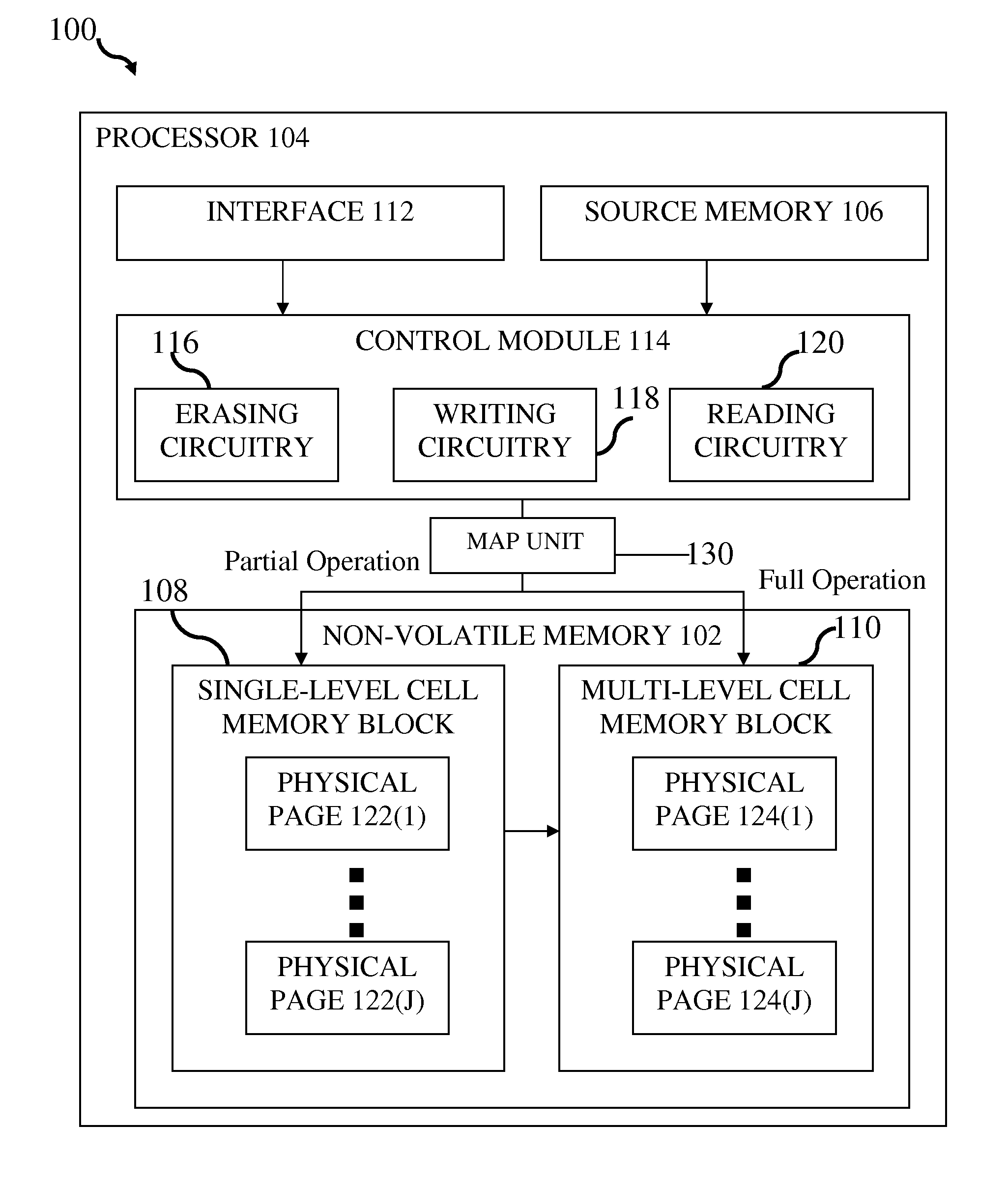

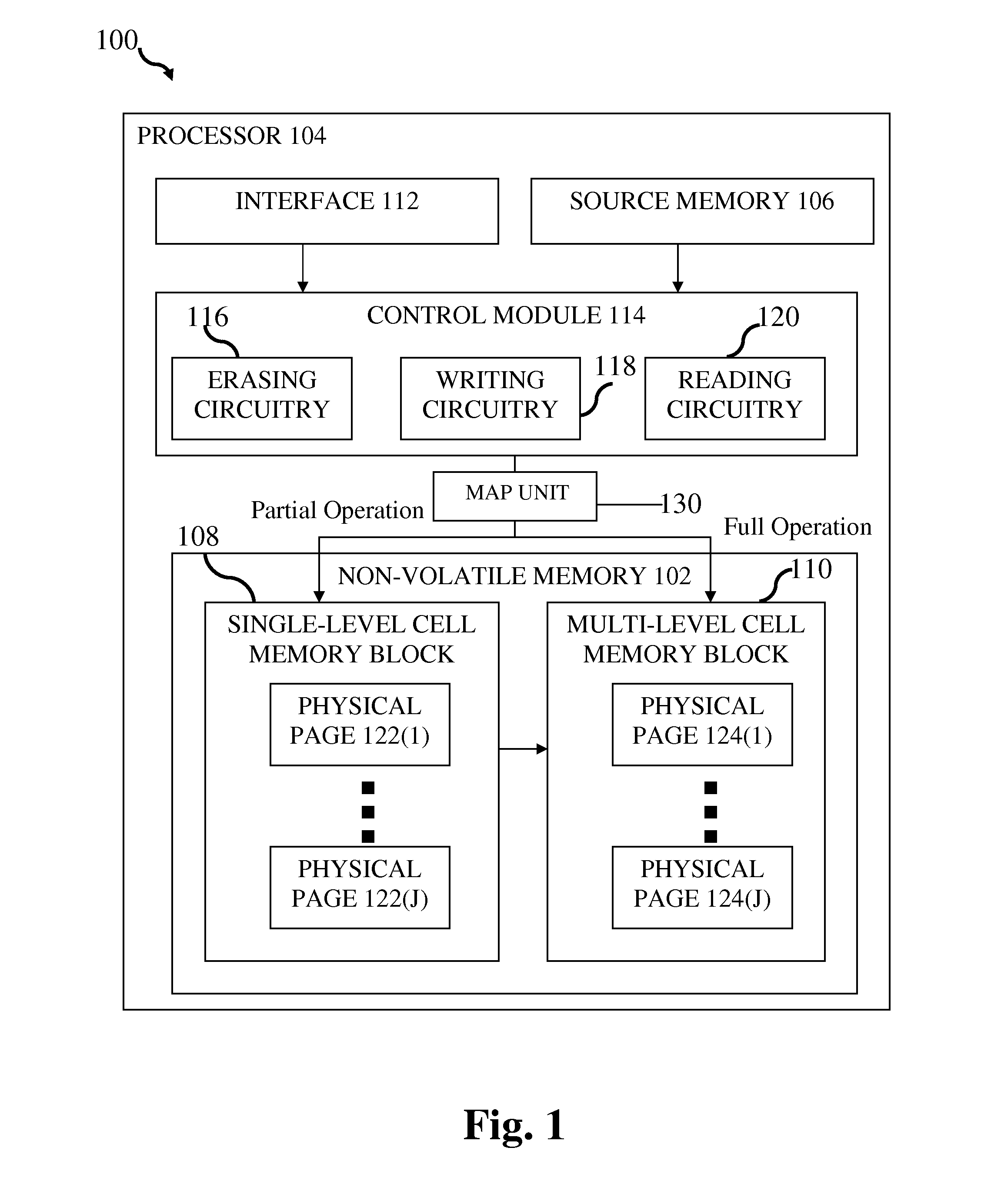

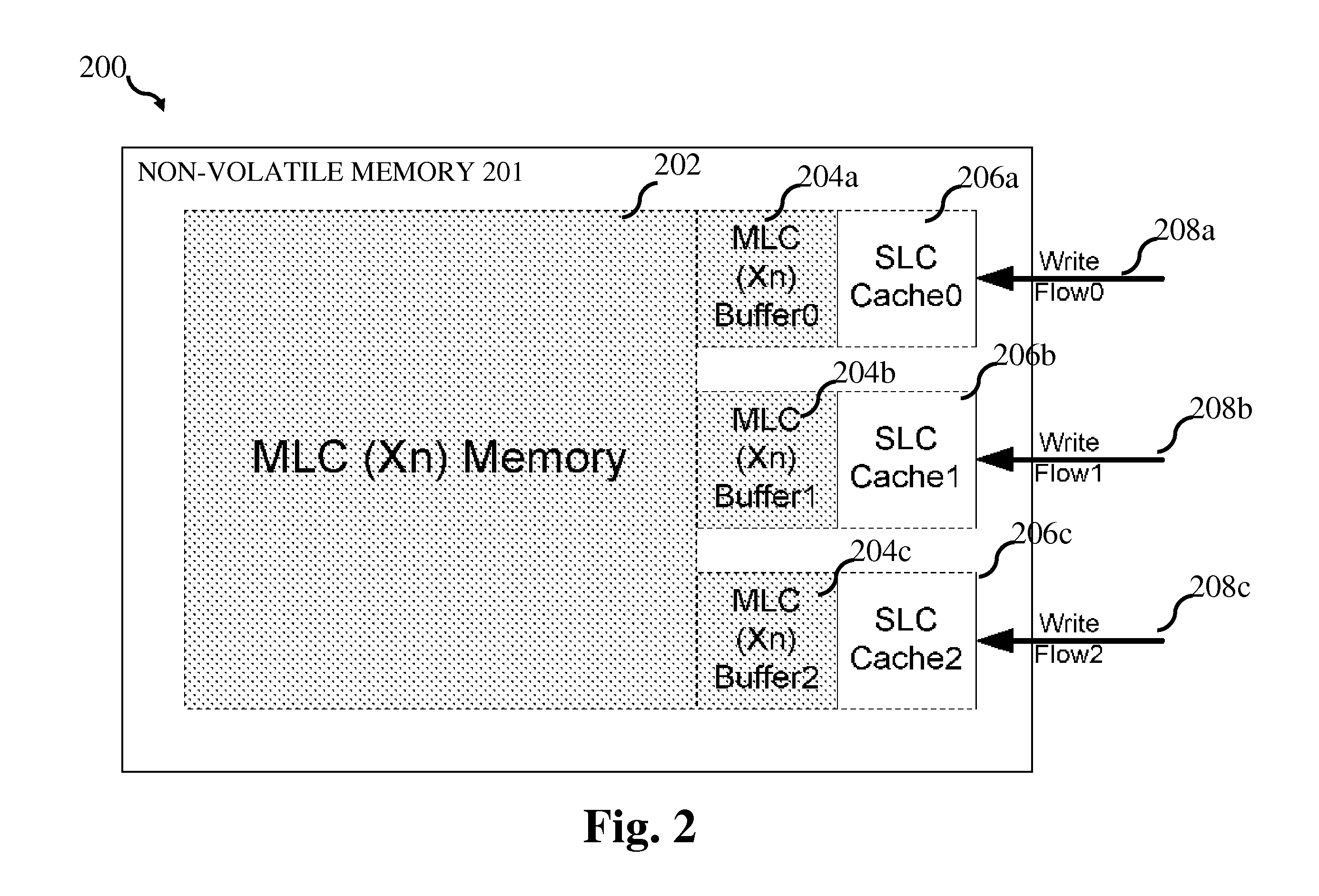

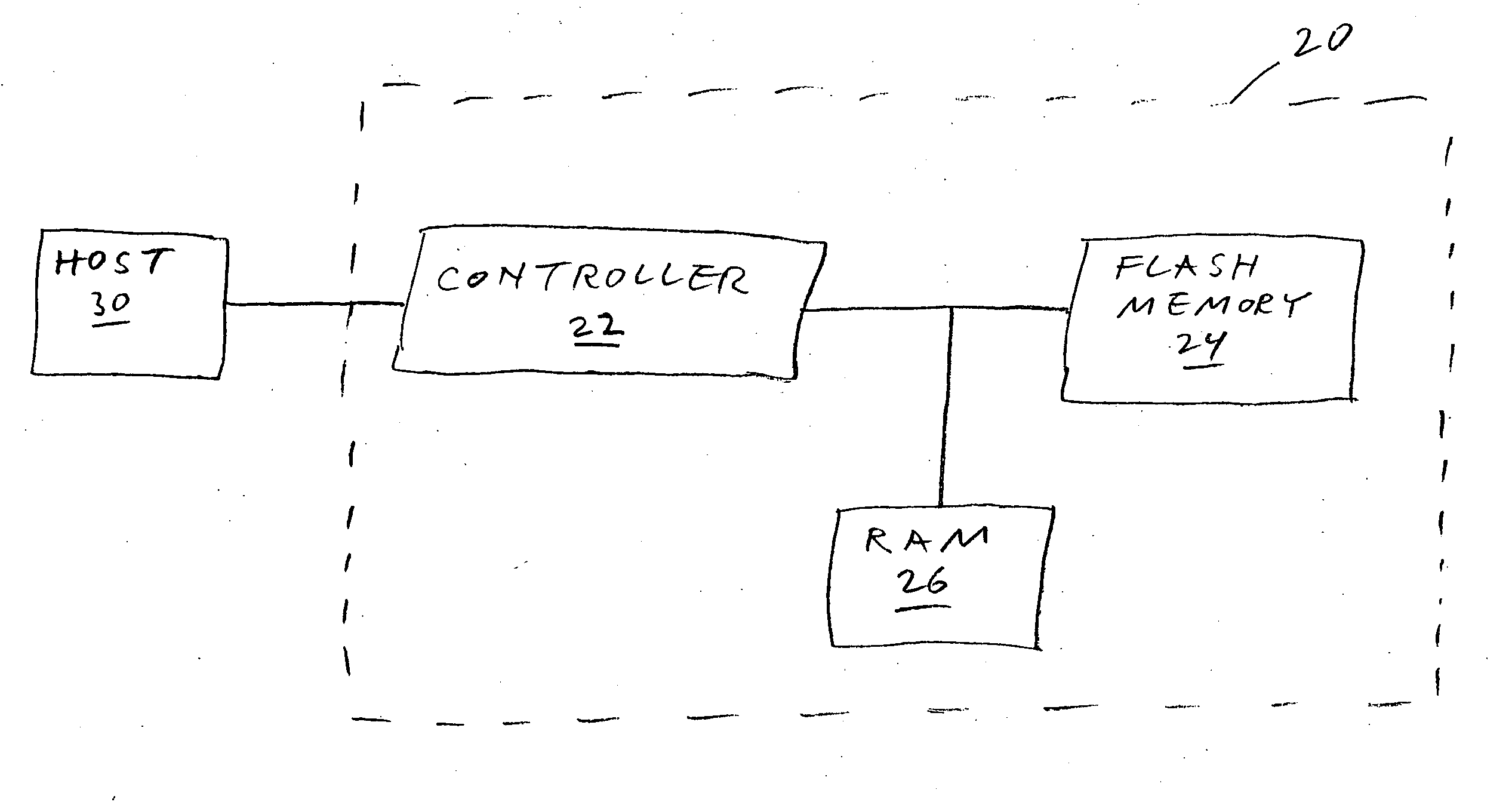

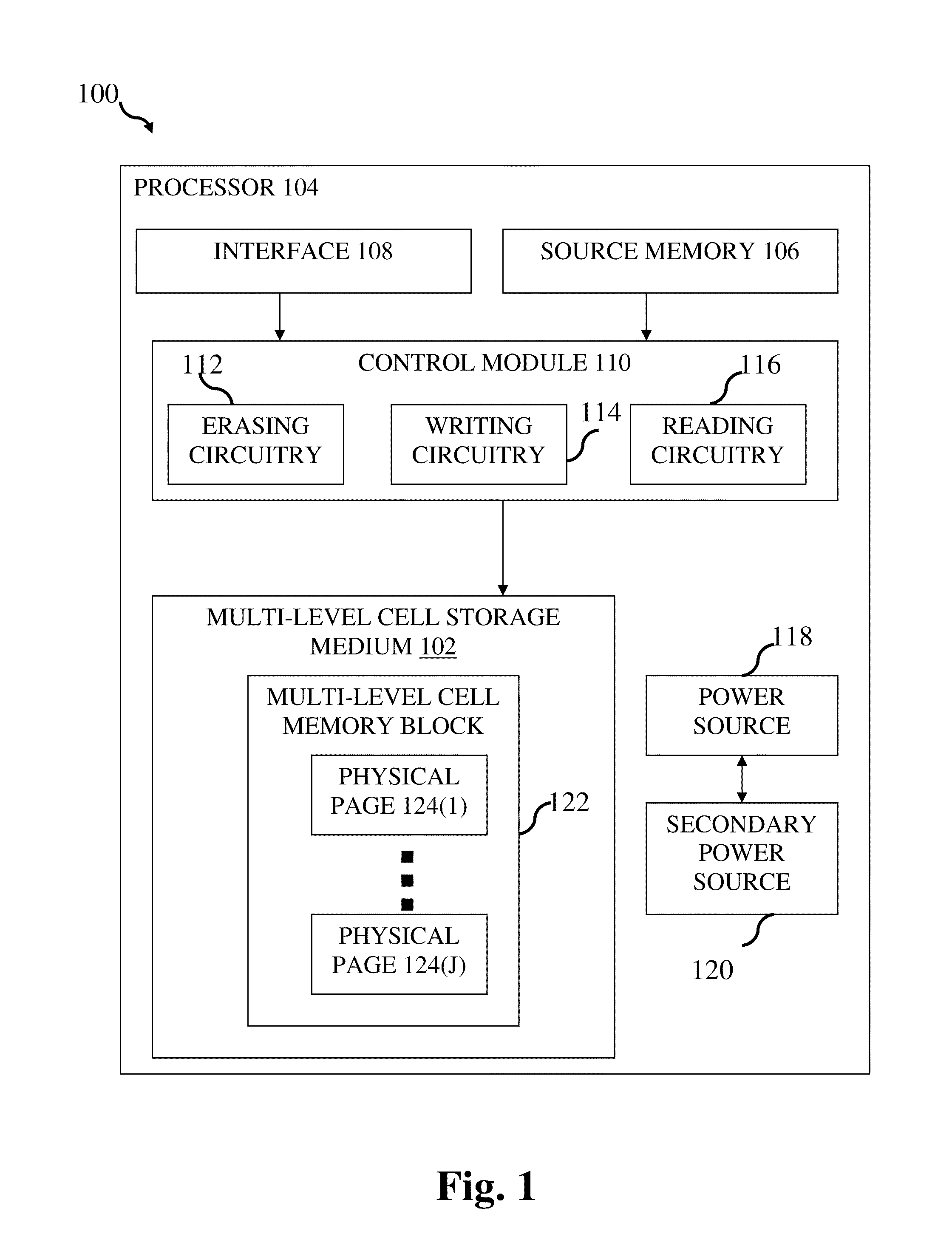

System and method for operating a non-volatile memory including a portion operating as a single-level cell memory and a portion operating as a multi-level cell memory

InactiveUS20110252187A1Reduce in quantityMemory architecture accessing/allocationMemory adressing/allocation/relocationData setSingle level

System and method for storing data in a non-volatile memory including a multi-level cell and single-level cell memory portions. To write a dataset to the non-volatile memory, if the size of the dataset is equal to the size of pages in the multi-level cell memory portion, the dataset may be written directly to the multi-level cell memory portion to fill an integer number of pages in a single write operation. However, if the size of the dataset is different than the size of the multi-level cell memory pages, at least a portion of the dataset may be temporarily written to the single-level cell memory portion until data is accumulated in a plurality of write operations having a size equal the size of the multi-level cell memory pages. The accumulated data may fill an integer number of the pages in the multi-level cell memory portion in a single write operation.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

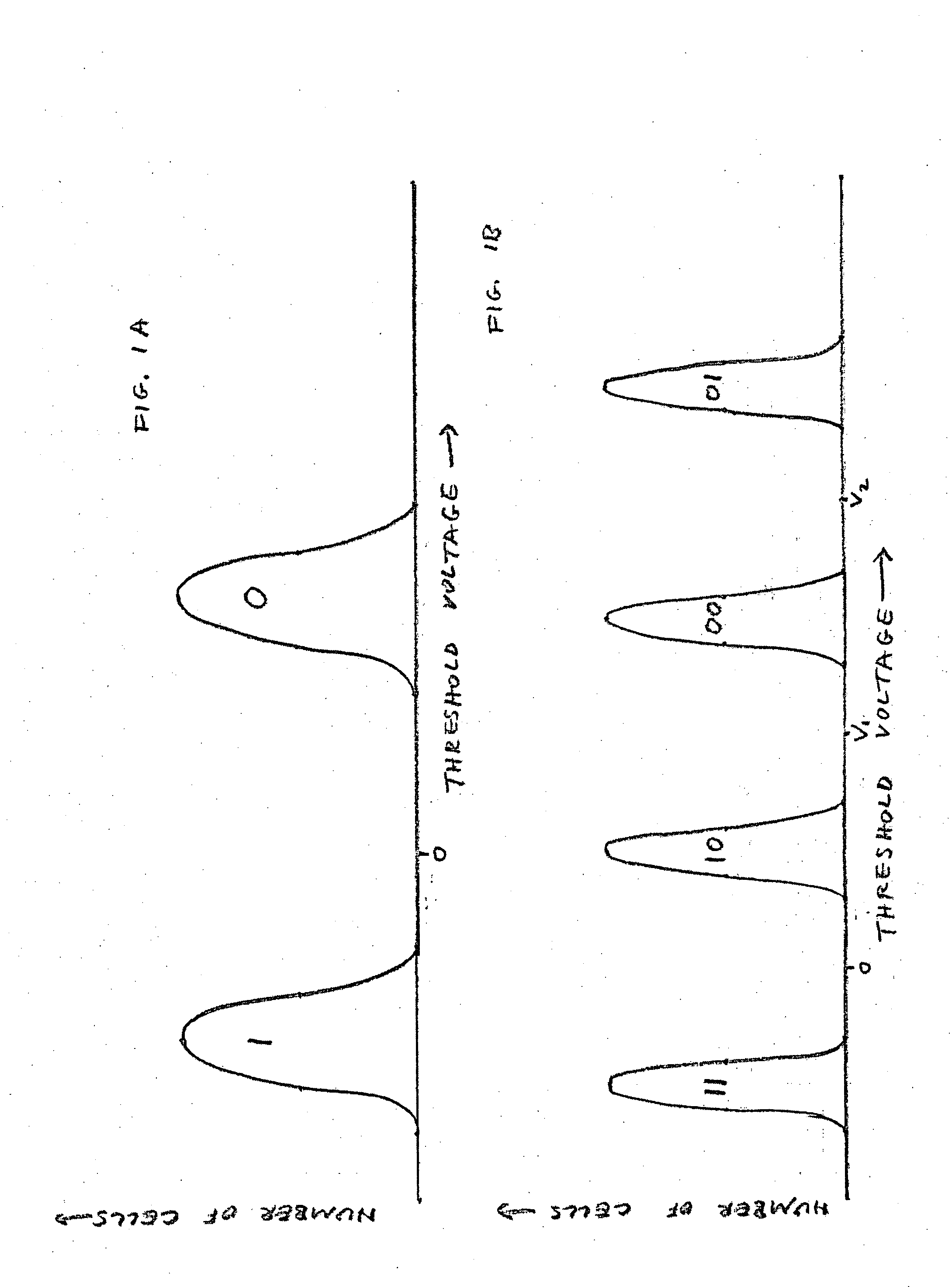

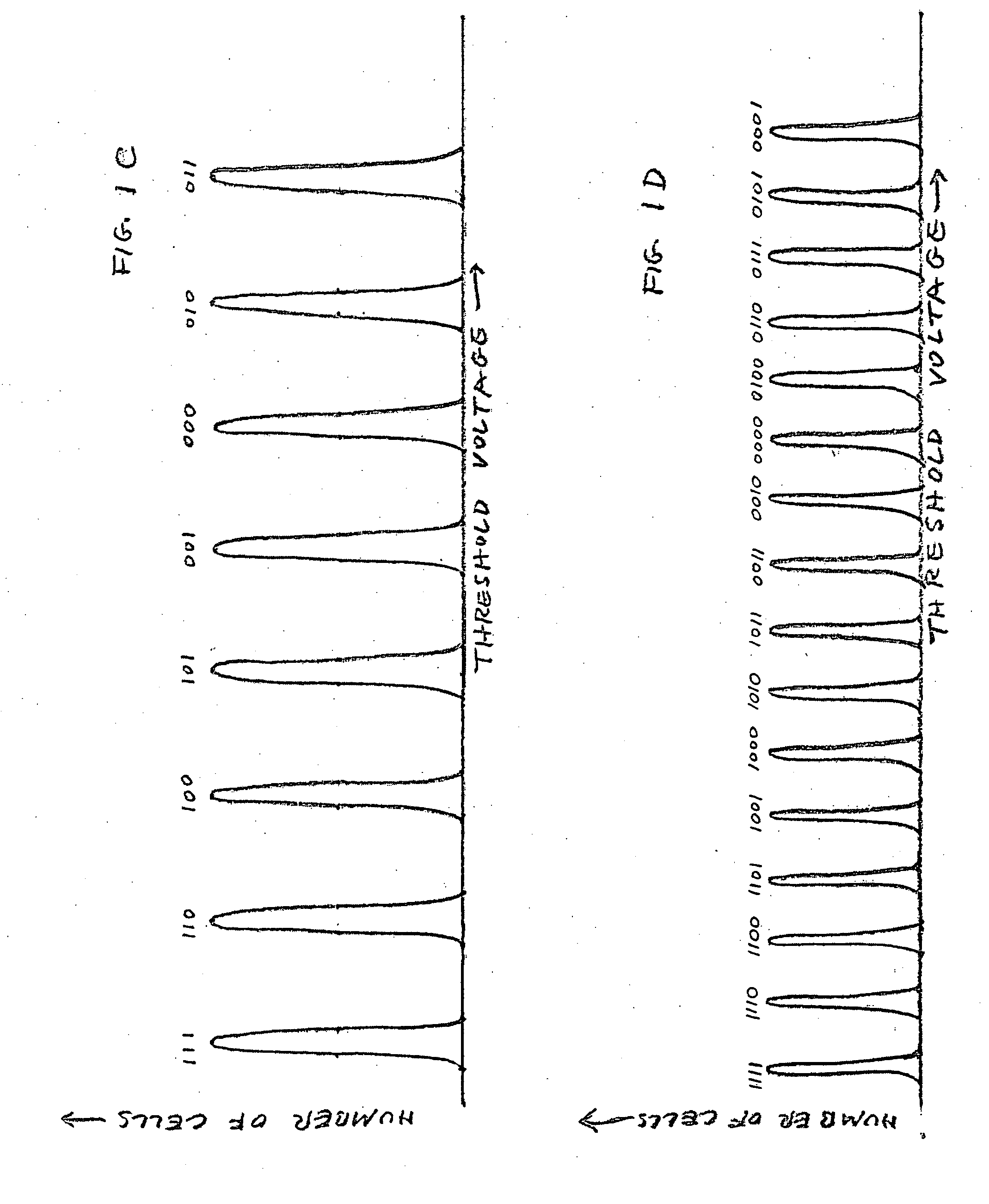

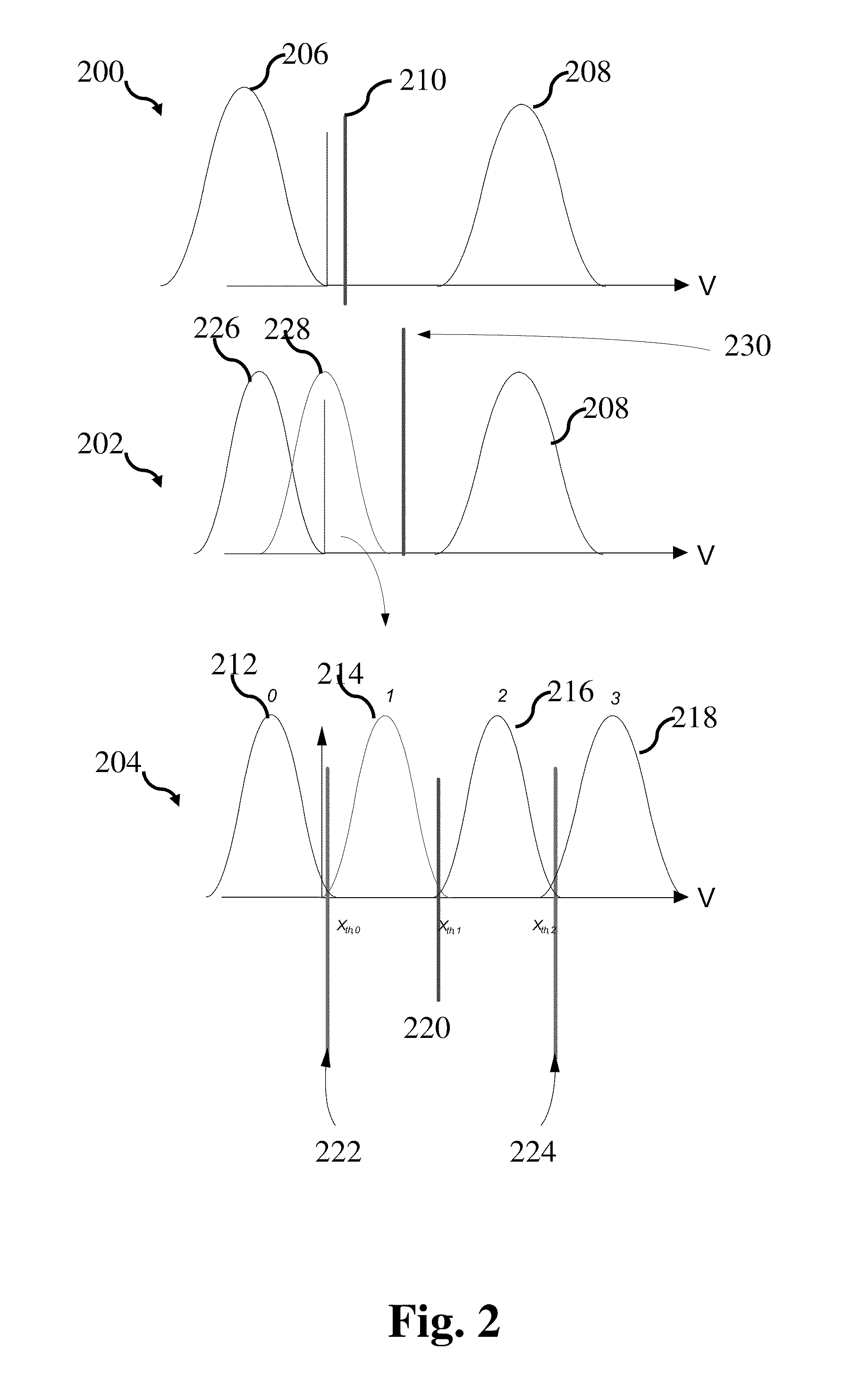

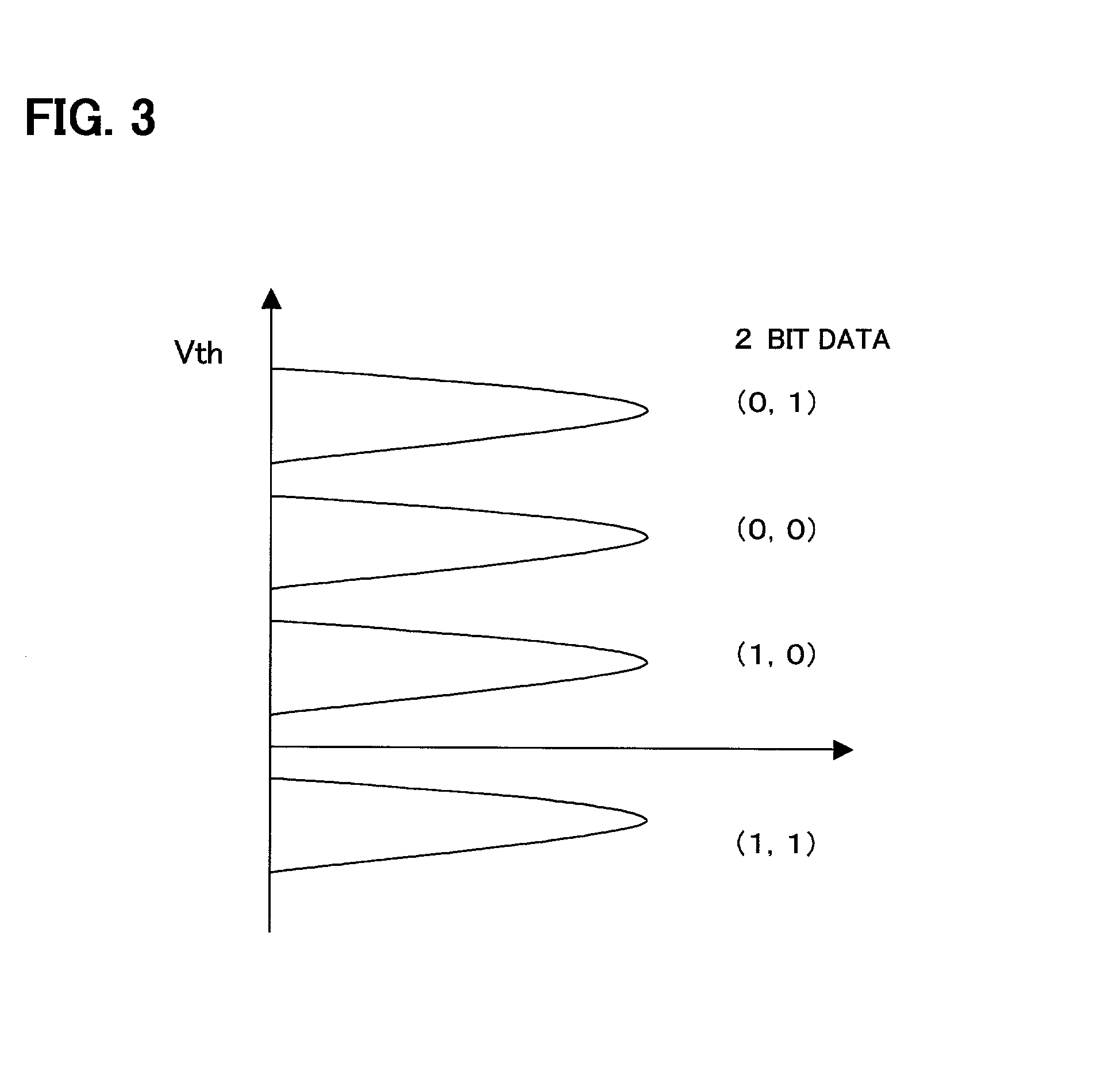

Probabilistic error correction in multi-bit-per-cell flash memory

InactiveUS20070086239A1Other decoding techniquesError detection/correctionComputer scienceCell memory

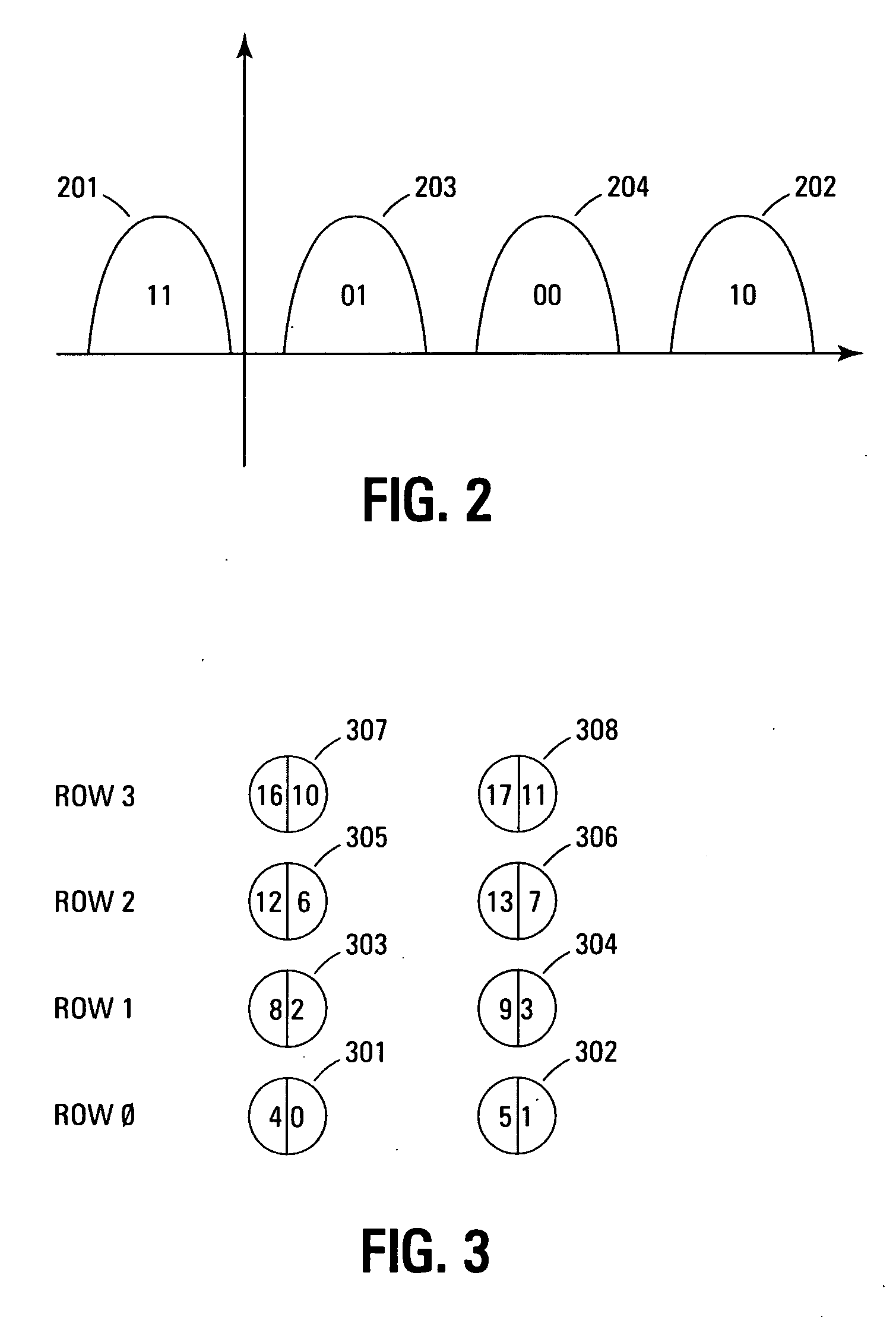

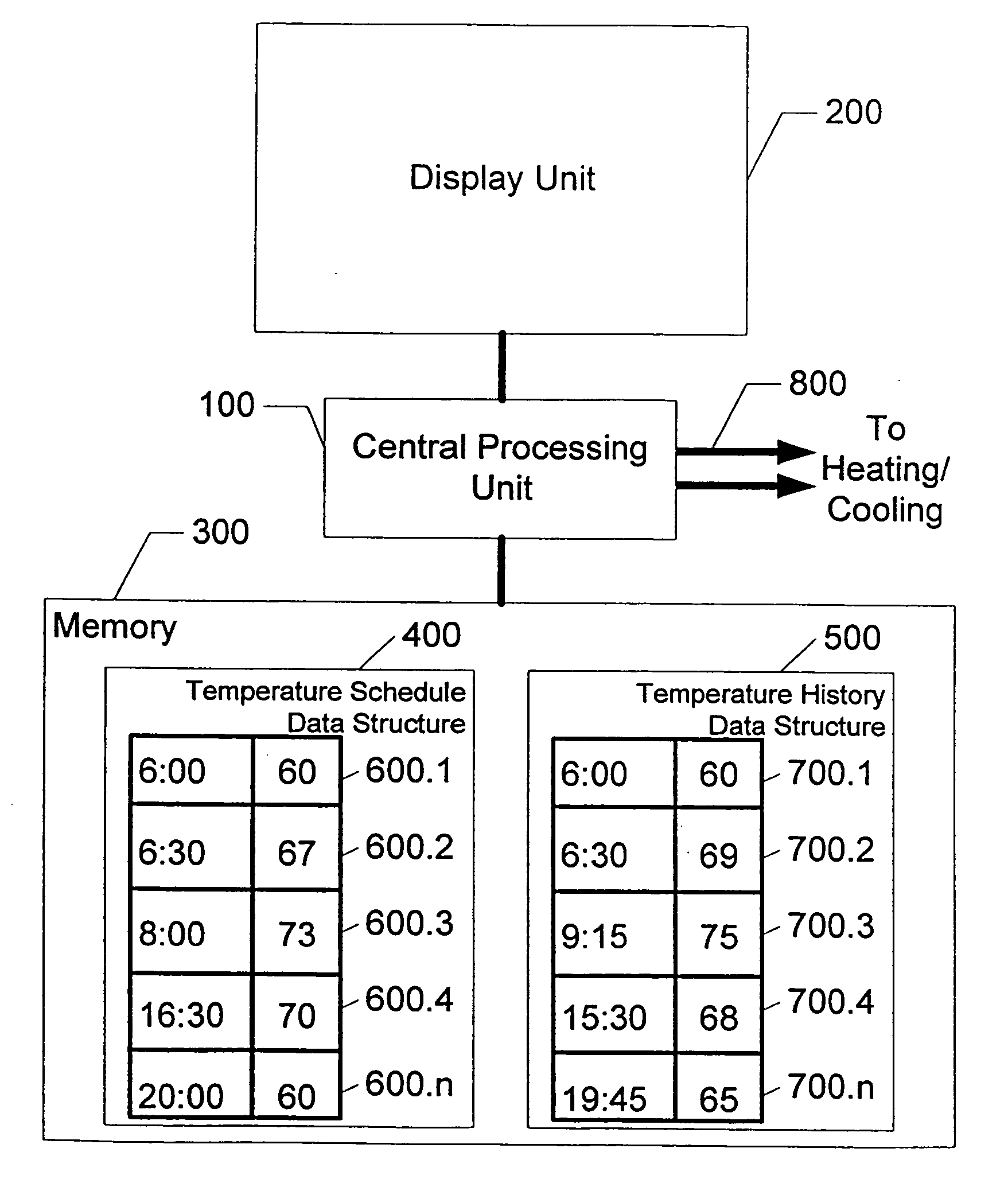

Data that are stored in cells of a multi-bit-per cell memory, according to a systematic or non-systematic ECC, are read and corrected (systematic ECC) or recovered (non-systematic ECC) in accordance with estimated probabilities that one or more of the read bits are erroneous. In one method of the present invention, the estimates are a priori. In another method of the present invention, the estimates are based only on aspects of the read bits that include significances or bit pages of the read bits. In a third method of the present invention, the estimates are based only on values of the read bits. Not all the estimates are equal.

Owner:RAMOT AT TEL AVIV UNIV LTD

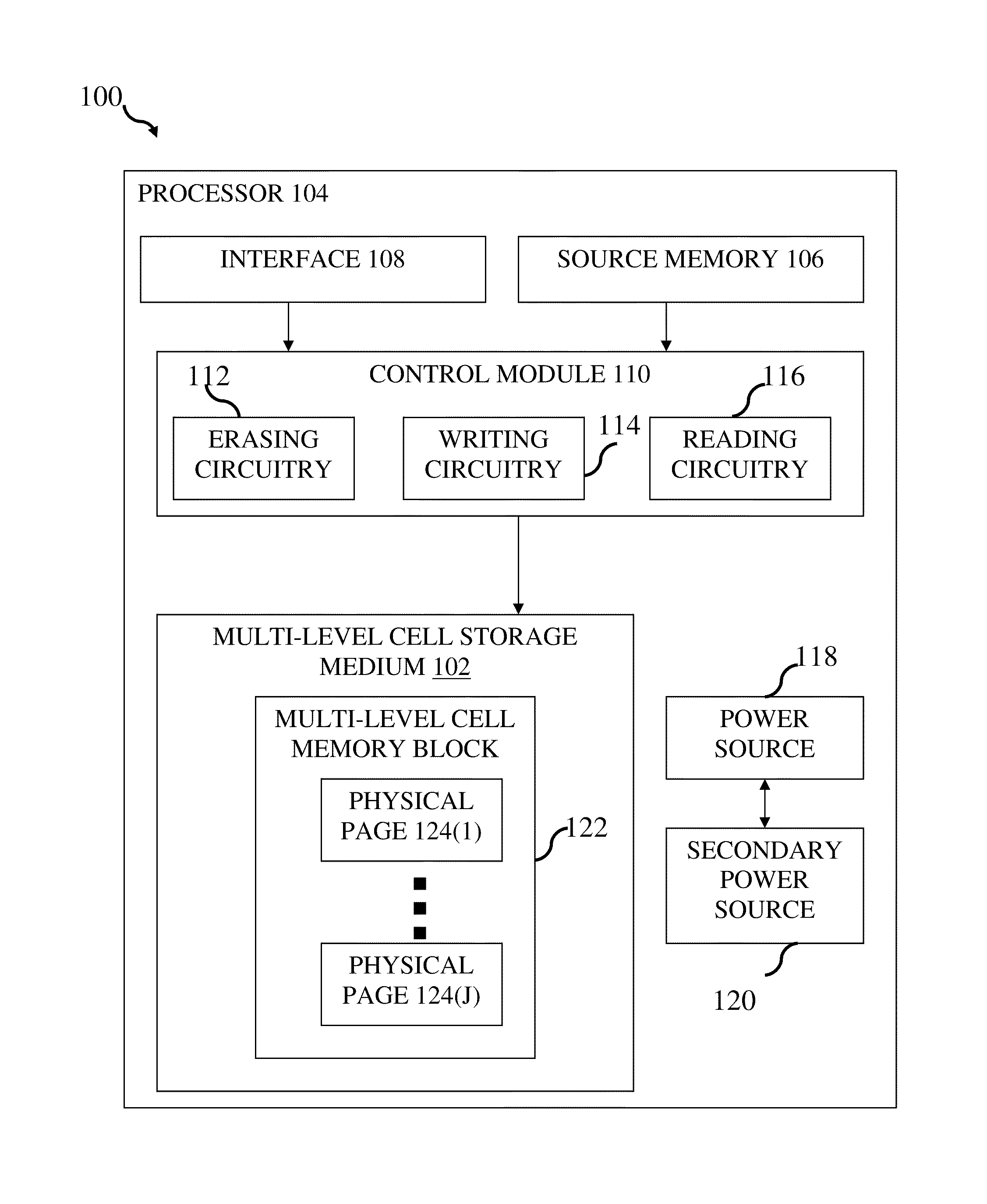

System and method for data recovery in multi-level cell memories

ActiveUS20120005558A1Read-only memoriesError correction/detection using block codesParallel computingMulti-level cell

A system and method are provided for data recovery in a multi-level cell memory device. One or more bits may be programmed sequentially in one or more respective levels of multi-level cells in the memory device. An interruption of programming a subsequent bit in a subsequent second or greater level of the multi-level cells may be detected. Data may be recovered from the multi-level cells defining the one or more bits programmed preceding the programming interruption of the second or greater level.

Owner:AVAGO TECH INT SALES PTE LTD

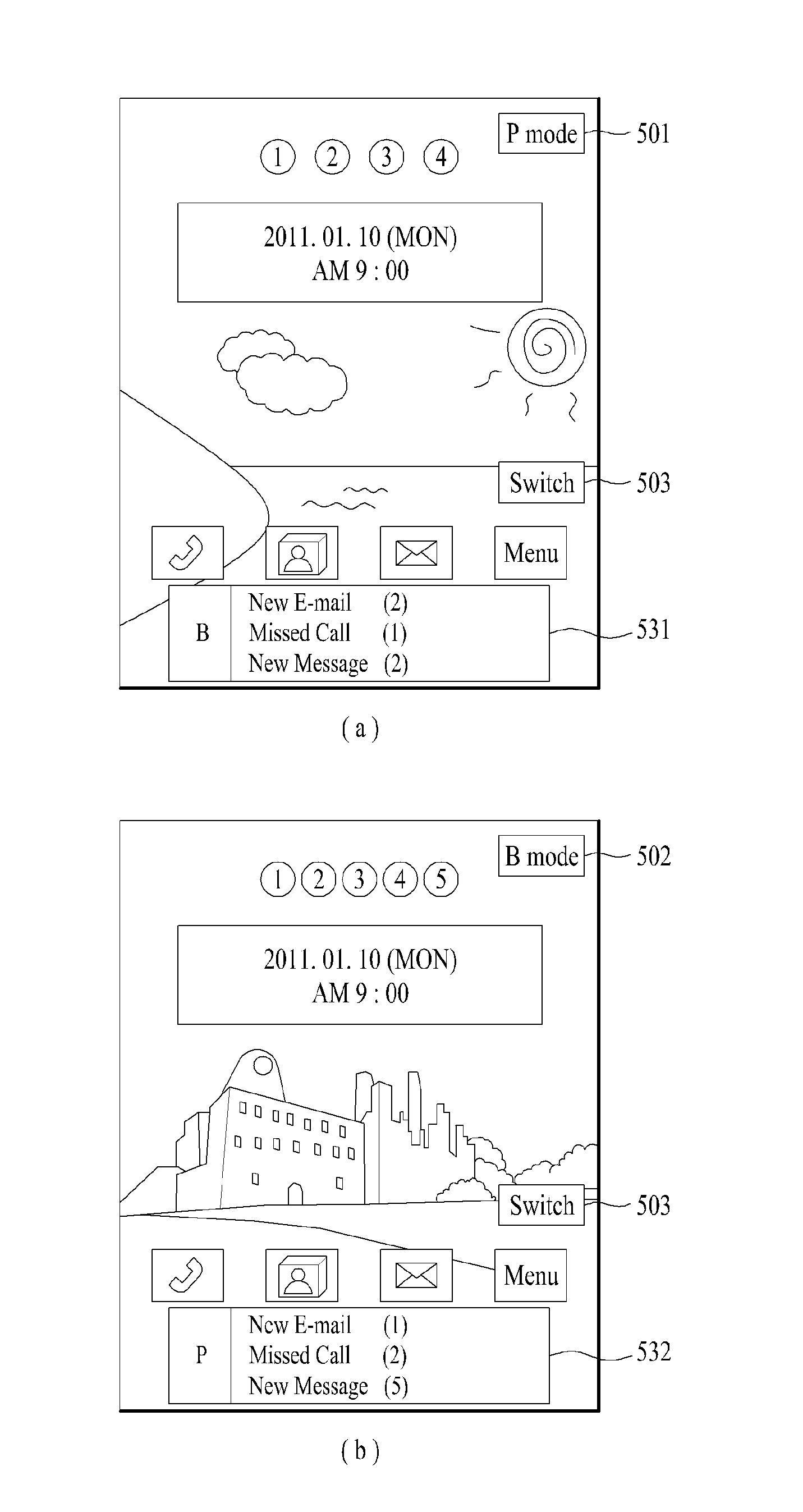

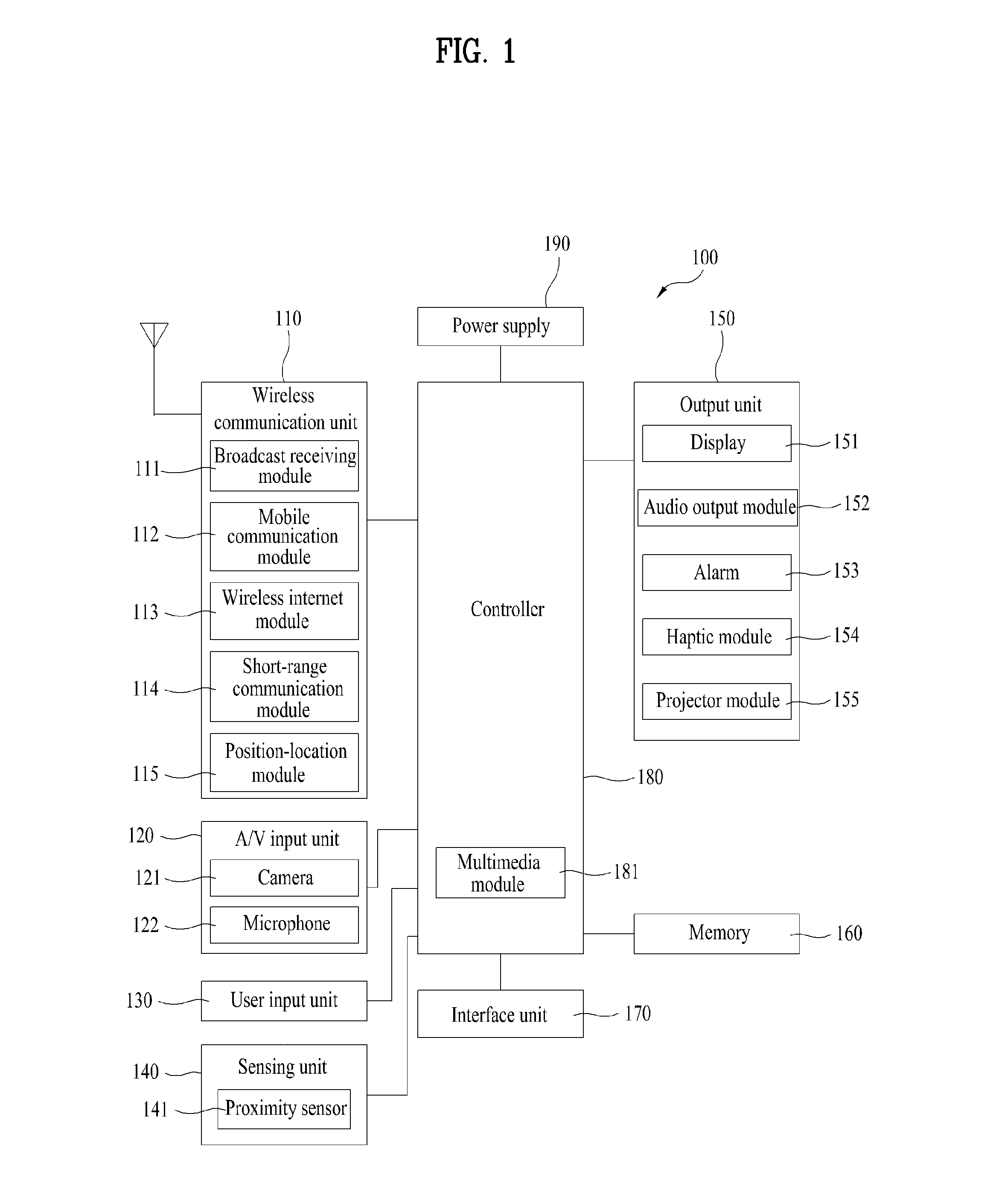

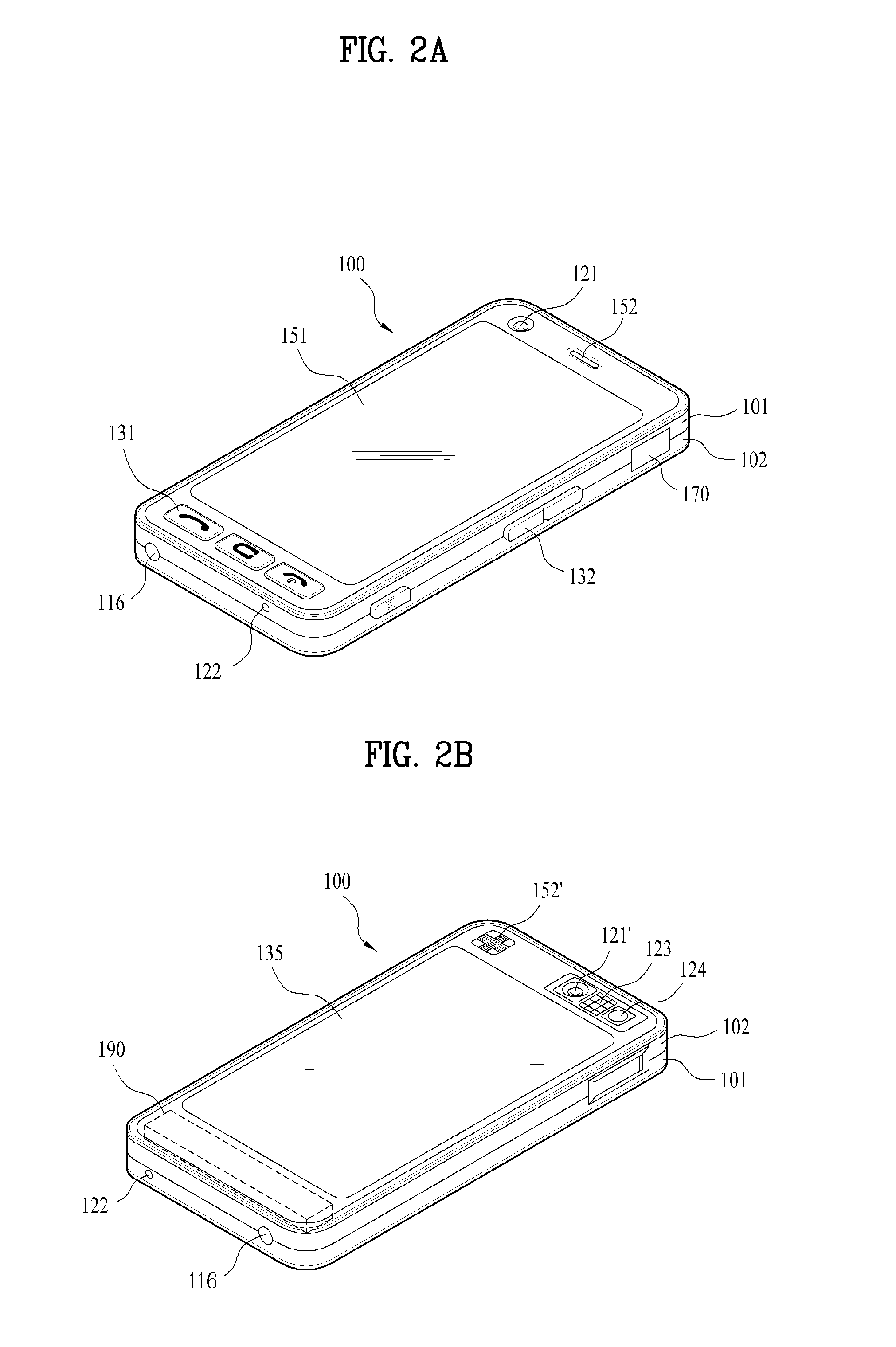

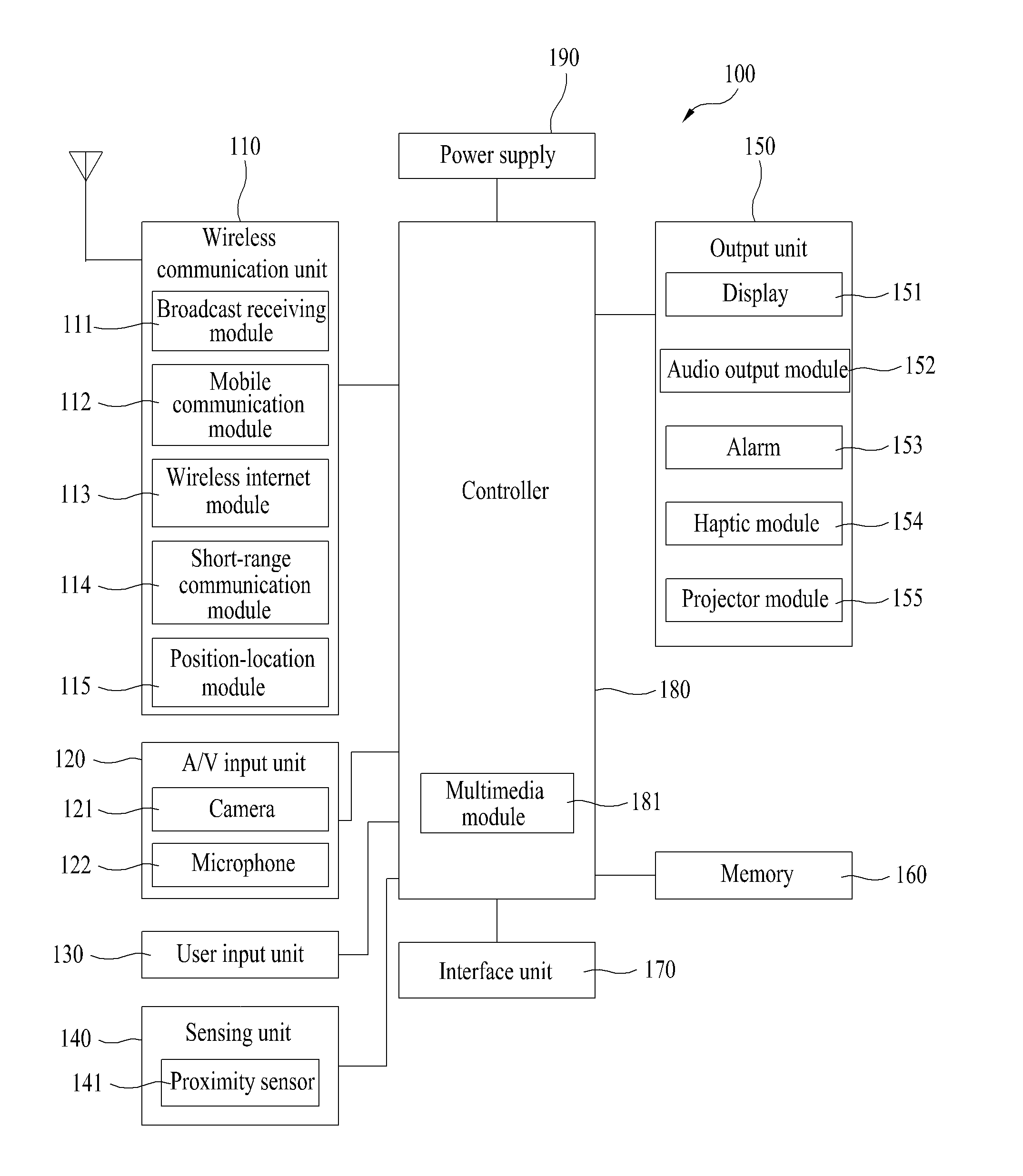

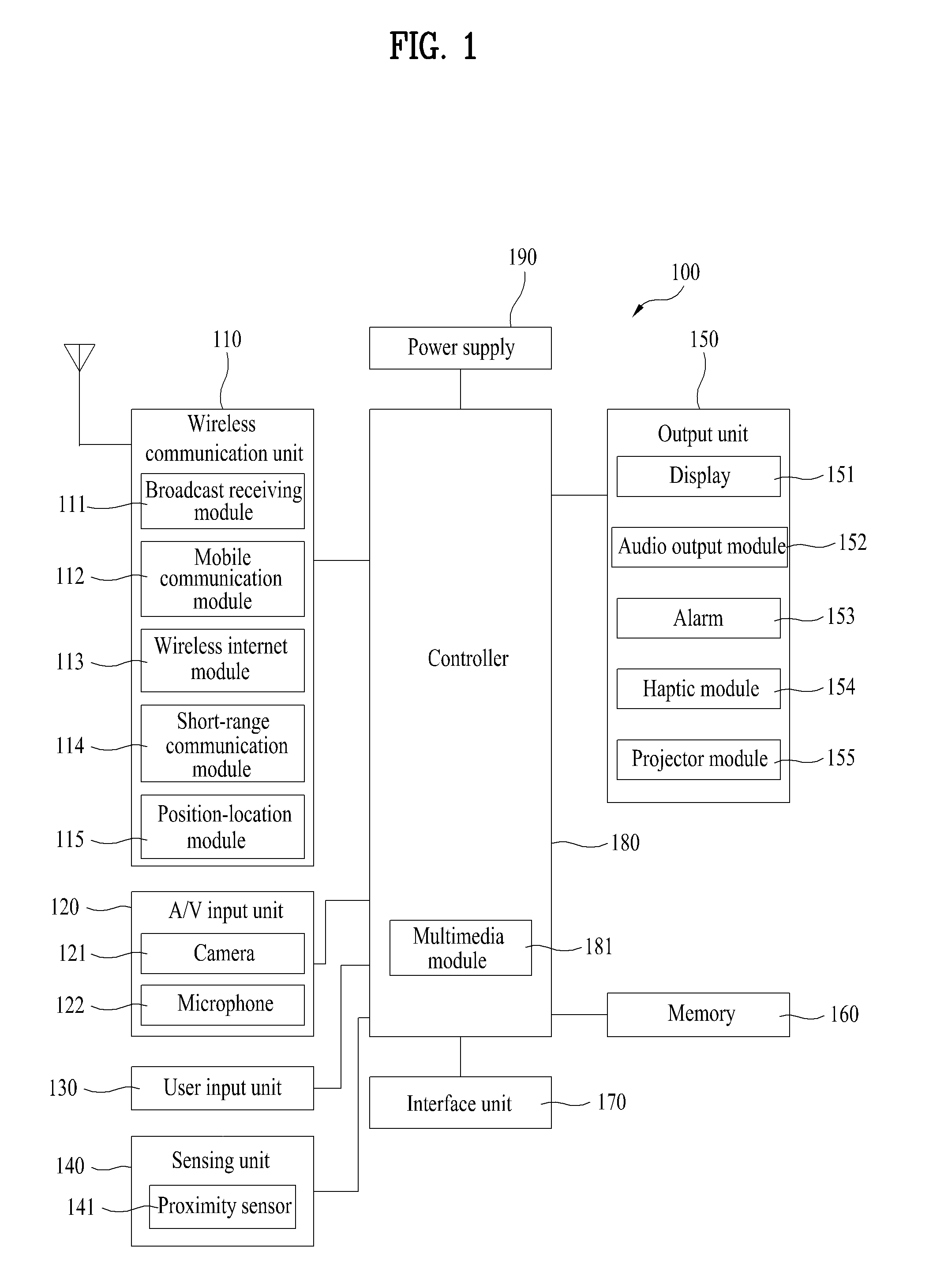

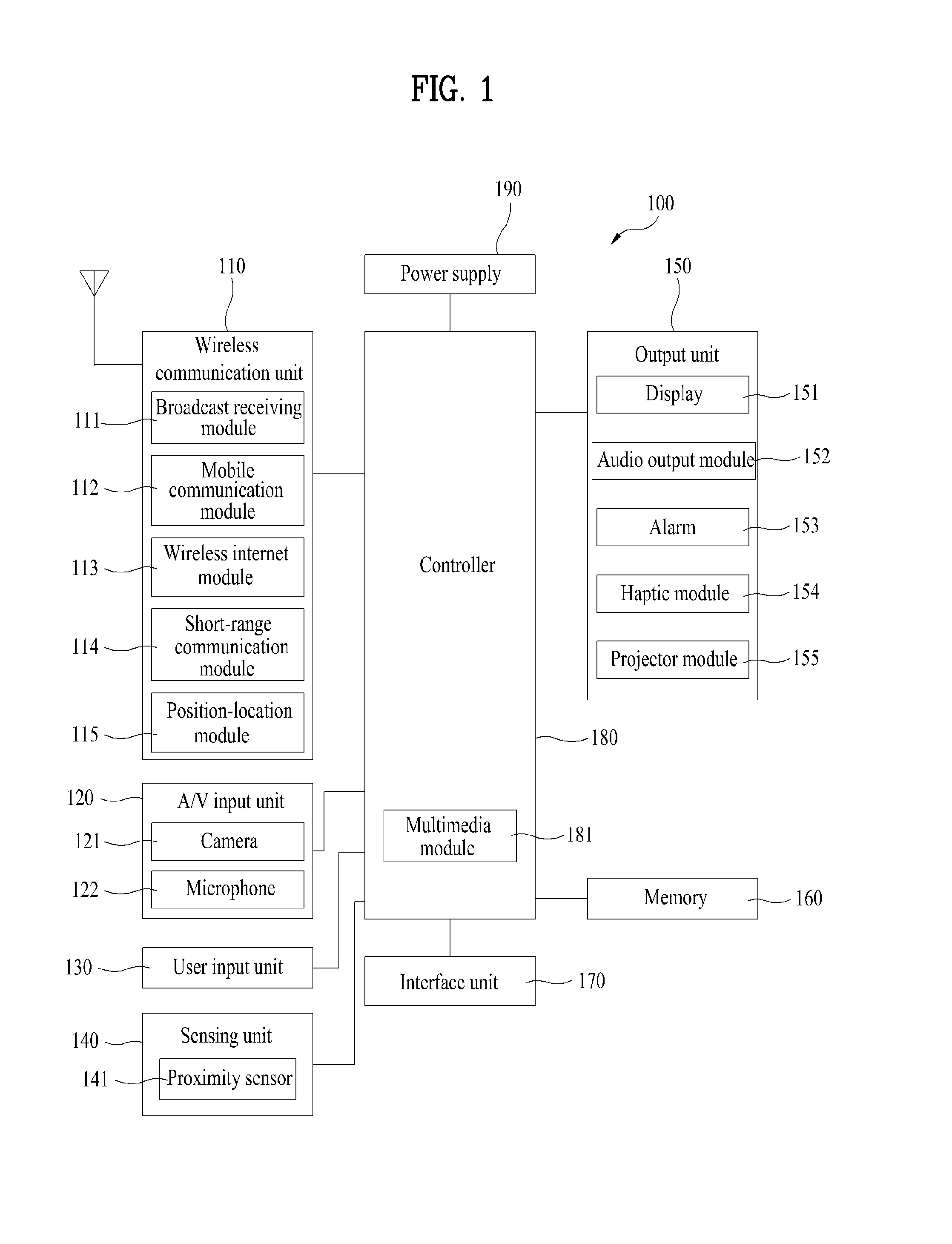

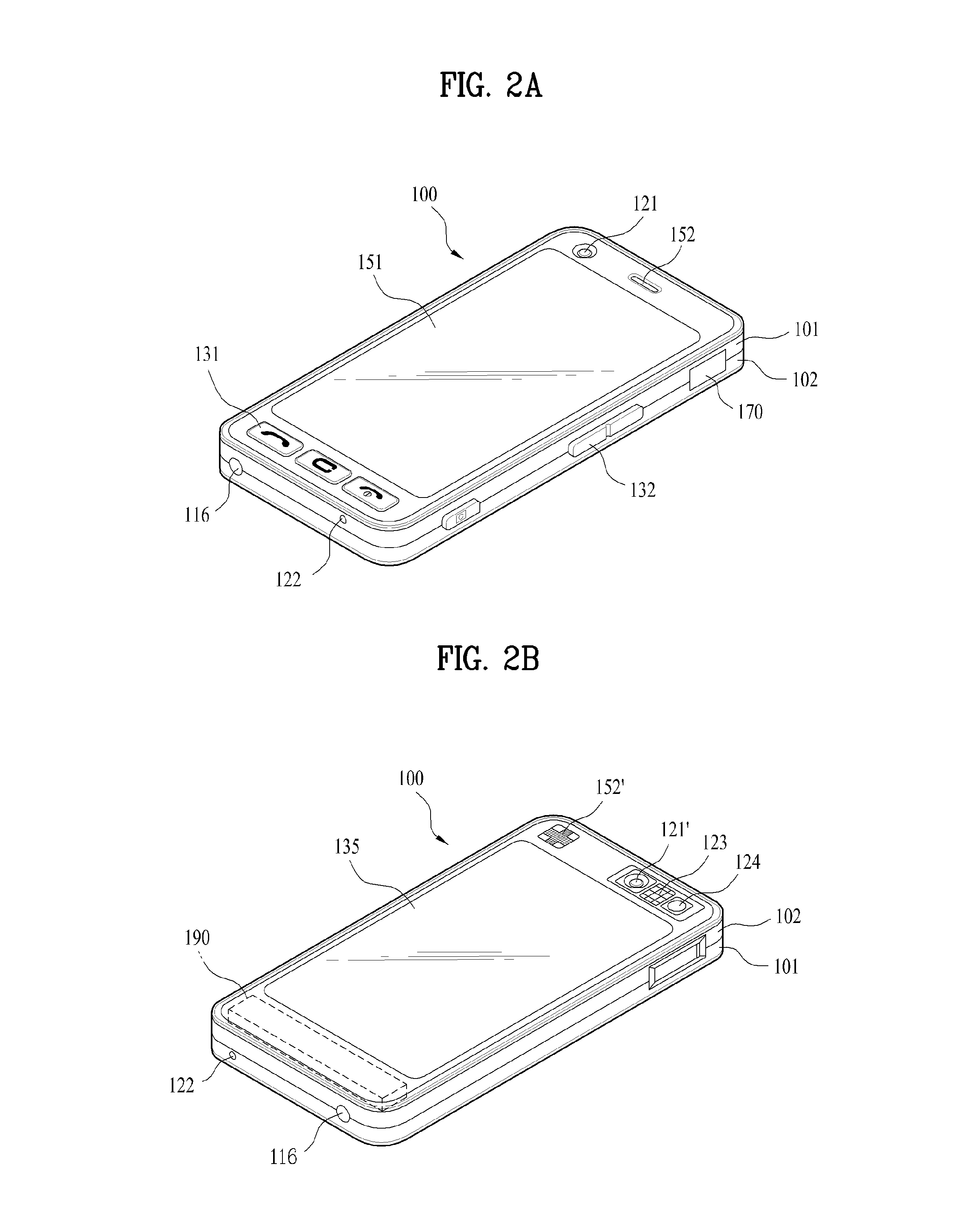

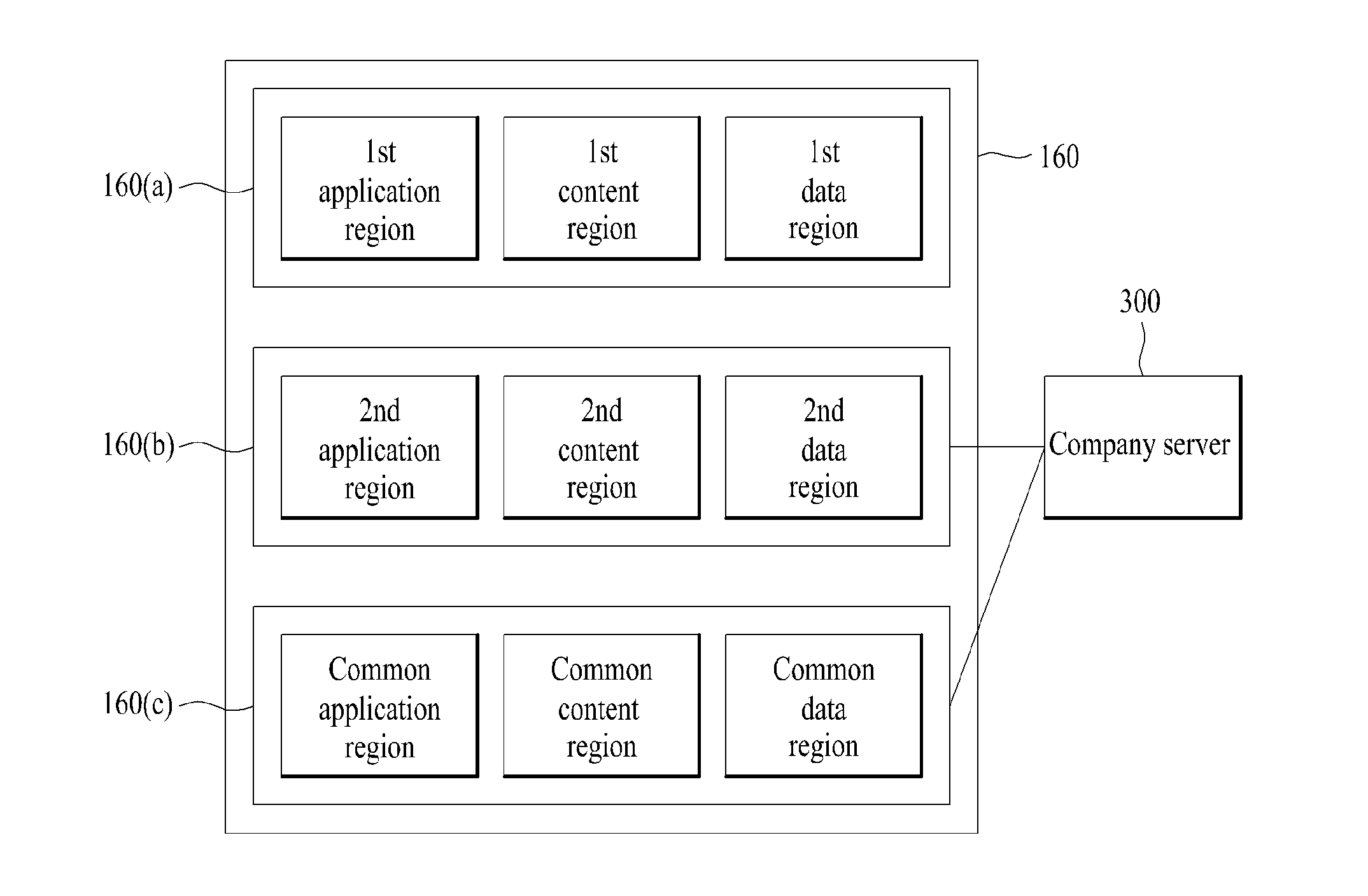

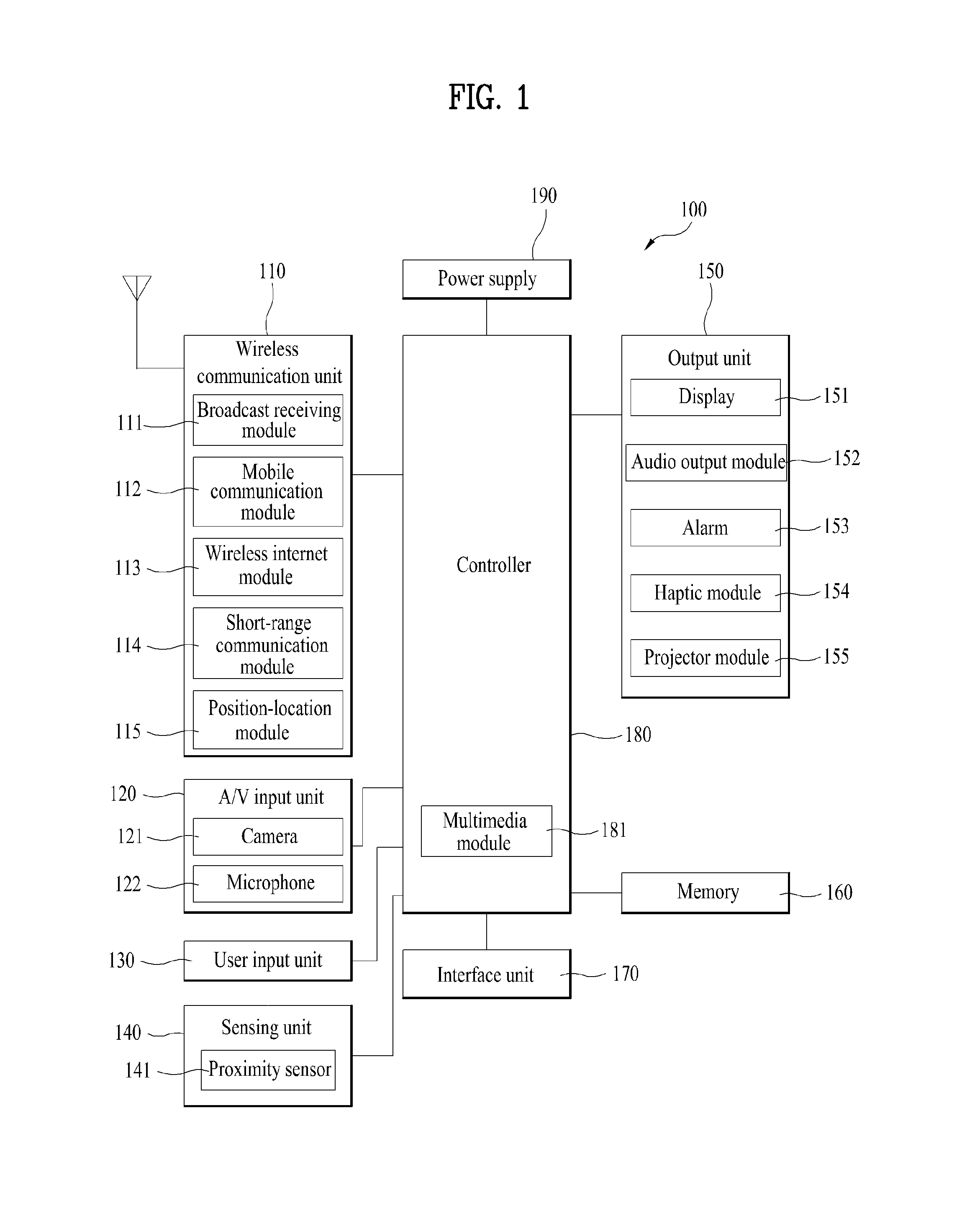

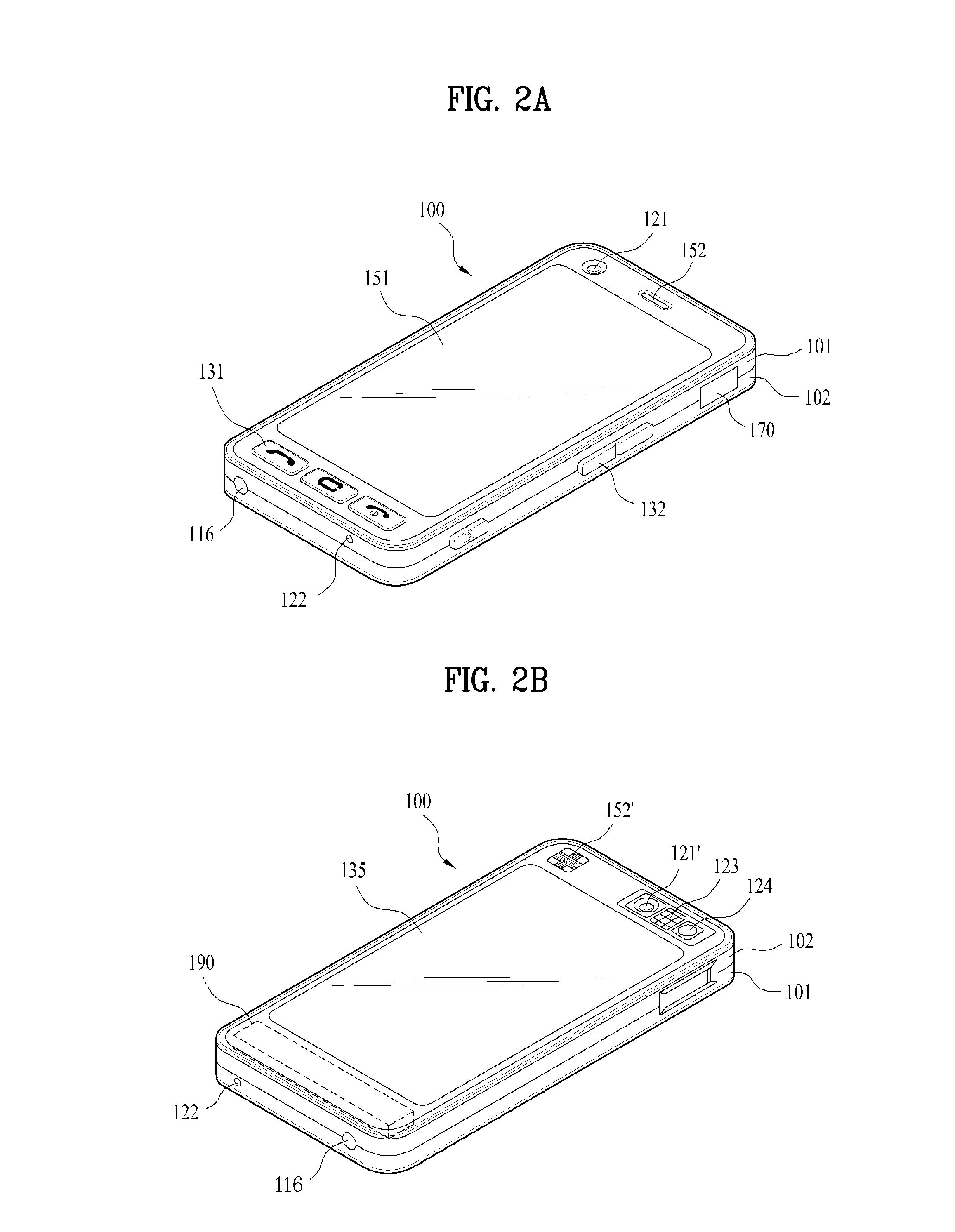

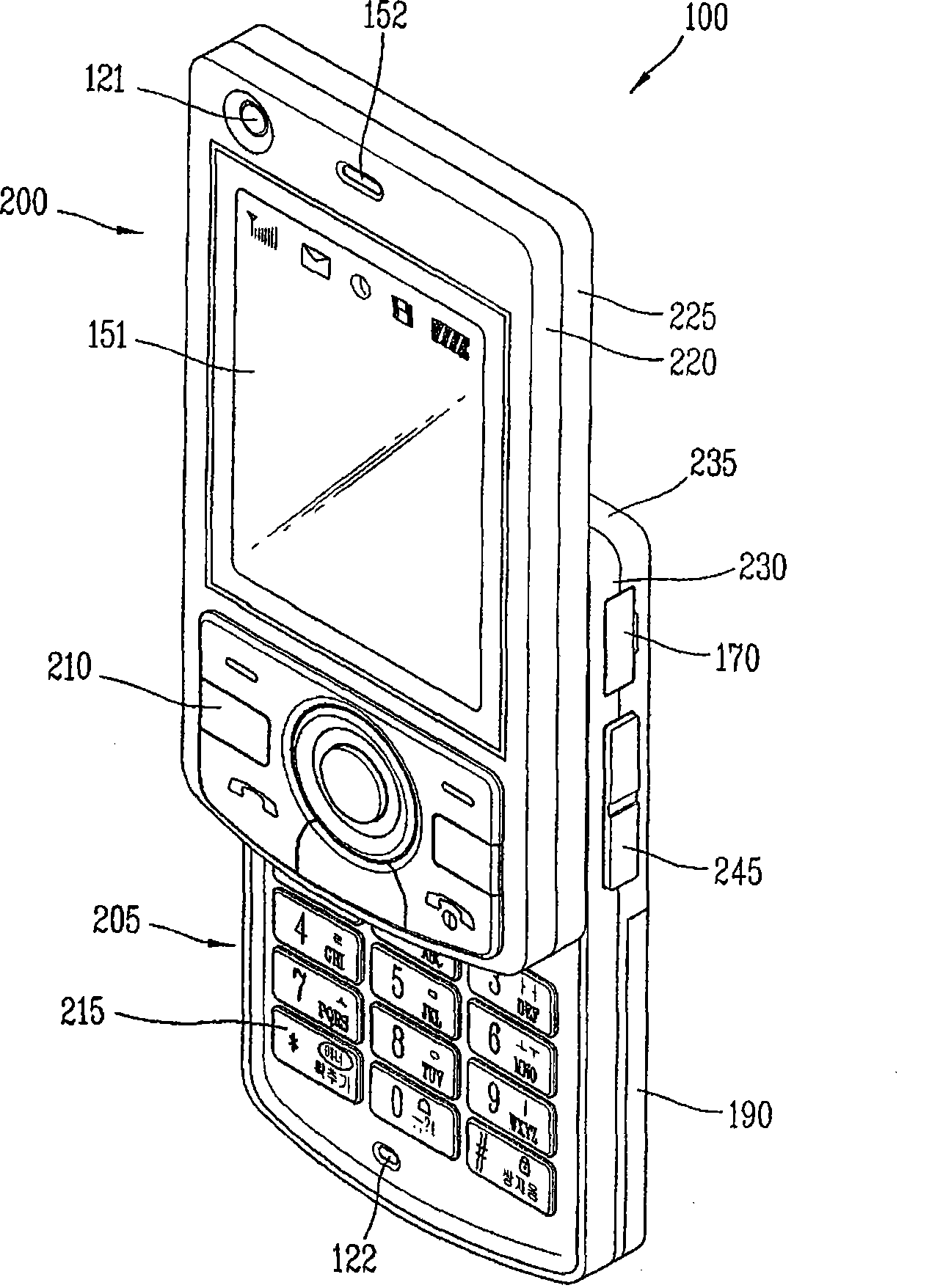

Mobile terminal and method of sharing information therein

ActiveUS20120166997A1Increase profitMaintain information securityDigital data protectionInternal/peripheral component protectionCommunication unitOperational system

A mobile terminal including a communication unit configured to communicate with at least one other terminal; a memory configured to store at least first and second operating systems including at least first and second modes, respectively; and a controller configured to execute the first and second operating systems, to simultaneously display first and second information screens on a display unit of the mobile terminal corresponding to the first and second modes, to receive a sharing signal requesting information from one of the first and second information screens be shared with the other of the first and second information screens, and to selectively share the requested information between the first and second information screens based on a predetermined criterion.

Owner:LG ELECTRONICS INC

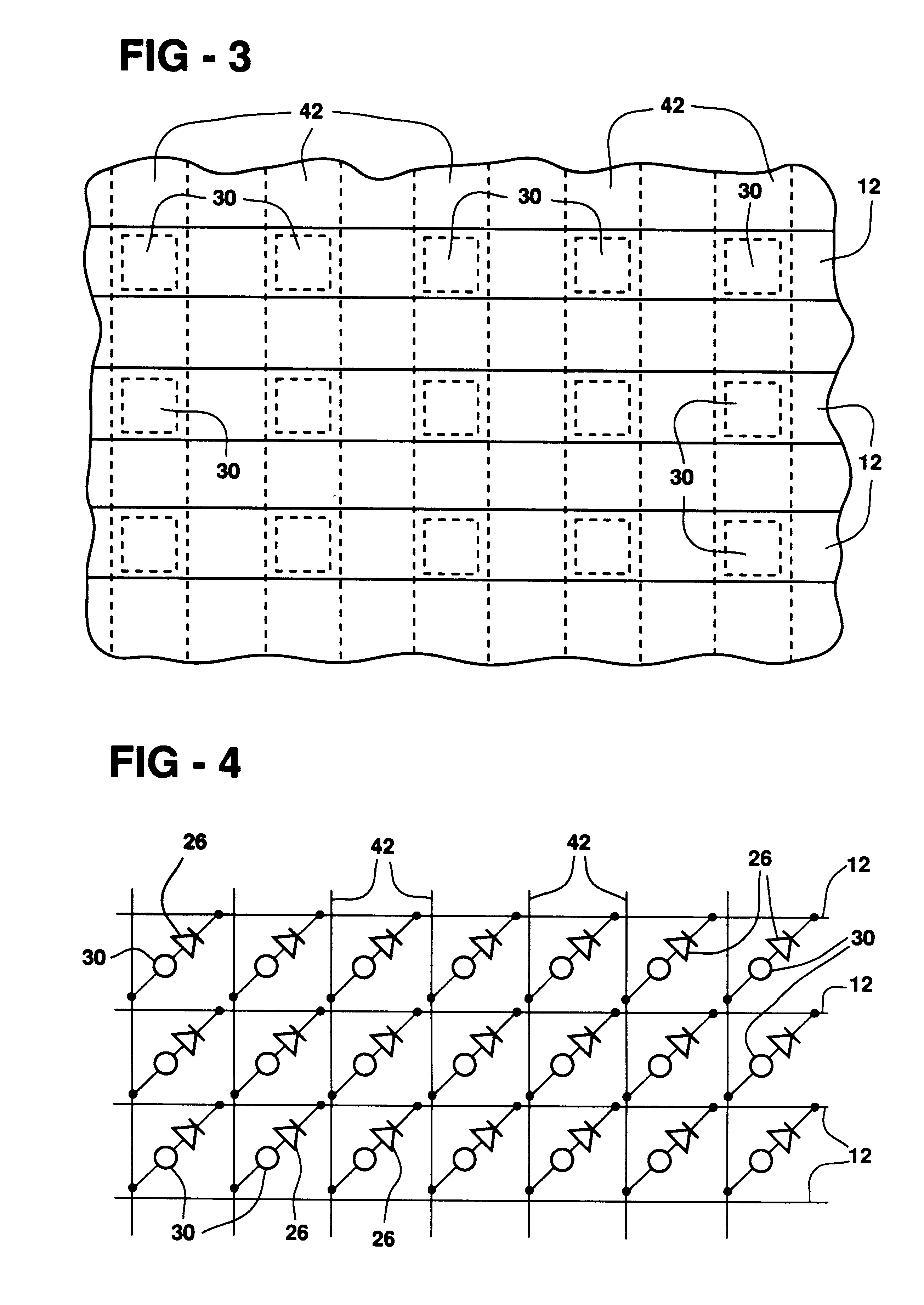

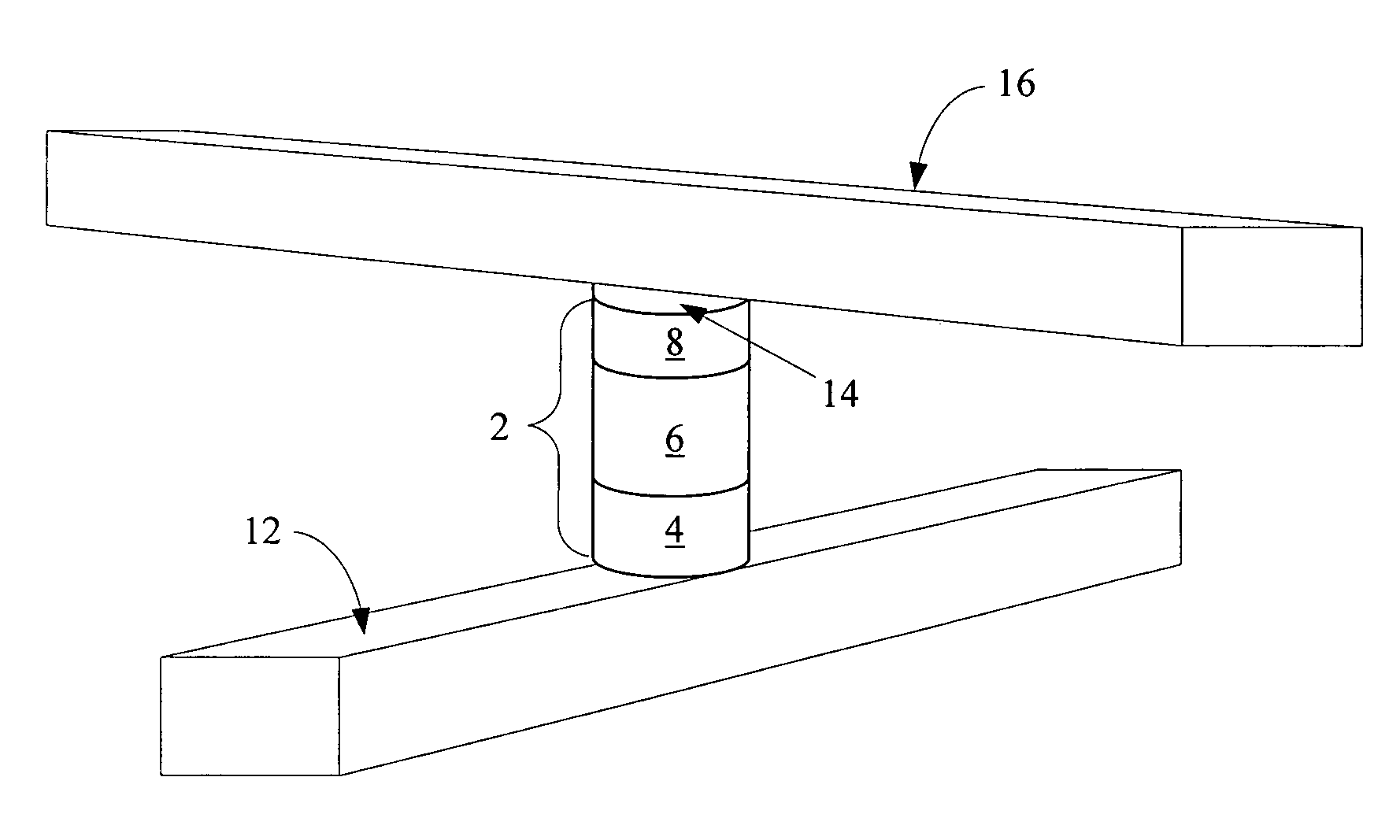

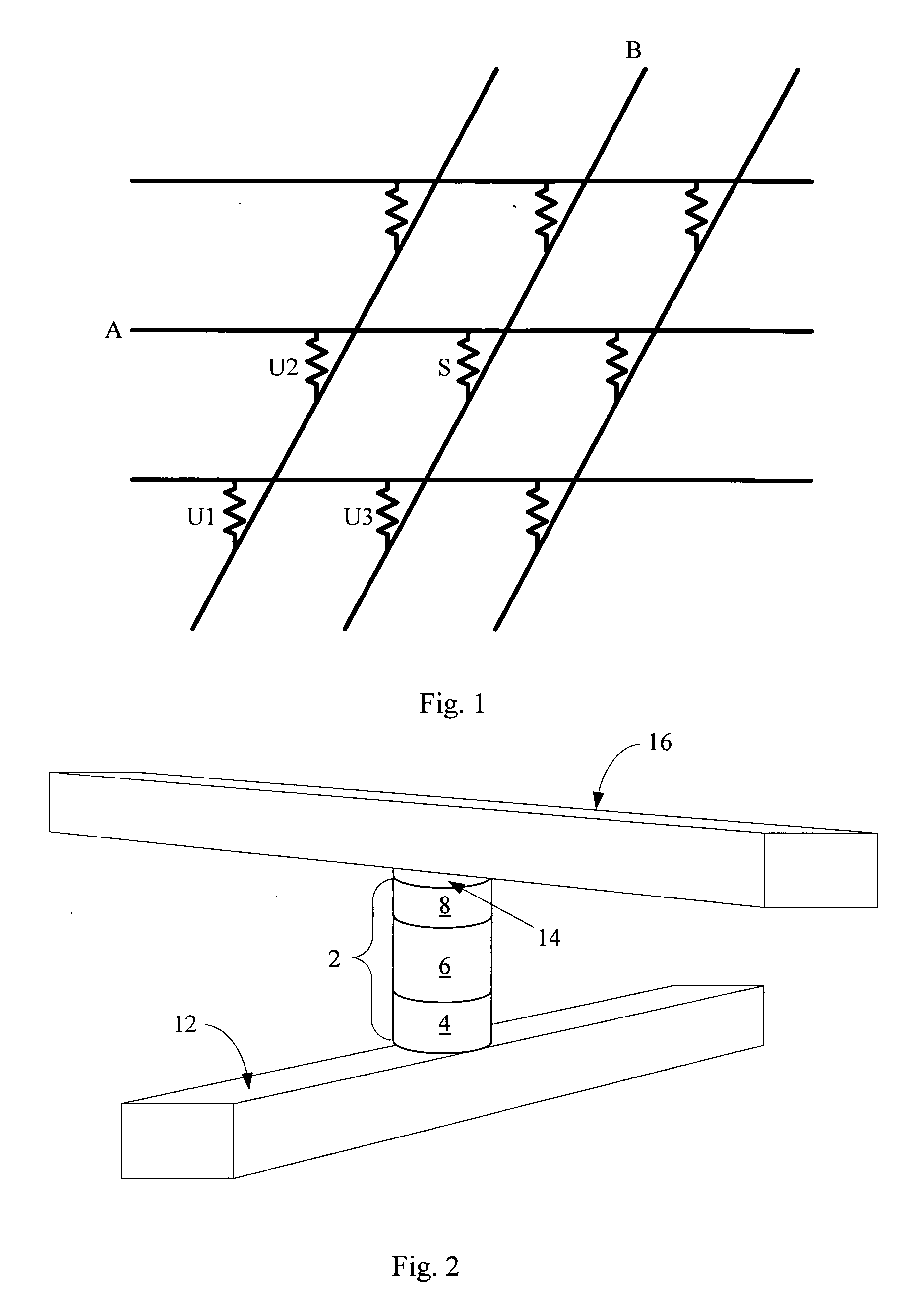

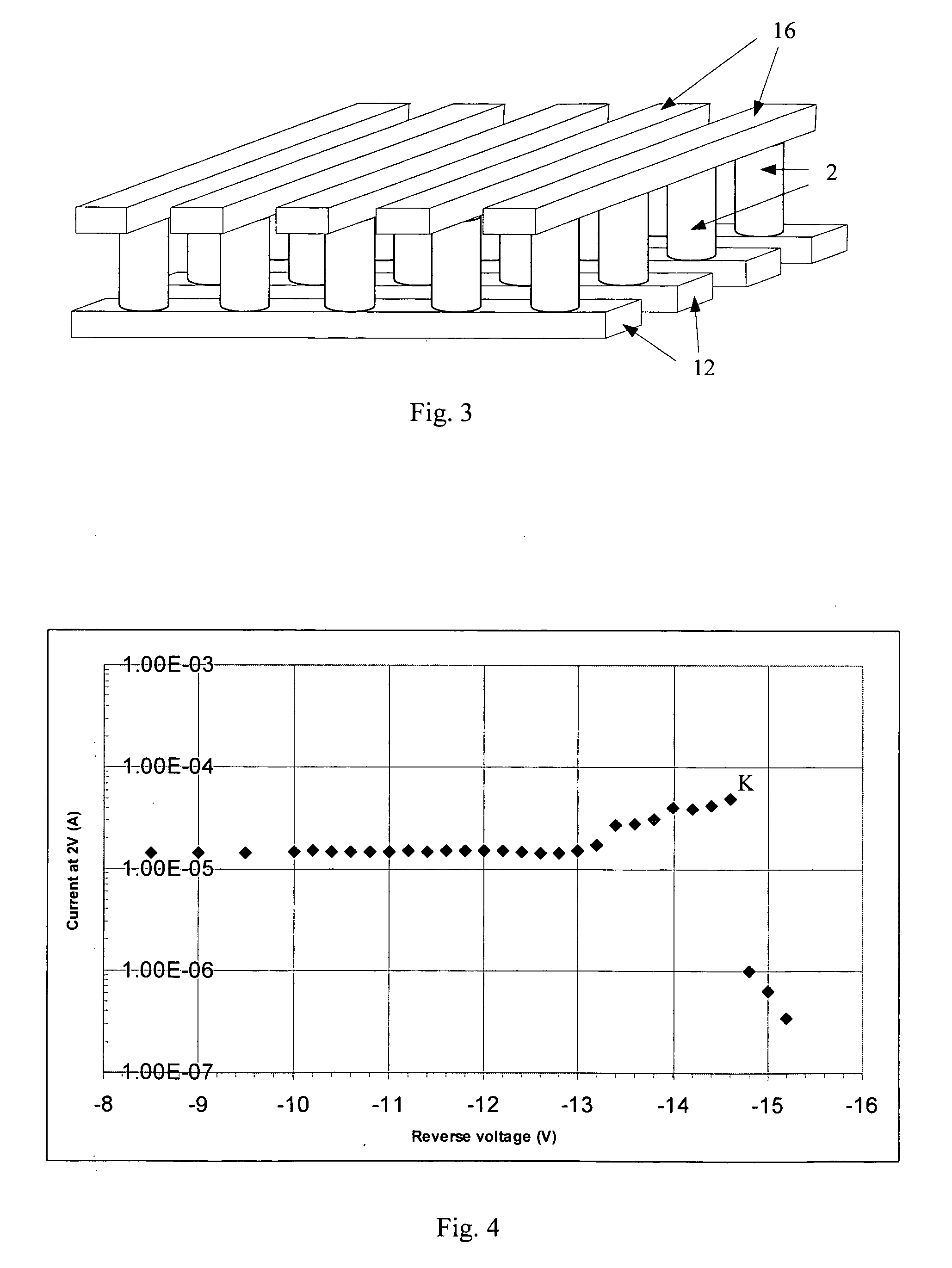

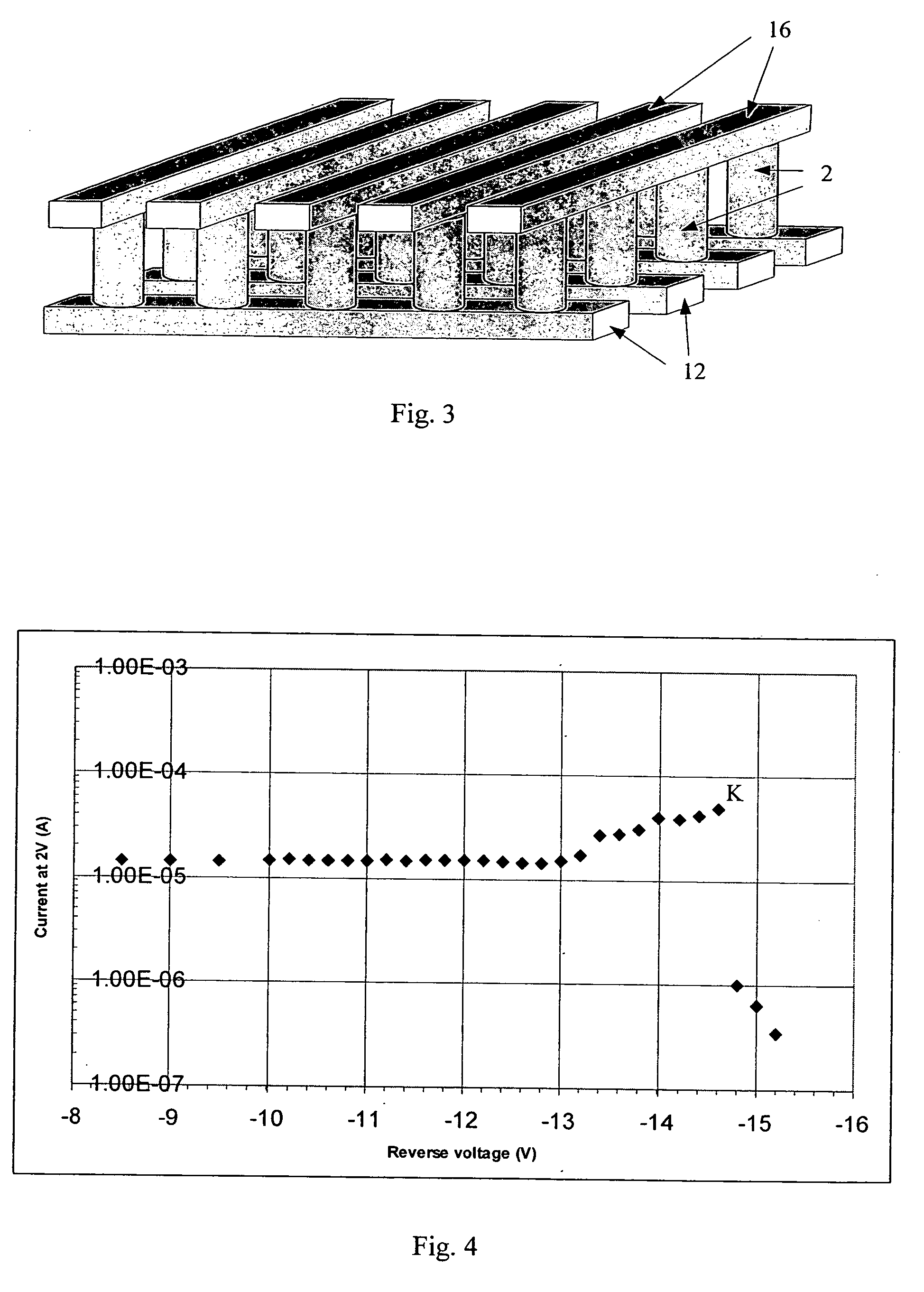

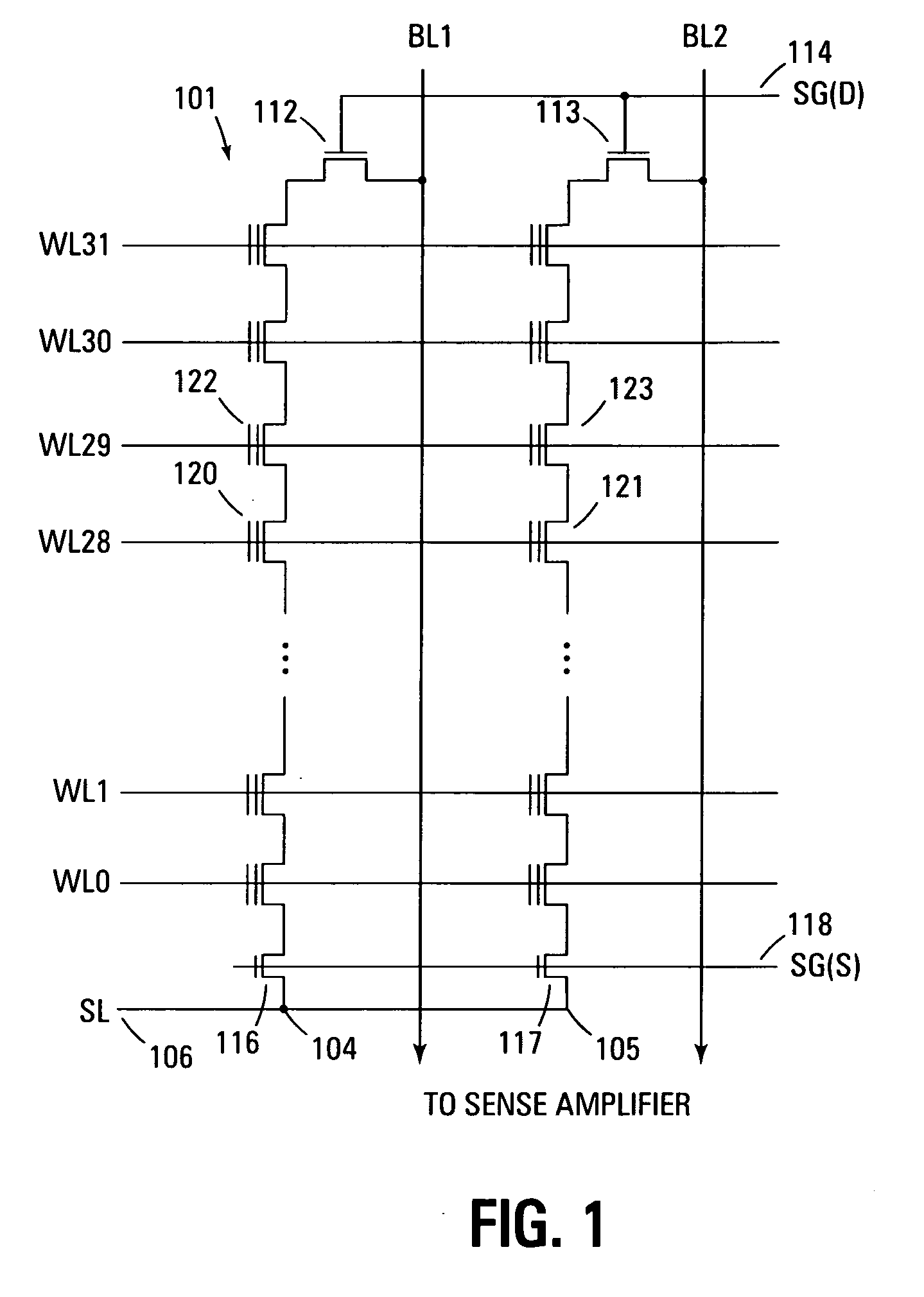

Multi-use memory cell and memory array

InactiveUS20070069276A1Solid-state devicesRead-only memoriesComputer architectureSemiconductor materials

A multi-use memory cell and memory array are disclosed. In one preferred embodiment, a memory cell is operable as a one-time programmable memory cell or a rewritable memory cell. The memory cell comprises a memory element comprising a semiconductor material configurable to one of at least three resistivity states, wherein a first resistivity state is used to represent a data state of the memory cell when the memory cell operates as a one-time programmable memory cell but not when the memory cell operates as a rewritable memory cell. A memory array with such memory cells is also disclosed. In another preferred embodiment, a memory cell is provided comprising a switchable resistance material, wherein the memory cell is operable in a first mode in which the memory cell is programmed with a forward bias and a second mode in which the memory cell is programmed with a reverse bias.

Owner:WODEN TECH INC

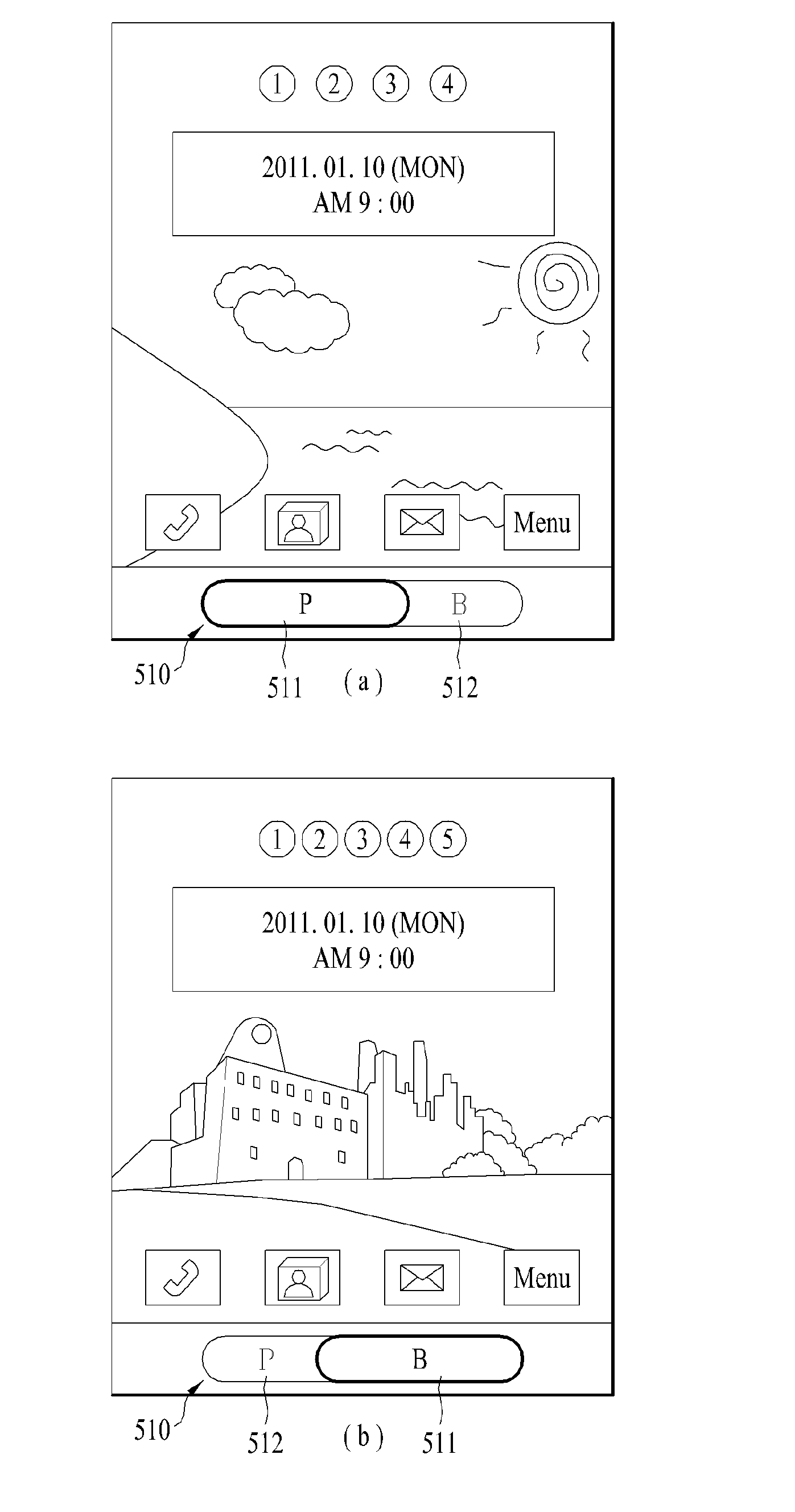

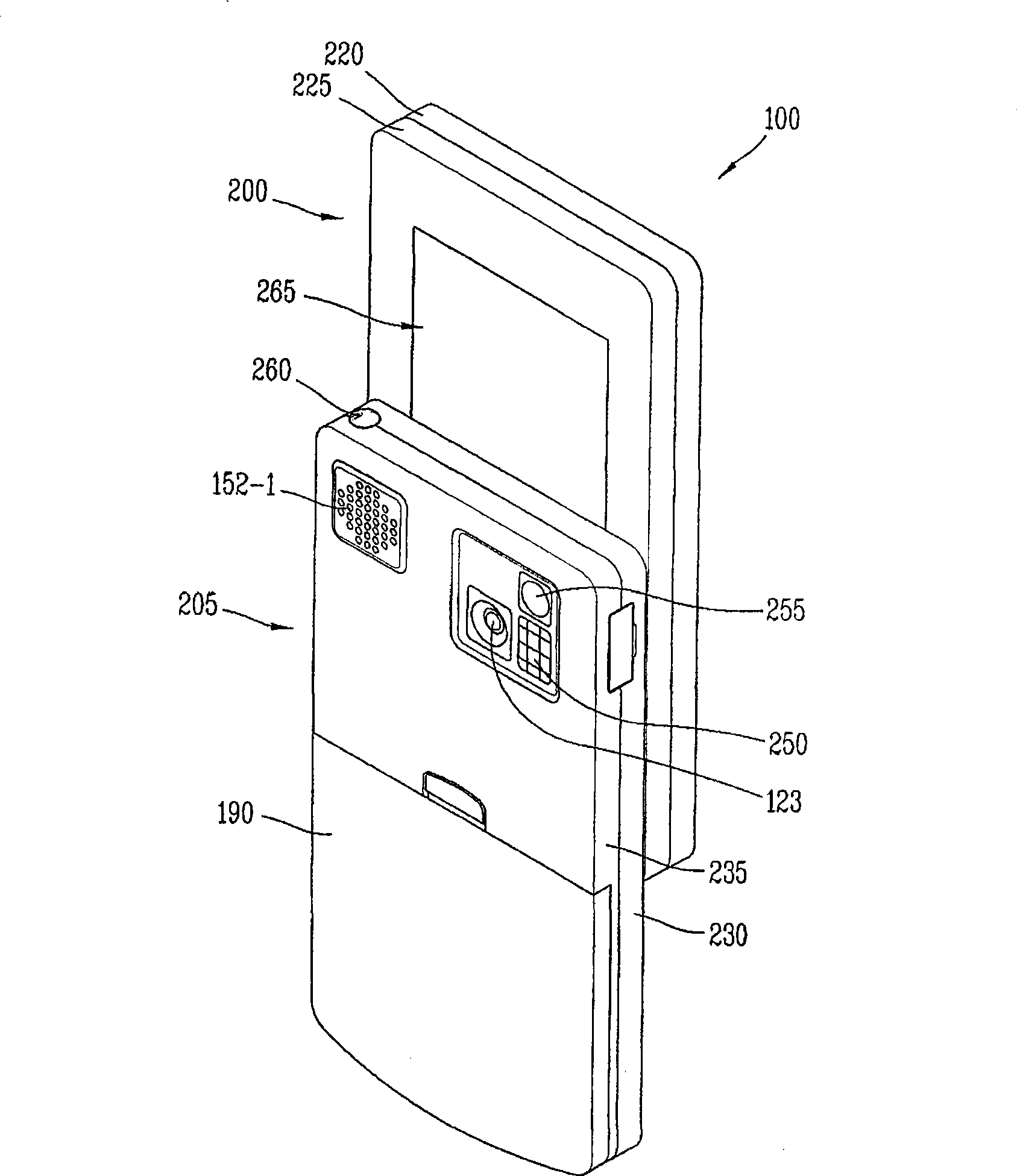

Mobile terminal and method of controlling a mode switching therein

InactiveUS20120157165A1Efficient executionSafety managementDigital data protectionInternal/peripheral component protectionCommunication unitOperational system

A mobile terminal including a communication unit configured to communicate with at least one external terminal; a memory configured to store at least first and second operating systems including at least first and second modes, respectively; and a controller configured to execute the first operating system and to activate the first mode corresponding to the first operating system, to display a first information screen on a display unit corresponding to the activated first mode, to receive a switching signal indicating the first mode is to be switched to the second mode, to attempt to switch to the second mode based on the received switching signal, and to restrict a specific application executing in the first mode when the second mode is not switched to.

Owner:LG ELECTRONICS INC

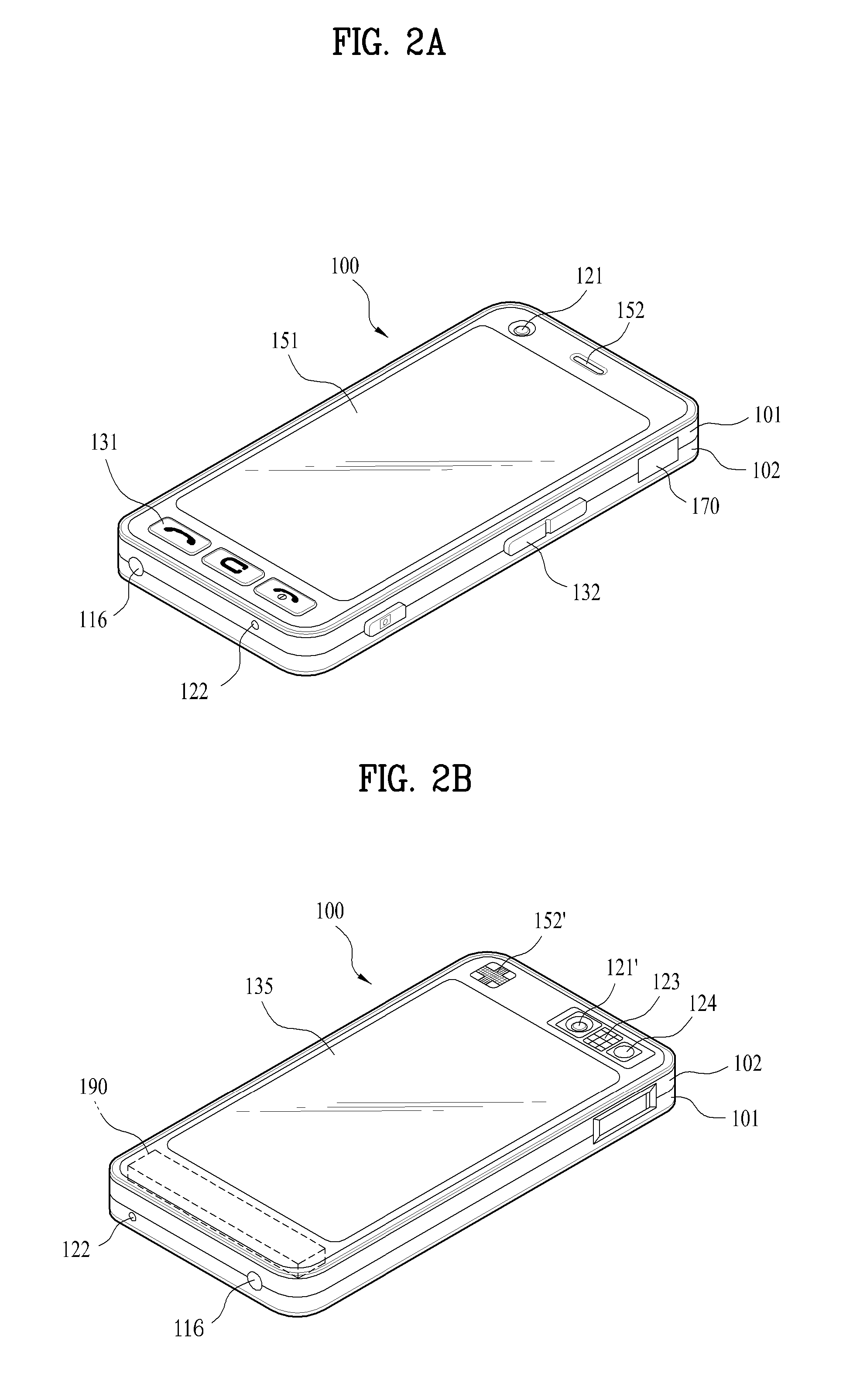

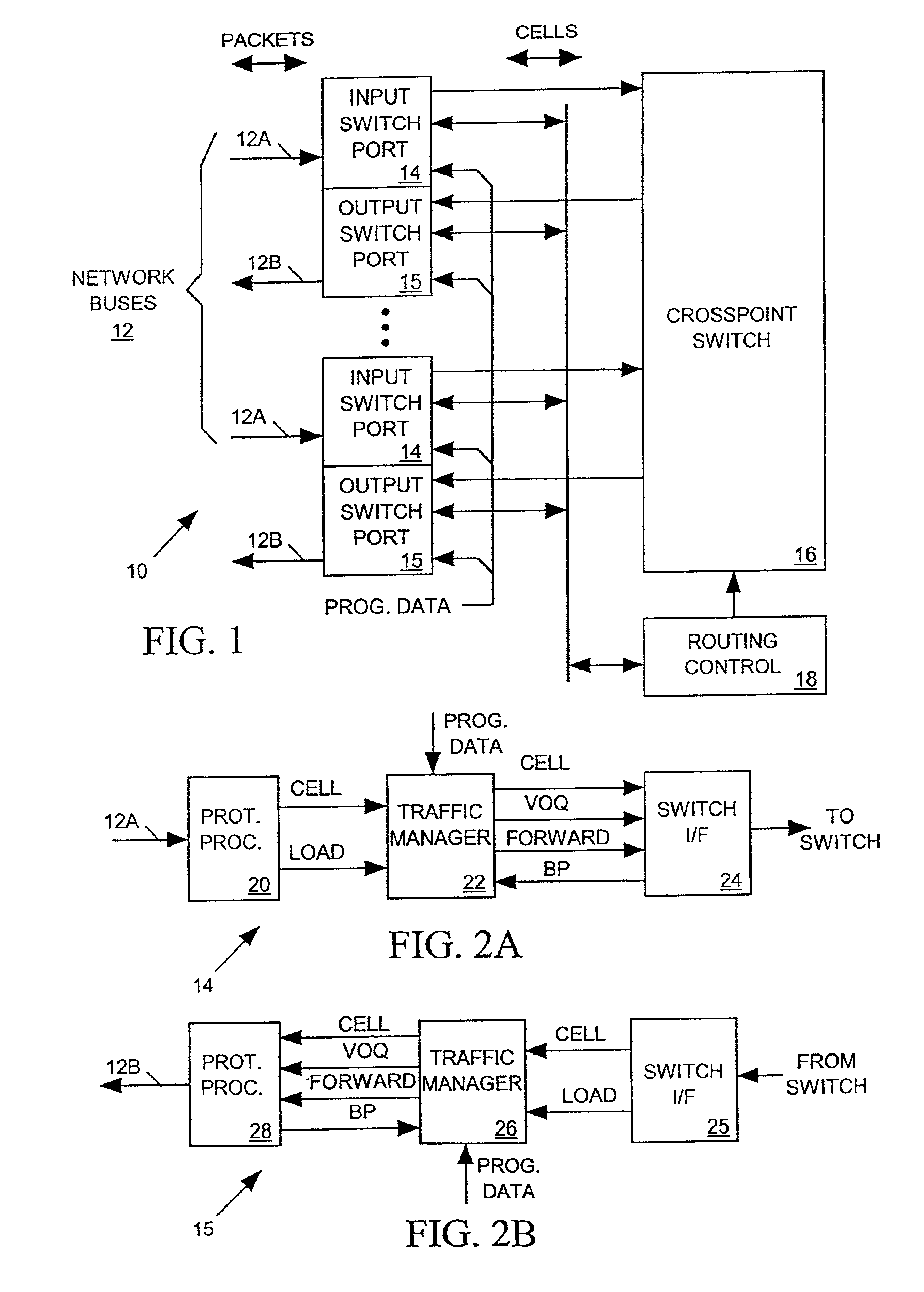

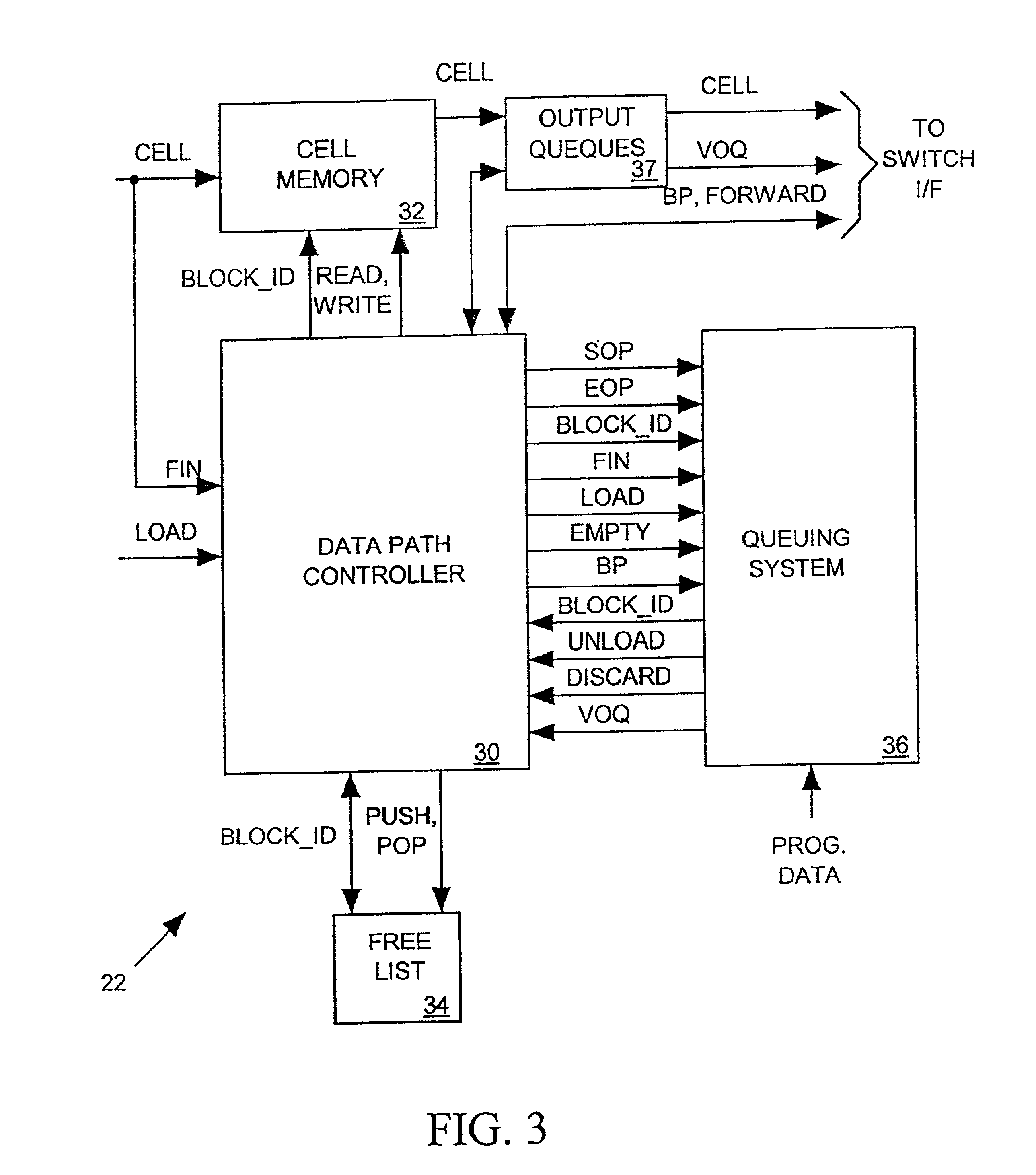

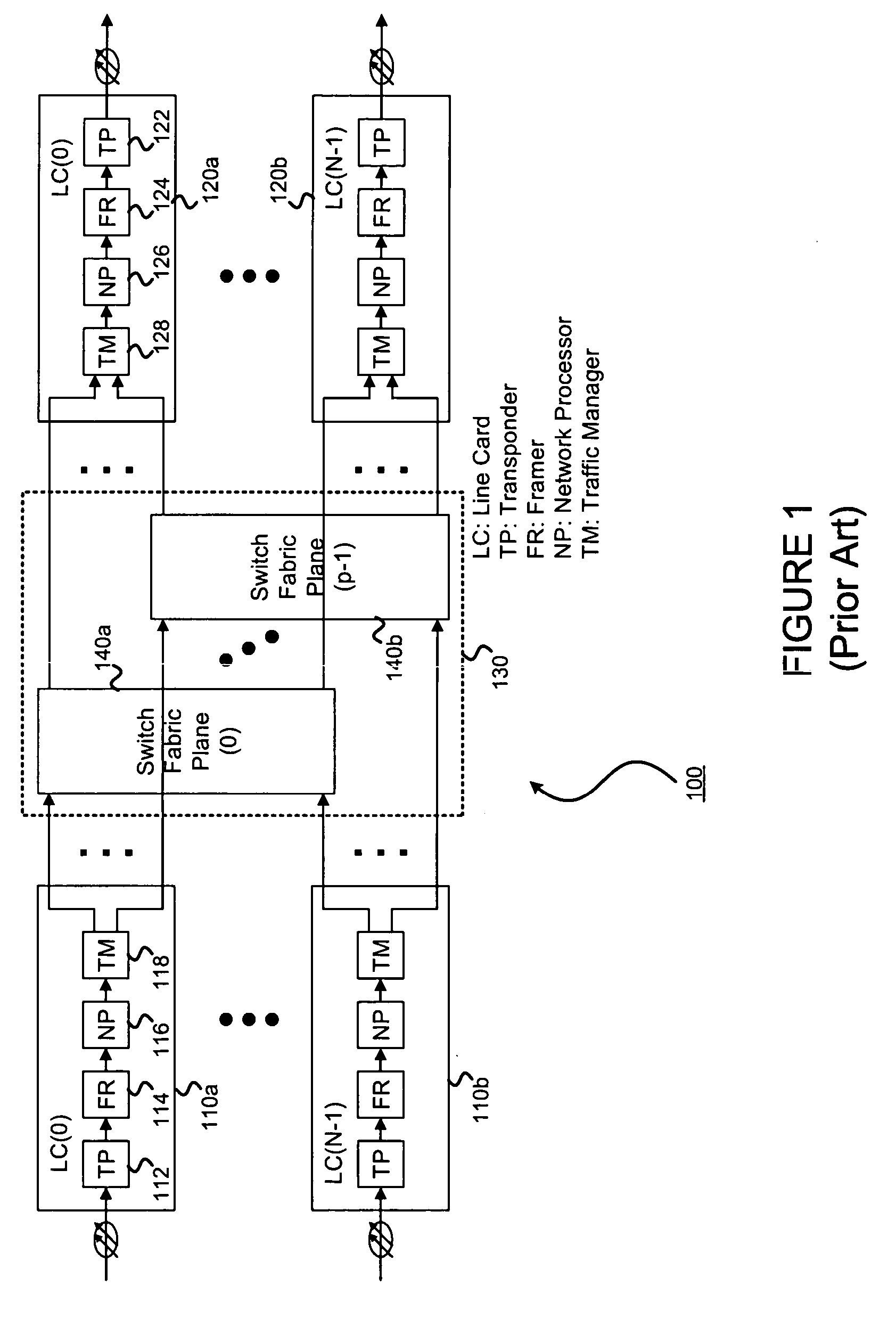

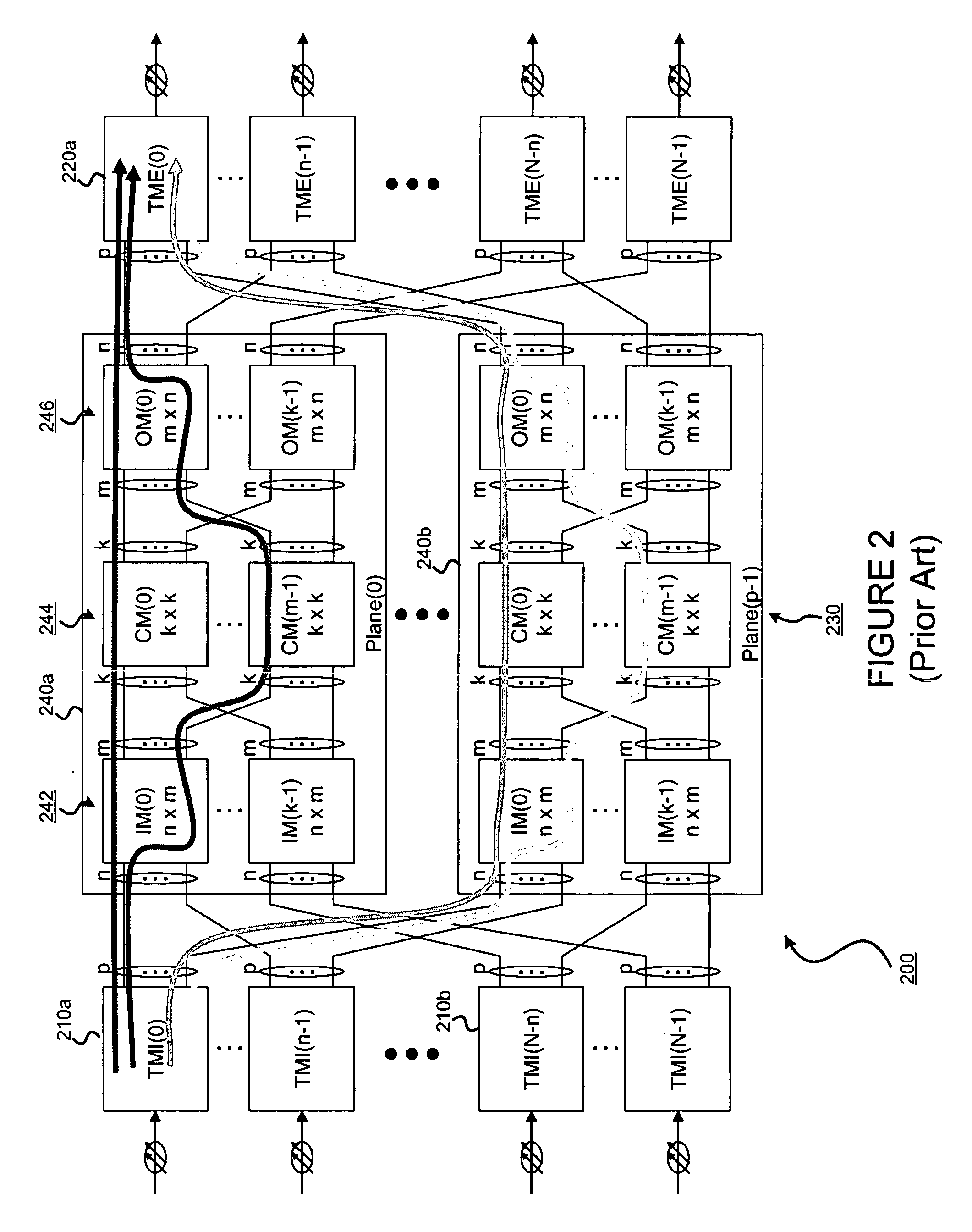

Traffic manager for network switch port

ActiveUS6959002B2Separate controlData switching by path configurationStore-and-forward switching systemsTraffic capacityNetwork switch

A traffic manager for a network switch input or output port stores incoming cells in a cell memory and later sends each cell out of its cell memory toward one of a set of forwarding resources such as, for example, another switch port or an output bus. Data in each cell references the particular forwarding resource to receive the cell. Each cell is assigned to one of several flow queues such that all cells assigned to the same flow queue are to be sent to the same forwarding resource. The traffic manager maintains a separate virtual output queue (VOQ) associated with each forwarding resource and periodically loads a flow queue (FQ) number identifying each flow queue into the VOQ associated with the forwarding resource that is to receive the cells assigned to that FQ. The traffic manager also periodically shifts an FQ ID out of each non-empty VOQ and forwards the longest-stored cell assigned to that FQ from the cell memory toward its intended forwarding resource. The traffic manager separately determines the rates at which it loads FQ IDs into VOQs and the rates at which it shifts FQ IDs out of each non-empty VOQ. Thus the traffic manager is able to separately control the rate at which cells of each flow queue are forwarded and the rate at which each forwarding resource receives cells.

Owner:ZETTACOM +1

Method for using a multi-use memory cell and memory array

A method for using a multi-use memory cell and memory array are disclosed. In one preferred embodiment, a memory cell is operable as a one-time programmable memory cell or a rewritable memory cell. The memory cell comprises a memory element comprising a semiconductor material configurable to one of at least three resistivity states, wherein a first resistivity state is used to represent a data state of the memory cell when the memory cell operates as a one-time programmable memory cell but not when the memory cell operates as a rewritable memory cell. A memory array with such memory cells is also disclosed. In another preferred embodiment, a memory cell is provided comprising a switchable resistance material, wherein the memory cell is operable in a first mode in which the memory cell is programmed with a forward bias and a second mode in which the memory cell is programmed with a reverse bias.

Owner:WODEN TECH INC

Mobile terminal and display controlling method therein

InactiveUS20130002725A1Easy accessCathode-ray tube indicatorsInternal/peripheral component protectionCommunication unitSystem controller

A mobile terminal including a communication unit configured to communicate with at least one external terminal; a memory configured to store at least first and second operating systems including at least first and second modes, respectively; and a controller configured to activate the first mode using the first operating system, to display, in a first display region of a display unit of the mobile terminal, the activated first mode, and to display in a second display region of the display unit, at least one second indicator that when selected, activates a second corresponding application in the second mode.

Owner:LG ELECTRONICS INC

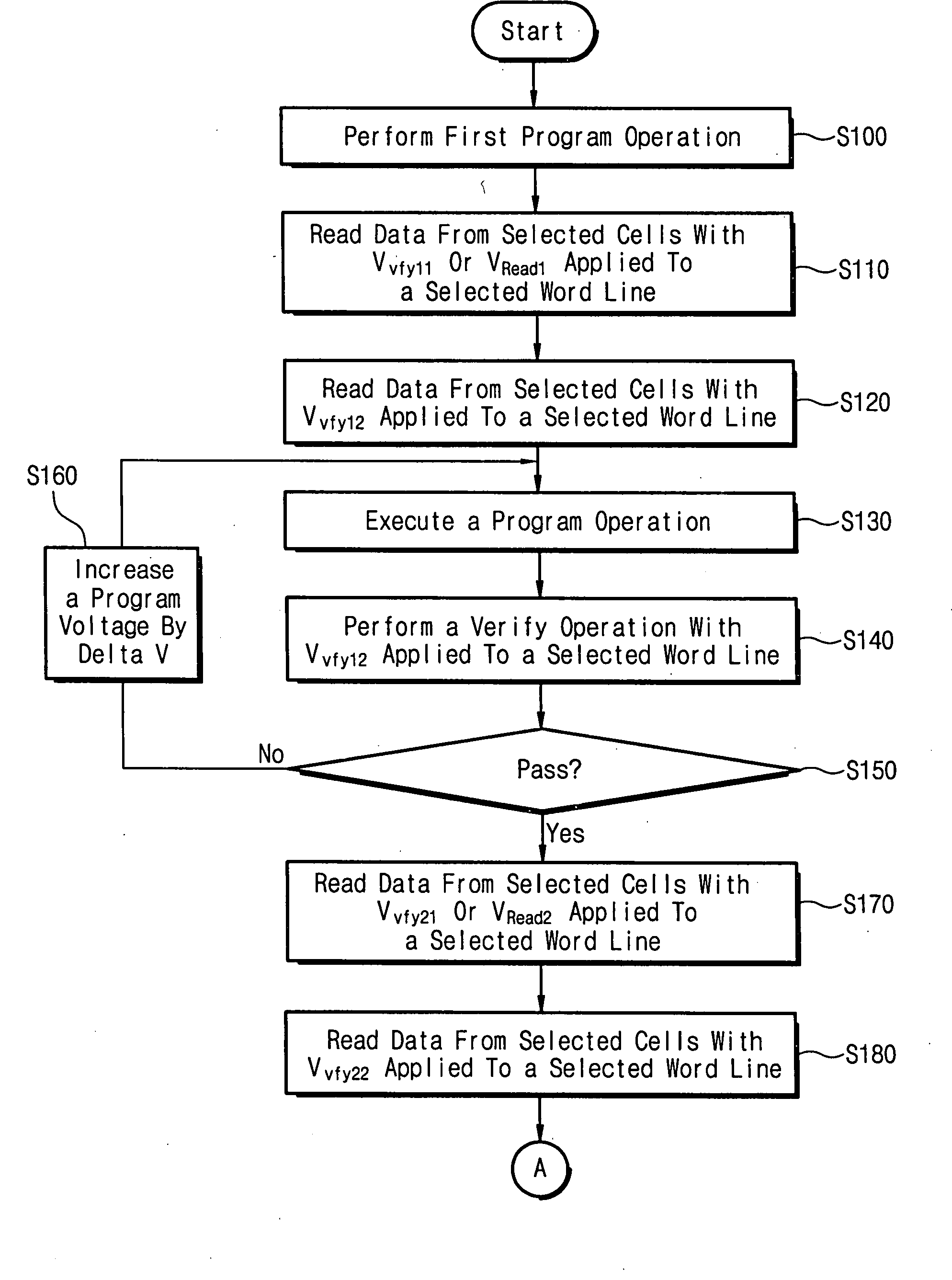

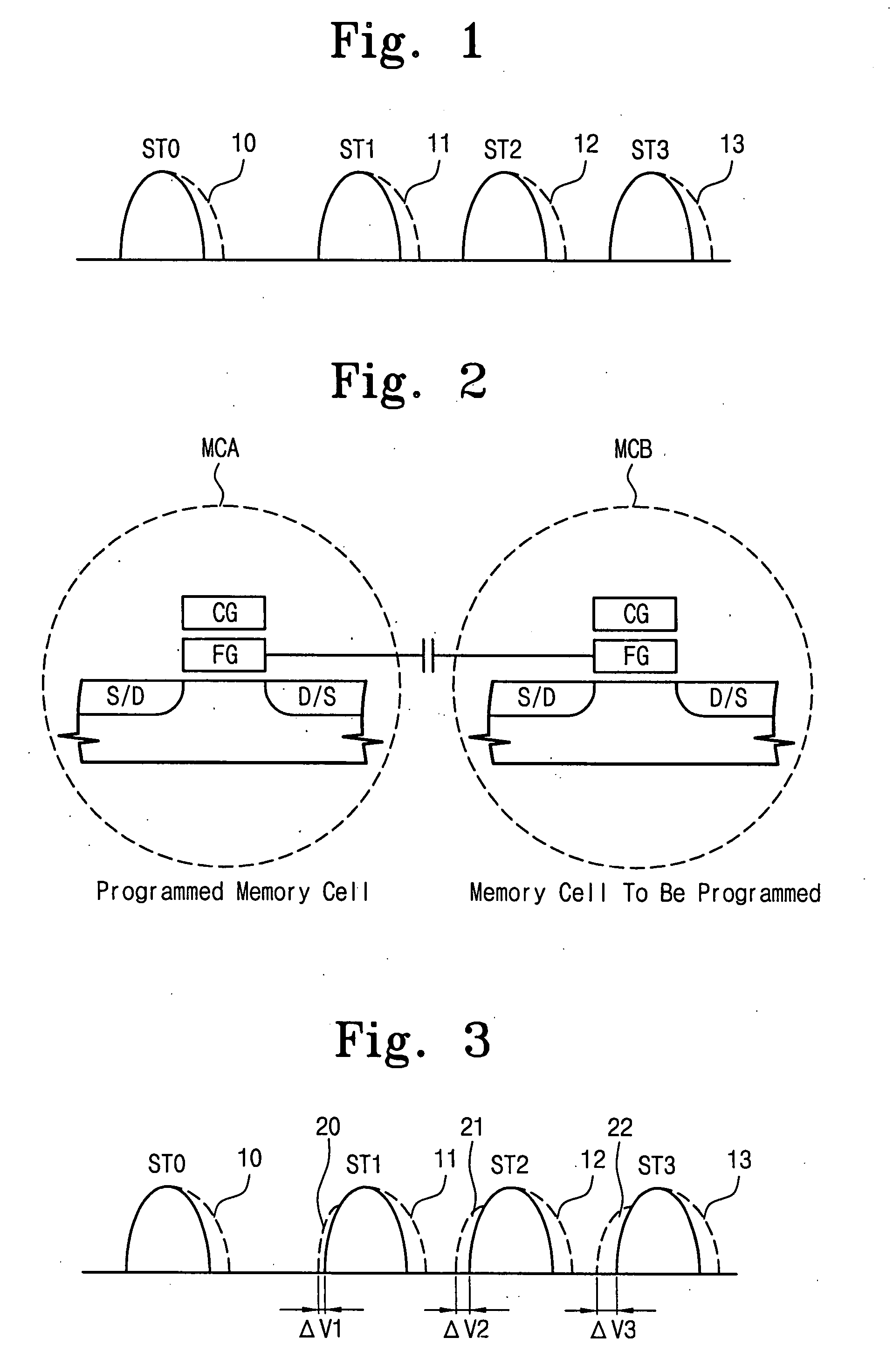

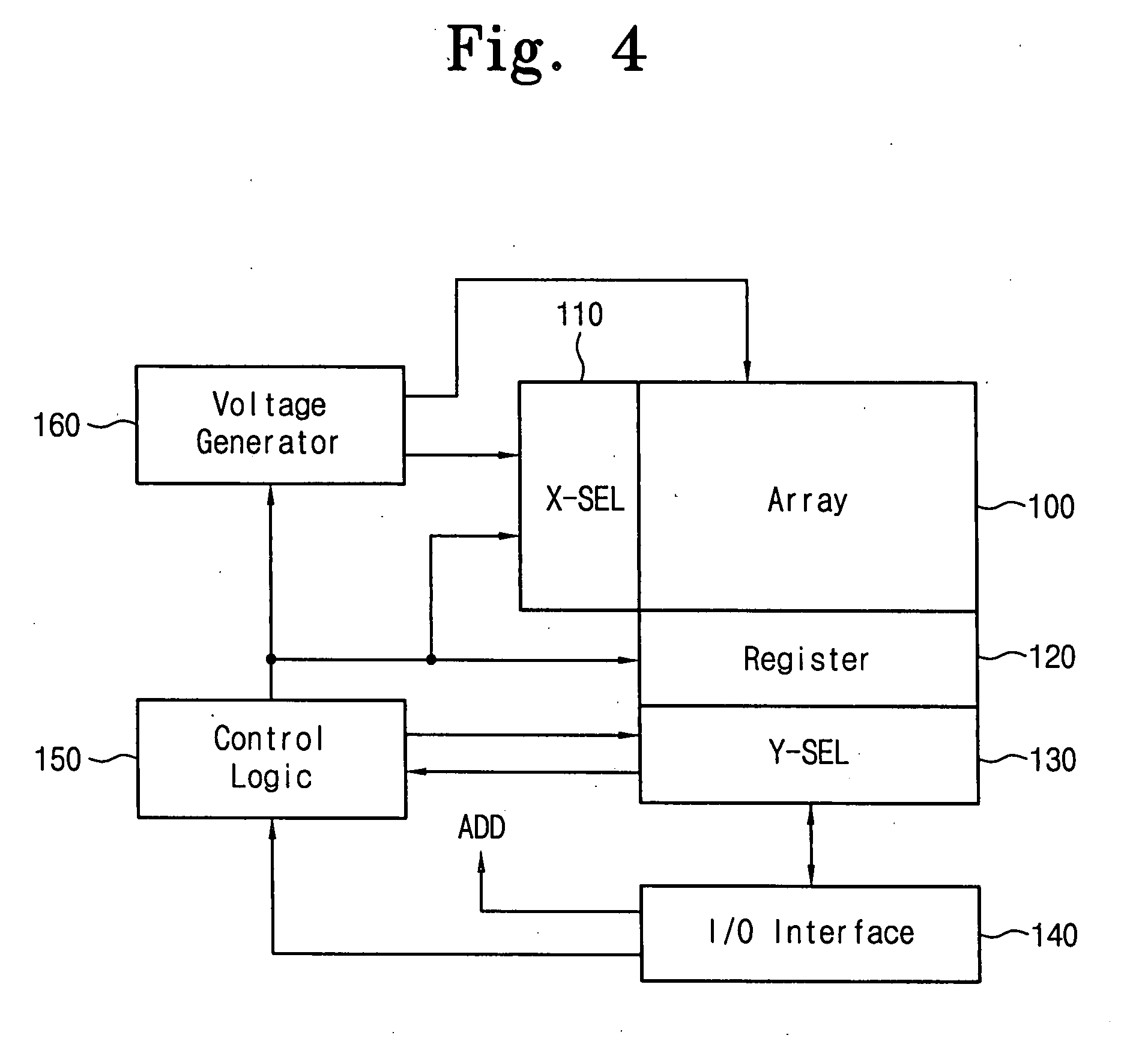

Program method of flash memory capable of compensating read margin reduced due to charge loss

The present invention provides a program method of a flash memory device including a plurality of memory cells for storing multi-bit data indicating one of a plurality of states. The memory cells are subjected to a primary program operation. Those memory cells arranged within a specific region of respective states are subjected to a secondary program operation to have a threshold voltage equivalent to or higher than a verify voltage used in the primary program operation. Thus, although a threshold voltage distribution is widened due to an electric field coupling / F-poly coupling and HTS, a read margin between adjacent states may be sufficiently secured using the program method.

Owner:SAMSUNG ELECTRONICS CO LTD

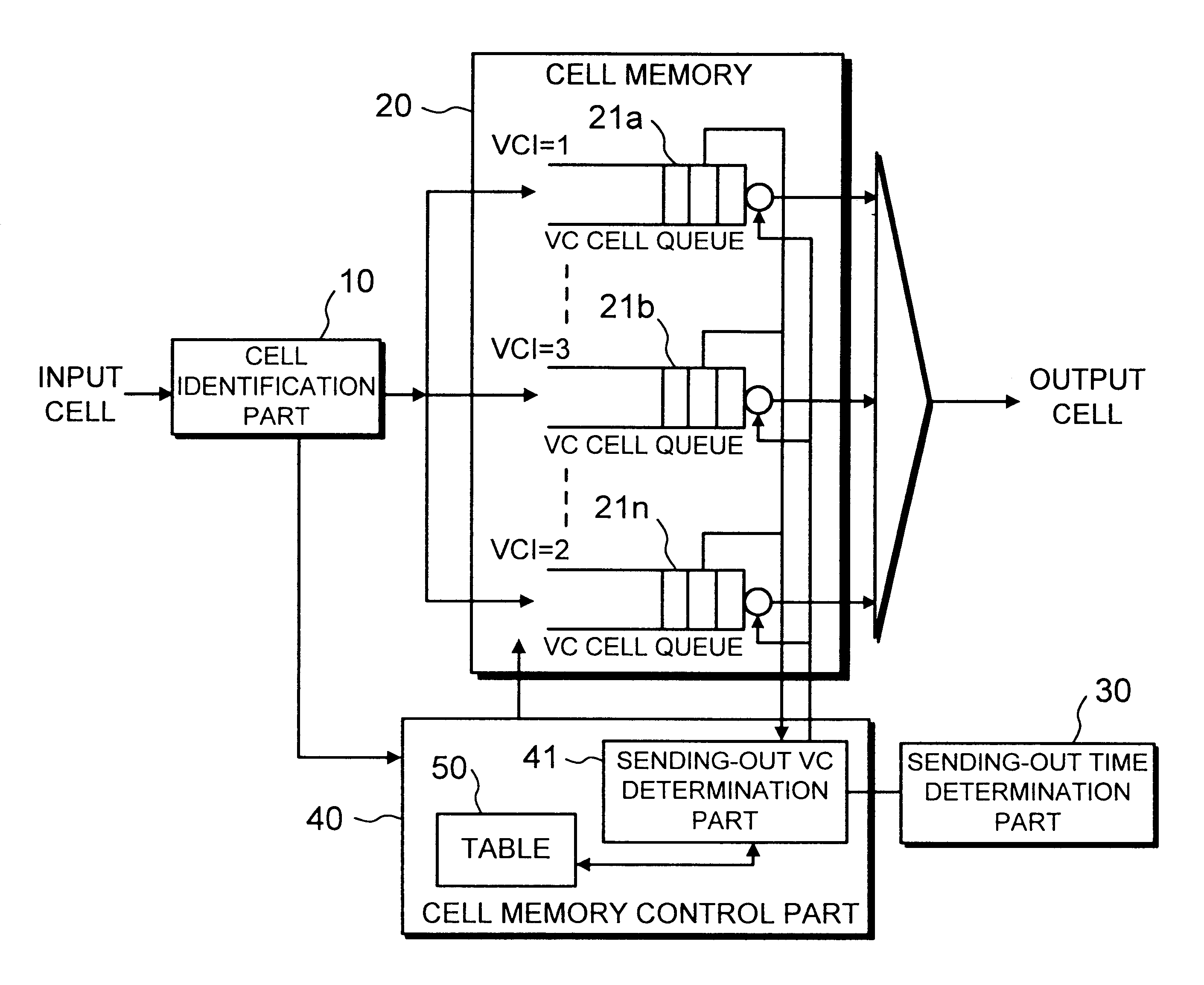

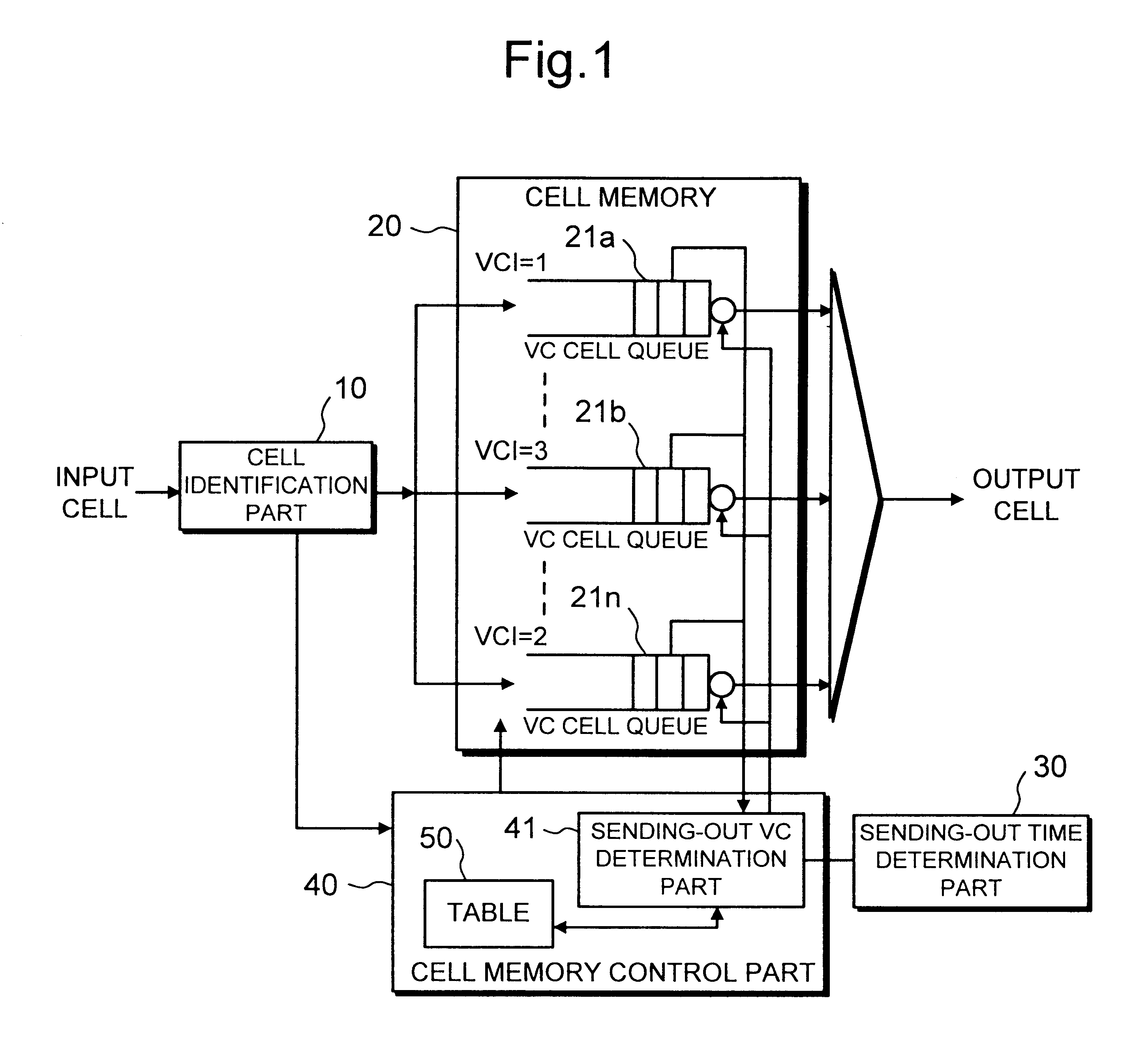

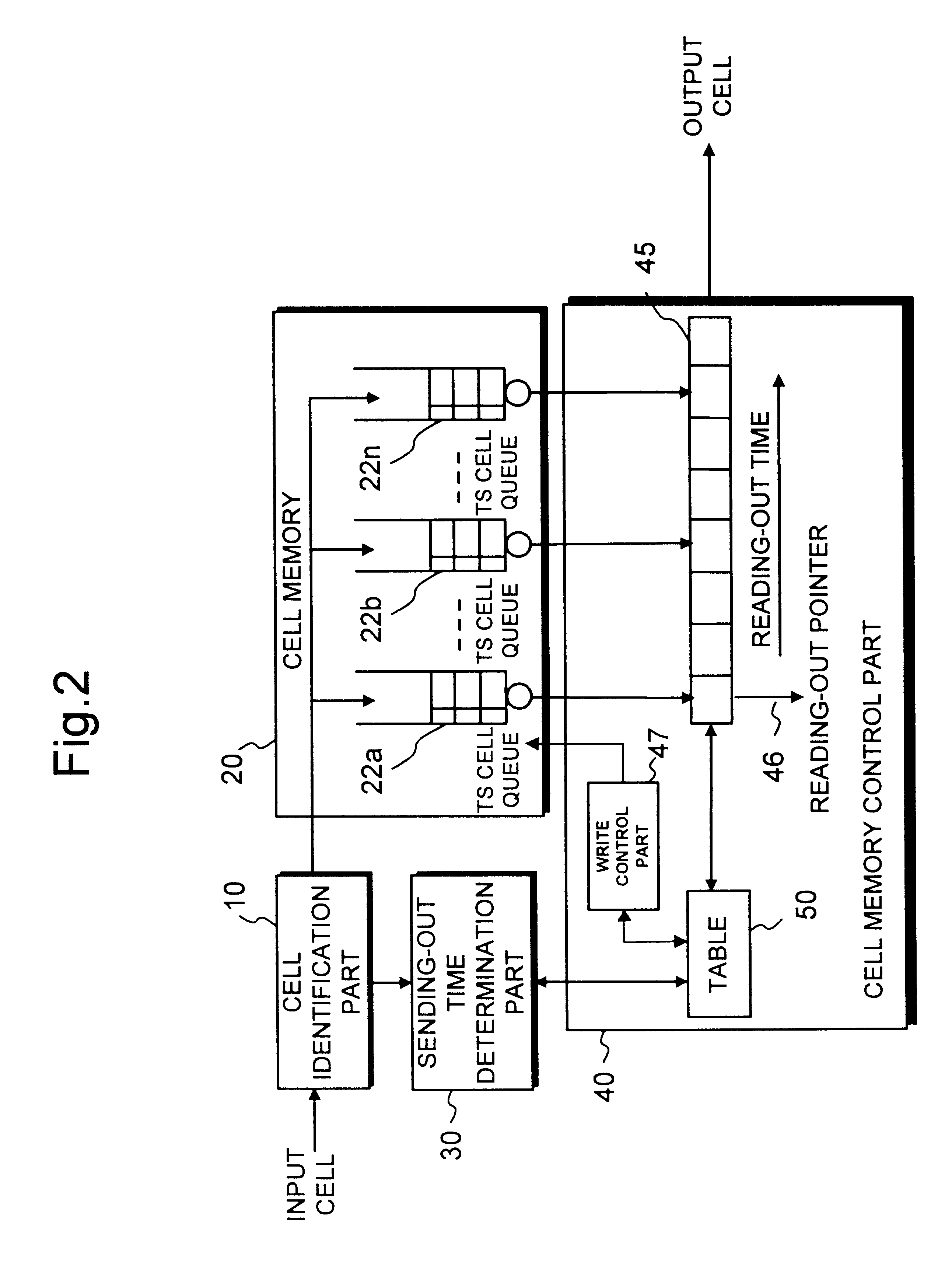

Traffic shaper

InactiveUS6704321B1Decreasing cell delay variationError preventionFrequency-division multiplex detailsCell delayDistributed computing

A traffic shaper for absorbing a cell delay variation of cell flow in each of virtual connections in an ATM (asynchronous transmission mode) network is realized. The traffic shaper comprises a cell identification part, a cell memory, a sending-out time determination part and a cell memory control part. The cell identification part is provided for identifying a virtual connection allocated to an input cell, the cell memory is provided for storing input cells into respective virtual queues, each queue is corresponding to the virtual connection, in accordance with the identified virtual connection of each input cell, the sending-out time determination part is provided for determining a sending-out time for each cell stored in the cell memory on the virtual connection basis, and the cell memory control part is provided for performing a cell output from each virtual queue in accordance with the sending-out time determined for each cell, and performing an output competition control by selecting a cell to be output among cells having the same sending-out time in different virtual queues in accordance with a predetermined output priority assigned to each virtual connection.

Owner:JUMIPER NETWORKS INC

Mobile terminal and display controlling method therein

InactiveUS20130007842A1Eliminate the problemDigital data processing detailsDevices with sensorCommunication unitOperational system

A mobile terminal including a communication unit configured to communicate with at least one external terminal; a memory configured to store at least first and second operating systems including at least first and second modes, respectively; and a controller configured to execute the first operating system and activate the first mode corresponding to the first operating system, display a first information screen on a display unit of the mobile terminal corresponding to the activated first mode, display an application execution history for the first mode and the second mode on a prescribed region of the first information screen of the first mode, and identifiably display whether applications included in the application execution history were executed in the first mode or the second mode.

Owner:LG ELECTRONICS INC

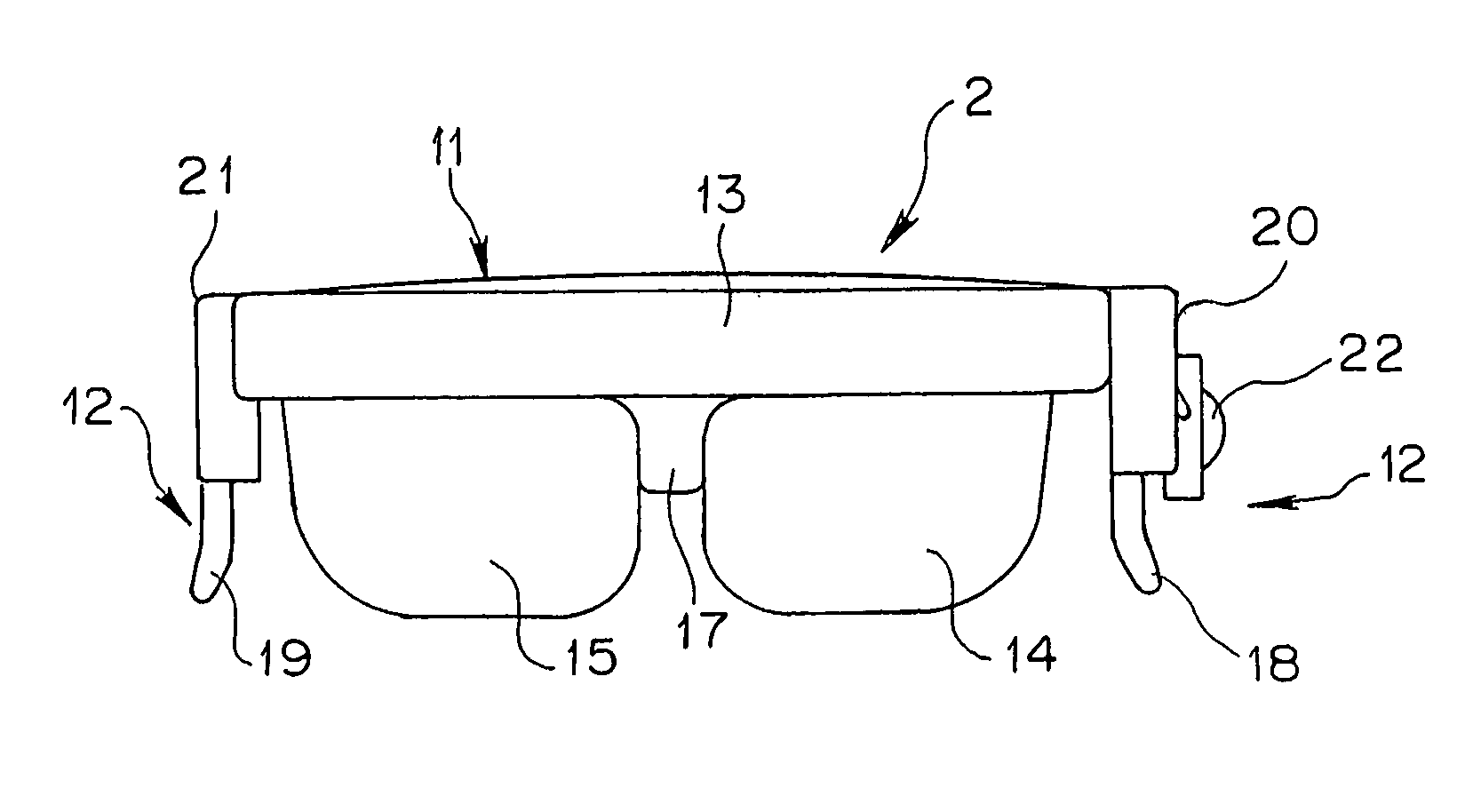

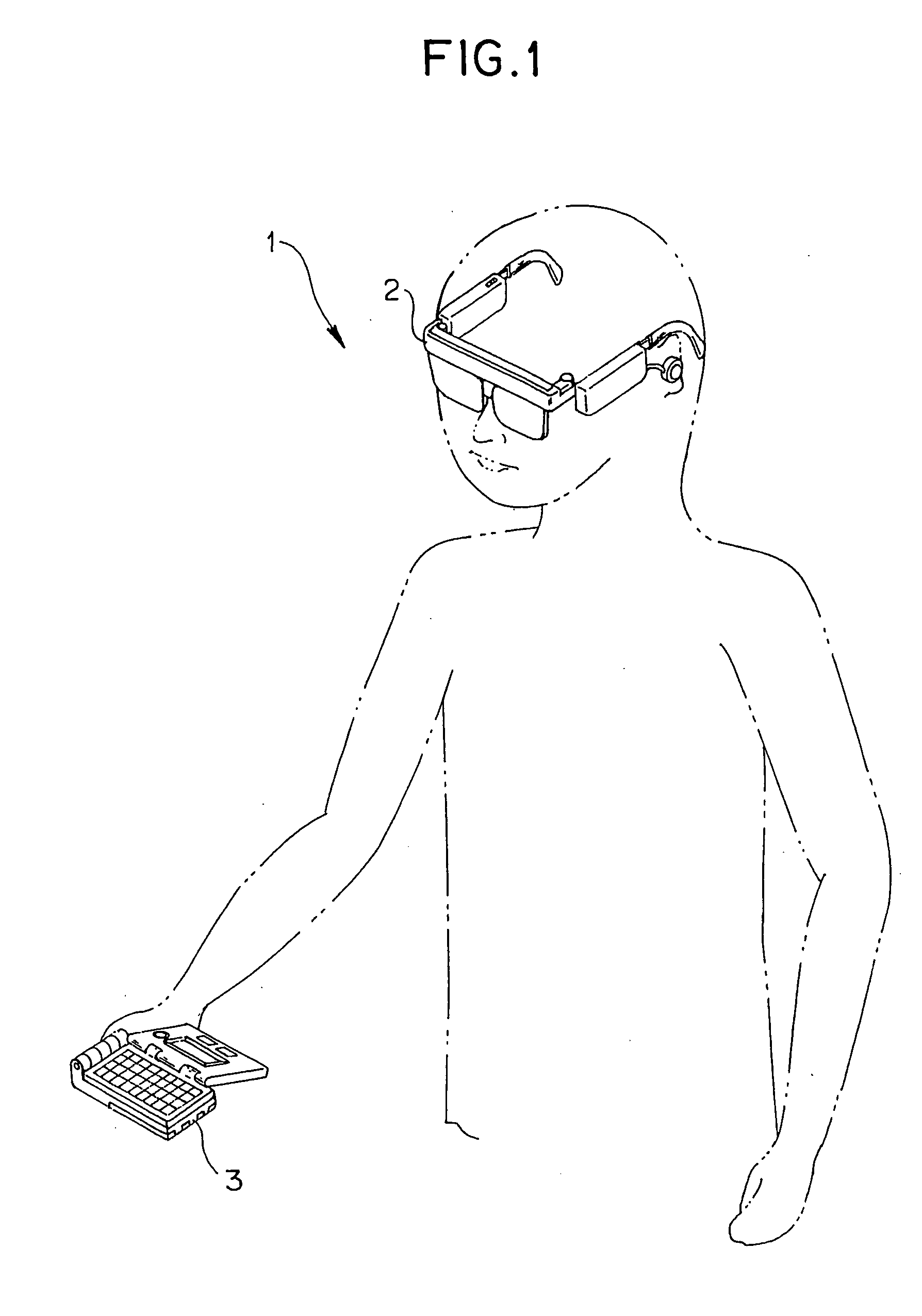

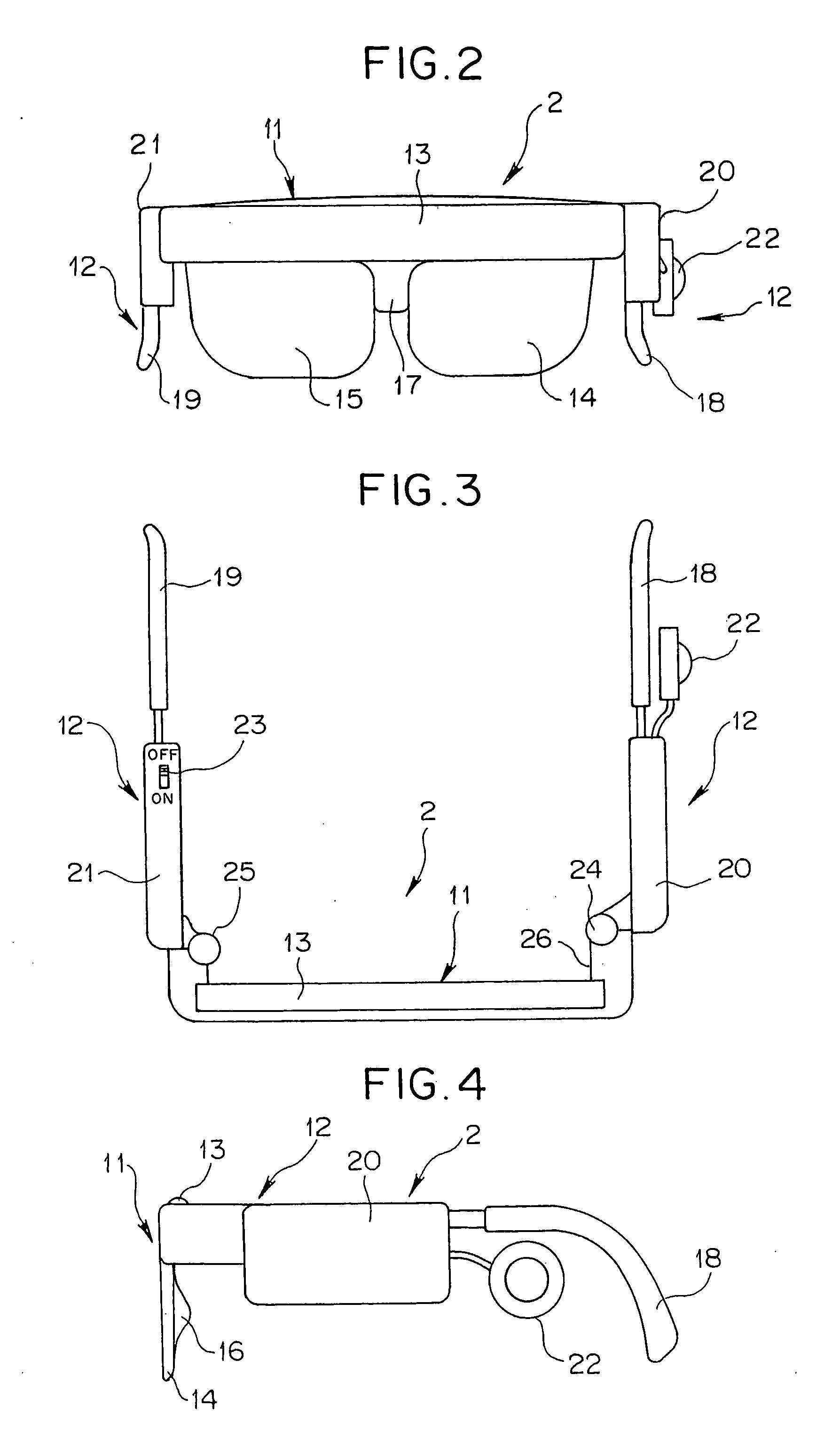

Information display system

InactiveUS20060017657A1Suppressing useless electric power consumptionCathode-ray tube indicatorsOptical elementsInformation display systemsUnit memory

An information display system according to the present invention includes a head-mounted unit for displaying images by projecting display data on eyes of an observer so that the images can be observed as virtual images and a main unit having a hard disk or a record memory for storing display original information, a main unit memory for temporarily storing the display data read out and converted from the display original information, an LCD for displaying images based on the display data, and a second operating switch including a display select switch for alternatively selecting any one of the displaying by the head-mounted unit and the displaying by the LCD.

Owner:OLYMPUS CORP

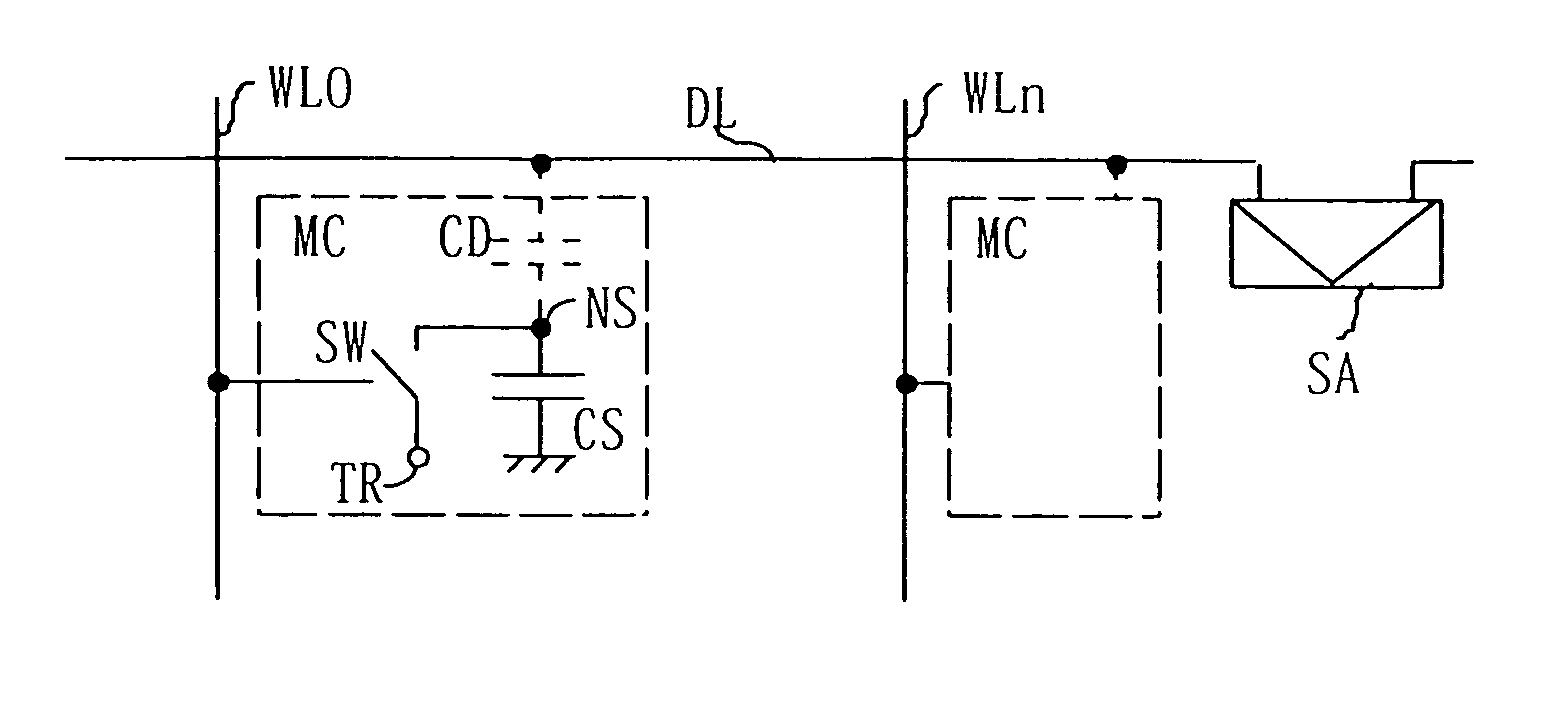

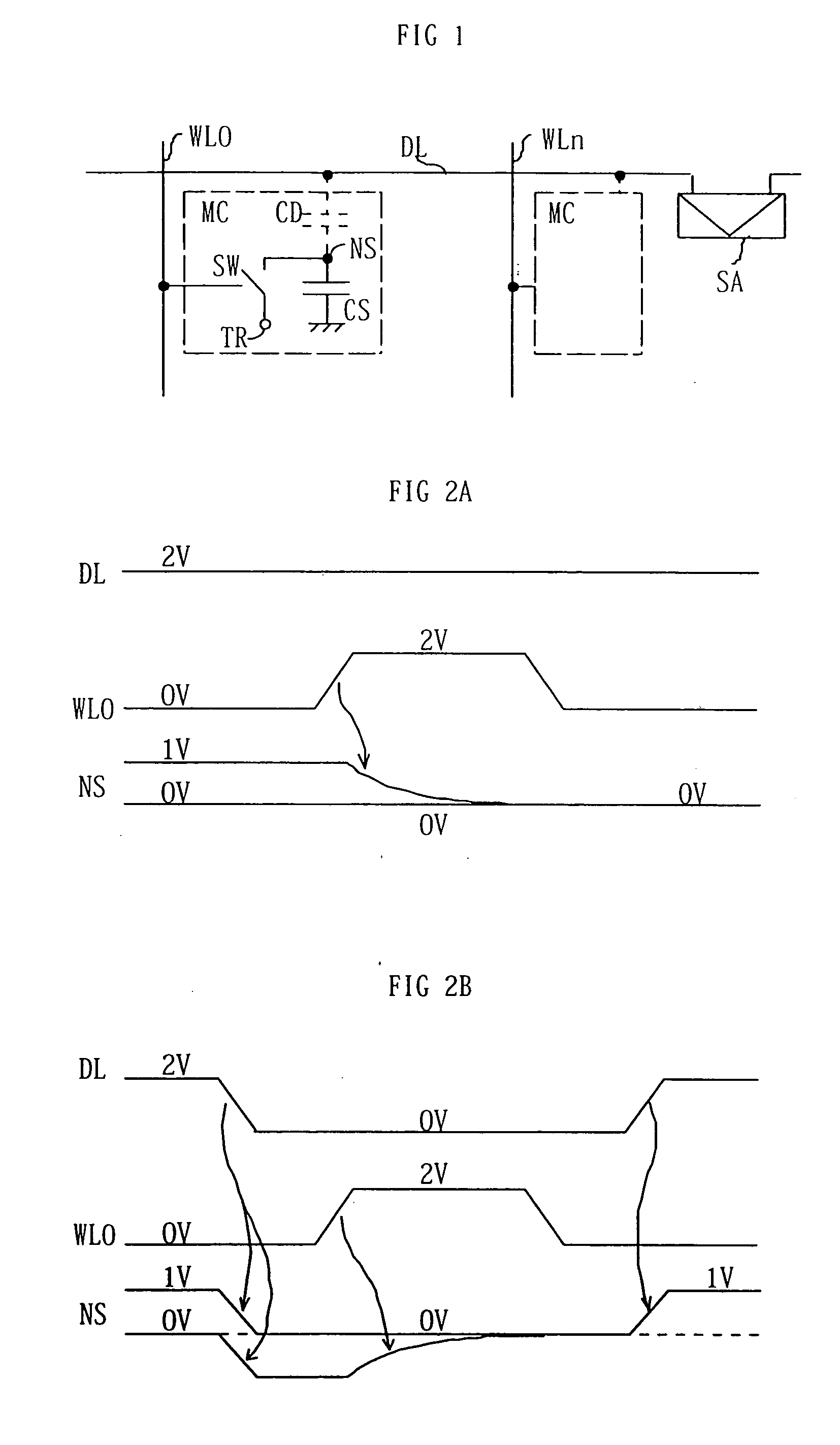

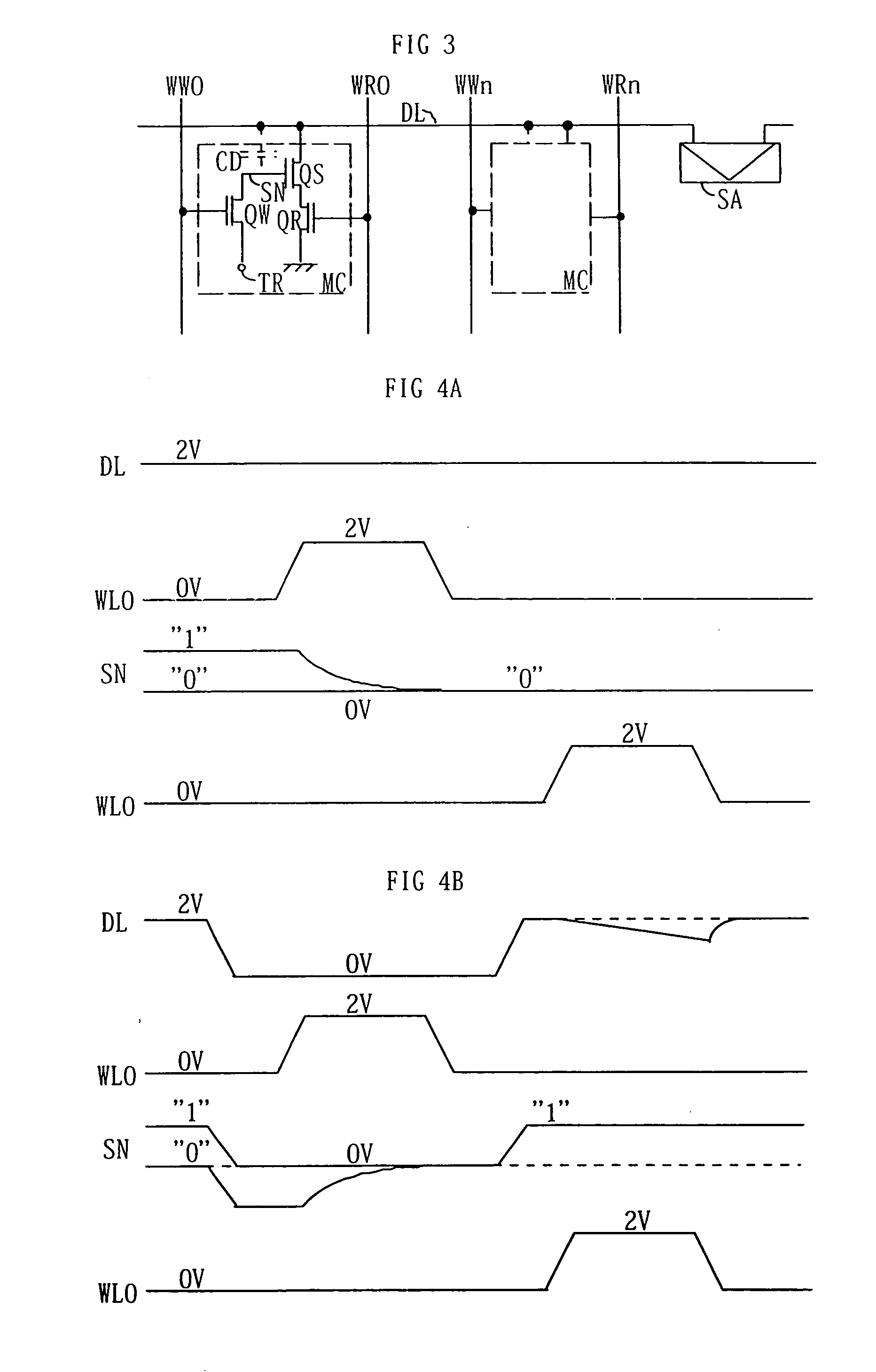

Semiconductor memories

InactiveUS20050237786A1Reduce areaReduce area requirementsTransistorSolid-state devicesHigh densityComputer science

A high integration dynamic random access memory is provided by this invention. Furthermore, a write method is provided such that cell size of two-and three-transistor gain cell memories is reduced. A dynamic memory incorporating a thin-channel transistor as the write element such that long data storage retention is achieved in the memory devices of this invention. A dynamic memory cell having low operating power and high density is also realized by this invention.

Owner:HITACHI LTD +1

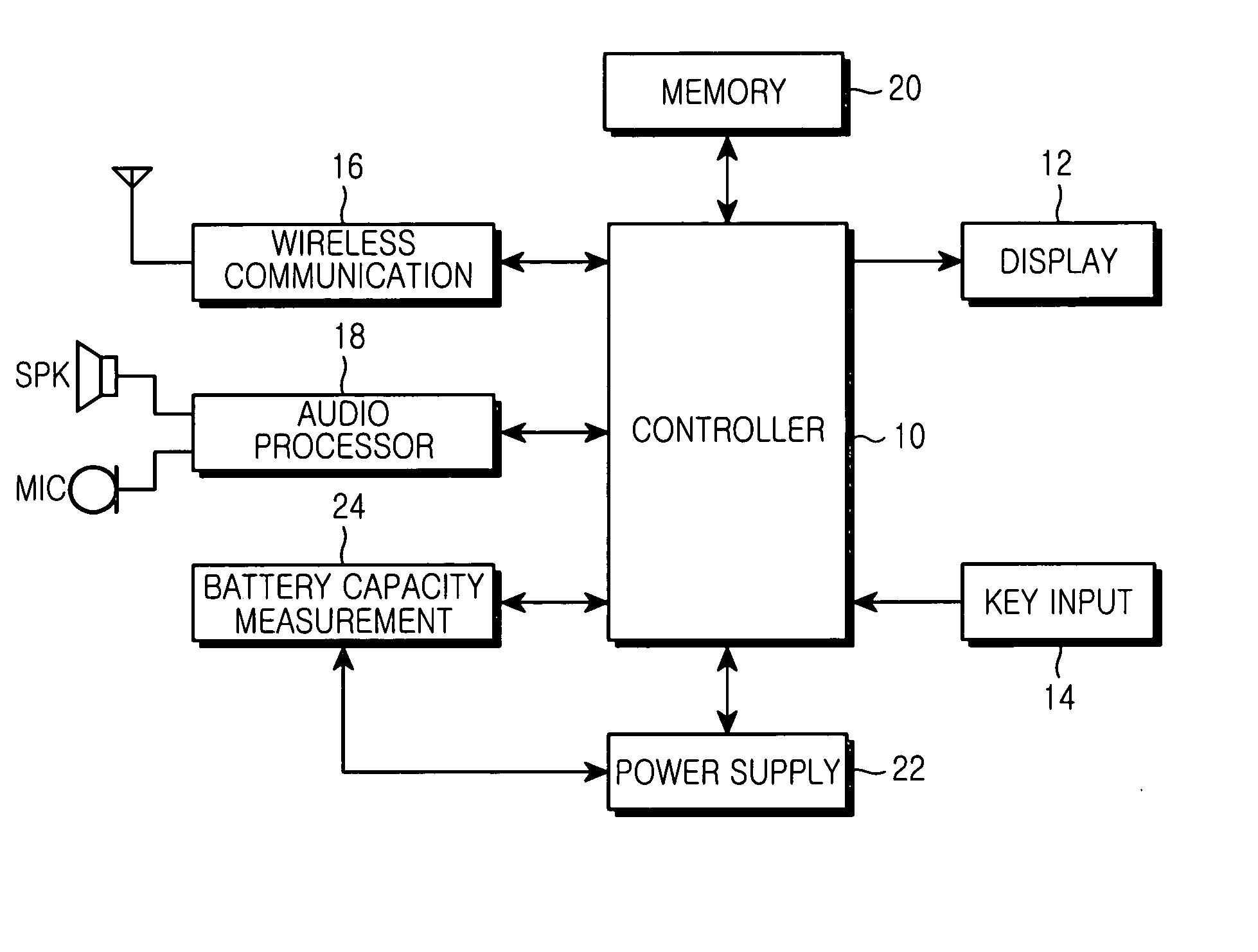

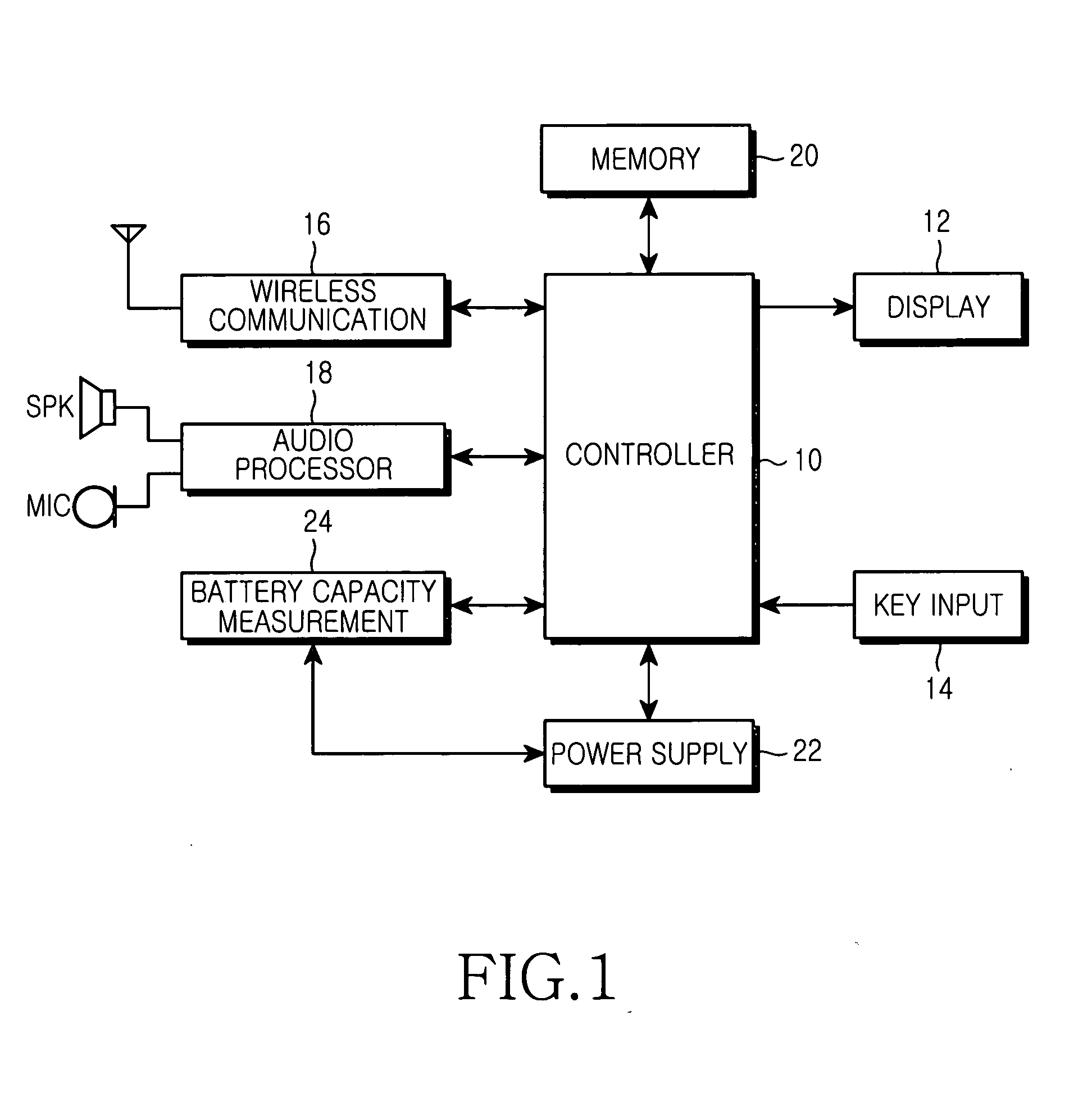

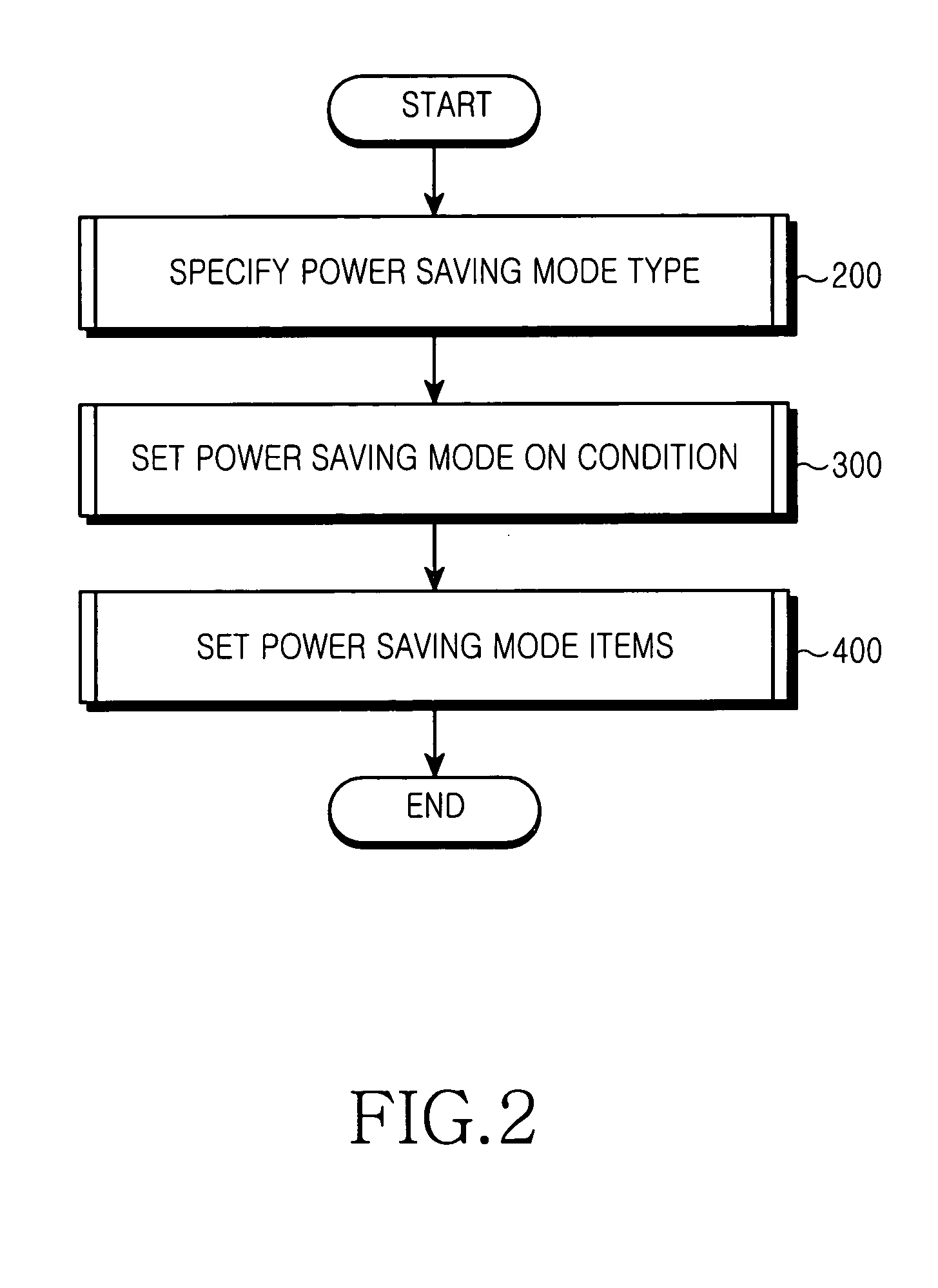

Apparatus and method for performing power saving control of mobile terminal

Disclosed is an apparatus and method for performing power saving control of a mobile terminal, which includes a battery capacity measurement unit, an input unit, a memory and a controller. Using the input unit, the user specifies a power saving mode type of the terminal and sets a power saving mode and power saving mode items corresponding to the specified power saving mode type. The memory stores information of the set power saving mode and the set power saving mode items in association with the specified power saving mode type. The controller performs power saving control corresponding to the set power saving mode items if battery capacity measured by the measurement unit is less than or equal to a preset battery capacity. The user can actively select how the terminal performs the power saving control, in their desired manners according to the remaining battery capacity.

Owner:QUALCOMM INC

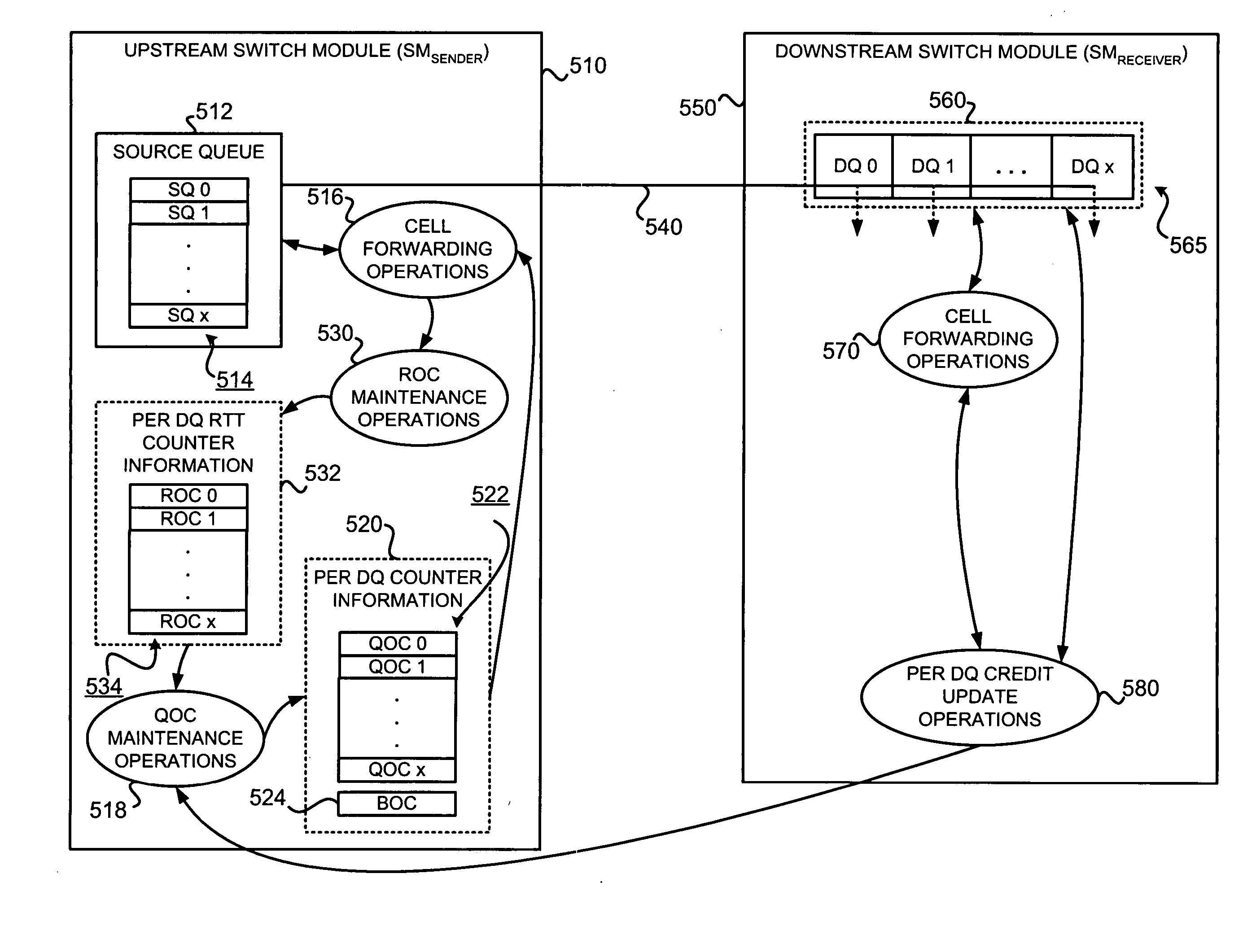

Switch module memory structure and per-destination queue flow control for use in a switch

ActiveUS20050002410A1Easy to useEasy to implementMultiplex system selection arrangementsData switching by path configurationTerm memoryDistributed computing

To use the memory space more effectively, cell memory can be shared by an input link and all output links. To prevent one flow from occupying the entire memory space, a threshold may be provided for the queue. The queue threshold may accommodate the RTT delay of the link. Queue length information about a downstream switch module may be sent to an upstream switch module via cell headers in every credit update period per link. Cell and / or credit loss may be recovered from. Increasing the credit update period reduces the cell header bandwidth but doesn't degrade performance significantly. Sending a credit per link simplifies implementation and eliminates interference between other links.

Owner:POLYTECHNIC INST OF NEW YORK

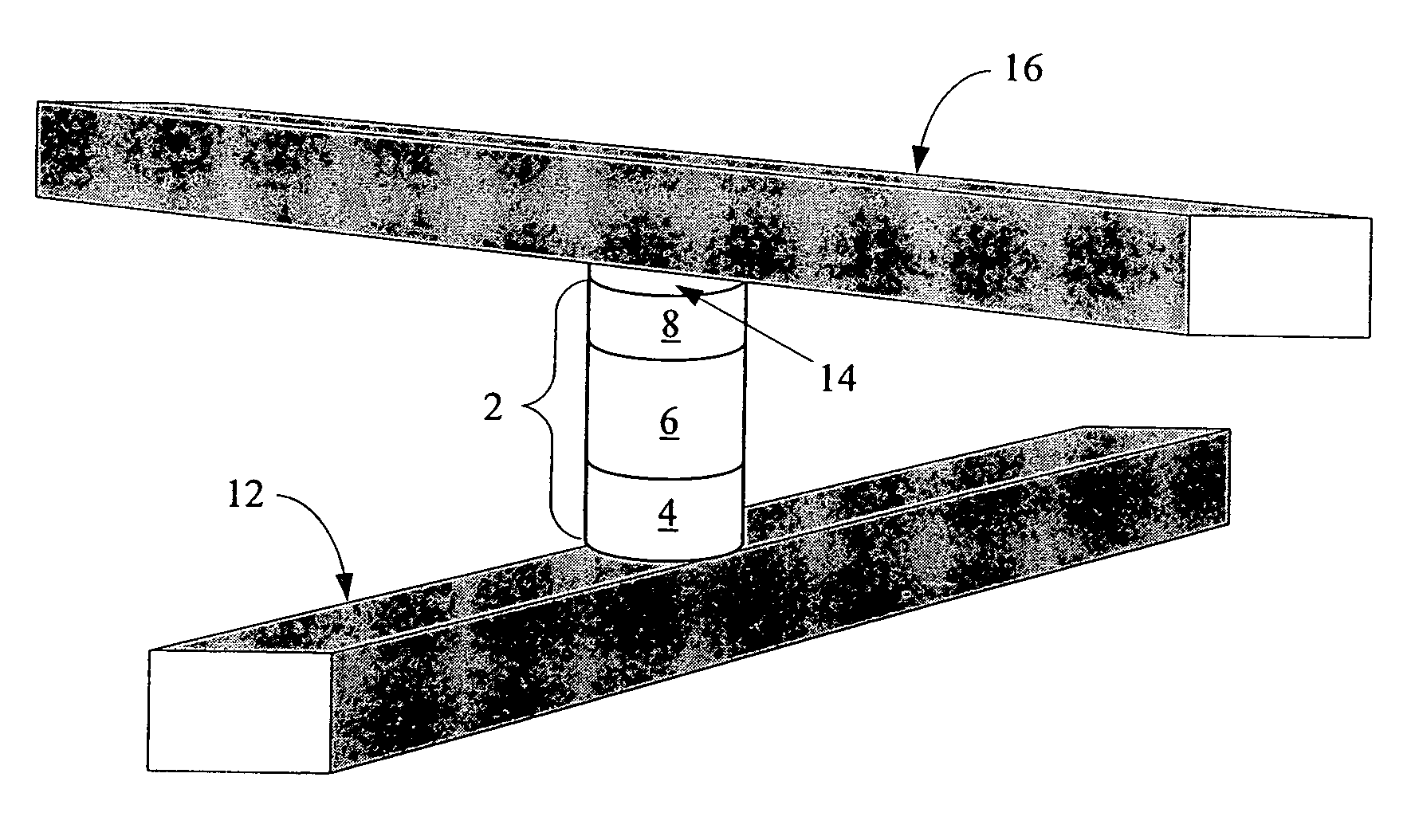

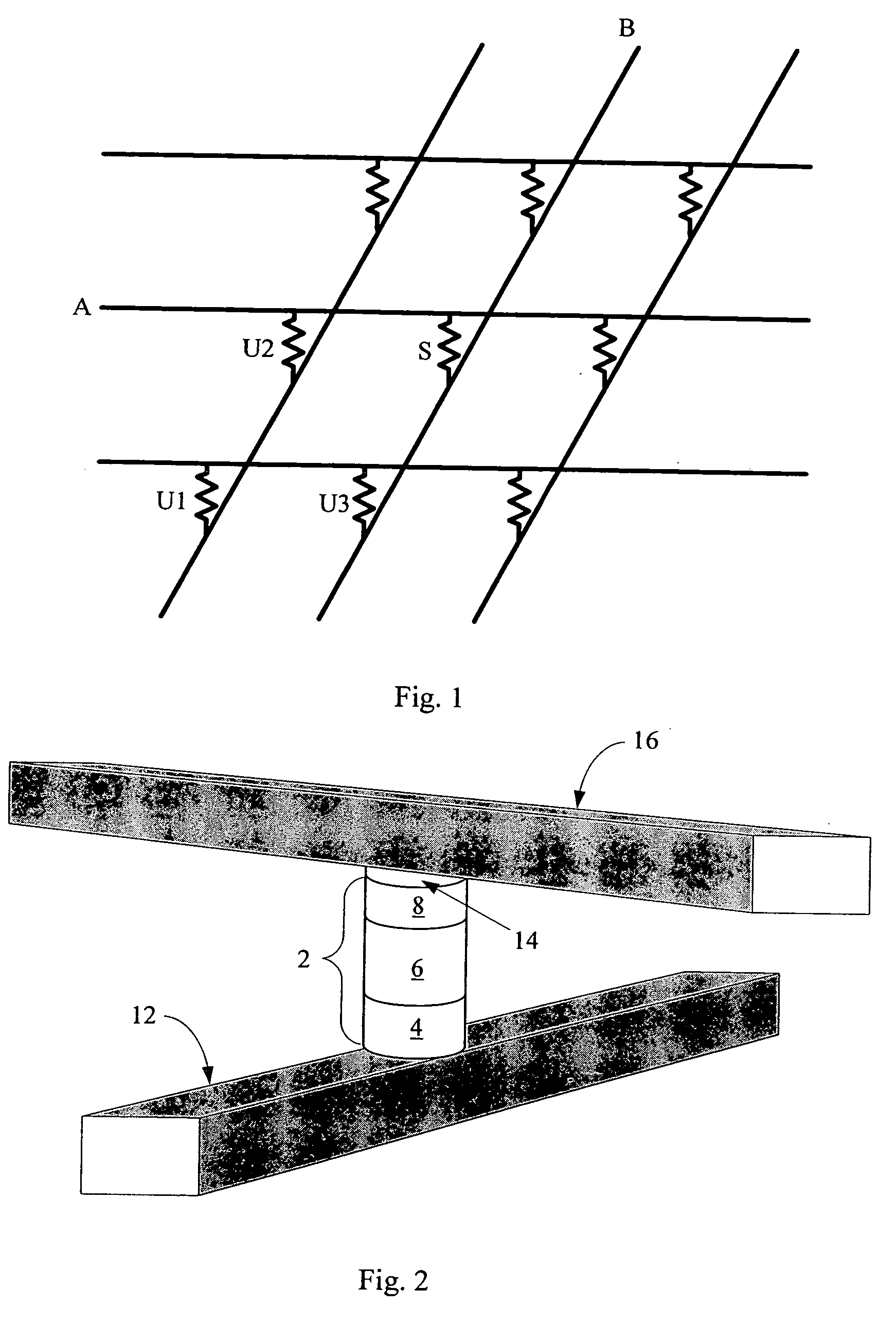

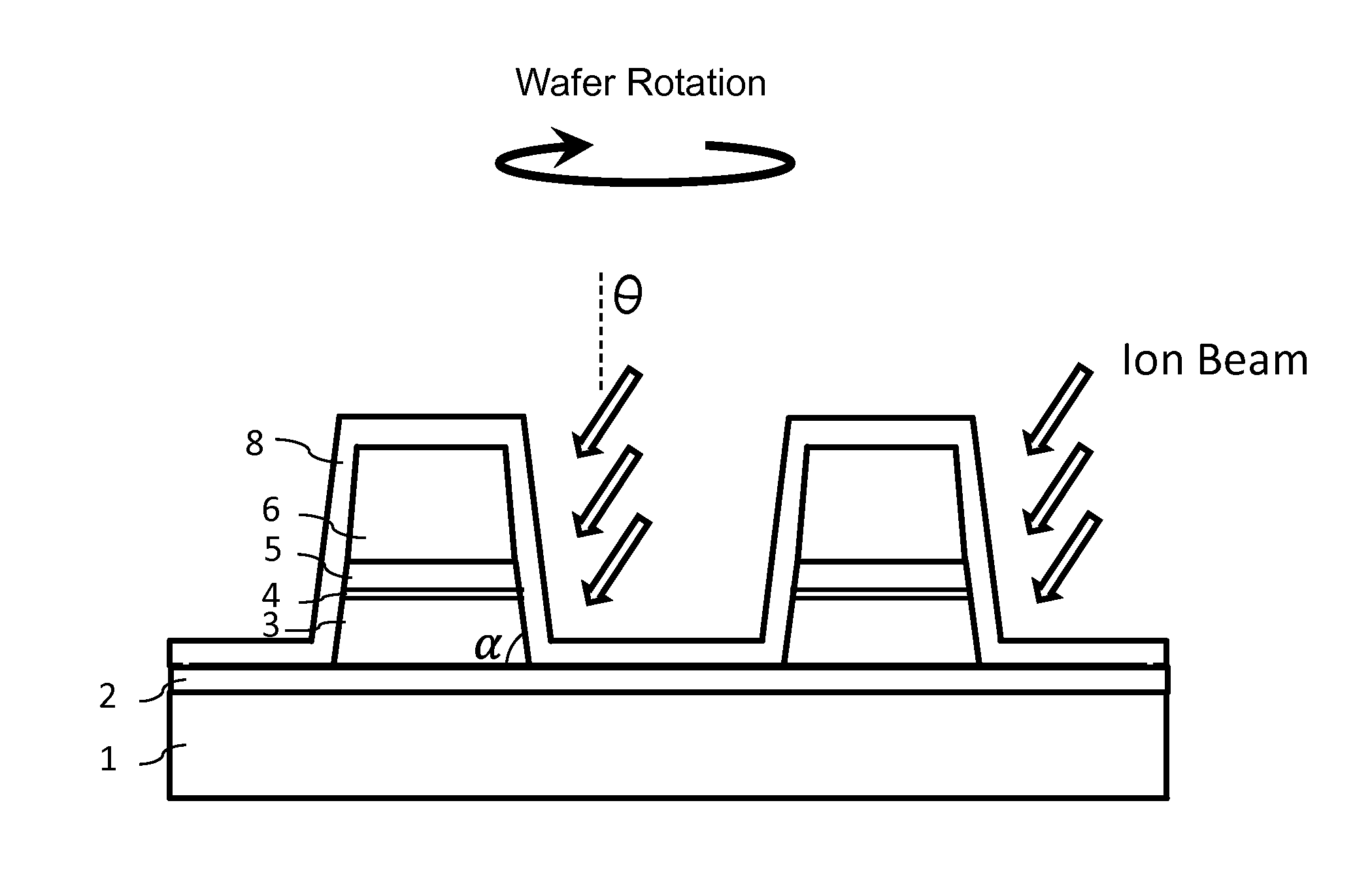

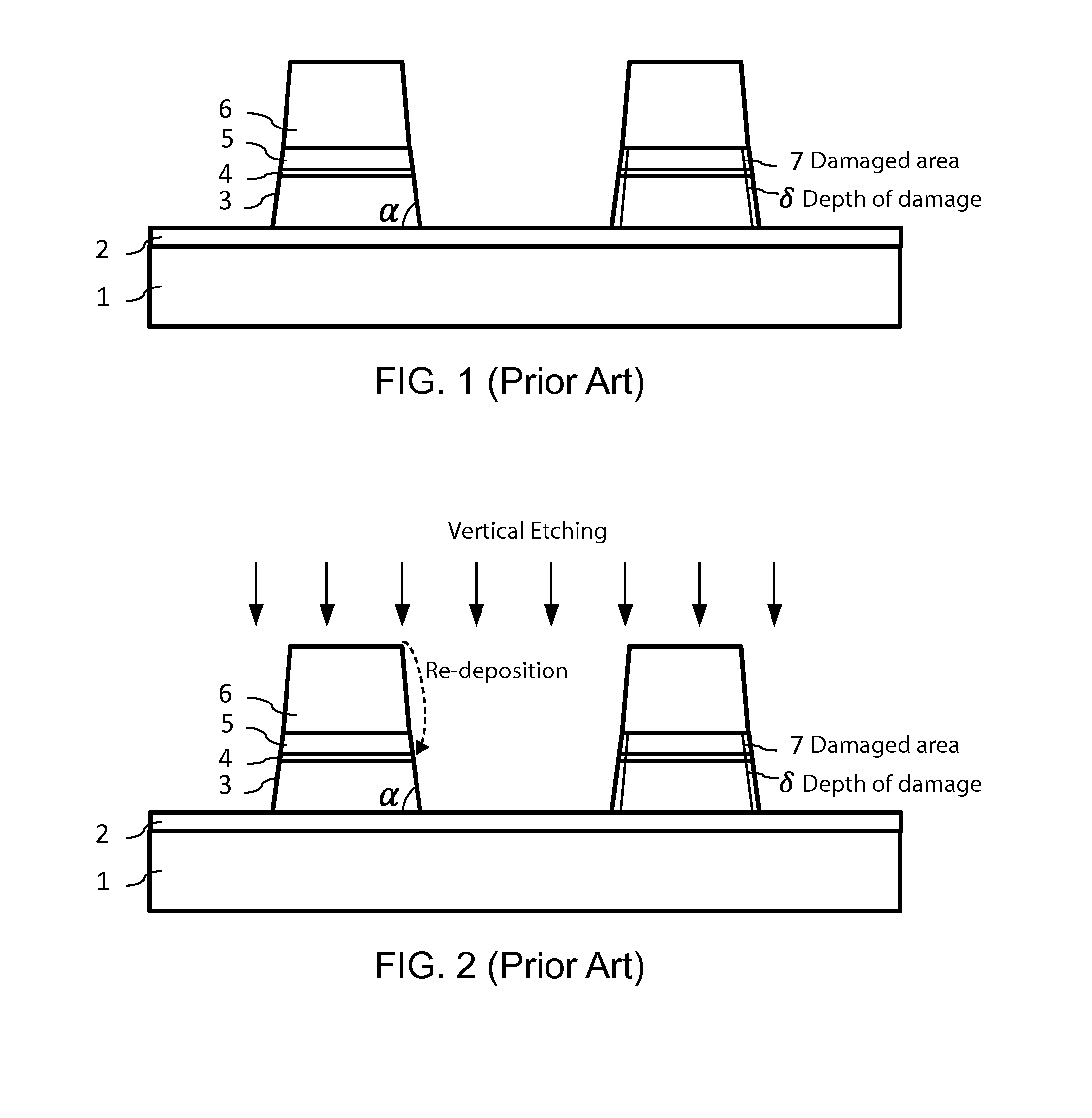

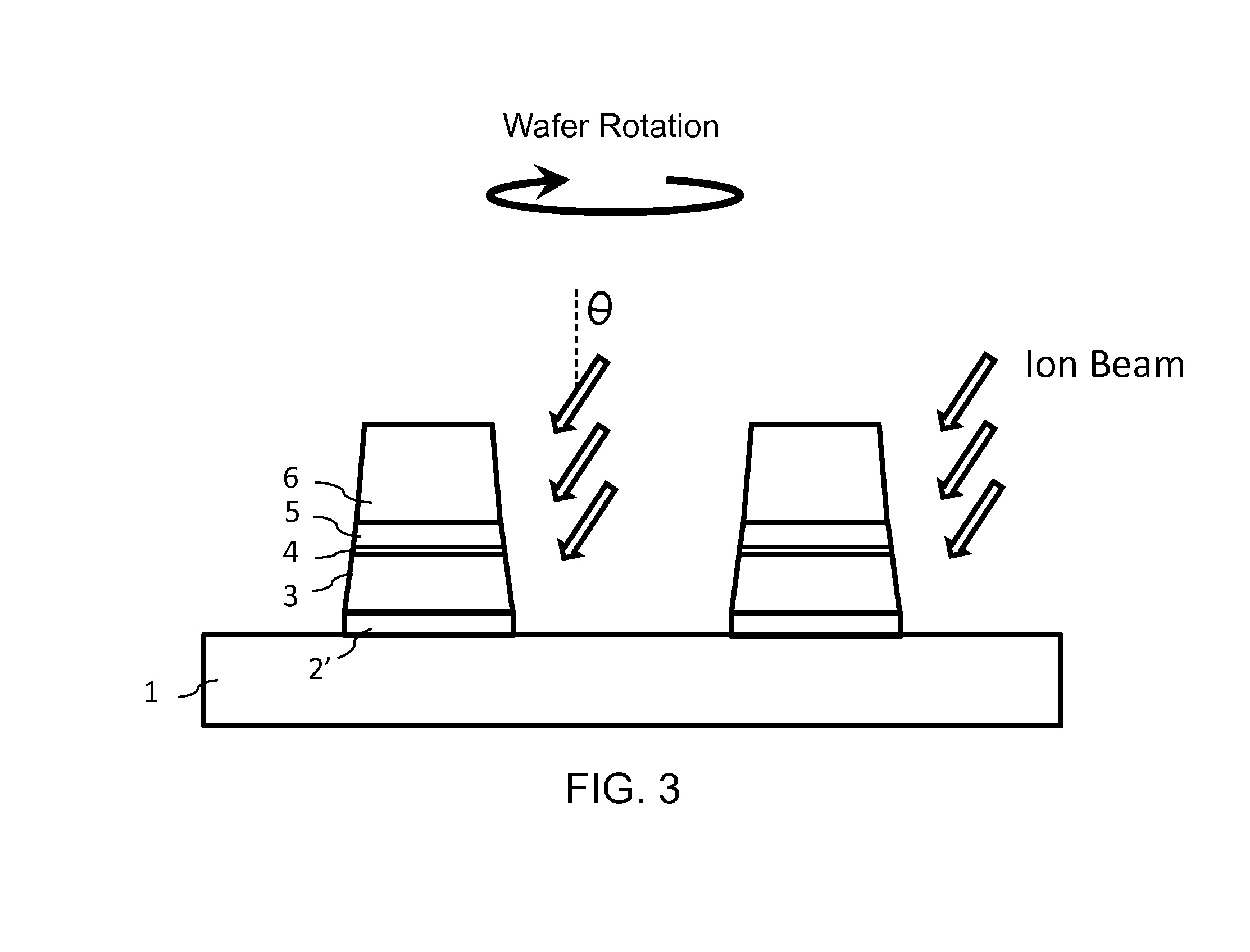

Mtj stack and bottom electrode patterning process with ion beam etching using a single mask

ActiveUS20140170776A1High selectivityAvoid damageSemiconductor/solid-state device manufacturingGalvano-magnetic device manufacture/treatmentEngineeringInductively coupled plasma

Fabrication methods using Ion Beam Etching (IBE) for MRAM cell memory elements are described. In embodiments of the invention the top electrode and MTJ main body are etched with one mask using reactive etching such as RIE or magnetized inductively coupled plasma (MICP) for improved selectivity, then the bottom electrode is etched using IBE as specified in various alternative embodiments which include selection of incident angles, wafer rotational rate profiles and optional passivation layer deposited prior to the IBE. The IBE according to the invention etches the bottom electrode without the need for an additional mask by using the layer stack created by the first etching phase as the mask. This makes the bottom electrode self-aligned to MTJ. The IBE also achieves MTJ sidewall cleaning without the need for an additional step.

Owner:AVALANCHE TECH

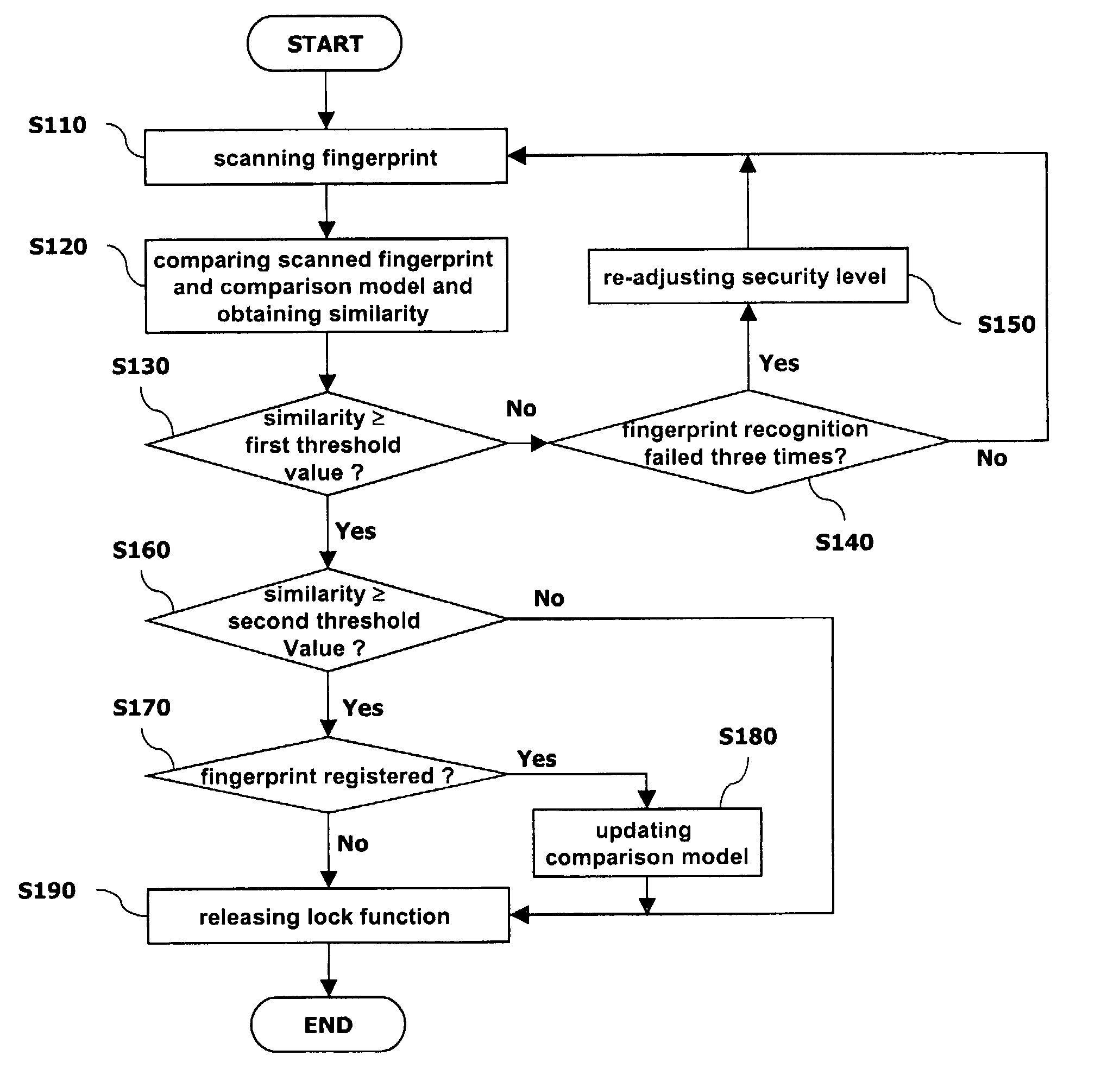

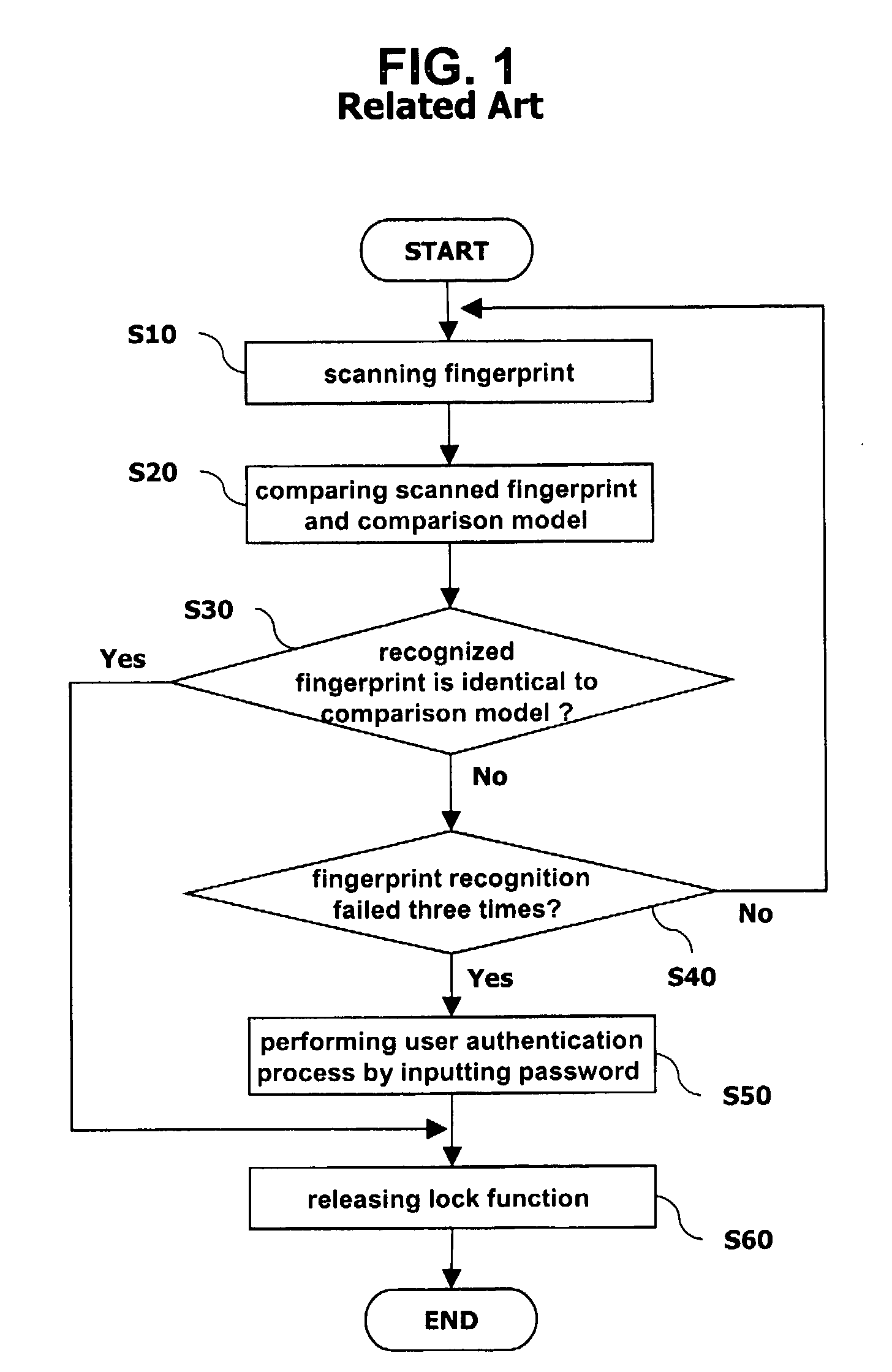

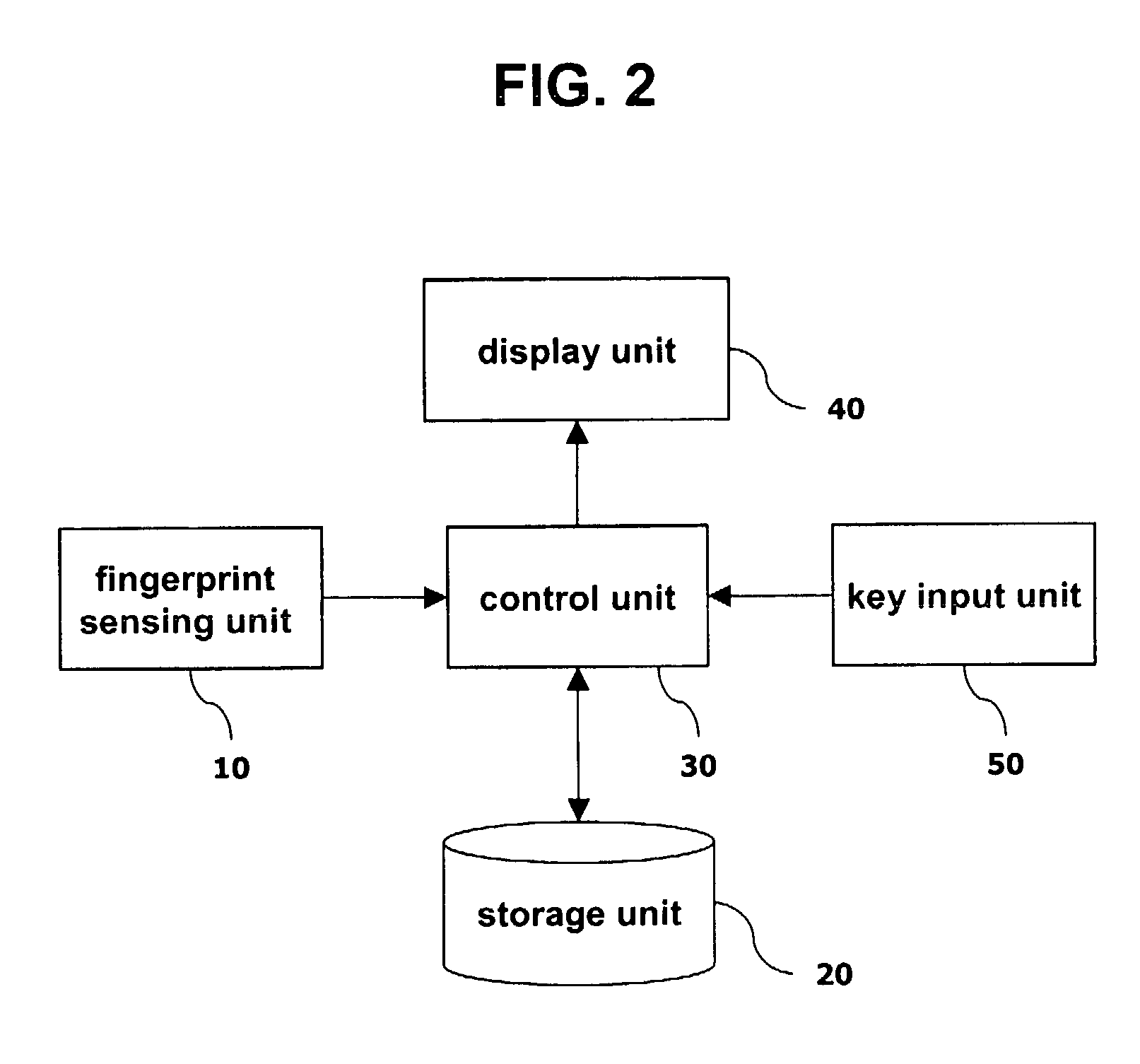

Apparatus and method of fingerprint recognition for a mobile terminal

InactiveUS20060210126A1Facilitate fingerprint recognitionLower security levelCharacter and pattern recognitionDiagnostic recording/measuringPattern recognitionModel control

An apparatus for recognizing a fingerprint includes a fingerprint sensing unit for scanning a fingerprint of a user; a storage using for storing a comparison model of the fingerprint of the user and various threshold values; a control unit for obtaining similarity between the fingerprint of the user scanned by fingerprint sensing unit and the comparison model stored in the storage unit, comparing it with a certain threshold value, and controlling a mobile terminal according to the comparison result; and a display unit for transferring a result (success or failure) of the fingerprint recognition or a request from the control unit to the user.

Owner:LG ELECTRONICS INC

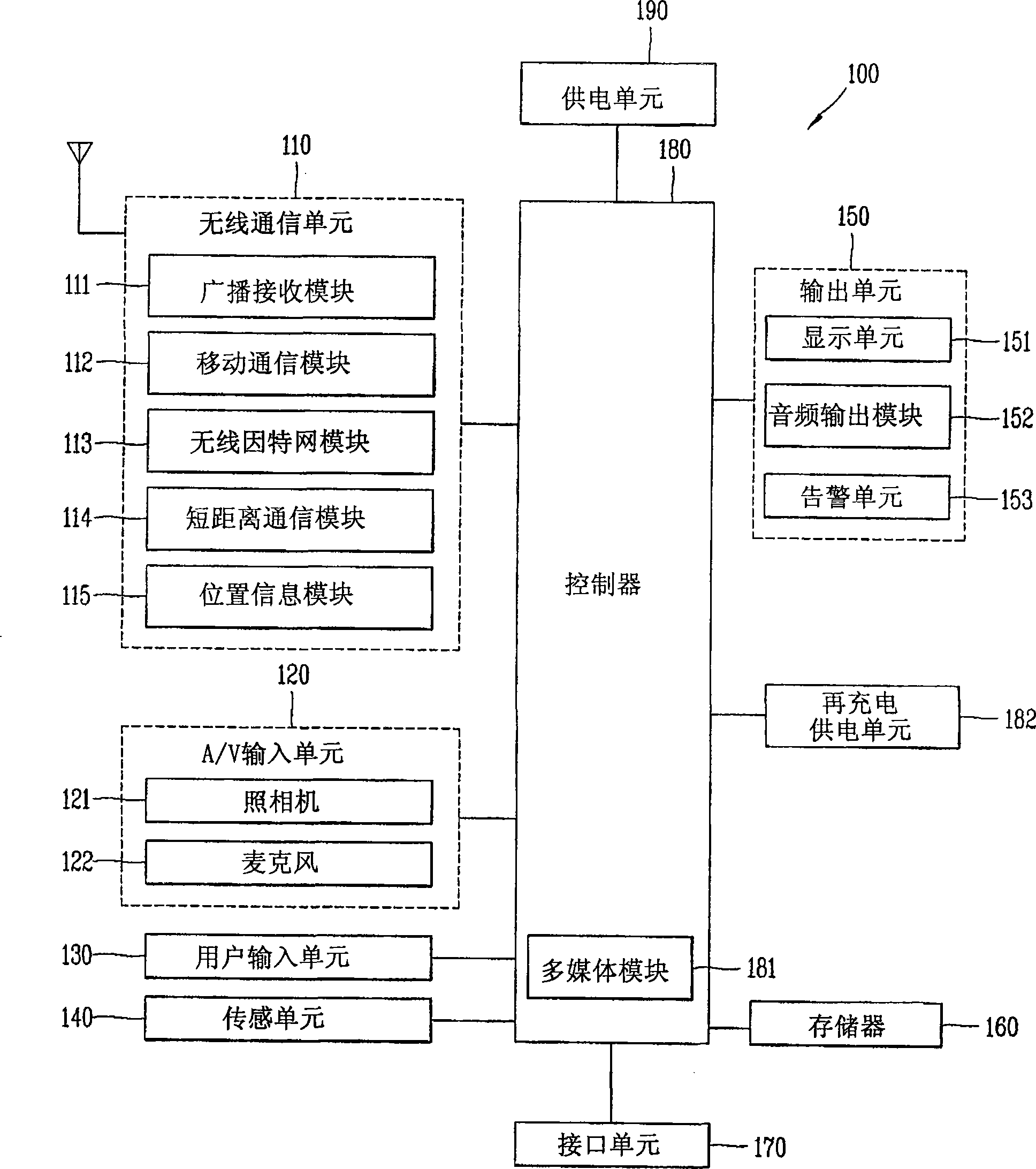

Mobile terminal having menu providing function for wireless recharging and recharging method thereof

InactiveCN101459981AImprove convenienceCircuit monitoring/indicationElectromagnetic wave systemTelecommunicationsElectrical battery

A mobile terminal is provided including a battery, an output unit, a memory, and a controller. The battery provides power. The output unit outputs a wireless recharge state. The memory stores recharge menus and recharge menu settings. The controller provides recharge menus for wireless recharging of the battery based on whether payment is required for the wireless recharging. The controller also performs a wireless recharging operation according to selection of the recharge menu settings.

Owner:LG ELECTRONICS INC

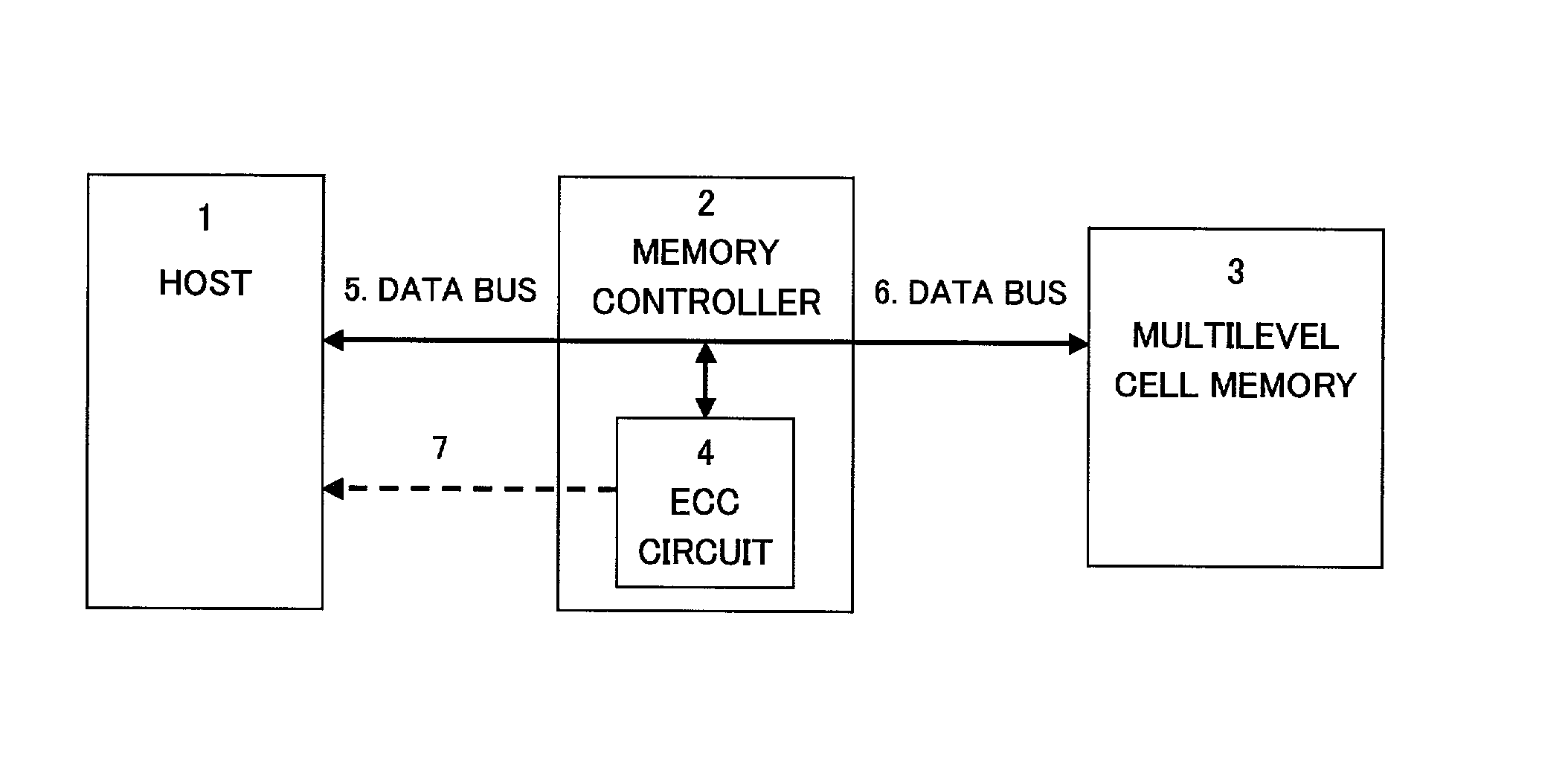

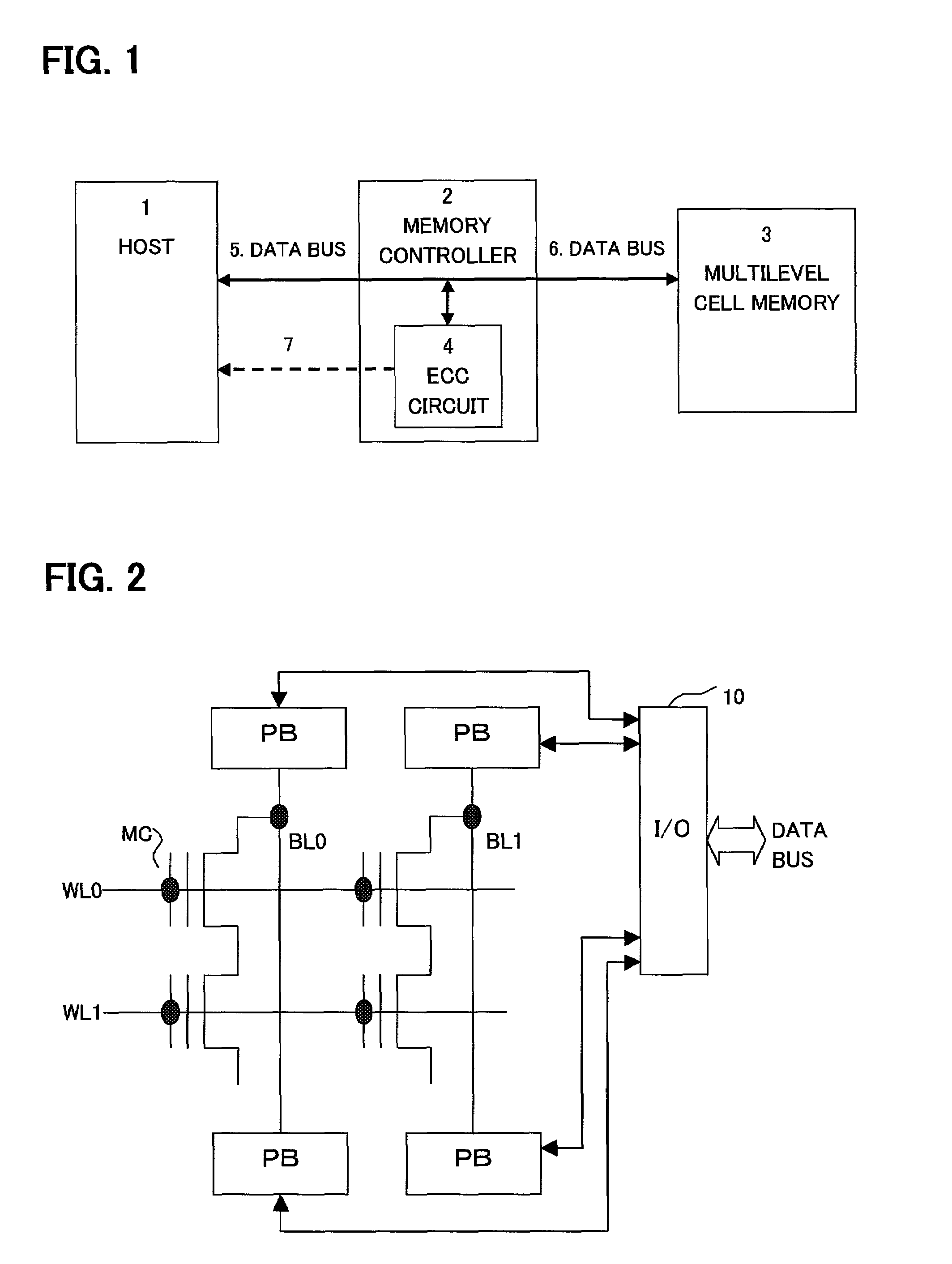

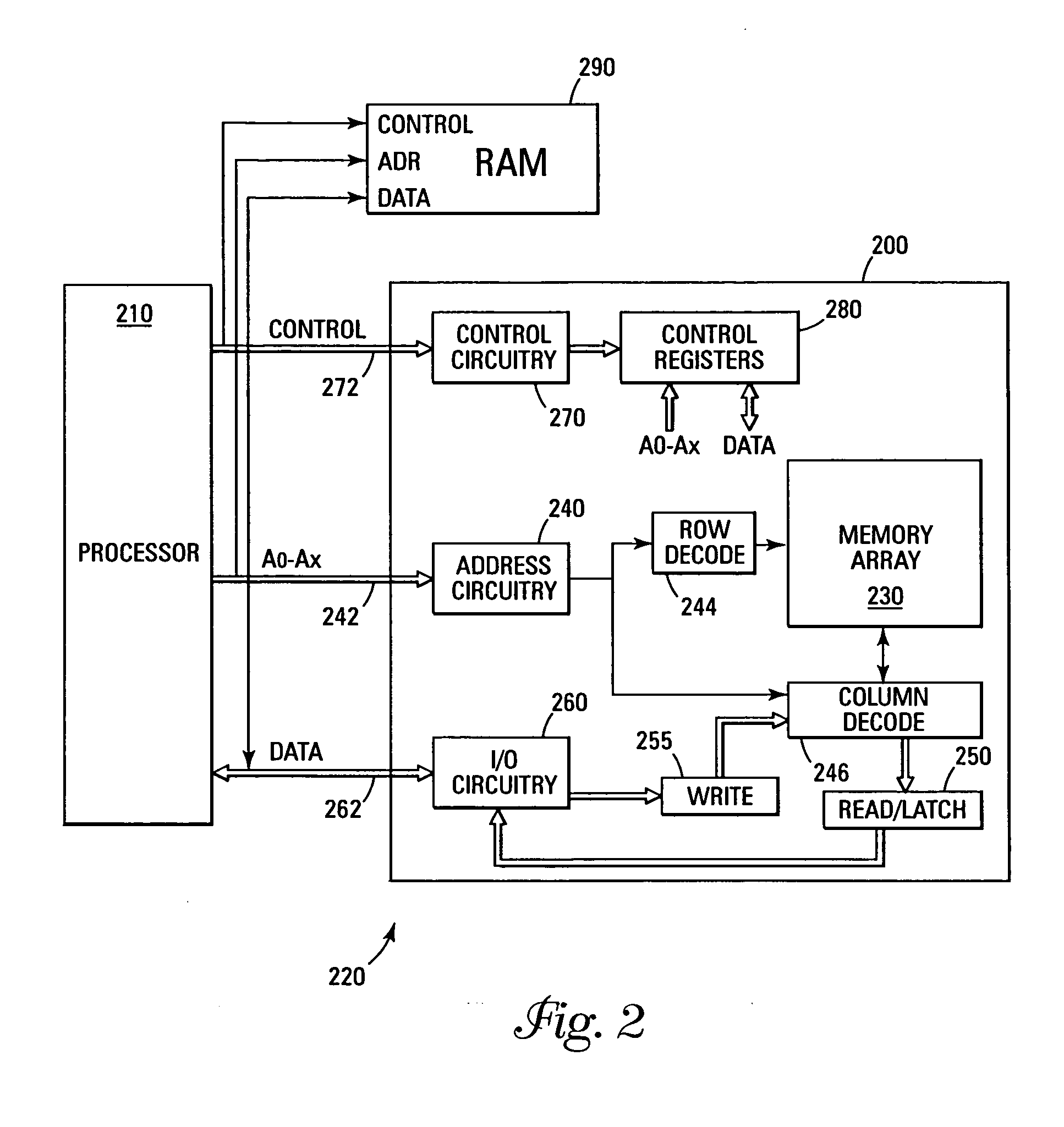

Memory controller for multilevel cell memory

InactiveUS7096406B2Configuration for division into data groups within the memory controller is comparatively simpleSimple configurationMemory loss protectionRead-only memoriesMemory controllerCorrection code

A N-level cell memory controlled by the memory controller of the invention have an internal configuration in which the plurality of data input / output terminals connected to the second data bus are separated into first through Mth data input / output terminal groups, such that there is no redundancy in the n bits of data associated with one N-level cell. Together with this, the memory controller separates the plurality of data bits on the first data bus into first through Mth data groups, the ECC circuits generate error-correction codes for each of these data groups, and the first through Mth data groups and first through Mth error correction codes are input to the first through Mth data input / output terminals of the N-level cell memory, via the second data bus.

Owner:FUJITSU LTD

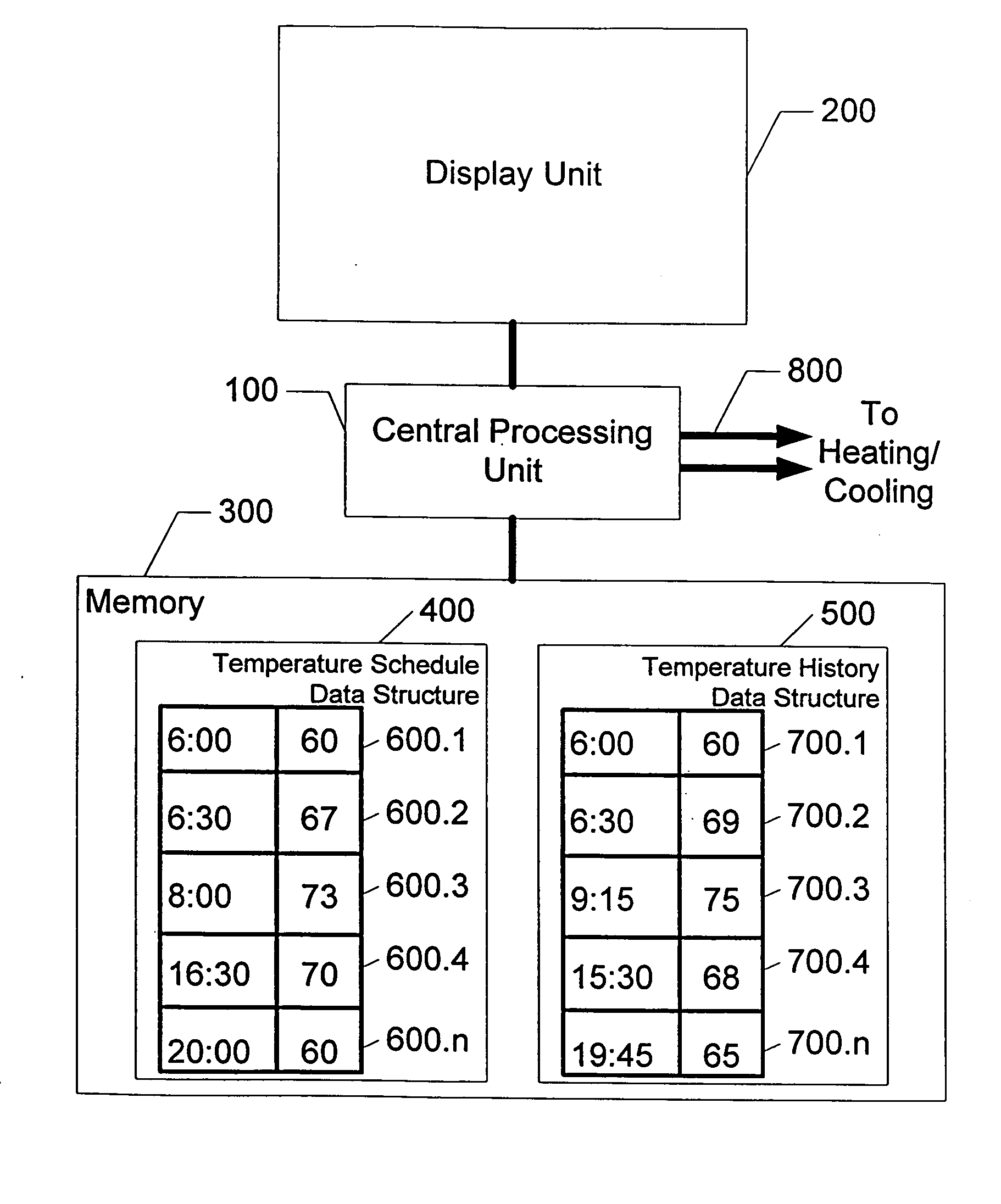

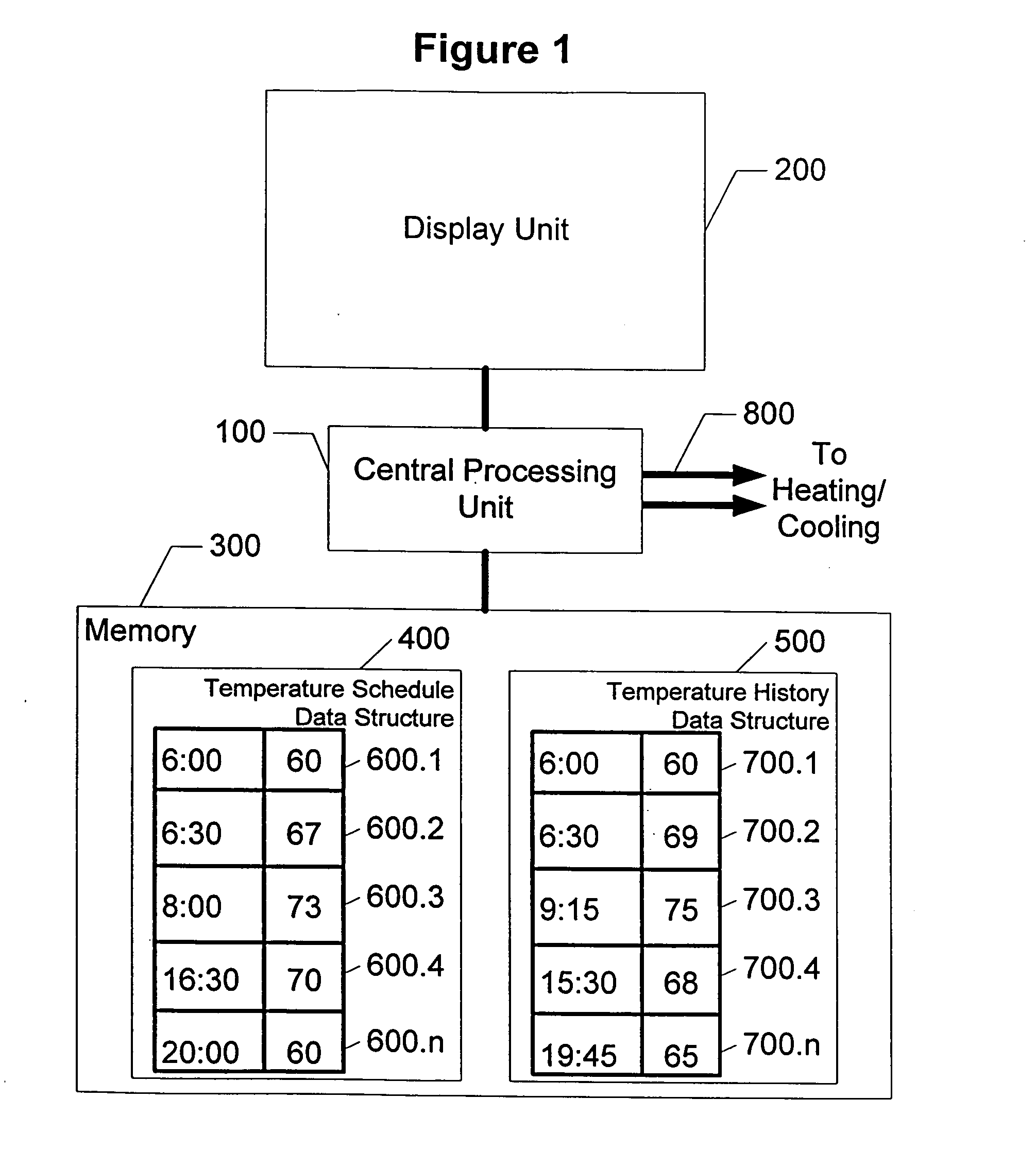

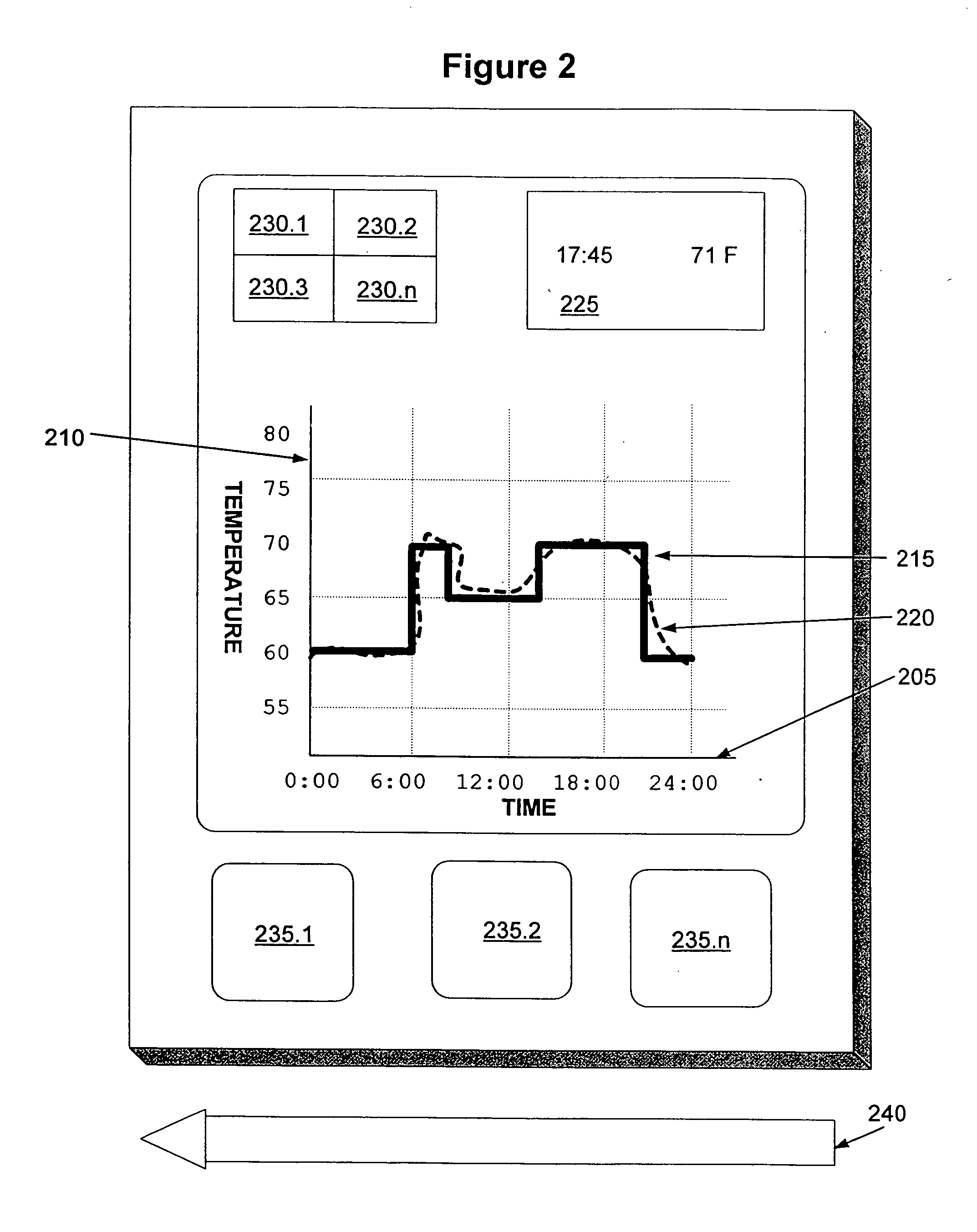

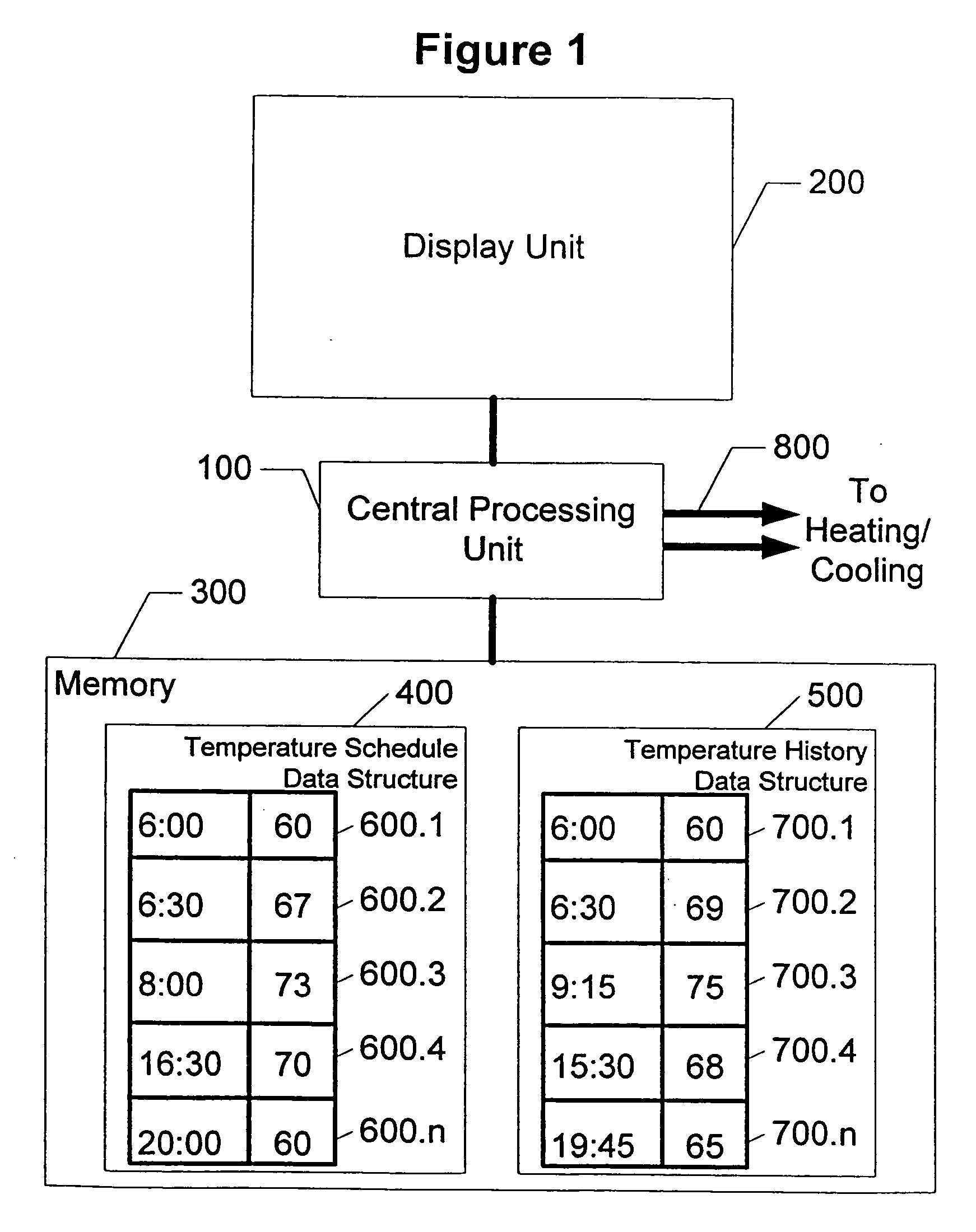

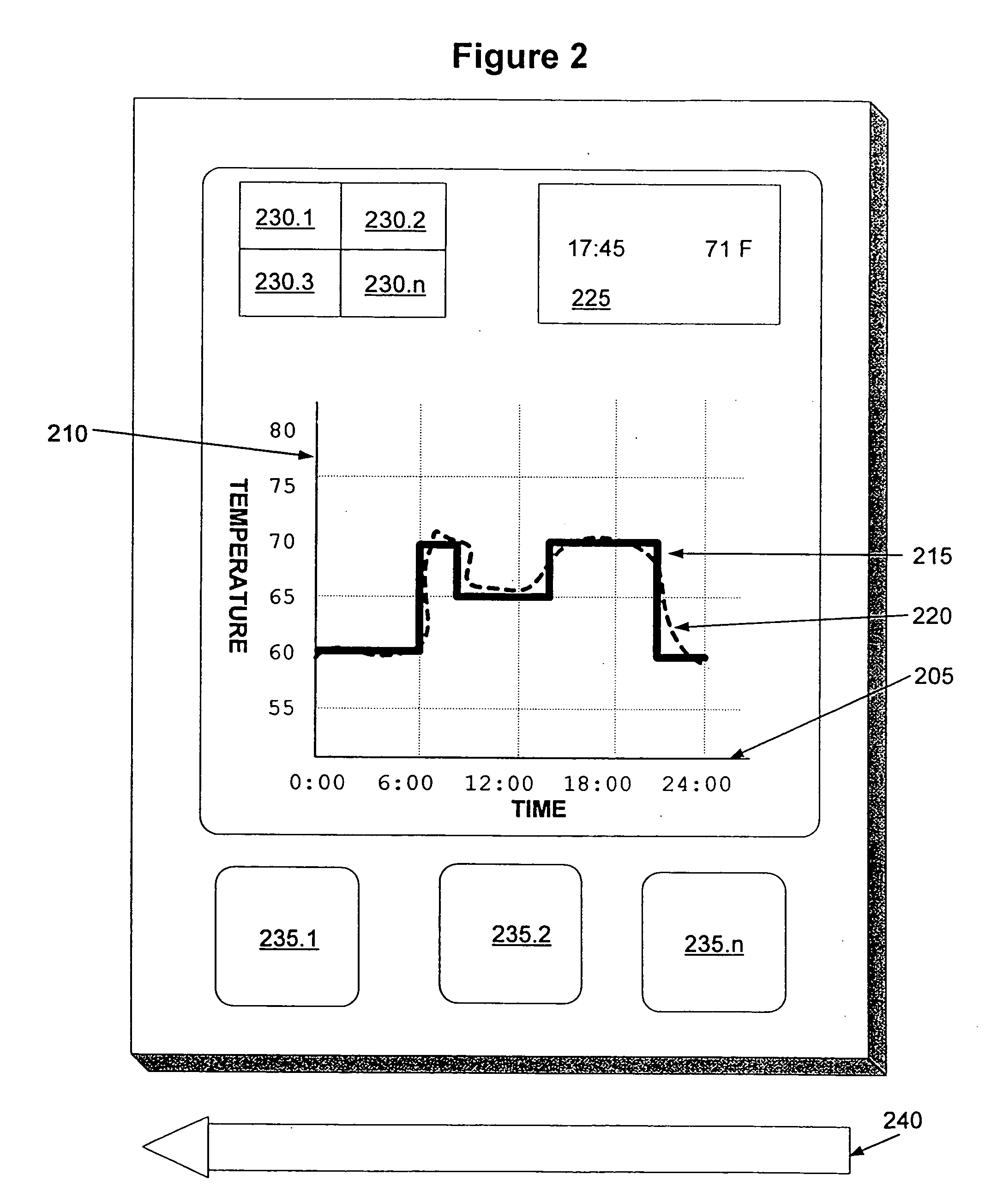

Graphical user interface system for a thermal comfort controller

InactiveUS20070198099A9Easily and intuitively programEasy programmingMechanical apparatusStatic/dynamic balance measurementGraphicsGraphical user interface

A graphical user interface system for a thermal comfort controller. The user interface system has a central processing unit coupled to a memory and a touch sensitive display unit. The memory stores a temperature schedule data structure and perhaps a temperature history data structure. The temperature schedule data structure is made up of at least one set-point. The temperature history data structure is made up of at least one Actual-Temperature-Point. The display presents the set-points and / or the Actual-Temperature-Points. One representation of the display is a graphical step-function. The user uses a finger or stylus to program the set-points by pointing and dragging a portion of the step-function.

Owner:ADEMCO INC

Multiple level cell memory device with single bit per cell, re-mappable memory block

InactiveUS20050286297A1Improve reliabilityError detection/correctionRead-only memoriesParallel computingStorage cell

A non-volatile memory device has a plurality of memory cells that are organized into memory blocks. Each block can operate in either a multiple level cell mode or a single bit per cell mode. One dedicated memory block is capable of operating only in the single bit per cell mode. If the dedicated memory block is found to be defective, a defect-free block can be remapped to that dedicated memory block location to act only in the single bit per cell mode.

Owner:ROUND ROCK RES LLC

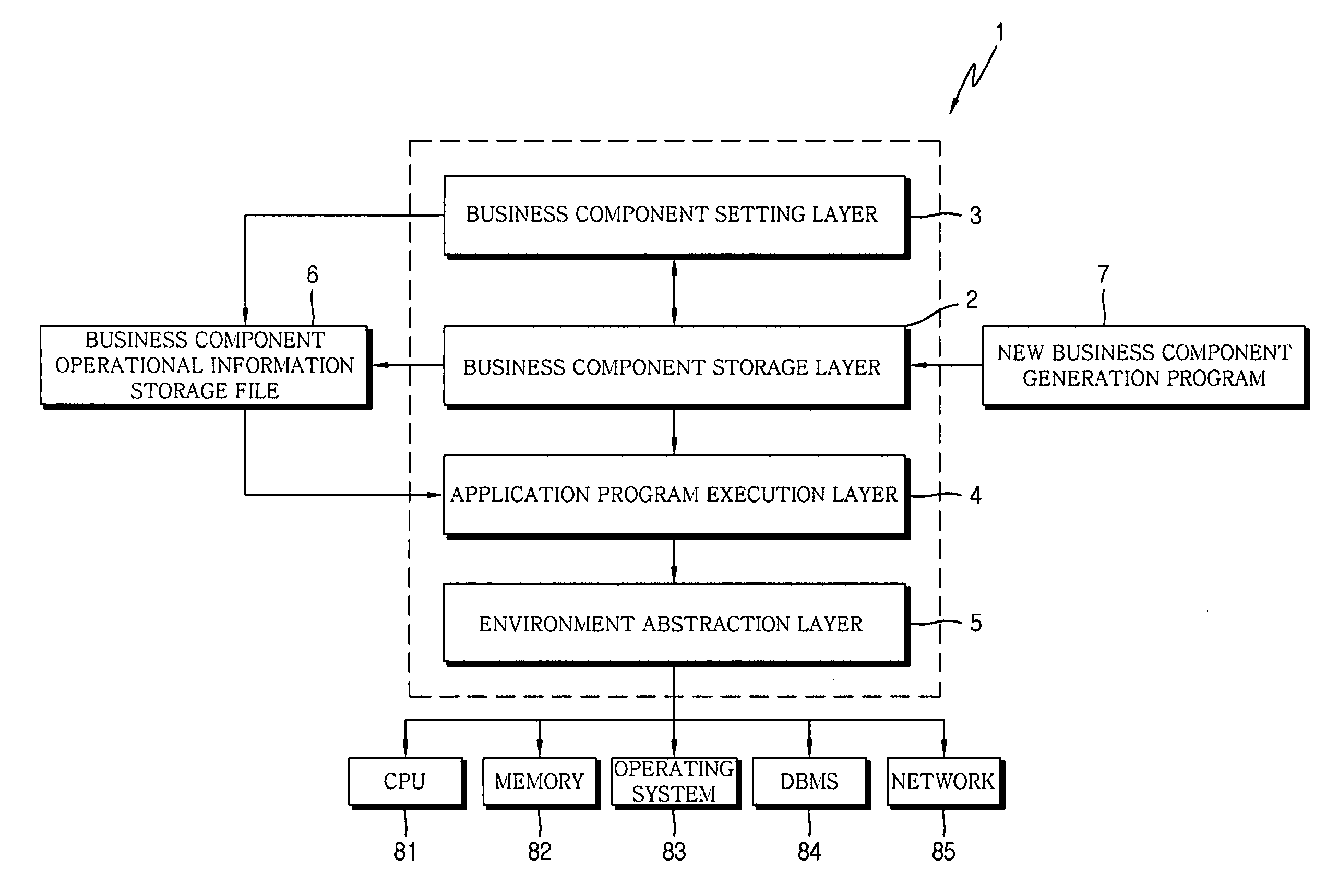

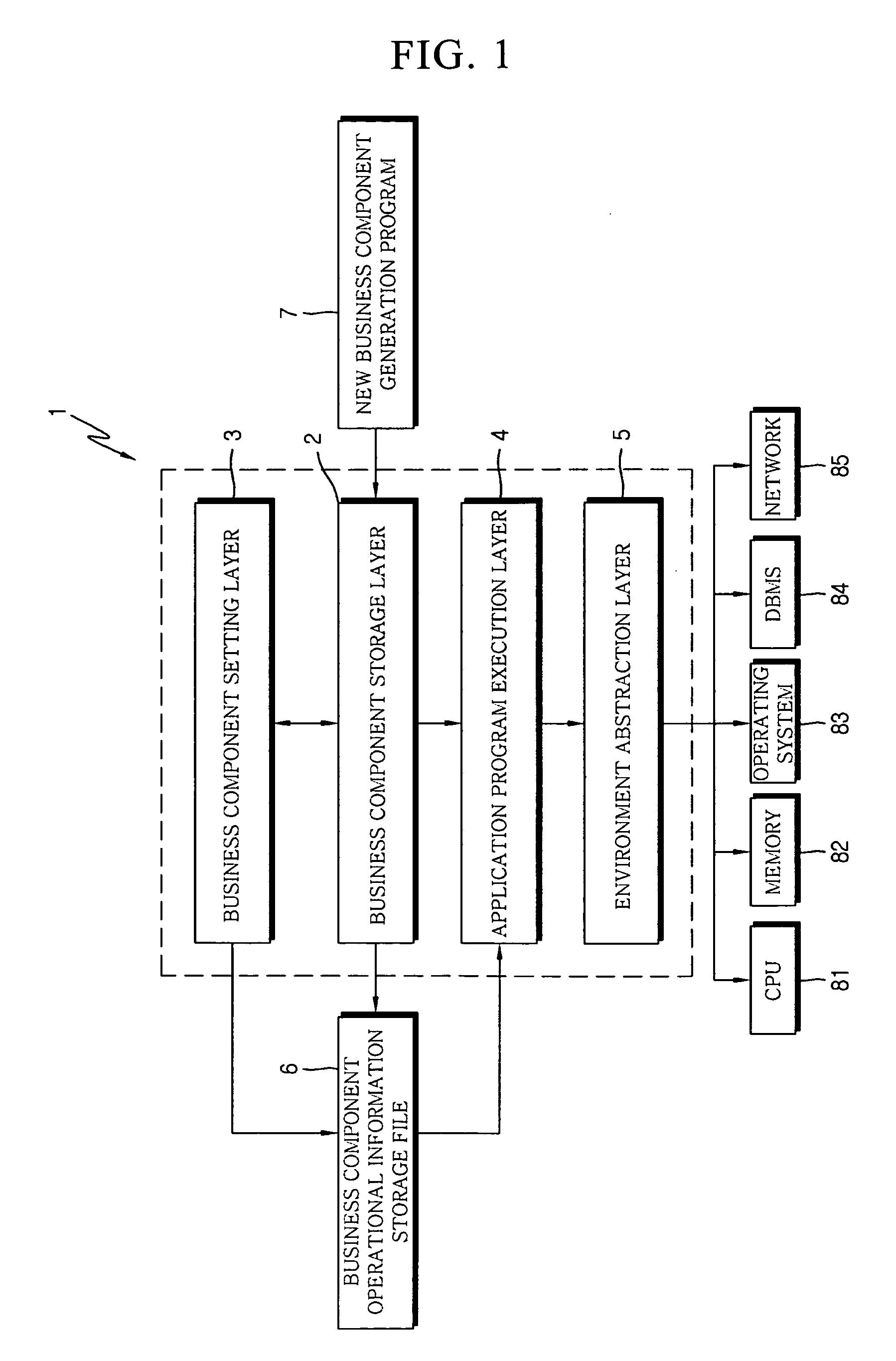

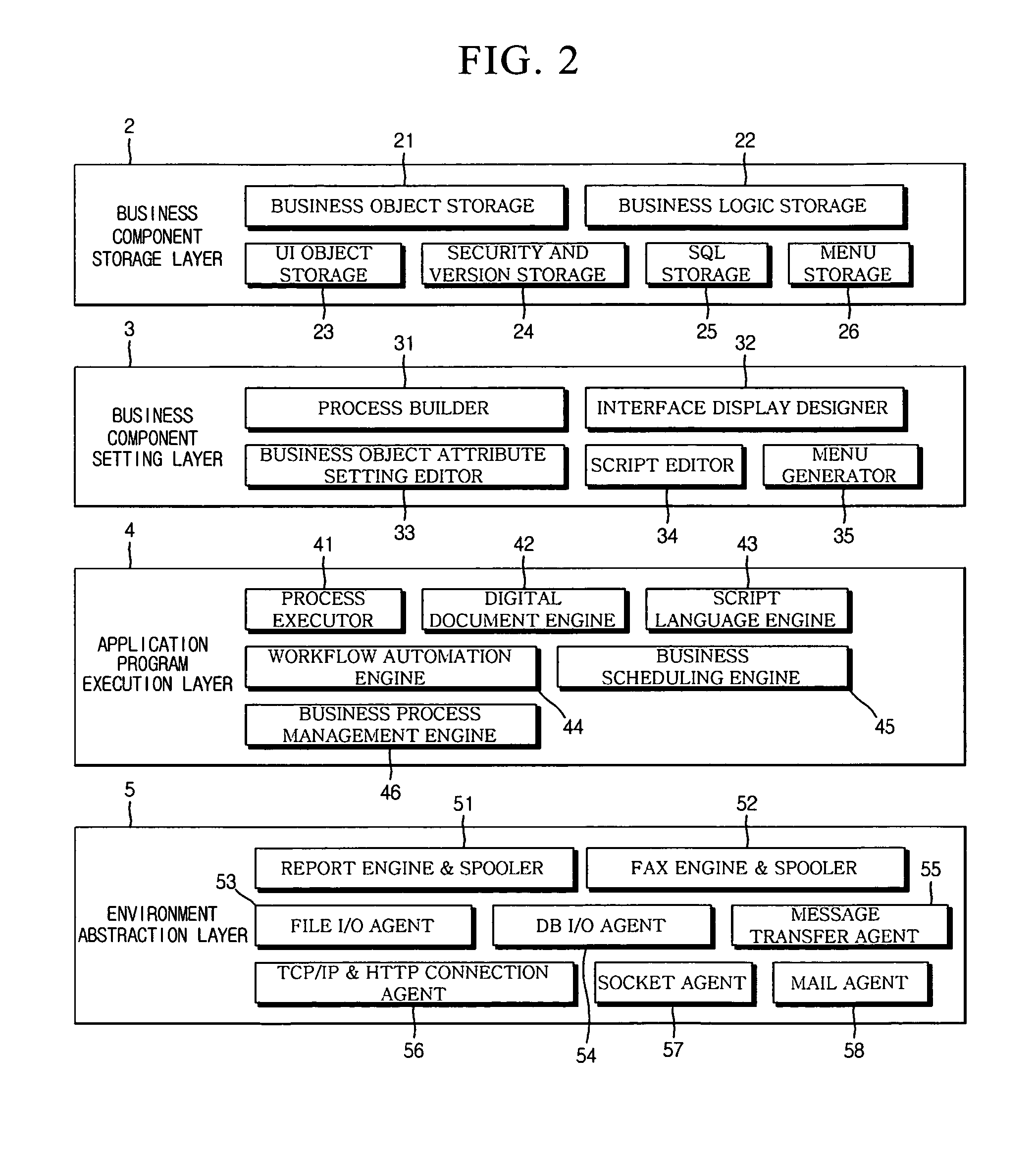

System and method for developing software based on business operating system

ActiveUS20070157165A1Improve and guarantee qualityImprove efficiencyDigital data processing detailsWriting boardsAbstraction layerOperational system

A software development system according to the present invention comprises a business component storage layer for storing at least one business standard component of a program; a business component setting layer for setting attribute information of each business standard object, including object type, operating method, execution condition, execution sequence and database (DB) connection information; an application program execution layer for operating and controlling the object in the business component storage layer by the attribute information of the objects set by the user, and performing comparison, execution or calculation according to logic defined in script language; and an environment abstraction layer for controlling information technology (IT) infrastructure including an operating system of a computer, a central processing unit (CPU), a memory, a database management system (DBMS), network and display apparatus.

Owner:KIM GILOONG

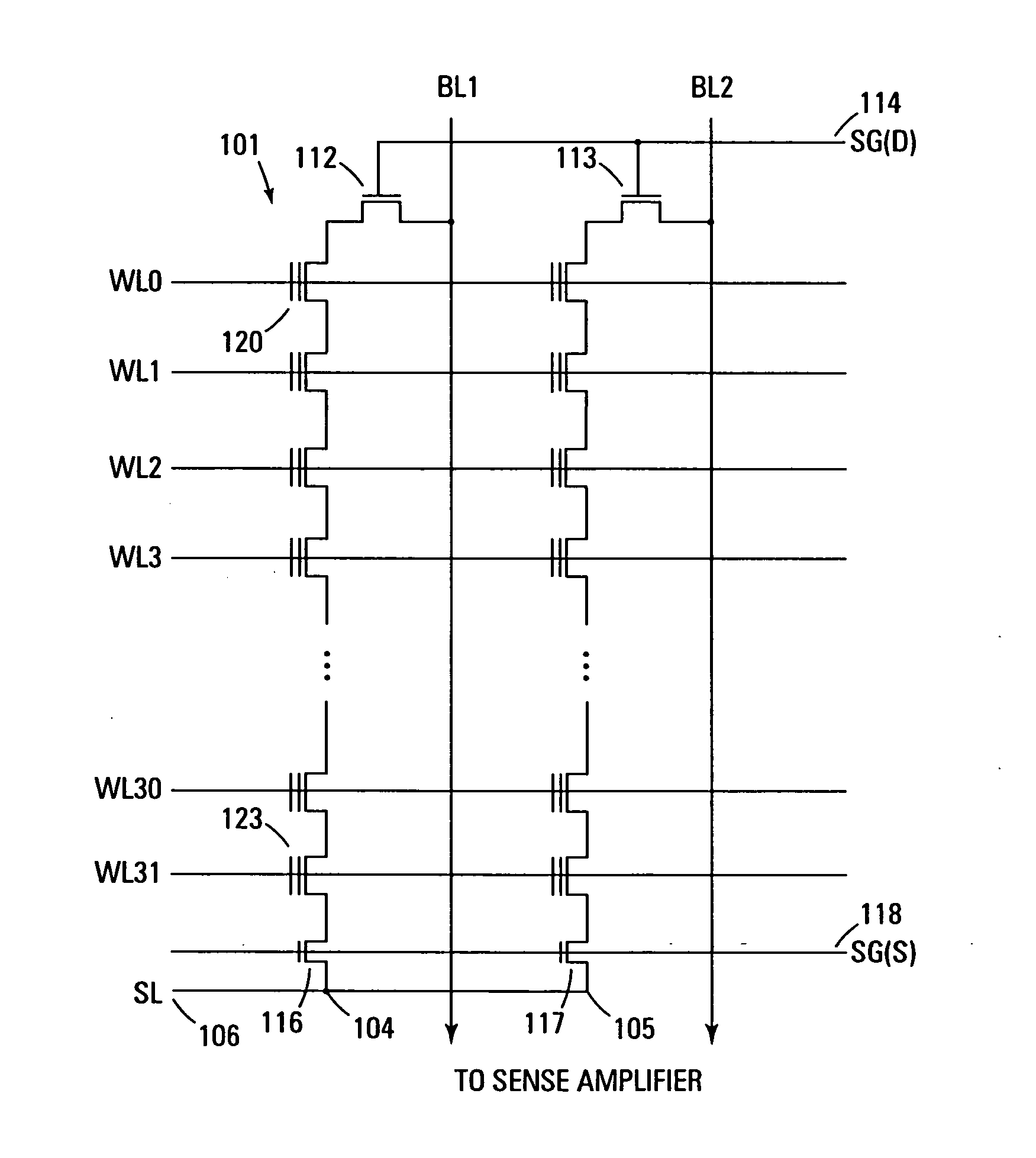

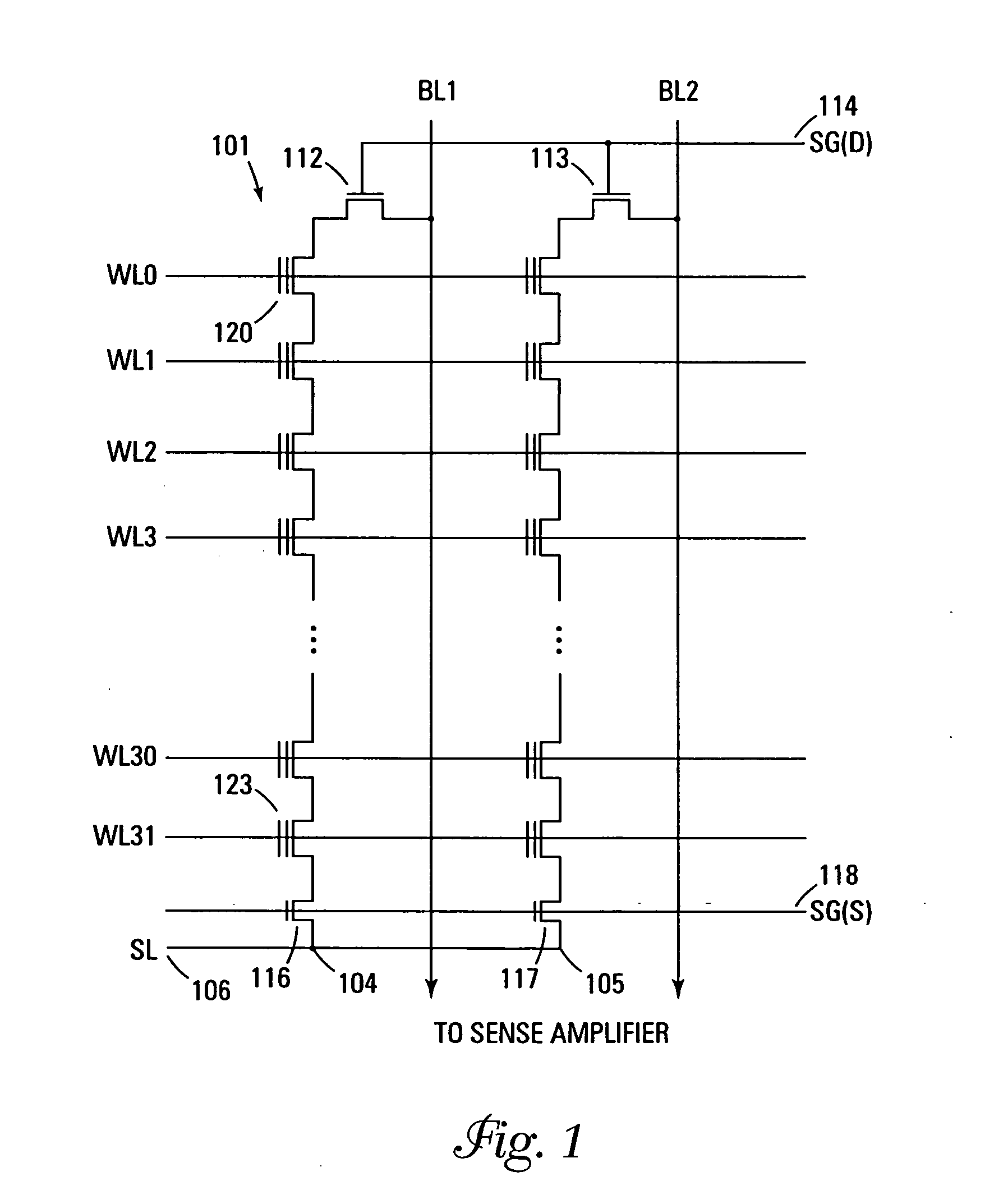

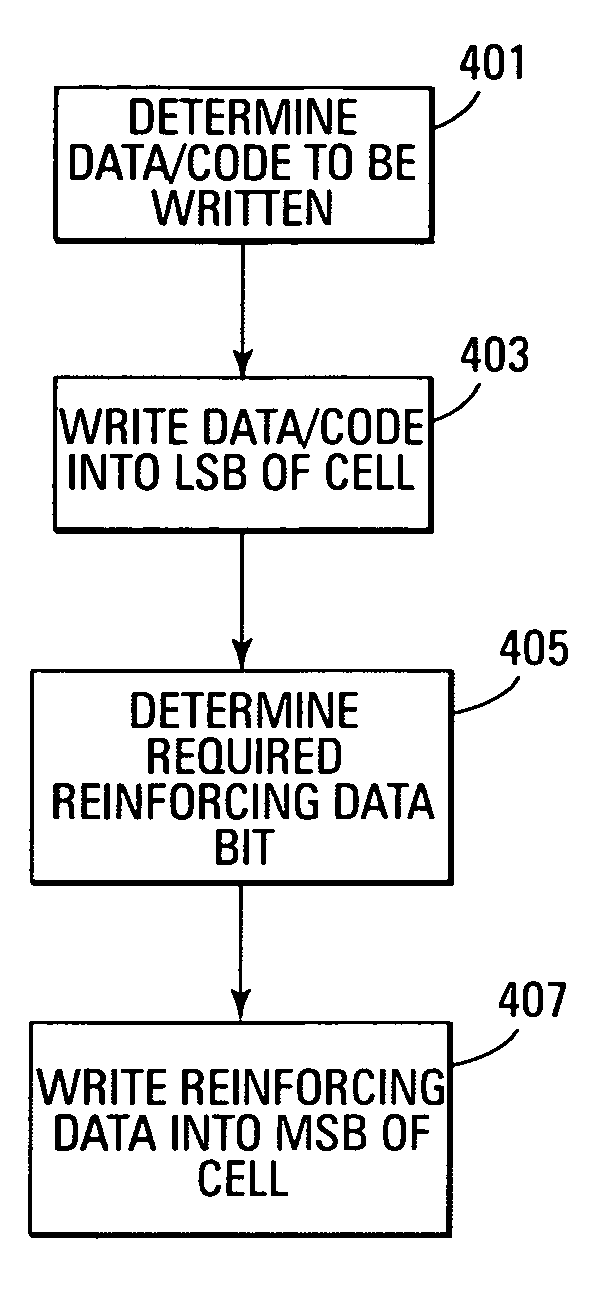

Single level cell programming in a multiple level cell non-volatile memory device

A multiple level cell memory array has an area that can be programmed as single level cells. The cells to be programmed are initially programmed with the desire data into either the least significant or most significant bit of the cell. A second programming operation the programs reinforcing data that adjusts the threshold level of the cell to the appropriate level for the desired data.

Owner:MICRON TECH INC

Graphical user interface system for a thermal comfort controller

InactiveUS20060027671A1Easily and intuitively programEasy programmingMechanical apparatusData processing applicationsGraphicsGraphical user interface

Owner:ADEMCO INC

Probabilistic error correction in multi-bit-per-cell flash memory

Data that are stored in cells of a multi-bit-per cell memory, according to a systematic or non-systematic ECC, are read and corrected (systematic ECC) or recovered (non-systematic ECC) in accordance with estimated probabilities that one or more of the read bits are erroneous. In one method of the present invention, the estimates are a priori. In another method of the present invention, the estimates are based only on aspects of the read bits that include significances or bit pages of the read bits. In a third method of the present invention, the estimates are based only on values of the read bits. Not all the estimates are equal.

Owner:RAMOT AT TEL AVIV UNIV LTD