Patents

Literature

800 results about "Single level" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

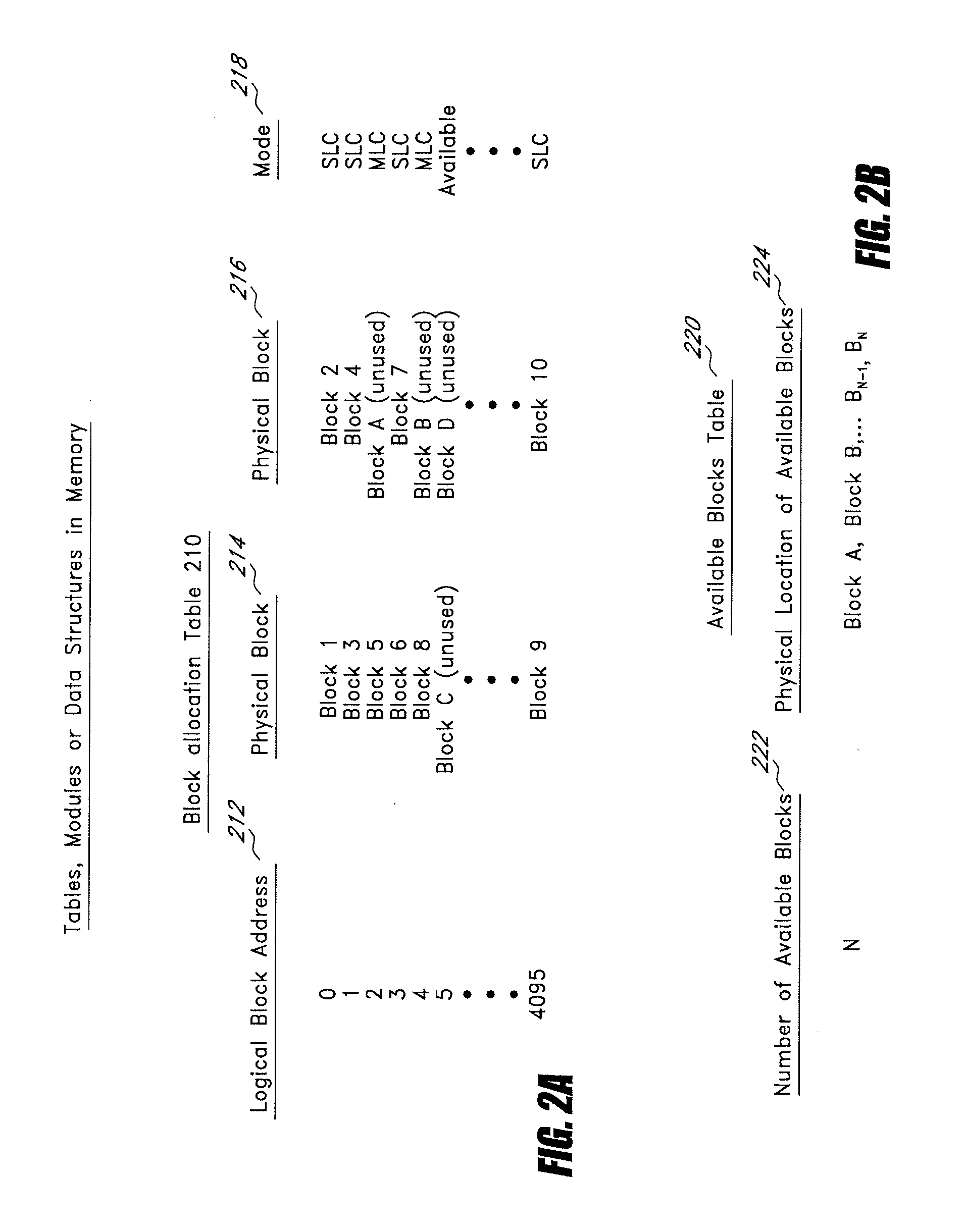

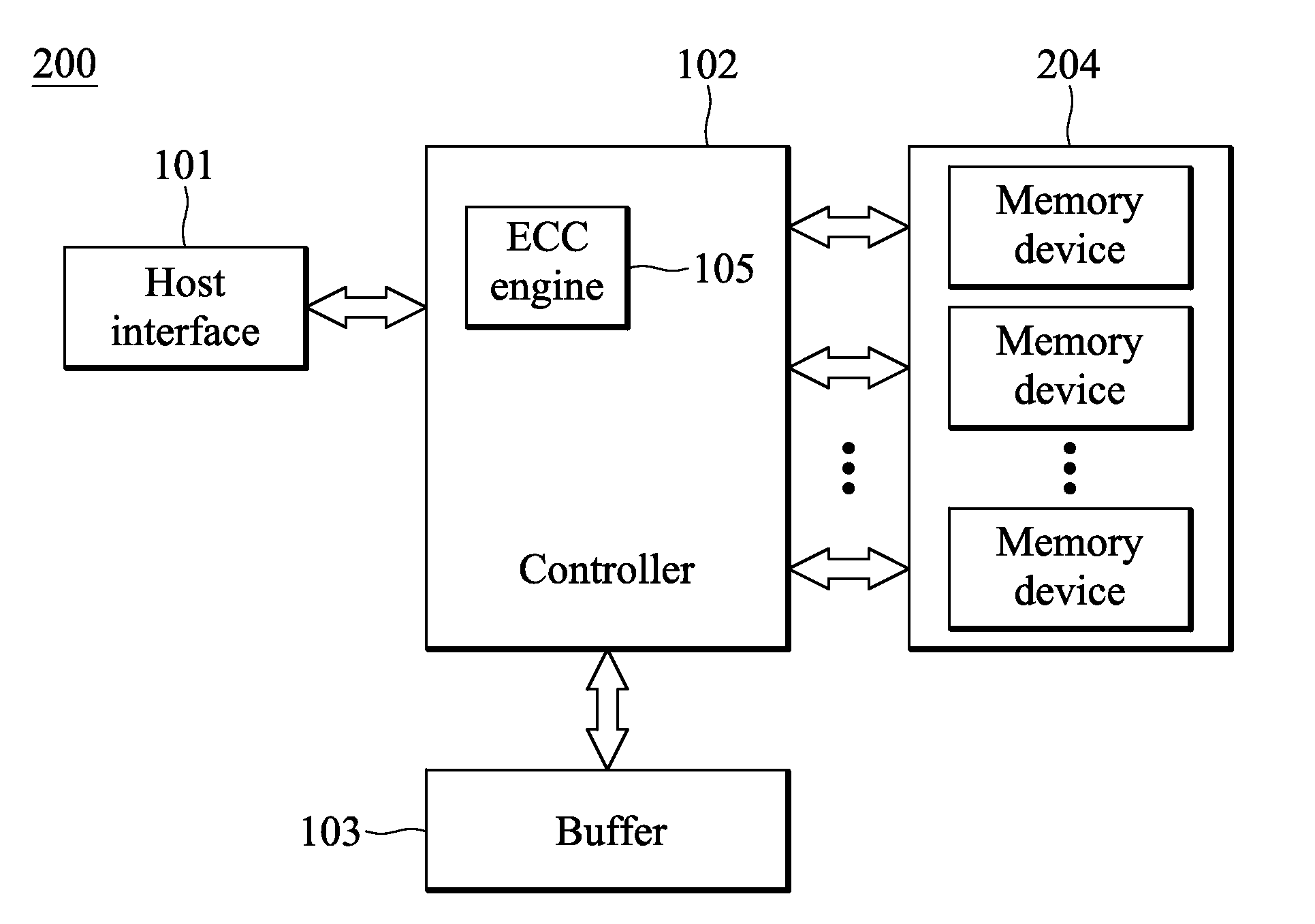

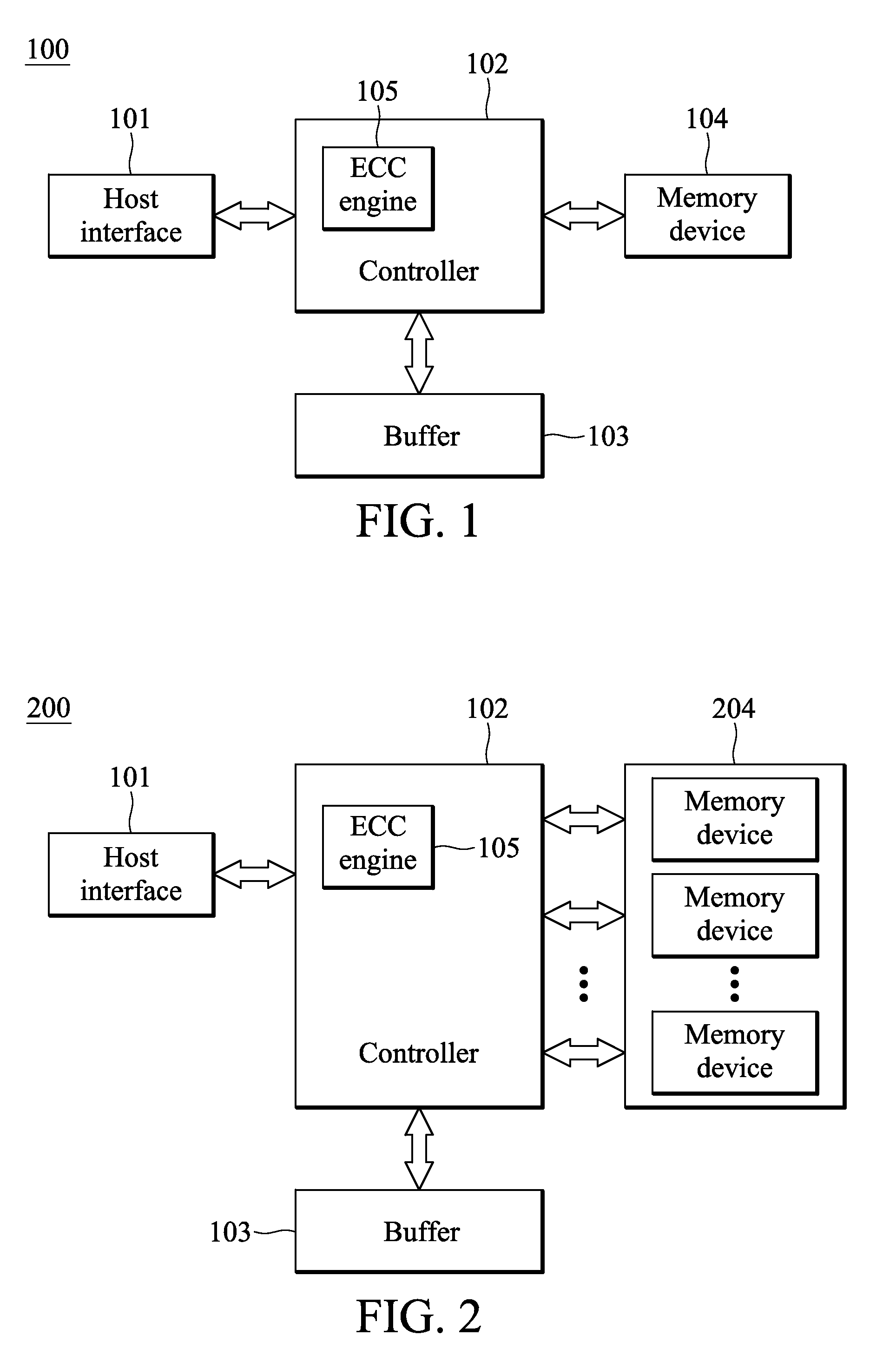

Hybrid 2-Level Mapping Tables for Hybrid Block- and Page-Mode Flash-Memory System

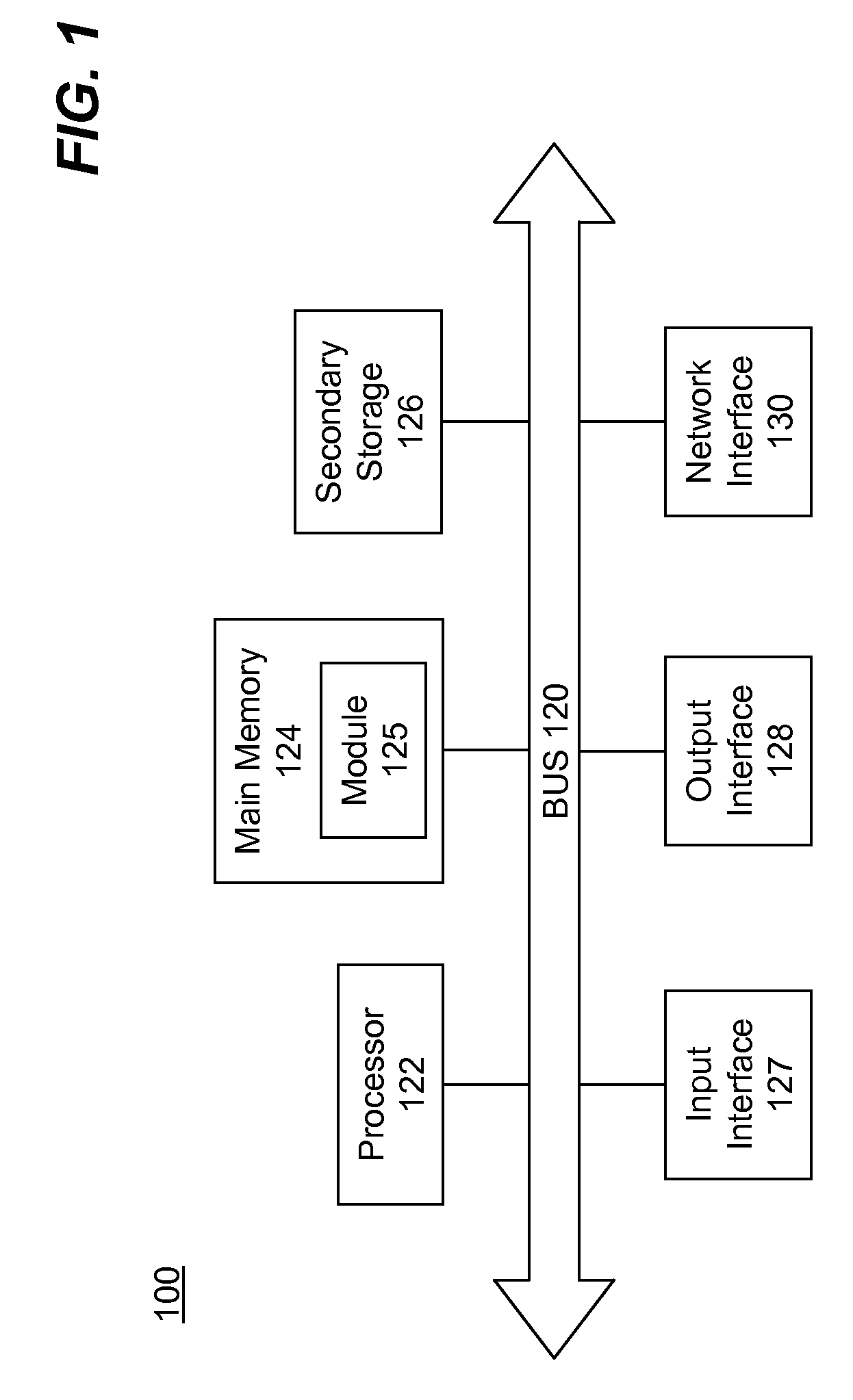

InactiveUS20090193184A1Memory architecture accessing/allocationMemory adressing/allocation/relocationVirtual fieldFrequency counter

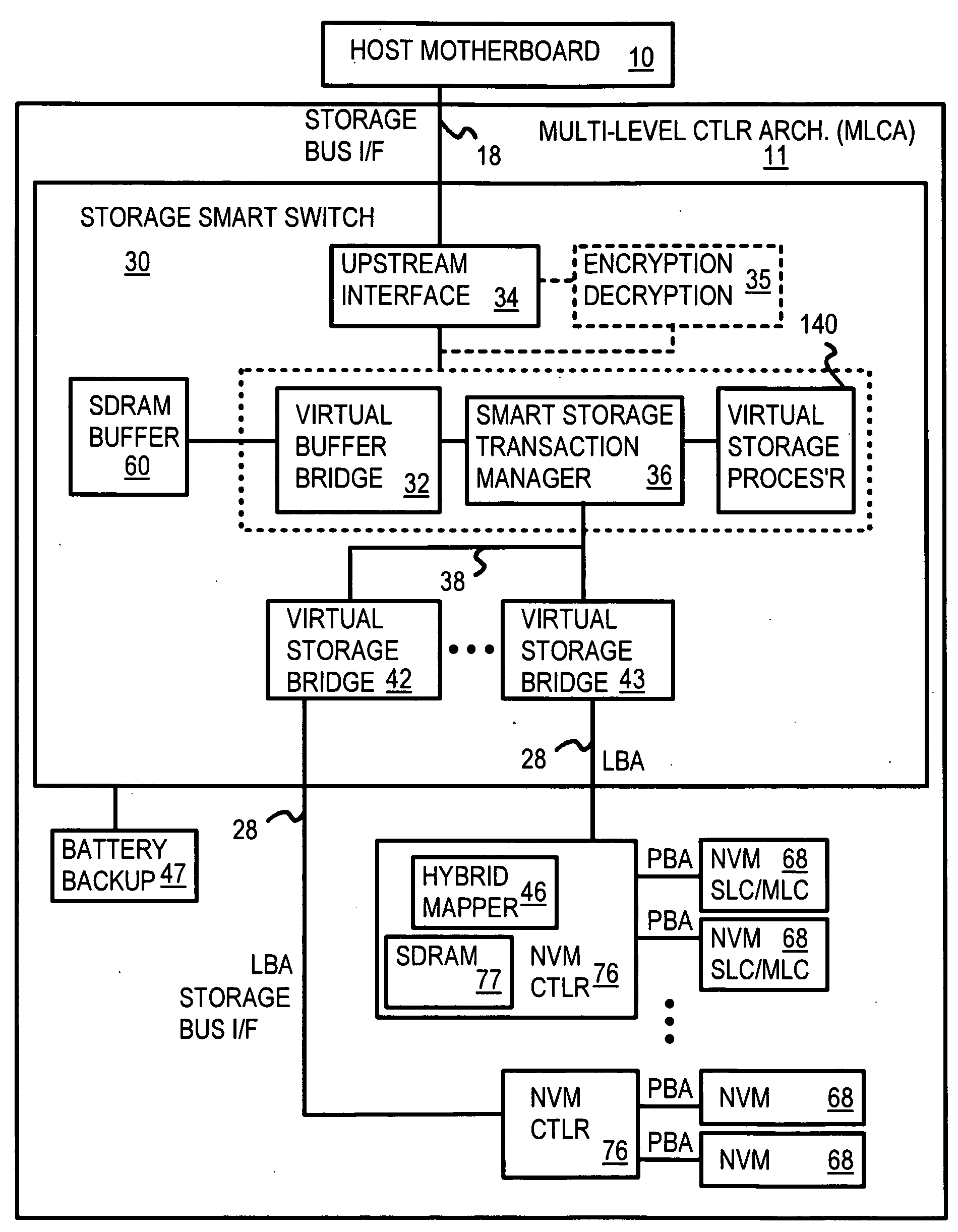

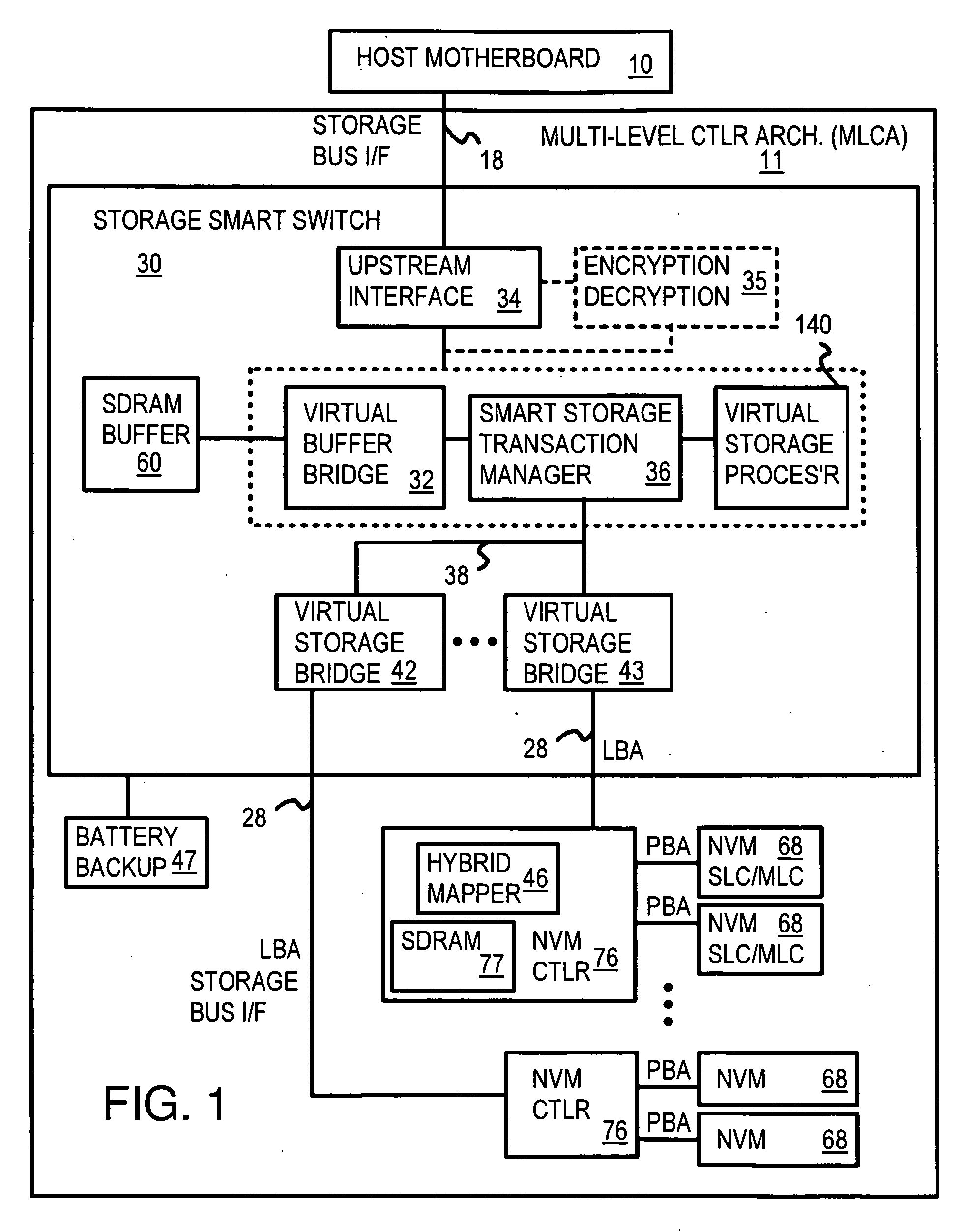

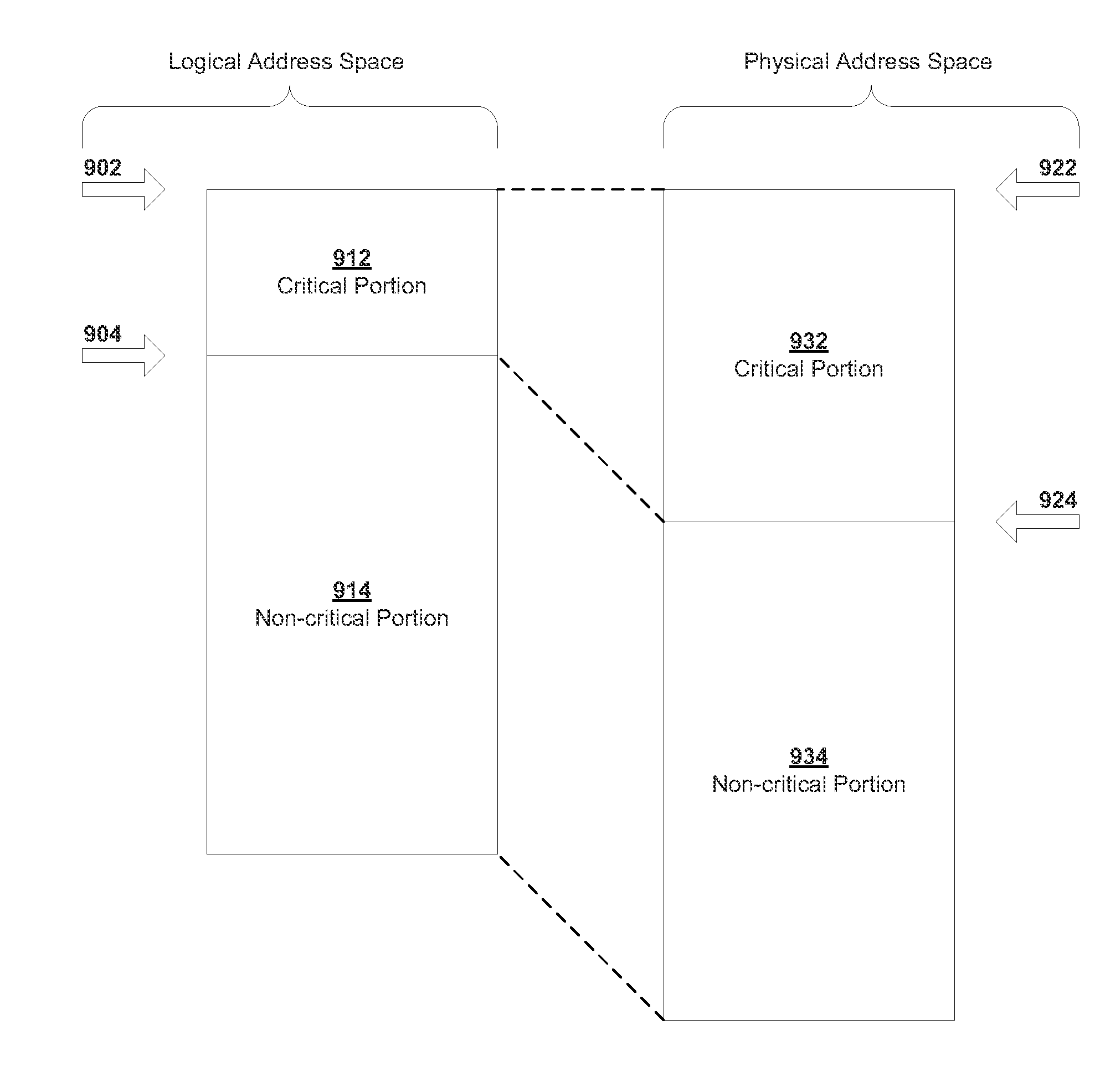

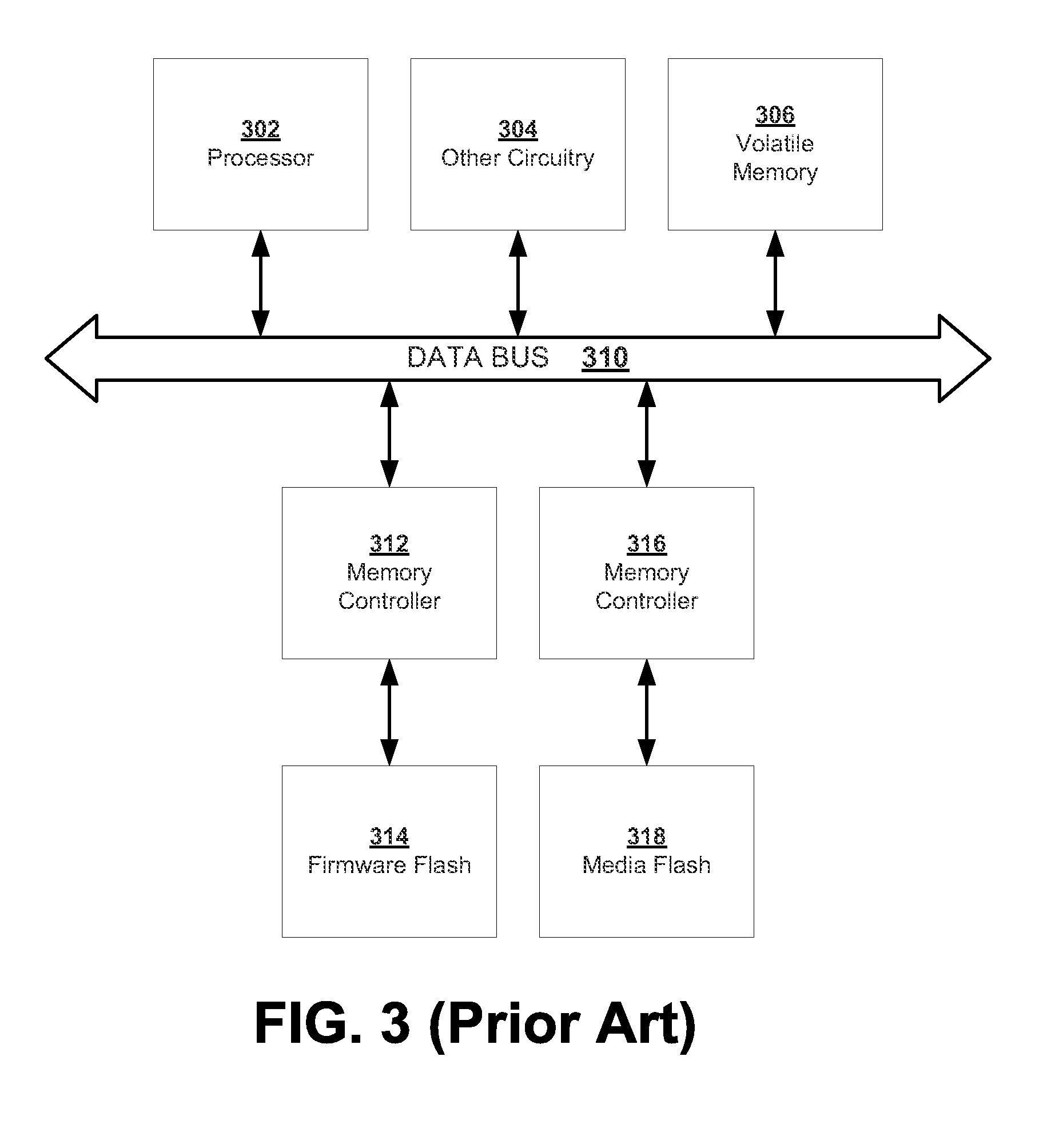

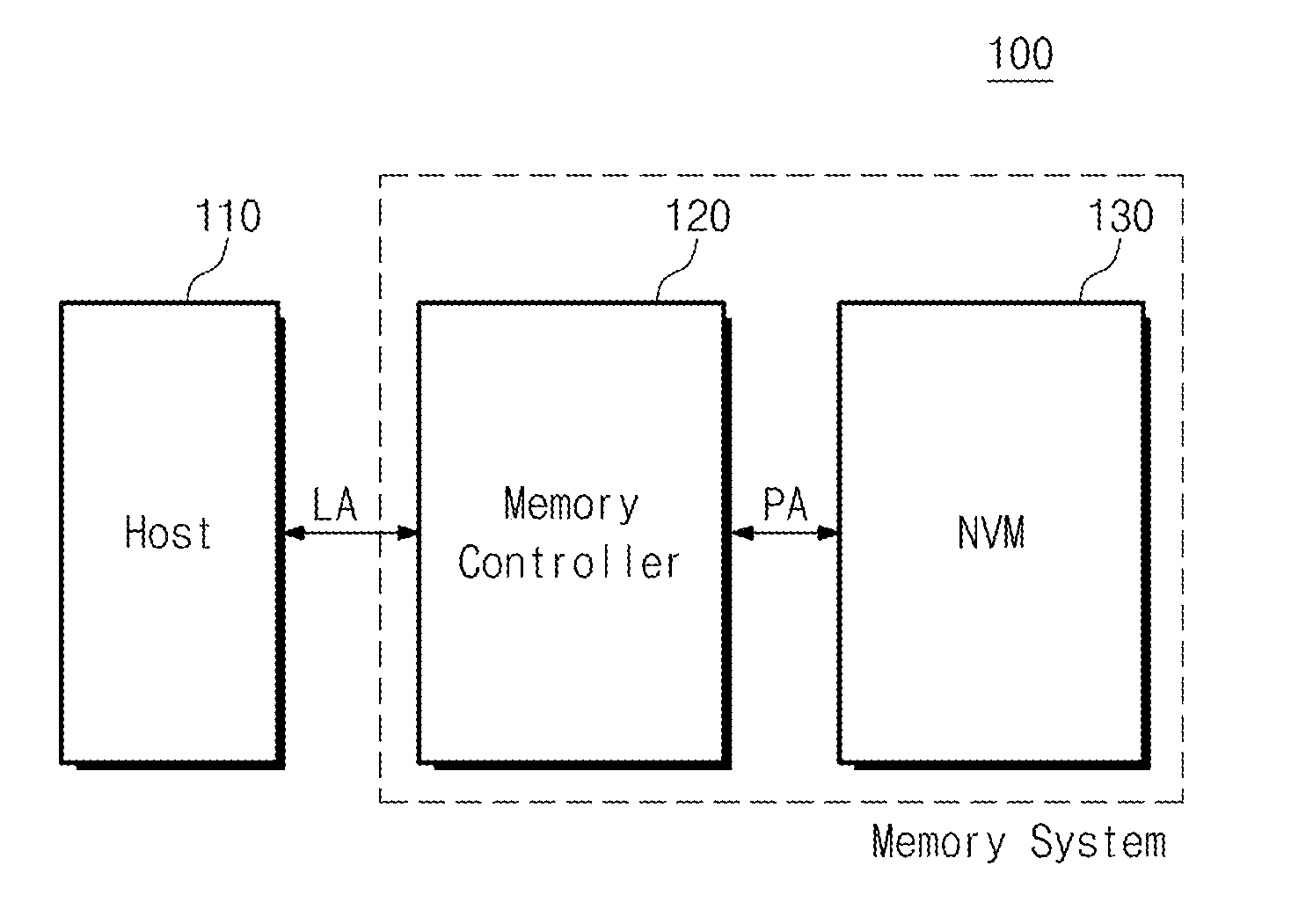

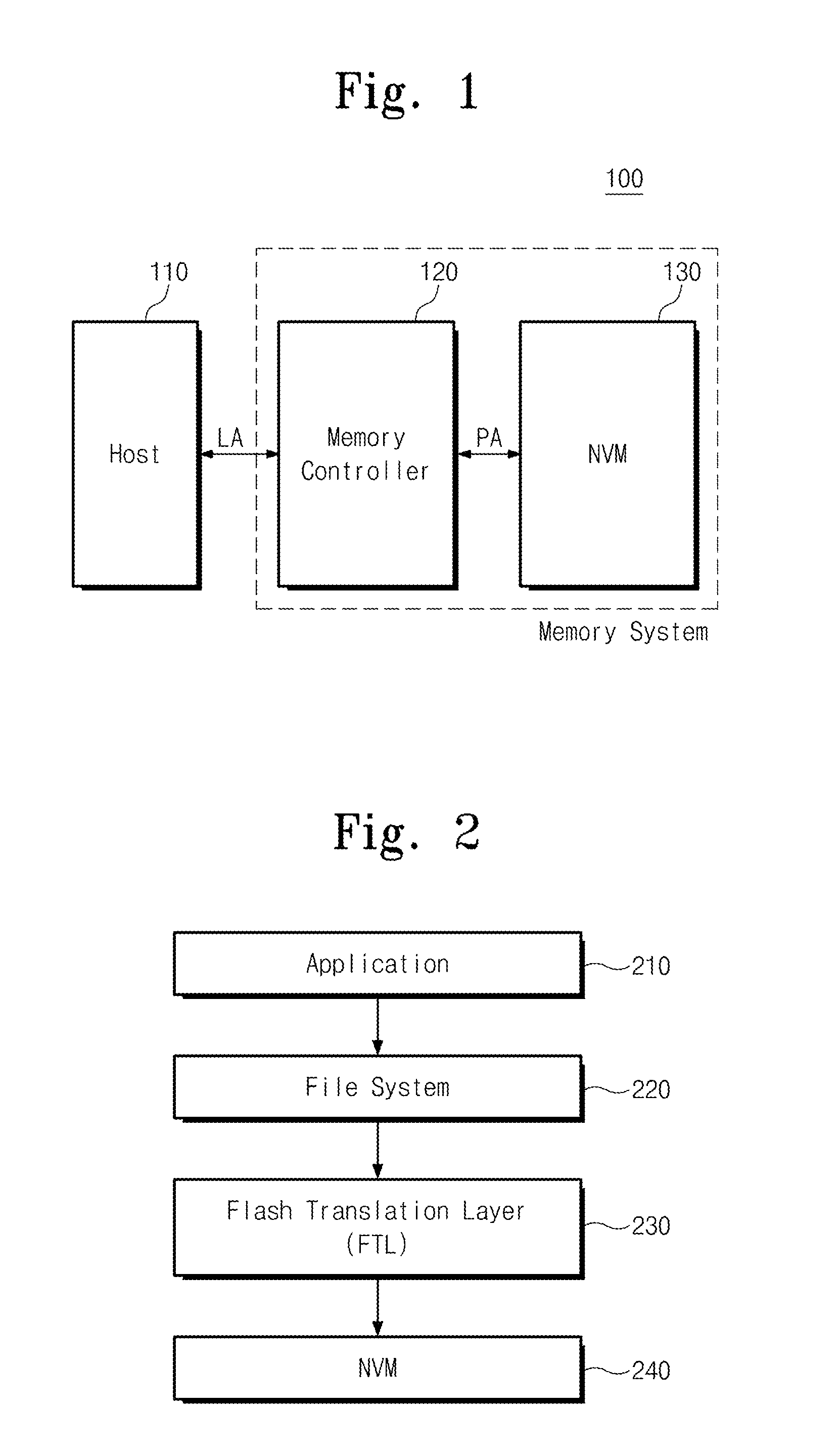

A hybrid solid-state disk (SSD) has multi-level-cell (MLC) or single-level-cell (SLC) flash memory, or both. SLC flash may be emulated by MLC that uses fewer cell states. A NVM controller converts logical block addresses (LBA) to physical block addresses (PBA). Most data is block-mapped and stored in MLC flash, but some critical or high-frequency data is page-mapped to reduce block-relocation copying. A hybrid mapping table has a first-level and a second level. Only the first level is used for block-mapped data, but both levels are used for page-mapped data. The first level contains a block-page bit that indicates if the data is block-mapped or page-mapped. A PBA field in the first-level table maps block-mapped data, while a virtual field points to the second-level table where the PBA and page number is stored for page-mapped data. Page-mapped data is identified by a frequency counter or sector count. SRAM space is reduced.

Owner:SUPER TALENT ELECTRONICS

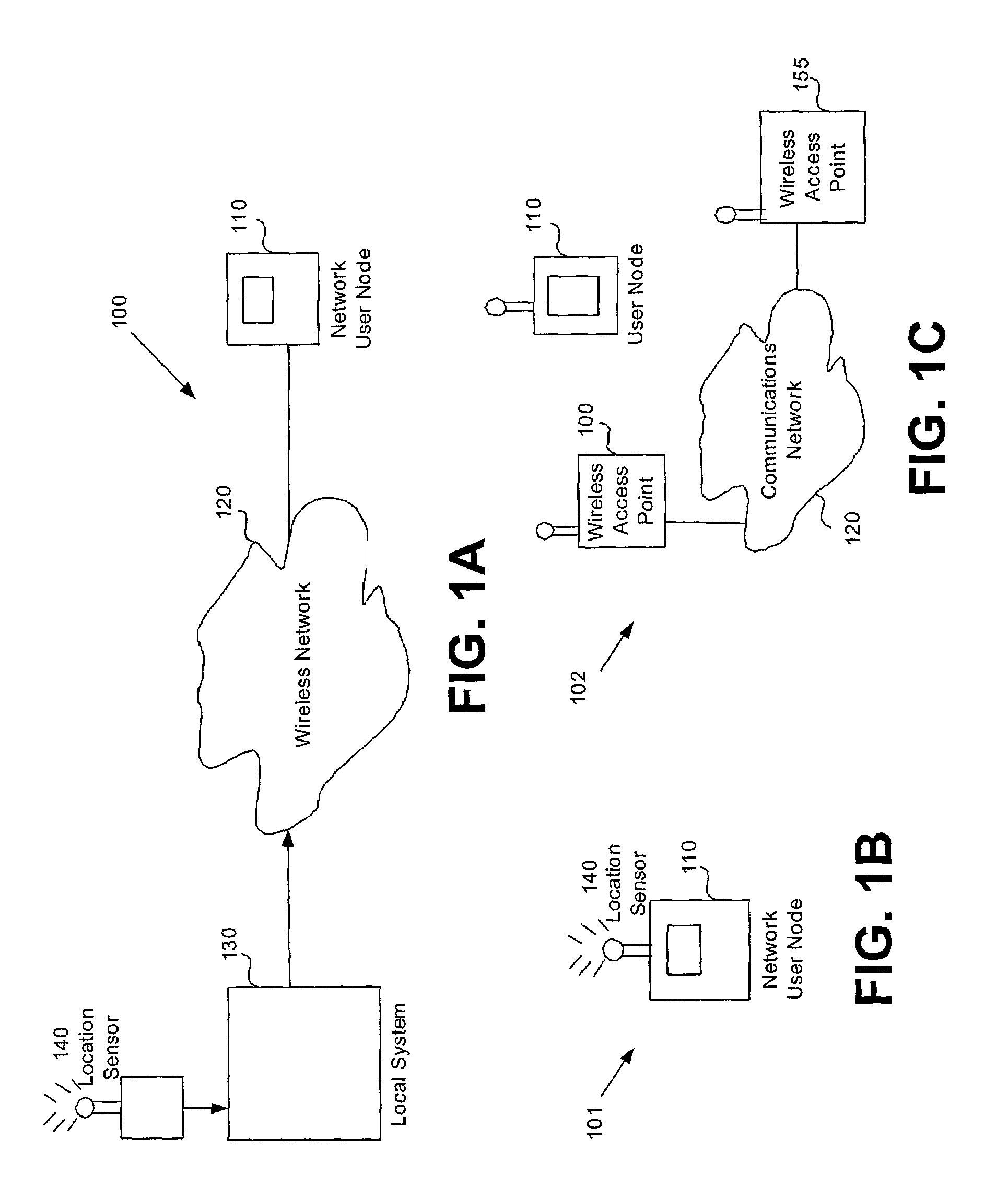

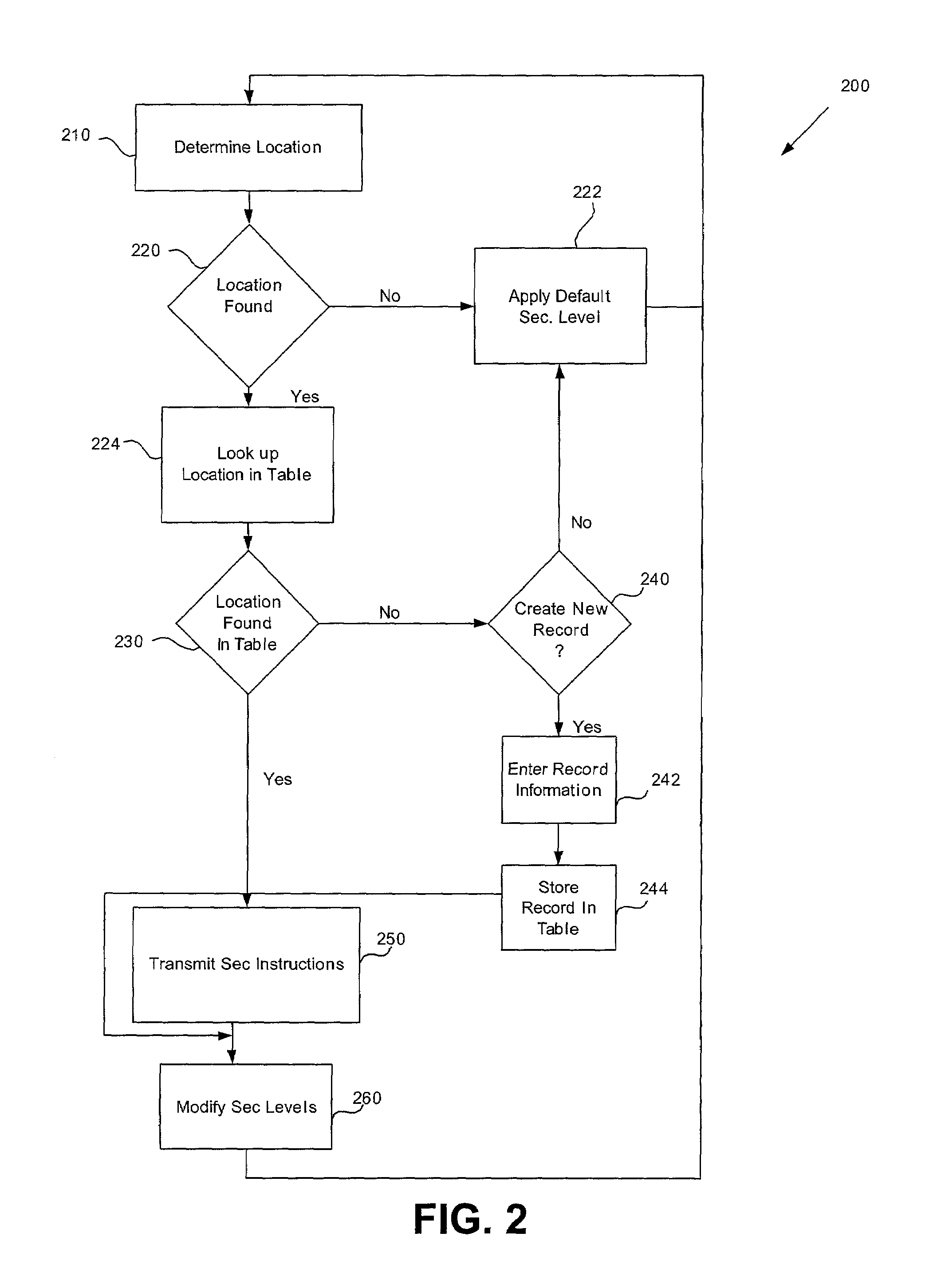

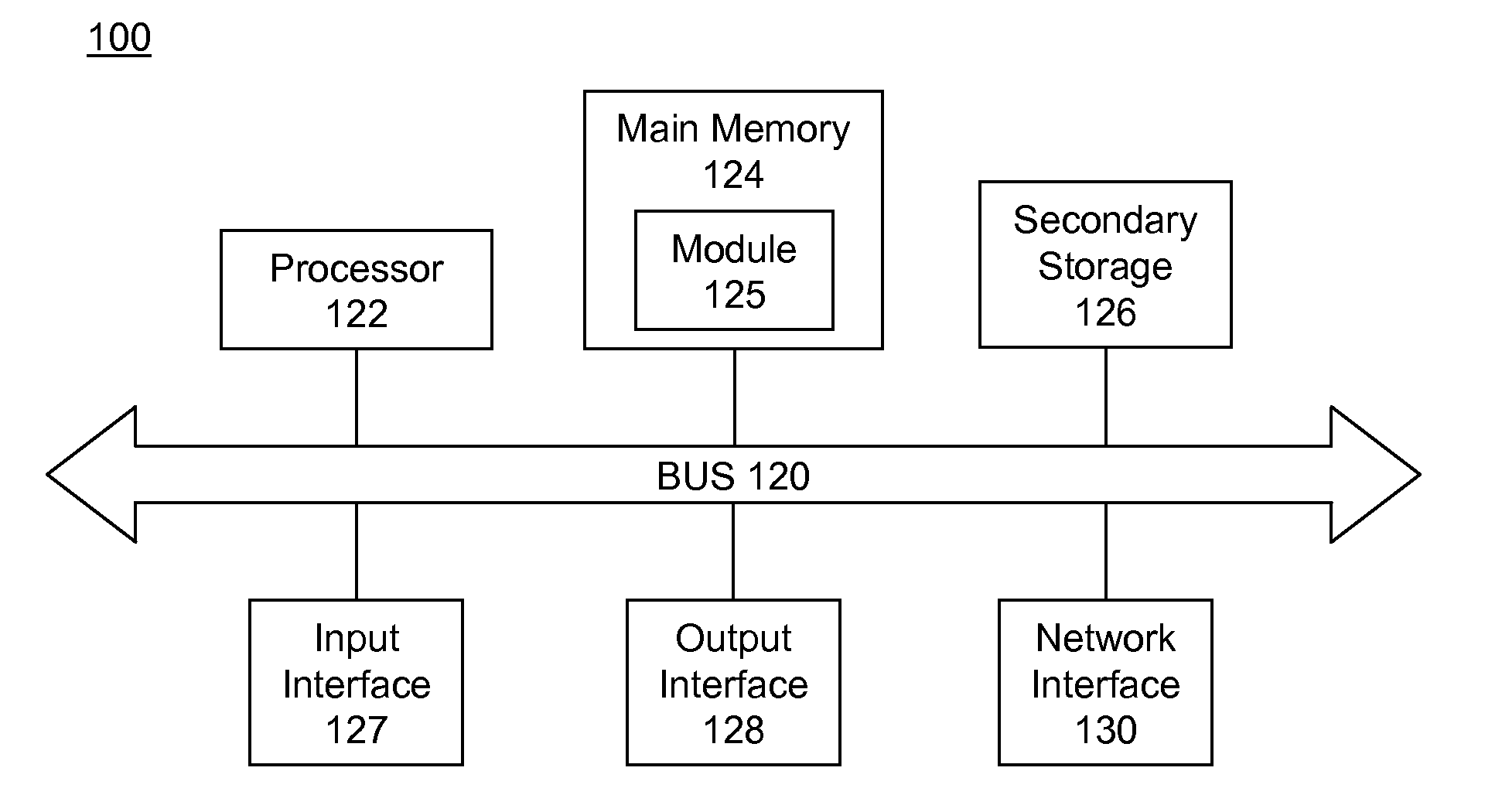

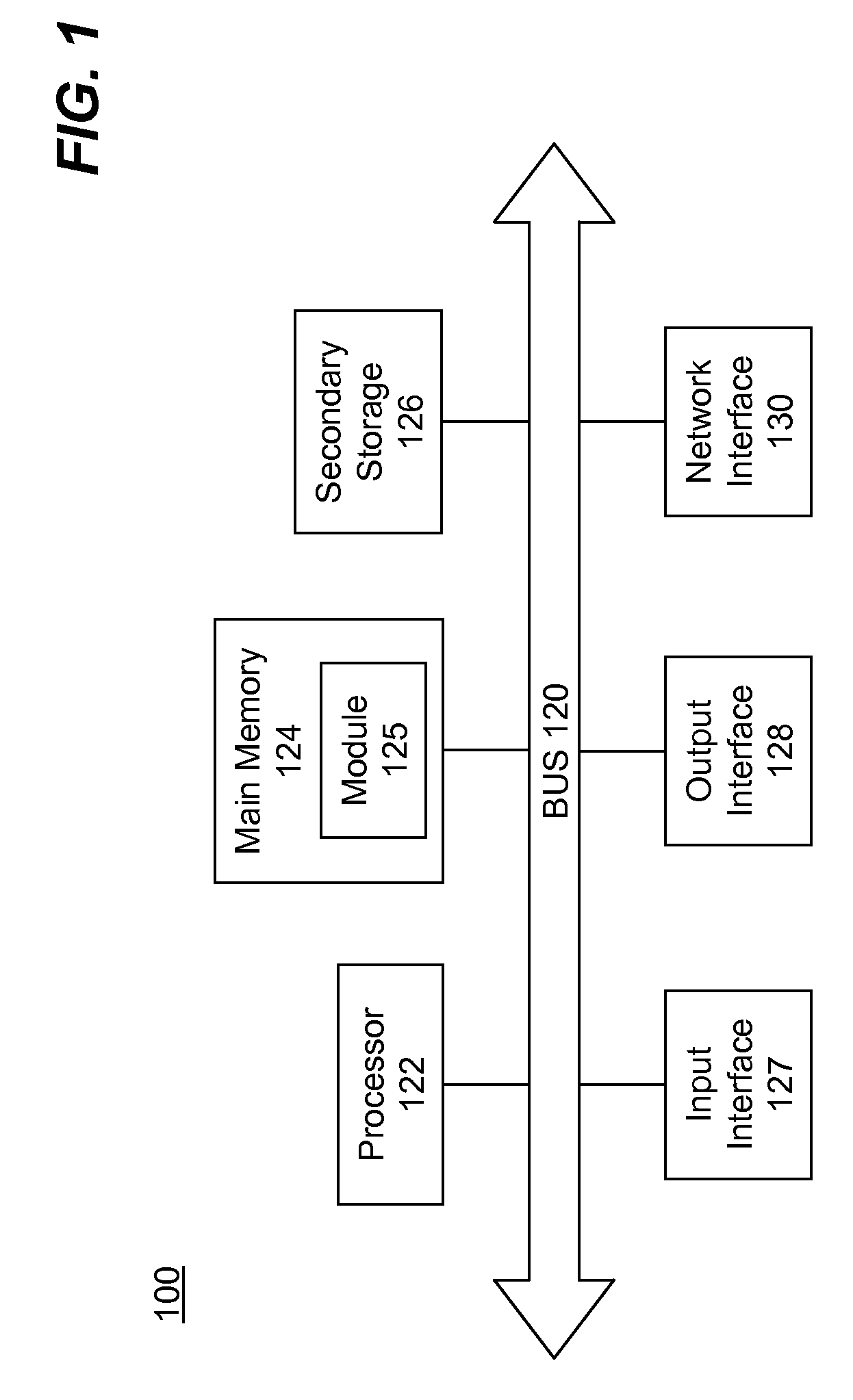

Location based security modification system and method

ActiveUS7591020B2Unauthorised/fraudulent call preventionEavesdropping prevention circuitsSingle levelSecurity level

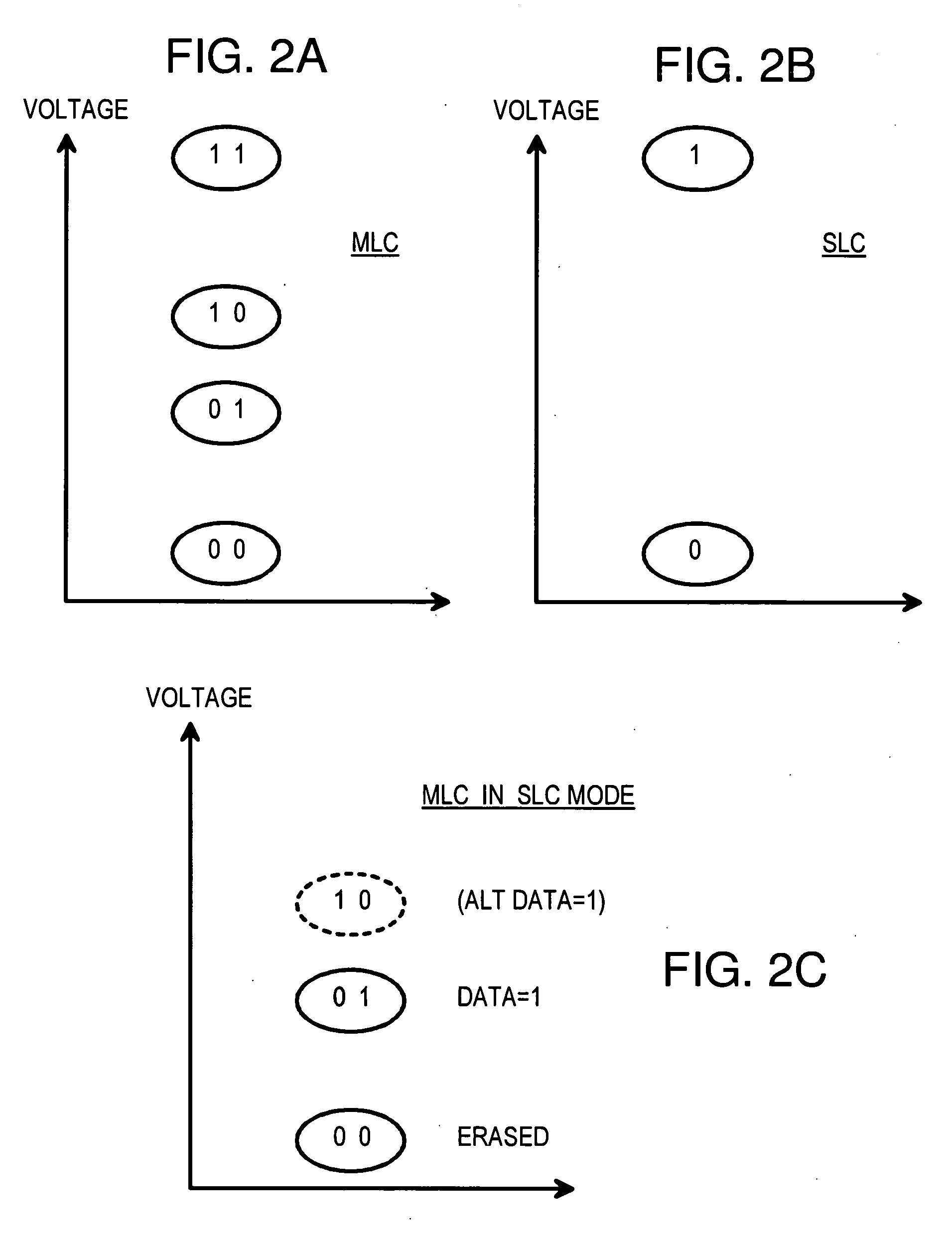

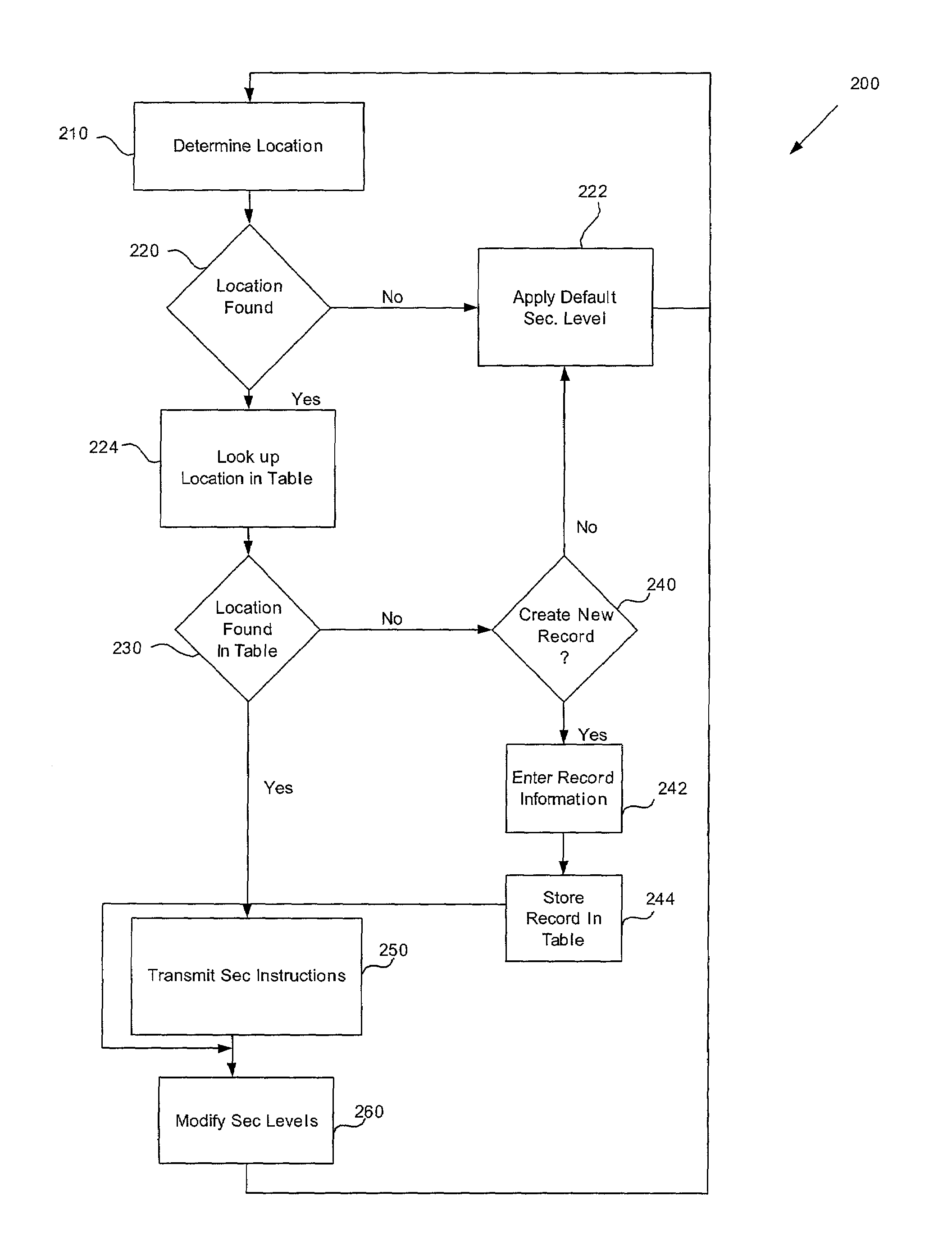

A method or system for providing a level of data security dependent on the location of the user of a wireless device is disclosed. One exemplary embodiment relates to a method of adjusting security for a network user node in communication with a network based upon the location of the node. The method is performed by determining the location of a network user node, selecting a single level of security from a group of more than two security levels based on the determined location, and modifying the security protection for the network user node based upon the selected level of security.

Owner:QUALCOMM INC

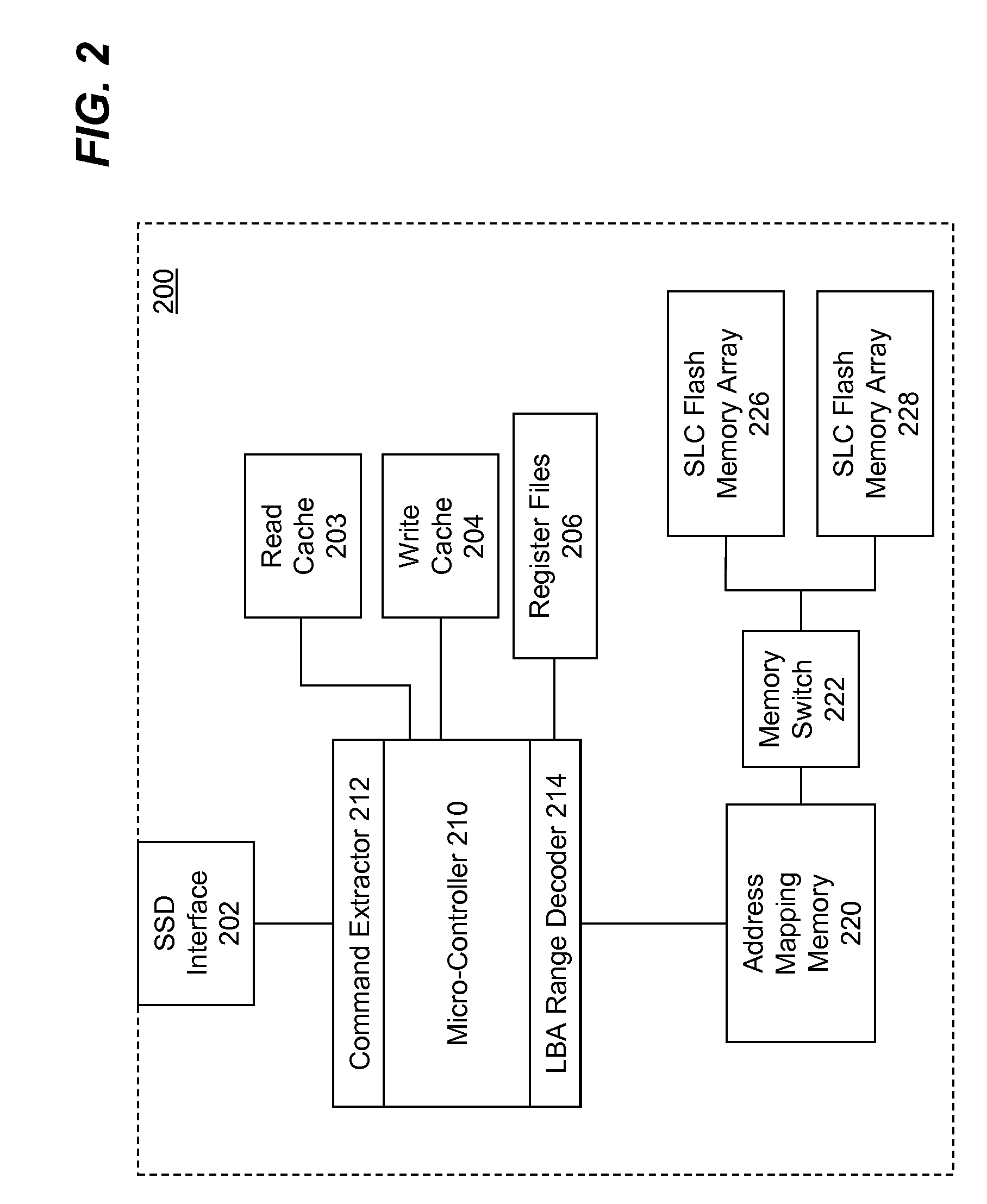

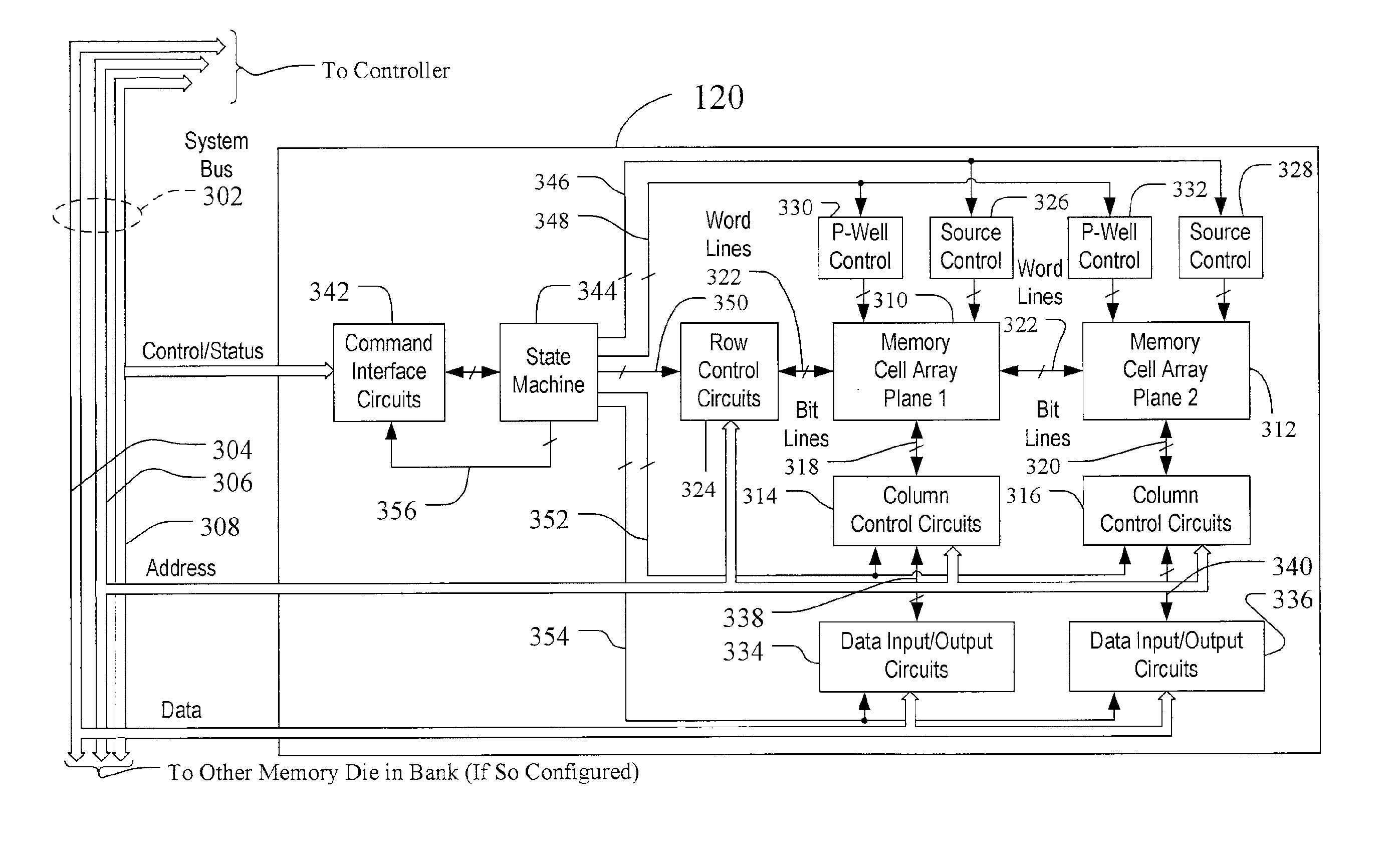

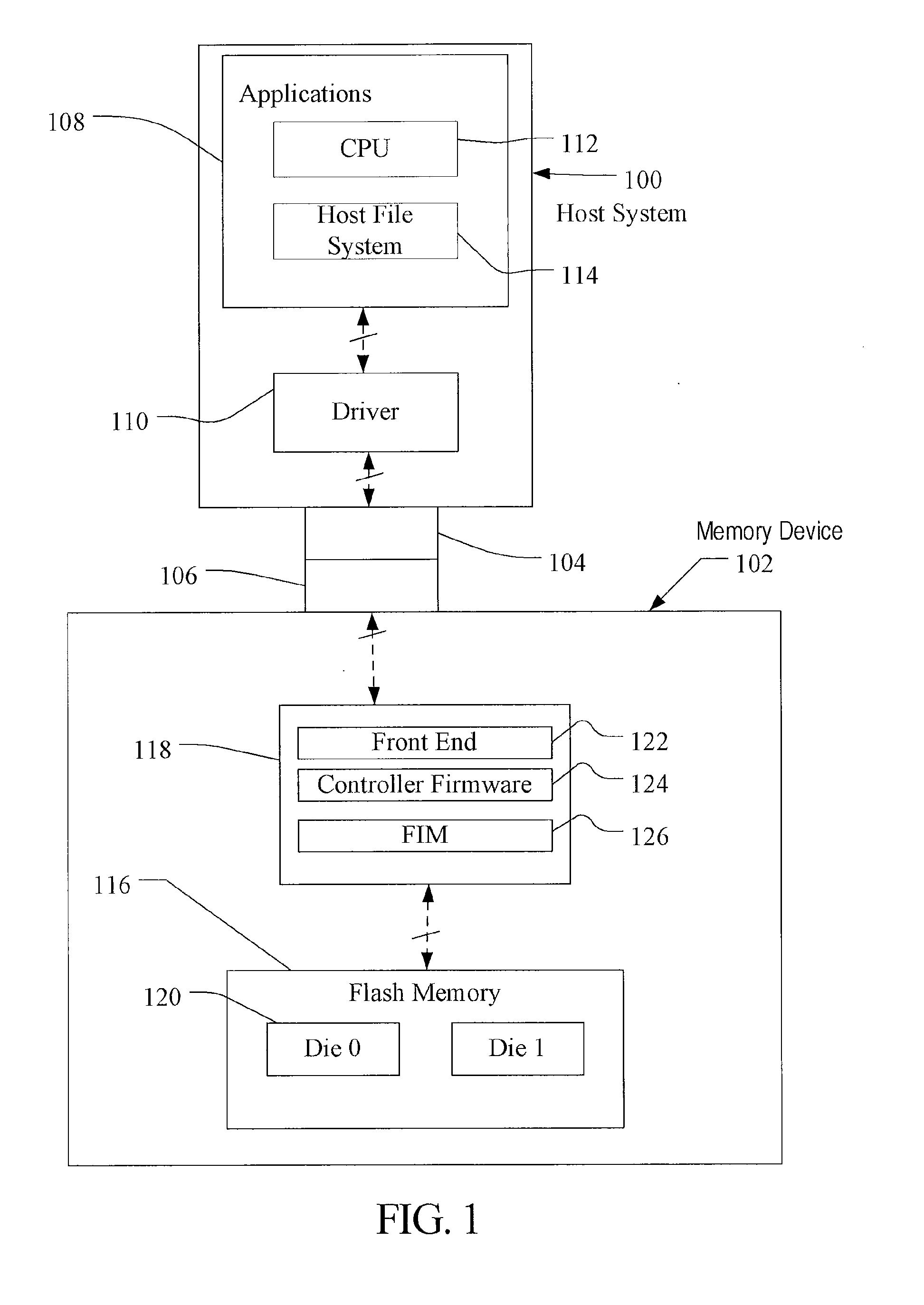

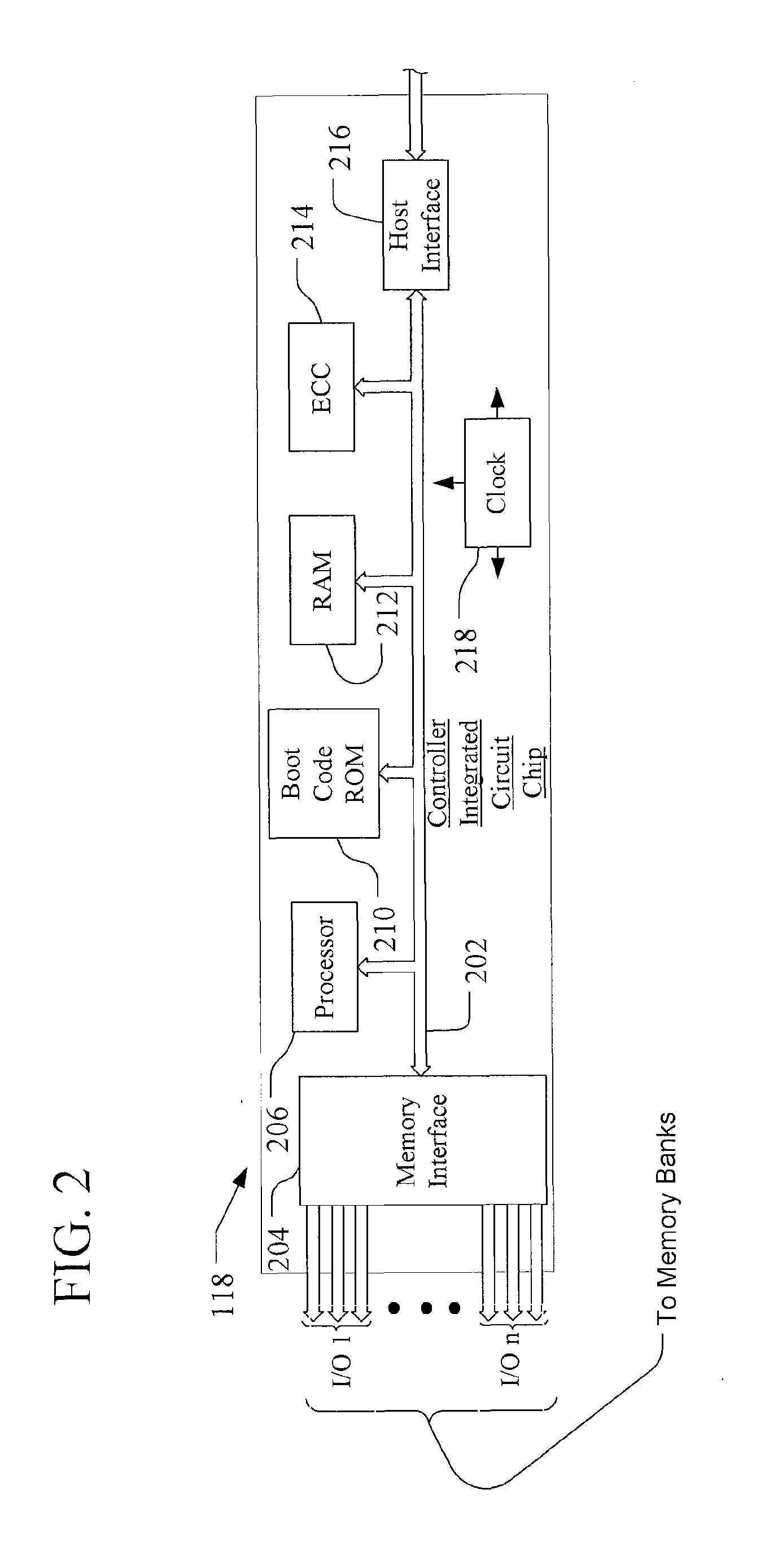

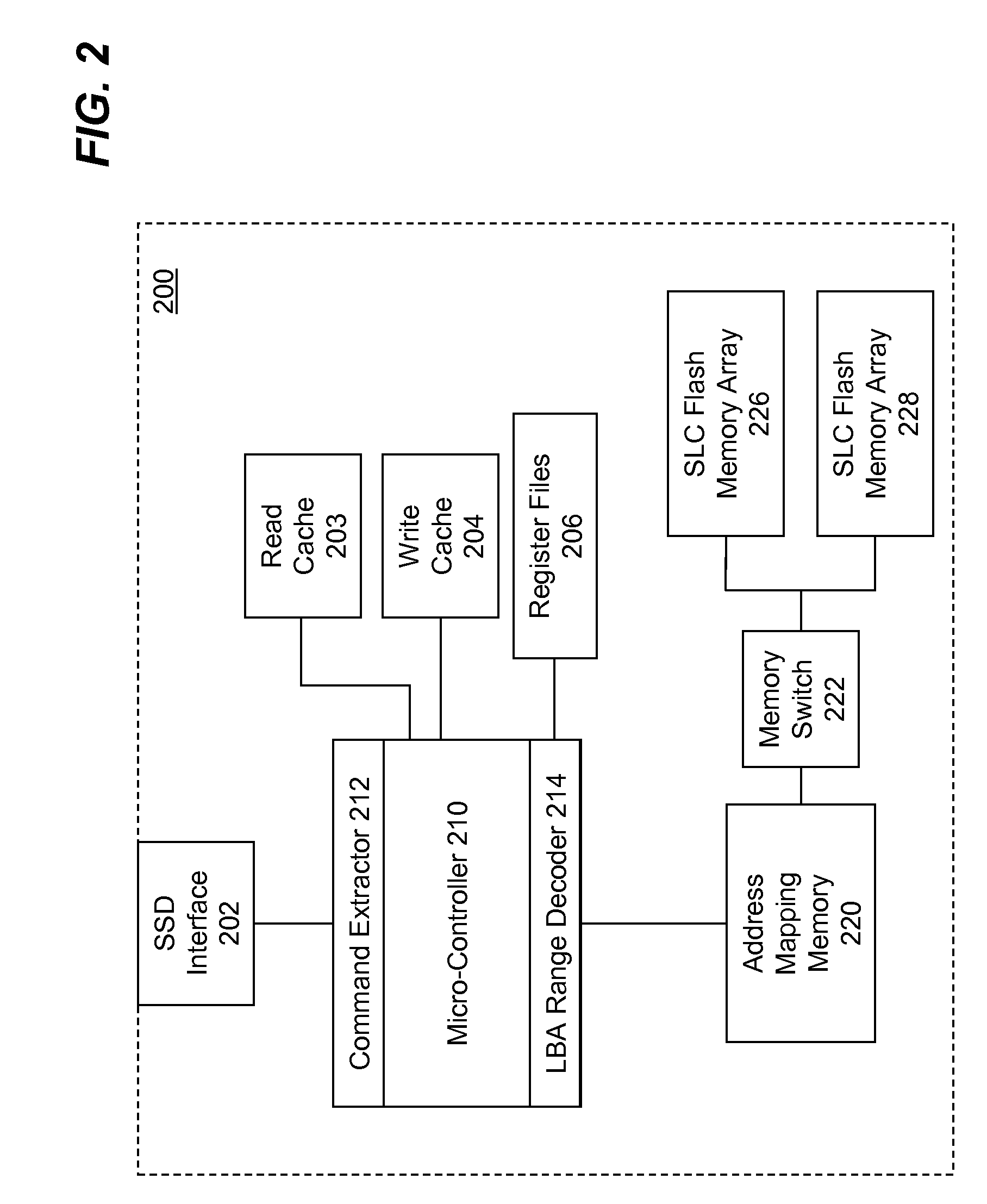

Hybrid SSD Using A Combination of SLC and MLC Flash Memory Arrays

InactiveUS20080215800A1Reduce manufacturing costAcceptable levelMemory architecture accessing/allocationInternal/peripheral component protectionData fileSingle level

Hybrid solid state drives (SSD) using a combination of single-level cell (SLC) and multi-level cell (MLC) flash memory arrays are described. According to one aspect of the present invention, a hybrid SSD is built using a combination SLC and MLC flash memory arrays. The SSD also includes a micro-controller to control and coordinate data transfer from a host computing device to either the SLC flash memory array of the MLC flash memory array. A memory selection indicator is determined by triaging data file based on one or more criteria, which include, but is not limited to, storing system files and user directories in the SLC flash memory array and storing user files in the MLC flash memory array; or storing more frequent access files in the SLC flash memory array, while less frequent accessed files in the MLC flash memory array.

Owner:SUPER TALENT TECH CORP

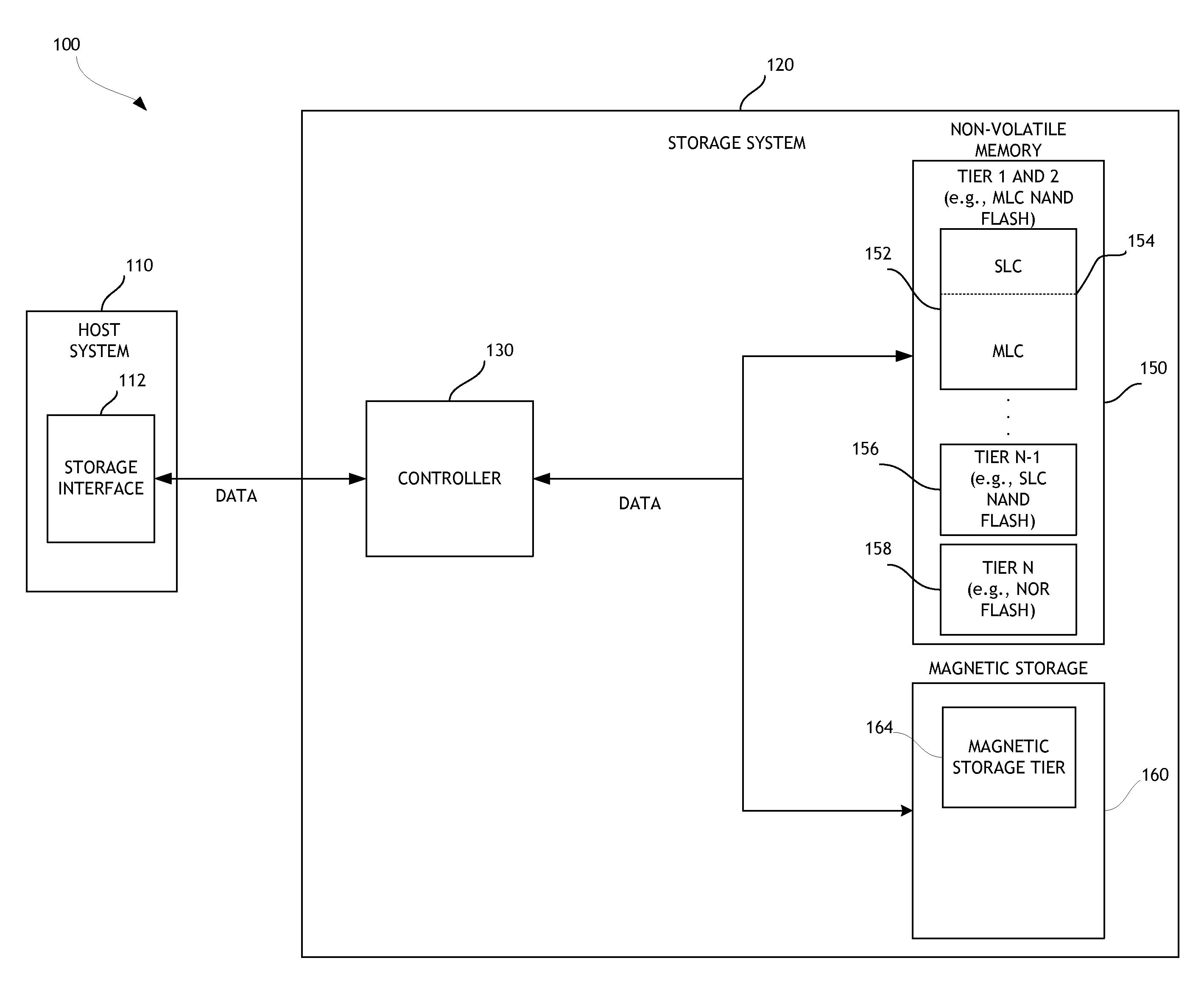

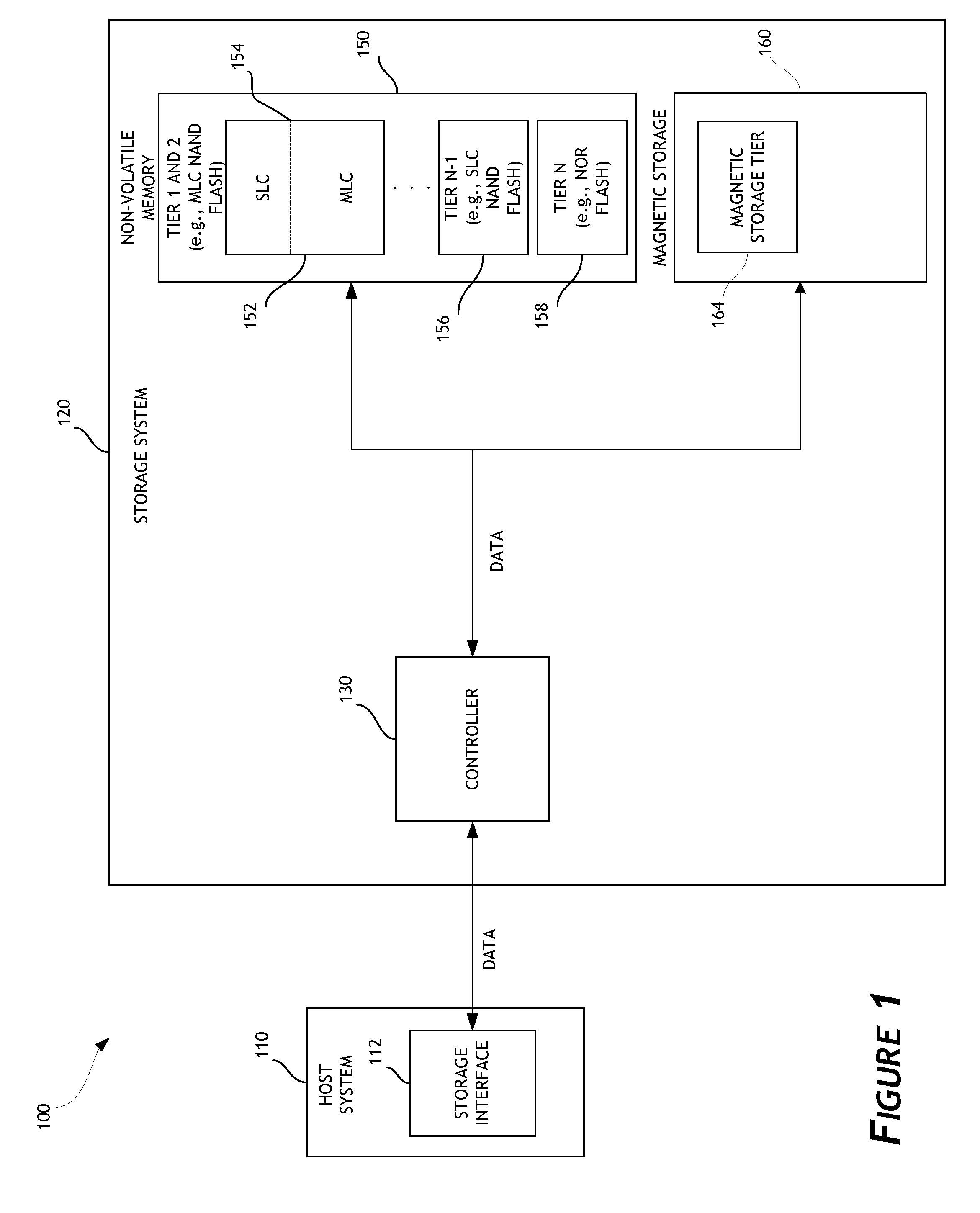

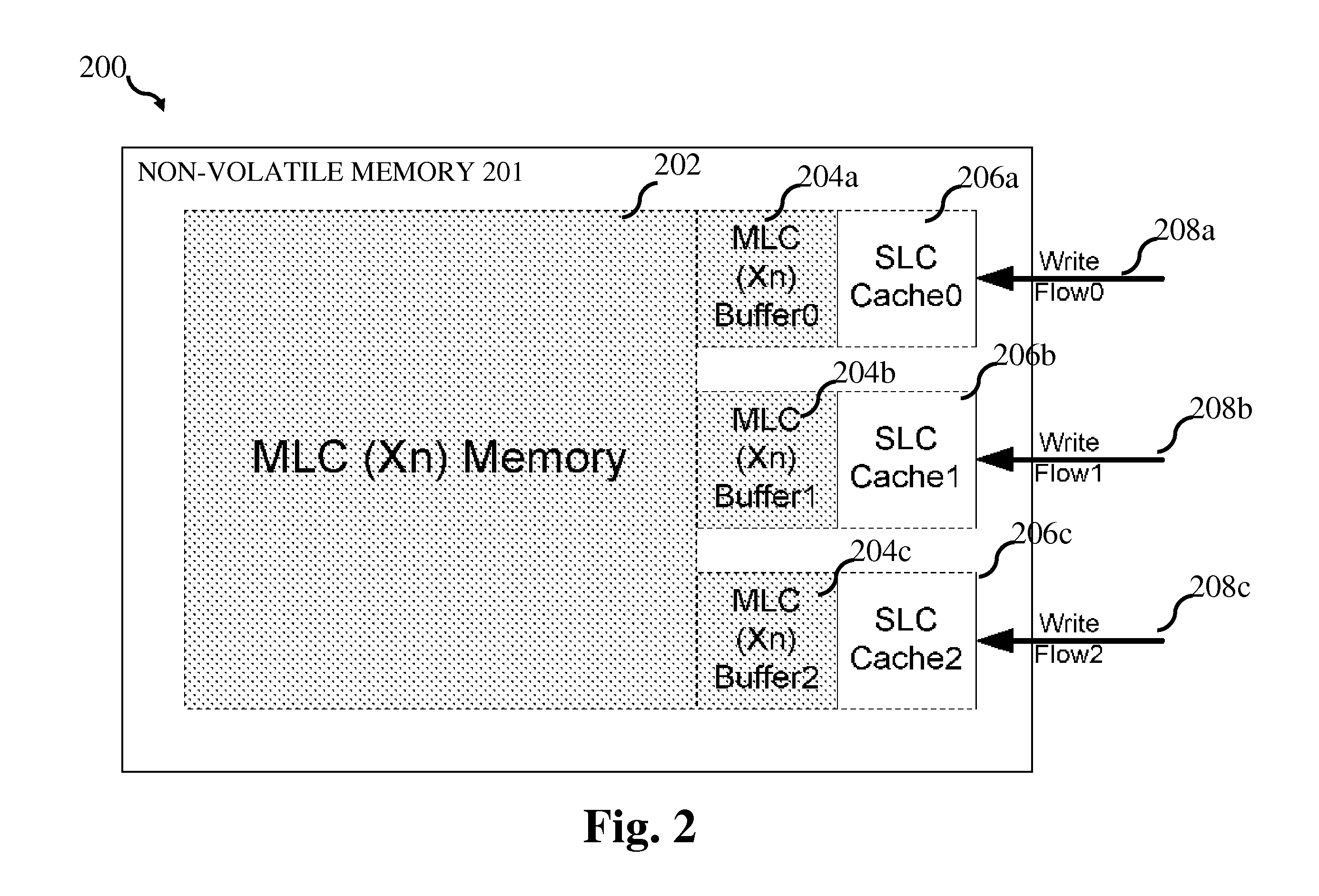

Disk drive data caching using a multi-tiered memory

ActiveUS20130132638A1Limit usable lifeReduce dataMemory architecture accessing/allocationEnergy efficient ICTSingle levelComputer science

A disk drive is disclosed that utilizes multi-tiered solid state memory for caching data received from a host. Data can be stored in a memory tier that can provide the required performance at a low cost. For example, multi-level cell (MLC) memory can be used to store data that is frequently read but infrequently written. As another example, single-level cell (SLC) memory can be used to store data that is frequently written. Improved performance, reduced costs, and improved power consumption can thereby be attained.

Owner:WESTERN DIGITAL TECH INC

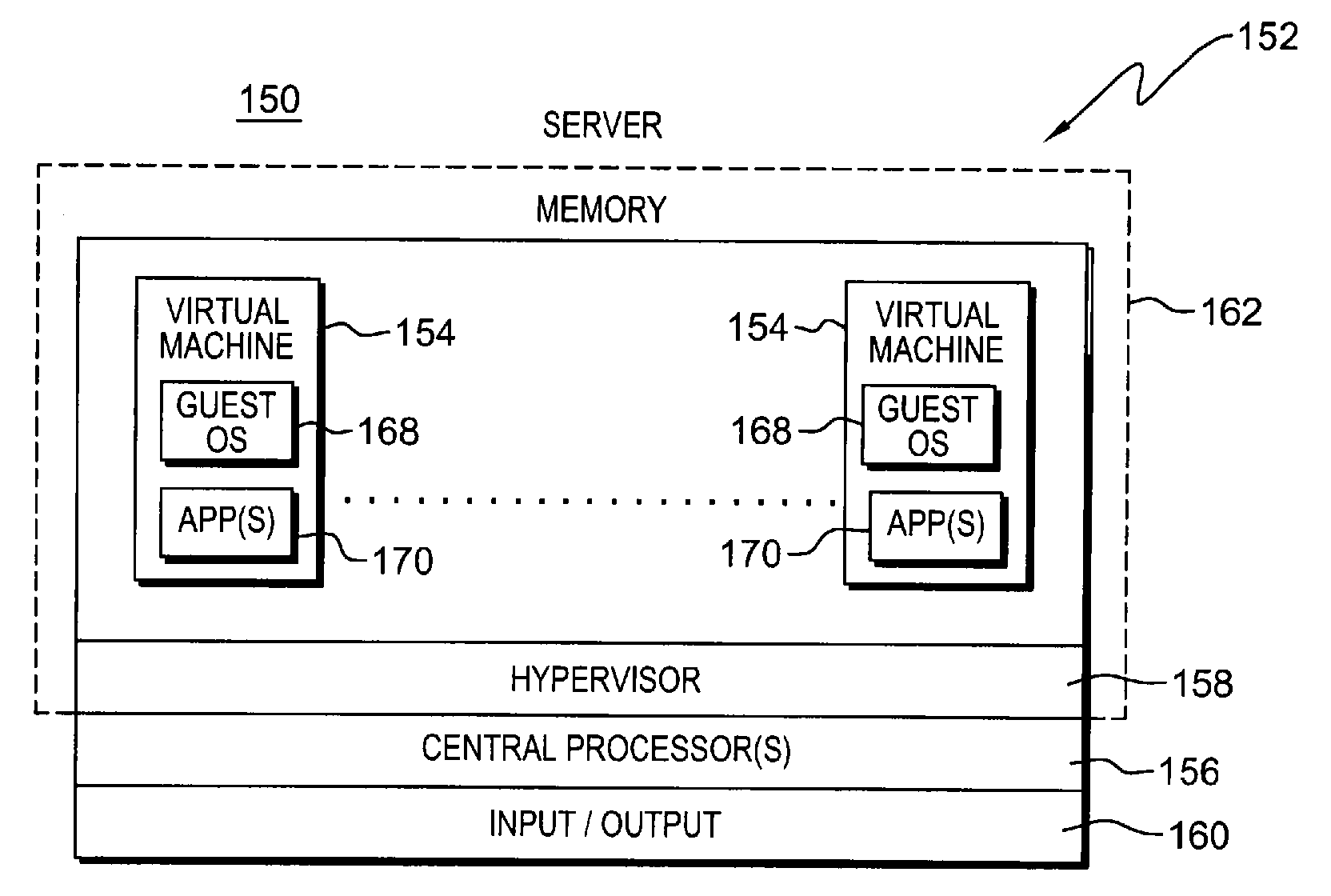

System supporting multiple partitions with differing translation formats

ActiveUS20140101361A1Memory architecture accessing/allocationMemory adressing/allocation/relocationSingle levelComputer science

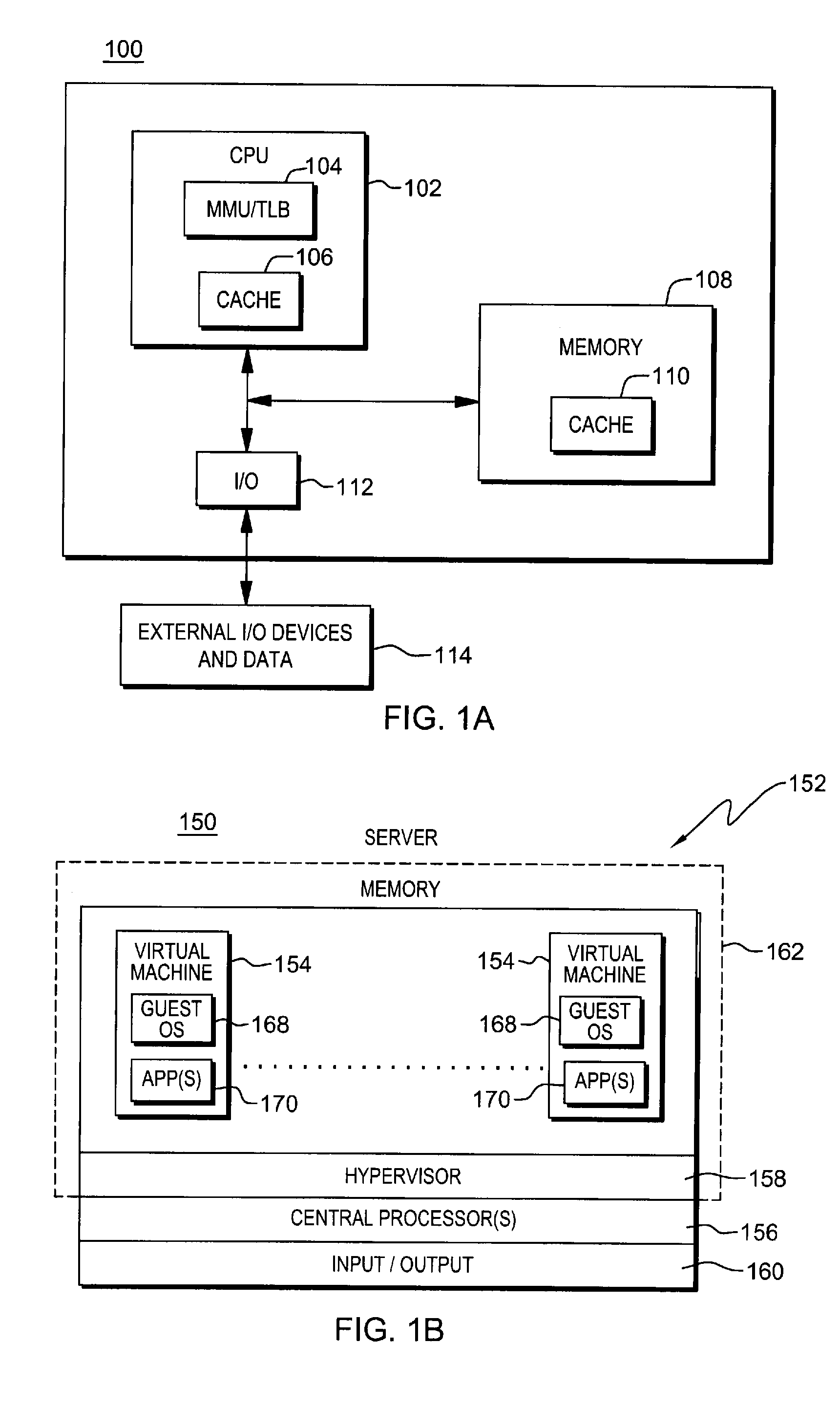

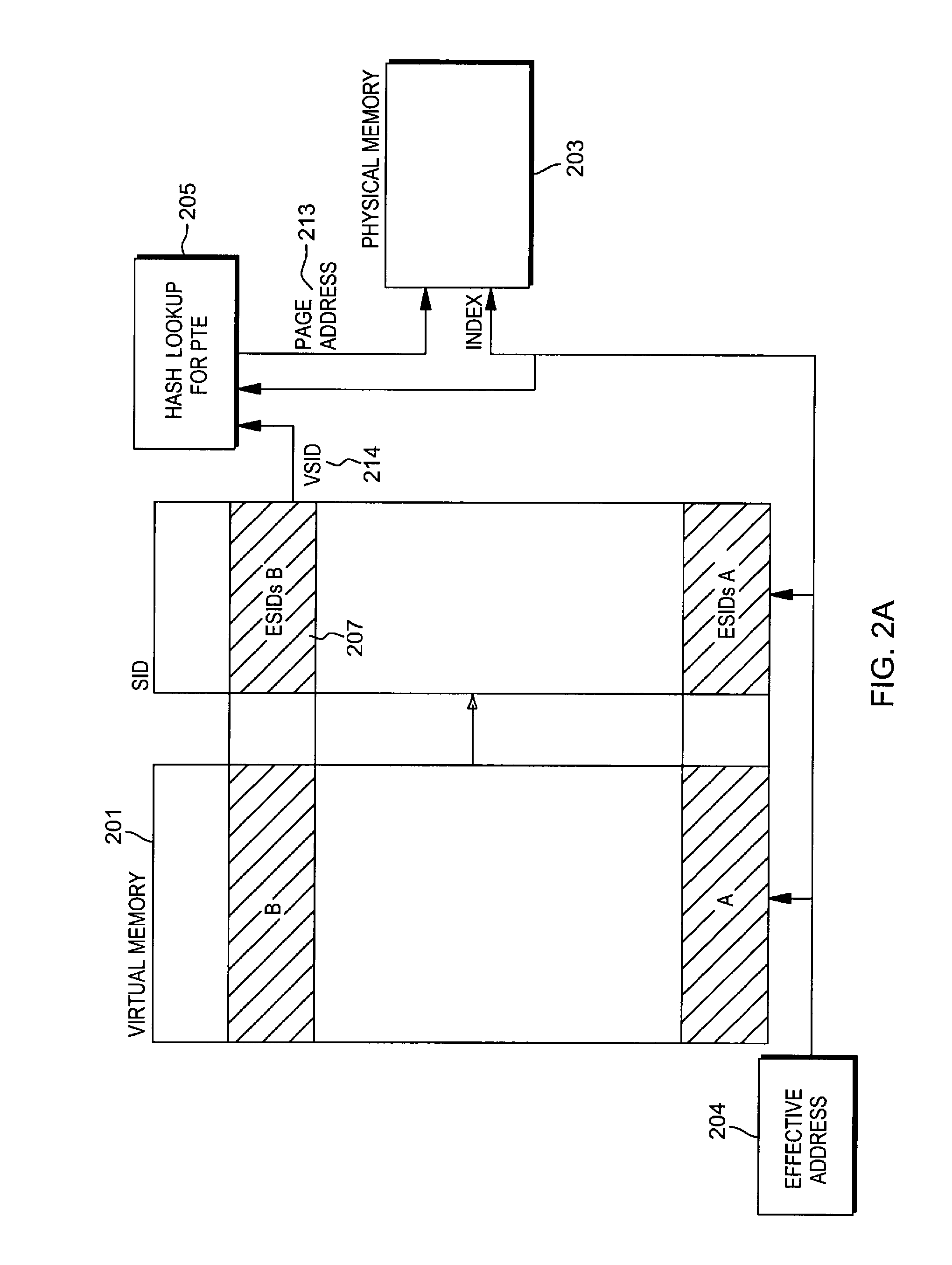

A system configuration is provided with multiple partitions that supports different types of address translation structure formats. The configuration may include partitions that use a single level of translation and those that use a nested level of translation. Further, differing types of translation structures may be used. The different partitions are supported by a single hypervisor.

Owner:IBM CORP

Plane decoding method and device for three dimensional memories

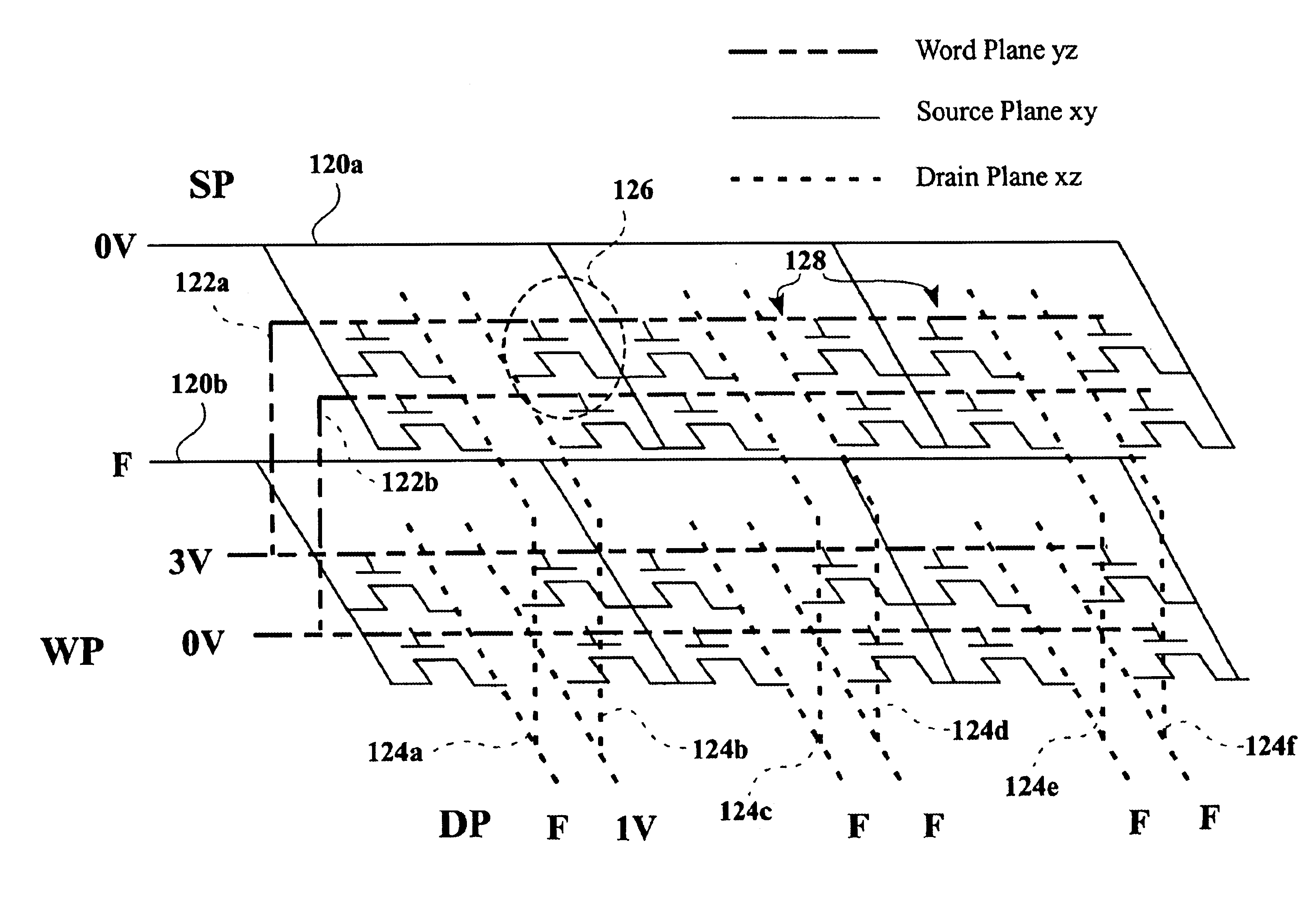

A multi-layer memory device is provided. The multi-layer memory device includes multiple layers of memory core cells. A word plane electrically connecting each first active terminal of the multiple layers of the memory core cells intersected by the word plane is included. A drain plane substantially orthogonal to the word plane is provided. The drain plane electrically connects each second active terminal of the multiple layers of the memory core cells intersected by the drain plane. A source plane substantially orthogonal to both the word plane and the drain plane is included. The source plane electrically connects each third active terminal of the memory core cells within a single level. In one embodiment, the memory core cells are defined by a device having three active terminals.

Owner:MACRONIX INT CO LTD

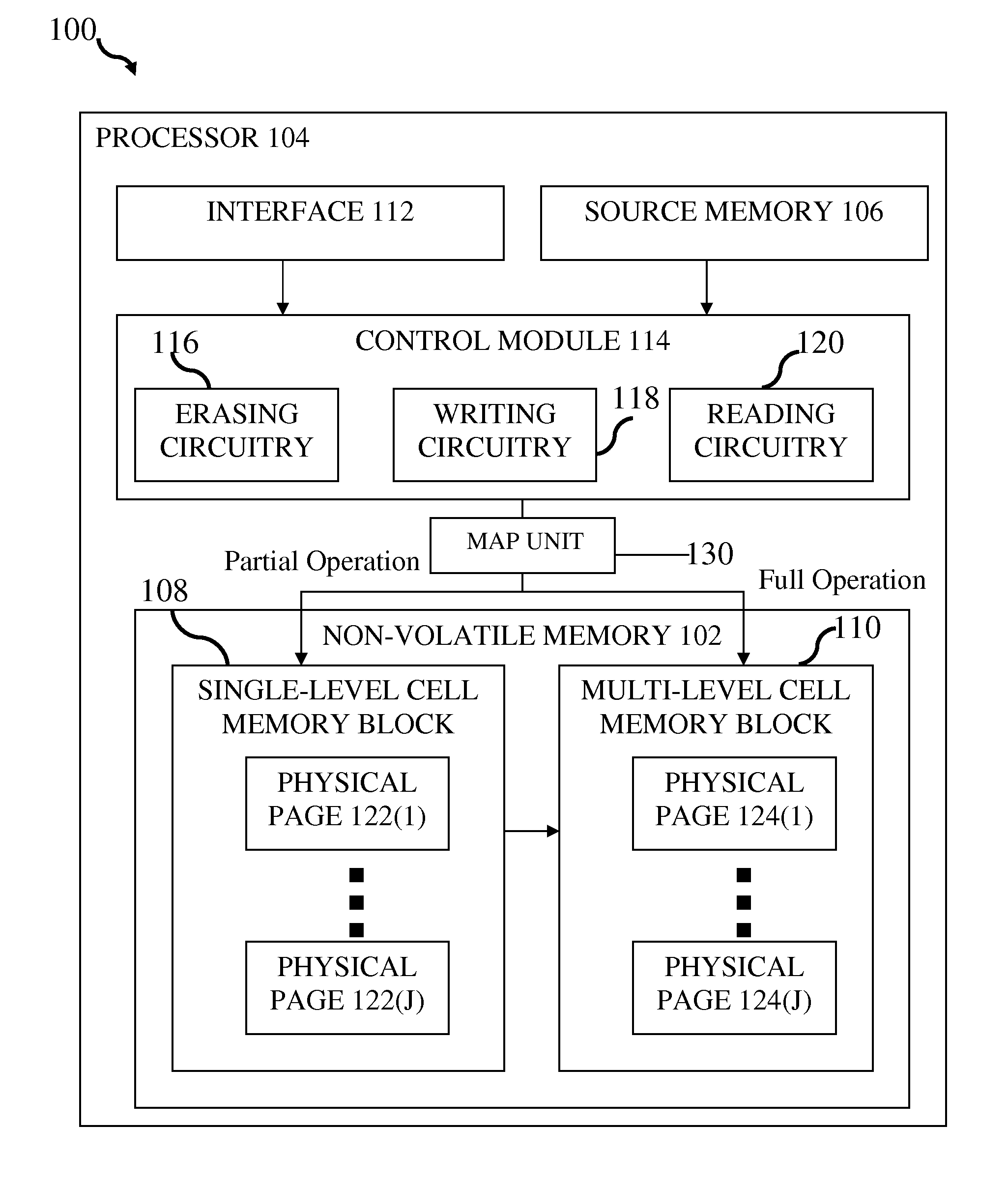

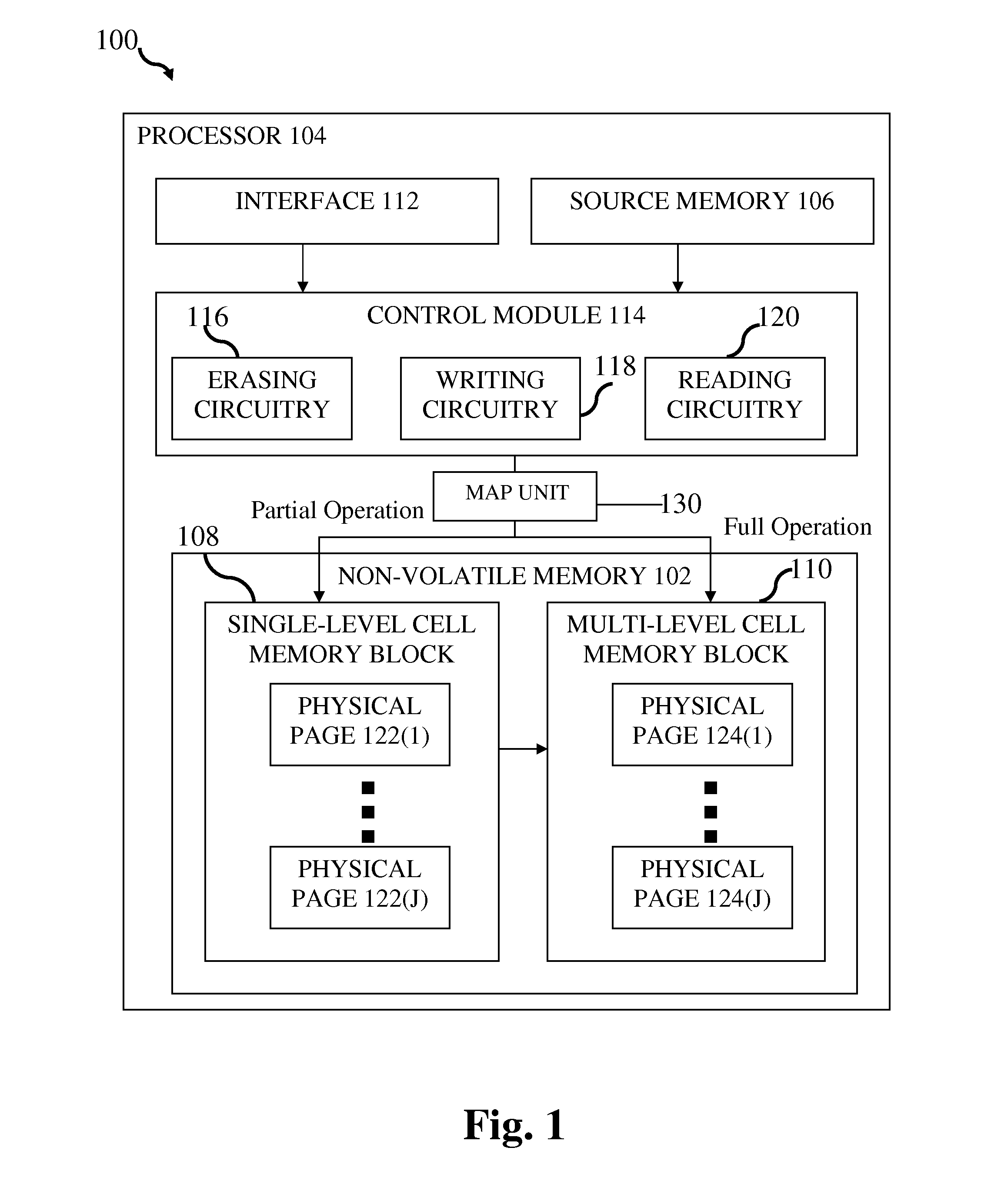

System and method for operating a non-volatile memory including a portion operating as a single-level cell memory and a portion operating as a multi-level cell memory

InactiveUS20110252187A1Reduce in quantityMemory architecture accessing/allocationMemory adressing/allocation/relocationData setSingle level

System and method for storing data in a non-volatile memory including a multi-level cell and single-level cell memory portions. To write a dataset to the non-volatile memory, if the size of the dataset is equal to the size of pages in the multi-level cell memory portion, the dataset may be written directly to the multi-level cell memory portion to fill an integer number of pages in a single write operation. However, if the size of the dataset is different than the size of the multi-level cell memory pages, at least a portion of the dataset may be temporarily written to the single-level cell memory portion until data is accumulated in a plurality of write operations having a size equal the size of the multi-level cell memory pages. The accumulated data may fill an integer number of the pages in the multi-level cell memory portion in a single write operation.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

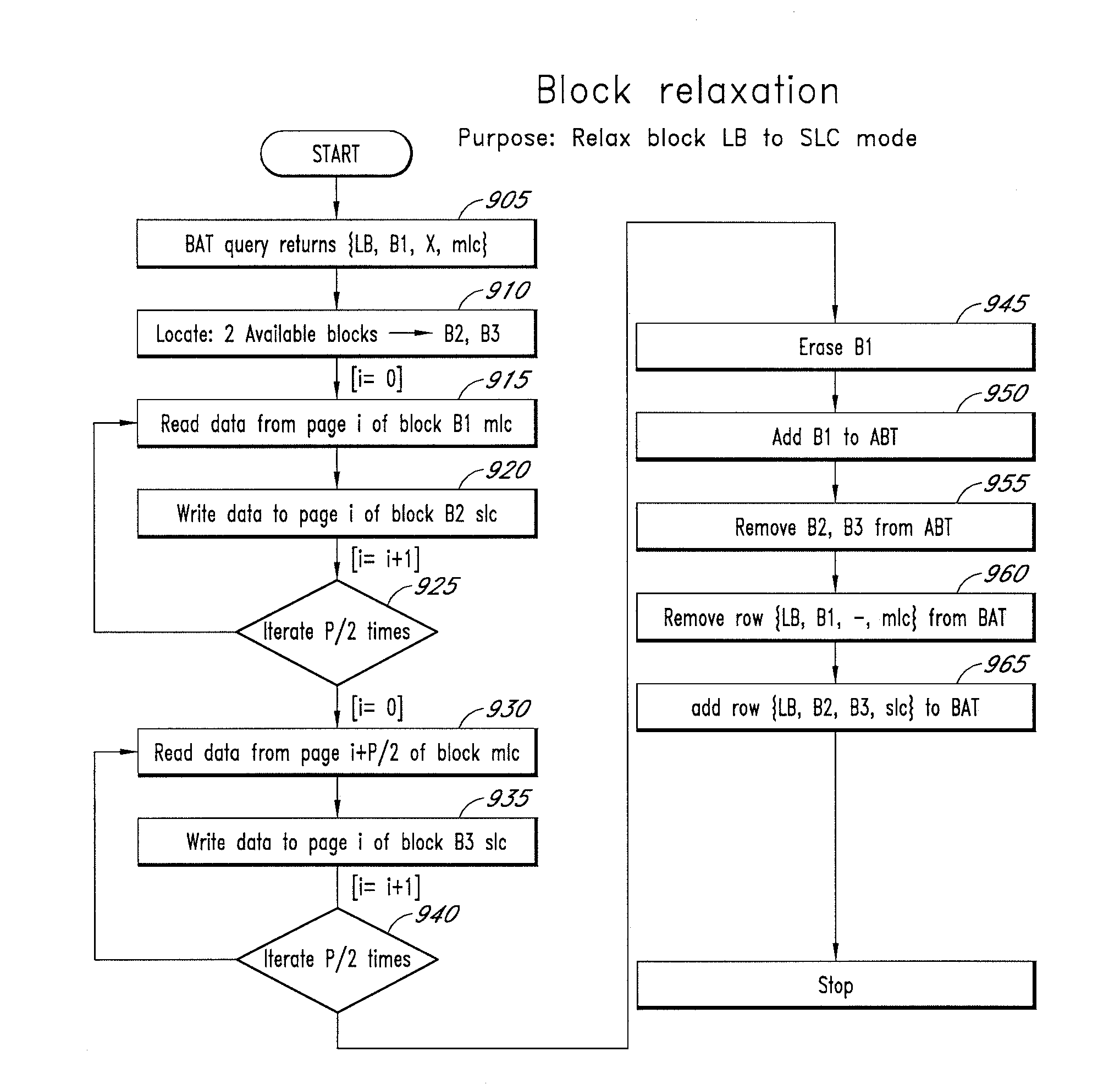

Dynamic slc/mlc blocks allocations for non-volatile memory

InactiveUS20100122016A1Memory architecture accessing/allocationMemory adressing/allocation/relocationParallel computingSingle level

Apparatus and methods are disclosed, such as those that provide dynamic block allocations in NAND flash memory between single-level cells (SLC) and multi-level cells (MLC) based on characteristics. In one embodiment, a memory controller dynamically switches between programming and / or reprogramming blocks between SLC mode and MLC mode based on the amount of memory available for use. When memory usage is low, SLC mode is used. When memory usage is high, MLC mode is used. Dynamic block allocation allows a memory controller to obtain the performance and reliability benefits of SLC mode while retaining the space saving benefits of MLC mode.

Owner:ROUND ROCK RES LLC

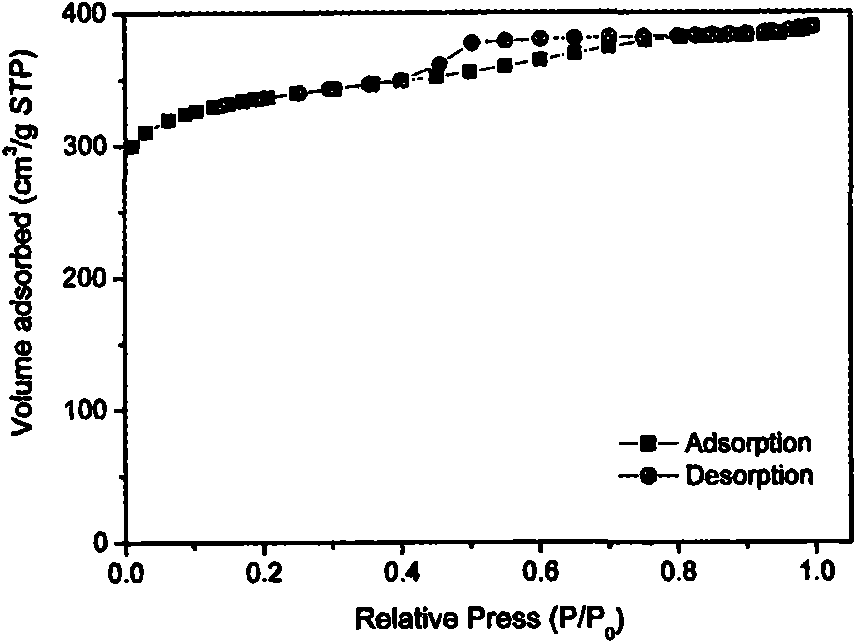

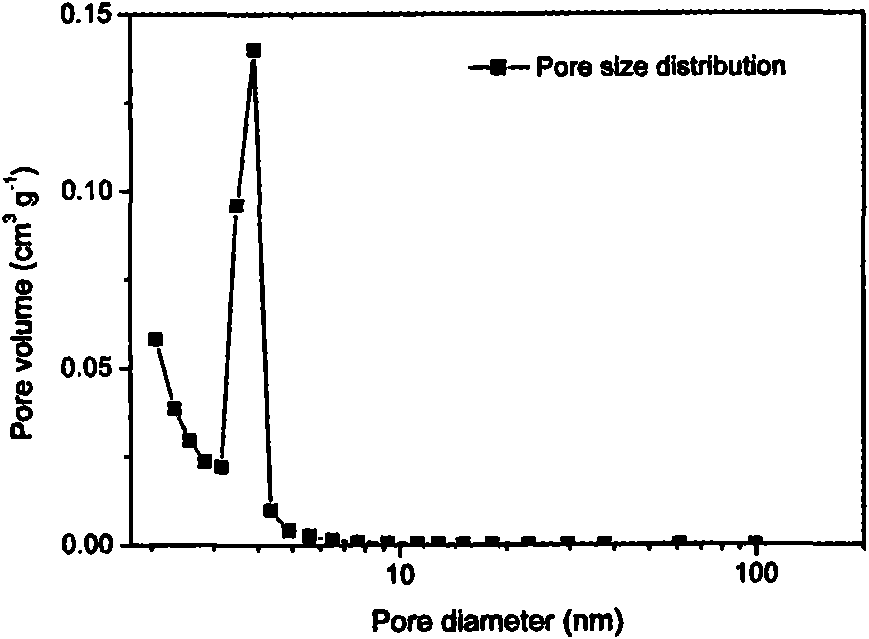

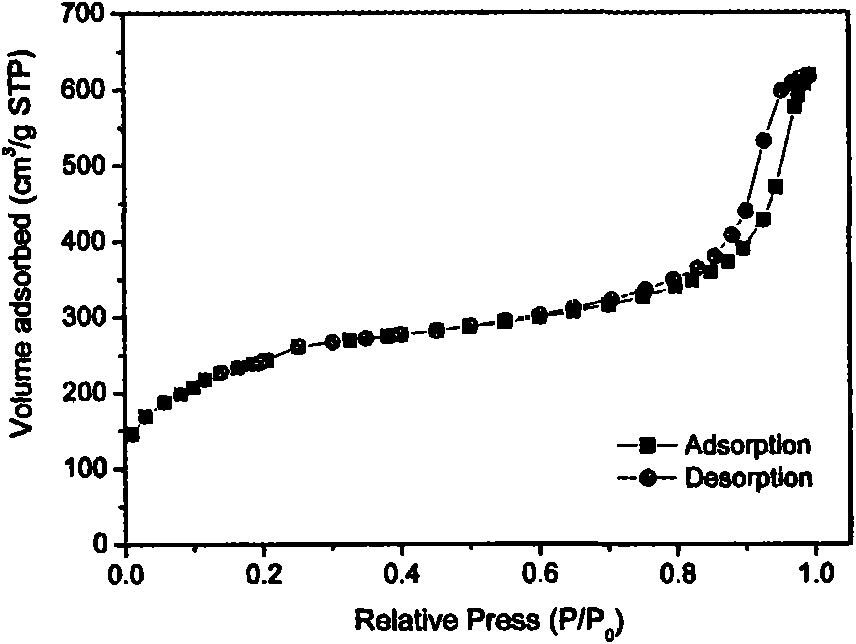

Nanometer hole metal-organic frame material in single-level or multilevel pore canal structure and preparation method thereof

The invention relates to a nanometer hole metal-organic frame material in a single-level or multilevel pore canal structure as well as a preparation method and the application thereof. The preparation method comprises the following steps: at least one metal salt and at least one polyfunctional group organic ligand reacts with at least one template agent in at least one solvent under the condition that no hole aid agent exists or only one hole aid agent exist, and single-level or multilevel nanometer holes or channels with the size of 0.5-100 nm exist in at least one direction in the internal space of the obtained metal-organic frame solid. The nanometer hole metal-organic frame material with large hole size and the nanometer hole metal-organic frame material in the layered multilevel pore canal structure can be obtained without the synthesis of the large-size organic ligand and have wide applications.

Owner:ANHUI UNIVERSITY

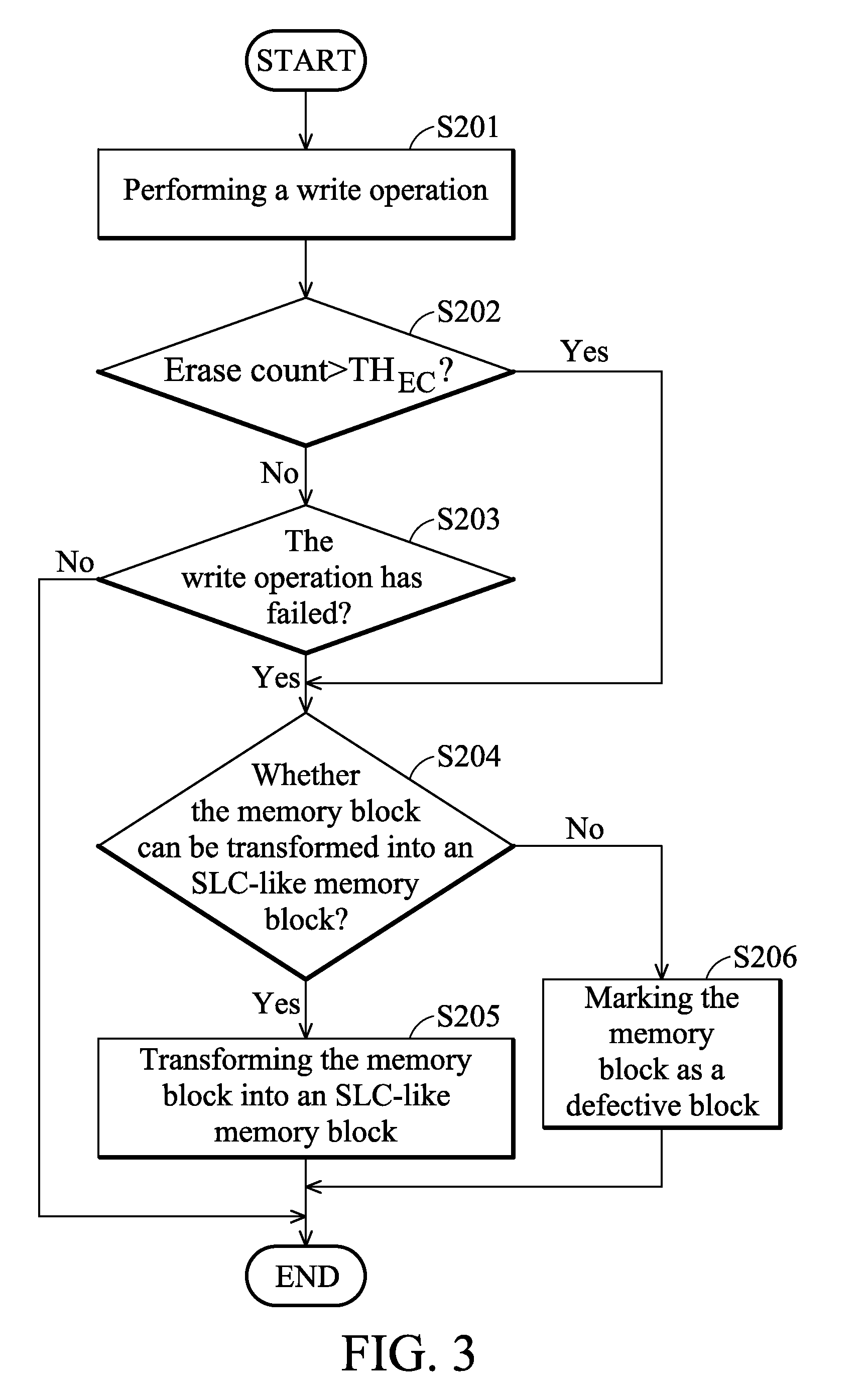

Method for managing device and solid state disk drive utilizing the same

InactiveUS20100332922A1Memory architecture accessing/allocationRead-only memoriesSingle levelMemory block

A solid state disk drive is provided. The solid state disk drive includes a multiple level cell (MLC) memory device and a controller. The MLC memory device includes memory blocks each comprising memory cells capable of storing more than a single bit of data per cell. The controller transforms at least one memory block into a single level cell (SLC)-like memory block, and accesses the memory block in an SLC manner.

Owner:MEDIATEK INC

SLC-MLC Wear Balancing

ActiveUS20130173844A1Memory architecture accessing/allocationRead-only memoriesSingle levelMulti-level cell

A method and system for SLC-MLC Wear Balancing in a flash memory device is disclosed. The flash memory device includes a single level cell (SLC) portion and a multi-level cell (MLC) portion. The age of the SLC portion and the MLC portion may differ, leading potentially to one portion wearing out before the other. In order to avoid this, a controller is configured to receive an age indicator from one or both of the SLC portion and the MLC portion, determine, based on the age indicator, whether to modify operation of the SLC portion and / or the MLC portion, and in response to determining to modifying operation, modify the operation of the at least one of the SLC portion or the MLC portion. The modification of the operation may thus balance wear between the SLC and MLC portions, thereby potentially extending the life of the flash memory device.

Owner:SANDISK TECH LLC

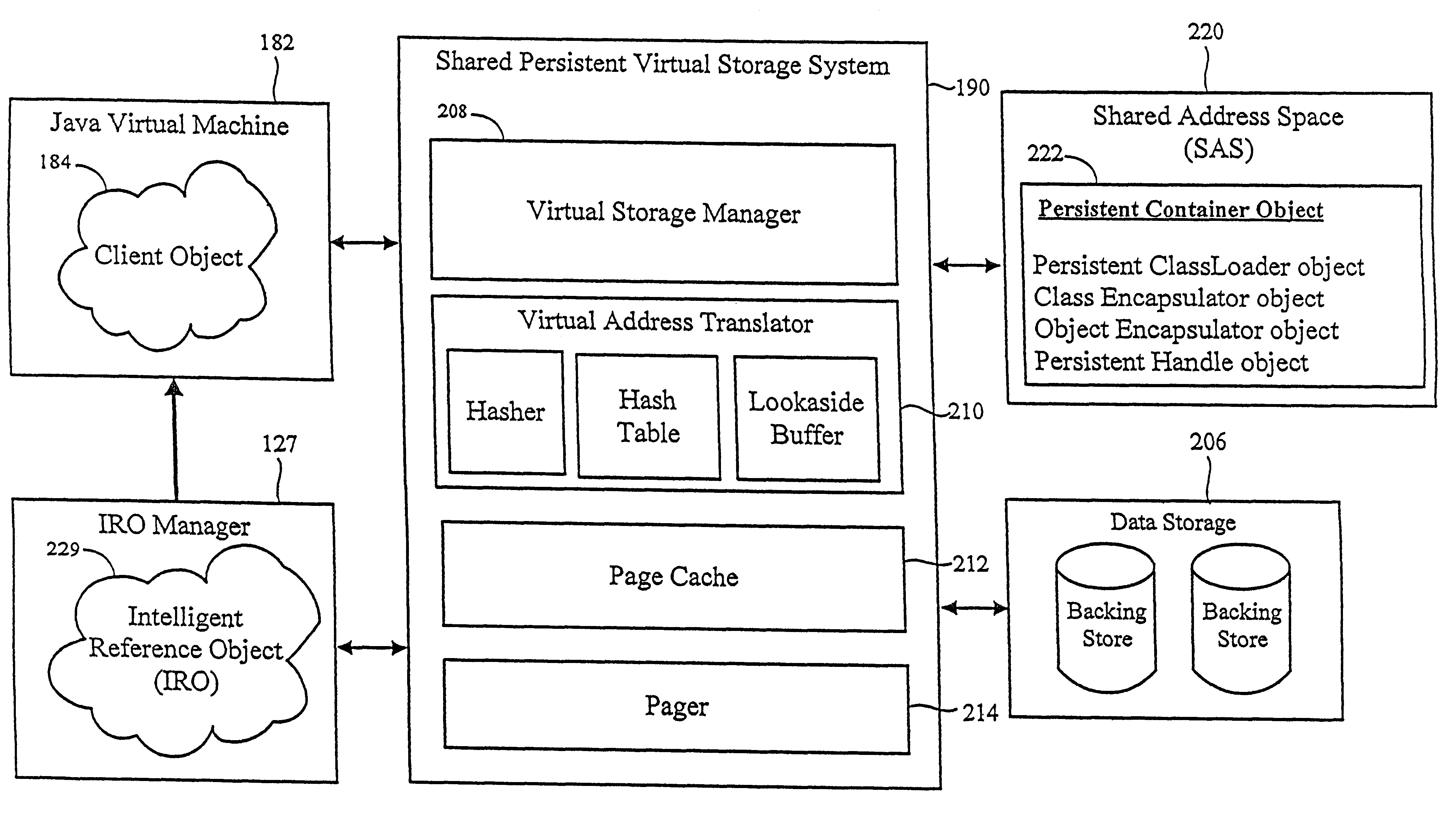

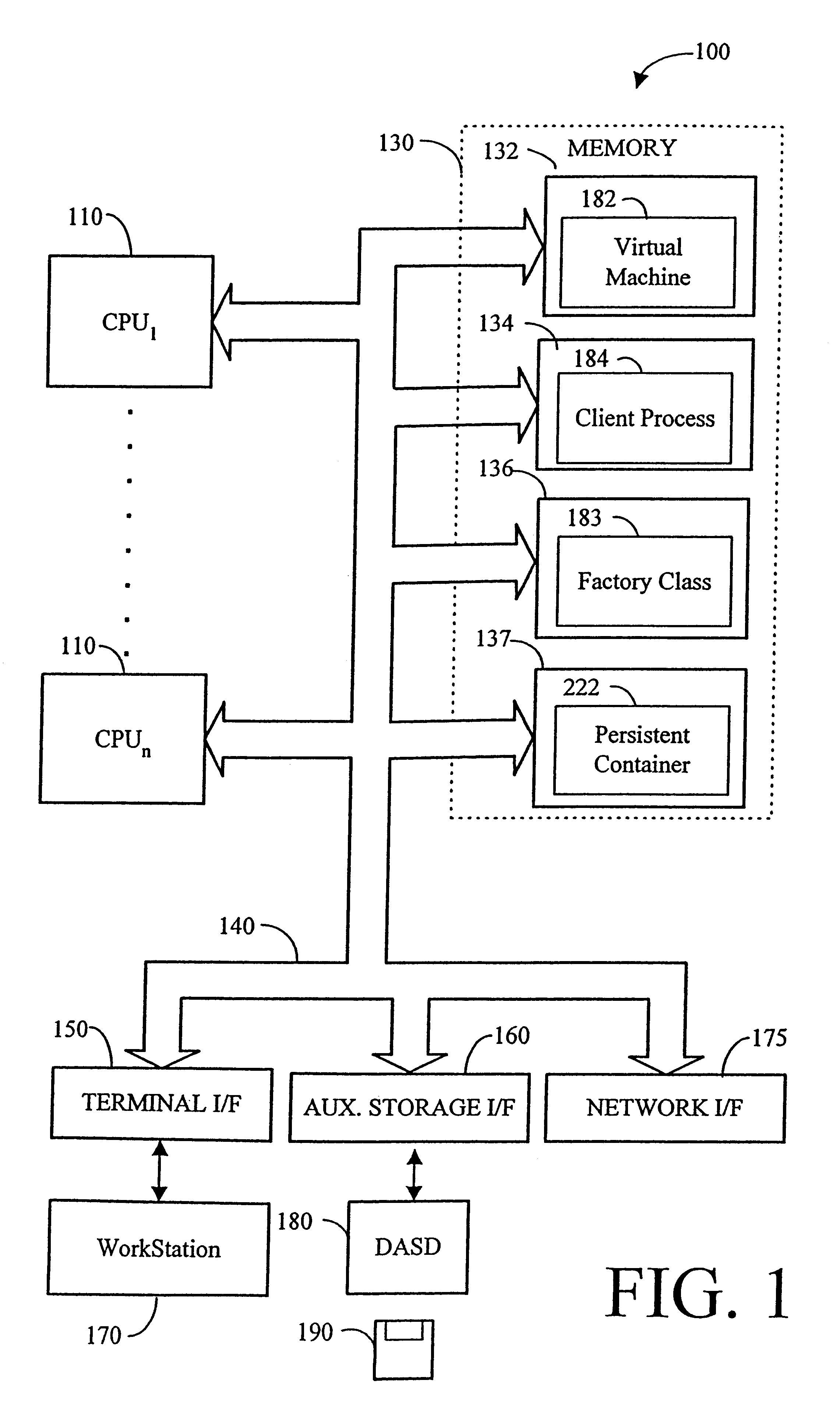

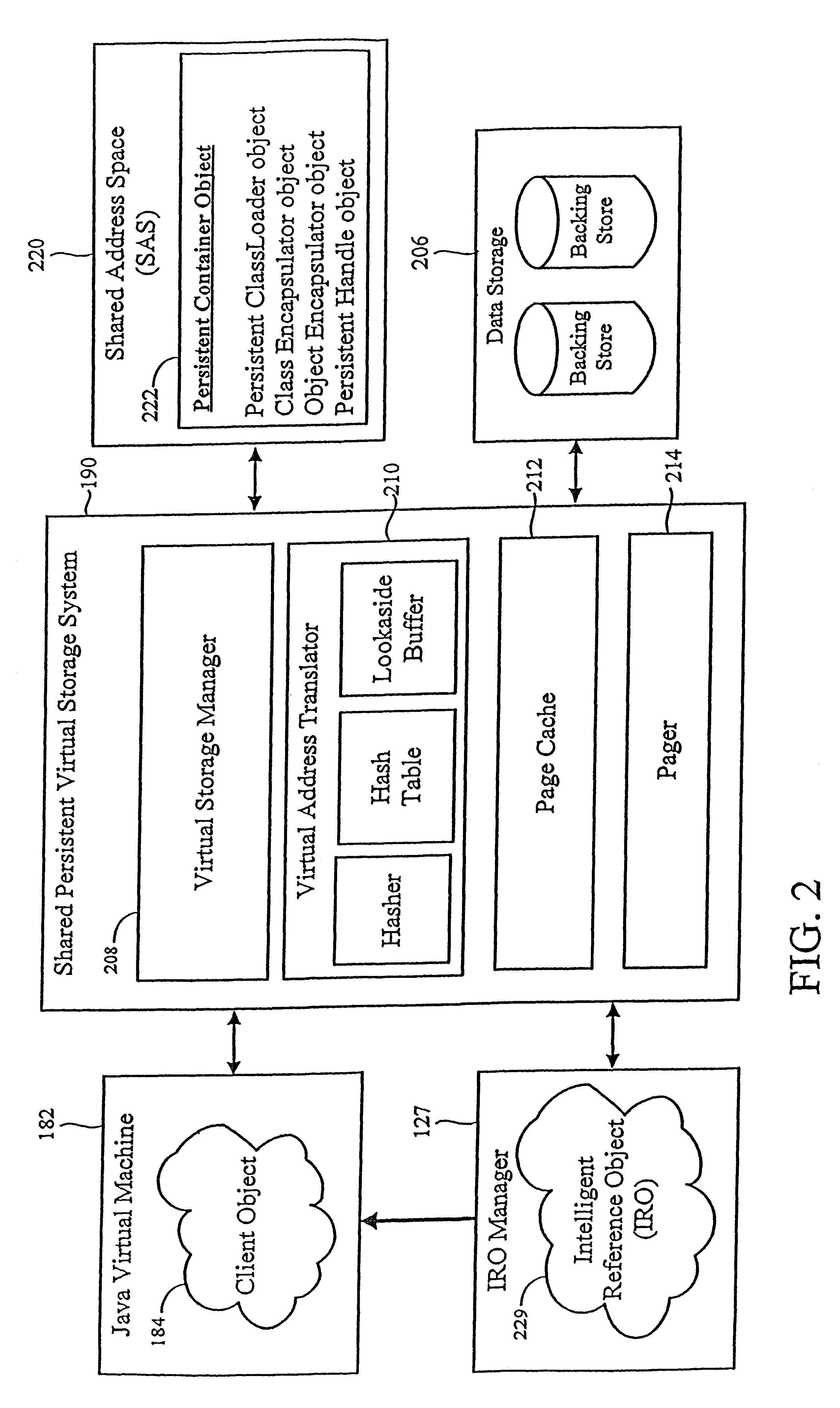

Virtual machine implementation for shared persistent objects

The preferred embodiment of the present invention facilitates the creation, storage and interaction of persistent objects using single level storage semantics on commodity systems. Specifically, the present invention defines several objects used to implement persistent objects in a shared address space. The preferred embodiment includes a Class Encapsulator class and the Object Encapsulator class that are preferably designed to encapsulate the class data and instance data, respectively. In particular, a Class Encapsulator object would preferably be created in a Persistent Container for each class of objects loaded into that Persistent Container. The Class Encapsulator object would include all of the specific data needed to implement its corresponding class. Likewise, an Object Encapsulator object would preferably be created to encapsulate each object to be stored persistently in the shared address space. A Persistent Handle class is preferably defined to store the shared address space address of the Class Encapsulator object and the Object Encapsulator object.

Owner:IBM CORP

Device, system, and method for reducing program/read disturb in flash arrays

A method, device and computer readable medium for programming a nonvolatile memory block. The method may include programming information, by a memory controller, to the nonvolatile memory block by performing a sequence of programming phases of descending bit significances. The device may include a nonvolatile memory block; and a memory controller that may be configured to determine a bit significance level of the nonvolatile memory block; program the nonvolatile memory block by performing at least one programming phase; and program the nonvolatile memory block to an erase value that may be higher than the pre-erase value; wherein the erase value and the pre-erase value may be selected based on the bit significance level of the nonvolatile memory block. The method may include packing three single level cell (SLC) nonvolatile memory blocks to one three-bit per cell nonvolatile memory block in order of the three SLC bit significances.

Owner:AVAGO TECH INT SALES PTE LTD

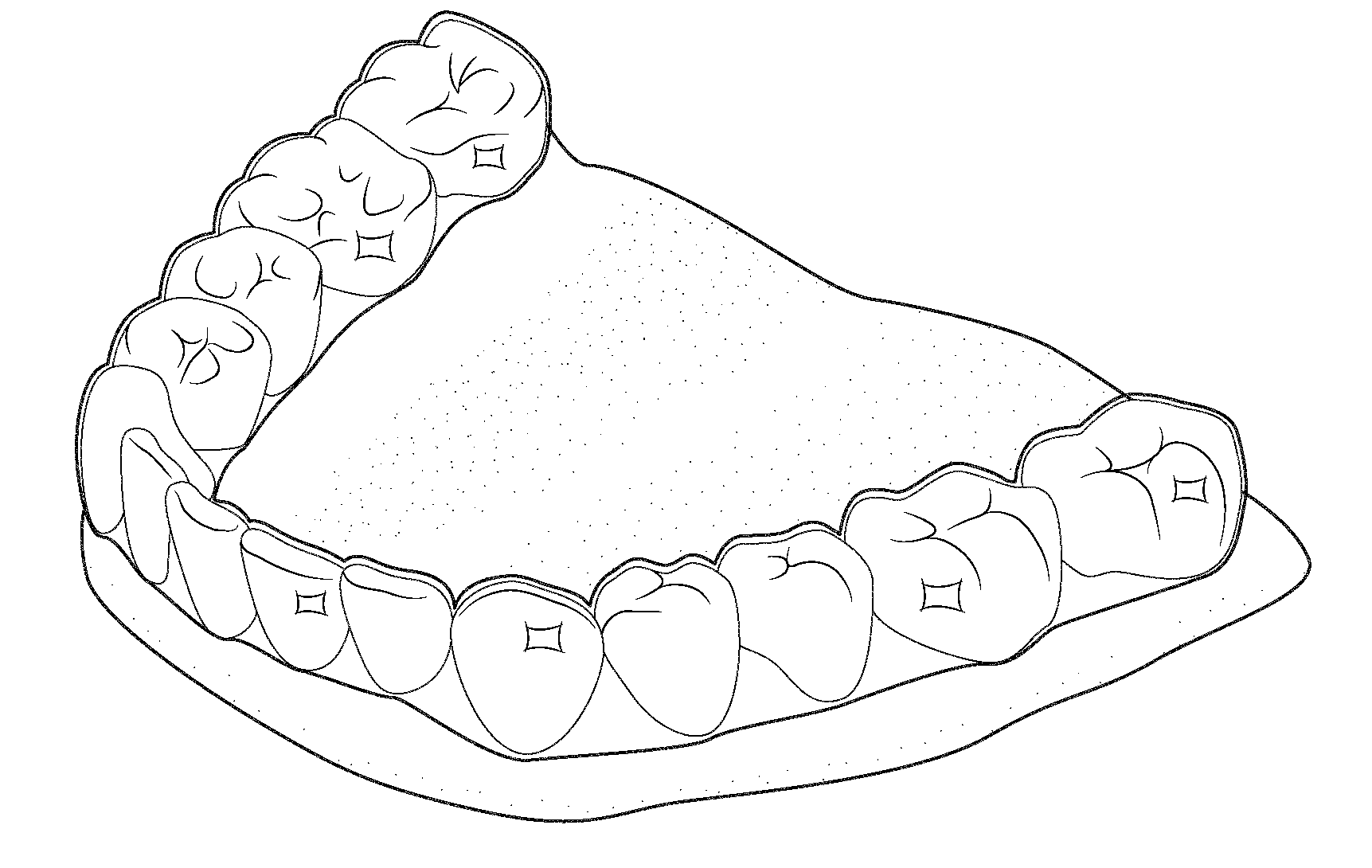

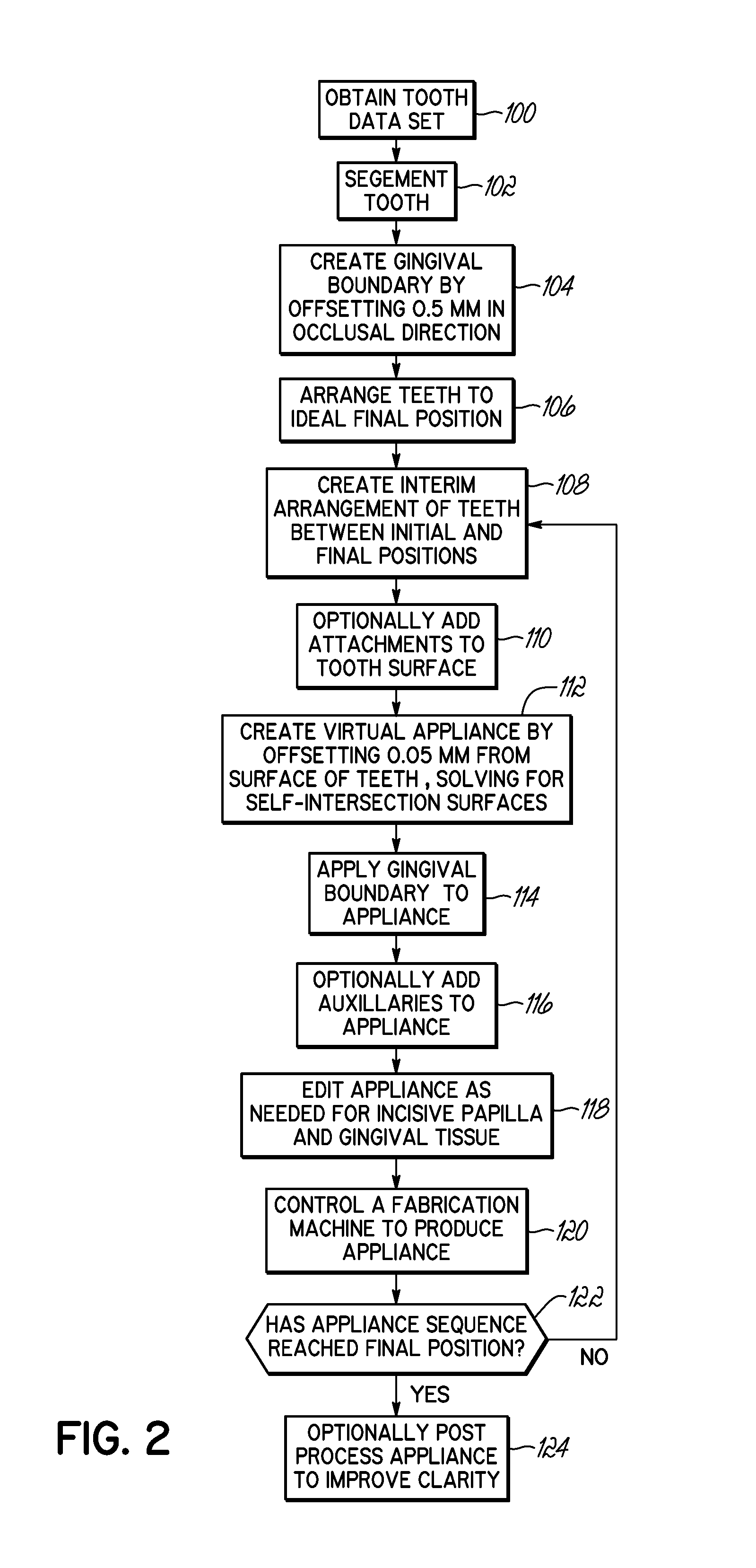

Direct manufacture of orthodontic aligner appliance

ActiveUS20130122448A1Fast deliveryAdditive manufacturing apparatusOthrodonticsSingle levelOrthodontics

A method for fabrication of an orthodontic device having tooth-fitting cavities, such as an aligner, using layer-by-layer printing of a single or multiple polymeric materials. The cavities of the appliance or an appliance mold are defined by the boundaries of the multiple layers, encapsulating up to fourteen teeth of a patient, and shaped to apply a load to at least one tooth that is sufficient to cause movement of the tooth, and remodeling of the adjacent bone. In the case where the cavities form an appliance mold, the mold is used to form a positive model and an appliance is formed thereon. A series of such appliances may be used to treat malocclusion of teeth, each appliance used in series to incrementally move one or more teeth from initial positions toward a desired final position. The appliance may be fabricated with a variety of disclosed materials, and may include auxiliary features for interaction with other orthodontic elements.

Owner:ORMCO CORP

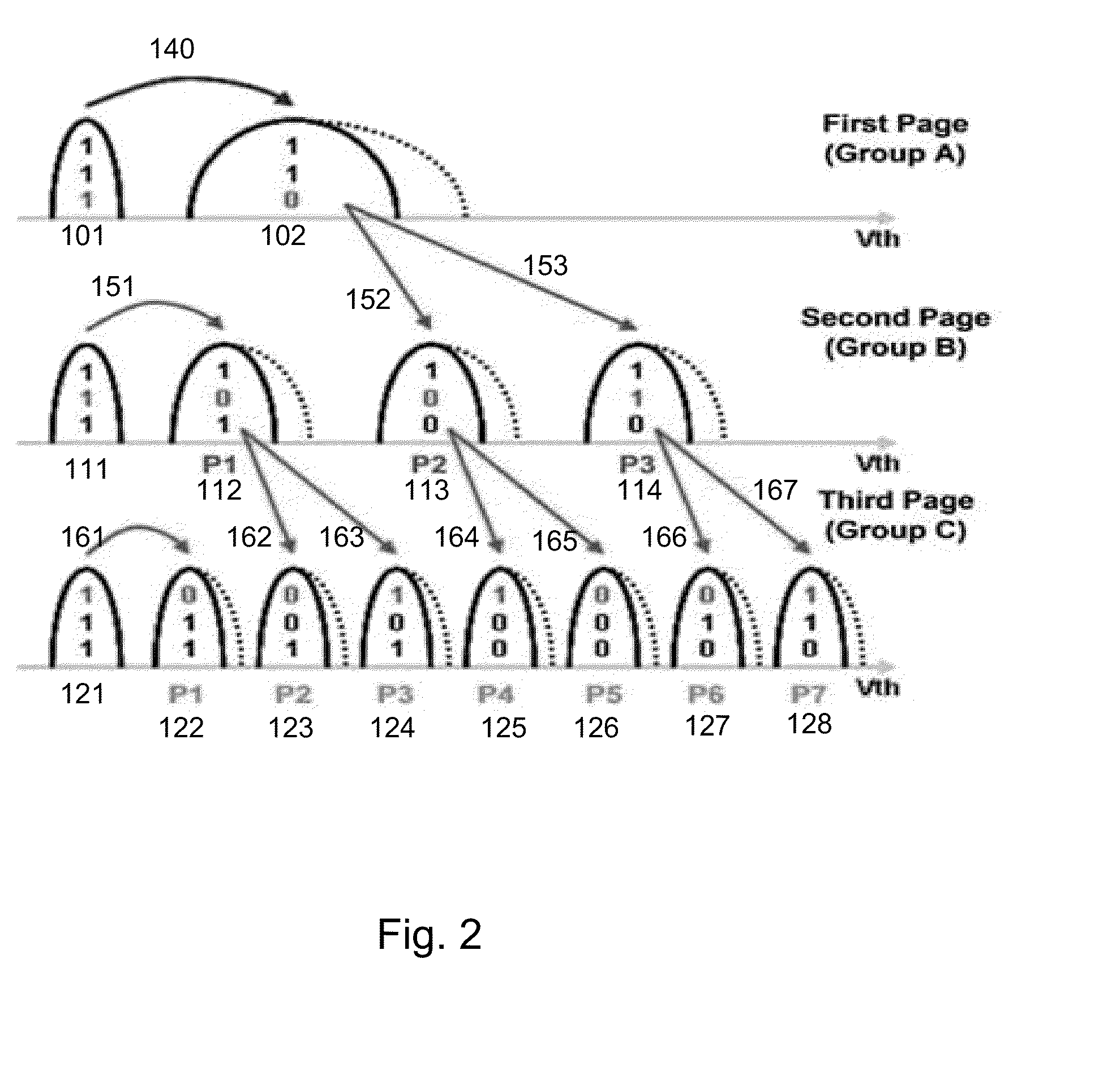

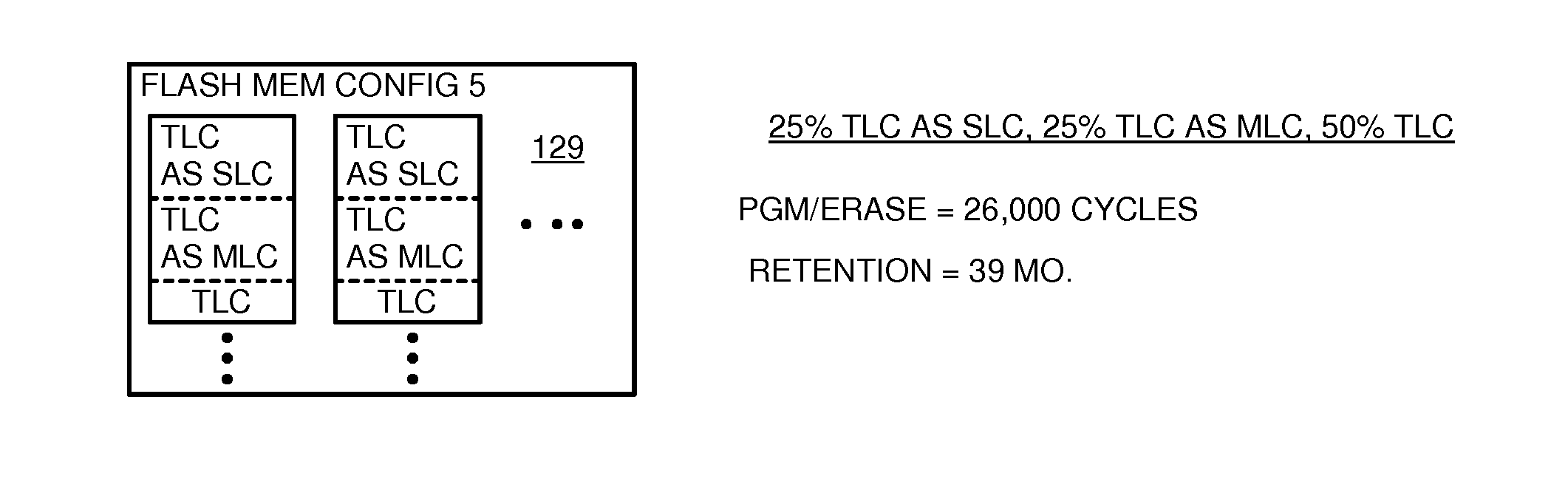

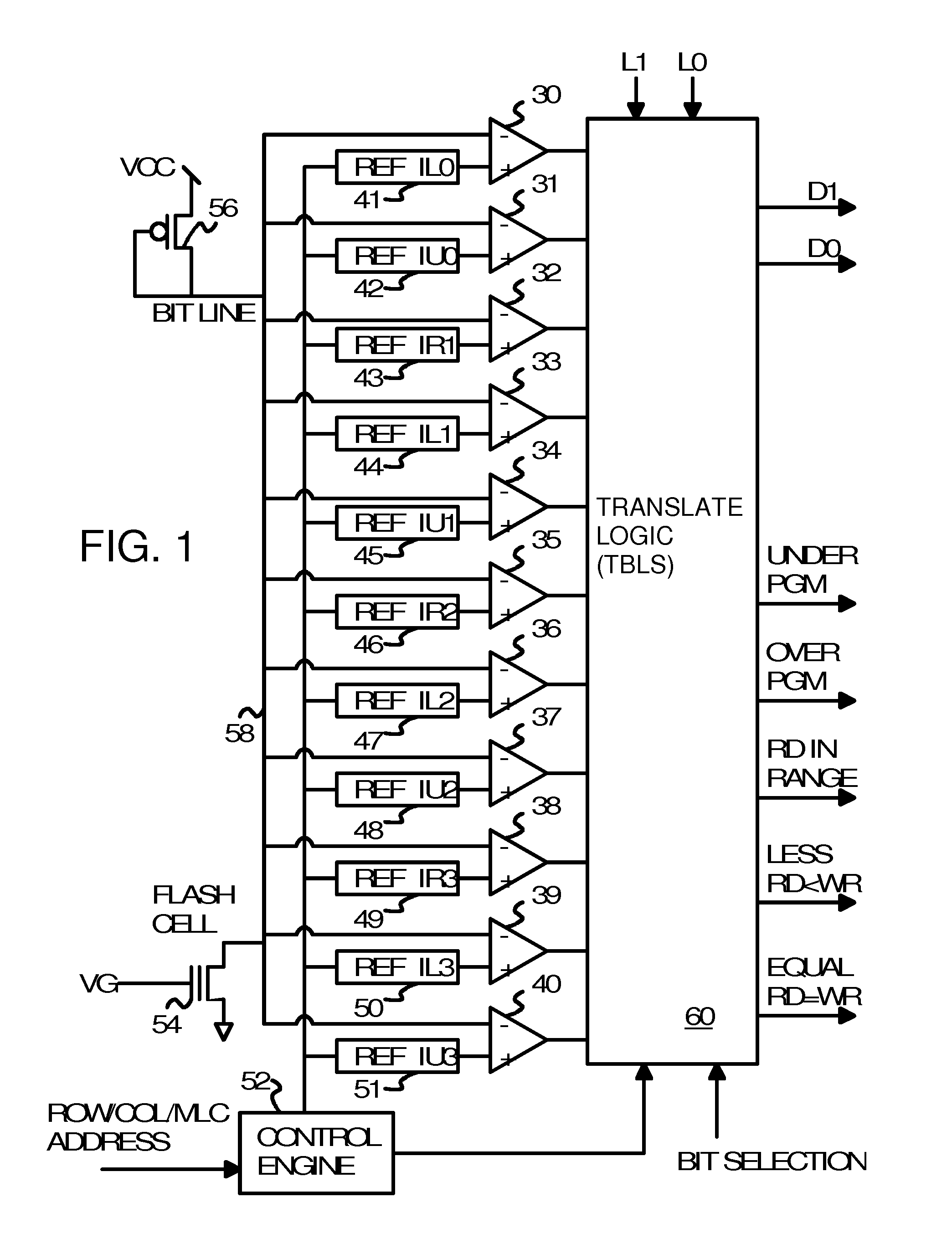

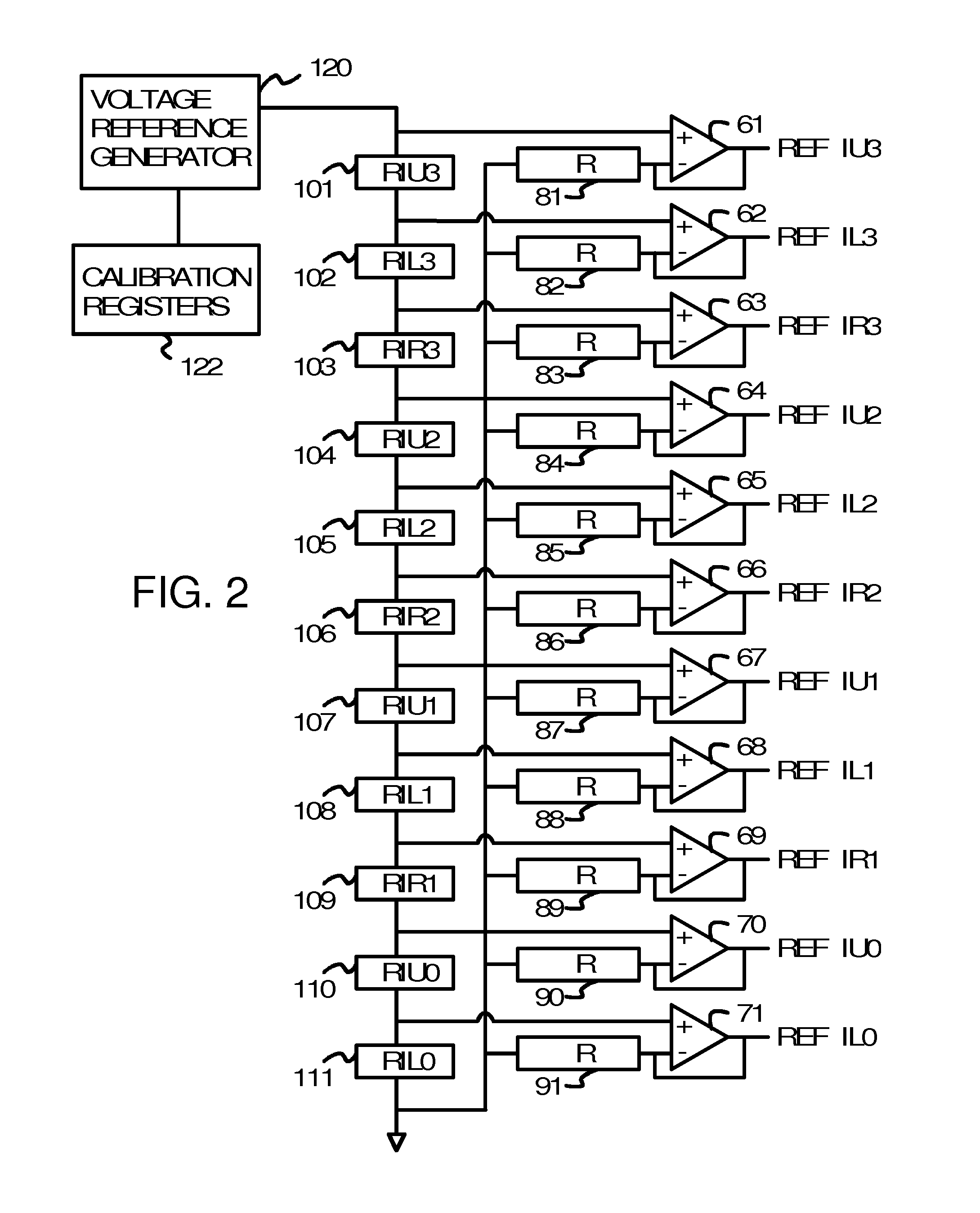

Endurance and retention flash controller with programmable binary-levels-per-cell bits identifying pages or blocks as having triple, multi, or single-level flash-memory cells

InactiveUS9123422B2Memory architecture accessing/allocationMemory adressing/allocation/relocationTruth valueRetention time

An retention flash controller reads assigned-level bits from a bad block / erase count table or from a page status table that indicate when flash memory cells operate as Triple-Level-Cell (TLC), Multi-Level-Cell (MLC), or Single-Level-Cell (SLC). Pages that fail as TLC or MLC are downgraded for use as SLC pages by changing the assigned-level bits. The level bits adjust truth tables used by translation logic that receives inputs from voltage comparators reading a bit line. The range of voltages for each logic level may be adjusted by the truth tables or by programmable registers. The programming voltage or programming pulses may be adjusted to increase endurance and the number of permitted program-erase cycles while reducing retention times before a refresh is needed of the flash cells. Mixed configurations of flash memory have MLC blocks and MLC as SLC blocks, or other combinations.

Owner:SUPER TALENT TECH CORP

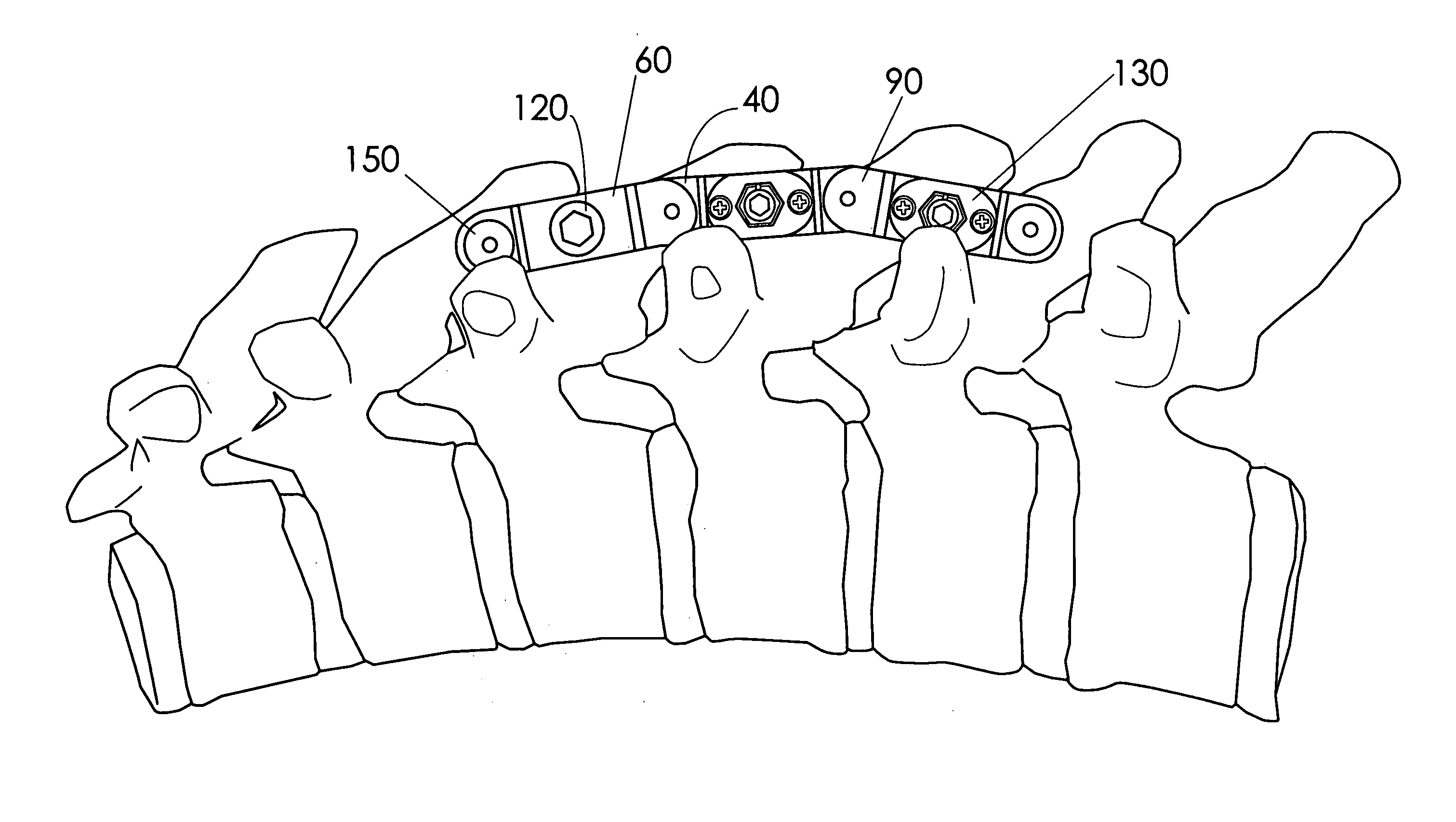

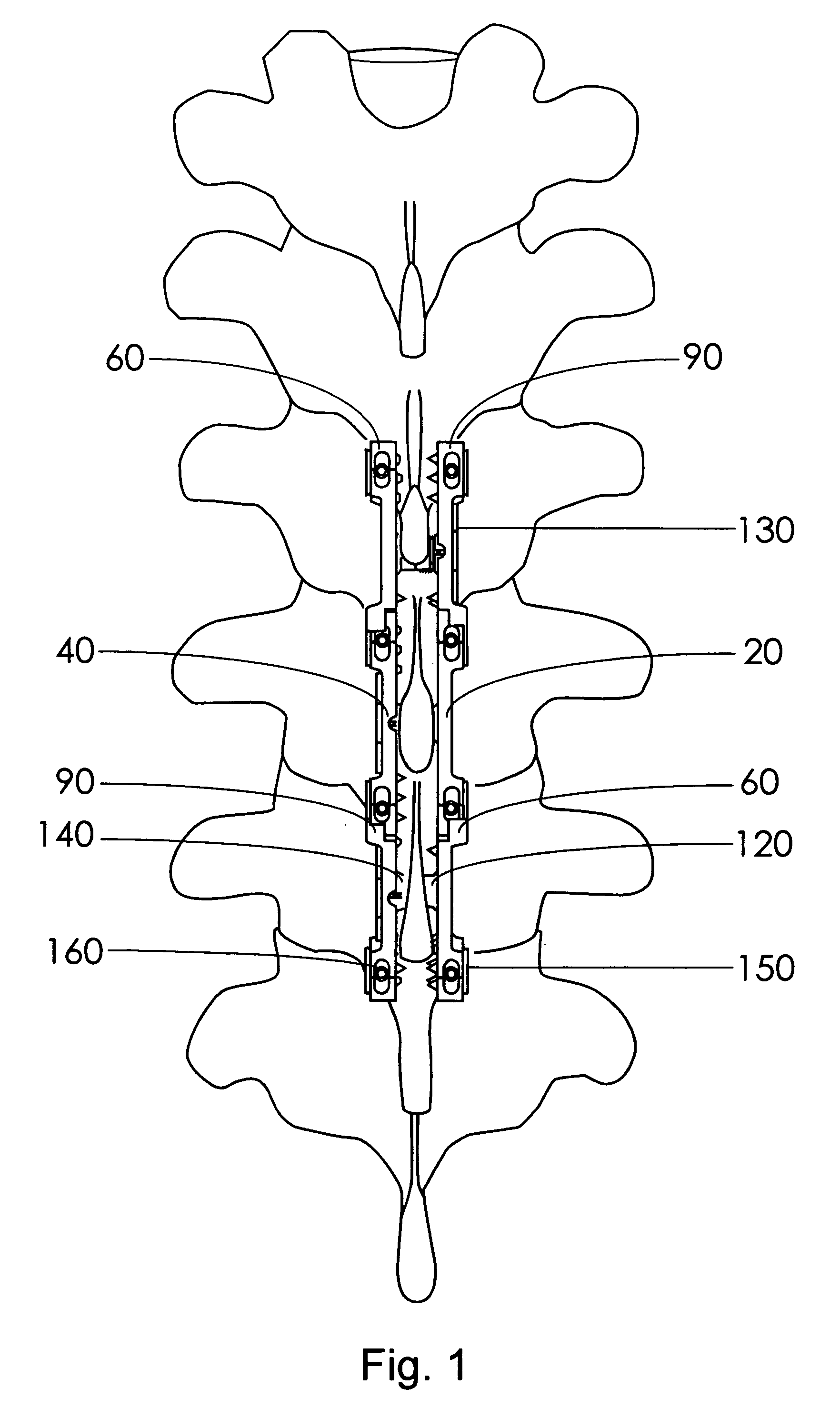

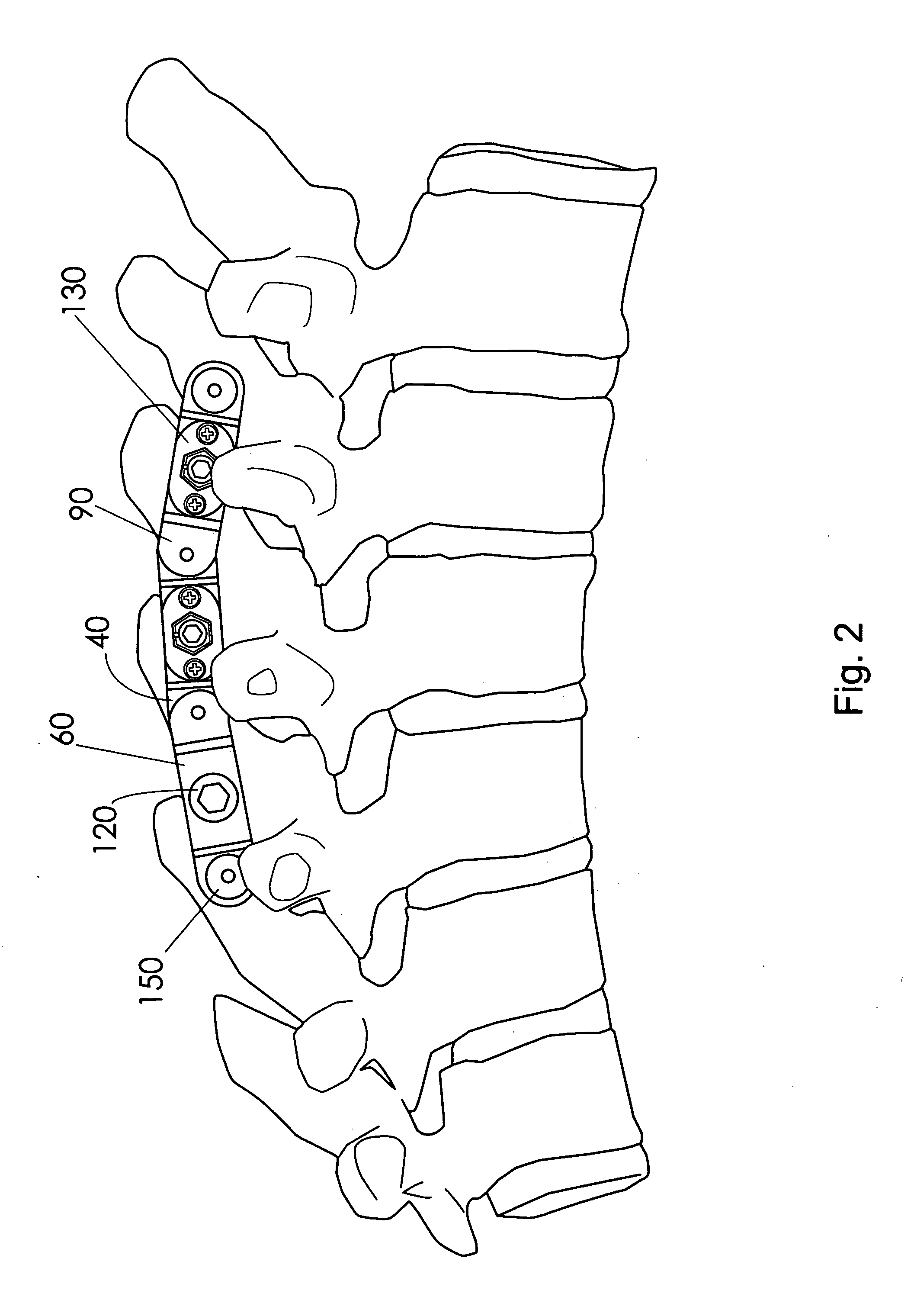

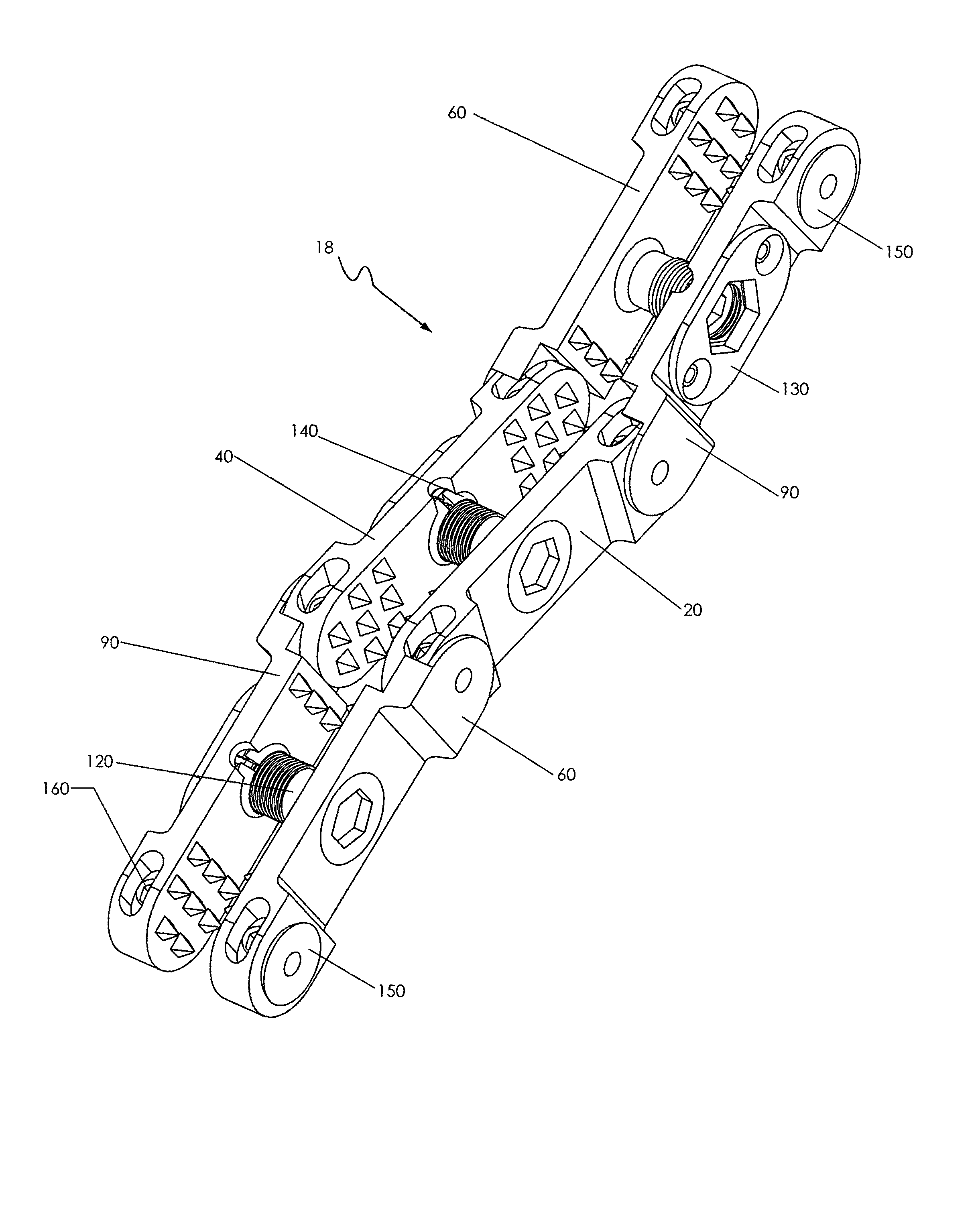

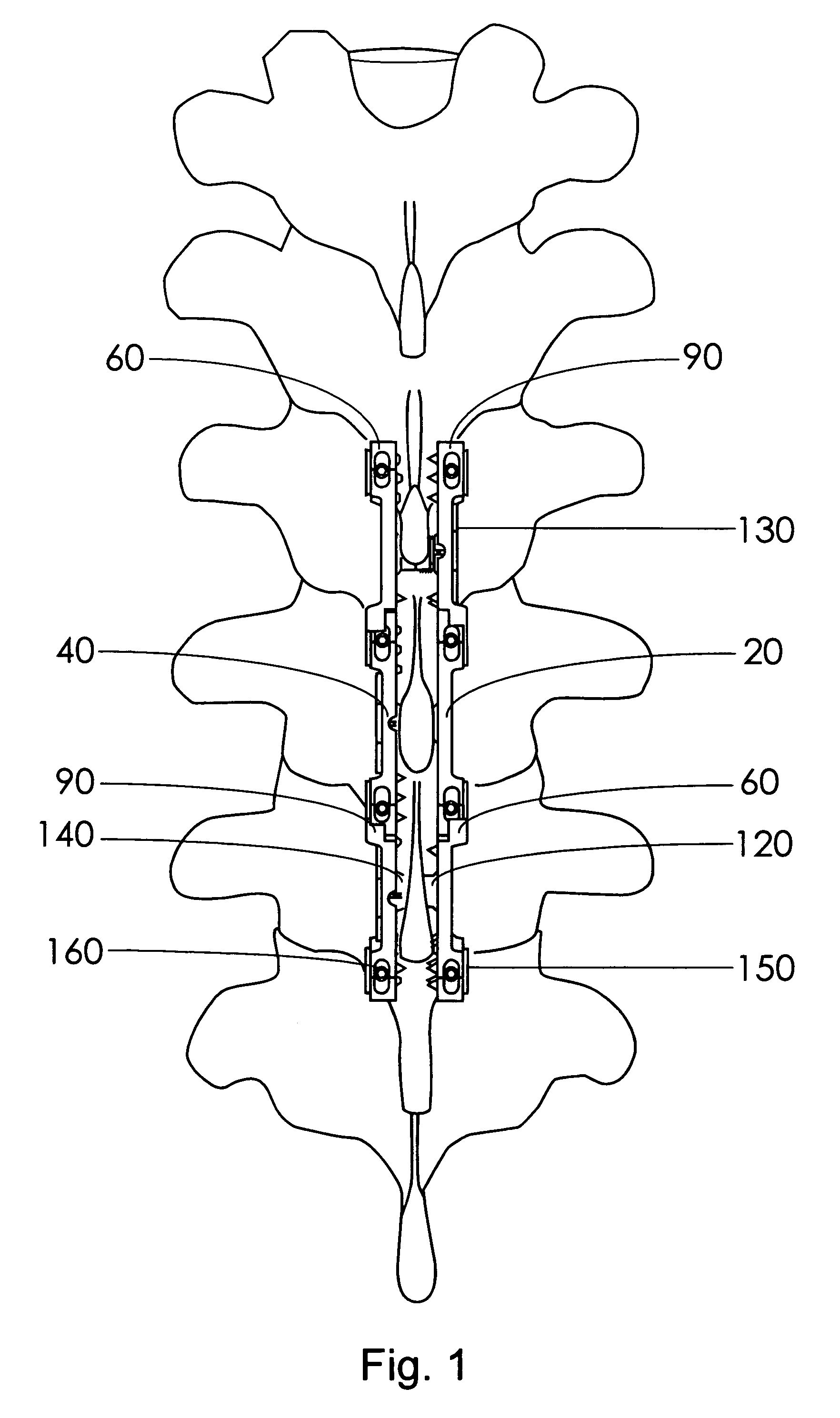

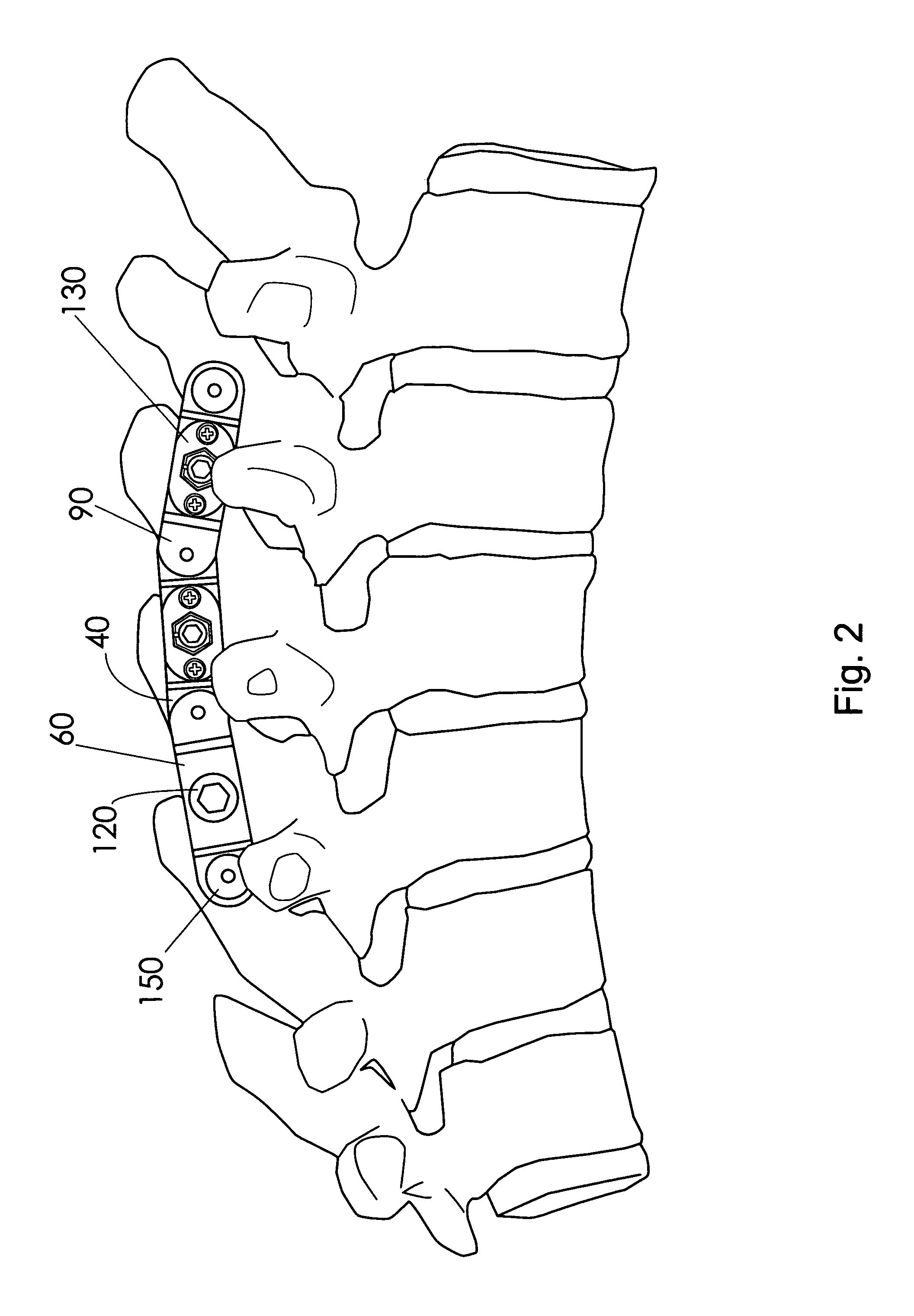

Spinous process stabilization device and method

InactiveUS20090264927A1Easy to integrateInternal osteosythesisJoint implantsCoronal planeEmbedded teeth

A fixation device to immobilize a spinal motion segment and promote posterior fusion, used as stand-alone instrumentation or as an adjunct to an anterior approach. The device functions as a multi-level fusion system including modular single-level implementations. At a single-level the implant includes a pair of plates spanning two adjacent vertebrae with embedding teeth on the medially oriented surfaces directed into the spinous processes or laminae. The complementary plates at a single-level are connected via a cross-post with a hemi-spherical base and cylindrical shaft passed through the interspinous process gap and ratcheted into an expandable collar. The expandable collar's spherical profile contained within the opposing plate allows for the ratcheting mechanism to be correctly engaged creating a uni-directional lock securing the implant to the spine when a medially directed force is applied to both complementary plates using a specially designed compression tool. The freedom of rotational motion of both the cross-post and collar enables the complementary plates to be connected at a range of angles in the axial and coronal planes accommodating varying morphologies of the posterior elements in the cervical, thoracic and lumbar spine. To achieve multi-level fusion the single-level implementation can be connected in series using an interlocking mechanism fixed by a set-screw.

Owner:GINSBERG HOWARD JOESEPH +2

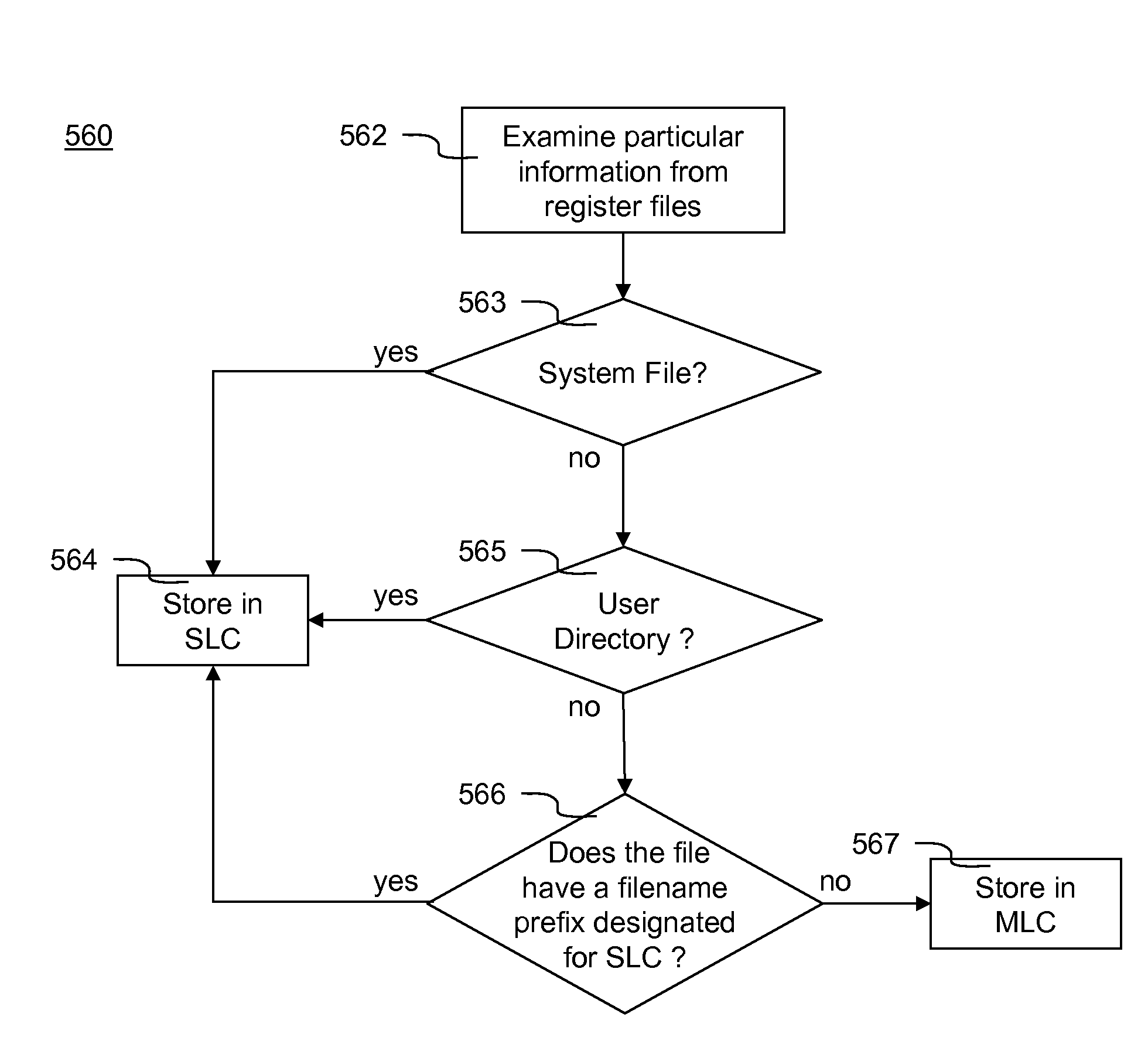

Hybrid SSD using a combination of SLC and MLC flash memory arrays

InactiveUS8078794B2Memory architecture accessing/allocationInternal/peripheral component protectionData fileSingle level

Hybrid solid state drives (SSD) using a combination of single-level cell (SLC) and multi-level cell (MLC) flash memory arrays are described. According to one aspect of the present invention, a hybrid SSD is built using a combination SLC and MLC flash memory arrays. The SSD also includes a micro-controller to control and coordinate data transfer from a host computing device to either the SLC flash memory array of the MLC flash memory array. A memory selection indicator is determined by triaging data file based on one or more criteria, which include, but is not limited to, storing system files and user directories in the SLC flash memory array and storing user files in the MLC flash memory array; or storing more frequent access files in the SLC flash memory array, while less frequent accessed files in the MLC flash memory array.

Owner:SUPER TALENT TECH CORP

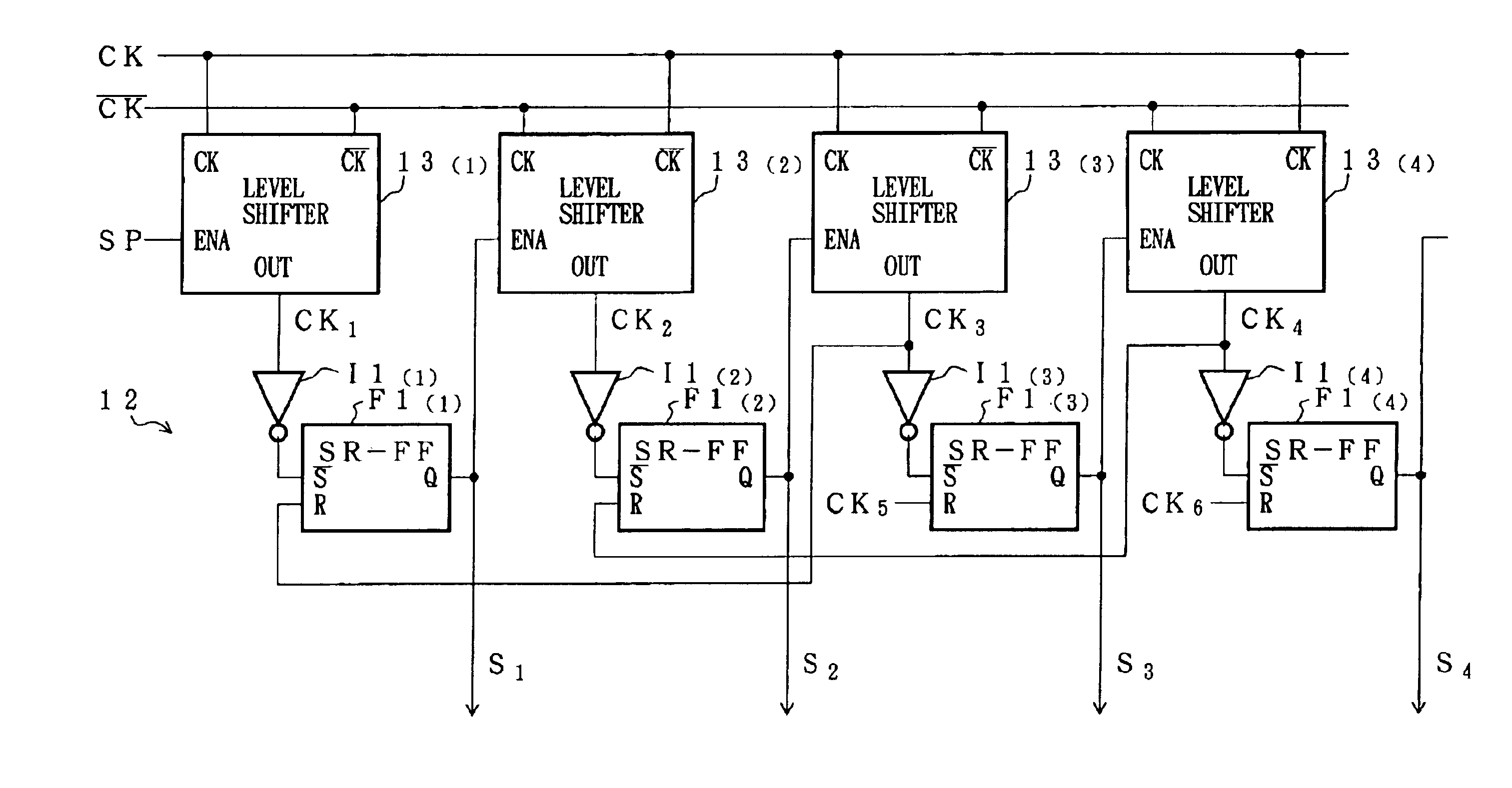

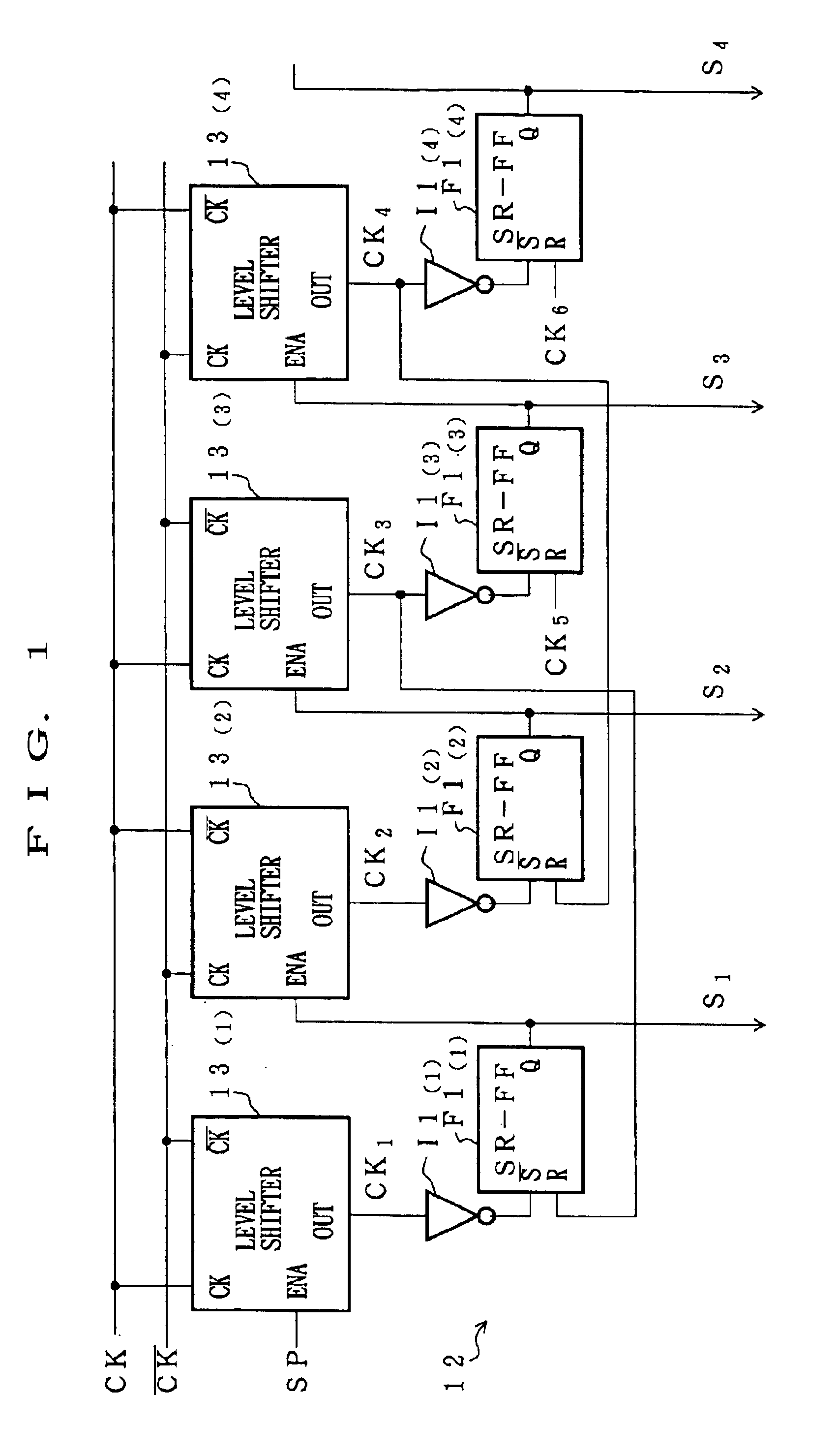

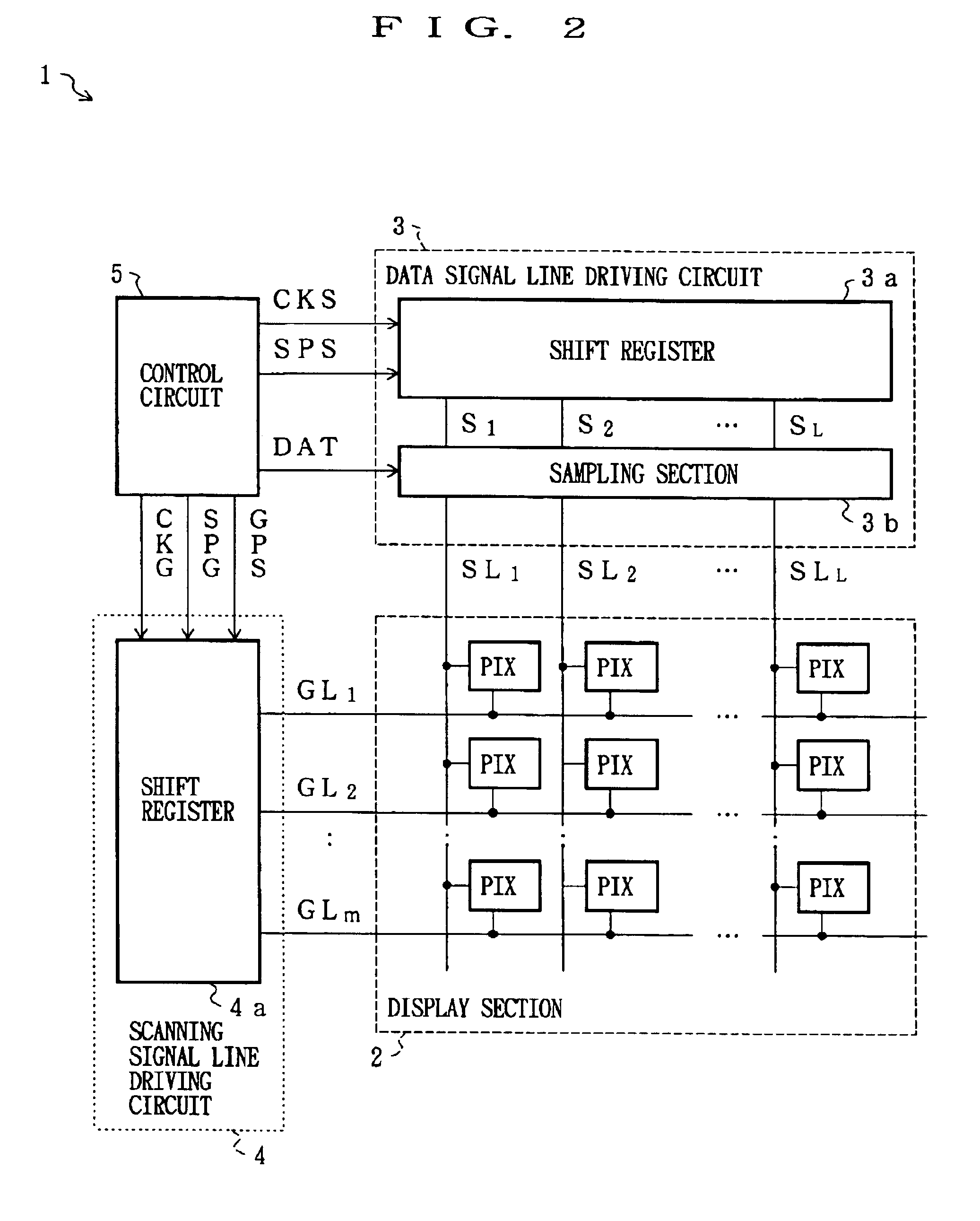

Shift register and image display apparatus using the same

InactiveUS6909417B2Reduce distanceReduce load capacityPulse generatorPulse automatic controlShift registerEngineering

A level shifter 13 is provided for each of SR flip flops F1 constituting a shift register 11. The level shifter 13 increases a voltage of a clock signal CK. This arrangement reduces a distance for transmitting a clock signal whose voltage has been increased, as compared with a construction in which a voltage of a clock signal is increased by a single level shifter and the signal is transmitted to each of the flip flops; consequently, a load capacity of the level shifter can be smaller. Furthermore, each of the level shifters is operated during a pulse output of the previous level shifter 13, and the operation is suspended at the end of the pulse output. Thus, the level shifters 13 can operate only when it is necessary to apply a clock signal CK to the corresponding SR flip flop F1. As a result, even when an amplitude of a clock signal is small, it is possible to reduce power consumption of the shift resister under normal operation.

Owner:SHARP KK

Multilayer winding inductor

ActiveUS20070267718A1Semiconductor/solid-state device detailsTransformers/inductances coils/windings/connectionsInductorEngineering

A multilayer winding inductor. The inductor at least includes multi-level interconnect and single-level interconnect structures. The multi-level interconnect structure includes a plurality of conductive plugs and a plurality of looped conductive traces overlapping and separated from each other. Each looped conductive trace has a gap to define first and second ends and at least two conductive plugs disposed between the neighboring looped conductive traces. The single-level interconnect structure is located over the multi-level interconnect structure, comprising an uppermost looped conductive trace and a second conductive plug. The uppermost looped conductive trace has a gap to define first and second ends, and the second conductive plug is disposed between the second end of the uppermost looped conductive trace and the first end of the looped conductive trace adjacent thereto, thereby electrically connecting the multi-level and single-level interconnect structures.

Owner:VIA TECH INC

Display device and methods of manufacturing and control

InactiveUS7199527B2High speedReduce power lossDischarge tube luminescnet screensSolid cathodesDisplay deviceVoltage drop

A flexible display device has one or more flexible electrode assemblies. Each of the electrode assemblies includes a hierarchical control arrangement for selectively activating electrodes of the display device. The hierarchical control arrangement includes high-level control elements and low-level control elements, each of the high-level control elements being operatively coupled to respective subsets of the low-level control elements, which in turn are coupled to respective groups of the electrodes. Exemplary control elements are microstructure elements containing imbedded microprocessors or integrated circuits. The use of a hierarchical control arrangement results in data signals having to pass through fewer control elements when compared with single-level arrangements. This increases operation speed and reduces power losses due to voltage drops across control elements. In addition, the number of connections to device(s) external to the display may thereby be reduced.

Owner:RUIZHANG TECH LTD CO

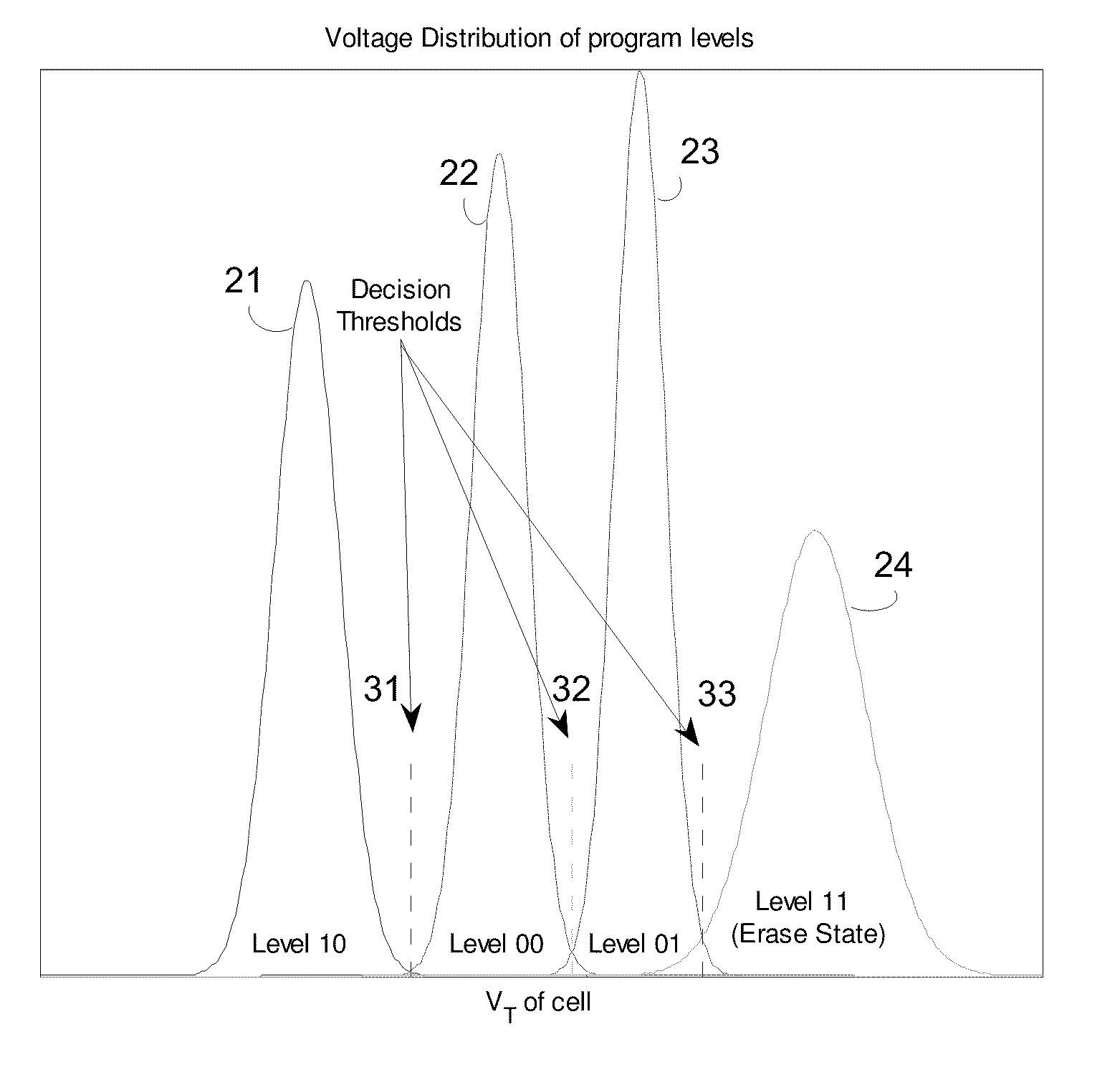

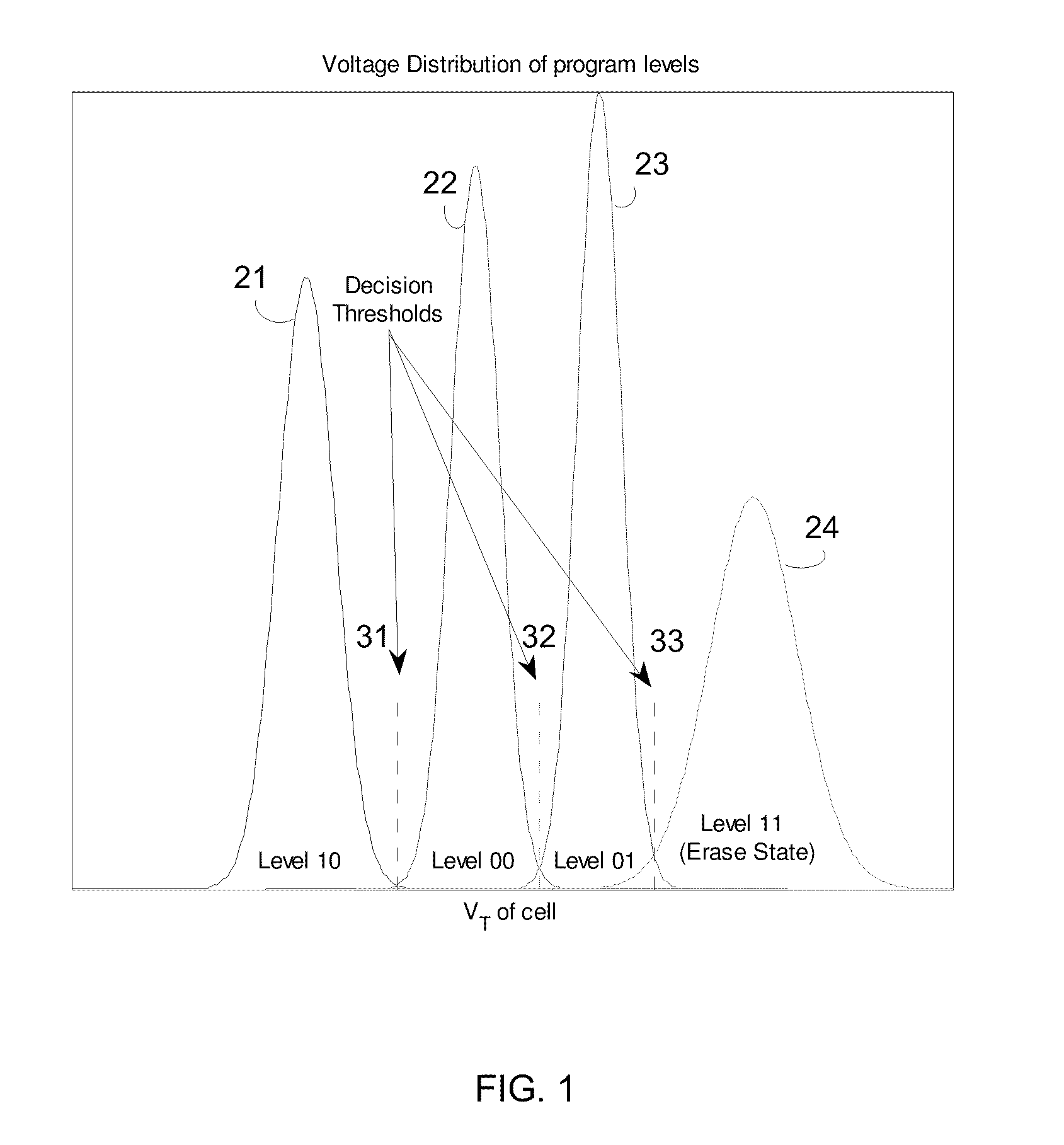

Systems and methods for reliable multi-level cell flash storage

ActiveUS20110302354A1Memory adressing/allocation/relocationRead-only memoriesSingle levelMulti-level cell

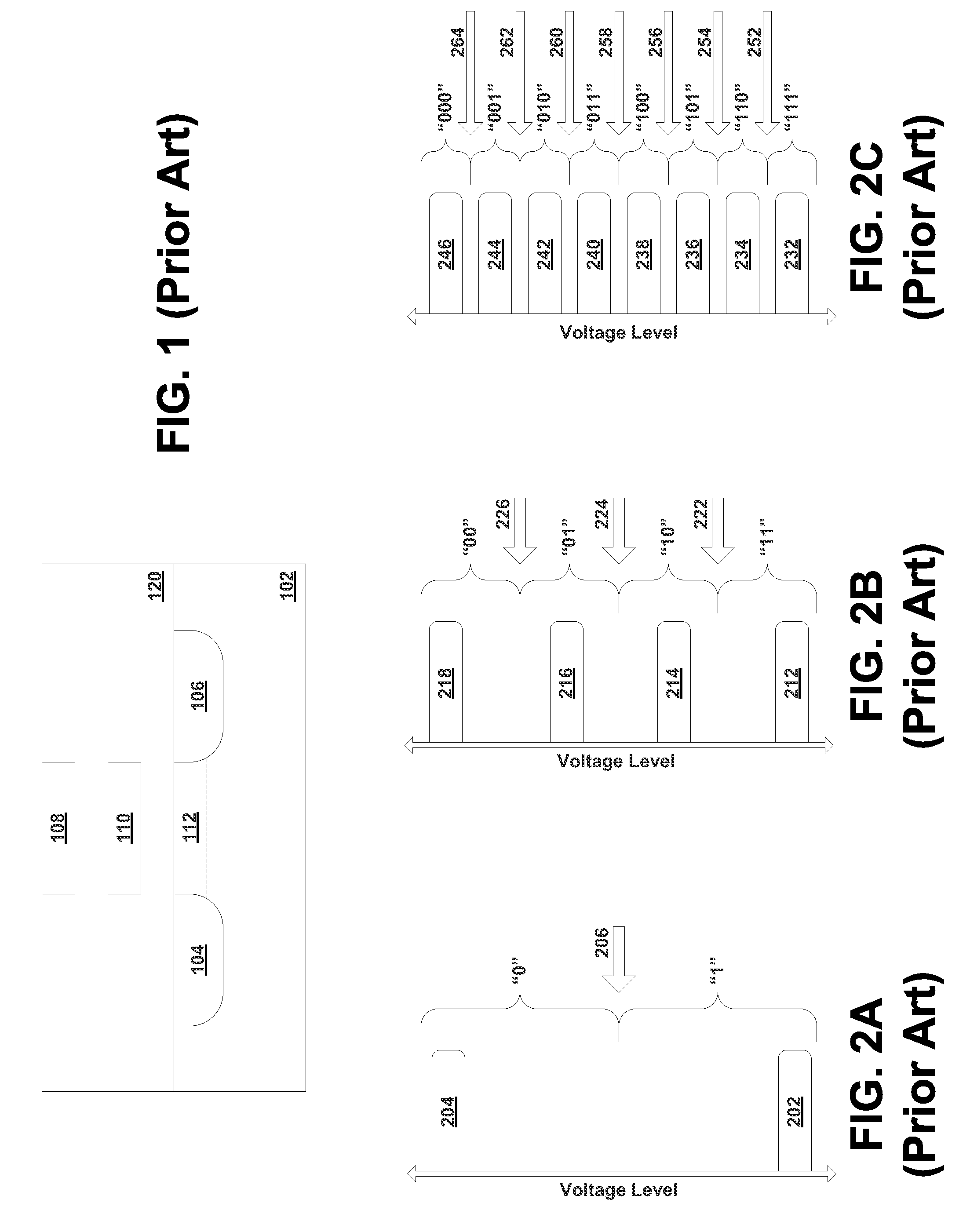

Multi-level cell (MLC) flash memory has become widely used due to their capacity to store more information in the same area as a single-level cell (SLC) flash memory. This makes MLC flash memory very attractive for storing media. Flash has also traditionally been used in electronic devices for firmware, but MLC flash is less reliable than SLC flash. For critical memory operations, MLC flash memory can be made as reliable as SLC flash by mapping one binary value to an MLC state corresponding to the highest threshold voltage and the other binary value to the MLC state corresponding the lowest threshold voltage when writing to the MLC flash, and by mapping all MLC states with corresponding threshold voltages above a central cutoff threshold voltage to one binary value and by mapping all MLC states with corresponding threshold voltages below a central cutoff threshold voltage to the other binary value.

Owner:SYNAPTICS INC

Memory system selecting write mode of data block and data write method thereof

ActiveUS20120005415A1Improve performanceMemory adressing/allocation/relocationSingle levelMulti-level cell

A method of performing a write operation in a nonvolatile memory device comprises storing write data in a log block used to update a data block, determining whether a write pattern stored in the log block is a sequential write pattern or a random write pattern, and selecting a new data block for storing merged data in the data block and the log block. The new data block is determined to be a single-level cell block or a multi-level cell block according to the determined write pattern.

Owner:SAMSUNG ELECTRONICS CO LTD

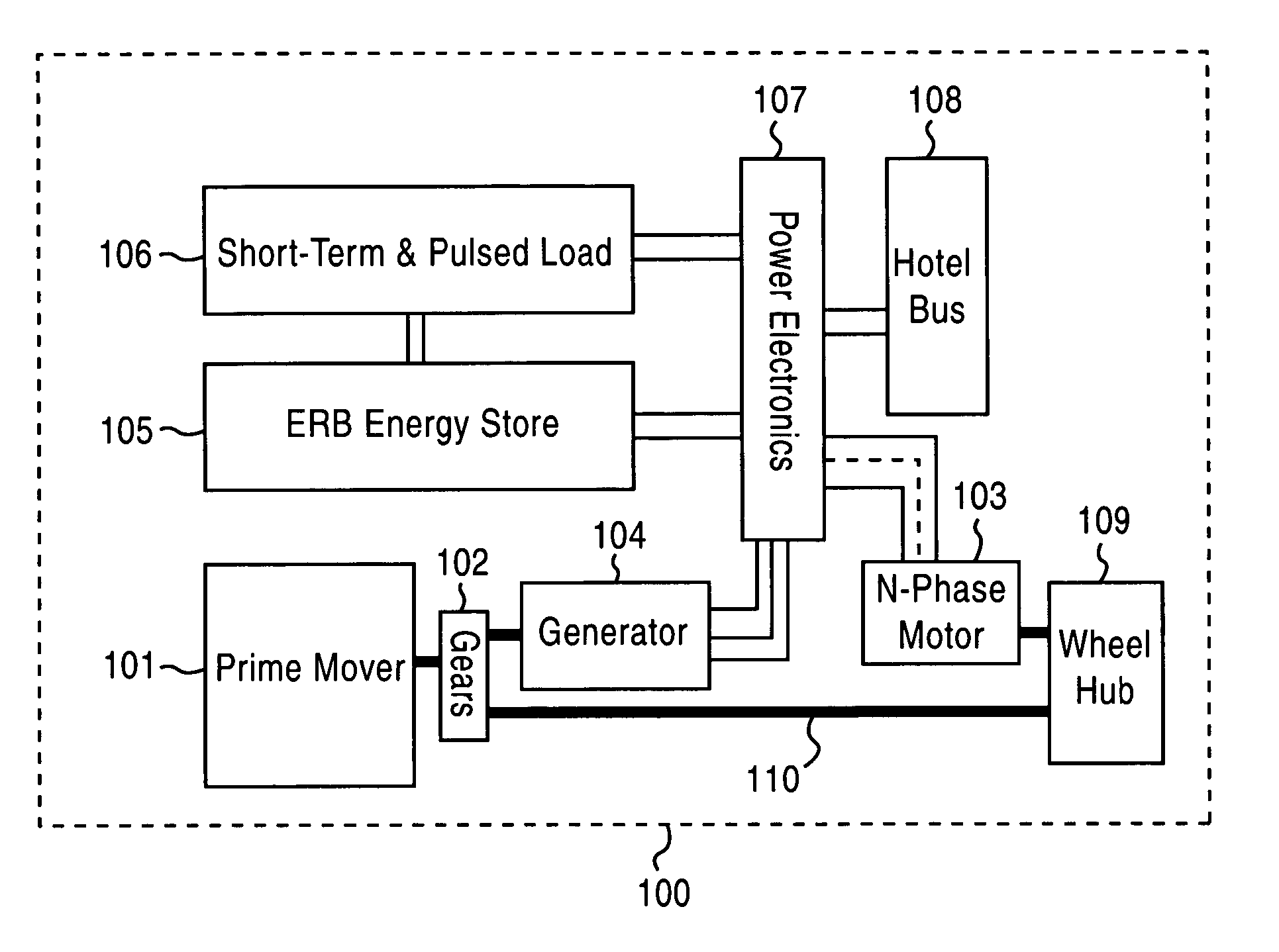

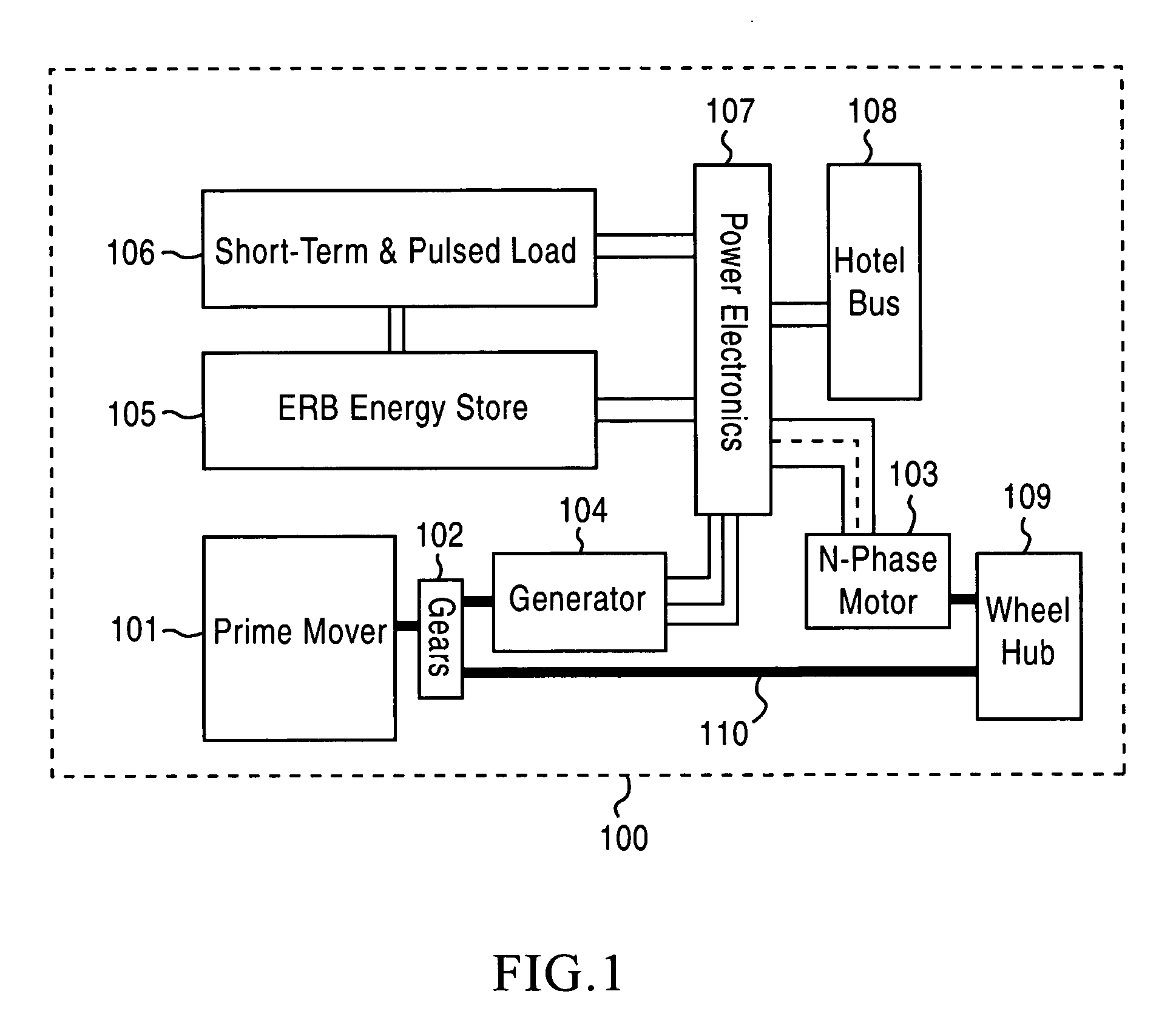

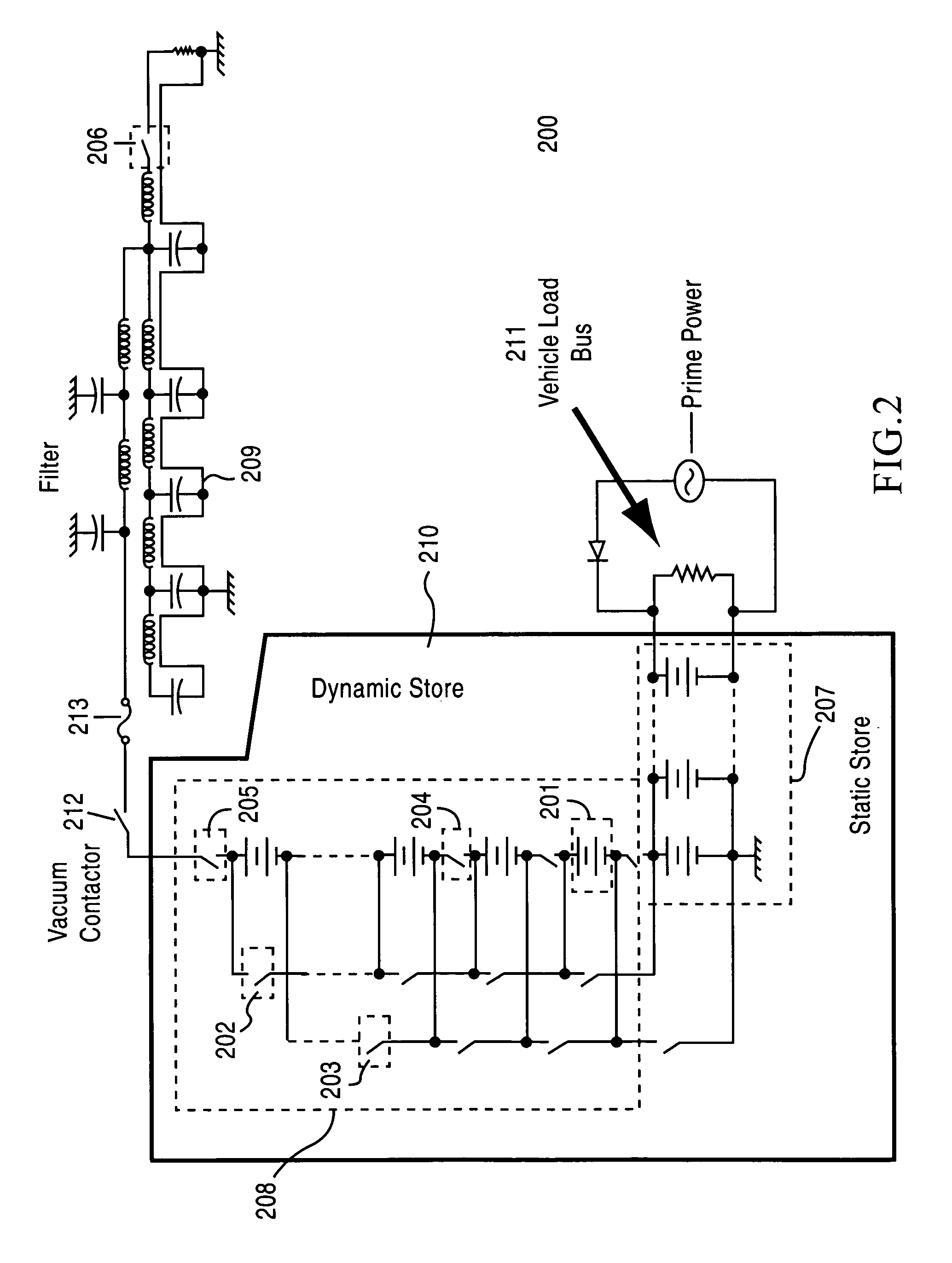

Modular electronically reconfigurable battery system

ActiveUS20070062744A1Efficient settingsHigh resolutionElectromagnetic launchersDc network circuit arrangementsPulse loadElectrical battery

An electronically reconfigurable battery includes a number of battery modules selectively interconnected by a number of electronic switches, wherein a selectable number of battery modules may be connected either in a series configuration or in a parallel configuration, as a result of placing selected switches of said plurality of switches in open states or closed states. In a parallel configuration, the battery provides power to a primary load, such as a propulsion load for a vehicle. In a series configuration, the battery is configured to provide a high voltage and high power output to a short-term and / or pulsed load, such as an additional load provided on the vehicle. Current from the battery is limited in one of three ways: a) by the batteries themselves; b) a current limiting device or system in series with the total erected battery; or c) a single level power converter or current limiter that is used to erect and charge the capacitor bank in a sequential one level at a time manner until the battery is fully erected and the capacitor is fully charged.

Owner:L 3 APPLIED TECH

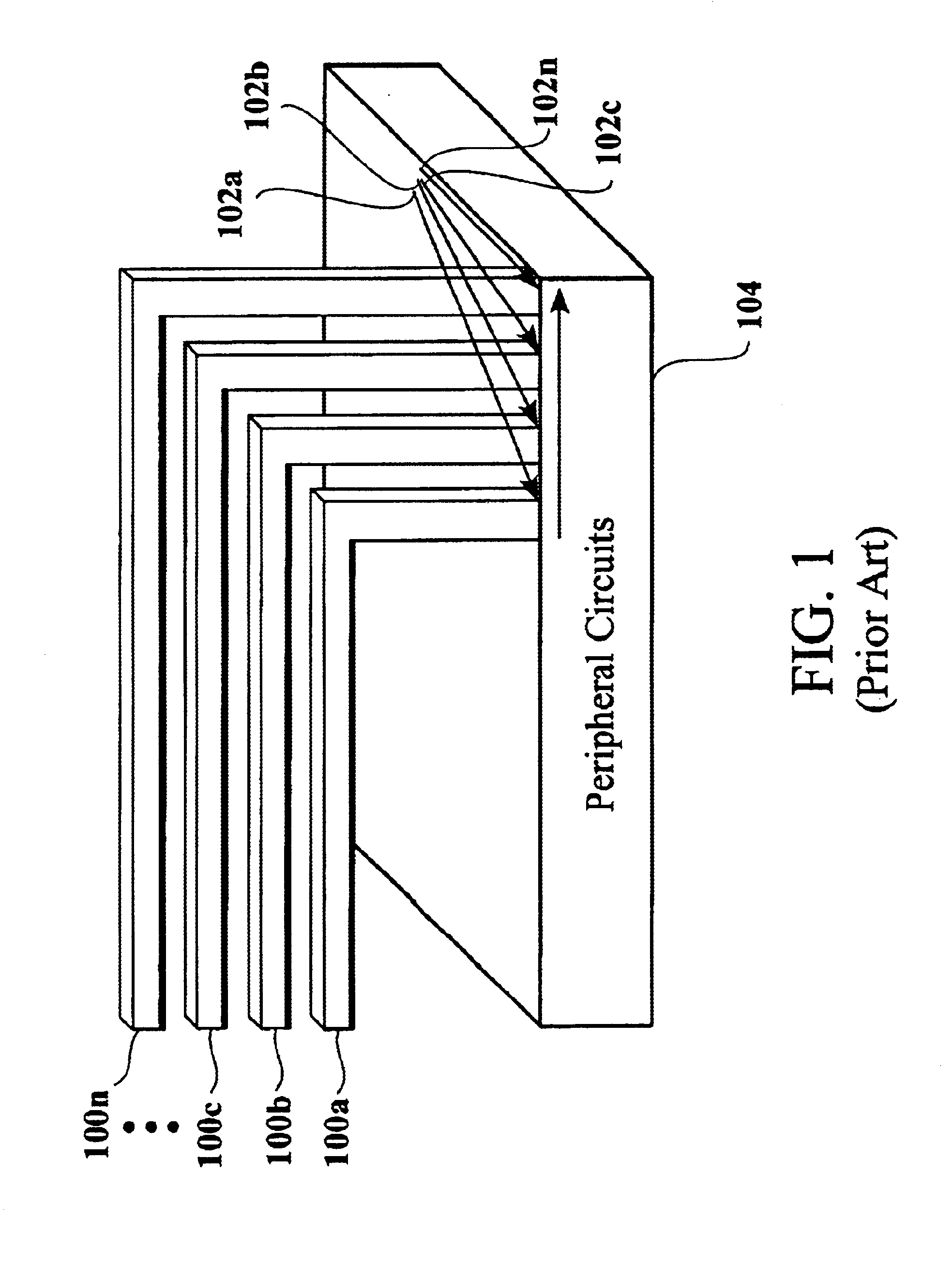

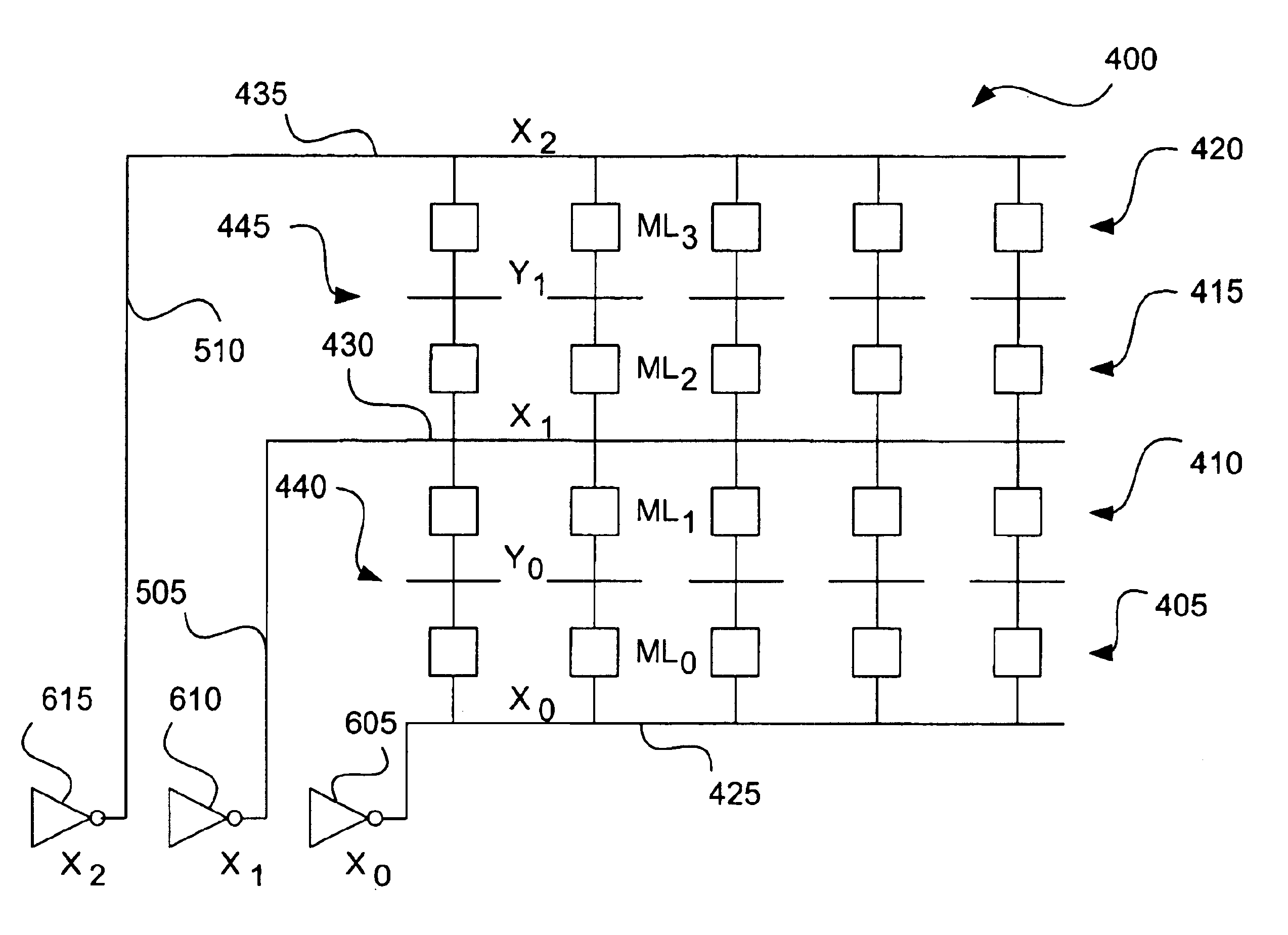

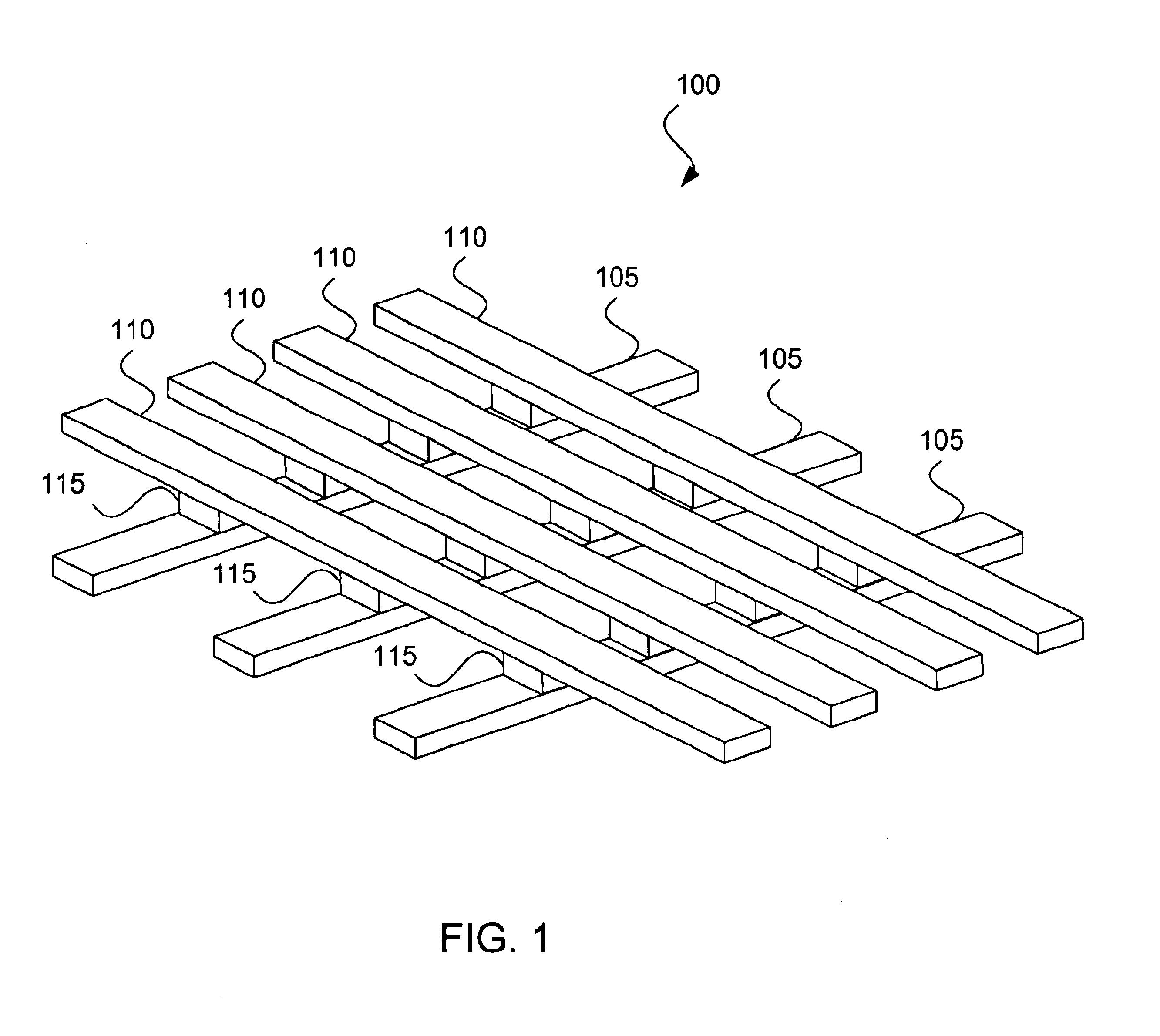

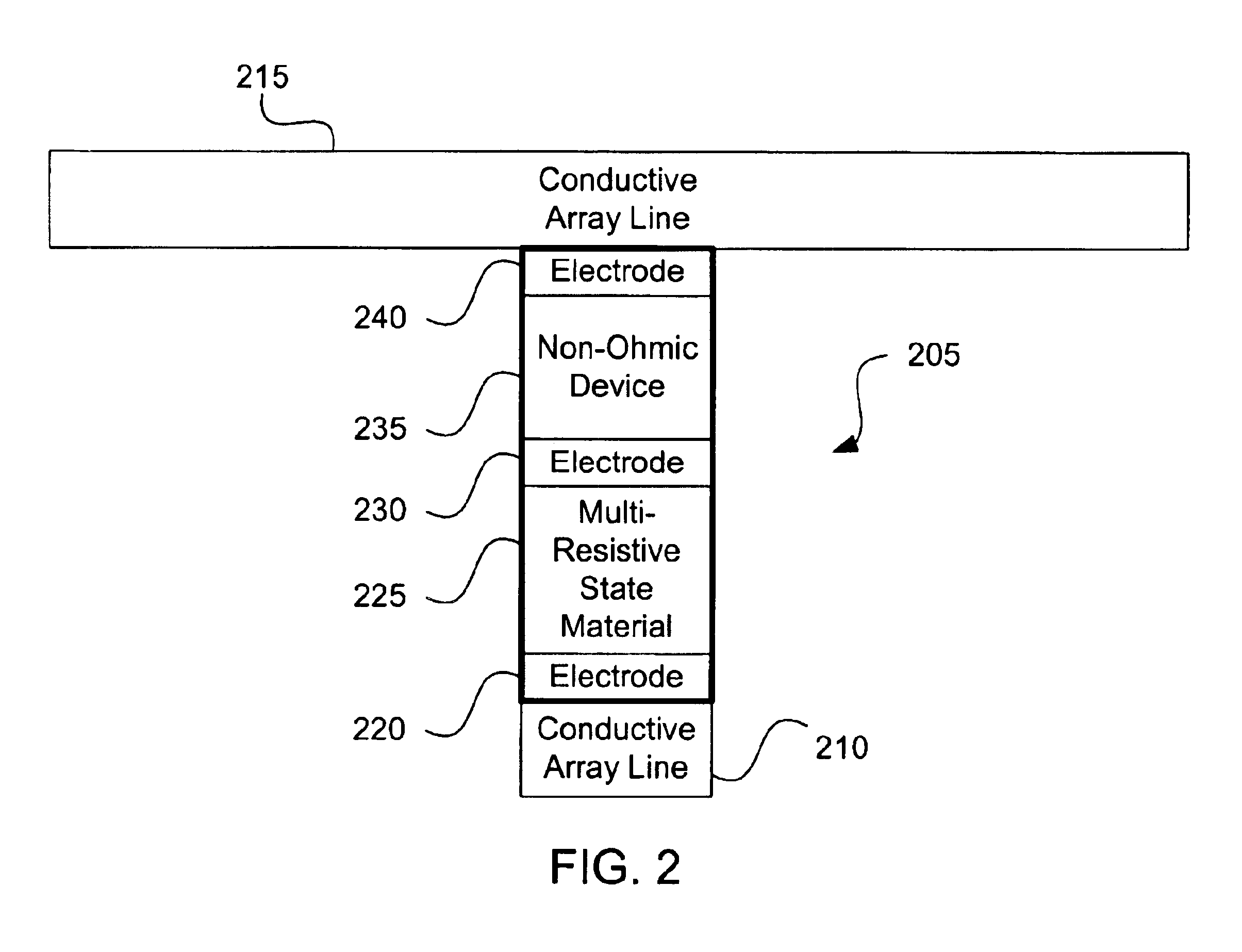

Cross point memory array with fast access time

Cross point array with fast access time. A cross point array is driven by drivers on a semiconductor substrate. The drivers for either a single-layer cross point array or for the bottom layer of a stacked cross point array can be positioned to improve access time. Specifically, if the x-direction drivers are positioned in the middle of the x-direction conductive array lines and the y-direction drivers are positioned in the middle of the y-direction conductive array lines, the access time will be improved.

Owner:UNITY SEMICON

Spinous process stabilization device and method

A fixation device is provided to immobilize a spinal motion segment and promote posterior fusion, used as stand-alone instrumentation or as an adjunct to an anterior approach. The device functions as a multi-level fusion system including modular single-level implementations. At a single-level the implant includes a pair of plates spanning two adjacent vertebrae with embedding teeth on the medially oriented surfaces directed into the spinous processes or laminae. The complementary plates at a single-level are connected via a cross-post passed through the interspinous process gap The freedom of rotational motion of both the cross-post and collar enables the complementary plates to be connected at a range of angles in the axial and coronal planes accommodating varying morphologies of the posterior elements in the cervical, thoracic and lumbar spine. To achieve multi-level fusion the single-level implementation can be connected in series using an interlocking mechanism fixed by a set-screw.

Owner:GINSBERG HOWARD JOESEPH +2

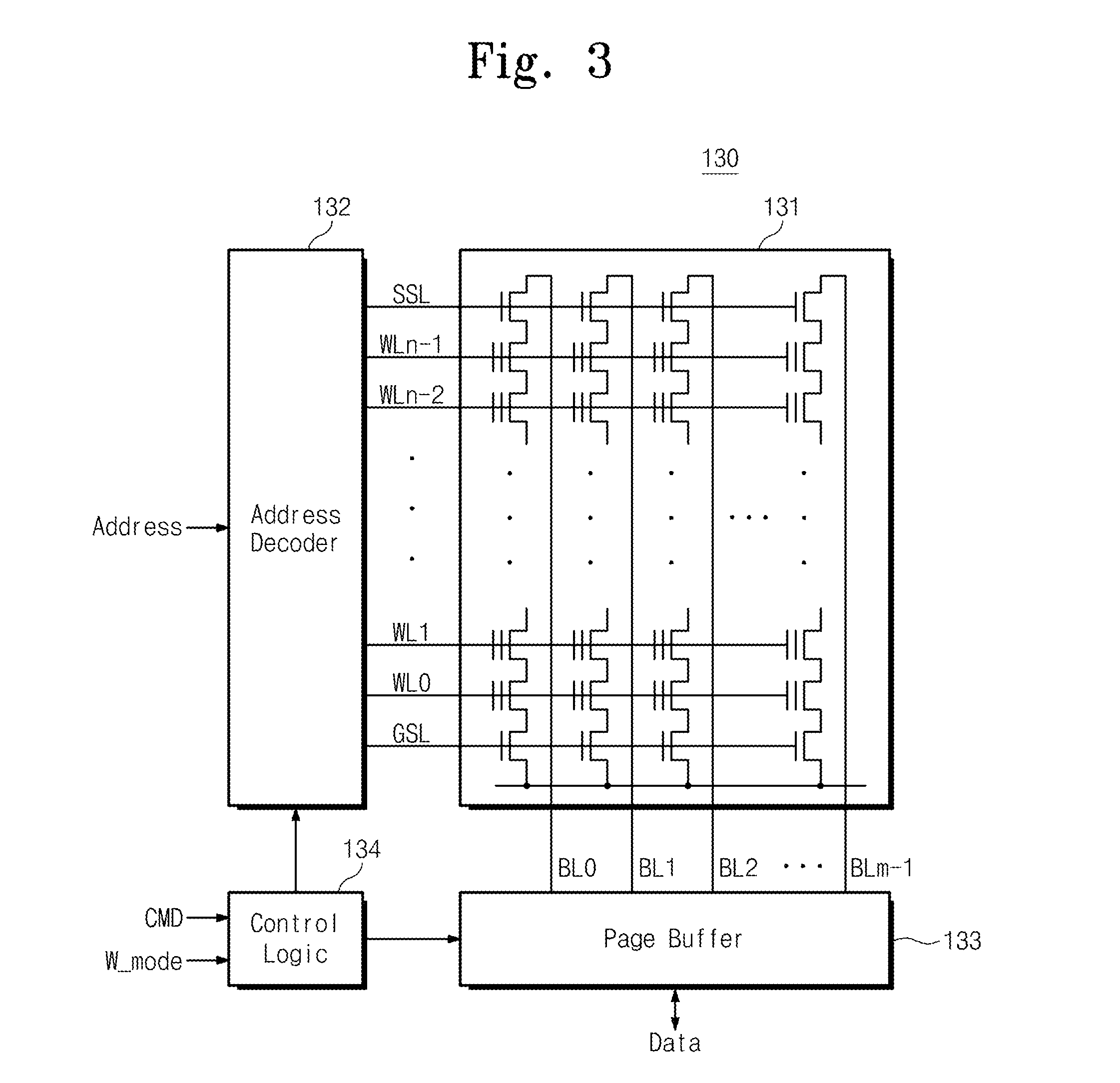

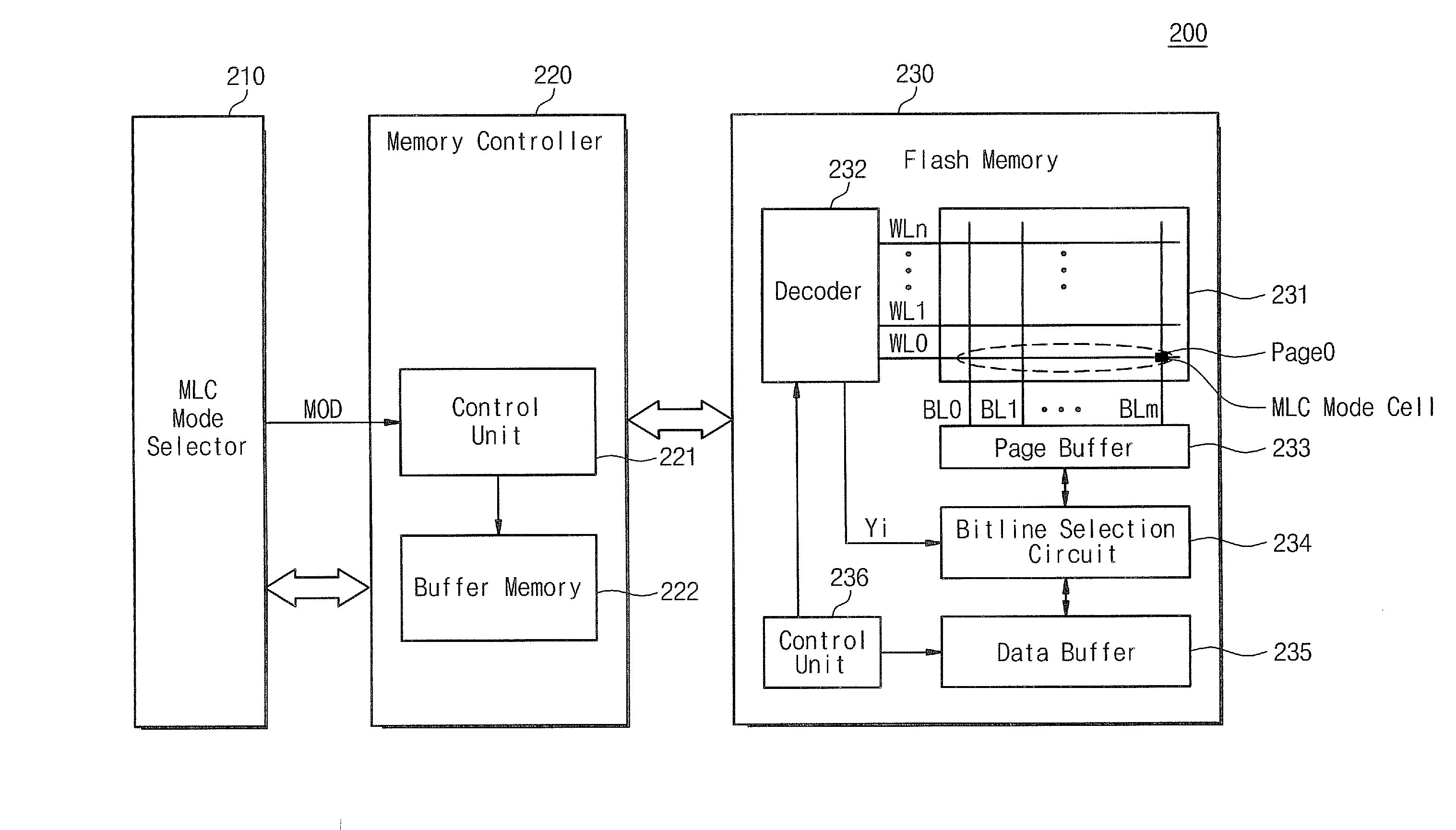

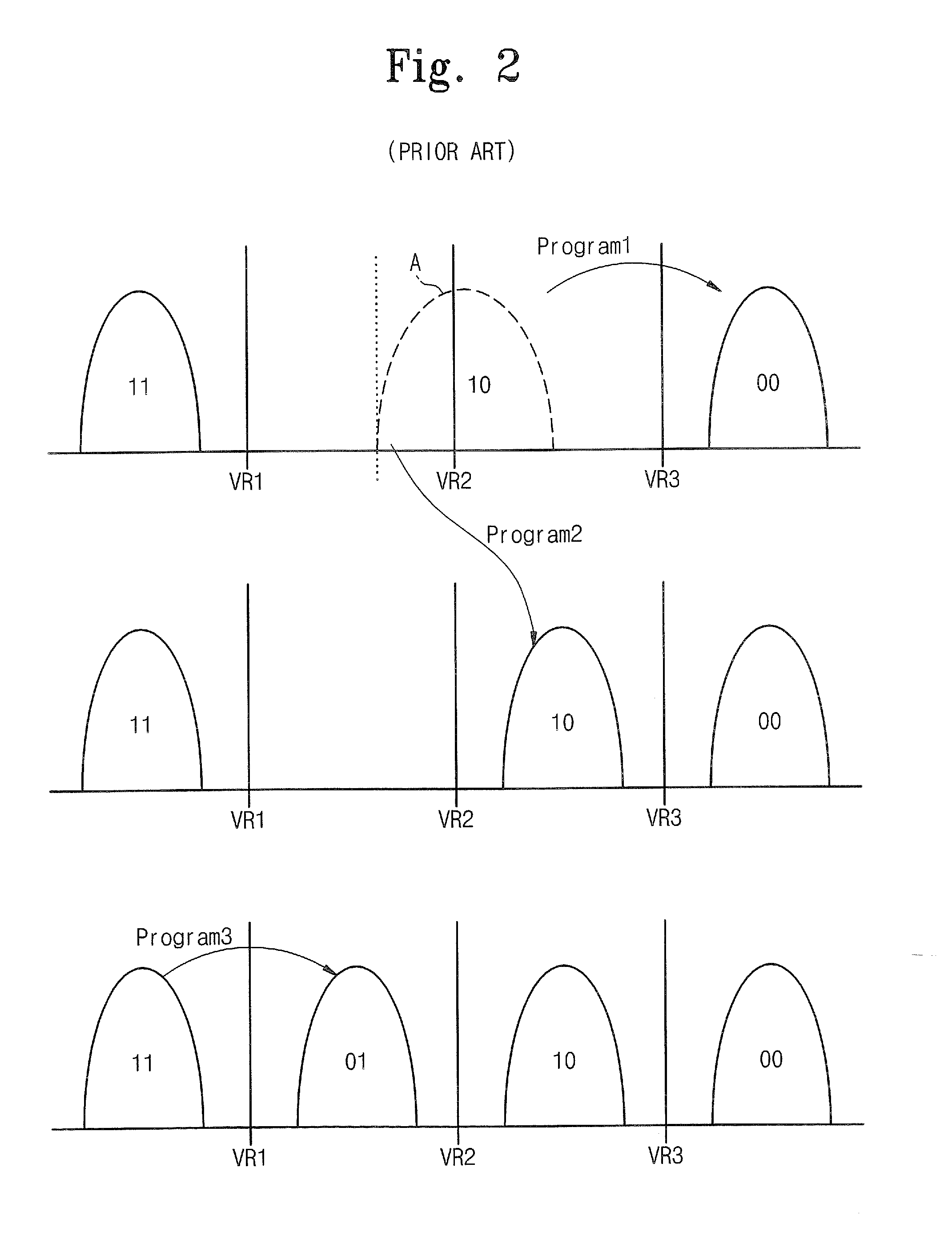

Nonvolatile memory devices including multiple user-selectable program modes and related methods of operation

A memory device includes a flash memory, a memory controller, and an MLC mode selector. The flash memory includes at least one memory cell configured to store multi-bit data therein. The MLC mode selector is configured to generate a mode selection signal indicating whether to store single-bit data or multi-bit data in the memory cell responsive to a user selection. The memory controller is configured to operate the flash memory in a single-level cell (SLC) program mode to store the single-bit data or a multi-level cell (MLC) program mode to store the multi-bit data based on the mode selection signal from the MLC mode selector. The memory device may be configured to store program mode information for the memory cell indicating whether the single-bit data or the multi-bit data is stored therein. Related systems and methods of operation are also discussed.

Owner:SAMSUNG ELECTRONICS CO LTD

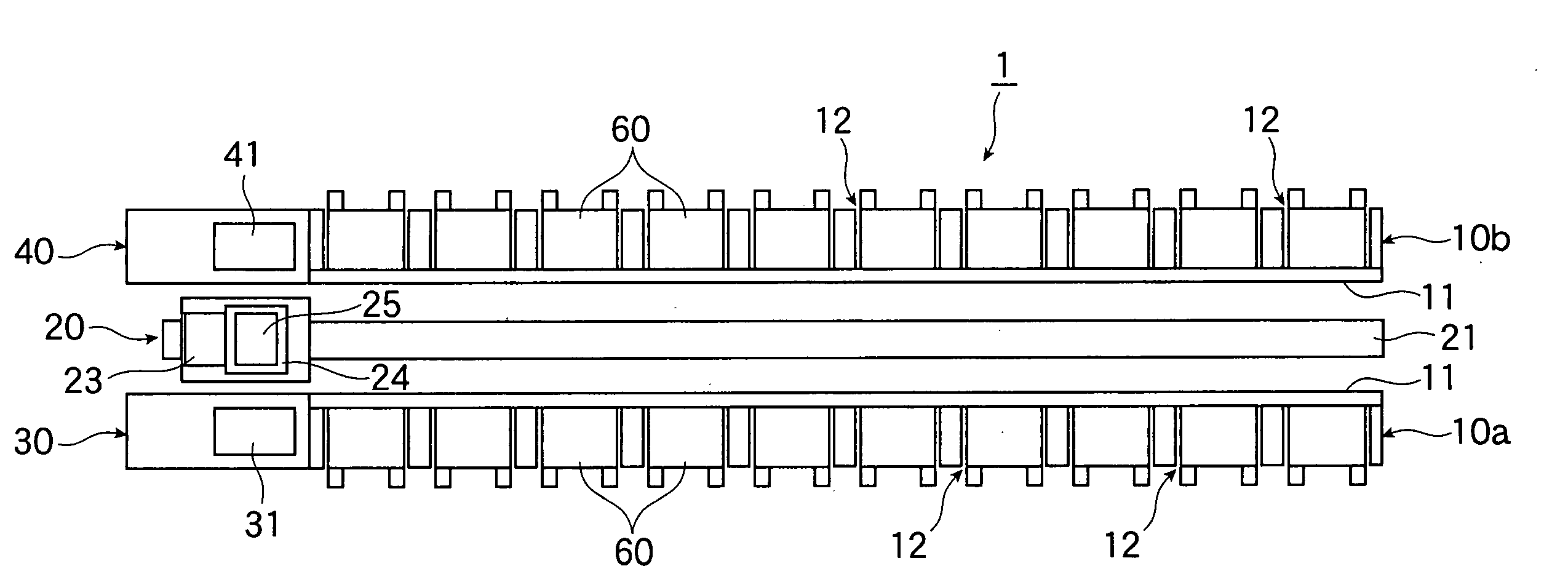

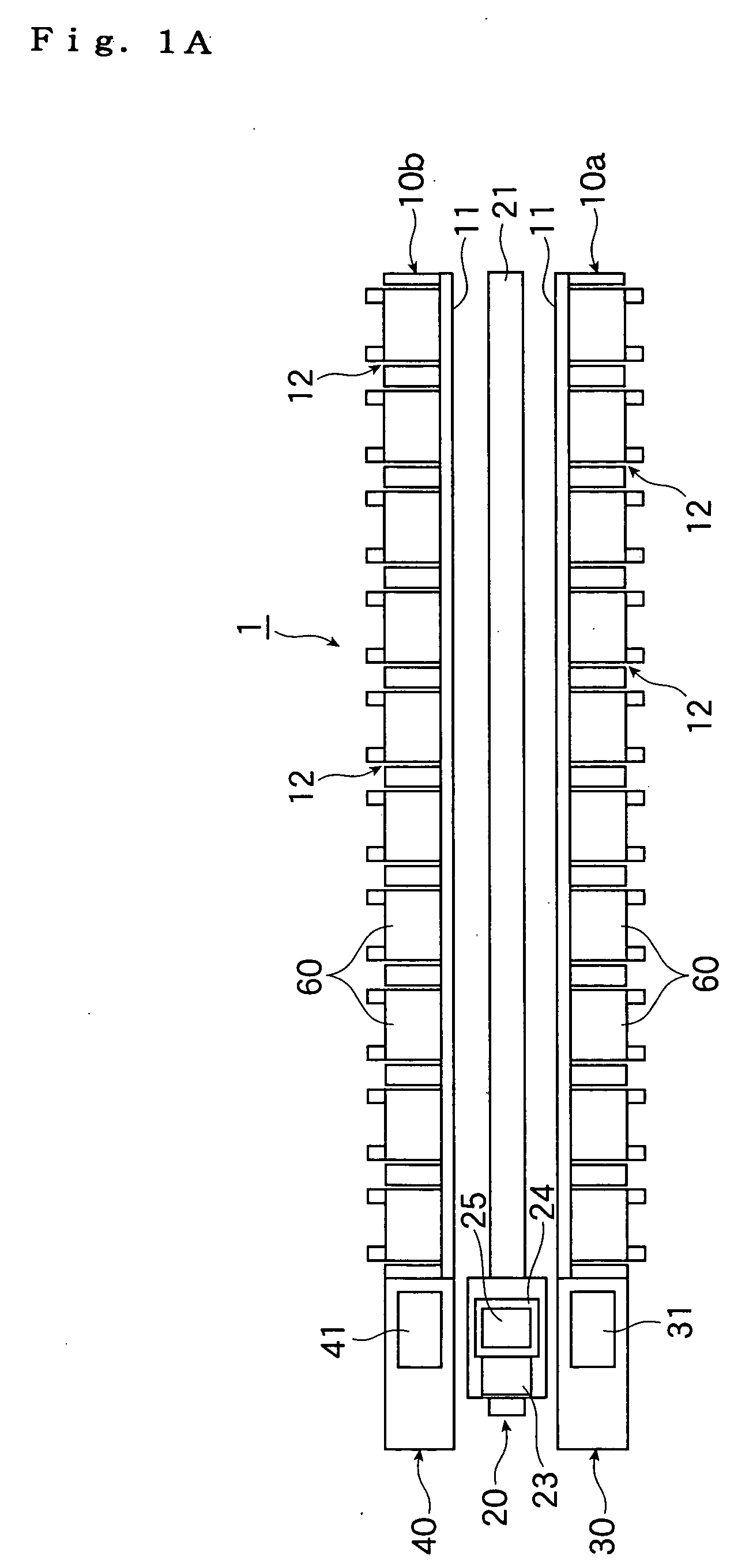

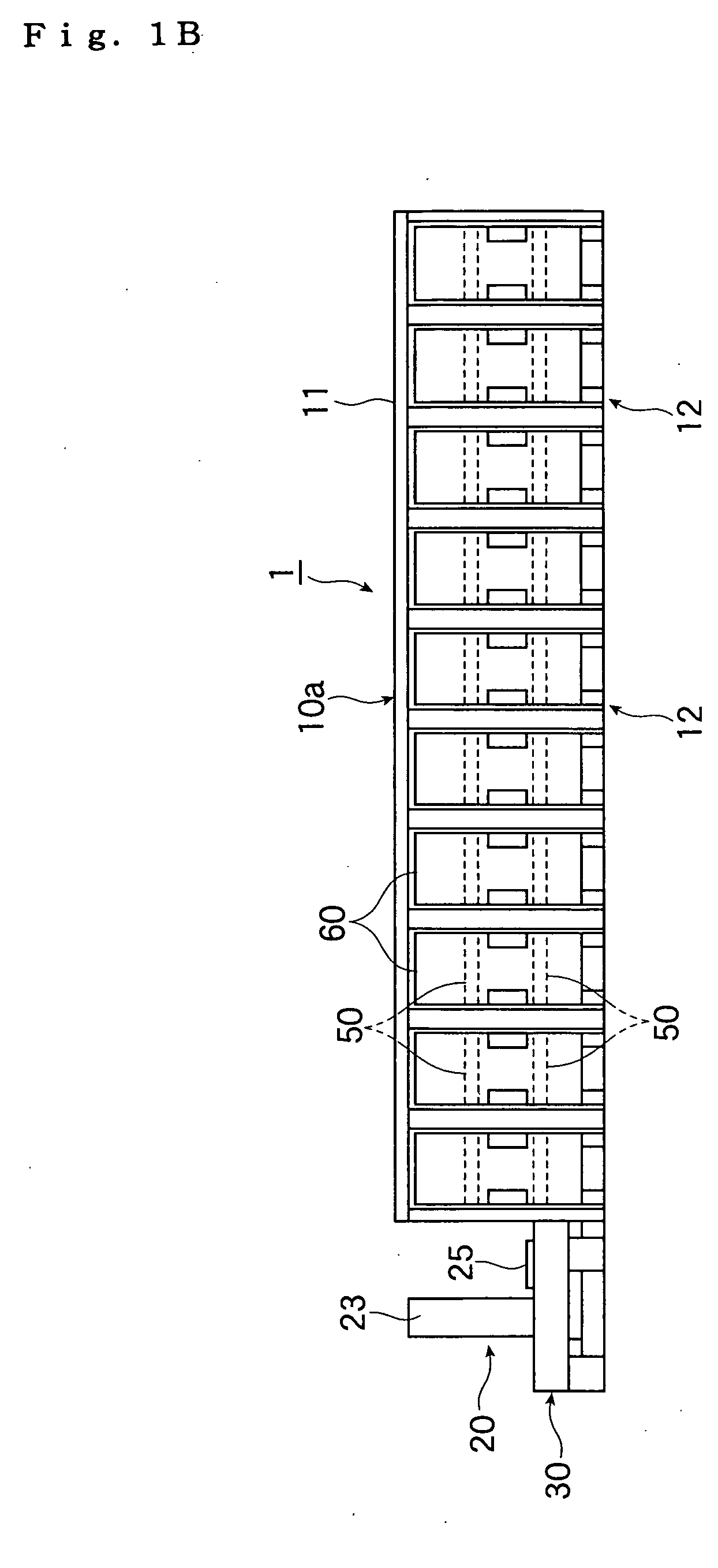

Automatic warehouse

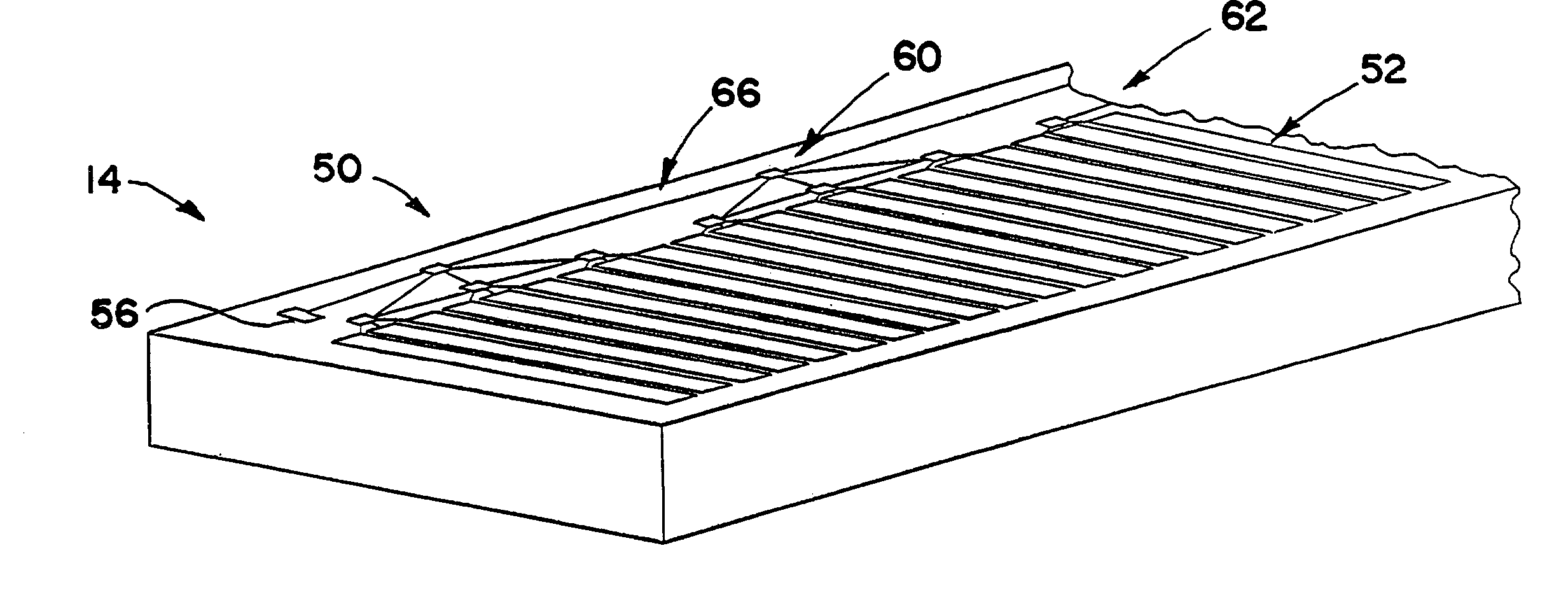

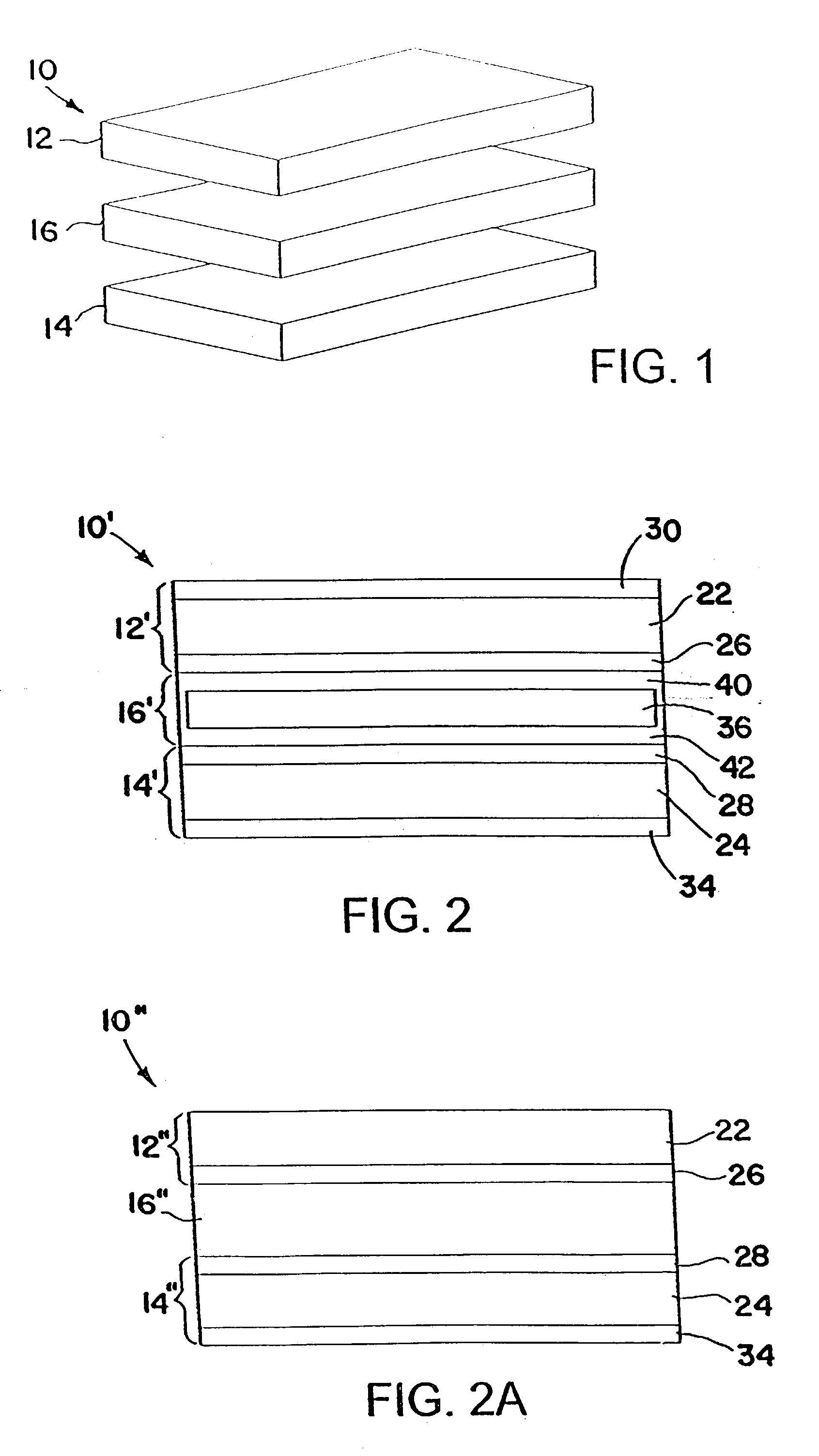

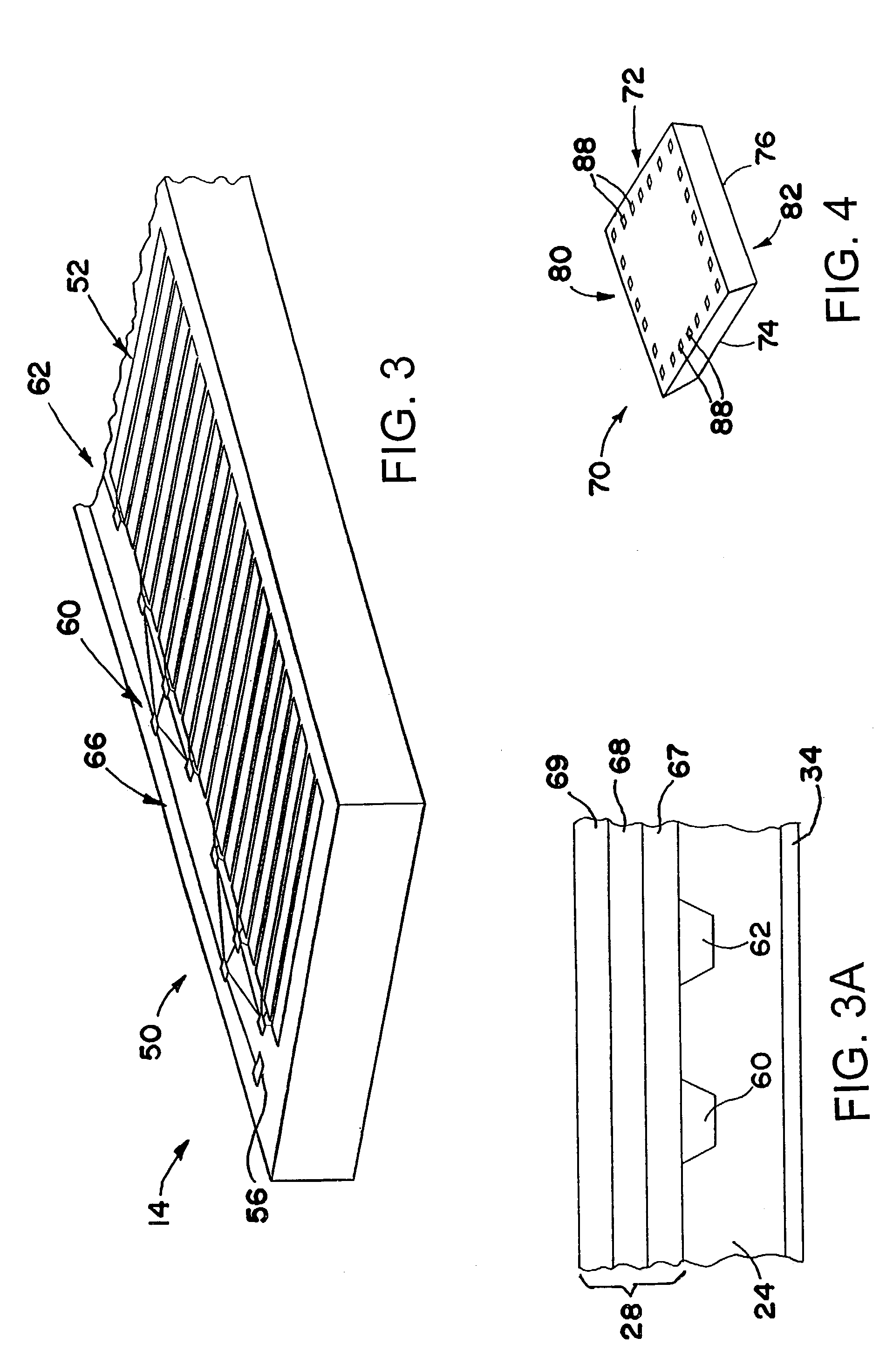

InactiveUS20090265031A1Increase freedomImprove storage efficiencyDigital data processing detailsStorage devicesEngineeringSingle level

An automatic warehouse 1 includes a plurality of shelves 50 and a conveyance device 20. The plurality of shelves 50 are arranged in a horizontal direction and in a single level or in a plurality of levels and adapted to store storage objects. The conveyance device 20 is adapted to transfer the storage objects between the same and each of the plurality of shelves 50. All of the plurality of shelves 50 are implemented by a plurality of shelves 50 provided in a plurality of carriages 60 capable of moving between the inside of the automatic warehouse and the outside of the automatic warehouse. By use of the plurality of carriages 60 which also function as storage shelves, there can be provided an automatic warehouse having high degree of freedom and good storage efficiency, enabling efficient use of factory space, and being capable of coping with cell production.

Owner:HIRATA & CO LTD

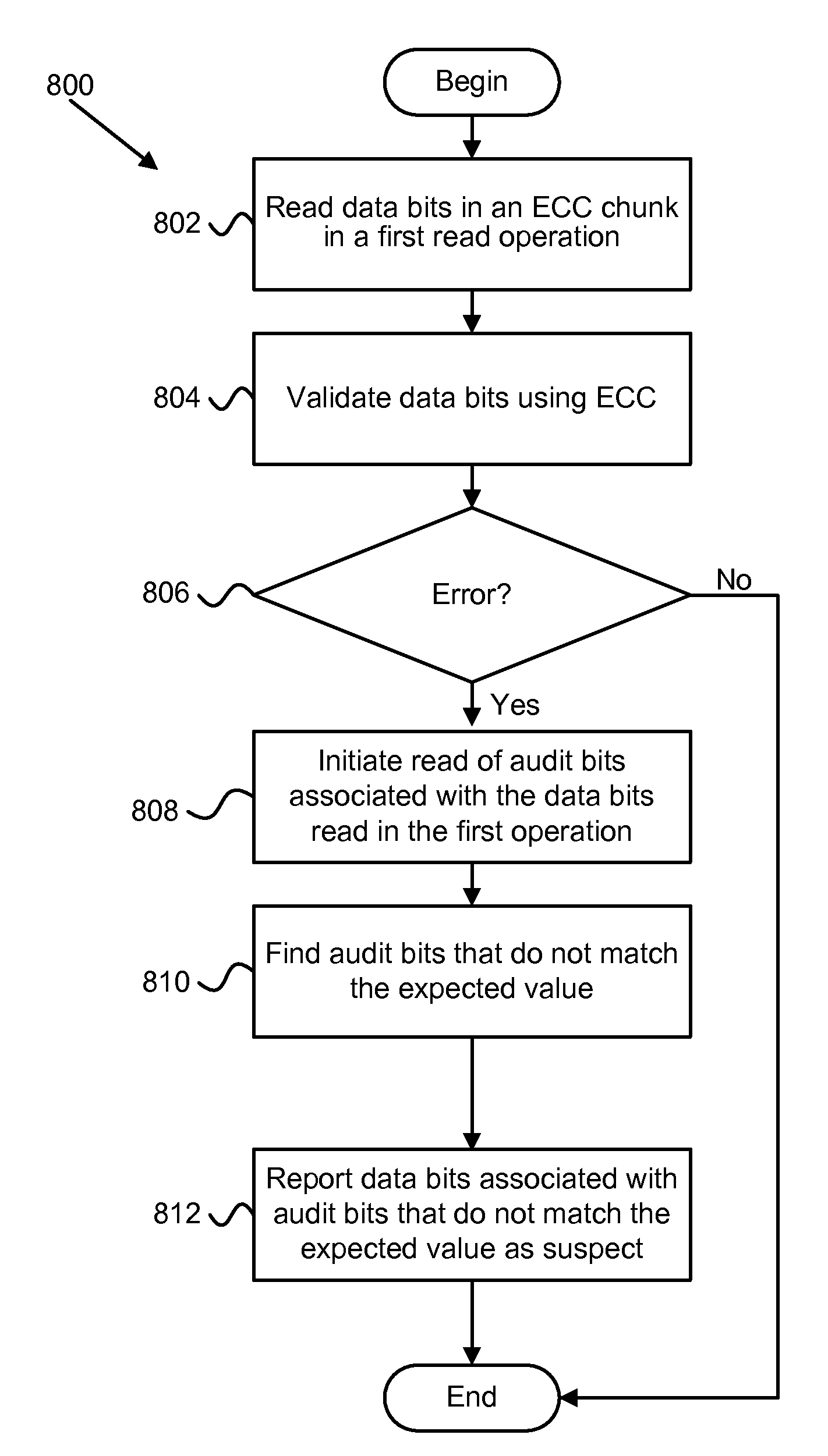

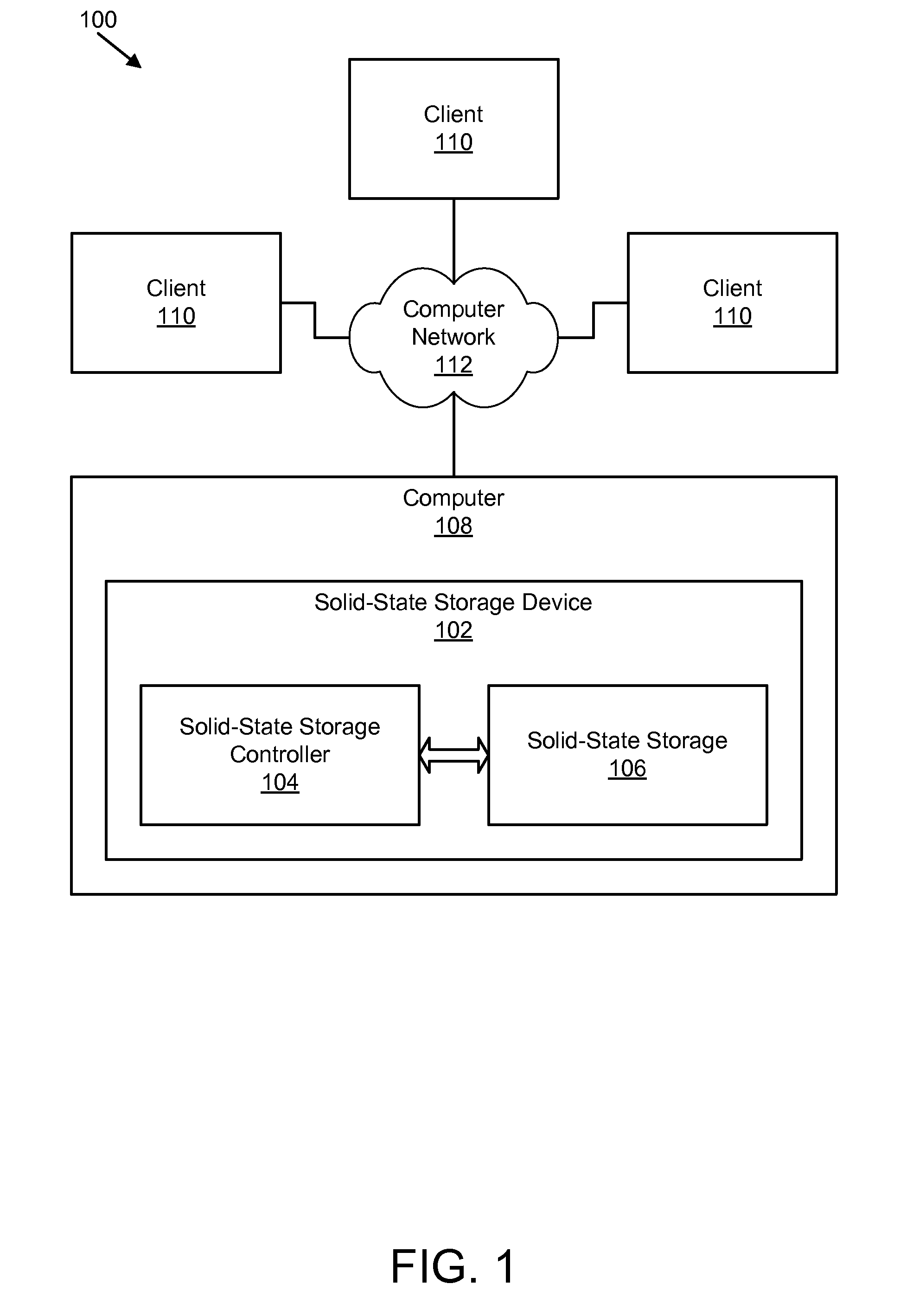

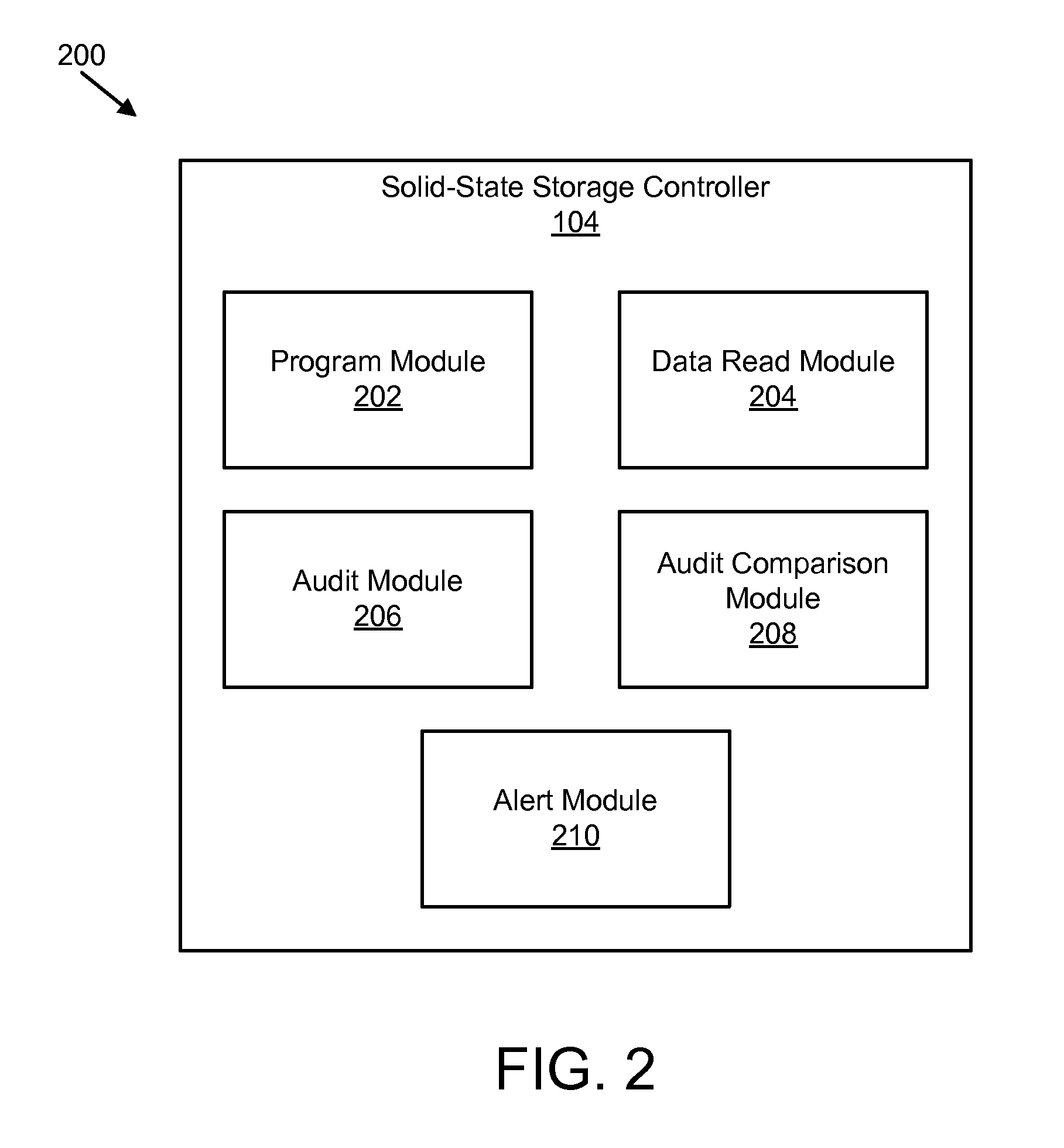

Apparatus, system, and method for using multi-level cell solid-state storage as single-level cell solid-state storage

ActiveUS20100235715A1Increase guard bandLow reliabilityMemory loss protectionRead-only memoriesSolid-state storageMultilevel memory

An apparatus, system, and method are disclosed for storing information in a storage device that includes multi-level memory cells. The method involves storing data that is written to the storage device in the LSBs of the multi-level memory cells, and storing audit data in the MSBs of the multi-level memory cells. The audit data can be read separately from the data and used to determine whether or not there has been any unintended drift between states in the multi-level cells. The audit data may be used to correct data when the errors in the data are too numerous to be corrected using error correction code (ECC). The audit data may also be used to monitor the general health of the storage device. The monitoring process may run as a background process on the storage device. The storage device may transition the multi-level memory cells to operate as single-level memory cells.

Owner:SANDISK TECH LLC

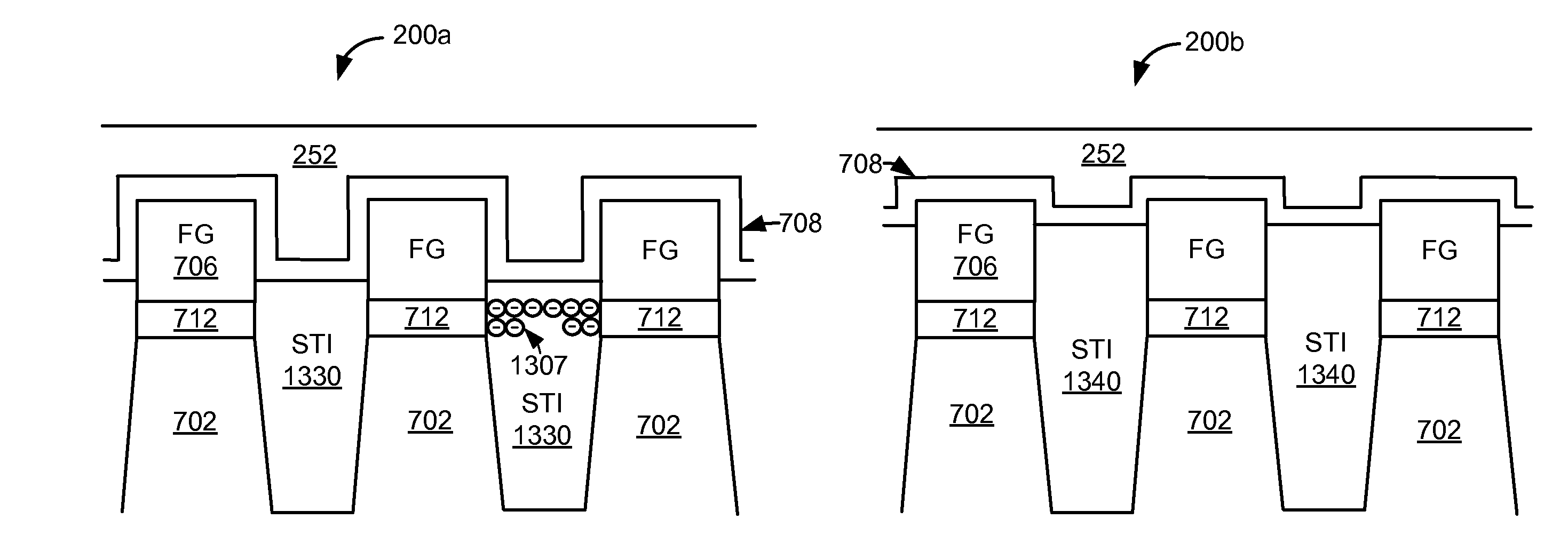

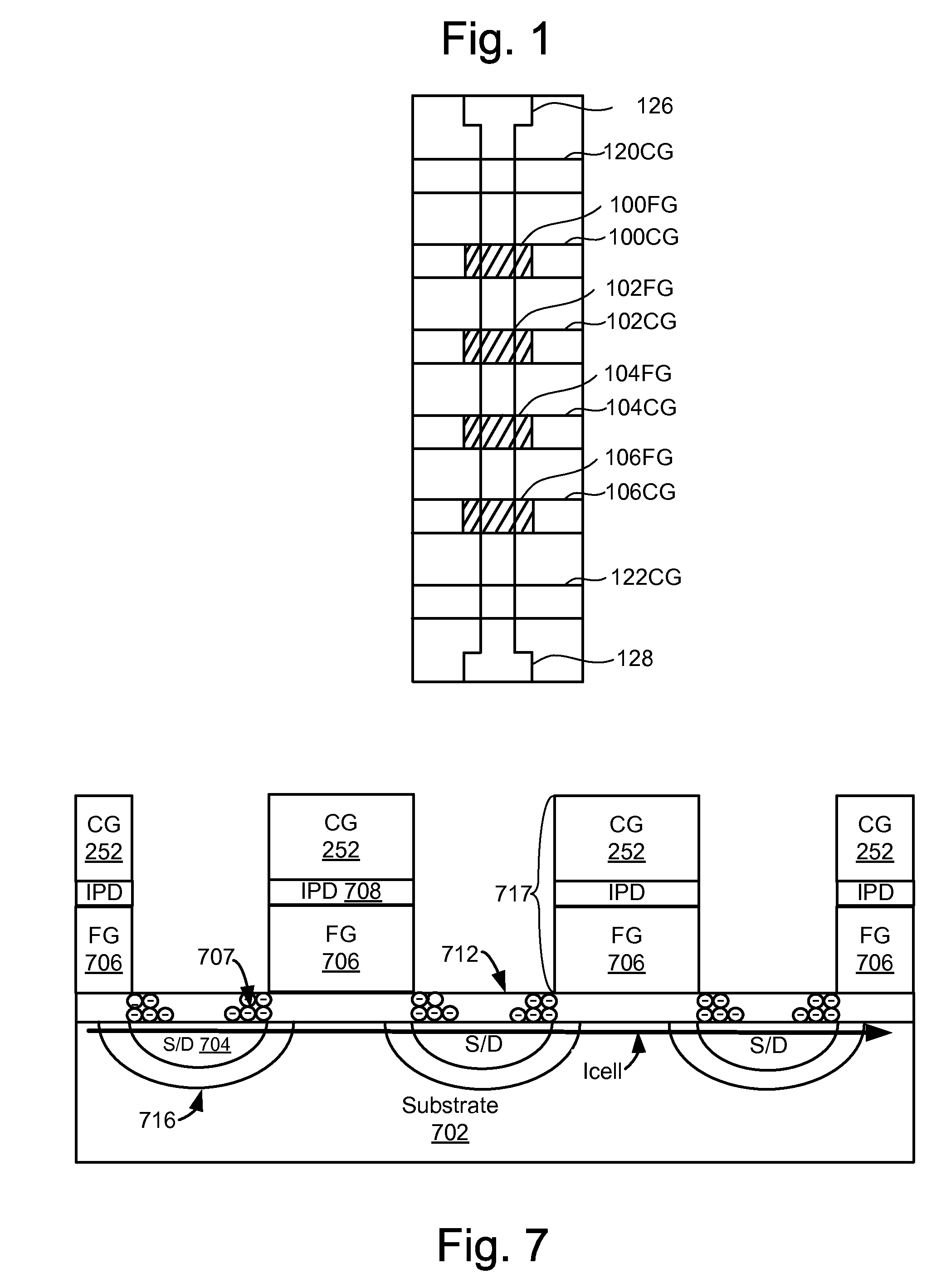

Fabricating and operating a memory array having a multi-level cell region and a single-level cell region

ActiveUS20100246257A1Improve staminaImprove reliabilityTransistorRead-only memoriesCell regionSingle level

Techniques are disclosed herein for applying different process steps to single-level cell (SLC) blocks in a memory array than to multi-level cell (MLC) blocks such that the SLC blocks will have high endurance and the MLC blocks will have high reliability. In some aspects, different doping is used in the MLC blocks than the SLC blocks. In some aspects, different isolation is used in the MLC blocks than the SLC blocks. Techniques are disclosed that apply different read parameters depending on how many times a block has been programmed / erased. Therefore, blocks that have been cycled many times are read using different parameters than blocks that have been cycled fewer times.

Owner:SANDISK TECH LLC

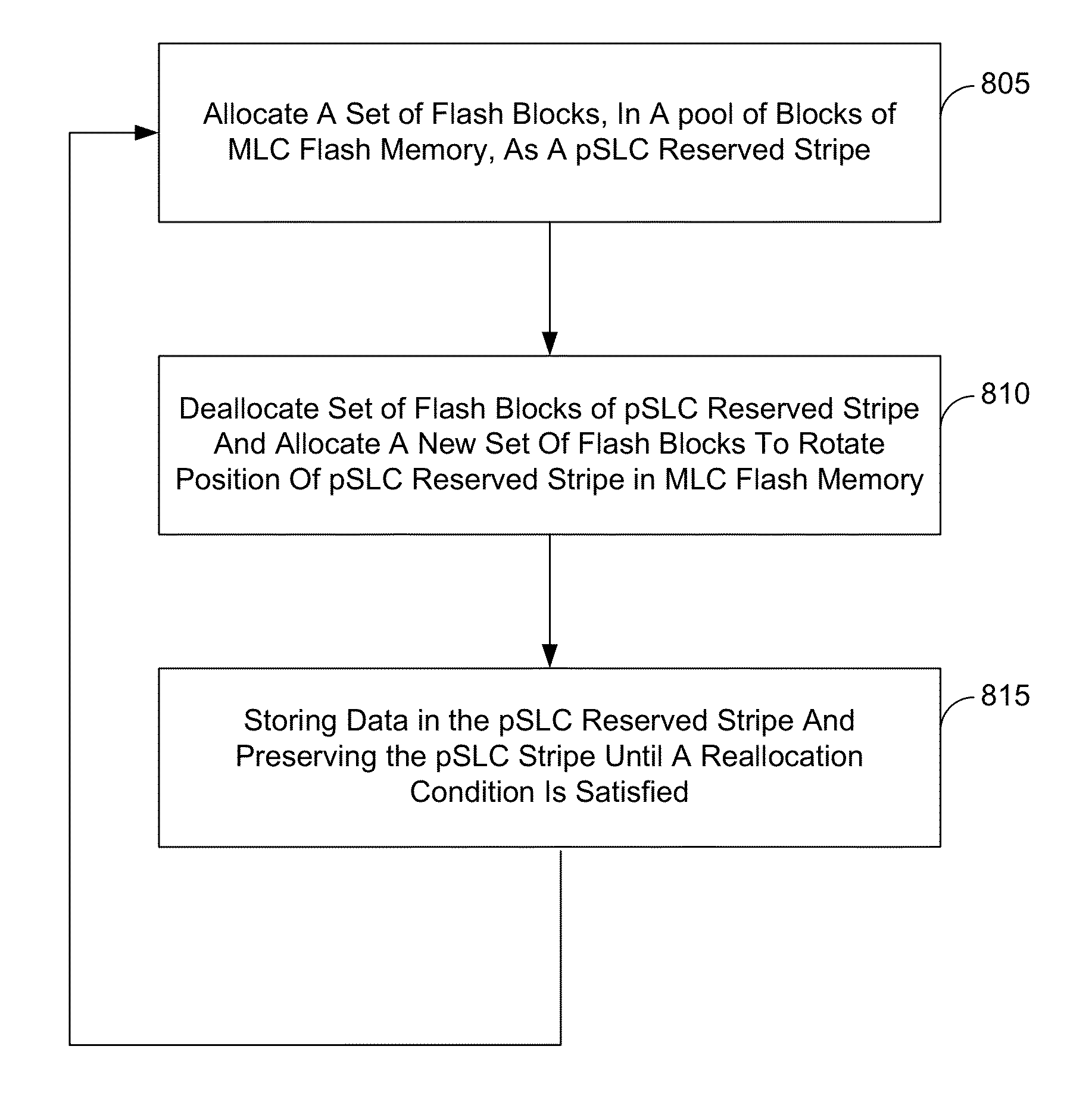

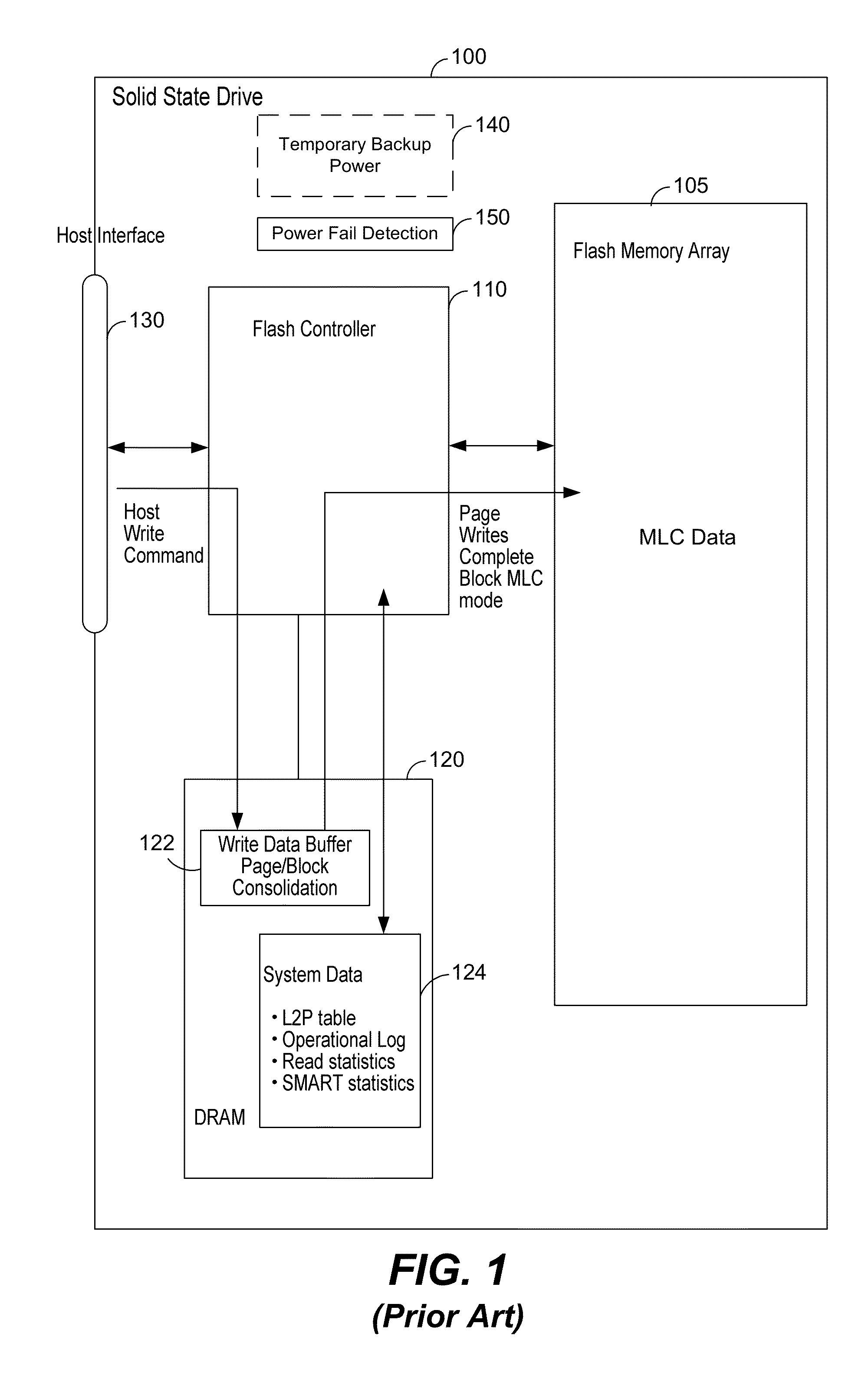

Power fail saving modes in solid state drive with mlc memory

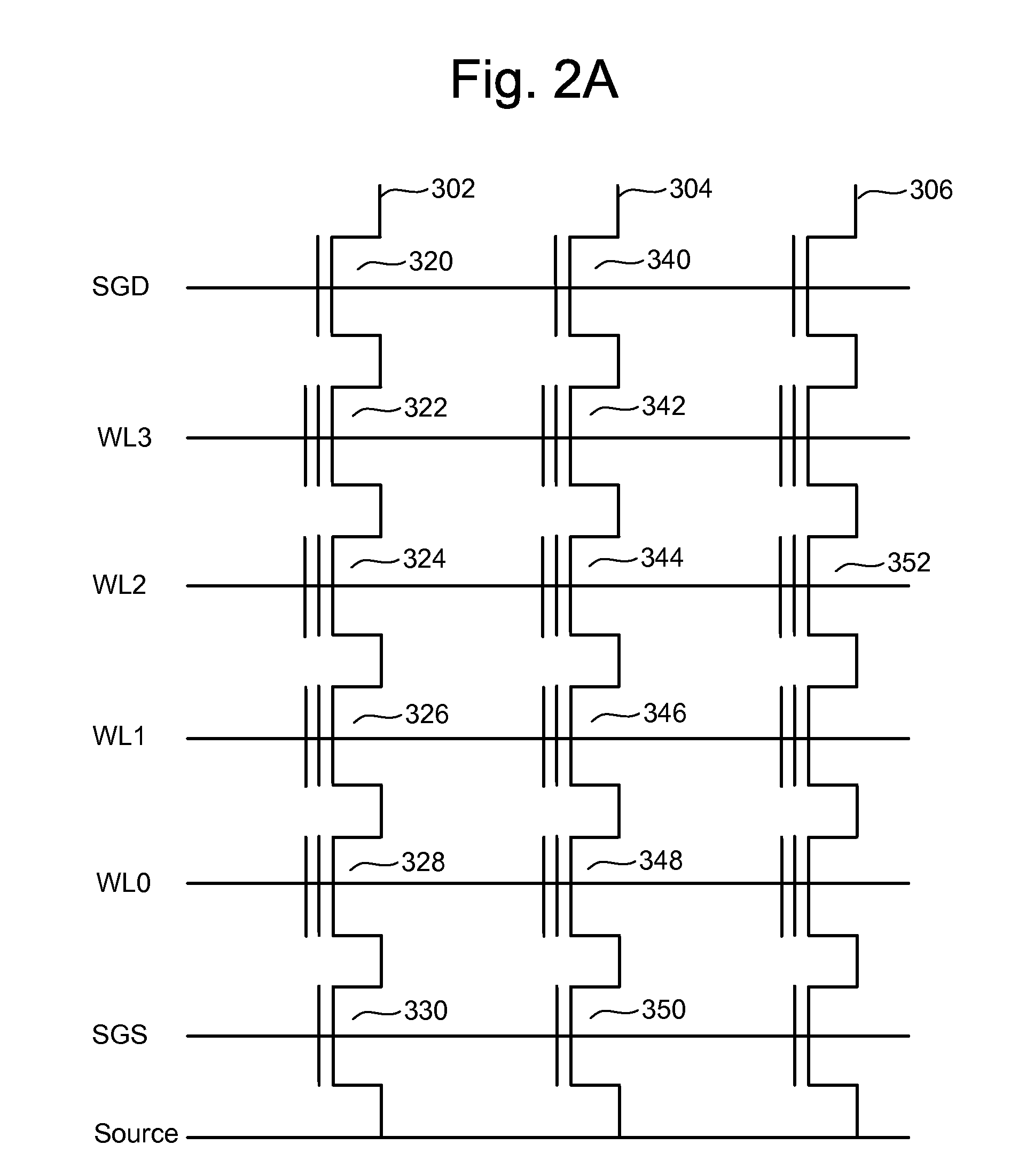

ActiveUS20160268000A1Reduce dwell timePrevent corruptionRead-only memoriesDigital storageWrite bufferStandby power

A solid state drive has a power failure savings mode that permits a reduction in holdup time for a temporary backup power supply. The solid state drive stores data in a multi-level cell (MLC) mode. In a power fail saving mode system metadata is written in a pseudo Single Level Cell (pSLC) mode. In the normal operating mode page writes are performed in complete blocks. In the power fail save saving mode data from a write buffer is written and additional dummy pages written to reduce the total number of pages that must be written to below a complete block size with the dummy pages providing protection from data corruption.

Owner:KIOXIA CORP