Patents

Literature

64 results about "Majority decision" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Majority decision. A majority decision (MD) is a winning criterion in several full-contact combat sports, such as boxing, kickboxing, Muay Thai, mixed martial arts and others sports involving striking.

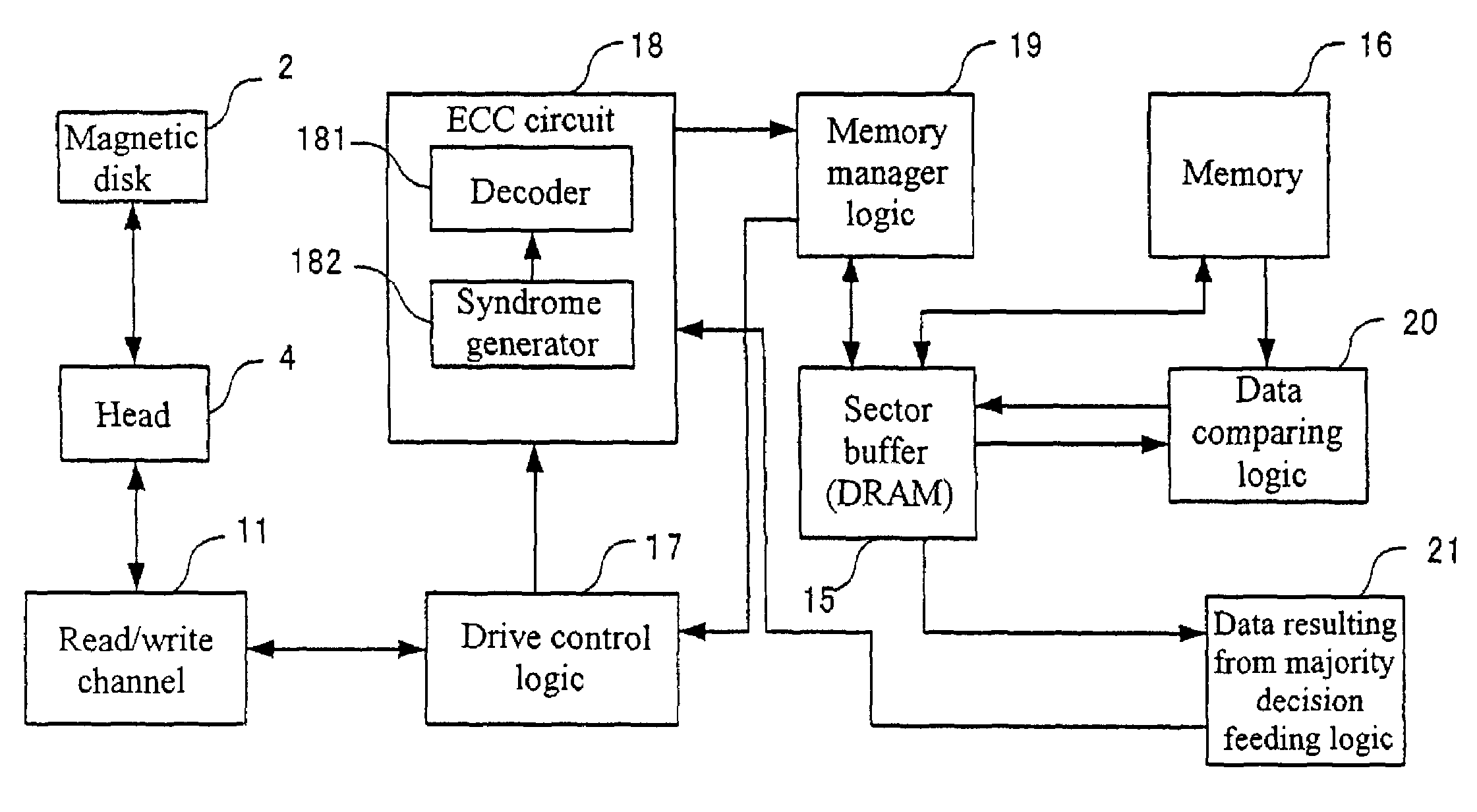

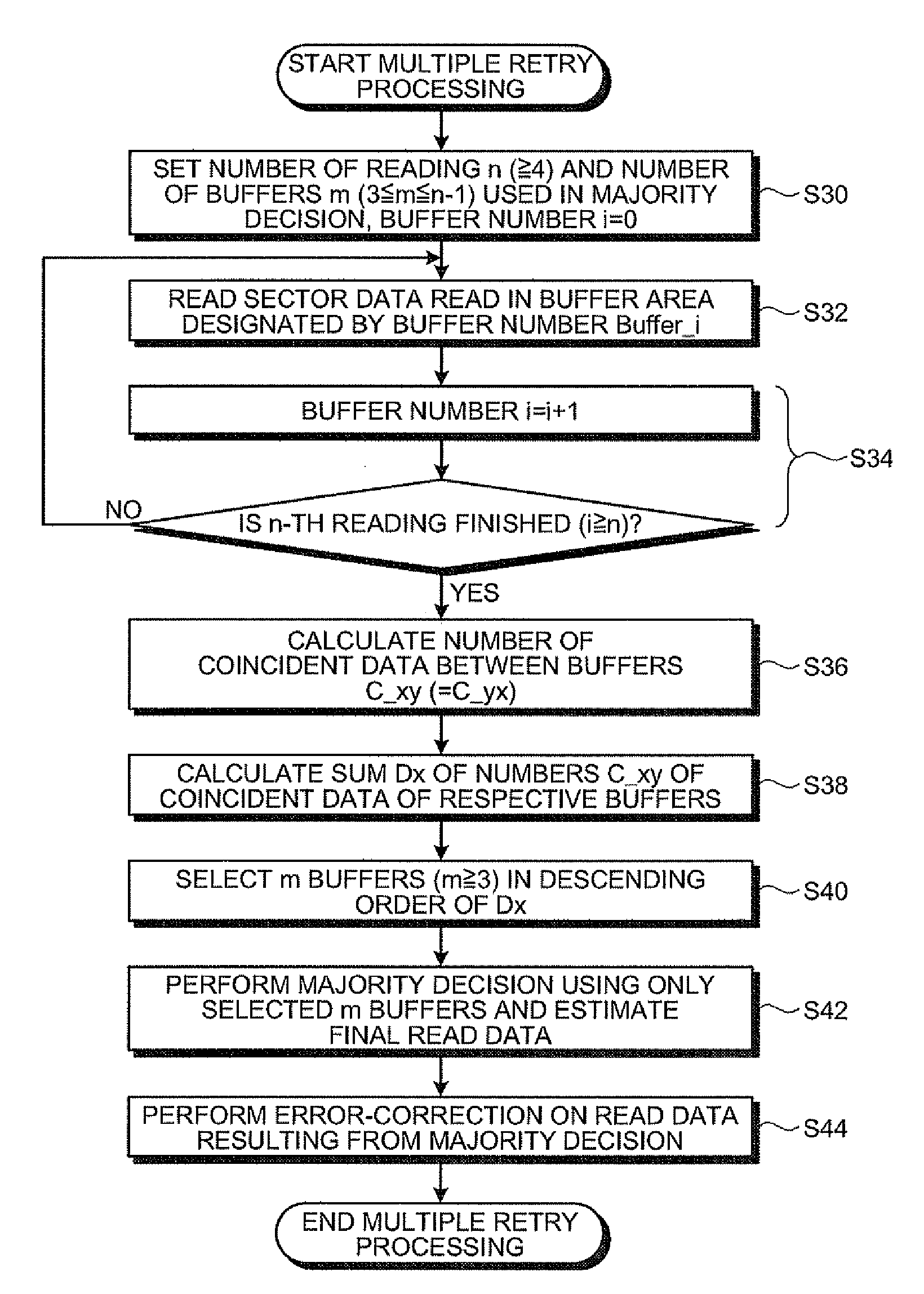

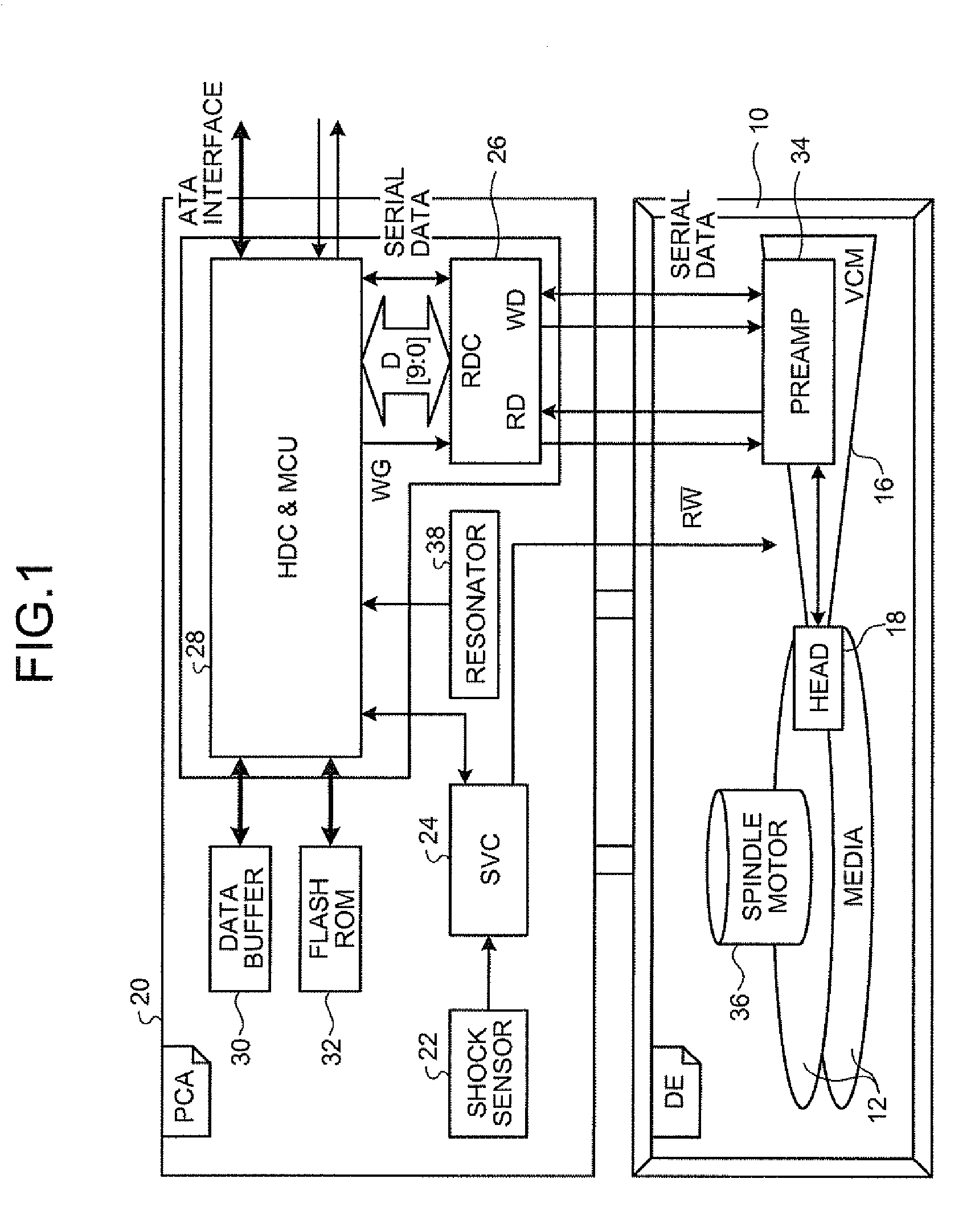

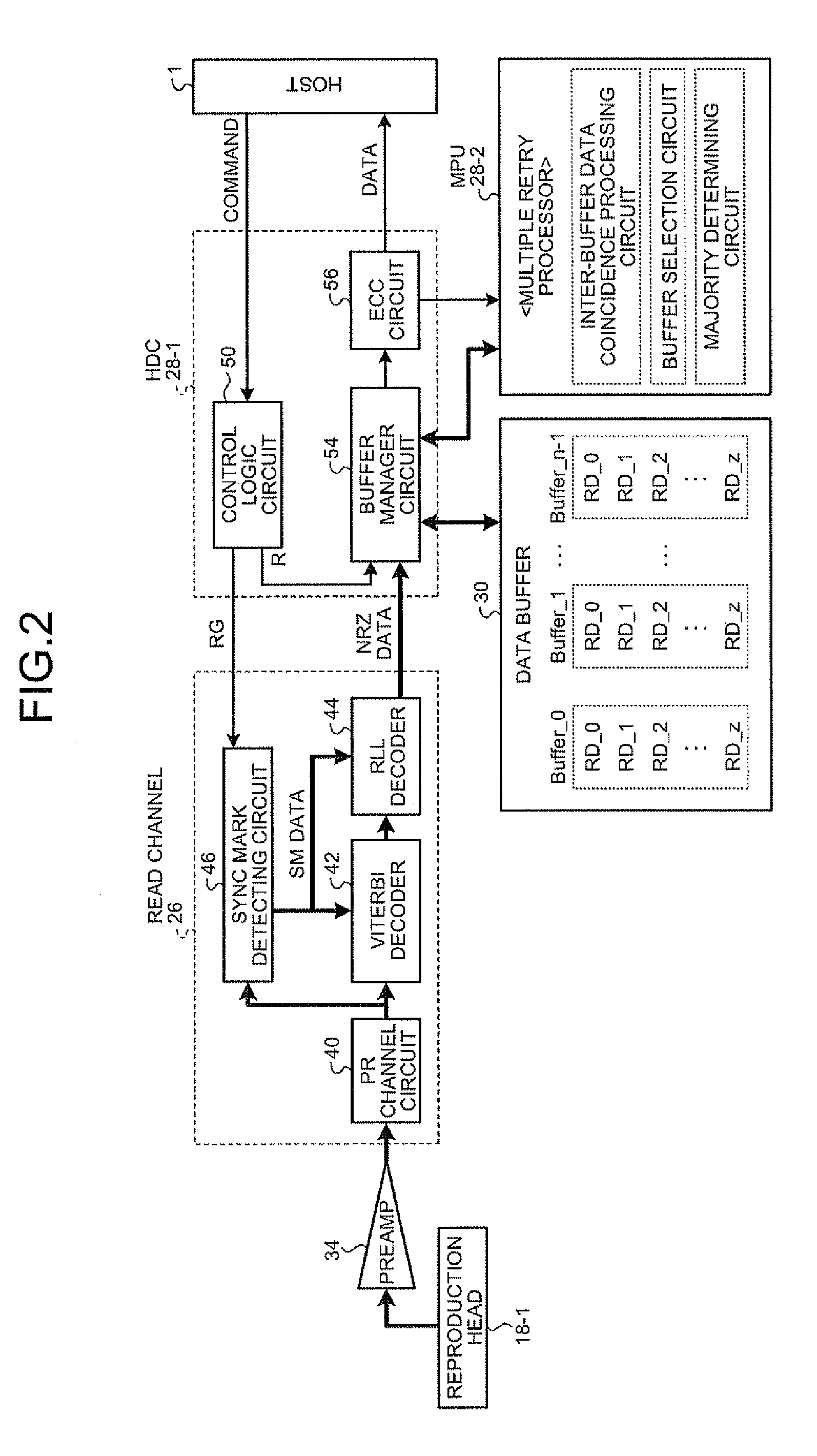

Data storage apparatus, read data processor, and read data processing method

ActiveUS6981205B2Improving error correcting probabilityIncrease probabilityInput/output to record carriersOther decoding techniquesComputer architectureData value

To improve the probability of error correction, thereby generating correct read data. Data is read from the same sector by a number of times and a majority decision is done in the same address, thereby the most frequently read value is regarded as the true data value in the address. For example, for an address 00, “00” is handled as a true data value.

Owner:LENOVO PC INT

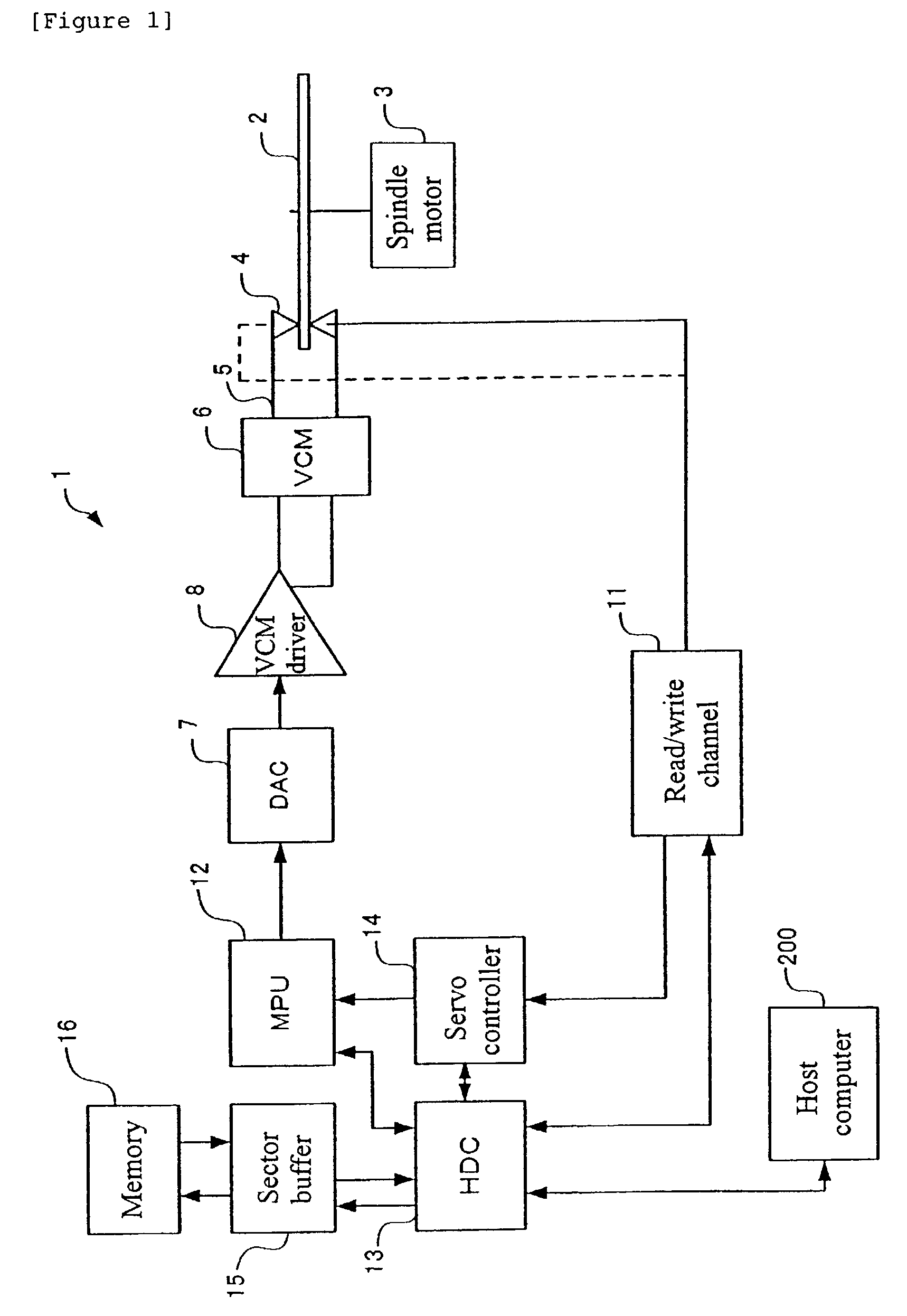

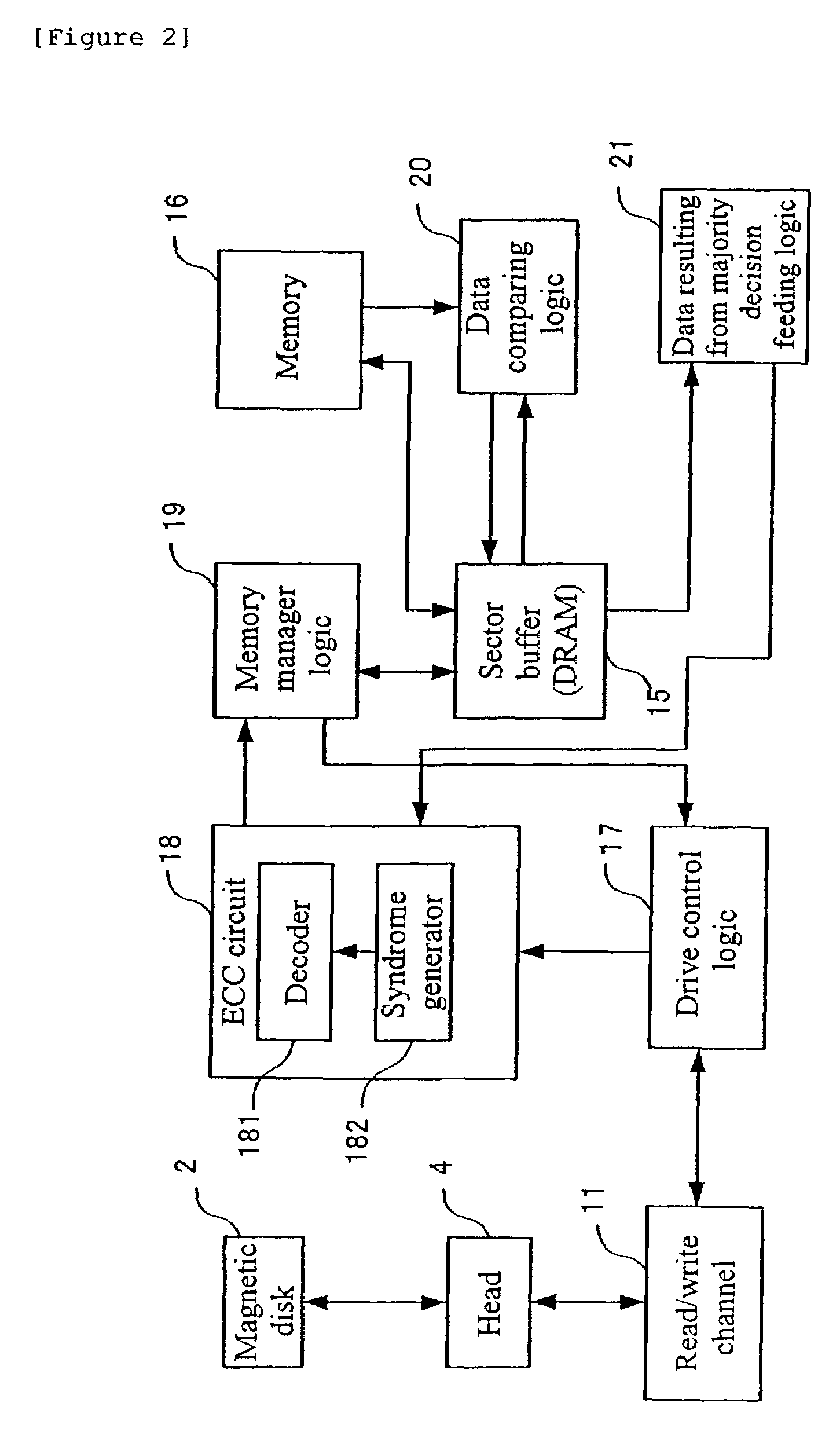

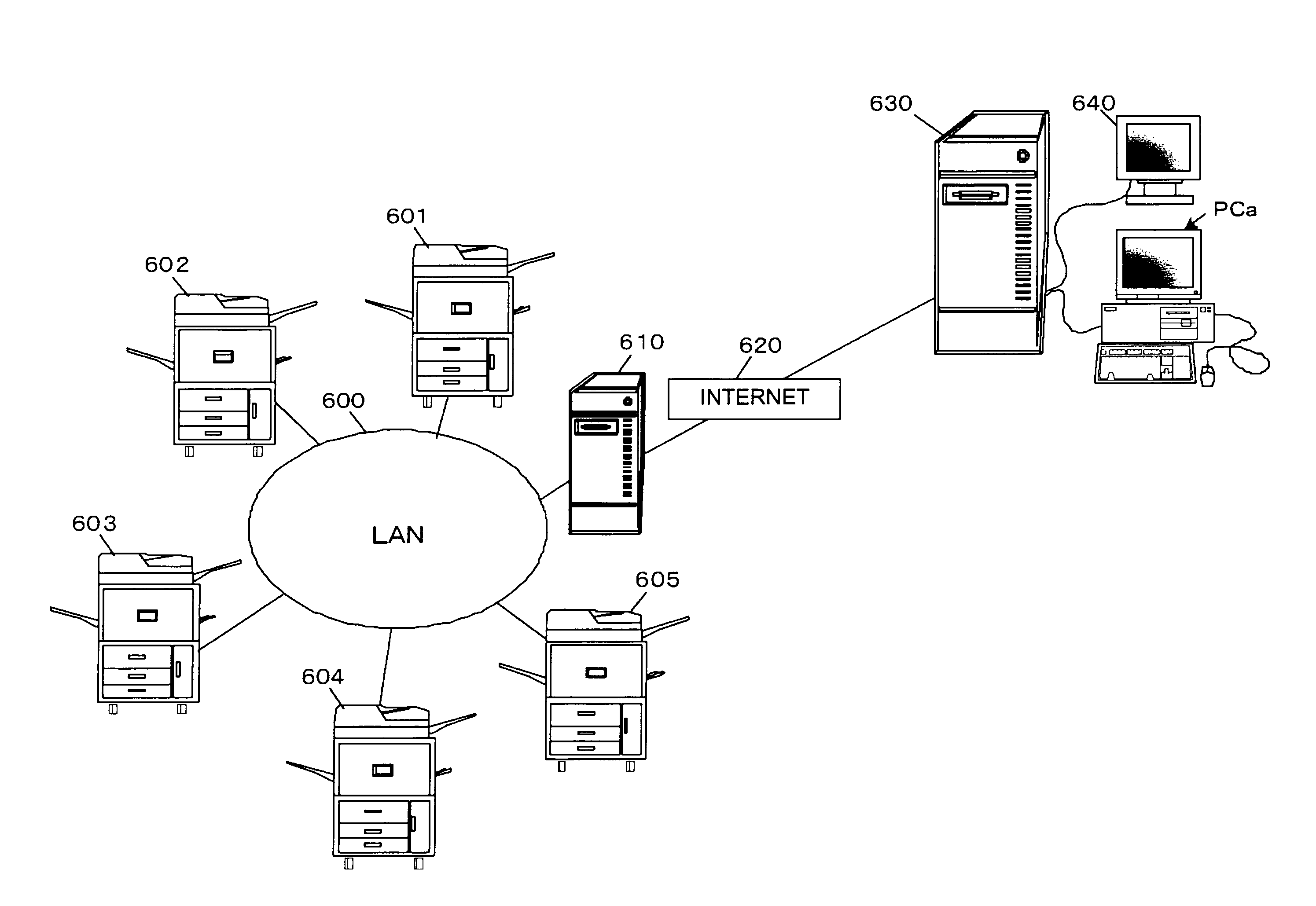

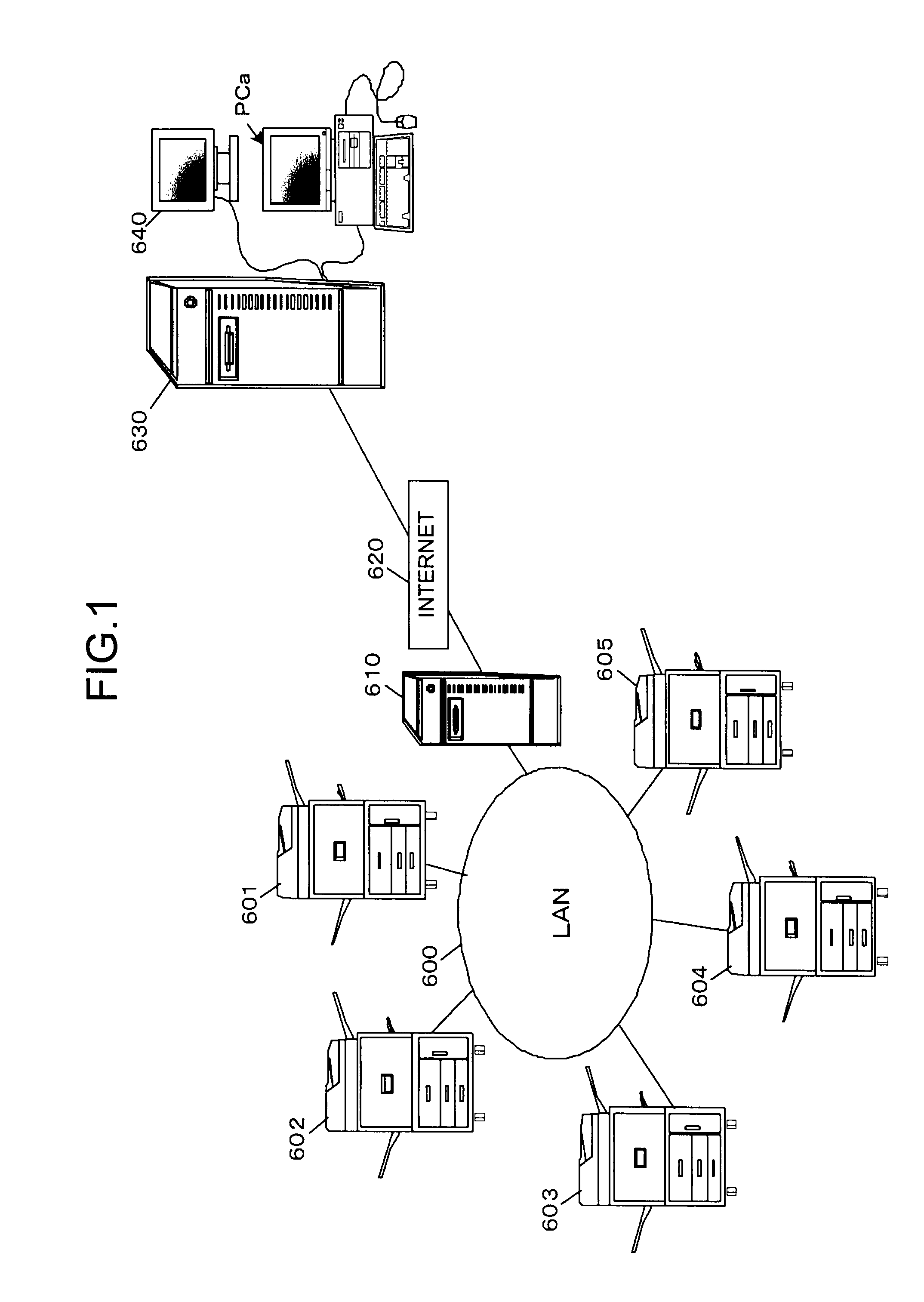

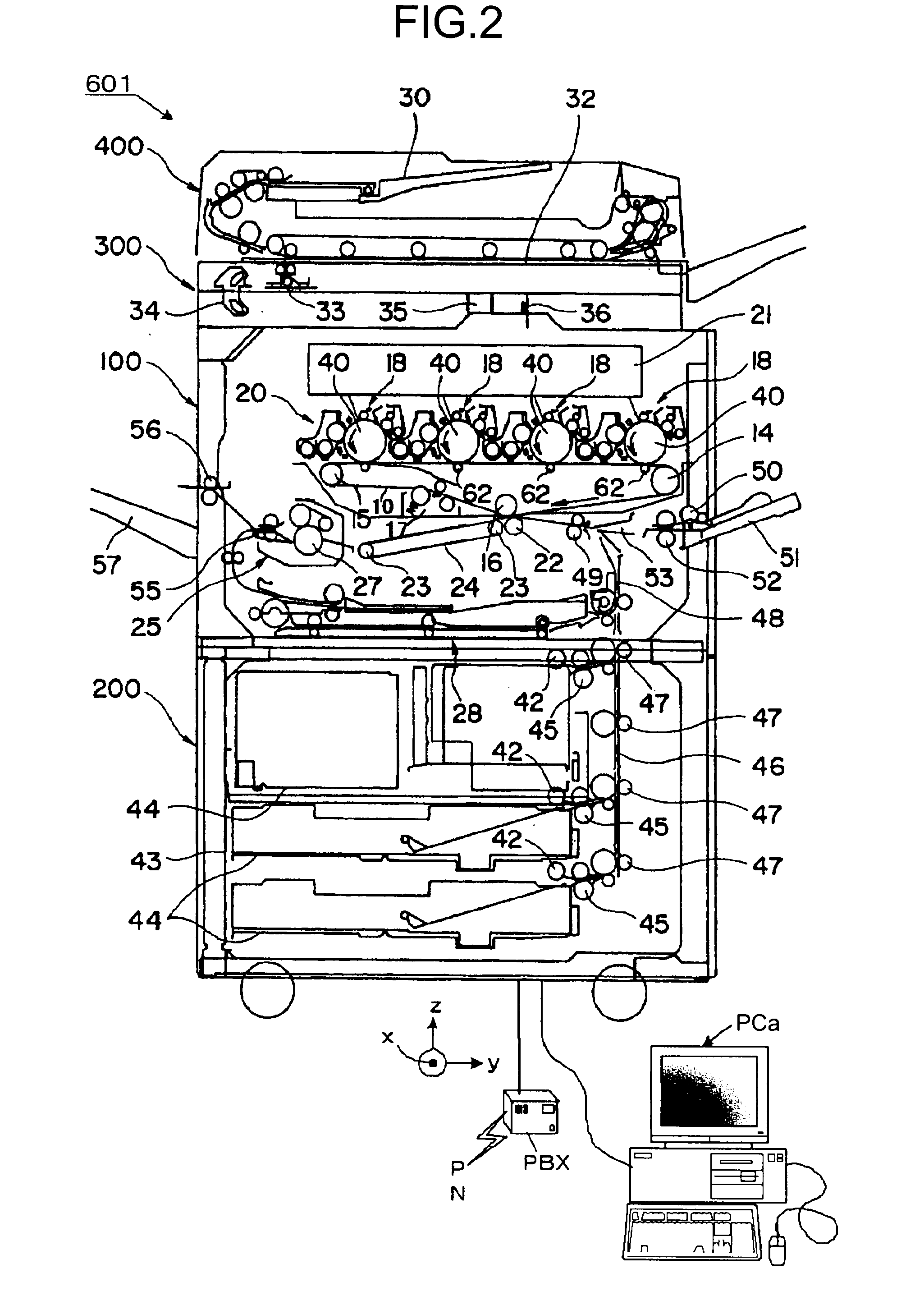

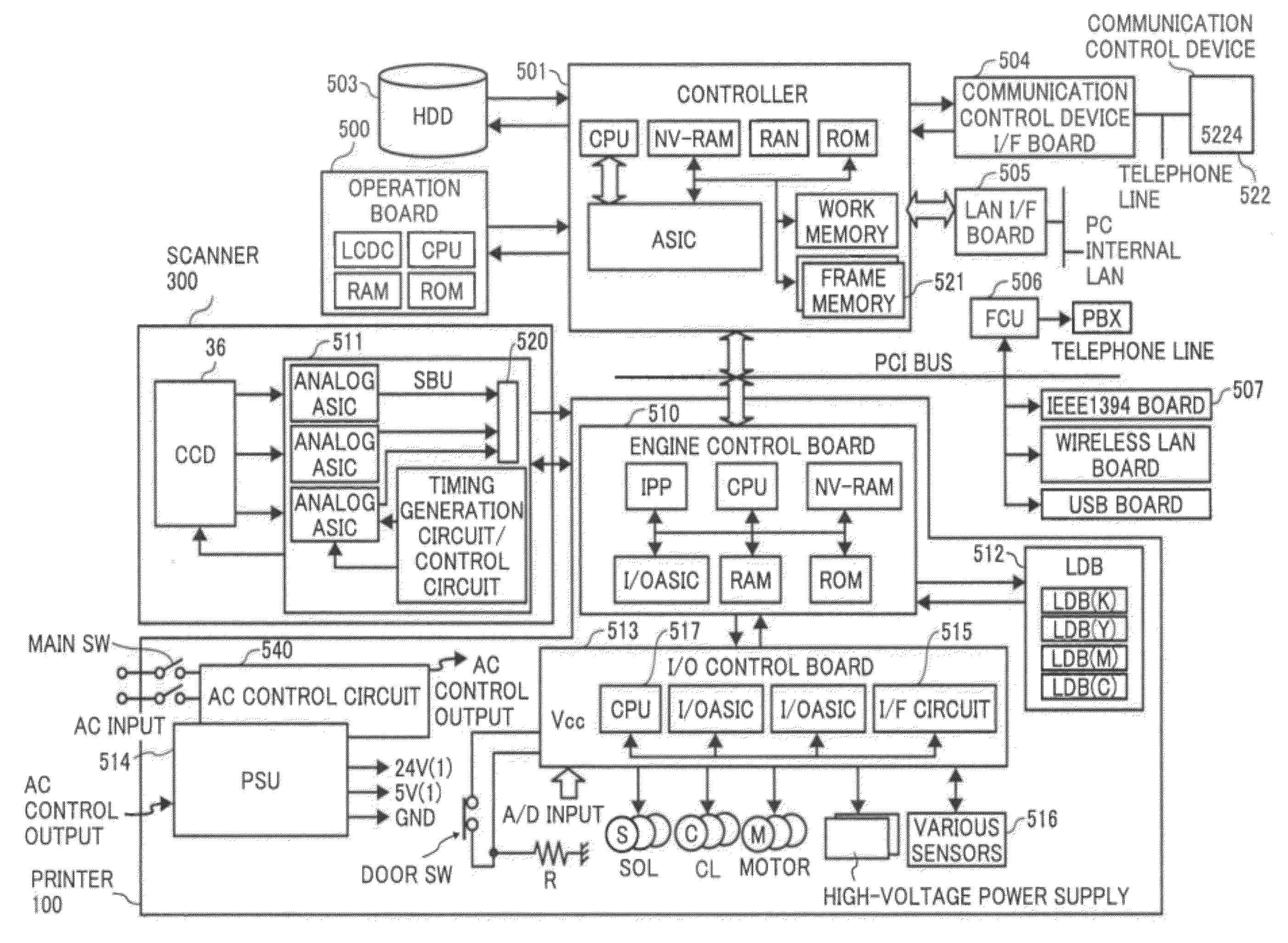

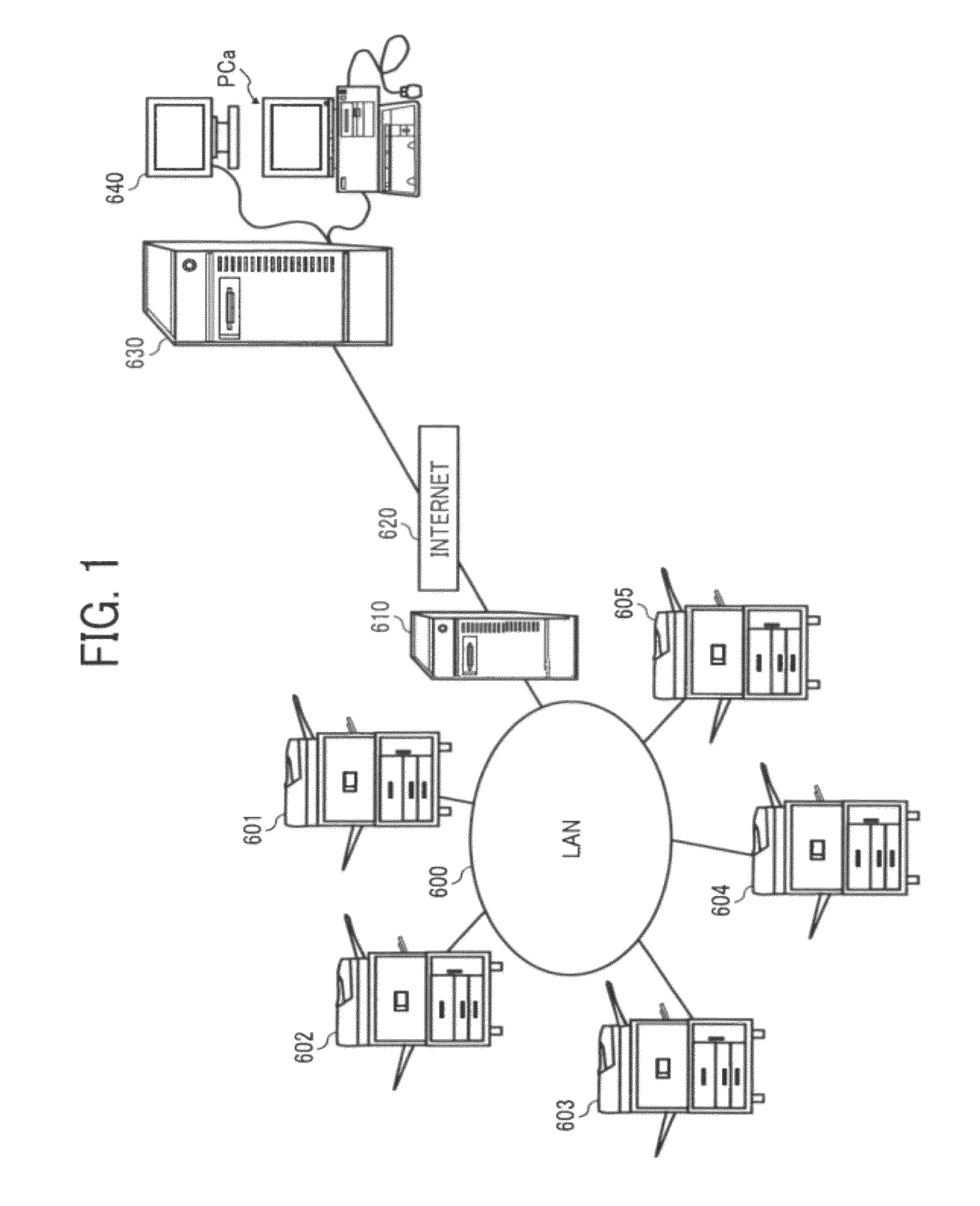

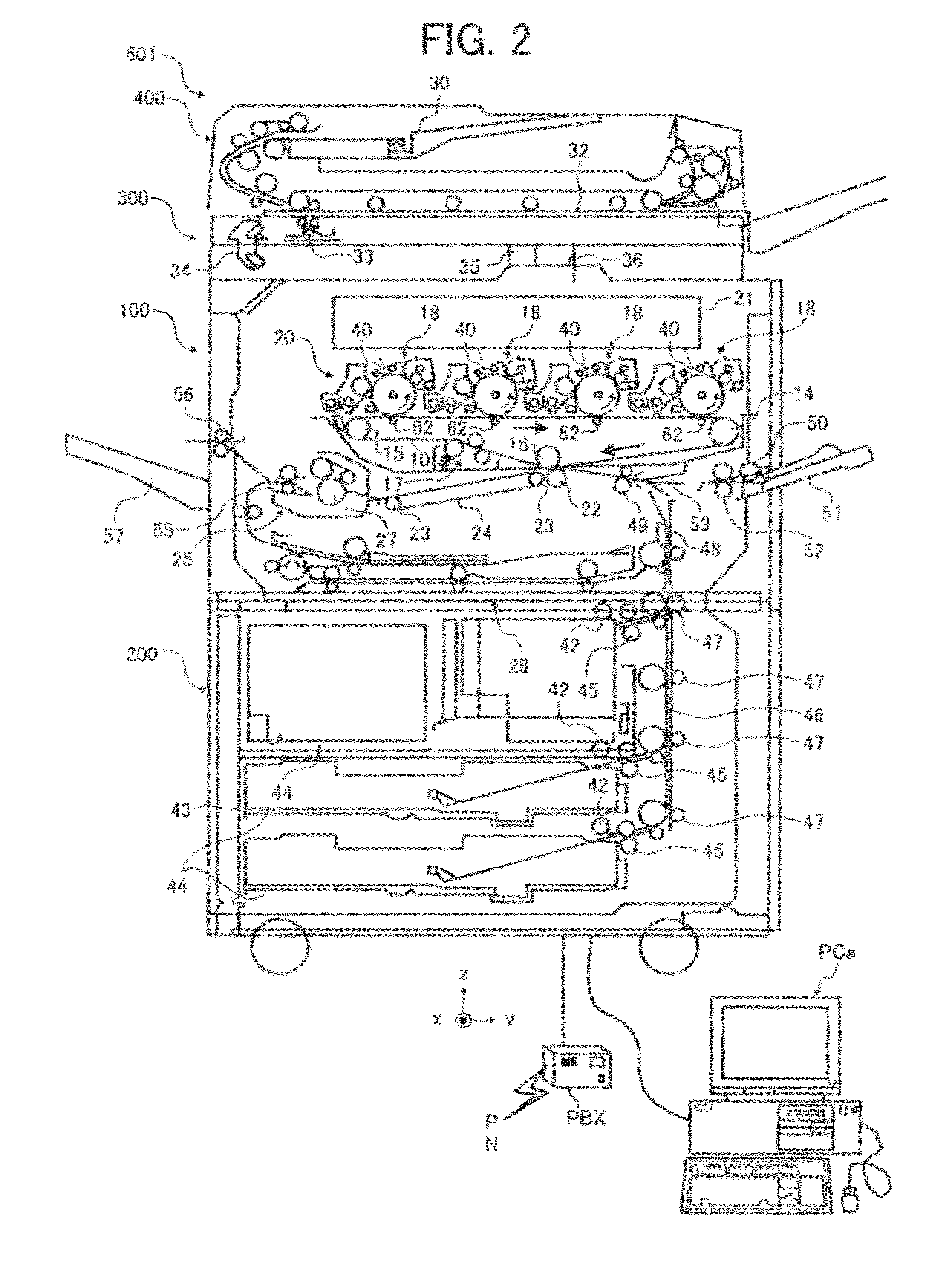

Management apparatus, management system, operation status determination method, and image forming apparatus

ActiveUS20090033993A1Solve problemsVisual presentationSpecial data processing applicationsImage formationData mining

A data collecting unit receives a plurality of types of status data from an image forming apparatus and stores the status data in a status database. A data generating unit generates a plurality of types of target data for determining a maintenance sign, based on the status data. A first determining unit determines whether each of the status data exceeds a predetermined reference value. A second determining unit performs weighted majority decision based on a determination result from the first determining unit and a weight value set for each of the status data, and determines whether there is a maintenance sign taking all the status data into consideration.

Owner:RICOH KK

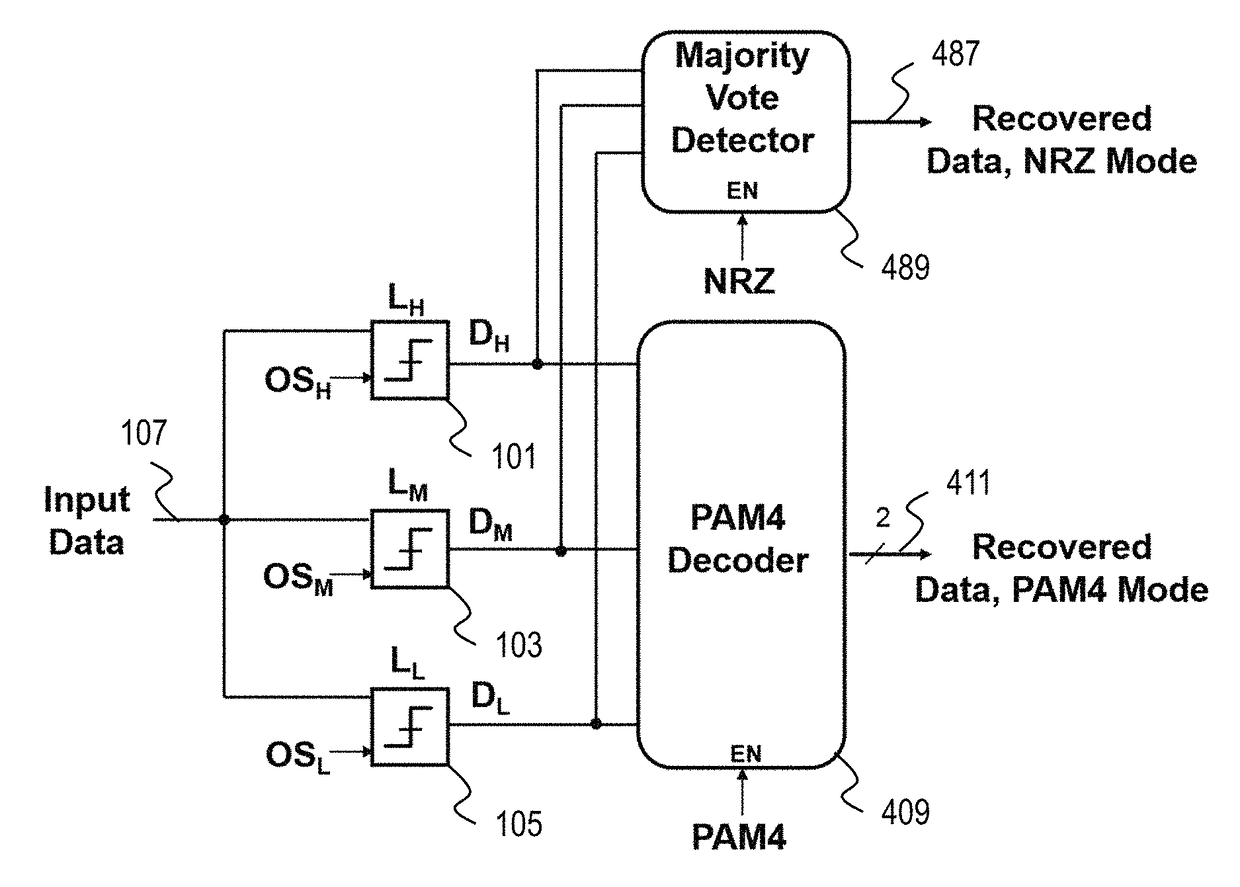

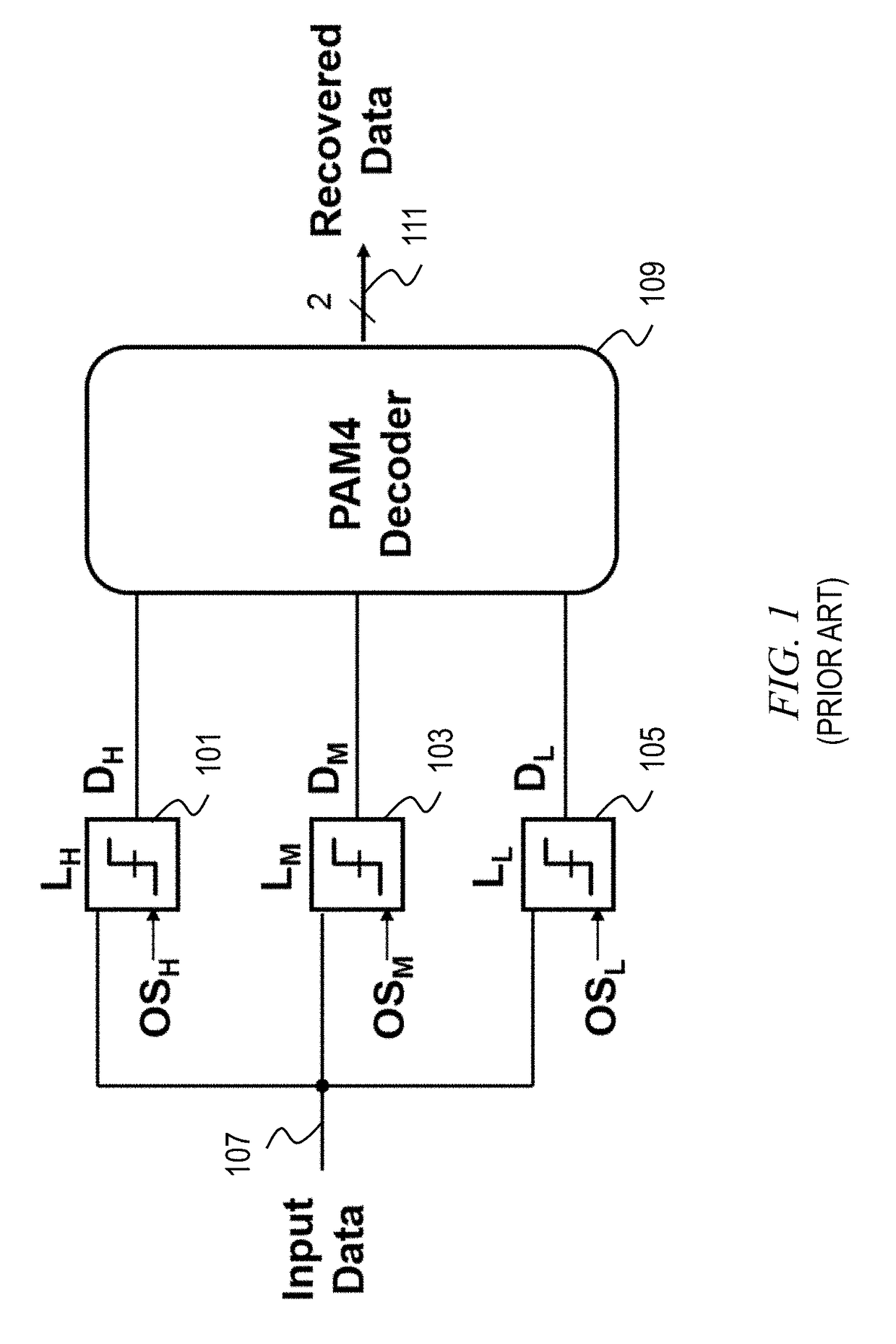

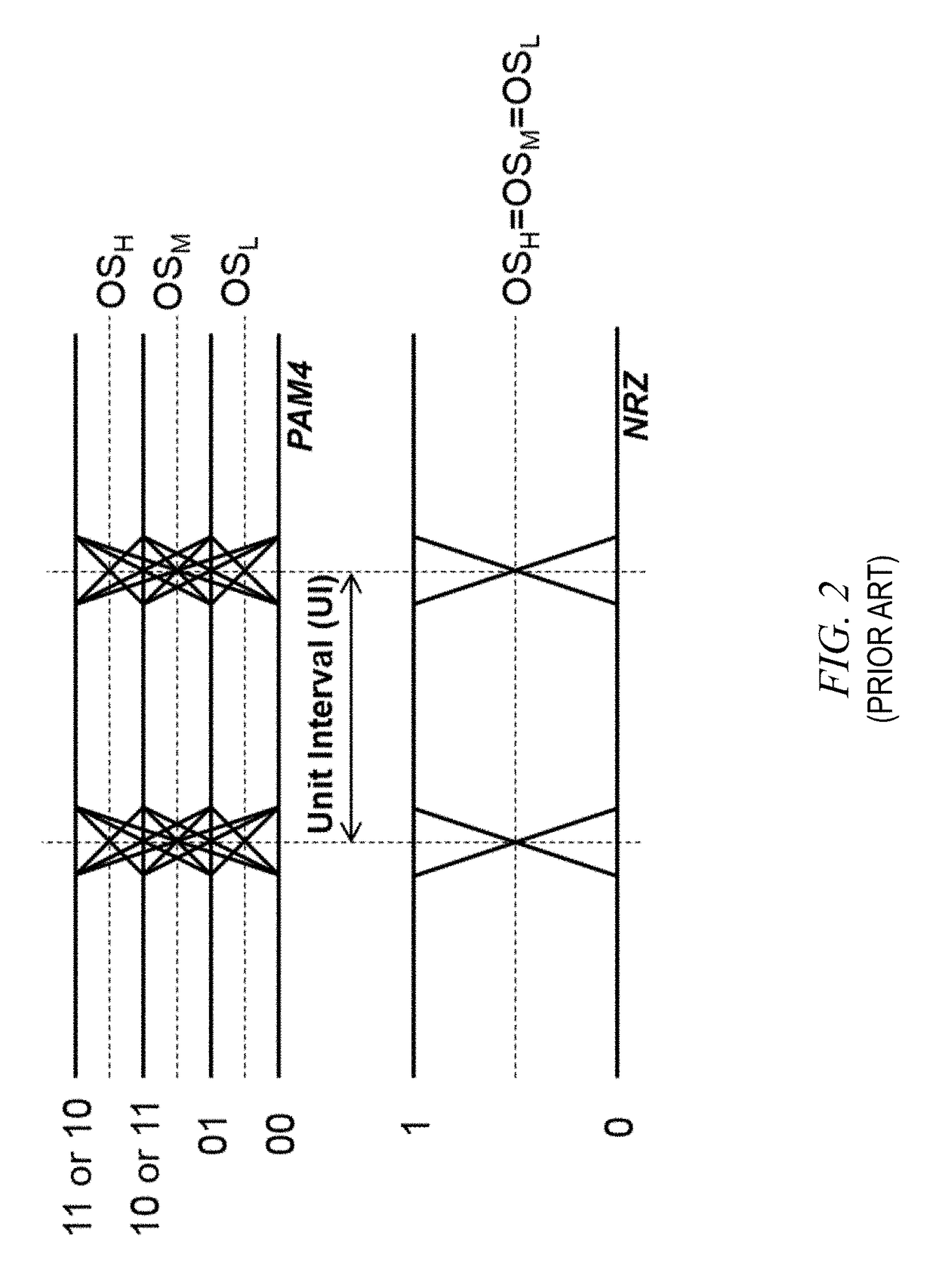

Dual-mode non-return-to-zero (NRZ)/ four-level pulse amplitude modulation (PAM4) receiver with digitally enhanced NRZ sensitivity

InactiveUS9699009B1Improve robustnessReduce sensitivityAmplitude-modulated carrier systemsSynchronising arrangementDual modeNon-return-to-zero

A four-level pulse amplitude modulation receiver has a four-level pulse amplitude modulation mode and a non-return-to-zero modulation mode. First, second, and third four-level pulse amplitude modulation samplers are coupled to an input. Each of the samplers has a corresponding output in turn including a corresponding binary decision of the first, second, and third samplers. A four-level pulse amplitude modulation decoder circuit has inputs coupled to the outputs of the samplers. The four-level pulse amplitude modulation decoder circuit is active in the four-level pulse amplitude modulation mode. The receiver also includes a non-return-to-zero majority voting circuit coupled to the outputs of the samplers. The non-return-to-zero majority voting circuit has an output and is configured to output a majority decision of the corresponding binary decisions of the samplers, and is active in the non-return-to-zero modulation mode.

Owner:IBM CORP

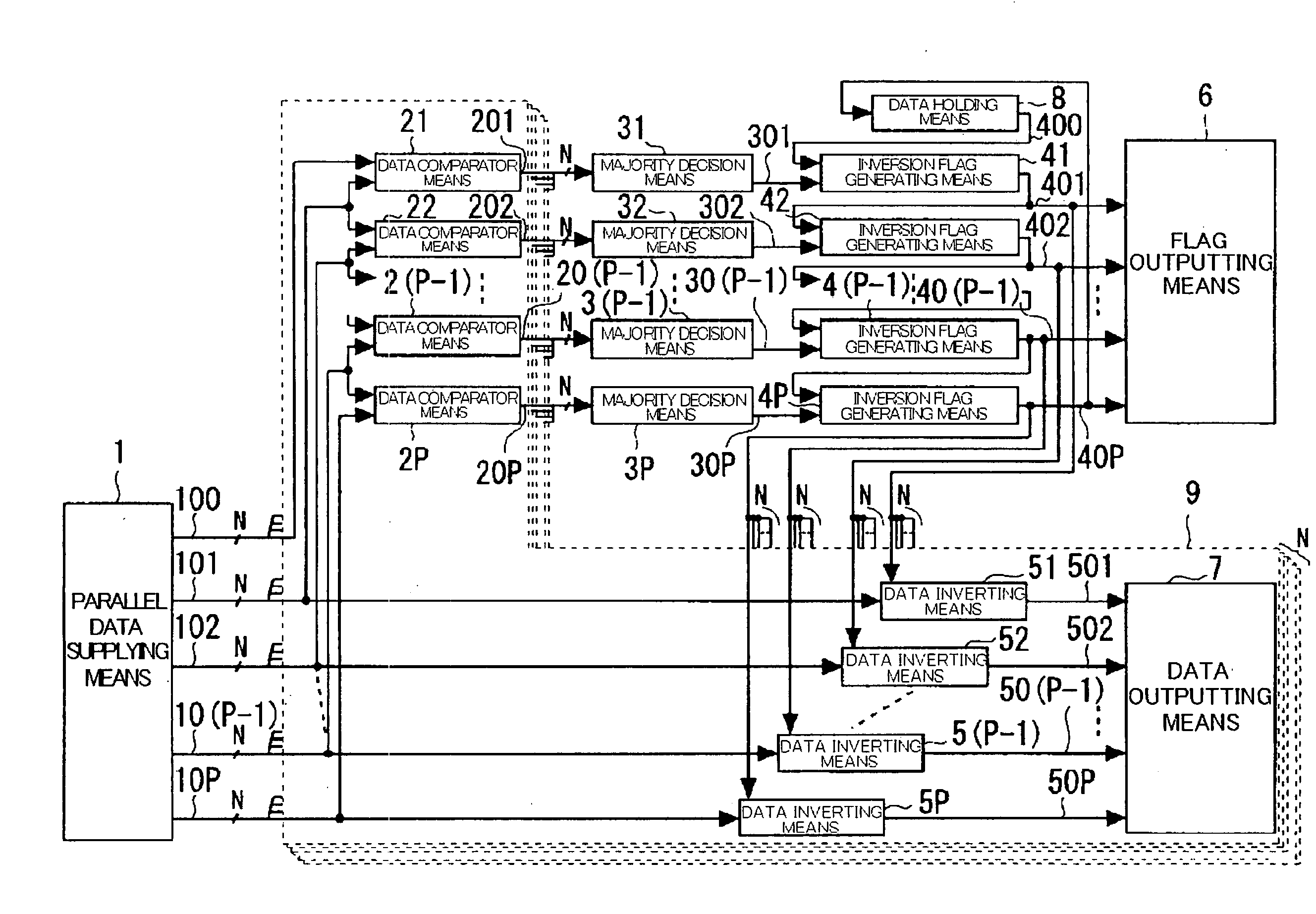

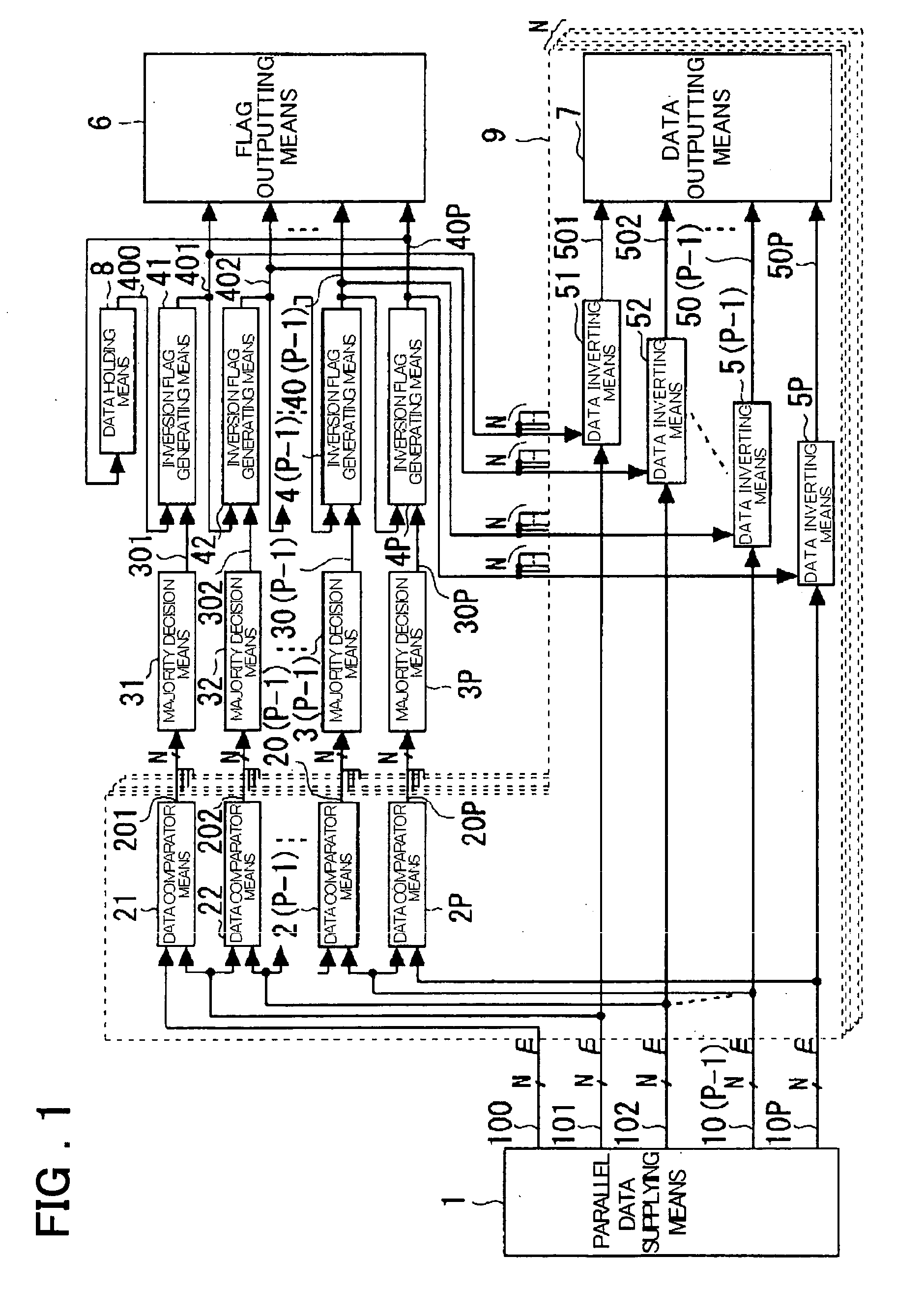

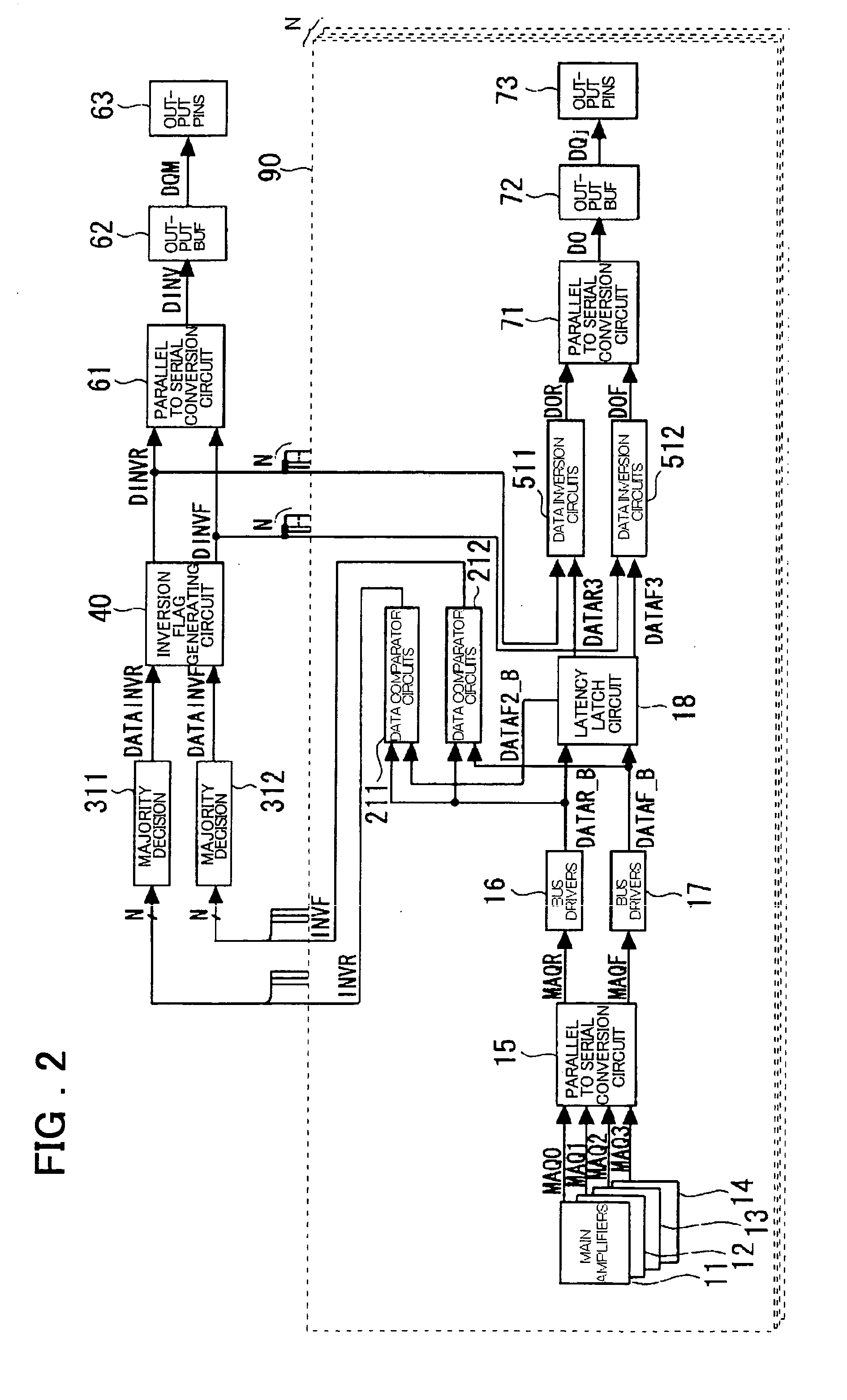

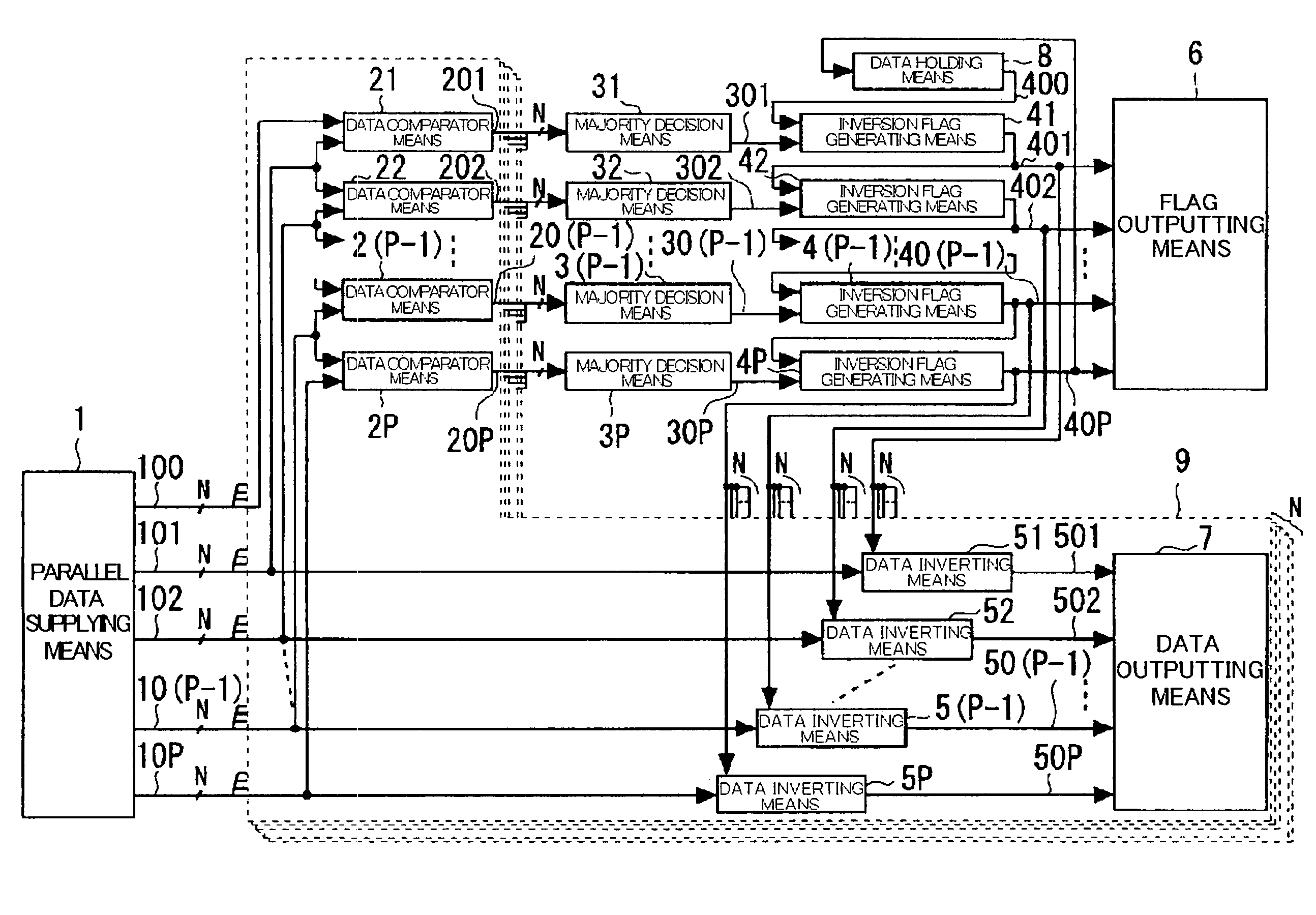

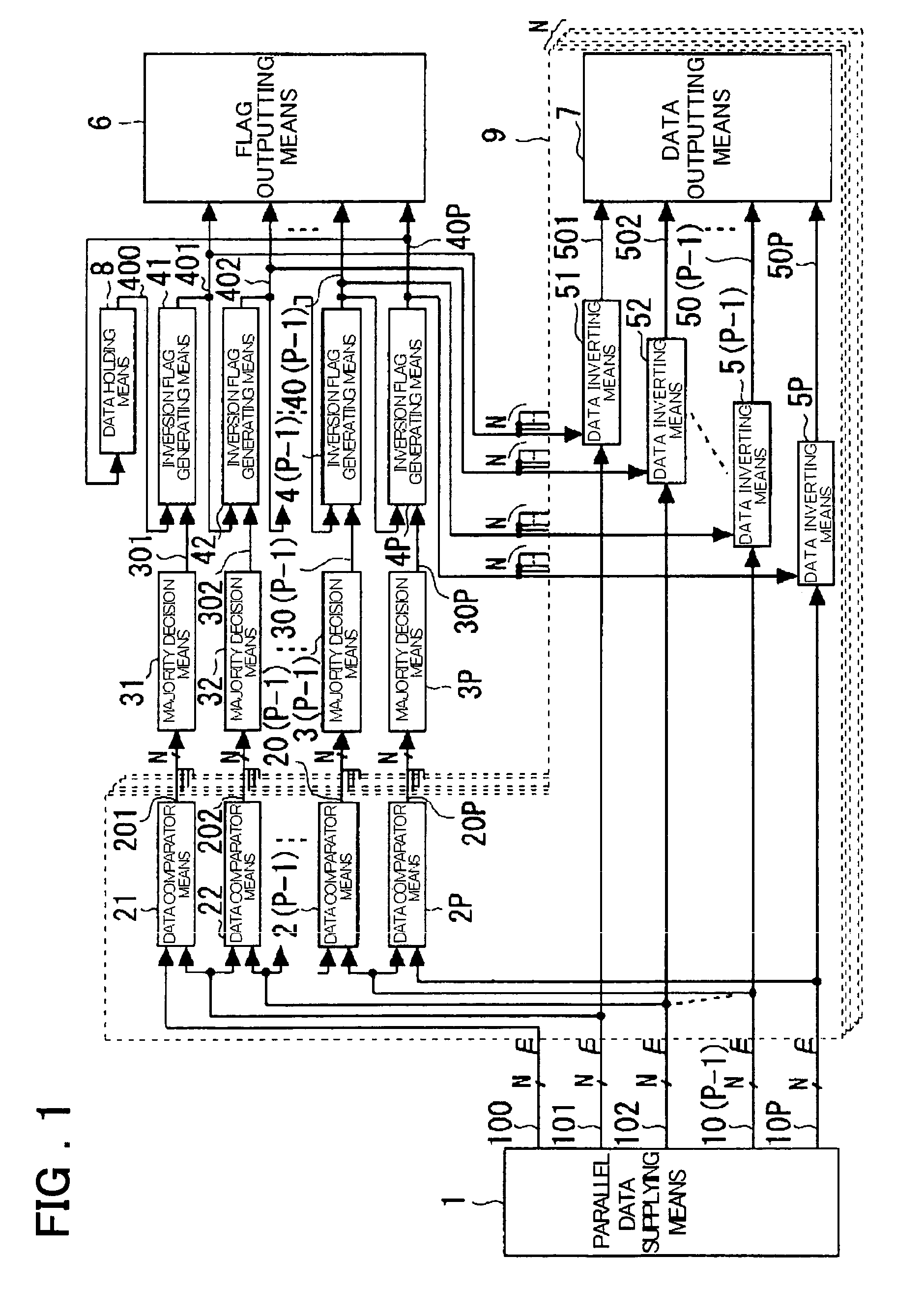

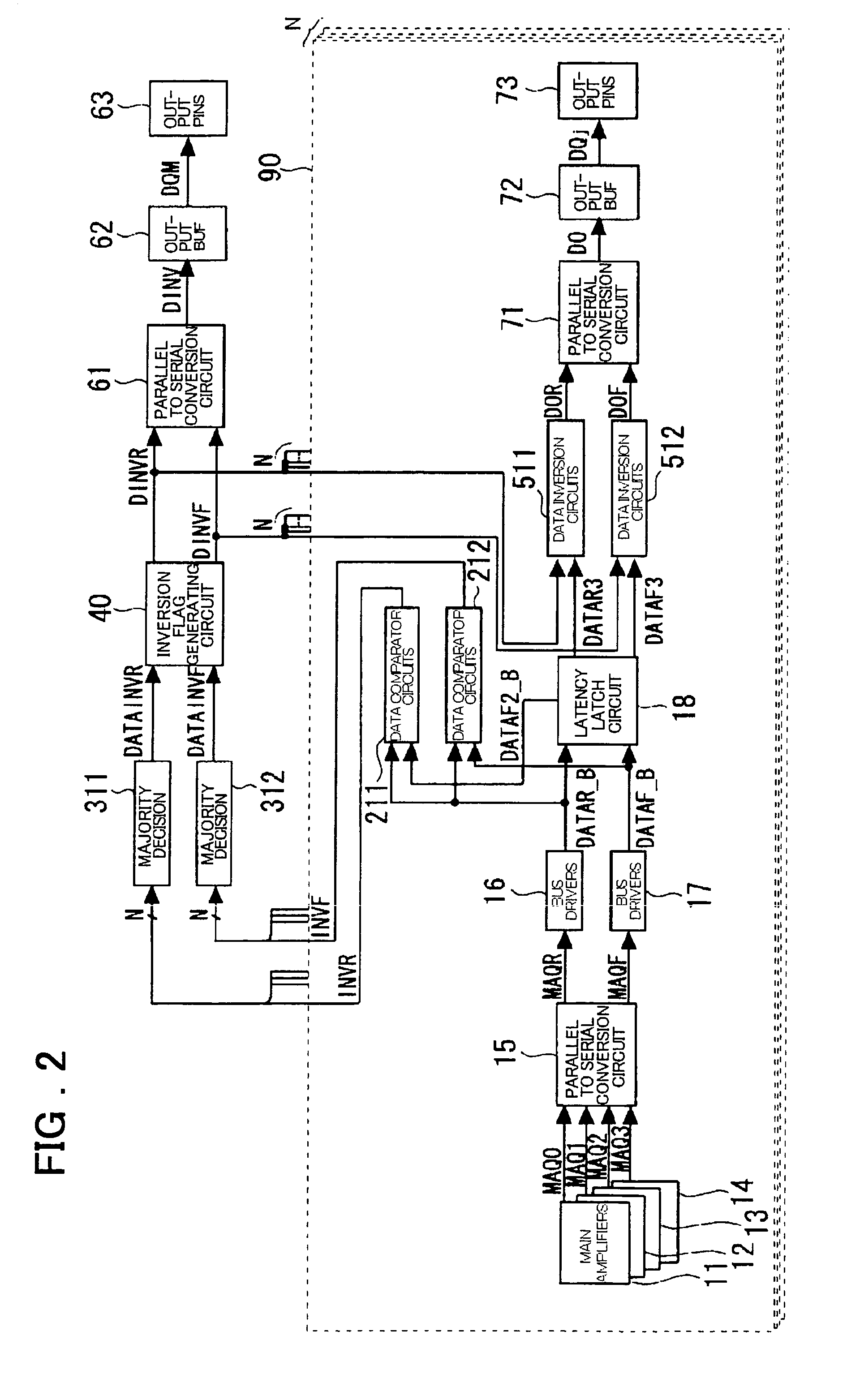

Data inversion circuit and semiconductor device

ActiveUS20040065904A1Digital data processing detailsSemiconductor/solid-state device manufacturingDecision circuitParallel computing

A parallel data outputting circuit equipped with a data inversion function, comprises P number of data comparator means, P number of majority decision circuits, P number of inversion flag generating means and P number of data inversion circuits, these being activated in parallel in one cycle. In generating an inversion flag indicating whether or not the parallel data are to be inverted and output in the inverted state, inversion flags are calculated from outputs of the inversion flag generating means and the inversion flag generating means of a cycle directly previous to a current cycle.

Owner:LONGITUDE LICENSING LTD

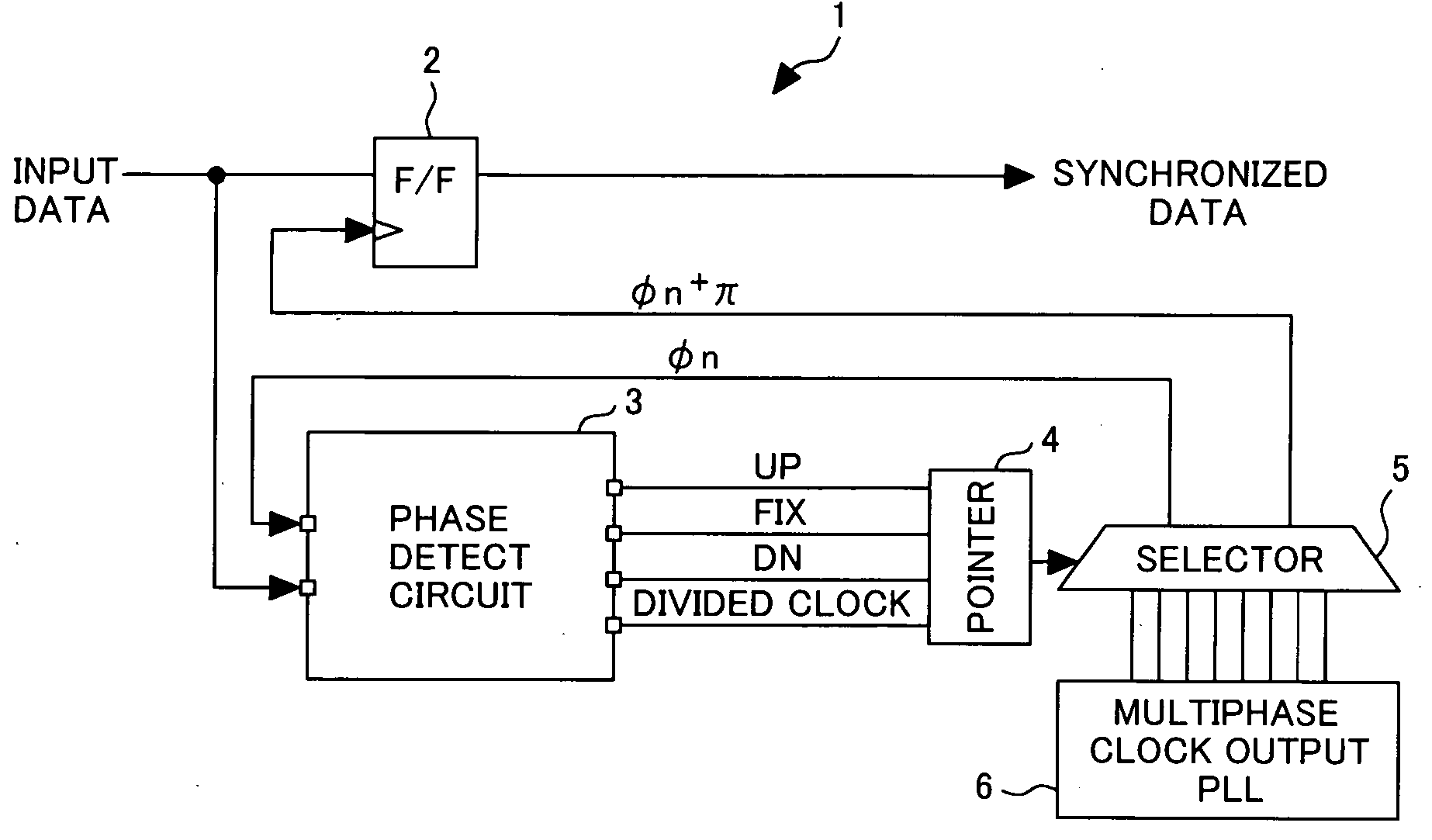

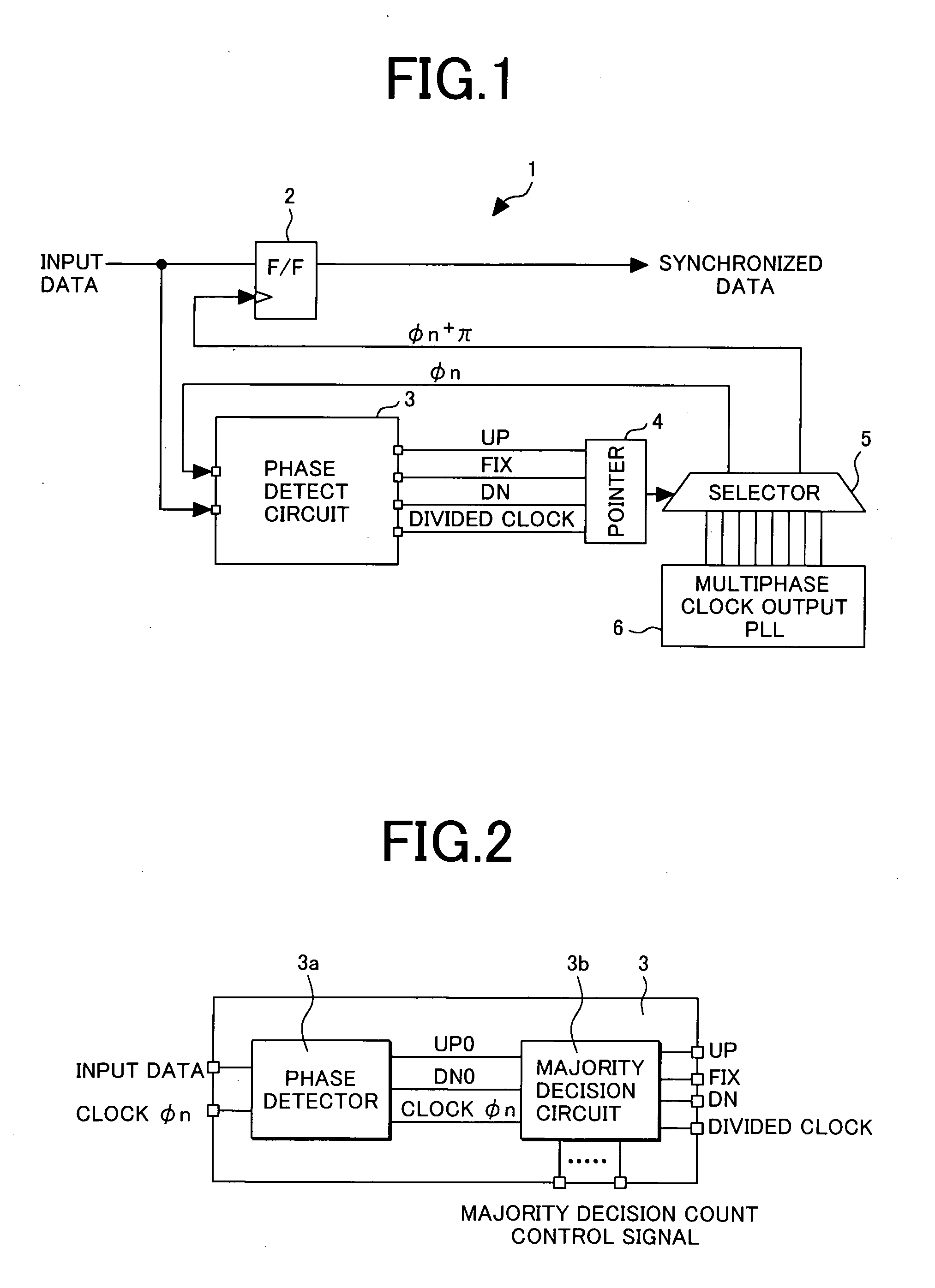

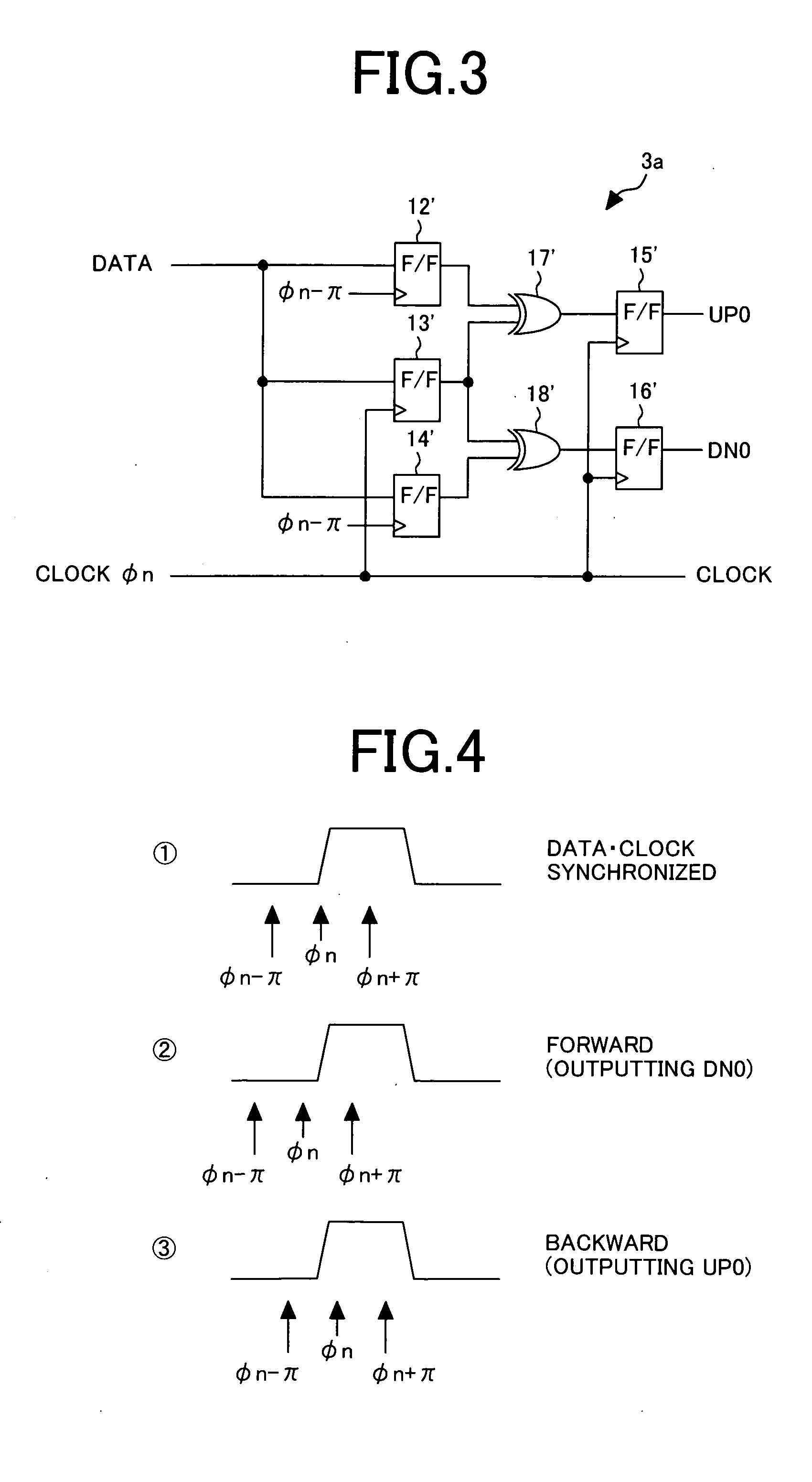

Semiconductor integrated circuit device

InactiveUS20050008111A1Reduce error ratePreventing following excessively the jittersPulse automatic controlSemiconductor/solid-state device detailsCounting NumberComputer science

An error rate of a bit synchronous circuit is decreased to a large extent by preventing following excessively the jitters included in input data. A phase detect circuit of a bit synchronous circuit includes a majority decision circuit. The majority decision circuit counts UP0 and DN0 signals as a phase comparison result of comparing phases by a UP0 counter and a DN0 counter for a period of time, and its count number is judged by a magnitude relation determination circuit. The magnitude relation determination circuit outputs an UP signal if the UP0 signal is majority, a DN signal if the DN0 signal is majority, and a FIX signal if the UP0 signal is equal to the DN0 signal. Accordingly, since it is possible to prevent following the jitters included in input data, etc., an error rate for bit synchronization can be reduced to a large extent.

Owner:HITACHI LTD

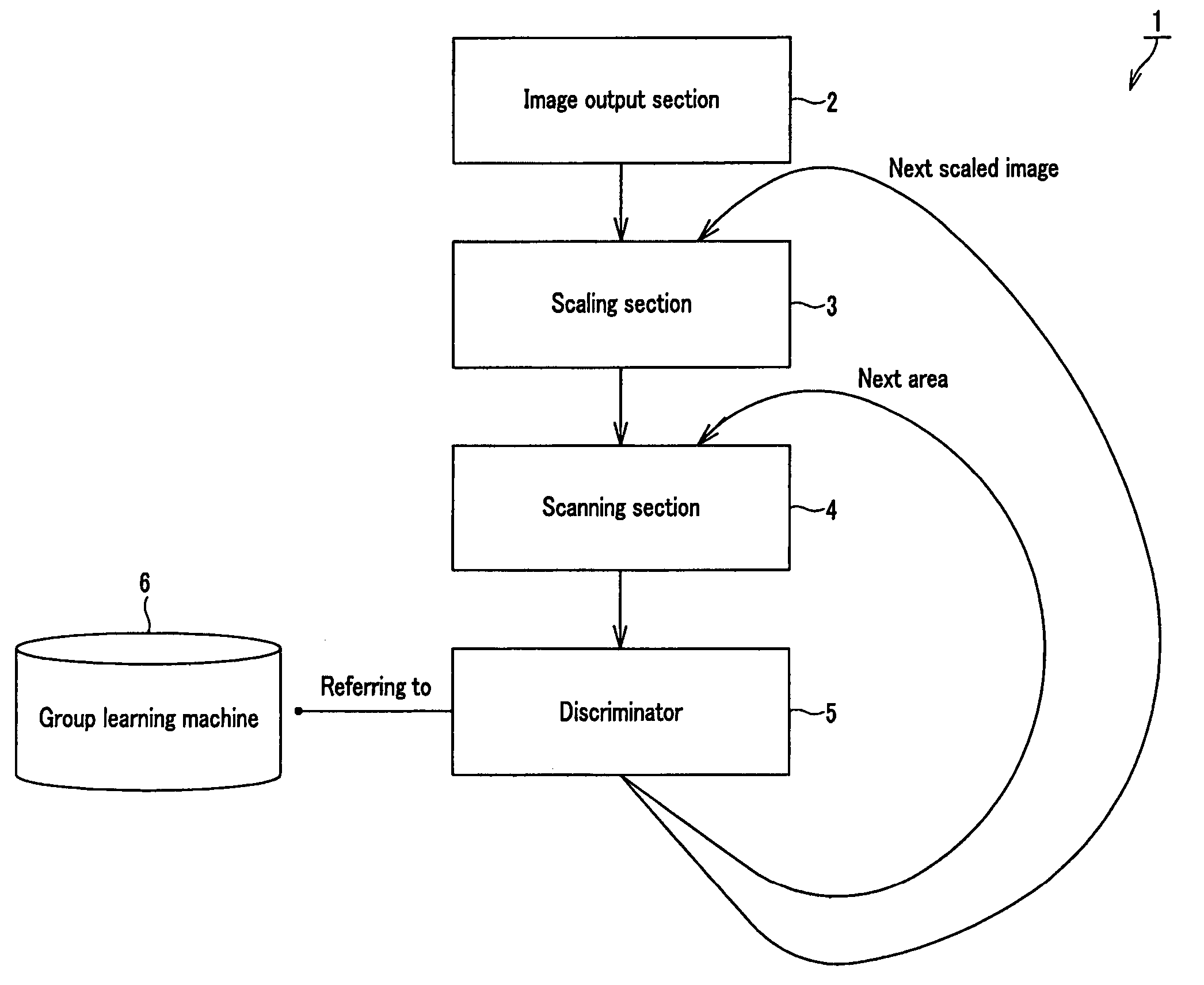

Device and method for detecting object and device and method for group learning

ActiveUS7574037B2High degreeSpeed up the computational processing operationsImage analysisCharacter and pattern recognitionPattern recognitionDiscriminator

An object detecting device for detecting an object in a given gradation image. A scaling section generates scaled images by scaling down a gradation image input from an image output section. A scanning section sequentially manipulates the scaled images and cutting out window images from them and a discriminator judges if each window image is an object or not. The discriminator includes a plurality of weak discriminators that are learned in a group by boosting and an adder for making a weighted majority decision from the outputs of the weak discriminators. Each of the weak discriminators outputs an estimate of the likelihood of a window image to be an object or not by using the difference of the luminance values between two pixels. The discriminator suspends the operation of computing estimates for a window image that is judged to be a non-object, using a threshold value that is learned in advance.

Owner:SONY CORP

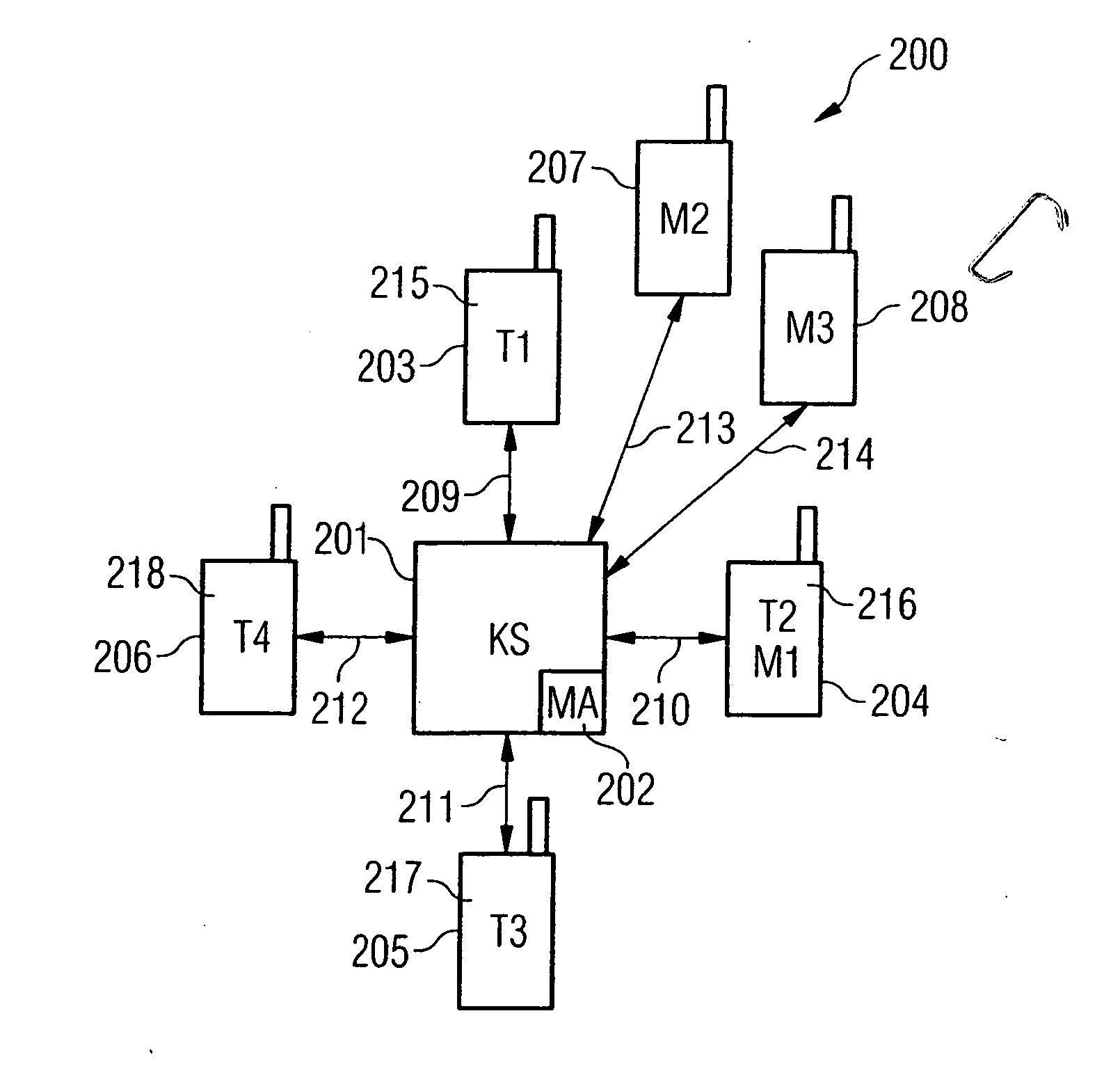

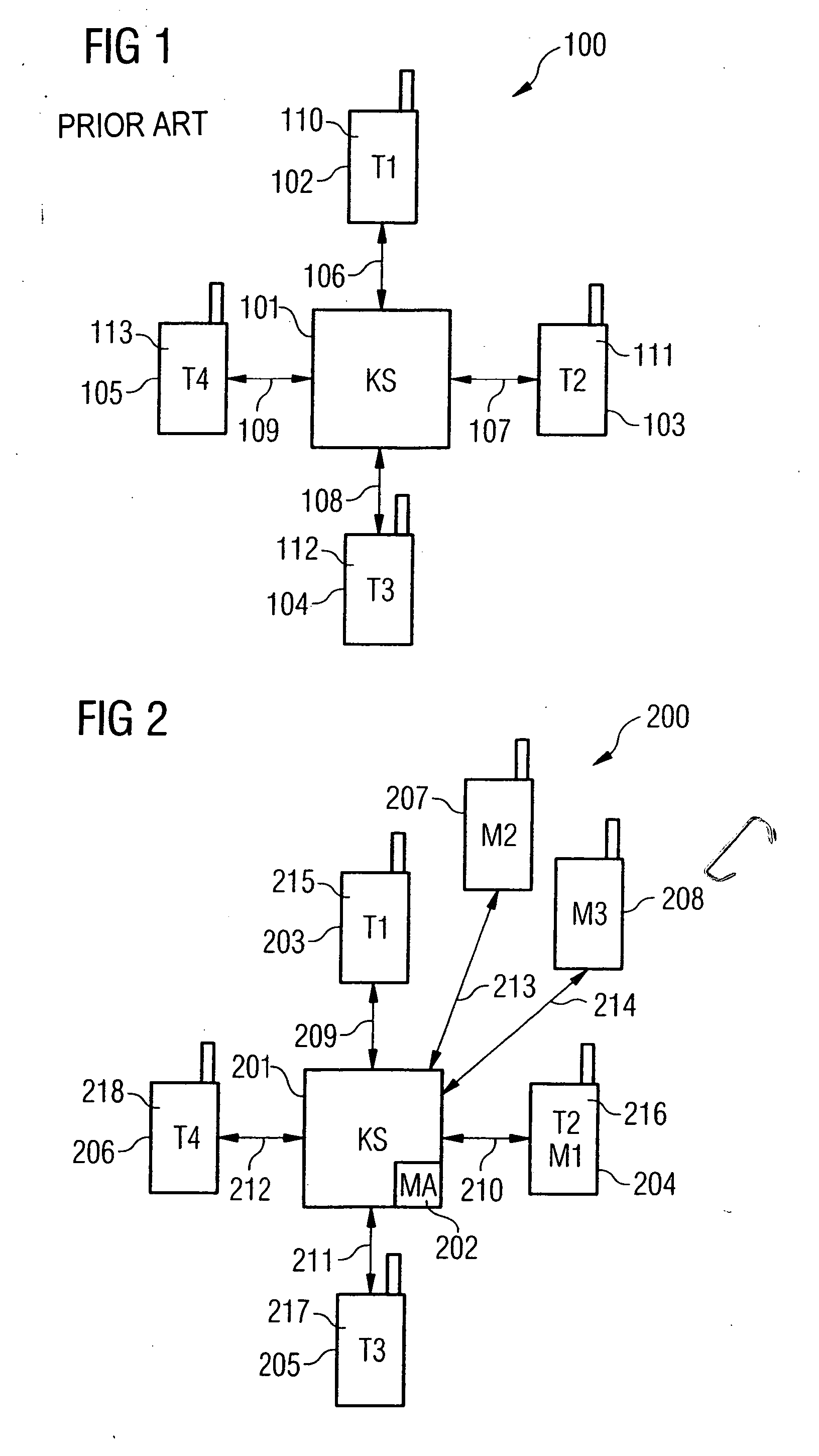

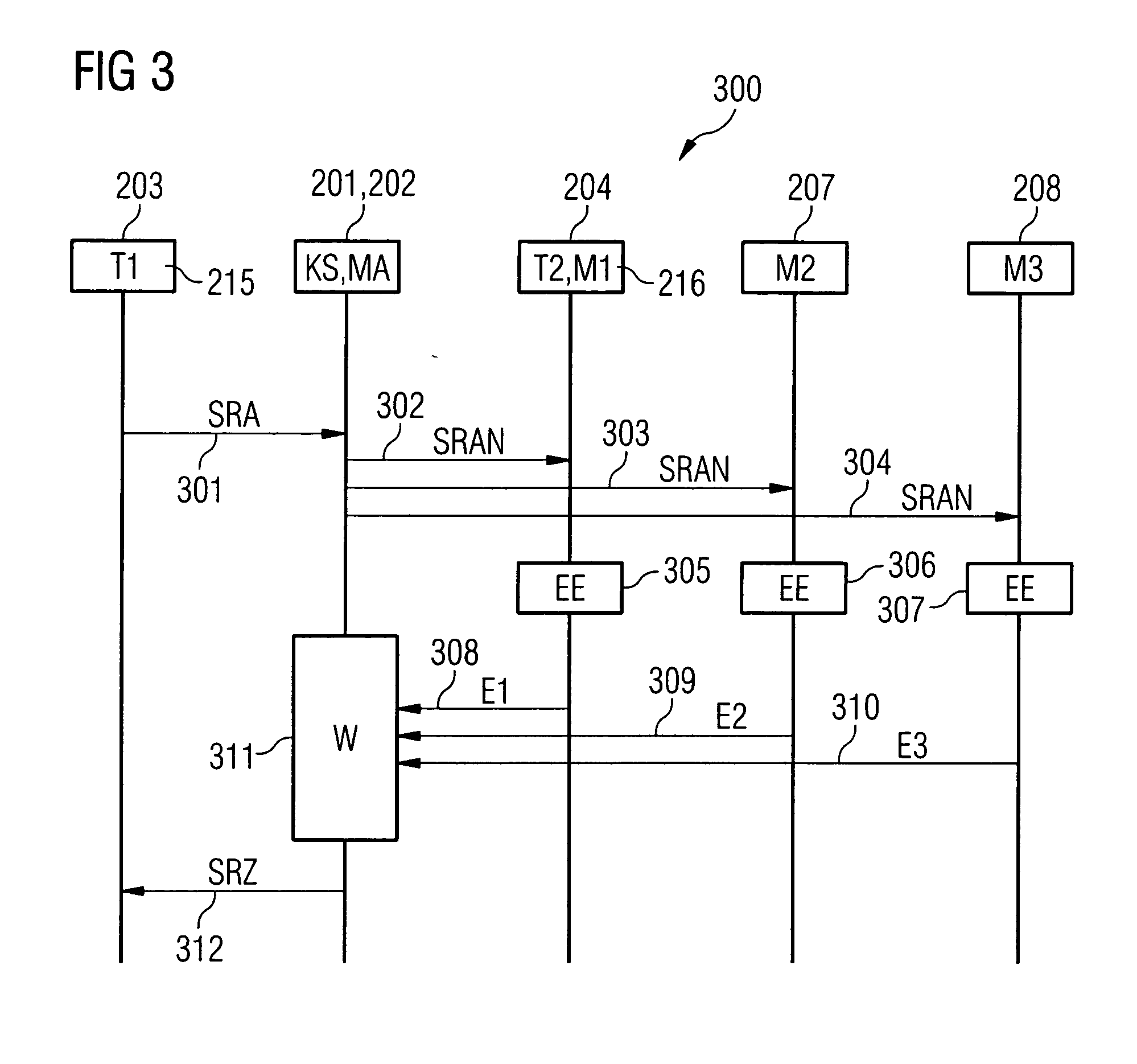

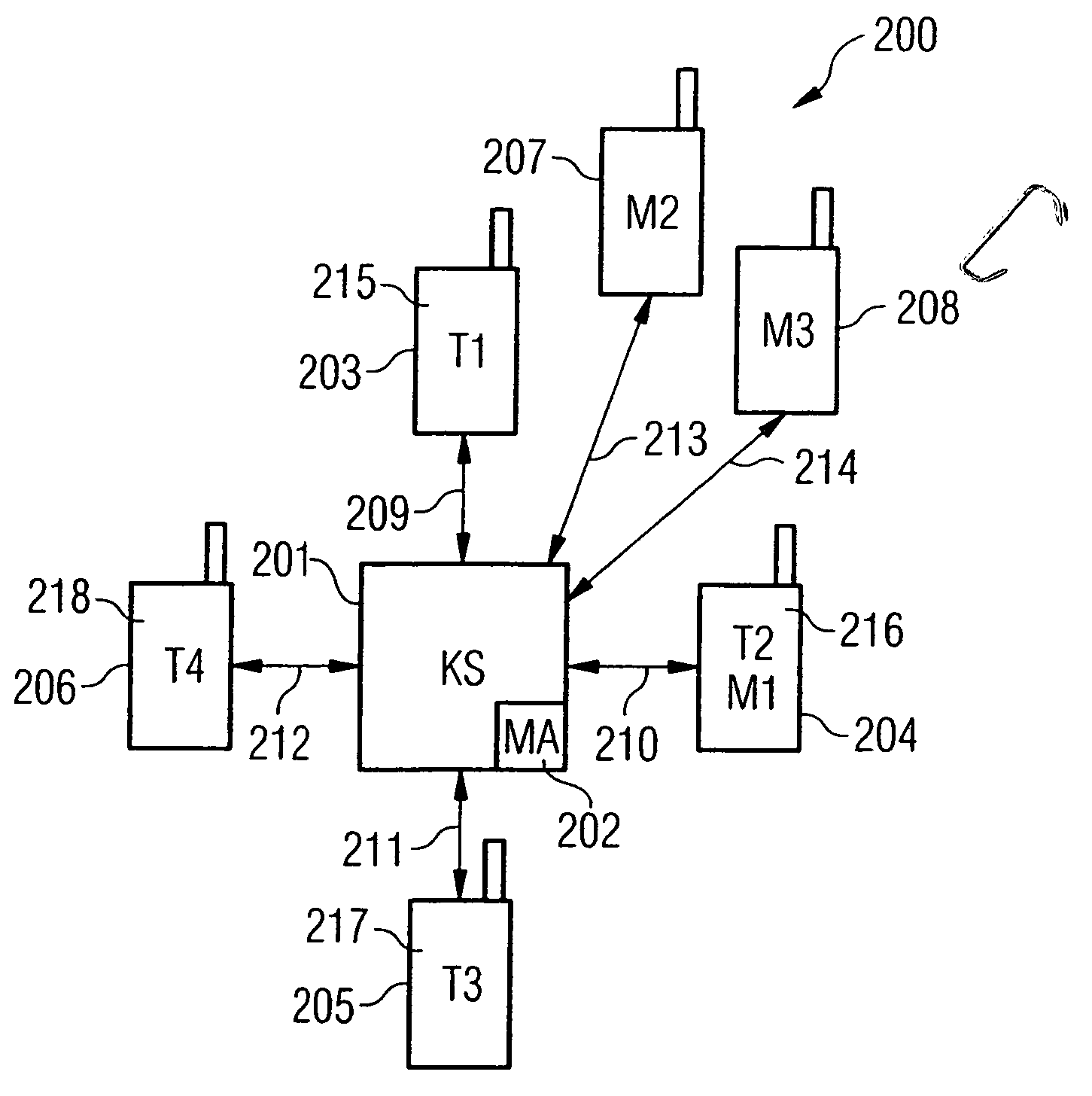

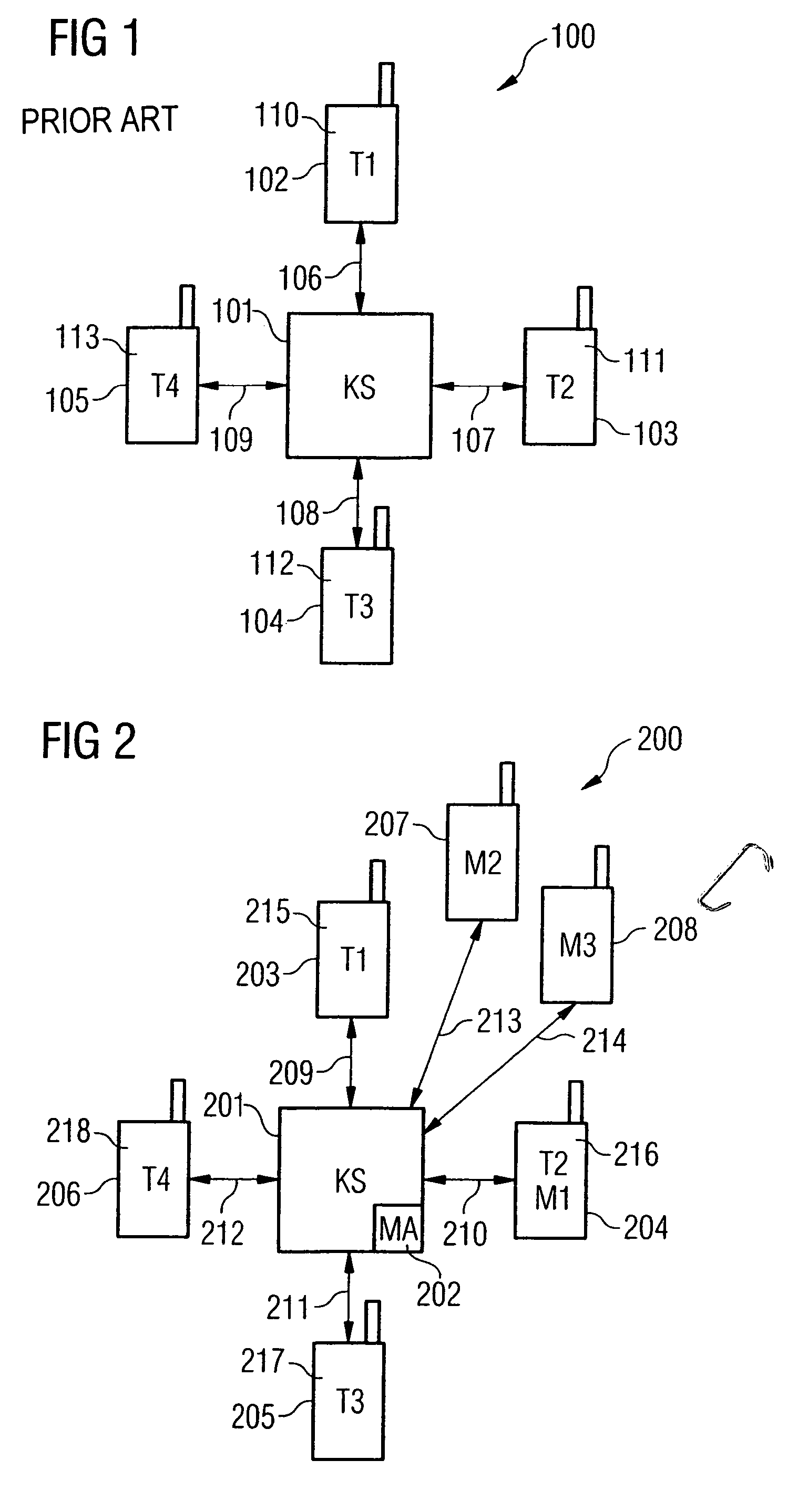

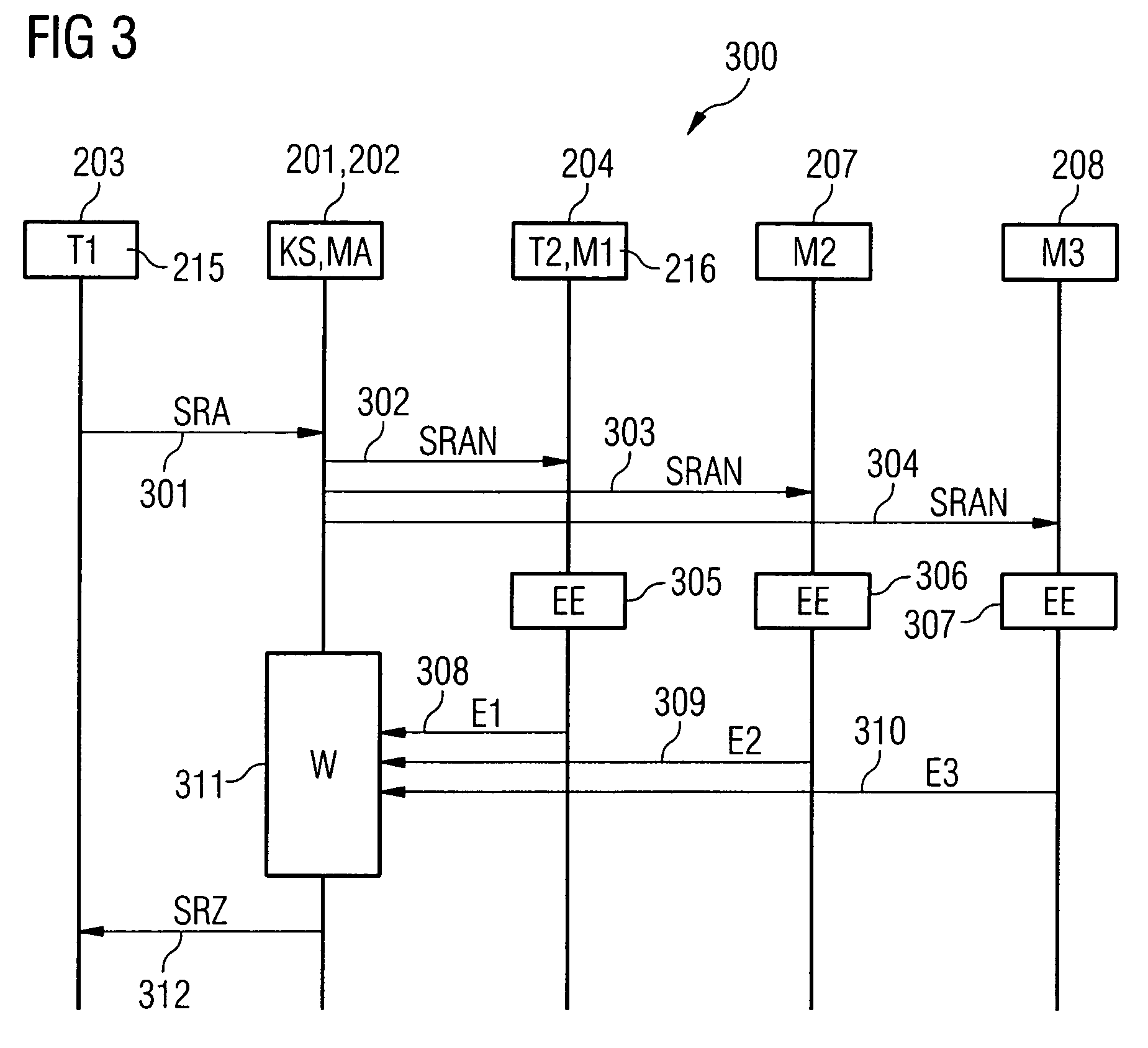

Communication system having conference server

InactiveUS20060234613A1Avoids lengthy discussionElectric current slaughtering/stunningSpecial service for subscribersControl communicationsConference control

A communication system having a conference server device, a conference control unit, a plurality of moderator units, and a plurality of telecommunication devices. The moderator units are used to control allocation of a communication right. The decisions of the moderator units regarding the allocation of the communication right are combined to form an unambiguous overall decision, and overall decision is made using a majority decision.

Owner:INTEL CORP

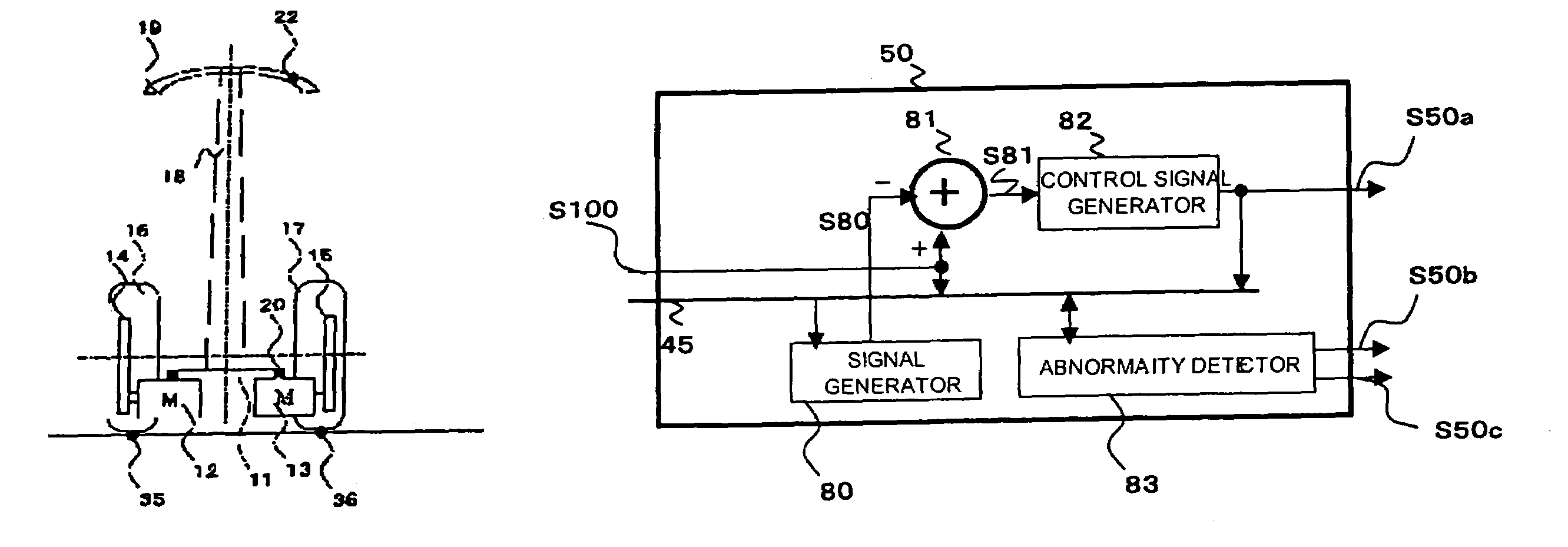

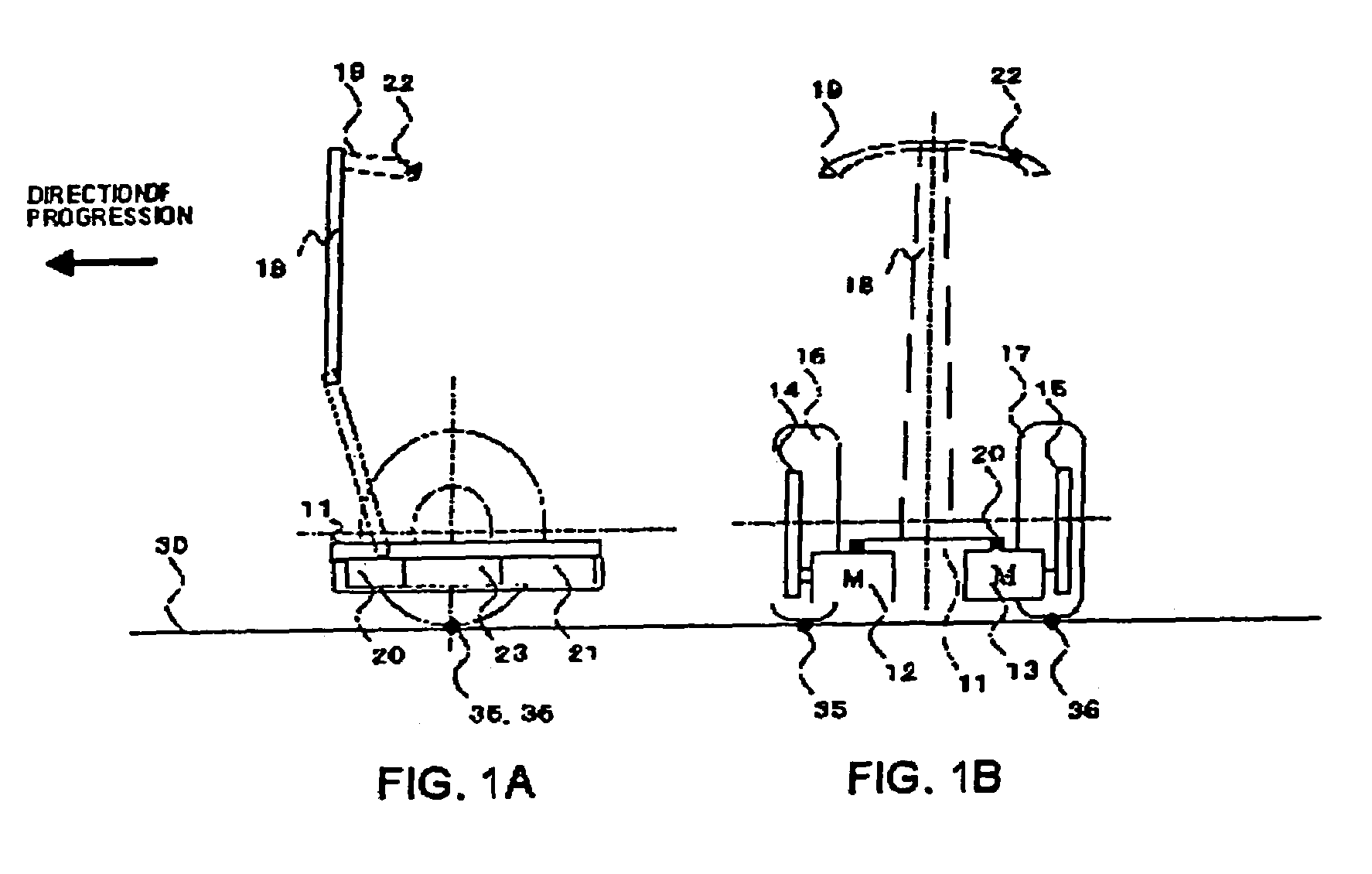

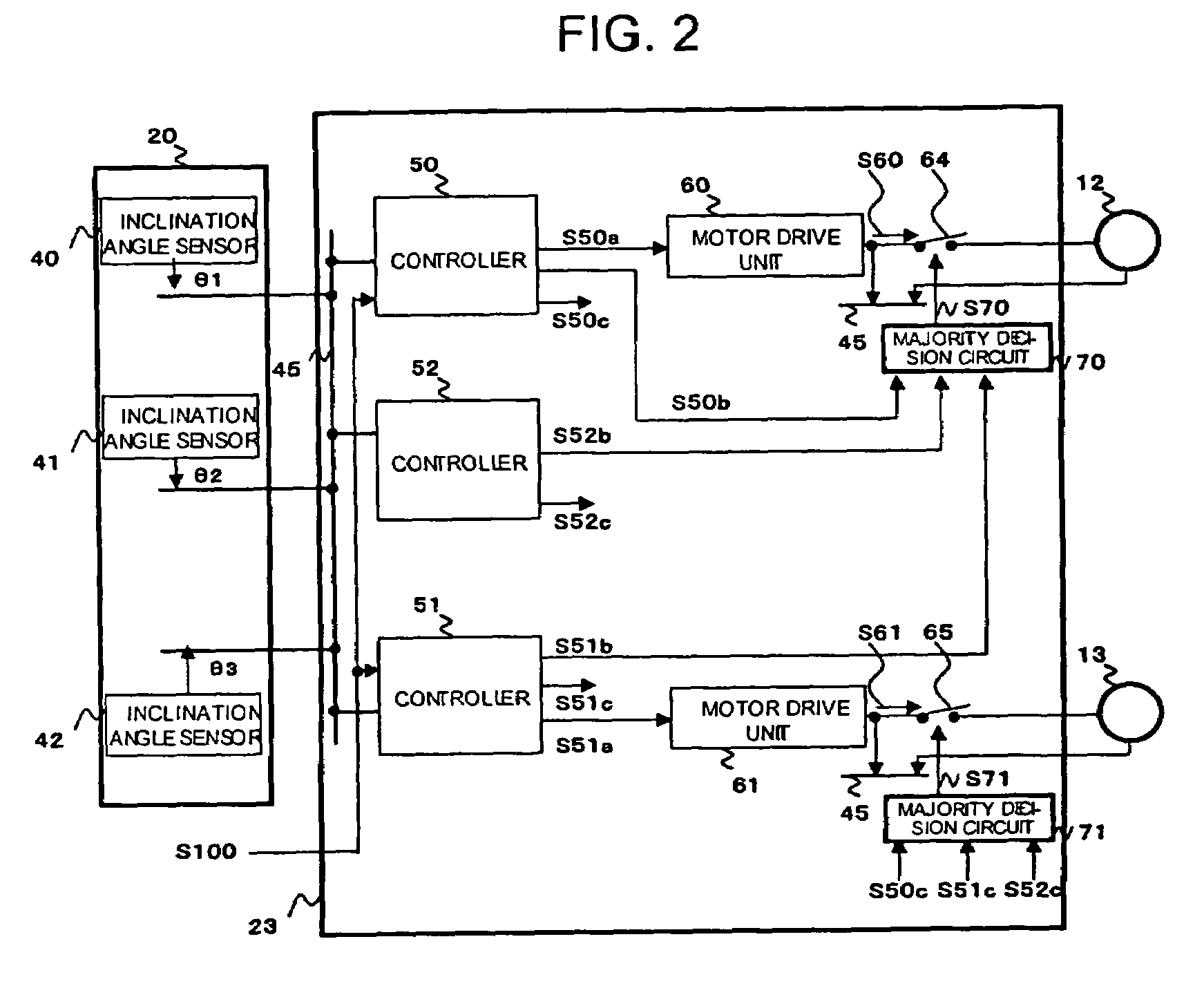

Drive control apparatus and method and two-wheeled vehicle

A drive control apparatus able to hold an autonomously stabilized posture by a small size configuration by independently detecting abnormalities in a drive system of a first motor and a drive system of a second motor at controllers, outputting the results to majority decision circuits, and having the majority decision circuits turn switches on / off by majority decision based on the results.

Owner:TOYOTA JIDOSHA KK +1

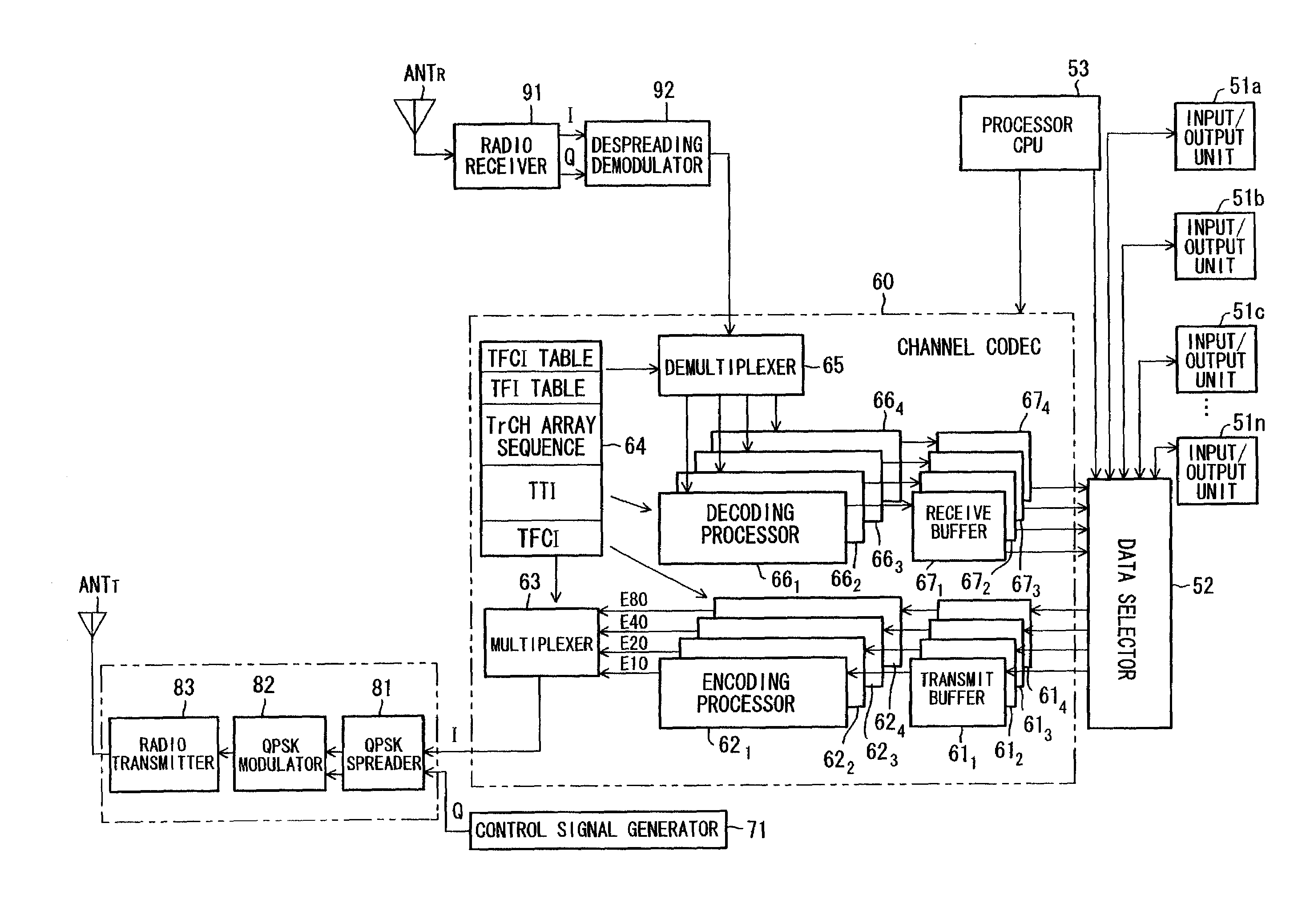

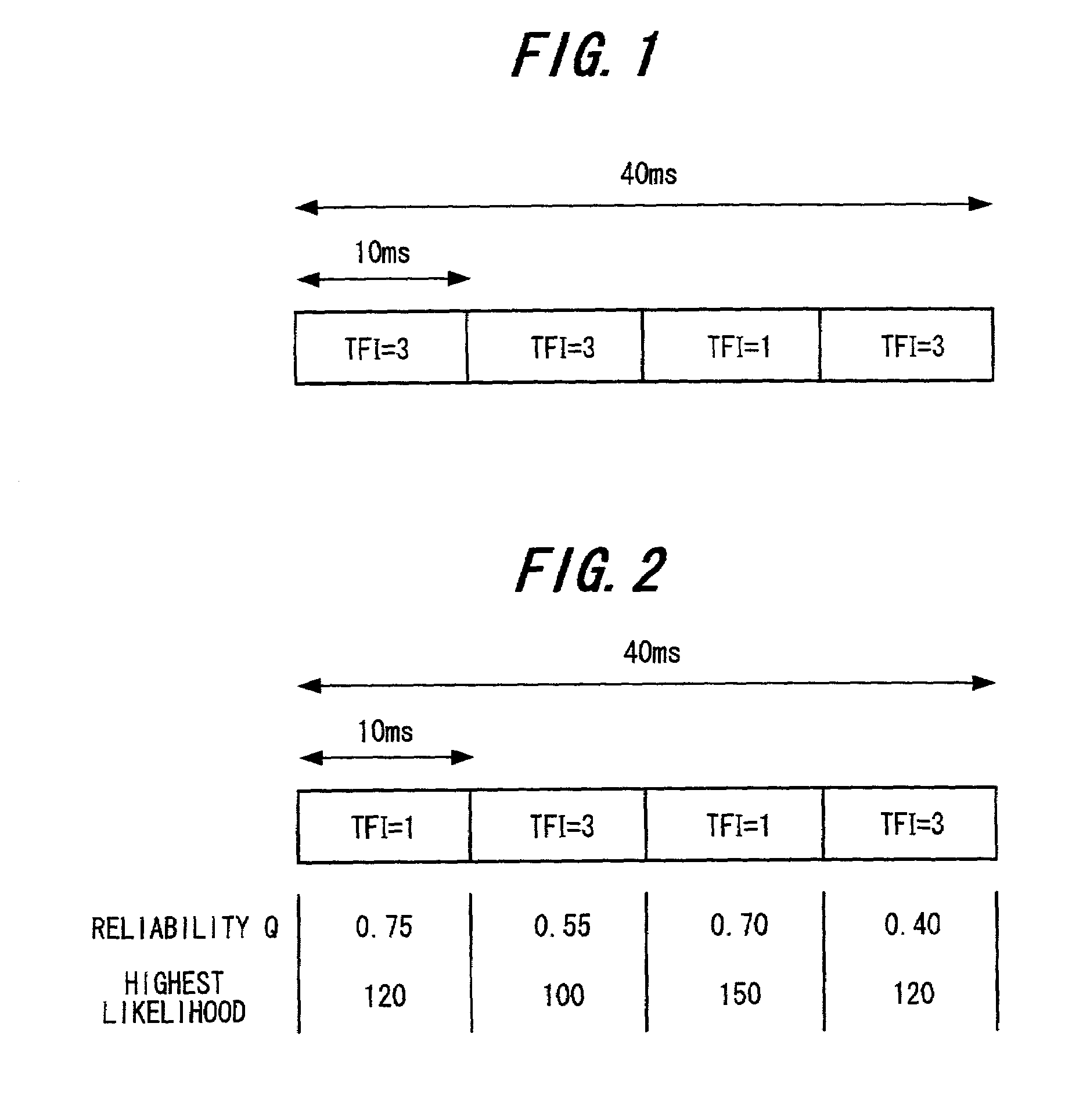

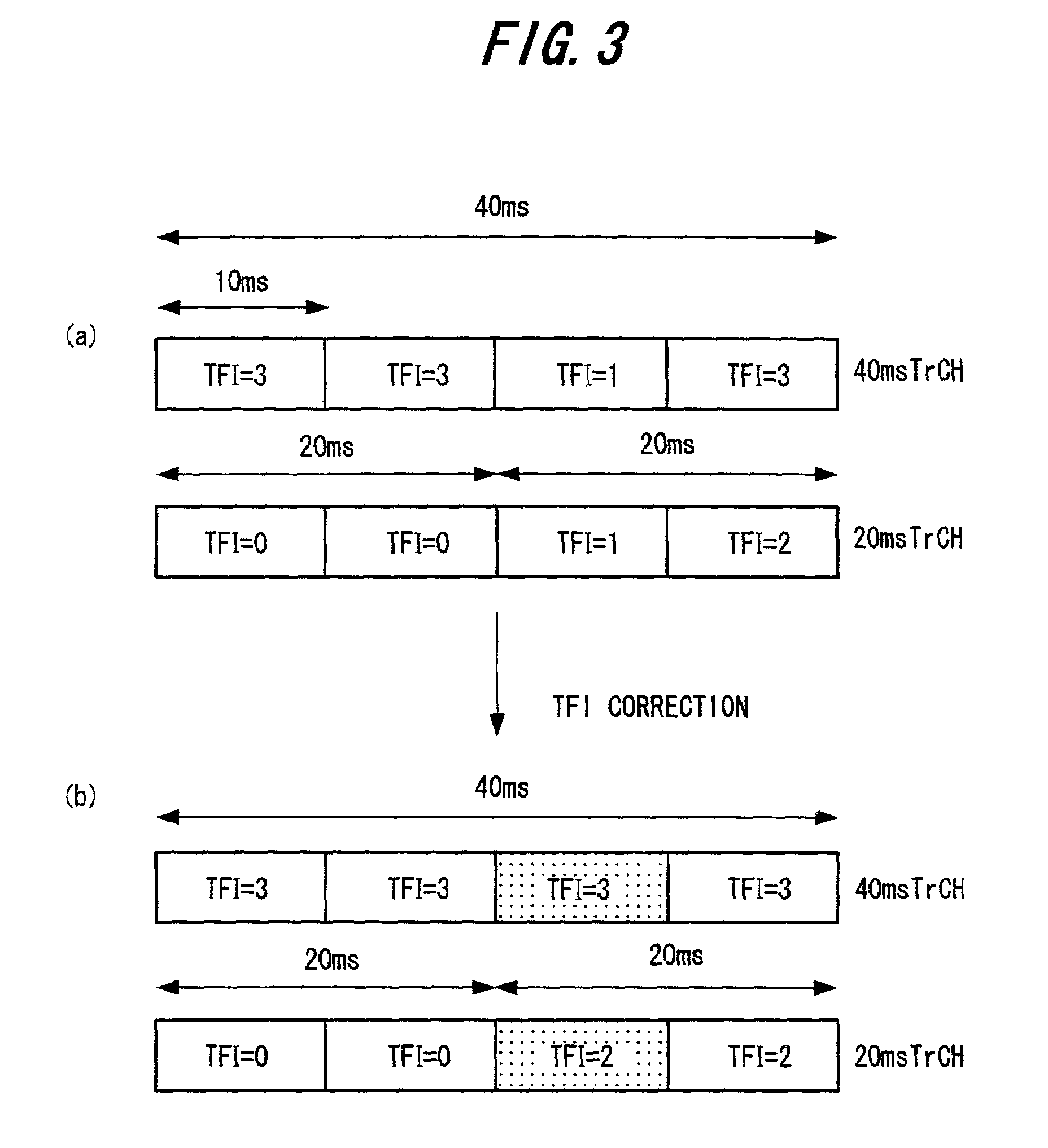

Transceiver apparatus and transceiving method in communication system

InactiveUS7130352B2Reduce reception errorsReduce errorsSecret communicationPulse demodulatorMultiplexingTransceiver

Disclosed is a communication system in which it is possible to detect a TFI (Transport Format Indicator) even if a TFCI (Transport Format Combination Indicator) cannot be decoded correctly. The system includes a transmitting apparatus which, when a transmission is made, encodes transmit data of each transport channel (TrCH) at a prescribed transmission time interval (TTI), partitions the encoded data at a frame period to obtain frame data of a prescribed bit length, multiplexes and transmits the frame data of each TrCH and transmits TFCI information that specifies the frame data length of each TrCH. The system includes a receiving apparatus for comparing, on a per-TrCH basis, the TFIs of a plurality of frames within a transmission time interval (TTI) conforming to the TrCH and, if TFIs differ, deciding the transport format (TFI) in this transmission time interval (TTI) by majority decision, etc.

Owner:FUJITSU LTD

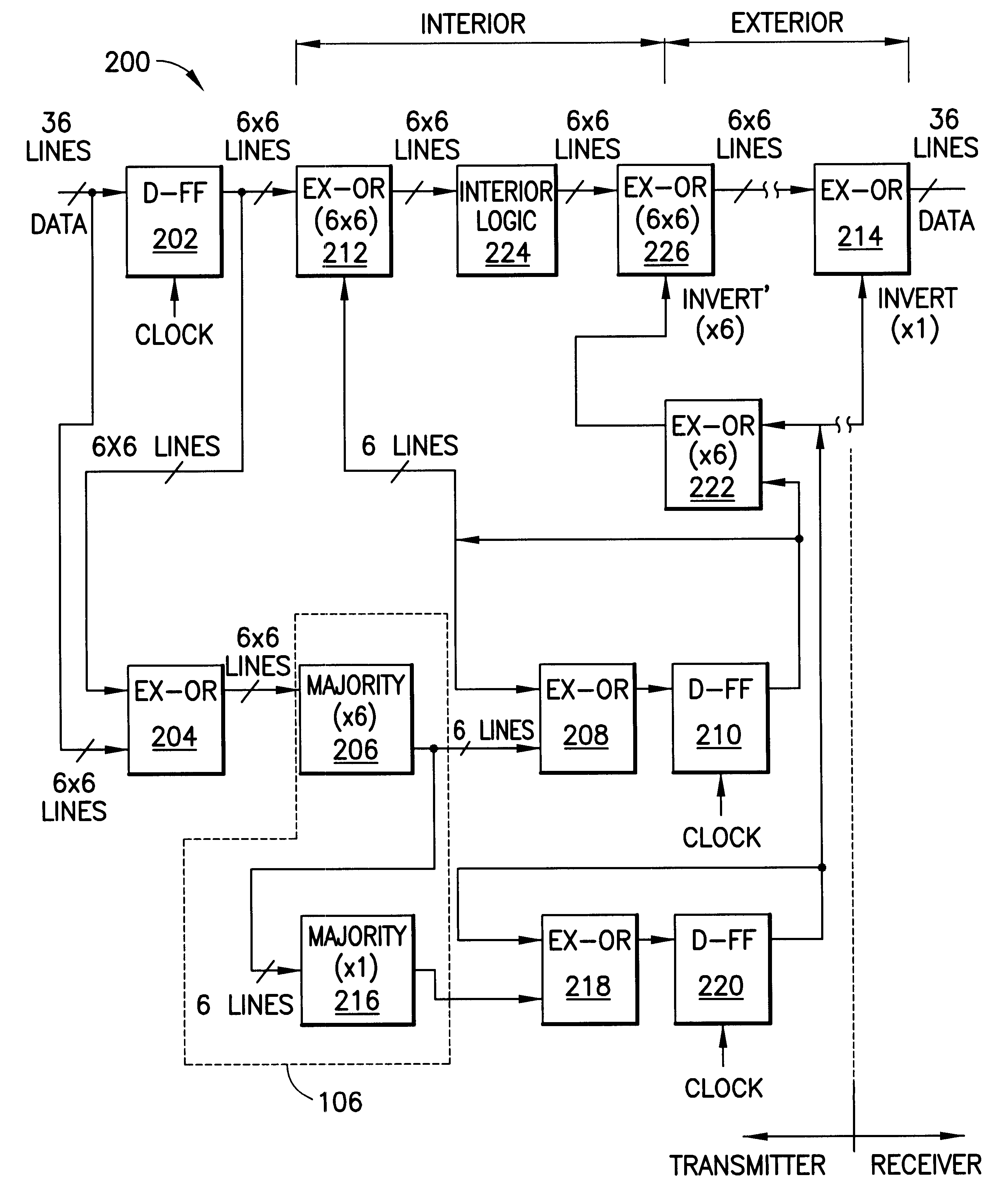

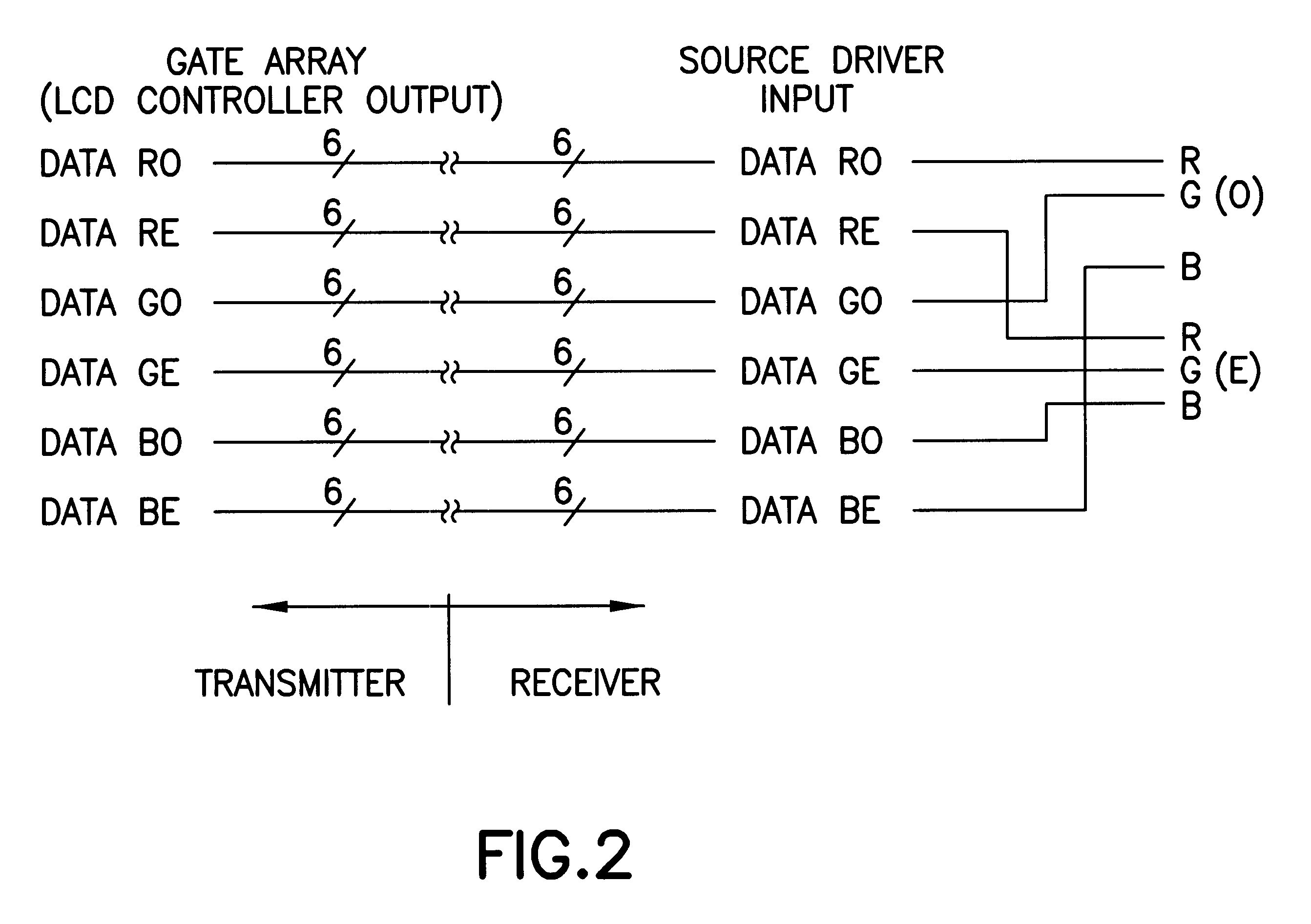

Data-transferring method and apparatus for reducing the number of data-bit changes

In transferring n data bits by the n data lines of an LCD, the n data lines are divided into s blocks each with m data bits (n=mxs). A majority decision is performed on the s blocks and is again performed on the s outputs from the s blocks. With this, a very small-scale and high-speed decision circuit can be realized. As a result, the effects of a reduction in unnecessary radiation by a reduction in the number of data-bit changes, a reduction in power dissipation by a reduction in the number of data-bit changes and the like are obtainable at realizable cost.

Owner:LENOVO (SINGAPORE) PTE LTD

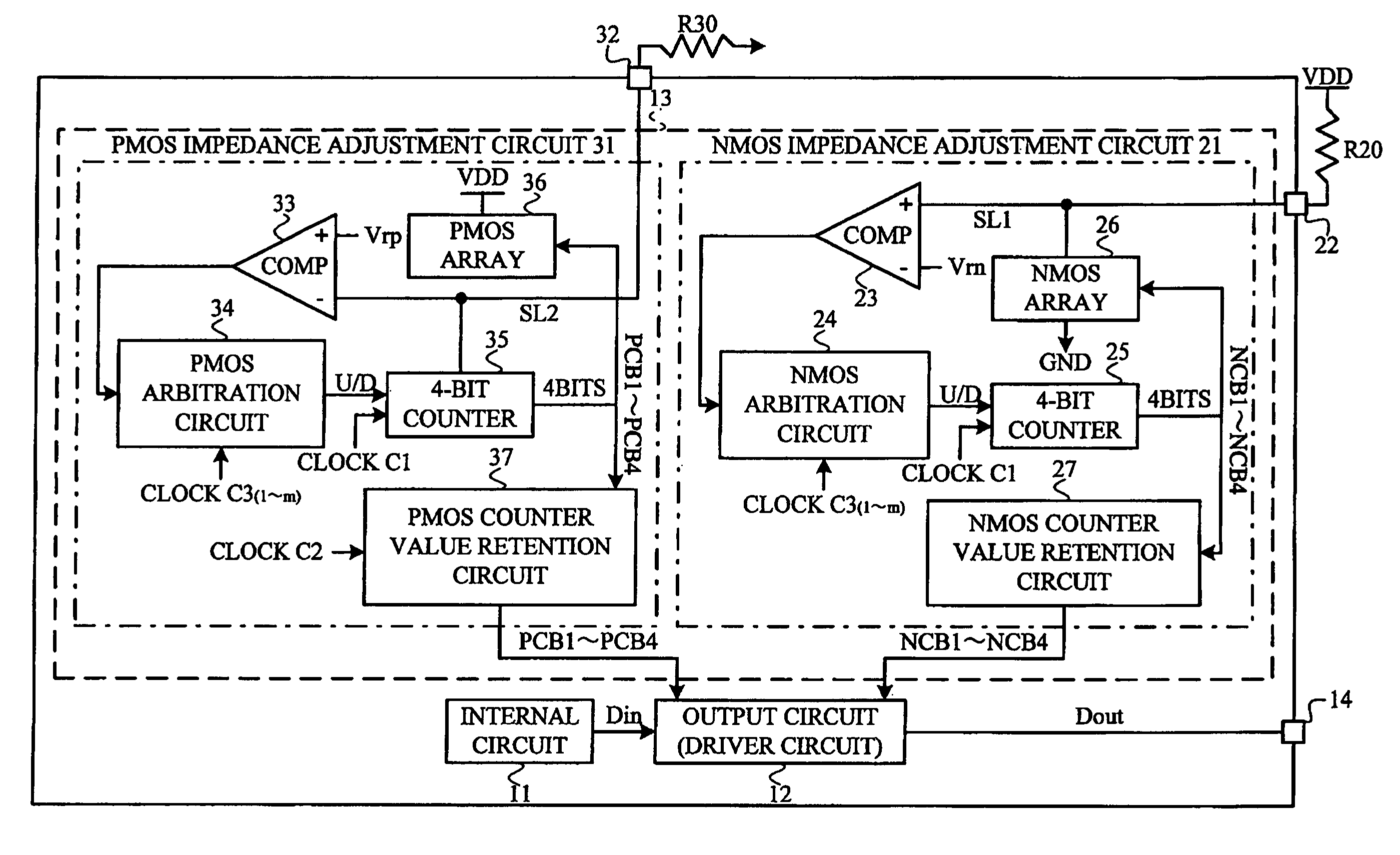

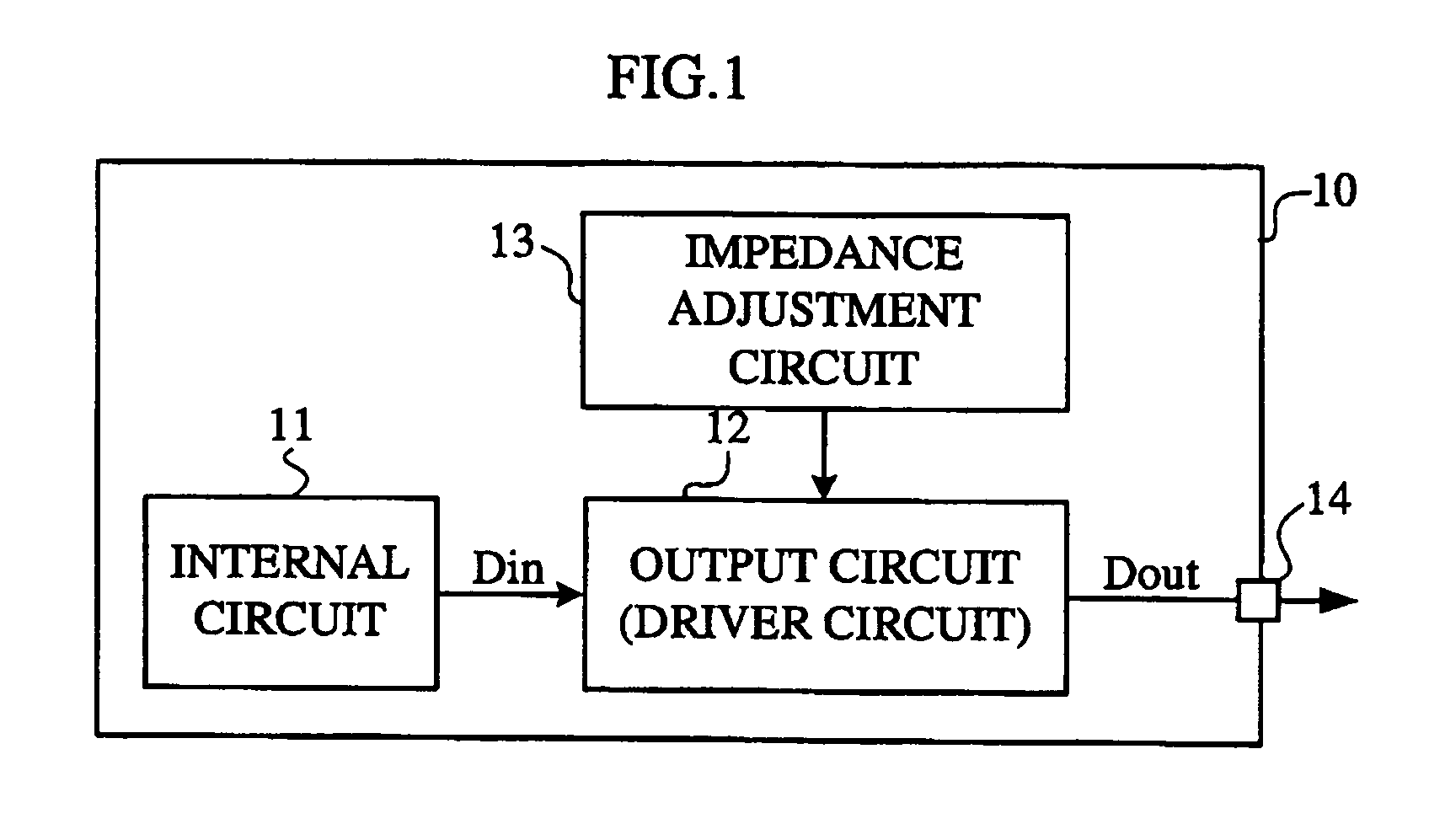

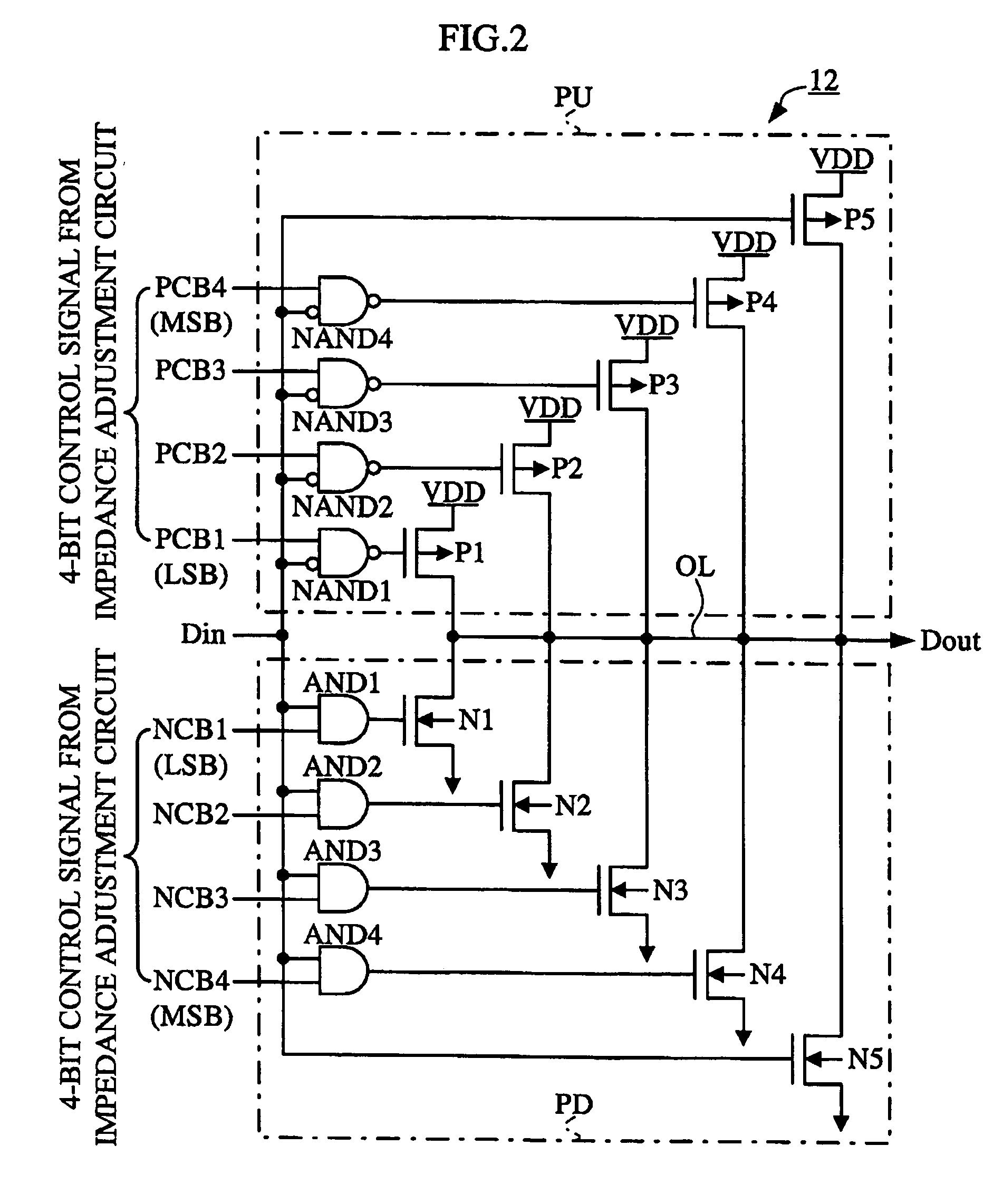

Impedance adjustment circuit, impedance adjustment method, and semiconductor device

InactiveUS7084663B2Avoid errorsExclude influenceInput/output impedence modificationReliability increasing modificationsControl signalEngineering

An impedance adjustment circuit has an external resistor, a comparator which compares the potential of one terminal of the external resistor with a predetermined voltage, a counter whose counted value changes in accordance with an output from the comparator and which outputs a control signal corresponding to the counted value, an NMOS array whose value of resistance changes in accordance with the control signal and which is connected to one terminal of the external resistor and an NMOS arbitration circuit which detects an output from the NMOS comparator a plurality of times and outputs a signal determined by a majority decision logic taken on the detected signals to the counter.

Owner:NEC CORP

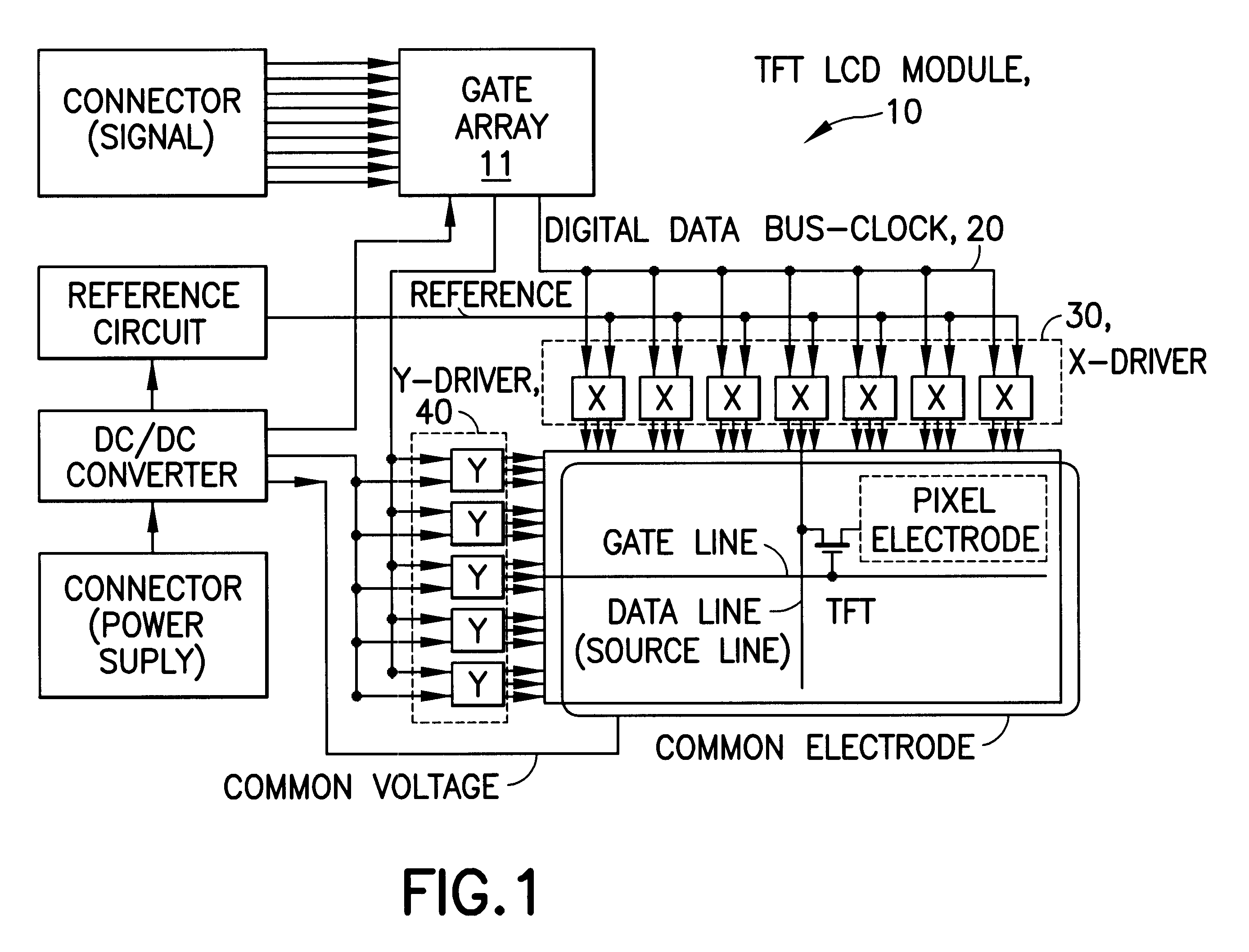

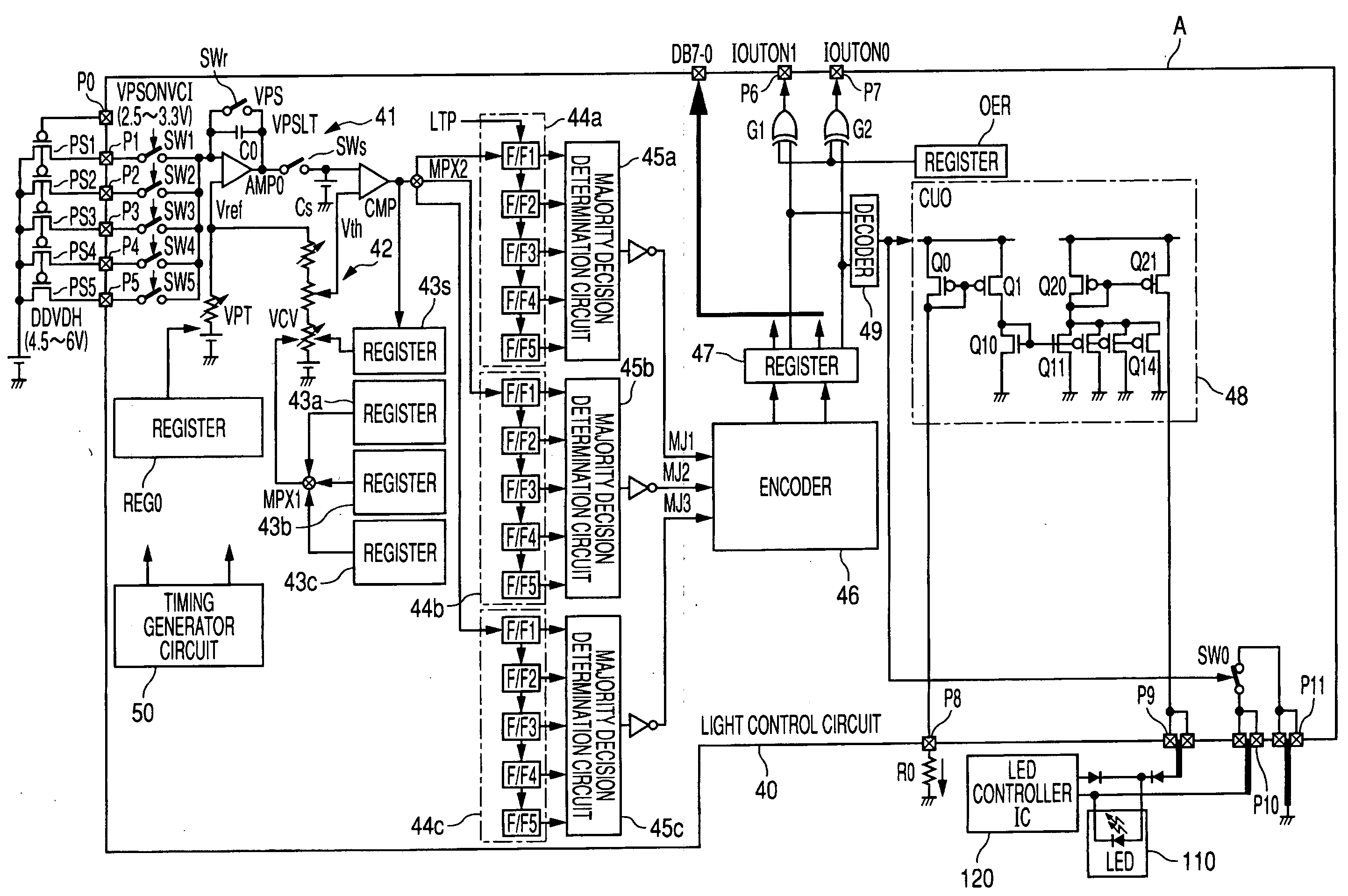

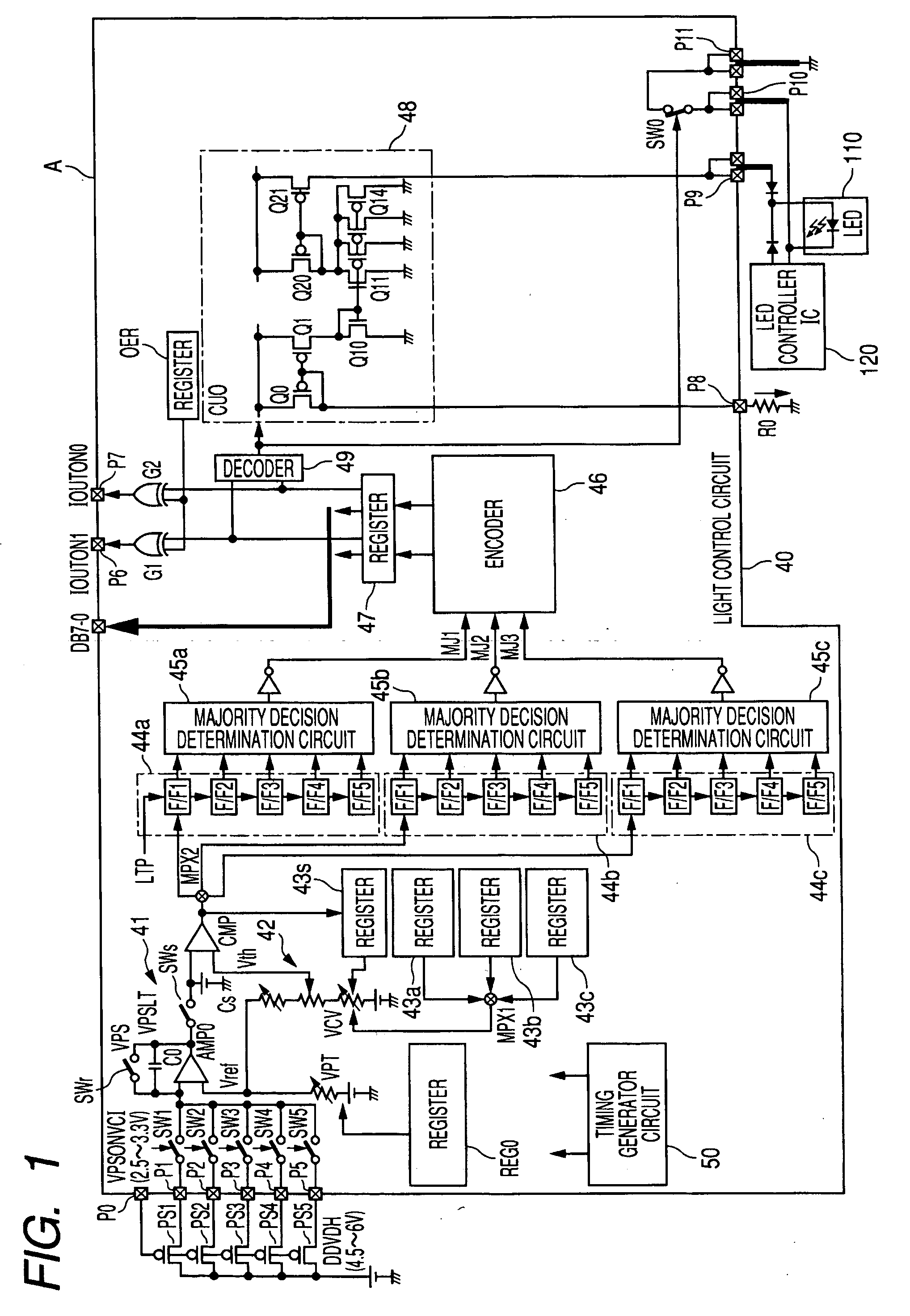

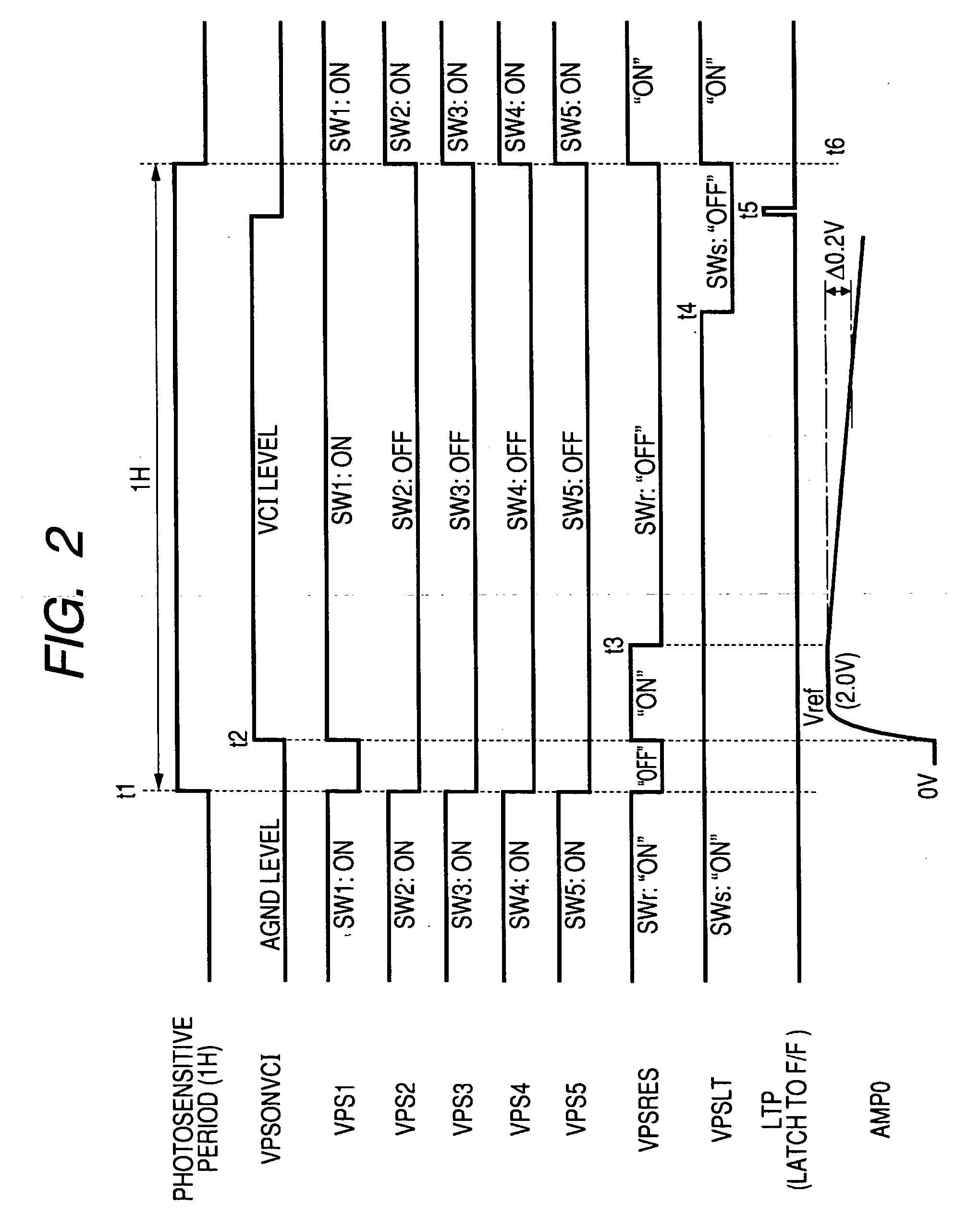

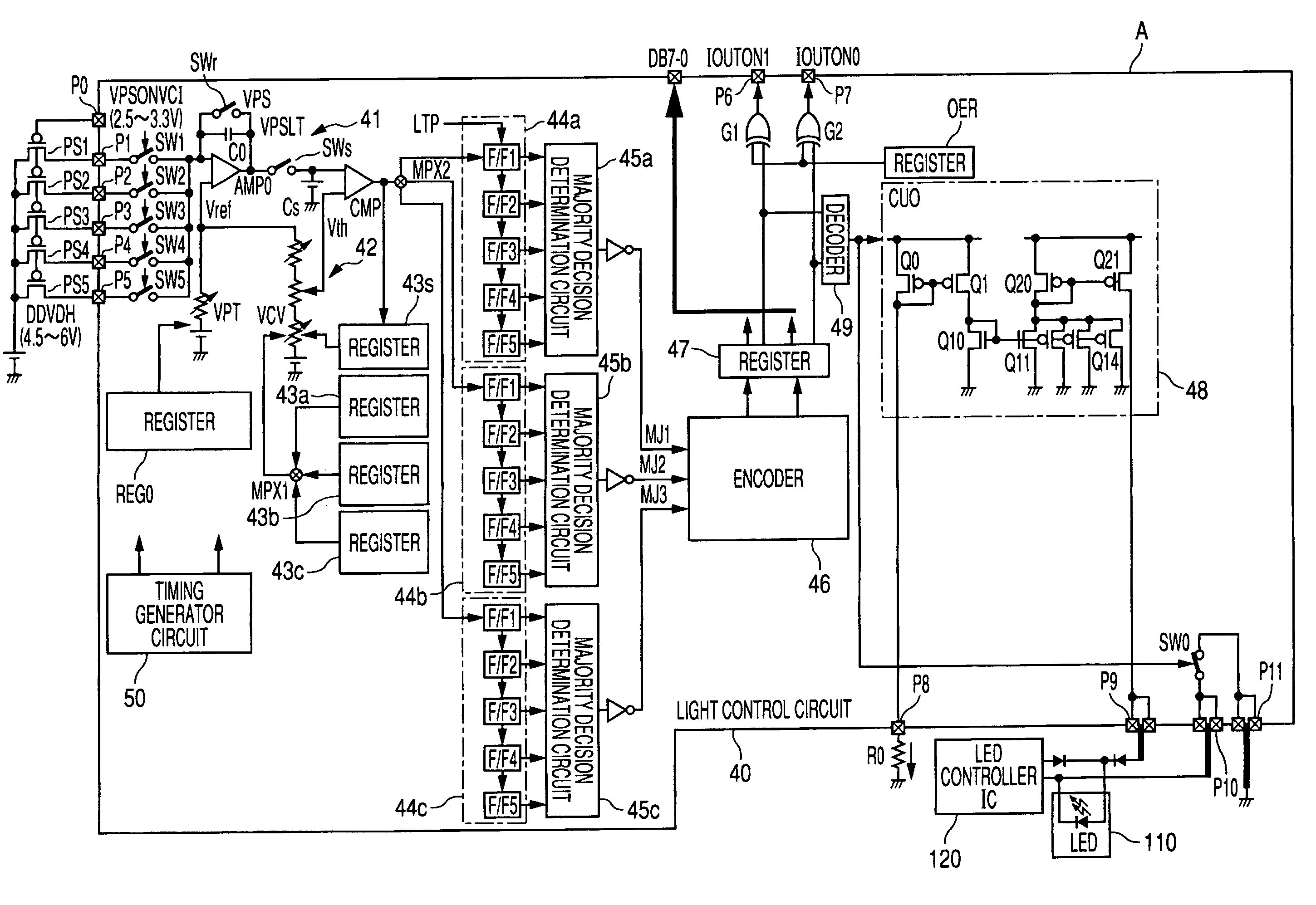

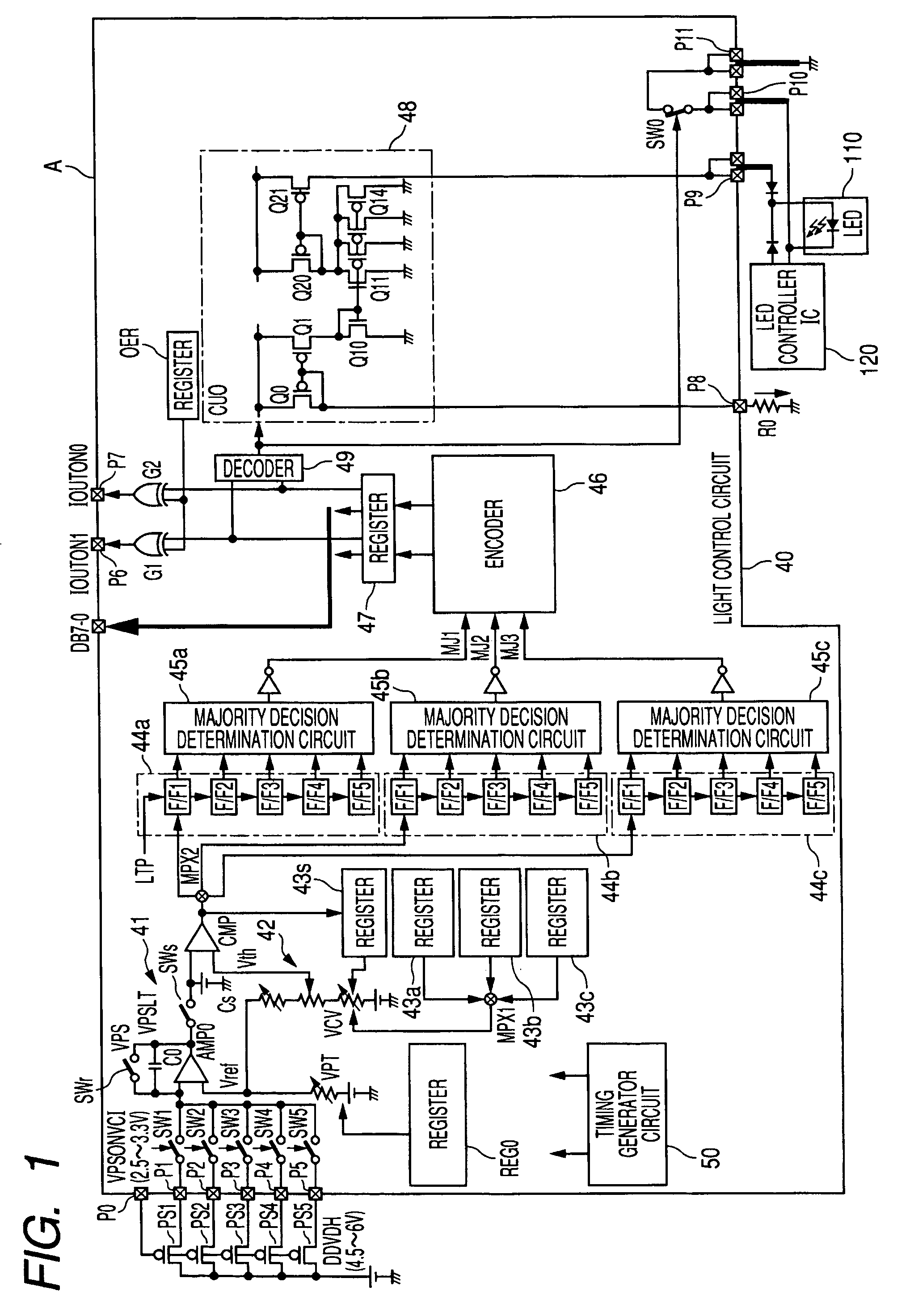

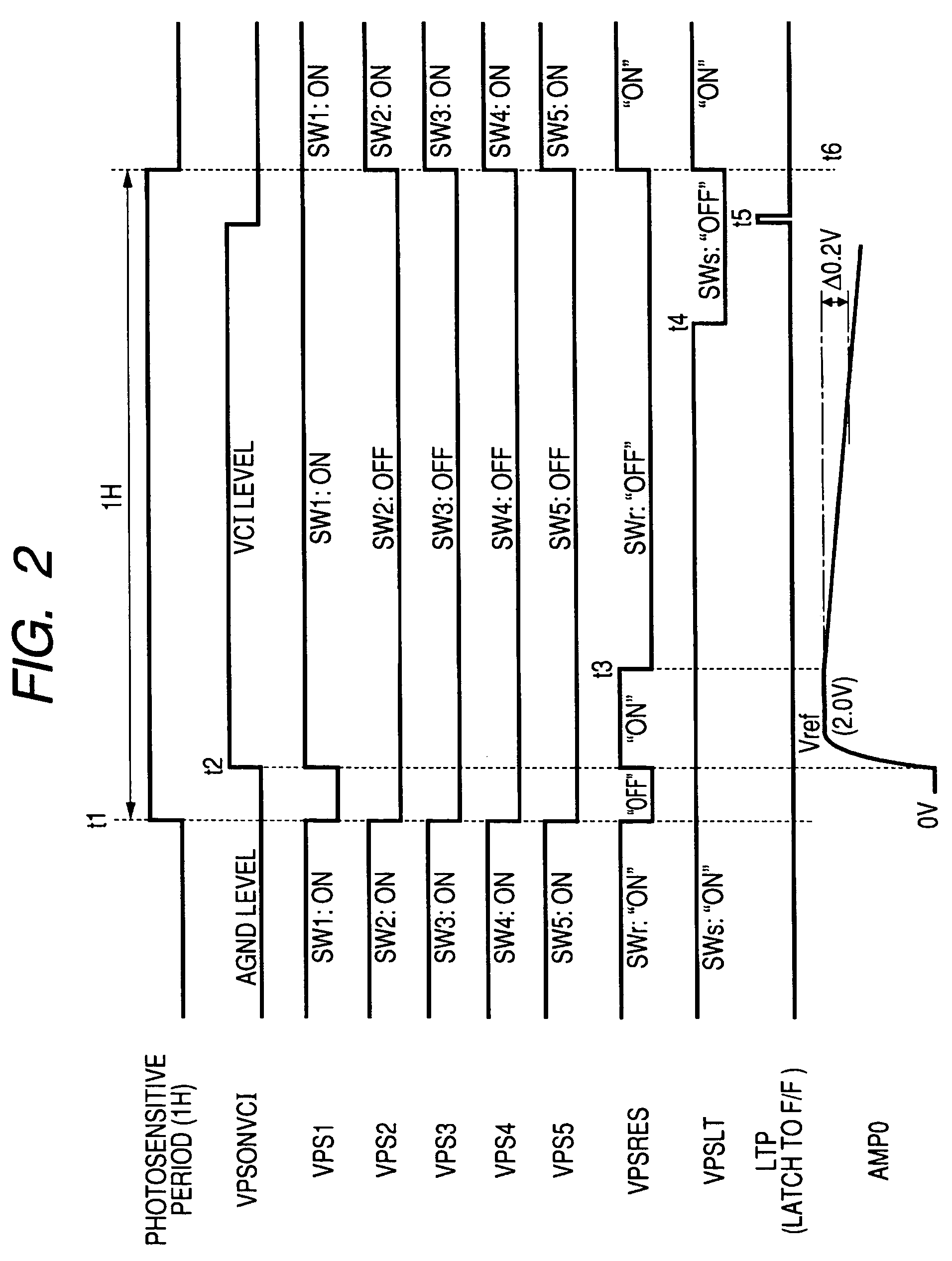

Light control circuit and a liquid-crystal-display control drive device

InactiveUS20070171182A1Reduce chip sizeLow costCathode-ray tube indicatorsInput/output processes for data processingLiquid-crystal displayComputational physics

A light control circuit that makes it possible to, when the light intensity of the area surrounding a display screen varies in a relatively short time, prevent the brightness of a backlight from being erroneously adjusted as the result of the variation being detected is provided. The light control circuit controls the backlight of a display panel. This light control circuit is provided with functions of performing the following operation: detection signals from multiple optical sensors are taken into a common sampling means in a time division manner to acquire multiple sampling values temporally dispersed; a surrounding light intensity is determined by majority decision based on the multiple sampling values, and the result of determination is externally outputted.

Owner:RENESAS ELECTRONICS CORP

Data inversion circuit and semiconductor device

ActiveUS6999352B2Digital data processing detailsSemiconductor/solid-state device manufacturingDecision circuitParallel computing

Owner:LONGITUDE LICENSING LTD

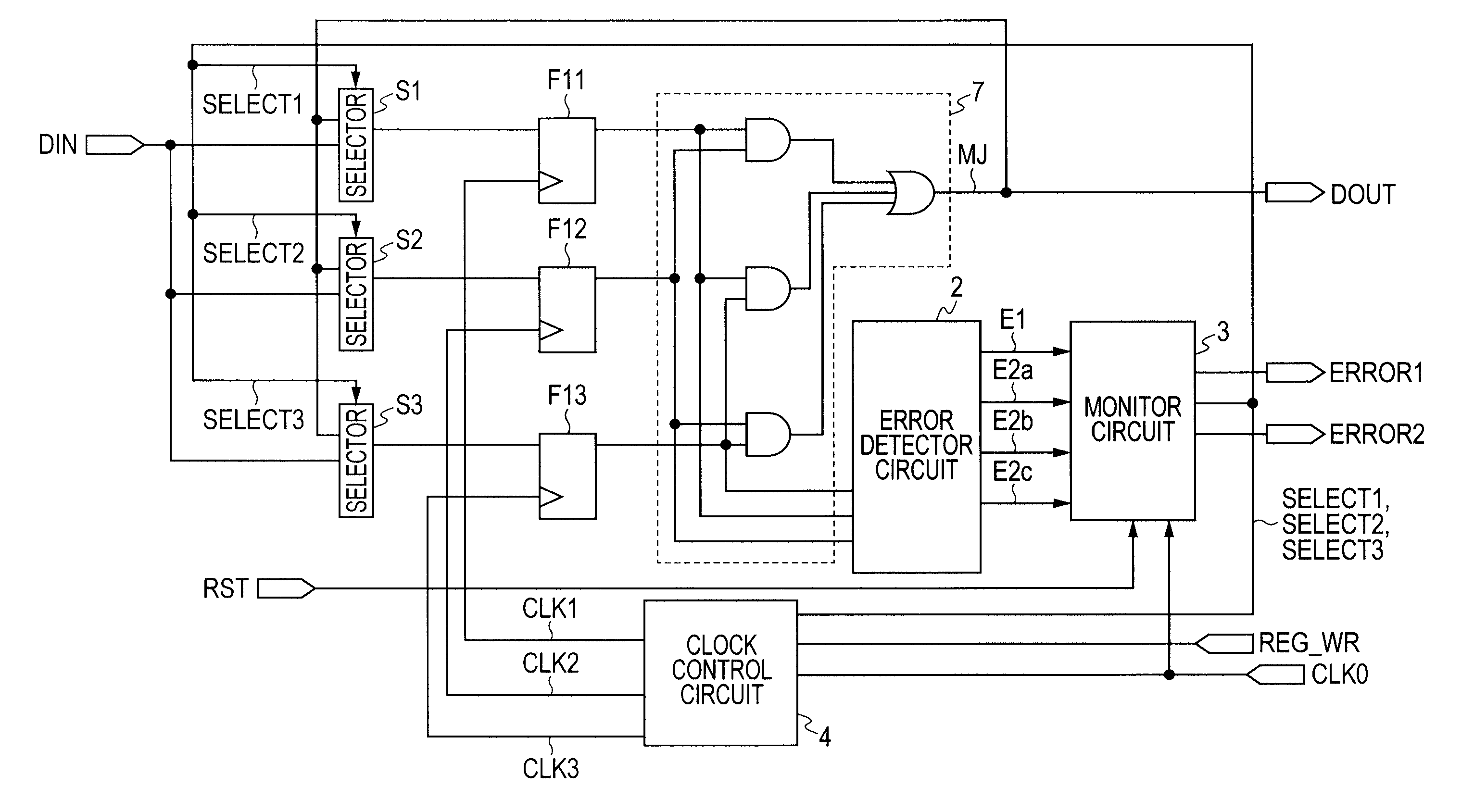

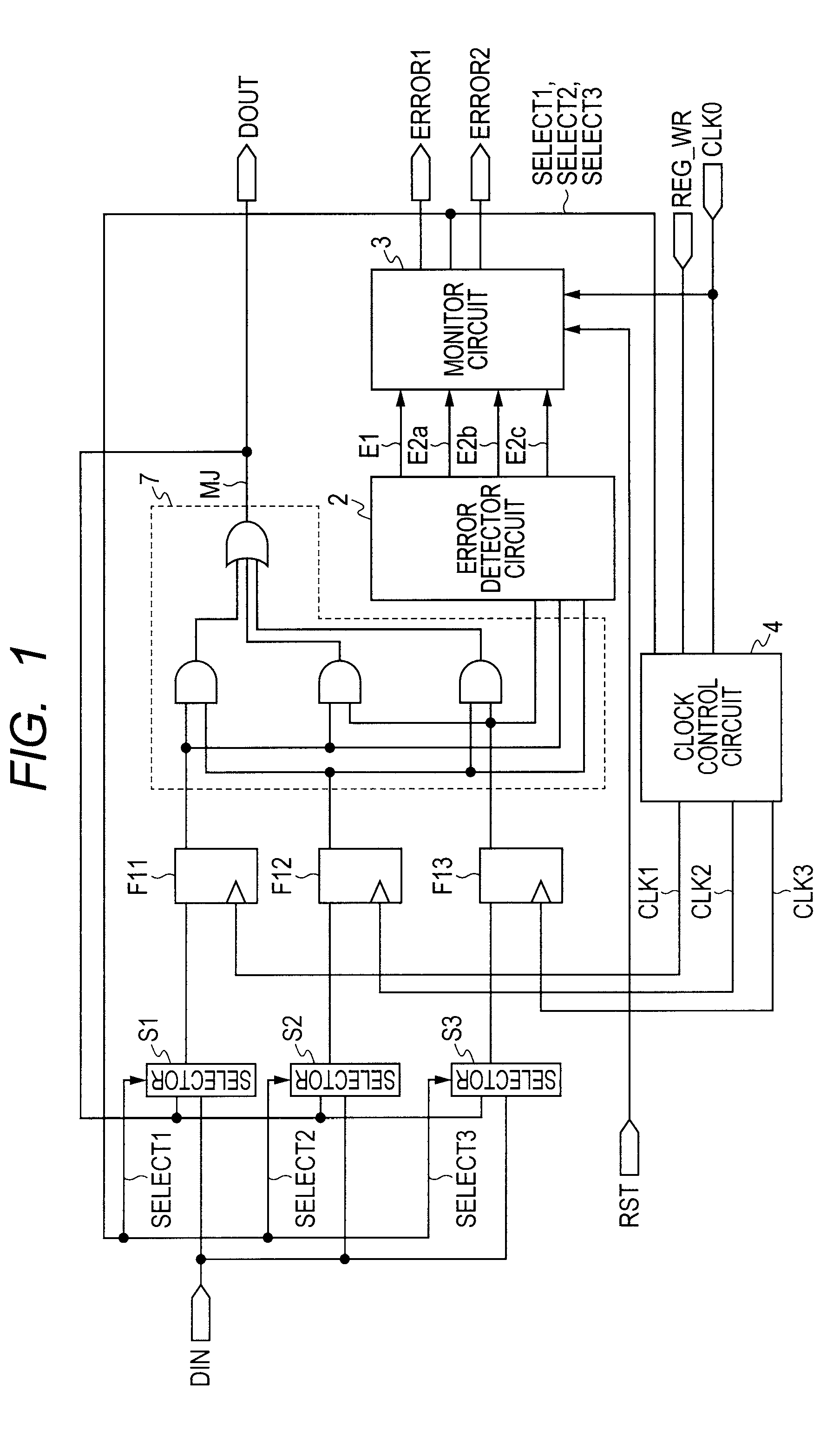

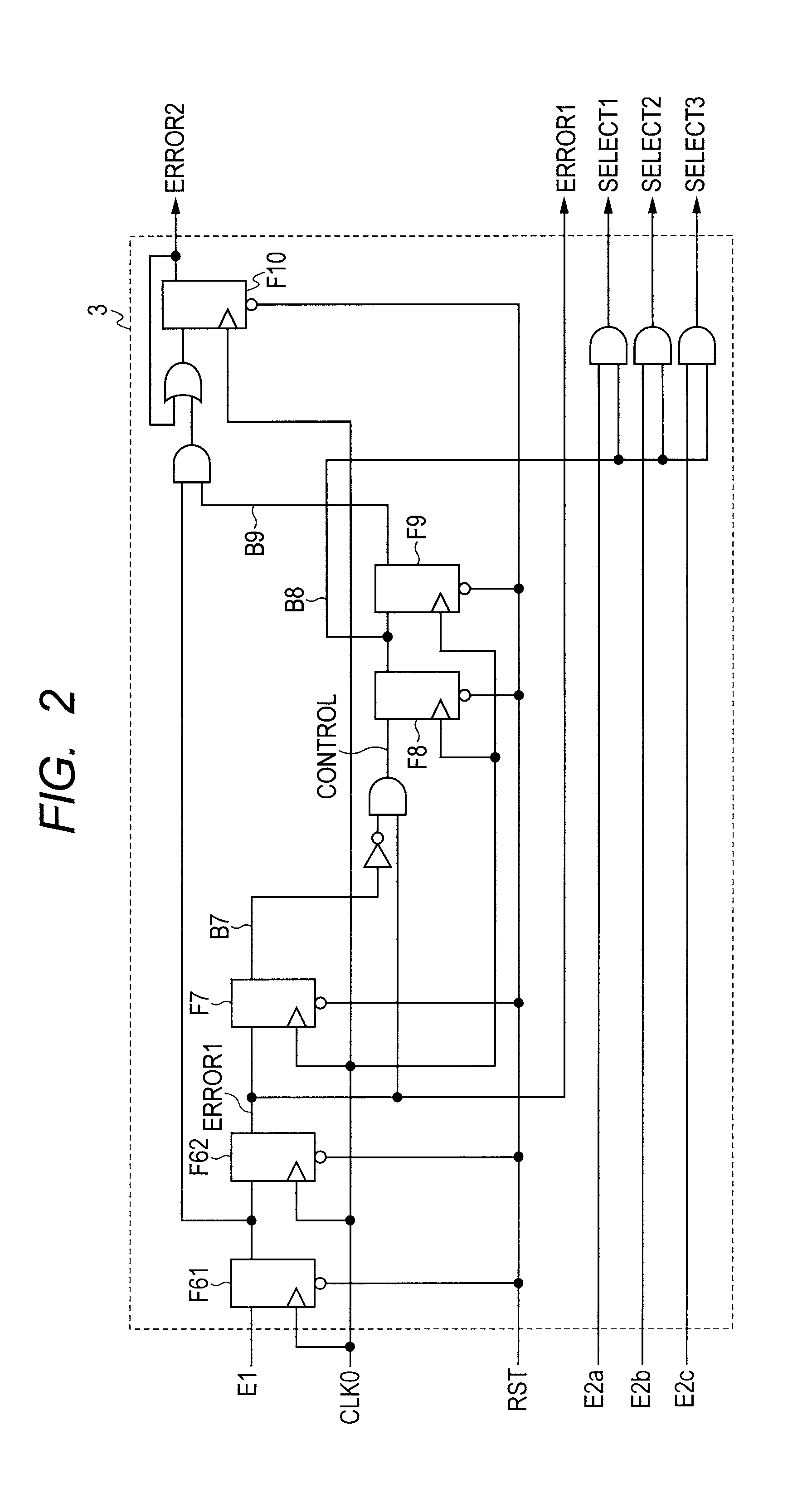

Semiconductor integrated circuit

ActiveUS20110219285A1Improve reliabilityFail-safe circuitsError correction/detection using block codesDetector circuitsSemiconductor

A semiconductor integrated circuit pertaining to the present invention comprises a plurality of storage elements for storing and holding an input signal, a majority circuit that outputs a result of a majority decision of outputs from the plurality of storage elements; an error detector circuit that detects a mismatch among the outputs of the plurality of storage elements and outputs error signals; and a monitor circuit that monitors the error signals from the error detector circuit, wherein the monitor circuit, based on the error signals, orders a refresh action that rewrites data for rectification to a storage element in which an output mismatch occurs out of the plurality of storage elements and, if rewrite and rectification by the refresh action are unsuccessful, sends a notification to an external unit or process.

Owner:RENESAS ELECTRONICS CORP

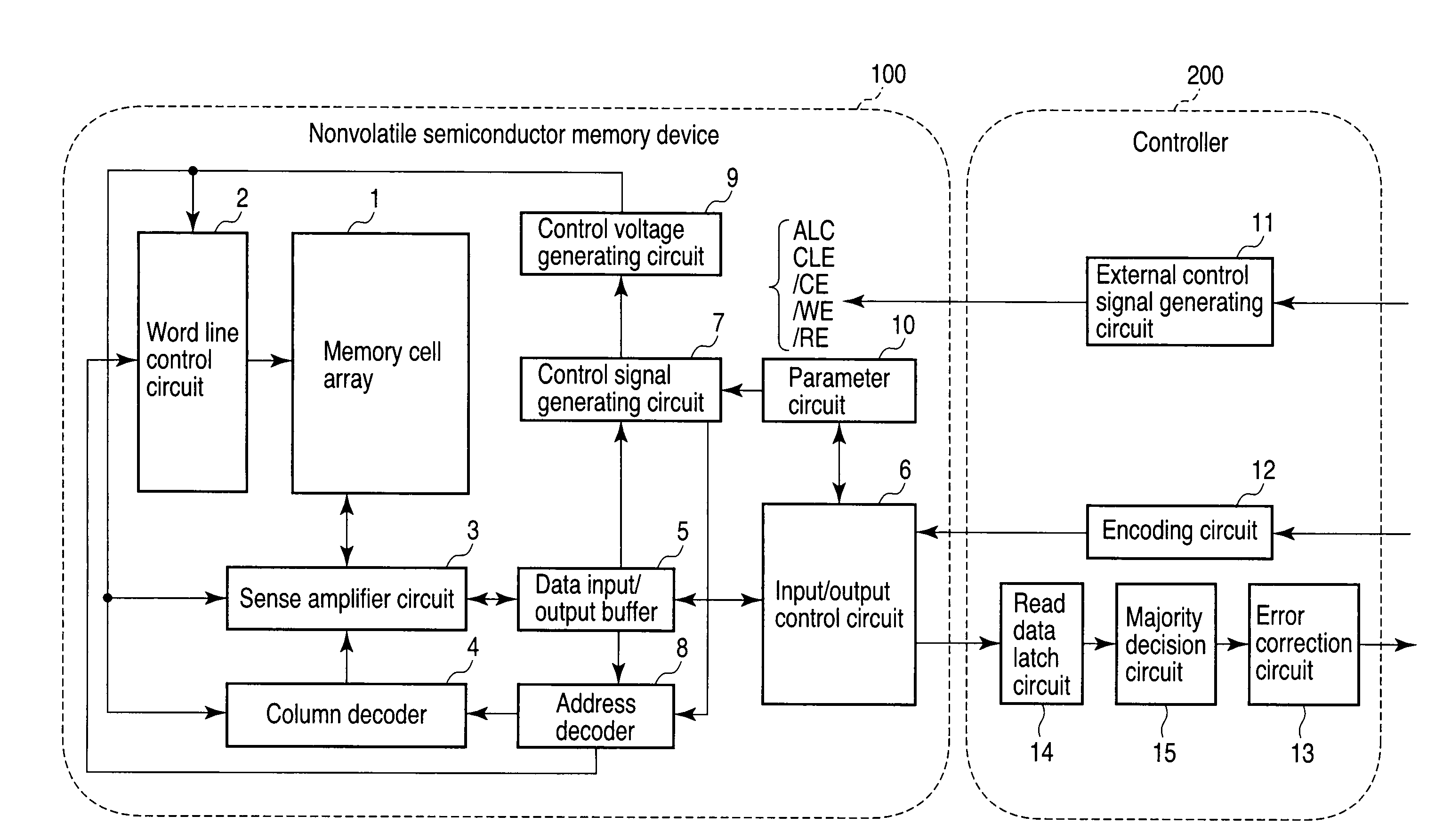

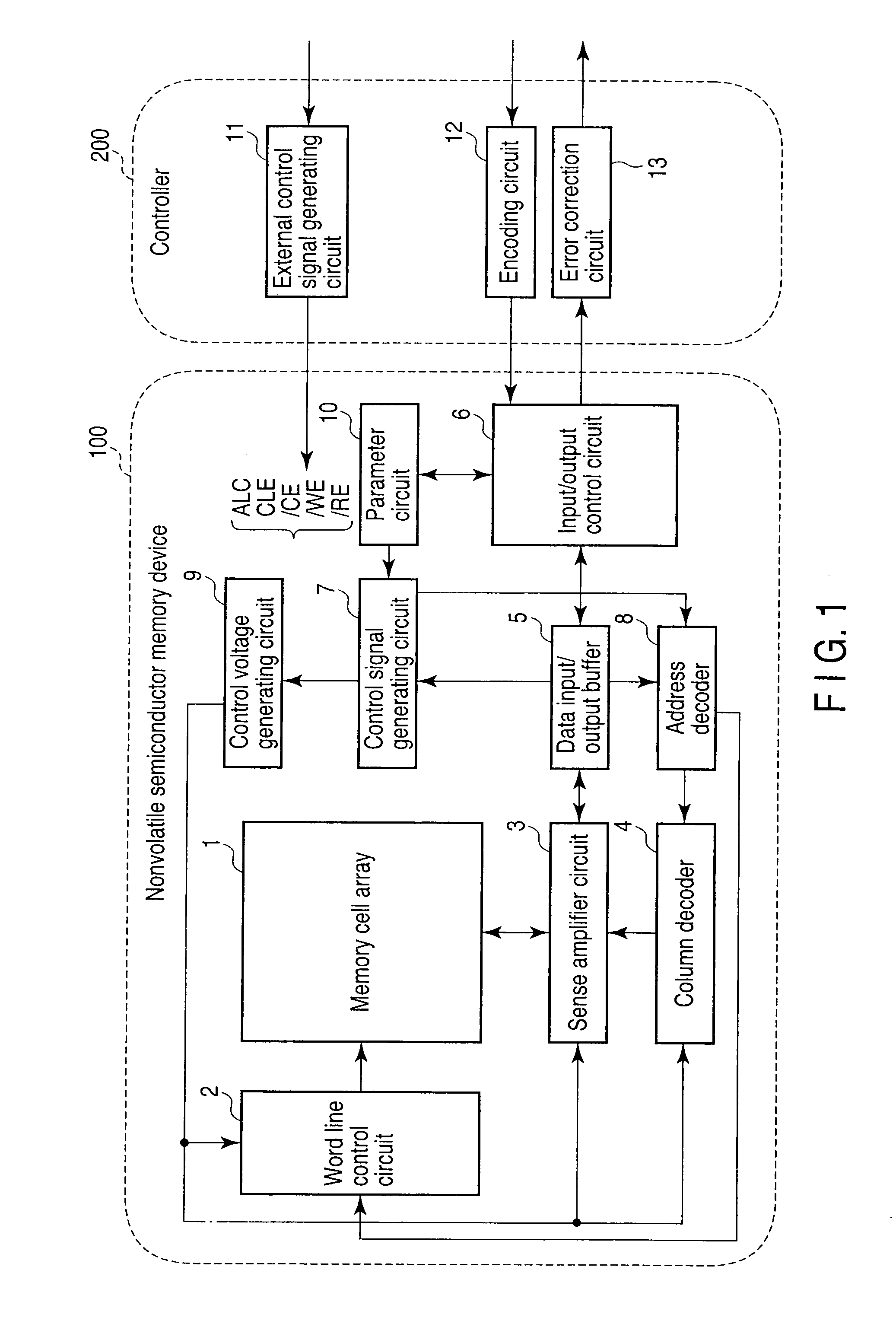

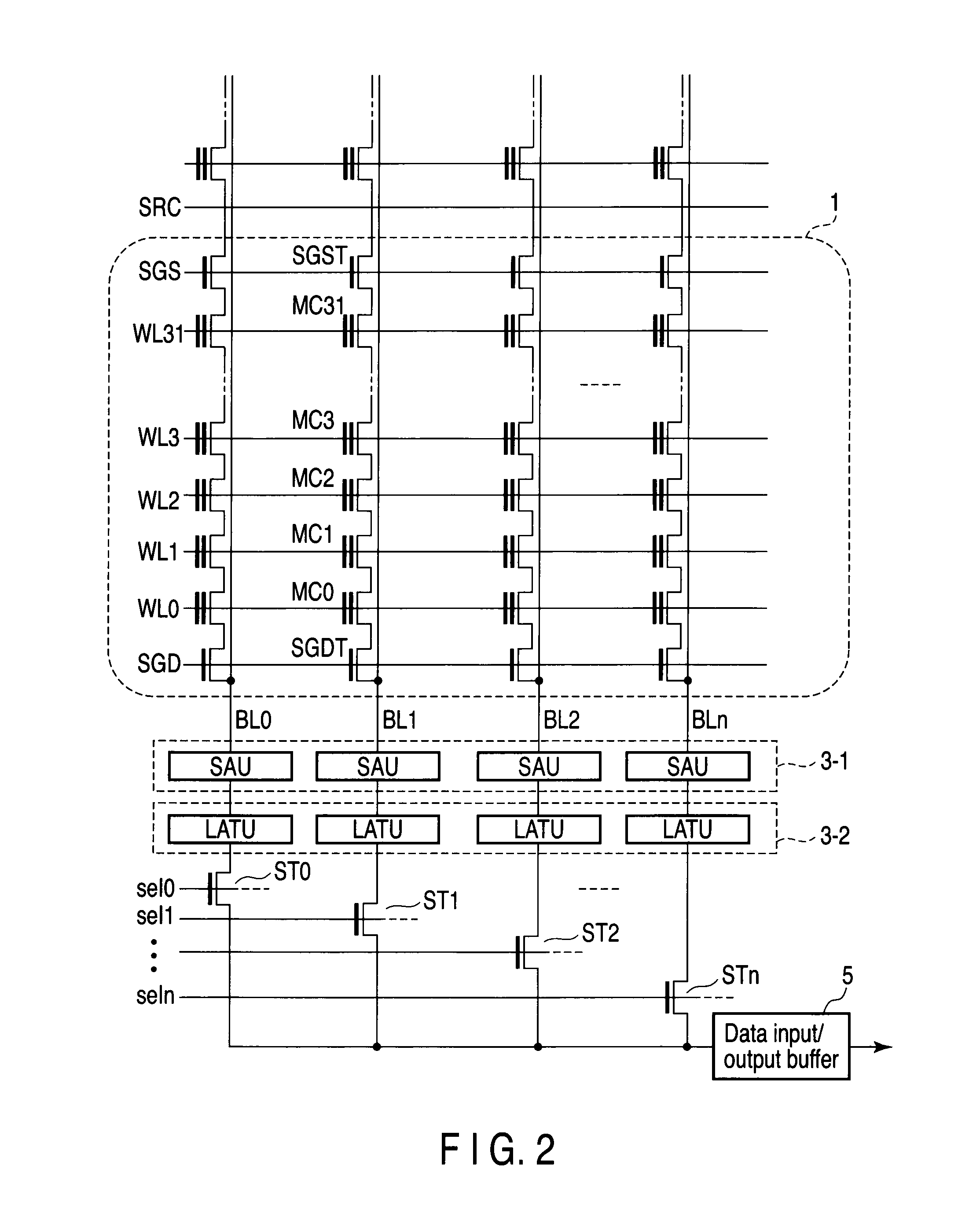

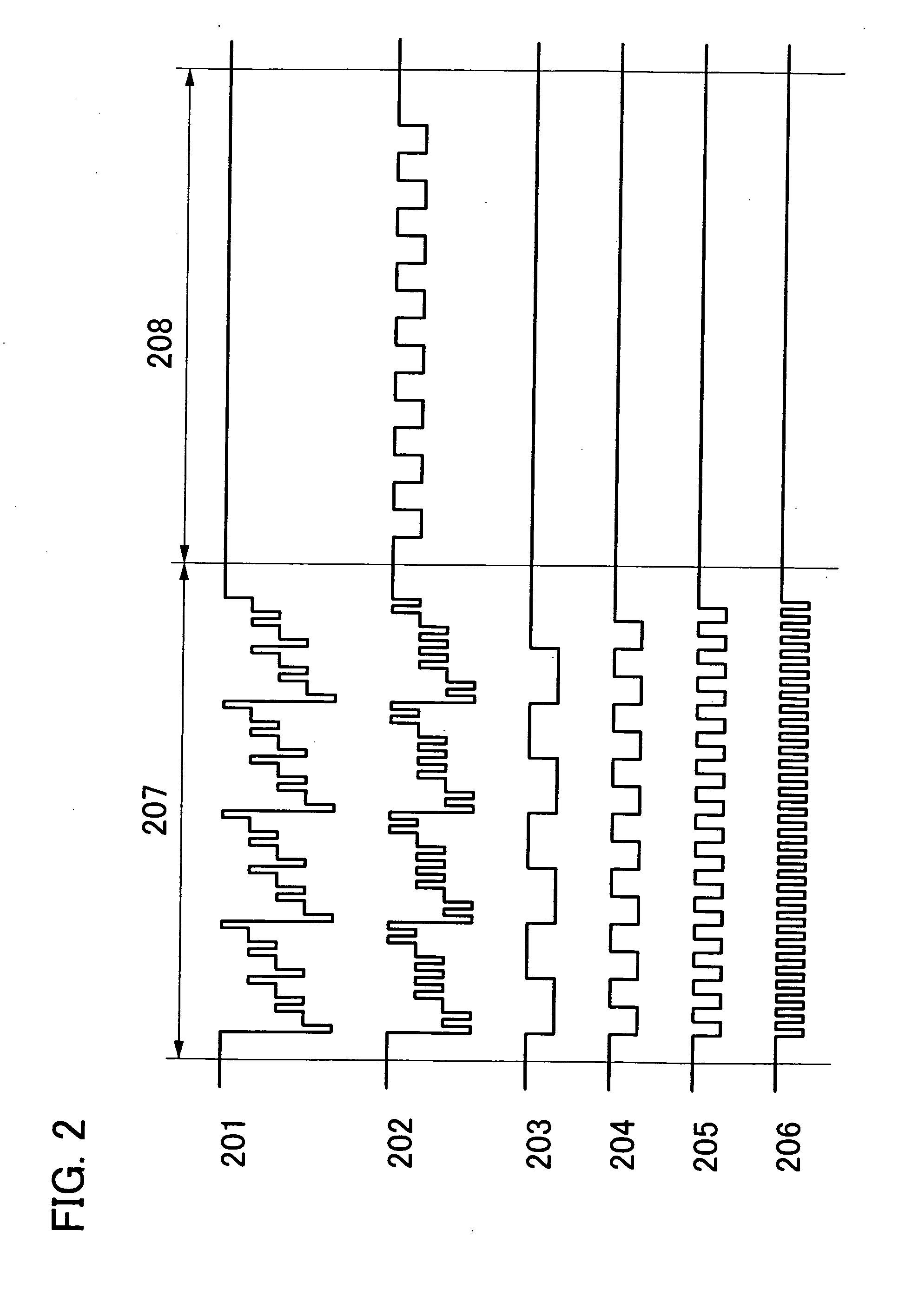

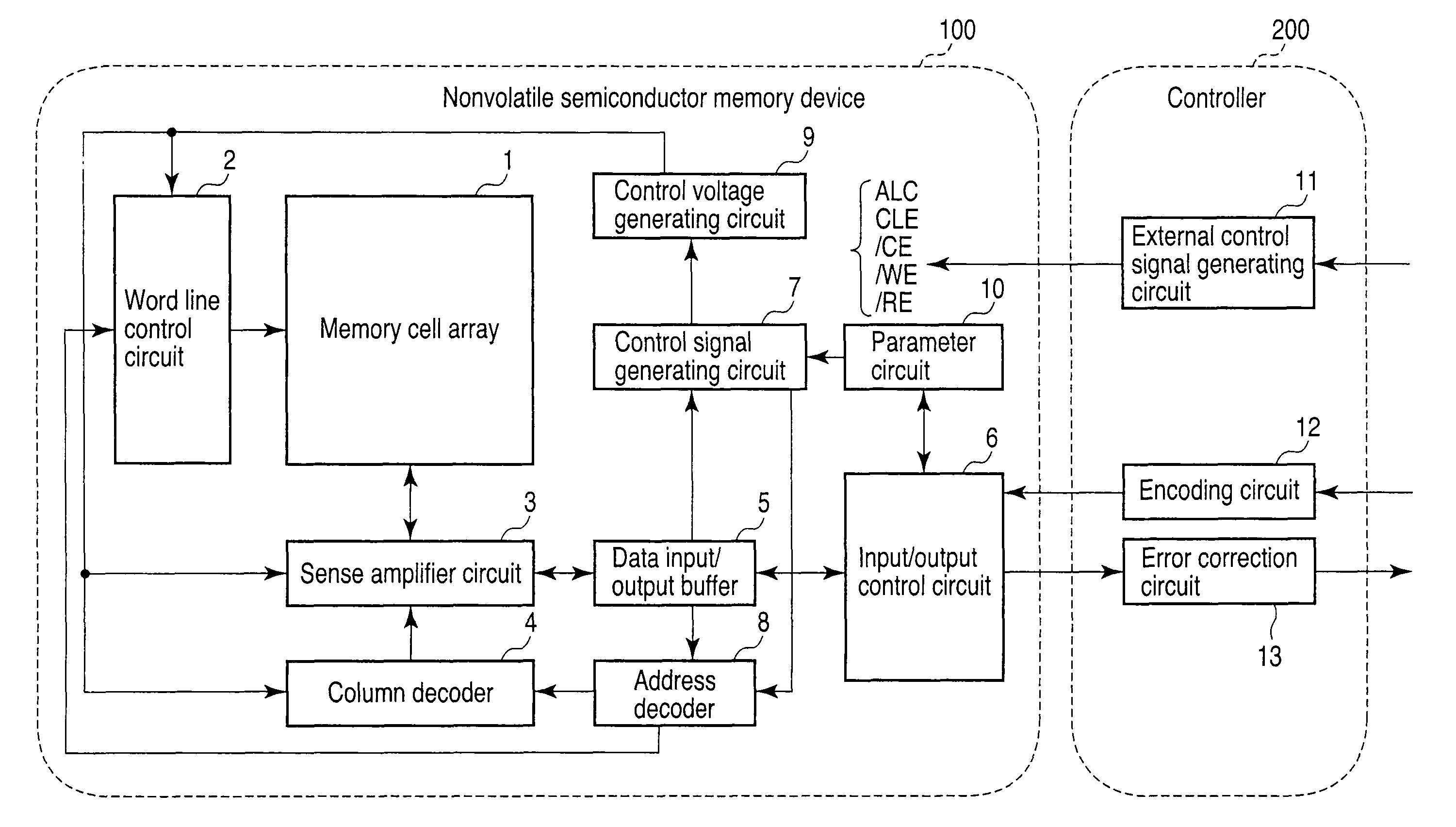

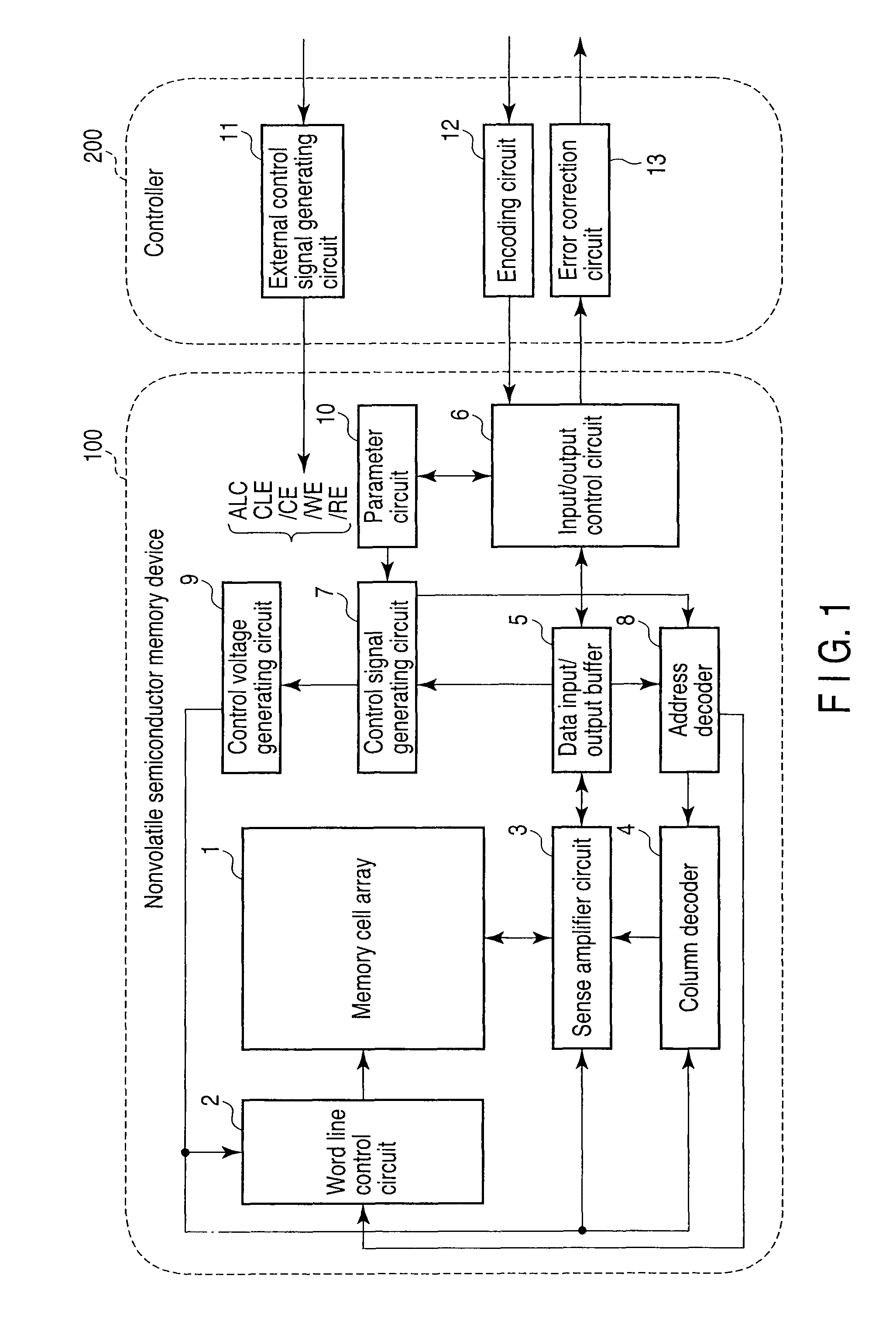

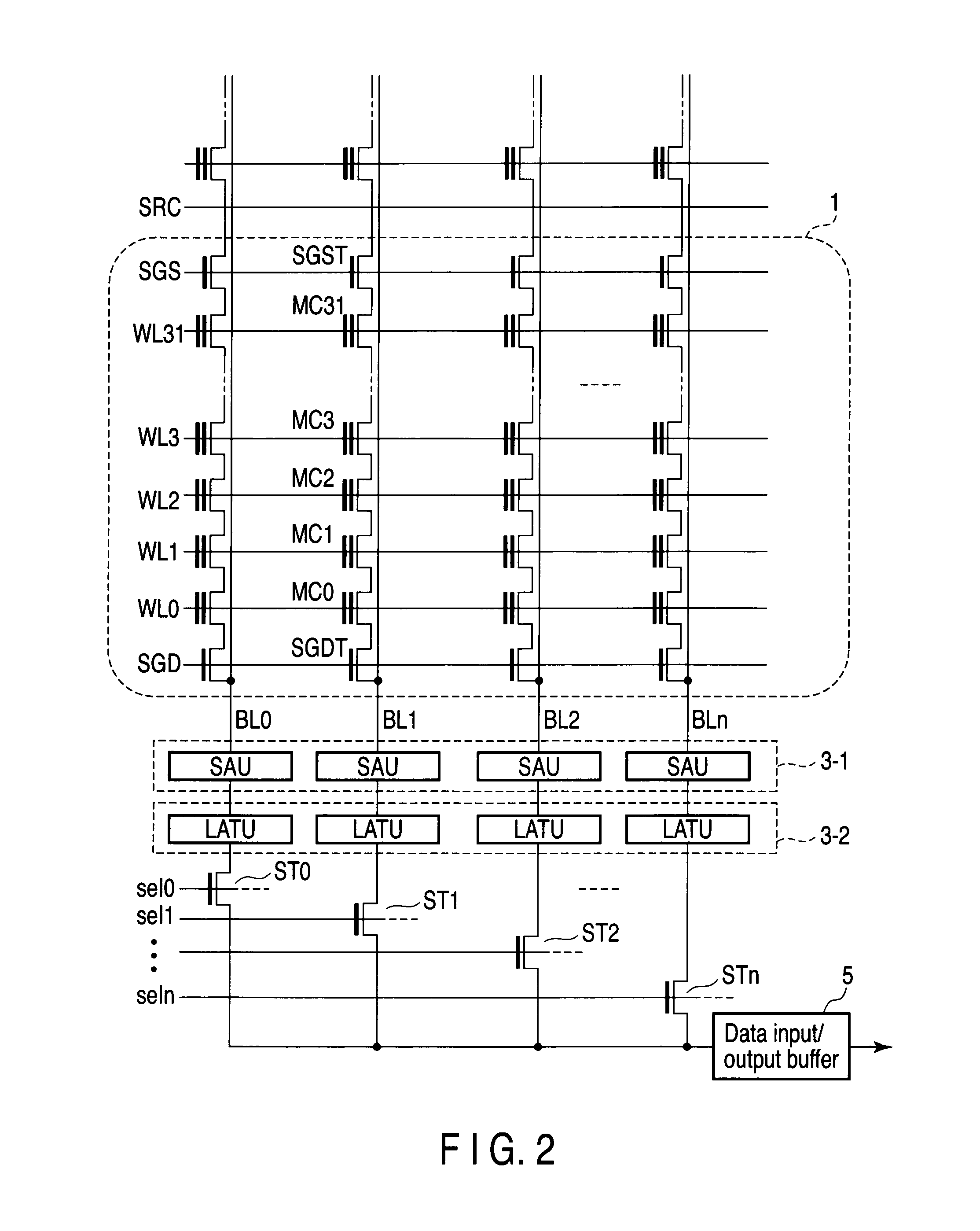

Nonvolatile semiconductor memory device which can electrically rewrite data and system therefor

InactiveUS20100177567A1Error detection/correctionRead-only memoriesComputer architectureHemt circuits

A nonvolatile semiconductor memory device includes a memory cell, latch circuits, and an arithmetic operation circuit. The memory cell stores data by a difference in threshold voltage. A read operation is performed twice or more on the memory cell under the same read conditions, and the latch circuits store a plurality of read data. The arithmetic operation circuit takes majority decision of the plurality of data stored in the latch circuits and decides data determined by the majority decision as data stored in the memory cell.

Owner:KK TOSHIBA

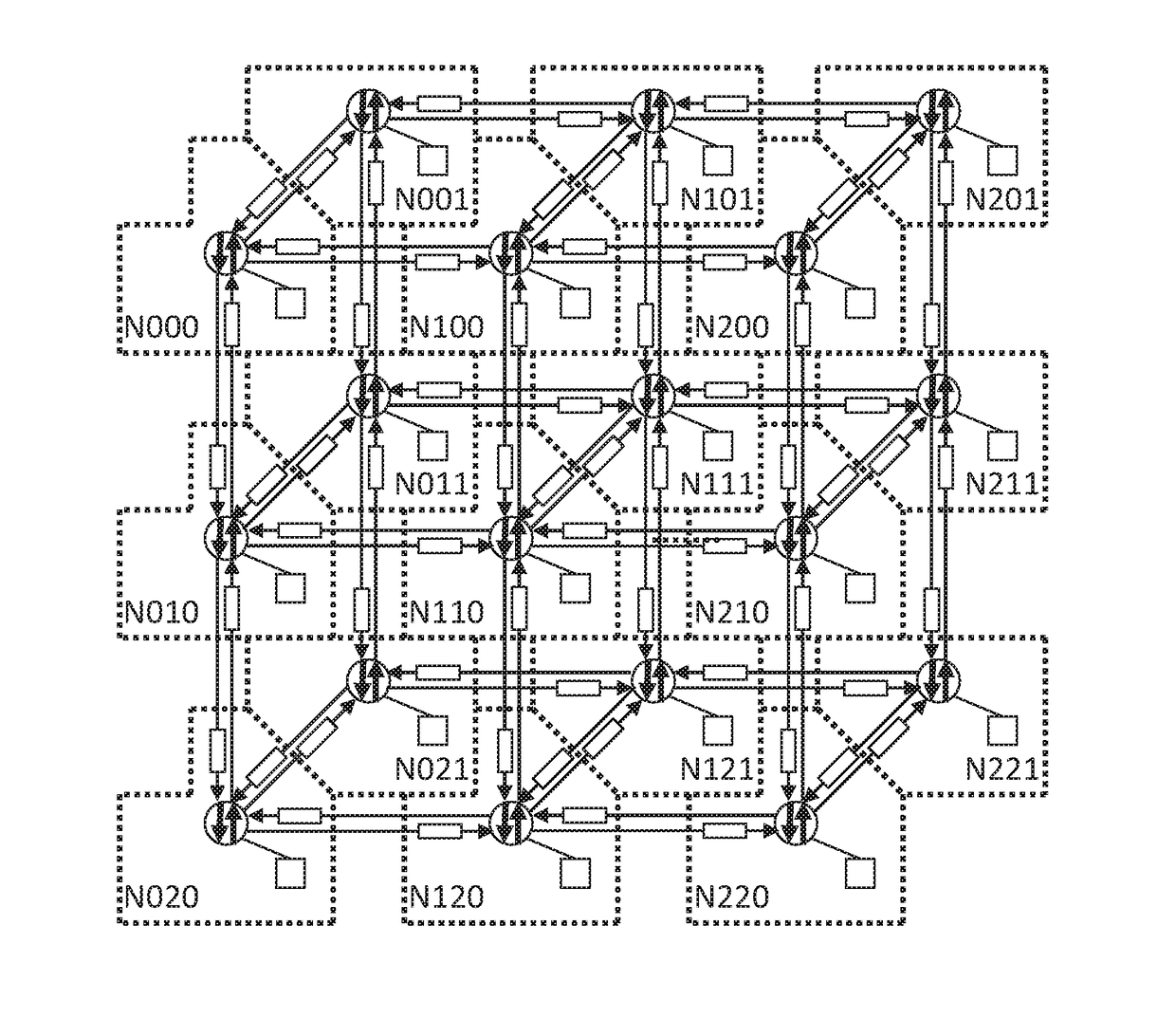

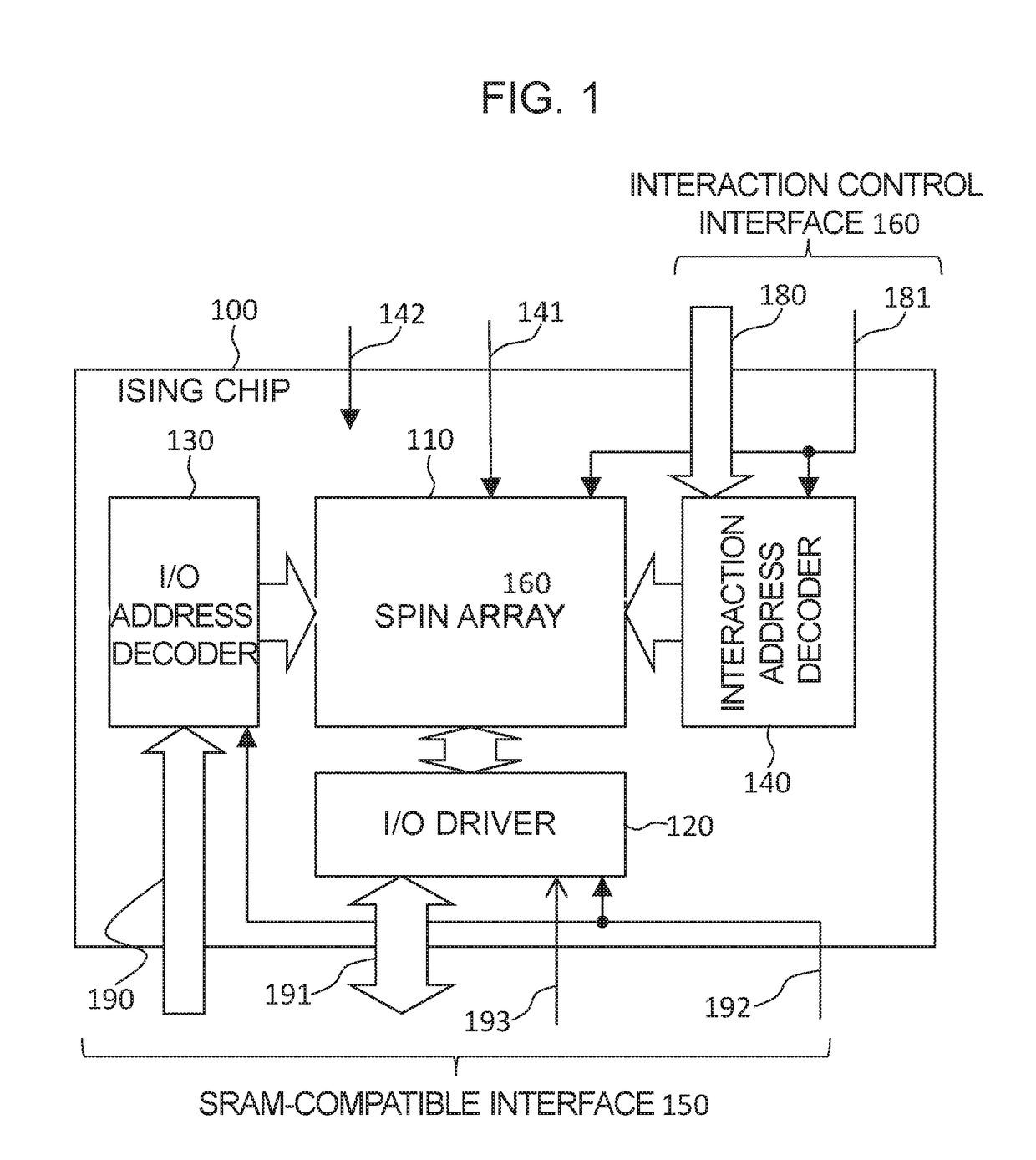

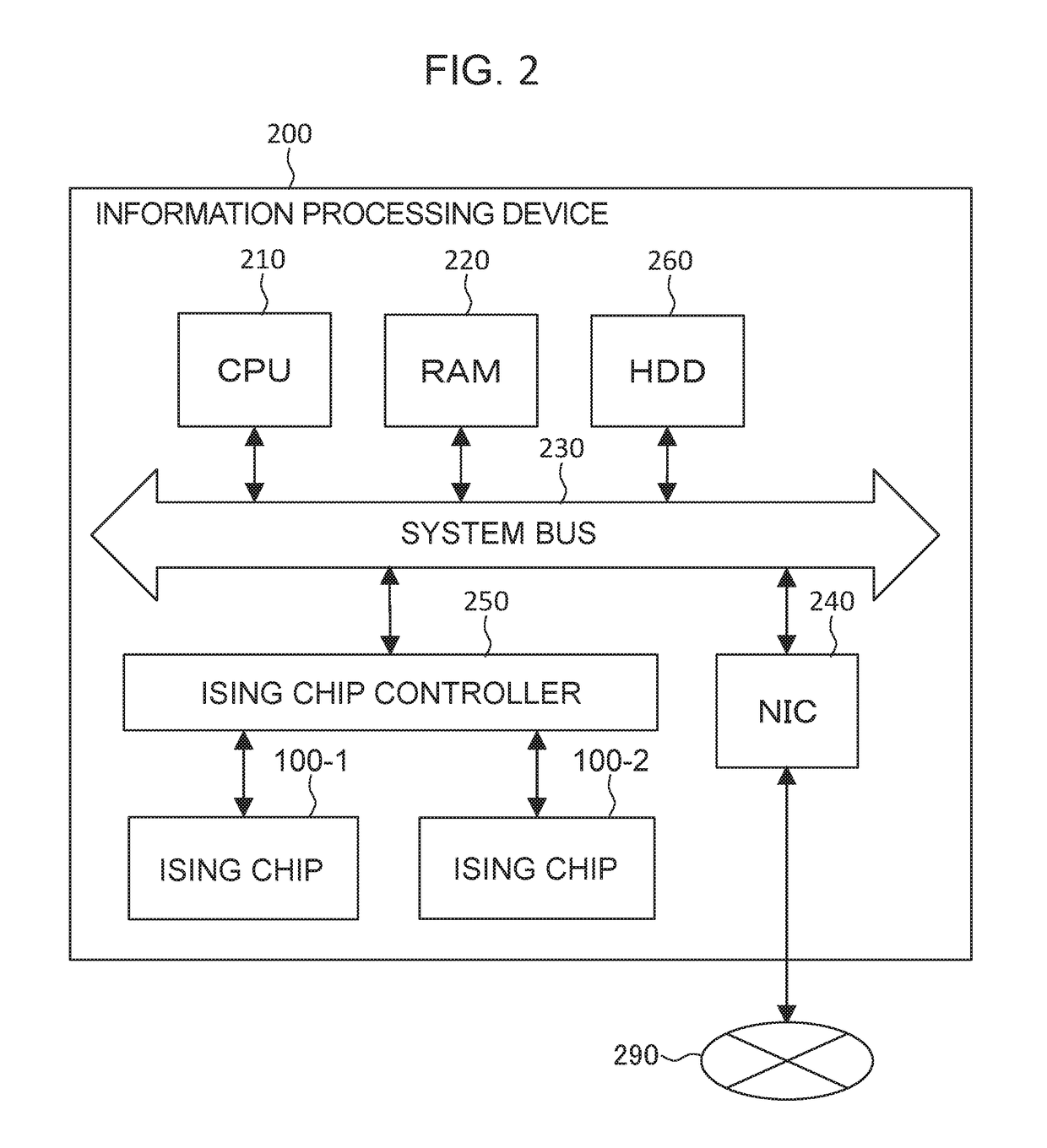

Semiconductor device and information processing device

InactiveUS20170068632A1Digital storagePower supply for data processingIsing modelInformation processor

A semiconductor device in which a ground state of an Ising model is realized, includes a spin array in which a spin unit is formed, the spin unit including a memory cell storing a value of one spin in an Ising model, a memory cell storing an interaction coefficient from an adjacent spin interacting with the spin, a memory cell storing an external magnetic field coefficient of the spin, and a circuit deciding a next state of the spin by binary majority decision logic based on a product of the value of each of the adjacent spins and the corresponding interaction coefficient, and the external magnetic field coefficient. The spin array is formed by having a plurality of the spin units, each having each spin allocated thereto, arranged and connected on a two-dimensional plane on a semiconductor substrate in the state where a topology of the Ising model is maintained.

Owner:HITACHI LTD

Communication system having conference server

InactiveUS7643628B2Avoids lengthy discussionElectric current slaughtering/stunningSpecial service for subscribersControl communicationsConference control

A communication system having a conference server device, a conference control unit, a plurality of moderator units, and a plurality of telecommunication devices. The moderator units are used to control allocation of a communication right. The decisions of the moderator units regarding the allocation of the communication right are combined to form an unambiguous overall decision, and overall decision is made using a majority decision.

Owner:INTEL CORP

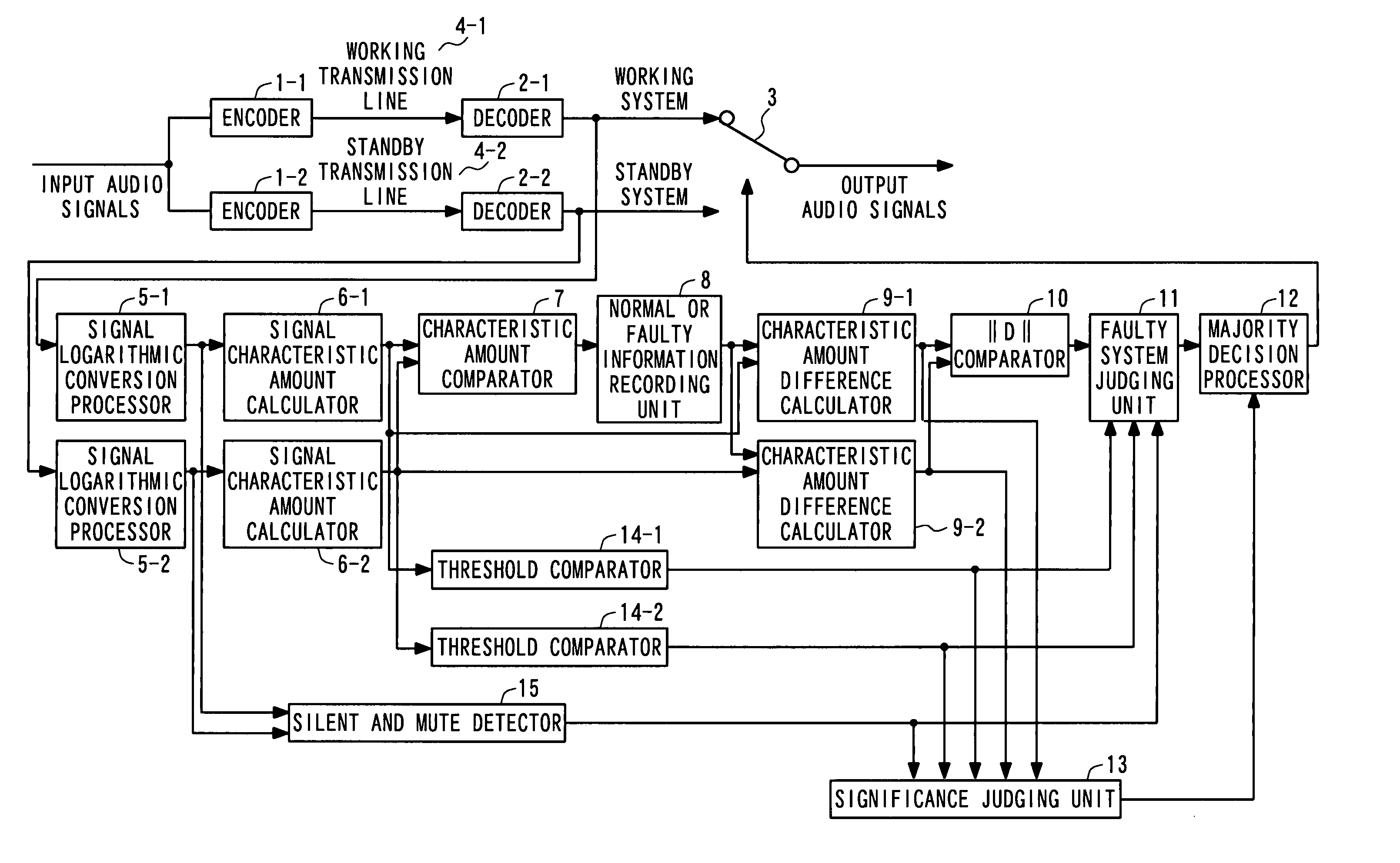

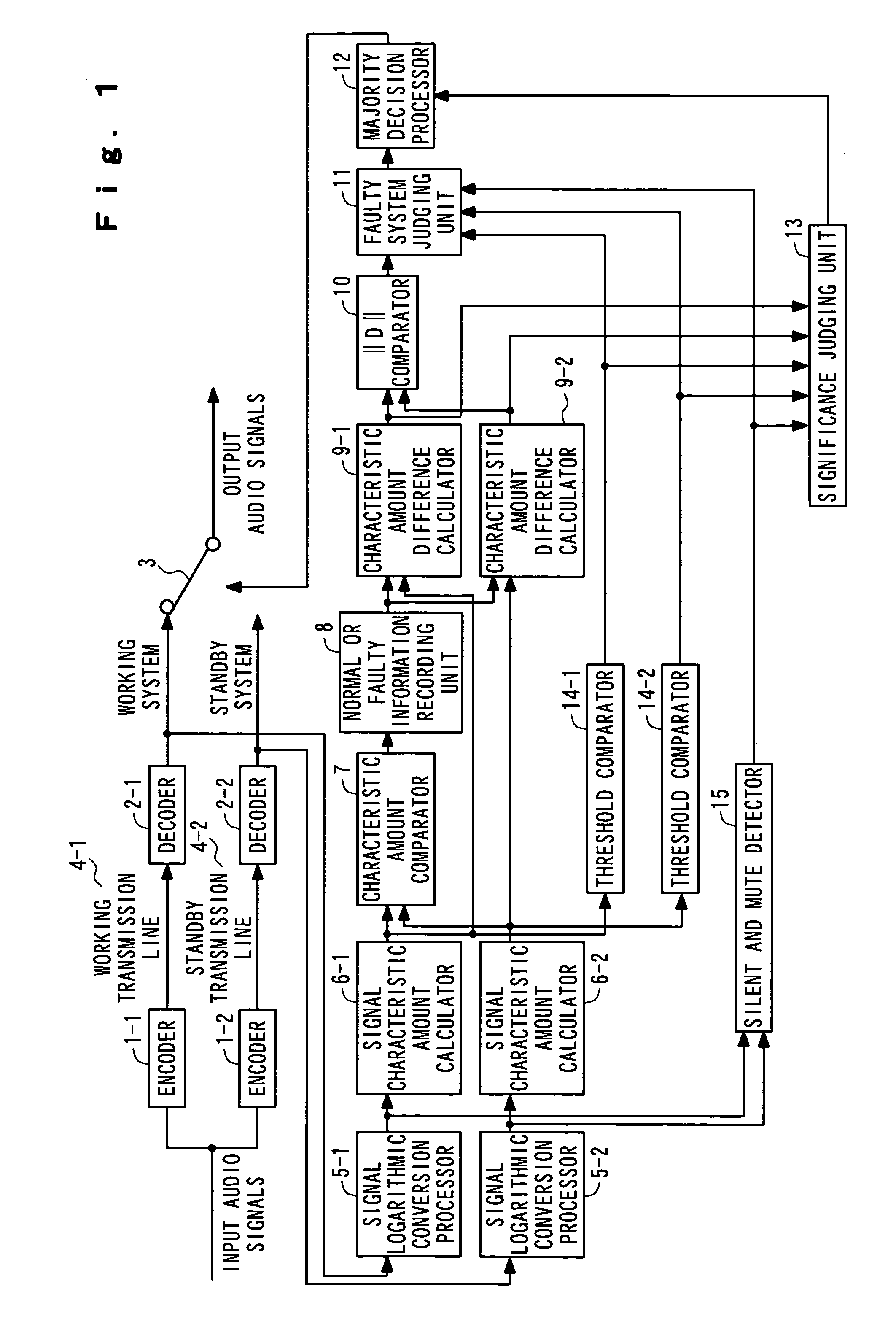

Apparatus for fault detection for parallelly transmitted audio signals and apparatus for delay difference detection and adjustment for parallelly transmitted audio signals

InactiveUS20050154952A1Continuous receptionEasy to adjustTelevision system detailsSubstation/switching arrangement detailsEngineeringAudio frequency

Characteristic amounts in each small region of audio signals transmitted in the working system and the standby system are extracted by characteristic amount calculators 6-1, 6-2. A characteristic amount comparator 7 compares the characteristic amounts and judges occurrence of a fault. Characteristic amount difference calculators 9-1, 9-2, ∥D∥ comparator 10, and faulty system judging unit 11 judges the system having a fault. Majority decision processor 12 and significance judging unit 13 enhance the reliability of the judgment. Delay difference of audio signals between systems is roughly detected by sub-sampling audio signals of two systems and comparing them, and then accurately detected without sub-sampling. Delay difference between audio signals is adjusted by the detected delay difference.

Owner:KDDI CORP

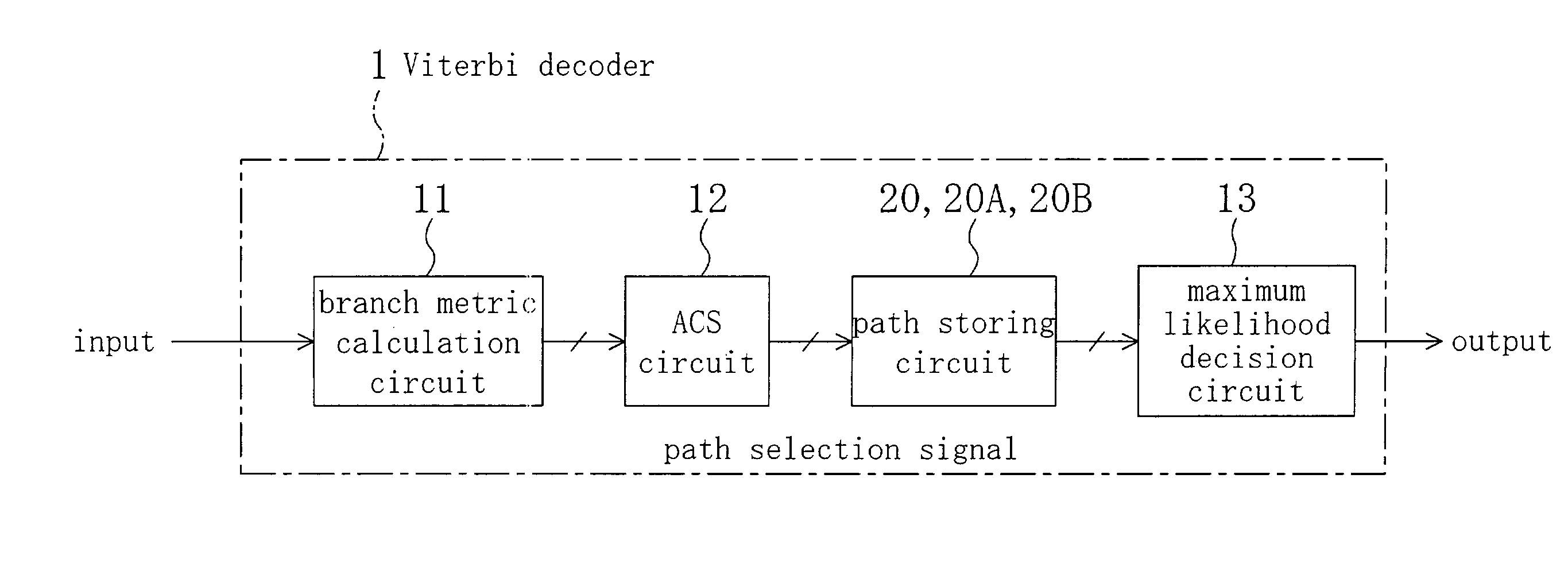

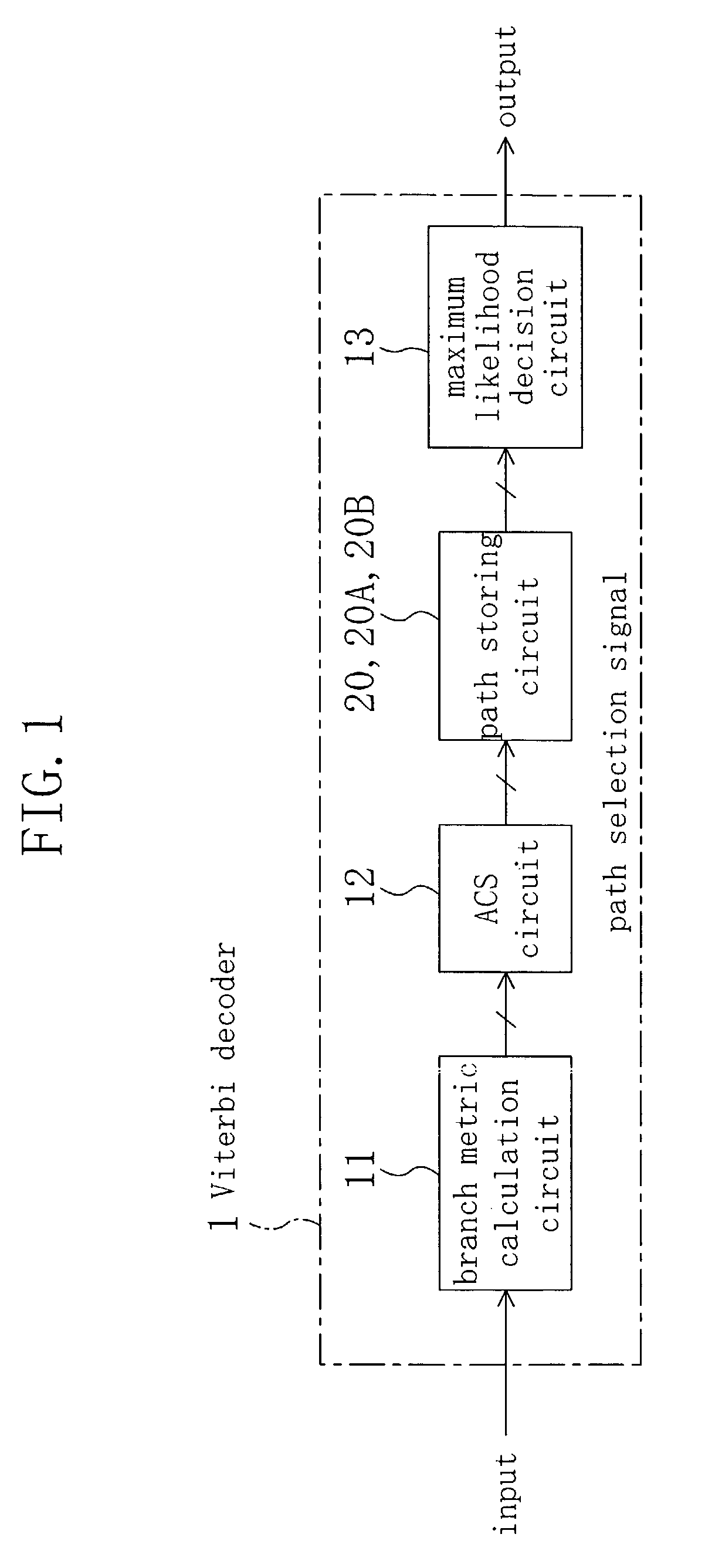

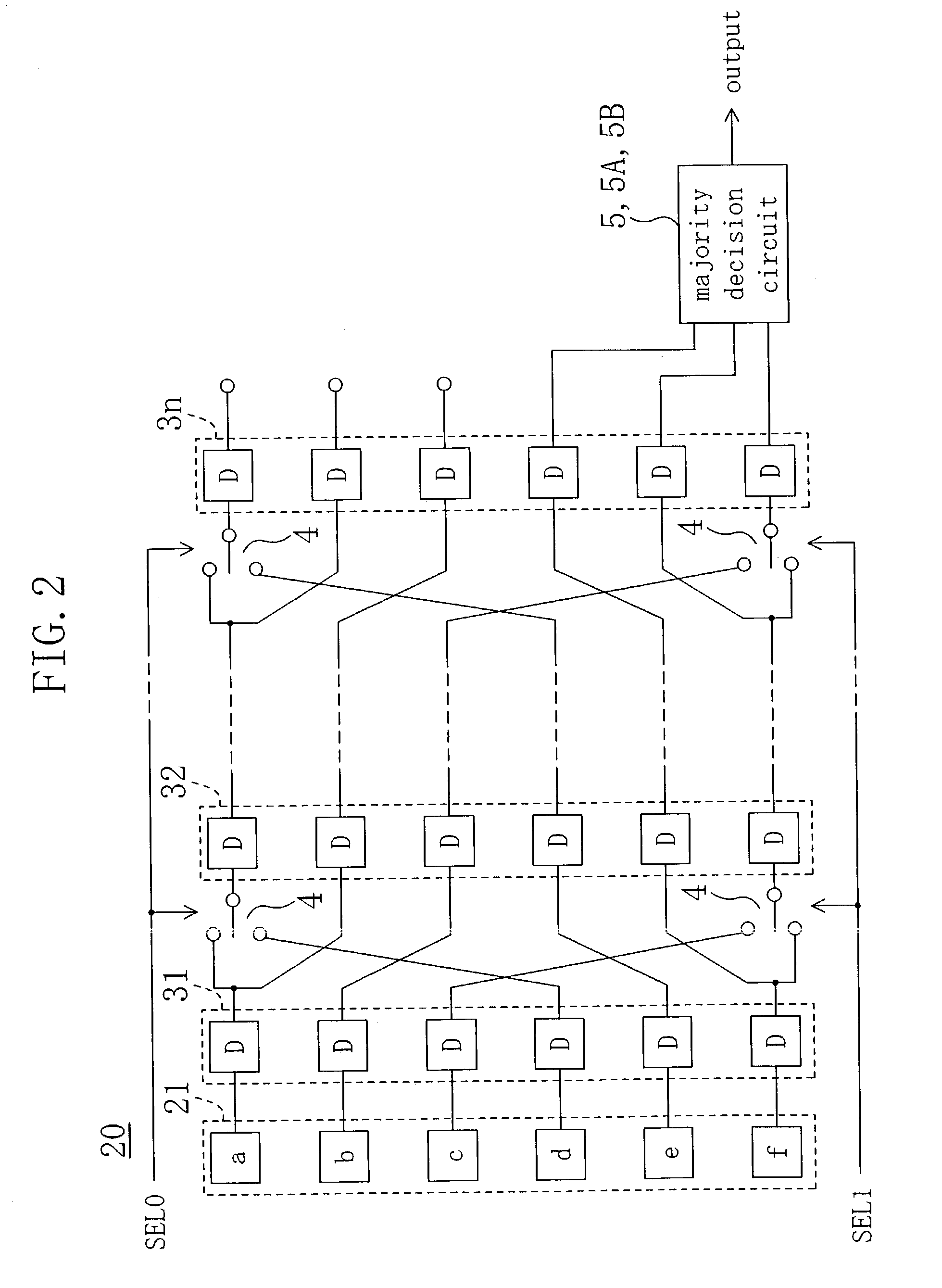

Viterbi decoder

InactiveUS7187729B2Improve performanceCircuit scale increaseTelevision system detailsError correction/detection using convolutional codesViterbi decoderEngineering

A path storing circuit has path holding parts at a plurality of stages storing a survivor path and corresponding to times. A majority decision circuit receives output values of three delay circuits including the top and bottom delay circuits each receiving a selected output of a selector out of six delay circuits in the path holding part at the final stage and makes a decision by a majority.

Owner:SOCIONEXT INC

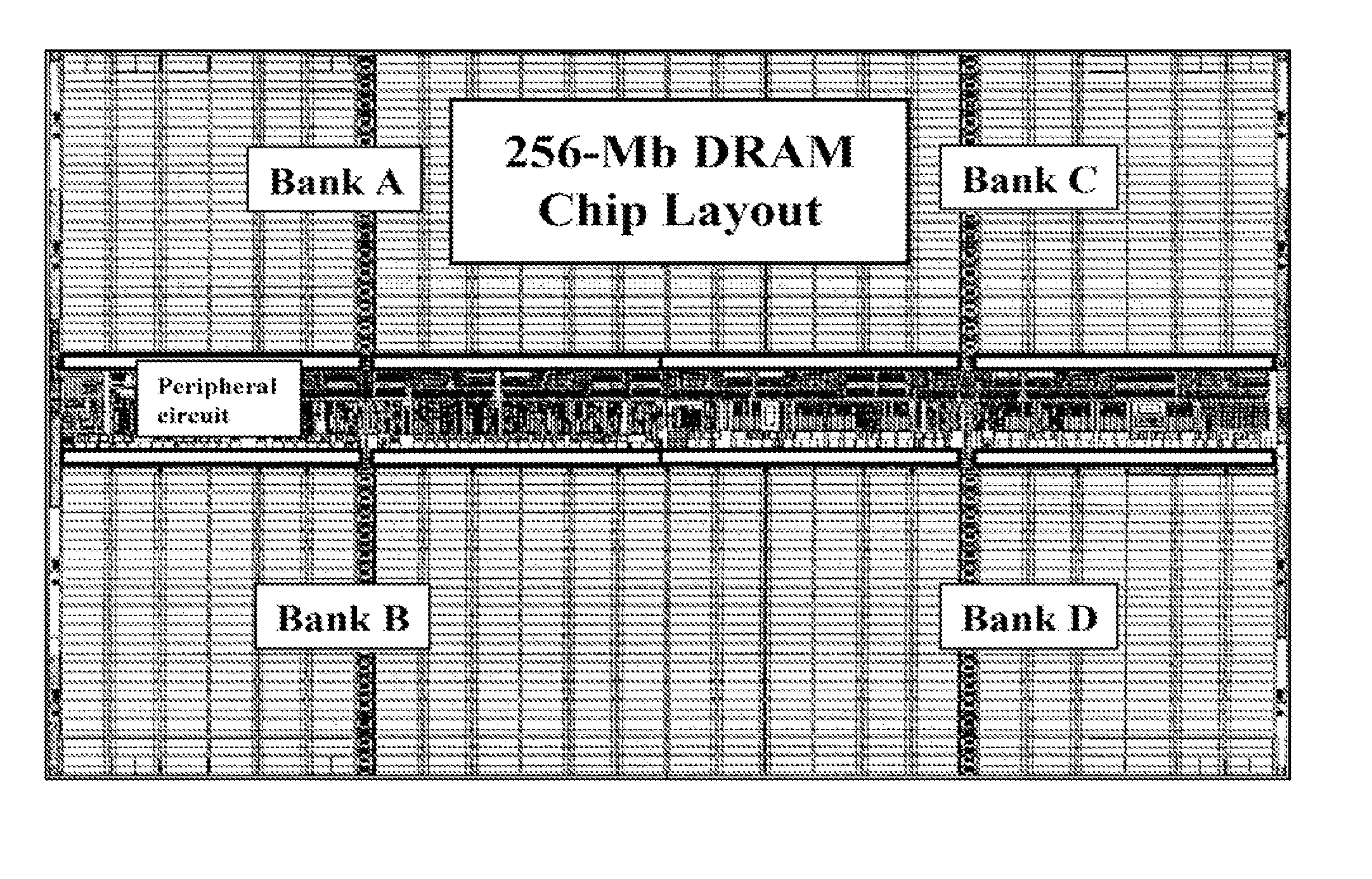

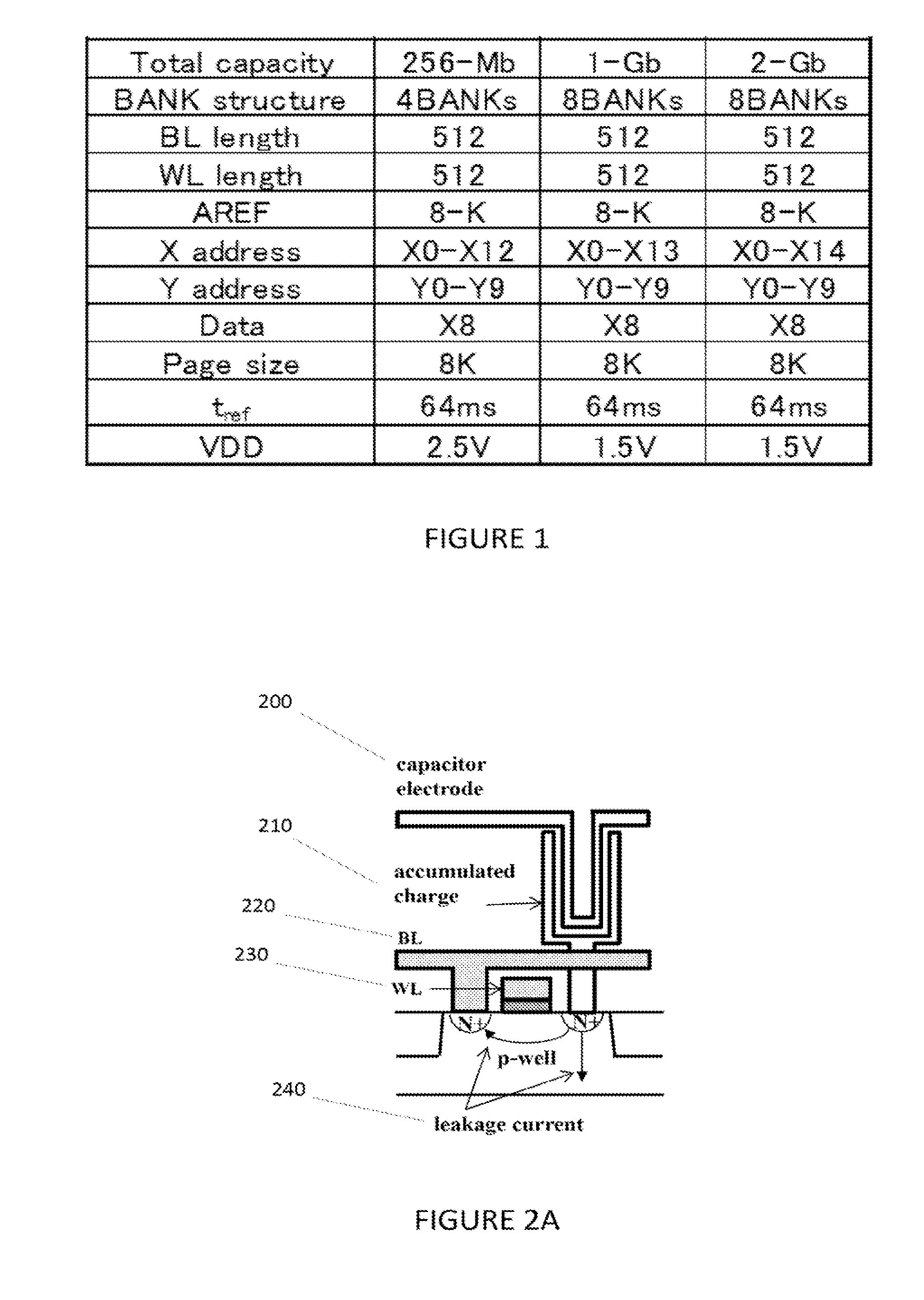

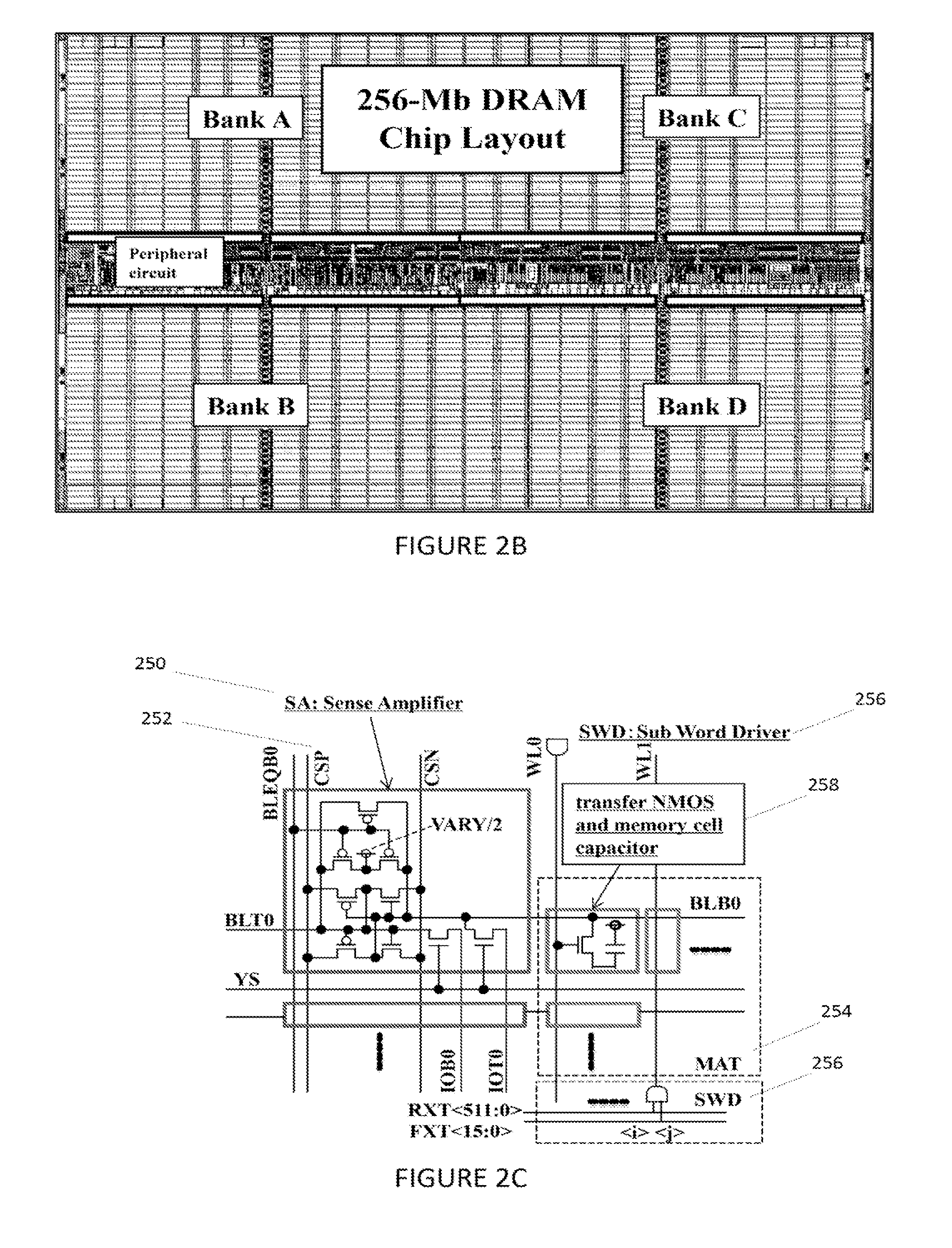

Partial access mode for dynamic random access memory

ActiveUS20150149717A1Efficient retentionReduce power consumptionDigital storageMemory systemsStatic random-access memoryRetention time

Some embodiments provide a method to reduce the refresh power consumption by effectively extending the memory cell retention time. Conversion from 1 cell / bit to 2N cells / bit reduces the variation in the retention time among memory cells. Although active power increases by a factor of 2N, the refresh time increases by more than 2N as a consequence of the fact that the majority decision does better than averaging for the tail distribution of retention time. The conversion can be realized very simply from the structure of the DRAM array circuit, and it reduces the frequency of disturbance and power consumption by two orders of magnitude. On the basis of this conversion method, some embodiments provide a partial access mode to reduce power consumption dynamically when the full memory capacity is not required.

Owner:MICRON TECH INC

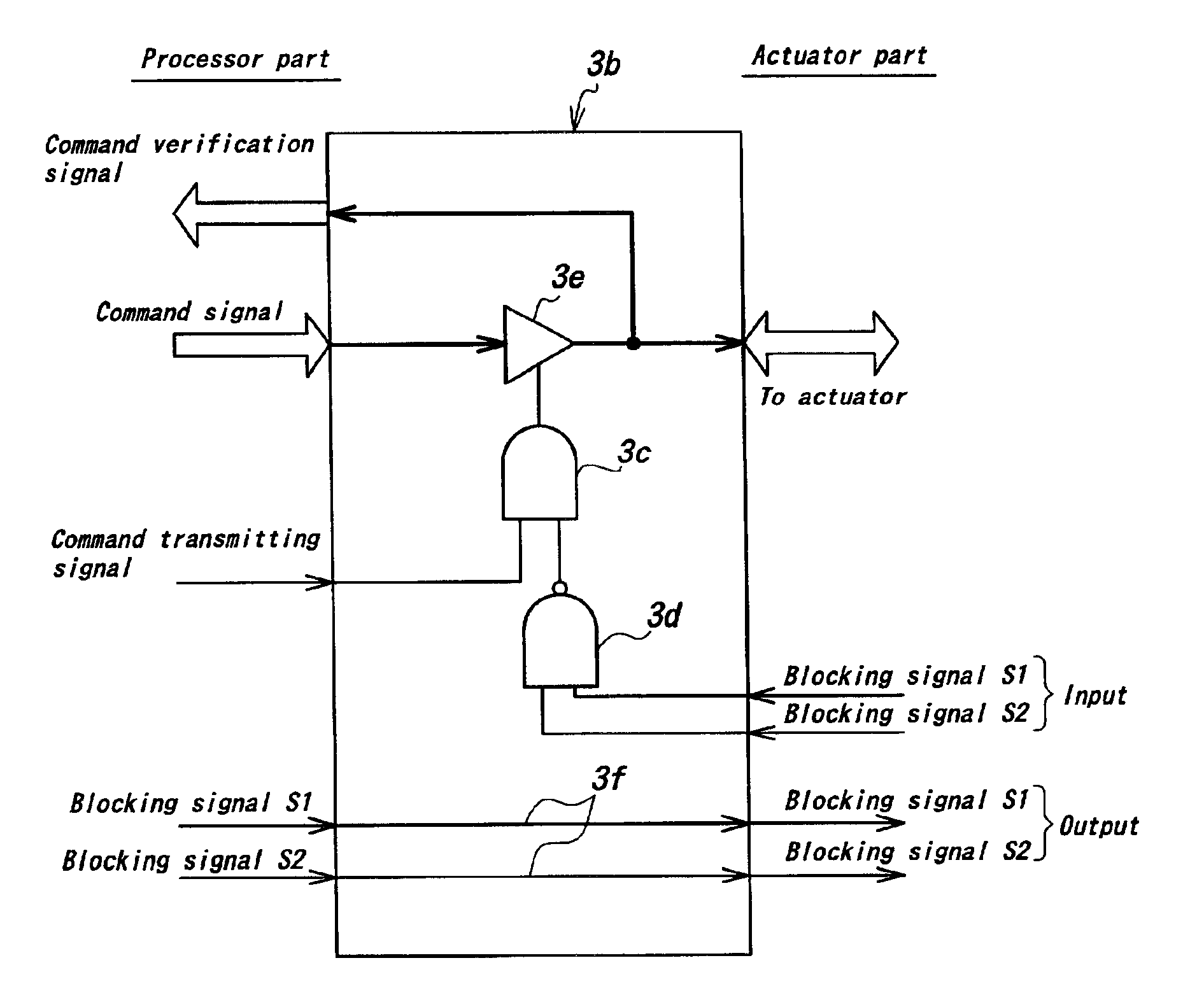

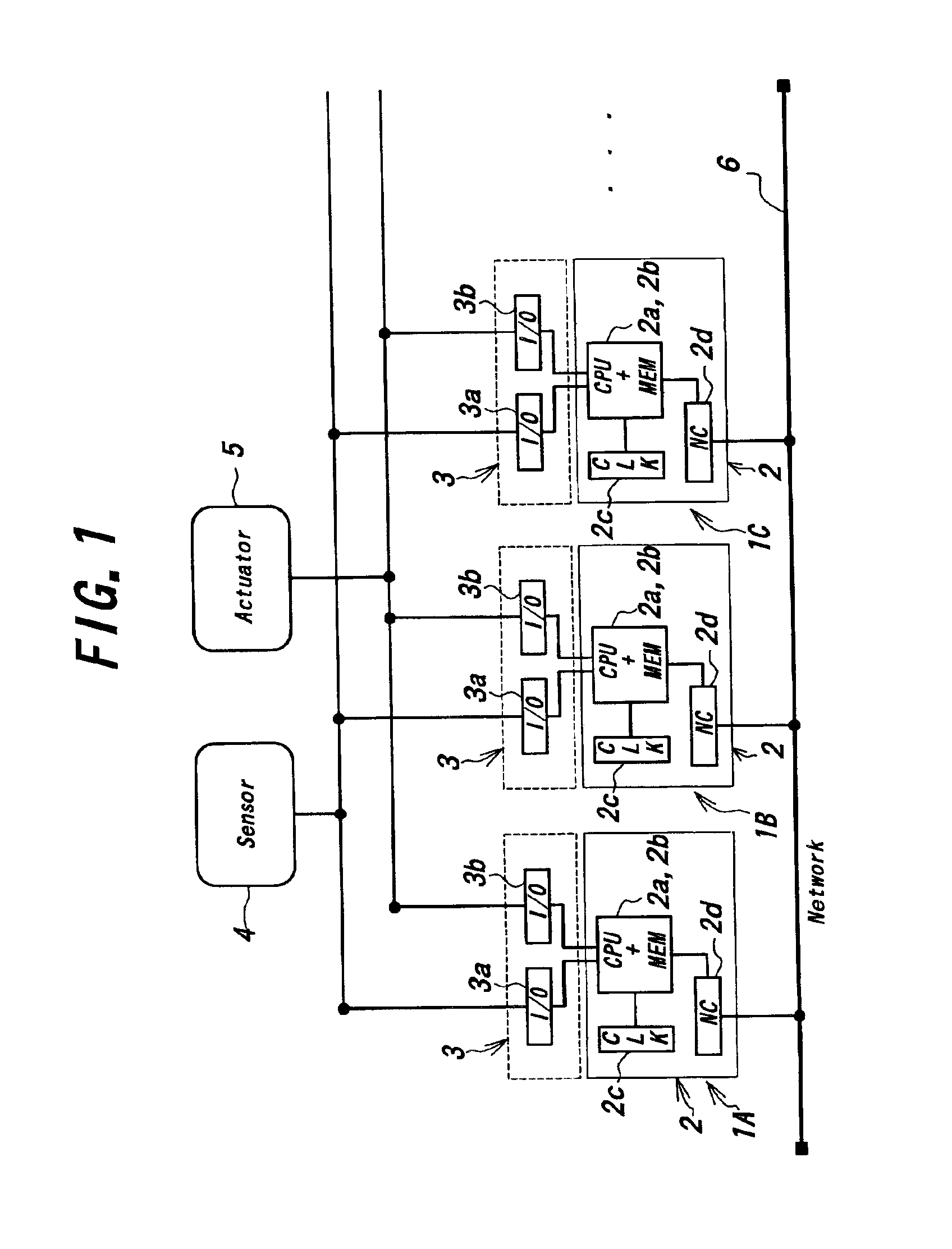

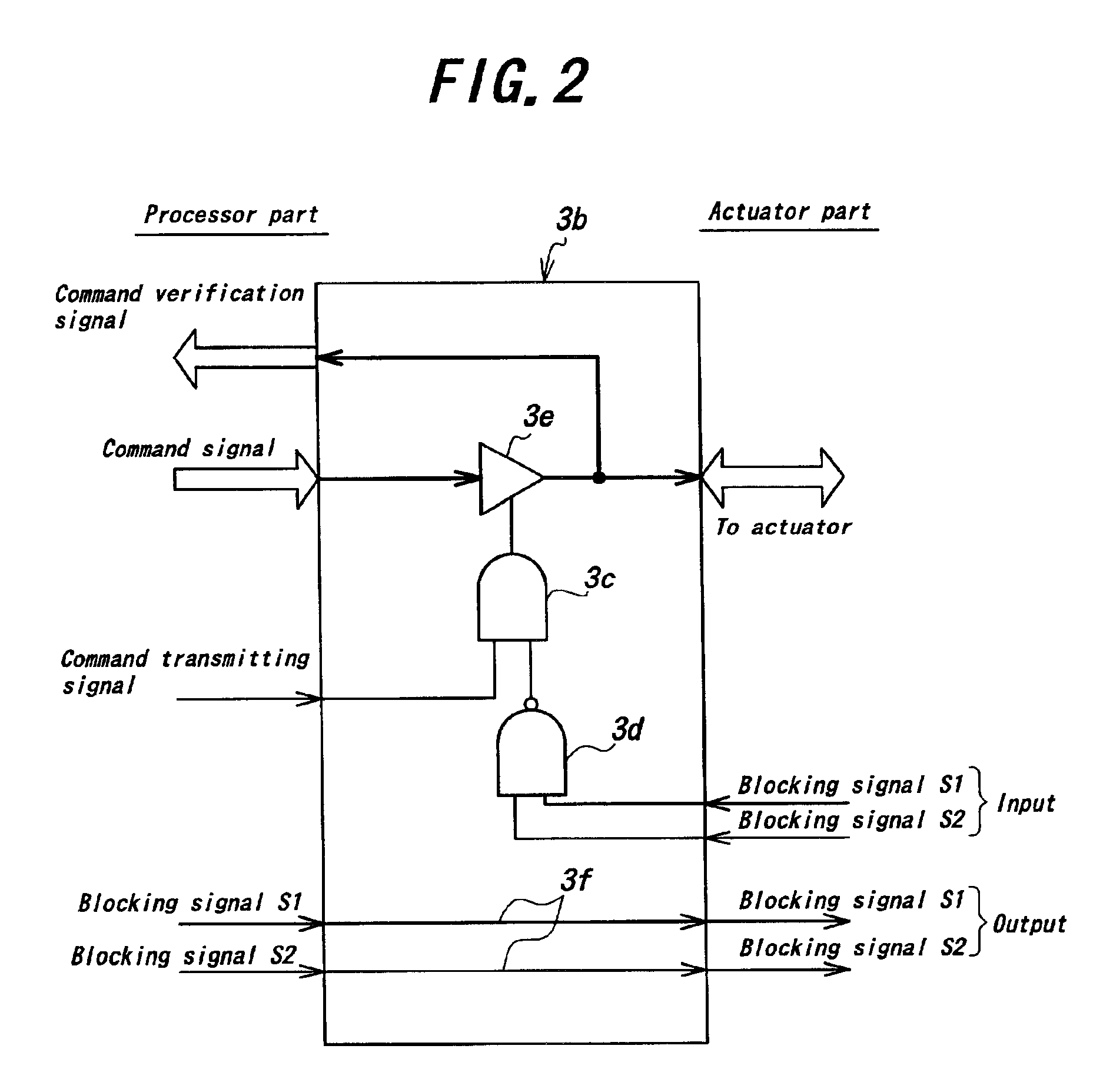

Redundant information processing system

InactiveUS6940811B2Solve the lack of reliabilityError preventionFrequency-division multiplex detailsInformation processingComputer hardware

A redundant information processing system with sufficient reliability is provided at a moderate cost without any part that could be a single fault point in the system. In the redundant information processing system in which an actuator 5 is controlled based on a signal from a sensor 4, each of processing devices 1A to 1C collects command signals from other processing devices and determines which command signal to be valid according to a logical decision, for example, a majority decision. When the command signals of more than two of the processing devices including the relevant processing device which determines are valid, the command signals are output according to priority while a control information blocking signal is output to a processing device other than those which are valid. When command signals of processing devices other than one which determines is valid, a processor part 2 does not output a command transmitting signal and does not either output the control information blocking signal to the other devices. When the number of control information blocking signals input from the other devices is less than two and the processor part outputs command transmitting signal, an interface part 3 outputs the command signal to the actuator 5. When the number of control information blocking signals input is two, the interface part 3 does not output the command transmitting signal even if the processor part outputs that command transmitting signal.

Owner:IHI AEROSPACE CO LTD +2

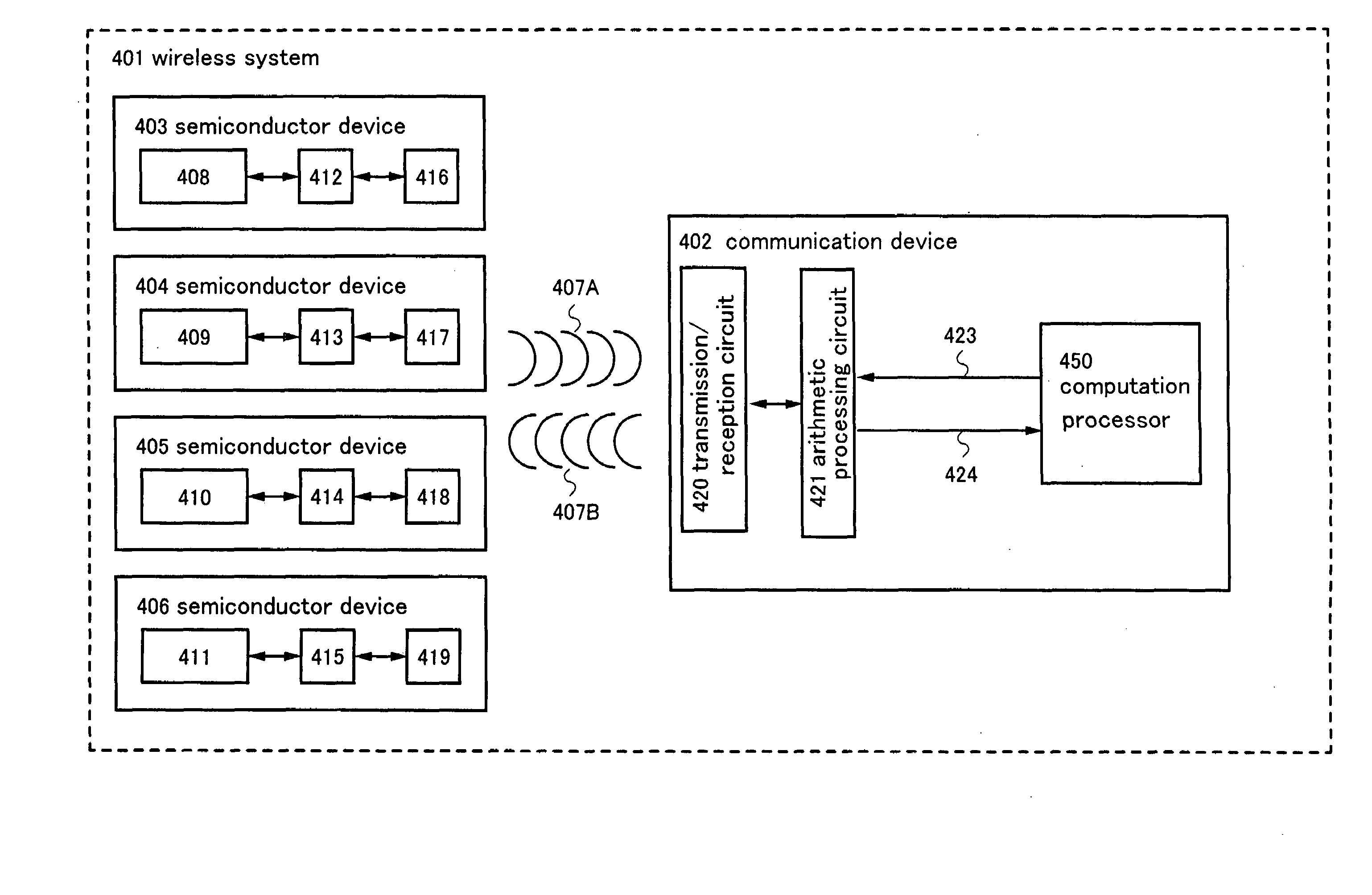

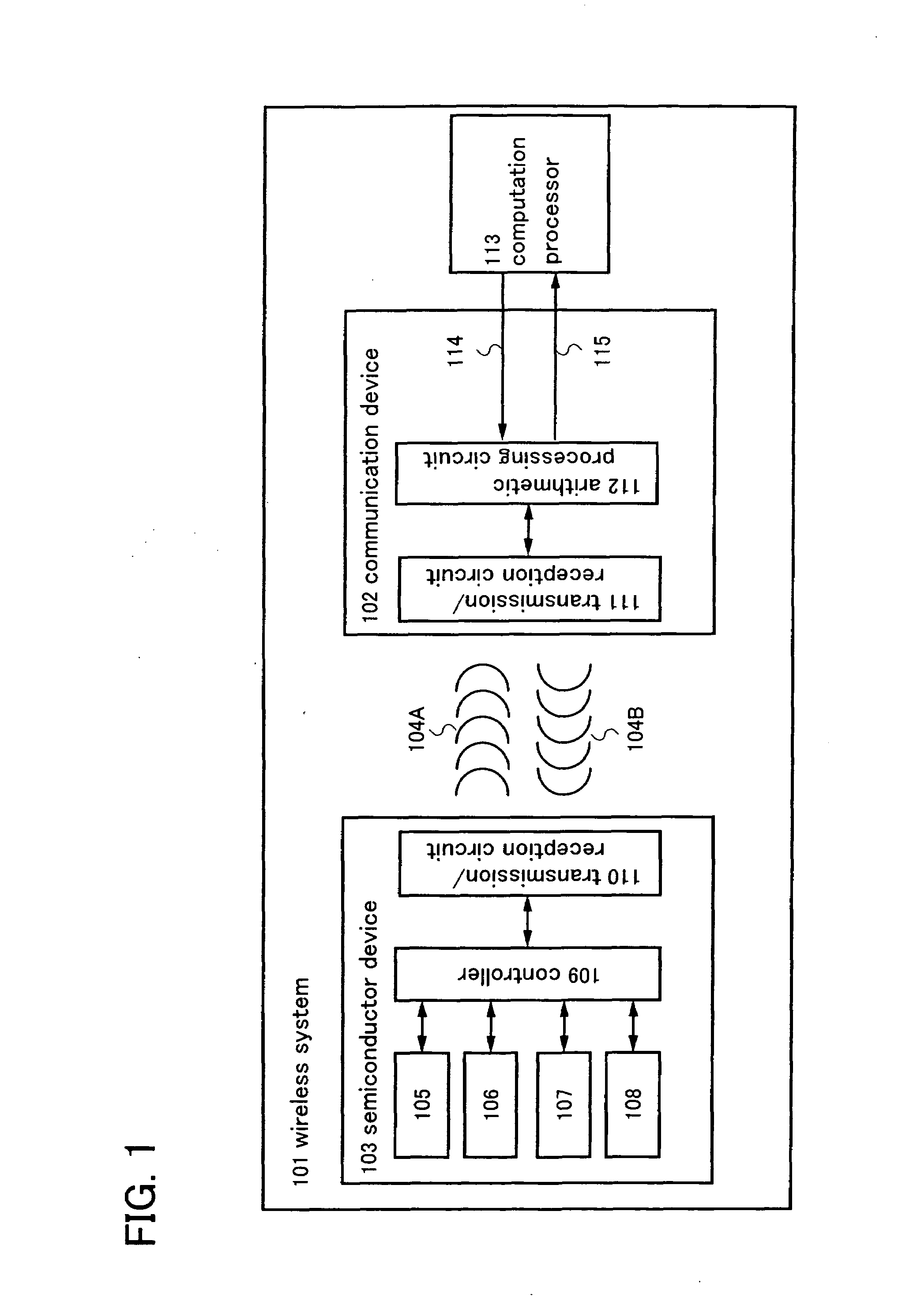

Wireless system, semiconductor device, and communication device

InactiveUS20080186182A1Improve reliabilityLow costError detection/correctionSubscribers indirect connectionHigh humidityEngineering

A semiconductor device is sometimes used in a bad environment like high temperature, low temperature, and high humidity, and is also used by being attached to a spot to which mechanical stress is added. Therefore, in order to improve reliability of a system using the semiconductor device, extremely high durability is required for the semiconductor device. However, since inexpensive price is also required for the semiconductor, a costly process cannot be used to improve durability. A wireless system includes a semiconductor device including a plurality of functional circuits each having the same function, and a communication device. The semiconductor device modulates and transmits a processing result of each functional circuit using subcarriers each having different frequencies. The communication device extracts a normal response by majority decision from a processing result of each functional circuit received. In this manner, a wireless system with high durability can be provided at low cost.

Owner:SEMICON ENERGY LAB CO LTD

Nonvolatile semiconductor memory device which can electrically rewrite data and system therefor

A nonvolatile semiconductor memory device includes a memory cell, latch circuits, and an arithmetic operation circuit. The memory cell stores data by a difference in threshold voltage. A read operation is performed twice or more on the memory cell under the same read conditions, and the latch circuits store a plurality of read data. The arithmetic operation circuit takes majority decision of the plurality of data stored in the latch circuits and decides data determined by the majority decision as data stored in the memory cell.

Owner:KK TOSHIBA

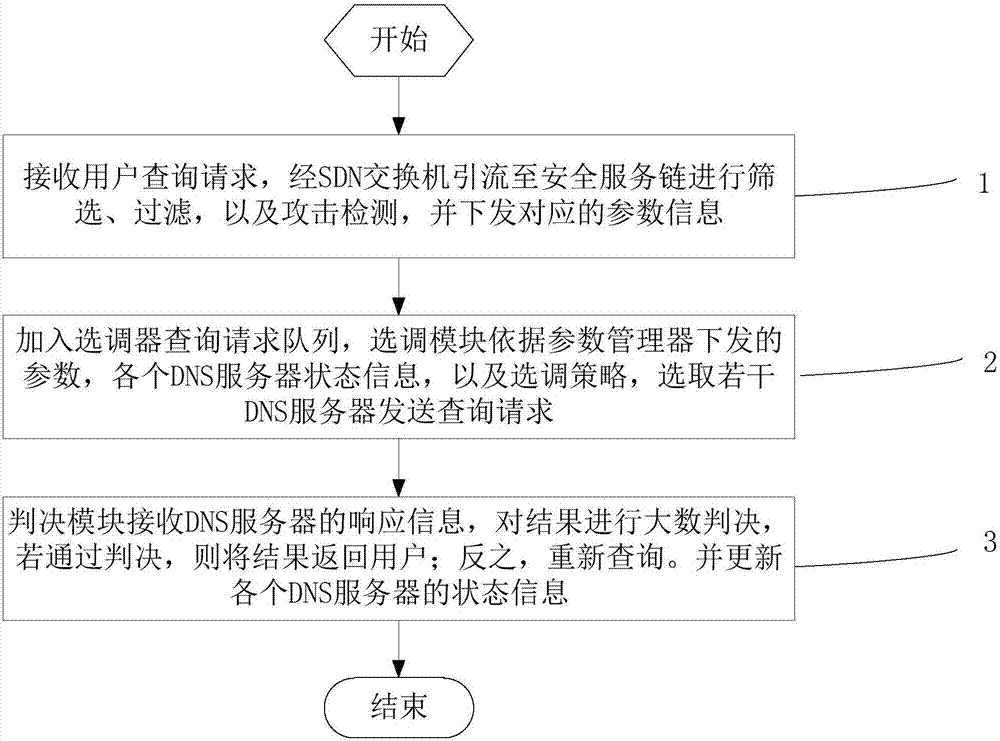

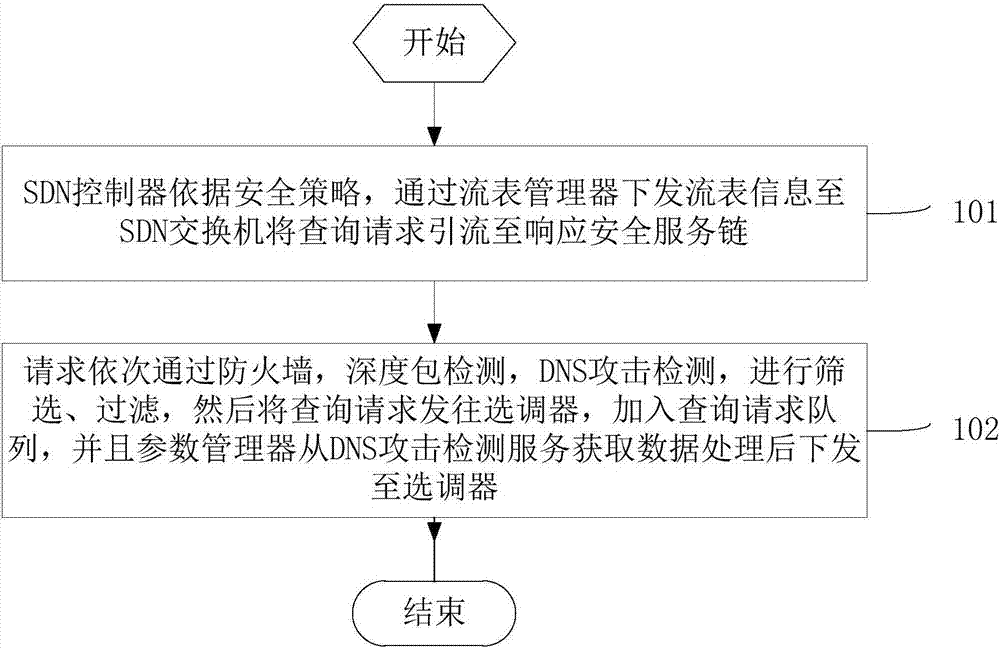

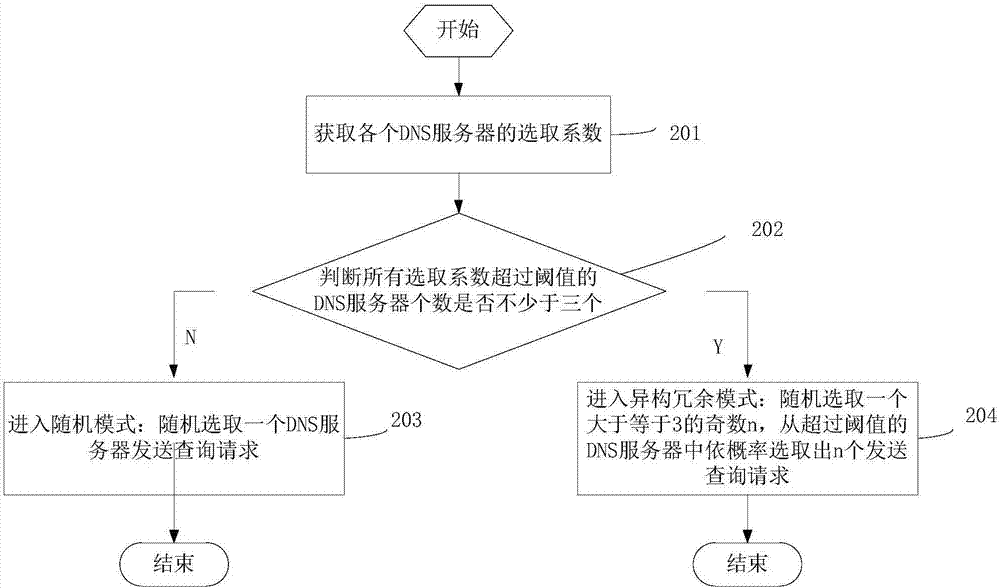

Mimic security method and device for recursive DNS server

ActiveCN106961422ASolve attacks such as cache poisoningGuaranteed reliabilityTransmissionComputer networkMajority decision

The invention discloses a mimic security method and a device for a recursive DNS server, overcoming the security threatening problem of the recursive DNS server. The method comprises the following steps: 1) receiving the inquiry requests of users; guiding the inquiry requests through a DNS switch to a security service chain where screening, filtering and attack detecting are performed to the requests; and obtaining the attack detecting data by a parameter manager followed by the delivering of corresponding parameter information to a transferring device; 2) for each inquiry request in the request queue of the transferring device, selecting by the transferring device a plurality of inquiry requests by the DNS server according to the parameter manager delivered parameters, the state information of various DNS servers and the transferring strategy; and 3) receiving the responding information of the DNS servers by a determining module; making the majority decision to the result; and updating the state information of the various servers in the DNS server pool. The method and the device of the invention solve the virus attacks to the cache of a recursive server without the modification of the DNS protocol or DNS inquiry responding procedure.

Owner:THE PLA INFORMATION ENG UNIV

Management apparatus, management system, operation status determination method, and image forming apparatus

Owner:RICOH KK

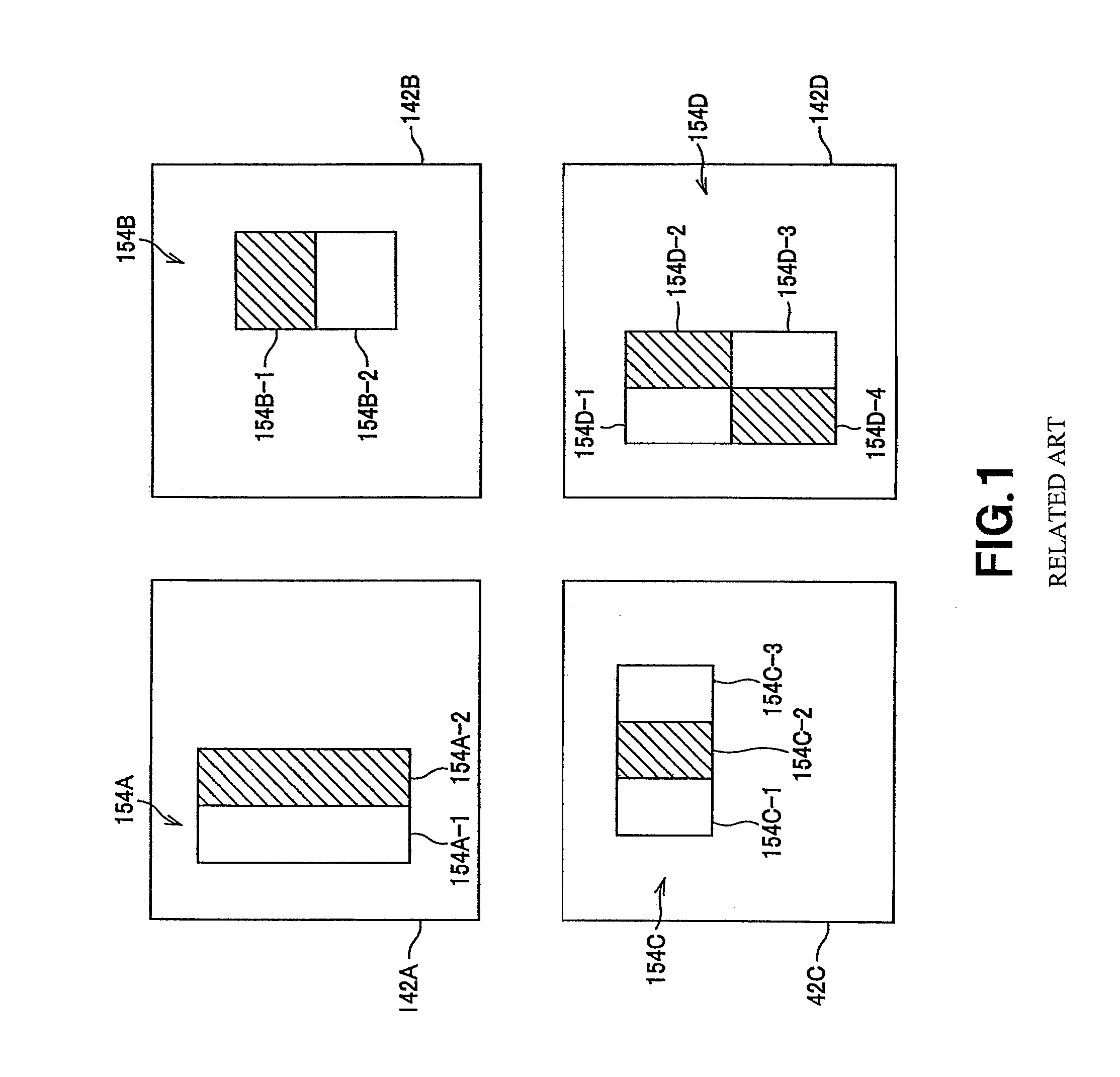

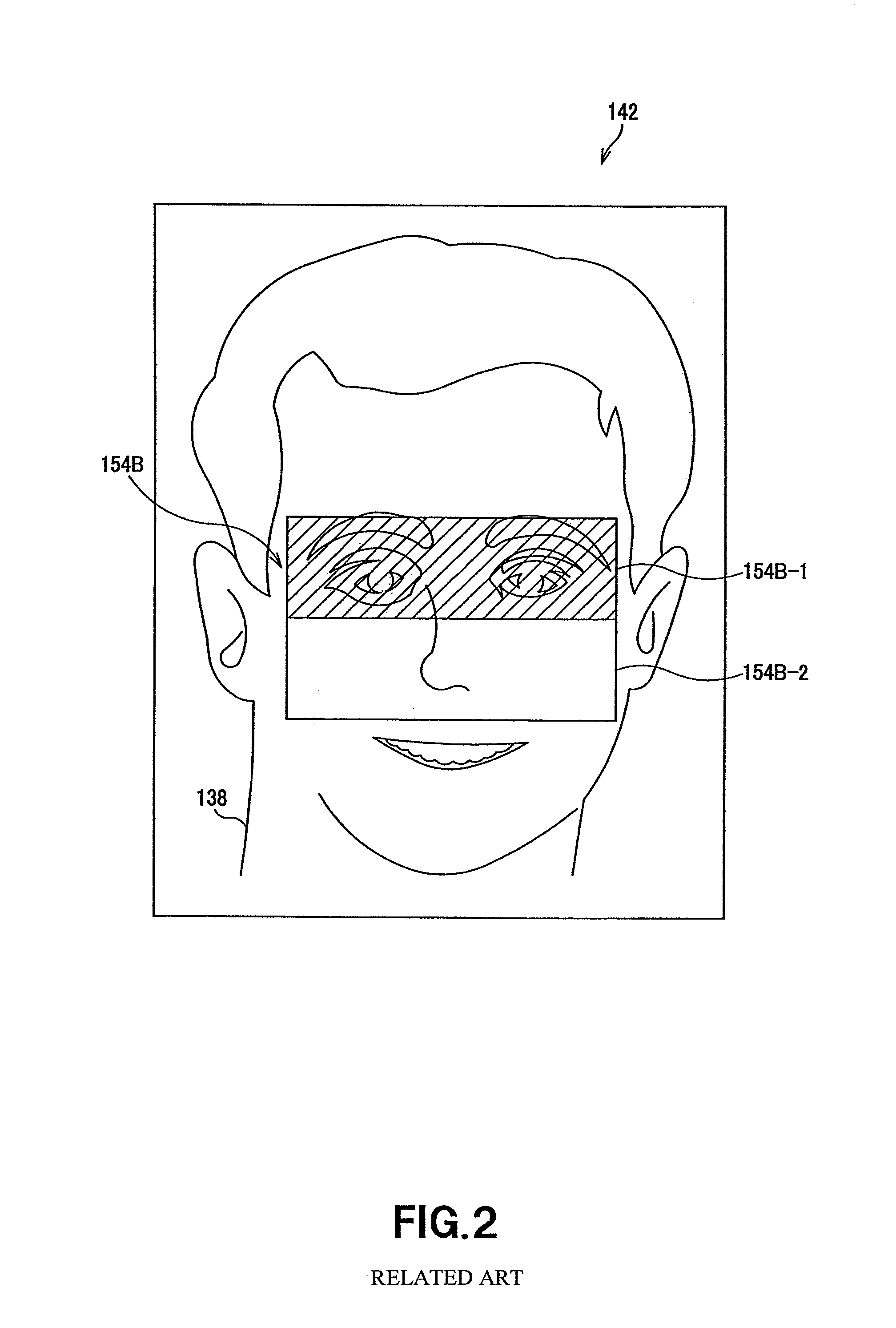

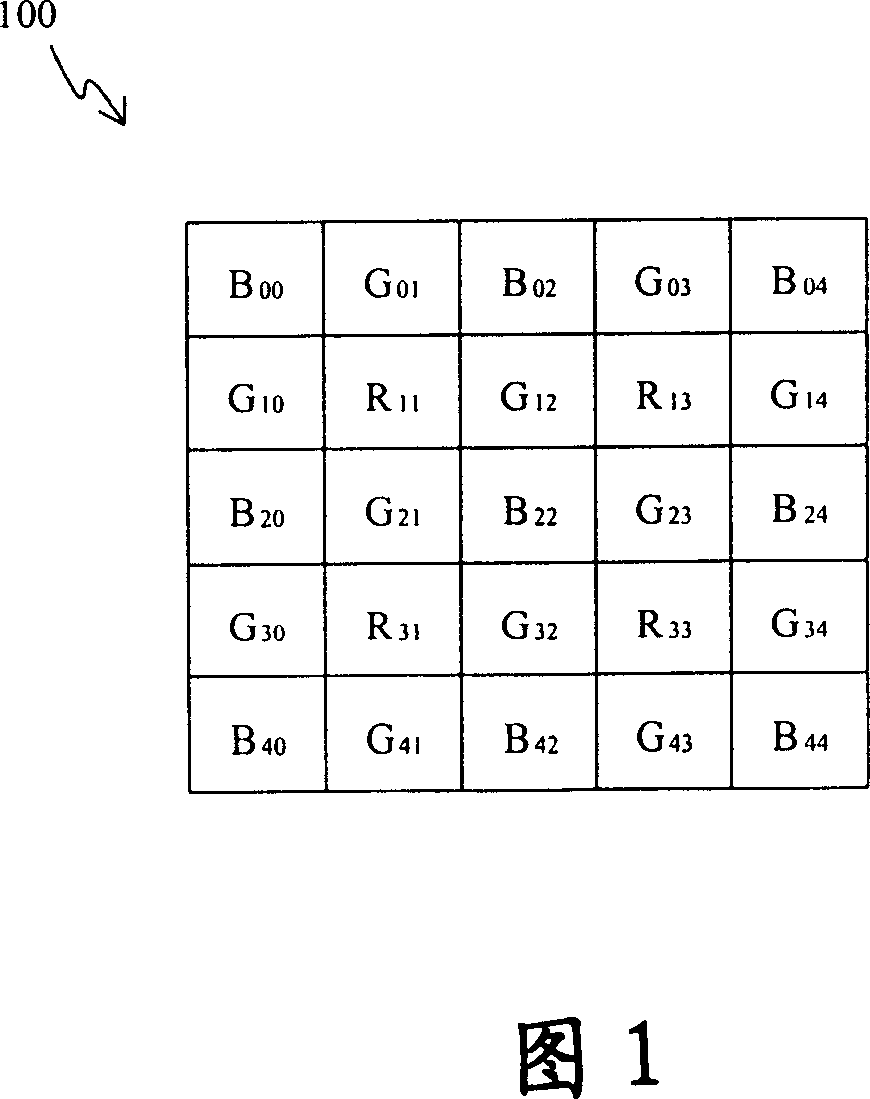

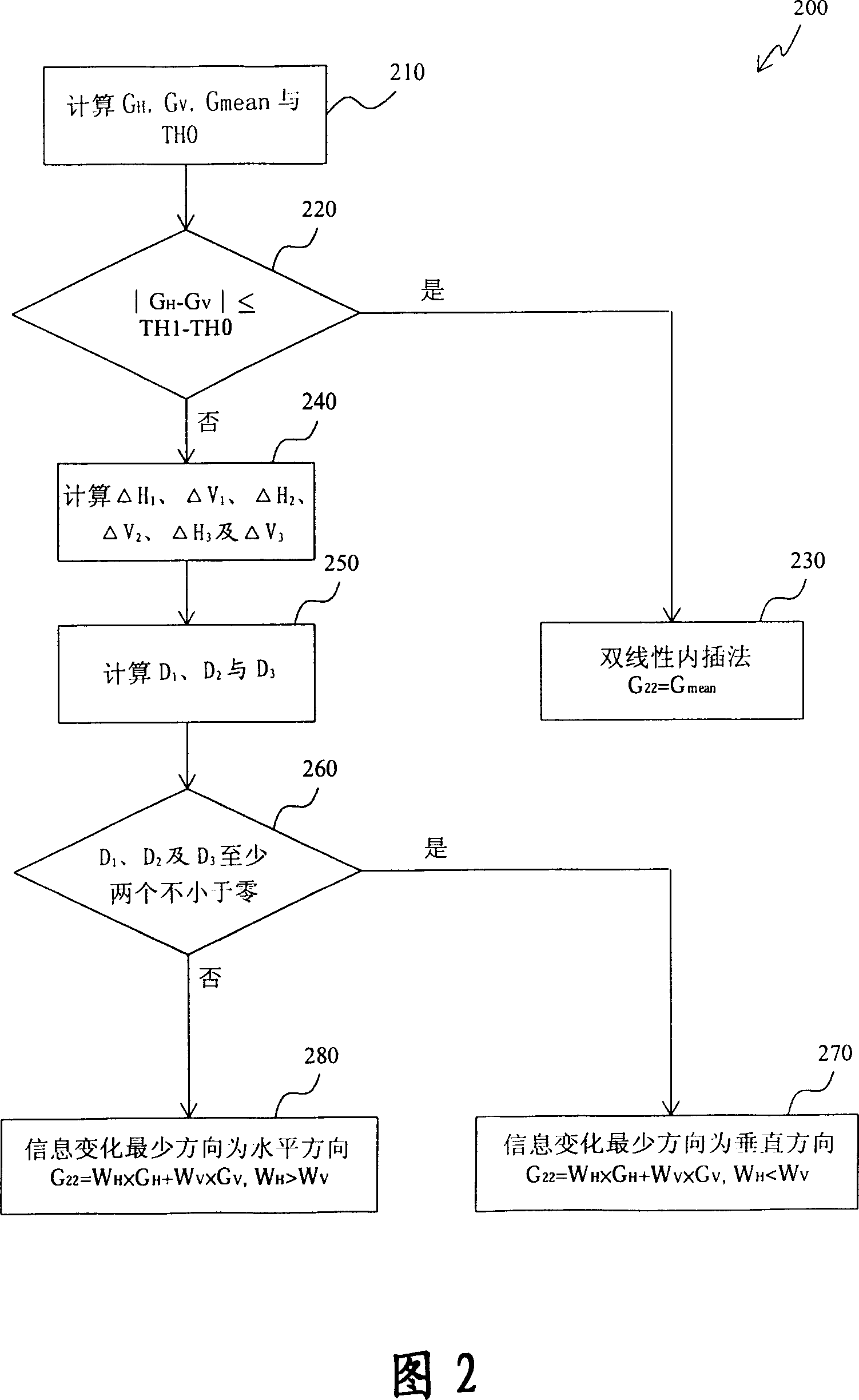

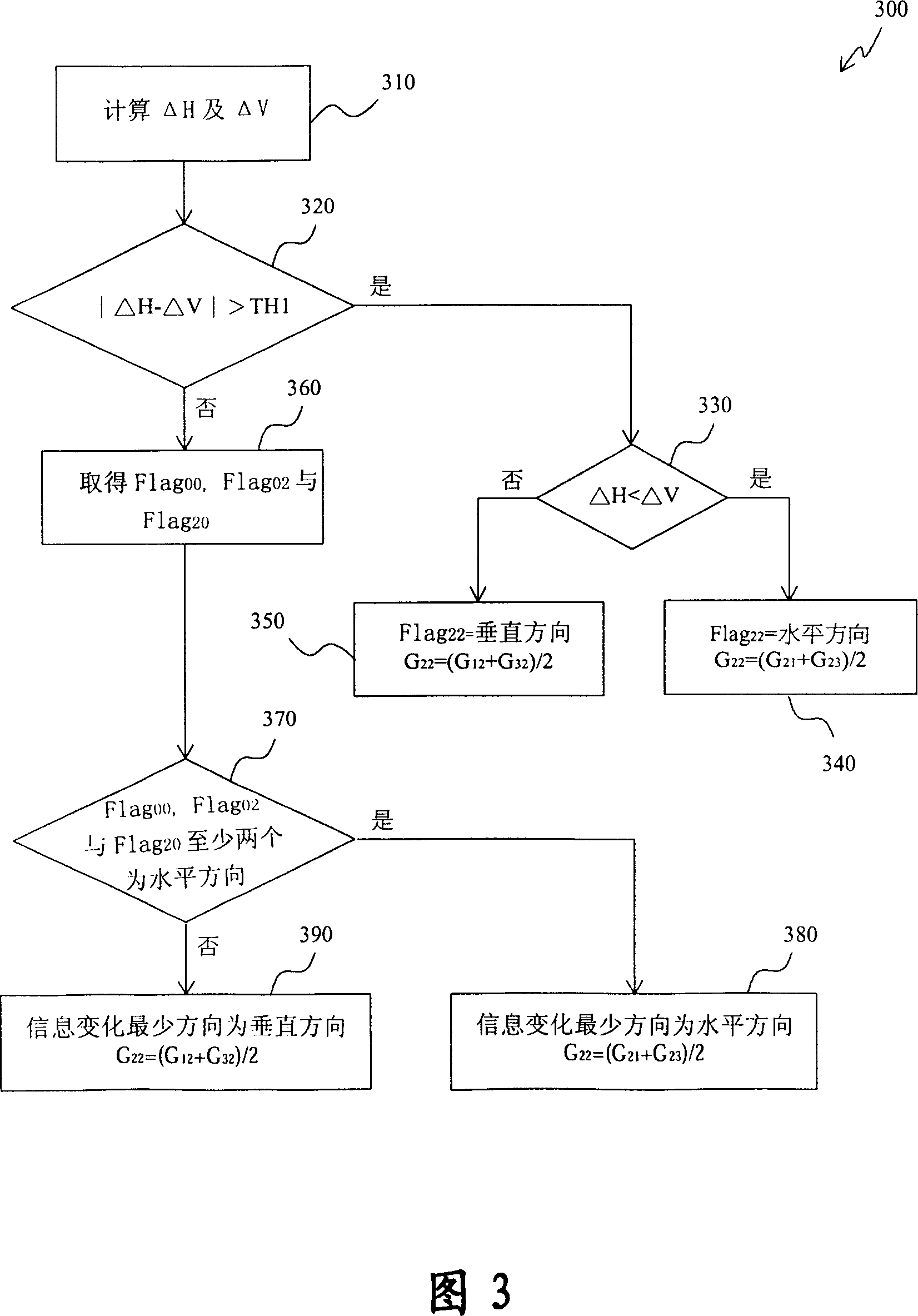

Method of deciding image local information change minimum direction using multiple decision

InactiveCN101001387AImprove accuracyColor signal processing circuitsPicture signal generatorsComputer visionVariation of information

Owner:ALTEK CORP

Storage device and data reading method thereof

InactiveUS20100095190A1Record information storageDigital signal error detection/correctionData storingData store

According to one embodiment, a data reading method of a storage device for reading data from a storage module, includes: reading data from the storage module; detecting an error in the data; reading, when the error is detected, the data several times; storing each data read several times in a buffer; calculating correlation between the data stored in the buffer; selecting data stored in the buffer with strong correlation so as to exclude data with low correlation from the selection; performing majority decision on the selected data or averaging the selected data; and outputting a result of the majority decision or the averaging as read data.

Owner:TOSHIBA STORAGE DEVICE CORP

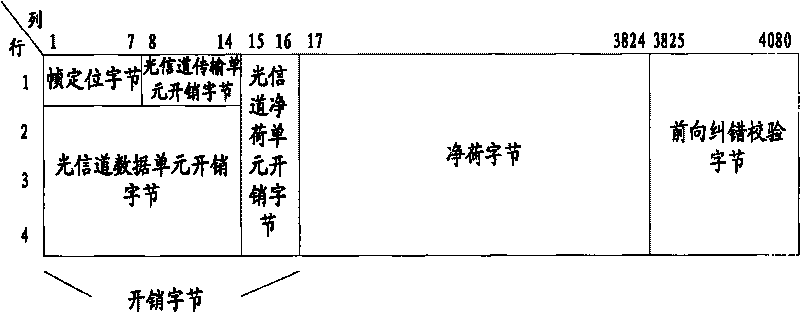

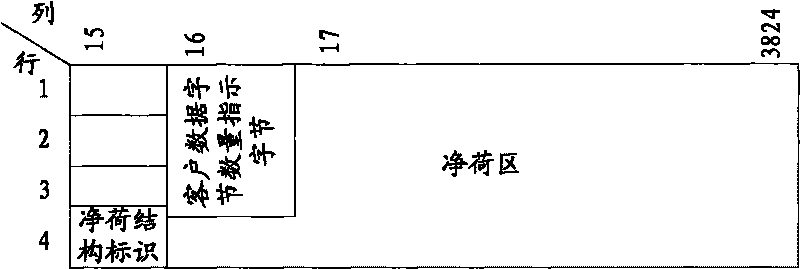

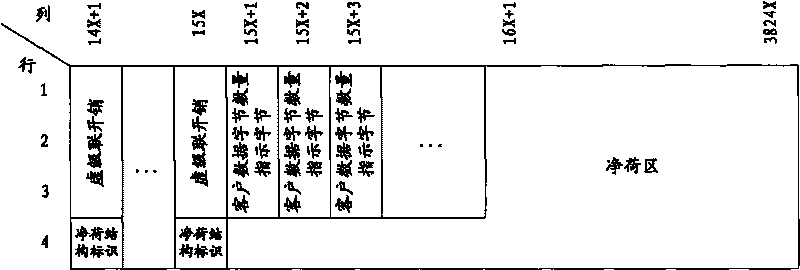

Method and device for sending and receiving mapping cost

ActiveCN101729188AReliable transmissionFlexible adjustmentMultiplex system selection arrangementsError preventionDependabilityData transmission

The invention discloses a method and device for sending and receiving mapping cost in adaptive constant bit rate service, belonging to the optical transport network field. The invention aims to solve the problem that the prior art can not provide the same adjustment ability for OPUk and OPUk-Xv and the adjustment speed is slow. The method and device for sending and receiving mapping cost transmit the change value of the number of a plurality of customer data bytes in OTN frame and a receiving terminal performs majority decision to obtain the correct number of customer data bytes, thus increasing the reliability of data transmission. The change value is transmitted in OTN frame to provide the same adjustment ability for OPUk and OPUk-Xv; and random adjustment of the quantitative value of the customer data bytes can be realized in a certain range.

Owner:HUAWEI TECH CO LTD

Light control circuit and a liquid-crystal-display control drive device

InactiveUS7808474B2Reduce chip sizeCathode-ray tube indicatorsInput/output processes for data processingLiquid-crystal displayComputational physics

A light control circuit that makes it possible to, when the light intensity of the area surrounding a display screen varies in a relatively short time, prevent the brightness of a backlight from being erroneously adjusted as the result of the variation being detected is provided. The light control circuit controls the backlight of a display panel. This light control circuit is provided with functions of performing the following operation: detection signals from multiple optical sensors are taken into a common sampling means in a time division manner to acquire multiple sampling values temporally dispersed; a surrounding light intensity is determined by majority decision based on the multiple sampling values, and the result of determination is externally outputted.

Owner:RENESAS ELECTRONICS CORP

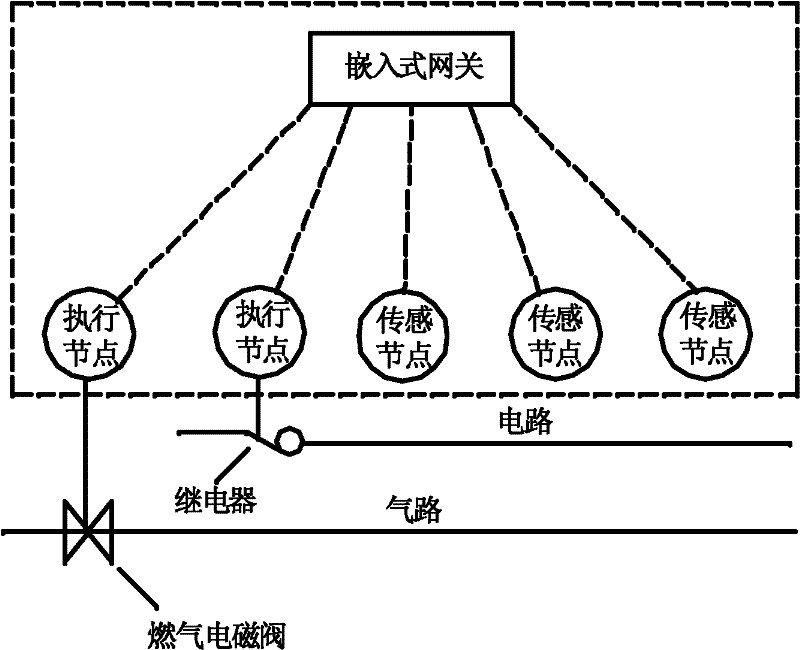

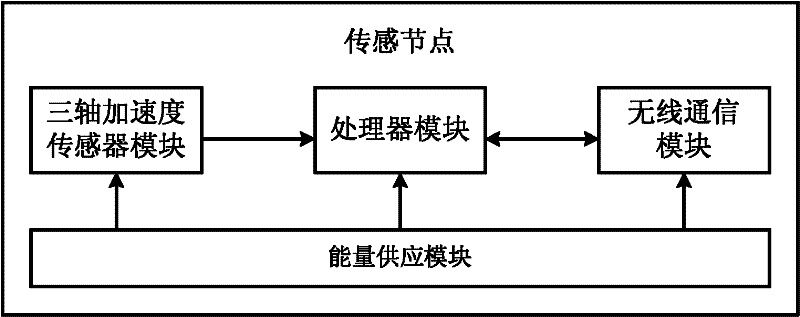

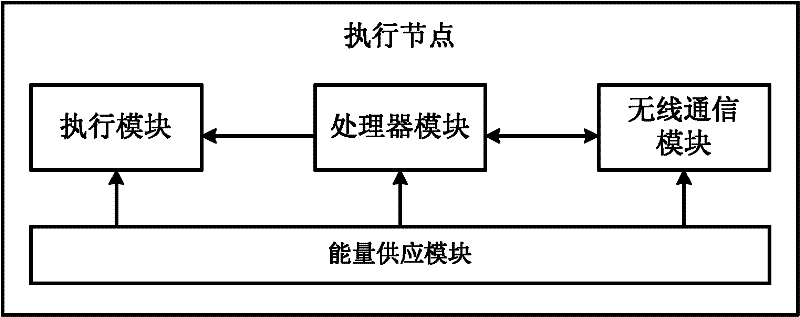

Earthquake emergency disaster prevention method and system based on Internet of things

The invention discloses an earthquake emergency disaster prevention method and system based on the Internet of Things. The method includes the following steps: S1, a sensing node uses a three-axis acceleration sensor to record seismic wave data and judges to obtain a judgment result; S2, an embedded gateway obtains the Judging the results and using the principle of minority obeying the majority to make earthquake emergency decision; S3, if the earthquake reaches a dangerous level, the embedded gateway sends emergency instructions to the execution node, and the execution node uses relays and gas solenoid valves to automatically cut off the circuit and gas circuit. In the present invention, the execution node uses the Internet of Things with self-organizing properties to automatically cut off the electric circuit and gas path in real time when the earthquake reaches a dangerous level, thereby effectively preventing the occurrence of secondary earthquake disasters, reducing the loss of earthquake disasters, and enabling residents to Life and property are protected from secondary disasters.

Owner:东北大学秦皇岛分校