Patents

Literature

207 results about "Non-return-to-zero" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

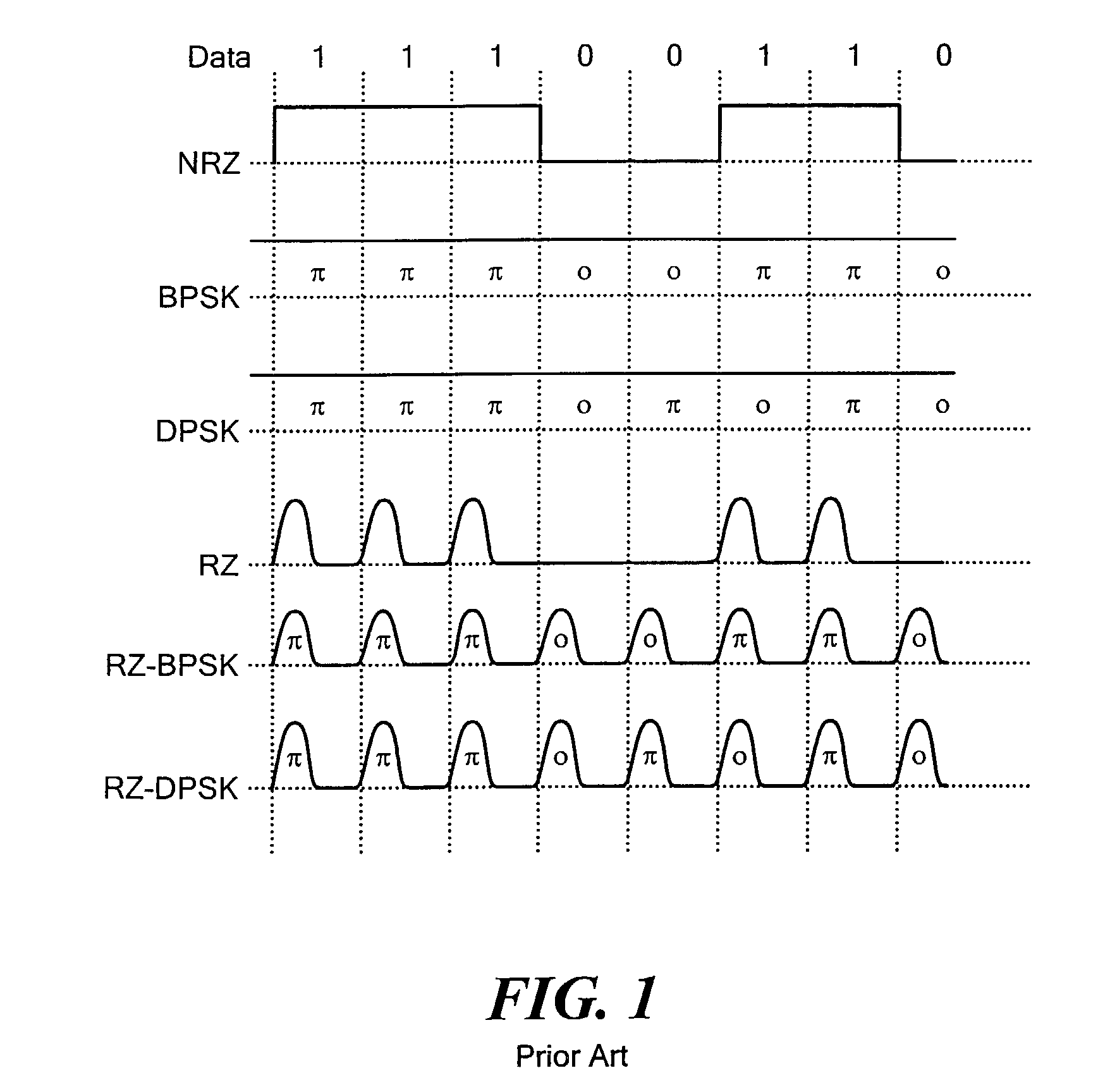

In telecommunication, a non-return-to-zero (NRZ) line code is a binary code in which ones are represented by one significant condition, usually a positive voltage, while zeros are represented by some other significant condition, usually a negative voltage, with no other neutral or rest condition. The pulses in NRZ have more energy than a return-to-zero (RZ) code, which also has an additional rest state beside the conditions for ones and zeros. NRZ is not inherently a self-clocking signal, so some additional synchronization technique must be used for avoiding bit slips; examples of such techniques are a run-length-limited constraint and a parallel synchronization signal.

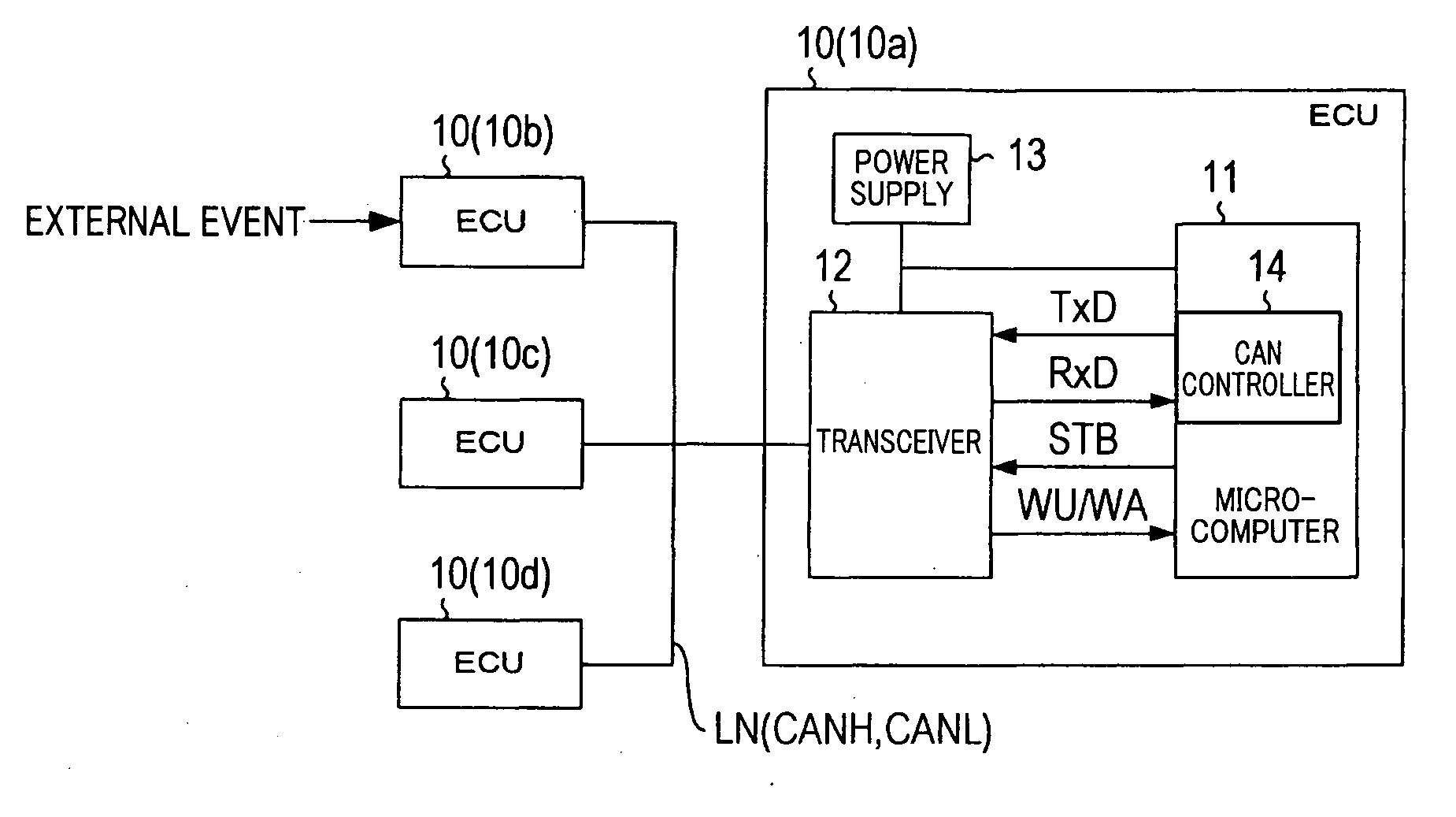

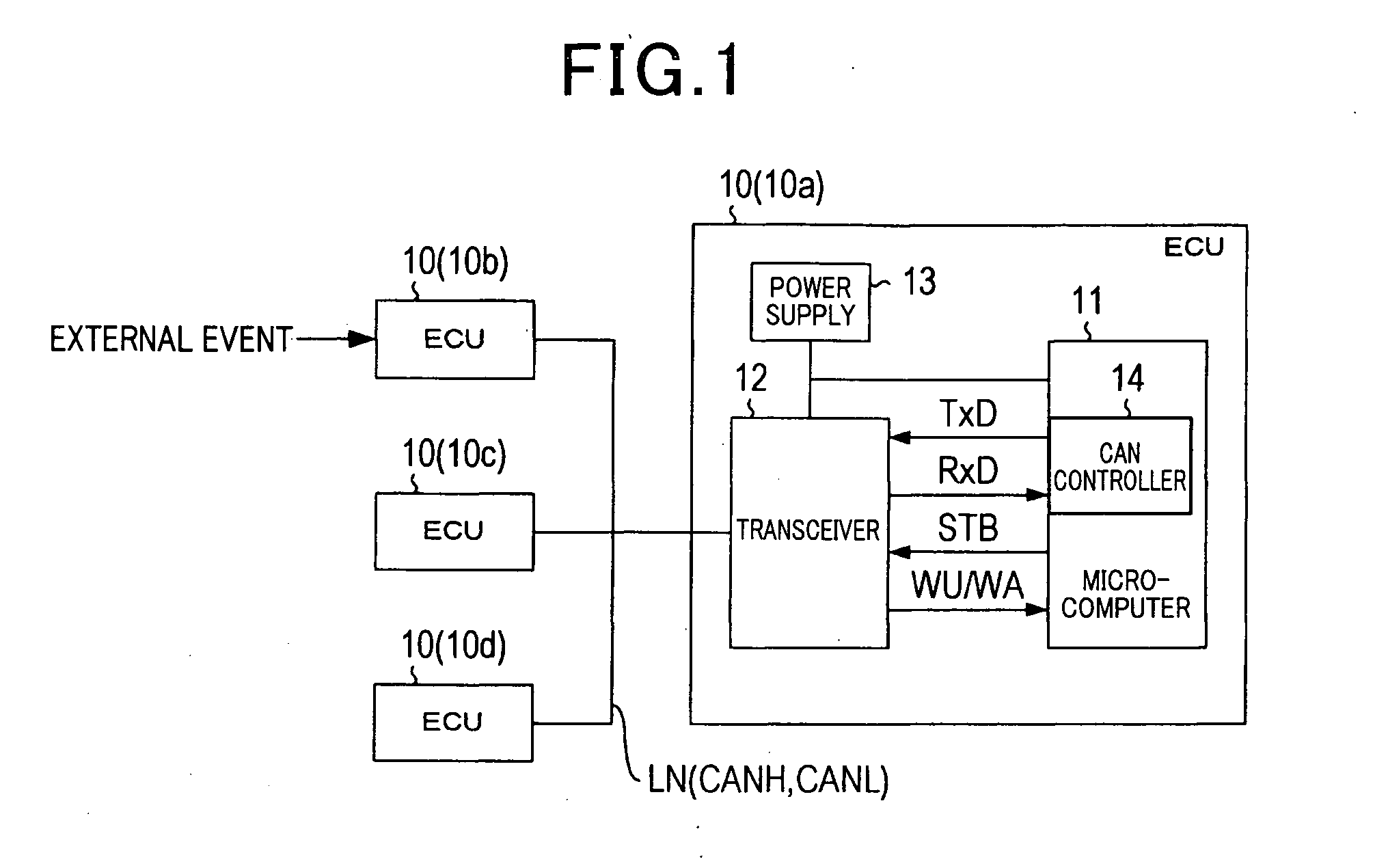

Communication system with a plurality of nodes communicably connected for communication based on NRZ (non return to zero) code

InactiveUS20120051241A1Increase power consumptionAverage power consumptionEnergy efficient ICTError preventionCommunications systemSignal on

In a communication system, plural nodes are communicably connected to a communication line and mutually communicate based on an NRZ (Non Return to Zero) code. Each node detects, as a data frame head, a dominant level when a signal on the line changes to a dominant level during a stand-by state of the line. An activation frame is transmitted during a sleep mode. The activation frame has an activation pattern area storing therein a bit pattern showing that the frame is the activation frame, a specific pattern area storing therein a bit pattern showing a node to be activated, a boundary position satisfying a predetermined boundary condition and being a boundary between the activation and specific pattern areas. Each node performs a switchover from the sleep mode to a normal mode based on the bit patterns in the activation and specific pattern areas and information given by the boundary position.

Owner:NIPPON SOKEN +1

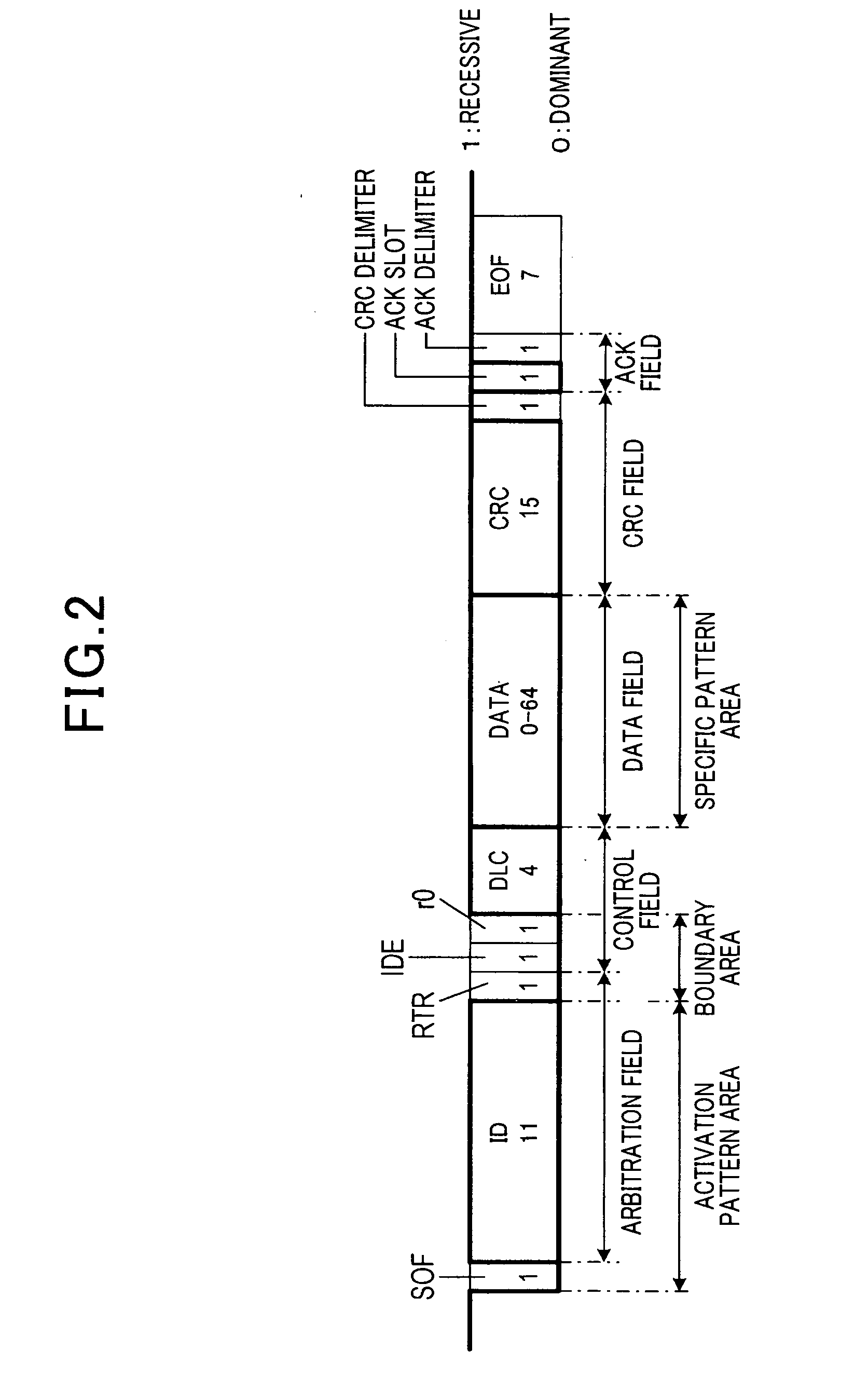

Method and apparatus for transmitting a signal using simultaneous FM and AM modulation

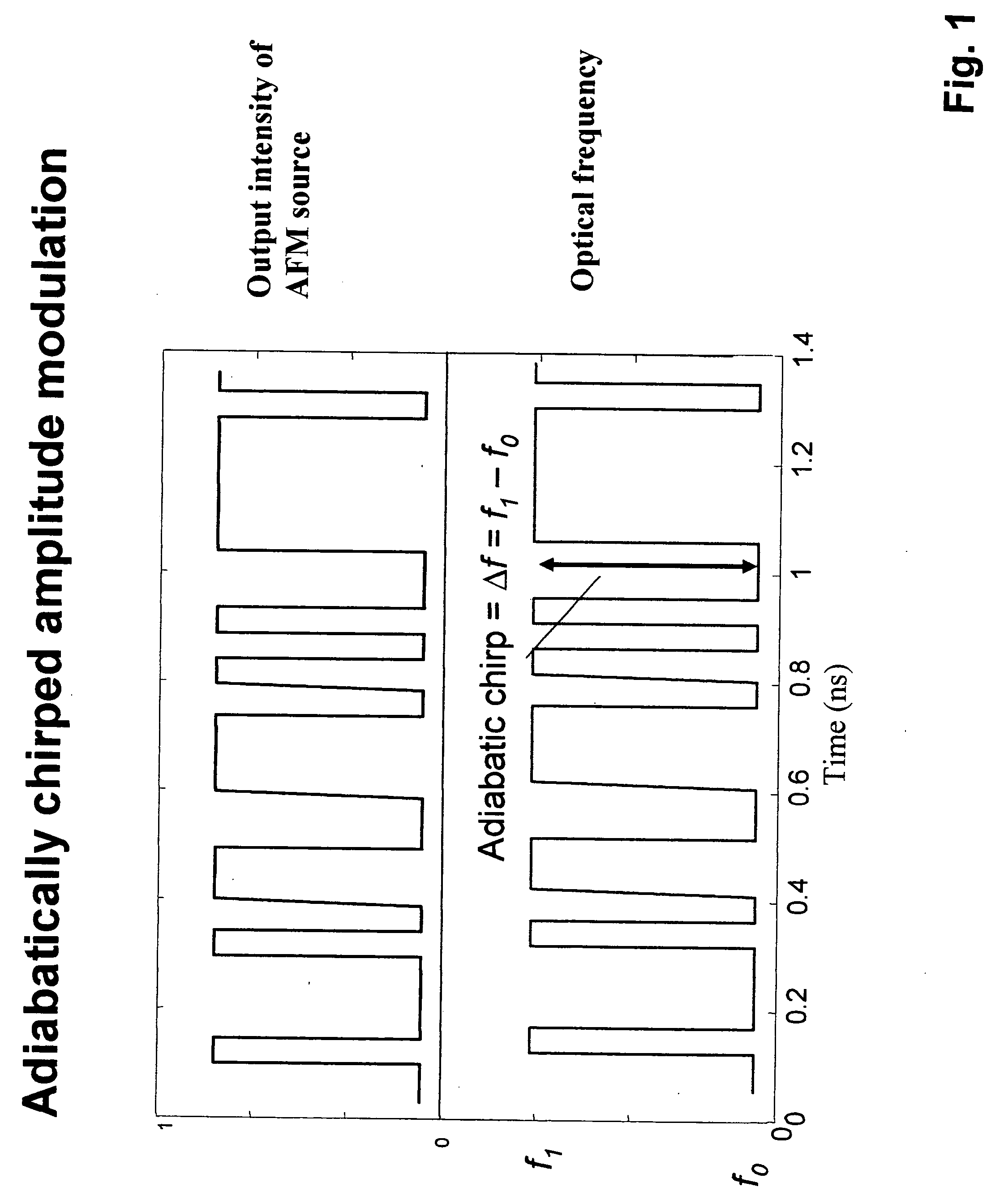

There is provided method for transmitting binary data contained in respective successive time cells, the data being in the form of an optical signal obtained by amplitude modulation and frequency modulation of an optical carrier wave, with a 0 bit data value having a 0 bit mean amplitude having a 0 bit amplitude time duration and a 0 bit frequency having a 0 bit frequency duration, and a 1 bit data value having a 1 bit mean amplitude having a 1 bit amplitude time duration and a 1 bit frequency having a 1 bit frequency duration; the improvement wherein: independently adjusting the 0 bit mean amplitude relative to the 1 bit mean amplitude; independently adjusting the 0 bit frequency relative to the 1 bit frequency; and independently adjusting time duration of the frequency profile of the 1 bit relative to the time duration of the amplitude profile of the 1 bit, whereby to extend the error-free propagation of the optical signal though a dispersive optical fiber beyond the dispersion limit. There is provided a method for transmitting Non-Return-To-Zero (NRZ) binary data contained in respective successive time cells, the data being in the form of an optical signal obtained by amplitude modulation and frequency modulation of an optical carrier wave, with a 0 bit data value having a 0 bit mean amplitude having a 0 bit amplitude time duration and a 0 bit frequency having a 0 bit frequency duration, and a 1 bit data value having a 1 bit mean amplitude having a 1 bit amplitude time duration and a 1 bit frequency having a 1 bit frequency duration; the improvement wherein: the phase across each 1 bit data value is substantially constant, and the phase of the carrier changes across each and every 0 bit by an amount equal to the product of the frequency difference between the 1 bit and the 0 bit and the duration of the 0 bit; whereby to extend the error-free propagation of the optical signal though a dispersive optical fiber beyond the dispersion limit. In accordance with one form of the present invention, there is provided a method for transmitting binary data contained in respective successive time cells, the data being in the form of an optical signal obtained by amplitude modulation and frequency modulation of an optical carrier wave, with a 0 bit data value having a 0 bit mean amplitude having a 0 bit amplitude time duration and a 0 bit frequency having a 0 bit frequency duration, and a 1 bit data value having a 1 bit mean amplitude having a 1 bit amplitude time duration and a 1 bit frequency having a 1 bit frequency duration; the improvement wherein: the amplitude profile of the 1 bit is substantially bell-shaped, and the frequency profile of the 1 bit is substantially square-shaped, with steeper rise and fall time and a wider flat top region; whereby to extend the error-free propagation of the optical signal though a dispersive optical fiber beyond the dispersion limit.

Owner:AZNA +1

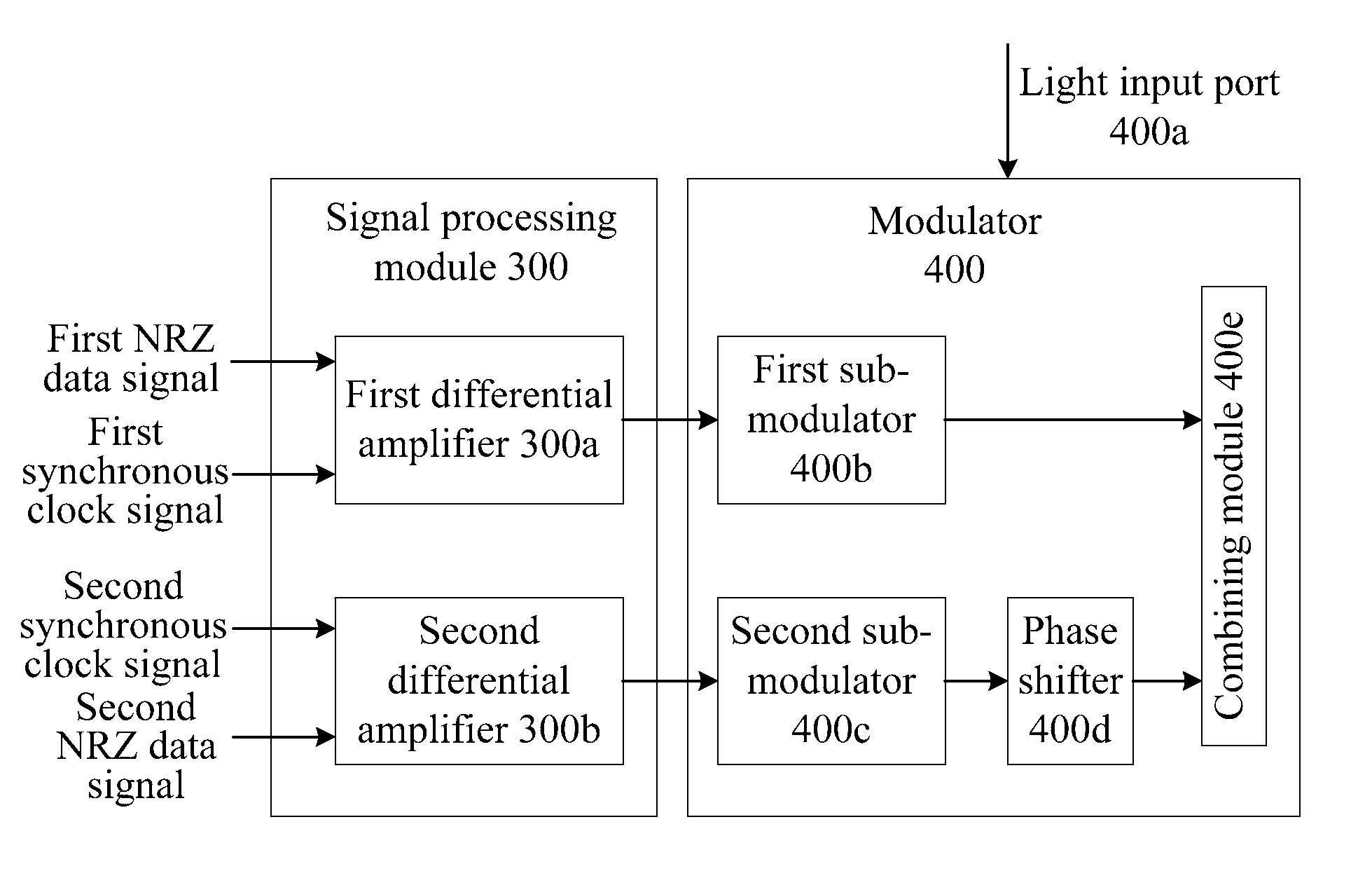

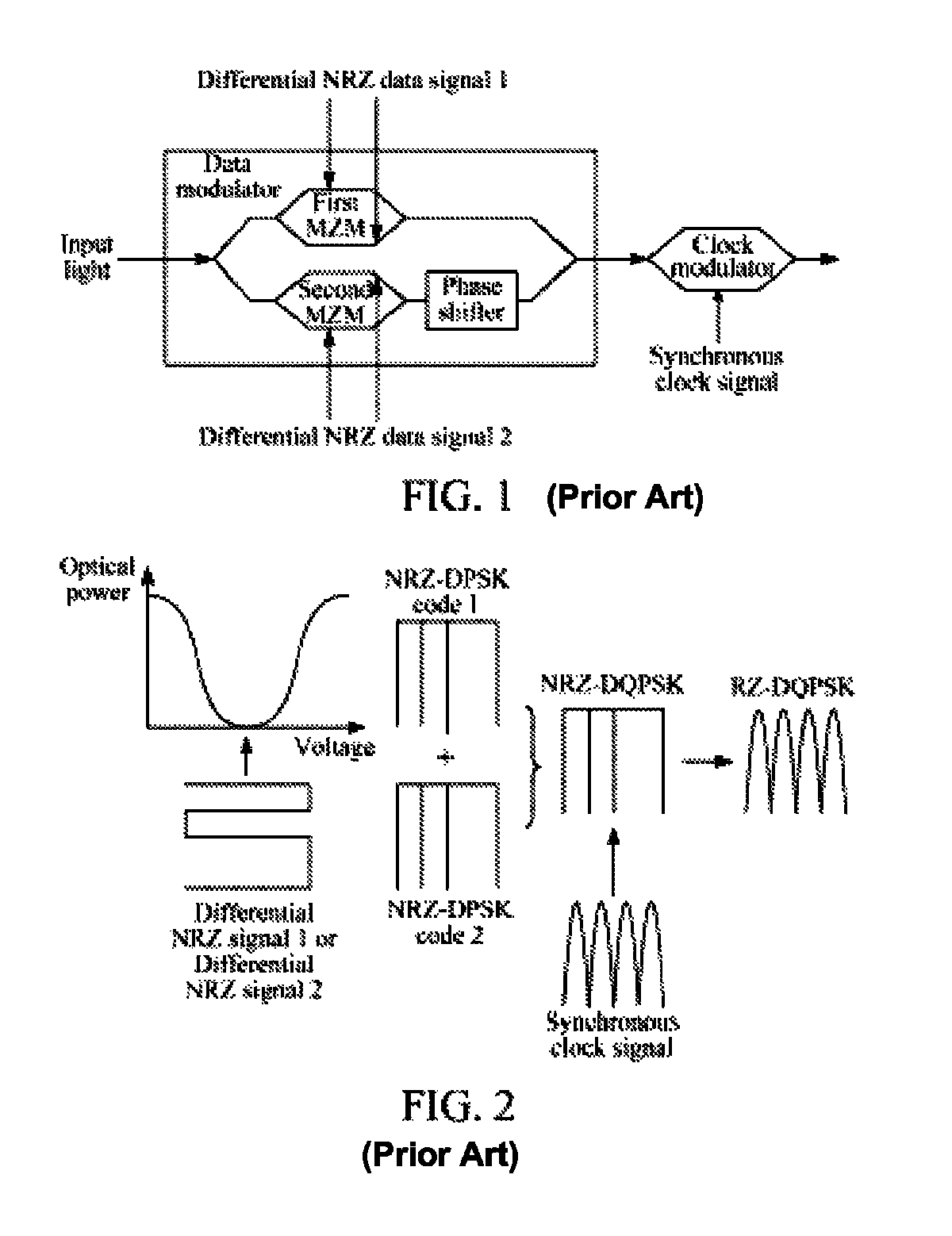

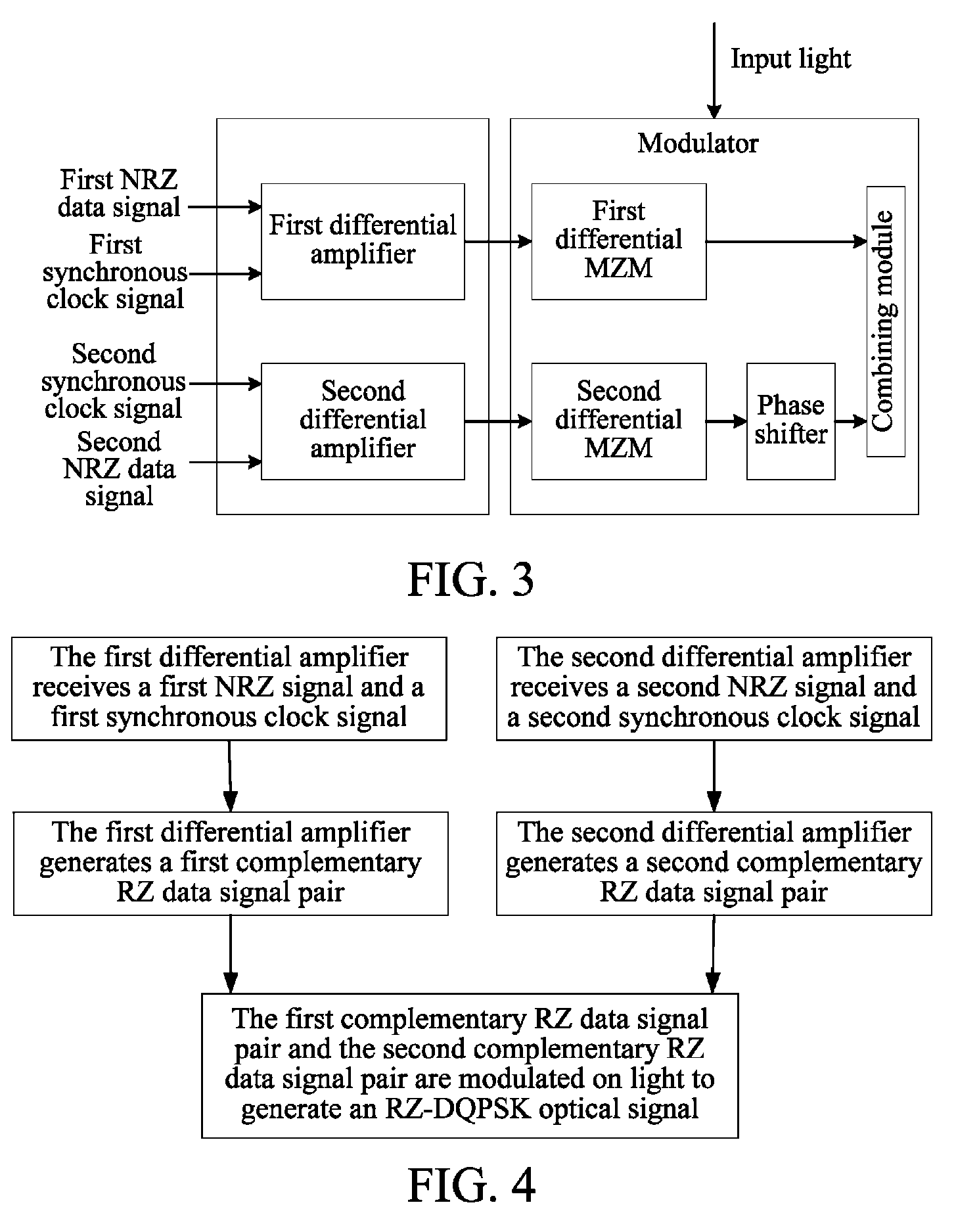

Method and device for generating optical signals

ActiveUS8831440B2Simple structureLow costElectromagnetic transmittersOptical NRZ to RZ conversionReturn-to-zeroSoftware engineering

The method includes: receiving a first Non Return to Zero (NRZ) data signal and a synchronous clock signal, and performing Return to Zero (RZ) processing to generate a first complementary RZ data signal pair; receiving a second NRZ data signal and a synchronous clock signal, and performing RZ processing to generate a second complementary RZ data signal pair; and modulating the first complementary RZ data signal pair and the second complementary RZ data signal pair on light to generate an RZ-Differential Quadrature Phase Shift Keying (RZ-DQPSK) optical signal. Through the method and device, RZ processing are performed on the NRZ data signals to generate the complementary RZ data signal pairs, and the complementary RZ data signal pairs are modulated on the light, thereby reducing the cost and the insertion loss of the entire device, lowering the requirements for input optical power and reducing the complexity of loop circuit control.

Owner:HUAWEI TECH CO LTD

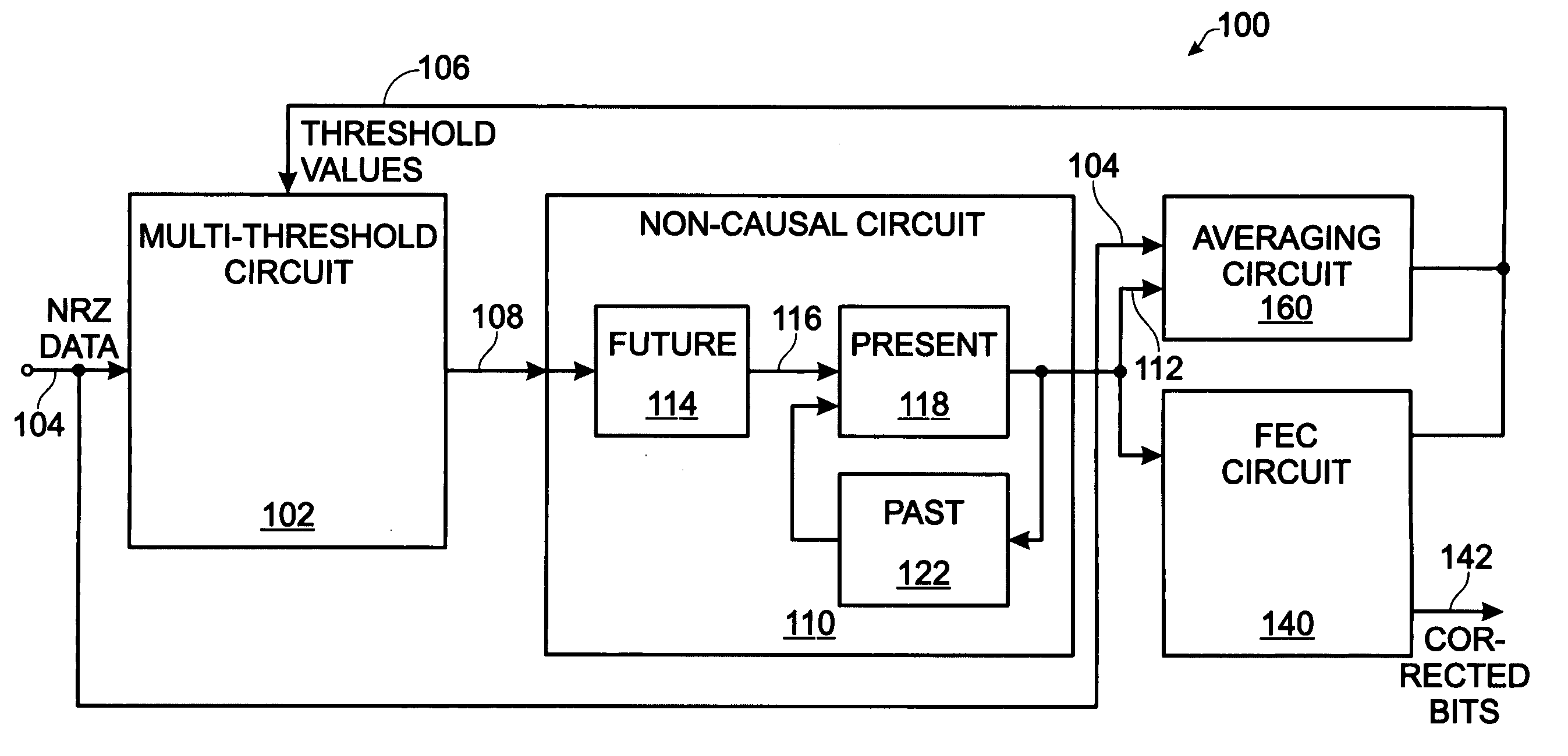

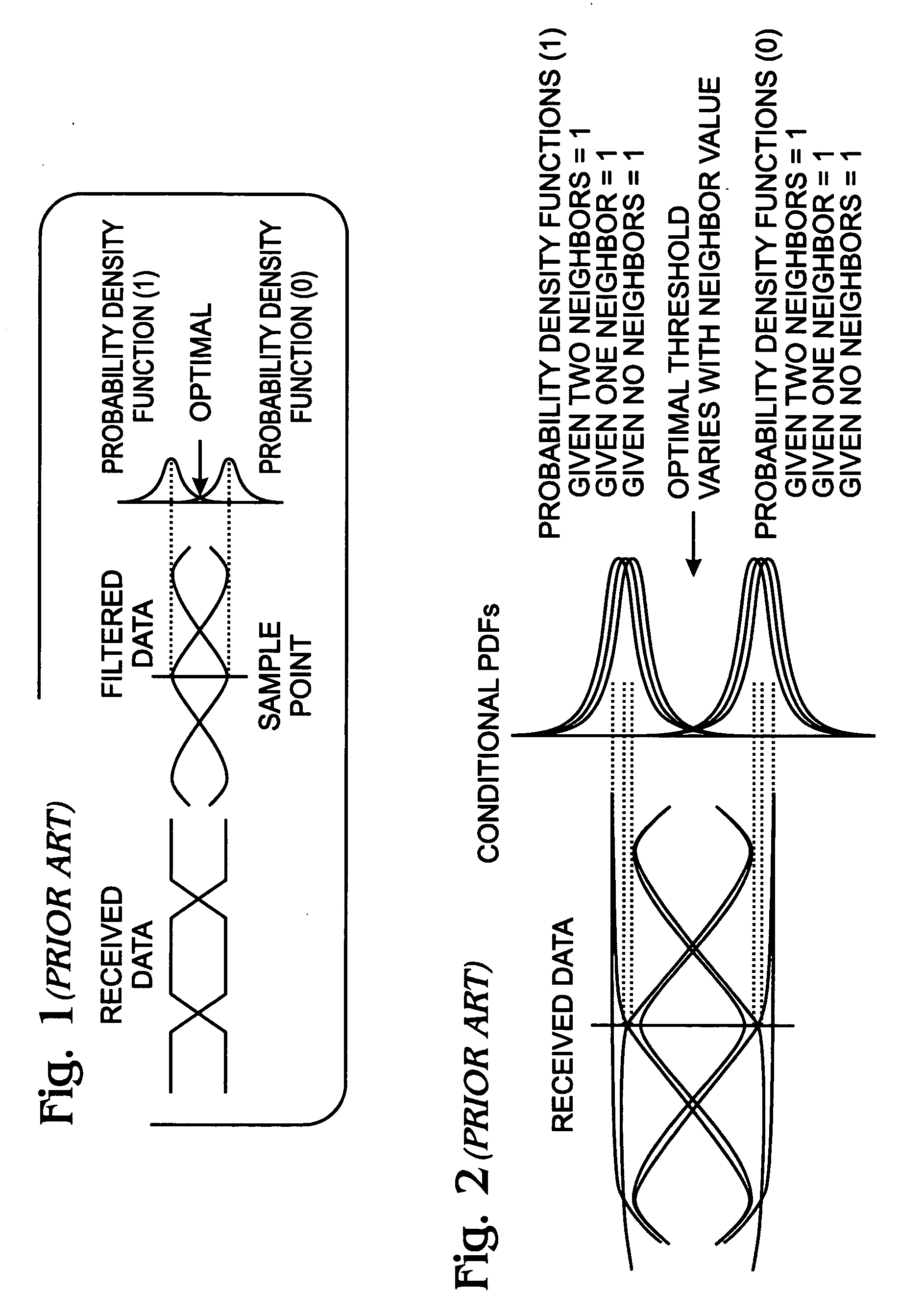

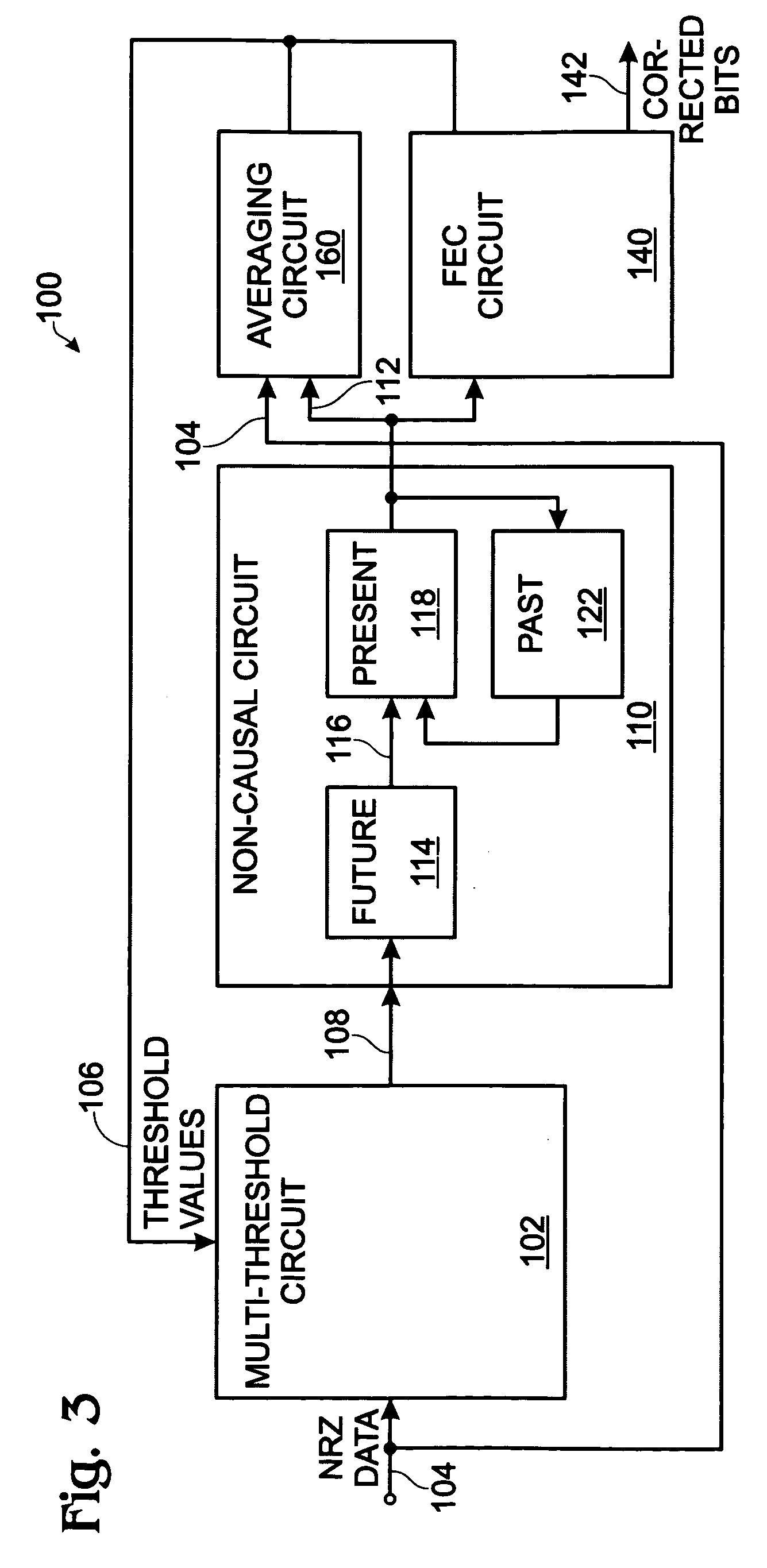

System for five-level non-causal channel equalization

InactiveUS20060256891A1Reduce impactOptimal mitigationError preventionCode conversionCommunications systemData stream

A system and method are provided for five-level non-causal channel equalization in a communications system. The method comprises: receiving a non-return to zero (NRZ) data stream input; establishing a five-level threshold; comparing the first bit estimate to a second bit value received prior to the first bit; comparing the first bit estimate to a third bit value received subsequent to the first bit; and, in response to the comparisons, determining the value of the first bit. Establishing a five-level threshold includes: establishing thresholds to distinguish a first bit value when the second and third bit values are a “1” value, when the second bit value is a “1” and the third bit value is a “0”, when the second bit value is a “0” and the third bit value is a “1”, when the second and third bit values are a “0” value, and an approximate midway threshold.

Owner:APPLIED MICRO CIRCUITS CORPORATION

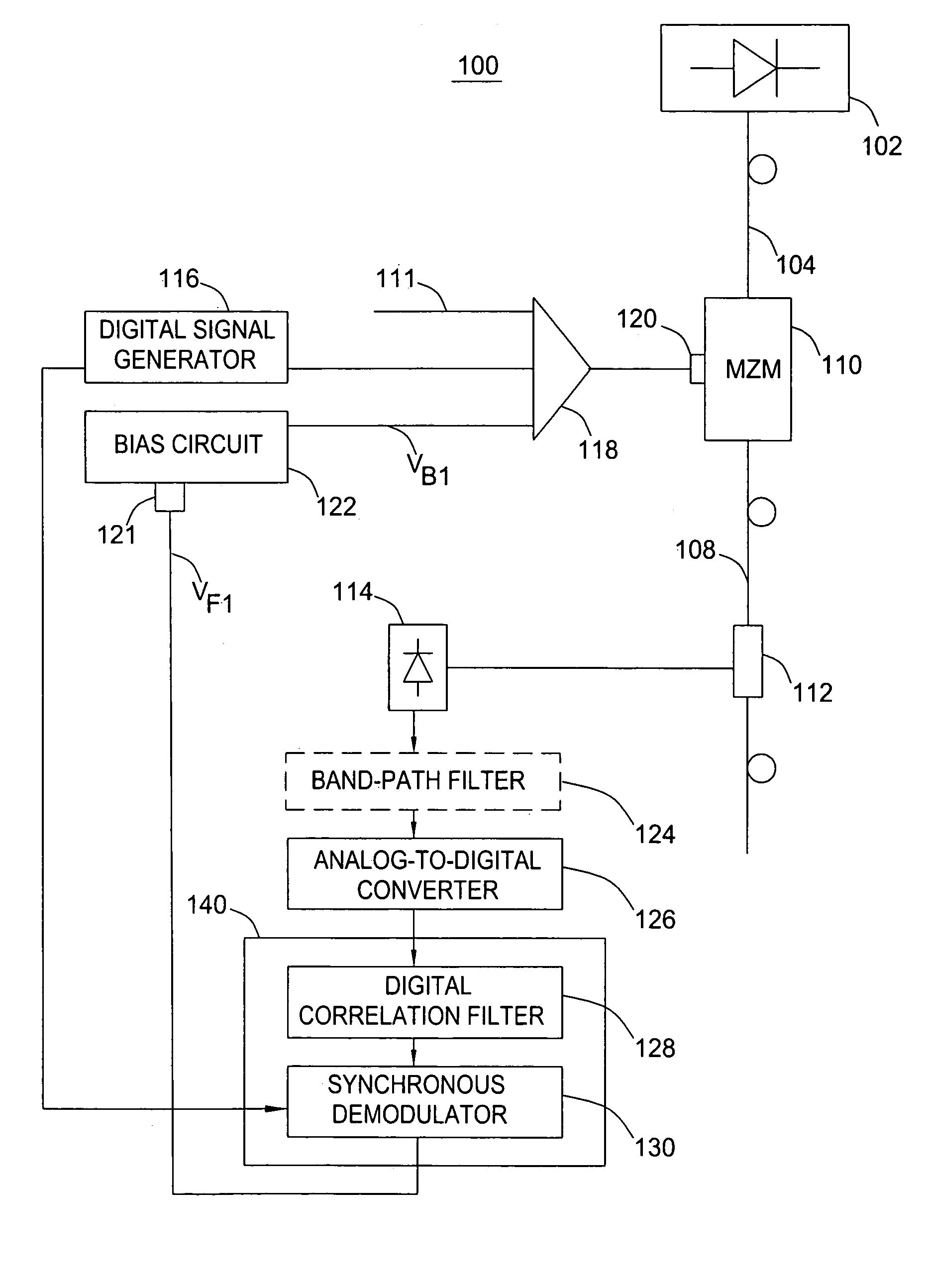

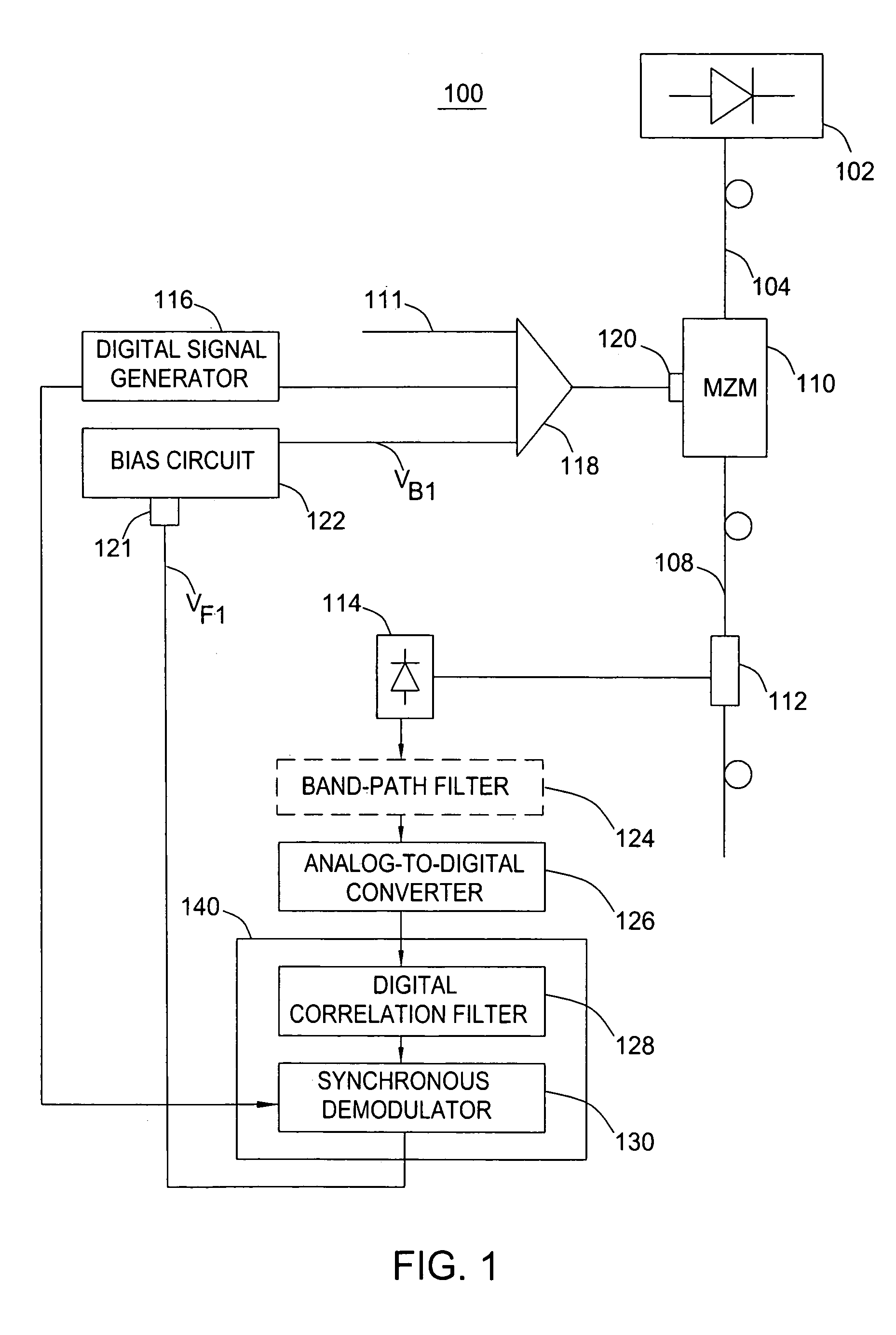

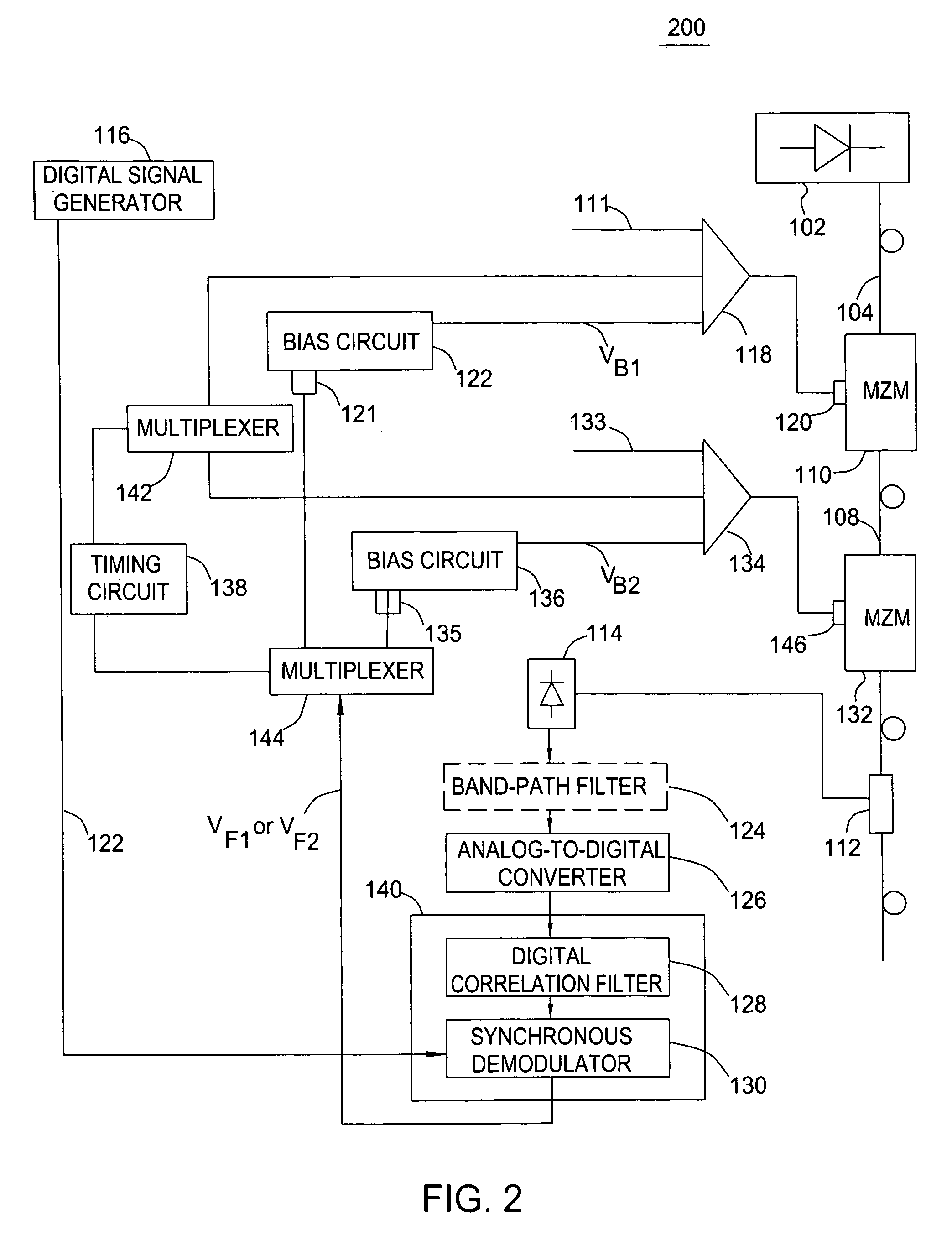

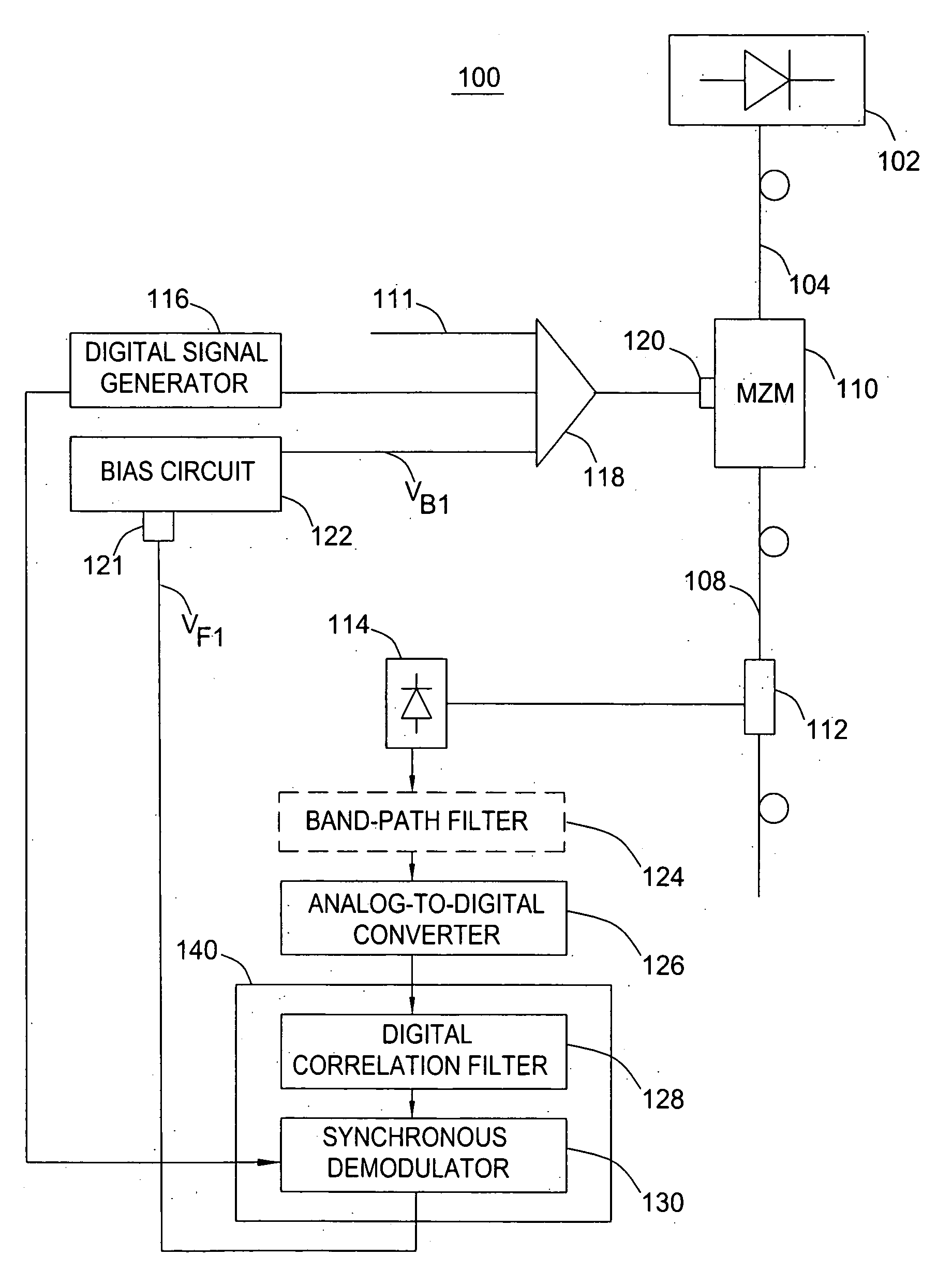

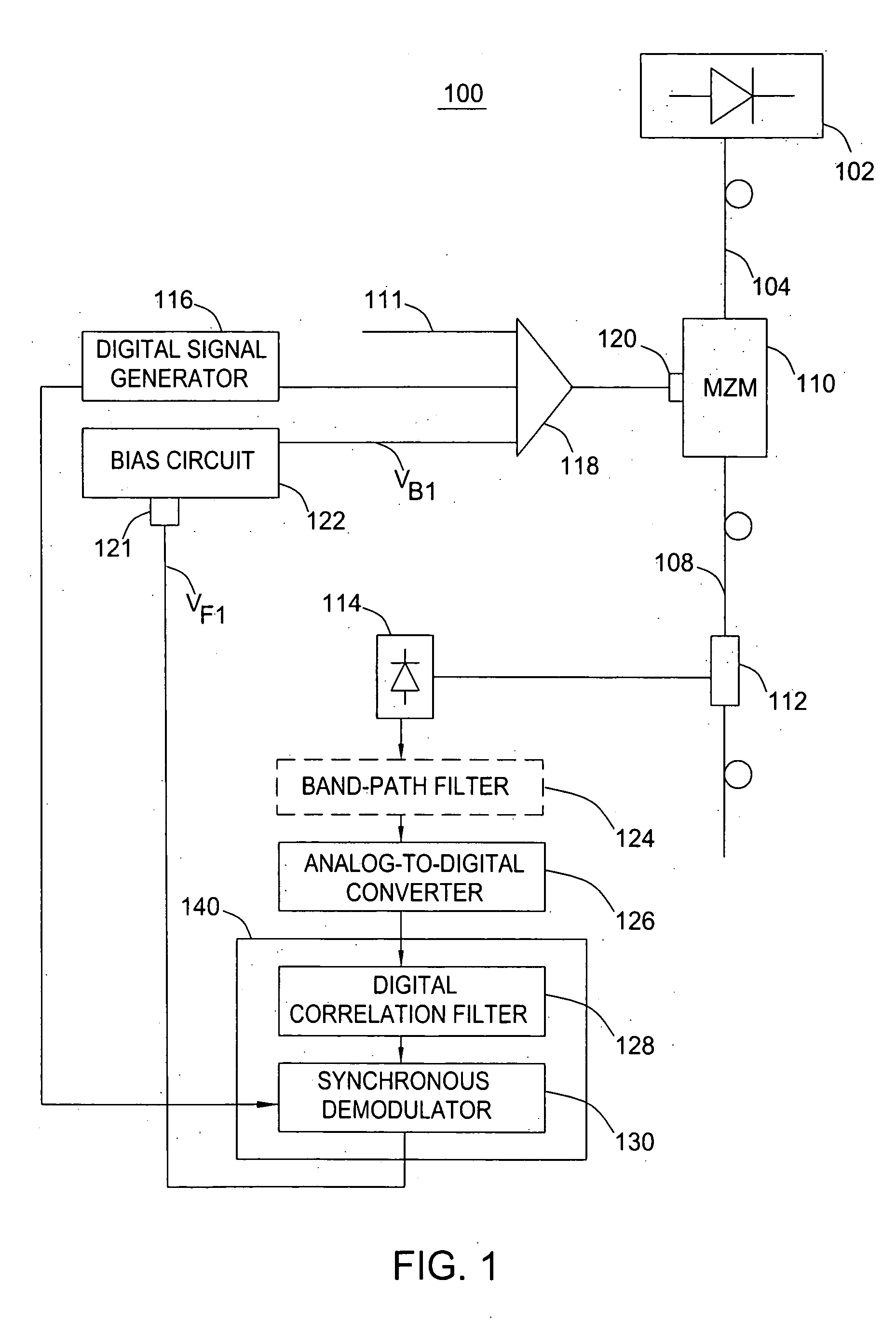

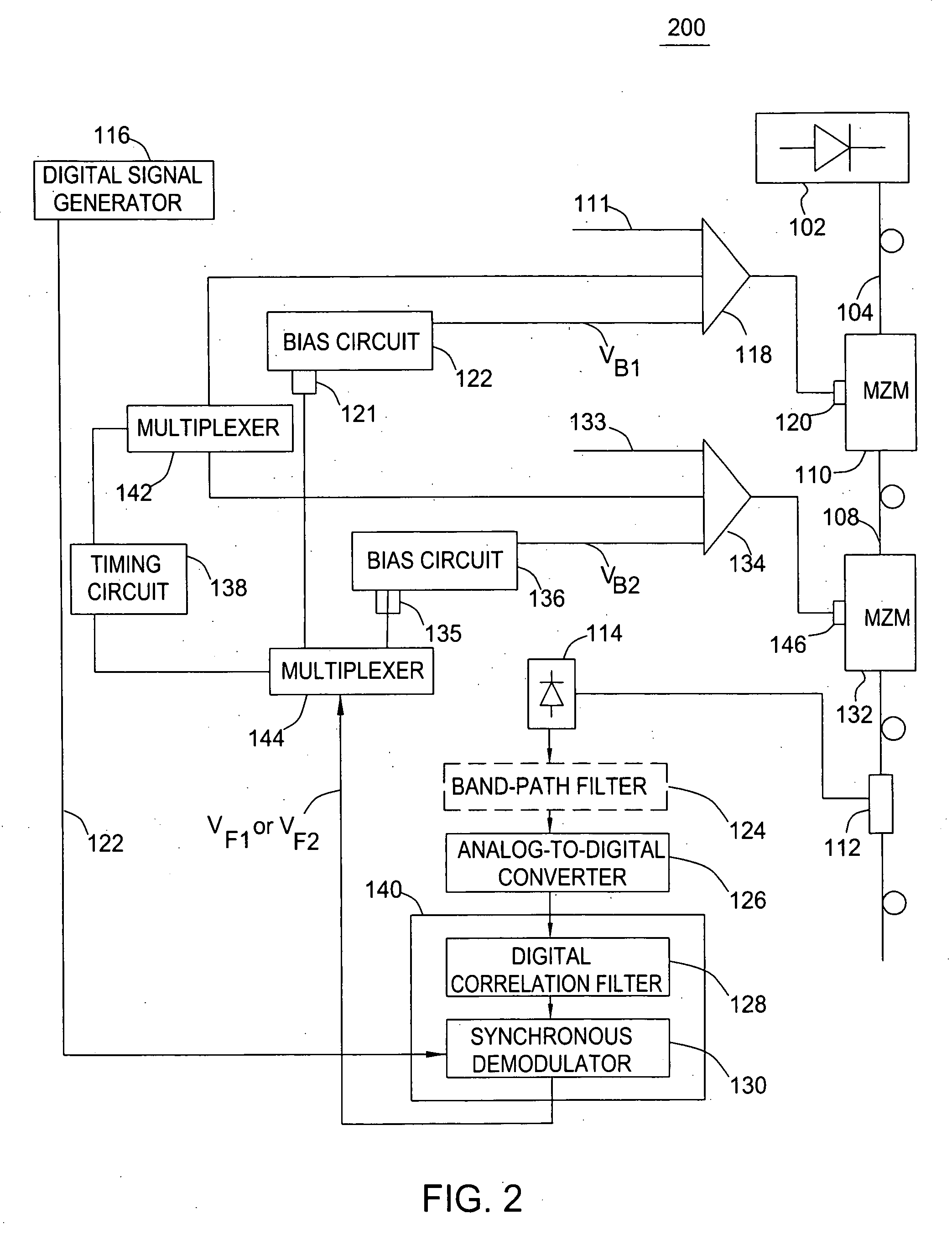

Method and apparatus for controlling a bias voltage of a Mach-Zehnder modulator

A method and apparatus for controlling a bias voltage of a Mach-Zehnder modulator (MZM) use a digital pilot signal and a digital correlation technique to produce a feedback signal for adjusting the bias voltage to the quadrature bias point. Embodiments of the invention include apparatuses performing a non-return-to-zero (NRZ), return-to-zero (RZ), or carrier suppressed RZ (CSRZ) high-speed optical modulation.

Owner:RPX CORP +1

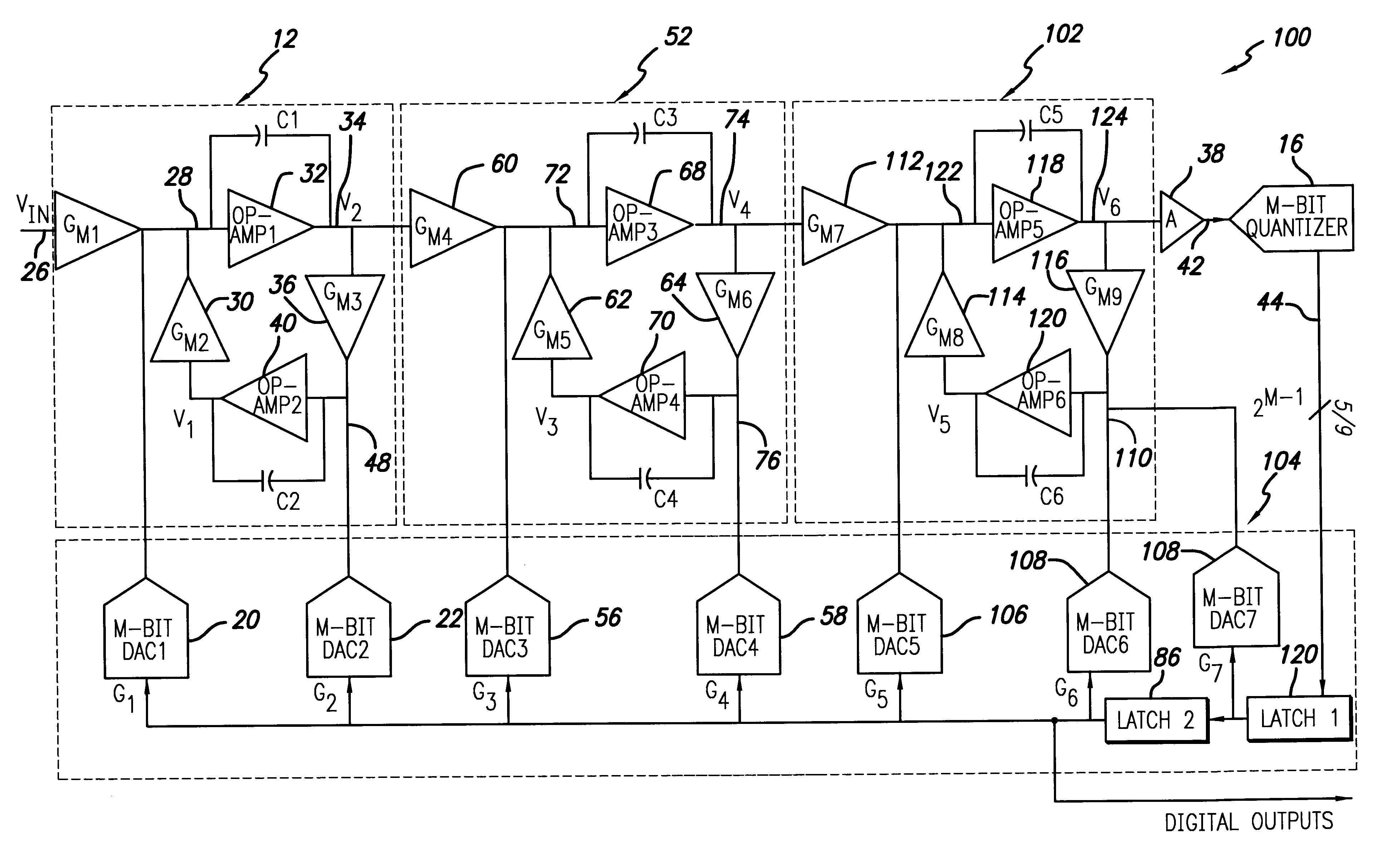

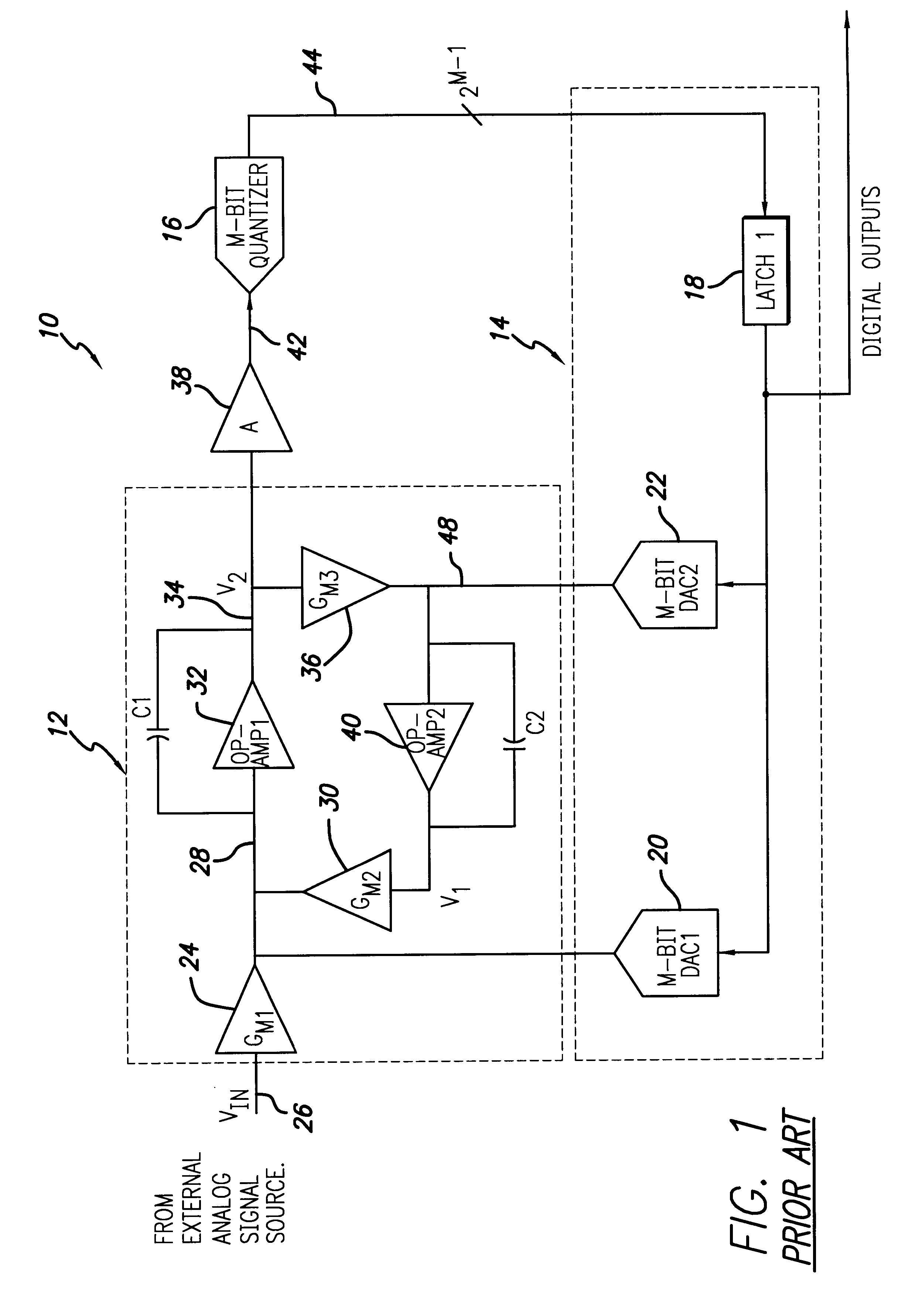

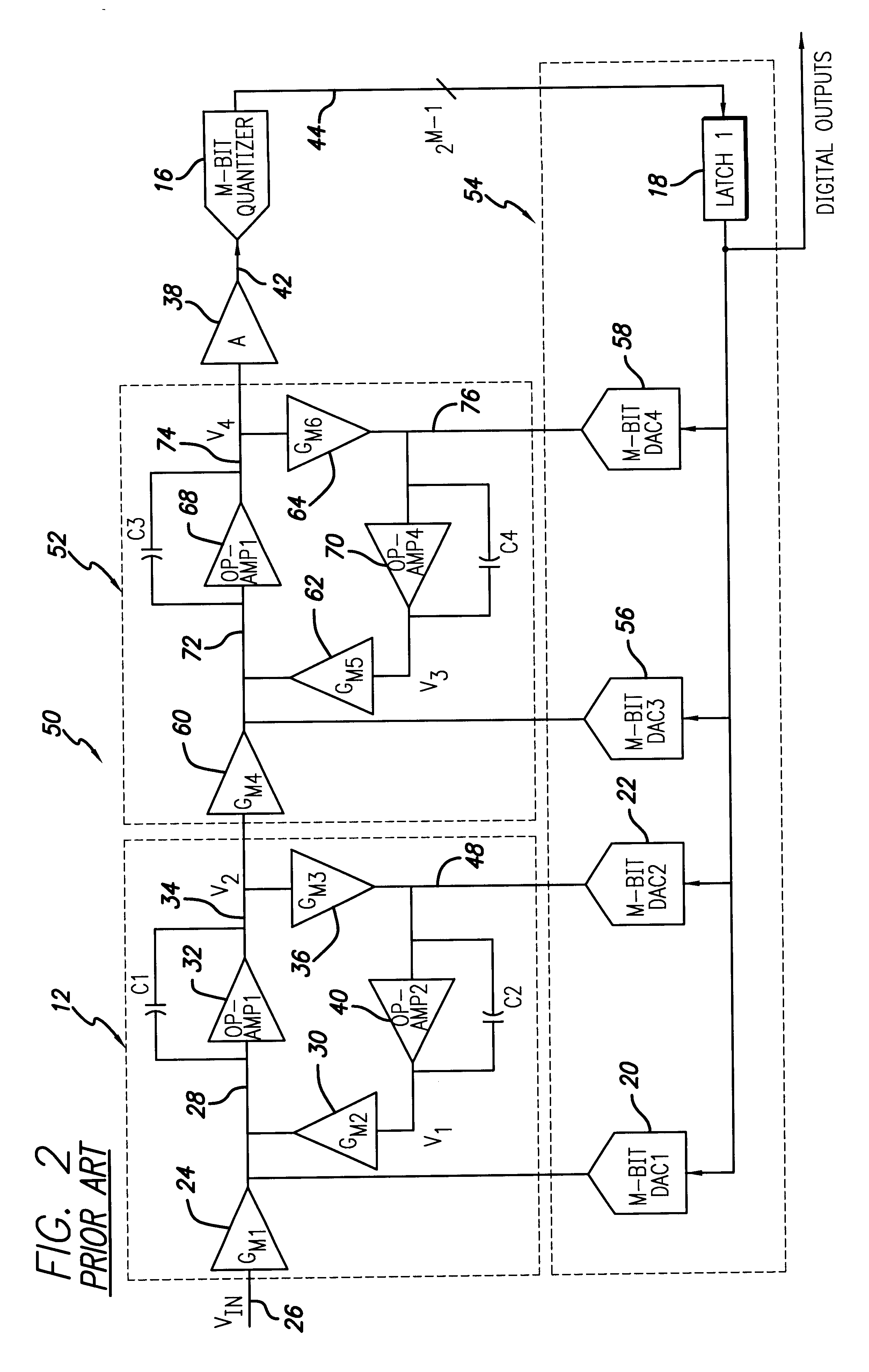

Excess delay compensation in a delta sigma modulator analog-to-digital converter

InactiveUS6414615B1Electric signal transmission systemsDelta modulationDigital analog converterAnalog signal

A high-performance delta sigma analog-to-digital converter. The high-performance delta sigma analog-to-digital converter includes a first mechanism for converting an input analog signal to a digital output signal. The first mechanism is characterized by a transfer function that is altered relative to an ideal transfer function. A second mechanism compensates for the alteration in the transfer function via a single additional digital-to-analog converter. In a specific embodiment, the alteration includes an additional pole and an additional zero induced by feedback delays in the first mechanism. The feedback delays include signal dependent jitter delay and feedback digital-to-analog converter cell switching delays. The second mechanism includes an additional latch that compensates for the signal dependent jitter delay. The first mechanism includes a resonator and a quantizer. The second mechanism includes a feedback path from an output of the quantizer to the resonator. The feedback path includes a first latch positioned between an output of the quantizer and the additional digital-to-analog converter. The additional latch is positioned at an output of the first latch and eliminates signal dependent jitter delay in the analog-to-digital converter. The additional feedback digital-to-analog converter is a non-return-to-zero digital-to-analog converter, an output of which is connected to the resonator.

Owner:RAYTHEON CO

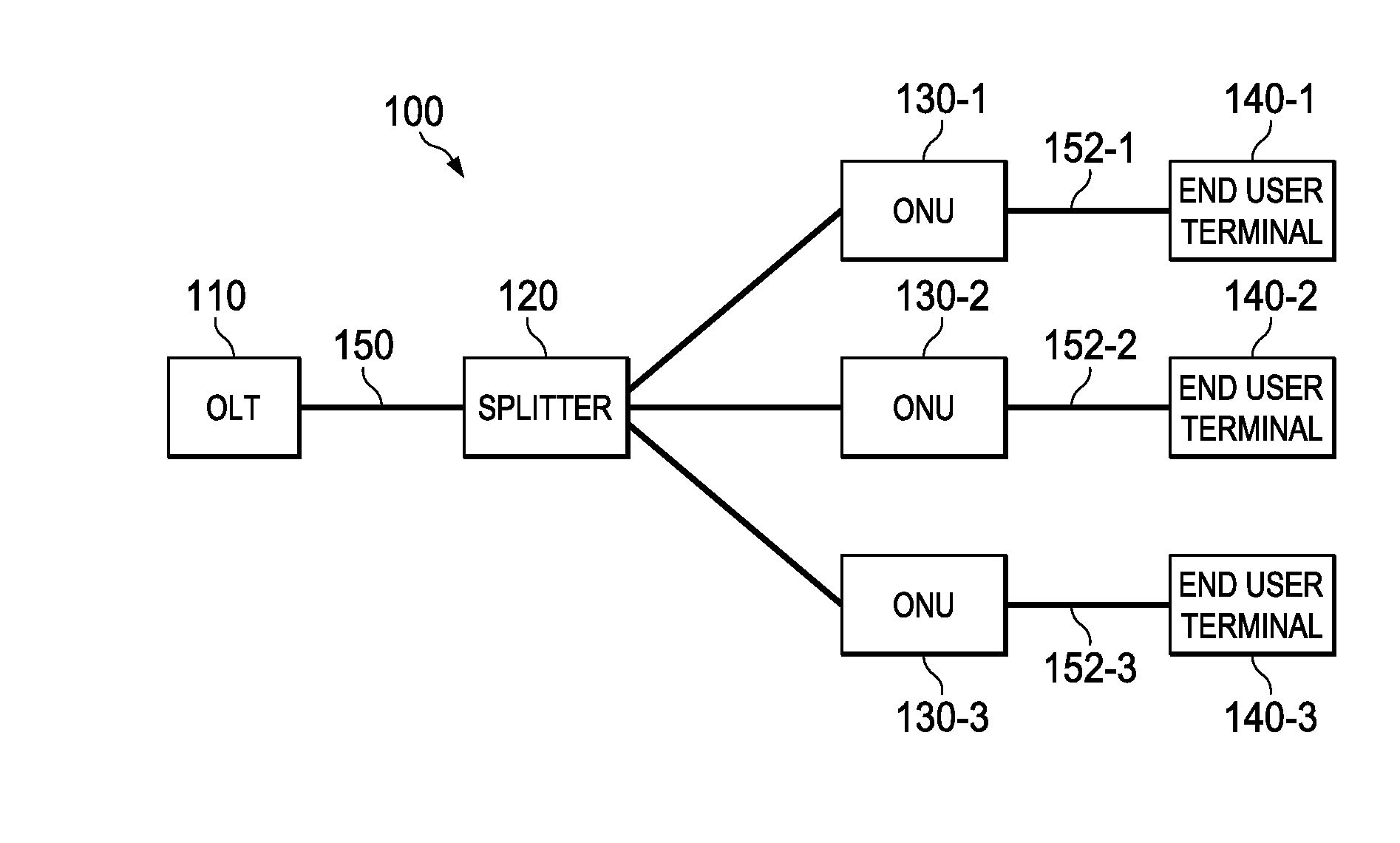

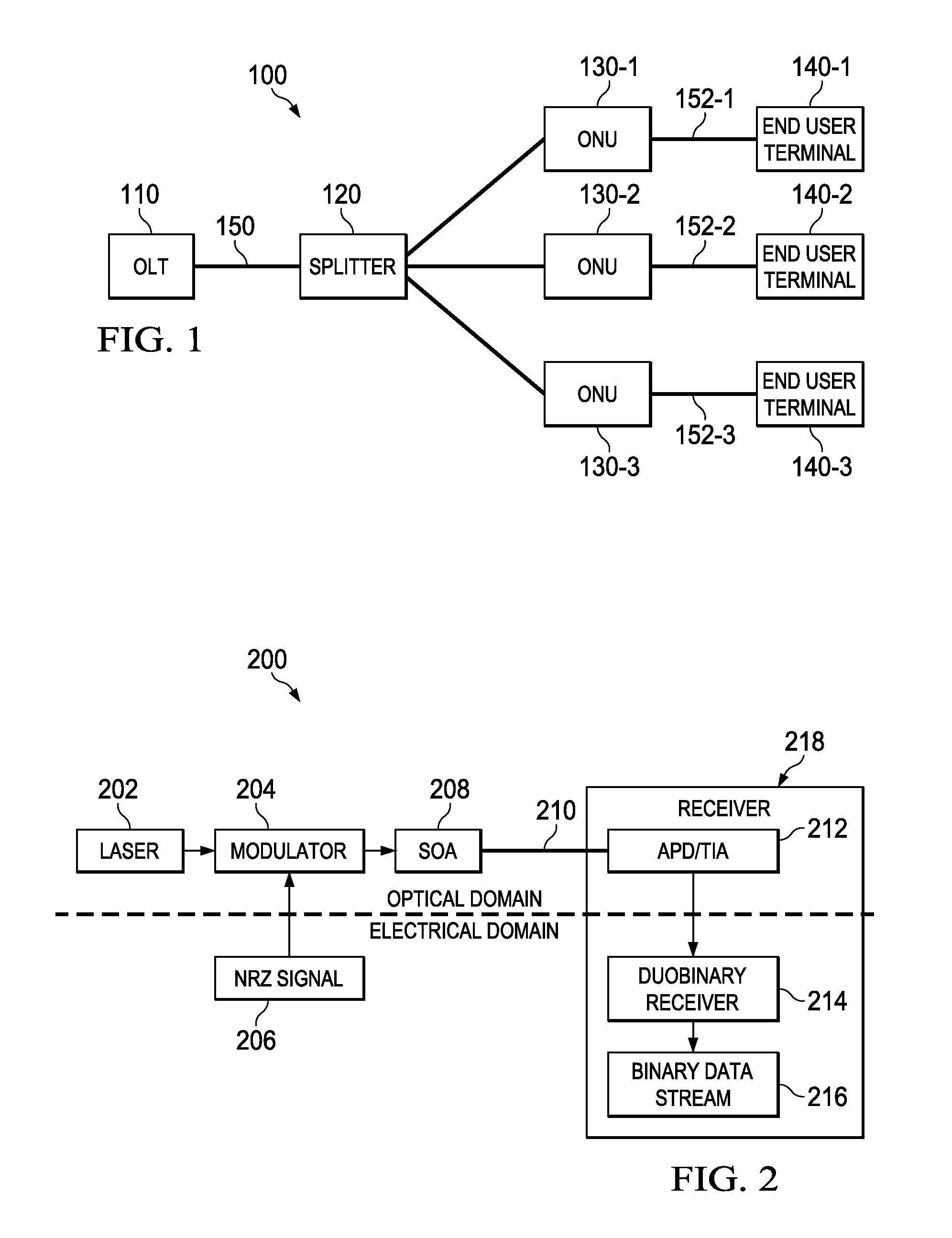

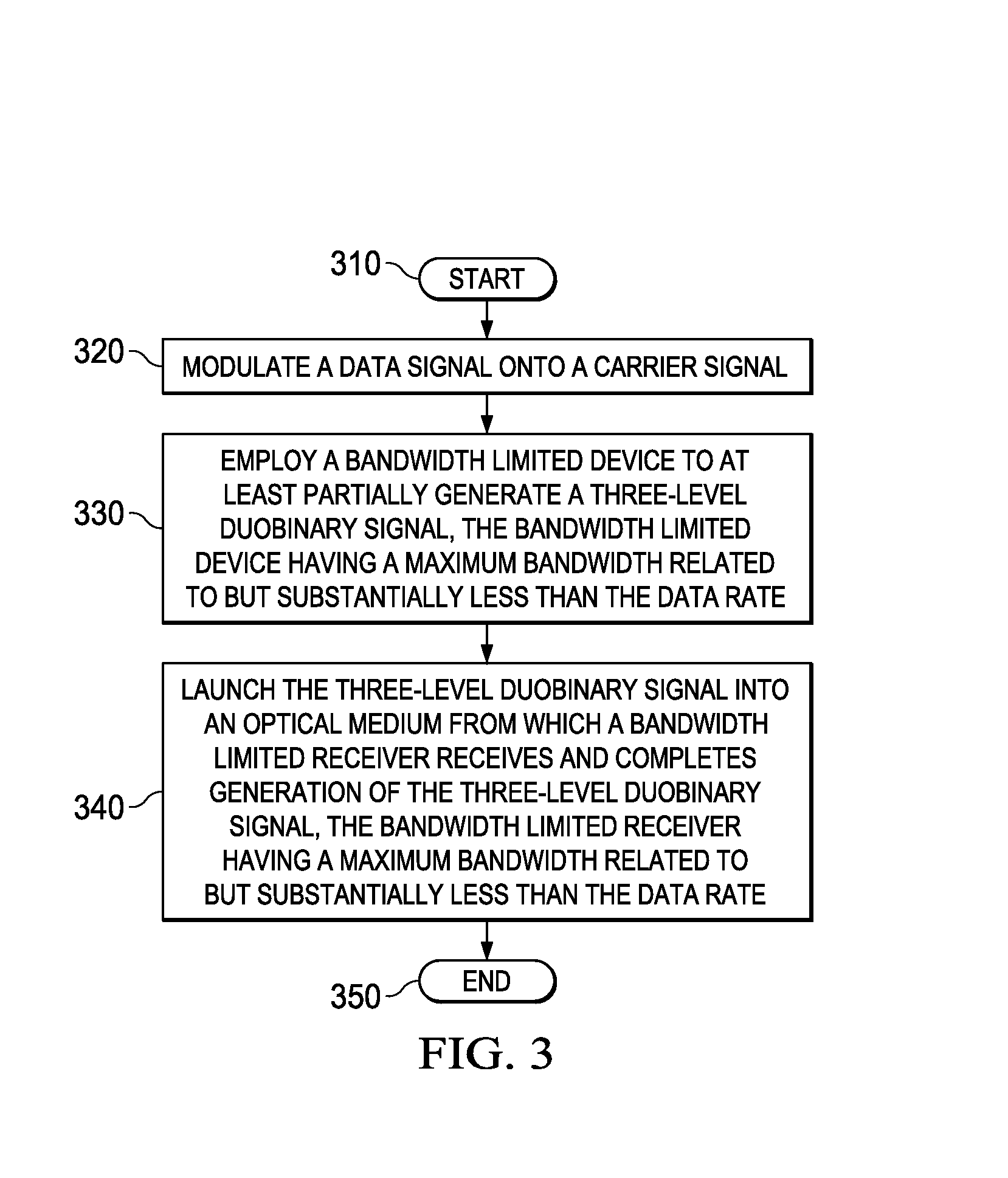

Optical network device employing three-level duobinary modulation and method of use thereof

Owner:ALCATEL LUCENT SAS

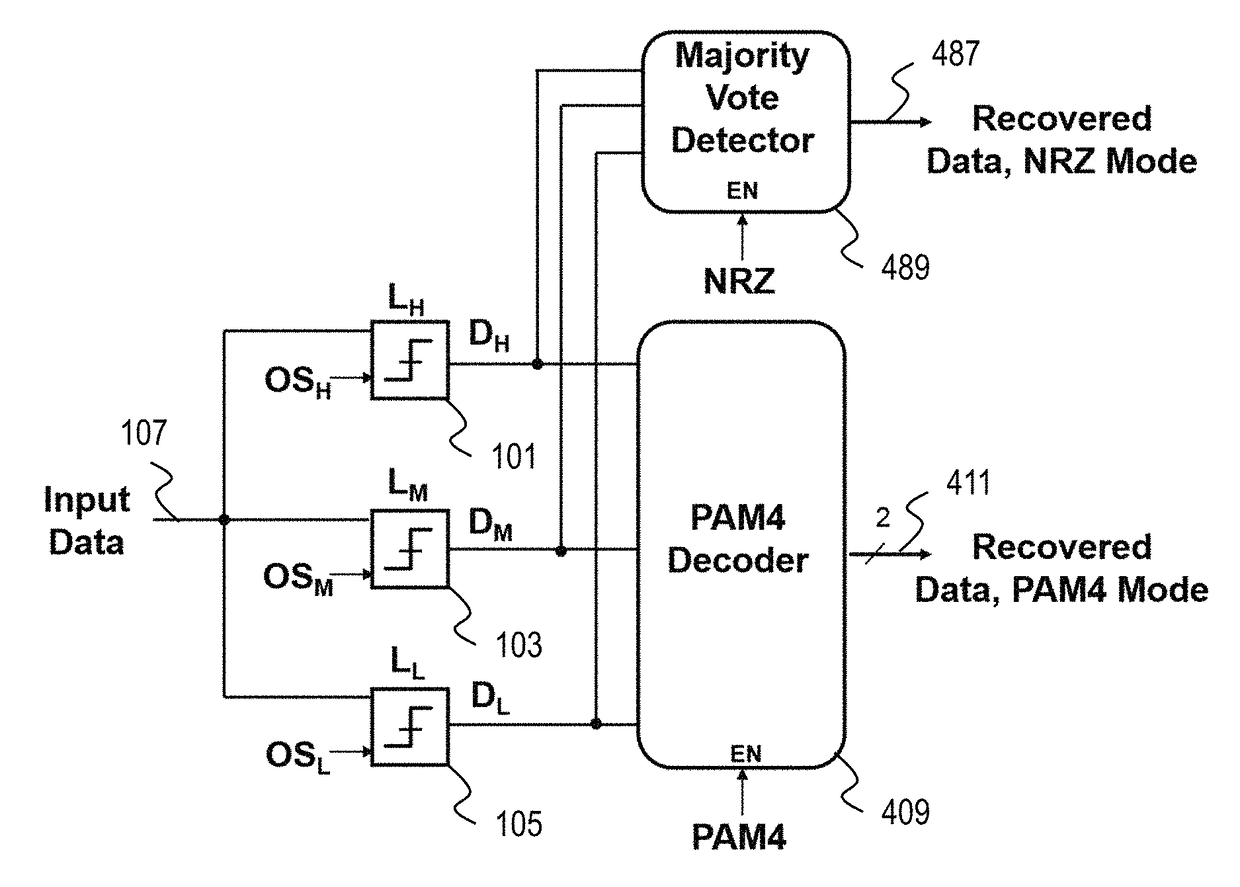

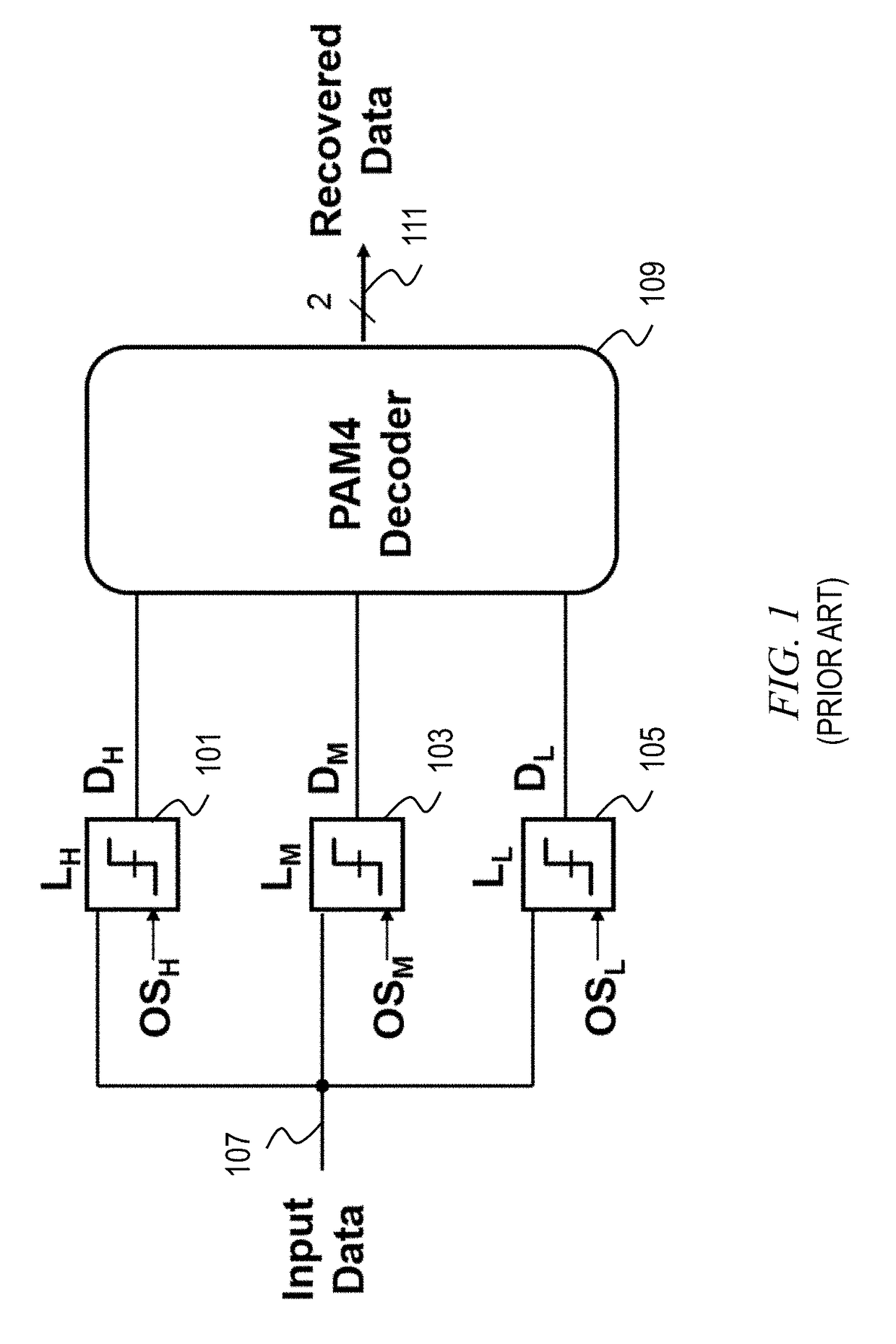

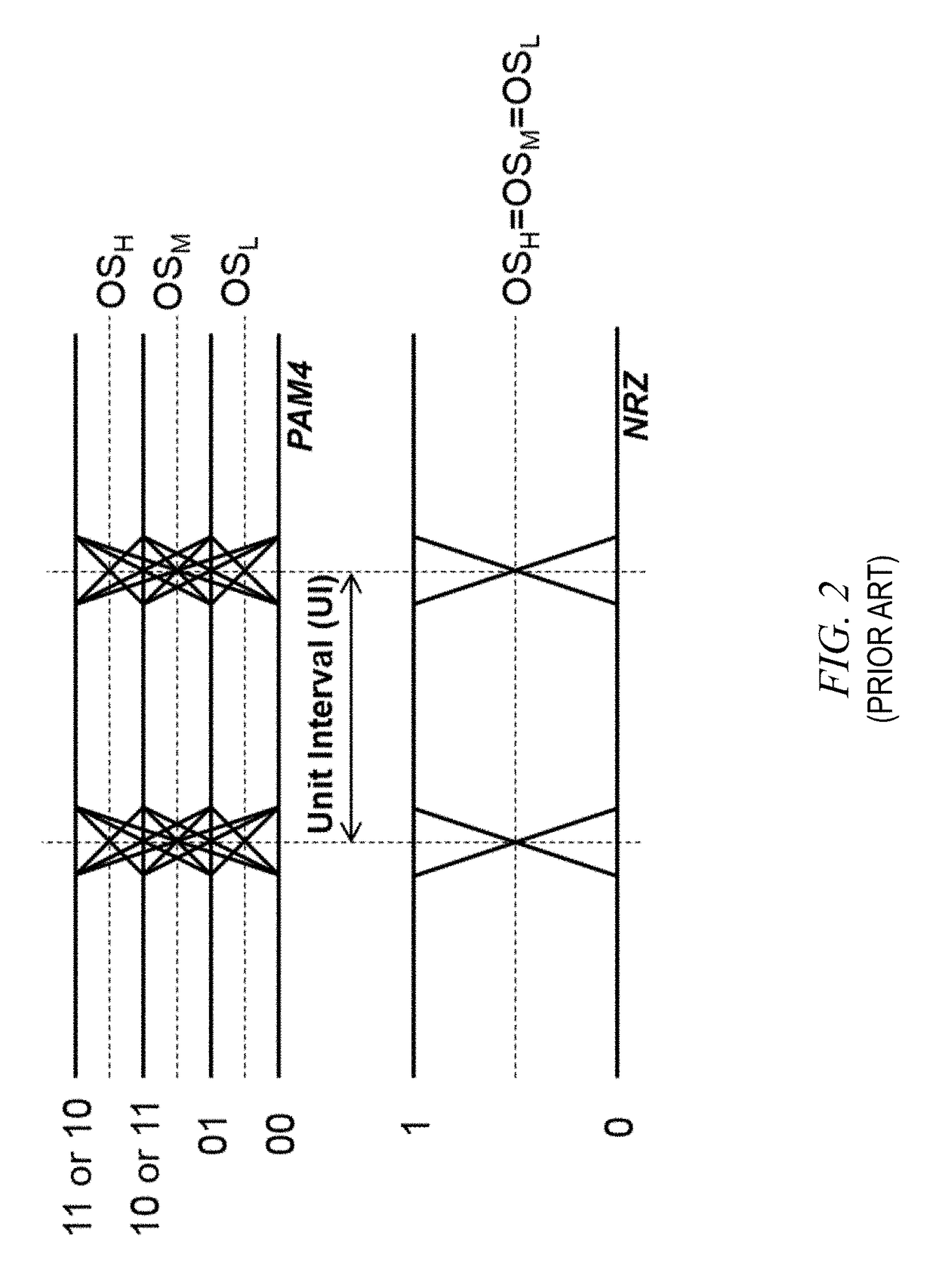

Dual-mode non-return-to-zero (NRZ)/ four-level pulse amplitude modulation (PAM4) receiver with digitally enhanced NRZ sensitivity

InactiveUS9699009B1Improve robustnessReduce sensitivityAmplitude-modulated carrier systemsSynchronising arrangementDual modeNon-return-to-zero

A four-level pulse amplitude modulation receiver has a four-level pulse amplitude modulation mode and a non-return-to-zero modulation mode. First, second, and third four-level pulse amplitude modulation samplers are coupled to an input. Each of the samplers has a corresponding output in turn including a corresponding binary decision of the first, second, and third samplers. A four-level pulse amplitude modulation decoder circuit has inputs coupled to the outputs of the samplers. The four-level pulse amplitude modulation decoder circuit is active in the four-level pulse amplitude modulation mode. The receiver also includes a non-return-to-zero majority voting circuit coupled to the outputs of the samplers. The non-return-to-zero majority voting circuit has an output and is configured to output a majority decision of the corresponding binary decisions of the samplers, and is active in the non-return-to-zero modulation mode.

Owner:IBM CORP

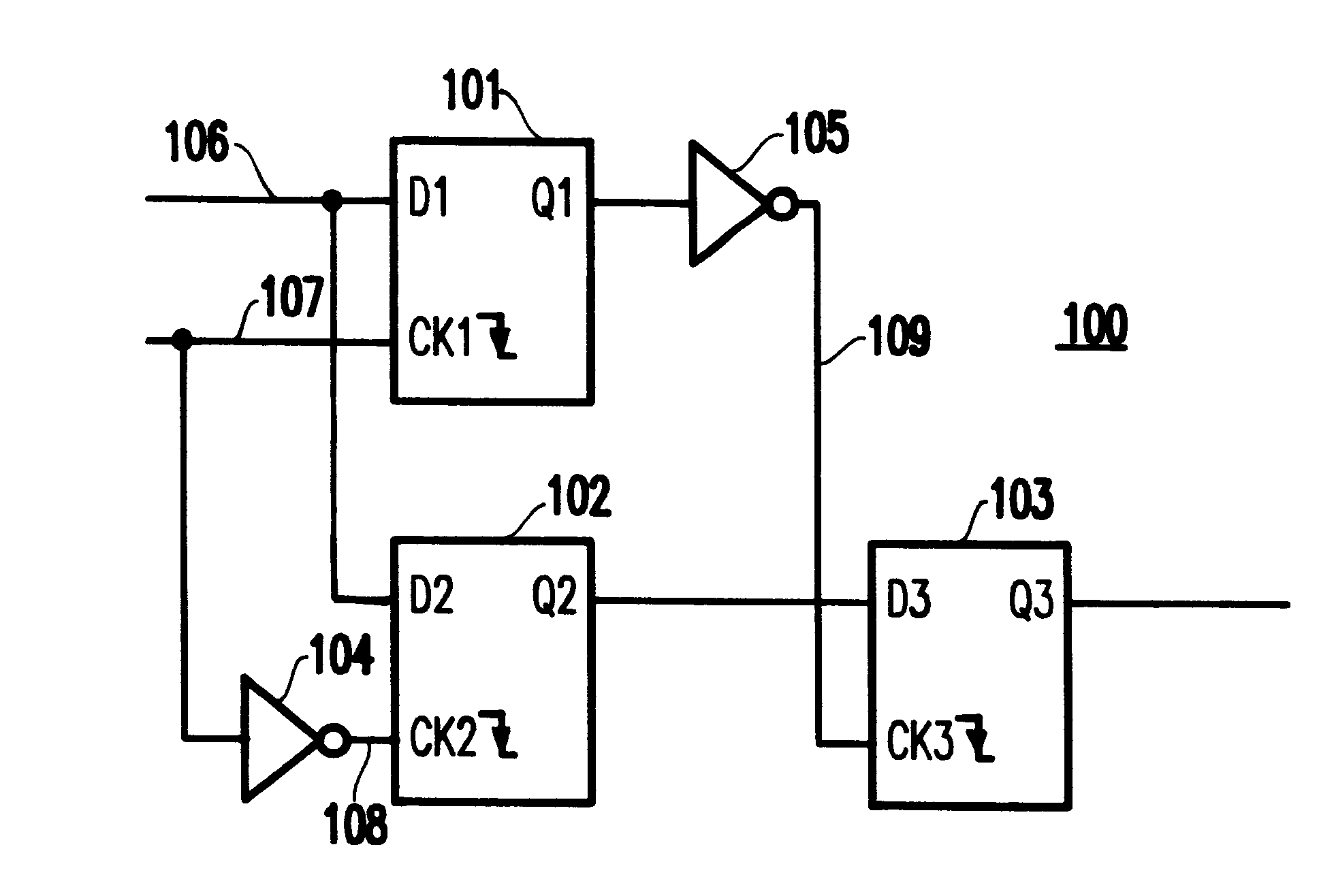

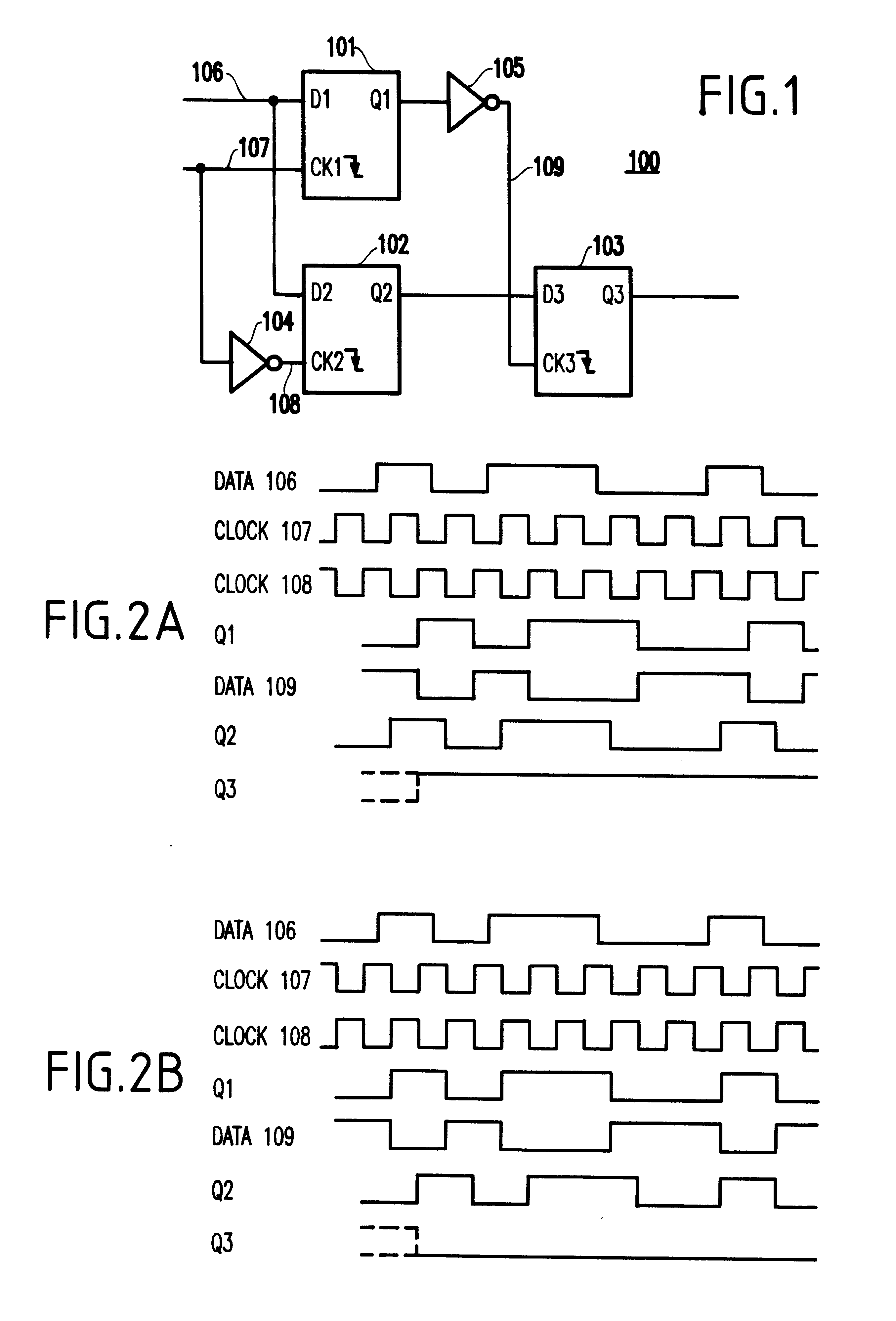

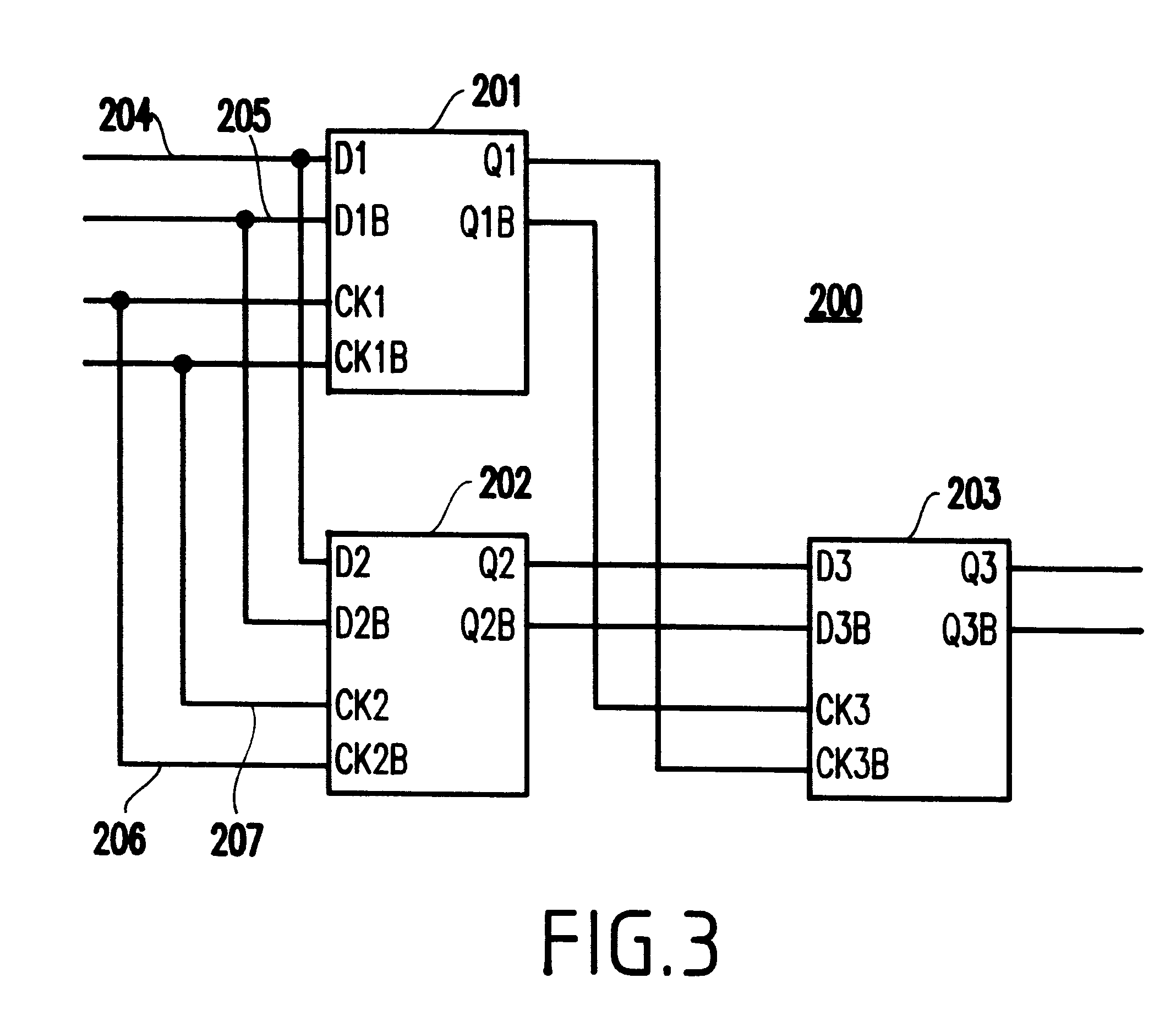

Binary self-correcting phase detector for clock and data recovery

InactiveUS6577694B1Optimize dataEasy to getVoltage-current phase angleOscillations comparator circuitsPhase detectorData signal

A phase detector for a clock and data recovery circuit from random non-return-to zero (NRZ) data signal includes a plurality (e.g., preferably three) edge-triggered flip-flops. The incoming NRZ data are sampled by a pair of edge-triggered flip-flops using the transition of the clock generated by the clock recovery circuit. A third edge-triggered flip-flop processes the outputs from the edge-triggered flip-flop pair to indicate whether the generated clock leads or lags the received data.

Owner:IBM CORP

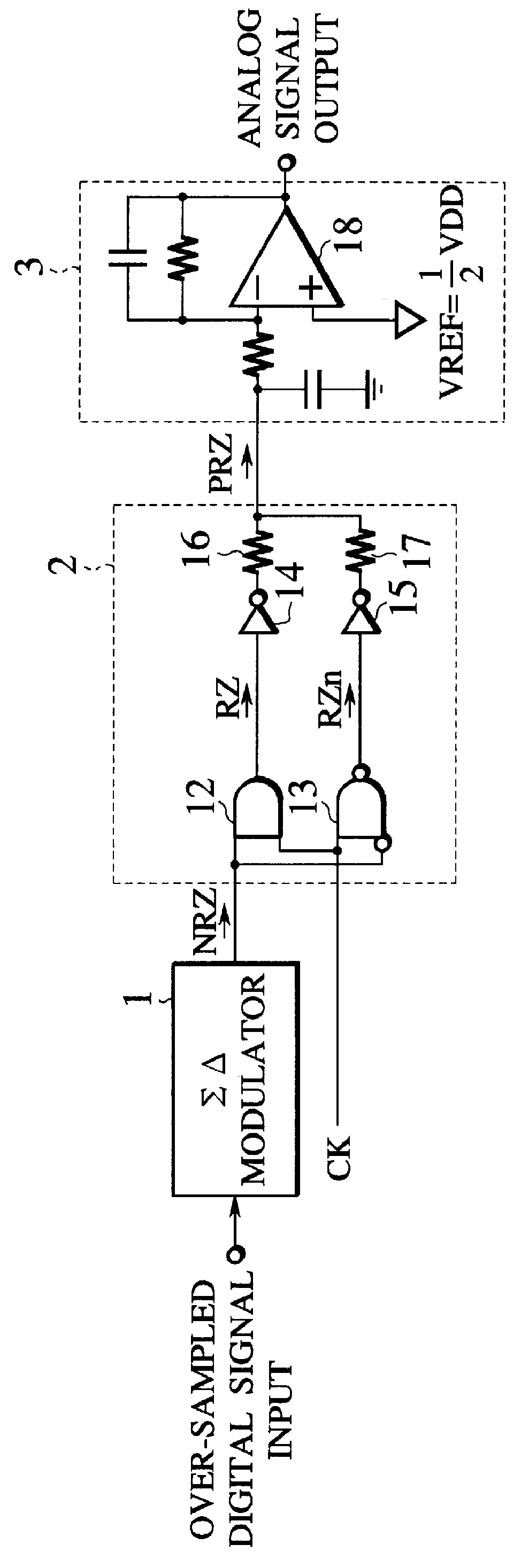

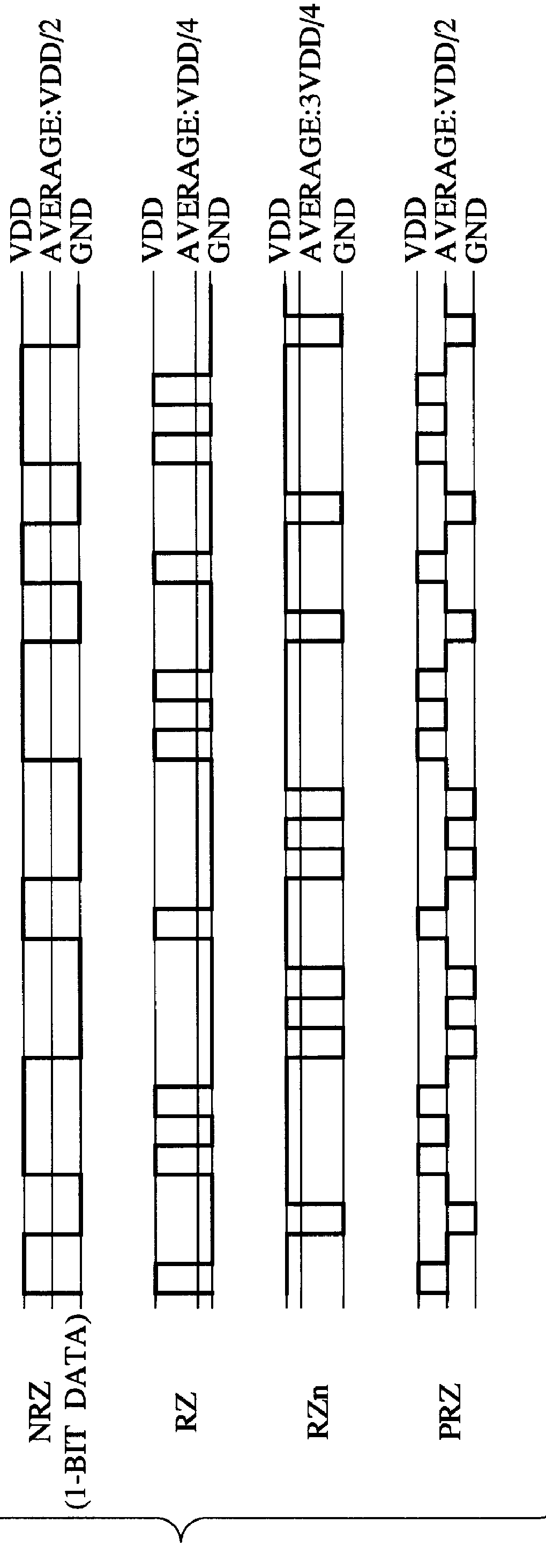

D/A converter

There is provided an over-sampling D / A converter which has a mute function for fixing an average DC potential of an analog output signal to a predetermined potential, and comprises a SIGMA DELTA modulator for receiving a multibit digital signal to which a DC offset value is added and then outputting a one-bit non-return-to-zero signal, a signal generator for receiving the non-return-to-zero signal and the clock signal, then generating a return-to-zero signal which is a logical multiplication of the non-return-to-zero signal and the clock signal and a complementary signal of the return-to-zero signal which is a logical addition of the non-return-to-zero signal and an inverted signal of the clock signal, and then adding the return-to-zero signal to the complementary signal of the return-to-zero signal to thus output a polar-return-to-zero signal, and an analog filter for receiving the polar-return-to-zero signal and then outputting an analog signal. Accordingly, because an average DC potential of an output signal at the time of the mute operation-ON is set substantially equal to the average DC potential of the output signal at the time of the mute operation-OFF, variation in the average DC potential in the output signal due to ON / OFF of the mute operation can be prevented. As a result, generation of audible click noises can be prevented.

Owner:KK TOSHIBA

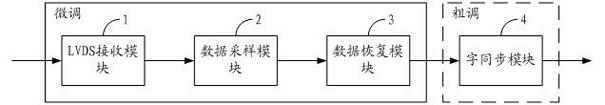

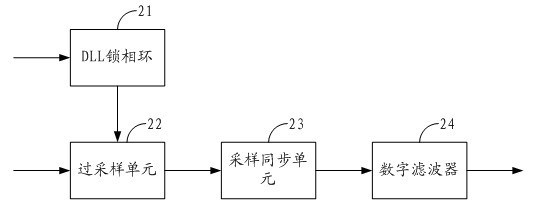

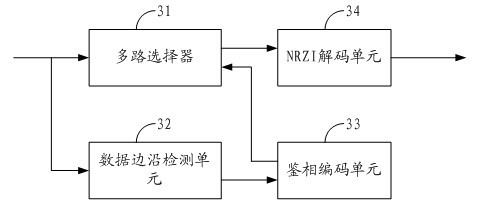

High-speed parallel interface circuit

The invention is suitable for the digital communication field, and provides a high-speed parallel interface circuit. The high-speed parallel interface circuit comprises a low voltage differential signaling (LVDS) receiving module, a data sampling module, a data restoring module and a word synchronization module, wherein the LVDS receiving module receives and shapes data; the data sampling module is connected with the LVDS receiving module and samples the data output by the LVDS receiving module under a plurality of phase clocks; the data restoring module is connected with the data sampling module, selects optimal sampling data from oversampling data output from the data sampling module and restores original data by non return to zero inverse (NRZI) decoding; and the word synchronization module is connected with the data restoring module and carries out shift adjustment to the data output by the data restoring module. In the high-speed parallel interface circuit, oversampling and word synchronization are combined to carry out accurate sampling restoration and synchronization to source-synchronous parallel data; and data in the center of an effective window can be dynamically and accurately sampled and restored in real time by dynamically synchronizing, filtering, discriminating phase, selecting the oversampling data and the like.

Owner:成都三零嘉微电子有限公司

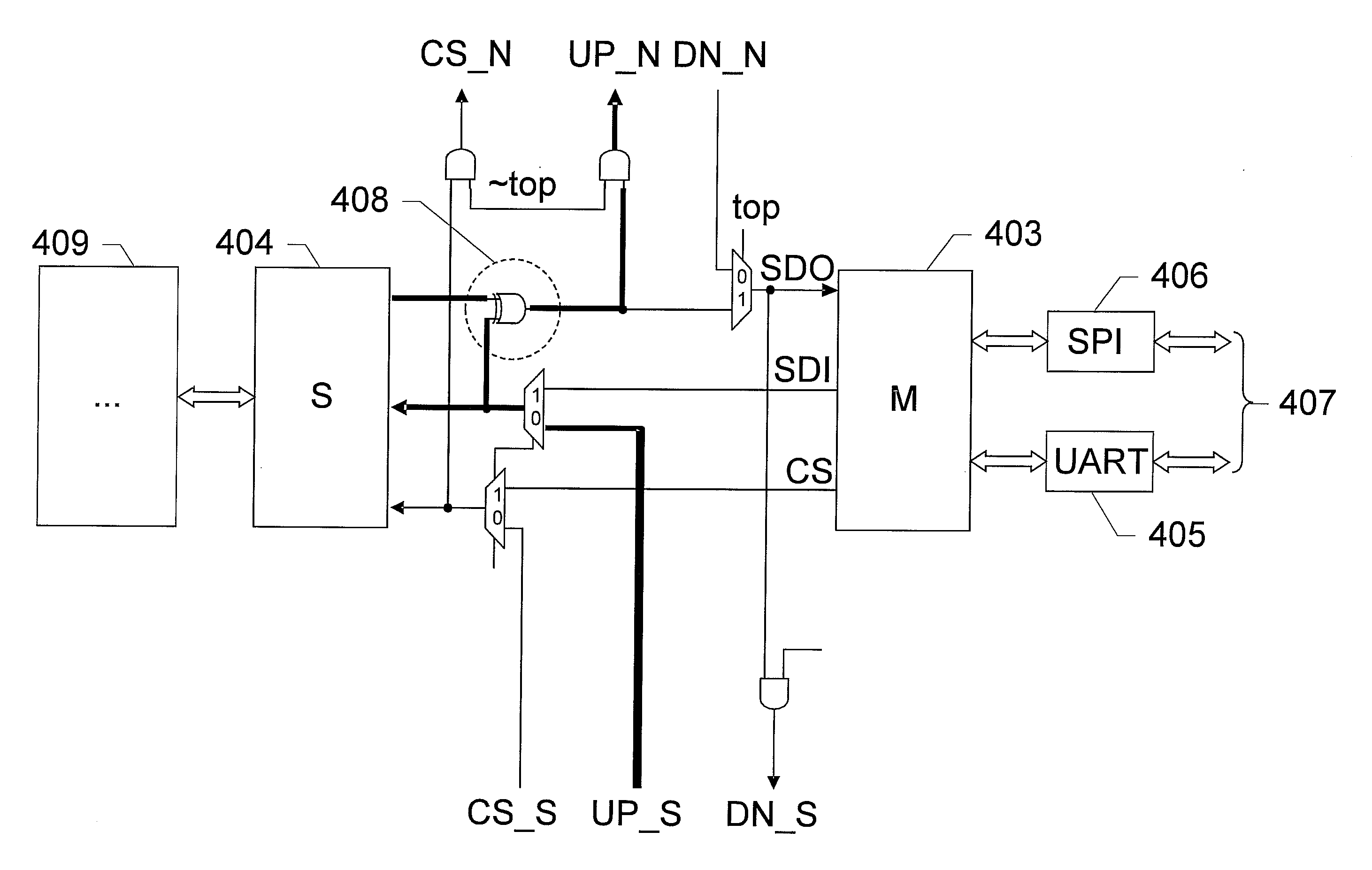

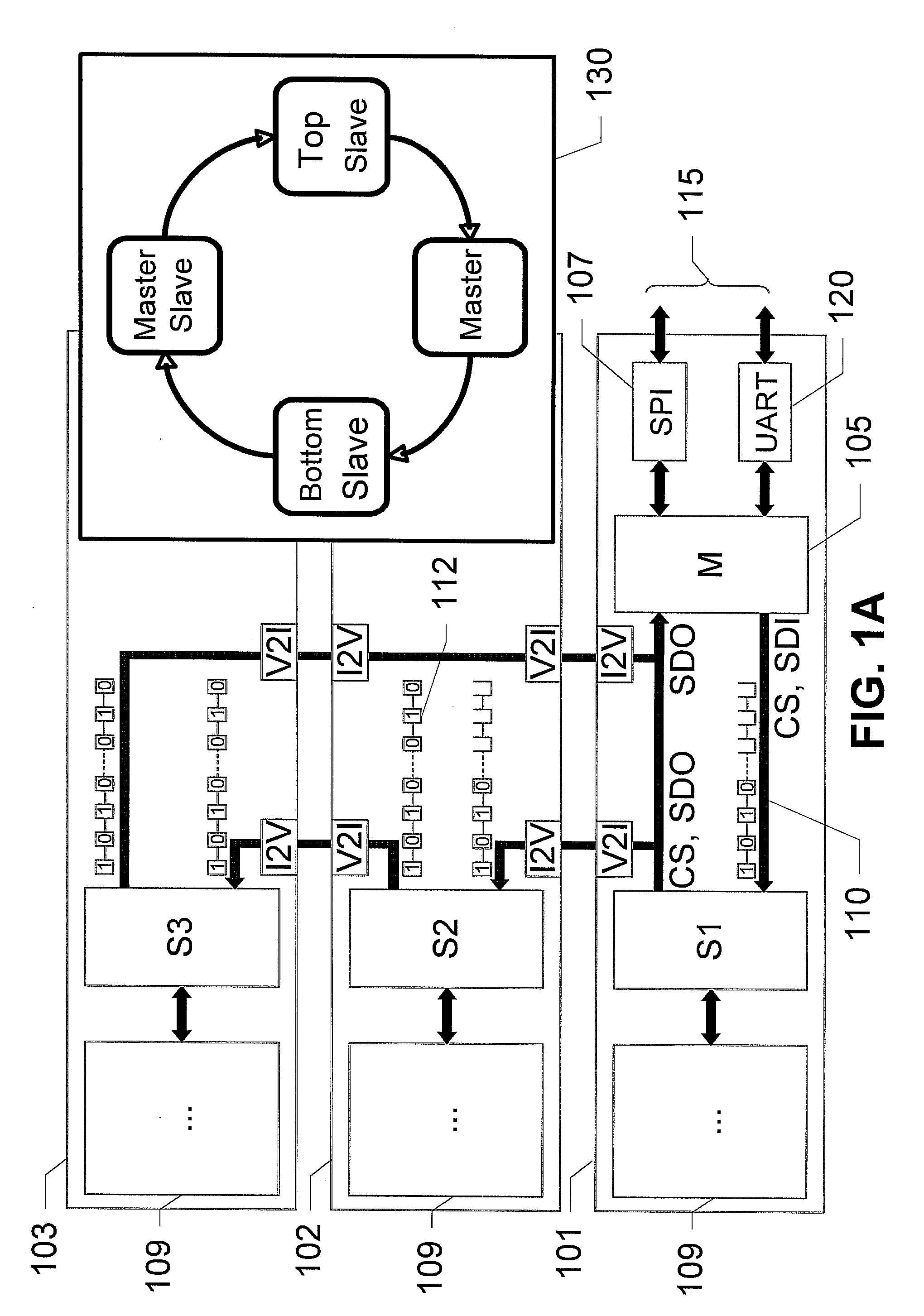

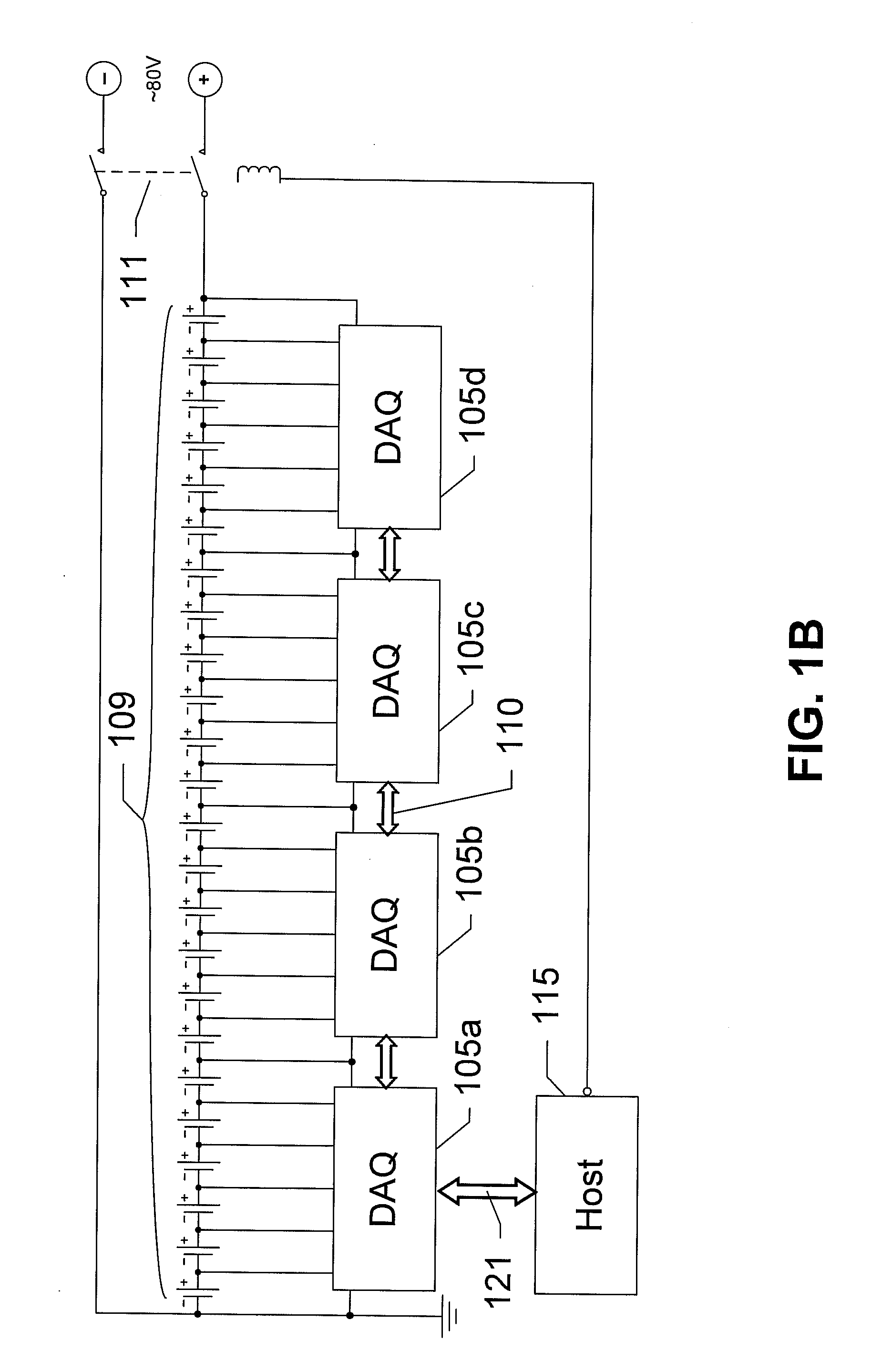

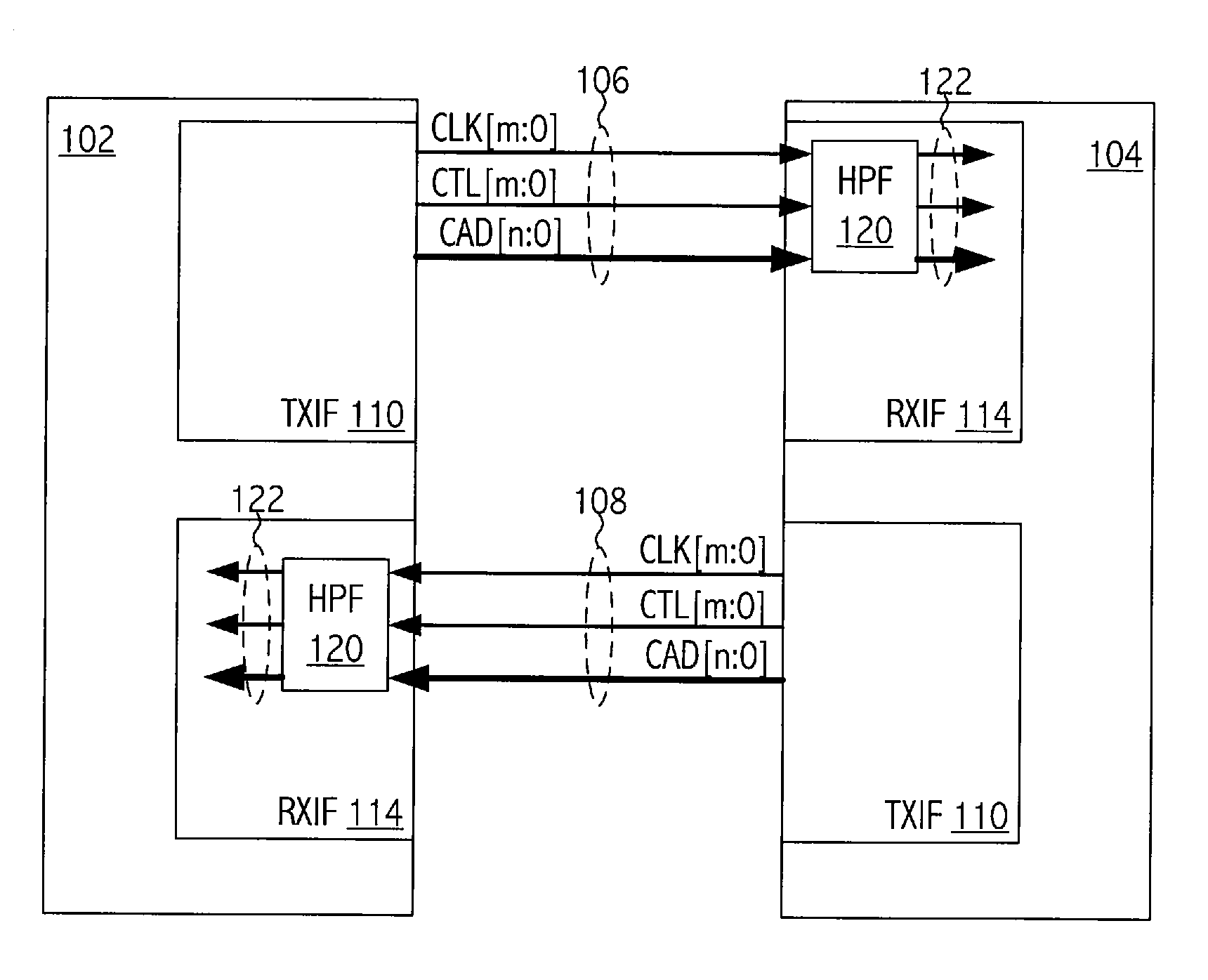

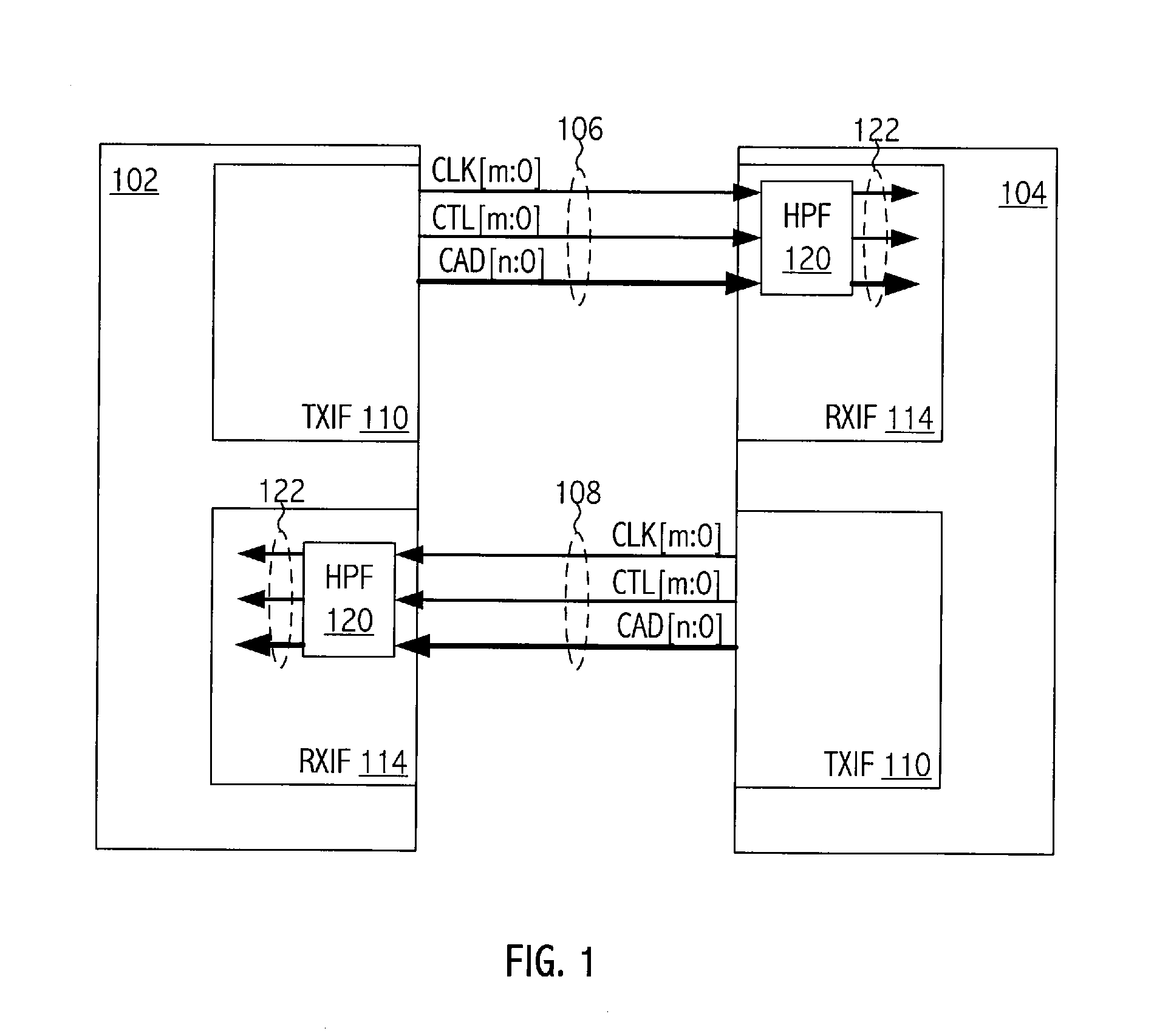

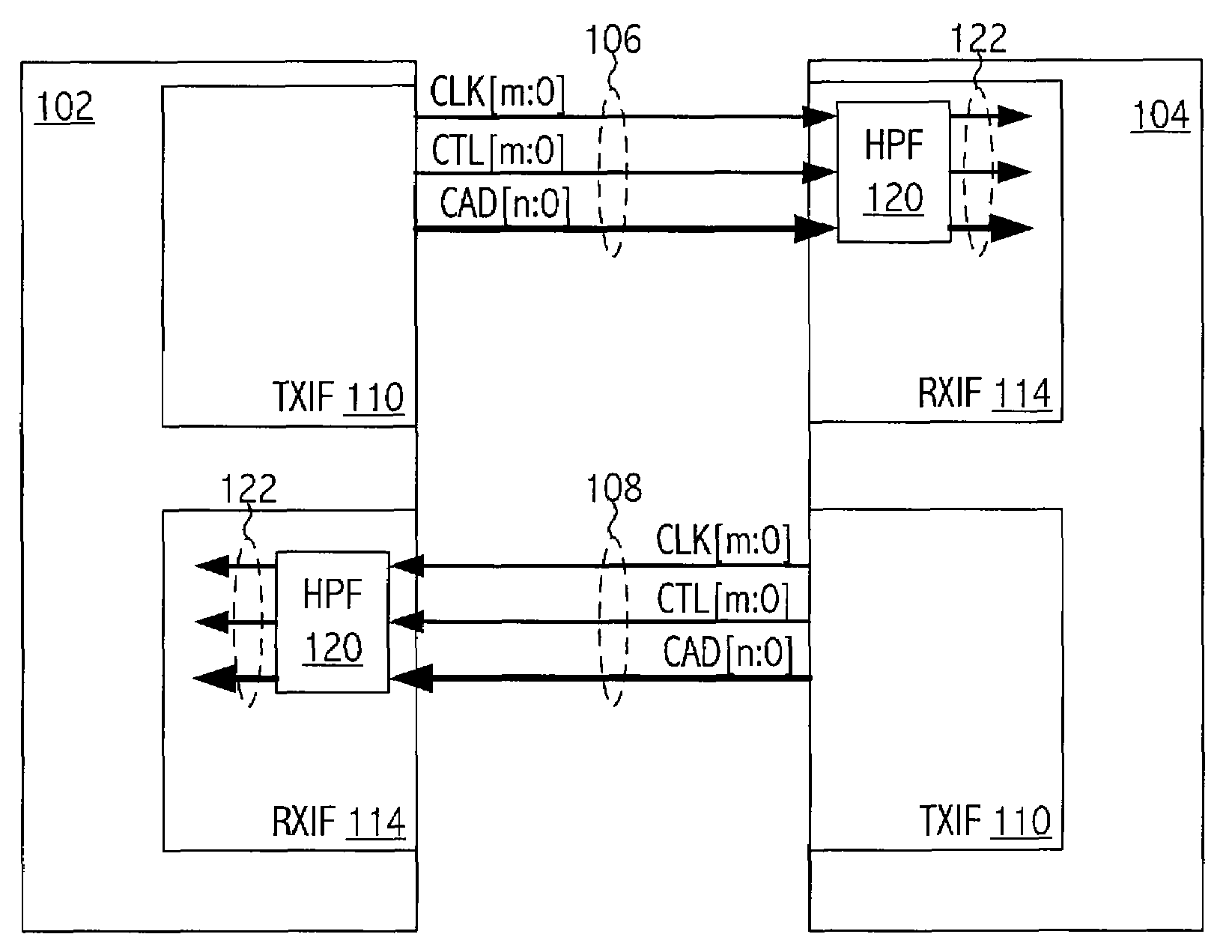

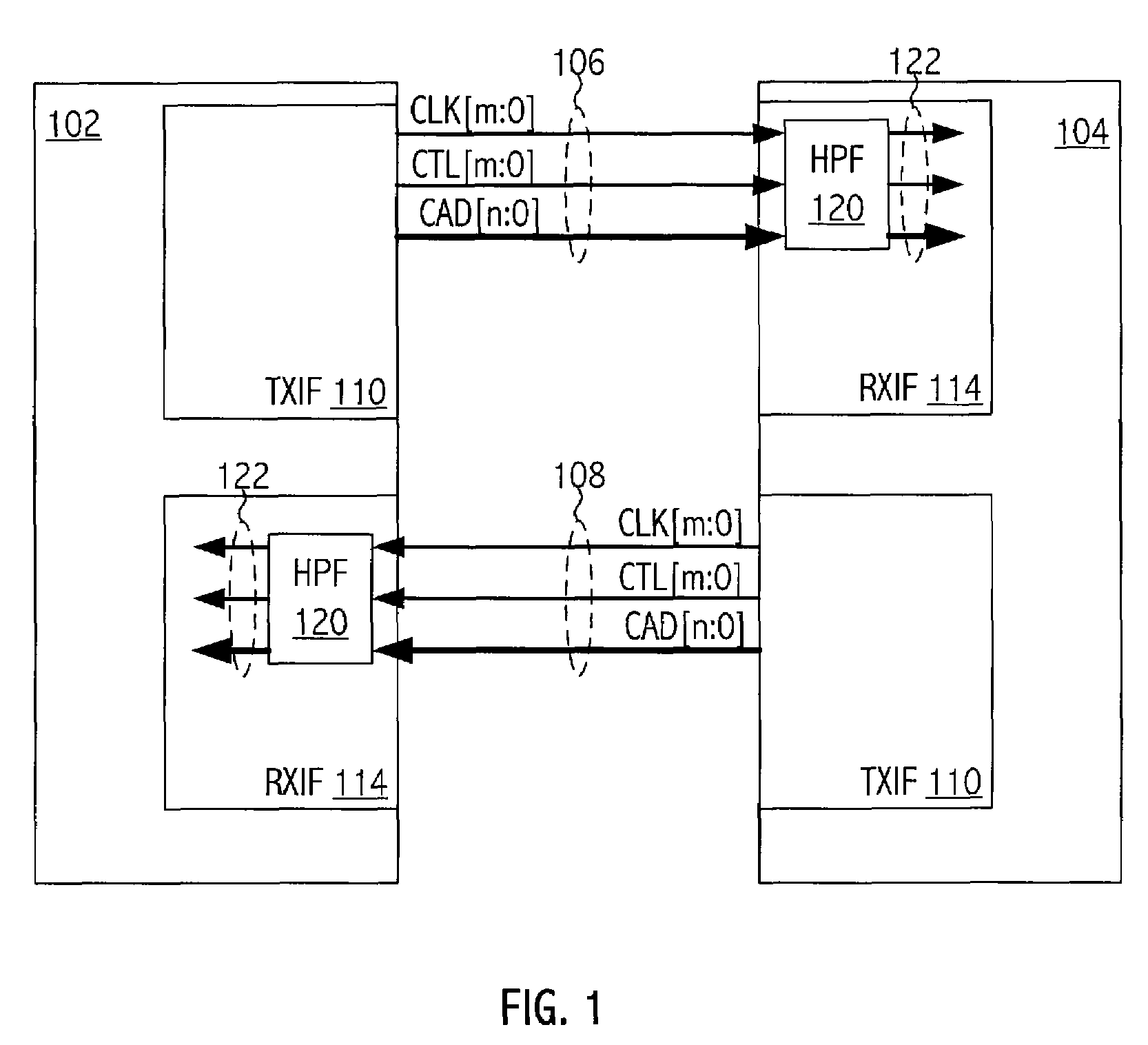

Serial communications protocols

ActiveUS20120297233A1Identical operationIdentical performancePulse automatic controlMultiple digital computer combinationsData streamData acquisition

Systems and methods are disclosed which relate to improving synchronization of clocks between a sender and a receiver communicating via an asynchronous serial interface. In a ring topology, a master device is connected to a plurality of slaves communicating using a bi-frequency encoded bit stream. A host device communicates with the master device using a non-return-to-zero data encoding. Each slave receives data from the master and sends it to the next slave in the ring unaltered unless the master indicates a requirement for a particular data, and transmits placeholder bits with a value of 0 around the ring. A particular slave can “fill-in” the placeholder bits with the information to be sent back to the master by inverting the placeholder bit. Clock synchronization between a receiving device and a transmitting device is improved using a fractional rate multiplier to generate a data sampling clock from a system clock. By adjusting the denominator, the sampling clock can be tuned to match the baud rate of the asynchronous serial data stream received from the transmitting device. Embodiments described include power management, data acquisition (DAQ), etc.

Owner:TEXAS INSTR INC

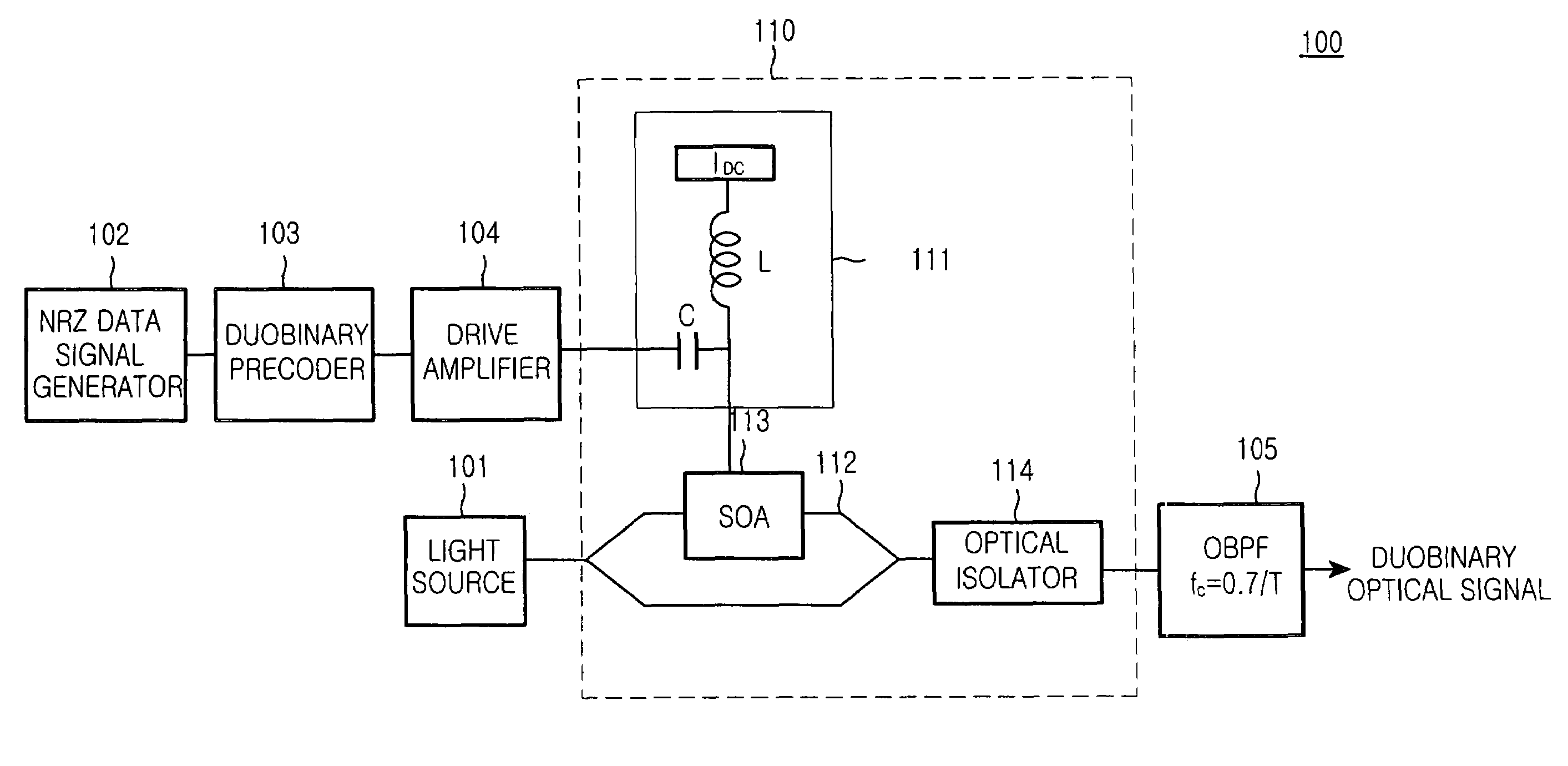

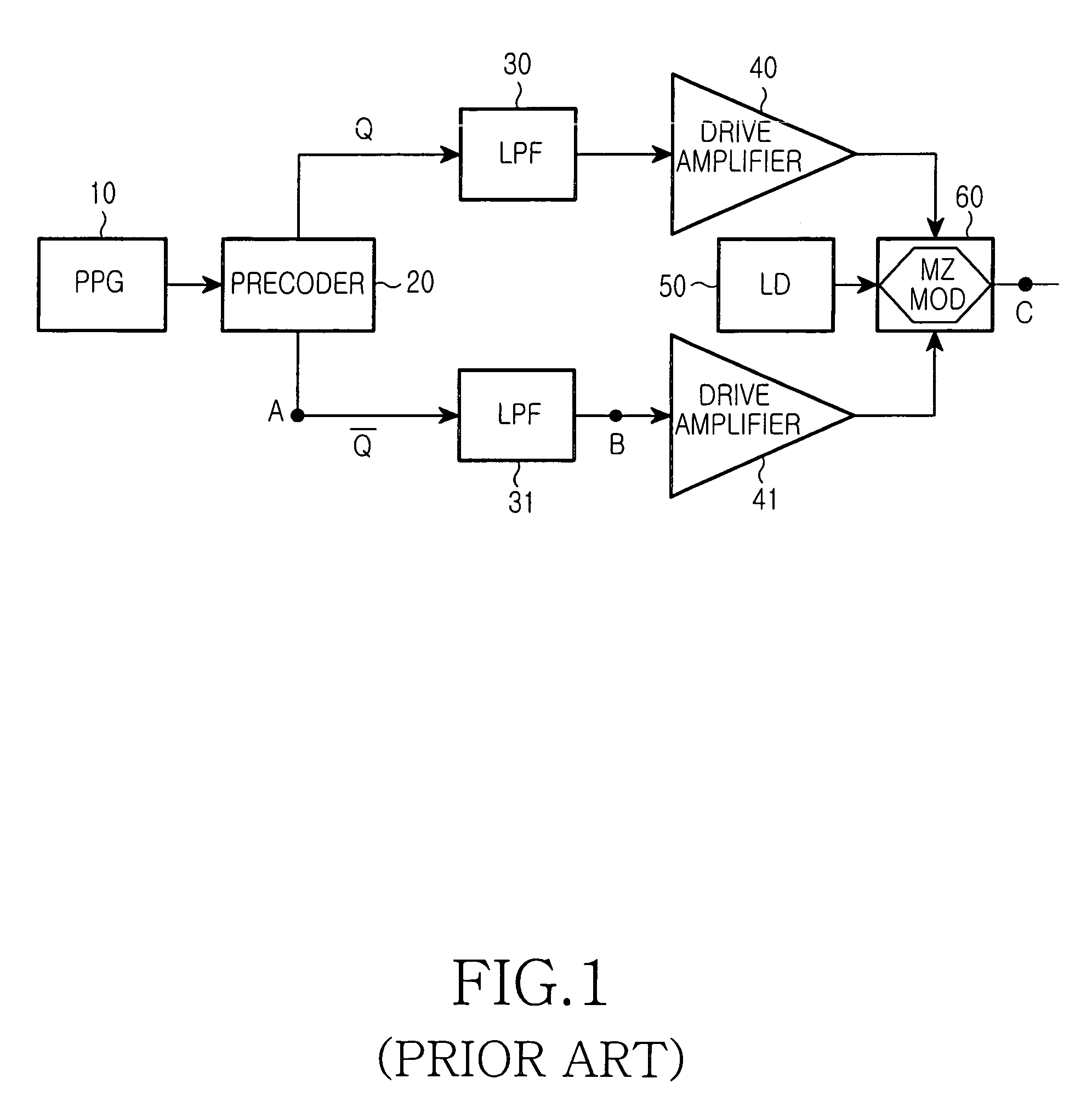

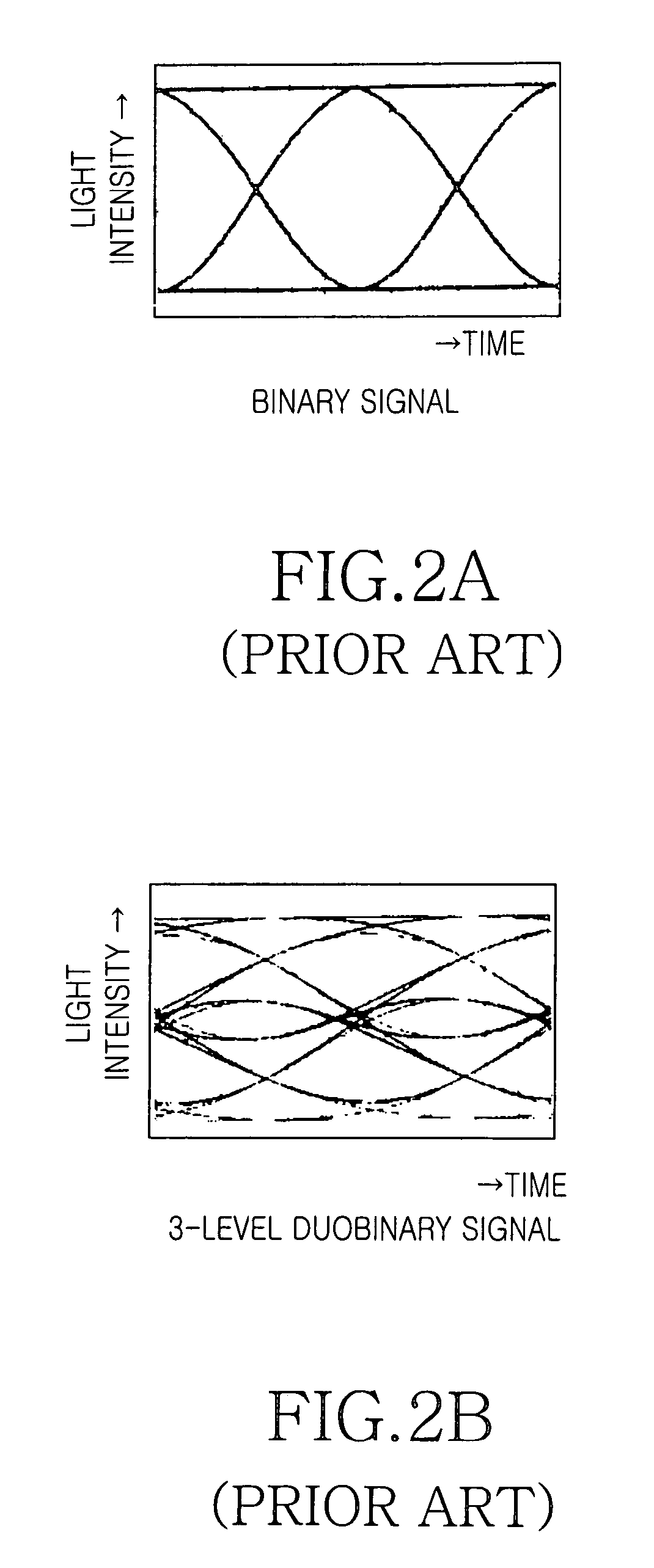

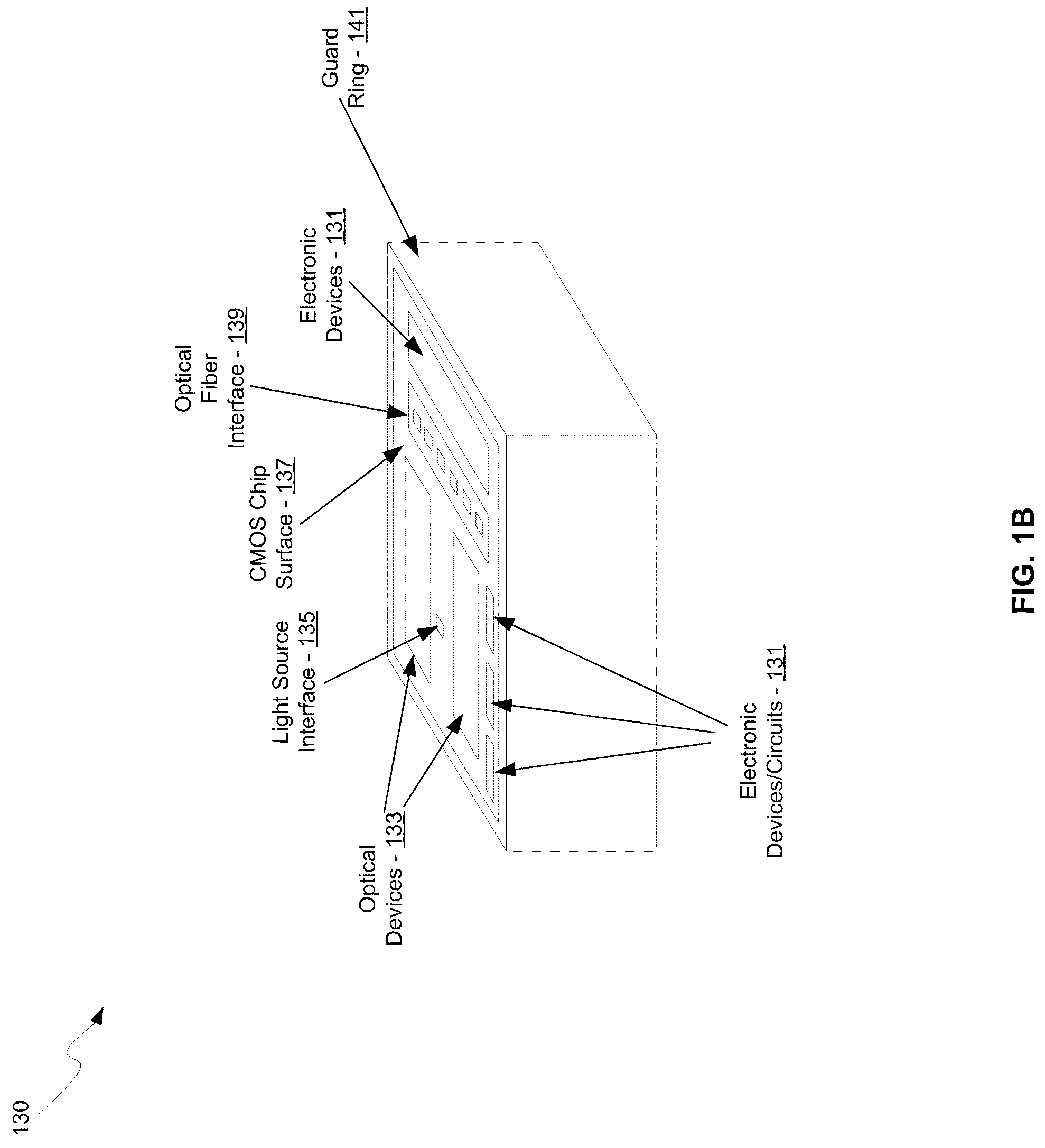

Duobinary optical transmission device using at least one semiconductor optical amplifier

InactiveUS7474858B2Spread the wordGood dispersionDistortion/dispersion eliminationElectromagnetic transmittersLow-pass filterCarrier signal

A duobinary optical transmission device provides duobinary optical transmission with improved quality by a technique that does not require an electrical low pass filter LPF.A duobinary optical transmission device includes at least one semiconductor optical amplifier (SOA). A light source outputs a carrier wave as an optical signal. A precoder encodes an input of a non-return-to-zero (NRZ) electrical signal. An interferometer type semiconductor optical amplification unit modulates the carrier wave according to a change of an applied bias current coupled to the encoded signal. An optical band pass filter (OBPF) receives the phase-modulated optical signal from the semiconductor optical amplification unit, filters the received phase-modulated optical signal according to a designated band, and outputs an optical duobinary signal.

Owner:SAMSUNG ELECTRONICS CO LTD

Decision feedback restore

ActiveUS20080057900A1Reduce and eliminate effectMultiple-port networksDelay line applicationsEngineeringNon-return-to-zero

An AC coupled receiver incorporates a decision feedback restore technique that is readily implemented on a monolithic integrated circuit to reduce or eliminate effects of baseline wander in a non-return-to-zero (NRZ) data receiver. In at least one embodiment of the invention, a method includes at least substantially attenuating at least a DC portion of a received signal to generate a first signal. The method includes generating a low frequency signal based at least in part on a reference signal selected from a plurality of reference signals. The method includes generating a restored signal based at least in part on the first signal and the low frequency signal.

Owner:ADVANCED MICRO DEVICES INC

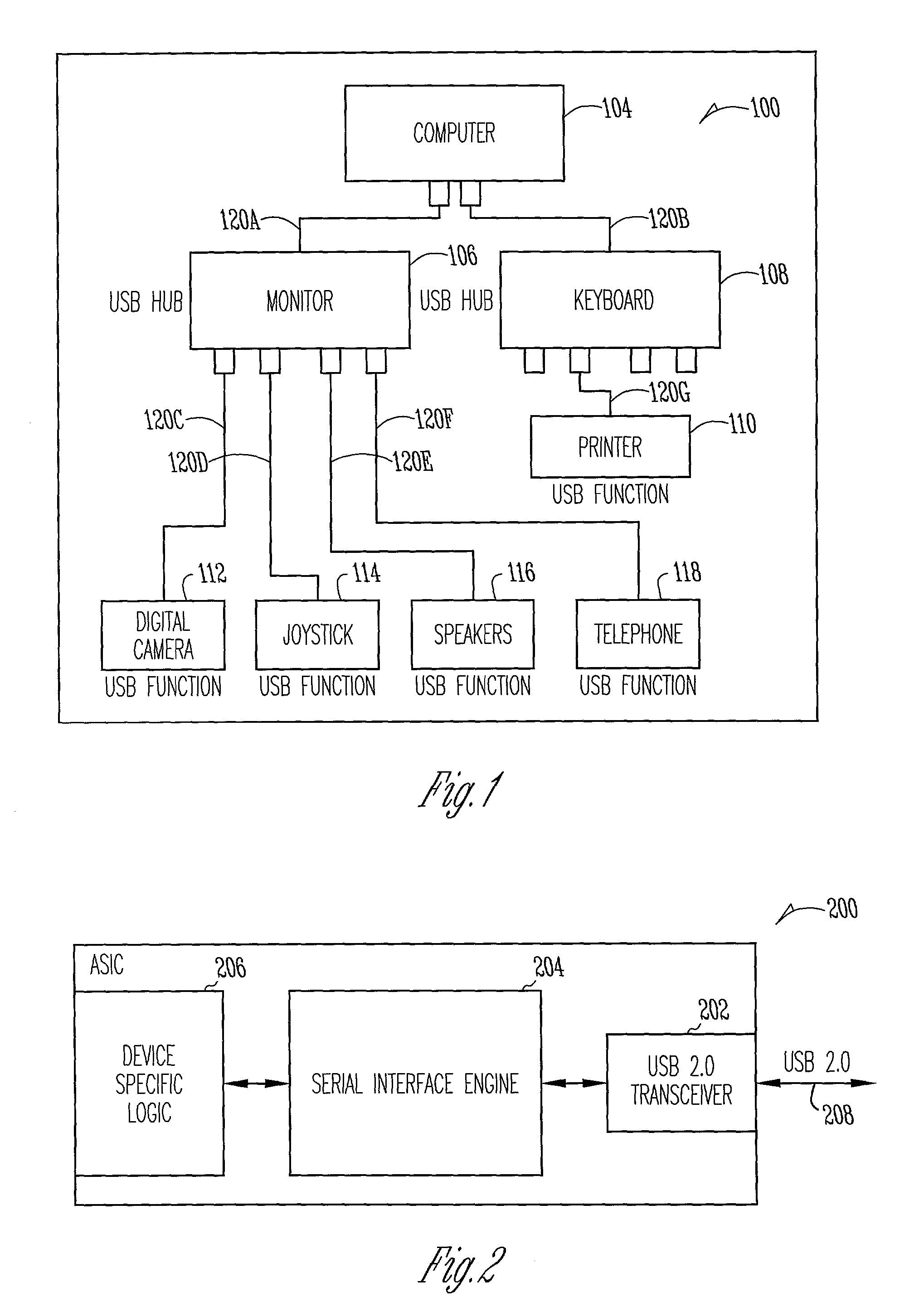

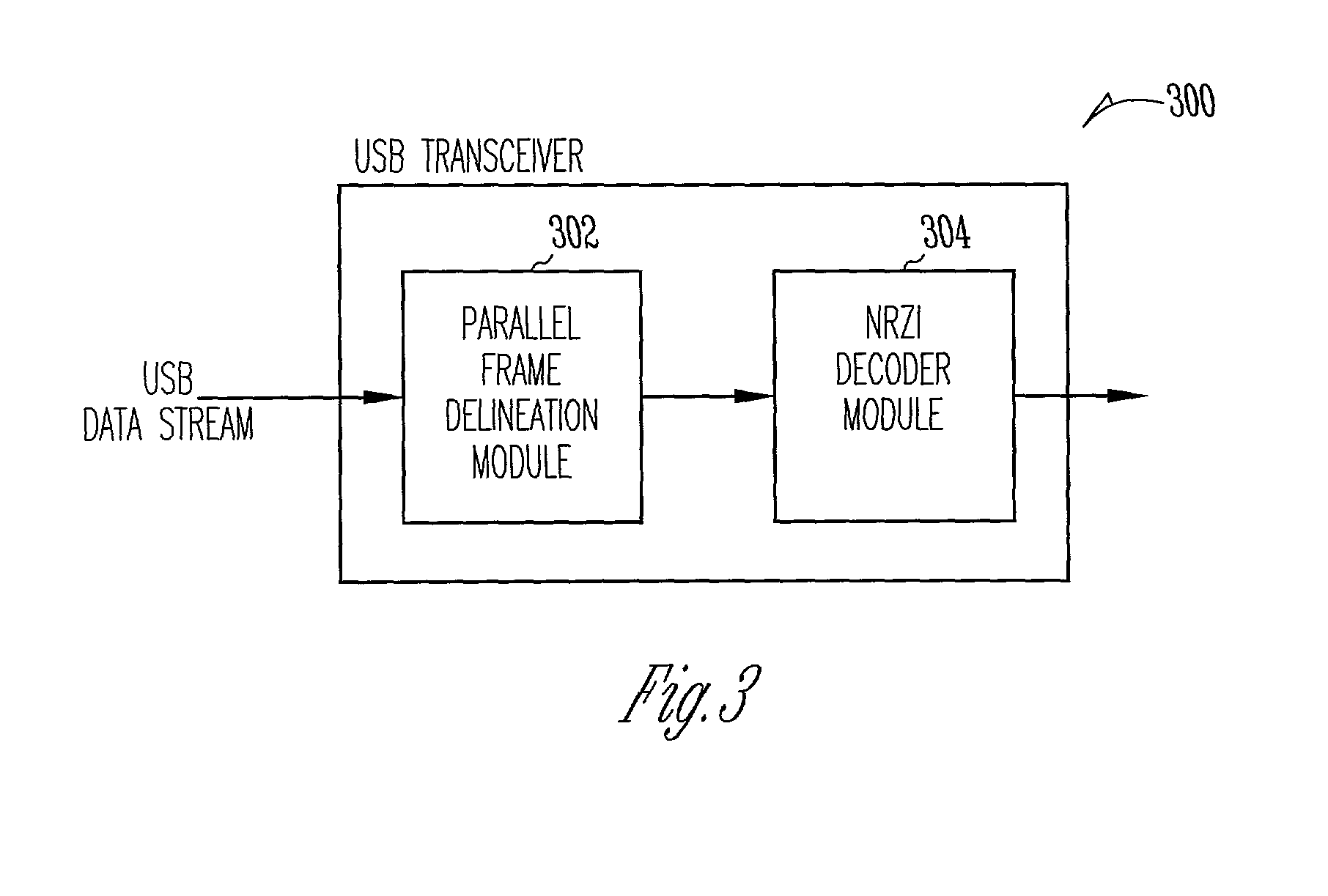

Pipelined, universal serial bus parallel frame delineator and NRZI decoder

A pipelined Universal Serial Bus (USB) parallel frame delineator and non-return to zero invert (NRZI) decoder is described. Using a three-stage pipeline and parallel data stream processing, a USB transceiver delineates received asynchronous frame boundaries within a USB peripheral NRZI data stream. Using asynchronous parallel data stream processing the USB transceiver concurrently decodes received NRZI encoded data.

Owner:INTEL CORP

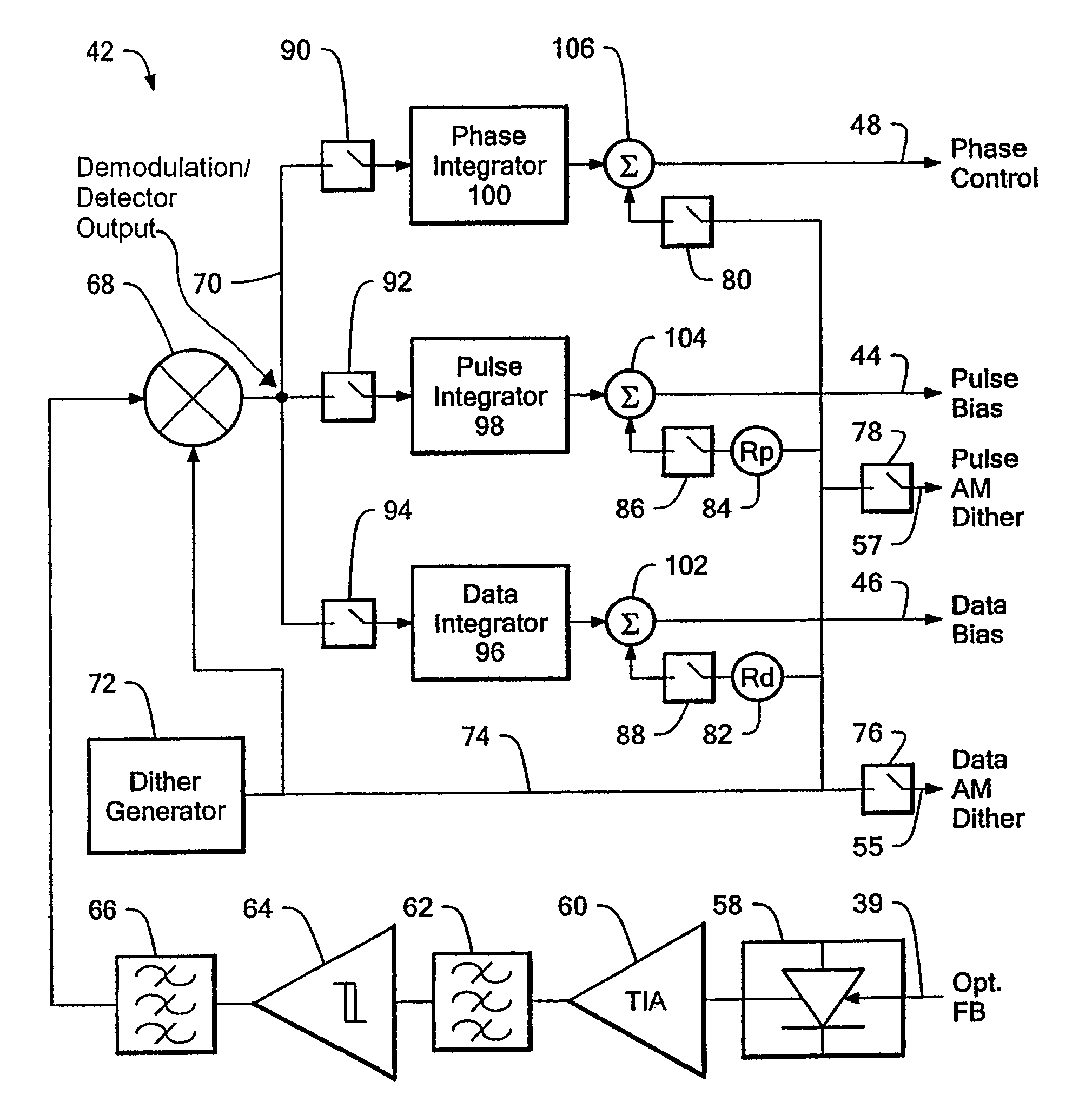

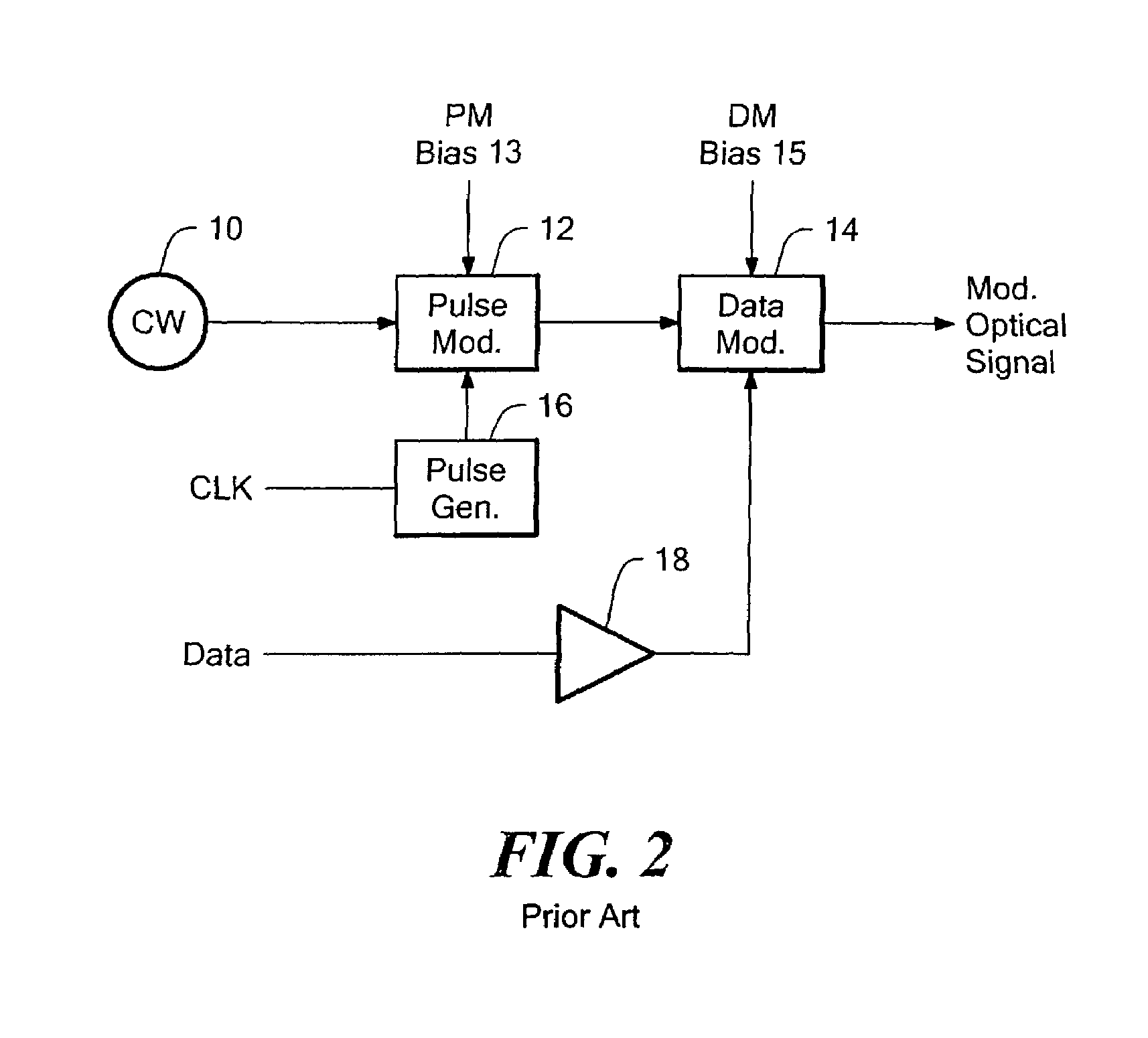

Control of an optical modulator for desired biasing of data and pulse modulators

ActiveUS7394992B2Sacrificing performanceStable and accurate operating pointTransmission monitoringElectromagnetic transmittersData streamPulse modulator

In an optical transmitter, continuous wave light from a laser passes through a data modulator (DM) for non-return-to-zero (NRZ) encoding of a data stream and through a pulse modulator to add return-to-zero encoding to the modulated optical signal. A modulator controller monitors the output optical signal power, optimizes the bias setting for the DM and the PM, and optimizes the phase relationship between the pulse and data components of the modulated optical signal. For each optimization, a low amplitude and low frequency dither signal is injected at appropriate points in the modulator. A single photo detector and electrical receiver are used in a multiplexed fashion to monitor the optical output signal and derive separate feedback signals. Remaining control circuitry forces a null in a respective residual dither component in the optical output signal to maintain the desired bias level or phase alignment.

Owner:LUMENTUM OPTICS INC

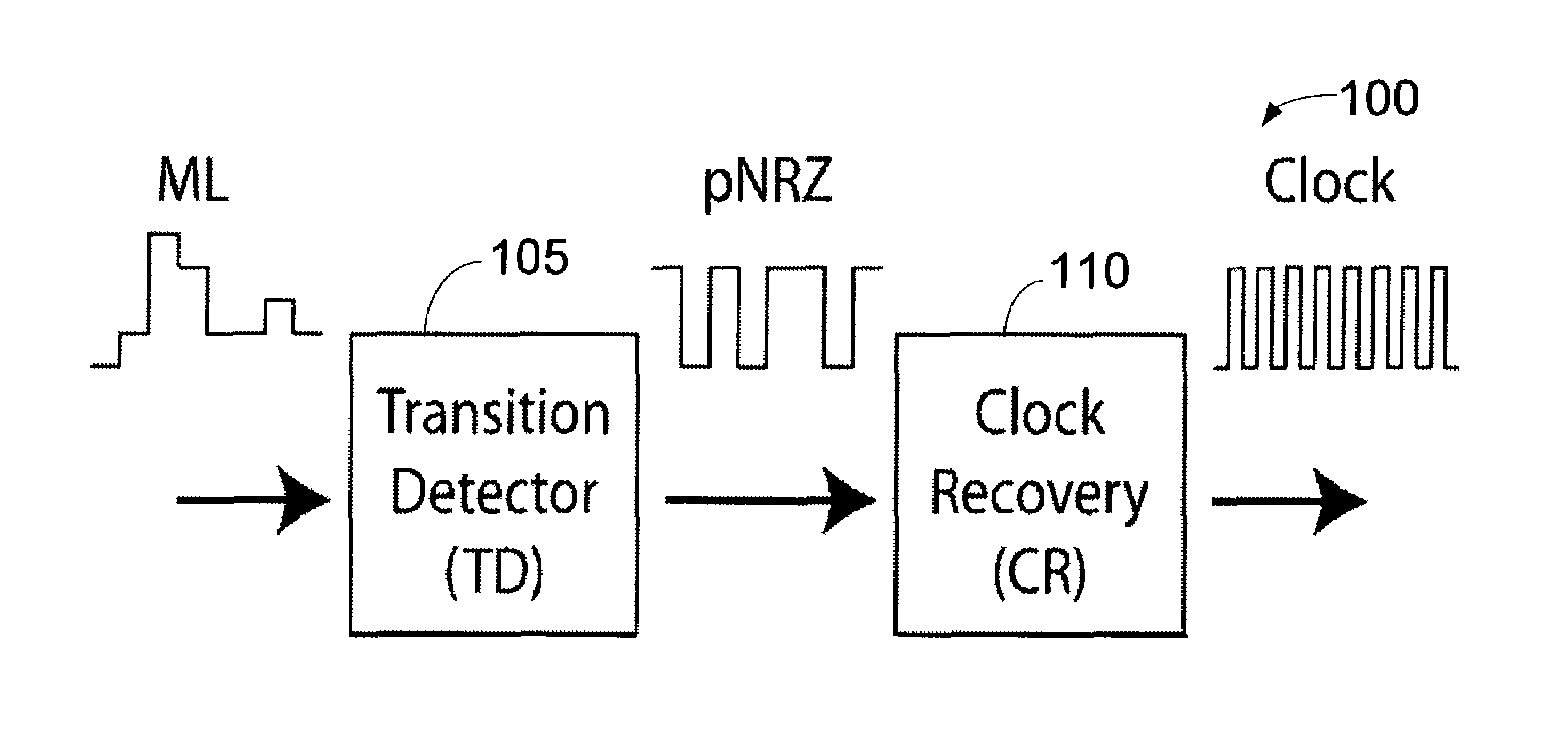

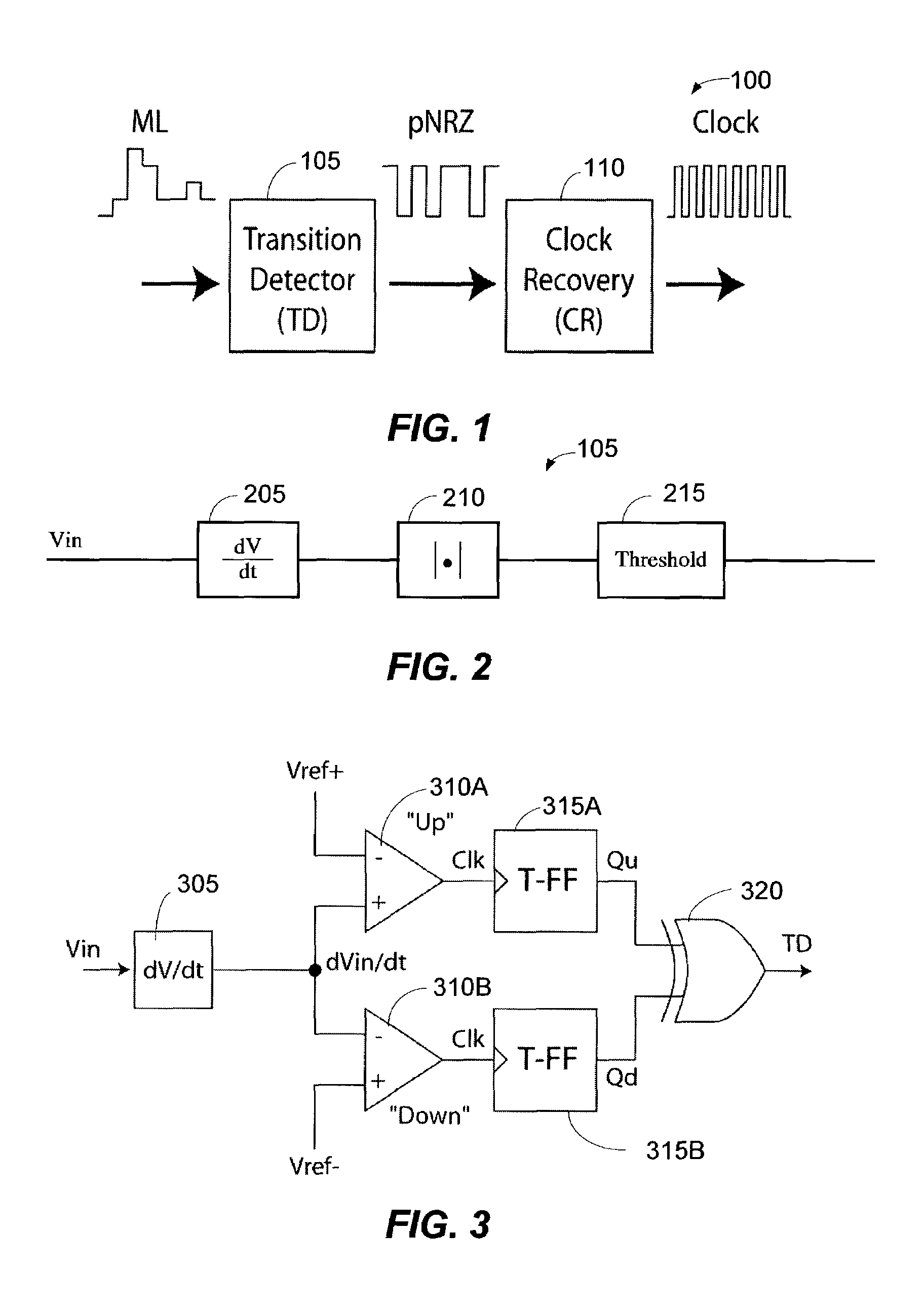

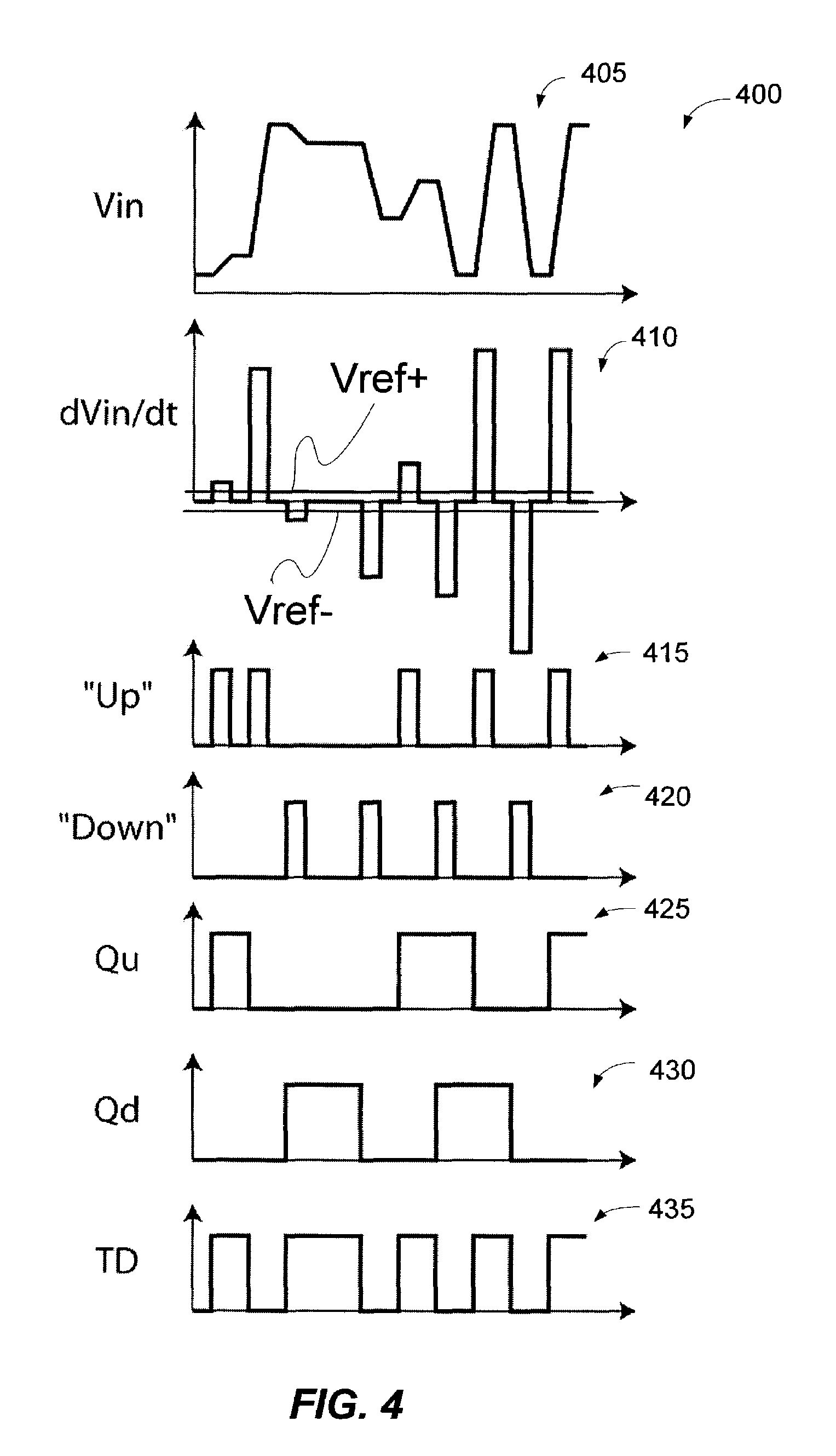

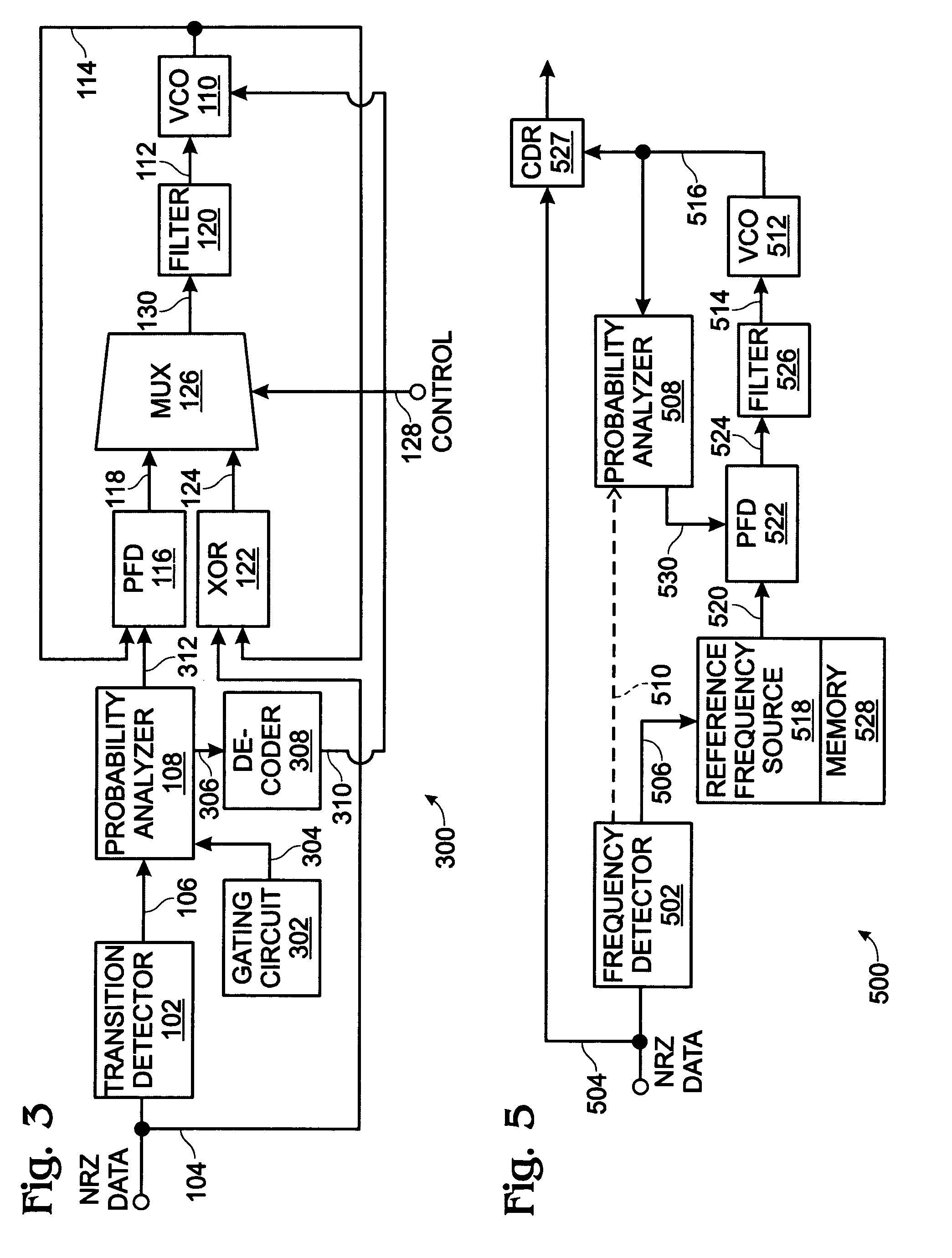

Multi-level signal clock recovery technique

ActiveUS7212580B2Dc level restoring means or bias distort correctionLine balance variation compensationClock recoveryEngineering

Clock recovery of a multi-level (ML) signal can be performed in a two-step process. First, the transitions within the ML signal can be detected by a novel transition detector (TD). And second, the output of the TD circuit can comprise a pseudo-non-return-to-zero (pNRZ) signal that can drive a conventional OOK clock recovery (CR) IC. The TD circuit can convert the edges of the ML signal into the pseudo-NRZ (pNRZ) signal. The TD circuit can capture as many transitions as possible to allow the conventional NRZ clock recovery (CR) chip to optimally perform. The TD circuit can differentiate the ML signal in order to detect the ML signal's transitions.

Owner:INTERSIL INC

Decision feedback restore of DC signals in a receiver

ActiveUS7720141B2Reduce and eliminate effectMultiple-port networksDelay line applicationsEngineeringNon-return-to-zero

An AC coupled receiver incorporates a decision feedback restore technique that is readily implemented on a monolithic integrated circuit to reduce or eliminate effects of baseline wander in a non-return-to-zero (NRZ) data receiver. In at least one embodiment of the invention, a method includes at least substantially attenuating at least a DC portion of a received signal to generate a first signal. The method includes generating a low frequency signal based at least in part on a reference signal selected from a plurality of reference signals. The method includes generating a restored signal based at least in part on the first signal and the low frequency signal.

Owner:ADVANCED MICRO DEVICES INC

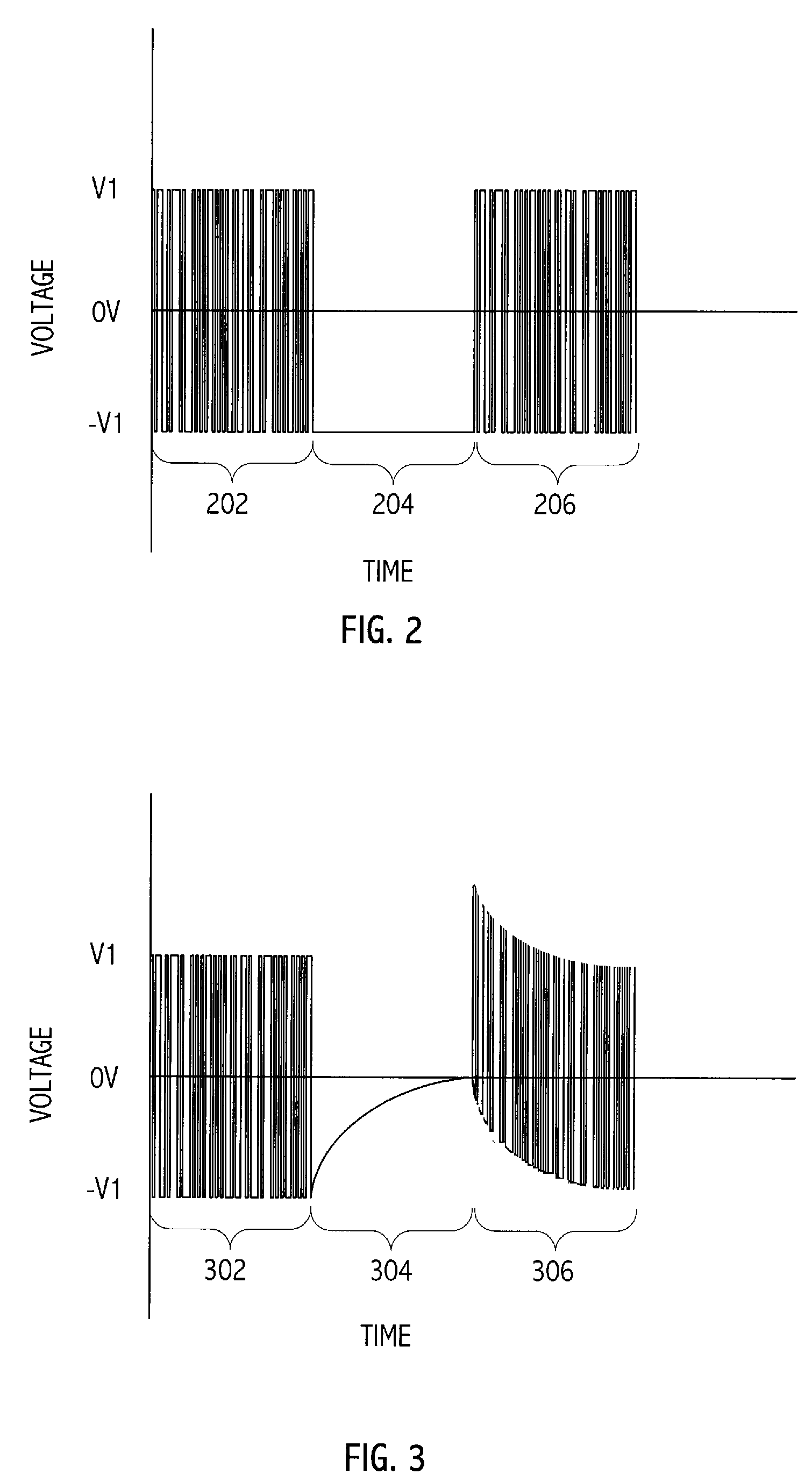

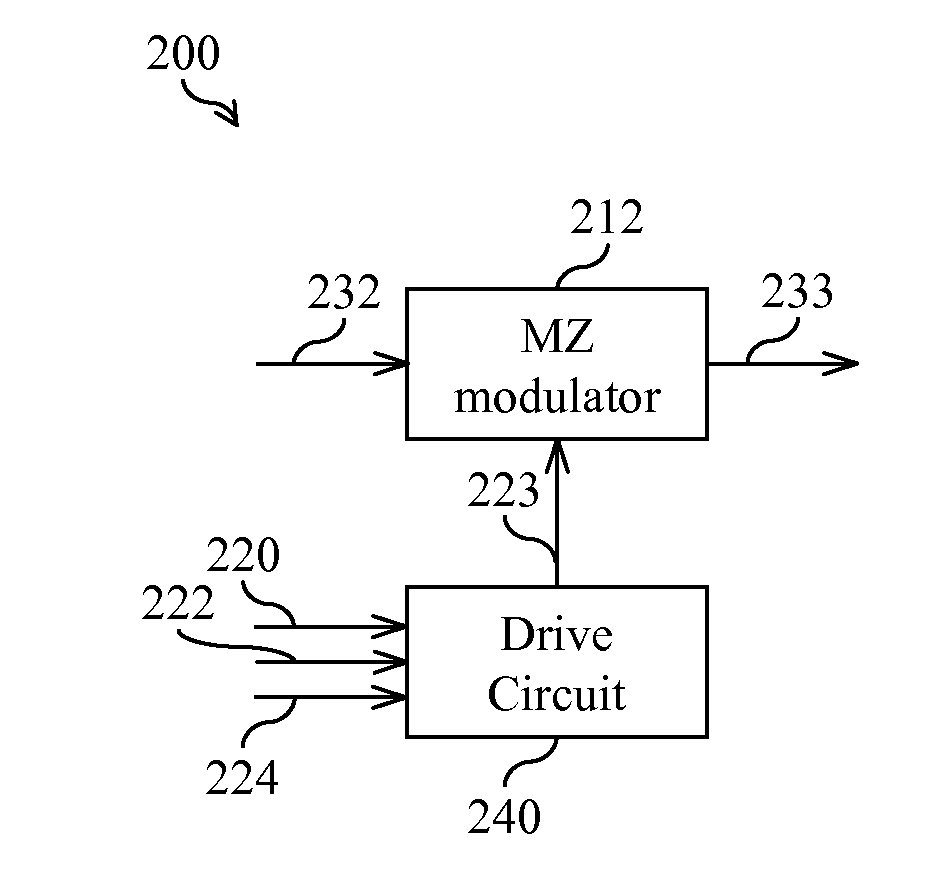

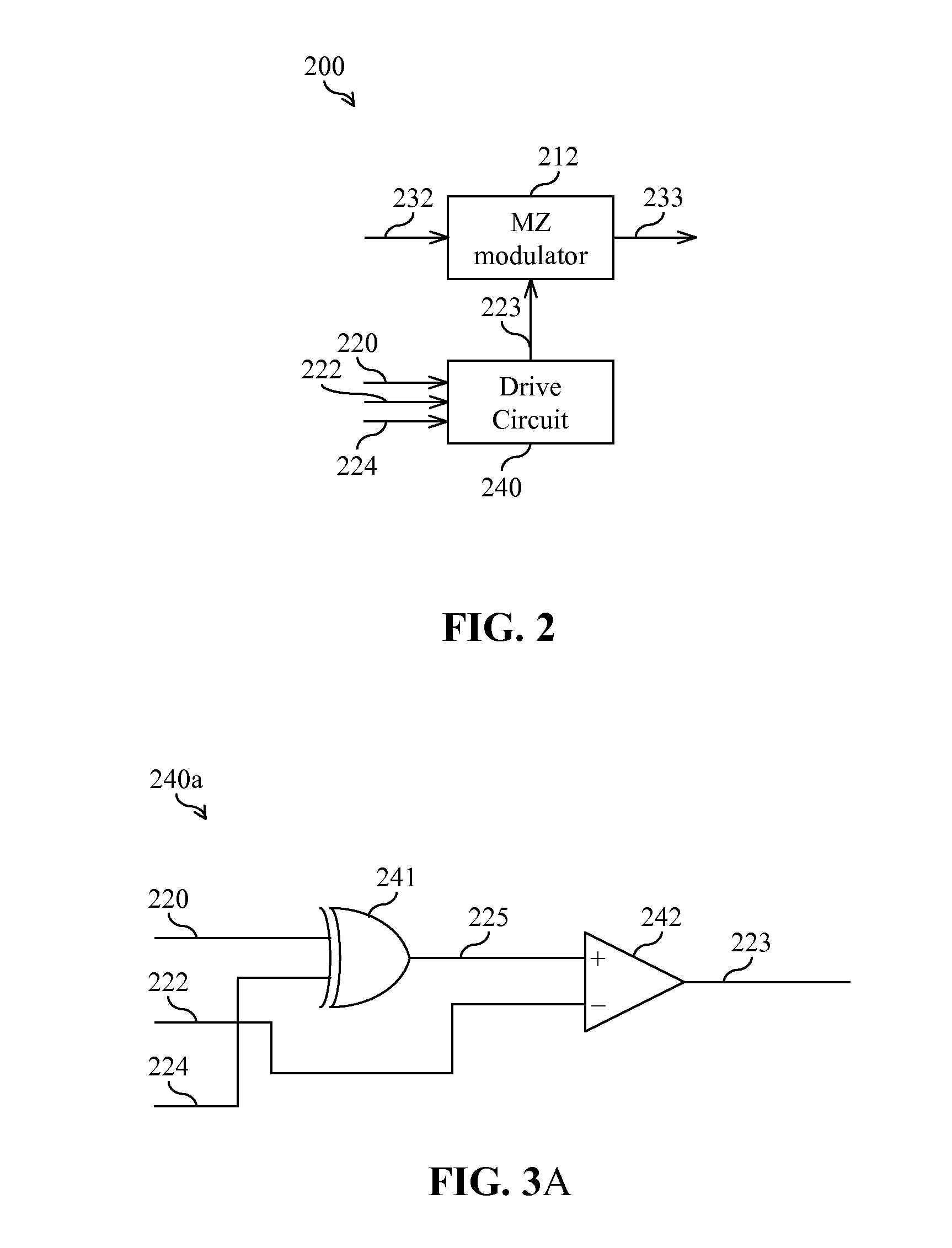

Modulation system and method for generating a return-to-zero (RZ) optical data signal

ActiveUS20110043888A1Simple methodElectromagnetic transmissionNon-linear opticsElectricityReturn-to-zero

A modulation system and a method for generating a return-to-zero (RZ) optical data signal are provided. The modulation system comprises a Mach-Zehnder (MZ) modulator and a drive circuit, which includes a logic XOR gate and a differential amplifier. The logic XOR gate applies a logic XOR operation to a non-return-to-zero (NRZ) electrical data signal and an inverse of an electrical clock signal to generate an electrical intermediate signal. The differential amplifier differentially amplifies the electrical intermediate signal and an inverse of the NRZ electrical data signal to generate an RZ electrical drive signal. The drive circuit drives the MZ modulator with the RZ electrical drive signal to generate the RZ optical data signal.

Owner:LUMENTUM OPERATIONS LLC

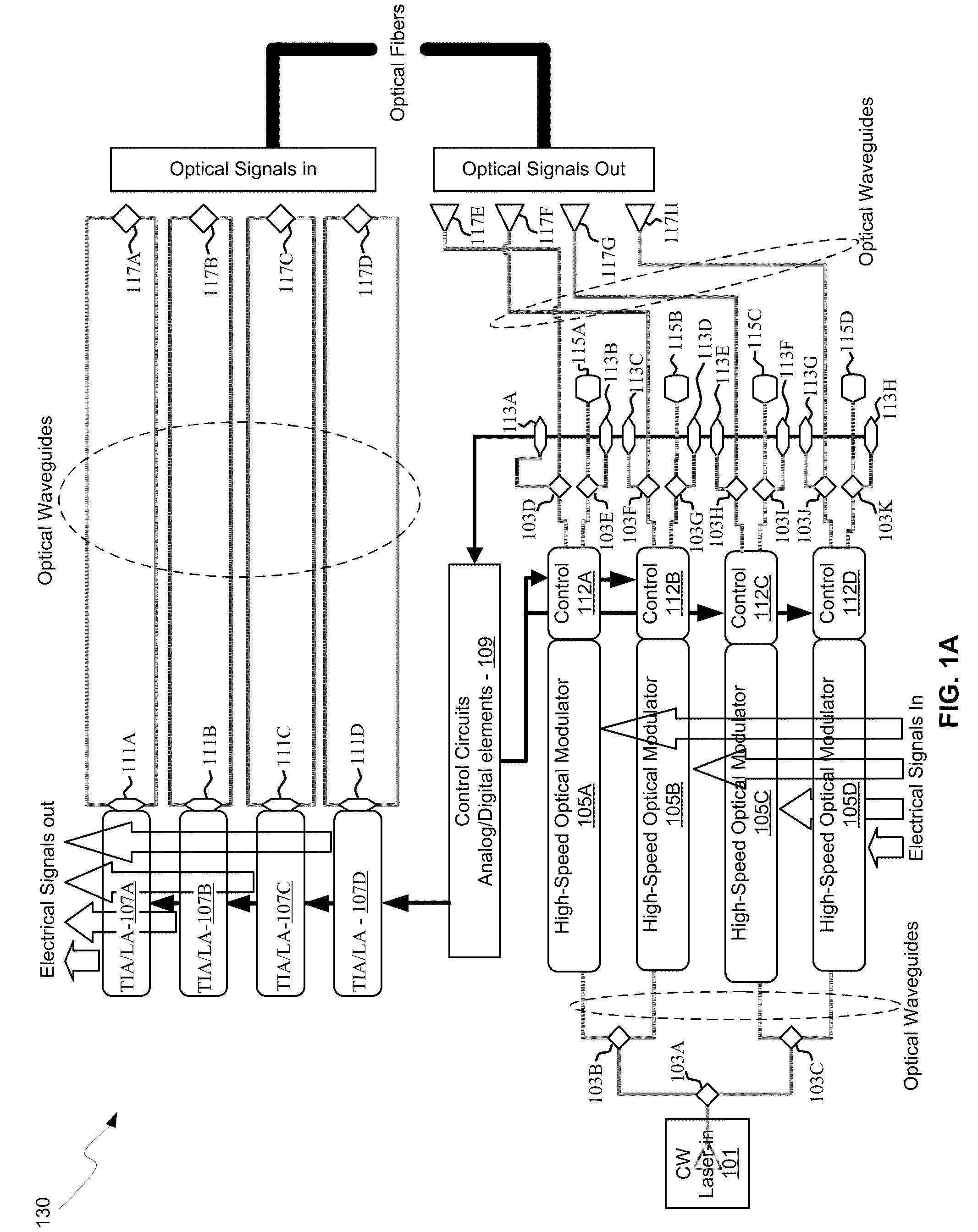

Method and system for a narrowband, non-linear optoelectronic receiver

Methods and systems for a narrowband, non-linear optoelectronic receiver are disclosed and may include amplifying a received signal, limiting a bandwidth of the received signal, and restoring the signal utilizing a level restorer, which may include a non-return to zero (NRZ) level restorer. The NRZ level restorer may include a pulse-triggered bistable circuit, which may include two parallel inverters, with one being a feedback path for the other. The inverters may be single-ended or differential. A photogenerated signal may be amplified in the receiver utilizing a transimpedance amplifier and programmable gain amplifiers (PGAs). A received electrical signal may be amplified via PGAs. The bandwidth of the received signal may be limited utilizing one or more of: a low pass filter, a bandpass filter, a high pass filter, a differentiator, or a series capacitance on the chip. The signal may be received from a photodiode integrated on the chip.

Owner:CISCO TECH INC

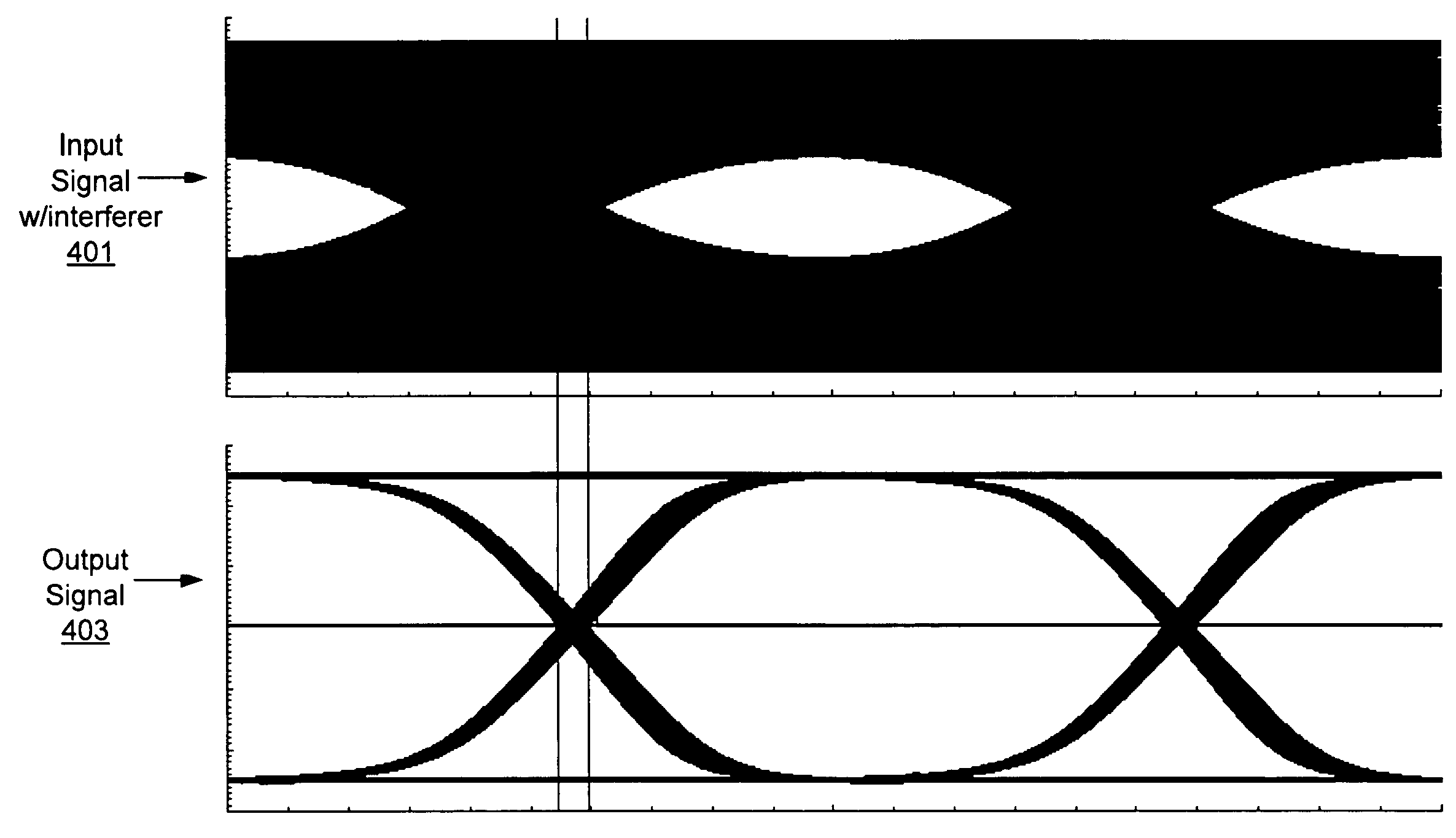

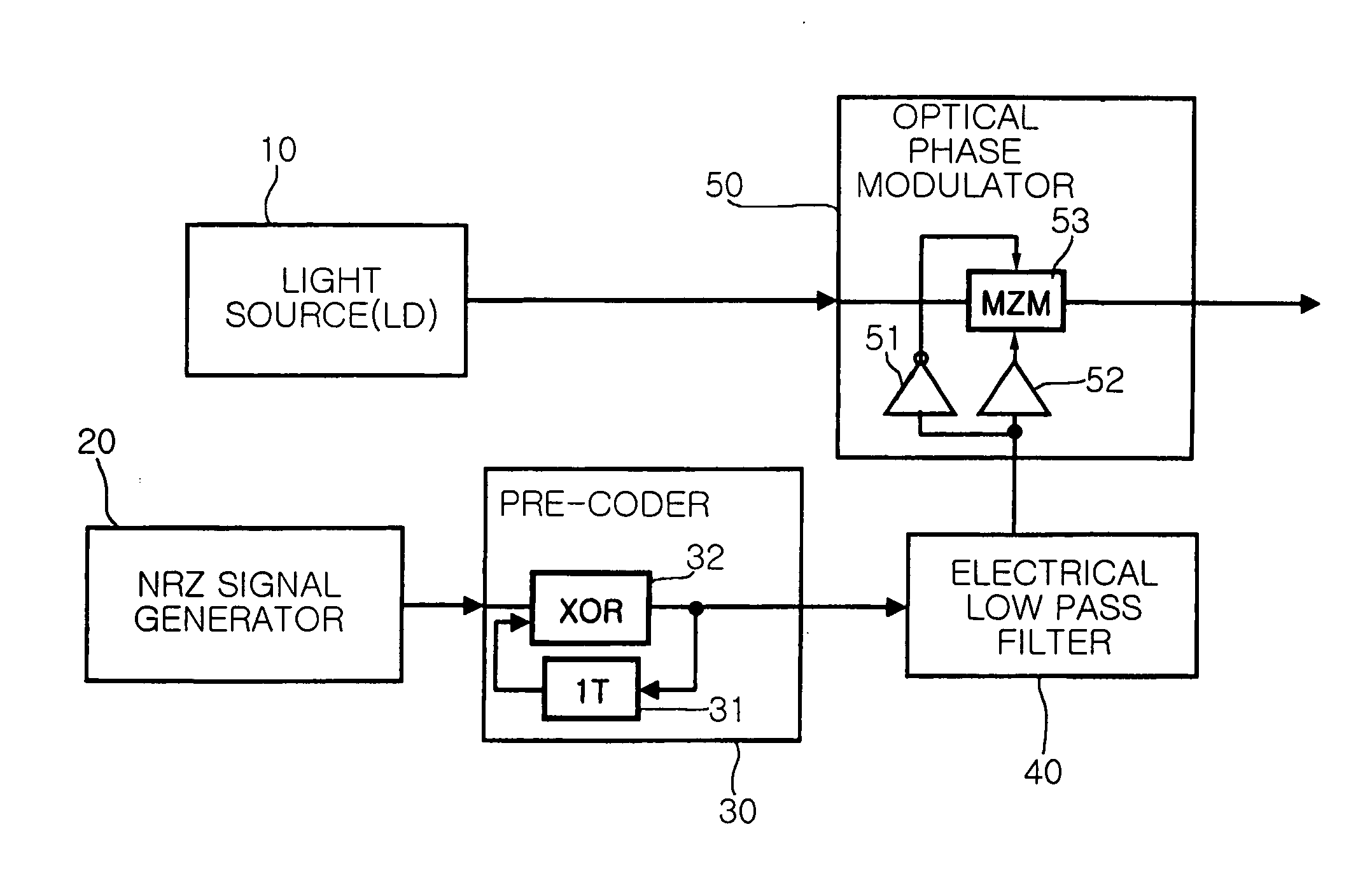

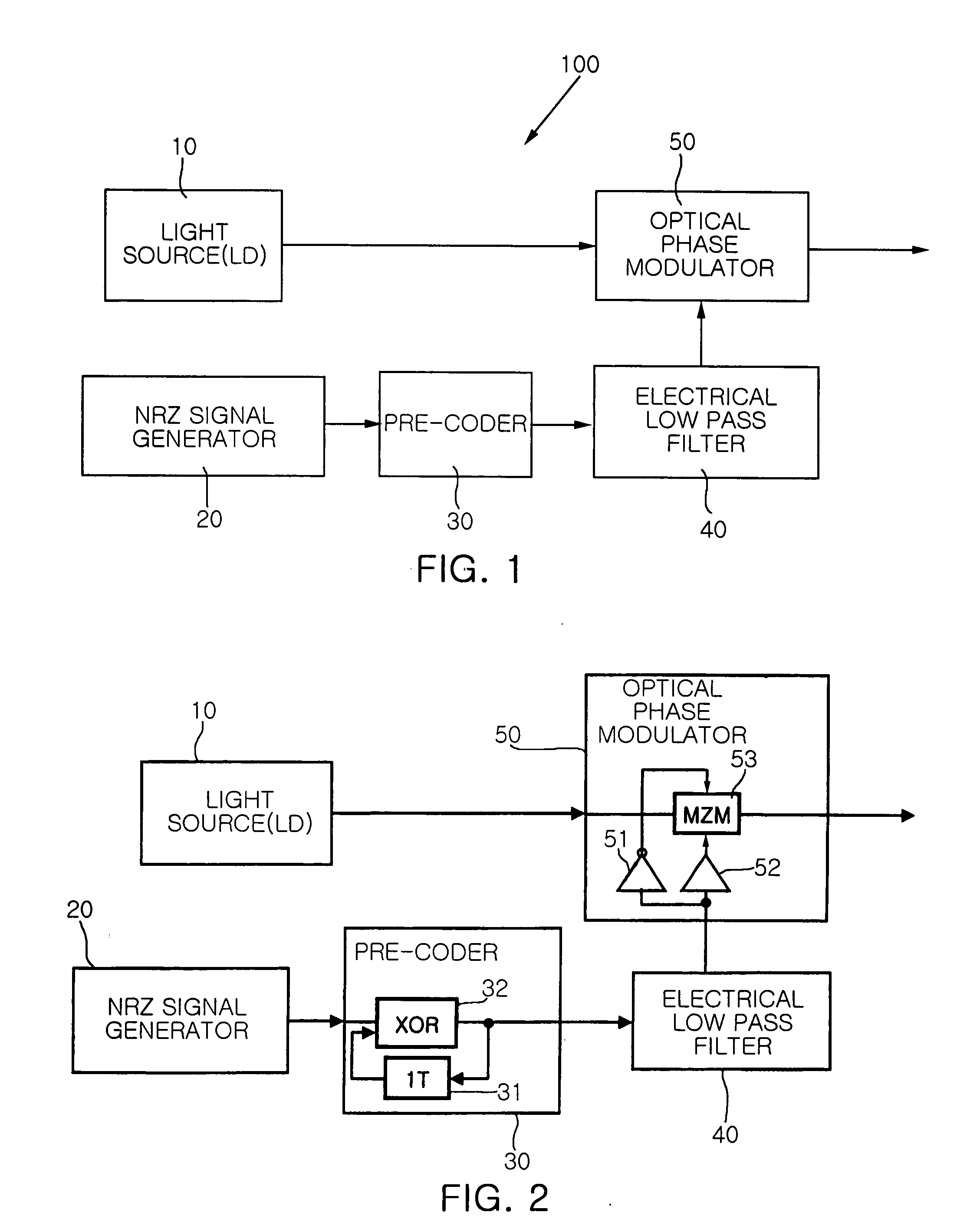

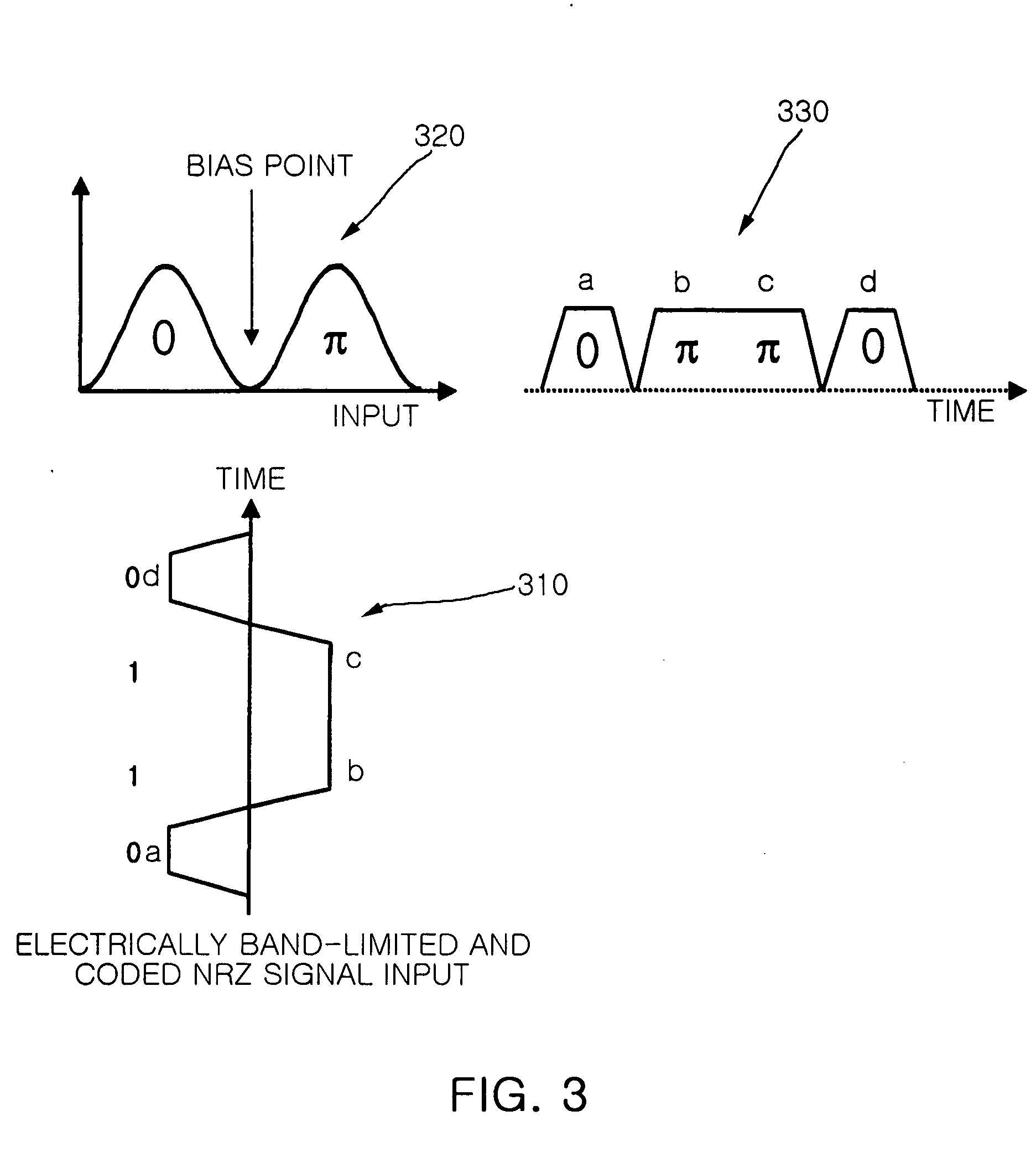

Apparatus and method for performing electrically band-limited optical differential phase shift keying modulation

InactiveUS20050135816A1Reduce crosstalkPhase-modulated carrier systemsElectromagnetic transmittersElectricityDifferential phase

The present invention relates to an apparatus and method for performing optical Differential Phase Shift Keying (DPSK) modulation, which transmits a phase difference between adjacent bits as information. The electrically band-limited optical DPSK modulating apparatus includes a light source, a Non-Return-to-Zero (NRZ) signal generator, a pre-coder, an electrical low pass filter, and a phase modulator. The NRZ signal generator generates a NRZ signal. The pre-coder codes the NRZ signal generated by the NRZ signal generator into a differential signal. The low pass filter electrically limits a bandwidth of the differential signal obtained through the pre-coder. The phase modulator modulates an optical signal input from the light source into a DPSK signal using the differential signal having the bandwidth electrically limited by the low pass filter.

Owner:ELECTRONICS & TELECOMM RES INST

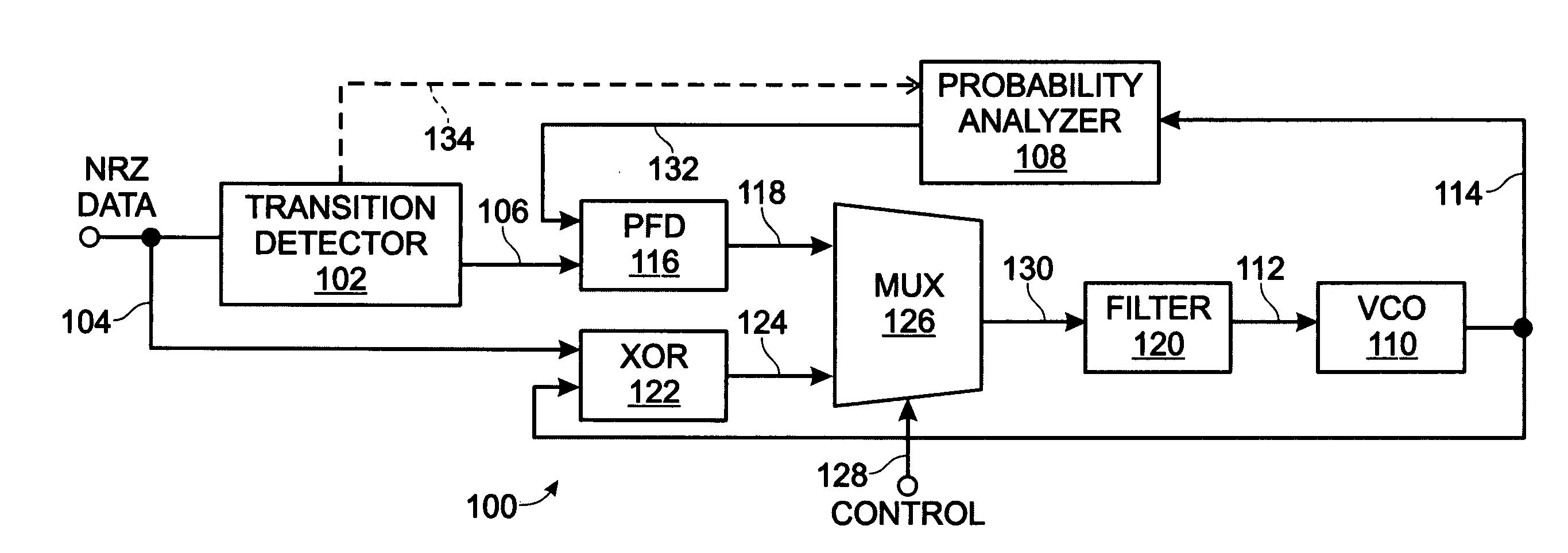

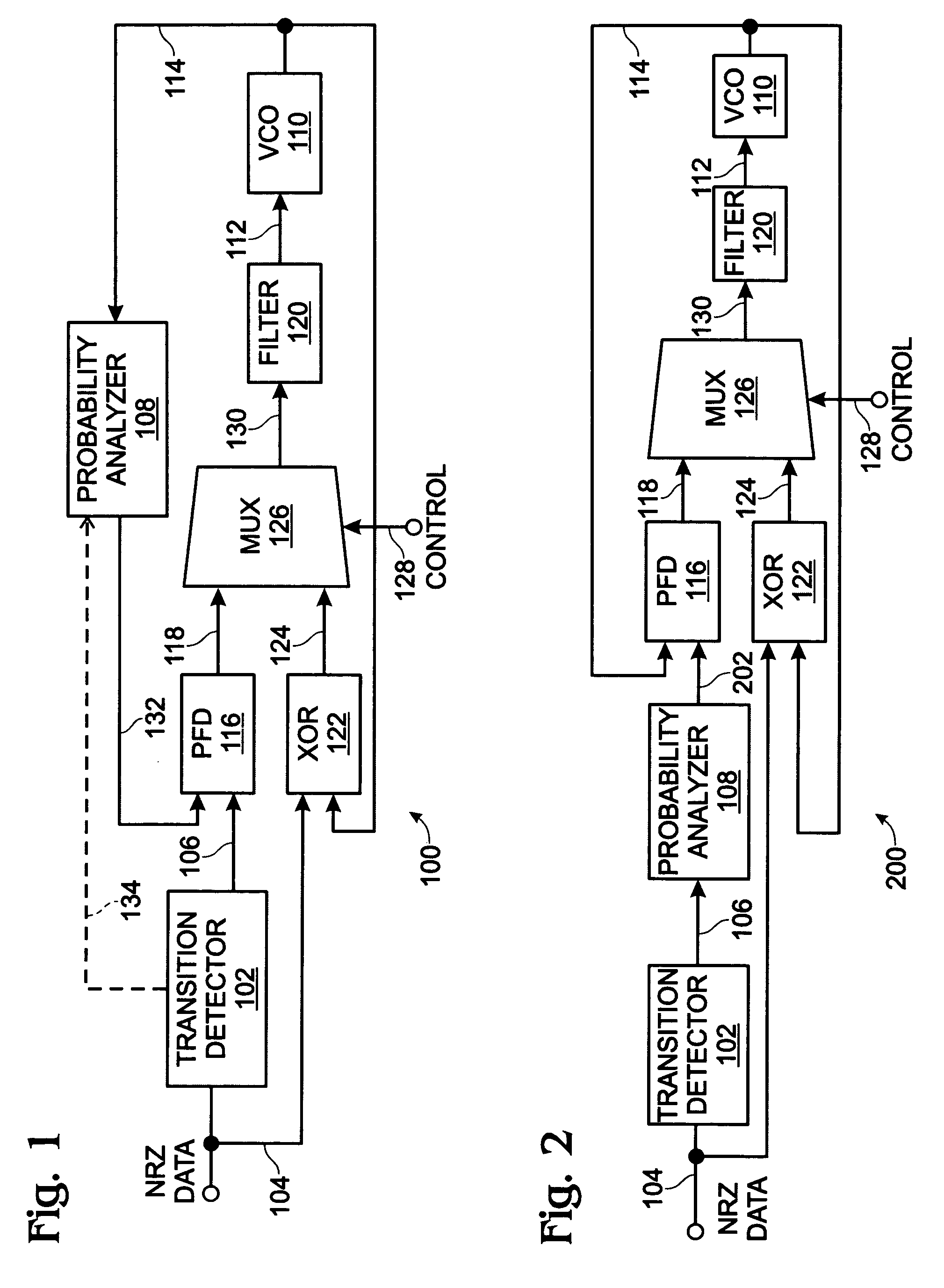

System and method for generating a reference clock

ActiveUS6985552B1Individual digits conversionAngle demodulation by phase difference detectionPhase detectorData stream

A system and method are provided for synchronizing a reference clock to a pseudorandom non-return to zero (NRZ) data stream in a clock data recovery system. The method comprises: sampling a pseudorandom NRZ data stream; determining a mean frequency of transitions (Fd) in the data stream; determining a transition probability (P) associated with the mean frequency of transitions; using a phase / frequency detector responsive to a VCO frequency, the mean frequency of transitions, and the transition probability; in response to using the phase / frequency detector, supplying a voltage controlled oscillator tuning voltage; generating the VCO frequency responsive to the tuning voltage; using a XOR phase detector to compare the VCO frequency to the NRZ data stream; in response to using the XOR phase detector, supplying a voltage controlled oscillator tuning voltage; and, generating the VCO frequency responsive to the tuning voltage. Also provided are a system and method for synchronizing a reference clock to a pseudorandom non-return to zero data stream in a clock data recovery system, and a system and method for generating a reference clock in the absence of a pseudorandom non-return to zero (NRZ) data stream in a system including a clock data recovery (CDR) unit.

Owner:MACOM CONNECTIVITY SOLUTIONS LLC

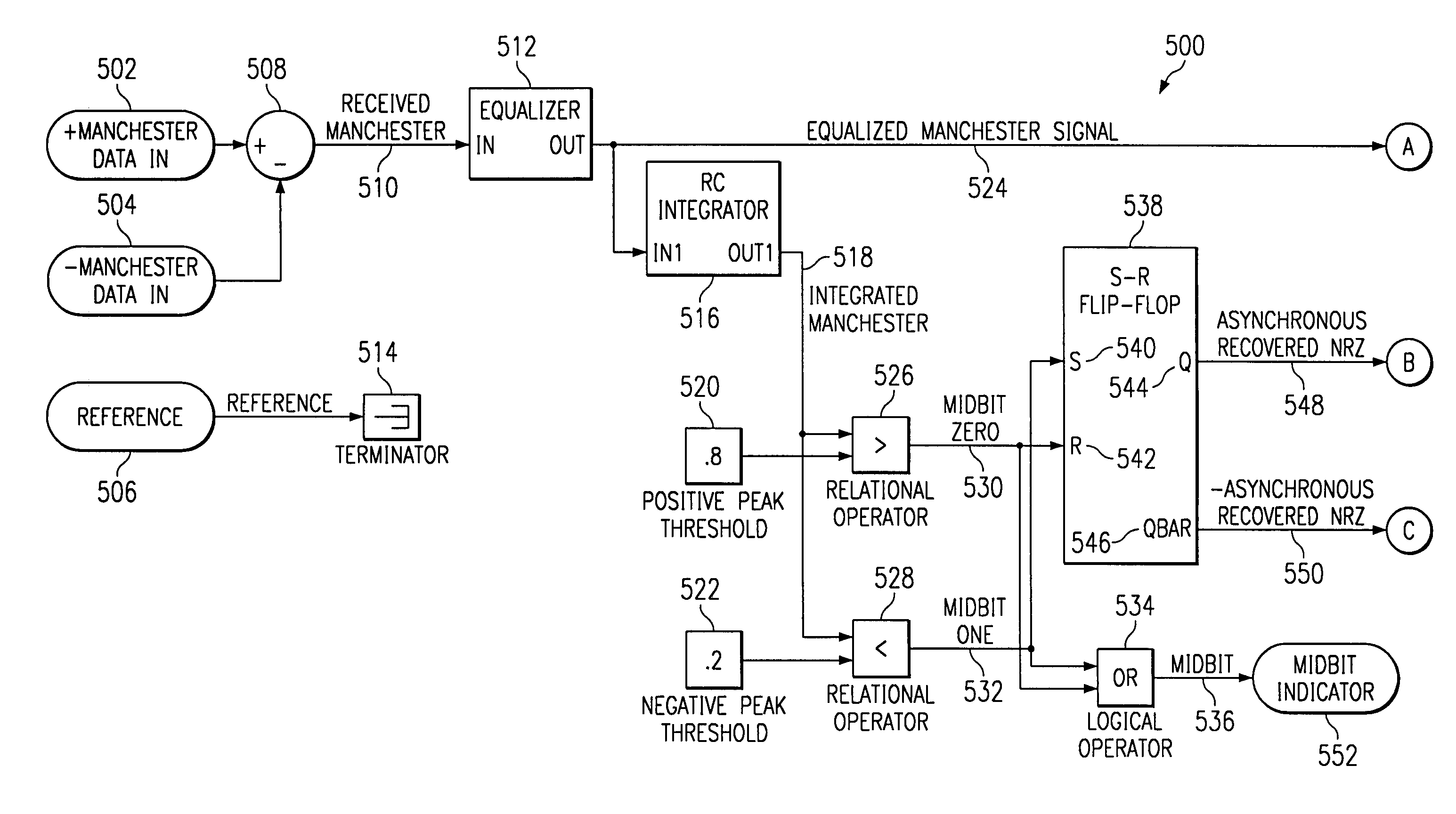

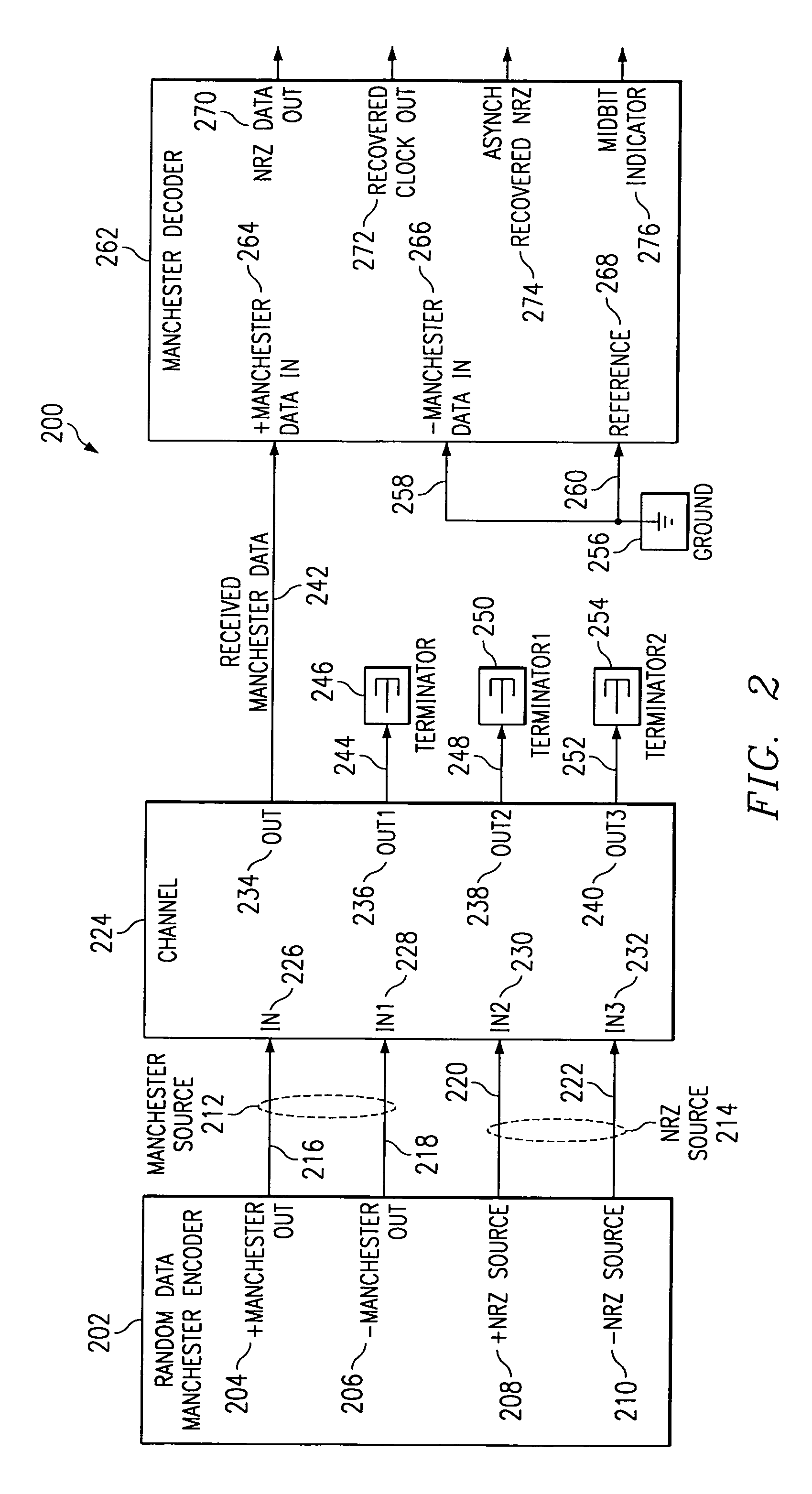

Method and system for clock/data recovery for self-clocked high speed interconnects

A method and system is provided for clock / data recovery for self-clocked high speed interconnects. A data signal is received and then equalized. The equalized data signal then provides the trigger to separate “ones” and “zeros” one-shots. The equalized Manchester data signal is also integrated, compared with a threshold value to determine the negative and positive peaks of the data signal. Then after the appropriate peak is determined, a mid-bit signal is sent as input to a set-reset flip-flop which thereby outputs an asynchronous recovered non-return to zero signal. This asynchronous recovered non-return to zero signal then provides an enable input to the “ones” one-shot and the complementary asynchronous recovered non-return to zero signal provides an enable input to the “zeros” one-shot. The “ones” one-shot outputs a “ones” clock signal and the “zeros” one-shot outputs a “zeros” clock signal. These two signals are verified and a recovered clock out signal is provided. The asynchronous recovered non-return to zero signal is supplied to a data flip-flop along with the recovered clock out signal and a constant and the result is a synchronous recovered non-return to zero signal.

Owner:IBM CORP

Method And System For Encoding And Decoding Information With Modulation Constraints And Error Control

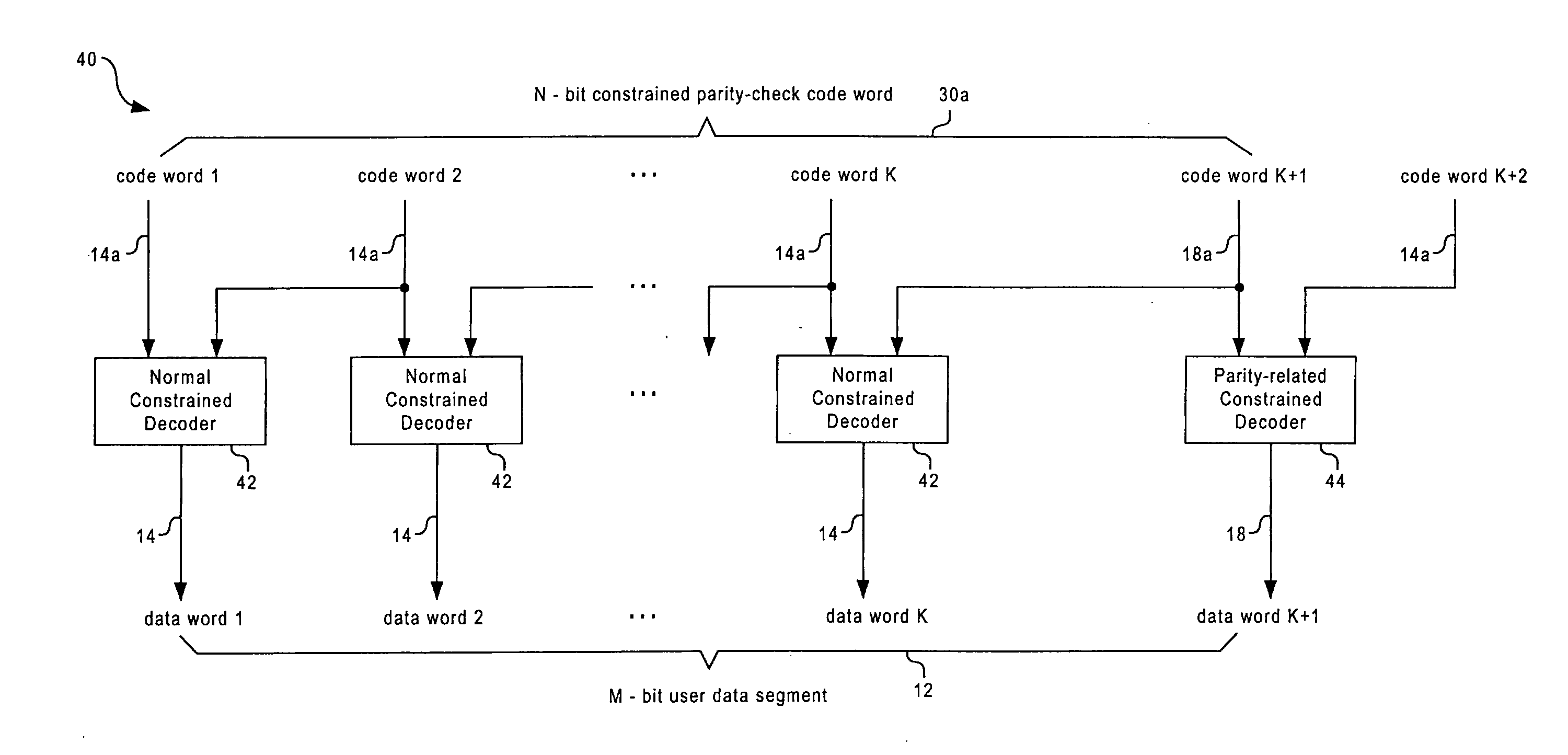

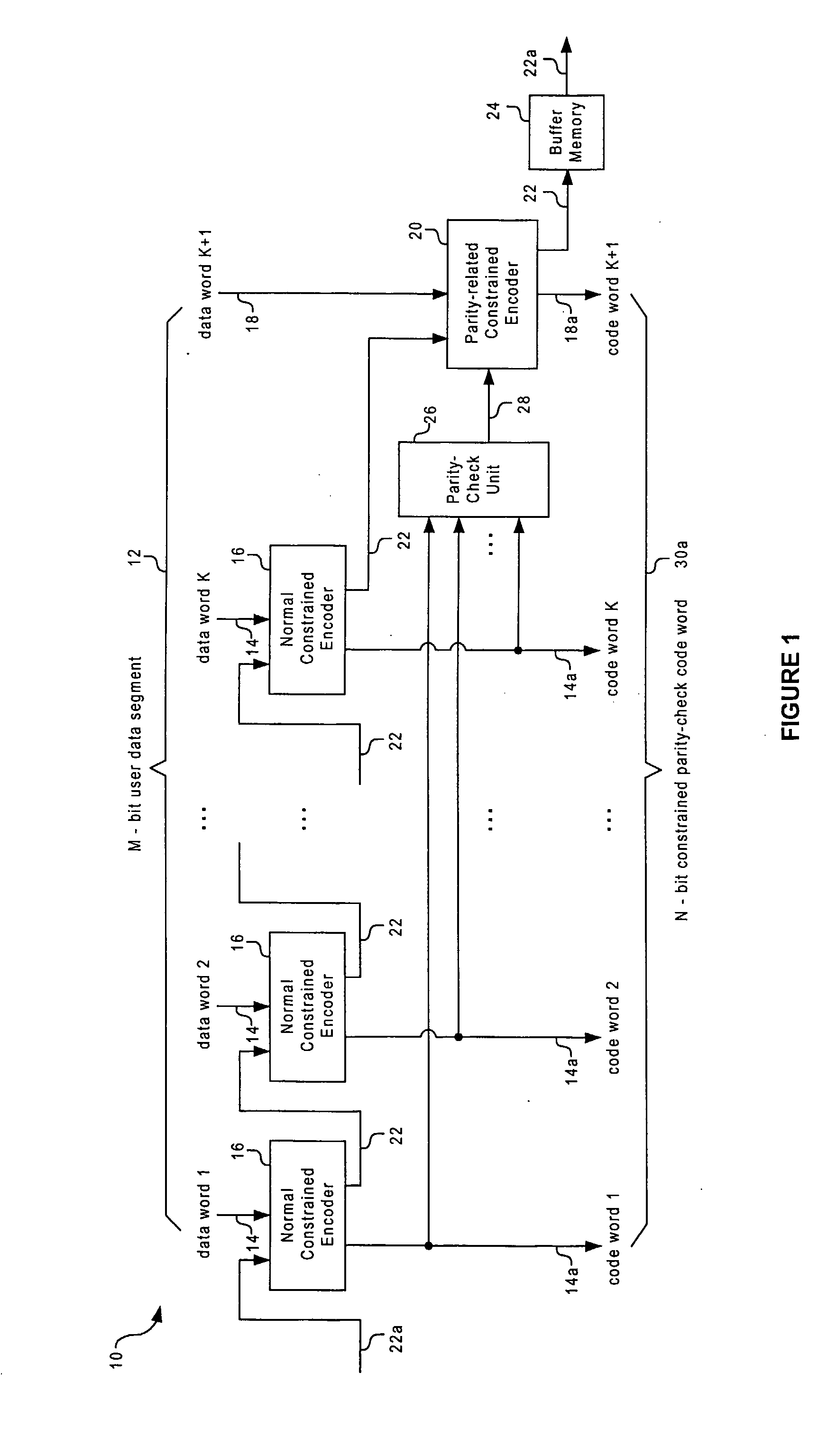

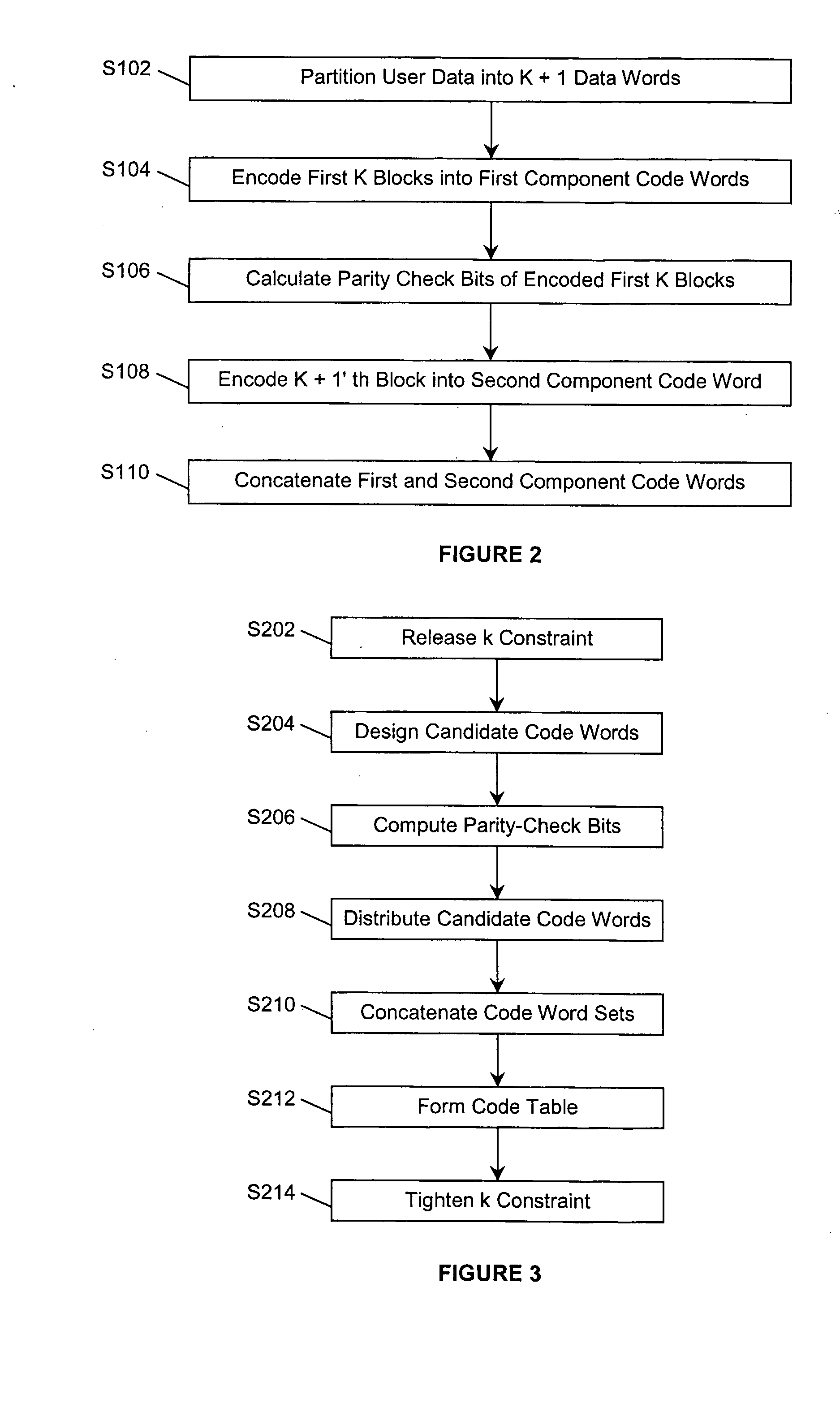

InactiveUS20080141095A1Simple hardware implementationReduce in quantityError correction/detection using multiple parity bitsRecord information storageBlock codeTheoretical computer science

A method and system for encoding a segment of user data words into a segment of code words so that both modulation constraints and a predetermined parity-check constraint are satisfied. Each segment of the user data is partitioned into several data words, and encoded separately by first and second types of component code, which are referred to as the normal constrained code and the parity-related constrained code, respectively. The parity-check constraint over the combined code word is achieved by concatenating the sequence of normal constrained code words with a specific parity-related constrained code word chosen from a candidate code word set. Both the component codes are finite-state constrained codes, which are designed to have rates close to the Shannon capacity. Furthermore, they are based on the same finite state machine (FSM), which enables them to be connected seamlessly, without violating the modulation constraints. Two preferred embodiments are provided to design a code in the non-return-to-zero inverted (NRZI) format and the non-return-to-zero (NRZ) format, respectively. Designing the codes in NRZ format may reduce the number of parity-check bits required for error detection and simplify error correction or post-processing. The parity-check constraint is defined by the parity-check polynomial or parity-check matrix of a systematic linear block code, which could detect any type of dominant error event as well as error event combinations of a given optical recording system. As a result, the information density of the system is improved.

Owner:AGENCY FOR SCI TECH & RES

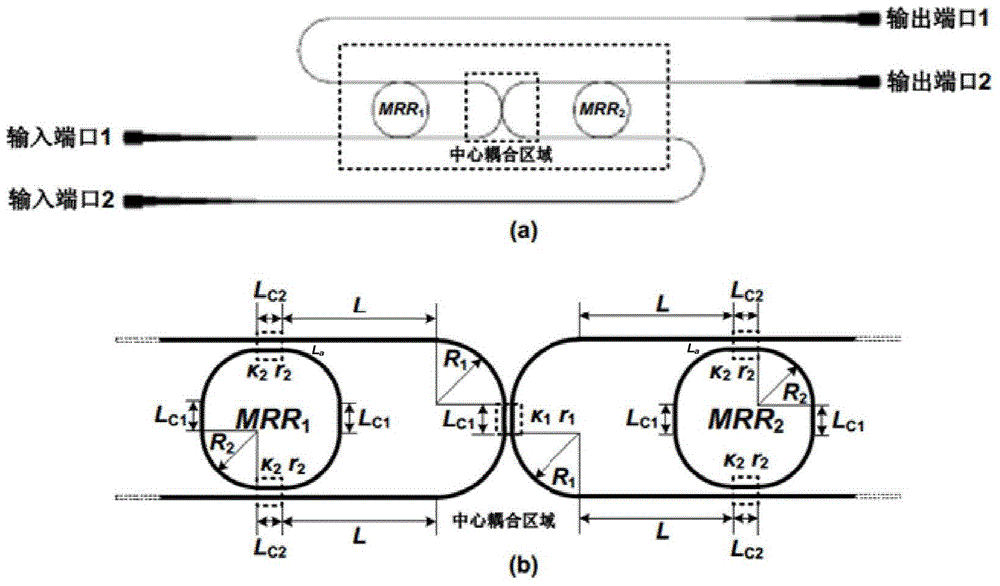

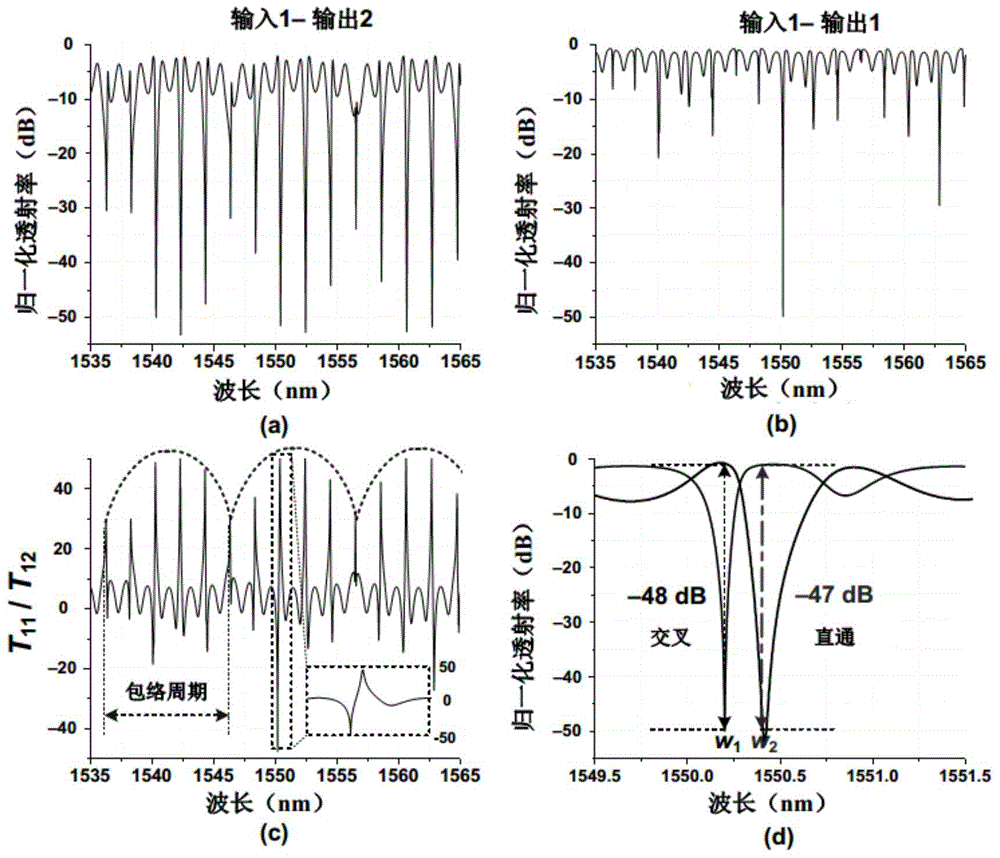

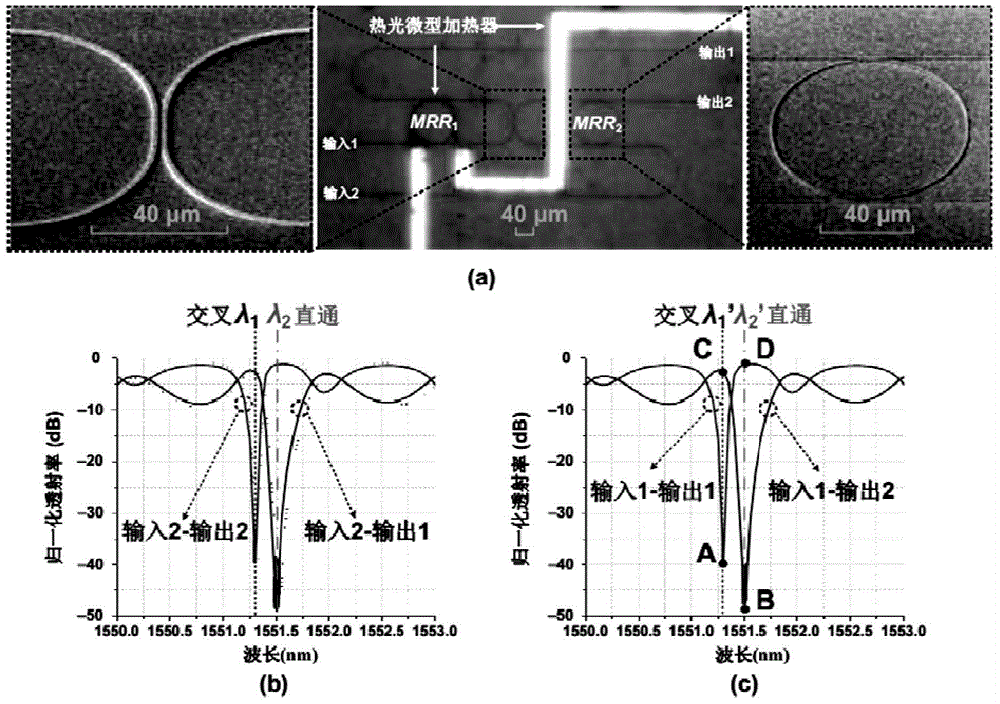

Non-blocking 2 * 2 optical switching node based on embedded type silicon substrate micro-ring resonant cavities

InactiveCN103986671AHigh extinction ratioLow crosstalk characteristicsMultiplex system selection arrangementsData switching networksSilicon on insulatorInput/output

The invention discloses a non-blocking 2 * 2 optical switching node based on embedded type silicon substrate micro-ring resonant cavities and belongs to the technical field of optical fiber communication. The non-blocking 2 * 2 optical switching node comprises two embedded type silicon substrate micro-ring resonant cavities which are arranged in a central-symmetry mode and are made of silicon wafers on insulators, and the resonant cavities are of an S-shaped structure. Two opposite U-shaped waveguides of the embedded type silicon substrate micro-ring resonant cavities form a directional coupler in a coupling mode. The outer sides of the two U-shaped waveguides are respectively provided with a micro-ring resonator. The optical switching node comprises four input-output switching ports which form two groups. Under crossing and shoot-through states, actually-measured extinction ratios reach 44.7 dB and 38.0 dB respectively, crosstalk values are lowered to -37.5 dB and -45.2 dB respectively, and for 10 Gb / s and 12.5 Gb / s non-return-to-zero (NRZ) signals, an error-code-free node switching function can be achieved.

Owner:SHANGHAI JIAO TONG UNIV

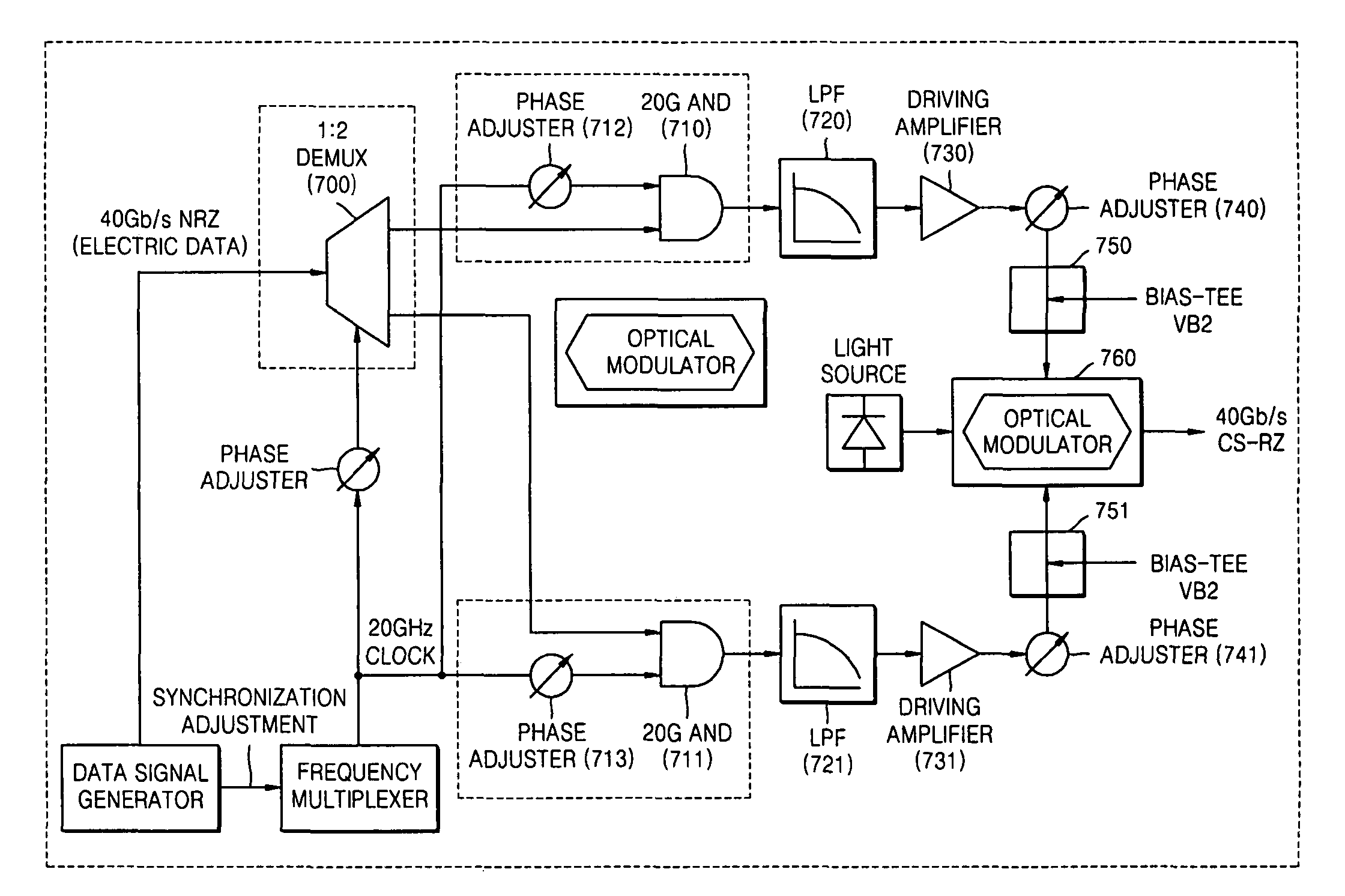

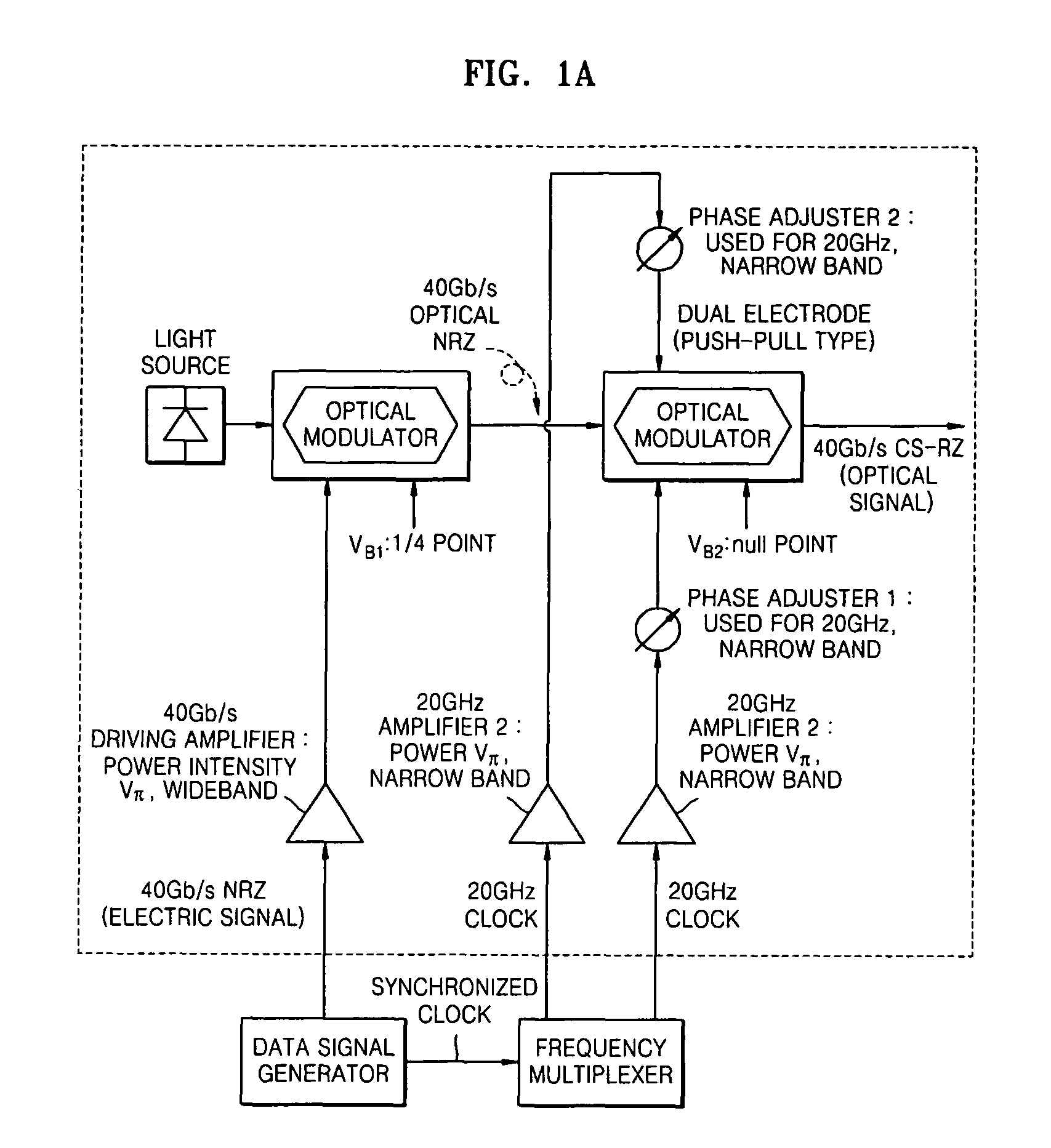

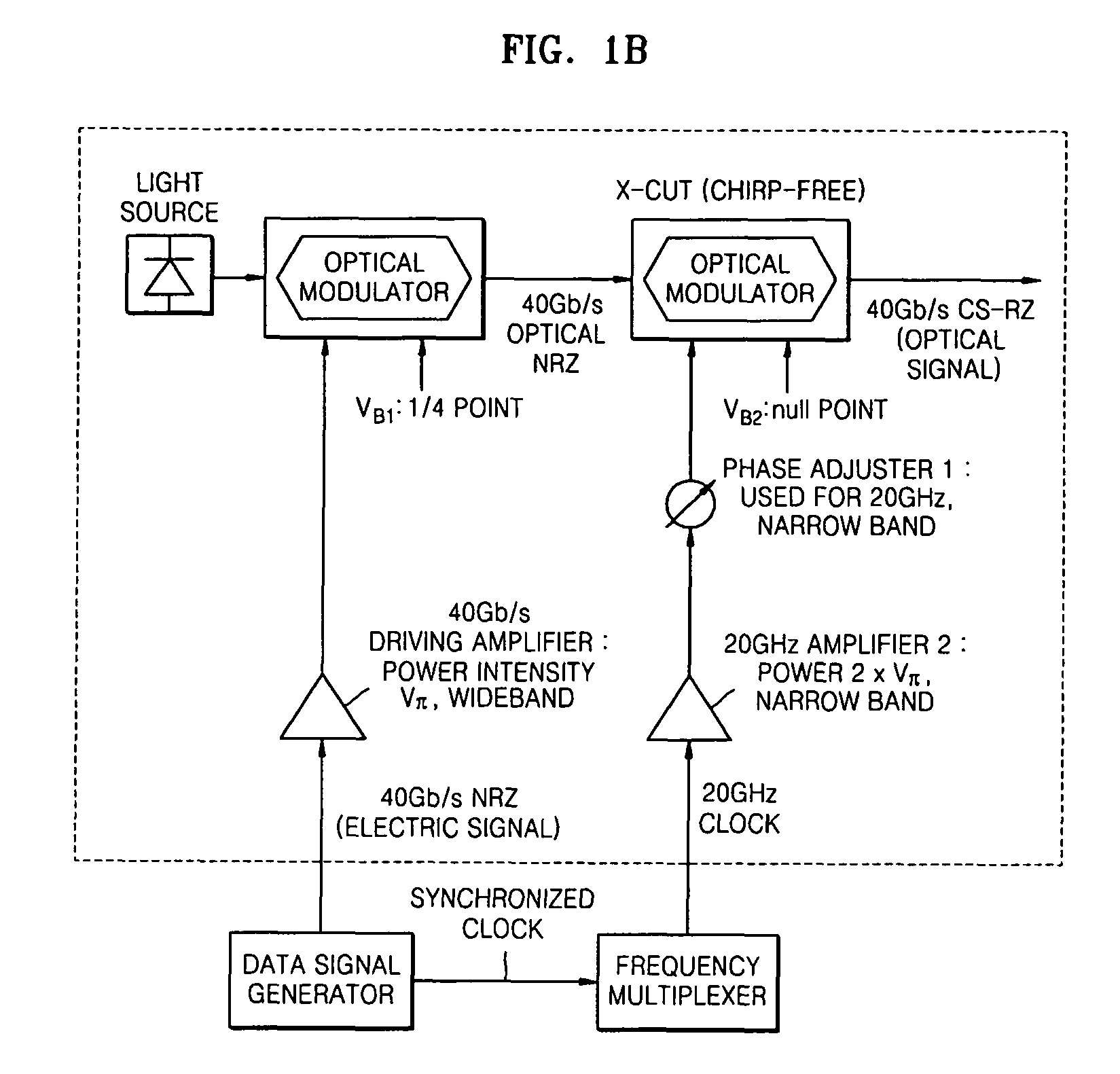

Apparatus and method to generate carrier suppressed-return to zero optical signal

Owner:ELECTRONICS & TELECOMM RES INST

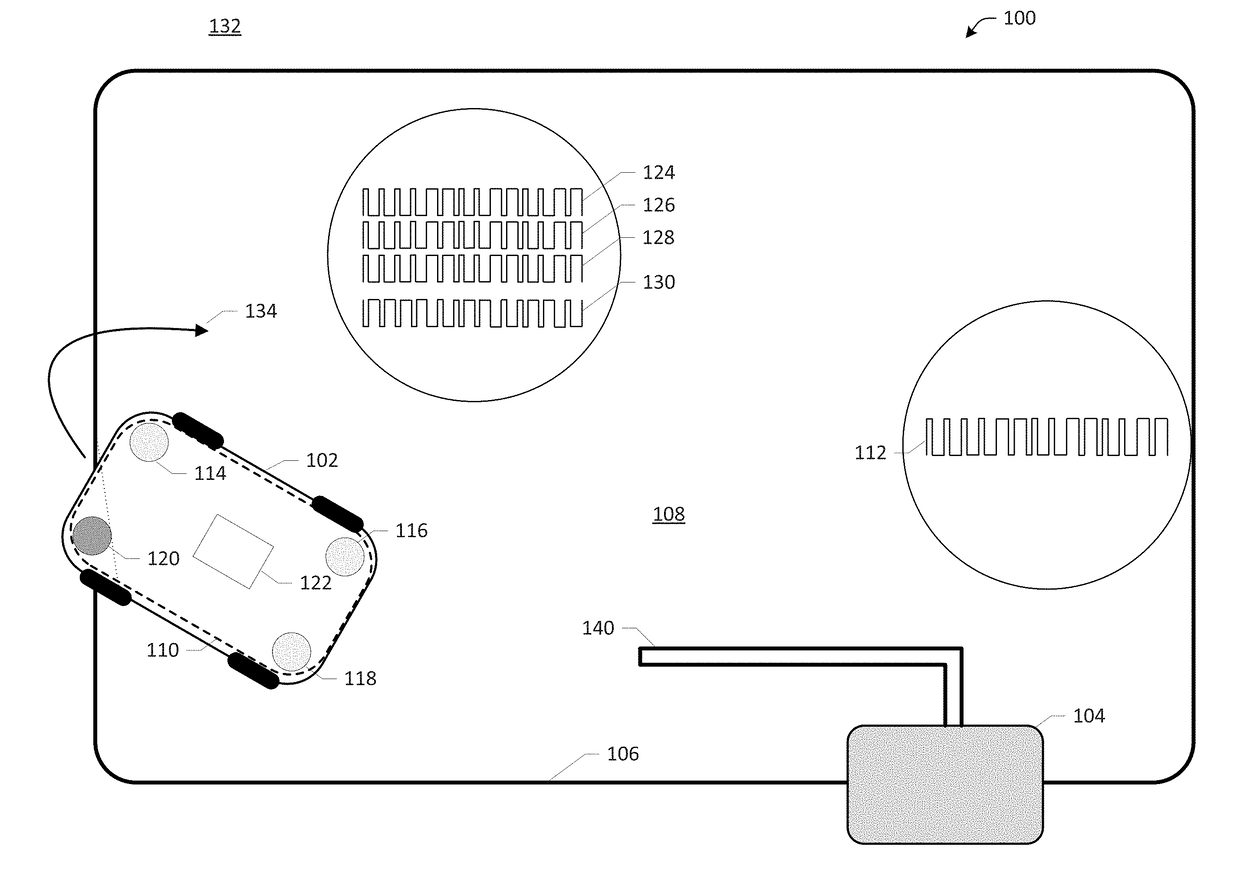

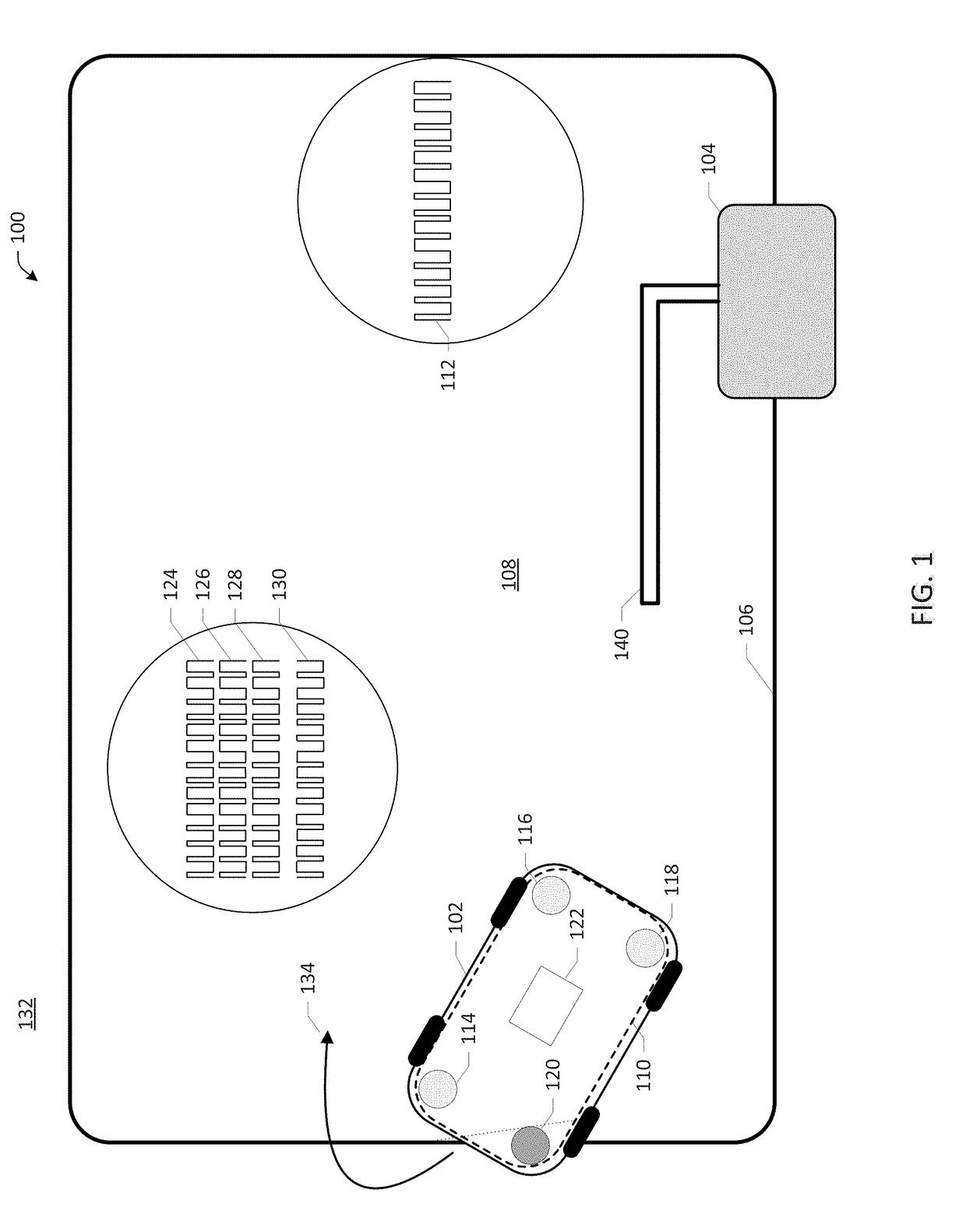

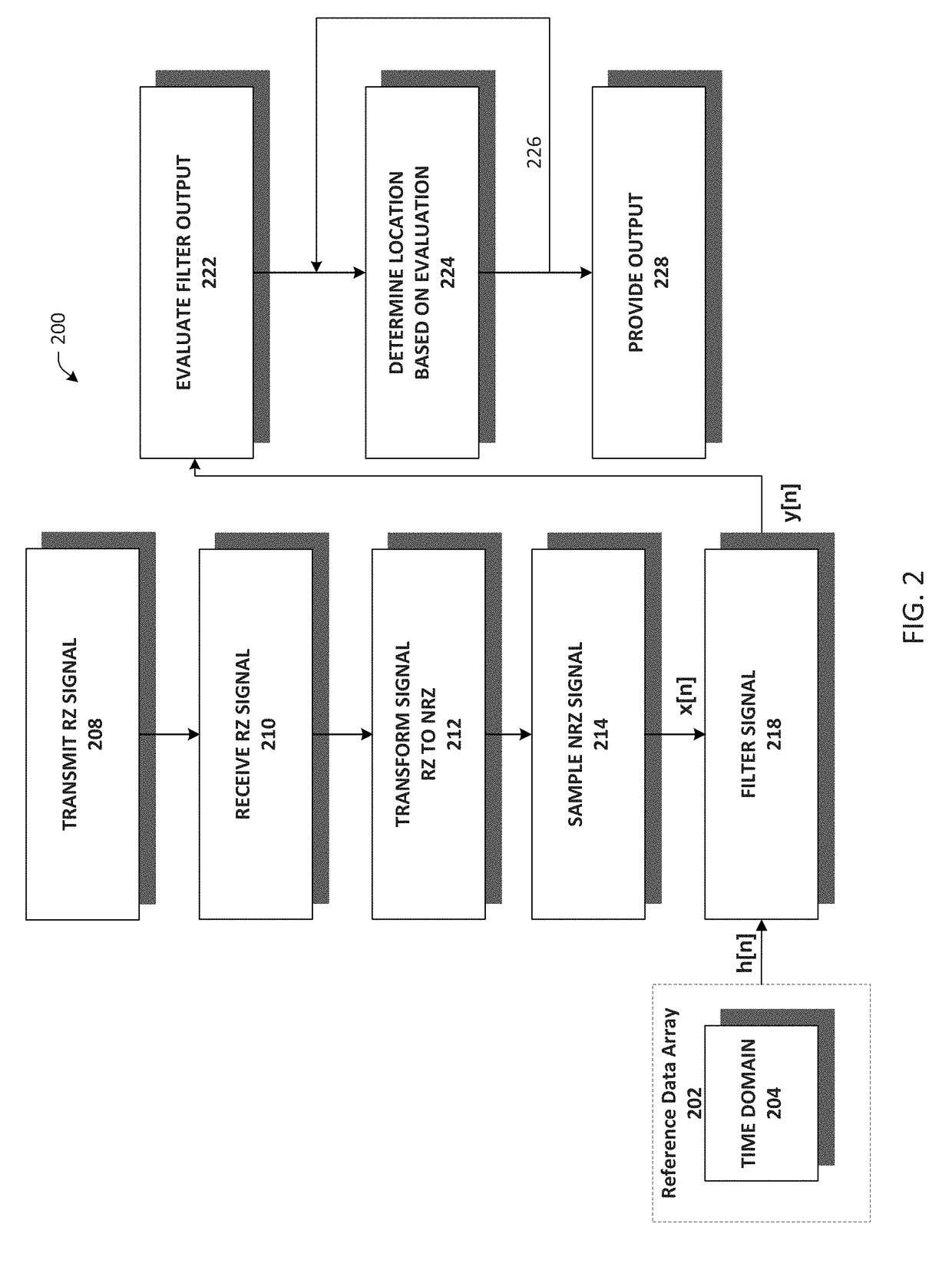

Autonomous mower navigation system and method

ActiveUS20170322562A1Well formedWave based measurement systemsCode conversionTime domainReturn-to-zero

A method for autonomous mower navigation includes receiving a return-to-zero encoded signal including a pseudo-random sequence, transforming the received signal to a non-return-to-zero representation, digitally sampling the non-return-to-zero signal representation in a time domain, filtering the sampled signal utilizing a reference data array based on the return-to-zero encoded signal to produce a filter output, and determining a location of the autonomous mower relative to a defined work area based on an evaluation of the filter output.

Owner:MTD PRODUCTS

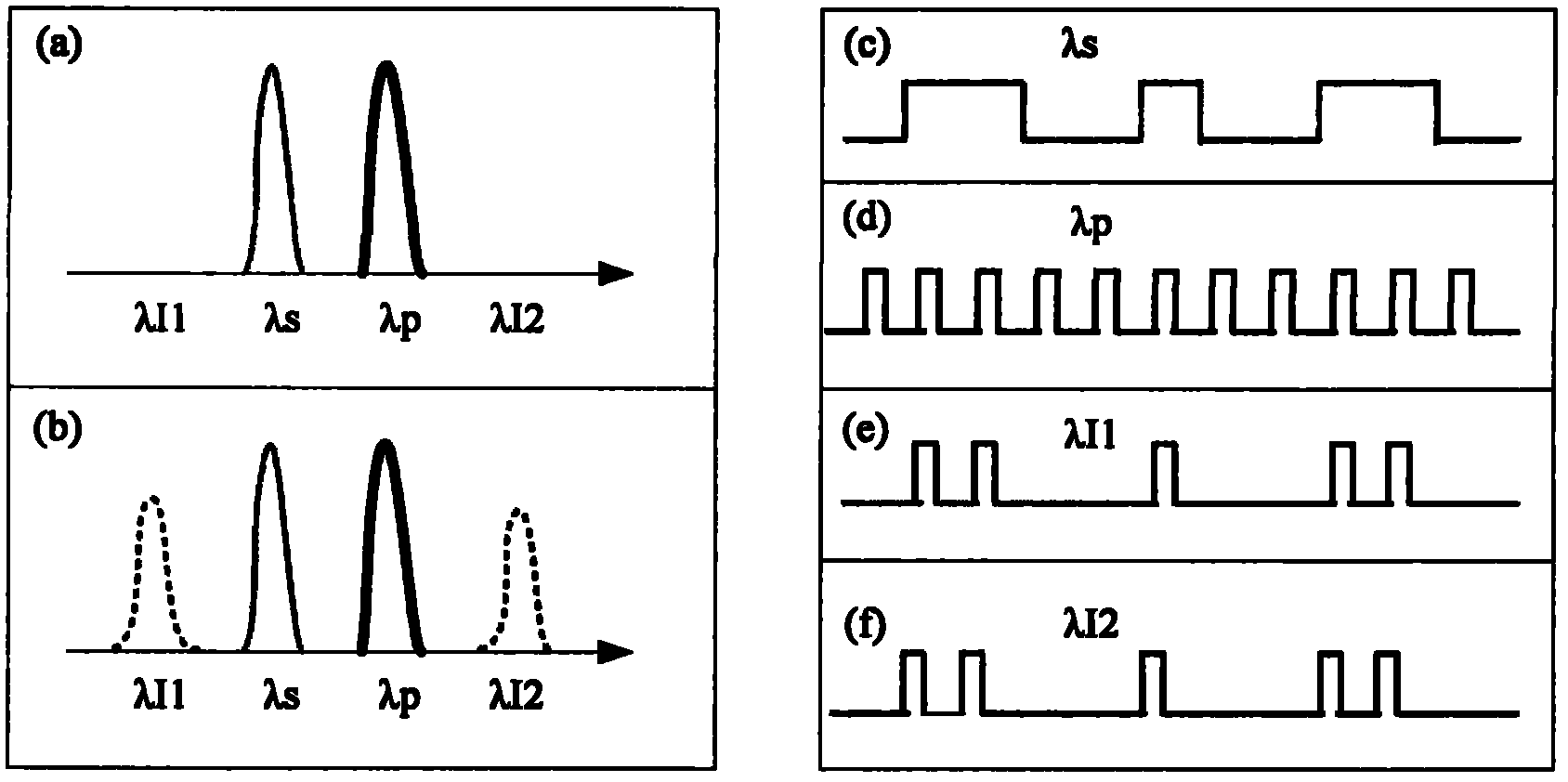

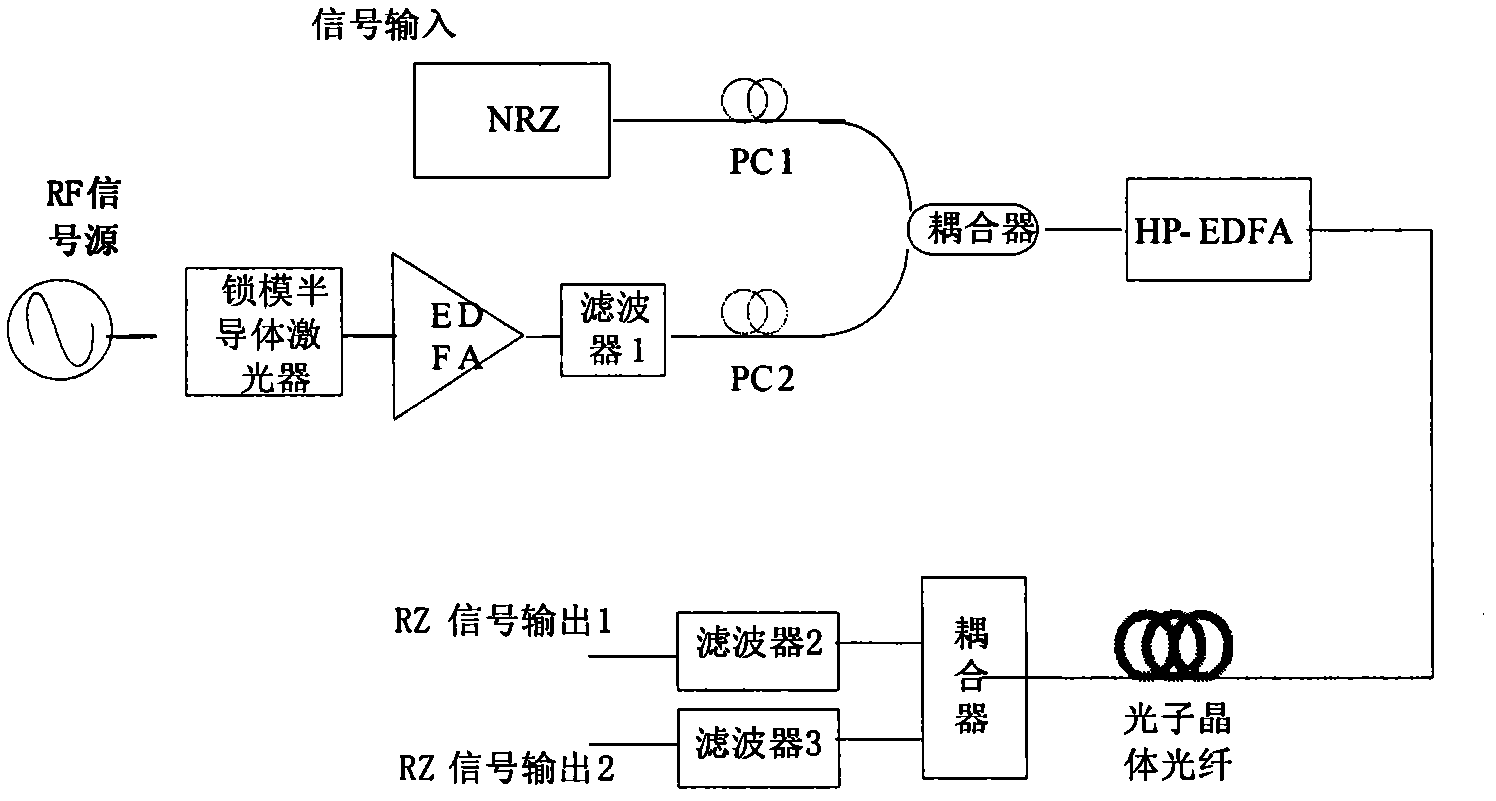

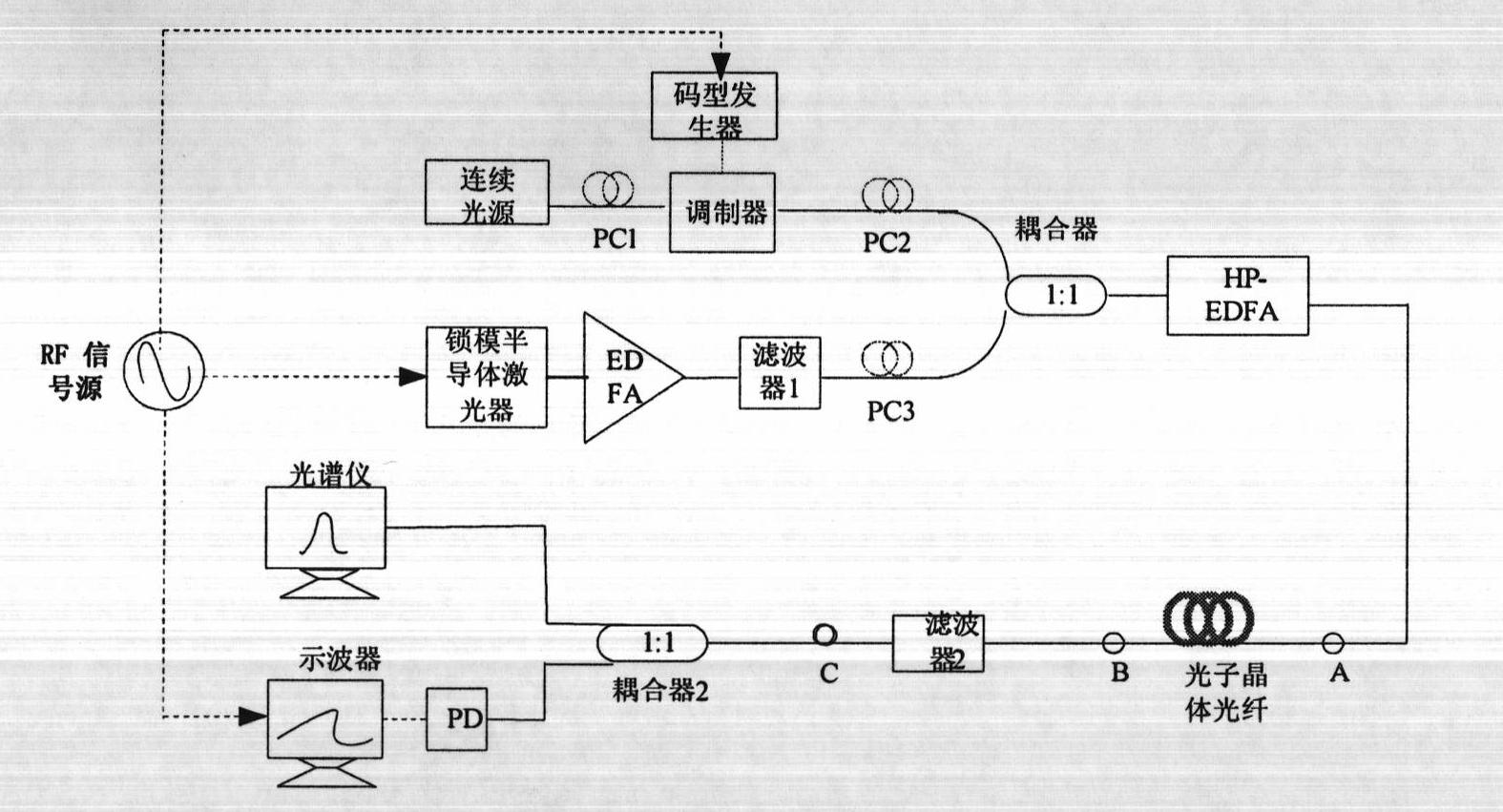

All-optical code conversion method with wavelength conversion function

InactiveCN102608832AOvercome the drawbacks of inflexible wavelength settingsLow waveguide efficiencyNon-linear opticsErbium dopingBand-pass filter

The invention discloses an all-optical code conversion method with a wavelength conversion function, which is characterized in that an RF (radio frequency) signal source sends out a radio-frequency signal with 10GHz recurrence frequency to be injected into a mode-locked semiconductor laser for active mode locking, the mode-locked semiconductor laser sends out an ultra-short pulse sequence with 10GHz recurrence frequency as pump light, an erbium-doped optical fiber amplifier is used for power amplification of the pump light prior to that spontaneous radiation noise is filtered by a filter 1, the pump light passes through a PC (polarization controller) 2 to realize optical coupling with an NRZ (non-return-to-zero) signal to be converted, and a PC1 on an NRZ signal light branch is used for adjusting the polarization state of a light beam. After coupling of the pump light and the NRZ signal, the pump light and the NRZ signal are injected into an overhigh-power erbium-doped optical fiber amplifier for power amplification prior to entering a 50-meter photonic crystal fiber and generating four-wave frequency mixing effect in the photonic crystal fiber, and two narrow-band optical filters are used for respectively filtering sidebands, so that a code conversion signal is obtained while wavelength conversion is completed, and a wavelength multicast function is realized.

Owner:XIAN UNIV OF POSTS & TELECOMM

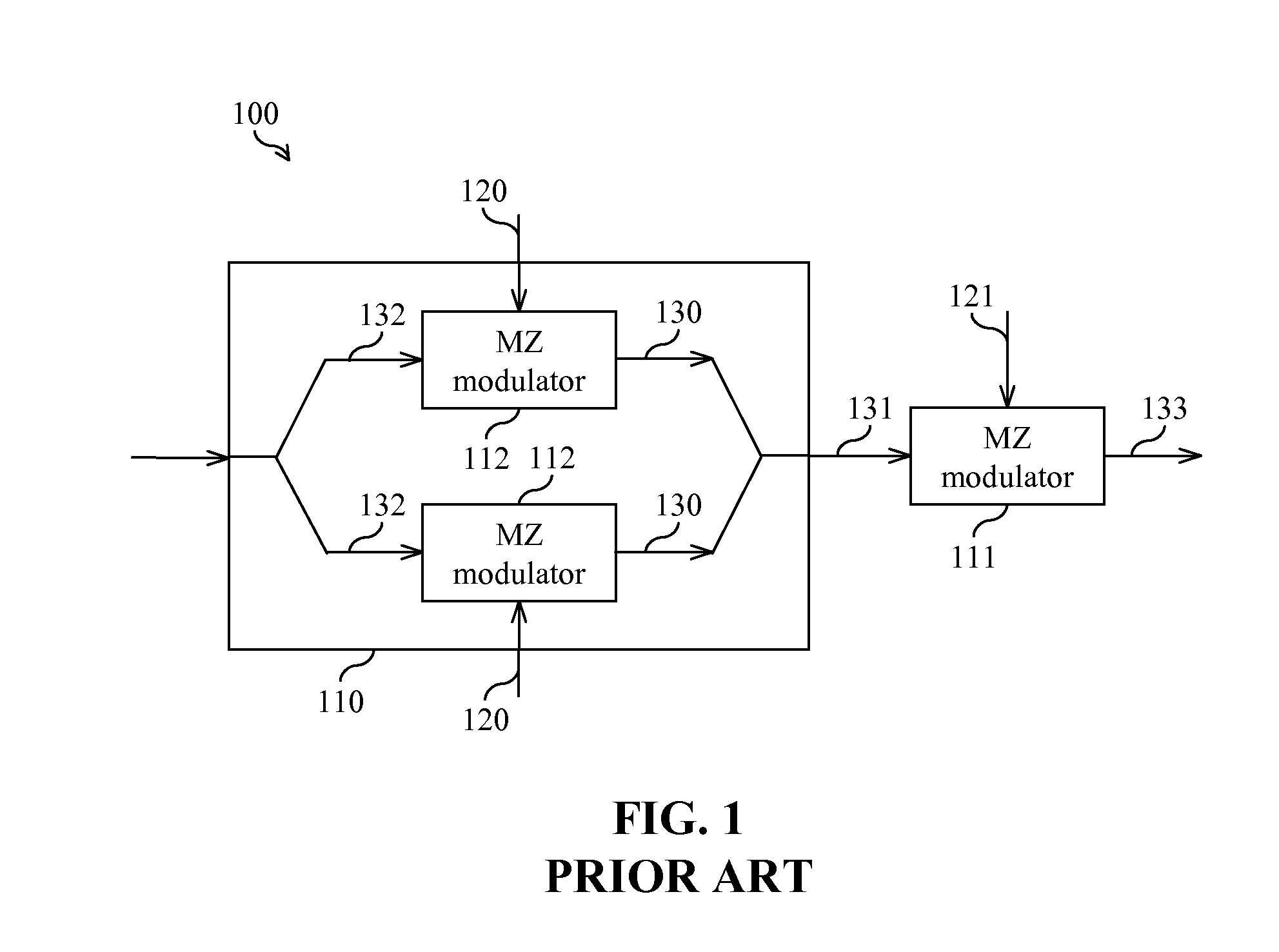

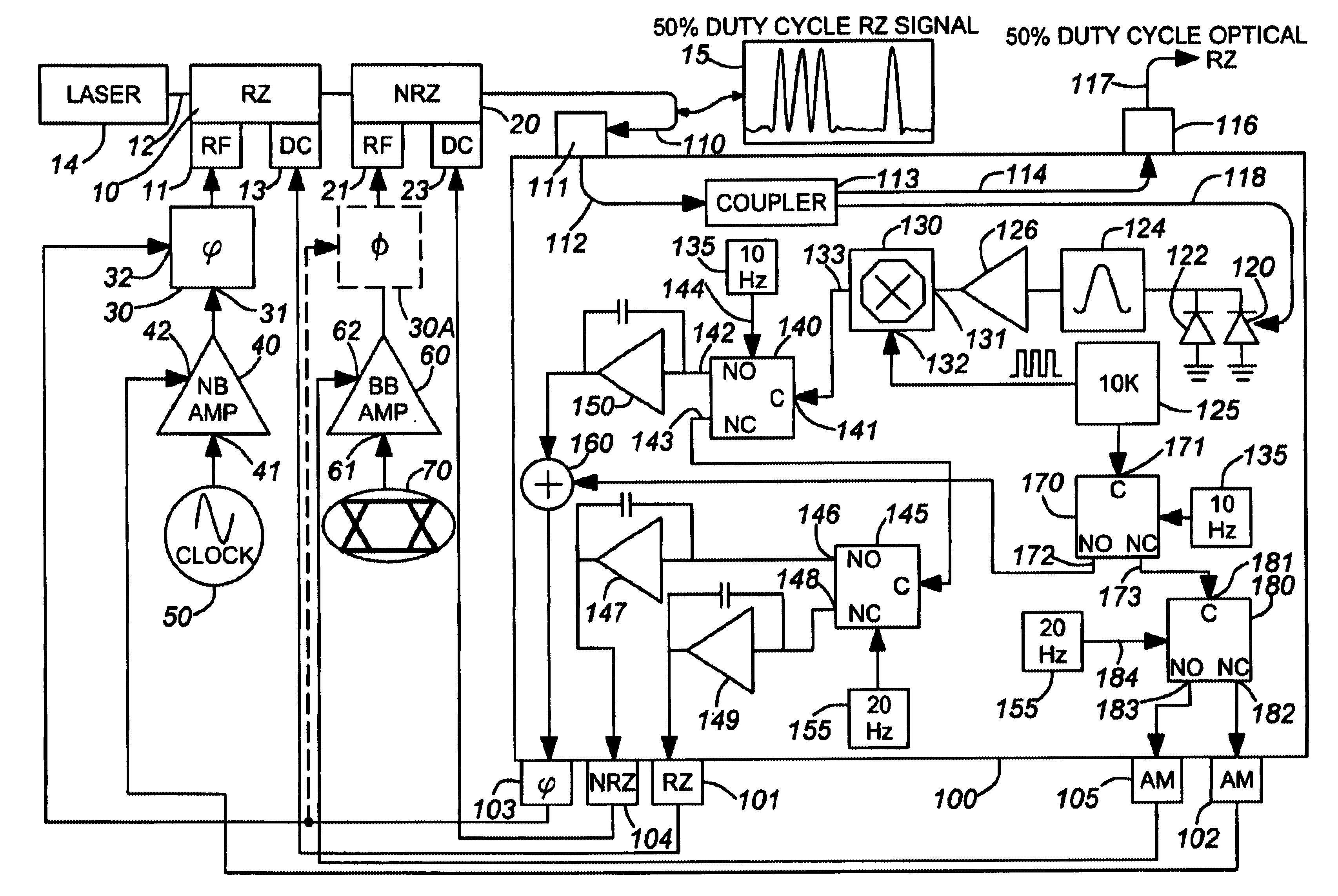

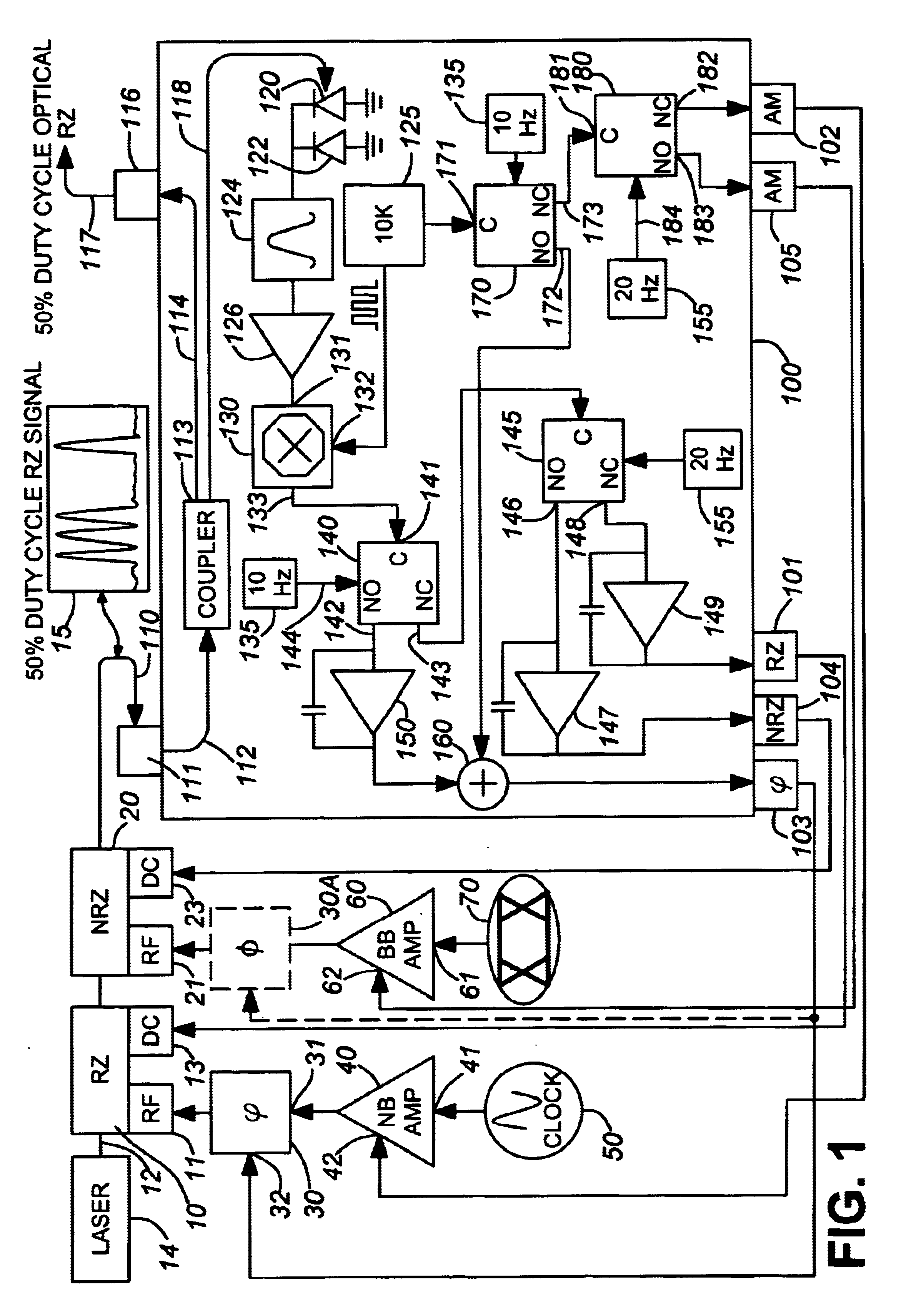

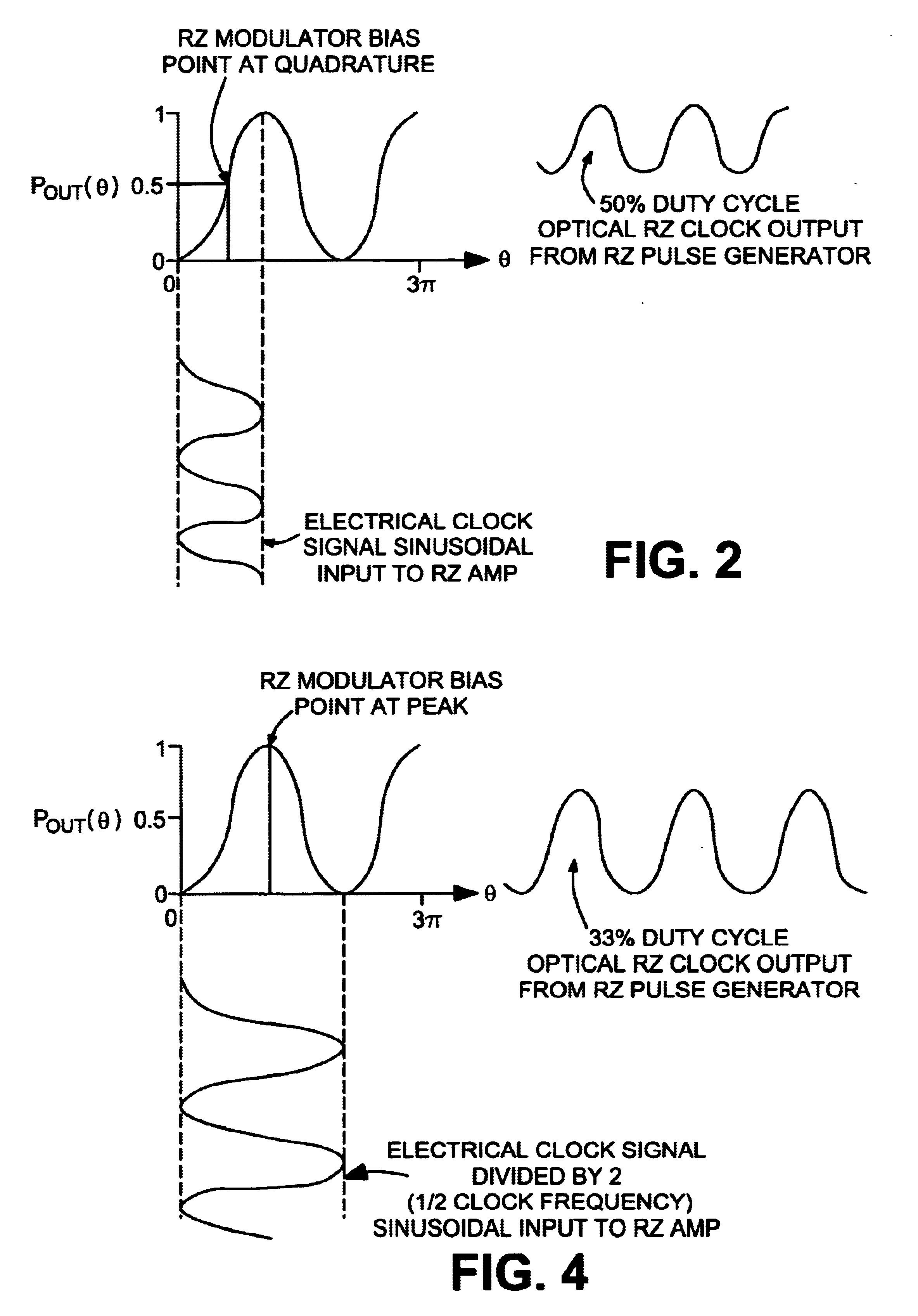

Cascaded RZ and NRZ laser modulators having RZ/NRZ phase alignment bias control

InactiveUS6917455B2Maximize RF powerDetection signalElectromagnetic transmissionNon-linear opticsReturn-to-zeroData signal

An optical transmitter architecture has a return-to-zero (RZ) laser modulator coupled in cascade with a non-return-to-zero (NRZ) laser modulator. Modulator bias and electronic phase delay bias are controlled using dither-based feedback, so as to align the phase of the RZ clock signal with that of the NRZ data. A first method uses an RZ quadrature AM dither or an RZ “hillclimber” bias dither, to apply a relatively low frequency dither signal to a variable RF delay for the RZ clock signal applied to the RZ modulator or NRZ data signal applied to the NRZ modulator. A second method is an RZ quadrature AM dither or “hillclimber” bias dither scheme that applies equal amplitude and opposite phase dither signals to perform complementary modulation of both the RZ and NRZ MZ modulators simultaneously.

Owner:LUMENTUM OPERATIONS LLC

Method and apparatus for controlling a bias voltage of a Mach-Zehnder modulator

A method and apparatus for controlling a bias voltage of a Mach-Zehnder modulator (MZM) use a digital pilot signal and a digital correlation technique to produce a feedback signal for adjusting the bias voltage to the quadrature bias point. Embodiments of the invention include apparatuses performing a non-return-to-zero (NRZ), return-to-zero (RZ), or carrier suppressed RZ (CSRZ) high-speed optical modulation.

Owner:RPX CORP +1