High-speed parallel interface circuit

An interface circuit, high-speed technology, applied in electrical components, digital transmission systems, transmission systems, etc., can solve problems such as difficulty in accurate sampling of clocks, difficulty in receiving data synchronously at the receiving end, and different data path delays.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

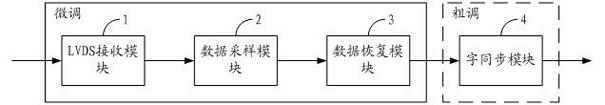

[0034] The transmission of high-speed parallel data consists of multiple channels. In the embodiment of the present invention, the high-speed parallel interface circuit structure of each channel is as follows: figure 1 shown. Each single channel (one-bit data path in parallel data) includes two parts: data sampling recovery (fine adjustment) and word synchronization (coarse adjustment).

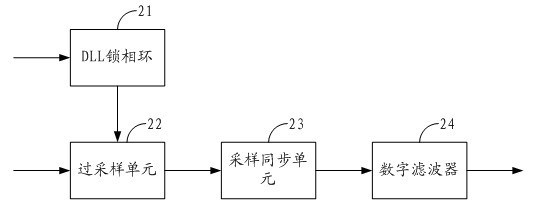

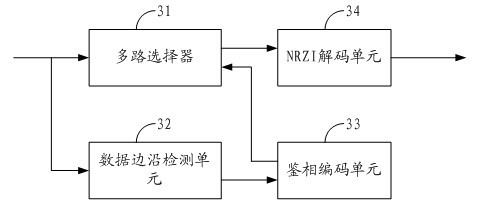

[0035] The data sampling recovery part includes a low voltage differential signal (LVDS) receiving module 1 , a data sampling module 2 and a data recovery module 3 which are electrically connected in sequence. T...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More