Patents

Literature

1004results about "Oscillations comparator circuits" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

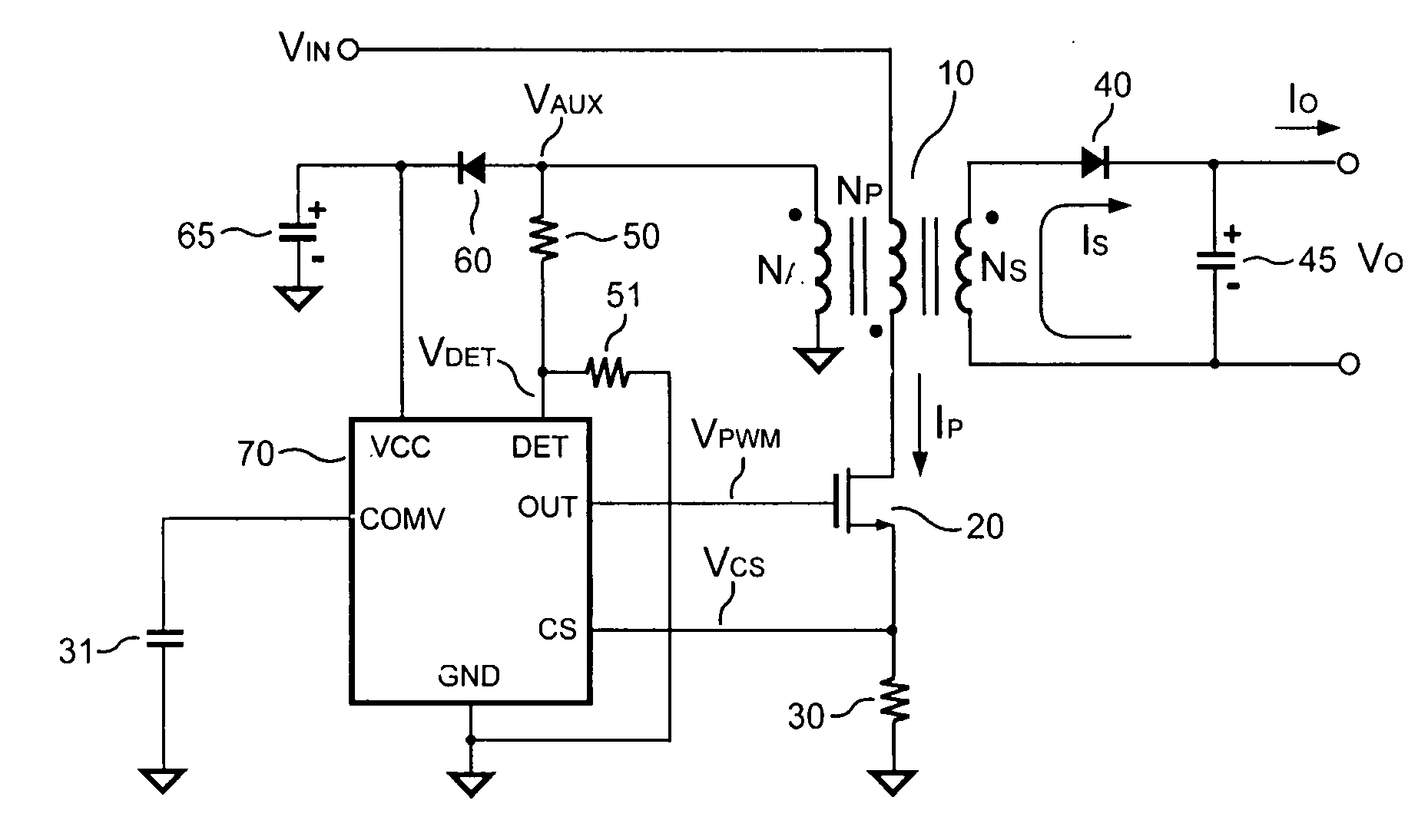

Switching control circuit having off-time modulation to improve efficiency of primary-side controlled power supply

ActiveUS7362593B2Save power consumptionLight load conditionEfficient power electronics conversionDc-dc conversionAudio power amplifierControl signal

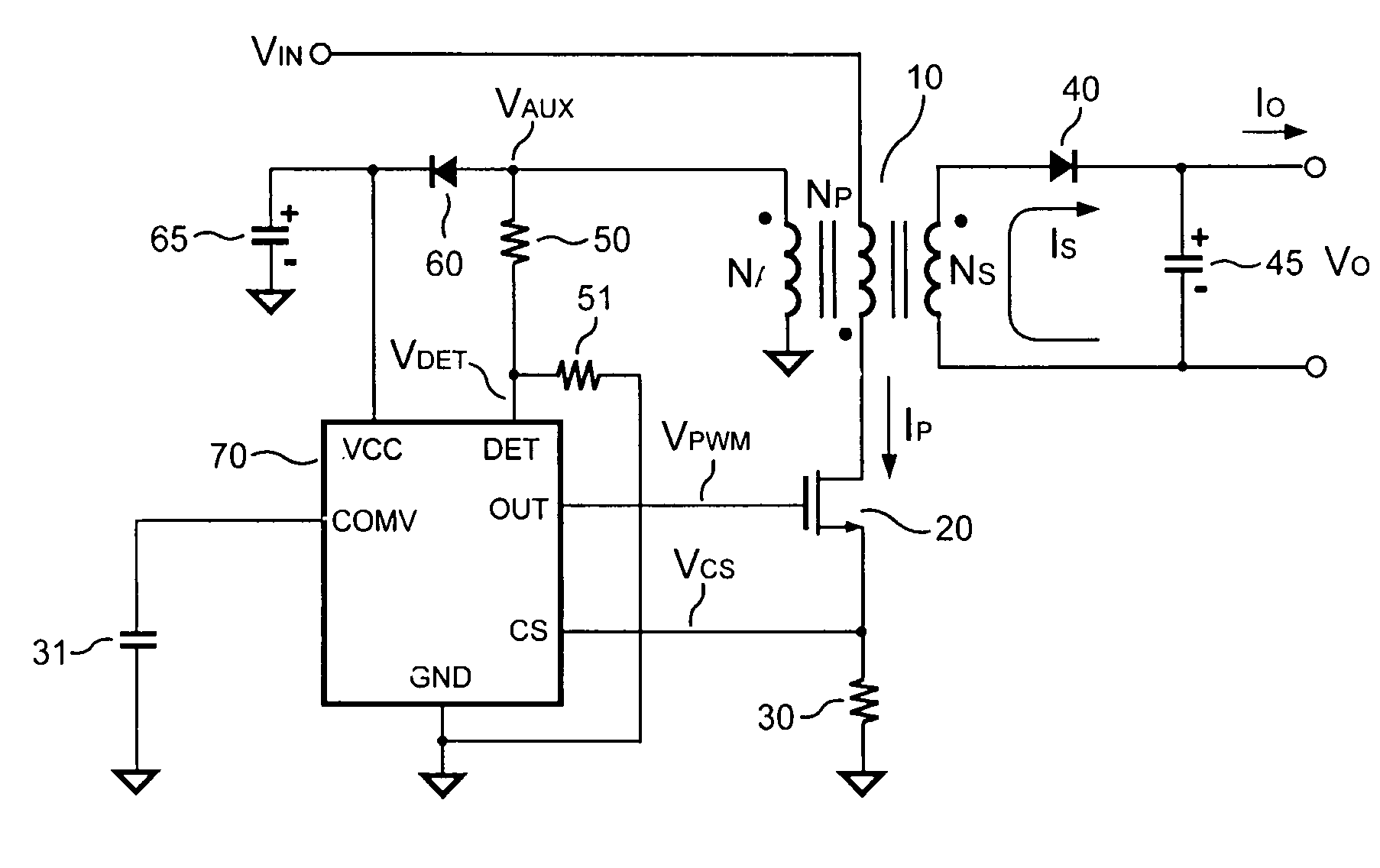

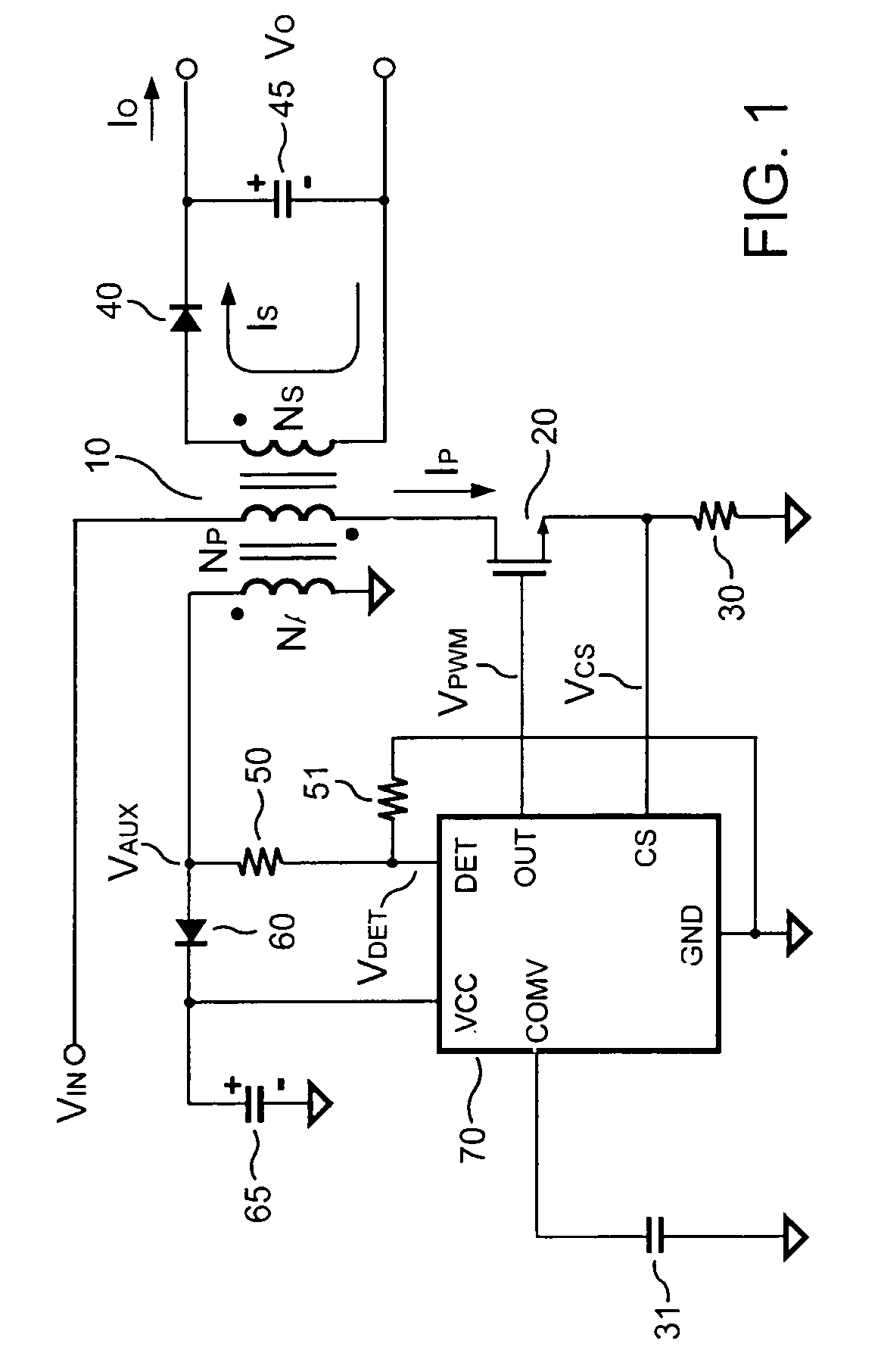

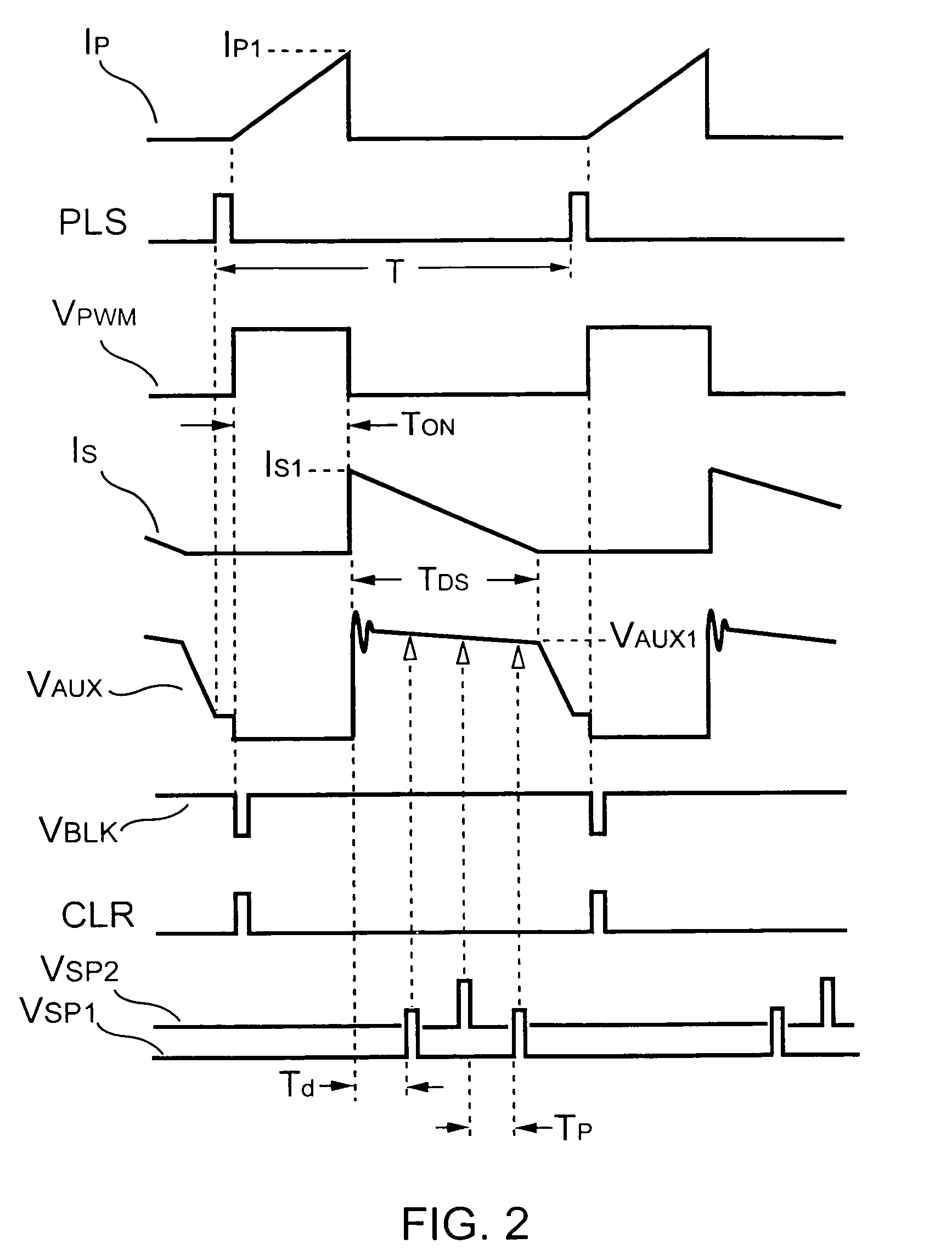

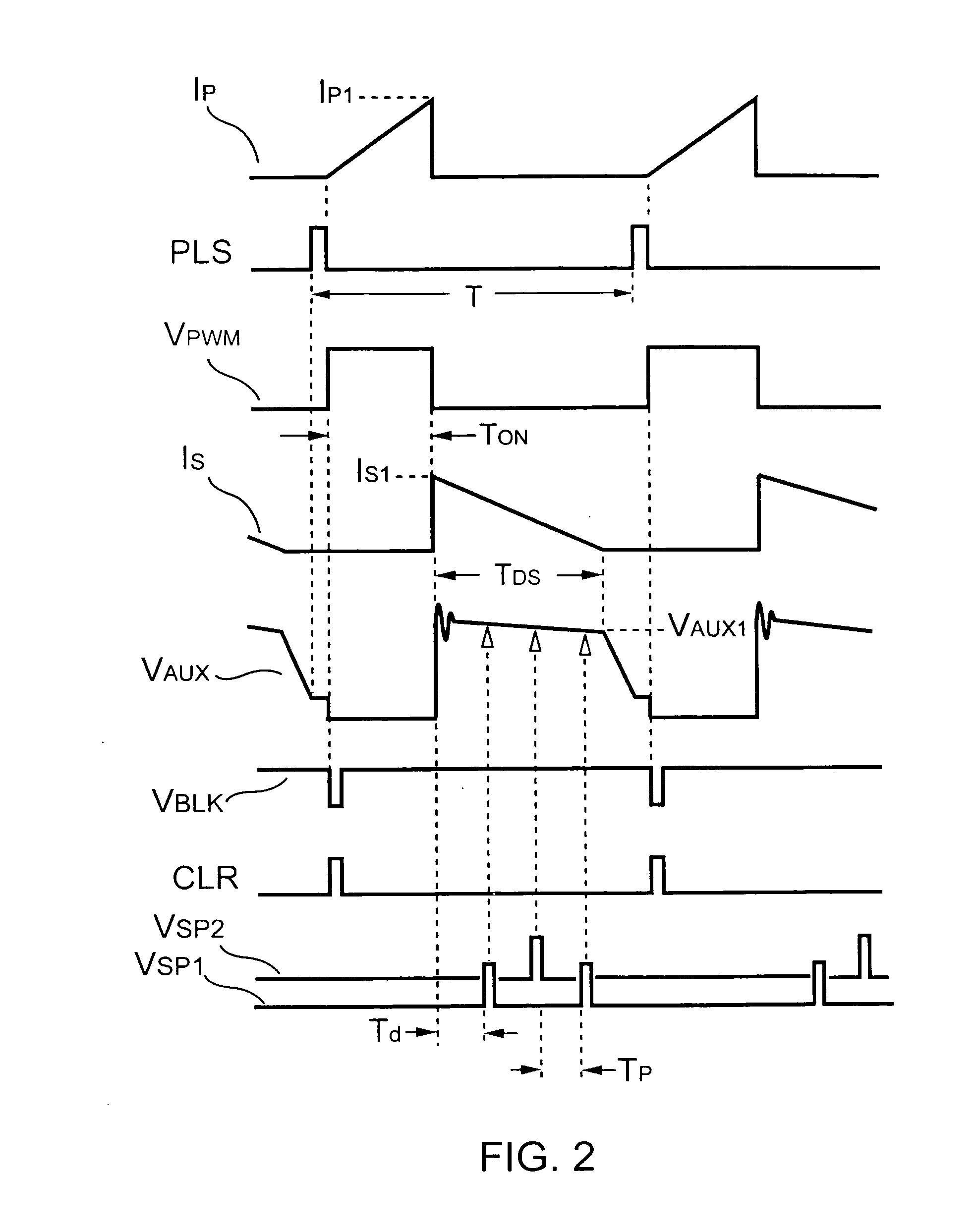

A voltage-waveform detector produces a voltage-feedback signal and a discharge-time signal by multi-sampling a voltage signal of a transformer. The discharge-time signal represents a discharge time of a secondary-side switching current. A voltage-loop error amplifier amplifies the voltage-feedback signal and generates a control signal. An off-time modulator correspondingly generates a discharge-current signal and a standby signal in response to the control signal and an under-voltage signal. The under-voltage signal indicates a low supply voltage of the controller. An oscillator produces a pulse signal in response to the discharge-current signal. The pulse signal determines the off-time of the switching signal. A PWM circuit generates the switching signal in response to the pulse signal and the standby signal. The standby signal further controls the off-time of the switching signal and maintains a minimum switching frequency. The switching signal is used for regulating the output of the power supply.

Owner:FAIRCHILD SEMICON CORP

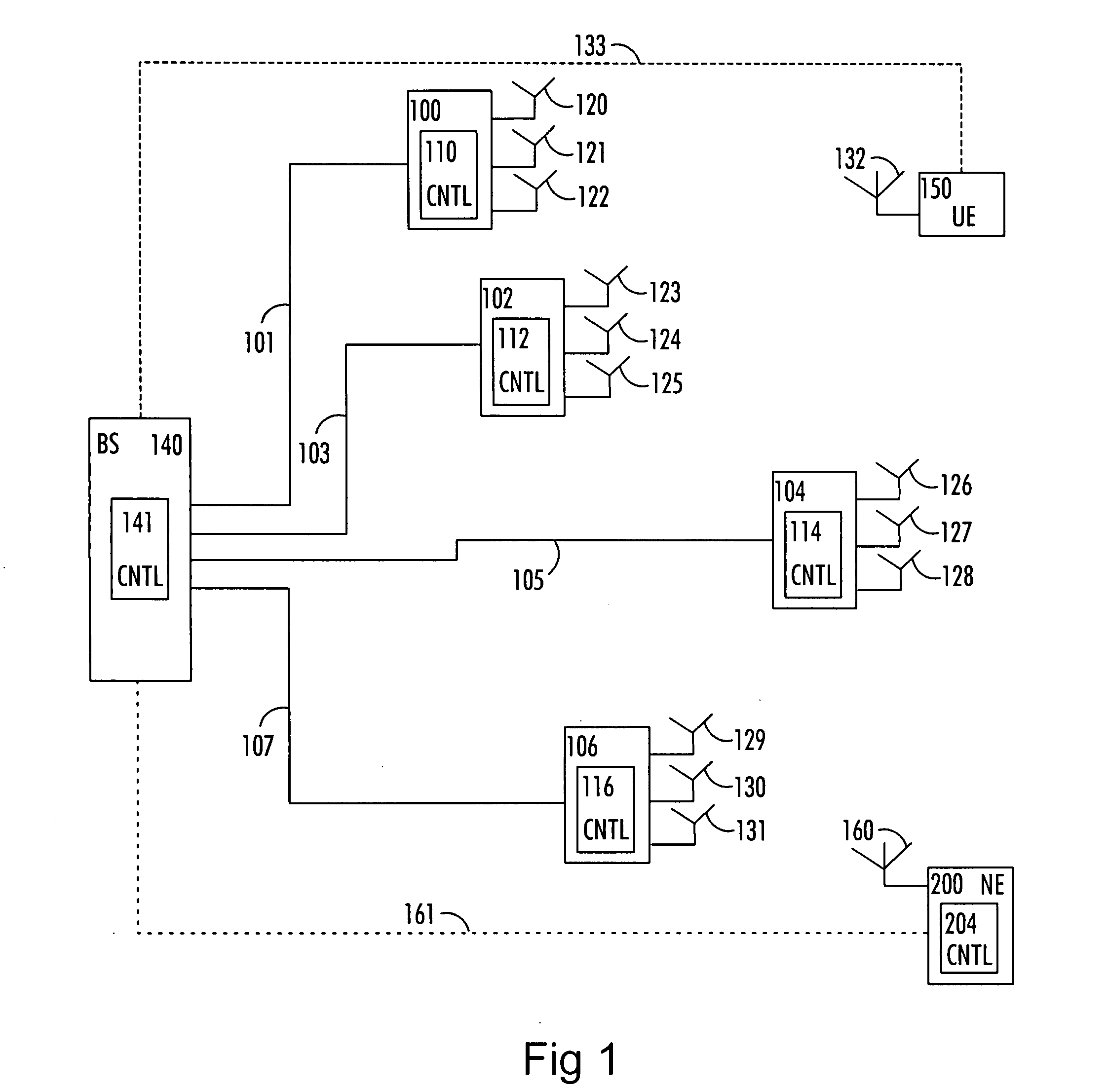

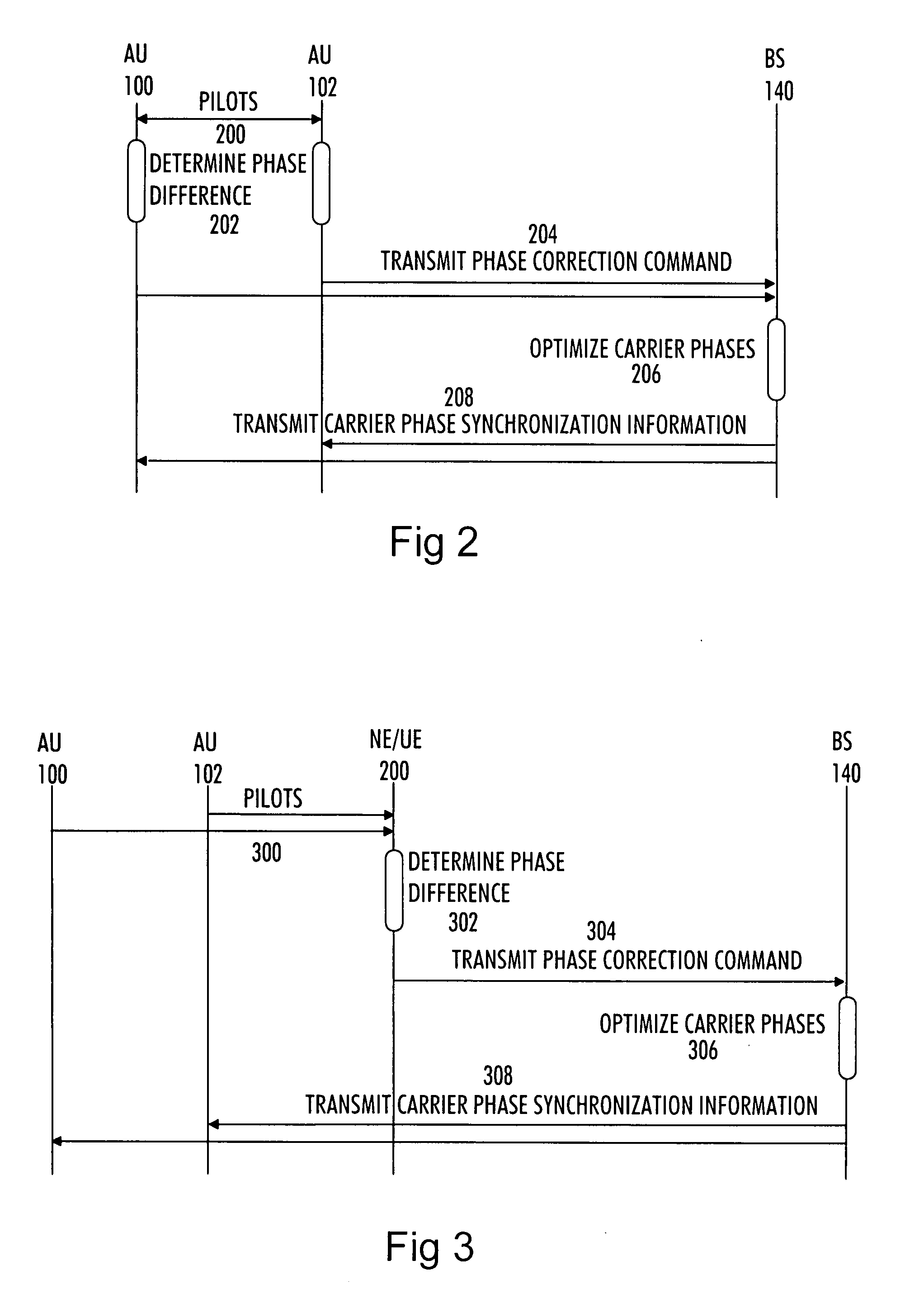

Communication method and system

ActiveUS20080150514A1Increase network capacityCooperate fullySite diversityReceivers monitoringPhase correctionCommon base

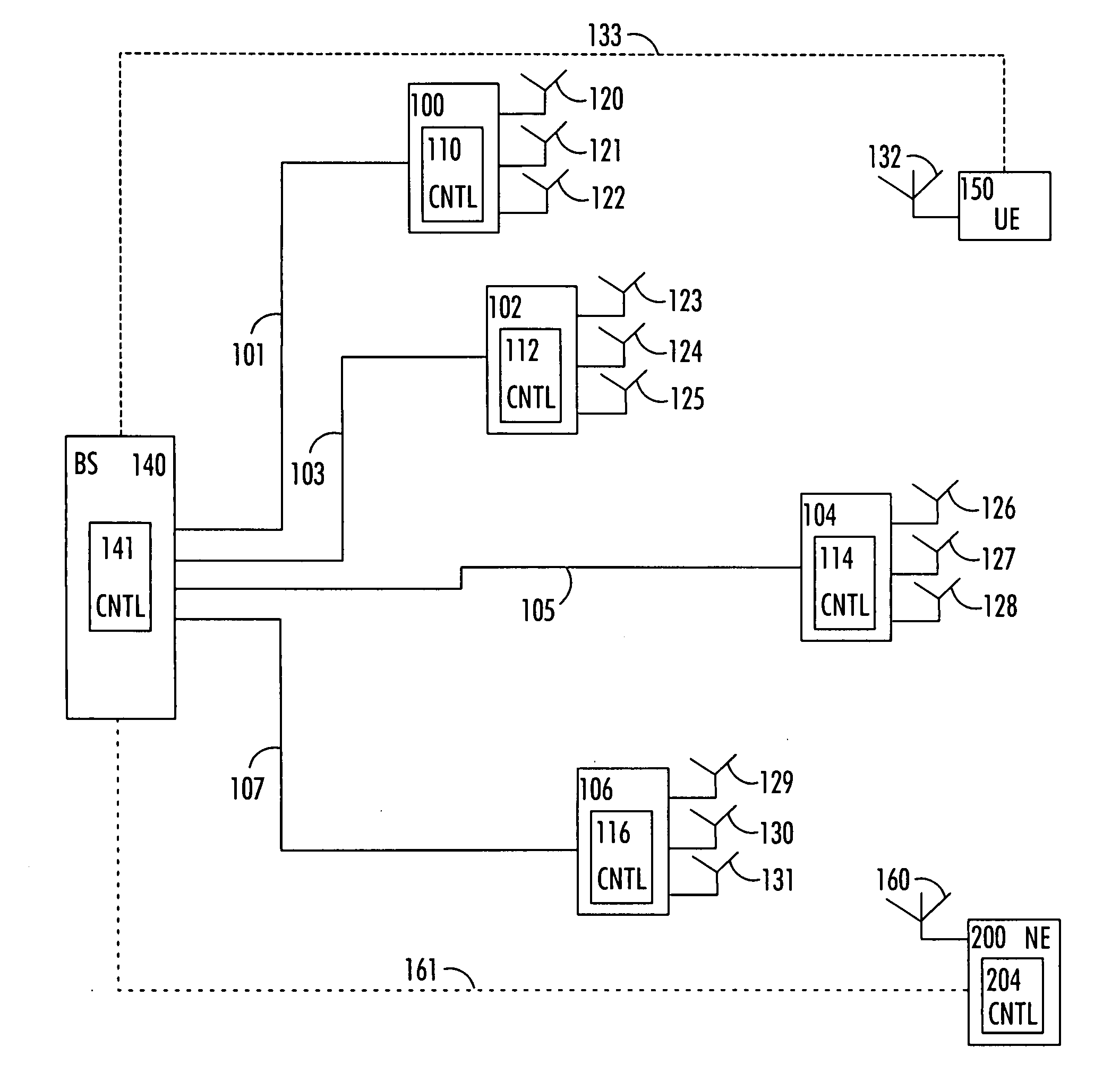

There is provided a method comprising: determining a phase difference between at least two antenna units of a distributed antenna system on the basis of at least one pilot signal received from at least one of a plurality of antenna units; and transmitting phase correction commands to a common base station of the plurality of antenna units on the basis of the determined phase difference in order to synchronize carrier phases between at least two antenna units of the distributed antenna system.

Owner:WSOU INVESTMENTS LLC

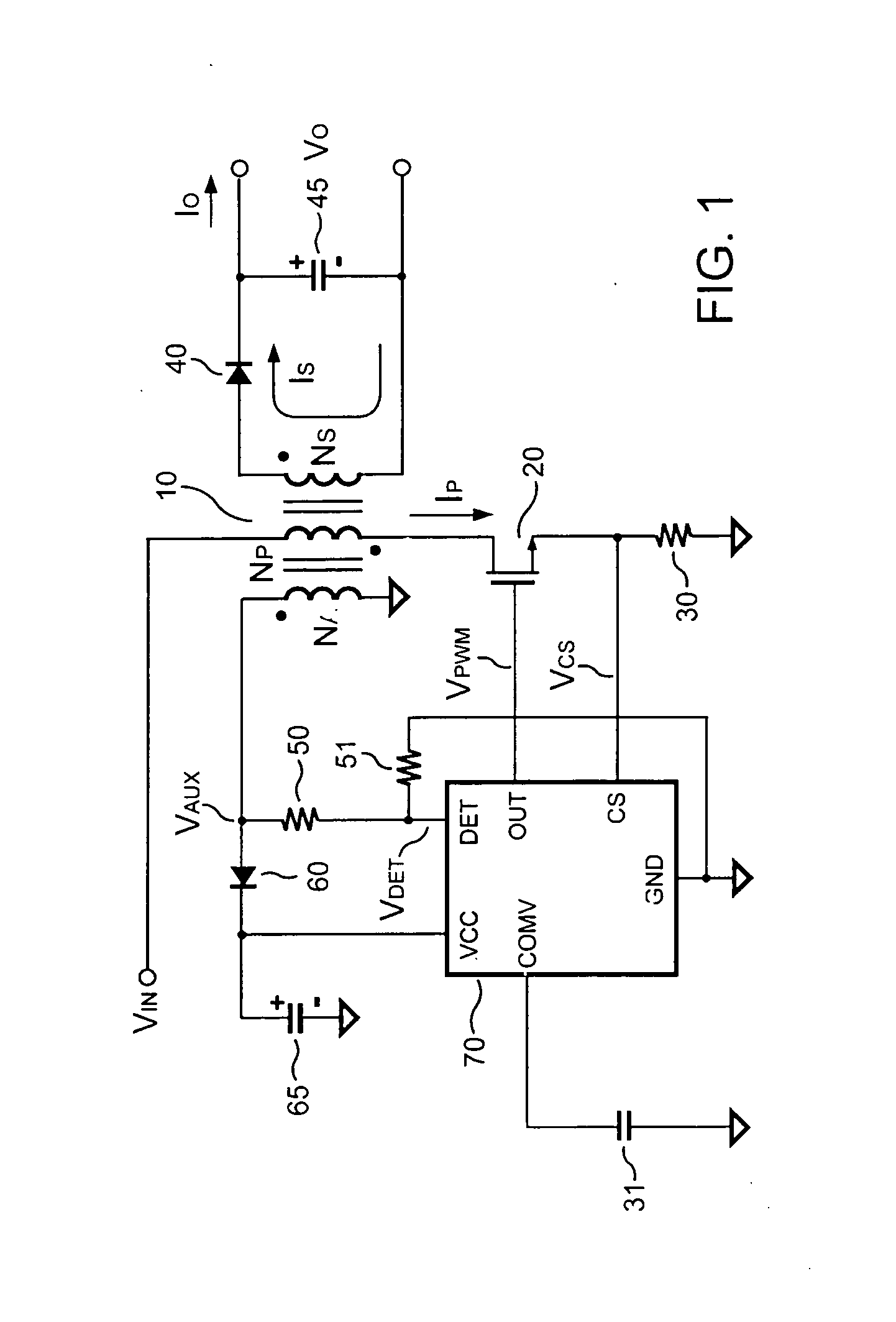

Switching control circuit having off-time modulation to improve efficiency of primary-side controlled power supply

ActiveUS20060055433A1Save power consumptionLight load conditionEfficient power electronics conversionDc-dc conversionControl signalSwitching frequency

A voltage-waveform detector produces a voltage-feedback signal and a discharge-time signal by multi-sampling a voltage signal of a transformer. The discharge-time signal represents a discharge time of a secondary-side switching current. A voltage-loop error amplifier amplifies the voltage-feedback signal and generates a control signal. An off-time modulator correspondingly generates a discharge-current signal and a standby signal in response to the control signal and an under-voltage signal. The under-voltage signal indicates a low supply voltage of the controller. An oscillator produces a pulse signal in response to the discharge-current signal. The pulse signal determines the off-time of the switching signal. A PWM circuit generates the switching signal in response to the pulse signal and the standby signal. The standby signal further controls the off-time of the switching signal and maintains a minimum switching frequency. The switching signal is used for regulating the output of the power supply.

Owner:FAIRCHILD SEMICON CORP

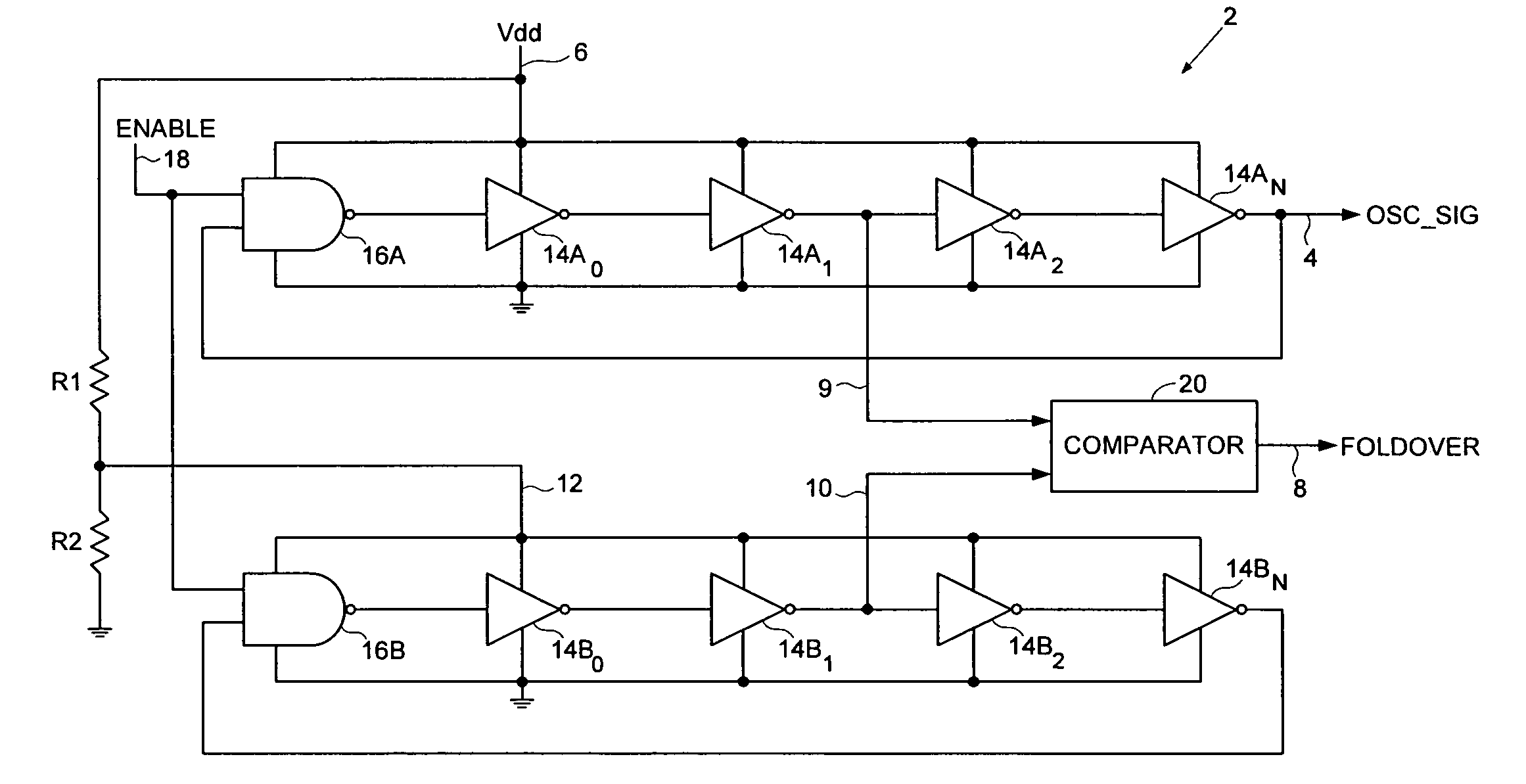

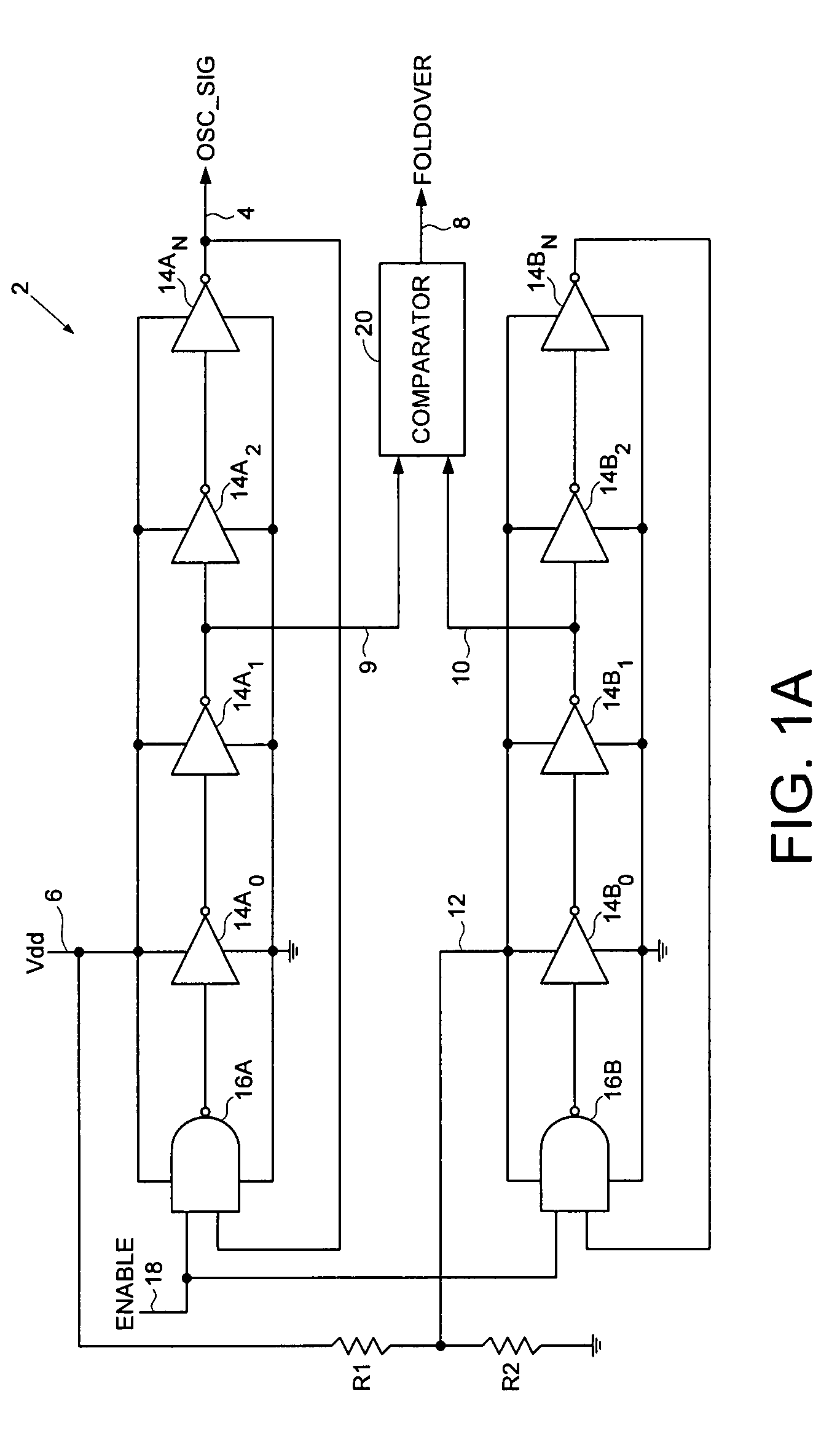

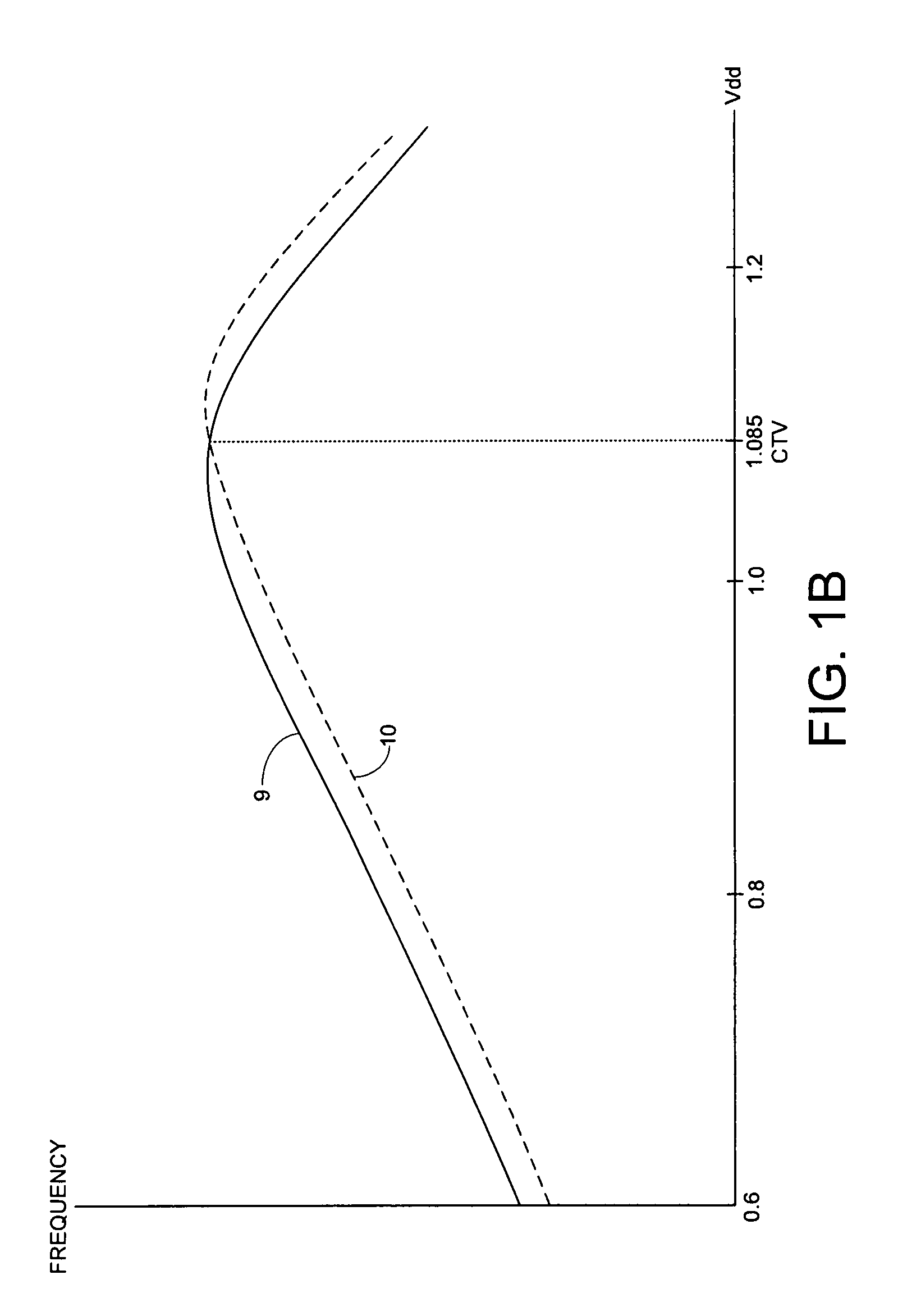

Oscillator comprising foldover detection

ActiveUS7733189B1High frequencyReduce frequencyElectrotherapyPulse automatic controlControl circuitVoltage

Control circuitry is disclosed including an oscillator operable to generate an oscillator signal. A frequency of the oscillator signal increases as an amplitude of a first voltage increases up to a threshold, and the frequency of the oscillator signal decreases as an amplitude of the first voltage exceeds the threshold. The oscillator is operable to generate a foldover signal indicating when the frequency of the oscillator signal is decreasing due to the first voltage exceeding the threshold.

Owner:WESTERN DIGITAL TECH INC

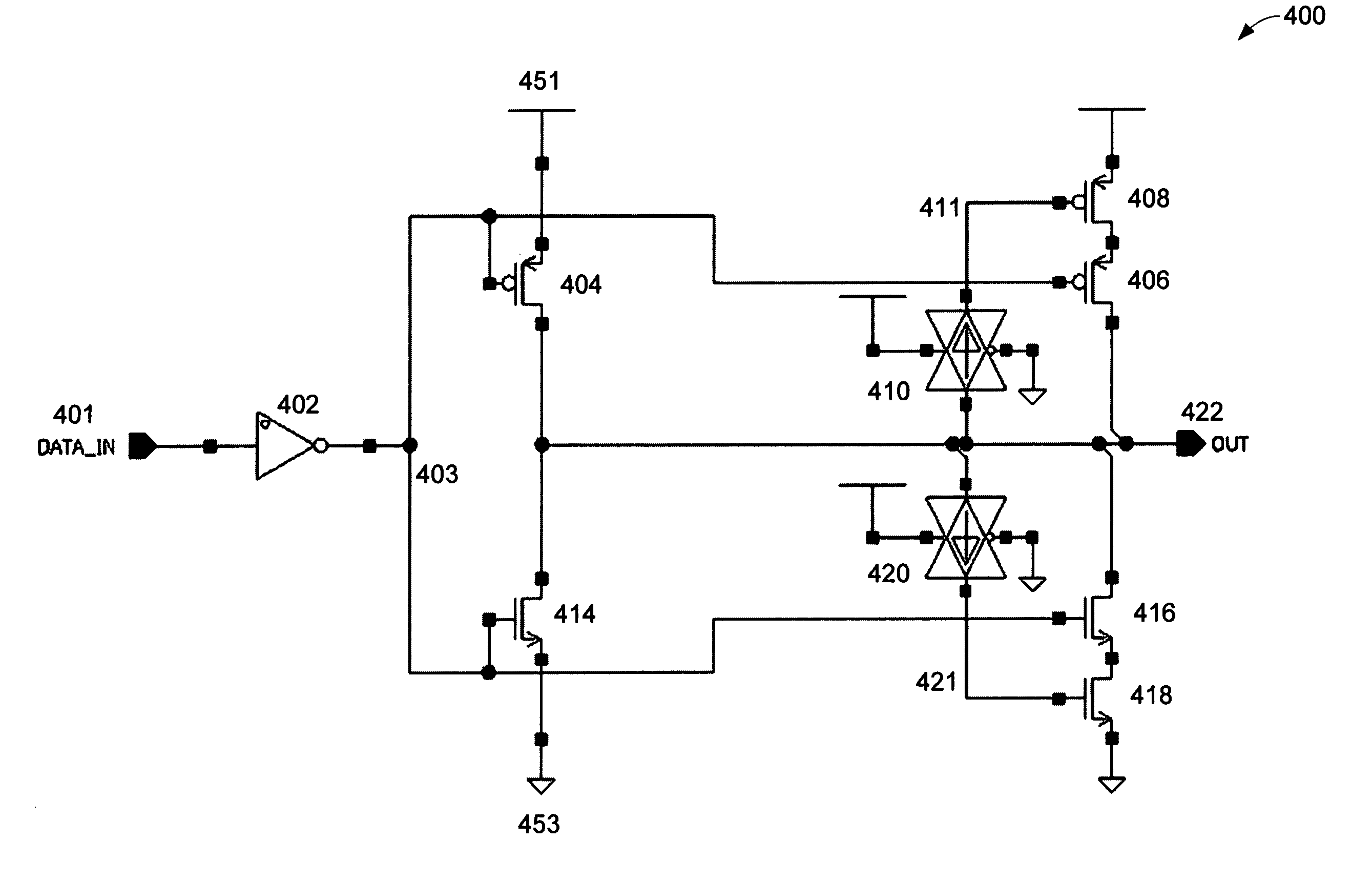

Method and apparatus for an output buffer with dynamic impedance control

Owner:INTEGRATED DEVICE TECH INC

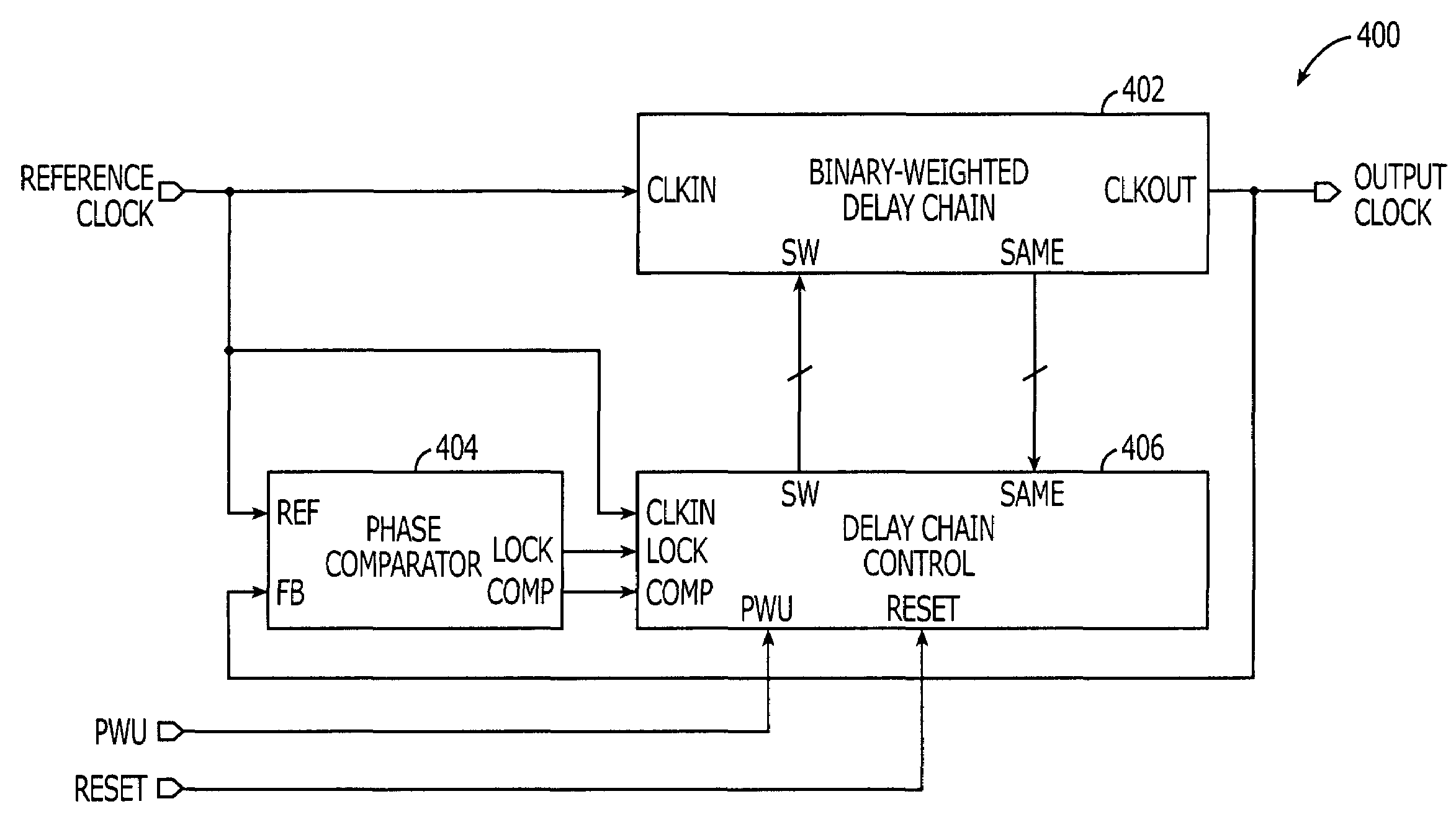

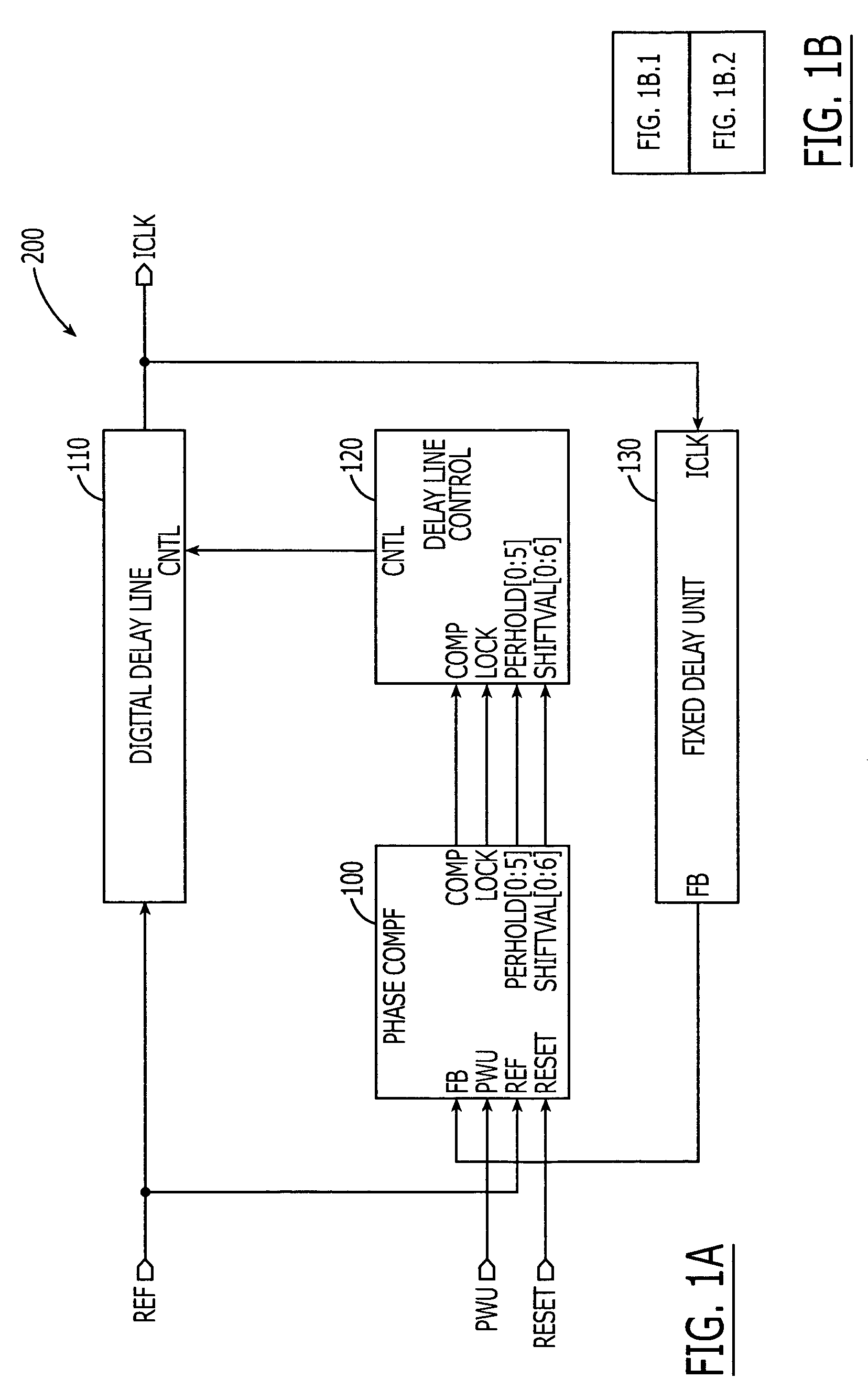

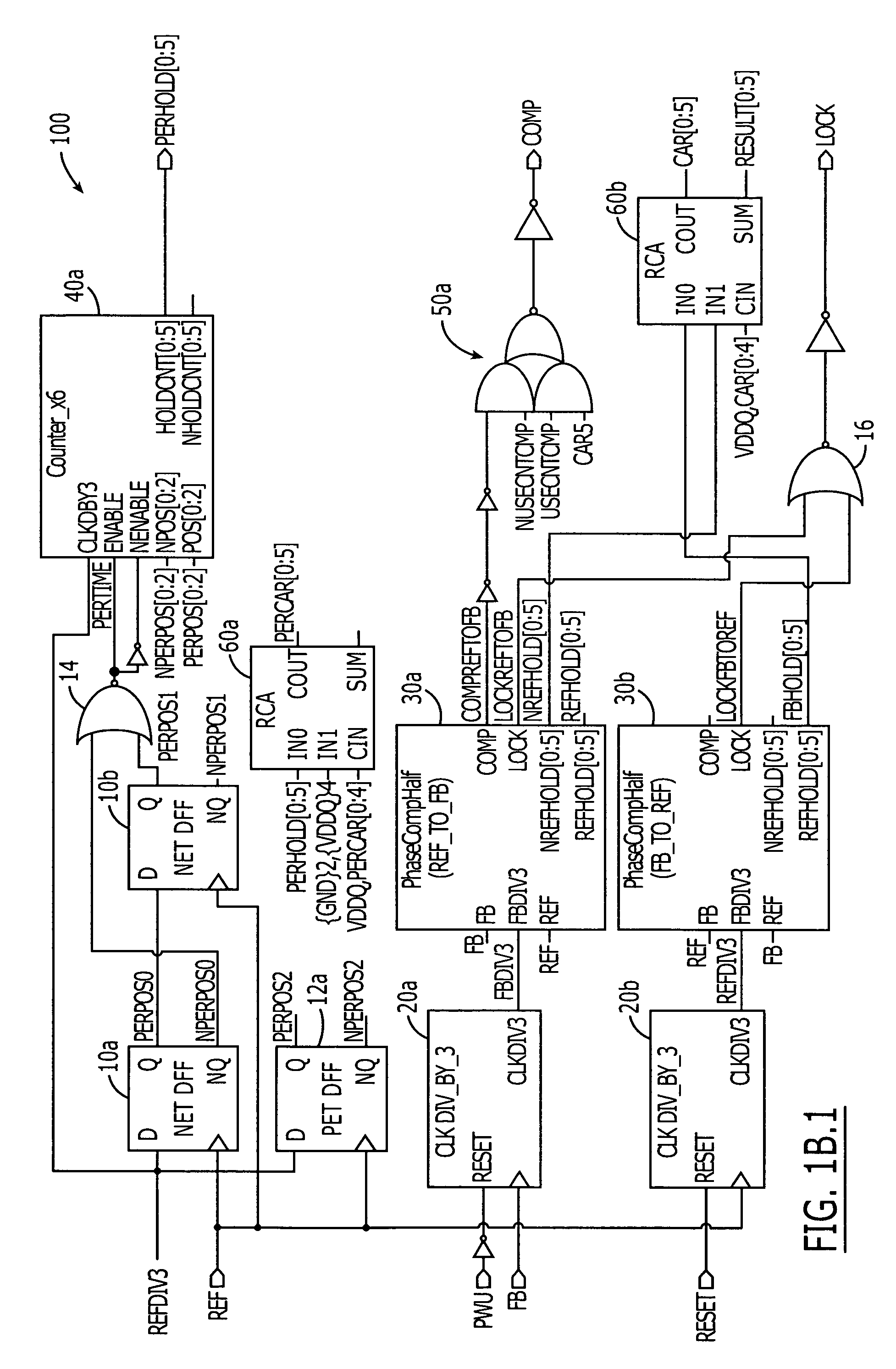

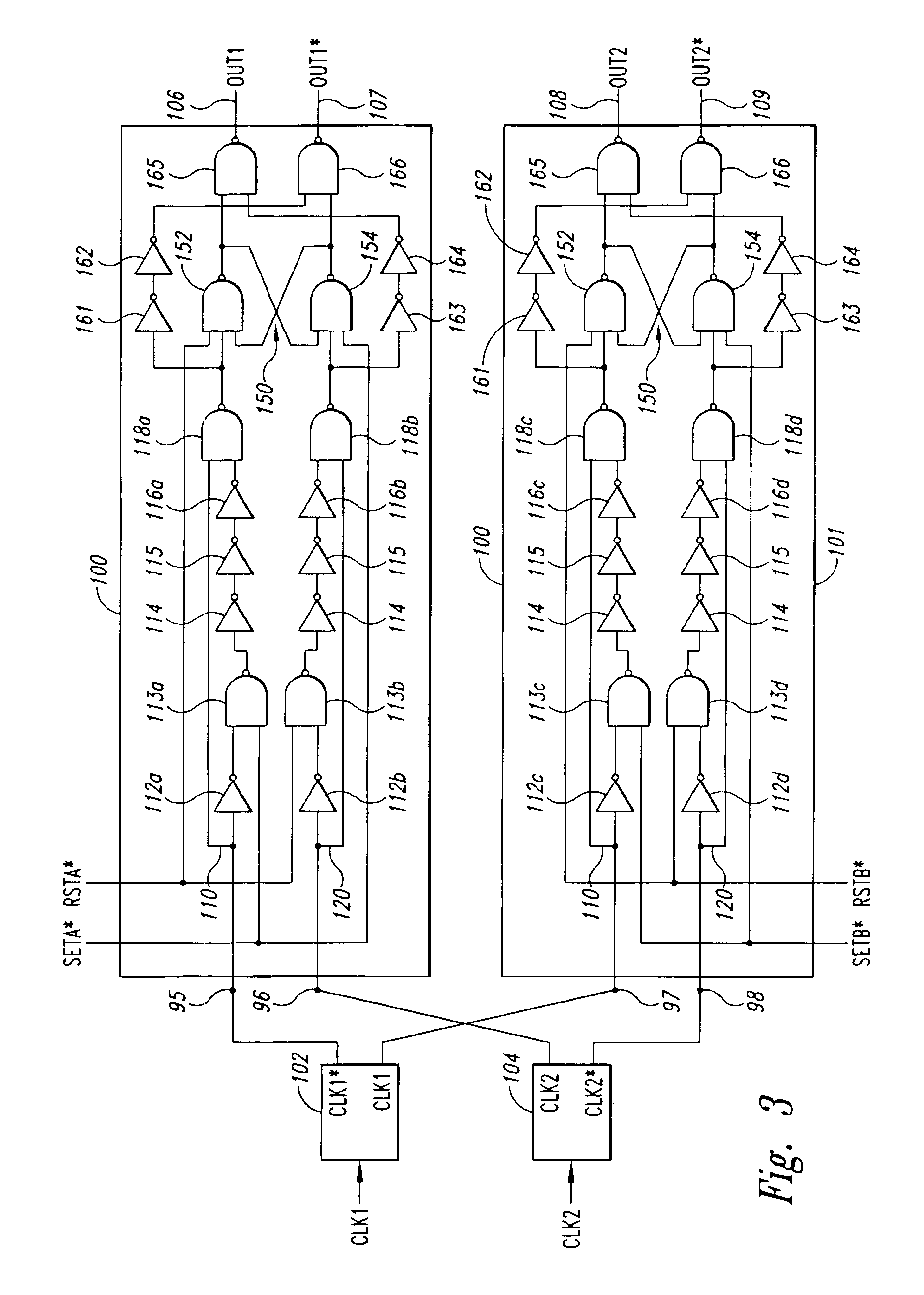

Delay-locked loop (DLL) integrated circuits having binary-weighted delay chain units with built-in phase comparators that support efficient phase locking

ActiveUS7119591B1Facilitates efficient locking of lockedMultiple input and output pulse circuitsPulse automatic controlDelay-locked loopEngineering

Owner:INTEGRATED DEVICE TECH INC

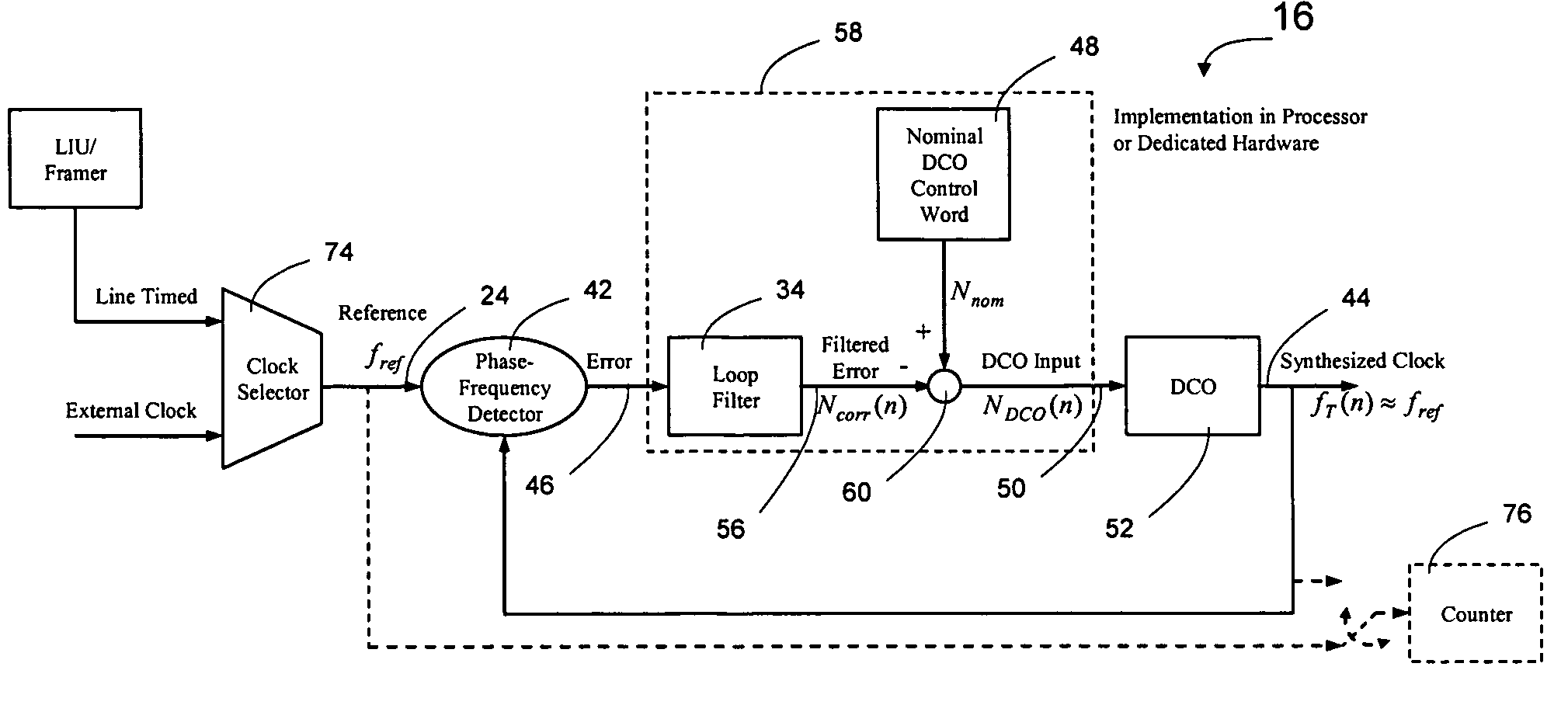

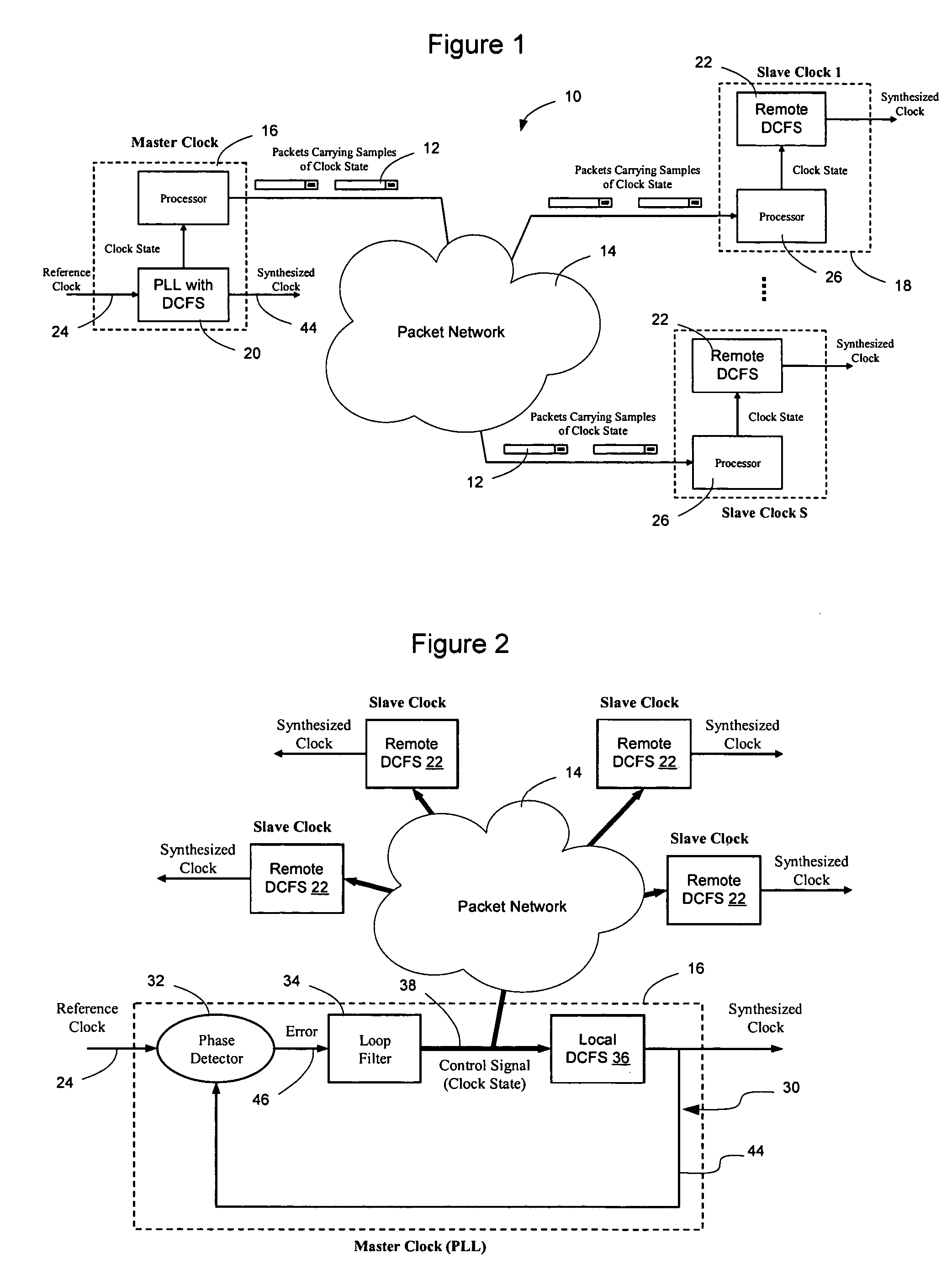

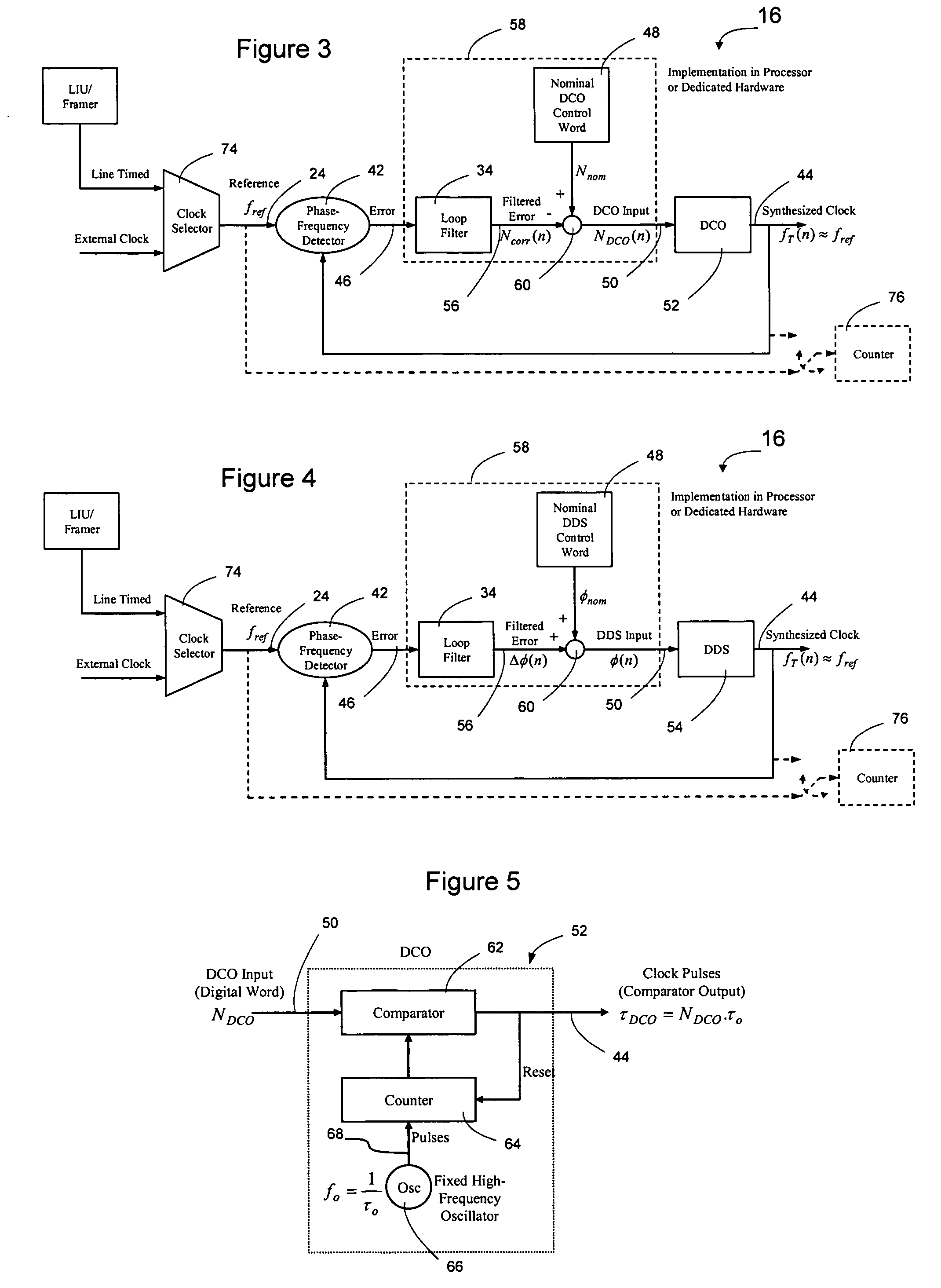

Method and apparatus for synchronizing clock timing between network elements

Network elements may be synchronized over an asynchronous network by implementing a master clock as an all digital PLL that includes a Digitally Controlled Frequency Selector (DCFS), the output frequency of which may be directly controlled through the input of a control word. The PLL causes the control word input to the master DCFS to be adjusted to cause the output of the master DCFS to lock onto a reference frequency. Information associated with the control word is transmitted from the master clock to the slave clocks which are also implemented as DCFSs. By using the transmitted information to recreate the master control word, the slaves may be made to assume the same state as the master DCFS without requiring the slaves to be implemented as PLLs. The DCFS may be formed as a digitally controlled oscillator (DCO) or as a Direct Digital Synthesizer (DDS).

Owner:CIENA

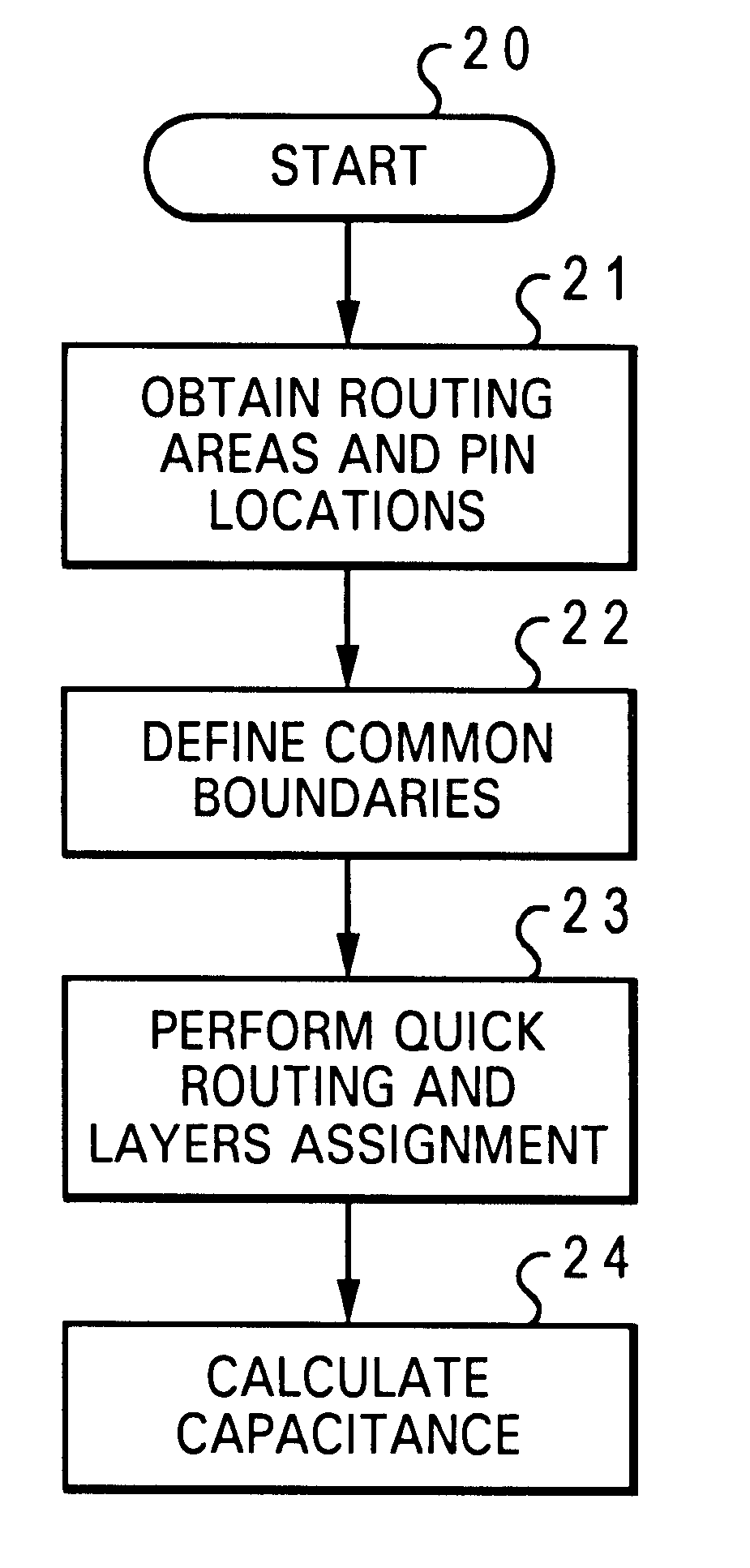

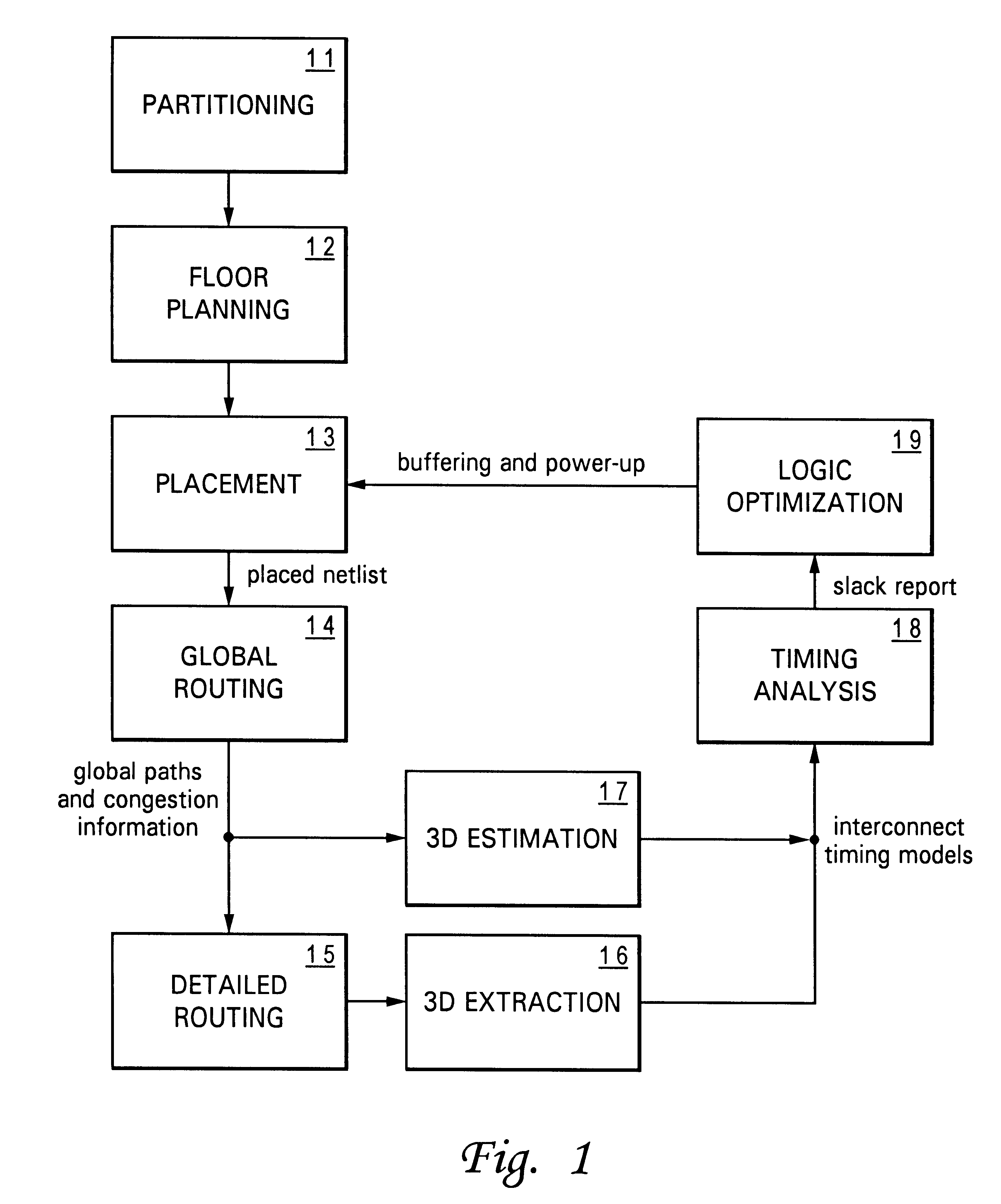

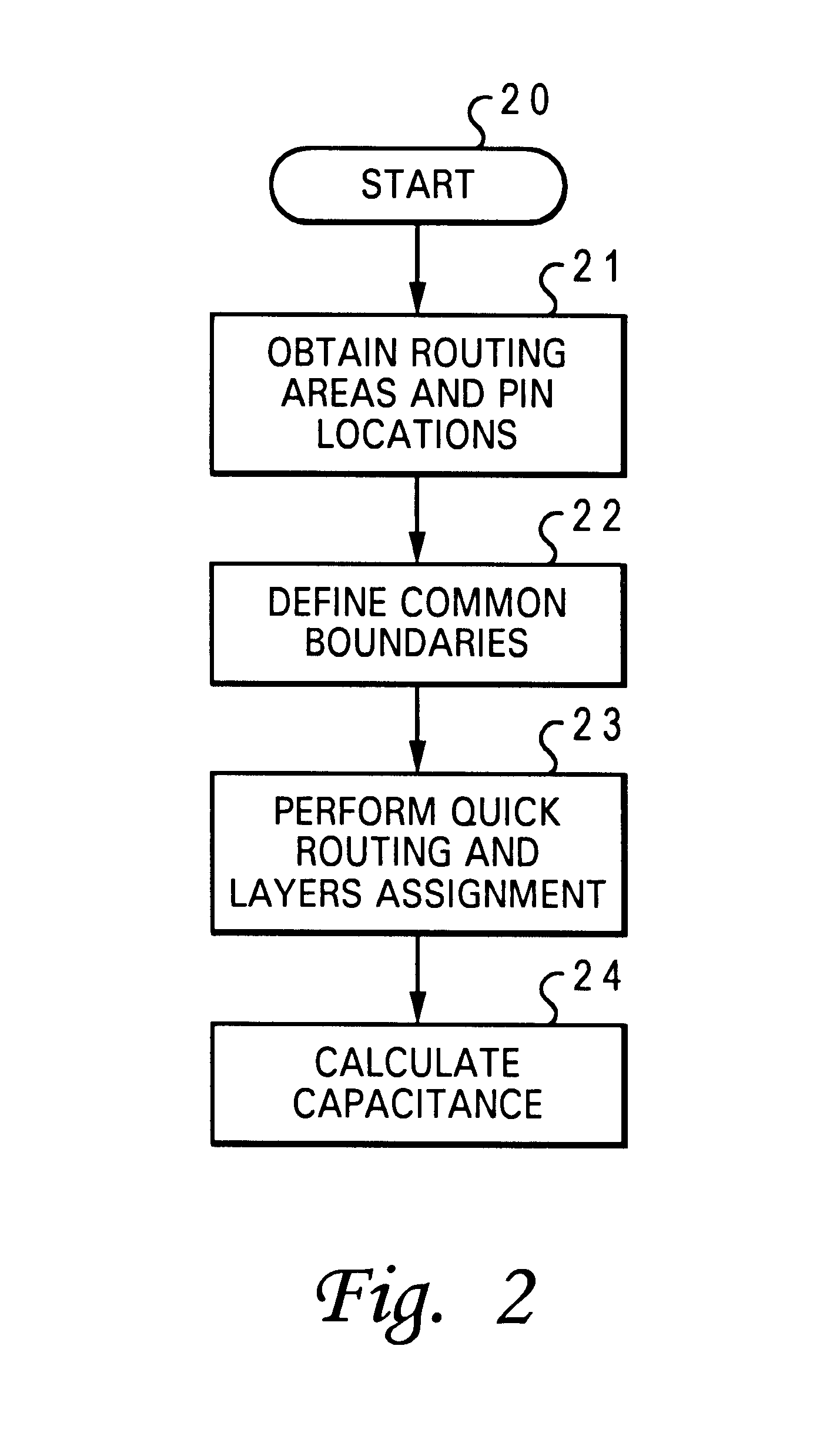

Method and system for performing capacitance estimations on an integrated circuit design routed by a global routing tool

A method for performing capacitance estimations on an integrated circuit design routed by a global routing tool is disclosed. Routing areas and pin locations of a net within an integrated circuit design are initially obtained from a global routing tool. Common boundaries among the routing areas are then defined. Before the performance of a detailed routing step, congestion information furnished by the global routing tool is utilized to perform probabilistic capacitance calculations for an interconnect that can be routed within the routing areas via the defined common boundaries to connect the pin locations.

Owner:IBM CORP

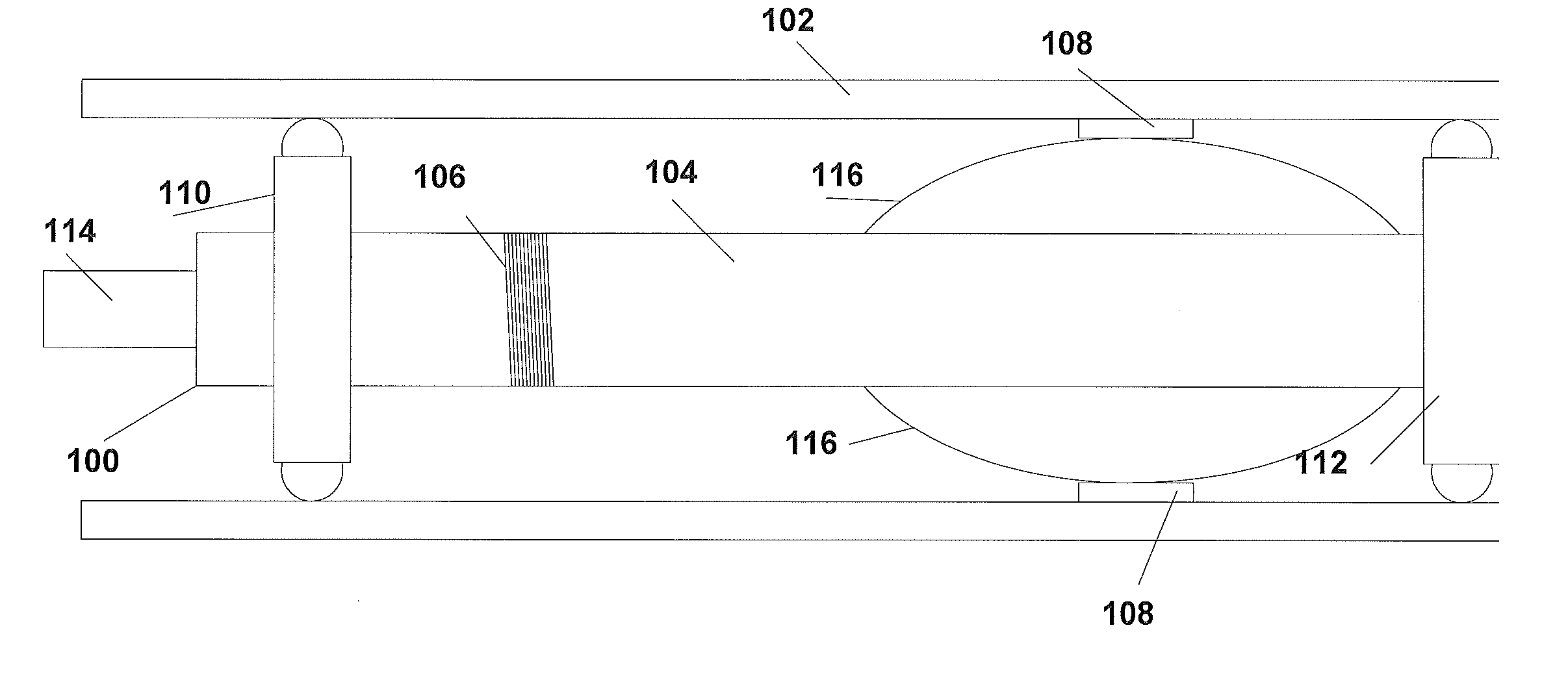

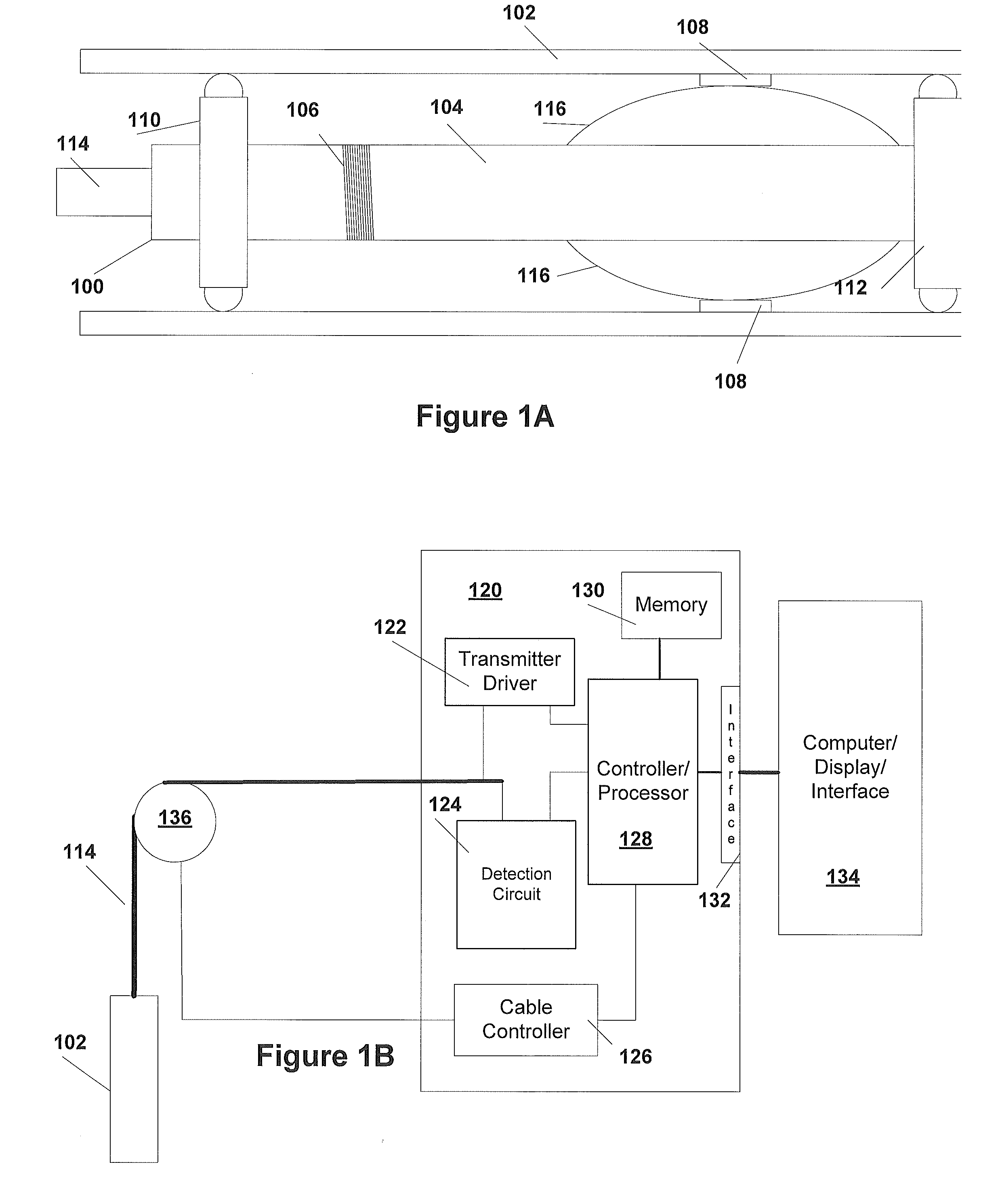

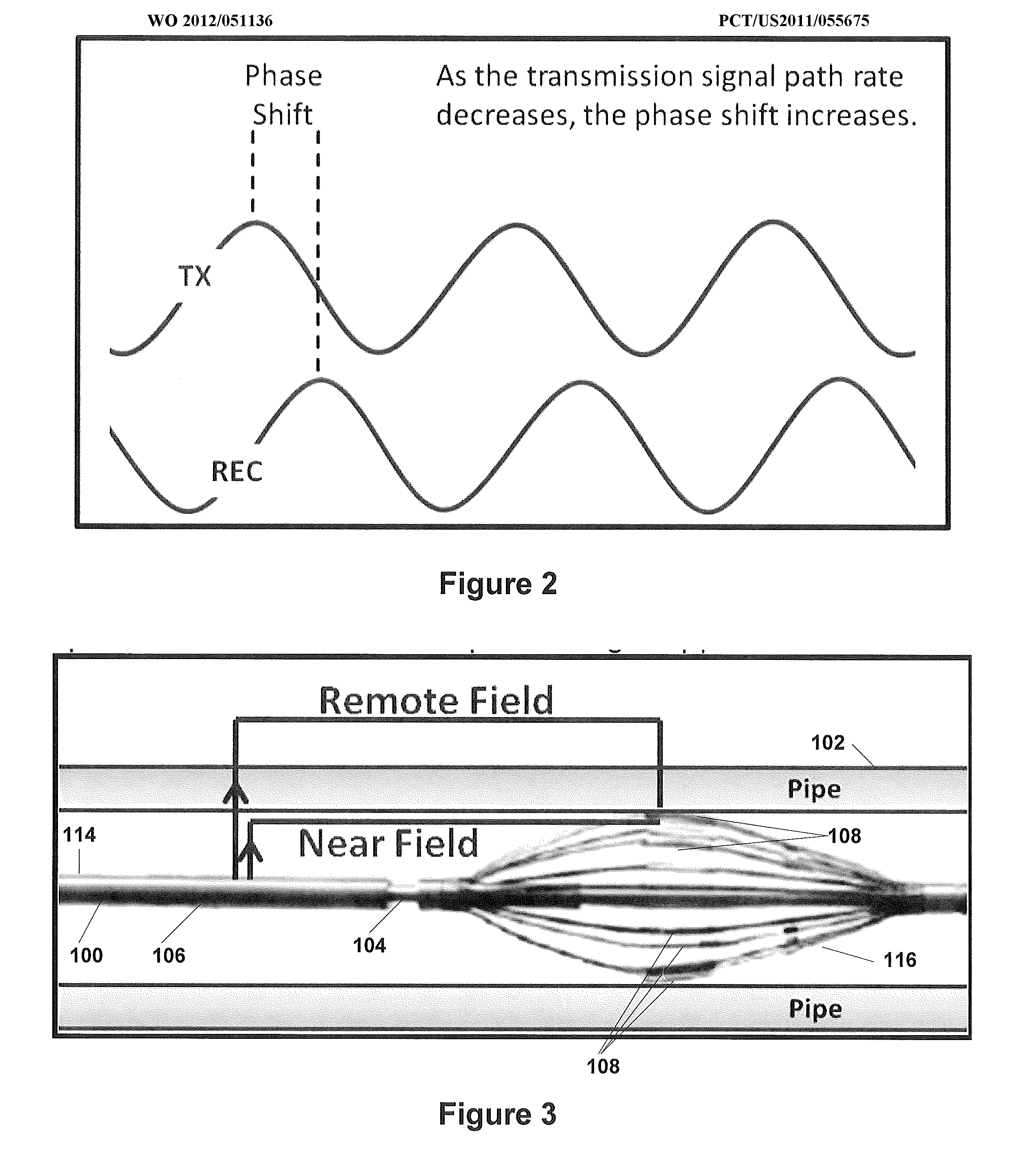

Method For Measuring Remote Field Eddy Current Thickness In Multiple Tubular Configuration

In accordance with aspects of the present invention, a method of inspecting a well tubular is disclosed. The method utilizes a probe with a transmitter and detectors spaced from the transmitter by at least twice the diameter of the pipe to be tested. In some cases where multi-tubular structures are tested, the probe can include further detectors spaced from the transmitter by at least twice the diameter of the outer pipes as well. The phase of signals detected by the detectors relative to the transmitter are utilized to detect faults in the pipes.

Owner:HALLIBURTON ENERGY SERVICES INC

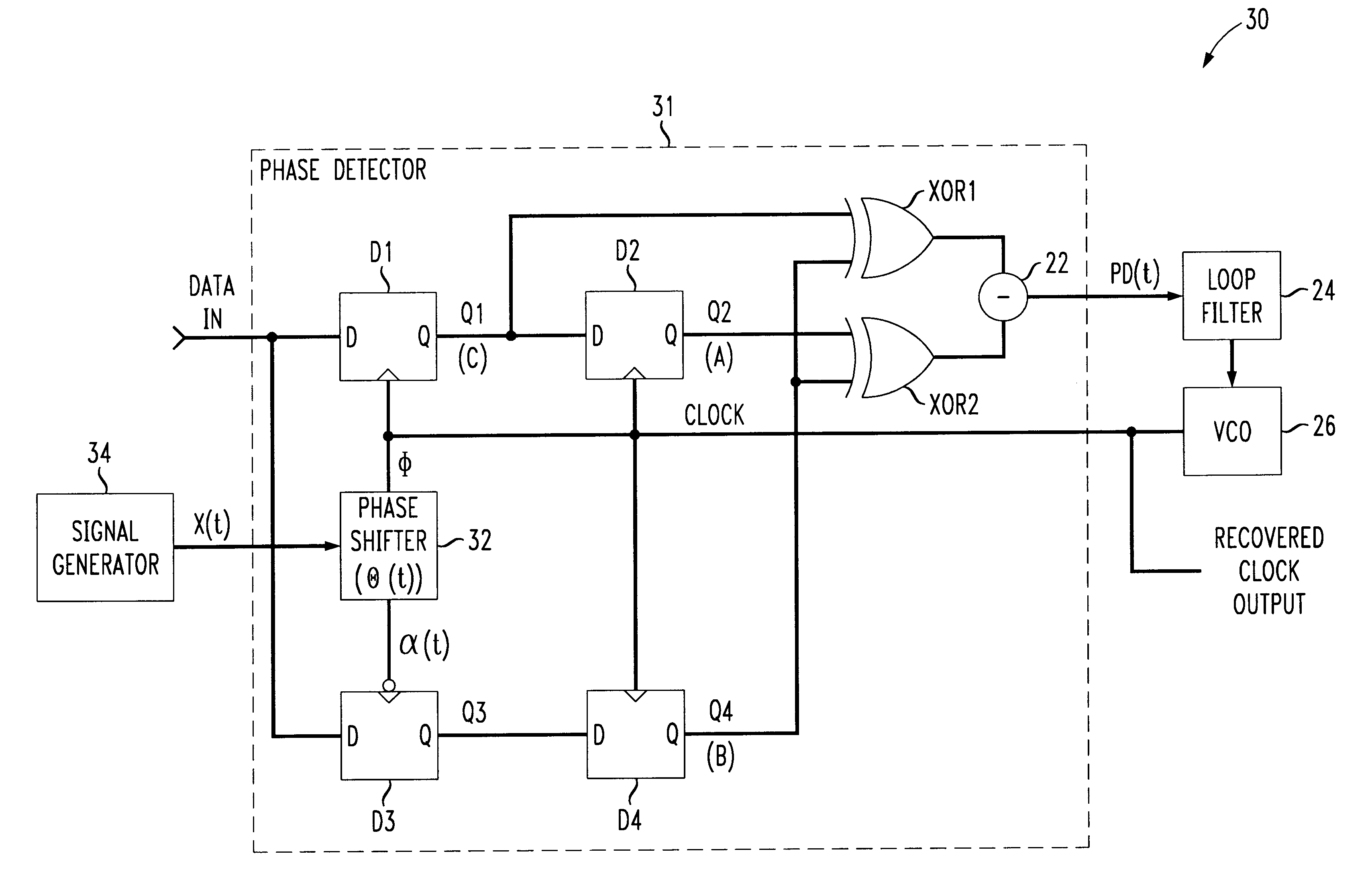

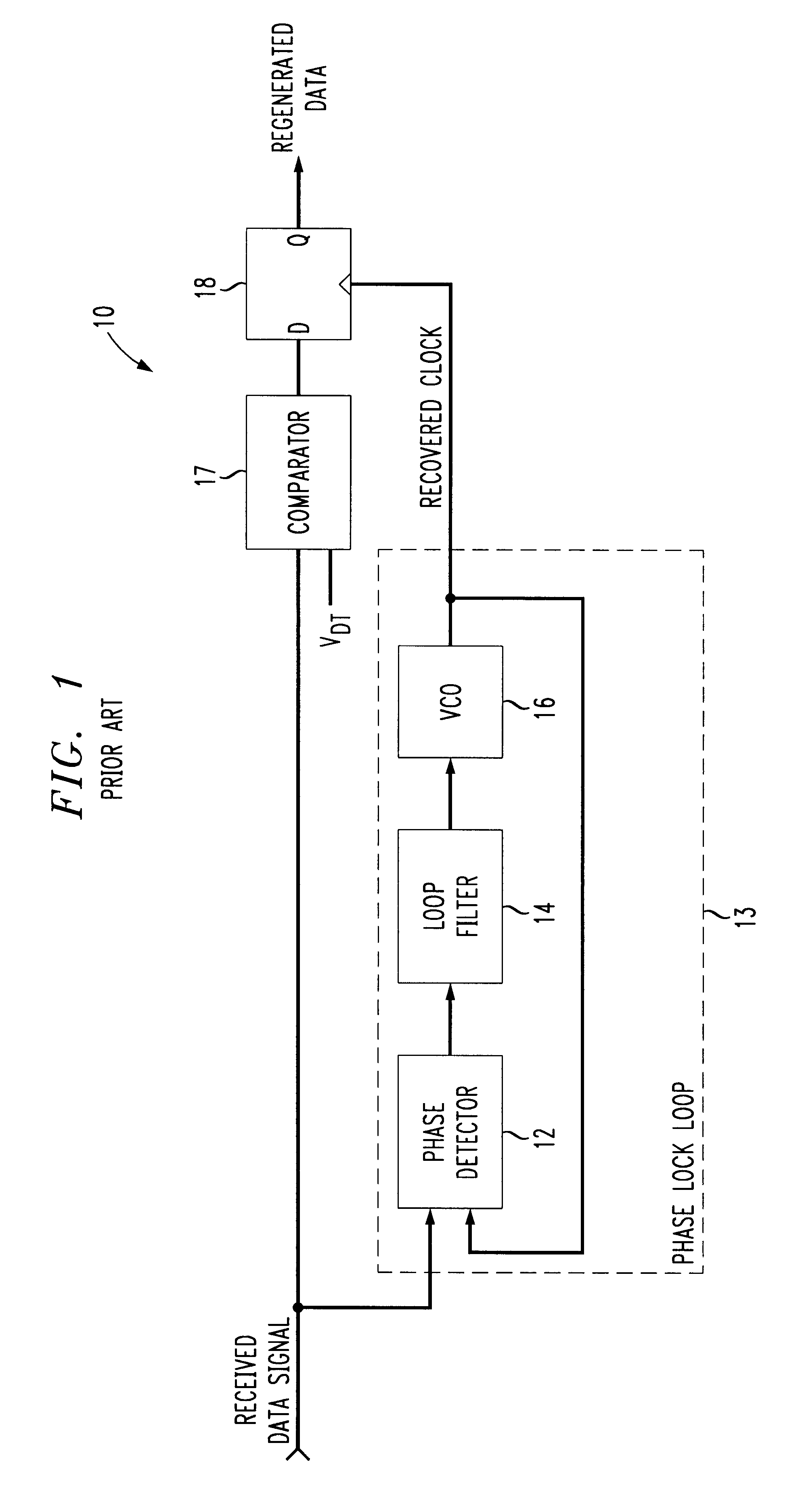

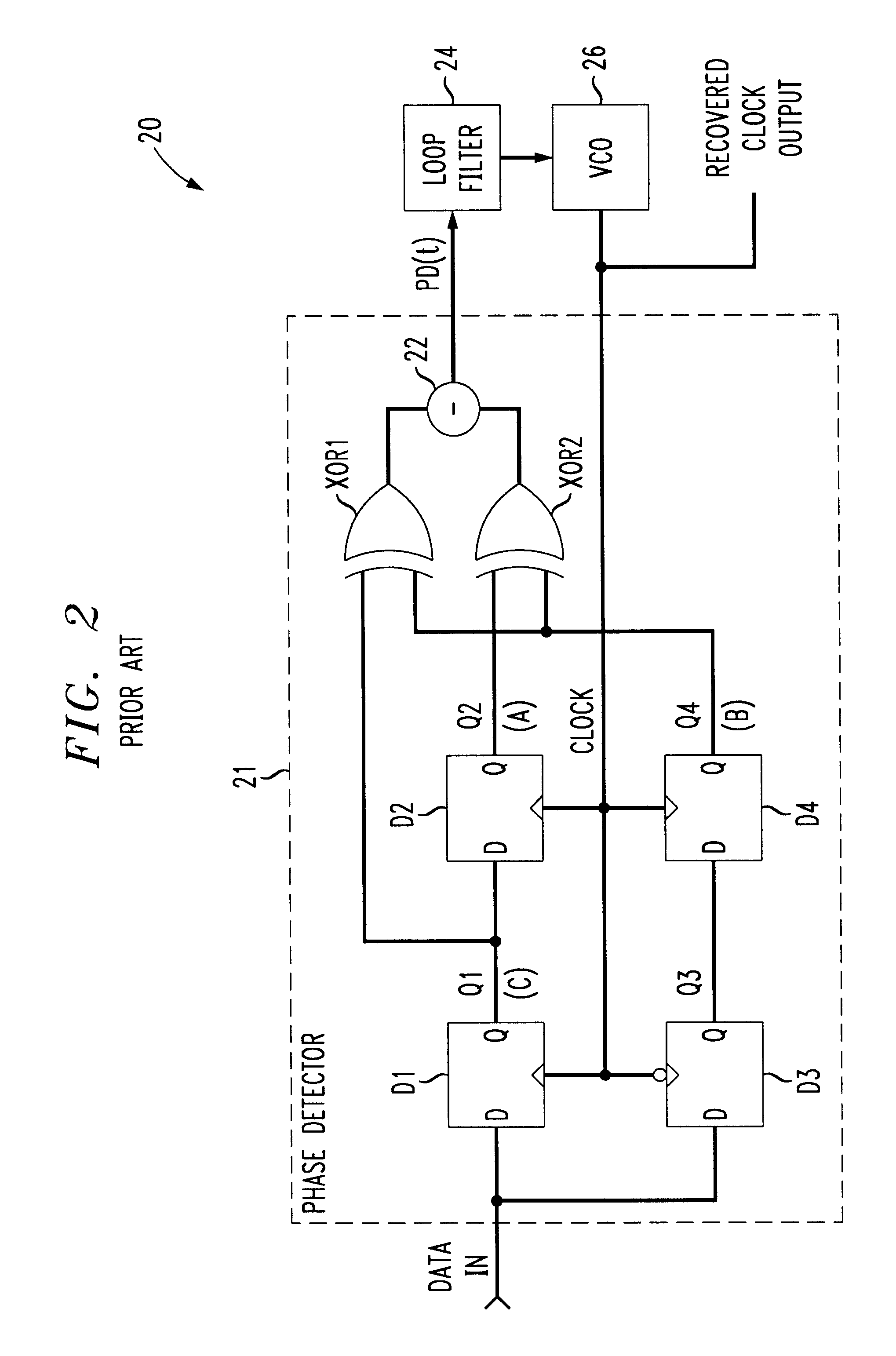

Self-aligned clock recovery circuit with proportional phase detector

InactiveUS6347128B1Pulse automatic controlGenerating/distributing signalsPhase differenceContinuous data

A self-aligned clock recovery circuit for synchronizing a local clock with an input data signal includes a sampling type phase detector for generating an output signal based on the phase difference between the local clock and the data signal timing. The phase detector obtains samples of consecutive data symbols at sampling times corresponding to transitions of the local clock, and obtains a data crossover sample at a sampling instant in between those of the consecutive data symbol samples. A phase shifter is employed to phase shift the local clock by an amount corresponding to a time varying modulation signal so as to obtain each data crossover sample at a variable sampling instant relative to the associated consecutive symbol samples. Logic circuitry determines whether the local clock appears to be early or late based on a comparison of the logic levels of the symbol samples and the associated data crossover sample, and provides a corresponding output signal through a filter to the local clock to adjust the clock accordingly. Since the relative sampling instants of successive data crossover samples are varied with time, the phase detector output signal amplitude is substantially proportional to the amount of phase error between the local clock and the symbol timing, thereby improving jitter properties of the clock recovery circuit.

Owner:AVAGO TECH INT SALES PTE LTD

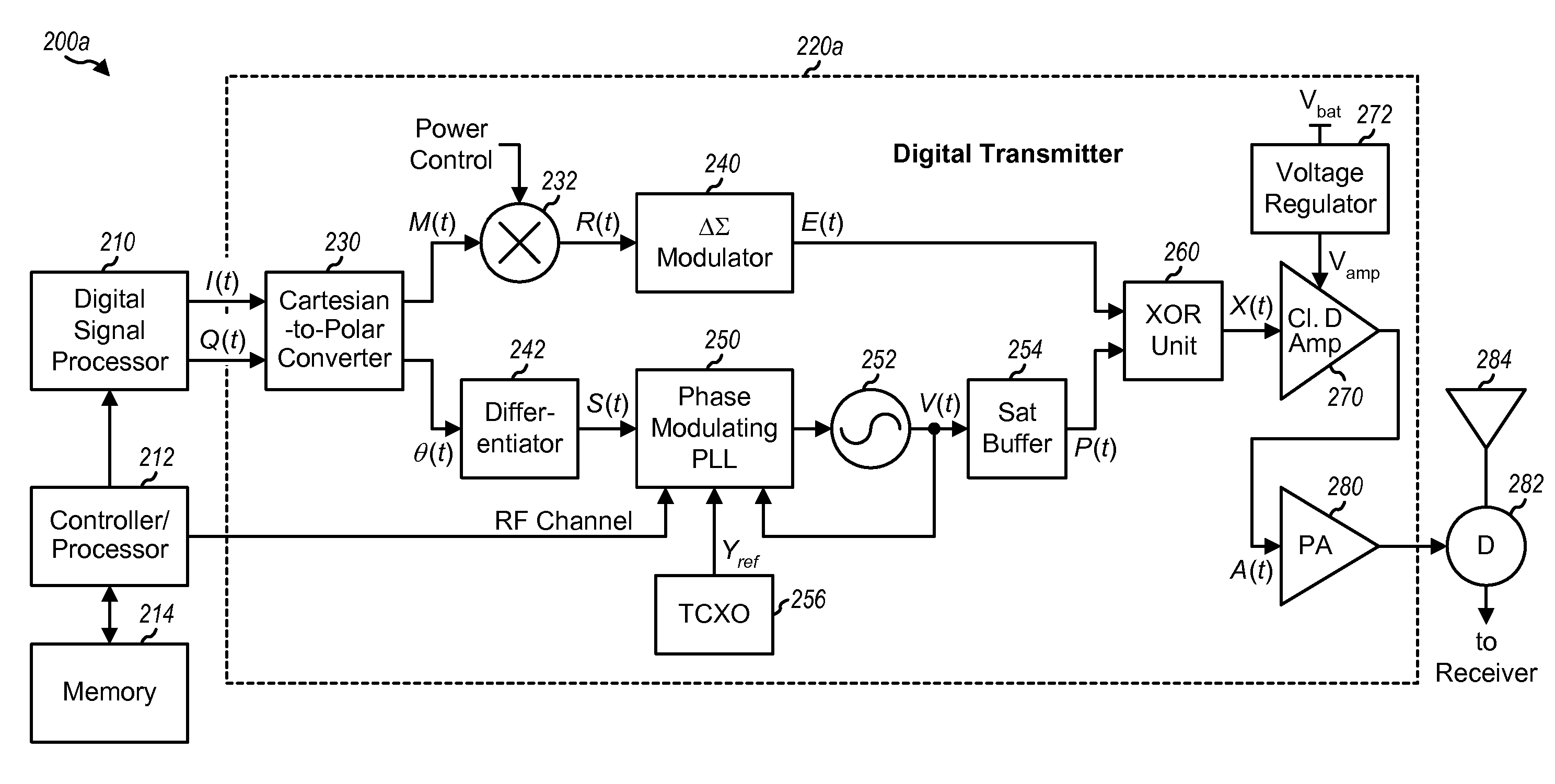

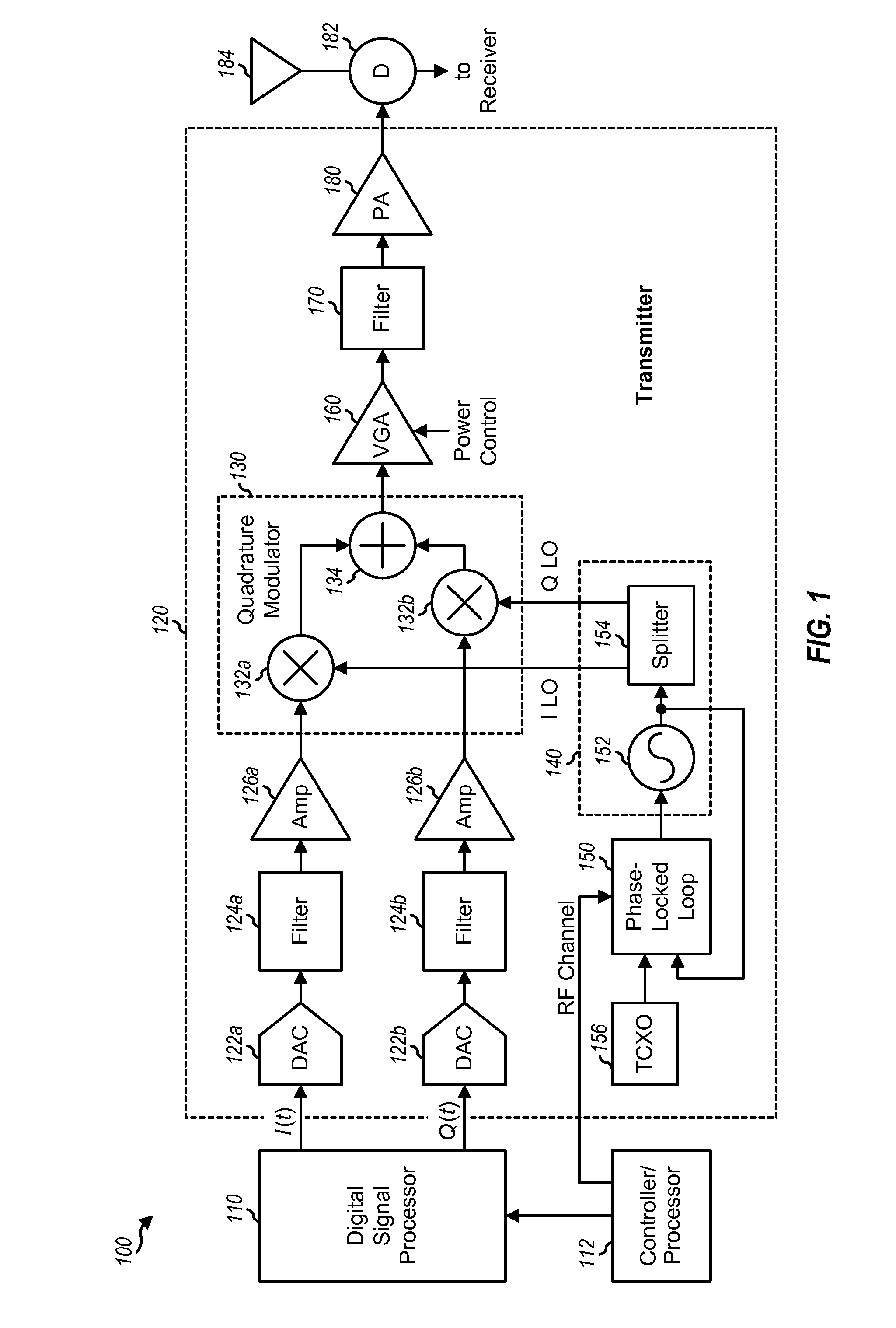

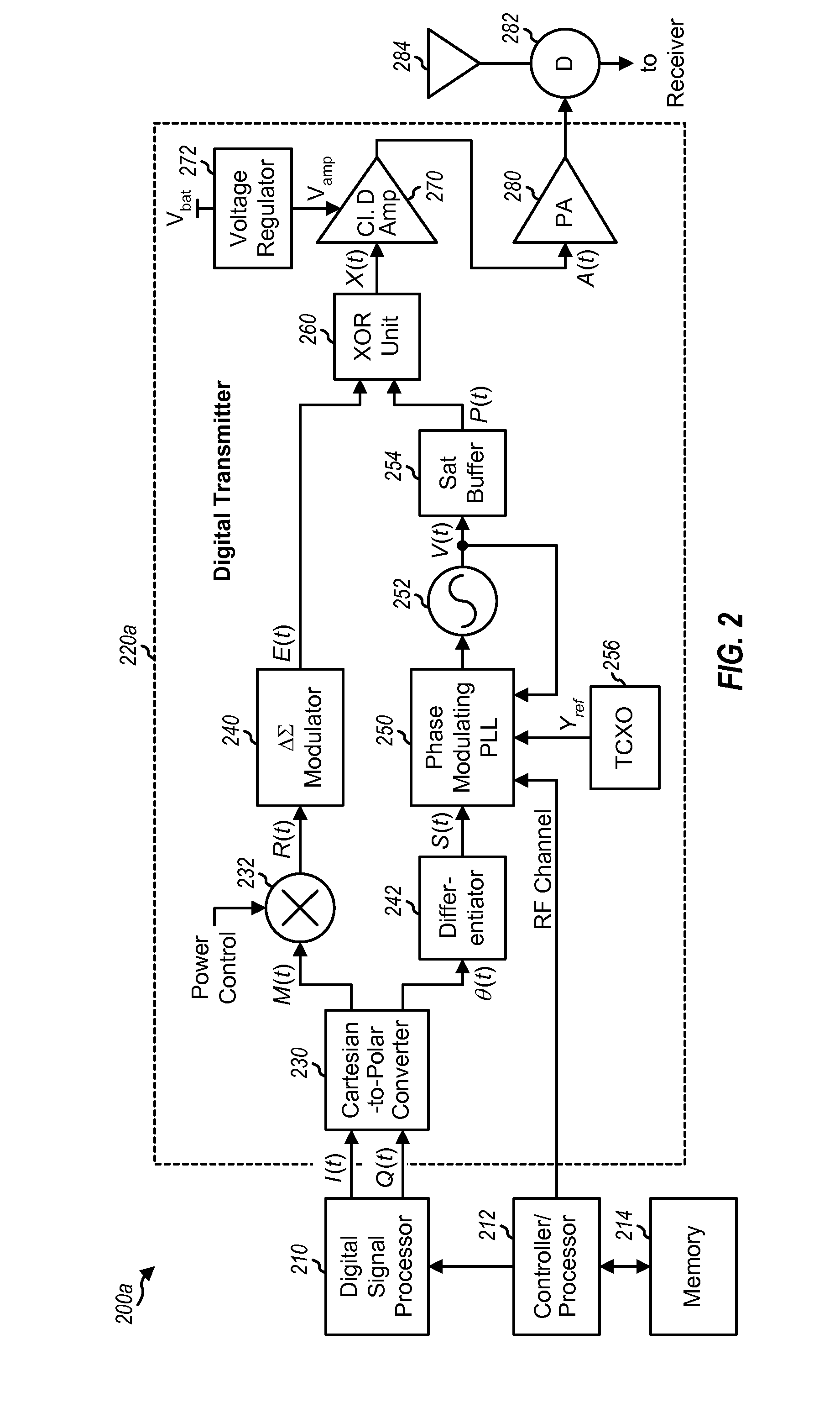

Digital transmitters for wireless communication

ActiveUS20070160164A1Easy to makeModulation with suppressed carrierAngle modulationAudio power amplifierExclusive or

Digital transmitters having improved characteristics are described. In one design of a digital transmitter, a first circuit block receives inphase and quadrature signals, performs conversion from Cartesian to polar coordinates, and generates magnitude and phase signals. A second circuit block (which may include a delta-sigma modulator or a digital filter) generates an envelope signal based on the magnitude signal. A third circuit block generates a phase modulated signal based on the phase signal. The third circuit block may include a phase modulating phase locked loop (PLL), a voltage controlled oscillator (VCO), a saturating buffer, and so on. A fourth circuit block (which may include one or more exclusive-OR gates or an amplifier with multiple gain states) generates a digitally modulated signal based on the envelope signal and the phase modulated signal. A fifth circuit block (which may include a class D amplifier and / or a power amplifier) amplifies the digitally modulated signal and generates an RF output signal.

Owner:QUALCOMM INC

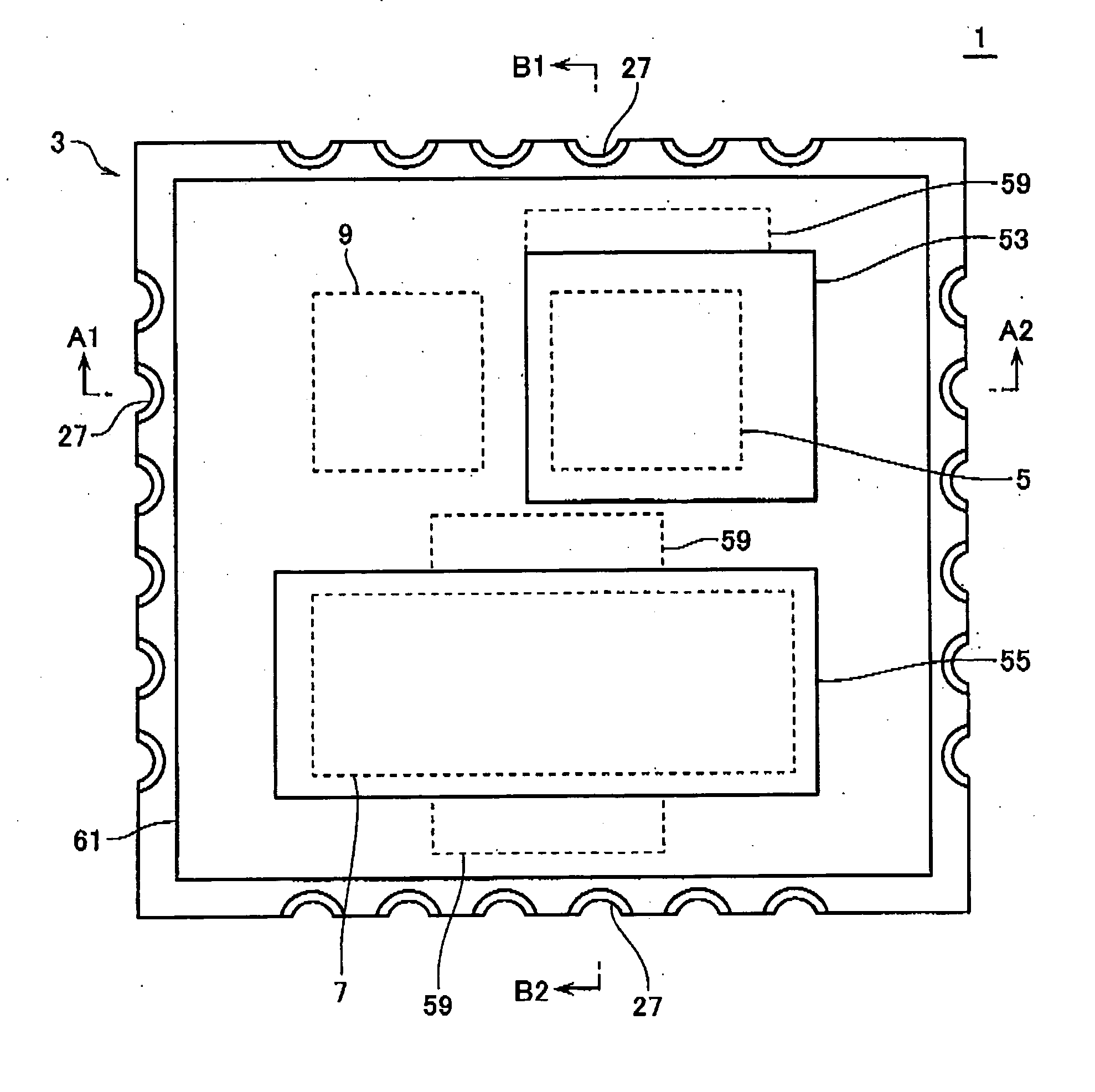

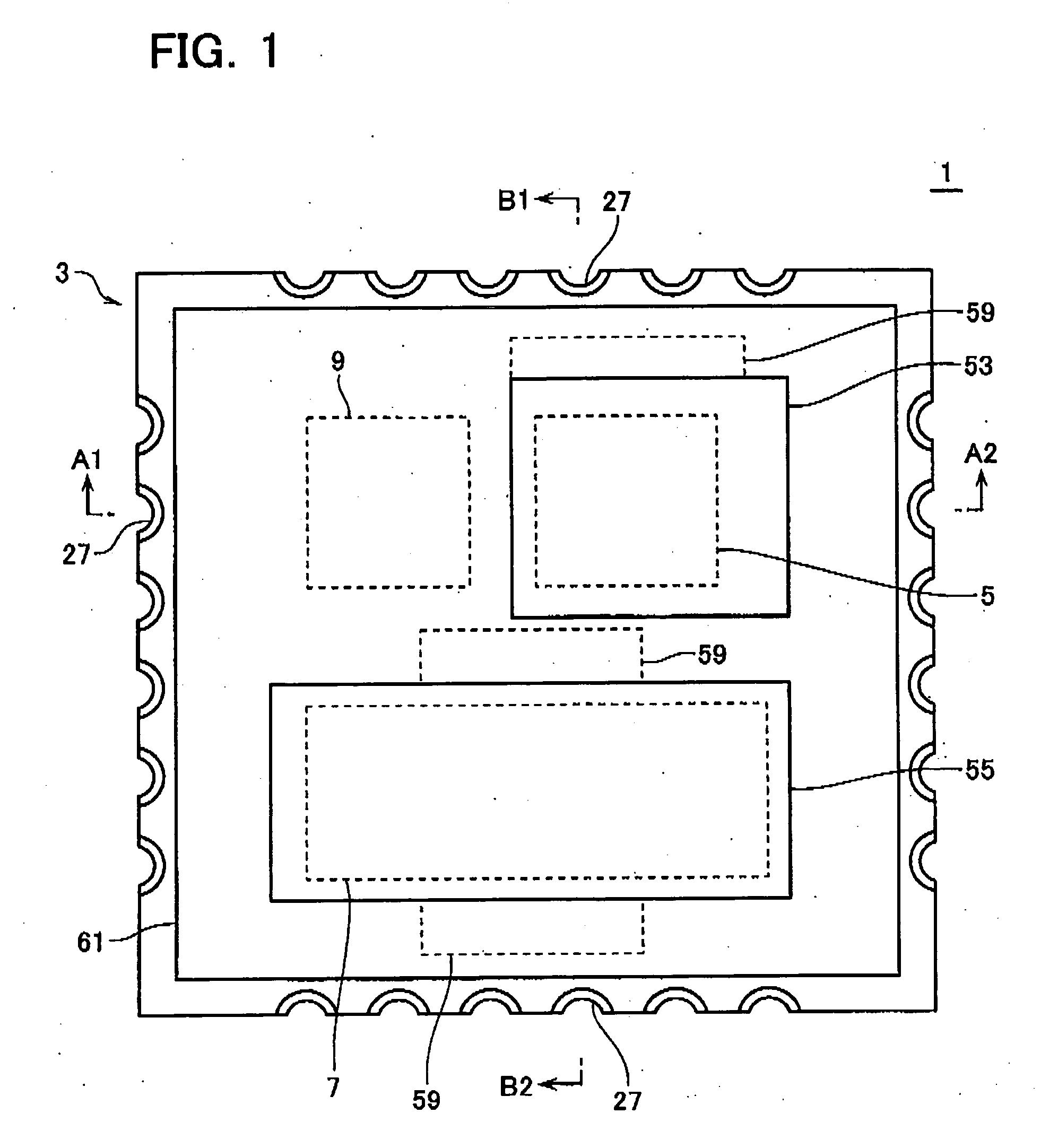

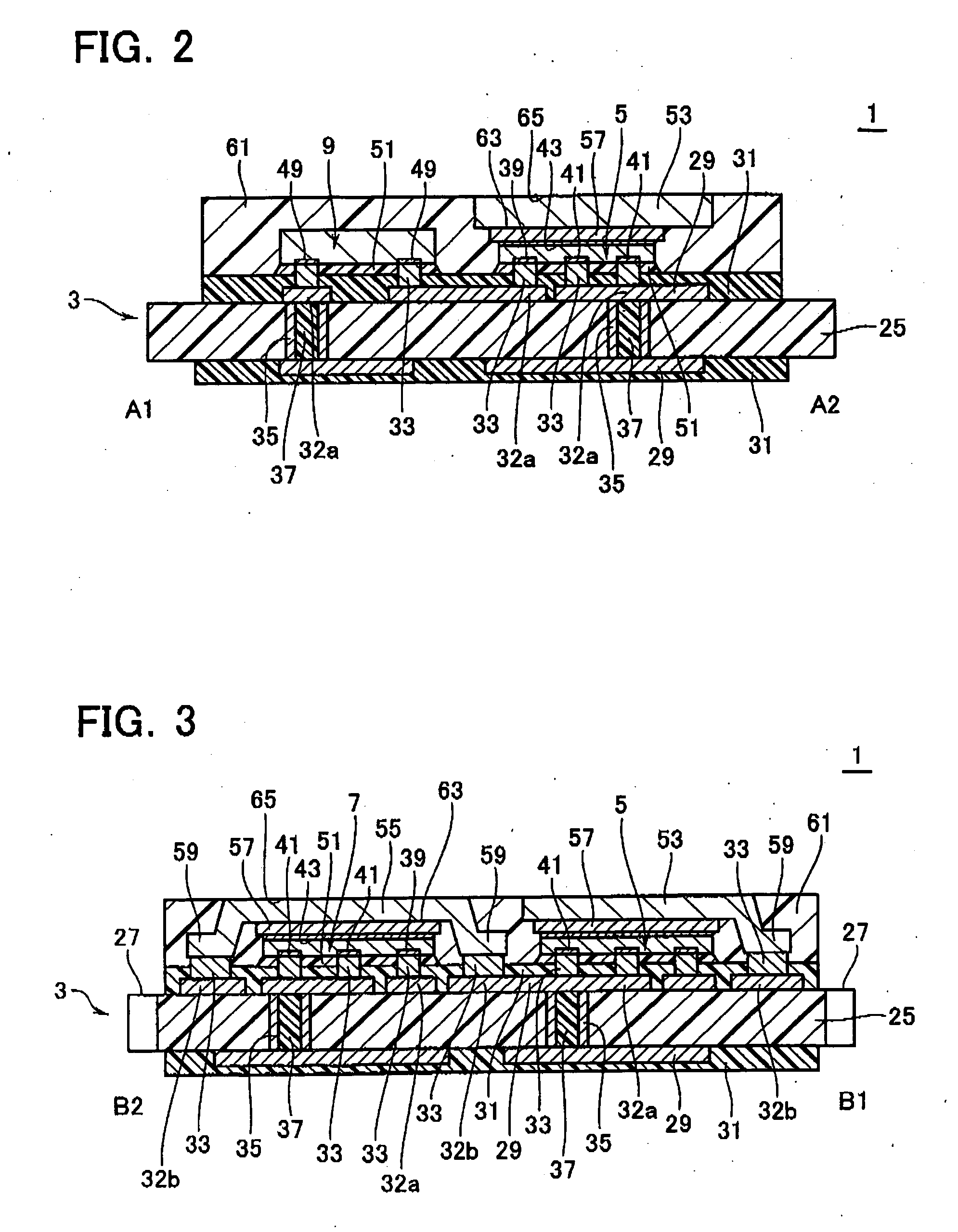

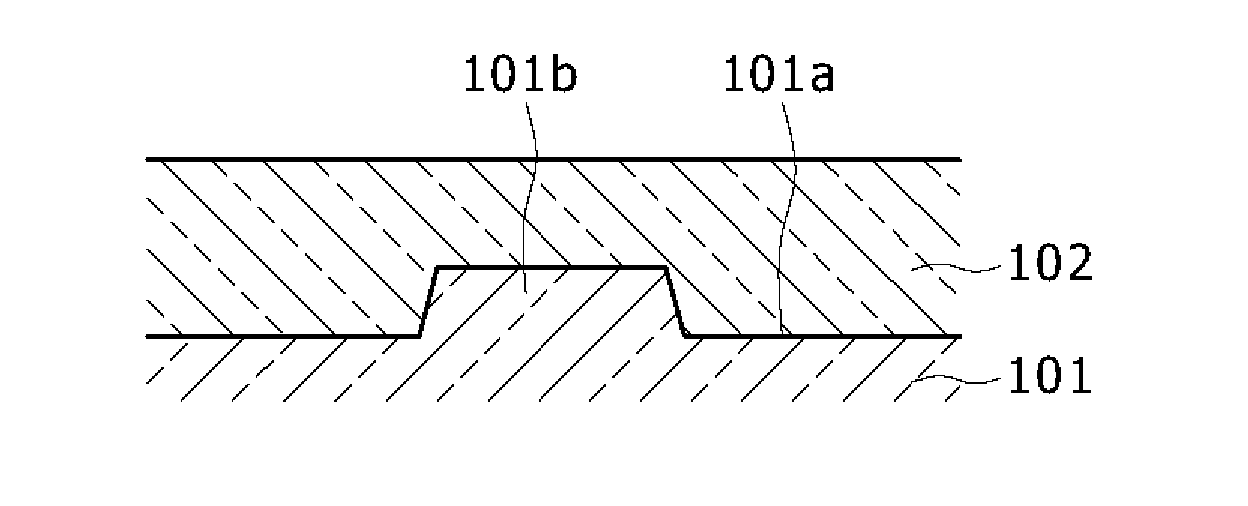

Semiconductor module

InactiveUS20060055432A1Semiconductor/solid-state device detailsSolid-state devicesPower switchingEngineering

A semiconductor module comprises a mounting board. A plurality of power switching device chips are mounted on the mounting board by flip-chip bonding. The chip has an upper surface and a lower surface and is configured to face the upper surface toward the mounting board. A drive IC chip is mounted on the mounting board by flip-chip bonding. The drive IC chip is operative to drive gates of transistors formed in the plurality of power switching device chips. A plurality of heat sink members are located on the lower surfaces of the plurality of power switching device chips, respectively. A resinous member is provided to seal the plurality of power switching device chips and the drive IC chip in a single package.

Owner:KK TOSHIBA

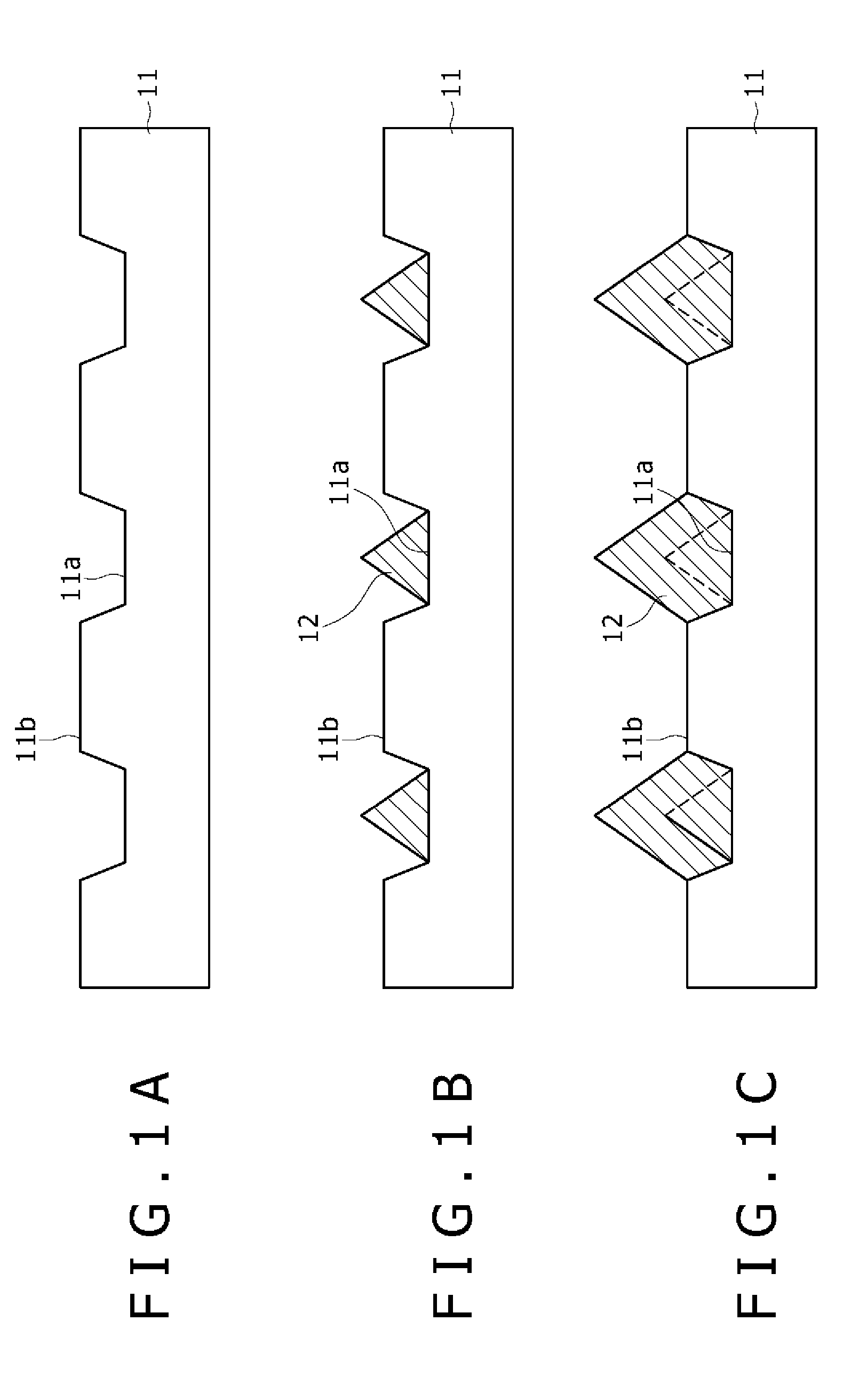

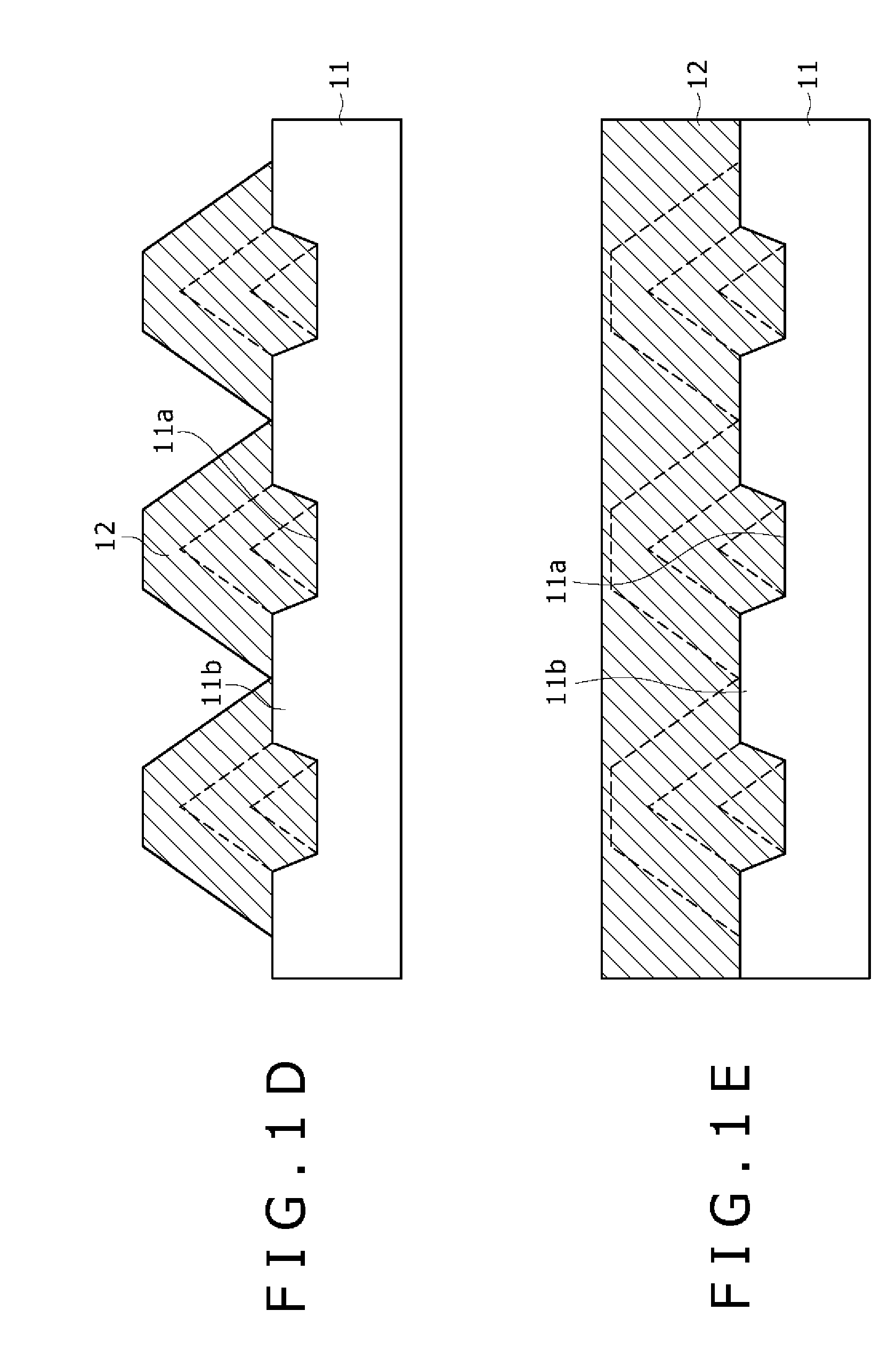

Light-emitting diode, method for making light-emitting diode, integrated light-emitting diode and method for making integrated light-emitting diode, method for growing a nitride-based iii-v group compound semiconductor, light source cell unit, light-emitting diode backlight, and light-emitting diode display and electronic device

InactiveUS20060258027A1Light emission efficiency is reducedImprove light emission efficiencySolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceEngineering

A method for making a light-emitting diode, which including the steps of: providing a substrate having at least one recessed portion on one main surface and growing a first nitride-based III-V group compound semiconductor layer through a state of making a triangle in section having a bottom surface of the recessed portion as a base thereby burying the recessed portion; laterally growing a second nitride-based III-V group compound semiconductor layer from the first nitride-based III-V group compound semiconductor layer over the substrate; and successively growing a third nitride-based III-V group compound semiconductor layer of a first conduction type, an active layer and a fourth nitride-based III-V group compound semiconductor layer of a second conduction type on the second nitride-based III-V group compound semiconductor layer.

Owner:SONY CORP

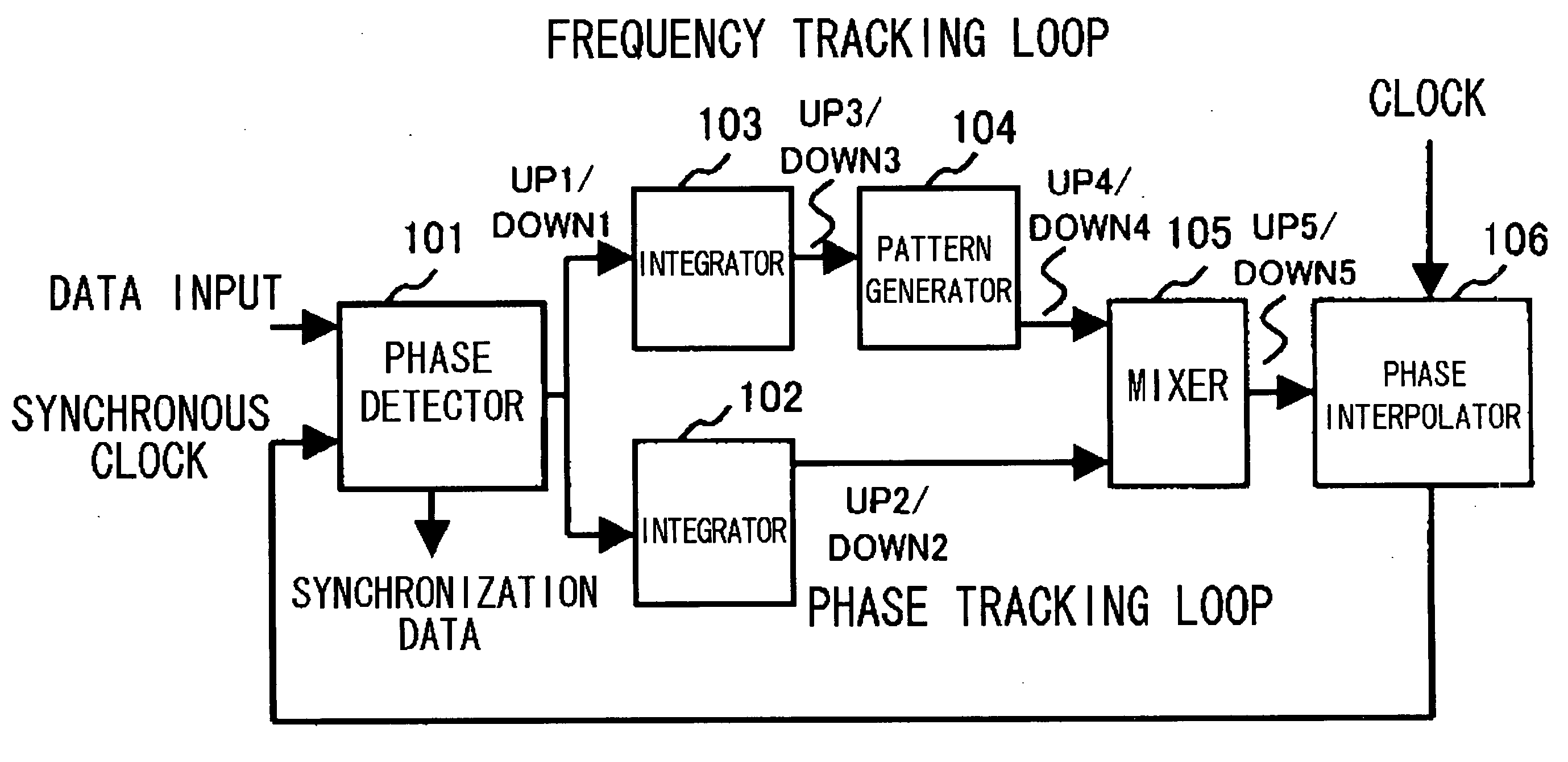

Clock and data recovery circuit

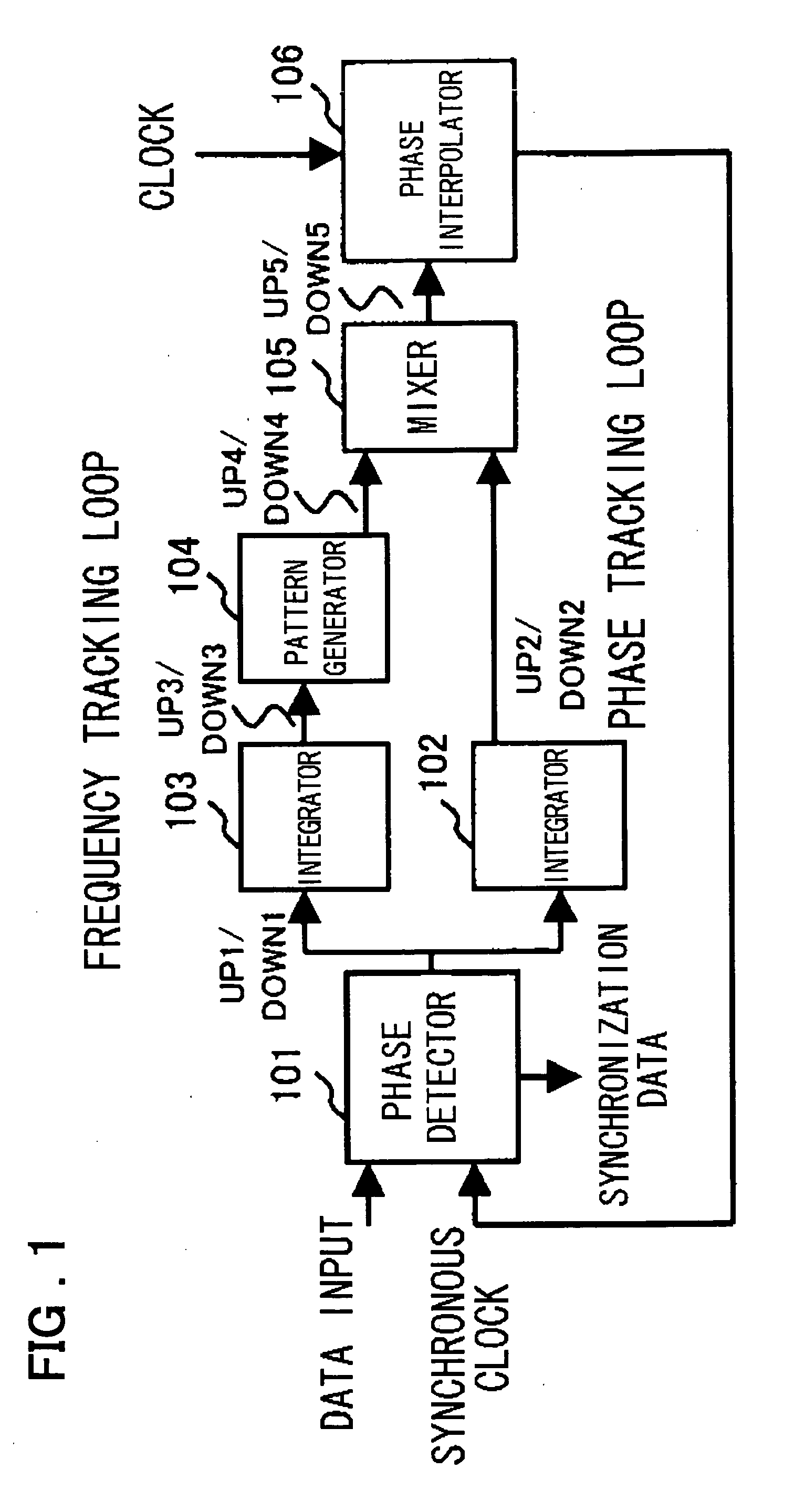

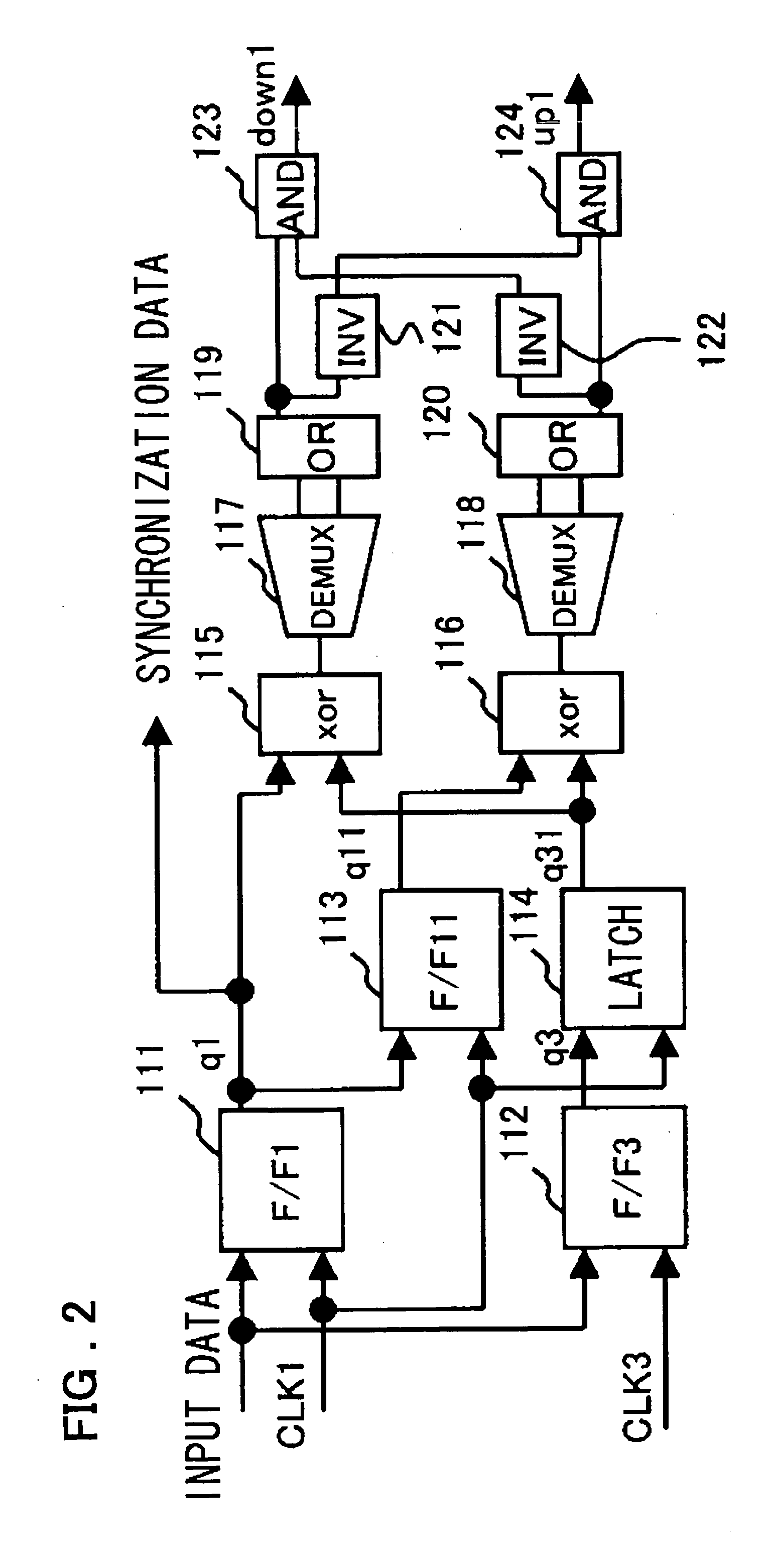

ActiveUS20040252804A1Increase in chip sizeIncreasing chip sizePulse automatic controlOscillations comparator circuitsPhase detectorIntegrator

A clock and data recovery circuit, for tracking frequency-modulated input data, comprises a phase detector for receiving a data signal and a synchronous clock signal, detecting a phase delay or a phase advance, and outputting an UP1 / DOWN1 signal, first and second integrators for integrating the UP1 / DOWN1 signal and outputting an UP2 / DOWN2 signal and an UP3 / DOWN3 signal, respectively, a pattern generator for receiving the UP3 / DOWN3 signal from the second integrator to output an UP4 / DOWN4 signal, a mixer for receiving the UP2 / DOWN2 signal from the first integrator and the UP4 / DOWN4 signal from the pattern generator and generating an UP5 / DOWN5 signal for output, and a phase interpolator for interpolating the phase of an input clock signal based on the UP5 / DOWN5 signal from the mixer, for output are provided. A clock signal output from the interpolator is fed back to the phase detector as the clock.

Owner:RENESAS ELECTRONICS CORP

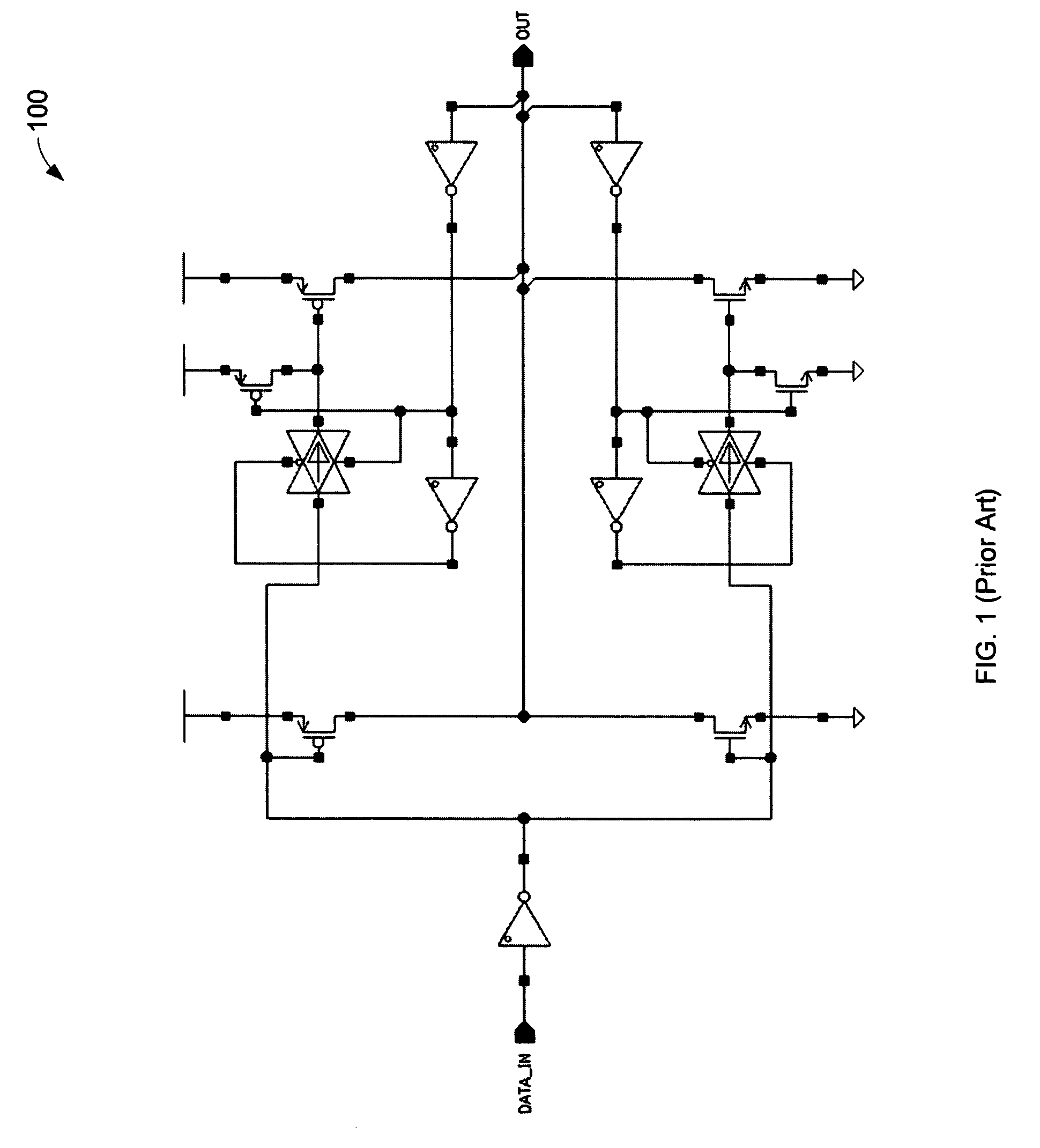

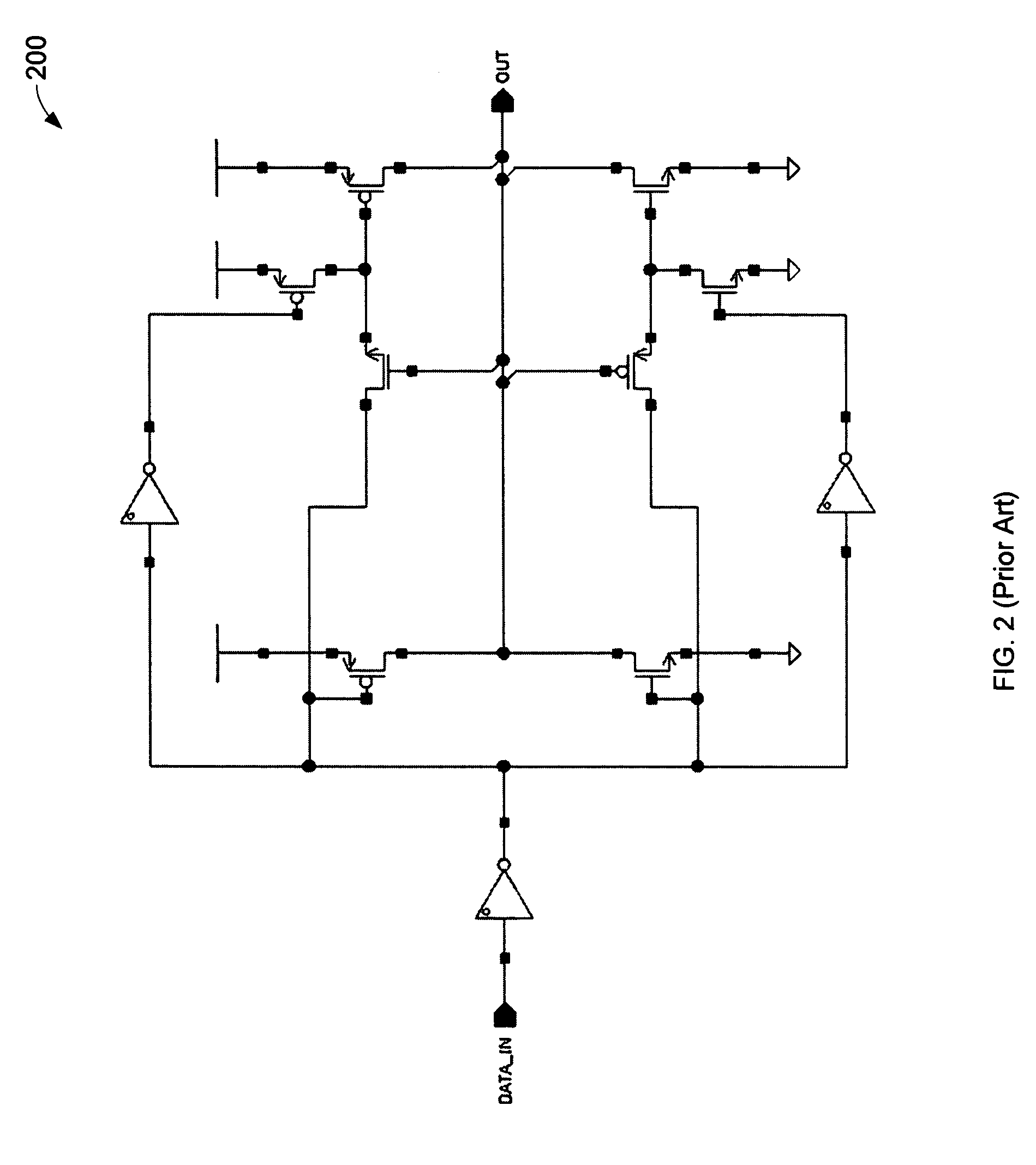

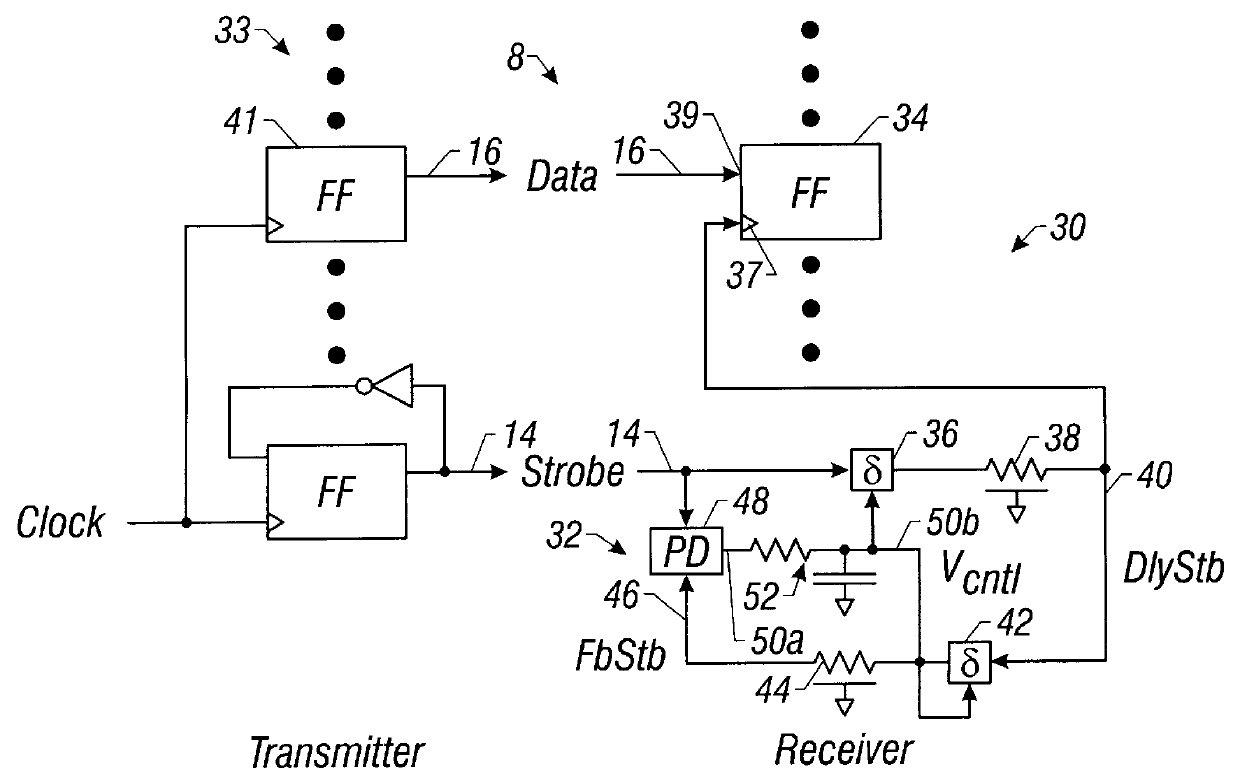

Timing control for input/output testability

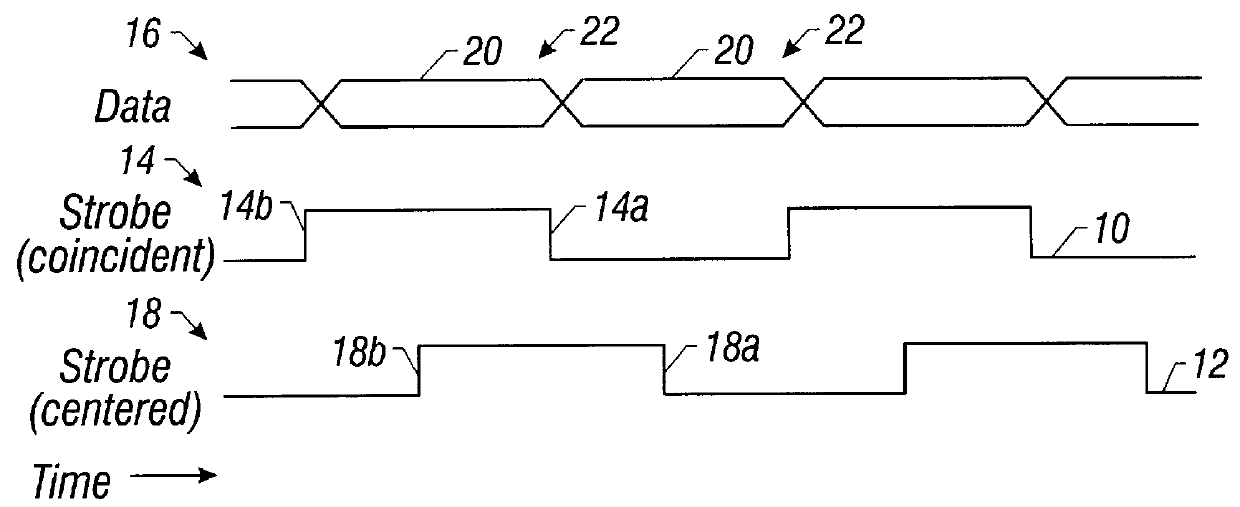

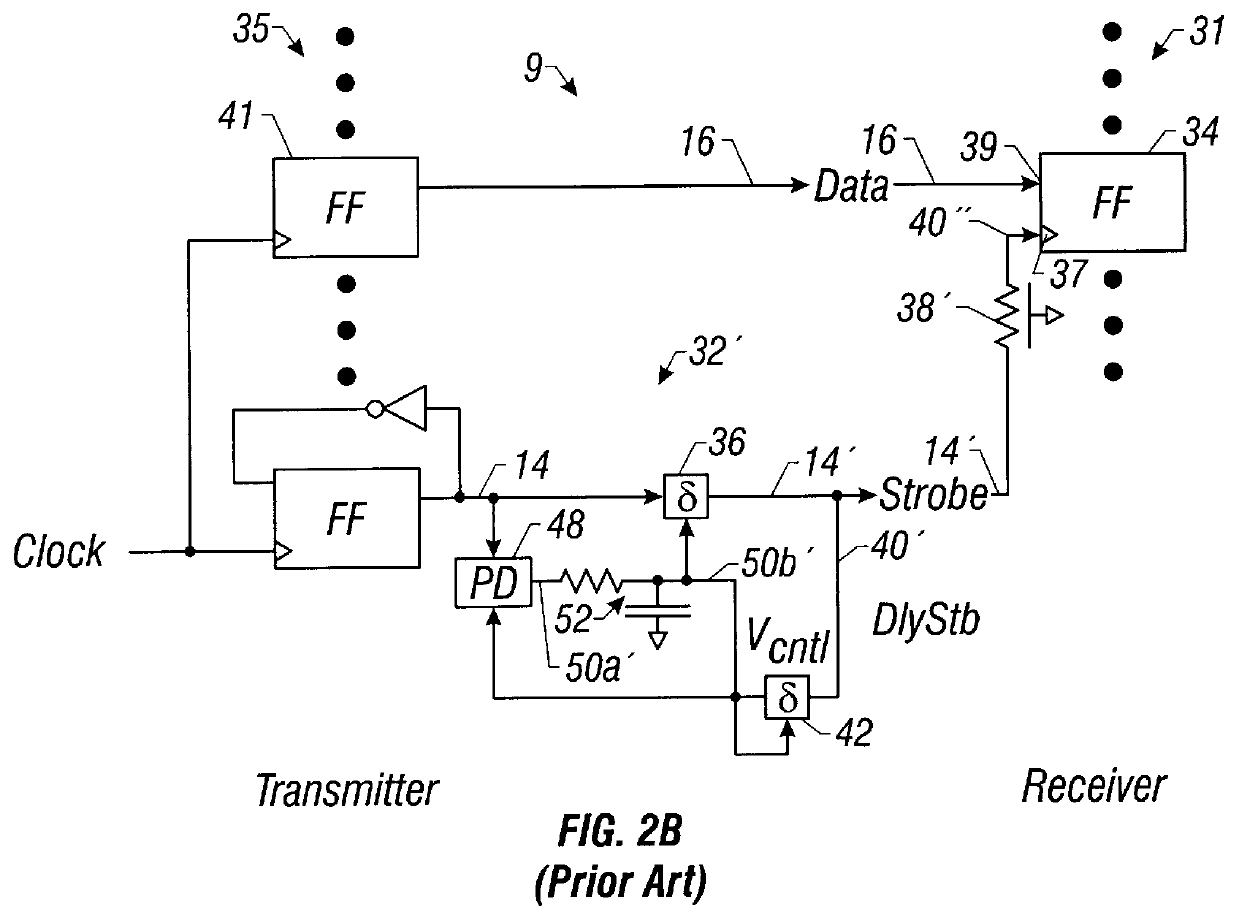

InactiveUS6085345AMultiple input and output pulse circuitsPulse automatic controlPhase differenceDelay-locked loop

Circuitry added to chips that use source synchronous techniques reduces difficulties associated with testing the chips. The circuitry increases the ability to use source synchronous techniques for data transmission. The circuitry is implemented in a delayed-lock loop (DLL) in either a transmitter (driver) or a receiver. The DLL measures the phase difference between a strobe signal and a delayed strobe signal. The DLL can be externally controlled by a source selectable input which allows the delay of the delayed strobe signal to be varied to test Tsetup and Thold in the receiver without varying the timings of the strobe signal and the data signals supplied to the chips. A timing measurement circuit having the strobe signal, the delayed strobe signal, and reference signals as inputs may be used to calibrate the phase difference between the strobe signal and delayed strobe signal.

Owner:INTEL CORP

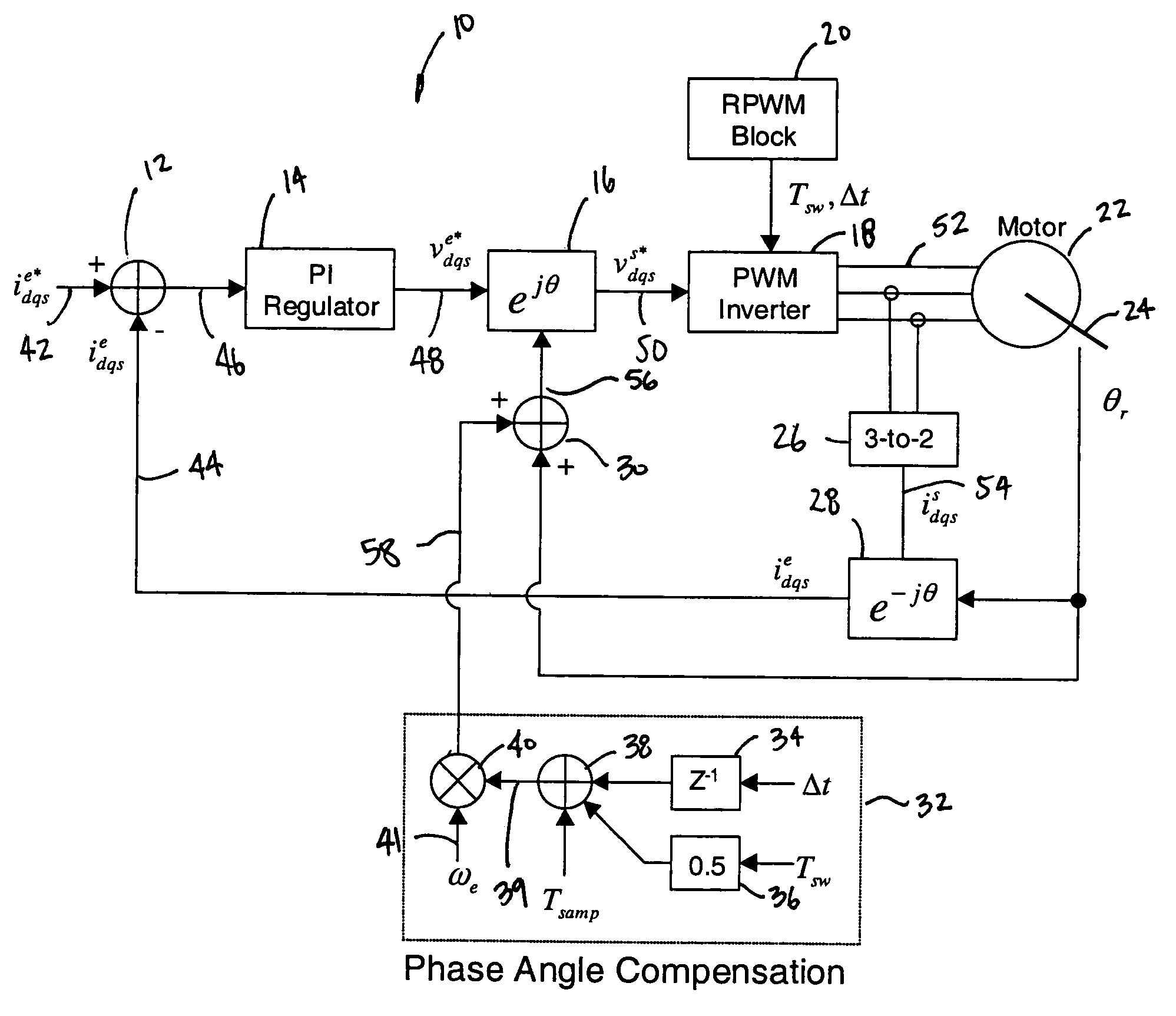

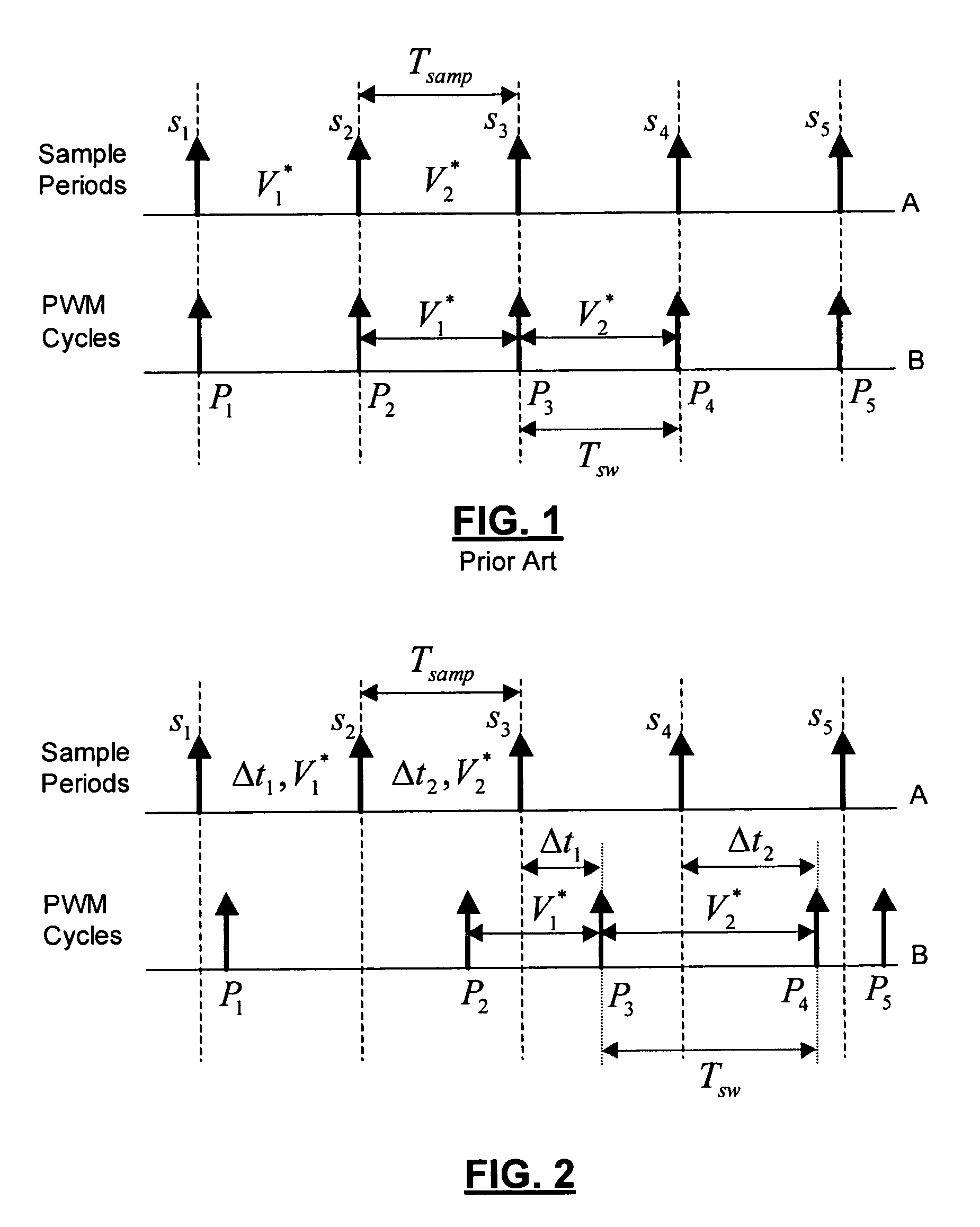

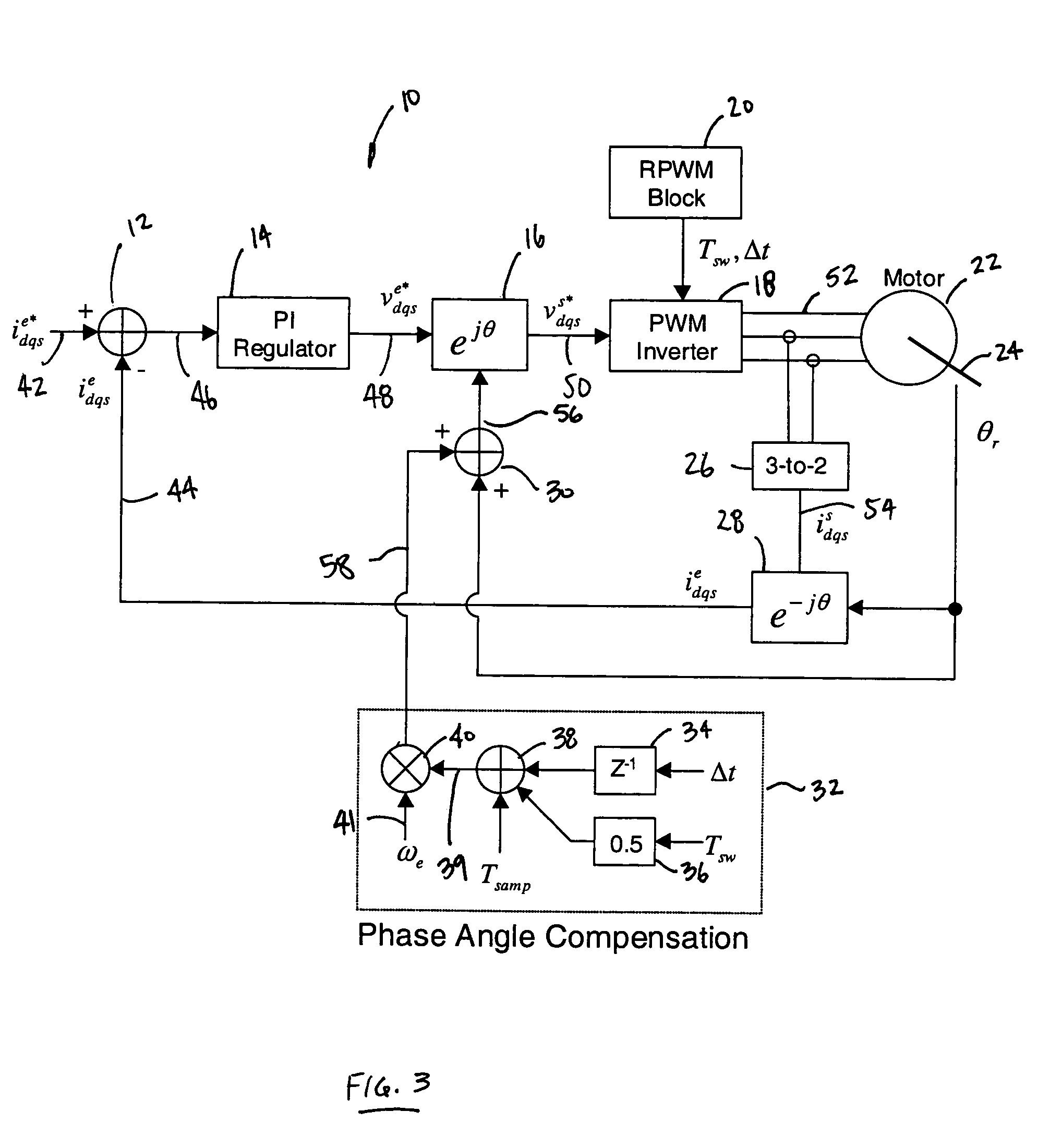

Delay compensation for stable current regulation when using variable-delay random PWM switching

ActiveUS6972534B1Easy constructionAC motor controlSynchronous motors startersSwitching cycleControl system

A control system for an electric machine having a rotor position sensor that generates a rotor position signal, a velocity module that generates an electric angular velocity value based on the rotor position signal, a random pulse width modulation module that generates a switching period and a delay for a current cycle, and a phase angle compensation module that sums a sample rate, one half of the switching period, and the delay of a previous cycle and that outputs a delay time. The phase angle compensation module further multiplies the delay time and the electric angular velocity value and generates a compensating angle.

Owner:GM GLOBAL TECH OPERATIONS LLC

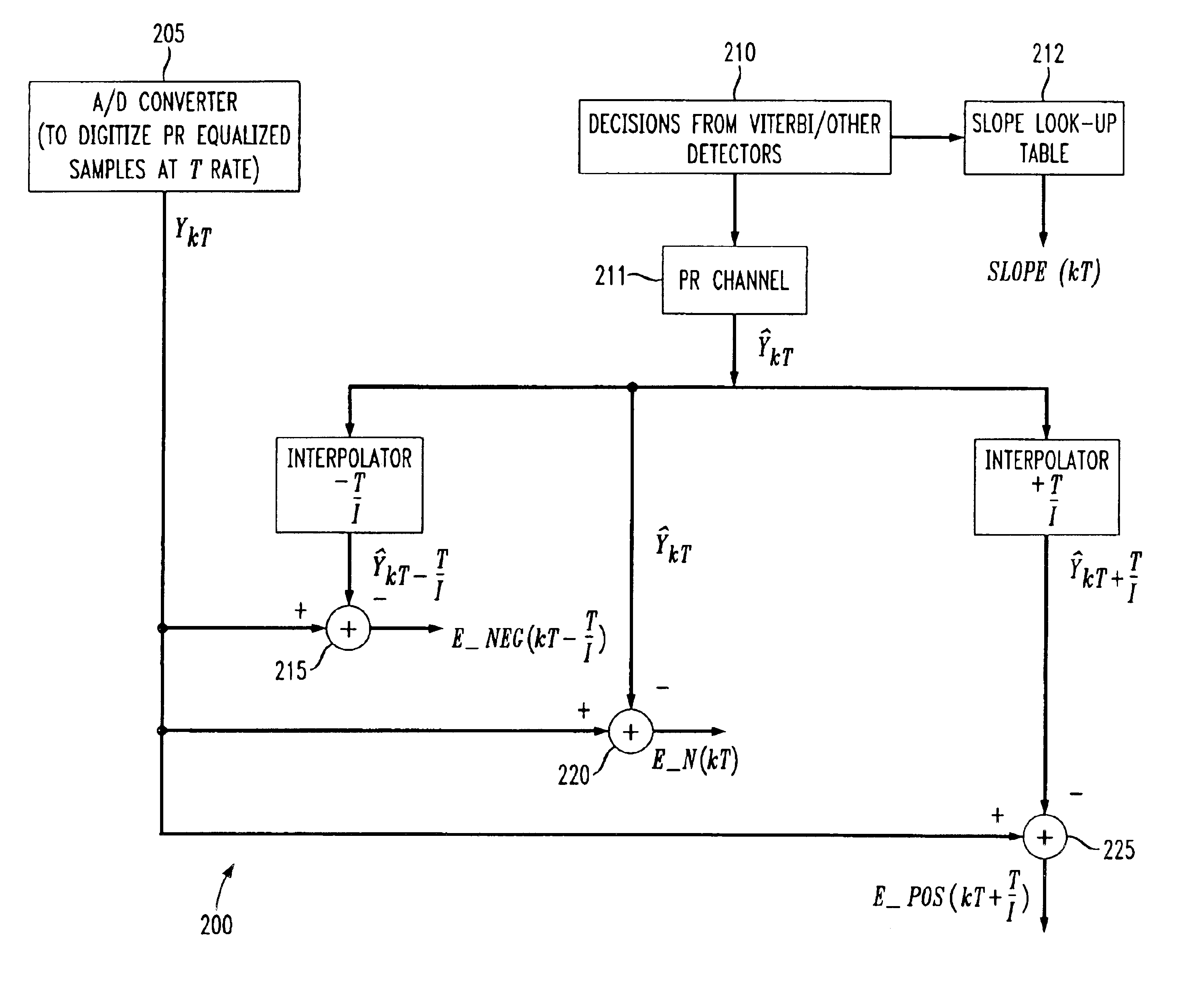

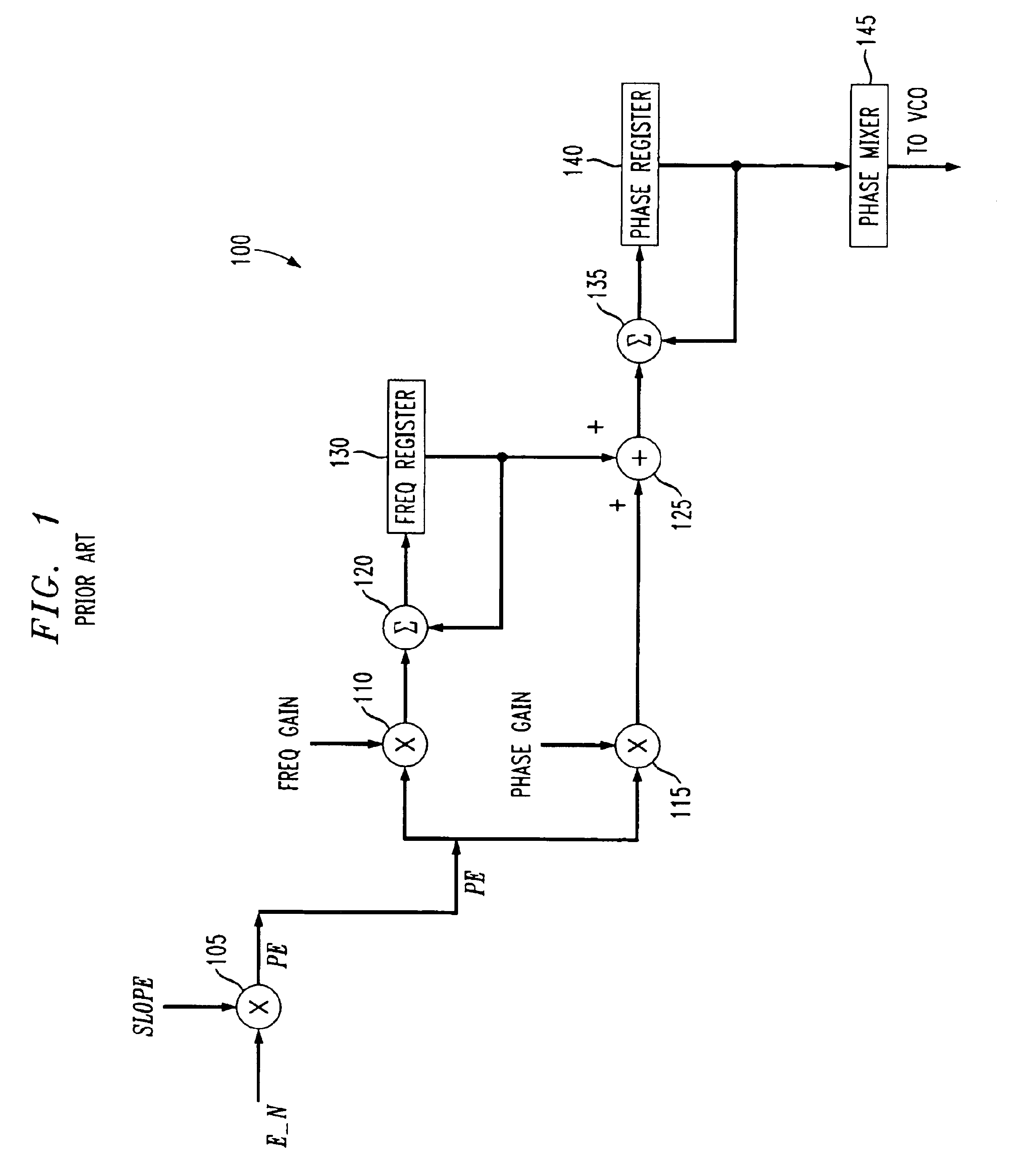

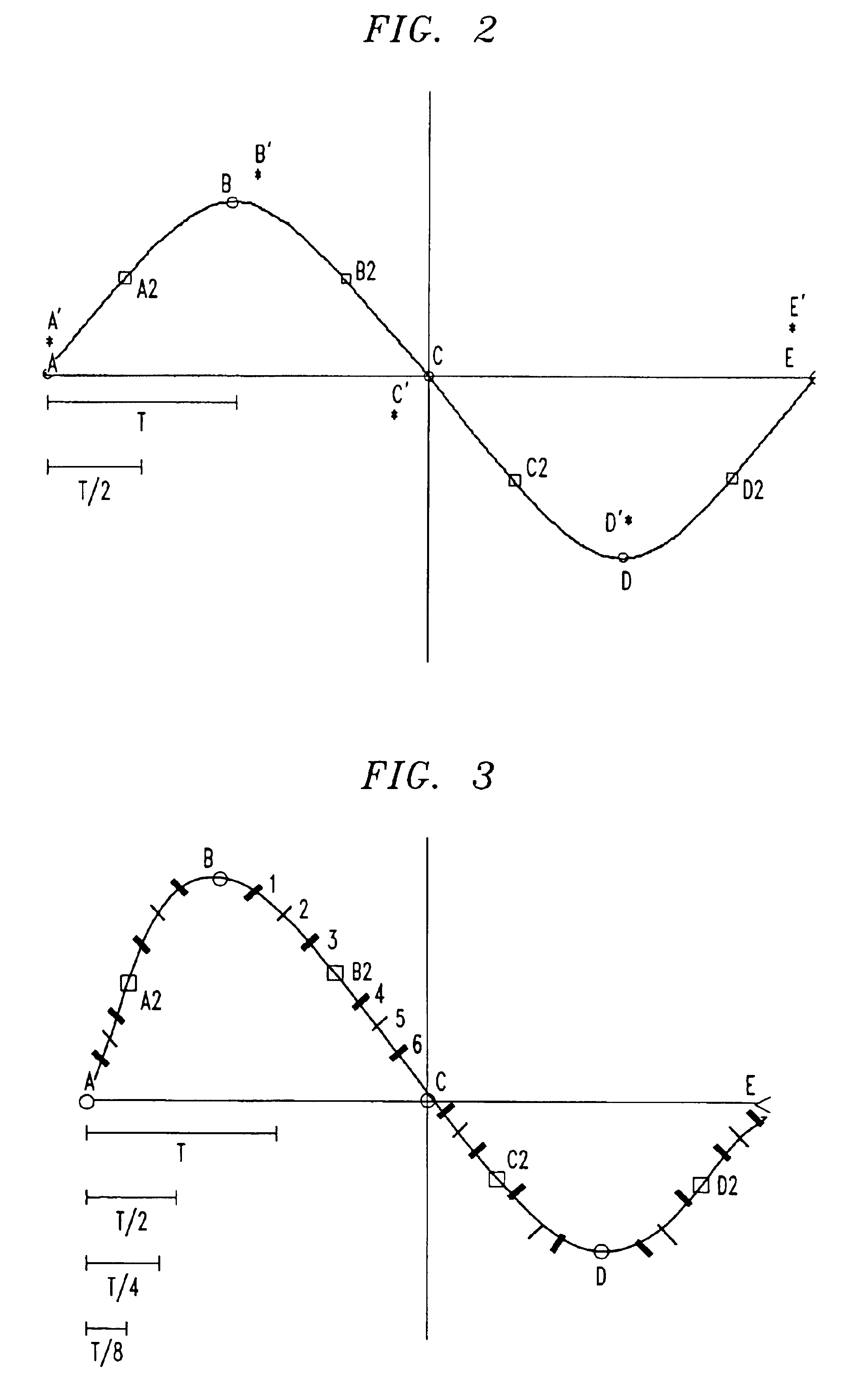

Scheme to improve performance of timing recovery systems for read channels in a disk drive

InactiveUS6856183B2Pulse automatic controlVoltage-current phase anglePhase locked loop circuitEngineering

A digital phase lock loop circuit including an error generation circuit for generating at least three error signals and a phase error adjustment circuit for generating at least one phase error adjustment signal from the at least three error signals. By using at least three error signals, as opposed to just one, the drift in the sampling phase of the recovered clock is easily detected and corrected to reduce burst errors and to improve loss of lock (LOL) performance.

Owner:BROADCOM INT PTE LTD

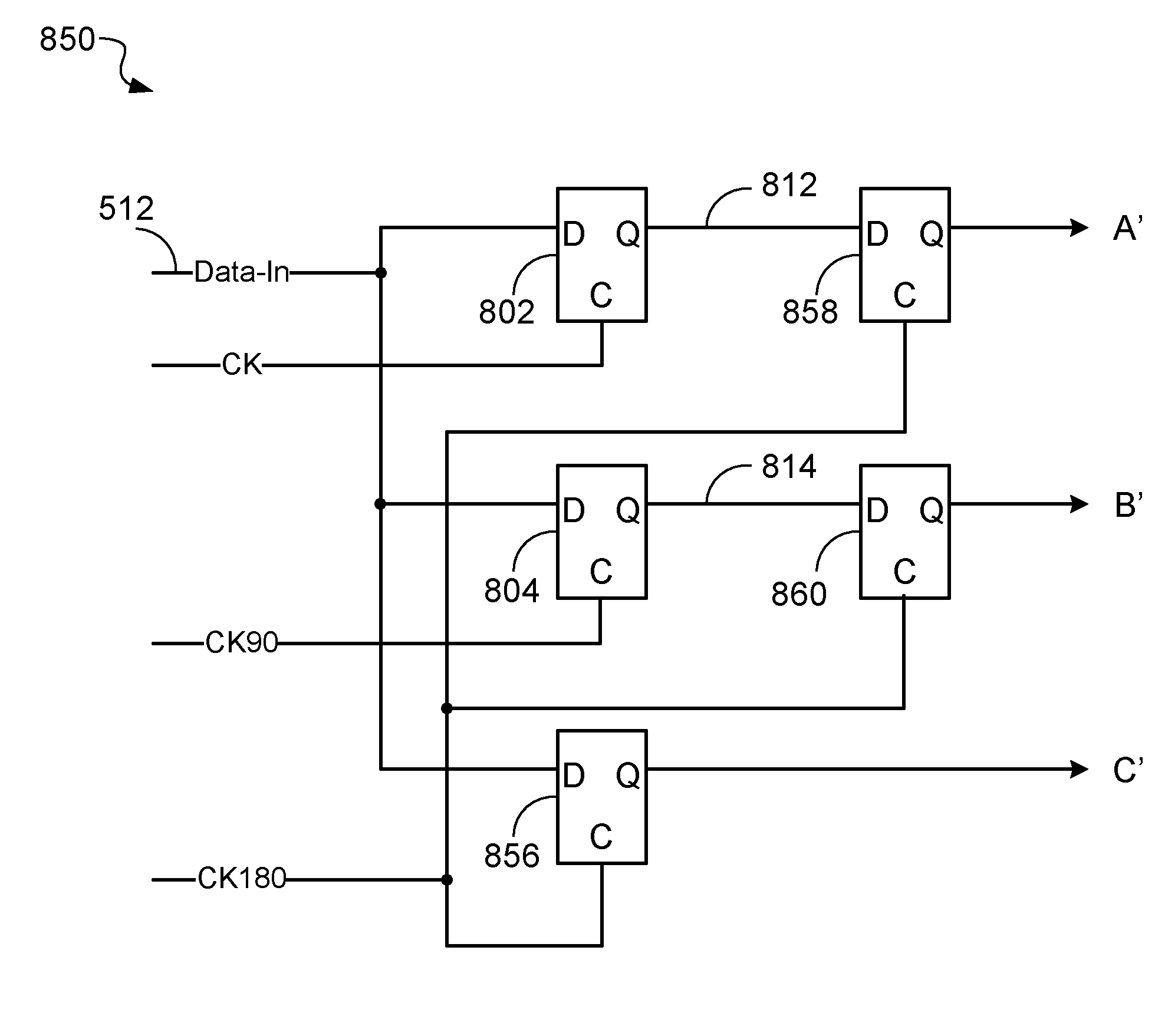

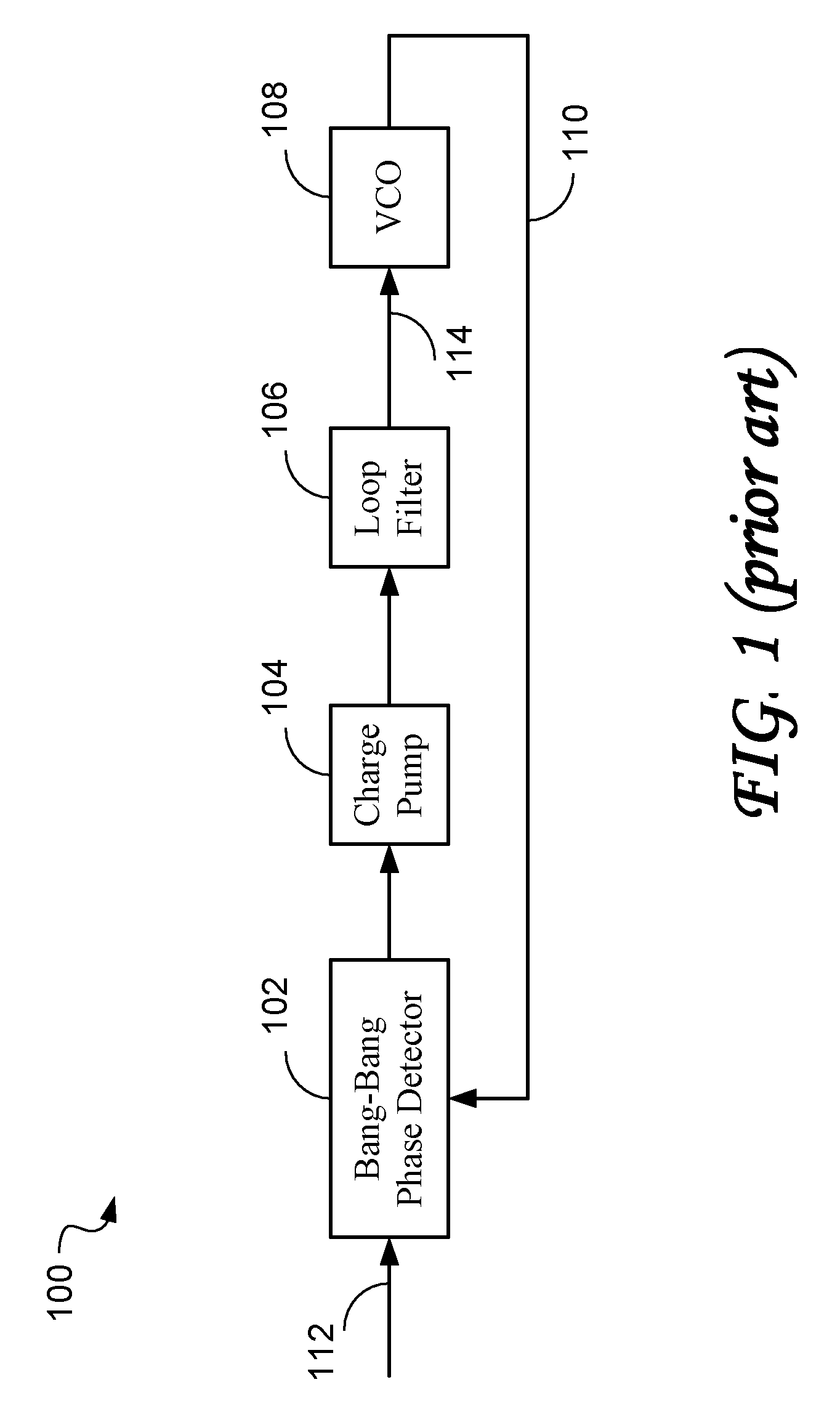

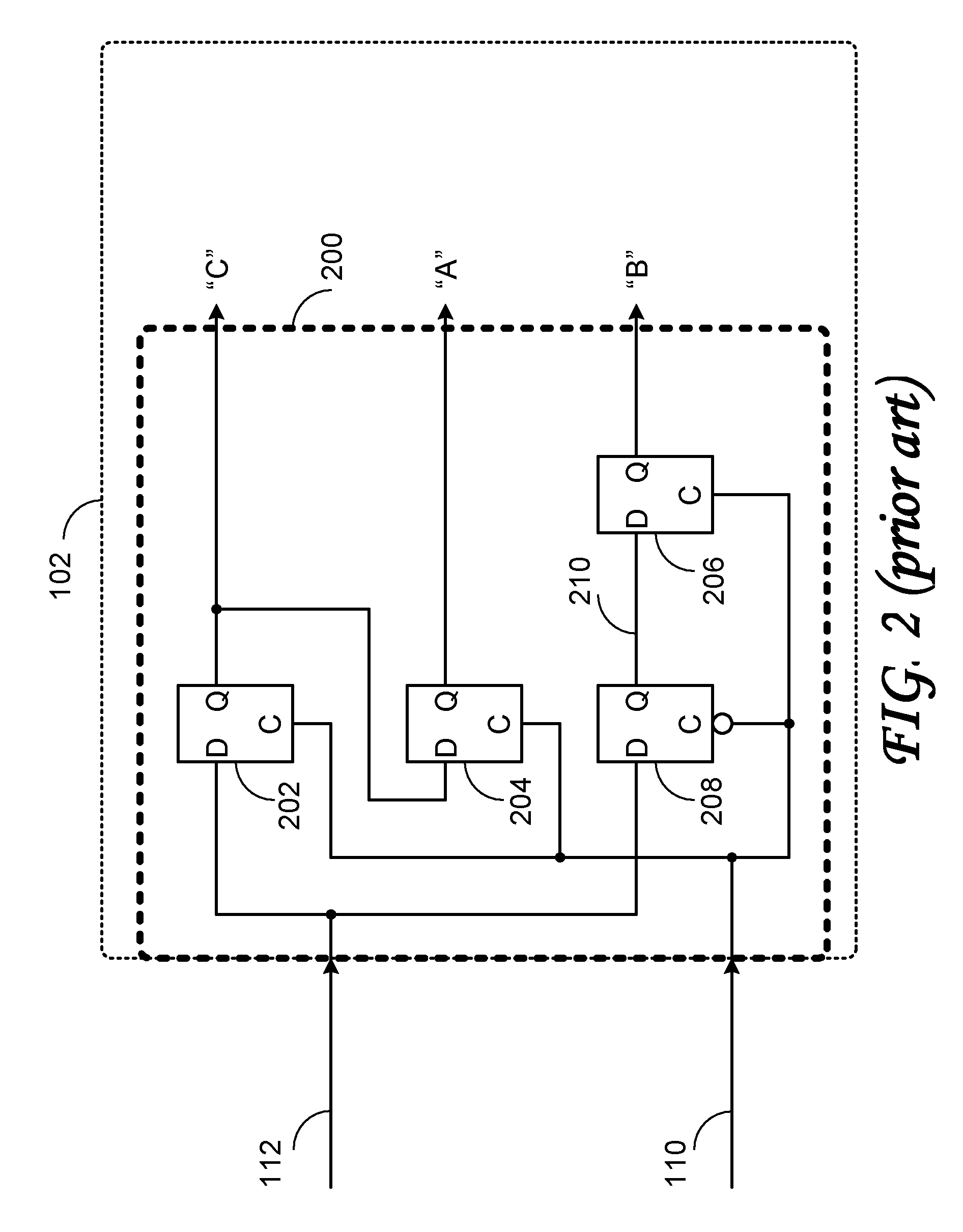

Bang-bang phase detector with sub-rate clock

ActiveUS8315349B2Oscillations comparator circuitsAngle demodulation by phase difference detectionData streamBang bang phase detector

Owner:RAMBUS INC

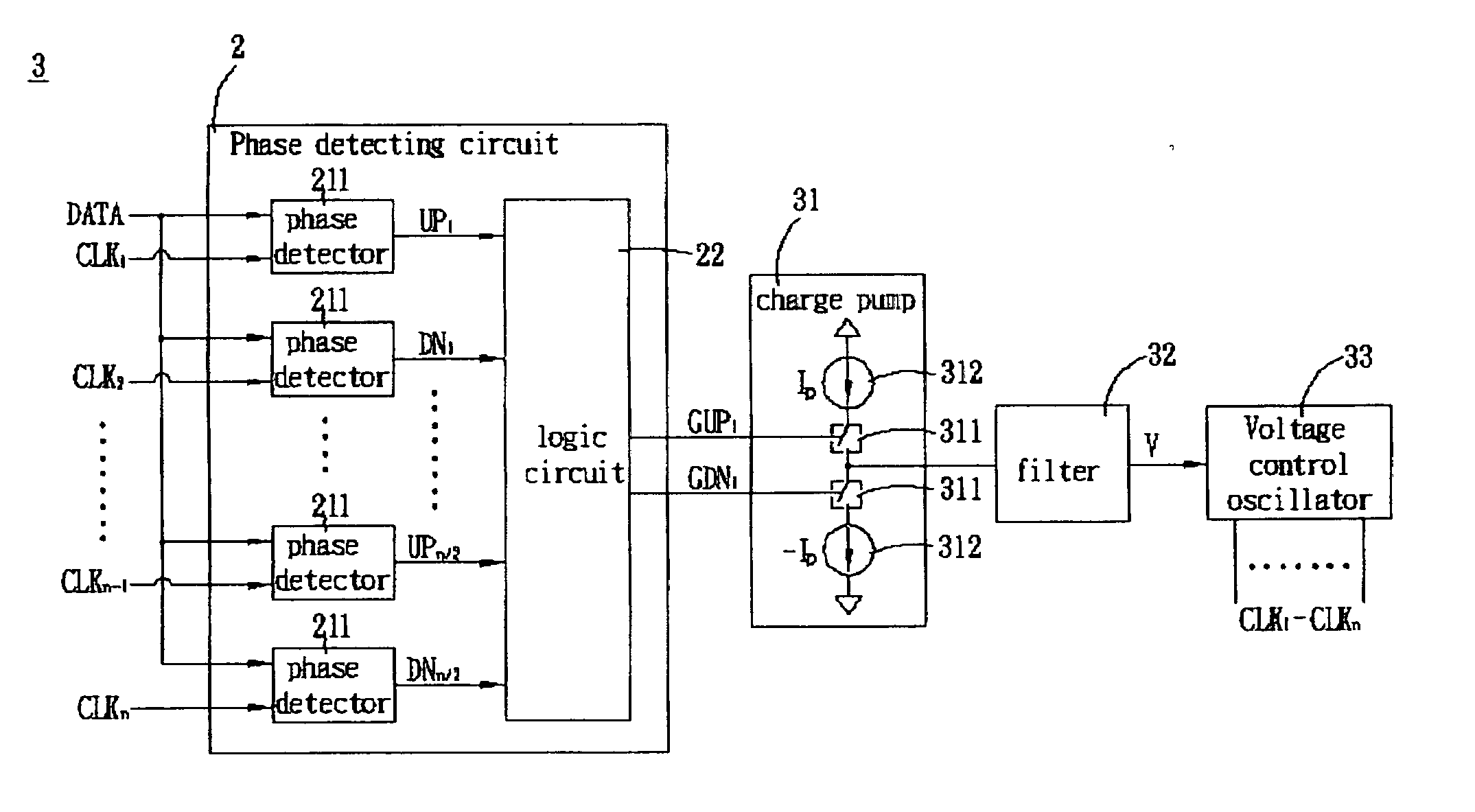

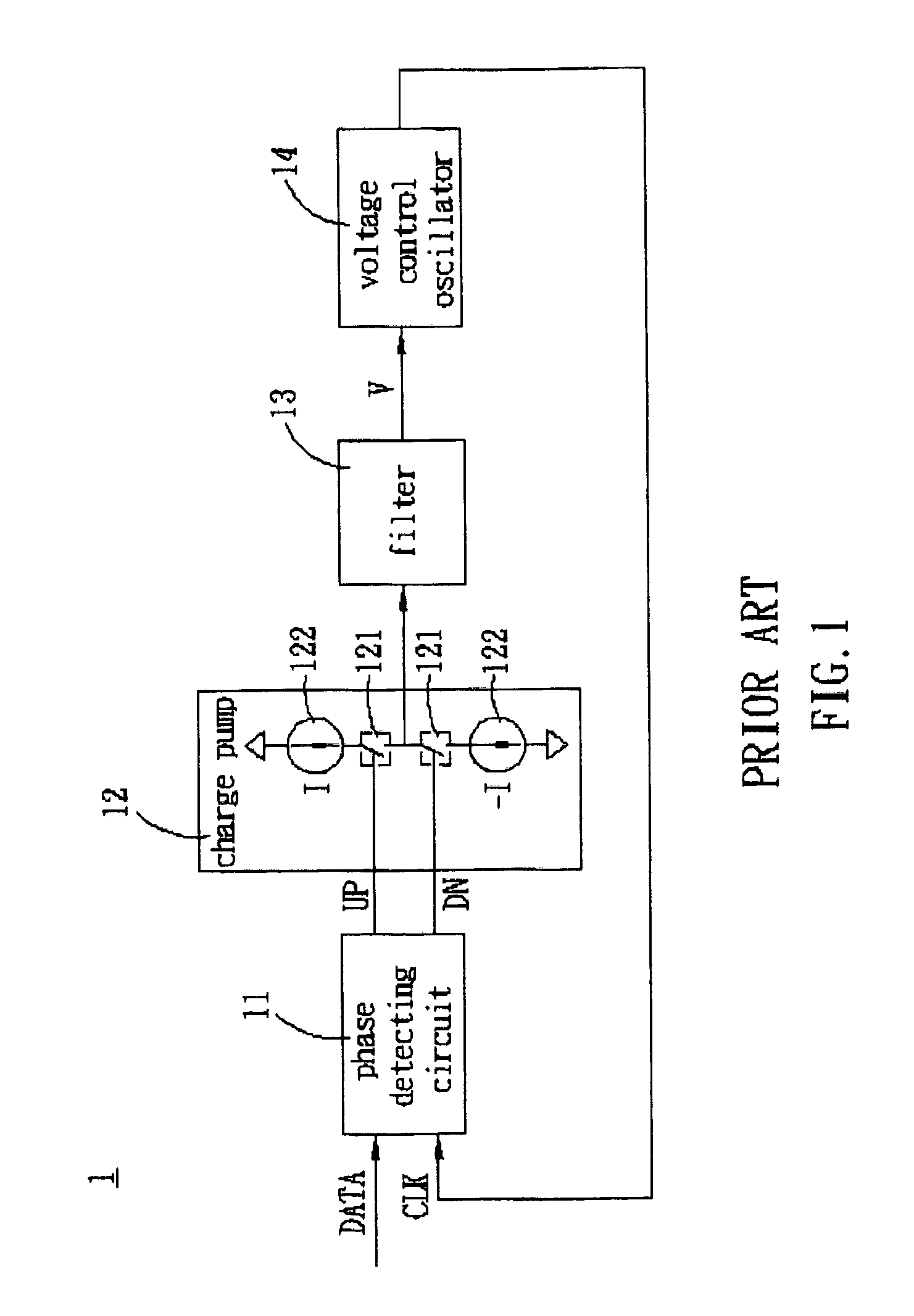

Phase detecting circuit having adjustable gain curve and method thereof

A phase detecting circuit having an adjustable gain curve includes a plurality of phase detectors and a logic circuit The phase detectors detect phase differences between a data signal and a plurality of clock signals by comparison to output a plurality of control signals. The clock signals have the same frequency but different phases, and the frequency of the data signal is a multiple of the frequency of the clock signals. The logic circuit performs various logic operations according to these control signals to output at least one set of gain control signals for adjusting a gain curve of the phase detecting circuit.

Owner:VIA TECH INC

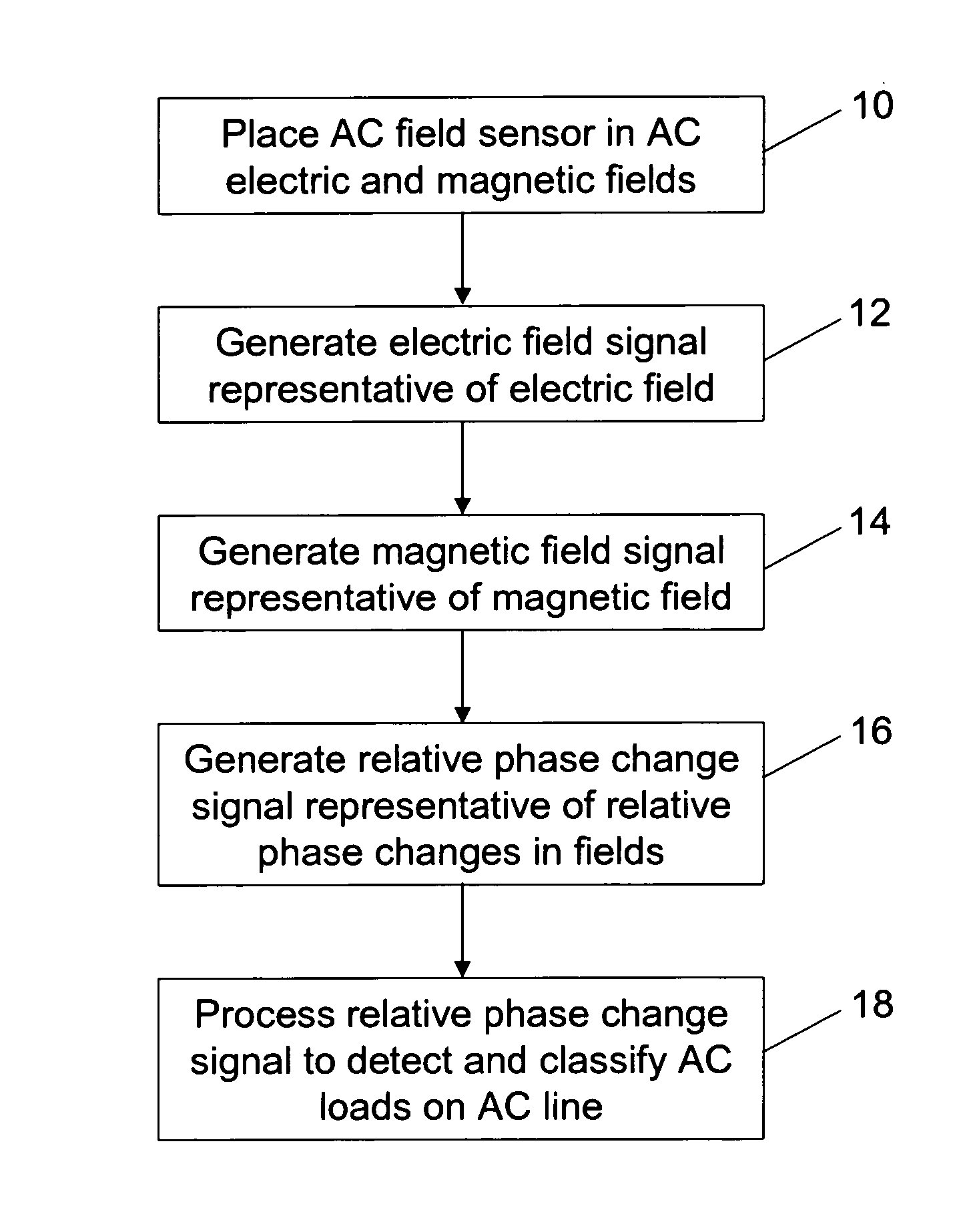

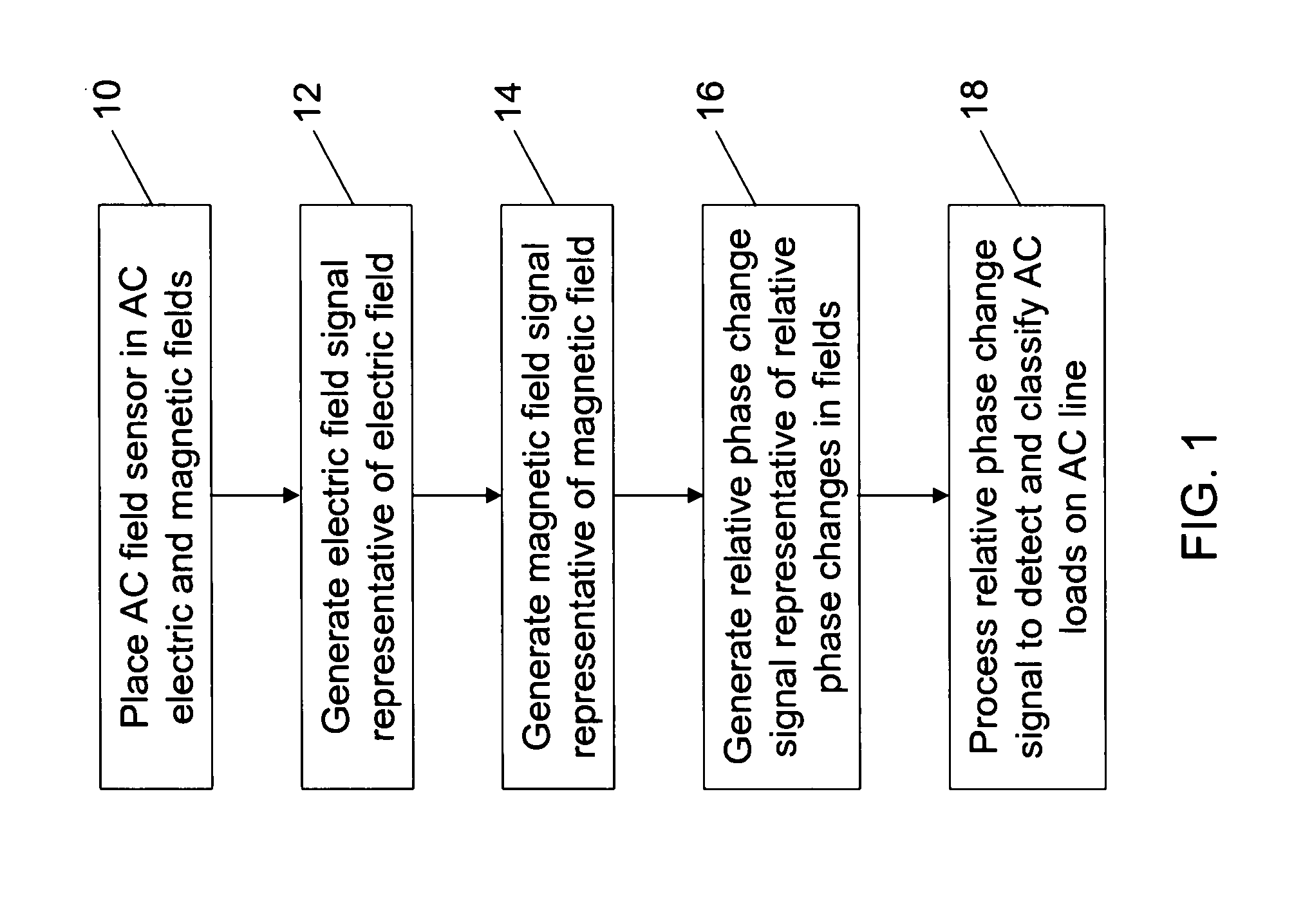

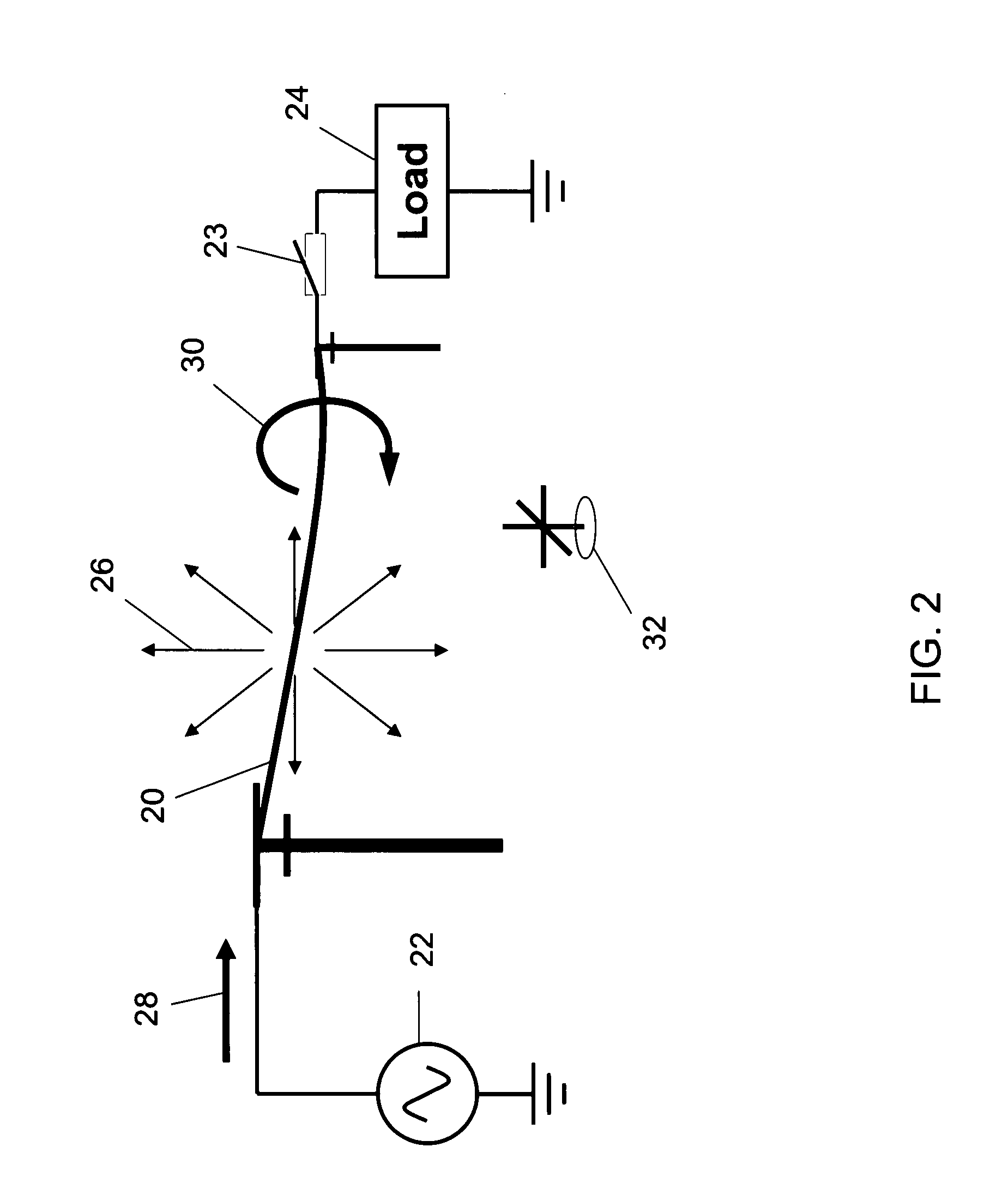

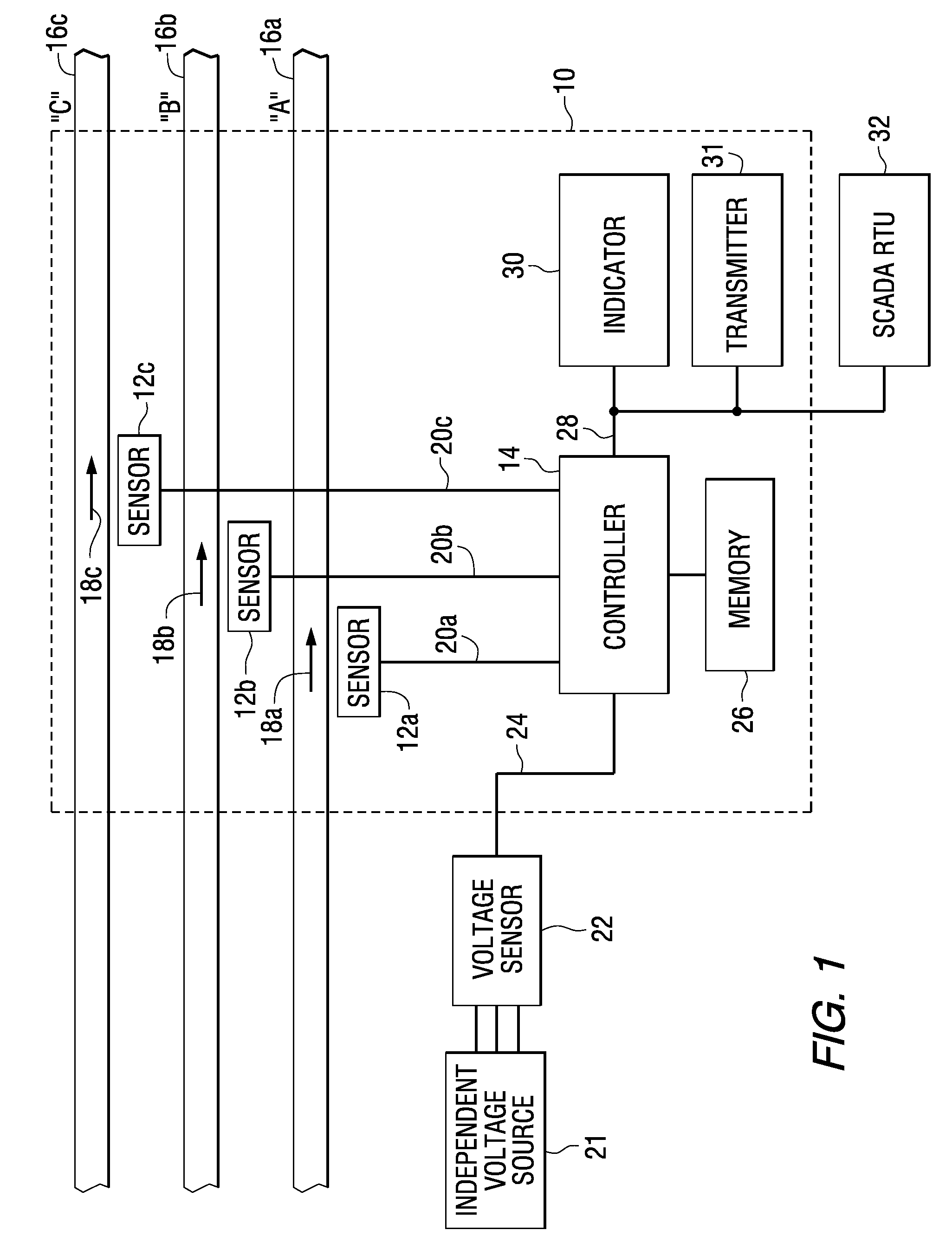

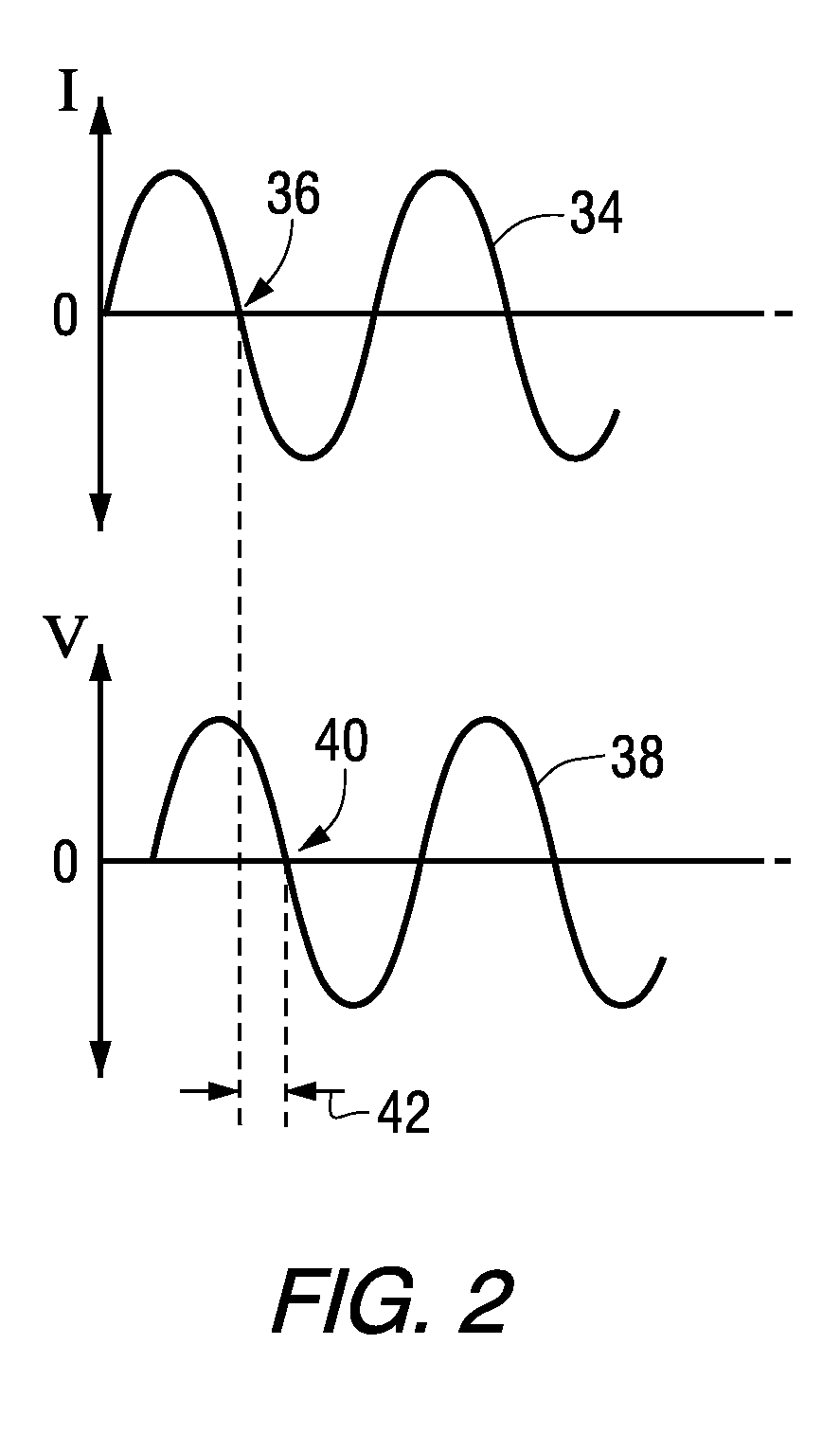

Methods for detecting and classifying loads on AC lines

InactiveUS20080048640A1Current/voltage measurementVoltage-current phase angleRelative magnitudeRelative phase

Methods for detecting and classifying loads on alternating current (AC) lines are provided. One such method includes the steps of placing an AC field sensor in AC electric and magnetic fields generated by an AC line, generating an electric field signal representative of the AC electric field received by the AC field sensor, generating a magnetic field signal representative of the AC magnetic field received by the AC field sensor, generating a relative phase signal representative of relative phase changes between the electric and magnetic fields, and processing the relative phase signal to detect and classify loads on the AC line. In another method, relative load vector signals representative of relative magnitude and phase changes in the magnetic field are generated and processed to detect and classify loads on the AC line.

Owner:US SEC THE ARMY THE

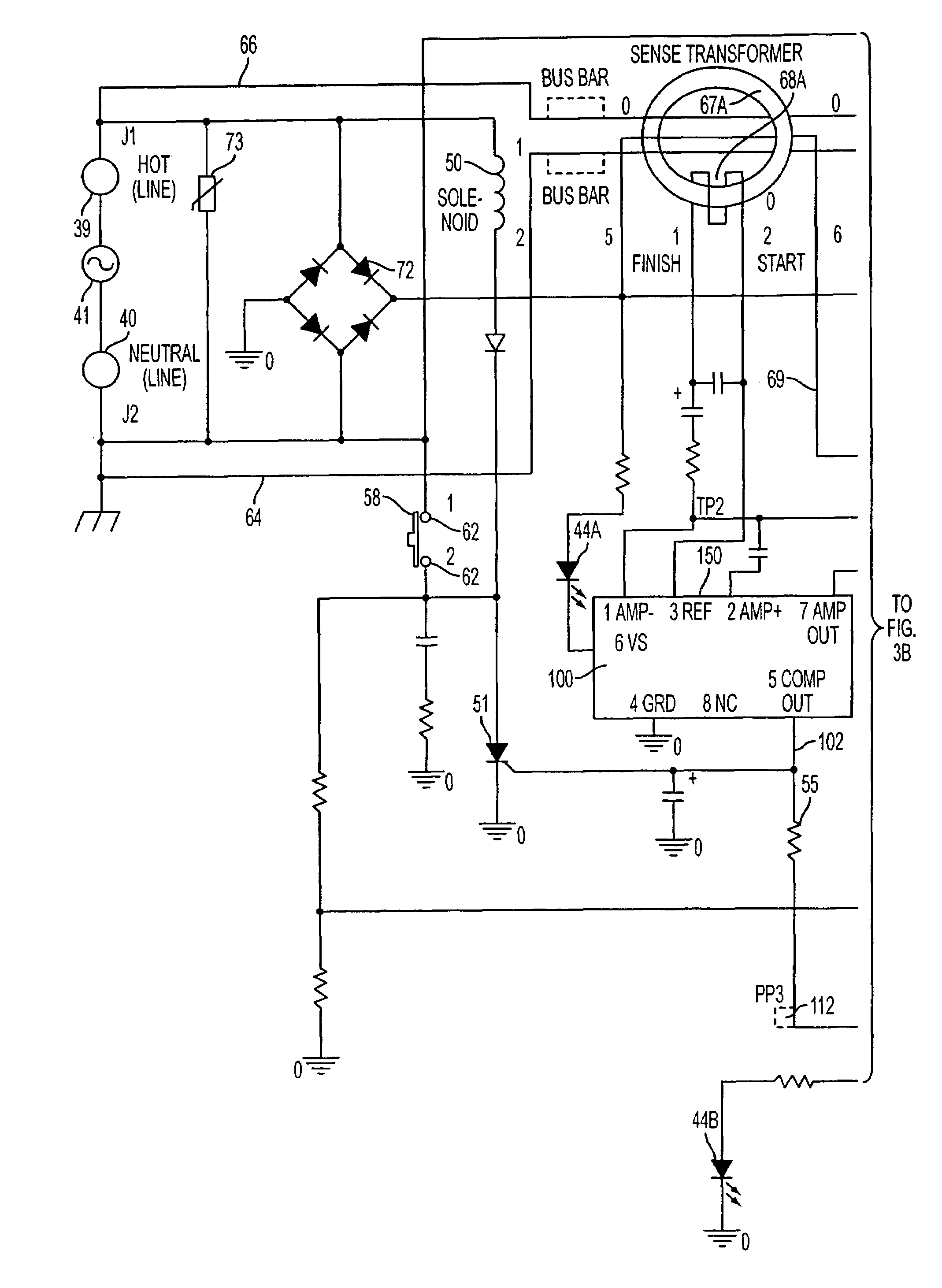

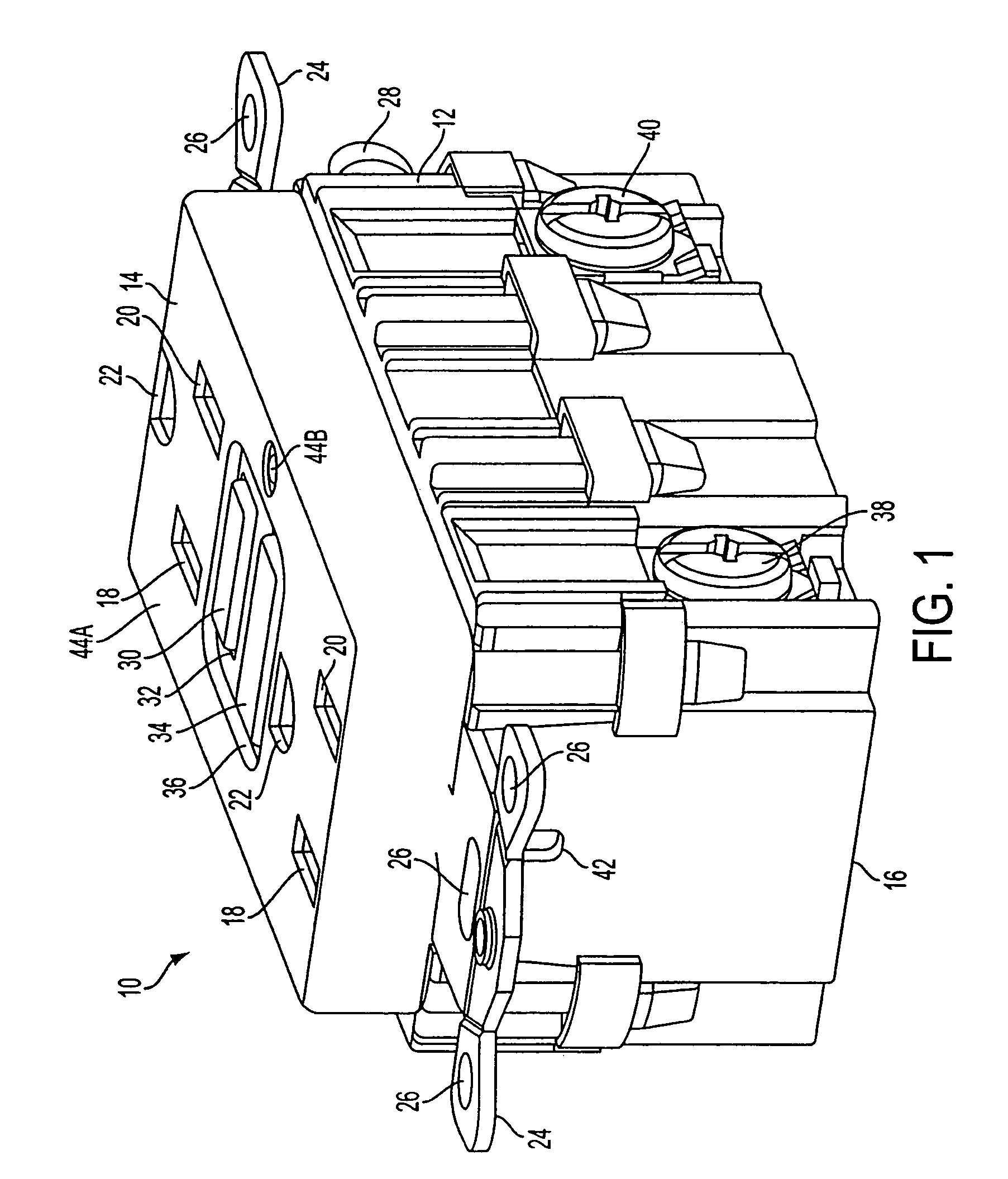

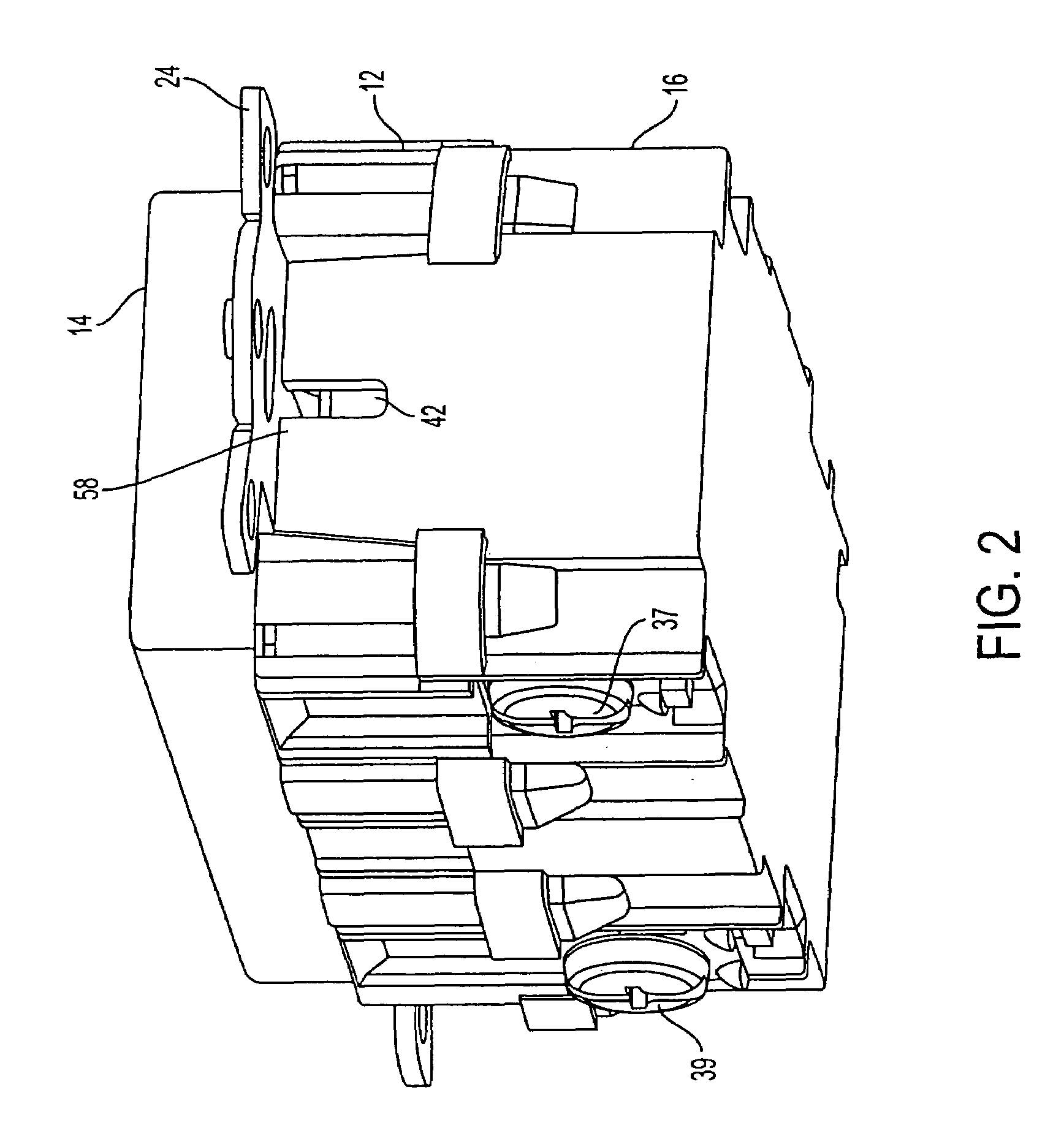

Self testing ground fault circuit interrupter (GFCI)

ActiveUS7443309B2Determines the operability of the switching deviceProtective switch detailsElectronic circuit testingStatus testGround failure

A self testing fault detector having a line side and a load side and a conductive path there between, said apparatus is provided. The self testing fault detector includes a controller, adapted to perform periodic status tests on a protection circuit of the self testing fault detector without interrupting power to the load.

Owner:HUBBELL INC

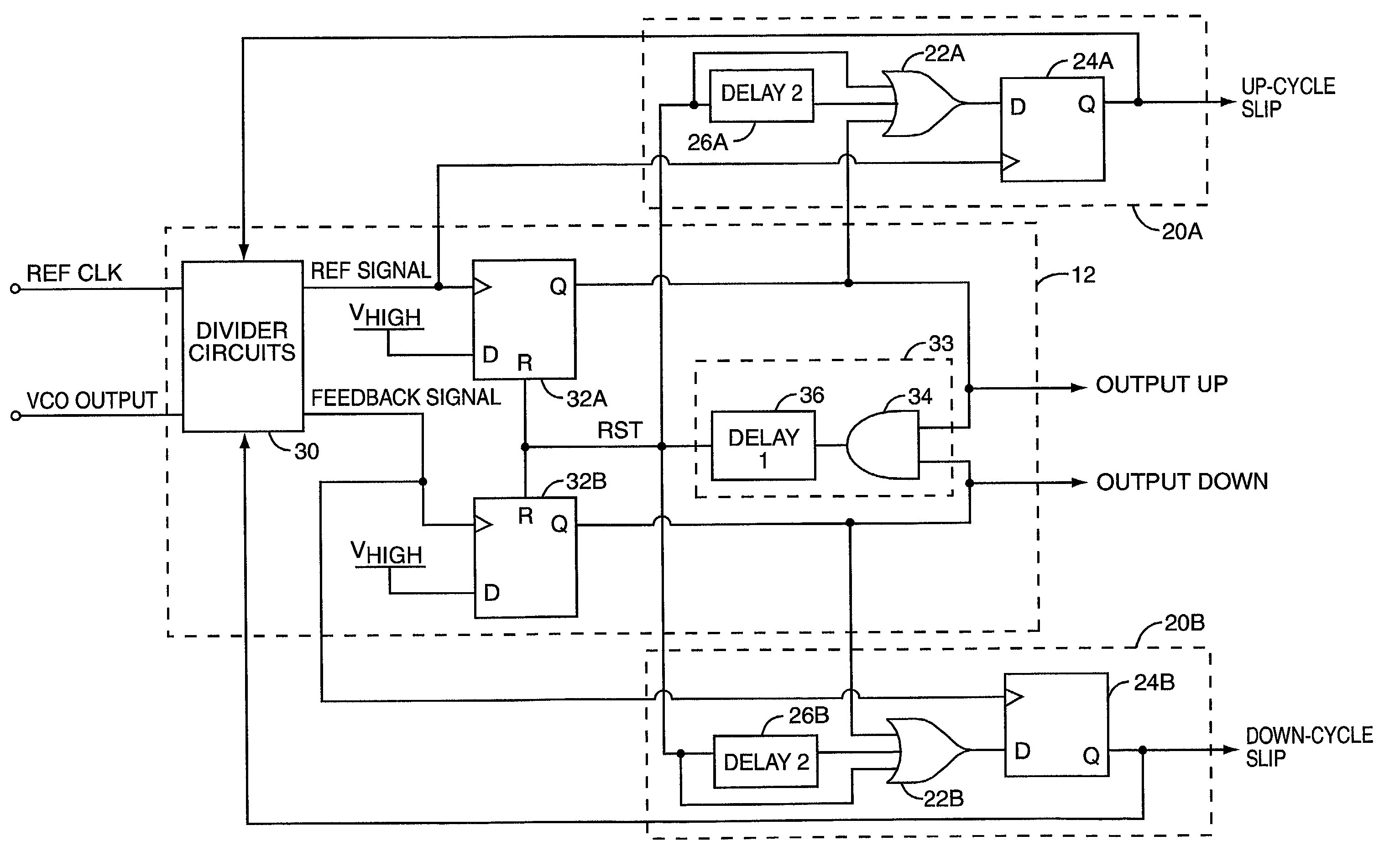

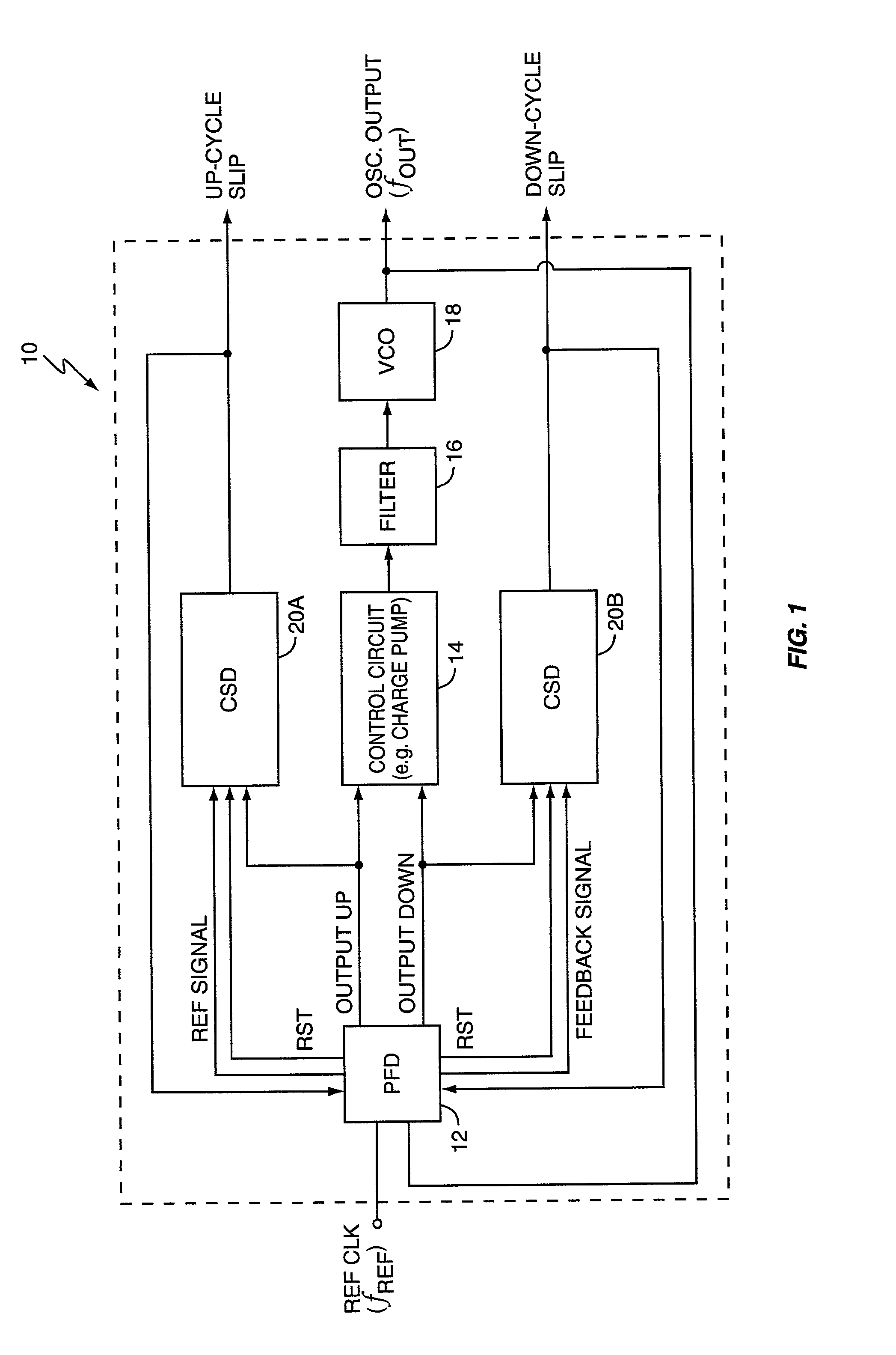

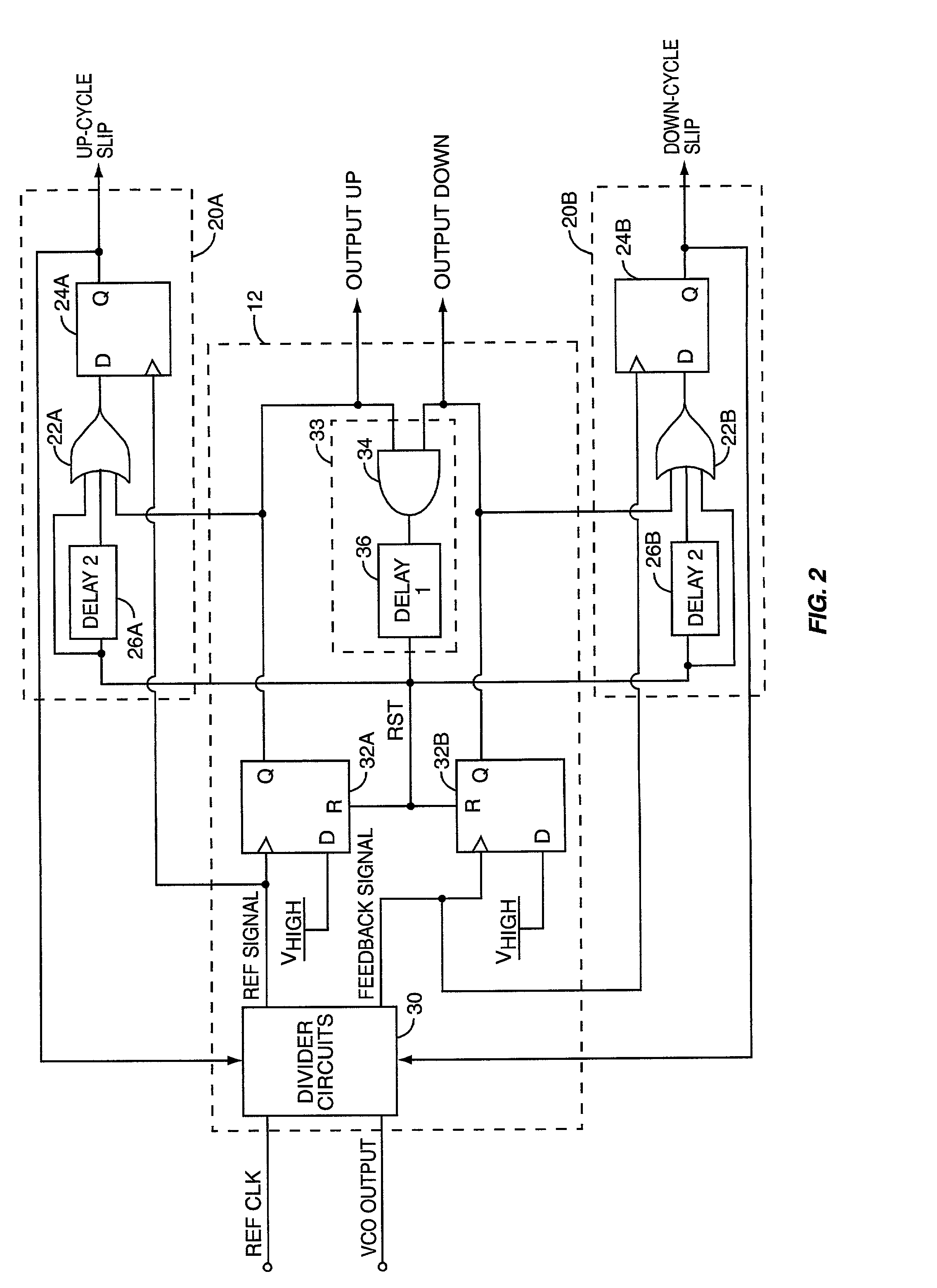

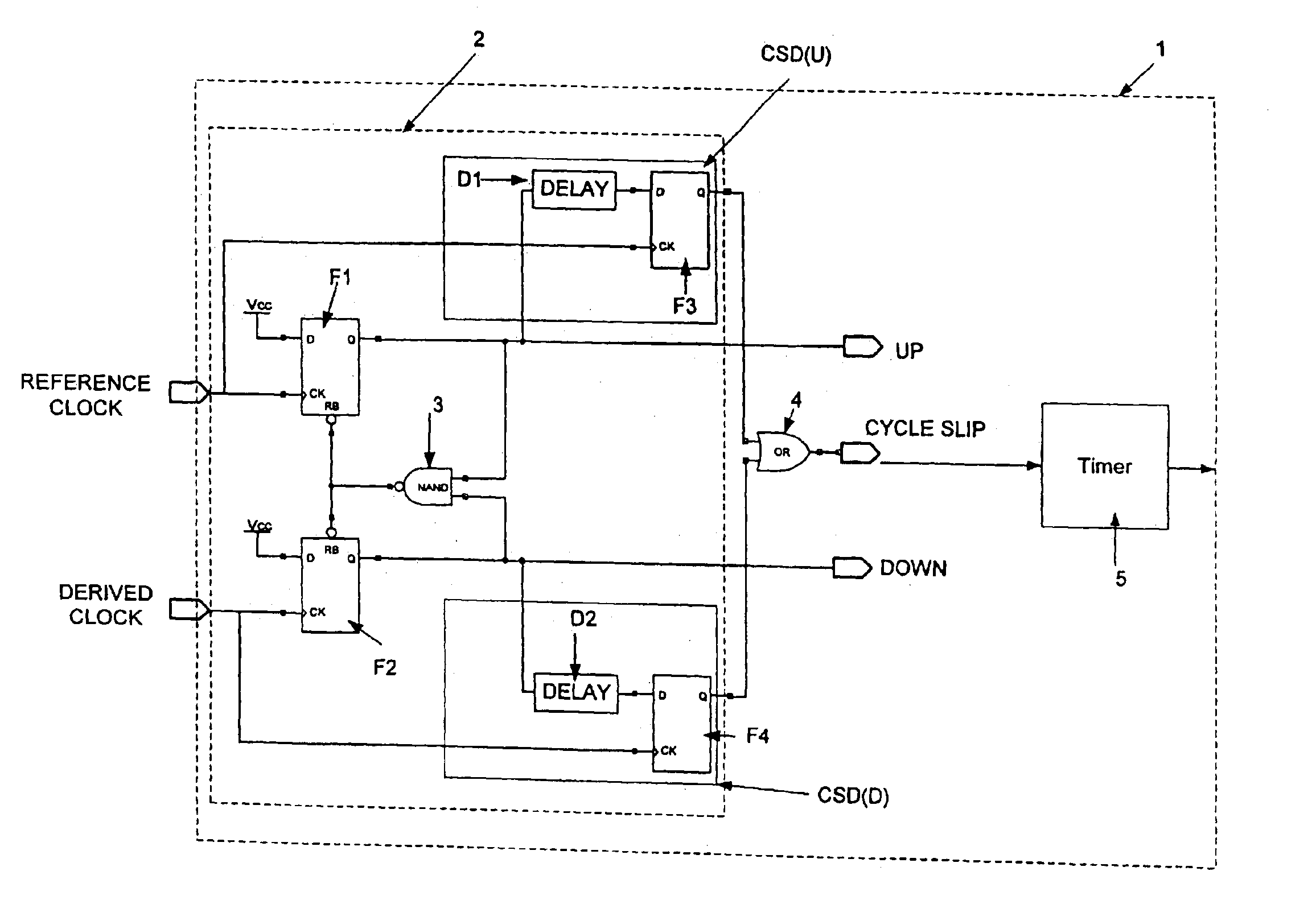

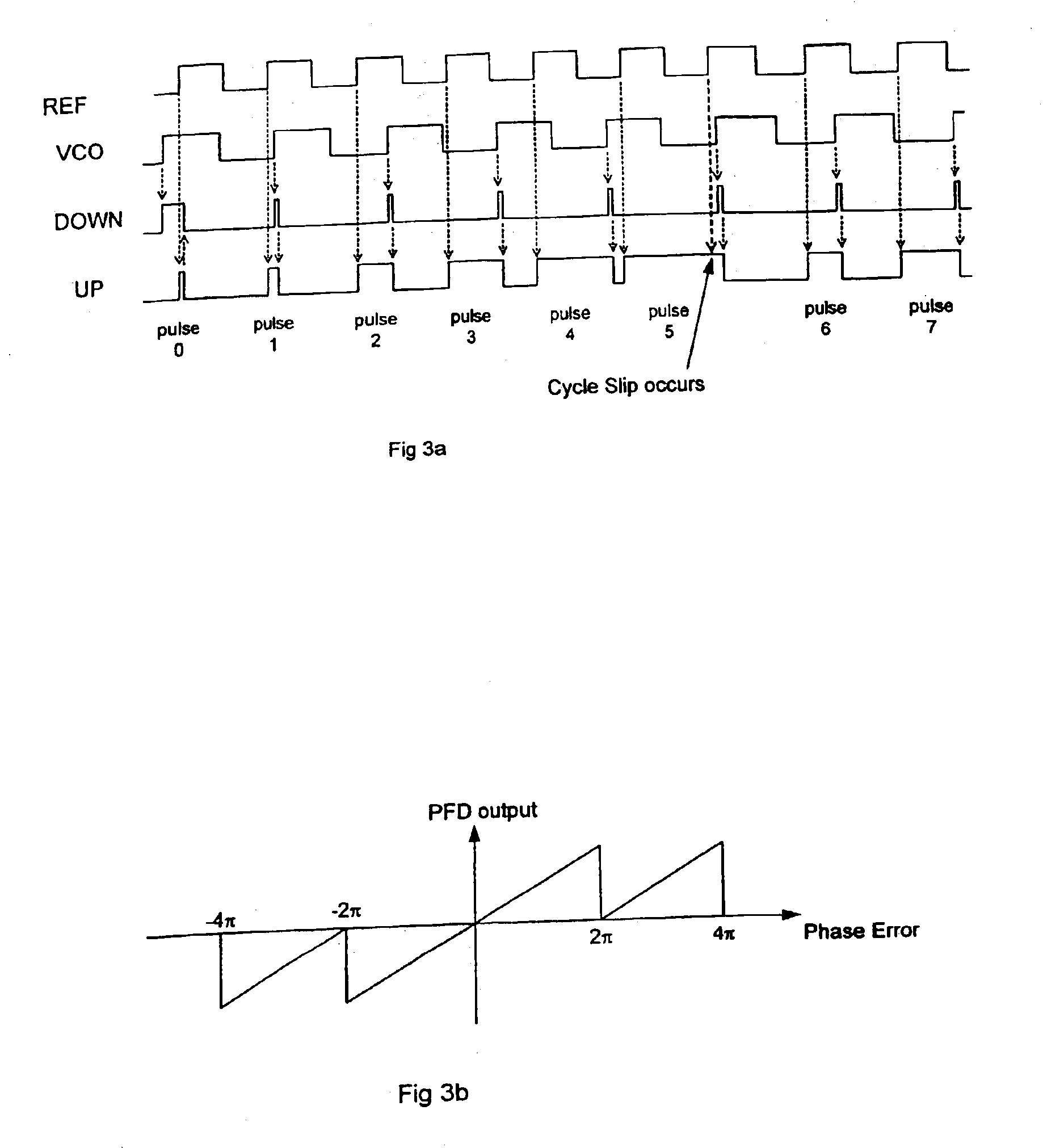

PLL cycle slip detection

InactiveUS7003065B2Pulse automatic controlVoltage-current phase angleControl signalPhase locked loop circuit

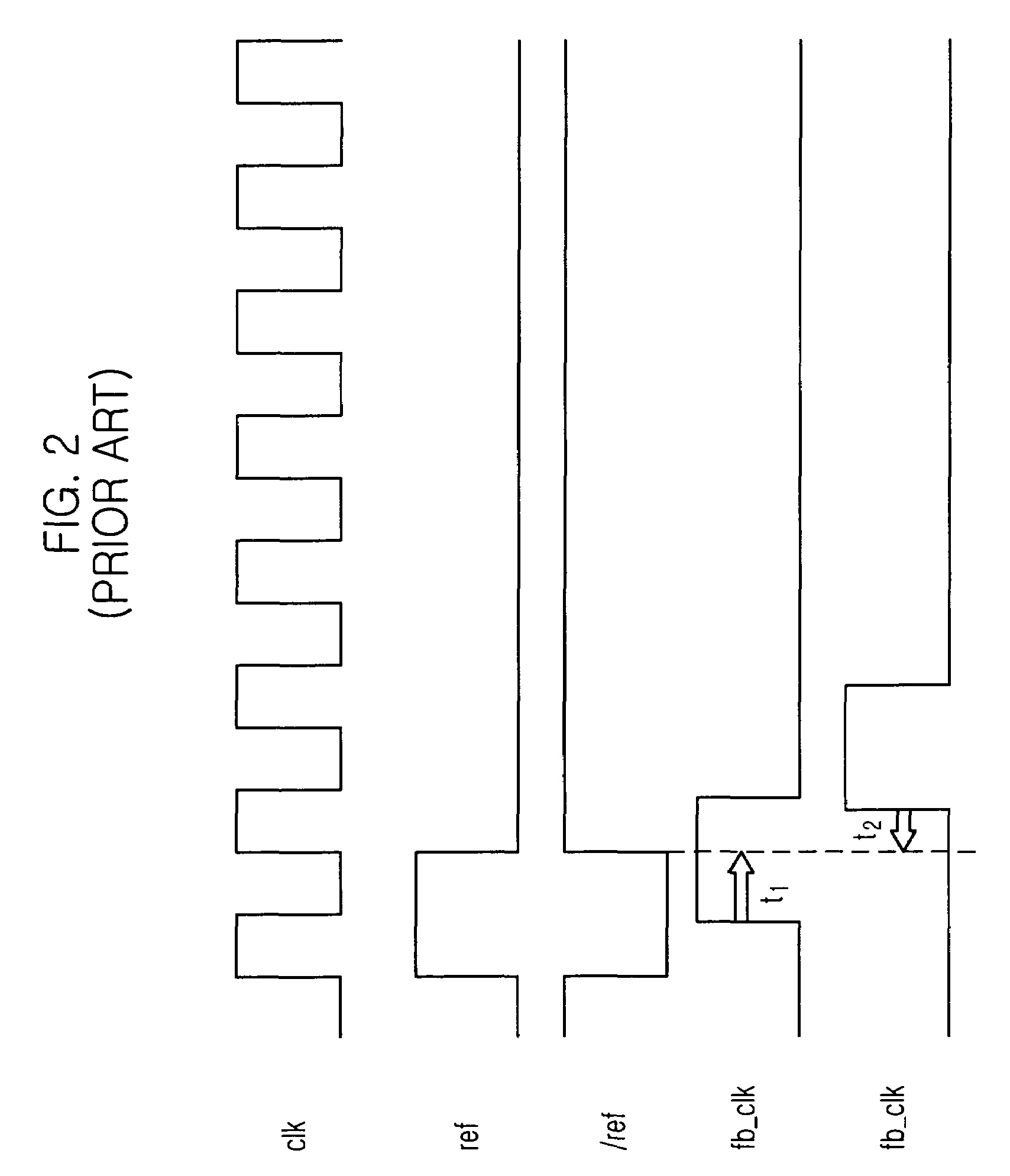

A cycle slip detector interfaces with a phase / frequency detector (PFD), such as might be used in a phase-locked loop circuit (PLL), and indicates when cycle slips occur in the PFD. Typically, the PFD generates output control signals as a function of the phase difference between first and second input signals, with the first input signal usually serving as a reference signal against which the PLL adjusts the second input signal. The PFD provides linear phase comparison between its input signals, provided their relative phase difference does not exceed ±2π radians. If one of the two signals leads or lags the other by more than that amount, a cycle slip occurs, and the PFD responds nonlinearly. The cycle slip detector provides logic for detecting and indicating leading and lagging cycle slips as they occur in the PDF, and is typically implemented as a minimal arrangement of logic gates and flip-flops.

Owner:ERICSSON INC

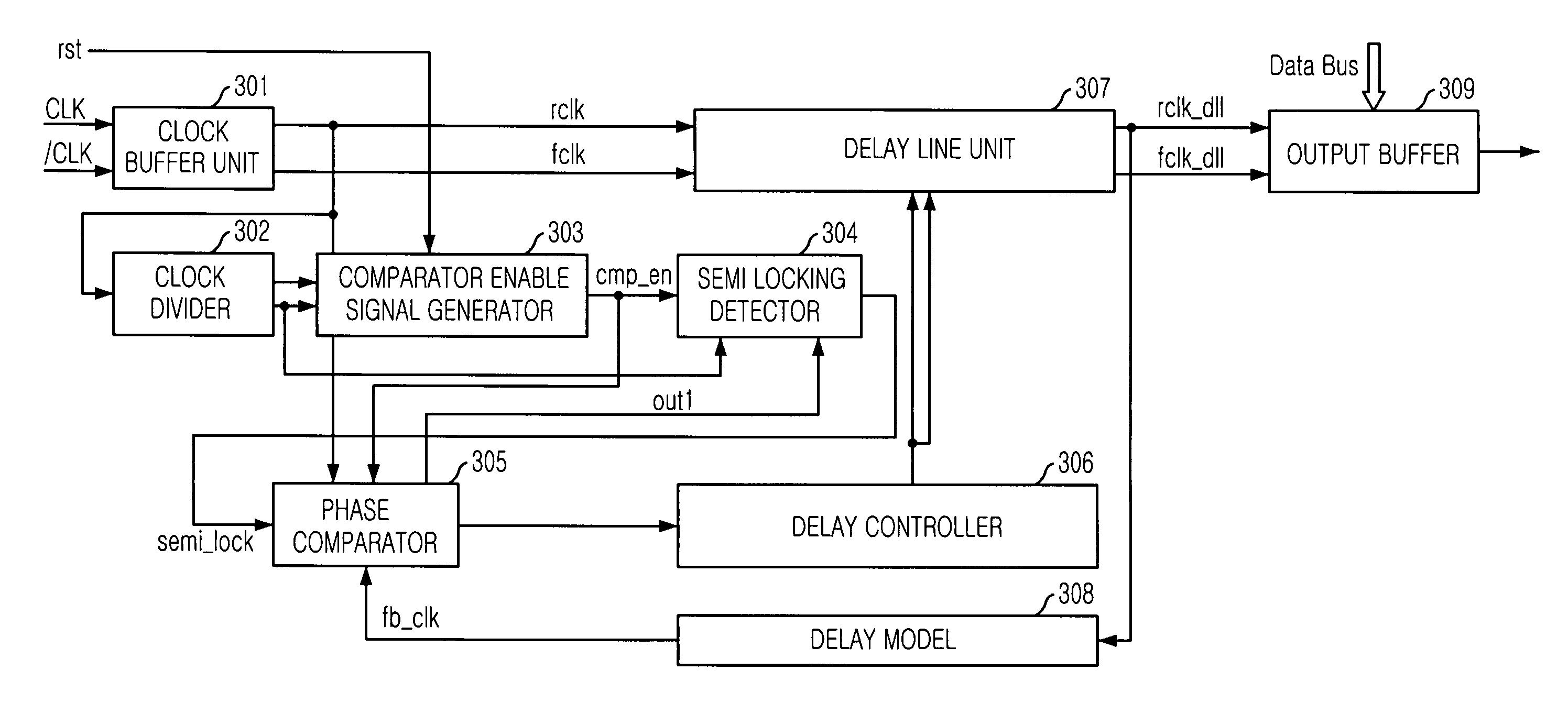

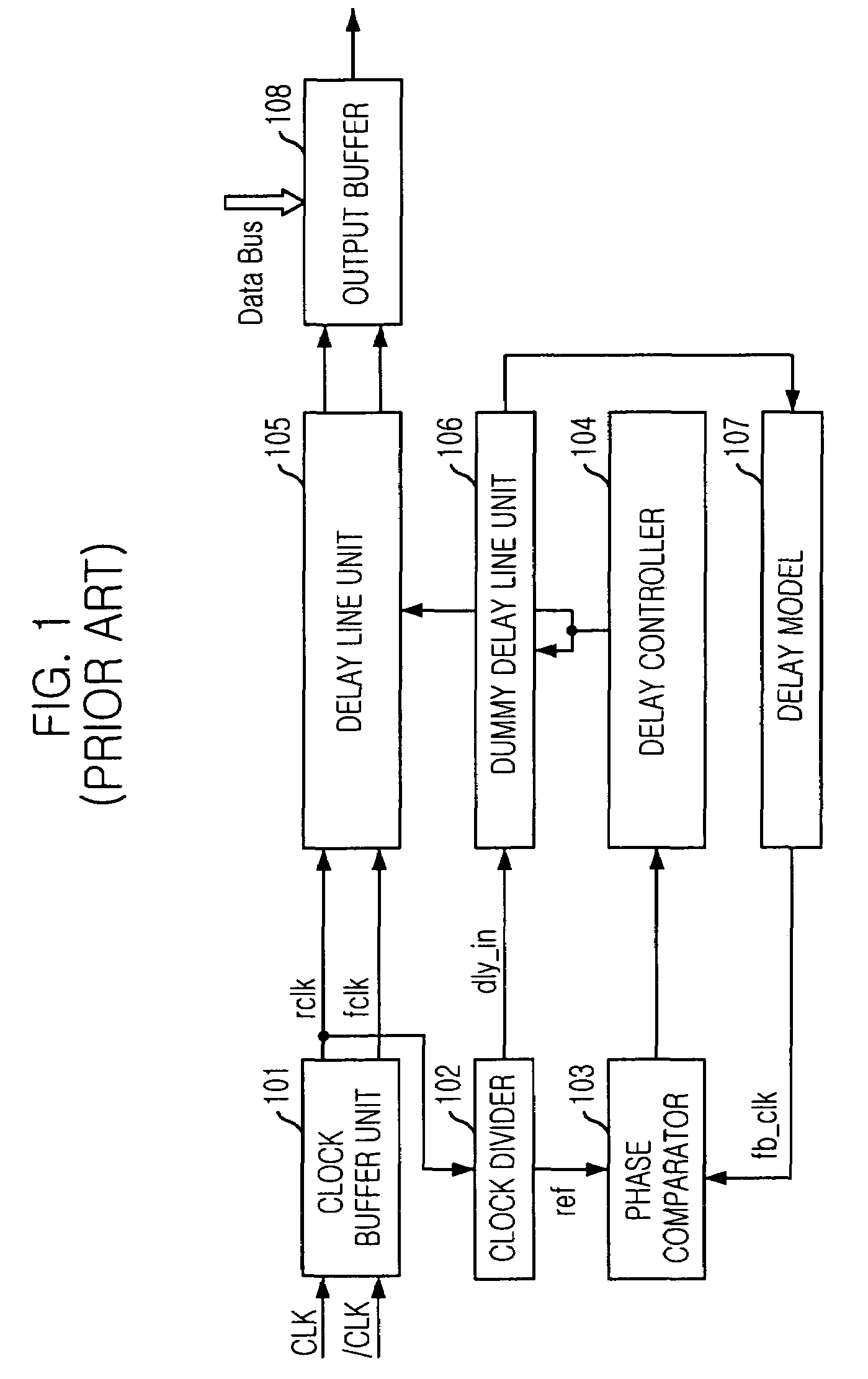

Delay locked loop in semiconductor memory device and its clock locking method

ActiveUS6989700B2Increase working frequencyGuaranteed uptimeMultiple input and output pulse circuitsPulse automatic controlOutput compareDelay-locked loop

A delay locked loop (DLL) for generating a delay locked clock signal, including: a comparator enable signal generator for generating a comparator enable signal in response to a reset signal and a plurality of clock divided signals; a semi locking detector for generating a semi locking detection signal in response to the comparator enable signal; a phase comparator enabled by the comparator enable signal for receiving a rising edge clock signal and a feed-backed clock signal in order to compare phases of the rising edge clock signal and the feed-backed clock signal and output the comparison result; and a DLL generator for generating the delay locked clock signal in response to the comparison result, wherein the comparator enable signal is generated by enlarging a pulse width of the reset signal by a predetermined amount.

Owner:SK HYNIX INC

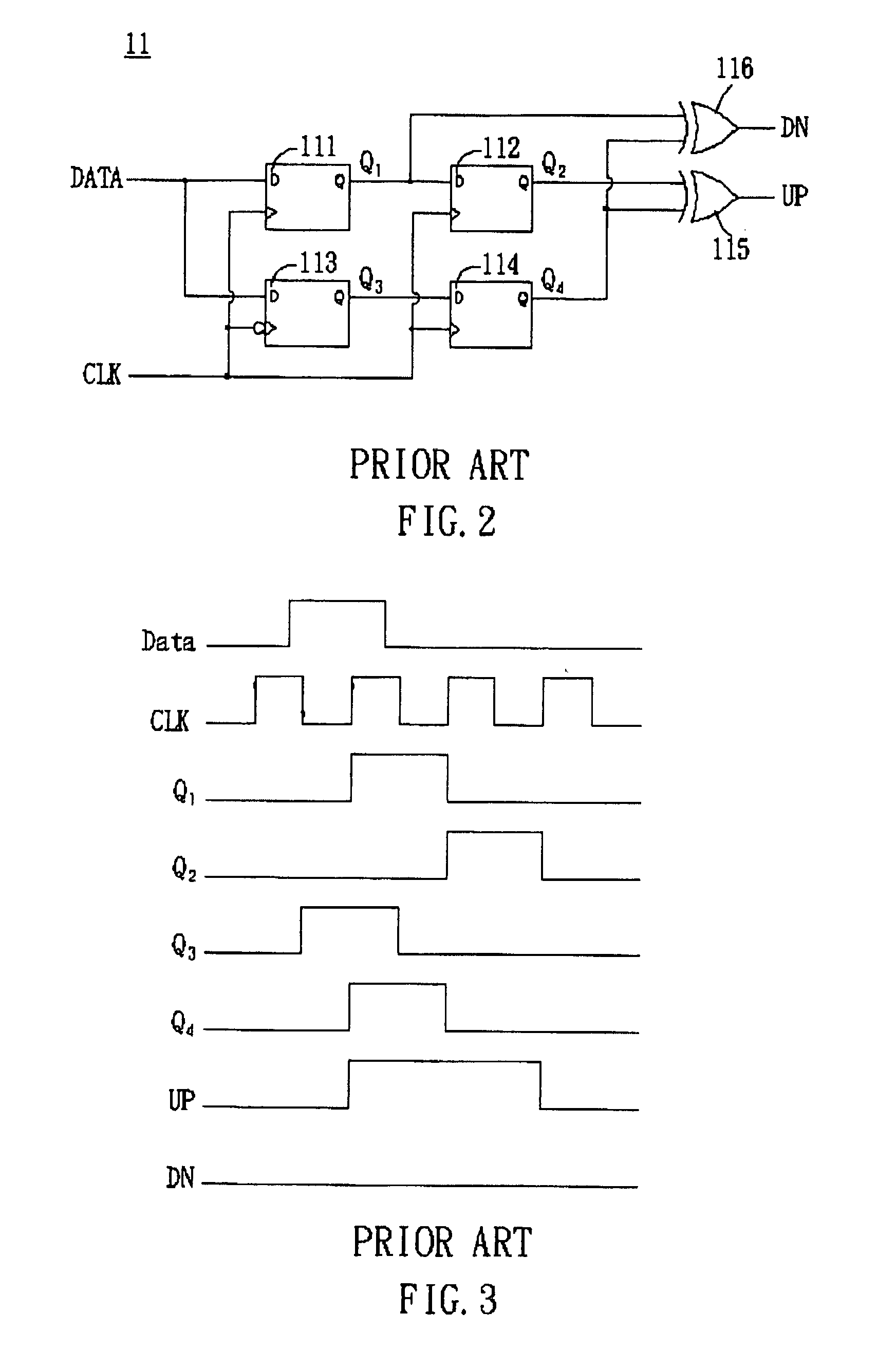

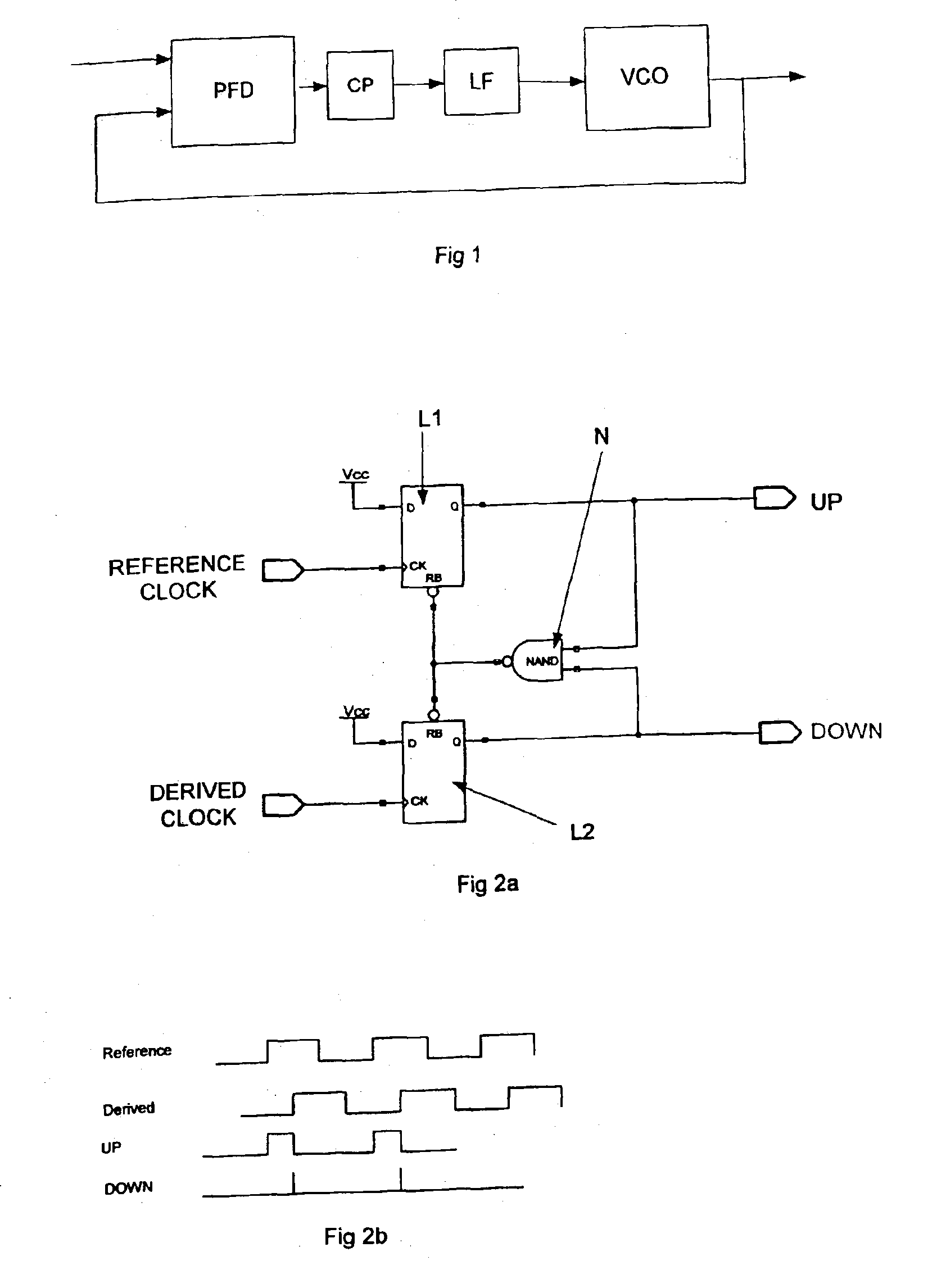

Phase/frequency detector and phase lock loop circuit

ActiveUS6856202B2Avoid the needHigh frequencyPulse automatic controlVoltage-current phase angleDetector circuitsControl signal

The present invention relates to cycle slip detectors for phase and frequency detectors (PFD) and to lock detectors for phase lock loop (PLL) circuits. The present invention provides a cycle slip detector circuit for use with a phase and frequency detector circuit having first and second signal inputs, and arranged to provide first and second PLL control signal outputs responsive to clock edges in the first and second input signals respectively; the cycle slip detector circuit comprising: means for determining a cycle slip between said input signals by determining when a delayed output signal coincides with a respective input signal.

Owner:CIRRUS LOGIC INC

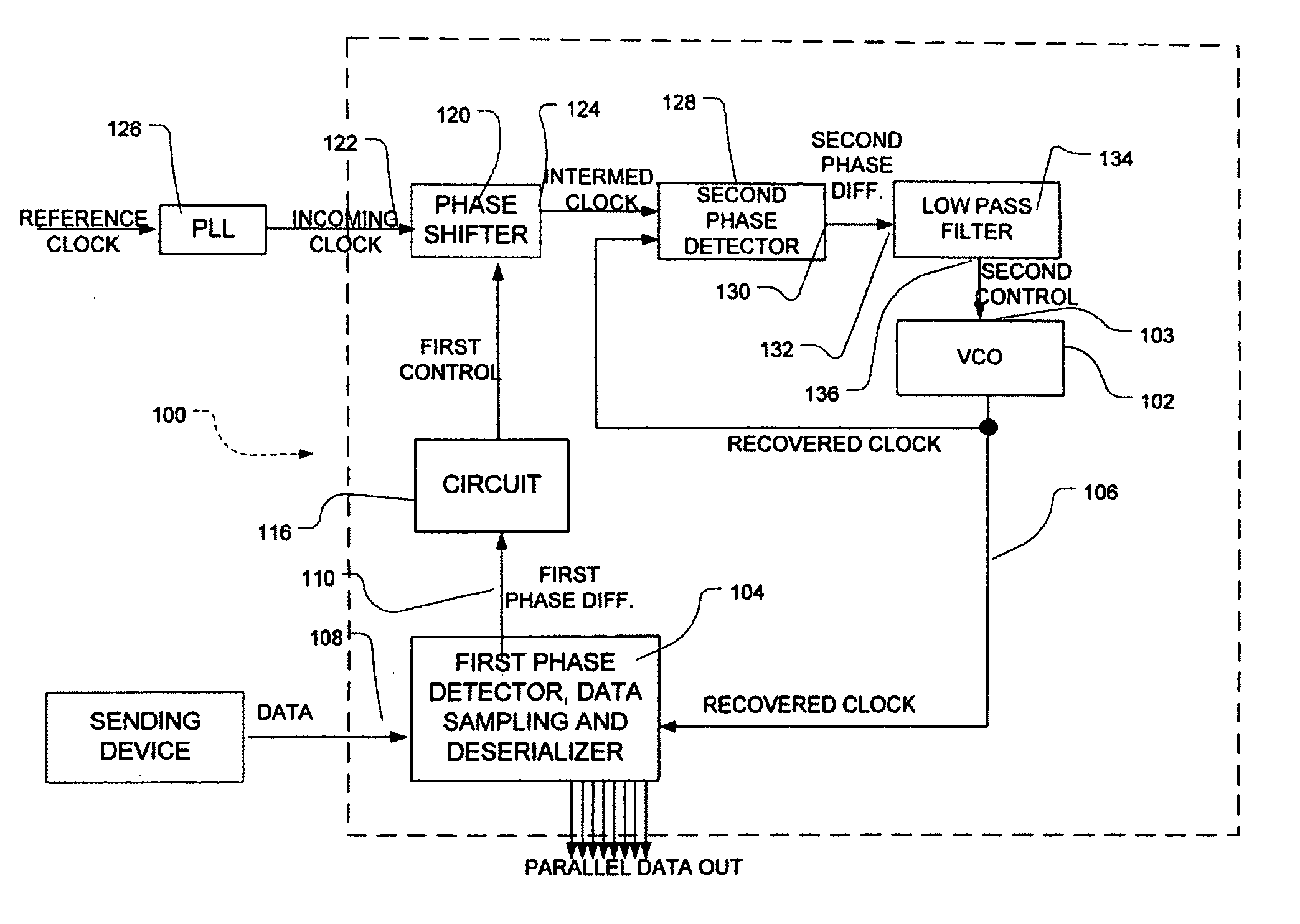

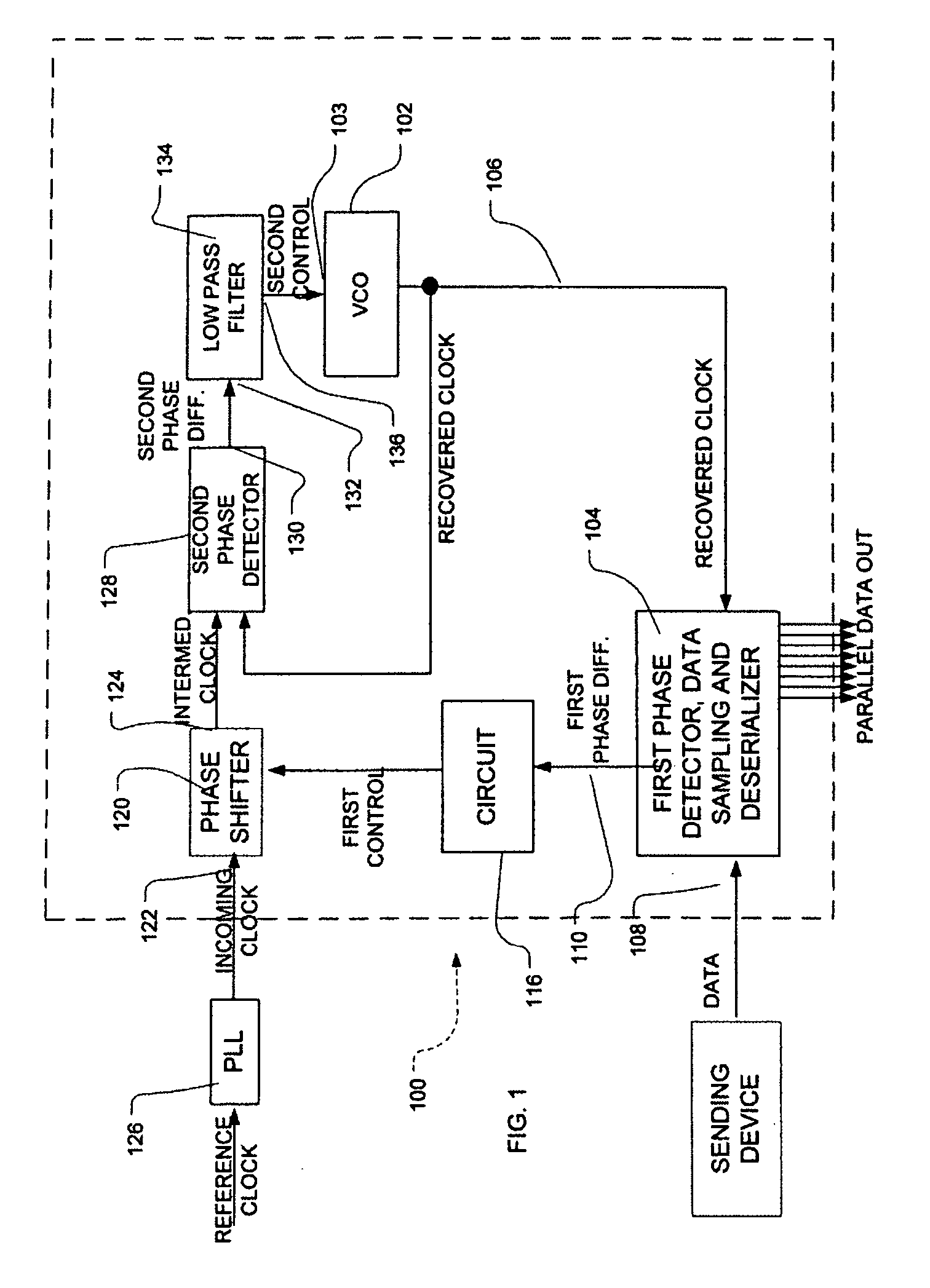

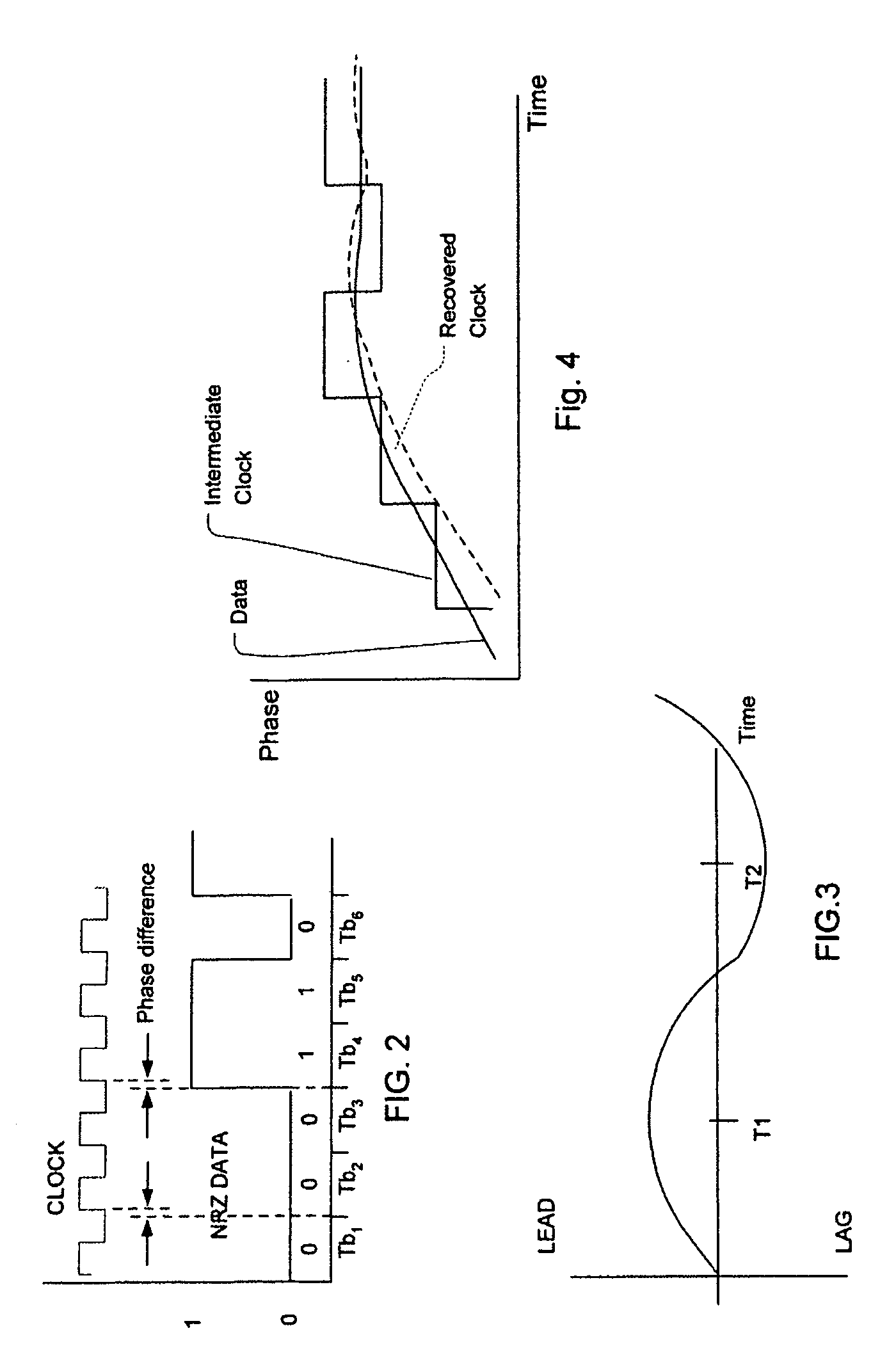

Low jitter clock recovery circuit

ActiveUS20070058768A1Pulse automatic controlOscillations comparator circuitsPhase detectorLow-pass filter

A clock recovery circuit includes a first phase detector for measuring the phase difference between a first clock signal from a voltage controlled oscillator (VCO) and a data signal. A phase shifter responsive to a control signal based on this phase difference adjusts the phase of an incoming clock signal to yield a second clock signal. The phase difference between the first clock signal and the second clock signal is measured and the resulting signal is low-pass filtered to derive a control signal for controlling the VCO. The phase locked loop including the VCO filters out jitter.

Owner:RAMBUS INC

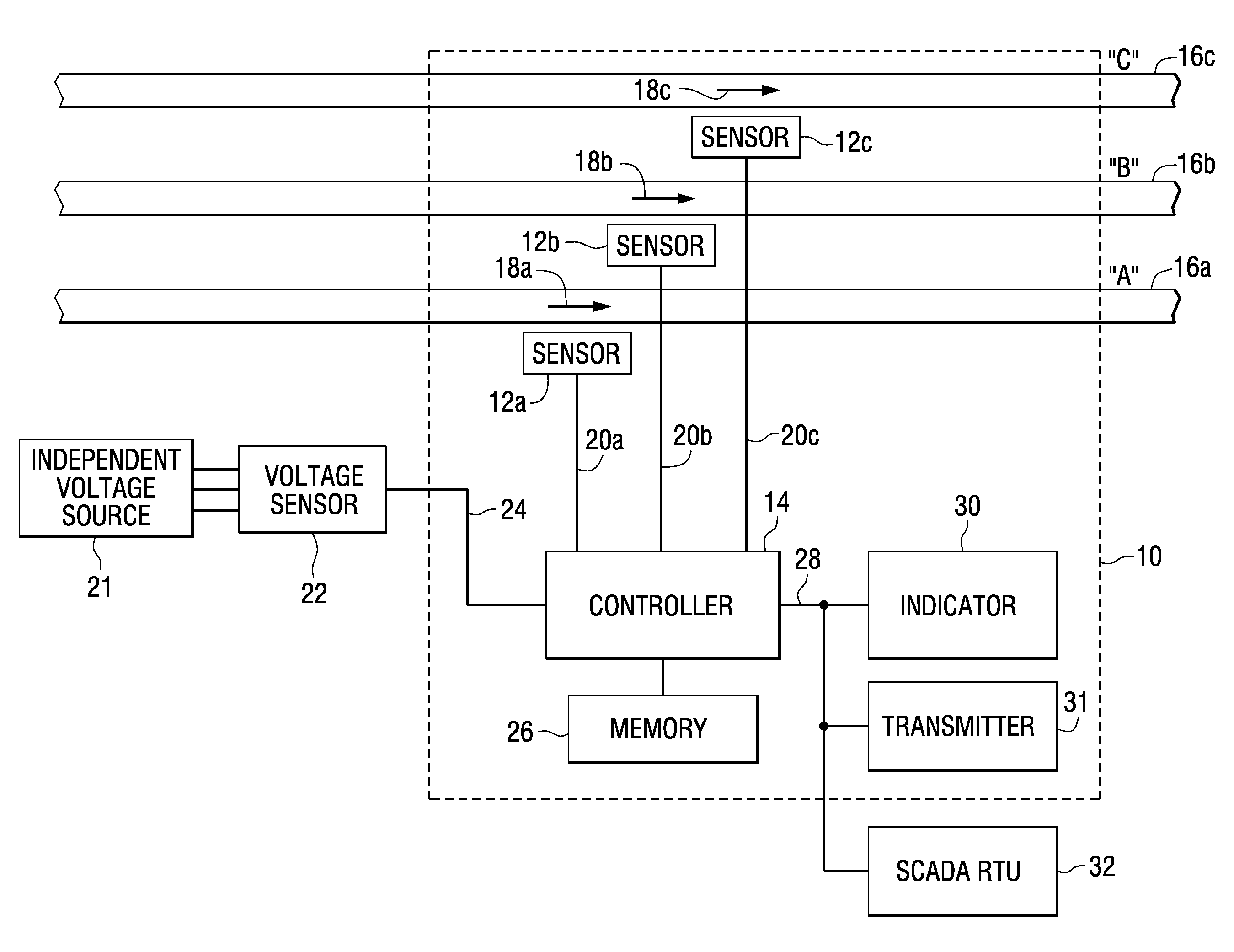

Directional fault current indicator

ActiveUS20090009180A1Voltage-current phase angleEmergency protective arrangements for automatic disconnectionElectrical conductorAngular degrees

A method for identifying a fault condition associated with a power line conductor of an electrical power distribution network. The method comprises determining a load current carried by the conductor is above a minimum load current, determining a learned phase angle relationship between the load current and a source signal, determining a load current magnitude, determining a real-time phase angle relationship between the load current and the source signal and indicating a fault condition when the real-time phase angle relationship is within a predetermined number of angular degrees of the learned phase angle relationship and when the load current magnitude exceeds a fault-indicating current.

Owner:THOMAS & BETTS INT INC

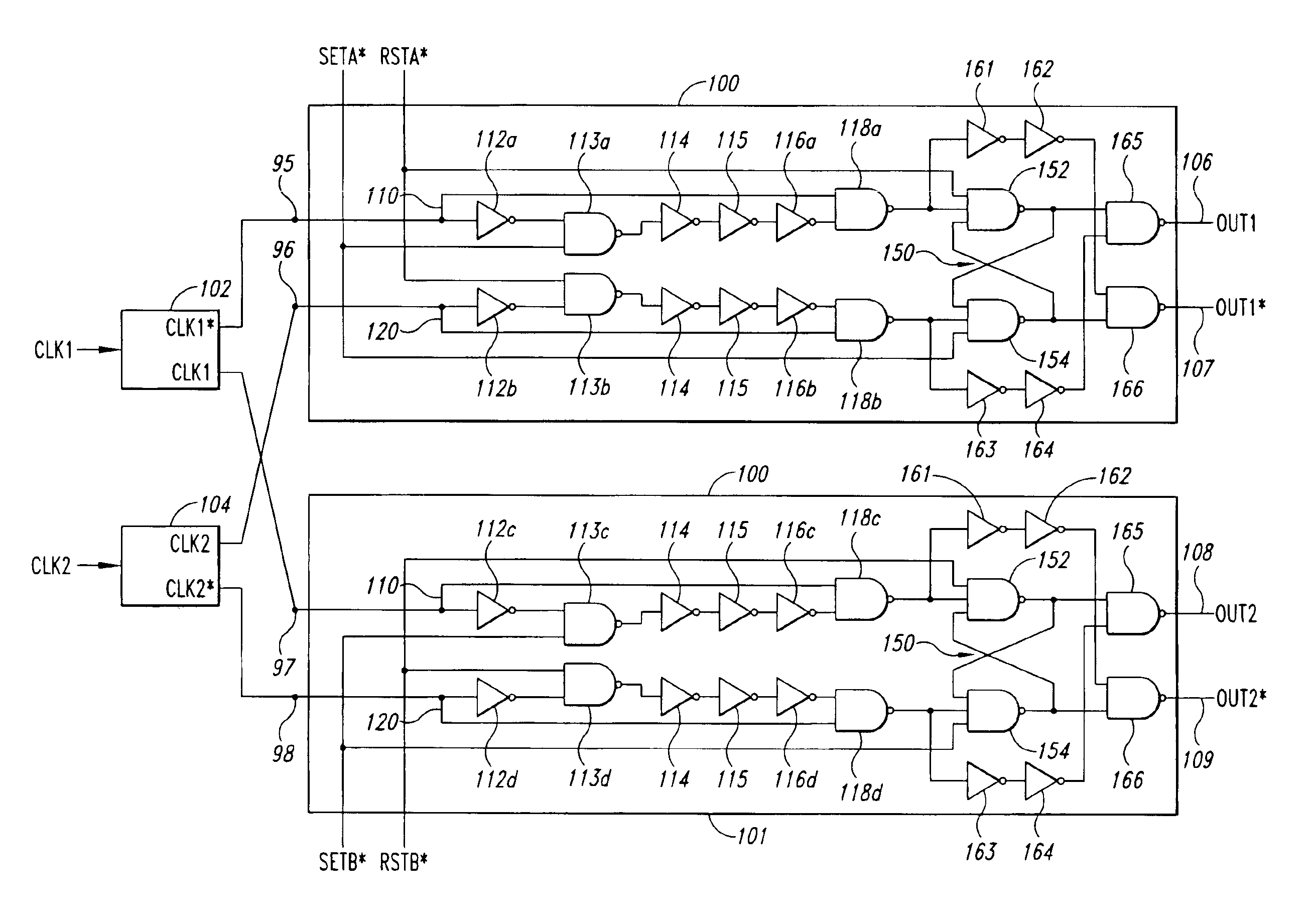

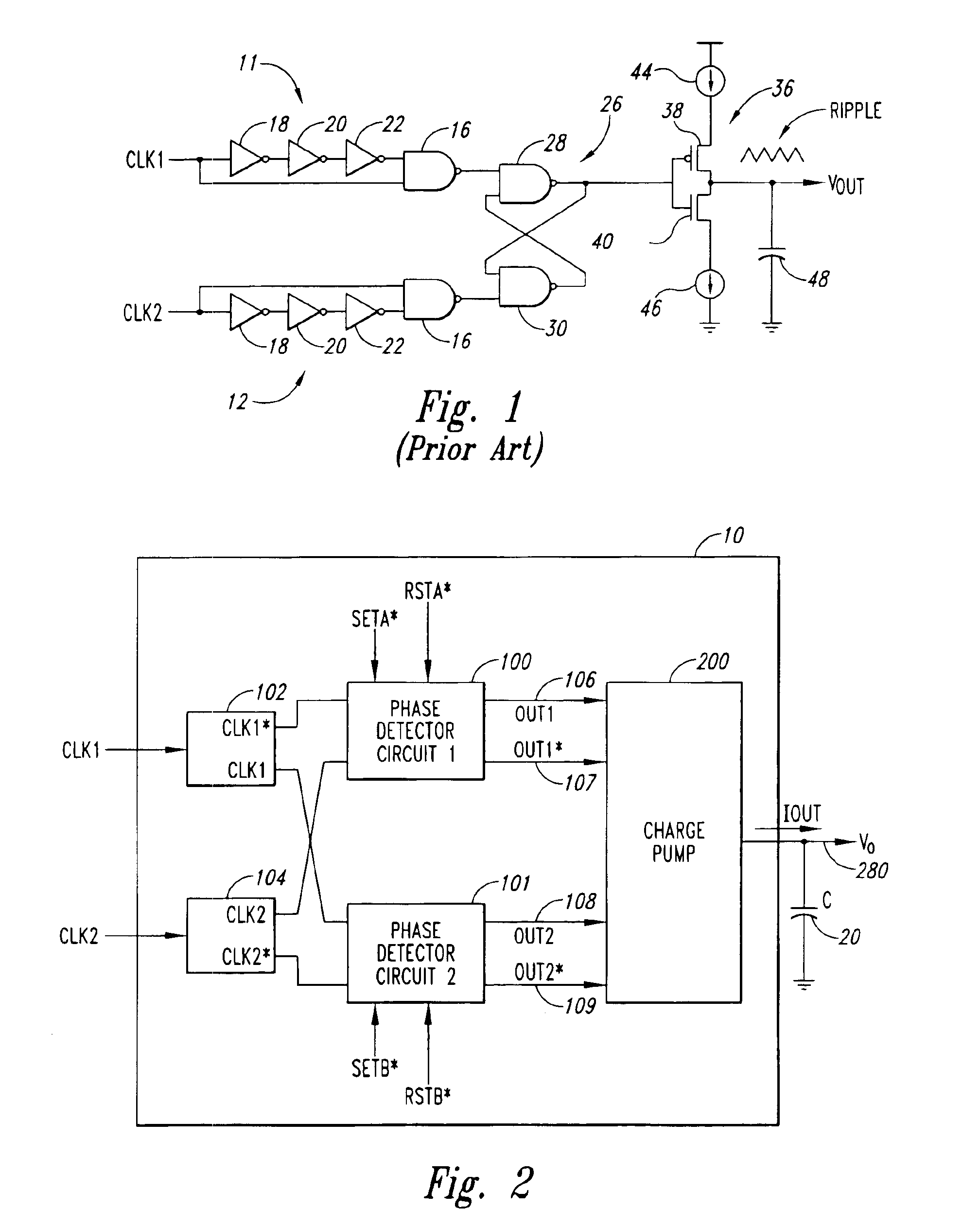

Method and apparatus for generating a phase dependent control signal

InactiveUS6952462B2Avoid problemsPulse automatic controlSingle output arrangementsPhase detectorPhase correlation

A phase detector generates a phase dependent control signal according to the phase relationship between a first and second clock signal. The phase detector includes first and second phase detector circuits receiving the first and second clock signals and generating select signals having duty cycles corresponding to the phase relationship between the clock edges of the first and second clock signals. The phase detector also includes a charge pump that receives select signals from the phase detector circuits and produces an increasing or decreasing control signal when the first and second clock signals do not have the predetermined phase relationship, and a non-varying control signal when the first and second clock signals do have the predetermined phase relationship. The control signal may be used to adjust the delay value of a voltage-controlled delay circuit in order to adjust the phase relationship between the first and second clock signals to have a predetermined phase relationship.

Owner:ROUND ROCK RES LLC

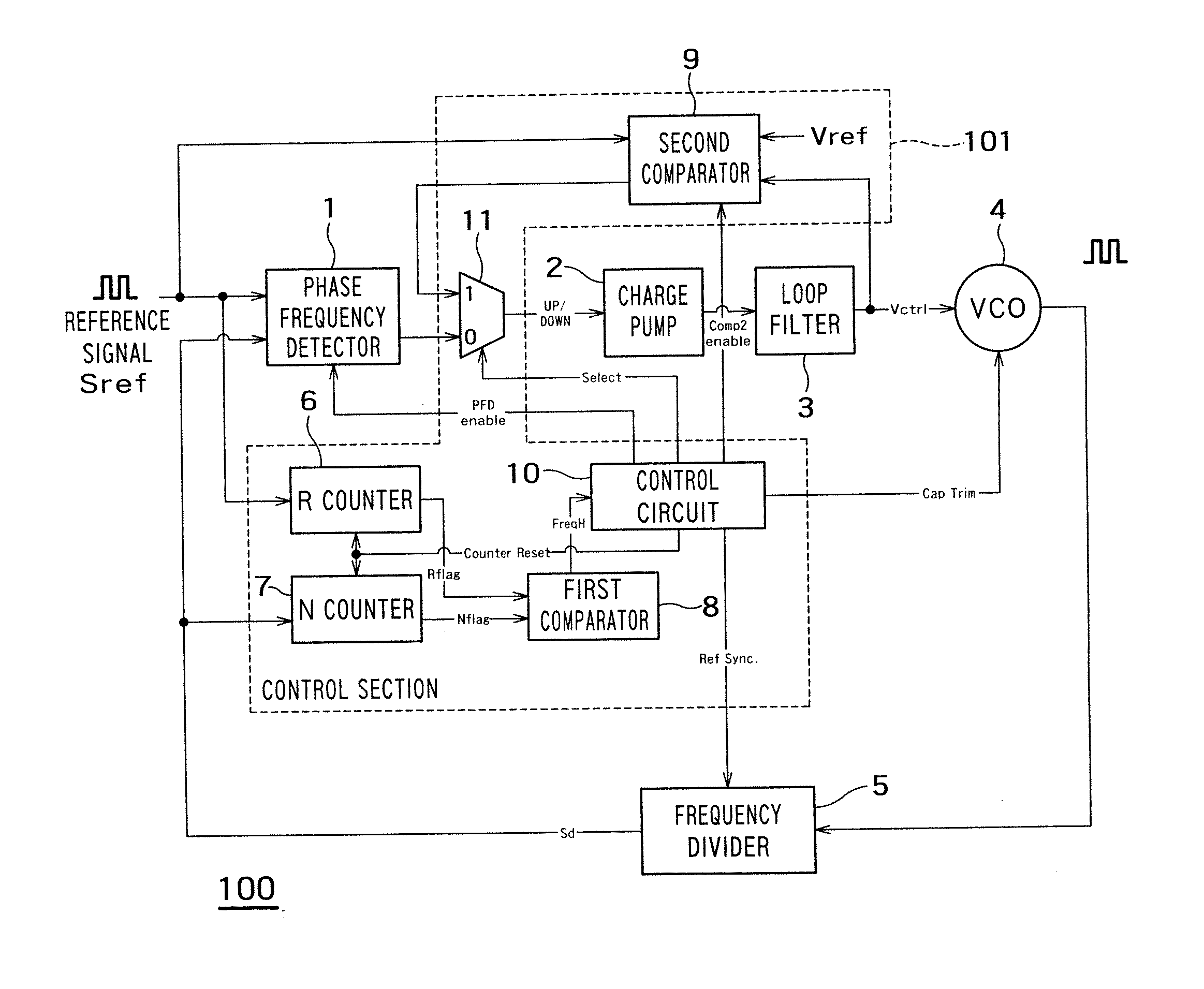

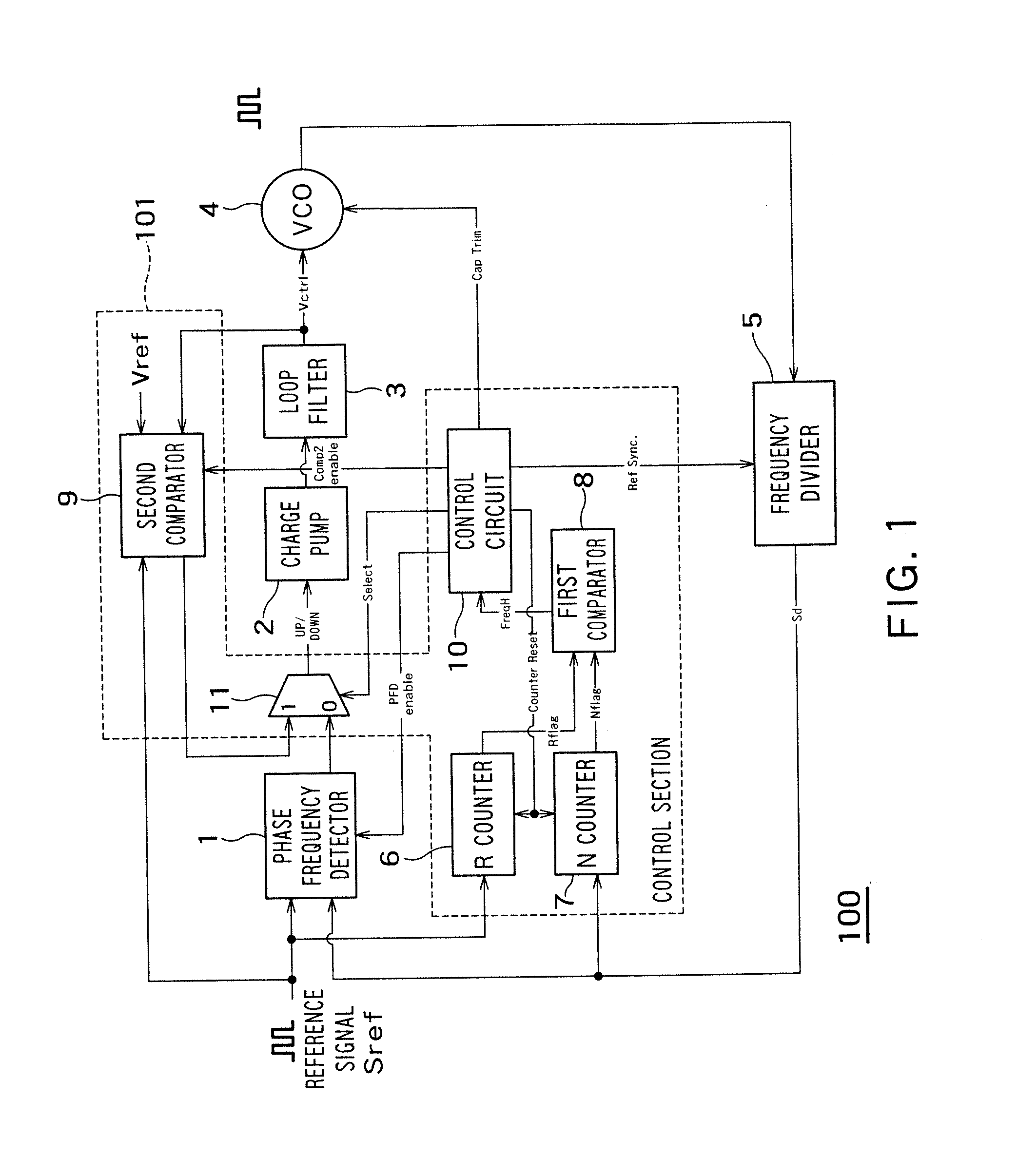

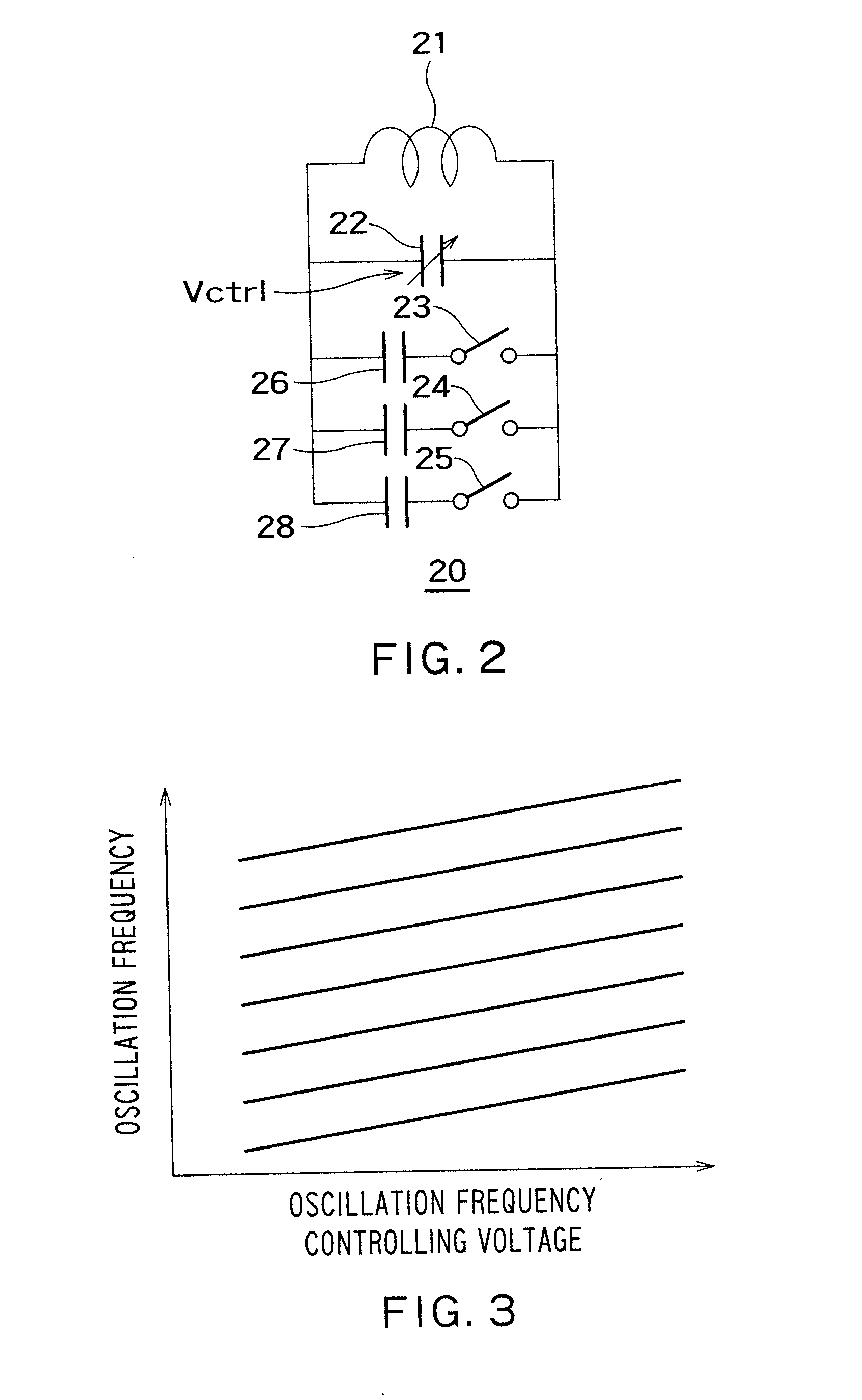

Controller for oscillator

An oscillator controller, has a phase frequency detector that compares a reference signal and a frequency-divided signal and outputs a phase difference signal; a charge pump that outputs a phase error signal according to the phase difference signal output from said phase frequency detector; a loop filter that filters the phase error signal output from said charge pump and outputs an oscillation frequency controlling voltage; a voltage-controlled oscillator that has an LC resonator having a coil, a variable capacitor connected to the opposite ends of the coil at the opposite ends thereof, and a capacitor connected in series with a switch between the opposite ends of said variable capacitor, the oscillation frequency of the voltage-controlled oscillator being controlled through adjustment of the capacitance value of said variable capacitor by said oscillation frequency controlling voltage; a frequency divider that divides the frequency of the output of said voltage-controlled oscillator and outputs said frequency-divided signal; a first counter that counts the number of waves of said reference signal to a desired number and outputs a first flag signal; a second counter that counts the number of waves of said frequency-divided signal to said desired number and outputs a second flag signal; a first comparator that compares said first flag signal and said second flag signal and outputs a frequency comparison signal; and a control circuit that controls said voltage-controlled oscillator, said first counter, said second counter and said frequency divider by outputting signals thereto.

Owner:KK TOSHIBA

Method and apparatus for phase detection in digital signals

InactiveUS6151356APulse automatic controlDc level restoring means or bias distort correctionDigital dataPropagation delay

The invention provides an improved method and apparatus for detecting the phase difference between a digital data signal and a clock signal. By ensuring that no pulse in the output phase signal is narrow enough to introduce a non-linearity, the present invention avoids a source of non-linearity exhibited in existing phase detectors. In addition, by ensuring that critical timing paths through the circuit contain similar circuit blocks, with similar propagation delays, relative time relationships are preserved from clock and data inputs to XOR inputs. The circuit is therefore largely insensitive to changes in the characteristics of the components so long as they all move together, as they would in an integrated circuit implementation.

Owner:RPX CLEARINGHOUSE

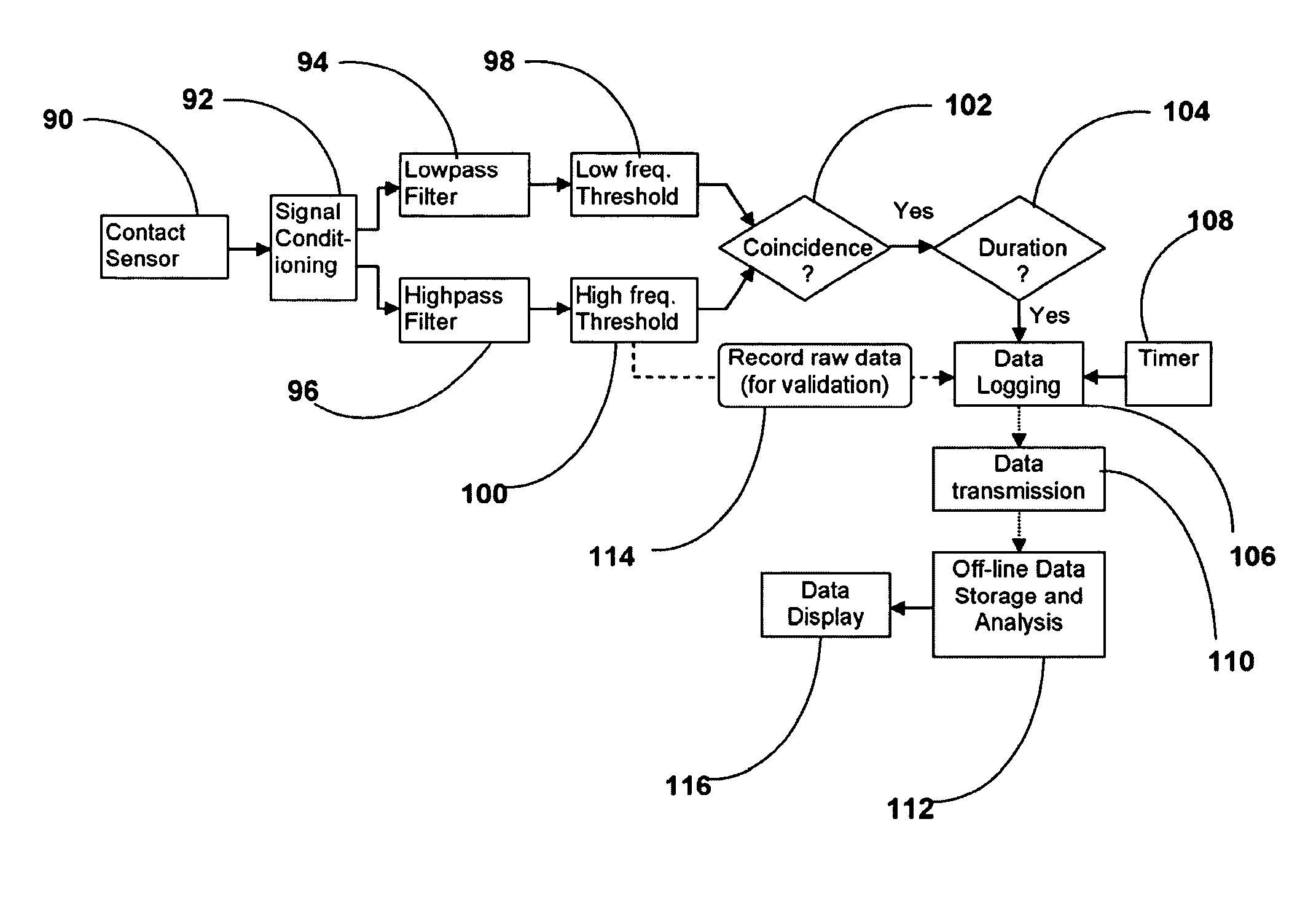

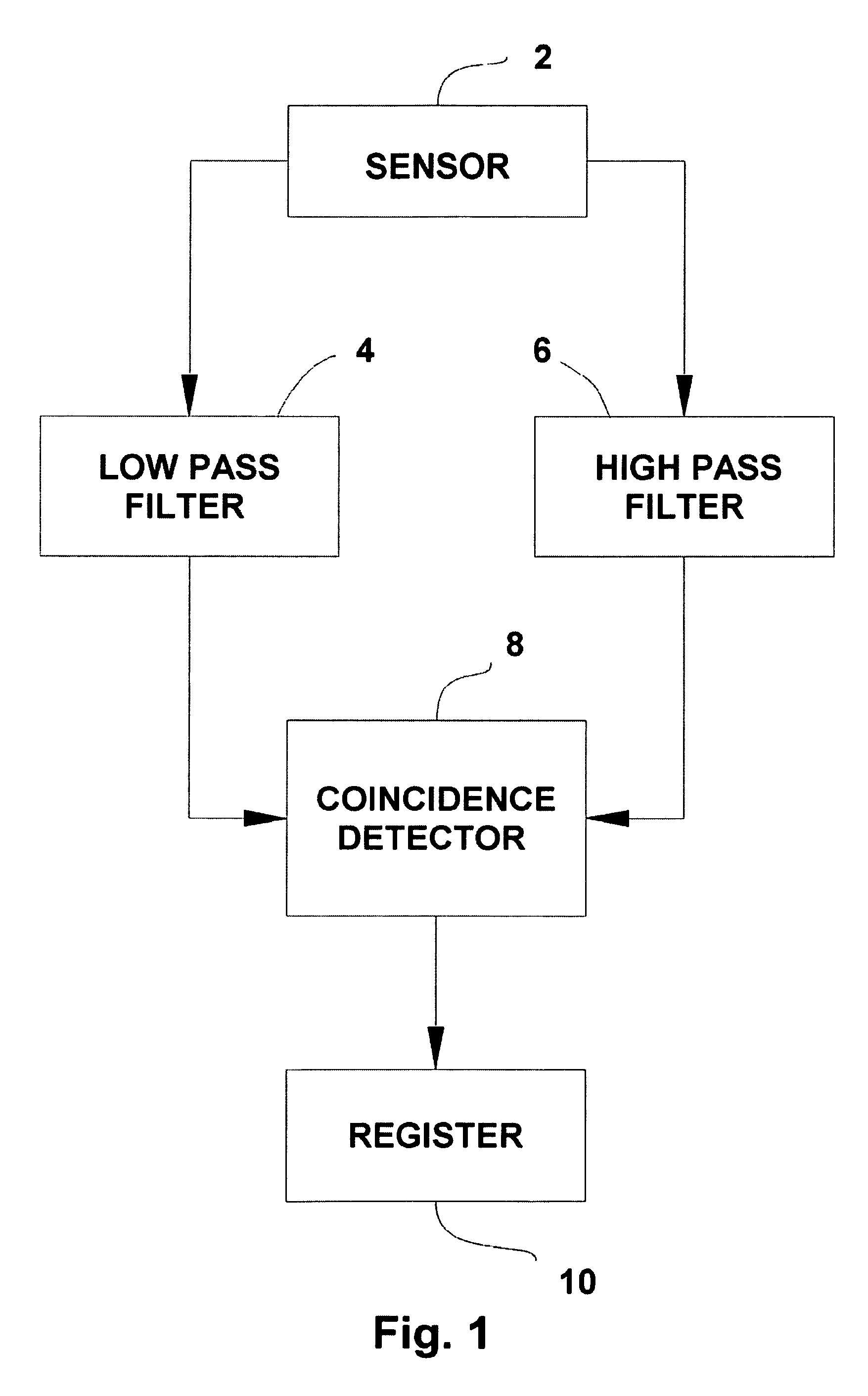

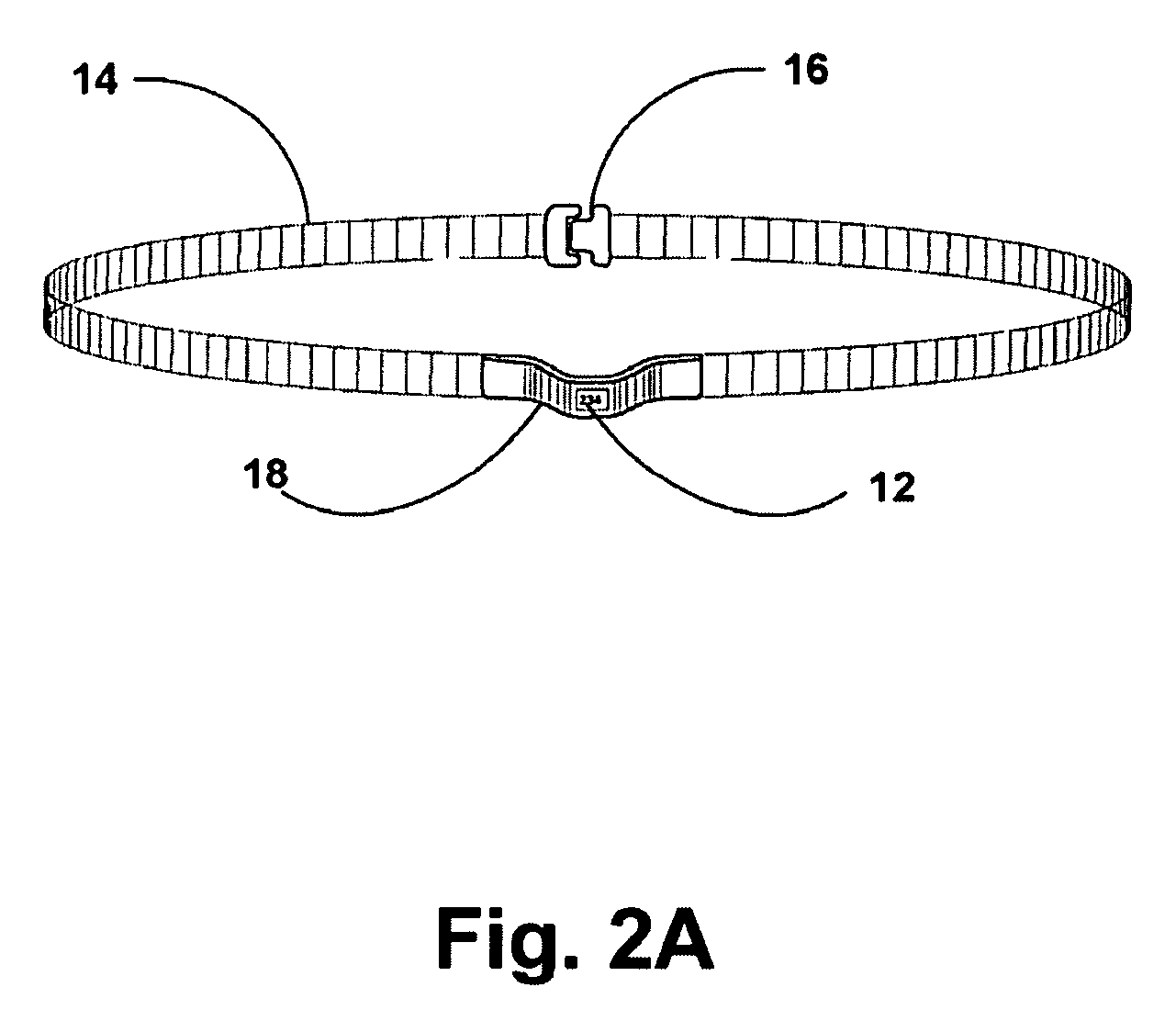

Cough detector

ActiveUS8241223B2Organ movement/changes detectionAuscultation instrumentsSonificationElectrical impedance

A device for detecting and counting coughing events is provided. In one embodiment a sensor for sensing and transducing low frequency and high frequency mechanical vibrations, sends signals to a coincidence detector that determines if high and low signals coincide. In another embodiment, ultrasonic energy is introduced to the trachea and if Doppler shift in frequency is detected, association is made to a coughing event. In another embodiment a change in the impedance of the neck is considered associated with coughing event if correlated over time with a specific mechanical frequency sensed.

Owner:RESPIRI LTD

Popular searches

Electric variable regulation Spatial transmit diversity Position fixation Substation equipment Individually energised antenna arrays Radio wave reradiation/reflection Pulse generation by logic circuits Voltage/current interference elimination Logic circuit coupling/interface arrangements Multi-tester circuits