Clock and data recovery circuit

a clock and data recovery technology, applied in the field of clock and data recovery circuits, can solve the problems of increasing power consumption, increasing chip size and power consumption, etc., and achieve the effects of increasing chip size, increasing power consumption, and increasing chip siz

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

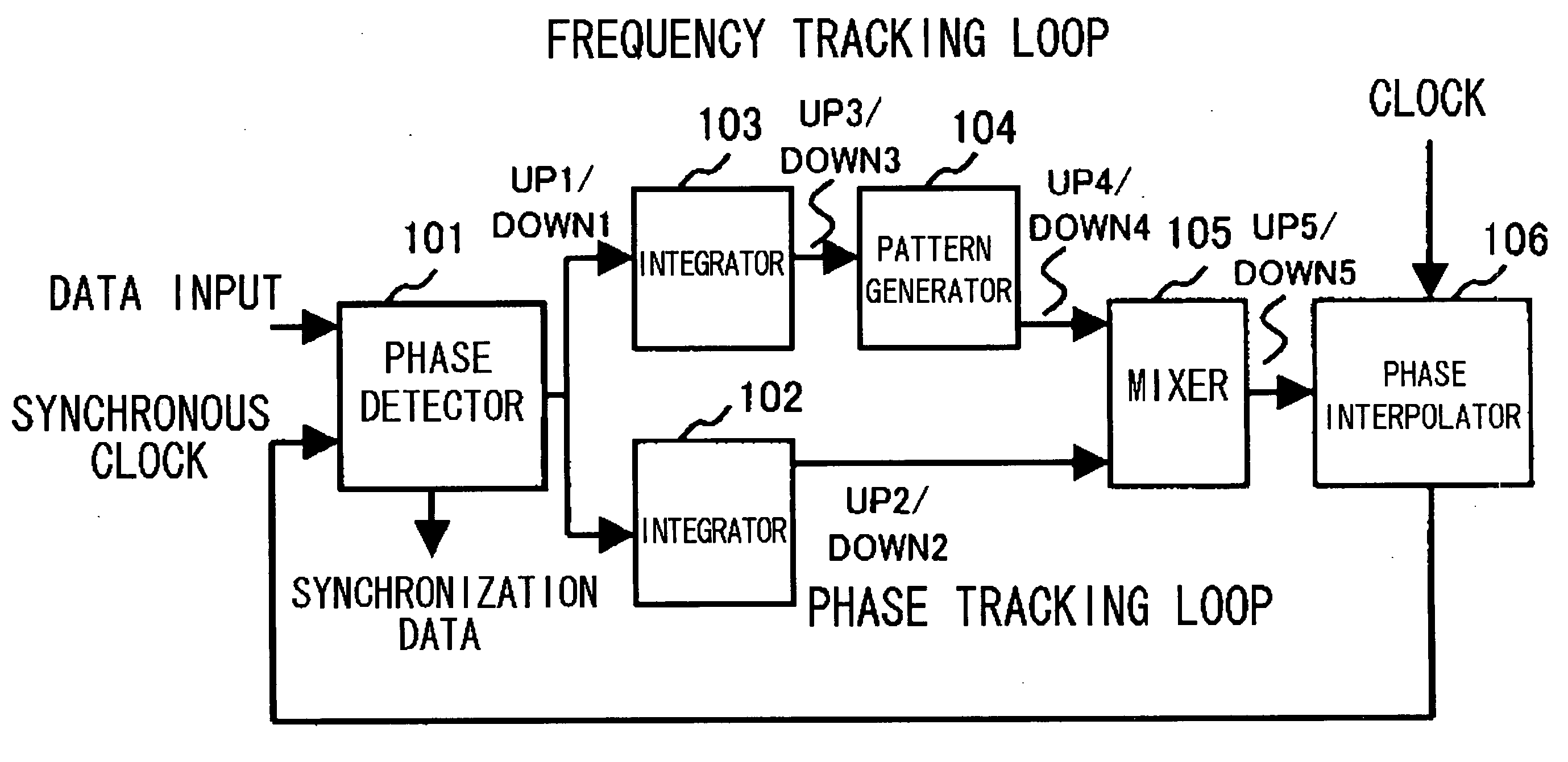

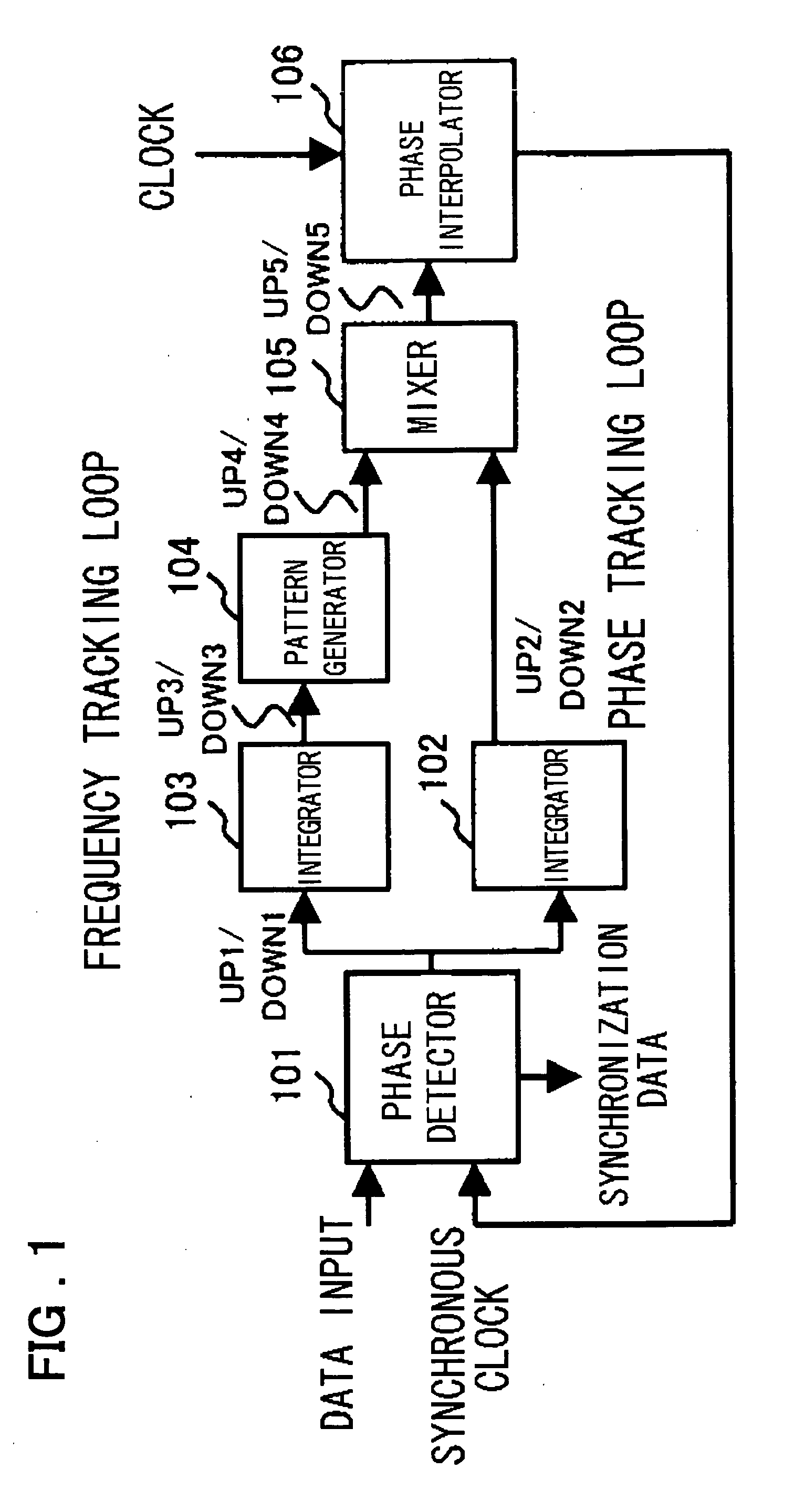

[0048] Embodiment modes of the present invention will be described. A device according to a preferred embodiment of the present invention includes a phase detector (101), a first integrator (102), a second integrator (103), a pattern generator (104), a mixer (105), and a phase interpolator (106). The phase detector (101) receives a data signal and a synchronous clock signal, detects a delay or an advance between the phases of the two input signals, and then outputs a first control signal (UP1 / DOWN1), according to the result of detection. The first integrator (102) integrates the first control signal output from the phase detector (101) to output a second control signal (UP2 / DOWN2). The second integrator (103) integrates the first control signal (UP1 / DOWN1) output from the phase detector (101) to output a third control signal. The pattern generator (104) inputs the third control signal (UP3 / DOWN3) from the second integrator (103) and then outputs a fourth control signal. The mixer (1...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More