Patents

Literature

87 results about "Asynchronous serial interface" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Asynchronous Serial Interface, or ASI, is a method of carrying an MPEG Transport Stream (MPEG-TS) over 75-ohm copper coaxial cable or multimode optical fiber. It is popular in the television industry as a means of transporting broadcast programs from the studio to the final transmission equipment before it reaches viewers sitting at home.

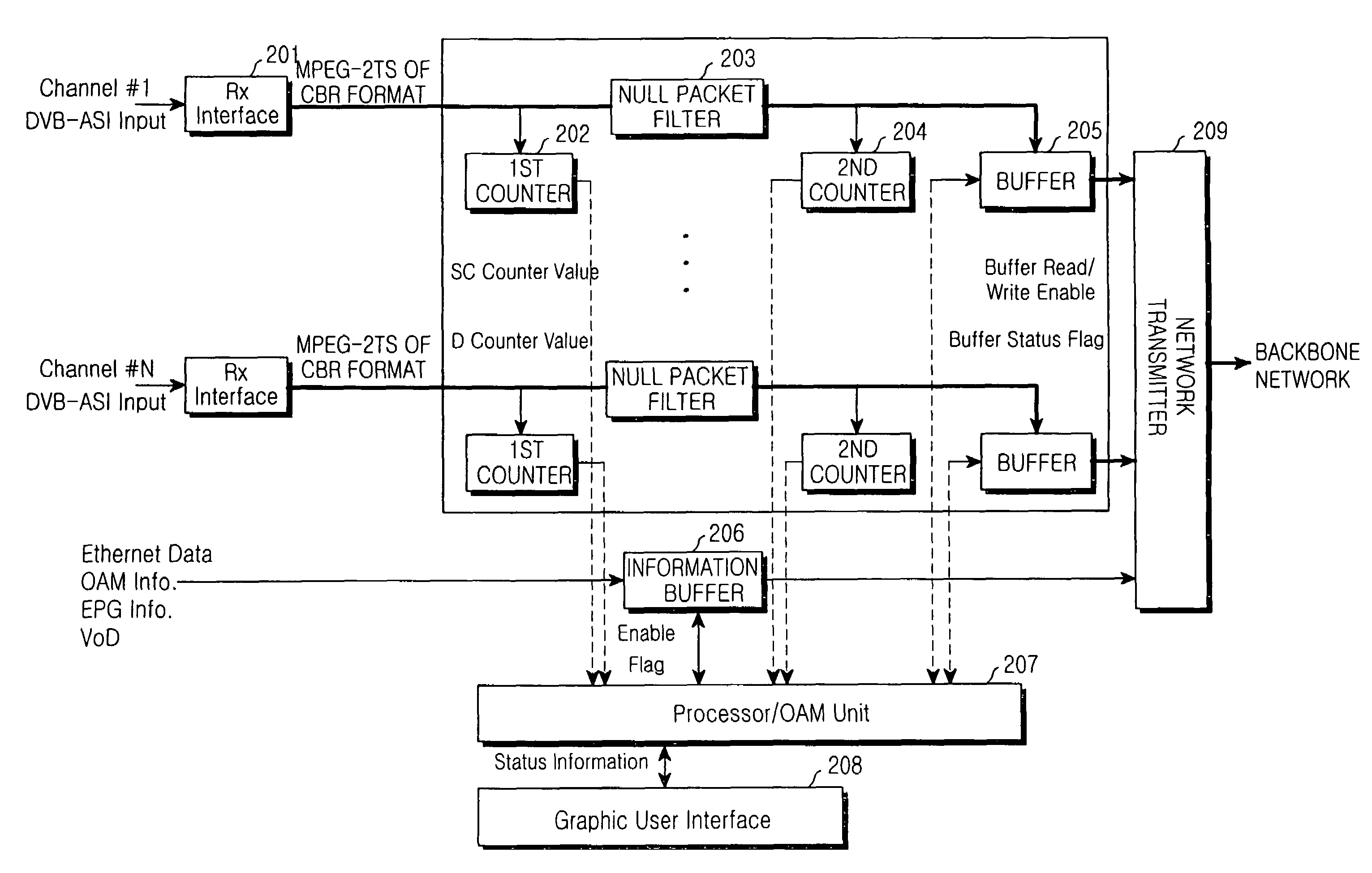

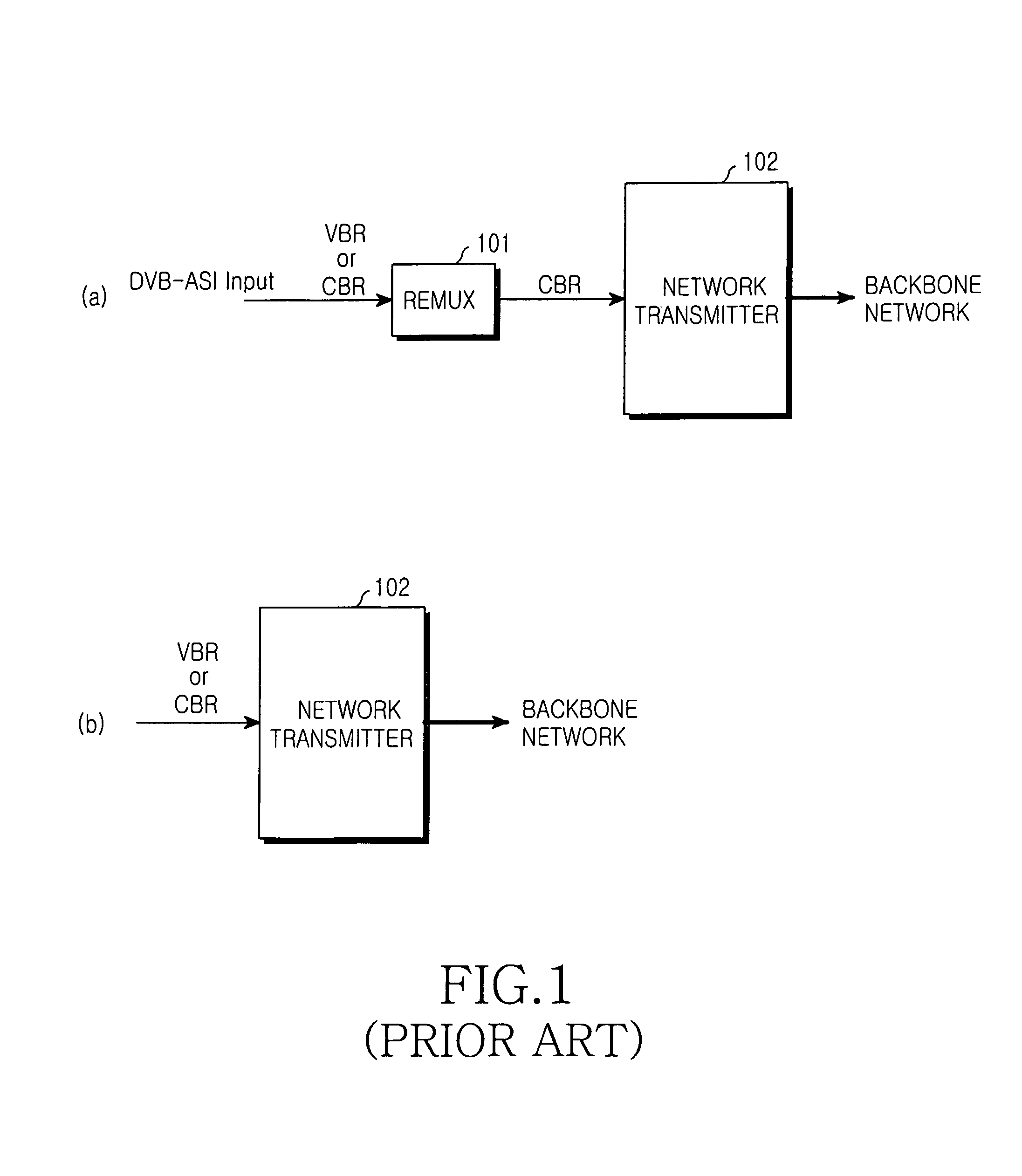

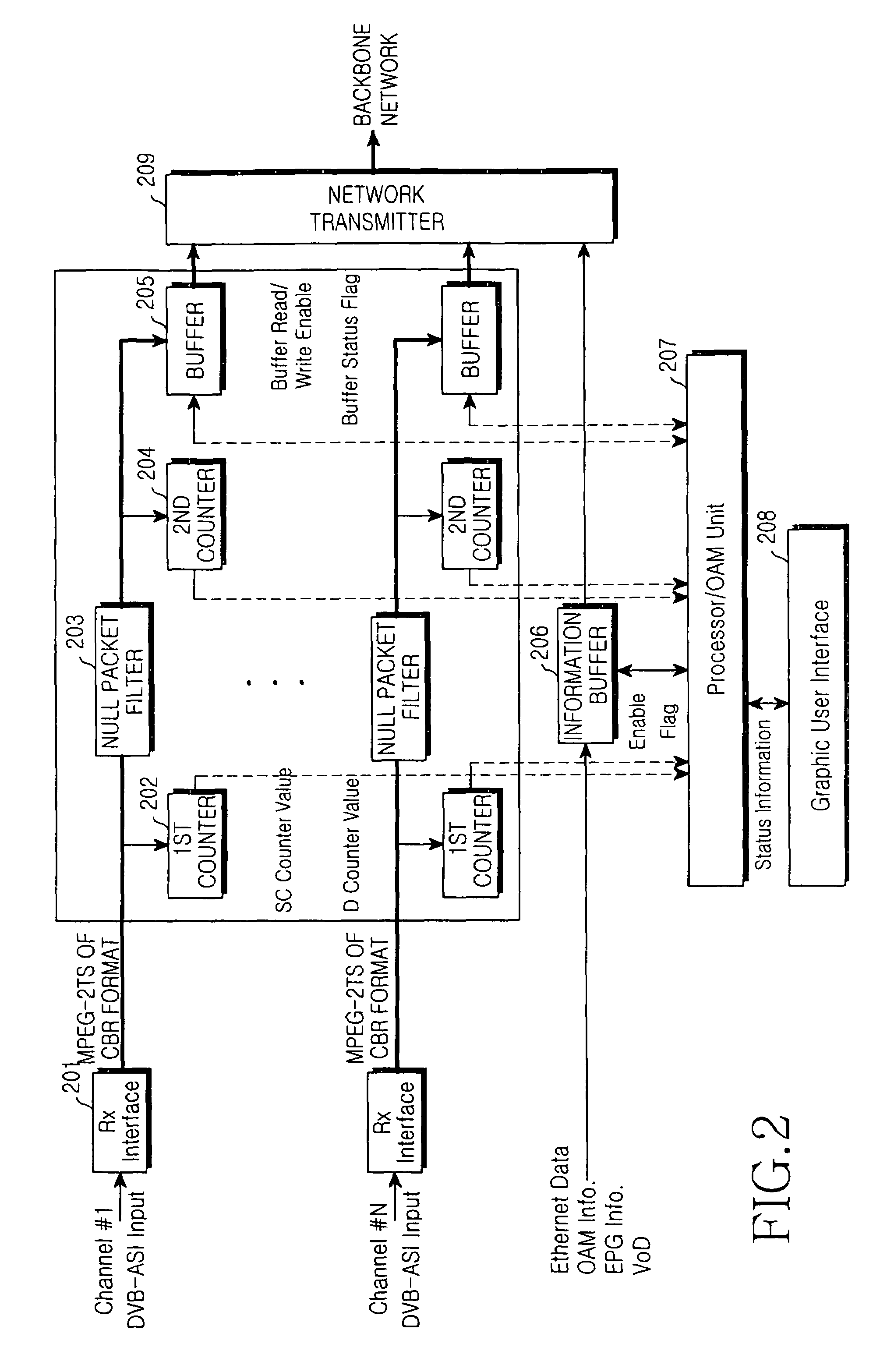

Device for filtering out null packet for MPEG-2 transmission

ActiveUS20050047341A1Avoid wastingError preventionFrequency-division multiplex detailsDigital videoData stream

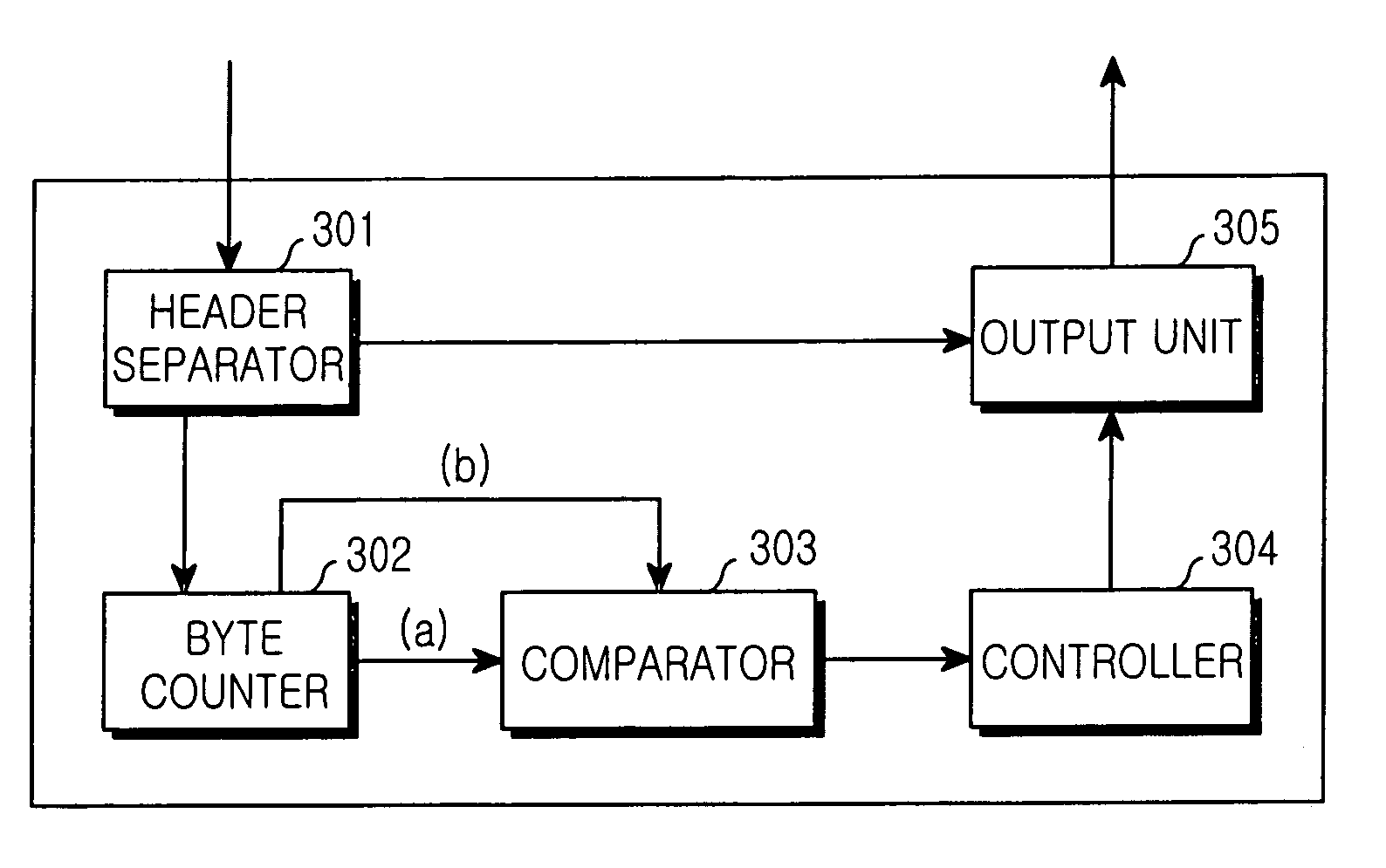

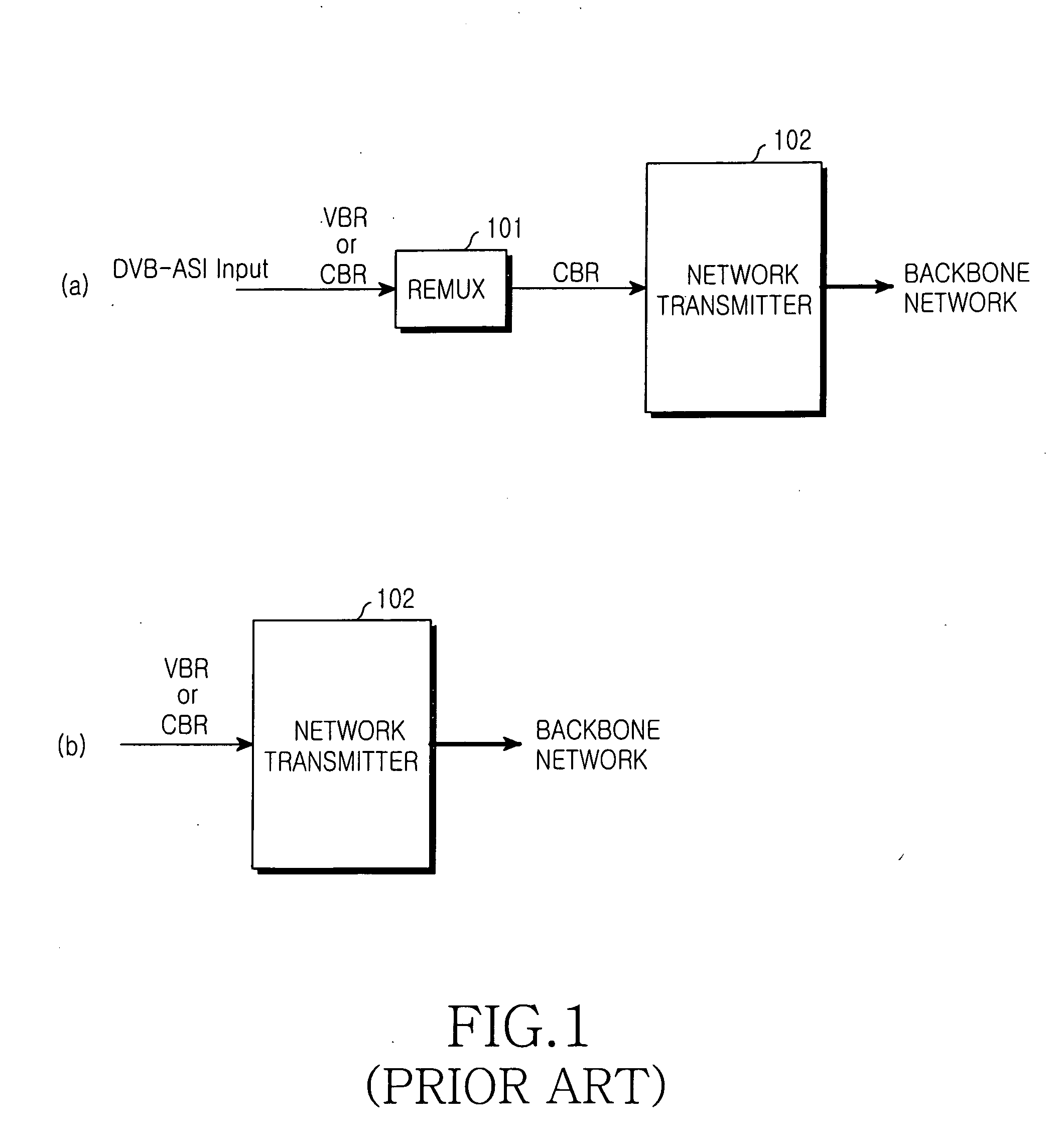

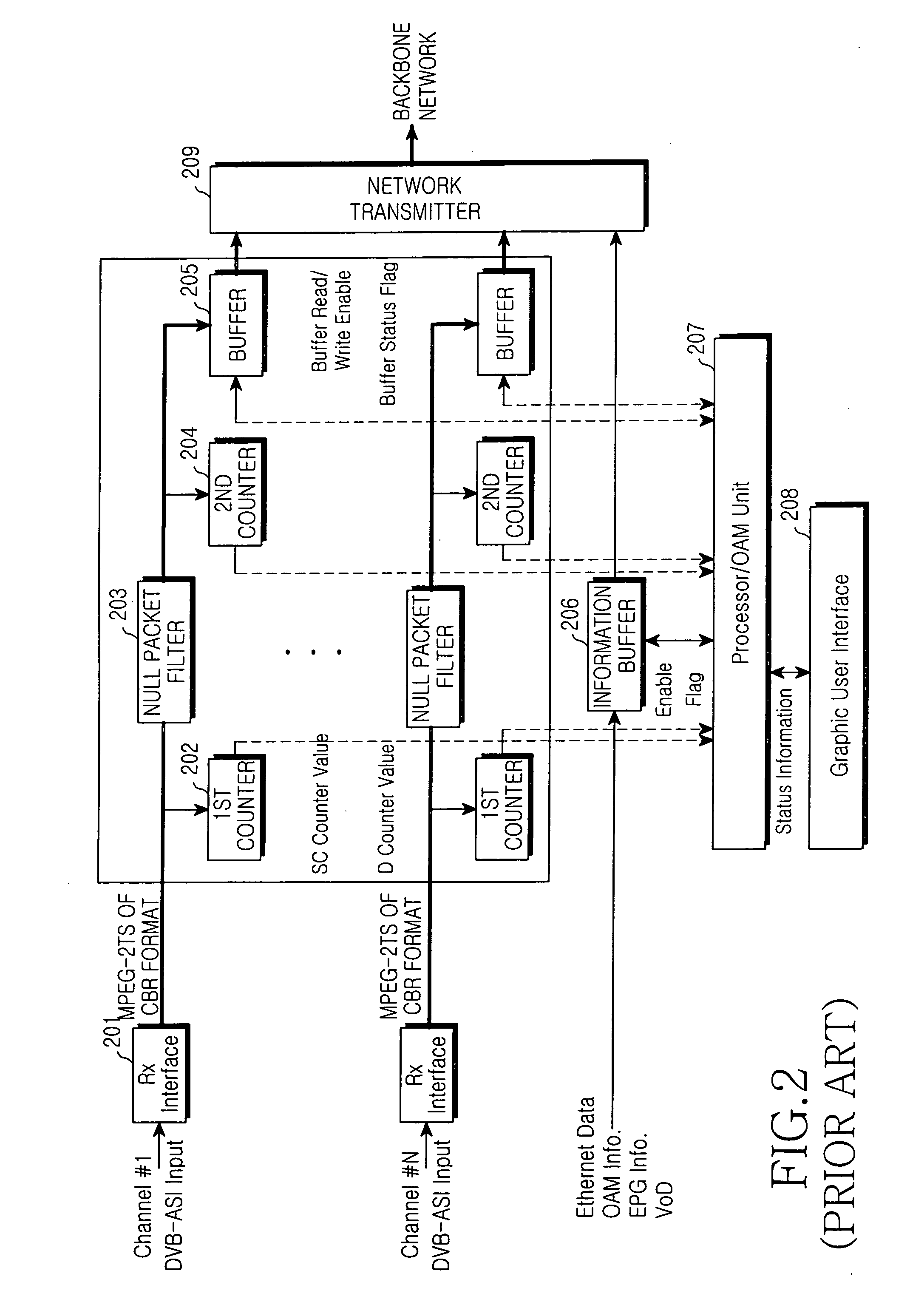

Disclosed is a device for filtering out a null packet in a data stream for example an MPEG-2 TS (Transport Stream) to avoid bandwidth waste when it is transmitted to a backbone network. The device includes a plurality of receiving interfaces, a filter unit, and a controller. The receiving interfaces receive parallel data, such as DVB-ASI (Digital Video Broadcasting-Asynchronous Serial Interface) inputs as channel-by-channel MPEG-2 data. The filter unit counts the respective numbers of data packets and non-data packets of the data input from the receiving interfaces and filters a null packet in the data. A network transmission unit transmits the filtered data to a backbone network. The controller calculates a bit rate based on both of the count numbers received from the filter unit.

Owner:SAMSUNG ELECTRONICS CO LTD

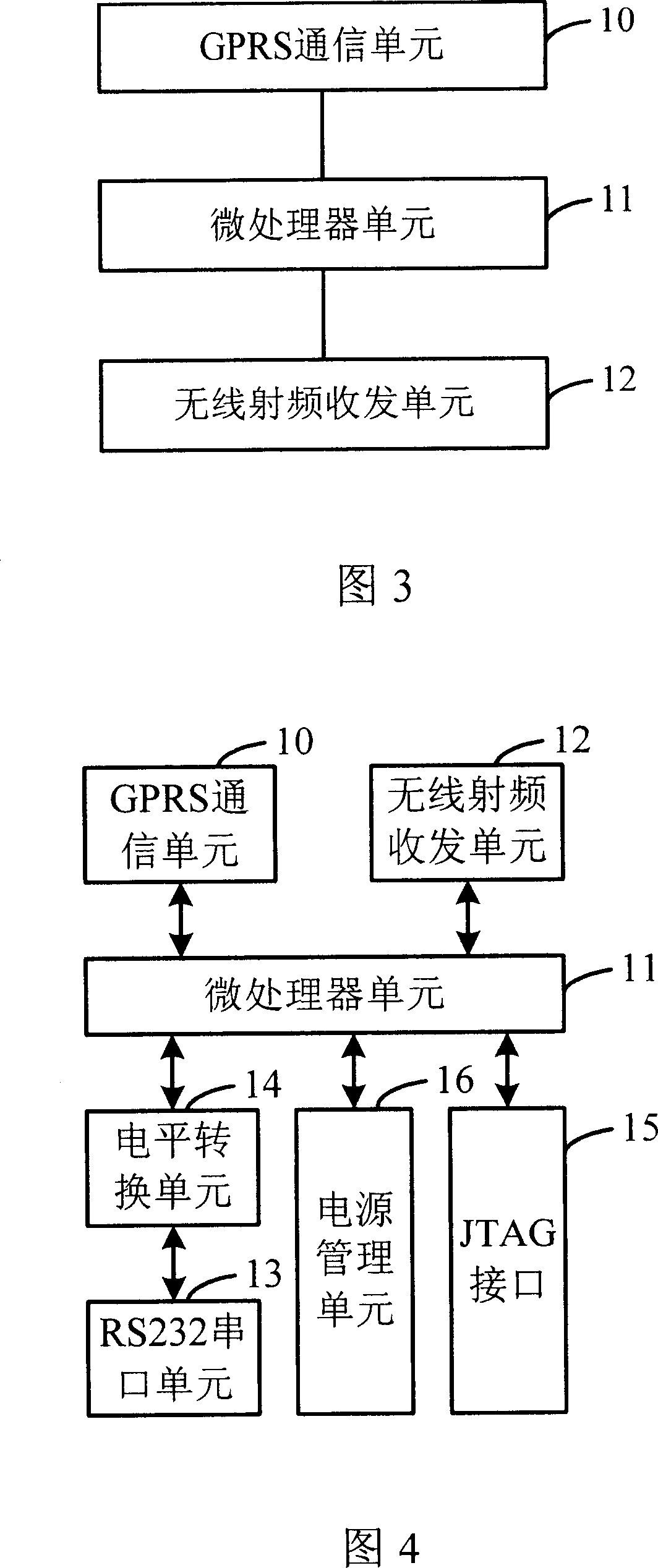

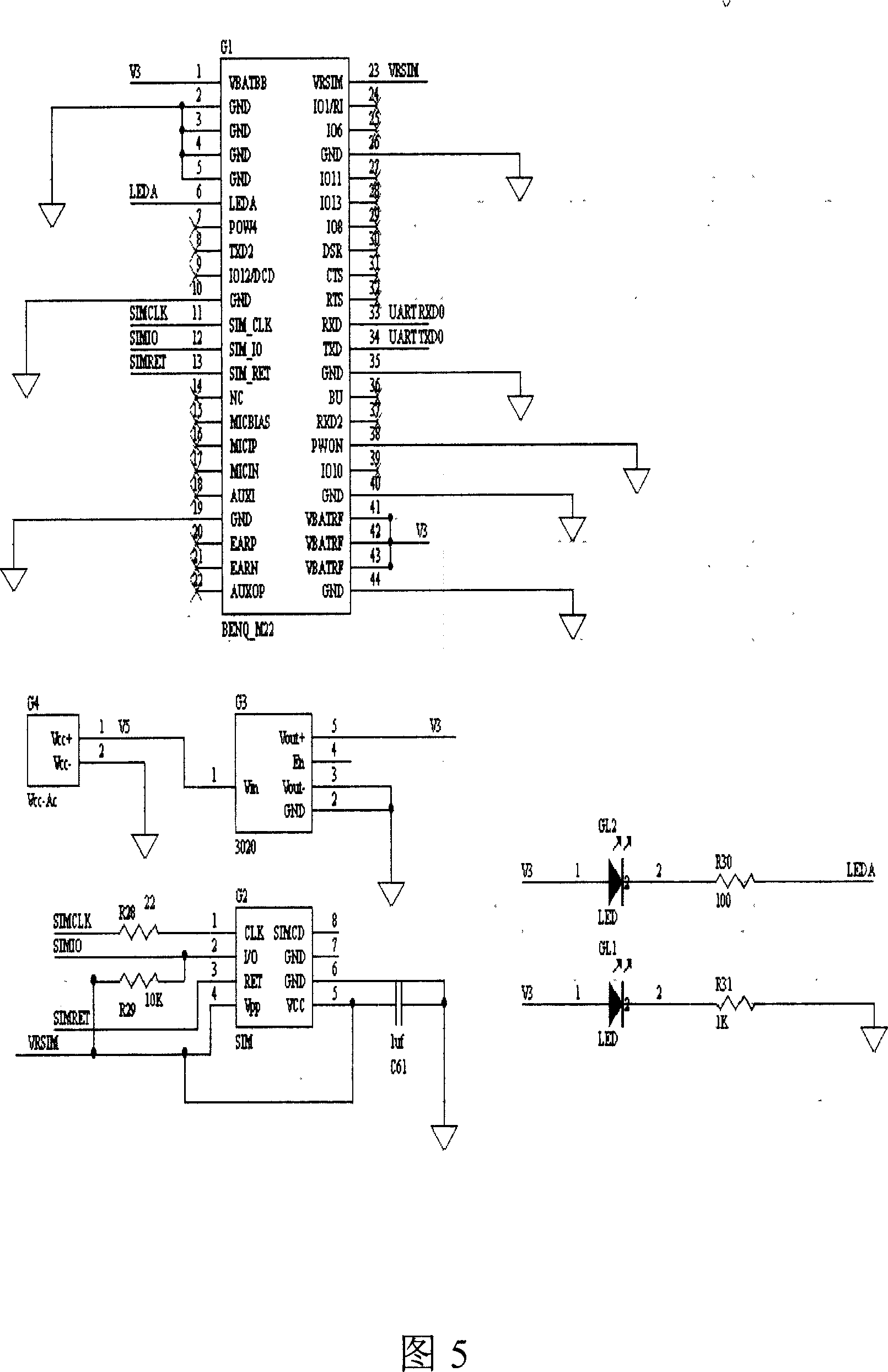

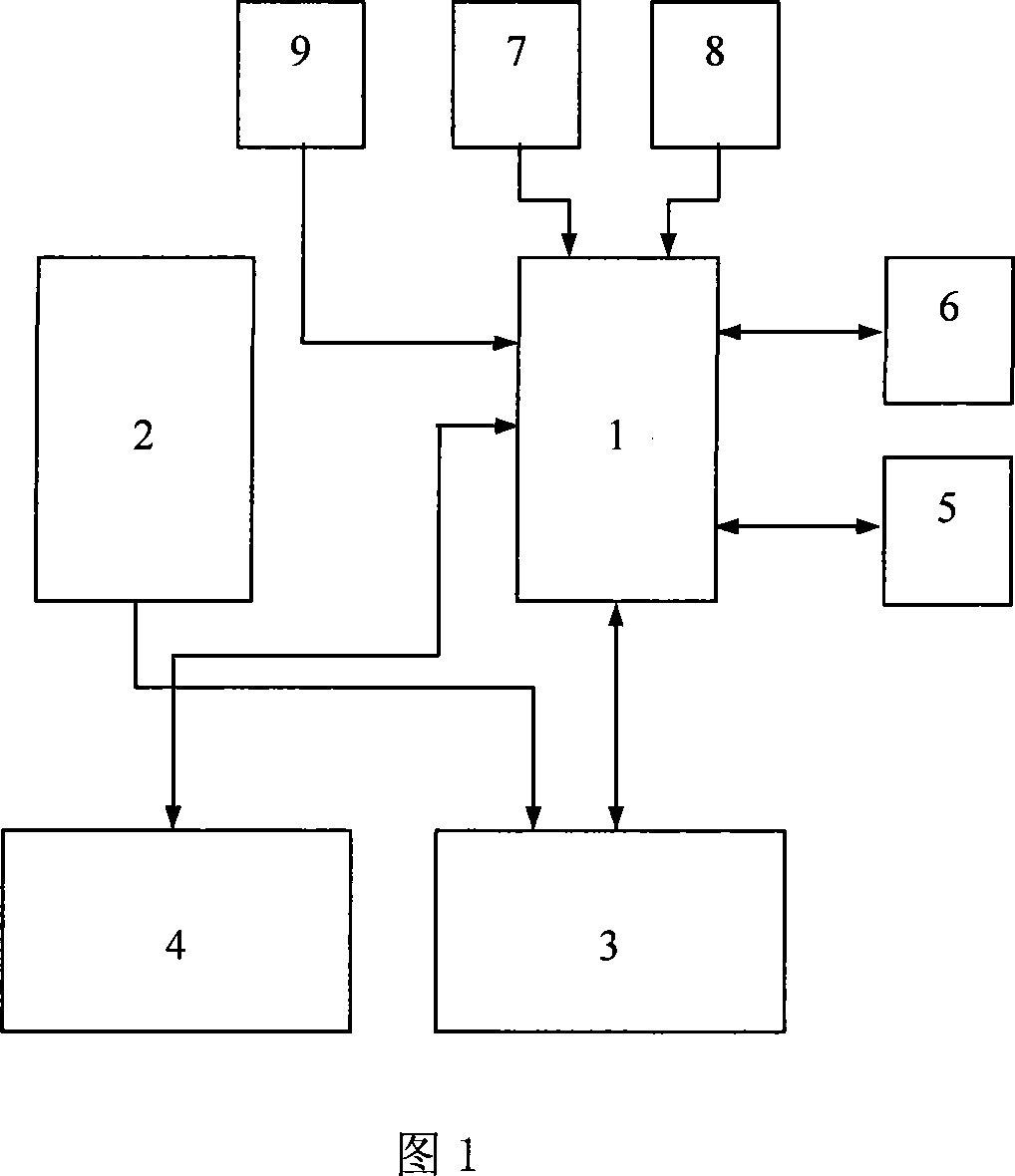

A wireless sensor network gateway device

InactiveCN101009619ALow costReduce power consumptionData switching by path configurationRadio/inductive link selection arrangementsLine sensorTransceiver

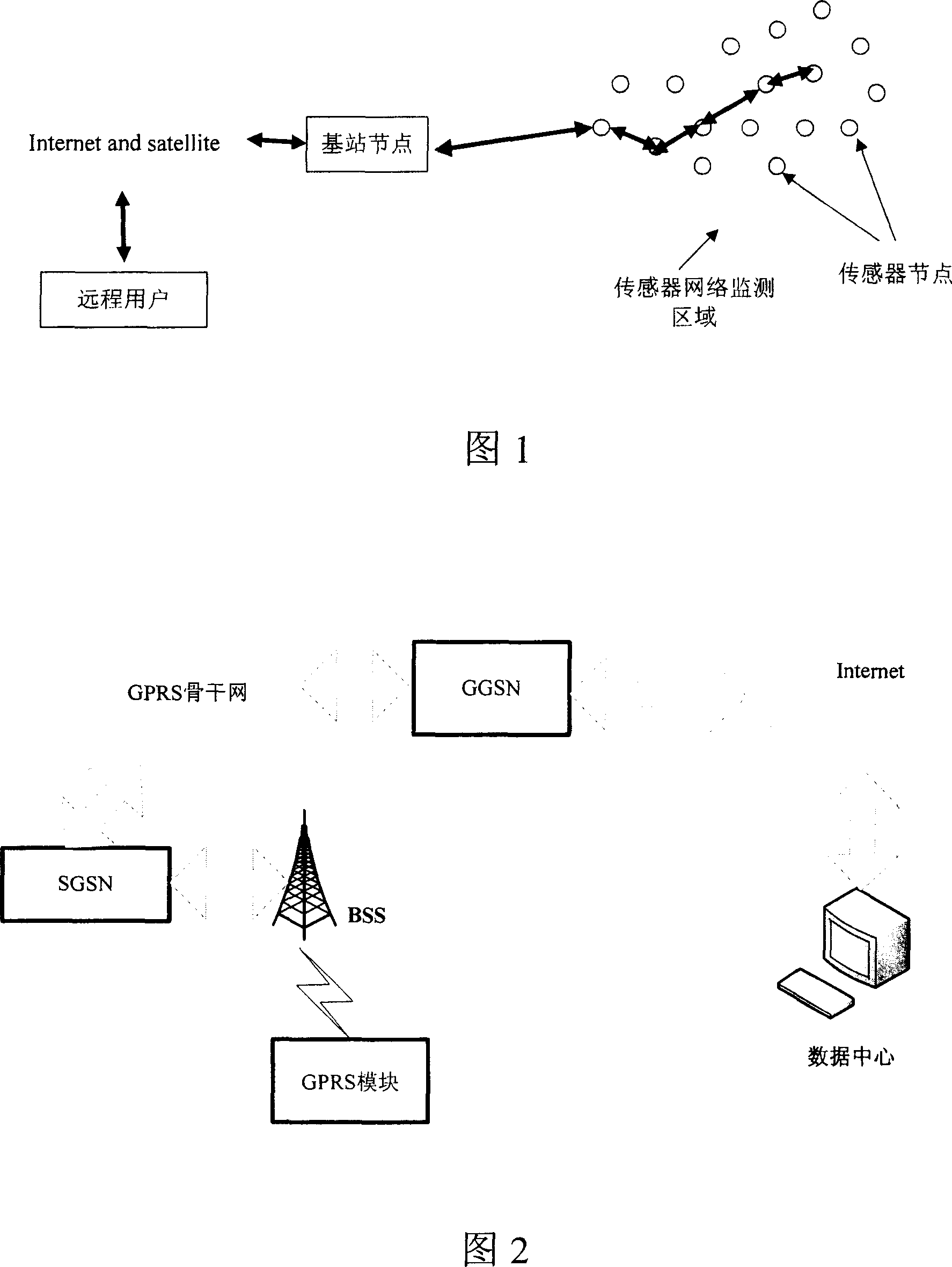

The disclosed gateway device for wireless sensor network comprises: a GPRS communication unit to communicate between the gateway and Internet or wireless communication network, a wireless RF transceiver for gateway and wireless sensor network, and a MPU to control the communication of former two units, wherein the MPU uses UART (general asynchronous serial interface) to communicate with the GPRS unit and SPI (synchronous serial interface) to communicate with the RF transceiver. This invention realizes reliable remote connection and bidirectional transmission for request in real application.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

Serial communications protocols

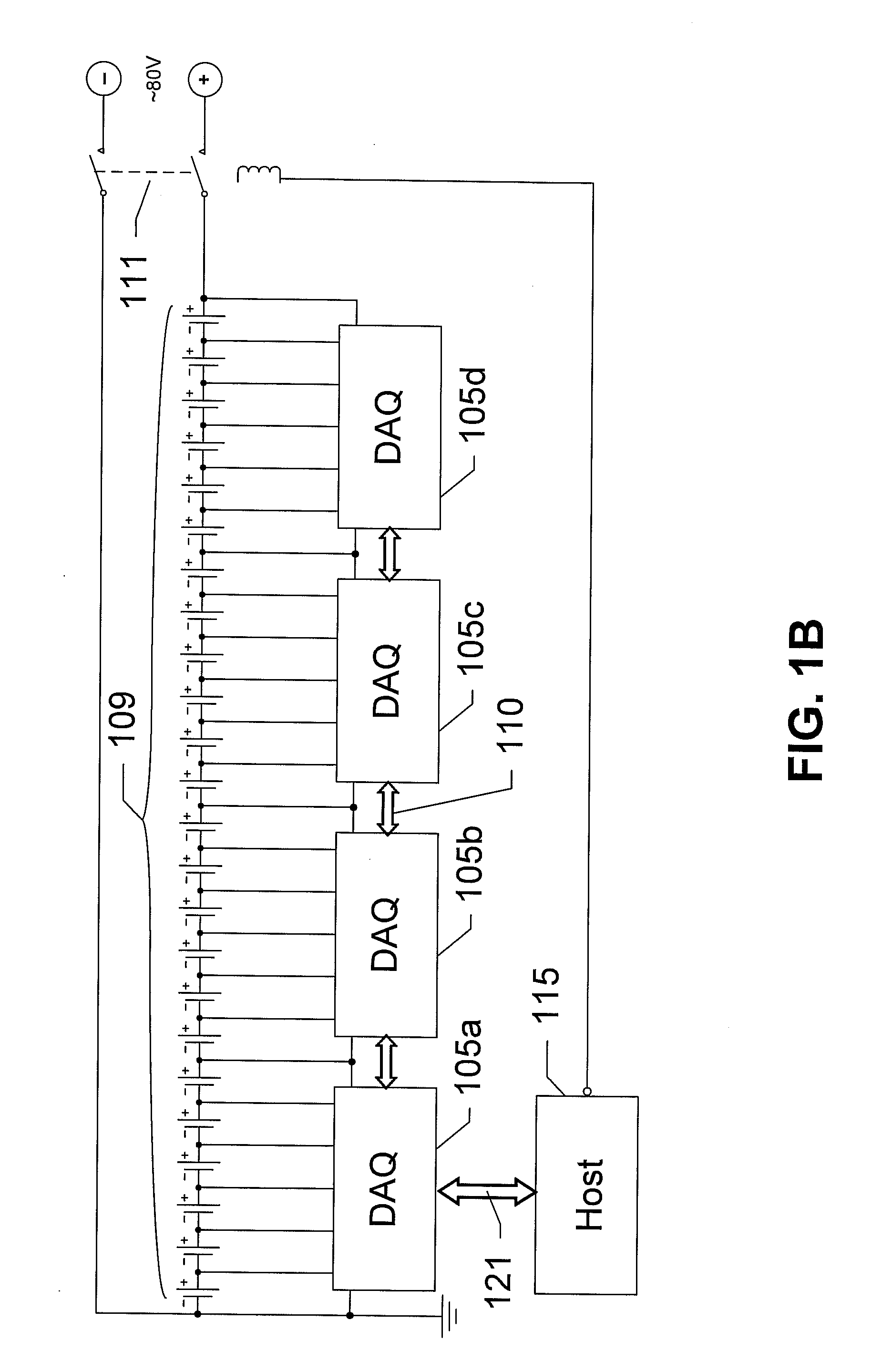

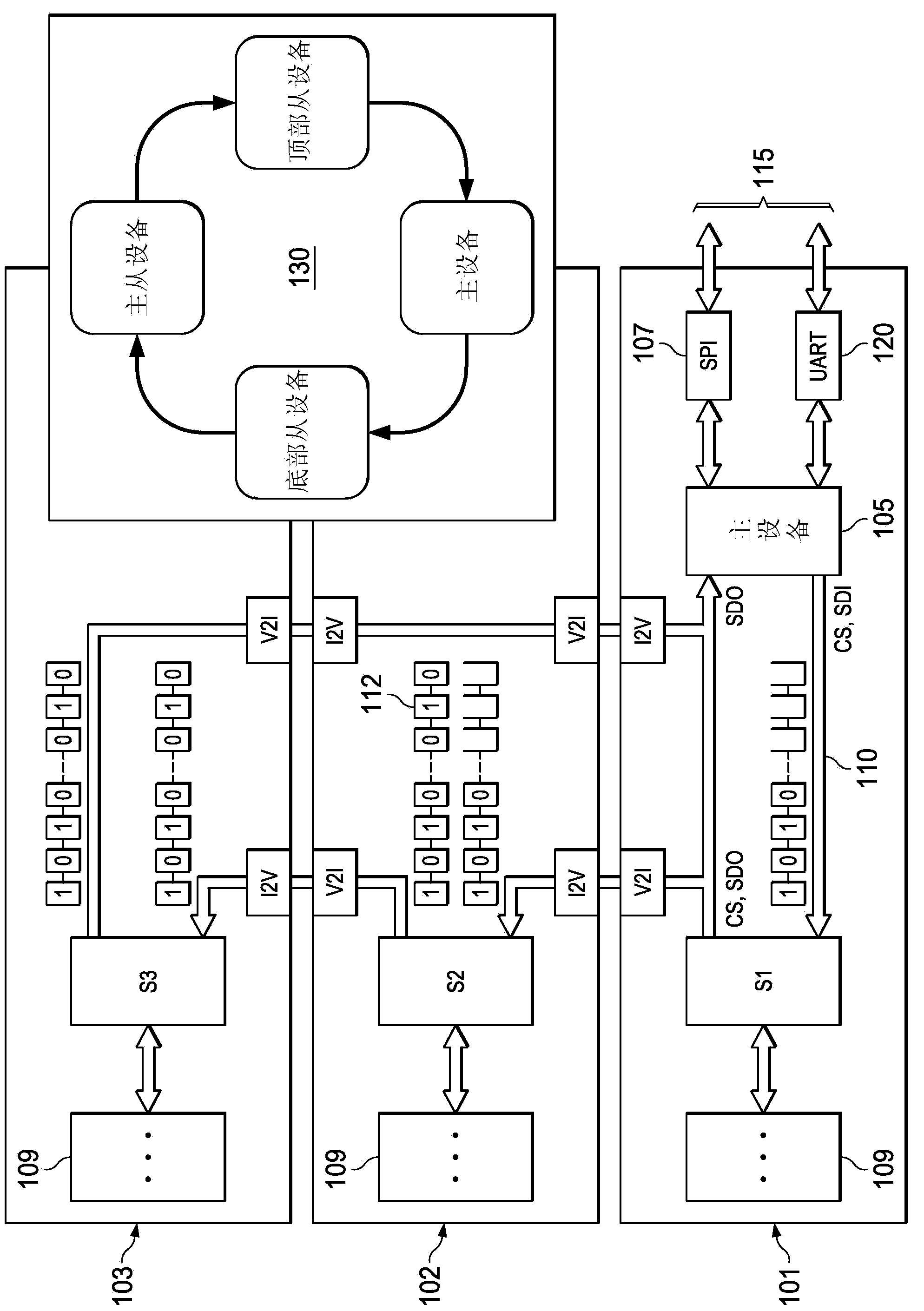

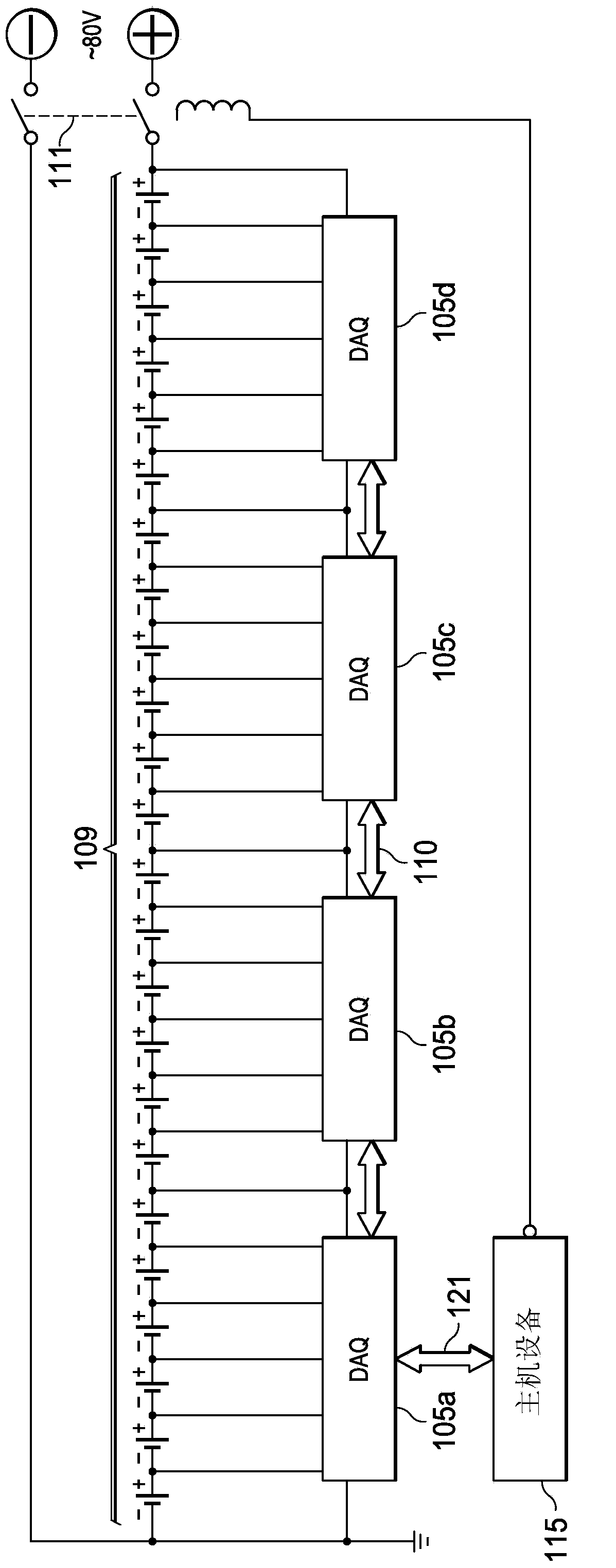

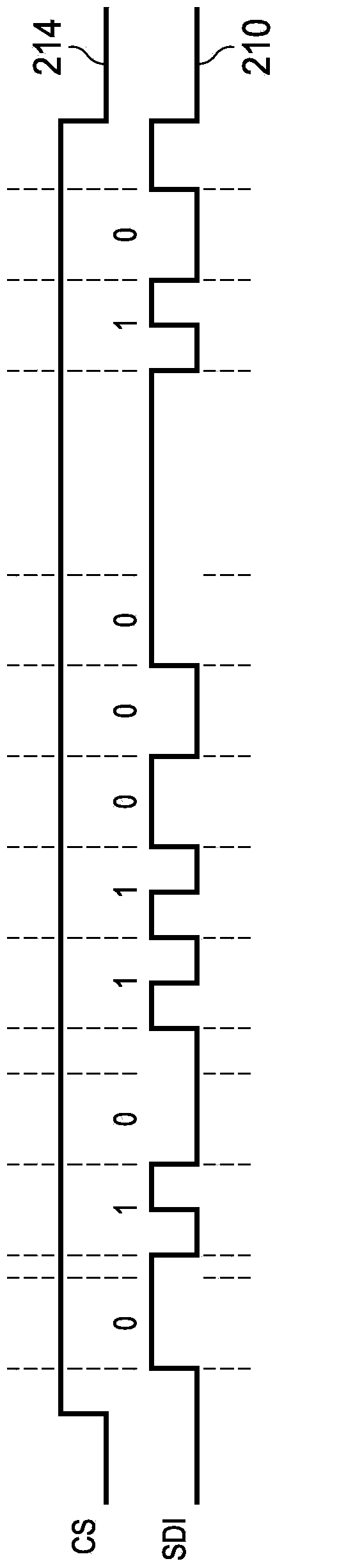

ActiveUS20120297233A1Identical operationIdentical performancePulse automatic controlMultiple digital computer combinationsData streamData acquisition

Systems and methods are disclosed which relate to improving synchronization of clocks between a sender and a receiver communicating via an asynchronous serial interface. In a ring topology, a master device is connected to a plurality of slaves communicating using a bi-frequency encoded bit stream. A host device communicates with the master device using a non-return-to-zero data encoding. Each slave receives data from the master and sends it to the next slave in the ring unaltered unless the master indicates a requirement for a particular data, and transmits placeholder bits with a value of 0 around the ring. A particular slave can “fill-in” the placeholder bits with the information to be sent back to the master by inverting the placeholder bit. Clock synchronization between a receiving device and a transmitting device is improved using a fractional rate multiplier to generate a data sampling clock from a system clock. By adjusting the denominator, the sampling clock can be tuned to match the baud rate of the asynchronous serial data stream received from the transmitting device. Embodiments described include power management, data acquisition (DAQ), etc.

Owner:TEXAS INSTR INC

Road lamp landscape lamp remote monitoring apparatus

InactiveCN101159088AApplicable to the field of remote measurement and controlLow costElectric signal transmission systemsElectric light circuit arrangementComputer moduleAsynchronous serial interface

The invention relates to a signal control device, in particular, a streetlight landscape light remote monitoring device. The working condition of all streetlight sites is polled in real time through the real-time monitoring of a streetlight landscape light remote monitoring terminal based on GPRS technique. When the streetlight sites fail, information about the failure can be rapidly transmitted to the monitoring center and processed as warning; therefore, the failure can be solved. When a telephone cable is cut and stolen, warning can be given to the monitoring center. A main control module, a switching value control detection module and a GPRS module are provided. The main control module is provided with a microprocessor, a power module and a time clock module. The communication terminal of the time clock module is connected with an I / O port. The control terminal of the switching value control detection module is axially connected with the electromagnetic coil terminal of an alternating current contactor. The detection terminal of the switching value control detection module is axially connected with the normally open and normally close contacting point of the alternating current contactor. The communication terminal of the switching value control detection module is connected with the I / O port of the microprocessor. The communication terminal of the GPRS module is connected with an asynchronous serial interface of the microprocessor.

Owner:XIAMEN INGOL DIGITAL TECH

Synchronous and asynchronous switchable serial interface based on FPGA and use method

InactiveCN107451087AImprove stabilityImprove accuracyElectric digital data processingTransceiverProcessor register

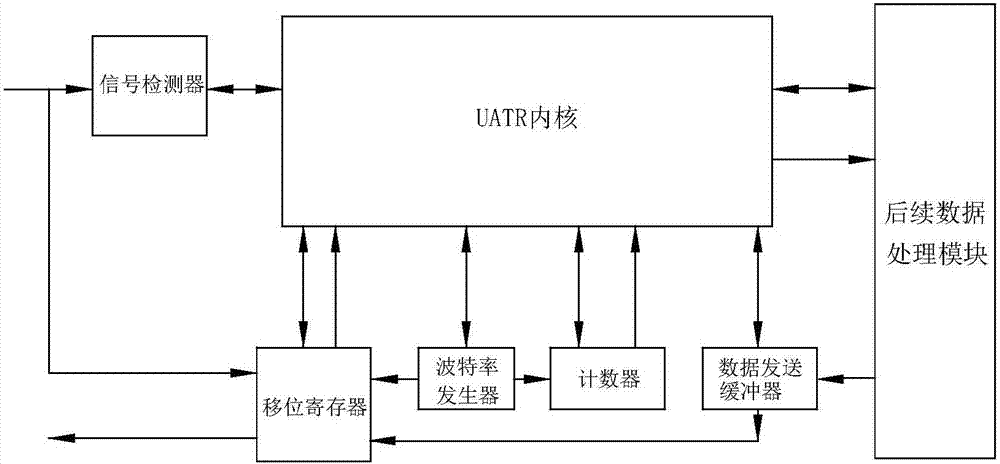

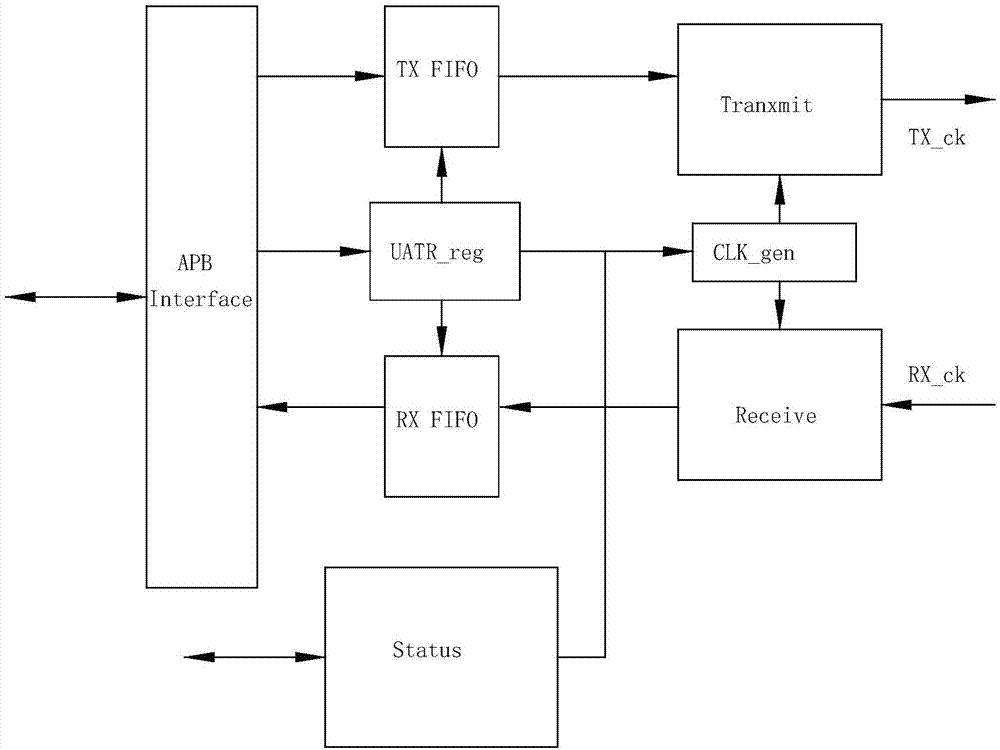

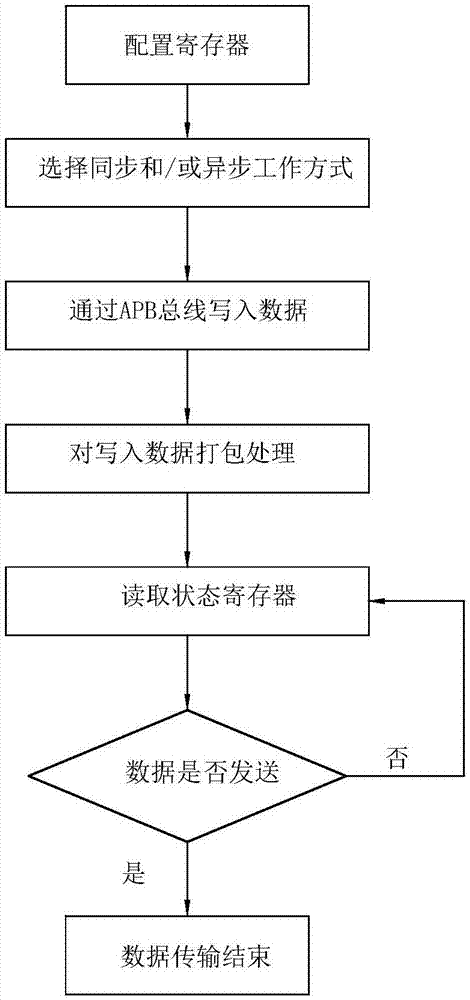

An FPGA-based heterosynchronous switchable serial port and a method of use thereof, the serial port includes a universal asynchronous transceiver, a sending register, and a receiving register, and the universal asynchronous transceiver is mounted on an APB bus for realizing CPU transfer to The universal asynchronous transceiver transmits data, and the described universal asynchronous transceiver is provided with a state detection register, and the sending pin and the receiving pin of the universal asynchronous transceiver are respectively connected to the control end of the sending module FIFO and the receiving module FIFO, and the universal asynchronous transceiver The clock module of the register and the field programmable gate array is connected, and the serial port can be set to synchronous mode or asynchronous mode through the register of the asynchronous transceiver, and the input end of the receiving module FIFO and the output end of the sending module FIFO are respectively connected The receiving module and the sending module, the clock module of the field programmable gate array are respectively connected with the control ends of the receiving channel and the sending channel. The invention supports two interface forms of synchronous serial port and asynchronous serial port, and is compatible with the UART protocol. In the asynchronous serial port mode, the frequency division precision is improved, the bit error rate is reduced, and the stability and accuracy of data are obviously improved.

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

Blue tooth multifunctional remote controller device and method for implementing voice communication

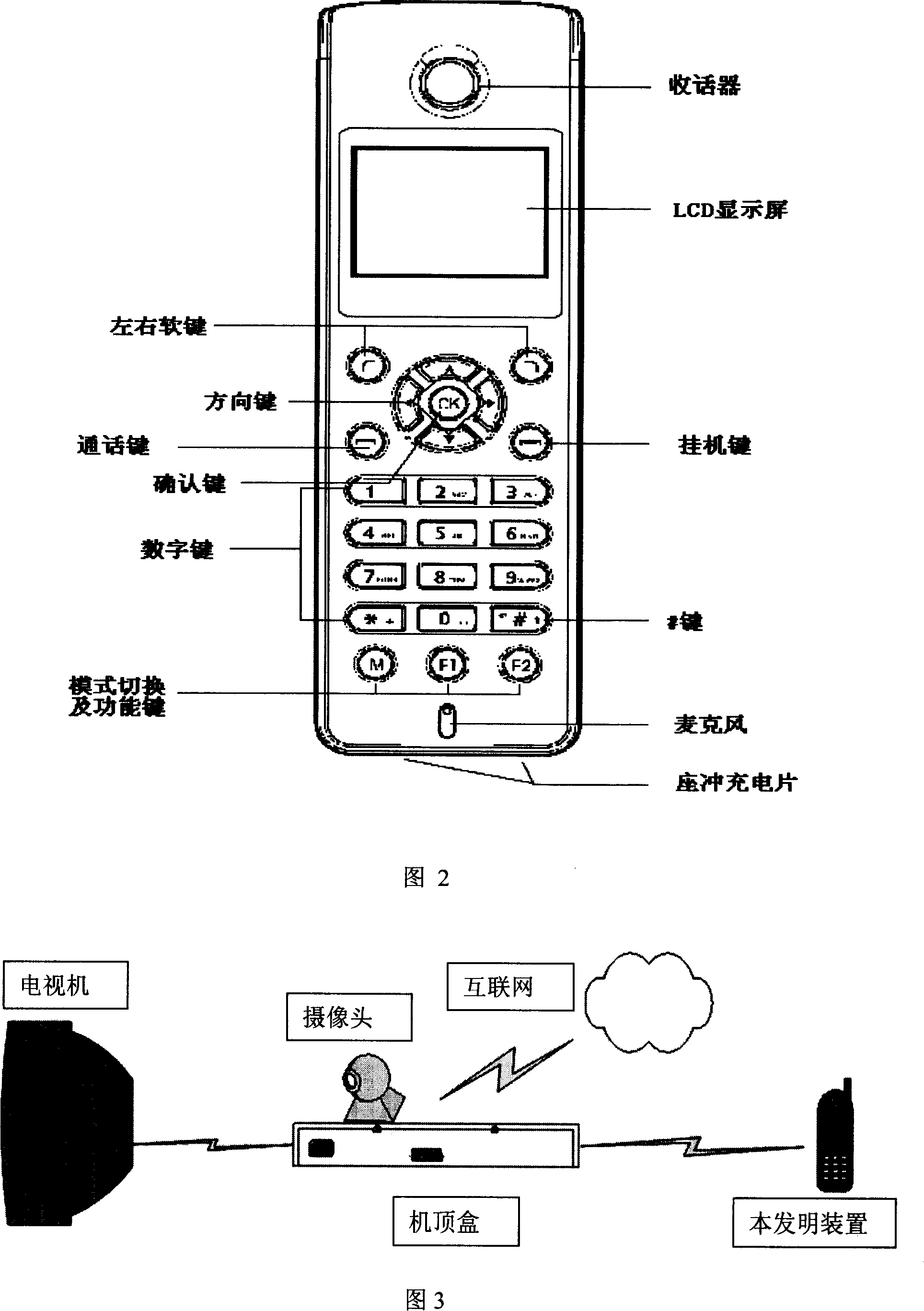

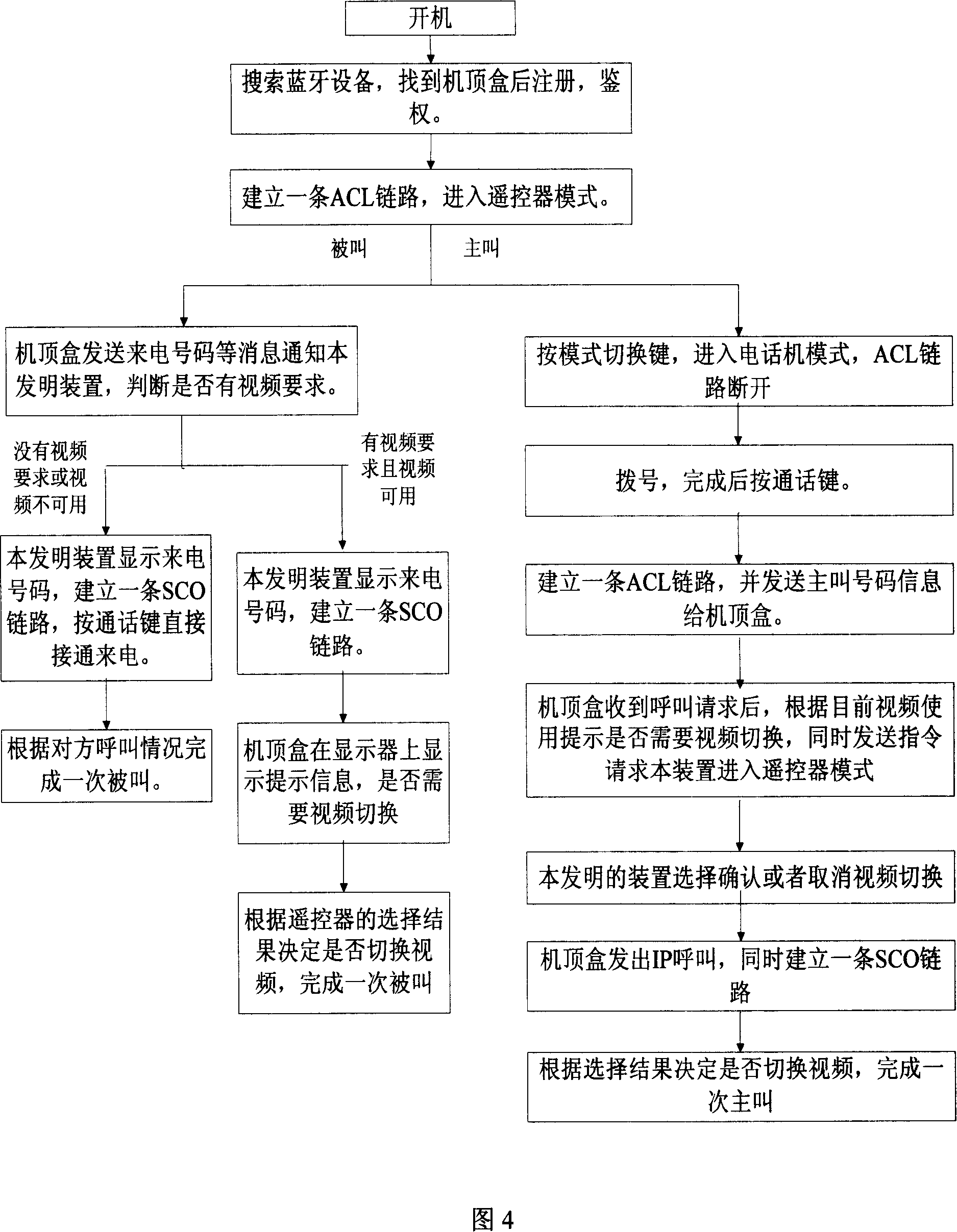

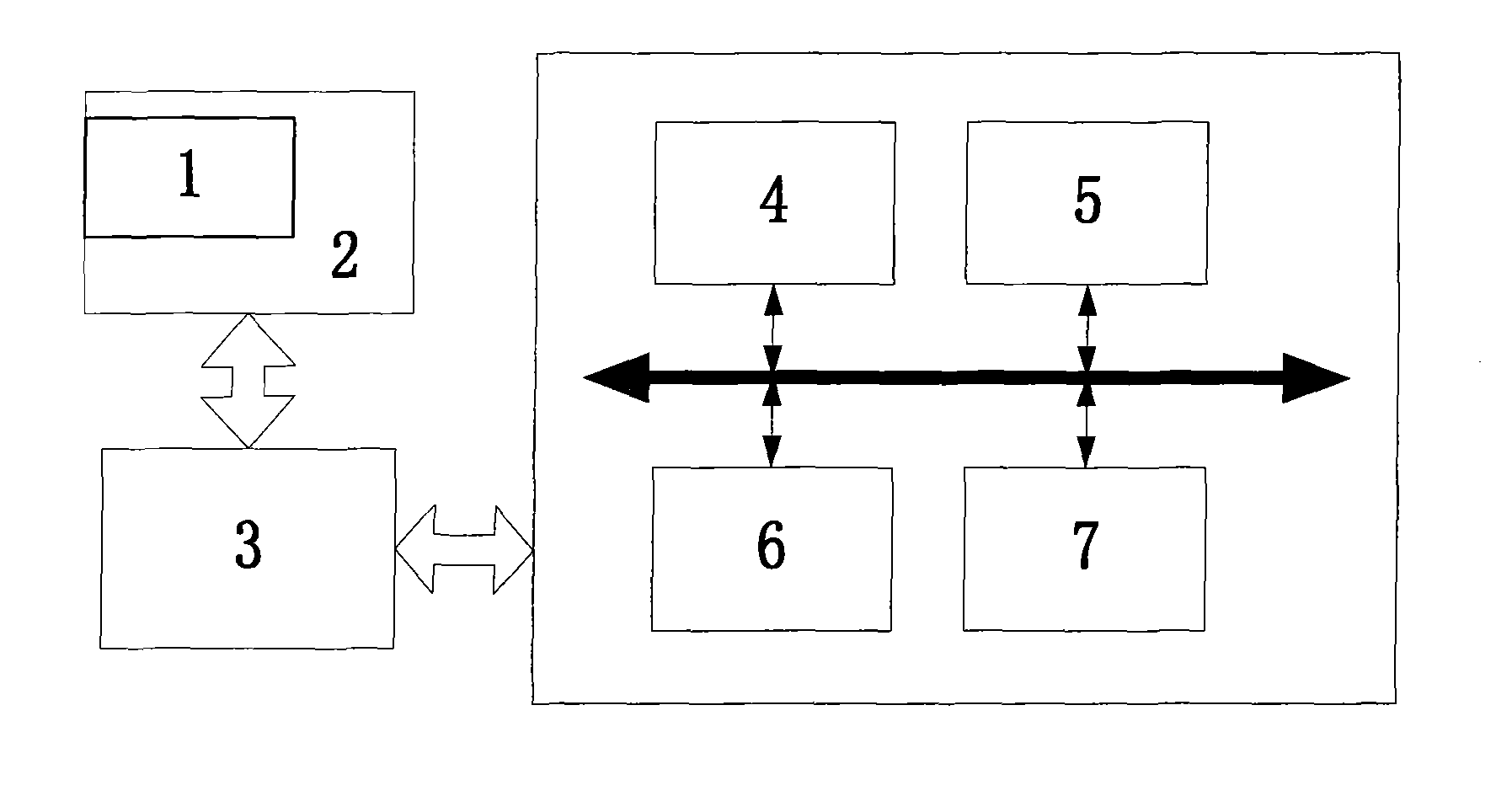

ActiveCN101132456AIncrease remote control distanceStrong penetrating powerTransmission systemsTelephonic communicationVoice communicationBluetooth

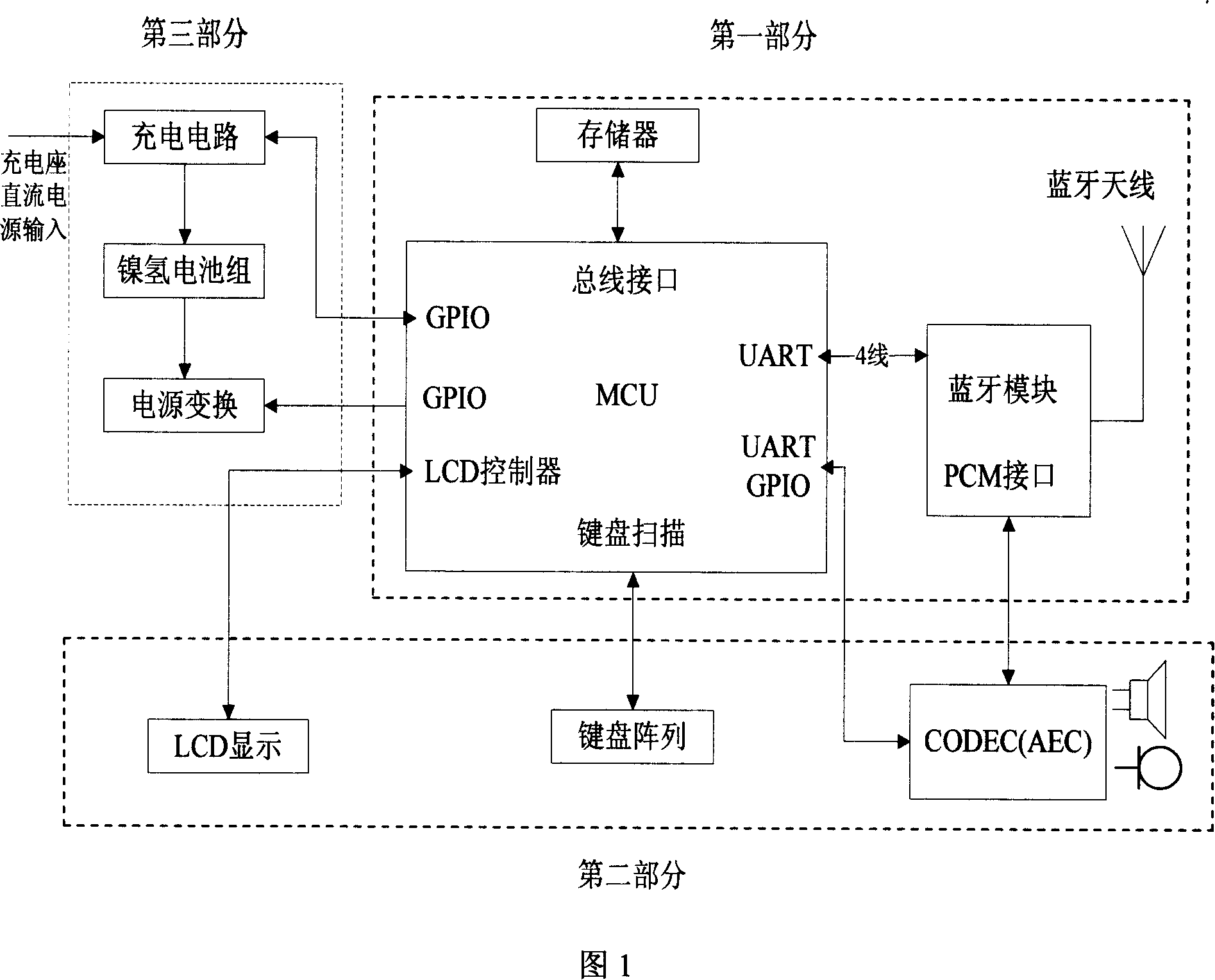

This invention discloses a blue-tooth multifunction remote controller and a method for realizing phone communication including: a blue-tooth module used in finishing RF T-R and its low baseband protocol process and providing control interfaces of a standard host computer and a processor module for finishing protocol stack process of middle and upper layers and the control of the whole system, in which, the processor module includes: a multi-point control unit, a 2-line asynchroinous serial interface, a 4-line asynchronous serial interface and at least one GPIO interface, and the blue-tooth module is connected with the multi-point control unit of the processor module via the 4-line asynchronous serial interface or the 2-line USB interface to further realize phone communication with the device and a set-top box.

Owner:ZTE CORP

Method for debugging 8051 core-based system on chip (SOC) on line

InactiveCN101963934AResolve mismatchShorten the timeDetecting faulty computer hardwareFault toleranceSerial line

The invention relates to a method for debugging an 8051 core-based system on chip (SOC) on line, and belongs to the technical field of integrated circuit design. On-line debugging software on a personal computer (PC) finishes communication with an asynchronous serial interface in the SOC through a serial line so as to realize on-line debugging. The system comprises the on-line debugging software on the PC, an RS232 conversion circuit and the 8051 core-based SOC. The method realizes the 51 instruction analysis, breakpoint processing, operation processing and content debugging of the SOC. Software codes are debugged on line by a few data lines after the mass production of chips is realized, so that the debugging work of the system is greatly simplified, the debugging time is shortened, the function optimization of the system is facilitated and the fault tolerance of the system is enhanced. Meanwhile, the scheme is simple and reliable, avoids using a logic analyzer and automatic test equipment to cause high cost, and can be applied to various SOCs taking an 8051 core as a control core.

Owner:SHANDONG UNIV

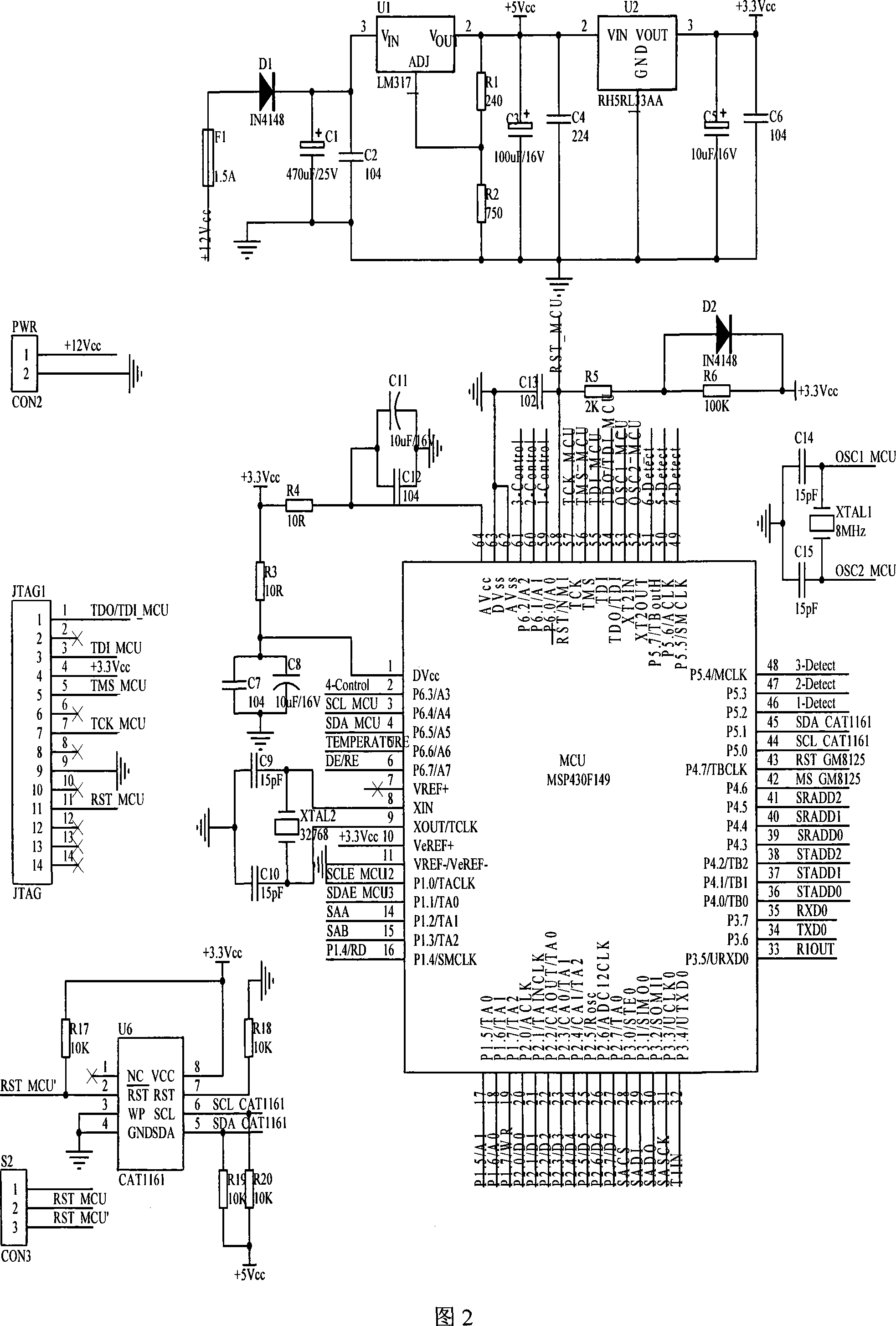

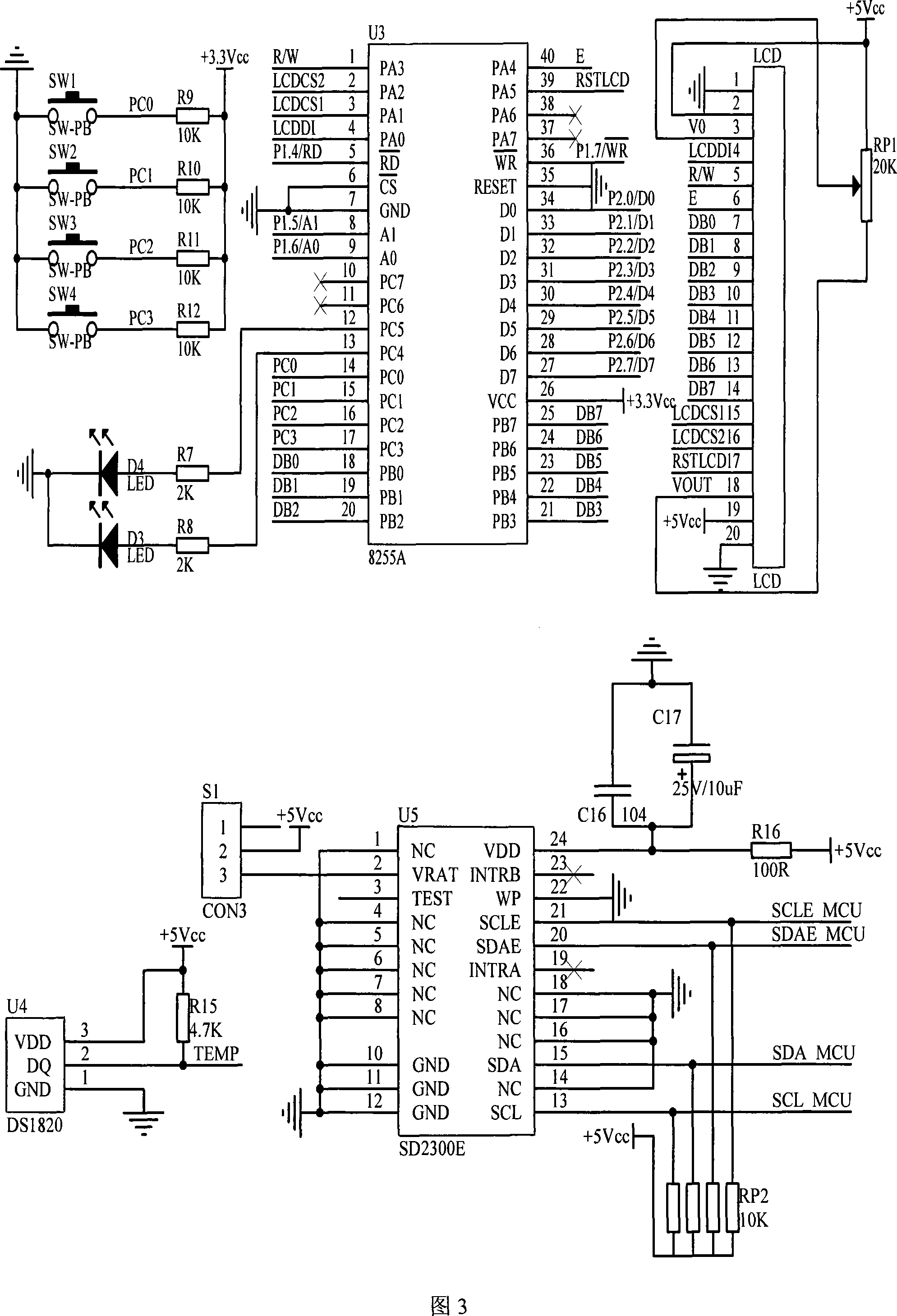

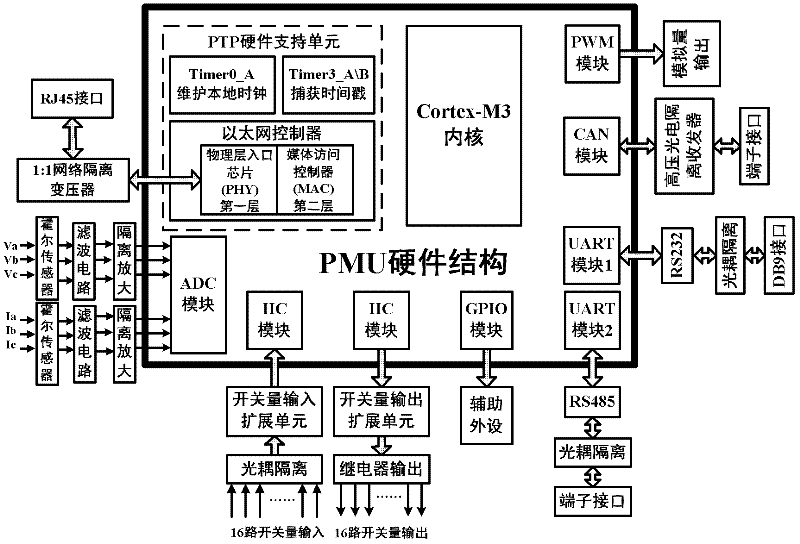

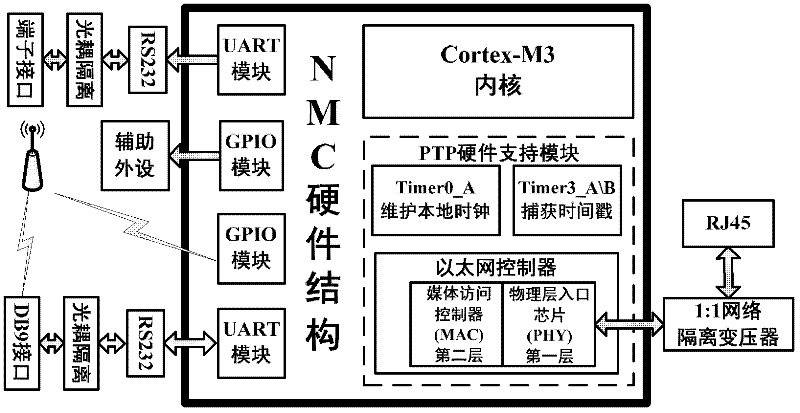

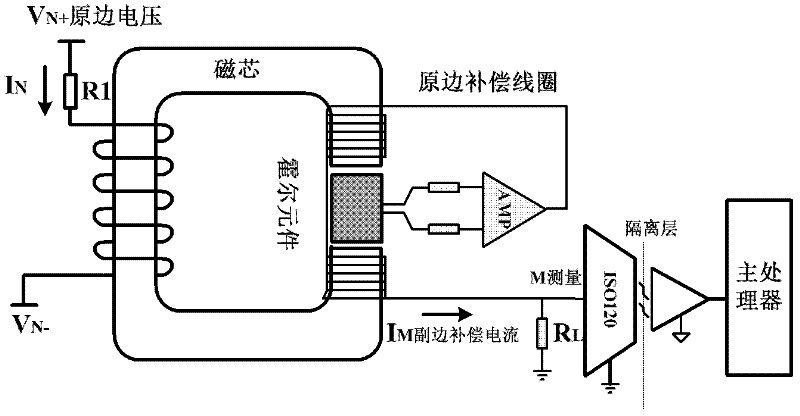

Synchronous phasor measuring device of ship electrical power system

InactiveCN102539916AGuaranteed uptimeRealize dynamic monitoring and analysisVoltage-current phase angleTransient analysisMeasurement point

The invention discloses a synchronous phasor measuring device of a ship electrical power system; the synchronous phasor measuring device comprises a processor, an analog-to-digital conversion module, a IIC extension switching value input module, a IIC extension switching value output module, a local area network controller module, a pulse width modulation module, a first asynchronous serial interface UART (Universal Asynchronous Receiver / Transmitter) module and a second asynchronous serial interface UART module and an Ethernet control module; the voltage and the magnitude-of-current of a measuring point of the ship electrical power system or the switching value of a relay or breaker of the electric power system are calculated and logically judged through the processor, then are respectively output through the IIC extension switching value output module and the pulse width modulation (PWM) module and finally are transmitted through the first asynchronous serial interface UART module, the second asynchronous serial interface UART module, the local area network controller module and / or the Ethernet control module. The synchronous phasor measuring device has the functions of dynamic measurement and transient measurement on the electric power system, can be used for carrying out transient analysis and dynamic monitoring on the ship electrical power system and simultaneously has the functions of onsite UART debugging and firmware upgrading of remote equipment by using an Ethernet RJ450 interface.

Owner:NAVAL UNIV OF ENG PLA

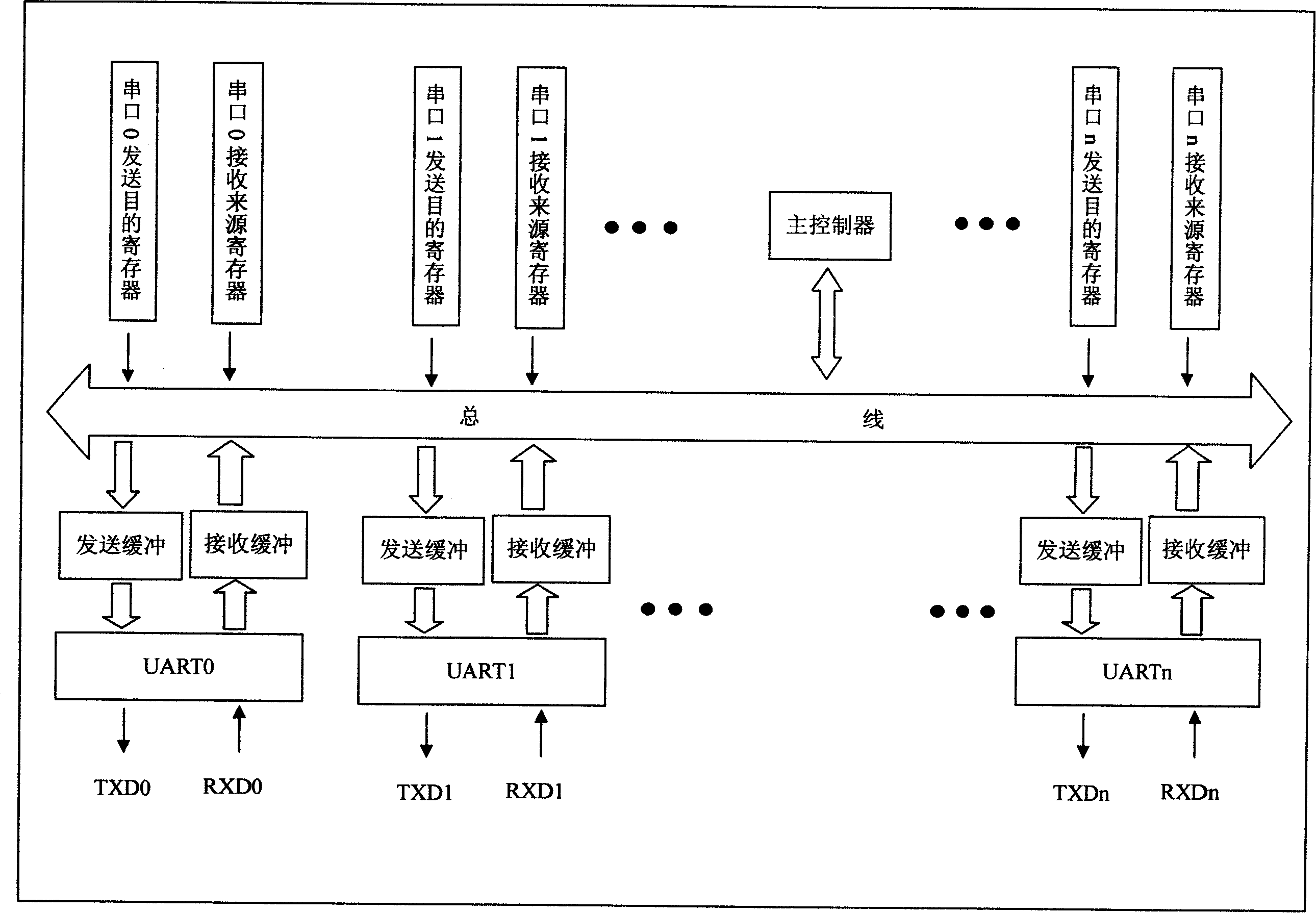

Asynchronous serial communication control device

InactiveCN101122894AEasy to useExpand the range of selectionElectric digital data processingAsynchronous serial communicationProcessor register

The present invention discloses an asynchronous serial communication controller, which includes over three asynchronous serial communication controller internal control logics, a sending port, a receiving port, a sending objective register and a receiving source register, which correspond with each asynchronous serial controller, and a main controller. The main controller processes the information frames, which are received from each asynchronous serial port, judges whether the information frame type is instruction frame or data frame and processes the information correspondingly. If the information frame is an instruction frame, the main controller operates on a relative register according to the contents of the instruction frame. If the information frame is a data frame, the main controller sends the data frame contents at a set data format and rate from the set serial port according to contents of relative registers. The present invention has the following advantages that the present invention supports several asynchronous serial interfaces to communicate directly and mutually at a high speed, improves system efficiency and is easy to use.

Owner:朱金怀

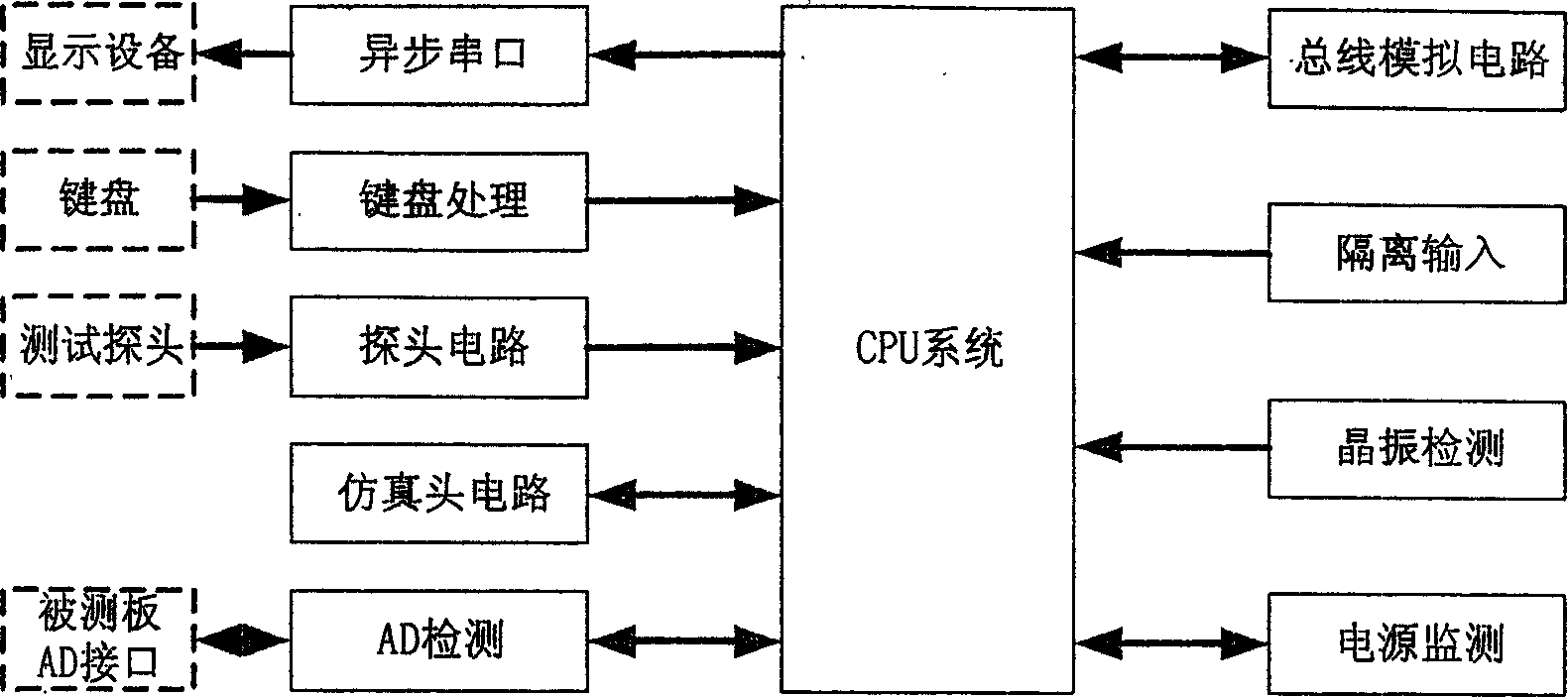

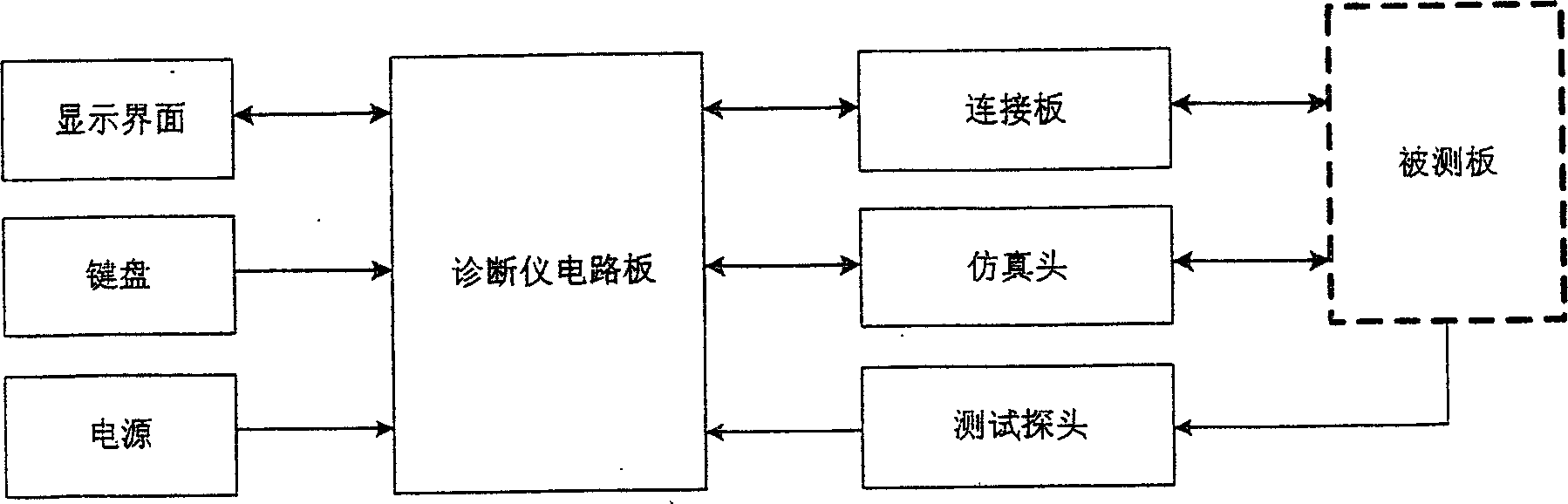

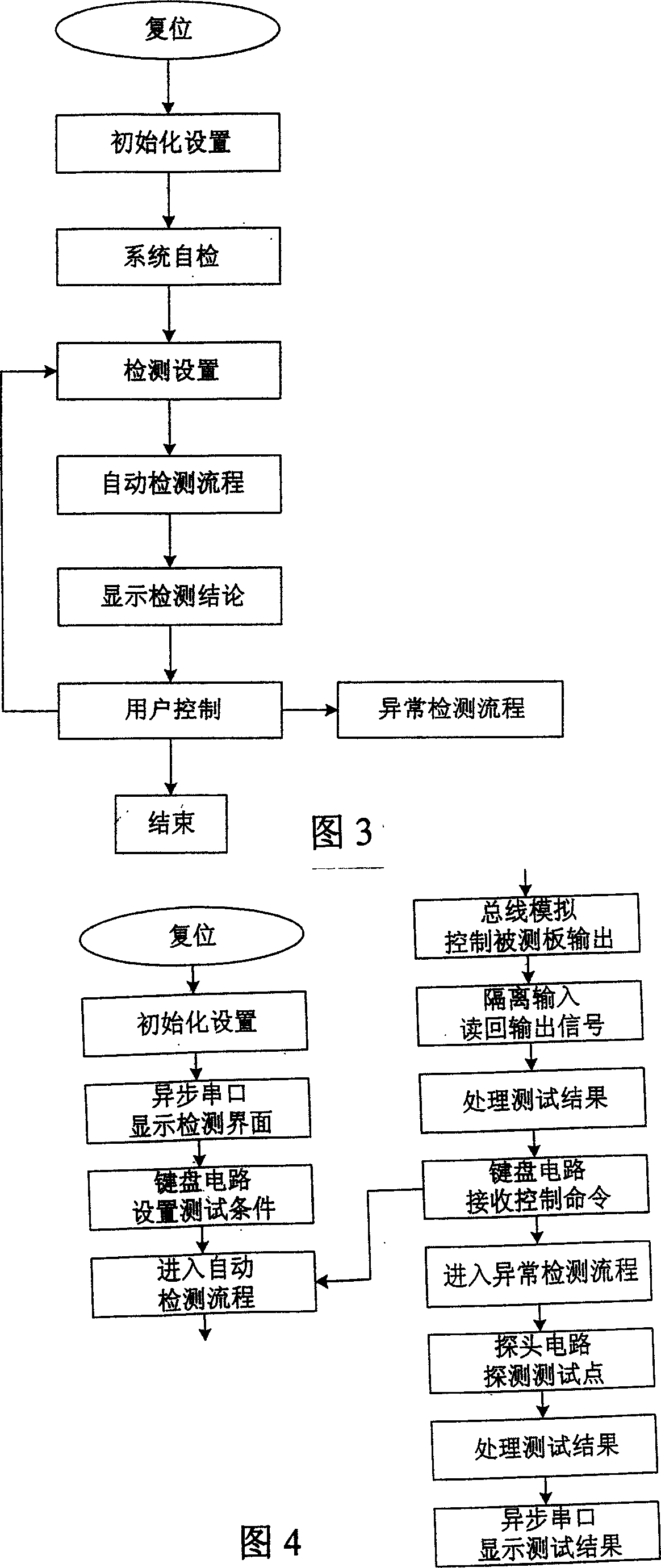

Locomotive signal failure diagnostic instrument

InactiveCN1528630ASimple and fast operationEasy to useRailway signalling and safetyFrequency counterProcedural approach

The invention relates to a locomotive signal failure diagnosis apparatus, its CPU system composed of CPU, memory, reset circuit, crystal vibration circuit and bus drive circuit. It is composed by its CPU system linked with the following modules: asynchronous serial interface module, keyboard processing module, simulation head module, A / D detecting module linked to A / D interface of the tested board, bus analog circuit module, isolating input module adopting photoelectric coupled circuit, crystal detecting module composed of testing control, data register and frequency counter, and power supply monitoring module as well as probe circuit module which is linked with a testing probe. Its operation is simple and convenient, and its detecting result is intuitionistic. It controls the tested board working by the program, so able to quickly obtain plenty of overall testing data, which cooperates with the testing pen, further determining the failure point.

Owner:BEIJING JIAOTONG UNIV

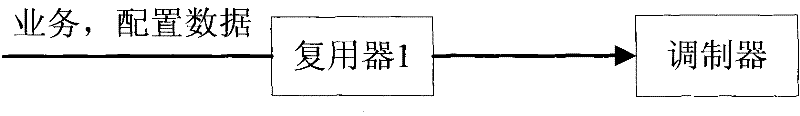

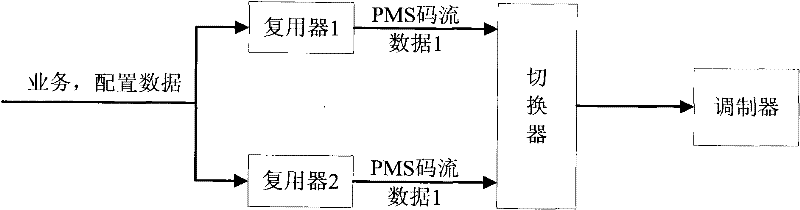

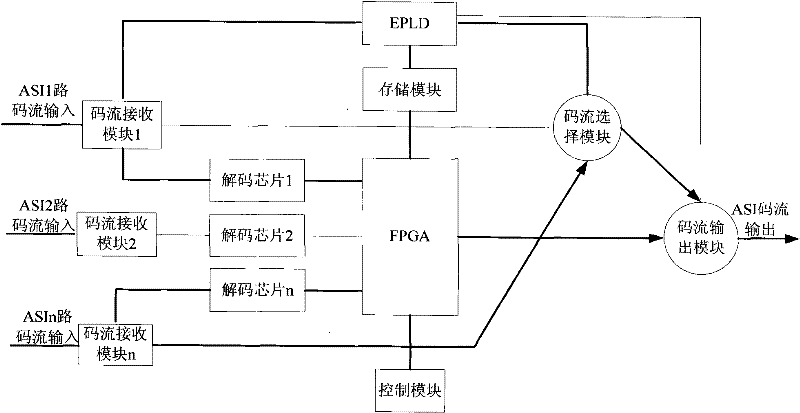

A switcher and method for selecting and outputting multiple signals

ActiveCN102300120AImprove stabilityImprove experienceSelective content distributionCustomer requirementsAsynchronous serial interface

The invention provides a switch and method for selectively outputting multiple signals. The method comprises the following steps of: making the switch receive multiple asynchronous serial interface (ASI) code streams; when the switch works in the field programmable gate array (FPGA) routing path mode, performing signal analysis on each received code stream; and outputting one of the ASI code streams serving as an output code stream to a modulator according to a preset rule. Due to the adoption of the technical scheme of the invention, the multiple received ASI code streams can be subjected to signal analysis, an ASI code stream with a better signal is selected for outputting, and the stability and user experience of a mobile multimedia broadcast system are improved; and a user-configurable switching strategy interface is provided, so that the user can combine a switching strategy which can meet the customer requirement to the maximum extent according to the practical service environment of the equipment.

Owner:ZTE CORP

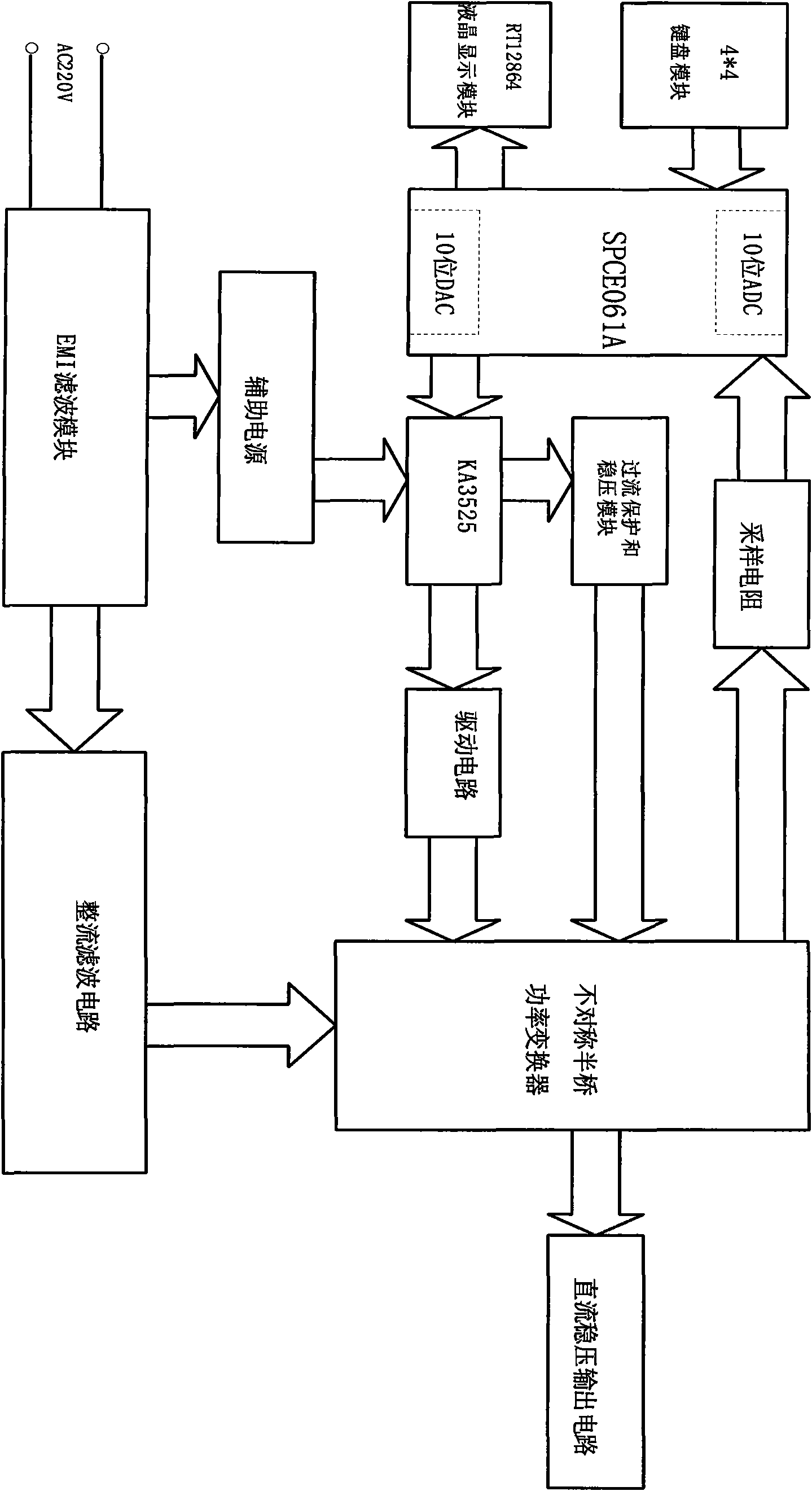

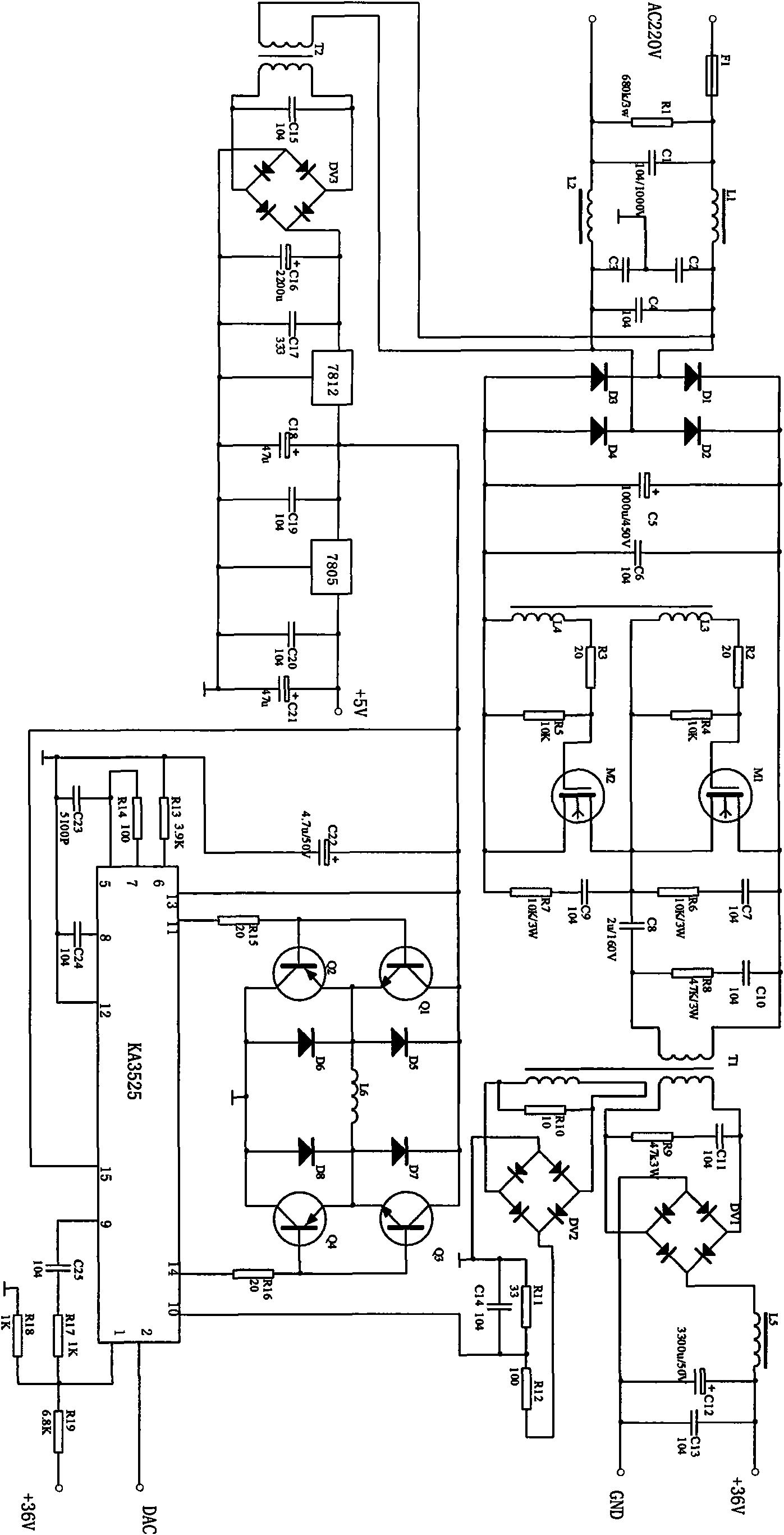

Design of singlechip-controlled switch power

InactiveCN101567637AMeet the needs of higher performance requirementsEasy to operateAc-dc conversionDc-dc conversionMicrocontrollerLow voltage

The invention discloses a design of singlechip-controlled switch power, which is characterized by comprising a numerical control switch power formation system of a singlechip and a numerical control system of a Sunplus singlechip switch power. The switch power formation system consists of an EML filter network, a rectifying filter circuit, a power converting circuit, a driving circuit, an output circuit, a voltage stabilizing circuit, an over-current protecting circuit and an auxiliary power circuit. The numerical control system of the switch power is controlled by an SPCE061A singlechip of Sunplus Company, the SPCE061A singlechip mainly comprises an input / output port, a timer / a counter, a D / A conversion, an A / D conversion, serial apparatus input output, a universal asynchronous serial interface, low voltage monitoring, reset, and the like. The invention has stable output voltage, high accuracy, wide adjustment range, high conversion efficiency and small power consumption and ripple current, thereby satisfying higher requirements on power source performance in laboratory and in life.

Owner:陈清尧

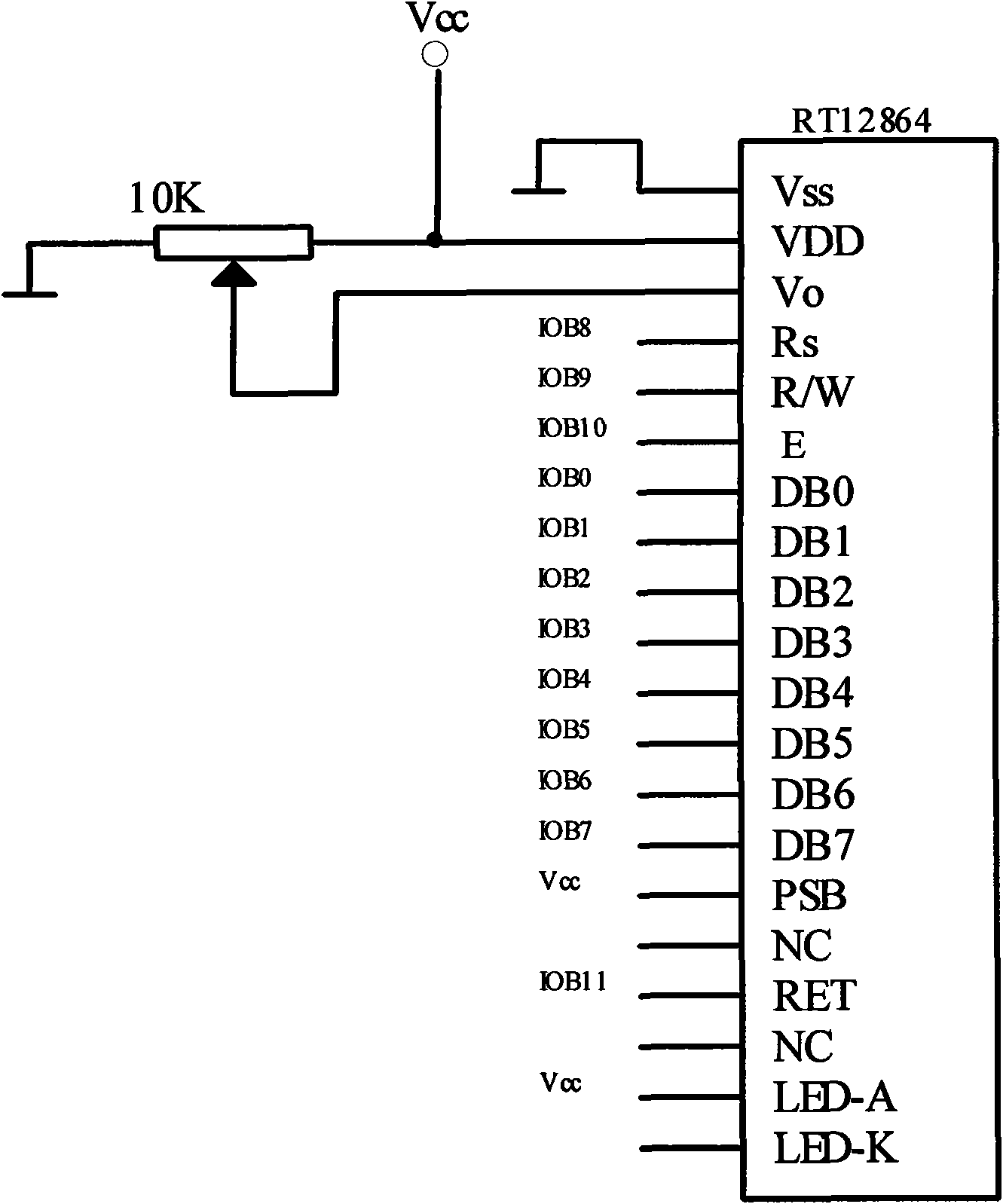

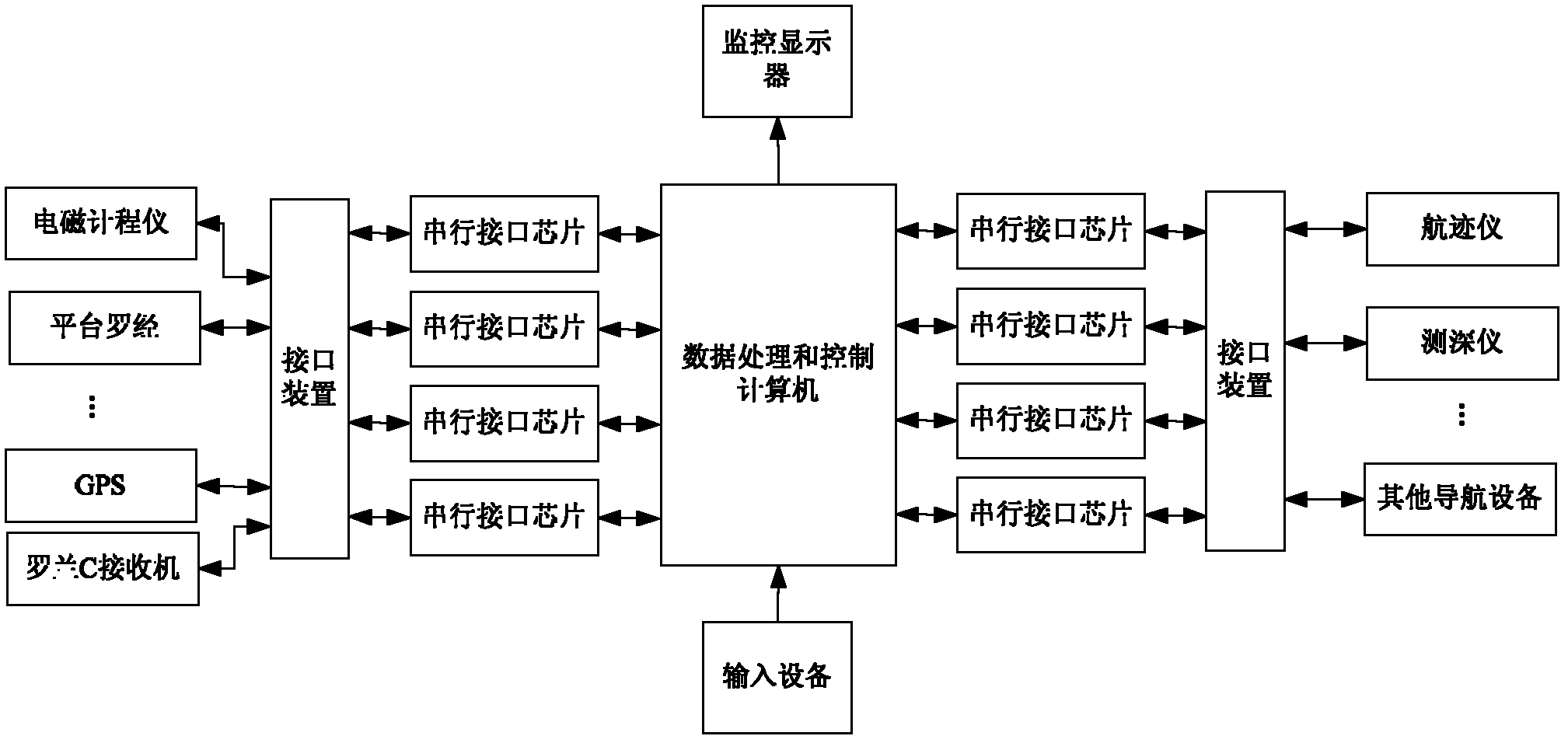

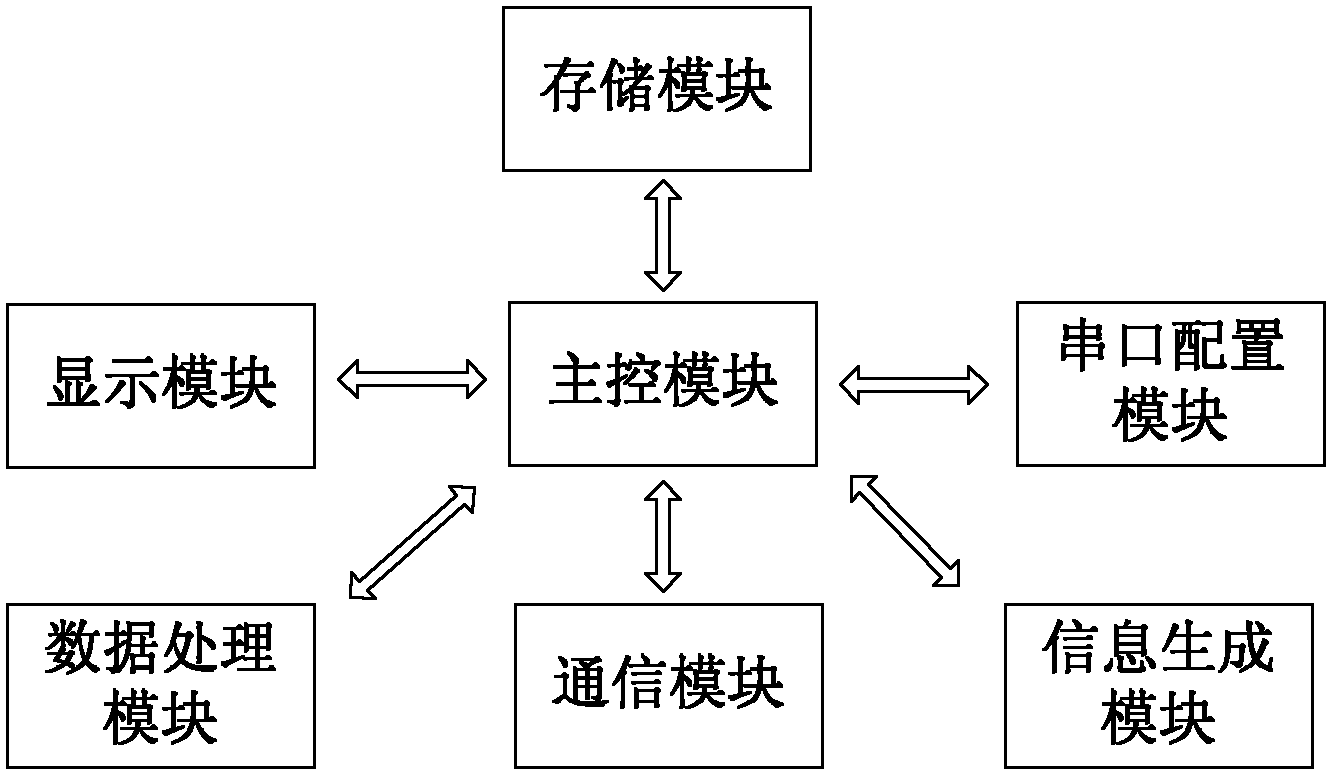

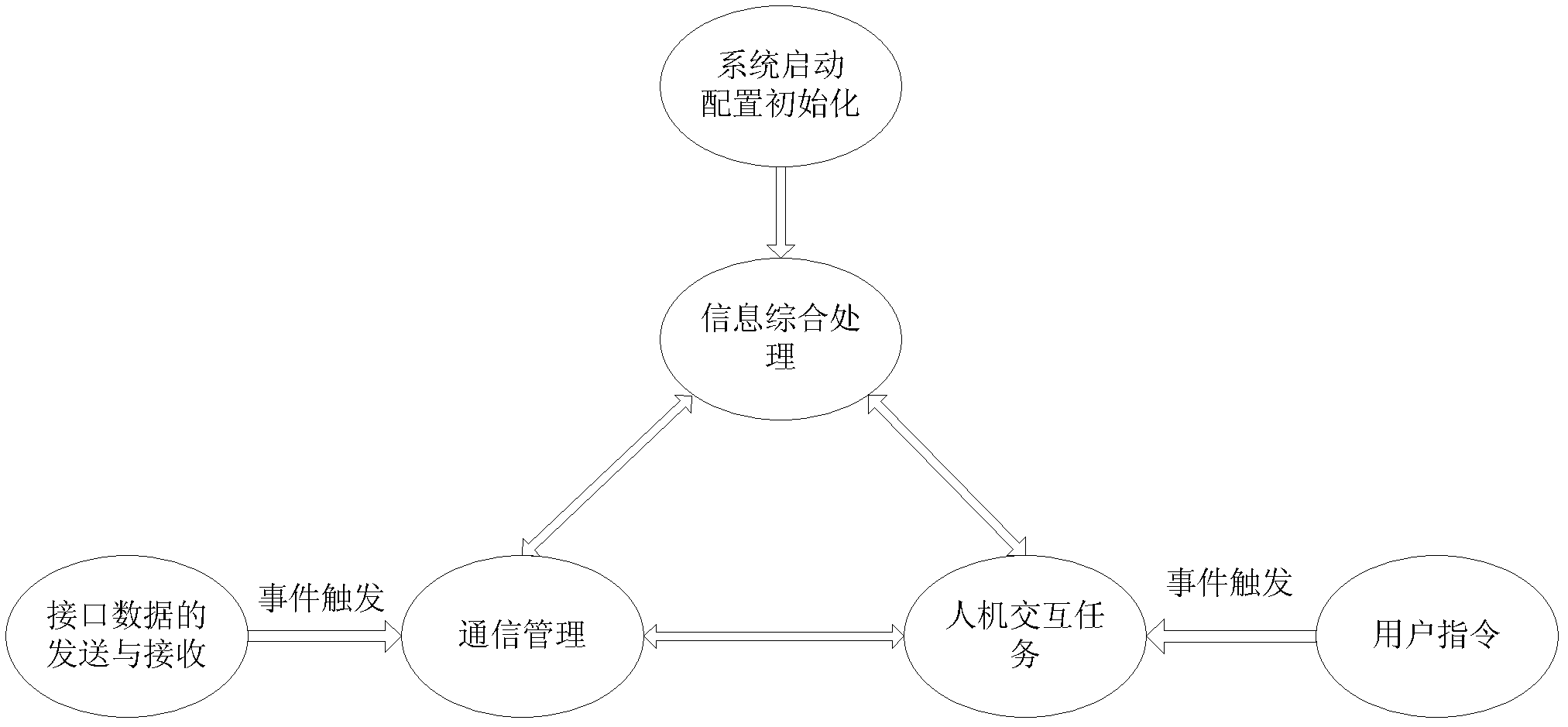

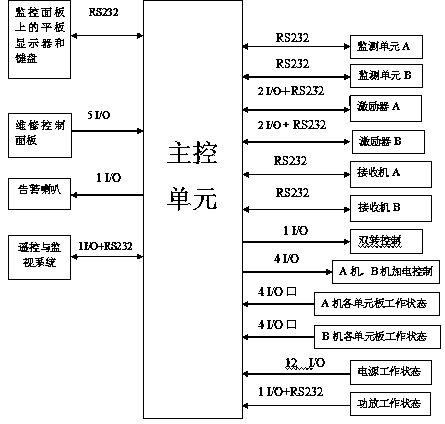

Multi-serial-port navigation information simulation integrated system

InactiveCN102506901ALess dependent on hardware structureIncrease flexibilityMeasurement devicesHardware structureHuman–machine interface

The invention relates to a multi-serial-port navigation information simulation integrated system, which is characterized in that hardware thereof includes a PC104 architectural computer, a monitoring display, an input device, an RS232 / RS485 asynchronous serial interface chip and an interface device. The monitoring display and the input device are connected with the PC104 architectural computer directly, the interface device is a drive card with eight serial ports and is connected with the PC104 architectural computer through the RS232 / RS485 asynchronous serial interface chip, the PC104 architectural computer realizes simulation of information of navigation equipment, a man-machine interaction interface is displayed in the monitoring display, and the interface device is connected with target equipment and can be provided with eight serial ports. The multi-serial-port navigation information simulation integrated system has the advantages of low dependence on hardware structure, low cost, high flexibility, convenience in carrying and use and reliable performance, and has the friendly man-machine interface.

Owner:BEIHANG UNIV

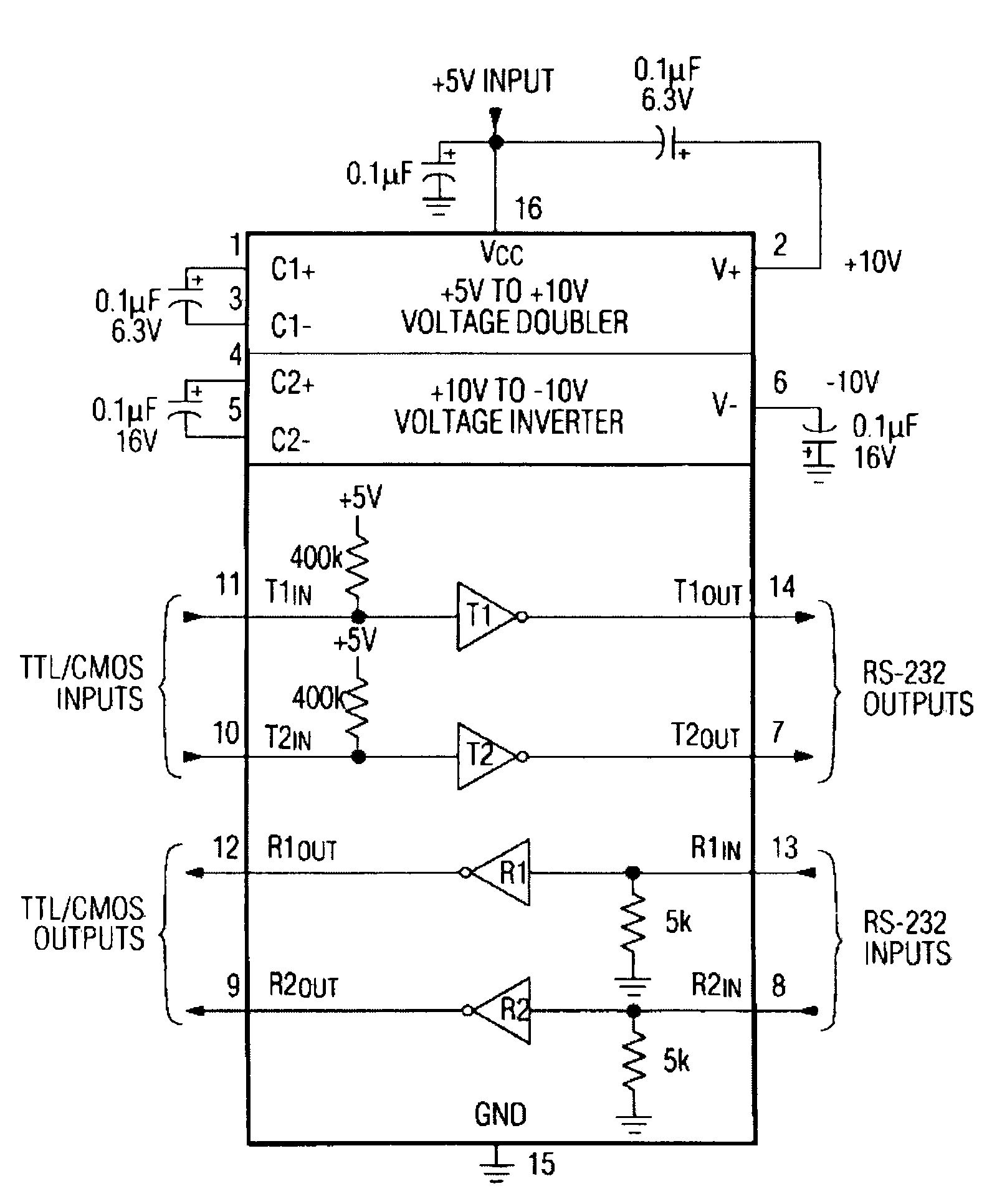

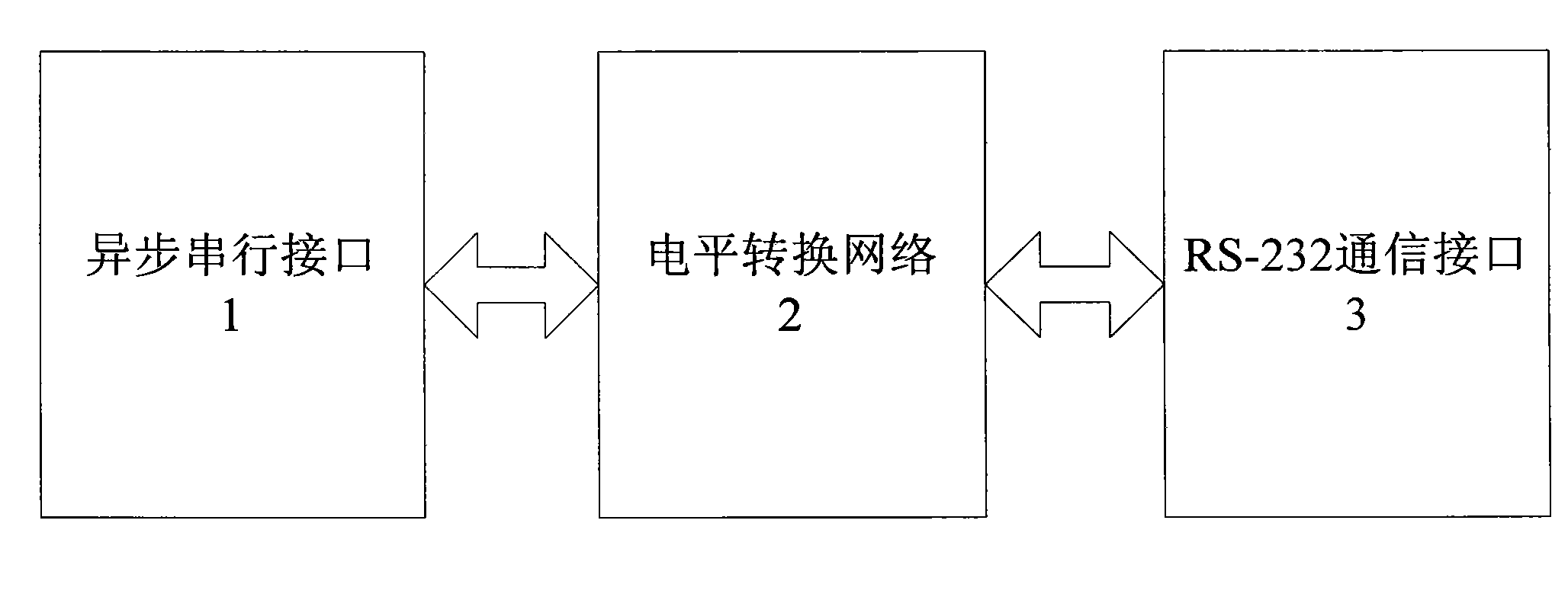

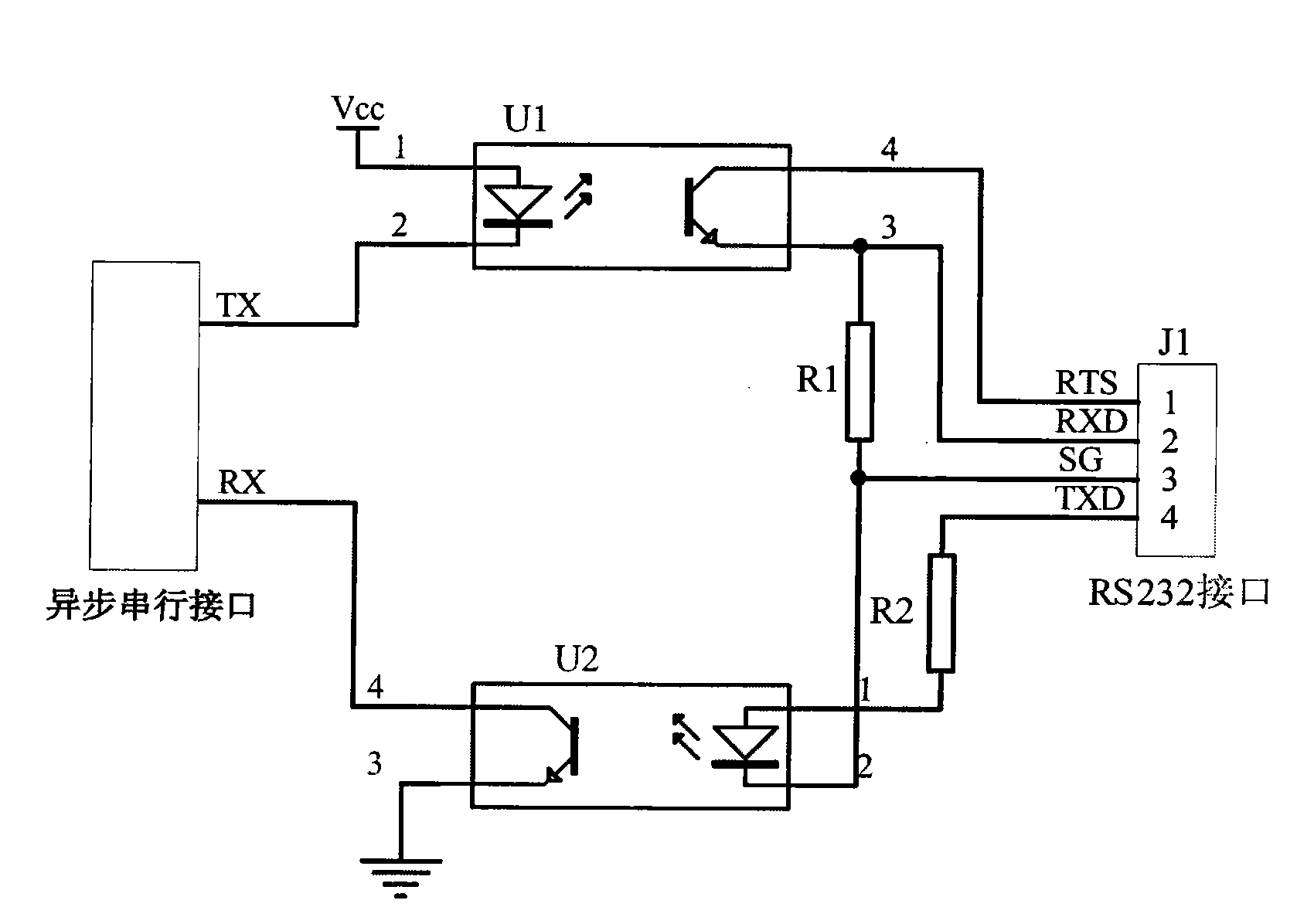

Level converting device

InactiveCN101662279AAchieve conversionAchieve electrical isolationLogic circuit coupling/interface arrangementsCommunication interfaceAsynchronous serial interface

The invention relates to a level converting device, which comprises an asynchronous serial interface and an RS-232 communication interface for transmitting data with the asynchronous serial interface,wherein the level converting device also comprises a level converting network which is connected between the asynchronous serial interface and the RS-232 communication interface; and the level converting network converts a TTL level sent by the asynchronous serial interface into an RS-232 level, and converts the RS-232 level sent from the RS-232 communication interface into the TTL level. Duringimplementation, the level converting device realizes the conversion between the TTL level and the RS-232 level through simple circuit connection, not only has low cost, but also realizes electrical isolation between a TTL circuit and an RS-232 circuit and has high communication band rate.

Owner:SHENZHEN KAIFA TECH

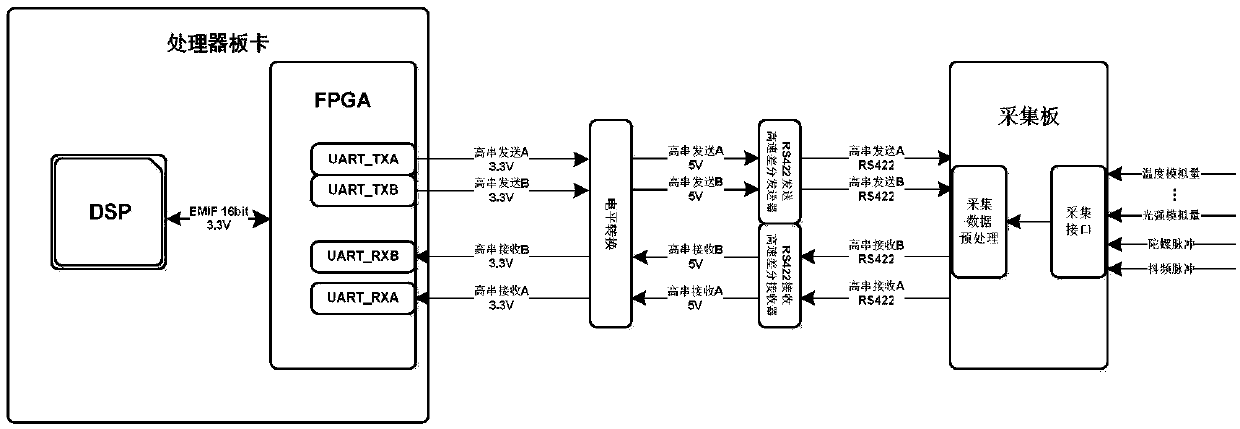

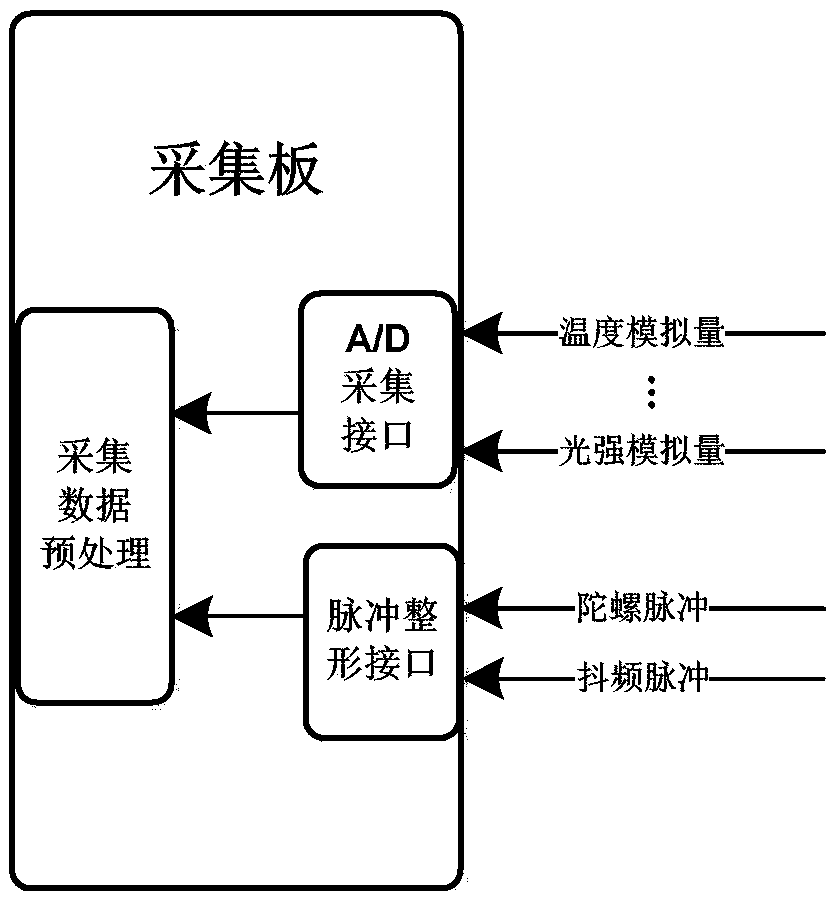

Sensor data intelligent collecting system for navigation system

PendingCN109586721AMeet processing power requirementsEnter exactlyMeasurement devicesAnalogue-digital convertersMarine navigationAsynchronous serial interface

The invention discloses a sensor data intelligent collecting system for a navigation system. The system can preprocess the collected sensor data prior to transmission to improve the anti-interferenceability of the collected data and have a certain error compensation capability, the preprocessing process does not need a remote main control processor for intervention, the system is integrated witha full-duplex and dual-redundant high-speed asynchronous serial interface with RS422 level so as to complete high-reliability and high-speed transmission and update of the inertial sensor measurementdata and facilitate timely navigation resolving task of the CPU.

Owner:XIAN AVIATION COMPUTING TECH RES INST OF AVIATION IND CORP OF CHINA

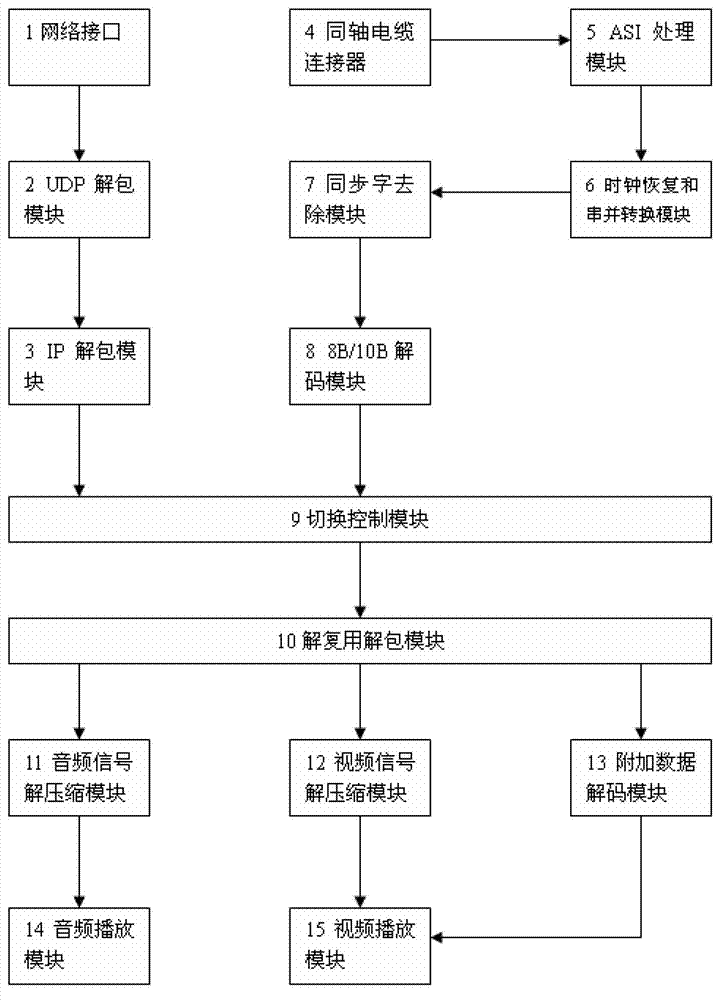

Multifunctional television capable of receiving wired television signals and network television signals

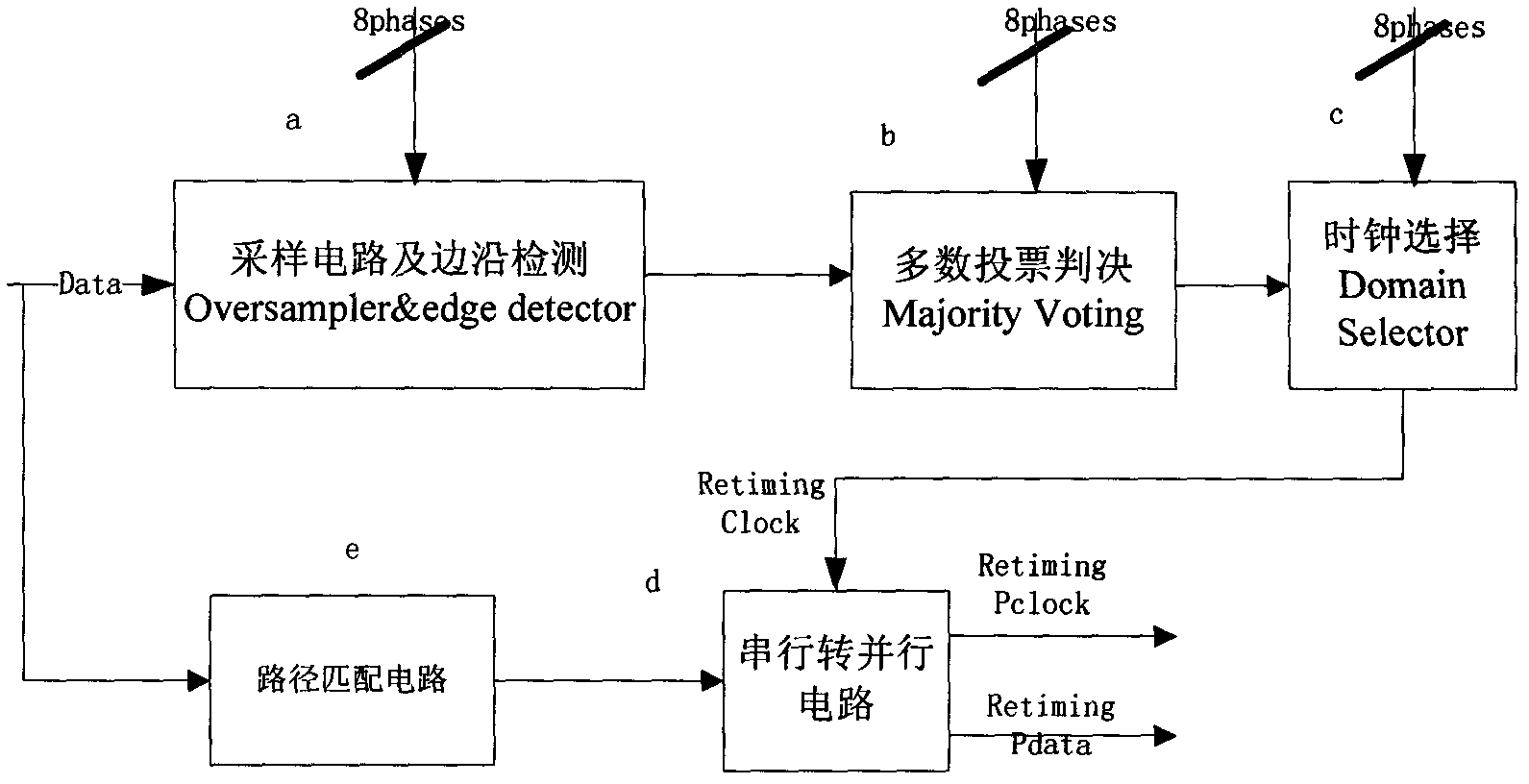

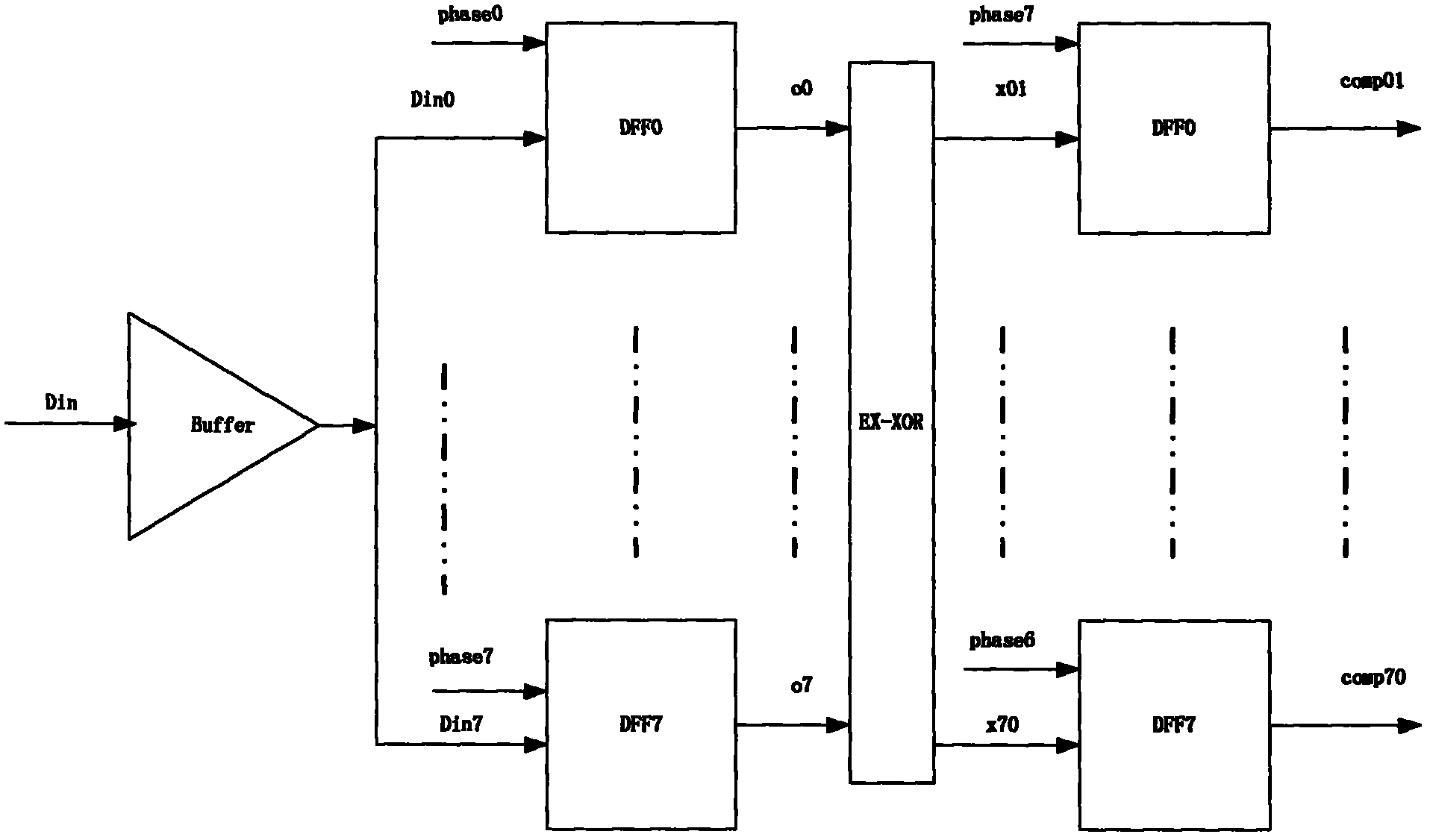

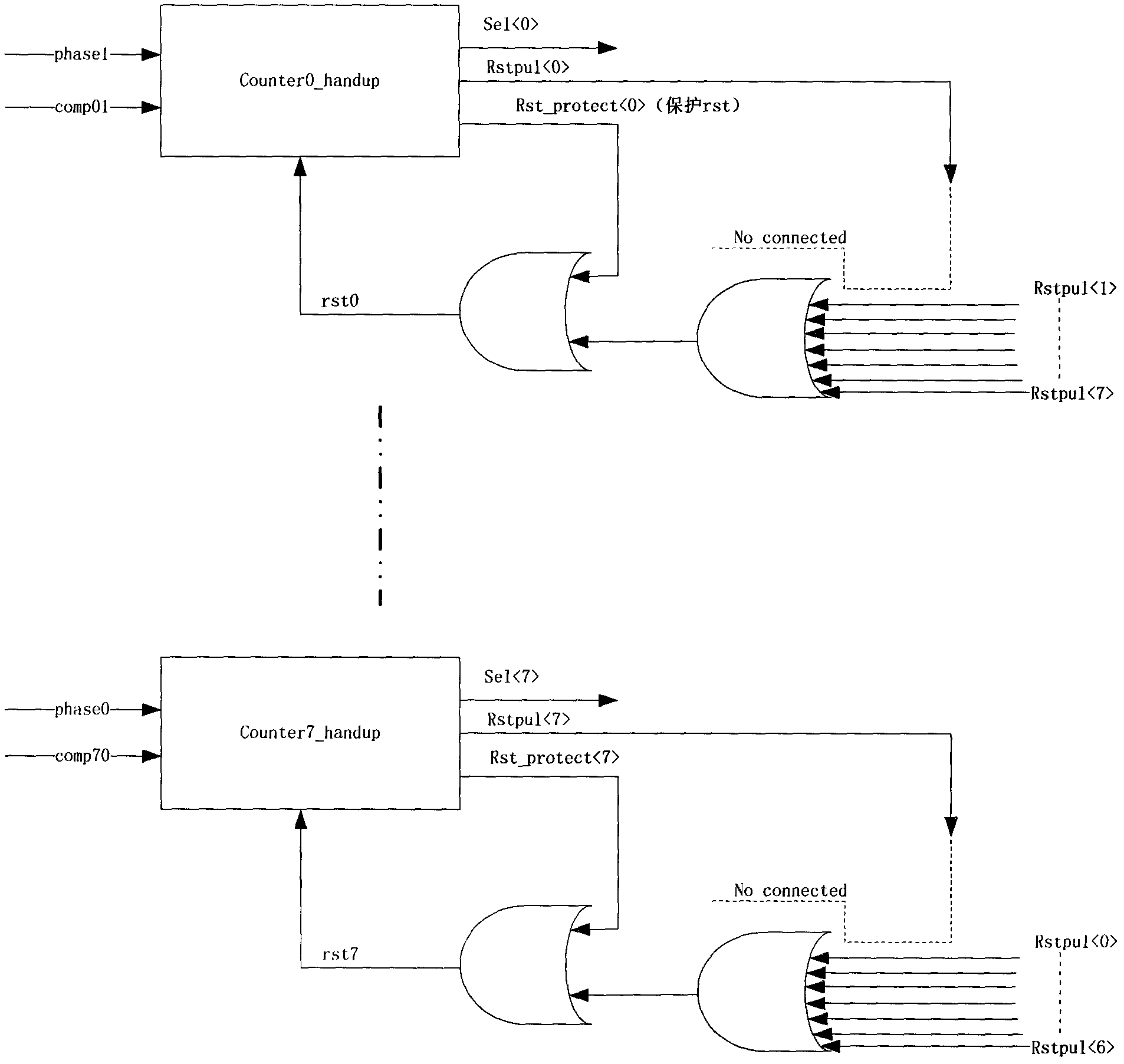

InactiveCN103313126AOvercome technical issues with changing TV typesSave resourcesSelective content distributionClock recoveryAsynchronous serial interface

The invention relates to a multifunctional television capable of receiving wired television signals and network television signals. The multifunctional television comprises a UDP (User Datagram Protocol) unpacking module, an IP (Internet Protocol) unpacking module, an ASI (Asynchronous Serial Interface) processing module, a timer recovery and serial-parallel conversion module, a synchronous character deletion module, a 8B / 10B decoding module, a demultiplexing and unpacking module and a conversion control module, wherein the UDP unpacking module and the IP unpacking module are sequentially connected and used for processing received network television signals so as to obtain a TS (Transmission Stream); the ASI processing module, the timer recovery and parallel-serial conversion module, the synchronous character deletion module and the 8B / 10B decoding module are sequentially connected and used for processing received wired television signals so as to obtain a TS; and the demultiplexing and unpacking module is used for demultiplexing and unpacking the TS from the network television signals and the TS from the wired television signals under the control of the conversion control module. Through the invention, the functions of a receiving device can be expanded, and the functions of receiving and playing the wired television signals and the network television signals are combined.

Owner:WUXI BEIDOUXINGTONG INFORMATION TECH

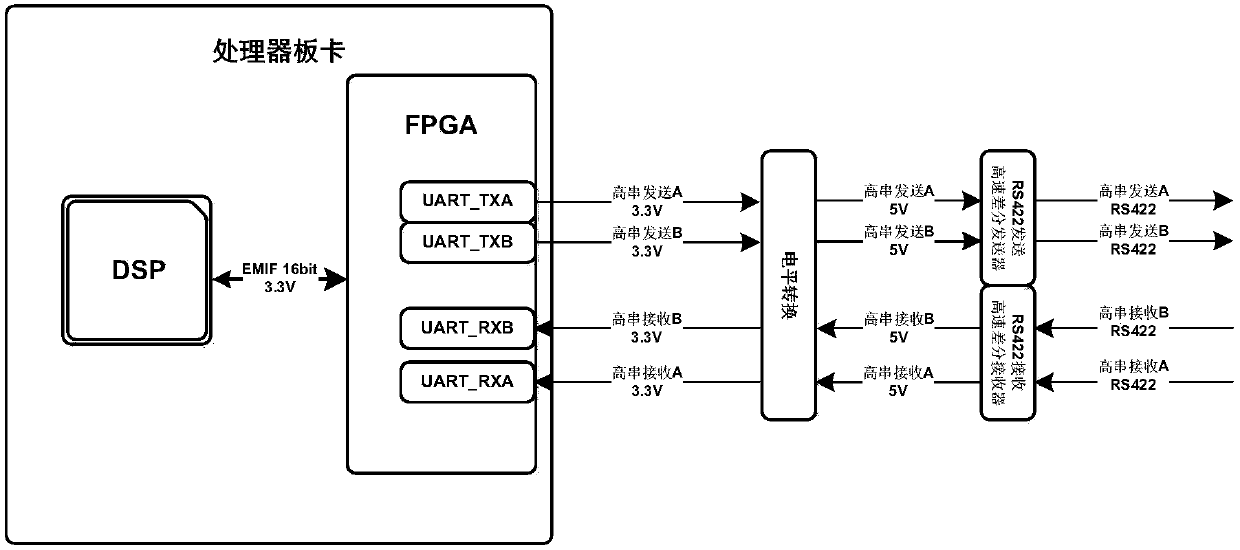

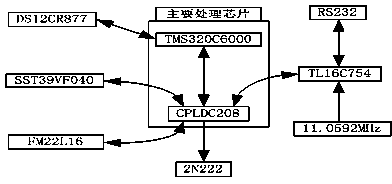

TACAN control system based on DSP

InactiveCN103676884AReal-timeTotal factory controlProgramme total factory controlControl systemAsynchronous serial interface

Owner:TIANJIN 764 COMM AIRMANSHIP

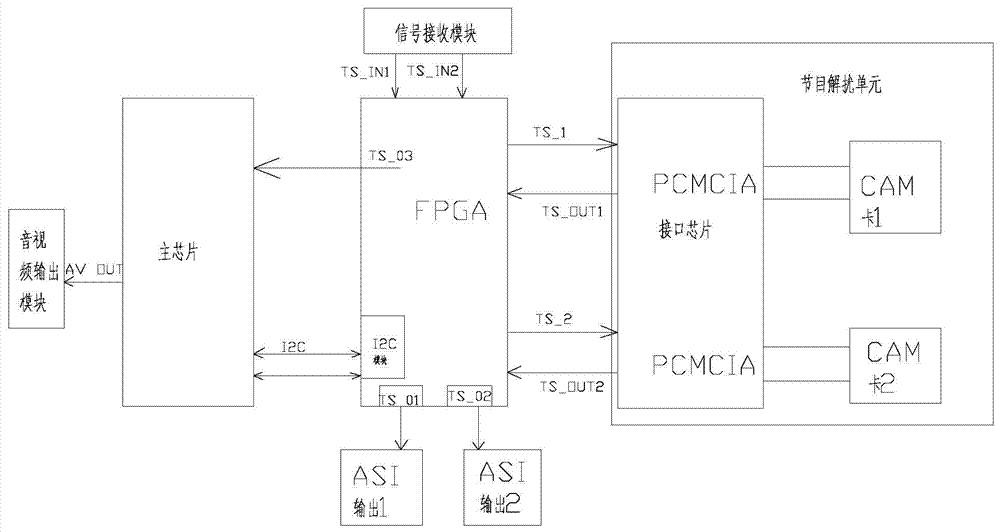

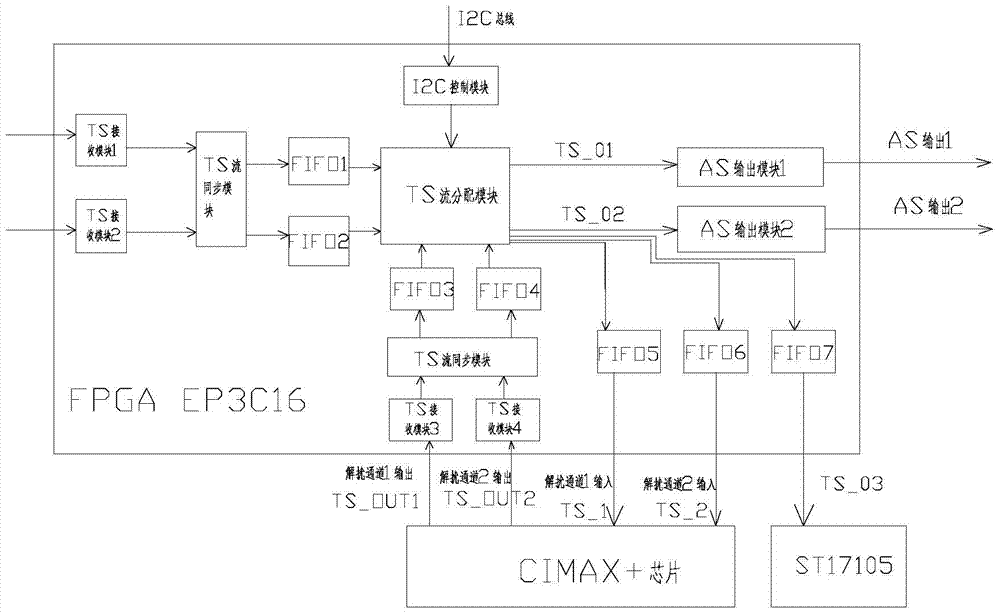

Decoder allowing independent descrambling of two television programs and controlling of distributed output of TS (transport streaming) flows

InactiveCN104519399AAssign output flexiblyImplement data conversionSelective content distributionComputer compatibilityConditional access

The invention discloses a decoder allowing independent descrambling of two television programs and controlling of distributed output of TS (transport streaming) flows. The decoder comprises an FPGA (field programmable gate array) module, a signal receiving module, a main chip module, a program descrambling module, an ASI (asynchronous serial interface) output module and an audio-video output module; the FPGA module is used for processing and distributing original encrypted TS flows and descrambled TS flows; the signal receiving module connected with the FPGA module is used for receiving two digital television programs of independent frequencies and outputting original TS flows; the main chip module connected with the FPGA module is used for controlling a system and decoding and playing audio-video; the program descrambling module connected with the FPGA module is used for descrambling the TS flows of the two television programs and outputting the descrambled TS flows through two PCMCIA (personal computer memory card international association) CAM (conditional access module) cards; the ASI output module connected with the FPGA module is used for converting and outputting parallel TS flows to an ASI interface; the audio-video output module connected with the main chip module is used for outputting descrambled and decoded television programs. The decoder has the advantages such as operational flexibility, high compatibility and low cost.

Owner:SICHUAN JIUZHOU ELECTRONICS TECH

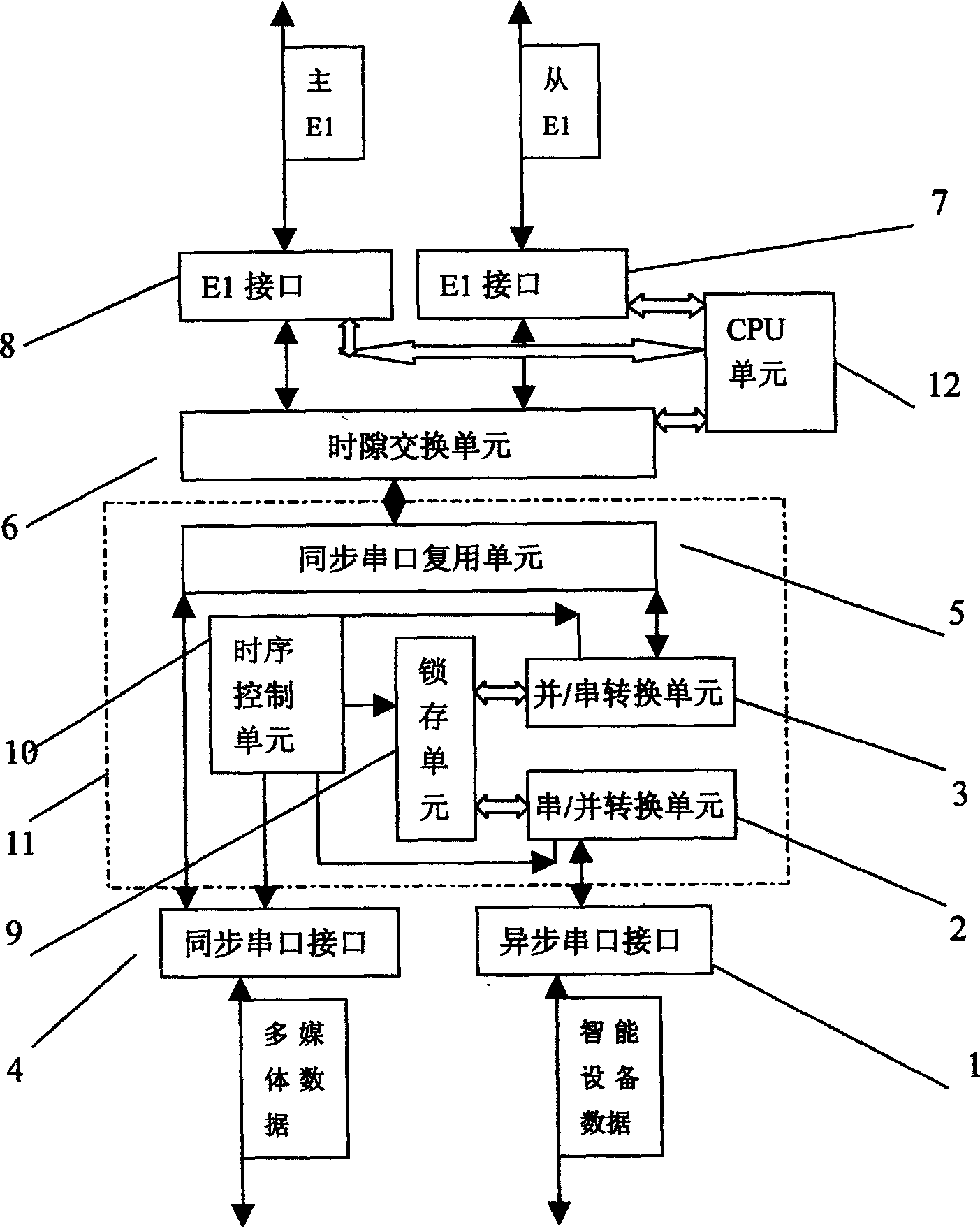

Remote monitoring data transmission method and implementing device therefor

InactiveCN1543130ALow maintenanceSimplify the amount of writingTransmission monitoringData switching networksAsynchronous serial interfaceTransformation unit

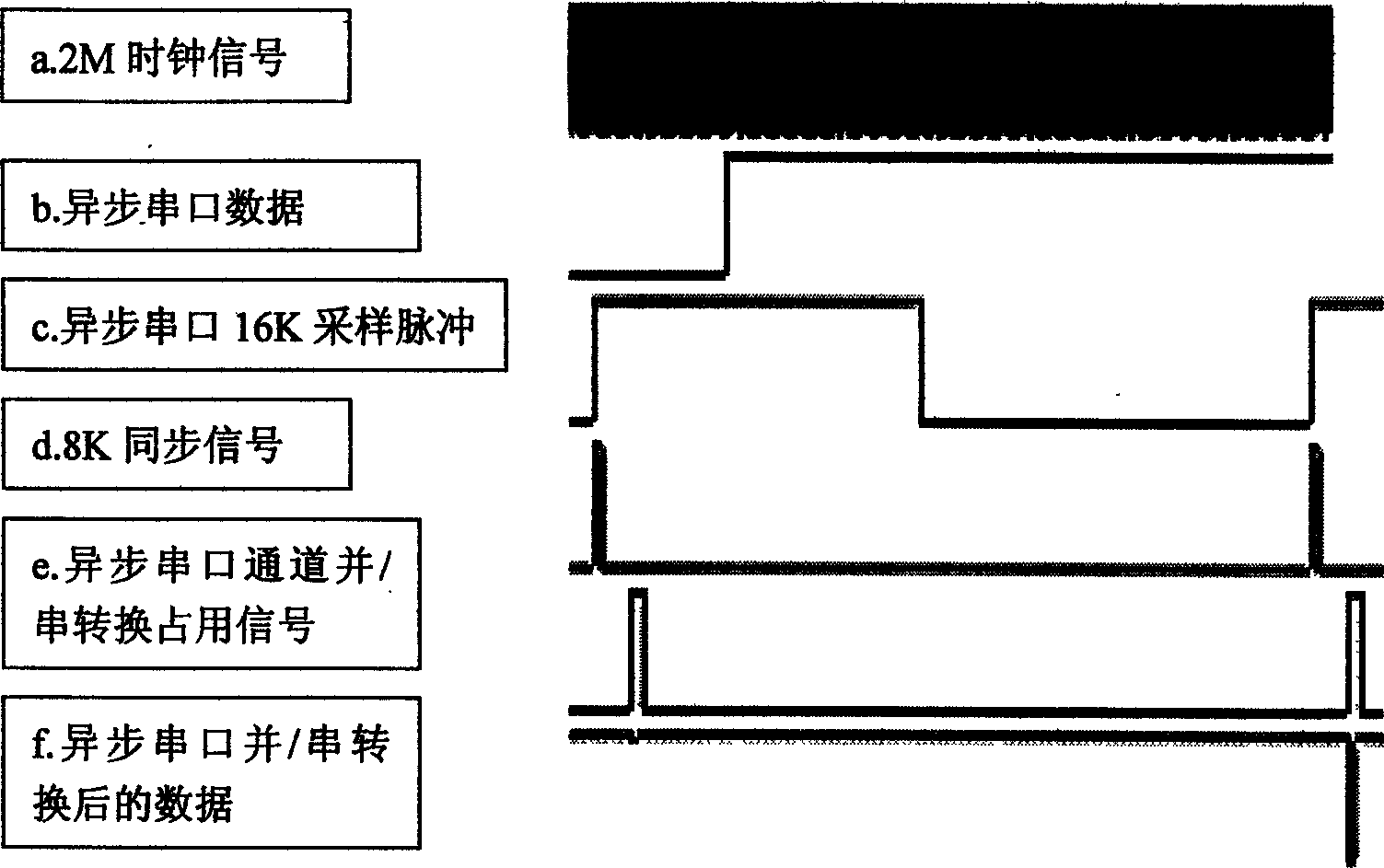

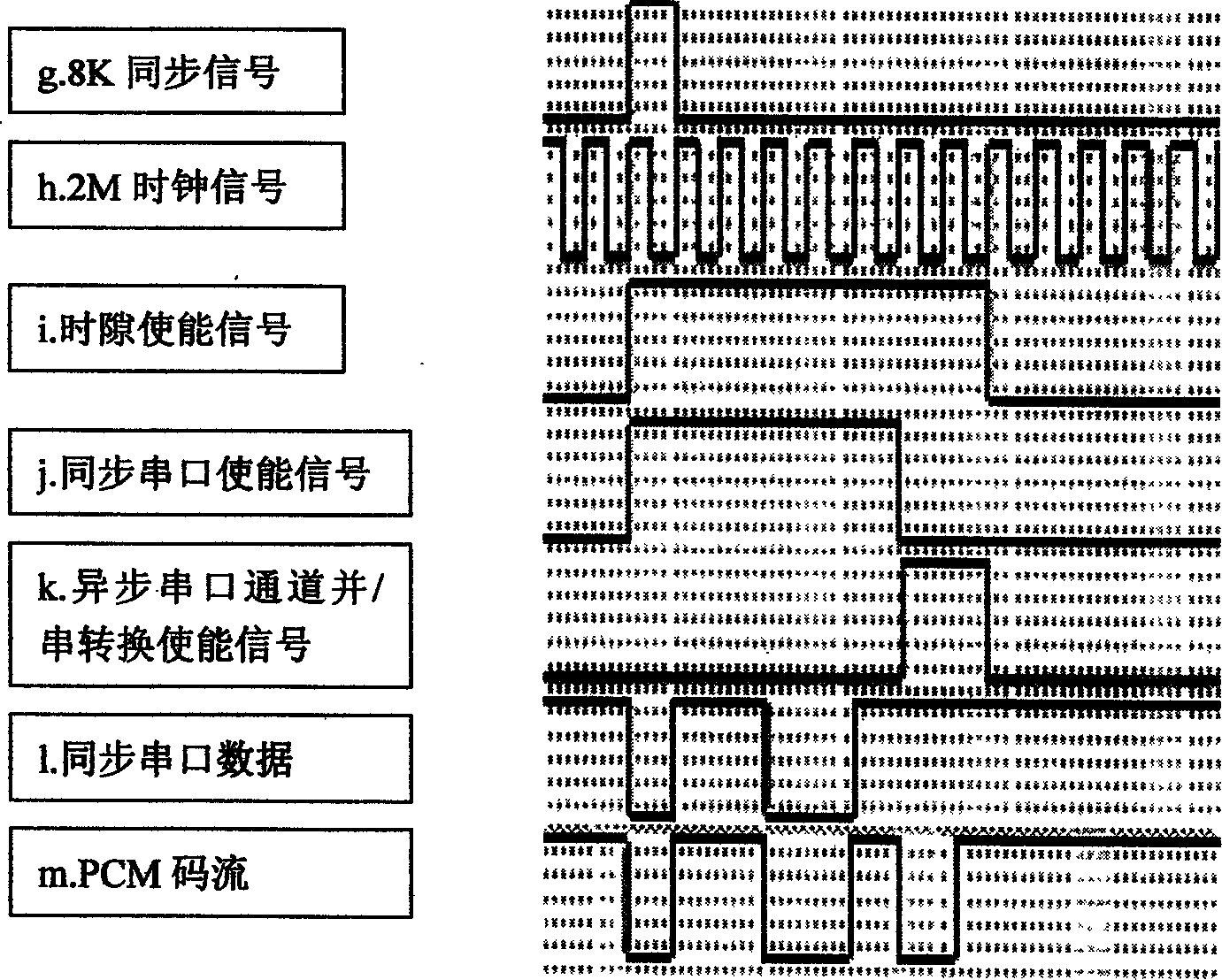

This invention relates to a transmission method and its application device for remote monitor data for solving the problem of unstable monitor system resulted from software reform on the basis of using transmission channel bandwidth as much as possible. This invention applies the following technology: an asynchronous serial interface outputs the data to a serial / parallel switch unit to finish the switch then the data is put in a latch unit which outputs it to a parallel / serial switch unit for switching then to be output to a synchronous serial multiplex unit multiplexed with the data to the unit from the synchronous serial interface to occupy a time slot together which is output to a time slot exchange unit exchanging it to a definite time slot to be merged with PCM stream from the slave E1interface and output from the master E1 interface.

Owner:ZTE CORP

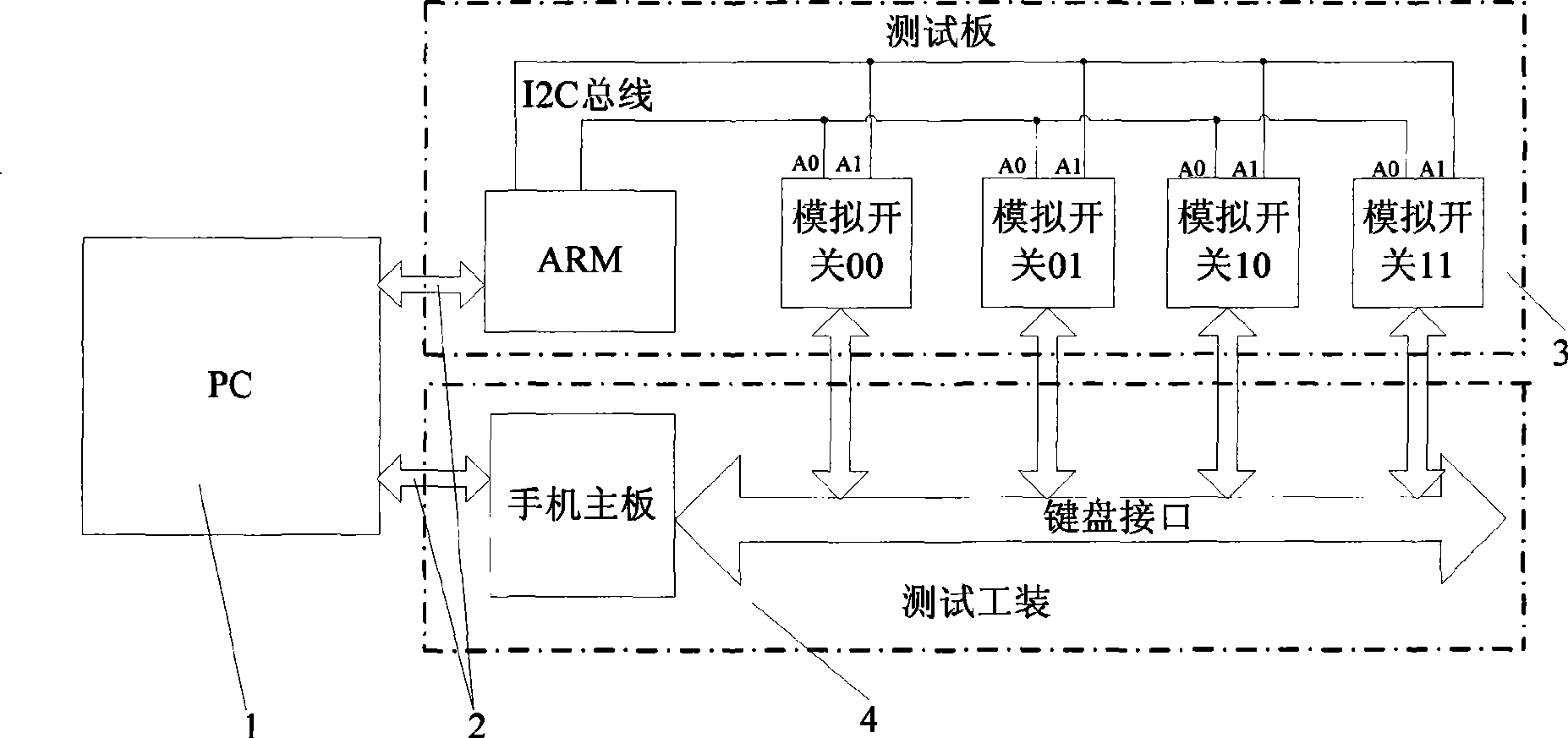

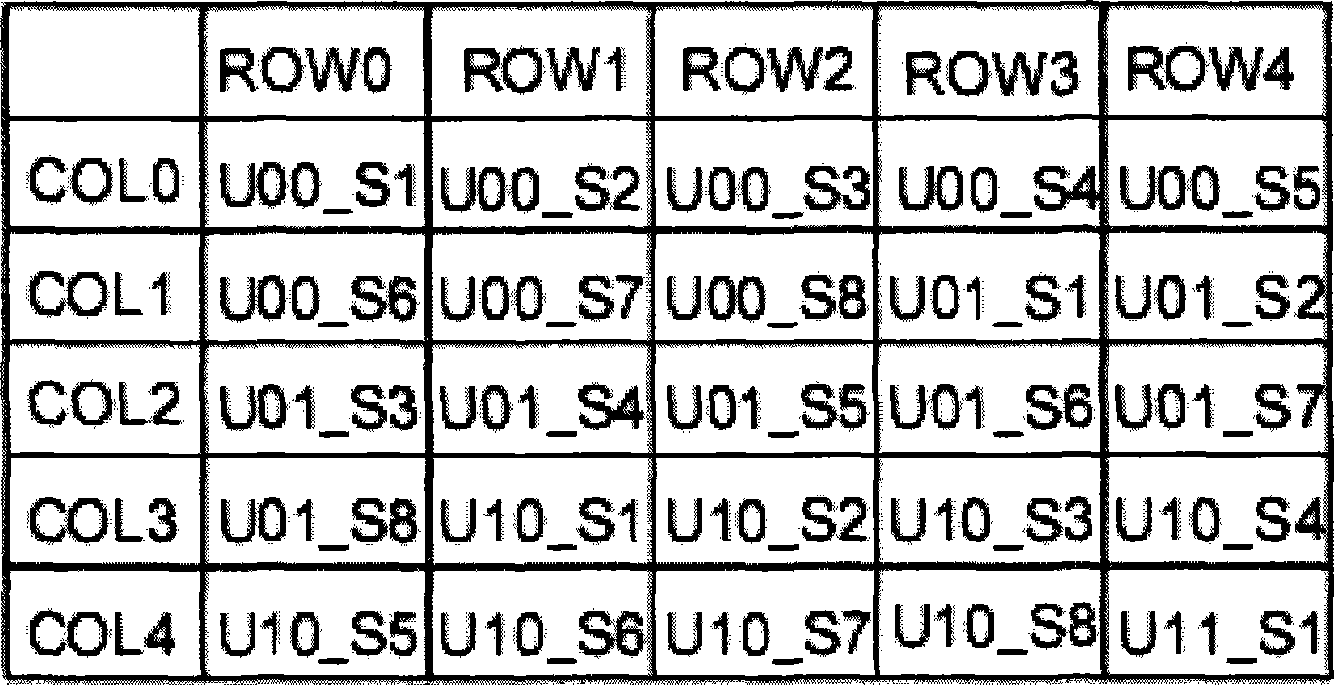

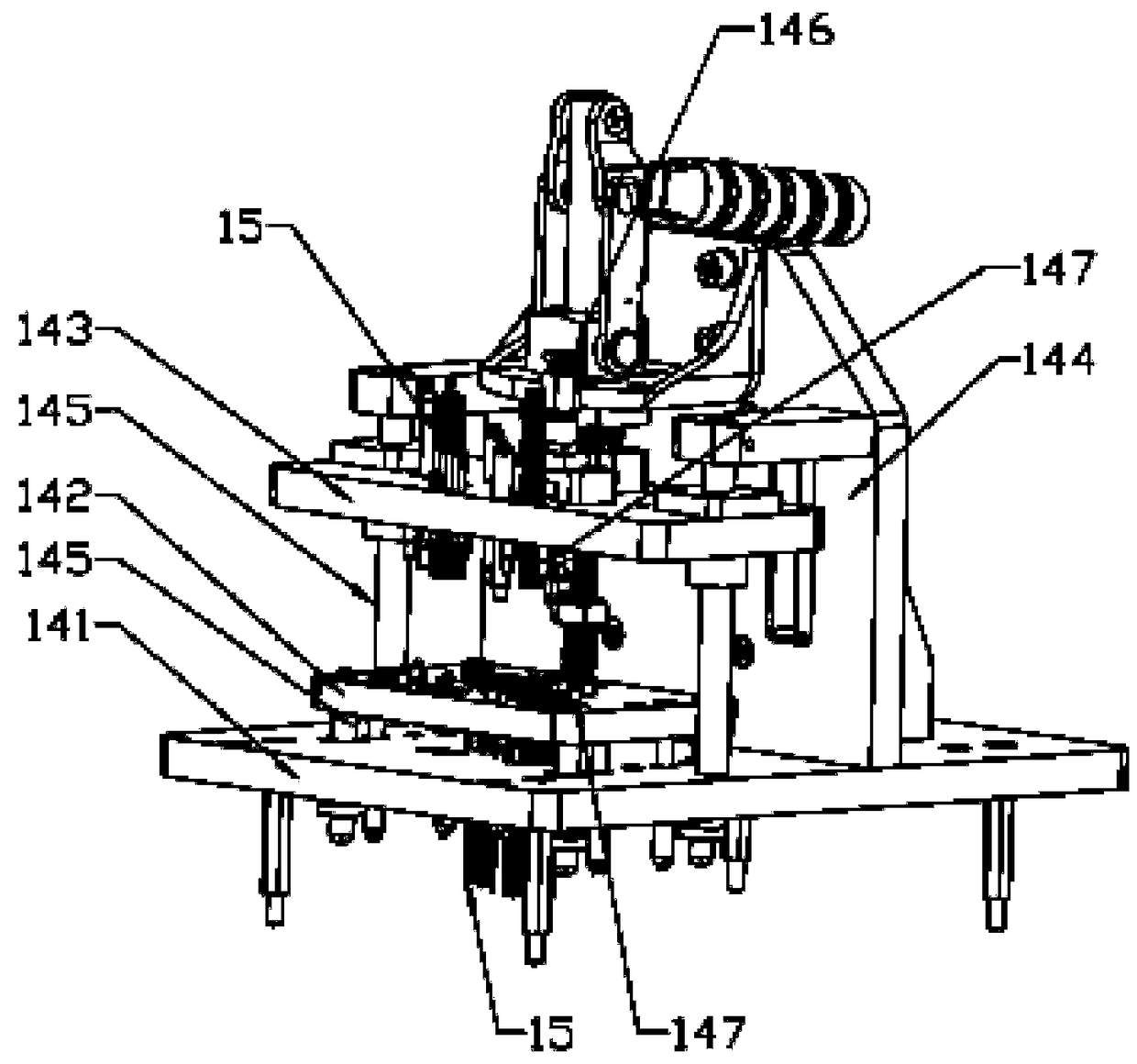

Keyboard test system and test method for intelligent mobile phone

InactiveCN101471977AEasy to operateSimple basis for judgmentSubstation equipmentAsynchronous serial interfaceSurface-mount technology

The invention relates to a keyboard testing system of an intelligent mobile phone and a testing method thereof. The keyboard testing system of the intelligent mobile phone comprises a computer, a testing board connected with the computer through an asynchronous serial interface and a mobile phone main board connected with a testing tool through the asynchronous serial interface. A keyboard interface on the mobile phone main board is connected to a plurality of analog switches on the testing board through the testing tool; and an ARM on the testing board is connected with the analog switches on the testing board through an IC bus. The keyboard testing system of the intelligent mobile phone and the testing method thereof are used for testing the keyboard of the intelligent mobile phone after adopting the mobile phone main board surface mount technology (SMT) and can provide simple operation for production workers, provide a simple judgment basis to obtain accurate detection results, reduce the number of production personnel and the production cost, improve the production efficiency, and improve the product quality.

Owner:SHANGHAI CHENXING ELECTRONICS SCI & TECH CO LTD

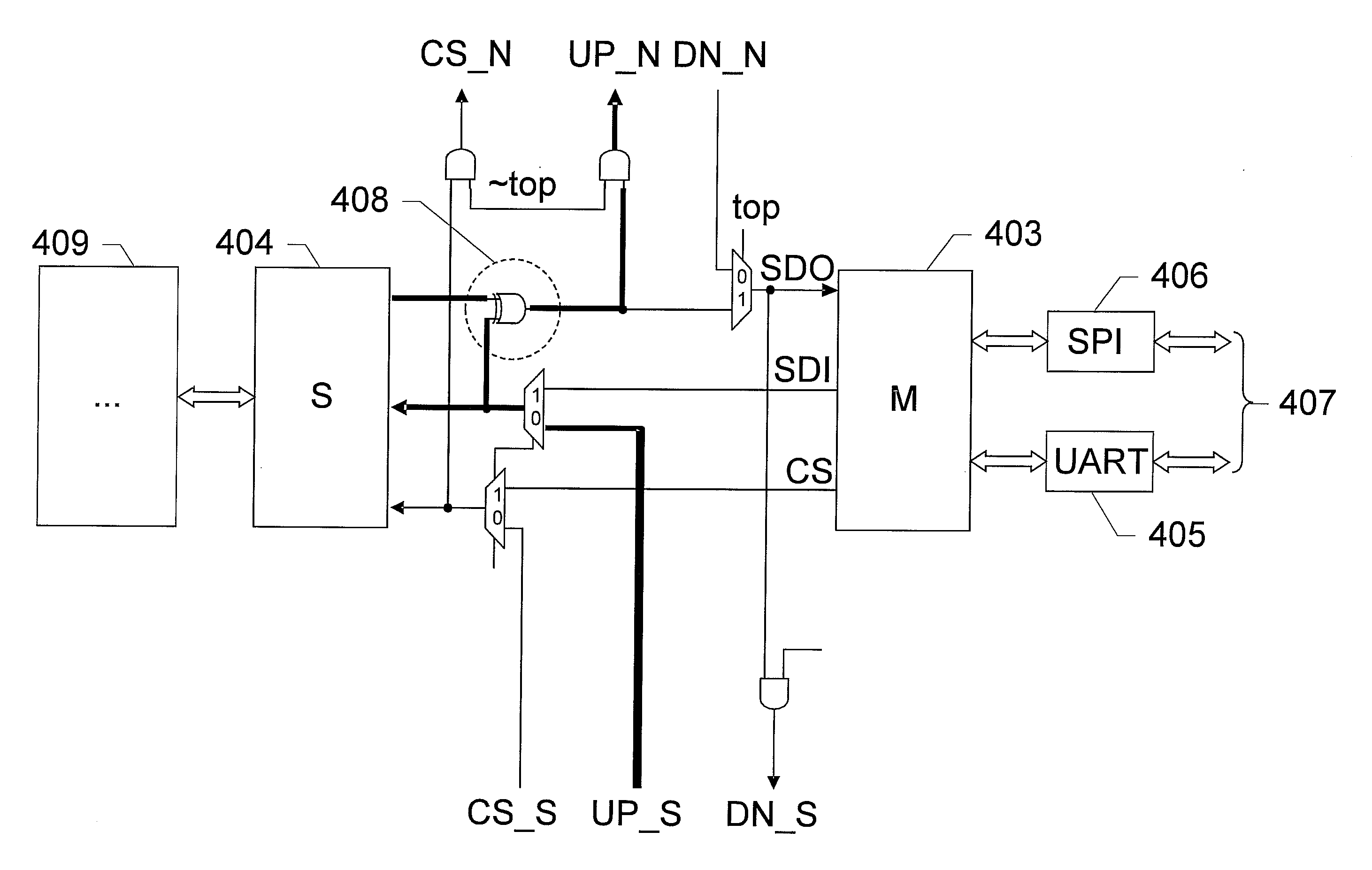

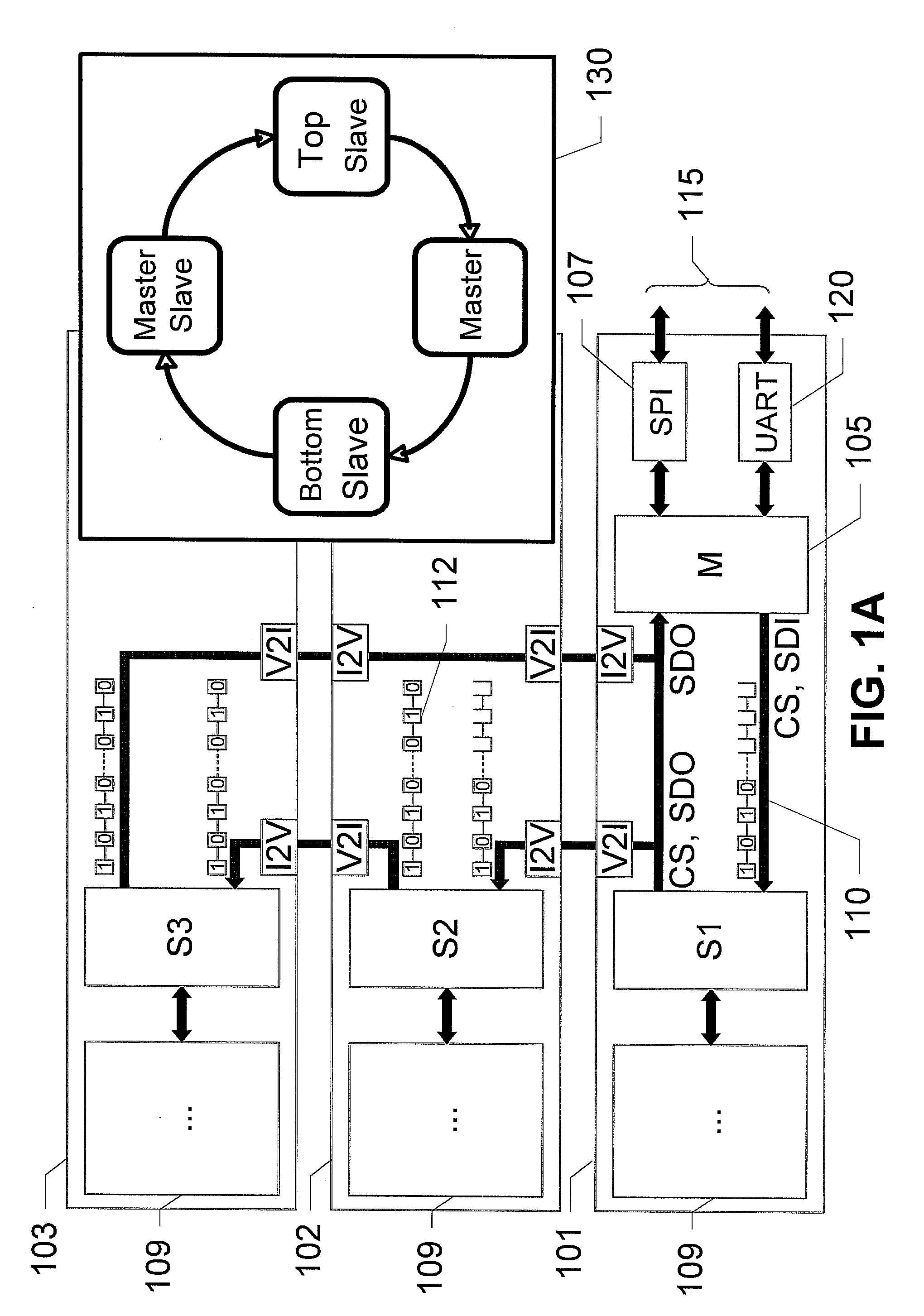

Serial communication protocols

ActiveCN103703716AReduces need for closely matched clocksPulse automatic controlLoop networksData streamData acquisition

Systems and methods are disclosed which relate to improving synchronization of clocks between a sender and a receiver communicating via an asynchronous serial interface. In a ring topology (130), a master device (105) is connected to a plurality of slaves (S1-S3) communicating using a bi-frequency encoded bit stream. A host device communicates with the master device using a non-return-to-zero data encoding. Each slave (SI-S3) receives data from the master (105) and sends it to the next slave in the ring unaltered unless the master indicates a requirement for a particular data, and transmits placeholder bits with a value of 0 around the ring. A particular slave can 'fill-in' the placeholder bits with the information to be sent back to the master by inverting the placeholder bit. Clock synchronization between a receiving device and a transmitting device is improved using a fractional rate multiplier to generate a data sampling clock from a system clock. By adjusting the denominator, the sampling clock can be tuned to match the baud rate of the asynchronous serial data stream received from the transmitting device. Embodiments described include power management, data acquisition (DAQ), etc.

Owner:TEXAS INSTR INC

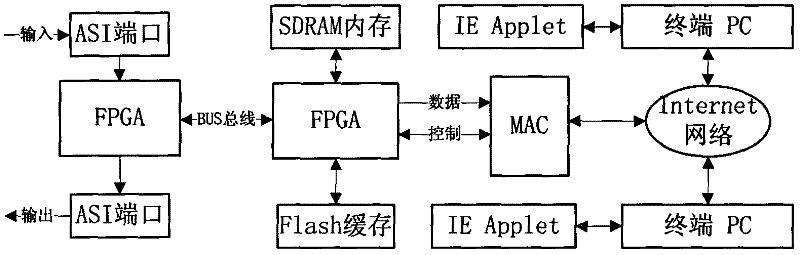

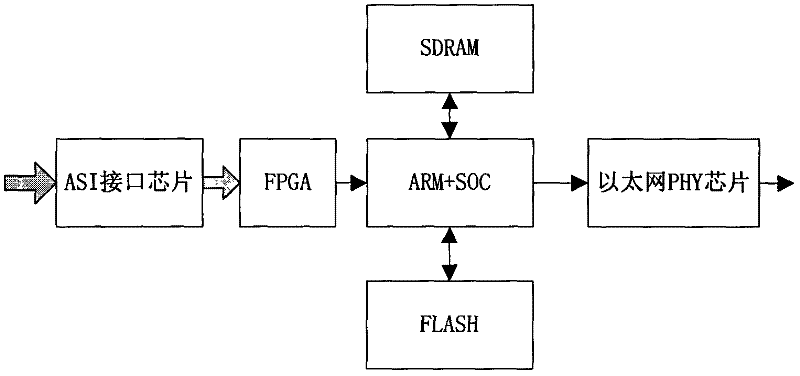

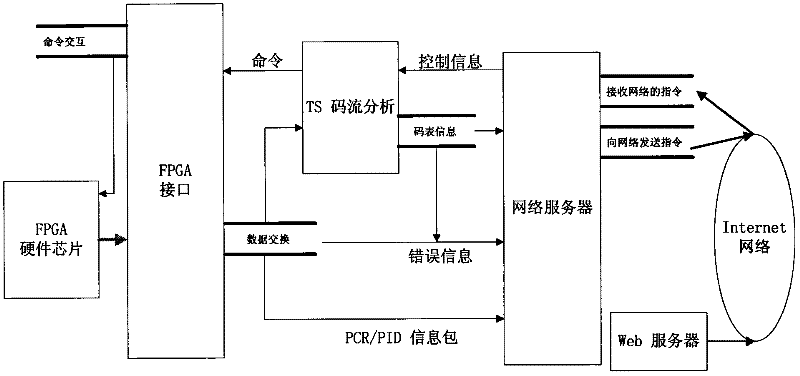

Embedded type based code stream analysis system

InactiveCN102421005ARecord in timeReal-time statistical bandwidth usageTelevision systemsSelective content distributionBase codeError check

The invention discloses an embedded type based code stream analysis system, comprising a hardware part and a software part. The hardware part is mainly composed of a FPGA (Field Programmable Gate Array) and an ARM (Advanced Risc Machine) and is further provided with peripheral chips, such as an ASI (Asynchronous Serial Interface) chip, an Ethernet interface chip, an SDRAM (Synchronous Dynamic random access memory), FLASH and the like, to constitute a complete embedded system. The software part comprises four modules, namely, an FPGA interface module, a TS (Transport Stream) code stream analysis module, a network server module and a web server module. According to the invention, TS code stream data can be subjected to synchronous byte extraction and packet sequence error check, a data stream can be monitored in real time, and error time and error conditions can be recorded in time.

Owner:GUANGZHOU ZHONGDA TELECOMM TECH

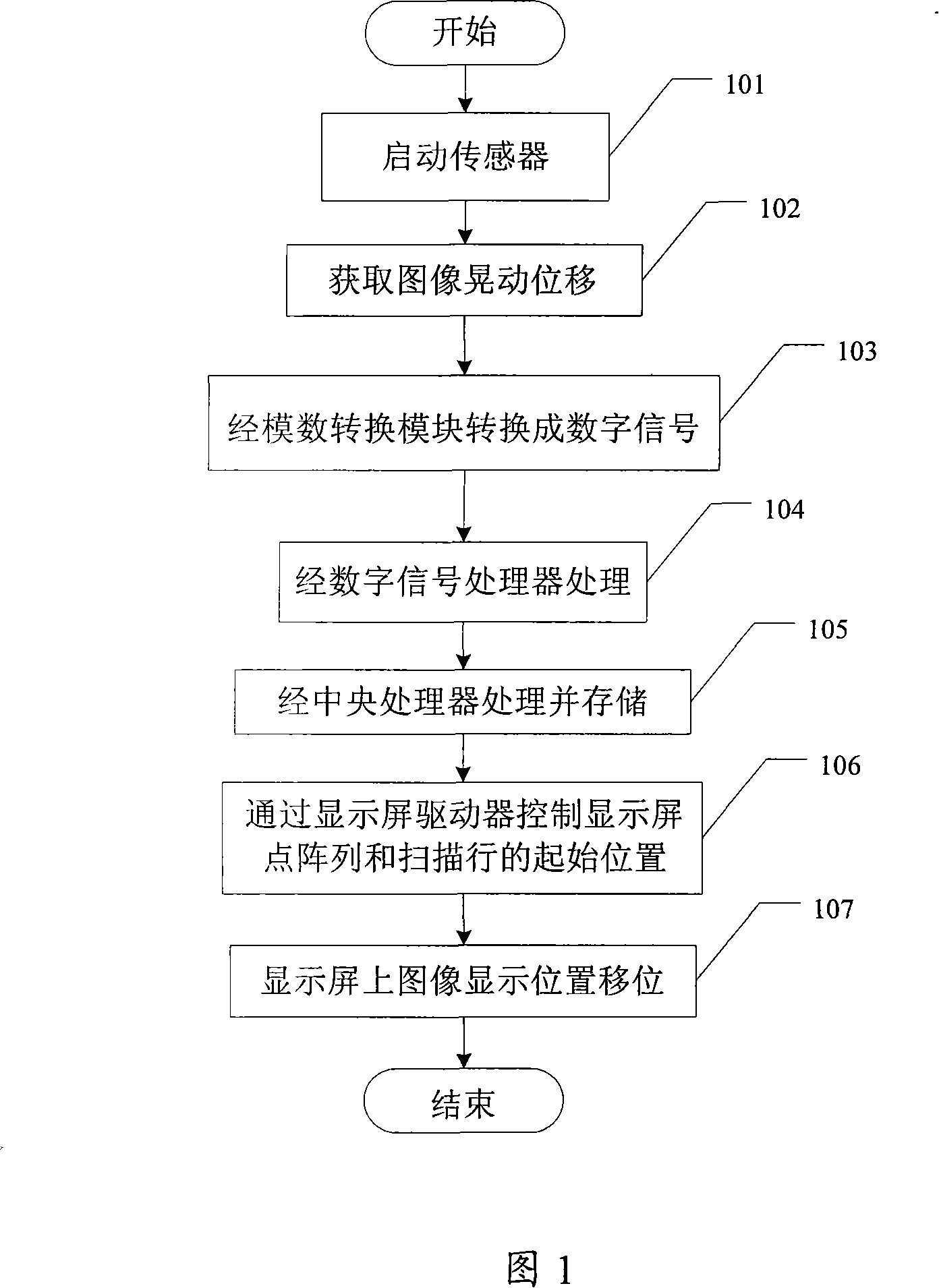

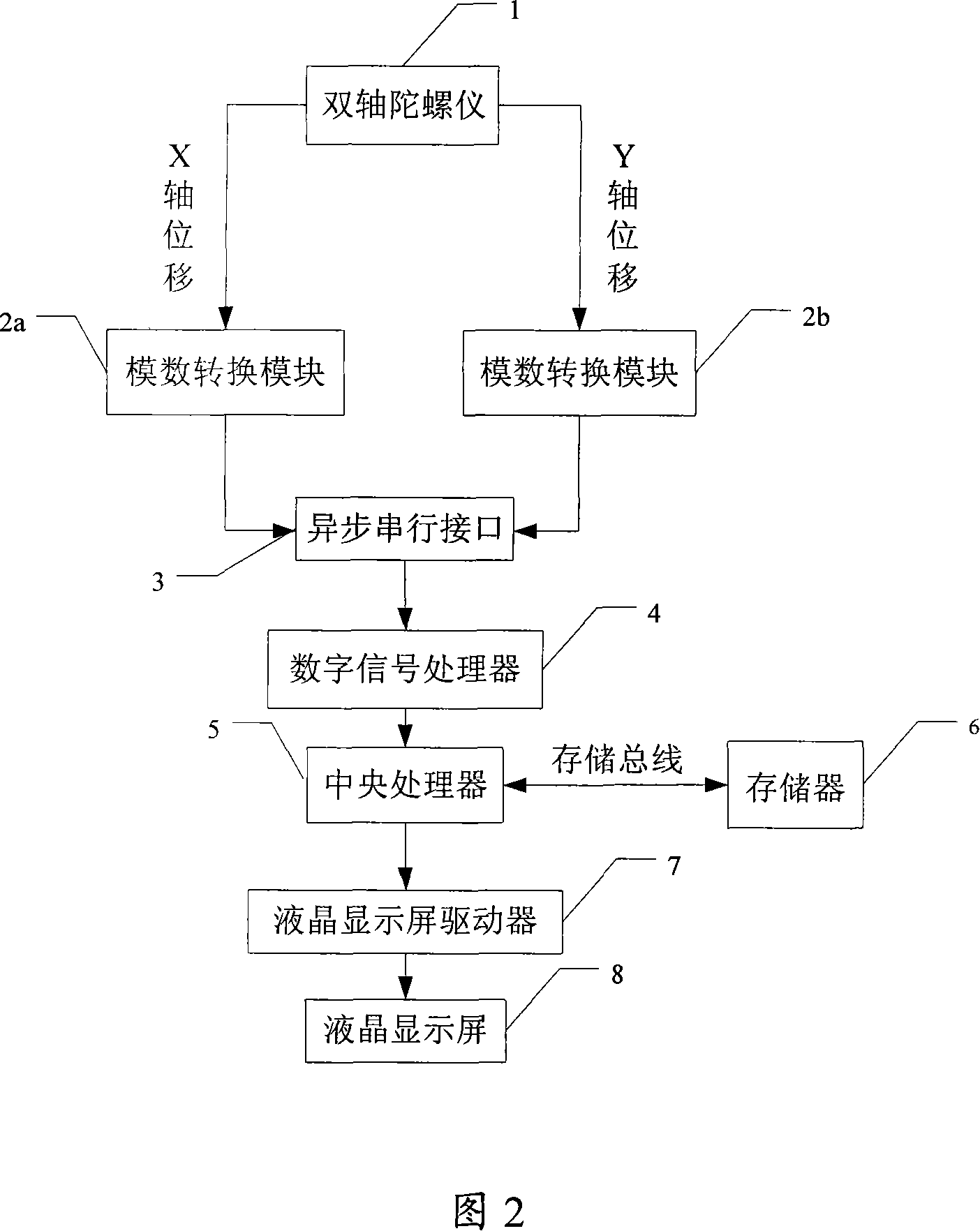

Method for stabilizing handhold equipment image and device

InactiveCN101159126AReduce visual fatigueEasy to operateCathode-ray tube indicatorsDigital signal processingAsynchronous serial interface

The invention discloses a method for stabilizing image of handheld equipment, which comprises the steps: (a) starting a sensor in the handheld equipment to acquire swaying data; and (b) converting an analog signal in the step (a) into a digital signal, transmitting the digital signal to a digital signal processor and a CPU for processing, controlling the start position of dot array and scan row of a display screen by a display screen driver to control the image position, and storing the position. The invention also discloses a device for implementing the method, which comprises the CPU, the sensor, an analog-digital conversion module, the digital signal processor, an asynchronous serial interface, the display screen driver, and the display screen and a storage, which are connected with each other in sequence, wherein the storage is connected with the CPU. The invention provides the method and a device for stabilizing image of the handheld equipment, which are capable of alleviating or eliminating visual fatigue caused by image of the handheld equipment in swaying environment.

Owner:KONKA GROUP

Serial clock restoring circuit in universal serial bus (USB) 2.0 high-speed mode

PendingCN102857220ASynchronisation information channelsPulse automatic controlAsynchronous serial interfaceUSB

The invention discloses a circuit which meets the speed requirements of USB2.0. The circuit is widely applied to asynchronous serial interface receiving ends and has the advantages of being large in data jitter tolerance range, quick in locking time and the like. The implementation method of the circuit is applied to and verified on 0.13 mu m process flow chips and 0.35 mu m process flow chips, and the circuit has obvious advantages in the aspects of power consumption, area and performance. Infringements of the circuit can be generally judged through analyses of implementation circuits of the circuit, and on the condition that the circuits can not be obtained, infringements can be judged according to backward analyses, such as dissection and photography, which are conducted on chips of the circuits. Organizations that can infringe include chip design companies with factories and without factories, research institutions, schools and the like.

Owner:LONTIUM SEMICON CORP

Device for filtering out null packet for MPEG-2 transmission

Disclosed is a device for filtering out a null packet in a data stream for example an MPEG-2 TS (Transport Stream) to avoid bandwidth waste when it is transmitted to a backbone network. The device includes a plurality of receiving interfaces, a filter unit, and a controller. The receiving interfaces receive parallel data, such as DVB-ASI (Digital Video Broadcasting-Asynchronous Serial Interface) inputs as channel-by-channel MPEG-2 data. The filter unit counts the respective numbers of data packets and non-data packets of the data input from the receiving interfaces and filters a null packet in the data. A network transmission unit transmits the filtered data to a backbone network. The controller calculates a bit rate based on both of the count numbers received from the filter unit.

Owner:SAMSUNG ELECTRONICS CO LTD

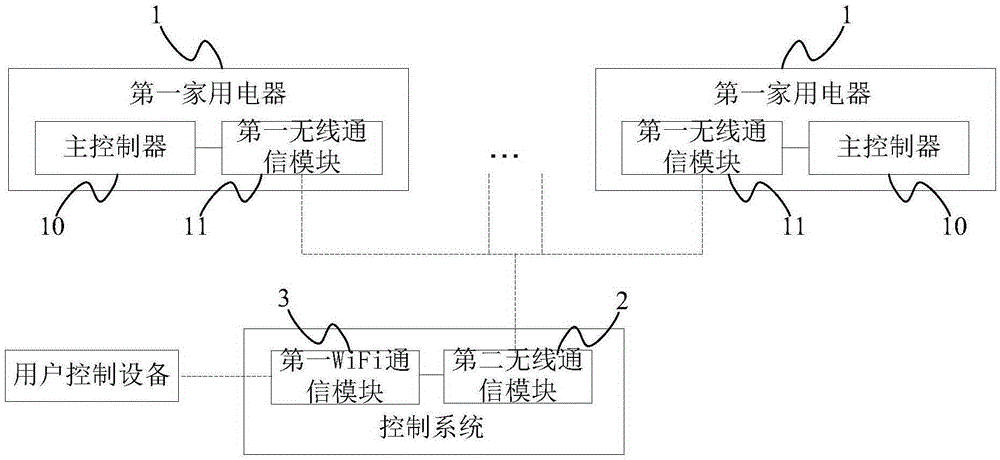

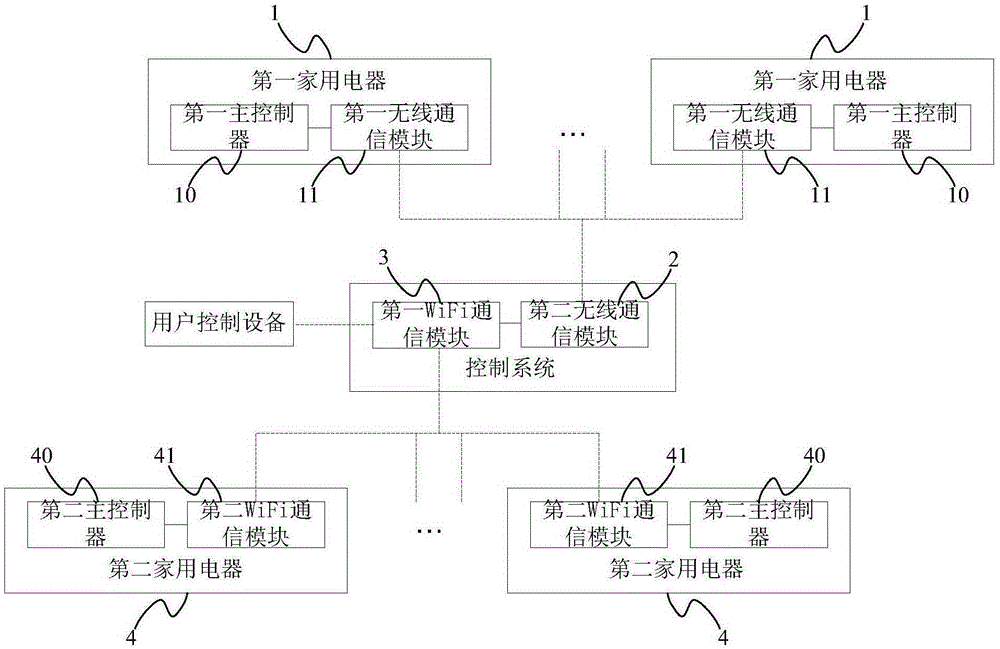

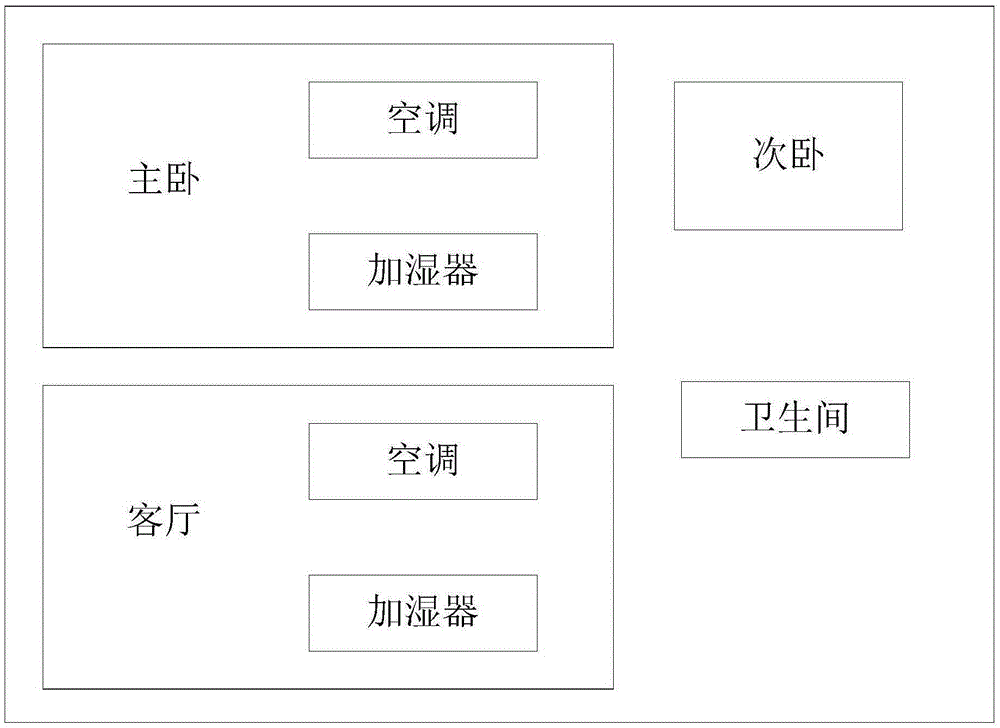

Household electrical appliance control method and system

The invention provides a household electrical appliance control method and system, and is applied to household electrical appliances including a first household electrical appliance. The first household electrical appliance comprises a first master controller and a first wireless communication module which is connected with the first master controller. The control system comprises a second wireless communication module and a first WiFi communication module. The first WiFi communication module is connected with the second wireless communication module through an asynchronous serial interface. The second wireless communication module is wirelessly connected with the first wireless communication module. The first WiFi communication module receives a control instruction inputted by a user through WiFi and performs format conversion on the control instruction and then transmits the control instruction to the second wireless communication module. The second wireless communication module transmits the control instruction to the first wireless communication module and transmits the control instruction to the first master controller through the first wireless communication module so as to control the first household electrical appliance and realize remote control of the household electrical appliances.

Owner:GREE ELECTRIC APPLIANCES INC

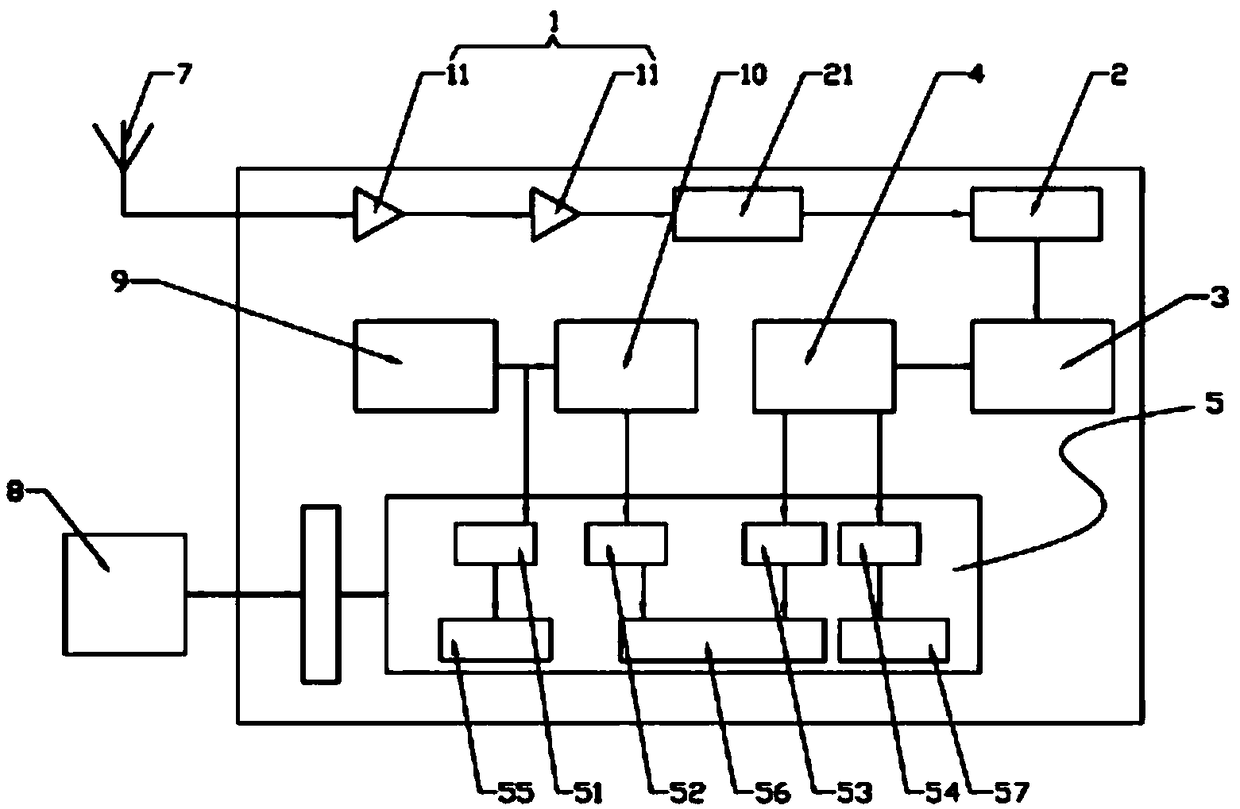

RF testing module and testing equipment containing the RF testing module

PendingCN108809448ALow costImplement WiFiTransmitters monitoringReceivers monitoringElectricityProgrammable logic device

The invention discloses a RF testing module which is reasonable in structure, high in universality and low in cost, and testing equipment containing the RF testing module. The invention comprises theRF testing module and the testing equipment containing the RF testing module; the RF testing module comprises a RF amplification module, a prescaler, a first waveform shaping circuit module, a complexprogrammable logic device, a microprocessor and an asynchronous serial interface electrically connected in order; the RF amplification module is electrically connected with an external antenna; the asynchronous serial interface is electrically connected with an external upper computer; the RF testing module further comprises a RMS detector and a second waveform shaping circuit module; the RMS detector is electrically connected with each of the external antenna, the second waveform shaping circuit module and the microprocessor; and the second waveform shaping circuit module is electrically connected with the microprocessor. The testing equipment disclosed by the invention is applied to the technical field of testing equipment of the security-protection sensor.

Owner:ZHONGSHAN BOCEDA ELECTRONICS TECH CO LTD

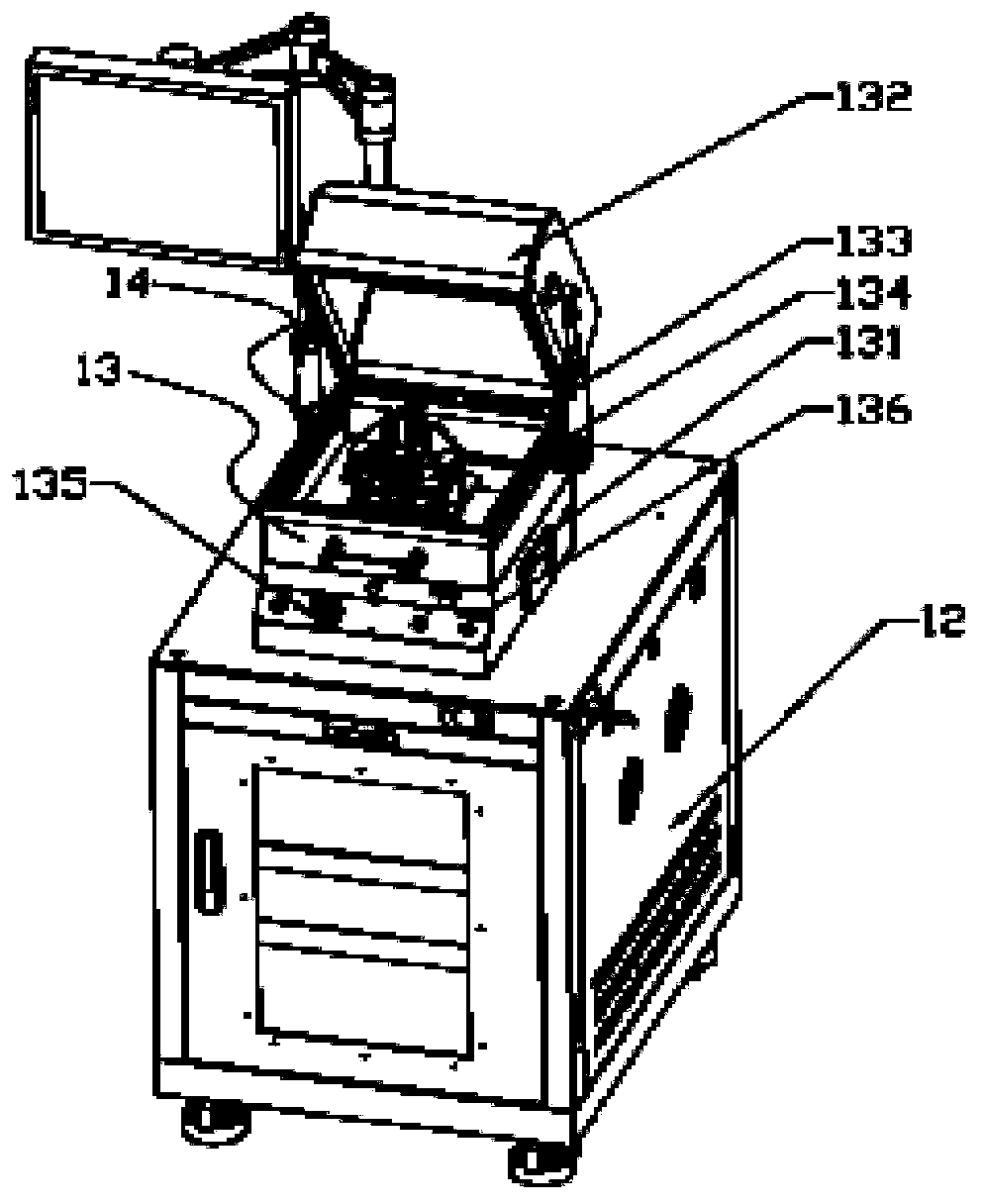

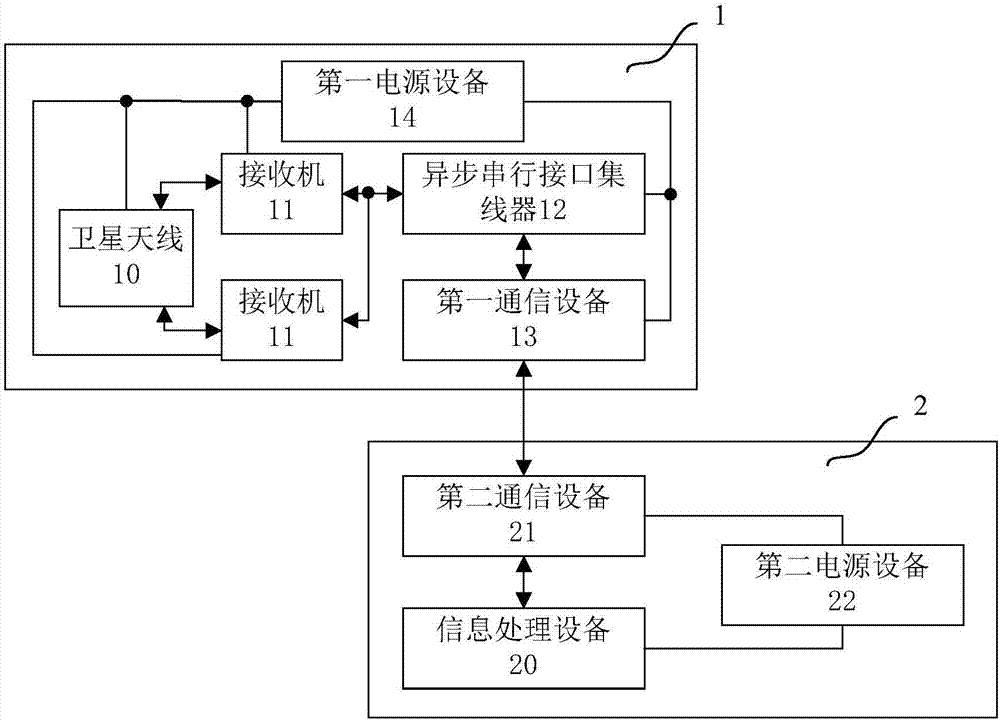

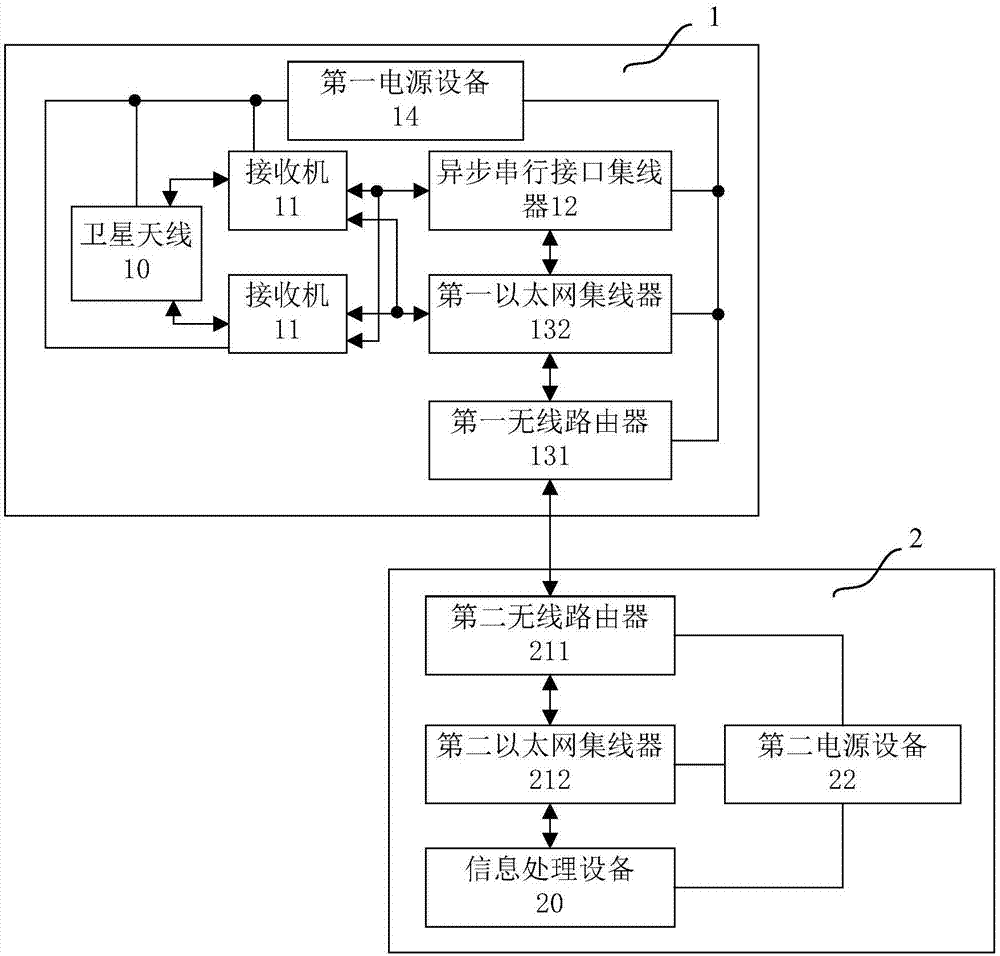

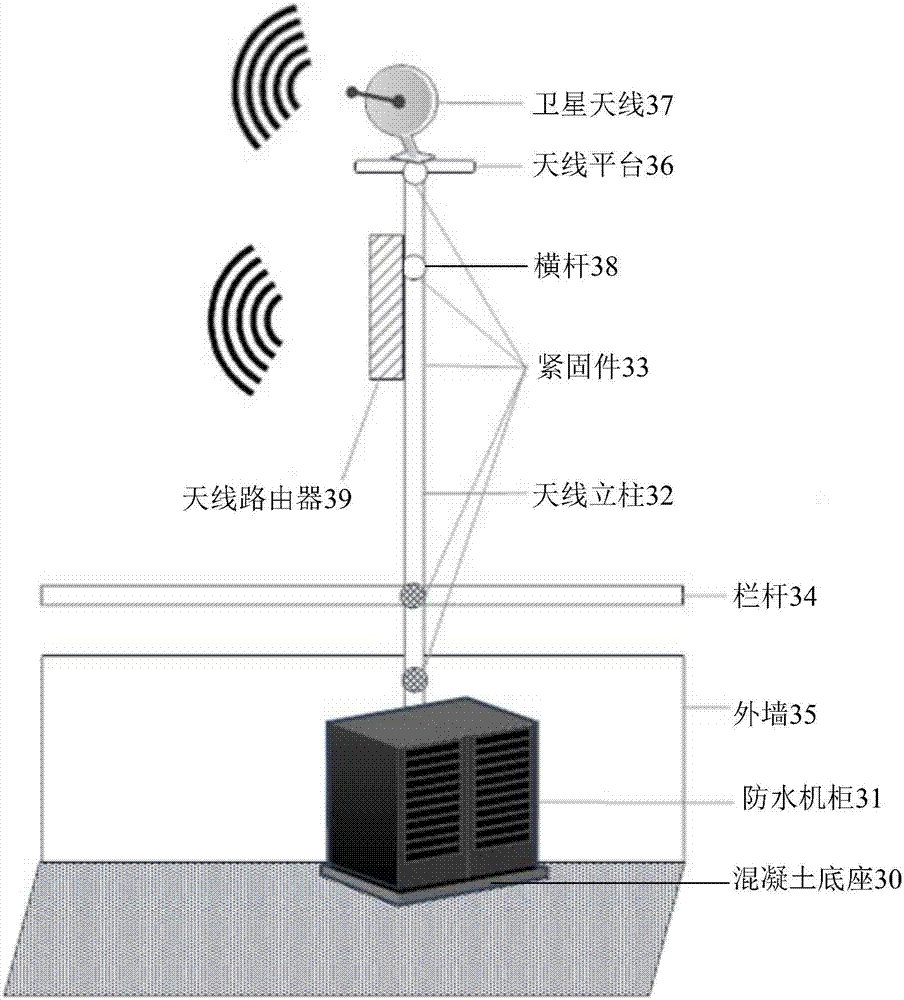

Small satellite ground station

ActiveCN107070533AImprove efficiencyImprove reliabilityRadio transmissionInformation processingSatellite data

The present invention provides a small satellite ground station. The small satellite ground station comprises an outdoor unit and an indoor unit. The outdoor unit comprises a satellite antenna, multiple receivers, an asynchronous serial interface hub, a first communication device, and a first power supply device. The multiple receivers are each in communicated connection with the satellite antenna and realize different satellite data communication functions. The asynchronous serial interface hub are connected with multiple receivers through multiple asynchronous serial interfaces. The first communication device establishes a network connection with the multiple receivers and the asynchronous serial interface hub so as to transmit satellite data from multiple receivers to the indoor unit. The first power supply device powers the above devices inside the outdoor unit. The indoor unit comprises an information processing device, a second communication device, and a second power supply device. The information processing device processes satellite data from the multiple receivers. The second communication device establishes a network connection with the first communication device and the information processing device, receives satellite data from the first communication device and transmits the satellite data to the information processing device. The second power supply device powers the above devices in the indoor unit.

Owner:PACIFIC TELECOM & NAVIGATION LTD

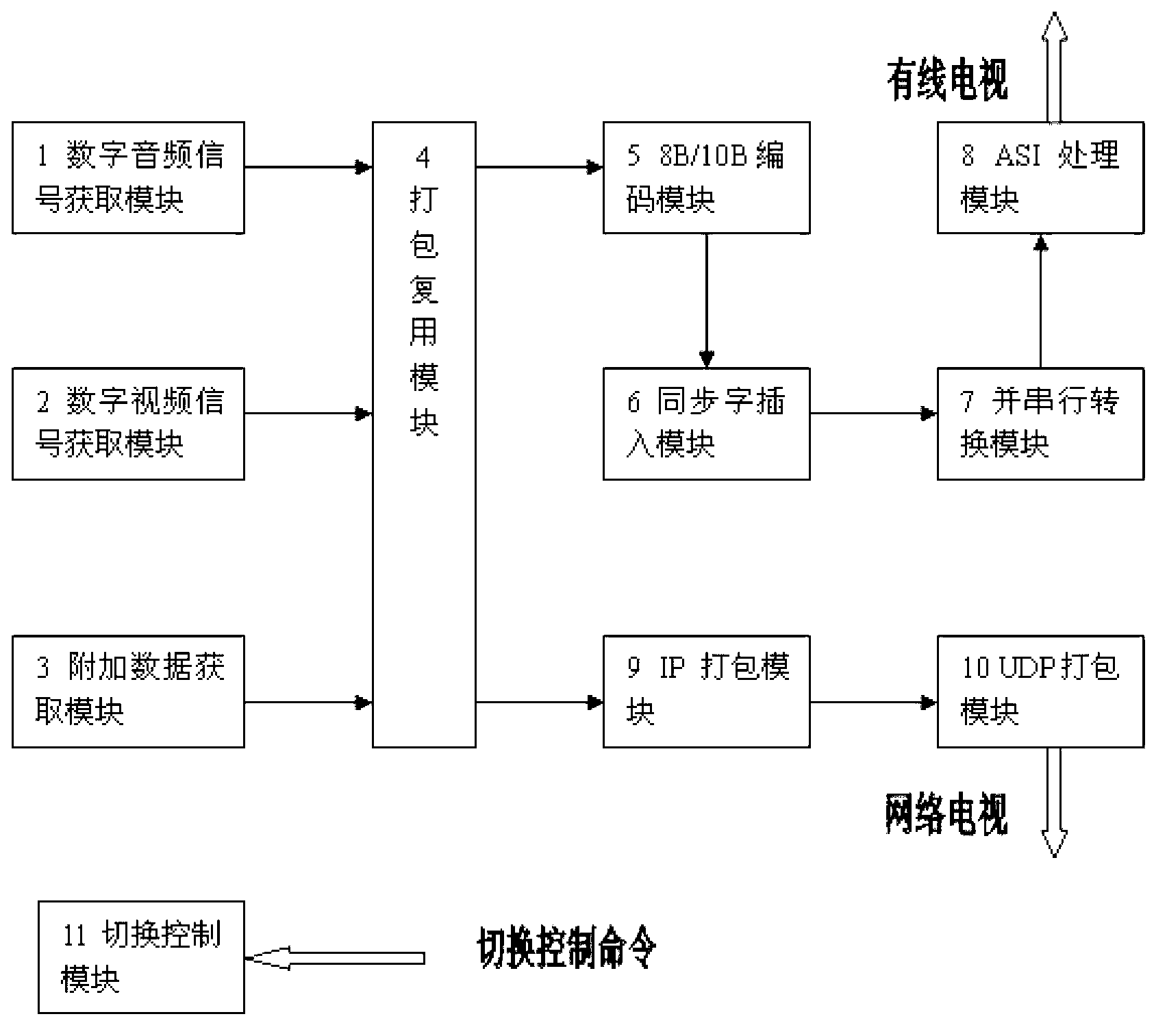

Television signal transmitter combining wired television transmission and network television transmission

InactiveCN103313101AExpansion of TV businessSave resourcesTelevision system detailsSelective content distributionDigital videoData acquisition

The invention relates to a television signal transmitter combining wired television transmission and network television transmission. The television signal transmitter comprises a digital voice signal acquisition module, a digital video signal acquisition module, an additional data acquisition module, a packing and multiplexing module, a 8B / 10B encoding module, a synchronous character insertion module, a serial-parallel conversion module, an asynchronous serial interface (ASI) processing module, an IP (Internet Protocol) packing module, a UDP (User Datagram Protocol) packing module and a conversion control module, wherein the packing and multiplexing module is connected with the digital voice signal acquisition module, the digital video signal acquisition module and the additional data acquisition module to be respectively used for receiving compressed voice data, compressed video data and encoded additional data, packing and multiplexing the data and processing the packed and multiplexed data under the control of the conversion control module so as to obtain wired television signals or network television signals. Through the invention, the functions of the transmitter can be expanded, and wired television signal transmission and network television signal transmission are combined.

Owner:航美传媒集团有限公司

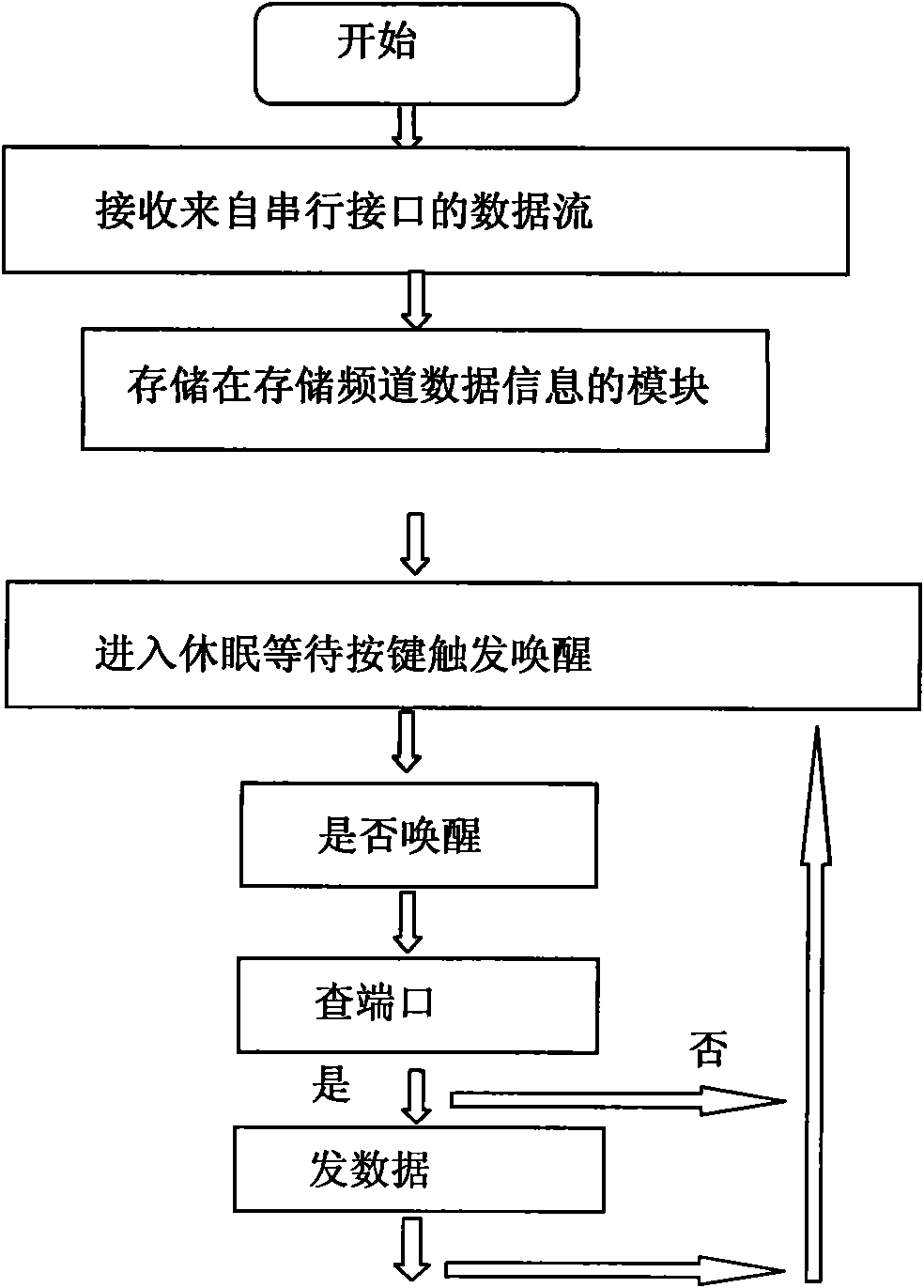

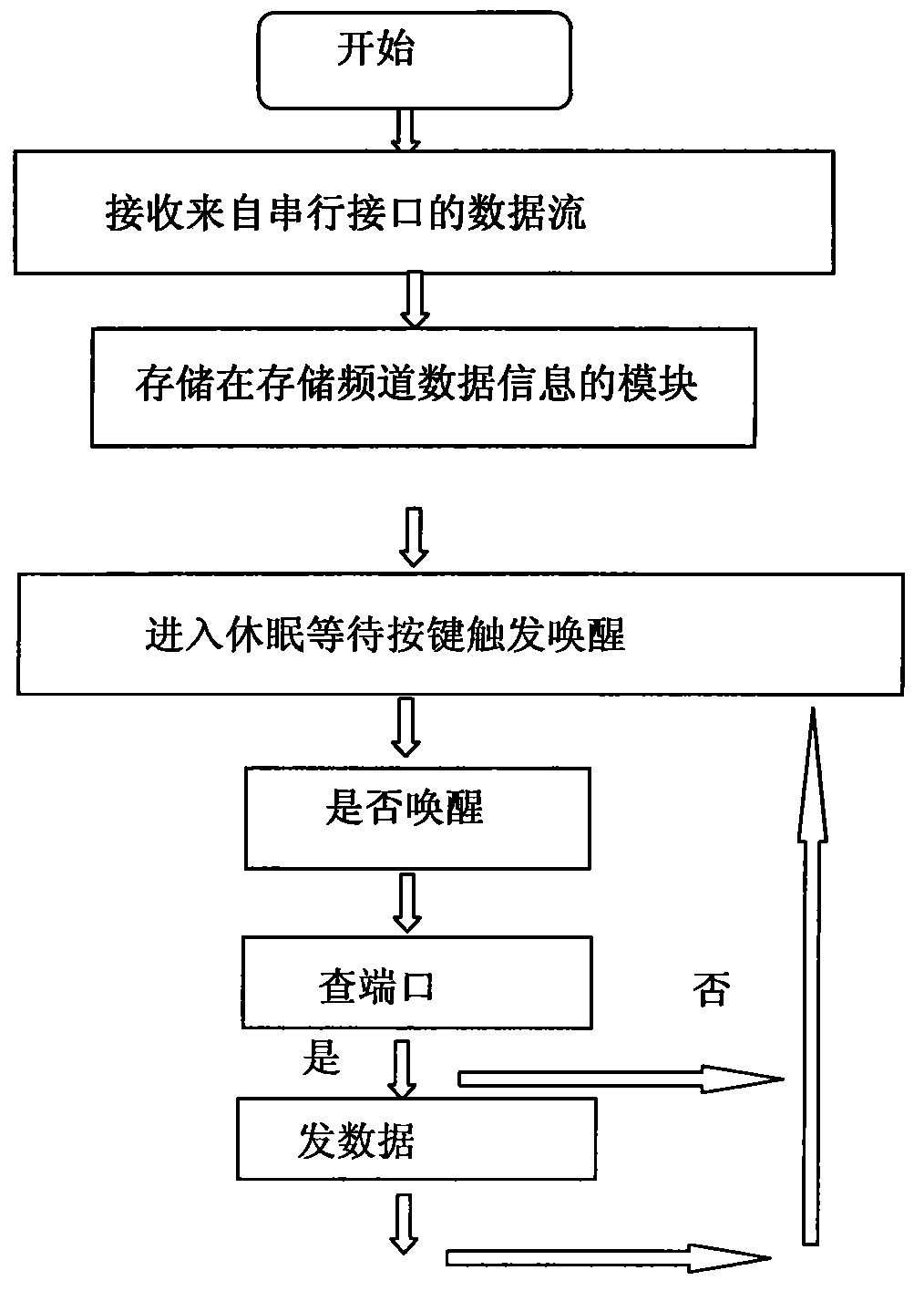

Television remote controller

InactiveCN102025931AEasy to useGood choiceTelevision system detailsColor television detailsVisually impairedChannel data

The invention provides a television remote controller. The television remote controller comprises a remote controller device and a module which is connected with a circuit board in the remote controller device for storing channel data information, wherein the module for storing the channel data information is connected with a data interface module which can be communicated with a central processing unit (CPU) main board or a computer; and a voice device is arranged in the remote controller device and connected with an asynchronous serial interface and the data interface module which is communicated with the CPU main board or the computer. The television remote controller can effectively help the visually impaired use the remote controller, so that the visually impaired can conveniently choose a channel program needed by the visually impaired.

Owner:JINGAN DISTRICT JUVENILE ACTIVITY CENT