Synchronous and asynchronous switchable serial interface based on FPGA and use method

A serial port, general-purpose asynchronous technology, applied in the direction of instruments, electrical digital data processing, etc., can solve the problem of increased bit error rate, etc., to achieve the effect of reducing bit error rate, improving frequency division precision, stability and accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] In order to make the purpose, technical solutions and advantages of the embodiments of the present invention clearer, the technical solutions in the embodiments of the present invention will be clearly and completely described below in conjunction with the drawings in the embodiments of the present invention. Obviously, the described embodiments It is a part of embodiments of the present invention, but not all embodiments.

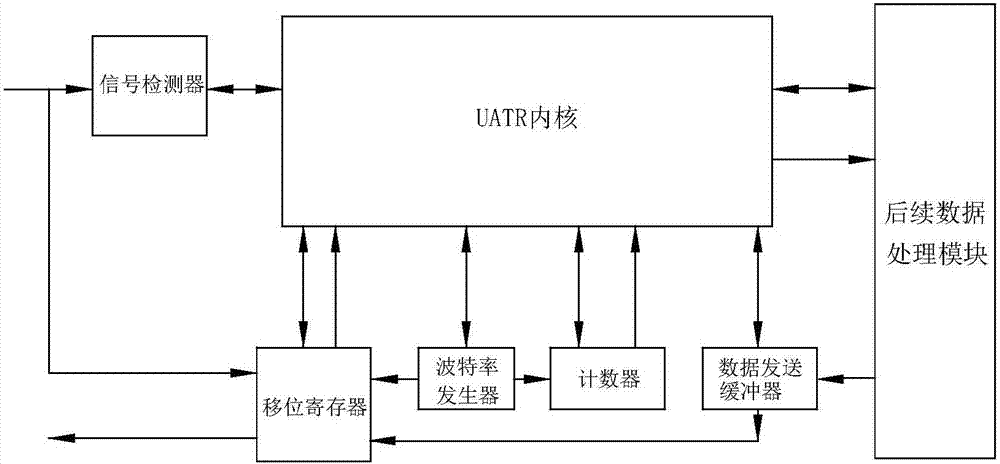

[0036] Such as figure 1 As shown, in the existing UART, the signal detector detects the data, sends the control signal to the UART core, the data is processed by the shift register and sent to the UART core, and the baud rate generator generates the baud rate for controlling the serial port The transmission rate on the line, the entire UART is connected to the back-end processing module through the TX / RX serial data line for data transmission, and CTS / RTS is a handshake signal, which is responsible for communicating with the back-end processing stat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More