Serial clock restoring circuit in universal serial bus (USB) 2.0 high-speed mode

A clock and circuit technology, applied in the field of data clock recovery, can solve the problems of superimposed noise and interference, amplitude attenuation, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

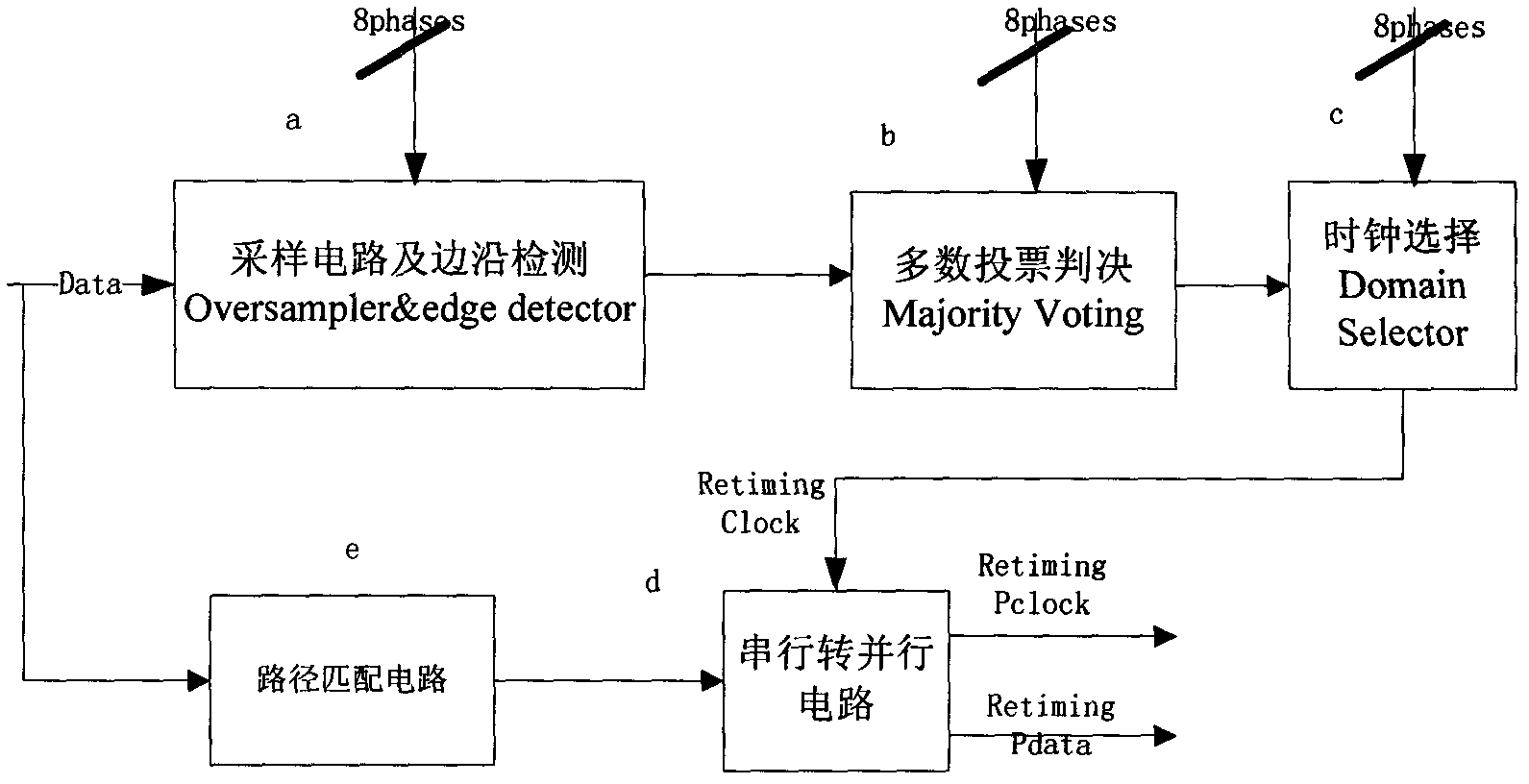

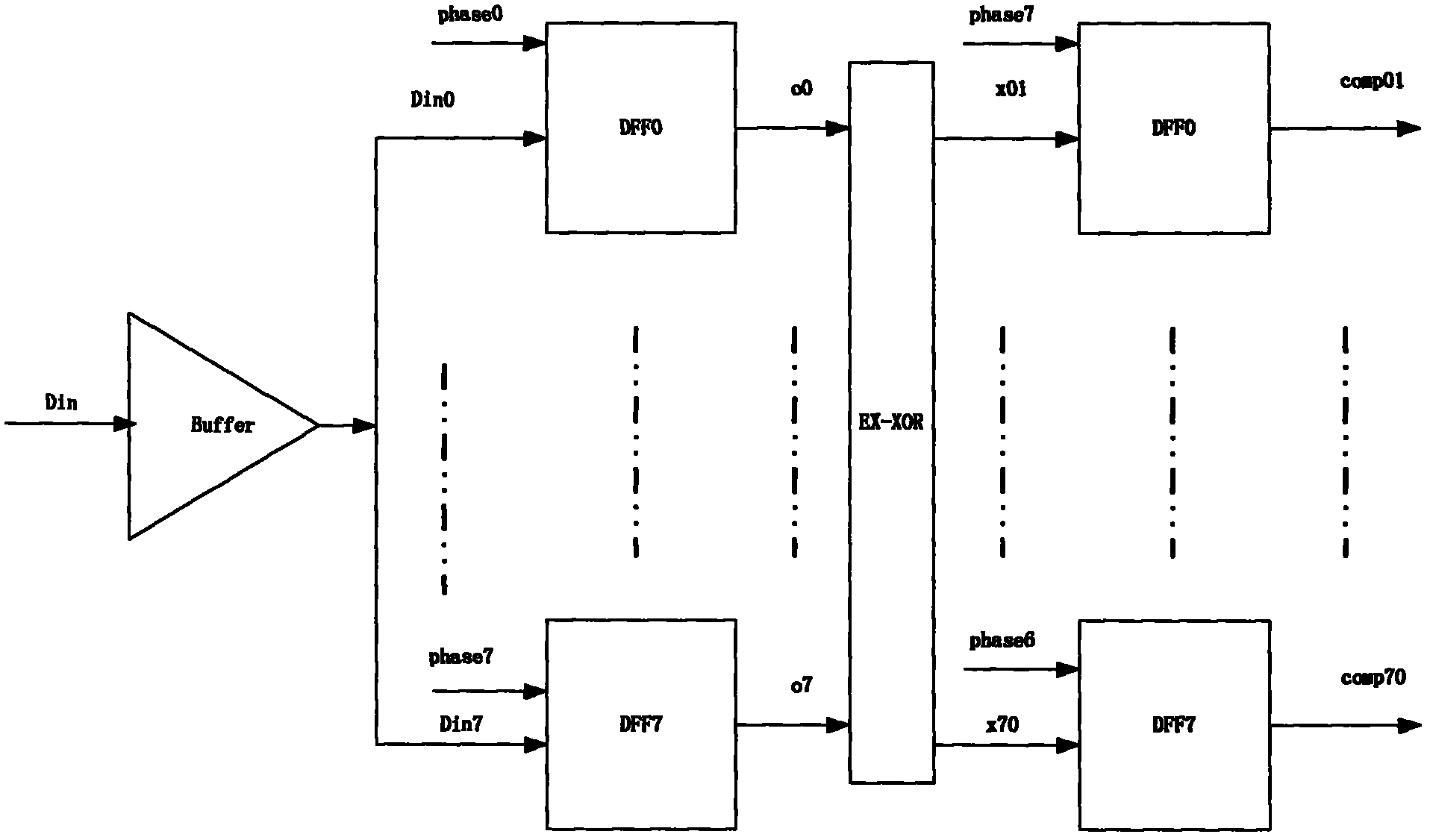

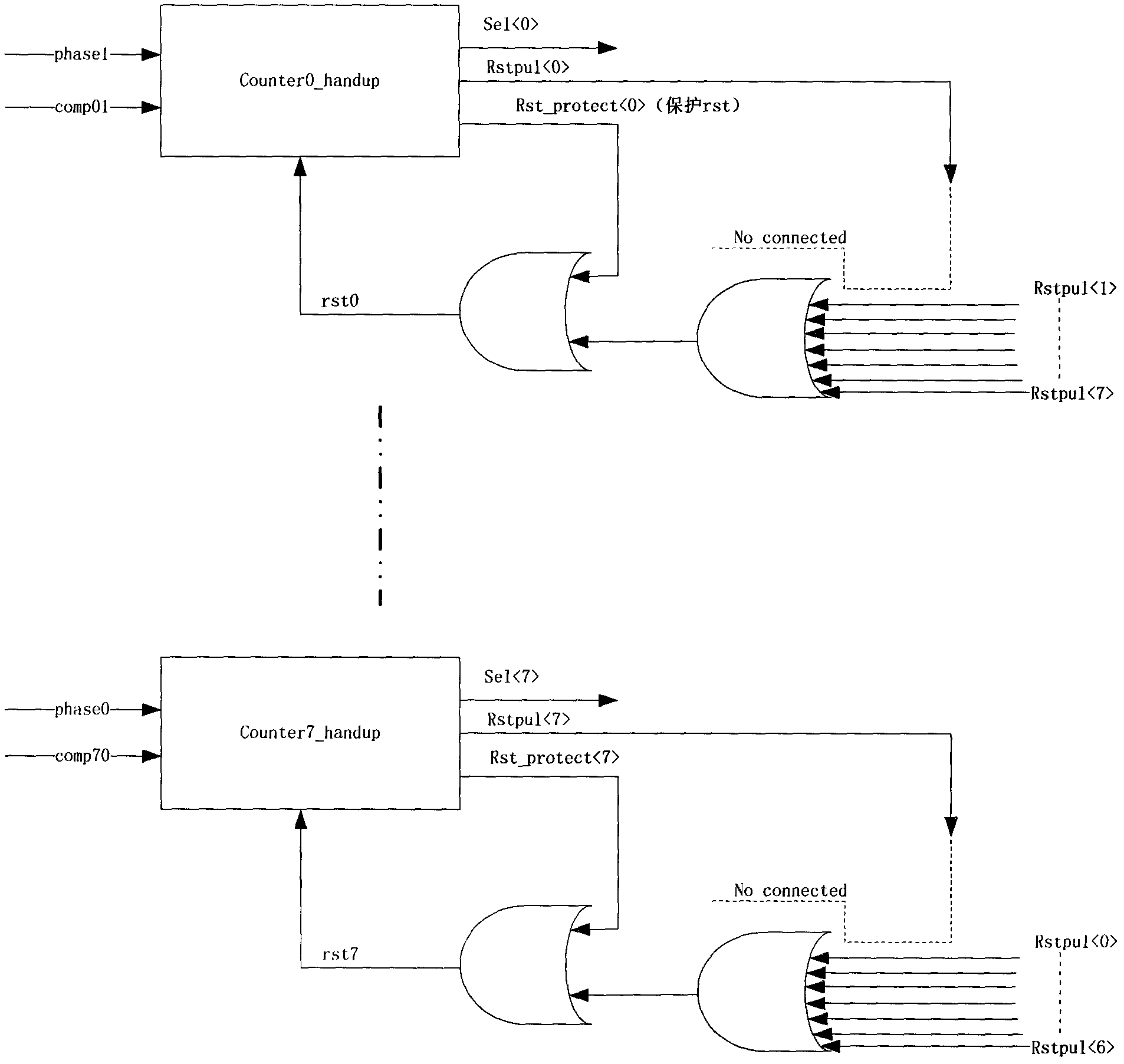

[0012] The implementation of this patent is in accordance with the content of Article 3, and the designed circuit meets the speed requirements of USB2.0, specifically as figure 2 , 3 , 4, and 5 are schematic illustrations. The implementation method described in this patent has been taped out and verified in 0.13um and 0.35um processes, and has obvious advantages in power consumption, area and performance.

[0013] The infringement of this patent can generally be judged by analyzing its implementation circuit. If the circuit cannot be obtained, it can be judged by the reverse analysis method of dissecting the chip and taking pictures. Institutions that may infringe include various chip design companies with or without factories, research institutions, schools, etc.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More