Patents

Literature

9476 results about "Master controller" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

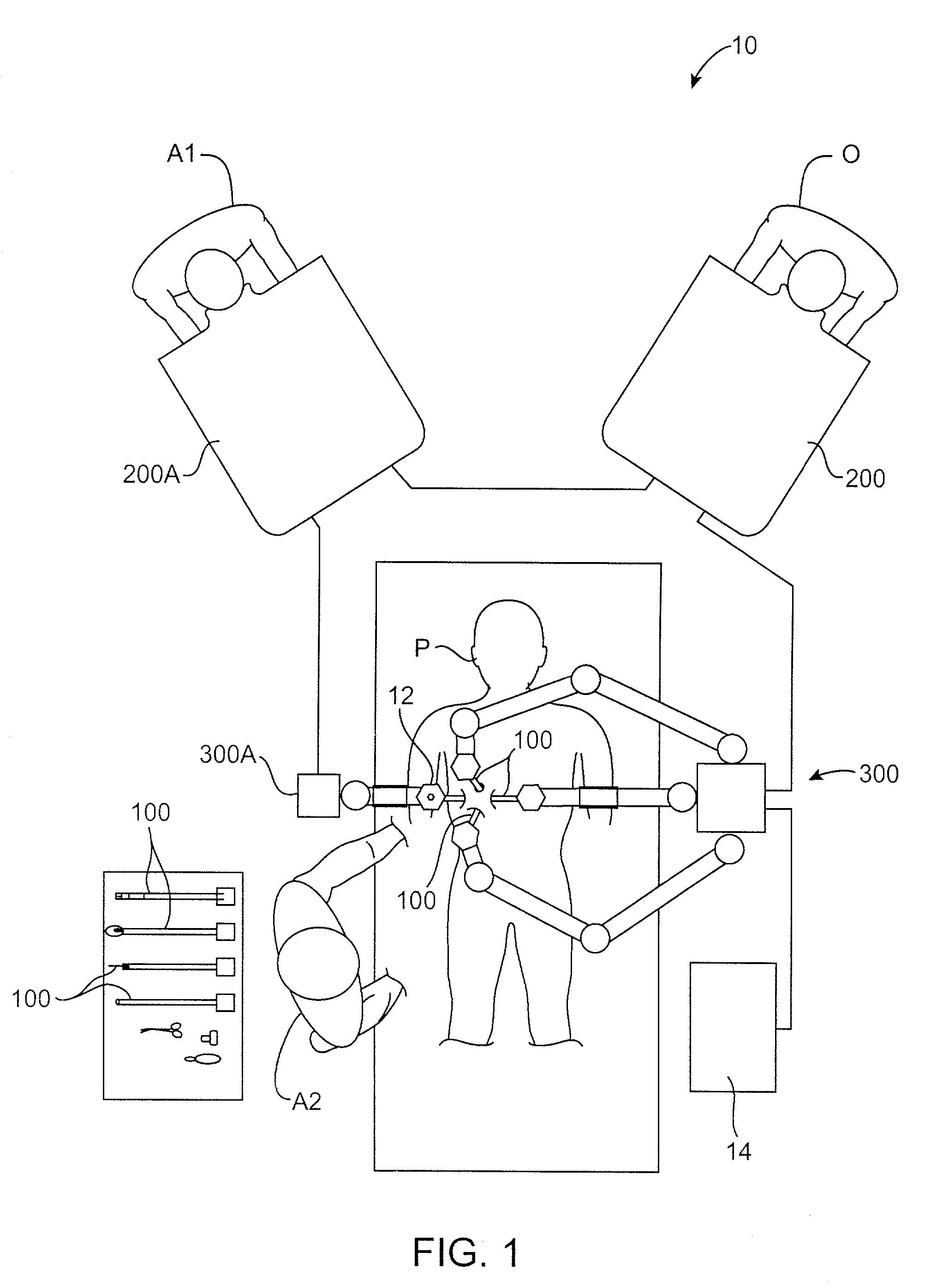

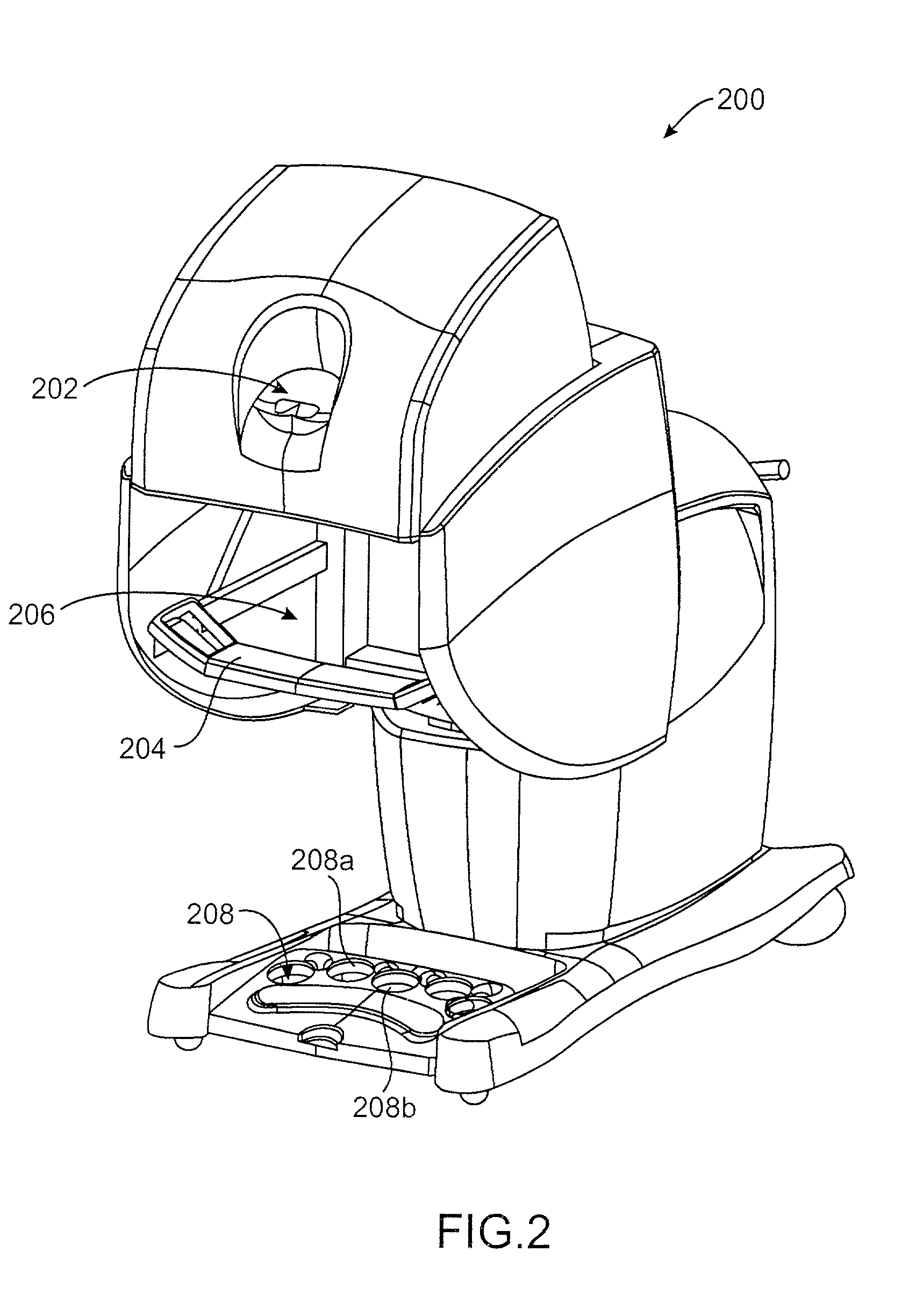

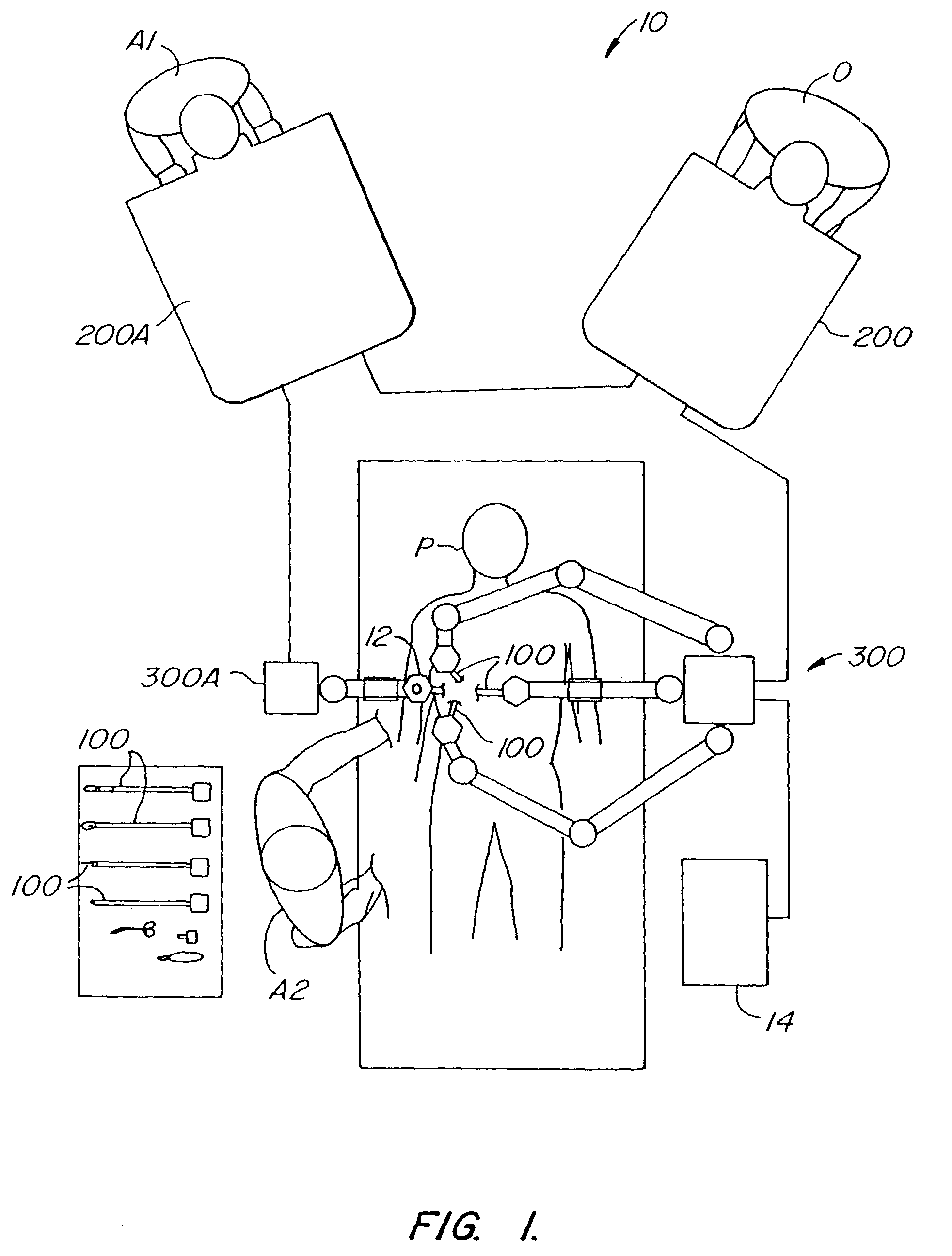

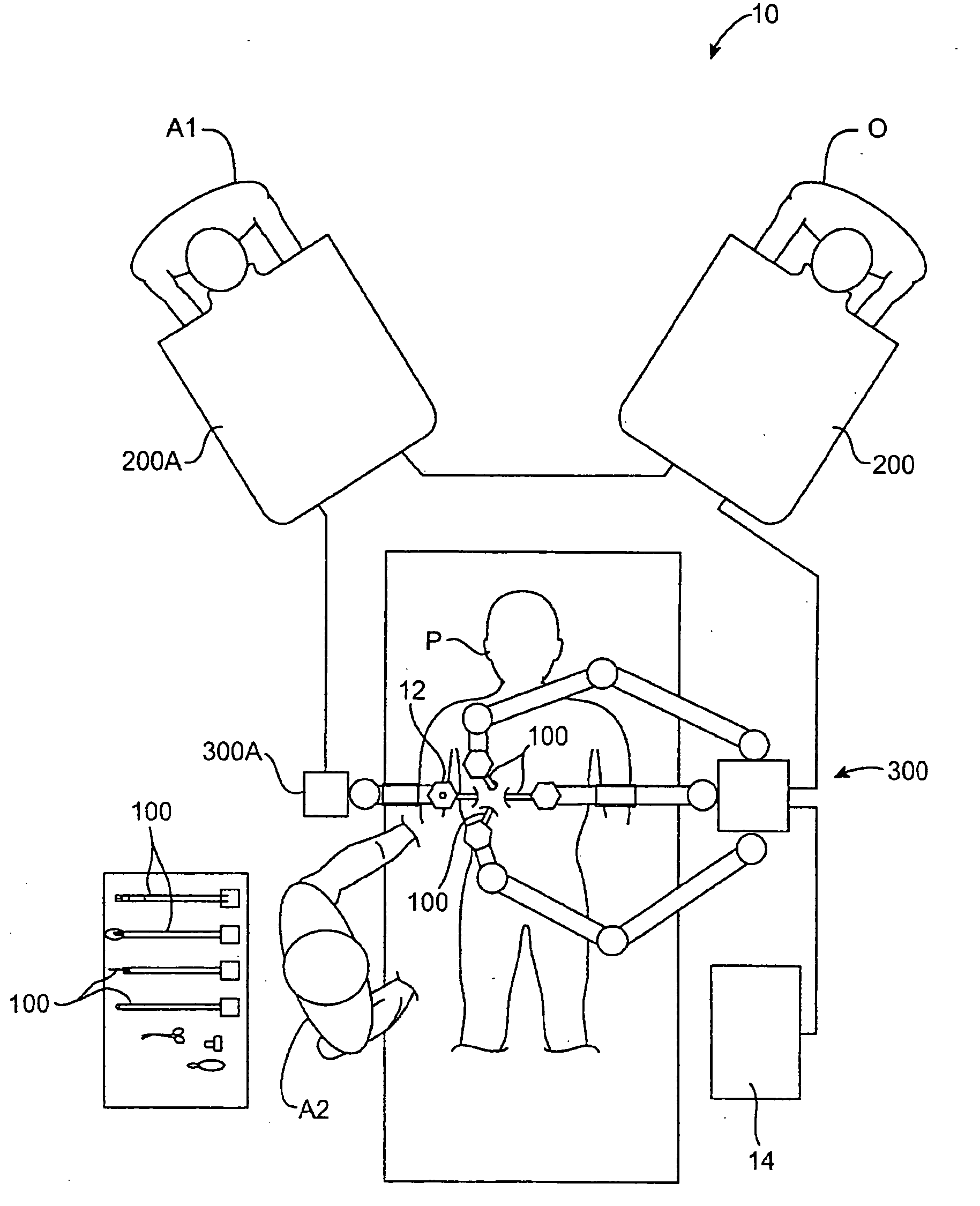

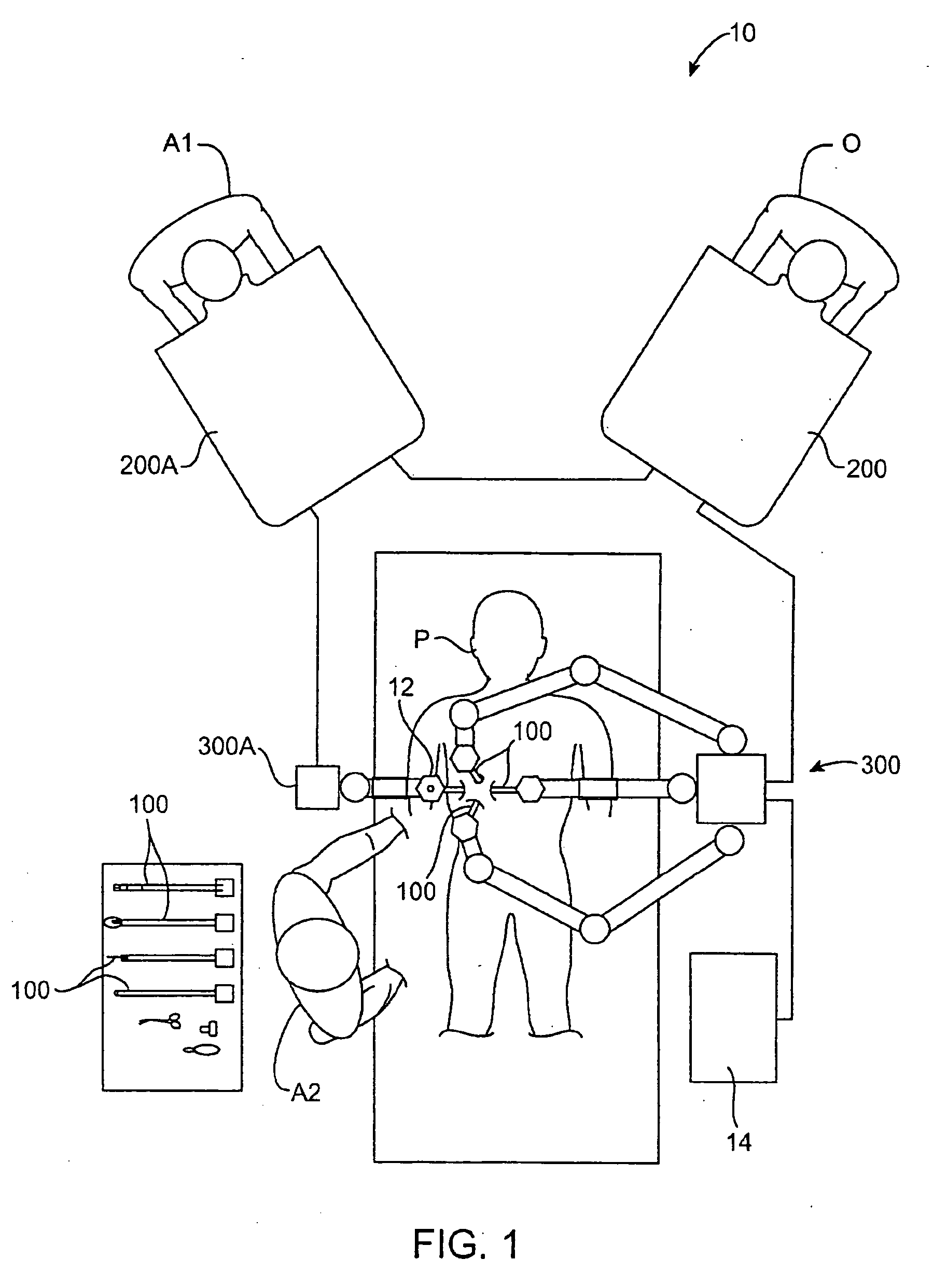

Repositioning and reorientation of master/slave relationship in minimally invasive telesurgery

InactiveUS7087049B2Easy SetupEasy to adjustDiagnostic recording/measuringSensorsEngineeringDegrees of freedom

The invention provides robotic surgical systems which allow selectable independent repositioning of an input handle of a master controller and / or a surgical end effector without corresponding movement of the other. In some embodiments, independent repositioning is limited to translational degrees of freedom. In other embodiments, the system provides an input device adjacent a manipulator supporting the surgical instrument so that an assistant can reposition the instrument at the patient's side.

Owner:INTUITIVE SURGICAL OPERATIONS INC

Repositioning and reorientation of master/slave relationship in minimally invasive telesurgery

InactiveUS20020128552A1Easy SetupEasy to adjustDiagnostic recording/measuringSensorsMaster controllerDegrees of freedom

The invention provides robotic surgical systems which allow selectable independent repositioning of an input handle of a master controller and / or a surgical end effector without corresponding movement of the other. In some embodiments, independent repositioning is limited to translational degrees of freedom. In other embodiments, the system provides an input device adjacent a manipulator supporting the surgical instrument so that an assistant can reposition the instrument at the patient's side.

Owner:INTUITIVE SURGICAL OPERATIONS INC

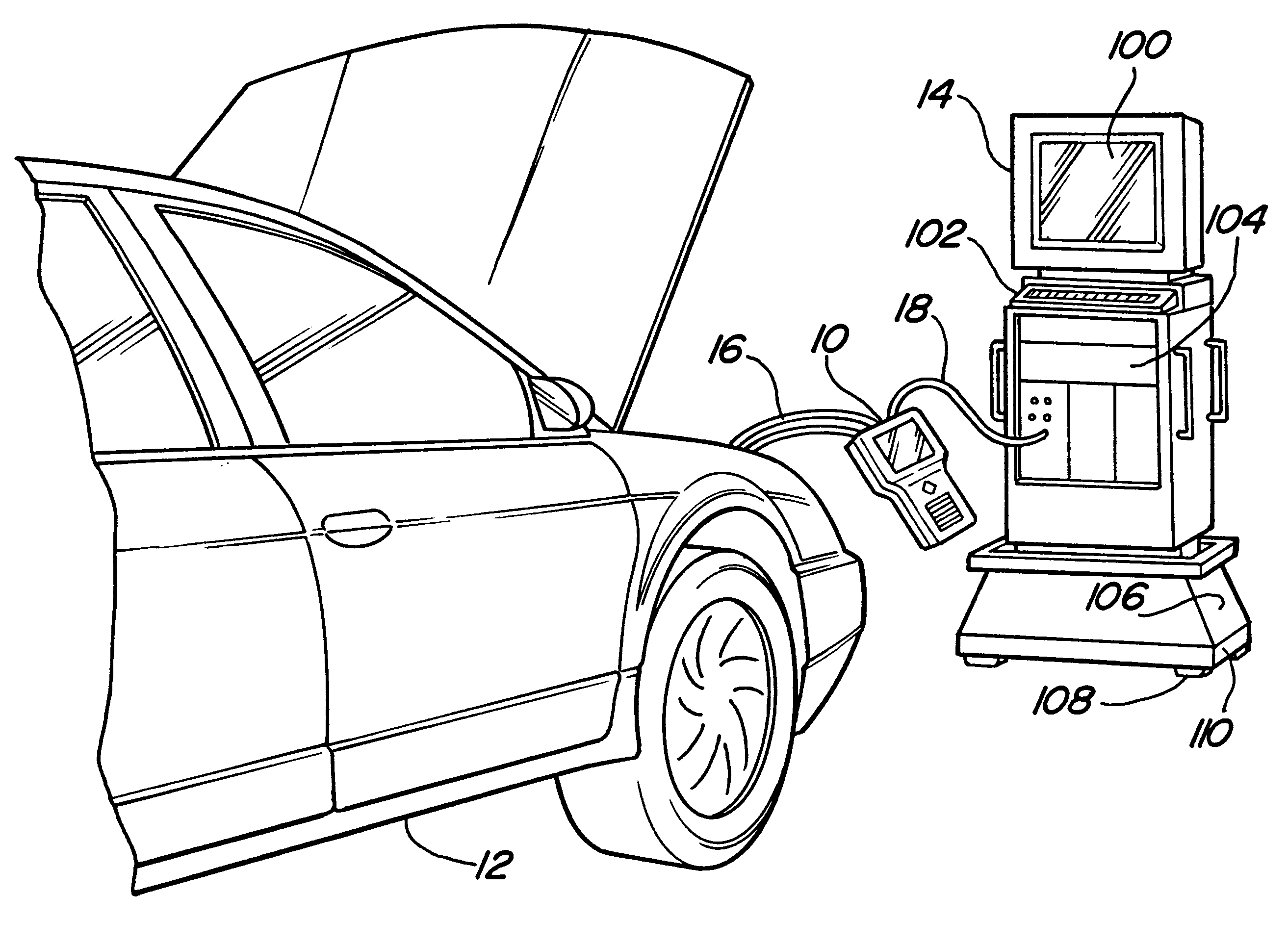

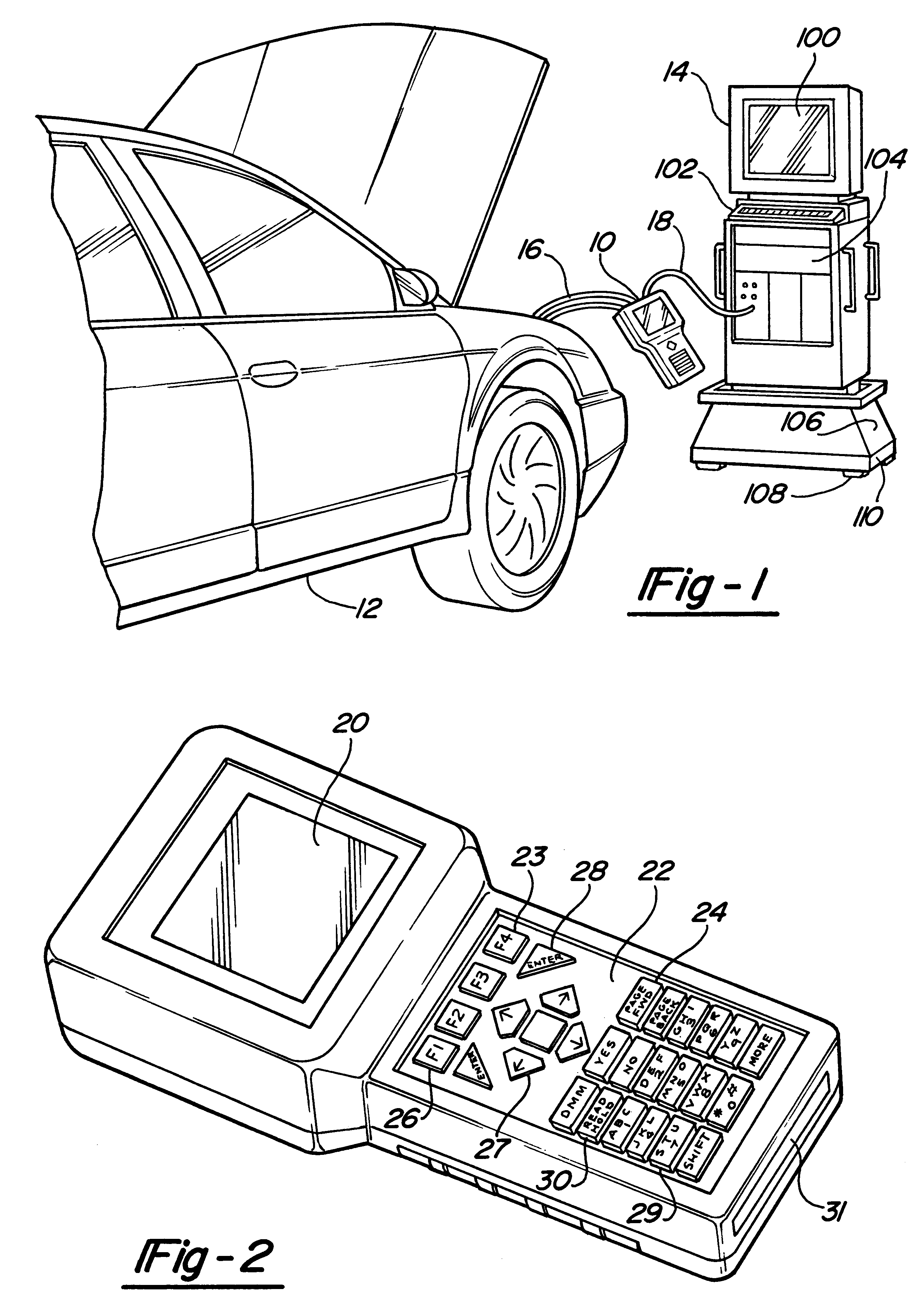

Automotive diagnostic service tool with hand held tool and master controller

InactiveUS6181992B1Reduce needQuick updateVehicle testingRegistering/indicating working of vehiclesOn boardMaster station

The present invention relates to a system and method for diagnosing and isolating problems and for monitoring operting conditions on an automobile. The system includes a hand held unit and a master station which can operate alone or in unison to accomplish functions such as logging and displaying data on a real-time basis, logging data remotely and displaying the data at a later time, diagnosing fault conditions, monitoring operating parameters, reprogramming on-board vehicle controllers, displaying service manual and service bulletin pages and ordering parts on-line.

Owner:FCA US

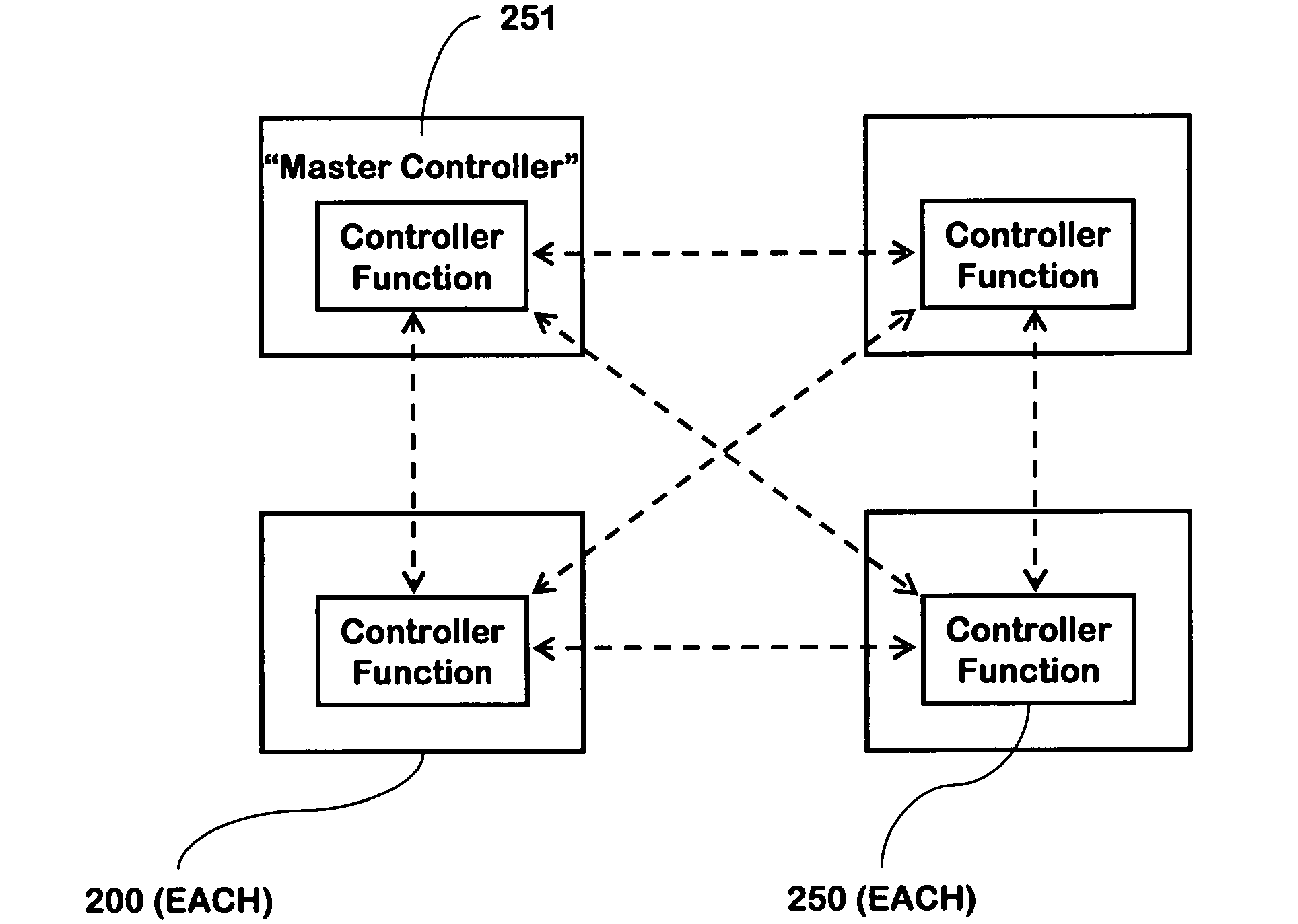

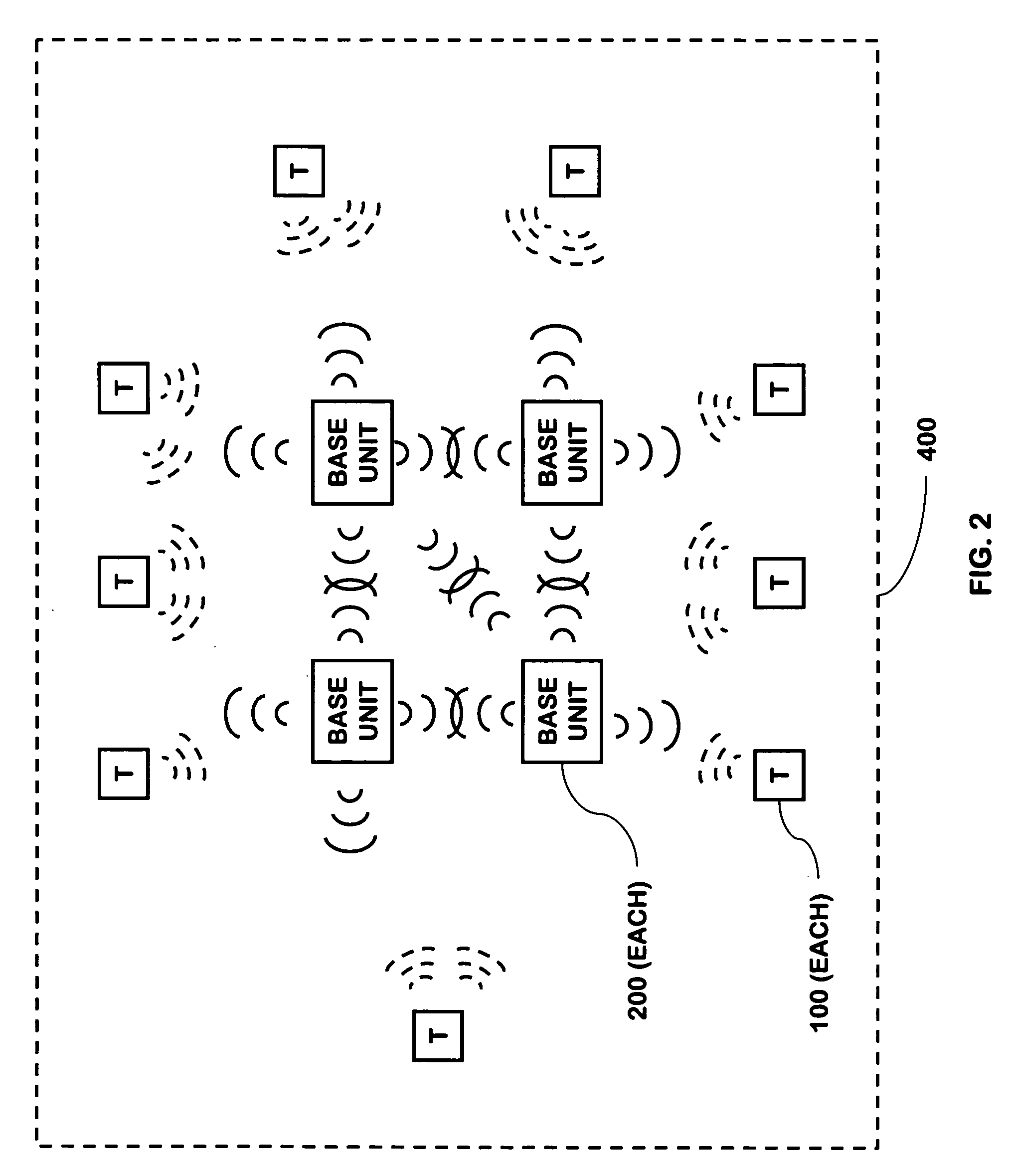

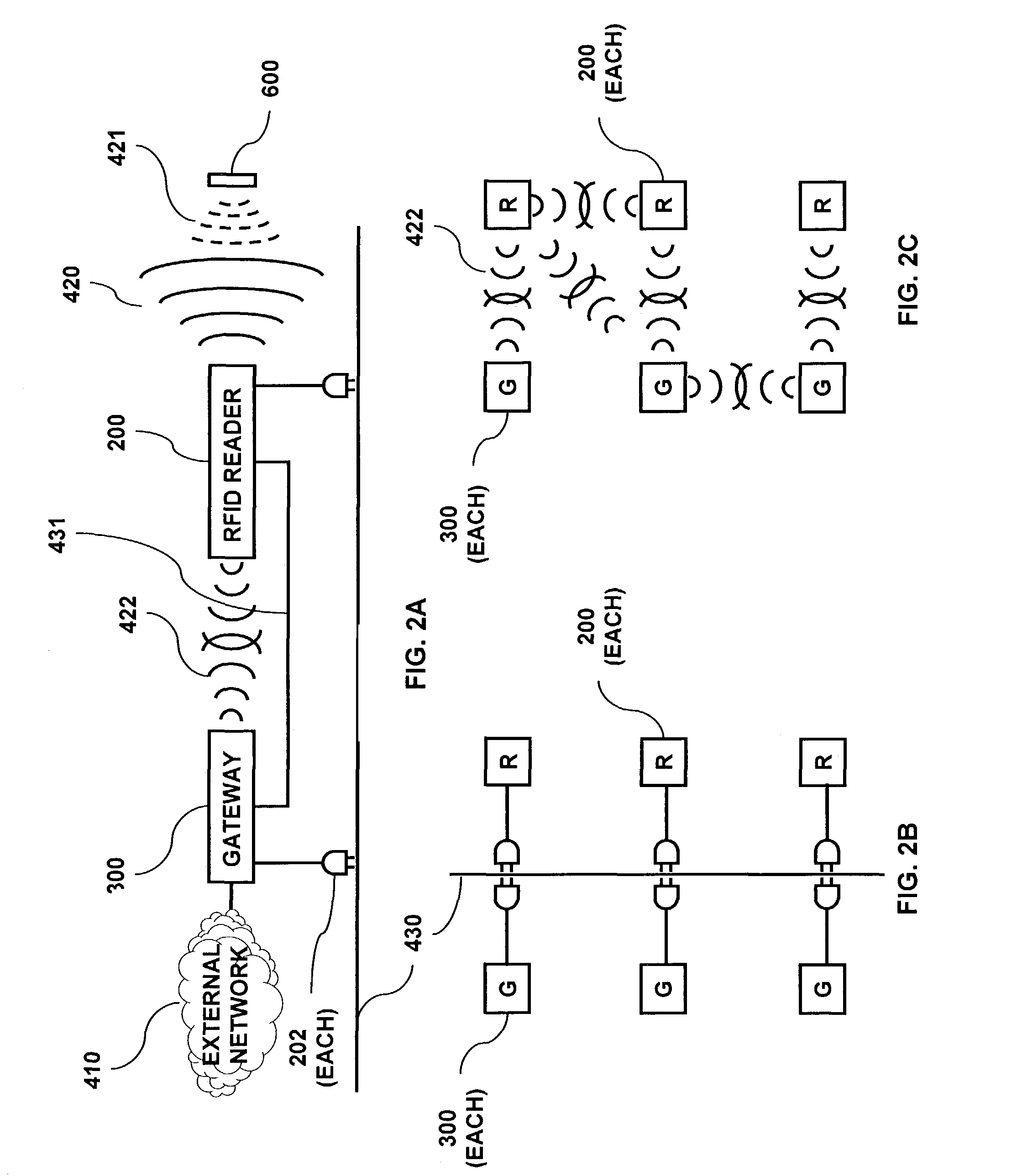

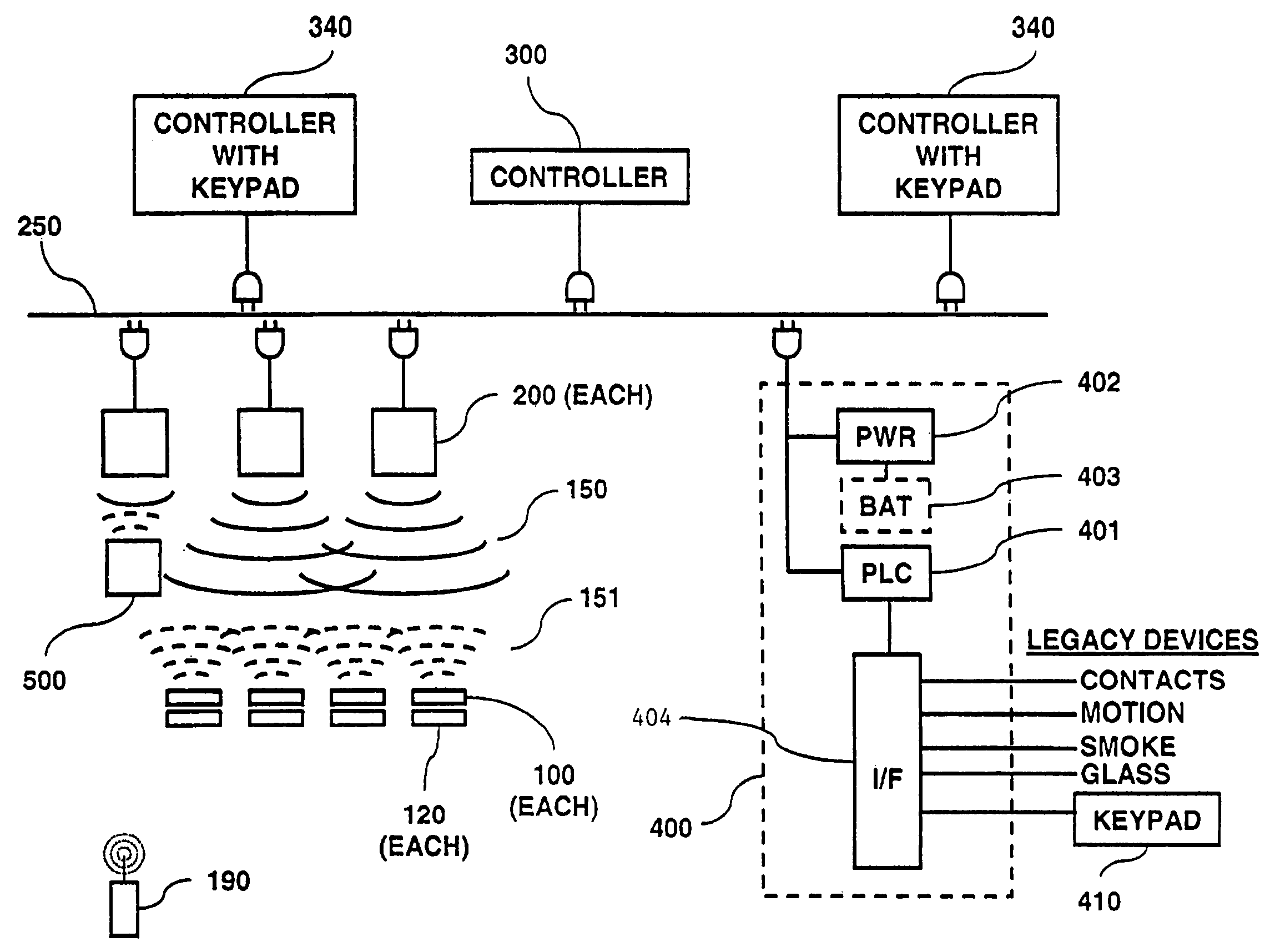

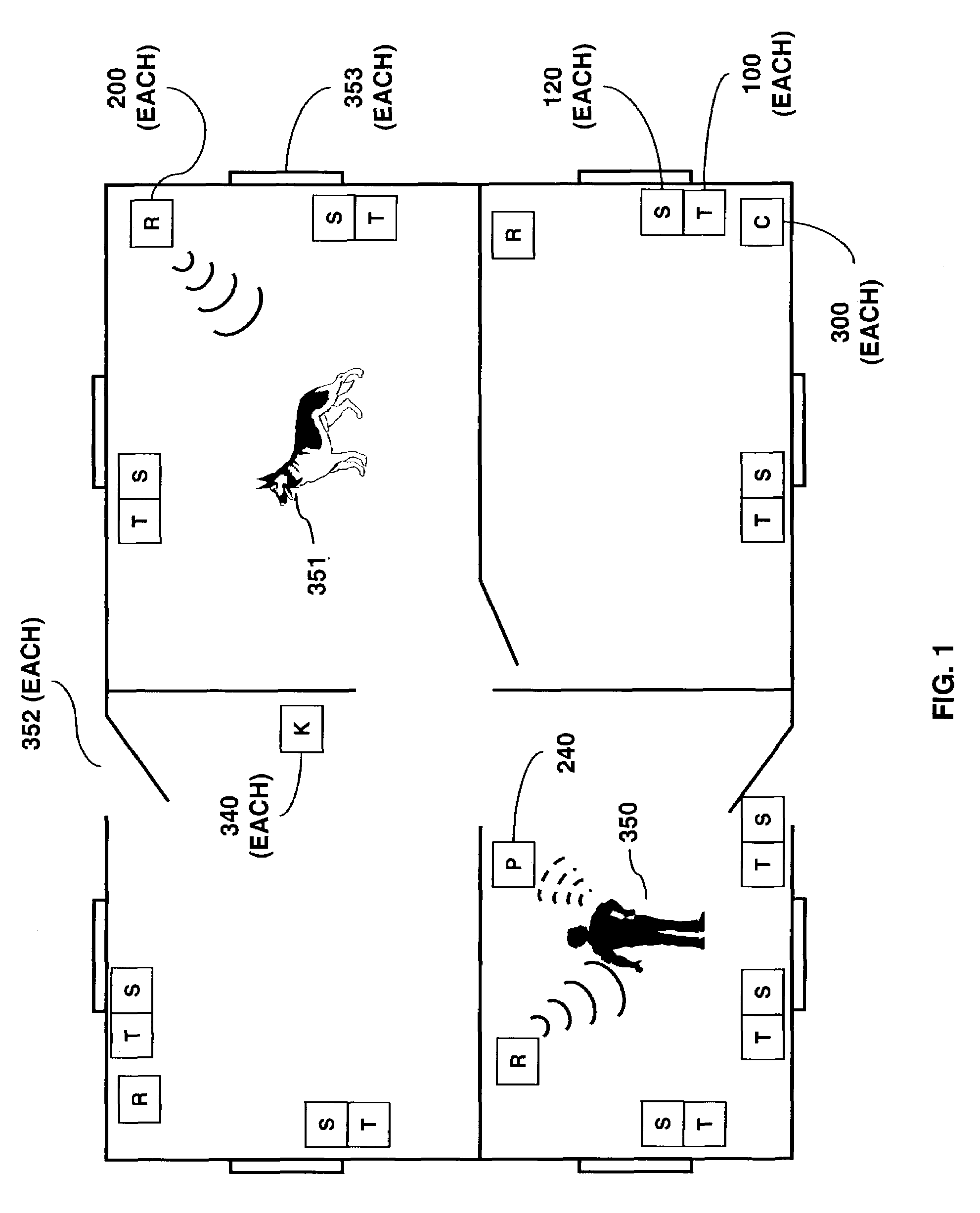

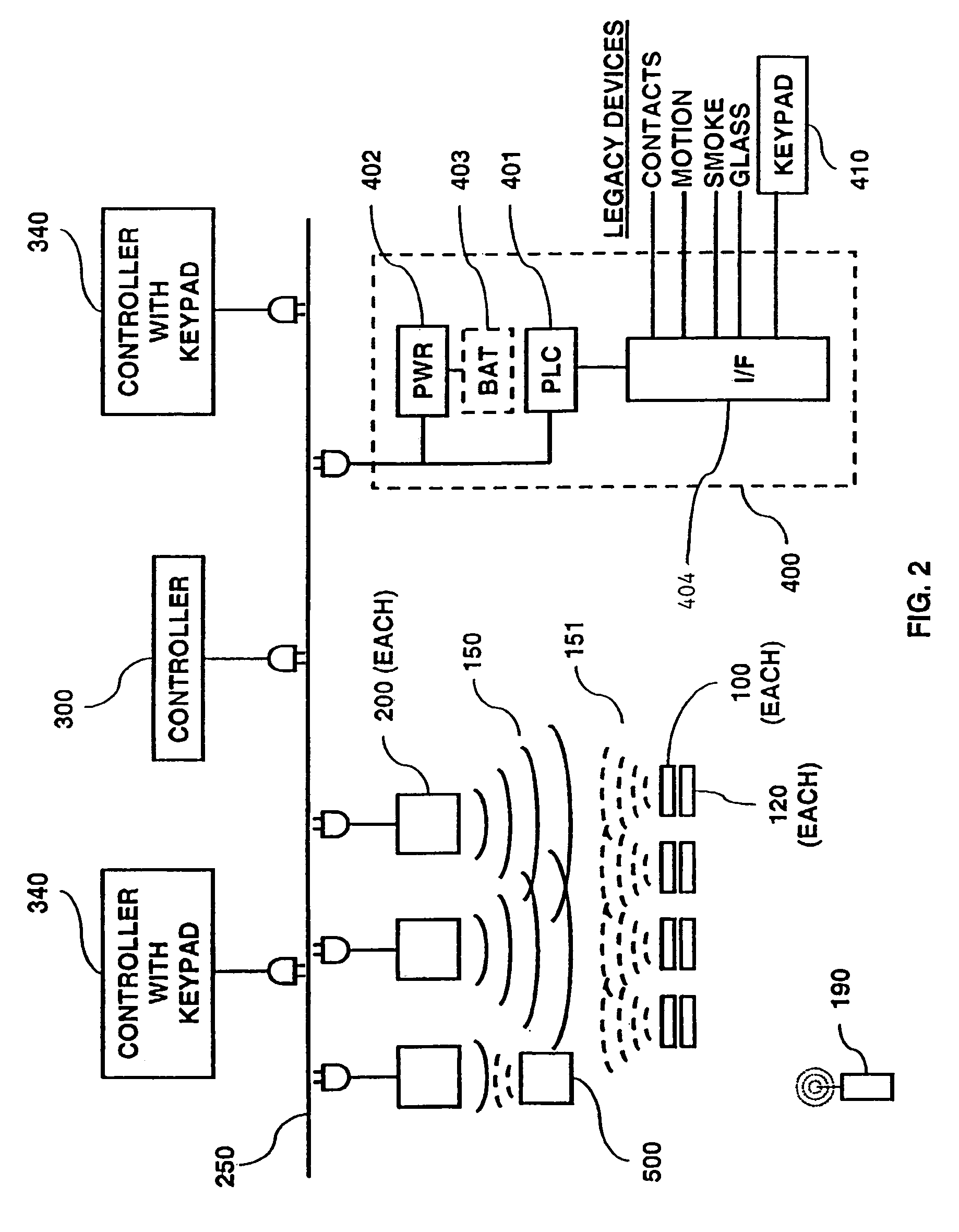

Multi-controller security network

InactiveUS7079020B2Improve reliabilityLow costMemory record carrier reading problemsElectric signalling detailsOperating energyMaster controller

A security network containing multiple controller functions that communicate using wireless communications. The controller functions are contained within base units. One controller function may be the master controller. Other controller functions may receive a copy of the configuration data contained within the master controller. If the master controller fails, another controller function may become the master controller. The controller functions may use encryption keys to encrypt and / or authenticate communications. Some base units may contain a telecommunications interface. Controller units may relay communications between themselves to reach a telecommunications interface. Controller functions located in different buildings may communicate. Controller functions may each receive wireless communications from a transponder and combine the received communications to reduce errors.

Owner:ADT US HLDG INC

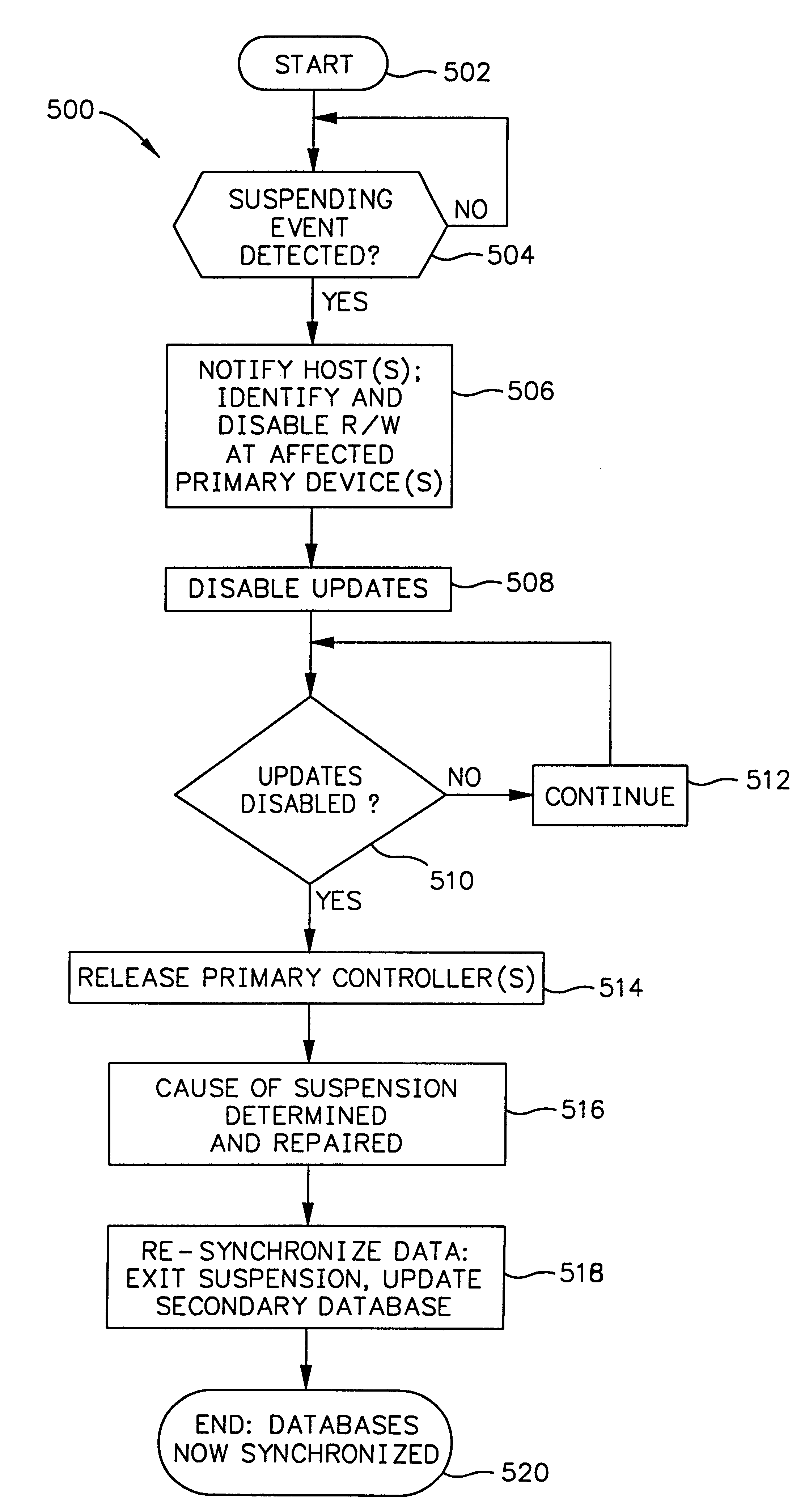

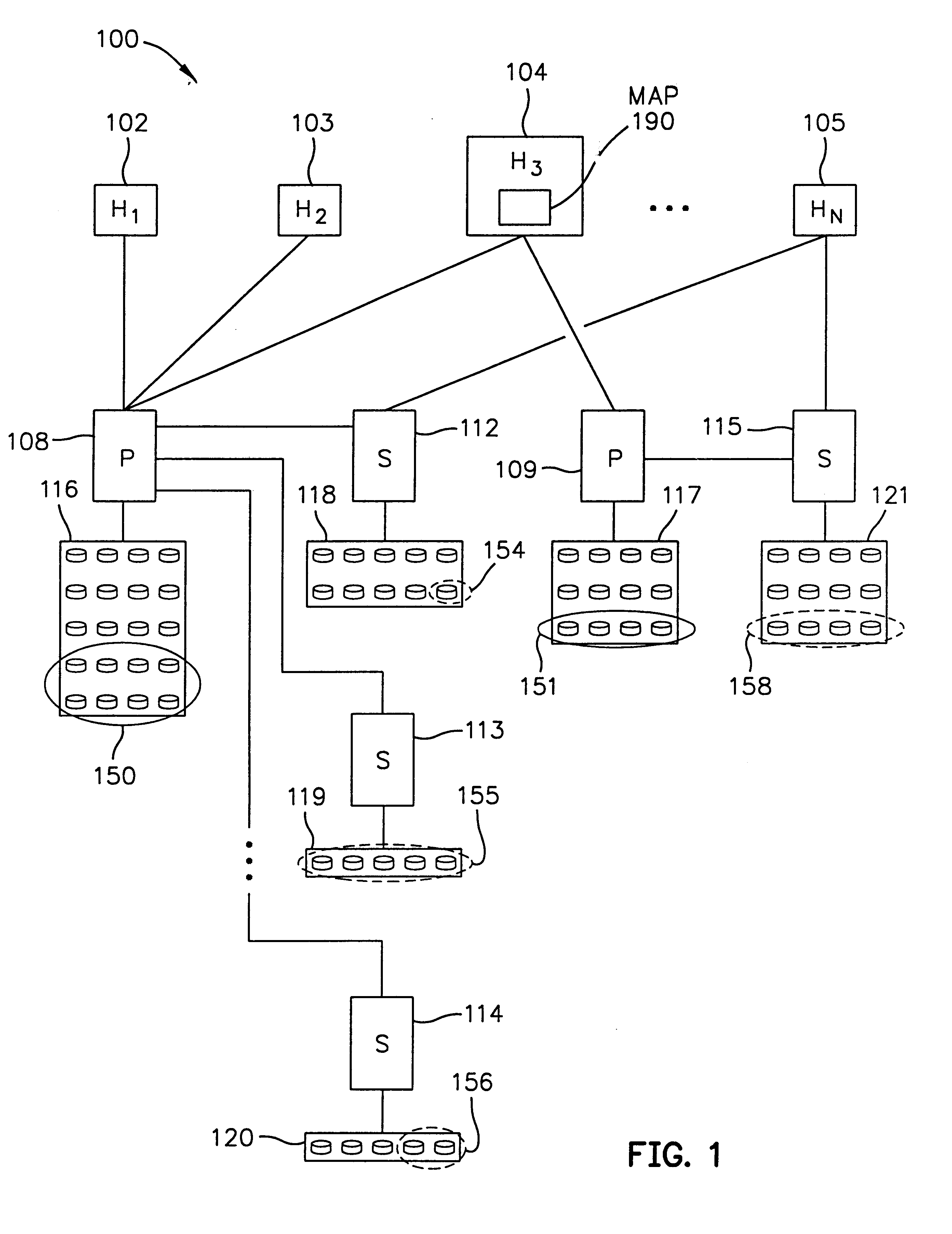

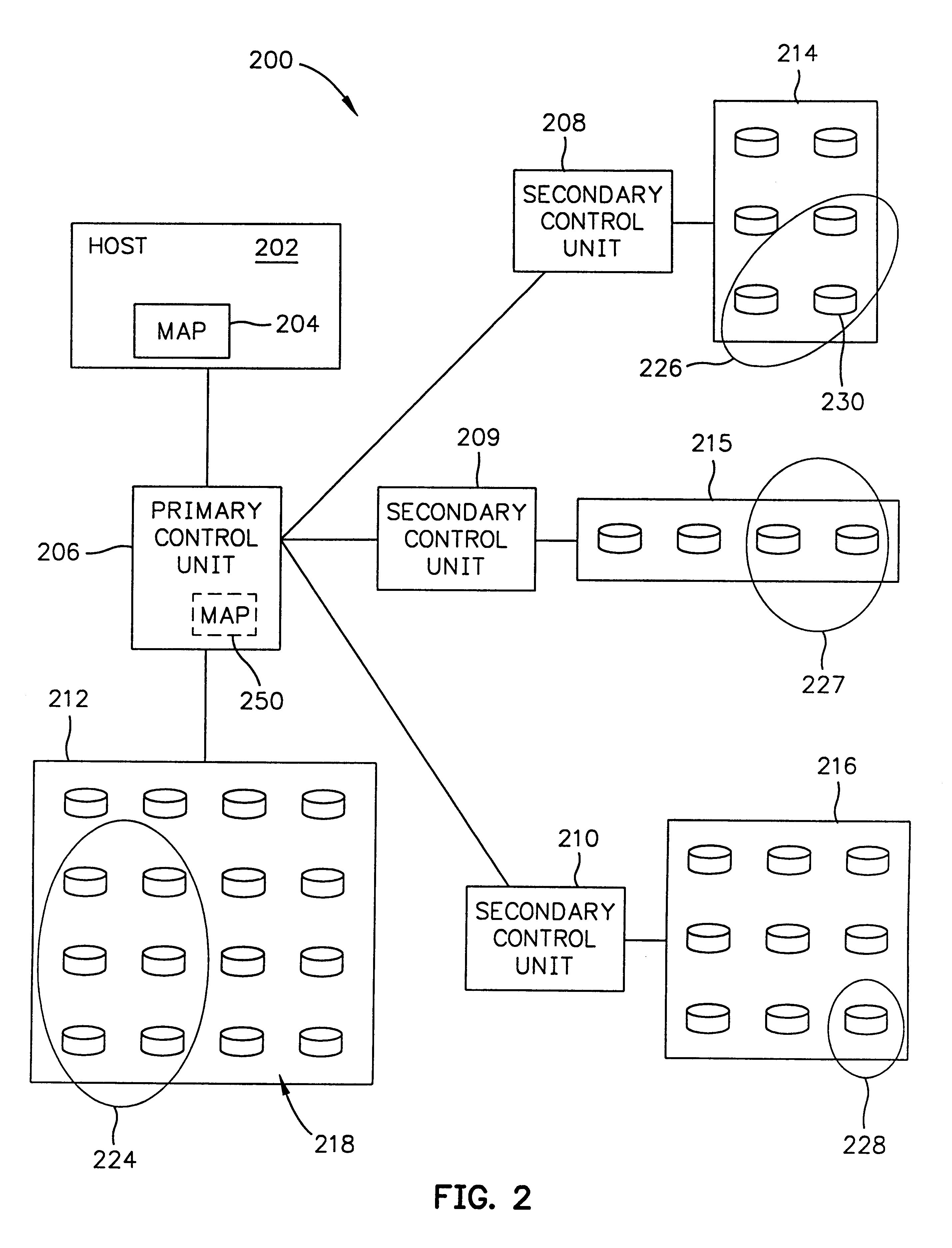

Database backup system ensuring consistency between primary and mirrored backup database copies despite backup interruption

InactiveUS6199074B1Data processing applicationsDigital computer detailsDatabase backupMaster controller

A database management system ensures consistency between primary and mirrored backup copies of a database, despite occurrence of a suspending condition interrupting the normal process of mirroring the primary database. One or more primary controllers are provided, each having a data storage unit with multiple primary data storage devices. Multiple secondary controllers each have multiple associated secondary data storage devices, each secondary controller being coupled to one primary controller. One or more primary databases reside on the primary devices, with a corresponding number of secondary databases residing on the secondary devices. Each secondary database mirrors a corresponding primary database. Either a host, attached to a primary controller, or one of the primary controllers itself, maintains a map cross-referencing each primary and secondary database with the primary and secondary devices containing portions thereof. If a predefined "suspending condition" affecting data mirroring occurs, the host or primary controller consults its map to identify all primary and secondary devices affected by the condition. Then, each primary controller stops all ongoing and future read / writes with each of its affected primary devices. Each primary controller also directs each secondary controller having an affected secondary device to stop mirroring the primary databases stored on that device. Then, the primary controller starts intermediate change recording and resumes read / writes with its primary devices. When the suspending condition ends, each primary controller applies the appropriate logged changes to its secondary database(s) and then reactivates each secondary database.

Owner:IBM CORP

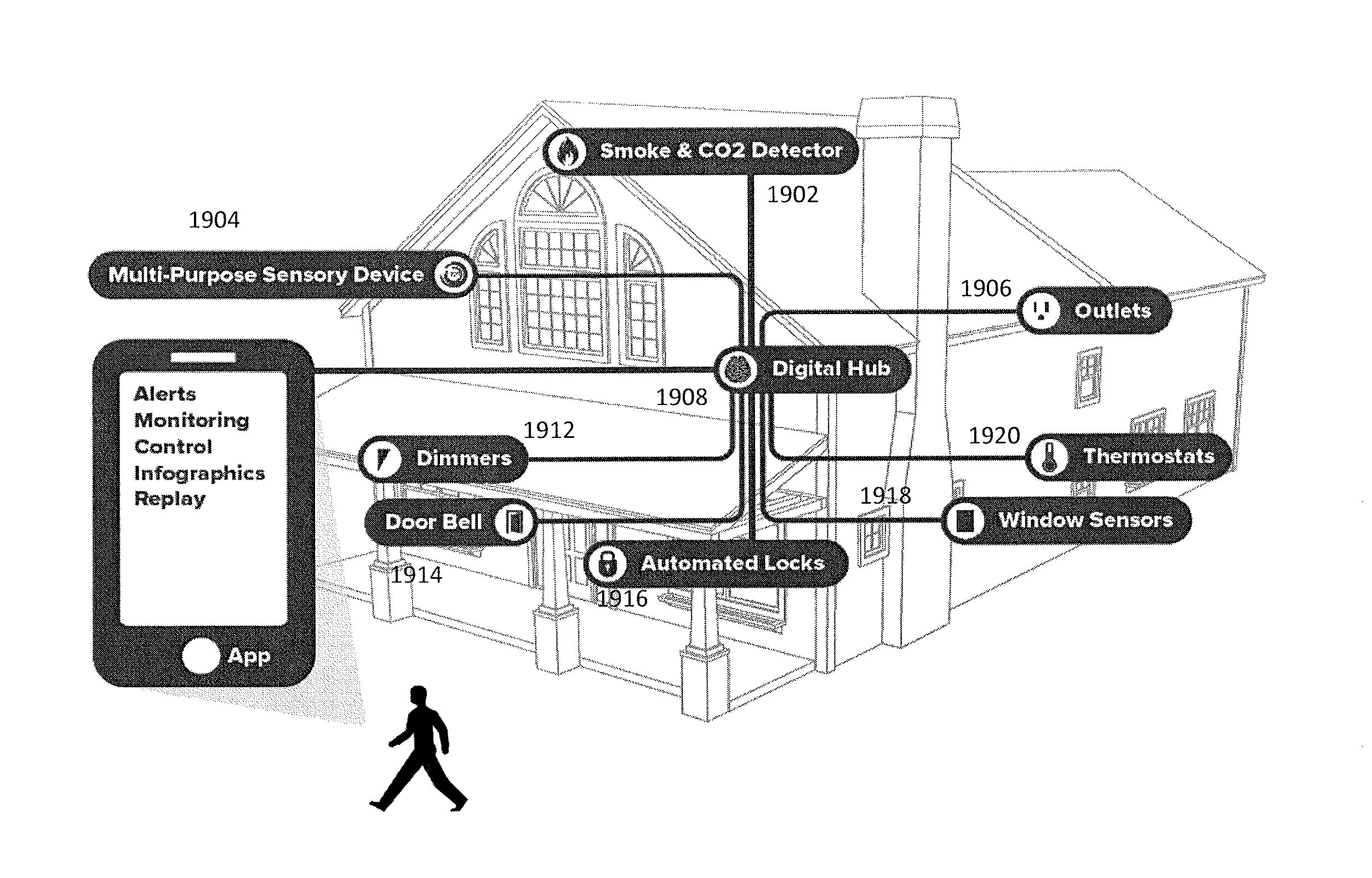

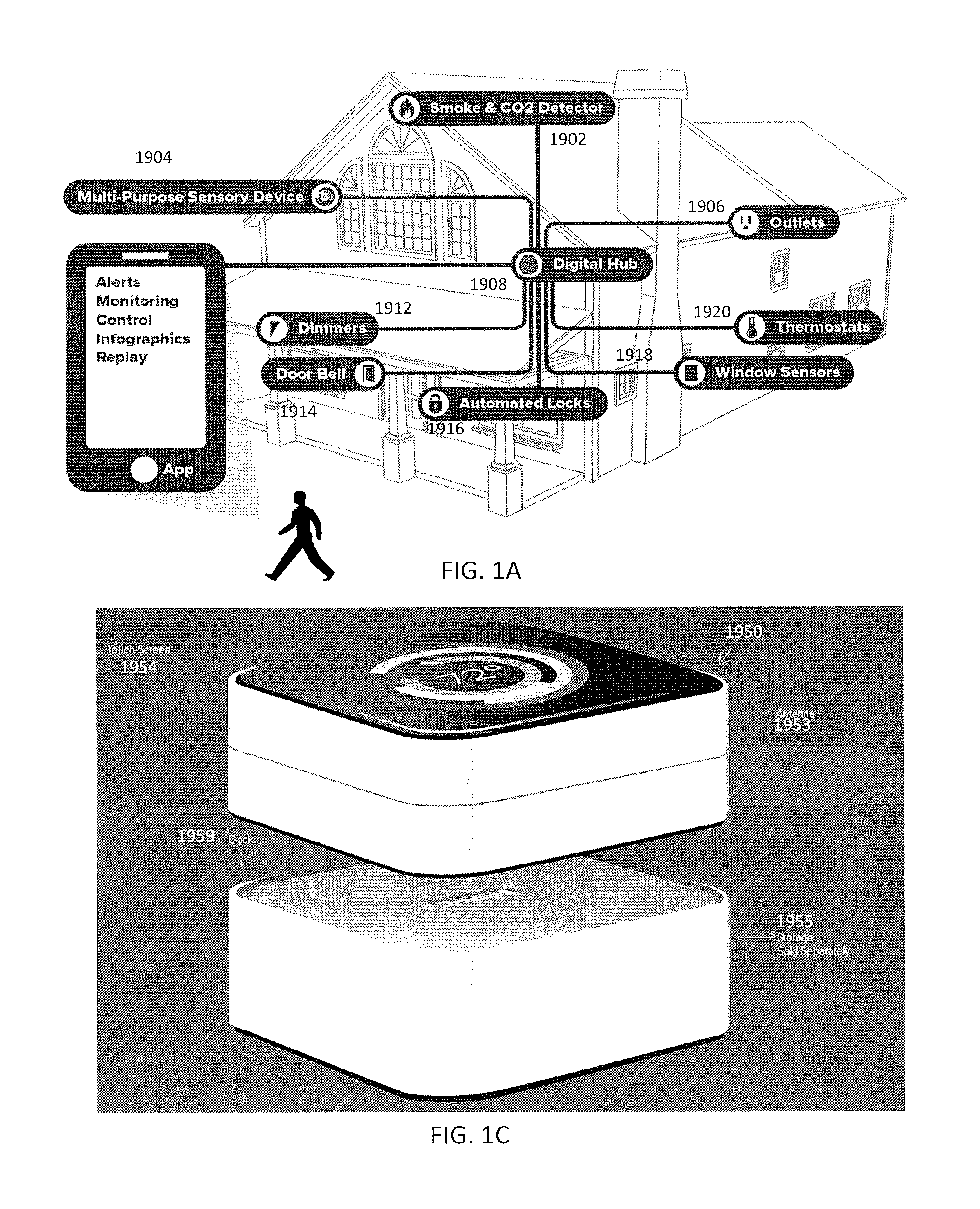

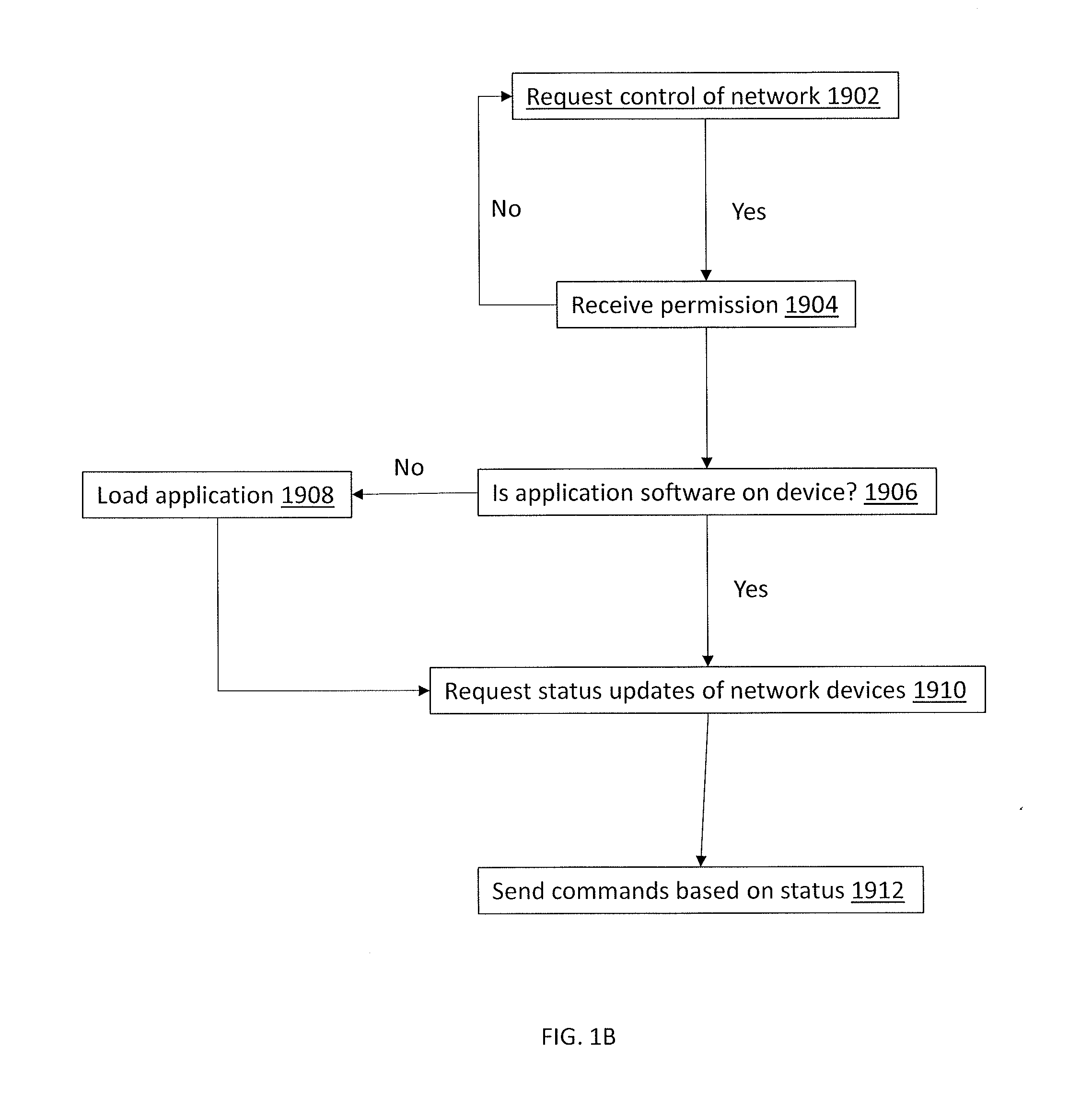

Wall-mounted interactive sensing and audio-visual node devices for networked living and work spaces

Described herein are networked (smart) living and work spaces, including a variety of different wireless nodes that may be distributed, including wall-mounted and / or retrofitted over existing electrical outlets and light switches, for providing data streams to a digital hub or master controller. For example, described herein are wall-mounted, interactive sensing and audio-visual node device for a networked living / working space.

Owner:UBIQUITI INC

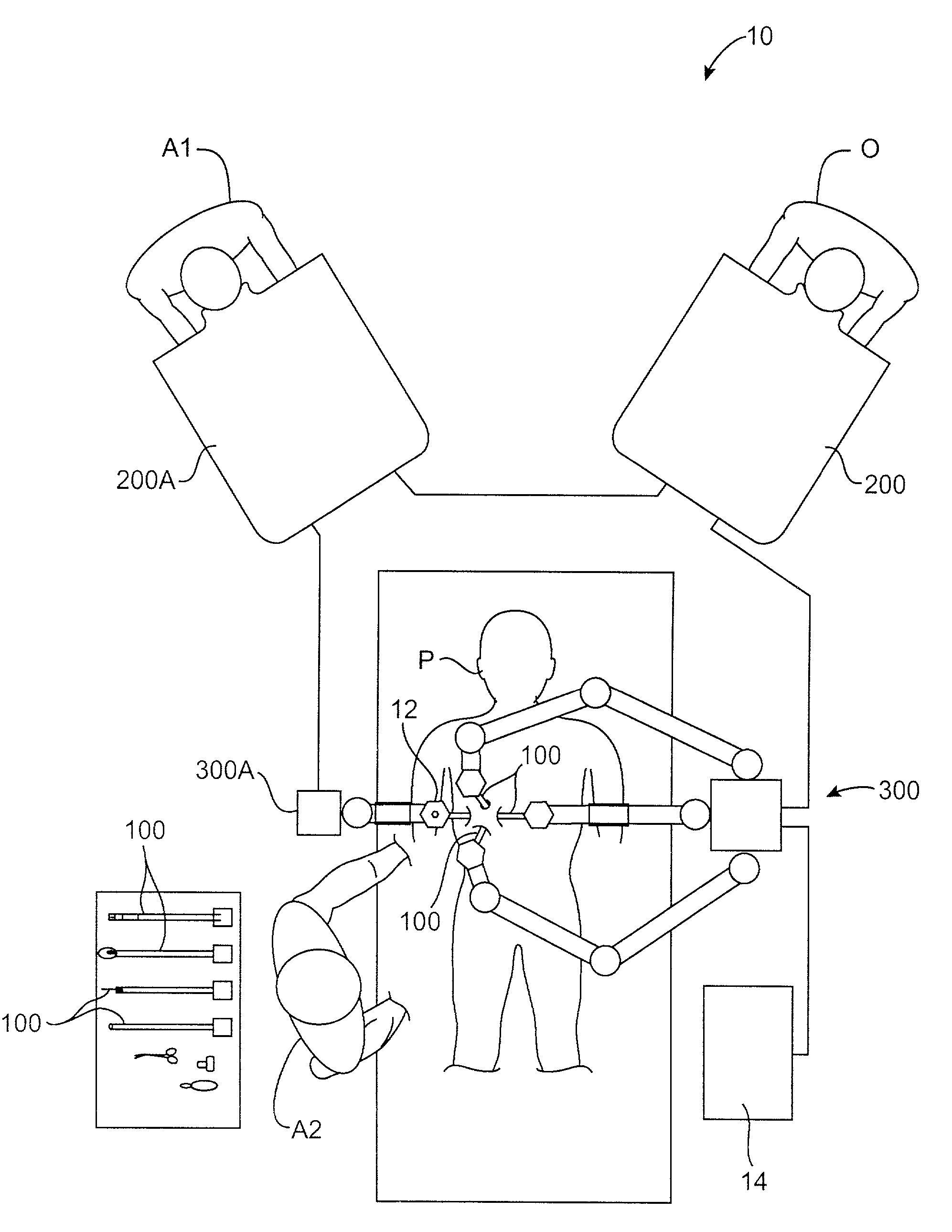

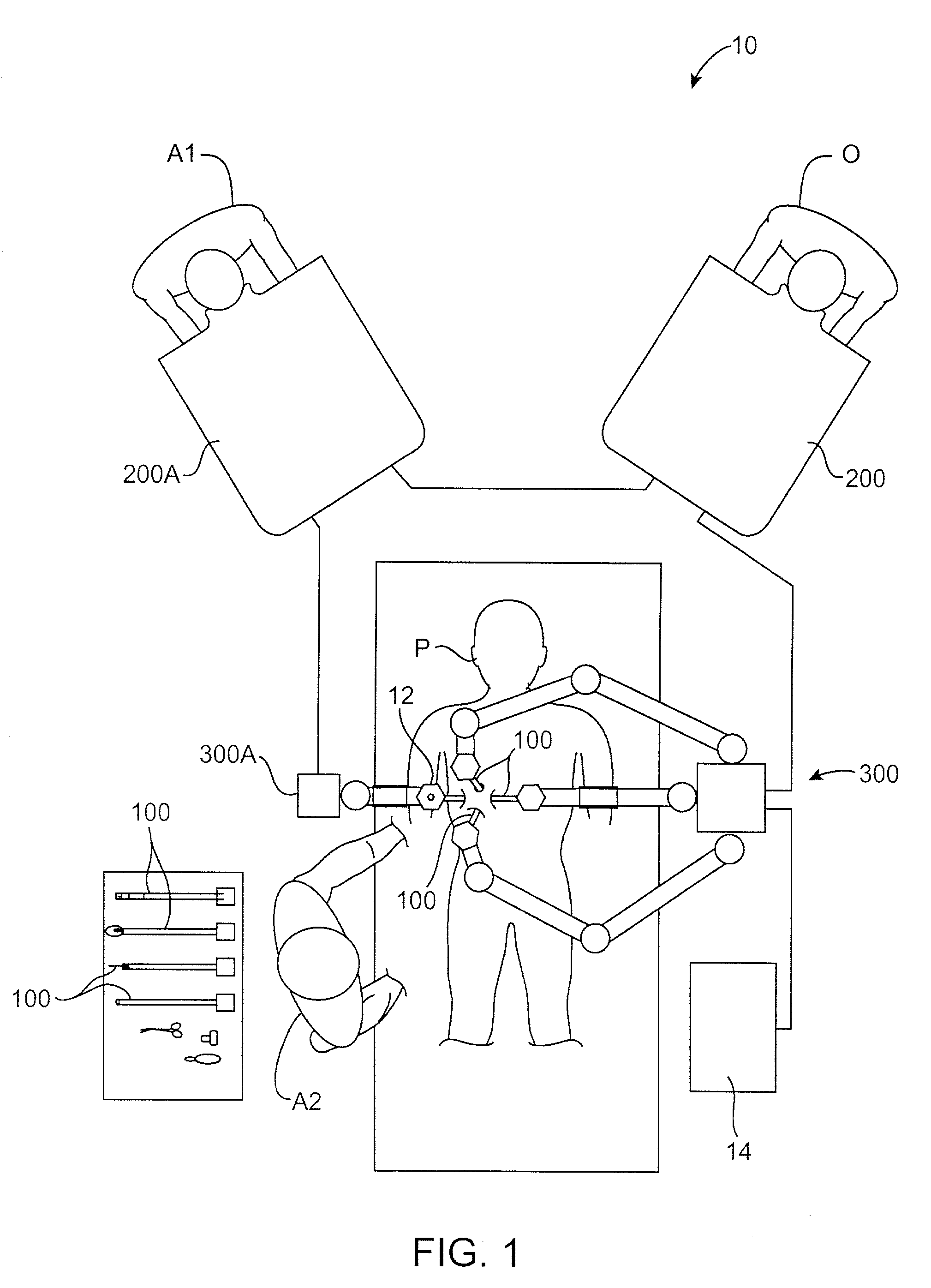

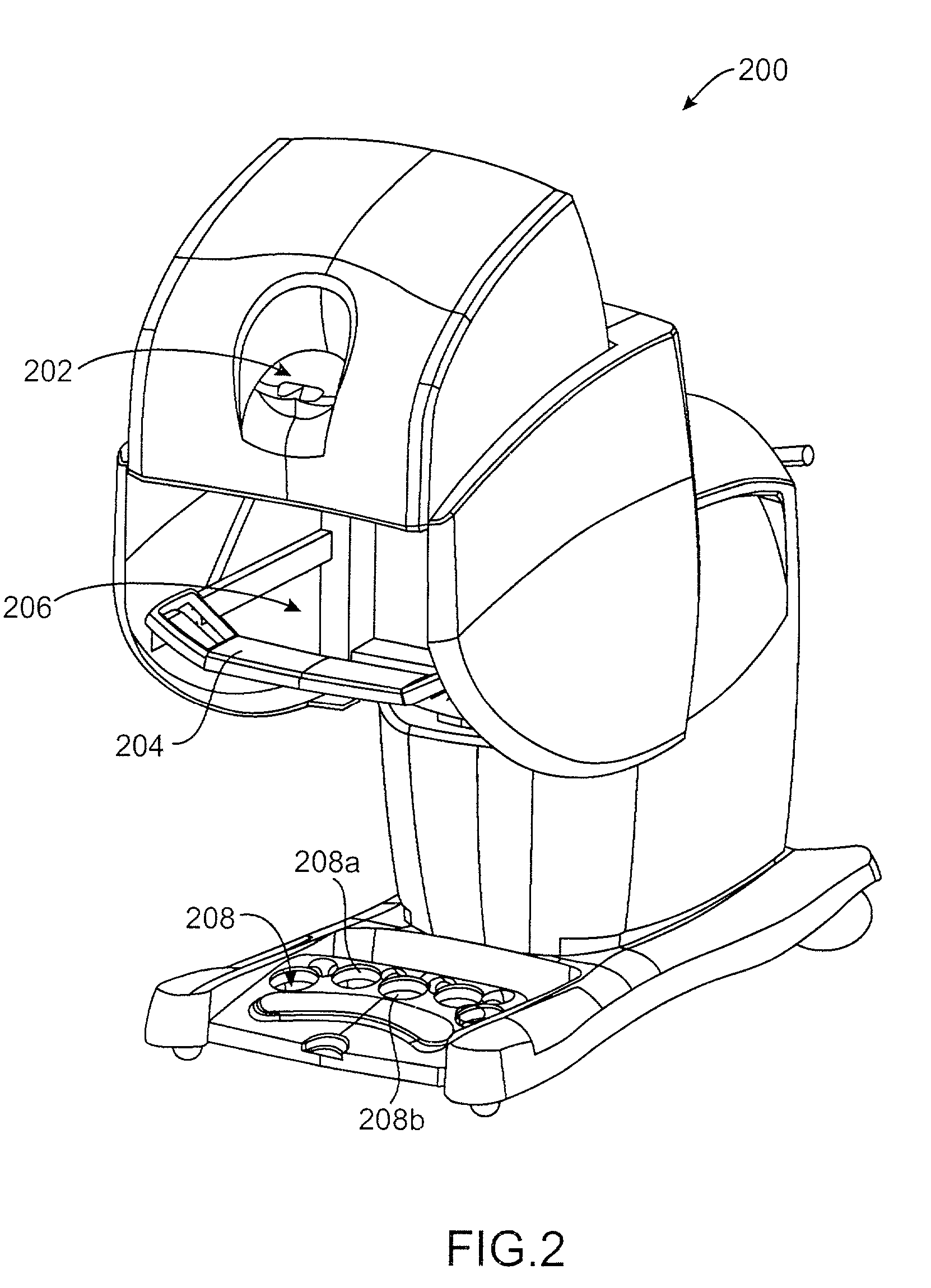

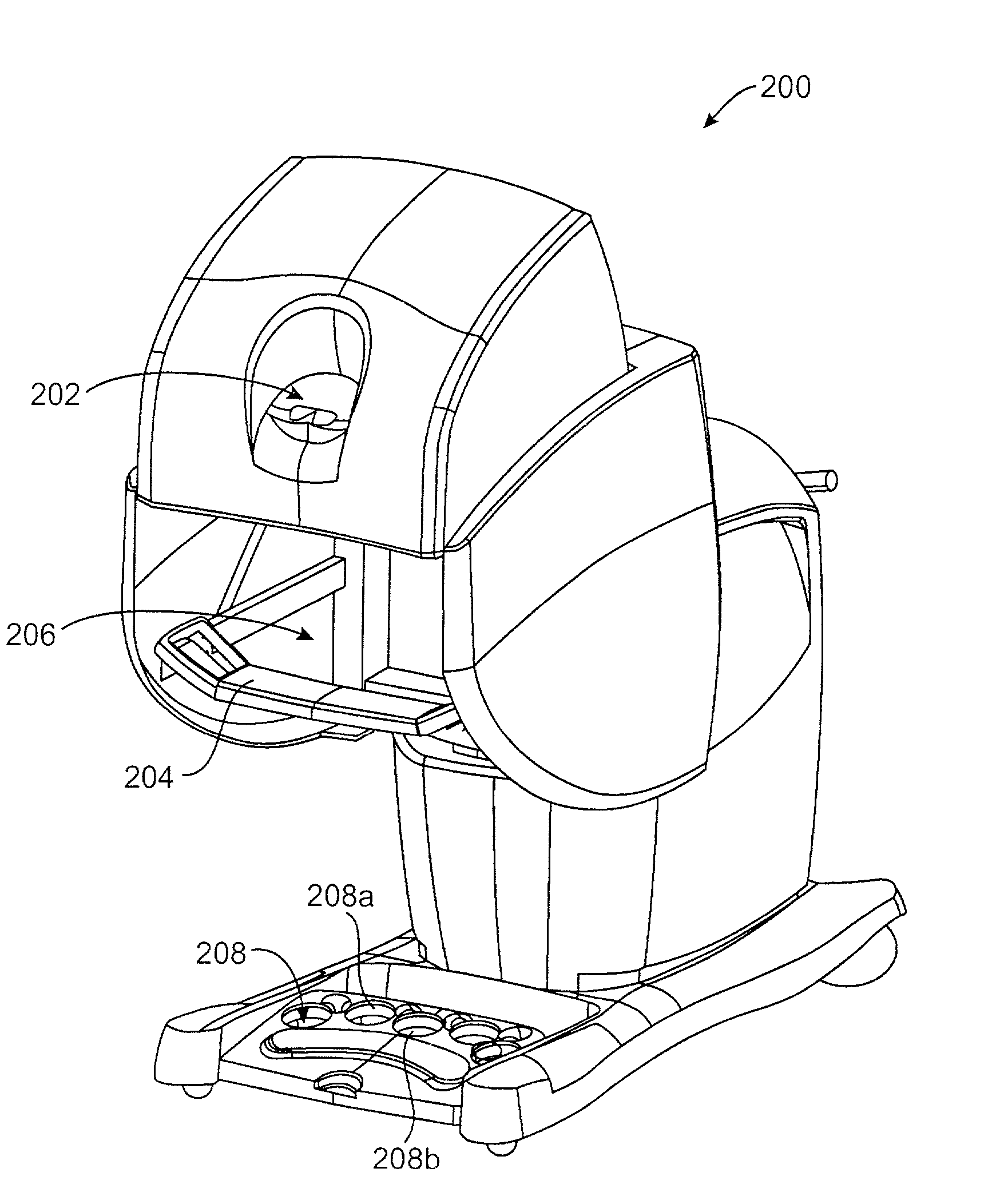

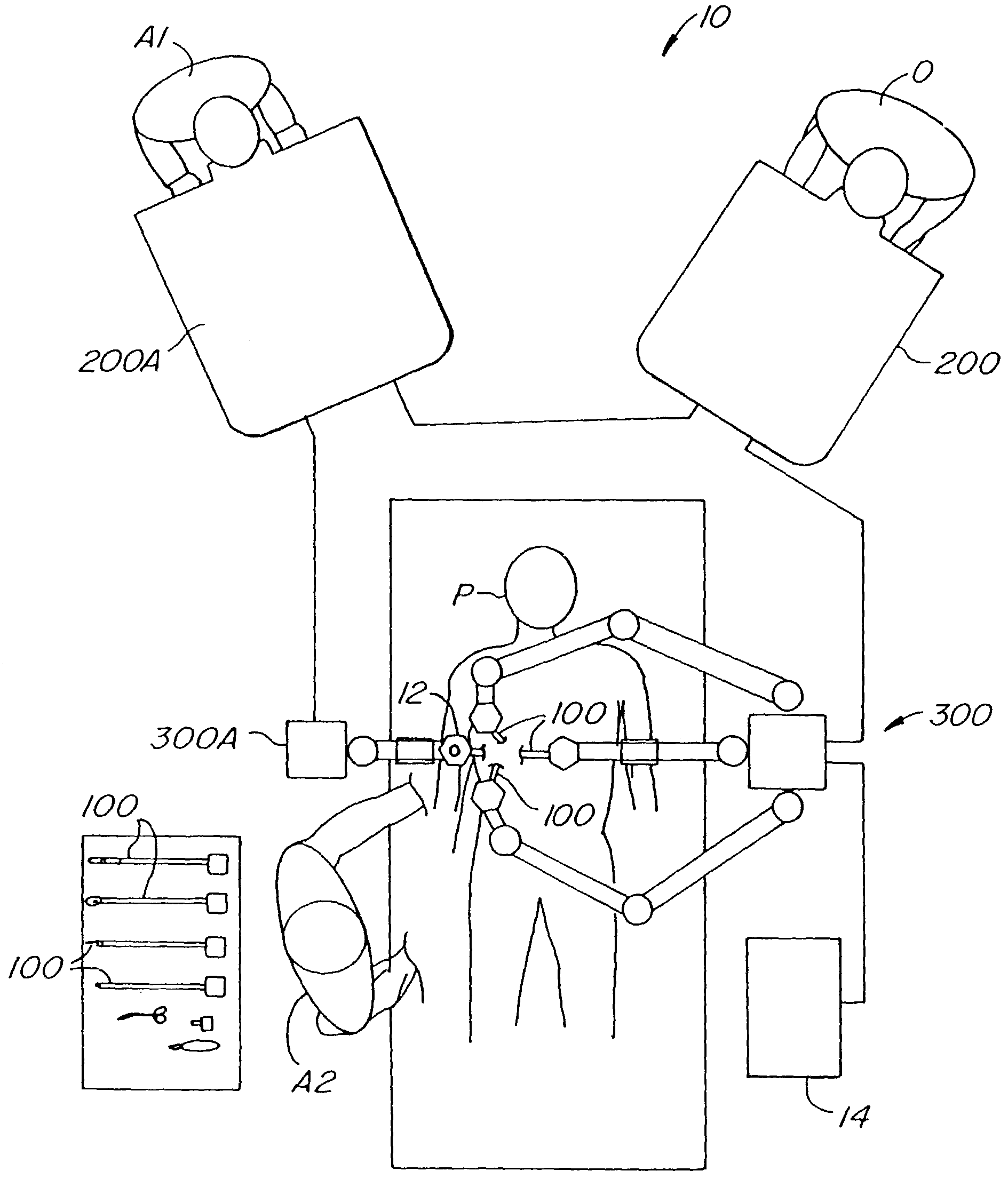

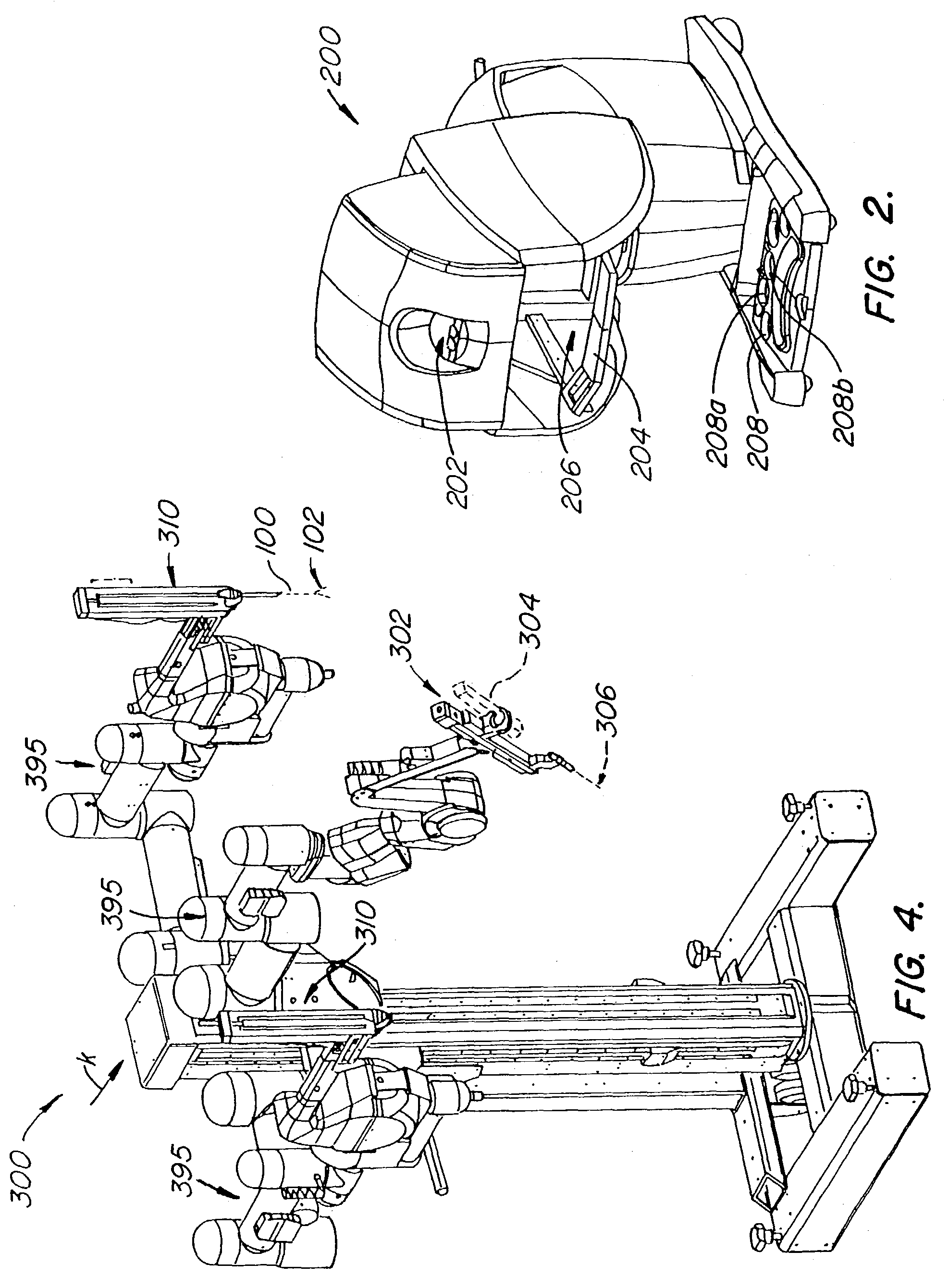

Cooperative minimally invasive telesurgical system

InactiveUS7865266B2Operative associations can be revisedAllocation is accurateMechanical/radiation/invasive therapiesDiagnosticsRobotic systemsIntermittent motion

Improved robotic surgical systems, devices, and methods include selectably associatable master / slave pairs, often having more manipulator arms than will be moved simultaneously by the two hands of a surgeon. Four manipulator arms can support an image capture device, a left hand tissue manipulation tool, a right hand tissue manipulation tool, and a fourth surgical instrument, particularly for stabilizing, retracting, tool change, or other functions benefiting from intermittent movement. The four or more arms may sequentially be controlled by left and right master input control devices. The fourth arm may be used to support another image capture device, and control of some or all of the arms may be transferred back-and-forth between the operator and an assistant. Two or more robotic systems each having master controls and slave manipulators may be coupled to enable cooperative surgery between two or more operators.

Owner:INTUITIVE SURGICAL OPERATIONS INC

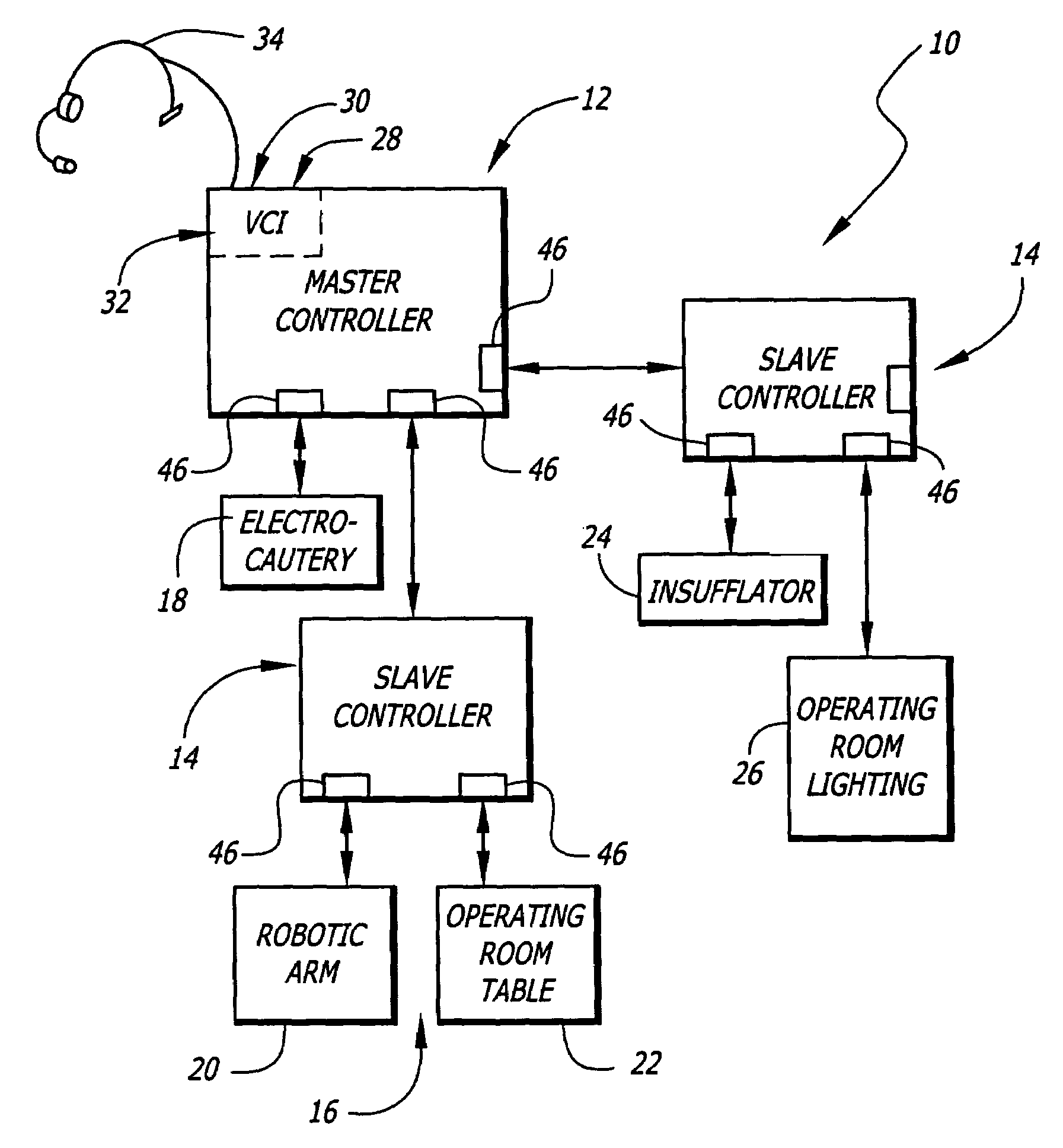

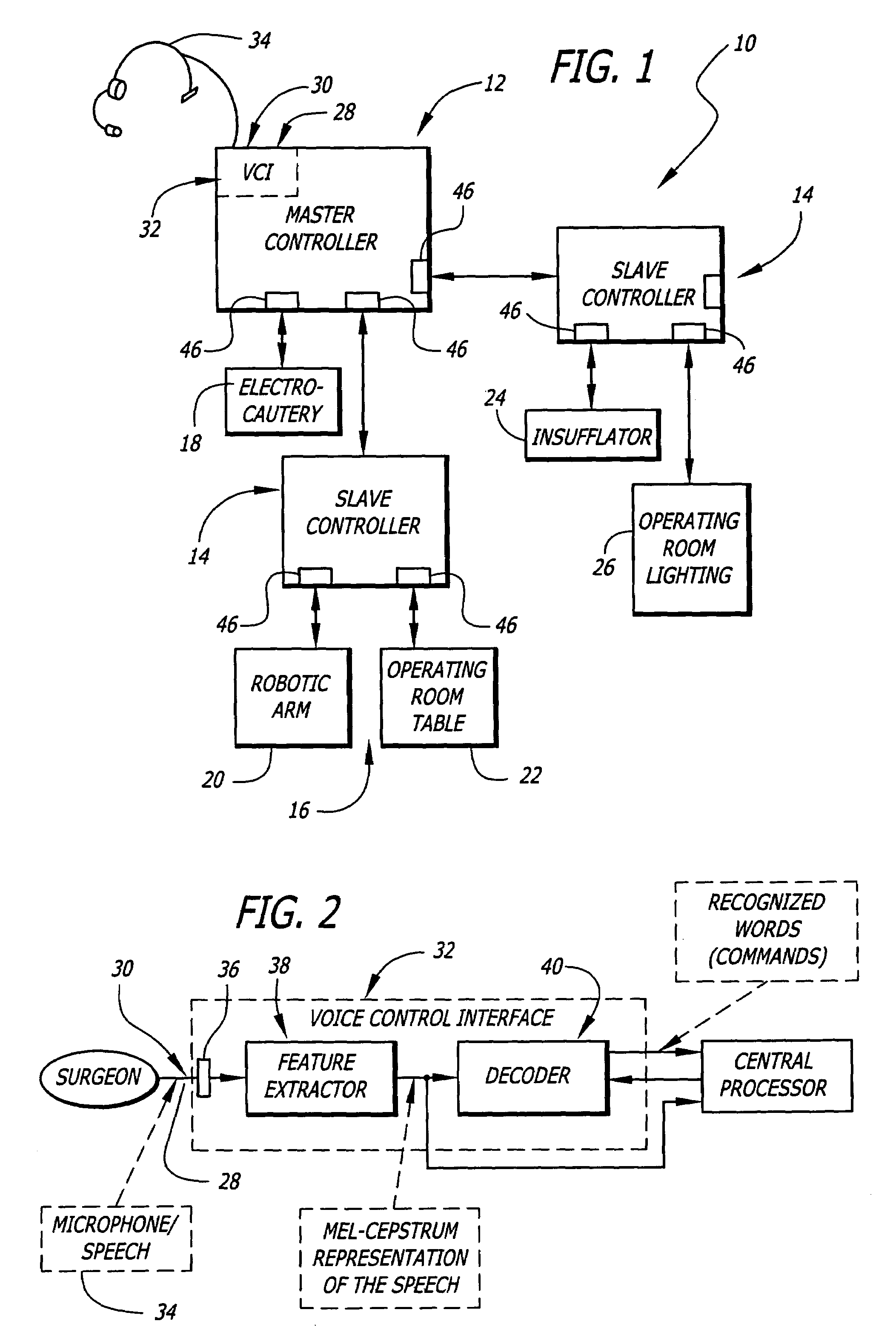

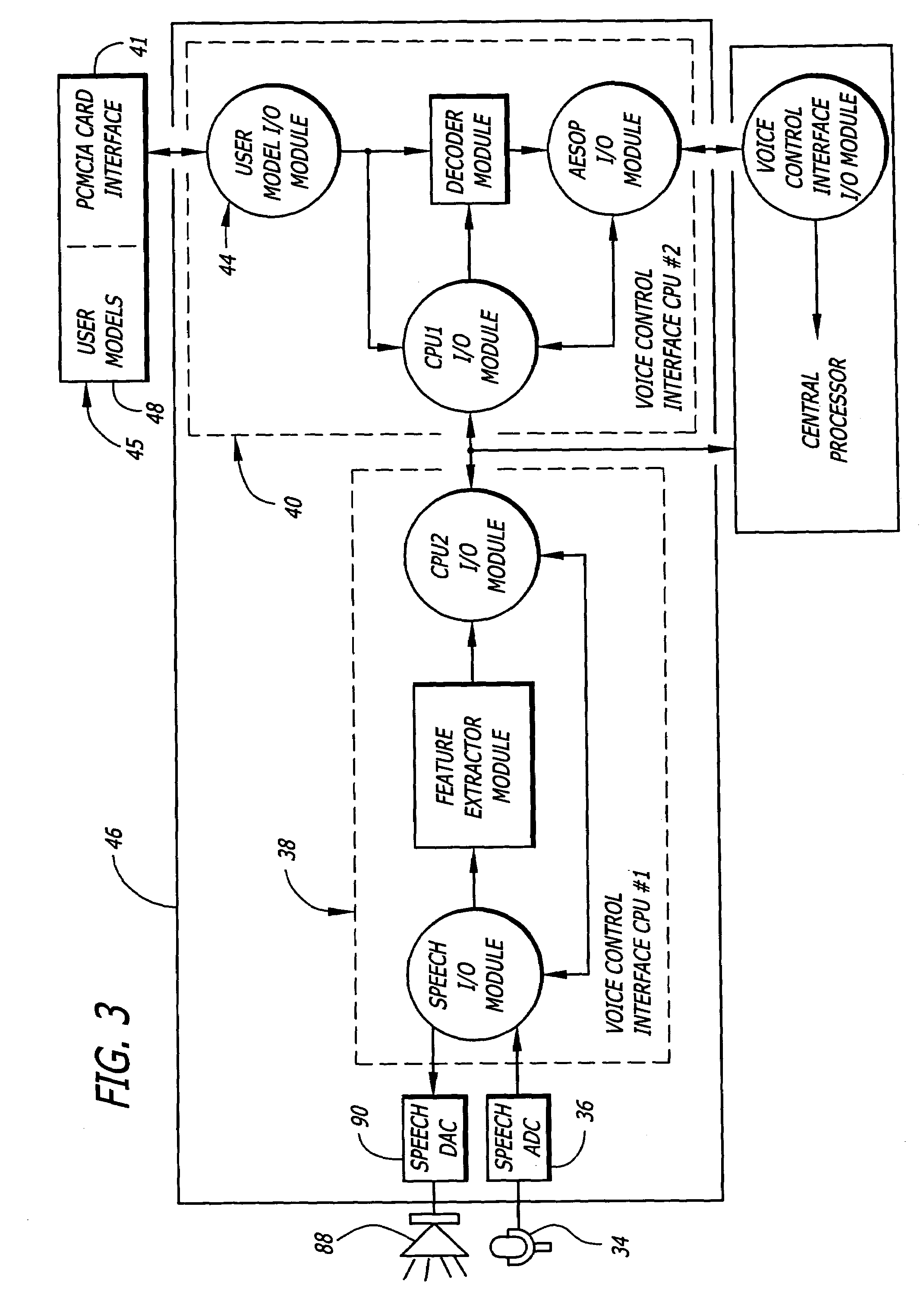

General purpose distributed operating room control system

The present invention pertains to control systems and provides a run time configurable control system for selecting and operating one of a plurality of operating room devices from a single input source, the system comprising a master controller having a voice control interface and means for routing control signals. The system additionally may include a plurality of slave controllers to provide expandability of the system. Also, the system includes output means for generating messages to the user relating to the status of the control system in general and to the status of devices connected thereto.

Owner:INTUITIVE SURGICAL OPERATIONS INC

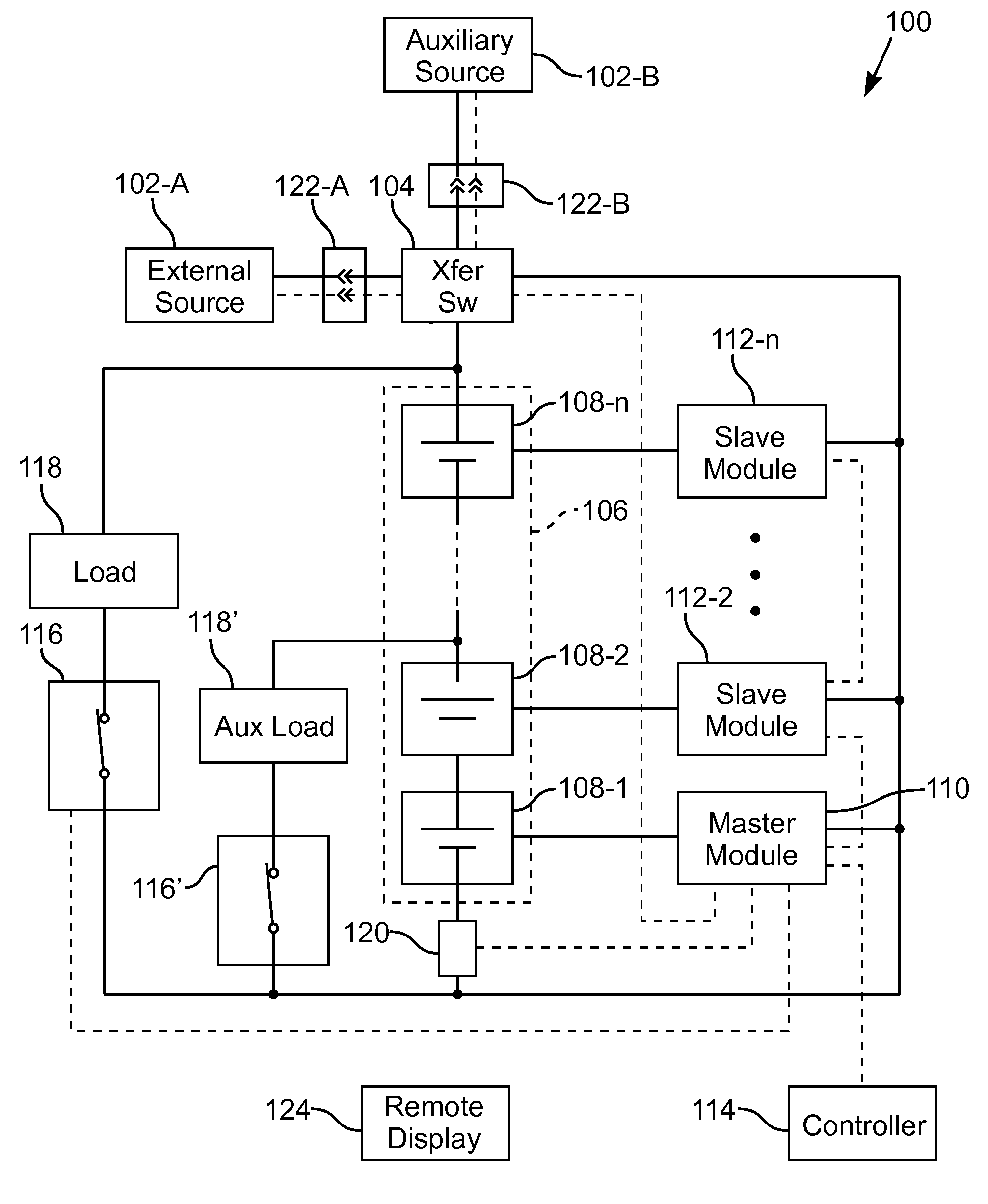

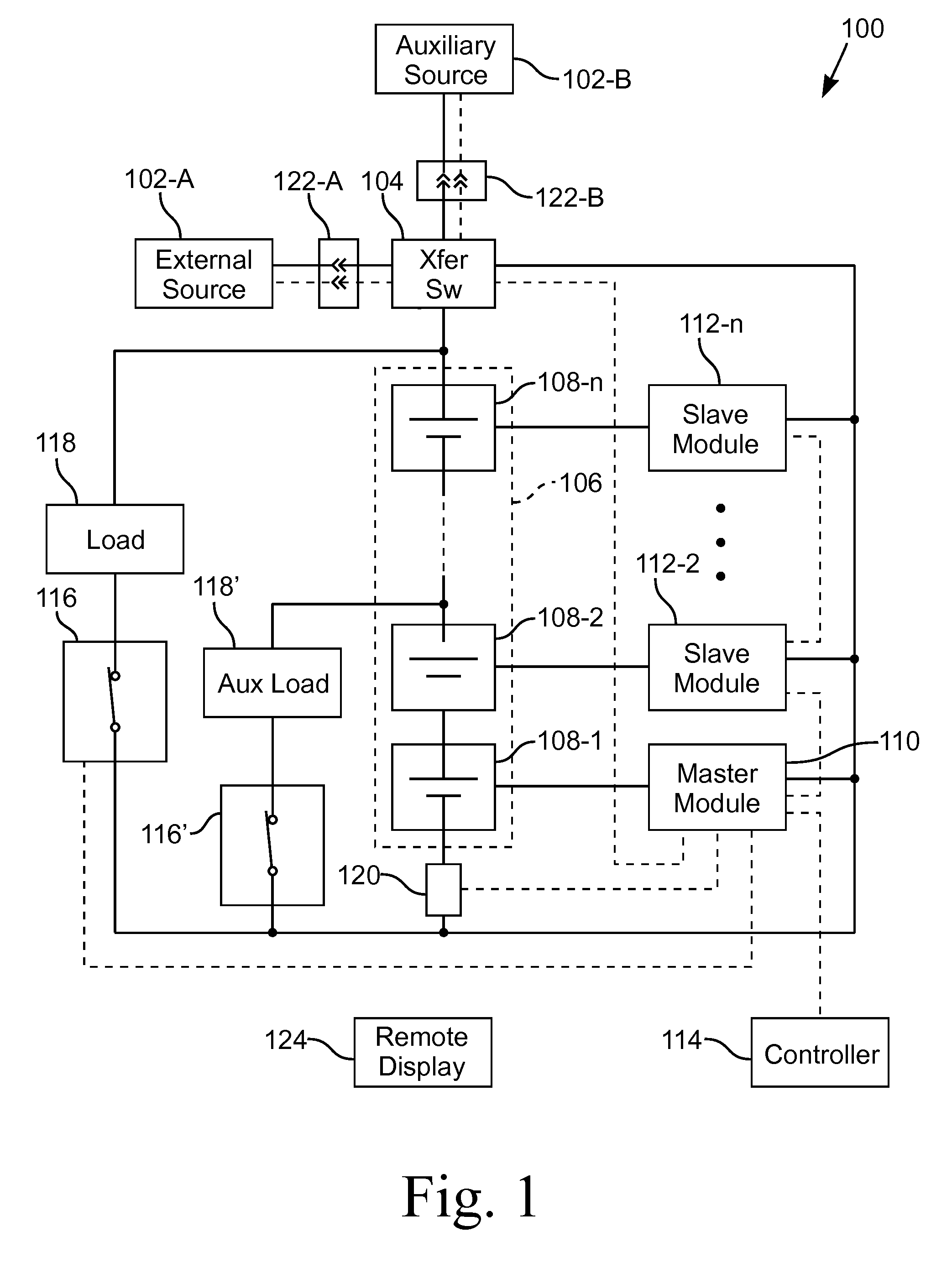

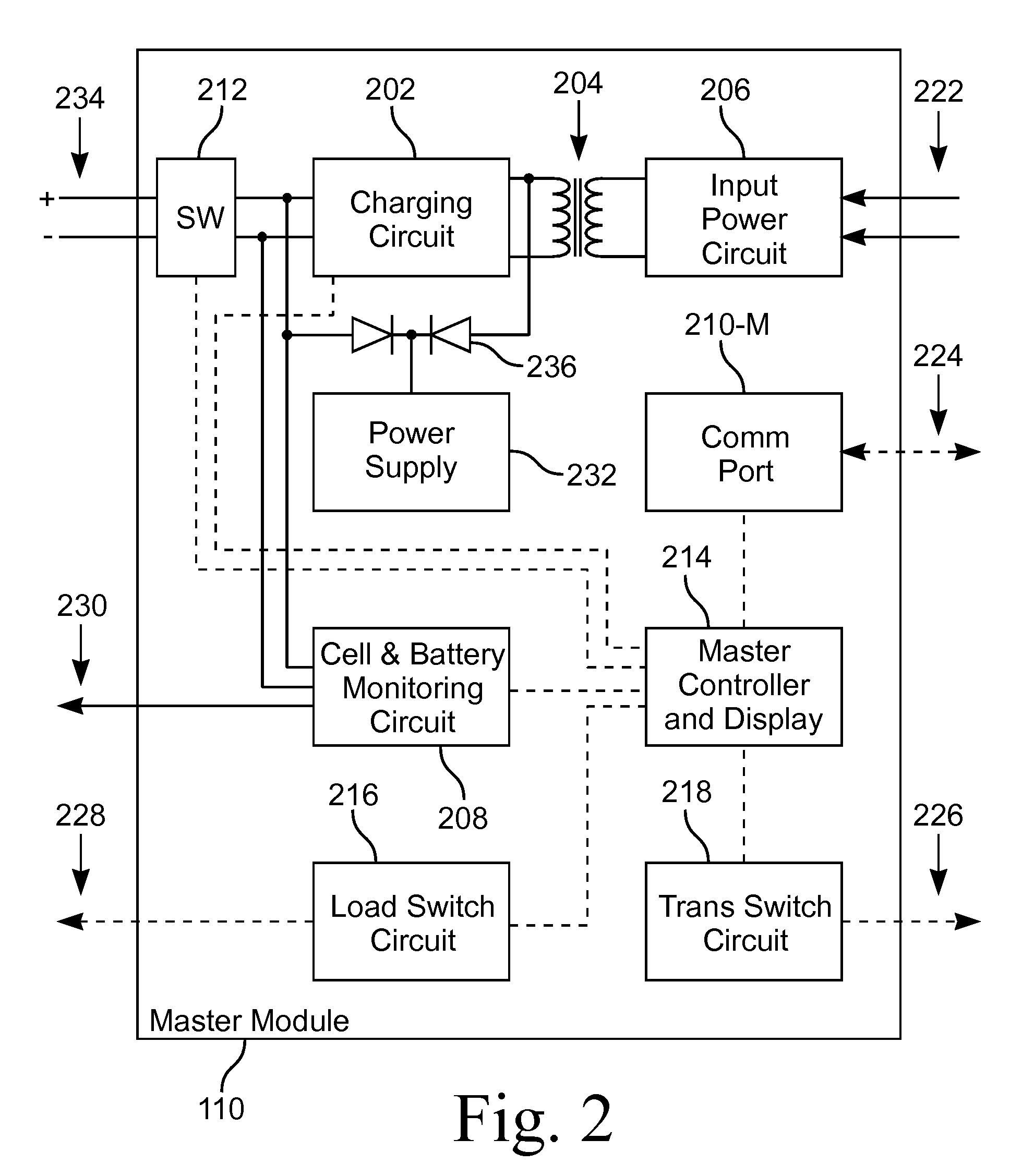

Battery management system

ActiveUS20090146610A1Easy maintenanceEasy to replaceCharge equalisation circuitSecondary cells charging/dischargingCritical levelTransfer switch

Apparatus for a modular battery management system with interchangeable slave modules connected to each cell and including a master module controlling and managing the battery system. All the modules receive power through a transfer switch that selectively switches between an external source, an auxiliary source, and the battery. The modules are configured to connect to a cell of the battery for charging and monitoring the cell individually. Each module is electrically isolated from the other modules. The modules are autonomous and shut down the battery and disconnect the module when a critical parameter of the cell is reached. When the battery is in service and a cell parameter approaches the critical level, the master controller instructs the corresponding slave module to charge the cell using battery power. The master module initializes the slave modules to uniquely identify the modules.

Owner:TRIGIANI ANTONIO

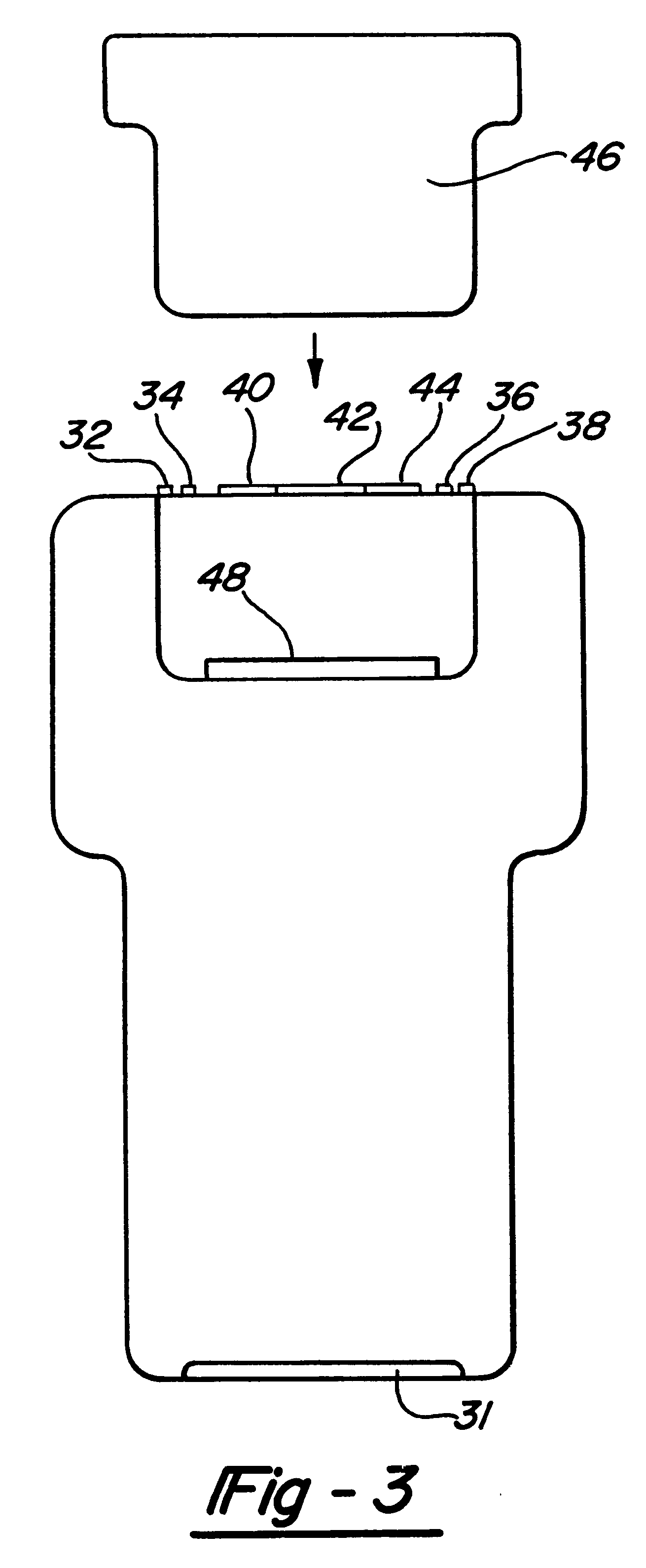

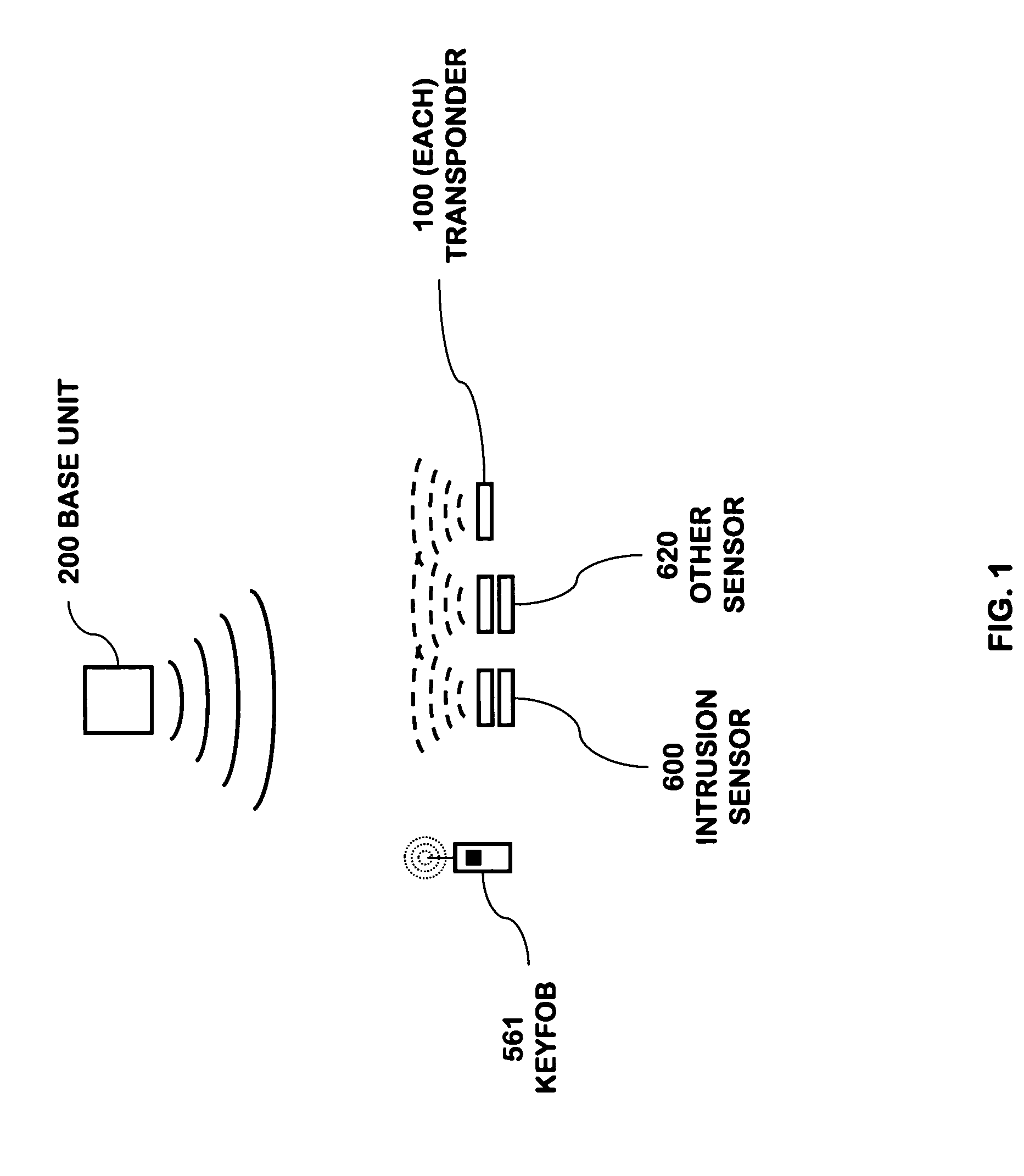

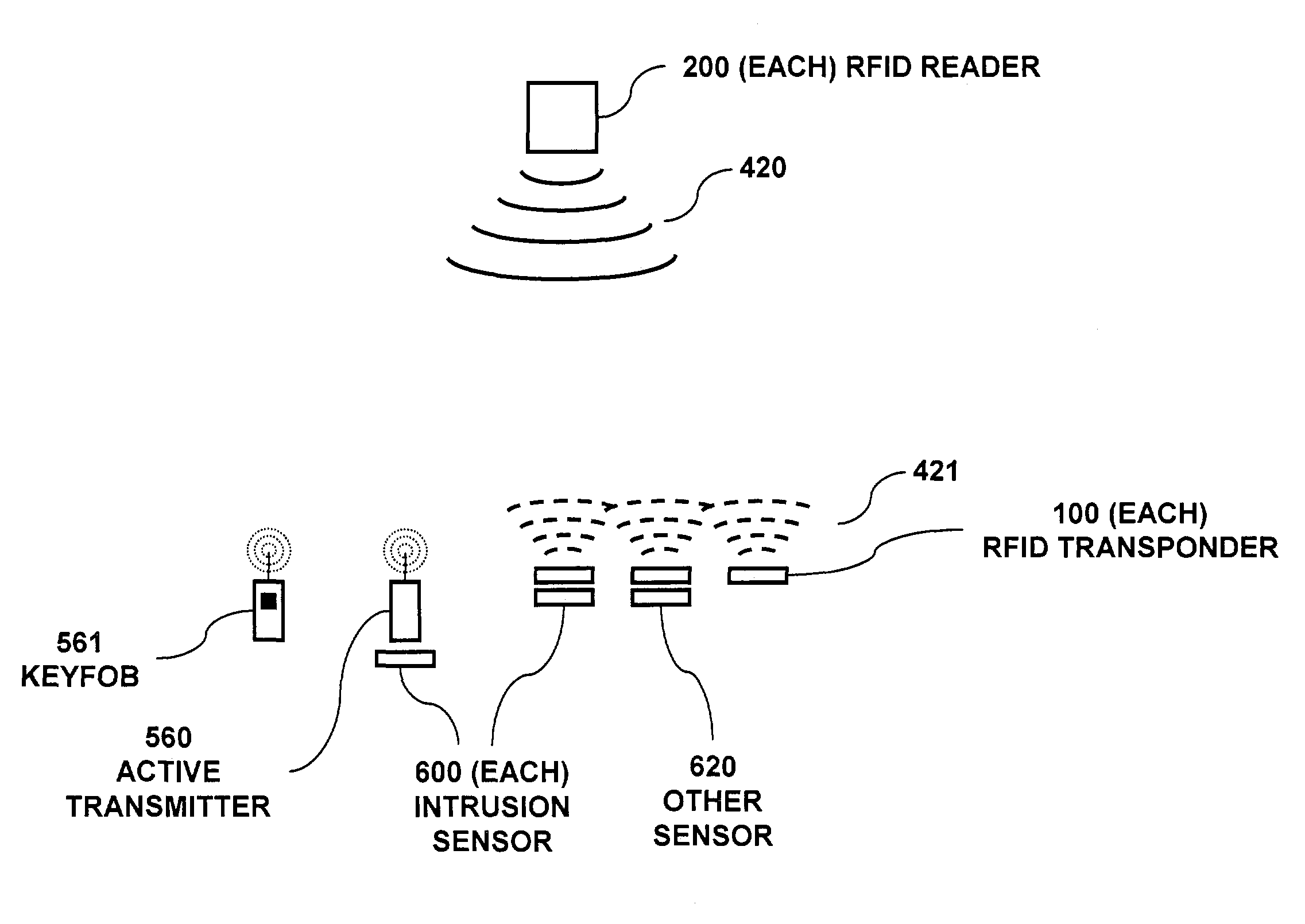

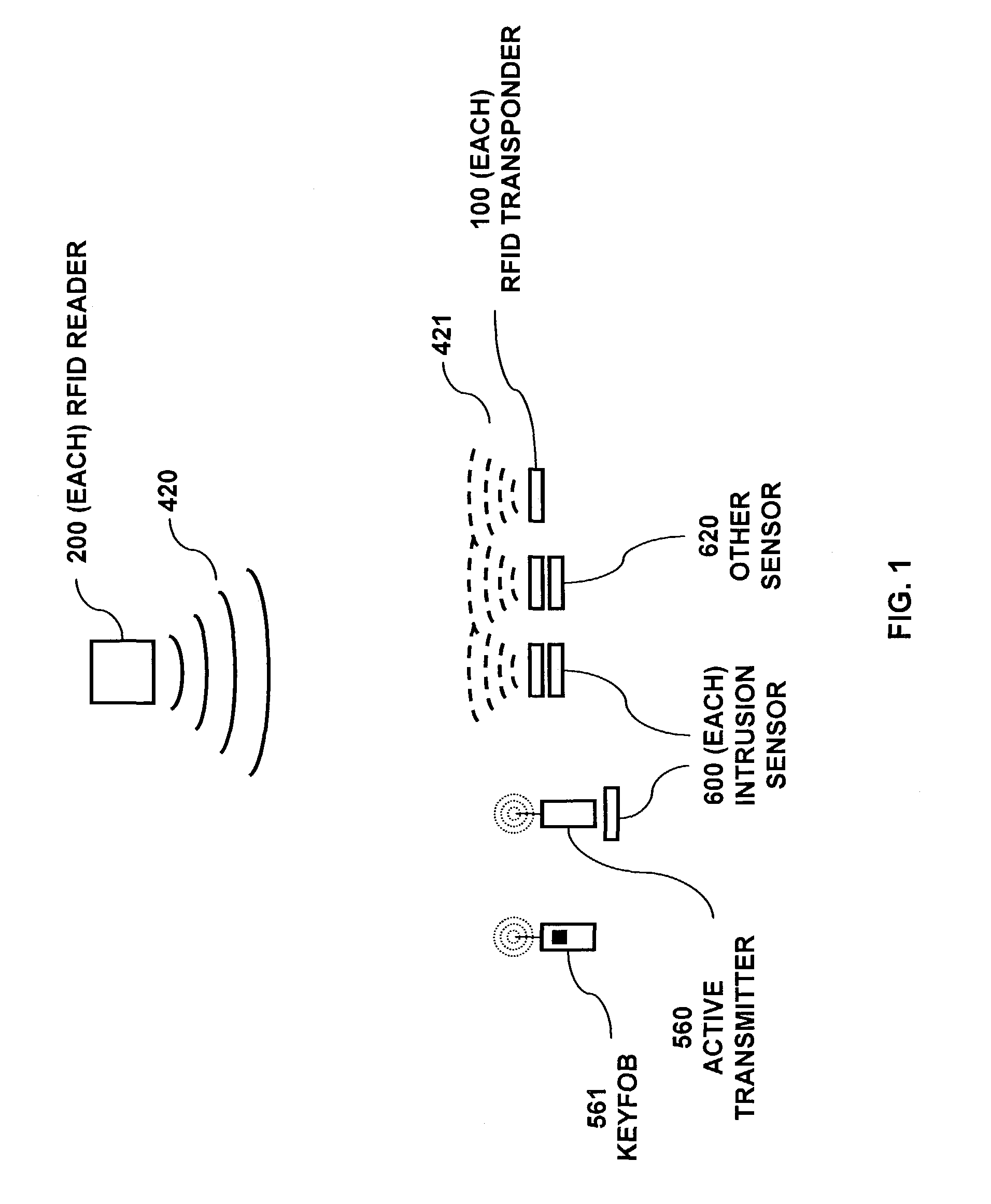

RFID reader for a security network

InactiveUS7023341B2Improve reliabilityLow costBurglar alarm by openingFrequency-division multiplex detailsComputer hardwareTransducer

An RFID reader for use in a security network based upon RFID techniques. The RFID reader can use wireless communications to communicate with RFID transponders and other devices in the security network. The RFID reader of the security network can be provided with multiple modulation techniques, multiple antennas, and the capability to vary its power level and carrier frequency. The RFID reader can transmit RF energy useful for detecting motion or for charging the batteries in RFID transponders. The RFID reader can contain an audio transducer, a camera, or various environmental sensors to detect parameters such as smoke, temperature, and water, among others. The program code of the RFID reader can be updated. A master controller within the security network can control operations within the RFID reader.

Owner:ADT US HLDG INC

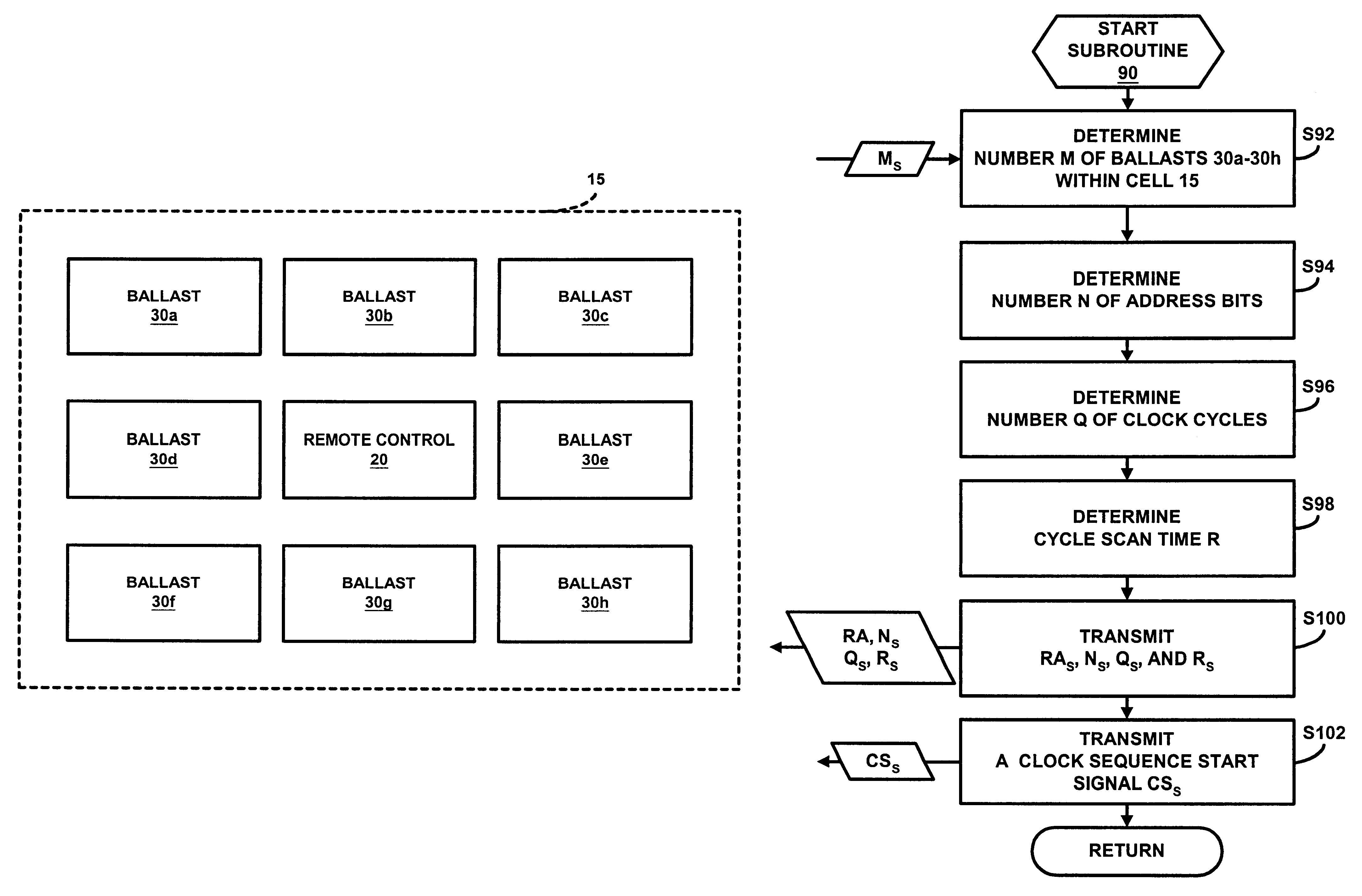

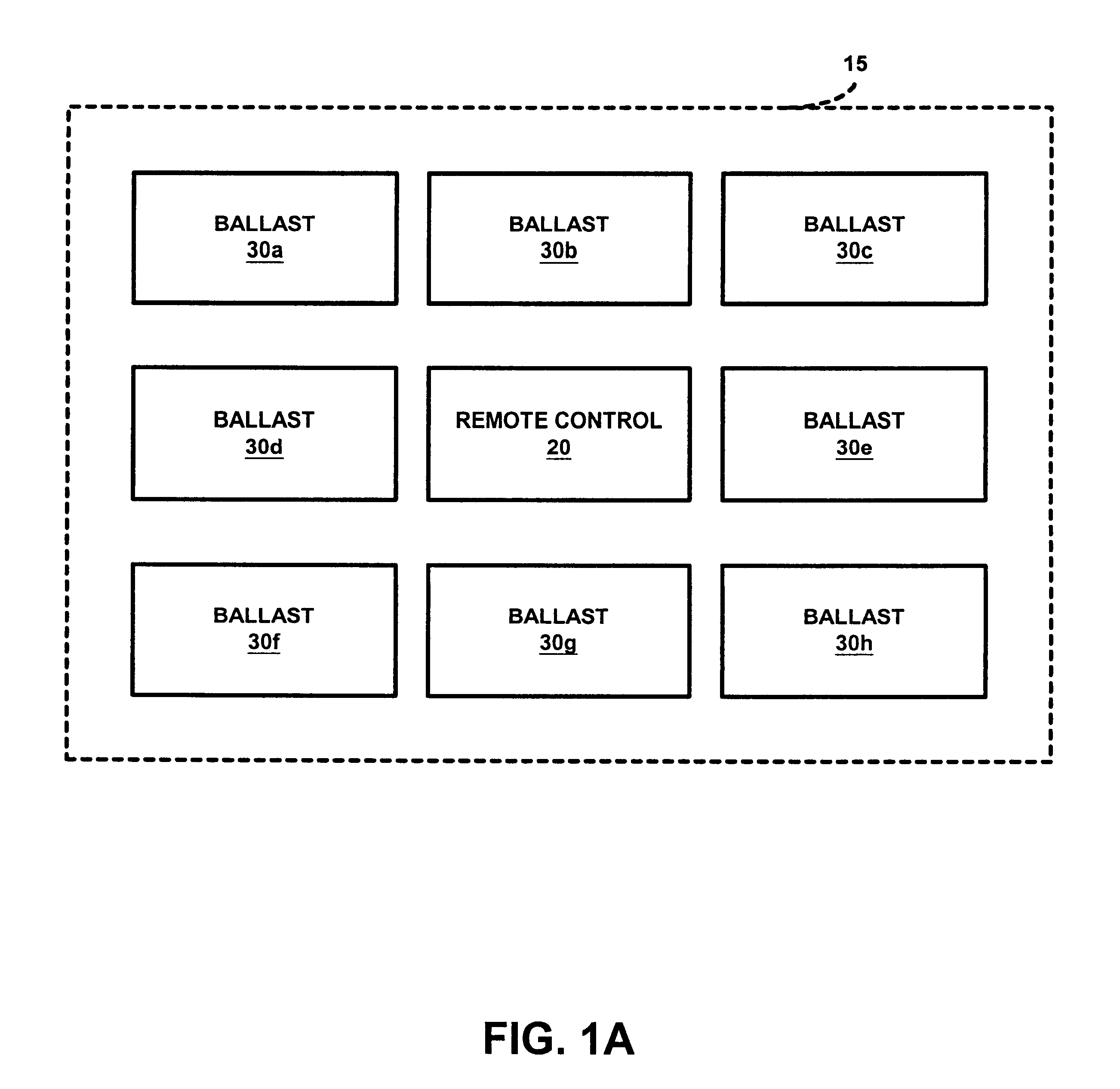

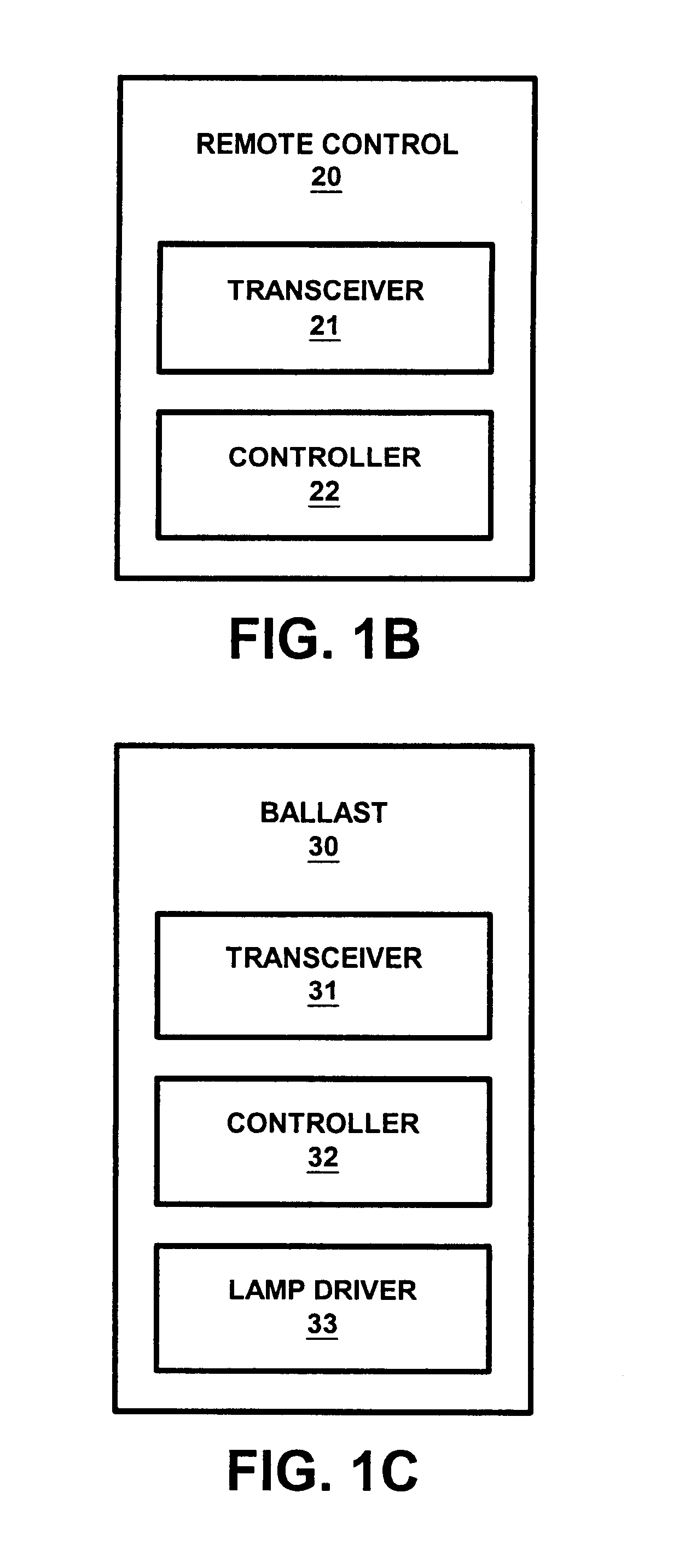

Method and system for assigning and binding a network address of a ballast

InactiveUS6831569B2Electric signal transmission systemsCircuit arrangementsRemote controlNetwork addressing

A system for implementing a method for initializing and binding ballasts is disclosed. The system comprises a remote control having a master controller and the ballasts each having a slave controller. The master controller and the slave controllers are operated to implement routines whereby the master controller generates a clock sequence of a plurality of clock cycles, and the slave controllers randomly generate addresses and direct a transmission of signals indicative of the generated random addresses to the master controller during corresponding clock cycles. In response thereto, the master controller assigns network addresses corresponding to the random addresses as indicated by the corresponding clock cycles. The master controller and the slave controllers are further operated to implement routines for verifying the assigned network addresses and routines for binding each network address to a command of the remote control.

Owner:SIGNIFY HLDG BV

Controller for a security system

InactiveUS7053764B2Improve reliabilityLow costFrequency-division multiplex detailsTelephonic communicationModem deviceMaster controller

A controller for use in a security system based upon RFID techniques. The controller can use power line carrier communications to communicate with other devices in the security system. The controller can use a modem or wireless module to connect to public networks. Multiple controllers can be used in a system, and the controllers can arbitrate to determine a master controller. The controller contains configuration data and tables that define the relationships between devices in the security system. The controller can receive communications from other devices in the system and can interface with legacy devices previously used with wired security systems. The controller can send messages based upon predetermined events, and can support a remote alerting function.

Owner:LIFESHIELD LLC

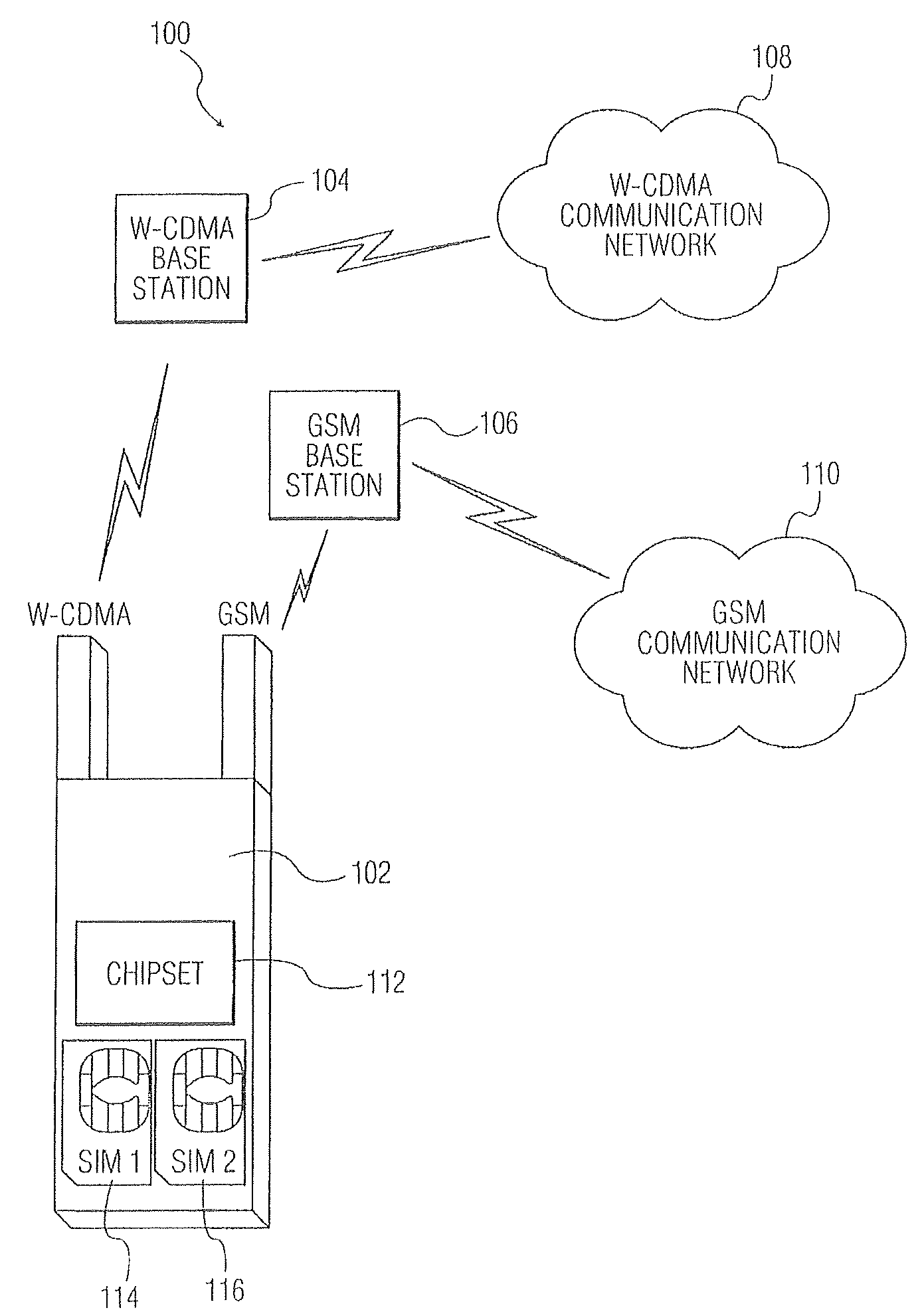

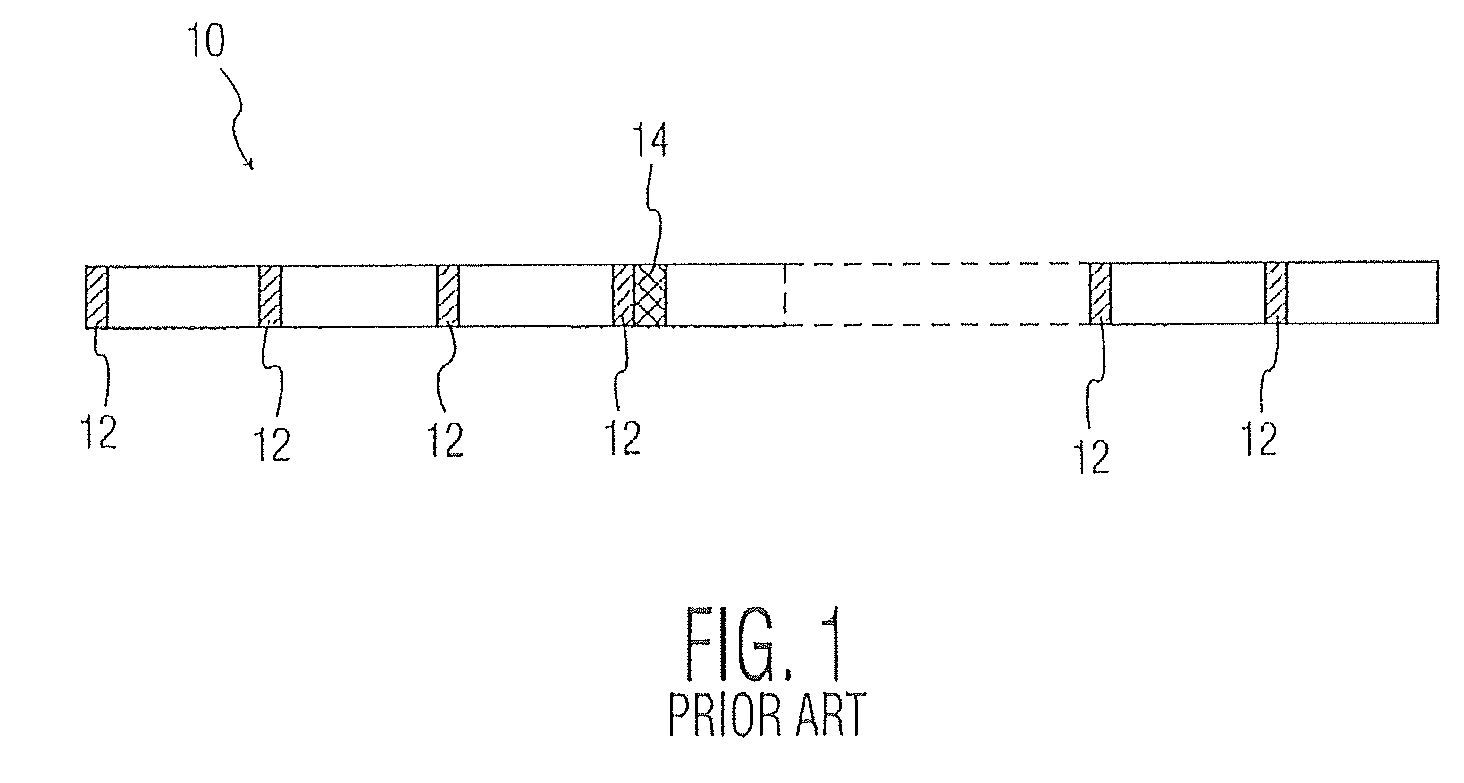

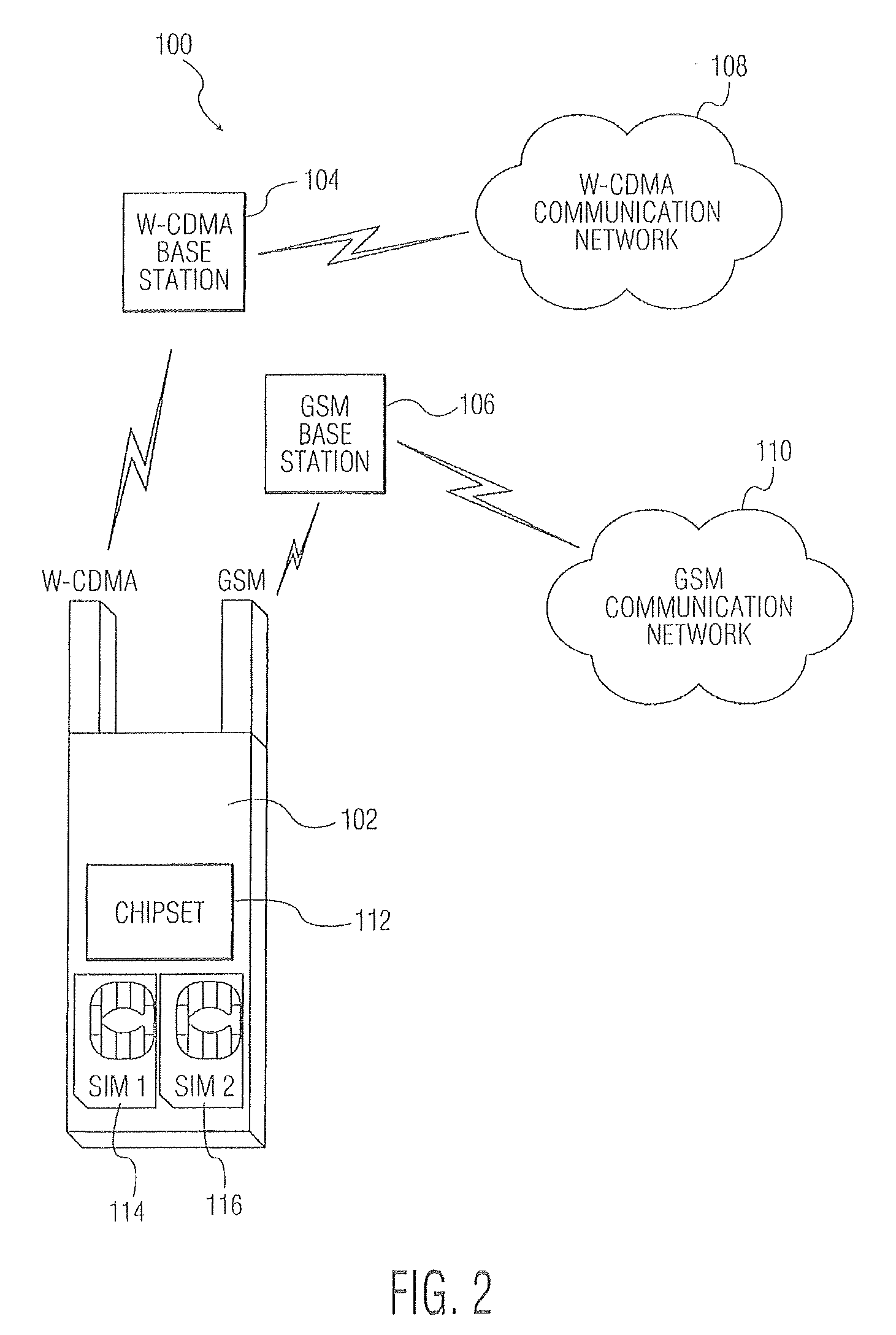

Method and system for enabling dual standby state in a wireless communications system

ActiveUS20090131054A1Facilitate a dual standby featurePower managementConnection managementCommunications systemMaster controller

A system and method having a multimode wireless communication terminal with at least two SIM card slots for use with at least two phone numbers simultaneously online (dual standby). The system includes a main controller, a primary mode module, a secondary mode module, and an inter-system measurement module. The main controller operates the multimode wireless communication terminal in single standby or dual standby state. The primary mode module enables the primary mode of operation for the multimode wireless communication terminal. The primary mode of operation is a default mode of operation. The secondary mode module enables the secondary mode of operation for the multimode wireless communication terminal. Paging information for the primary mode of operation and the secondary mode of operation are monitored at their respective monitoring rates using a TDM method. Switching between the primary and secondary modes of operation is executed by an inter-system handover module. During the dual standby state, both the inter-system measurement and handover are initiated by the terminal itself. The multimode wireless communication terminal is used in a multimode wireless communication system.

Owner:TELEFON AB LM ERICSSON (PUBL)

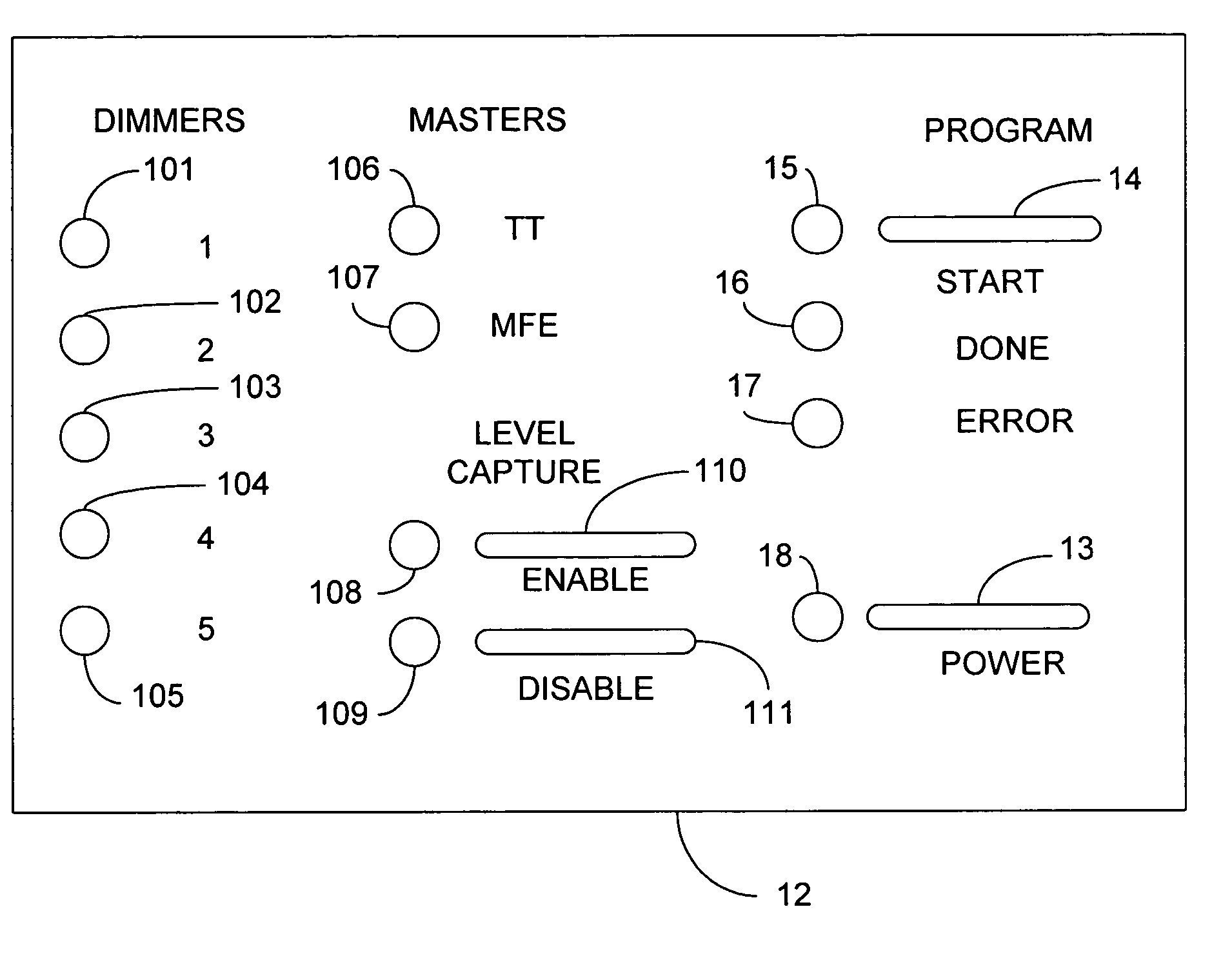

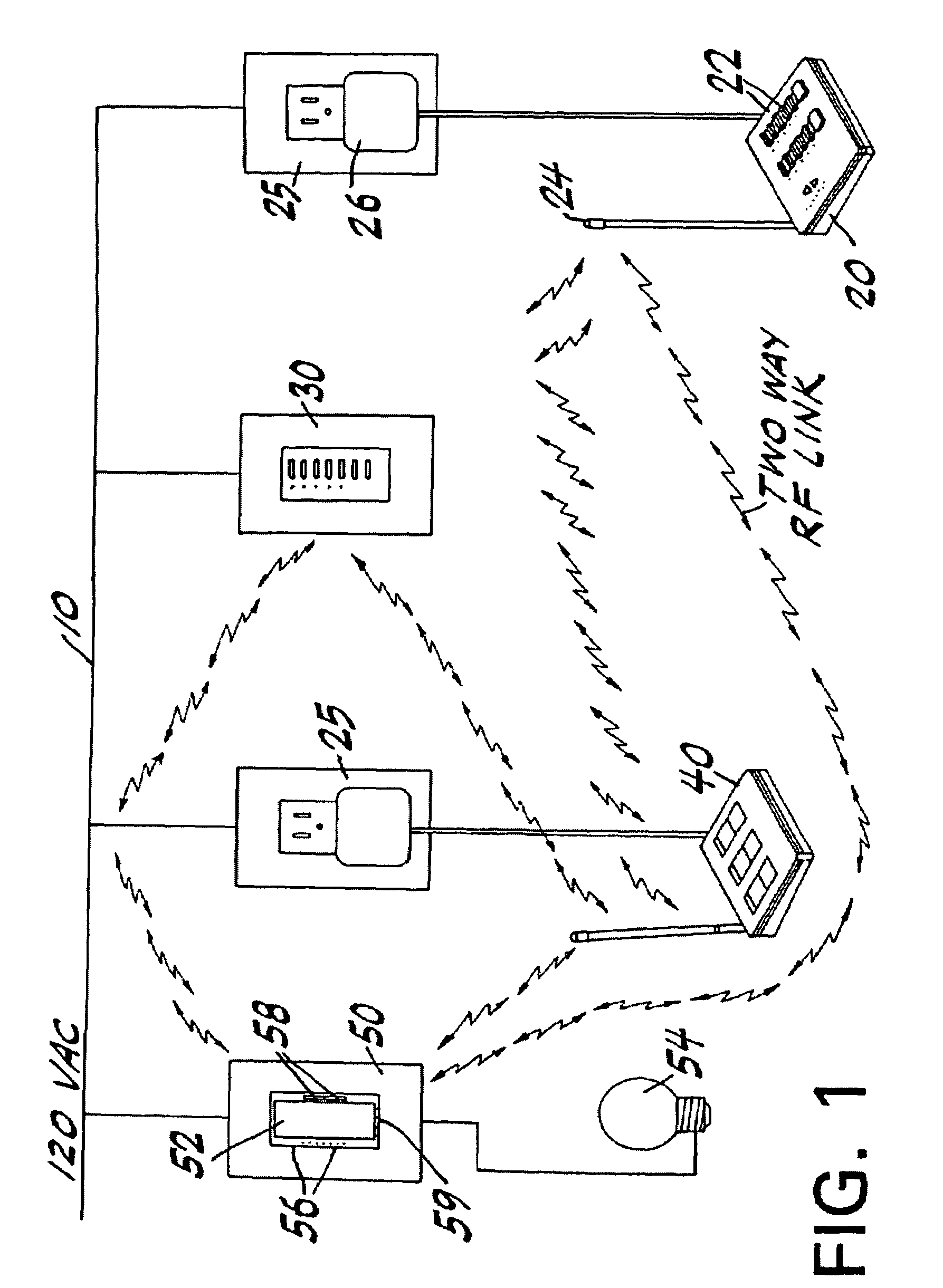

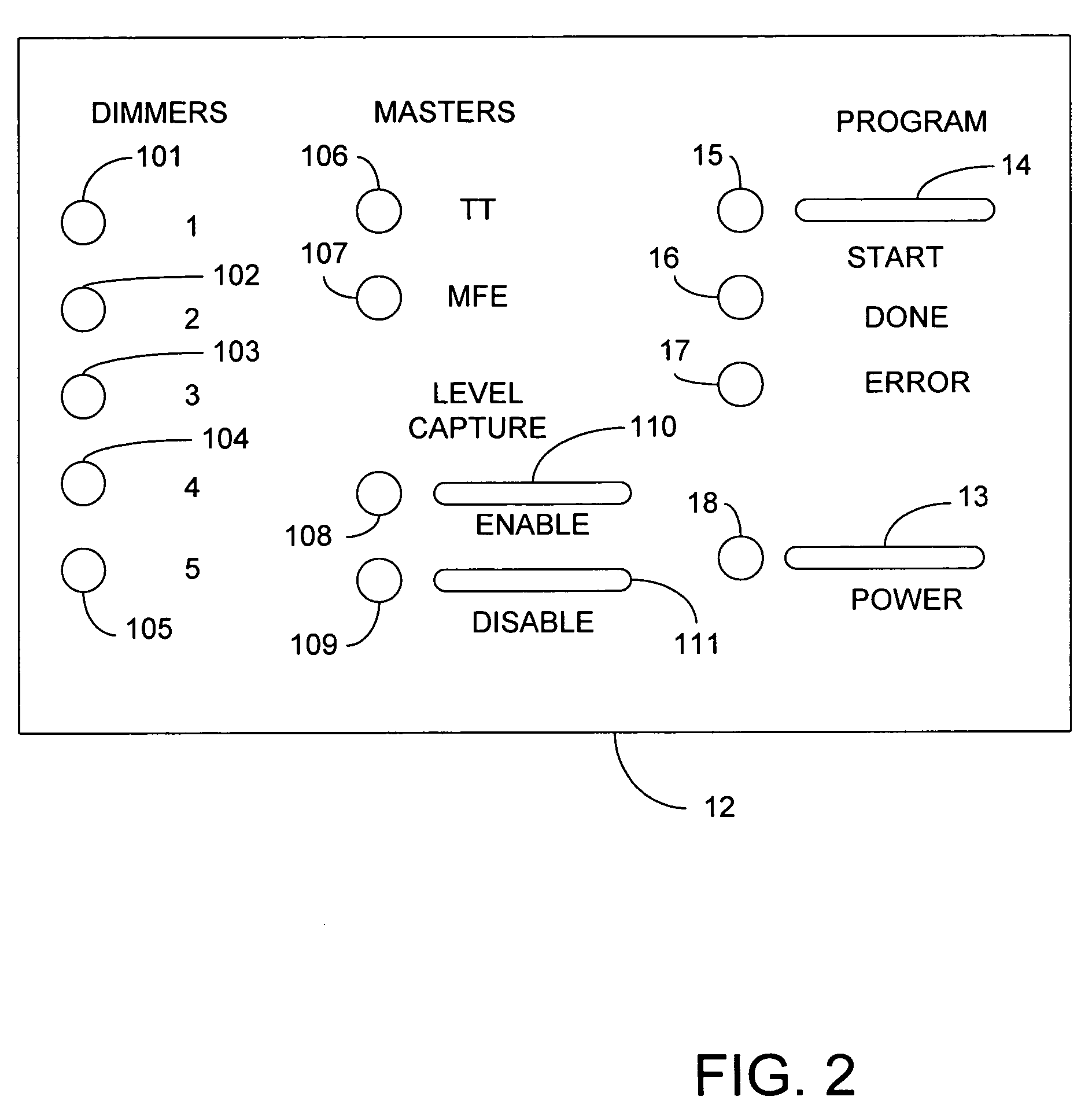

Radio frequency lighting control system programming device and method

ActiveUS7126291B2Lighten the taskSave programming timeElectrical apparatusComputer controlMaster controllerLighting system

An independent radio frequency programming device automates a setup process for a lighting system with lighting control devices and master controls. The programming device intercepts communications between the lighting control devices and the master control during an initial setup phase. A start function permits the programming device to provide automated setup information to the master controls. Once the automated setup process completes, the lighting system is fully programmed with behavior functions for all lighting control devices.

Owner:LUTRON TECH CO LLC

Repositioning and reorientation of master/slave relationship in minimally invasive telesuregery

InactiveUS20060241414A1Easy SetupEasy to adjustComputer controlSimulator controlEngineeringMaster controller

The invention provides robotic surgical systems which allow selectable independent repositioning of an input handle of a master controller and / or a surgical end effector without corresponding movement of the other. In some embodiments, independent repositioning is limited to translational degrees of freedom. In other embodiments, the system provides an input device adjacent a manipulator supporting the surgical instrument so that an assistant can reposition the instrument at the patient's side.

Owner:INTUITIVE SURGICAL OPERATIONS INC

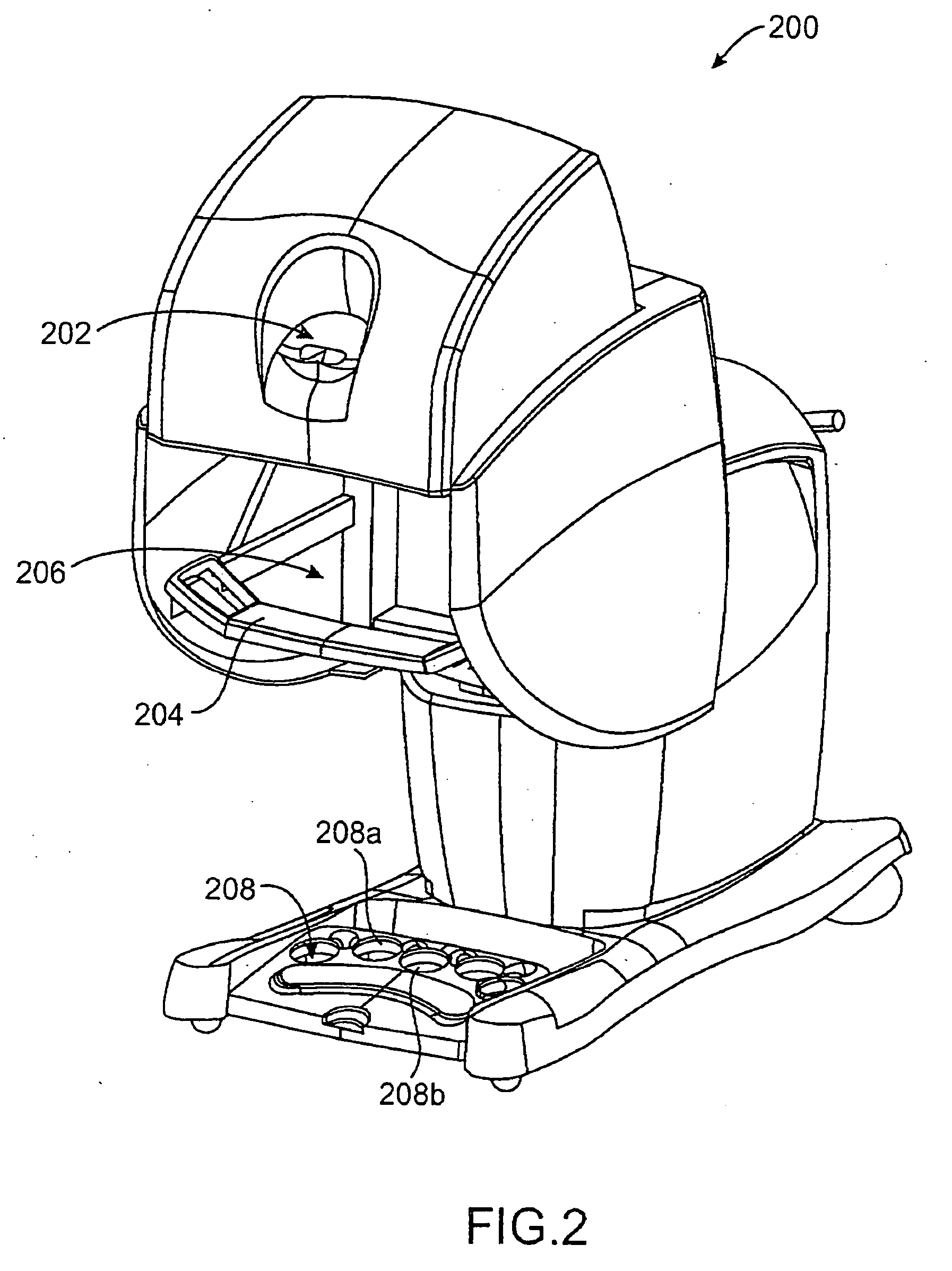

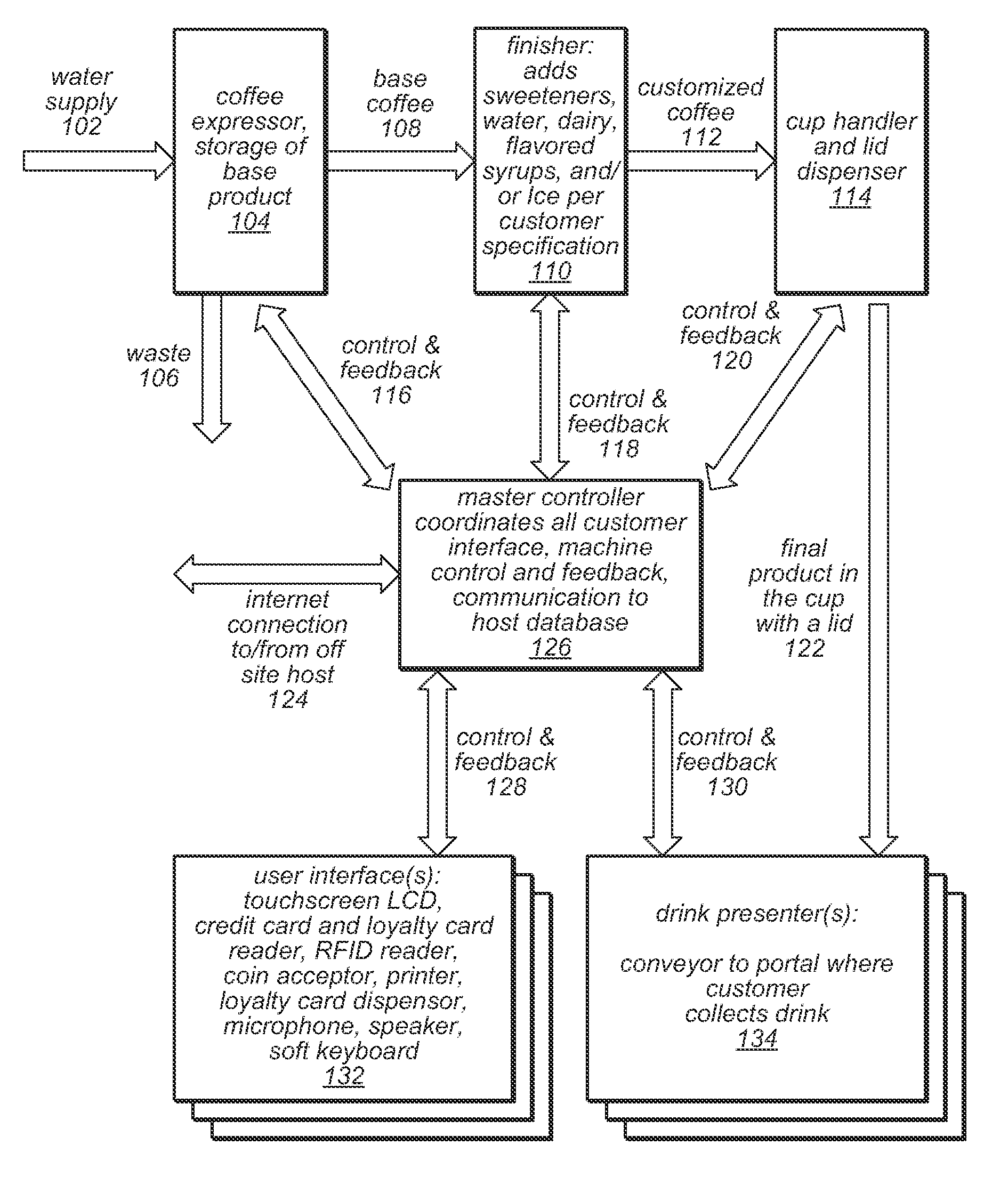

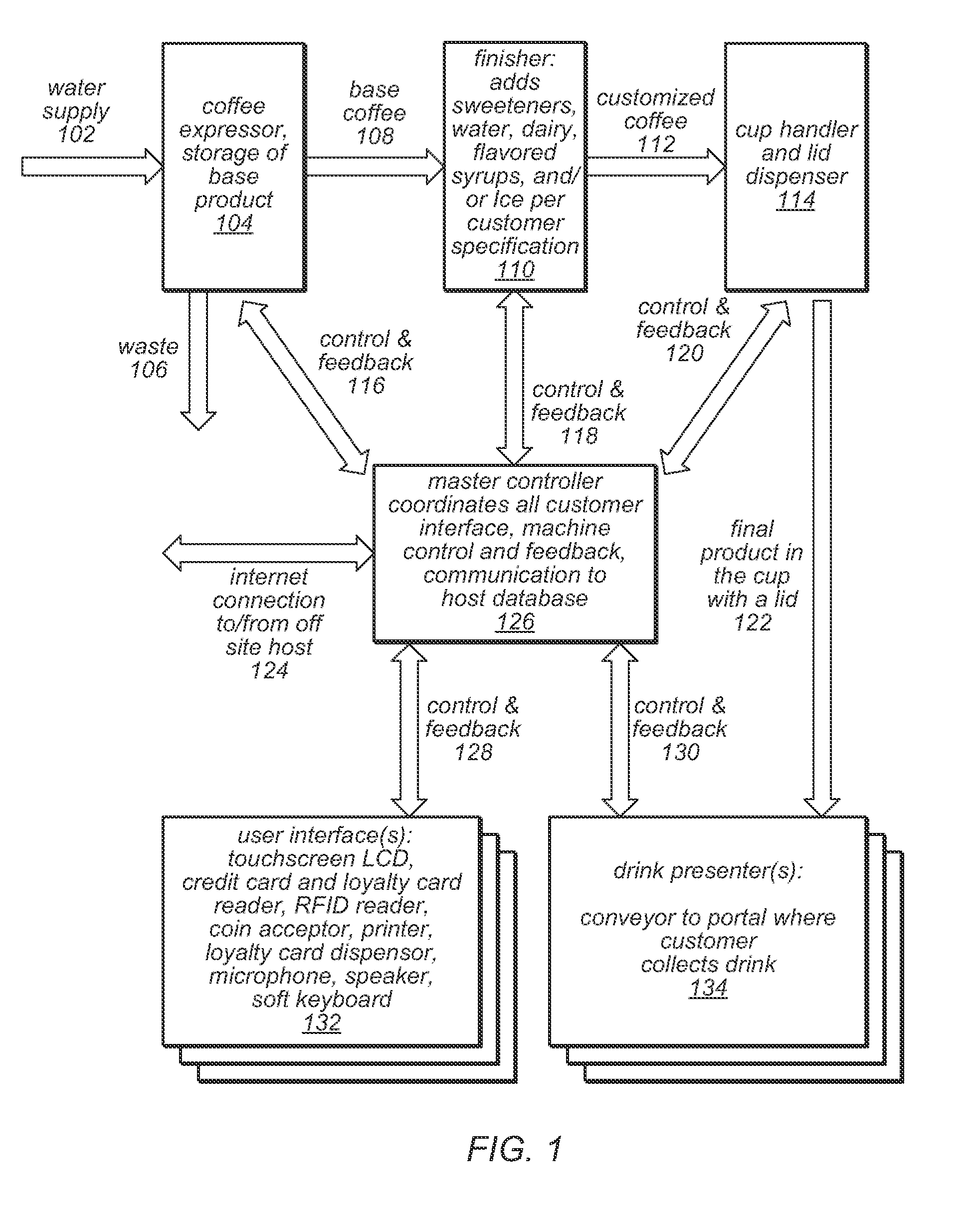

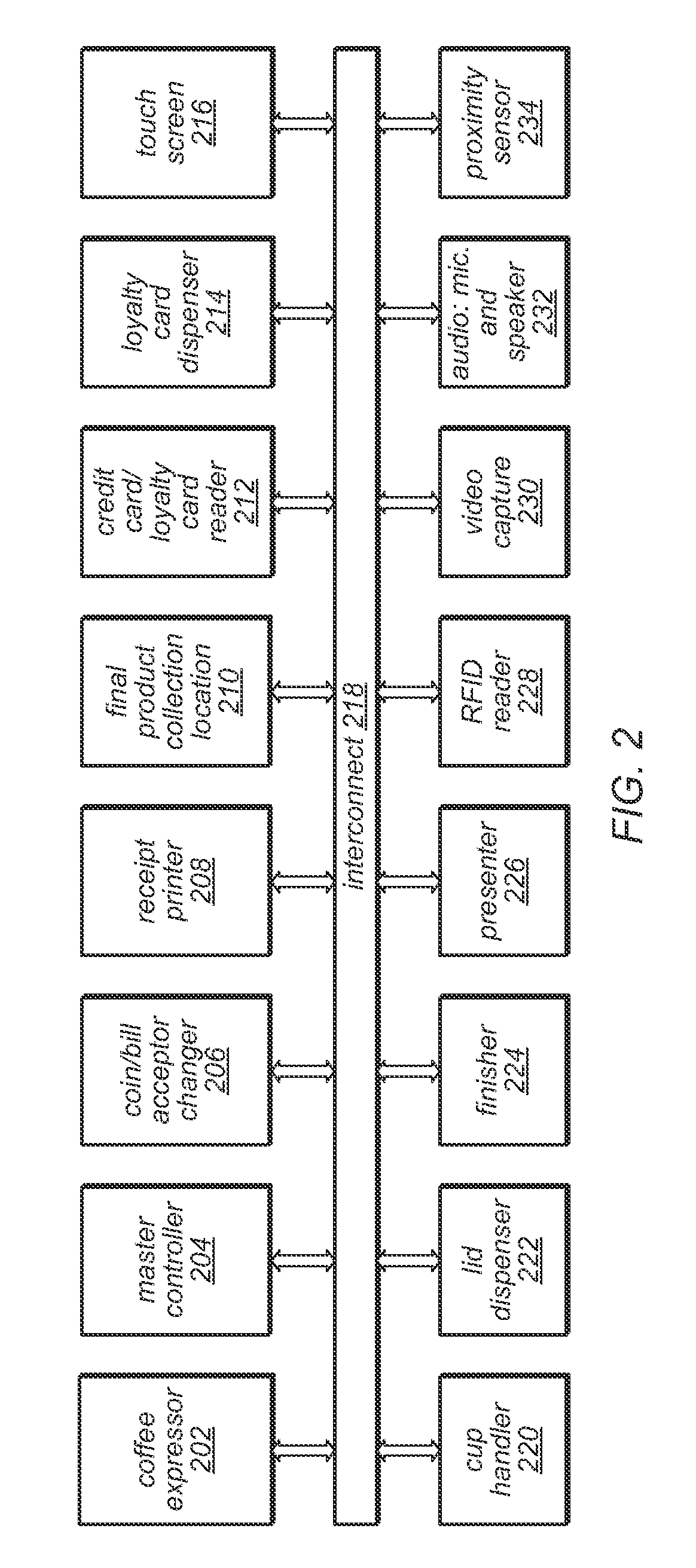

Apparatus and Method for Brewed and Espresso Drink Generation

An apparatus that generates brewed beverages by performing one or more chemical and / or mechanical processes may receive requests to produce specified brewed beverages. The apparatus may include a master controller that initiates and controls performance of the chemical and / or mechanical processes to produce the specified beverages. The master controller may adaptively apply one or more process accelerators during the performance of one of the chemical or mechanical processes to accelerate the process or to achieve a desired qualitative or quantitative characteristic for a beverage or a component thereof. The adaptive application of one or more process accelerators may be dependent on a multiple-variable process profile developed for the process and / or a specified beverage. For example, the pressure in a steam wand and / or the depth of the wand may be varied during a process to froth milk in order to produce frothed milk having a desired temperature.

Owner:COSTA COFFEE

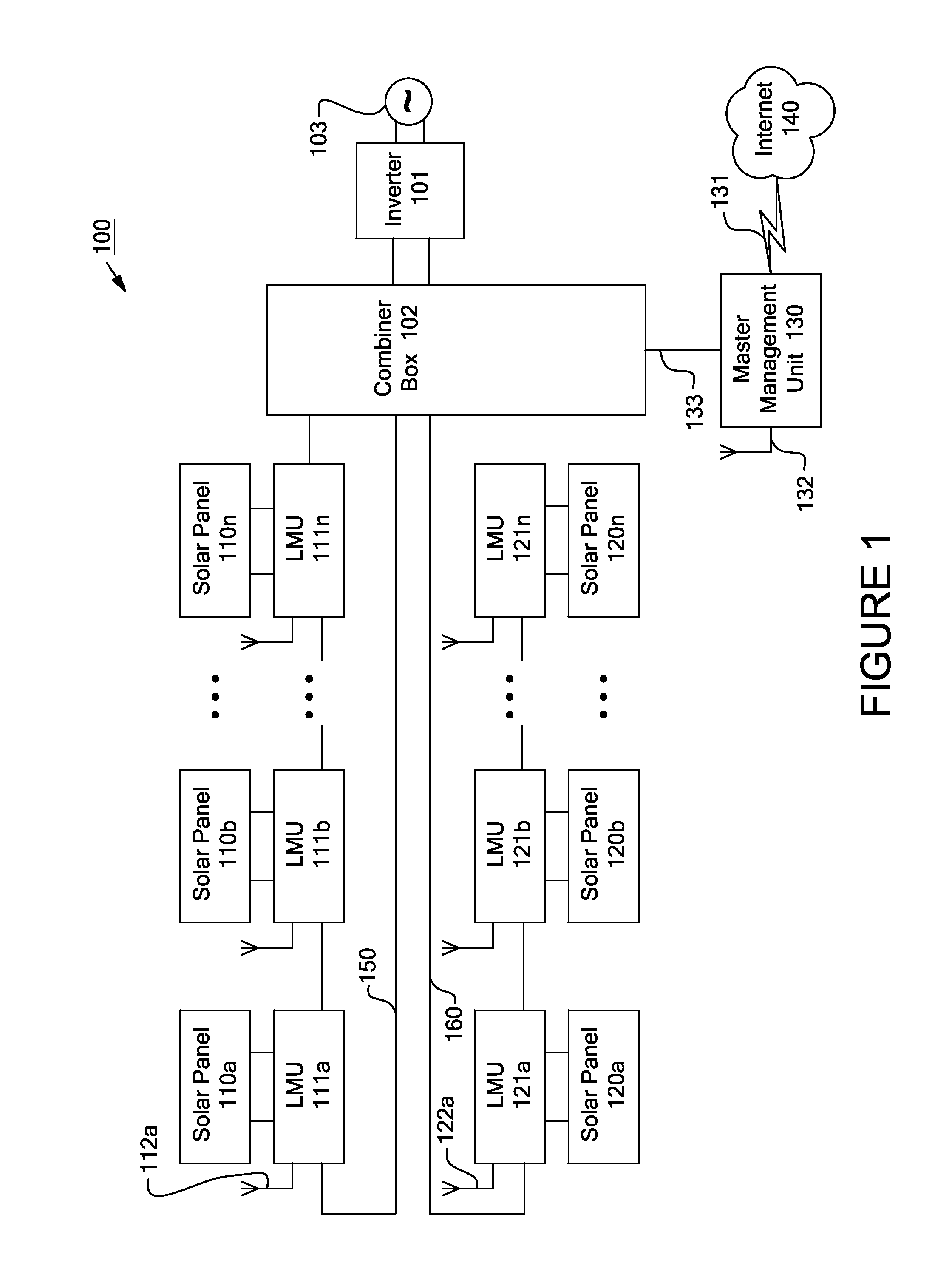

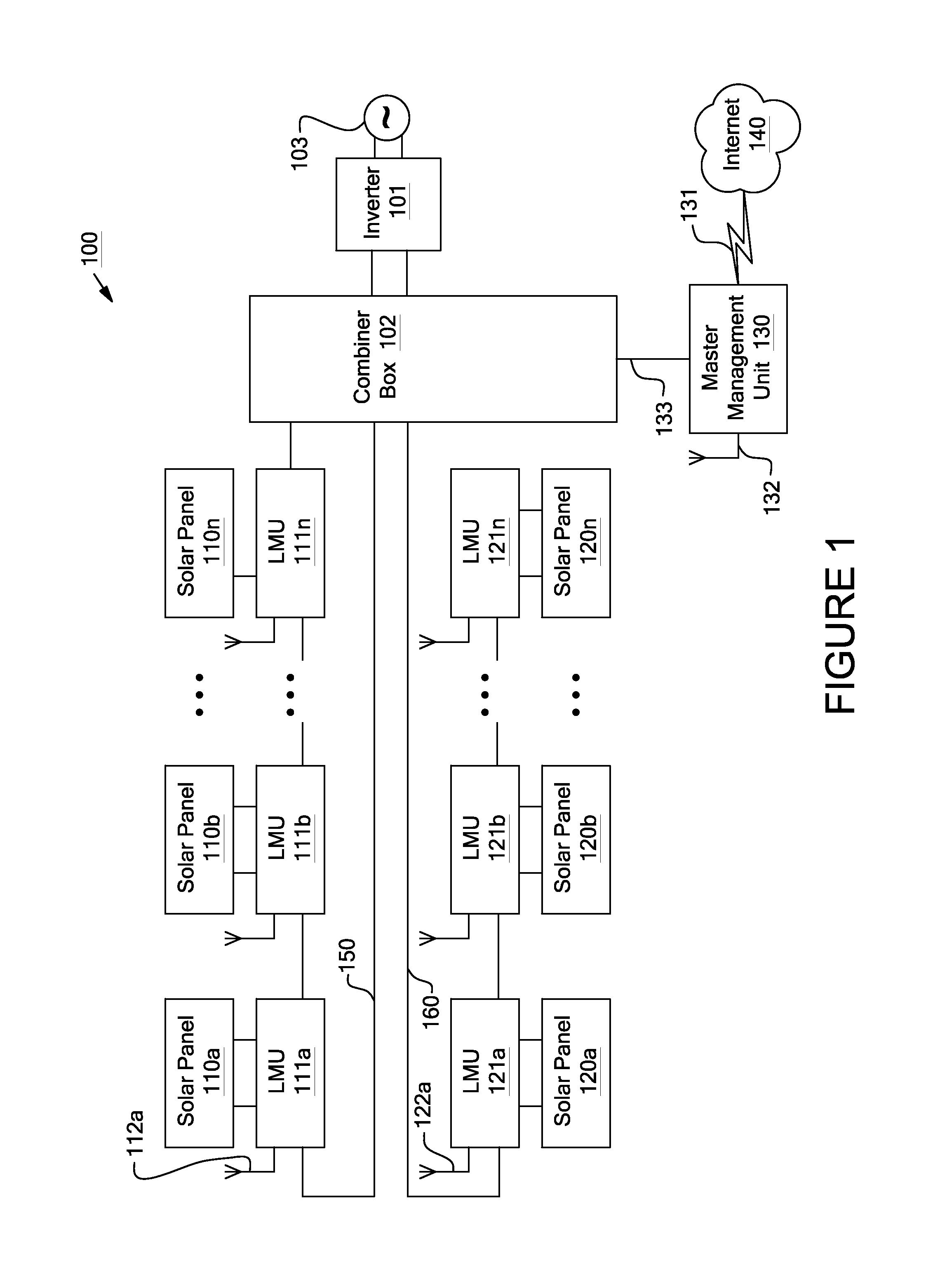

Systems and methods for an identification protocol between a local controller and a master controller in a photovoltaic power generation system

Owner:NEWLIGHT CAPITAL LLC

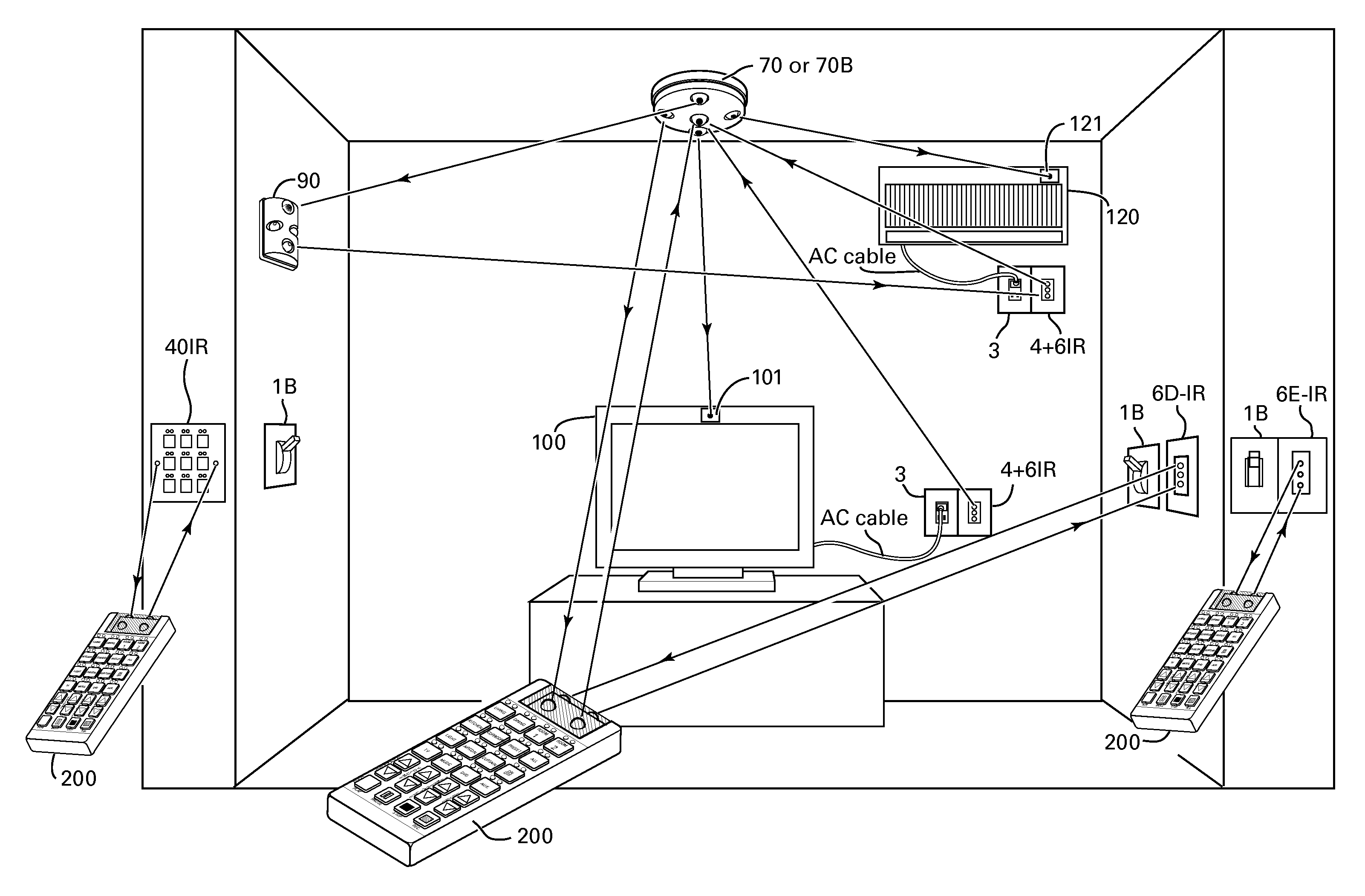

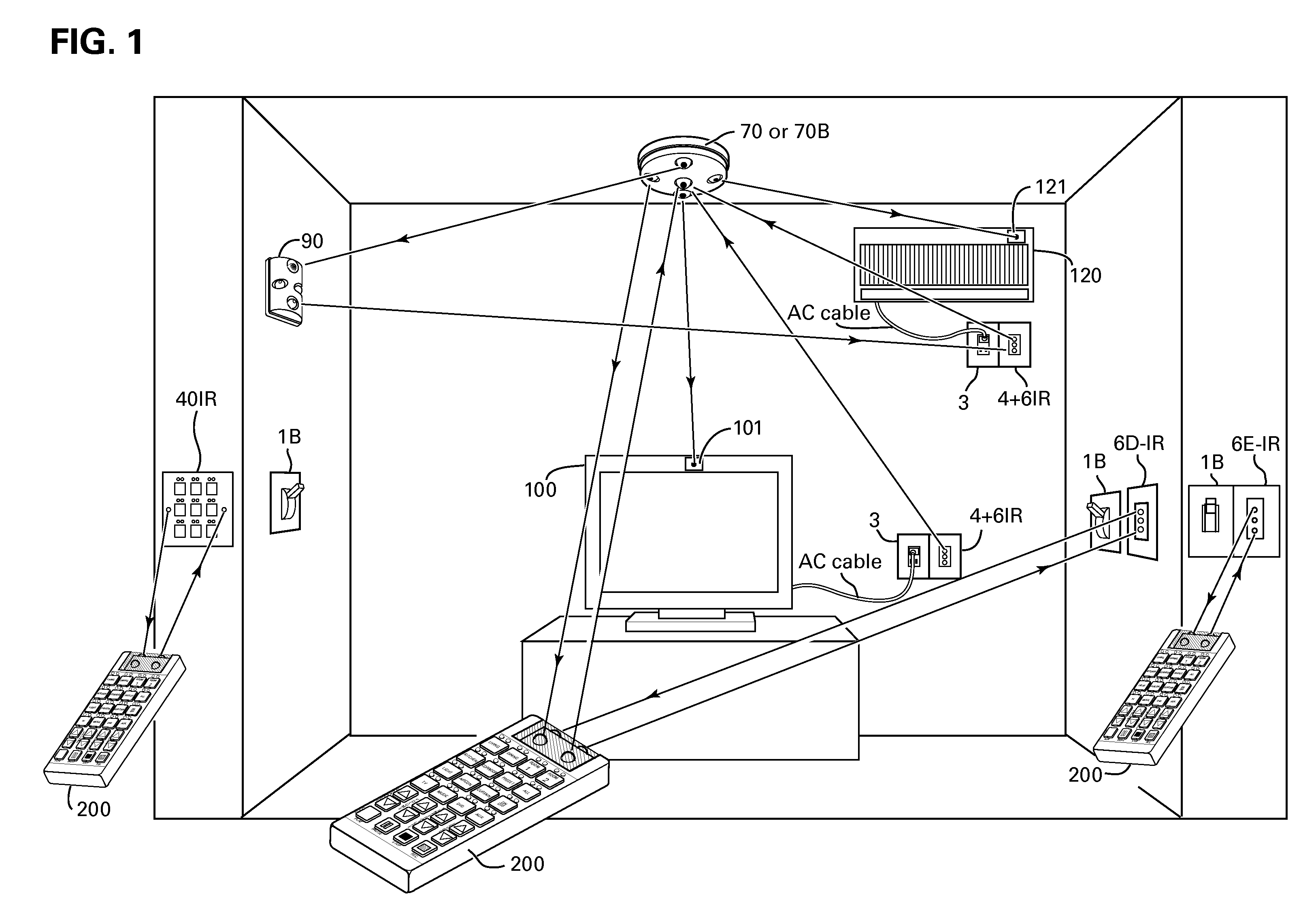

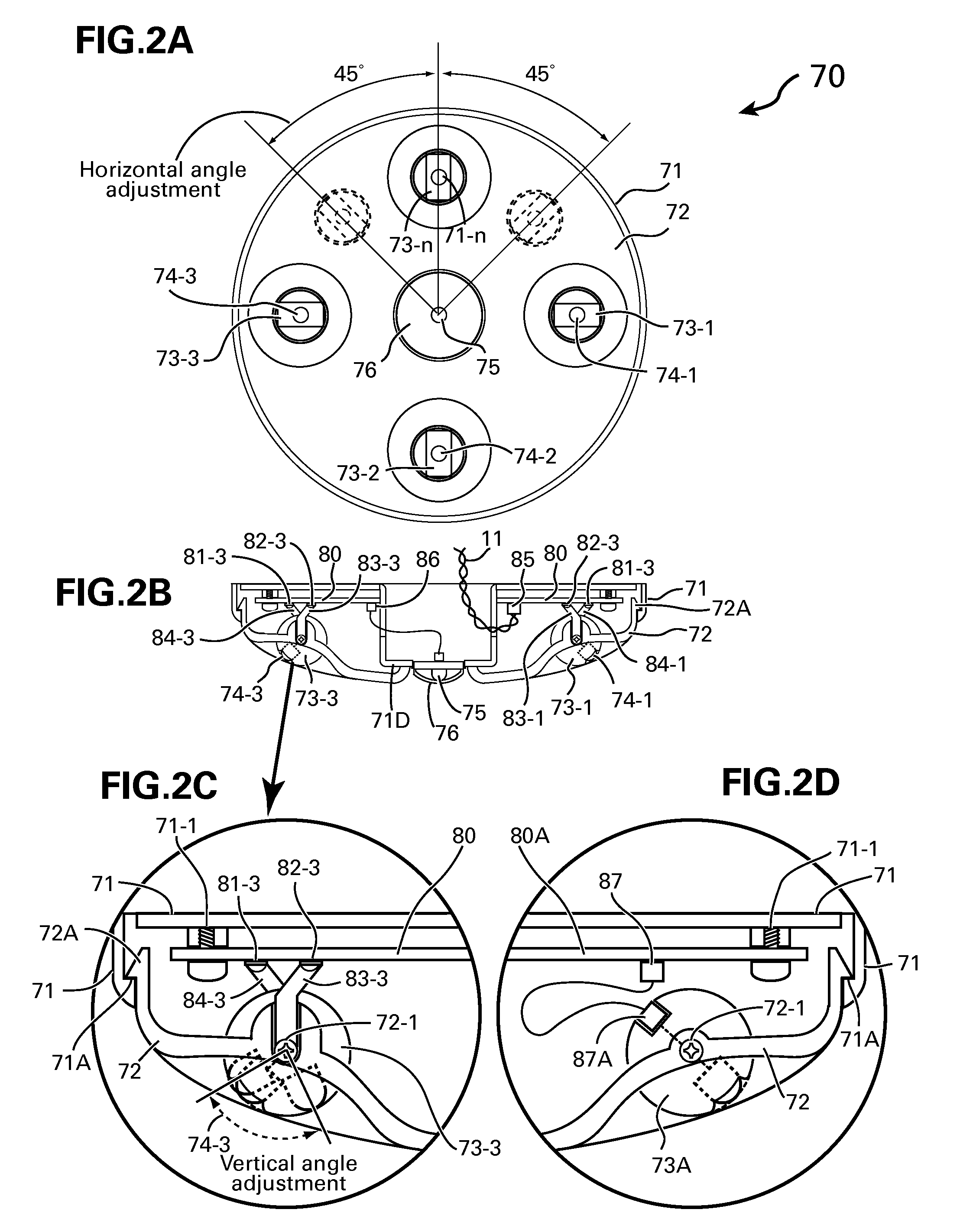

Method and apparatus for operating AC powered appliances via video interphones, two way IR drivers and remote control devices

InactiveUS7639907B2Effectively close missing linkLow costNon-electrical signal transmission systemsCoupling light guidesHand heldEngineering

A method for coupling at least one of a wall mount and a ceiling mount adjustable IR driver with a two way IR network of a home automation system controlled by a main controller selected from a group comprising a dedicated controller, a video interphone and a shopping terminal, the IR driver includes a plurality of adjustable IR transmitters and at least one IR receiver for propagating IR commands to at least one of hand held IR remote control units, electrical appliances and devices selected from a group comprising a remotely operated relays, an AC current sensors and a keypads, and for receiving from at least one of the devices a status data, said IR commands include at least a power on-off command for switching an appliance on and off and the status data pertaining to the on and off statuses of a commanded appliance.

Owner:ELBEX VIDEO LTD

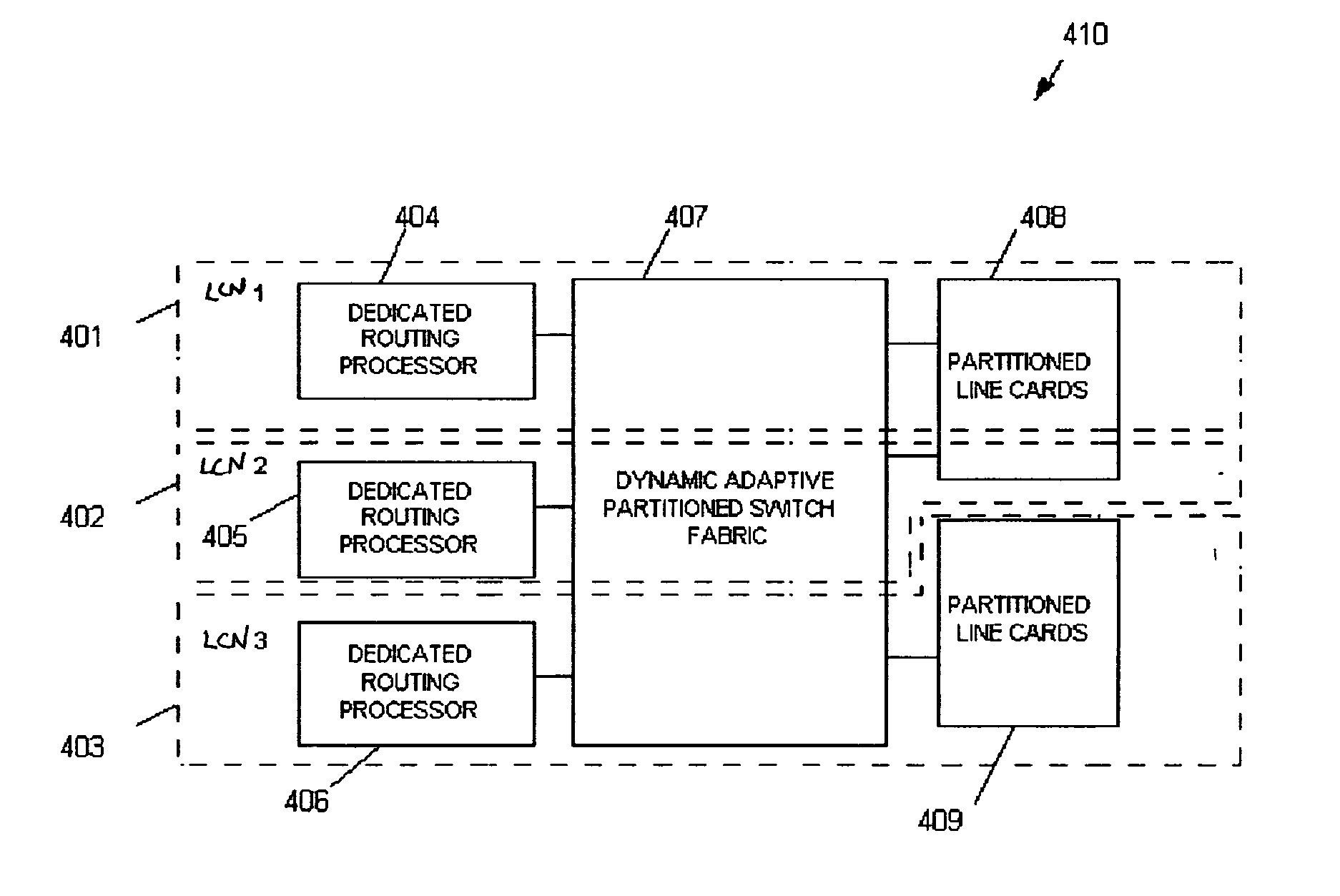

System, method and apparatus for sharing and optimizing packet services nodes

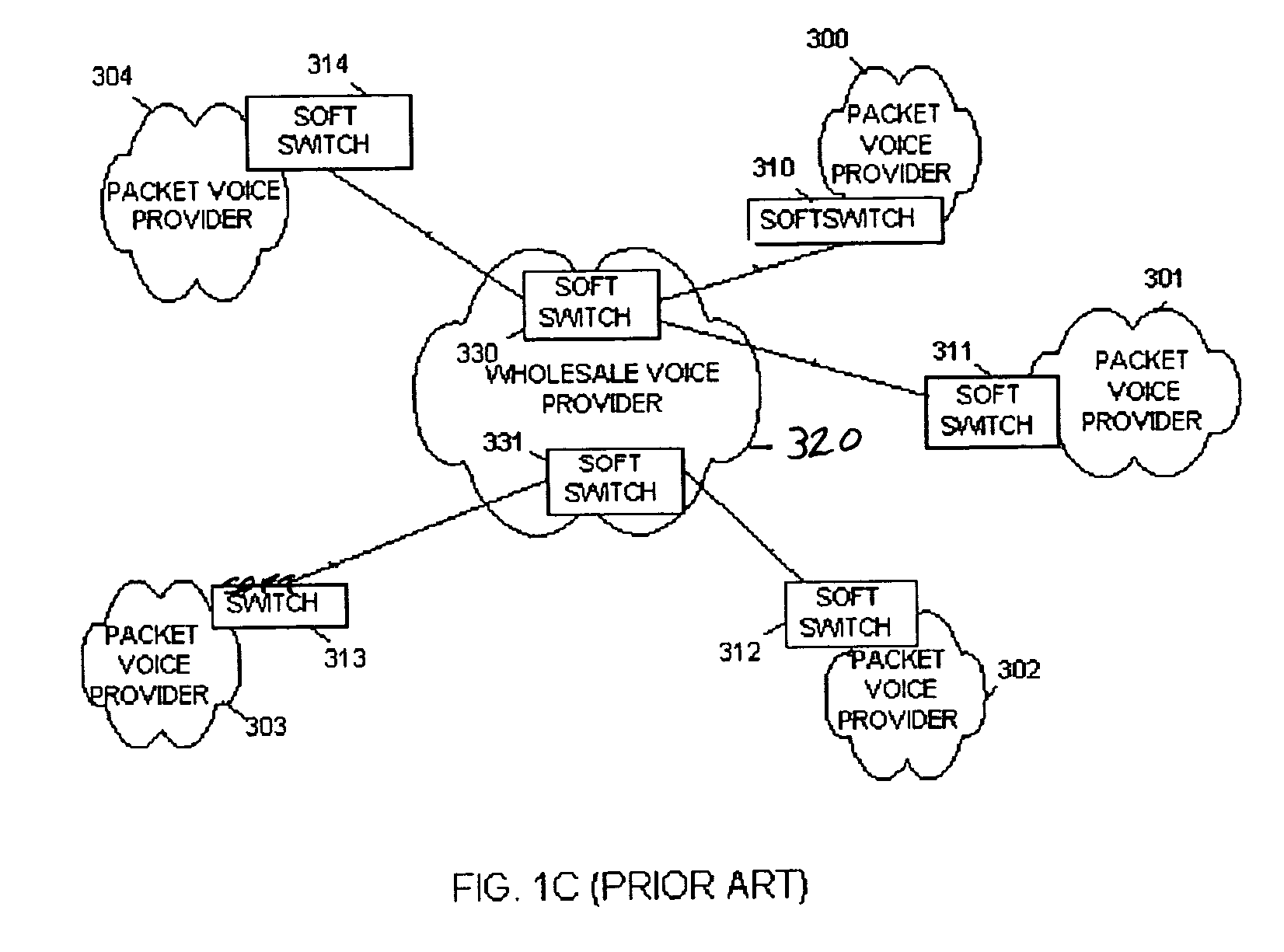

InactiveUS20040066782A1Lower capital expenditureWide area networksReal-time webTelecommunications network

A dedicated, optimized, secure and private apparatus, system and method is provided for service providers to dynamically share the resources of a single packet services node within a telecommunications network. The apparatus, method and system uses real-time dynamic software partitioning, with low-level dynamic hardware reconfiguration and adaptation, to enable real-time network, software and hardware resource allocation. The packet services node is configured as a unified and integrated switch (UIS) that can be segmented into a number of logical communication nodes (LCN). Each LCN operates as a secure, independent, private and dynamically configured packet services node. A master controller is responsible for the allocation of resources to LCNs based on resource availability and / or a predefined resource allocation configuration between the operator of the UIS and the user of the LCN.

Owner:NASSAR AYMAN ESAM

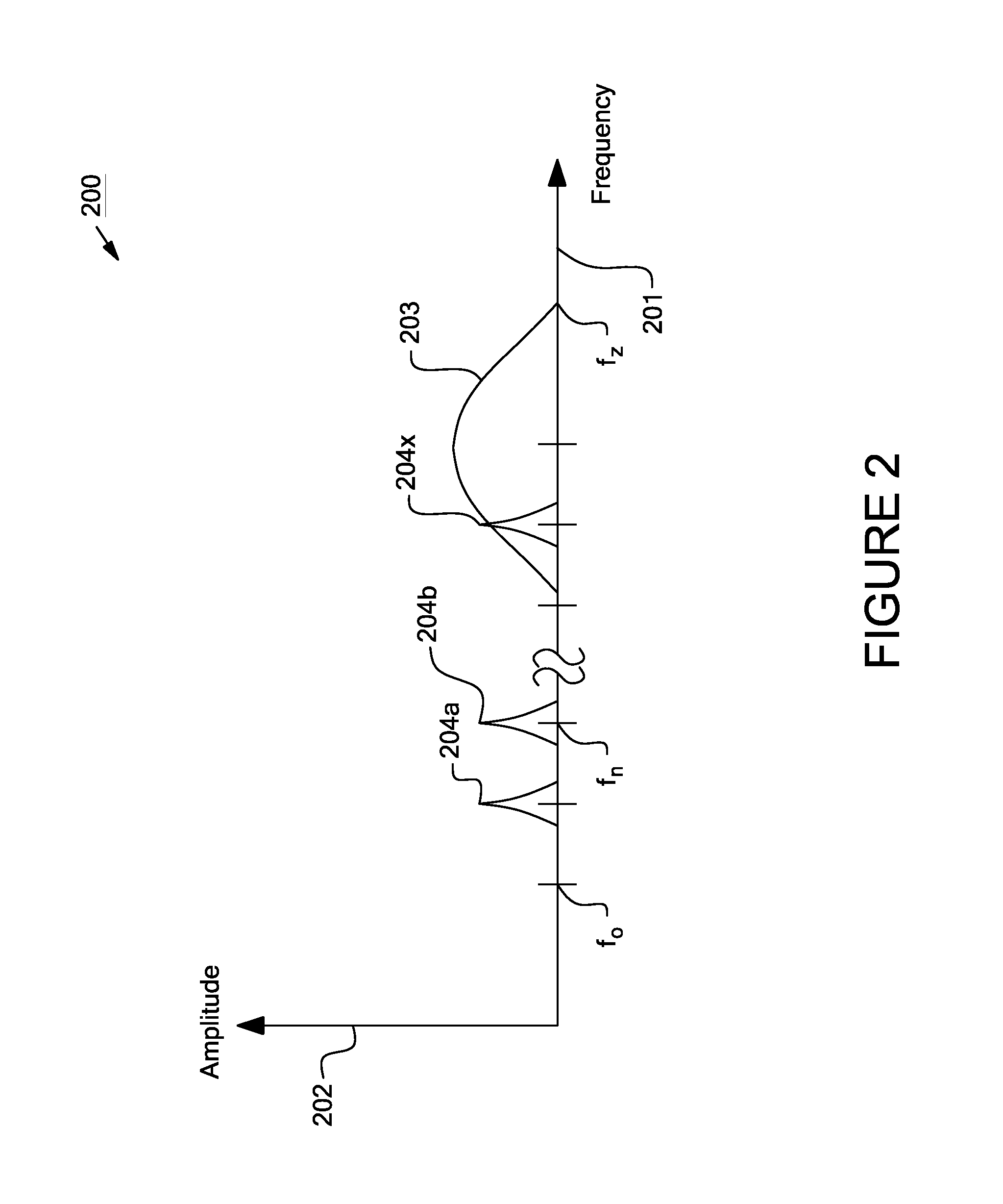

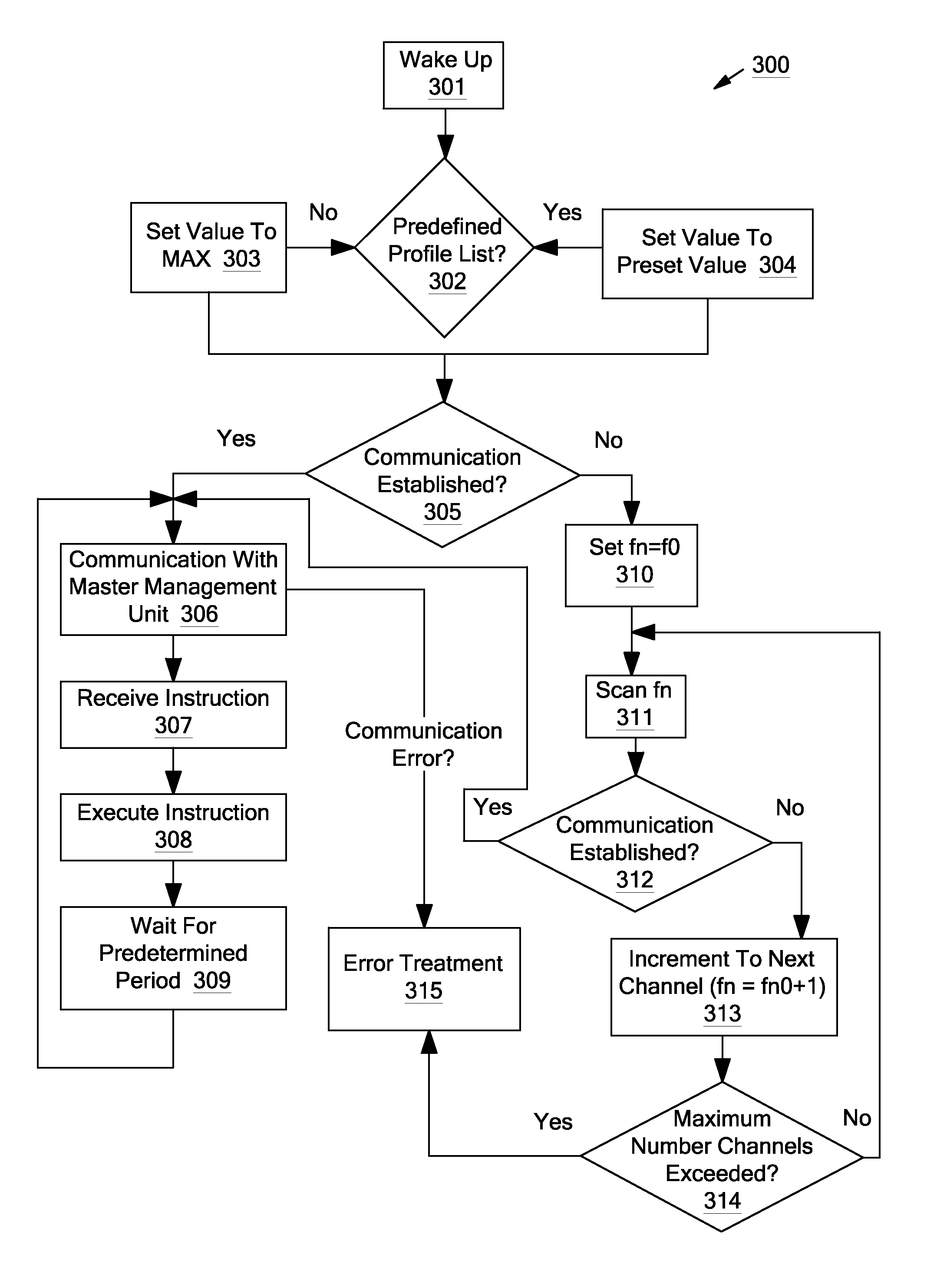

Systems and methods for a communication protocol between a local controller and a master controller

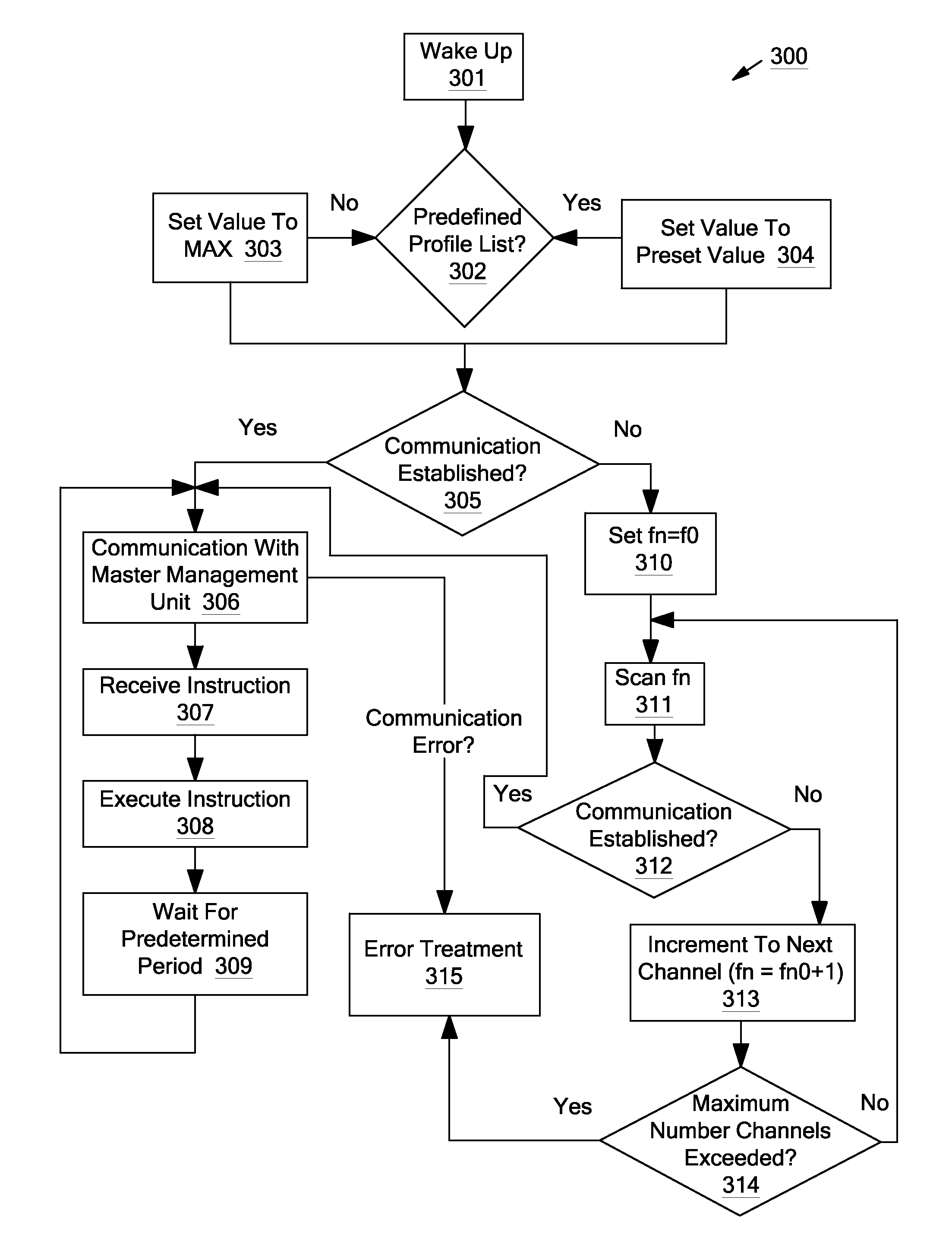

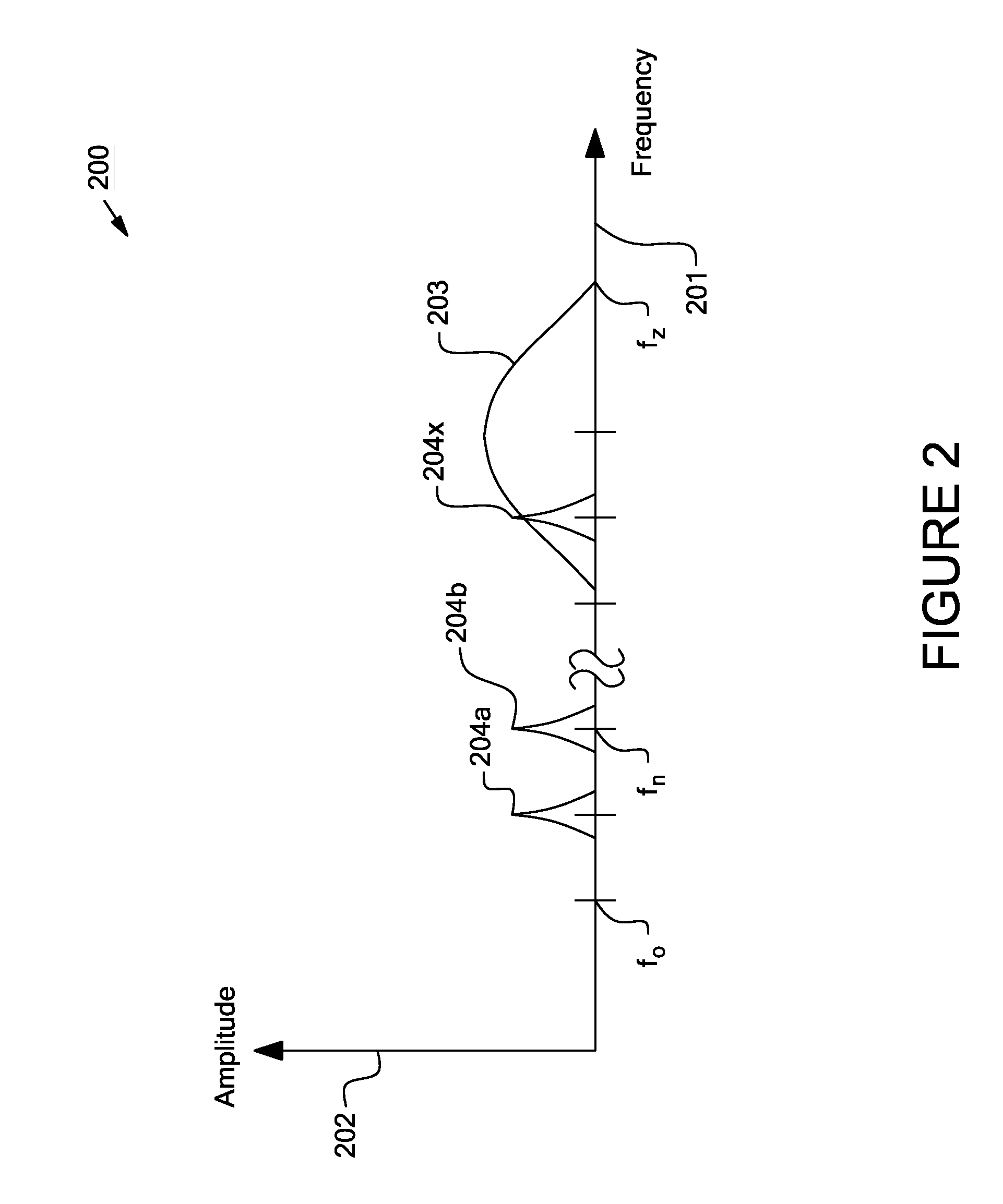

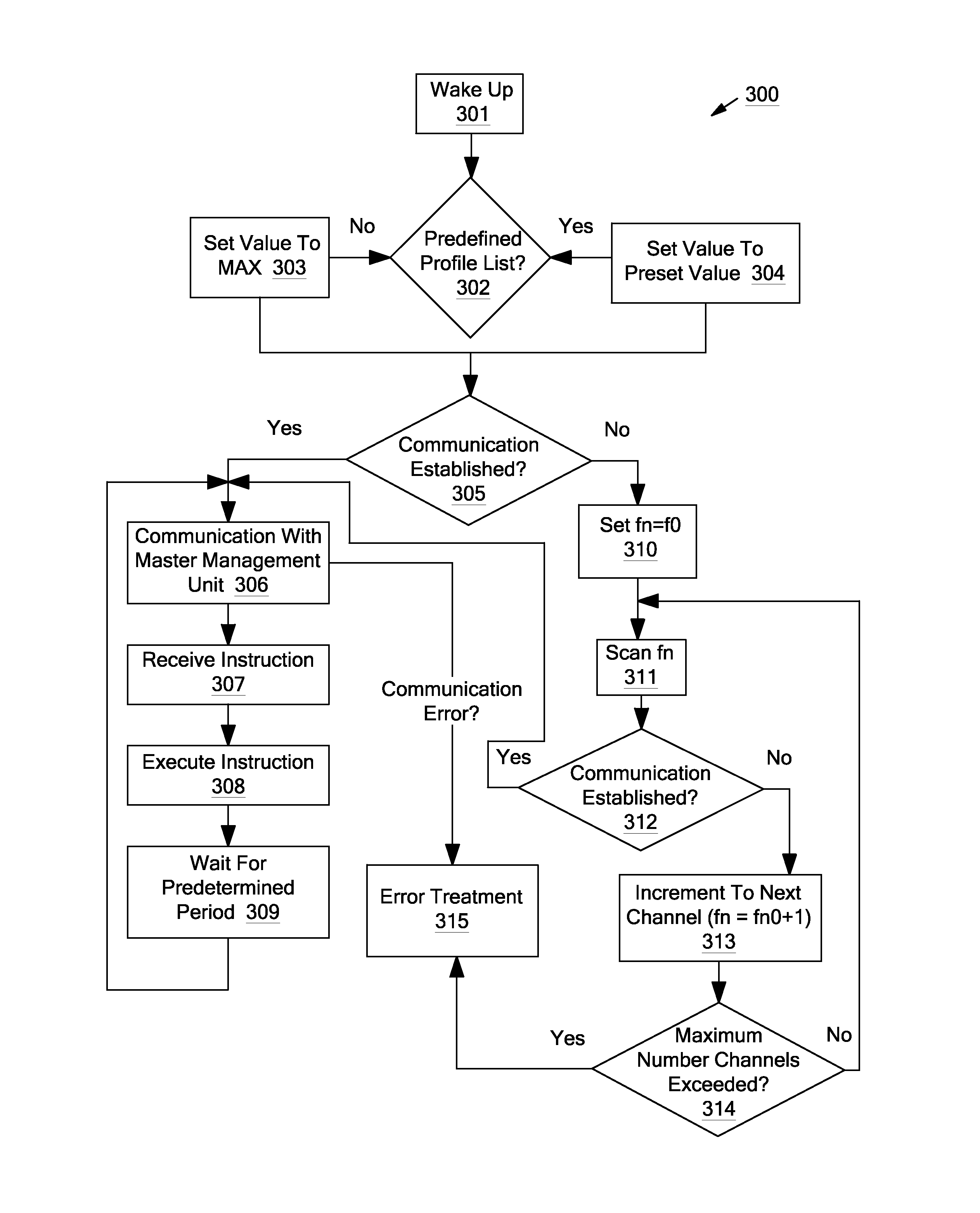

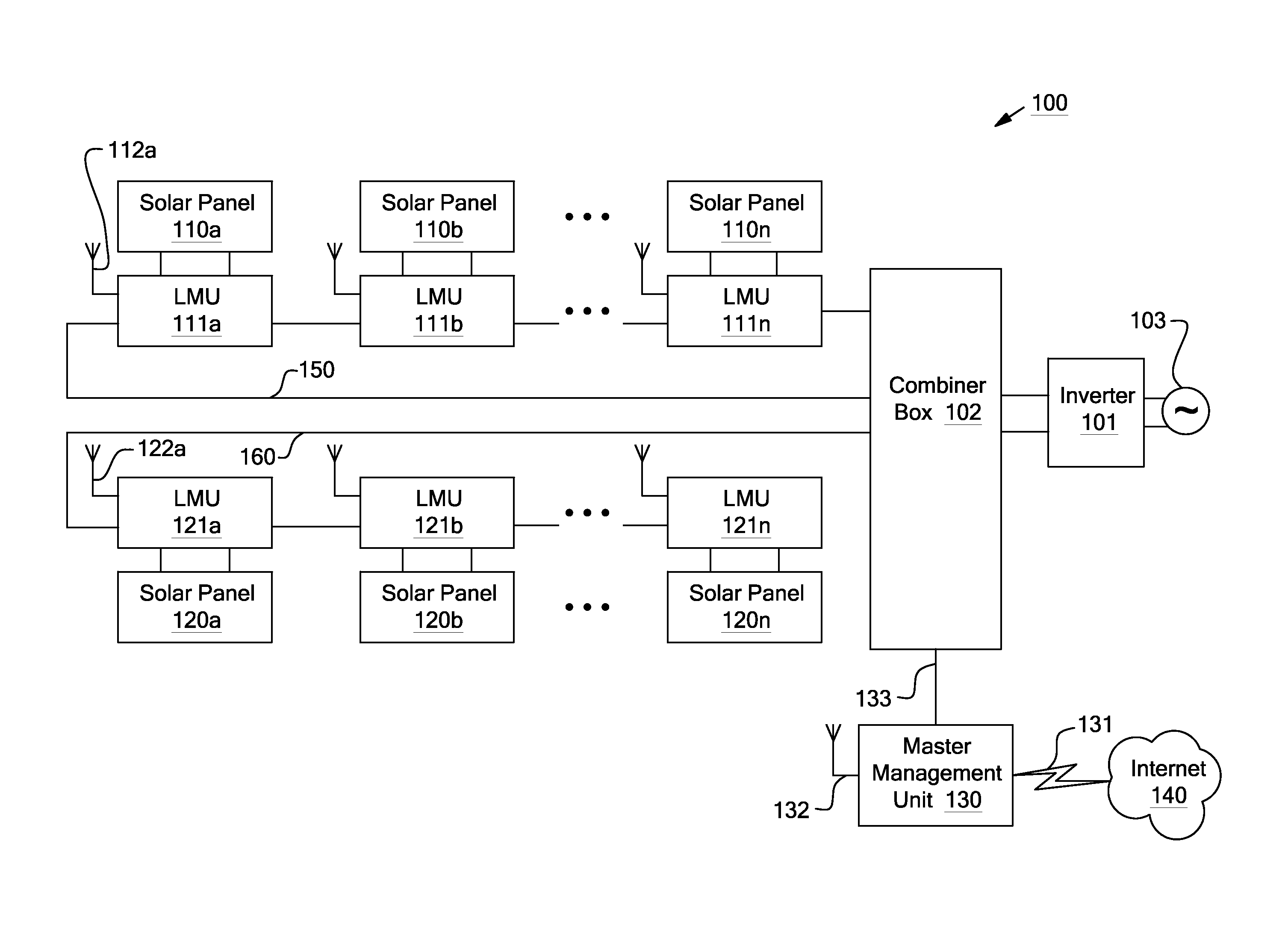

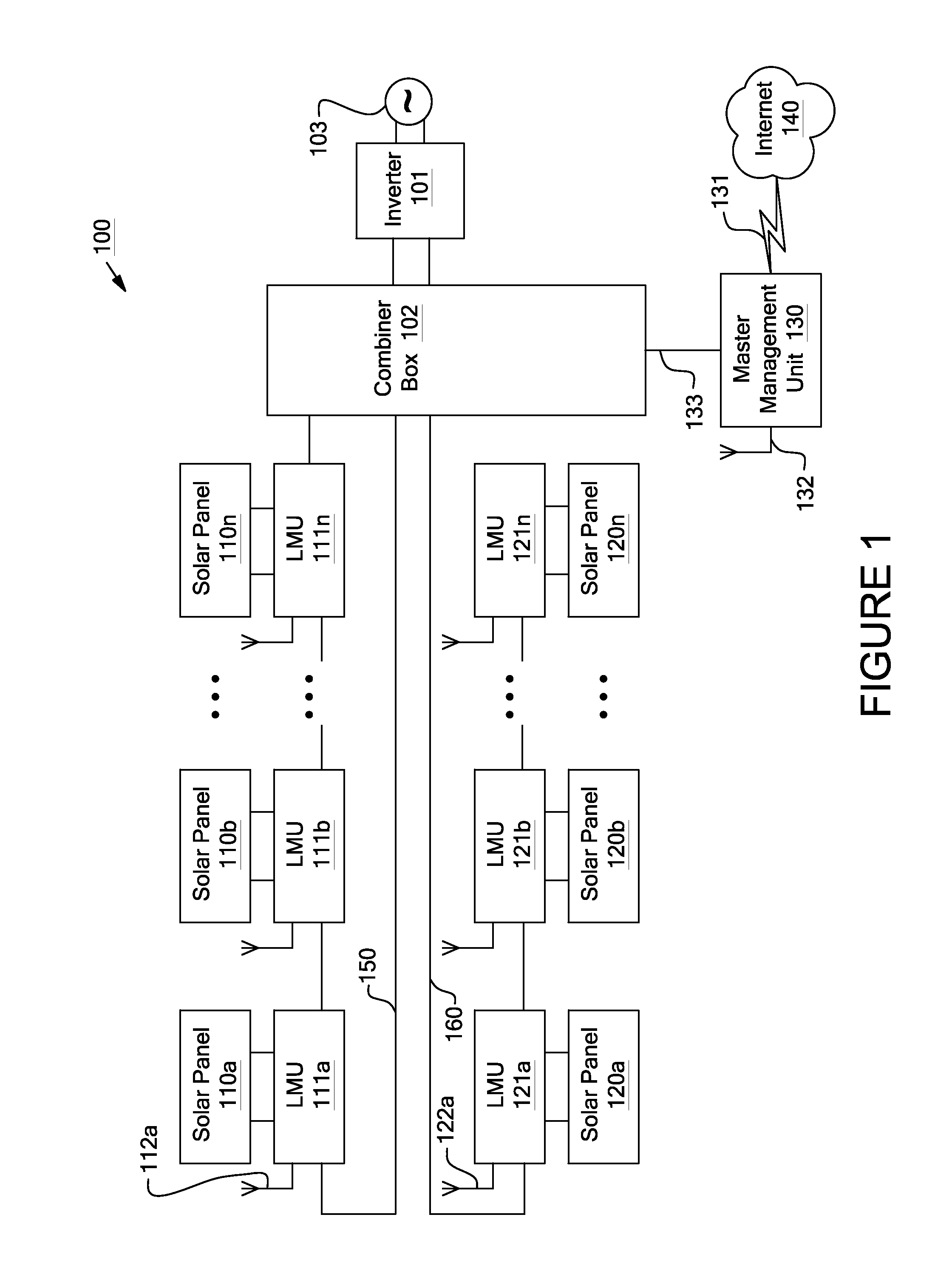

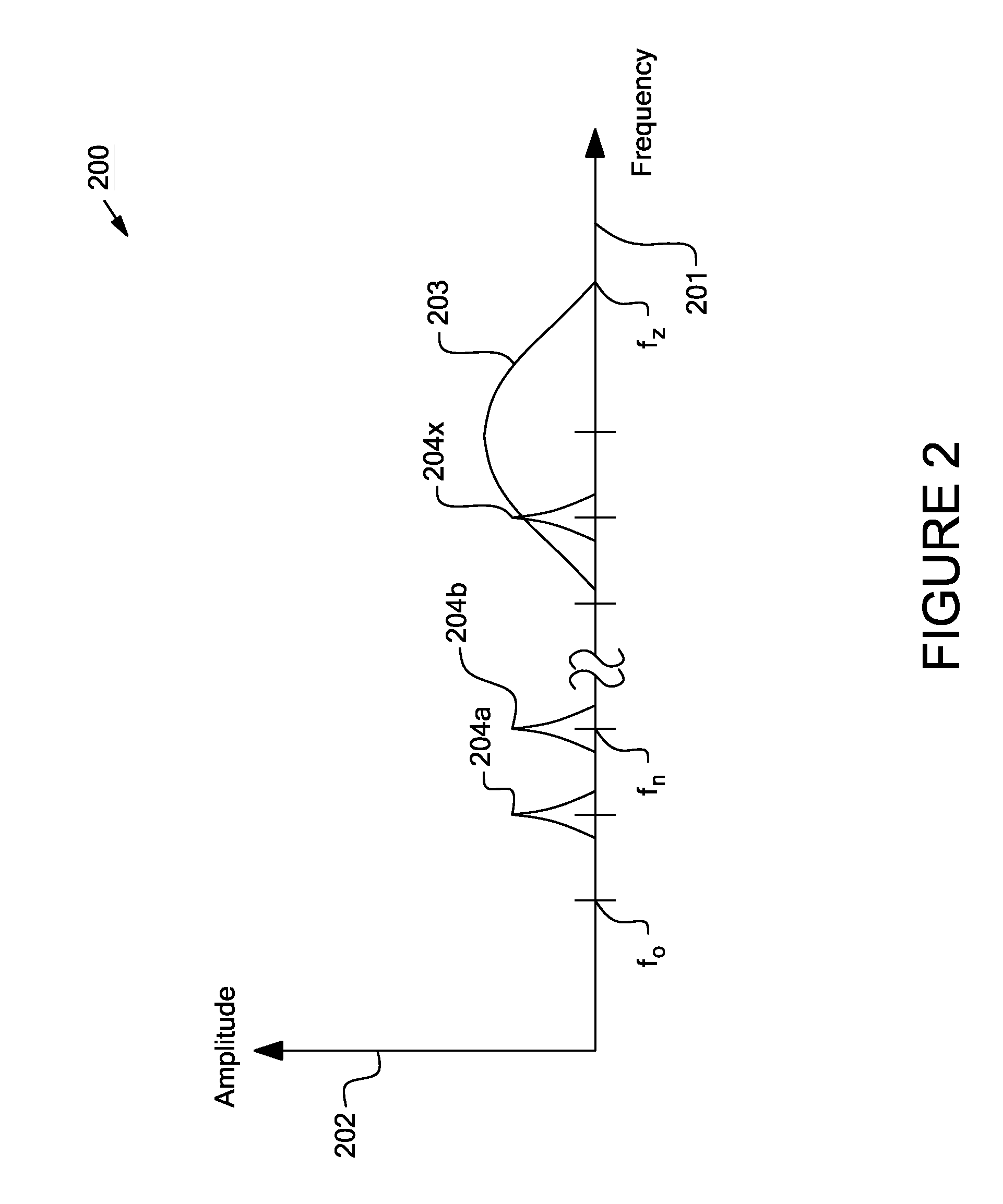

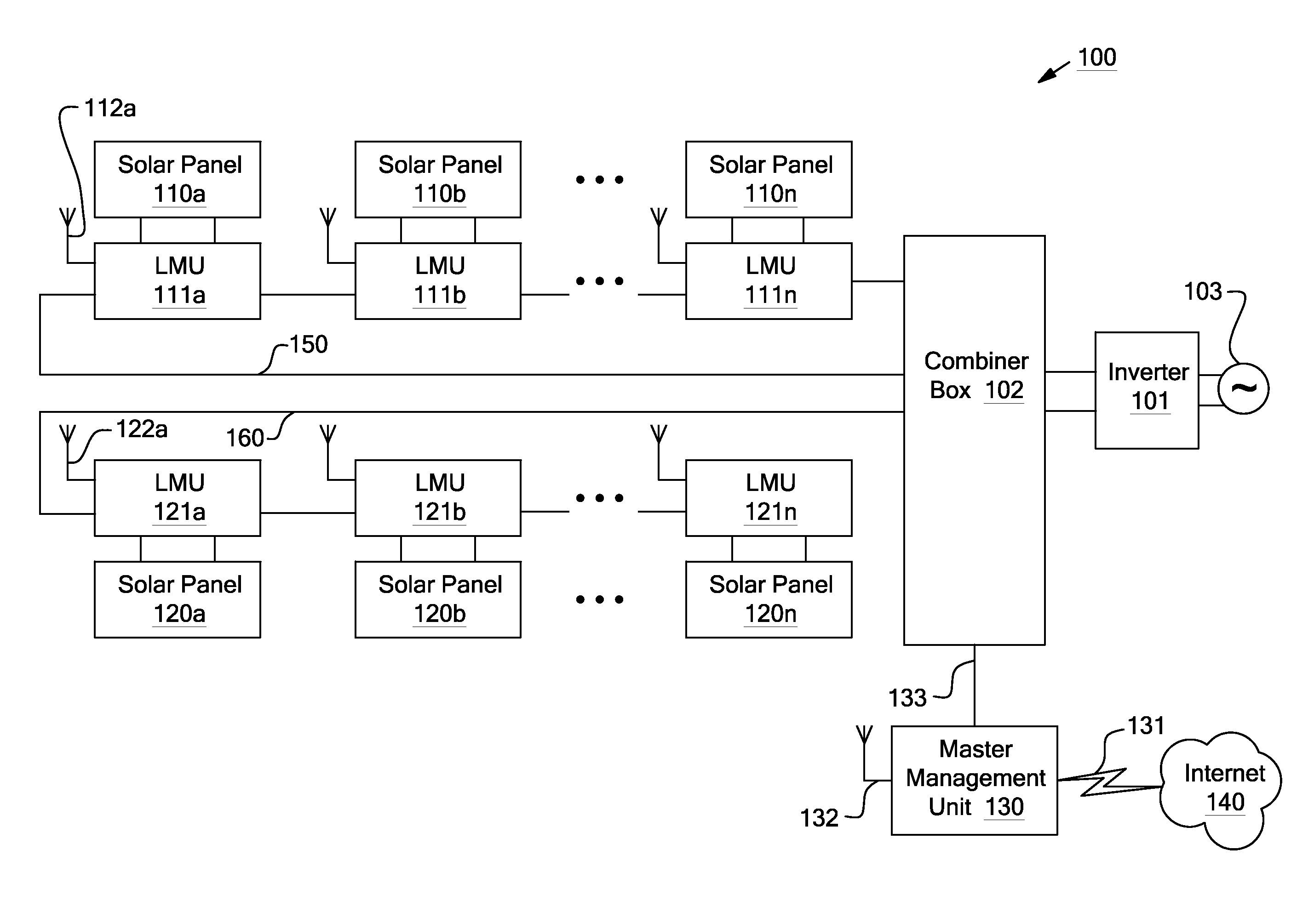

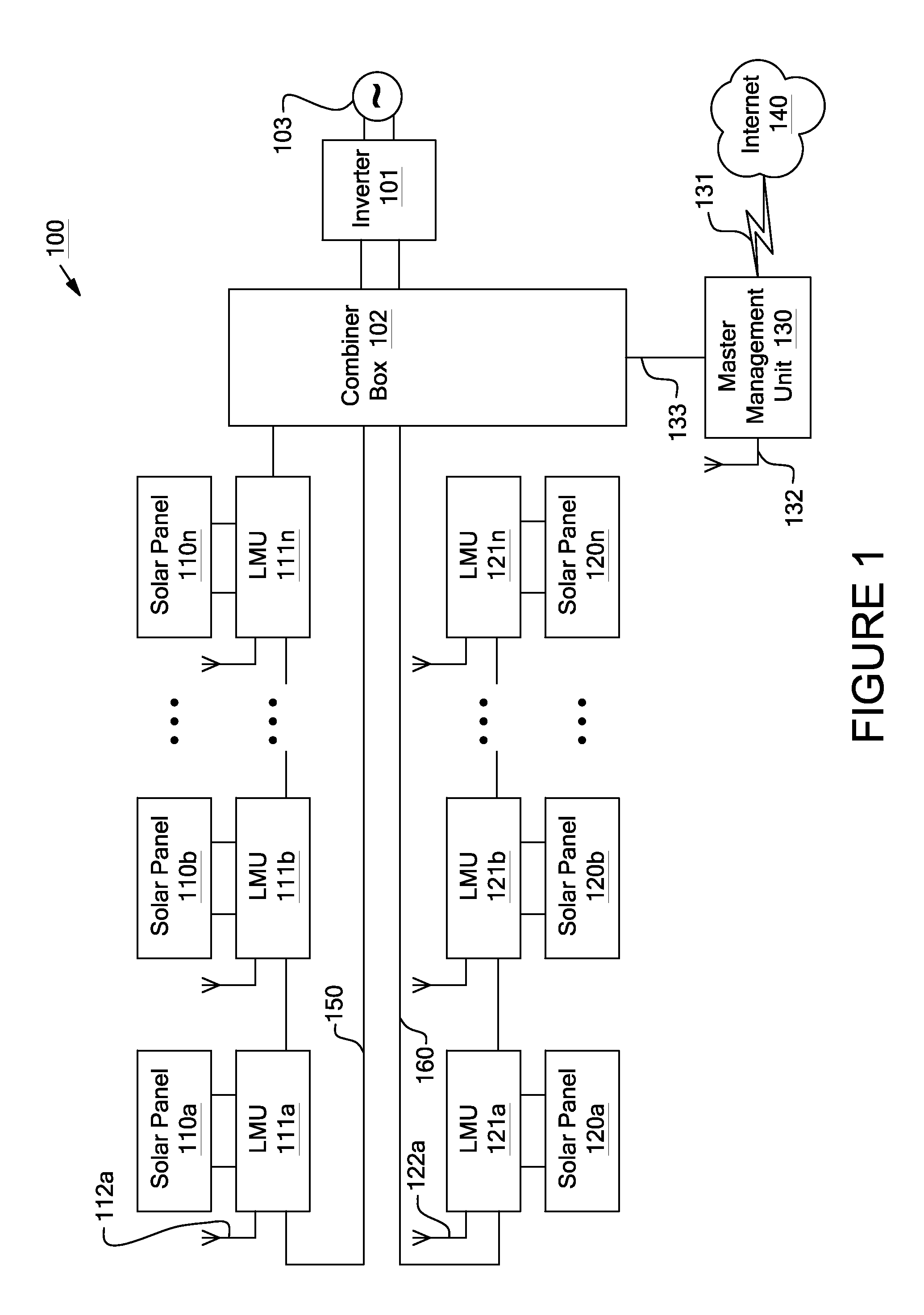

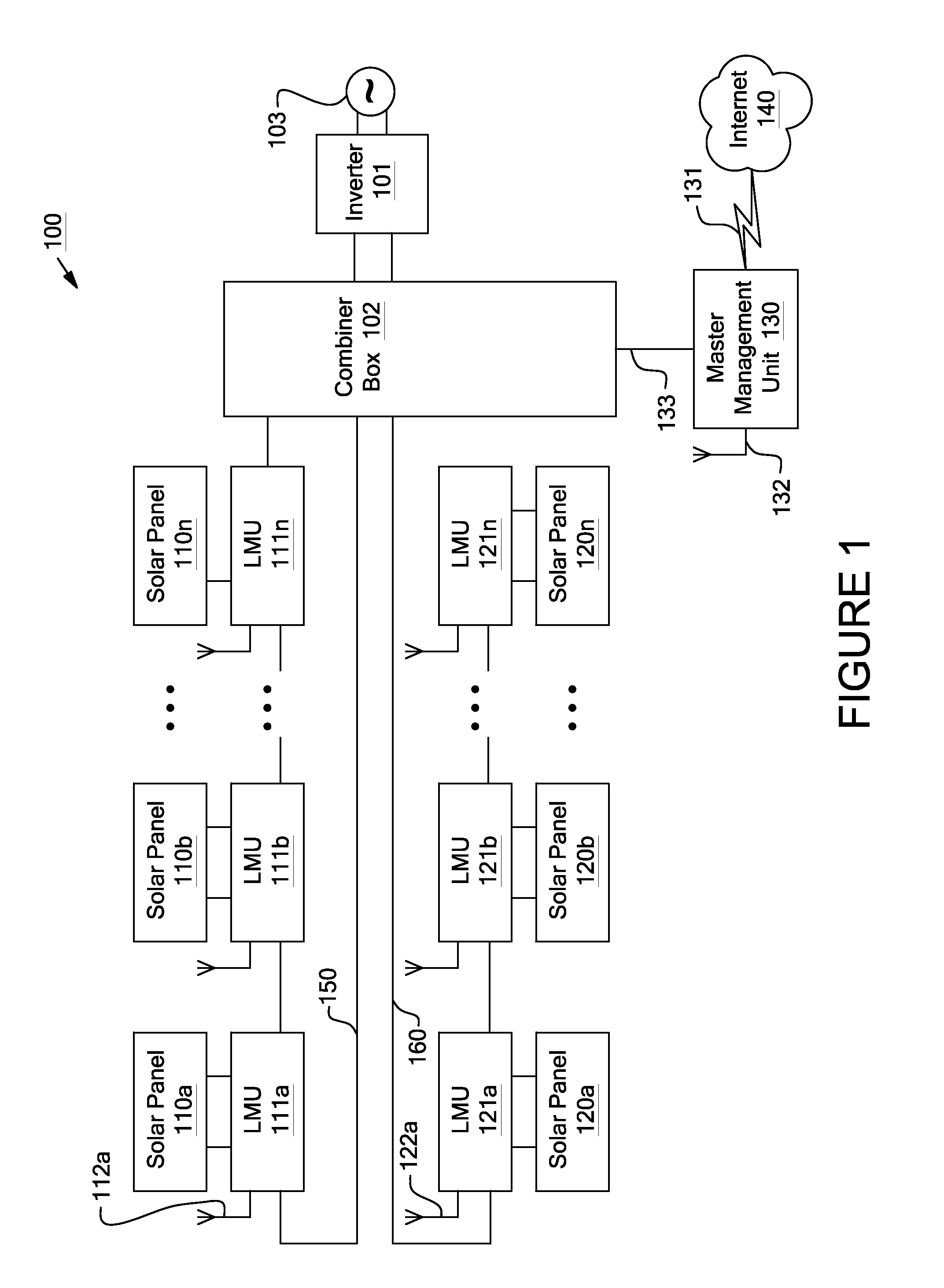

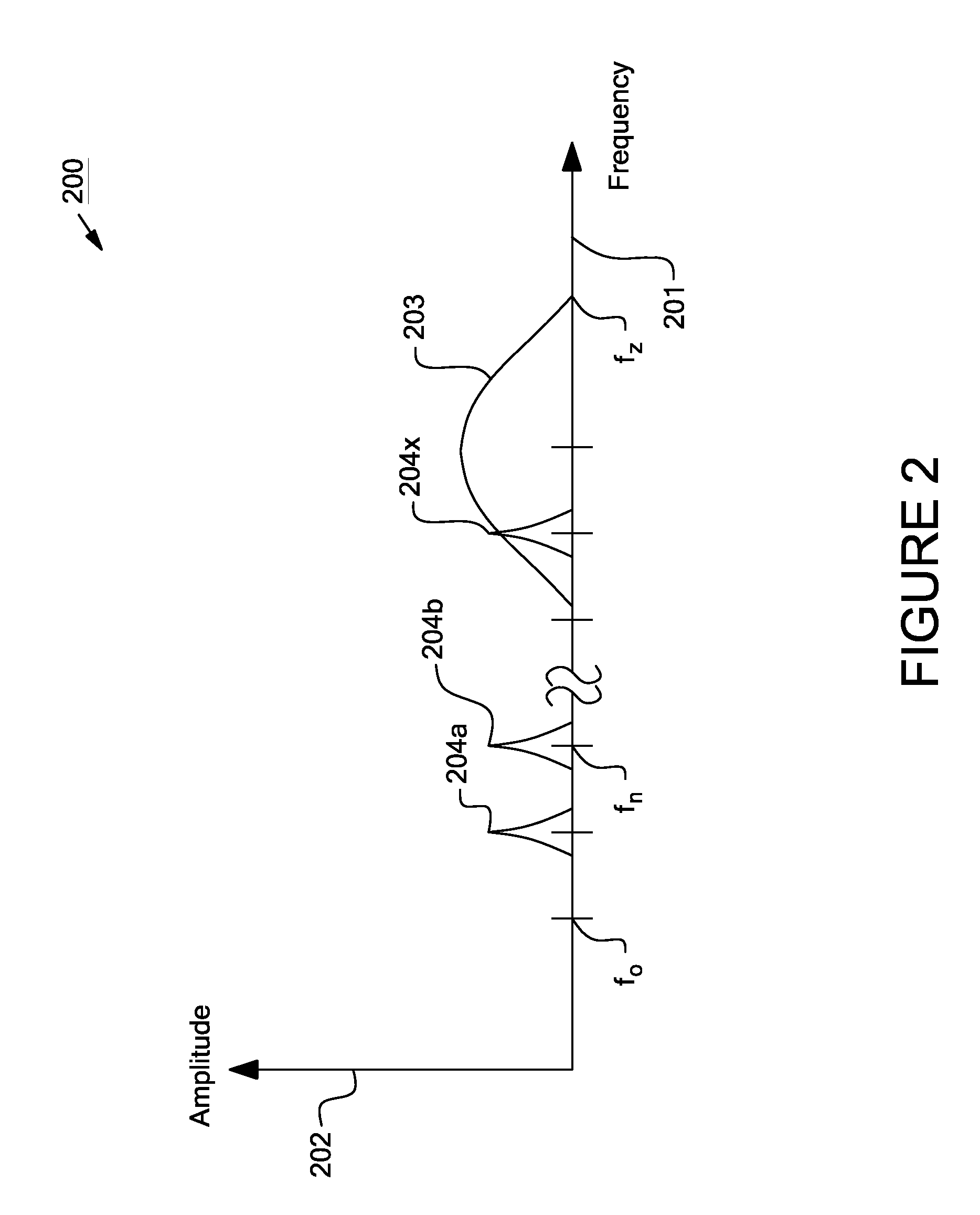

Systems and methods for local management units in a photovoltaic energy system. In one embodiment, a method implemented in a computer system includes: attempting to communicate on a first active channel with a master management unit from a local management unit that controls a solar module; if communication with the master management unit on the first active channel has not been established, attempting to communicate on a second active channel with the master management unit.

Owner:NEWLIGHT CAPITAL LLC

Systems and Methods for an Identification Protocol Between a Local Controller and a Master Controller

ActiveUS20110173276A1Generation forecast in ac networkLevel controlManagement unitComputerized system

Systems and methods for local and master management units in a photovoltaic energy system. In one embodiment, a method implemented in a computer system includes sending a first identification code from a local management unit to a master management unit. The first identification code is associated with the first local management unit, and the local management unit controls a solar module. An authentication of the first identification code is received from the master management unit. In response to receiving the authentication, active operation of the local management unit is continued (e.g., for a set time period).

Owner:NEWLIGHT CAPITAL LLC

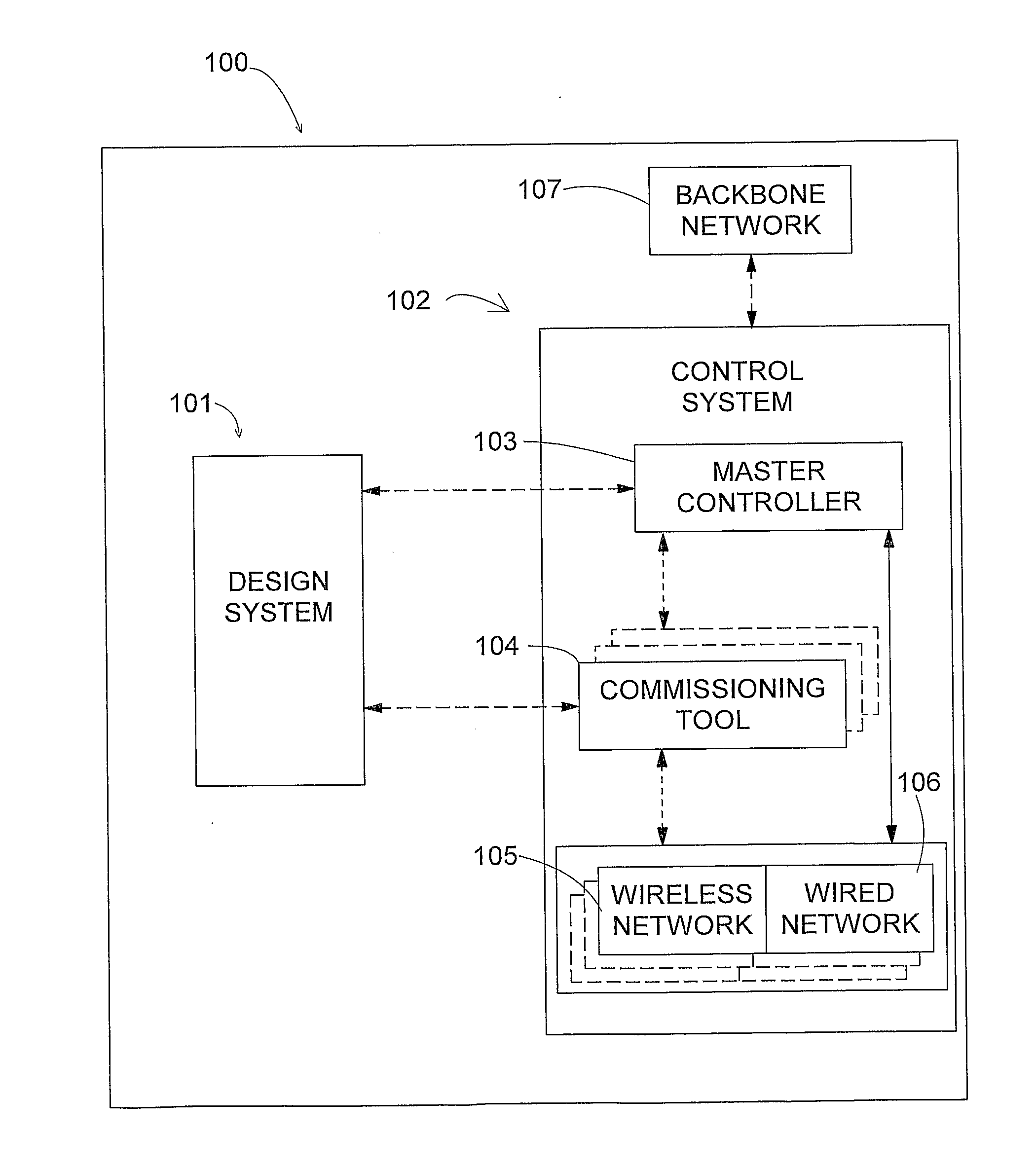

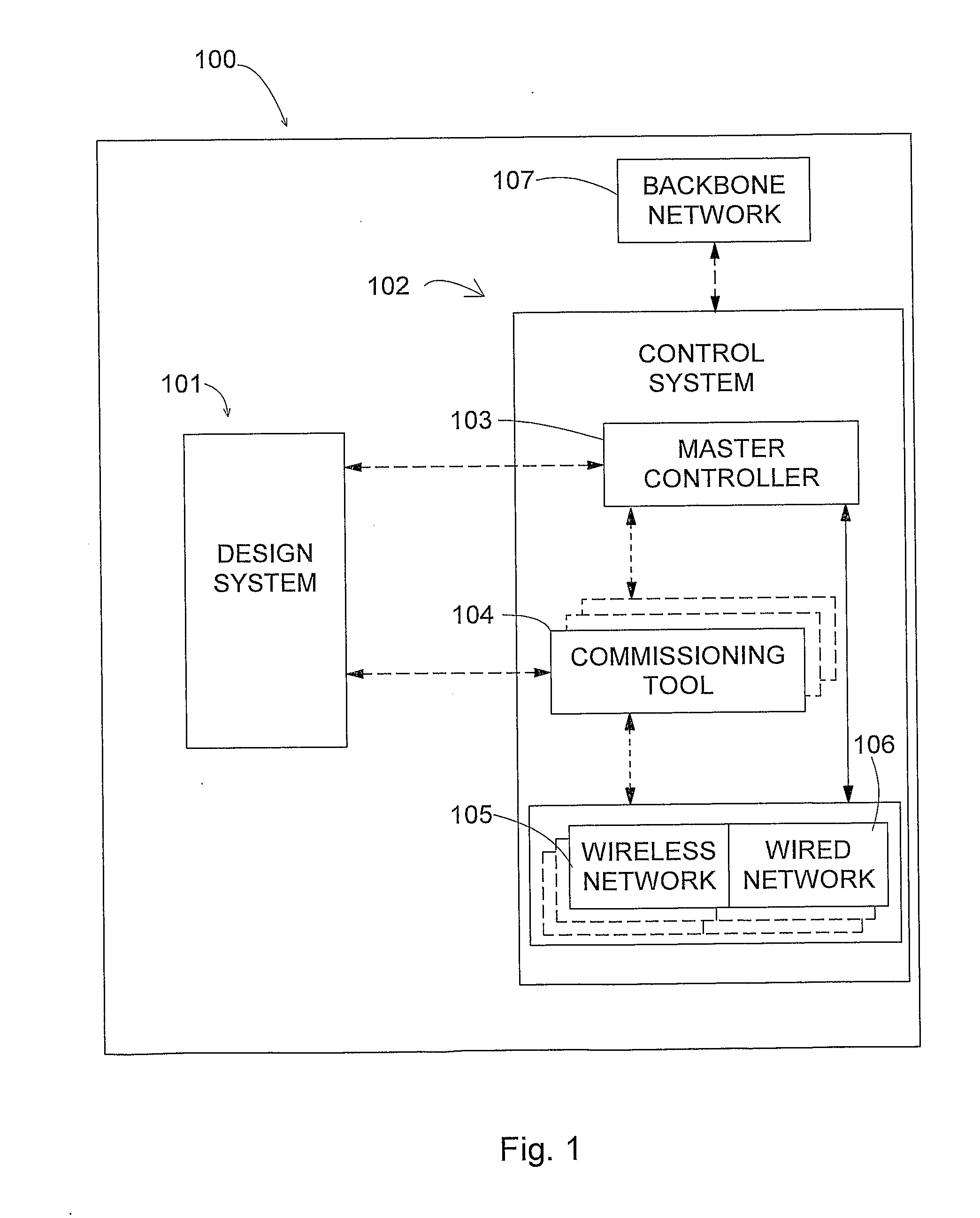

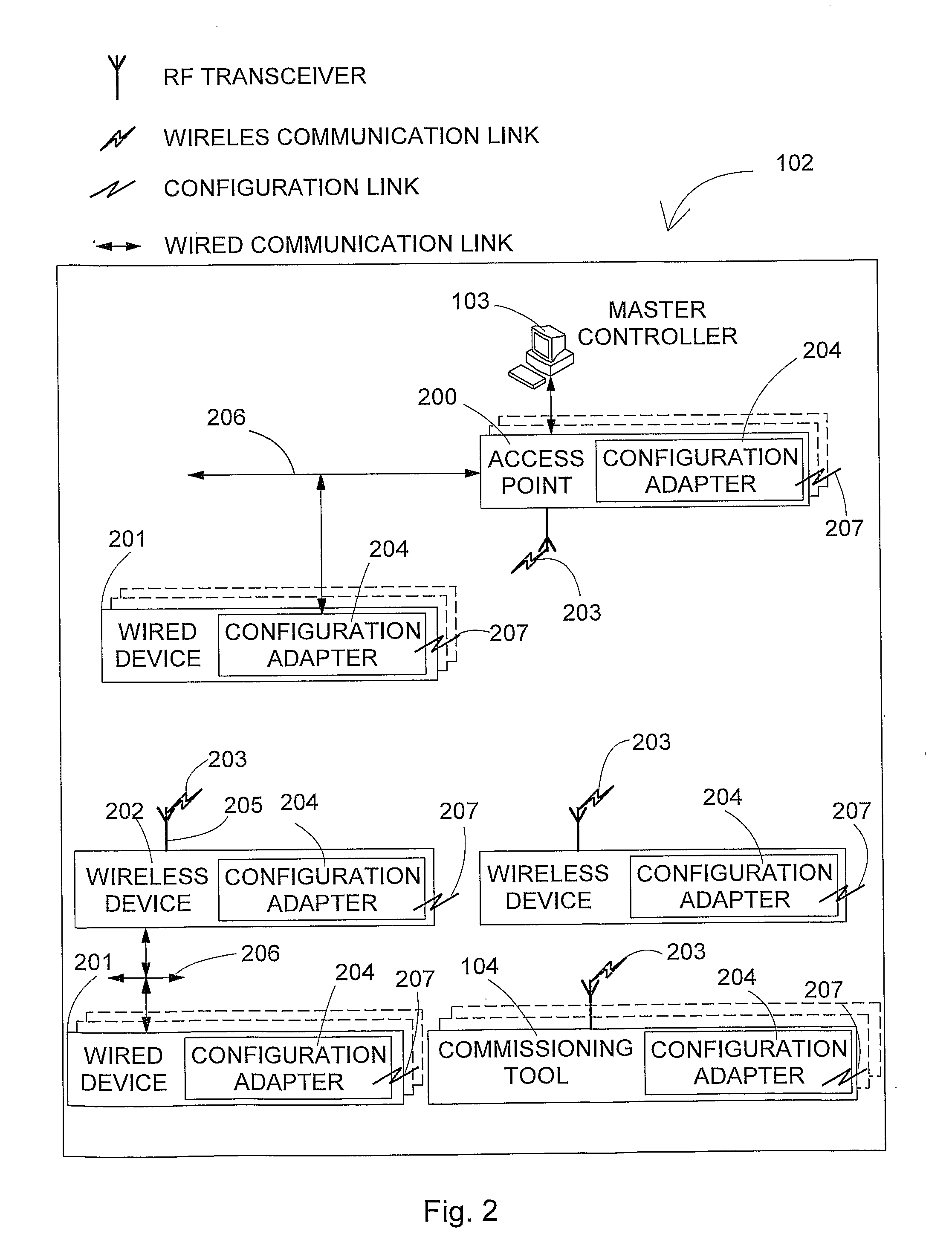

Design and control systems, commissioning tools, configuration adapters and method for wireless and wired networks design, installation and automatic formation

ActiveUS20110007665A1Digital computer detailsData switching by path configurationElectricityTelecommunications link

Design and control systems, commissioning tools, configuration adapters and a method for wireless and wired networks design, installation and automatic formation, including binding of the networks devices are provided. In the design system a scheme that uniquely identifies each network device by its type and its physical location is created and information for logical binding between the devices is prepared. In the design system is also created a device mapping that maps between the devices on the scheme and their network configuration data such as, radio IDs and startup attribute sets and wired communication link address. The data prepared in the design system is transferred to or accessed by a master controller and dedicated commissioning tools in the control system. According to devices' physical locations, appropriate configuration data is loaded from the commissioning tools into the devices through dedicated configuration adapters. The devices and their configuration adapters not necessarily have to be powered-up during configuration data loading. After power-up, the devices automatically update themselves with the loaded configuration data and the control system may initialize itself and identifies all the devices. The master controller in the control system uses the design system defined binding information and transmits binding commands for creating logical links between the devices and so networks may be automatically formed.

Owner:TRIDINETWORKS

Systems and Methods for an Identification Protocol Between a Local Controller and a Master Controller

Systems and methods for local and master management units in a photovoltaic energy system. In one embodiment, a method implemented in a computer system includes sending a first identification code from a local management unit to a master management unit. The first identification code is associated with the first local management unit, and the local management unit controls a solar module. An authentication of the first identification code is received from the master management unit. In response to receiving the authentication, active operation of the local management unit is continued (e.g., for a set time period).

Owner:NEWLIGHT CAPITAL LLC

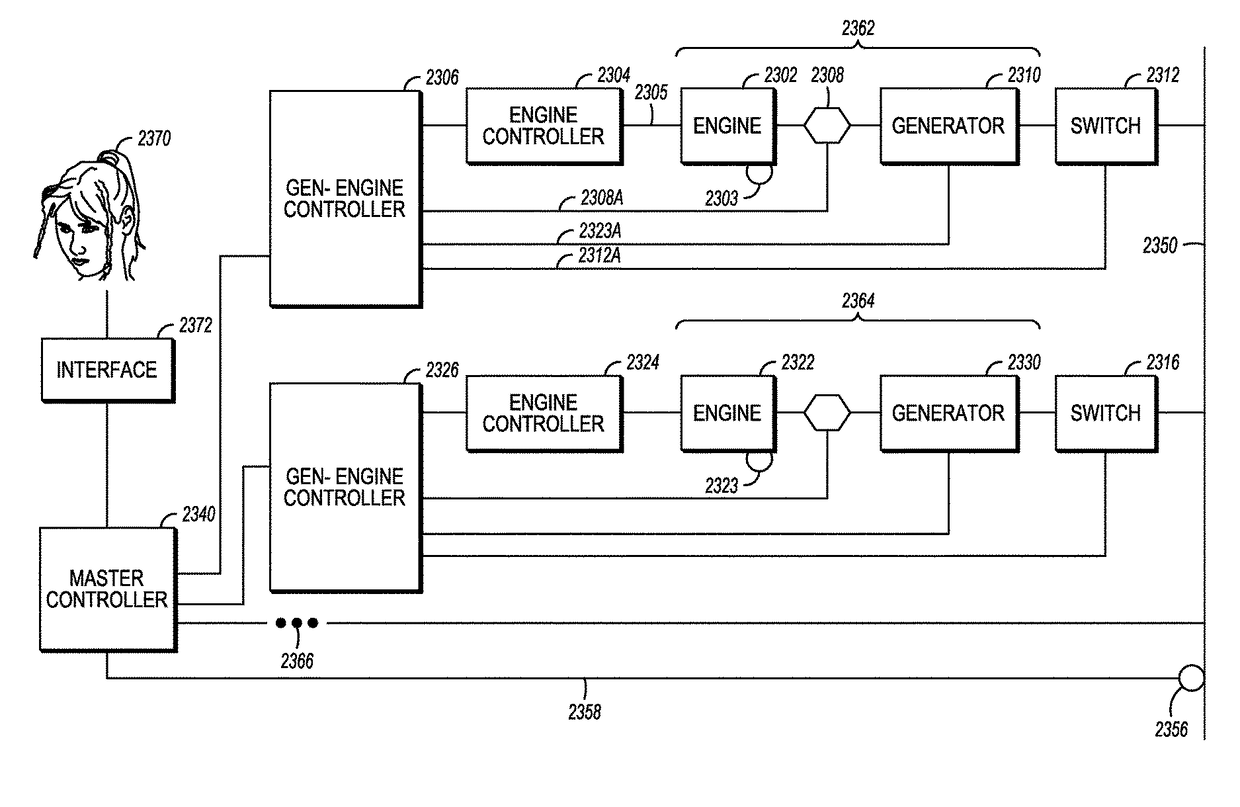

System and method for automatically controlling one or multiple turbogenerators

At least one controller manages a gas turbine engine driving a generator directly or indirectly coupled to the engine. The controller is programmed to automatically determine and adjust inputs to the gas turbine engine in order to cause the generator to produce a user-specified electrical output. Multiple sets of generator, engine, and controller may be used, in which case a master controller individually manages the other controllers to collectively provide the a user-specified electrical output.

Owner:TURBINE POWERED TECH LLC

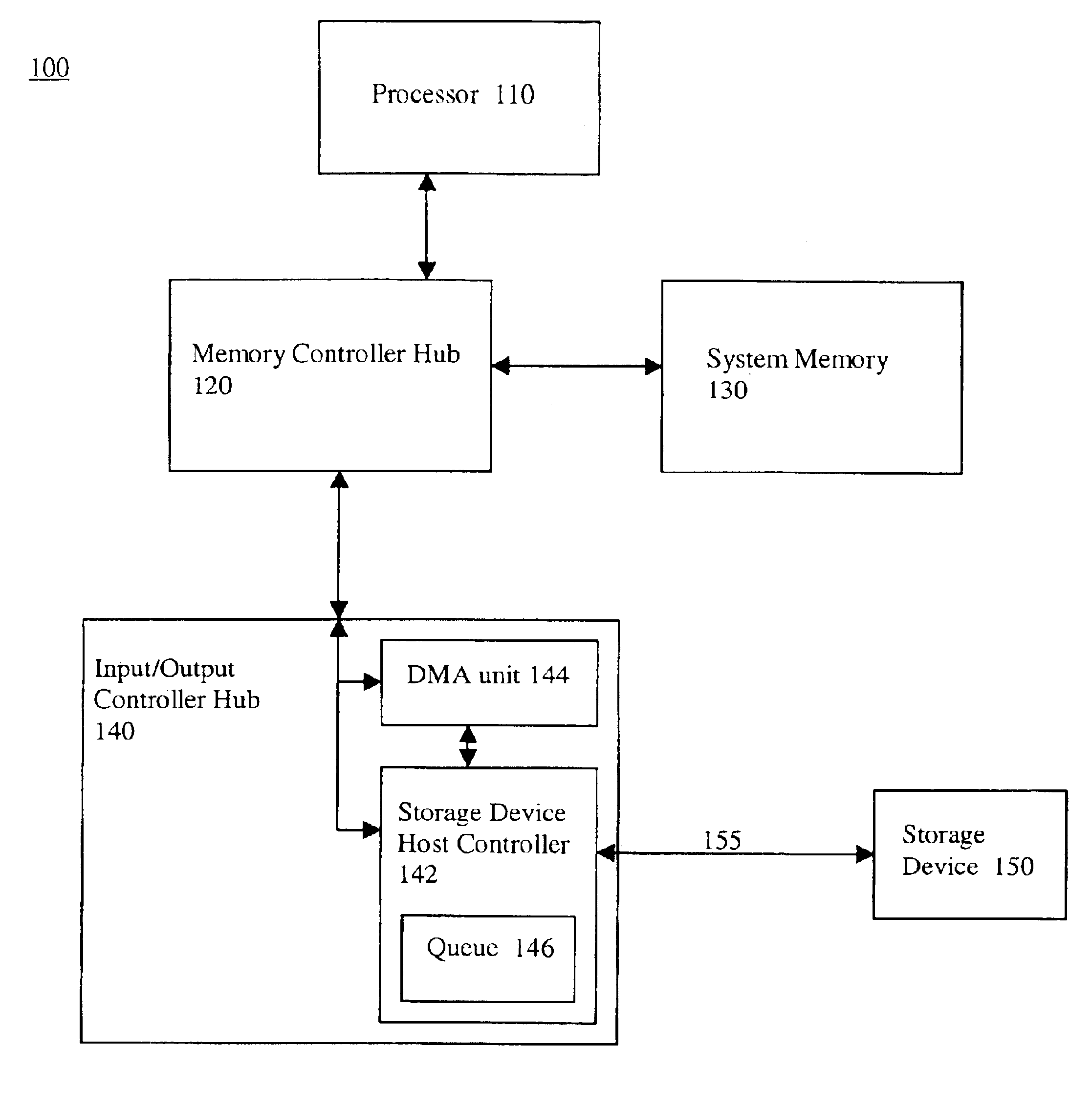

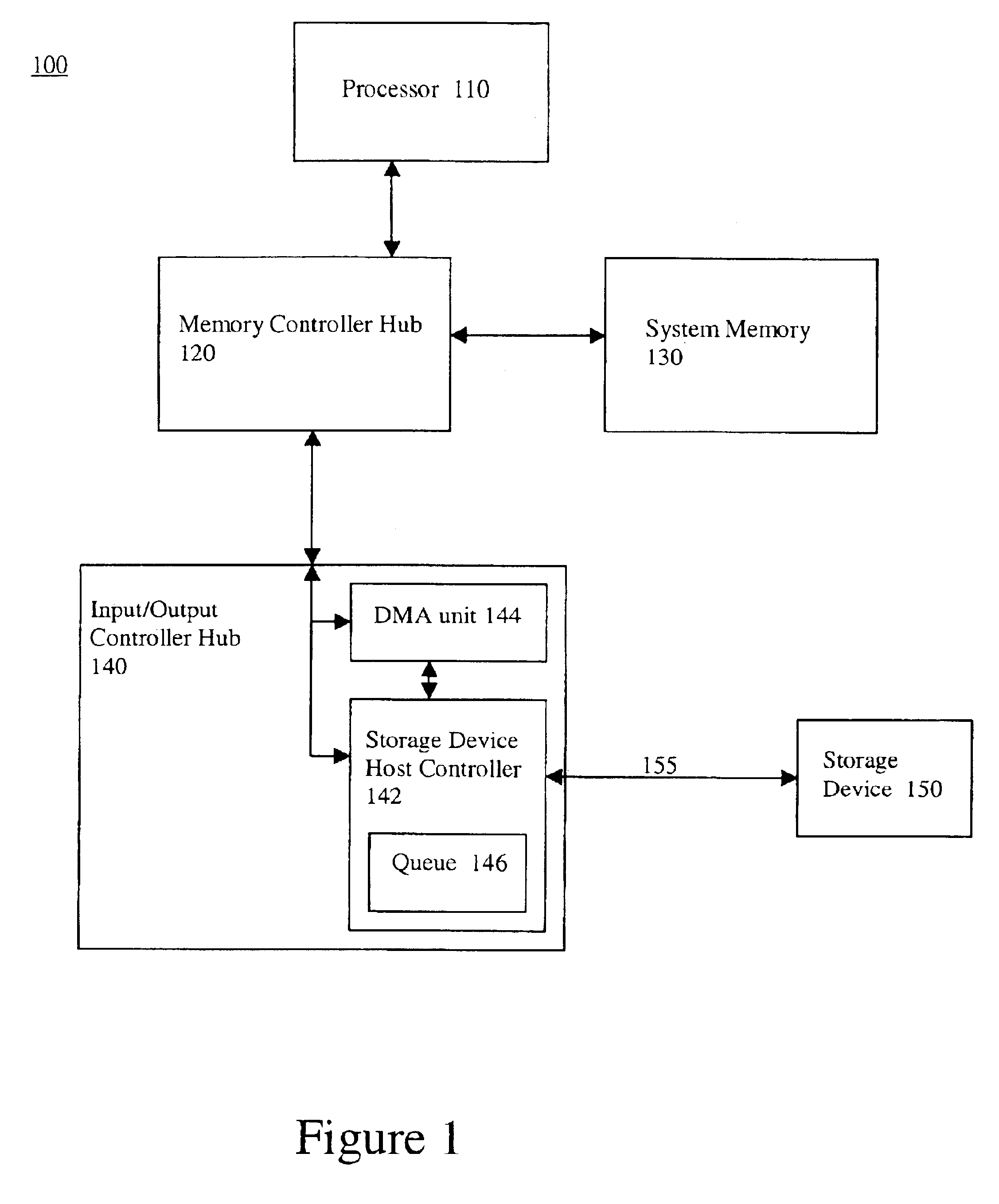

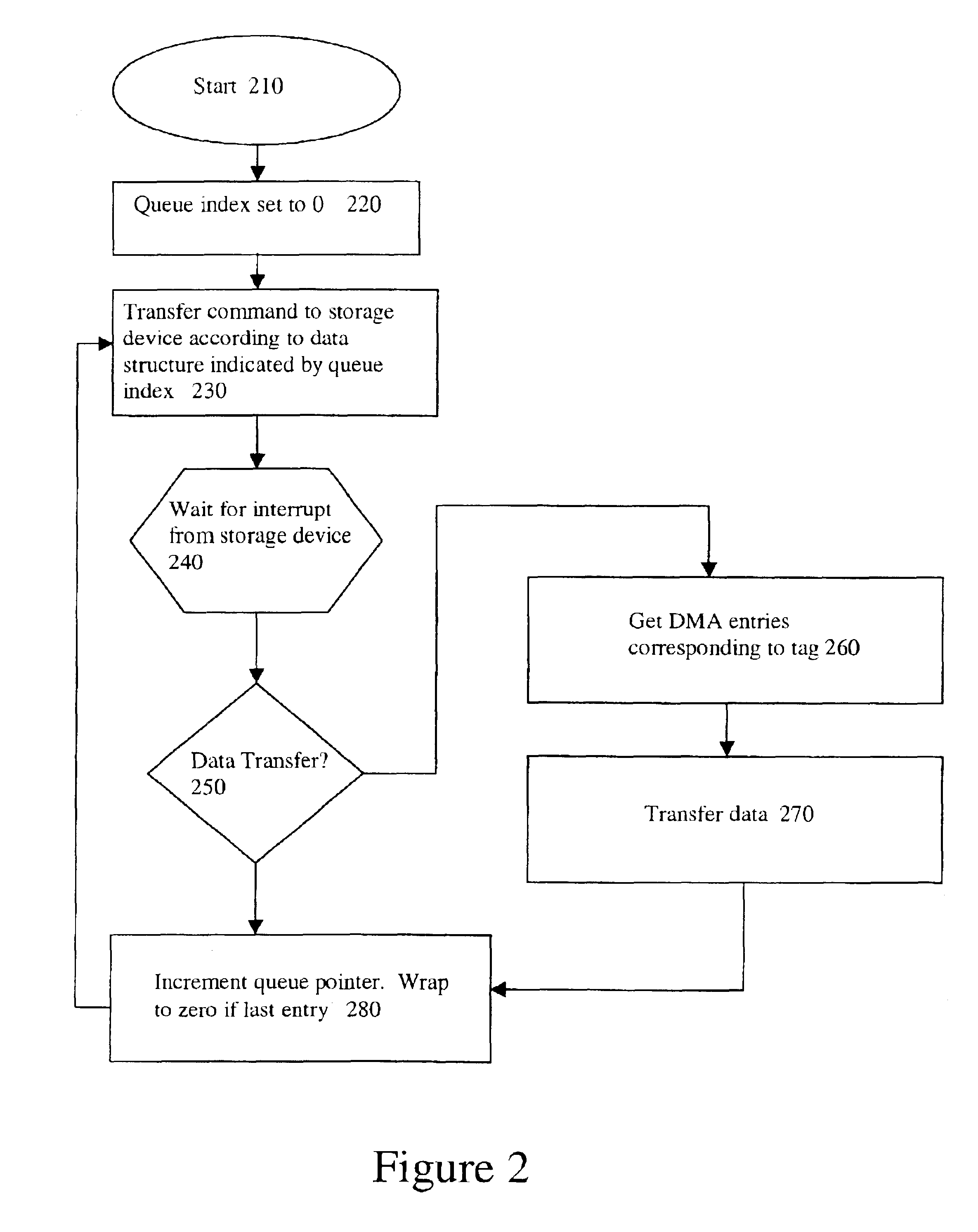

Hardware assisted ATA command queuing

One embodiment involves having a processor writing disk drive command information for a number of data transactions to cacheable system memory. The processor then performs a single write transaction to a disk drive host controller. The disk drive host controller then causes a DMA transfer to occur which reads the command information located in system memory and stores the command information in a queue. Once the host controller has the command information, it programs the disk drive with information corresponding to a queue entry over a serial interconnect. The disk drive signals an interrupt after it processes the command information. The disk drive host controller does not forward the interrupt to the processor, but services the interrupt itself. The disk drive host controller reads from the disk drive to determine the disk drive status. The disk drive can signal that it is ready to execute the programmed command, or it can signal that it is not ready to perform the programmed command but is ready to receive additional command programming information corresponding to another queue entry, or it may signal that it is ready to execute a previously programmed command. The disk drive host controller then performs the required operations using the information stored in the queue without involving the processor. Because the processor is only involved in setting up a command block in system memory and in signaling the disk drive host controller that the command block is ready for reading, the processor is freed up to perform other tasks and overall system performance is improved.

Owner:INTEL CORP

Systems and Methods for a Communication Protocol Between a Local Controller and a Master Controller

ActiveUS20110161722A1Error preventionPhotovoltaic energy generationManagement unitComputerized system

Systems and methods for local management units in a photovoltaic energy system. In one embodiment, a method implemented in a computer system includes: attempting to communicate on a first active channel with a master management unit from a local management unit that controls a solar module; if communication with the master management unit on the first active channel has not been established, attempting to communicate on a second active channel with the master management unit.

Owner:NEWLIGHT CAPITAL LLC

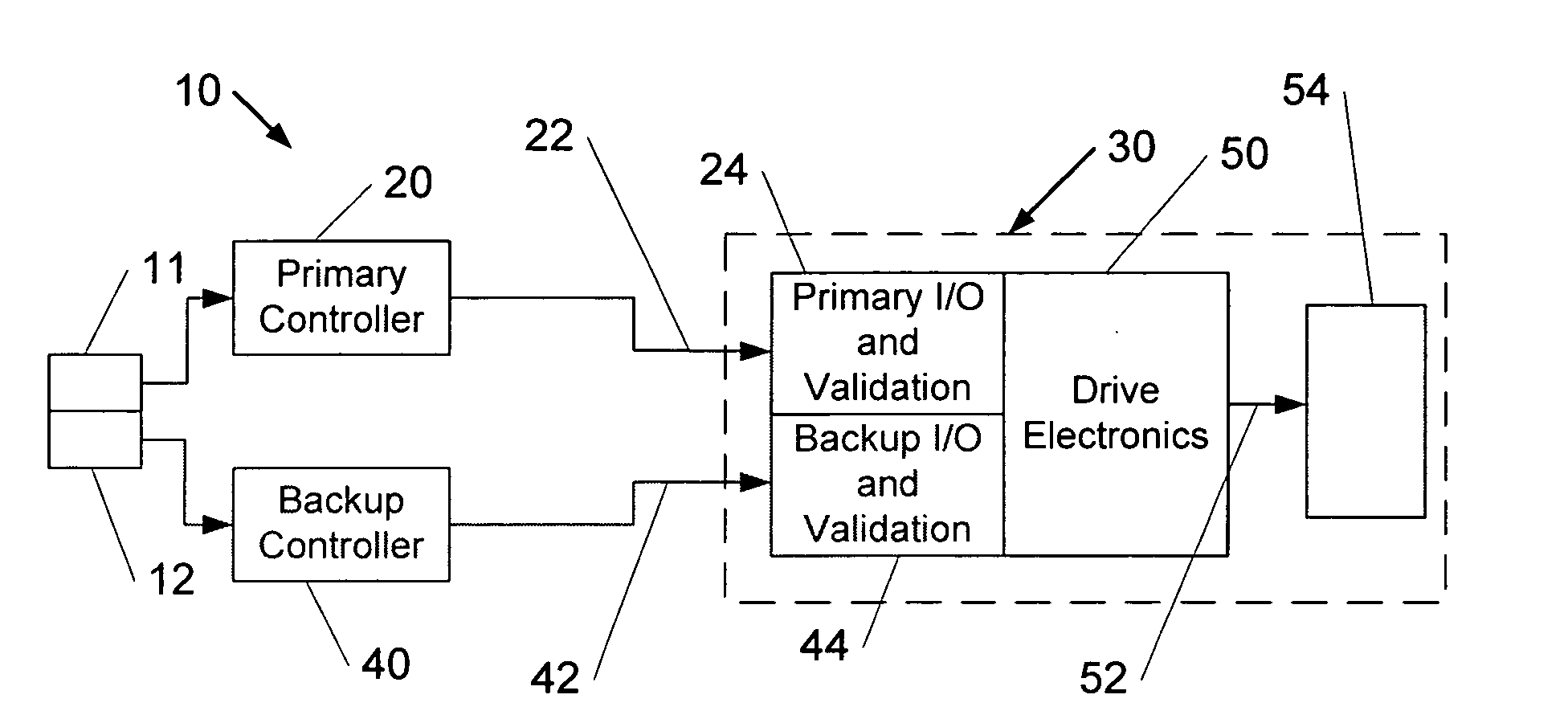

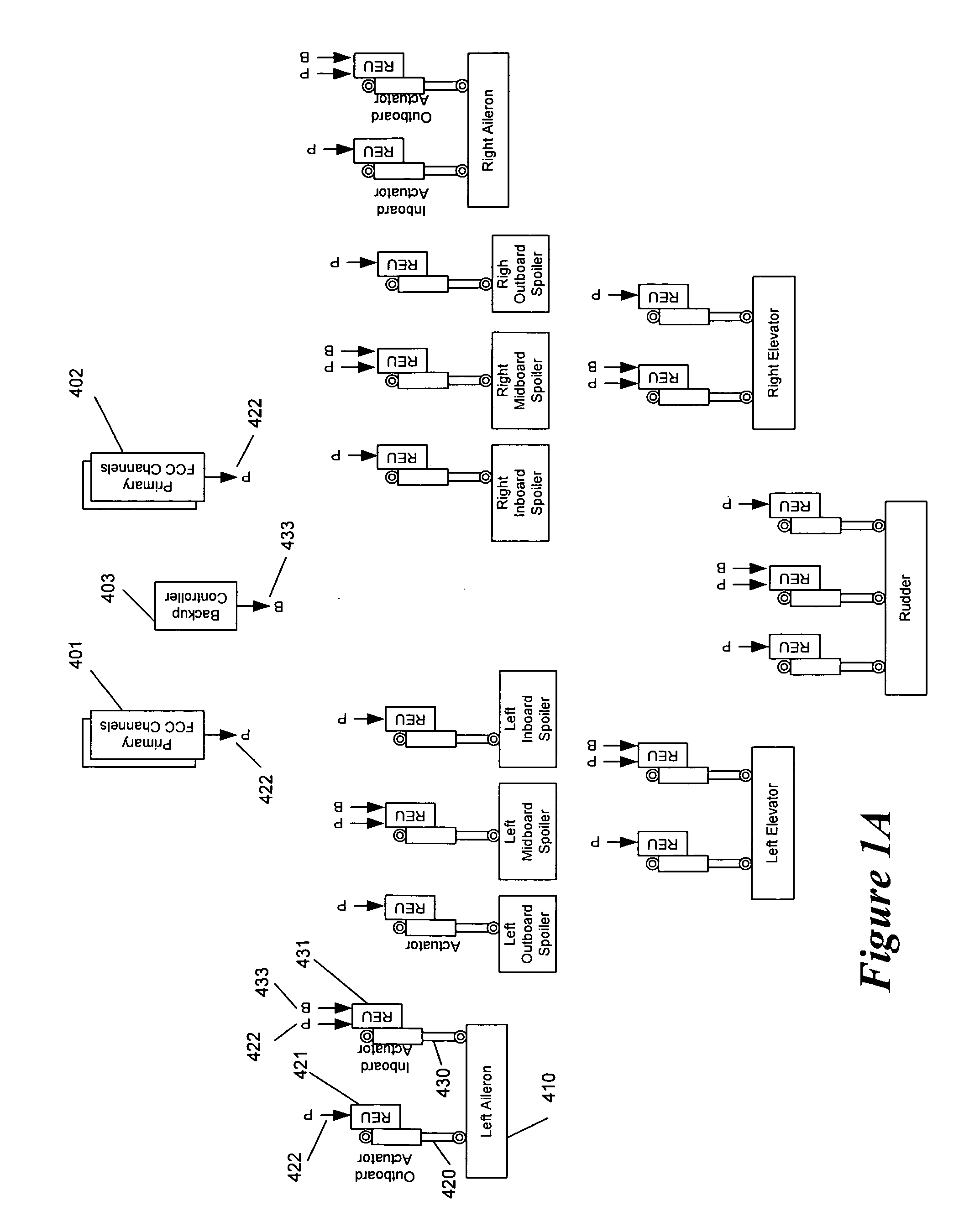

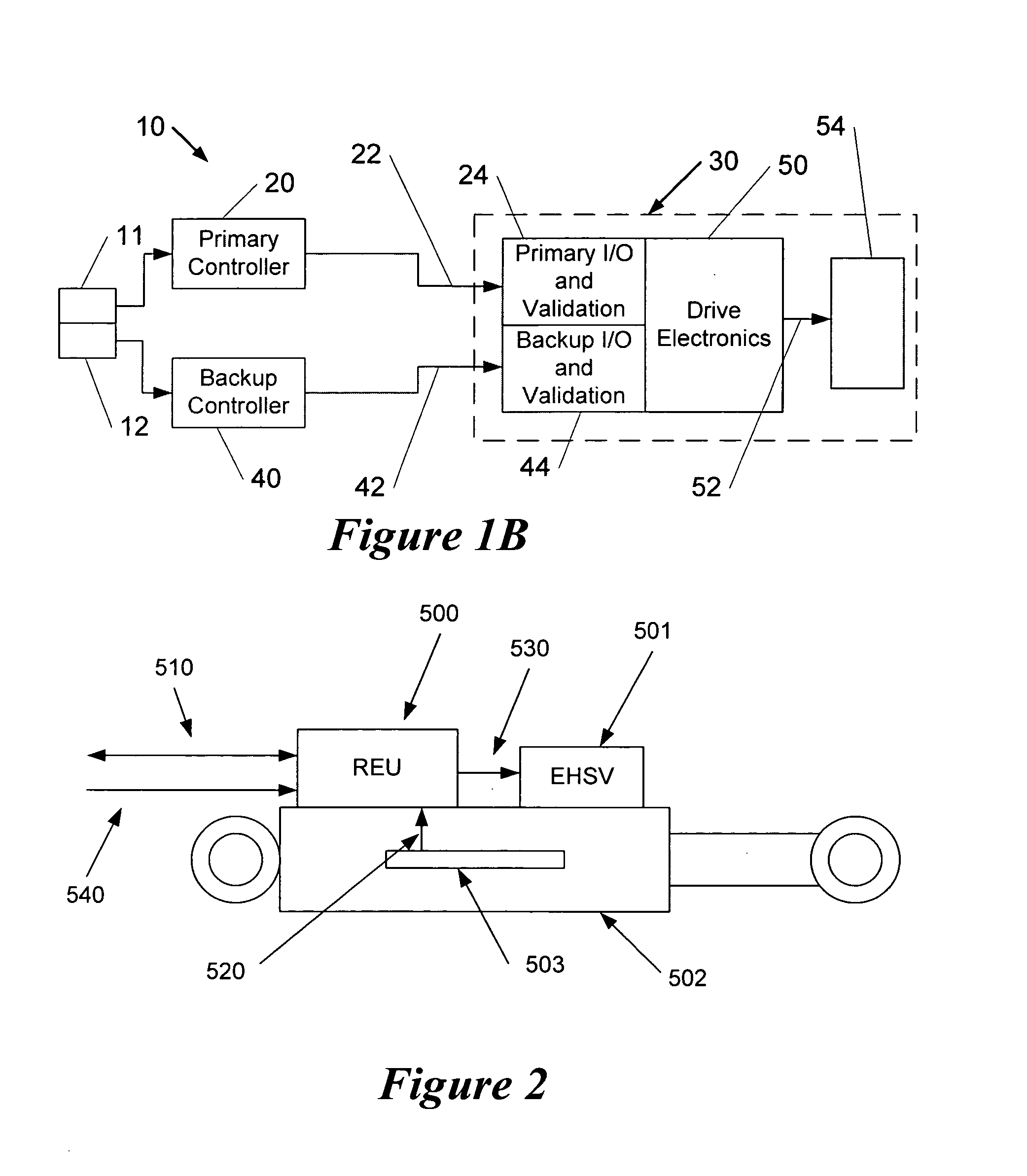

Apparatus and method for backup control in a distributed flight control system

ActiveUS20070164166A1Without compromisingWith power amplificationActuated automaticallyControl signalMaster controller

Embodiments of the invention relate to a flight control system for controlling an aircraft during flight. The flight control system may include a primary controller configured to receive an input from a pilot and to output a primary control signal and a primary transmission path connected to the primary controller and configured to relay the primary control signal. The flight control system may also include a backup controller configured to receive the input from the pilot and to output a backup control signal and a backup transmission path connected to the backup controller and configured to relay the backup control signal. Additionally, the flight control system may include an actuator having a remote electronics unit configured to receive the primary control signal and the backup control signal and to determine if the primary control signal is available and valid. The remote electronics unit may be configured to output an actuator command based on the primary control signal if the primary control signal is available and valid and to output the actuator command based on the backup control signal if the primary control signal is unavailable or invalid.

Owner:GULFSTREAM AEROSPACE CORP

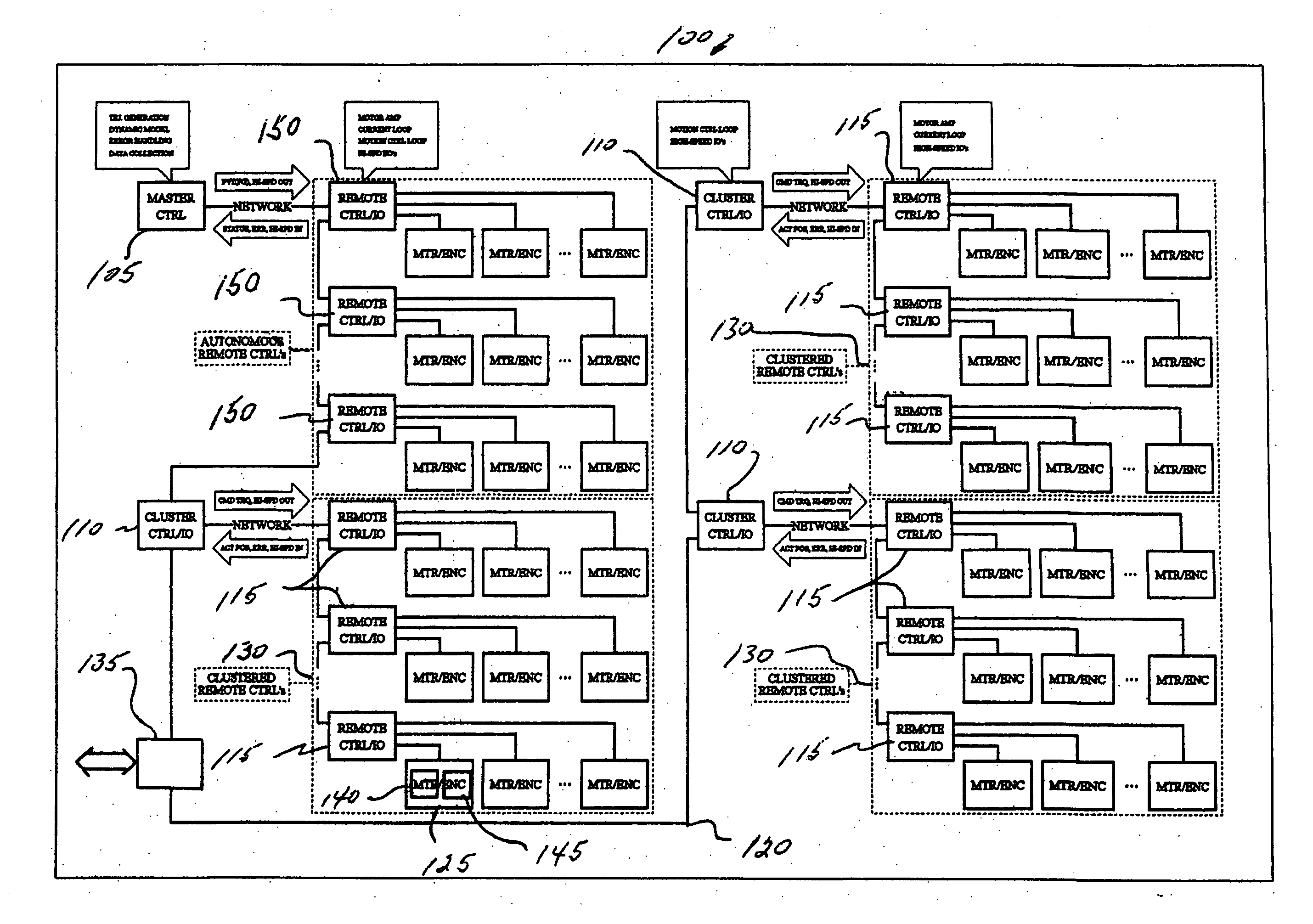

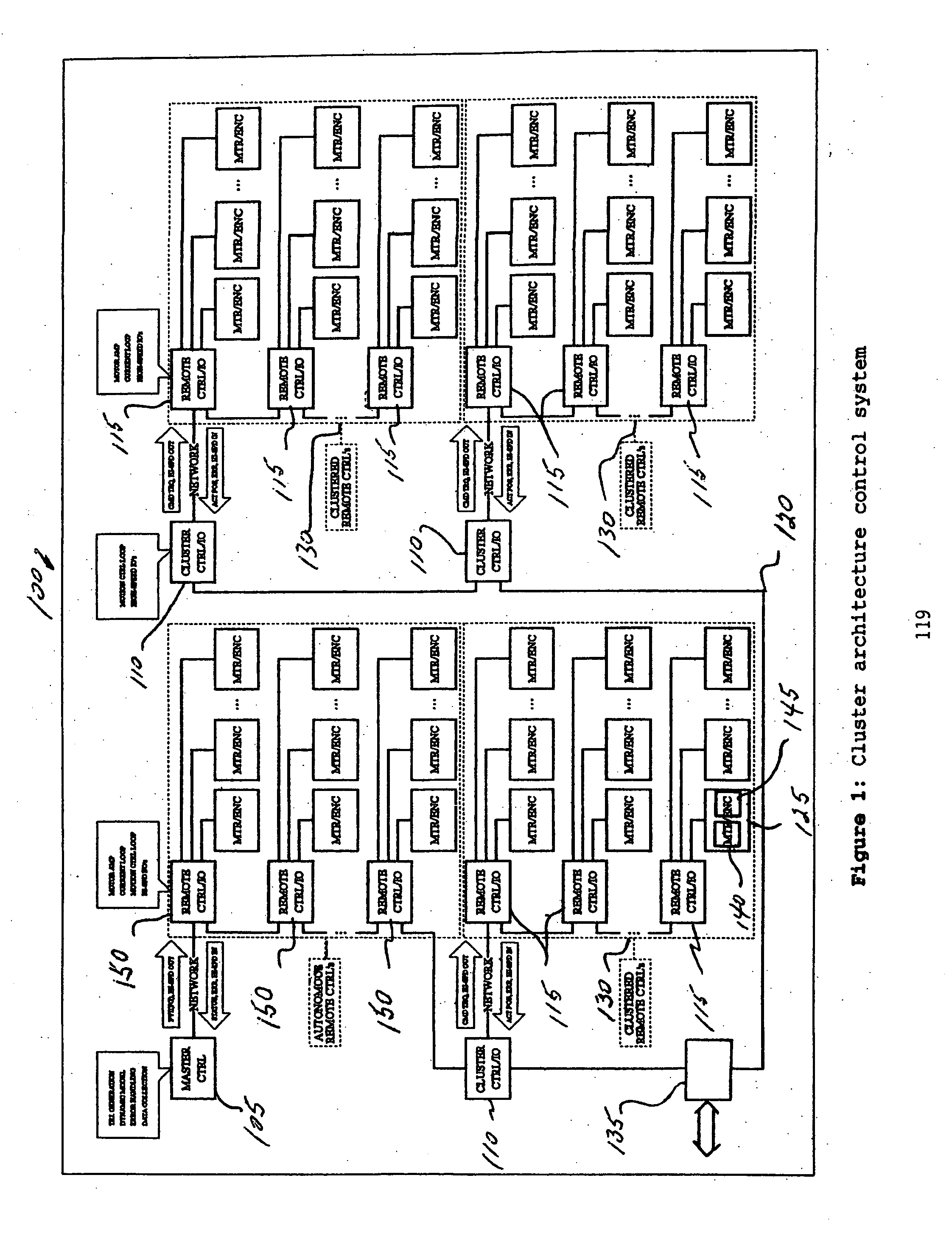

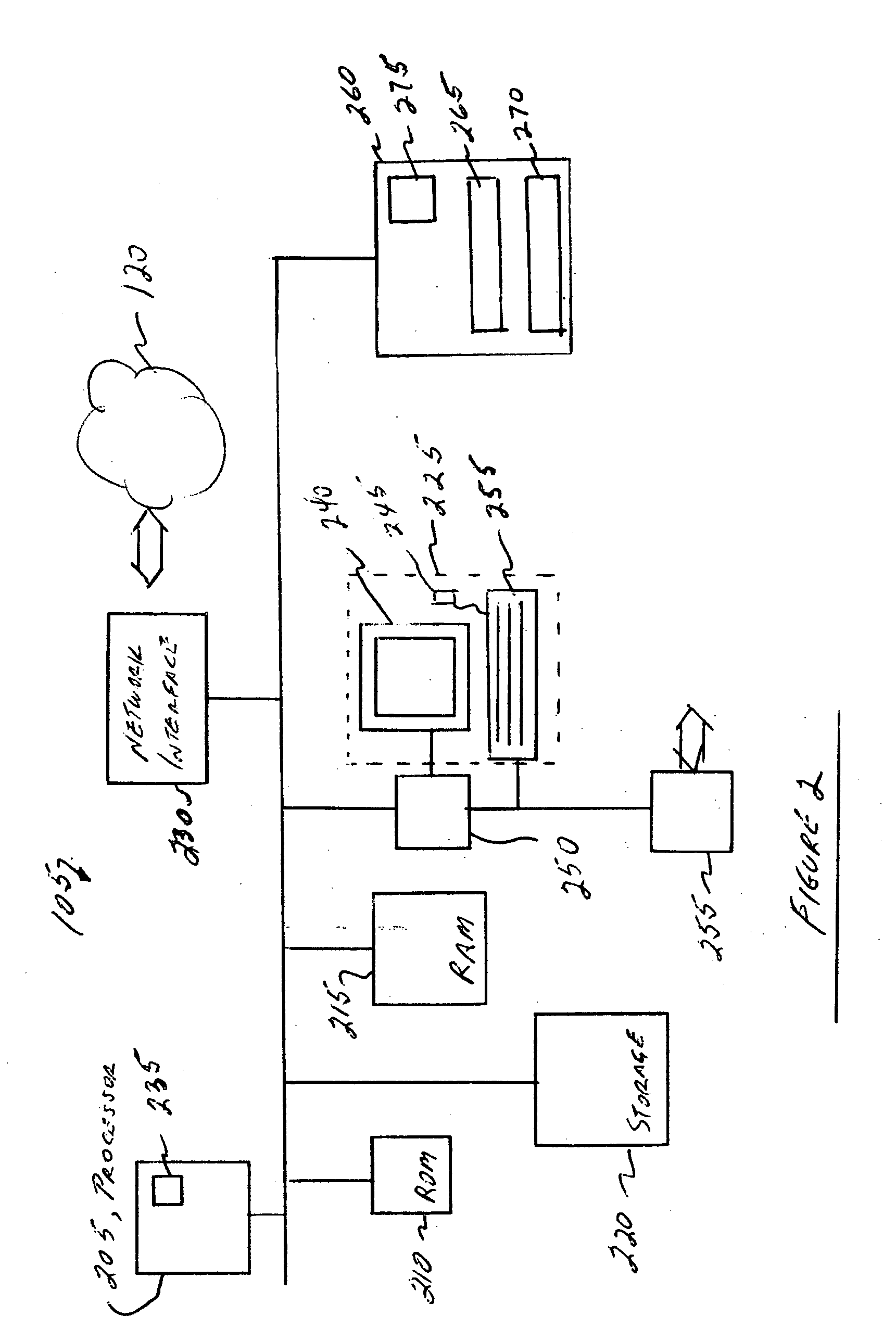

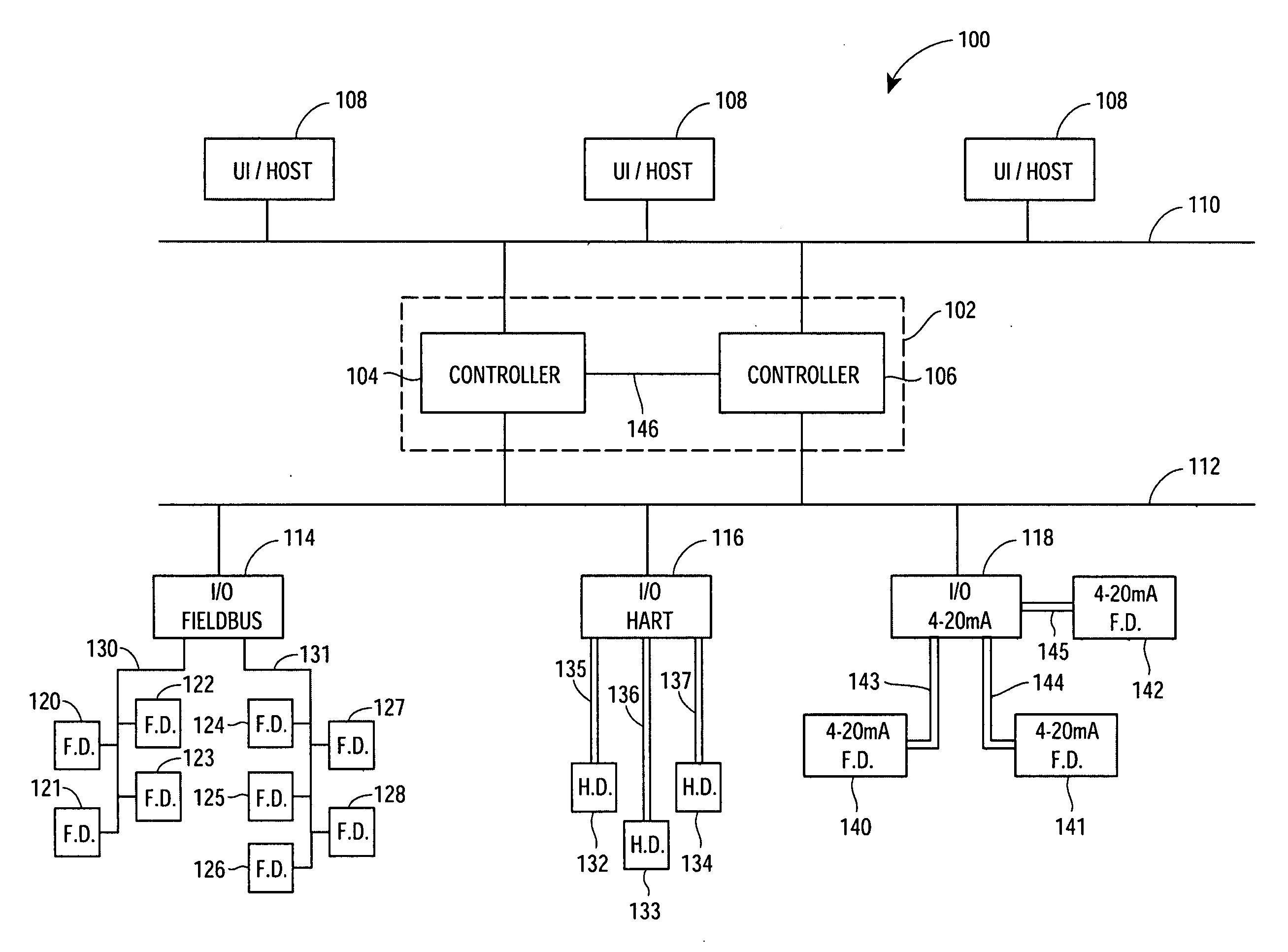

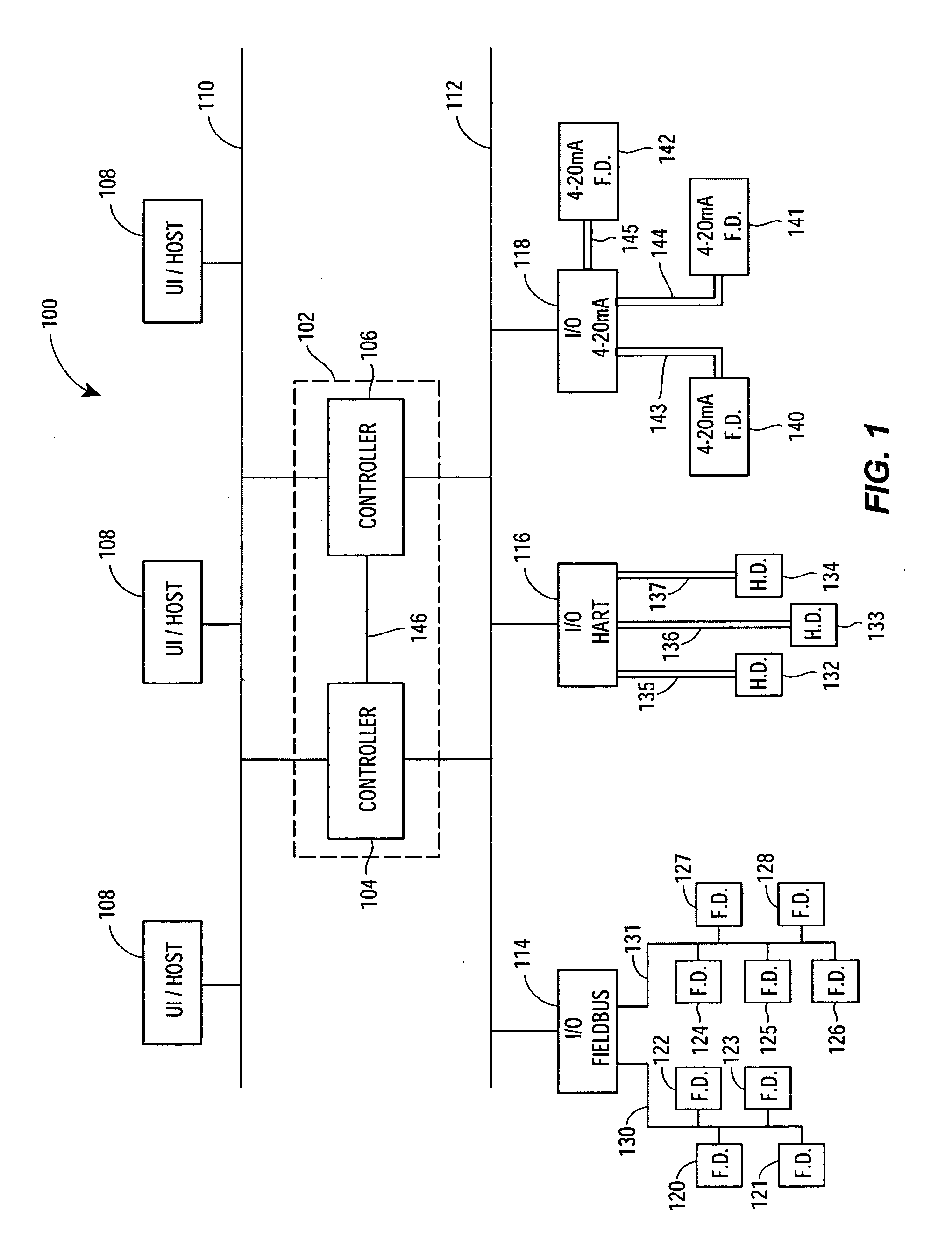

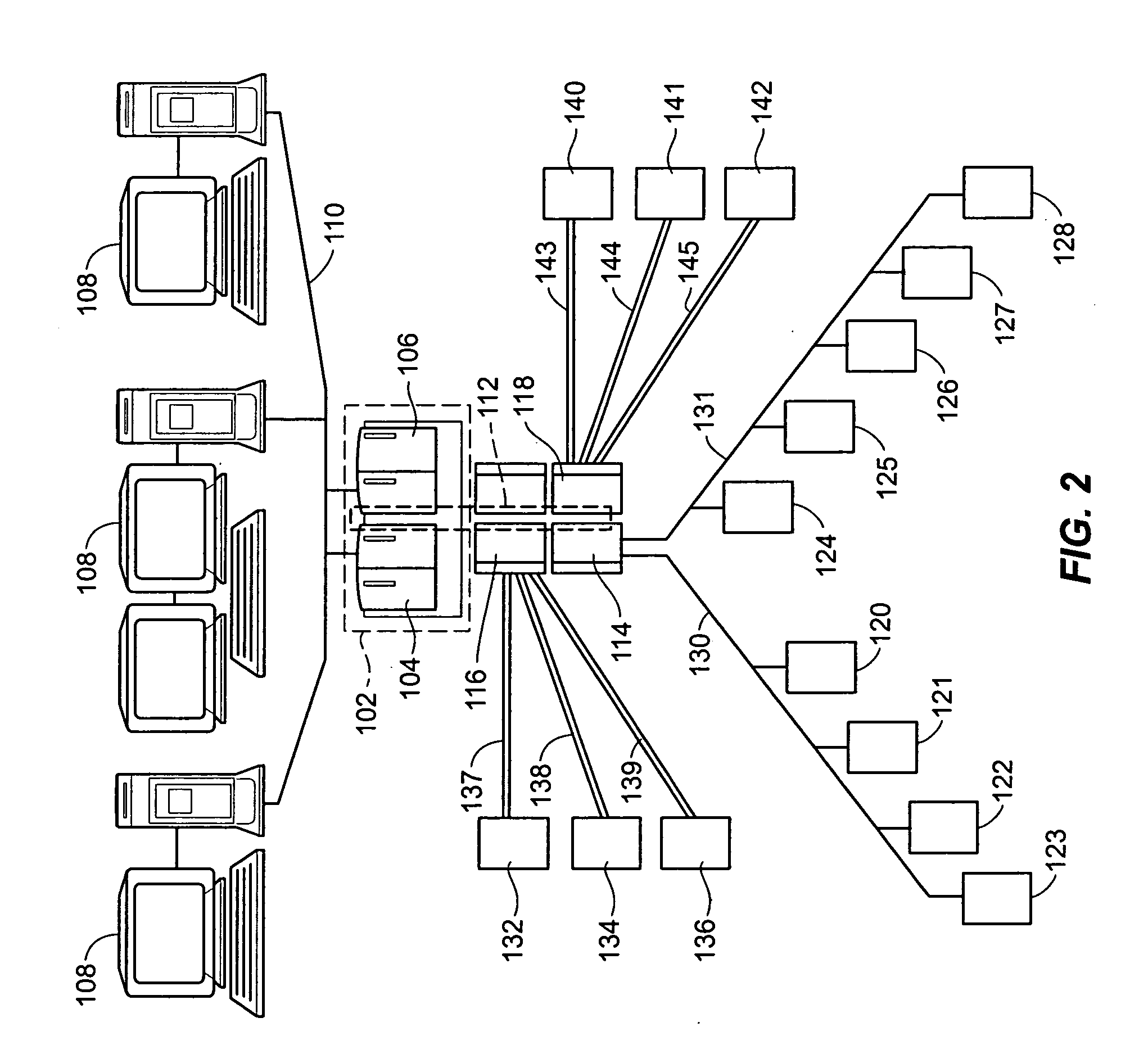

Scalable motion control system

ActiveUS20070010898A1Maintain integrityEasy to implementLiquid surface applicatorsComputer controlDirect controlMaster controller

A control system includes a clustered architecture having a master controller, a central control section including one or more first remote controllers under direct control of the master controller, and a distributed control section including a cluster controller controlled by the master controller. The cluster controller controls the activities of one or more second remote controllers. Each of the first and second remote controllers are utilized to drive one or more axes.

Owner:BOOKS AUTOMATION US LLC

Method for redundant controller synchronization for bump-less failover during normal and program mismatch conditions

The present invention relates generally to process control systems and devices and, more particularly, to an apparatus for and a method of implementing redundant controller synchronization for bump-less failover during normal and mismatch conditions at the redundant controllers. The redundant controllers are configured to transmit state information of the process control areas of the primary controller to the backup controller that is necessary for synchronizing the redundant controllers but is not typically transmitted to other devices during the performance of process control functions. Synchronization messages are transmitted from the primary controller to the backup controller each time one of the control areas executes to perform process control functions. In other aspects, the redundant controllers are configured to determine state information at the backup controller from other process control network information during a fallover of the primary controller where a mismatch condition exists between the control areas of the two controllers during the downloading of reconfigurations, and to initialize the backup controller at startup when the mismatch condition exists.

Owner:EMERSON PROCESS MANAGEMENT POWER & WATER SOLUTIONS

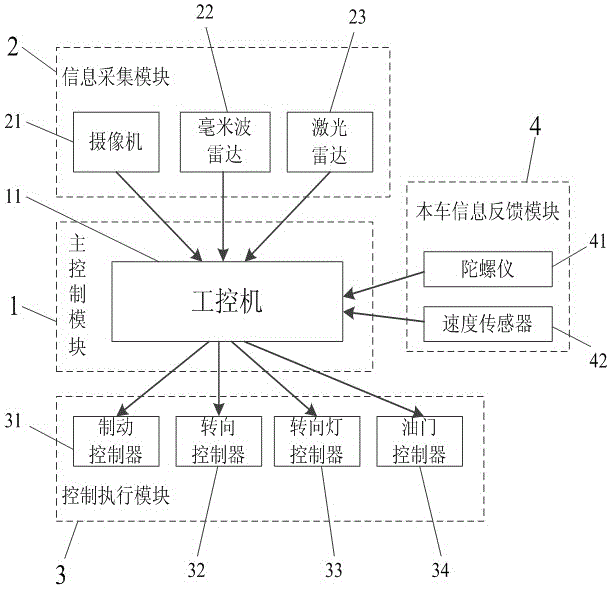

Autonomous lane-changing decision making system for pilotless automobile

ActiveCN105015545AStrong targetingSimple decision makingExternal condition input parametersDriver input parametersAnalogue computationDecision system

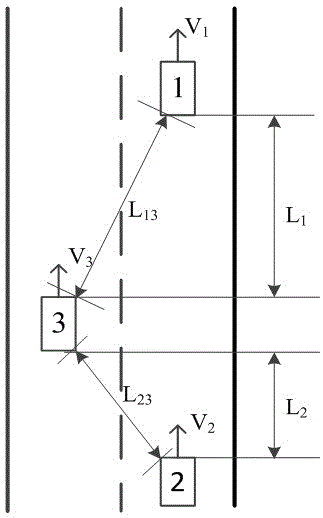

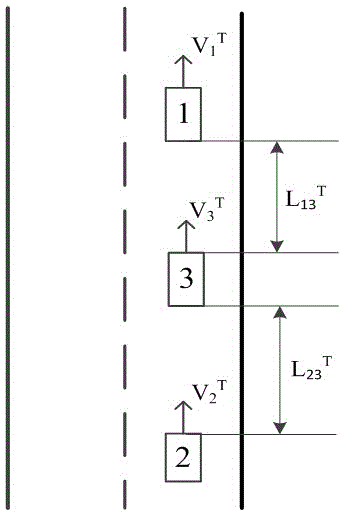

The invention discloses an autonomous lane-changing decision making system for a pilotless automobile. First, through an information collecting module, environment information such as a lane line, an obstacle, speeds of surrounding interactive vehicles, distances between the surrounding interactive vehicles and the pilotless automobile and so on is obtained; the obtained information is transmitted to a main control module; the main control module is used for analyzing the received information, judging whether a lane-changing condition is satisfied or not, carrying out analog computation on the received information to obtain a lane-changing scheme and transmitting the lane-changing scheme to a control executing module; and then a vehicle controller is used for controlling a steering direction, speed and so on of the pilotless automobile according to a decision signal so that the running lane of the pilotless automobile is changed. In the lane-changing process, the information collecting module is required to monitor the environment and the surrounding vehicles in real time; meanwhile, the operation status of the pilotless automobile also needs to be fed back to the main controller in real time so that the pilotless automobile can adjust decision information in time in case of an emergency; therefore, a purpose that the running lane of the pilotless automobile is autonomously changed is safely and effectively realized.

Owner:INNER MONGOLIA MAIKU INTELLIGENT VEHICLE TECH