Patents

Literature

3688 results about "Simple circuit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Laser programmable electrically readable phase-change memory method and device

InactiveUS6850432B2Simple and low power-consumingSimple and low and electrical circuitRead-only memoriesDigital storagePhase-change memoryEngineering

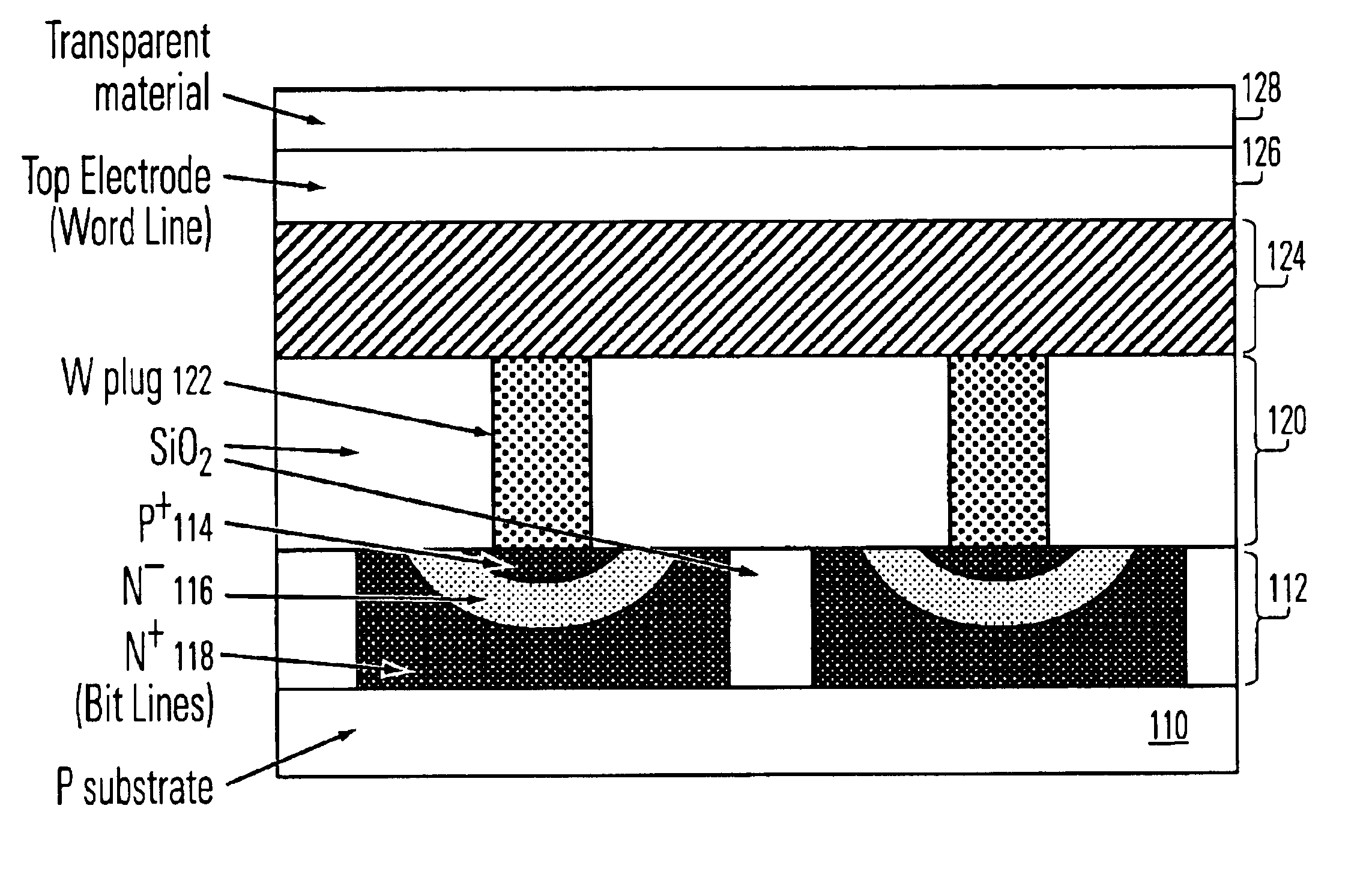

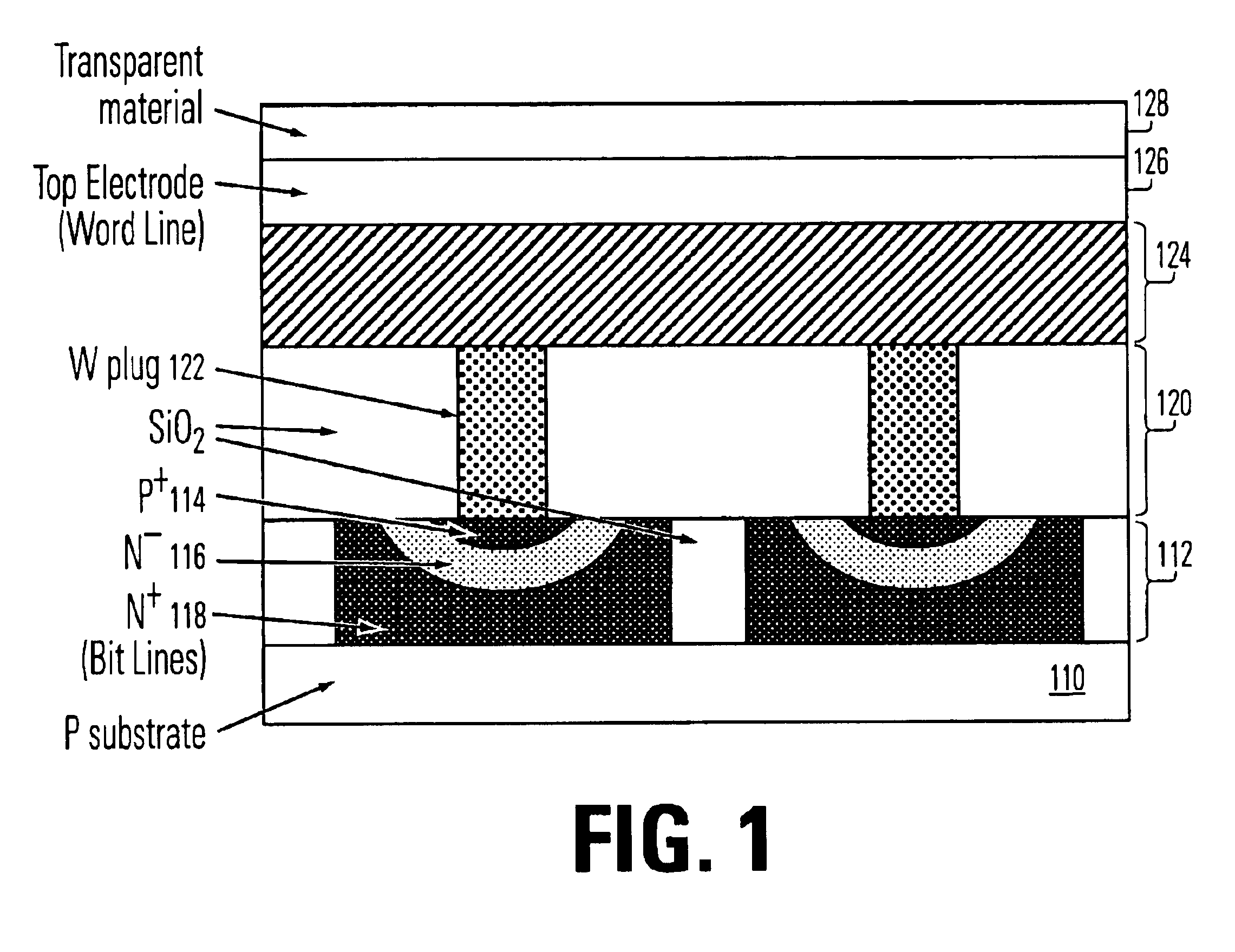

Roughly described, a phase-change memory such as a chalcogenide-based memory is programmed optically and read electrically. No complex electrical circuits are required for programming the cells. On the other hand, this memory can be read by electrical circuitry directly. The read out speed is much faster than for optical disks, and integrated circuit chips made this way are more compatible with other electrical circuits than are optical disks. Thus memories according to the invention can have simple, low power-consuming, electrical circuits, and do not require slow and power-hungry disk drives for reading. The invention therefore provides a unique low power, fast read / write memory with simple electrical circuits.

Owner:MACRONIX INT CO LTD

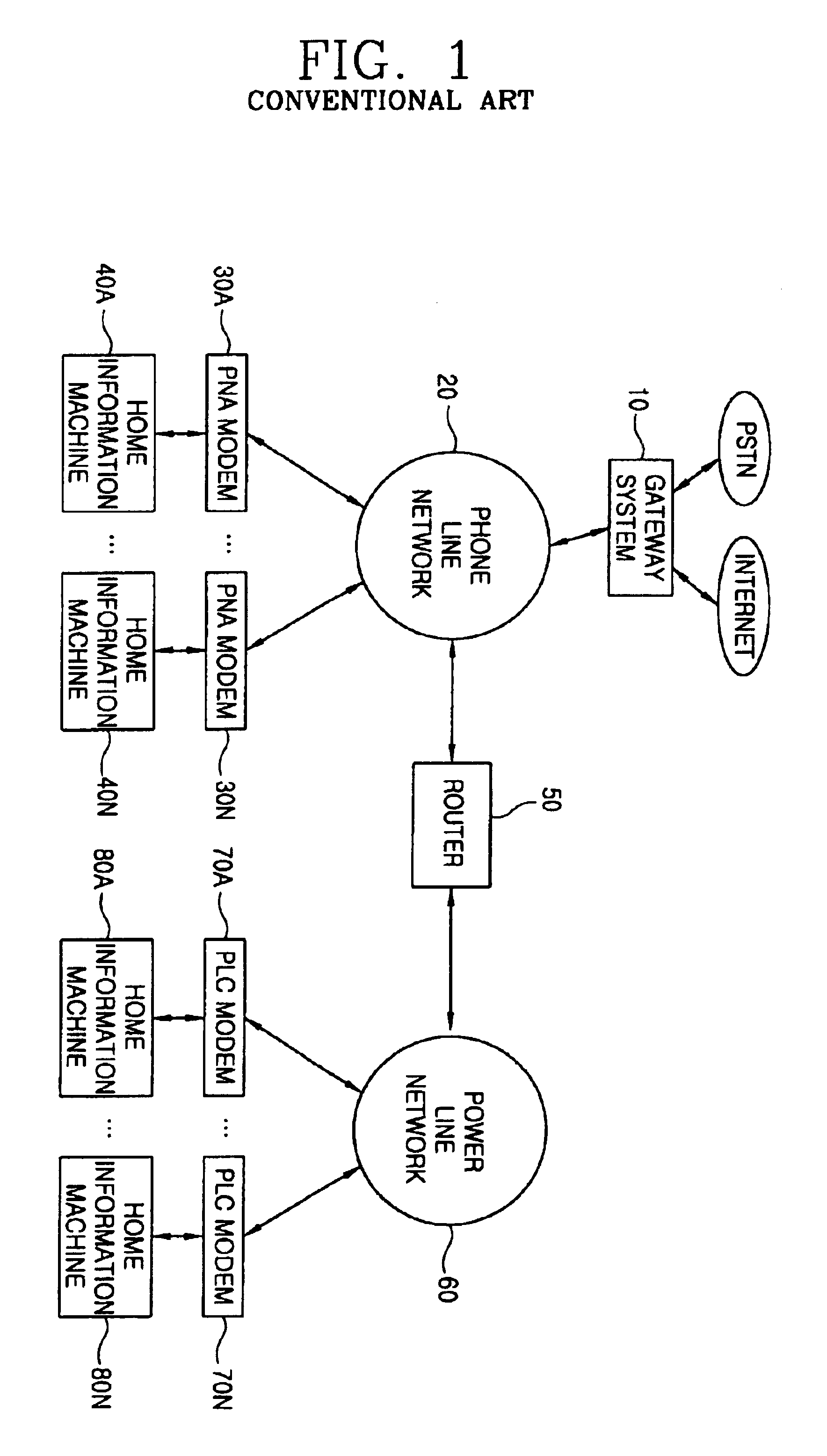

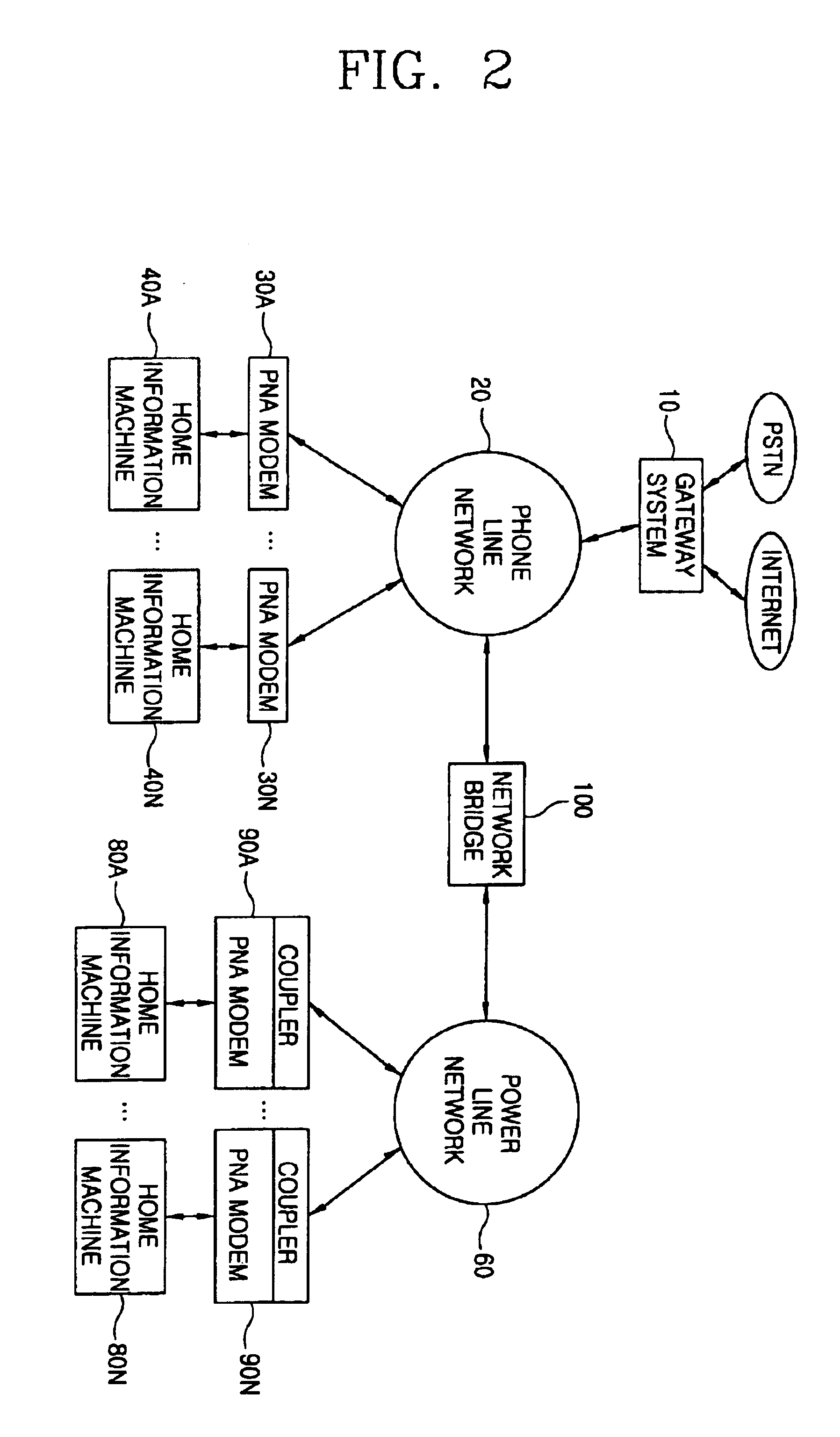

Network infrastructure integrated system

InactiveUS6904134B2Systems using filtering and bypassingInterconnection arrangementsPower line networkNetwork connection

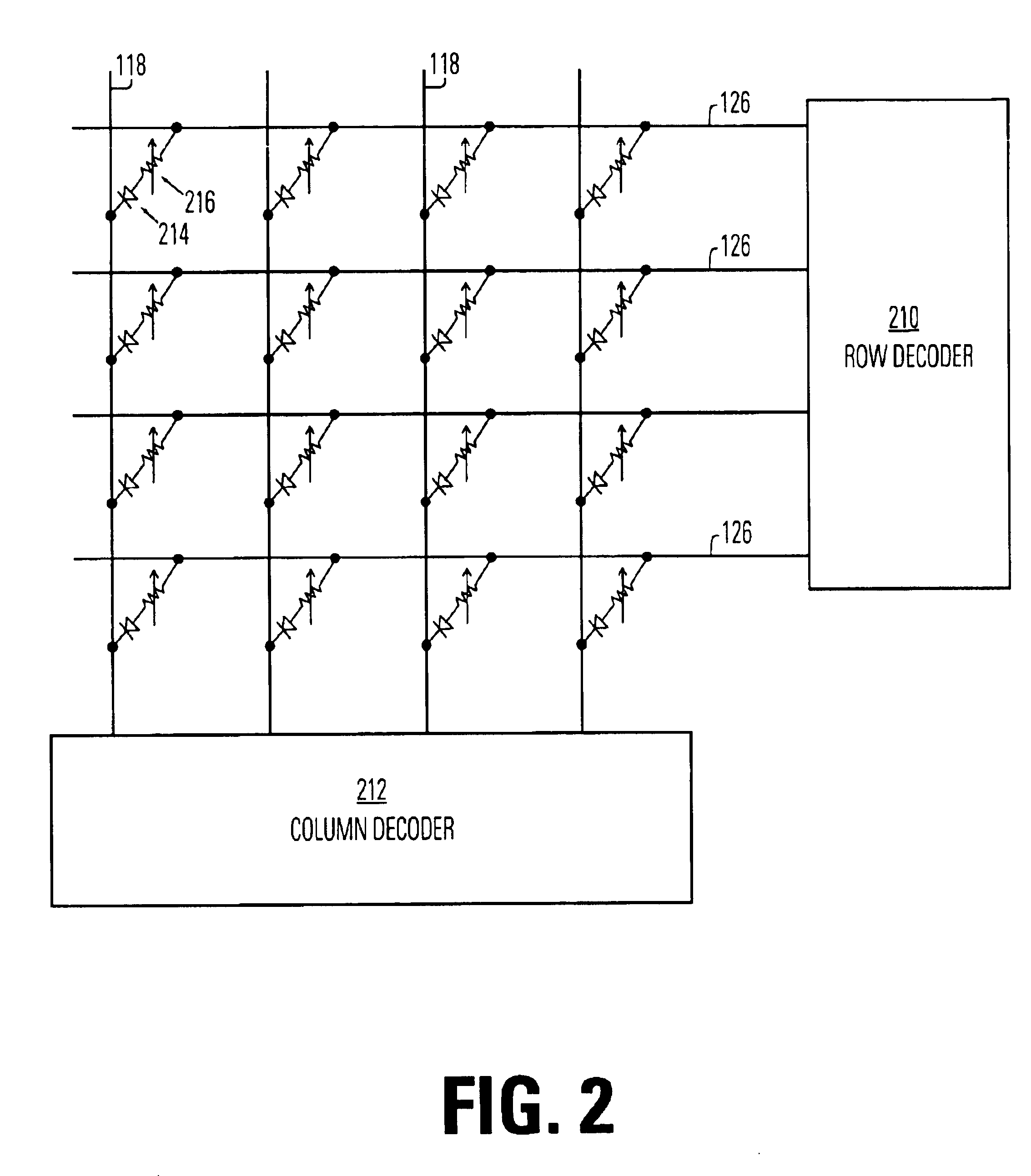

A network infrastructure integrated system which is able to integrate a telephone line network and a power line network as a single network using a simple circuit includes a first network to which a plurality of Home Information Machines are connected; a second network to which a plurality of Home Information Machines are connected; and a network bridge connected between the first and second networks and enabling the Home Information Machines to share respective applications and data with each other, whereby the cost can be reduced, the interchangeability is increased, and the accessibility to the network can be increased by using both the power lines and the telephone lines.

Owner:LG ELECTRONICS INC

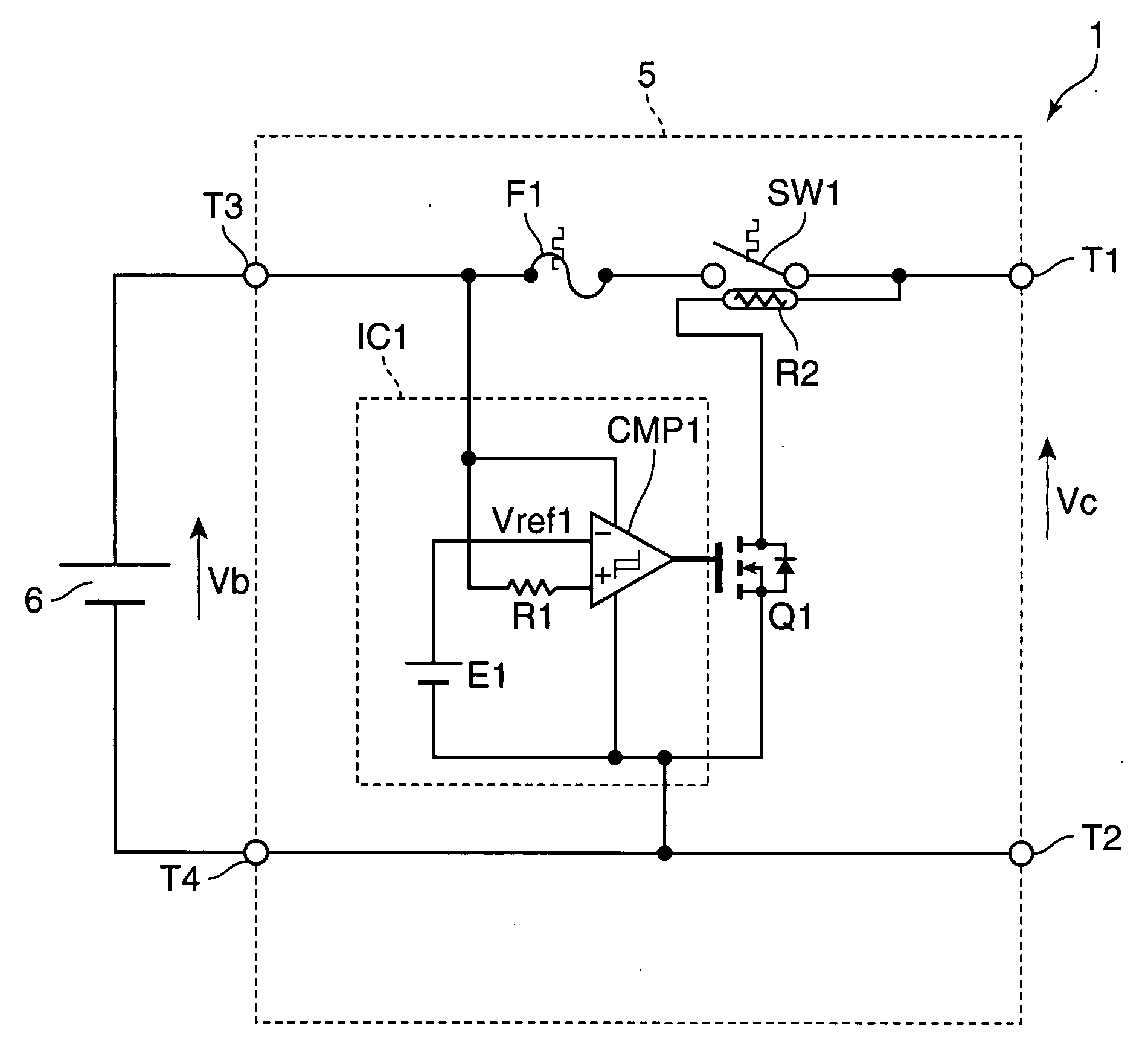

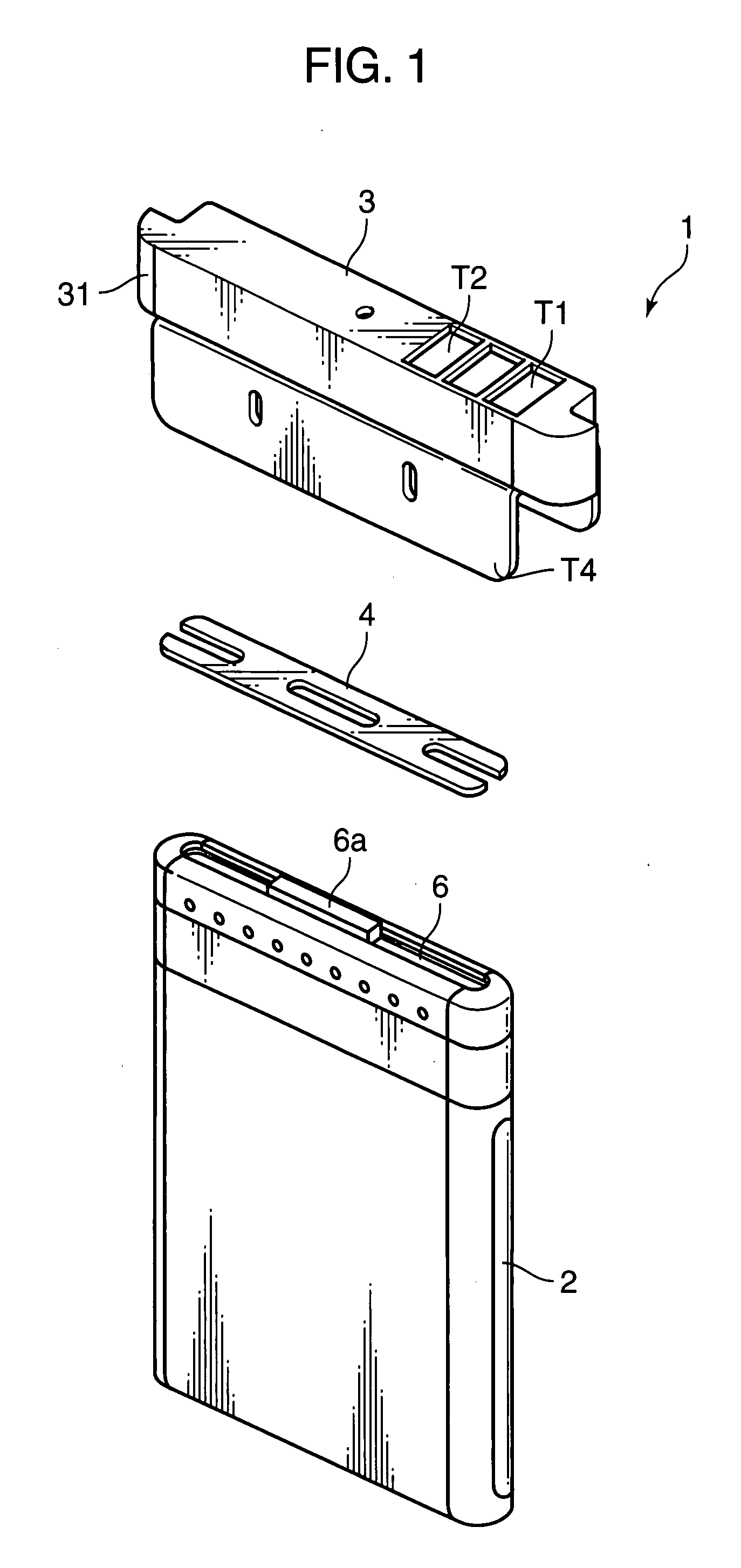

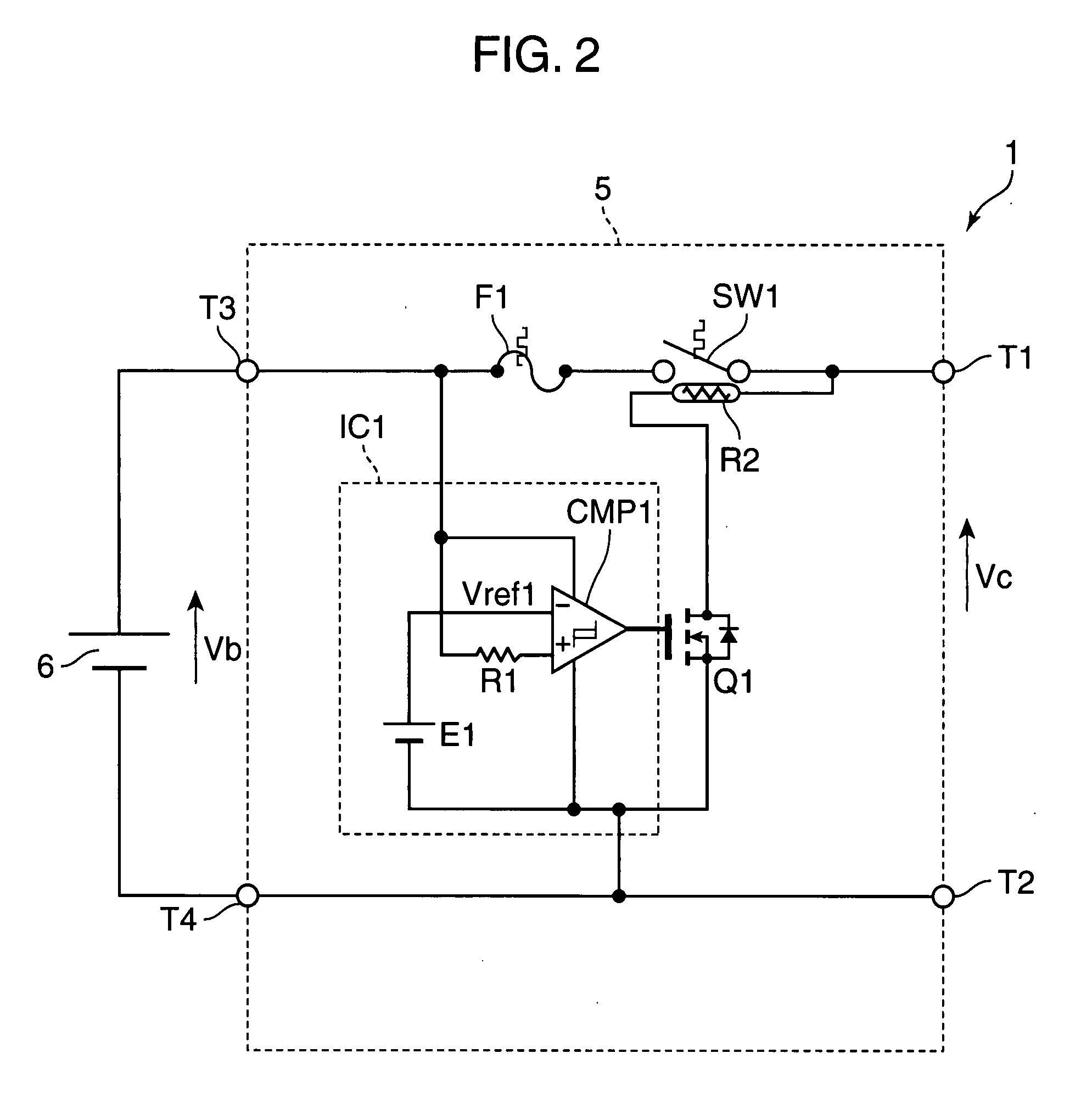

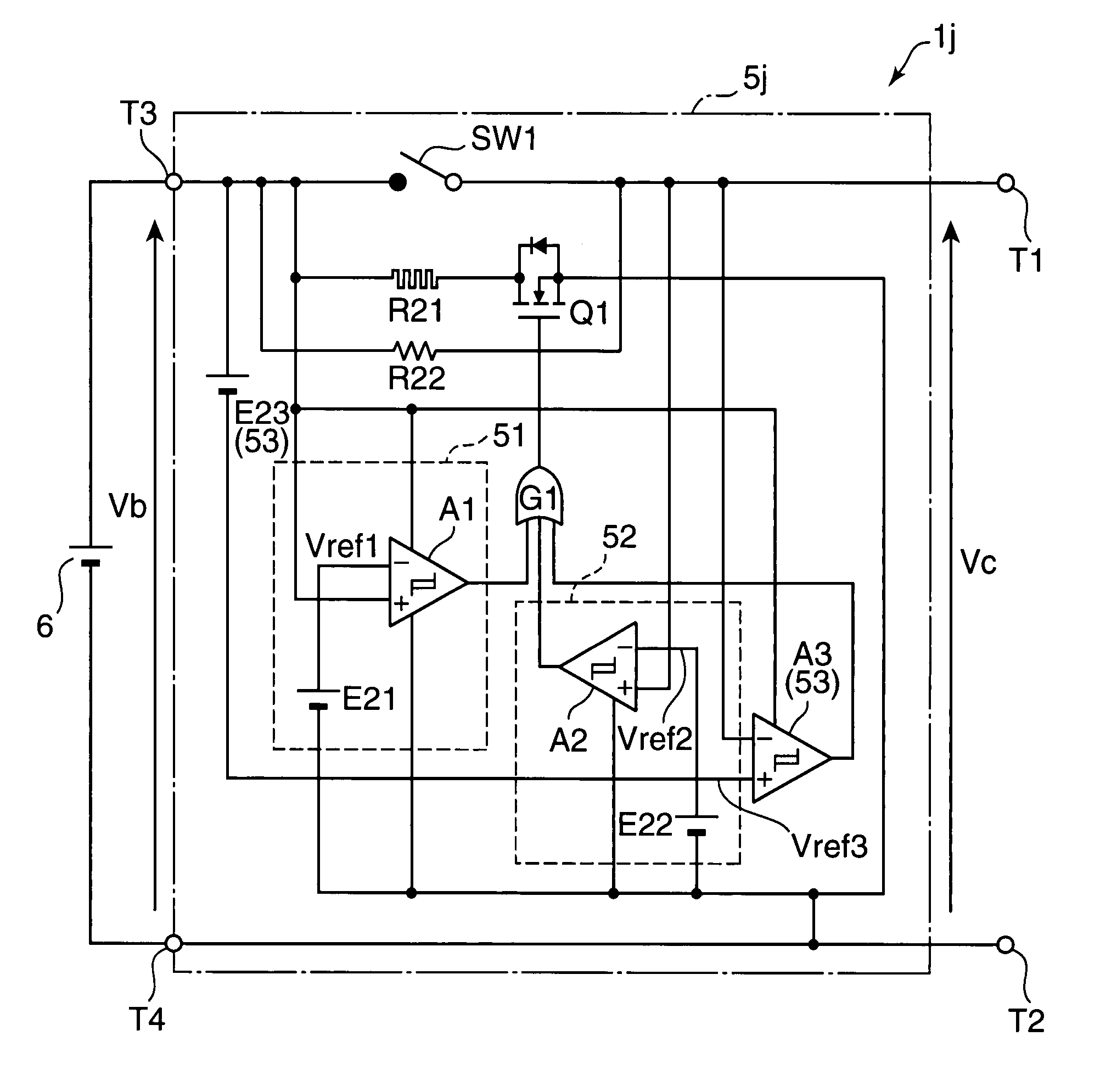

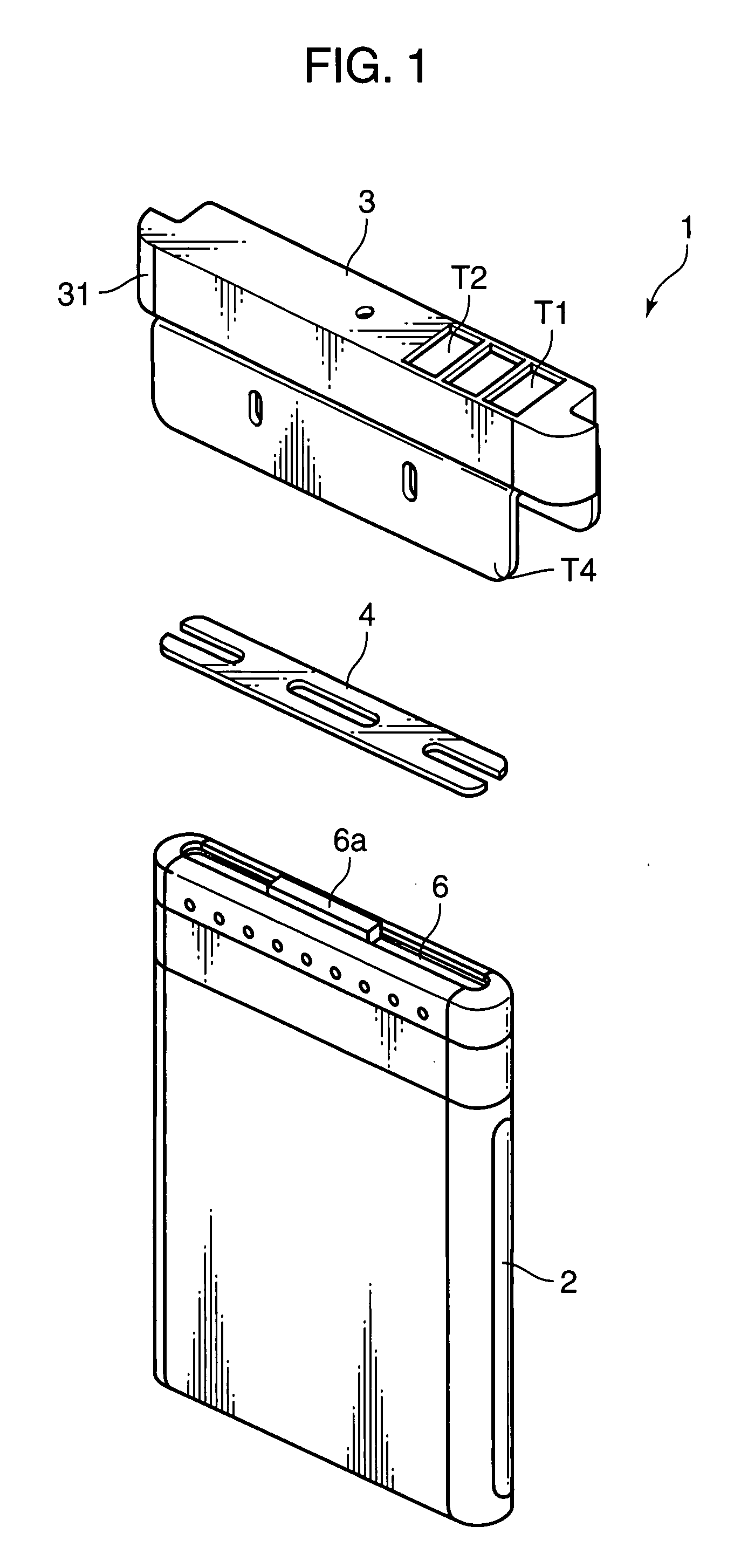

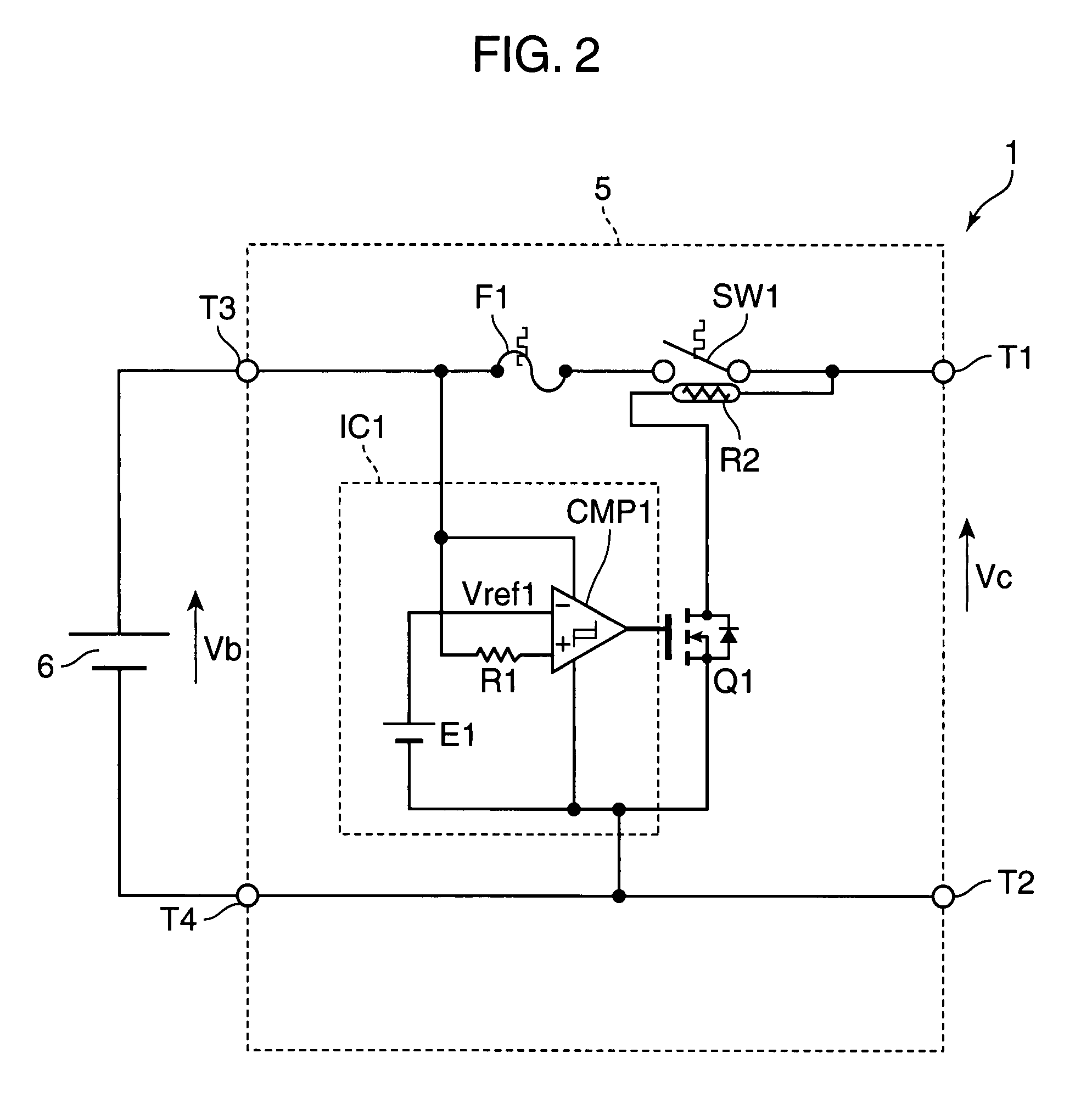

Secondary Battery Protection Circuit, Battery Pack and Thermosensitive Protection Switch Device

InactiveUS20080116851A1Reduced characteristicsReduce degradationElectrothermal relaysEmergency protective circuit arrangementsEngineeringDischarge current

A protection circuit is provided for protecting a secondary battery from overcharging and excessive discharge current by a simple circuit. The protection circuit is provided with a connection terminal (T3) for connecting the secondary battery (6); a connection terminal (T1) for connecting a charging device for charging the secondary battery (6) and / or a load device driven by a discharge current from the secondary battery (6); a bimetal switch (SW1) that is provided between the connection terminals (T1, T3) and turned off in the case of exceeding a specified temperature set beforehand; a heater (R2) for heating the bimetal switch (SW1); and an integrated circuit (IC1) for turning the bimetal switch (SW1) off by causing the heater (R2) to generate heat if a voltage applied to the connection terminal (T3) by the secondary battery (6) exceeds a preset reference voltage.

Owner:PANASONIC CORP

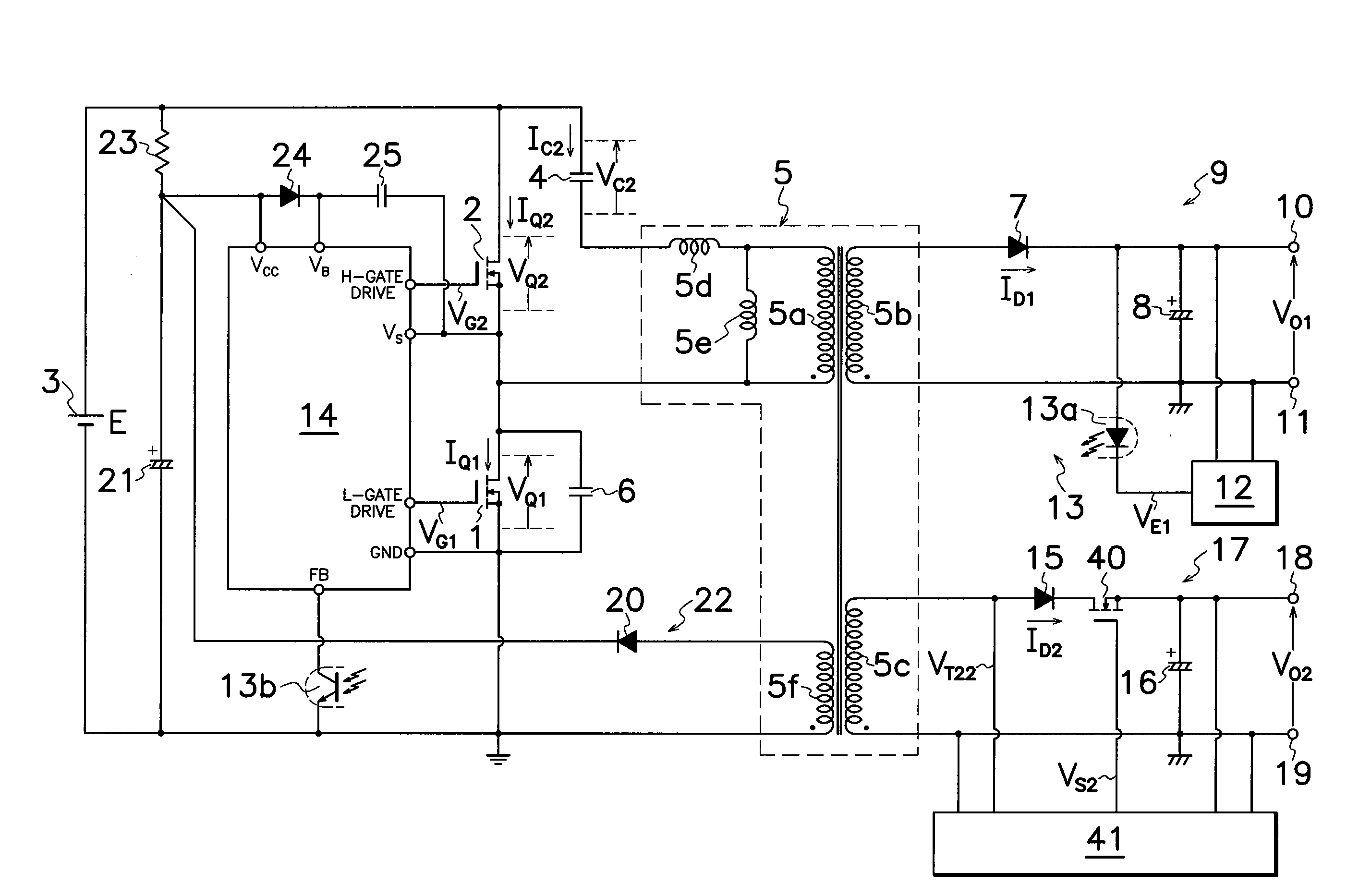

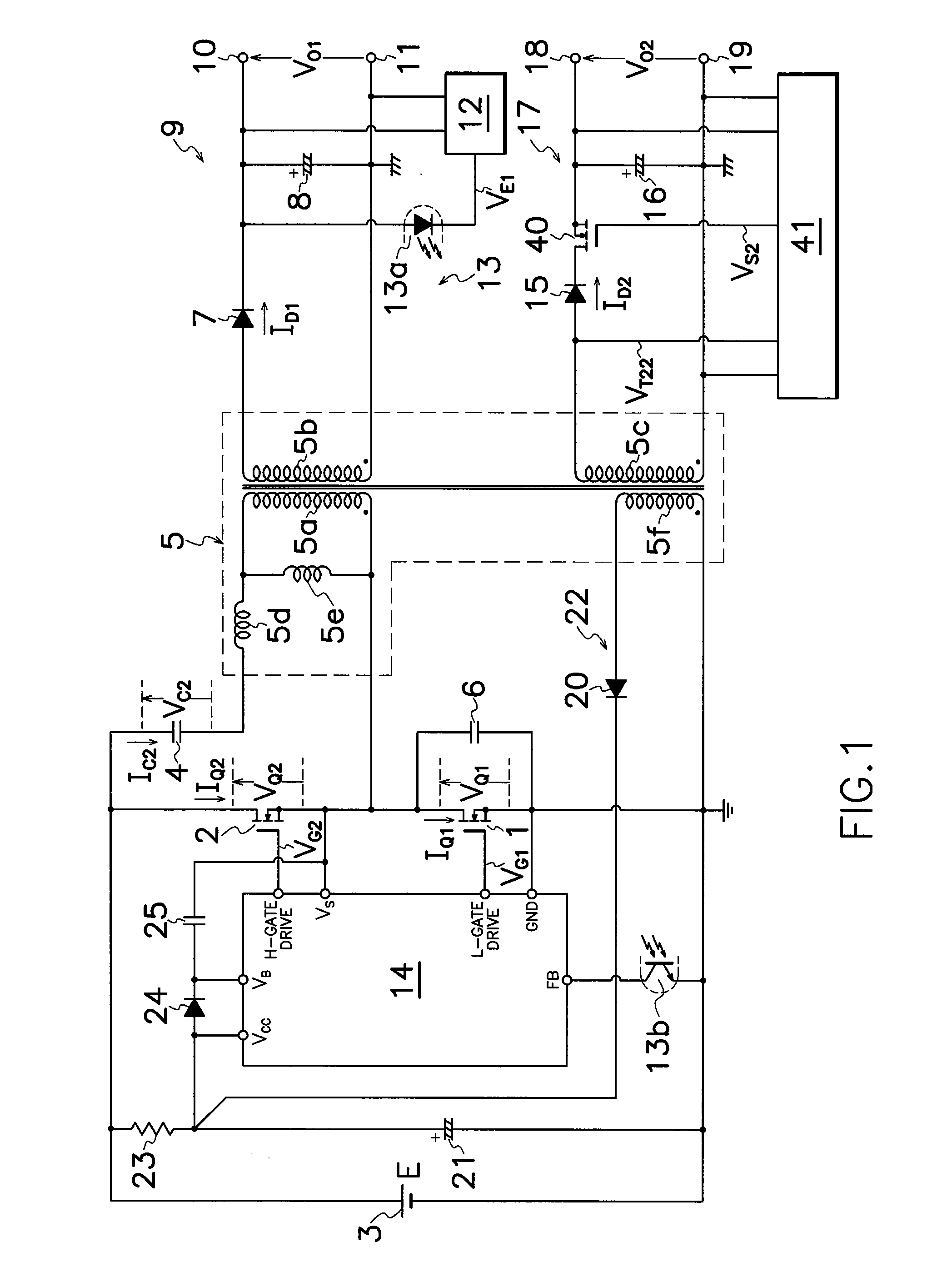

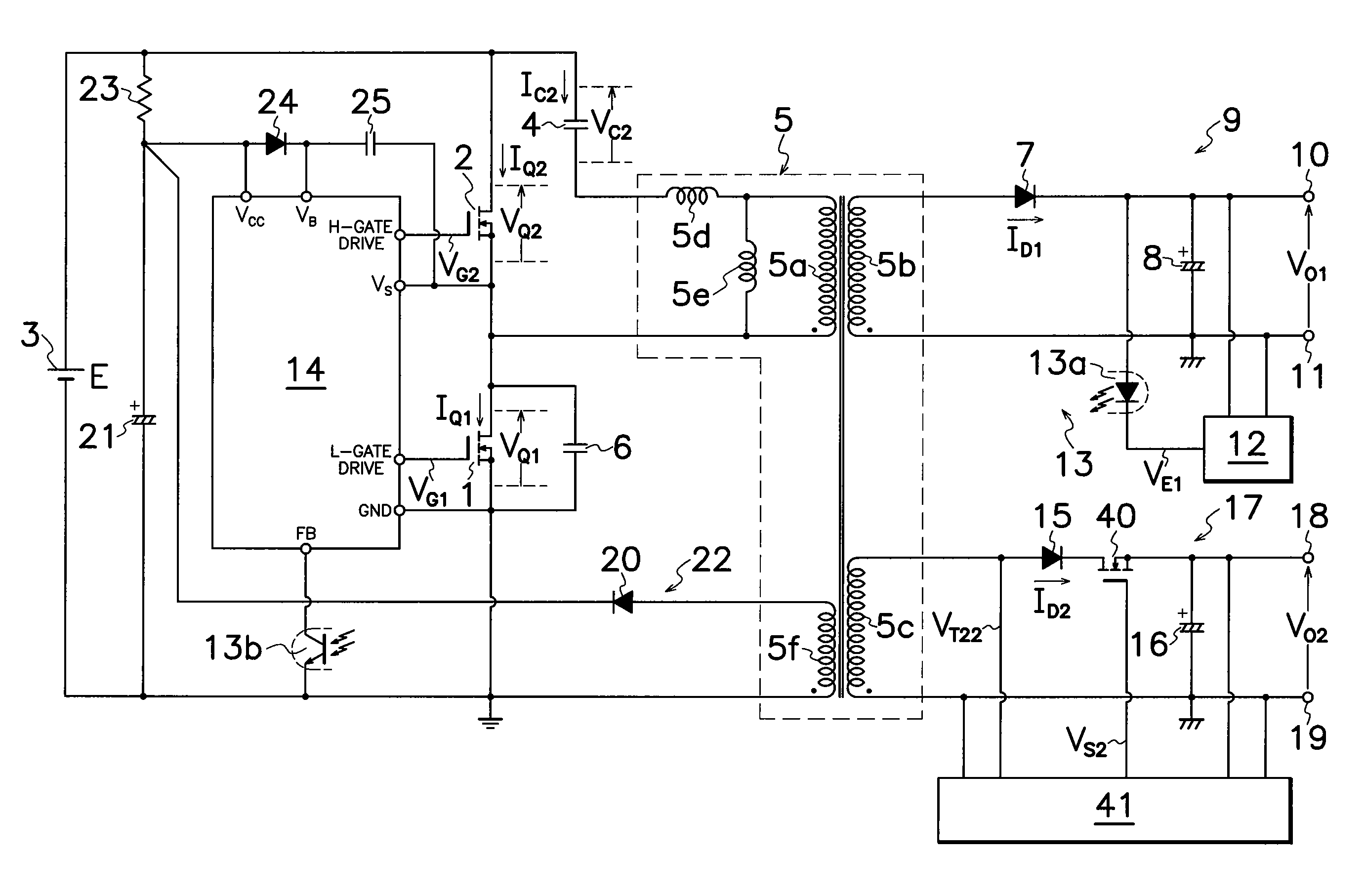

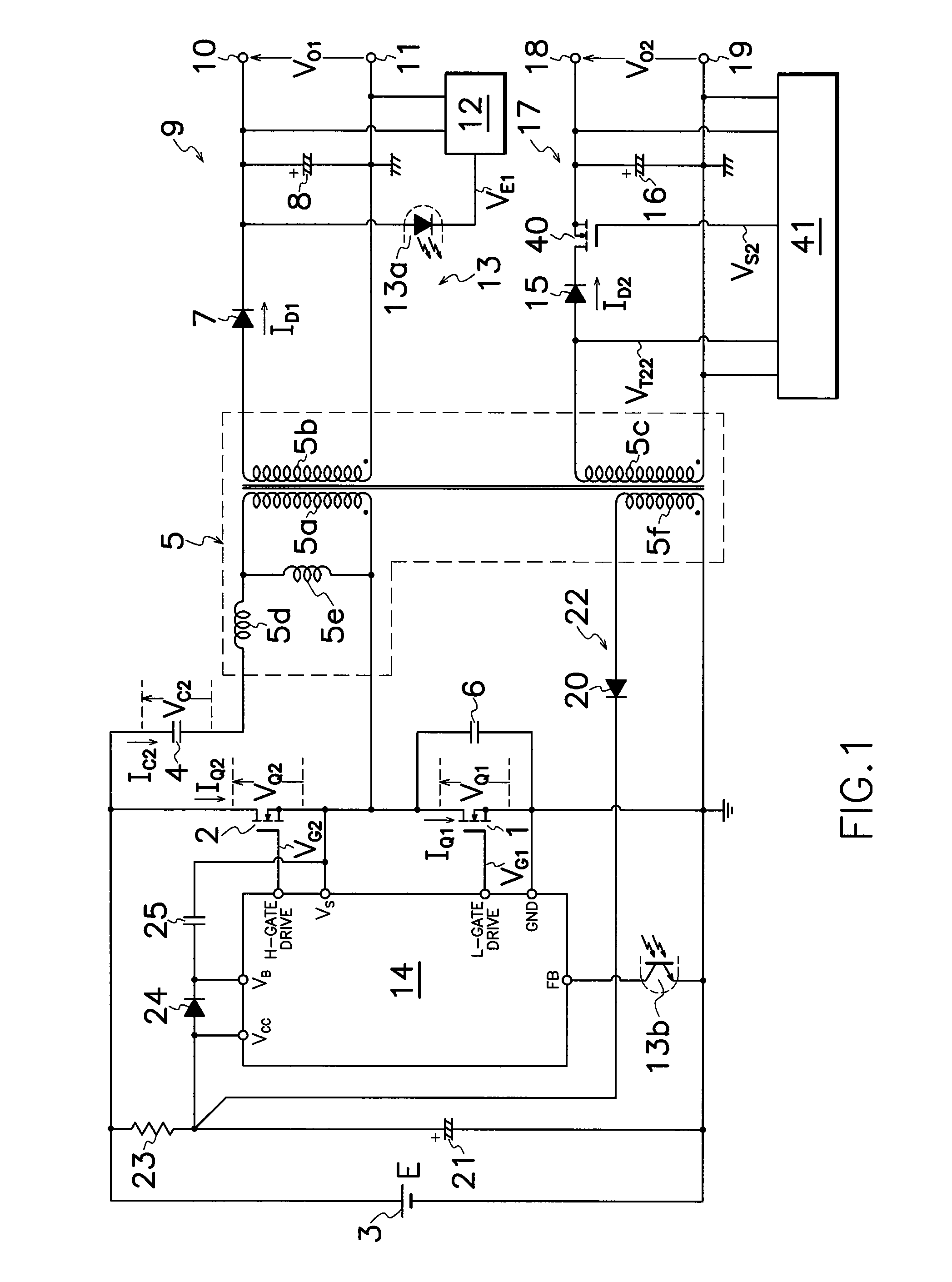

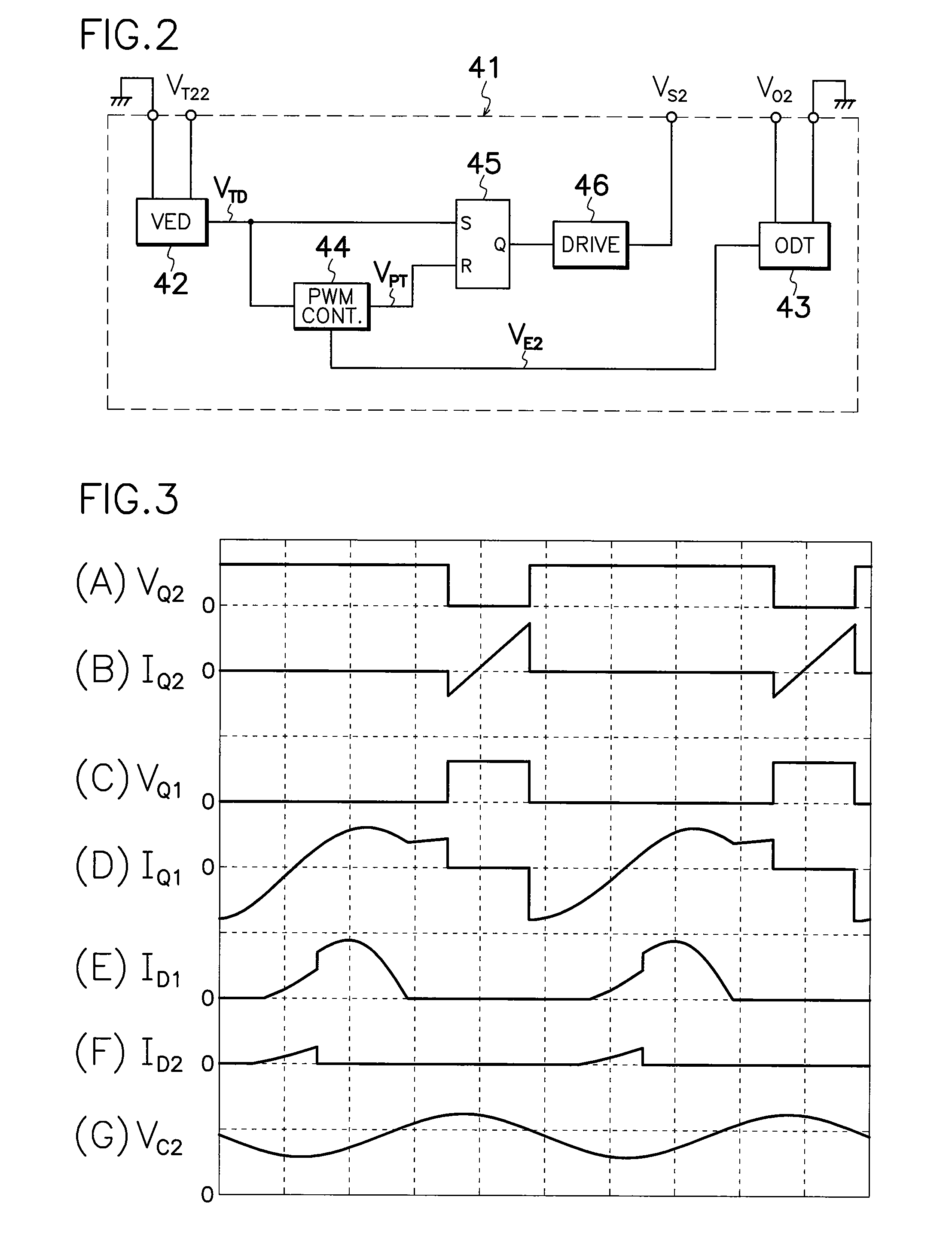

Current resonant dc-dc converter of multi-output type

InactiveUS20090251925A1Extended service lifeImprove power conversion efficiencyAc-dc conversion without reversalEfficient power electronics conversionDc dc converterTransformer

A current resonant DC-DC converter of multi-output type is provided which comprises an output-regulatory MOS-FET 40 connected between a secondary winding 5c of a transformer 5 and a smoothing capacitor 16 in a second rectifying smoother 17, and an output control circuit 41 for controlling the on-off operation of output-regulatory MOS-FET 40 based on voltage VO2 from smoothing capacitor 16 in second rectifying smoother 17. By turning the on-off operation of output-regulatory MOS-FET 40 in synchronization with switching frequency of first or second MOS-FETs 1, 2, an ideal cross regulation among respective DC outputs can be obtained, providing the inexpensive converter with simple circuit alteration capable of producing highly stable DC outputs with high power conversion efficiency, high accuracy and less power conversion loss.

Owner:SANKEN ELECTRIC CO LTD

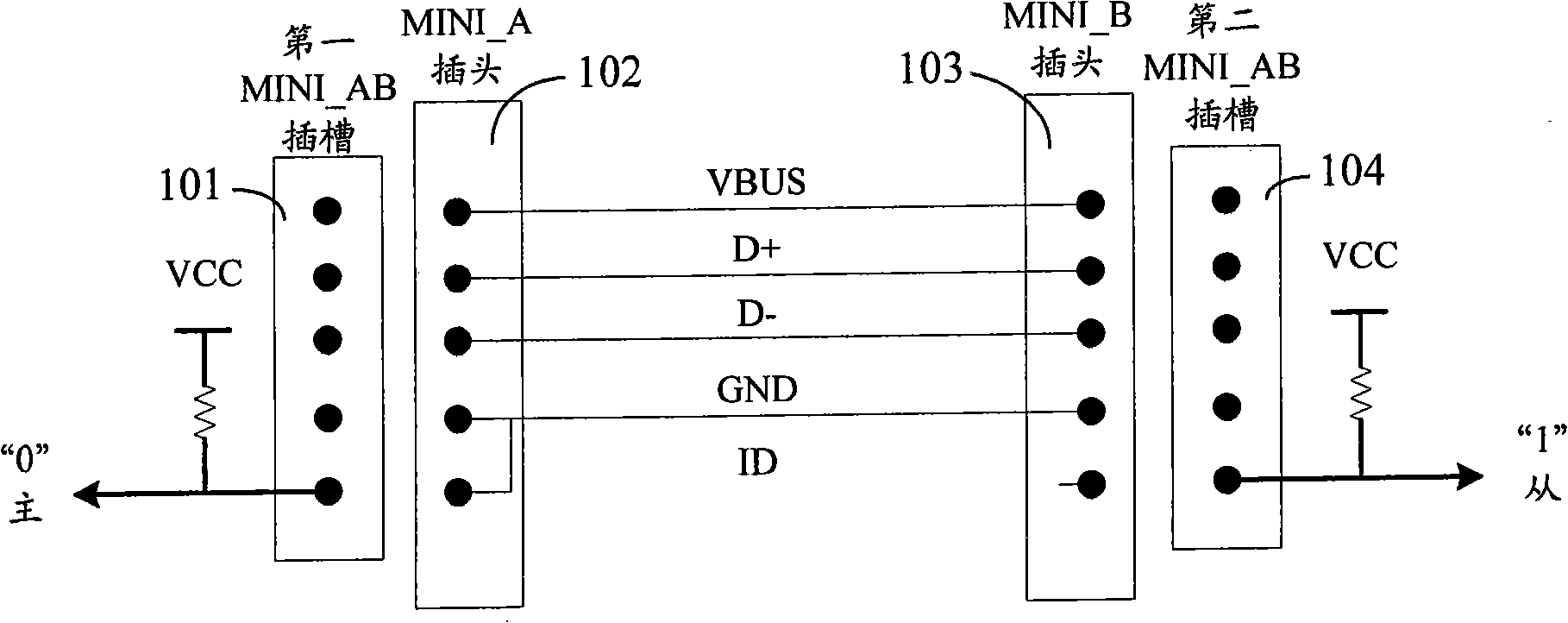

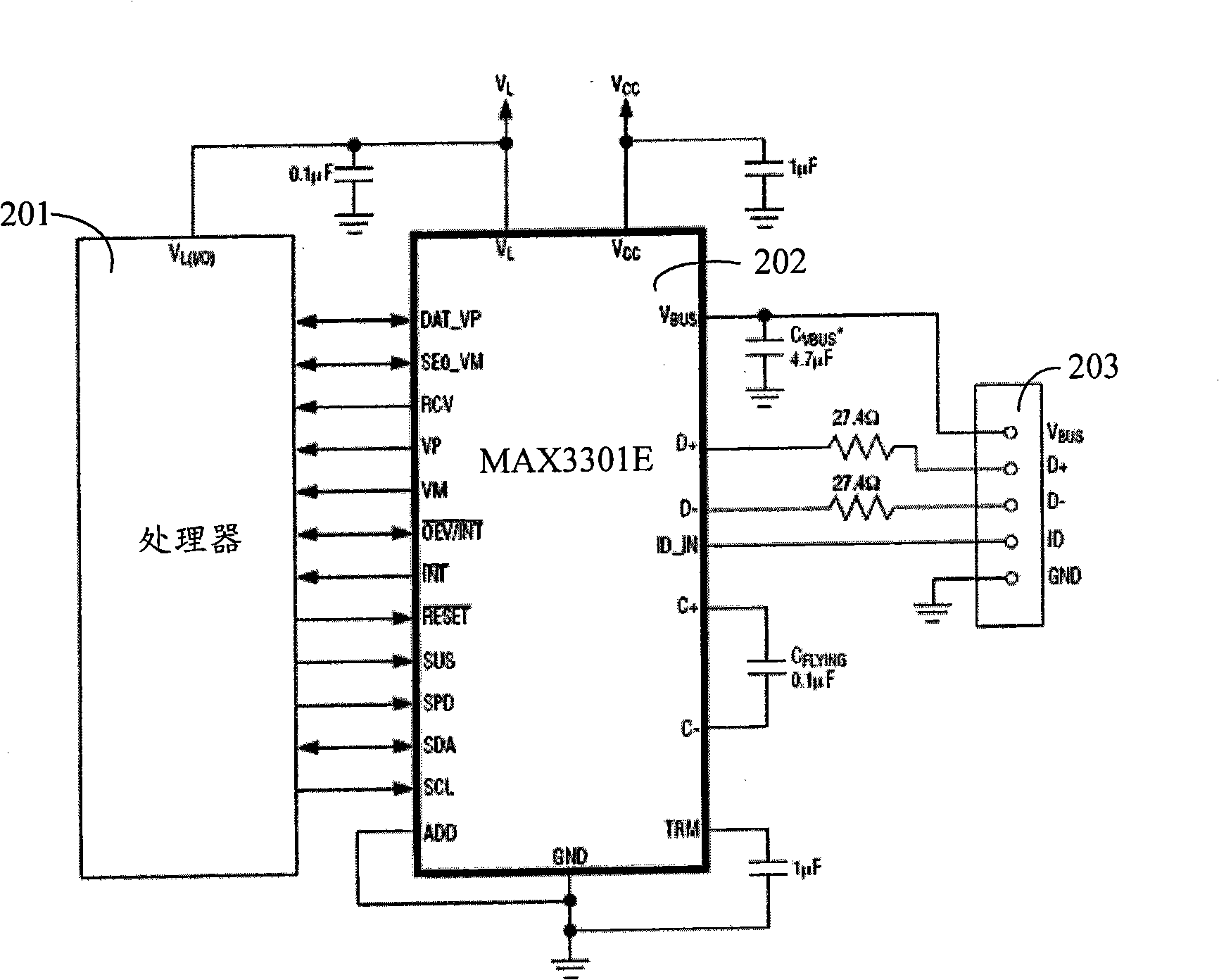

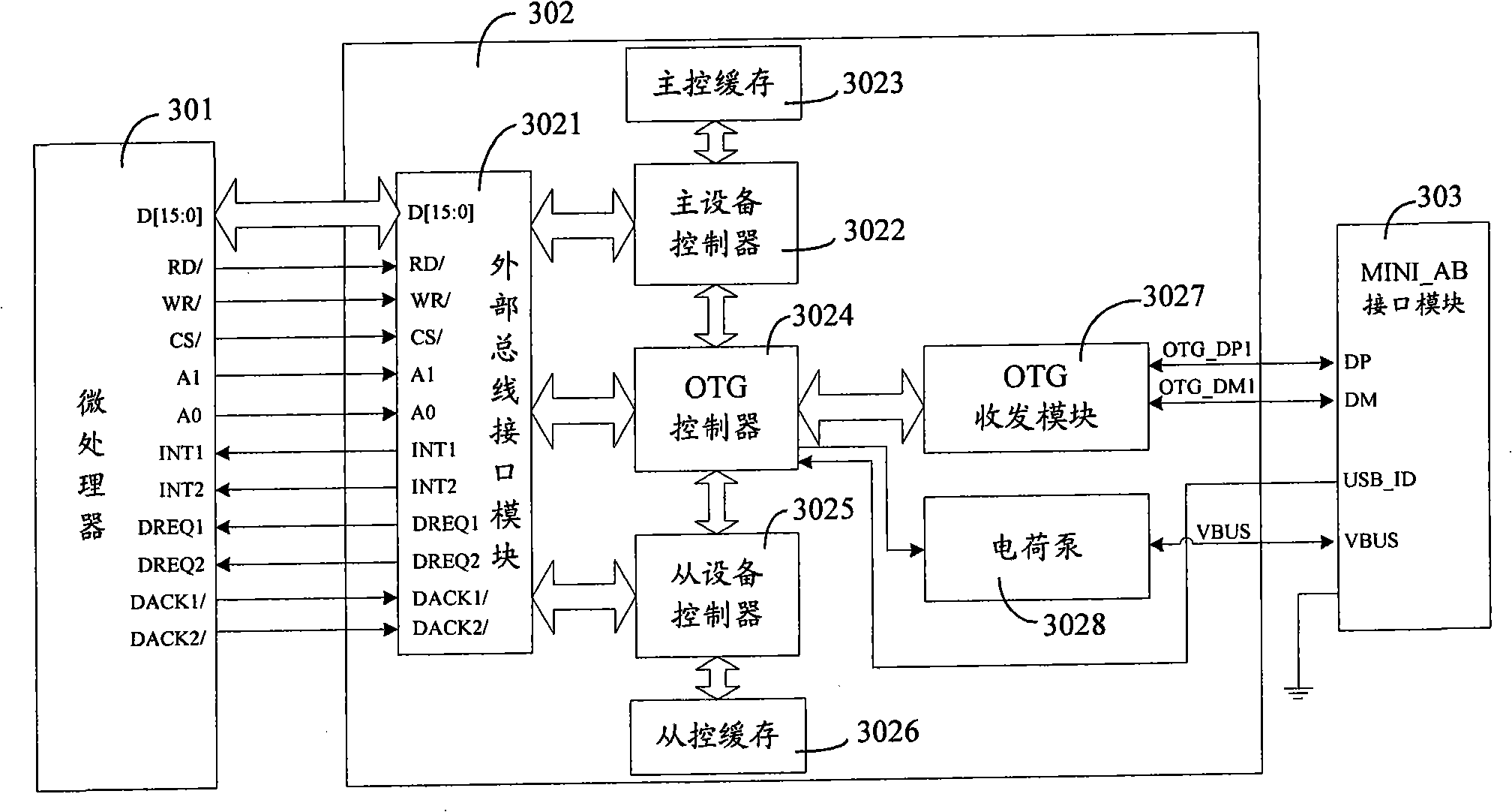

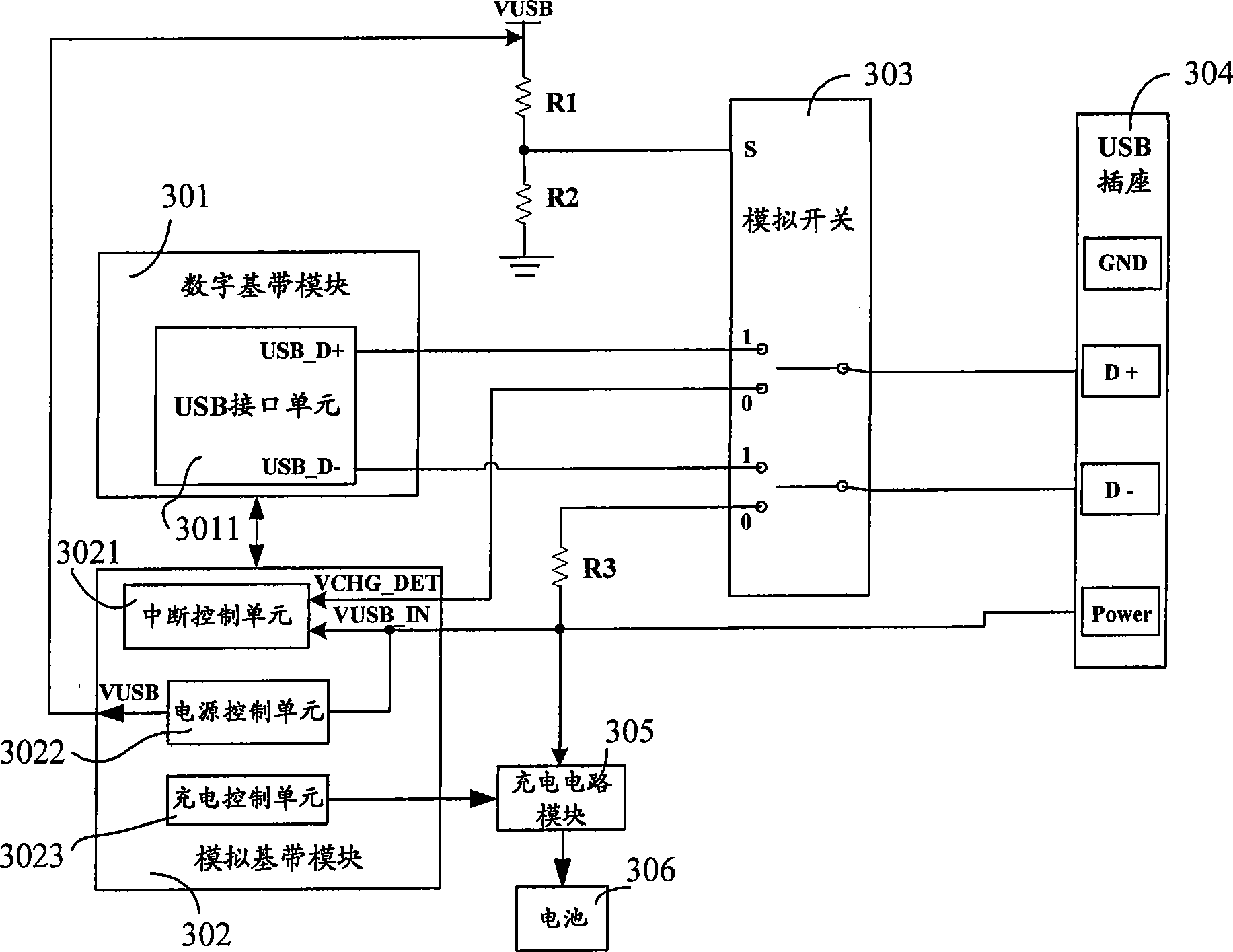

Method and apparatus for implementing general-purpose serial bus USB OTG

ActiveCN101359316AImplement USB OTG functionLow costElectric digital data processingGeneral purposeData interface

The invention discloses a method which realizes the universal serial bus USB OTG and includes that the processor detects the principal- subordinate identification interface signal though the second GPIO and judges the level of the principal-subordinate identification interface signal; if the principal-subordinate identification interface signal is low level, the USB principle device controller is started; if the principal-subordinate identification interface signal is high level, the USB subordinate device controller is started; meanwhile, the invention also discloses a device which realizes the universal serial bus USB OTG; the device comprises a processor, a plurality of analog switches, a power module and a MINI_AB interface module; wherein, the processor includes a USB principle device controller, a USB subordinate device controller, four GPIO interfaces, two data interface signals, a power interface signal and a principal-subordinate identification interface signal. The method and the device which realize the universal serial bus USB OTG provide the client with a set of universal serial bus USB OTG solution which has the advantages of simple circuit, low cost, convenient application, wide application range and reliable performance.

Owner:LEADCORE TECH

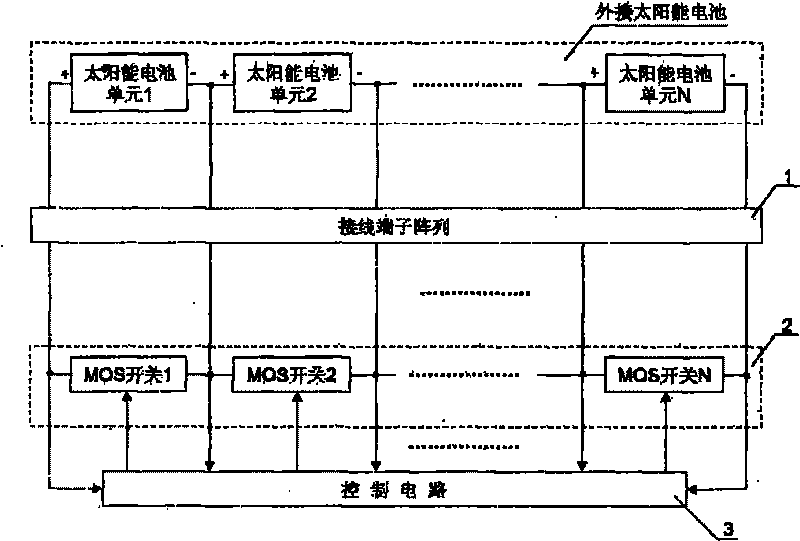

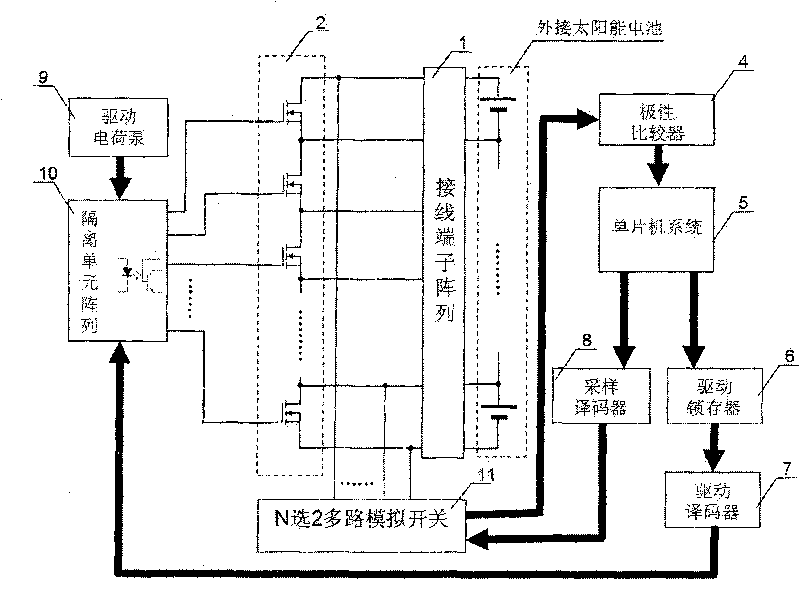

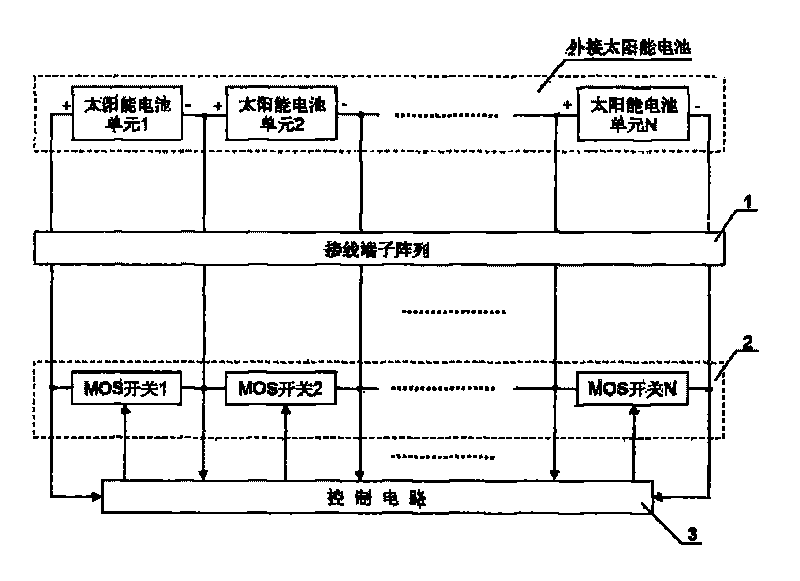

Dynamic interconnected control system and control method for solar battery pack

InactiveCN101697462ASolve problems where a failure can affect the entire systemPV power plantsElectrical testingElectricityElectrical battery

The invention provides a dynamic interconnected control system and a control method for a solar battery pack, which comprises a plurality of MOS switch units, a connection terminal array and a control unit, wherein MOS switches are connected in series to form an array; each electric node of the MOS switch array is connected with a corresponding node of the connection terminal; the MOS switches are electrically connected with a control unit; and the control unit controls switch-on / switch-off of the MOS switches according to the state of the solar battery unit connected with the connection terminal array. The method comprises the following steps of: connecting a plurality of MOS switch units in series; connecting each solar battery unit and an MOS switch in parallel and electrically connecting the solar battery unit and the control unit; using the control unit to monitor the state of each solar battery unit and controlling the switch-on / switch-off of the MOS switches according to the state of the solar battery unit. The dynamic interconnected control system and the control method for the solar battery pack provided by the invention solve the problem that the entire system is affected when a single solar battery unit fails by using a very simple circuit structure.

Owner:HEBEI INST OF LASER

Current resonant DC-DC converter of multi-output type

InactiveUS7768801B2Ac-dc conversion without reversalEfficient power electronics conversionDc dc converterTransformer

A current resonant DC-DC converter of multi-output type is provided which comprises an output-regulatory MOS-FET 40 connected between a secondary winding 5c of a transformer 5 and a smoothing capacitor 16 in a second rectifying smoother 17, and an output control circuit 41 for controlling the on-off operation of output-regulatory MOS-FET 40 based on voltage VO2 from smoothing capacitor 16 in second rectifying smoother 17. By turning the on-off operation of output-regulatory MOS-FET 40 in synchronization with switching frequency of first or second MOS-FETs 1, 2, an ideal cross regulation among respective DC outputs can be obtained, providing the inexpensive converter with simple circuit alteration capable of producing highly stable DC outputs with high power conversion efficiency, high accuracy and less power conversion loss.

Owner:SANKEN ELECTRIC CO LTD

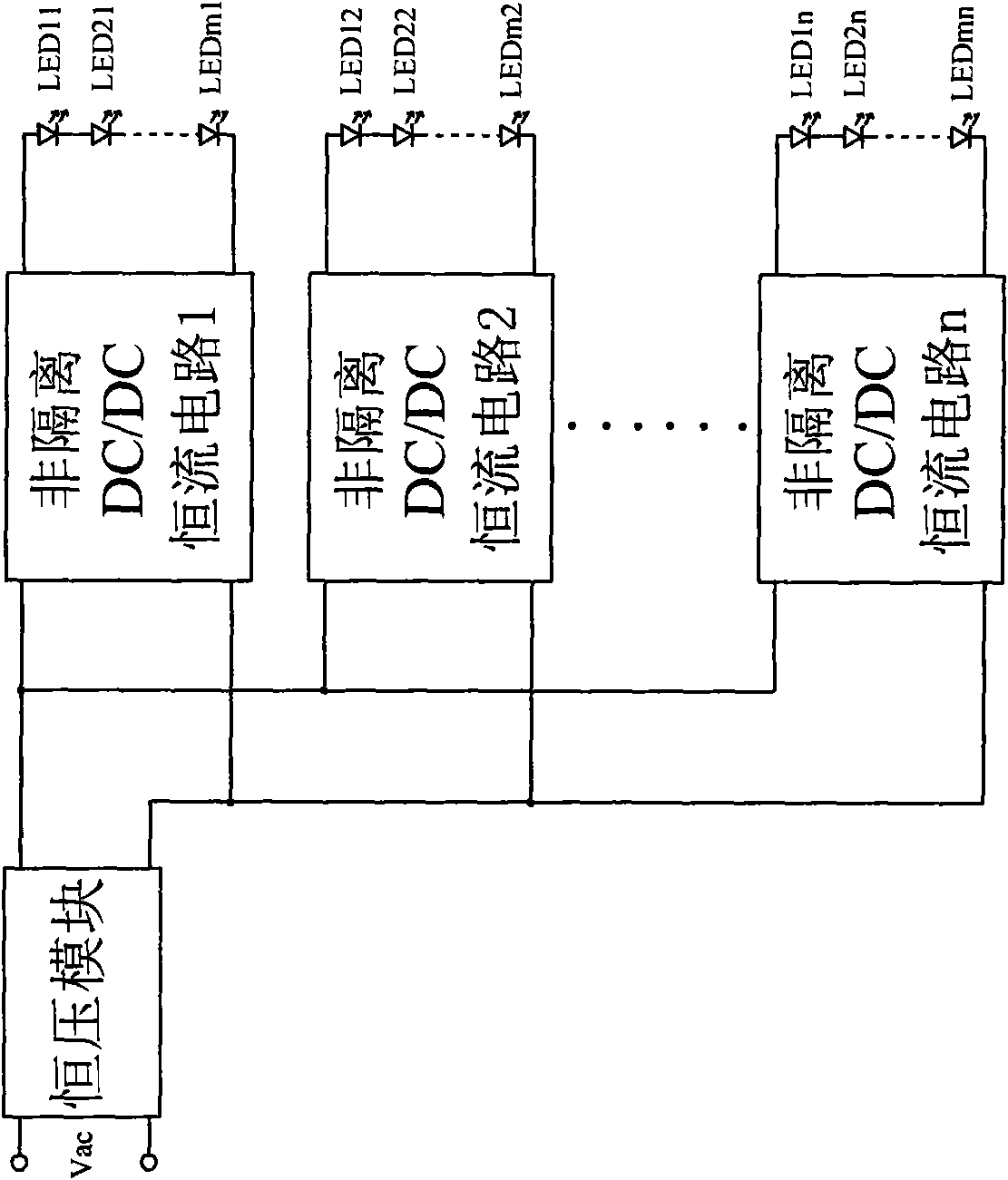

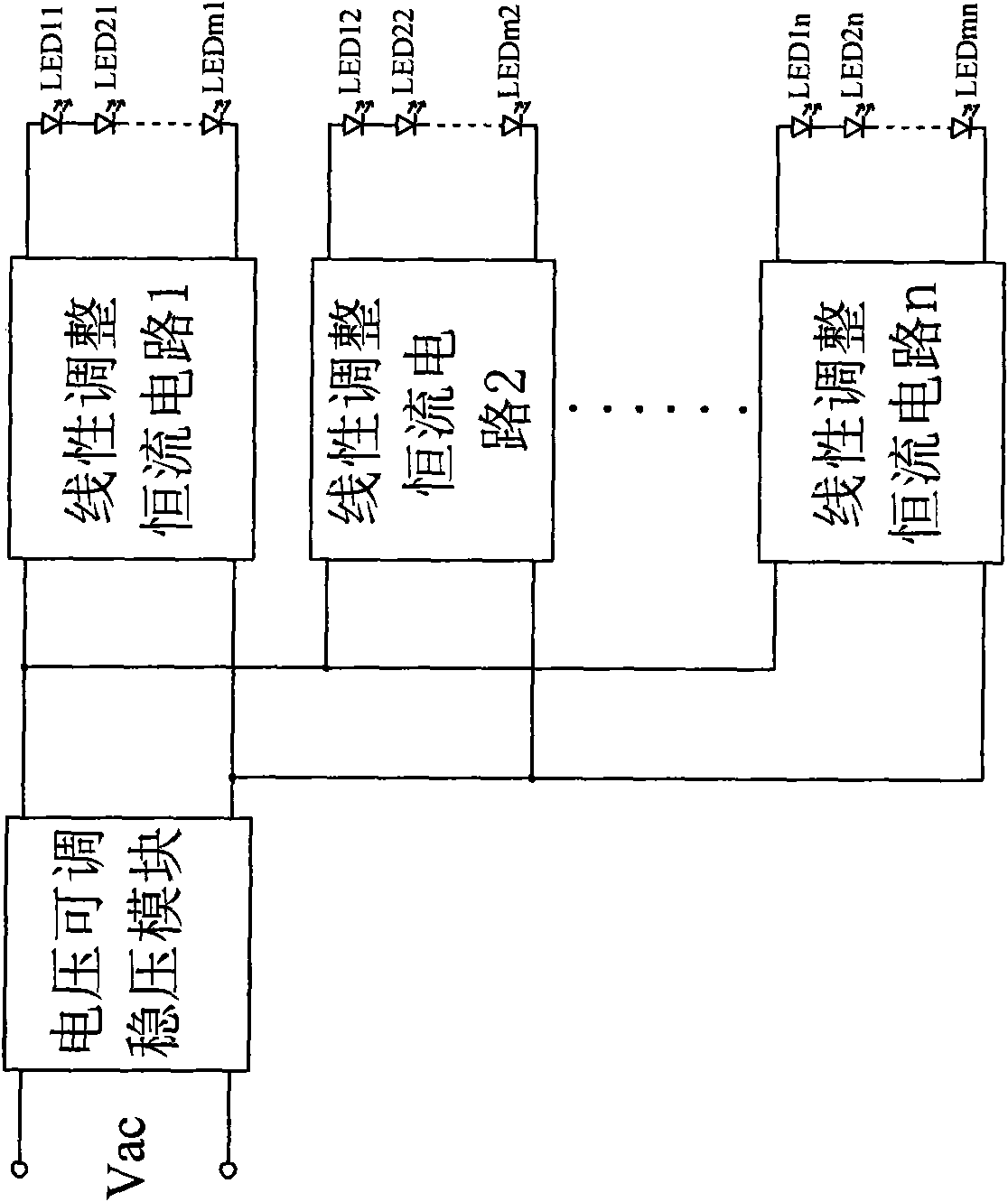

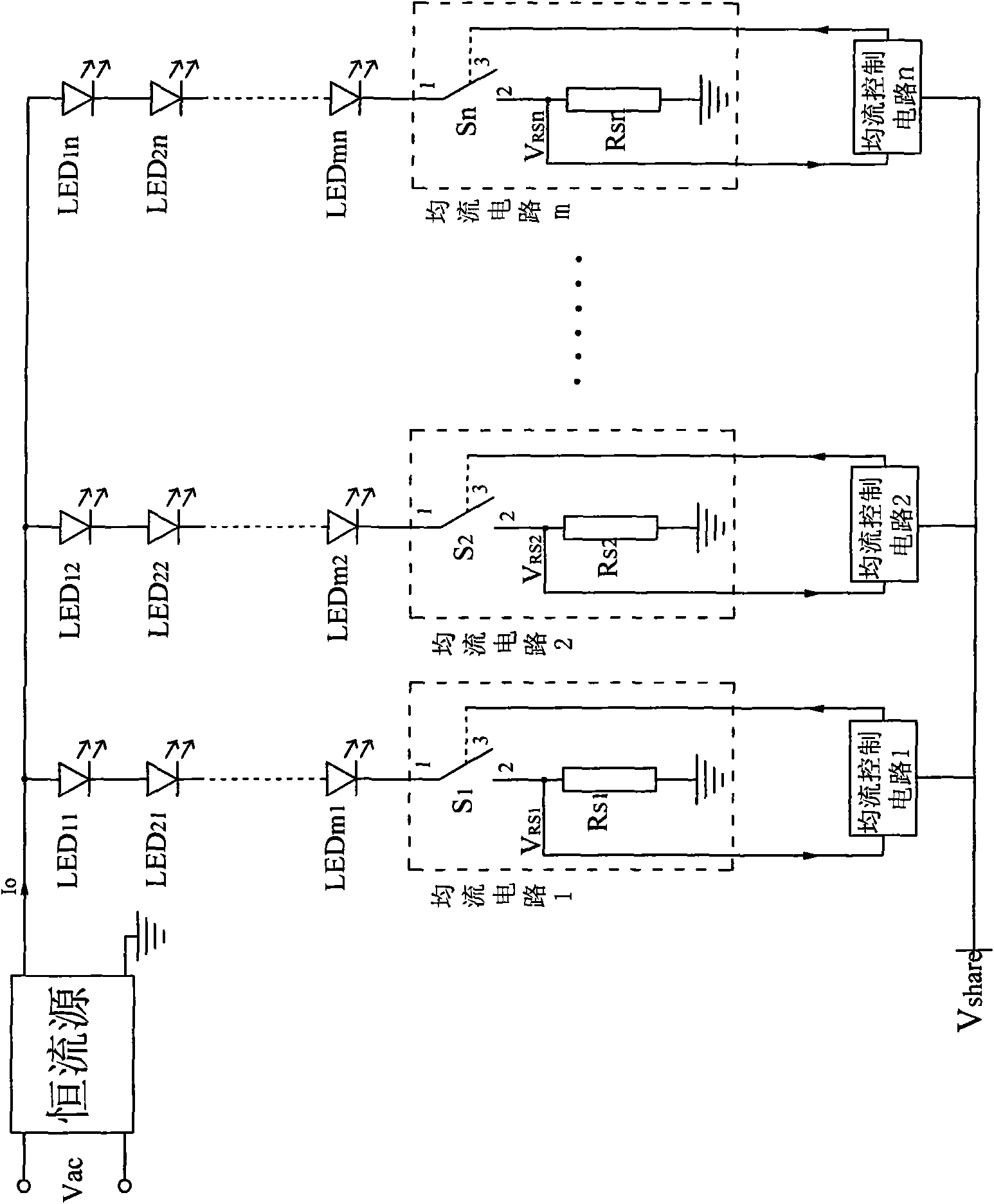

Multichannel constant-current control circuit applicable to LED driver

ActiveCN101674693ASimple structureLow costElectrical apparatusPoint-like light sourceElectrical resistance and conductancePower flow

The invention discloses a multichannel constant-current control circuit applicable to an LED driver, comprising a single output constant-current source and a plurality of channels of output circuits.The multichannel constant-current control circuit is characterized in that each output circuit comprises a current equalizing circuit, a current equalizing control circuit and a load consisting of a plurality of LED lamps; the input of each channel of current equalizing control circuit is from a sampling signal of the sampling resistor to output current, and becomes a public connecting wire afterbeing converted by the current equalizing circuit; the public connecting wire is connected with the other channels to form a current equalizing bus; each channel of current sampling signal and the current equalizing bus voltage are compared and adjusted in the current equalizing control circuit; and an output signal of the current equalizing control circuit can control the size of impedance of a liner adjusting tube of the corresponding current equalizing circuit, then control the size of each channel of current and realize current equalization. The multichannel constant-current control circuit has simple circuit structure and low cost, and is applicable to standard multichannel constant current control of the rear stage of a single-channel constant current power supply.

Owner:INVENTRONICS HANGZHOU

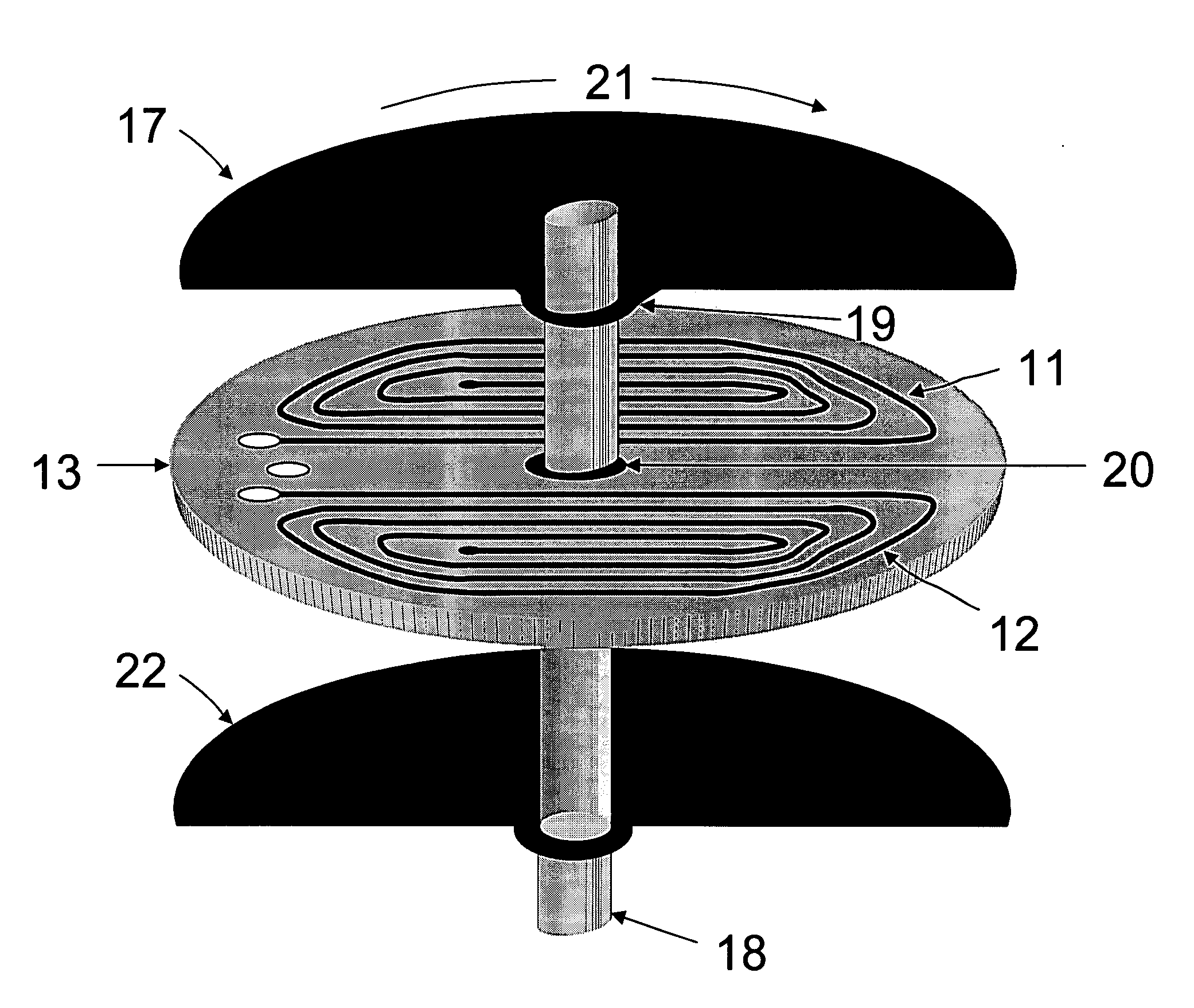

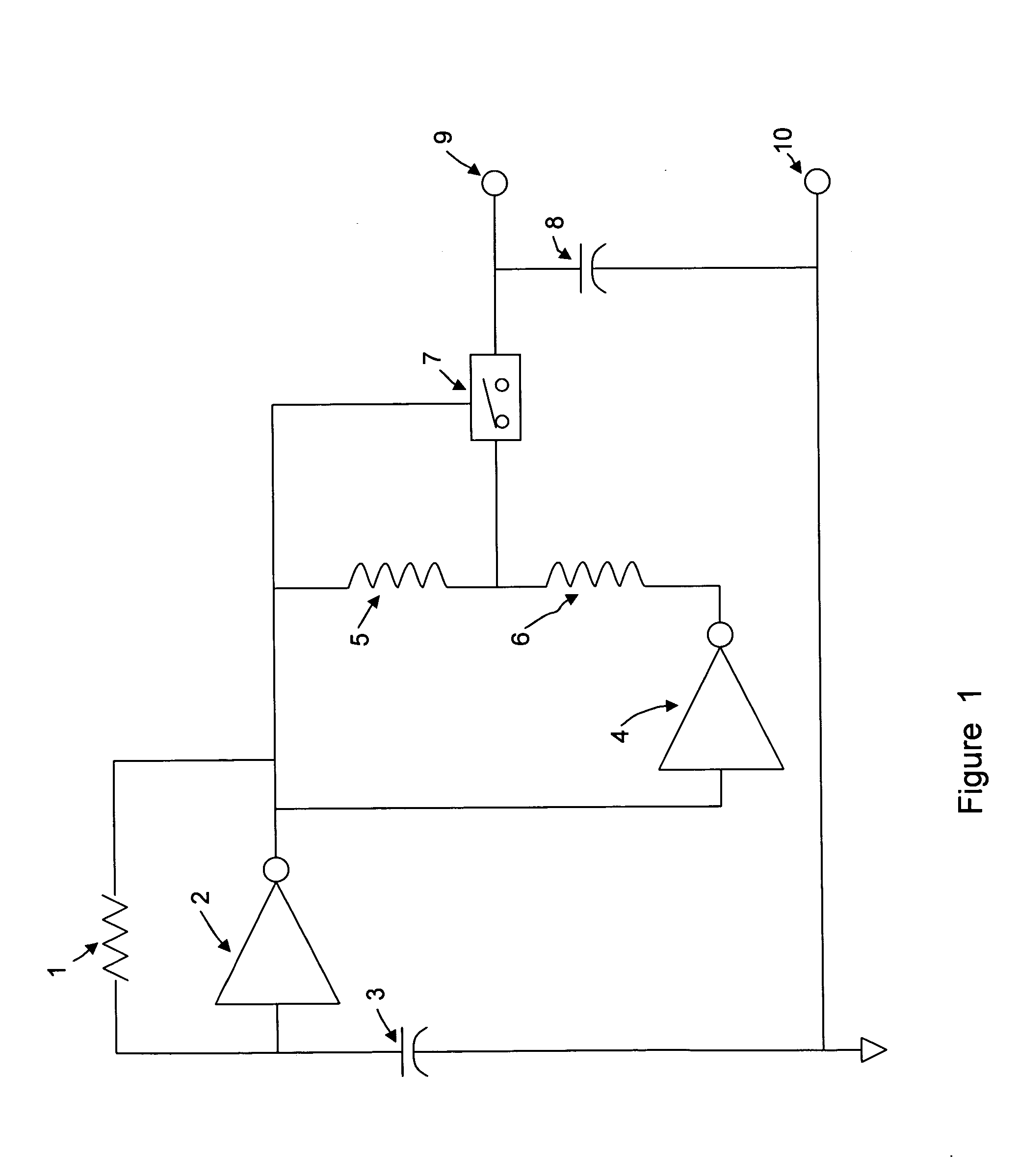

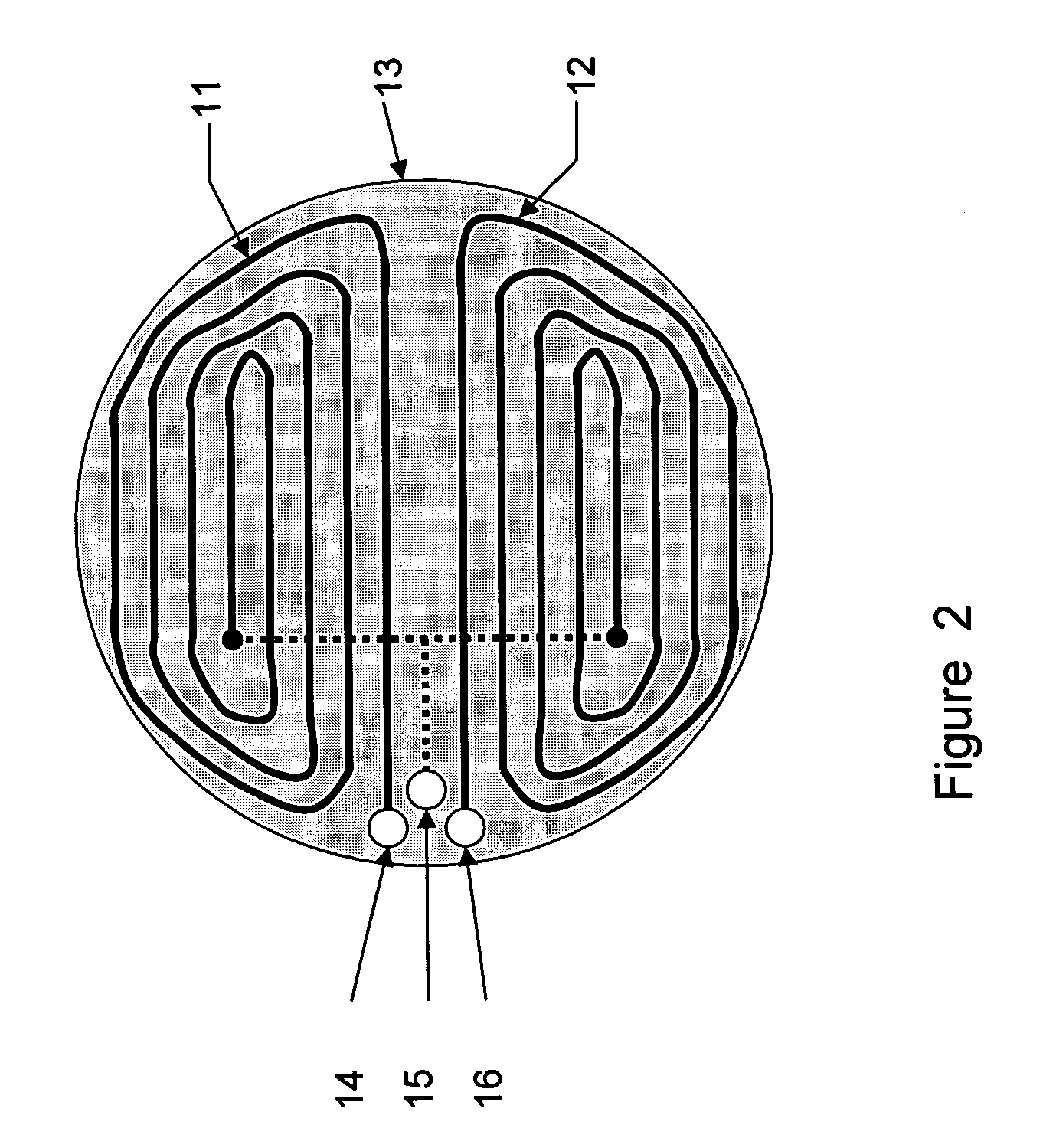

Simplified inductive position sensor and circuit configuration

ActiveUS20050253576A1Reduce errorsLess sensitivityUsing electrical meansConverting sensor output electrically/magneticallyPlanar substrateEngineering

Inductive position sensors and circuit configurations are disclosed for the measurement of linear, rotary, or curved position along a motion axis. The simplified sensor structures combine one or two parts of a movable core element with a simple planar substrate having first and second inductances connected in series. Movement of the core element in parallel to the planar substrate causing the impedance of at least one of the inductances to change. Simple circuit configurations are taught by which the impedance change is converted into a useful output signal that indicates position along the motion axis.

Owner:NYCE DAVID SCOTT

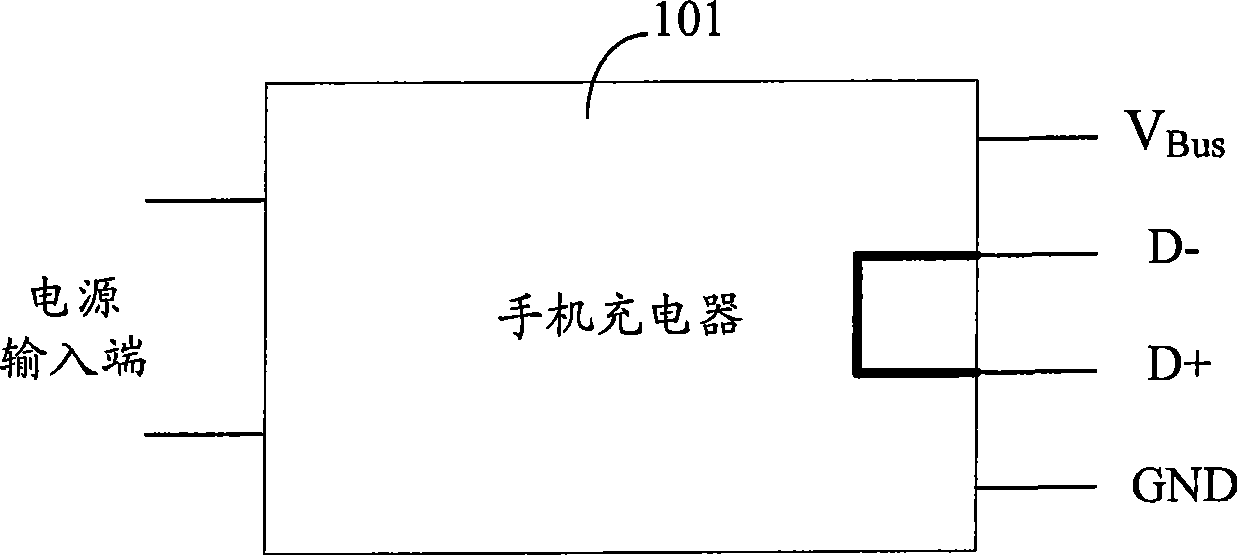

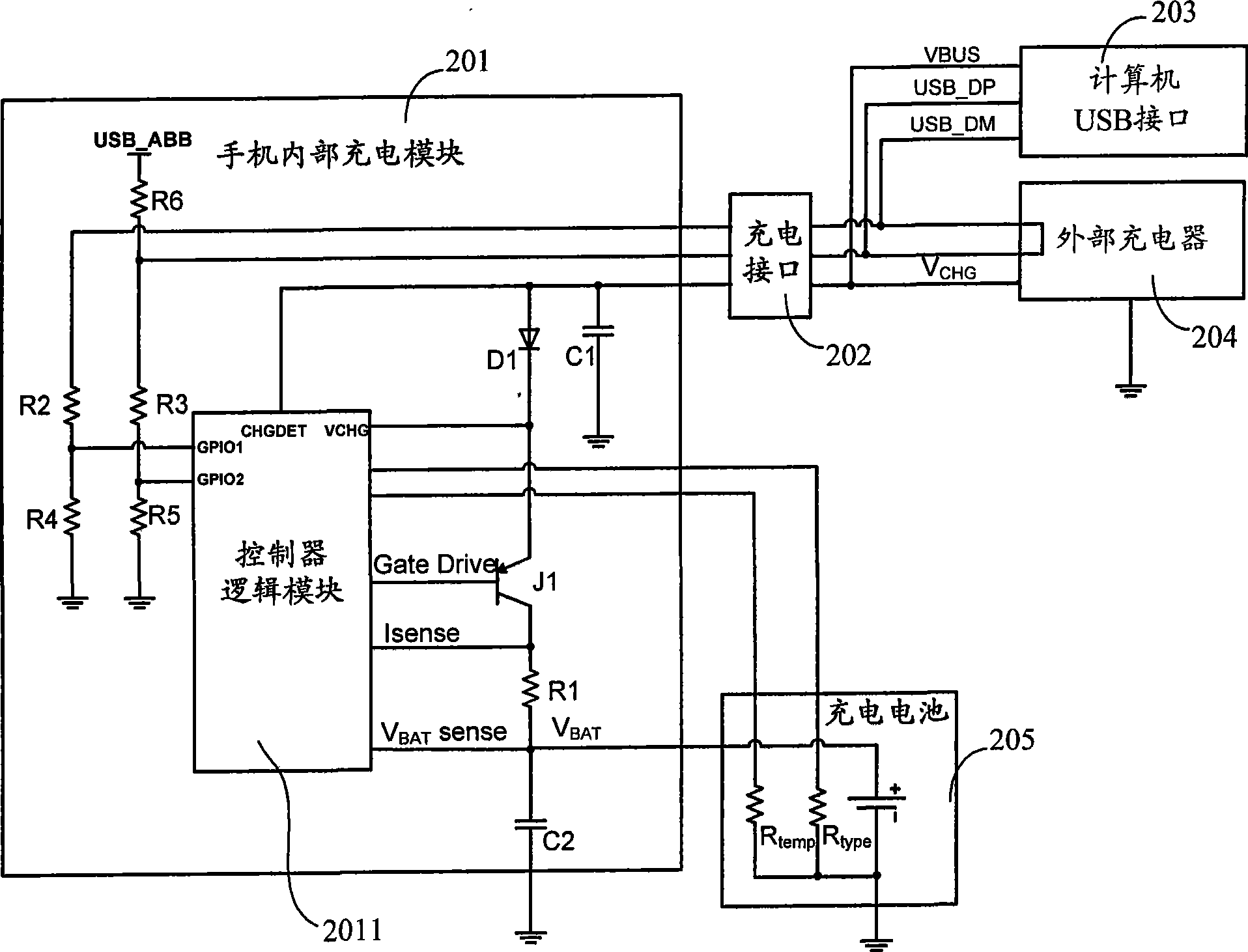

Device and method for terminal charger charging, USB charging and data communication

ActiveCN101383627AAvoid loadSimple structureRadio/inductive link selection arrangementsTransmissionSignal qualityUSB

The invention discloses a method for terminal charger charge, USB charge and data communication. The method includes the steps that a processor detects the triggering condition that the USB insertion interrupts and the charger insertion interrupts, if both interrupts are triggered, a charger is confirmed to be inserted in the terminal, and the charger charge process starts; if the condition that only the USB insertion interrupts is triggered, the condition that a USB data wire is inserted in the terminal is confirmed, the USB charge process starts, and USB data transmission is carried out. Meanwhile, the invention discloses a device for terminal charger charge, USB charge and data communication, which comprises a processor, a USB interface module and a selecting module, wherein the selecting module comprises a selecting end and two single input and double output switches. The invention provides users with a solution proposal that has the advantages of simple circuit structure, small resource occupation and great improvements of signal quality and data transmission reliability and integrates the functions of terminal charger charge, USB charge and data communication into a whole.

Owner:LEADCORE TECH

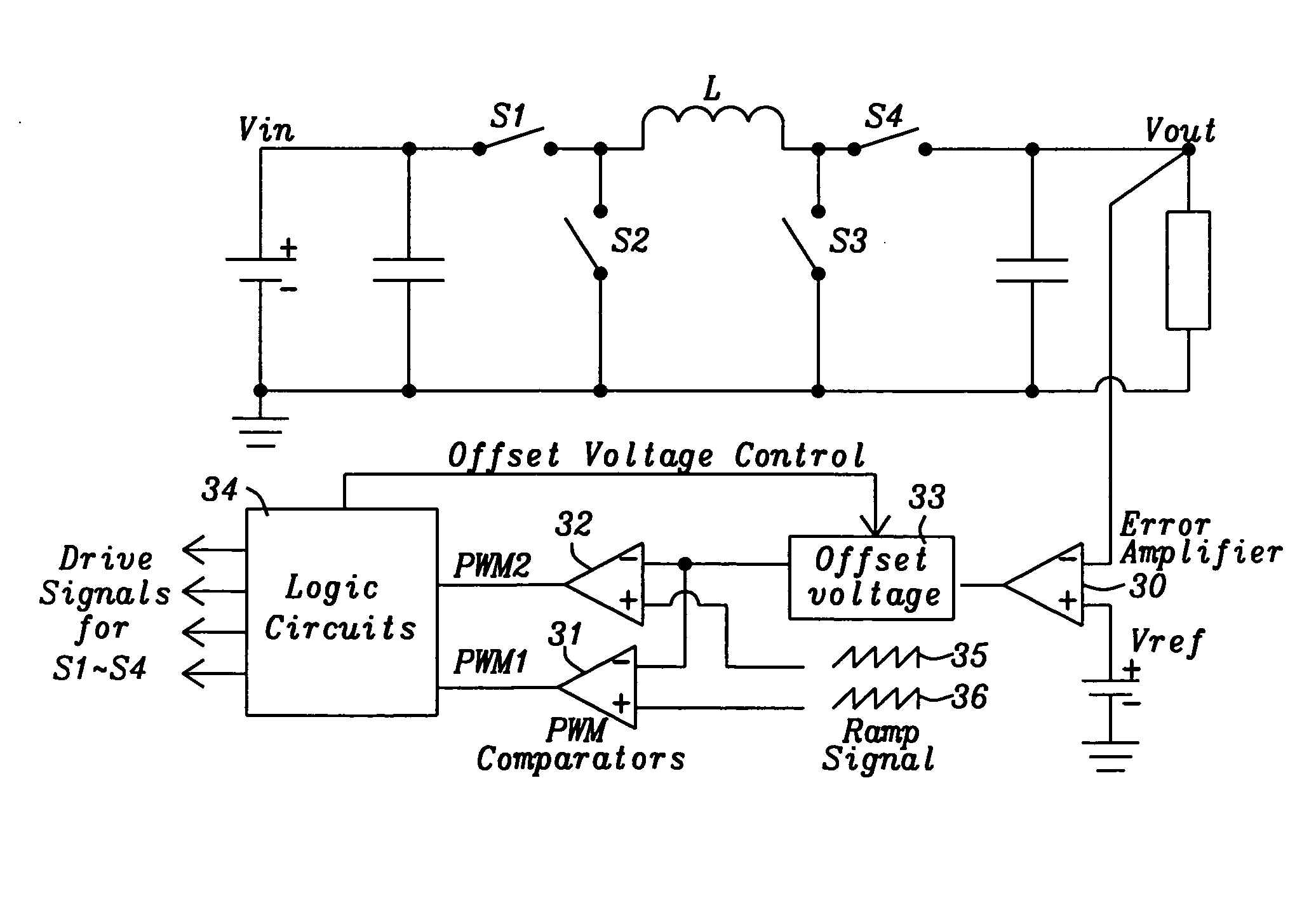

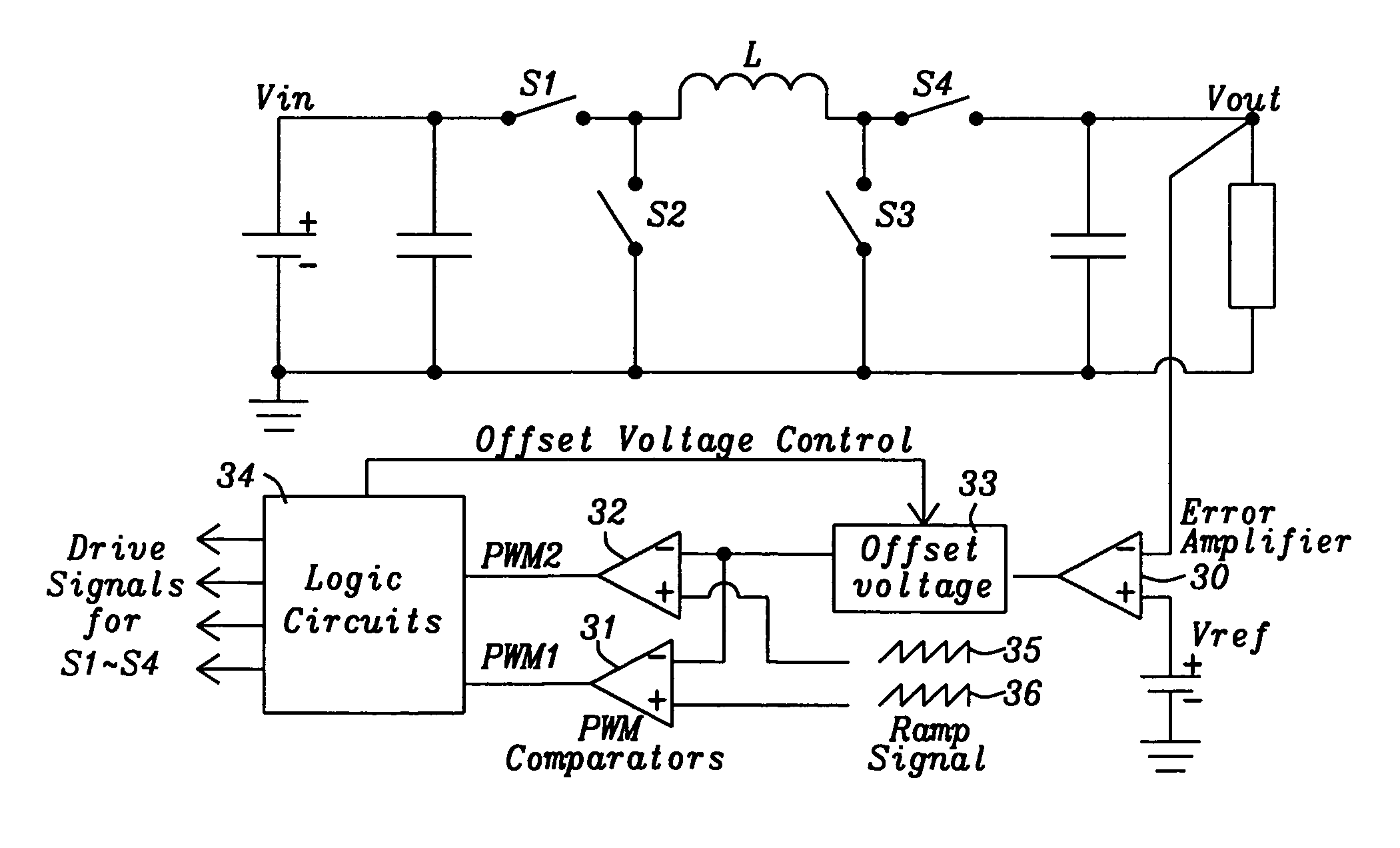

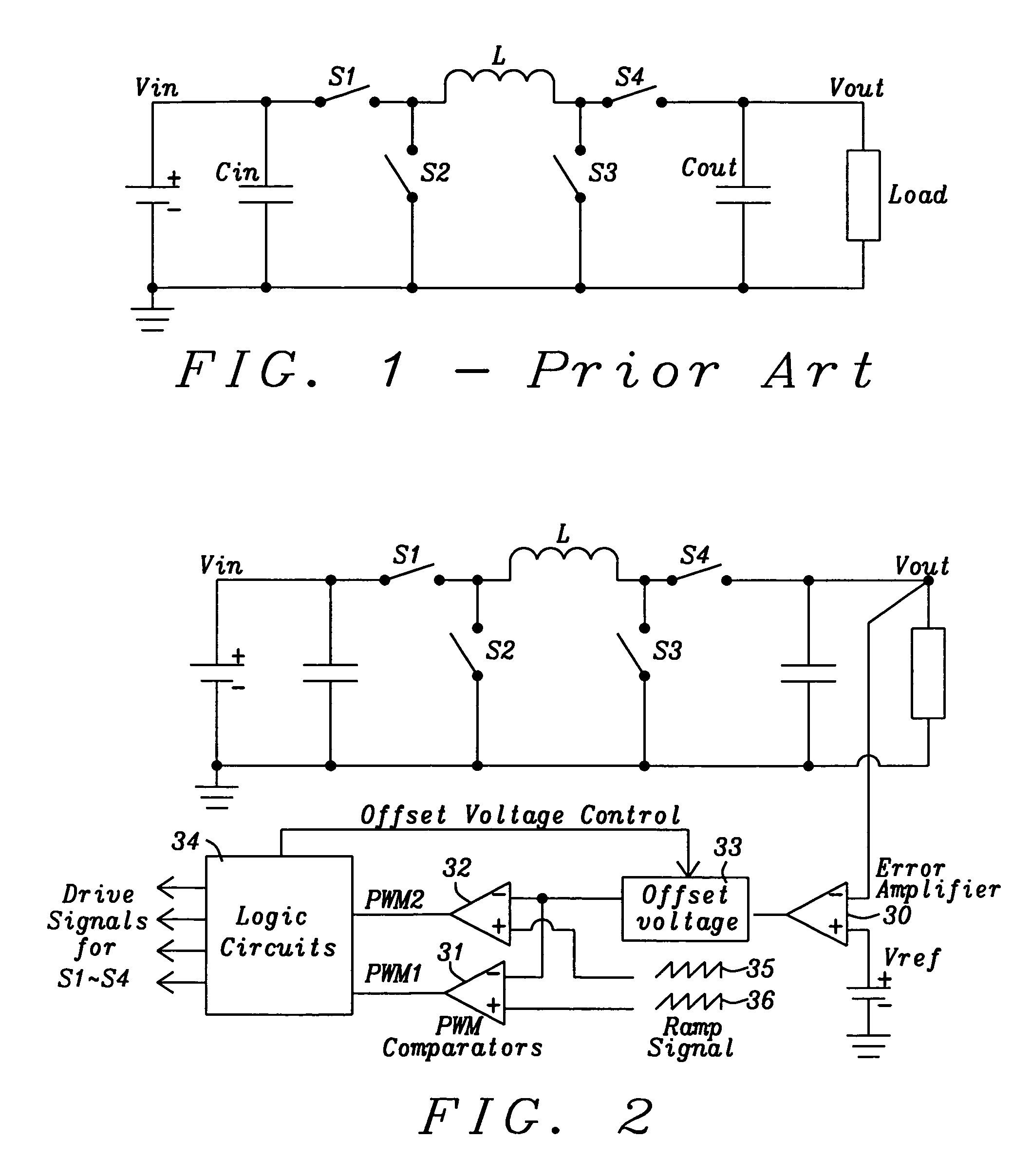

Circuit of high efficient buck-boost switching regulator and control method thereof

ActiveUS20120146594A1Improve efficiencyDc-dc conversionAc network voltage adjustmentSwitching frequencyEngineering

Owner:DIALOG SEMICONDUCTOR GMBH

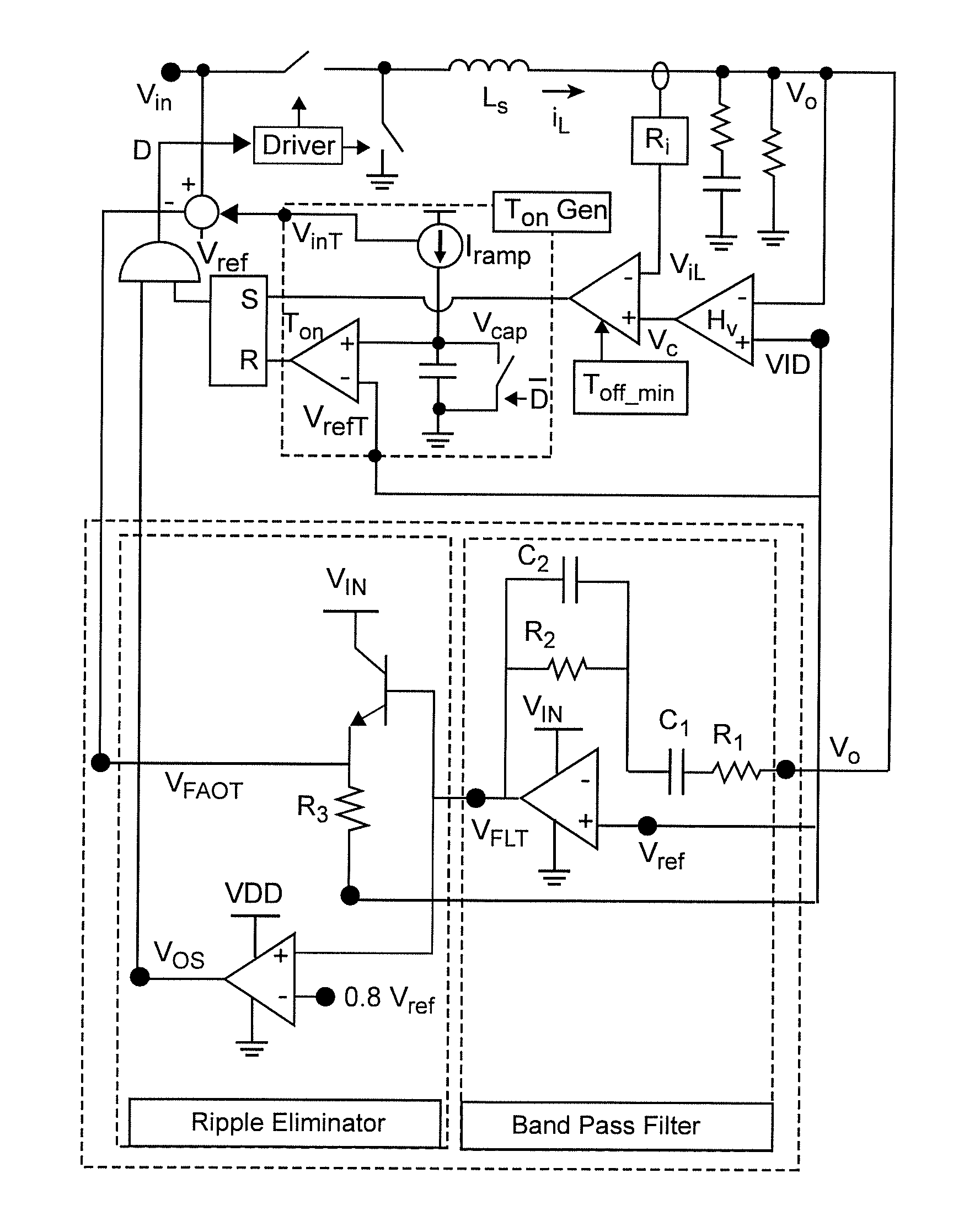

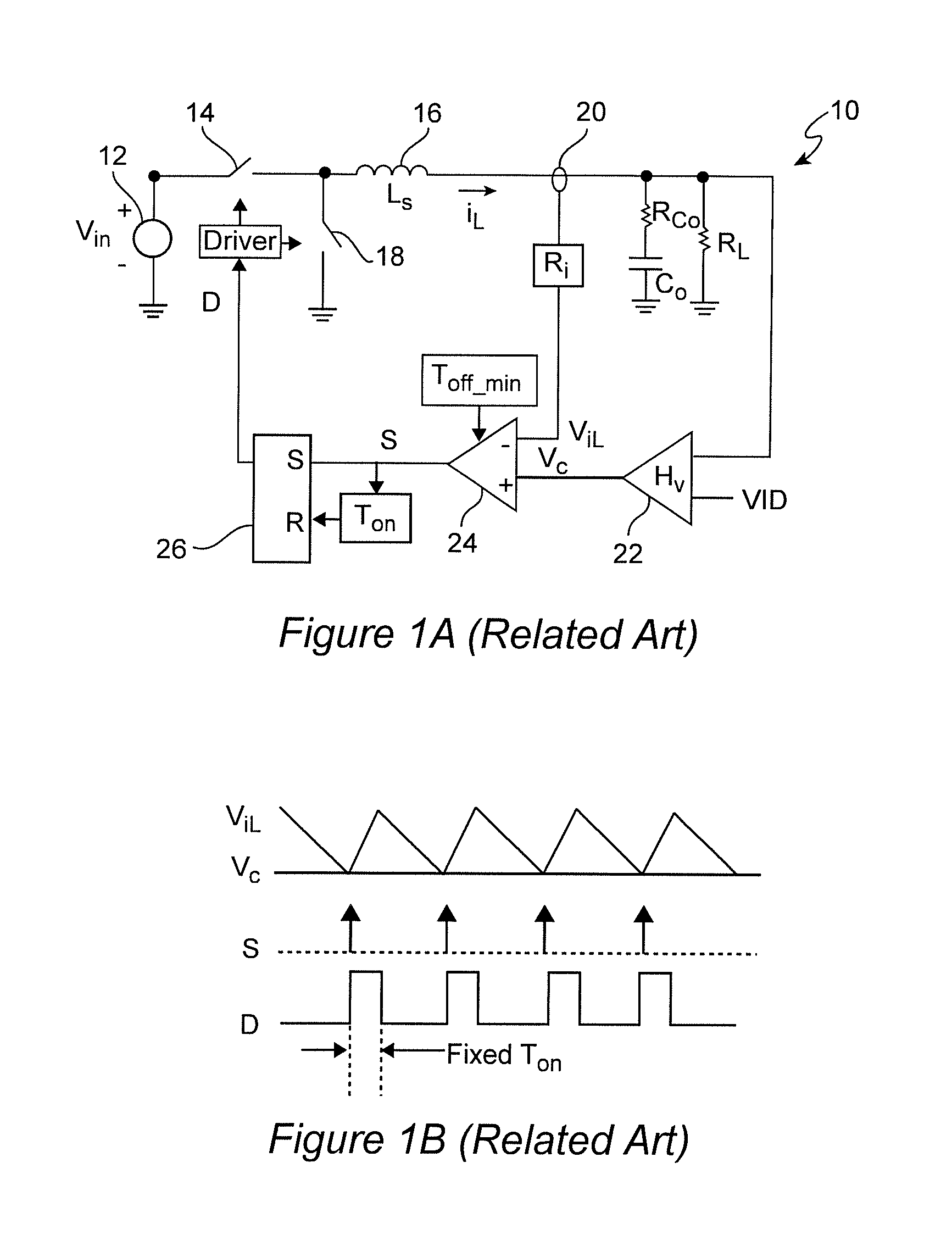

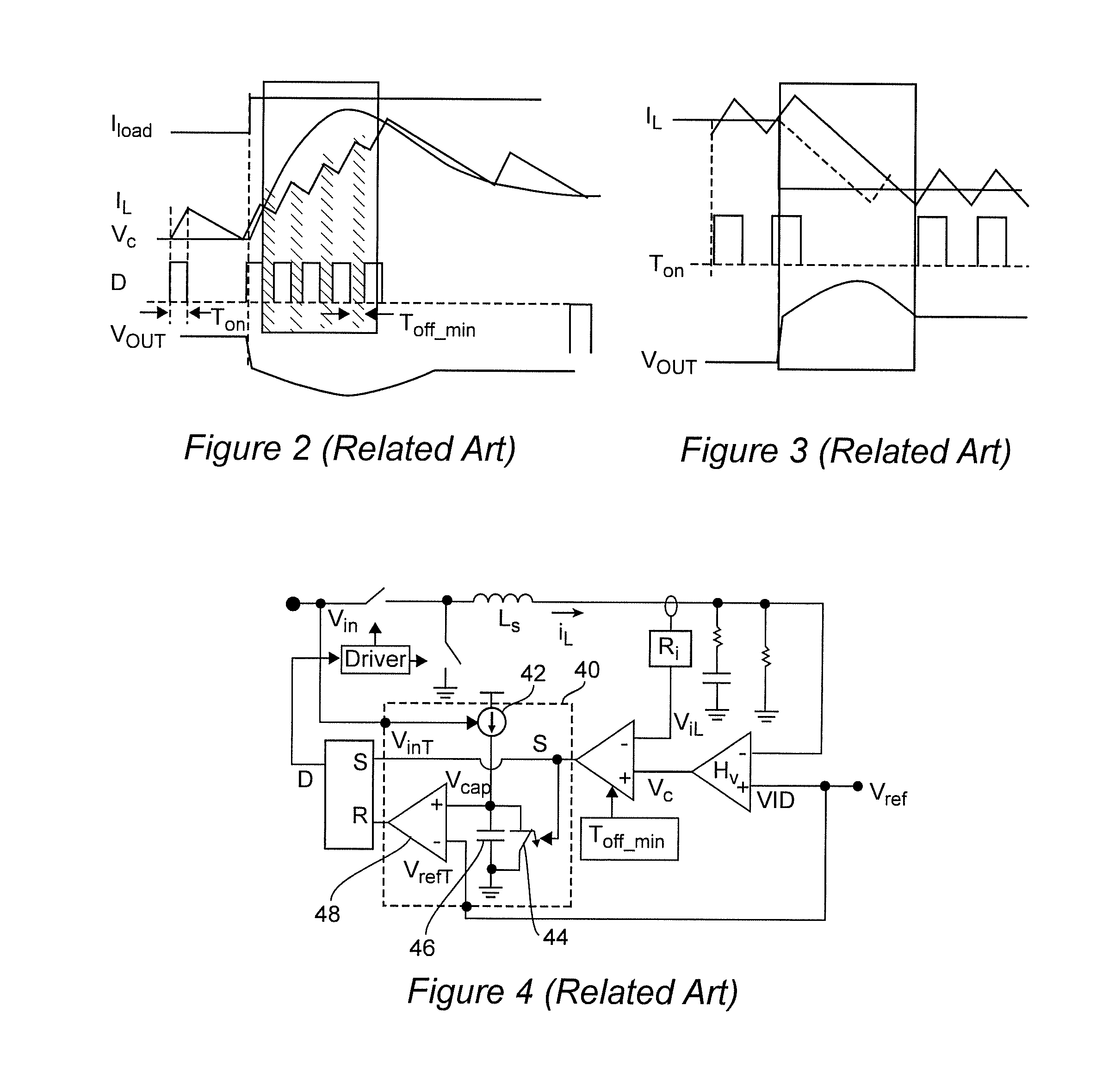

Transient Performance Improvement for Constant On-Time Power Converters

ActiveUS20150280556A1Transient response of powerIncreased and decreasedDc-dc conversionElectric variable regulationCapacitanceElectrical polarity

Response of a variable frequency switching constant on-time or adaptive on-time controlled power converter to a large step-up or step-down change in load is improved with a simple circuit that detects magnitude and polarity of a change in output voltage and initiates, extends or terminates conduction of power pulses from an input source through said power converter. Both the amplitude and duration of undershoot or overshoot of the transient response are reduced or, alternatively, the capacitance of an output filter may be significantly reduced and still provide comparable transient performance. The fast adaptive on-time control is applicable to multi-phase power converters using phase managers or one or more phase-locked loops for interleaving of power pulses.

Owner:VIRGINIA TECH INTPROP INC

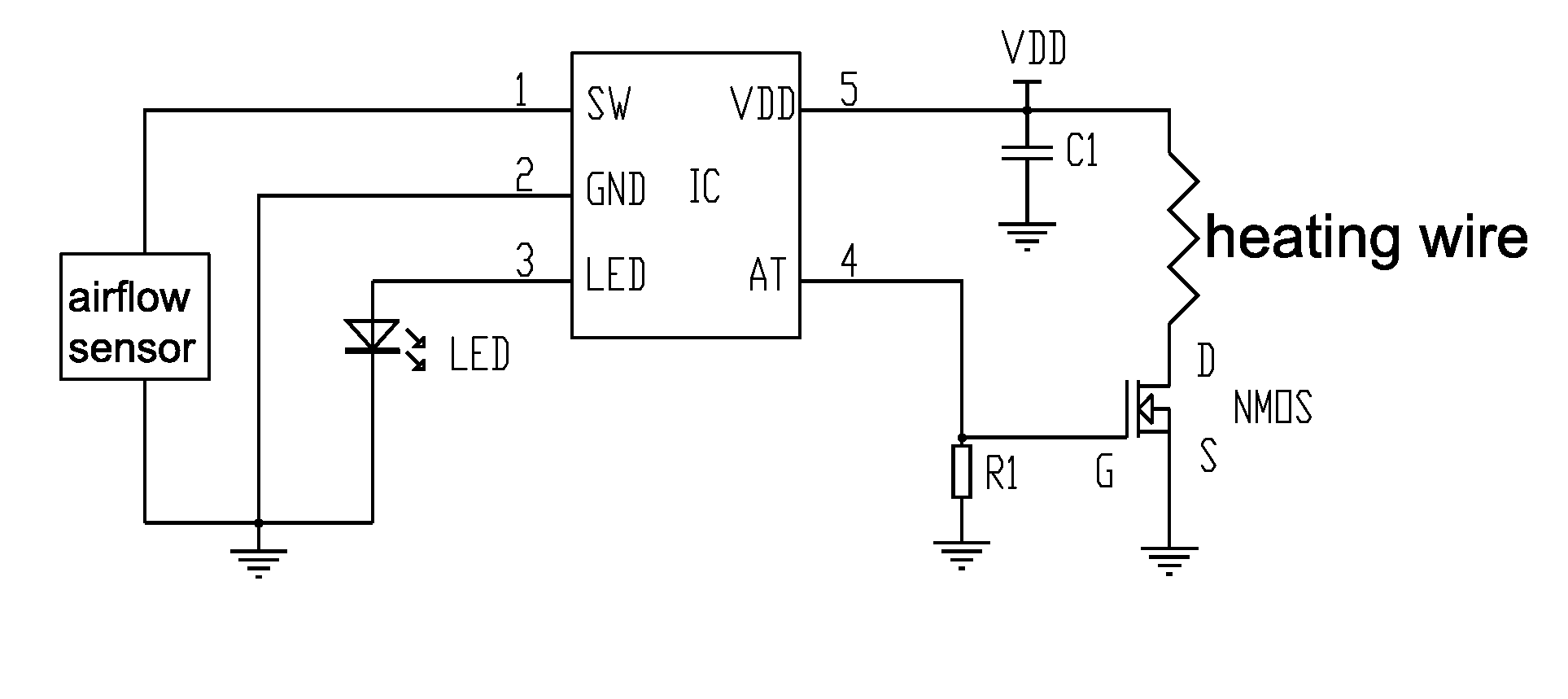

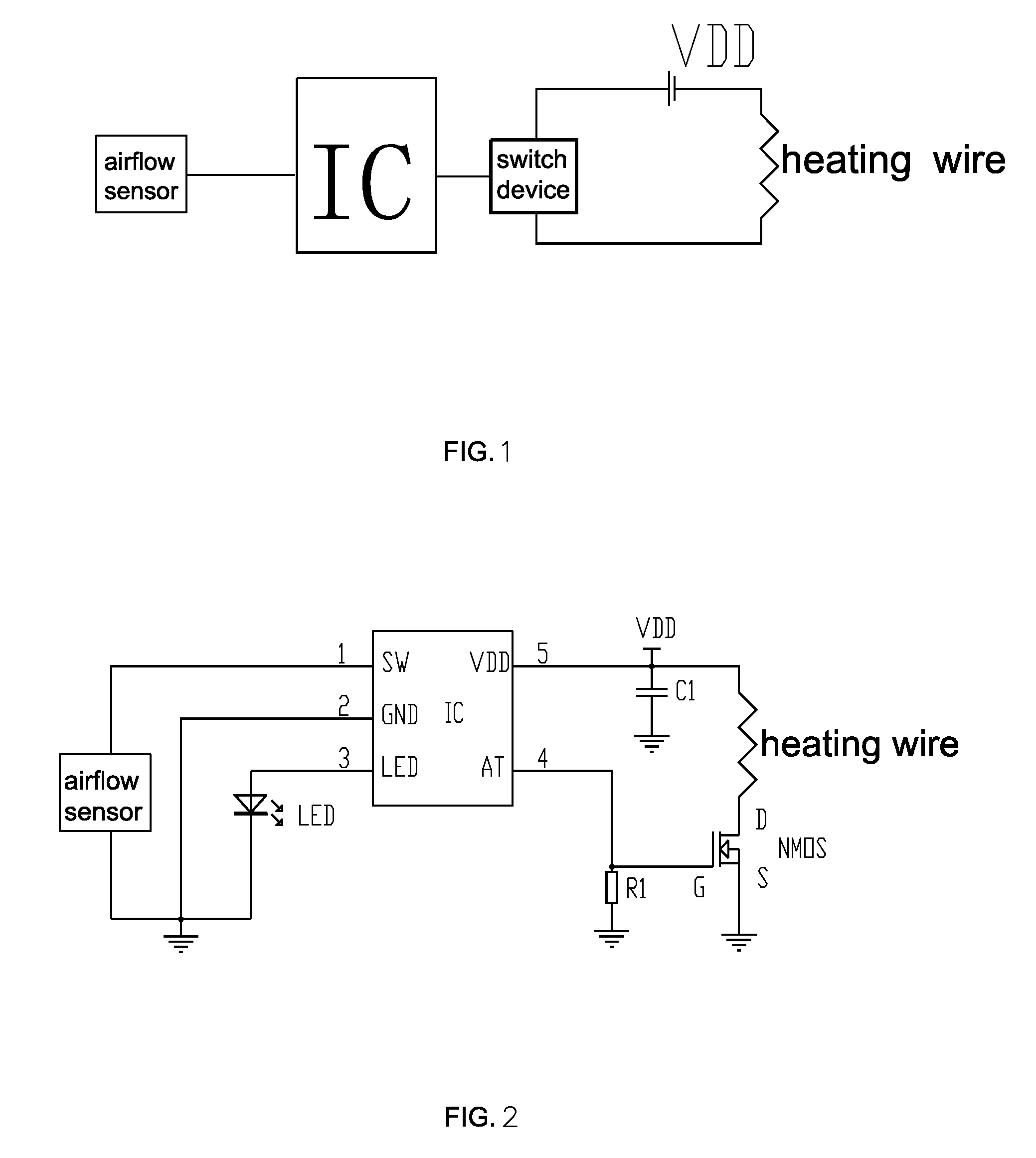

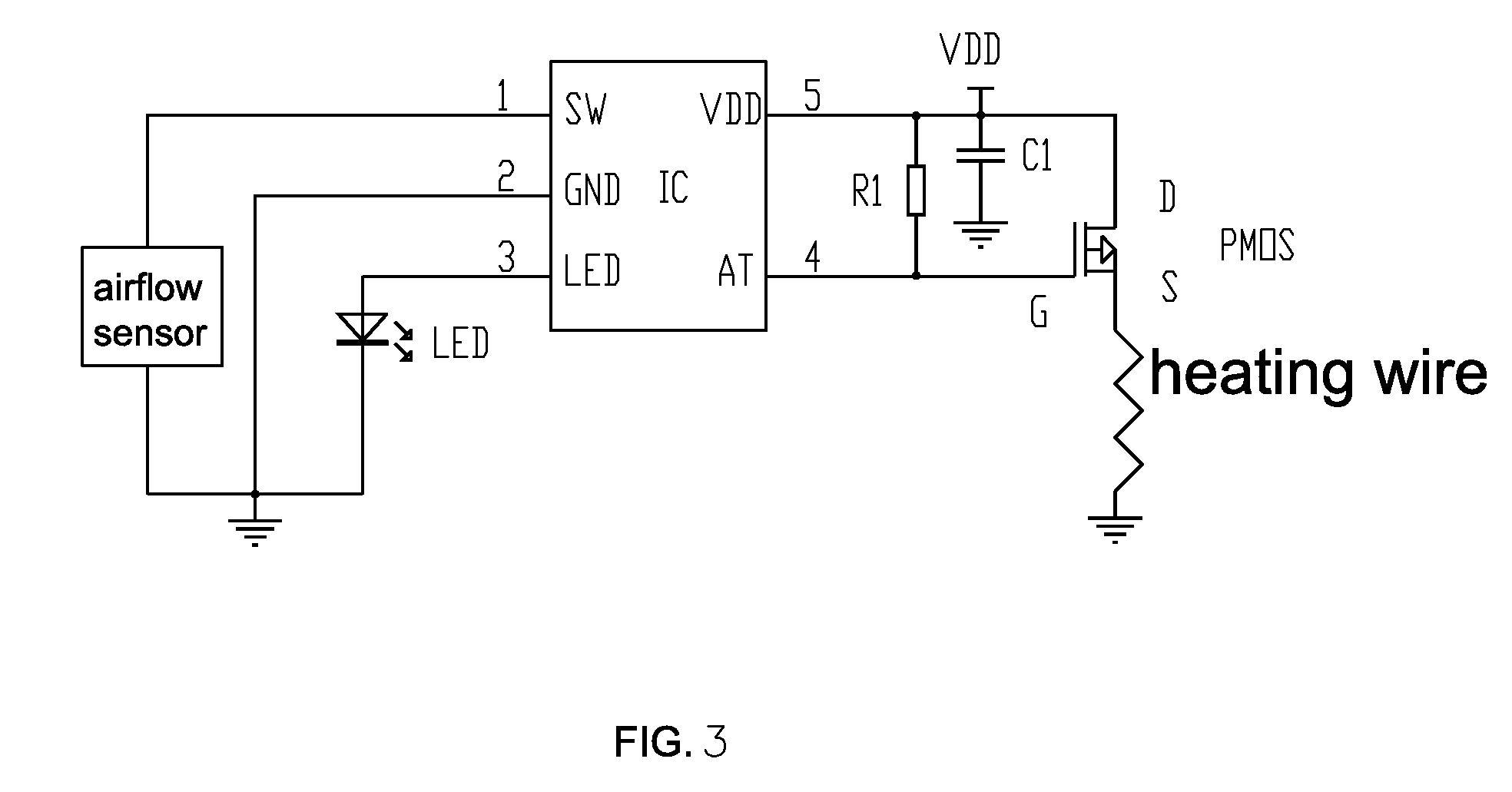

Electronic cigarette circuit

InactiveUS9060388B2High power outputReduce the amount of solutionTobacco devicesOhmic-resistance heatingHotlineEngineering

This invention discloses an electronic cigarette circuit, including an IC, an airflow sensor connected to the IC, a heating wire and a power supply VDD connected to the IC and the heat wire, the electronic cigarette circuit further including a switch device, the switch device being connected with the heating wire and the power supply VDD to form a circuit loop. The electronic cigarette circuit of the present invention adopts a switch device placed outside the IC, and the IC, the heating wire and the power supply form the circuit loop, so as to achieve high power output to the heating wire, and a large amount of smoke, with a simple circuit structure for ease mass production.

Owner:HUIZHOU KIMREE TECH

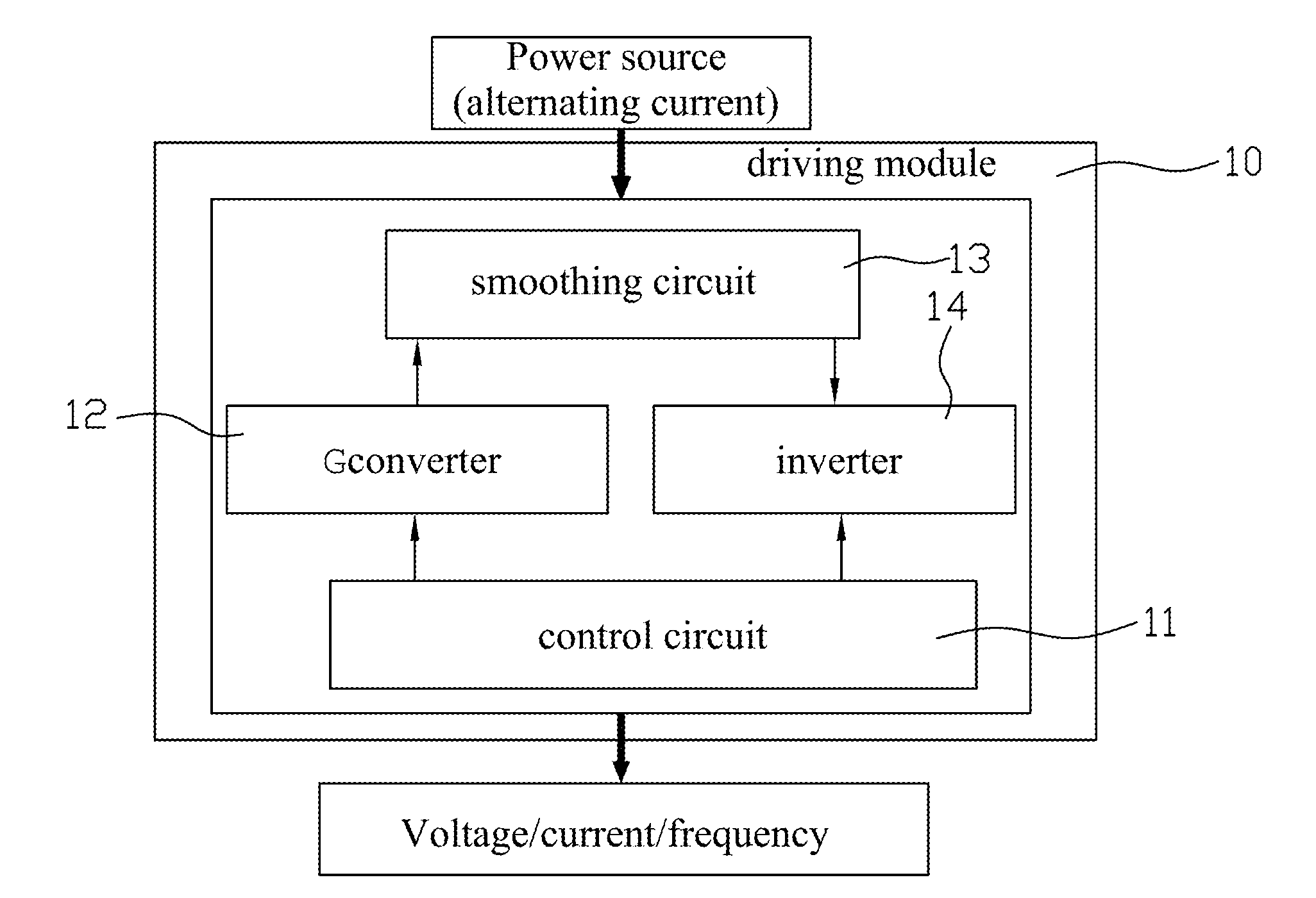

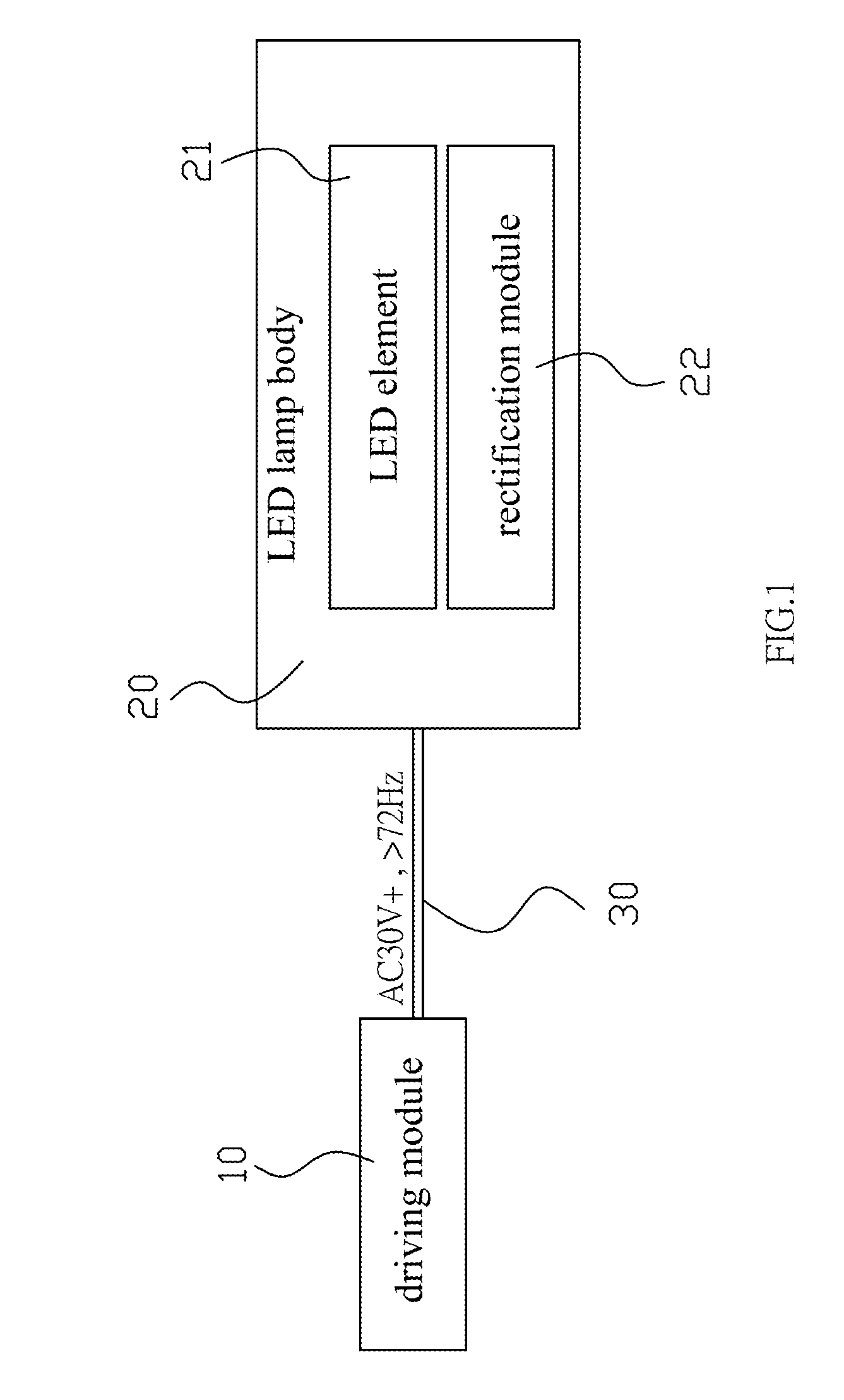

Light emitting diode illumination device and method for controlling electric current

InactiveUS20110006703A1Effectively improving the flicker phenomenonIncrease light sourceElectrical apparatusElectroluminescent light sourcesElectric power transmissionEngineering

A light emitting diode (LED) illumination device utilizes a power transmission line to electrically connect a driving module and at least one LED lamp body. The driving module outputs a high frequency alternating power having above 30 voltages and above 72 Hz frequencies through frequency modulation. Each LED lamp body has at least one LED element and a rectification module. The high frequency alternating power generated from the driving module is modulated by the rectification module into a direct power to drive the LED element. Accordingly, the flicker phenomenon on the light source can be effectively improved, and the filter component installed inside each LED lamp body can be omitted. A simple circuit is used to reliably drive the LED element to achieve goals of rapidly developing products and saving costs.

Owner:LEXTAR ELECTRONICS CORP

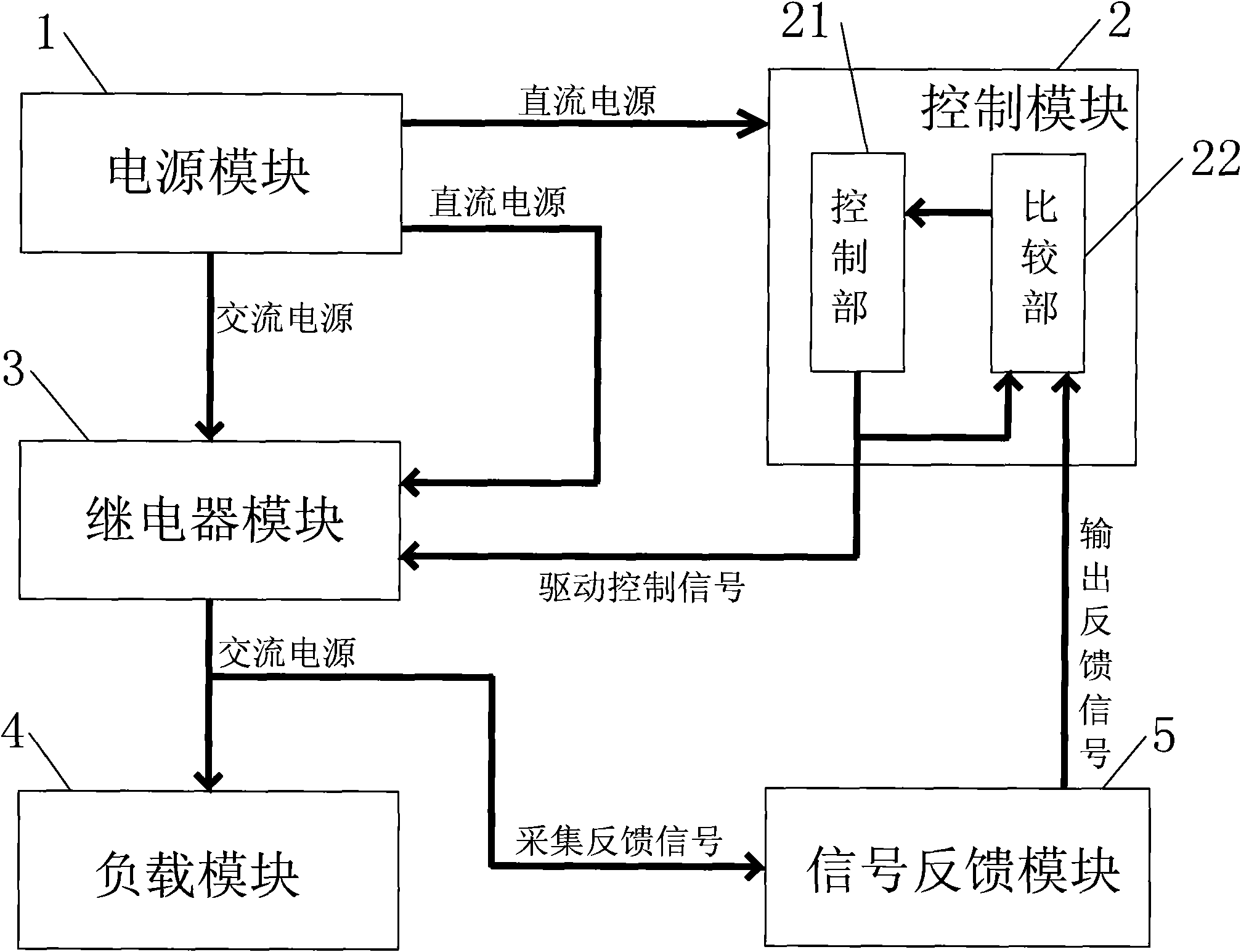

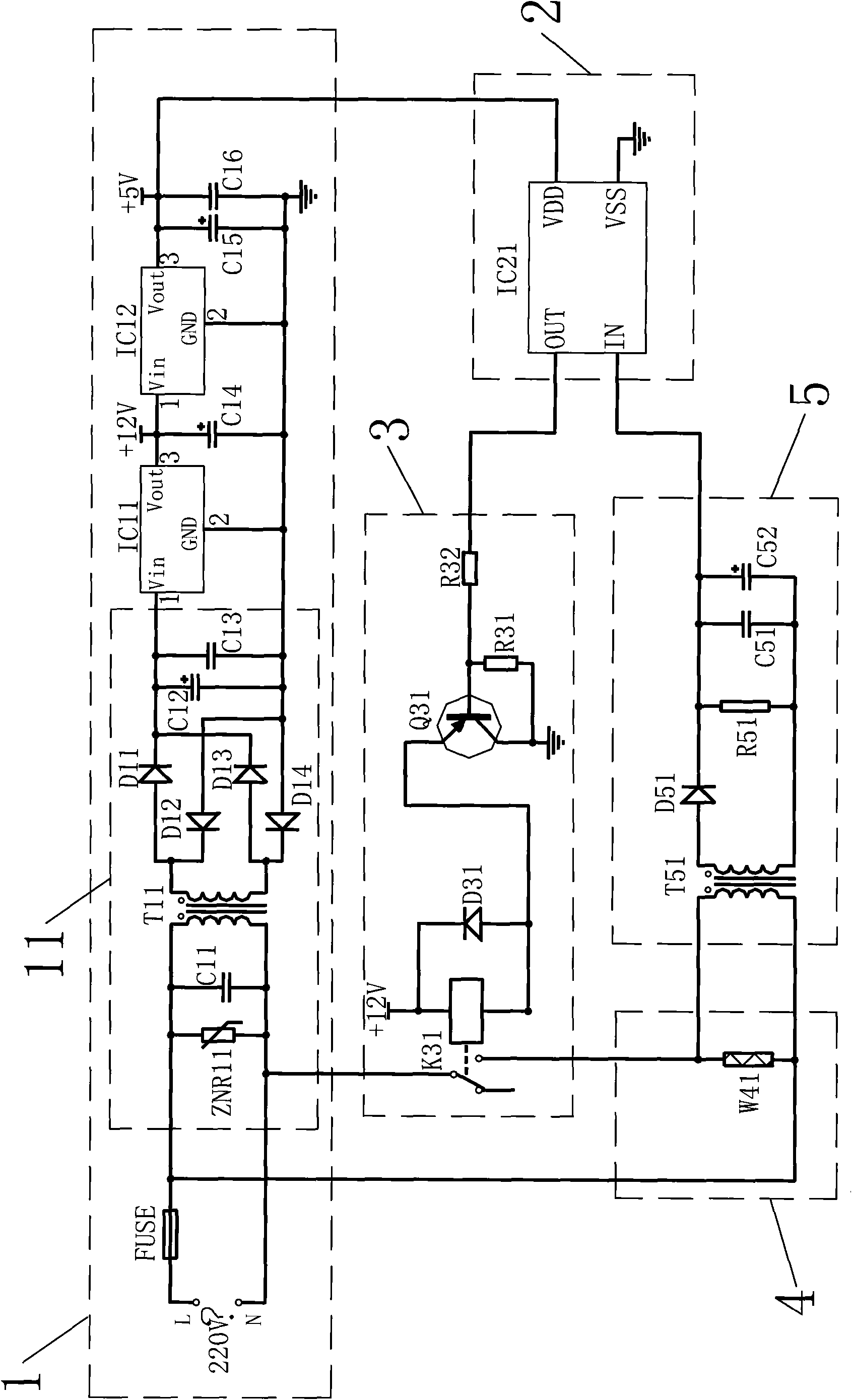

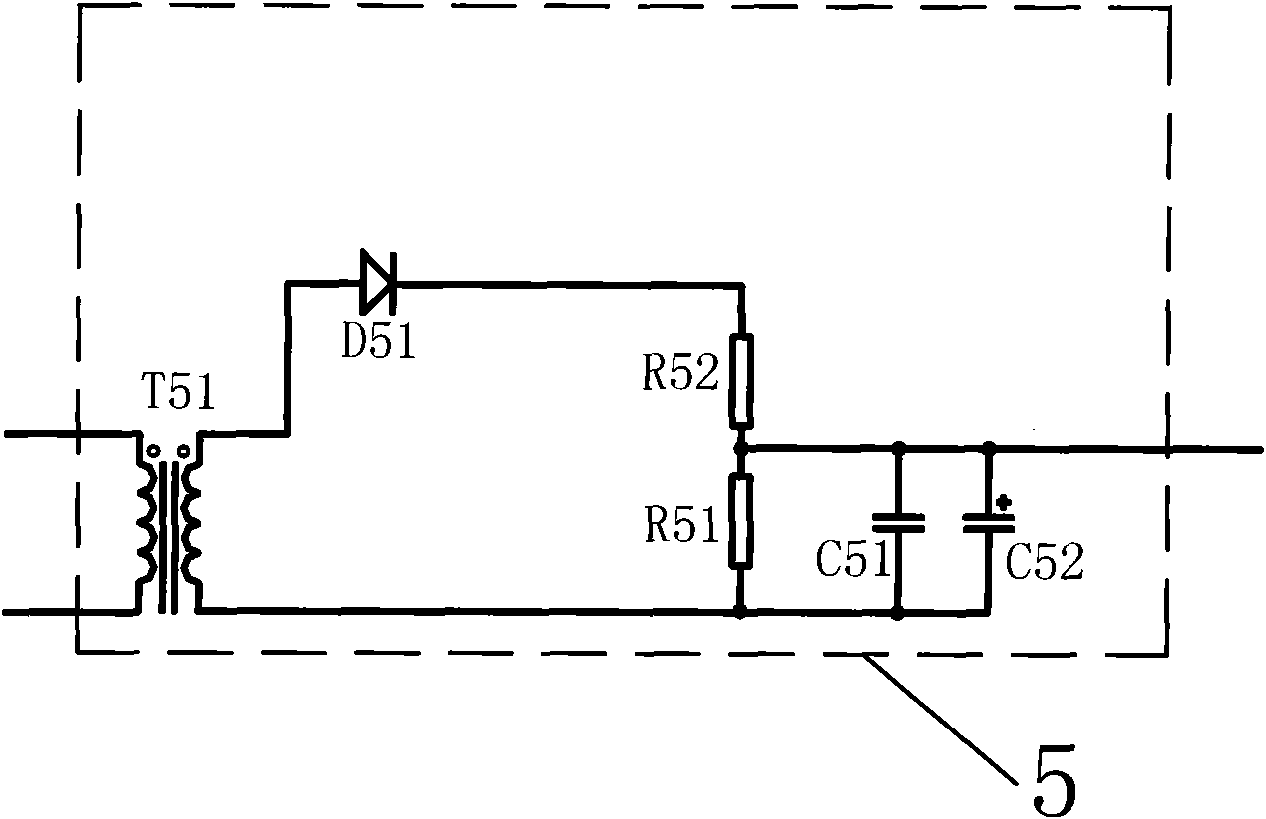

Relay fault detecting circuit

The invention discloses a relay fault detecting circuit belonging to the field of relays and comprising a power supply module which can provide a low-voltage DC power supply and a high-voltage AC power supply, a relay module, a control module and a signal feedback module, wherein the control module and the relay module are respectively provided with the low-voltage DC power supply by the power supply module; the control module is connected with the control end of the relay module, and the connecting and disconnecting of the switching end of the relay module is controlled by a driving control signal of the control module; one end of the switching end of the relay module is connected with the output end of the high-voltage AC power supply of the power supply module, and the other end is a load connecting end which is connected with the control module through a signal feedback circuit; and the control module is used for detecting and controlling the fault of the relay module through comparing the driving control signal with a feedback signal. The invention can judge the fault that a relay cannot be connected or disconnected, can simultaneously detect faults of a plurality of relays and has simple circuit design and convenient use.

Owner:MIDEA GRP CO LTD

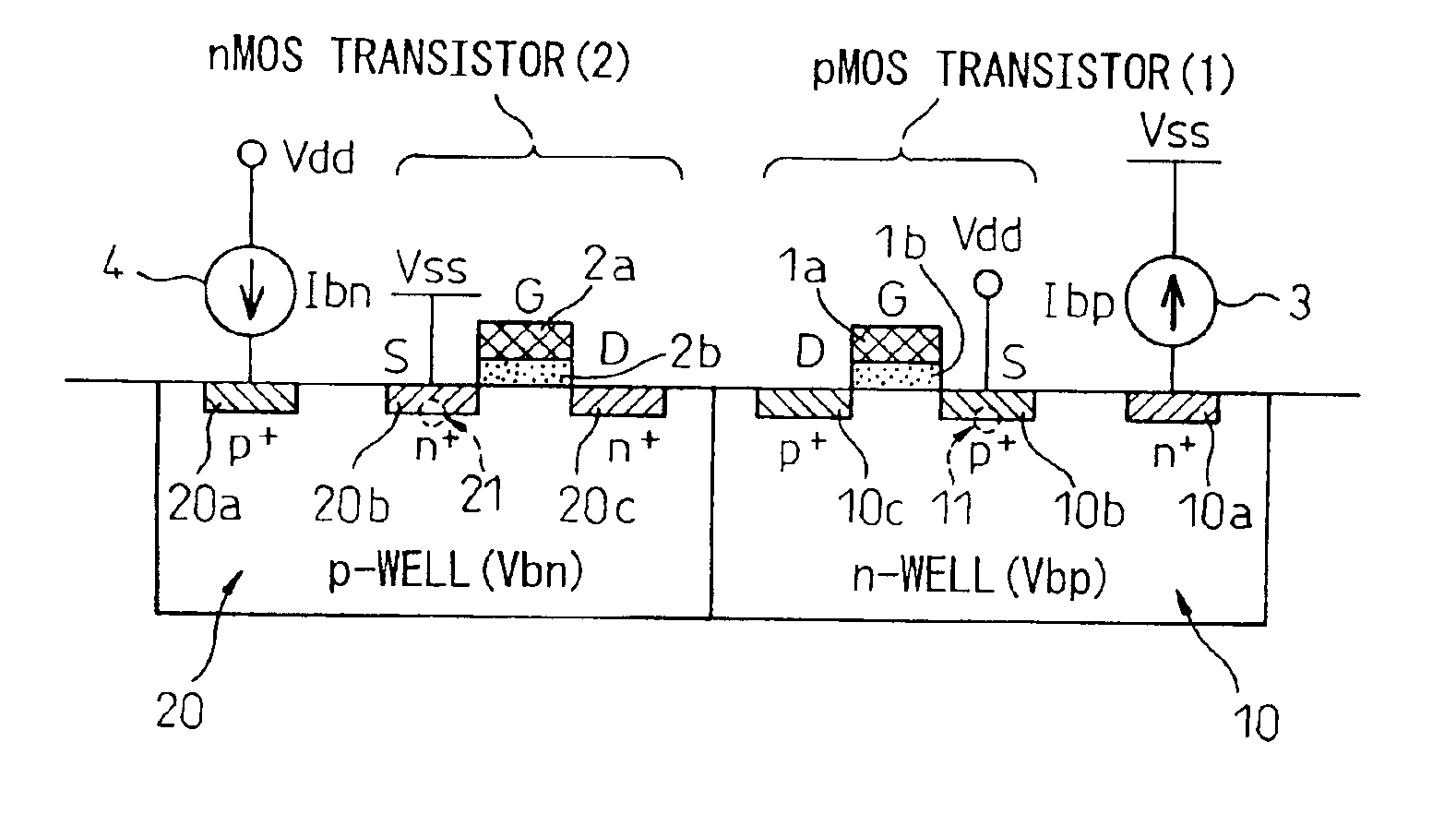

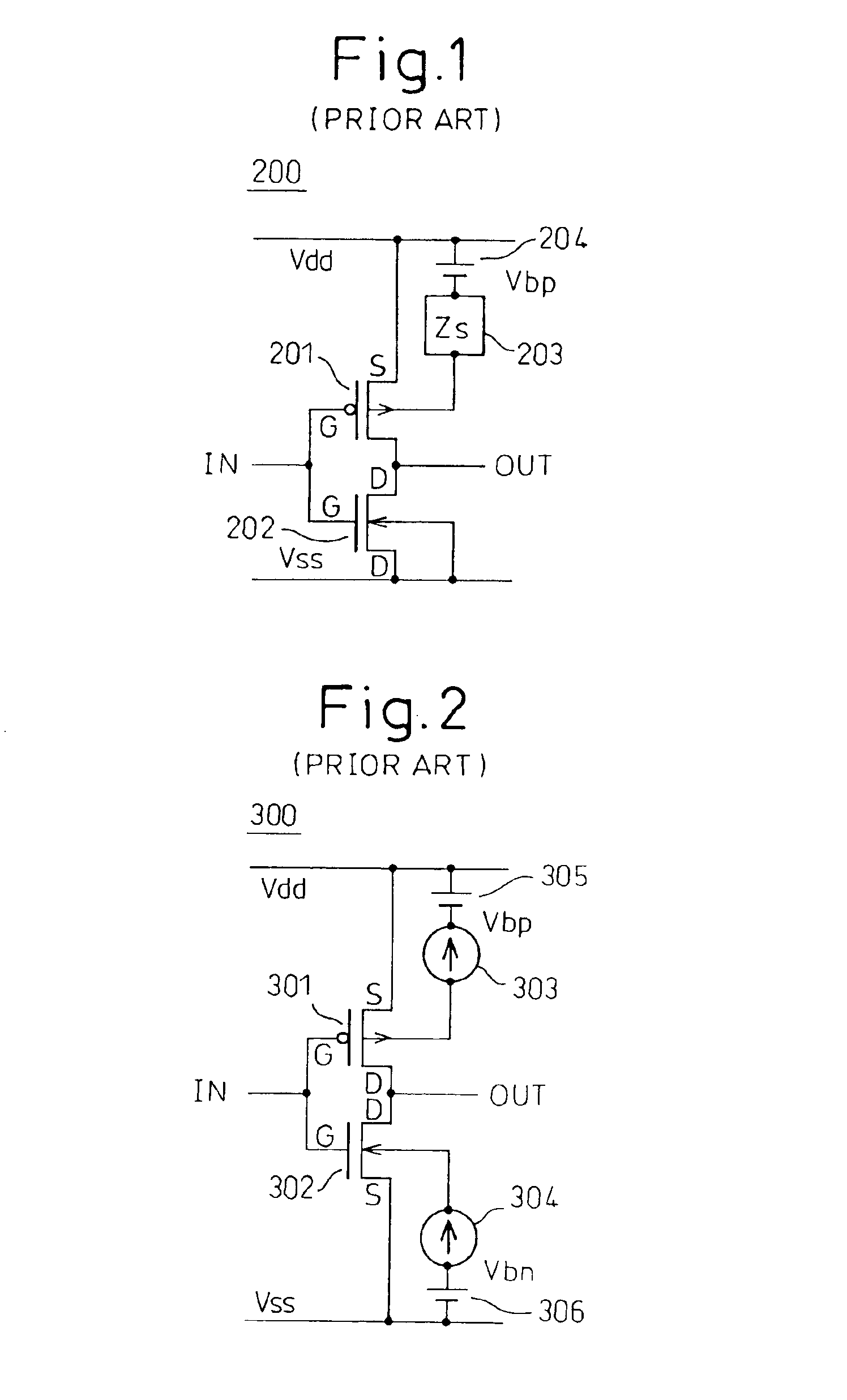

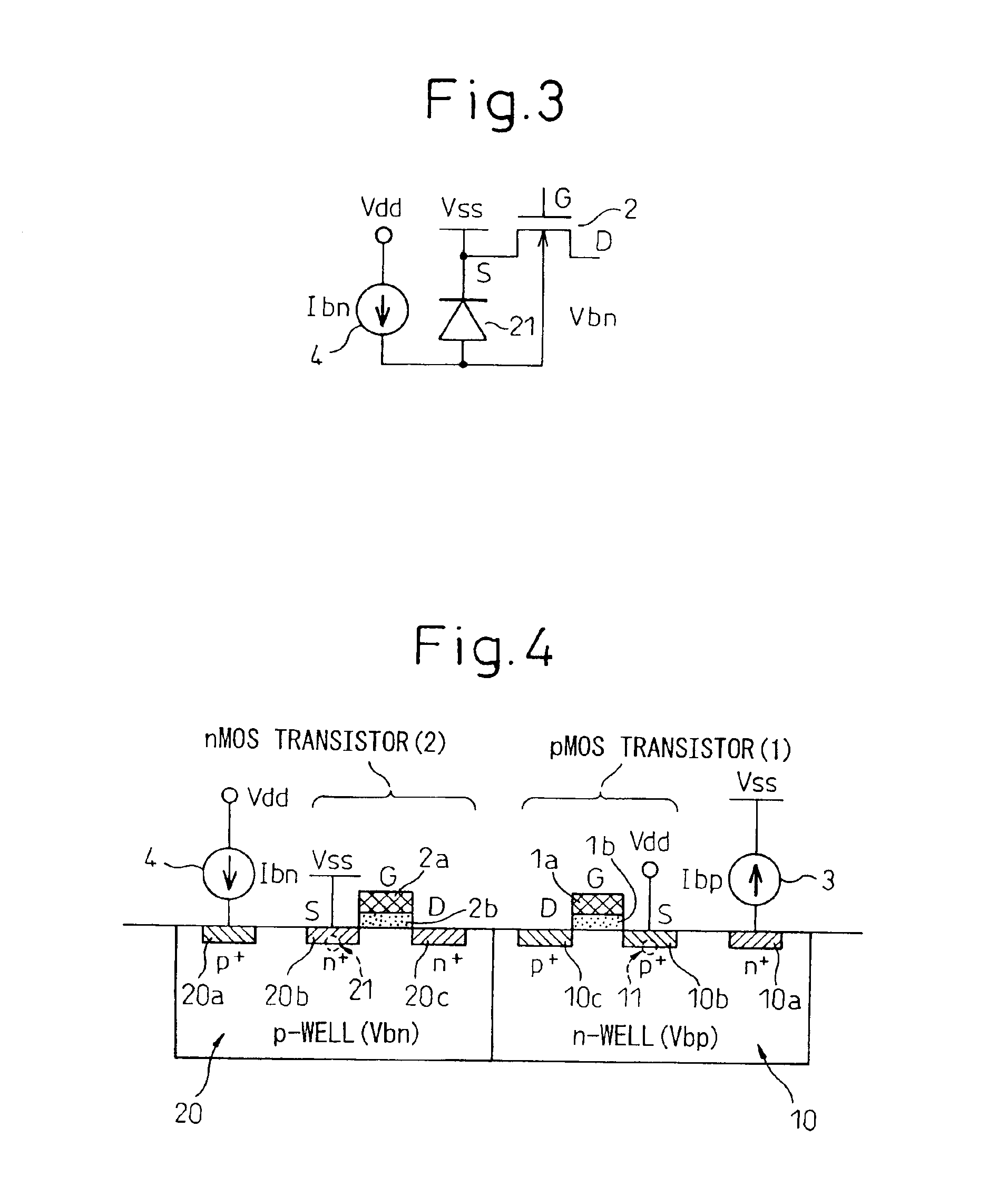

Semiconductor integrated circuit device having body biasing circuit for generating forward well bias voltage of suitable level by using simple circuitry

InactiveUS6864539B2Simple circuitTransistorSwitching accelaration modificationsSemiconductorSimple circuit

A semiconductor integrated circuit device has a MISFET and a body biasing circuit. The MISFET has a source electrode and a drain electrode of a first conductivity type and a gate electrode, and the MISFET is formed in a well of a second conductivity type. The body biasing circuit generates a voltage in the well by passing a prescribed current in a forward direction into a diode which is formed from the well and the source electrode of the MISFET.

Owner:RENESAS ELECTRONICS CORP

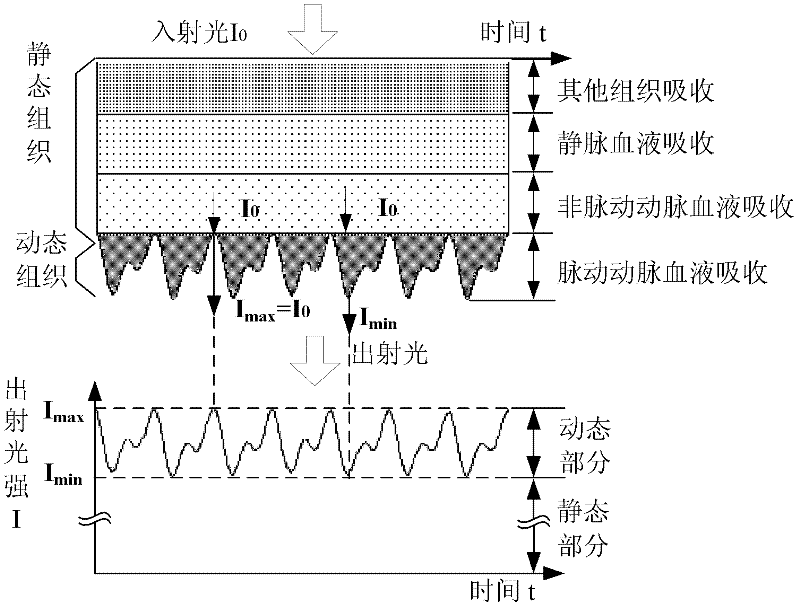

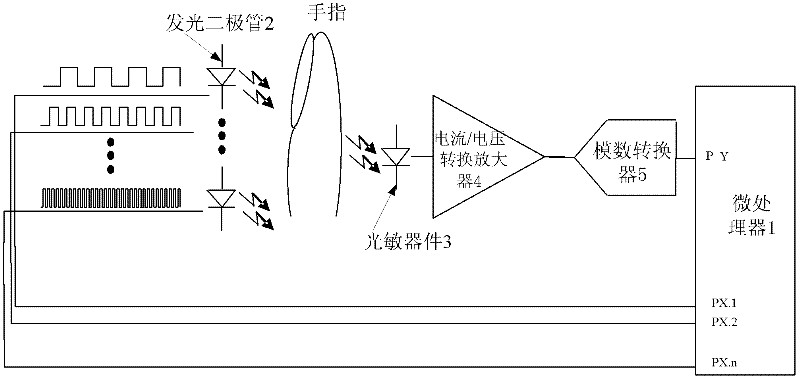

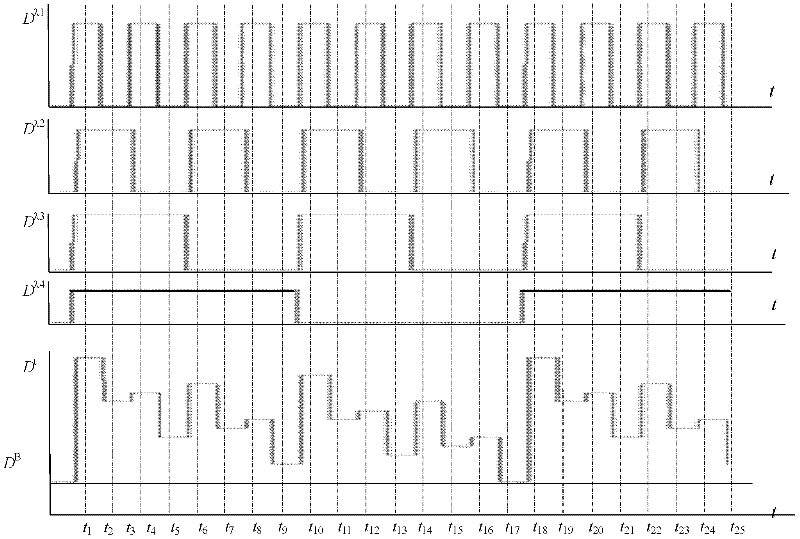

Device and method for measuring square wave modulated photoelectric volume pulse wave

ActiveCN102389313AAccurate measurementNo need to debugCatheterDiagnostic recording/measuringMeasurement devicePeak value

The invention discloses a device and a method for measuring square wave modulated photoelectric volume pulse wave. A microprocessor outputs square waves which have different frequencies and form a double ratio relationship; the square waves drive at least two light-emitting diodes; the light from the light-emitting diodes are received by a photosensitive device after passing through tested finger; the photosensitive device converts the light into a voltage signal; the voltage signal is converted into a predefined amplitude value voltage signal by a current / voltage conversion amplifier; an analogue-to-digital converter converts the predefined amplitude value voltage signal into a digital signal; the microprocessor processes the digital signal to obtain photoelectric volume pulse wave and valley value and peak value thereof, and gets spectrum value by the valley value and the peak value. The measurement method comprises the following steps of: separating the digital signal to obtain the photoelectric volume pulse wave and removing interference of background light by the microprocessor; getting the valley value and the peak value according to the photoelectric volume pulse wave; and calculating the valley value and the peak value to obtain light absorbance difference, and obtaining the spectrum value by the light absorbance difference. The accurate measurement, simple circuit and low cost are realized.

Owner:TIANJIN UNIV

Secondary battery protection circuit, battery pack and thermosensitive protection switch device

InactiveUS7952330B2Avoid feature degradationReduced characteristicsSecondary cellsElectric powerSimple circuitBattery pack

A protection circuit is provided for protecting a secondary battery from overcharging and excessive discharge current by a simple circuit. The protection circuit is provided with a connection terminal (T3) for connecting the secondary battery (6); a connection terminal (T1) for connecting a charging device for charging the secondary battery (6) and / or a load device driven by a discharge current from the secondary battery (6); a bimetal switch (SW1) that is provided between the connection terminals (T1, T3) and turned off in the case of exceeding a specified temperature set beforehand; a heater (R2) for heating the bimetal switch (SW1); and an integrated circuit (IC1) for turning the bimetal switch (SW1) off by causing the heater (R2) to generate heat if a voltage applied to the connection terminal (T3) by the secondary battery (6) exceeds a preset reference voltage.

Owner:PANASONIC CORP

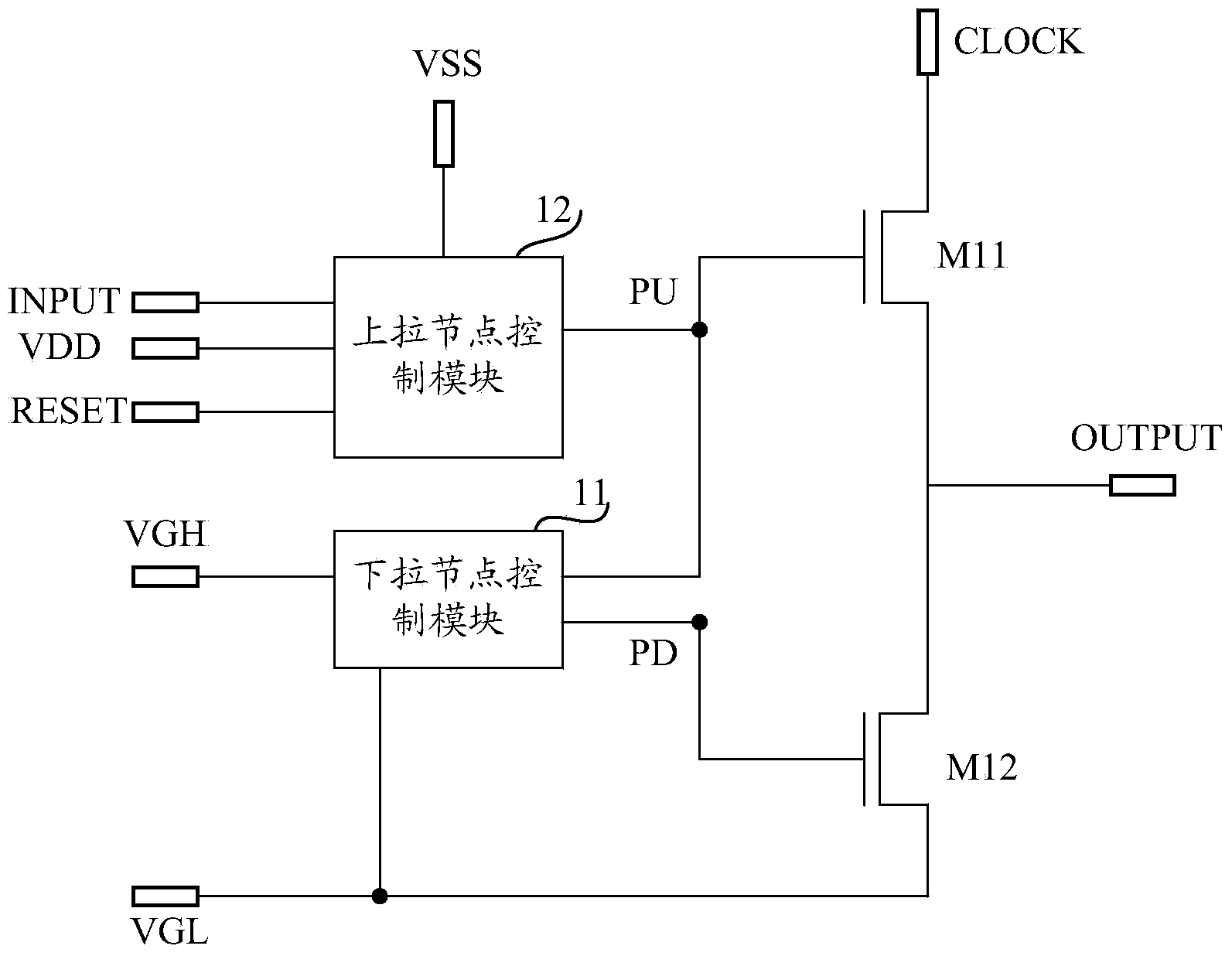

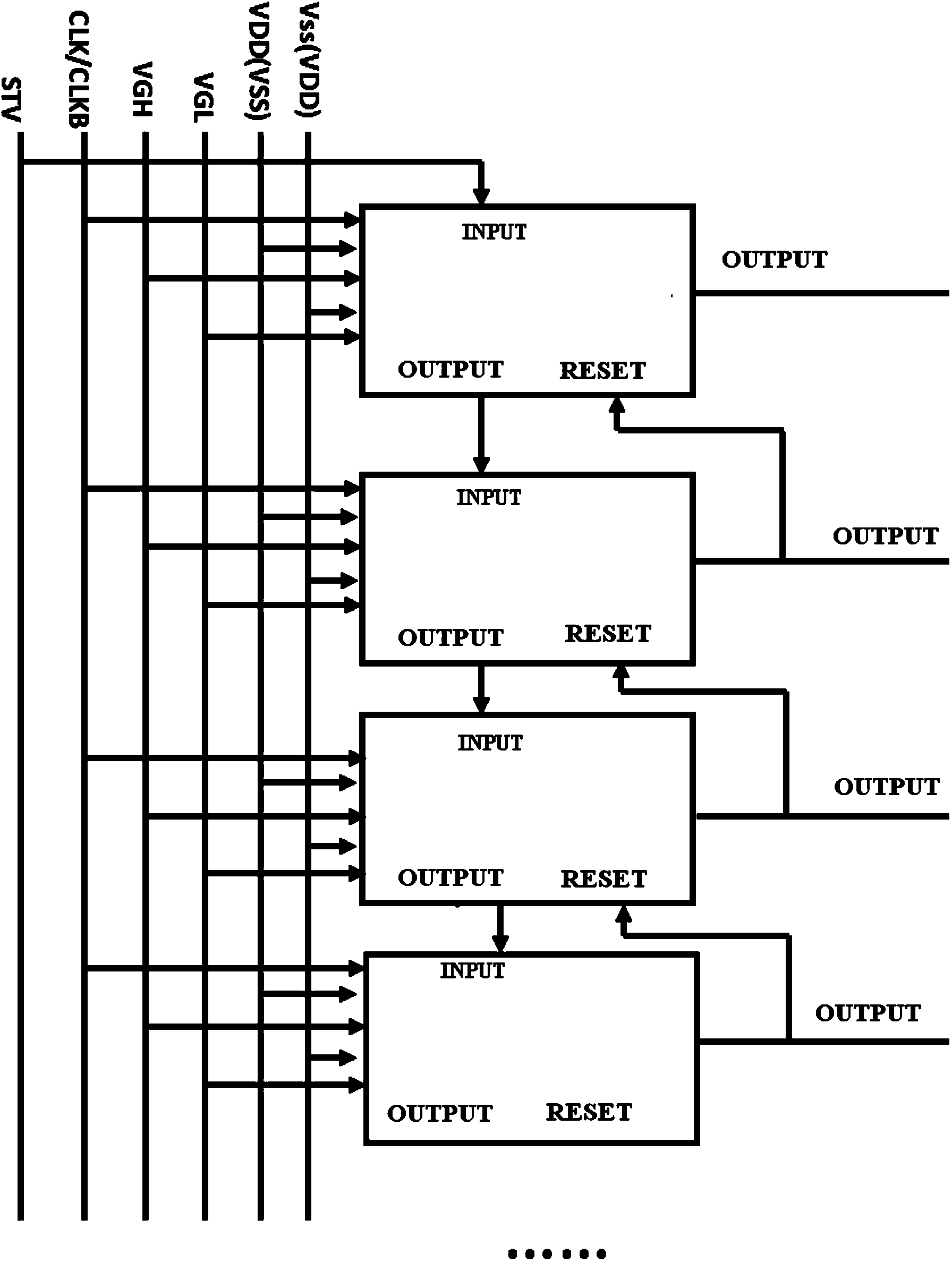

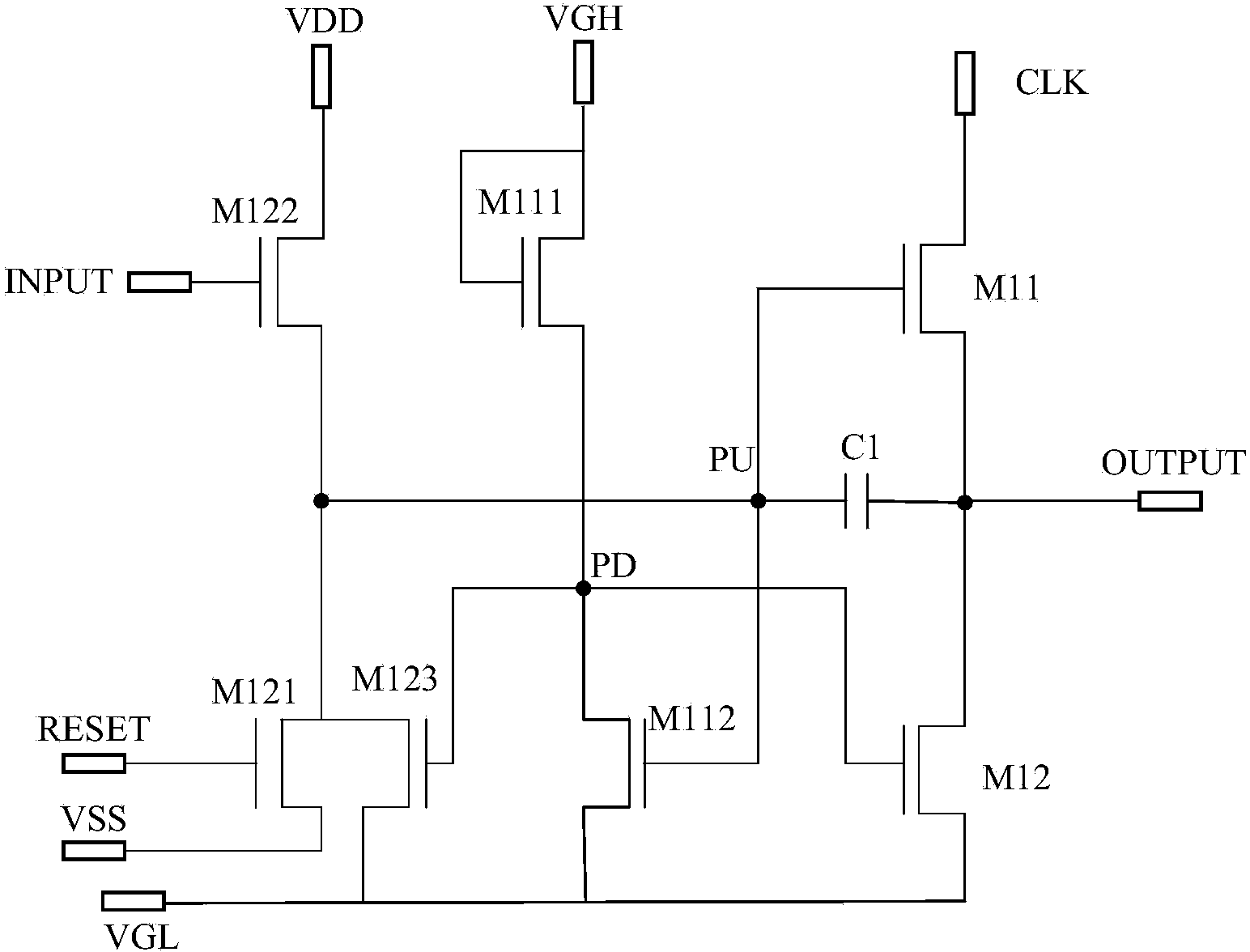

Shifting register unit and driving method thereof, shifting register and display device

InactiveCN104392704ASimple structureRealize bi-directional scanning functionStatic indicating devicesDigital storageShift registerProcessor register

The invention provides a shifting register unit and a driving method thereof, a shifting register and a display device. The shifting register unit comprises a grid driving signal output end, a clock signal end, a pull-up transistor, a pull-down transistor, a pull-down node control module and a pull-up node control module, wherein the pull-down node control module controls the potential of a pull-down node to be a low potential in an input stage, controls shutoff of the pull-down transistor in an output stage, and controls turn-on of the pull-down transistor in a resetting stage, so that the grid driving signal output end outputs a low level; the pull-up node control module controls the potential of a pull-up node to be pulled up to a high potential in an input stage, and controls turn-on of the pull-up transistor in an output stage, so that the grid driving signal output end outputs a clock signal, controls the potential of the pull-up node to be pulled down to a low level in a resetting stage, and controls shutoff of the pull-up transistor in a remaining stage. By adopting a simple circuit structure, a two-way scanning function is realized so as to reduce the power consumption.

Owner:HEFEI BOE OPTOELECTRONICS TECH +1

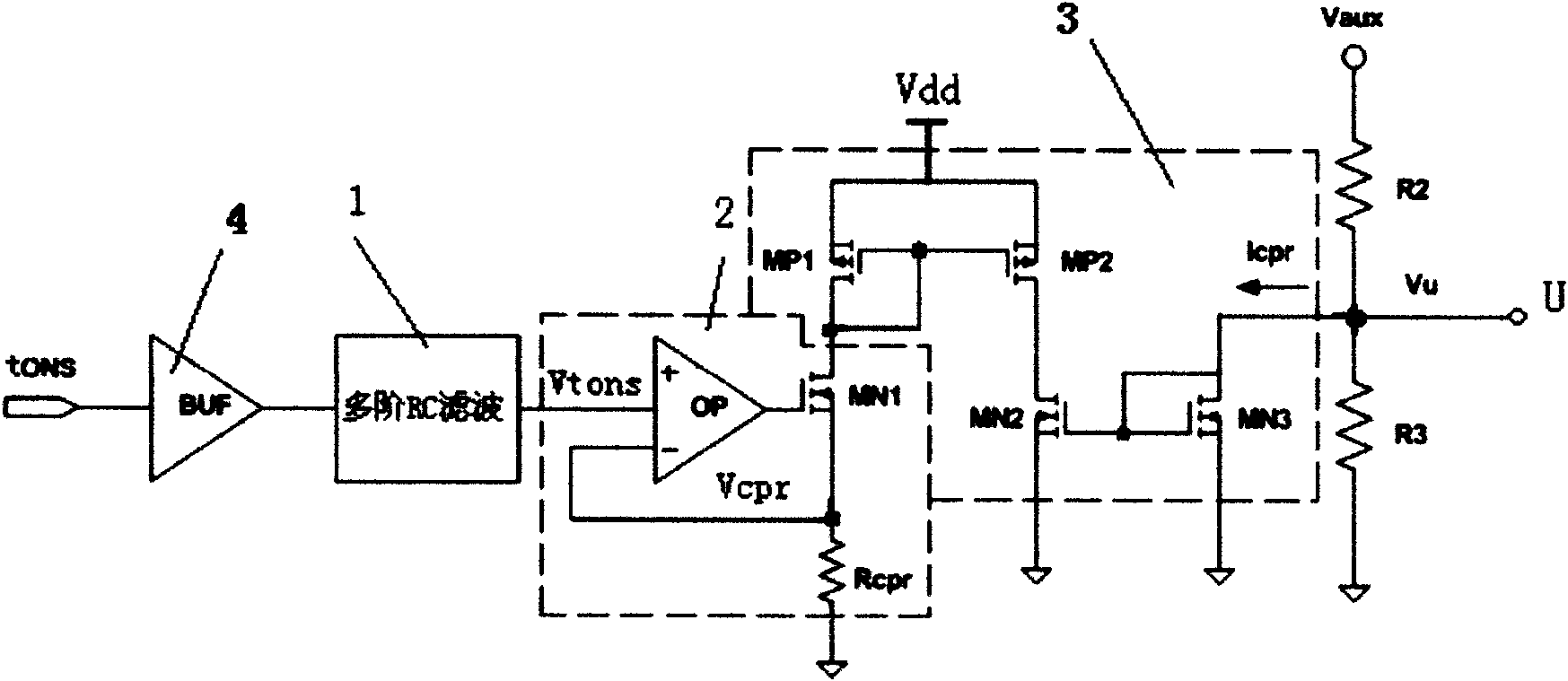

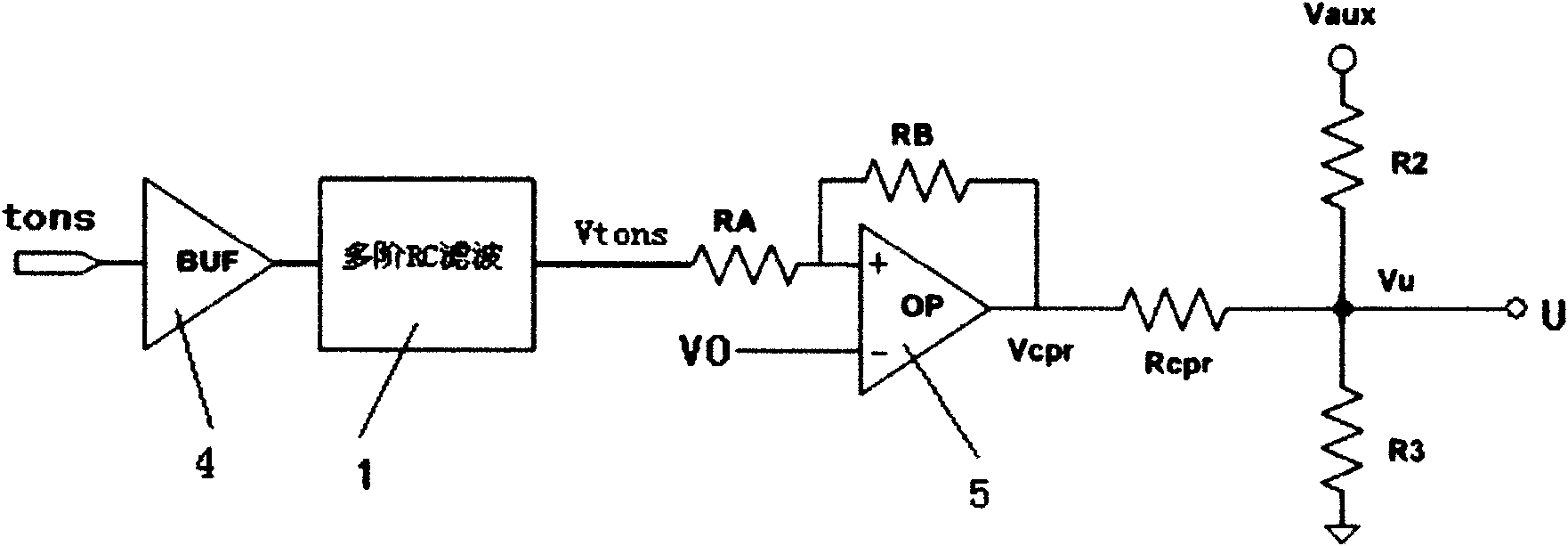

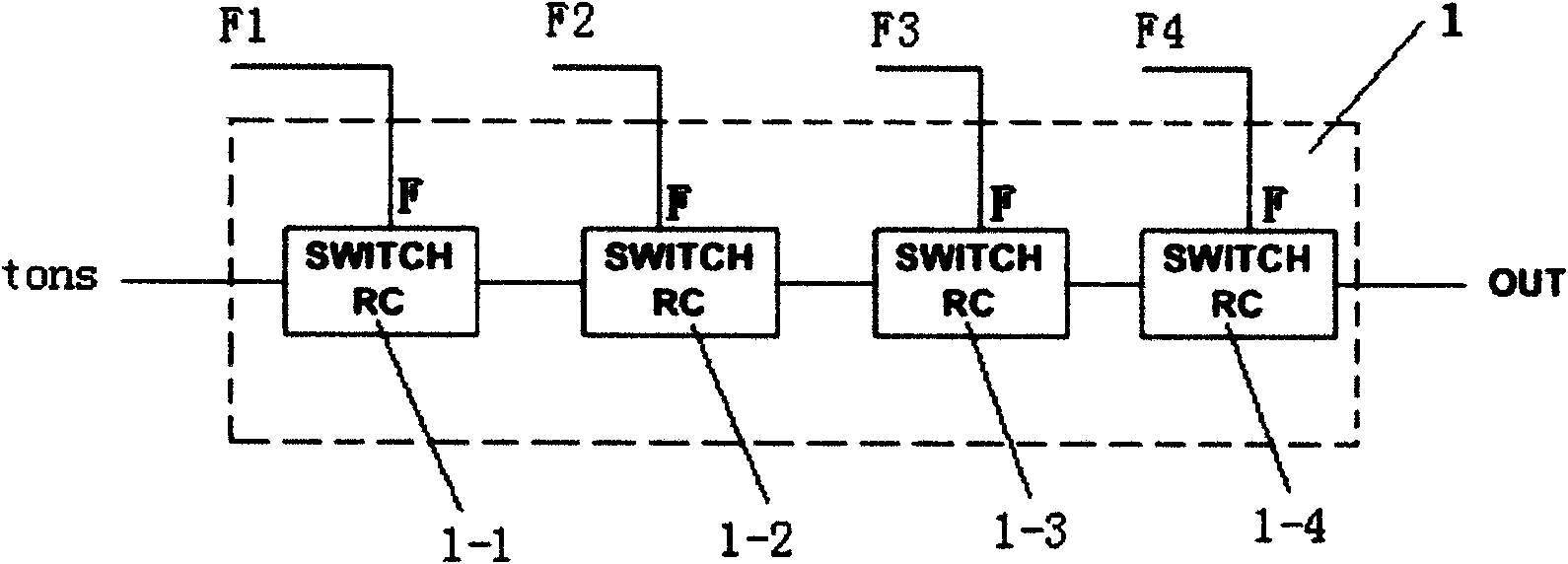

Line loss compensation circuit for switch power supply

InactiveCN101860243AImprove performanceSimple structureAc-dc conversionCapacitanceElectrical resistance and conductance

The invention relates to a line loss compensation circuit for a switch power supply, which is divided into a current-type line loss compensation circuit and a voltage-type line loss compensation circuit, wherein the current-type circuit comprises a multi-stage RC low pass filter, a voltage / current switching circuit and a current mirroring circuit, and the voltage-type circuit comprises a multi-stage RC low pass filter, a subtractor and a compensating resistance. The invention can produce a compensating current of Icpr or a compensating voltage of Vcpr which is proportionable to an output current of Iout, and the compensating current or the compensating voltage is used for offsetting voltage drop of an output wire caused by change of Iout, thereby recovering voltage stabilizing control function of a control loop to secure constant output. The invention has the advantages of skilful design idea and simple circuit and is easy to realize. The improvement of the invention is that: the switch RC filter is adopted to greatly reduce volume of an electric capacity of the RC filter, thereby facilitating integration, further improving circuit performance and simplifying circuit structure, and strengthening operation reliability of the switch power supply.

Owner:西安英洛华微电子有限公司

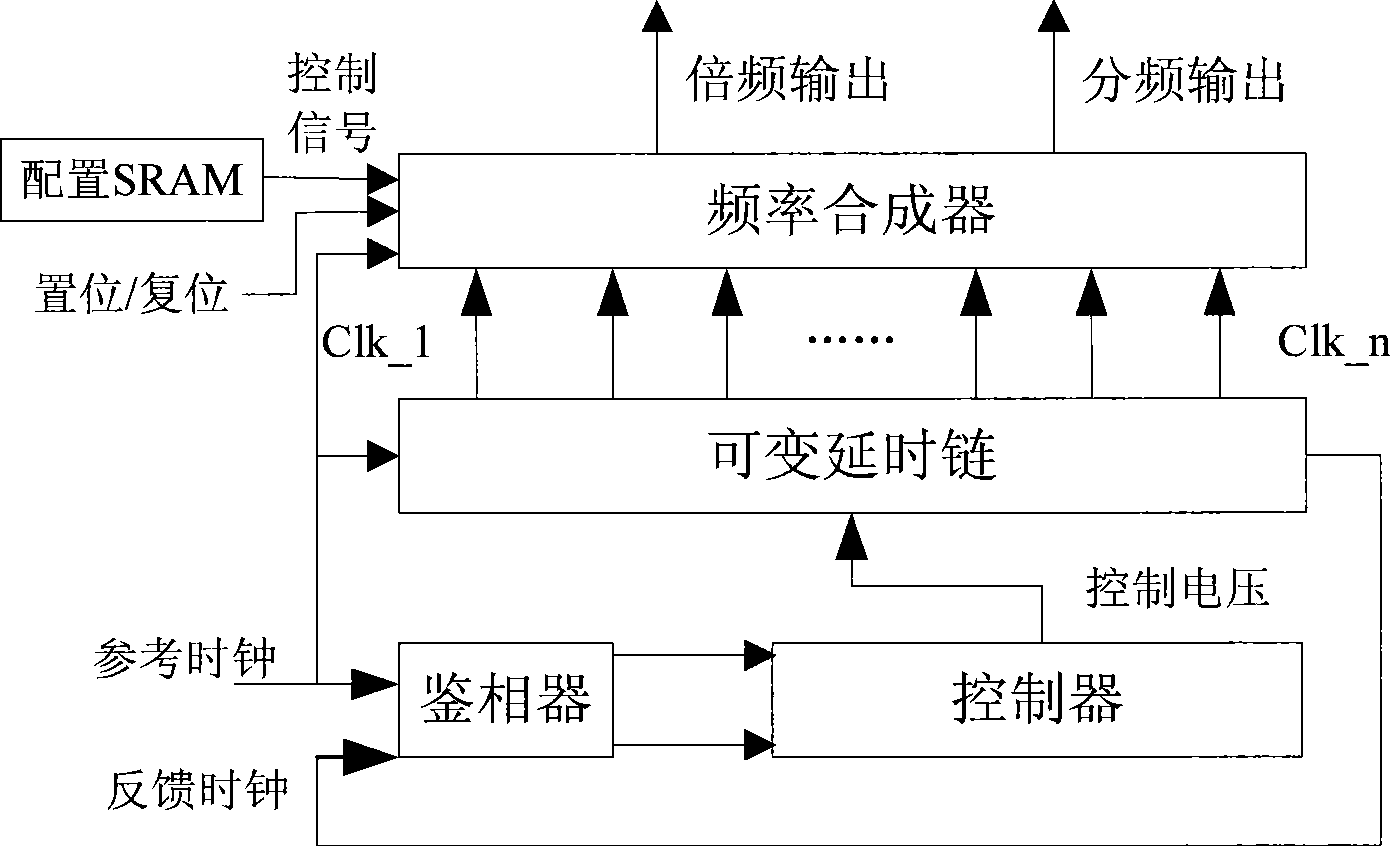

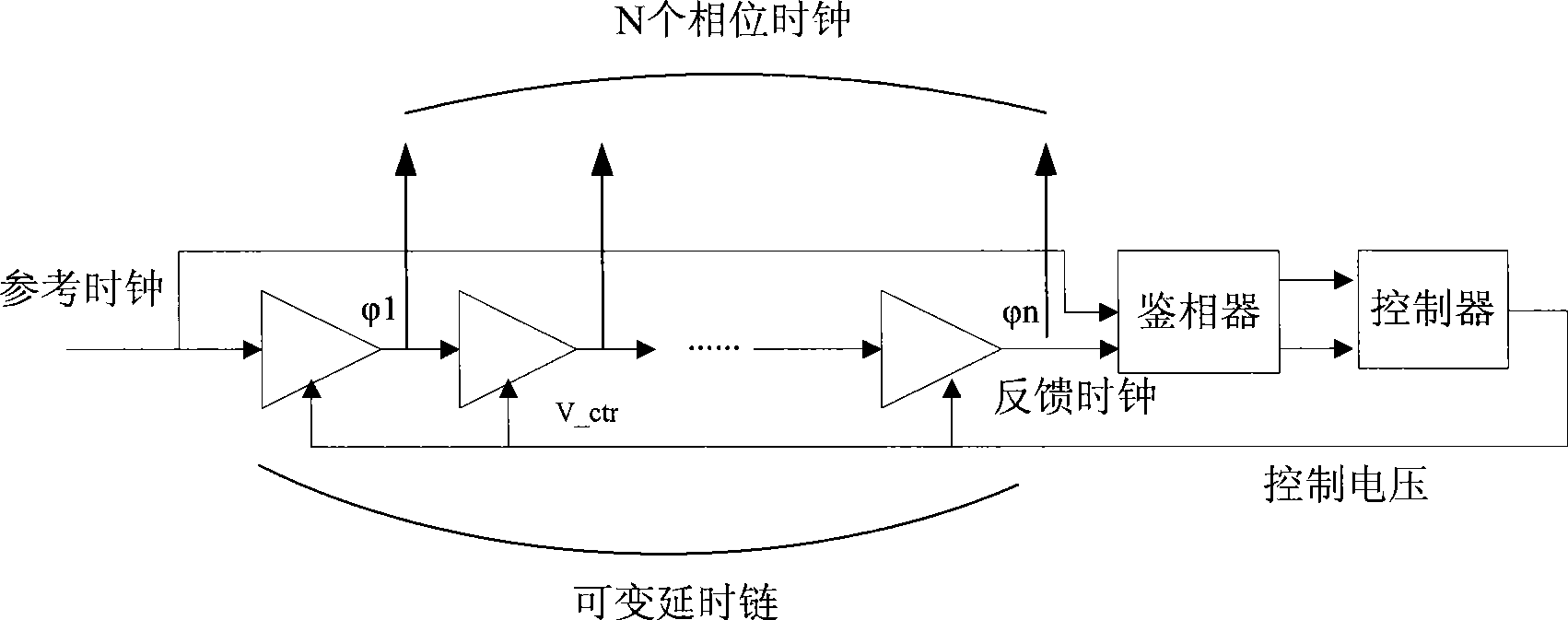

Configurable frequency synthesizer circuit based on time-delay lock loop

ActiveCN101478308AImprove reusabilityAbsolute stabilityPulse automatic controlDiscriminatorTime delays

The invention relates to a configurable frequency synthesis circuit based on a delay locked loop. The circuit comprises the delay locked loop, a frequency synthesizer and a configuring SRAM, wherein, the delay locked loop consists of a phase discriminator, a controller and a variable delay chain; and the frequency synthesizer consists of a frequency doubling synthesizer and a frequency division synthesizer. The phase discriminator receives a reference clock and a feedback clock and outputs comparison signals and locking signals after phase demodulation comparison; the comparison signals and the locking signals are processed by the controller, and the controller outputs control voltage then in order to enable the variable delay chain to generate N phase clocks that are output to the frequency synthesizer; and the frequency doubling synthesizer and the frequency division synthesizer enable the set / reset time of a R / S trigger in the frequency doubling synthesizer to generate frequency doubling clock signals under the control of the configuring SRAM, and lead the set / reset time of the R / S trigger in the frequency division synthesizer to generate frequency division clock signals. The configurable frequency synthesis circuit has simple circuit organization, flexibly changes a frequency synthesis coefficient by changing the code flow value in the embedded configuring SRAM so as to obtain a frequency division coefficient and a frequency doubling coefficient as required, and can be applied to a field programmable logic array.

Owner:BEIJING MXTRONICS CORP +1

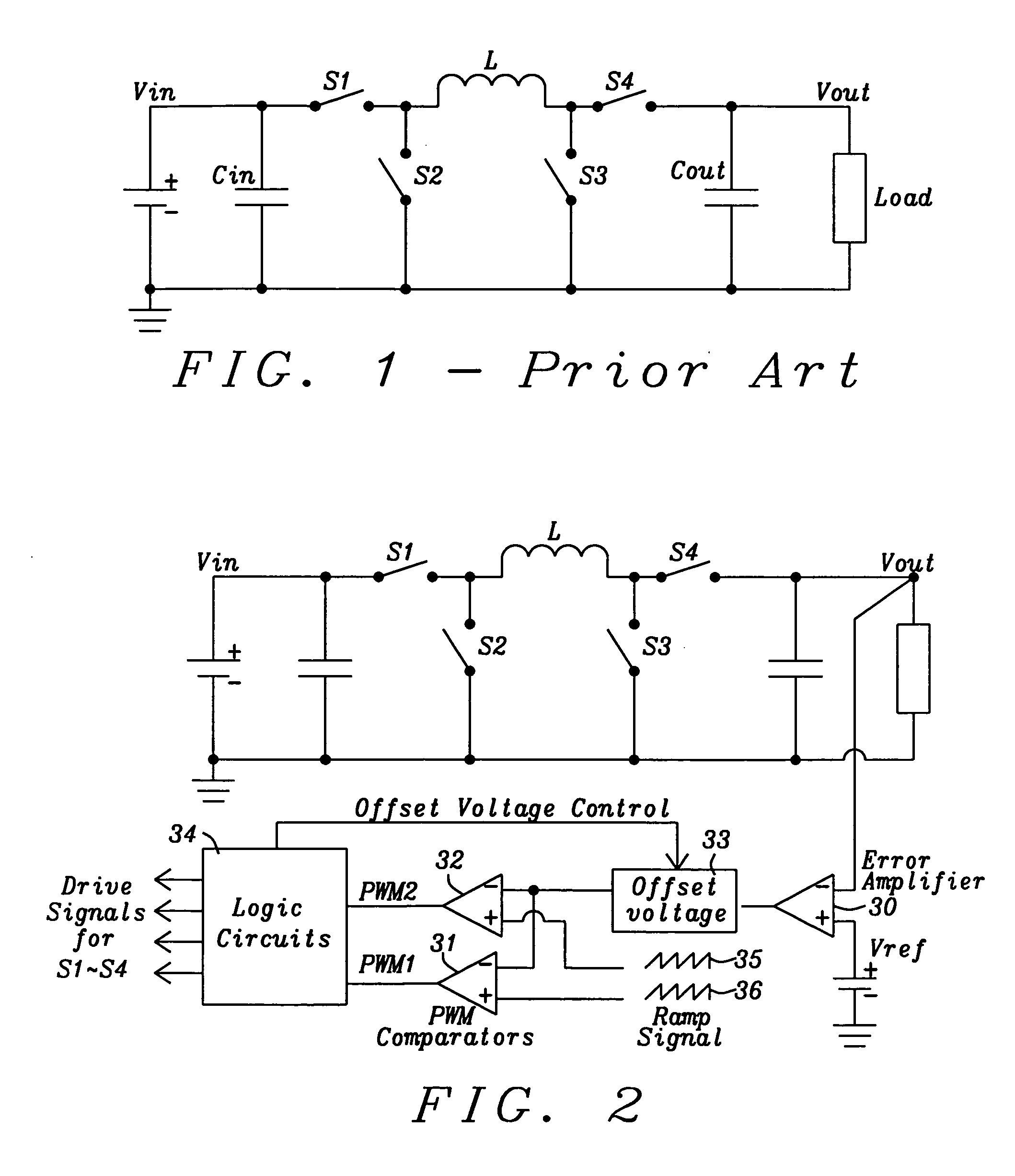

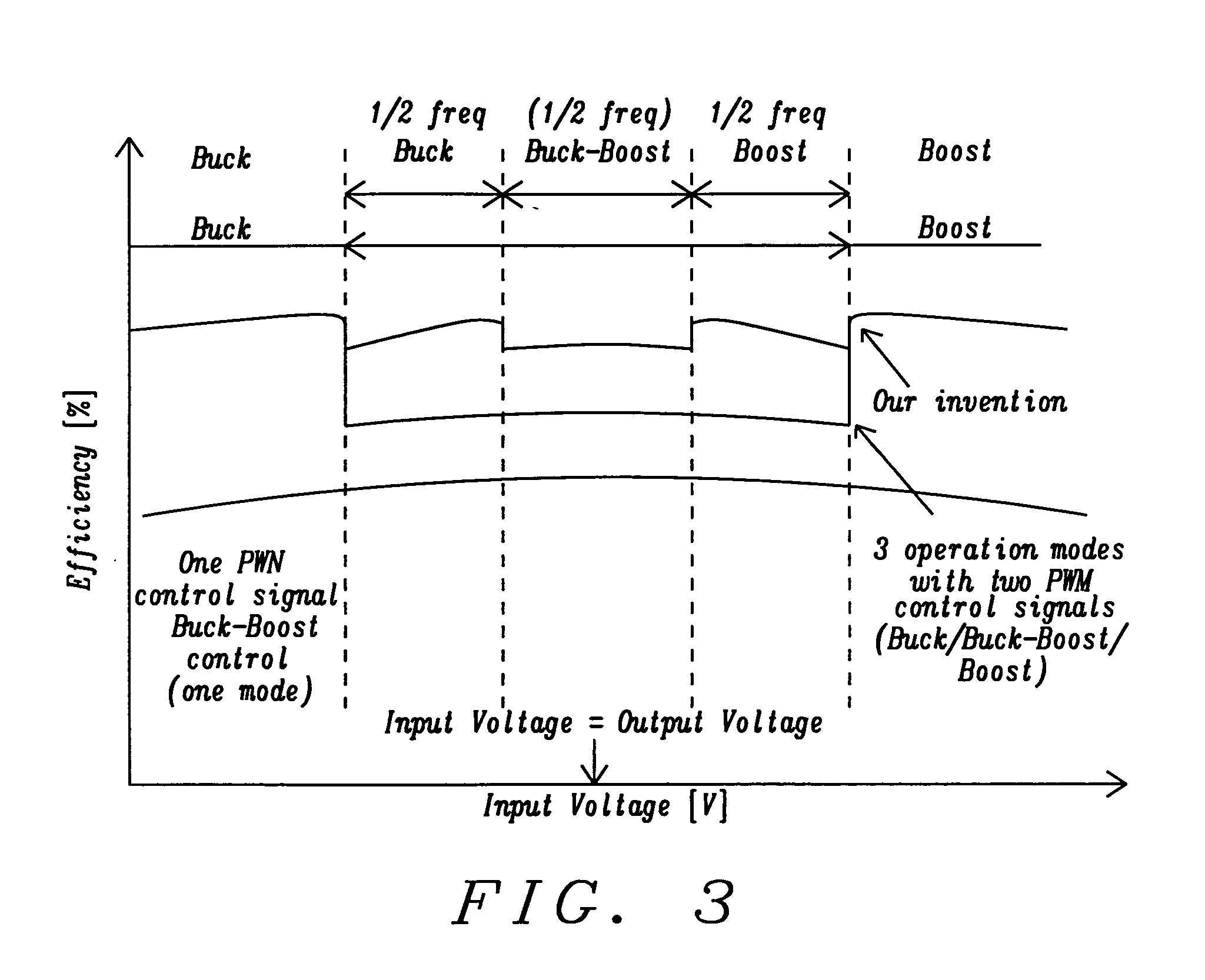

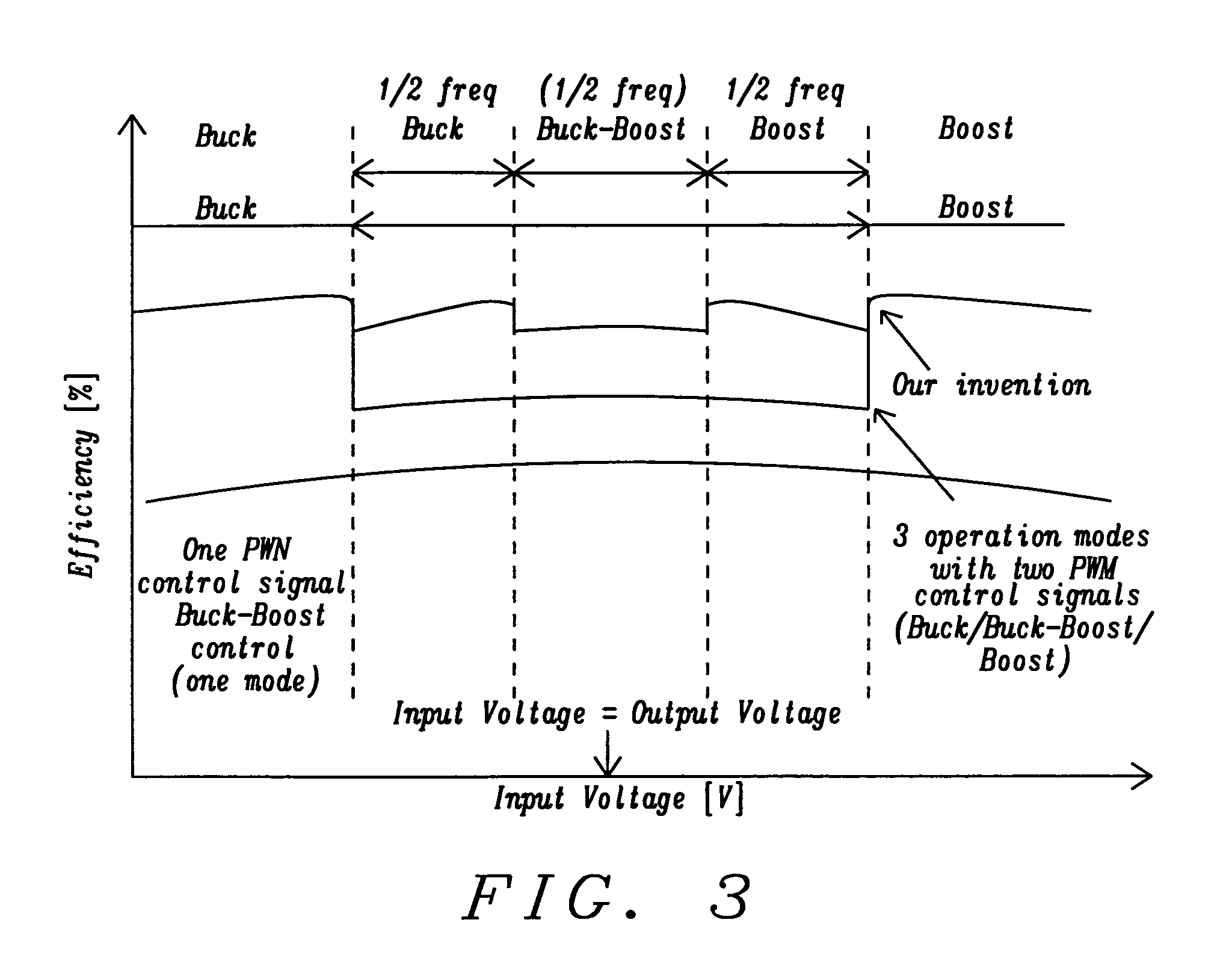

Buck-boost converter with improved efficiency operation

ActiveUS8860387B2Improve efficiencyDc-dc conversionAc network voltage adjustmentEngineeringSwitching frequency

Systems and methods for providing a buck-boost converter with an improved efficiency are disclosed. The buck-boost converter disclosed operates in 5 different modes, namely in buck mode, half frequency buck mode, half frequency buck-boost mode, half frequency boost mode, and in boost mode. In half frequency buck mode, buck-boost mode, and in half frequency boost mode the switching frequency is halved compared to the switching frequency of buck or boost mode. A simple circuit implementation by adding two offset voltages in ramp signals or PWM comparators enables to halve the switching frequency if required.

Owner:DIALOG SEMICONDUCTOR GMBH

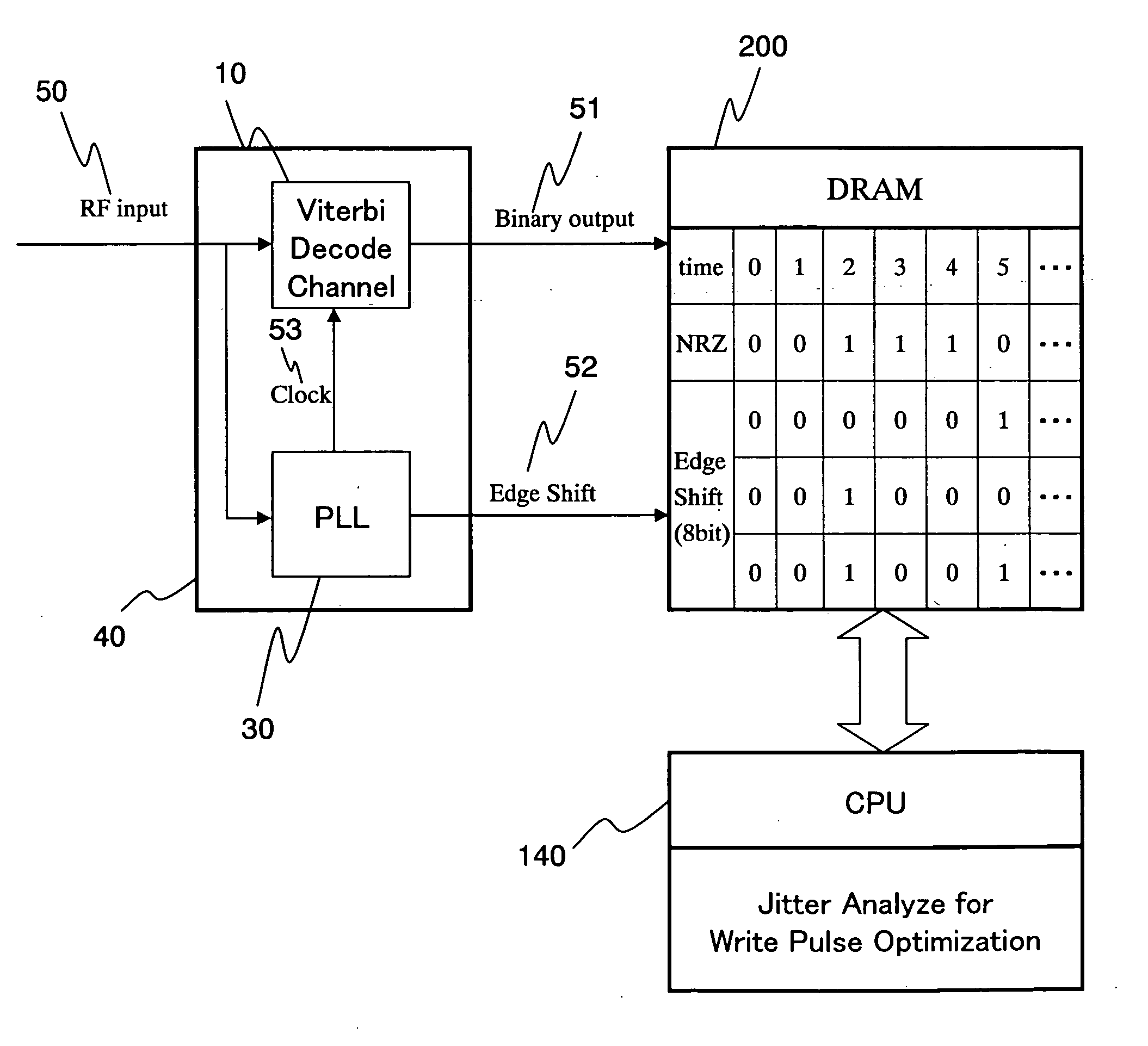

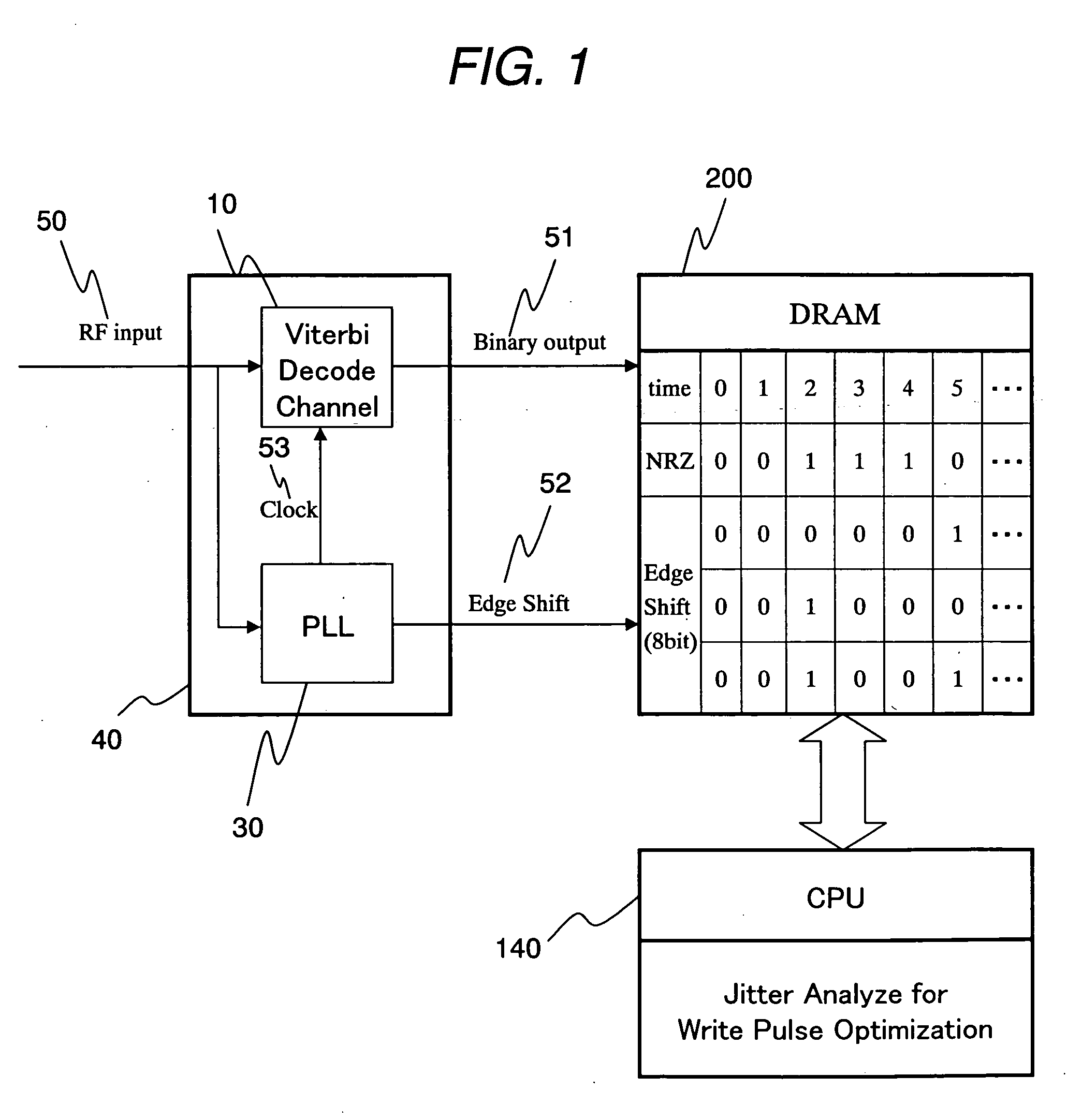

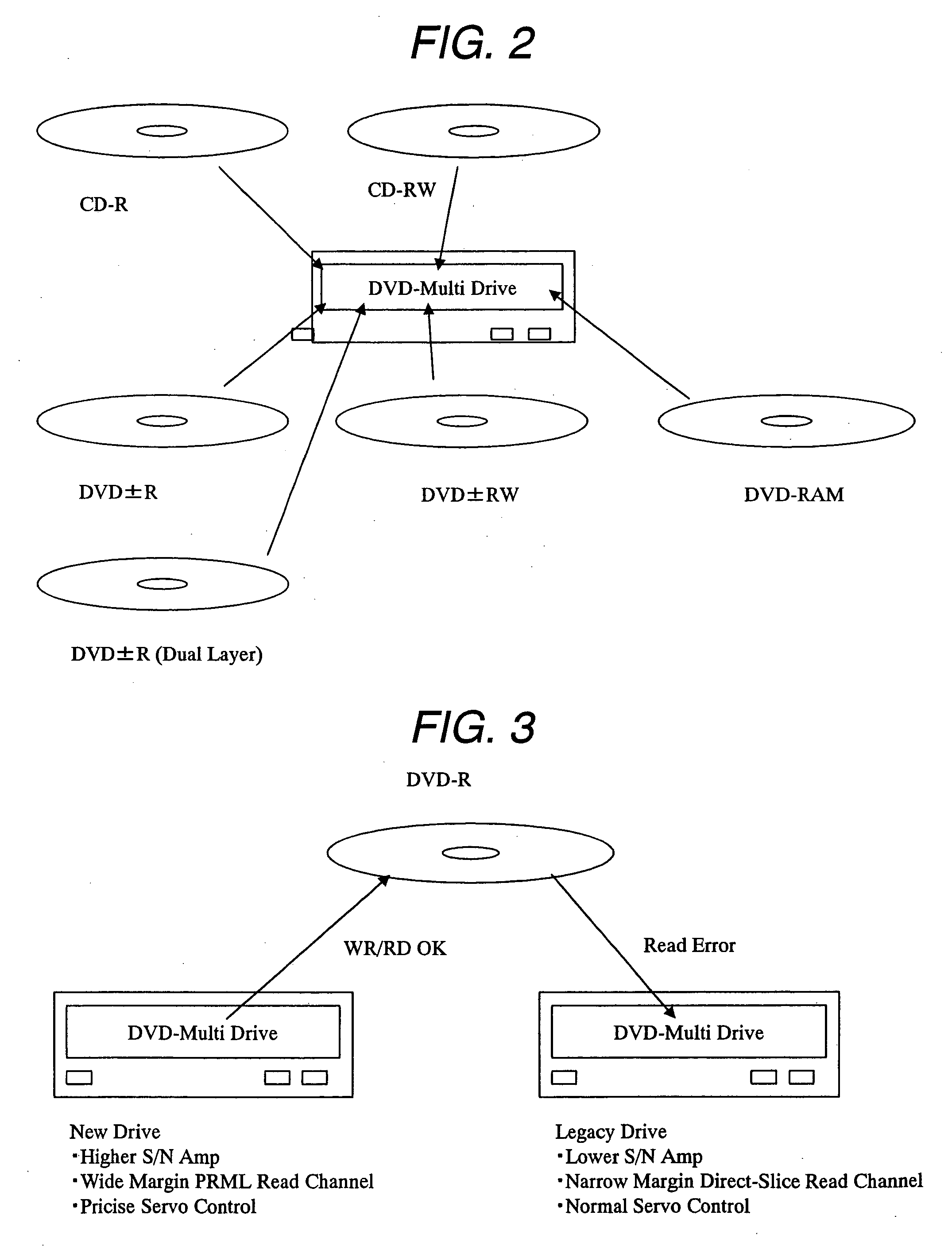

Recording method and optical disc apparatus

InactiveUS20060083135A1Short timeTelevision system detailsModification of read/write signalsDigital dataExternal storage

In a recordable optical disc apparatus, the efficiency of the work necessary for optimizing the write pulse condition (write strategy) is improved and the read compatibility among drive units is ensured by a minimum addition of circuitry. An edge shift amount or a read signal and a binarized result are stored in an external memory as digital data and are later processed by analysis software in a host PC. The write pulse shape and power conditions can be optimized to individual optical disc media in a short time by means of a simple circuit. Further, by optimizing the write pulse shape and power condition in view of the PRML class or the difference in NA of the head, any deterioration of read compatibility can be avoided.

Owner:HITACHI LTD +1

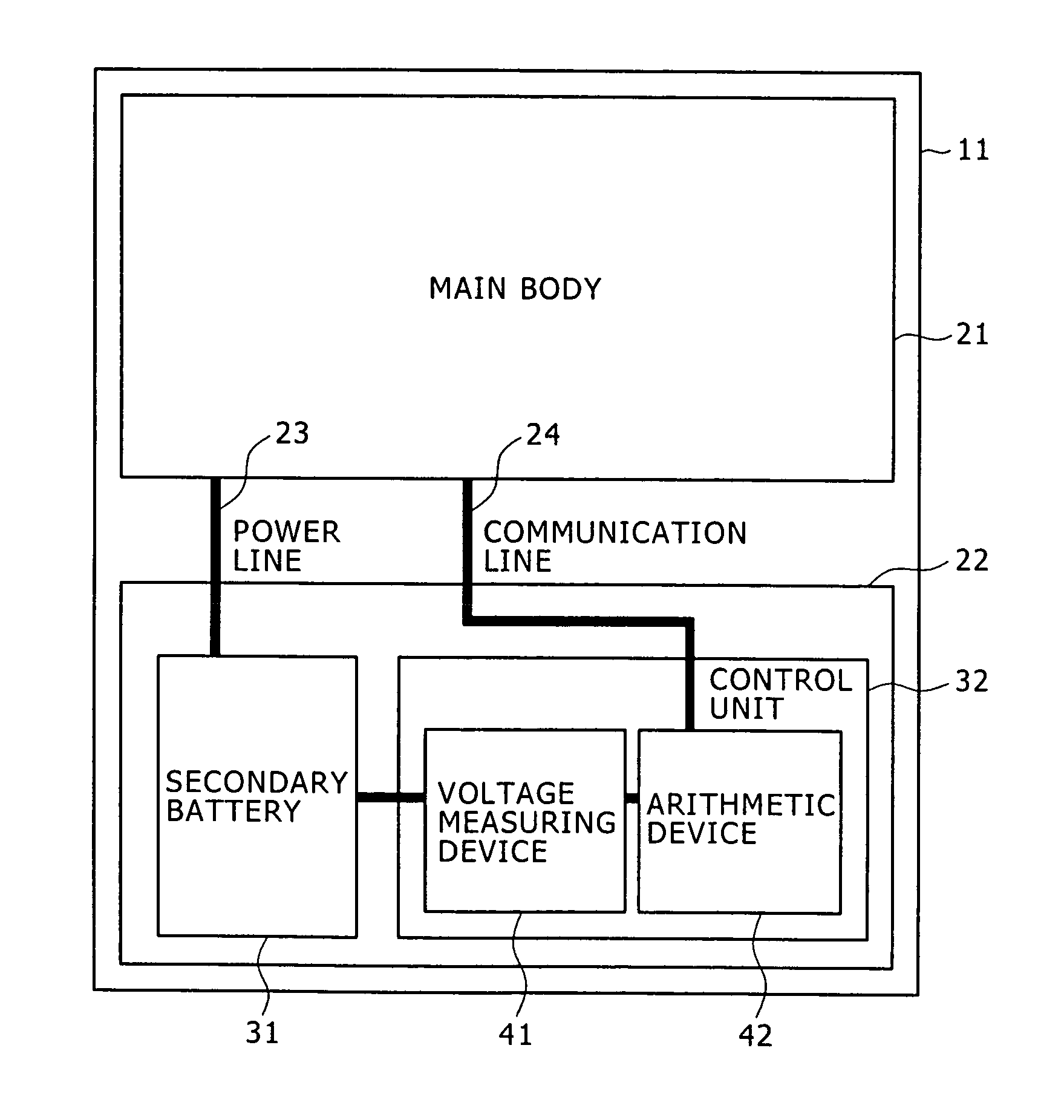

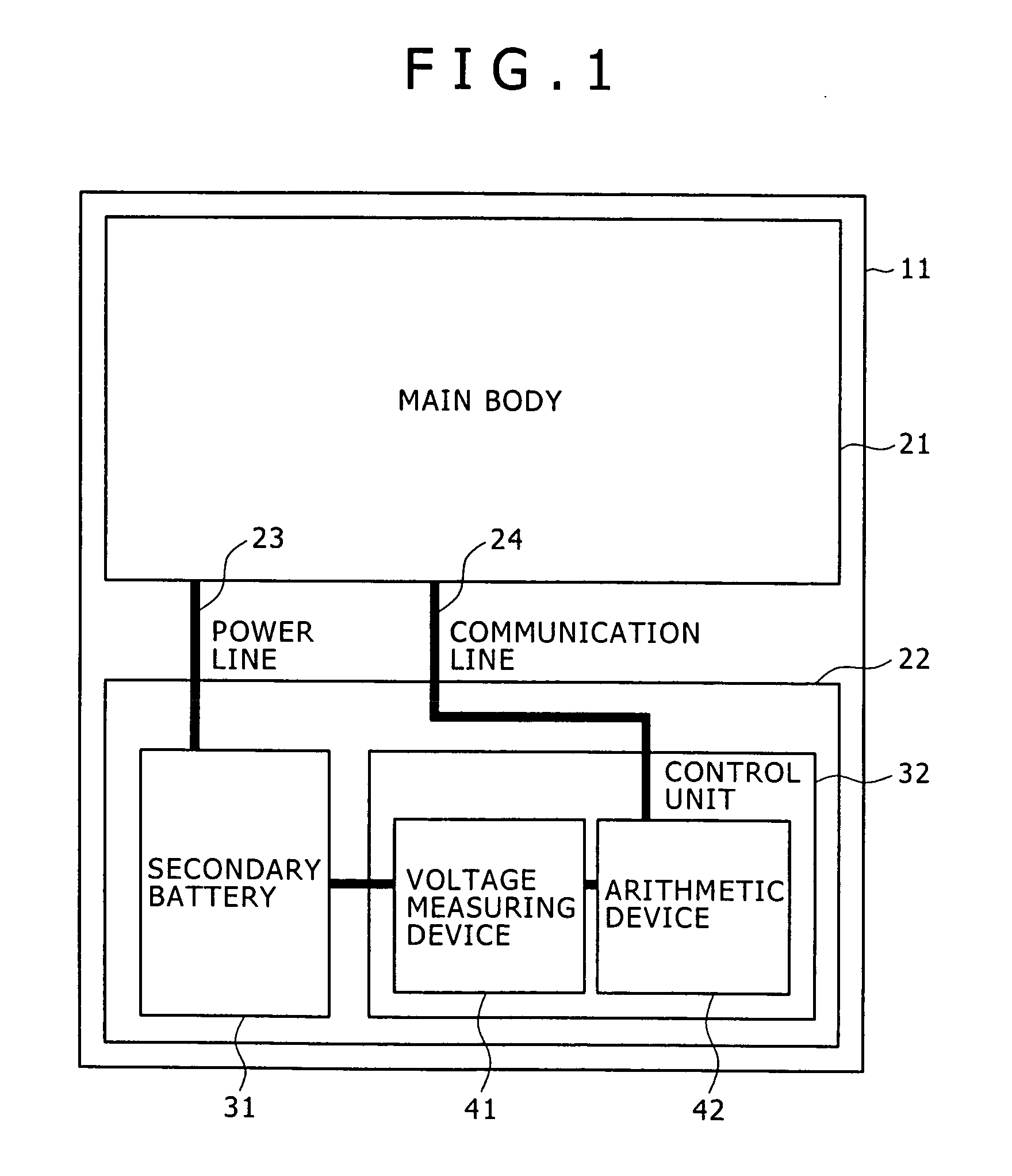

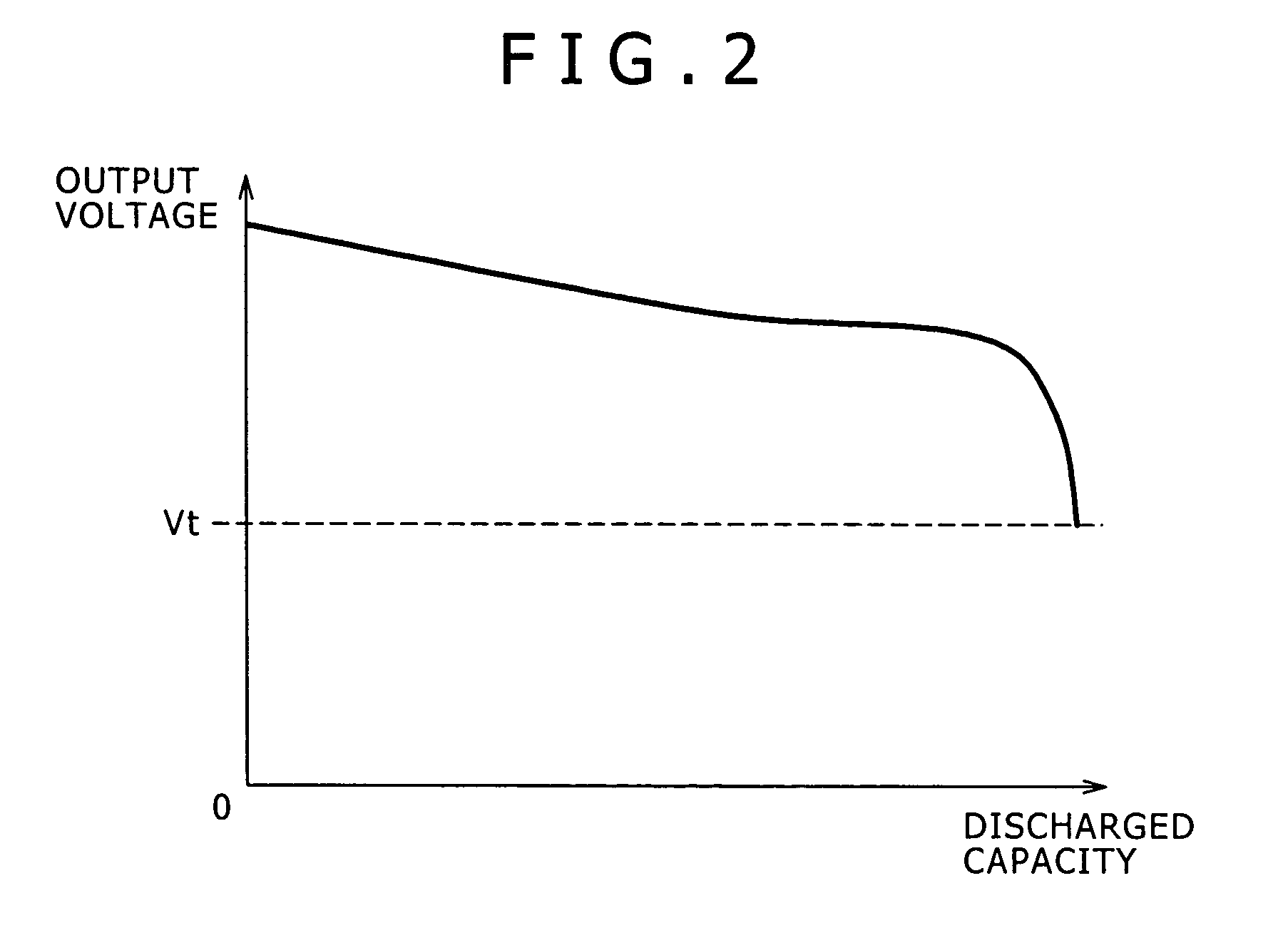

Battery remaining capacity calculating method, battery remaining capacity calculating device, and battery remaining capacity calculating program

ActiveUS20070114971A1Reduce the number of partsAddress rising pricesBatteries circuit arrangementsMaterial analysis by electric/magnetic meansElectrical batteryEngineering

A battery remaining capacity calculating method, a battery remaining capacity calculating device, and a battery remaining capacity calculating program that make it possible to estimate the remaining capacity of a secondary battery with high accuracy using a relatively simple circuit configuration. An output voltage value of the secondary battery is measured, a use mode of the secondary battery is divided into a high consumption mode in which the output voltage value is not lower than a threshold value and a low consumption mode in which the output voltage value is lower than the threshold value, a remaining capacity in the low consumption mode is calculated on a basis of a predetermined reference voltage curve as a discharge characteristic of the secondary battery and the output voltage value, and a remaining capacity in the high consumption mode is calculated supposing that there is little change in the remaining capacity at a time of change from the low consumption mode to the high consumption mode. In the high consumption mode, the remaining capacity may be calculated on a basis of a reference remaining capacity as a remaining capacity before the use mode change, a start voltage as an output voltage at a time of a start of the high consumption mode, a predetermined cutoff voltage of the secondary battery, and the output voltage value.

Owner:MURATA MFG CO LTD

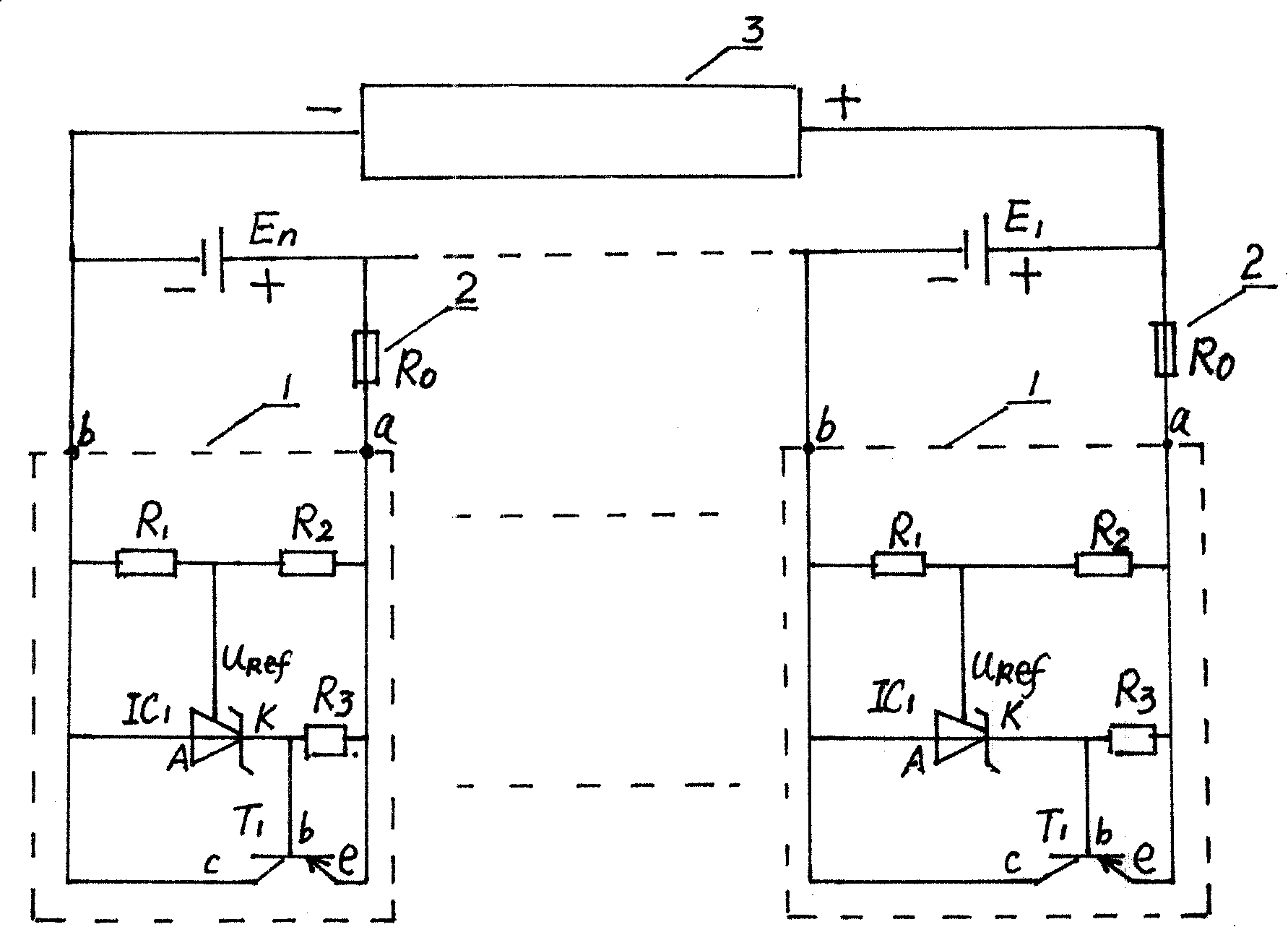

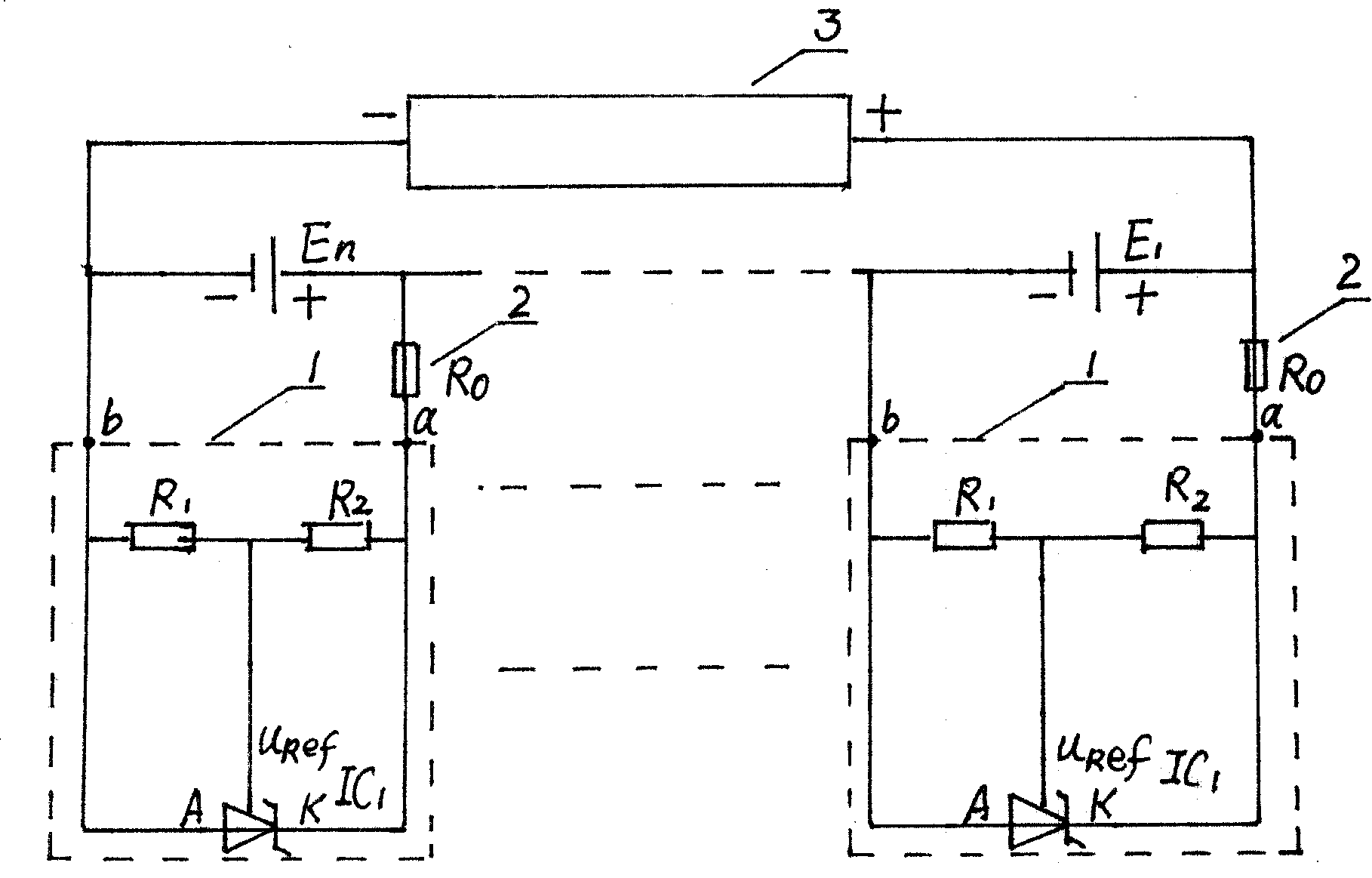

Automatic equalization charging equipment charged by series storage battery

InactiveCN101162847ADoes not affect storageSmall static working currentBatteries circuit arrangementsElectric powerEngineeringEqualization

The present invention relates to an automatic balance charging device for charging series storage battery, which is arranged on each battery of the series storage battery one to one. The balance charging device comprises an accurate voltage balance current shunt [1] and a limiting fuse [2] in series. The present invention enables the battery of the series storage battery to obtain balance charging in long term automatically, thereby greatly prolonging the real service life of the storage battery. The present invention is characterized by simple circuit, small volume, low cost and good using effect, thereby being applicable to various series storage battery which can automatically solve the balance charging problem without any measures.

Owner:伍占禧

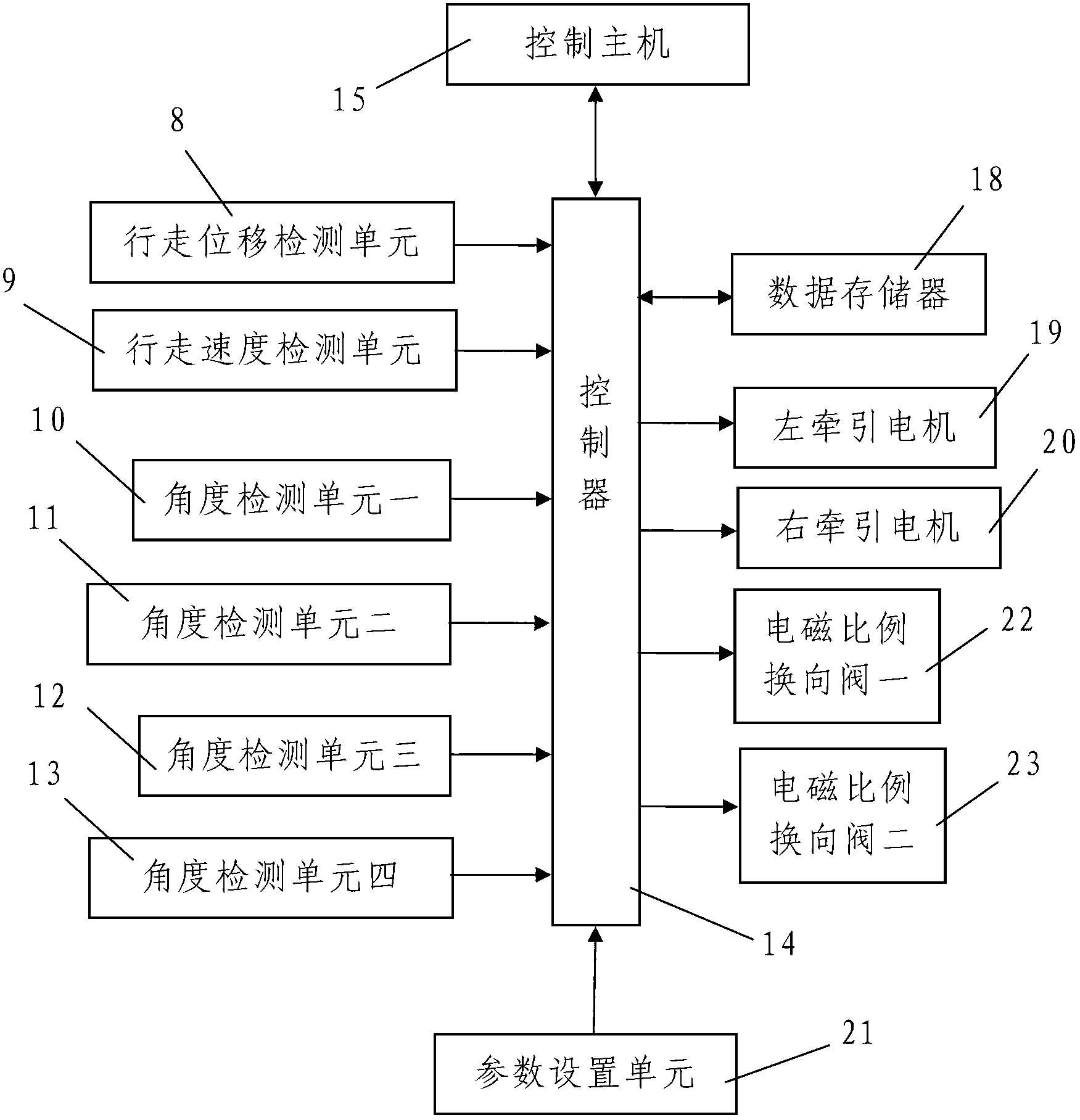

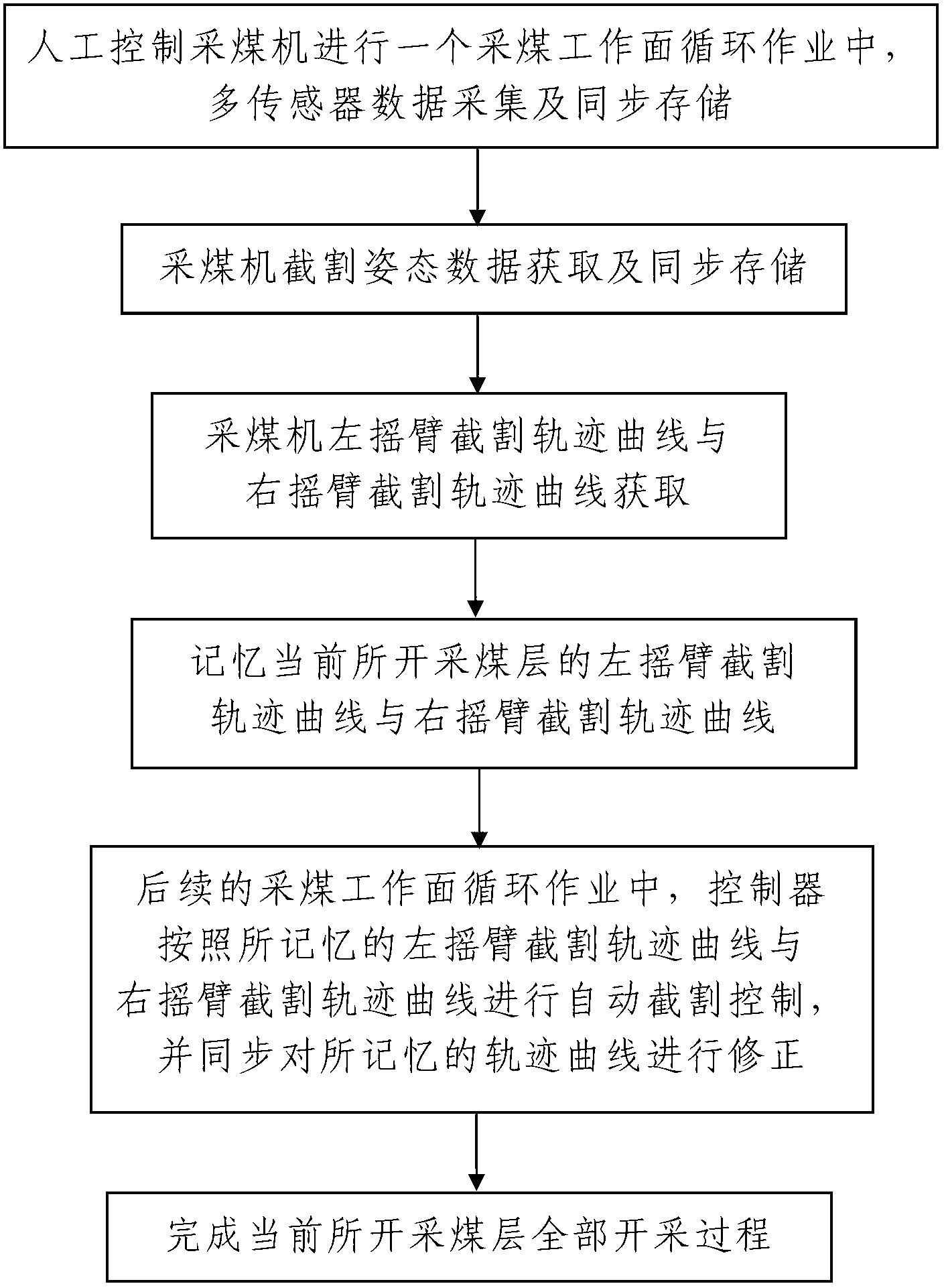

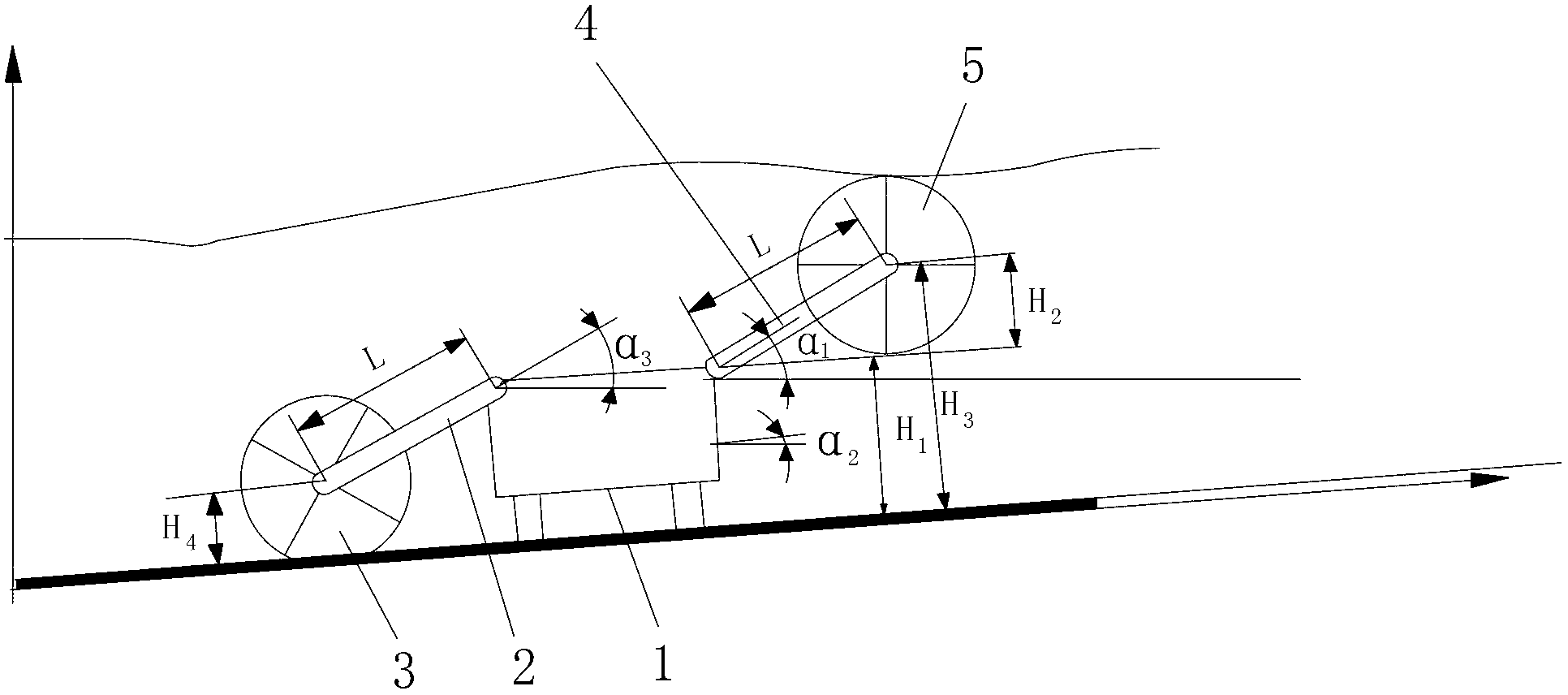

Automatic cutting control system and automatic cutting control method for coal cutter

ActiveCN102797462AEasy installation and layoutLow input costSlitting machinesControl systemEngineering

The invention discloses an automatic cutting control system and an automatic cutting control method for a coal cutter. The control system comprises a controller, a data storage device, a working condition detection apparatus for the coal cutter and a control host. The working condition detection apparatus for the coal cutter comprises a walking displacement detection unit, an angle detection unit one for detecting the swing angle of a right rocker arm, an angle detection unit two for detecting the inclination angle of a working face, an angle detection unit three for detecting the swing angle of a left rocker arm, and an angle detection unit four for detecting the upward or downward angle of the coal cutter. A left height adjustment oil cylinder and a right height adjustment oil cylinder are both controlled by the controller. The control method comprises the steps of: 1) learning and memorizing the cutting trace of the currently working coal seam; 2) accomplishing the automatic coal cutting according to the memorized trace, and adjusting the memorized trace in real time; 3) repeating step 2) until all the exploration processes of the currently working coal seal is finished. The system of the invention is advantageous by a simple circuit, a reasonable design, a convenient control method, and good application effect, and can realize the automatic cutting control of the coal cutter.

Owner:XIAN COAL MINING MACHINERY

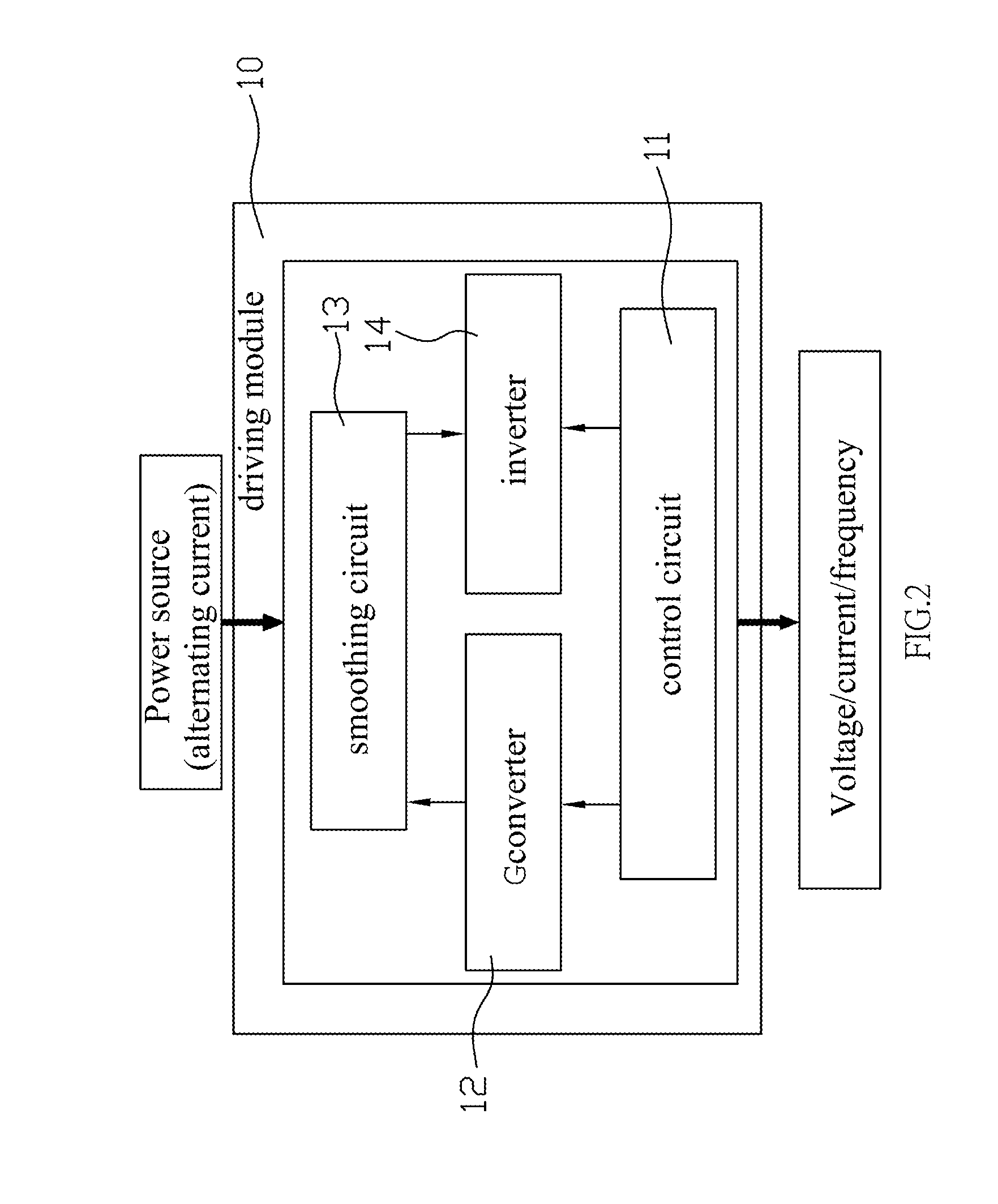

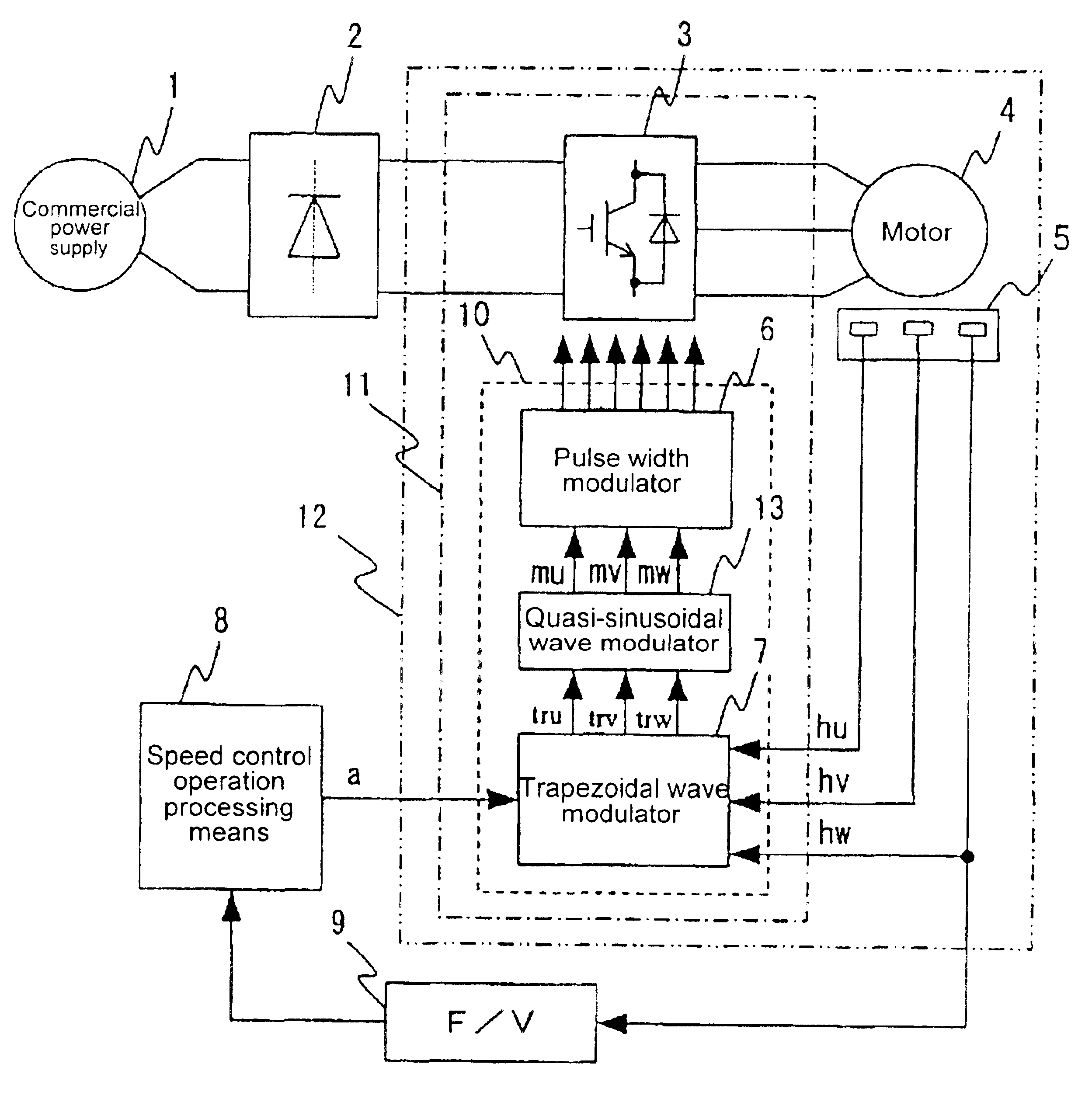

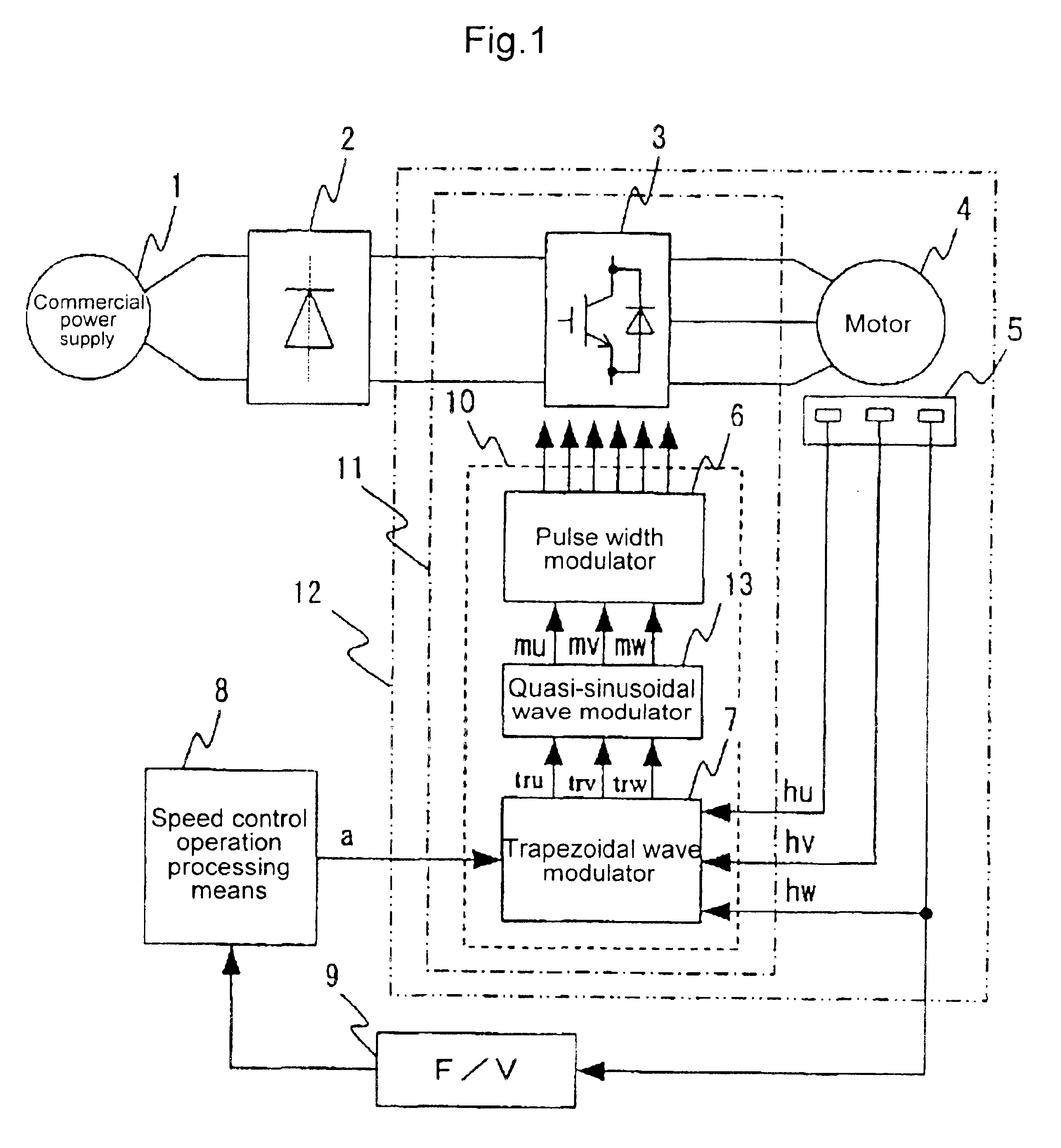

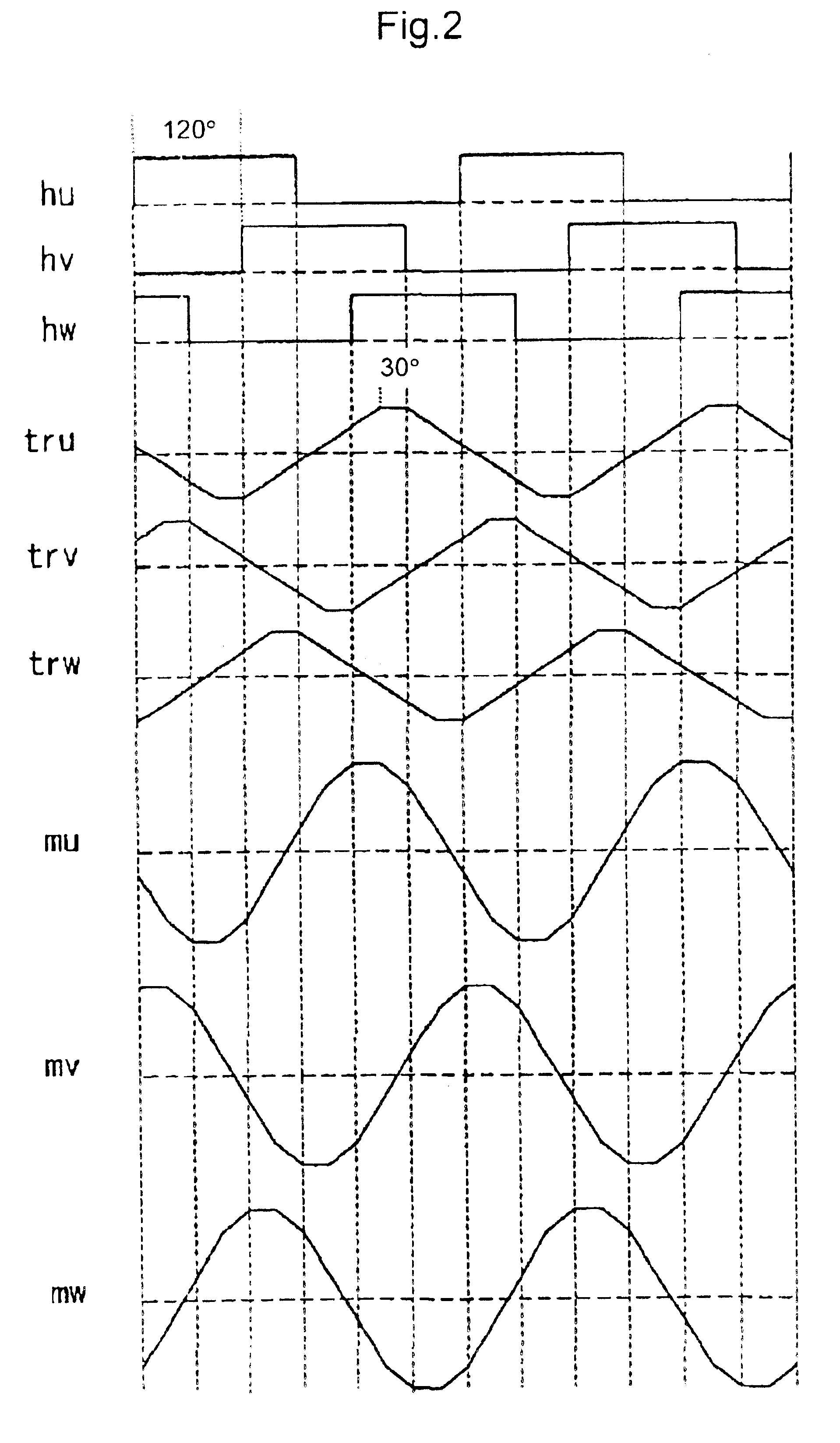

Driving equipment and semiconductor equipment for alternating-current motor

InactiveUS6828752B2Reducing torque ripplesSimple circuitSingle-phase induction motor startersTorque ripple controlCarrier signalMagnetic poles

The present invention enables modulated wave signals having extremely small waveform distortion to be generated using a relatively simple circuit, and thereby it is possible to hold down vibrations and noise of a motor, which are attributable to torque ripples. In order to remove defects of the conventional techniques, the circuit generates a plurality of trapezoidal wave signals having at least two constant levels based on position sensing signals of magnetic pole of a motor, generates quasi-sinusoidal wave signals at a quasi-sinusoidal wave modulator based on the plurality of trapezoidal wave signals, and compares the quasi-sinusoidal wave signals with a carrier wave so as to perform PWM control of an inverter.

Owner:HITACHI LTD

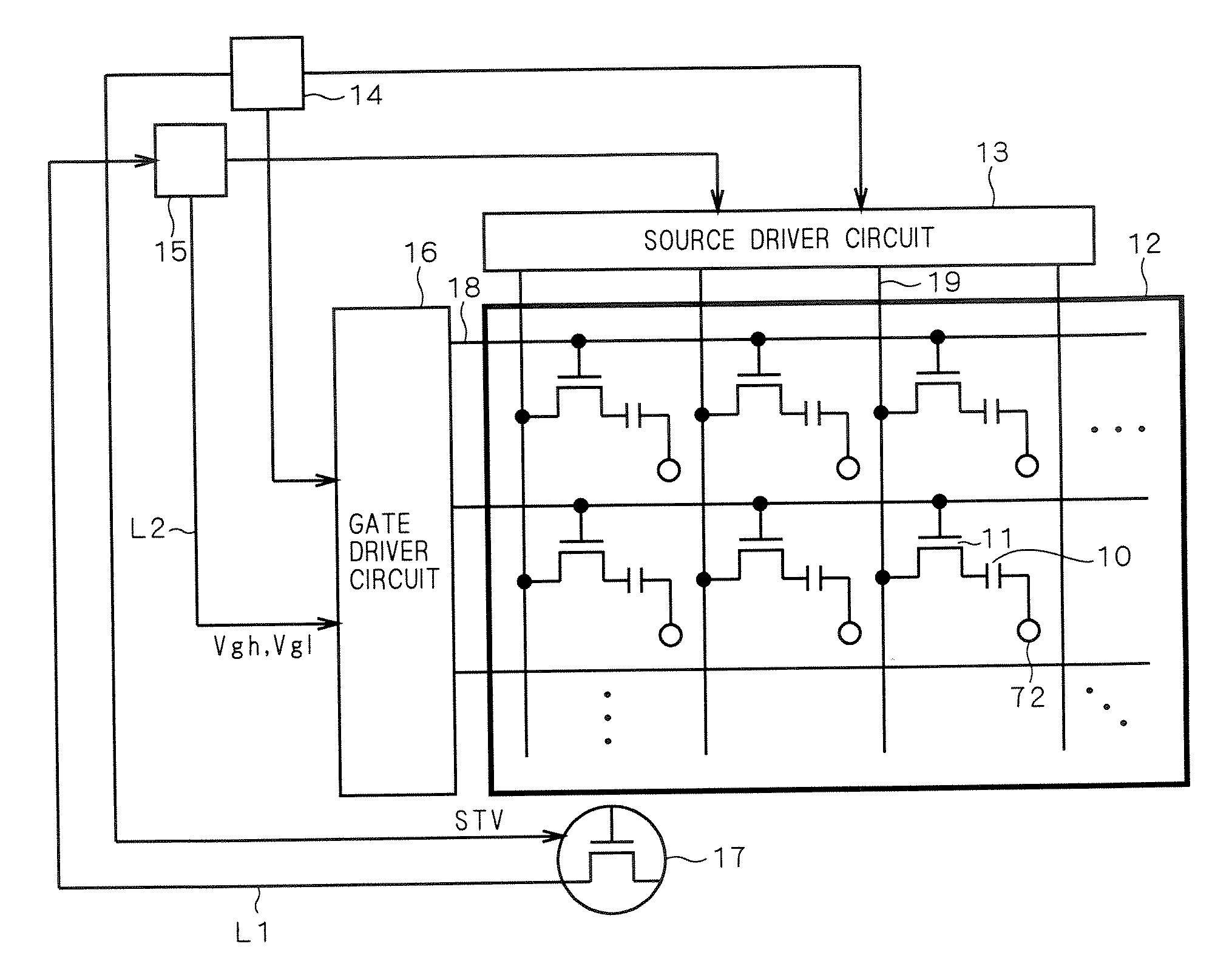

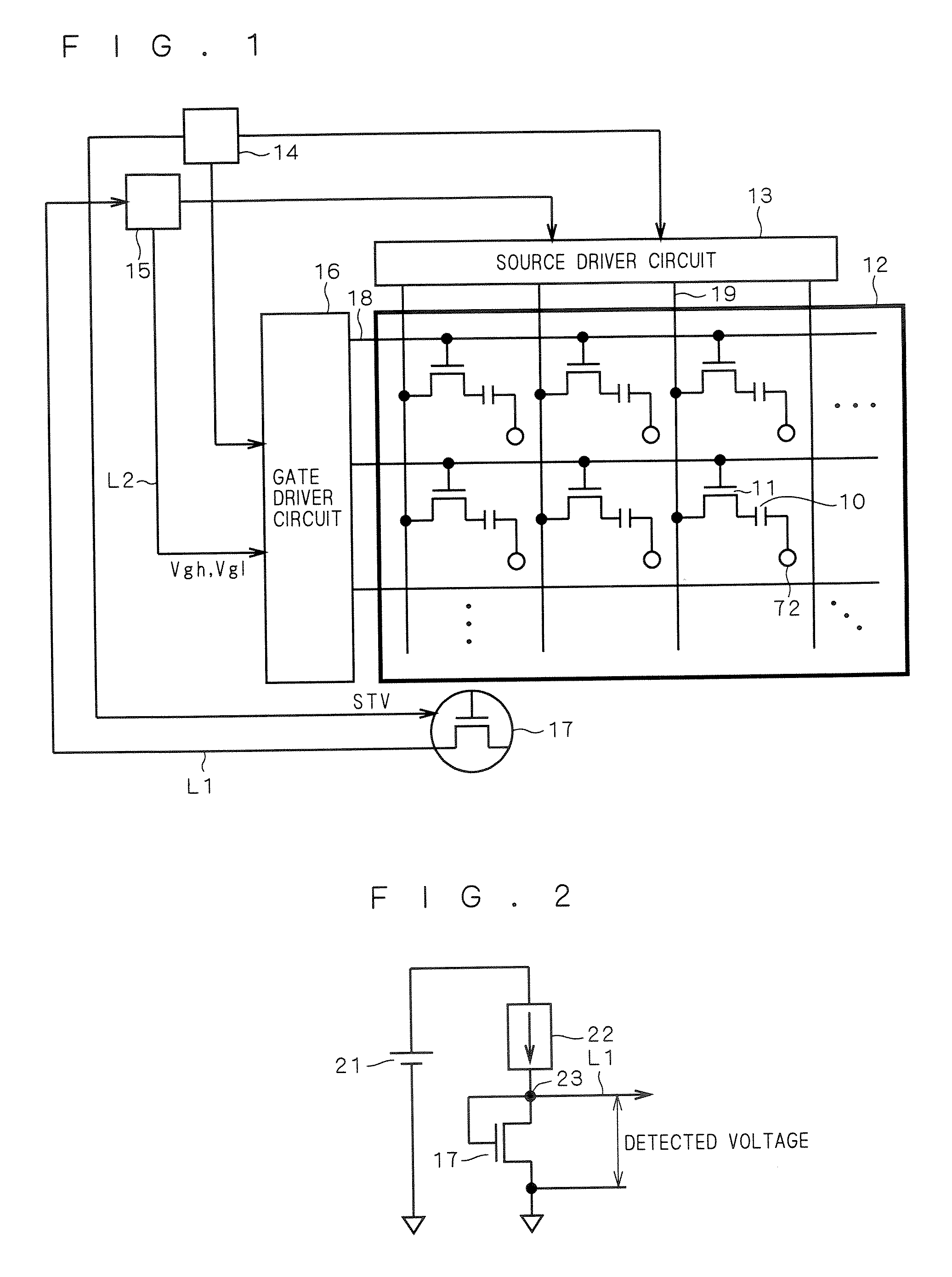

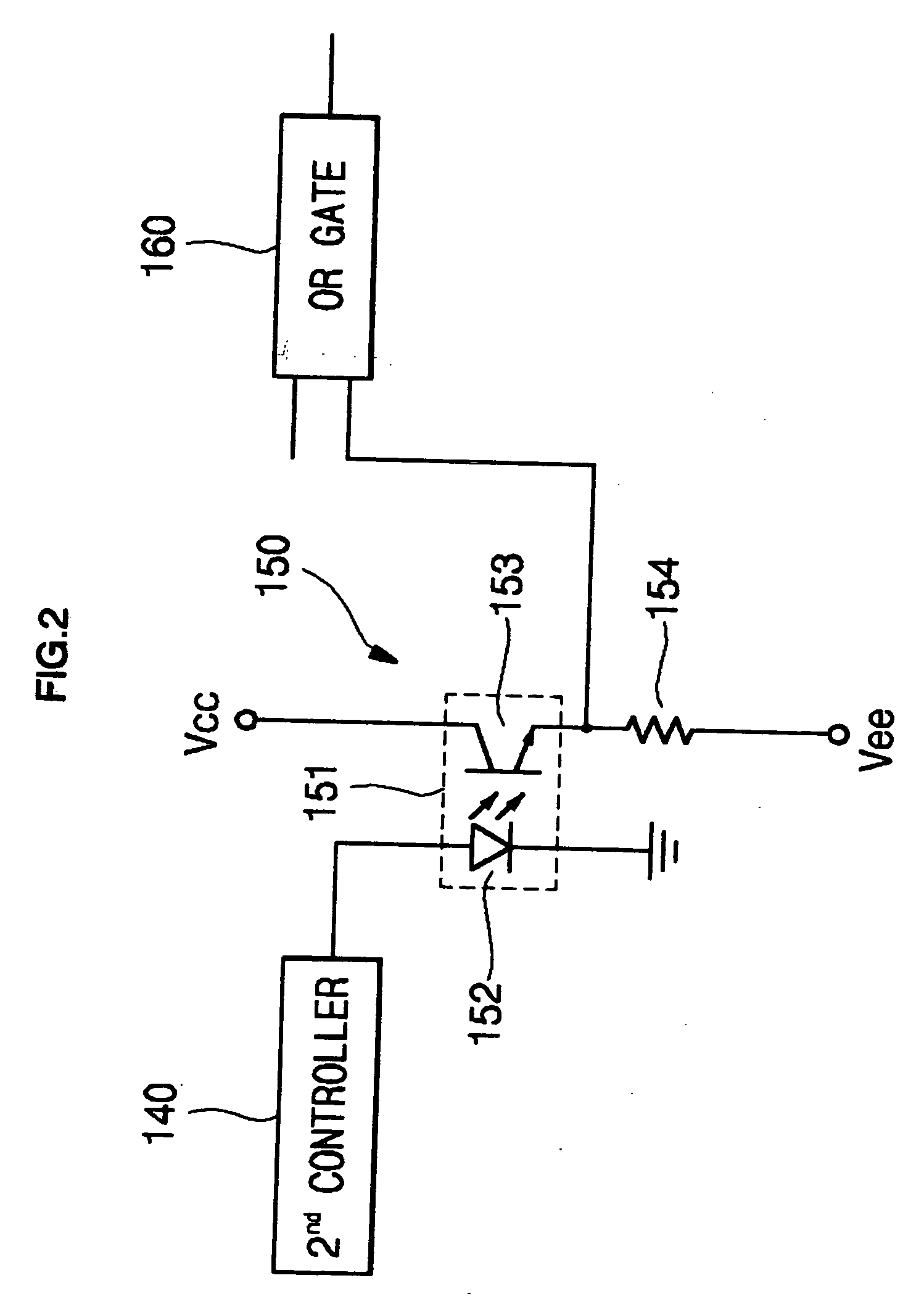

Display device

InactiveUS20070052646A1Simple circuit configurationIncrease the driving voltageStatic indicating devicesNon-linear opticsDisplay deviceSimple circuit

There is disposed a TFT for detecting characteristic having the same characteristic as a pixel TFT disposed at a pixel. The TFT for detecting characteristic detects a gate on voltage for driving the pixel TFT. The TFT for detecting characteristic is driven so as to agree with the pixel TFT in a period of the on state. This provides a display device that is capable of driving the pixel TFT at its optimum driving voltage with a simple circuit configuration, even when the characteristic of the pixel TFT is subjected to temperature change, aged change, and individual variations.

Owner:MITSUBISHI ELECTRIC CORP

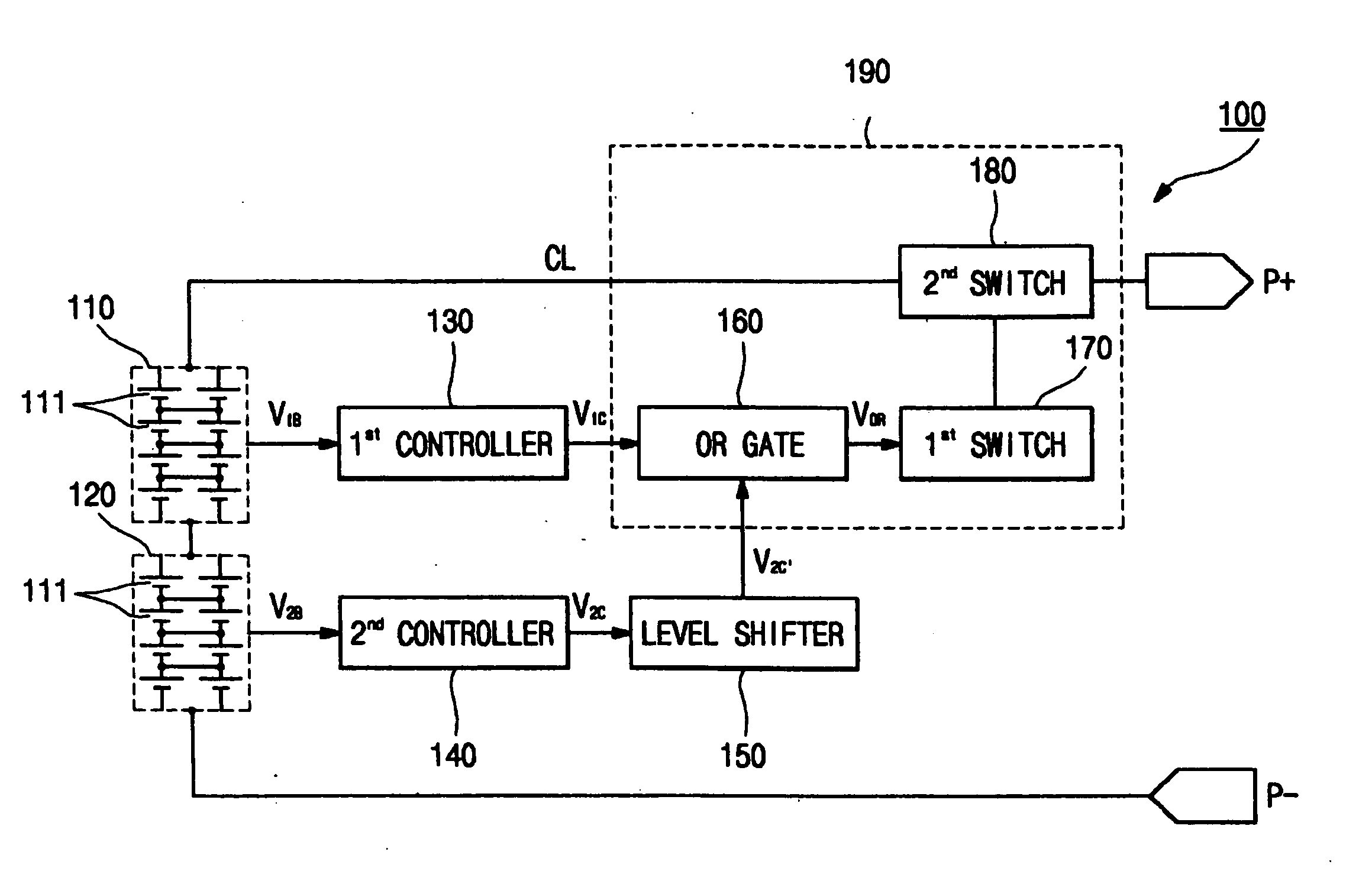

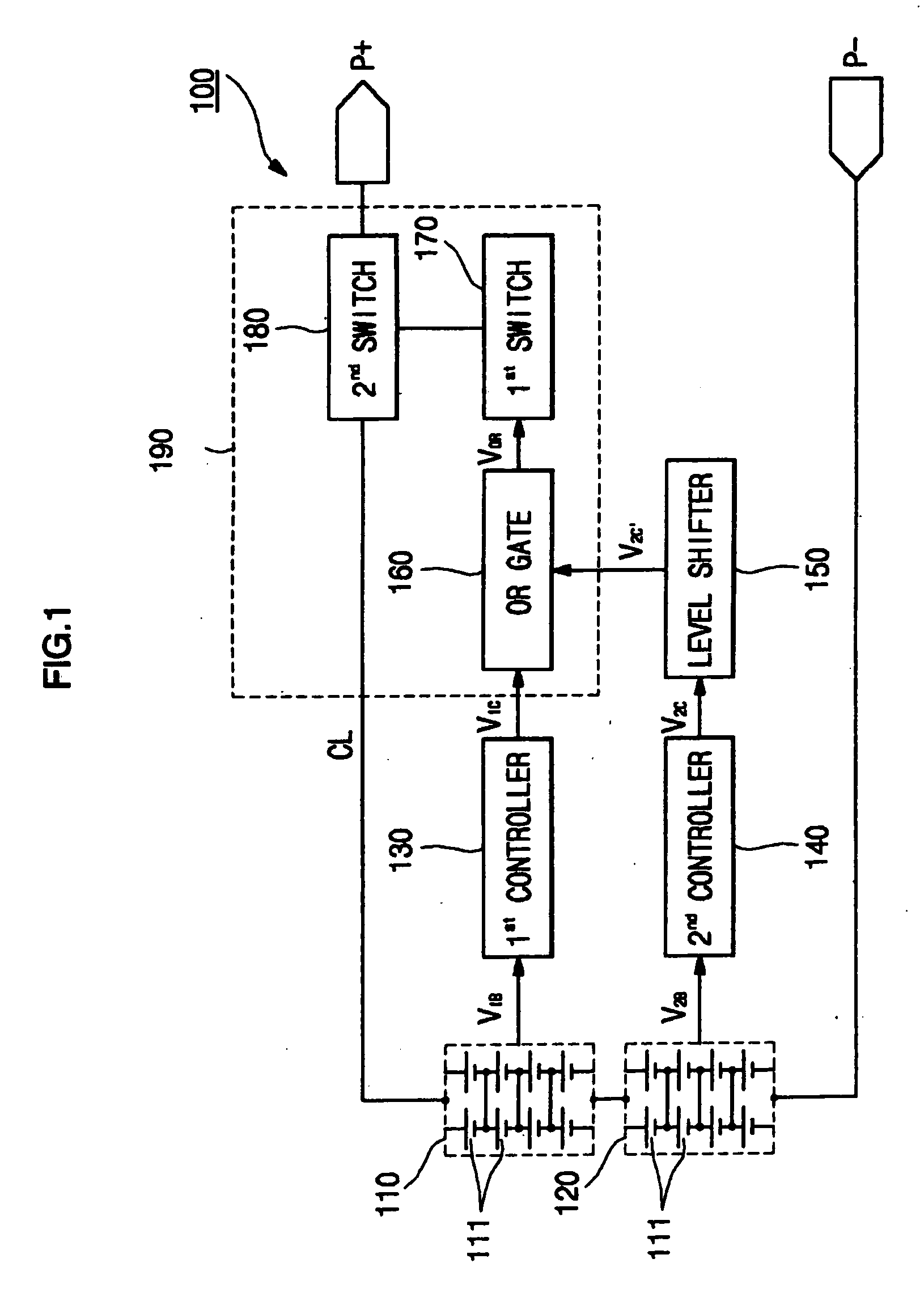

Protective circuit for a secondary battery pack and method of operating the same

InactiveUS20060077603A1Simple circuit configurationPreventing the secondary battery banks from overcharging or over-dischargingCharge equalisation circuitIndicating/monitoring circuitsEngineeringLevel converter

A protective circuit for a secondary battery pack advantageously having a simple circuit configuration while maintaining the safety of banks in the circuit. Each protective circuit has banks adapted to be charged or to discharge voltage, each bank being coupled to a controller that senses the charging or discharging voltage of the bank and outputs a predetermined value if overcharging or over-discharging is sensed. A level shifter is adapted to shift the voltage output from the controller to an adjusted voltage approximately equal to the voltage output from one of the other controllers. A switching means controls the stopping of charging or discharging of the banks.

Owner:SAMSUNG SDI CO LTD

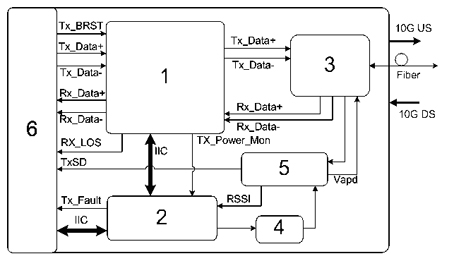

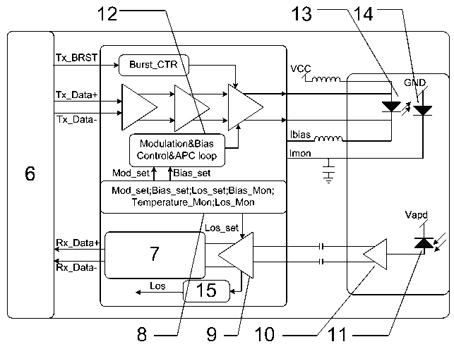

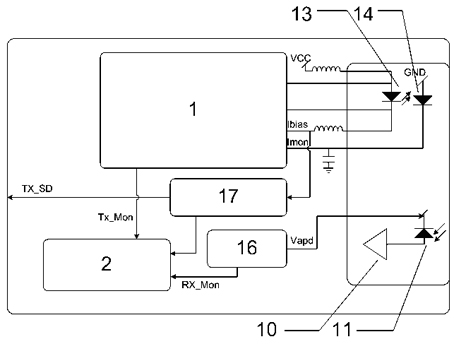

10G Ethernet passive network single-fiber bidirectional optical module

ActiveCN101895350AReduce optical power degradationGuaranteed working characteristicsMultiplex system selection arrangementsElectromagnetic transceiversMicrocontrollerPassive networks

The invention discloses a 10G single-fiber bidirectional optical module, which comprises a burst laser driver, a burst light power indicator, a microcontroller, a single-fiber bidirectional optical device, an avalanche photoelectric diode bias control circuit, a limiting amplifier, a receiving end light power monitor and an SFP+ connector, wherein the microcontroller is mainly used for controlling the burst laser driver and the limiting amplifier; the single-fiber bidirectional optical device is connected between the burst laser driver and the limiting amplifier to realize conversion between electrical signals and light signals; and the avalanche photoelectric diode bias control circuit supplies a high bias voltage to a receiving end avalanche photoelectric diode and performs voltage compensation on the receiving end avalanche photoelectric diode according to the temperature property. The 10G single-fiber bidirectional optical module has the advantages of low design cost, simple circuit design and capability of meeting the requirement of a 10G EPON ONU symmetrical scheme.

Owner:SOURCE PHOTONICS CHENGDU