Patents

Literature

5702 results about "External circuit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

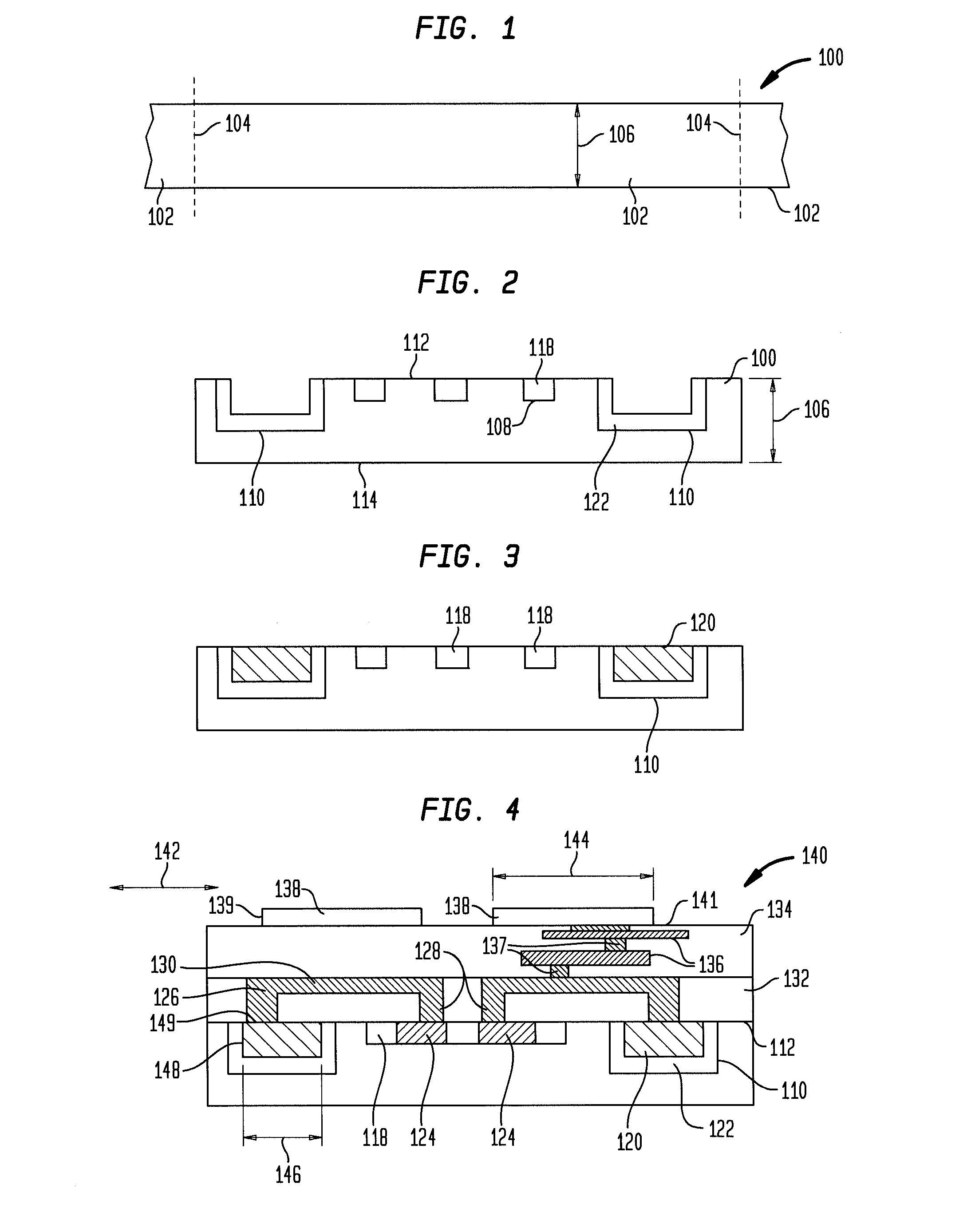

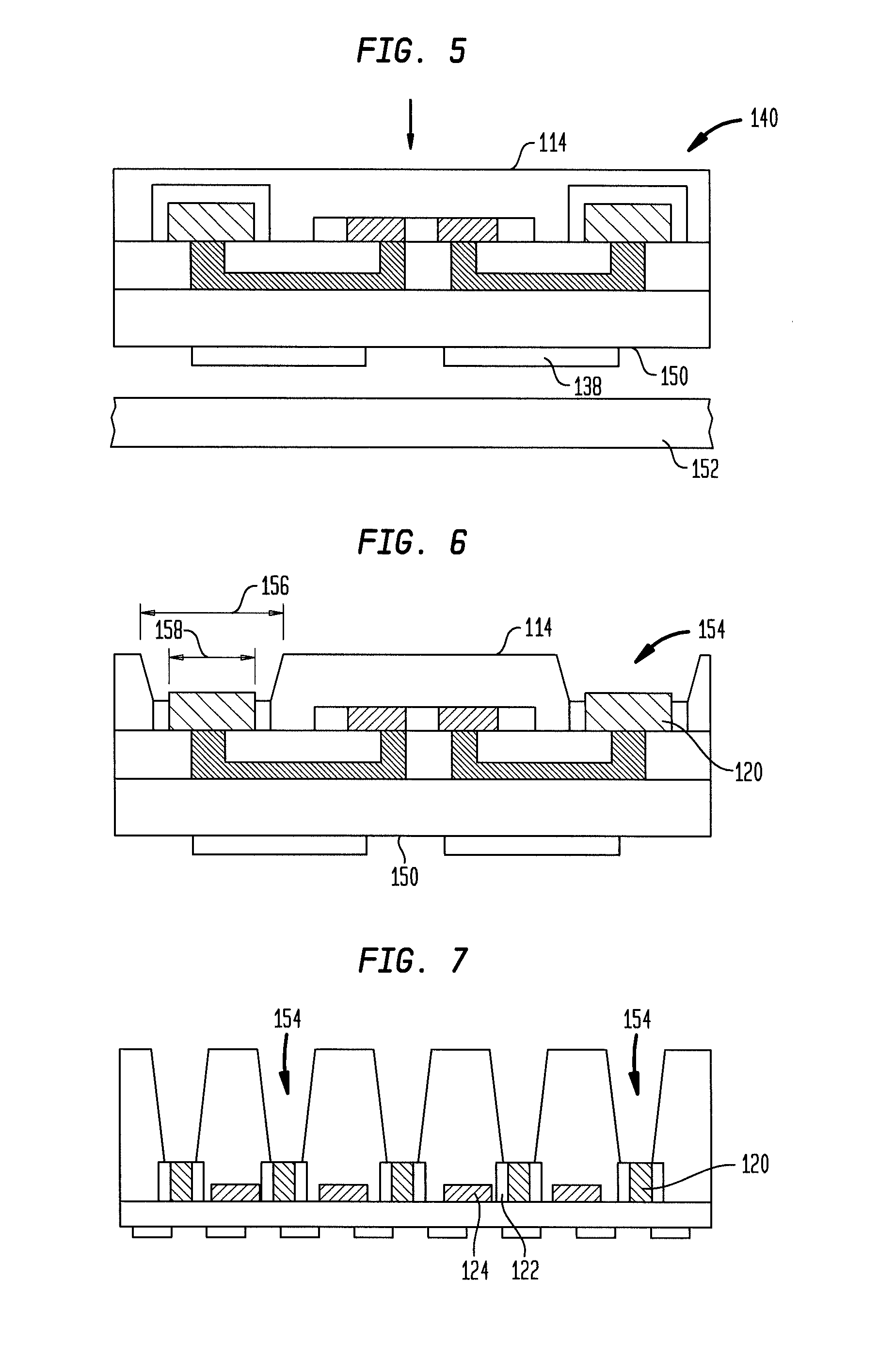

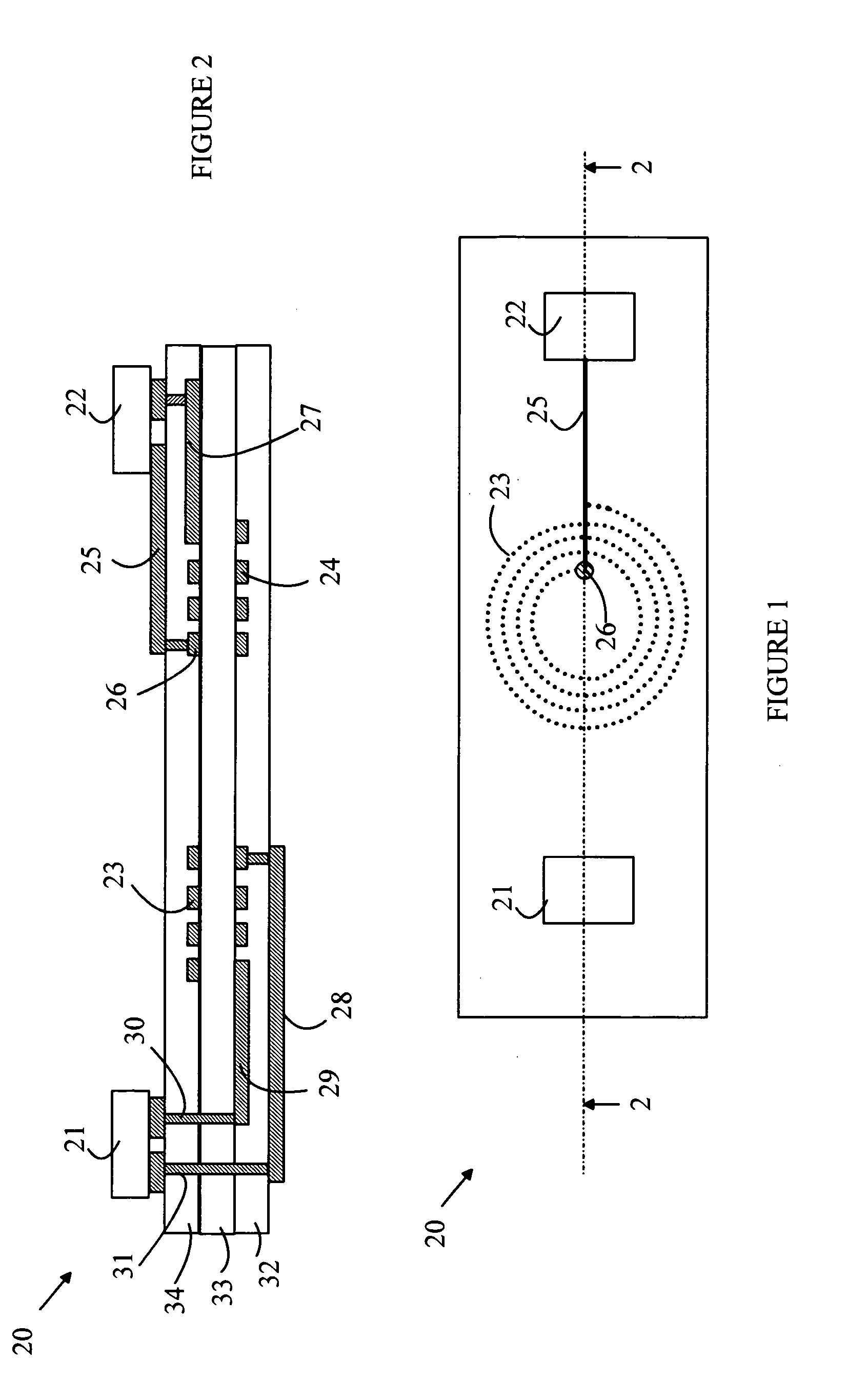

System-in packages

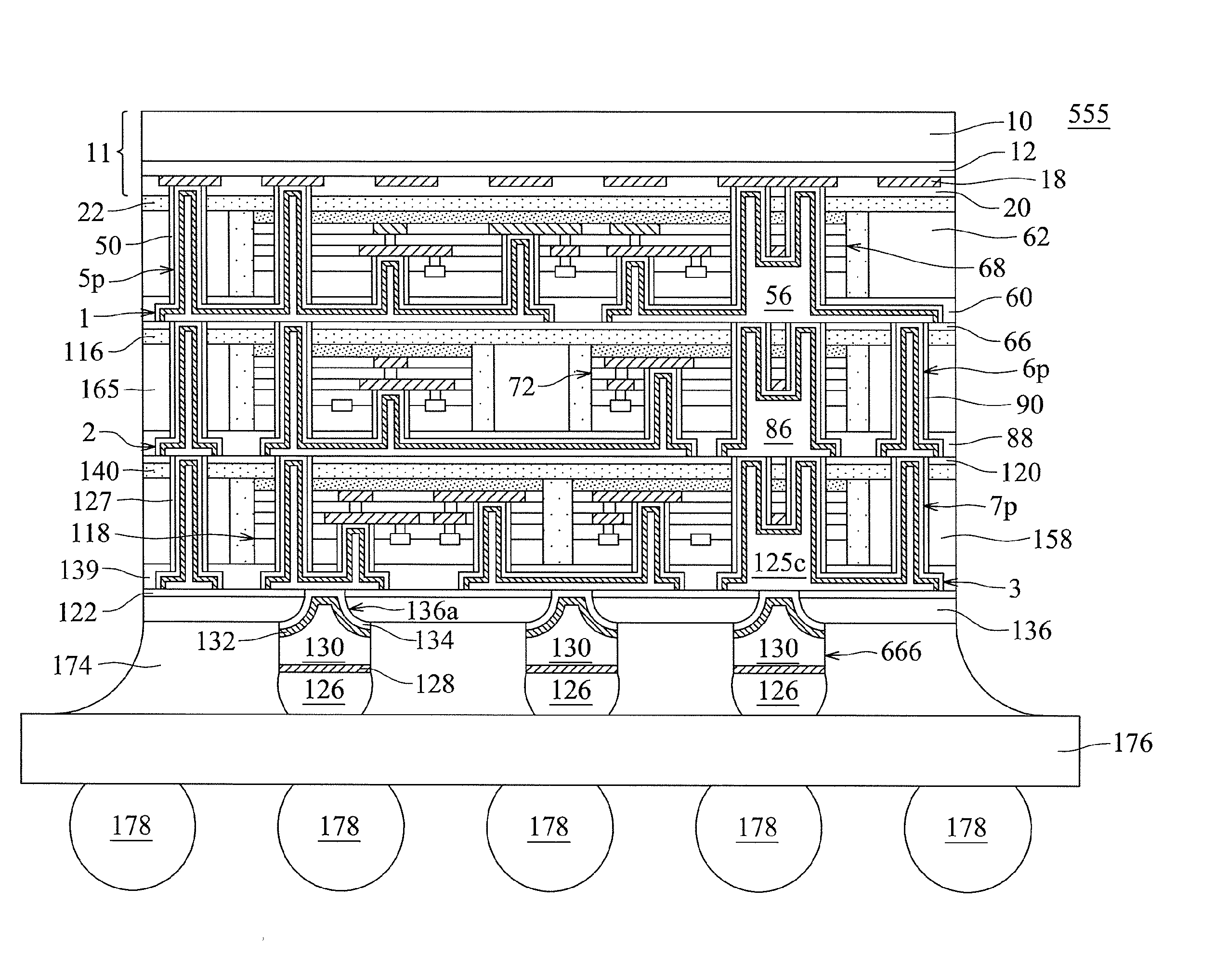

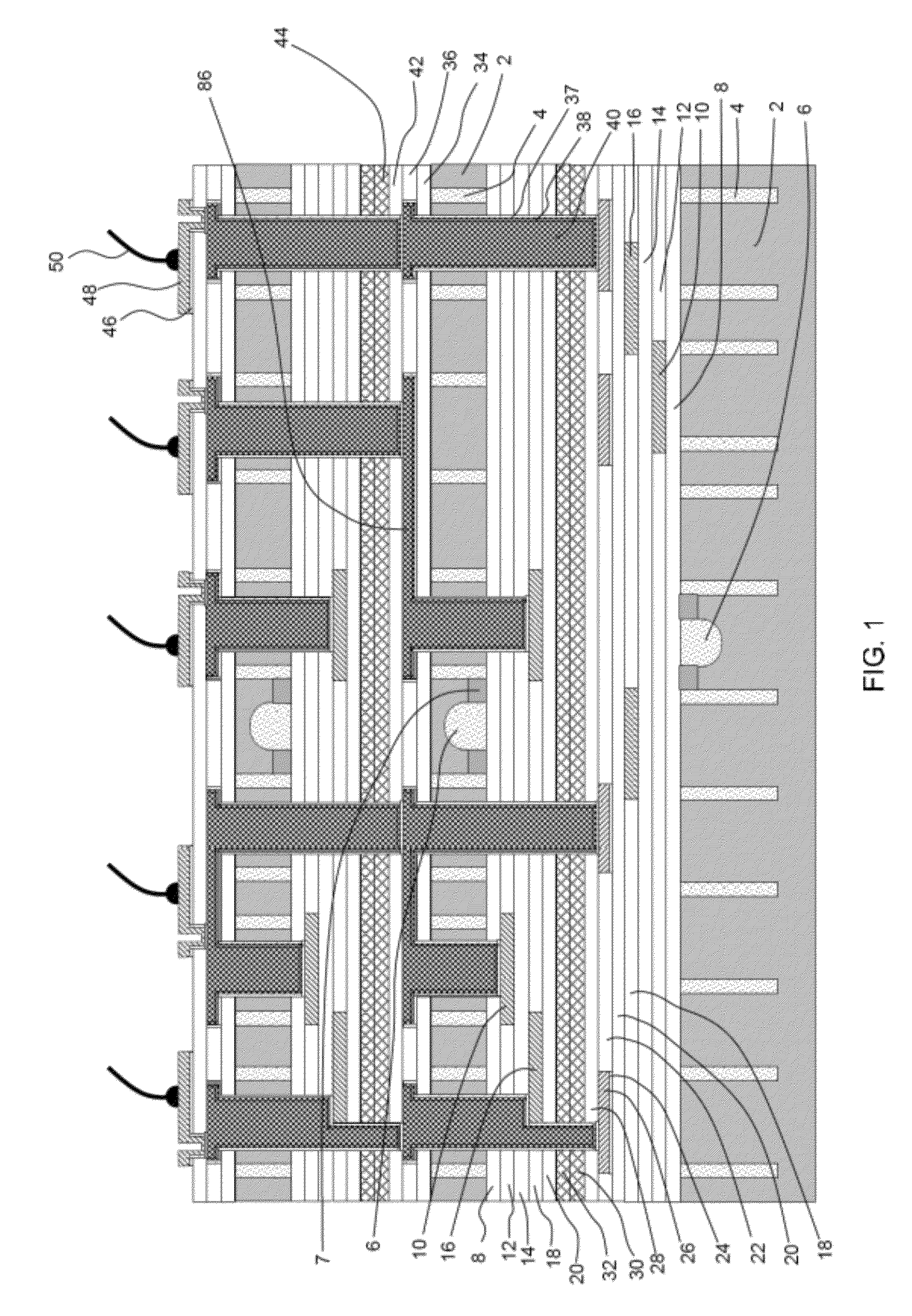

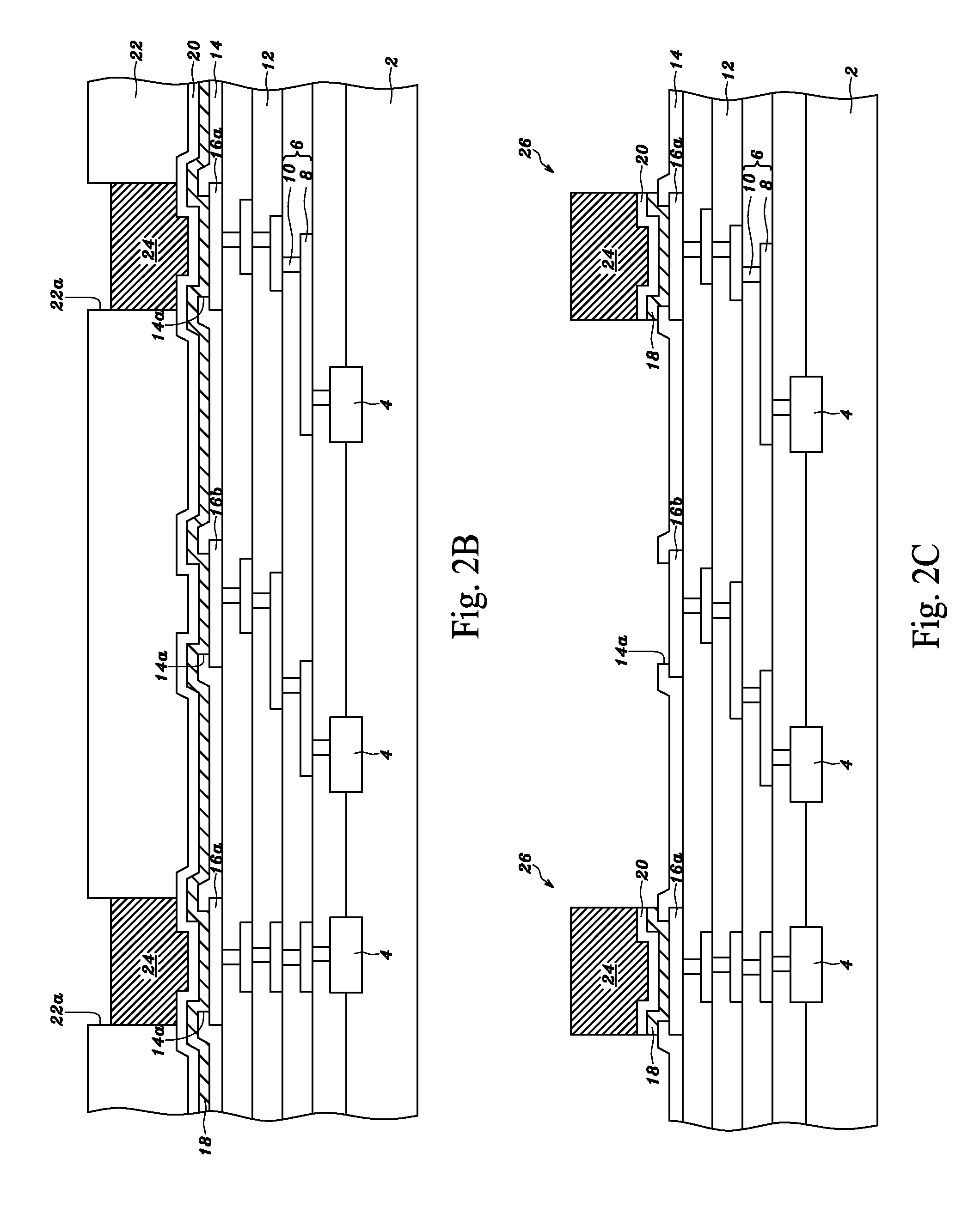

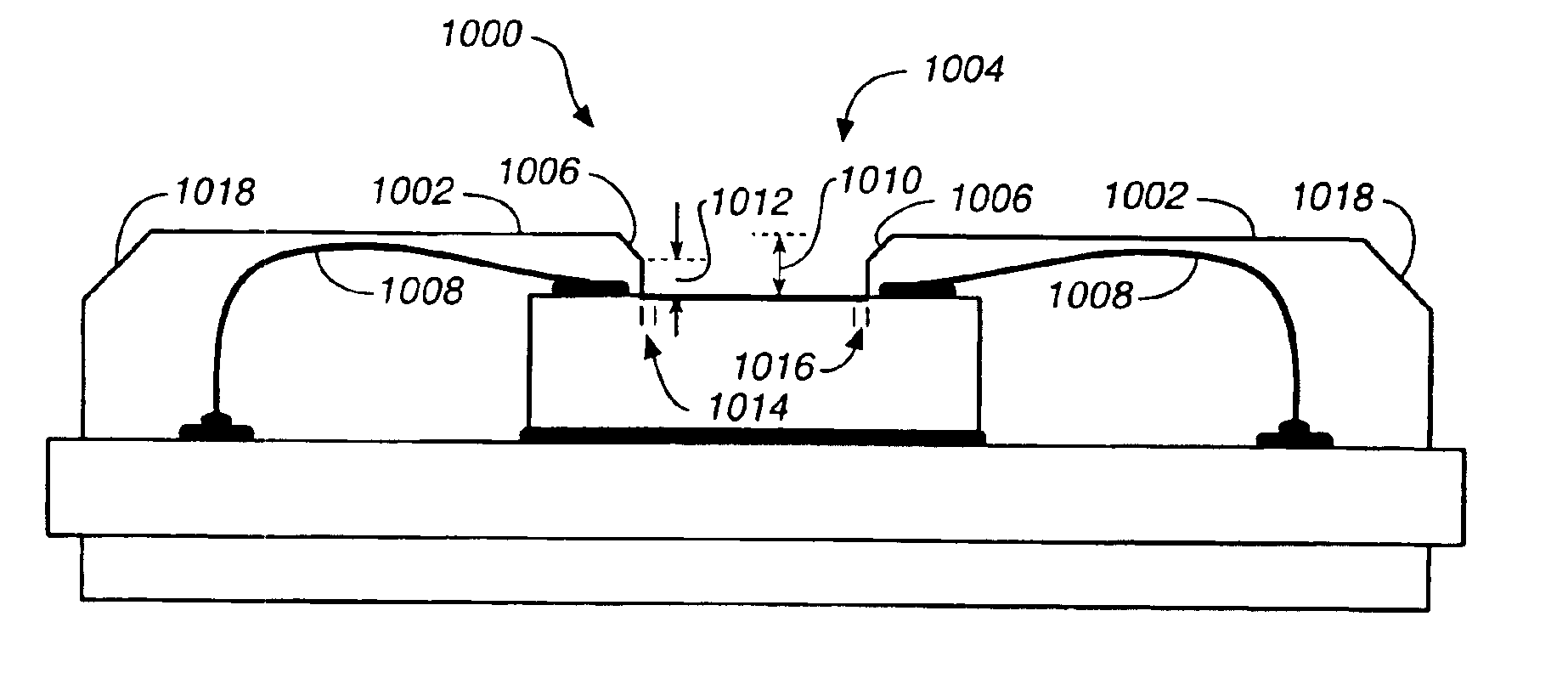

ActiveUS20110026232A1Improve uniformitySemiconductor/solid-state device detailsCircuit arrangements on support structuresMetal interconnectSystem in package

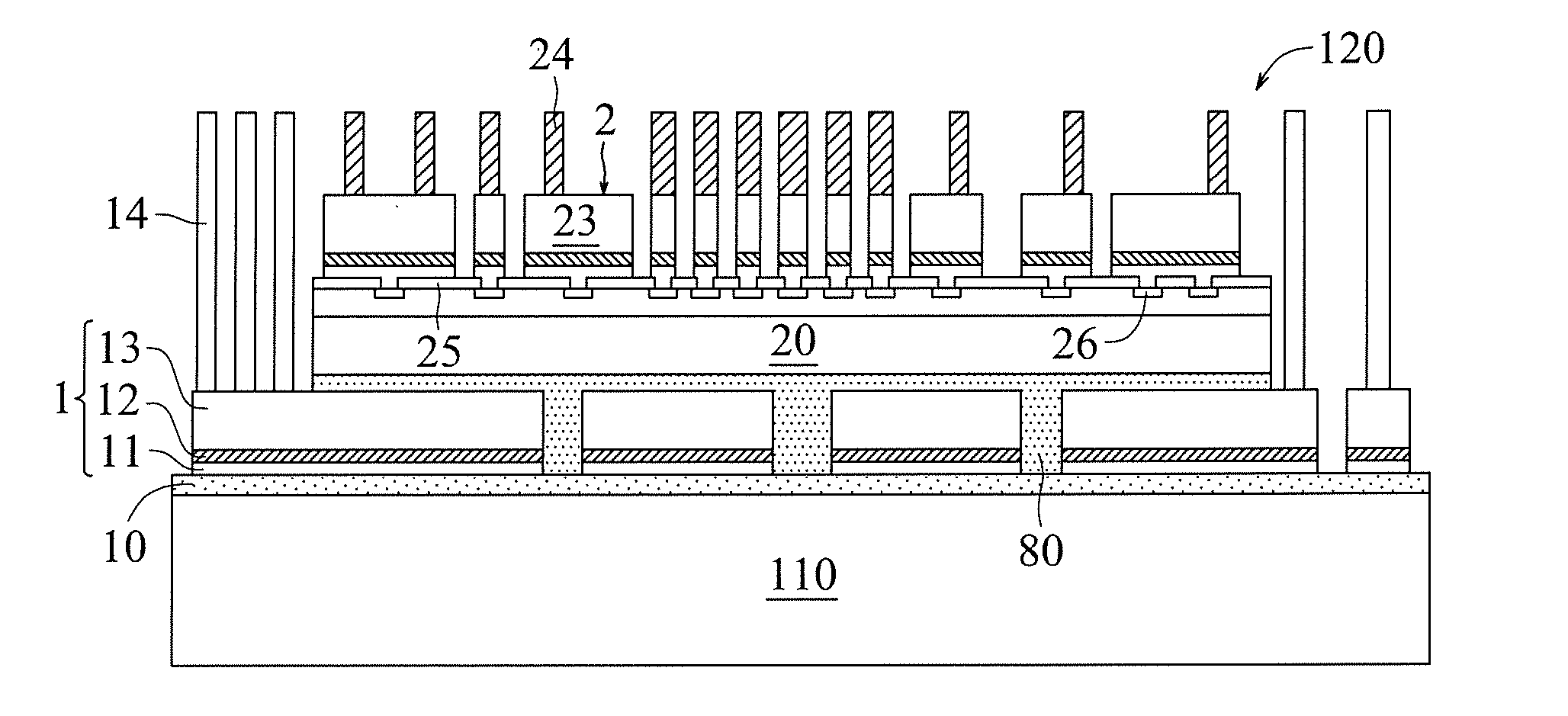

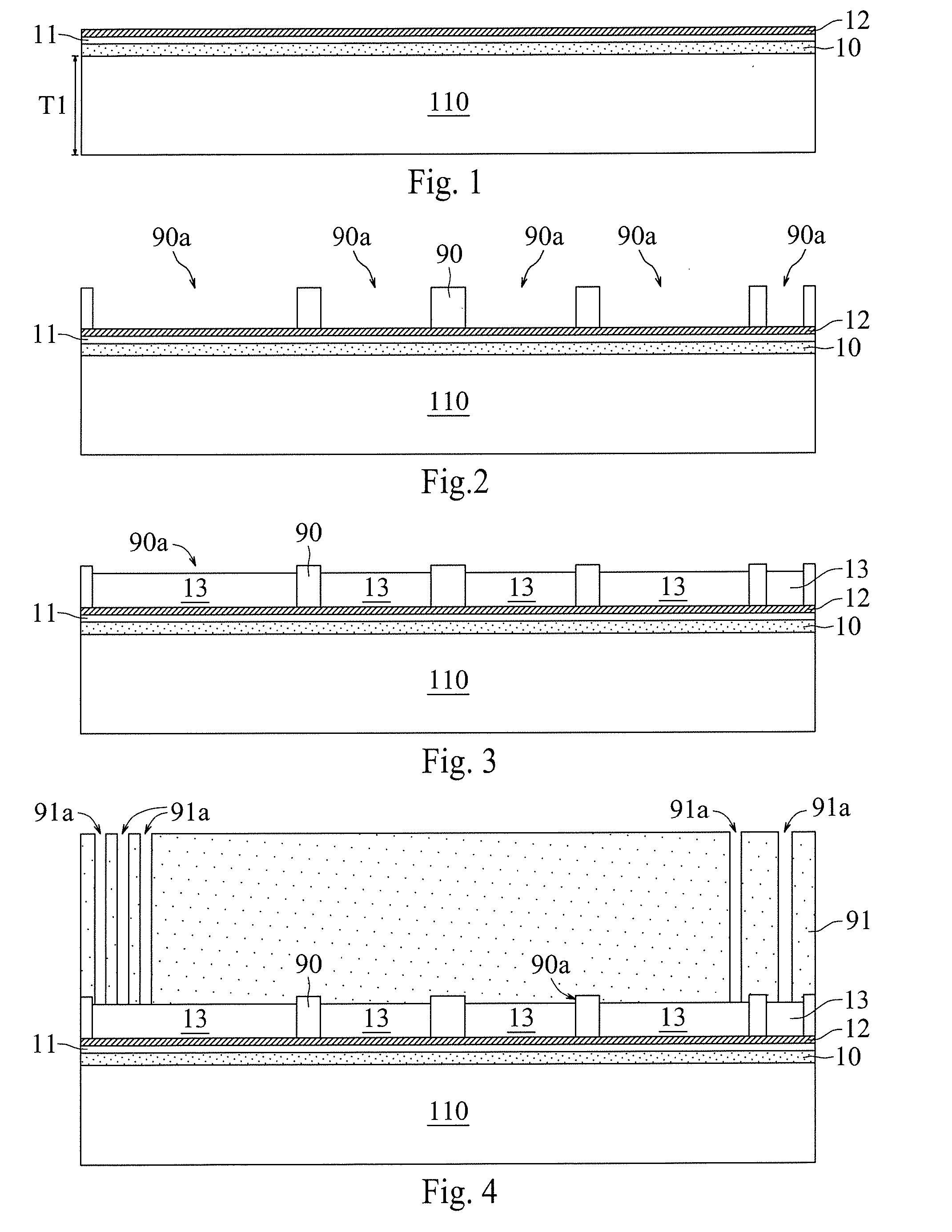

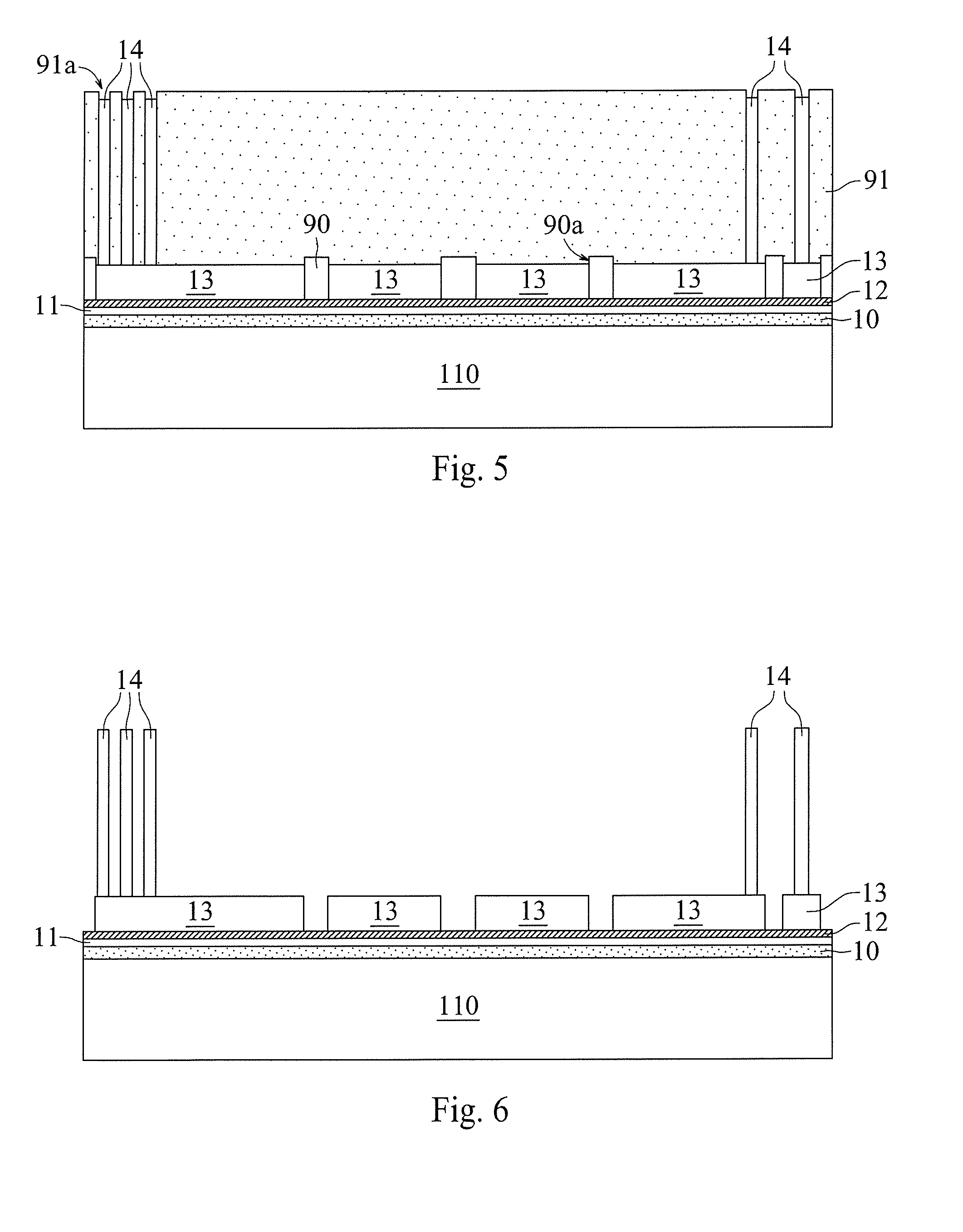

System-in packages, or multichip modules, are described which can include multi-layer chips and multi-layer dummy substrates over a carrier, multiple through vias blindly or completely through the multi-layer chips and completely through the multi-layer dummy substrates, multiple metal plugs in the through vias, and multiple metal interconnects, connected to the metal plugs, between the multi-layer chips. The multi-layer chips can be connected to each other or to an external circuit or structure, such as mother board, ball grid array (BGA) substrate, printed circuit board, metal substrate, glass substrate, or ceramic substrate, through the metal plugs and the metal interconnects.

Owner:QUALCOMM INC

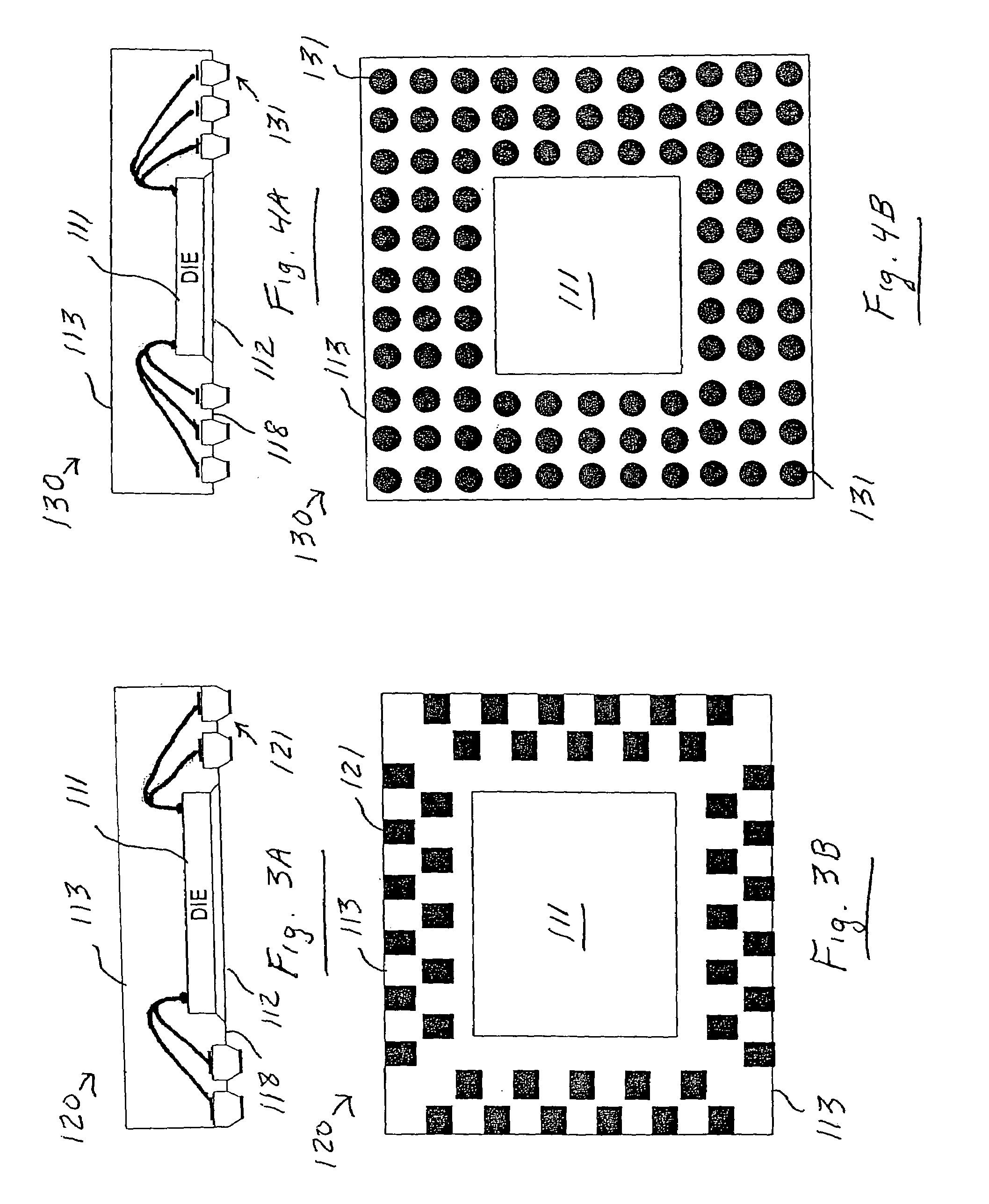

Multichip Packages

InactiveUS20120193785A1Semiconductor/solid-state device detailsSolid-state devicesData connectionEngineering

Multichip packages or multichip modules may include stacked chips and through silicon / substrate vias (TSVs) formed using enclosure-first technology. Enclosure-first technology may include forming an isolation enclosure associated with a TSV early in the fabrication process, without actually forming the associated TSV. The TSV associated with the isolation enclosure is formed later in the fabrication process. The enclosure-first technology allows the isolation enclosures to be used as alignment marks for stacking additional chips. The stacked chips can be connected to each other or to an external circuit such that data input is provided through the bottom-most (or topmost) chip, data is output from the bottom-most (or topmost) chip. The multichip package may provide a serial data connection, and a parallel connection, to each of the stacked chips.

Owner:MEGIT ACQUISITION

System-in packages

ActiveUS8503186B2Improve uniformityCircuit arrangements on support structuresSemiconductor/solid-state device detailsMetal interconnectSystem in package

Owner:QUALCOMM INC

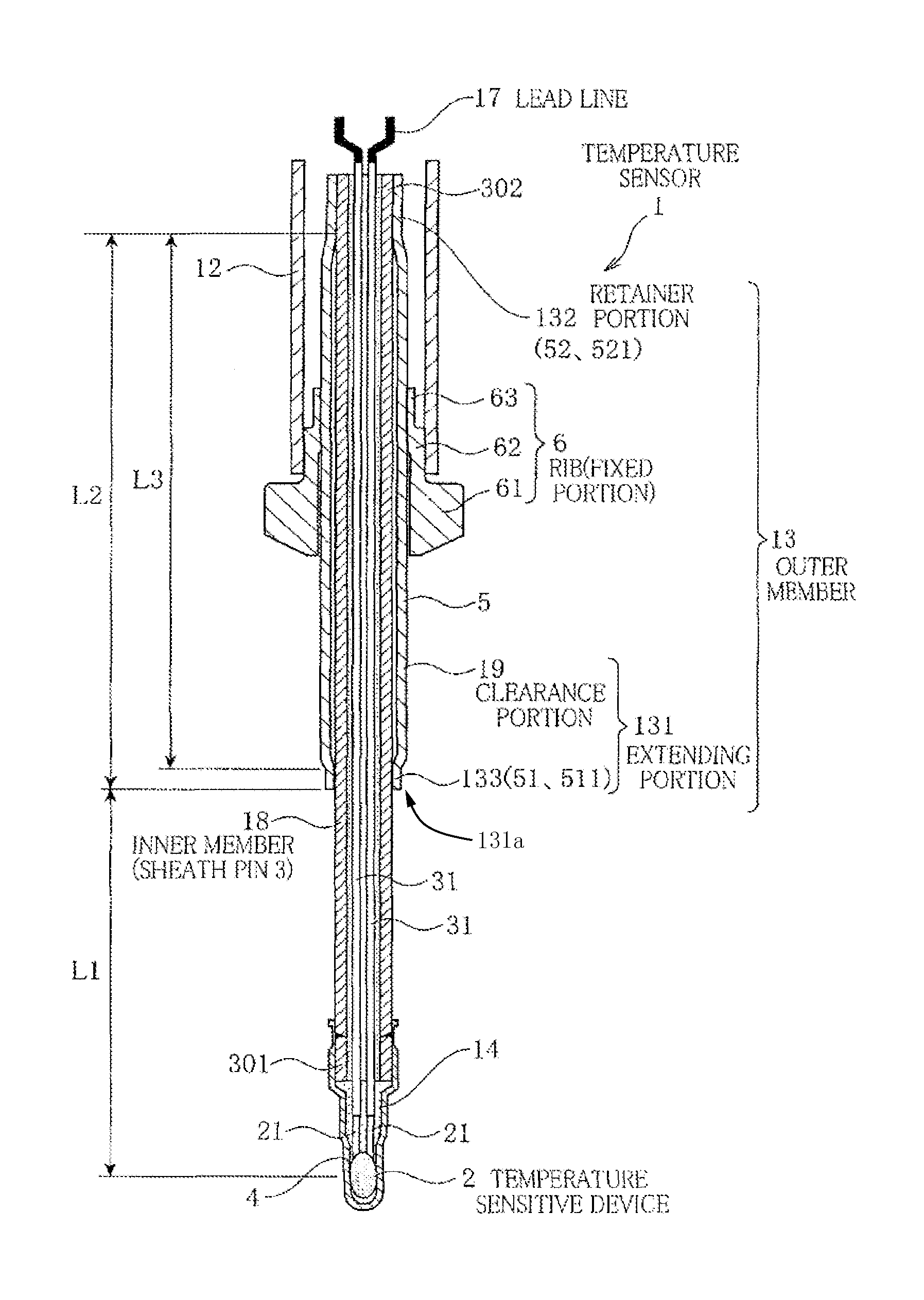

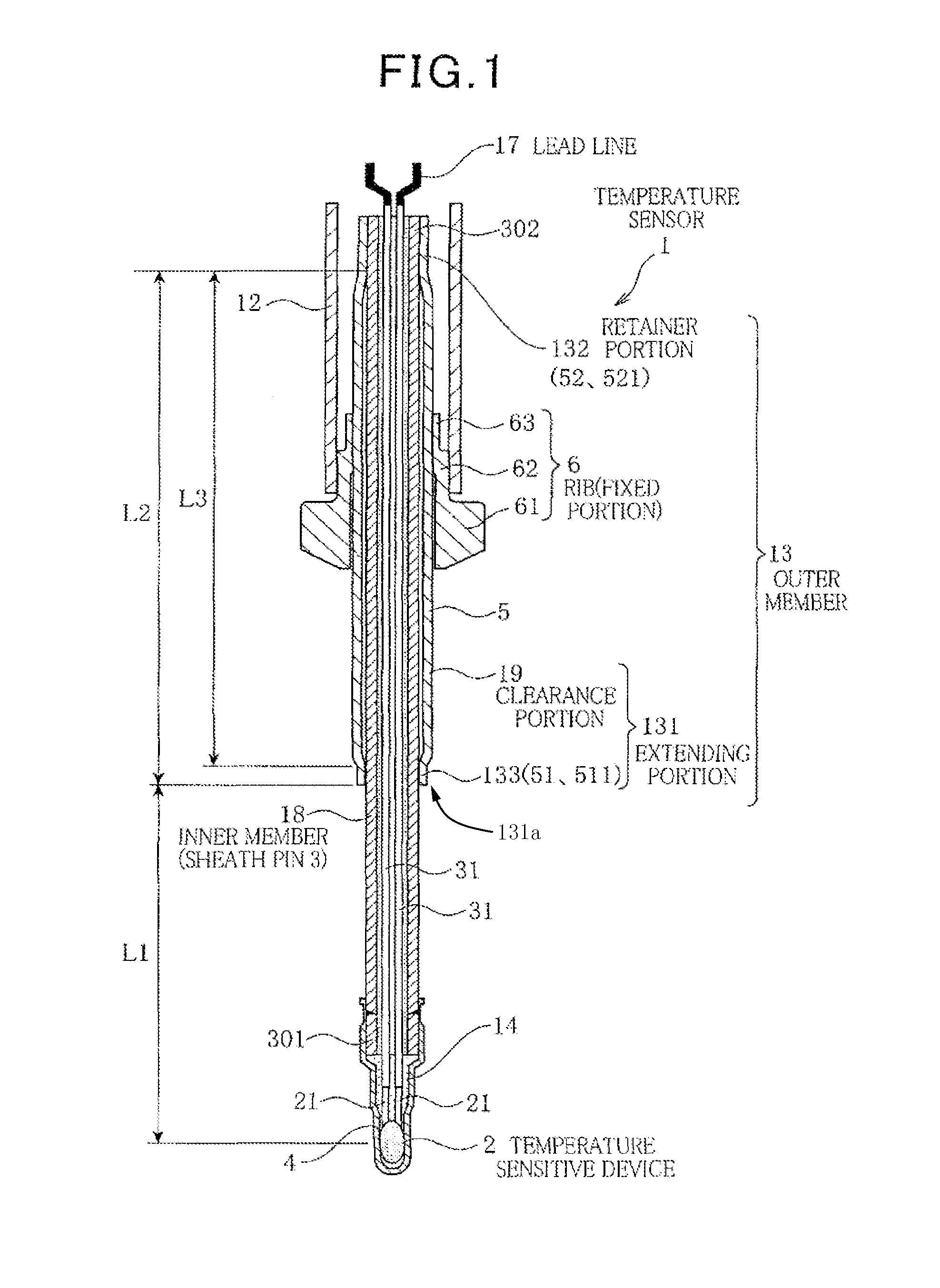

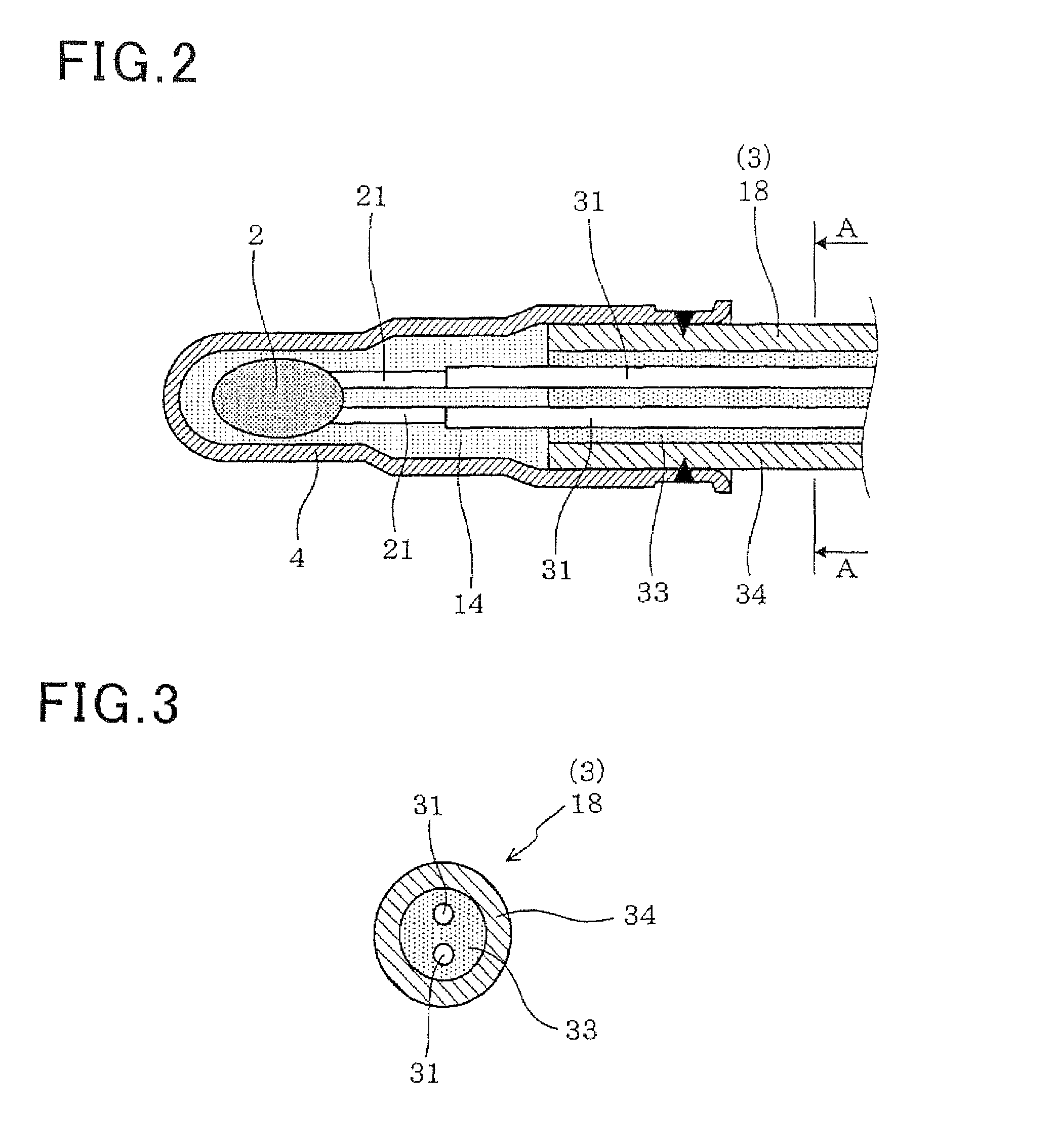

Temperature sensor

ActiveUS8864375B2Reduce vibrationReduce the overall heightThermometer detailsTemperature measurement in motorsInternal combustion engineExhaust pipe

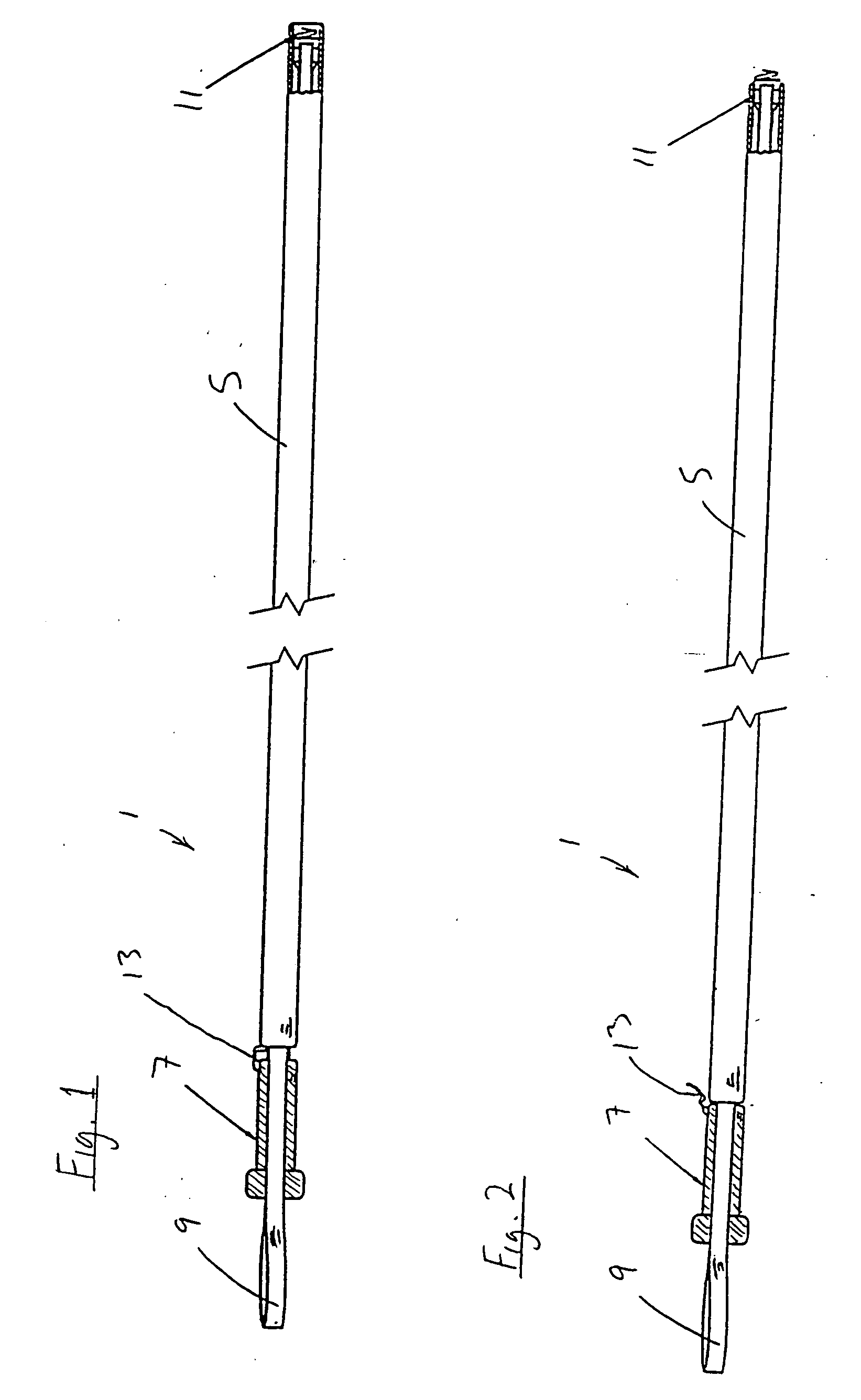

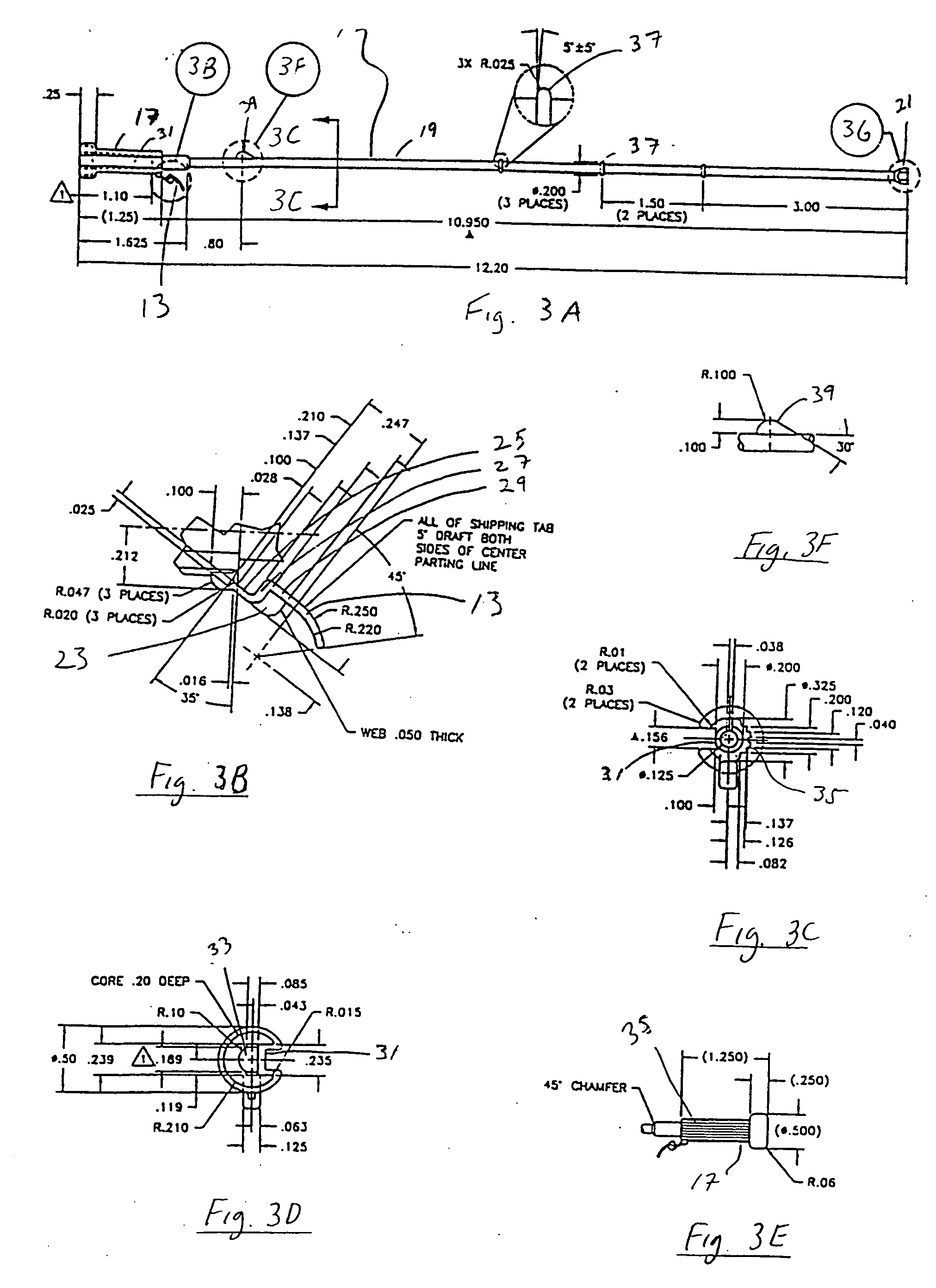

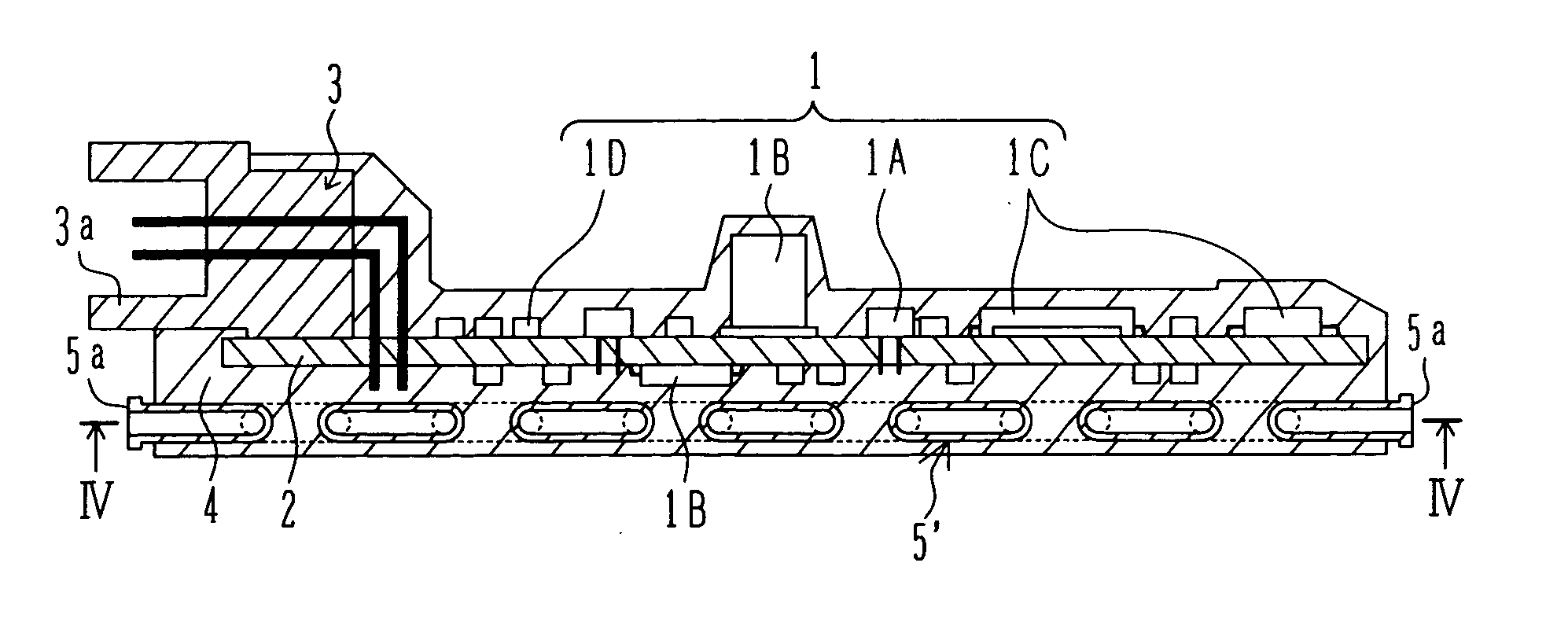

The temperature sensor 1 is equipped with a temperature sensitive device 2 to be disposed inside an exhaust pipe of an internal combustion engine, signal lines 31 connected at a top end side to the temperature sensitive device 2 and at a rear end side to leads for connection with an external circuit, an inner member 18 having a sheath pin 3 in which the signal lines 31 are disposed, and an outer member 13 disposed to cover at least a portion of an outer periphery of the inner member 18. The outer member 13 includes a fixed portion (rib 6) to be fixed to an upper wall of the exhaust pipe, a retainer portion 132 retaining the inner member 18, and an extending portion 131 formed closer to a top end side than the retainer portion 132. The extending portion 131 includes a clearance portion 19 disposed so as to have an air gap between itself and the inner member 18 and a front interference portion 133 disposed in a condition that a maximum air gap between the front interference portion 133 and the inner member 18 in a radius direction is 0.2 mm or less.

Owner:DENSO CORP

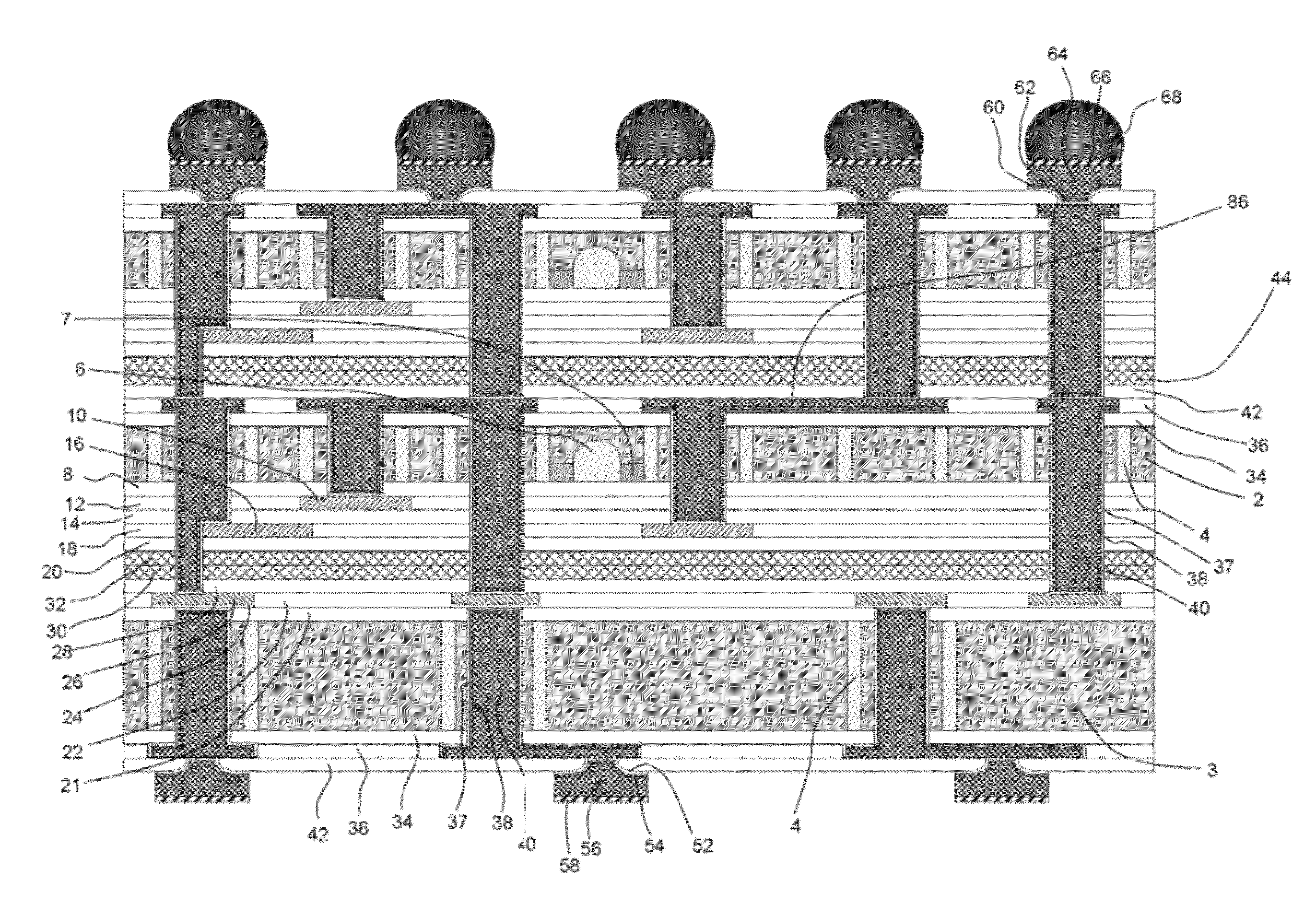

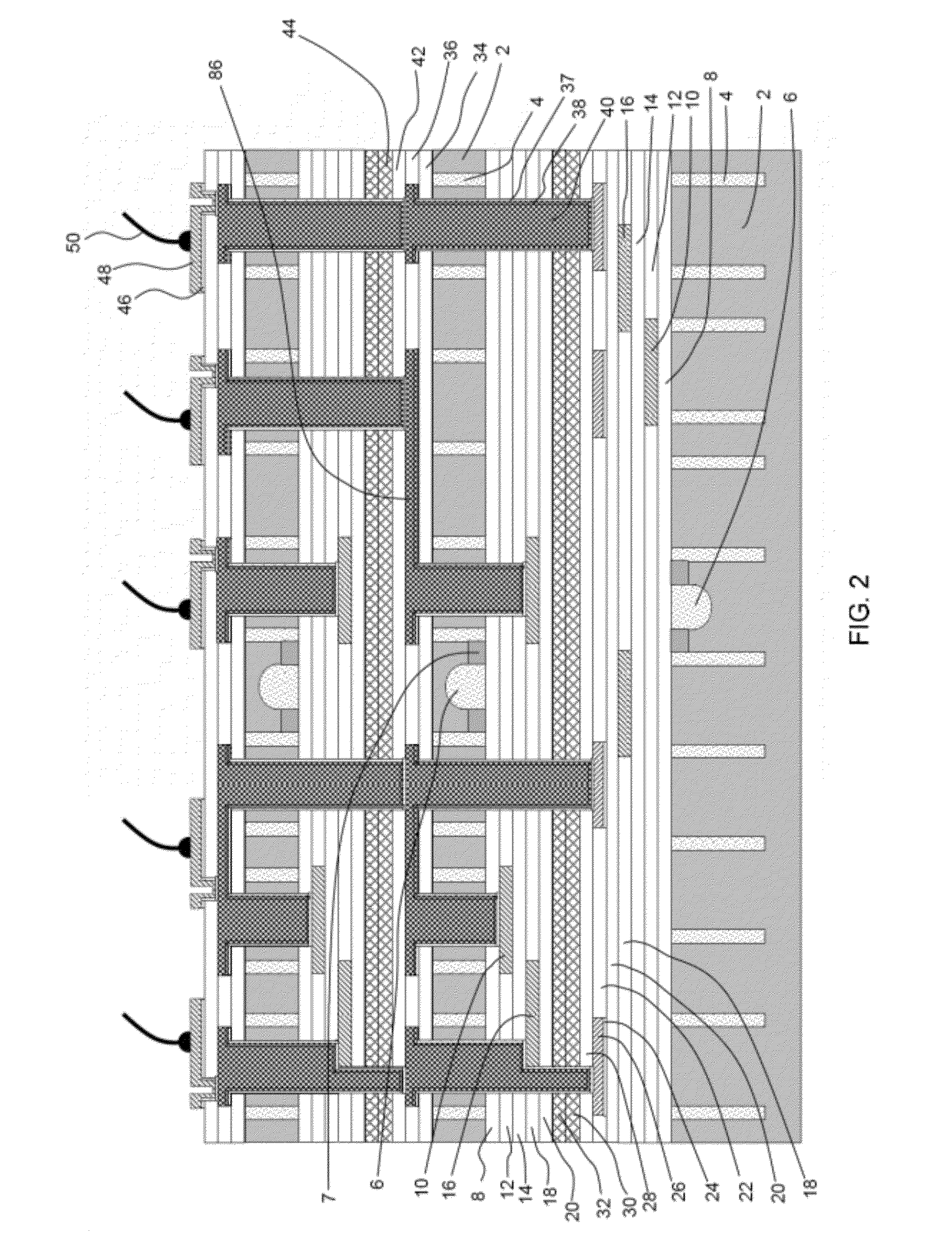

Microelectronic elements with rear contacts connected with via first or via middle structures

ActiveUS20120018863A1Semiconductor/solid-state device detailsSolid-state devicesElectricityElectrical connection

A microelectronic unit includes a microelectronic element, e.g., an integrated circuit chip, having a semiconductor region of monocrystalline form. The semiconductor region has a front surface extending in a first direction, an active circuit element adjacent the front surface, a rear surface remote from the front surface, and a conductive via which extends towards the rear surface. The conductive via can be insulated from the semiconductor region by an inorganic dielectric layer. An opening can extend from the rear surface partially through a thickness of the semiconductor region, with the opening and the conductive via having respective widths in the first direction. The width of the opening may be greater than the width of the conductive via where the opening meets the conductive via. A rear contact can be electrically connected to the conductive via and exposed at the rear surface for electrical connection with an external circuit element, such as another like microelectronic unit, a microelectronic package, or a circuit panel.

Owner:TESSERA INC

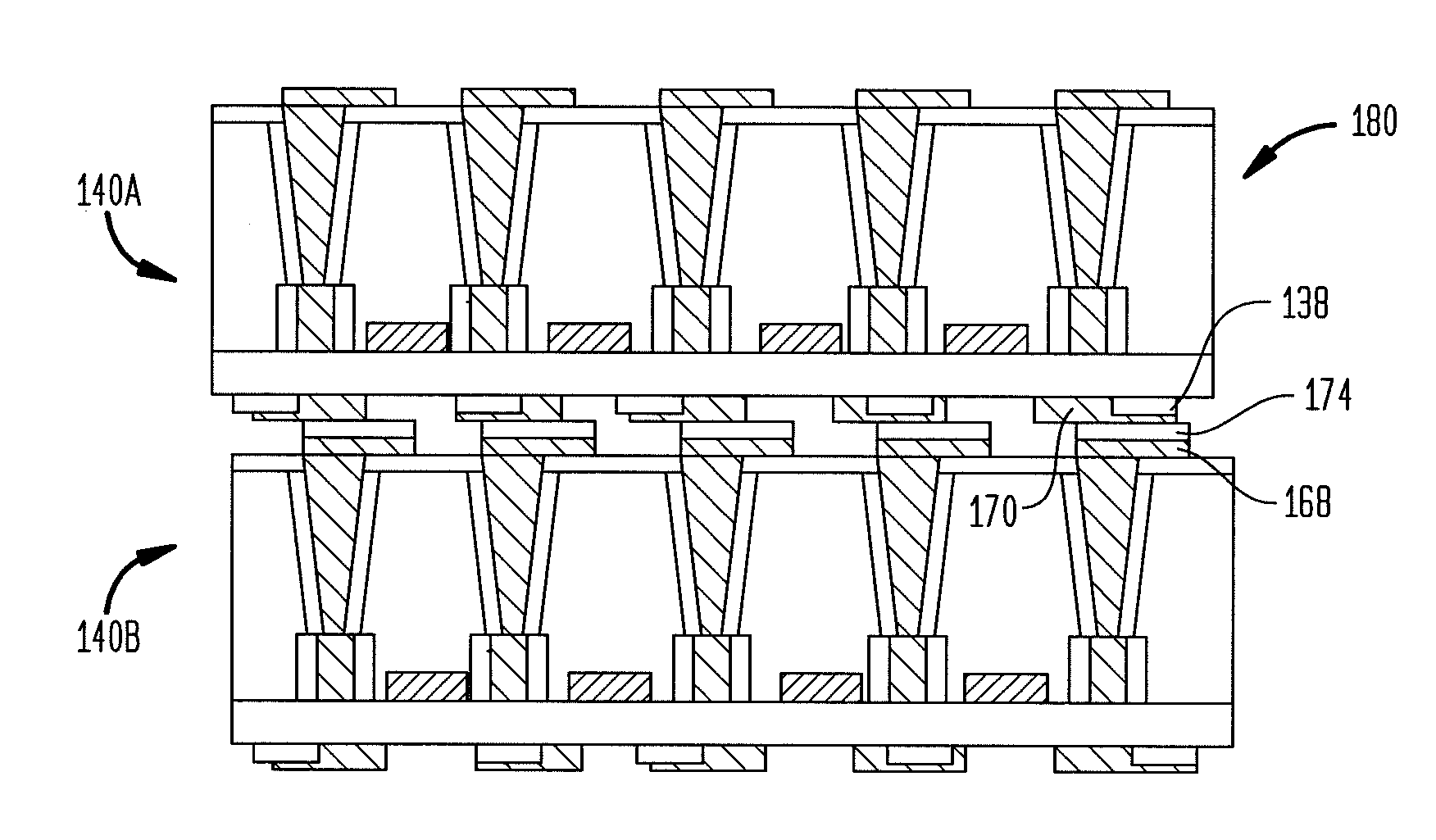

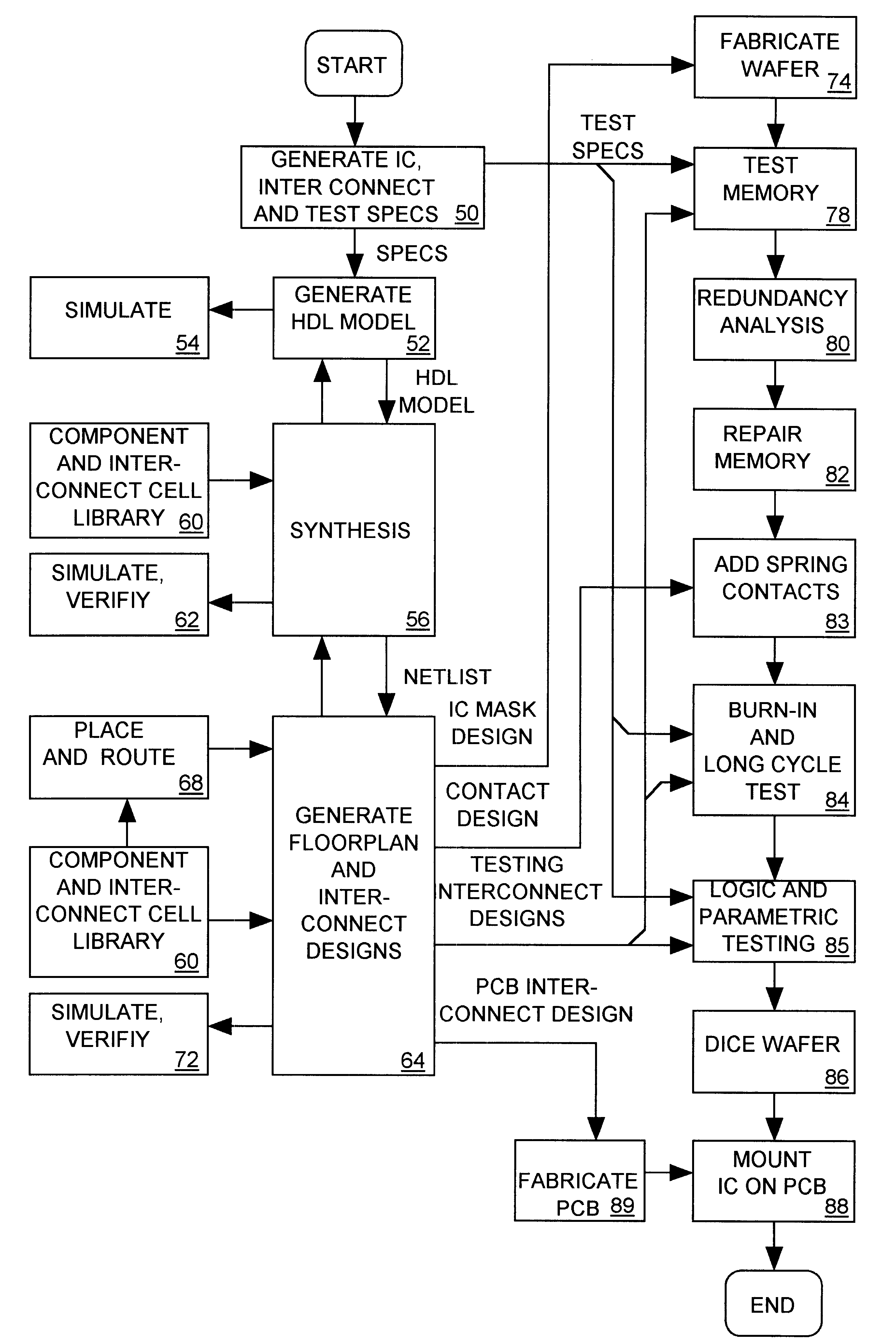

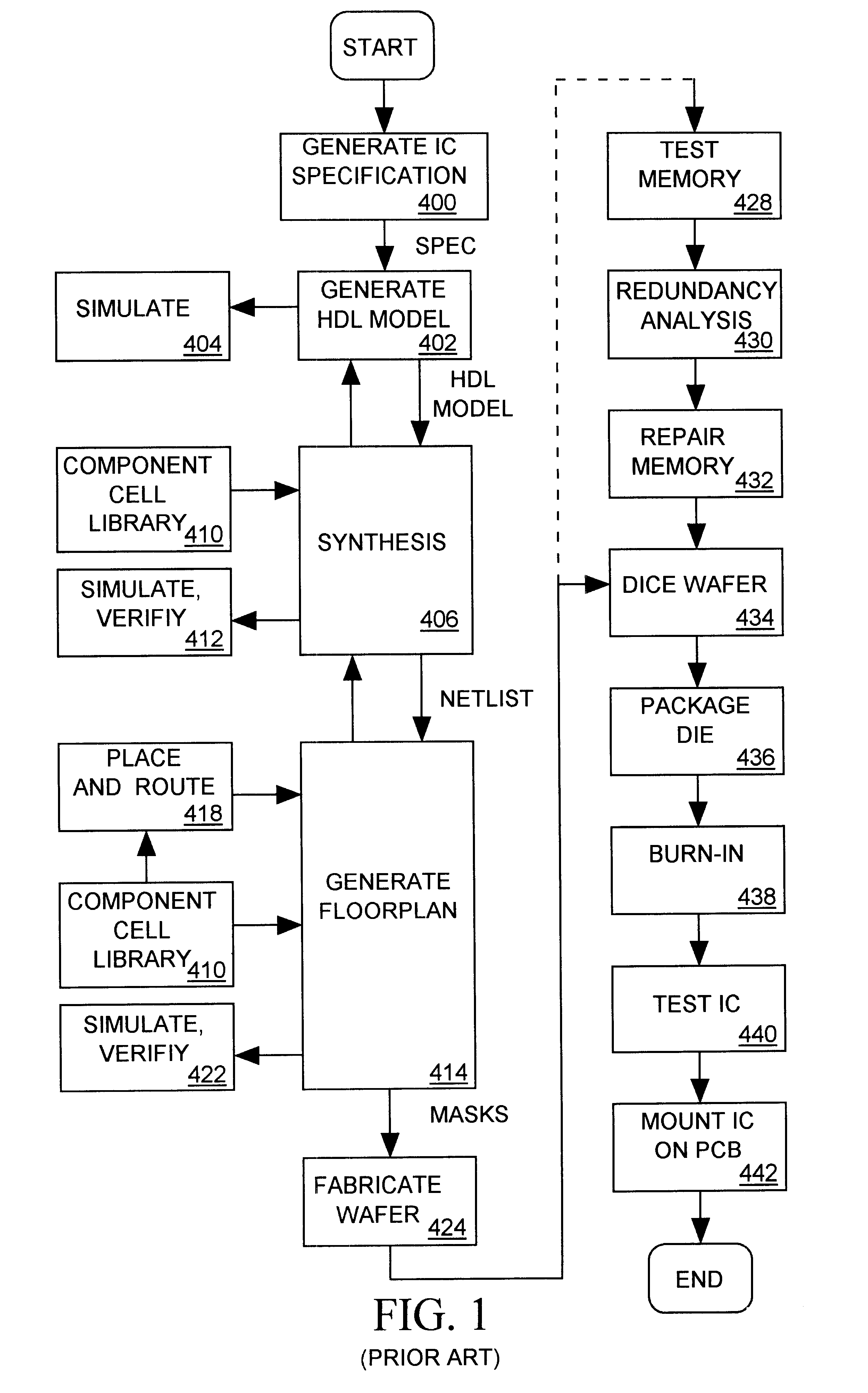

Method of designing, fabricating, testing and interconnecting an IC to external circuit nodes

InactiveUS6539531B2Easy to optimizeMultiple-port networksSemiconductor/solid-state device detailsEngineeringInterconnection

Owner:FORMFACTOR INC

Chip package and method for fabricating the same

ActiveUS20070205520A1Semiconductor/solid-state device detailsSolid-state devicesAnisotropic conductive filmLead bonding

A chip package includes a semiconductor substrate, a first metal pad over the semiconductor substrate, and a second metal pad over the semiconductor substrate. In a case, the first metal pad is tape automated bonded thereto, and the second metal pad is solder bonded thereto. In another case, the first metal pad is tape automated bonded thereto, and the second metal pad is wirebonded thereto. In another case, the first metal pad is solder bonded thereto, and the second metal pad is wirebonded thereto. In another case, the first metal pad is bonded to an external circuitry using an anisotropic conductive film, and the second metal pad is solder bonded thereto. In another case, the first metal pad is bonded to an external circuitry using an anisotropic conductive film, and the second metal pad is wirebonded thereto.

Owner:SUMITOMO ELECTRIC IND LTD +1

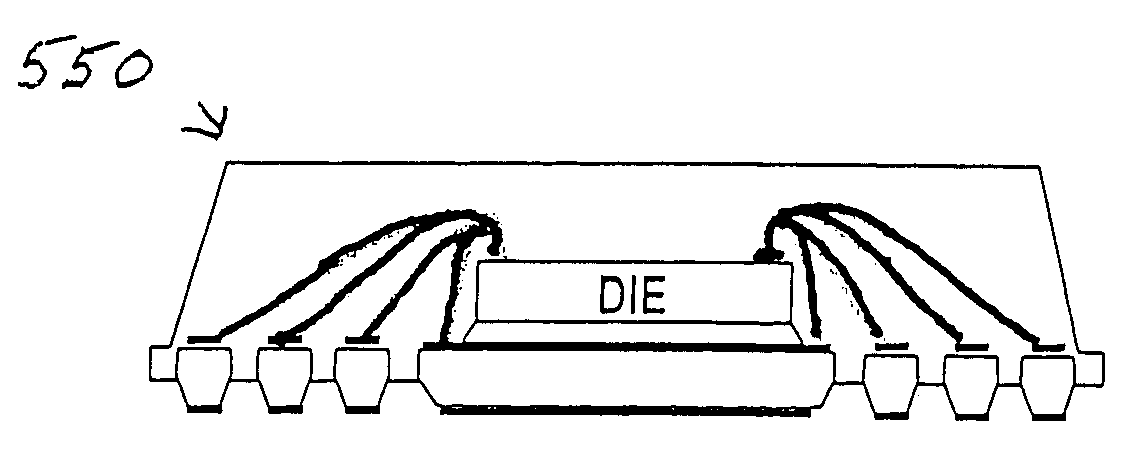

Flat no-lead semiconductor die package including stud terminals

ActiveUS7060535B1Semiconductor/solid-state device detailsSolid-state devicesSemiconductor chipMetal sheet

A flat no-lead semiconductor die package contains a plurality of studs that protrude from the bottom surface of the capsule and act as electrical contacts, allowing the package to be mounted on a flat surface such as a printed circuit board, while permitting external circuit to be located on the flat surface directly beneath the package. The package may or may not contain a die-attach pad. The die may be mounted flip-chip style on the stud contacts and die-attach pad. A method of fabricating the package includes etching an upper portion of a metal sheet through a mask layer, attaching dice at locations on the surface of the metal sheet, forming a layer of molding compound over the dice, etching the lower portion of the metal sheet through a second mask layer, and separating the packages with a dicing saw or punch tool.

Owner:UTAC HEADQUARTERS PTE LTD

High power LED package

InactiveUS20050274959A1Heat radiation property can be improvedIncrease powerSolid-state devicesSemiconductor devicesLiquid-crystal displayEngineering

Disclosed is a high power LED package, including an LED; a silicon submount to which the LED is flip chip bonded; a reflective film formed on the silicon submount and electrically connected to the LED to increase light emitting efficiency of the LED; electrical wires connected to the reflective film to connect the LED to an external circuit; an insulating body formed below the silicon submount; a heat sink formed below the insulating body; an insulating substrate formed on the heat sink; and metal lines formed on the insulating substrate and connected to the electrical wires. In the LED package, since the silicon submount having the LED flip chip bonded thereto is directly attached to the heat sink, heat generated upon operation of the LED can be effectively radiated. Also, the LED package has a simple structure, thus having drastically decreased manufacturing costs. The high power LED can be applied to backlight units of LCDs or general illumination fixtures, and as well, to backlight units of conventional PCS phones or LED packages for key pads, therefore increasing the light properties of the LED. In particular, the LED package has an array of two or more submounts each having an LED flip chip bonded thereto, and thus, it can be applied to a module of a backlight unit for LCDs, thus having remarkably reduced manufacturing costs.

Owner:LG ELECTRONICS INC

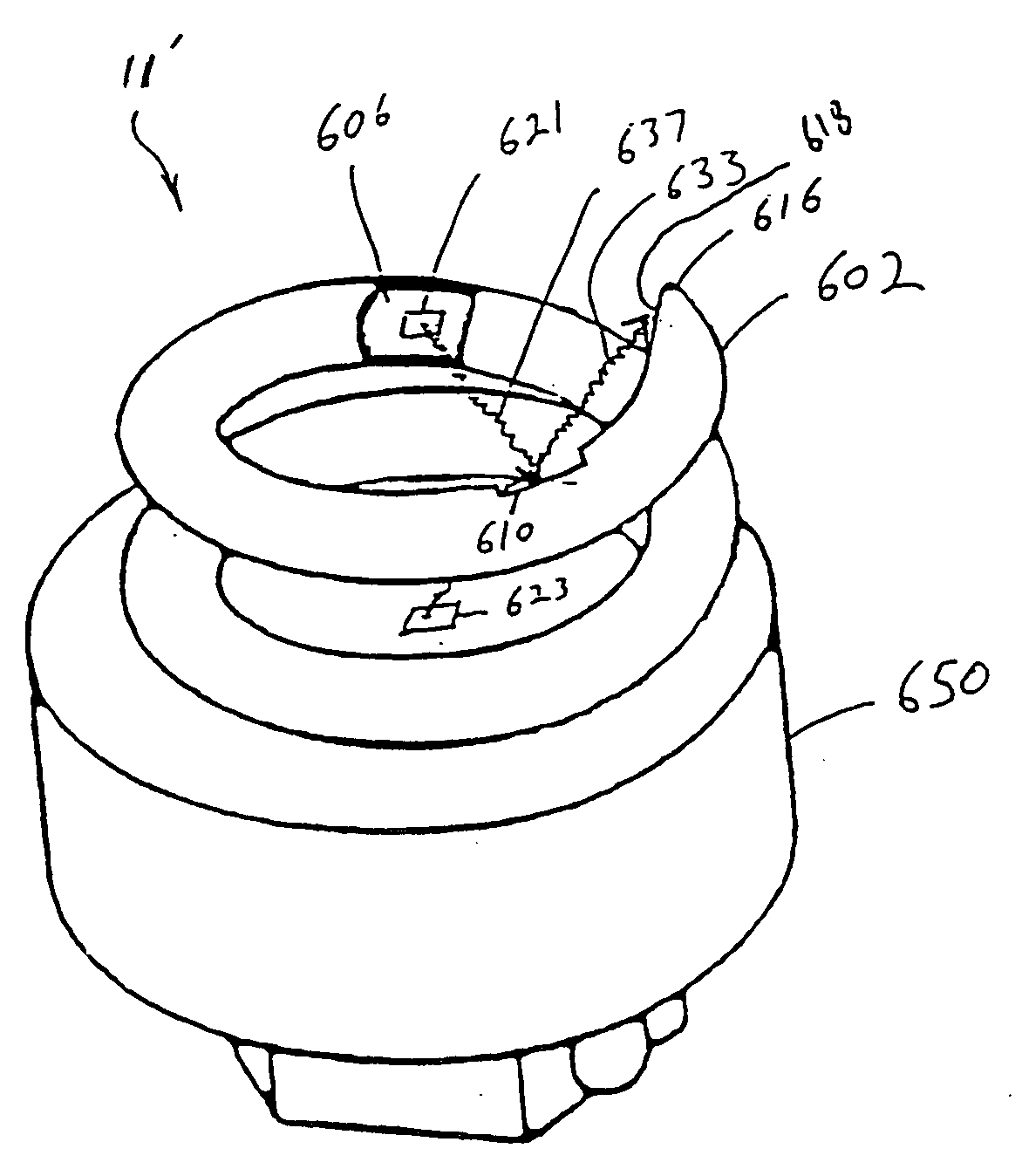

Fetal oximetry system and sensor

InactiveUS20050283059A1Improve accuracyUsable signal timeSensorsBlood characterising devicesFetal monitoringLength wave

Owner:RIC INVESTMENTS LLC

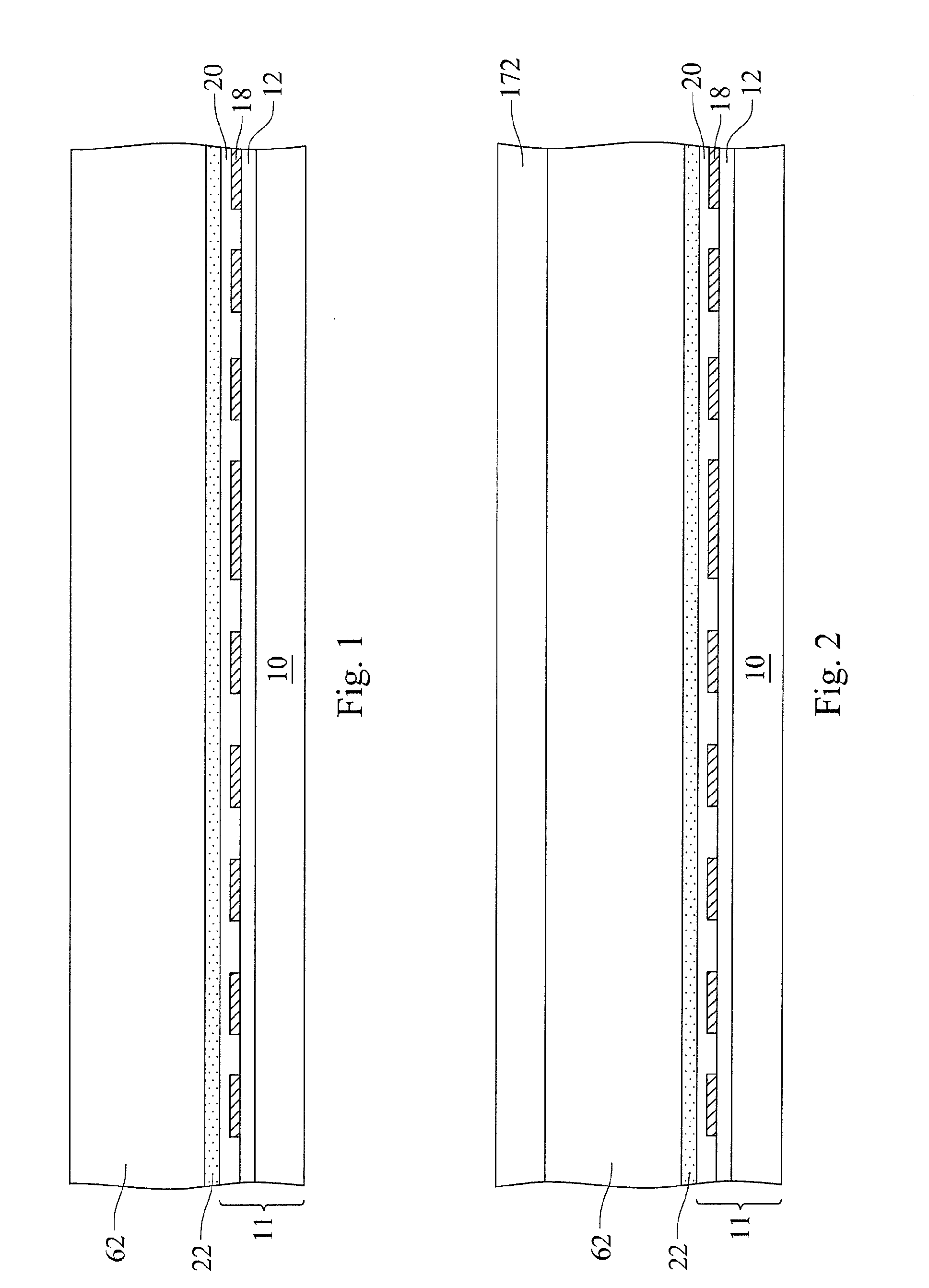

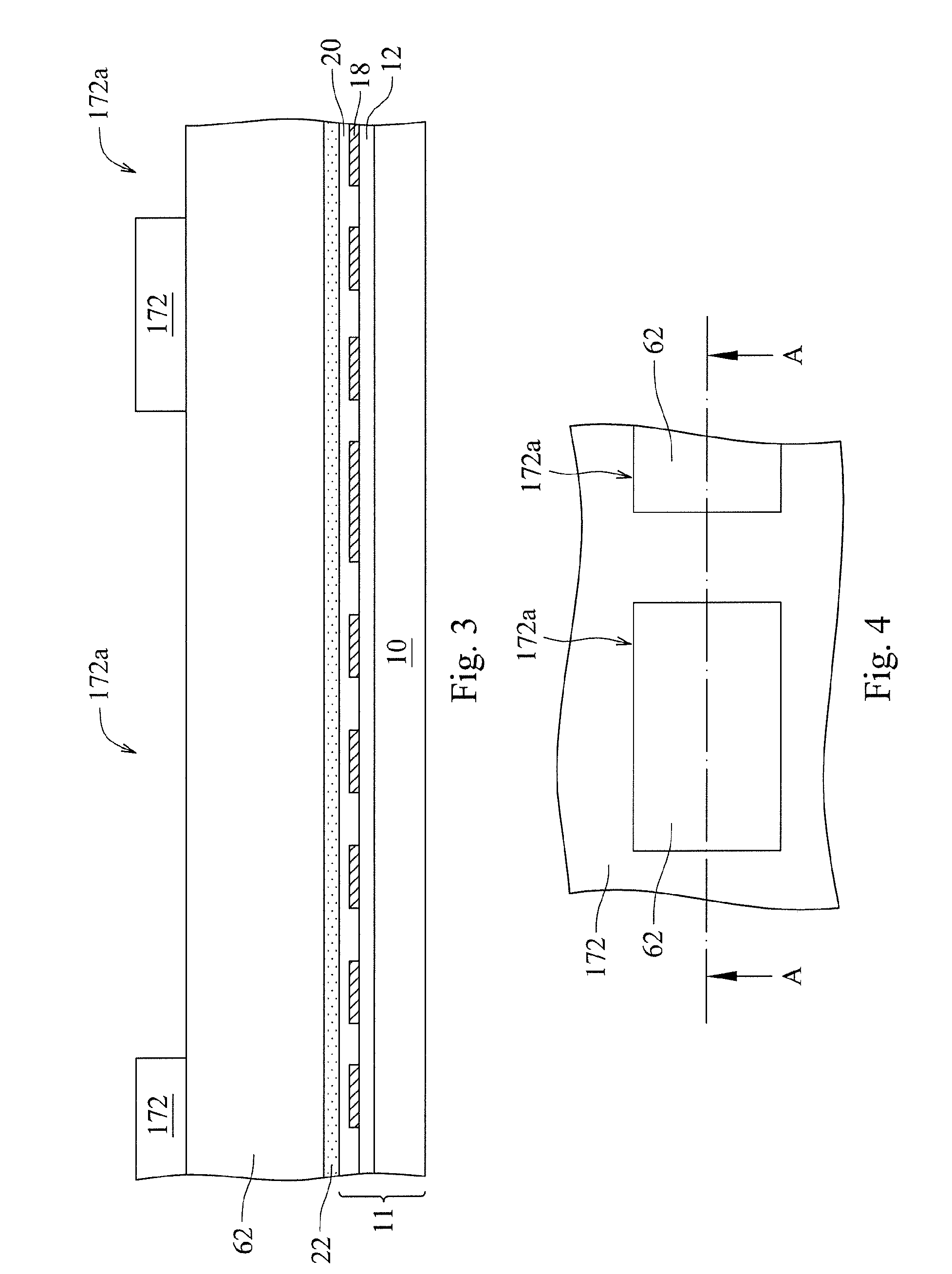

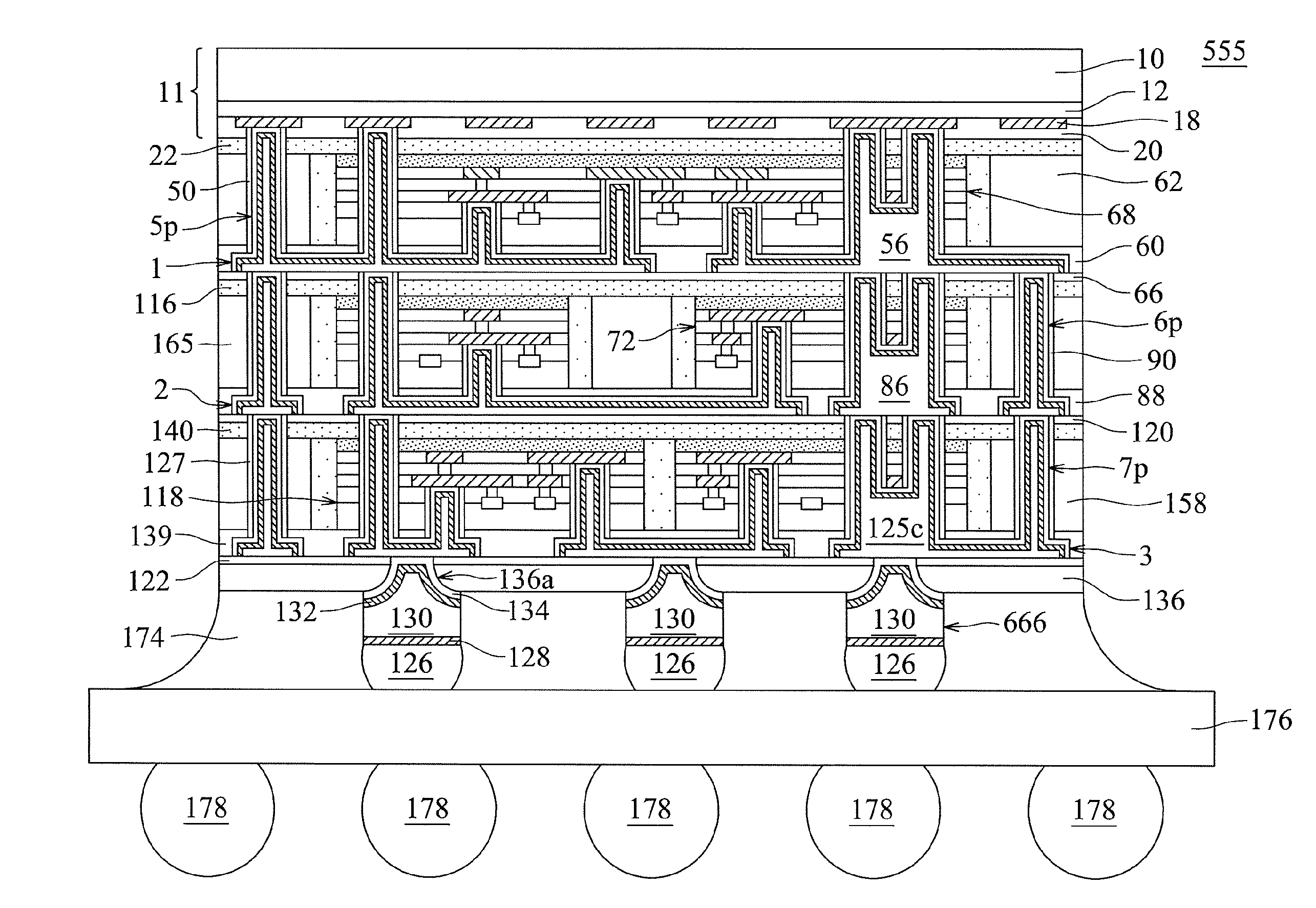

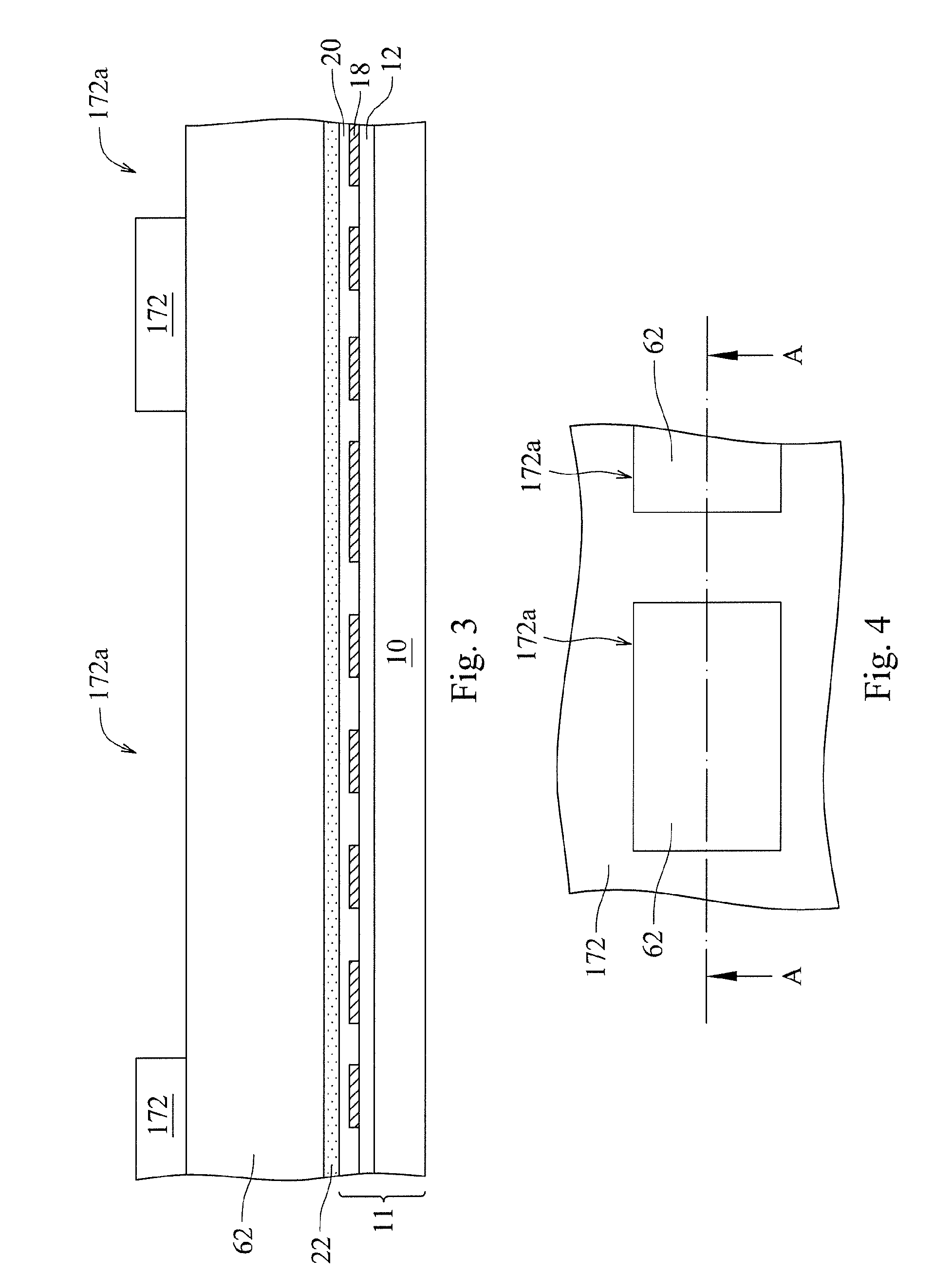

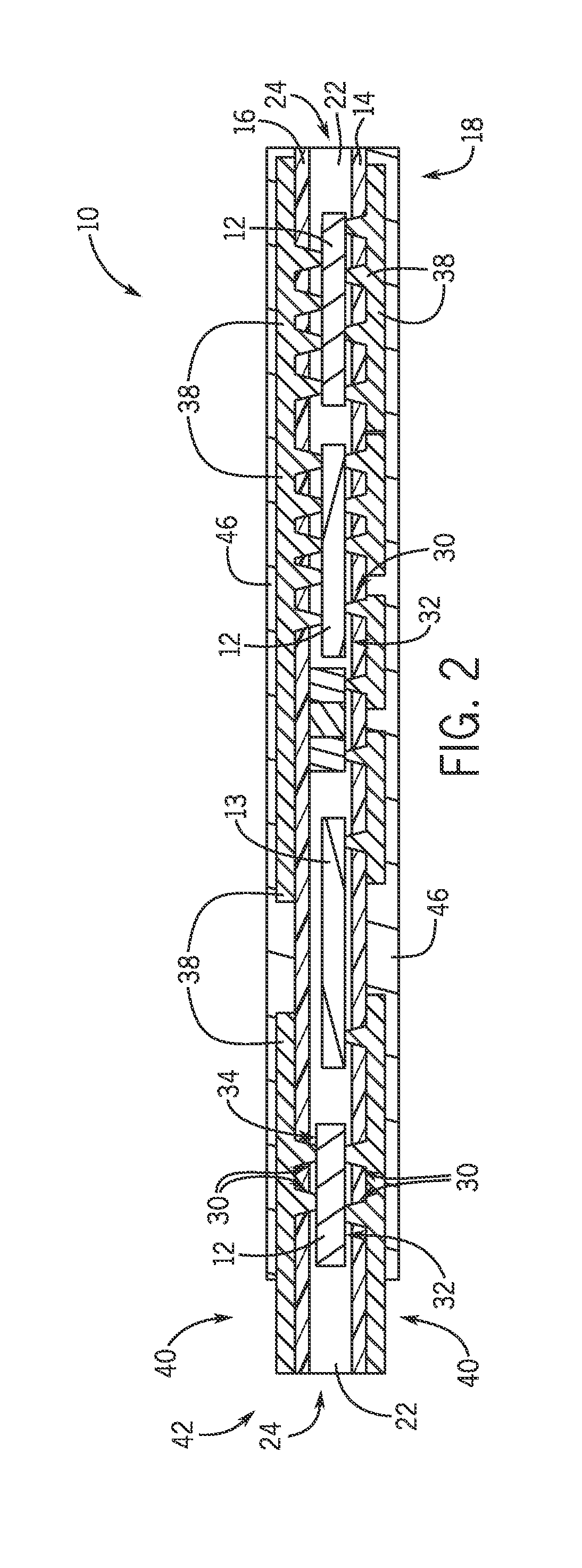

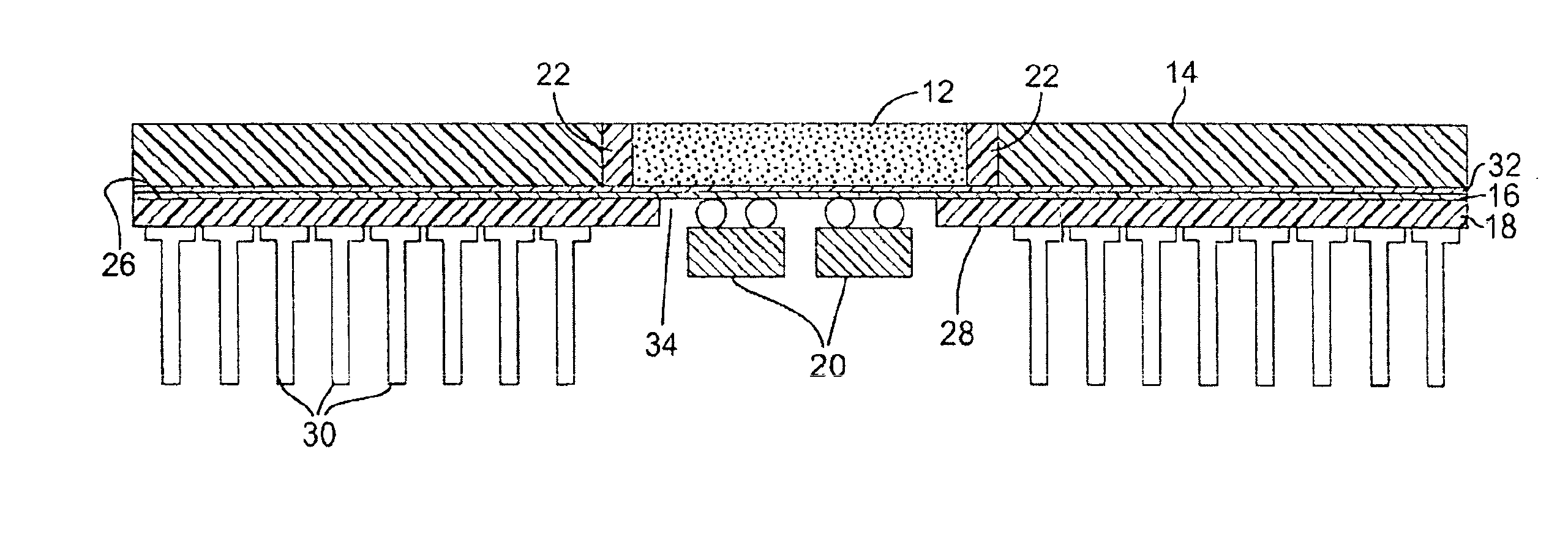

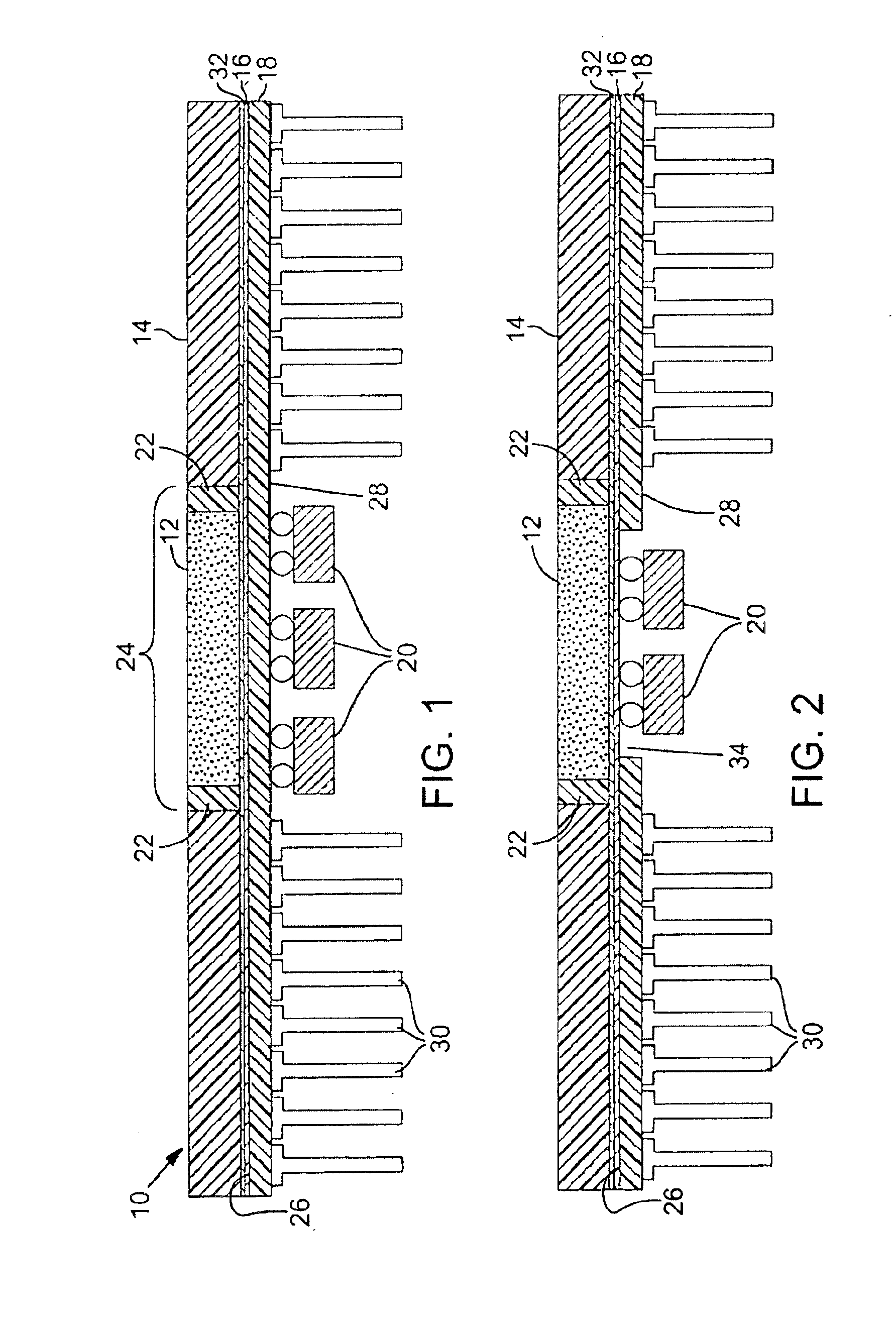

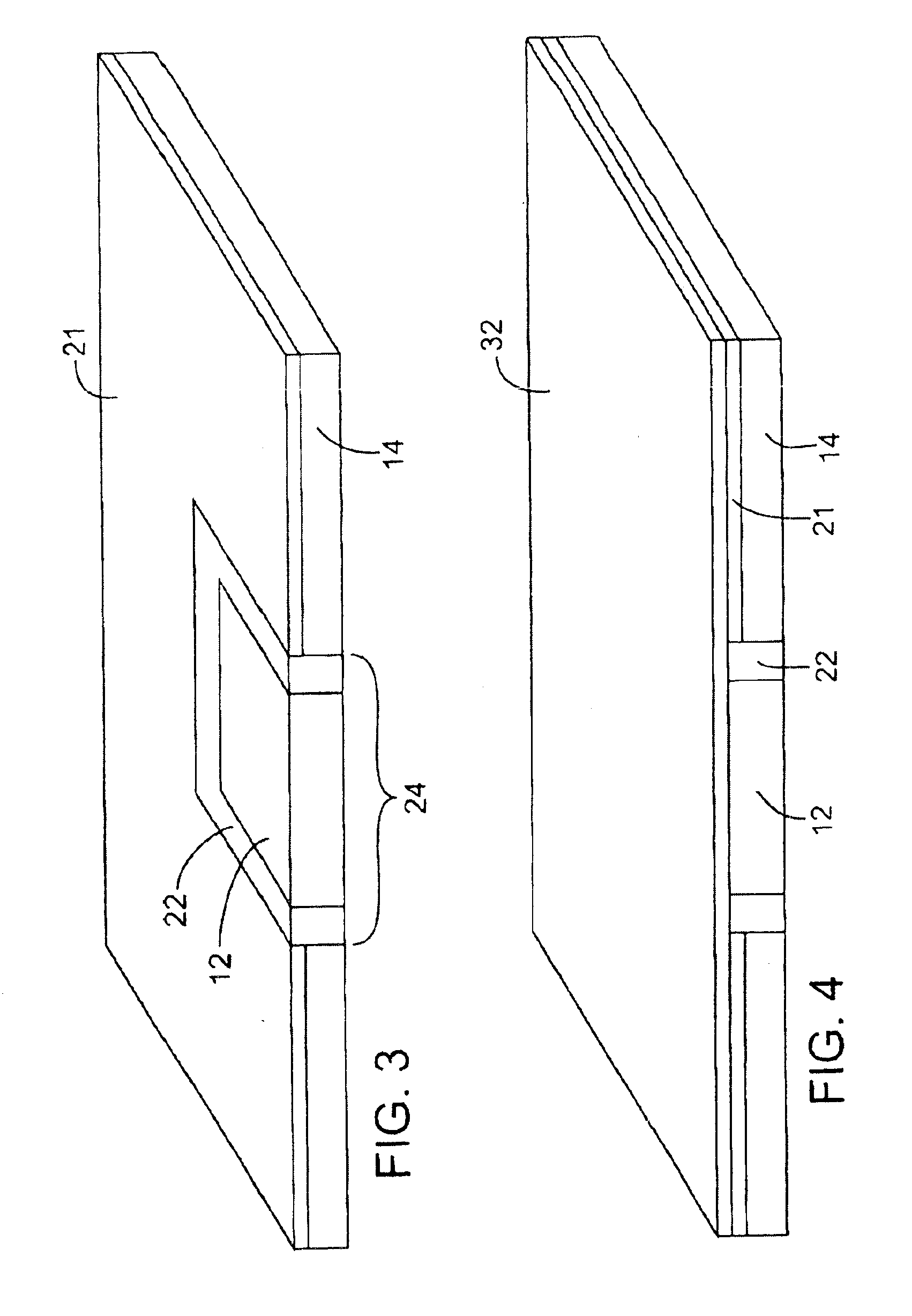

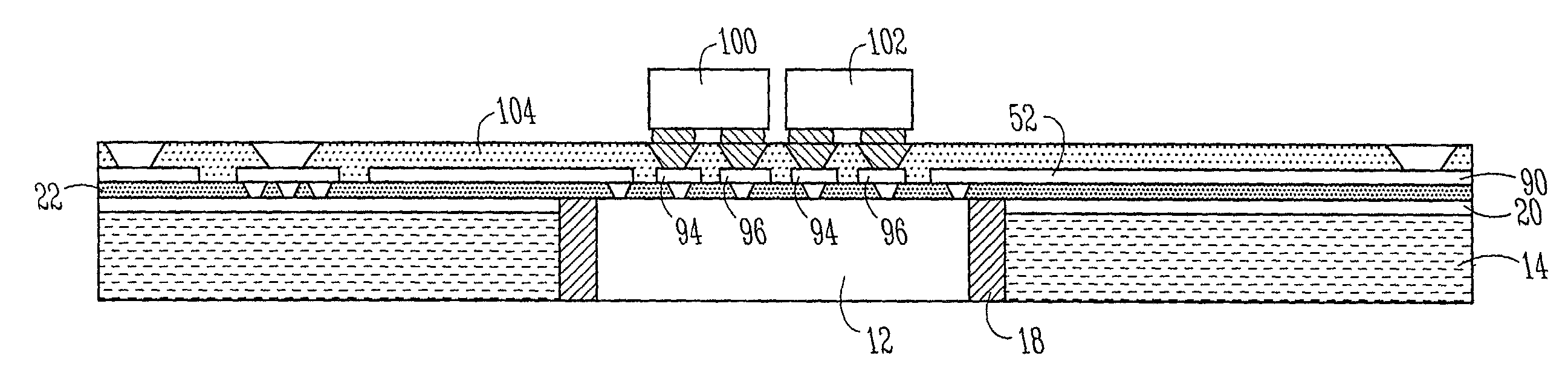

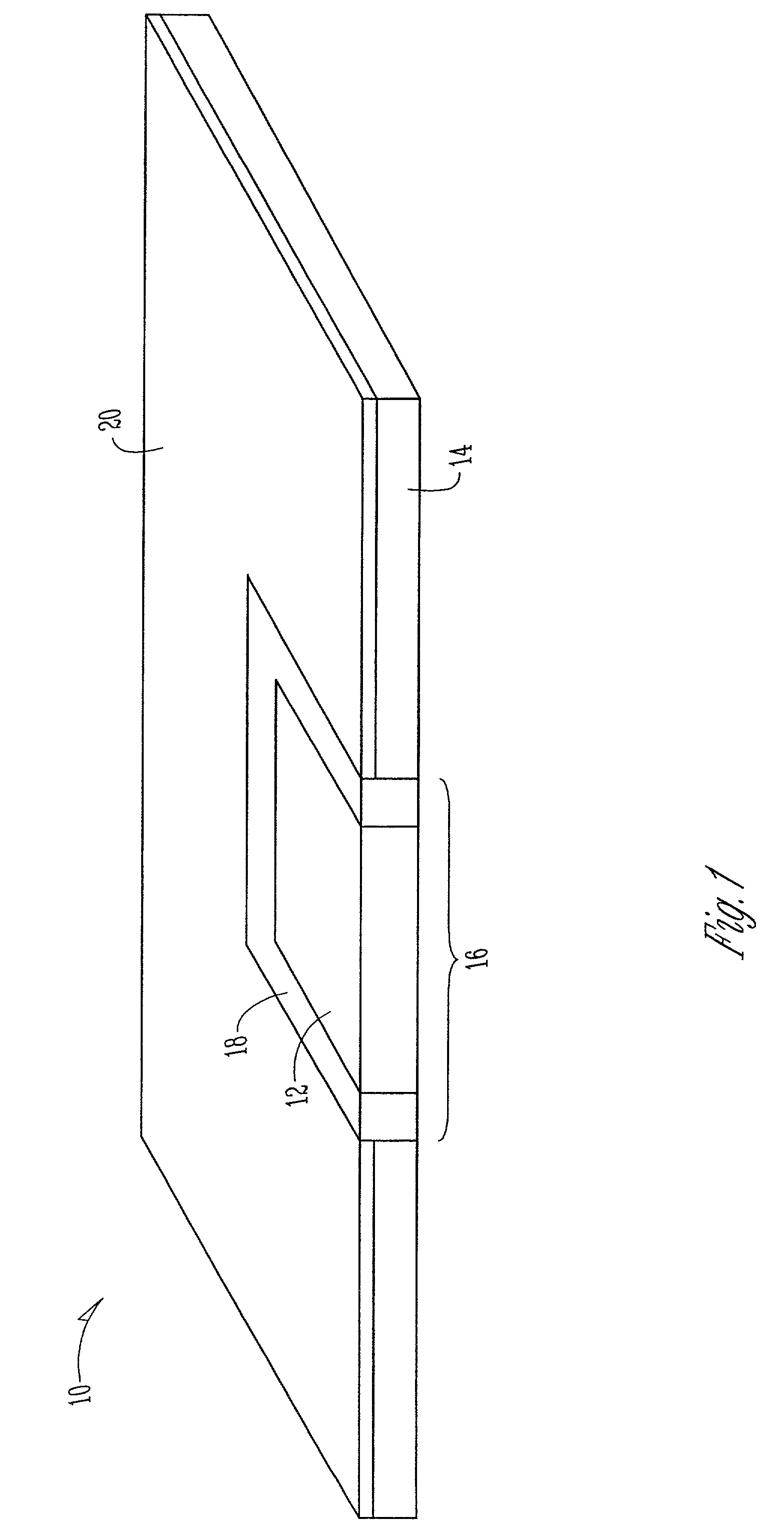

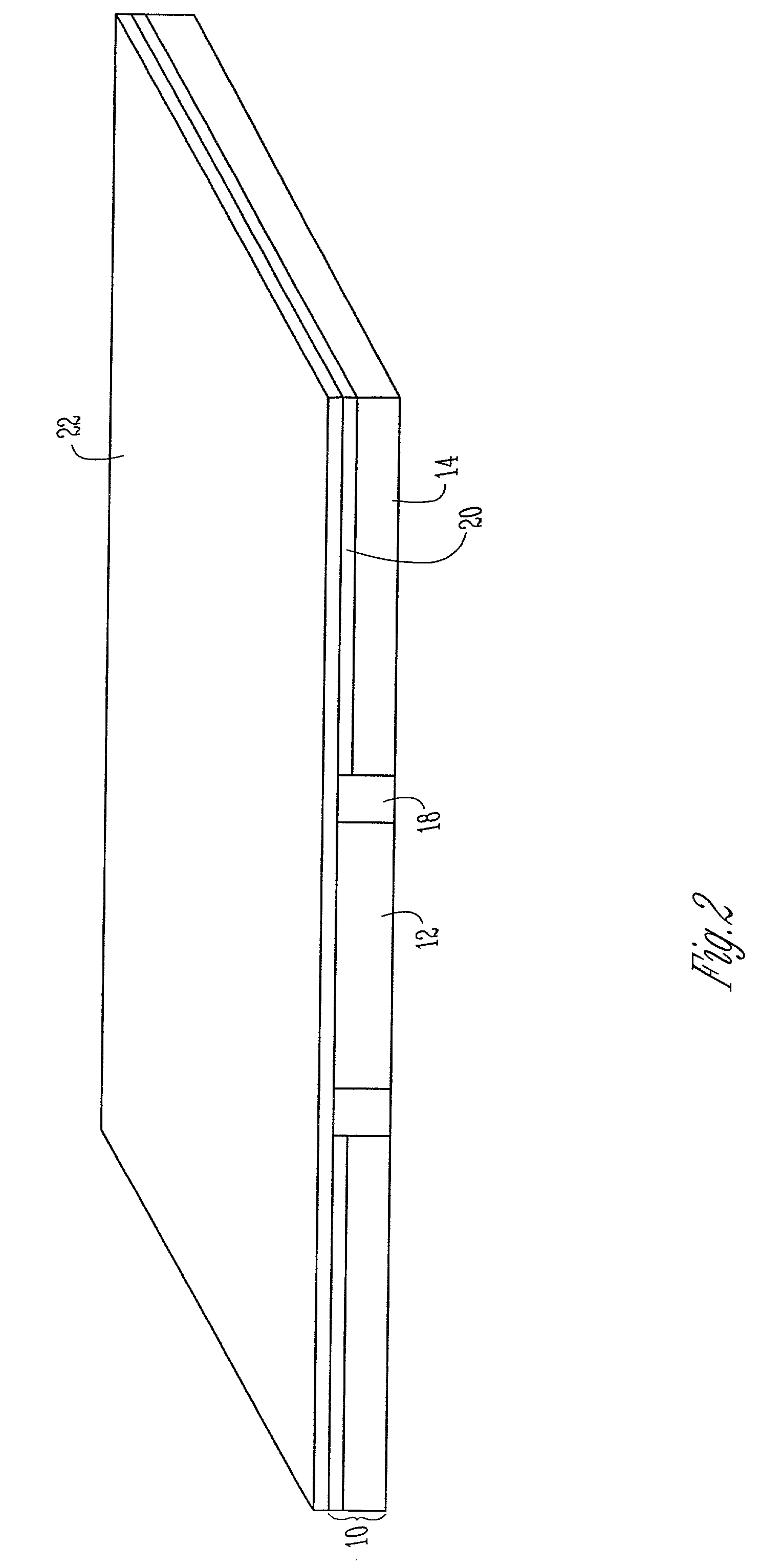

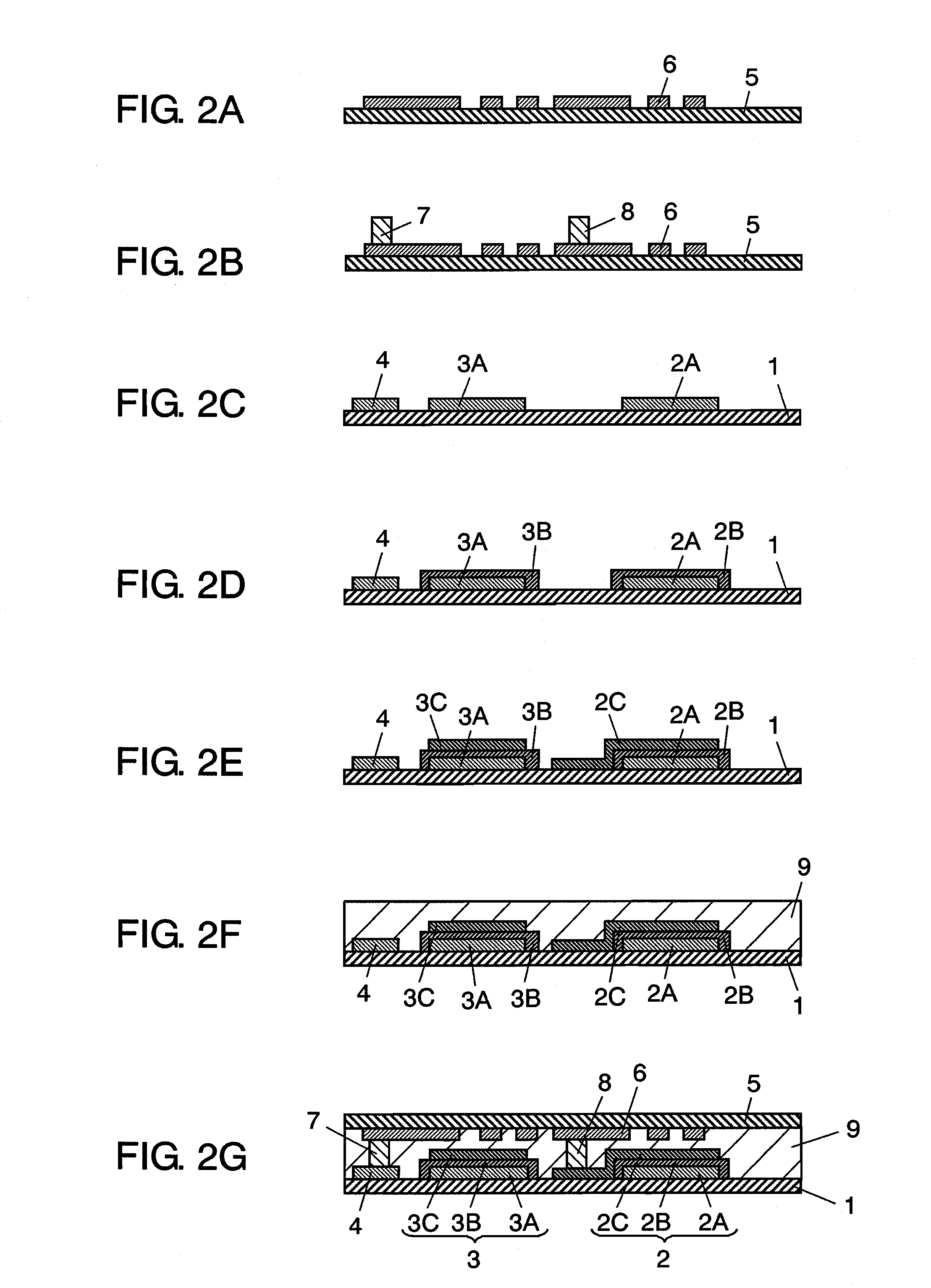

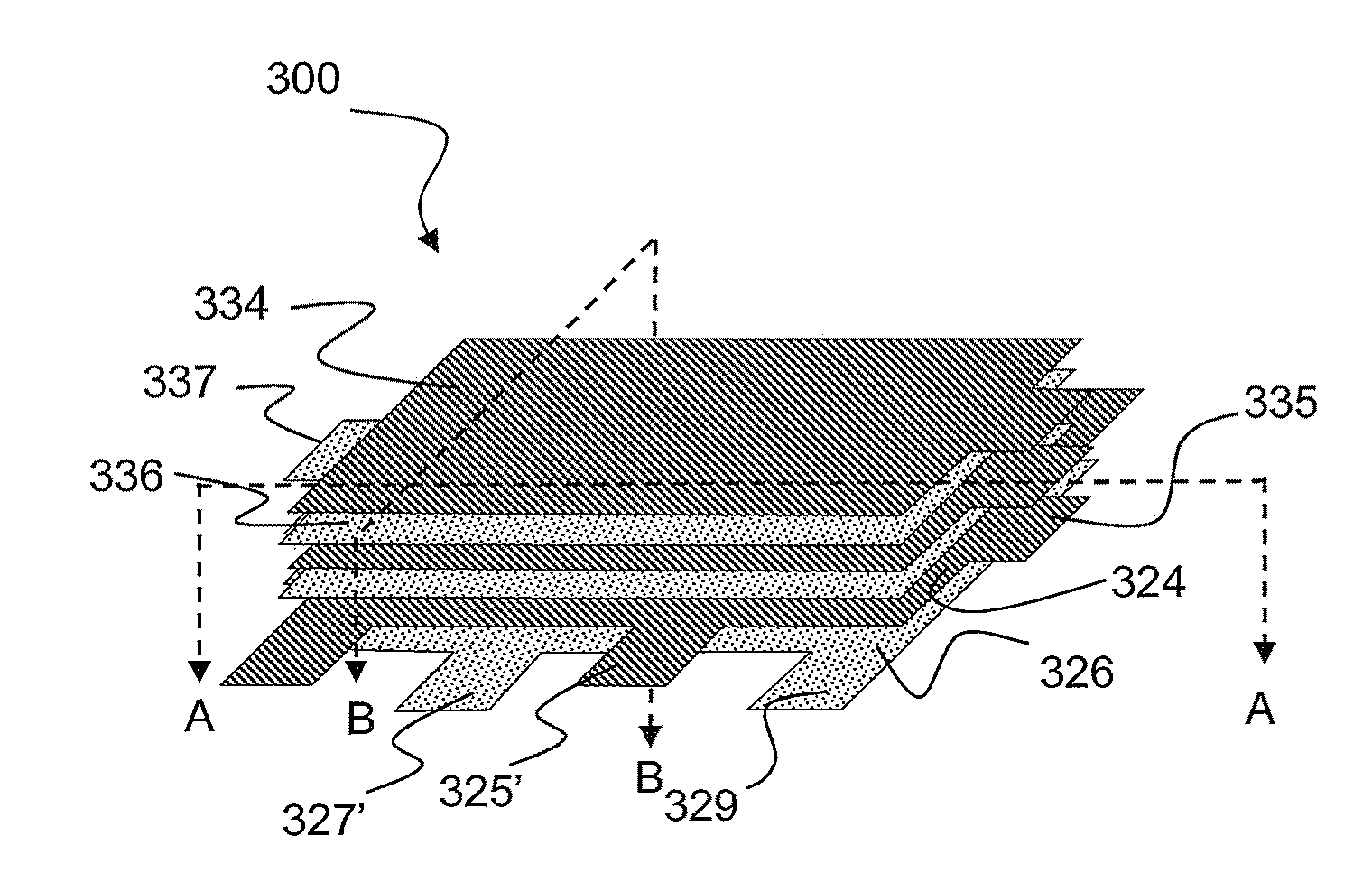

Ultra-thin embedded semiconductor device package and method of manufacturing thereof

ActiveUS20150255418A1Final product manufactureSemiconductor/solid-state device detailsMetal interconnectEngineering

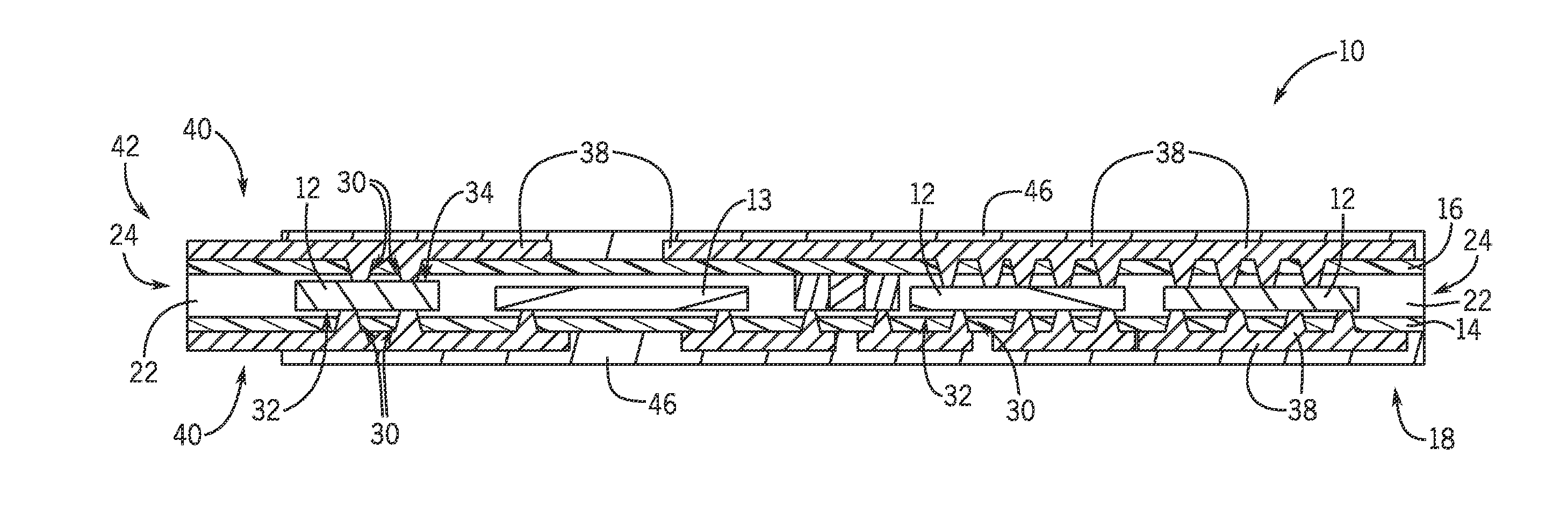

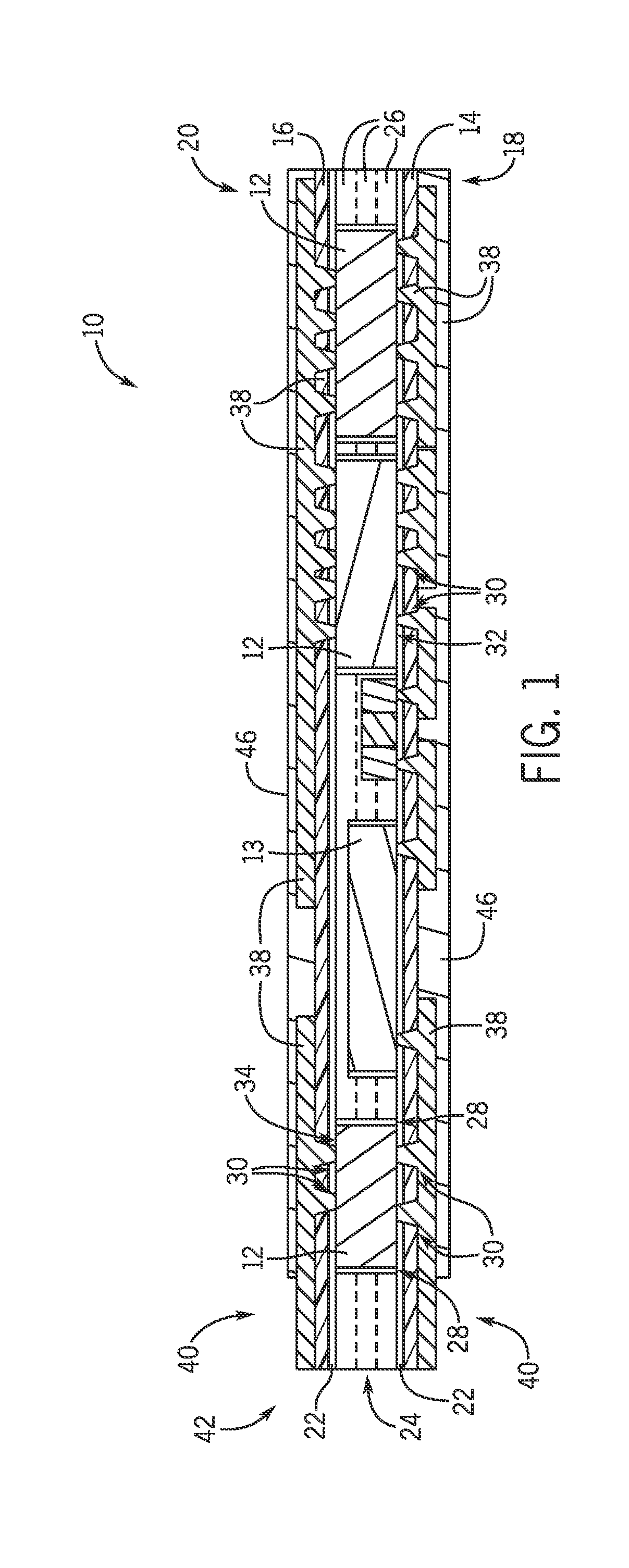

A package structure includes a first dielectric layer, semiconductor device(s) attached to the first dielectric layer, and an embedding material applied to the first dielectric layer so as to embed the semiconductor device therein, the embedding material comprising one or more additional dielectric layers. Vias are formed through the first dielectric layer to the at least one semiconductor device, with metal interconnects formed in the vias to form electrical interconnections to the semiconductor device. Input / output (I / O) connections are located on one end of the package structure on one or more outward facing surfaces thereof to provide a second level connection to an external circuit. The package structure interfits with a connector on the external circuit to mount the package perpendicular to the external circuit, with the I / O connections being electrically connected to the connector to form the second level connection to the external circuit.

Owner:GENERAL ELECTRIC CO

High performance, low cost microelectronic circuit package with interposer

InactiveUS6888240B2Semiconductor/solid-state device detailsSolid-state devicesPin grid arrayInterposer

A low cost technique for packaging microelectronic circuit chips fixes a die within an opening in a package core. At least one metallic build up layer is then formed on the die / core assembly and a grid array interposer unit is laminated to the build up layer. The grid array interposer unit can then be mounted within an external circuit using any of a plurality of mounting technologies (e.g., ball grid array (BGA), land grid array (LGA), pin grid array (PGA), surface mount technology (SMT), and / or others). In one embodiment, a single build up layer is formed on the die / core assembly before lamination of the interposer.

Owner:INTEL CORP

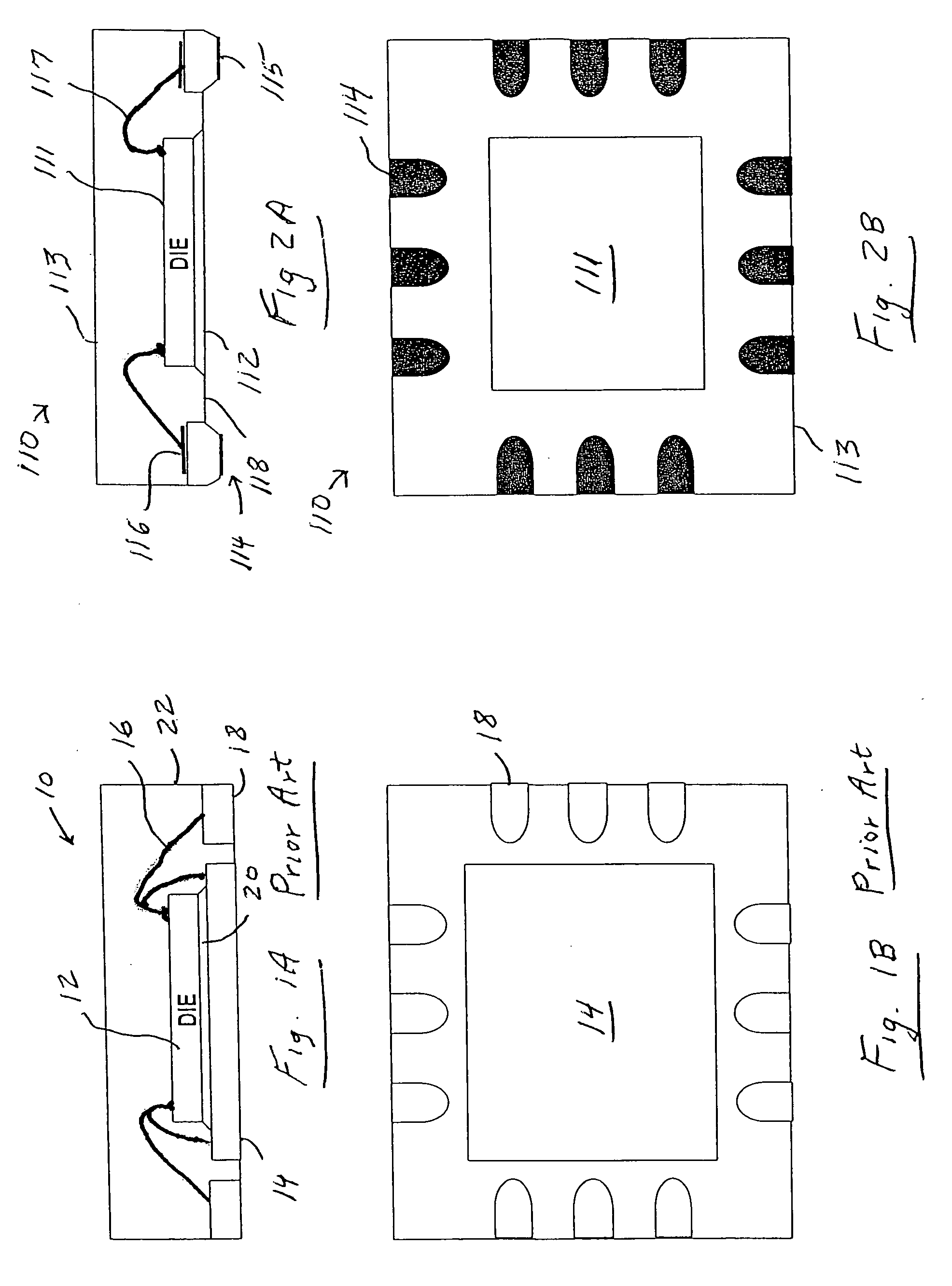

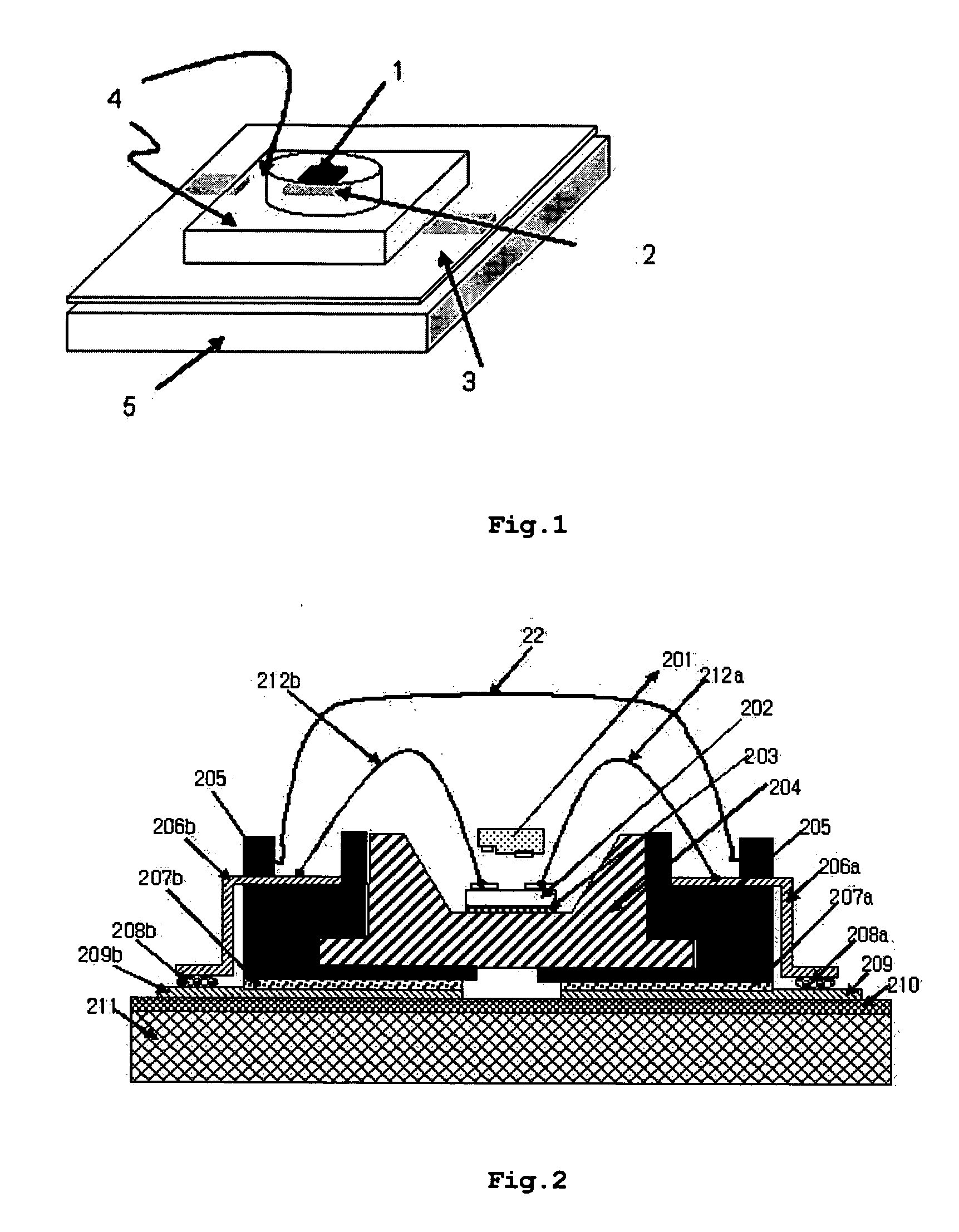

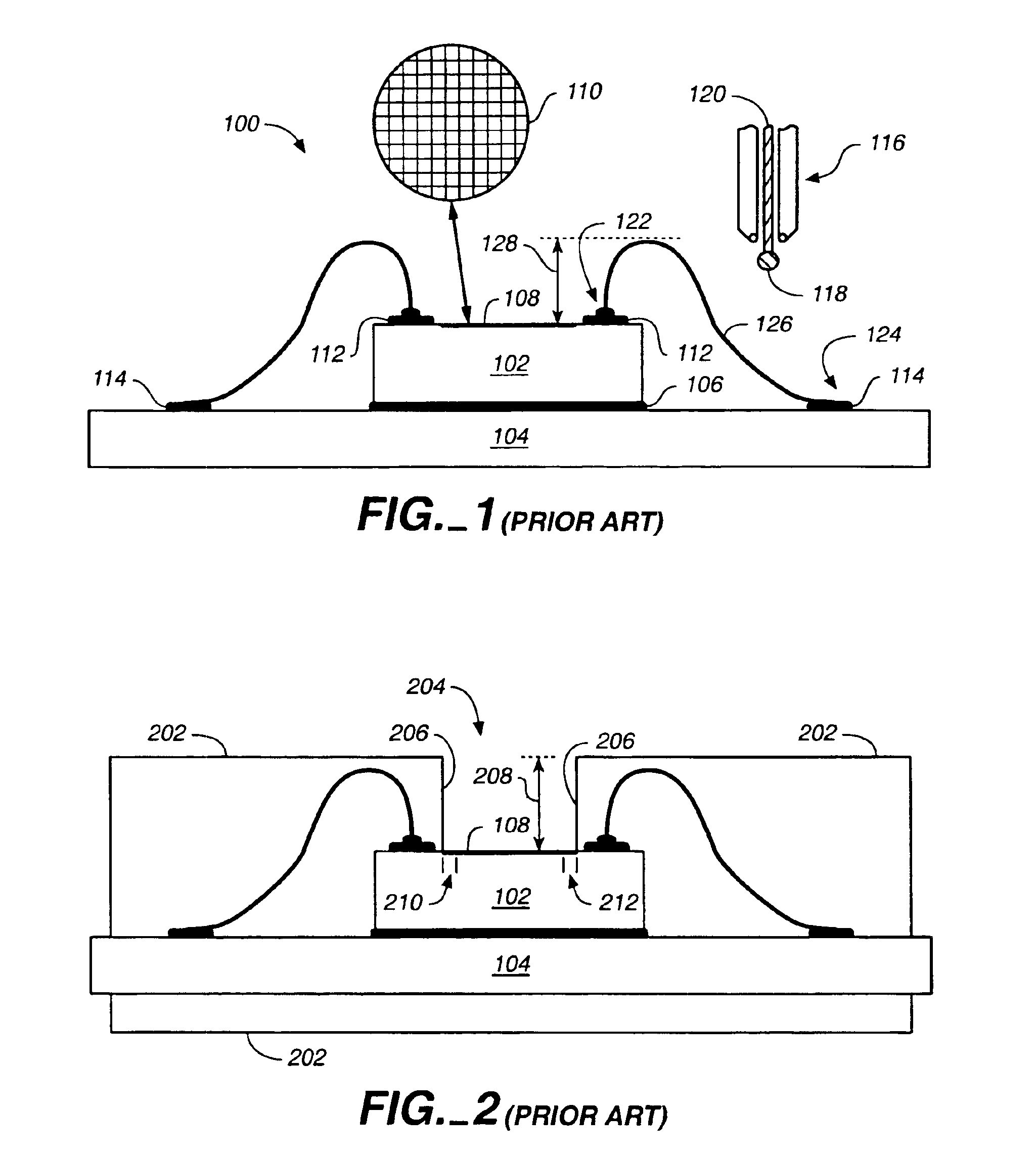

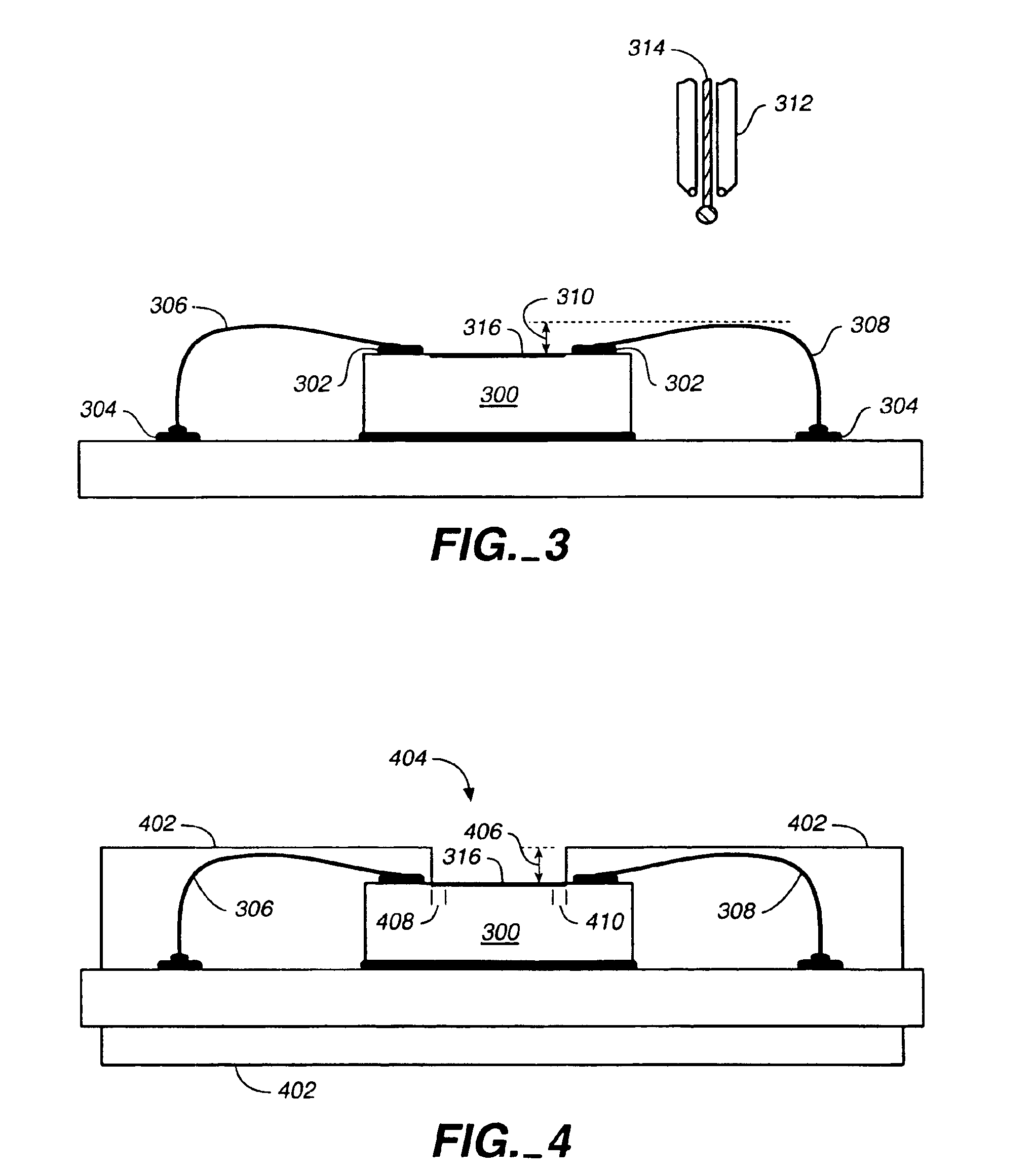

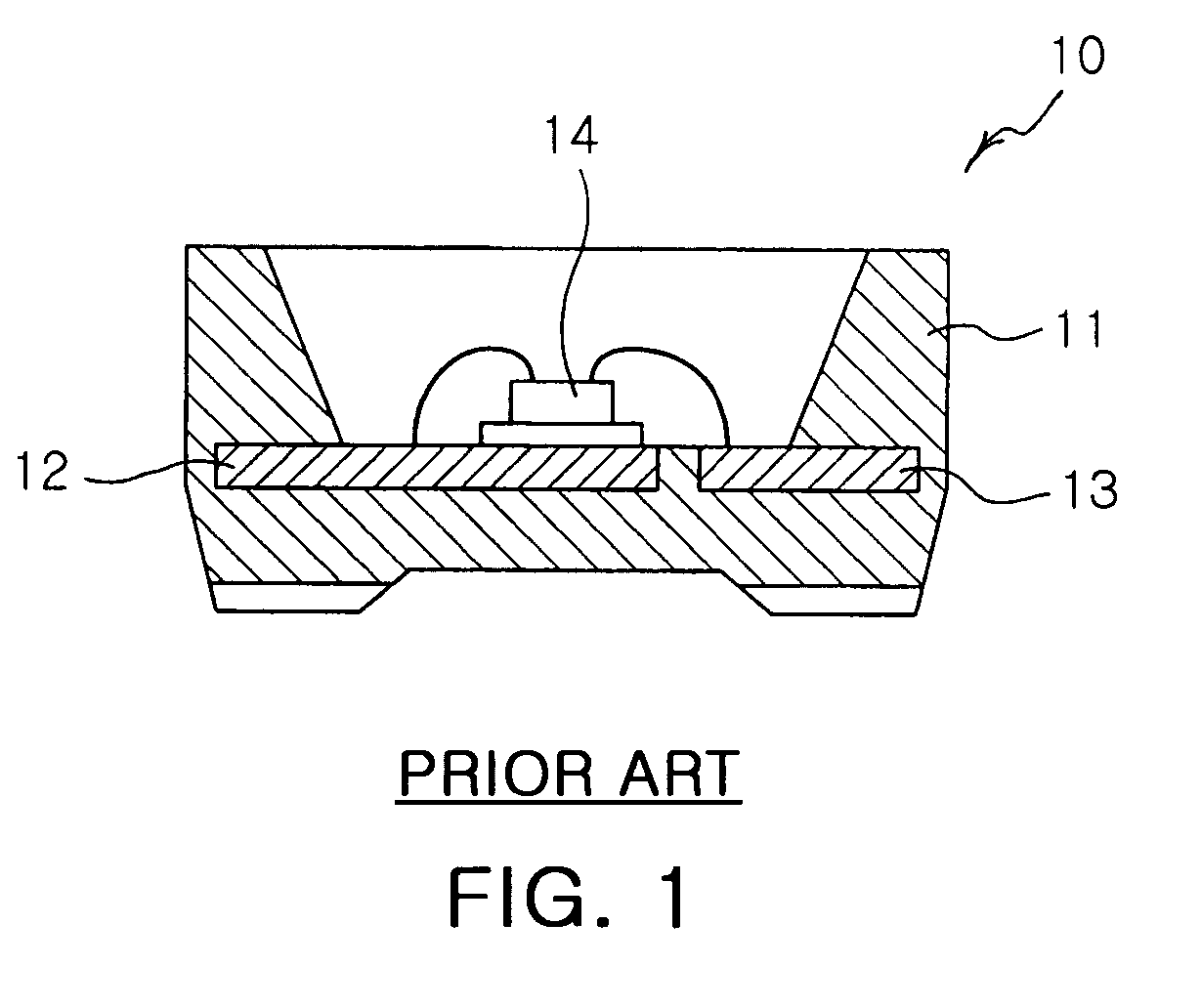

System for providing an open-cavity low profile encapsulated semiconductor package

InactiveUS6962282B2Small possible sizeReduce the overall heightPrinted circuit assemblingLine/current collector detailsSensor arrayLead bonding

System for providing an open-cavity semiconductor package. The system includes a method for wire bonding a finger sensor die to an external circuit. The finger sensor die includes a sensor array having one or more die contacts that are wire bonded to one or more external contacts of the external circuit so that a usable portion of the sensor array is maximized. The method comprises steps of forming a ball at a first end of a bonding wire, forming an electrically conductive connection between the ball and a selected external contact of the external circuit, extending the bonding wire to a selected die contact so as to form a wire loop having a low loop height, and forming an electrically conductive stitch connection between a second end of the bonding wire and the selected die contact.

Owner:SOCIONEXT INC

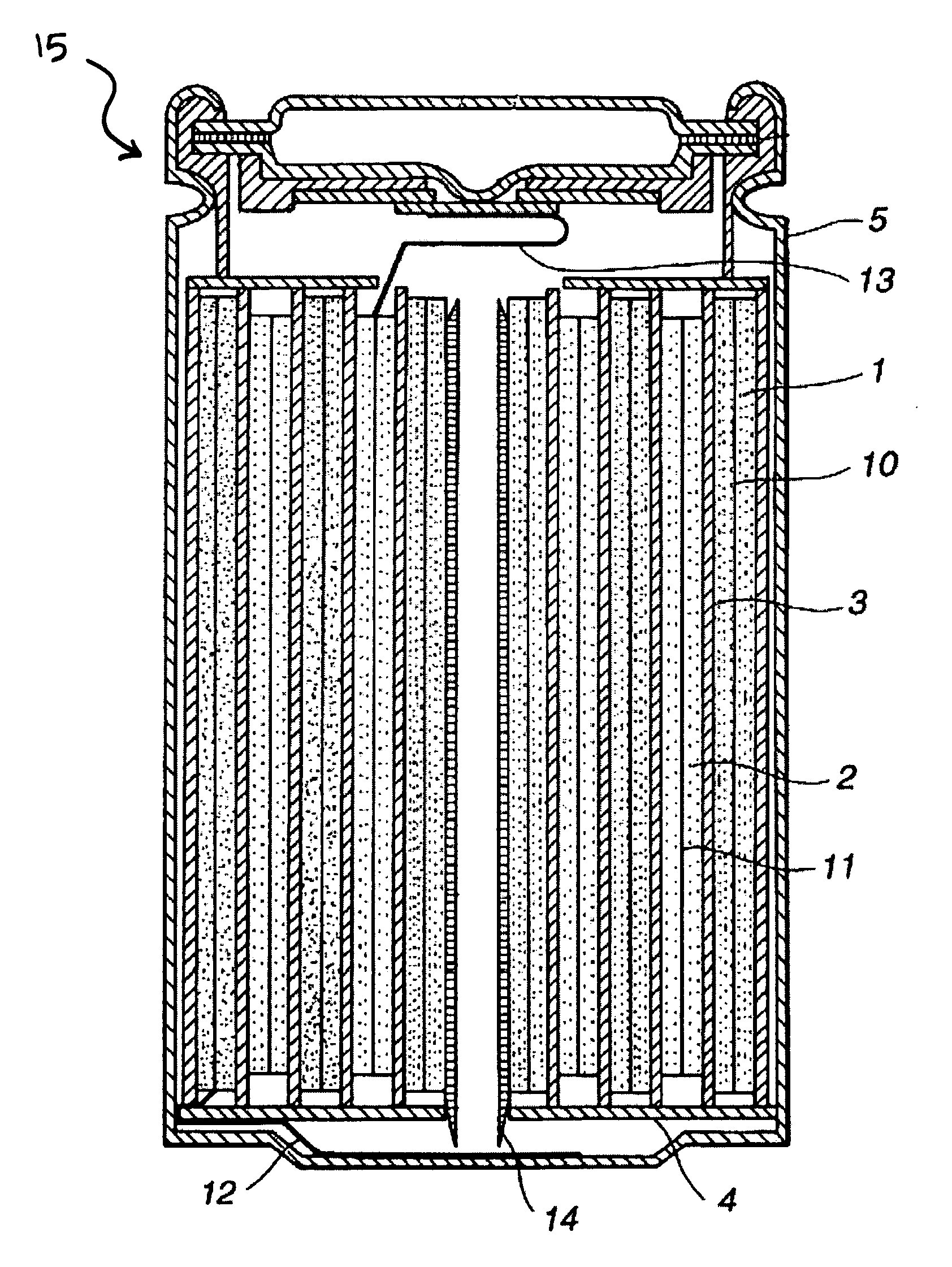

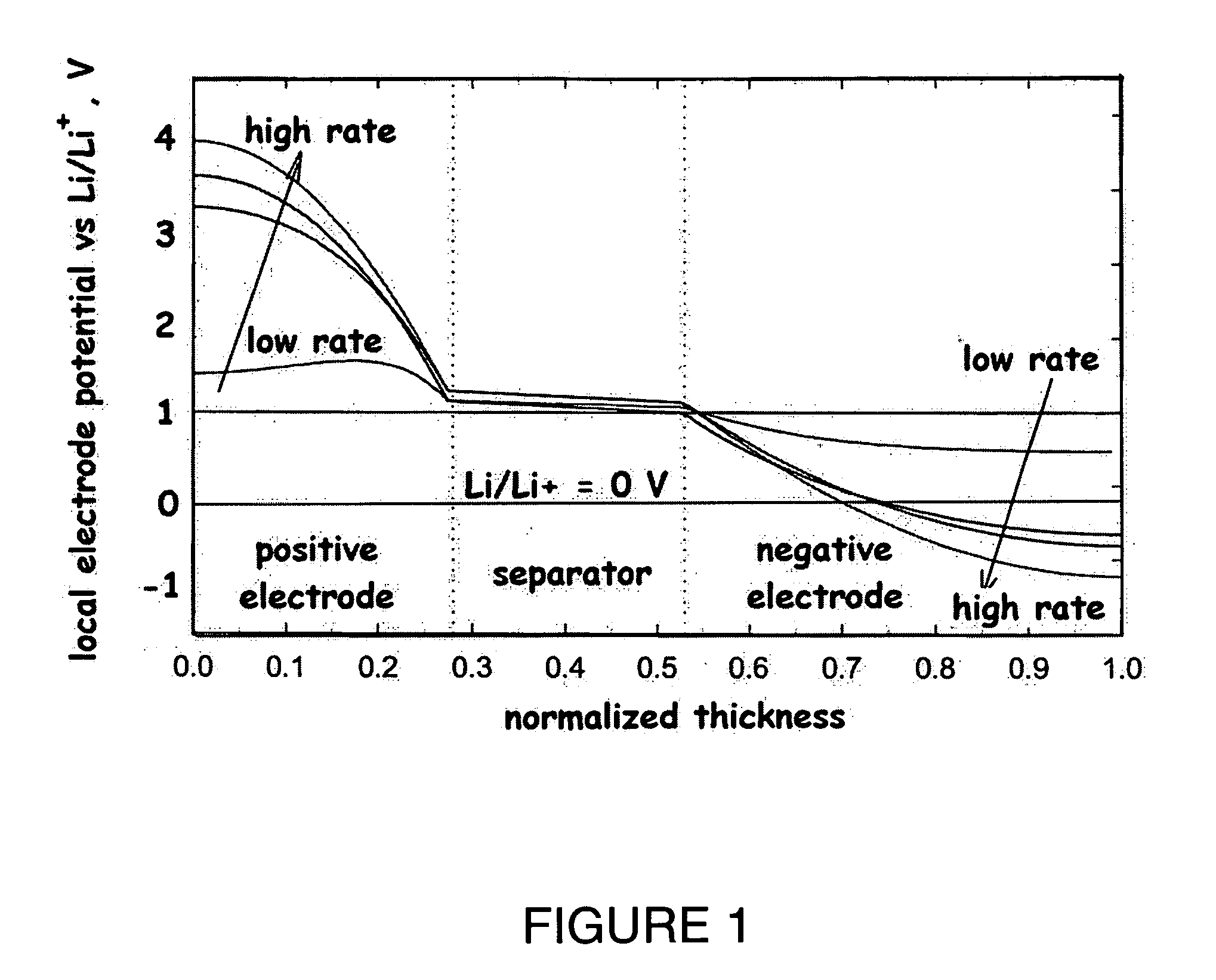

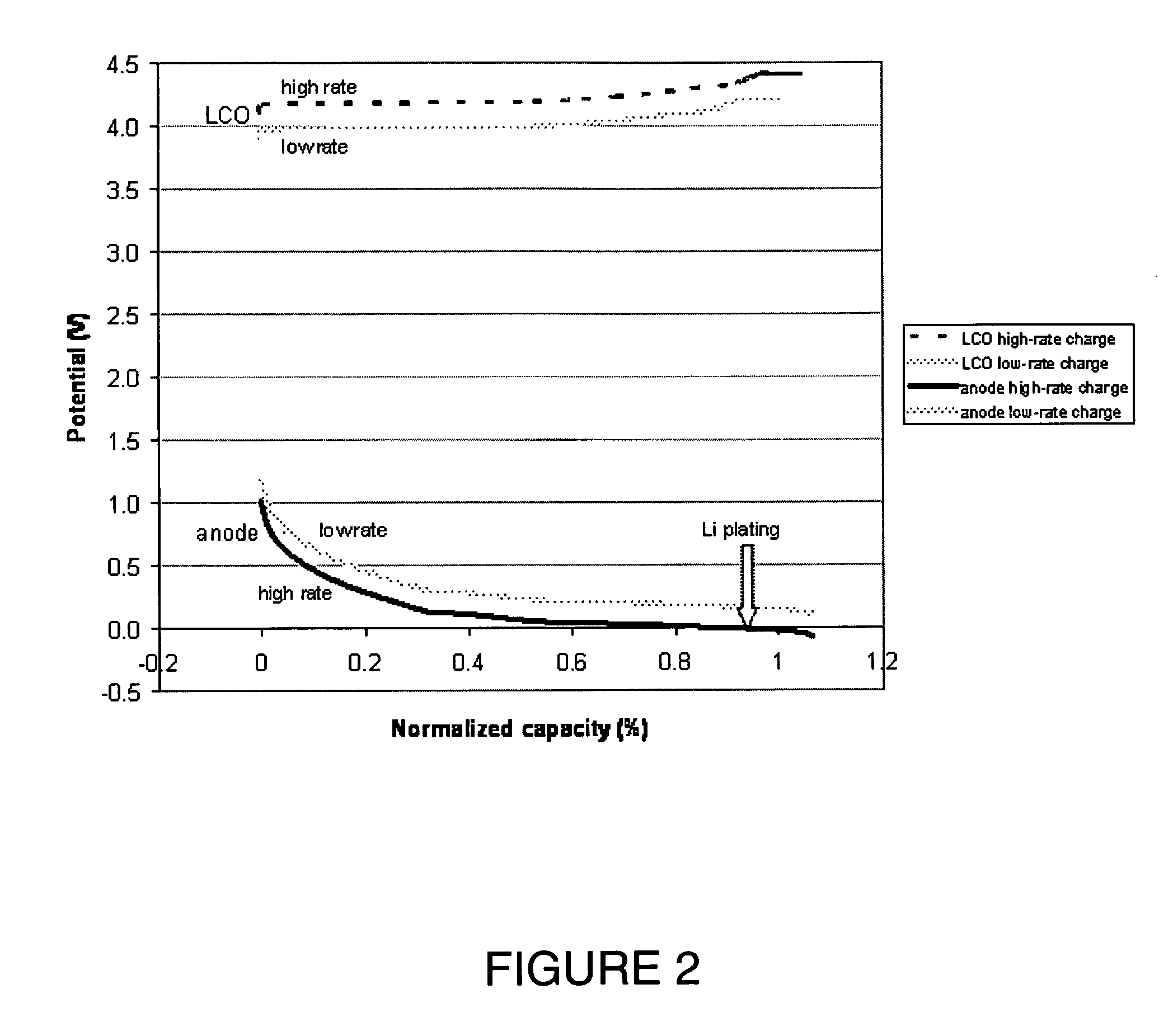

Lithium secondary cell with high charge and discharge rate capability

ActiveUS20050233219A1Final product manufactureActive material electrodesElectrode potentialMetallic lithium

A high capacity, high charge rate lithium secondary cell includes a high capacity lithium-containing positive electrode in electronic contact with a positive electrode current collector, said current collector in electrical connection with an external circuit, a high capacity negative electrode in electronic contact with a negative electrode current collector, said current collector in electrical connection with an external circuit, a separator positioned between and in ionic contact with the cathode and the anode, and an electrolyte in ionic contact with the positive and negative electrodes, wherein the total area specific impedance for the cell and the relative area specific impedances for the positive and negative electrodes are such that, during charging at greater than or equal to 4C, the negative electrode potential is above the potential of metallic lithium. The current capacity per unit area of the positive and negative electrodes each are at least 3 mA-h / cm2, the total area specific impedance for the cell is less than about 20 Ω-cm2, and the positive electrode has an area specific impedance r1 and the negative electrode has an area specific impedance r2, and wherein the ratio of r1 to r2 is at least about 10.

Owner:A123 SYSTEMS LLC

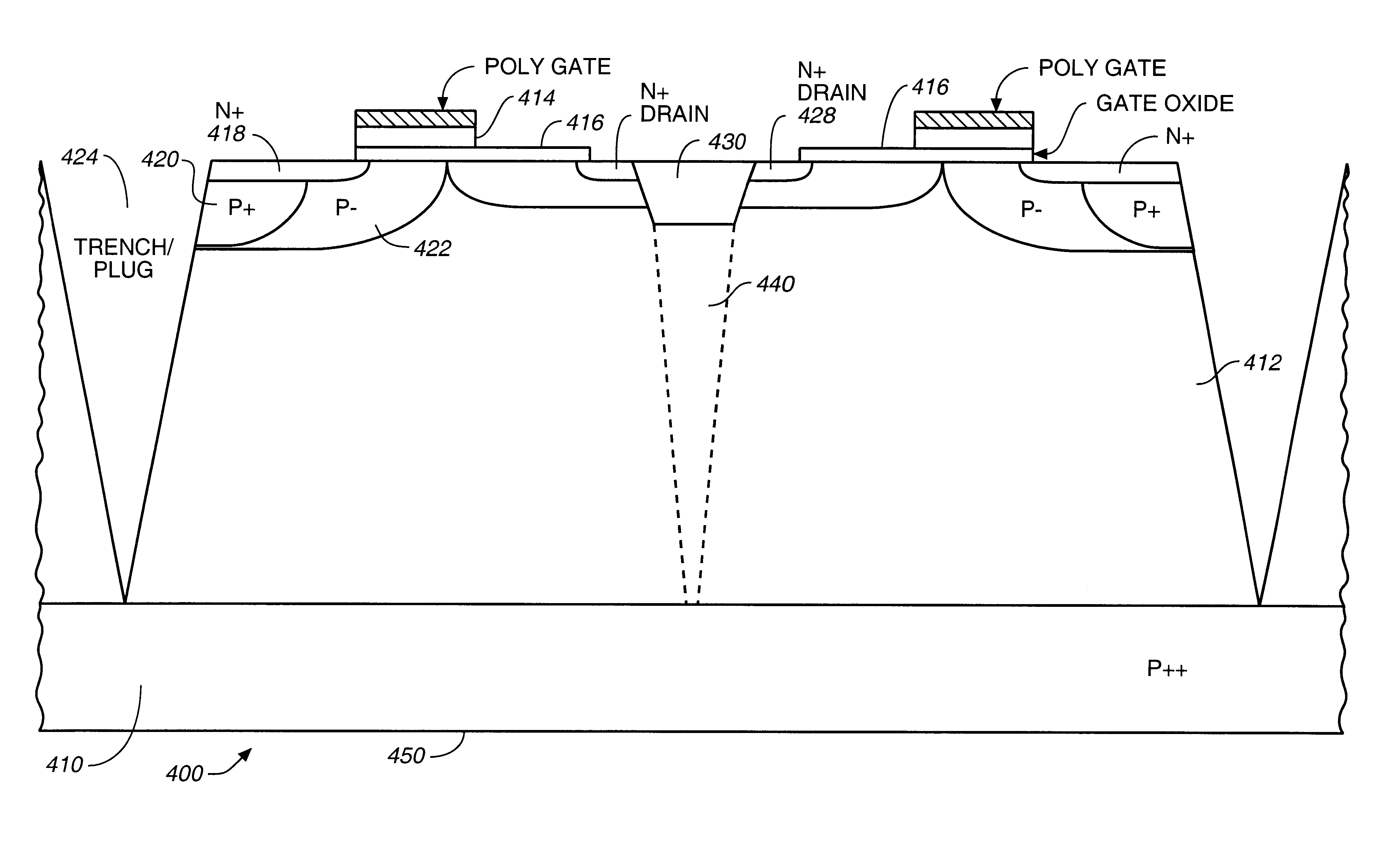

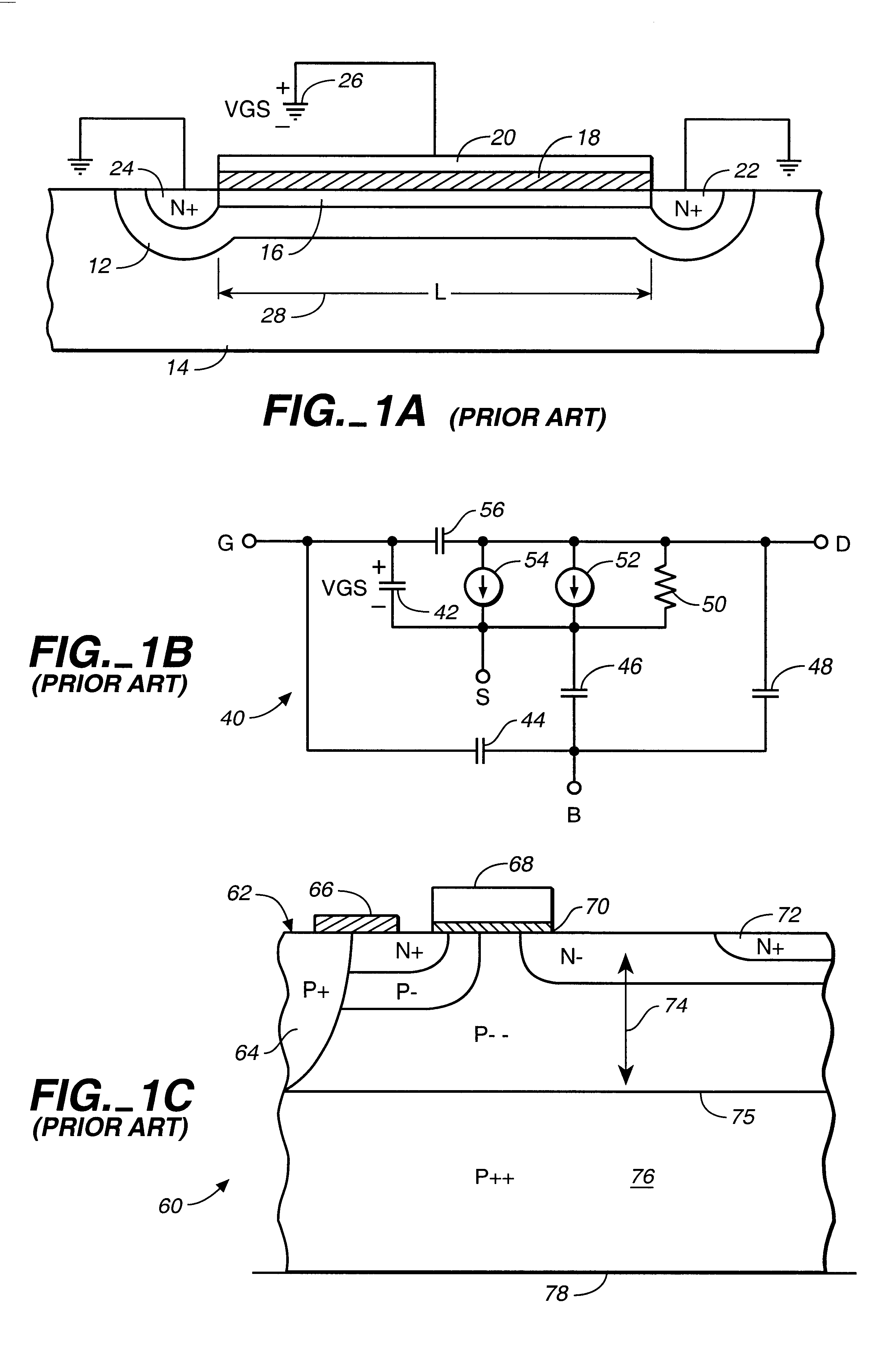

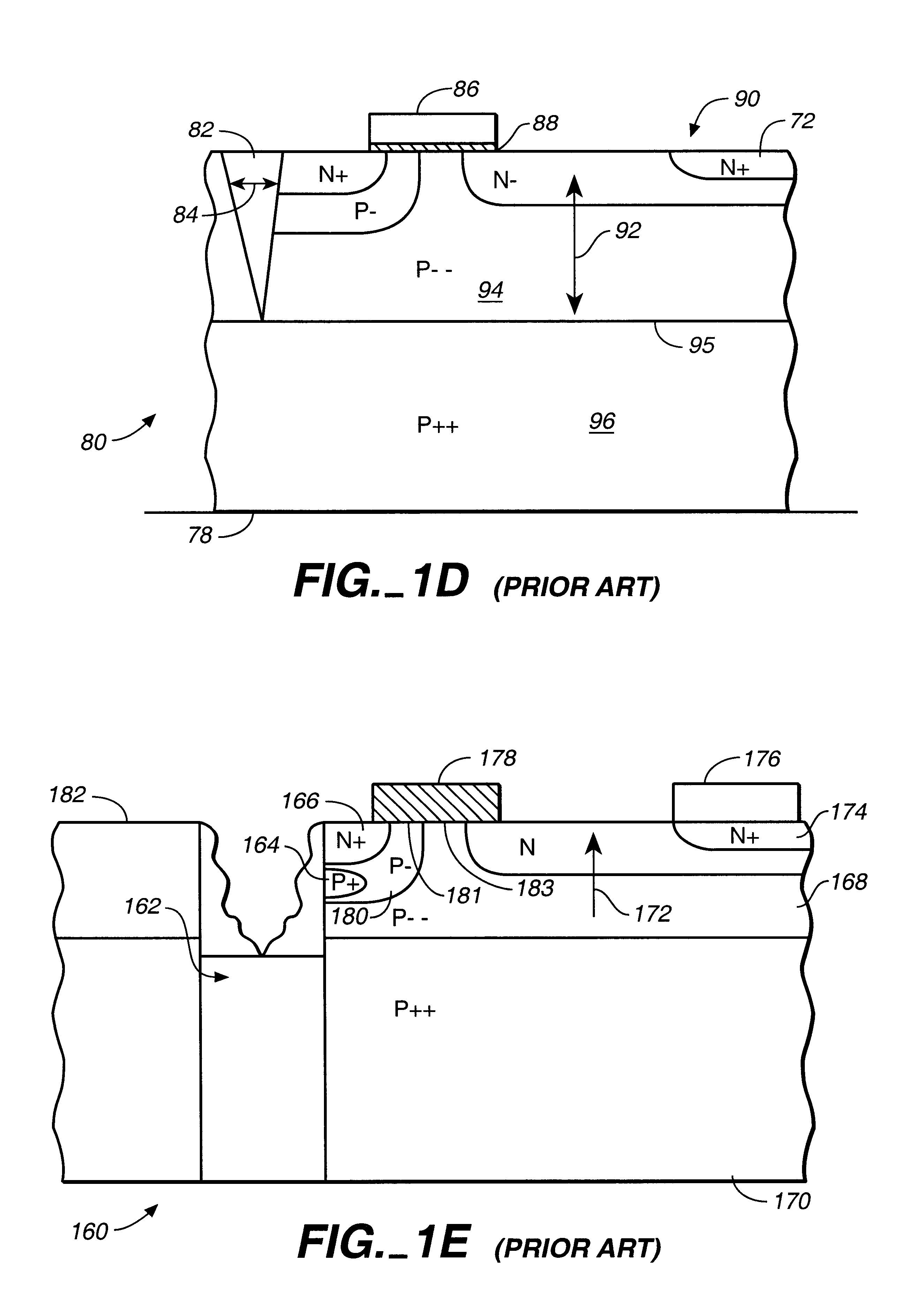

Lateral RF MOS device with improved drain structure

InactiveUS6222233B1Semiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceEngineering

The lateral RF MOS device having a conducive plug in the source region and an oxide plug in the drain region is disclosed. The oxide plug in the drain region reduces the drain-source capacitance, improves the matching ability to the outside circuitry, and results in a lateral RF MOS device having a wider BW, and an improved power efficiency than a prior art lateral RF MOS device. The oxide plug can comprise a shallow plug or a deep plug. The shallow oxide plug results in a lesser reduction in the drain-source capacitance but is relatively easy to fabricate. The deep oxide plug results in a higher reduction in the drain-source capacitance but is relatively difficult to fabricate.

Owner:QORVO US INC

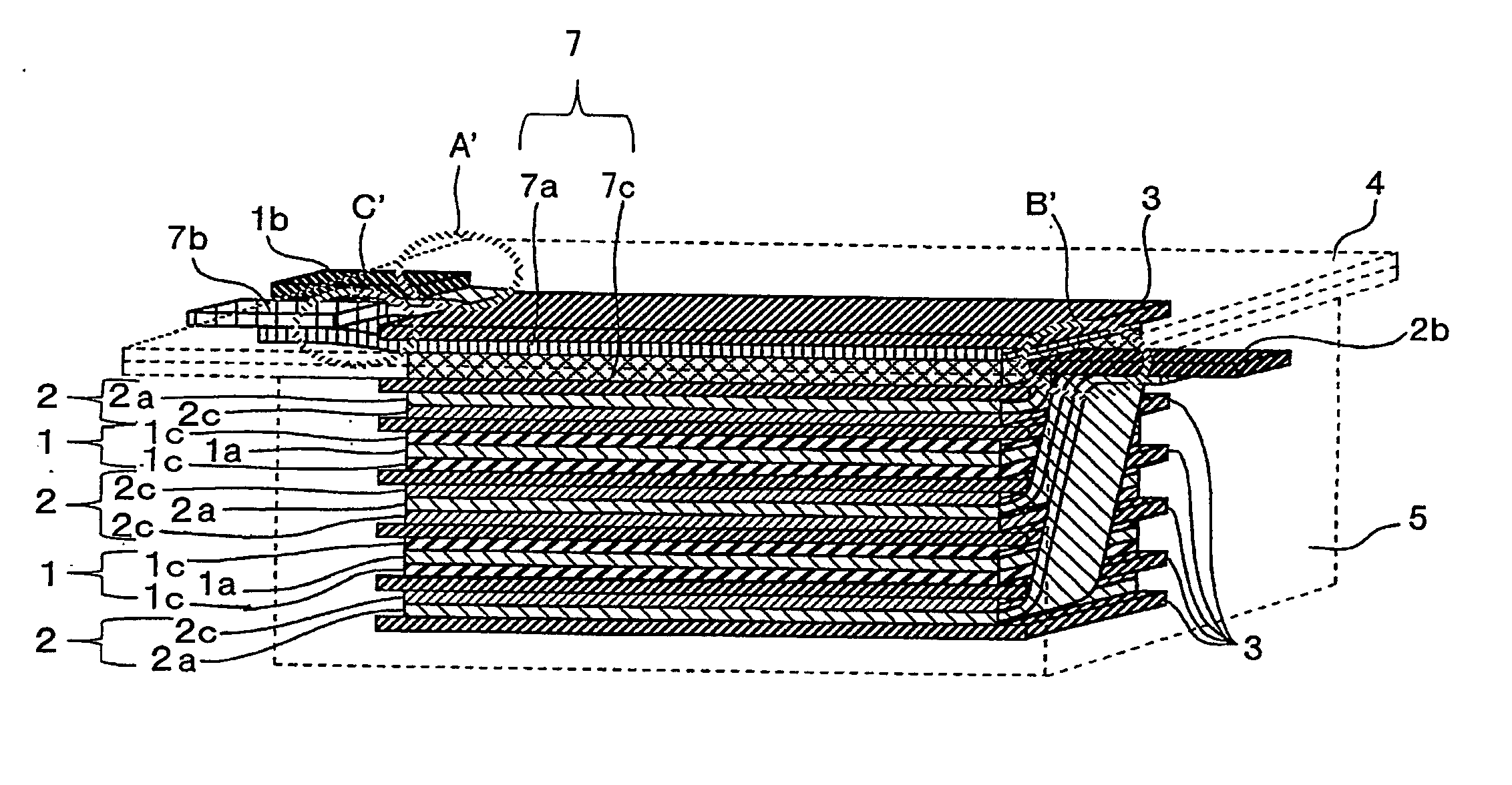

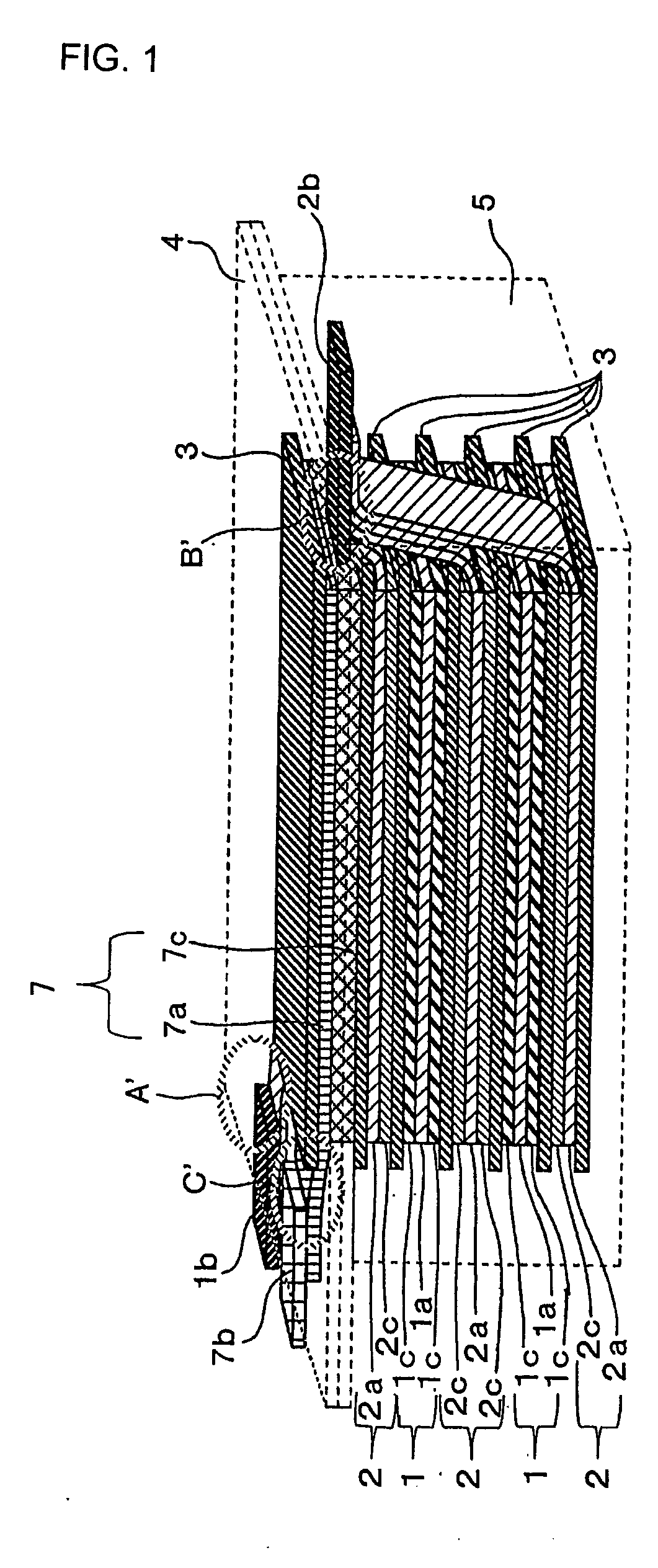

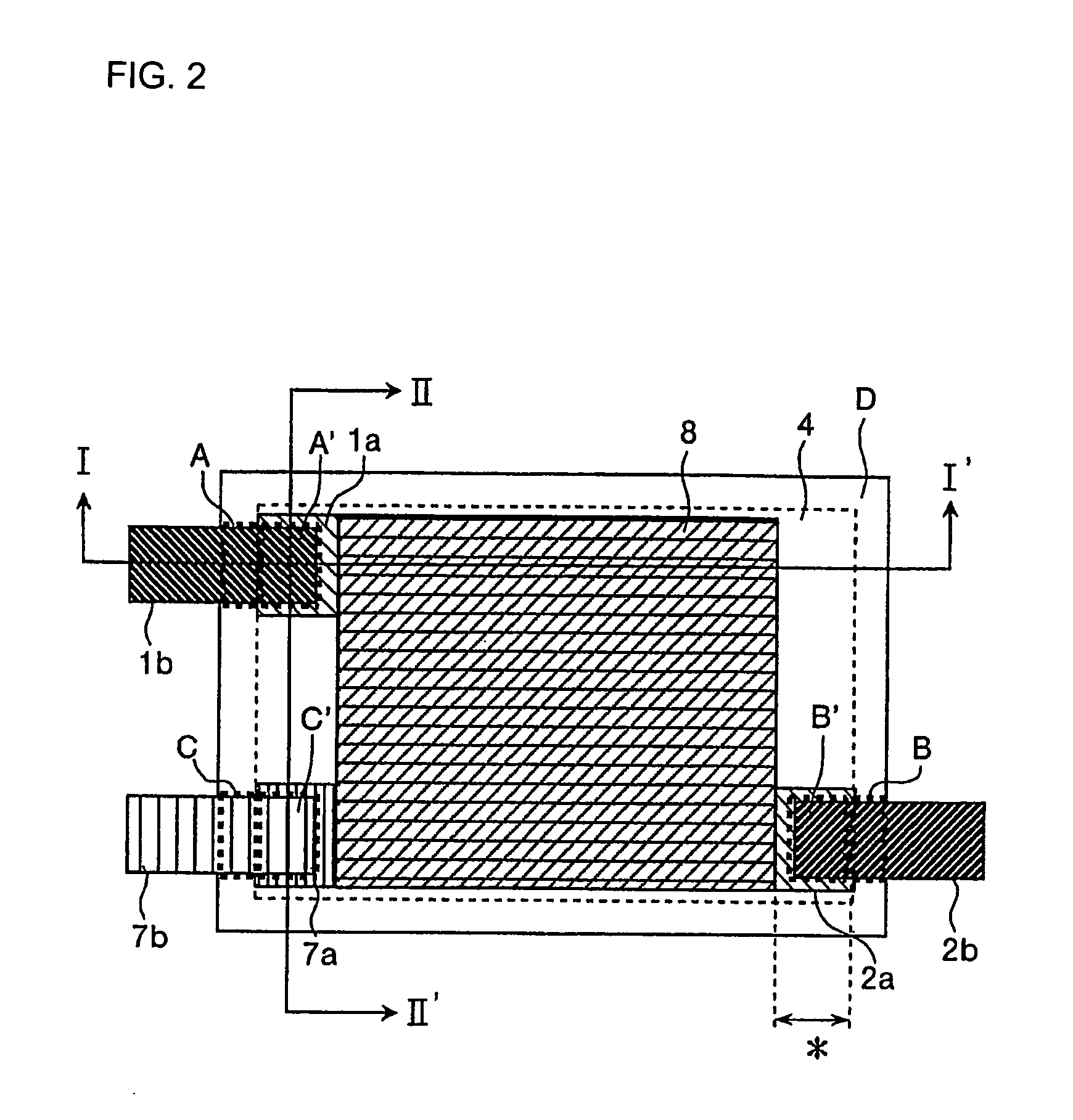

Electrical storage device and manufacturing electrical storage device

InactiveUS20060057433A1Improve breakdown voltageIncrease energy densityFinal product manufactureElectrolyte/reactants regenerationElectrode potentialShape change

An electrical storage device of the present invention is characterized in that a positive electrode, a negative electrode, a lithium electrode, and an electrolyte capable of transferring lithium ion is included, the lithium electrode is arranged to be out of direct contact with the negative electrode, and lithium ion can be supplied to the negative electrode by flowing a current between the lithium electrode and the negative electrode through an external circuit. With the above characteristic, problems such as non-uniform carrying of lithium ion to the negative electrode, shape-change of a cell, and temperature increase of an electrolytic solution under incomplete sealing of a cell and the like can be easily solved. A using method of the electrical storage device is characterized in that, by using the lithium electrode as a reference electrode, the positive electrode potential and negative electrode potential can be measured, and the potential of the positive or negative electrode can be controlled when the electrical storage device is charged or discharged. Therefore, the potentials of the positive electrode and negative electrode can be monitored, thereby it can be easily determined whether deterioration of the electrical storage device is caused by the positive electrode or the negative electrode. Also, it is possible to control the device with the potential difference between the negative electrode and reference electrode, that is, the negative potential. In addition, when characteristics deteriorate such as the internal resistance increase, an appropriate amount of lithium ion can be supplied to the negative electrode and / or positive electrode by the lithium electrode.

Owner:FUJI JUKOGYO KK

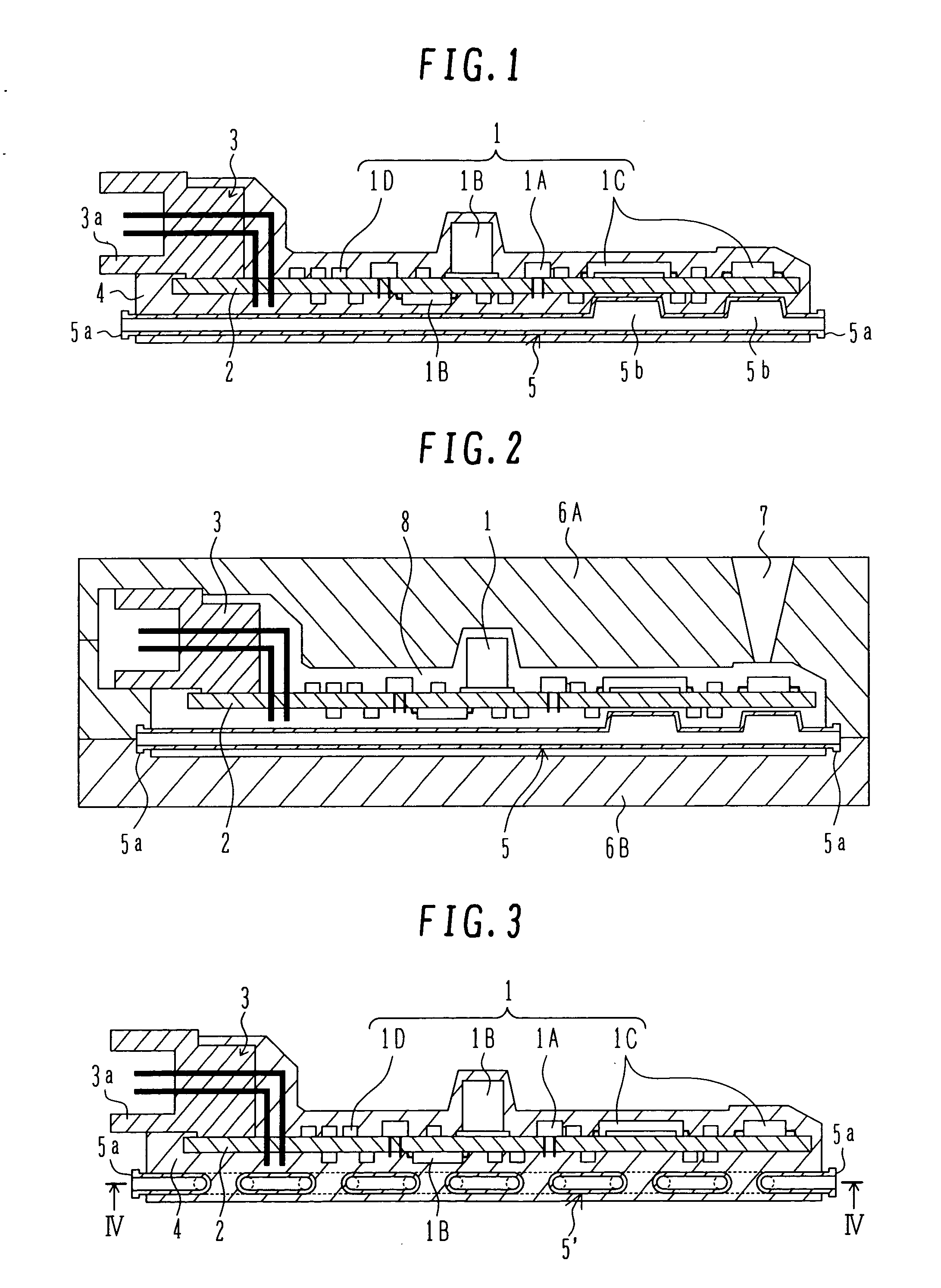

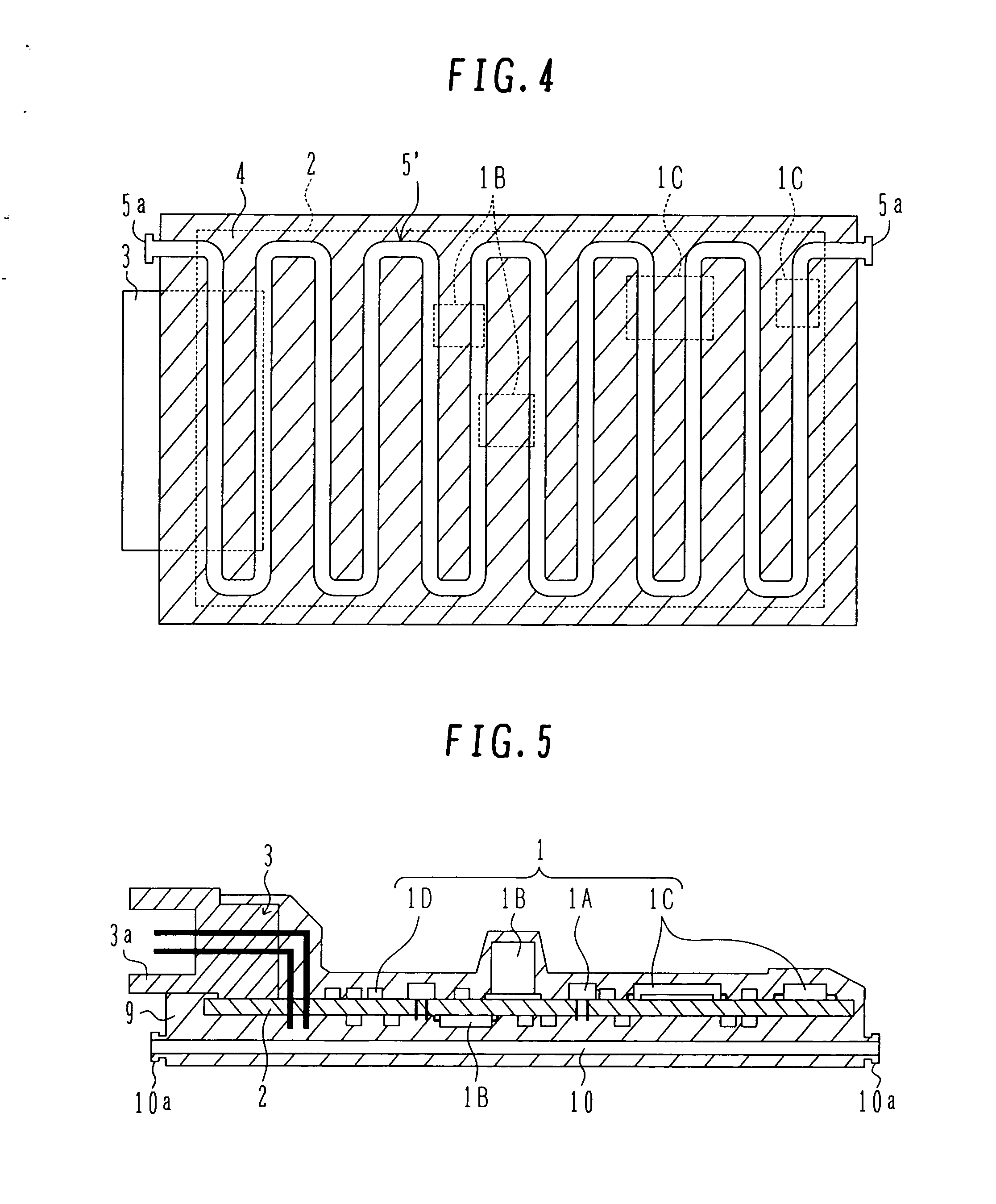

High frequency module

InactiveUS20030169575A1Efficiently dissipatedLow costSemiconductor/solid-state device detailsSolid-state devicesAudio power amplifierElectrical conductor

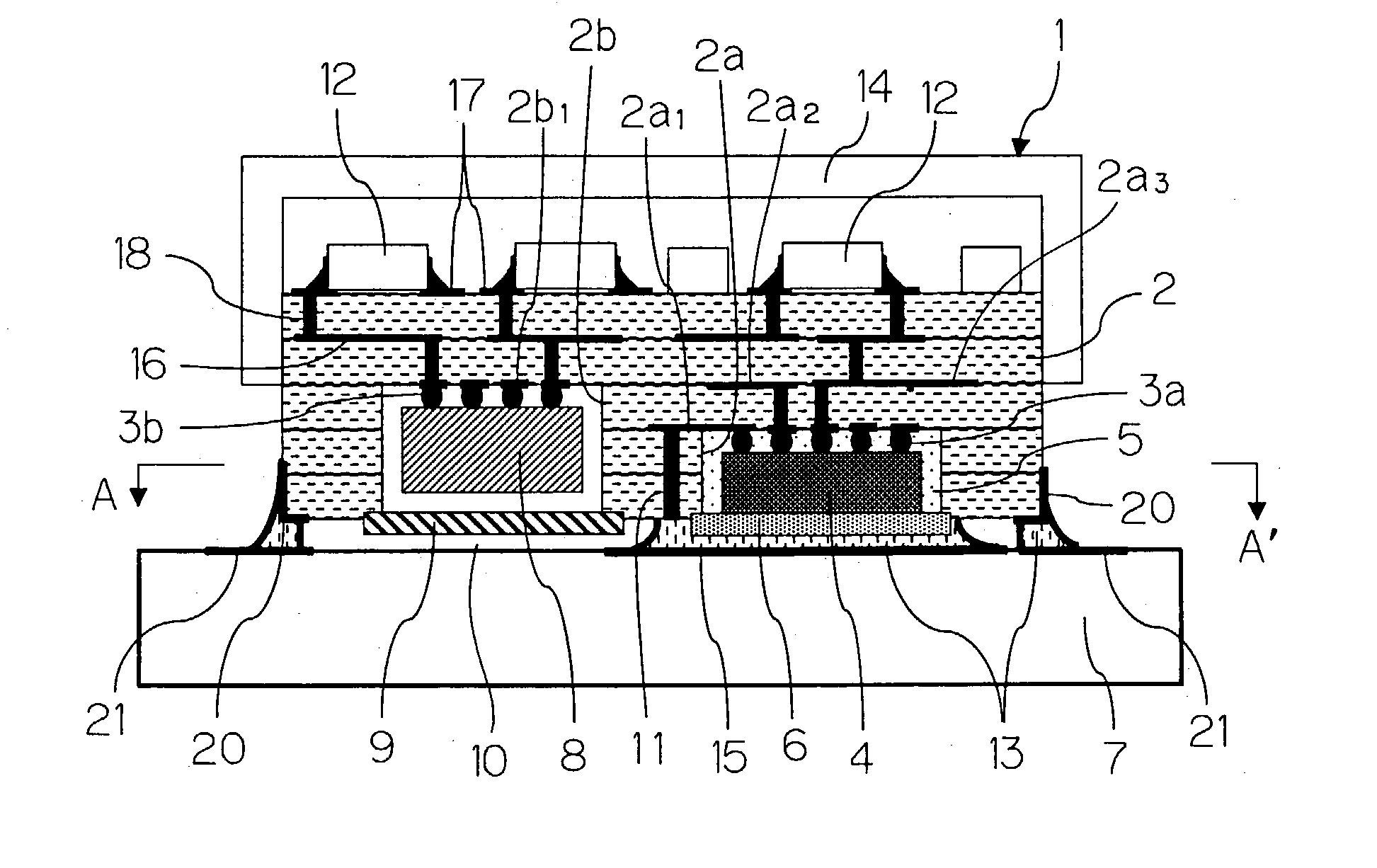

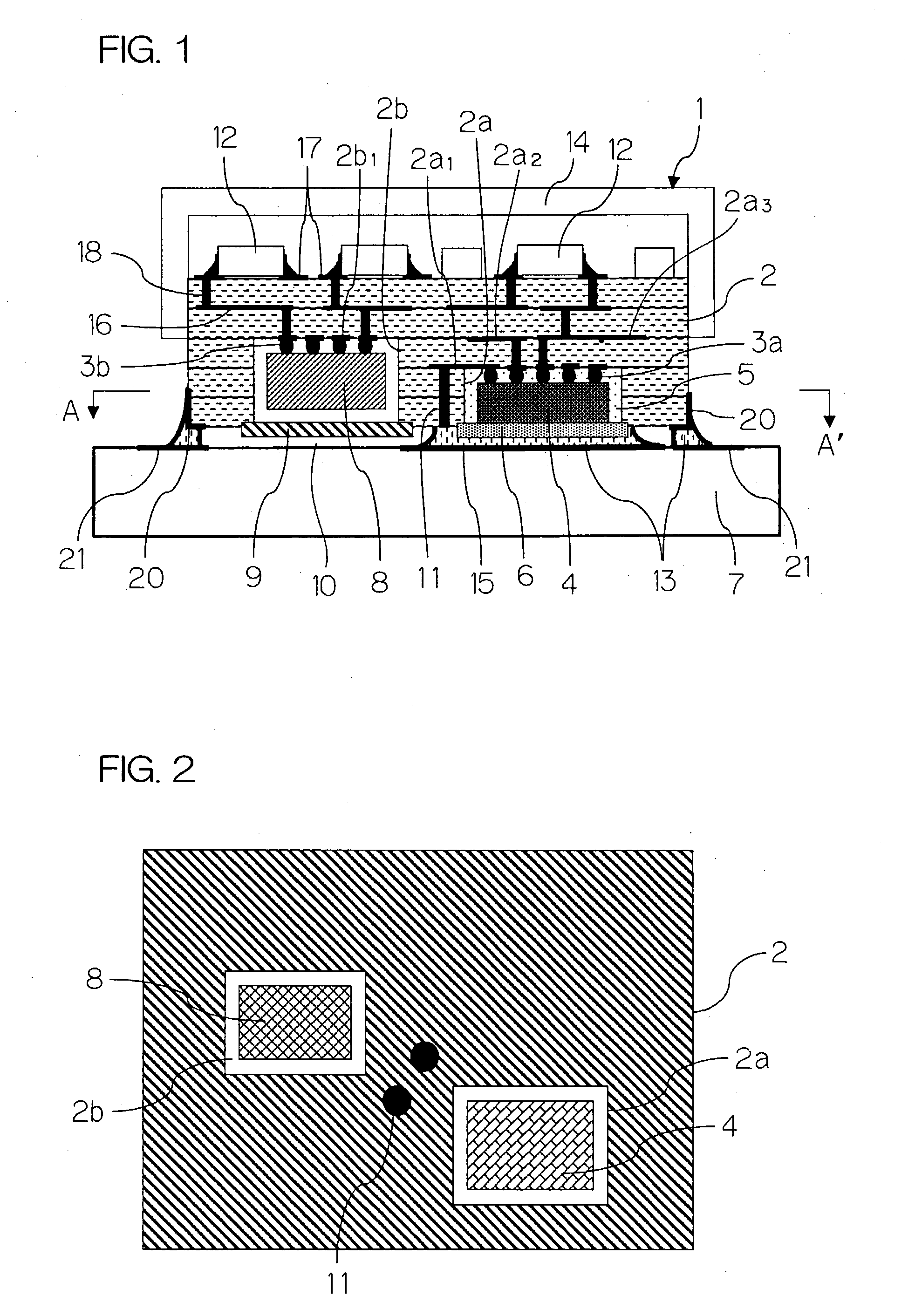

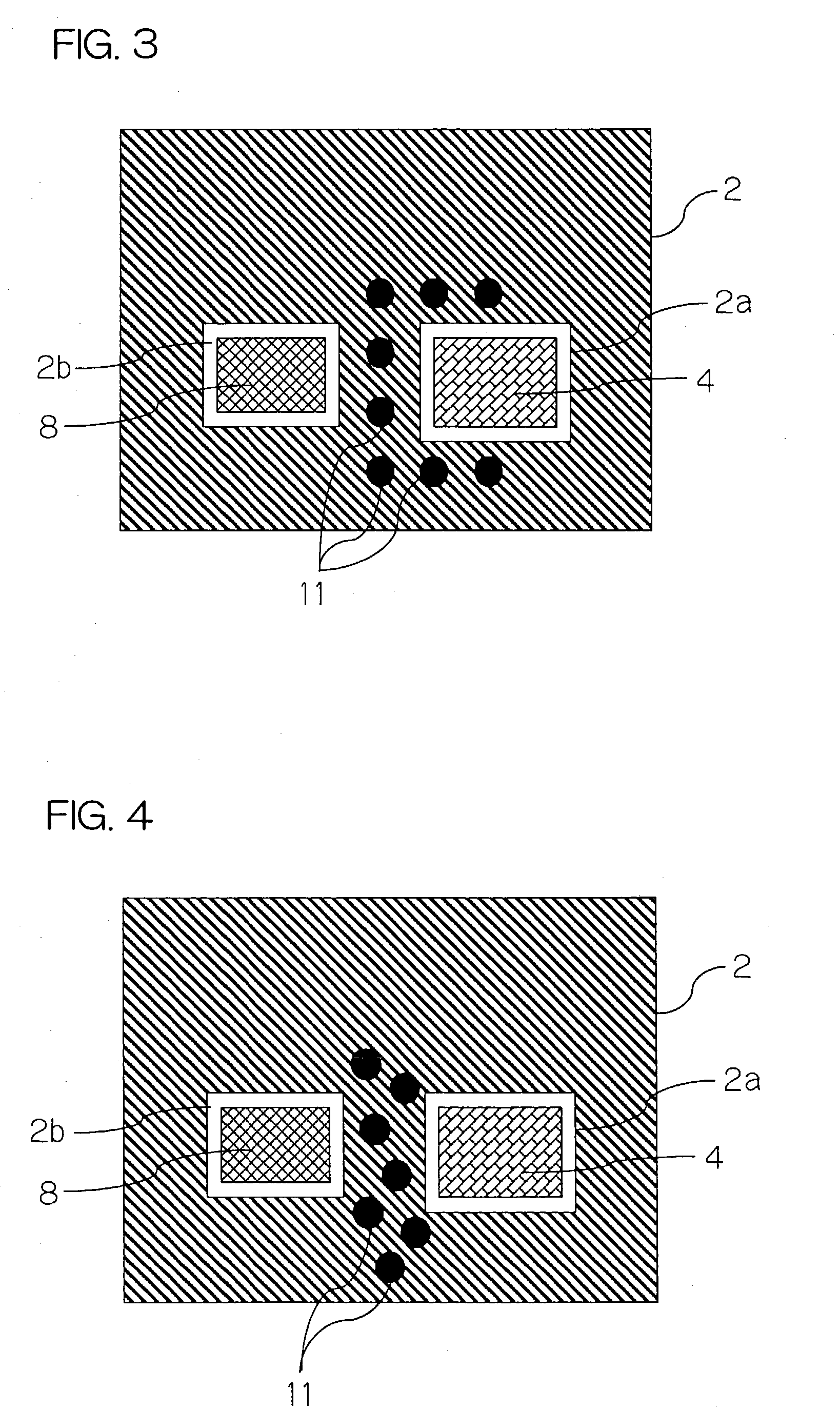

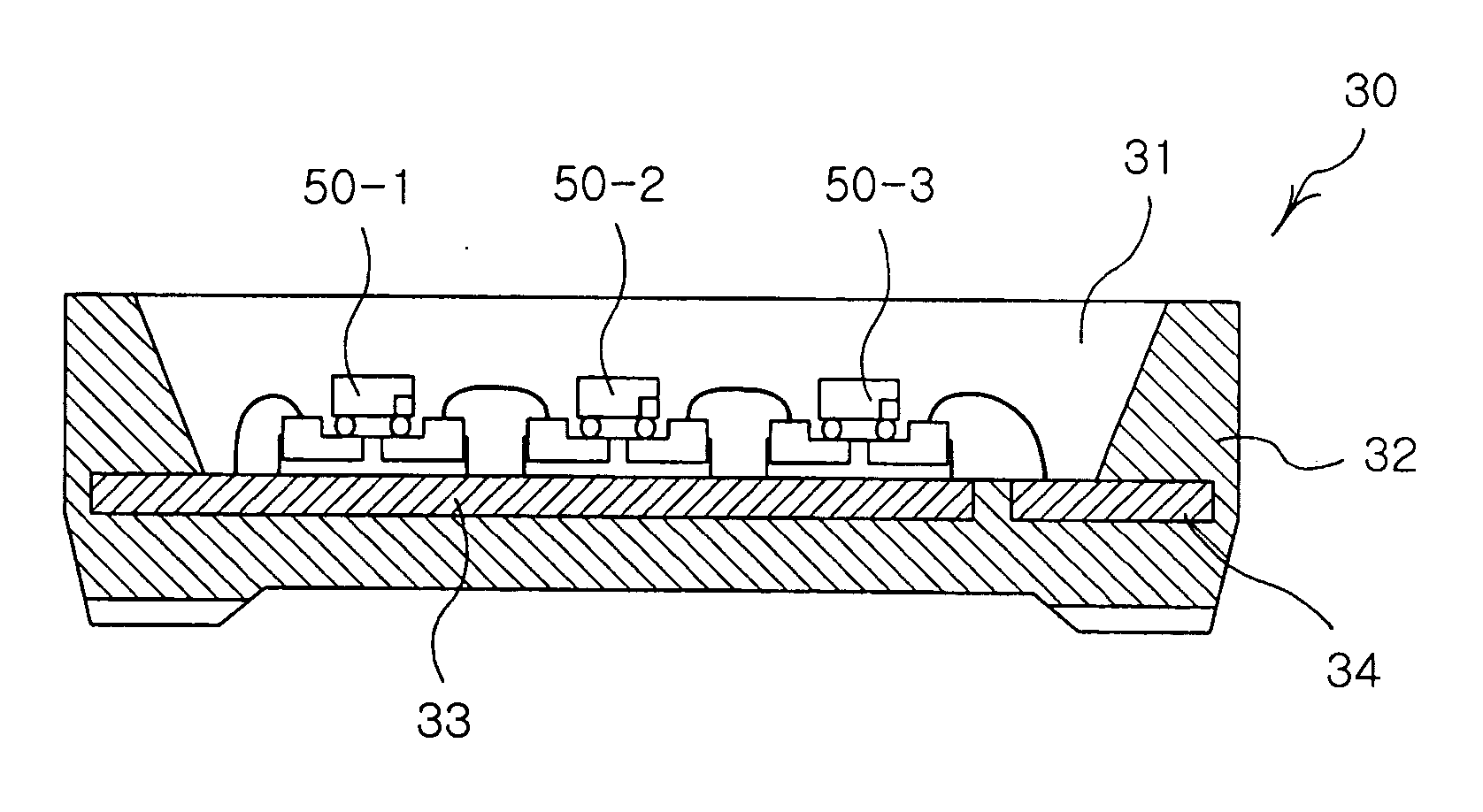

There is presented a high frequency module, in which a recess 2a for mounting power amplifier device is formed on a lower surface of a dielectric substrate 2, and a recess 2b for mounting surface acoustic wave filter is formed on an upper surface of the dielectric substrate 2, and a power amplifier device 4 and a surface acoustic wave filter 8 are mounted through conductive bumps 3a and 3b on the recesses 2a and 2b, respectively. In addition, a through-hole conductor 11 whose one end is exposed at the lower surface of the dielectric substrate 2 is provided between the recesses 2a and 2b. The exposed end of the through-hole conductor 11 is attached to a thermal dissipation conductor 15 on an upper surface of an external electric circuit board 7 through a brazing material 13.

Owner:KYOCERA CORP

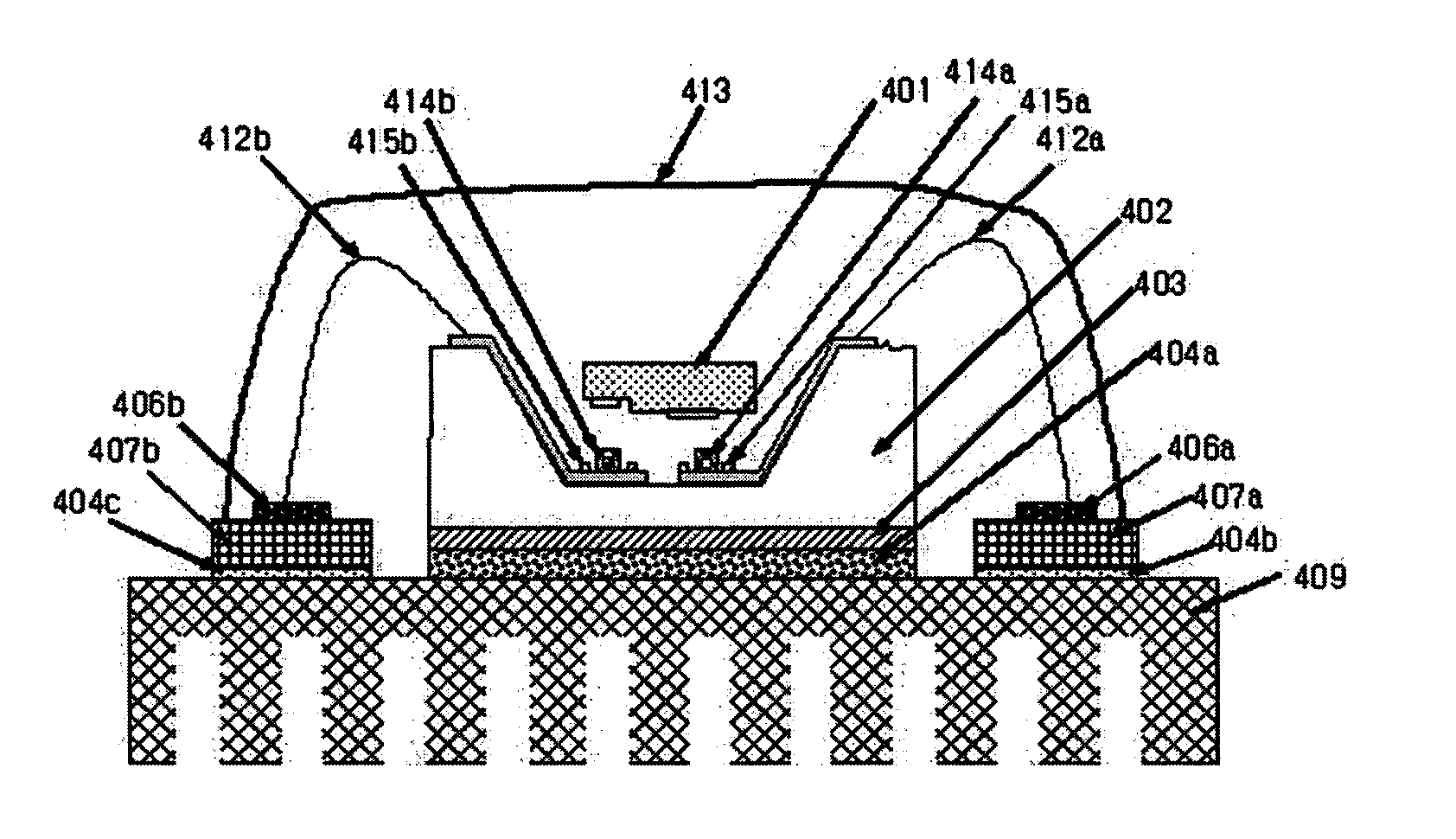

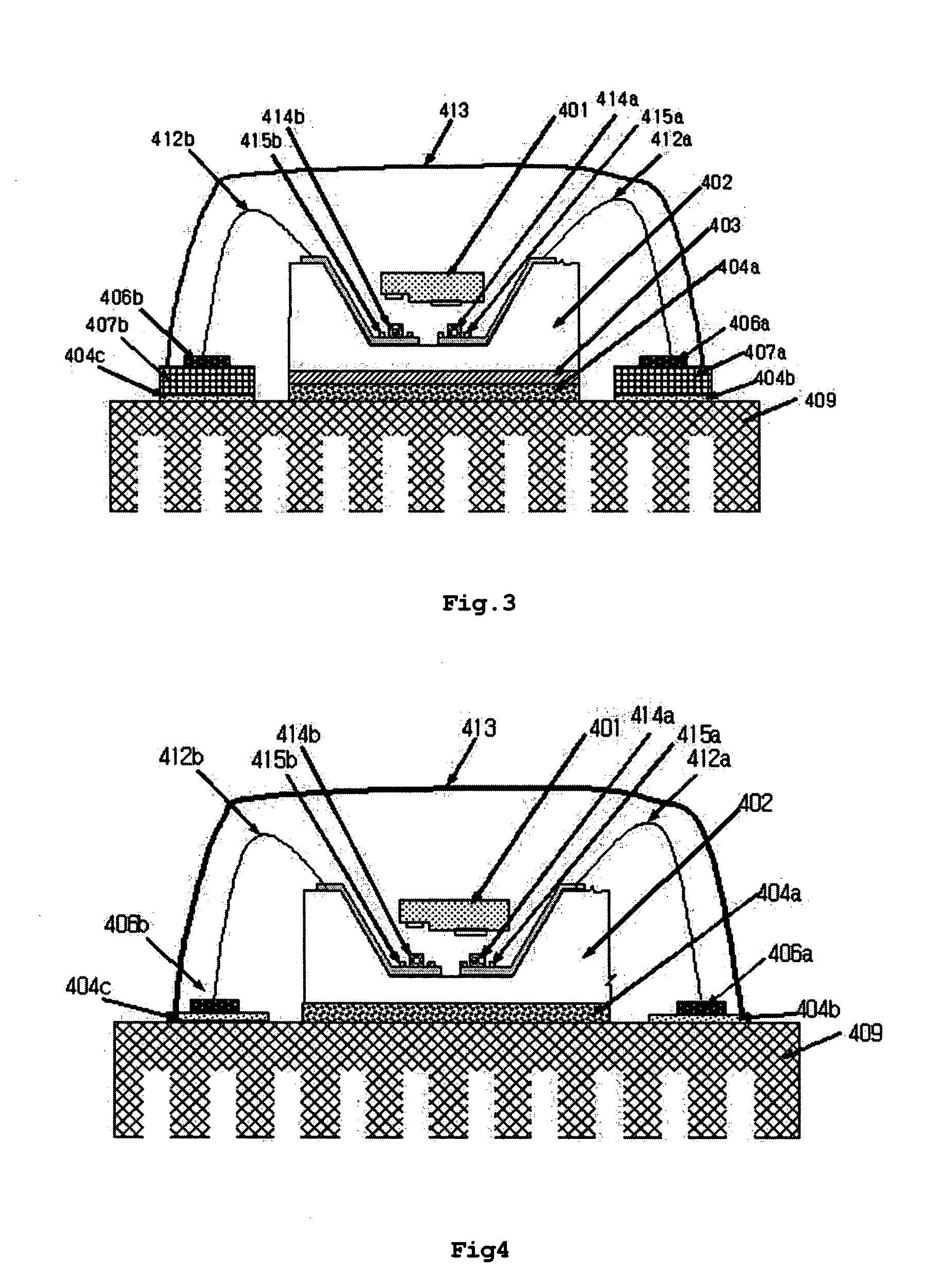

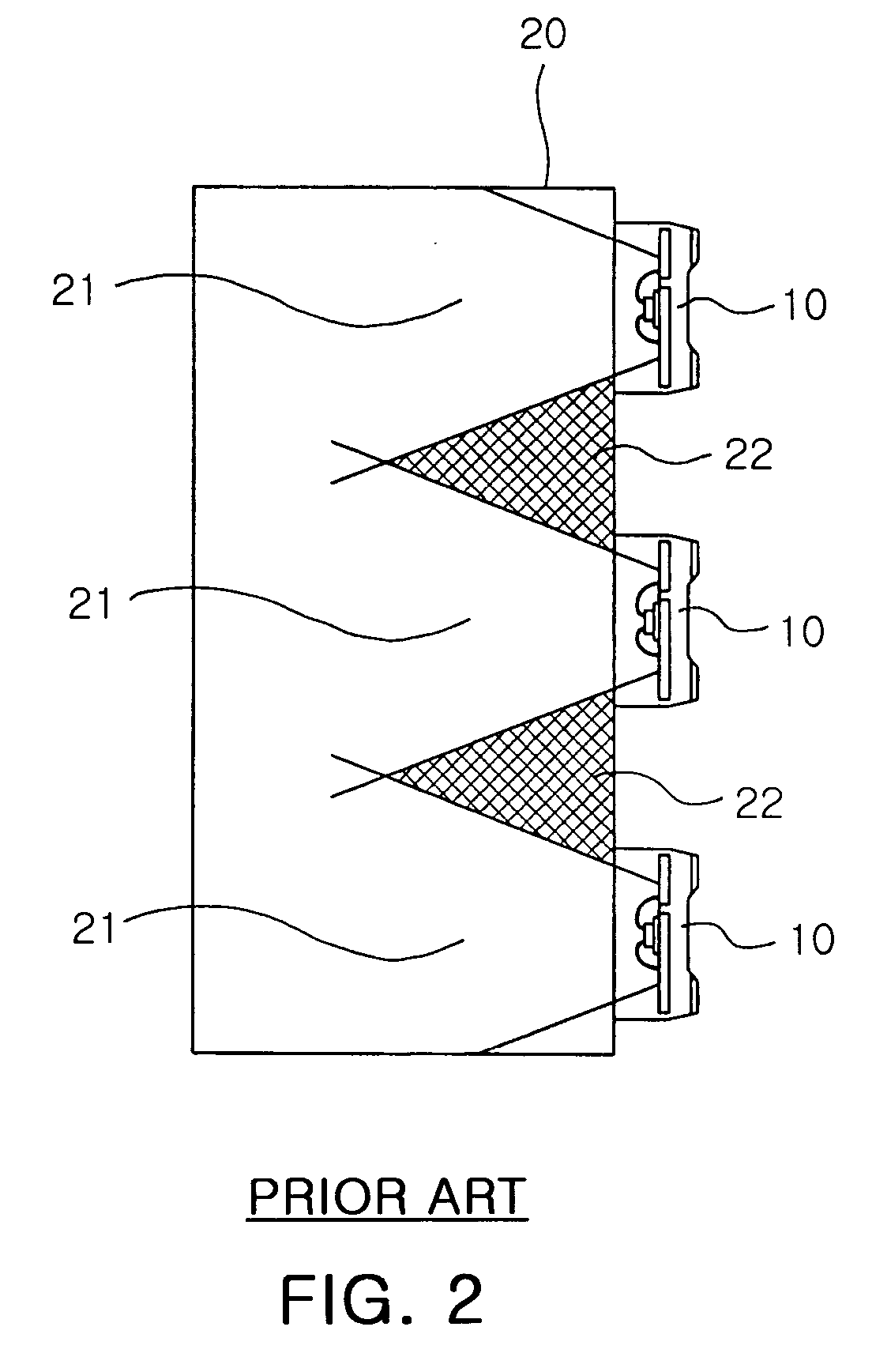

LED package for backlight unit

ActiveUS20060023451A1Avoid deformationImprove image qualityLighting support devicesGlass furnace apparatusEngineeringDie bonding

Disclosed herein is an LED package for a backlight unit. The LED package includes a plurality of LEDs, a die bonding part, a wire bonding part and a body. The die bonding part, on which the plurality of LEDs is arranged, allows the first electrodes of the LEDs to be electrically connected to an external circuit. The wire bonding part is spaced apart from the die bonding part by a predetermined distance to be insulated from the die bonding part and allows the second electrodes of the LEDs to be electrically connected to the external circuit so that the LEDs are operated. The body has a molding cup which is used to fill a space above the LEDs with transparent resin and a base on which the die bonding part and the wire bonding part are arranged.

Owner:SAMSUNG ELECTRONICS CO LTD

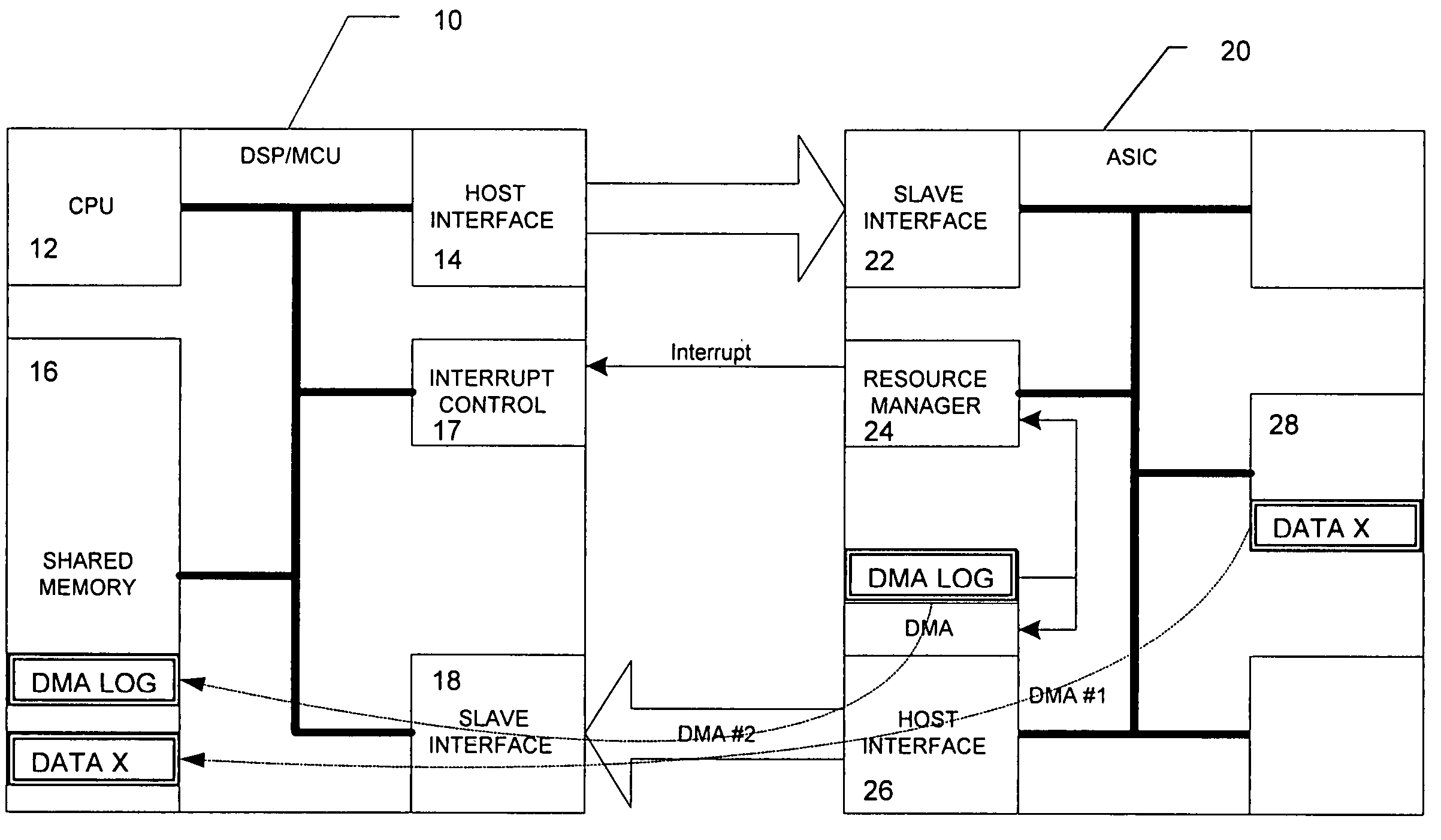

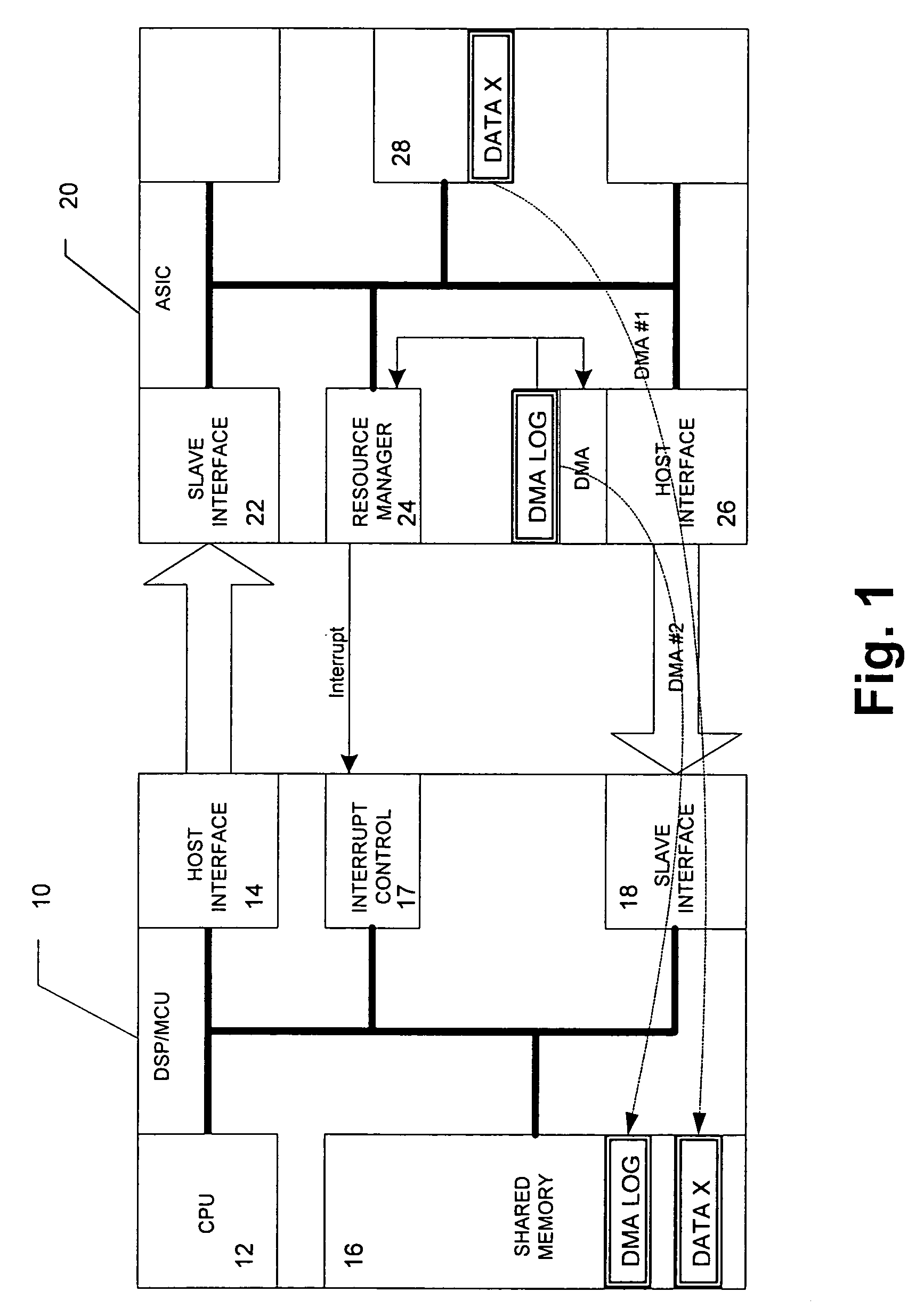

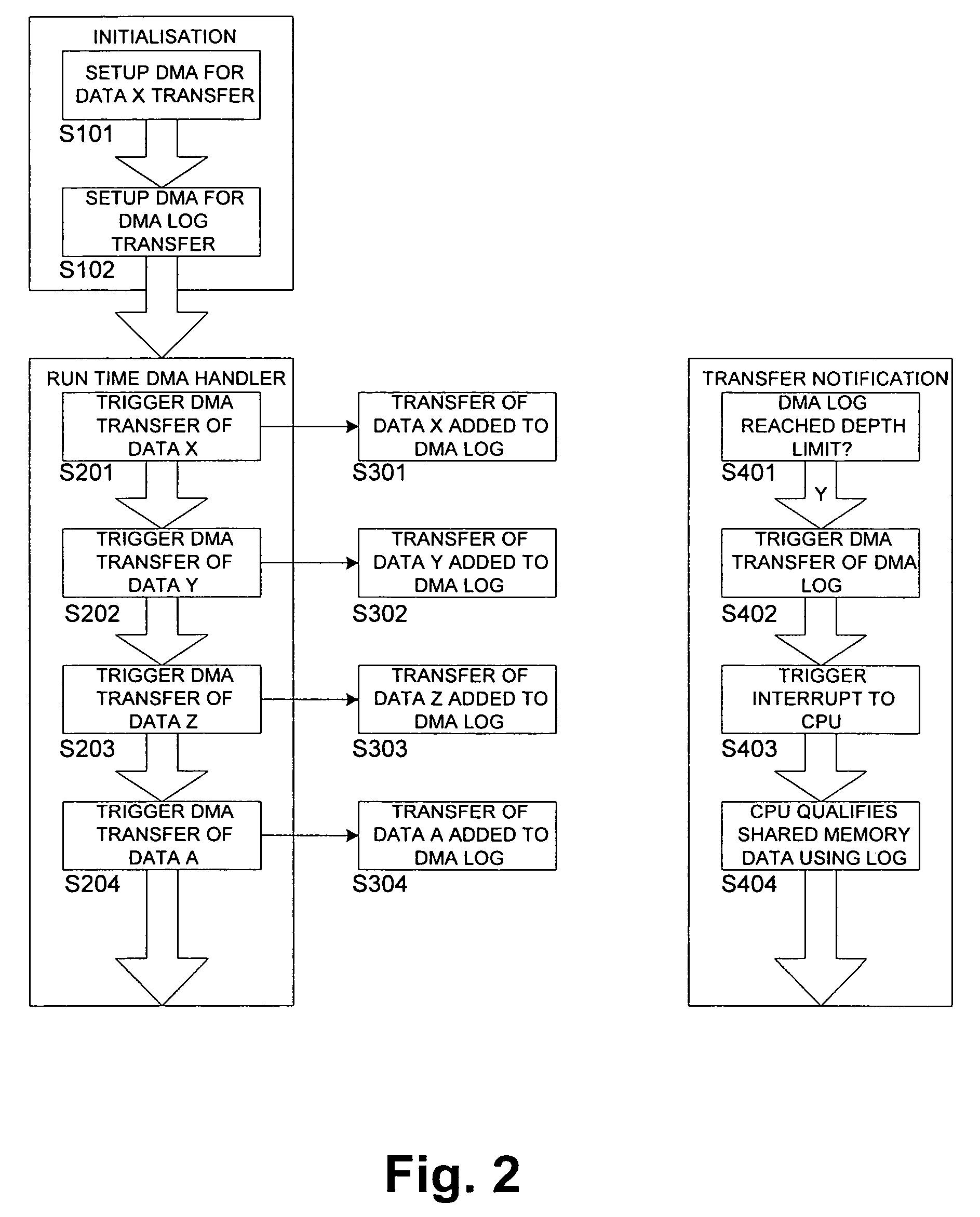

DMA data transfer between low-overhead processor and connected external circuitry using transactions log

InactiveUS7293119B2Reduce loadReduce overheadDigital computer detailsSpecific program execution arrangementsTransaction logData transmission

Owner:NOKIA SOLUTIONS & NETWORKS OY

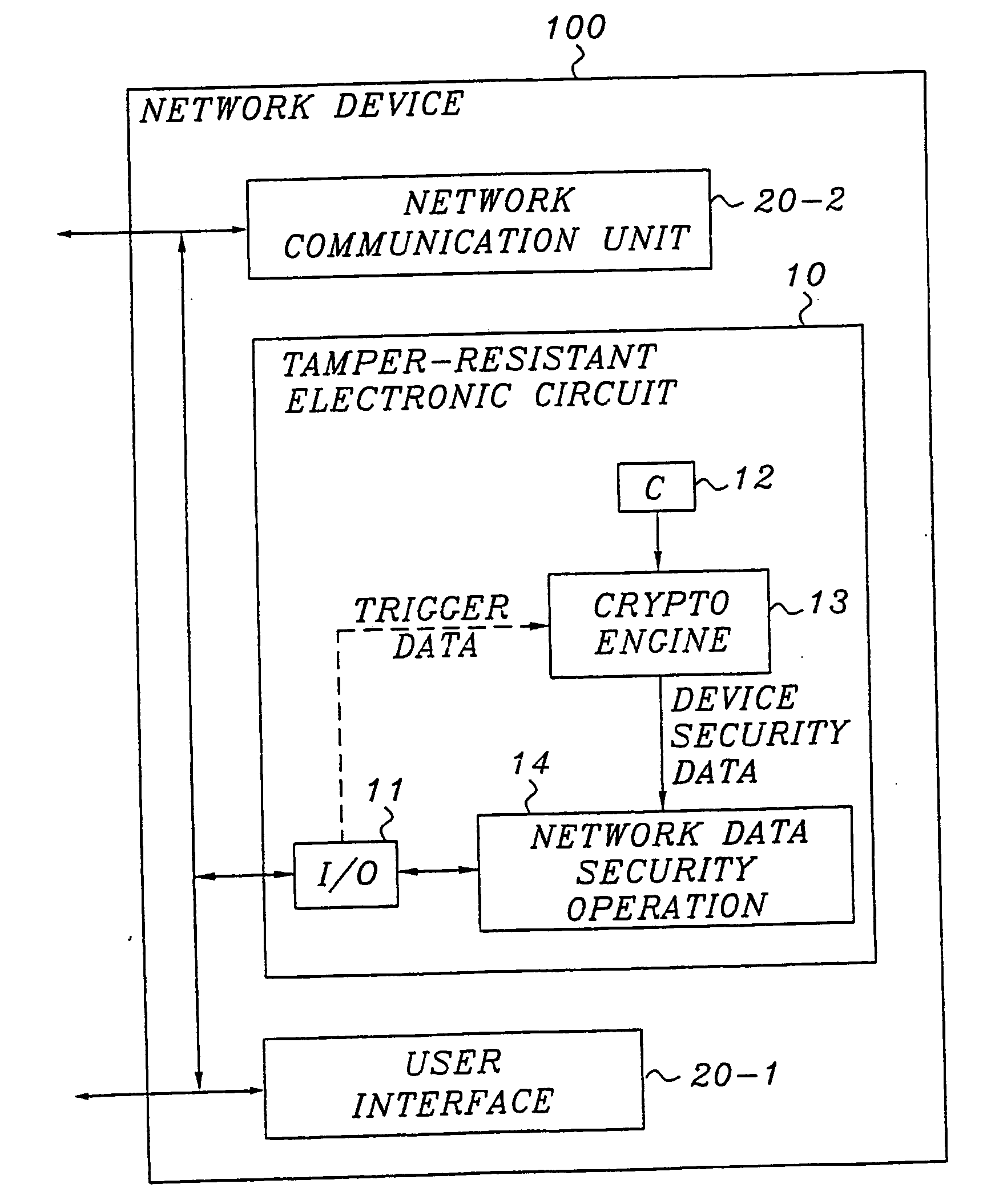

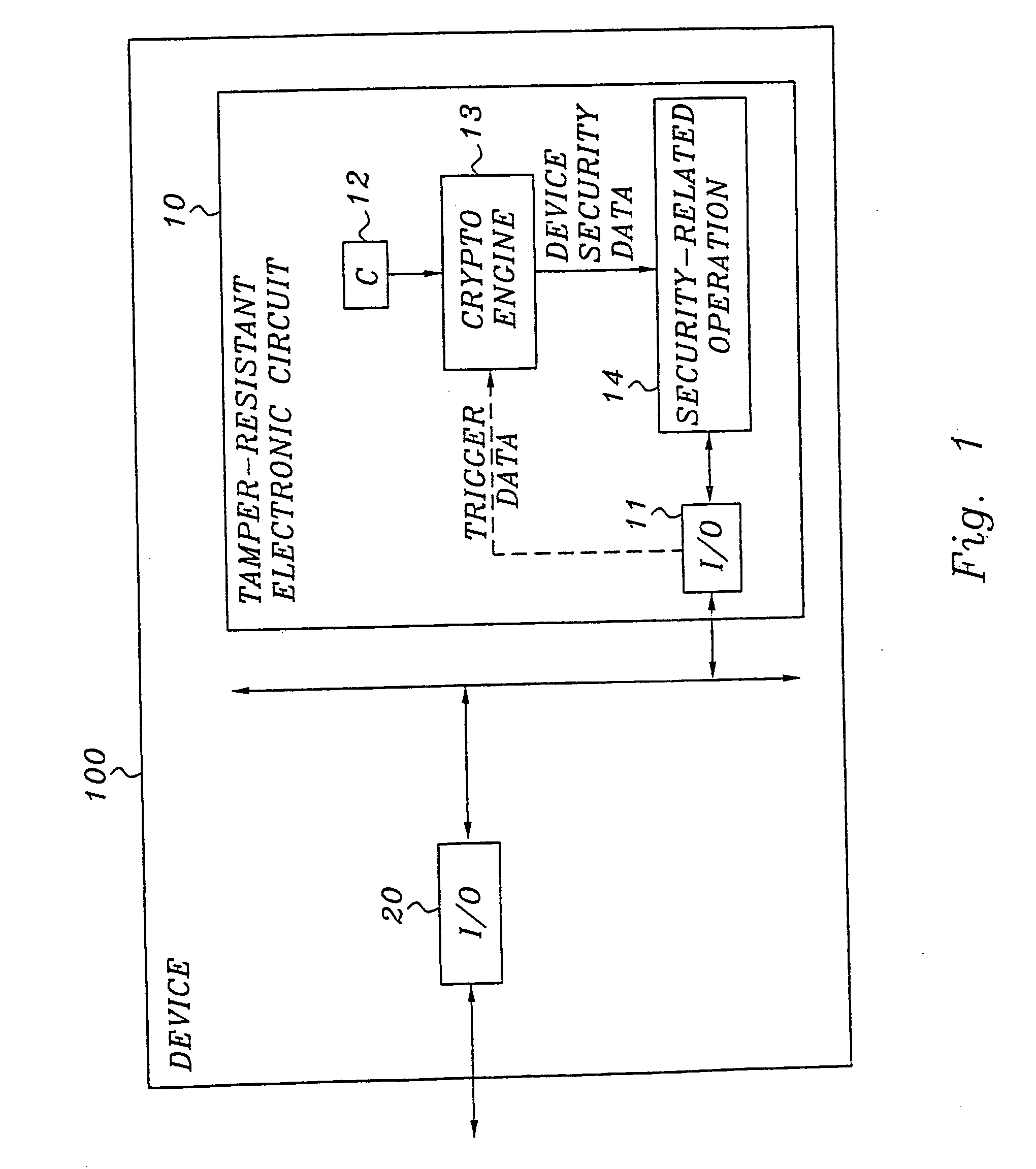

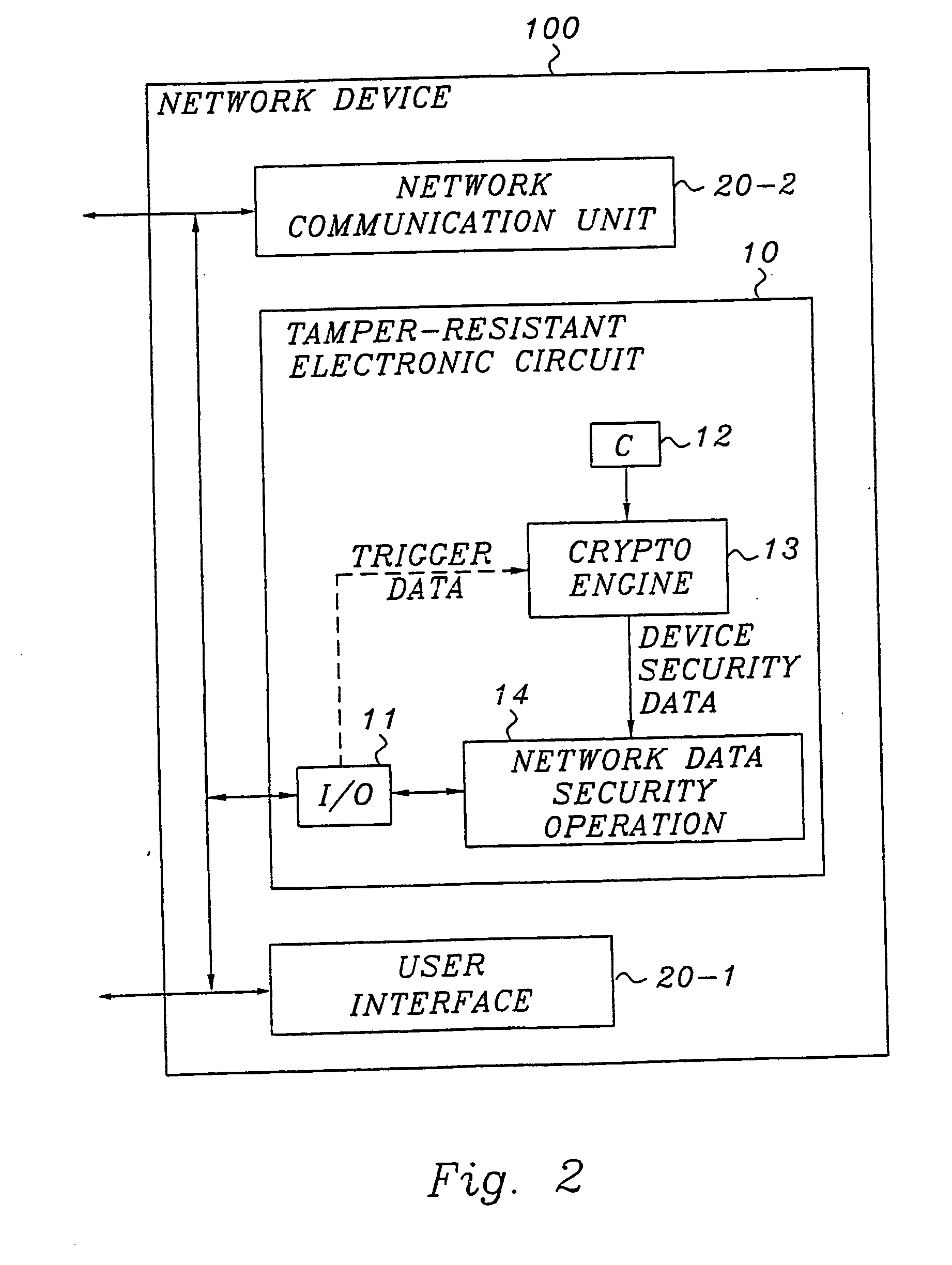

Secure implementation and utilization of device-specific security data

ActiveUS20060101288A1Easy accessImprove securityKey distribution for secure communicationVolume/mass flow measurementExternal circuitComputer security

The invention concerns a tamper-resistant electronic circuit configured for implementation in a device. The electronic circuit securely implements and utilizes device-specific security data during operation in the device, and is basically provided with a tamper-resistantly stored secret not accessible over an external circuit interface. The electronic circuit is also provided with functionality for performing cryptographic processing at least partly in response to the stored secret to generate an instance of device-specific security data that is internally confined within said electronic circuit during usage of the device. The electronic circuit is further configured for performing one or more security-related operations or algorithms in response to the internally confined device-specific security data. In this way, secure implementation and utilization device-specific security data for security purposes can be effectively accomplished. The security is uncompromised since the stored secret is never available outside the electronic circuit, and the device-specific security data is internally confined within the circuit during usage or operation of the device.

Owner:TELEFON AB LM ERICSSON (PUBL)

Photo-catalytic reactor

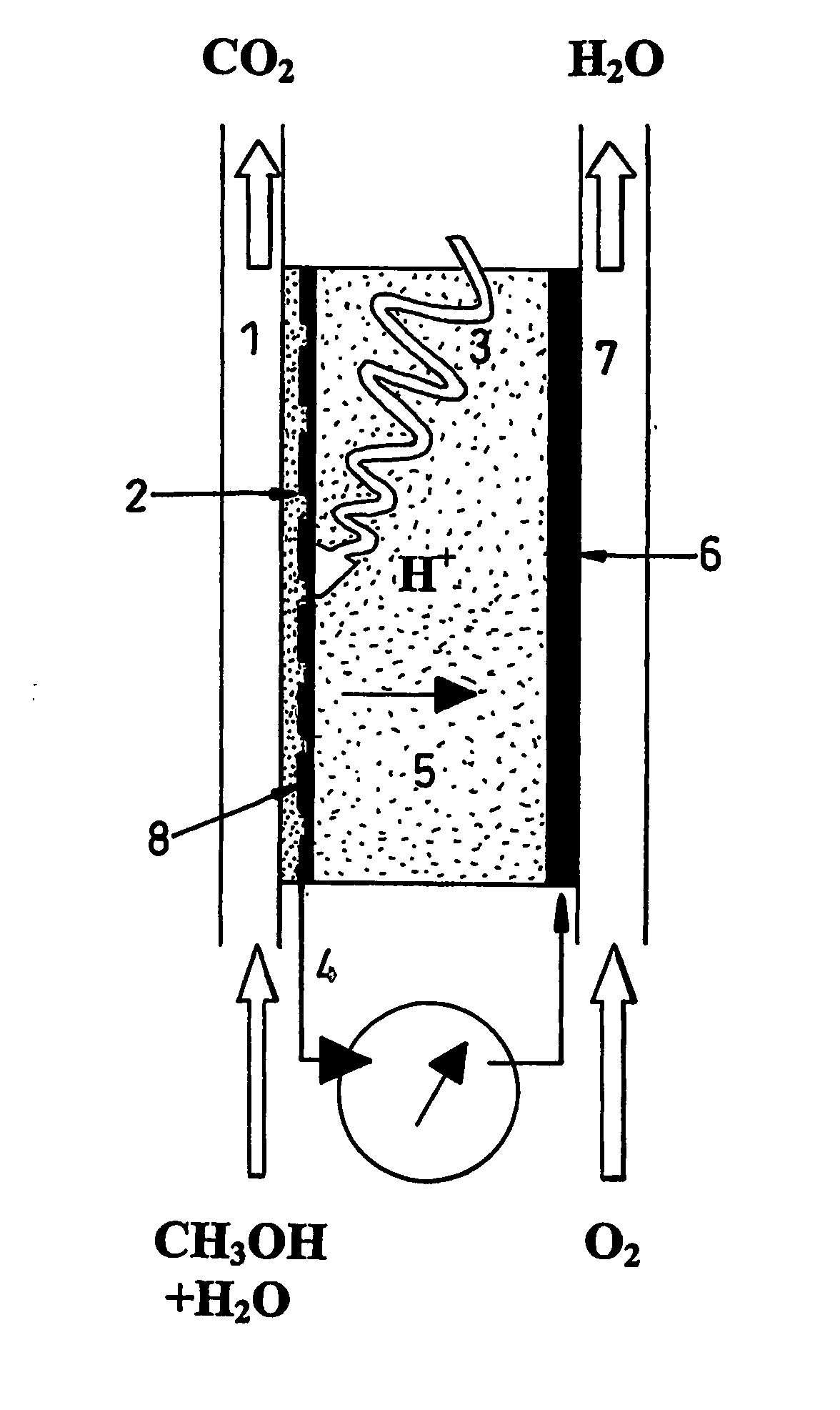

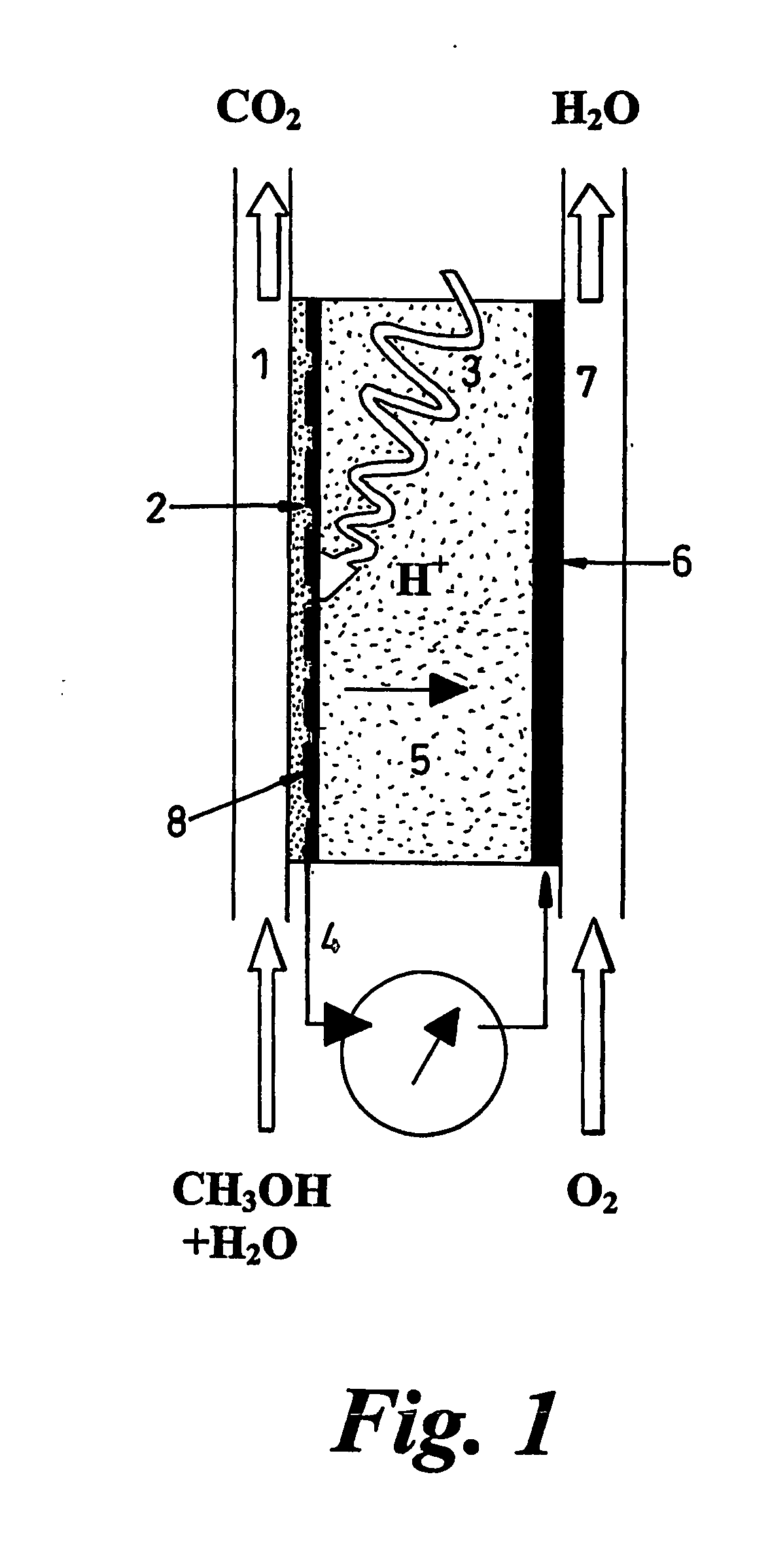

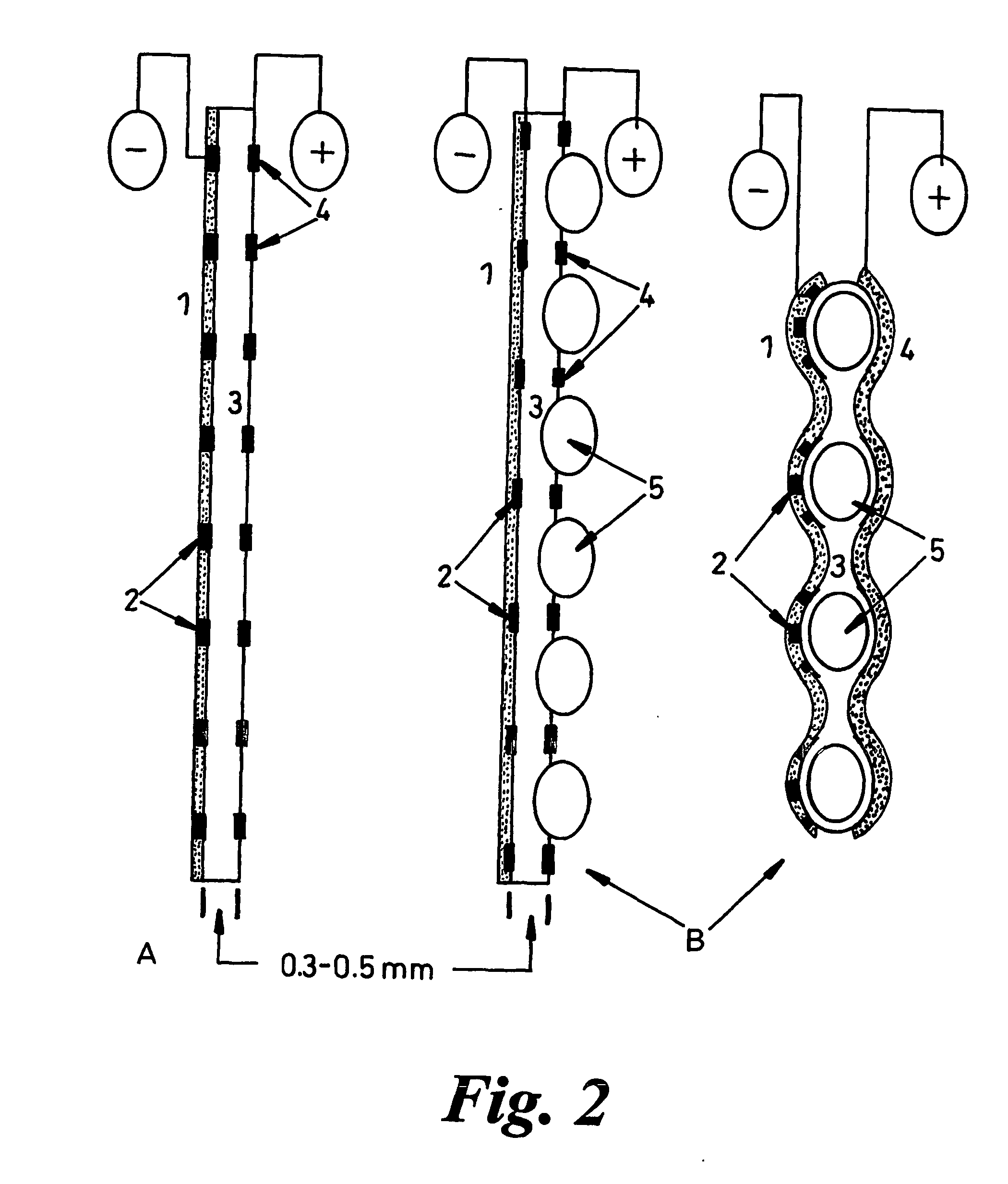

ActiveUS20060246342A1Reduce deliveryEasy to demonstrateDeferred-action cellsFuel cells groupingElectron holePhotocatalytic reaction

A photocatalytic reactor, capable of generating an electric current by consumption of a fuel containing organic material, comprises a direct oxidation fuel cell including an anode and a cathode. The anode is a photocatalysis-assisted anode which comprises a photocatalyst on a surface of an electrically-conductive substrate so arranged as to be receptive to light. A light-transmissive proton-conductive membrane is arranged between the anode and the cathode, such that light passes through said membrane as a final stage in the optical path to the photocatalyst. The photocatalyst promotes oxidation of organic material and generates electron-hole pairs. The reactor, configured to support multiple cells in a stacked array, is provided with inlet(s) for introducing said fuel and connector(s) for connection to an external electrical circuit.

Owner:THE UNIV COURT OF THE UNIV OF ABERDEEN REGENT WALK

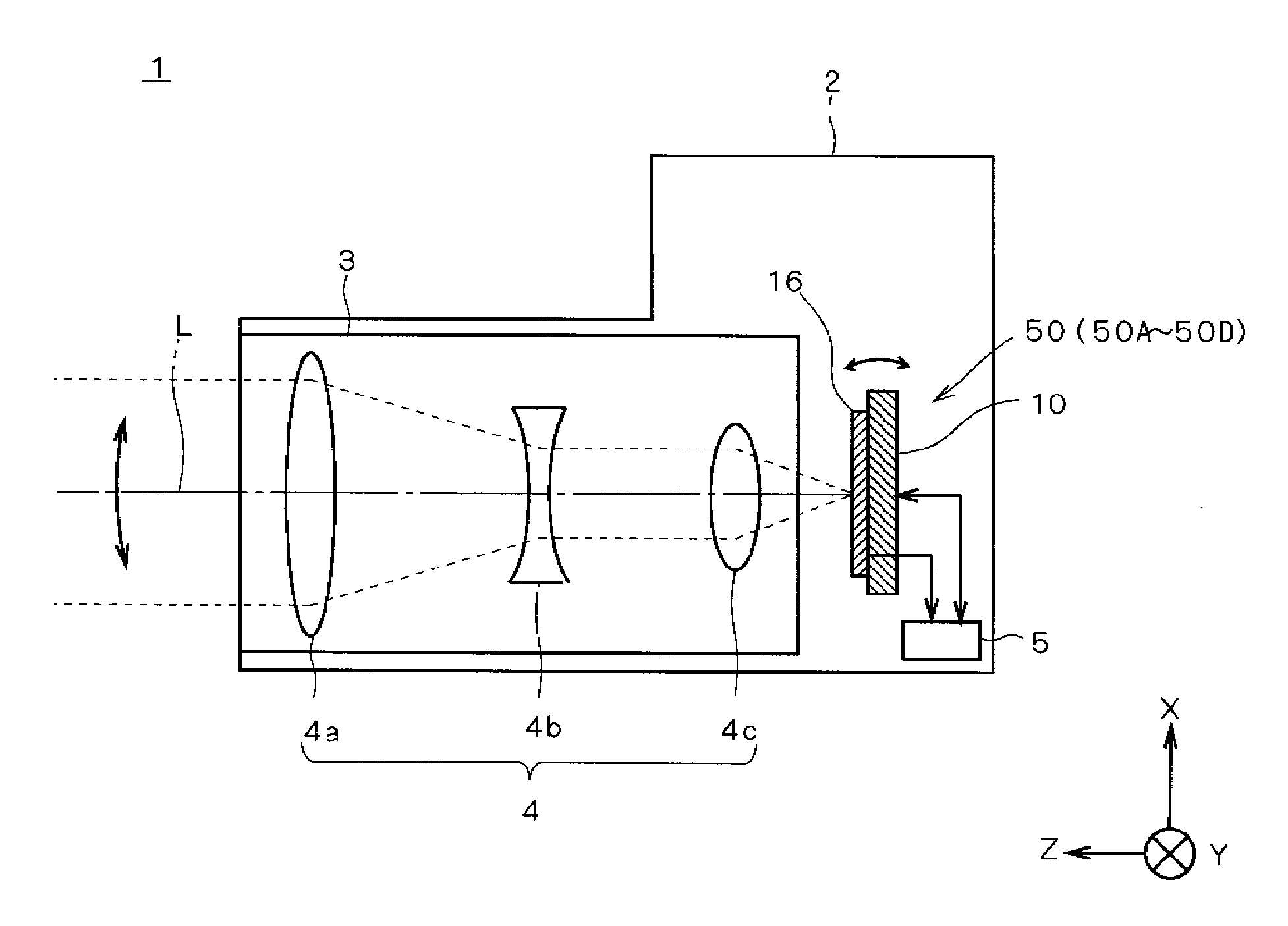

Image sensor device

InactiveUS20080198249A1Improve accuracyInhibition resistanceTelevision system detailsTelevision system scanning detailsElectricityEngineering

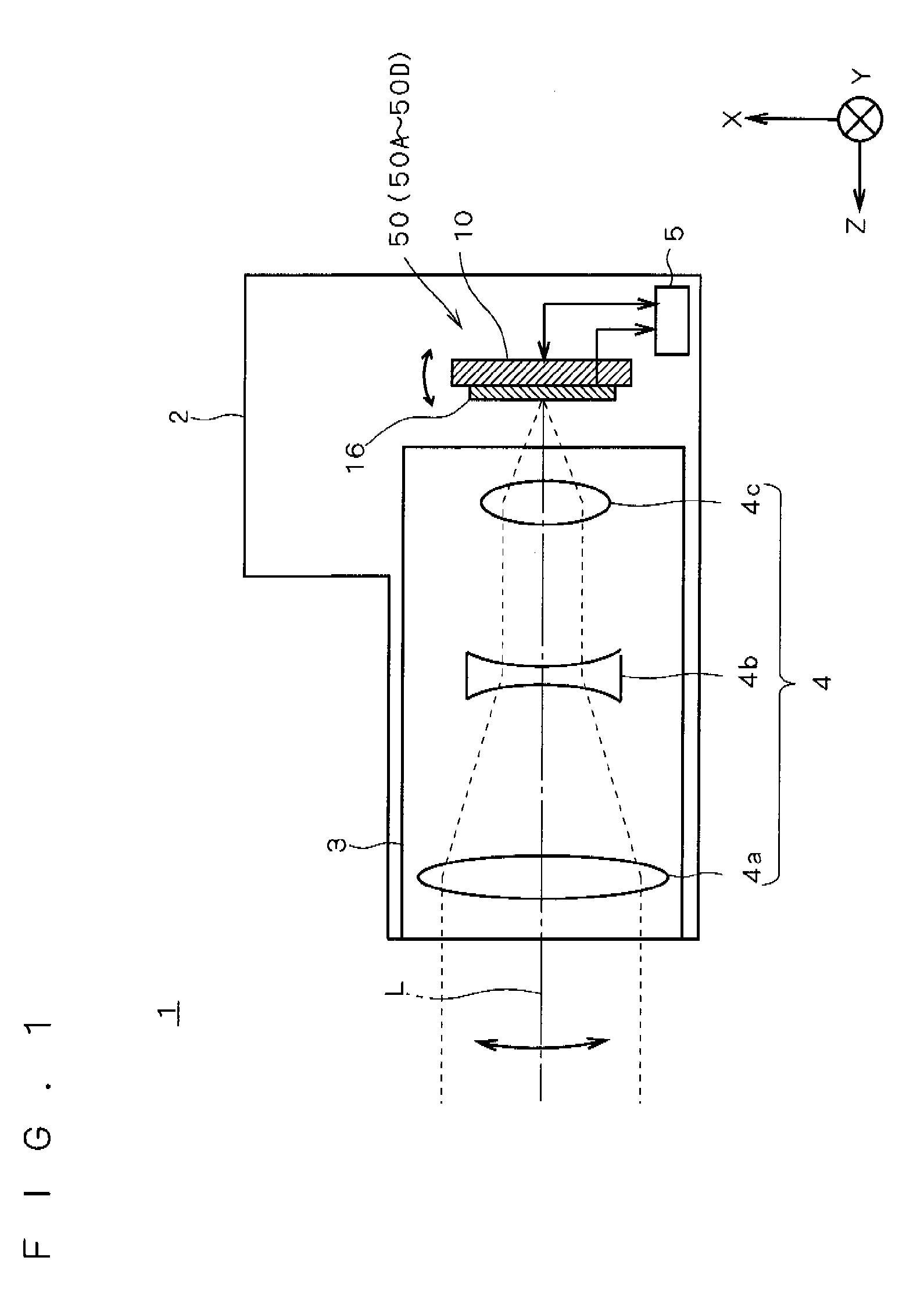

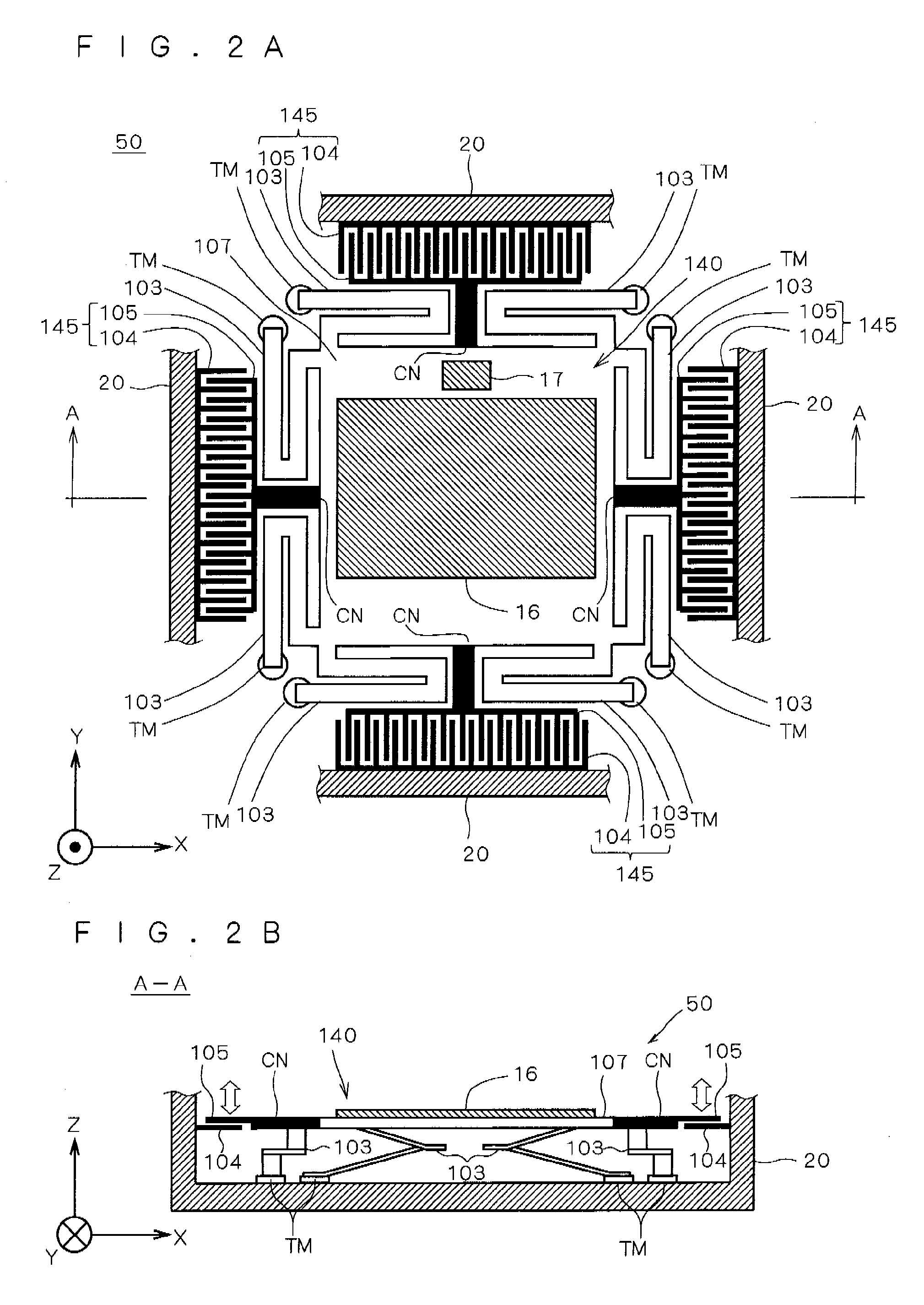

An object of the present invention is to provide a small-sized image sensor device having high precision of moving an object to be moved. The image sensor device includes: a fixed unit; a movable unit including an image sensor; a beam unit fixed to the fixed unit and movably supporting the movable unit; a driving unit for applying a driving force for moving the movable unit; and a wire unit provided for the beam unit and electrically connecting the image sensor and an external circuit.

Owner:KONICA MINOLTA OPTO

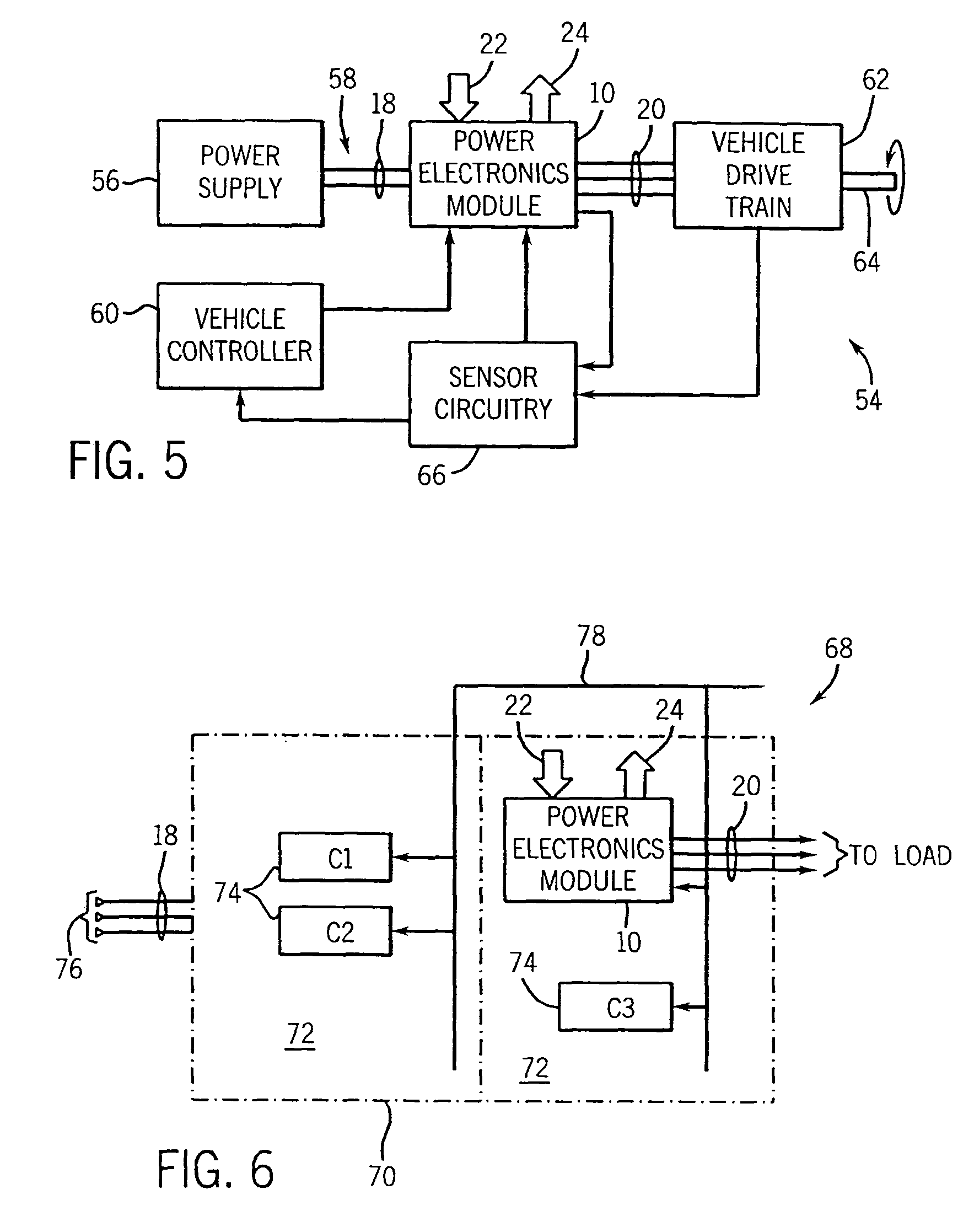

Power converter connection configuration

InactiveUS7450388B2Small and light and efficient configurationImprove performanceMagnetic/electric field screeningDigital data processing detailsModular unitModularity

Owner:ROCKWELL AUTOMATION TECH

Low cost microelectronic circuit package

InactiveUS7183658B2Semiconductor/solid-state device detailsSolid-state devicesMicroelectronic circuitsExternal circuit

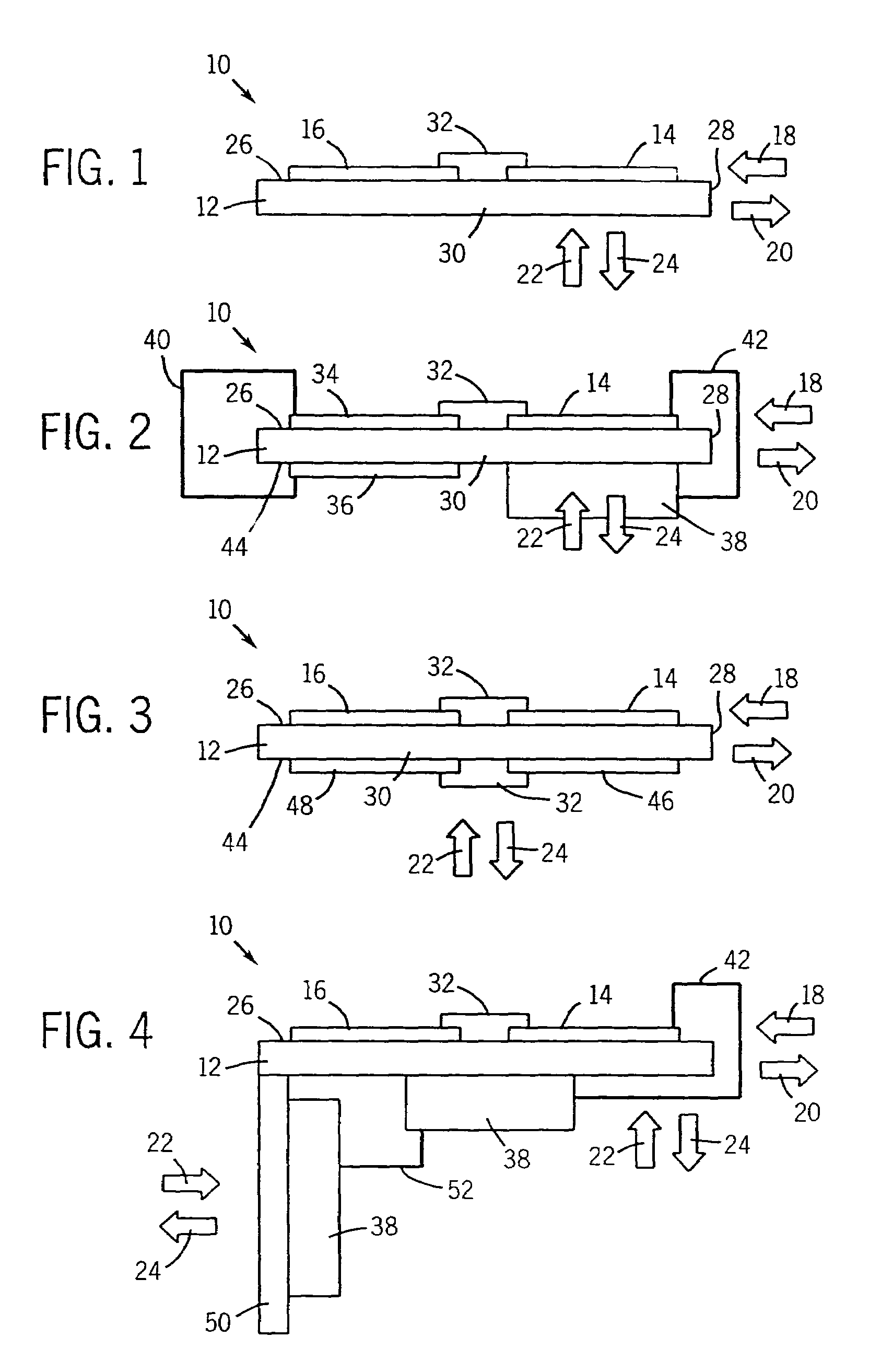

A low cost microelectronic circuit package includes a single build up metallization layer above a microelectronic die. At least one die is fixed within a package core using, for example, an encapsulation material. A single metallization layer is then built up over the die / core assembly. The metallization layer includes a number of landing pads having a pitch that allows the microelectronic device to be directly mounted to an external circuit board. In one embodiment, the metallization layer includes a number of signal landing pads within a peripheral region of the layer and at least one power landing pad and one ground landing pad toward a central region of the layer.

Owner:INTEL CORP

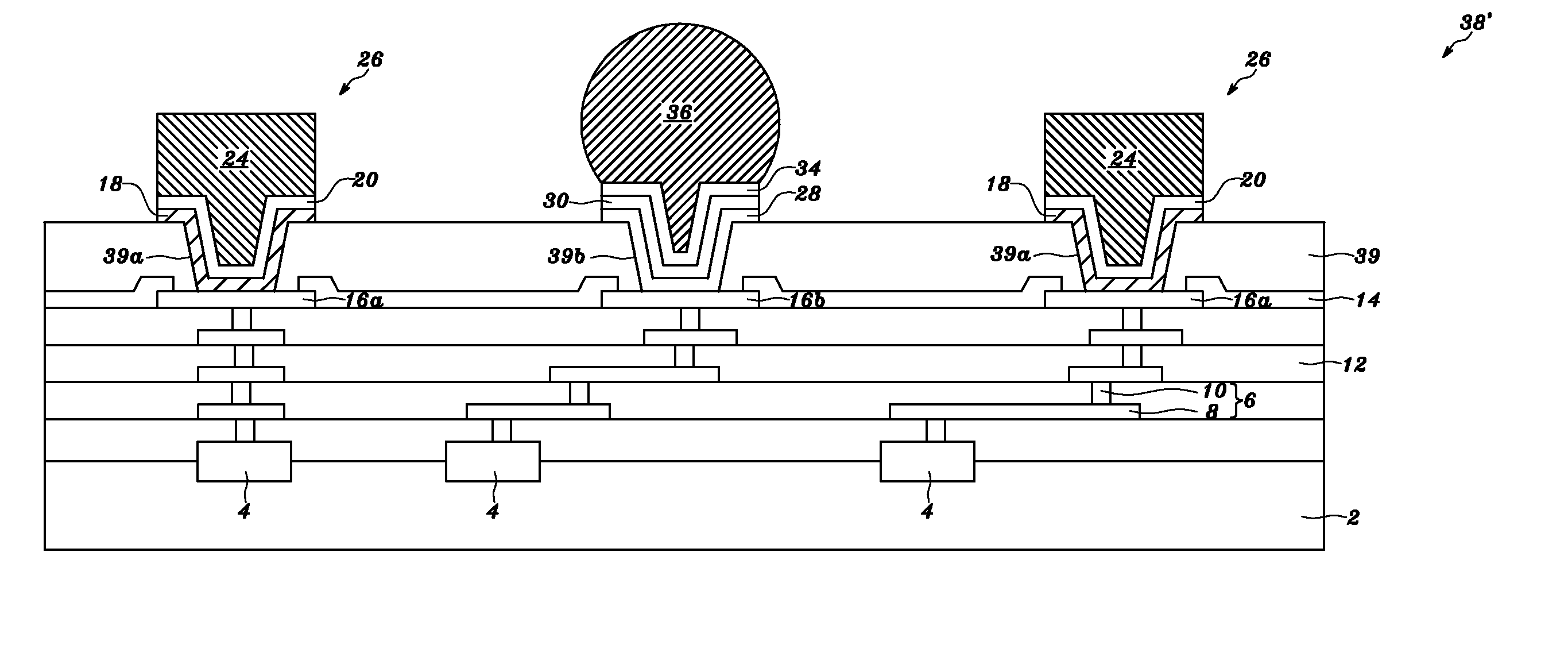

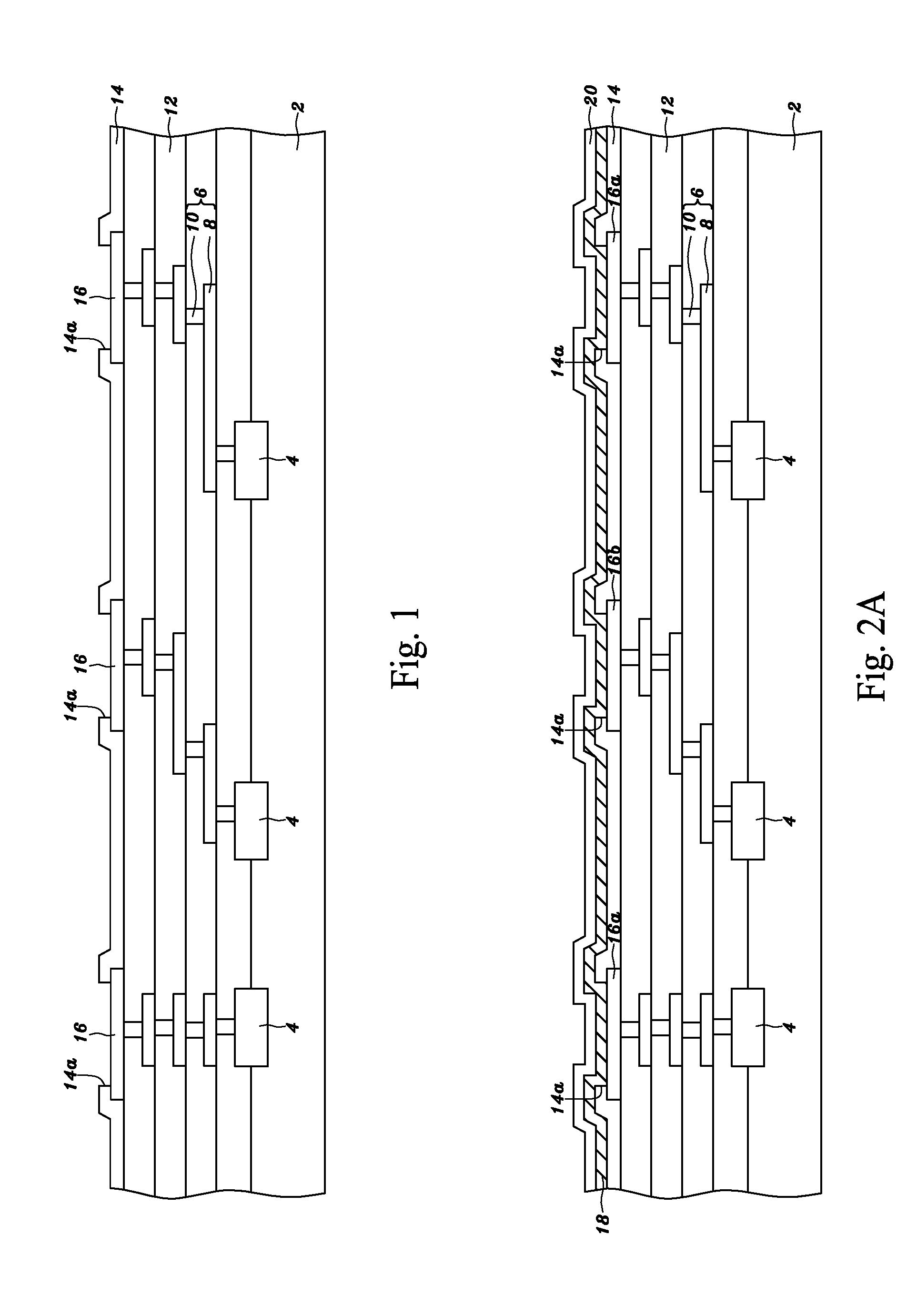

System-in packages

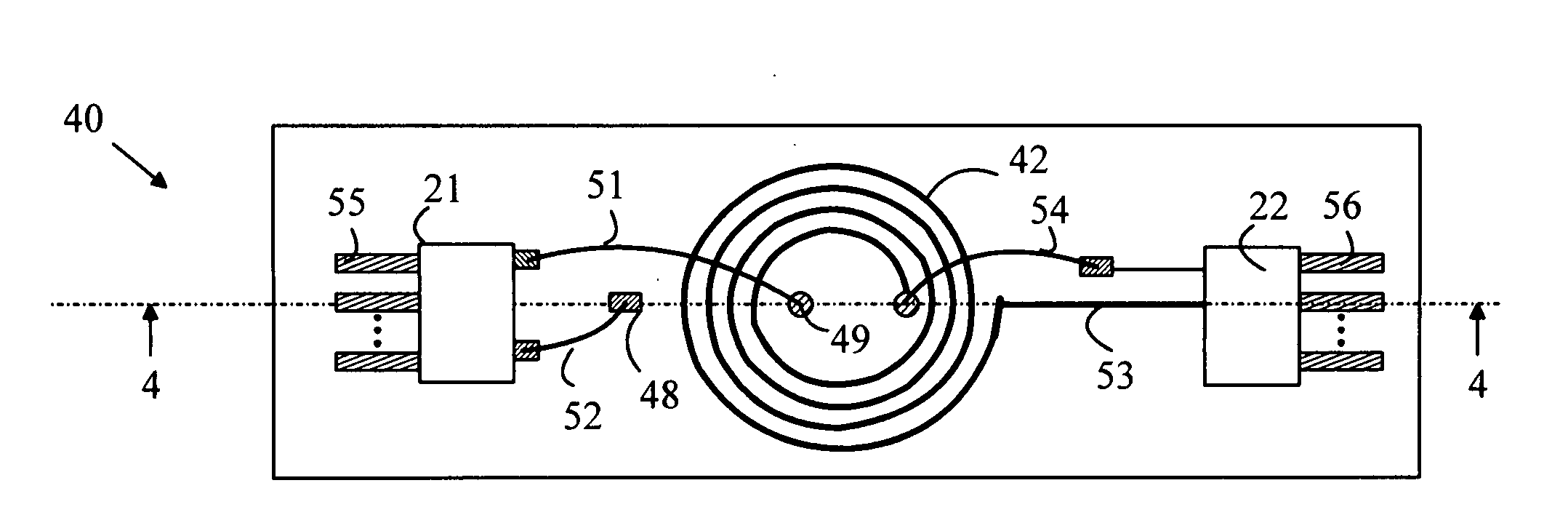

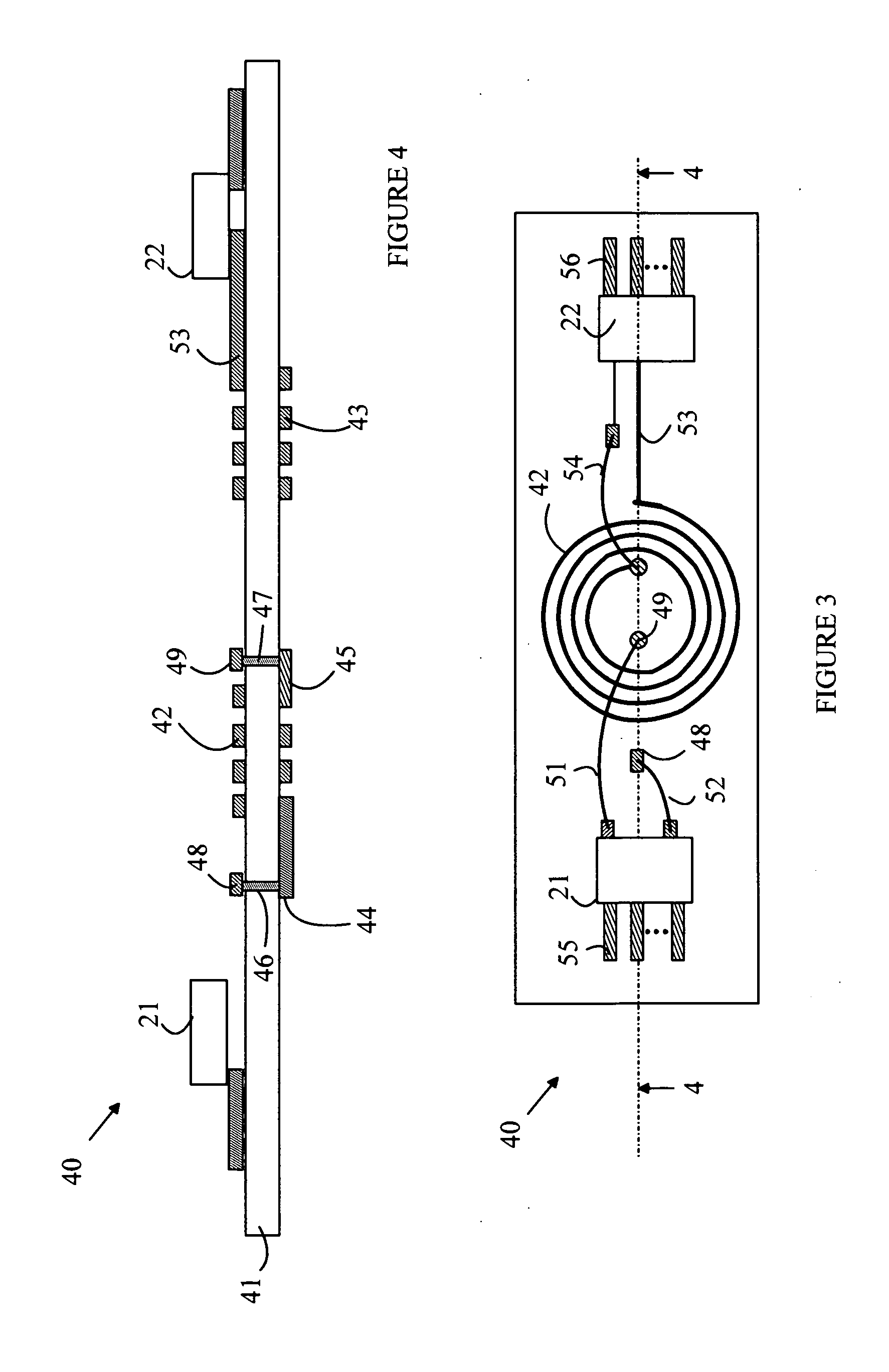

ActiveUS20100290191A1Good electromagnetic field shieldImprove routing densitySemiconductor/solid-state device detailsSolid-state devicesSystem in packageExternal circuit

System-in packages, or multichip modules, are described which can include multi-layer chips in a multi-layer polymer structure, on-chip metal bumps on the multi-layer chips, intra-chip metal bumps in the multi-layer polymer structure, and patterned metal layers in the multi-layer polymer structure. The multi-layer chips in the multi-layer polymer structure can be connected to each other or to an external circuit through the on-chip metal bumps, the intra-chip metal bumps and the patterned metal layers. The system-in packages can be connected to external circuits through solder bumps, meal bumps or wirebonded wires.

Owner:QUALCOMM INC

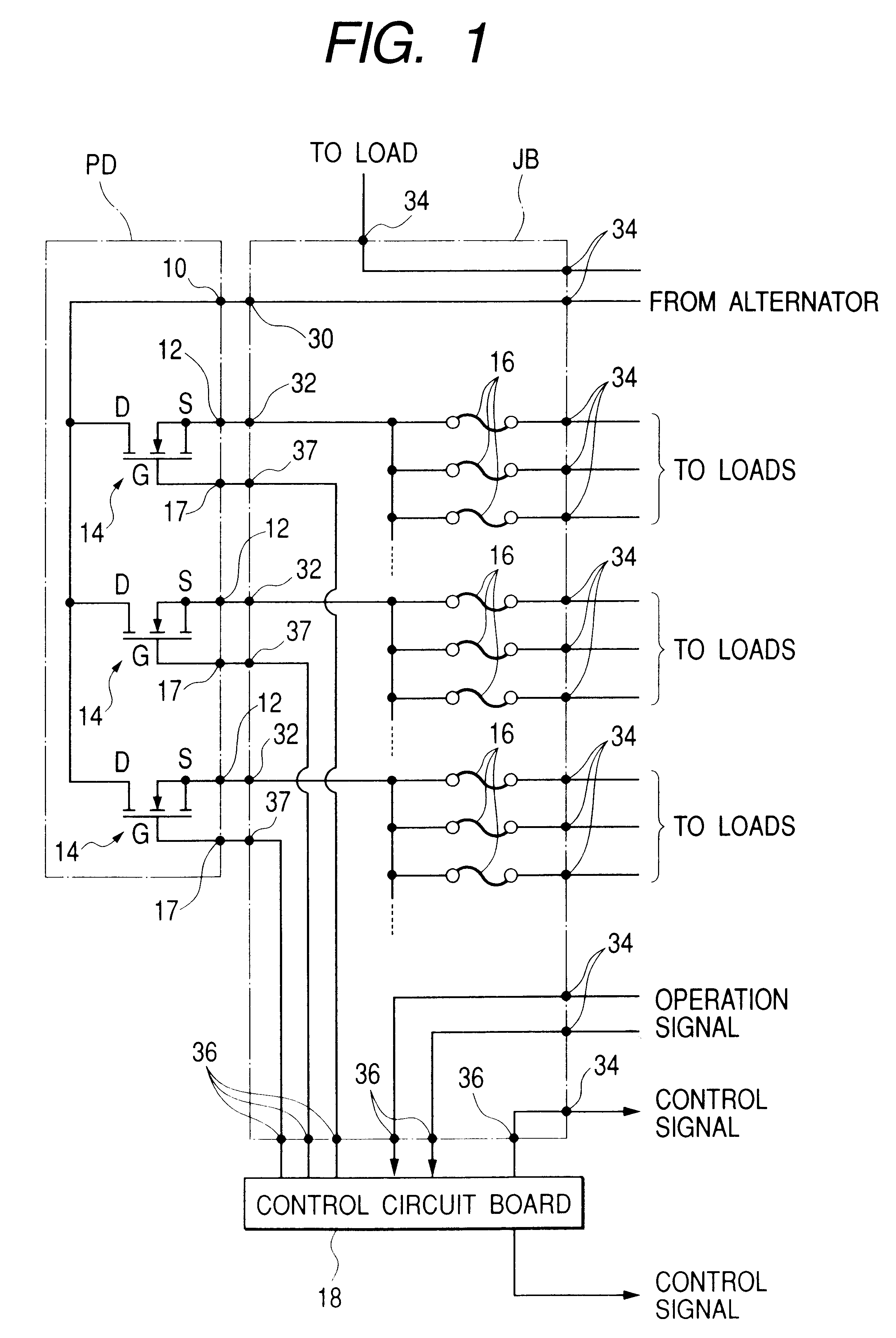

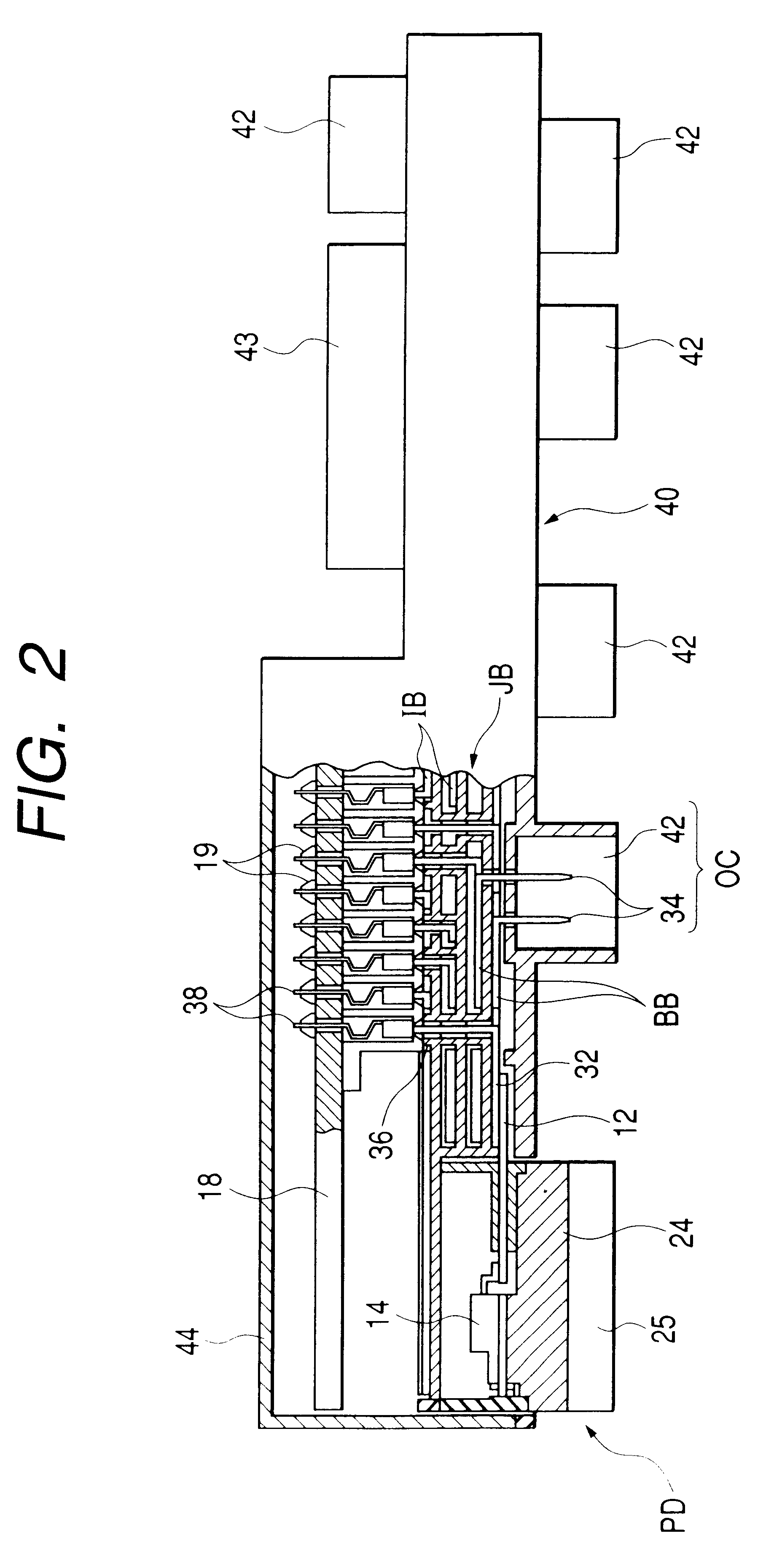

Engine control circuit device

InactiveUS20060012034A1Improve heat resistanceReduce expansionSemiconductor/solid-state device detailsPrinted circuit aspectsHeat resistanceControl circuit

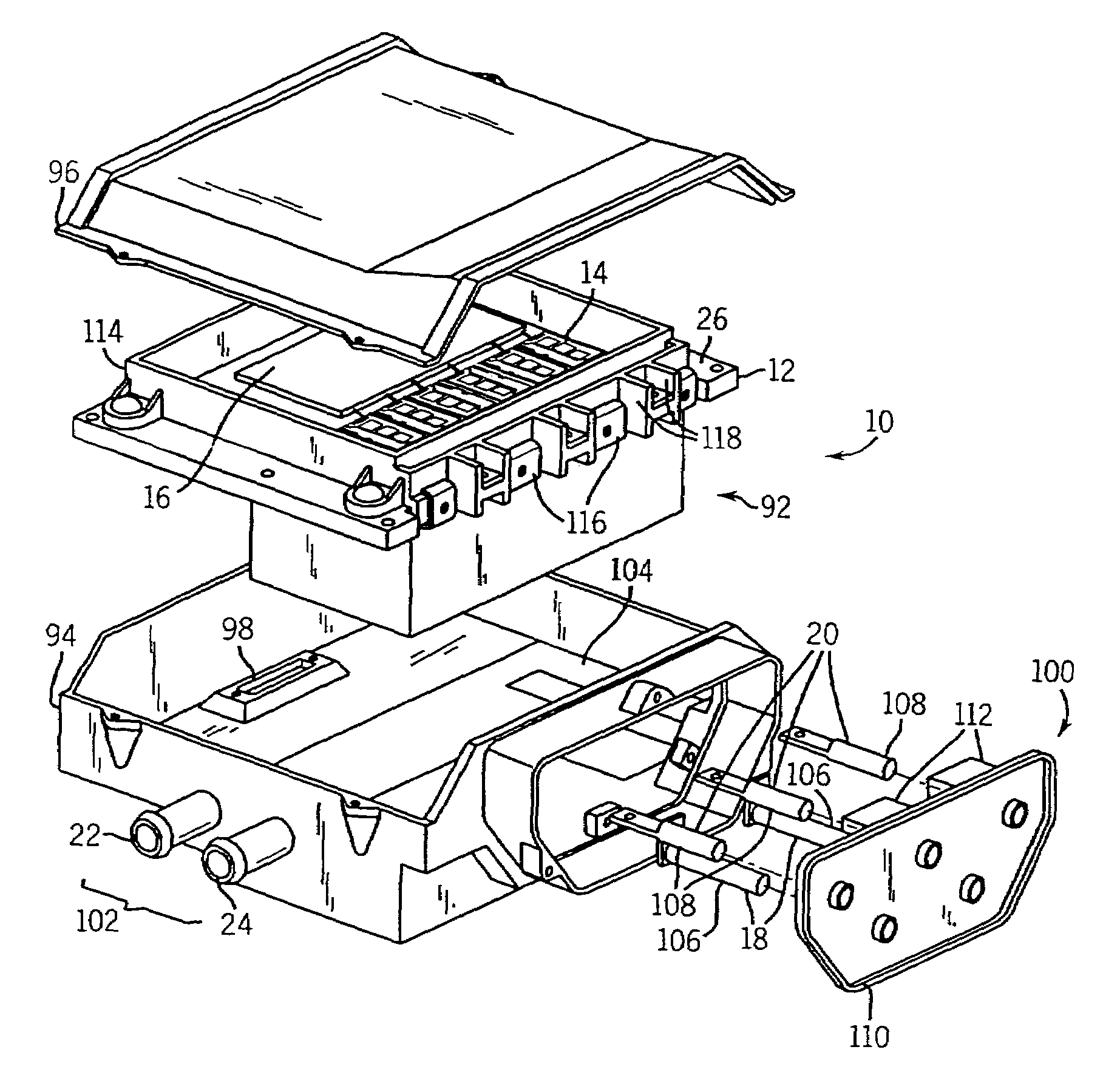

An engine control circuit device which has higher heat resistance and can be installed in a place exposed to severe thermal environments. In an engine control circuit device comprising a circuit board on which a plurality of packaged electronic parts are mounted, and a connector mounted on the circuit board for connection to an external circuit, the device further comprises a resin portion formed of a thermo-setting resin and covering the connector except for a connecting portion thereof and the circuit board, and a cooling pipe integrally molded in the resin portion and allowing a coolant to flow through it, thereby cooling the resin portion.

Owner:HITACHI LTD

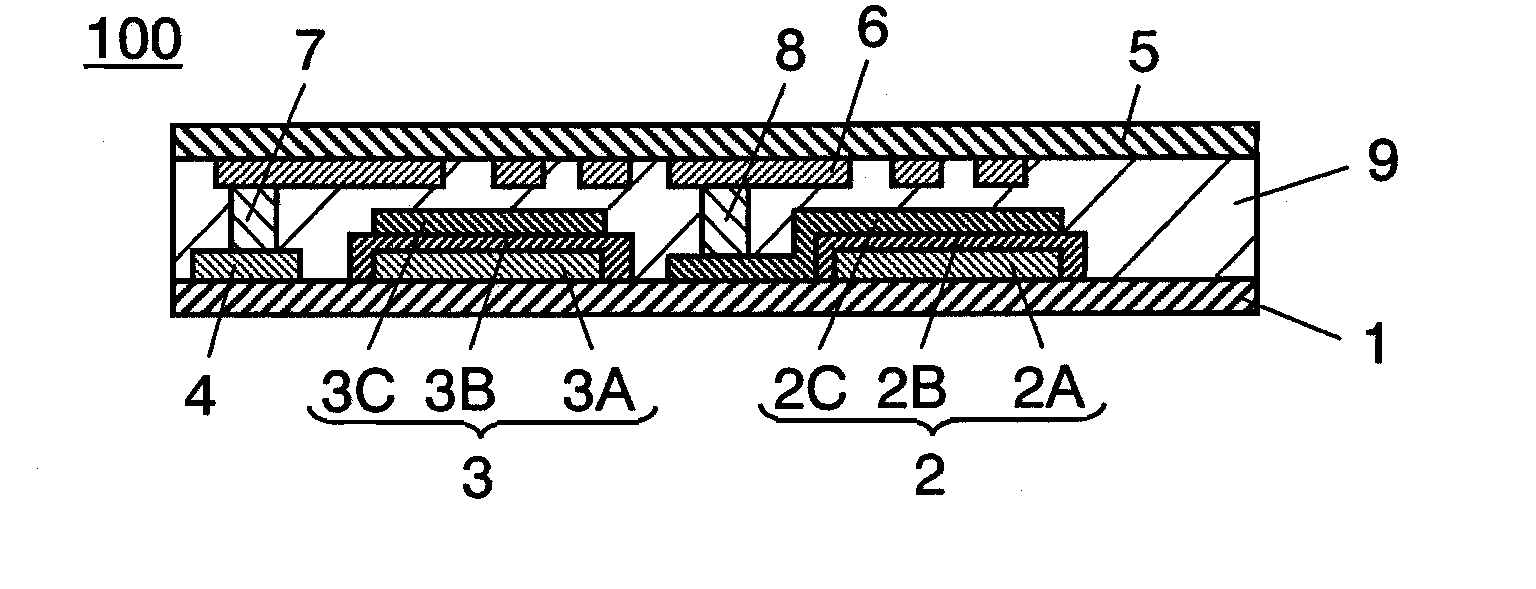

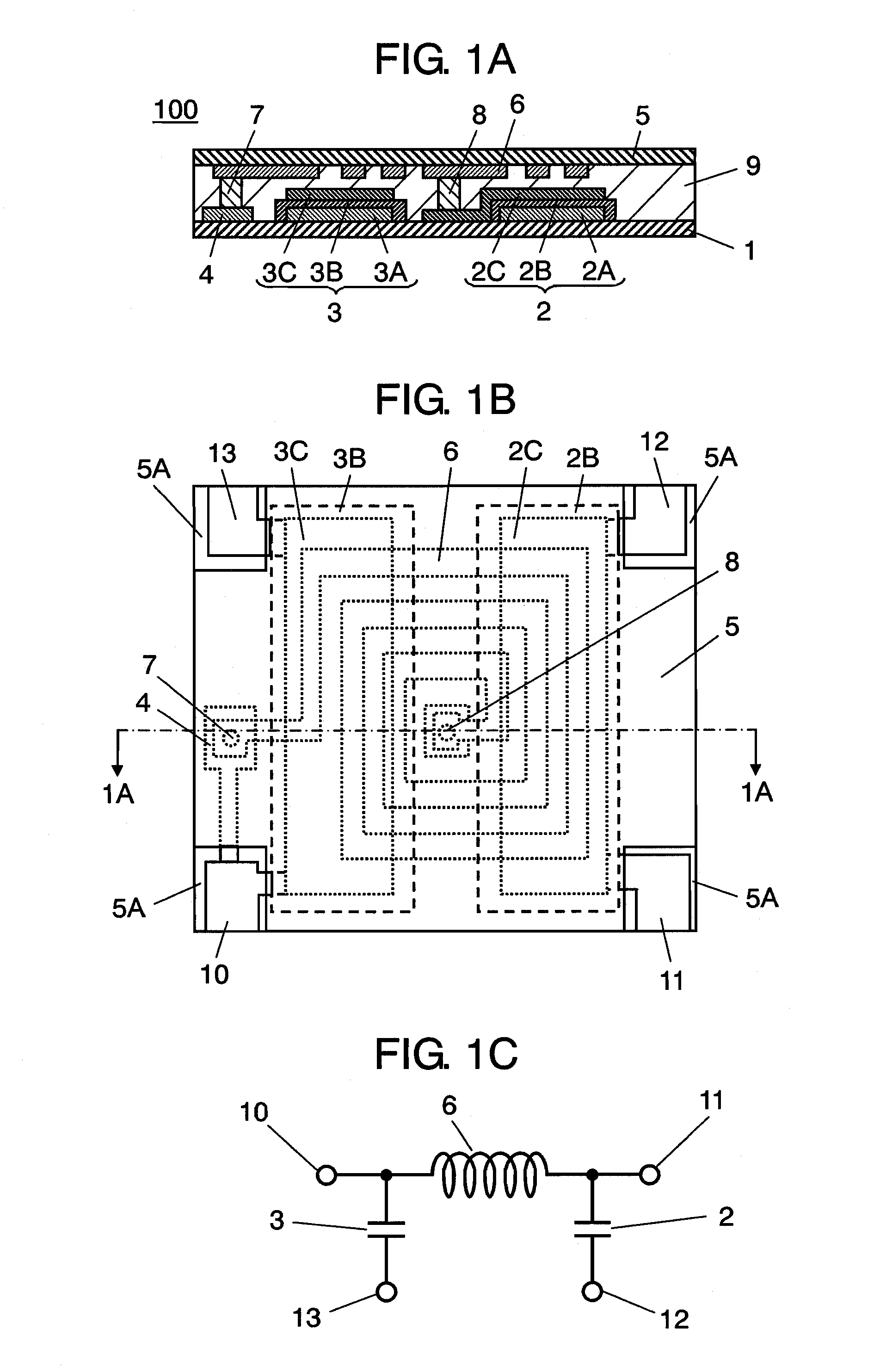

Sheet-like composite electronic component and method for manufacturing same

InactiveUS20100090781A1Avoid defectsGood yield rateMultiple-port networksPrinted circuit detailsElectrical conductorEngineering

To provide a configuration including a first sheet substrate, on which a first thin film electronic component is formed on at least one main face, and an external connection terminal for connecting to an external circuit is formed one main face or the other face; a second sheet substrate, on which a second thin film electronic component is formed on at least one face; an insulator connection resin layer for fixing the first sheet substrate and the second sheet substrate opposing the first thin film electronic component against the second thin film electronic component; and an interlayer connection conductor for electrically connecting electrode terminals, which have been set in advance, of the first thin film electronic component and the second thin film electronic component.

Owner:PANASONIC CORP

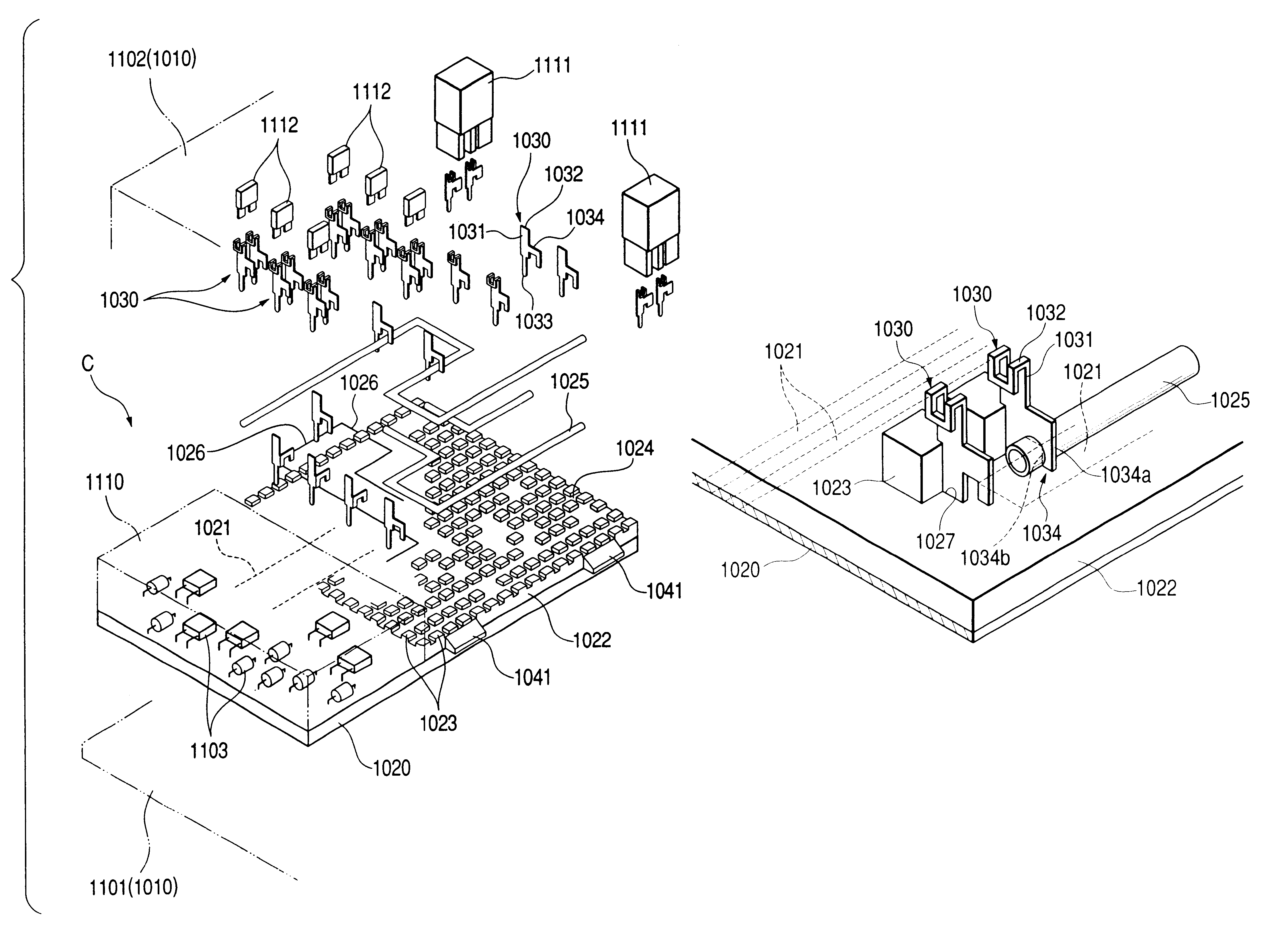

Terminal that provides connection between a wire circuit and a printed circuit, and electric junction box including said terminal

A terminal is mounted on an electric wiring board that has both a wire circuit formed by a wire and a printed circuit formed by a printed conductor. The terminal includes a connecting portion capable of electrically connecting an internal circuit of the electric wiring board to an external circuit, a lead portion capable of being electrically connected to the printed circuit of the electric wiring board, and a press-fitting portion capable of being electrically connected to the wire circuit. The electric wiring board may be mounted in an electric junction box. A load supporting member may be provided which transfer a load acting on the terminal from a connector of the external circuit to the housing. The load supporting member may include an engaging portion provided at an end surface of a wiring circuit board, and a retaining portion provided on a side wall of the housing.

Owner:AUTONETWORKS TECH LTD +2

Galvanic isolator

InactiveUS20080061631A1Easy to understandAvoid insufficient thicknessMultiple-port networksNear-field transmissionFlexible circuitsEngineering

A galvanic isolator having a split circuit element, a polymeric substrate, a transmitter and receiver is disclosed. The split circuit element has first and second portions, the first portion being disposed on a first surface of the substrate and the second portion being disposed a second surface of the substrate. The transmitter receives an input signal and couples a signal derived from the input signal to the first portion. The receiver is connected to the second portion of the circuit element and generates an output signal that is coupled to an external circuit. The galvanic isolator can be economically fabricated on conventional printed circuit board substrates and flexible circuit substrates.

Owner:AVAGO TECH INT SALES PTE LTD

Controlled esr low inductance capacitor

InactiveUS20100188799A1Improve current cancellationIncrease path lengthFixed capacitor electrodesFixed capacitor dielectricElectrical resistance and conductancePath length

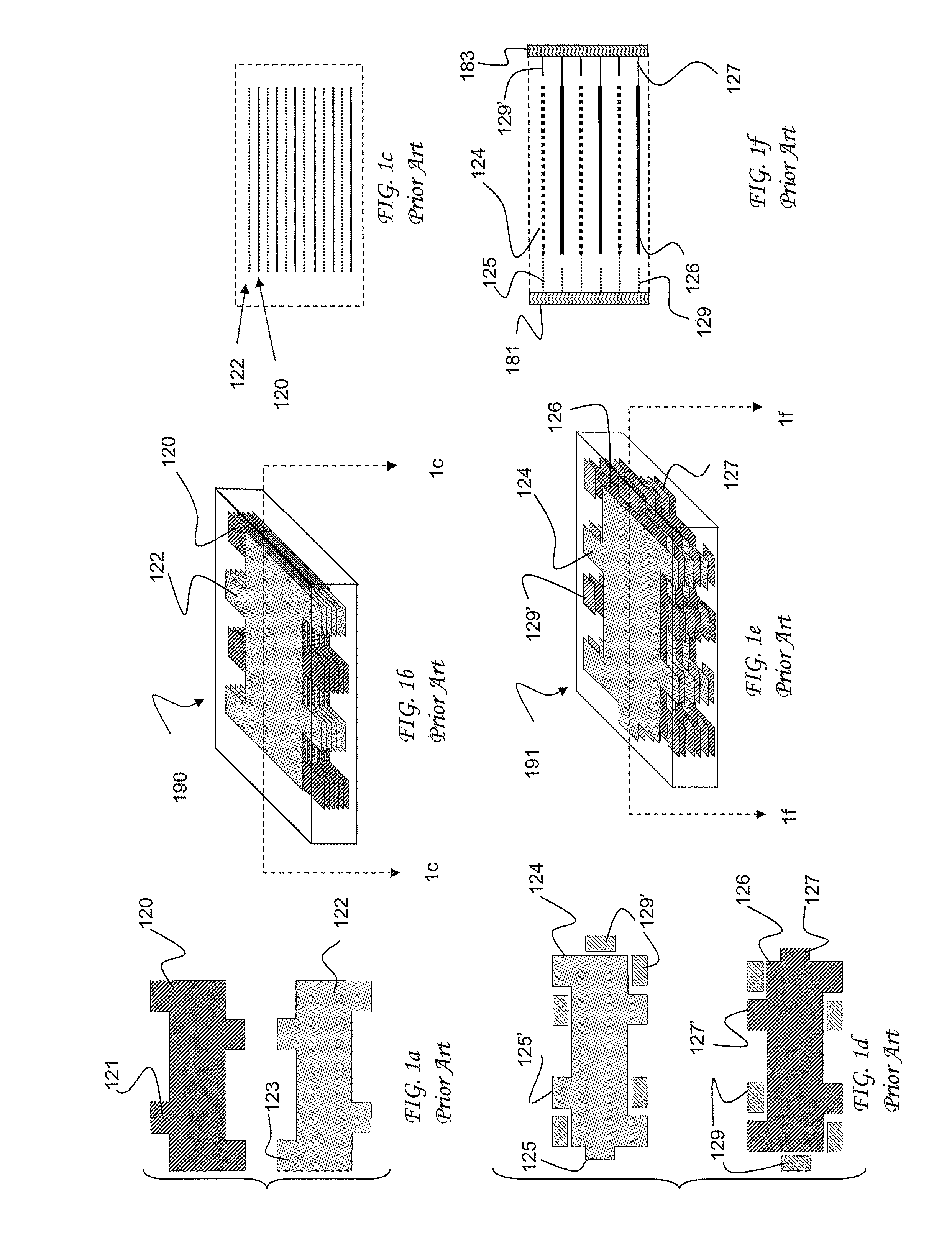

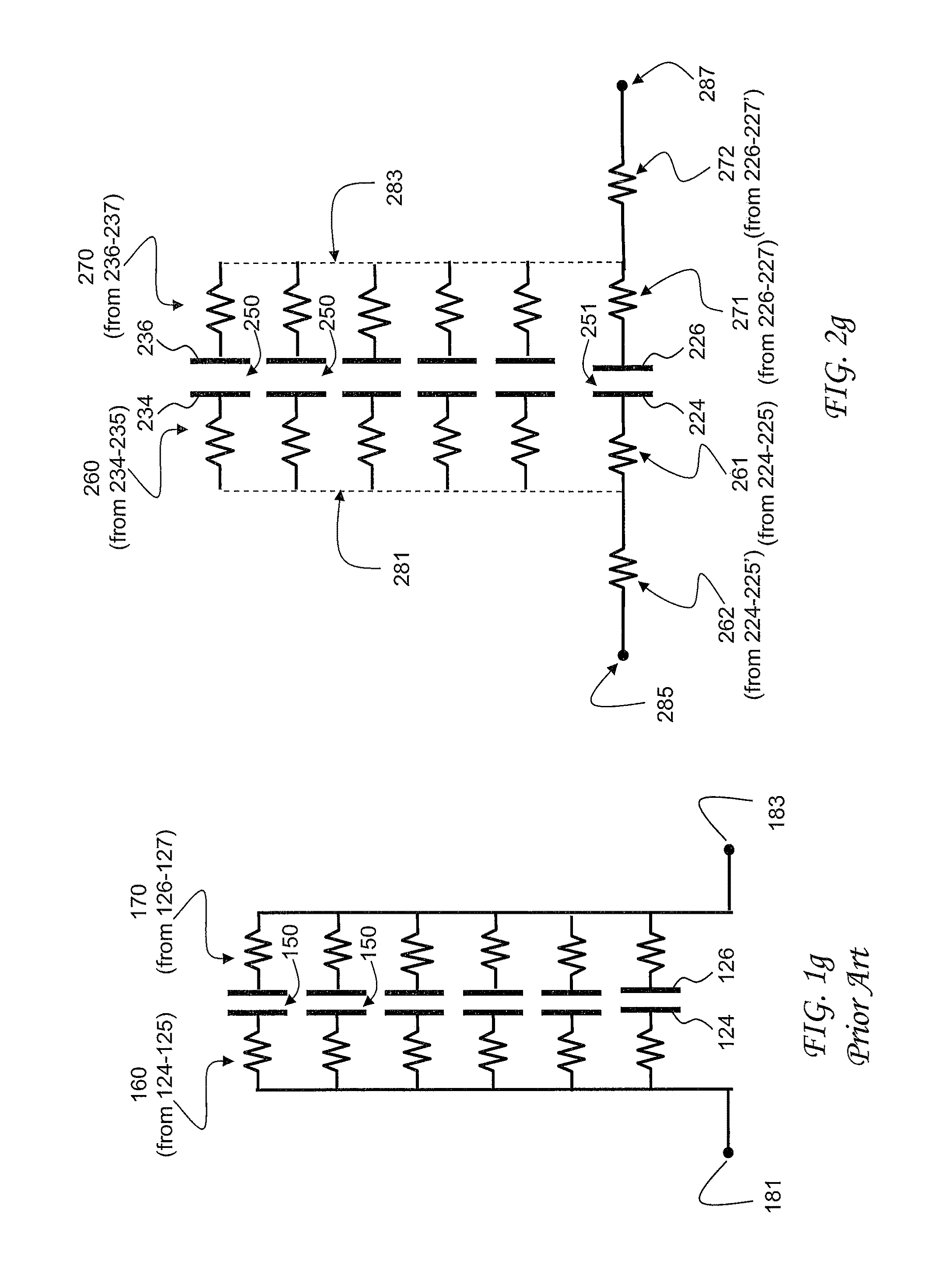

Multilayer capacitors incorporate both low inductance (ESL) and controlled Equivalent Series Resistance (ESR) features into a cost-effective unitary device. Internal electrode patterns generally include one or more pairs of mother electrodes adapted for external connection (e.g., to a circuit, another electrical component, circuit board, or other mounting environment), and multiple pairs of daughter electrodes adapted only for internal connection to other electrodes (e.g., other daughter electrodes and / or selected mother electrodes) without direct connection to an external circuit. Mother and daughter electrodes are interdigitated with electrode tab features, where daughter electrodes have internal-connection tabs, and mother electrodes have both internal-connection tabs and circuit-connection tabs, all of which are connected to respective internal-connection or circuit-connection terminals. ESR is increased by the parallel connection between mother and daughter electrodes as well as other optional features such as but not limited to resistive terminations, resistive connectors, serpentine terminations and increased current path lengths.

Owner:AVX CORP