Patents

Literature

167results about How to "Reduce decoding delay" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

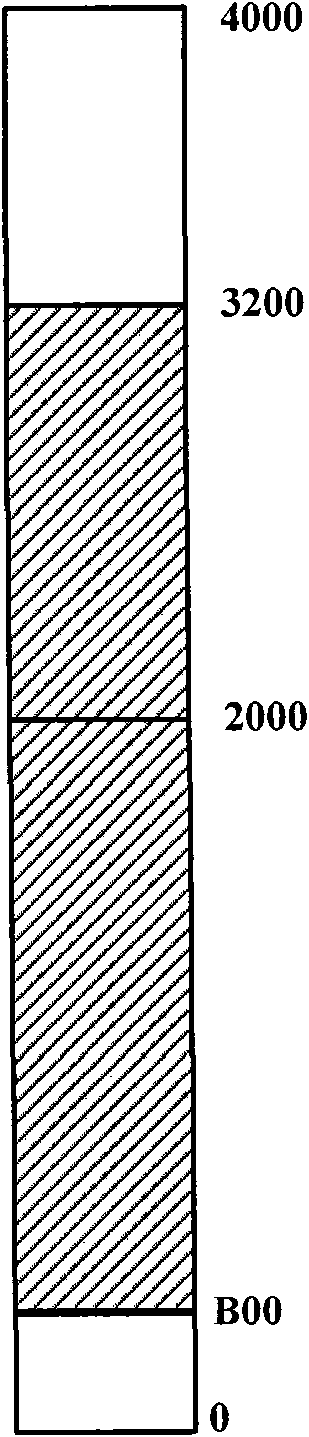

Application Year

Inventor

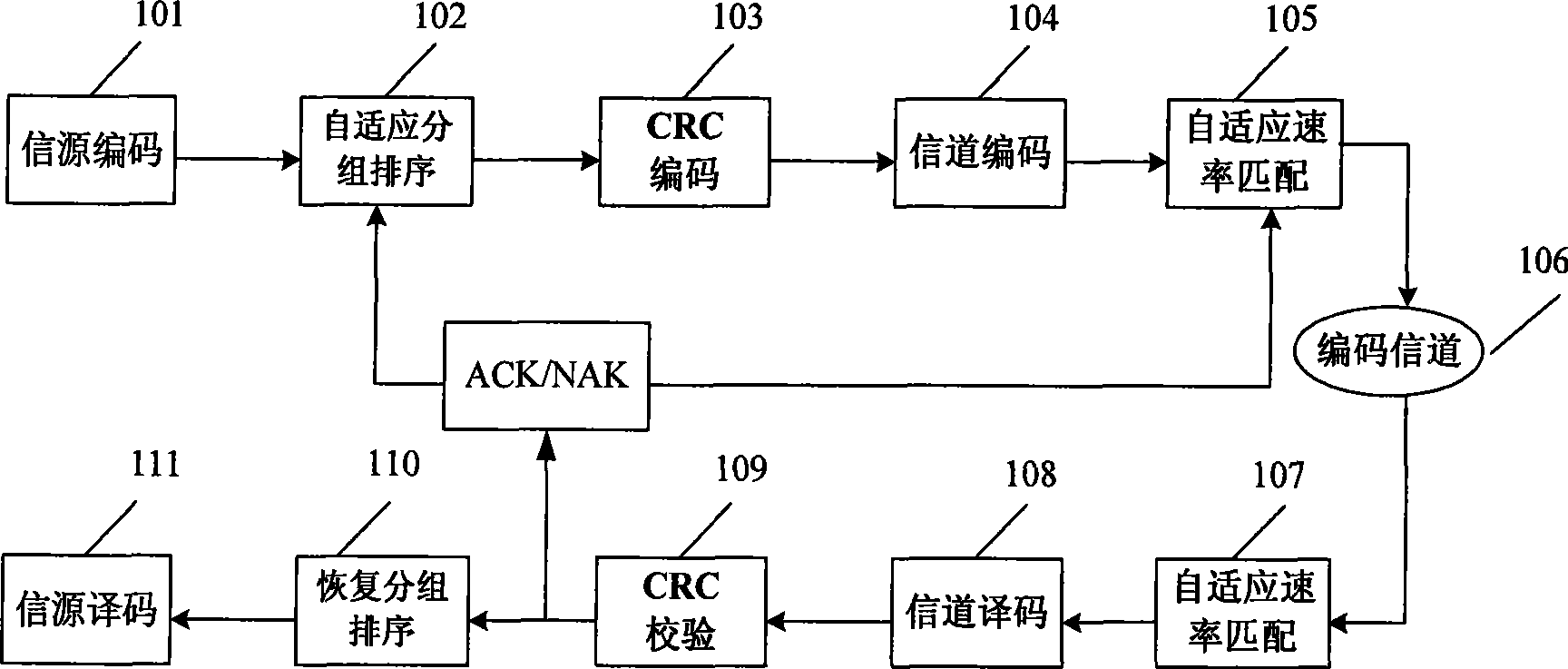

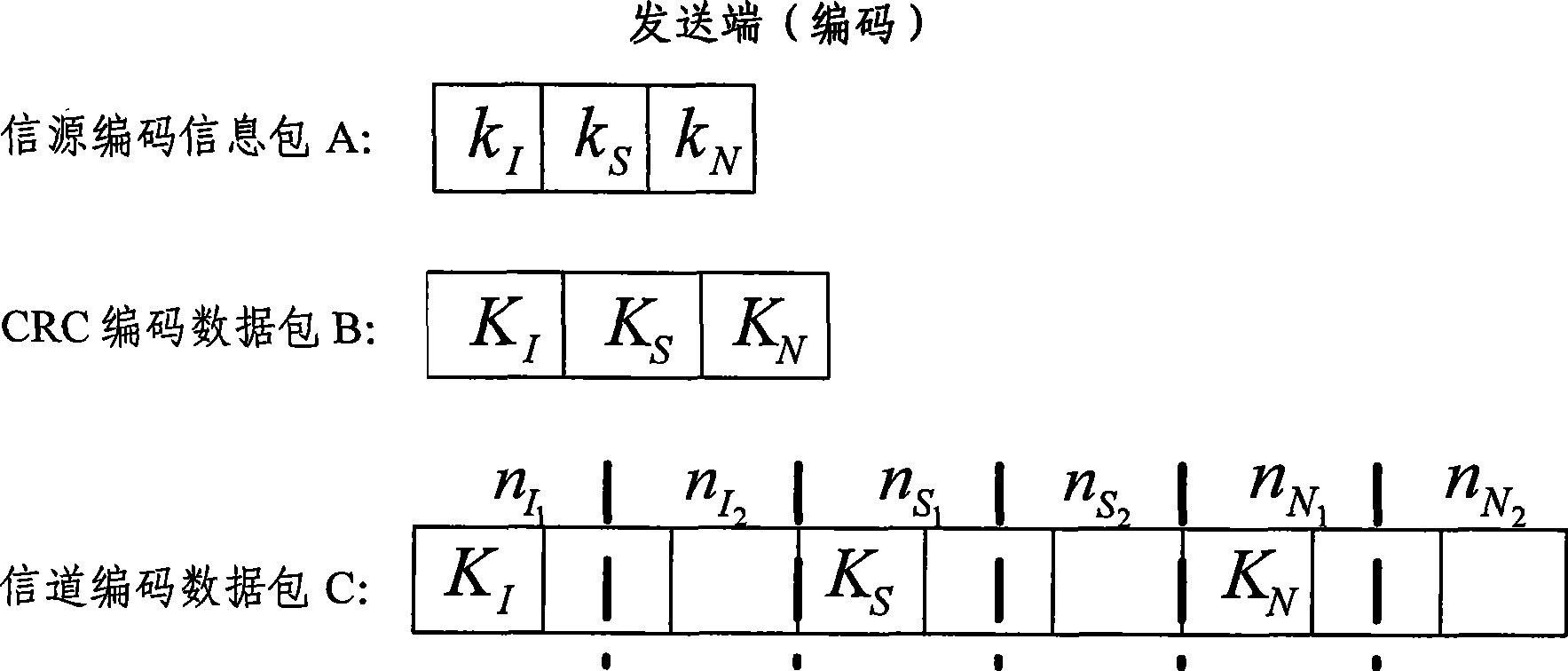

Signal source and channel combined optimized adaptive error control method

InactiveCN101478373AAvoid wastingImprove transmission qualityError preventionNetwork traffic/resource managementChannel codeSelf adaptive

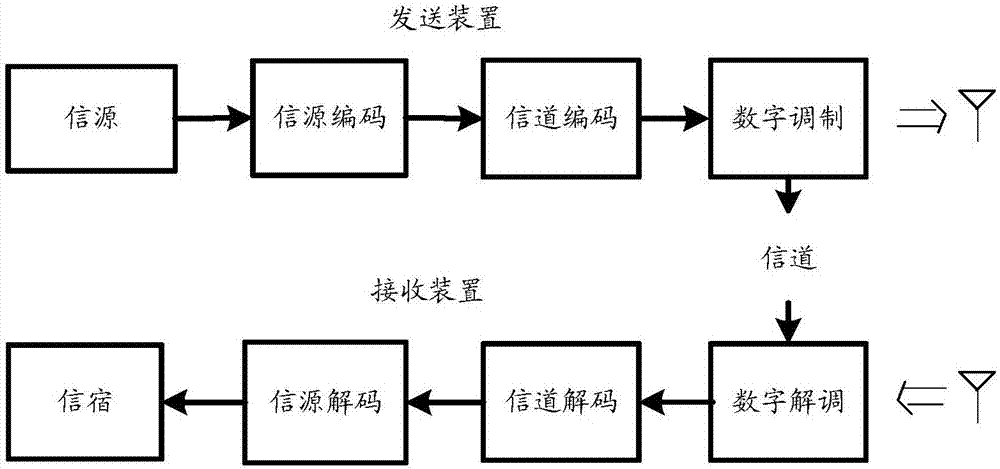

The invention discloses an adaptive error control method for source channel coding combined optimization, which is characterized in that the source coding output code streams are classified to the following three grades according to the significance: significance, secondary significance and non-significance; and during the channel coding process, the source code streams of the three graders undergo the adaptive unequal error protection by means of variable-velocity forward error control / hybrid automatic repeat request (FEC / HARQ), so as to allow the transmission rate and the channel coding rate of the source code streams to be adjusted adaptively according to the time-varying fading characteristics of the wireless channel, thereby optimizing the transmission quality of the source code streams and improving the transmission efficiency and the channel utilization rate of the whole system. The method comprises the six steps, overcomes the problems of contradiction and resource waste caused by the independent coding of the source and the channel in the prior communication system, achieves the effect of adaptive combined optimization of the source code stream transmission rate and the channel coding rate based on the time-varying fading characteristics of channel, and has good application prospects.

Owner:BEIHANG UNIV

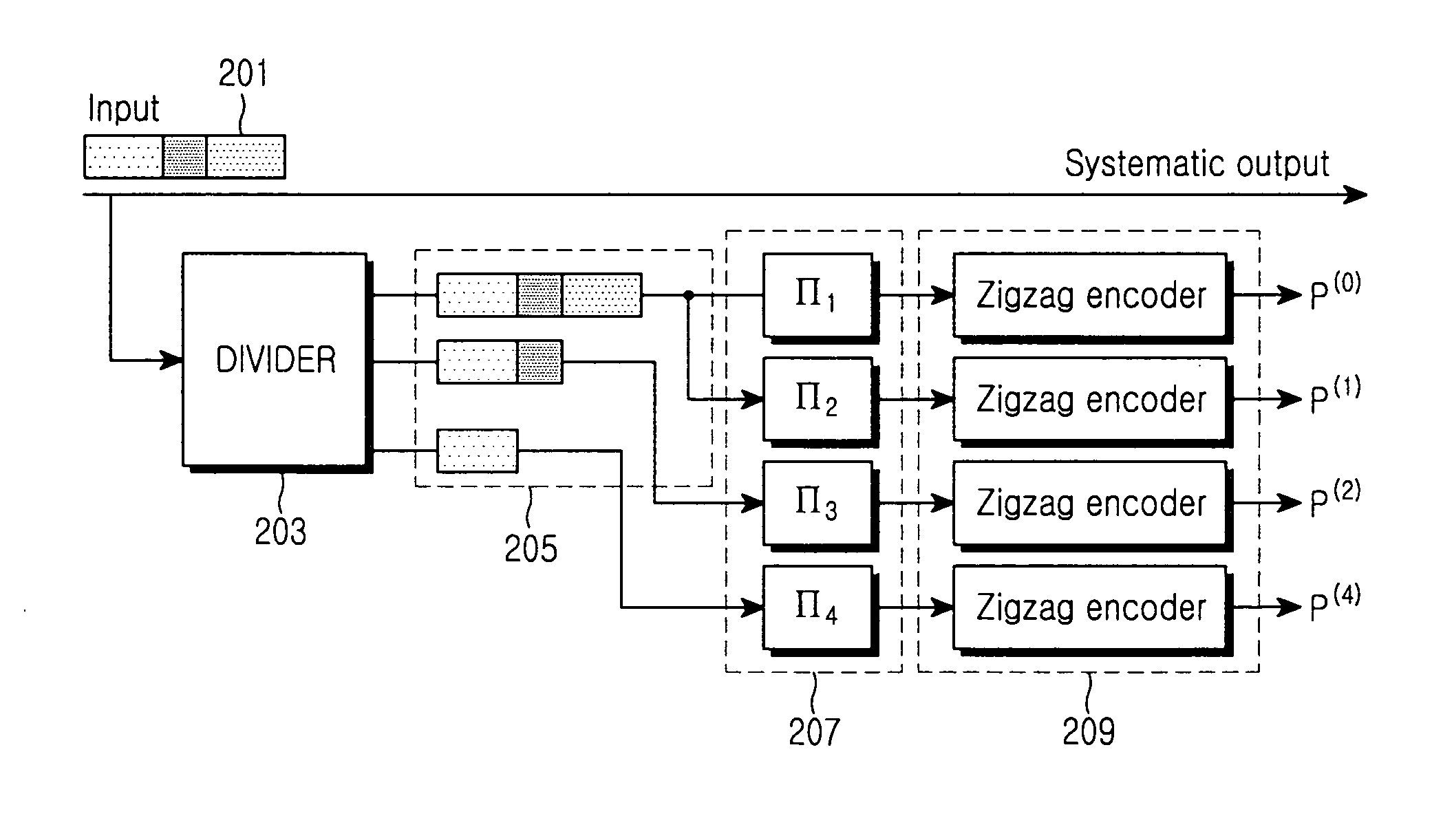

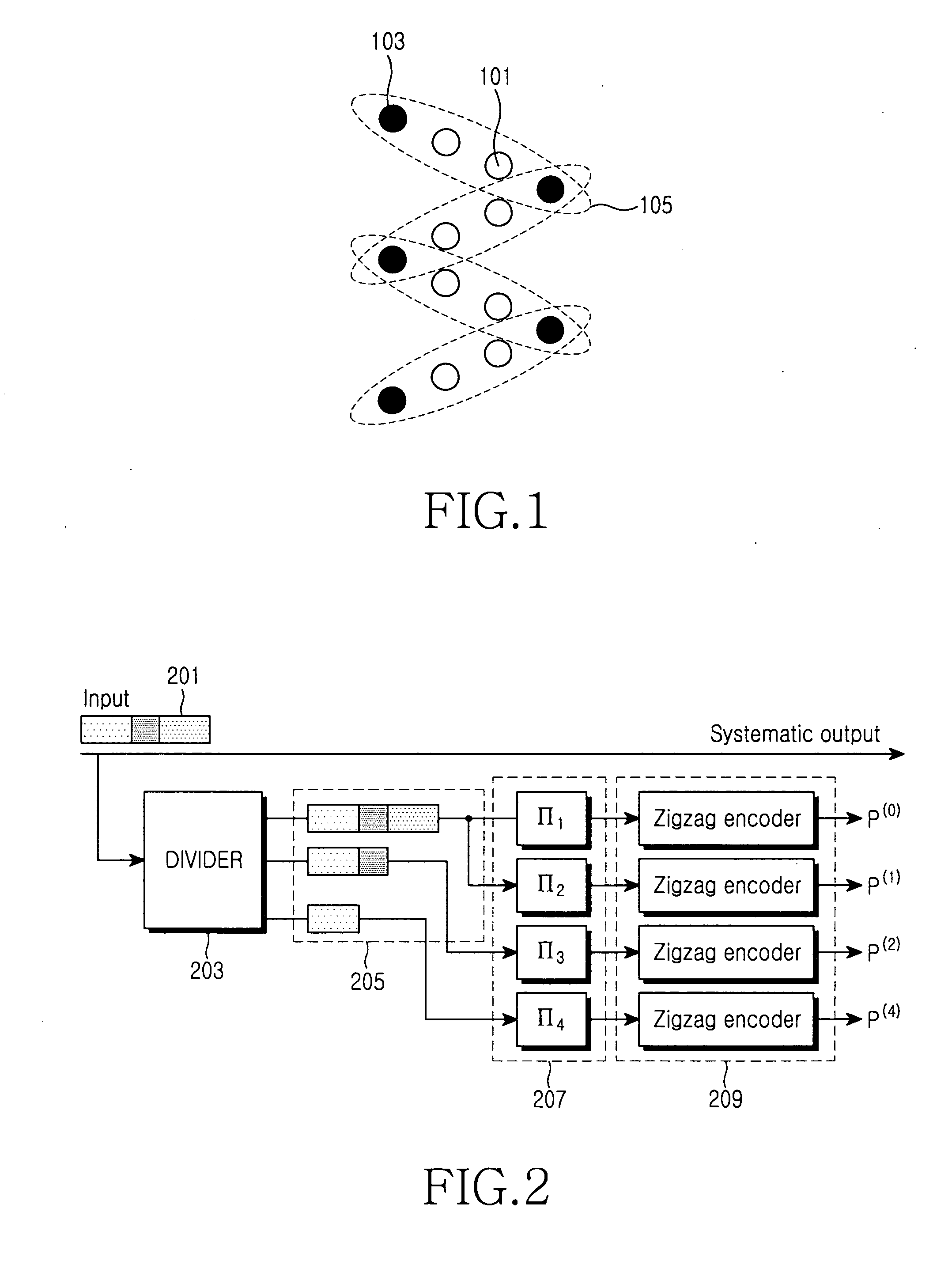

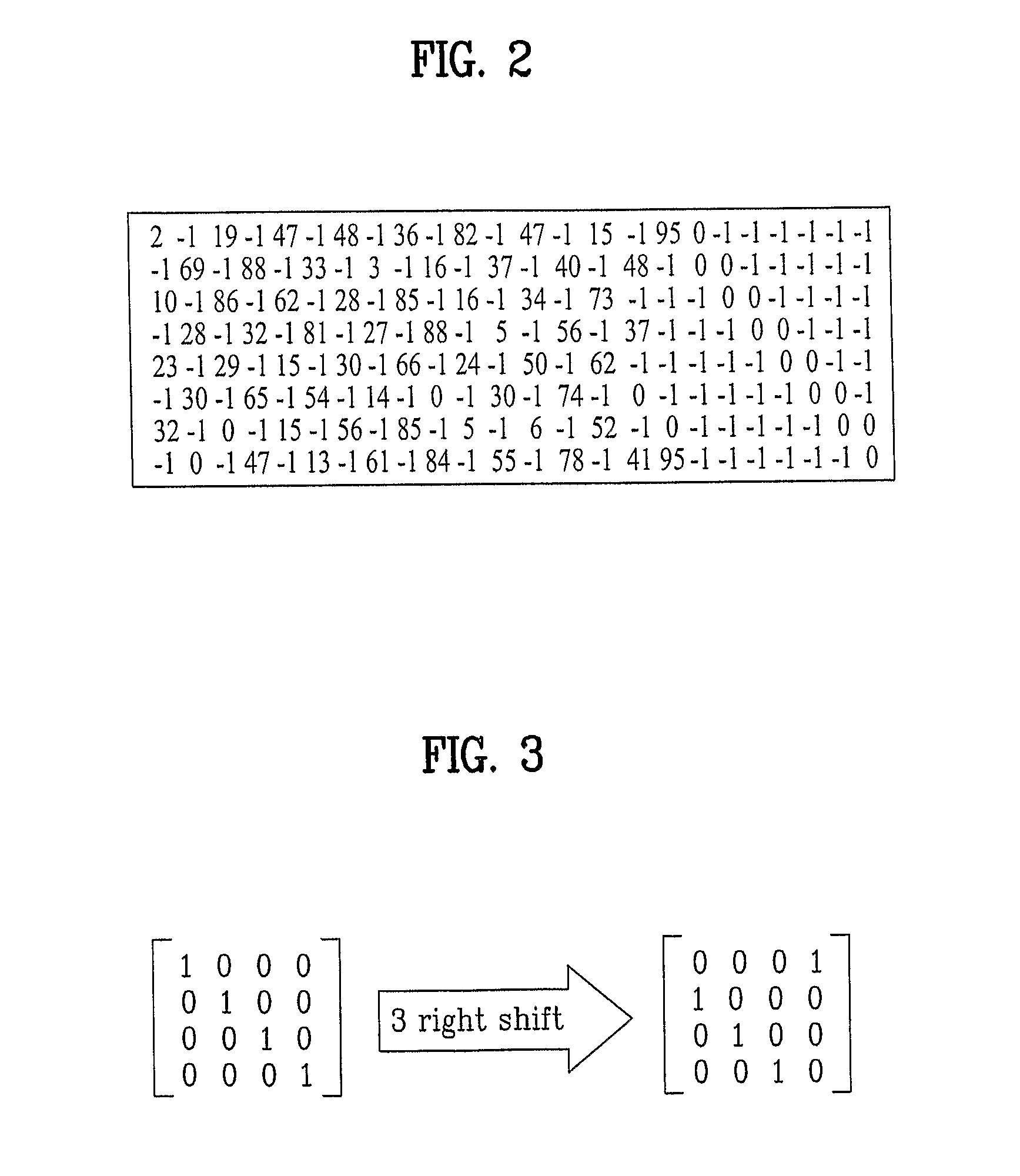

Apparatus and method for generating low density parity check code using zigzag code in a communication system

InactiveUS20060190801A1Avoid performanceImprove system efficiencyCode conversionCoding detailsCommunications systemAlgorithm

A method for generating a low-density parity check (LDPC) code supporting various code rates. The method includes finding a plurality of parity check matrixes showing the best performance at a predetermined code rate; matching the parity check matrixes in terms of the number of ‘1’s per row in units of sub-matrixes of each of the matrixes; and converting the plurality of parity check matrixes into one matrix, and combining punctured zigzag codes generated for every code rate into one punctured zigzag code.

Owner:SAMSUNG ELECTRONICS CO LTD +1

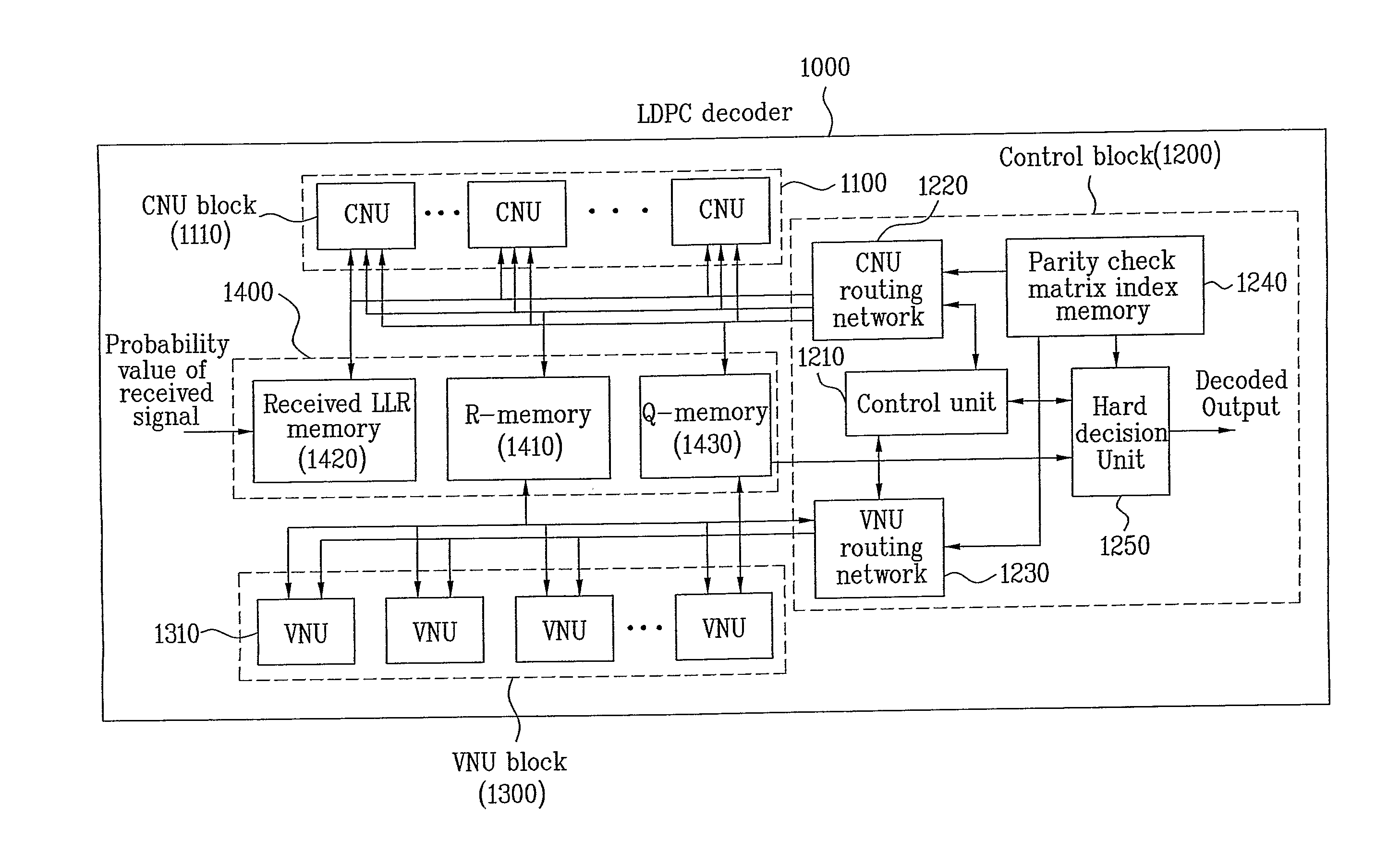

Method and apparatus for performing decoding using LDPC code

InactiveUS20110010602A1Improve decoding performanceReduce decoding delayError correction/detection using multiple parity bitsCode conversionTheoretical computer scienceParity-check matrix

A method of performing decoding using an LDPC code is disclosed. The method of performing decoding an encoded codeword using a parity check matrix, comprises decoding the codeword using the parity check matrix, wherein the parity check matrix includes a plurality of layers, each of which includes at least one or more rows split exclusively from a specific row of a base parity check matrix.

Owner:LG ELECTRONICS INC

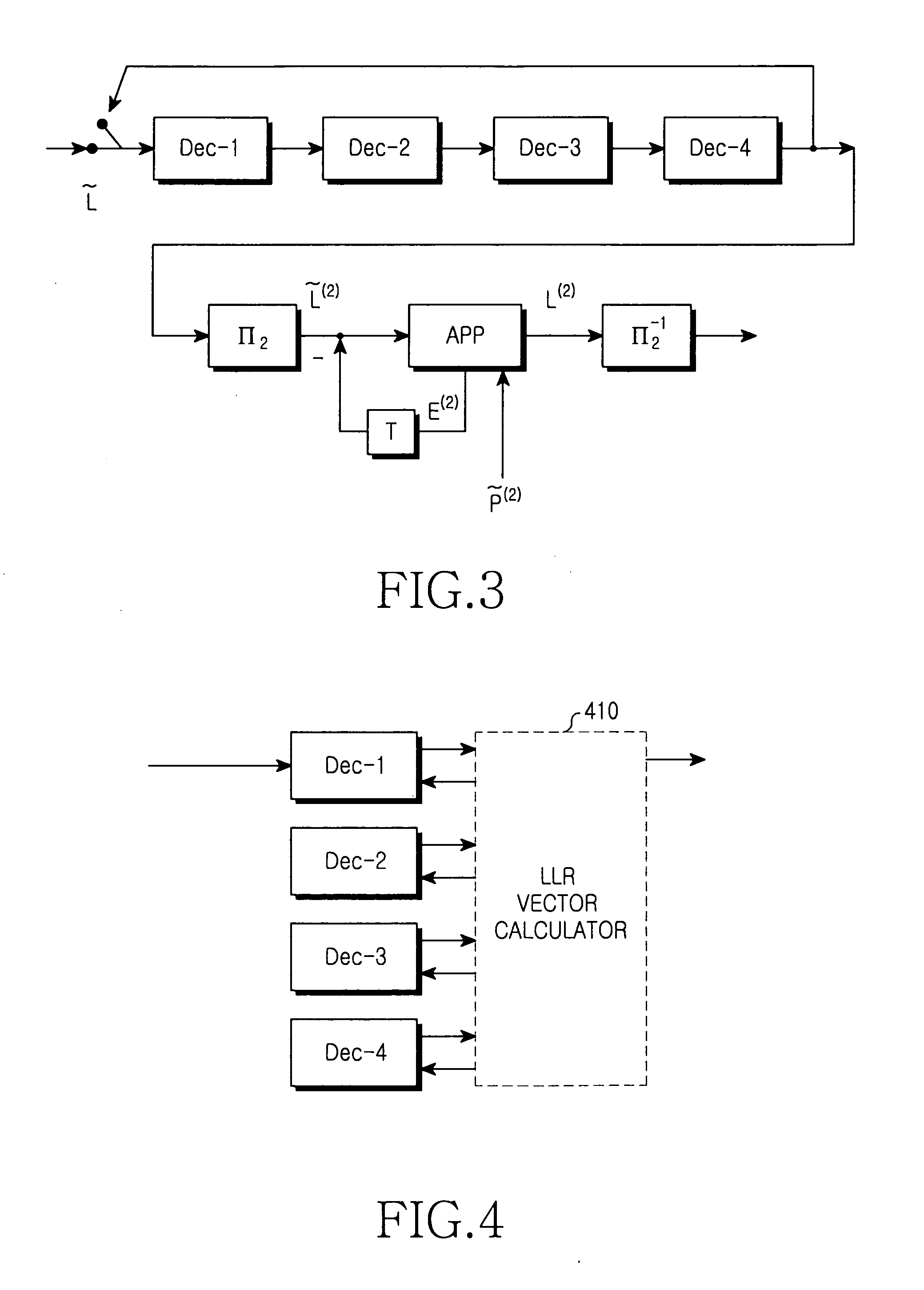

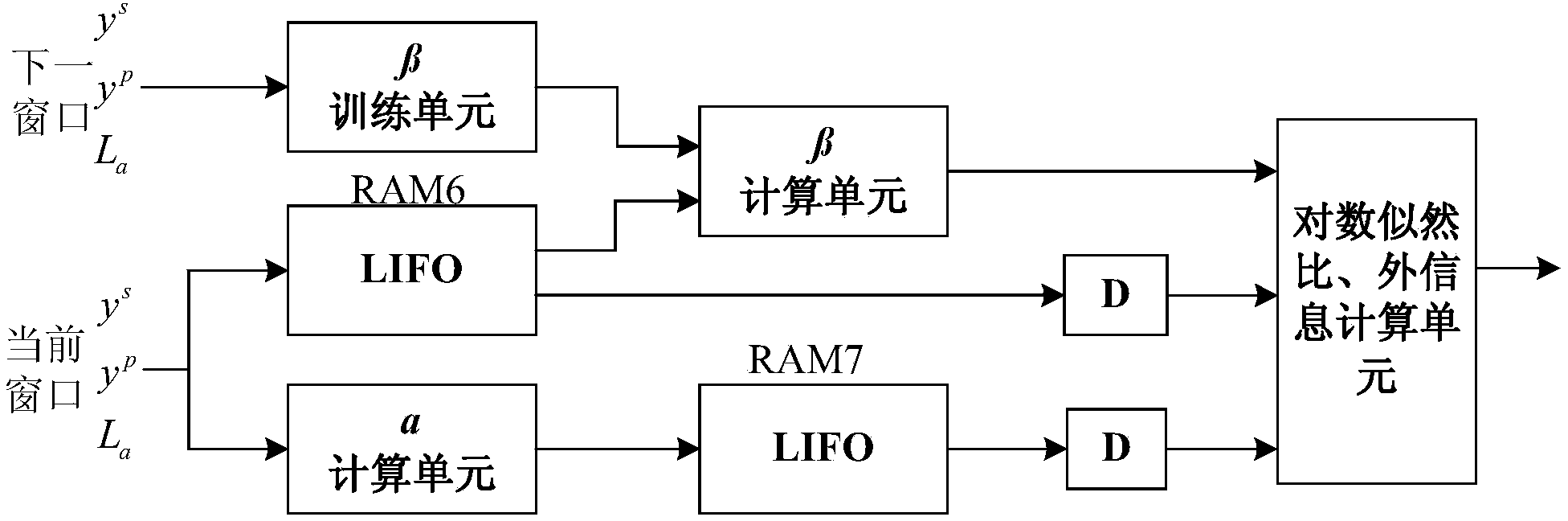

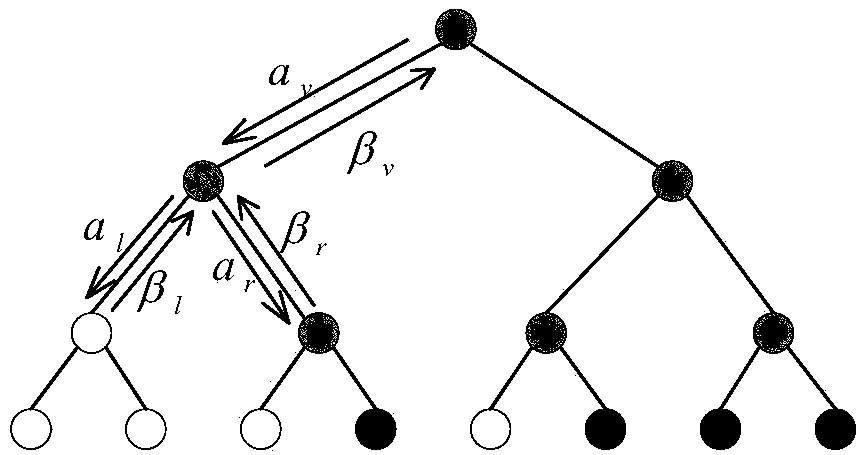

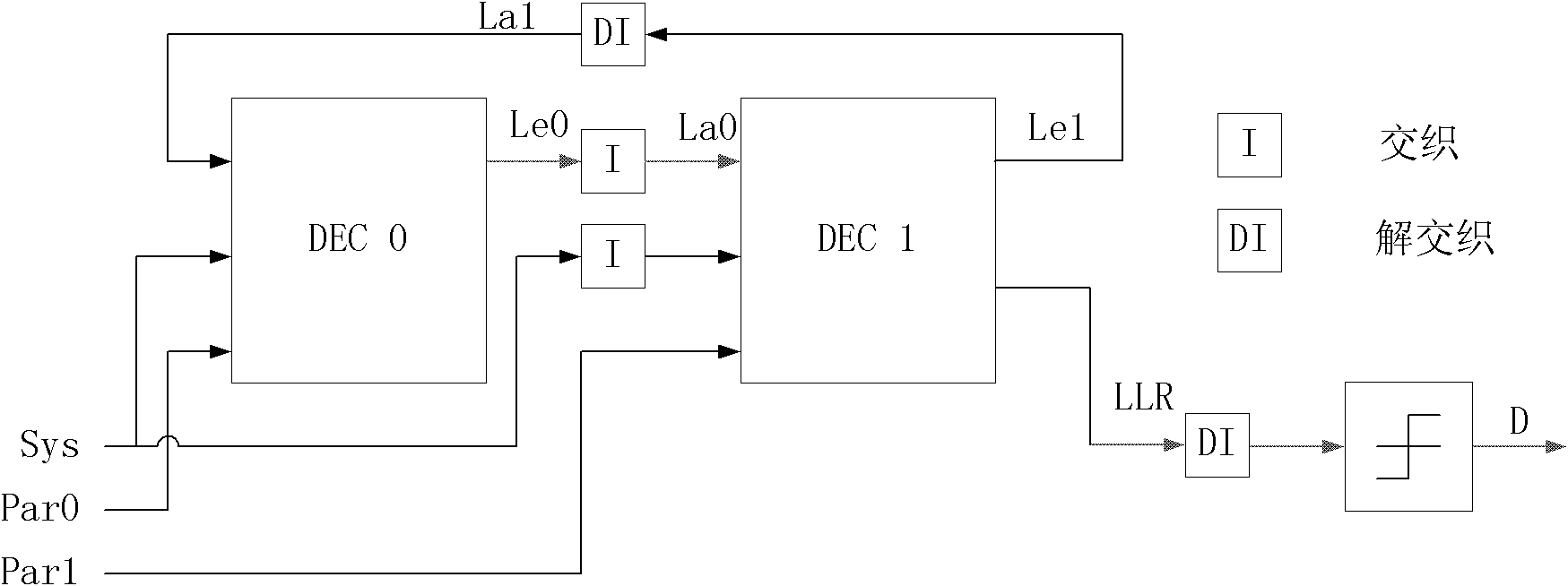

Method and apparatus for parallel turbo decoding in long term evolution system (LTE)

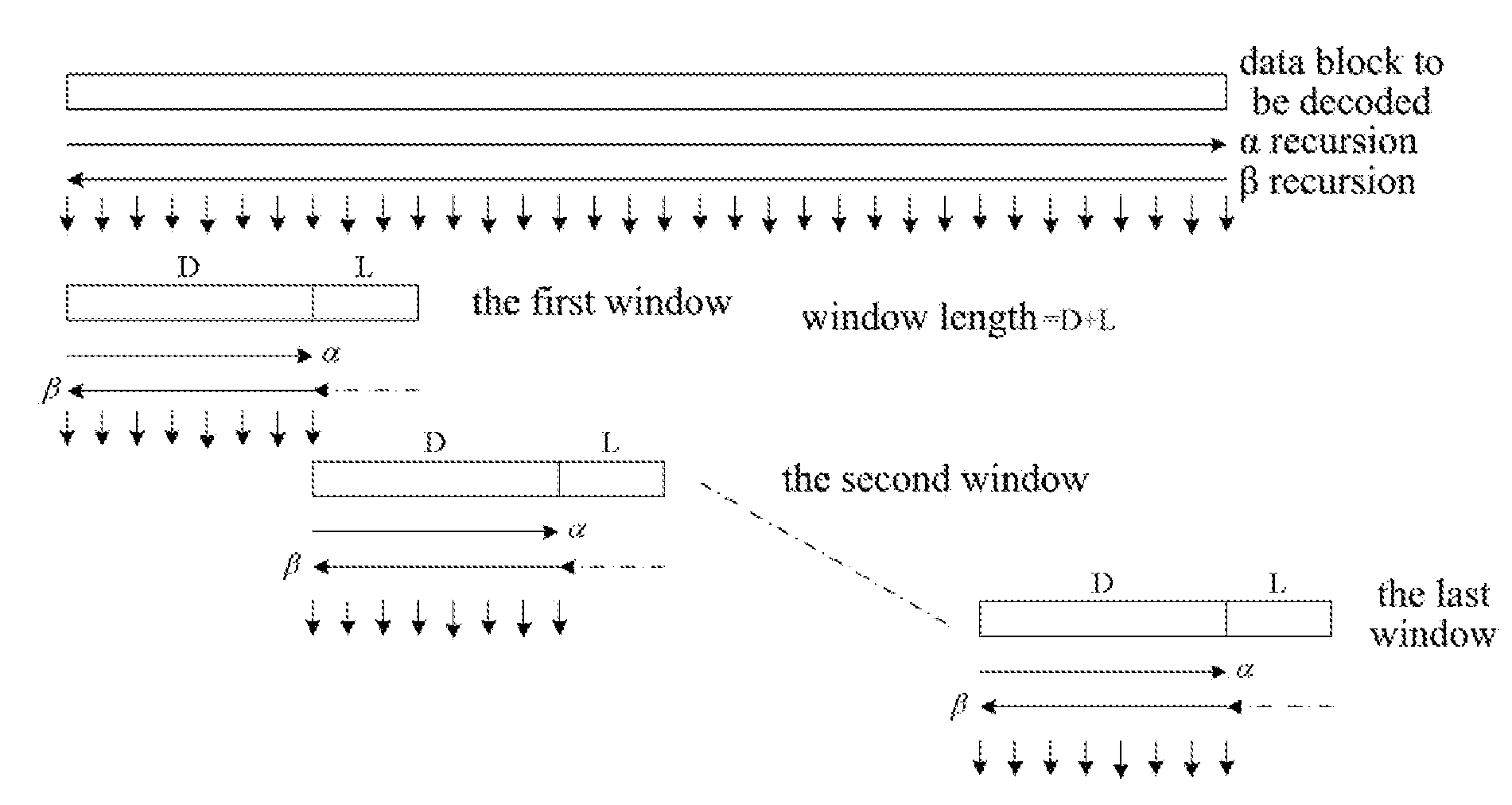

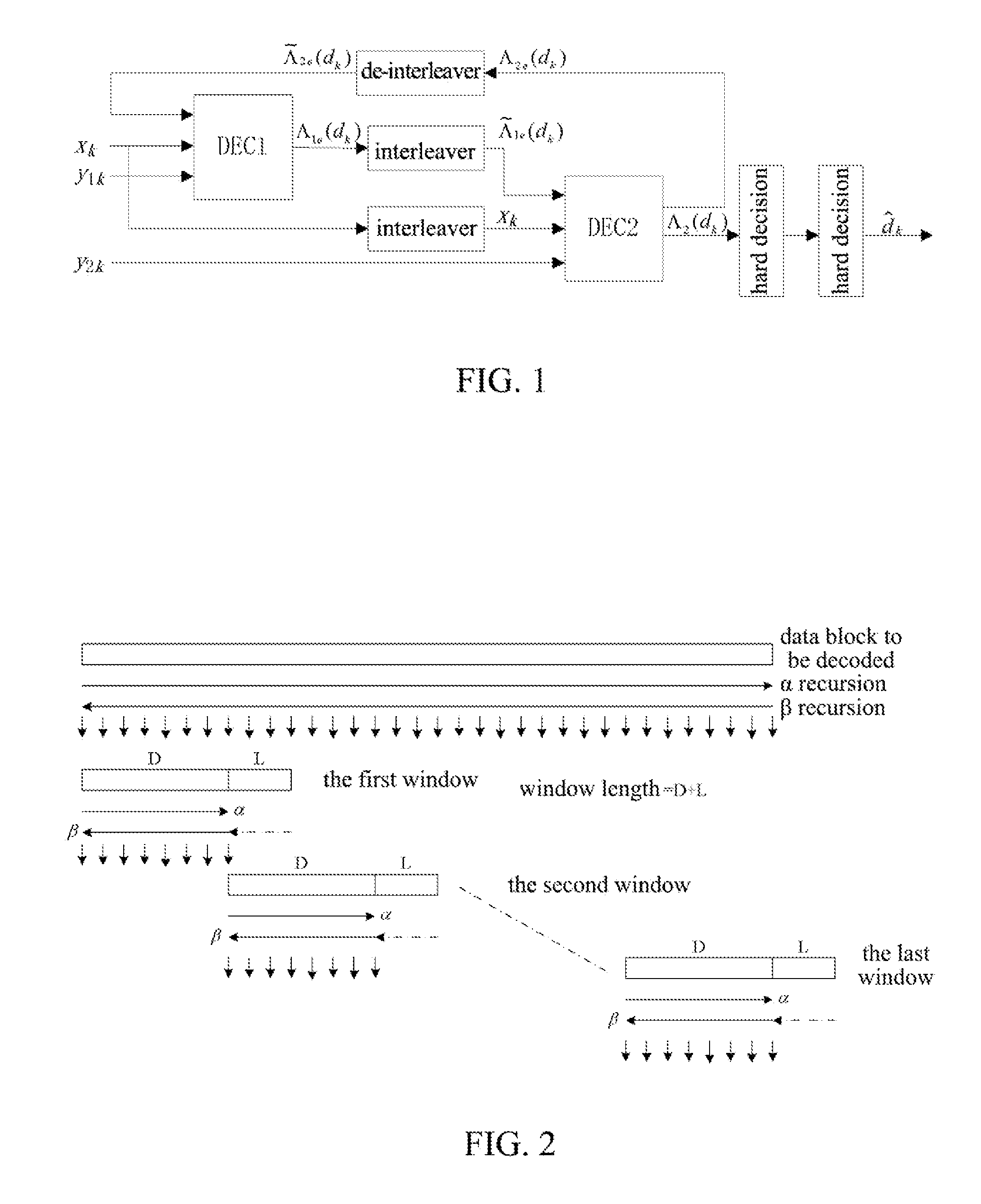

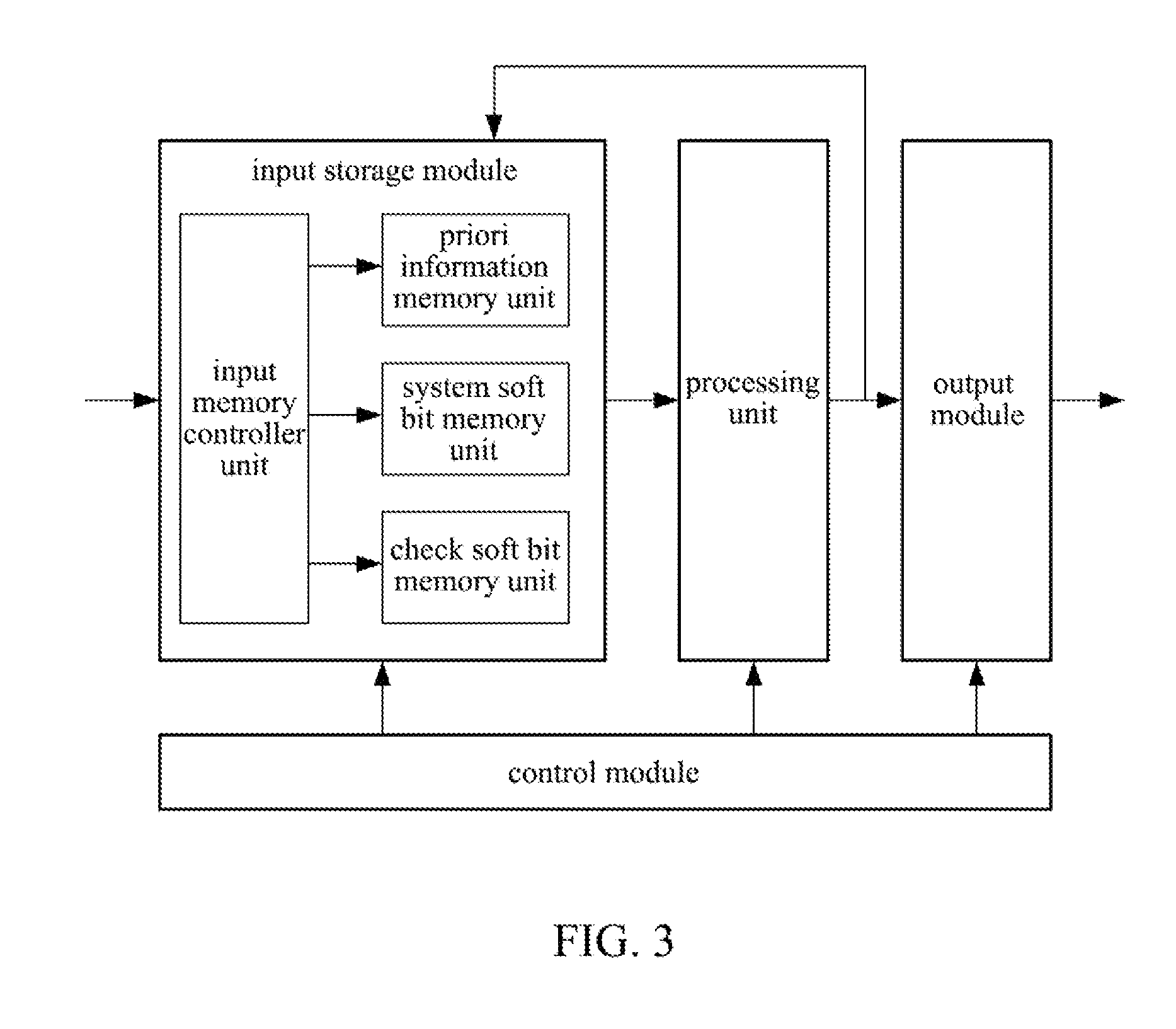

InactiveUS20120106683A1Reduce consumptionReduce processing latencyOther decoding techniquesCode conversionSlide windowComputer science

Provided are a method and an apparatus for parallel Turbo decoding in LTE, comprising: storing input check soft bits and a frame to be decoded, when storing said frame, dividing the frame into blocks, storing each block respectively as system soft bits; simultaneously performing component decoding once for several blocks of one said frame, and in the process of component decoding, dividing each block into several sliding windows according to a sliding window algorithm, calculating the following parameters according to system soft bits, check soft bits and priori information: branch metric value γ, forward state vector α, backward state vector β, LLR, and priori information, storing the priori information for use in a next component decoding; completing a decoding process after several component decoding; performing a hard decision on LLR, and if judged that a result of the hard decision meets an iteration ending condition, outputting a decoding result, otherwise, performing next iteration decoding.

Owner:ZTE CORP

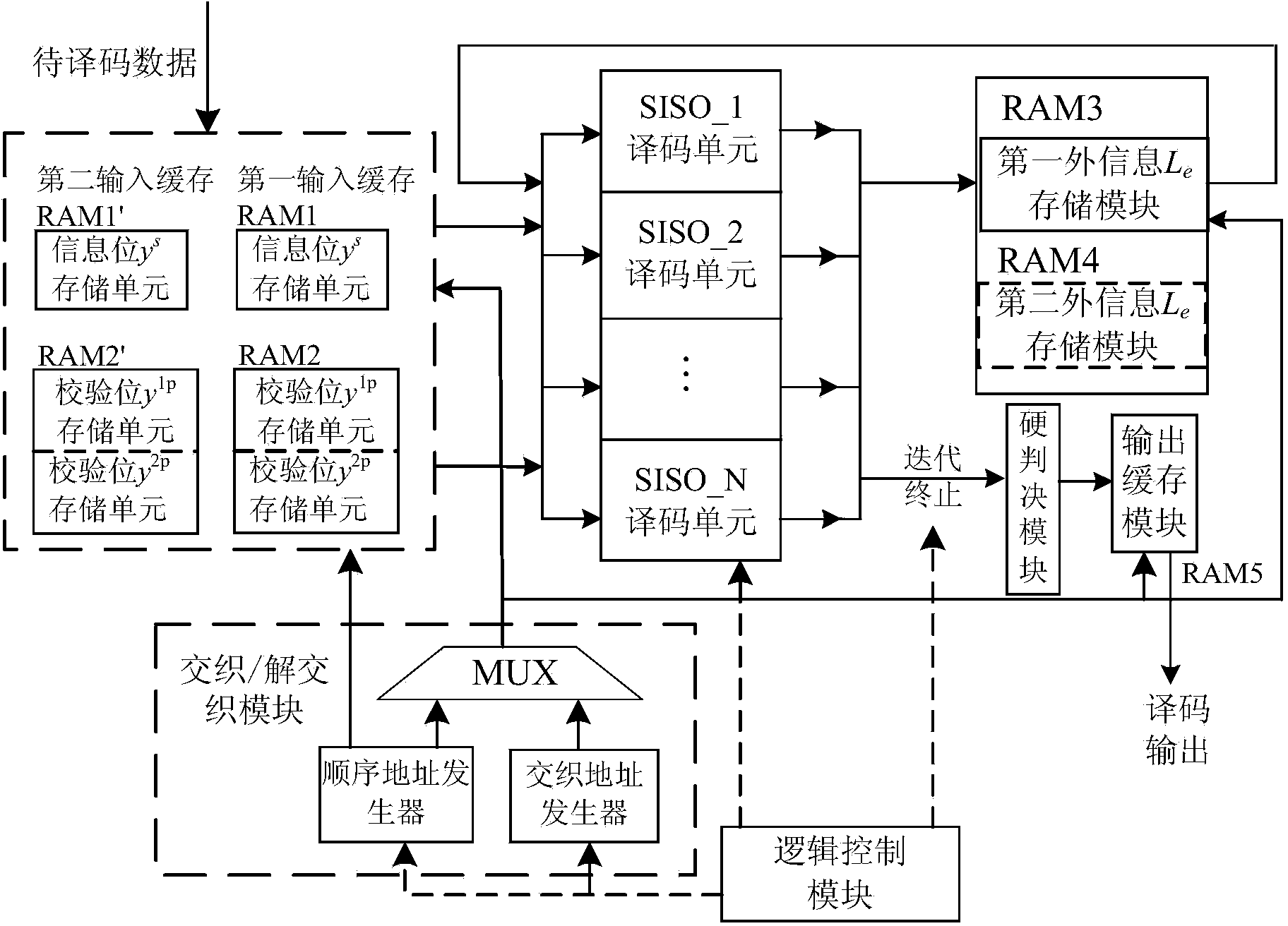

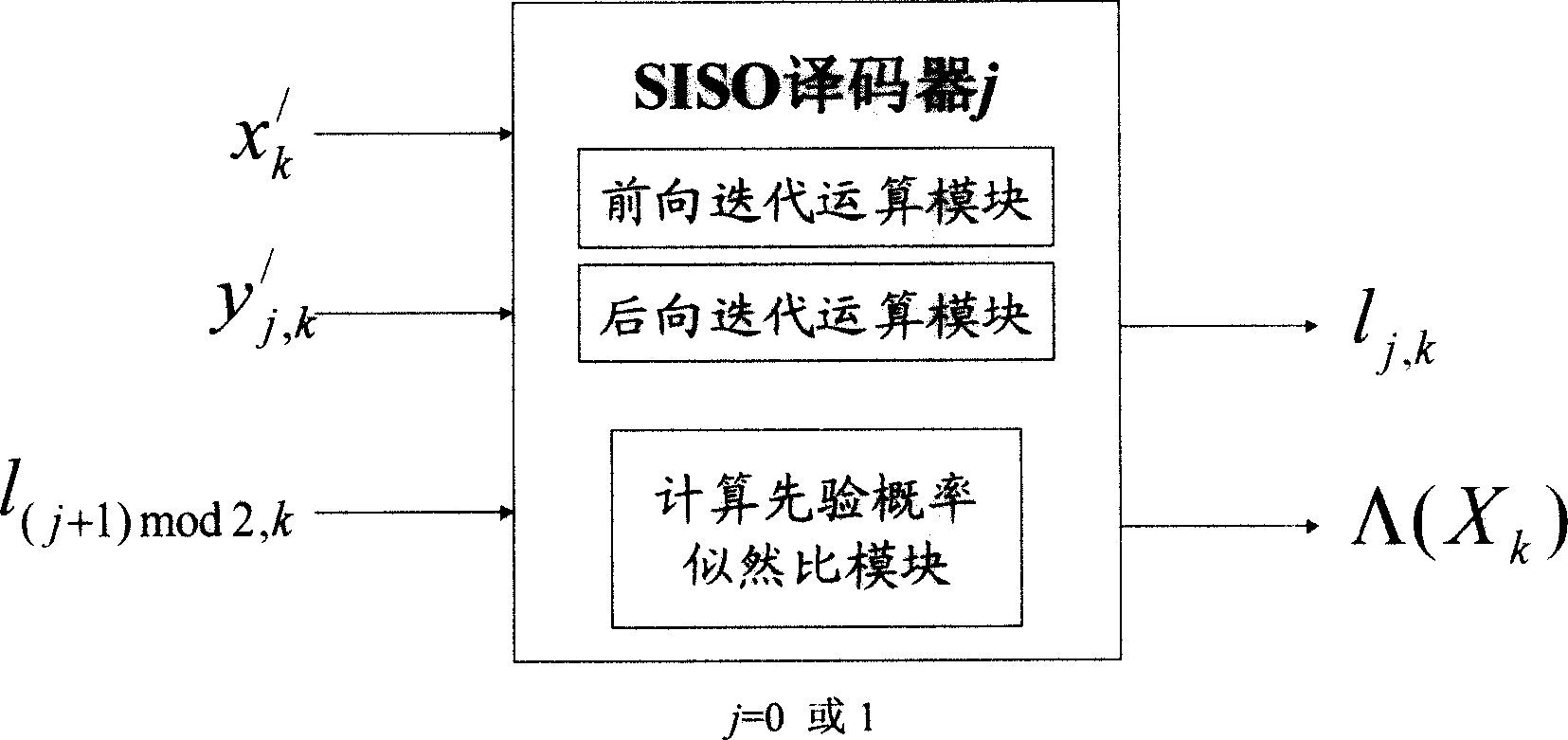

Turbo code high-speed decoding method based on parallel and windowing structure

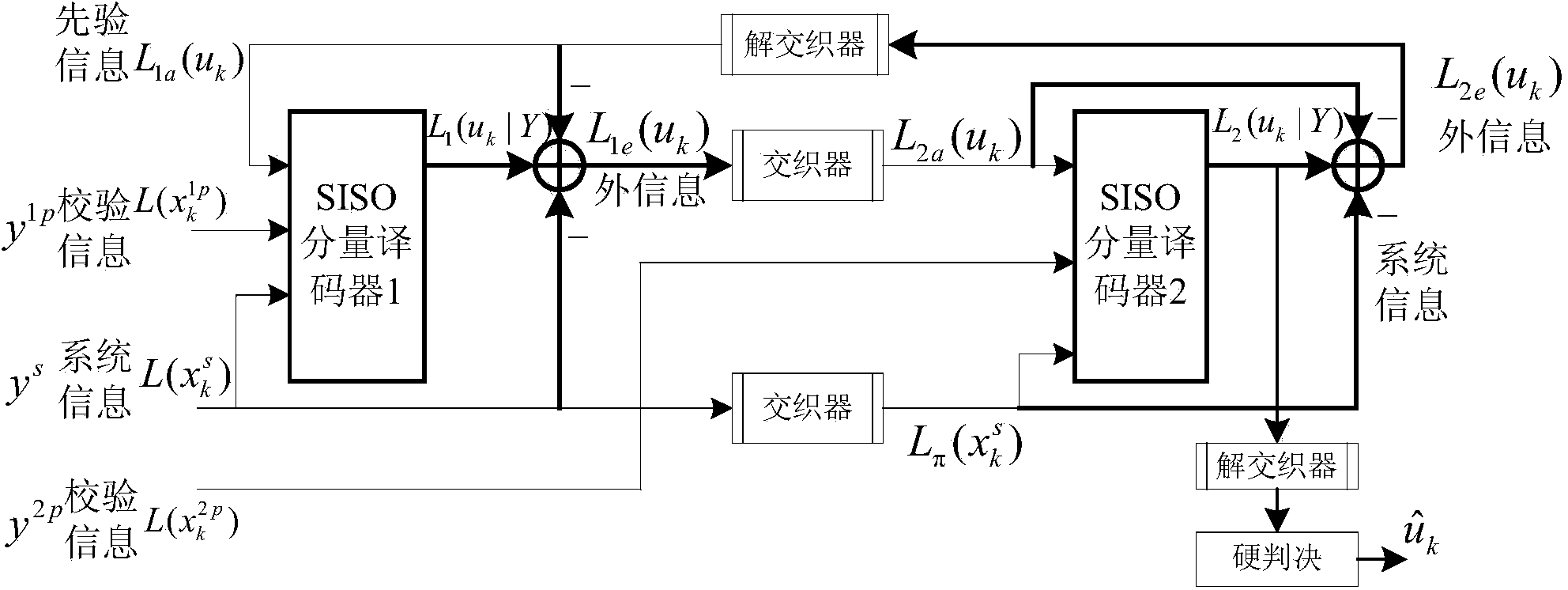

ActiveCN103873073AIncrease decoding speedReduce the number of RAMError correction/detection by combining multiple code structuresSlide windowComputer module

The invention relates to a Turbo code high-speed decoding method based on a parallel and windowing structure, wherein the method is achieved through a Turbo code high-speed decoder. The method relates to a first input buffer module, a second input buffer module, a first extrinsic information storage module, a second extrinsic information storage module, a interweaving / de-interweaving module, N SISO decoding units, a hard-decision module and an output buffer module, wherein the first input buffer module and the second input buffer module continuously receive data frames input from the exterior in a ping-pong operating mode, first component decoding and second component decoding iterated for the first time are completed through the N SISO decoding units, in this way, first component decoding and second component decoding iterated for the Nth time are completed, iteration is ended, LLR information obtained through the second component decoding iterated for the Mth time is subjected to de-interweaving, the de-interweaving result is subjected to a hard decision, and finally, the hard decision result is stored in the output buffer module. According to the method, the advantages of parallel decoding and sliding window decoding are combined, the decoding running speed is substantially increased, and the good decoding property is achieved.

Owner:BEIJING RES INST OF TELEMETRY +1

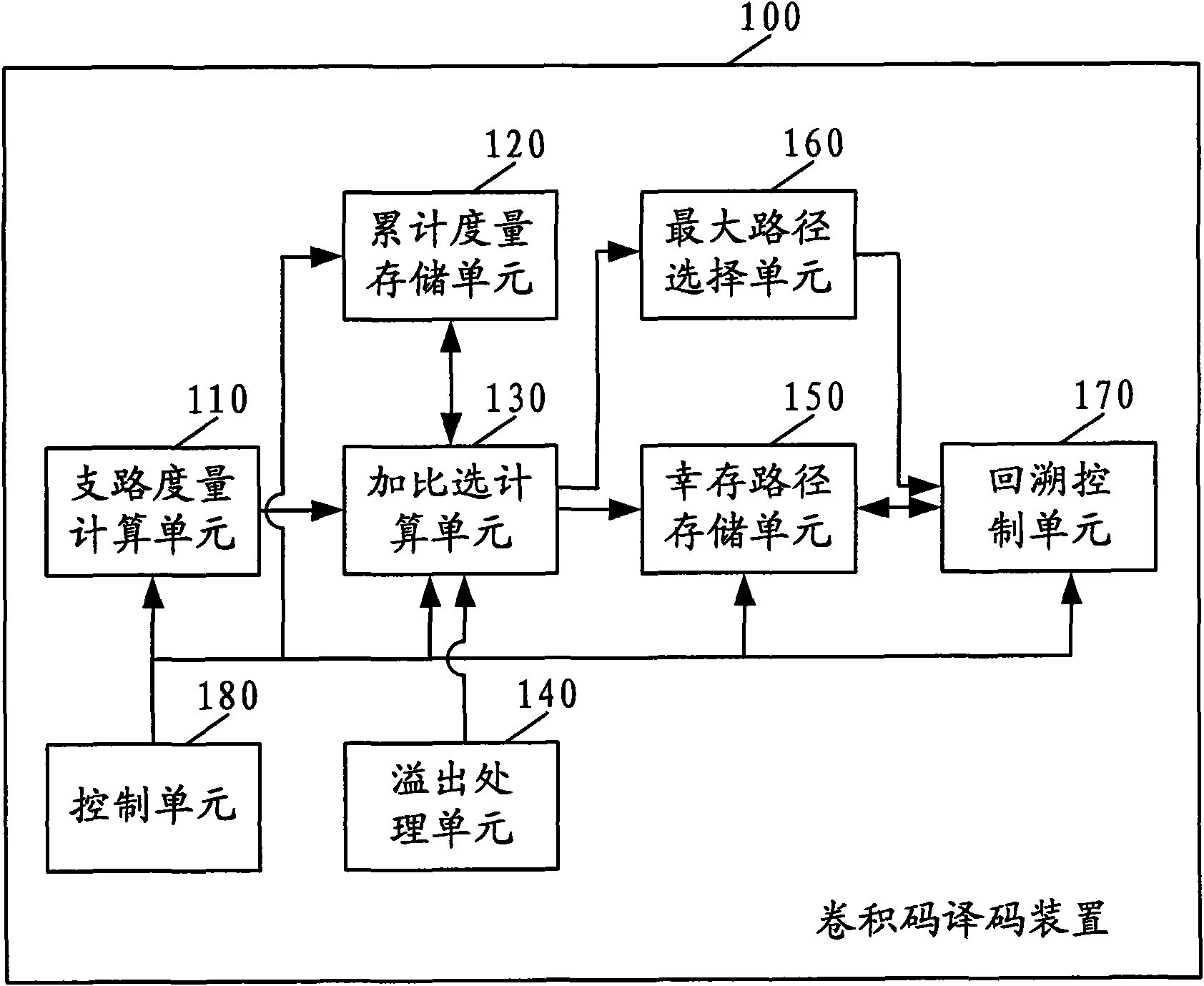

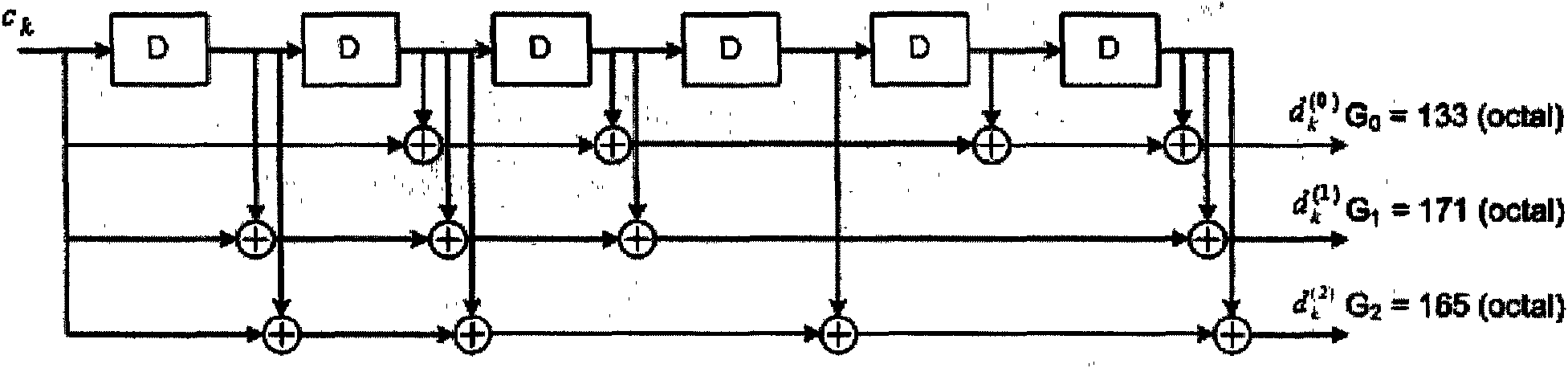

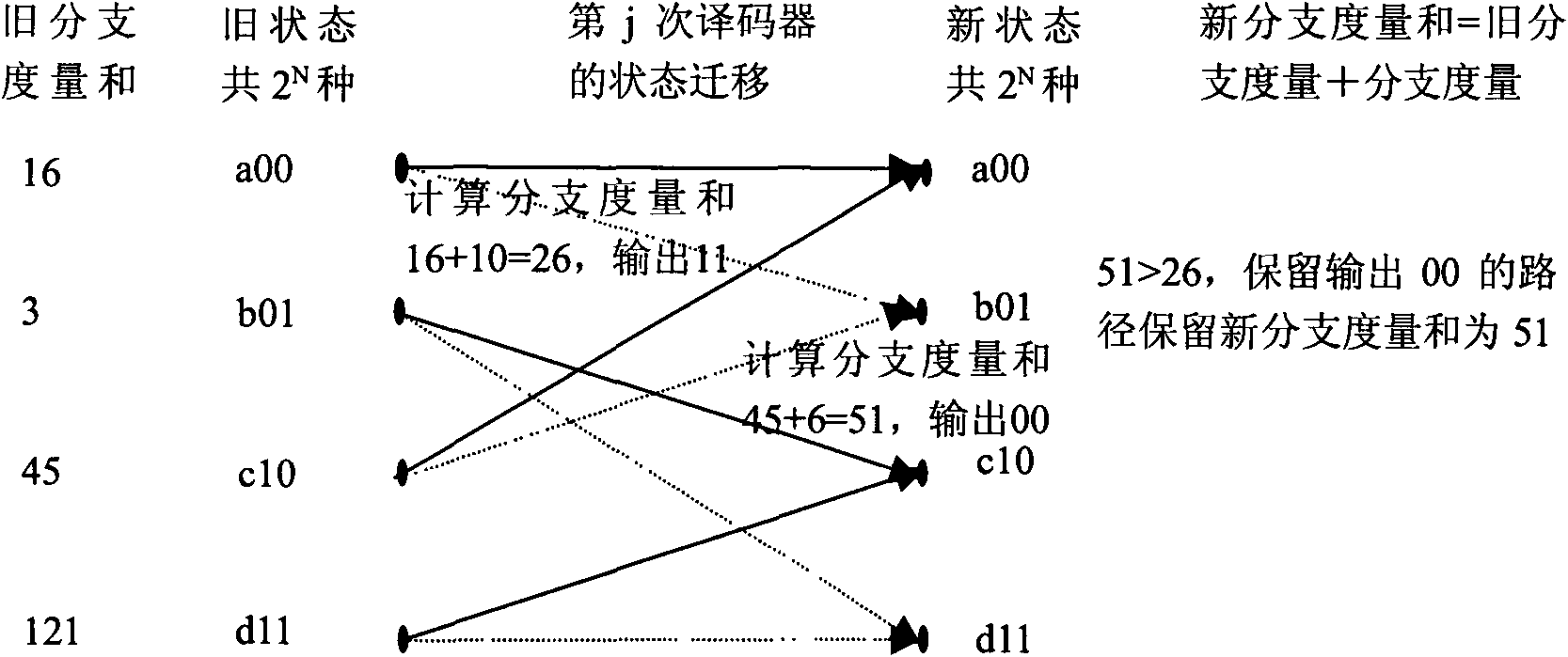

Method and device for decoding convolution code

ActiveCN101997553AHigh speedImprove performanceError correction/detection using convolutional codesConvolutional codeConvolution theorem

The invention discloses a method and device for decoding a convolution code. The device comprises a branch measure calculating unit, an accumulated measure storage unit, an add-compare-select calculating unit, an overflow processing unit, a survival path storage unit and a backtracking control unit, wherein the branch measure calculating unit is used for calculating a branch measure value; the accumulated measure storage unit is used for storing an accumulated survival path measure value; the add-compare-select calculating unit is used for carrying out adding-comparison-selection operation; the overflow processing unit is used for generating a subtraction enabling signal according to the state change of the highest order of the accumulated measure value in the accumulating process and controlling the add-compare-select calculating unit to carry out subtraction operation on the accumulated survival path measure value; the survival path storage unit is used for storing a survival path; and the backtracking control unit is used for backtracking the survival path and outputting a decoding result. The method and the device can solve the overflow problem of the survival path measure value in the accumulating process.

Owner:SANECHIPS TECH CO LTD

Encoding method, decoding method, devices and equipment

PendingCN107342774AAccelerated detection purposeReduce decoding delayCode conversionConnection managementComputer engineeringDecoding methods

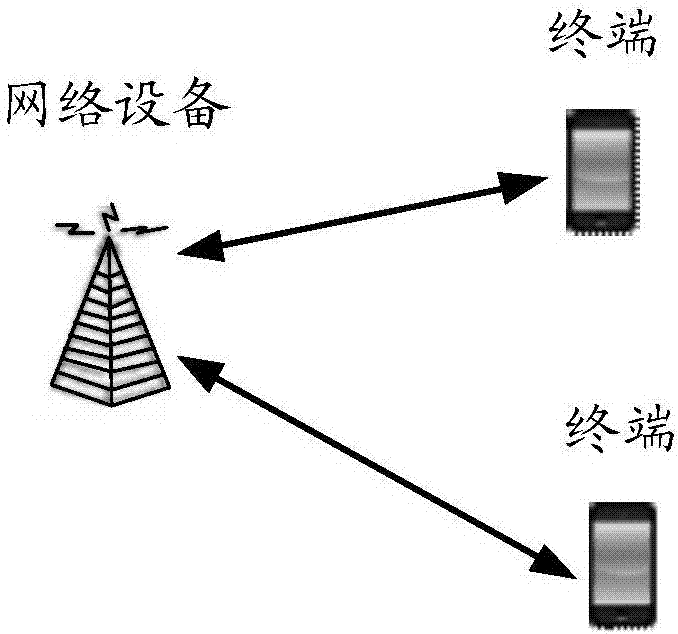

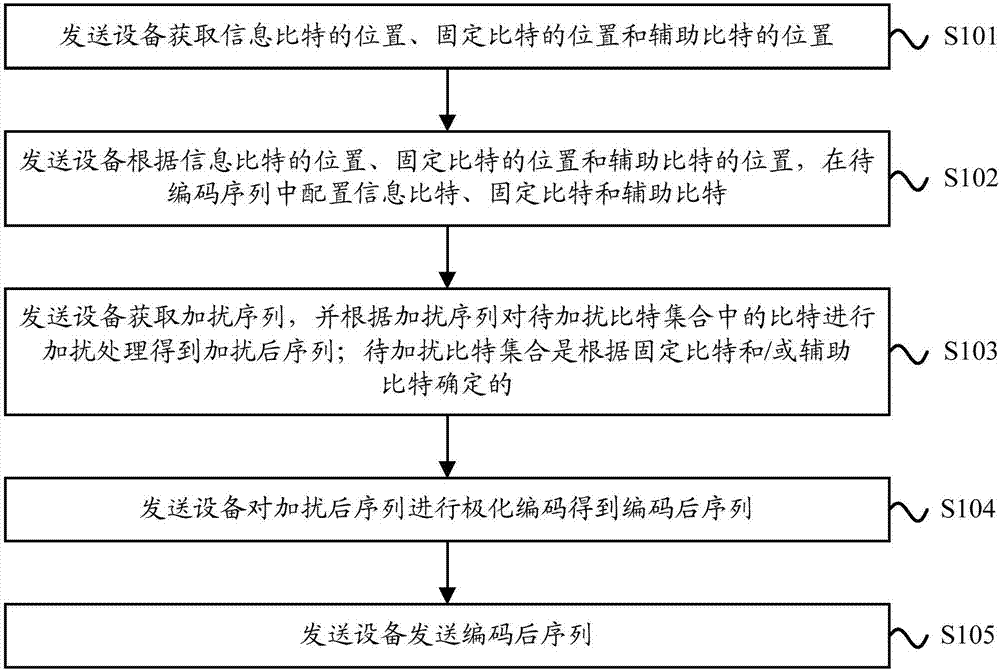

The application provides an encoding method, a decoding method, devices and equipment. The method comprises the following steps: sending equipment determines the location of an information bit, the location of a fixed bit and the location of an auxiliary bit, configures the information bit, the fixed bit and the auxiliary bit in a sequence to be encoded according to the determined locations, and then obtains a scrambling sequence, determines a bit set to be scrambled in the fixed bit and / or the auxiliary bit, scrambles the bits in the bit set to be scrambled according to the scrambling sequence to obtain a scrambled sequence, then performs polarization coding to obtain an encoded sequence, and sends the encoded sequence; and receiving equipment performs decoding verification after receiving a sequence to be decoded, performs verification when decoding to the location of the scrambled bit, and ends the decoding process if the verification fails. Thereby, signals that do not belong to the sending equipment can be excluded in advance, the decoding delay can be reduced, and the detection can be accelerated.

Owner:HUAWEI TECH CO LTD

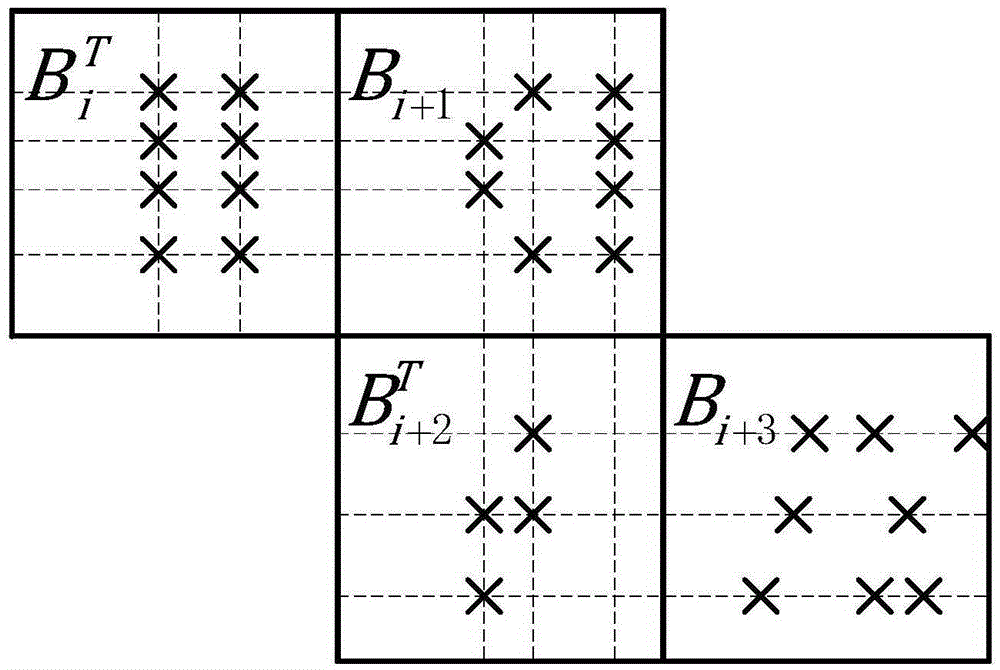

Coding and decoding methods of ode of tail-biting staircase codes

ActiveCN105429646AGuaranteed error correction performanceTroubleshoot issues where uncorrected errors are affecting overall performanceError correction/detection using convolutional codesError correction/detection by combining multiple code structuresComputer architectureBlock code

The invention relates to a tail-biting staircase code coding method. The tail-biting staircase code coding method comprises the following steps: 1) selecting an (n, k) linear block code as a component code, wherein n represents a code length, n belongs to (500, 5000), and k represents an information length before coding; and 2) grounding received information according to a mode in staircase codes, constructing a matrix B<1>, B<2>, B<3>, ..., B<n>, adding a full-zero matrix participating the coding to a lower part of B<1>, coding the residual matrix using the component code then, generating a check bit matrix while the coding, completing end-to-end connection of codes of a final matrix and a first matrix in a group then, finally replacing the full-zero matrix complemented in the B<1> with the check bit matrix, and completing the coding. The coding method is advantageous in that, through adoption of the novel coding scheme, the novel tail-biting staircase codes have a characteristic of the block code, coding processes between groups are mutually independent, information of each matrix in the groups is still contained in the two component codes, and error correction performance is guaranteed.

Owner:NANJING UNIV

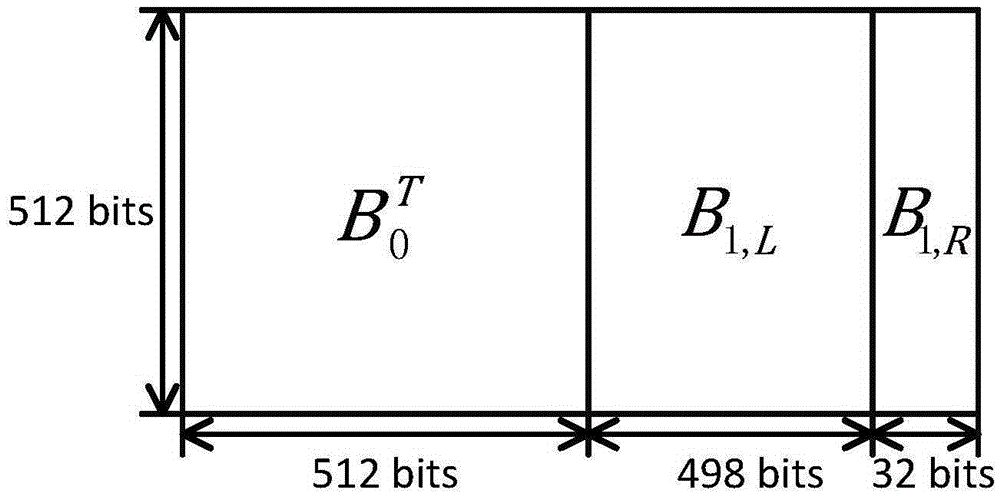

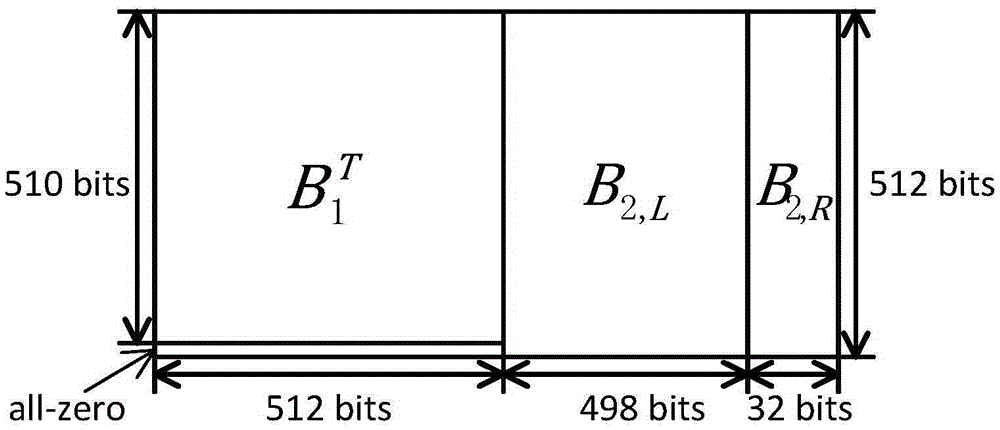

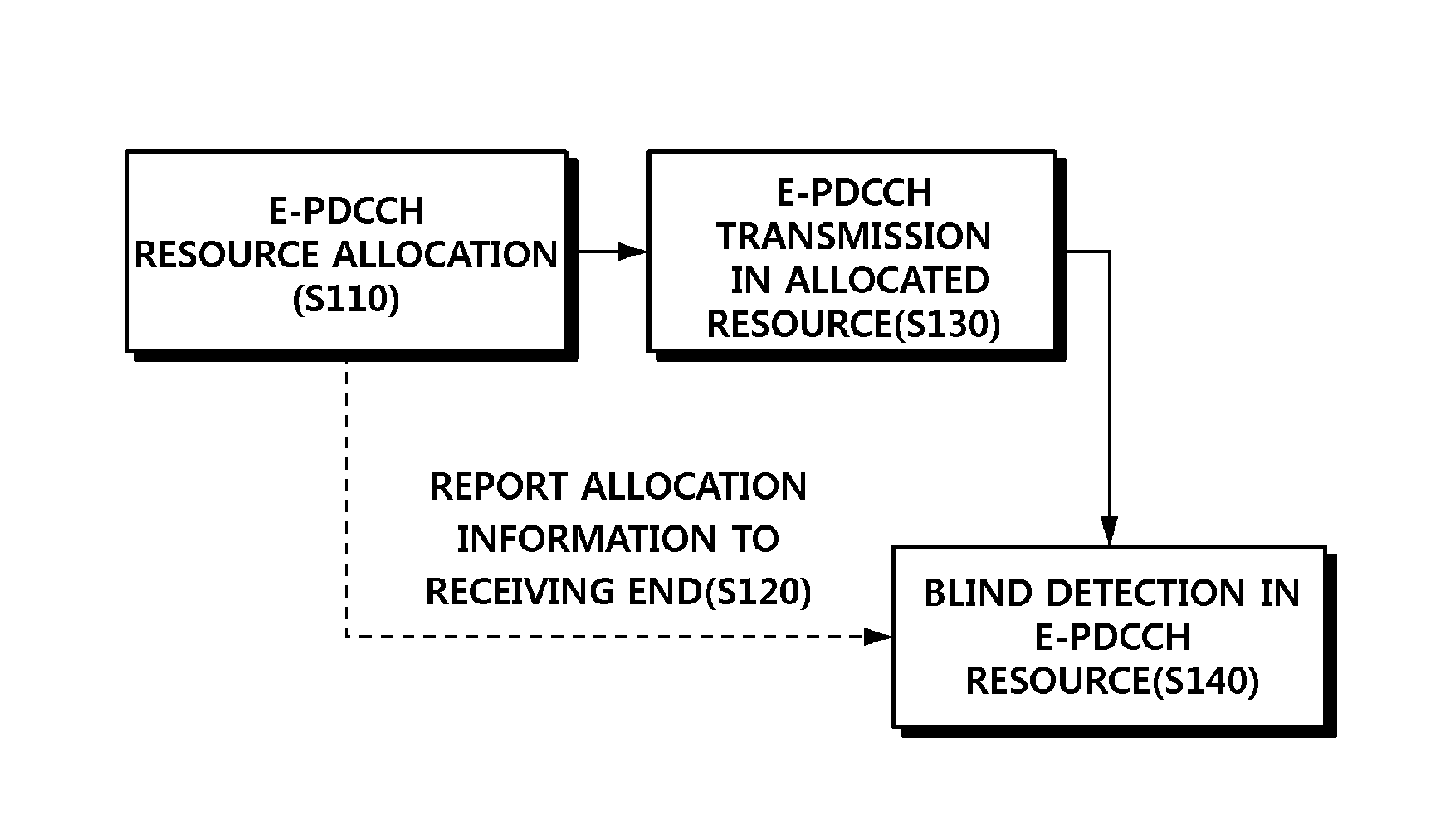

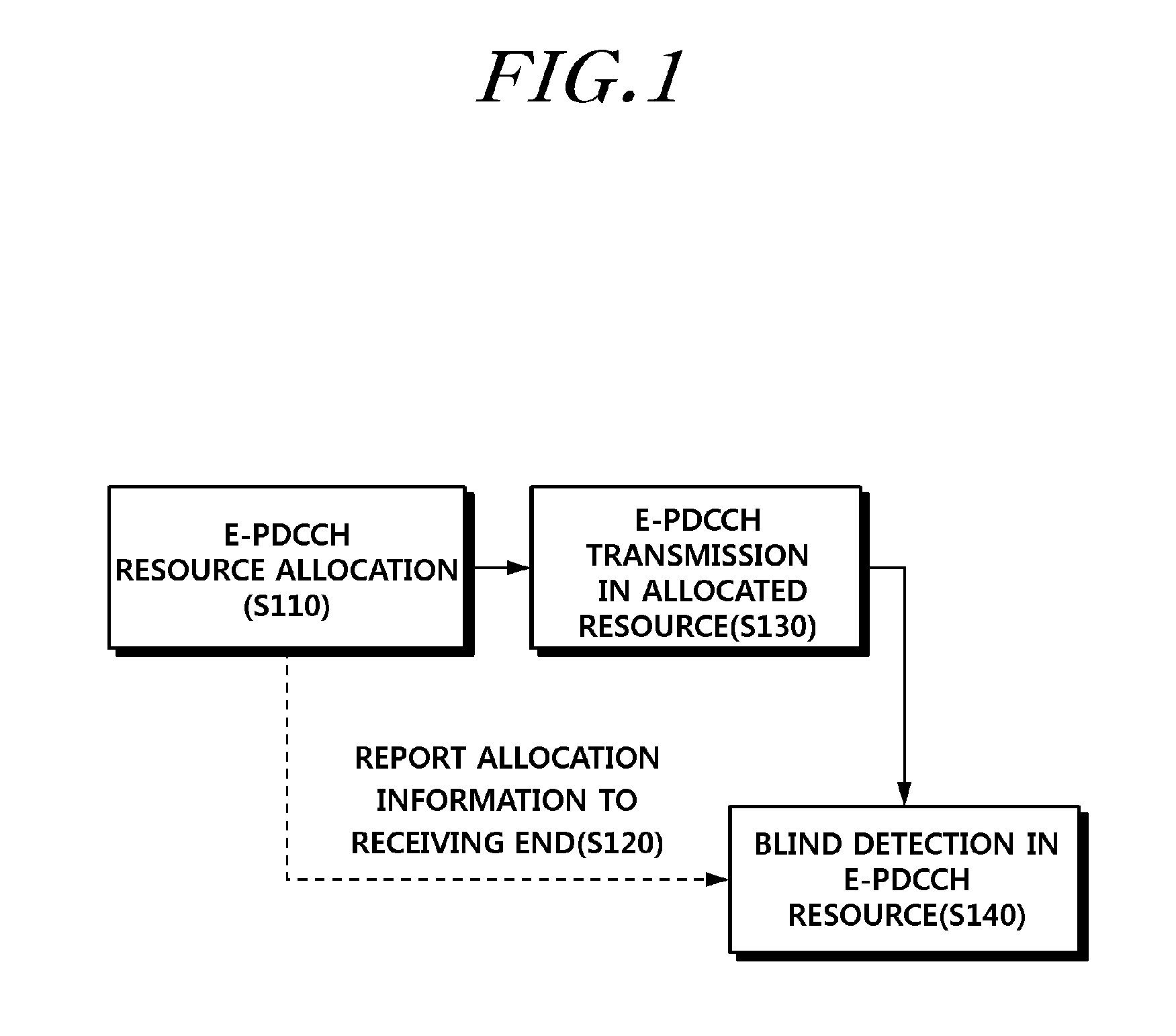

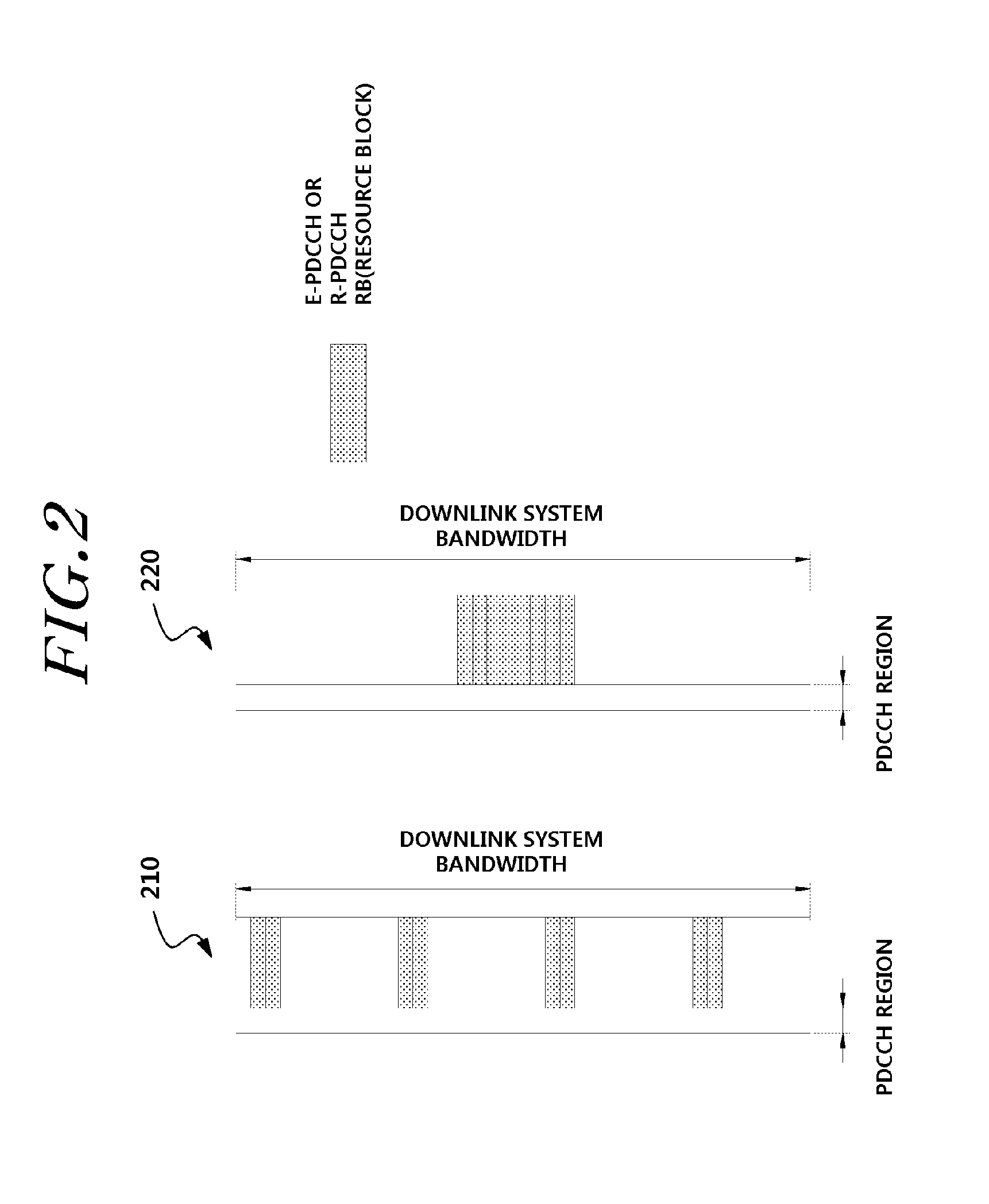

E-pdcch mapping, and method and apparatus for transmission and reception in wireless communication system

InactiveUS20140286292A1Reduce complexityReduce decoding delayReceiver specific arrangementsSignal allocationCommunications systemResource allocation

The present invention relates to E-PDCCH (Extended PDCCH) mapping, and a method and an apparatus for transmission and reception in a wireless communication system. The E-PDCCH mapping and the transmission method according to one embodiment of the present description, includes the steps of: enabling a base station to perform distributed resource allocation for two or more regions to which the E-PDCCH is transmitted; and mapping the E-PDCCH to be transmitted to a user terminal by applying a mapping rule to resources of one or more regions among the two or more regions. The mapping rule includes at least one of a first mapping rule for mapping the E-PDCCH to a resource within a pre-indicated region in the terminal, and a second mapping rule for mapping the E-PDCCH according to an aggregation level of the E-PDCCH.

Owner:PANTECH CO LTD

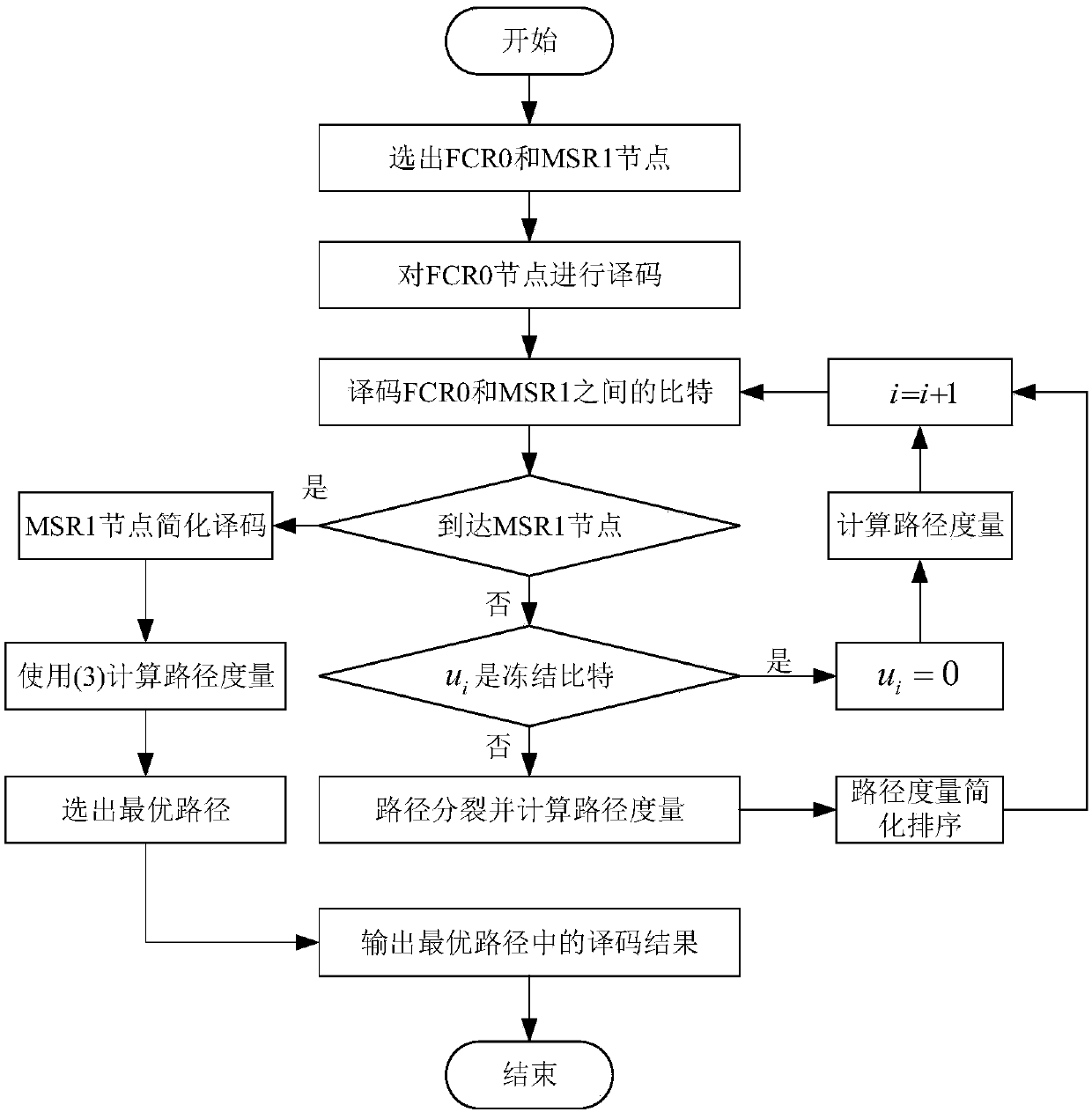

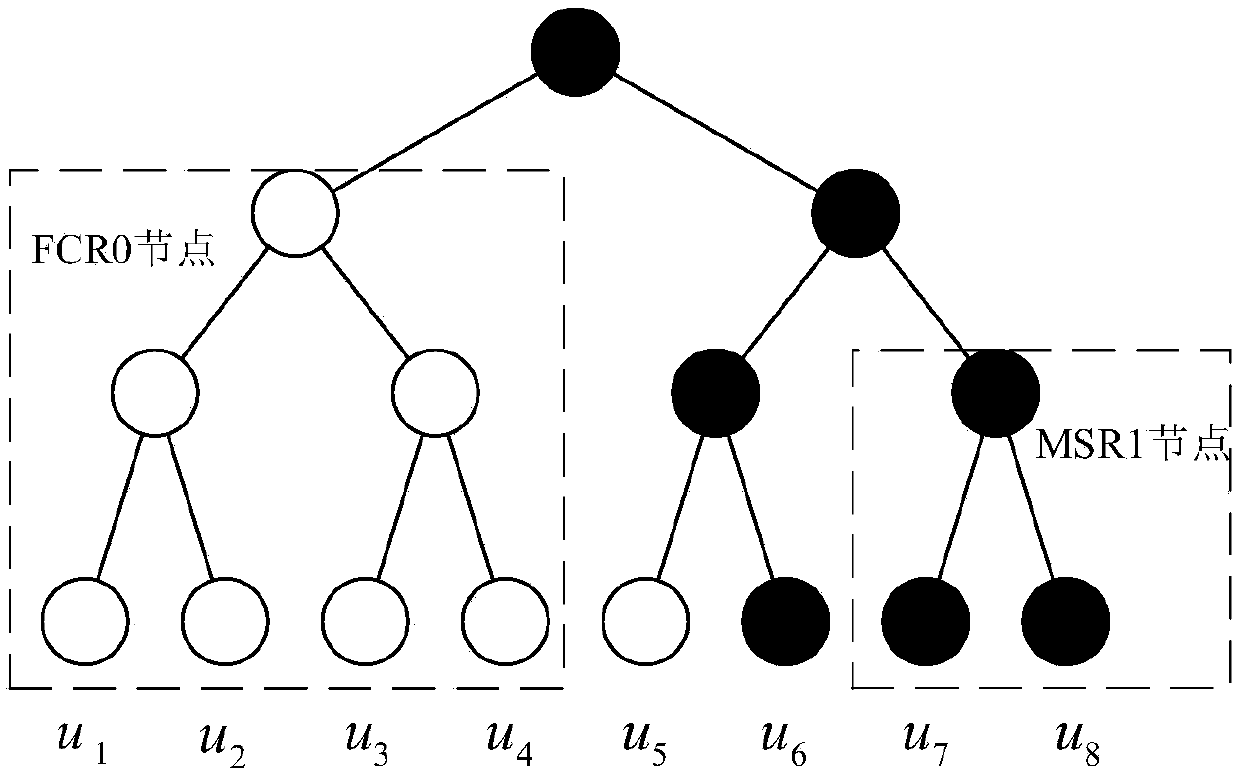

Polar code decoding method with low delay and complexity

ActiveCN108063649ASimplified decoding calculationReduce decoding delayError preventionOther decoding techniquesDecoding methodsLow delay

The invention discloses a polar code decoding method with low delay and complexity. The polar code decoding method adopts an SCL method for decoding and comprises the following steps of (1) selectingan FCR0 node and an MSR1 node from a bit sequence to be coded; (2) for the FCR0 node, directly acquiring a decoding result according to a value of a freezing bit stored by a receiver; (3) for a bit sequence between the FCR0 node and the MSR 1 node, if the current bit sequence to be coded is the frozen bit, connecting a path in the step (2) and directly acquiring a decoding result according to a value of the freezing bit stored by the receiver, and if the current bit sequence to be coded is an information bit, connecting a freezing bit decoding path, and reserving a path with a smaller path metric through path splitting and simplified path metric; (4) for the MSR1 node, carrying out direct judgment decoding by using an LLR, and connecting to the step (3), and connecting to all paths reserved in the step (3); and (5) for the path in the step (4), selecting a decoding sequence corresponding to a path with the minimum path metric as decoding output. The polar code decoding method has lowerdelay and complexity.

Owner:白盒子(上海)微电子科技有限公司

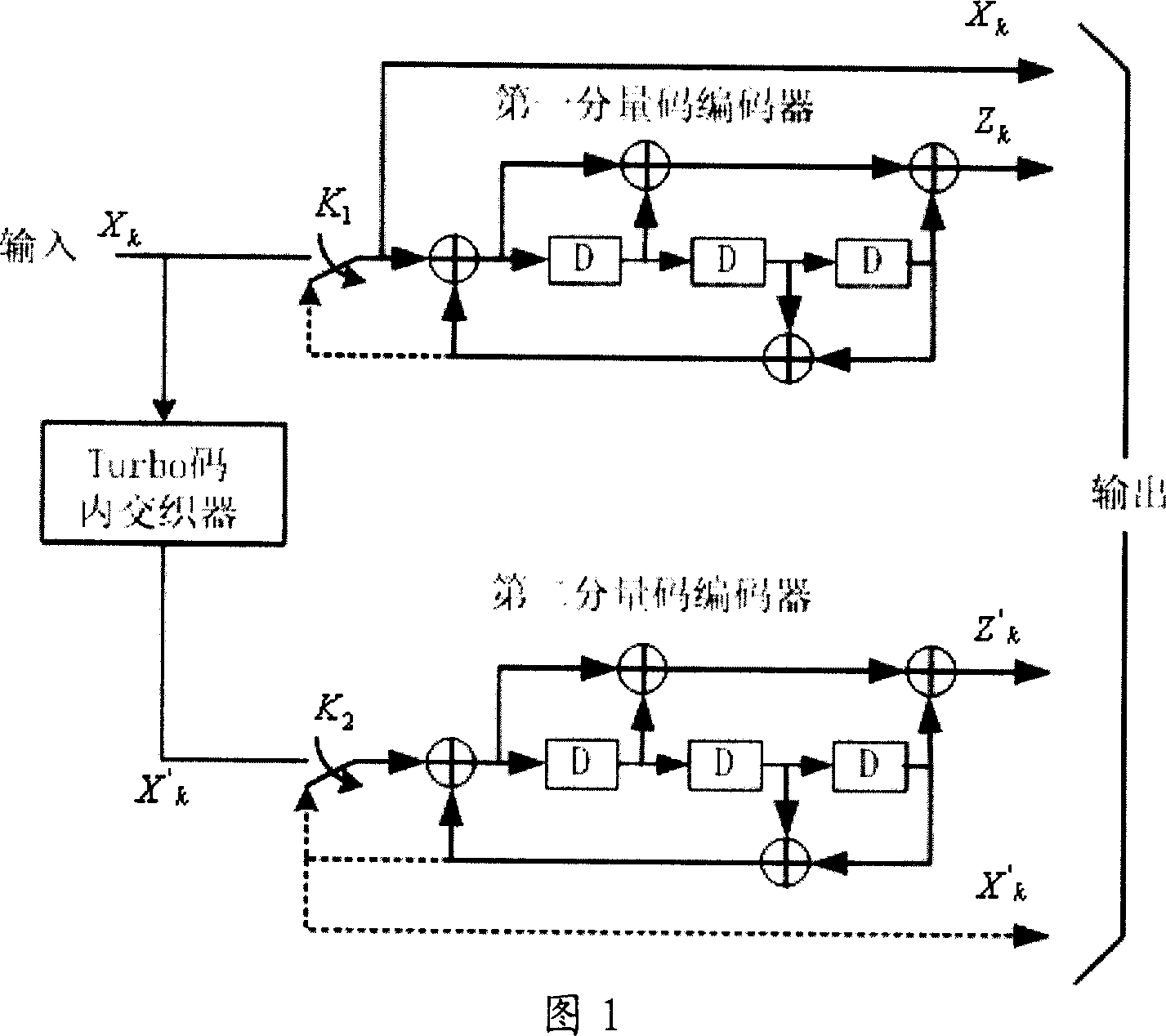

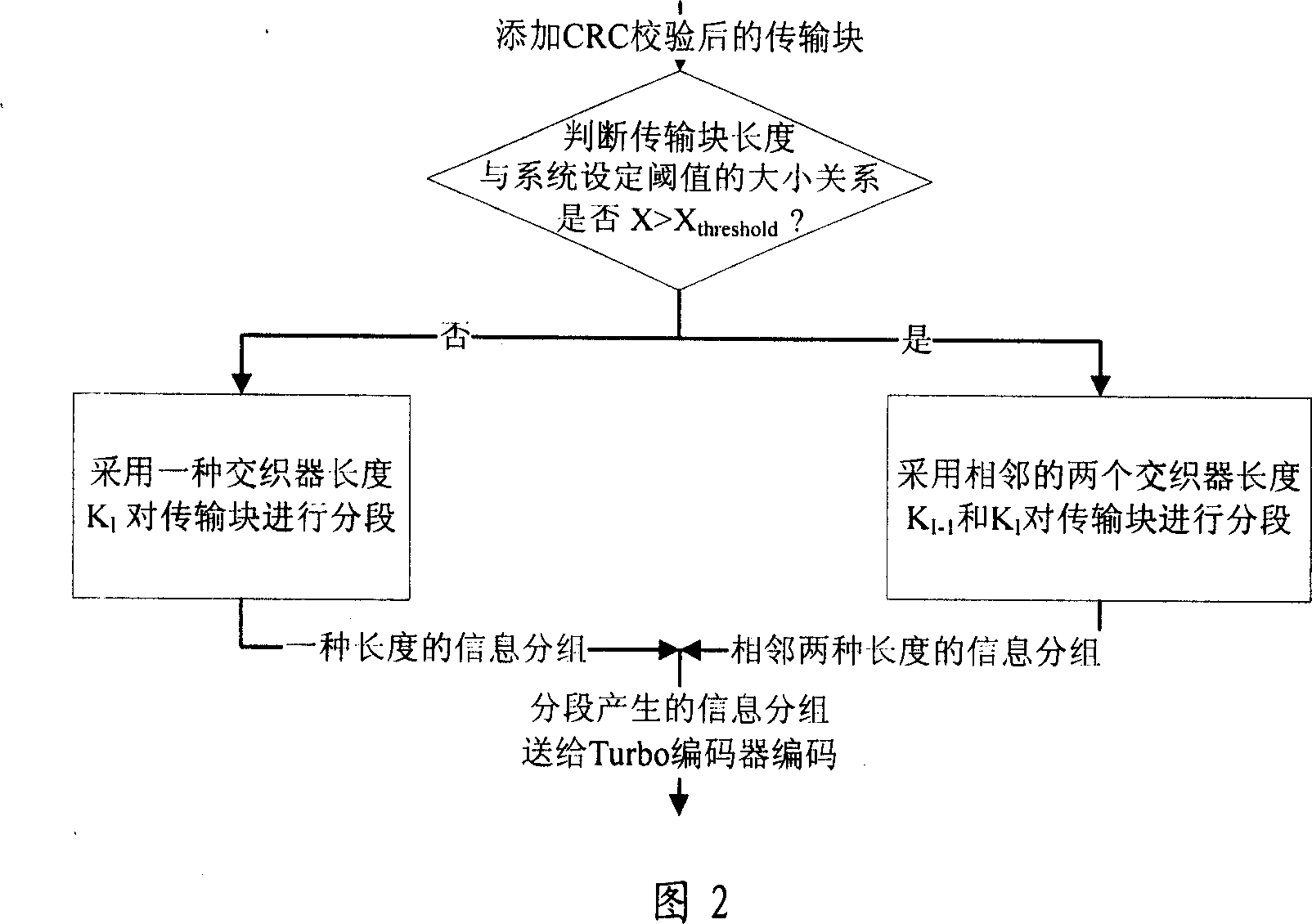

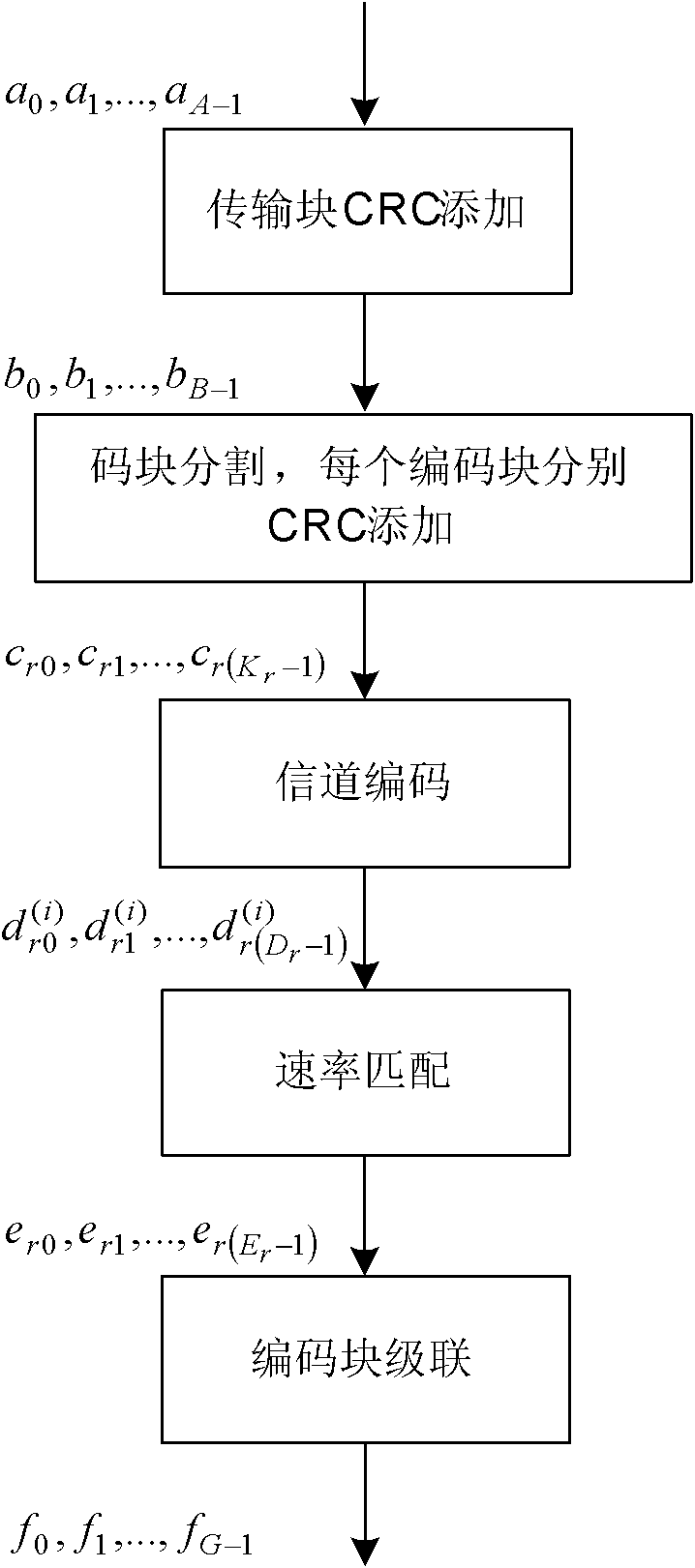

A Turbo code transmission block segmenting method

InactiveCN101060481AReduce the numberReduce in quantityError preventionError correction/detection using interleaving techniquesRound complexityTurbo coded

The disclosed segmenting method for Turbo code comprises: deciding whether the transmission block length over the system-set threshold; if equal or less than the threshold, using interlace device length KI for segmentation; or else, using near KI-1 and KI for segmentation. This invention ensures system performance, reduces filling-bit number, and decreases the complexity and time delay.

Owner:ZTE CORP

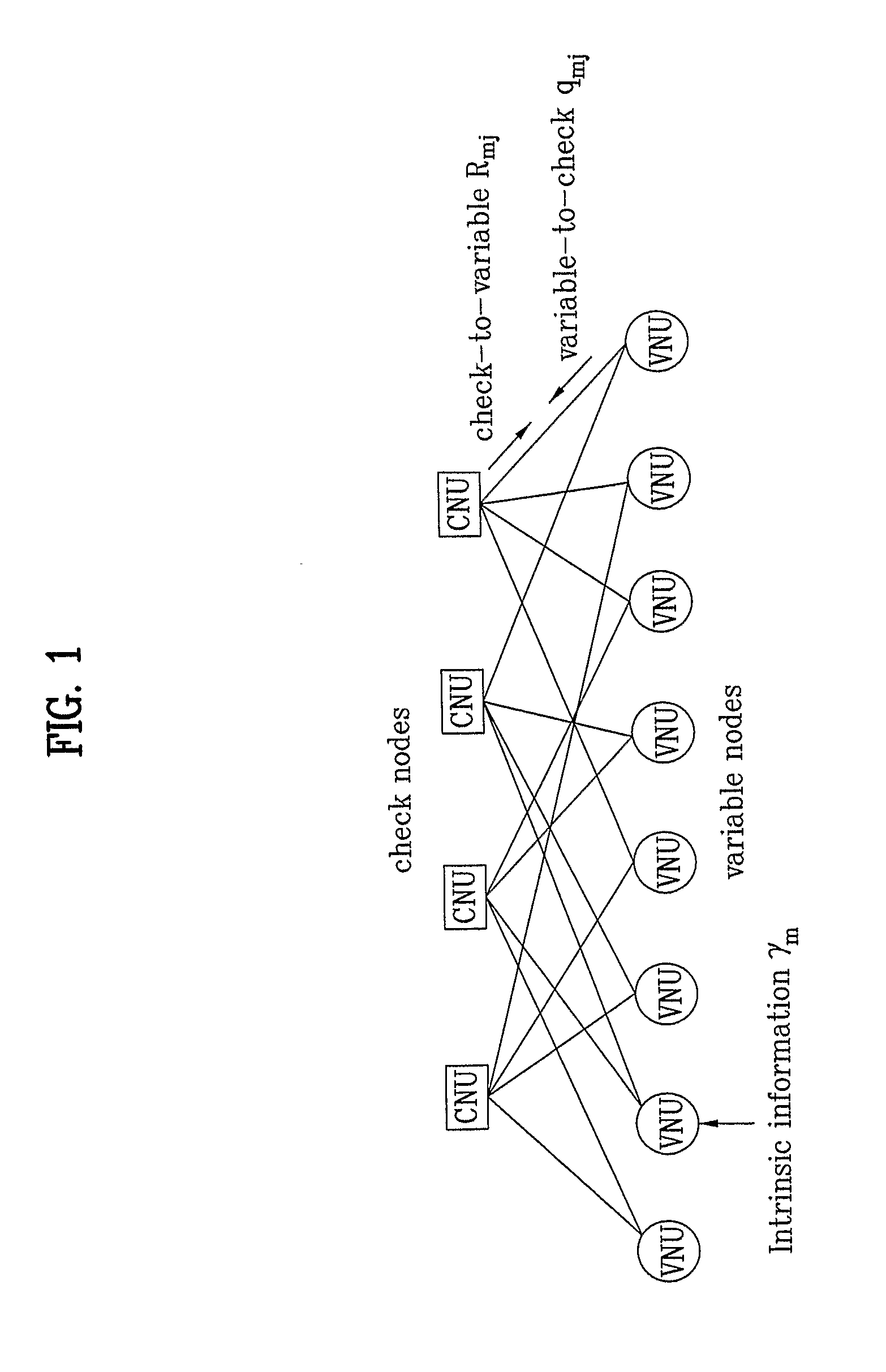

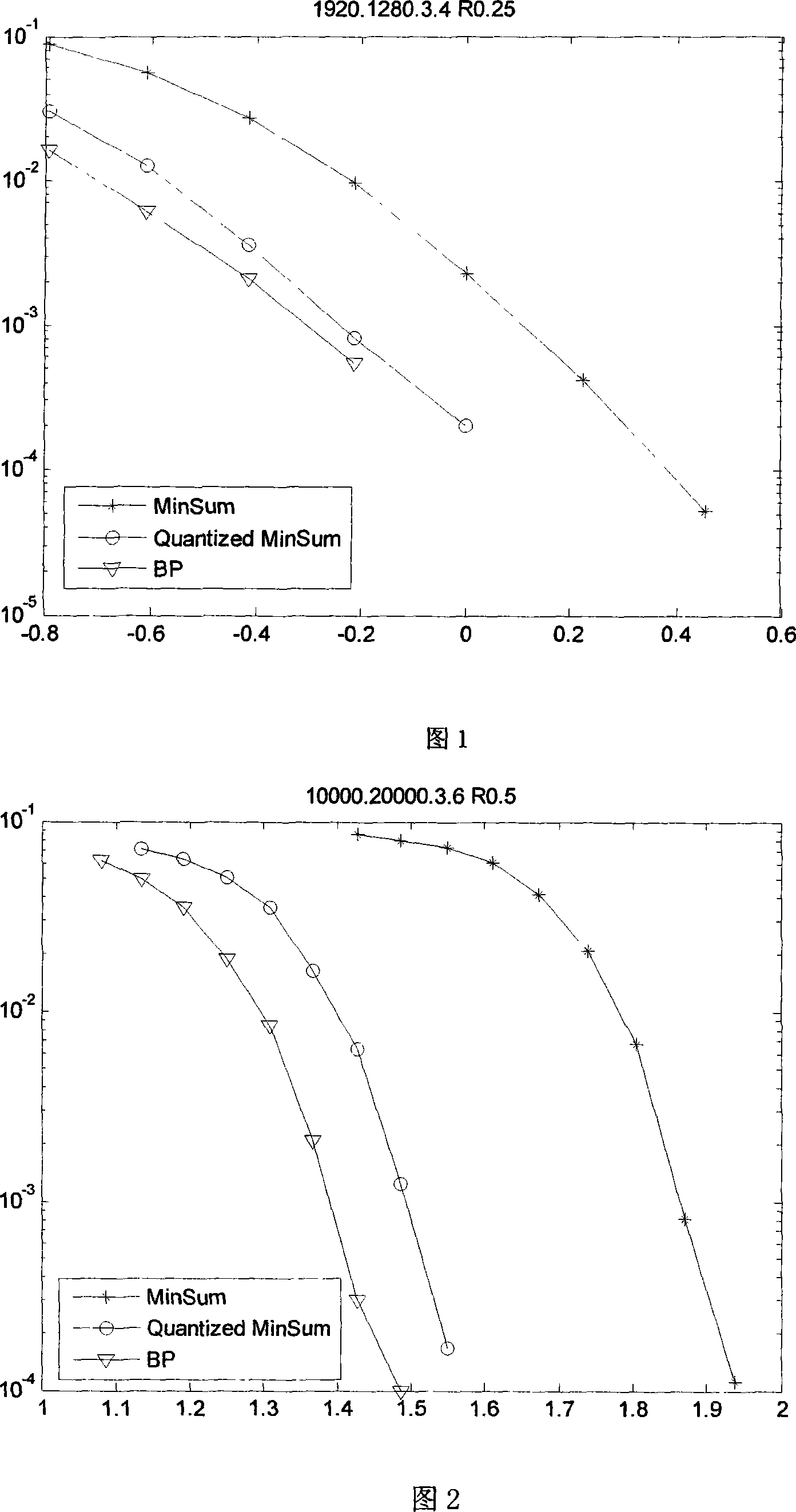

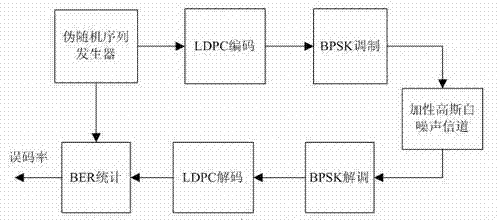

Quantified minimizing and coding method for low-density parity code

ActiveCN101132252ASimplified Computational ComplexityImprove decoding performanceError preventionError correction/detection using multiple parity bitsDecoding methodsLow density

A minimum sum decoding method for quantization of low density odd-even check codes is a circulation method including the following steps: 1, using information received by a channel to initialize a varible node decoder, 2, every variable node inputs the information to a check node connected with it by the edge, which computes related logarithm likelihood ratio information , 3, the check node carries out equal distance quantization then transmits it to an adjacent variable node decoder, 4, every check node inputs the information to a variable node connected with it by edge to compute related logrithm likelihood ratio information, 5, carrying out hard judgment to the logrithm likelihood ratio information output by step 4 and stopping the decoding if the code meets a check matrix and outputting successful information, if iteration time reaches to a preset maximum one, then the decode is stopped and fail information is output, otherwise it is switched to step 2.

Owner:HUAWEI TECH CO LTD

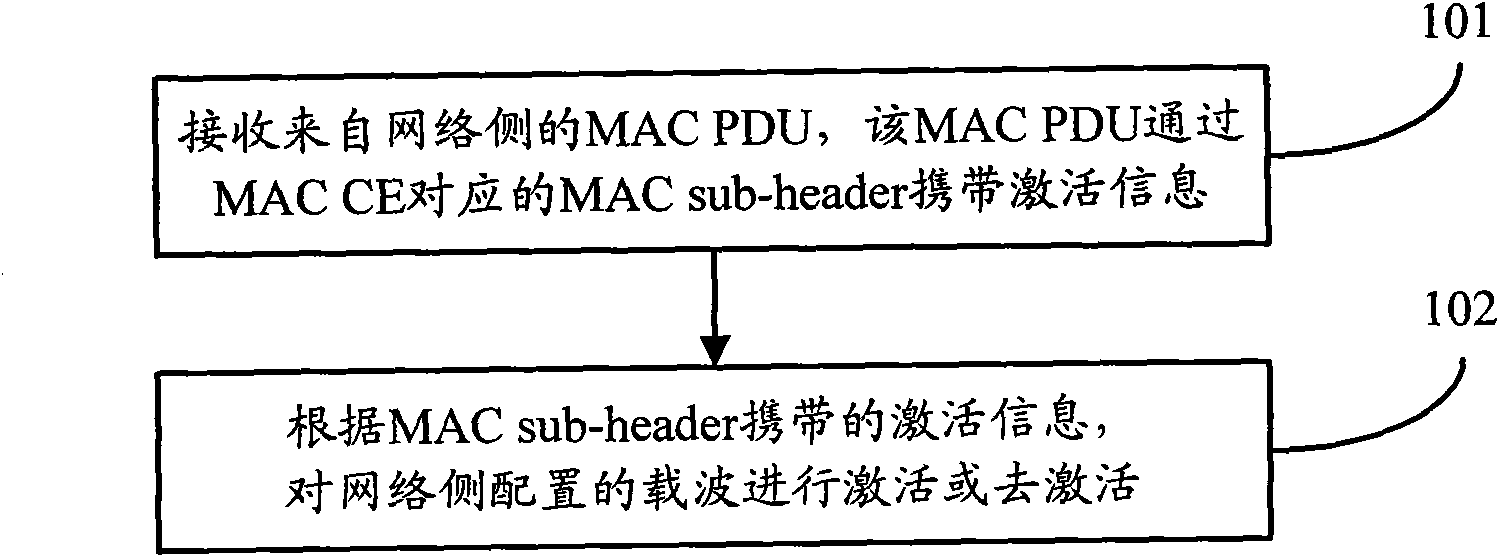

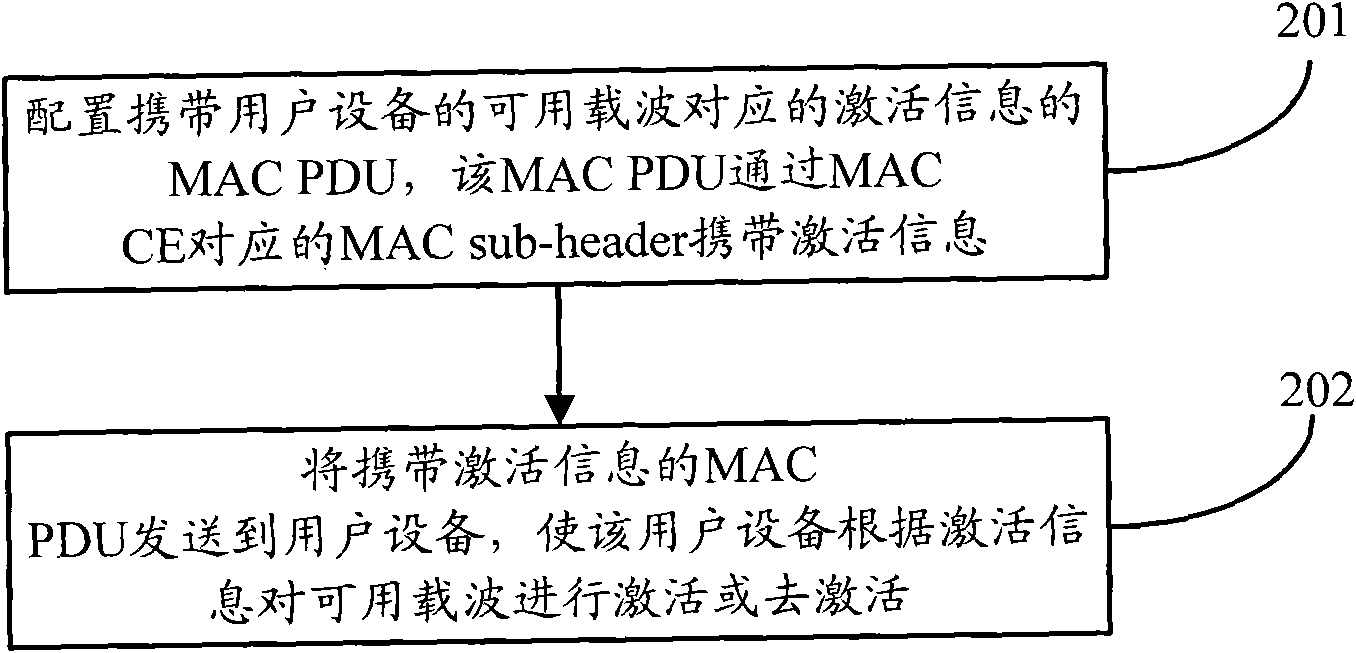

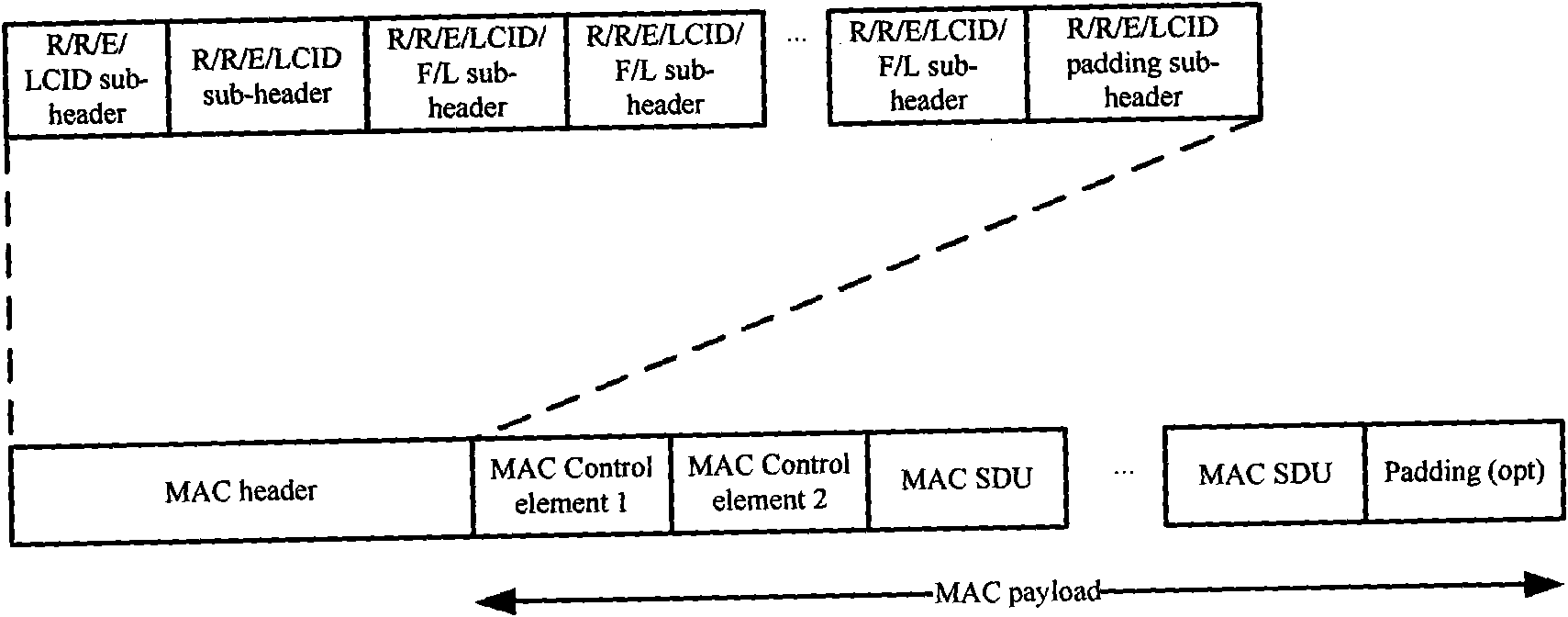

Method, device and system for activating carrier waves

ActiveCN102123487AReduce decoding delaySave powerPower managementNetwork traffic/resource managementCarrier signalBiological activation

The embodiment of the invention discloses a method for activating carrier waves, which comprises the following steps of: receiving a media access control protocol data unit (MAC PDU) from a network side, wherein the MAC PDU carries activation information through a media access control sub-header (MAC sub-header) corresponding to a media access control control element (MAC CE); and activating or deactivating the carrier waves configured on the network side according to the activation information carried by the MAC sub-header. The embodiment of the invention saves the electric quantity of user equipment (UE). The embodiment of the invention also discloses a device and a system applying the method.

Owner:CHINA MOBILE COMM GRP CO LTD

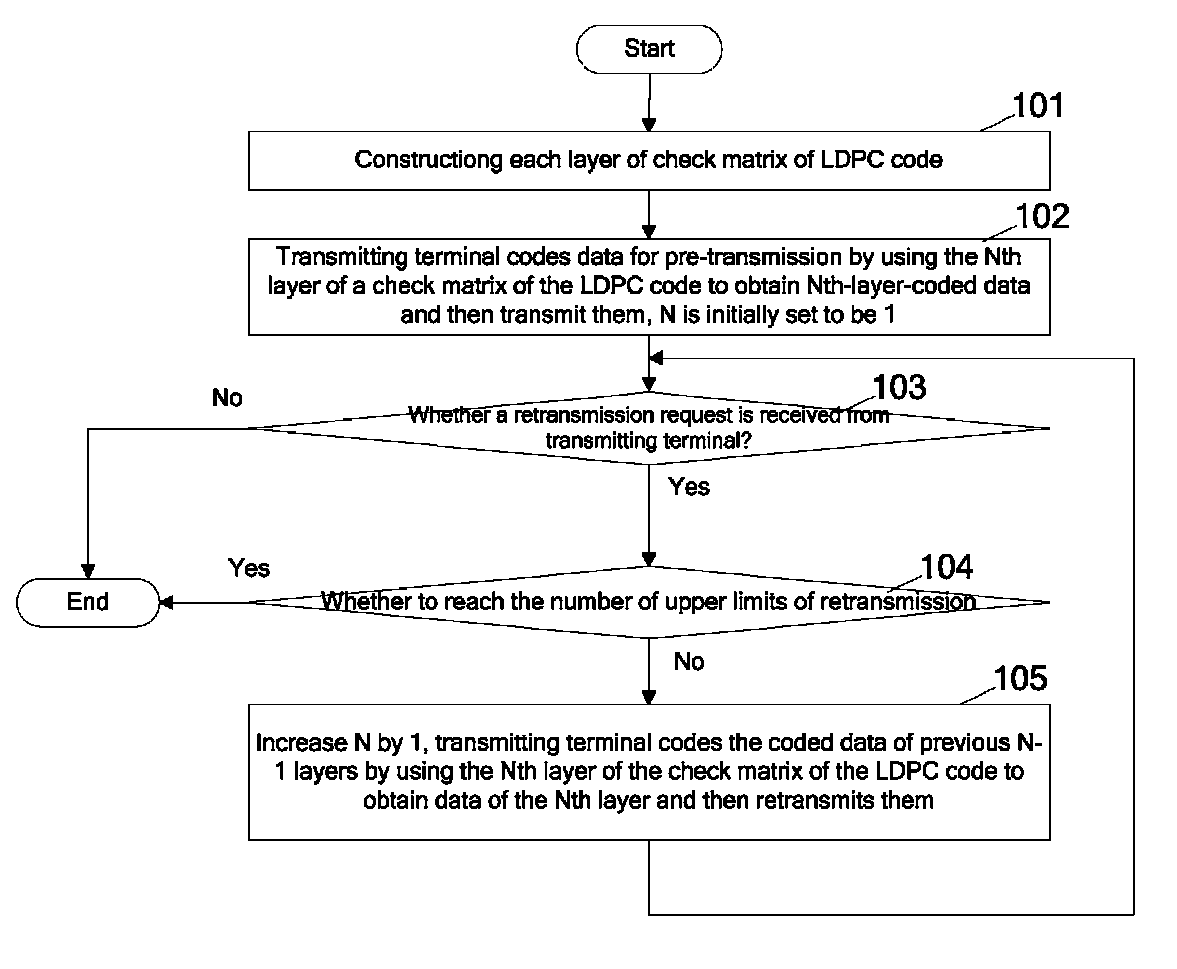

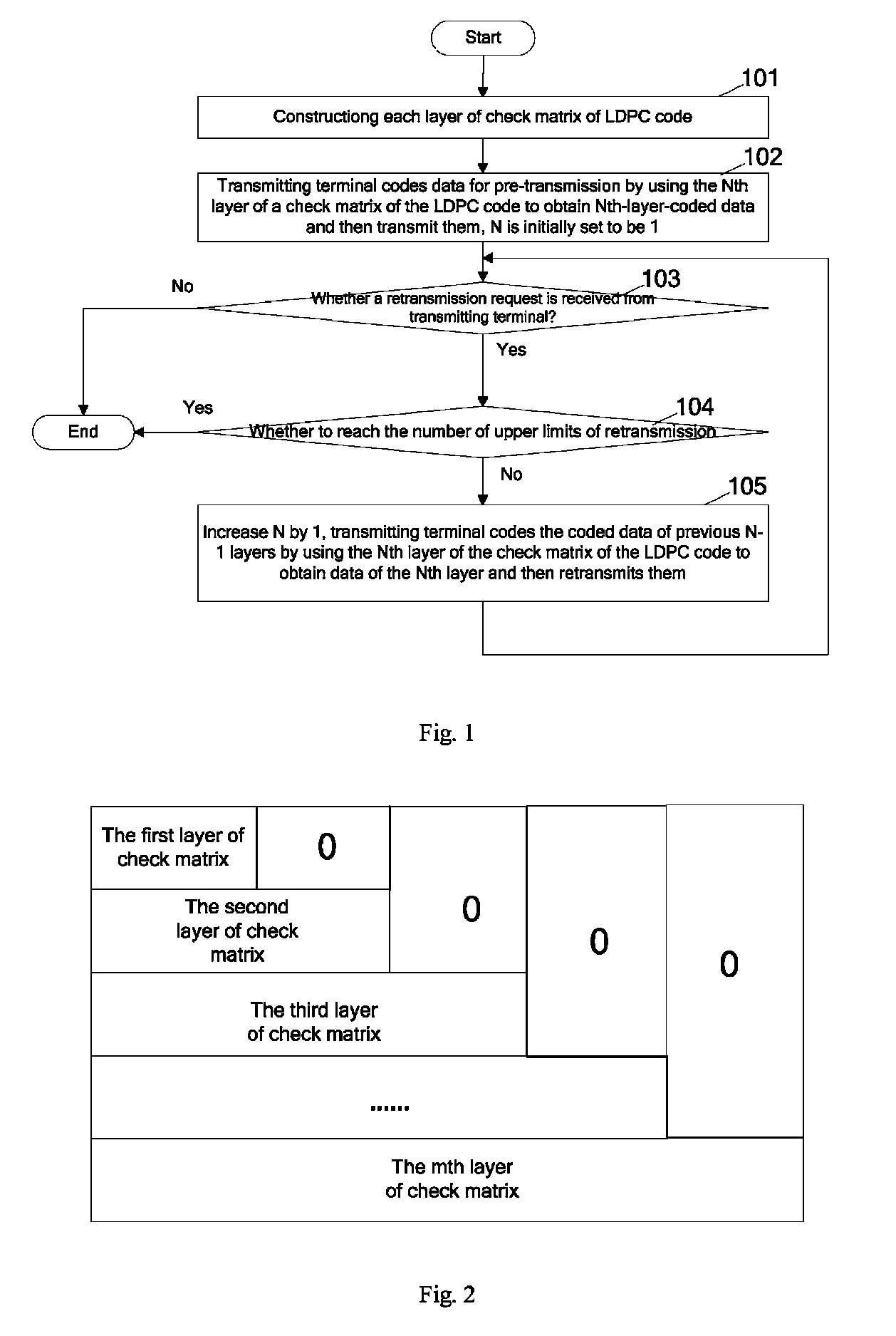

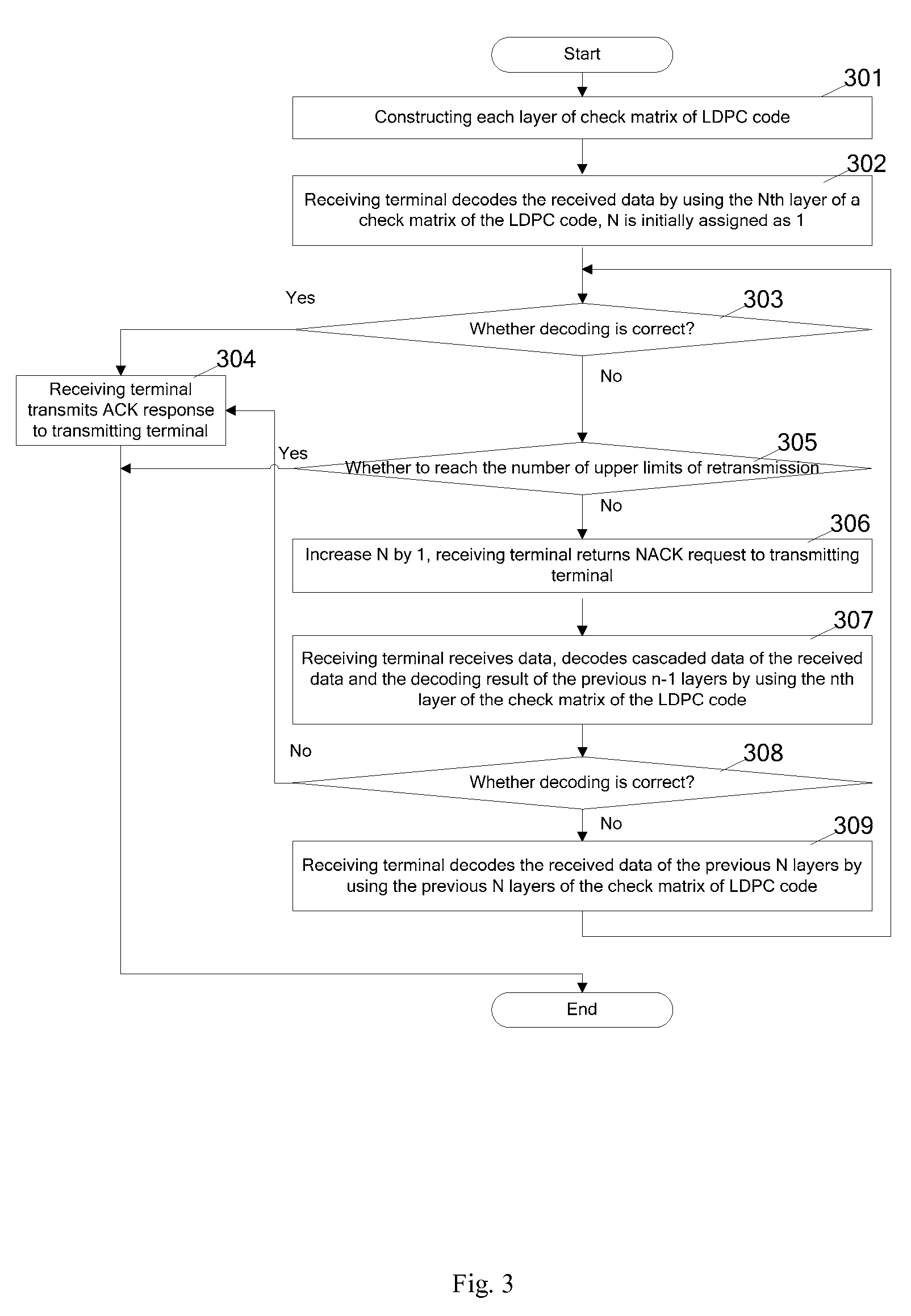

Method, apparatus and system for coding and decoding of LDPC codes

ActiveUS8418015B2Reduce system costReduce decoding delayError prevention/detection by using return channelTransmission systemsLow densityError correcting

The present invention discloses a method, an apparatus and a system for low-density parity-check (LDPC) coding and decoding. The coding method includes the following steps: constructing each layer of a check matrix of a layered LDPC code used as an error correcting code; when data is initially sent by a data transmitting terminal, performing first-layer-coding of the data to be sent by using the first layer of a check matrix of the LDPC code, sending the first-layer-coded data; when data for (n−1)th retransmission is sent by the data transmitting terminal, performing nth-layer-coding of the data by using the nth layer of a check matrix of the LDPC code, sending the nth-layer-coded data, wherein n is an integer no less than 2. It is possible to reduce the system overhead, decrease the decoding delay, and improve the decoding performance by using the technical solution of the present invention which is also adapted to high-speed data services.

Owner:DATANG MOBILE COMM EQUIP CO LTD

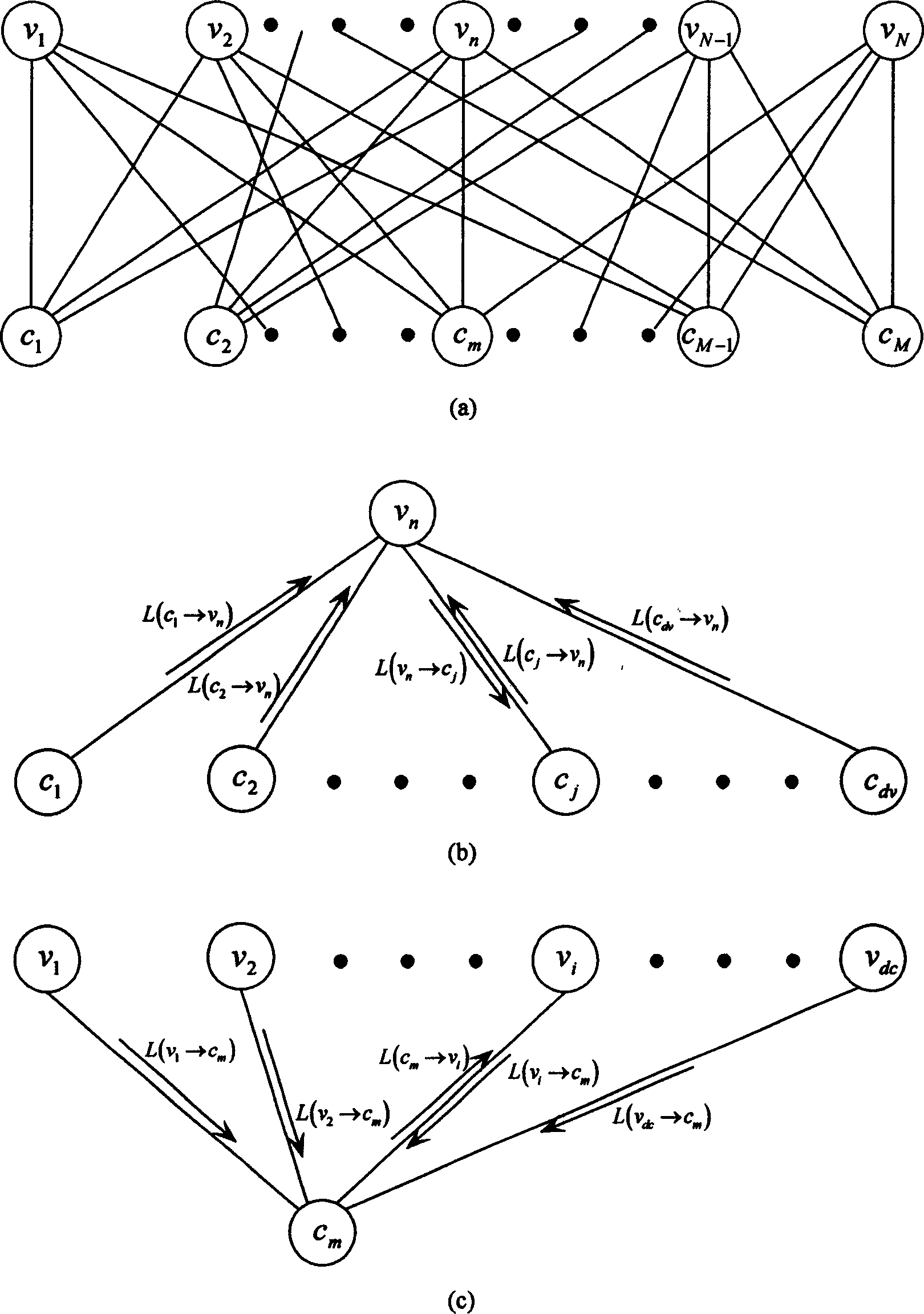

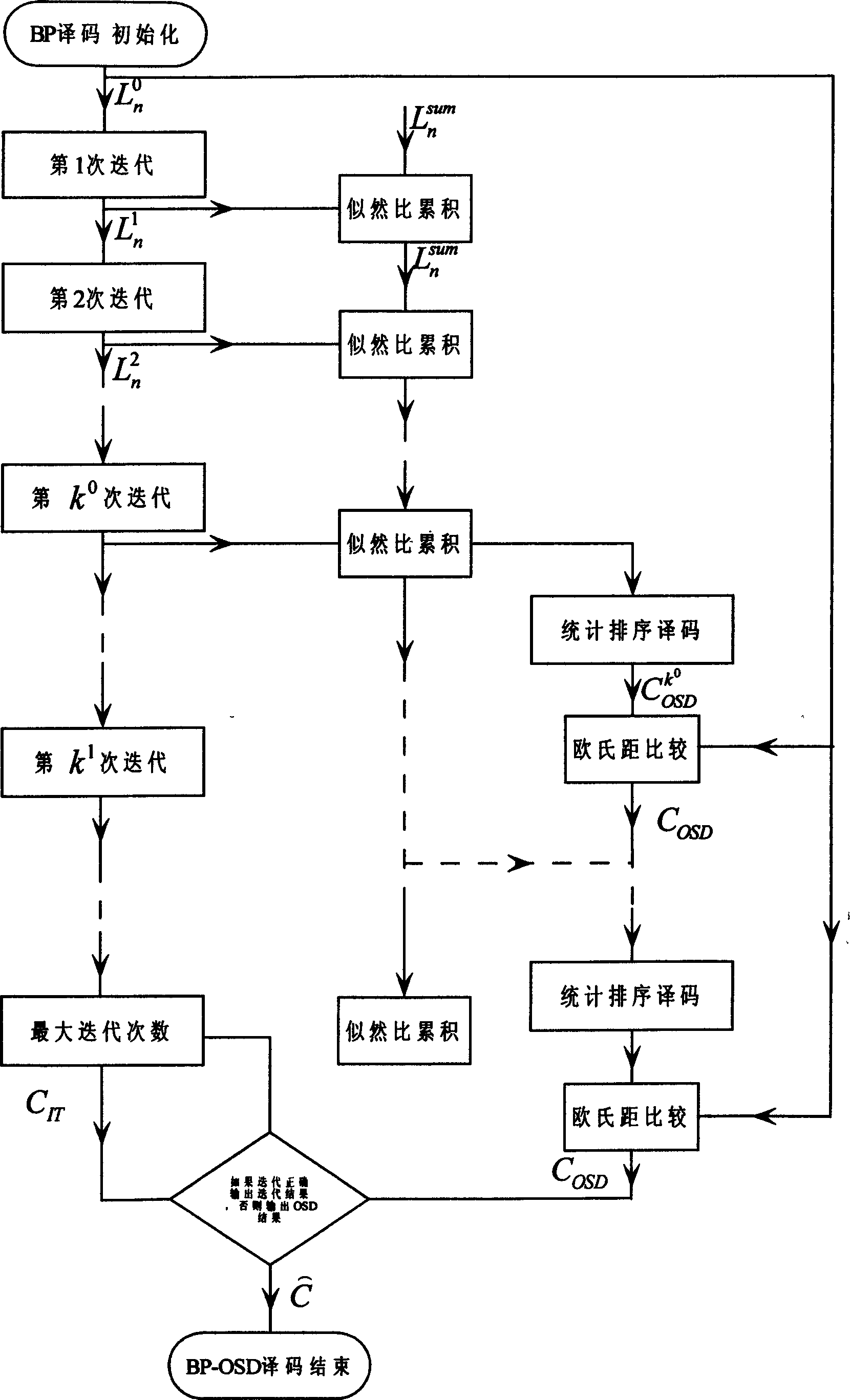

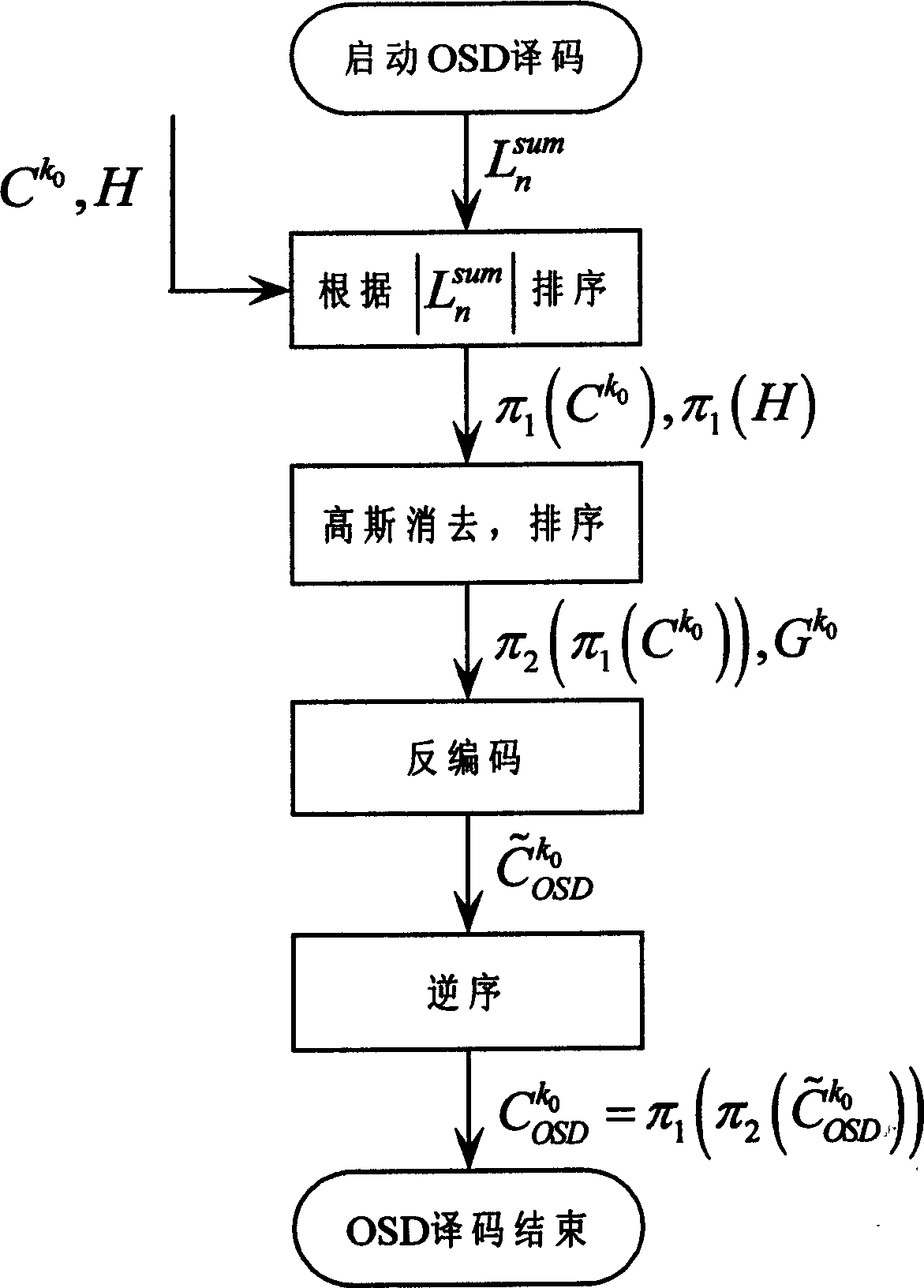

Low density odd-even check code iterative sequencing statistical decoding method

InactiveCN1859013ACorrectly decoded resultEliminate vibrationError correction/detection using multiple parity bitsSingle error correctionLikelihood-ratio testLow density

This invention relates to an iteration sort statistic decode method for low density odd-even check codes (LDPC), in the process of decoding, a sort statistic decoding method is applied to assist the iteration decode based on the amplitude of the accumulation value of the likelihood ratio output in iteration each time by all variable nodes, namely, the variable nodes output and accumulate the likelihood ratios and the absolute value of the accumulated likelihood ratio is defined as the stability of the current iterated nodes then to sort the columns of the nodes and the check matrixes for ascending order based on the stability and carrying out gauss elimination to the sorted matrixes to generate a matrix combining the system after the gauss eliminatioin and code the sorted two stabilized node information sequences to get a set of code words for selection, if there is no final output for the iteration decode, then the code words for selection with the smallest Euclidean distance are selected and received as the decode output.

Owner:SOUTHEAST UNIV

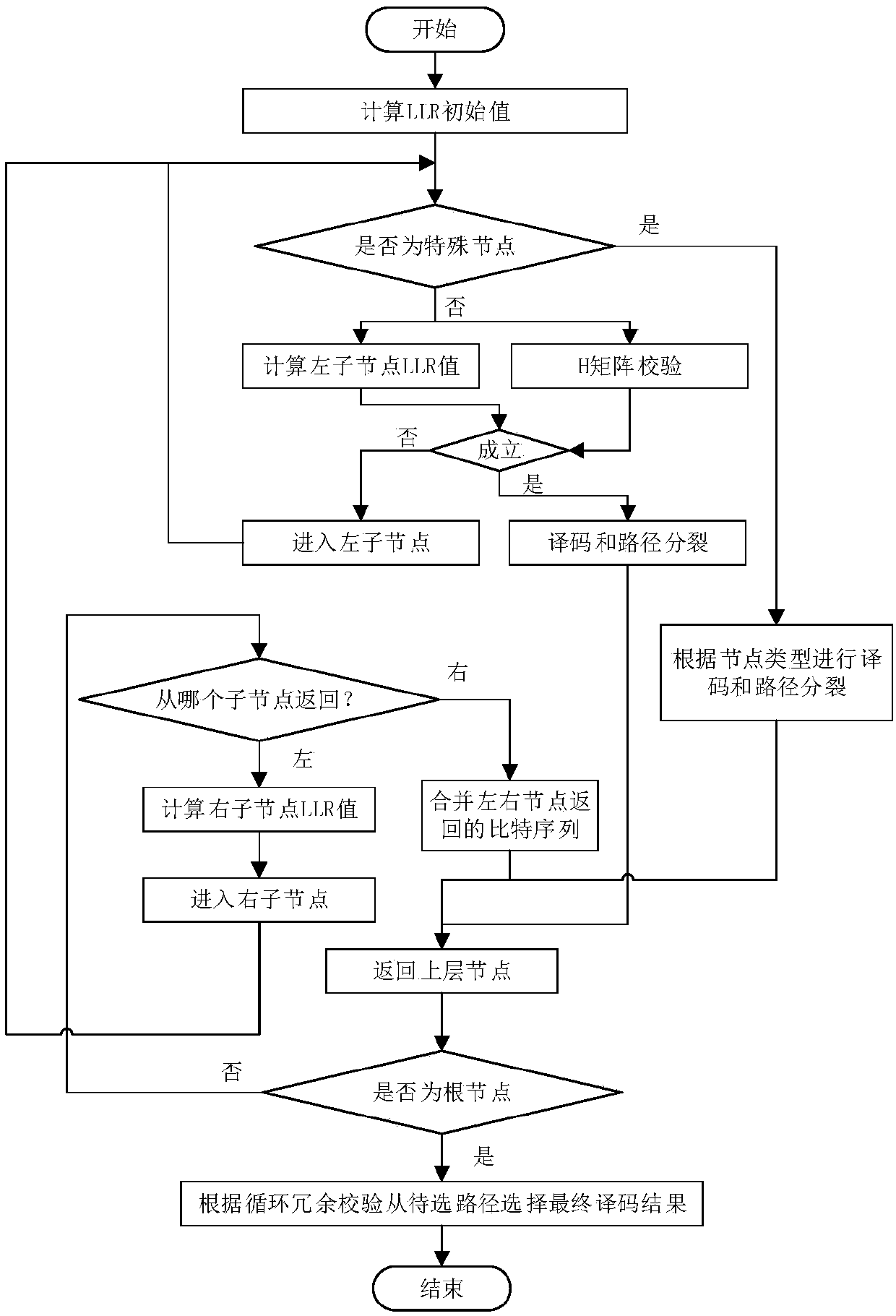

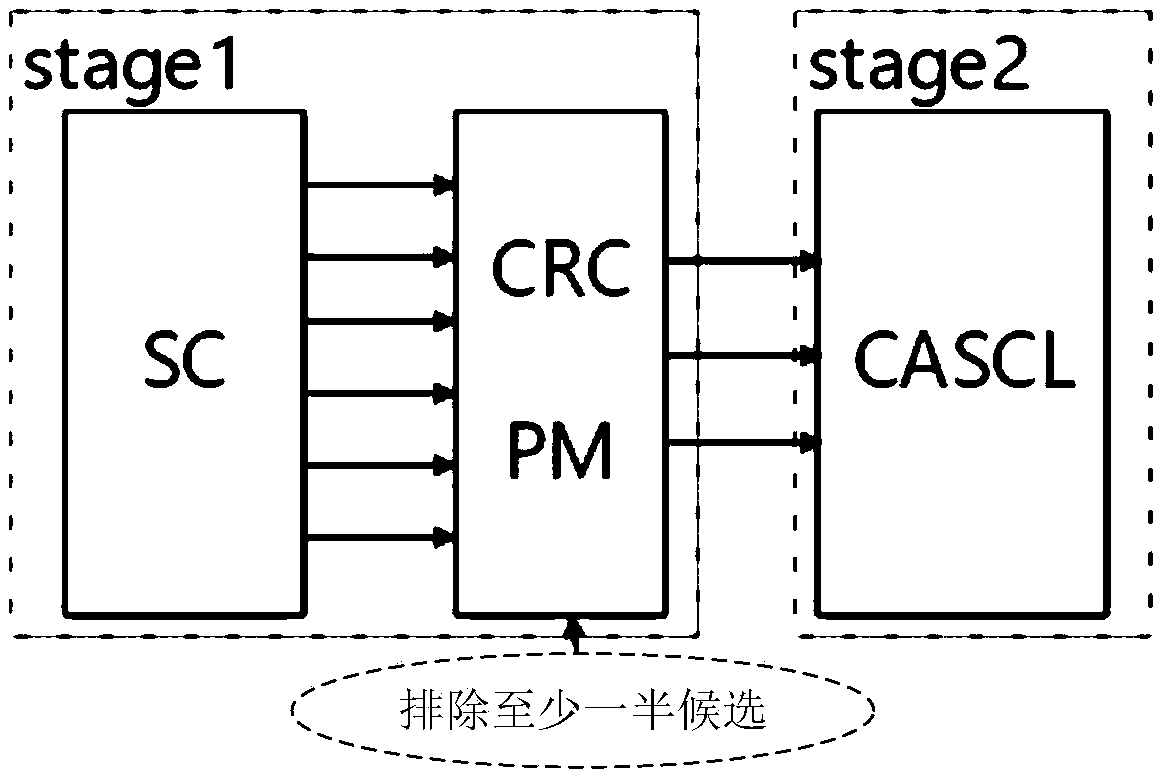

Method for reducing decoding time delay of polarization code

ActiveCN107248866AReduce decoding delayChannel coding adaptationError correction/detection using linear codesComputation complexitySignal-to-noise ratio (imaging)

The invention discloses a method for reducing decoding time delay of a polarization code. The method comprises that an initial value of a logarithm likelihood ratio is calculated; recursive traversal is carried out on a decoding tree; special nodes carry out decoding in the traversal process; non-special nodes use a verification matrix to reduce decoding time delay in the traversal process; and a final decoding result is selected according to cyclic redundancy check. In the process of recursive traversal of the decoding tree in polarization code decoding, the verification matrix of the polarization code is used for verification, recursive traversal is not carried out on sub-nodes any more when verification fails, the decoding time delay is reduced effectively, and determination via the verification matrix can be carried out with other steps simultaneously, so no extra decoding time delay is caused. The method of the invention can be used to reduce decoding time delay of a successive cancel method substantially; compared with a classic low-time-delay brief propagation decoding method, the time delay characteristic of the method in the invention can approach that of brief propagation decoding, and the method of the invention is better than brief propagation decoding in the aspects of error rate performance and computing complexity; and the higher the signal to noise ratio is, the more obviously the decoding time delay is reduced.

Owner:上海瀚芯实业发展合伙企业(有限合伙)

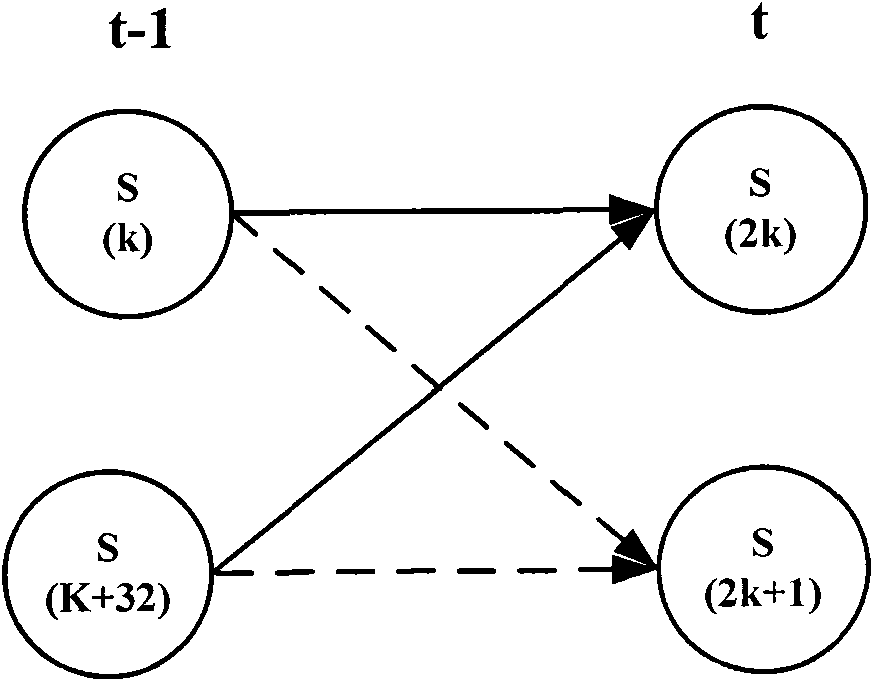

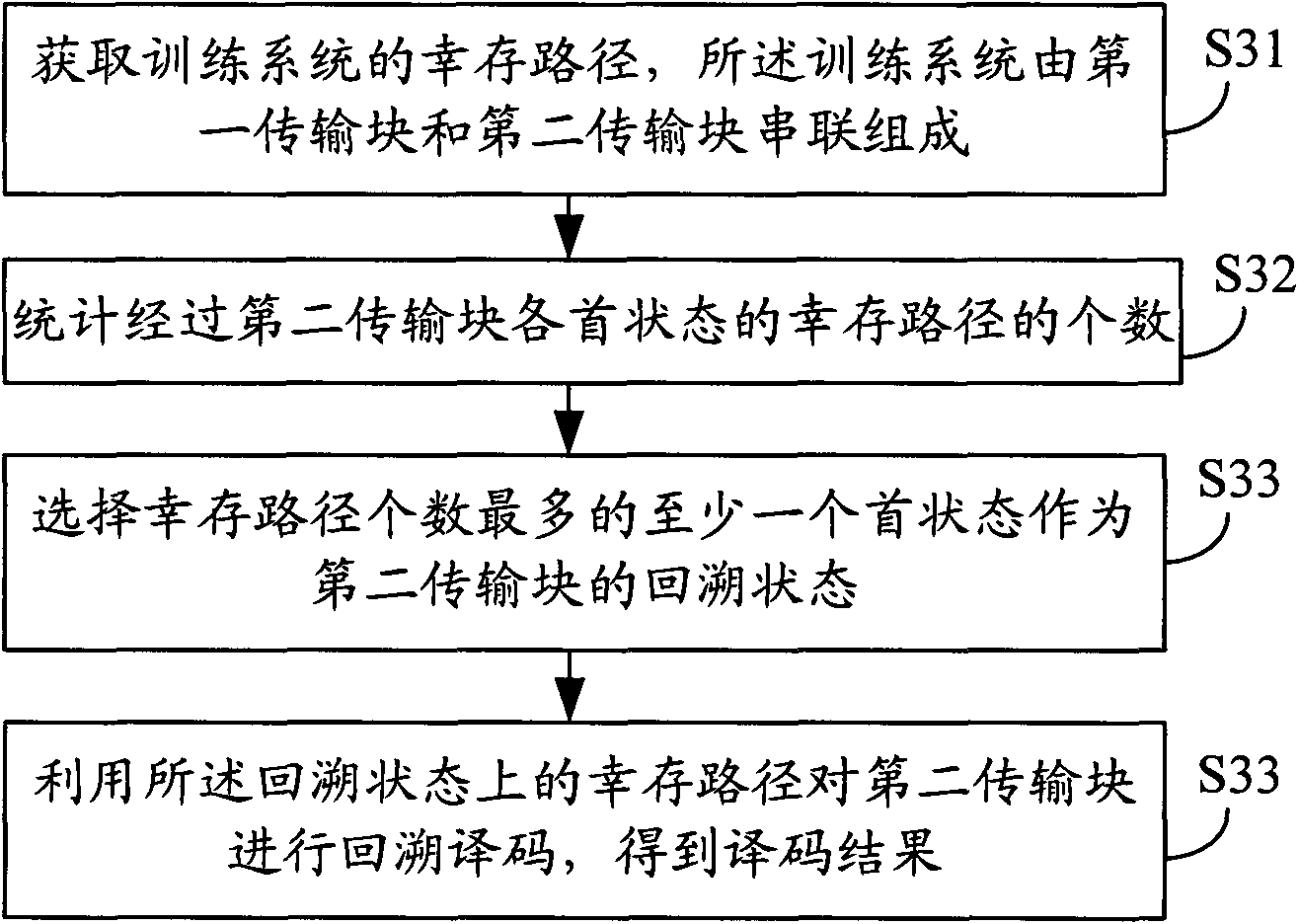

Method and device for tail biting decoding

InactiveCN101667840AReduce decoding delayImprove accuracyError correction/detection using convolutional codesUnequal/adaptive error protectionTail-bitingComputer science

The embodiment of the invention provides a method and a device for tail biting decoding, aiming at improving the accuracy of determining backtracking state and reducing the decoding delay. The method provided by the embodiment of the invention comprises the following steps: acquiring a survivor path of a training system formed by the series connection of a first transmission block and a second transmission block; counting the number of survivor paths passing through each first state of the second transmission block; selecting at least one initial state with maximum survivor paths as the backtrack state of the second transmission block; and obtaining a decoding result by utilizing the survivor paths on the backtracking state to perform backtrack decoding of the second transmission block.

Owner:HUAWEI TECH CO LTD

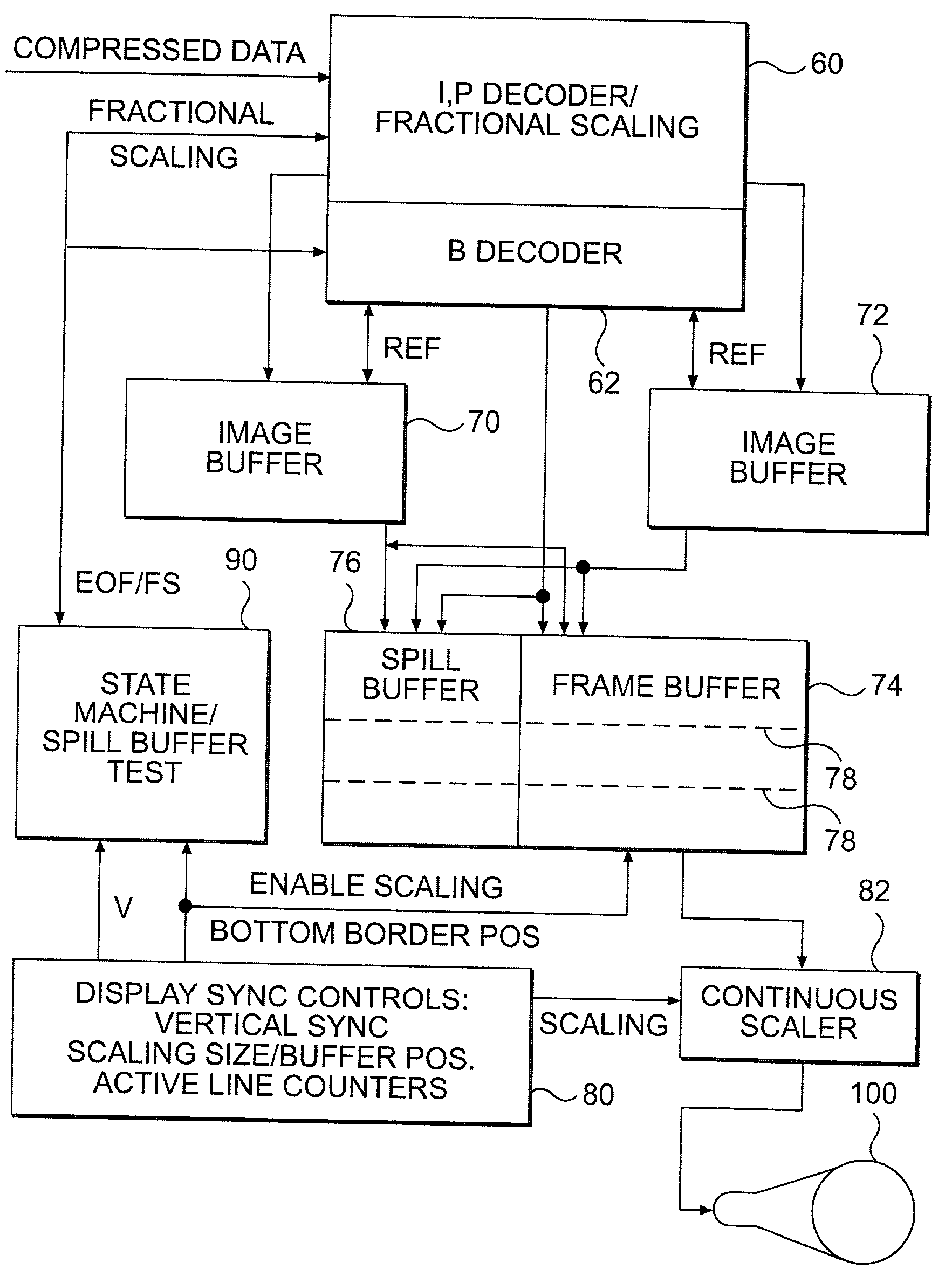

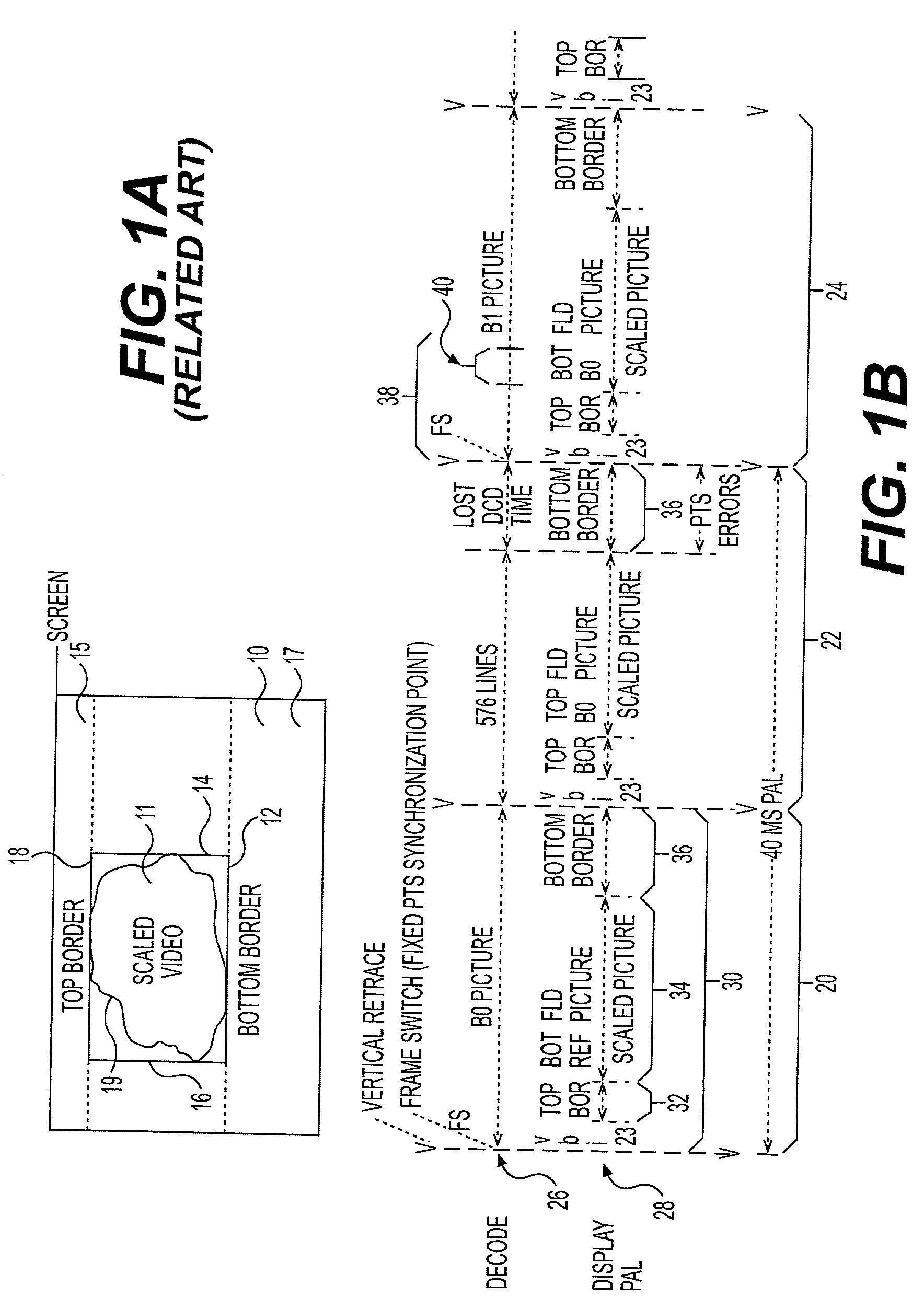

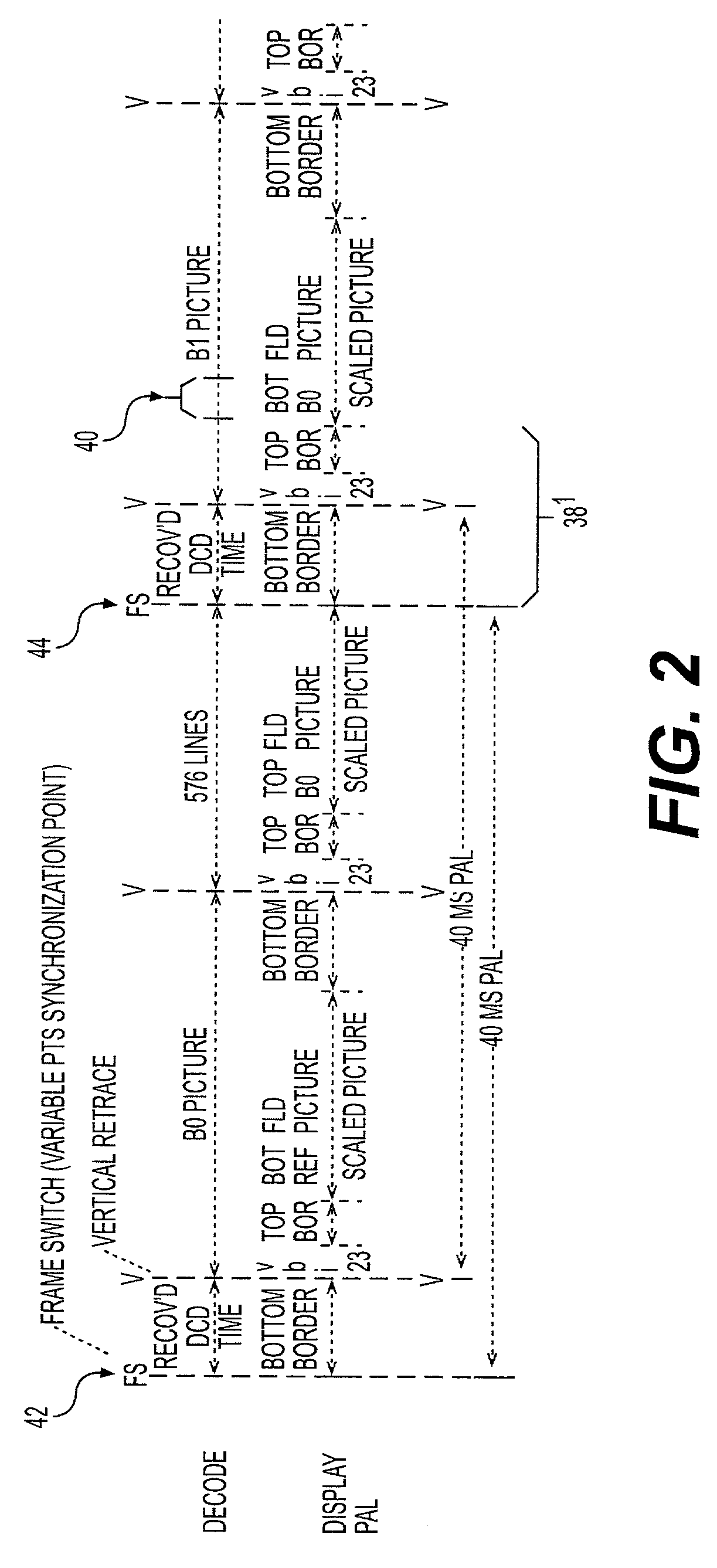

Low latency video decoder with high-quality, variable scaling and minimal frame buffer memory

ActiveUS7729421B2Reduce decoding delaySynchronization errorTelevision system detailsPicture reproducers using cathode ray tubesImage resolutionLatency (engineering)

Owner:TWITTER INC

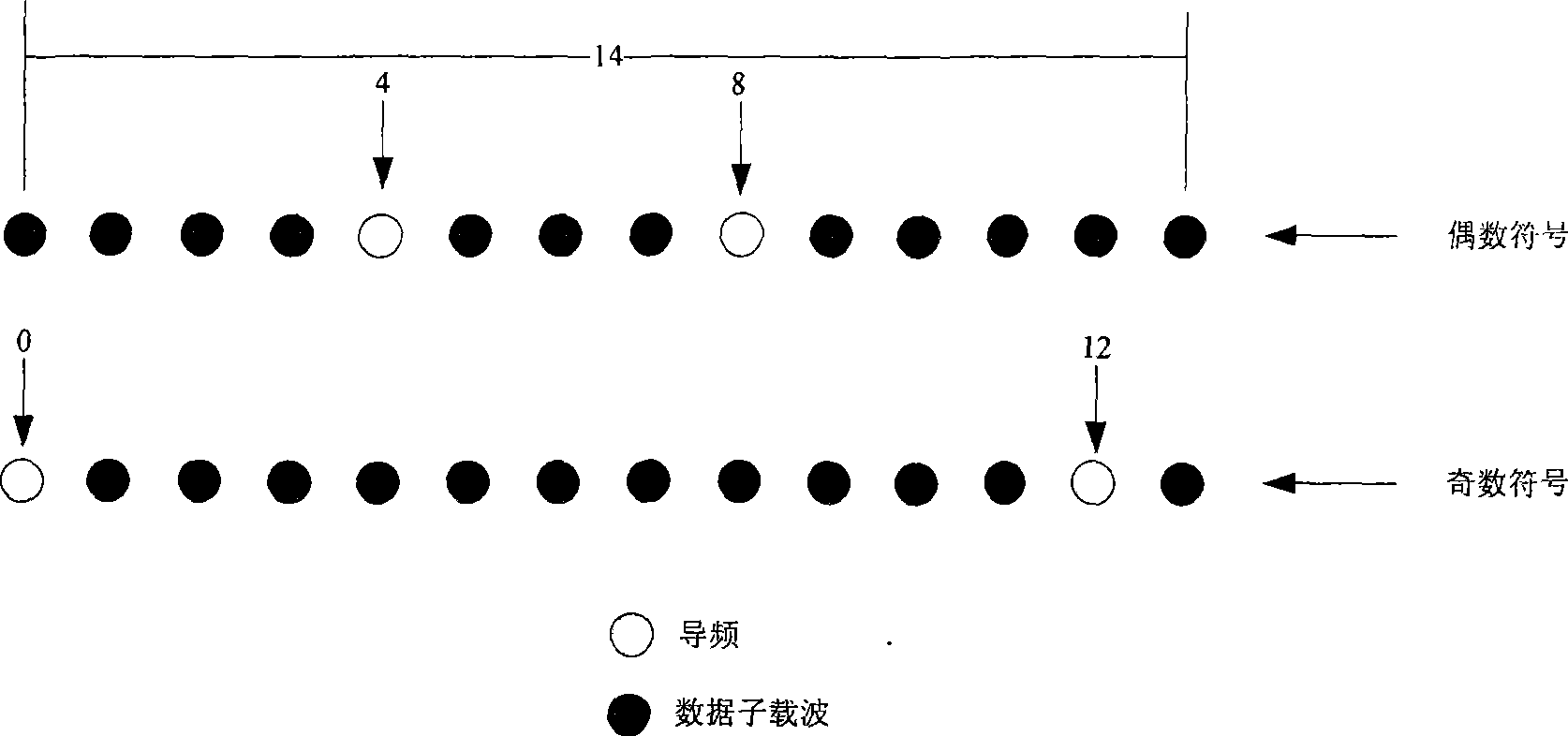

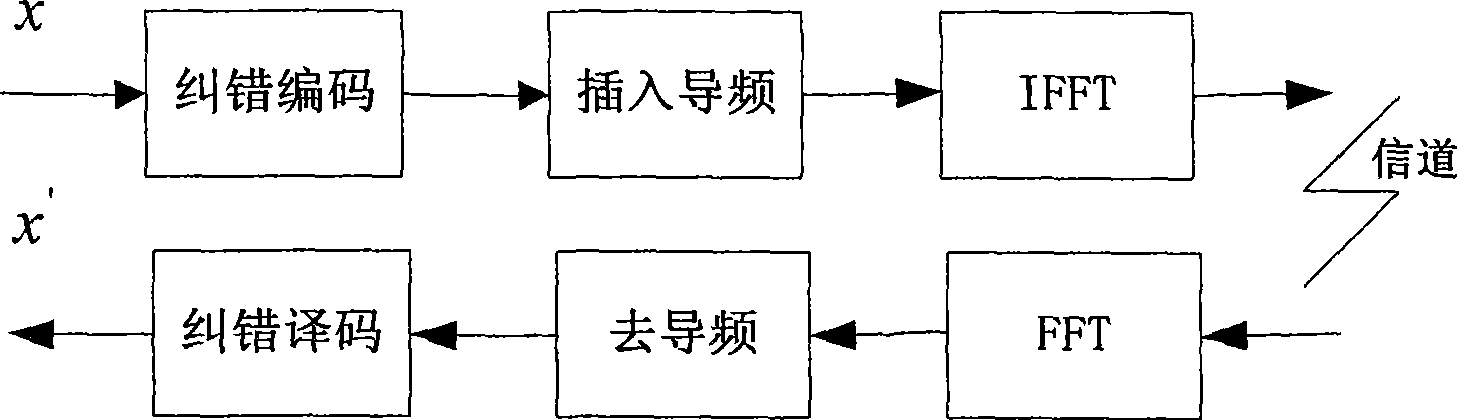

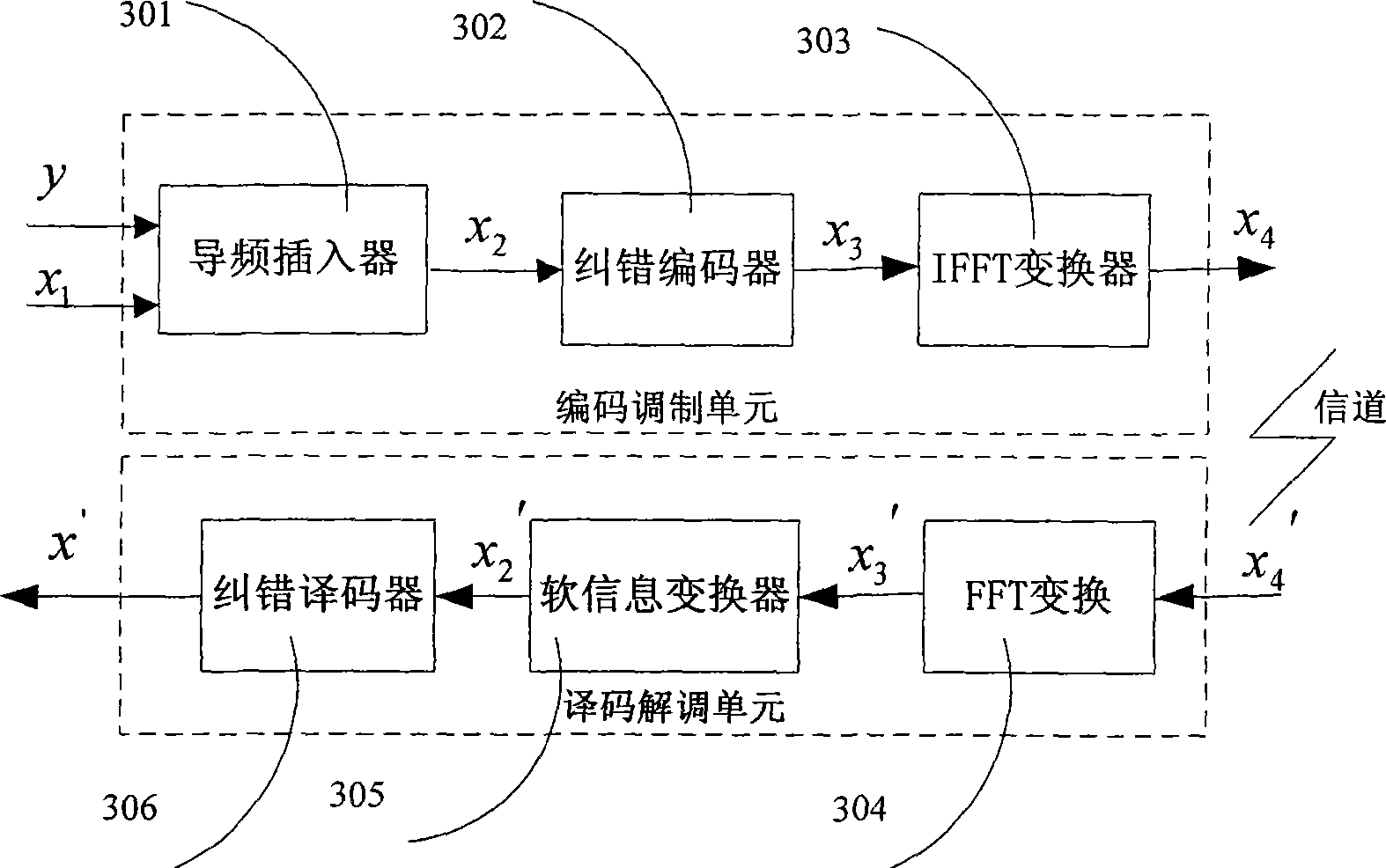

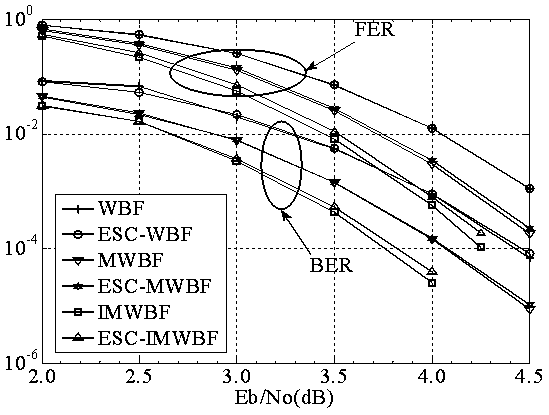

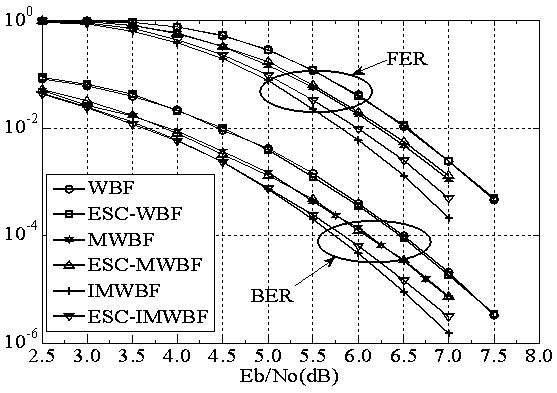

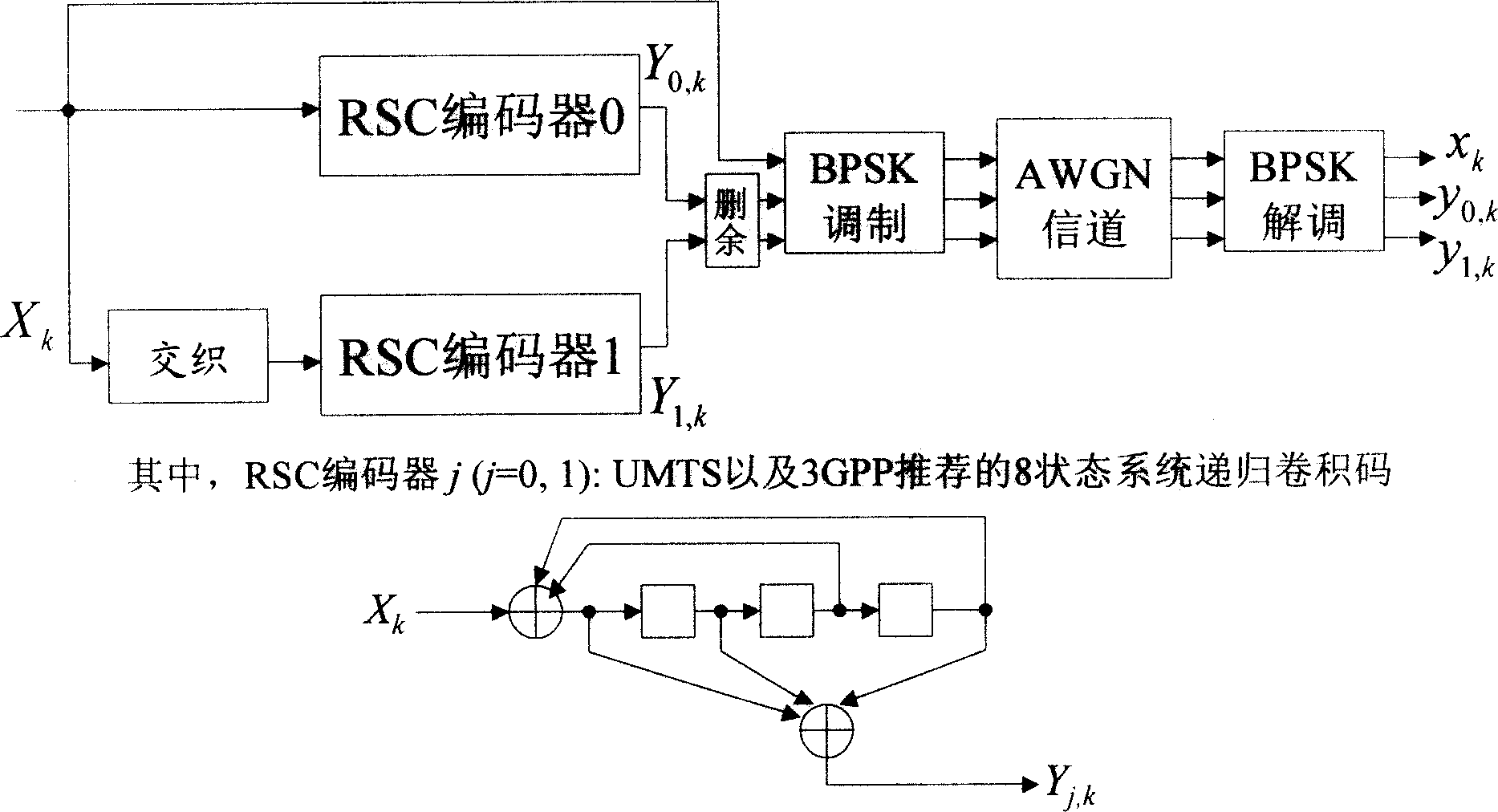

Encoding and decoding method for improving decoding efficiency by pilot frequency information and device thereof

InactiveCN101534127AFast convergenceImprove decoding performanceCode conversionCoding detailsTime delaysError correcting

The invention discloses an encoding and decoding method for improving decoding efficiency by pilot frequency information and a device thereof. The method comprises the following steps that: pilot frequency sequences are evenly inserted into an information sequence before encoding, and the information sequence is subjected to error correction encoding by an error correcting code; the encoded information sequence is generated into an OFDMA symbol after IFFT conversion, and is transmitted to a receiving end; the receiving end carries out FFT conversion on the received information sequence to obtain soft information corresponding to the information sequence which is encoded by a transmitting end; the positions of the pilot frequency sequences inserted into the information sequence are set into corresponding soft information values according to values of the pilot frequency sequences; and the information is subjected to error correcting decoding to obtain transmitting information of the transmitting end. The method and the device can improve the velocity of convergence and decoding performance of an error correcting decoder, reduce the times of decoding iteration, reduce decoding time delay, and simplify the process of decoding.

Owner:西安新邮通信设备有限公司

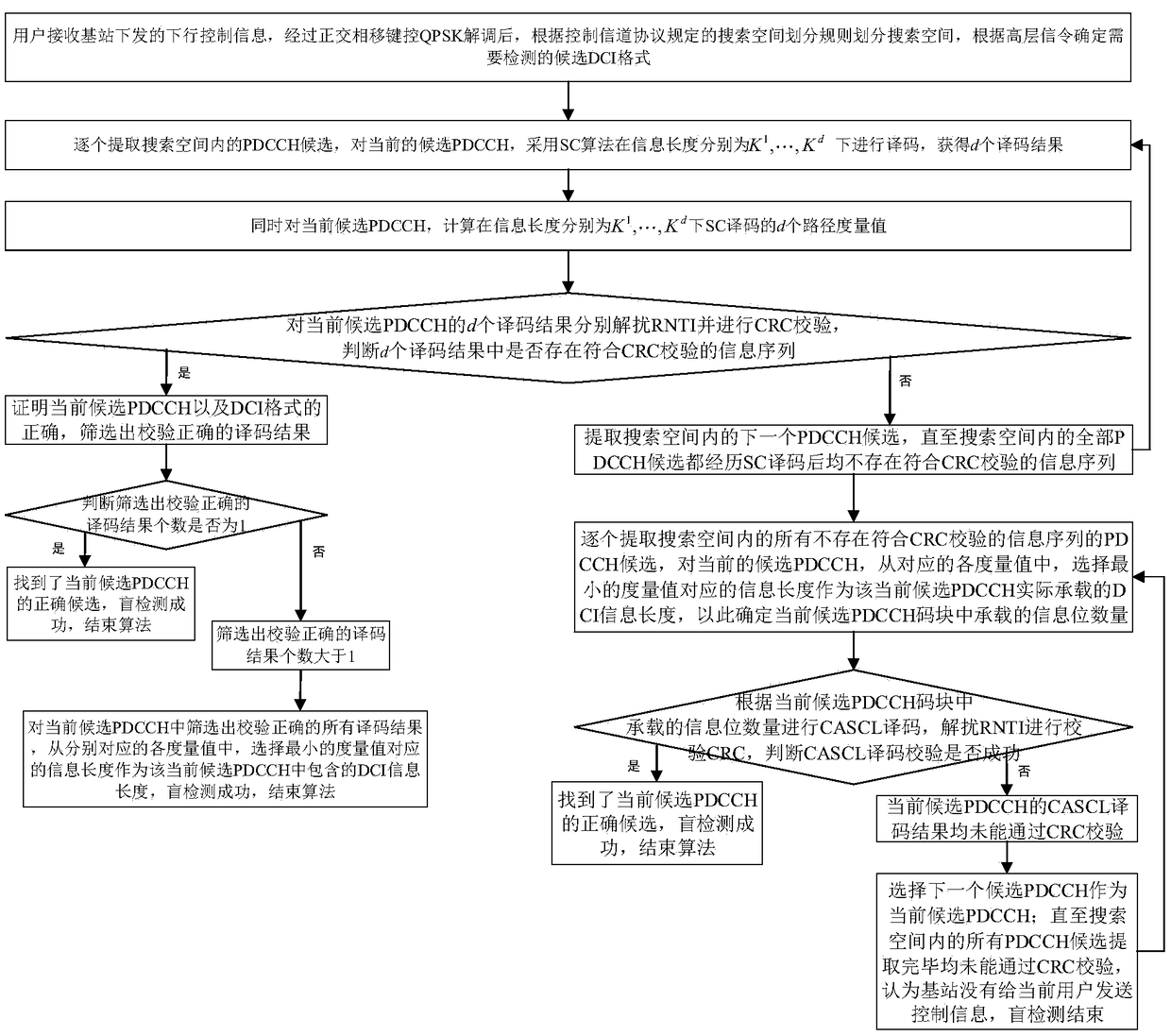

Polarization code-based low-complexity PDCCH (Physical Downlink Control Channel) channel blind detection method

ActiveCN109286473AReduce decoding timesReduce the complexity of blind detectionReceiver specific arrangementsControl channelEngineering

The invention discloses a polarization code-based low-complexity PDCCH (Physical Downlink Control Channel) channel blind detection method, which belongs to the field of communication. Firstly, a candidate DCI (Downlink Control Information) format which needs to be detected is determined; PDCCH candidates are then extracted one by one for decoding, d decoding results are obtained, and d path metricvalues CM are calculated at the same time; a decoding result which is checked to be correct is screened from the d decoding results; when the number of results is greater than 1, the information length corresponding to the smallest metric value is selected as the result for the current candidate PDCCH; when all PDCCH candidates do not have an information sequence conforming to CRC check, the information length corresponding to the smallest metric value CM is selected as the DCI information length actually carried by the current candidate PDCCH; and finally, CASCL decoding is carried out according to the information digit number carried in the current candidate PDCCH, an RNTI is descrambled for checking the CRC, if the CASCL decoding succeeds in checking, the correct result of the currentcandidate PDCCH is found out, or otherwise, a next candidate PDCCH is selected until the search is completed. The complexity of blind detection is reduced, and the practicability is good.

Owner:BEIHANG UNIV

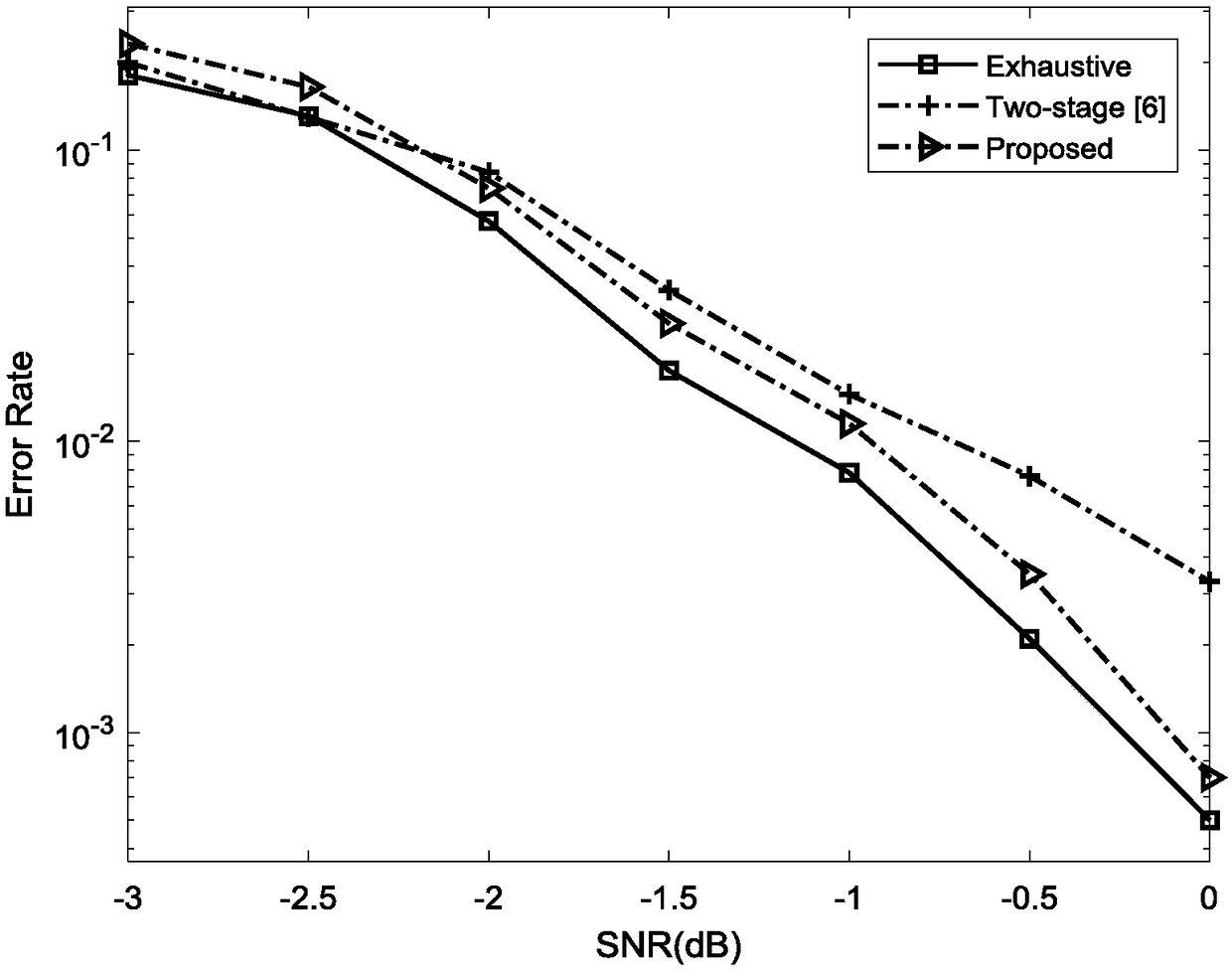

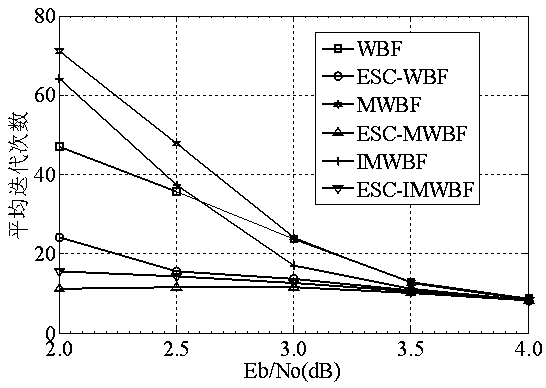

Ahead-of-time stopping method of low complexity LDPC code weighting bit flipping decoding algorithm

InactiveCN104009763AAvoid wastingReduce decoding delayError correction/detection using multiple parity bitsSystem timeComputer science

The invention discloses an ahead-of-time stopping method of a low complexity LDPC code weighting bit flipping decoding algorithm. The method includes the steps that S1, initializing is conducted; S2, the syndrome s is calculated through z, wherein the s={s1, ...sm, ...sM}= zH<T>, sm=mod(sigma n<A (m) zn, 2), the expression of the sm is shown in the specification; S3, when the s is equal to zero, iteration is stopped, and decoding output is z; when the s is not equal to zero, if k>=Kmax, decoding fails, and decoding is over; if k<Kmax and k=k+1, the flipping function {En, 1<=n<=N} of each information node is calculated; the maximum value (please see the specification for the formula) of the flipping function is solved, and if MAX<0, decoding is over; otherwise, the z is updated, and iteration continues. According to the ahead-of-time stopping method of the low complexity LDPC code weighting bit flipping decoding algorithm, after the flipping function {En, 1<=n<=N} of each information node is obtained through calculation, the maximum value of the flipping function is solved, if MAX<0, the iterative process is stopped directly, wherein the expression of the MAX is shown in the specification, and otherwise iteration still continues according to the original steps; the non-error correction frame decoding process can be discovered and stopped in time, waste of hardware resources is avoided, and decoding time delay is lowered. Simulation results show that under the condition that the bit error rate and the frame error rate basically remain unchanged, the average iterations of the weighting bit flipping decoding algorithm can be greatly decreased, and therefore the system time delay and the implementation complexity are lowered.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

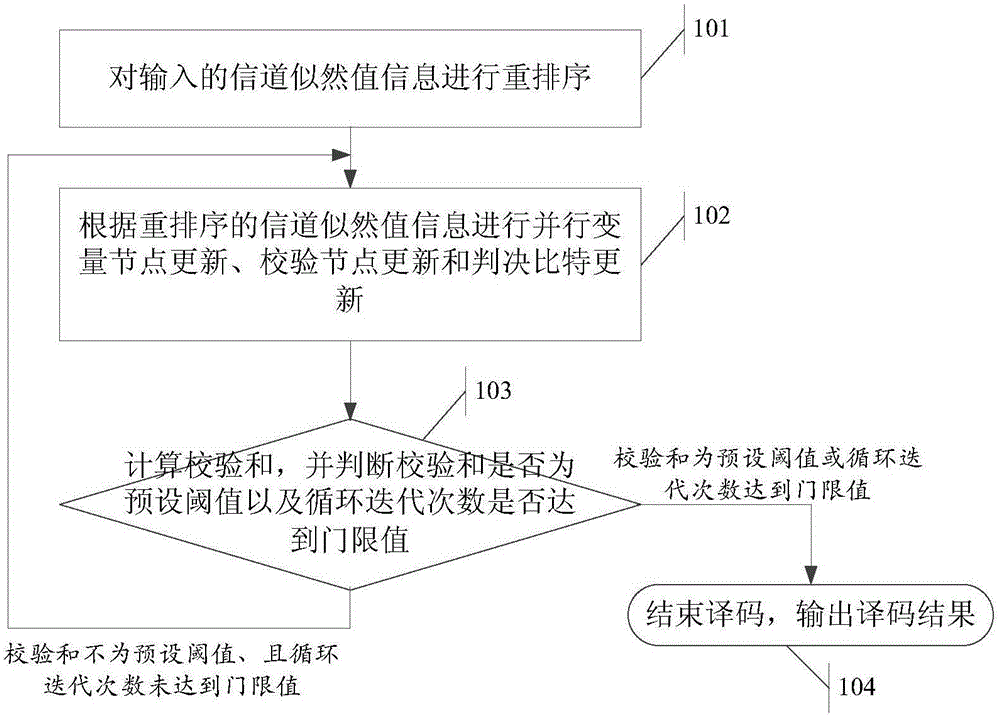

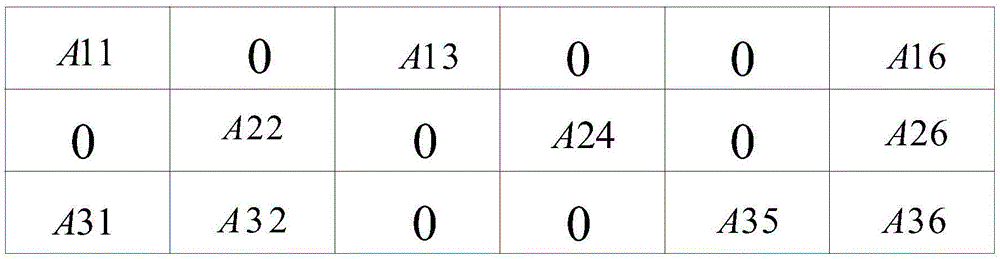

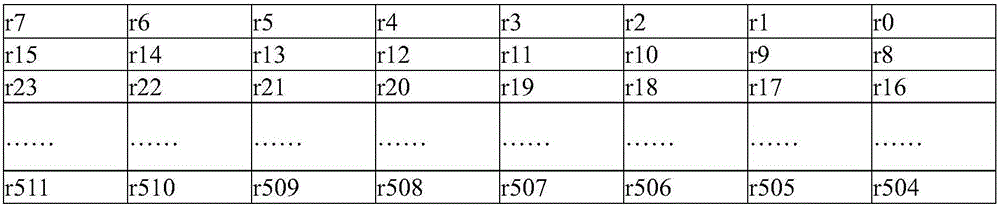

Decoding method and device of low density parity code LDPC

ActiveCN105049060AReduce consumptionSimple control logicError correction/detection using multiple parity bitsParallel computingLow-density parity-check code

The invention discloses a decoding method and device of a low density parity code LDPC. In the implementation process of decoding a binary LDPC (Low Density Parity Code) code by adopting MS, during initialization, a parallel input sequence of channel likelihood information is rearranged according to the structural features of a check matrix, and during each updating, a variable node is updated in parallel according to the sequence; compared to a multiframe parallel decoding structure, the method reduces the complexity of decoding delay, memory space of a decoder and interface control logic on the premise of no loss of performance.

Owner:SPACE STAR TECH CO LTD

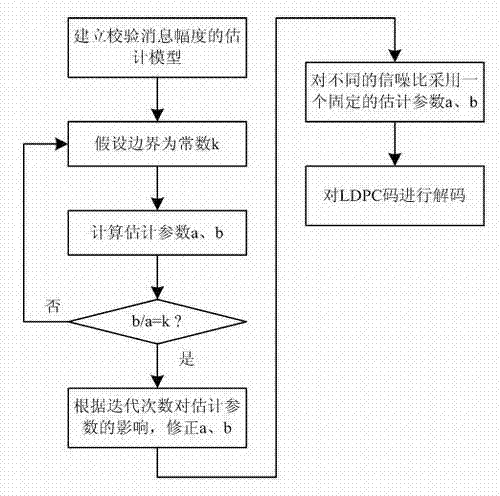

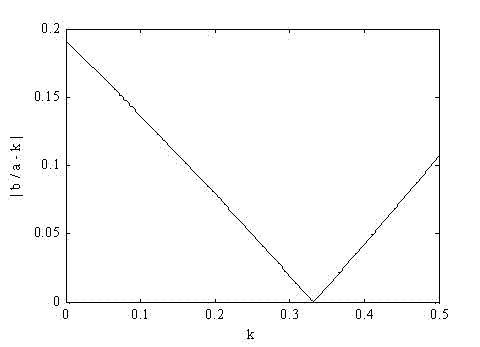

Mini-sum decoding correcting method based on linear minimum mean error estimation

InactiveCN102811065AQuick fixEasy to implementError correction/detection using multiple parity bitsSignal-to-noise ratio (imaging)Estimation methods

The invention relates to a mini-sum decoding correcting method based on linear minimum mean error estimation. The method comprises the steps of establishing a model on a check message amplitude by a linear minimum mean error estimation method, and accelerating the determination of an estimation parameter by a golden section search algorithm to enable the estimation value approach to the check message amplitude in an error back propagation (BP) method; and revising the estimation parameter by taking the influence of the iterative times on the estimation parameter into consideration. According to the mini-sum decoding correcting method, a fixed estimation parameter is applied to different signal to noise ratios, so as to ensure the decoding performance and to reduce the expense of the hardware; the low density parity check (LDPC) code is decoded after the estimation parameter is obtained. The method not only ensures an excellent decoding performance but guarantees a rapid calculation of the estimation parameter; and is low in decoding complexity and simple in implementation of the hardware.

Owner:FUZHOU UNIV

Dynamic allocation method for decoding iteration of transmission block of topological code of long term evolution (LTE) system

ActiveCN102130747AImprove decoding performanceReduce decoding delayError preventionComputer architectureTopological order

The invention provides a dynamic allocation method for decoding iteration of a transmission block of a topological code of a third generation partnership project (3GPP) long term evolution (LTE) system. According to the method, within the maximum processing time delay of the transmission block, the remained iterative decoding time delay of encoding blocks which are decoded successfully in advanceis re-allocated to the encoding blocks which cannot be successfully decoded temporarily by effectively utilizing decoder hardware resources and the processing time delay allocated to the current transmission block, so that the decoding performance of the whole transmission block is improved. The method mainly comprises the following steps of: limiting the processing time delay of the transmissionblock by setting the maximum iterations of each encoding block, wherein the each encoding block of the transmission block in the LTE adopts an iterative decoding algorithm based on maximum posterior probability; firstly, carrying out iterative decoding on the encoding blocks sequentially, carrying out cyclic redundancy check simultaneously, and counting the iterations for dynamic allocation according to a check result; and when decoding of all of the encoding blocks is finished, averagely allocating the counted iterations to the encoding blocks which are not decoded successfully, and continuing carrying out the iterative decoding on the encoding blocks according to the iterations obtained by allocation.

Owner:SOUTHEAST UNIV

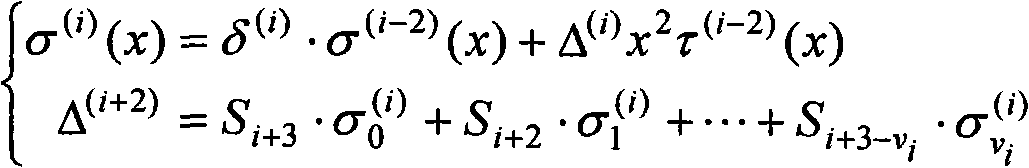

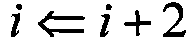

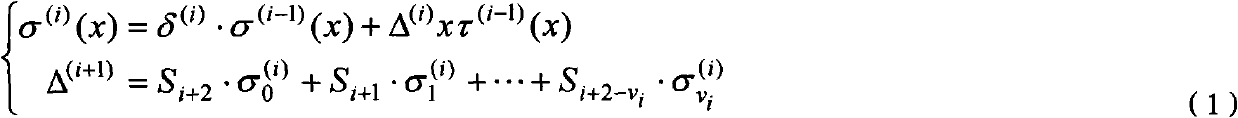

Method and device for computing error location polynomial in decoding through binary BCH (Bose-Chaudhuri-Hocquenghem) code

InactiveCN101951265AReduce decoding delayReduce power consumptionCyclic codesError locationComputer engineering

The invention discloses a method and a device for computing an error location polynomial in decoding through a binary BCH (Bose-Chaudhuri-Hocquenghem) code. The method comprises the following steps of: (1) starting iteration from an even number according to a computed syndrome, initializing a step-length initial value i and computing the initial parameter of the error location polynomial; (2) computing the ith iterated error location polynomial and an i+2nd iterated correction term; (3) judging and computing the parameter of the next iterative computation; (4) setting the step length of value buil-up constant of i to be 2, i.e. i<=i+2; (5) comparing the value of iteration times with 2t-1, selecting to continue iteration according to a comparison result, and turning to the step (2), or ending the iteration and turning to a step (6) for processing; and (6) outputting the i-2nd iterated error location polynomial, and finishing the computation. The invention also greatly reduces the power consumption of a decoding circuit while reducing the binary BCH decoding delay.

Owner:ALLWINNER TECH CO LTD

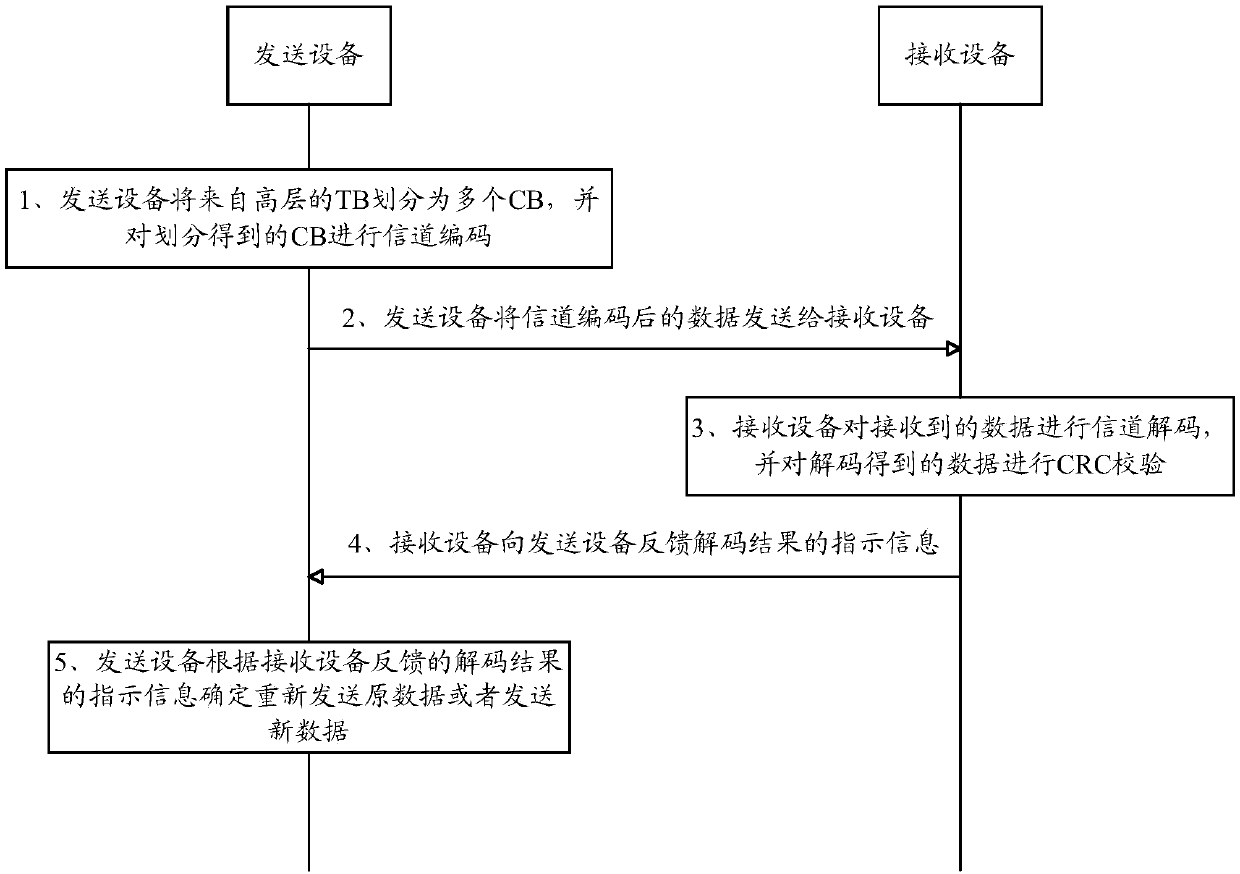

Data transmission method and apparatus

ActiveCN108347295ASave data transmission signalingImprove accuracyForward error control useTransmission rate adaptationData transmissionCoding block

The invention discloses a data transmission method and apparatus. The method comprises the steps of enabling a receiving device to receive at least two packets of data from a sending device, each packet including at least one information CB (Code Block); enabling the receiving device to perform decoding on information CBs in the each packet and send indication information to the sending device, the indication information including information for indicating a decoding error packet, and information for indicating the number M of information CBs with a decoding error in the decoding error packet, and the decoding error packet being a packet where an information CB with the decoding error is located; enabling the receiving device to receive first check CBs from the sending device, the numberN of the first check CBs being greater than or equal to the M, and the first check CBs being obtained by encoding the information CBs in the decoding error packet; and enabling the receiving device toperform decoding on the information CBs in the decoding error packet according to the first check CBs. By adopting the data transmission method and apparatus provided by the embodiments of the invention, the data transmission method and apparatus have the advantages that the decoding complexity of transmission data can be reduced, the data transmission efficiency is improved and the transmissionresources are saved.

Owner:HUAWEI TECH CO LTD

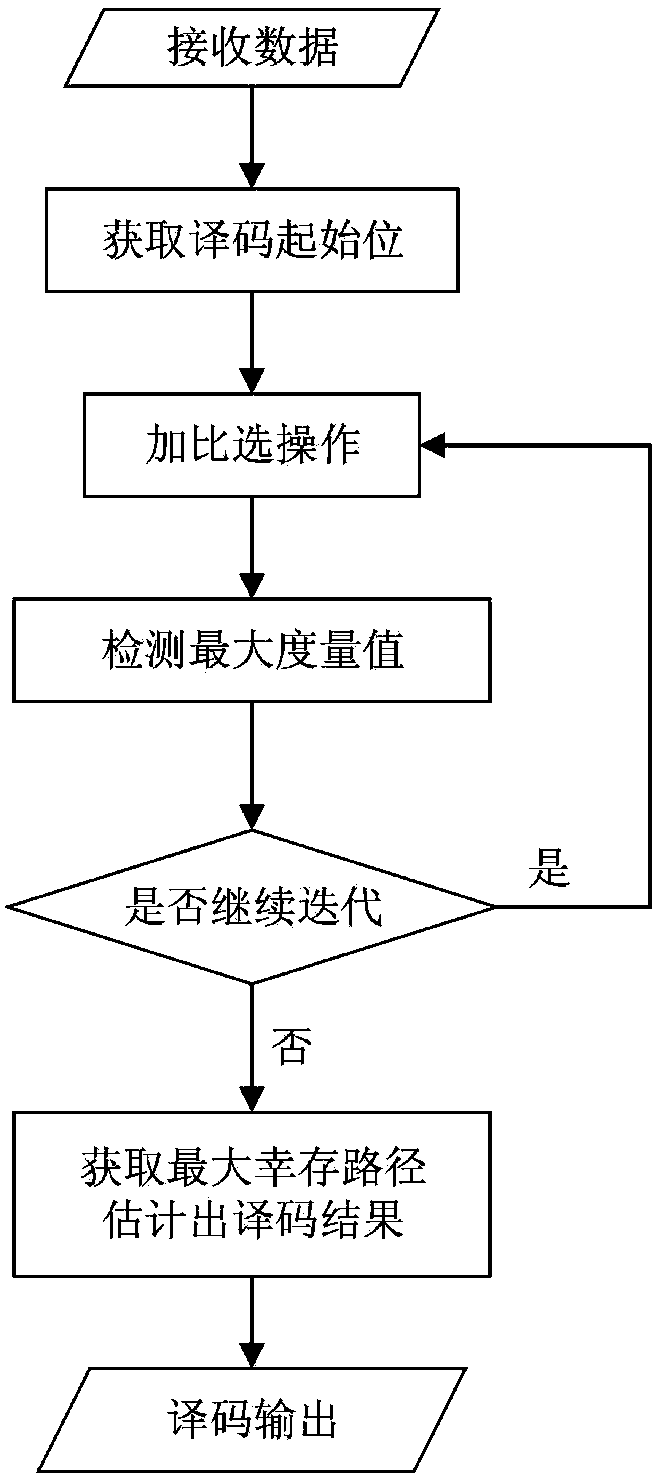

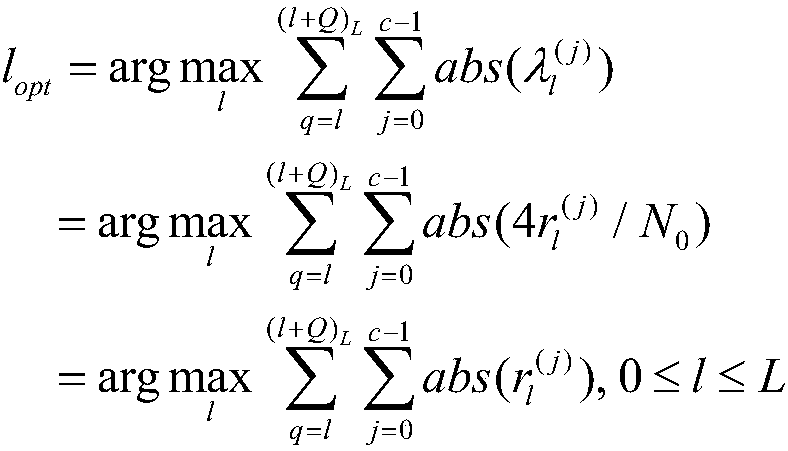

CVA-based tail-biting convolutional code channel decoding method

ActiveCN107911195AReduce decoding delayImprove decoding efficiencyError correction/detection using convolutional codesError preventionDependabilityTail-biting

The invention claims a CVA-based tail-biting convolutional code channel decoding method, which relates to the field of mobile communication technology. In order to reduce the decoding complexity and increase the decoding efficiency, the present invention proposes a decoding algorithm based on the Circular Viterbi Algorithm (CVA). The decoding start position of the highest reliability is determinedbased on the likelihood ratio information of a received information sequence. The Viterbi decoding is modified from the start position, by adding a comparison and selection process, impossible statepositions are deleted, and after several iterations of search, less surviving states converge in surviving paths, the state of the largest measurement value is selected as the start position of the final decoding, and a decoding result is estimated according to its corresponding surviving path. The algorithm has a faster convergence speed, the decoding efficiency is further improved, and the decoding delay is reduced.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

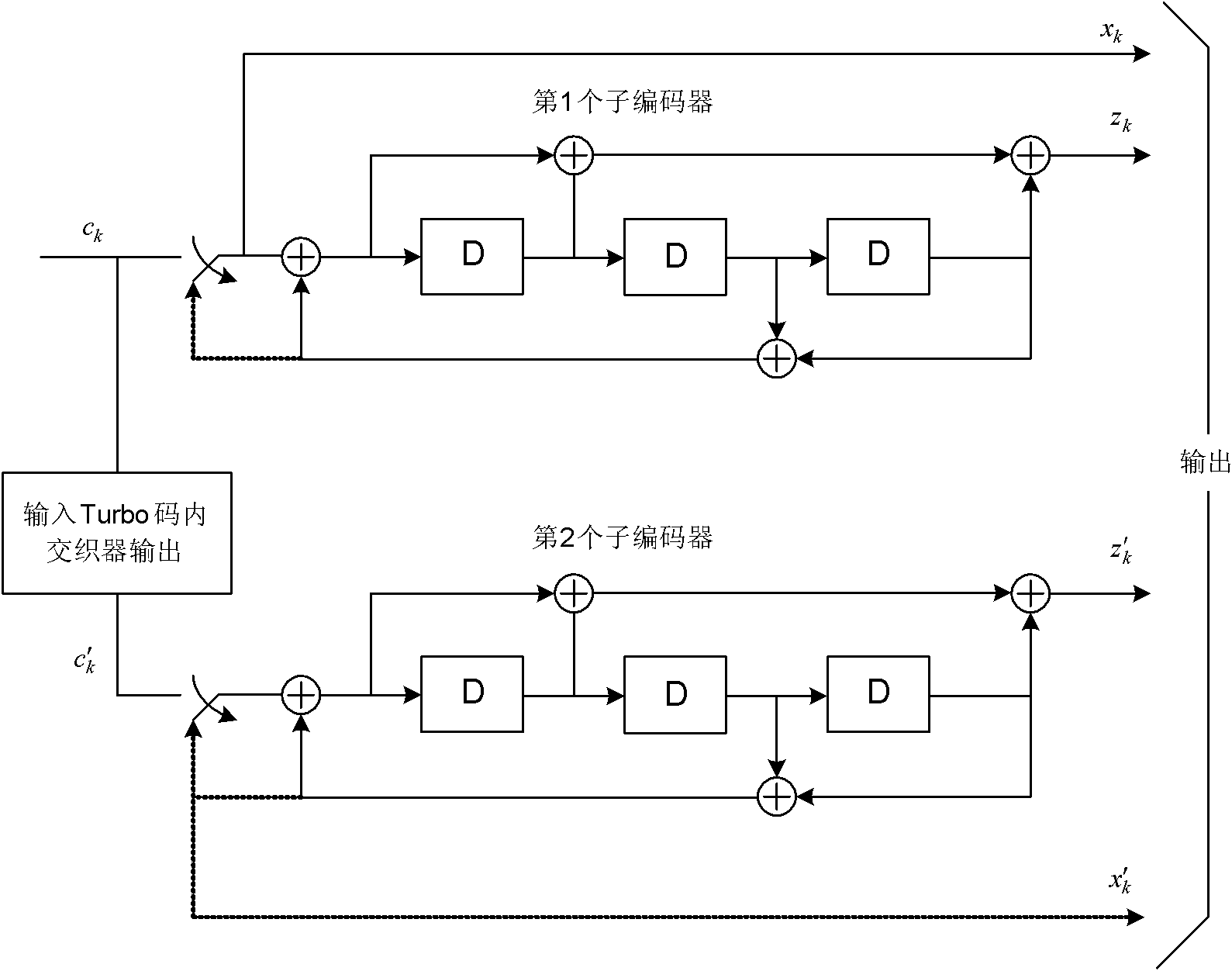

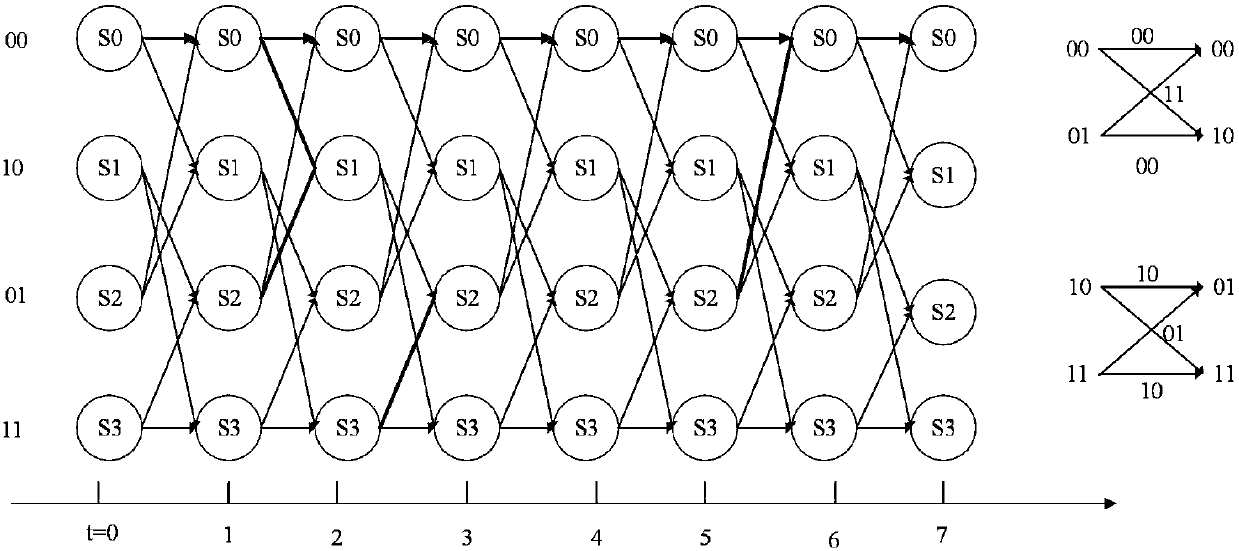

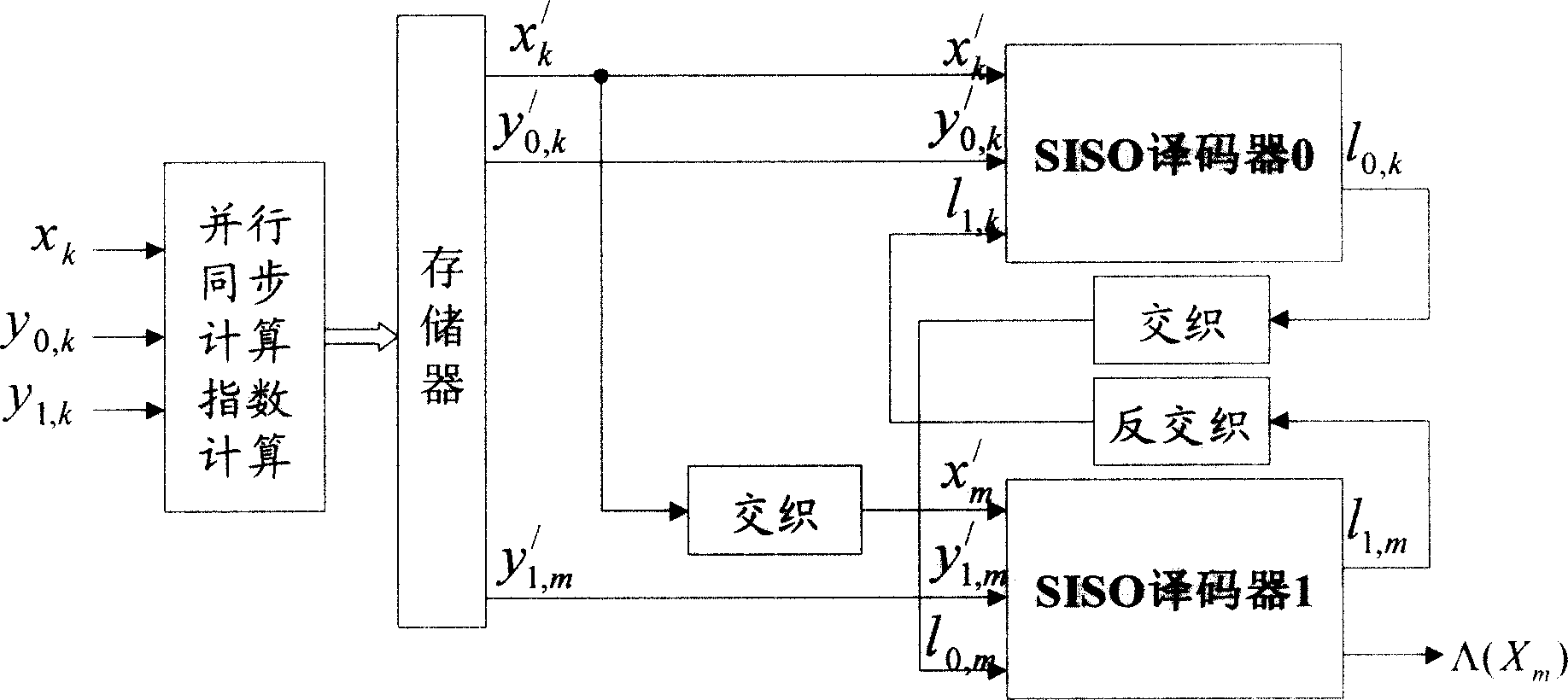

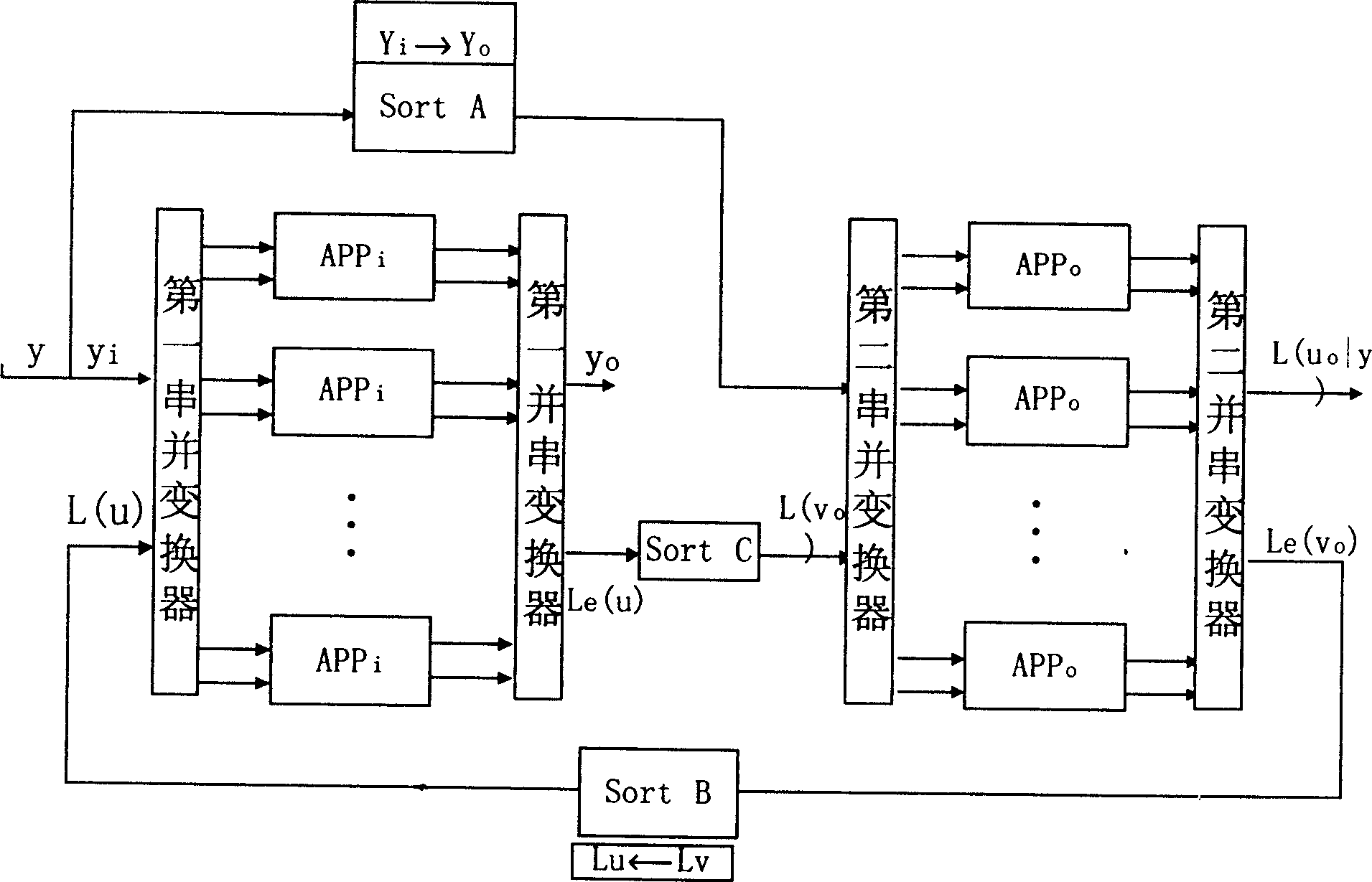

Non-logarithm-domain high-speed maximum posteroir probability Turbo decoding method

InactiveCN1710815AImprove computing efficiencyReduce decoding delayError correction/detection by combining multiple code structuresDecoding methodsStandard map

Unipolar binary signal (0,1) instead of traditional bipolar binary signal (+1, -1) is adopted in the disclosed decoding method to realize calculation of probability measure of state transition so as to obtain high speed decoding algorithm of iteration in software in and software out (SISO) in non-logarithm field. The SISO decoding algorithm of iteration eliminates a great lot exponential operation and logarithm operation, which is must be carried out in standard MAP decoding procedure of iteration. Comparing with standard MAP decoding method, the invention possesses same performance of optimal error correction. Comparing with LOG-MAP decoding method based on logarithm field, the invention possesses quicker decoding speed. Decoding delay of the invention is very close to approximate method MAX - LOG - MAP of LOG - MAP logarithm.

Owner:SOUTHWEST JIAOTONG UNIV

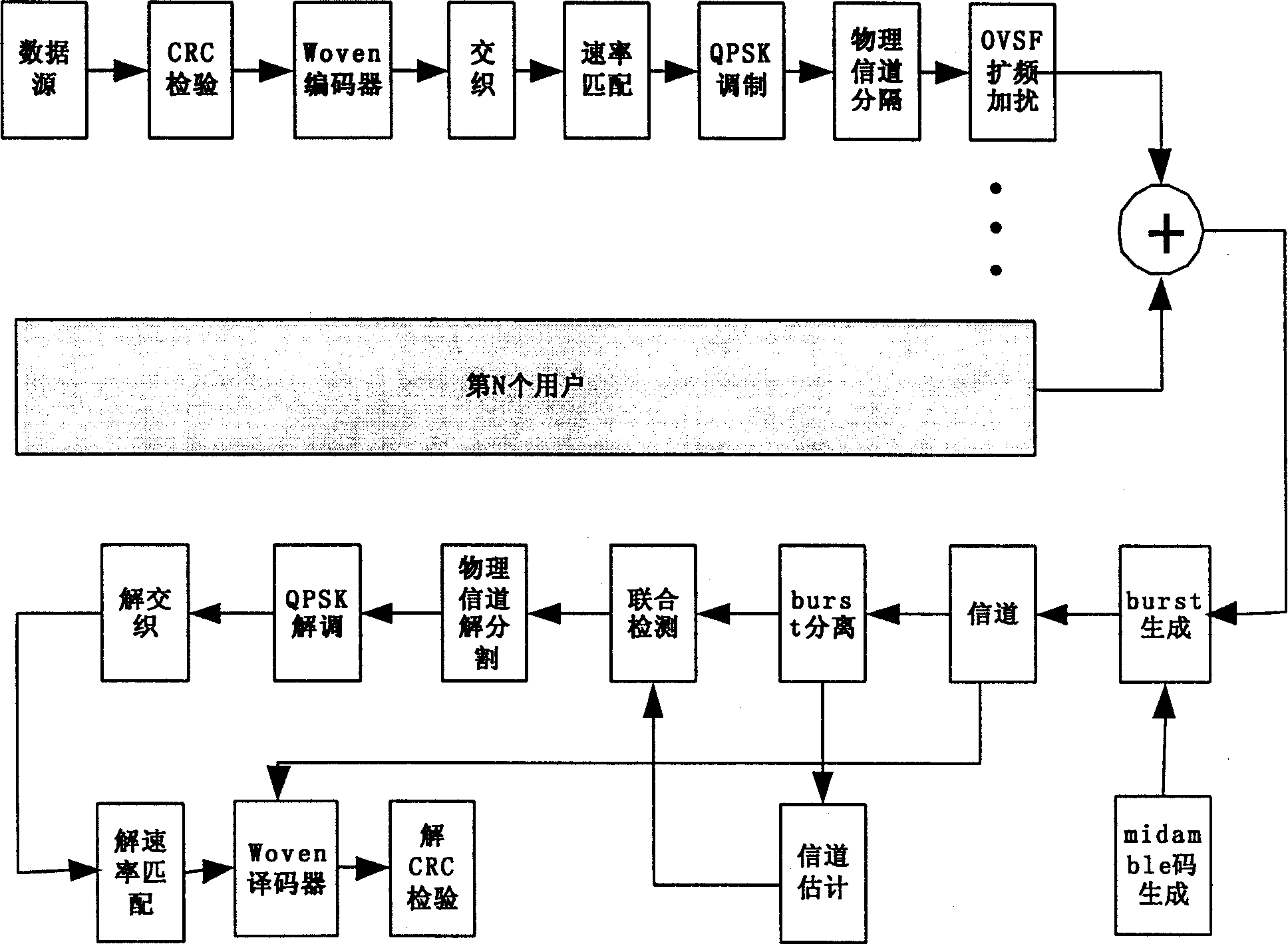

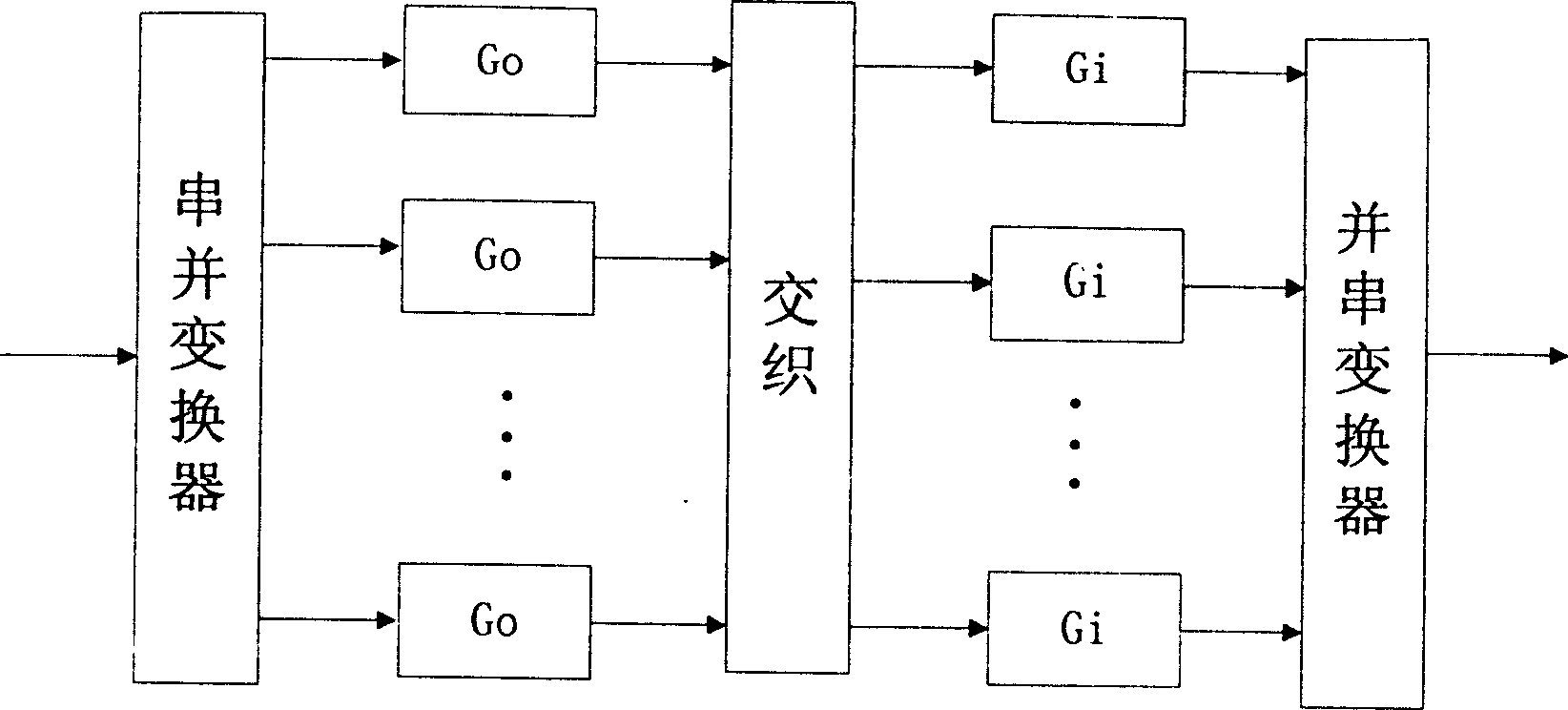

Woven convolutional code error detection and correction coder, encoder in TD-SCDMA system

InactiveCN1738229AReduce complexityGuaranteed Bit Error RateError correction/detection using convolutional codesError preventionComputer hardwareTime delays

The invention relates to the channel error-correcting coding technique which can protect the Woven convolution code error-corrector in the TD-CDMA system. The invention replaces the Turbo code in present channel coding with the Woven convolution code error-corrector and encoder which uses a series of encoders to replace the internal and external encoders of step-connected code. The Woven convolution code uses two steps of coding structure, while the iterated decoding structure is used for decoding. Since the simple convolution component code and the paralleling decoding structure are used in the invention, the time delay of decoding and the operational complexity are reduced markedly. So the Woven convolution code more fits the high-speed high-real time service to improve the property of system compared to the Turbo code.

Owner:SHENZHEN TINNO WIRELESS TECH

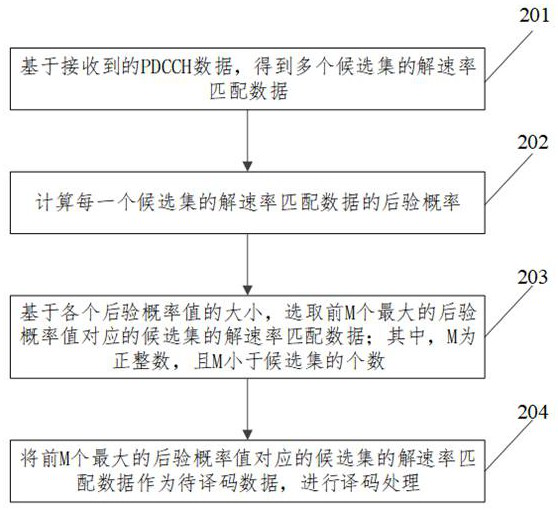

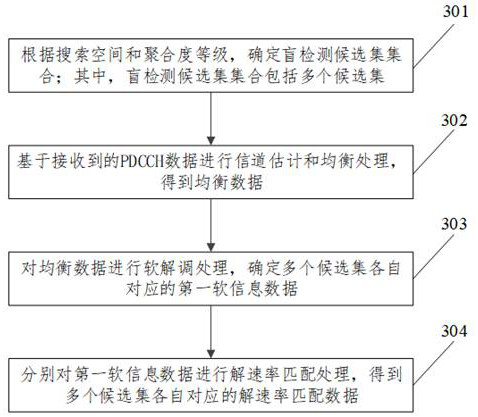

Physical downlink control channel detection method and device, equipment and storage medium

ActiveCN113938257AReduce the number of decodingReduce decoding delayReceiver specific arrangementsChannel coding adaptationDecoding methodsTime delays

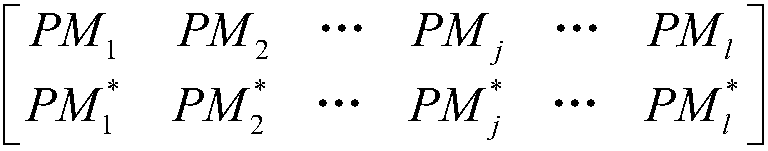

The invention relates to a physical downlink control channel detection method and device, equipment and a storage medium. The method comprises the following steps: based on received PDCCH (Physical Downlink Control Channel) data, obtaining rate de-matching data of a plurality of candidate sets; calculating a posterior probability value of rate de-matching data of each candidate set; based on the magnitude of each posterior probability value, selecting rate de-matching data of the candidate set corresponding to the first M maximum posterior probability values; wherein M is a positive integer, and M is smaller than the number of the candidate sets; and taking the rate de-matching data of the candidate set corresponding to the first M maximum posterior probability values as to-be-decoded data, and performing decoding processing. The method and the device are used for solving the problem of relatively large time delay caused by a decoding method in related arts.

Owner:GUANGZHOU HUIRUI SITONG INFORMATION SCI & TECH CO LTD