Patents

Literature

58results about How to "Improve decoding throughput" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

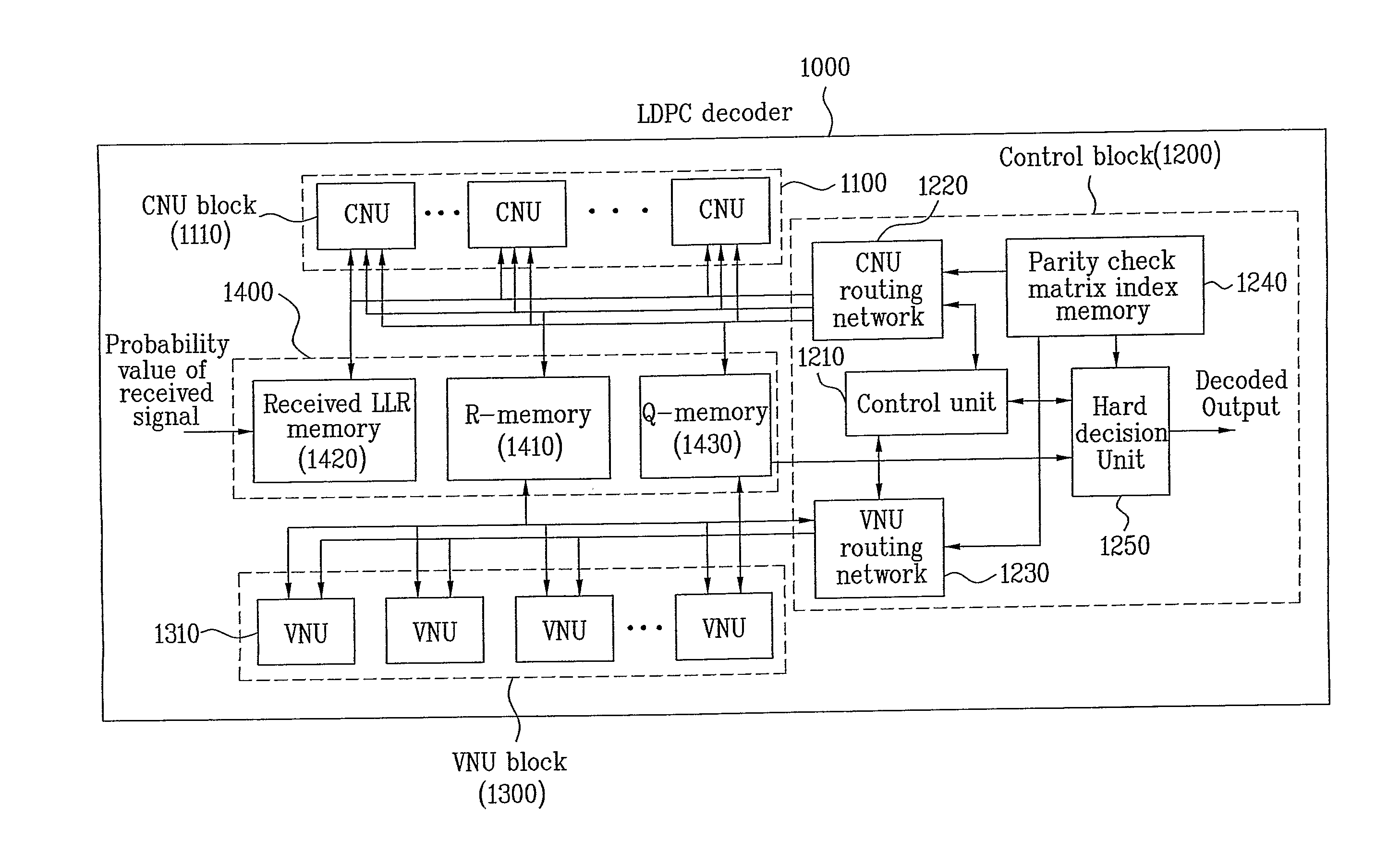

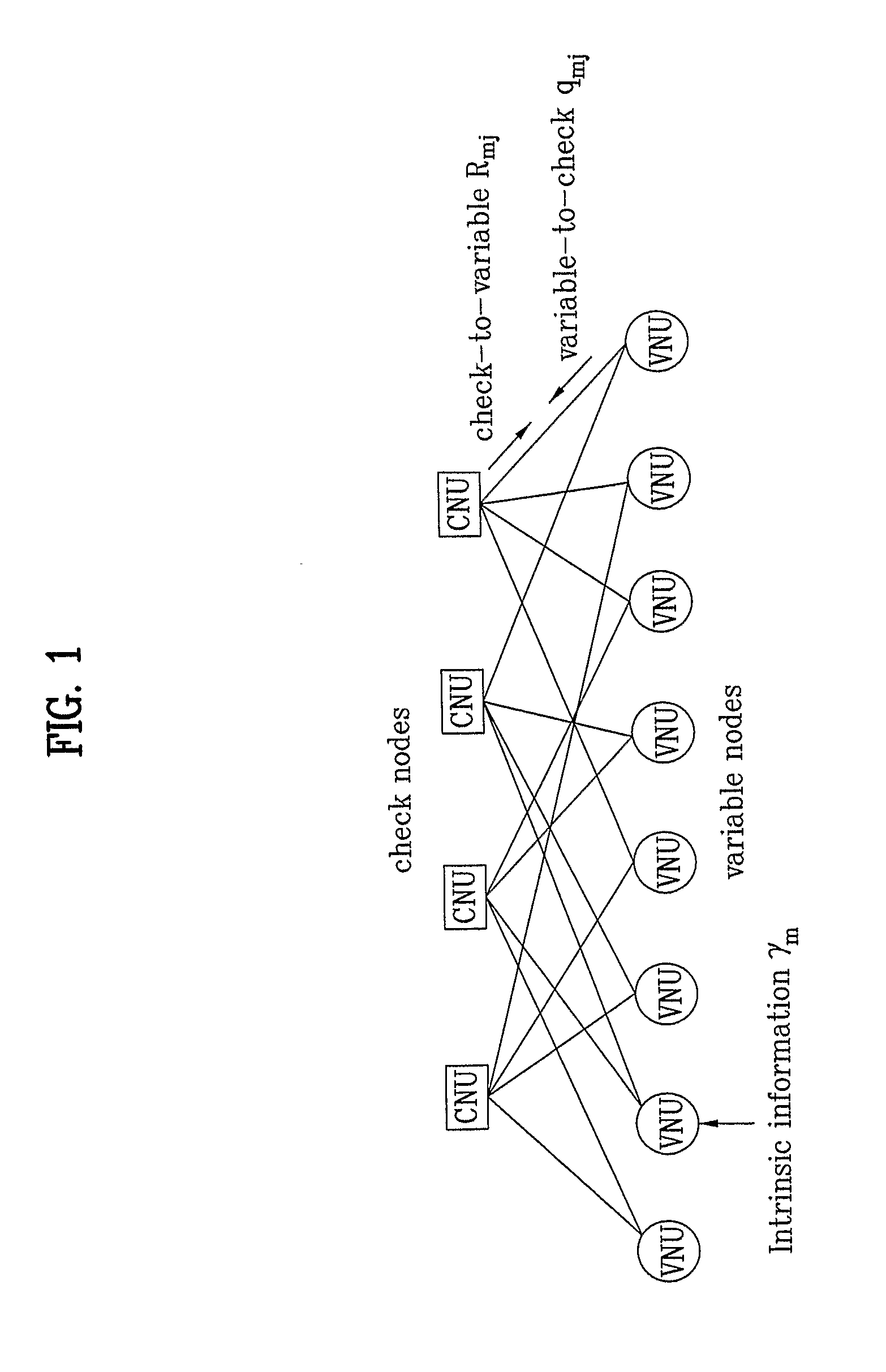

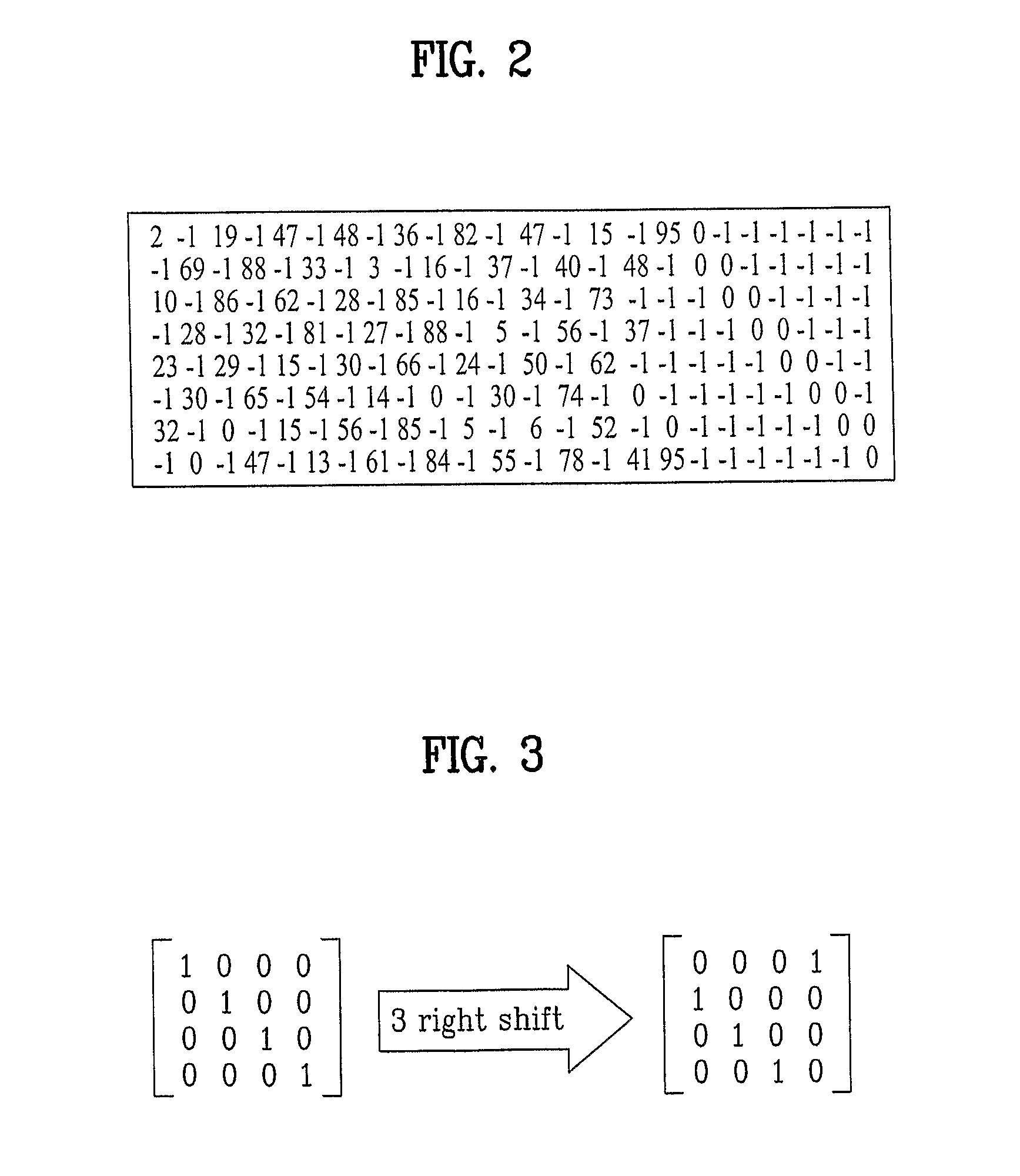

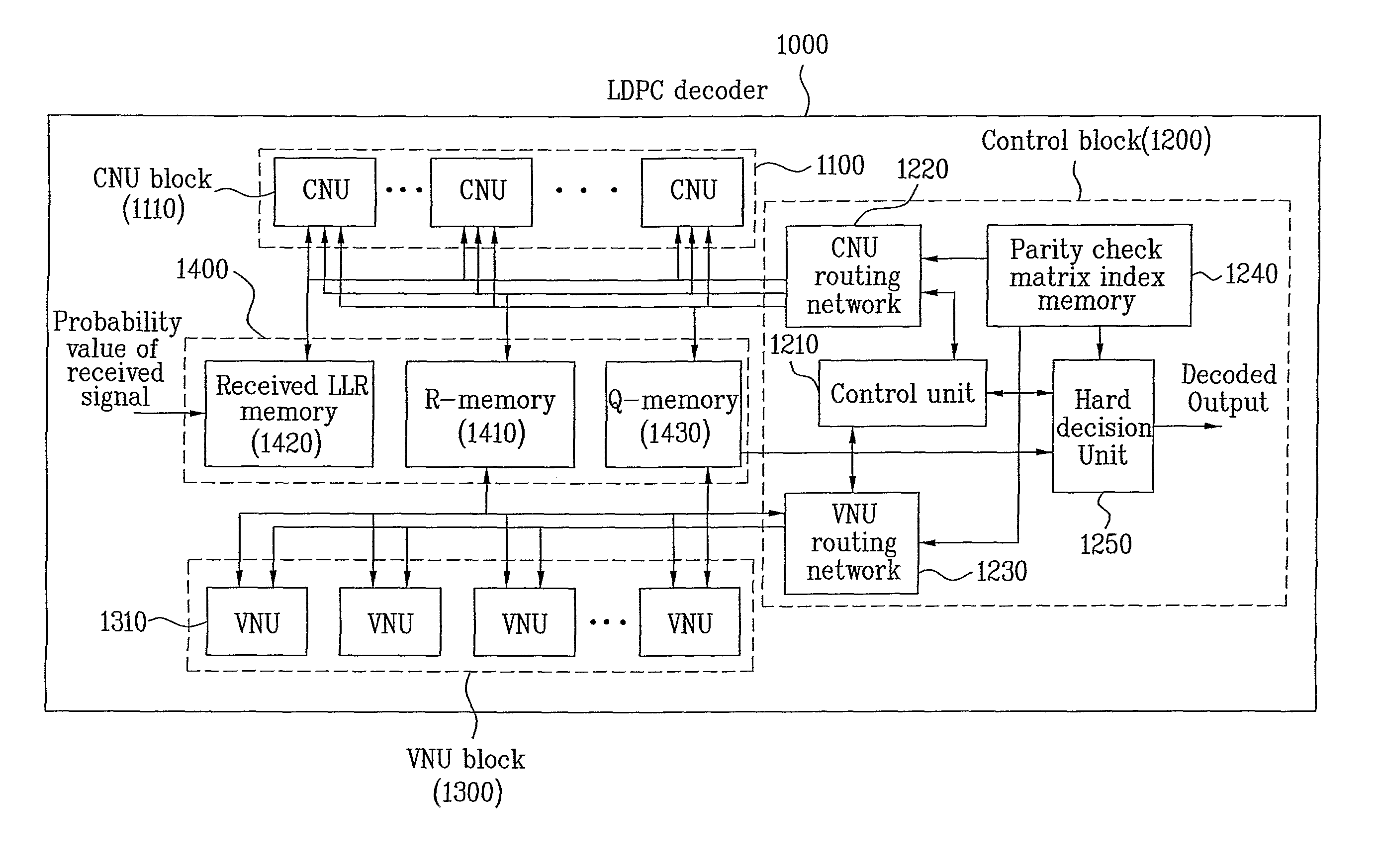

Method and apparatus for performing decoding using LDPC code

InactiveUS20110010602A1Improve decoding performanceReduce decoding delayError correction/detection using multiple parity bitsCode conversionTheoretical computer scienceParity-check matrix

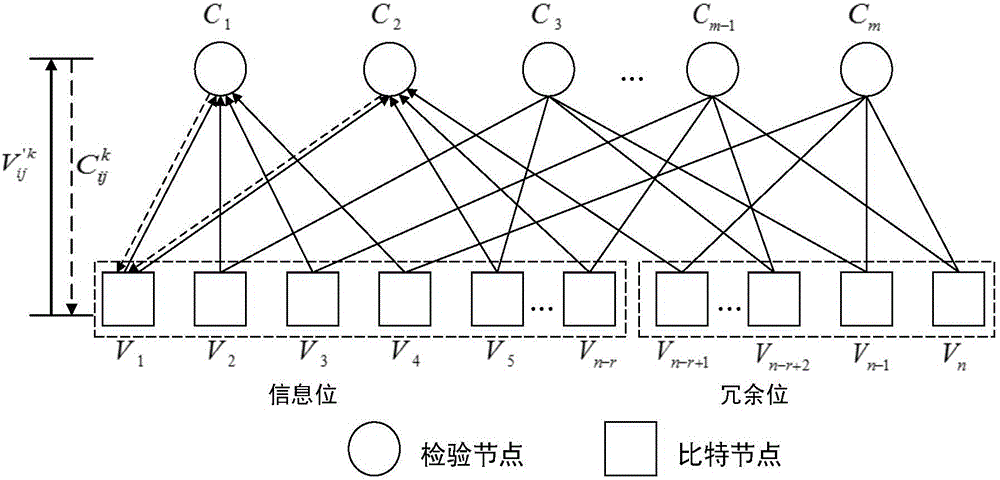

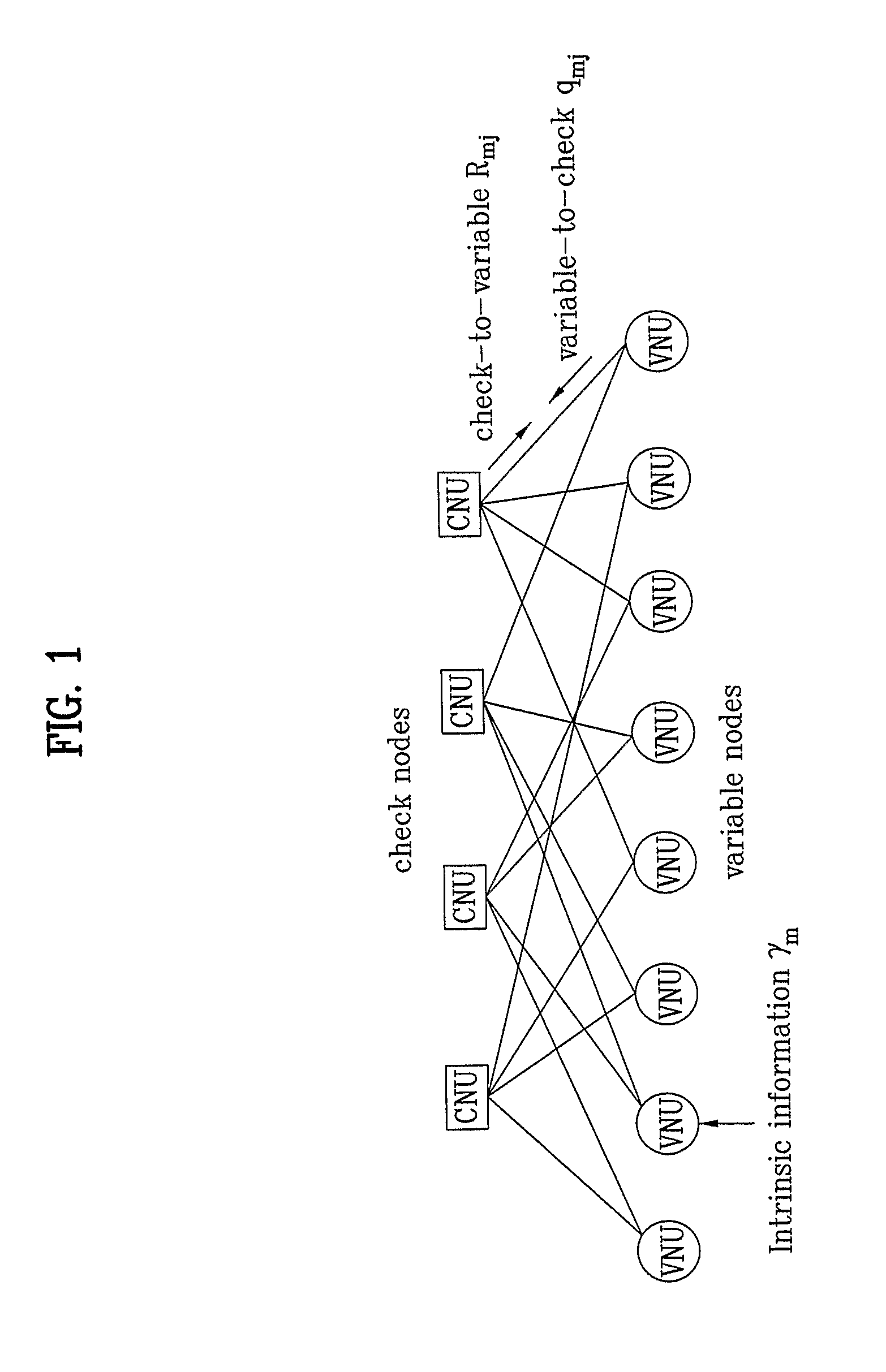

A method of performing decoding using an LDPC code is disclosed. The method of performing decoding an encoded codeword using a parity check matrix, comprises decoding the codeword using the parity check matrix, wherein the parity check matrix includes a plurality of layers, each of which includes at least one or more rows split exclusively from a specific row of a base parity check matrix.

Owner:LG ELECTRONICS INC

Multiple-rate, quasi-cycling and low density decoder for parity check codes

InactiveCN101951264AIncrease profitMeet the requirements of different code ratesError correction/detection using multiple parity bitsMultiplexingMemory bank

The invention discloses a multiple-rate, quasi-cycling and low density decoder for parity check codes, comprising a variable node information memory bank, a check matrix information memory bank, a symbol memory bank, an intermediate information memory bank, a variable node processor set, a check node processor set and a shifter set. The decoder uses two adjacent submatrixes as the basic unit of the check node update and the variable node update to perform concurrent operation, thereby greatly enhancing the throughput rate of coding; meanwhile due to that the QC-LDPC codes with different code rates share the same memory unit and hardware resource, the decoder realizes the full multiplexing of hardware units such as check node processors and variable node processors, the structure of the decoder can be designed regardless of the specific code rate, and the decoding with multiple rates is realized by using the hardware resource of single code rate, thereby enhancing the use ratio of the hardware.

Owner:NINGBO UNIV

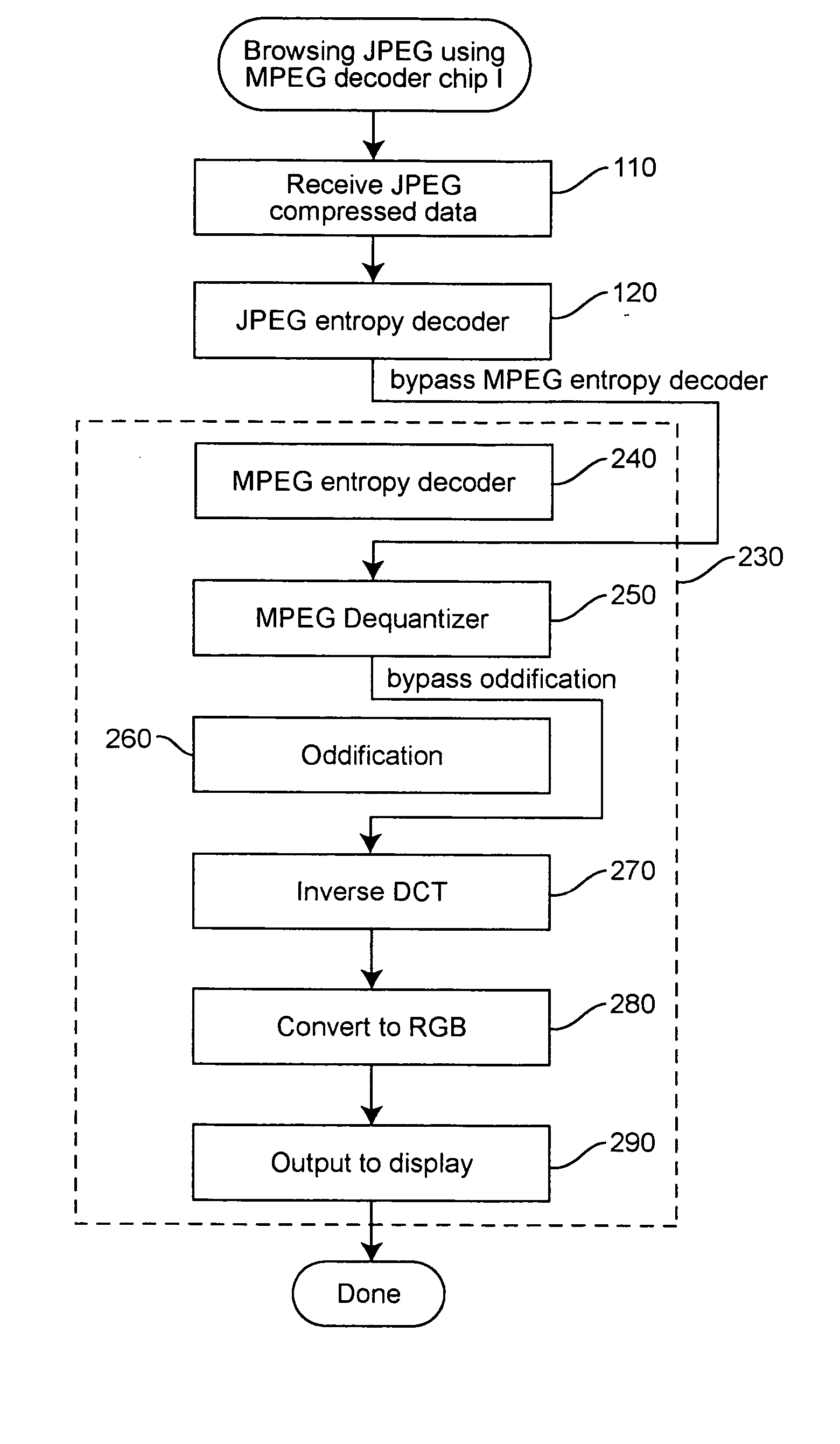

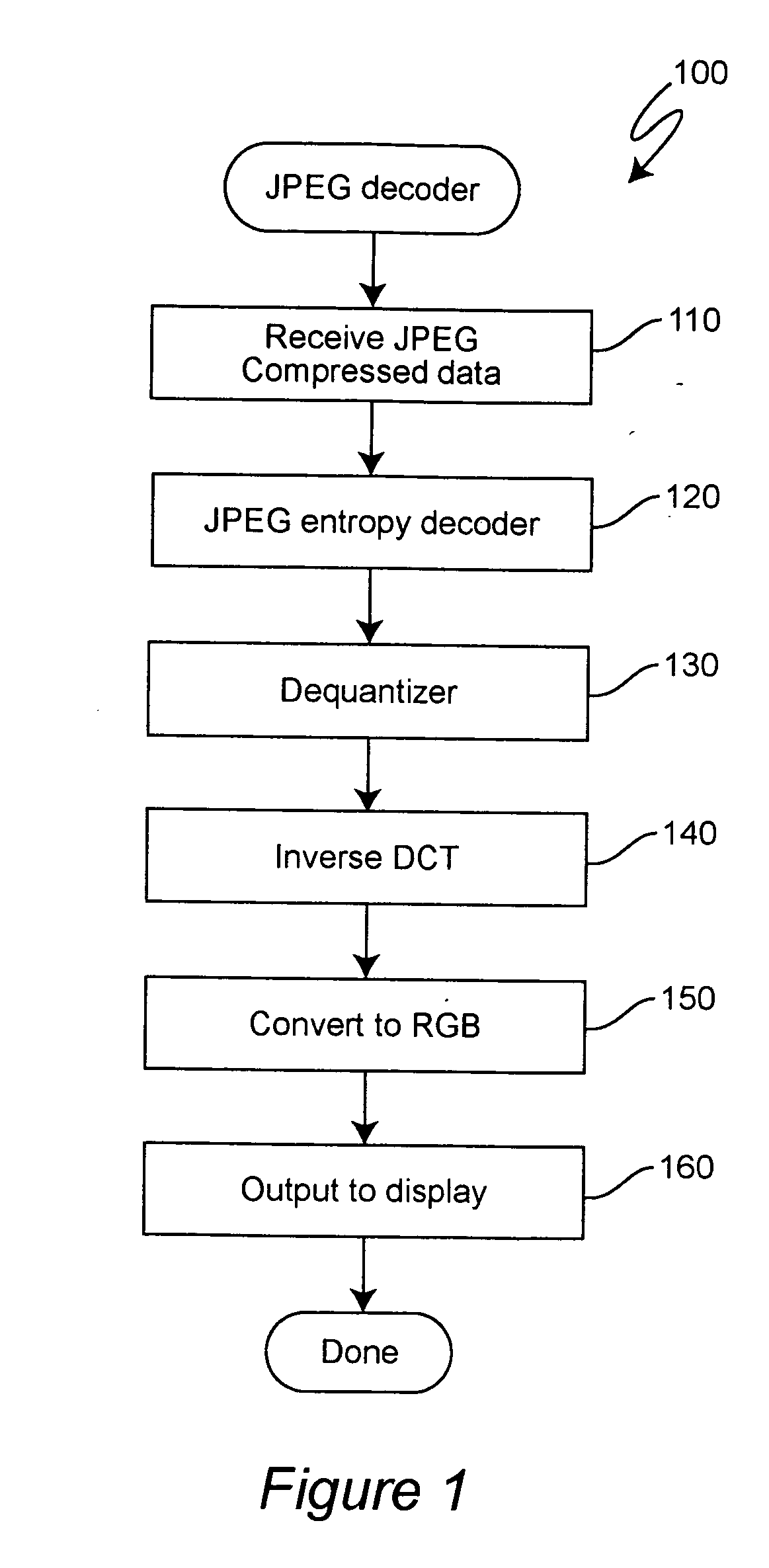

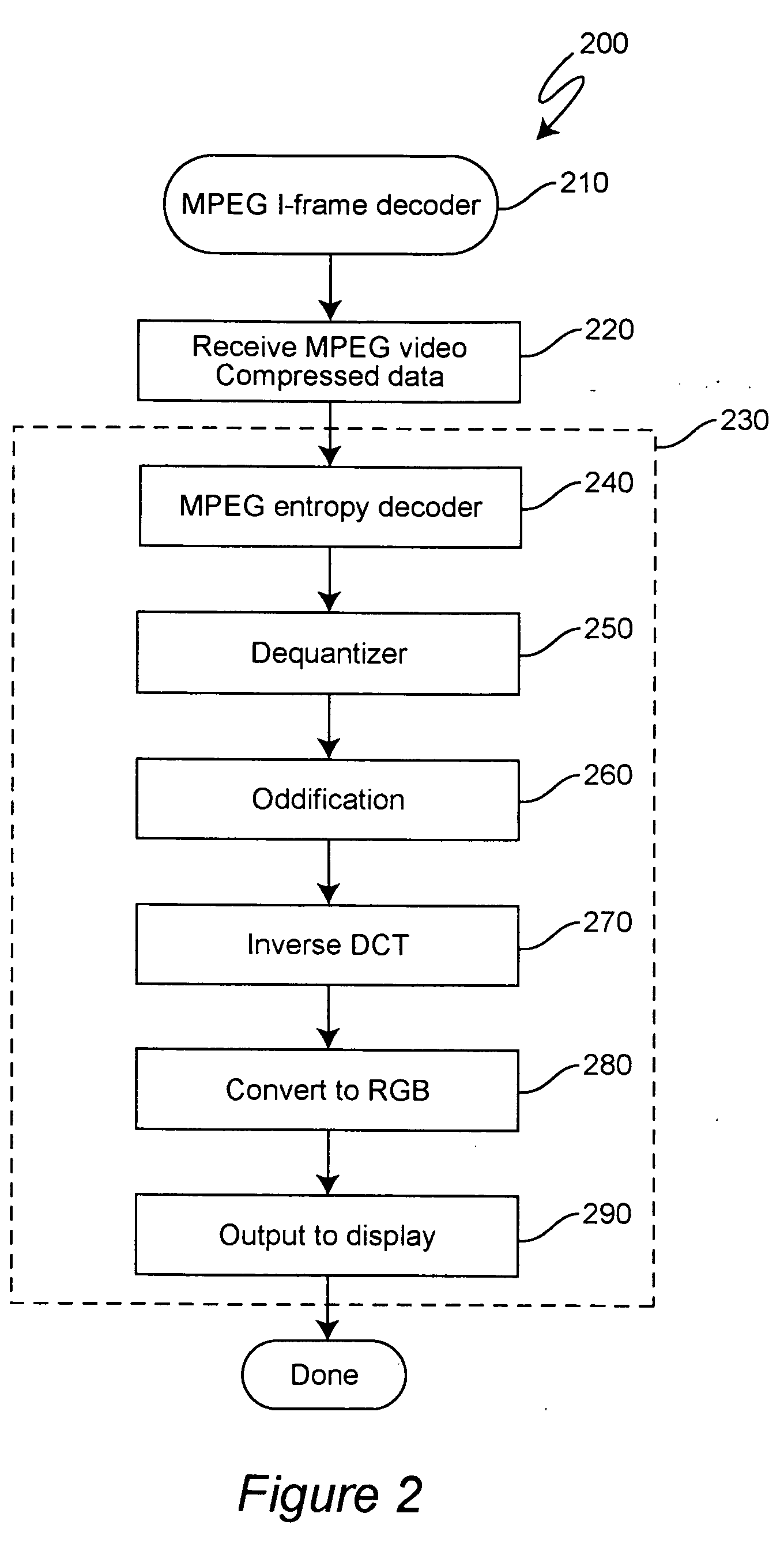

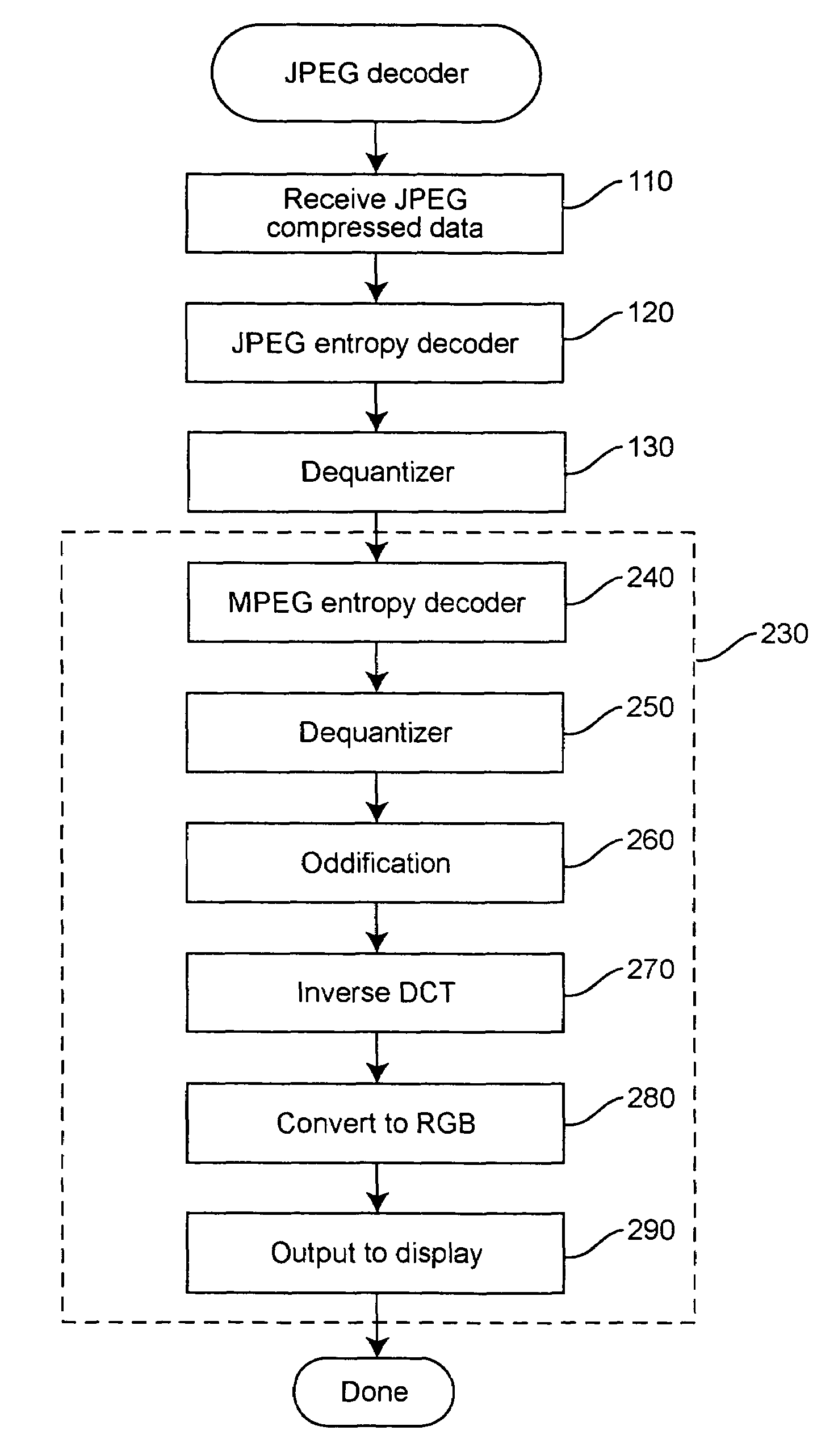

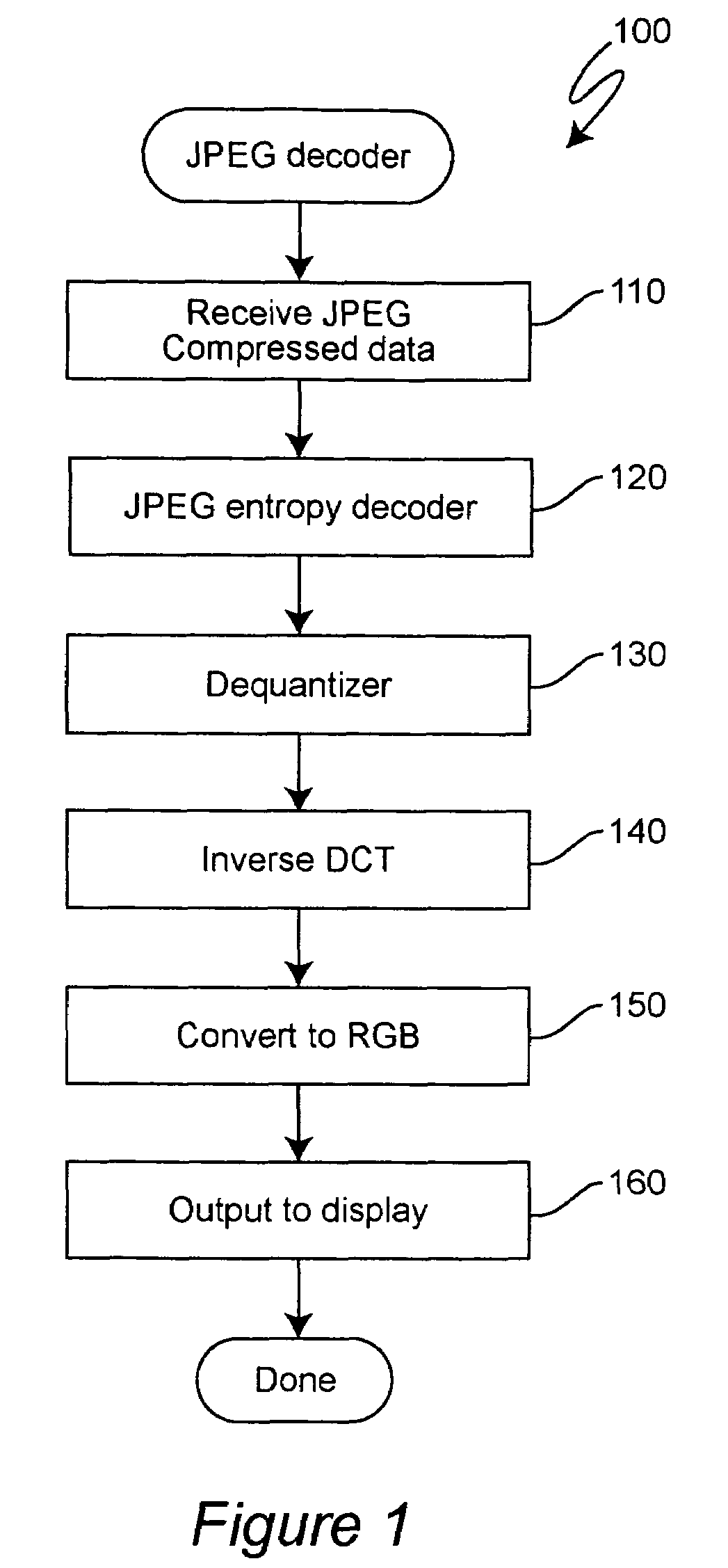

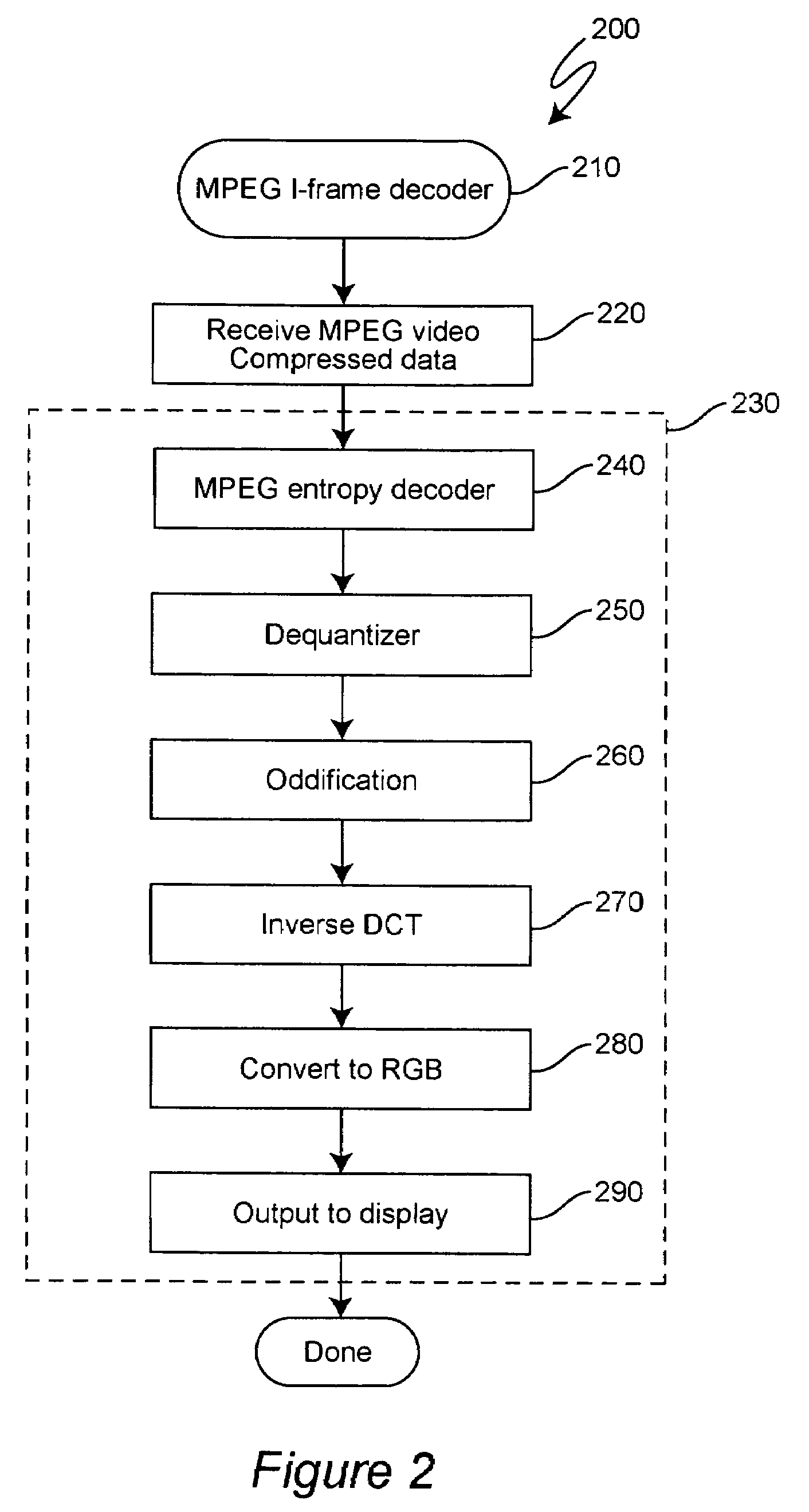

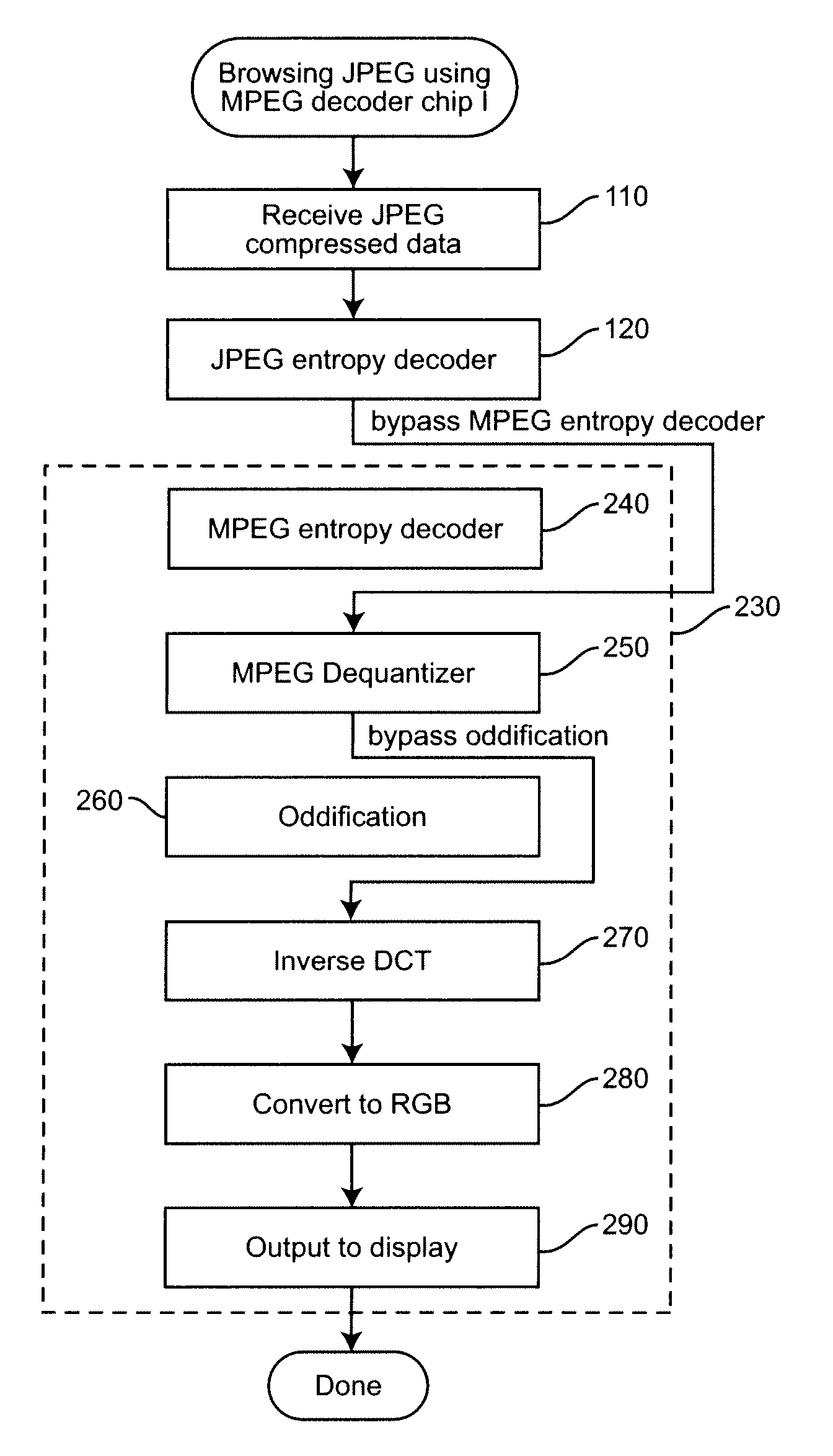

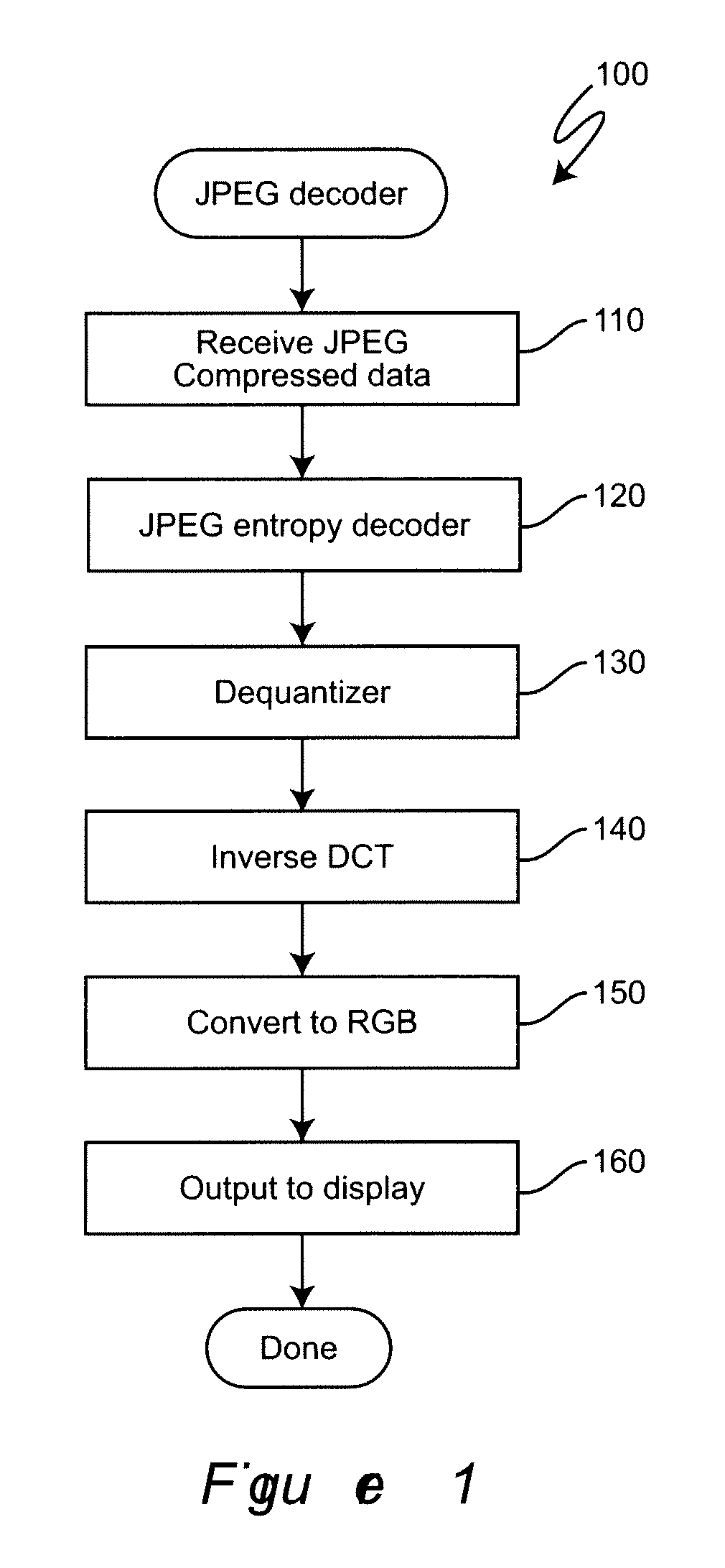

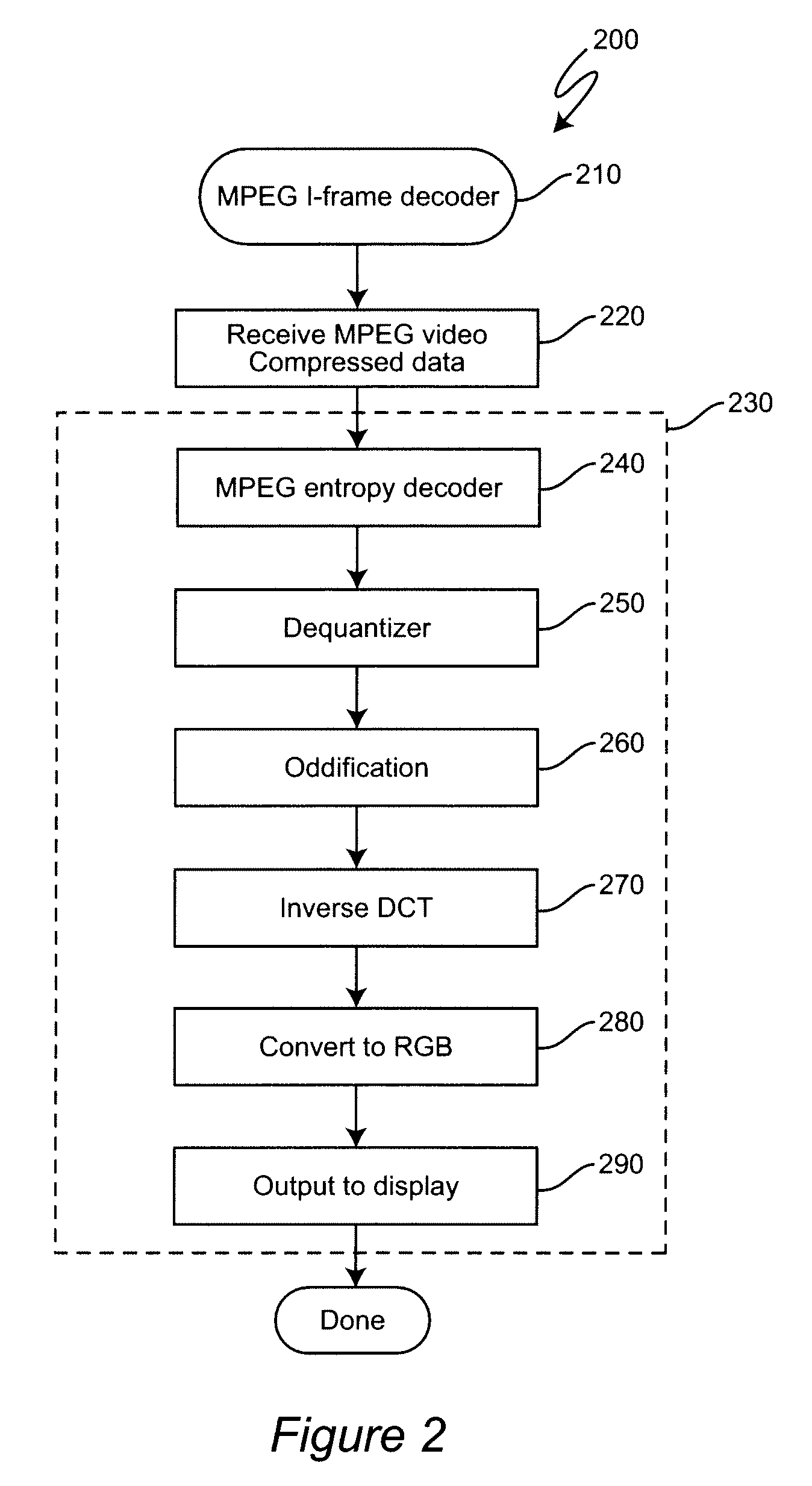

Browsing JPEG images using MPEG hardware chips

InactiveUS20050047666A1Rapid browsingHigh qualityCharacter and pattern recognitionTelevision systemsJPEGSoftware

Rapid throughput of still image compressed data (e.g. JPEG) is achieved for presentation of images in rapid succession for browsing or browsing by panning within large images by using a hardware decoder adapted for presentation of moving images to reduce the processing load which must be performed in accordance with software although the still image data is incompatible with still image data in many respects; some of which necessarily lead to a loss of image fidelity. The still image data is partially decoded (e.g. entropy decoded) in software processing and re-encoded and reformatted to a form which can at least be accepted by the hardware decoder even though not compliant with any particular moving picture data standard (e.g. MPEG). Storage in the hardware decoder is reallocated to provide, in combination with a reduction of slower software processing, a throughput increase of four-fold or more. Software processing of the still image data is also allowed to proceed and the result substituted for the result of the hardware decoding if a given image is viewed for a time sufficient for the software image processing to be completed.

Owner:IBM CORP

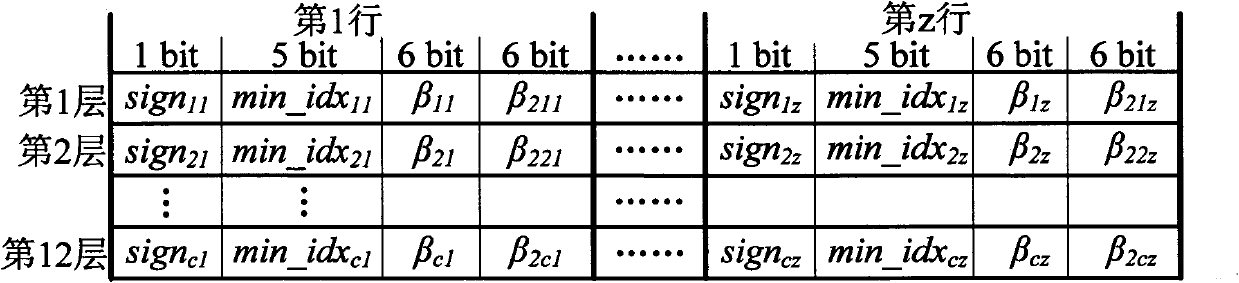

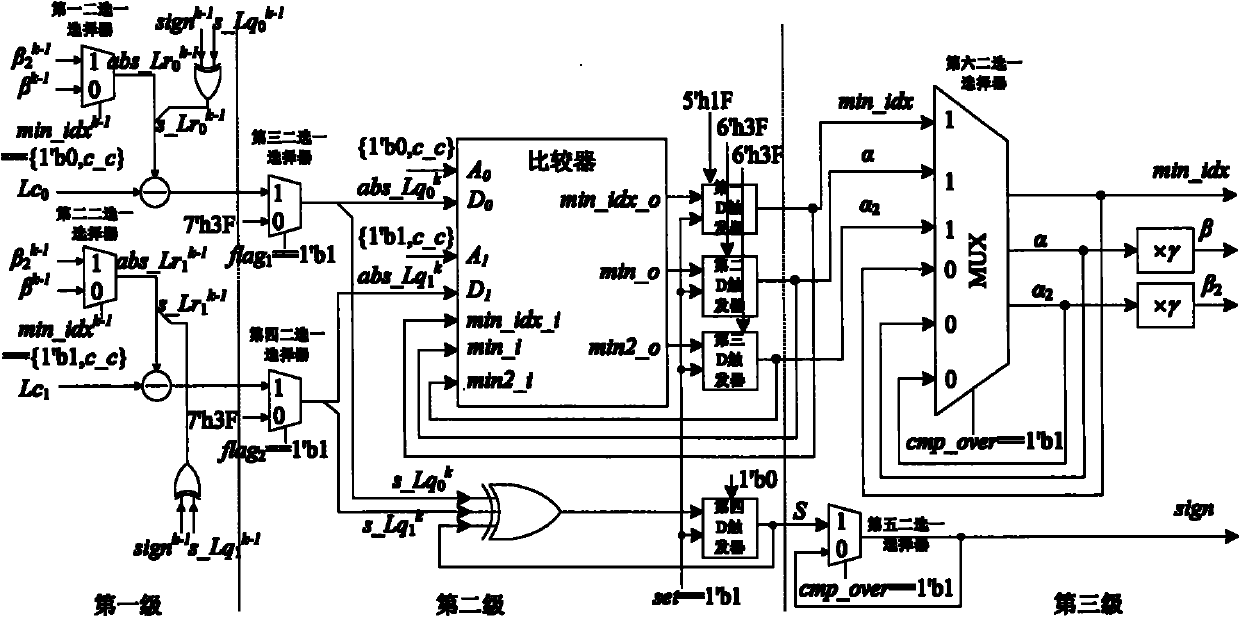

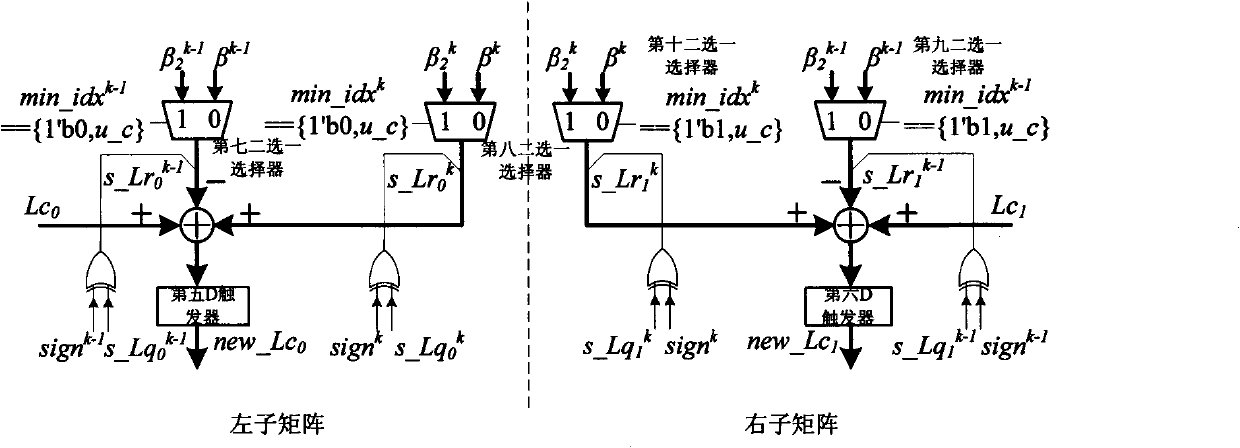

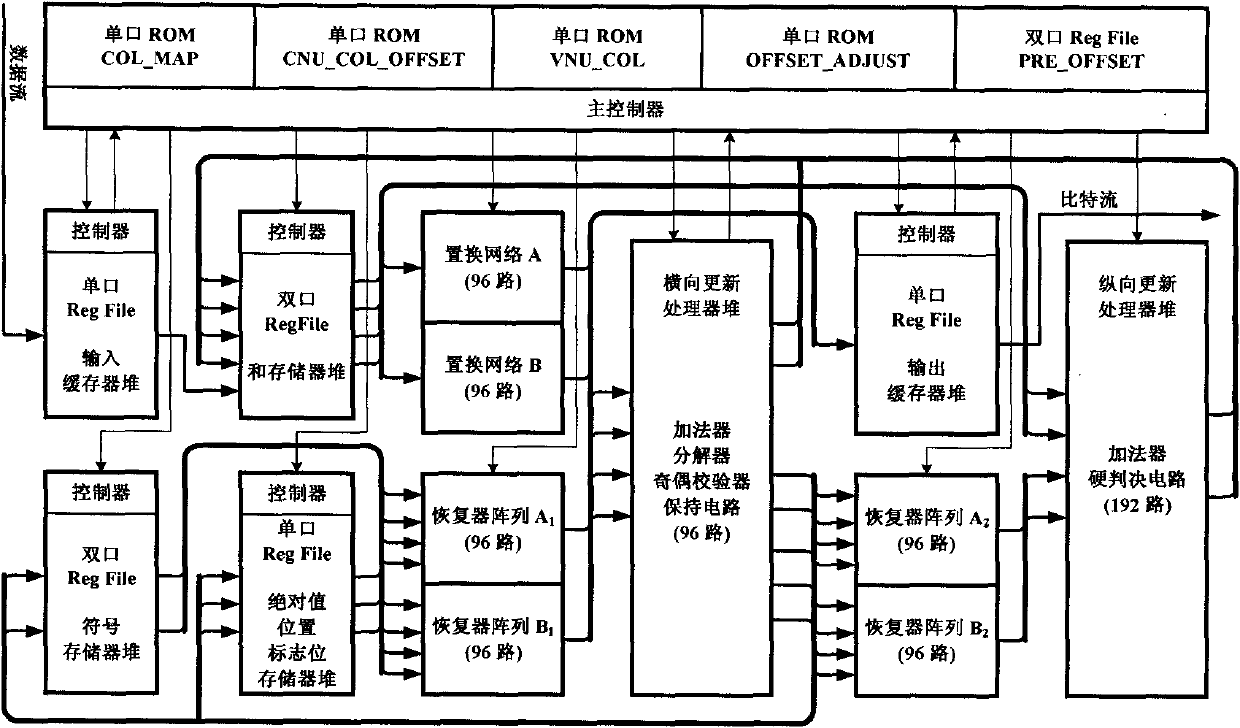

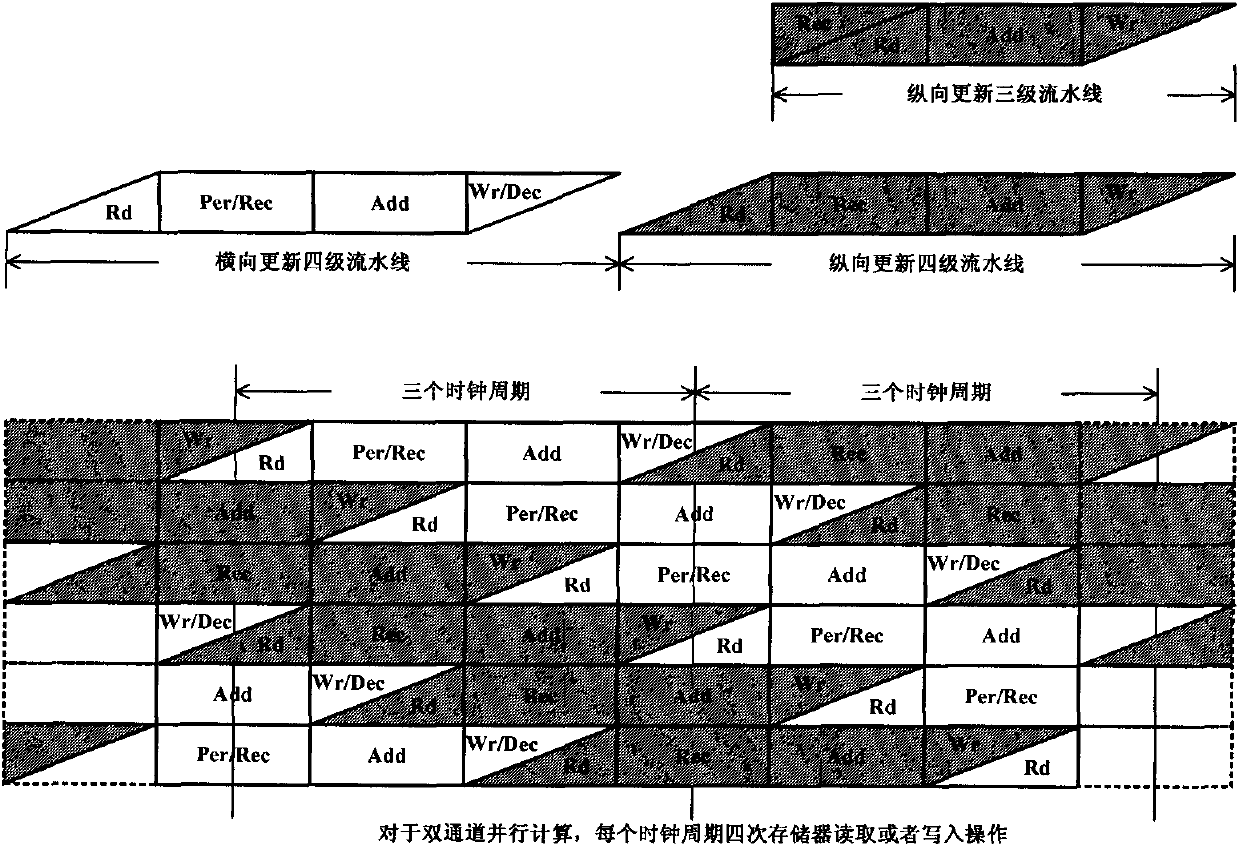

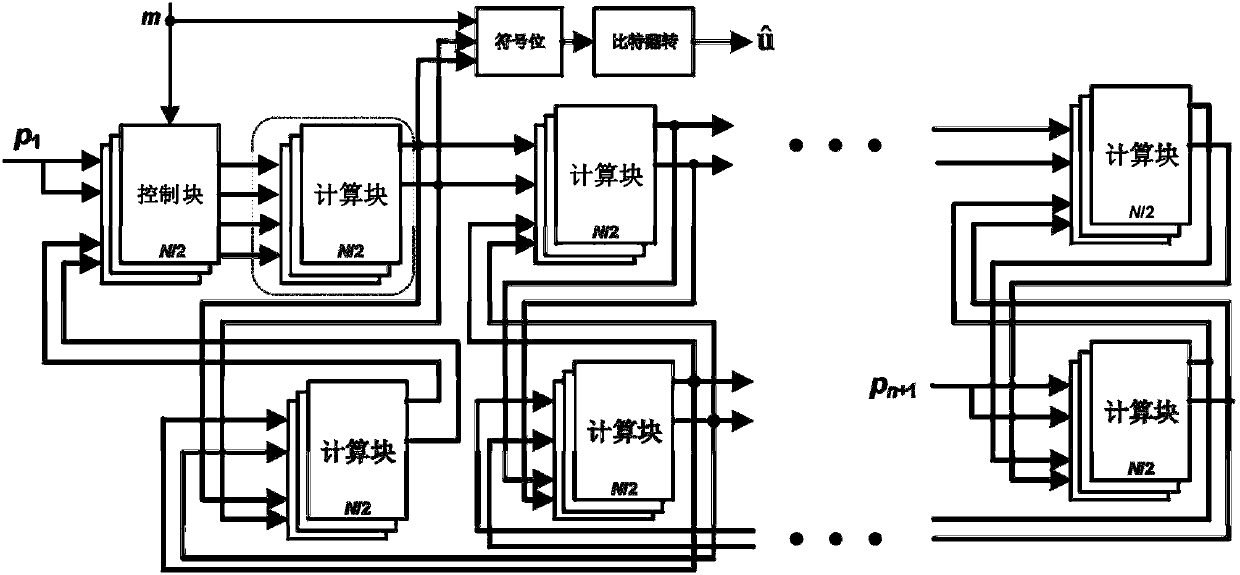

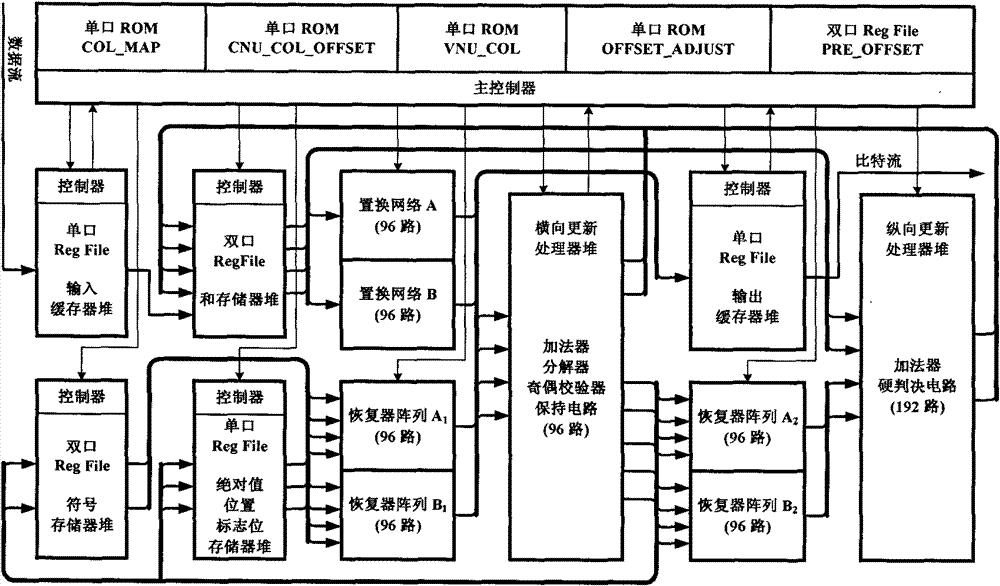

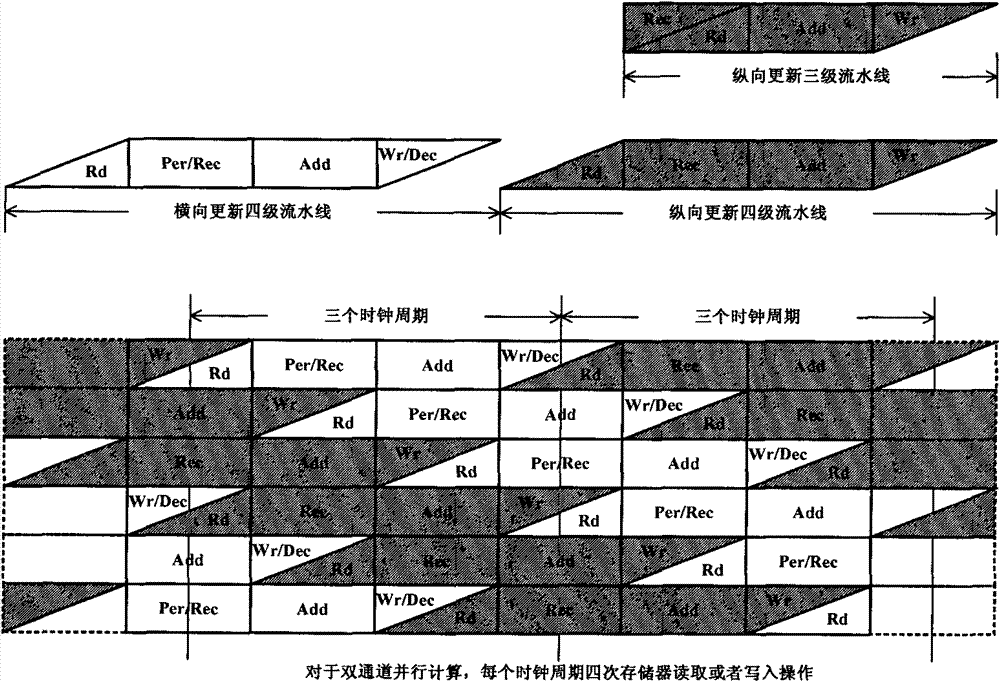

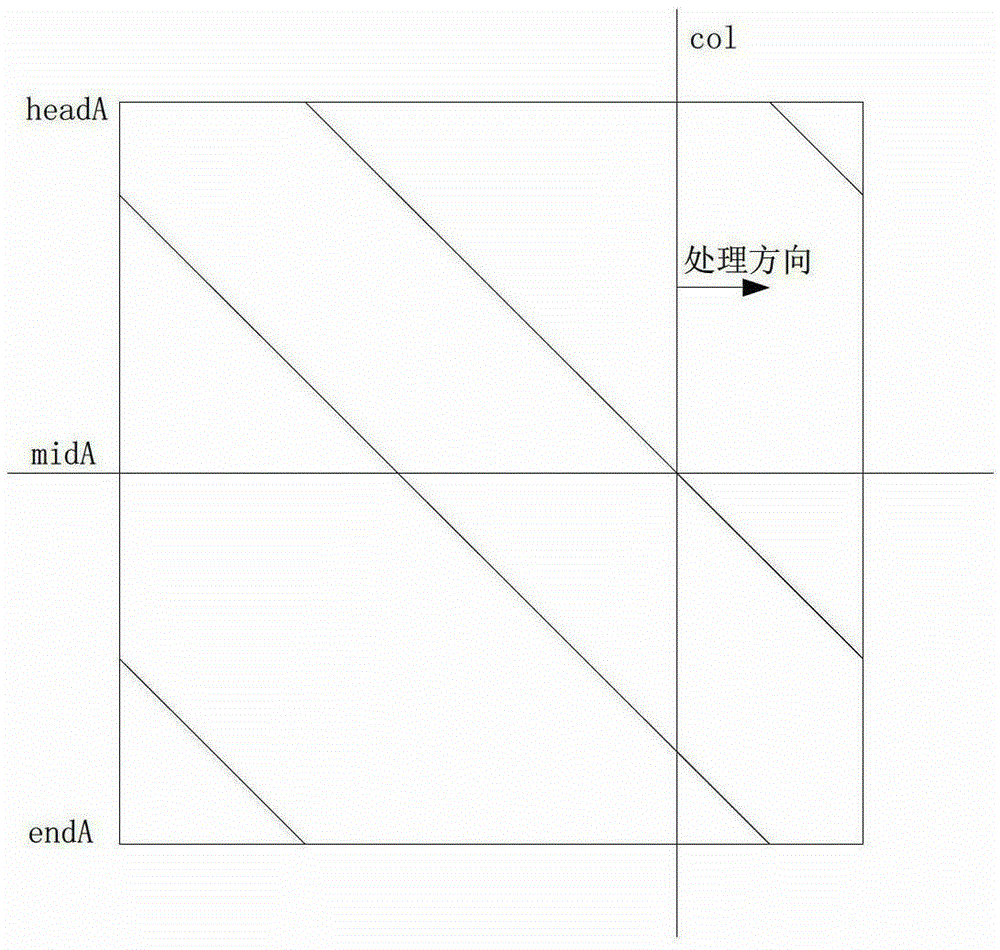

Ultrahigh-speed and low-power-consumption QC-LDPC code decoder based on TDMP

InactiveCN101771421AReduce visitsAvoid access violationsError correction/detection using multiple parity bitsComputer architectureParallel computing

The invention belongs to the technical field of wireless communication and micro-electronics, in particular to an ultrahigh-speed low-power-consumption and low-density parity check code (QC-LDPC) decoder based on TDMP. Through symmetrizing six grades of production lines, interlacing row blocks and line blocks, re-sequencing nonzero sub matrixes, carrying out four-quadrant division on a sum value register pile and adopting the technology of reading and writing the bypass, the decoder carries out serial scanning in the row sequence, two nonzero sub matrixes are respectively processed in each clock period during horizontal updating and vertical updating. The horizontal updating and the vertical updating are fully overlapped. Particularly, the sum value register pile stores the sum values of variable nodes, and is also used as an FIFO for storing transient external information transferred between two phases. The structure of the decoder has strong configurability, can be easily transplanted into any other irregular or irregular QC-LDPC codes, and has the excellent decoding performance, the peak frequency can reach 214 MHz, the thuoughput can reach about 1 gigabit per second, and the chip power consumption is only 397 milliwatts.

Owner:FUDAN UNIV

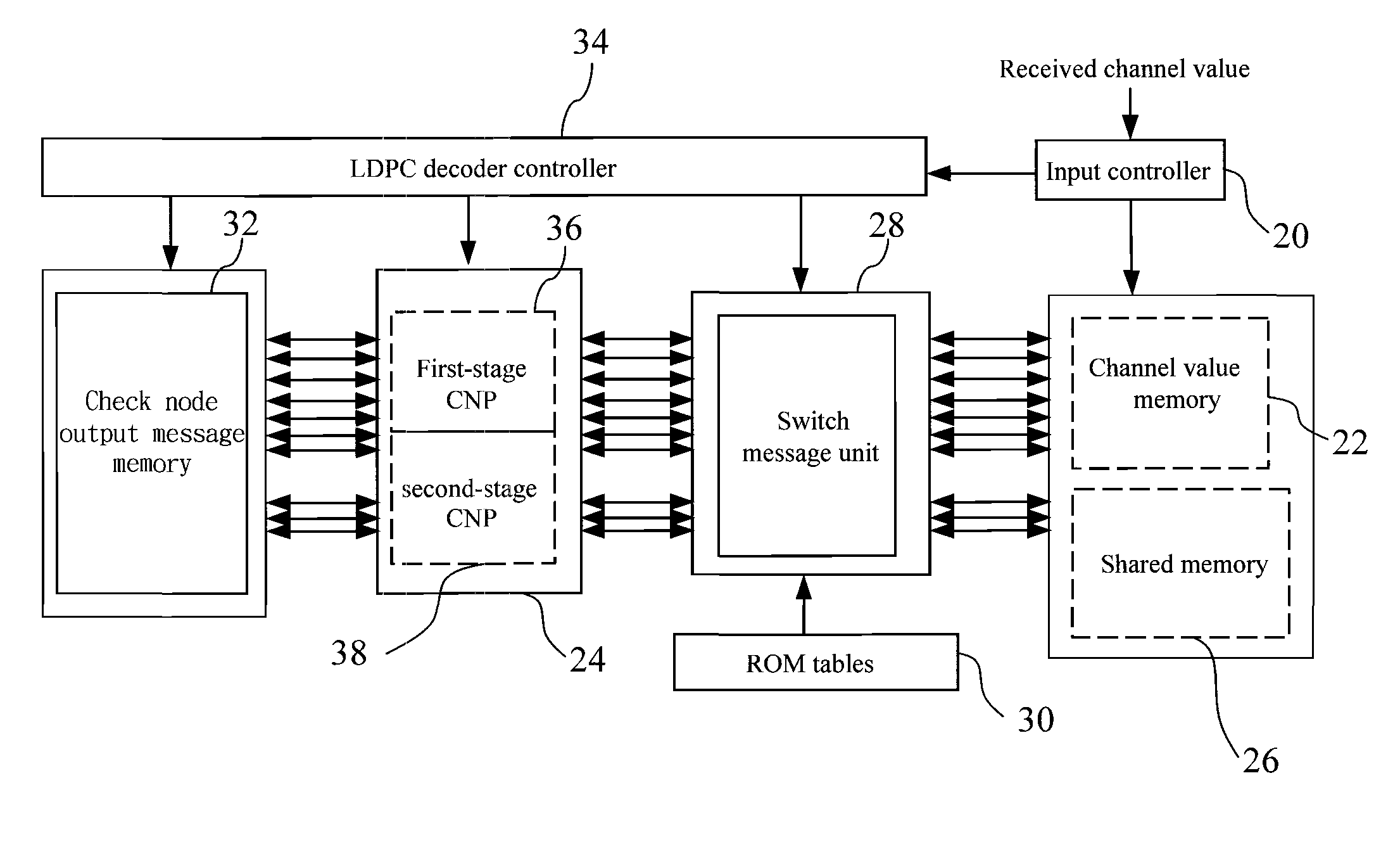

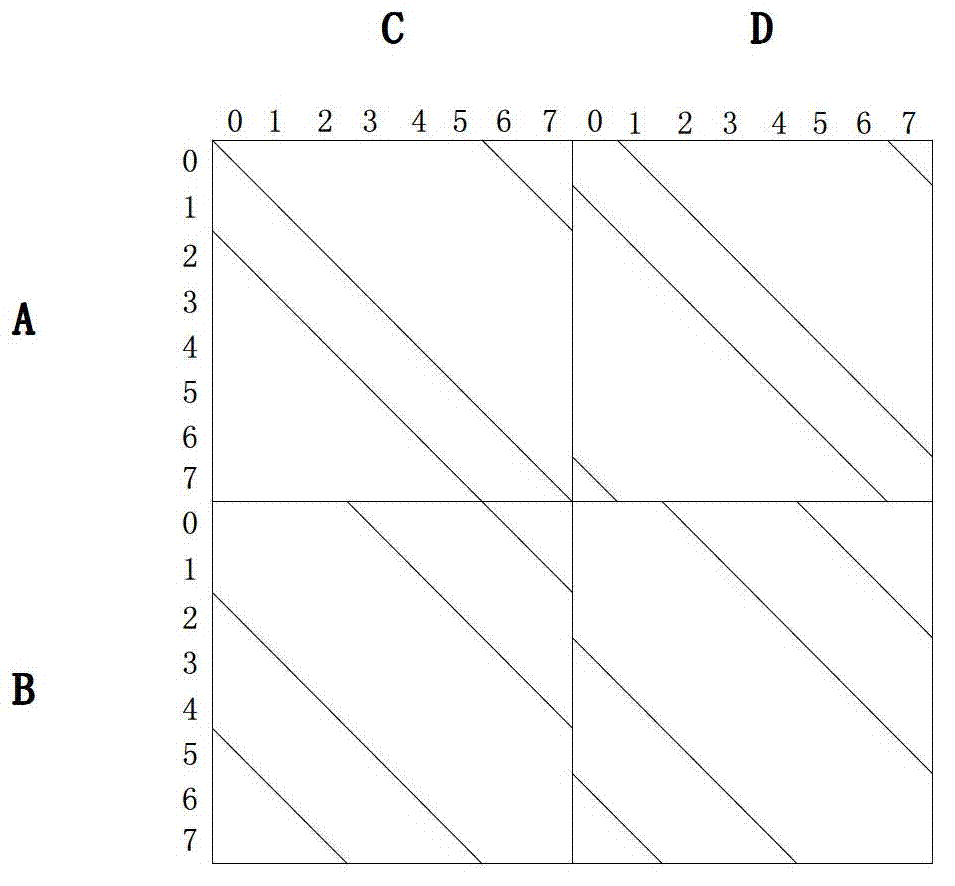

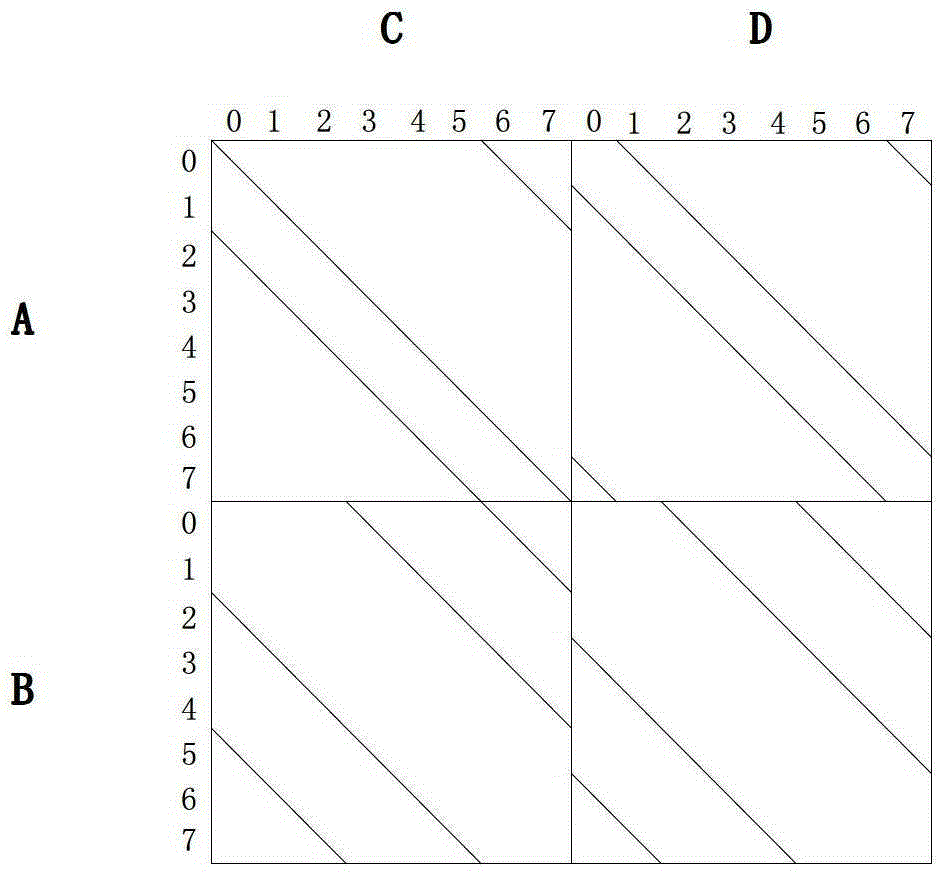

Edge-based decoders for low-density parity-check codes

ActiveUS8429483B1Improve decoding throughputError detection/correctionCode conversionData retrievalParity-check matrix

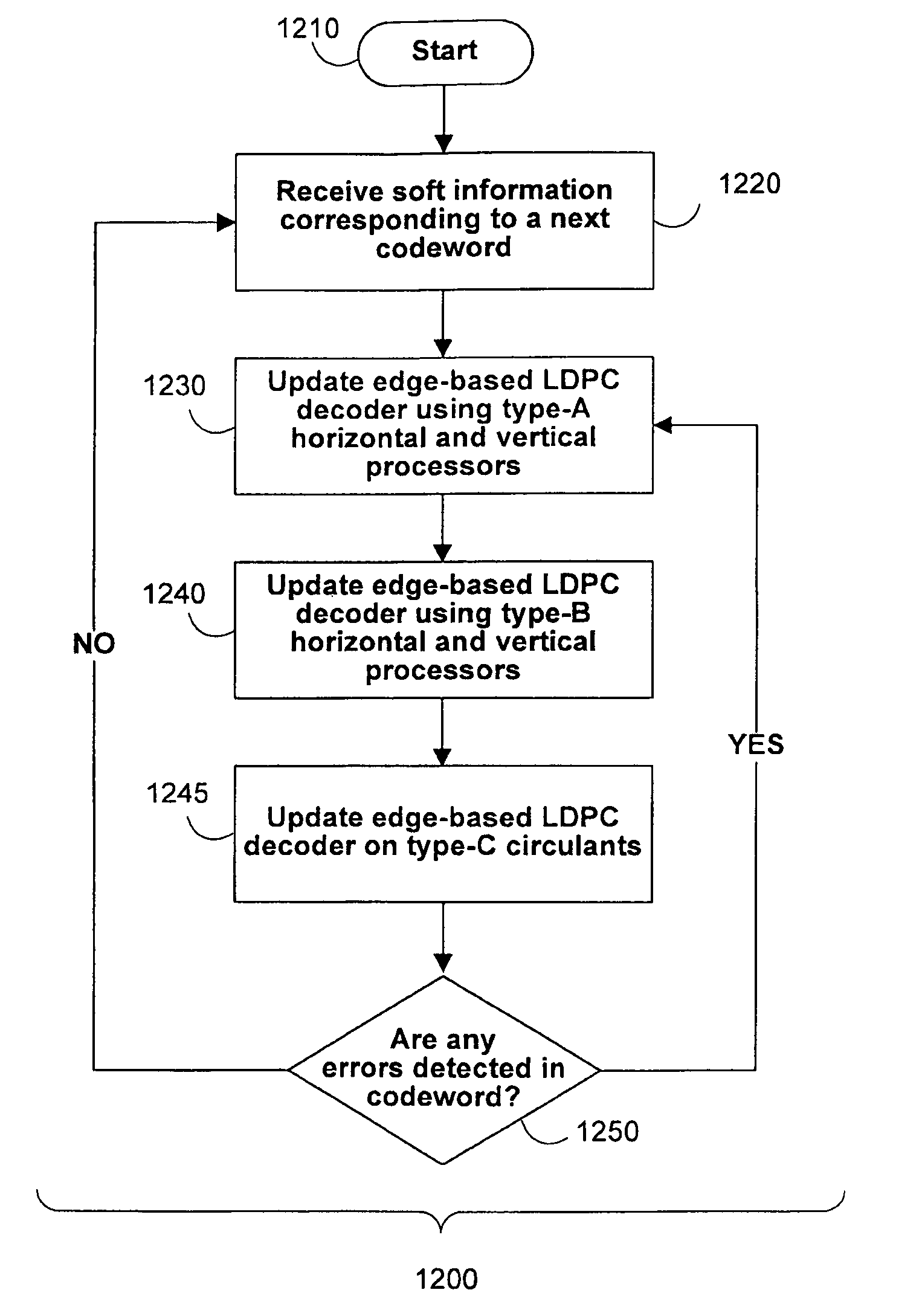

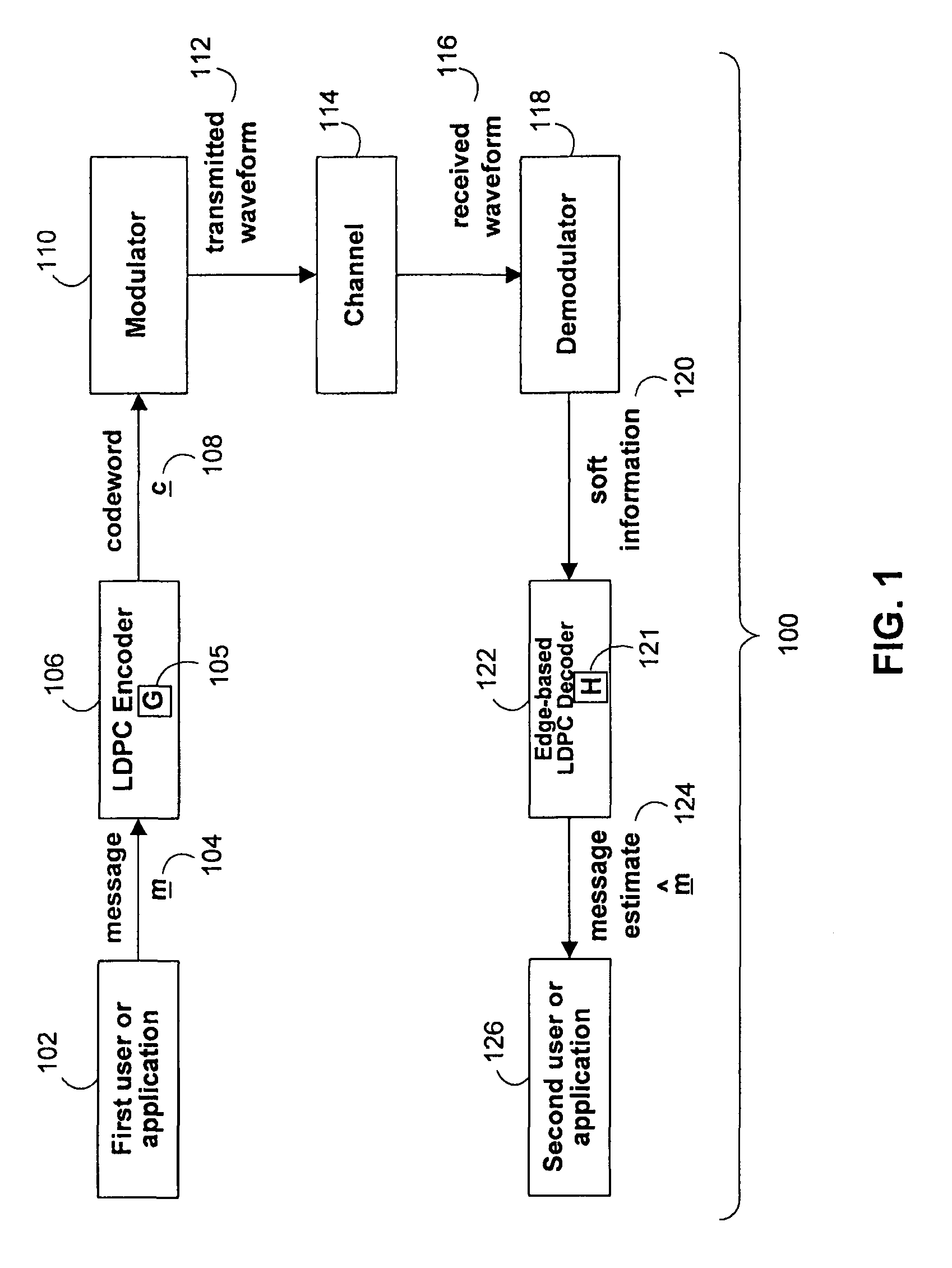

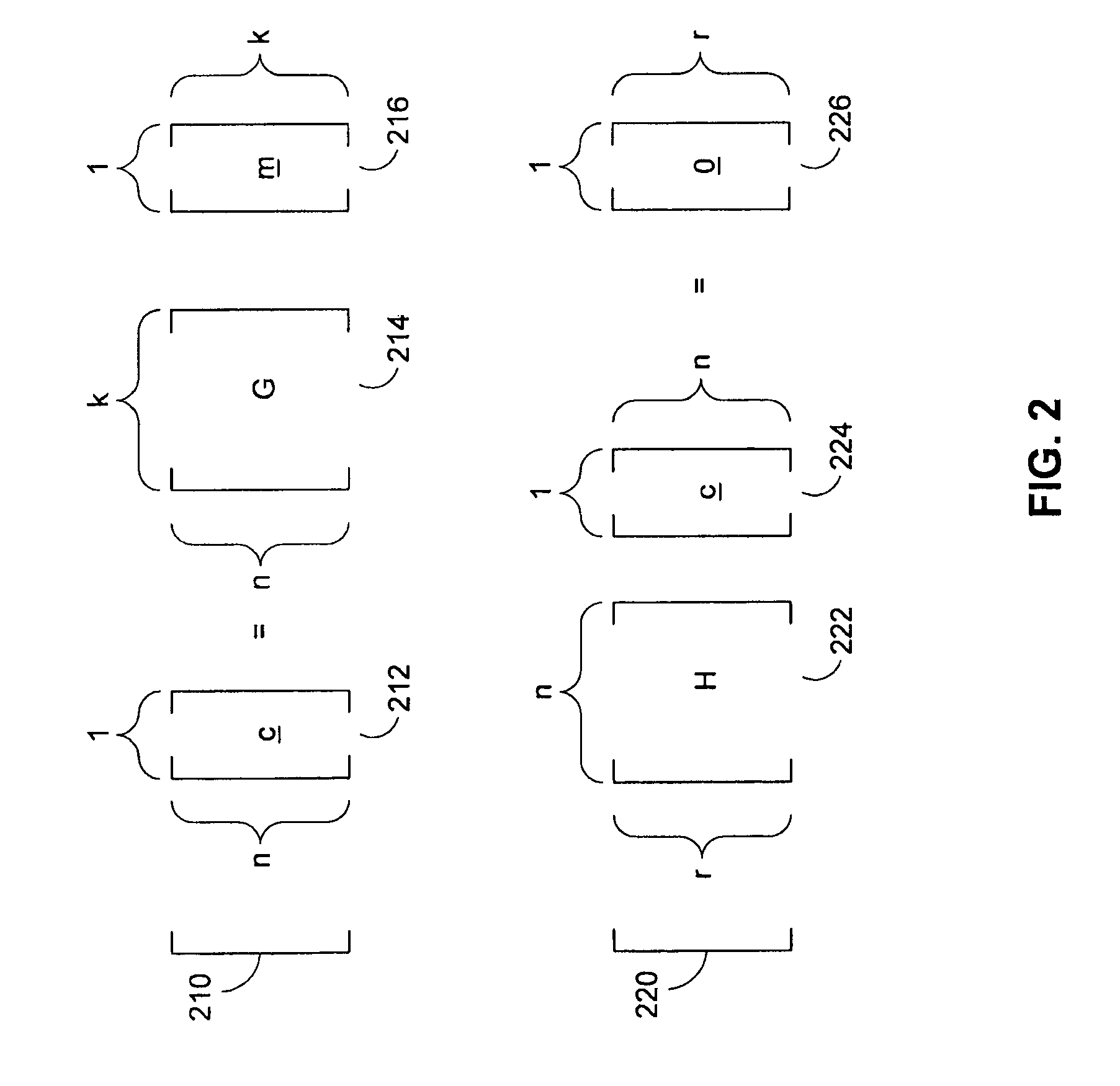

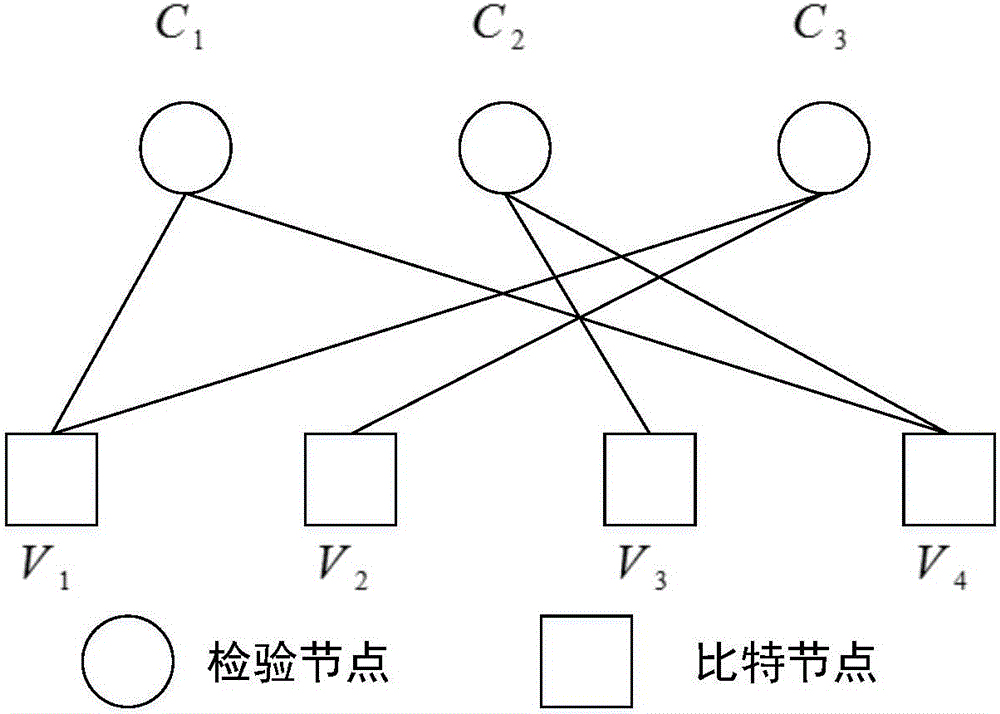

Systems, methods, and apparatus are provided for increasing decoding throughput in an LDPC decoder, such as in a wireless communications receiver or in a data retrieval unit. A checker-board parity check matrix and edge-based LDPC decoder structure are provided in which both vertical and horizontal processors are used simultaneously. Horizontal processors may be grouped into type-A and type-B horizontal processors, and similarly, vertical processors may be grouped into type-A and type-B vertical processors. Type-A processors may be used in different clock cycles than type-B processors to update memory locations in a decoding matrix without causing memory access conflicts.

Owner:MARVELL ASIA PTE LTD

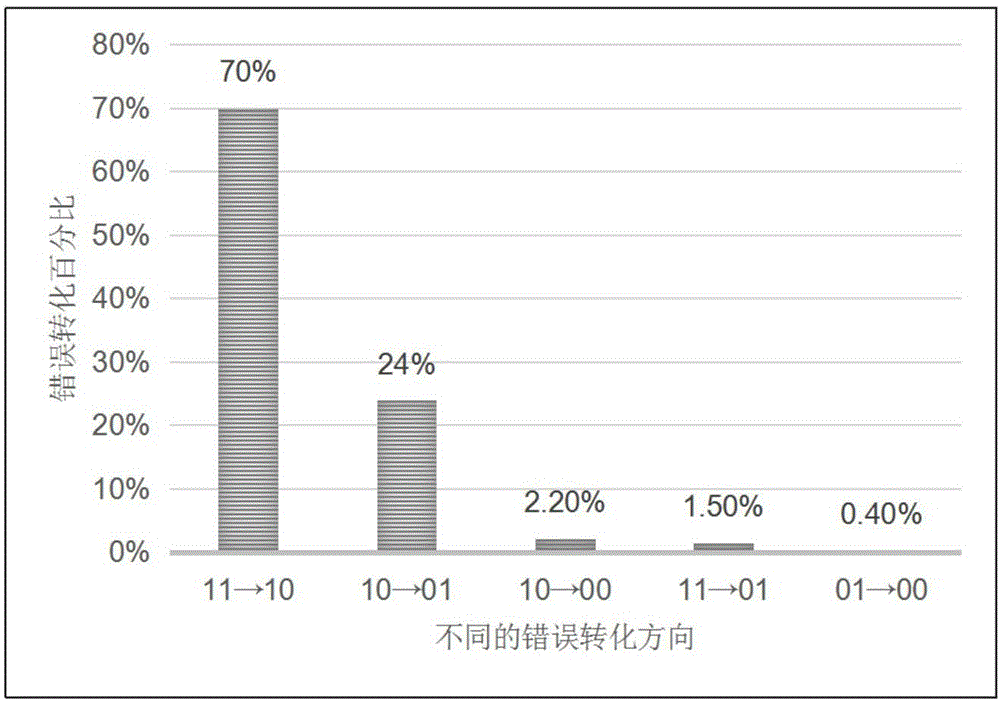

LDPC (low density parity check) decoding optimization method based on flash programming interference error perception

ActiveCN106371943AImprove decoding accuracyImprove decoding throughputError correction/detection using multiple parity bitsCode conversionLow densityDependability

The invention discloses an LDPC (low density parity check) decoding optimization method based on flash programming interference error perception. Along with the increase of NAND flash-memory storage density, more bit information is stored in each unit; the coupling interference along the units is high; the serious programming interference errors are caused, so that the traditional BCH code cannot ensure the data reliability; the LDPC code has error-correcting performance superior to that of the BCH code, and is applied to an NAND flash-memory storage system. The used optimized LDPC decoding algorithm has important significance. Through observation, the programming interference errors have value correlative characters; when the LDPC decoding is performed, the value correlative characters of the programming interference errors can be blended into the LDPC decoding process; the additional information is provided for bit judgment, so that the bit judgment precision is improved; the decoding convergence speed is accelerated; the LDPC decoding delay is reduced.

Owner:HUAZHONG UNIV OF SCI & TECH

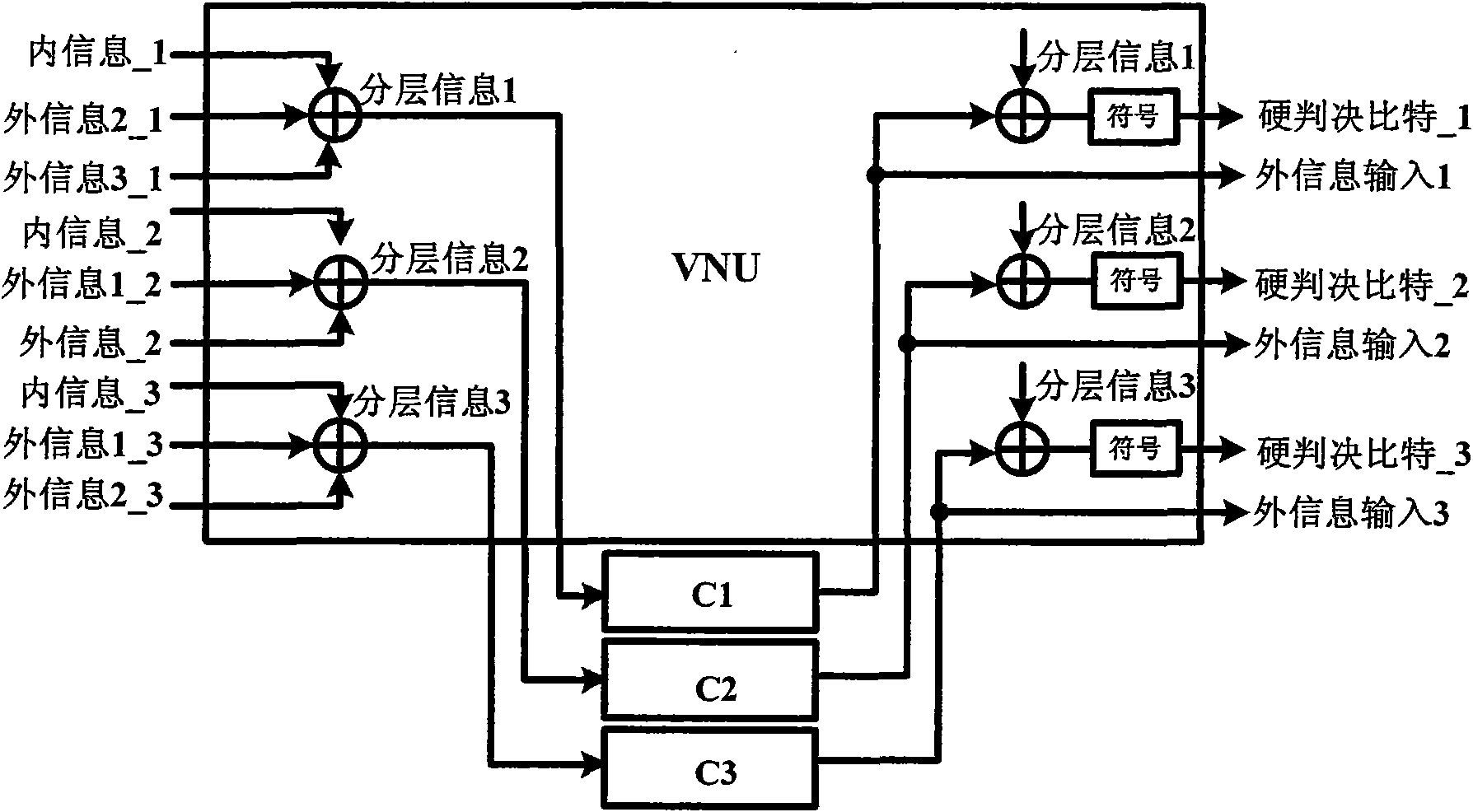

Parallel hierarchical decoder for low density parity code (LDPC) in mobile digital multimedia broadcasting system

InactiveCN101931416AReduce the number of iterationsImprove bit error performanceError correction/detection using multiple parity bitsSignal-to-noise ratio (imaging)Parallel computing

The invention discloses a parallel hierarchical decoder for a low density parity code (LDPC) in a mobile digital multimedia broadcasting system. The parallel hierarchical decoder adopts a partially parallel structure and is characterized in that: 1) each line of a check matrix is taken as a layer, check nodes of each layer are updated sequentially for each variable node, the variable node is updated after the check nodes of each layer are updated and a value obtained after updating is used in the updating of the check nodes of a next layer until an iteration is finished; and 2) the check nodes of a plurality of lines are selected for parallel computation under the condition that 1) is met, so that a partially parallel decoding structure can be realized. Compared with the conventional LDPC decoder, the parallel hierarchical decoder has the advantages of reducing average iteration times needed when a decoding convergence condition [bit error rate (BER) is less than or equal to 10 to 6] is met under the condition of the same signal to noise ratio and the same maximum iteration time, achieving higher error code performance, greatly increasing decoding throughput rate or effectively reducing power consumption and improving the error code performance of a system.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

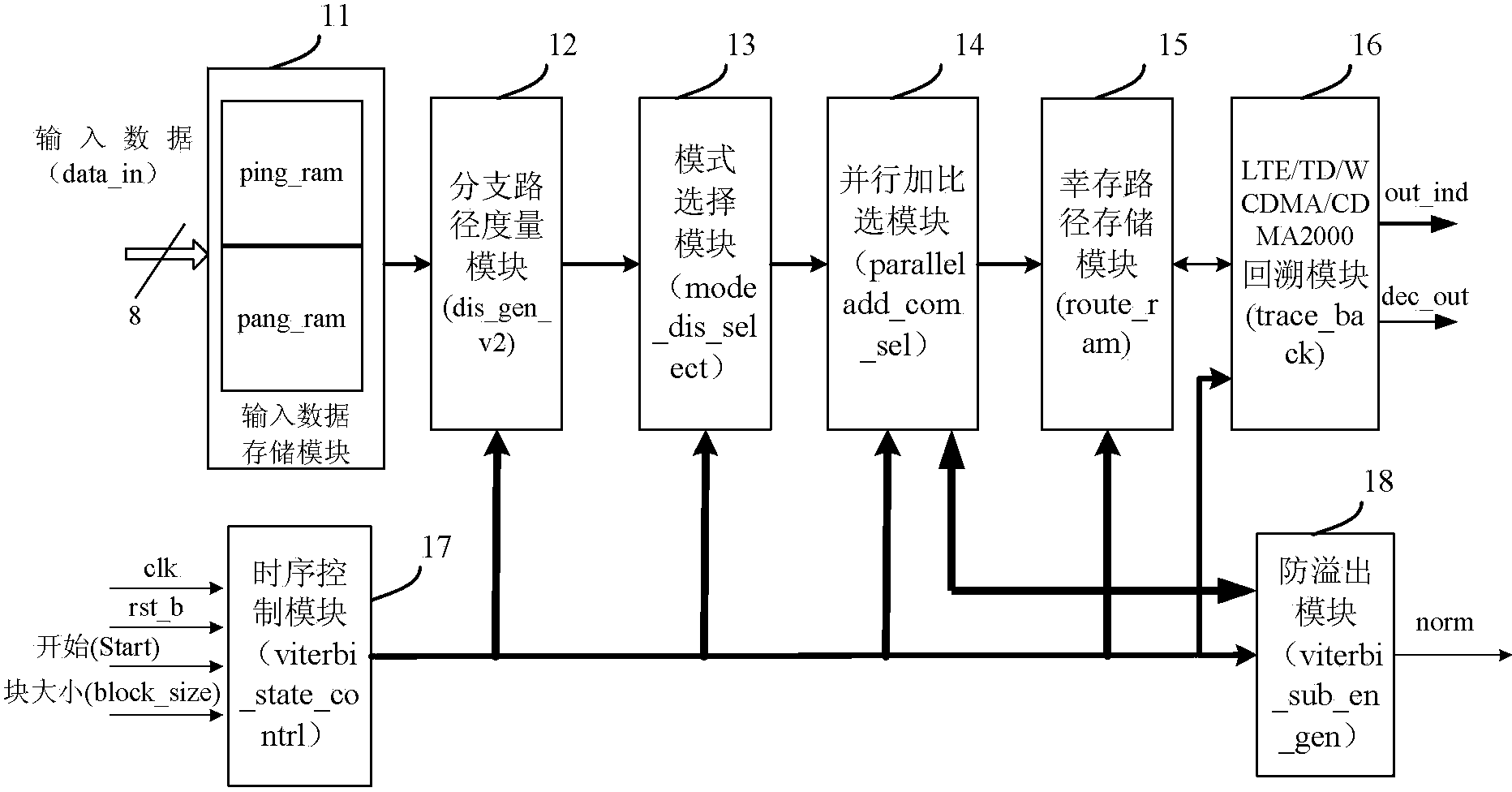

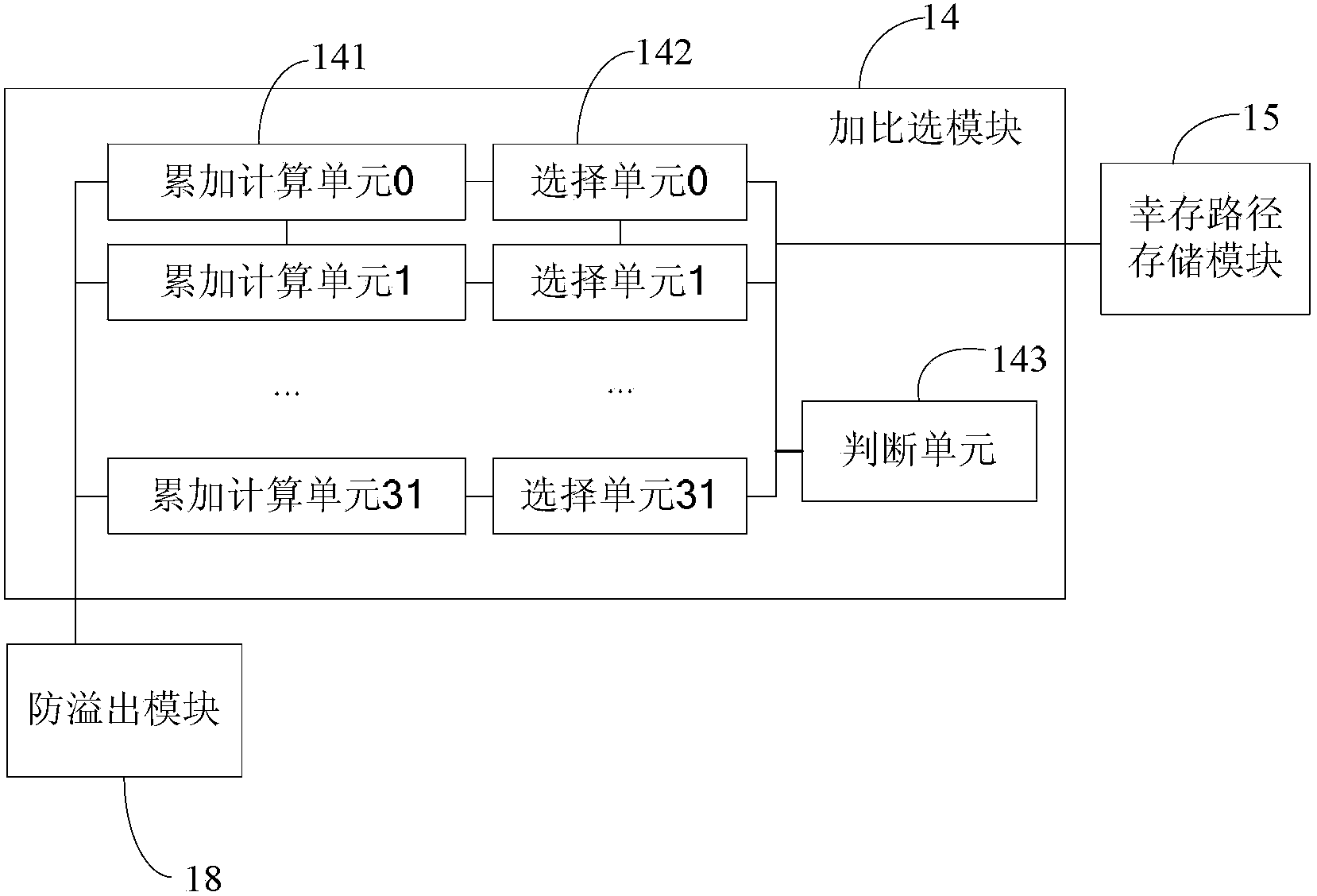

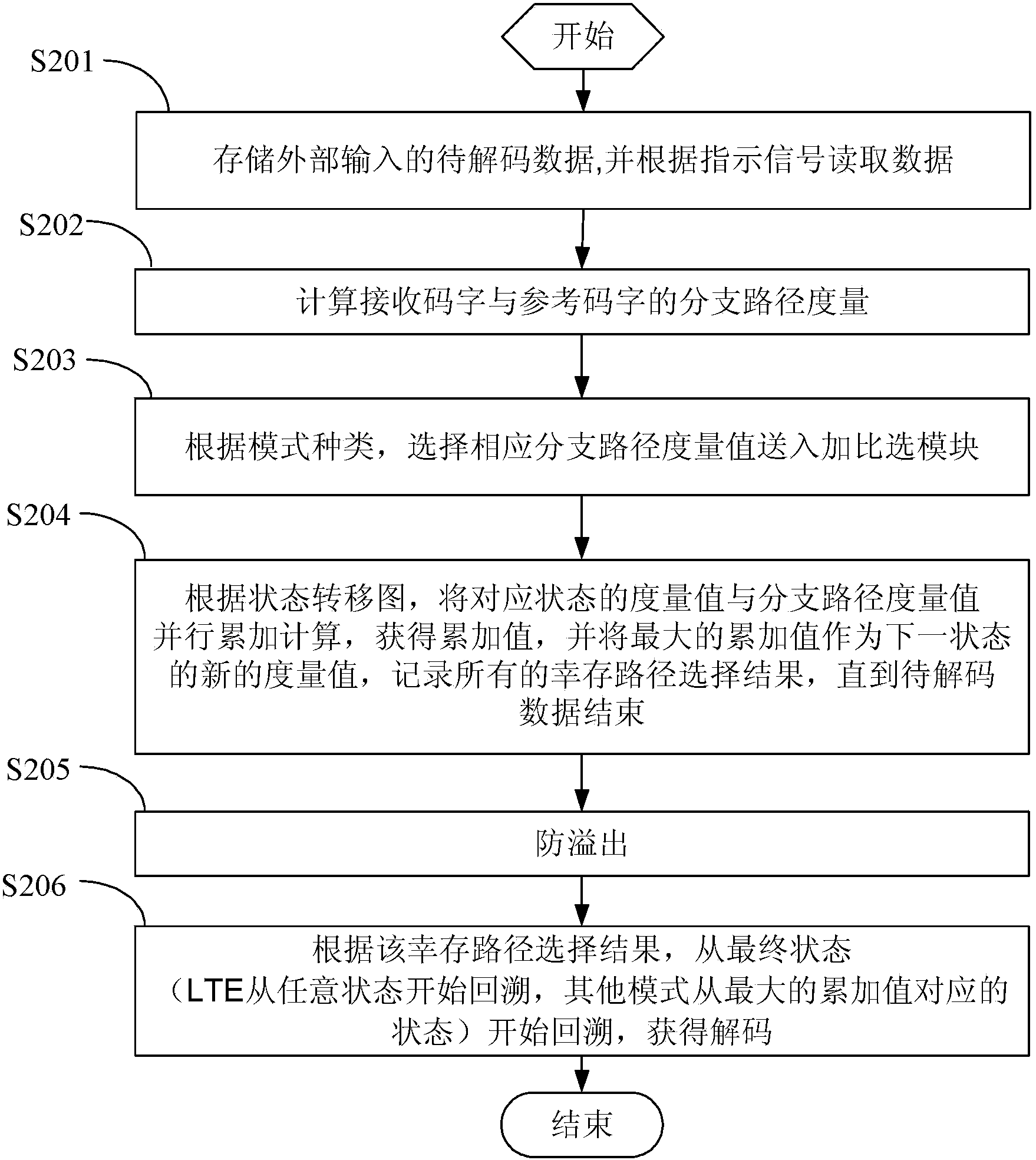

Multi-mode viterbi decoding apparatus and decoding method thereof

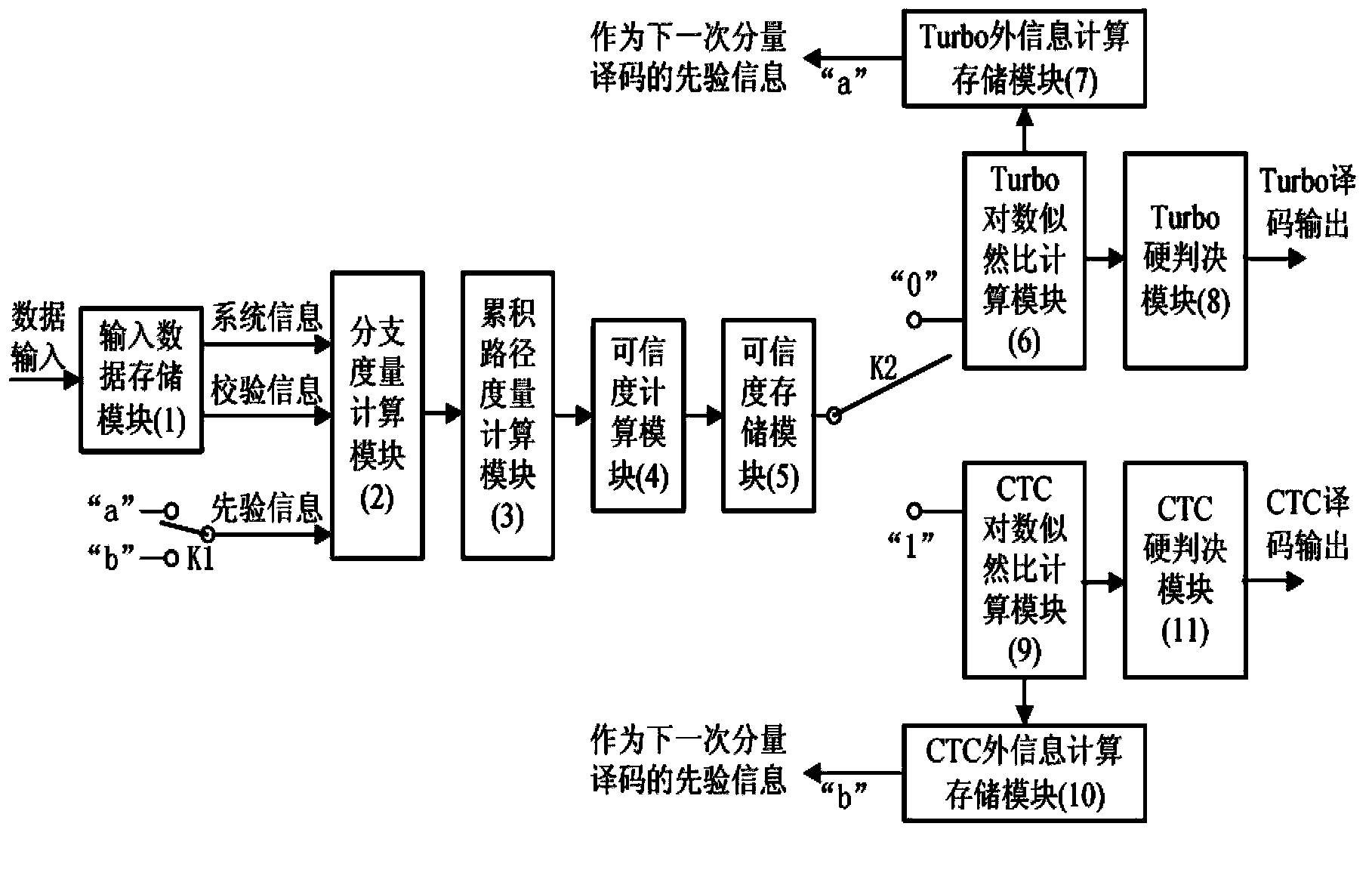

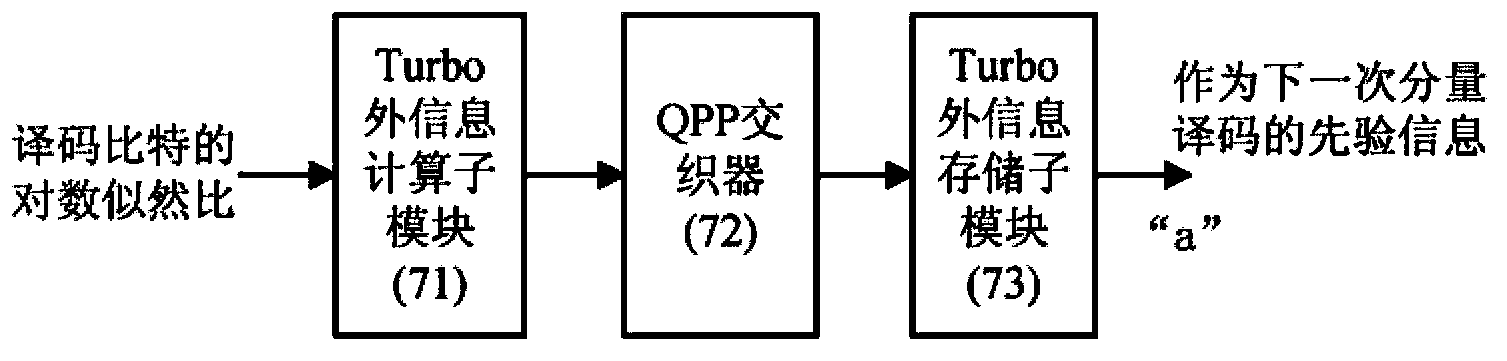

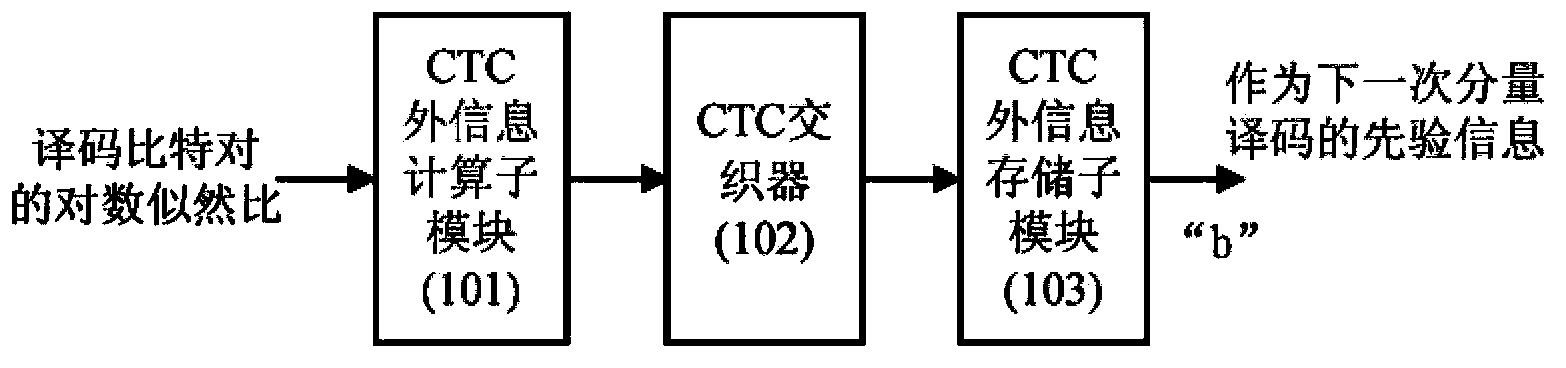

ActiveCN103427850ASimple designImprove decoding throughputOther decoding techniquesDecoding methodsComputer science

The invention provides a multi-mode viterbi decoding apparatus and a decoding method thereof. The decoding apparatus comprises an input data storage module, a branch path metric module, a mode selection module, a parallel add-compare-select module, a residual path storage module, a backtracking module and a sequential control module, wherein the parallel add-compare-select module is used for performing accumulative calculation on the metric values and branch path metric values of corresponding states according to a state transfer graph for obtaining accumulative values, and sending residual path selection results to the residual path storage module by taking the greatest accumulative value as the new metric value of a next state until data to be decoded ends; and the backtracking module is used for selecting different backtracking modes according to different encoding modes, and begins backtracking from any a state or the state corresponding to the greatest accumulative value so as to obtain decoding results according to the residual path selection results stored by the residual path storage module. By using the multi-mode viterbi decoding apparatus and the decoding method thereof, enormous resources can be shared, design can be optimized, and the decoding throughput can be improved.

Owner:SANECHIPS TECH CO LTD

Browsing JPEG images using MPEG hardware chips

InactiveUS7254272B2Quick ViewSignificant loss of image fidelityCharacter and pattern recognitionTelevision systemsComputer hardwareImaging processing

Rapid throughput of still image compressed data (e.g. JPEG) is achieved for presentation of images in rapid succession for browsing or browsing by panning within large images by using a hardware decoder adapted for presentation of moving images to reduce the processing load which must be performed in accordance with software although the still image data is incompatible with still image data in many respects; some of which necessarily lead to a loss of image fidelity. The still image data is partially decoded (e.g. entropy decoded) in software processing and re-encoded and reformatted to a form which can at least be accepted by the hardware decoder even though not compliant with any particular moving picture data standard (e.g. MPEG). Storage in the hardware decoder is reallocated to provide, in combination with a reduction of slower software processing, a throughput increase of four-fold or more. Software processing of the still image data is also allowed to proceed and the result substituted for the result of the hardware decoding if a given image is viewed for a time sufficient for the software image processing to be completed.

Owner:INT BUSINESS MASCH CORP

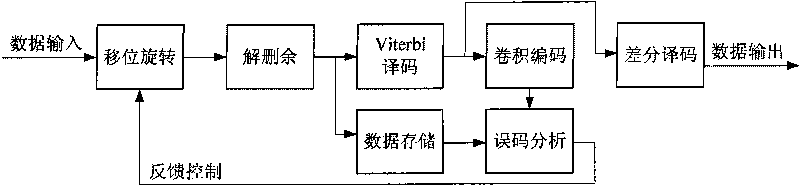

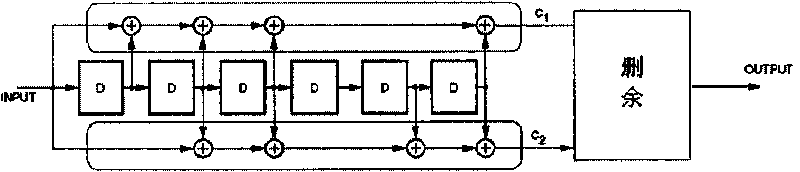

Parallel multicode-rate convolutional code decoding method and realization device thereof

InactiveCN101764622AMeet the requirements of high-speed information transmission communication systemImprove decoding throughputError correction/detection using convolutional codesControl signalAmbiguity

The invention discloses a parallel multicode-rate convolutional code decoding method and a realization device thereof. The parallel multicode-rate convolutional code decoding method comprises the following steps of: S1. receiving Nin paths of parallel input signals, and shifting the input signals under the effect of a shifting control signal and outputting the input signals, wherein output signals are also Nin paths of parallel signals, and the Nin is positive integers; S2. partially eliminating the phase ambiguity of the output signals; S3. taking the signals processed in the S2 as effectivedata, adding guard intervals for the effective data to assemble into a data frame, and taking the data frame as the input of a parallel convolutional code; S4. carrying out the convolutional decodingon the assembled data frame after being processed in the step S3; and S5. merging multipath outputs of the parallel convolutional decoding into one path and outputting in parallel. The invention provides the parallel multicode-rate convolutional code decoding method aiming at the defect that the throughput rate of the traditional convolutional decoding can not satisfy high-speed communication, improves the decoding throughput rate and the effective payload velocity by adopting a parallel partitioning processing technology, and can satisfy requirements of high-velocity information transmissioncommunication systems, such as satellite communication, and the like.

Owner:TSINGHUA UNIV

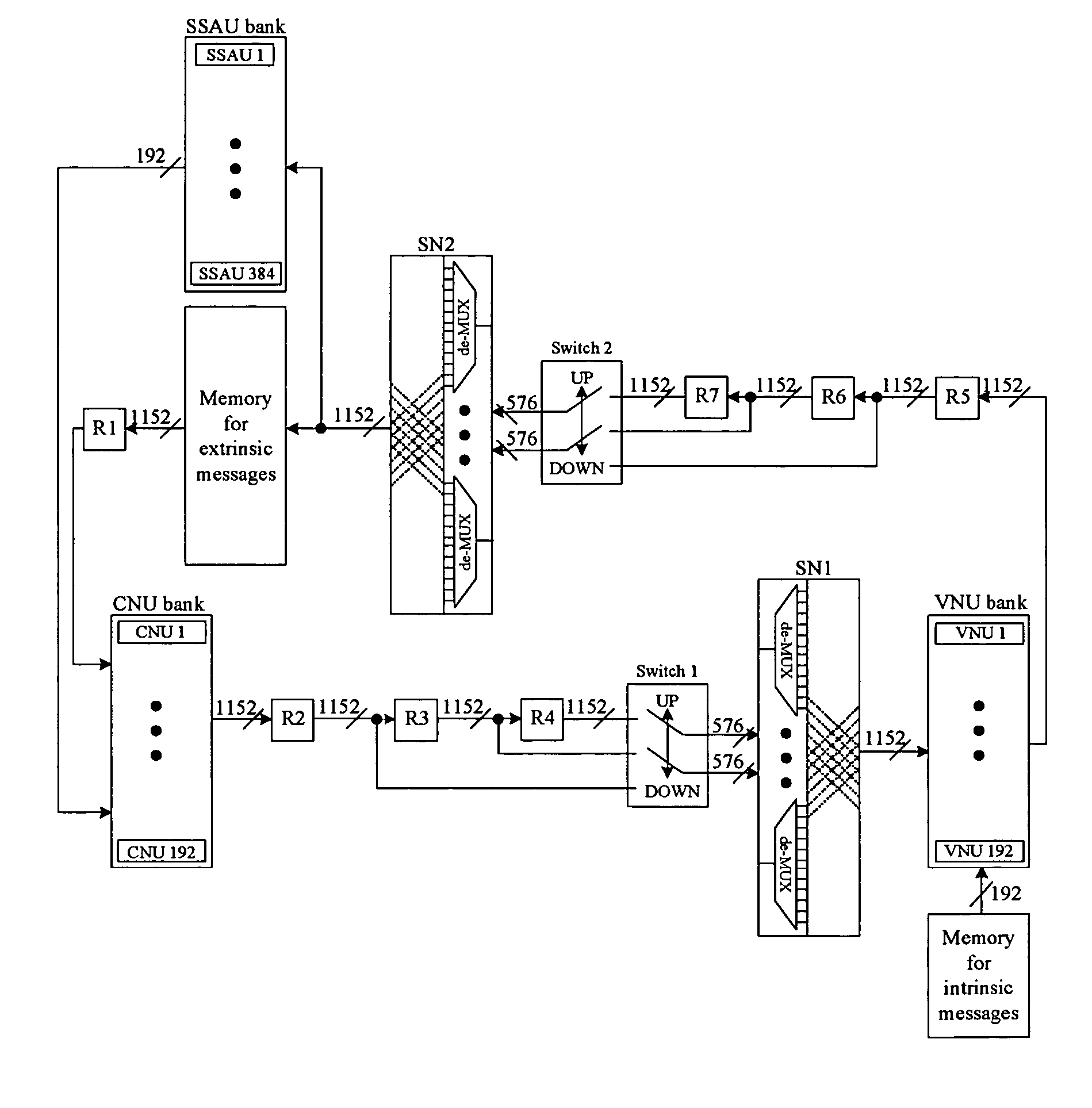

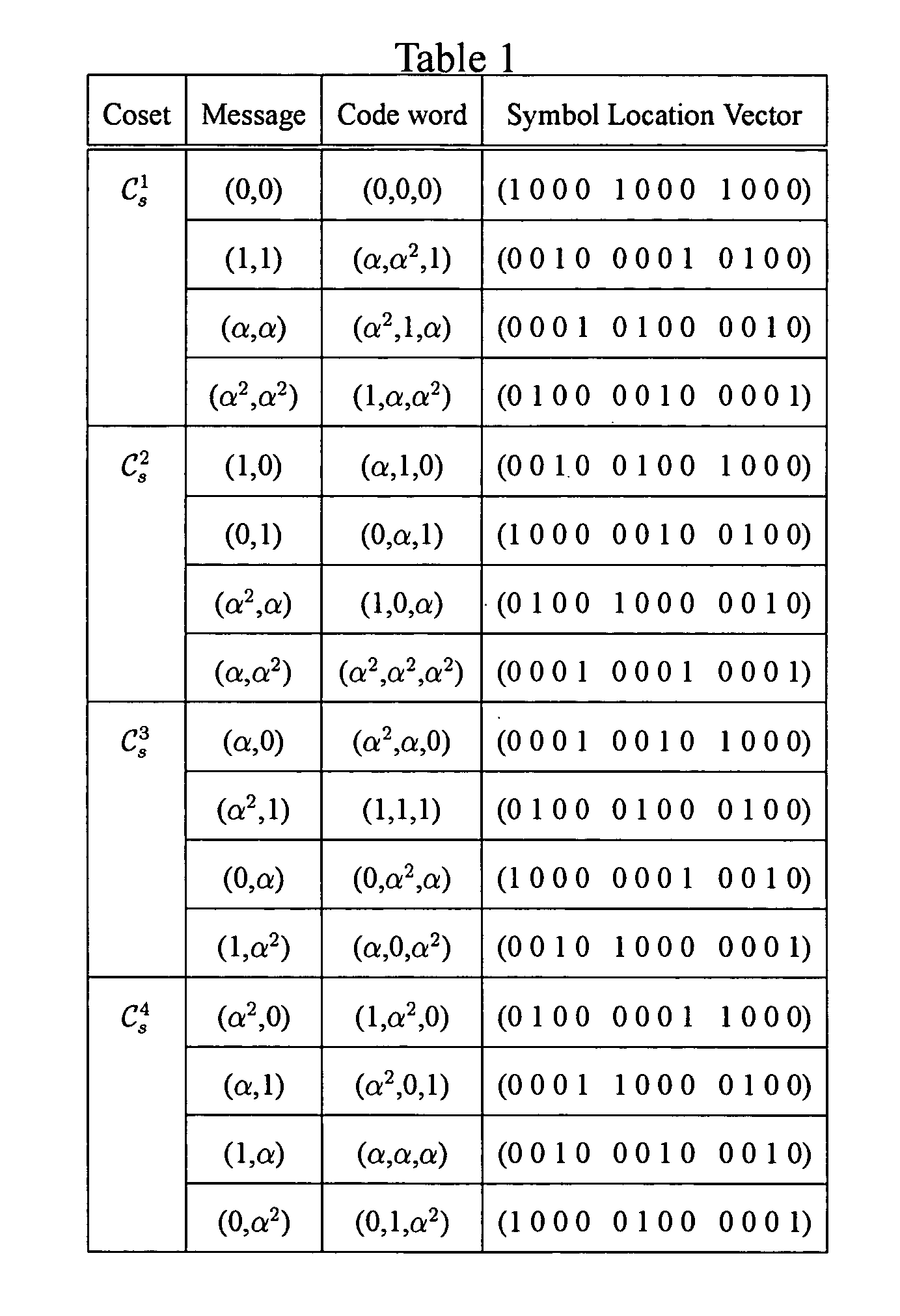

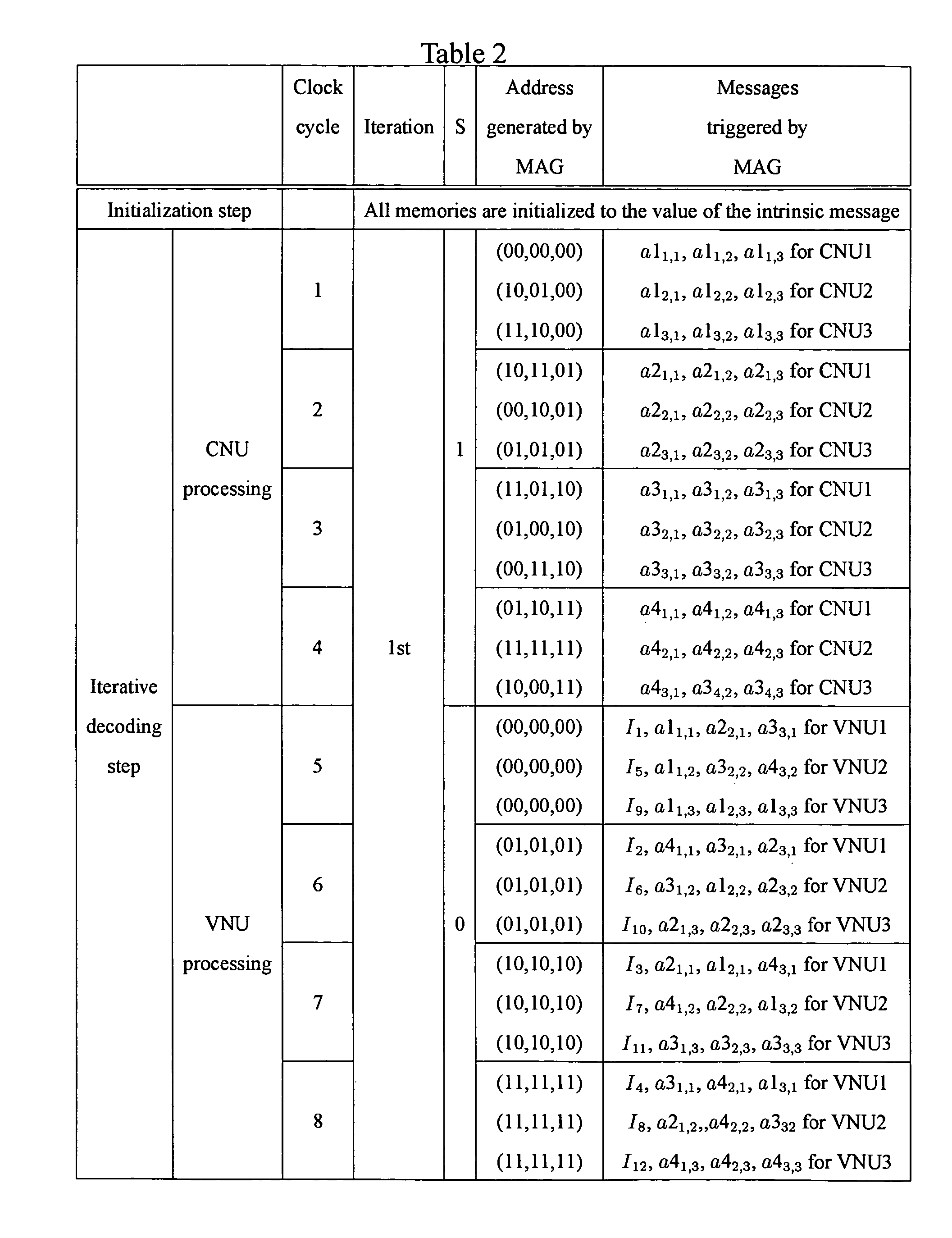

System and method for designing RS-based LDPC code decoder

InactiveUS7716553B2Low costImprove decoding throughputData representation error detection/correctionCode conversionMemory addressComputer architecture

Owner:PARHI KESHAB K

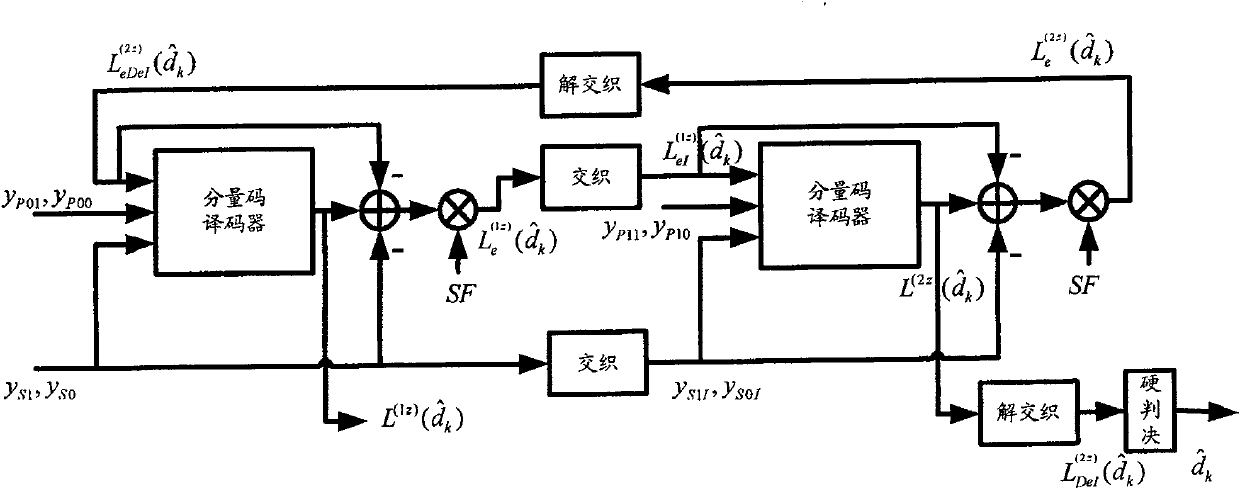

General high-performance Radix-4SOVA decoder and decoding method

InactiveCN103354483AAvoid disadvantagesImprove decoding performanceError preventionComputer architectureSecondary component

The invention discloses a general high-performance Radix-4SOVA decoder and a decoding method. In the prior art, in the Radix-4SOVA decoder, only a binary system Turbo code based on bit interleaving is supported. By using the decoder and the method of the invention, the above problem is mainly solved. The method has the following steps of receiving channel information and storing; reading the channel information of a first component code, carrying out first component decoding which means that a branch metric, a cumulative path metric, credibility, a log-likelihood ratio and extrinsic information are successively calculated, interleaving the extrinsic information and storing; reading the channel information of a second component code and completing secondary component decoding; determining whether a maximum iteration is reached; if the maximum iteration is not reached, starting next iteration decoding; otherwise, carrying out hard decision on the log-likelihood ratio so as to obtain an estimation value of a decoding bit and finishing the decoding. According to the invention, a credibility updating method based on a bit pair is used; the general and configurable high performance decoding of a binary system Turbo code and a duobinary system convolution Turbo code can be realized; the method can be used in a general and configurable Turbo decoder in a LTE and WiMAX system.

Owner:XIDIAN UNIV

Method and apparatus for performing decoding using LDPC code

InactiveUS8347170B2Improve decoding throughputLower latencyError correction/detection using multiple parity bitsCode conversionTheoretical computer scienceParity-check matrix

Owner:LG ELECTRONICS INC

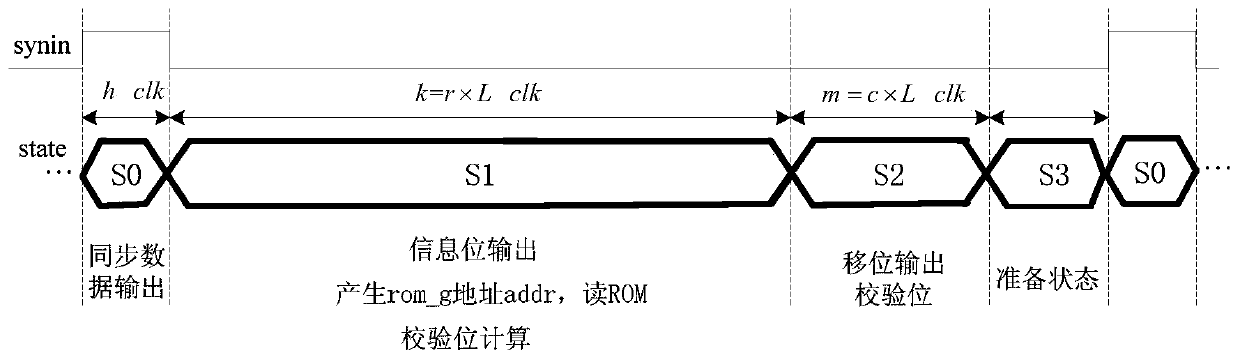

high-speed code rate compatible LDPC encoder of a QC-LDPC code based on an FPGA

ActiveCN109802687AAchieving code rate compatibilityImprove job stabilityError correction/detection using multiple parity bitsHigh level techniquesComputer architectureTime delays

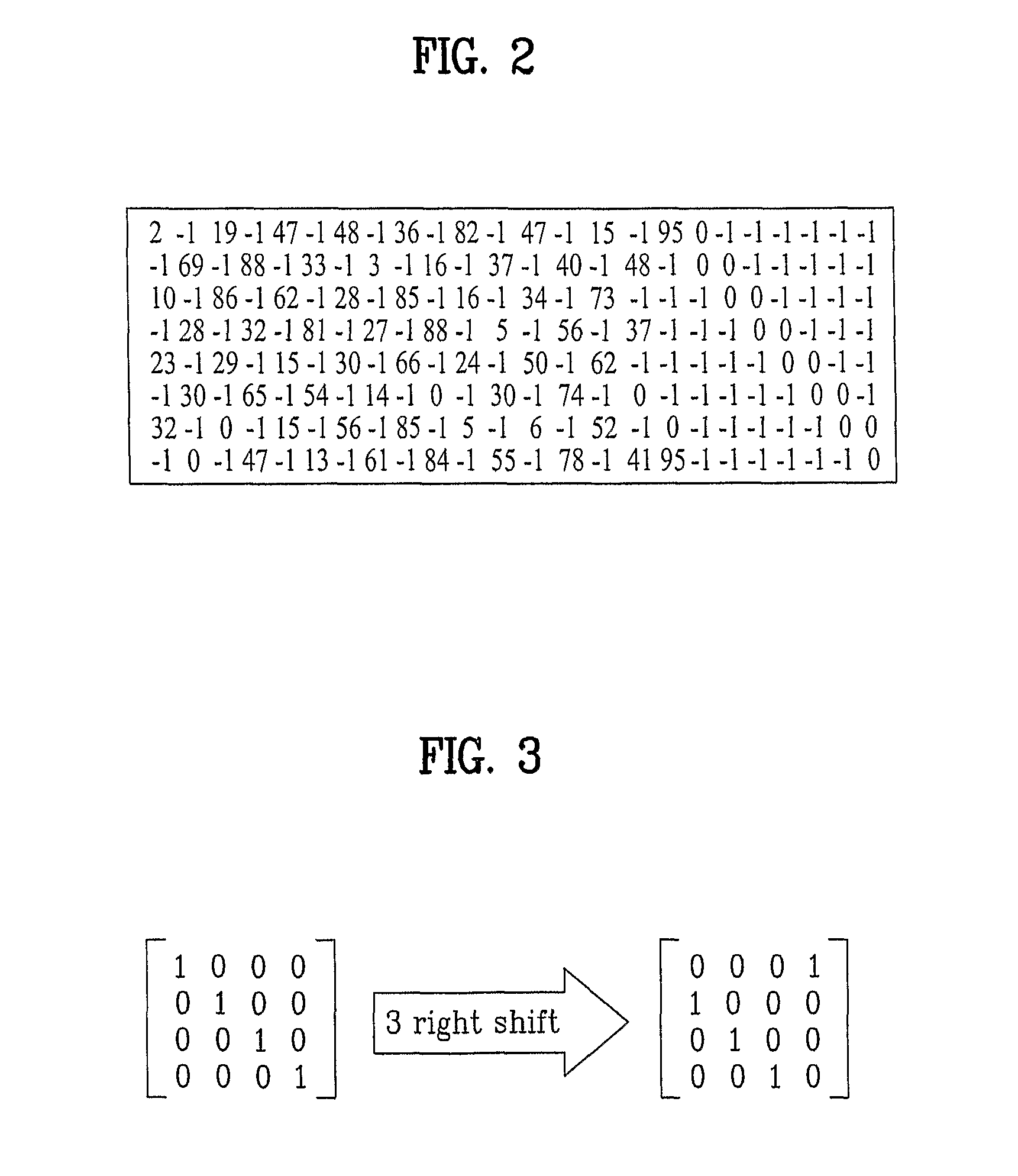

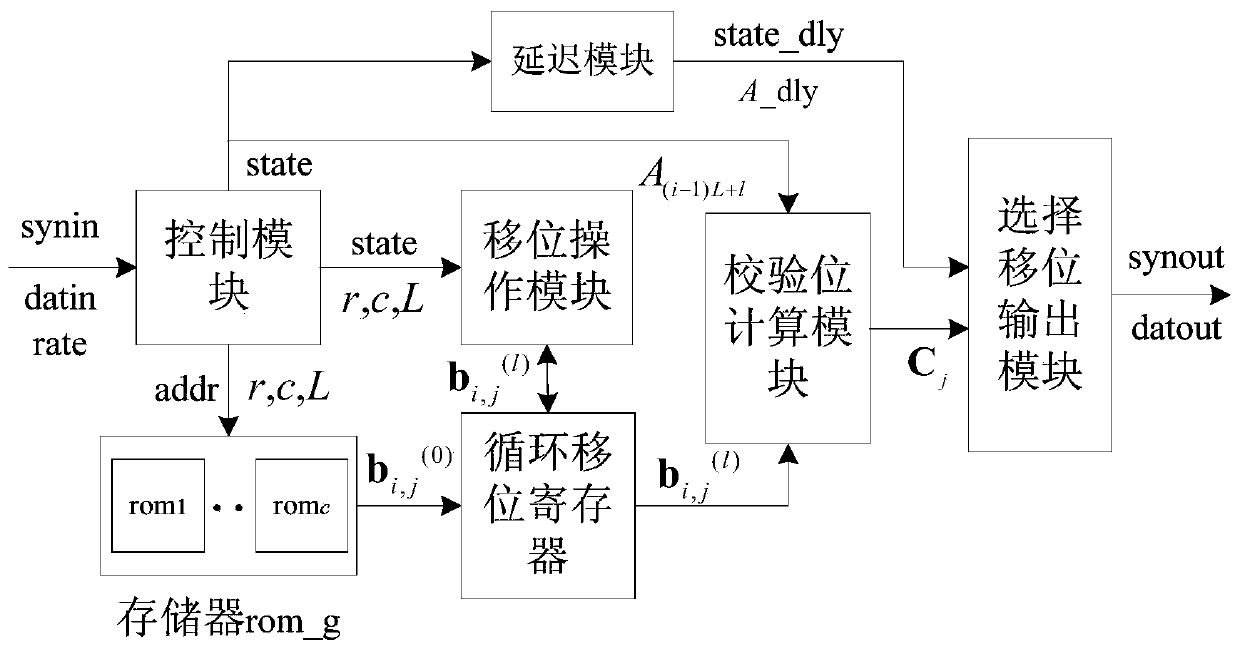

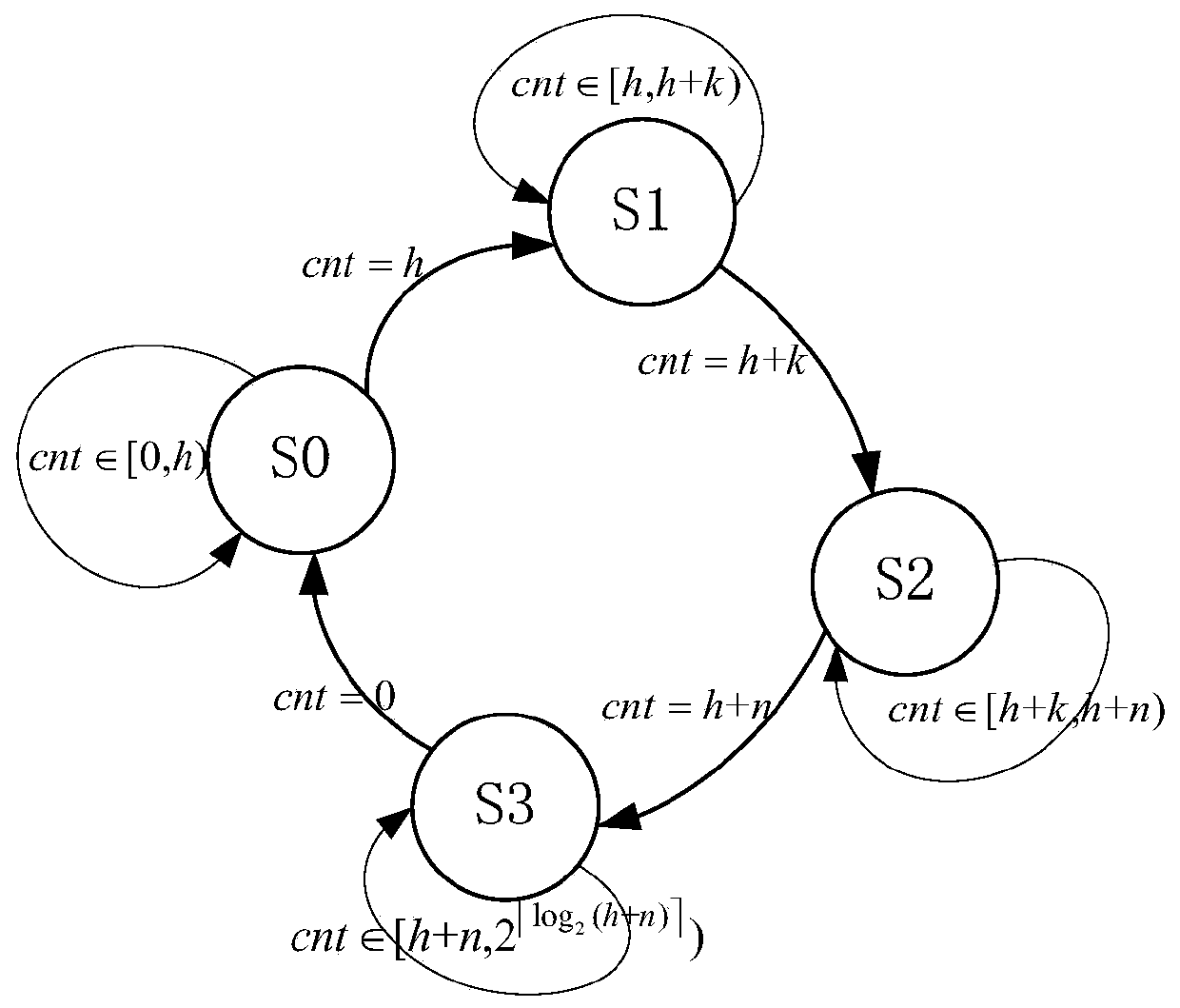

The invention discloses a high-speed code rate compatible LDPC encoder of a QC-LDPC code based on an FPGA. The method comprises the following steps of sending a column vector of a component of each information sub-block of an input information sequence to a check bit calculation module through a control module; performing time delay on a column vector of a component of the information sub-block through a delay module, and sending the column vector to a selective shift output module; enabling the shift operation module to determine a shift method of the cyclic shift register according to the code rate rate rate of the encoder, and send the shift method to the cyclic shift register; According to a shift method for determining the cyclic shift register, performing shift operation on the firstrow data bi, j (0) of the cyclic sub-matrixes Bi, j, calculating to obtain a check vector according to a result after the shift operation and information bit by bit of an input information bit sequence, and sending the check vector to a selective shift output module; And selecting a shift output module, and outputting the check vector and the column vector of the component of the information sub-block at different times. The high-speed code rate compatible encoder architecture disclosed by the invention can realize resource sharing between different code rates to the greatest extent.

Owner:XIAN INSTITUE OF SPACE RADIO TECH

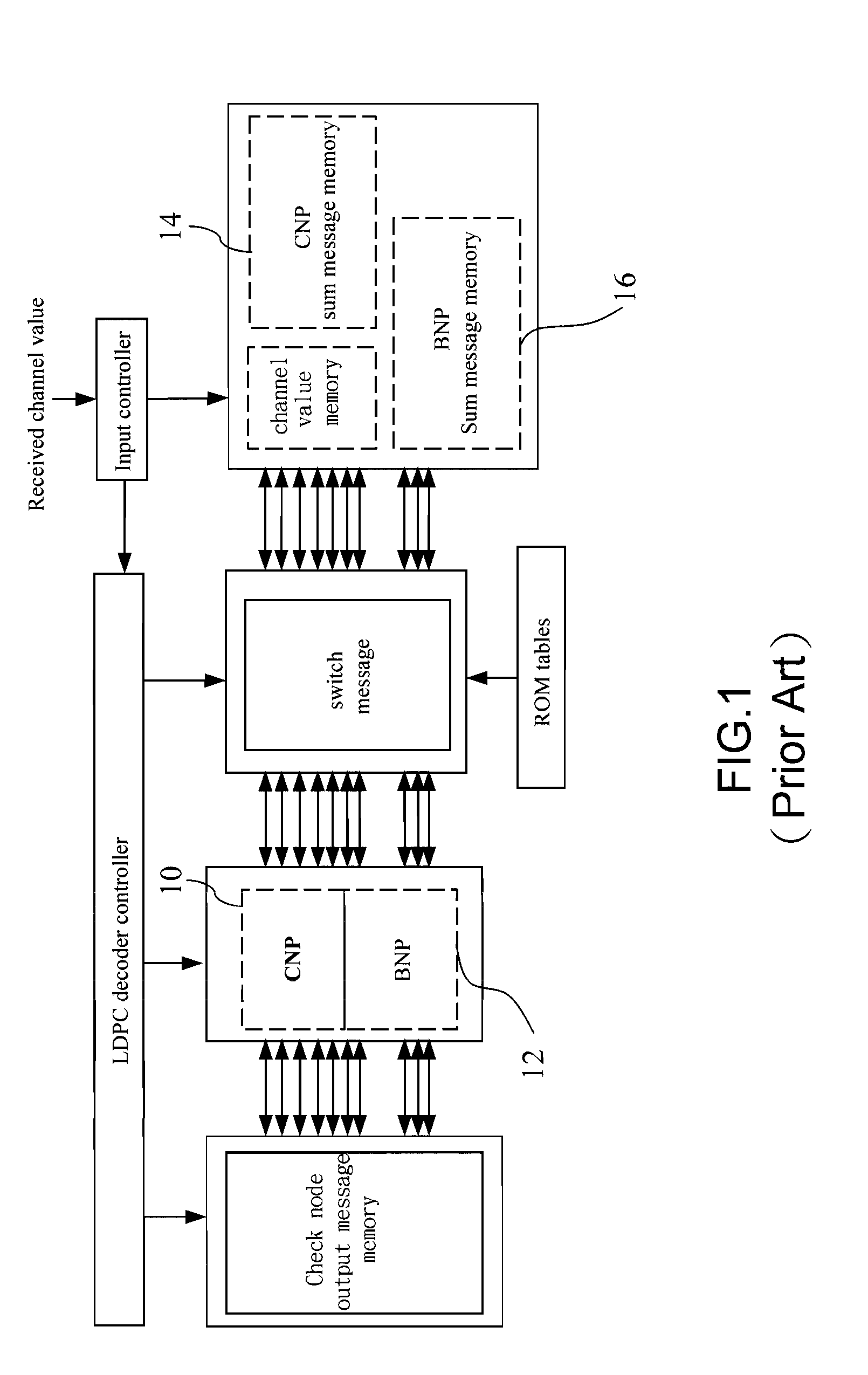

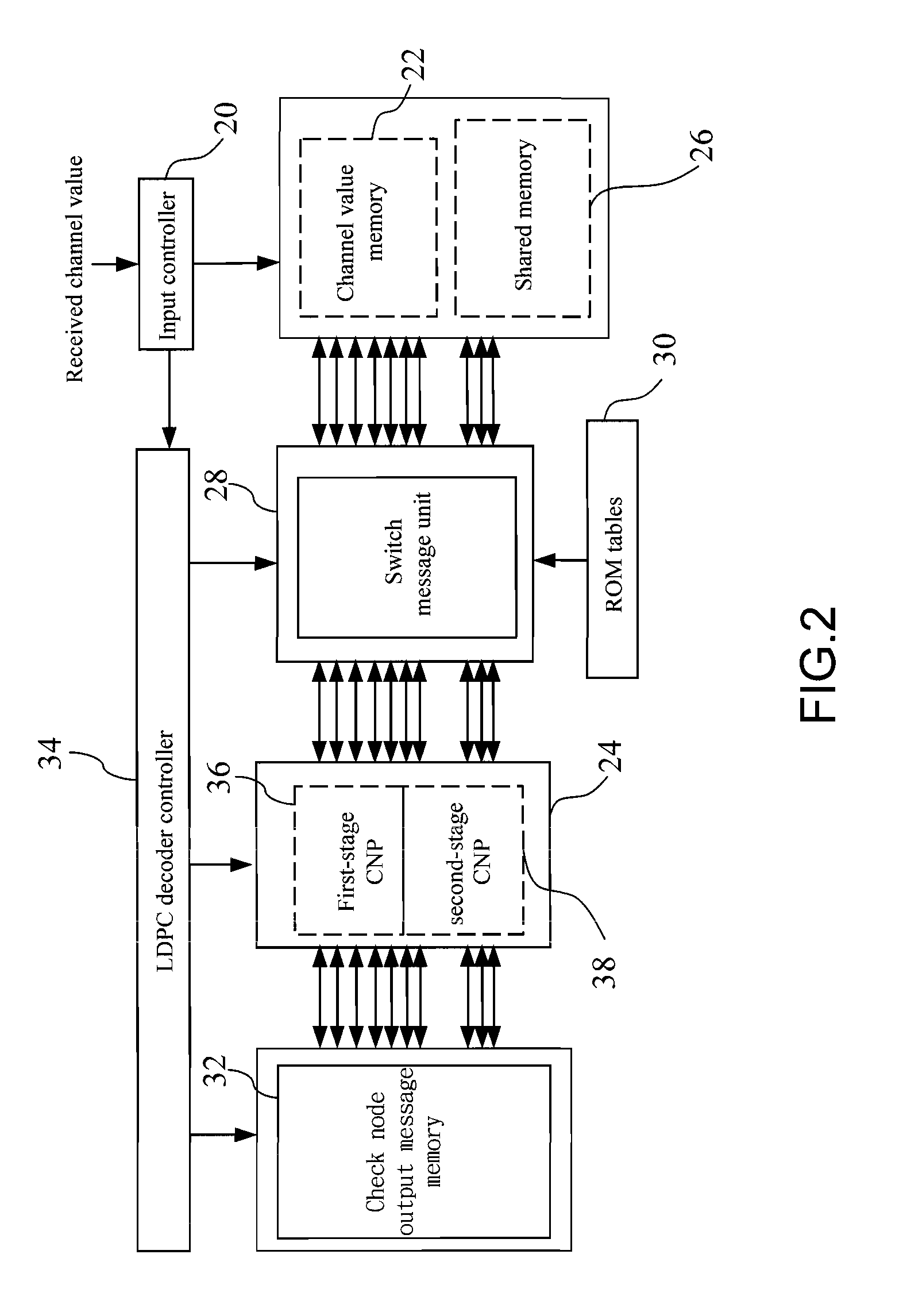

Operating method applied to low density parity check (LDPC) decoder and circuit thereof

ActiveUS20090037799A1Small sizeImprove decoding throughputError detection/correctionOther error detection/correction/protectionLow densityComputer science

An operating method applied to low density parity check (LDPC) decoders and the circuit thereof are proposed, in which original bit nodes are incorporated into check nodes for simultaneous operation. The bit node messages are generated according to the different between the newly generated check messages and the previously check node messages. The bit node messages can be updated immediately, and the decoder throughput can be improved. In the other way, the required memory of LDPC decoders can be effectively reduced, and the decoding speed can also be enhanced.

Owner:NAT CHIAO TUNG UNIV

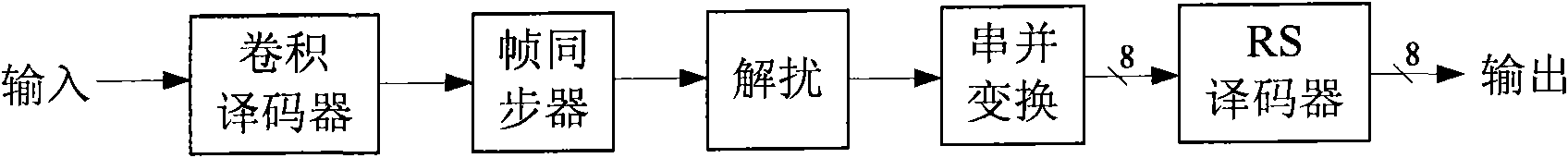

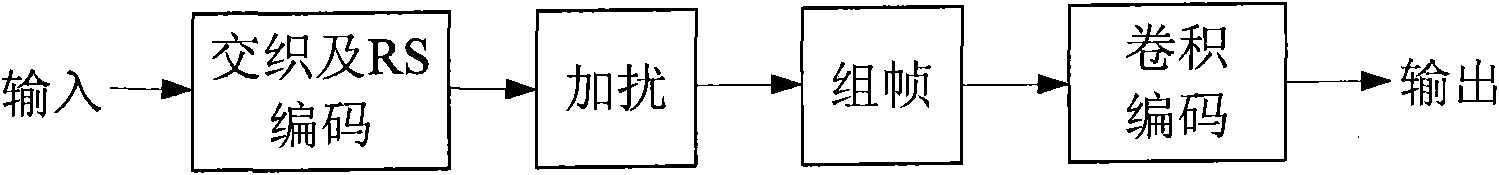

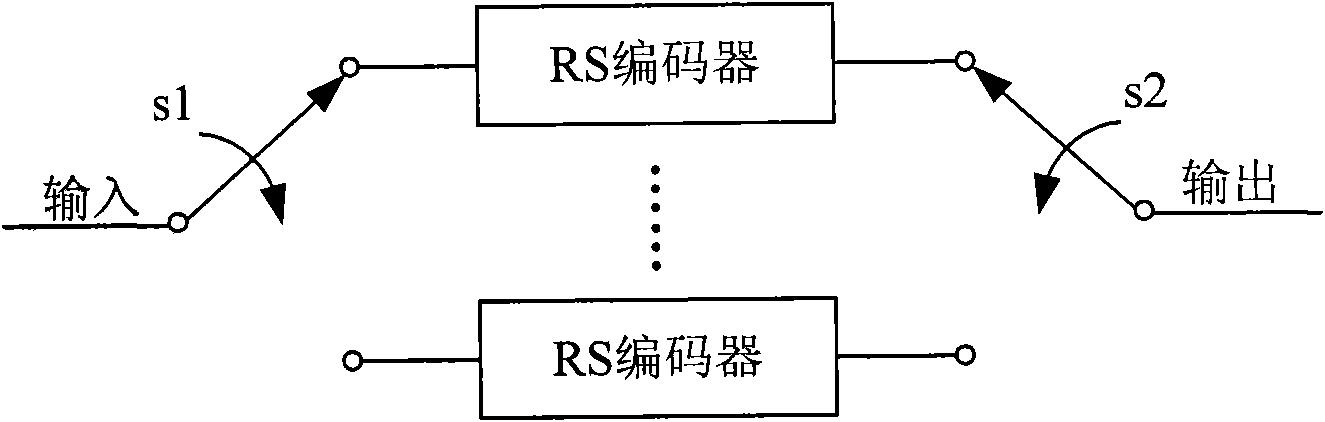

Parallel folding-RS cascade coding method and realizing device thereof

InactiveCN101777927AImprove decoding throughputIncrease speedError correction/detection by combining multiple code structuresDecoding methodsComputer architecture

The invention discloses a parallel folding-RS cascade coding method and a realizing device thereof. The method comprises the following steps of: S1, blocking the received Nin path input data into folding coding frame as the input of the parallel folding coding; S2, performing parallel winding coding on the folding coding frame output in the step S1 and outputting valid data in the folding coding frame; S3, combining multi-path output of the parallel folding coding into one path of data and outputting the data in parallel by taking a field as a unit, wherein the bit width of the field is NRS bit; S4, searching the field on the initial position of a frame synchronous identifier word in the data output in the step S3 as well as the position in the field, outputting RS signal frame body data and identifying the initial position of the frame body; S5, descrambling the data output in the step S4 in parallel; and S6, performing symbol-solving interlacing and RS coding on the data descrambledin the step S5. The invention improves the coding throughput rate and effective net load rate of the folding-RS cascade coder and can satisfy the coding requirement in the high-rate information transmission application occasions for satellite communication, and the like.

Owner:TSINGHUA UNIV

Operating method and circuit for low density parity check (LDPC) decoder

ActiveUS8108762B2Small sizeImprove decoding throughputError detection/correctionCode conversionLow densityComputer science

Owner:NAT CHIAO TUNG UNIV

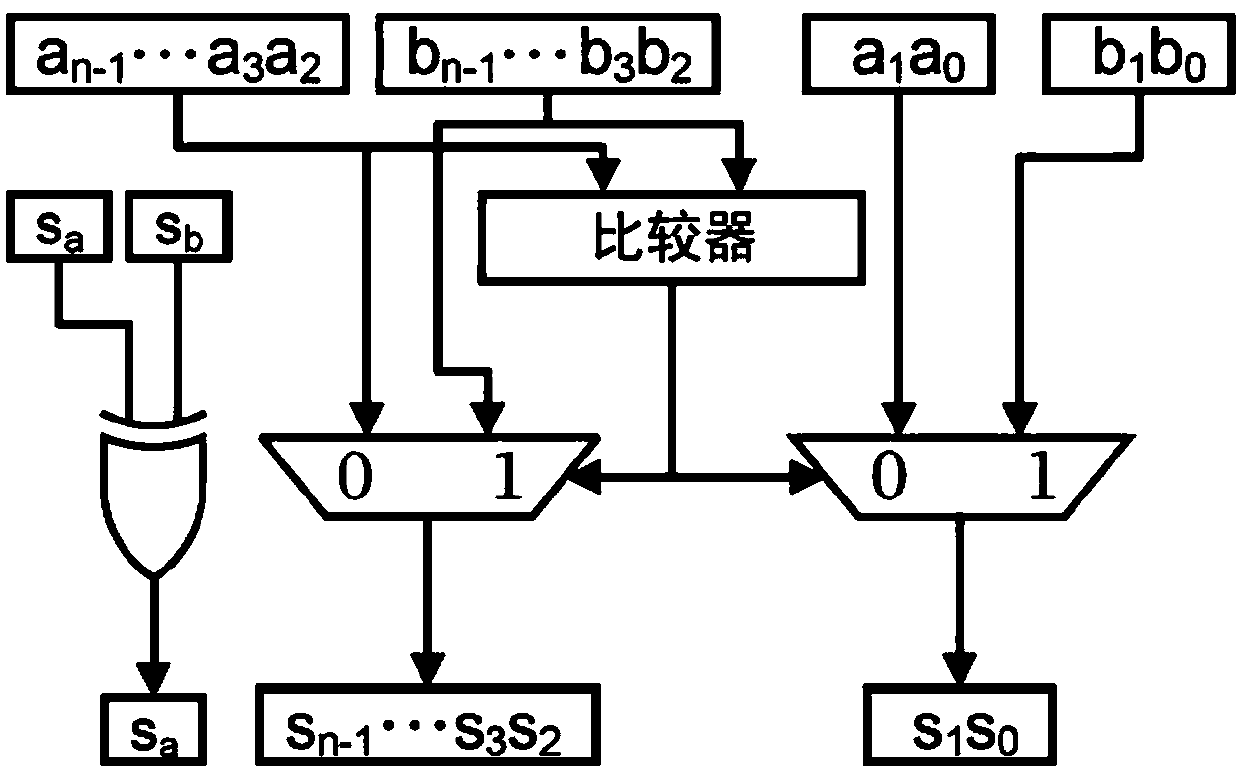

Approximate calculation-based polarization code belief propagation decoding method and decoder

ActiveCN108449091AReduce consumptionLimit decoding throughputError correction/detection using linear codesApproximate computingBelief propagation

The invention discloses an approximate calculation-based polarization code belief propagation decoding method and decoder. Approximate optimization treatment is executed for two types of decoding nodes in the conventional polarization code belief propagation decoder, thus, for the first type of node which realizes absolute value comparison operation of input data, when comparing input data absolute value size, only front section bits of the input data are compared, and bits of the back is ignored; and for the second type of node which realizes additive operation for the input data, a full adder and a full subtractor simultaneously perform operation for the absolute value of the input data, and a control number is generated according to an absolute value comparison result for performing screening, and a plus one unit in the operation only acts on the bits of the back part of the input data. According to the method and the decoder provided by the invention, key path delay and hardware consumption of the whole decoder are reduced by means of the approximate calculation. A simulation result shows that the method and the decoder provided by the invention can effectively reduce hardwareconsumption of the decoder and improve decoding efficiency.

Owner:SOUTHEAST UNIV

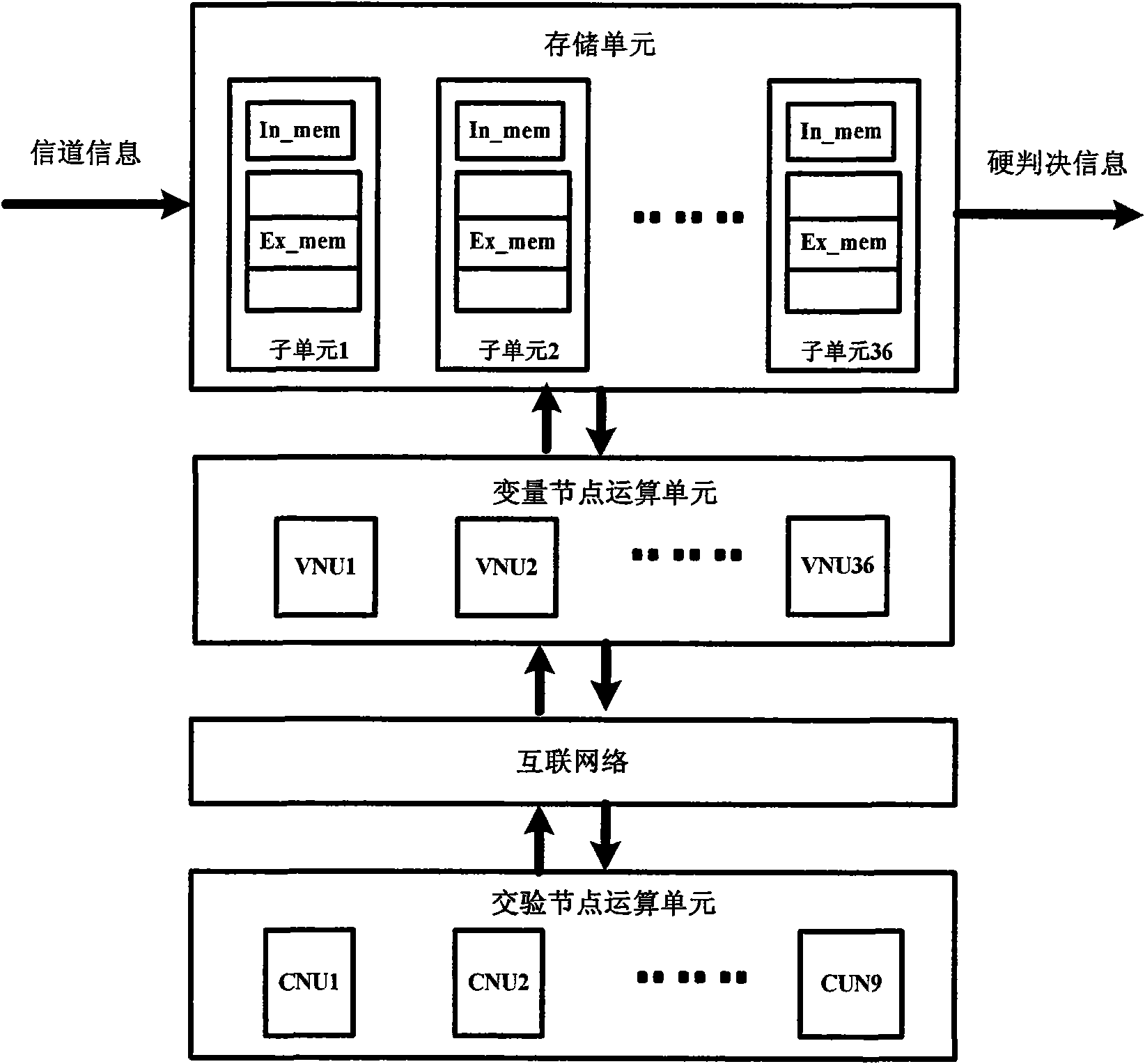

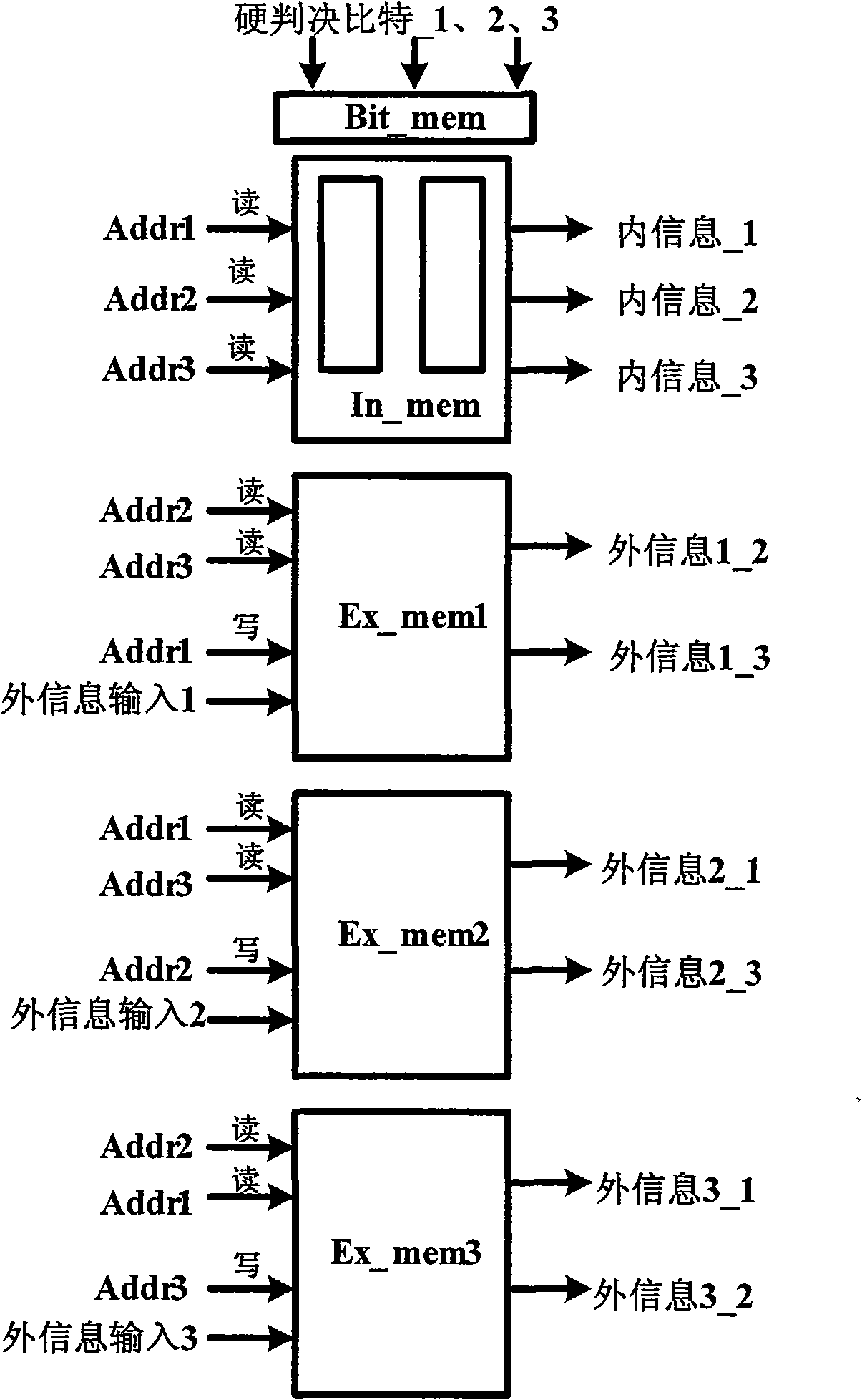

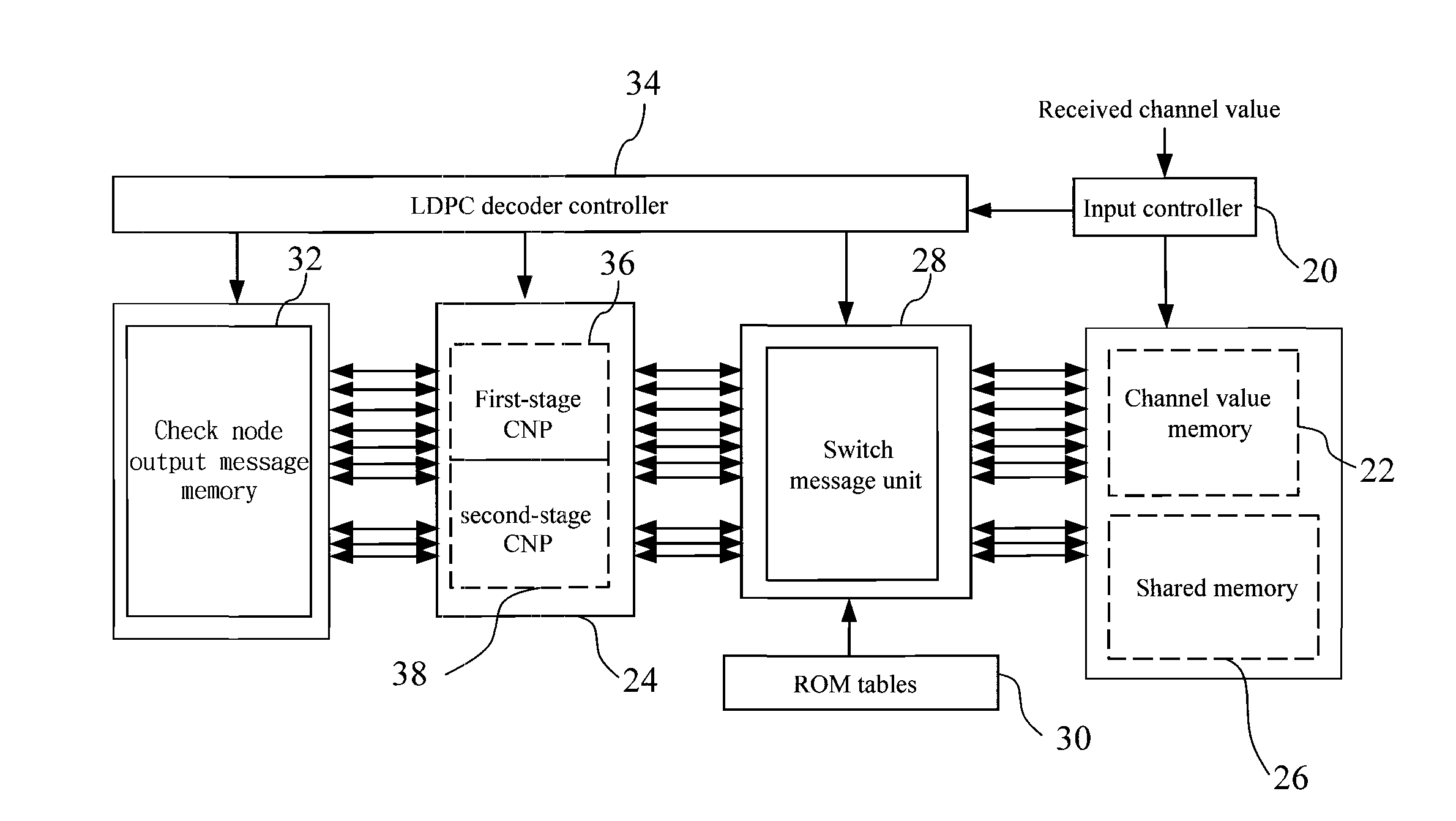

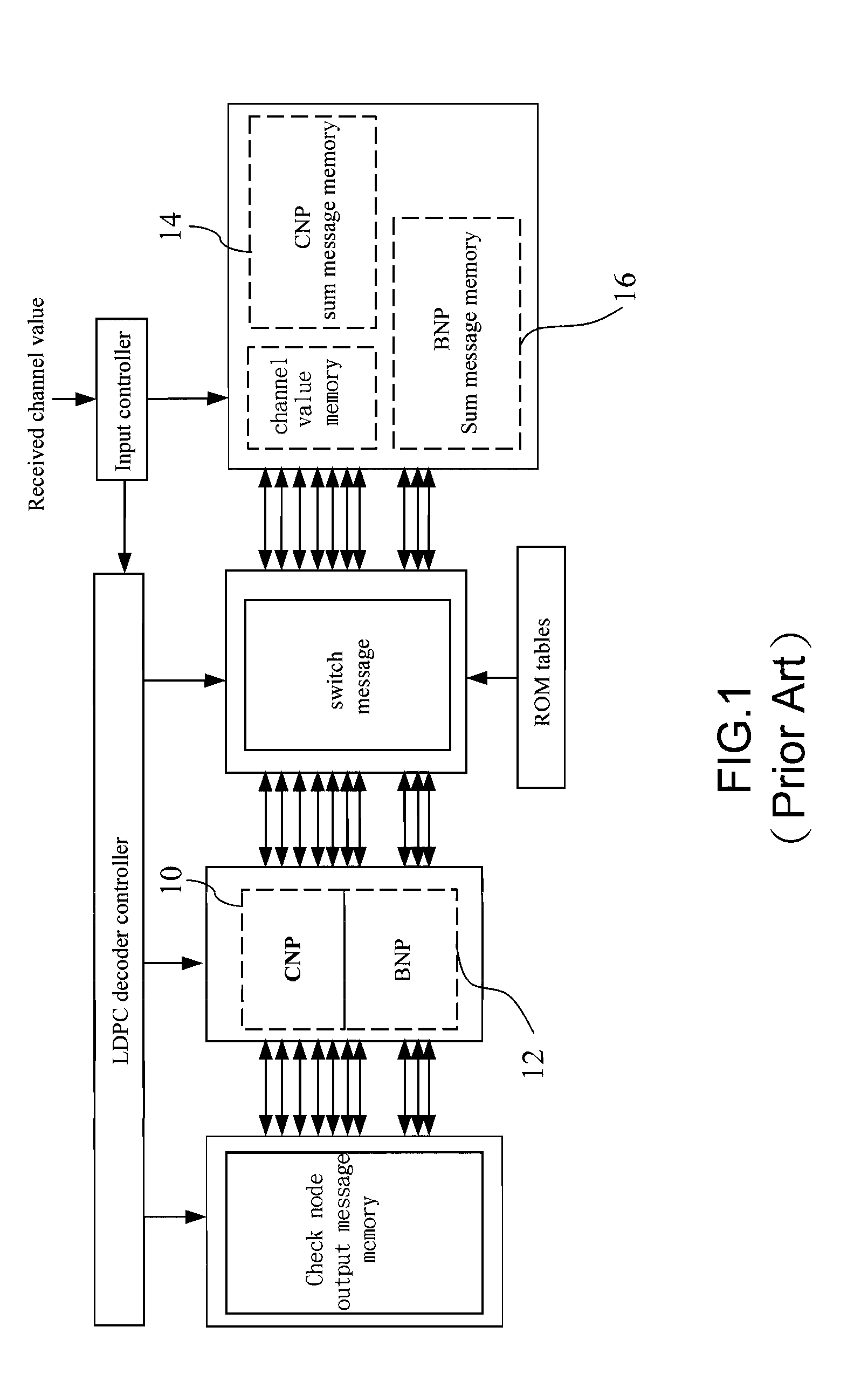

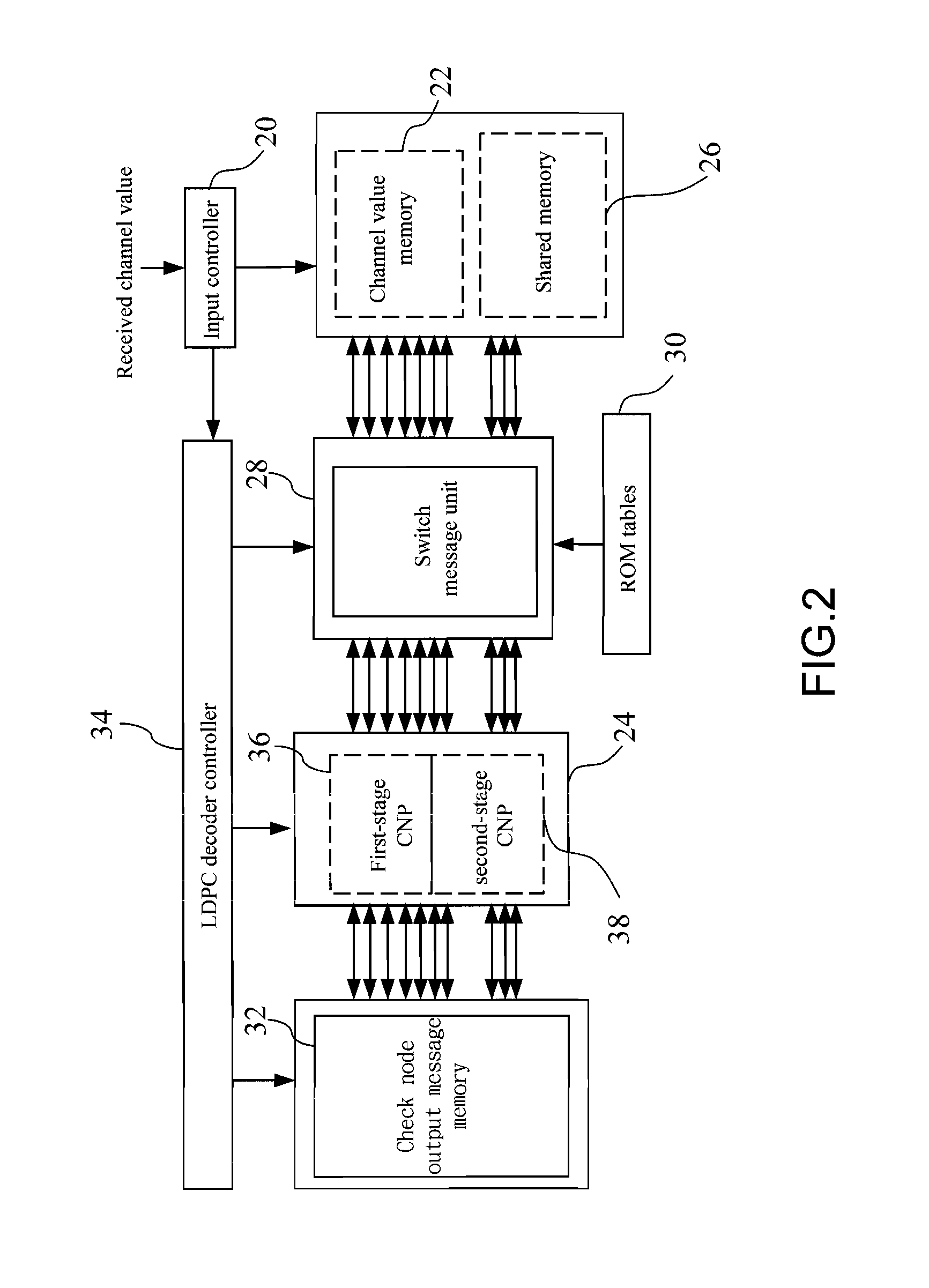

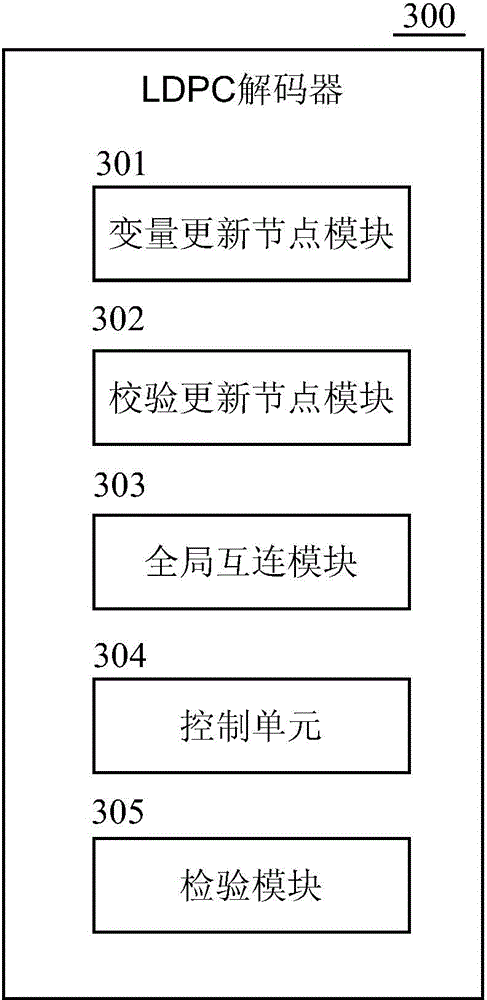

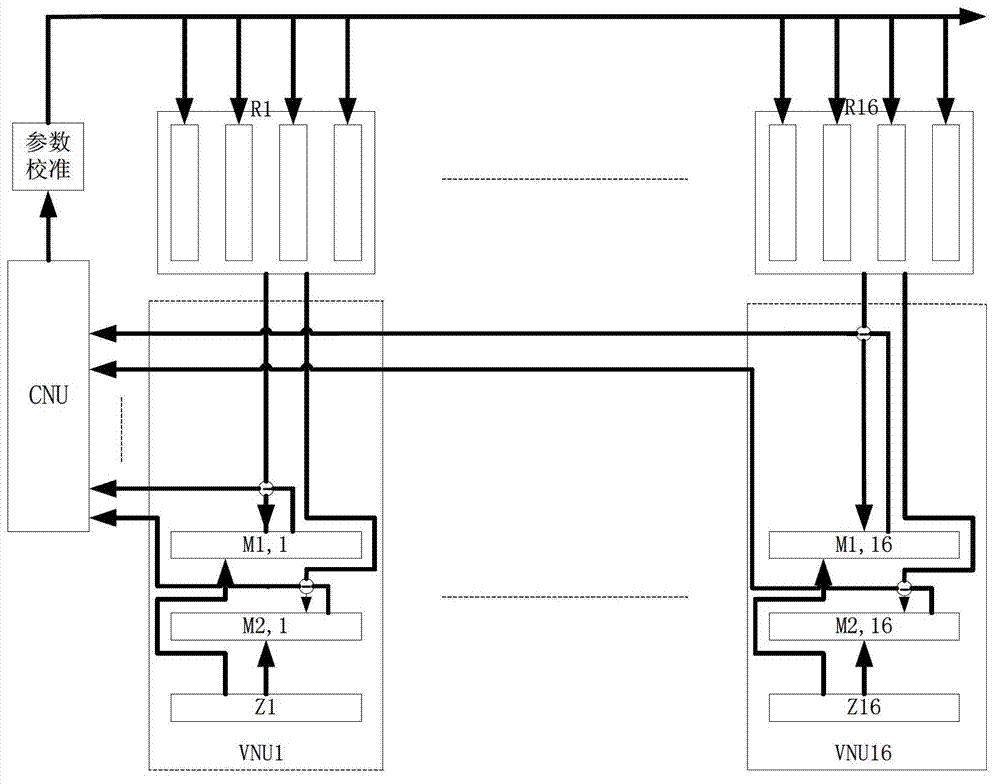

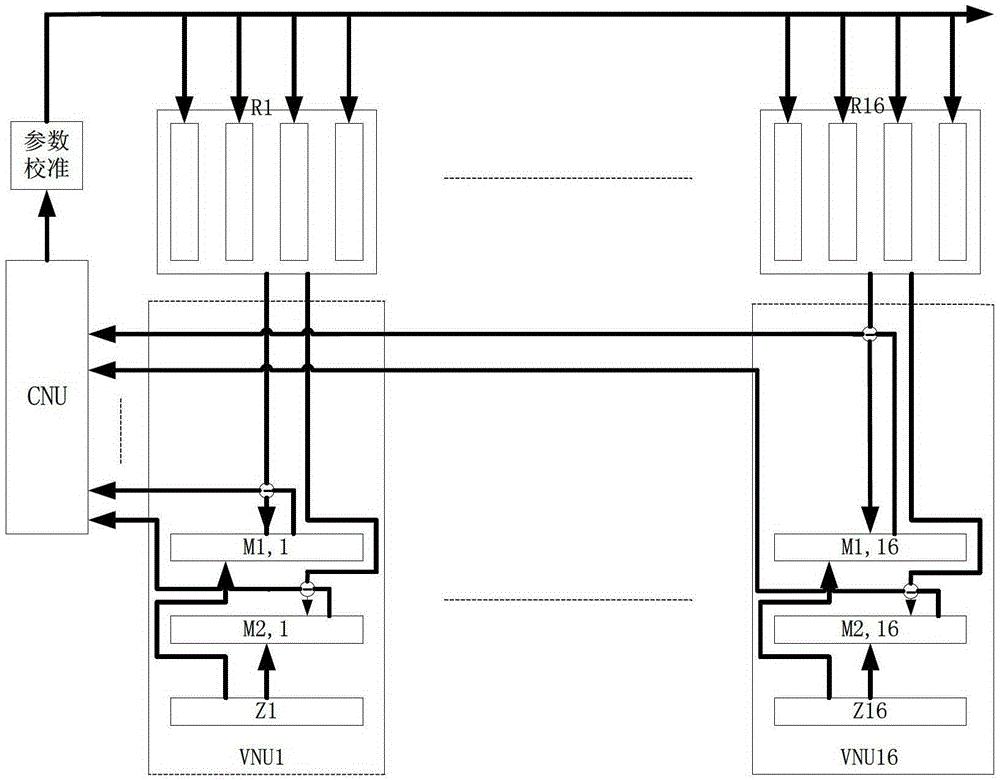

LDPC (low density parity check) decoder and LDPC decoding method

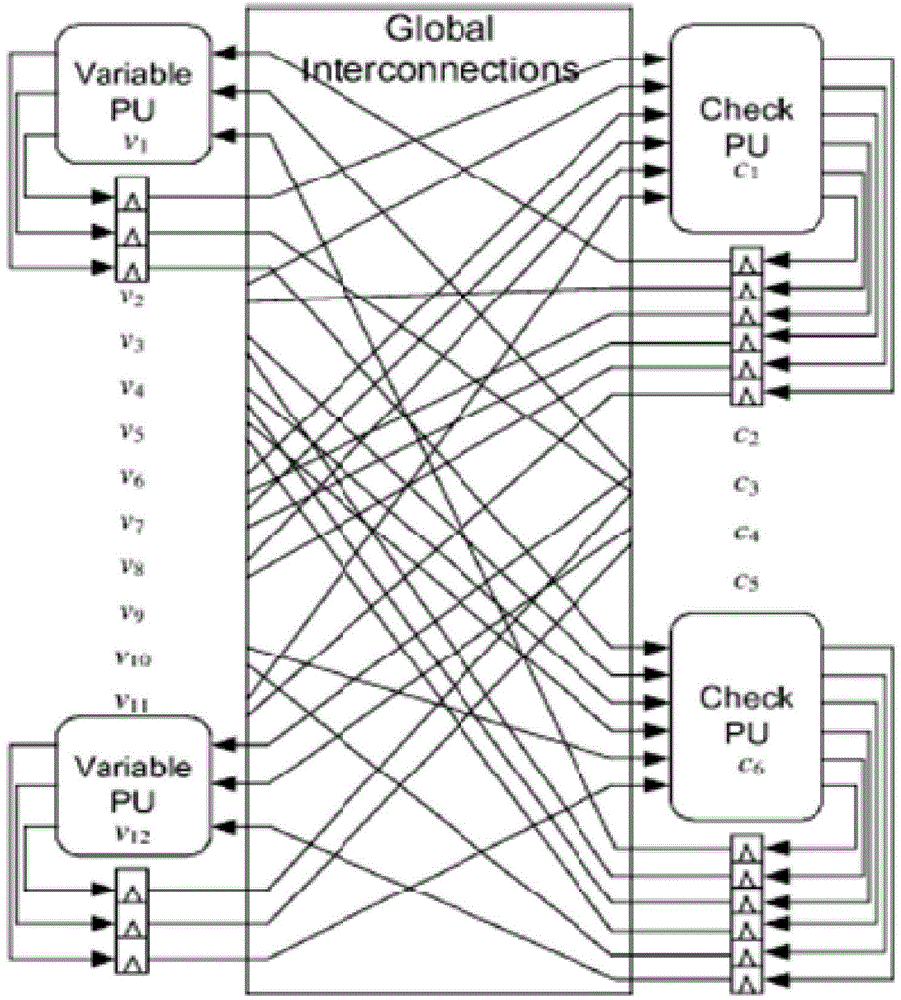

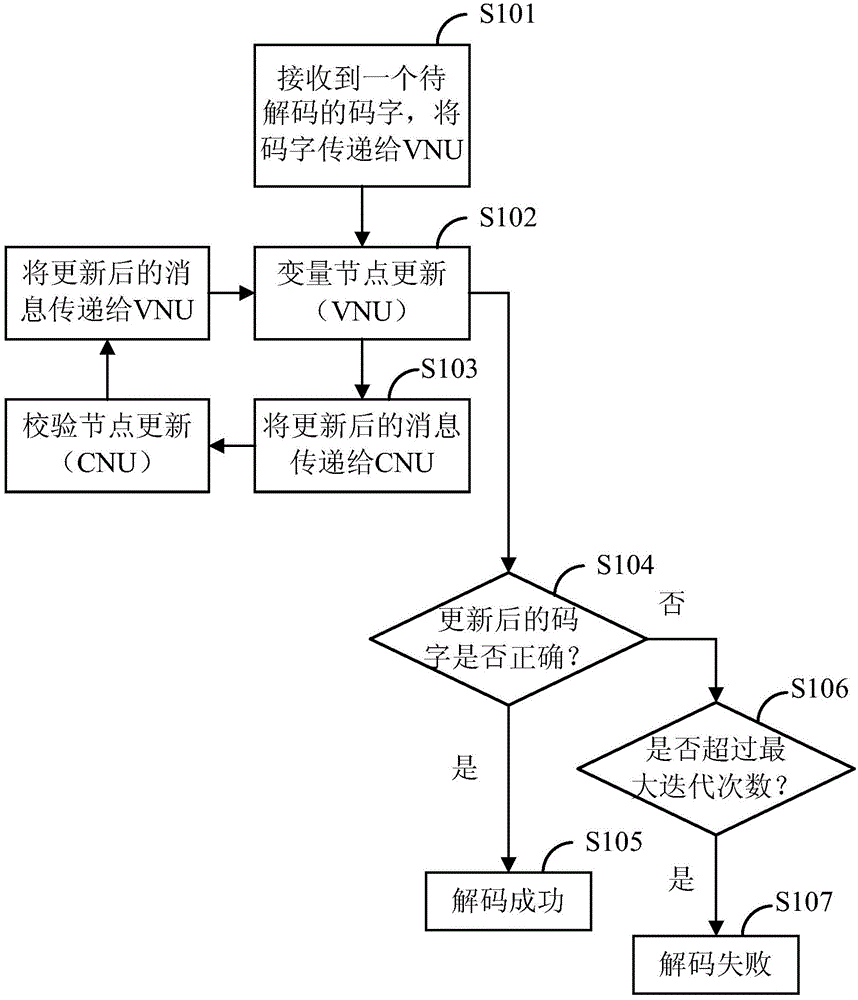

ActiveCN104796156AImprove decoding throughputEfficient use ofError correction/detection using multiple parity bitsInterconnectionLow density

The invention provides an LDPC (low density parity check) decoder and an LDPC decoding method. The LDPC decoder comprises a variable update node module, a check update node module, a global interconnection module and a control unit, wherein the variable update node module comprises M variable update node calculation units which are used for carrying out variable node update calculation on an inputted message, thereby acquiring an updated message of variable nodes; the check update node module comprises N check update node calculation units which are used for carrying out check node update calculation on the inputted message, thereby acquiring updated message of check nodes; the global interconnection module is used for mutually connecting each of the M variable update node calculation units and each of the N check update node calculation units; and the control unit is used for carrying out control, thereby enabling the acquired updated message of the variable nodes to be transmitted to each of the N check update node calculation units, enabling the updated message of the check nodes to be transmitted to each of the M variable update node calculation units, and being capable of decoding two different code words parallelly.

Owner:LENOVO (BEIJING) CO LTD

Parallel soft elimination decoding method and related device

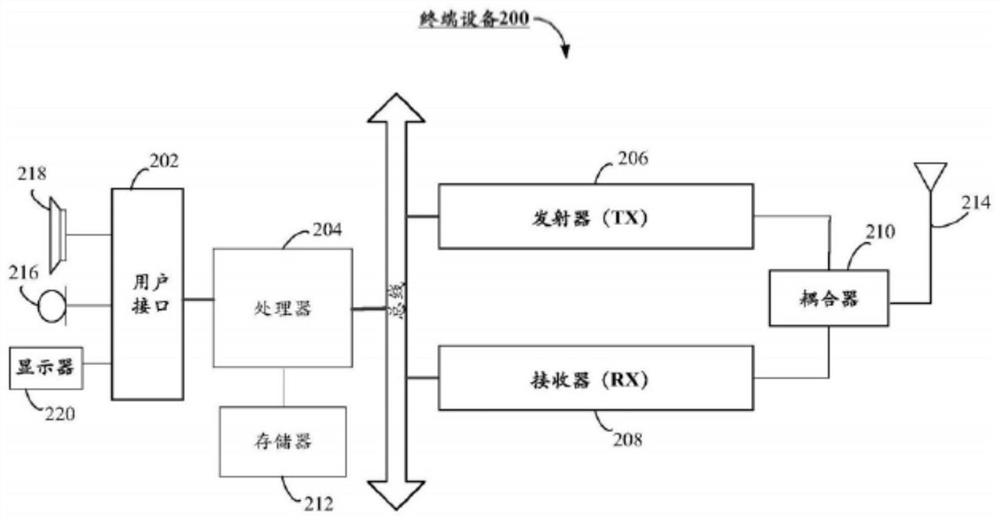

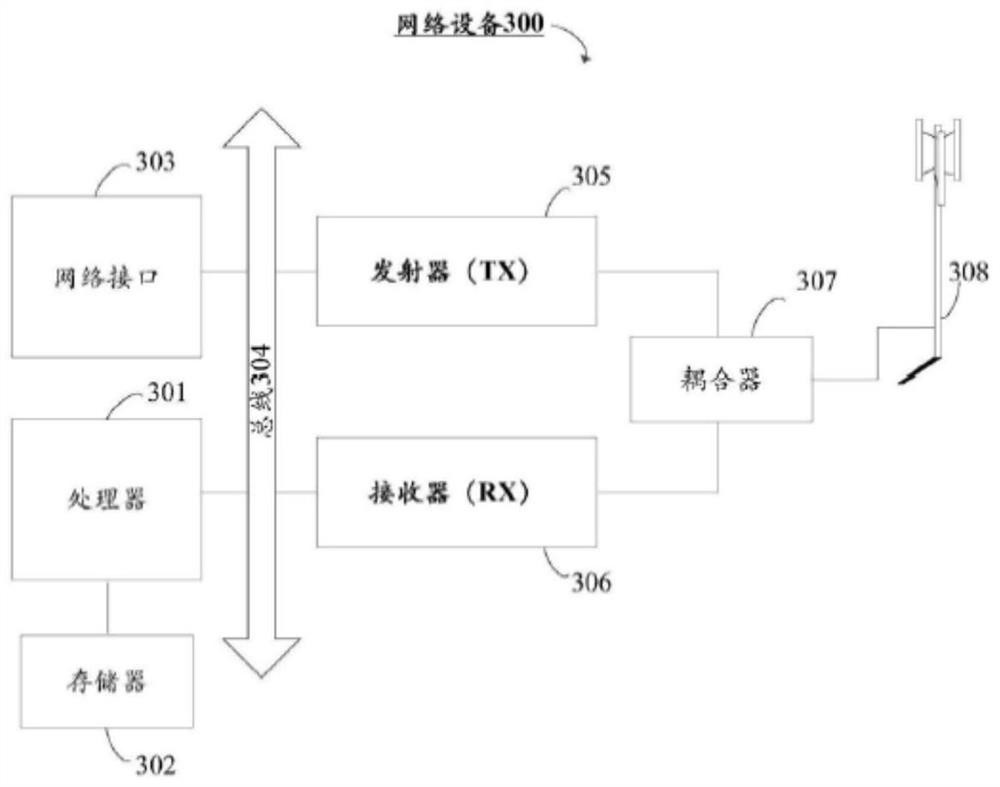

PendingCN113055022AImprove efficiencyMeet soft bit outputError correction/detection using multiple parity bitsCode conversionDecoding methodsTheoretical computer science

The embodiment of the invention discloses a parallel soft elimination decoding method and a related device. The method comprises the steps: obtaining a to-be-decoded sequence, and enabling the bit length of the to-be-decoded sequence to be N; according to N, determining a hierarchy range s to 0 of a log likelihood ratio (LLR) updating mechanism of the sequence to be decoded, hierarchy m to hierarchy 0 forming sub-blocks for non-parity check PC bit parallelization decoding processing, and N = 2s + 1; carrying out lLR layer-by-layer iteration updating on the sequence to be decoded according to the hierarchy range s-0 until the preset maximum iteration number is reached, and obtaining the target log likelihood ratio LLR of the information bit direction of the sequence to be decoded, wherein the information bit direction is the LLR transmission direction from the high hierarchy to the low hierarchy; and decoding according to the target LLR in the information bit direction to obtain a decoding result. By adopting the embodiment of the invention, the requirements of soft bit output and high decoding performance can be met.

Owner:HUAWEI TECH CO LTD

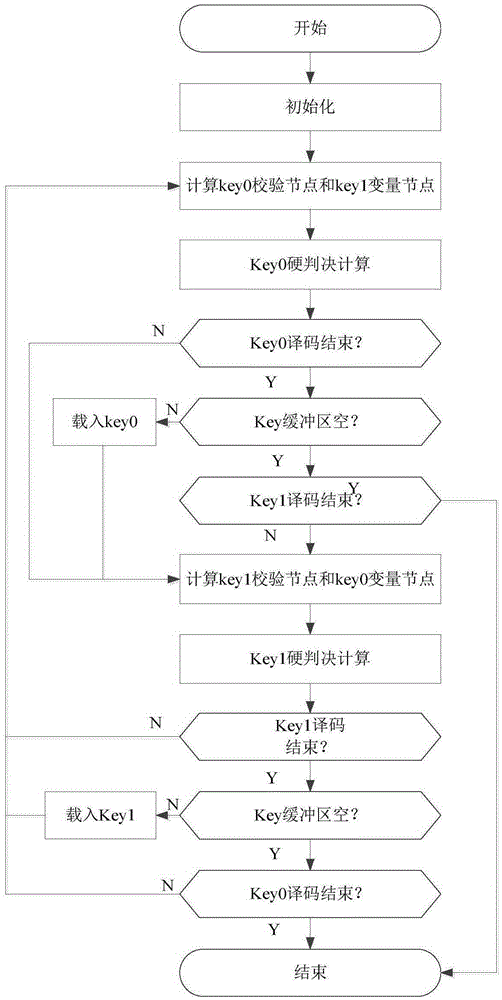

Quantum key distribution random low-density parity-check (LDPC) code parallel decoding method

ActiveCN105306198AImprove decoding throughputMeet performance needsKey distribution for secure communicationError preventionQuantum key distributionTheoretical computer science

The invention discloses a quantum key distribution random low-density parity-check (LDPC) code parallel decoding method. The method comprises the following steps: S1, performing initialization: loading two key strings, namely key0 and key1, from a key string storage module, and finishing variable node decoding of the key0; S2, calculating key0 check node information and key1 variable node information; S3, performing a key0 hard decision calculation; S4, loading the key0: loading a new key string into an LDPC decoder key0 buffer area from the key string storage module; S5, calculating key1 check node information and key0 variable node information; S6, performing a key1 hard decision calculation; and S7, loading the key1: loading a new key string into a decoder key1 buffer area from the key string storage module. The method has the advantage that the overall efficiency and performance can be improved.

Owner:NAT UNIV OF DEFENSE TECH

Browsing JPEG Images Using MPEG Hardware Chips

InactiveUS20070189616A1Quick ViewSignificant loss of image fidelityColor television with pulse code modulationColor television with bandwidth reductionImaging processingJPEG

Rapid throughput of still image compressed data (e.g. JPEG) is achieved for presentation of images in rapid succession for browsing or browsing by panning within large images by using a hardware decoder adapted for presentation of moving images to reduce the processing load which must be performed in accordance with software although the still image data is incompatible with still image data in many respects; some of which necessarily lead to a loss of image fidelity. The still image data is partially decoded (e.g. entropy decoded) in software processing and re-encoded and reformatted to a form which can at least be accepted by the hardware decoder even though not compliant with any particular moving picture data standard (e.g. MPEG). Storage in the hardware decoder is reallocated to provide, in combination with a reduction of slower software processing, a throughput increase of four-fold or more. Software processing of the still image data is also allowed to proceed and the result substituted for the result of the hardware decoding if a given image is viewed for a time sufficient for the software image processing to be completed.

Owner:INT BUSINESS MASCH CORP

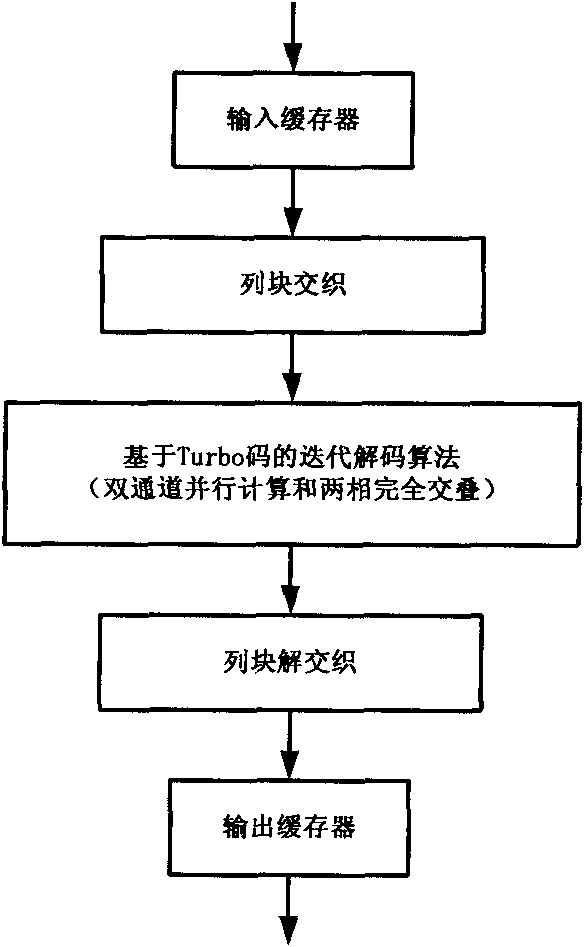

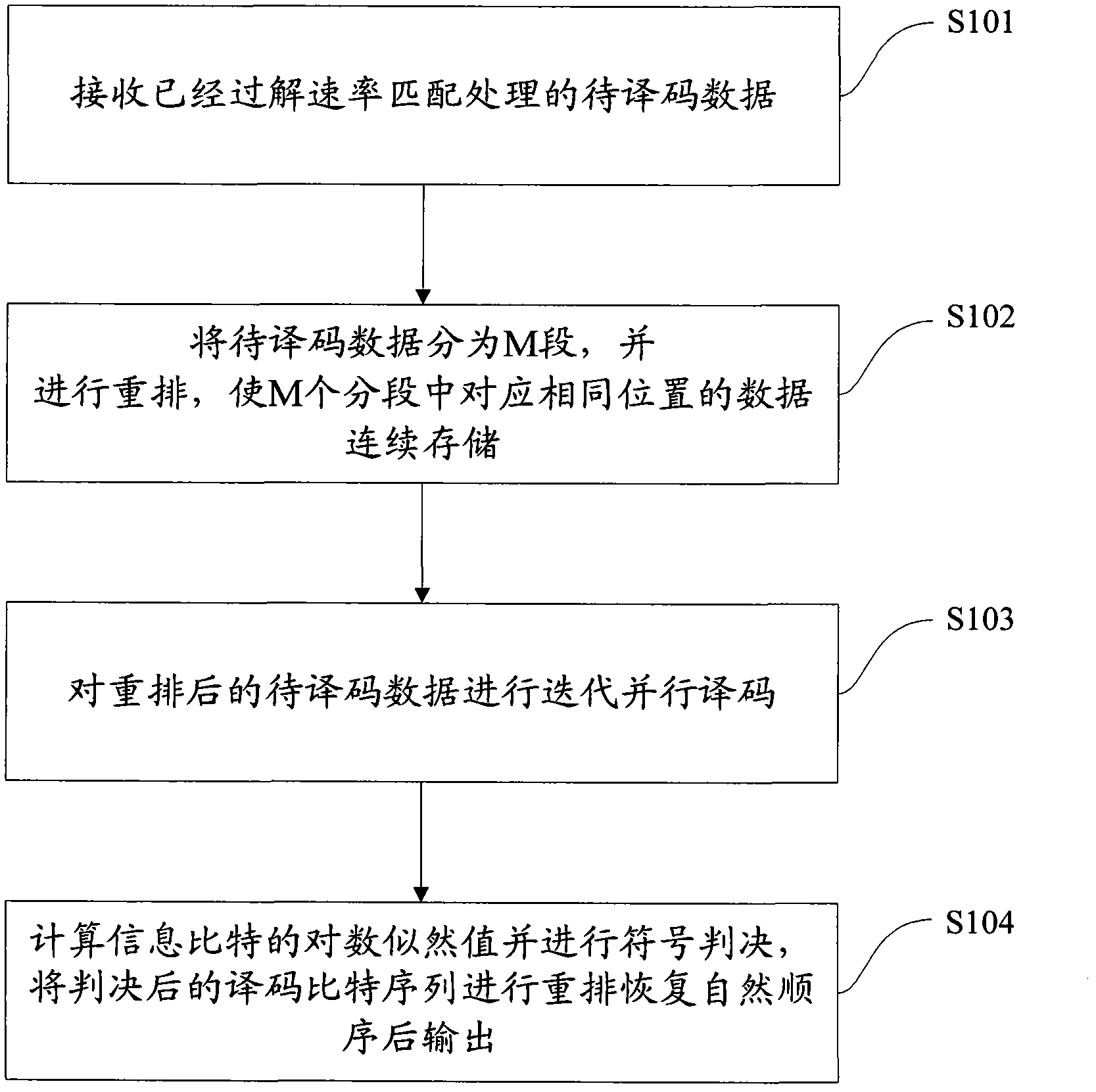

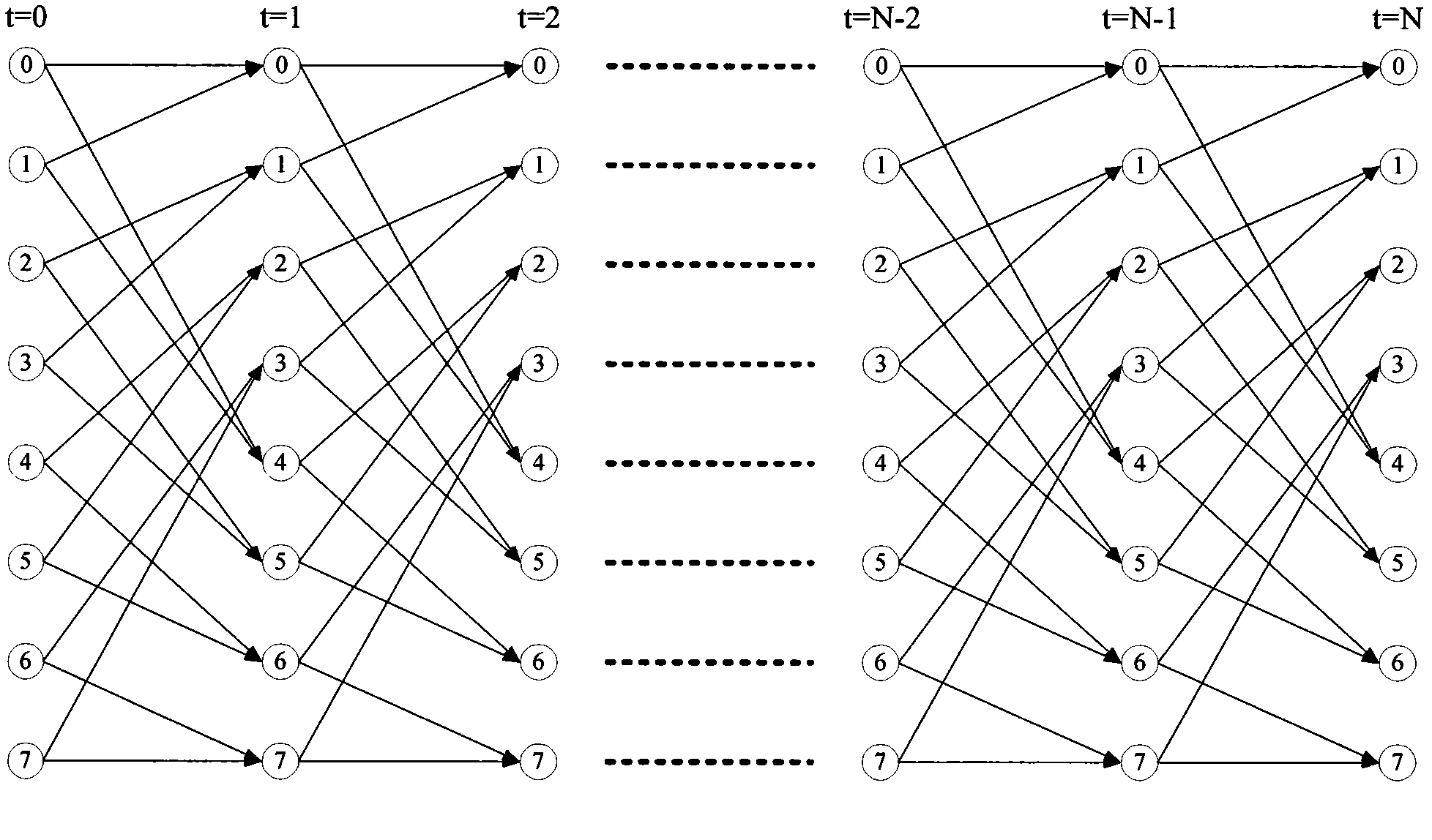

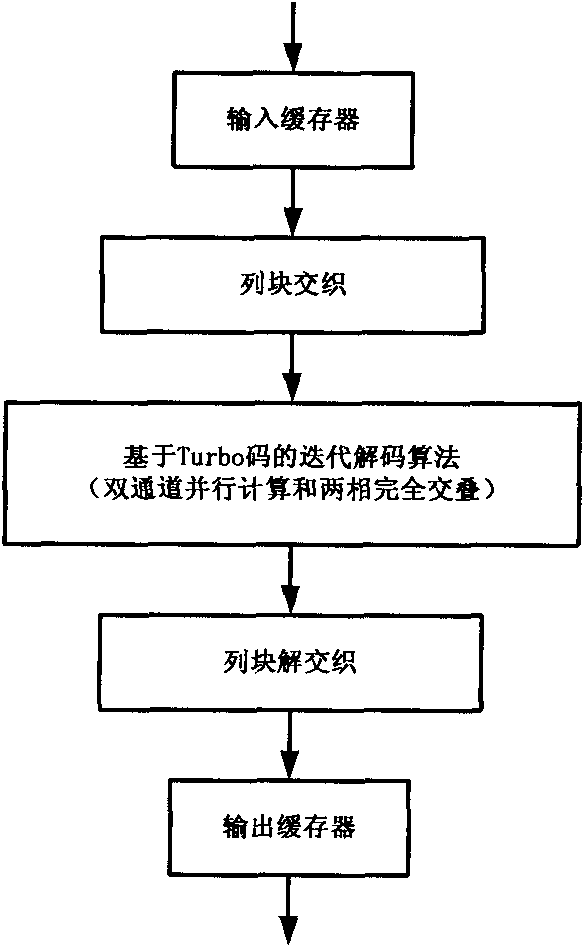

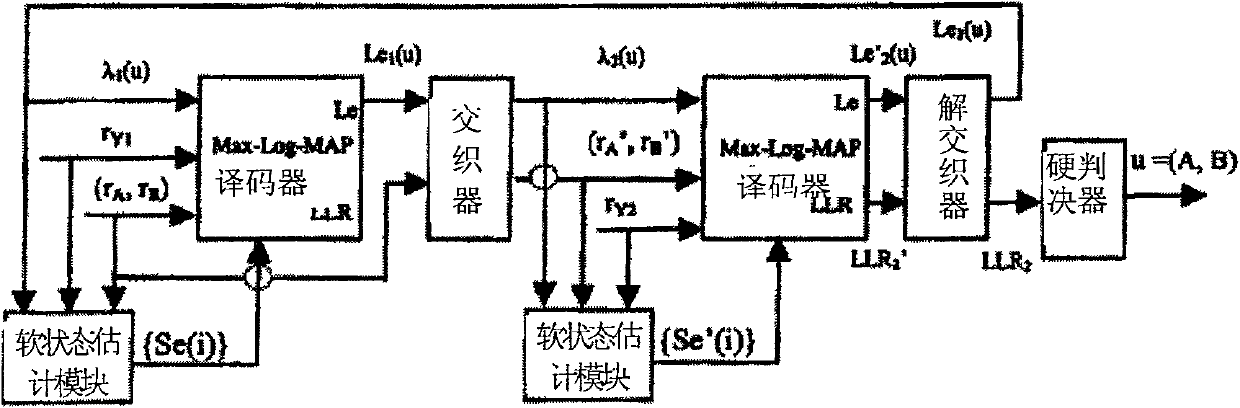

High-speed parallel Turbo decoding method and system in software radio system

ActiveCN102594507AIncrease flexibilityPracticalError preventionError correction/detection using interleaving techniquesComputer hardwareSoftware define radio

The invention provides high-speed parallel Turbo decoding method and system in a software radio system. The method comprises the following steps: dividing data to be decoded into M segments, and reordering the data to continuously store the corresponding data at the same positions in the M segments; carrying out iterative decoding on the reordered data to be decoded, comprising the processes of performing parallel component code decoding on the data in the M segments and performing interlacing and de-interlacing on the exchange external information of the two component codes through an interlacing list calculated in advance; and calculating the log likelihood of a system bit, performing symbol judgment, and reordering the judged decoding bit sequences to recover the natural sequence. According to the embodiment of the invention, the high-speed parallel Turbo decoding in the software radio system is realized, the decoding time is greatly reduced and the decoding throughout rate is improved.

Owner:因诺微科技(天津)有限公司

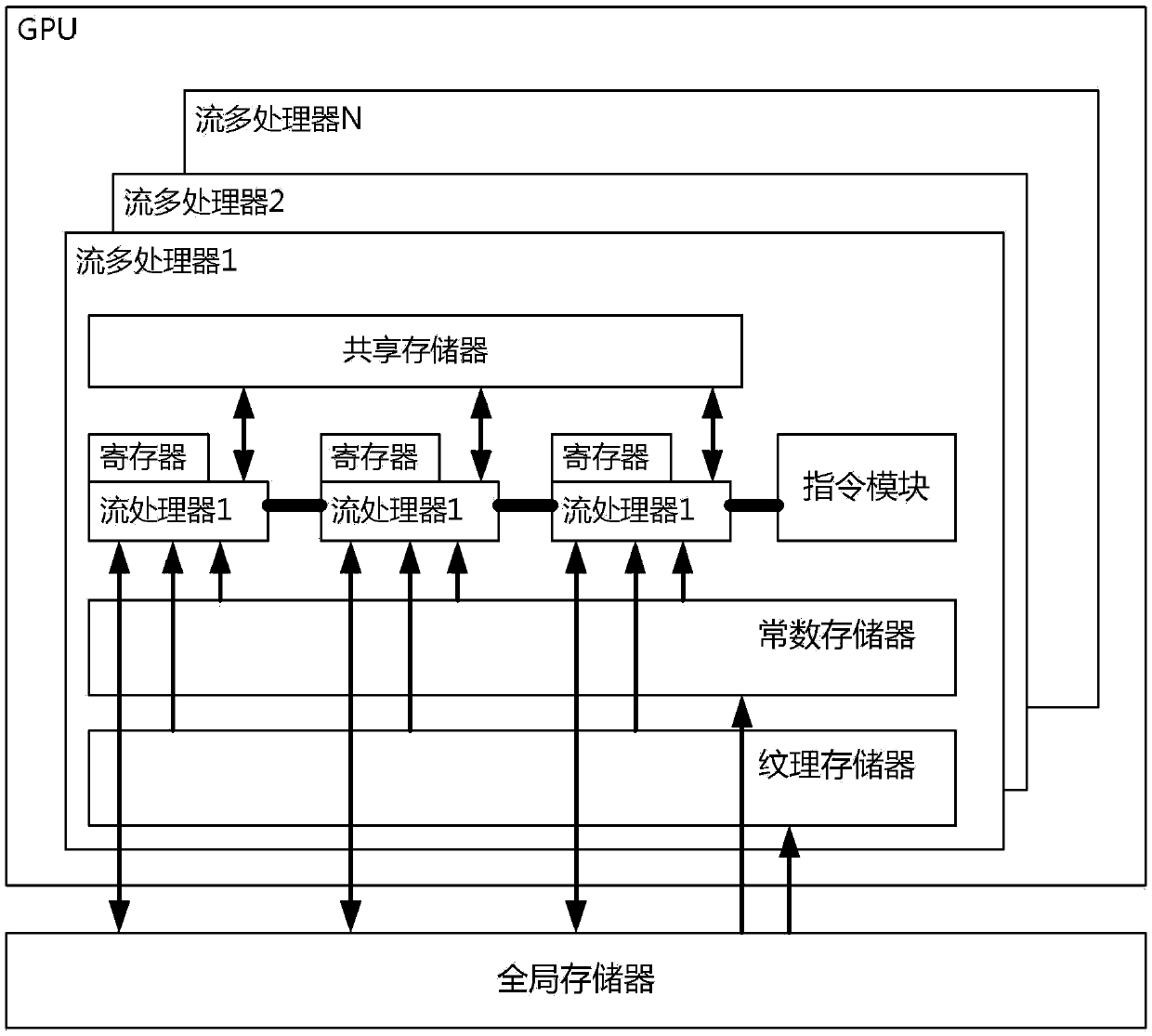

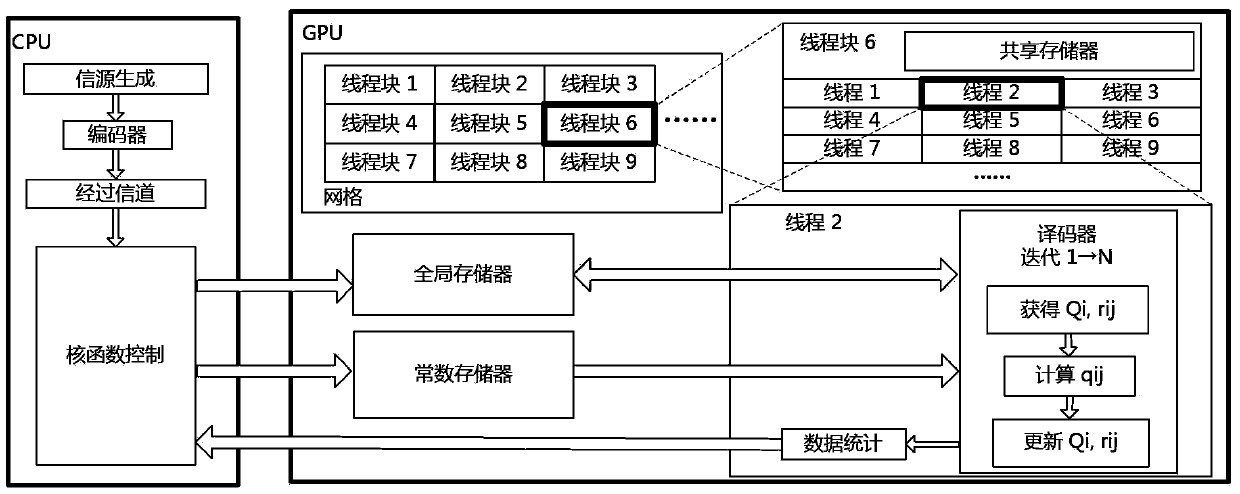

Accelerated decoding method of qc-ldpc code based on gpu architecture

ActiveCN102932003BAccelerated decodingAchieve parallelizationError correction/detection using multiple parity bitsCore functionGraphics processing unit

Owner:SHANGHAI JIAOTONG UNIV

Method for decoding LDPC (Low Density Parity Check) codes

ActiveCN103117751AEnhanced couplingImprove throughputError correction/detection using multiple parity bitsDecoding methodsLow density

The invention discloses a method for decoding LDPC codes. The method for decoding the LDPC codes includes the following steps of determining a multiplexed line of a check matrix, determining a first check node calculation part, a second check node calculation part, a first variable node calculation part and a second variable node calculation part of a decoding unit, subjecting the multiplexed line to a first processing in the K times iteration processing, subjecting the first variable node calculation part to a K-1 times variable node update calculation when the first check node calculation part is subjected to a K times check node update calculation, subjecting the multiplexed line to a second processing, and subjecting the second check node calculation part to a K times check node update calculation while the second variable node calculation part is subjected to a K times variable node update calculation. Compared with the sequence of the variable node calculation and the check node calculation in the traditional method, the method for decoding the LDPC codes improves the decoding handling capacity of the LDPC codes.

Owner:SPACE STAR TECH CO LTD

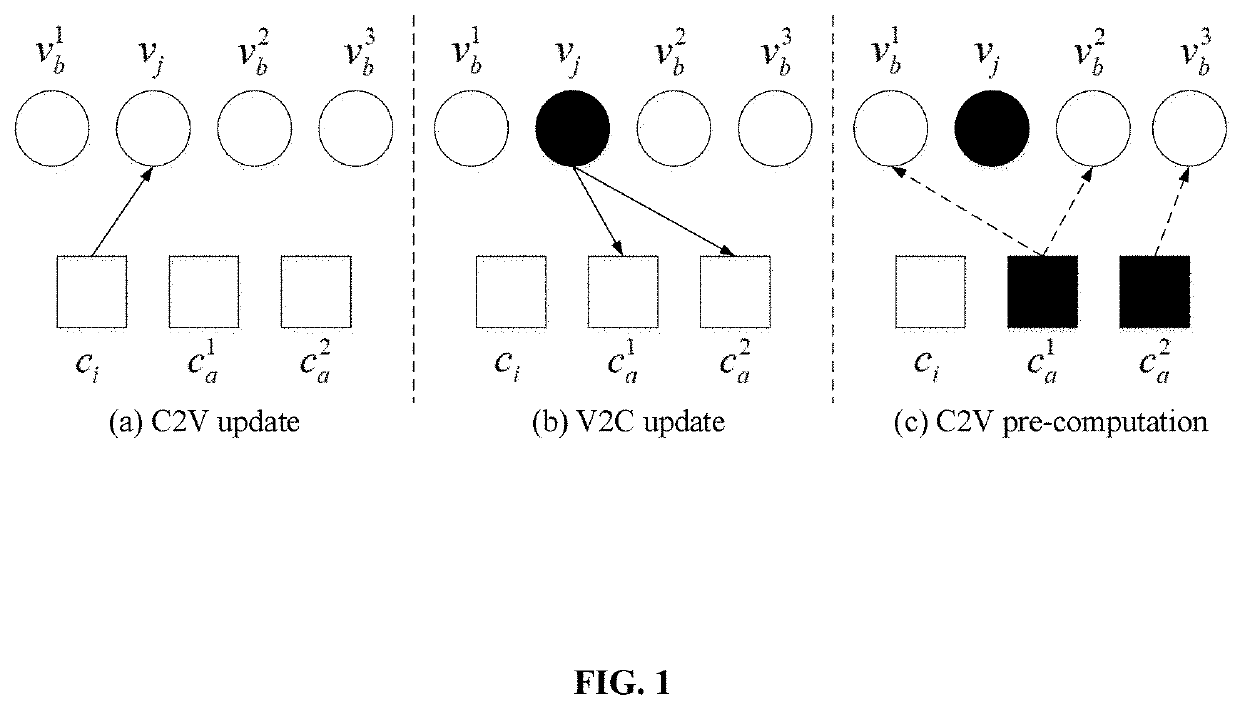

Decoding method of LDPC codes based on partial average residual belief propagation

ActiveUS20220329262A1Improve decoding throughputReduce errorsOther decoding techniquesError correction/detection using multiple parity bitsBelief propagationComputer science

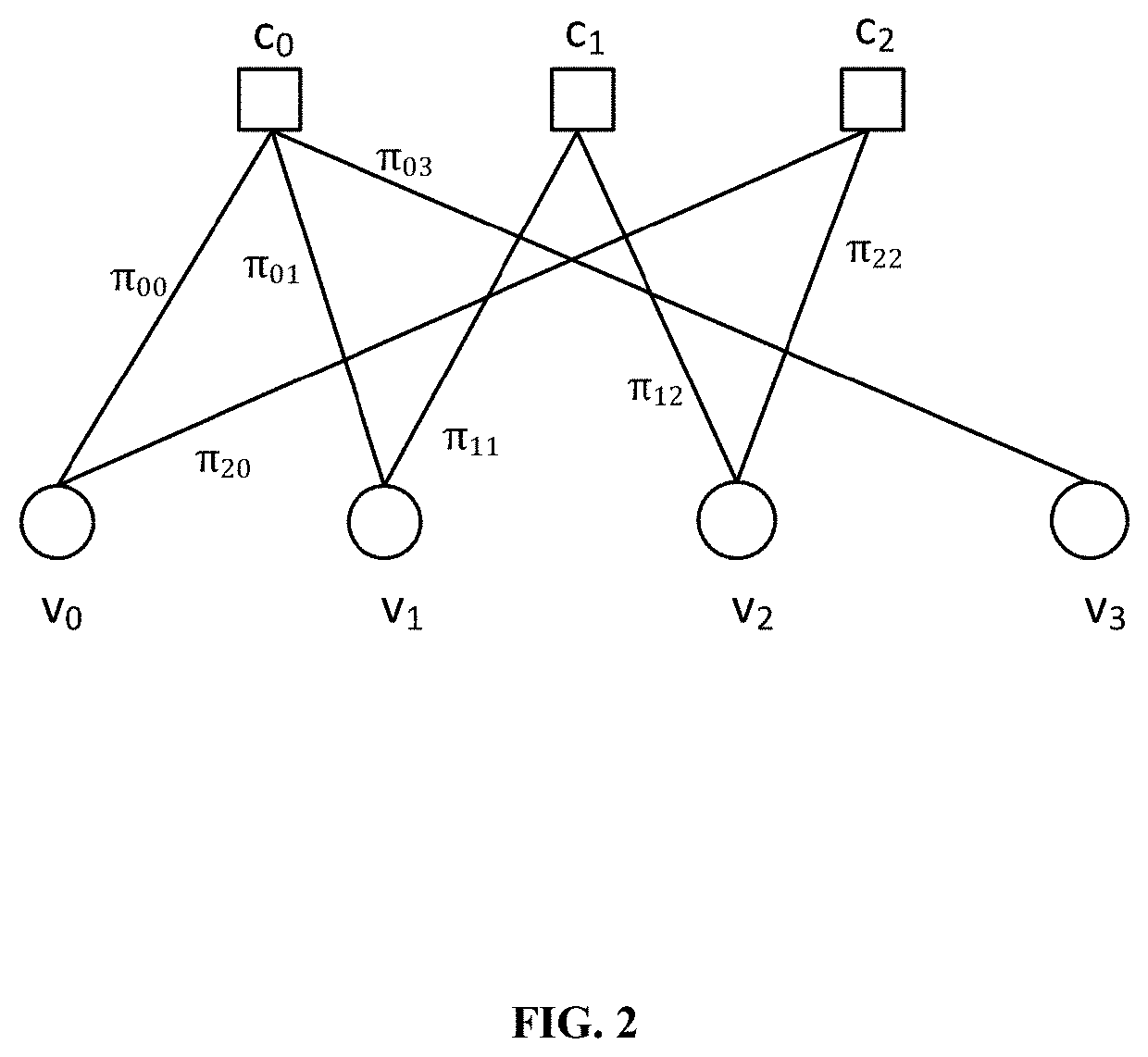

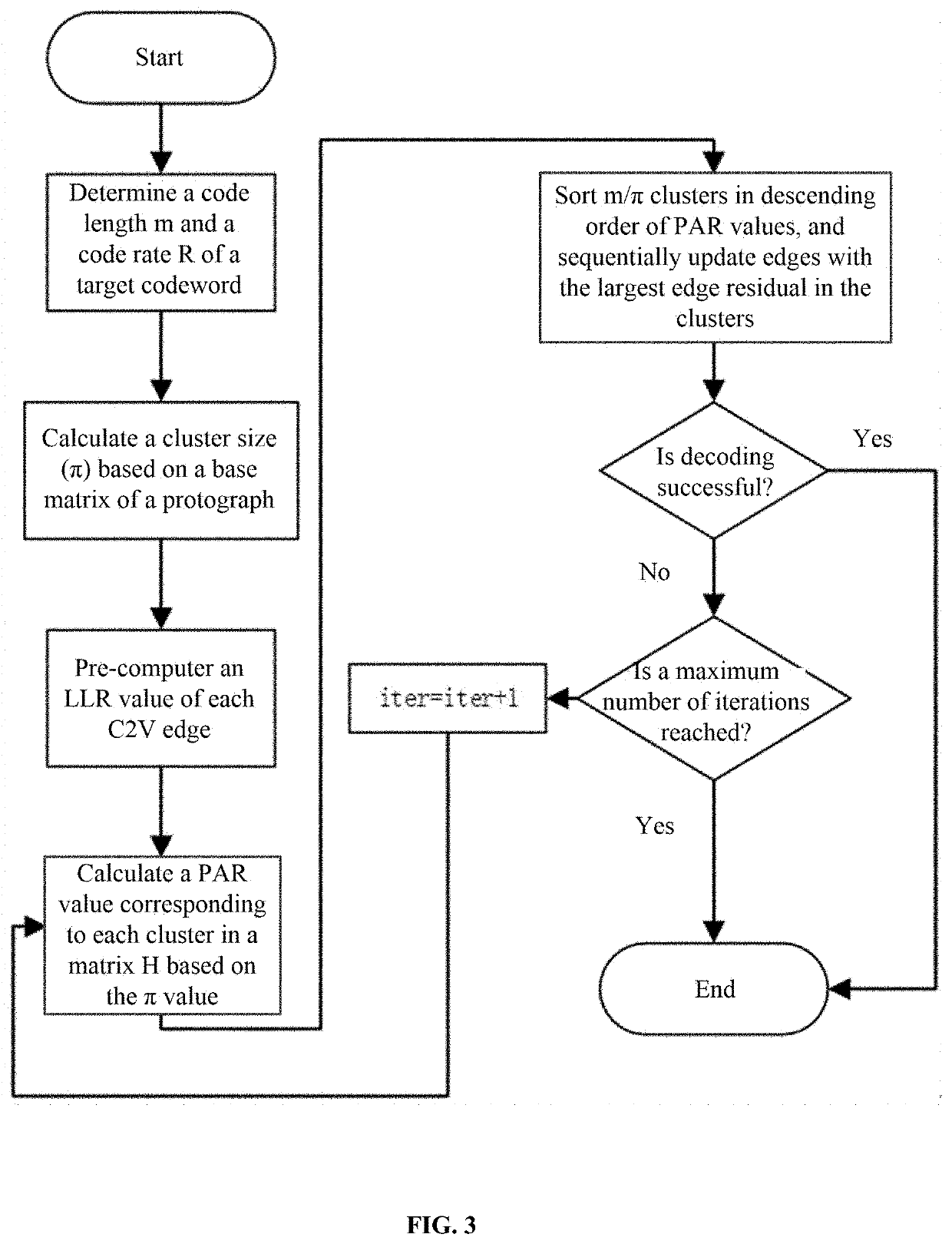

A decoding method of low-density parity-check (LDPC) codes based on partial average residual belief propagation includes the following steps: S1: calculating a size of a cluster π in a protograph based on a code length m and a code rate of a target codeword; S2: pre-computing an edge residual rc<sub2>i< / sub2>→v<sub2>j < / sub2>corresponding to each edge from a variable node to a check node in a check matrix H; S3: calculating, based on π, a partial average residual (PAR) value corresponding to each cluster in the check matrix H; S4: sorting m / π clusters in descending order of corresponding PAR values, and updating an edge with a largest edge residual in each cluster; S5: updating edge information mc→v<sub2>i < / sub2>from a check node ci to a variable node vj, and then updating a log-likelihood ratio (LLR) value L(vj) of the variable node vj; and S6: after the updating, making a decoding decision.

Owner:SUN YAT SEN UNIV

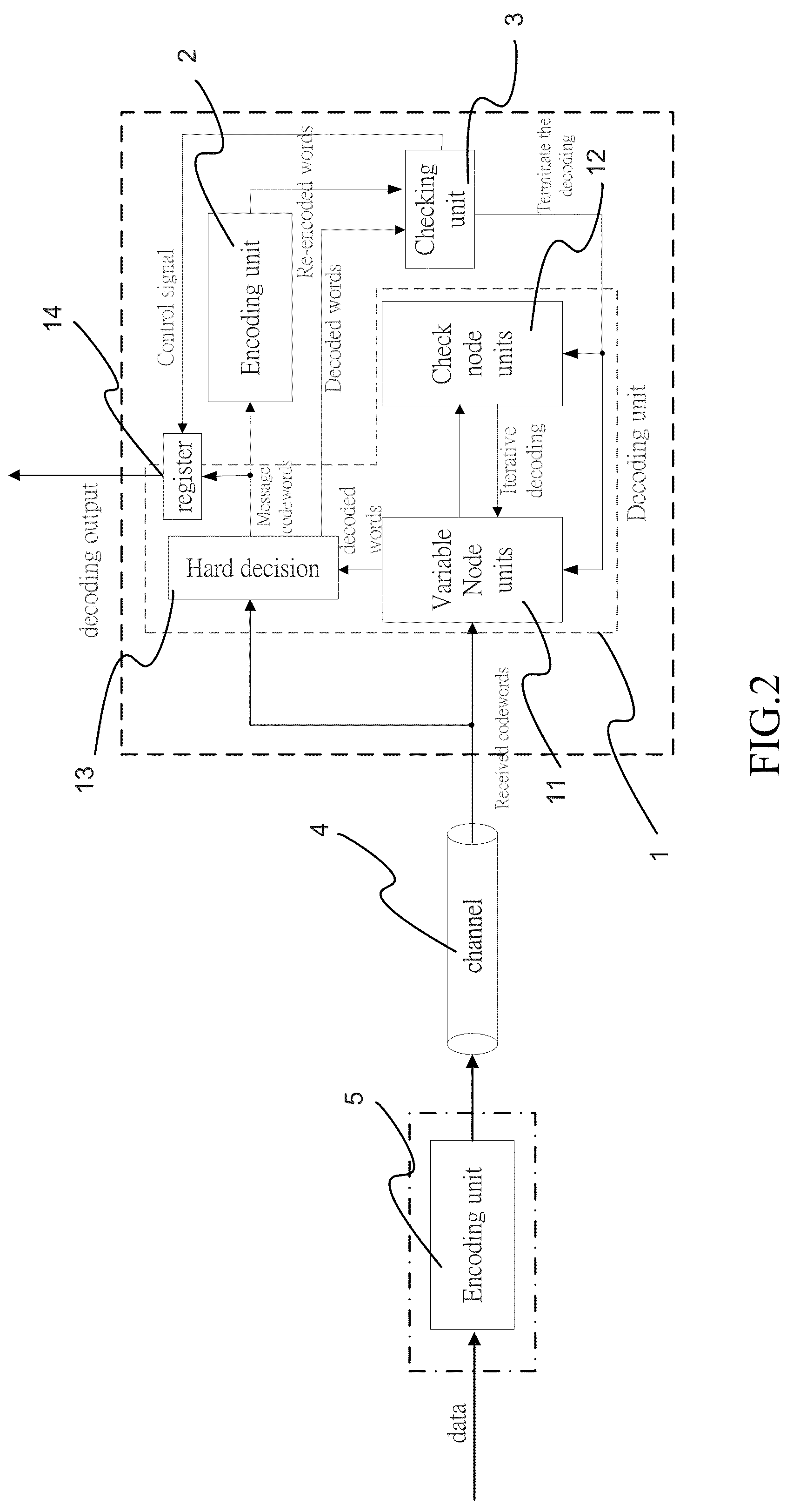

Method of early termination of channel decoding by re-encoding

ActiveUS8977934B2Save power consumptionSimple structureOther decoding techniquesError correction/detection using multiple parity bitsComputer hardwareHardware complexity

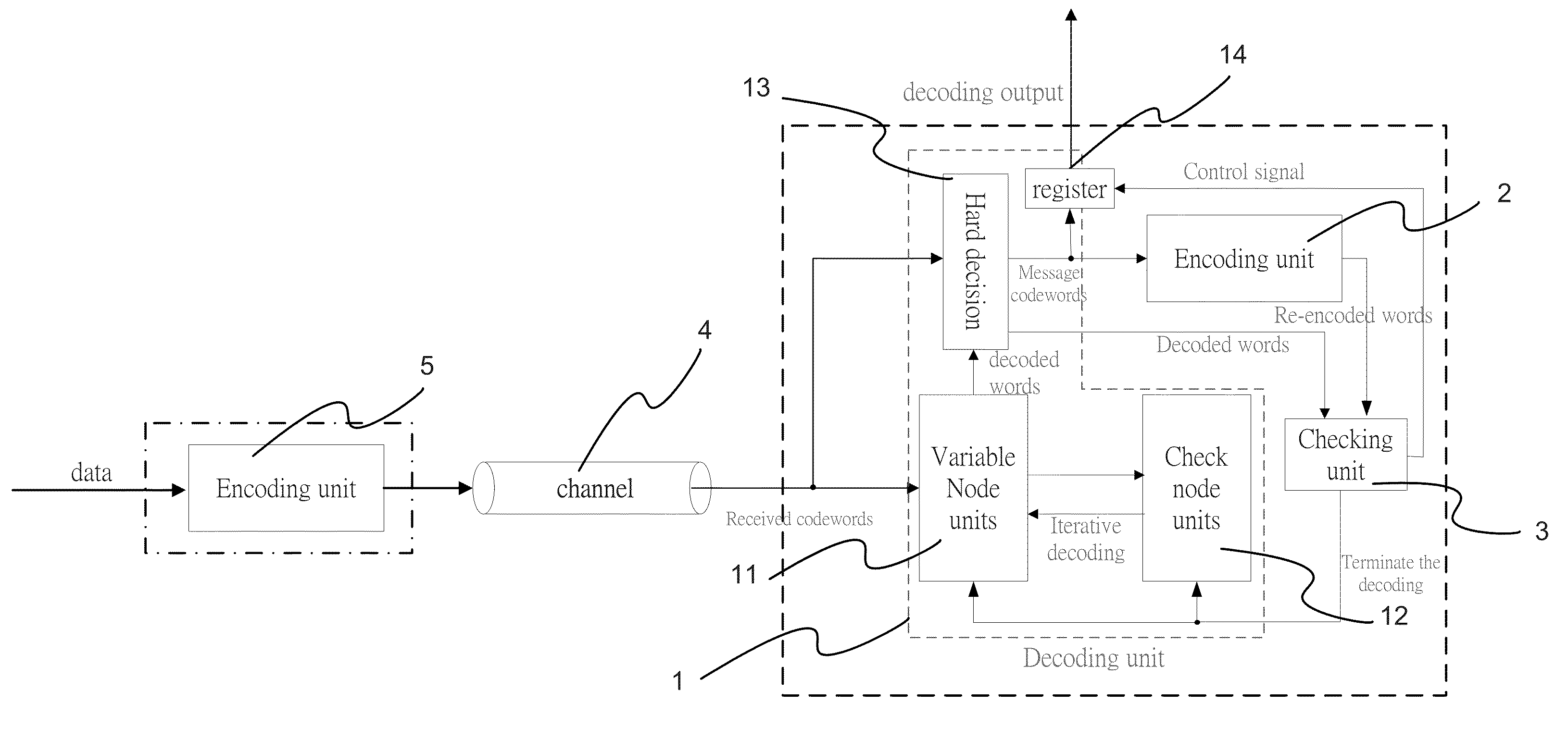

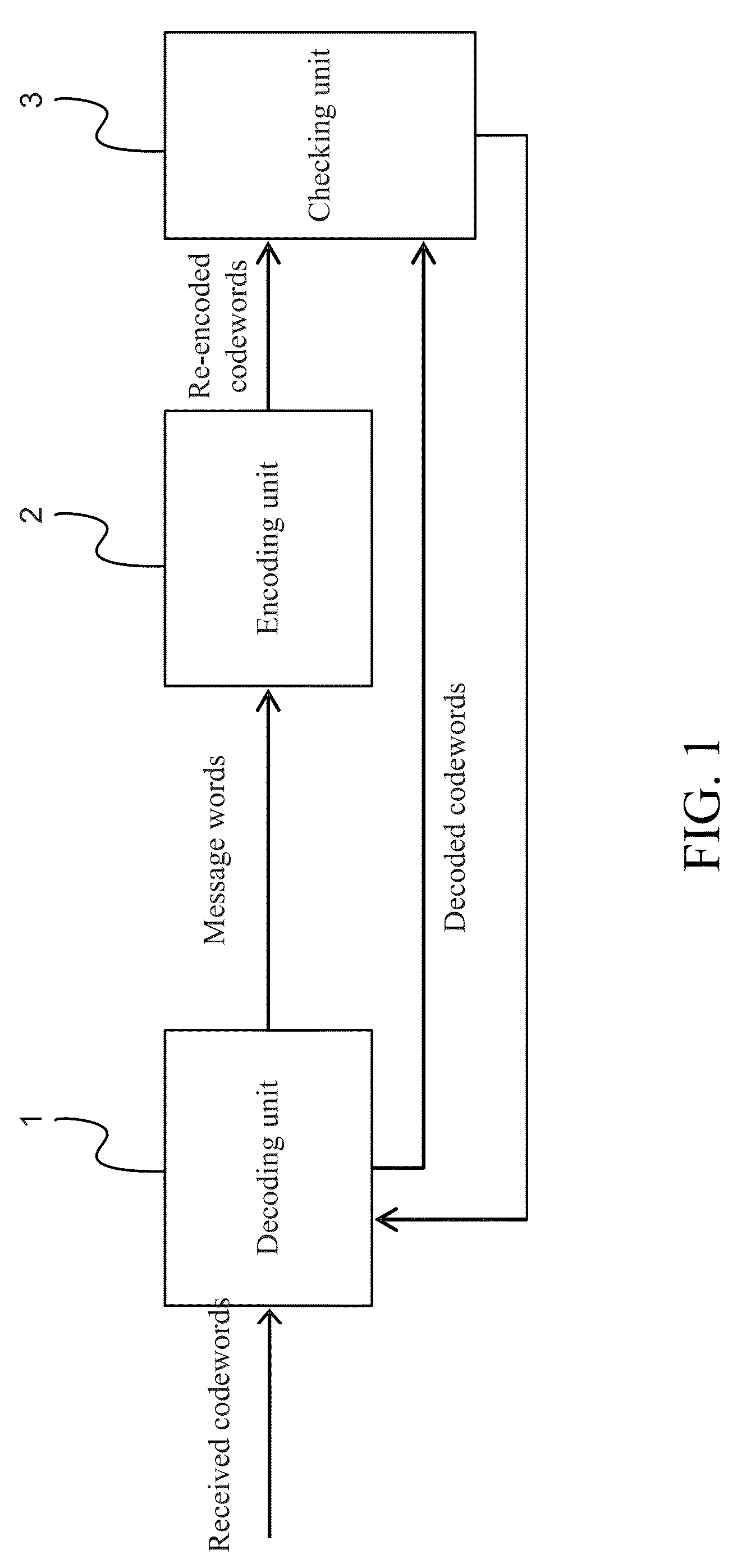

A system providing early termination for channel decoding by re-encoding including a decoding unit, an encoding unit connected to the decoding unit, and a checking unit connected to the decoding unit and to the encoding unit. Via the system, decoded message words produced from the decoding unit are sent back to the encoding unit for re-encoding. Re-encoded words are compared to the decoded codewords by the checking unit and, if they are completely the same, the decoding action of the decoding unit is terminated. The system reduces power consumption and offers a simplified structure, improved decoding throughput, and reduced hardware complexity.

Owner:NATIONAL TSING HUA UNIVERSITY

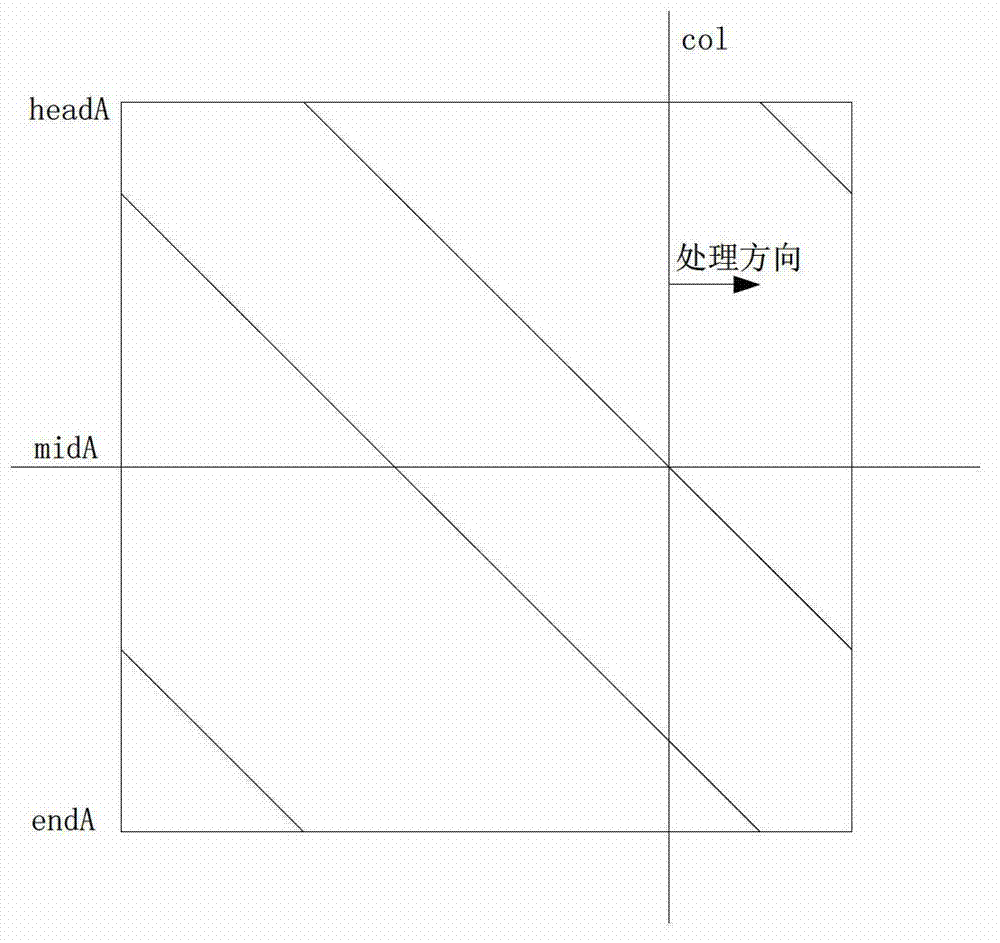

Ultrahigh-speed and low-power-consumption QC-LDPC code decoder based on TDMP

InactiveCN101771421BReduce visitsAvoid access violationsError correction/detection using multiple parity bitsFour quadrantsProduction line

The invention belongs to the technical field of wireless communication and micro-electronics, in particular to an ultrahigh-speed low-power-consumption and low-density parity check code (QC-LDPC) decoder based on TDMP. Through symmetrizing six grades of production lines, interlacing row blocks and line blocks, re-sequencing nonzero sub matrixes, carrying out four-quadrant division on a sum value register pile and adopting the technology of reading and writing the bypass, the decoder carries out serial scanning in the row sequence, two nonzero sub matrixes are respectively processed in each clock period during horizontal updating and vertical updating. The horizontal updating and the vertical updating are fully overlapped. Particularly, the sum value register pile stores the sum values of variable nodes, and is also used as an FIFO for storing transient external information transferred between two phases. The structure of the decoder has strong configurability, can be easily transplanted into any other irregular or irregular QC-LDPC codes, and has the excellent decoding performance, the peak frequency can reach 214 MHz, the thuoughput can reach about 1 gigabit per second, and the chip power consumption is only 397 milliwatts.

Owner:FUDAN UNIV

ldpc decoding method

ActiveCN103117751BEnhanced couplingImprove throughputError correction/detection using multiple parity bitsDecoding methodsLdpc decoding

The invention discloses a method for decoding LDPC codes. The method for decoding the LDPC codes includes the following steps of determining a multiplexed line of a check matrix, determining a first check node calculation part, a second check node calculation part, a first variable node calculation part and a second variable node calculation part of a decoding unit, subjecting the multiplexed line to a first processing in the K times iteration processing, subjecting the first variable node calculation part to a K-1 times variable node update calculation when the first check node calculation part is subjected to a K times check node update calculation, subjecting the multiplexed line to a second processing, and subjecting the second check node calculation part to a K times check node update calculation while the second variable node calculation part is subjected to a K times variable node update calculation. Compared with the sequence of the variable node calculation and the check node calculation in the traditional method, the method for decoding the LDPC codes improves the decoding handling capacity of the LDPC codes.

Owner:SPACE STAR TECH CO LTD

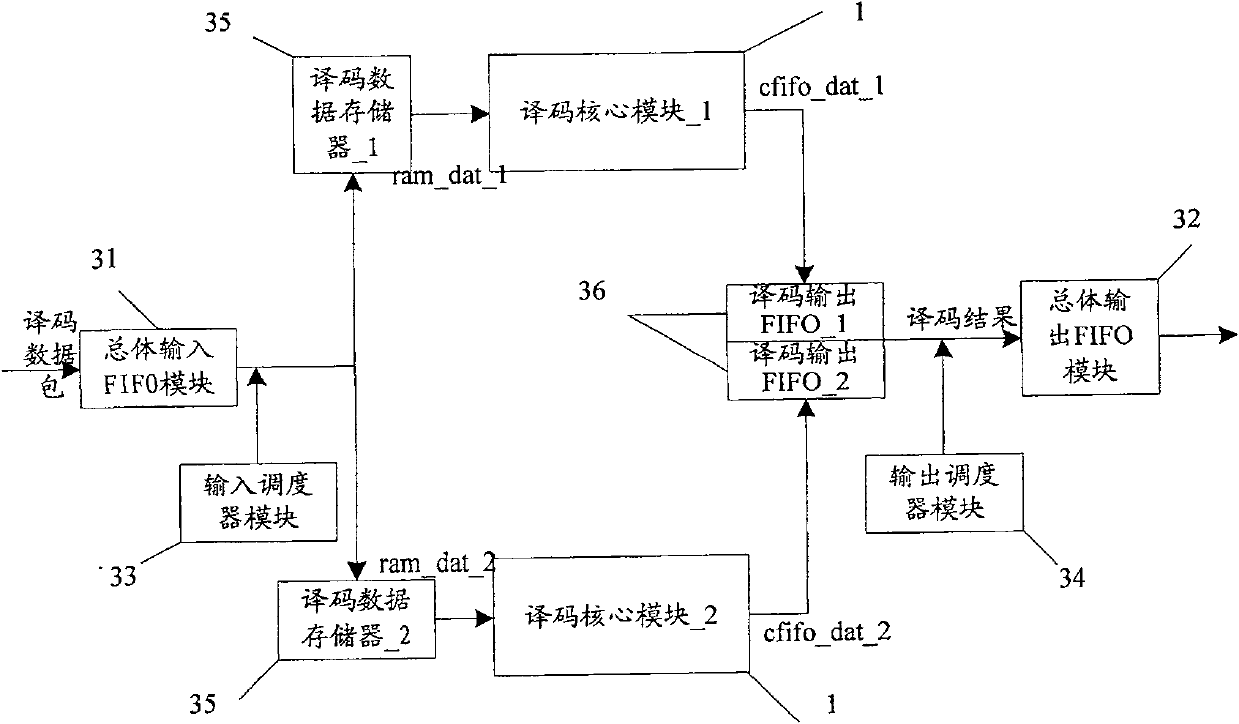

Duo-binary system CTC code translator

InactiveCN100589329CIncrease the number ofImprove decoding throughputError correction/detection using convolutional codesError correction/detection by combining multiple code structuresData memoryComputer engineering

The invention relates to a dual-binary CTC decoder, comprising a total input FIFO module (31)connected with an input, a total output FIFO module (32)connected with an output, a parallel cascade decodecore module (1)connected with the total input FIFO module via a decode data memory (35)on the input and connected with the total output FIFO module via a decode core module output FIFO (36)on the output, an input distribution module (33)for controlling the connection between the decode data memory and the total input FIFO module, and an output distributing module (34)for controlling the connection between the decode core module output FIFO and the total output FIFO module. The invention has expandable structure, which can increase decode core module number according to decode throughout, to realize high-speed decoding and meet IEEE standard.

Owner:ZTE CORP +1