Accelerated decoding method of qc-ldpc code based on gpu architecture

A GPU architecture and decoding technology, applied in the field of decoding systems, can solve the problems of high complexity and cost, low versatility and configurability, long development cycle, etc., to achieve easy implementation, improve decoding throughput, and achieve The effect of parallelization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0057] The present invention will be described in detail below in conjunction with specific embodiments. The following examples will help those skilled in the art to further understand the present invention, but do not limit the present invention in any form. It should be noted that those skilled in the art can make several modifications and improvements without departing from the concept of the present invention. These all belong to the protection scope of the present invention.

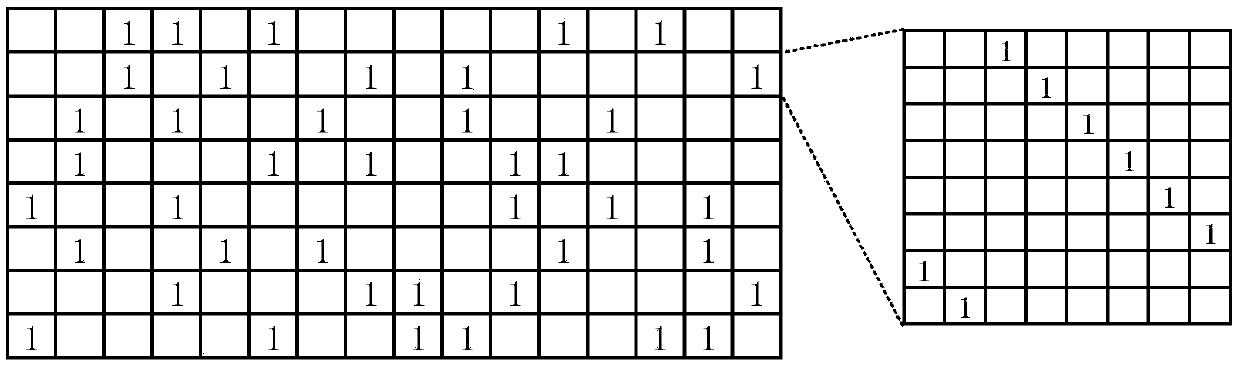

[0058] Such as figure 1 Shown is a schematic diagram of the structure of the H matrix of the QC-LDPC code constructed by the quasi-cyclic extension method. Take the WiMAX codeword with a code length of 2304 and a code rate of 0.5 as an example, input the mother matrix of the decoded code word, calculate the check matrix with a maximum row weight of 7, a maximum column weight of 6, code length N=2304, code rate R=0.5, QC expansion factor Z_f=96.

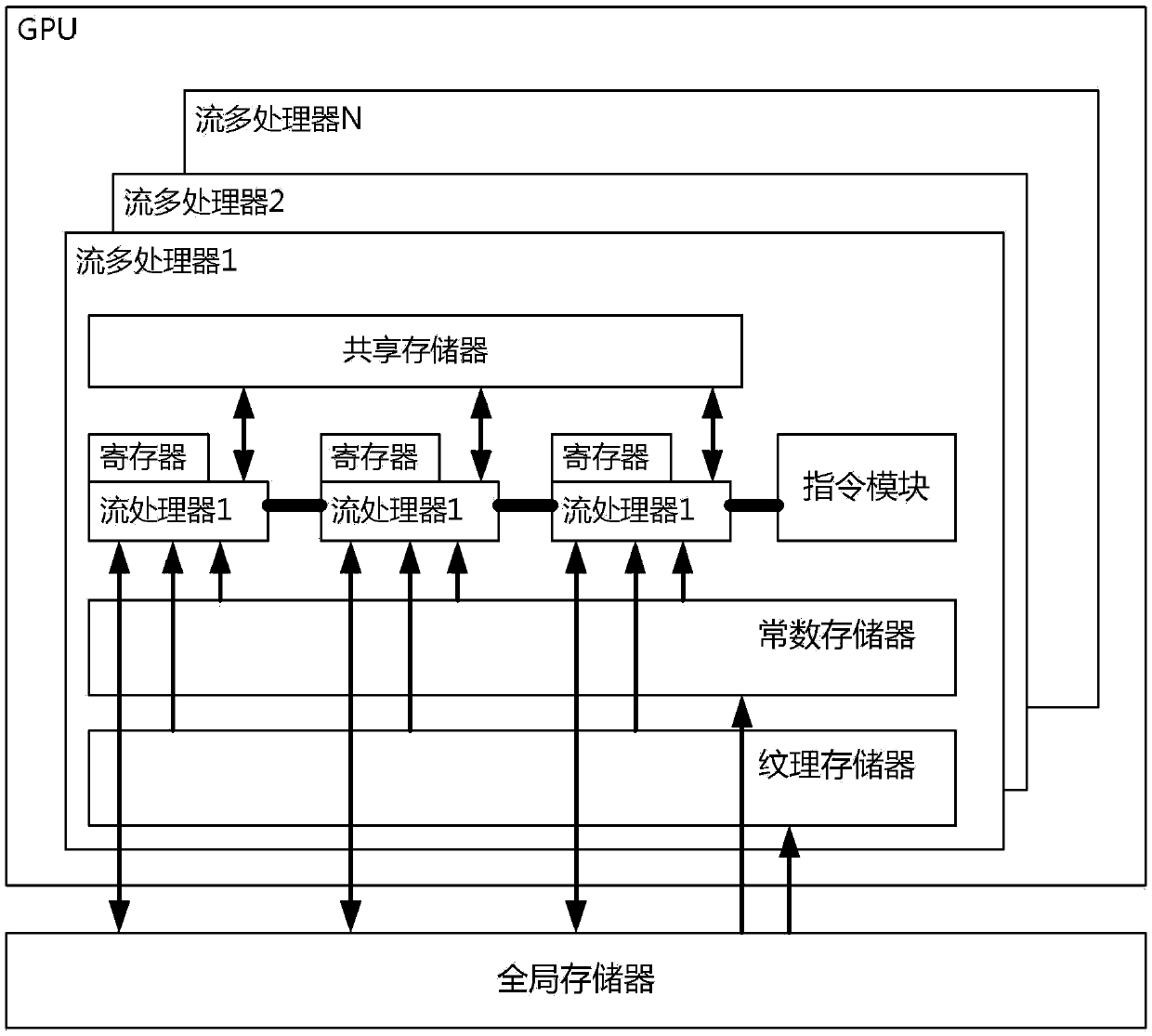

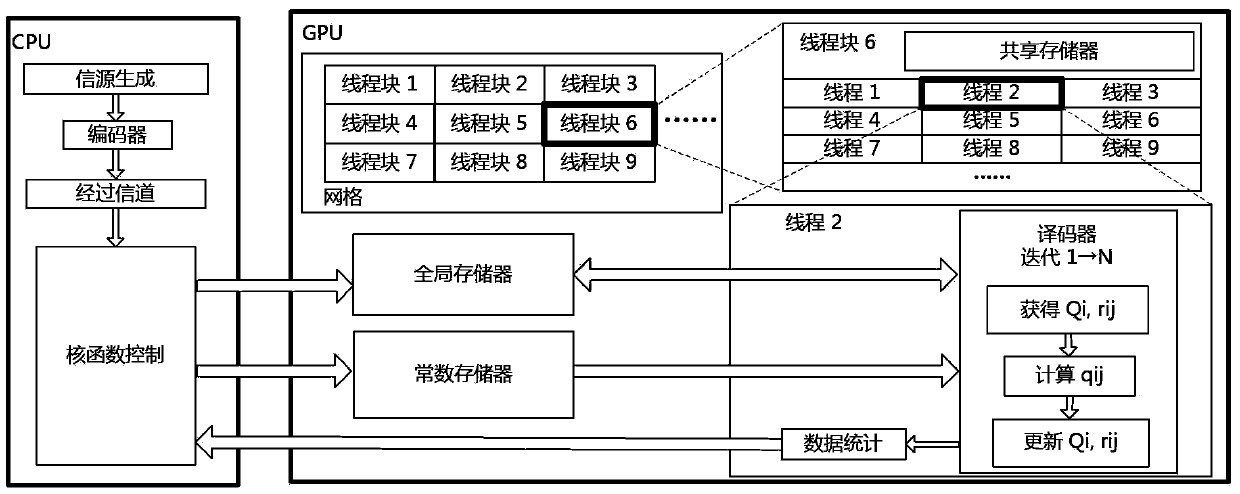

[0059] Such as figure 2 As shown, a schematic d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More