Ultrahigh-speed and low-power-consumption QC-LDPC code decoder based on TDMP

A decoder and restorer technology, applied in the application of multi-bit parity error detection coding, error correction/detection using block codes, data representation error detection/correction, etc., can solve decoding complexity and performance degradation Medium, low decoding complexity, poor performance, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

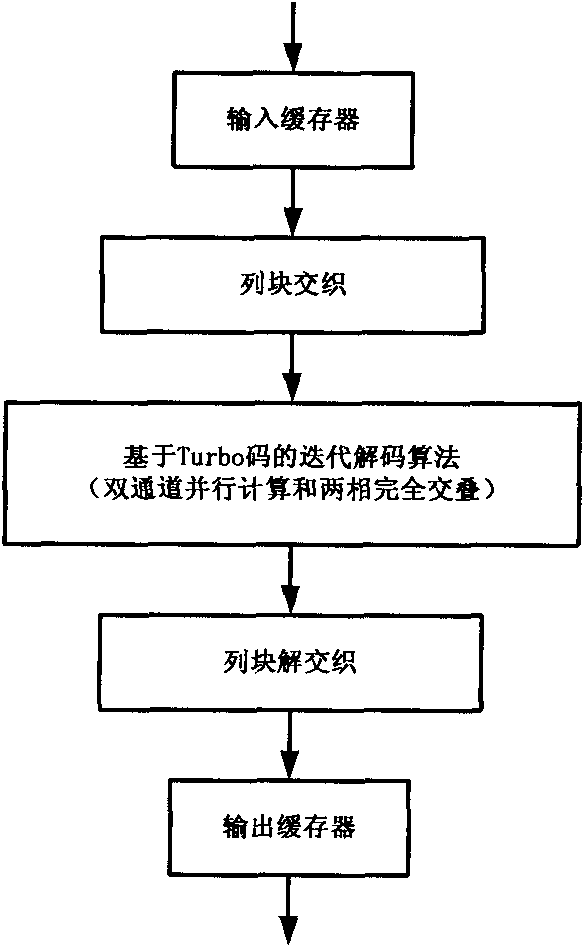

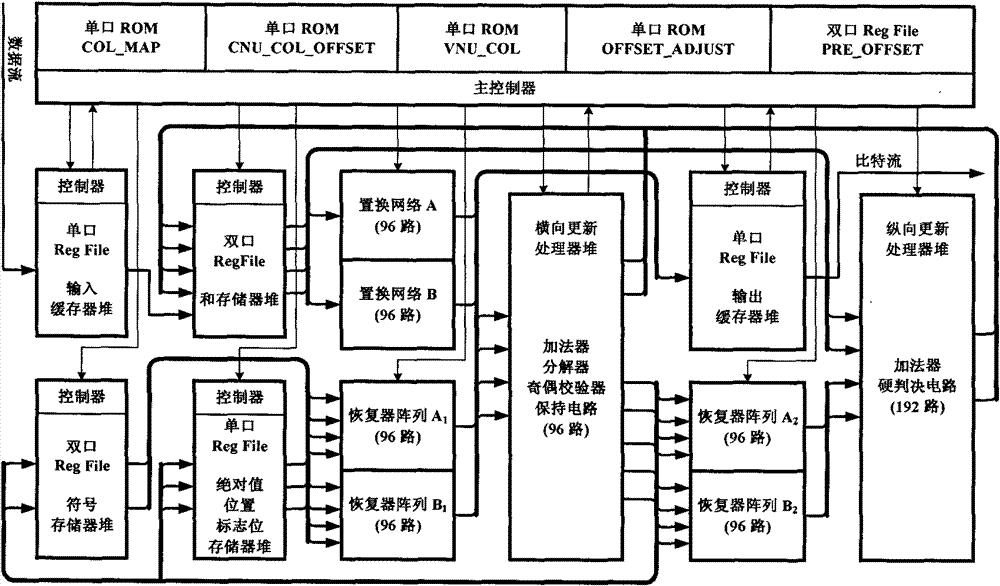

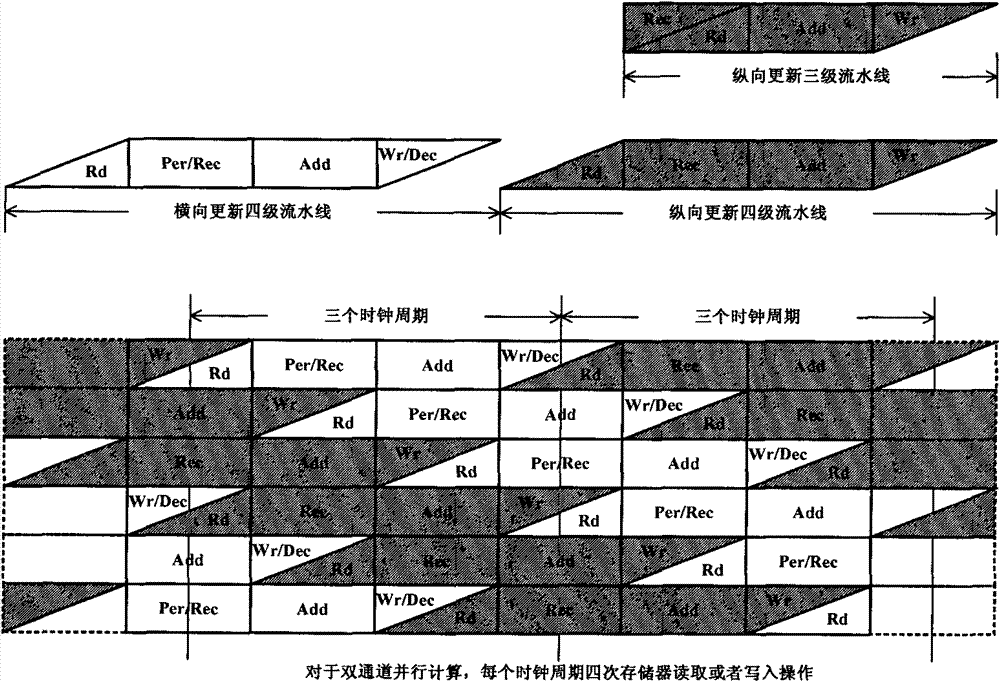

[0098] The decoder adopts an improved TDMP (Turbo-Decoding Message-Passing) decoding algorithm, that is, the soft-input and soft-output engine (SISO Engine) in the TDMP algorithm is replaced by the Normalized Min-Sum algorithm. Each row block corresponds to a subcode (sub-iteration); all subcodes concatenated together correspond to one iteration. Information is passed not only between different iterations, but also between different subcodes (sub-iterations). At the same time, each line only needs to save the check node information components: minimum and second minimum absolute value, minimum value position, sign and flag. Therefore, the decoder can not only achieve the same fast convergence speed as the TDMP algorithm, but also reduce memory resources to the greatest extent. In addition, horizontal update and vertical update adopt dual-channel parallel computing and two-phase complete overlapping technology, which further improves the throughput of the decoder and the utili...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More