Patents

Literature

87results about How to "Avoid access violations" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Intelligent vision based vehicle law-violation parking detection system and method

InactiveCN104616501AAvoid access violationsReduce workloadRoad vehicles traffic controlVision sensorImaging processing

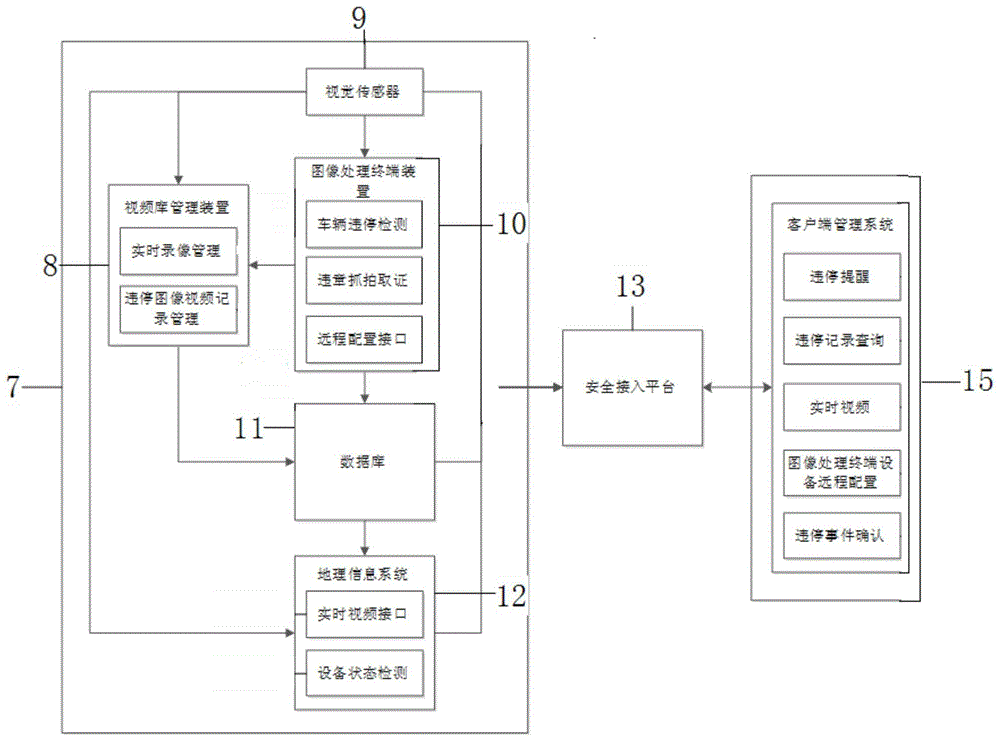

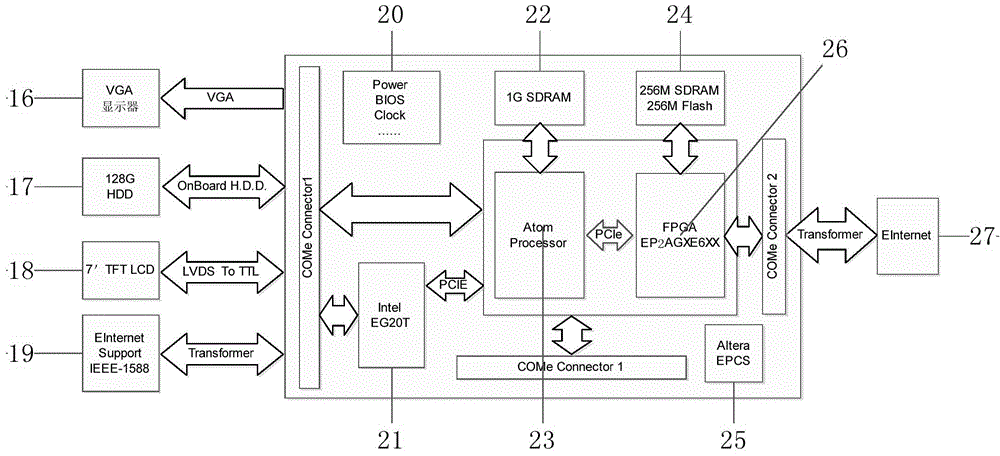

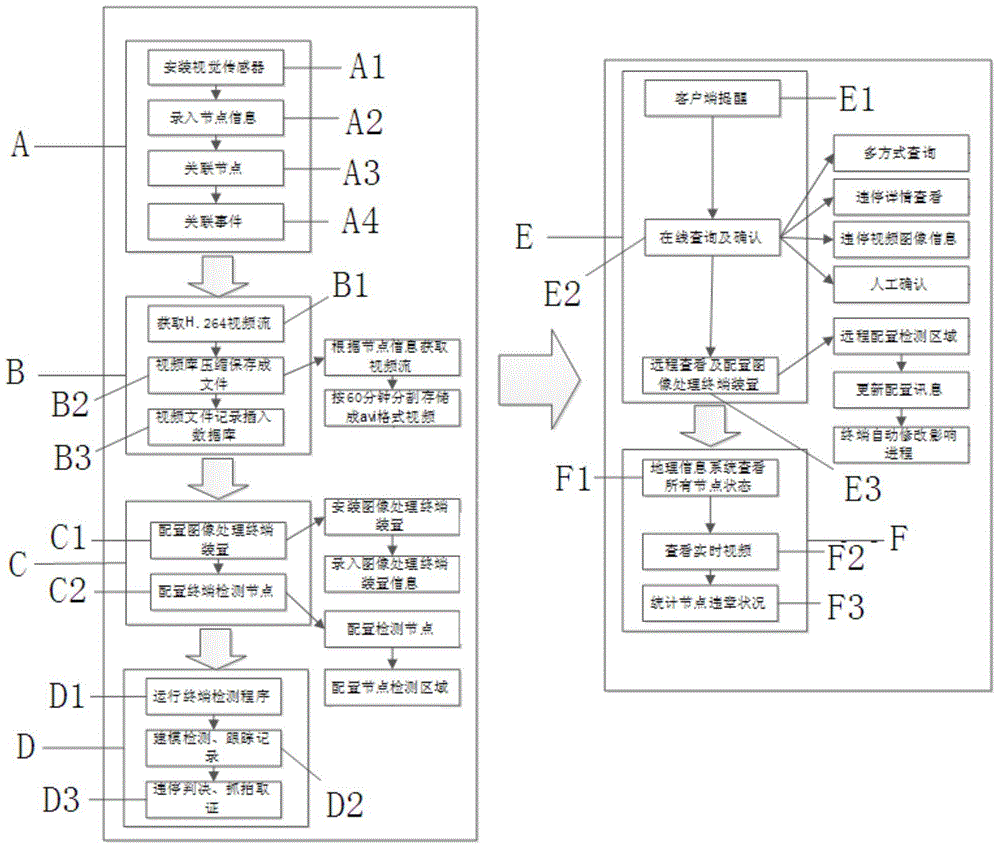

The invention discloses an intelligent vision based vehicle law-violation parking detection system and method. The detection system is that the output end of a visual sensor node is connected with an image processing terminal device and a video database management device, the image processing terminal device is connected with the video database management device, the image processing terminal device and the video database management device are jointly connected with a database, the database is connected with a geographical information system, the visual sensor node, the image processing terminal device, the video database management device, the database and the geographical information system form an image processing private network, the image processing private network is connected with a data private network through a safety access platform, a client-side management system is arranged in the data private network, automatically detects law-violation parking behaviors of vehicles, automatically records law-violation videos and performs timely processing, 'second accidents' caused by processing lag are avoided, data safety is ensured, data integrity and confidentiality can be effectively protected, and the intelligent vision based vehicle law-violation parking detection system and method have good application prospect.

Owner:HOHAI UNIV CHANGZHOU

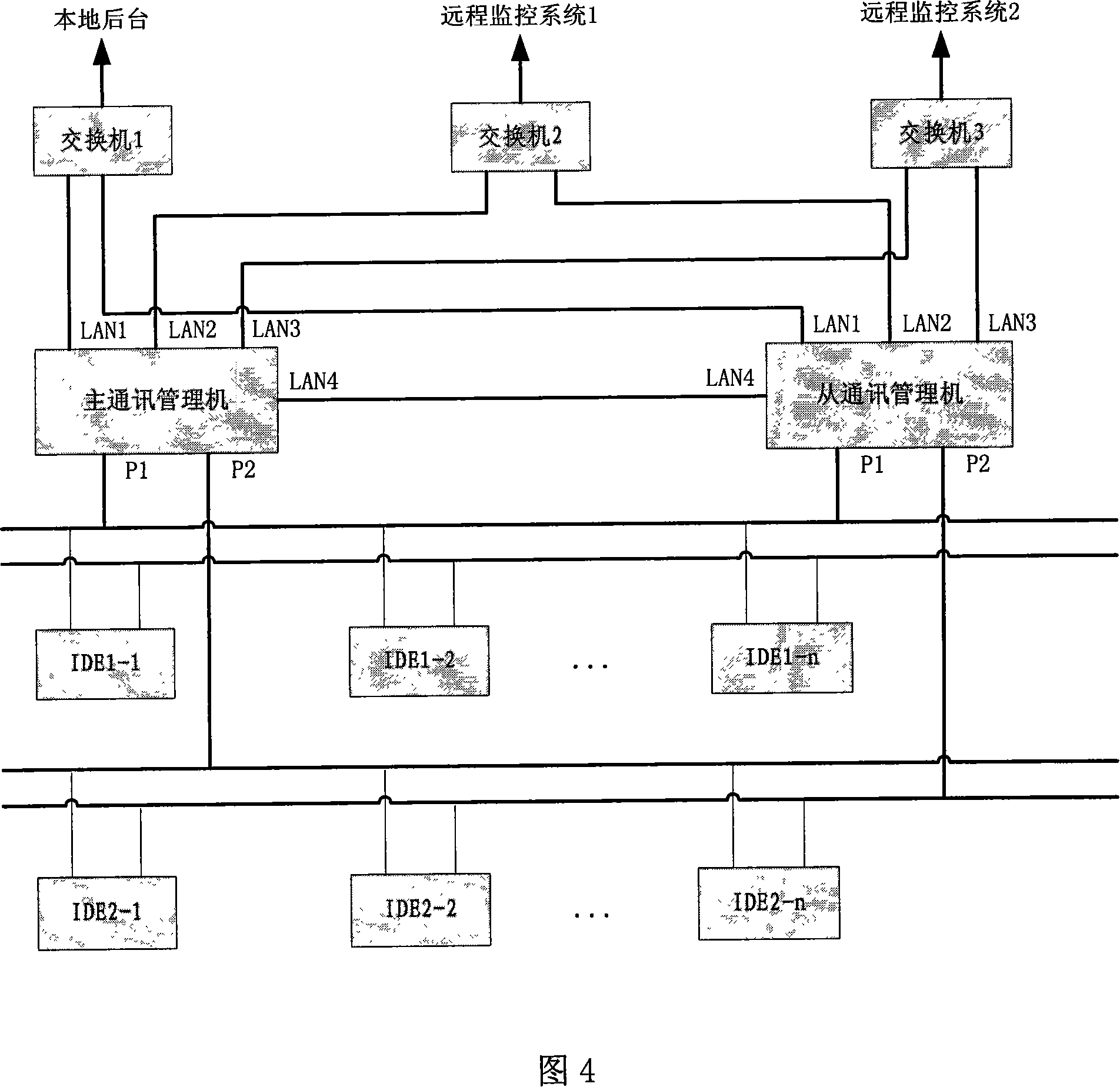

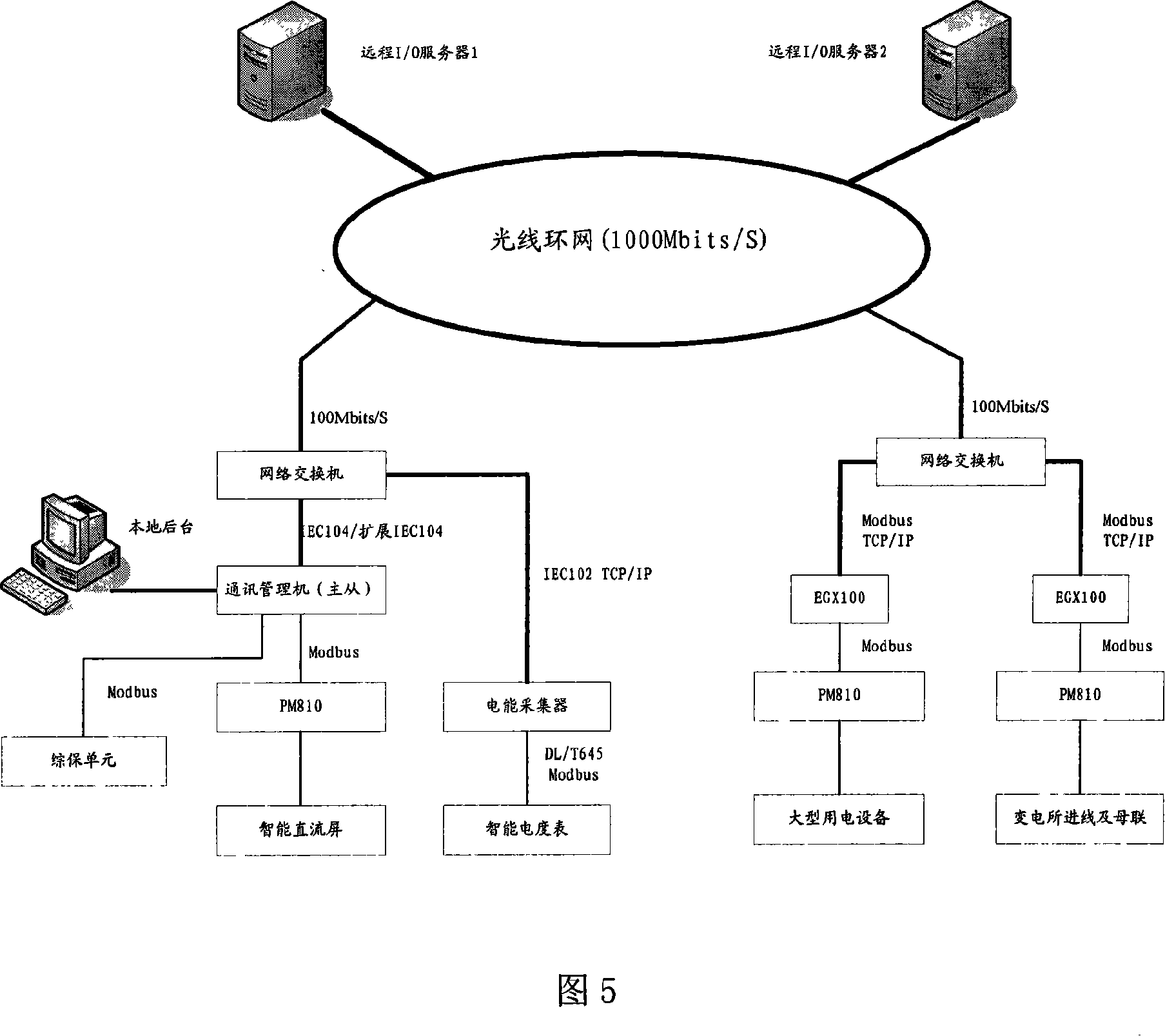

Transforming plant intelligent electronic equipment access system

InactiveCN101109951AImprove reliabilityGuaranteed real-time and reliabilityTotal factory controlProgramme total factory controlData transmissionRS-485

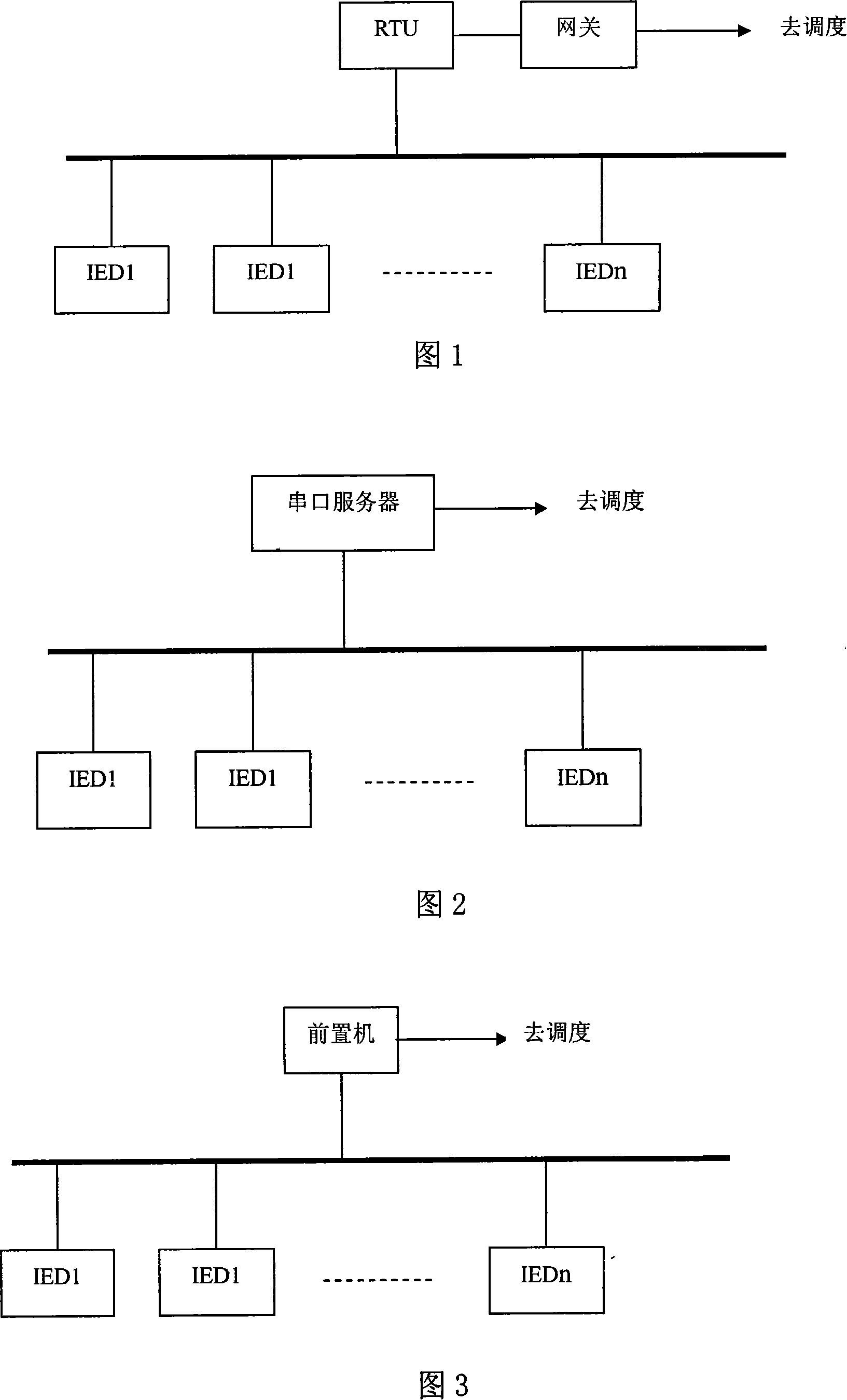

A system used for connecting with the intelligent electronic equipment in the transformer substation, so as to realize the tele-mechanics transmission of ''four remote'' date for the equipment in the transformer substation. The system adds a communication layer between the equipment in the isolated layer and the monitored control system of the transformer substation. The communication layer adopts the communication supervisor which is constituted by the high performance embedded system. Simultaneously, the data acquisition for the site equipment RS 485channel is completed and the communication protocol conversion is finished for the Ethernet transmission. Also, both the two-equipment and the double-channel redundancy communication can be realized to improve the reliability of data acquisition and communication as well as guarantee the reliability and the real time of the electric system's tele-mechanic data transmission, so as to solve such problems as the access conflict among a plurality of the primary stations at RS 485 port of the intelligent electronic equipment in the isolated layer as well as the remote control limits exist in a plurality of the monitored control system. Therefore, an effective access method is provided for the equipment in the middle isolated layer of the transformer substation's automation system to directly go through the Ethernet for completing the monitoring function.

Owner:JIGANG GRP +1

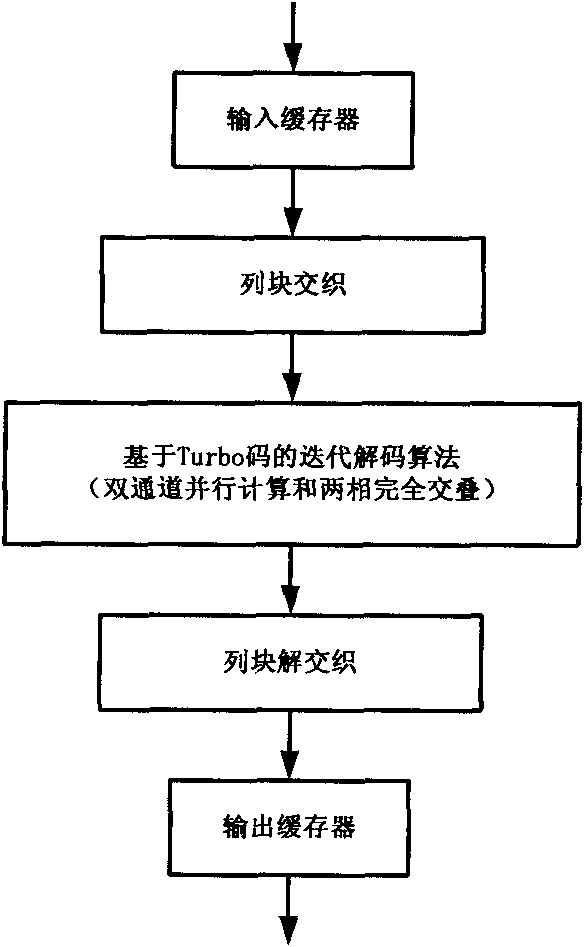

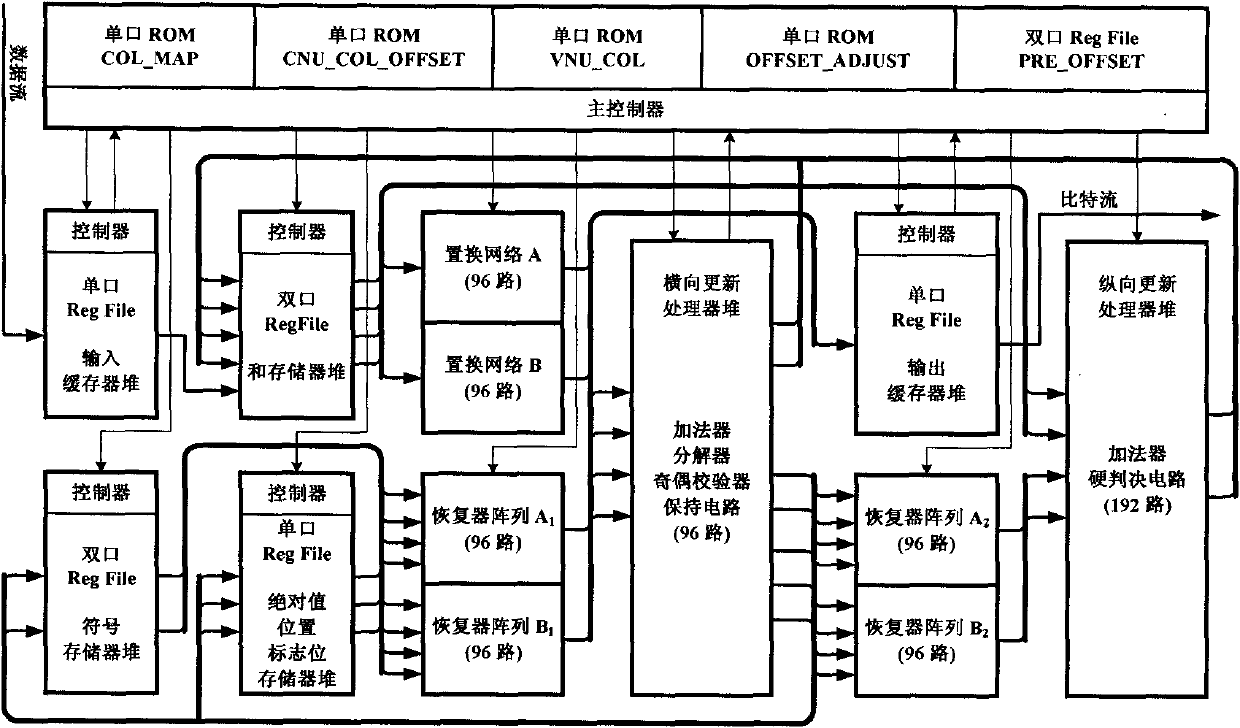

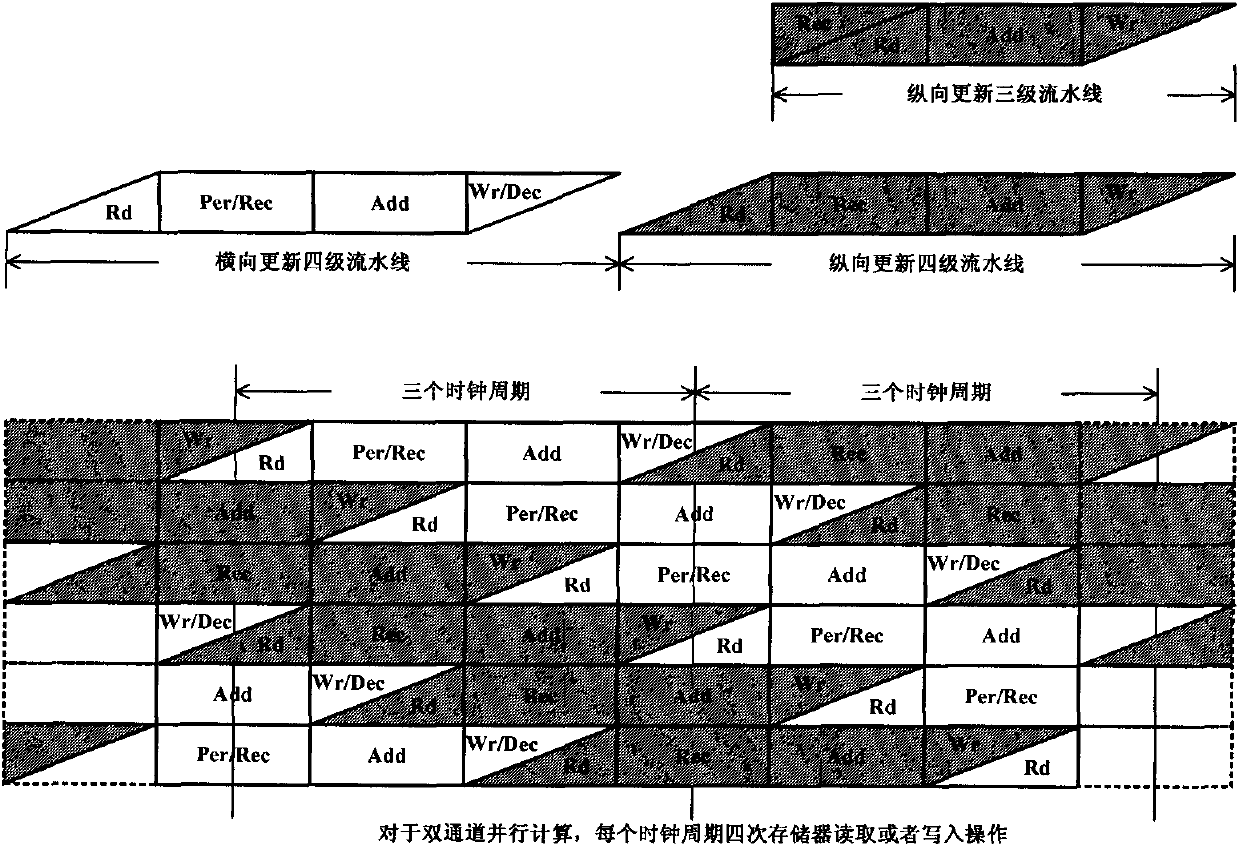

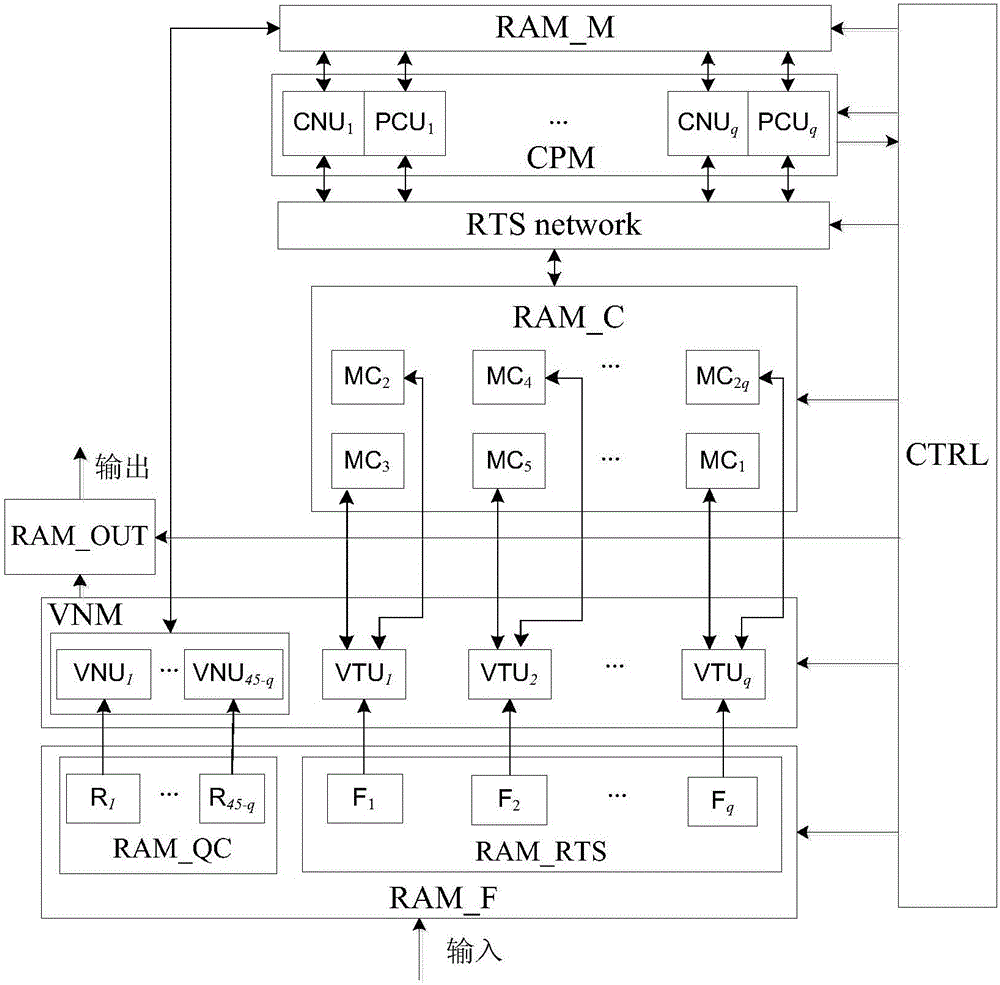

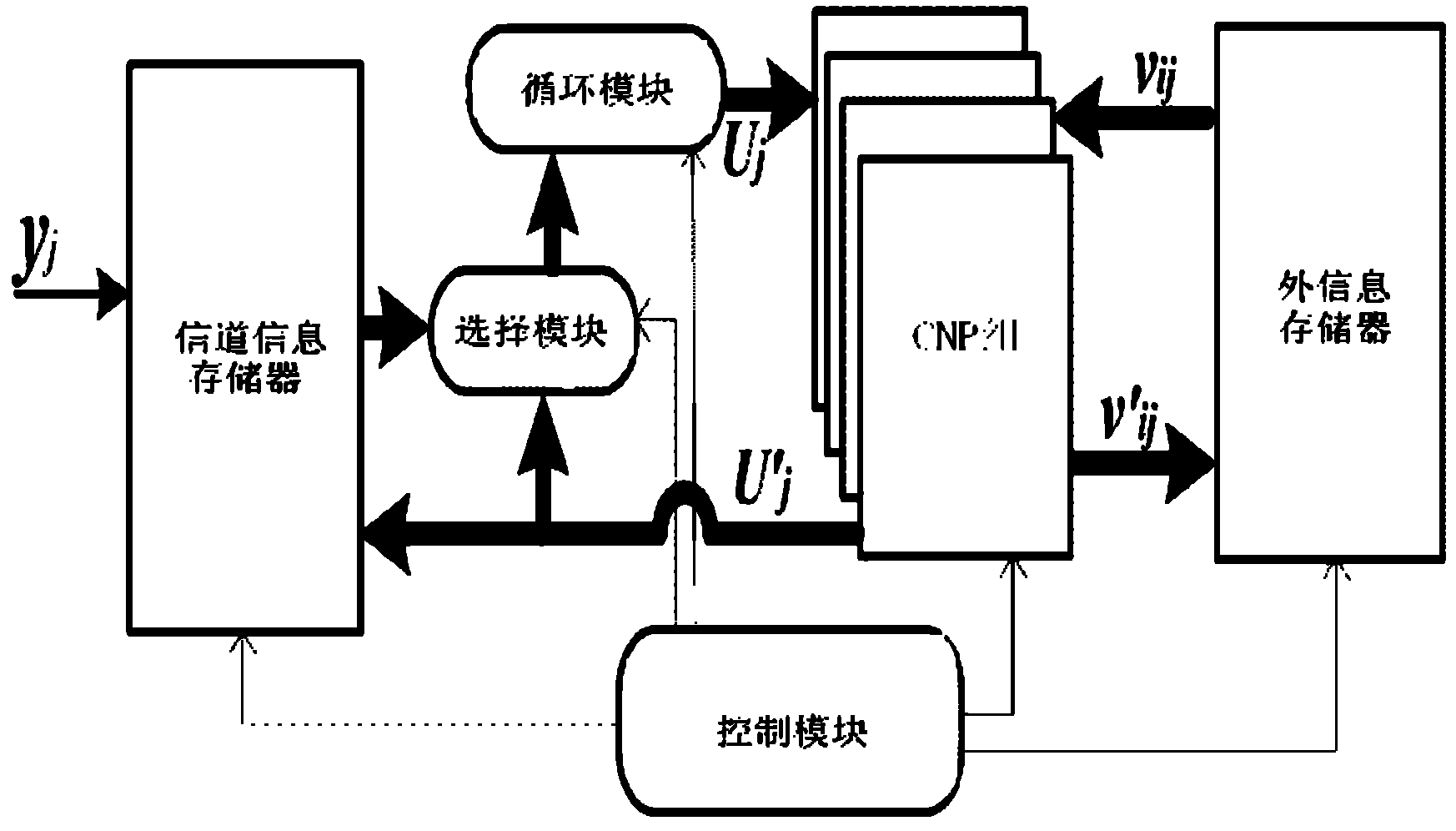

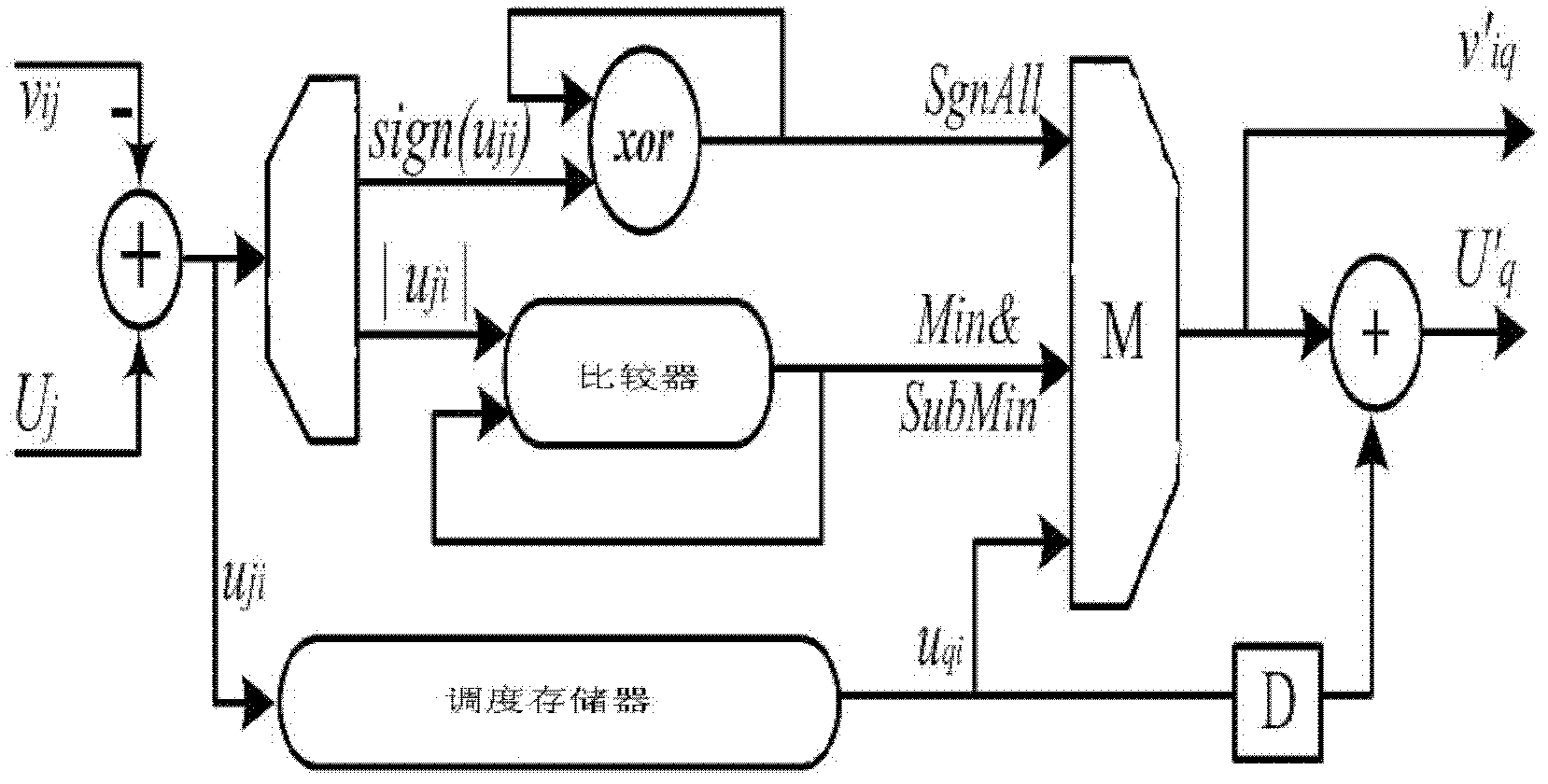

Ultrahigh-speed and low-power-consumption QC-LDPC code decoder based on TDMP

InactiveCN101771421AReduce visitsAvoid access violationsError correction/detection using multiple parity bitsComputer architectureParallel computing

The invention belongs to the technical field of wireless communication and micro-electronics, in particular to an ultrahigh-speed low-power-consumption and low-density parity check code (QC-LDPC) decoder based on TDMP. Through symmetrizing six grades of production lines, interlacing row blocks and line blocks, re-sequencing nonzero sub matrixes, carrying out four-quadrant division on a sum value register pile and adopting the technology of reading and writing the bypass, the decoder carries out serial scanning in the row sequence, two nonzero sub matrixes are respectively processed in each clock period during horizontal updating and vertical updating. The horizontal updating and the vertical updating are fully overlapped. Particularly, the sum value register pile stores the sum values of variable nodes, and is also used as an FIFO for storing transient external information transferred between two phases. The structure of the decoder has strong configurability, can be easily transplanted into any other irregular or irregular QC-LDPC codes, and has the excellent decoding performance, the peak frequency can reach 214 MHz, the thuoughput can reach about 1 gigabit per second, and the chip power consumption is only 397 milliwatts.

Owner:FUDAN UNIV

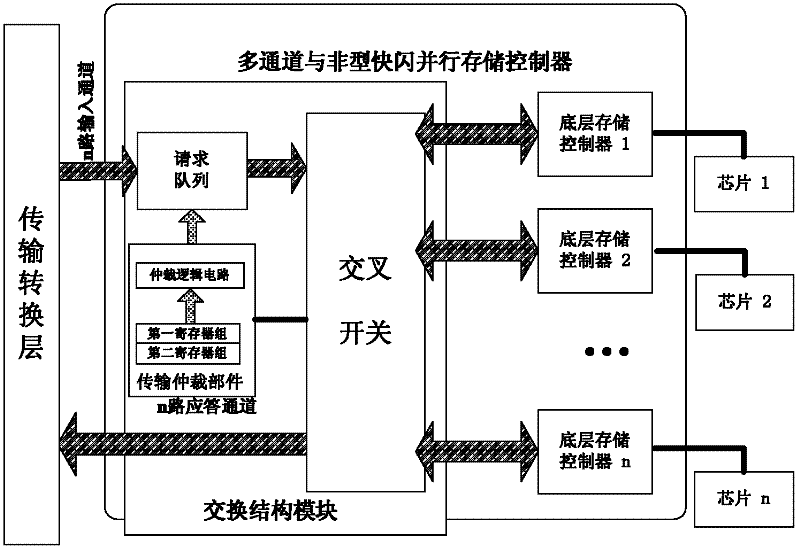

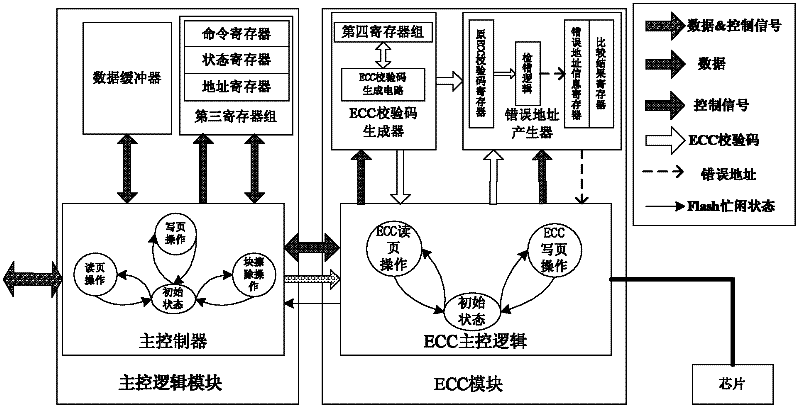

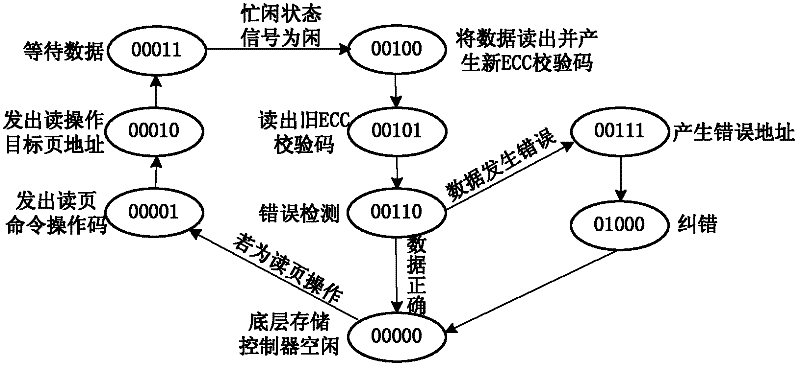

Multichannel NAND flash parallel memory controller

ActiveCN102541678AAvoid access violationsIncrease Aggregate BandwidthRedundant data error correctionCrossbar switchError checking

The invention discloses a multichannel NAND flash parallel memory controller and aims to provide a memory controller which is capable of providing larger aggregation bandwidth and has high data reading and writing reliability. The multichannel NAND flash parallel memory controller comprises a switching structure module and n bottom-layer memory controllers, wherein the switching structure module comprising a request queue, a transmission arbitration member and a crossbar switch is used for carrying out transmission arbitration on requests of a plurality of channels; each bottom-layer memory controller consisting of a master control logic module and an ECC (Error Checking and Correcting) module is used for generating a control signal meeting a chip time sequence requirement and carrying out ECC on data; the master control logic module comprises a data buffer, a third register group and a master controller, and the ECC module comprises an ECC master control logic, an ECC check code generator and an error address generator. By using the multichannel NAND flash parallel memory controller, a parallel access mechanism of a multichannel NAND flash chip is realized, the aggregation bandwidth is effectively increased, the requirement of data intensive calculation for large bandwidth is met, an ECC function is realized, and the data reliability is improved.

Owner:NAT UNIV OF DEFENSE TECH

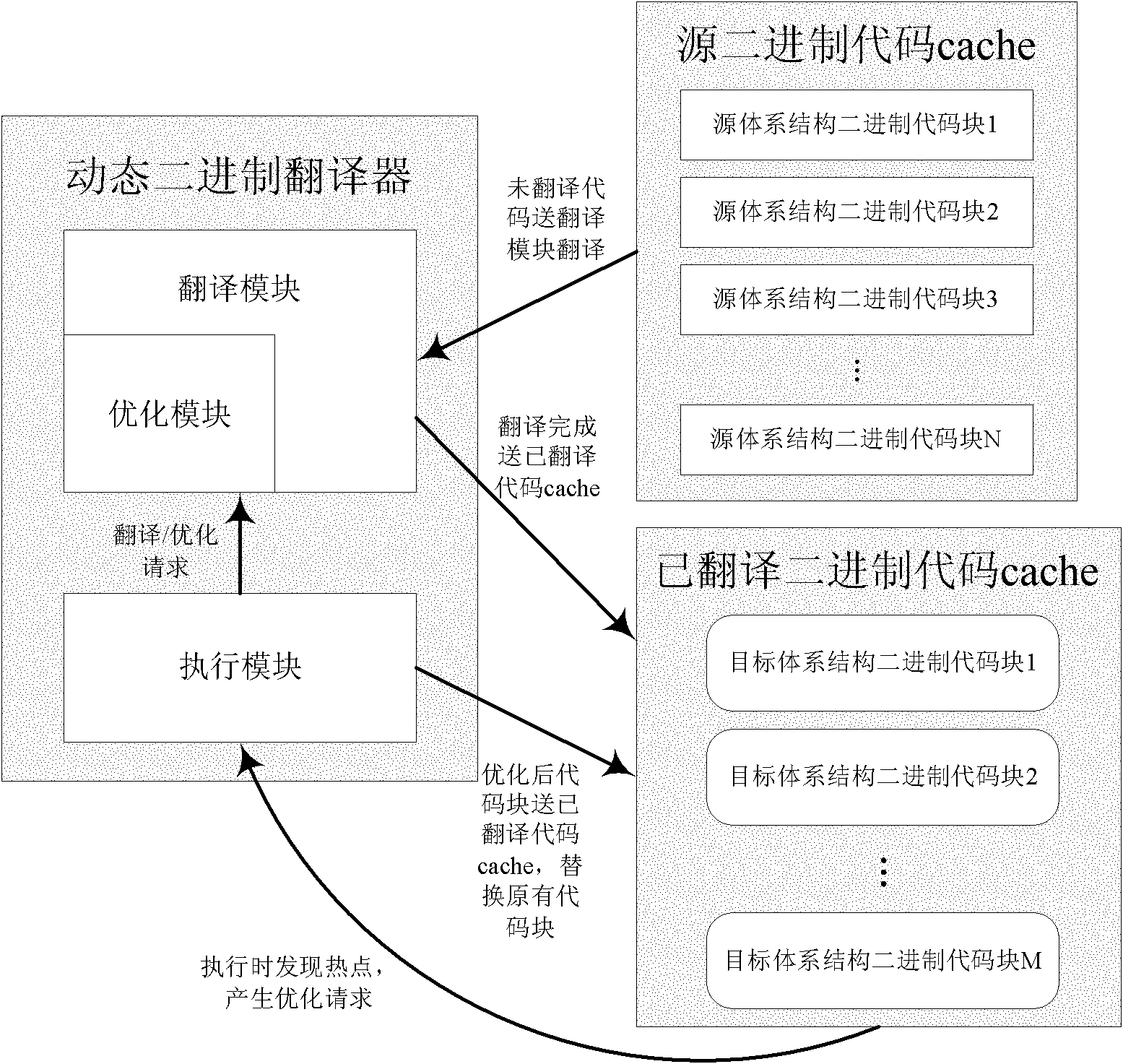

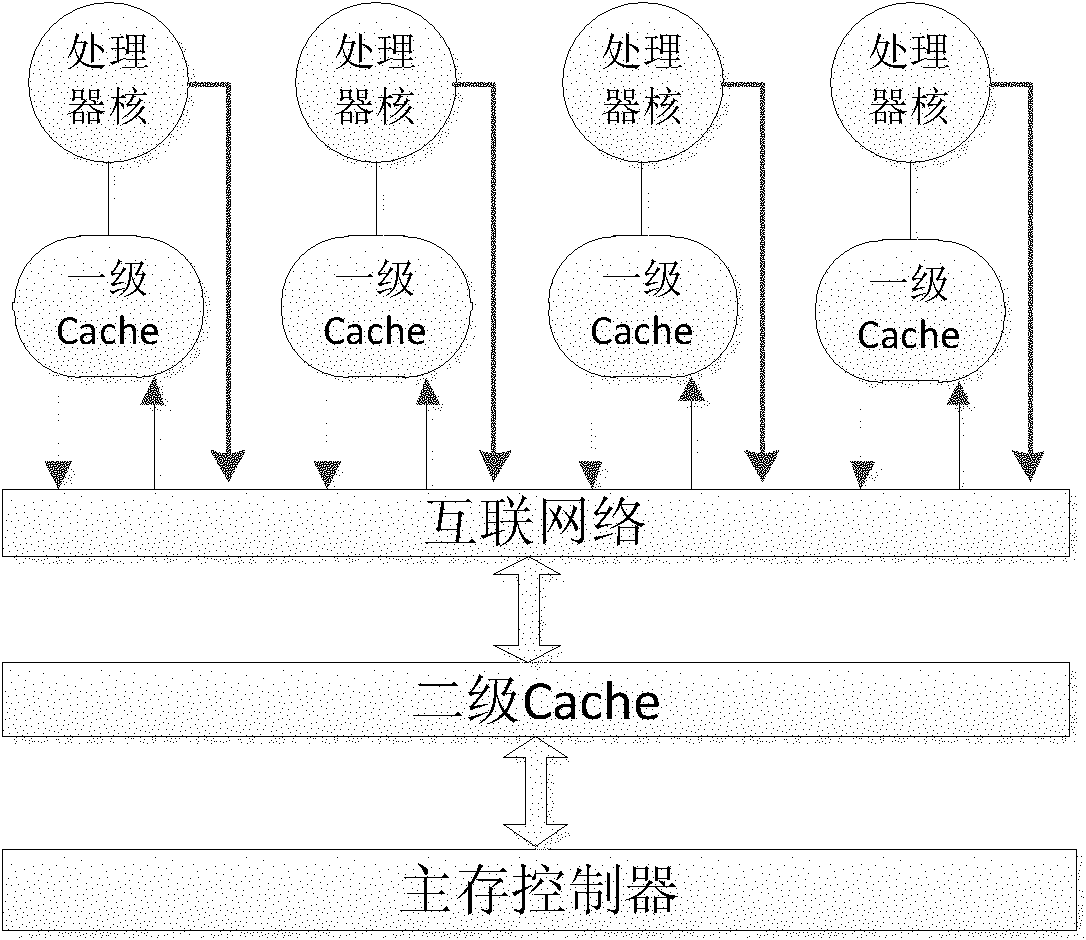

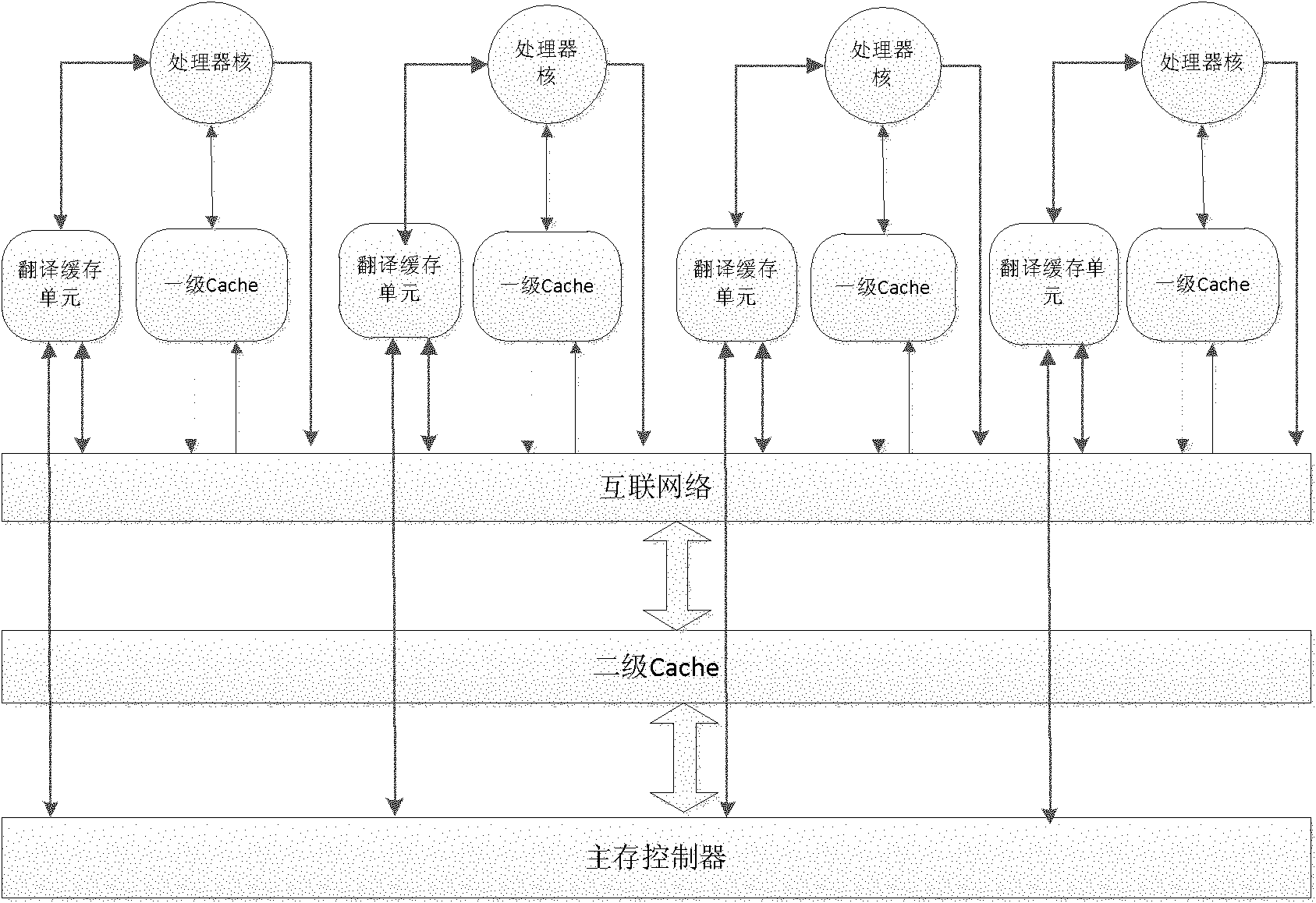

Multicore architecture supporting dynamic binary translation

InactiveCN102073533AReduce overheadReduce page access latencyMemory adressing/allocation/relocationMultiple digital computer combinationsMulticore architectureParallel computing

The invention discloses a multicore architecture supporting dynamic binary translation, aiming to solve the problems of Cache access conflict, main memory conflict and the like during dynamic binary translation. The multicore architecture comprises a plurality of processor cores, a plurality of primary Caches, a plurality of translation cache units, a secondary Cache and a main memory controller,wherein the primary Caches and the translation cache units are private for each processor core; the secondary Cache and the main memory controller are shared by all the processor cores; each translation cache unit comprises a communication control unit, a cache management unit and a data memory unit; the communication control unit comprises a multi-channel selector, a communication control unit controller, a transmission bus and three registers; the cache management unit comprises a page replacement component and a cache management control component; and the data memory unit comprises a source architecture binary code cache area, a target architecture binary code cache area and a page mapping table. The multicore architecture has the following technical effects: the data access latency isreduced, the translation throughput is high and the Cache access conflict is less.

Owner:NAT UNIV OF DEFENSE TECH

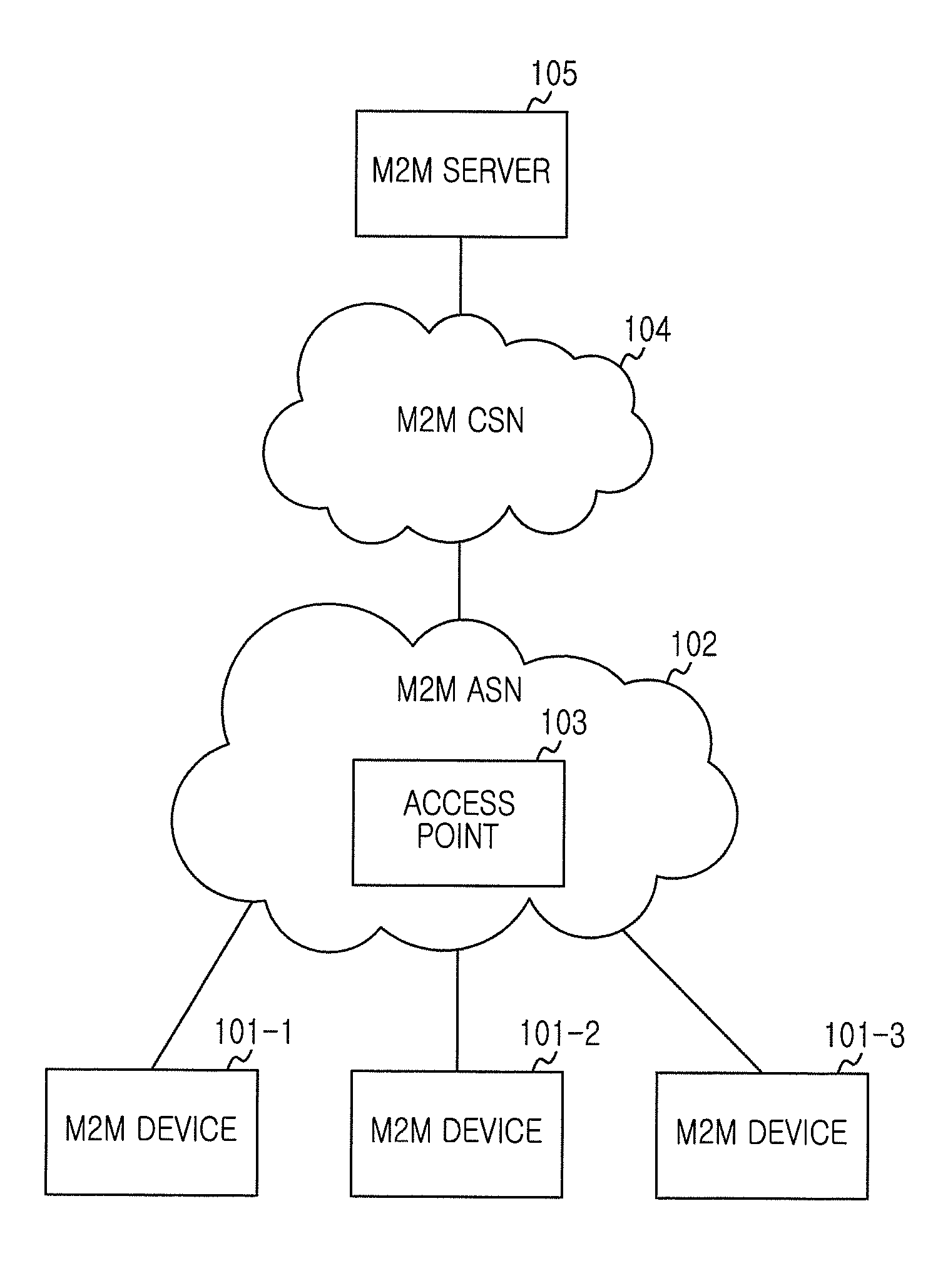

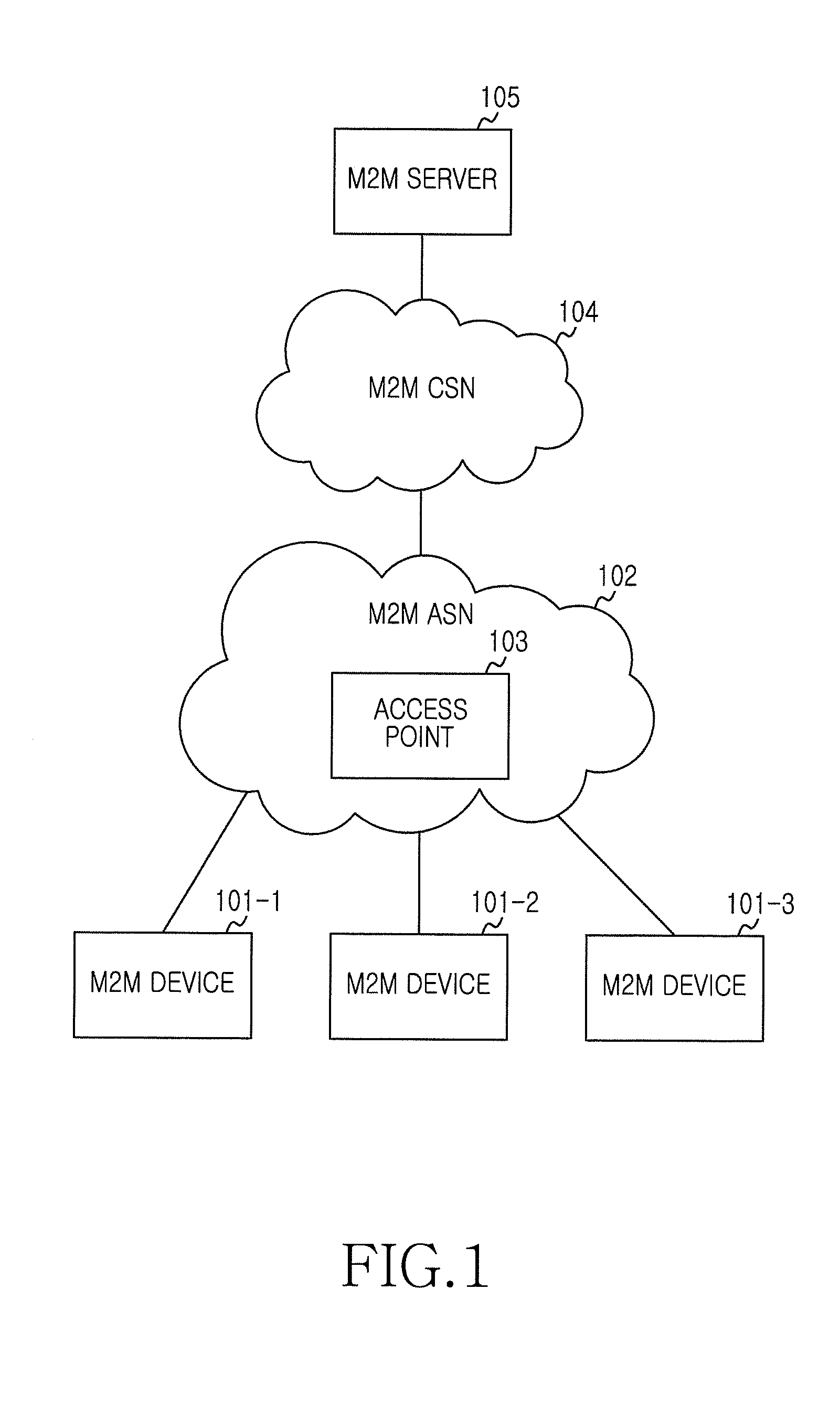

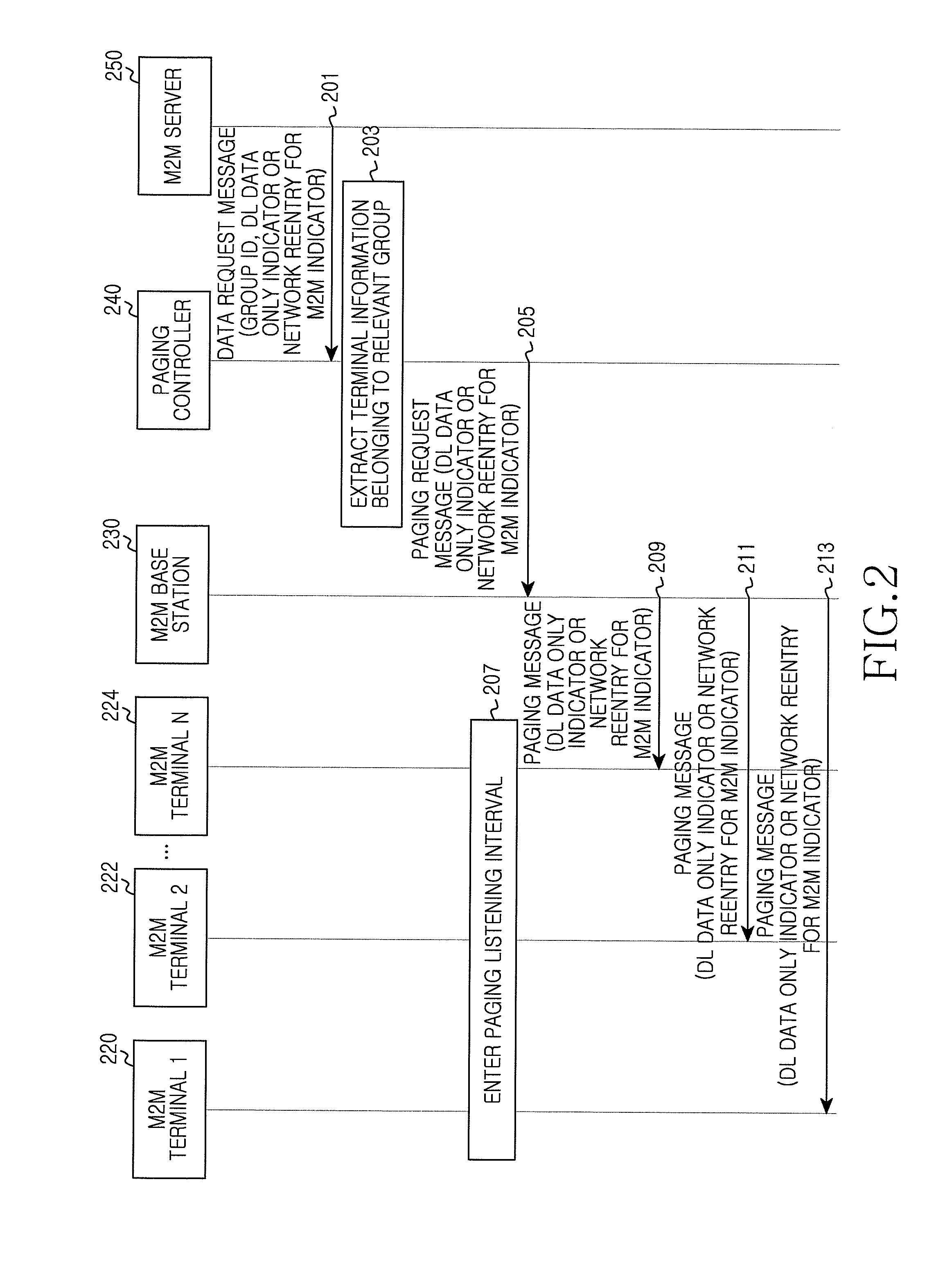

Method and apparatus for reducing access overhead from paged device in machine to machine communication system

ActiveUS20120093052A1Reduce access overheadAvoid access violationsPower managementTransmission systemsCommunications systemComputer science

An apparatus for an idle mode terminal is configured to perform a method for operating the idle mode terminal in a Machine to Machine (M2M) communication system. A paging message is received from the base station during a paging listening interval. The Apparatus determines whether an indicator indicating receipt of multicast group data is included in the paging message. When the indicator indicating the receiving of multicast group data is included, data transmitted via a downlink resource that uses an identifier mask of a multicast group to which a terminal belongs is received. Thereafter, a paging non-listening interval is entered.

Owner:SAMSUNG ELECTRONICS CO LTD

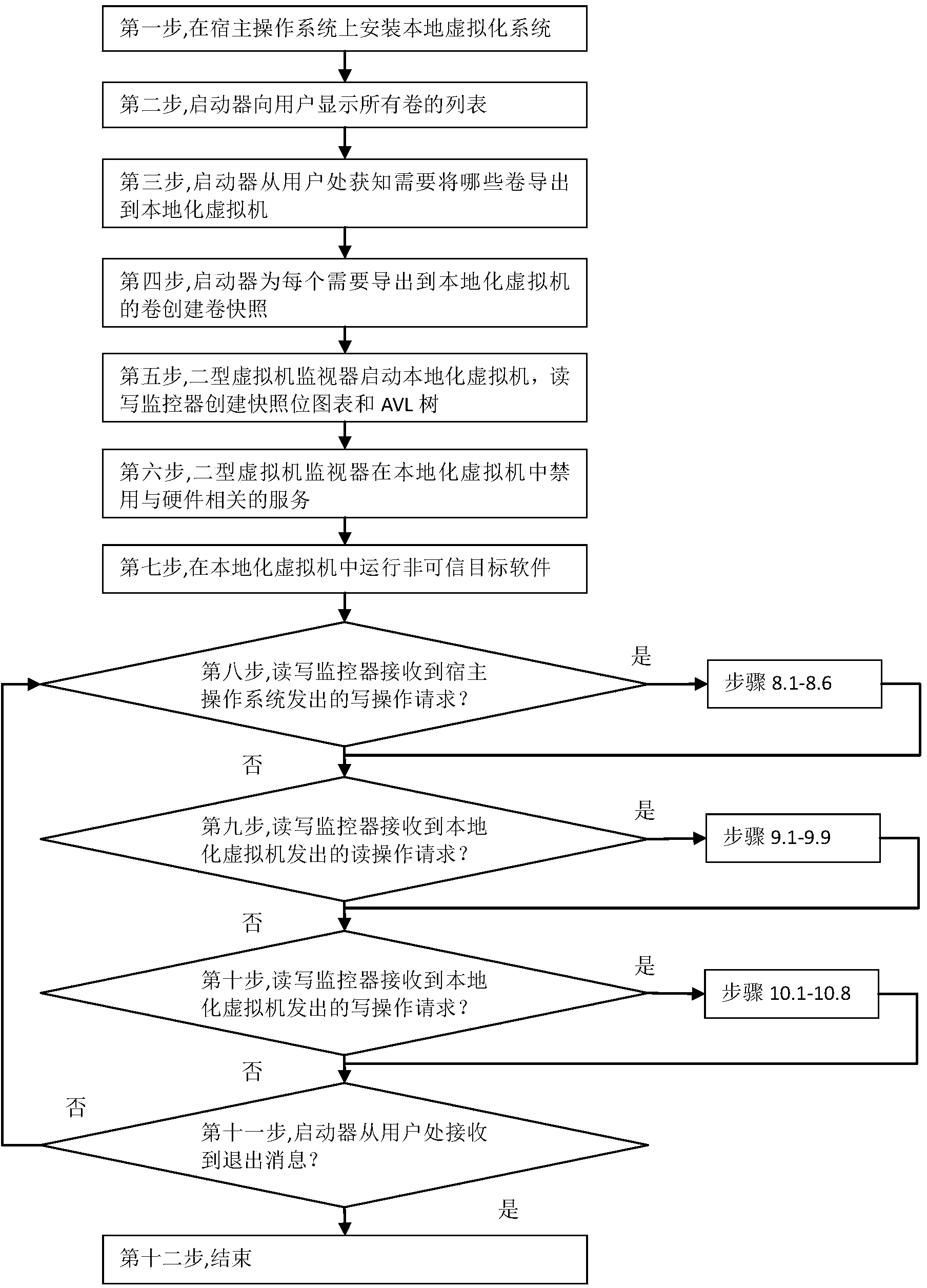

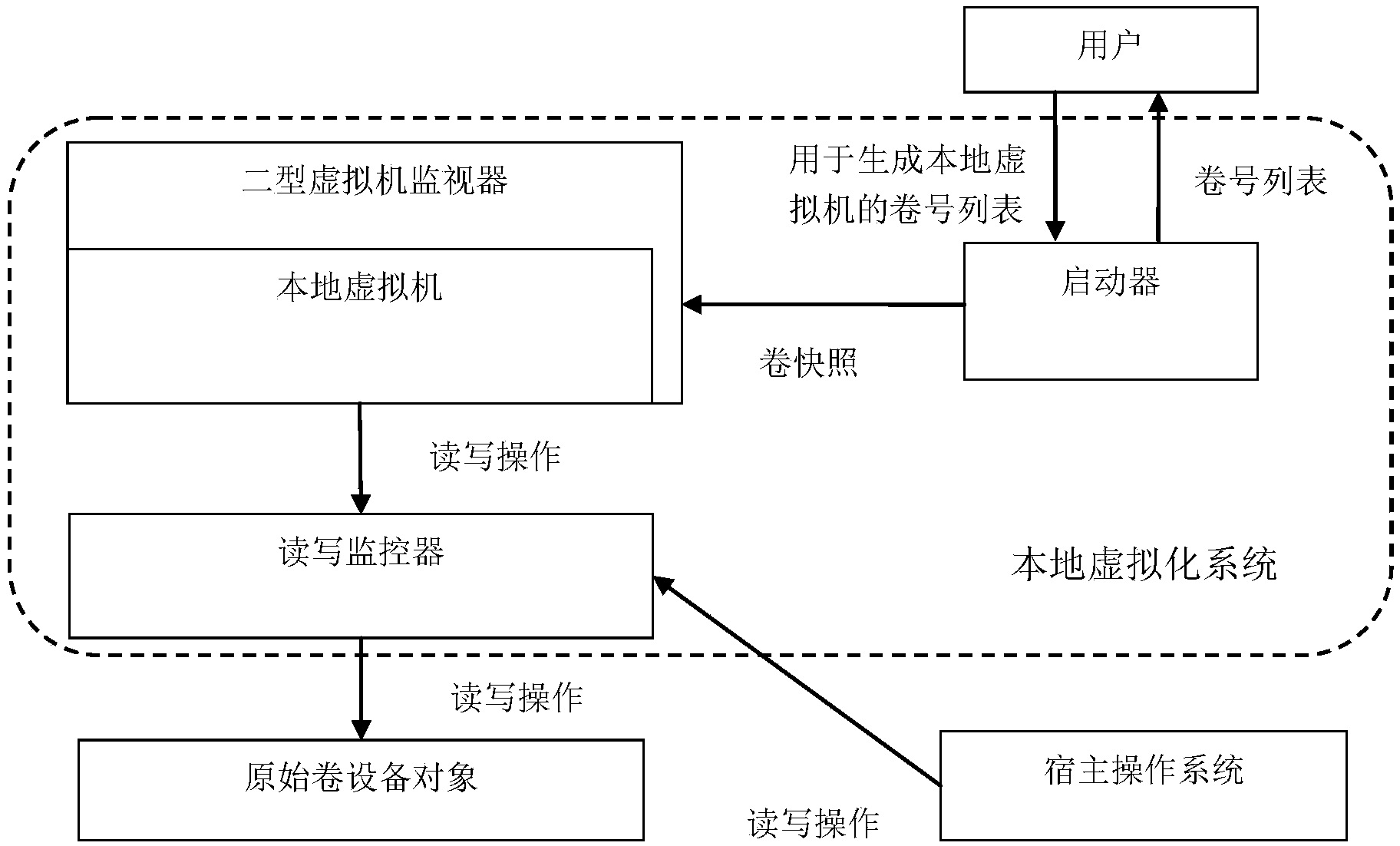

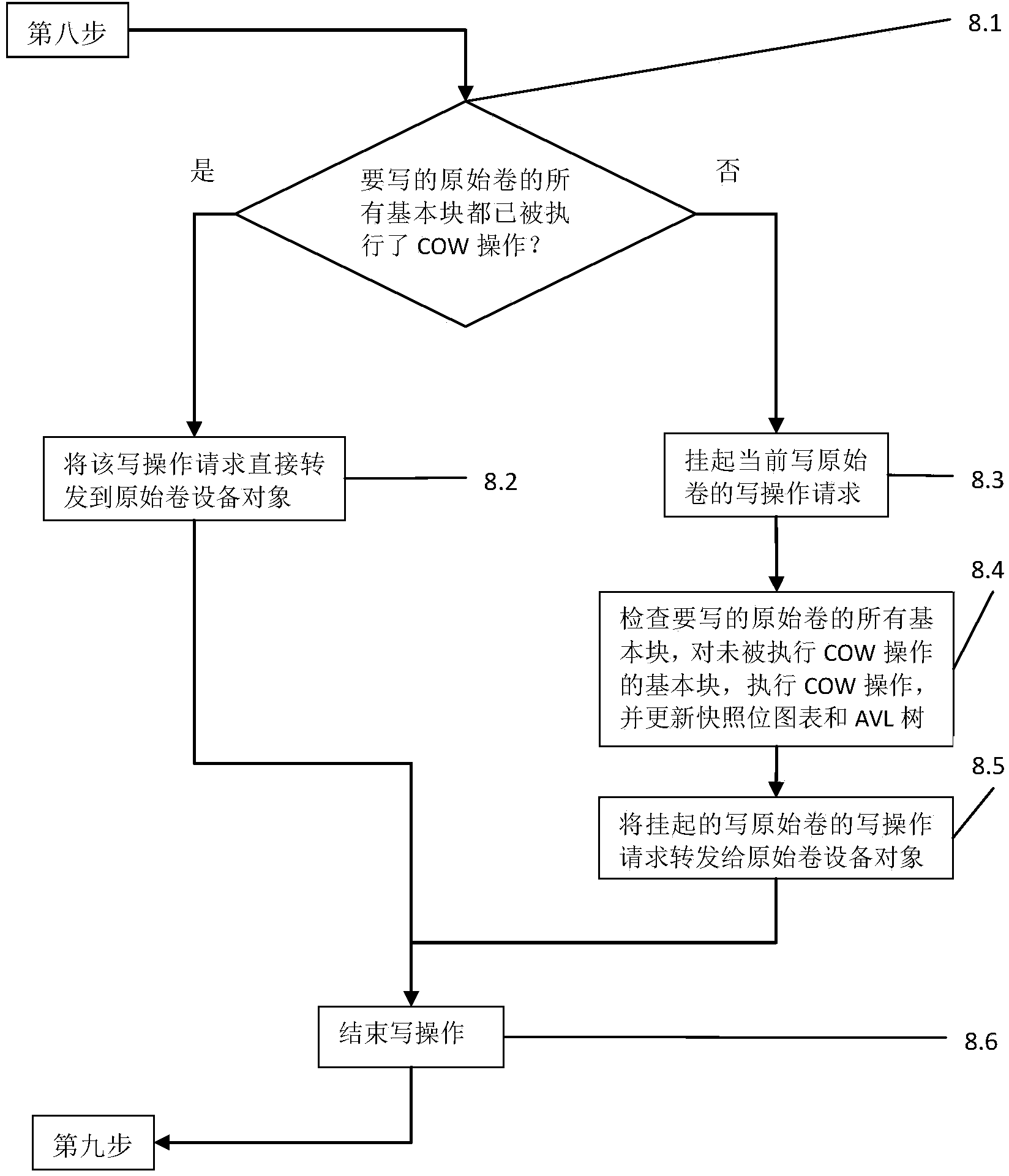

Method for running programs in isolation manner on basis of local virtualization mechanism

InactiveCN103914647ARealize safe isolation operationAvoid access violationsPlatform integrity maintainanceVirtualizationOperational system

The invention discloses a method for running programs in an isolation manner on the basis of a local virtualization mechanism. The method aims to solve the problem that an existing method for running programs in an isolation manner cannot simultaneously meet three application constraints required when non-trusted software is executed. The technical scheme includes that a local virtualization system which comprises a type-two virtual machine monitor, a starter and a read-write monitor is installed in a host operating system, the type-two virtual machine monitor starts a local virtual machine according to volume snapshots provided by the starter, and the read-write monitor performs read-write operation on an original volume device object in a unified manner according to a principle that 'basic blocks in a snapshot space only can be written by the virtual machine and original basic blocks only can be written by a host machine'. The method has the advantages that a host computation environment can be reconstructed on a personal computing platform, file system access conflict of the local virtual machine and the host operating system can be prevented, and non-trusted software can effectively and safely run in an isolation manner.

Owner:NAT UNIV OF DEFENSE TECH

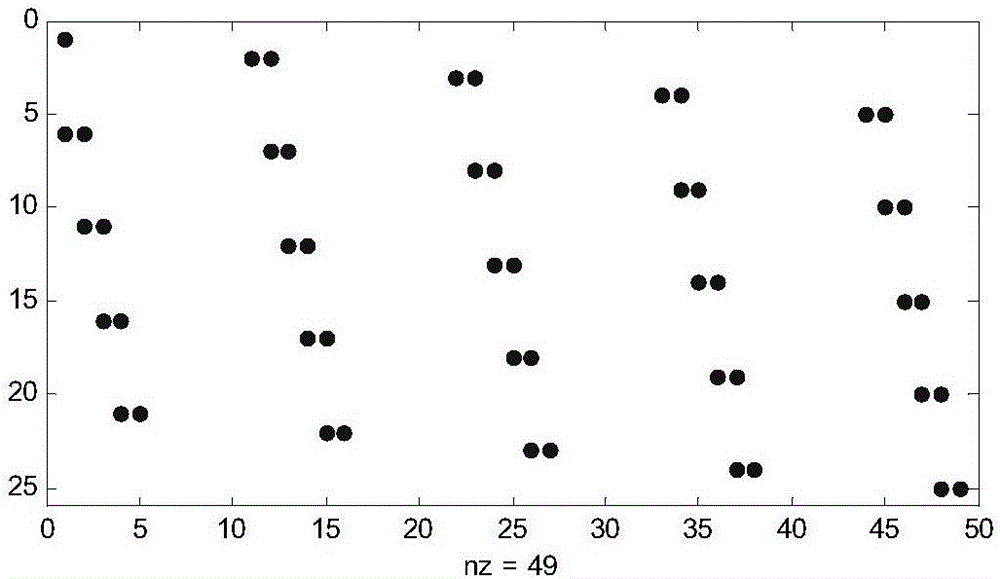

FPGA-based high-speed adaptive DVB-S2 LDPC decoder and decoding method

ActiveCN106571829AReduce complexityDoes not affect decoding performanceError correction/detection using multiple parity bitsCode conversionDVB-S2Decoding methods

The invention relates to an FPGA-based high-speed adaptive DVB-S2 LDPC decoder and a decoding method. the method comprises steps: (1) matrix transformation is carried out, the generated left matrix has a quasi-cyclic structure, and the right matrix is a new matrix for a triangle-to-dual-diagonal (RTS) sub matrix; (2) RAM and iteration times are initialized; (3) the two parts of matrixes complete variable node information updating and data write back; (4) node information updating and write back are verified, a syndrome vector s is calculated, and one is added to the iteration times iter; (5) if the syndrome vector s is equal to 0 or the maximum iteration times are reached, a sixth step is carried out, or otherwise, the third step is carried out for next-round iteration processing; and (6) a decoding judgment bit is read, and a decoding codeword is outputted.

Owner:XIAN INSTITUE OF SPACE RADIO TECH

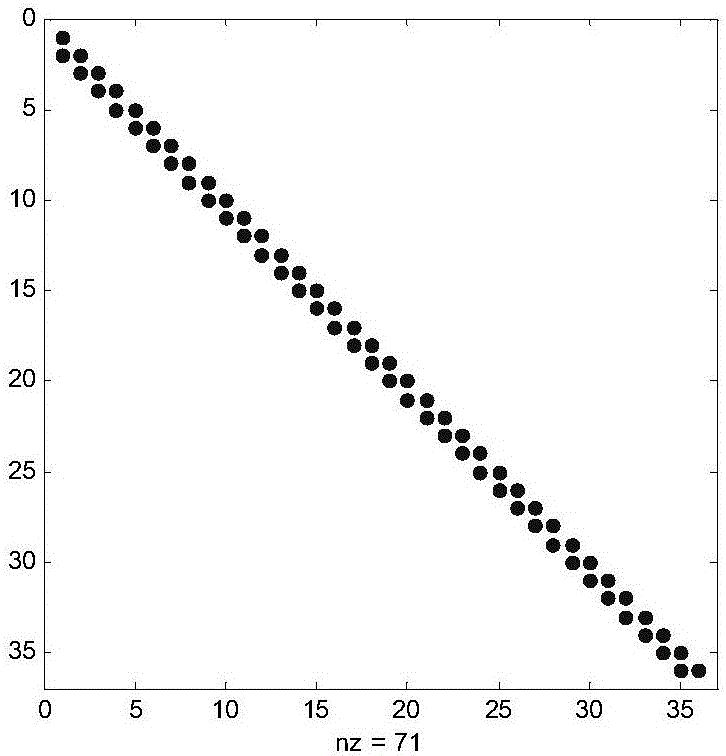

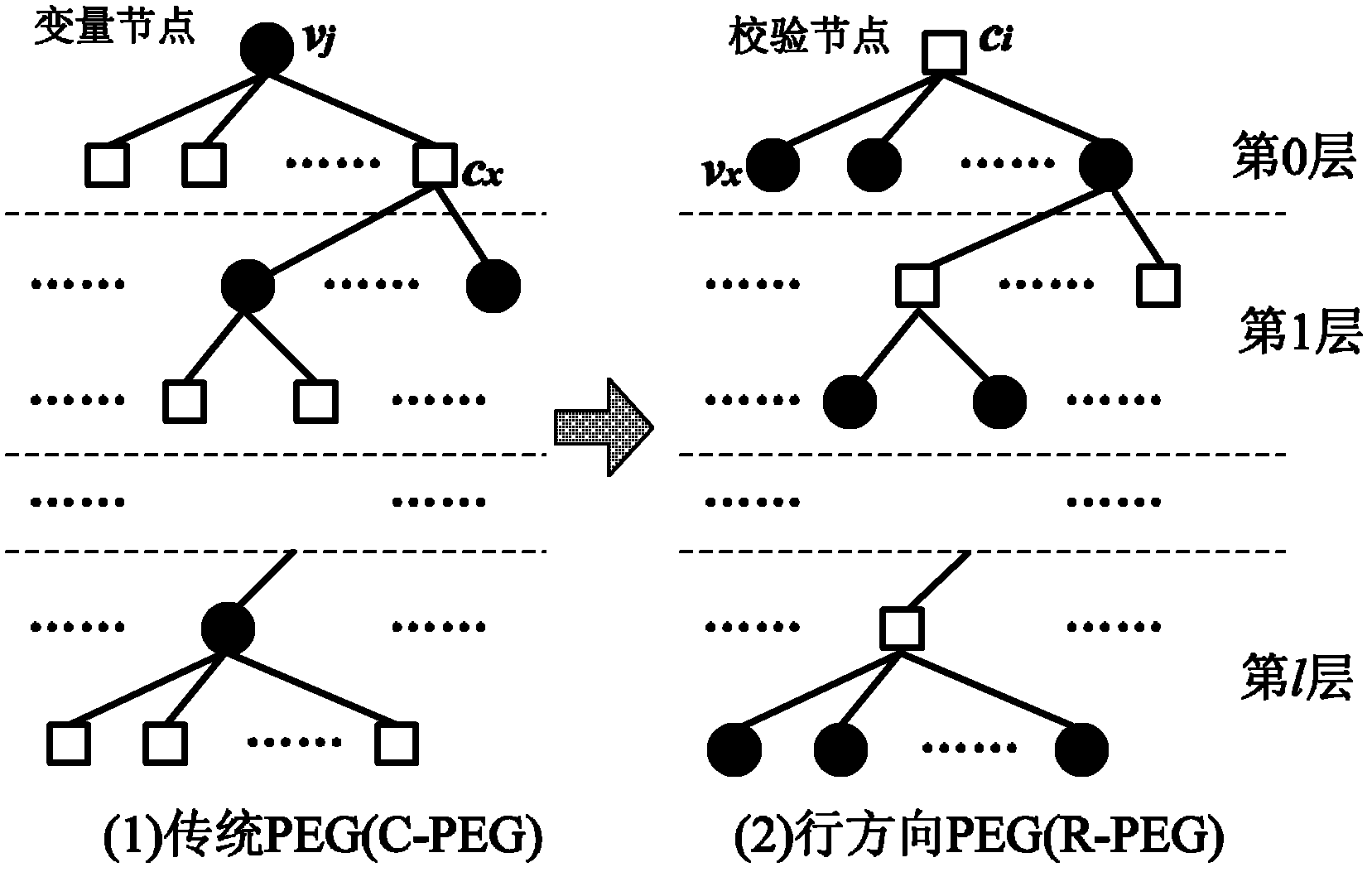

Quasi-cyclic low-density parity-check (LDPC) code construction method capable of eliminating decoder access conflict

InactiveCN103220002AReduce wasteAvoid access violationsError correction/detection using multiple parity bitsTanner graphAlgorithm

The invention relates to a quasi-cyclic low-density parity-check (LDPC) code construction method. A quasi-cyclic LDPC code to be constructed is represented by a tree graph model Tanner graph, and the quasi-cyclic check matrix parameter is that the size of a basis matrix is m * n, the size of a Block matrix is p * p, and basis matrix variable nodal point dimensionality distribution is represented by dv. The method comprises the follow steps: (1) determining check nodal point homogenization dimensionality distribution (dc) according to the basis matrix variable nodal point dimensionality distribution (dv) and adding all the n variable nodal points to the Tanner graph according to the dimensionality distribution (dc); (2) adding m check nodal points to the Tanner graph line by line and selecting pre-selected variable nodal points, determining the variable nodal points reaching a weight preset value according to side boundary weight and serving as an alternative set, and obtaining the variable nodal points with avoiding degree (ADeg) equal to or larger than delay (DLY) in a screening mode from the alternative set; and (3) determining the side boundary weight in the Tanner graph according to the points obtained from the step (2), adding corresponding sides to the Tanner graph, obtaining the quasi-cyclic LDPC code according to the Tanner graph, and achieving the construction of the quasi-cyclic LDPC code.

Owner:PEKING UNIV

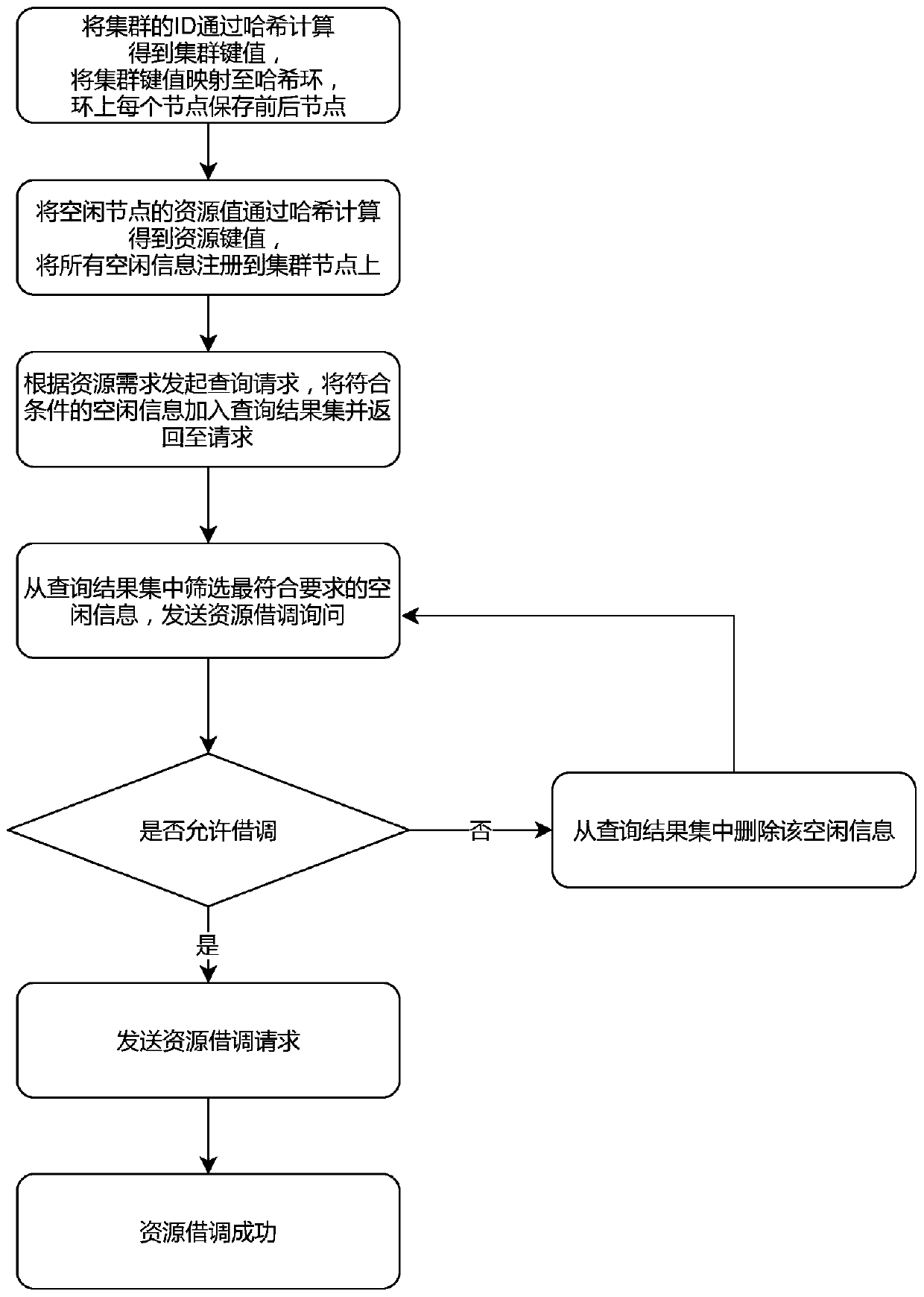

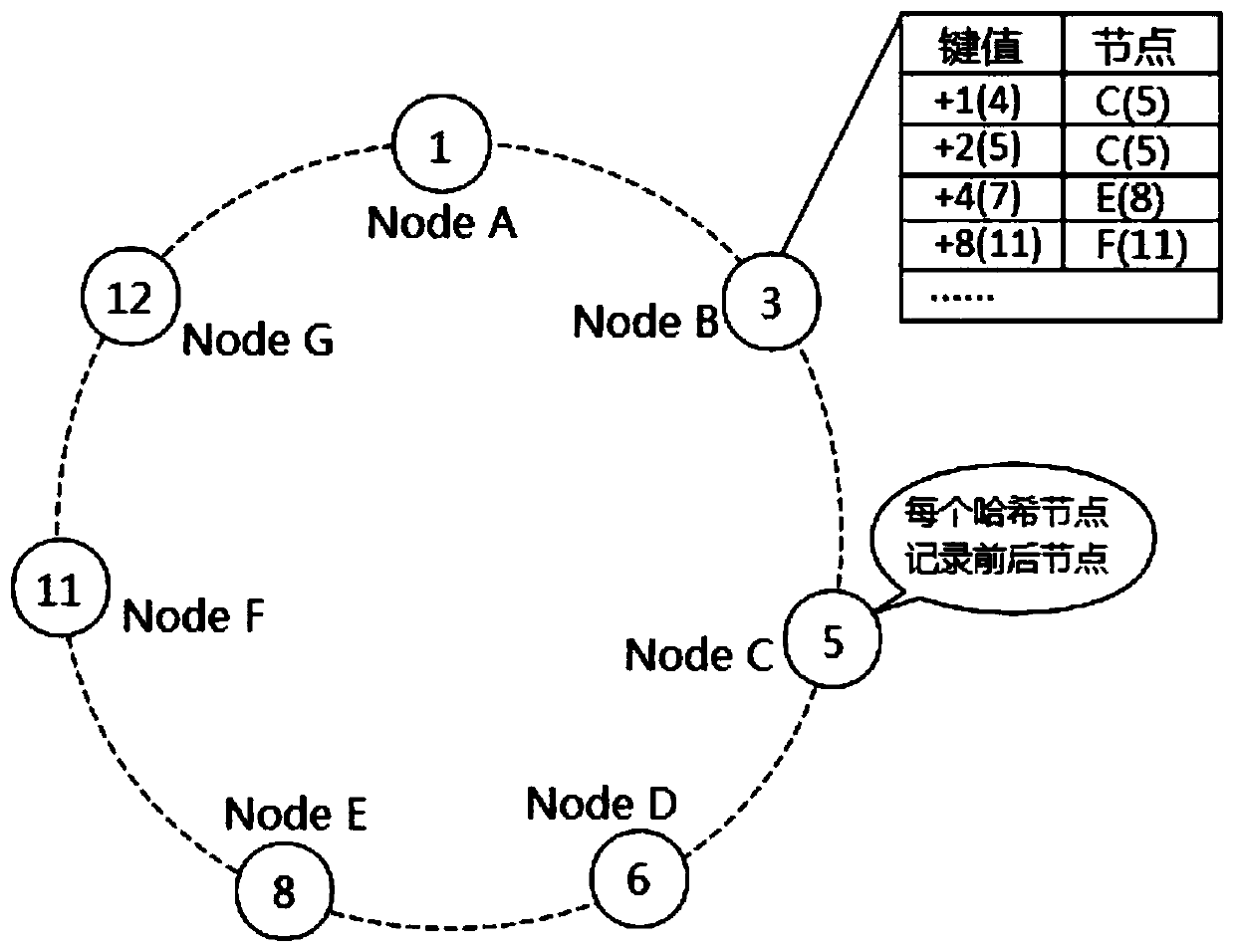

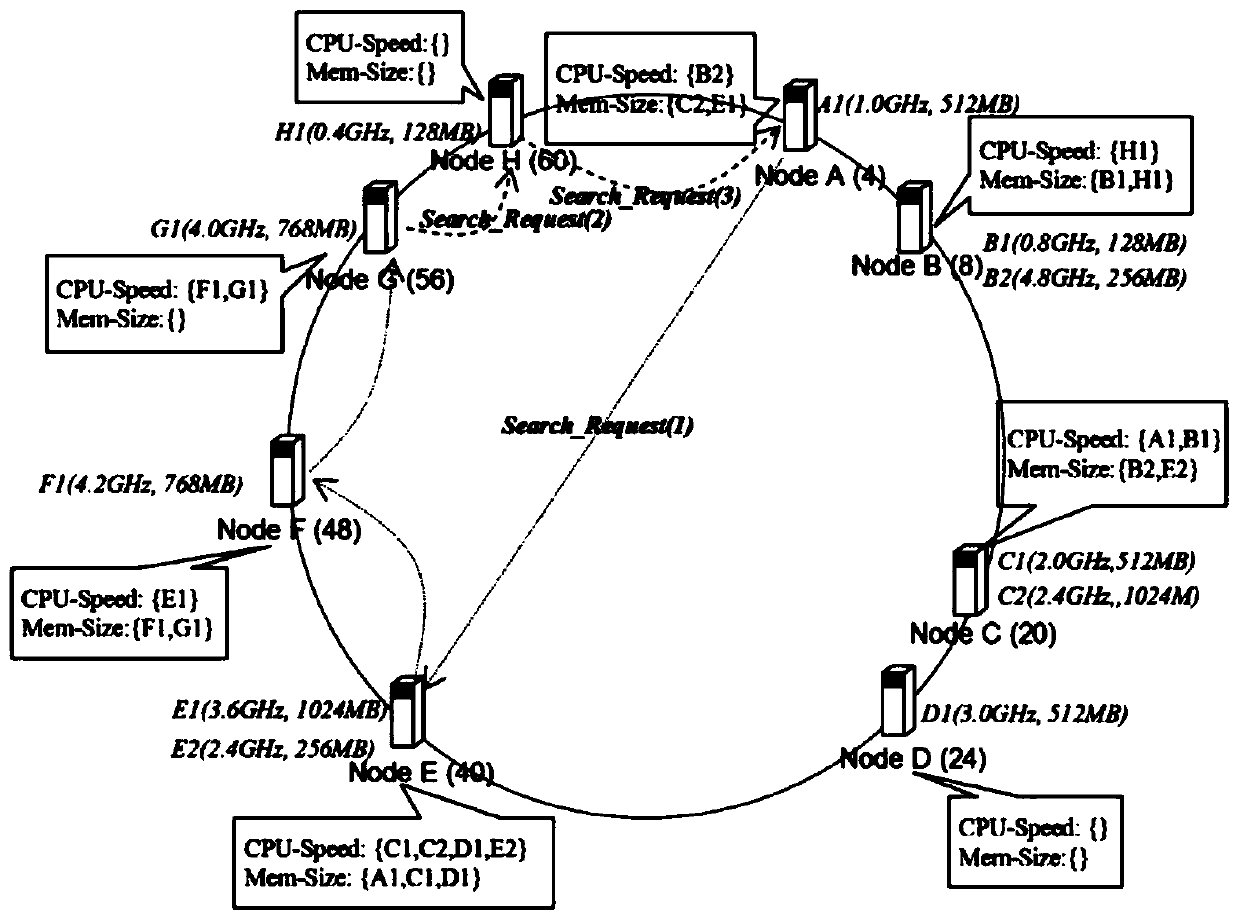

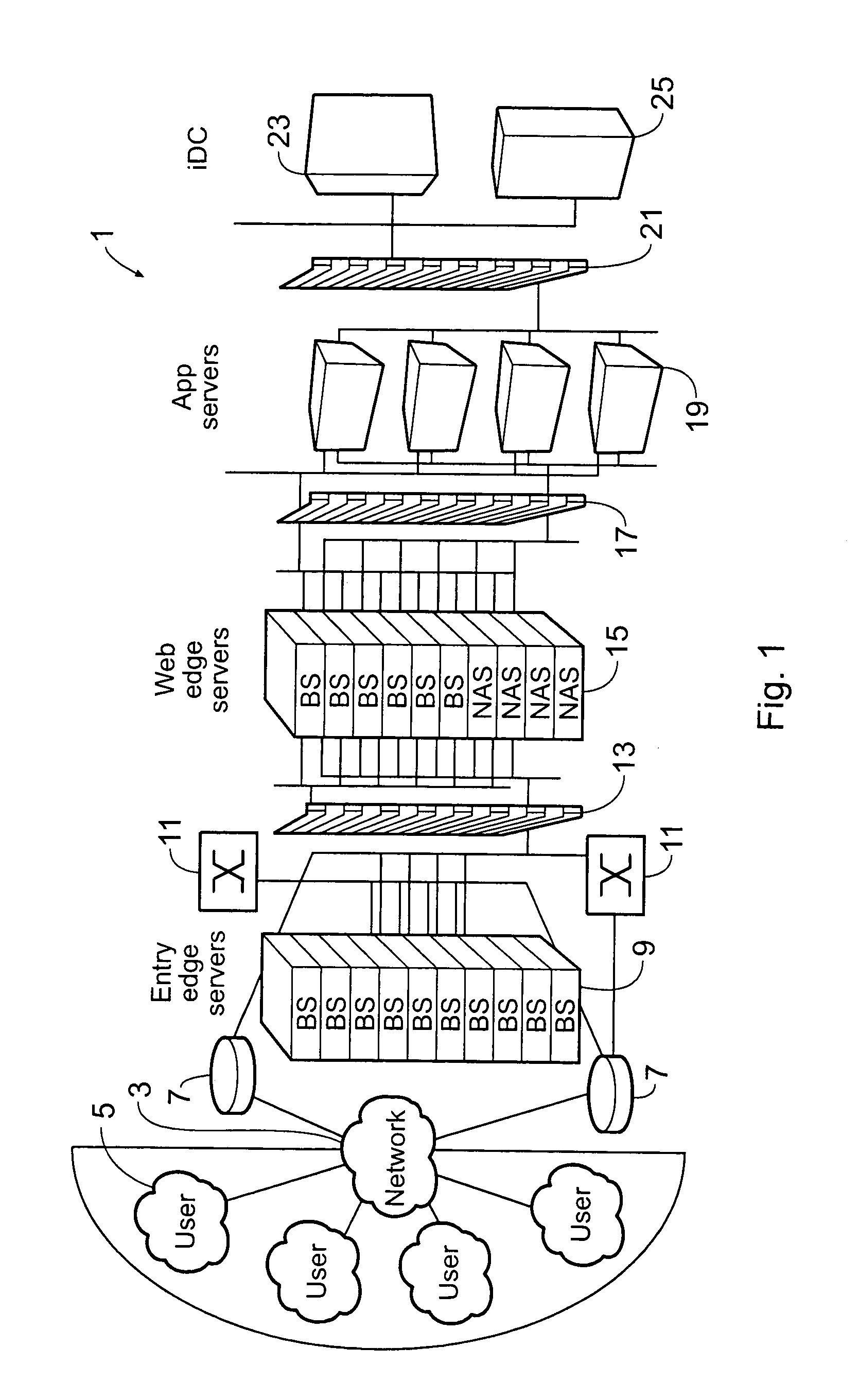

Edge cluster resource processing method and system

ActiveCN111147546AEfficient use ofAvoid wastingResource allocationTransmissionShardParallel computing

The invention provides an edge cluster resource processing method and system. The method comprises the steps: carrying out the Hash calculation of ID values of all clusters to obtain a cluster key value and mapp the cluster key value to a resource Hash ring, enabling each node, i.e., a cluster node, on the ring to store a precursor node and a subsequent node of the node to form a traversable ring;carrying out hash calculation on the idle resource value to obtain a resource key value, the digit of the resource key value being the same as the digit of the cluster key value, registering all idleinformation on the corresponding cluster node, and each cluster node being capable of storing a plurality of idle information; initiating a query request, adding the value meeting the condition intoa query result set, and returning the query result set to the request; screening out the idle information which most meets the requirements from the query result set, and sending a resource secondmentquery to ensure that secondment succeeds. The problem of resource fragmentation is solved, resources are effectively utilized and resource waste is avoided; in addition, a locking mechanism is adopted during resource scheduling so that the problem of resource access conflicts is avoided.

Owner:中科大数据研究院

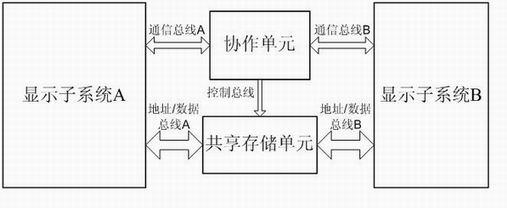

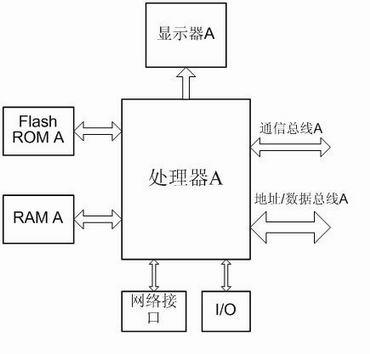

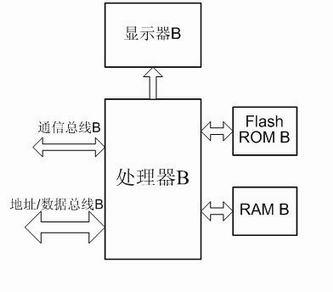

Information display device based on dual processor cooperation

InactiveCN102184157AGuaranteed uptimeProcessing speedDigital computer detailsImage data processing detailsInformation typeRandom access memory

The invention discloses an information display device based on dual processor cooperation, which comprises two display subsystems, a cooperation unit and a sharing storage unit, wherein the two display subsystems are respectively connected to the cooperation unit through the respective communication buses of the two display subsystems and are connected to the sharing storage unit through the respective address / data buses of the two display subsystems; the cooperation unit is connected to the sharing storage unit by a control bus; the cooperation unit is used for performing the cooperative work, data exchange and data sharing of the two display subsystems; the cooperation unit is communicated with processors of the two display subsystems through a protocol; information type and data format transferred between the cooperation unit and the processors are defined in the communication protocol; the cooperation unit is used for specifically managing a distributed processing task in the whole system, including the activation, scheduling and tracking of each process and the communication and synchronization among processes related to the distributed processing task. The sharing storage unit is used for storing various information and data which are used by the two display subsystems; and under the control of the cooperation unit, the subsystems access the RAM (random-access memory)in the sharing storage unit in sequence through the respective address / data buses of the subsystems. By using the device provided by the invention, the running property of dual processor system can be efficiently promoted, the executing efficiency of concurrent process in the system can be improved, the access conflict of sharing resource is avoided, and the processing speed of complex task is increased.

Owner:EAST CHINA NORMAL UNIV

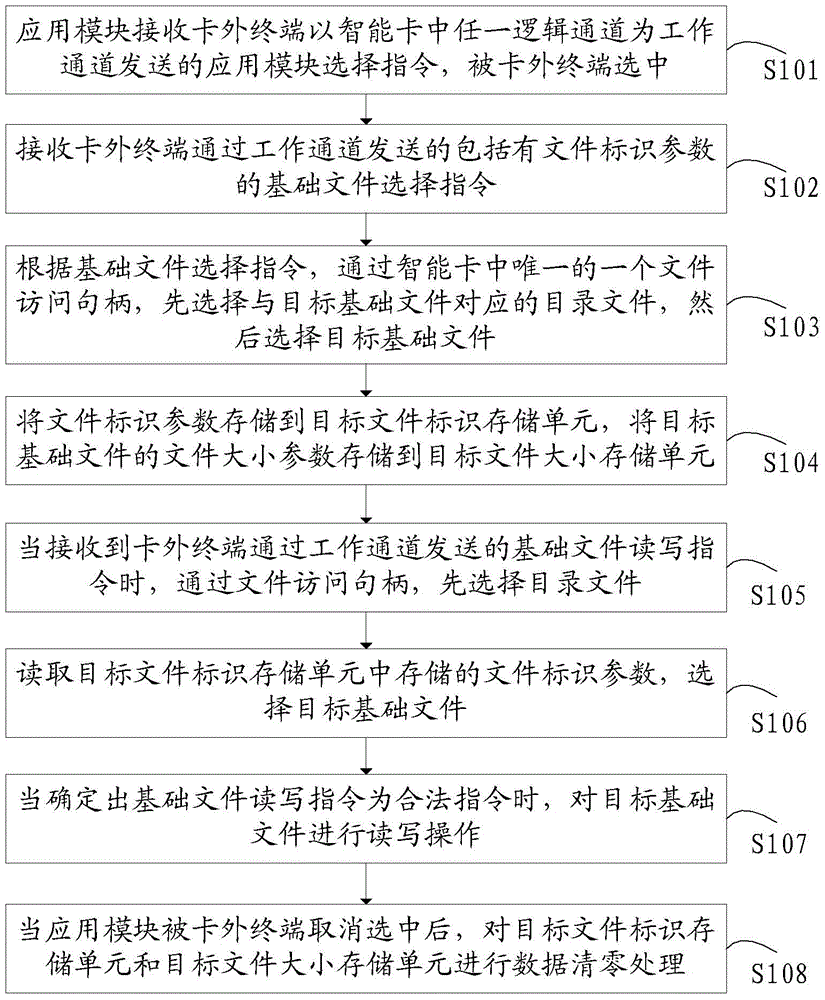

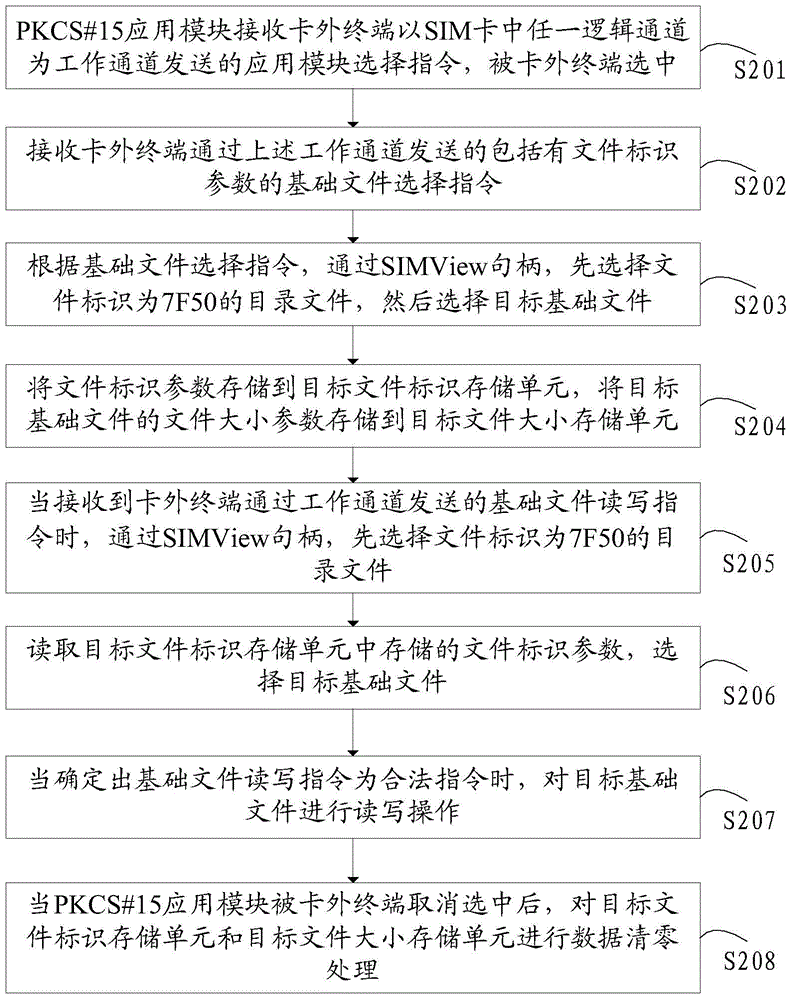

Method for accessing file system of smart card through application module

ActiveCN104484619AAvoid access violation situationsAvoid access violationsDigital data protectionFile systemSmart card

The application discloses a method for accessing a file system of a smart card through an application module, which is applied to smart cards. In the method, when a basic file selection instruction sent by an external terminal is executed by the application module of the smart card, a directory file, which corresponds to a target basic file, in the file system of the application module is first selected, so that a file access handle in the smart card points to the directory file, consequently, the target basic file located under the directory file can be selected, the circumstance of file access conflict which is caused when a file is directly selected under the premise that the file access handle possibly points to an unexpected file is prevented, and thereby the problem of file access conflict which can take place when the external terminal selects a file in the file system of the smart card through the application module is solved.

Owner:EASTCOMPEACE TECH

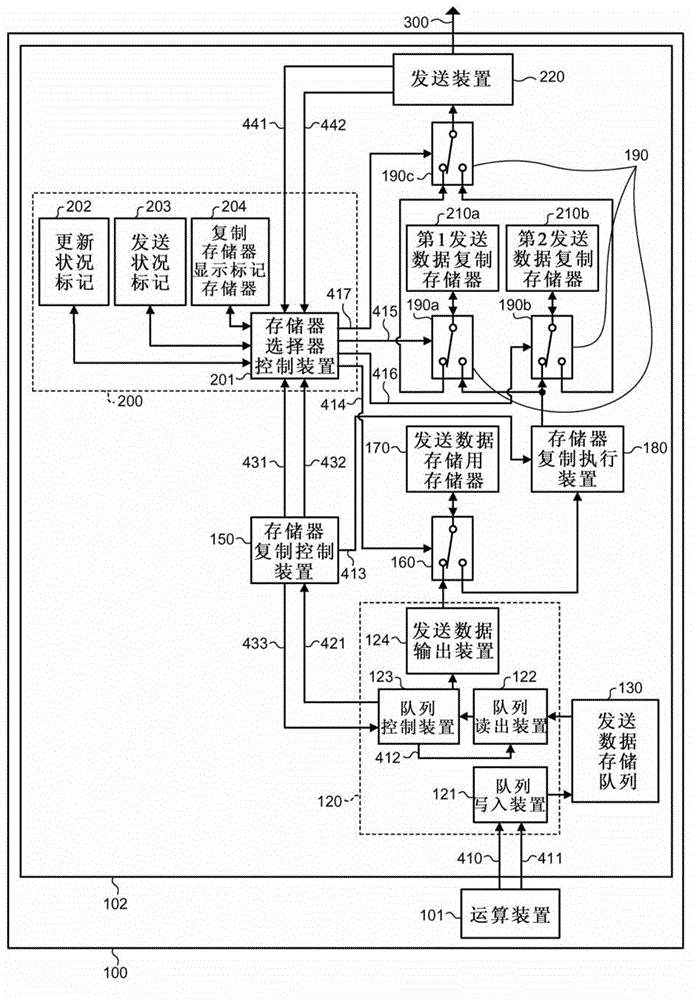

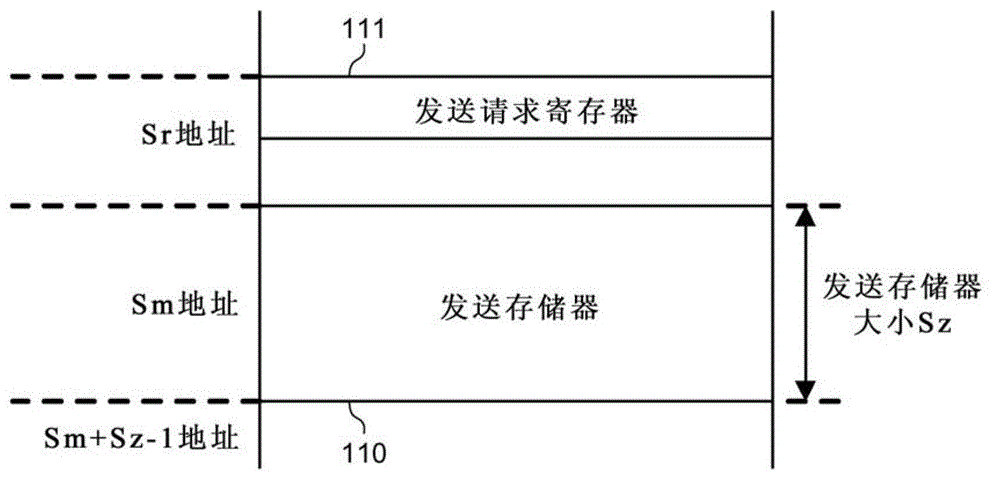

Transmission control device, memory control device, and plc provided with the transmission control device

InactiveCN102754089AGuaranteed simultaneityShorten execution cycleProgramme controlInput/output to record carriersData storingData store

Provided is a transmission control device provided with data store memory into which data is written; a plurality of data copy memories into which the data that have been written into the data store memory are copied; a non-readout copy memory selection means for selecting one of the data copy memories from which the data has not been read out from among the plurality of the data copy memories; a memory copy means for copying the data that has been written into the data store memory into the data copy memory that has been selected by the non-readout copy memory selection means; a readout copy memory selection means for selecting the data copy memory into which the memory copy means has copied the data from among the plurality of data copy memories; and a data output means for reading out the data from the data copy memory that has been selected by the readout copy memory selection means and outputting thereof to the transmission means.

Owner:MITSUBISHI ELECTRIC CORP

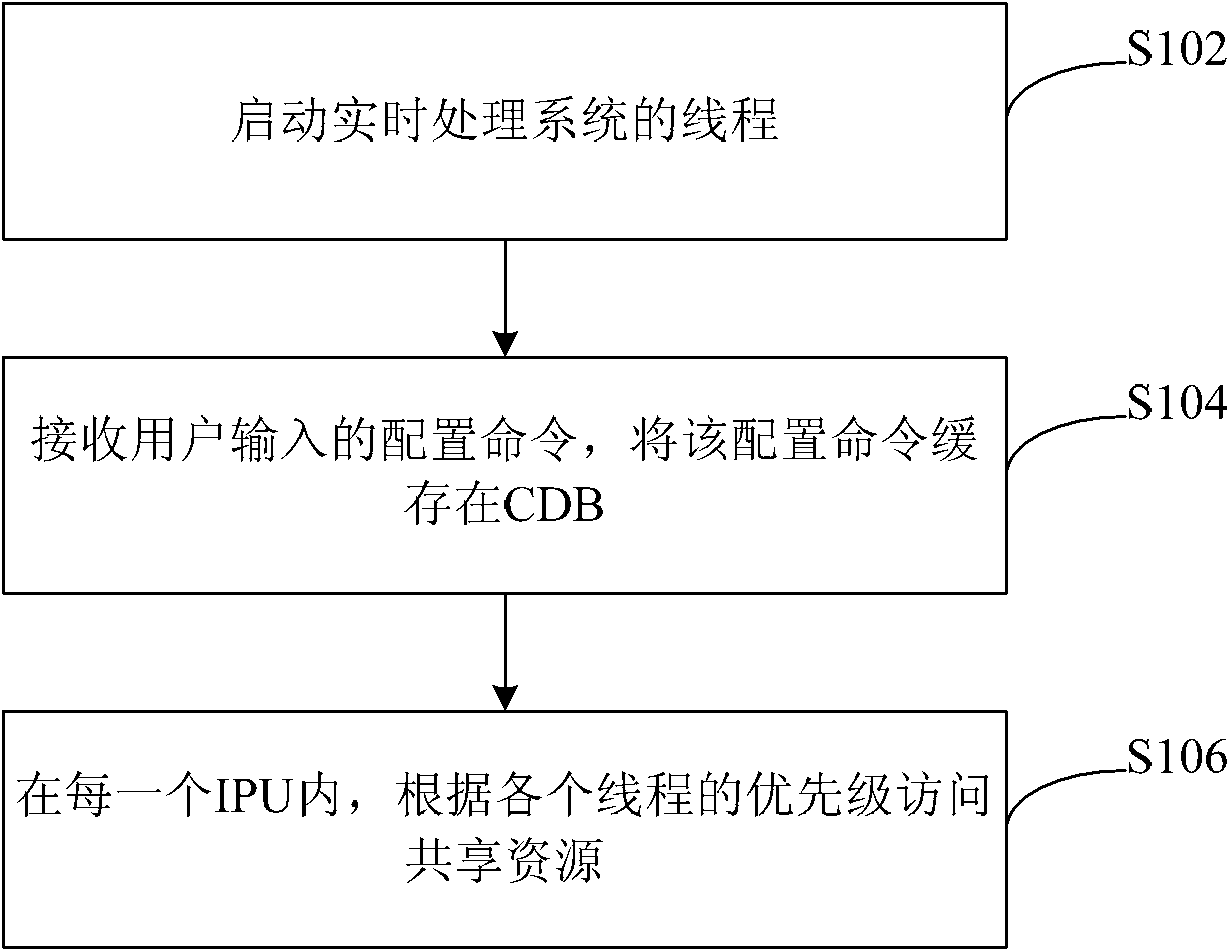

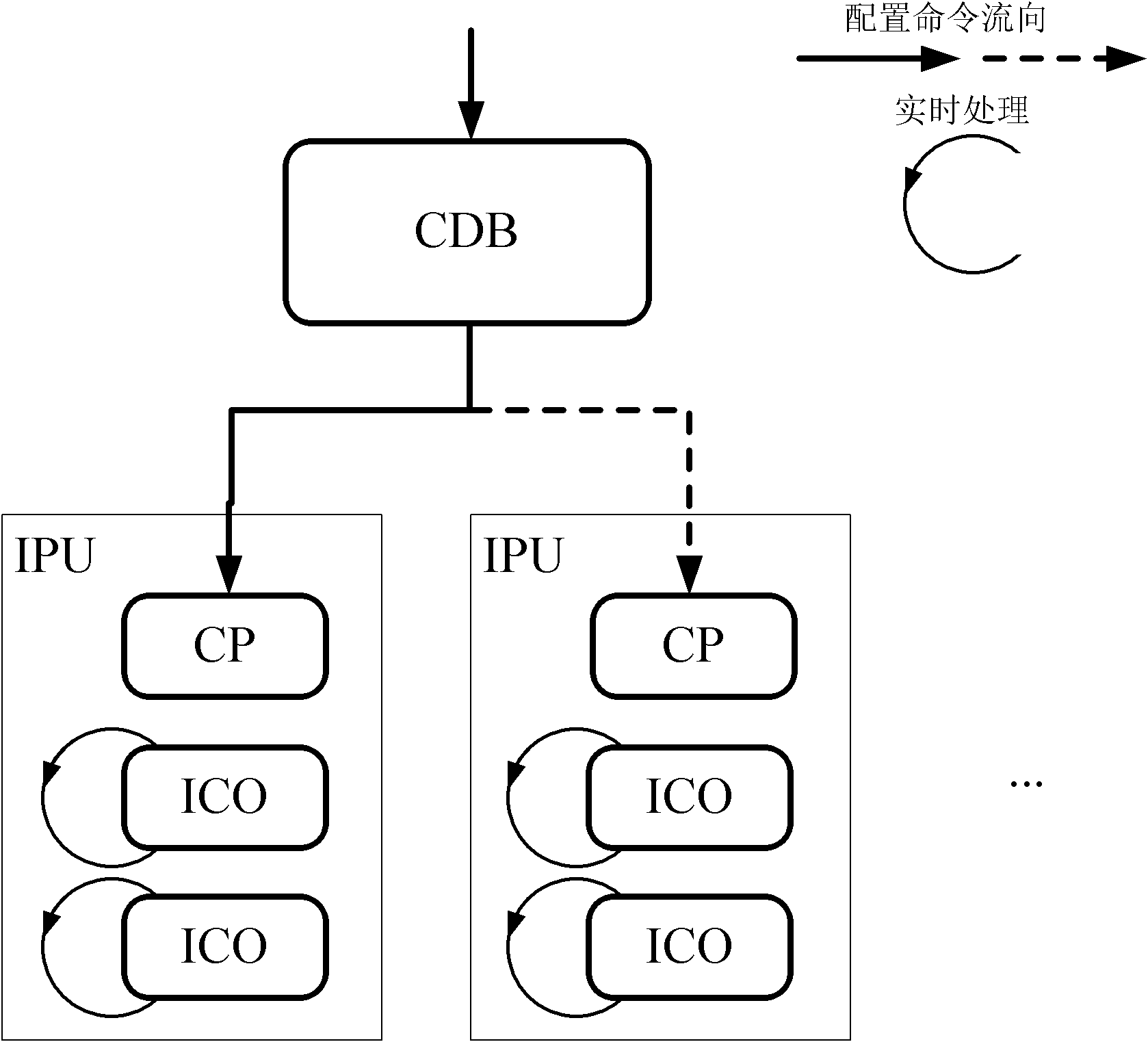

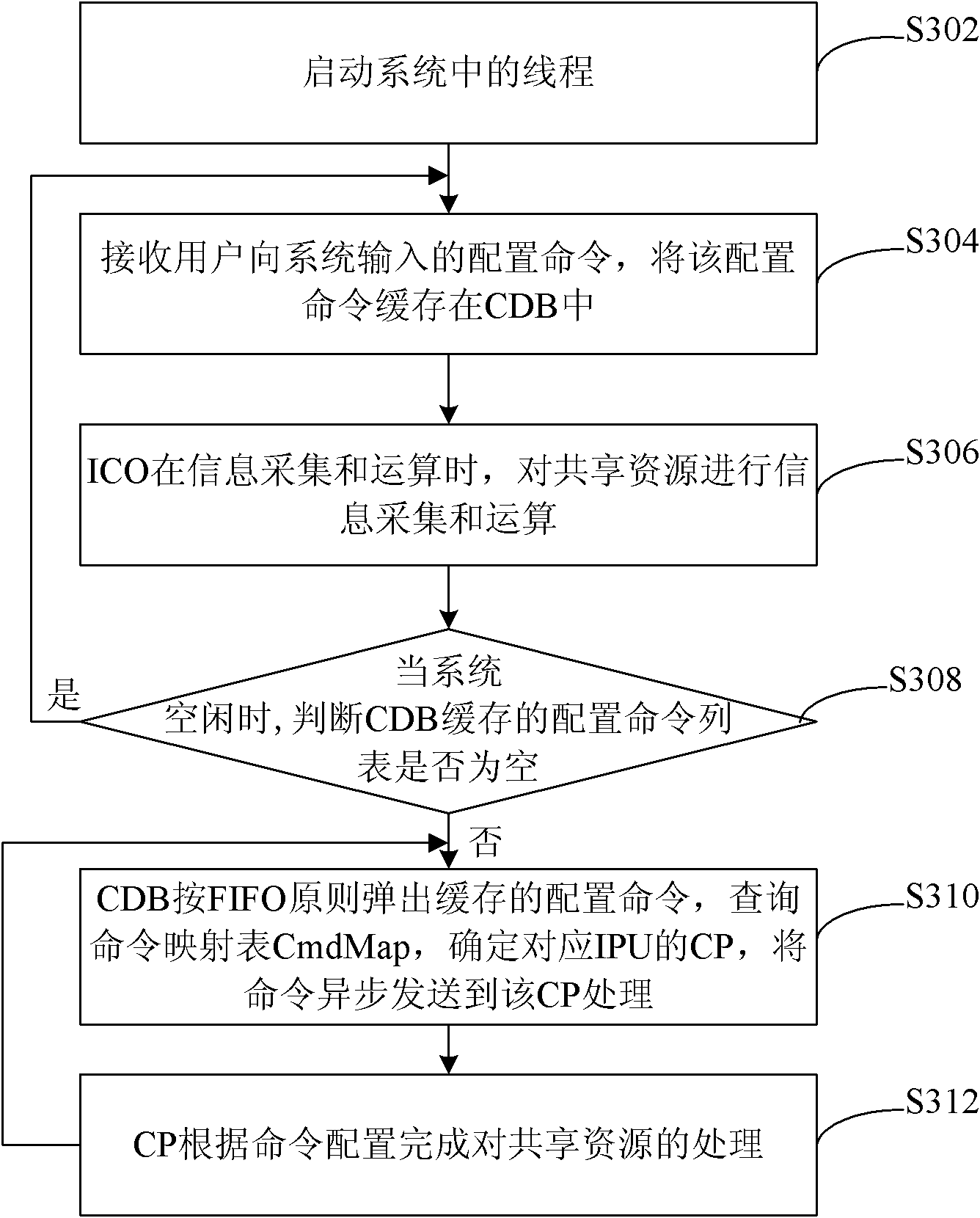

Accessing method for real-time processing shared resource in system and real-time processing system

ActiveCN102831007AAvoid access violationsFix hangProgram initiation/switchingProgram synchronisationReal-time computingHandling system

The invention discloses an accessing method for real-time processing a shared resource in a system and a real-time processing system. The method comprises the following steps: starting a thread of the real-time processing system, wherein the real-time processing system comprises a plurality of input preparation units (IPU), every IPU comprises a content provider (CP) thread and an icon file (ICO) thread; the relative priorities between the threads in the IPU is that the priority level of the CP thread is greater than that of the ICO thread; receiving a configuring order of a user input and buffering the configuring order in a command descriptor block (CDB), the priority level of the CDB thread is less than that of the ICO thread; and in every IPU, the shared resource can be accessed according to the priority level of every thread. Through the invention, the problem that the system hanging is easy to be caused by semaphore locking method is resolved, the stability and the reliability of the system are enhanced.

Owner:ZTE CORP

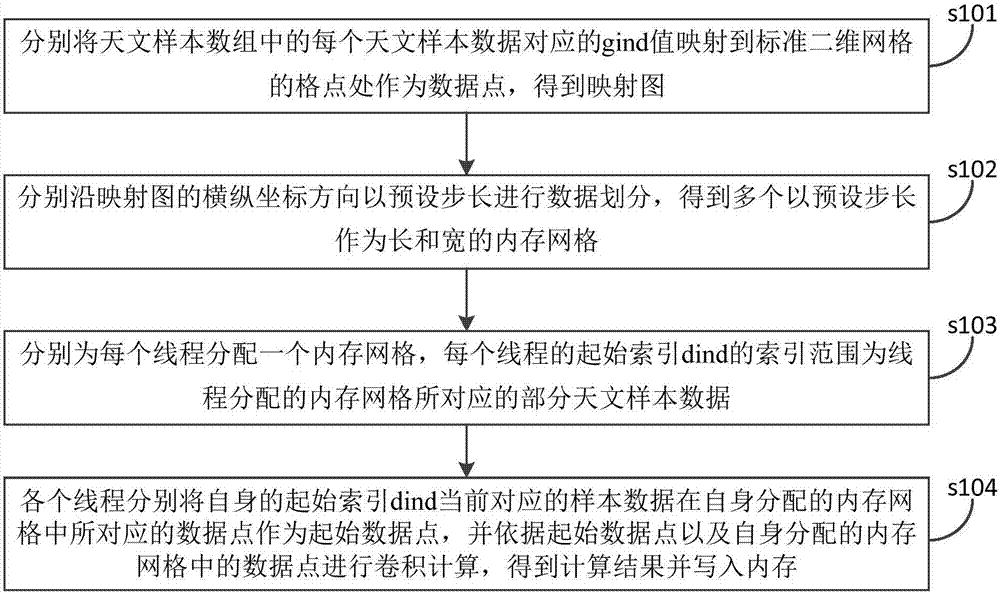

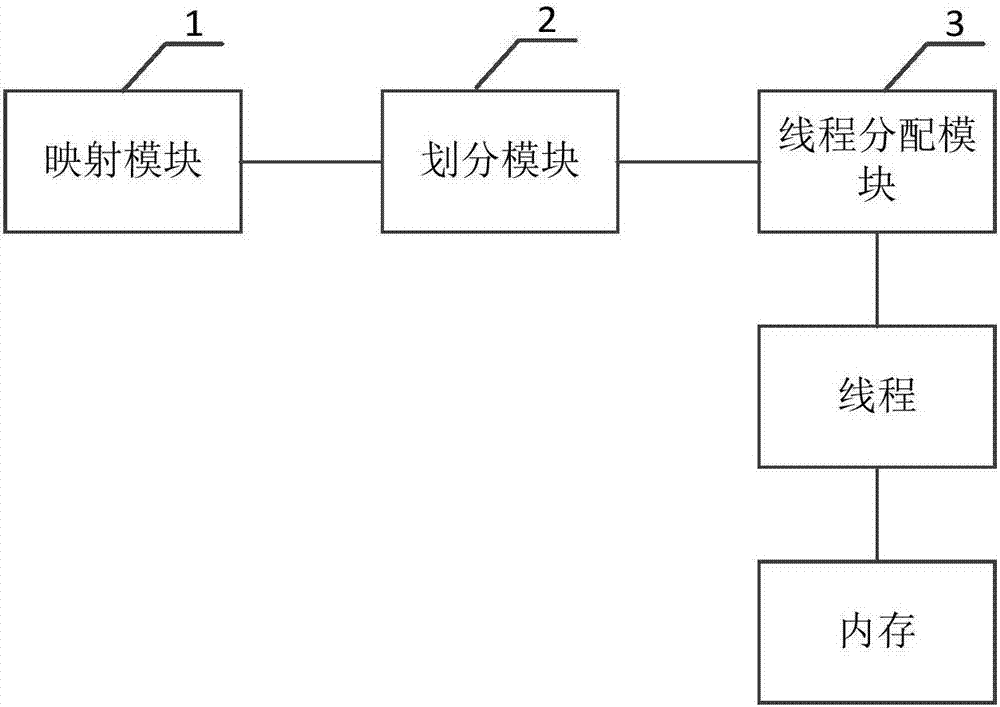

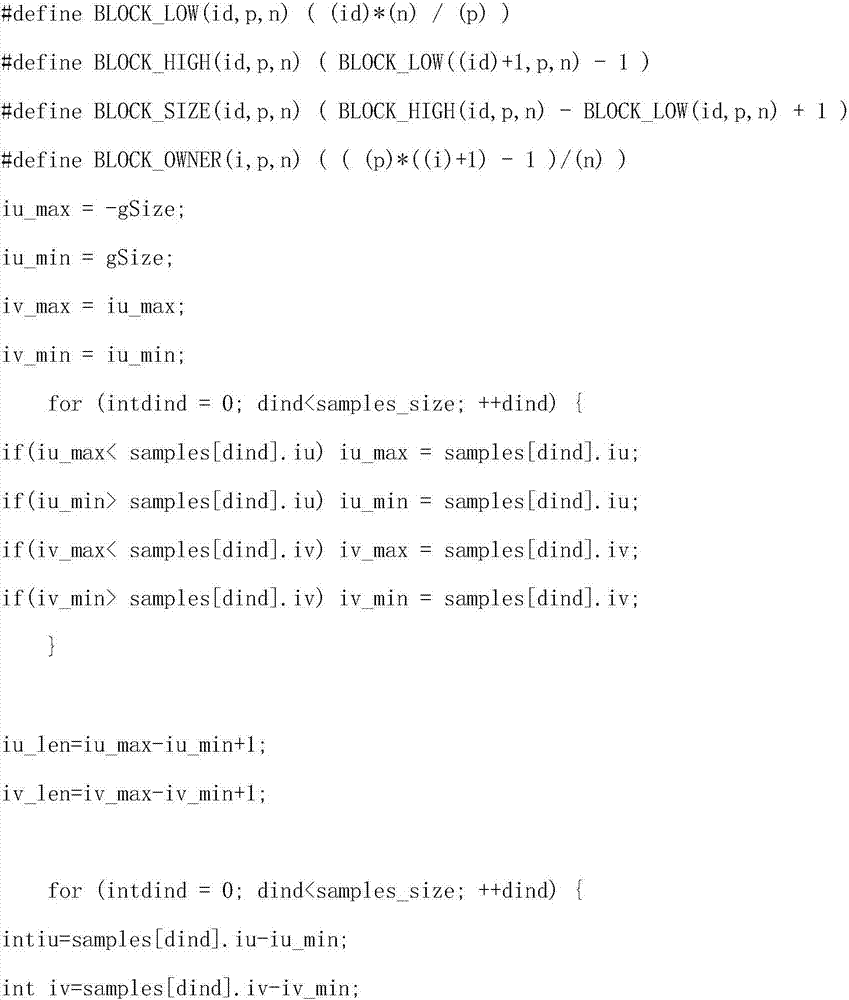

Parallel calculation method and apparatus used for astronomical software Griddding

ActiveCN106897131AAvoid access violationsEasy to handleProgram initiation/switchingProgram synchronisationArray data structureParallel processing

The invention discloses a parallel calculation method and apparatus used for astronomical software Griddding. The method comprises the steps of mapping a gind value corresponding to each piece of astronomical sample data in an astronomical sample array to a grid point of a standard two-dimensional grid to serve as a data point, thereby obtaining a mapping graph; performing data division by a preset step length along horizontal and longitudinal coordinates of the mapping graph to obtain a plurality of memory grids taking the preset step length as the length and the width; allocating a memory grid to each thread, wherein an index range of a starting index dind of each thread is partial astronomical sample data corresponding to the memory grid; taking the data point corresponding to the sample data currently corresponding to the starting index dind of each thread as a starting data point, performing convolutional calculation according to the starting data point and the data point in the memory grid allocated to each thread to obtain a calculation result, and writing the calculation result in a memory. According to the method and the apparatus, the access conflict of each thread to the memory can be avoided as far as possible, so that the parallel processing capability and the memory access efficiency of a Gridding program are improved.

Owner:INSPUR BEIJING ELECTRONICS INFORMATION IND

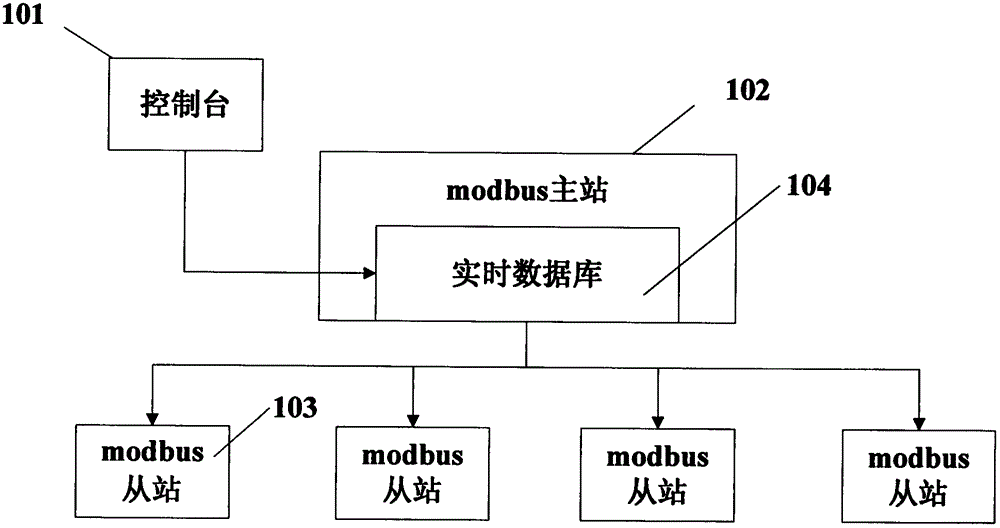

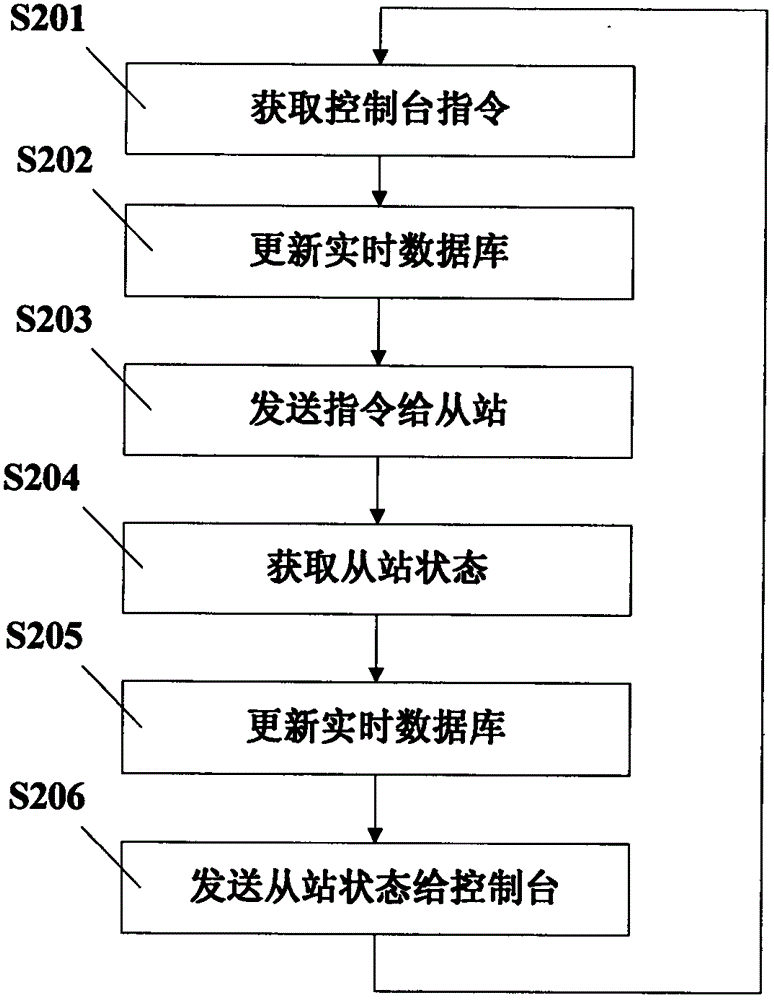

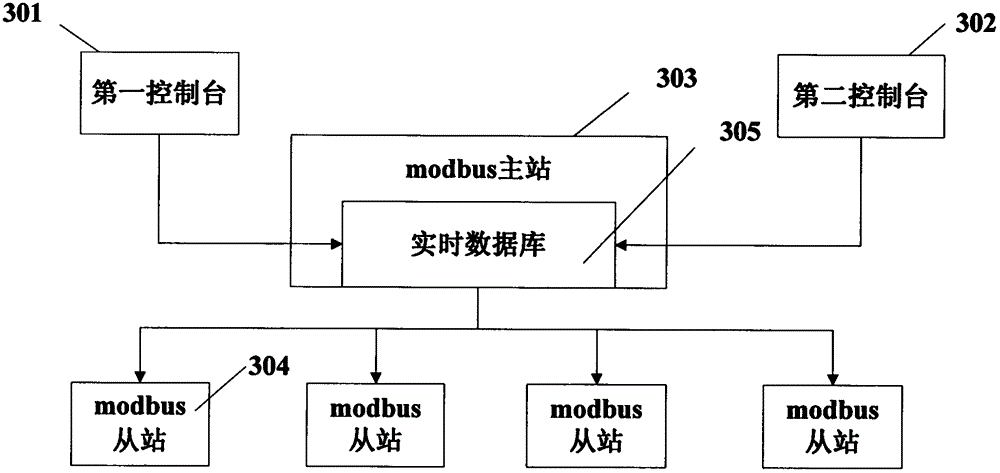

Method for avoiding modbus real-time database access conflict

InactiveCN102722535AAvoid access violationsAddress effectivenessSpecial data processing applicationsDatabase accessOperating system

The invention discloses a method for avoiding modbus real-time database access conflict. The method comprises the following steps of: performing update operation on a database by a console in a modbus master station, caching an instruction of the update operation in an instruction buffer area, and comparing the instruction with the previous buffer instruction. Only when the instruction is changed, the instruction is updated to the database; the instruction is stored by an instruction buffer; and in a cyclic list of the modbus master station, each update operation instruction aiming at the database has the corresponding instruction buffer, and the buffers are cleared when starting and before entering a cycle. The method can ensure that the sent instruction is accurately executed when two consoles have only one sending instruction in a multi-console modbus system, and the real-time database access conflict is solved.

Owner:周明 +1

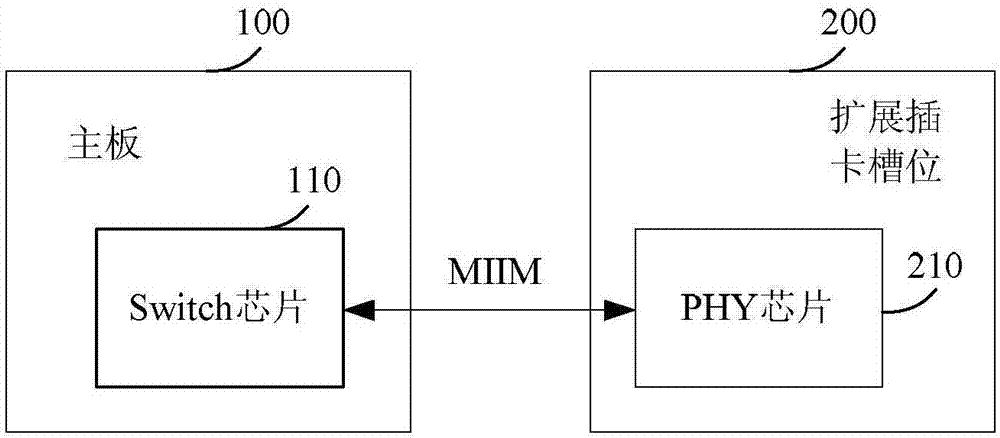

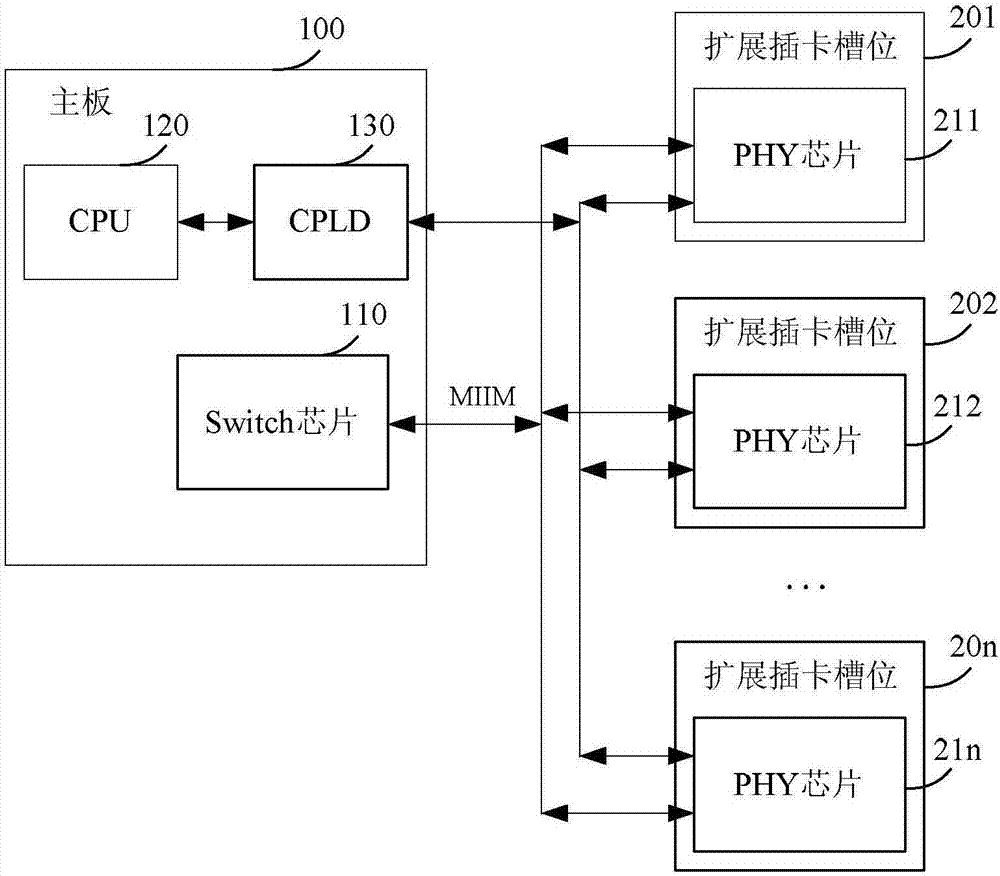

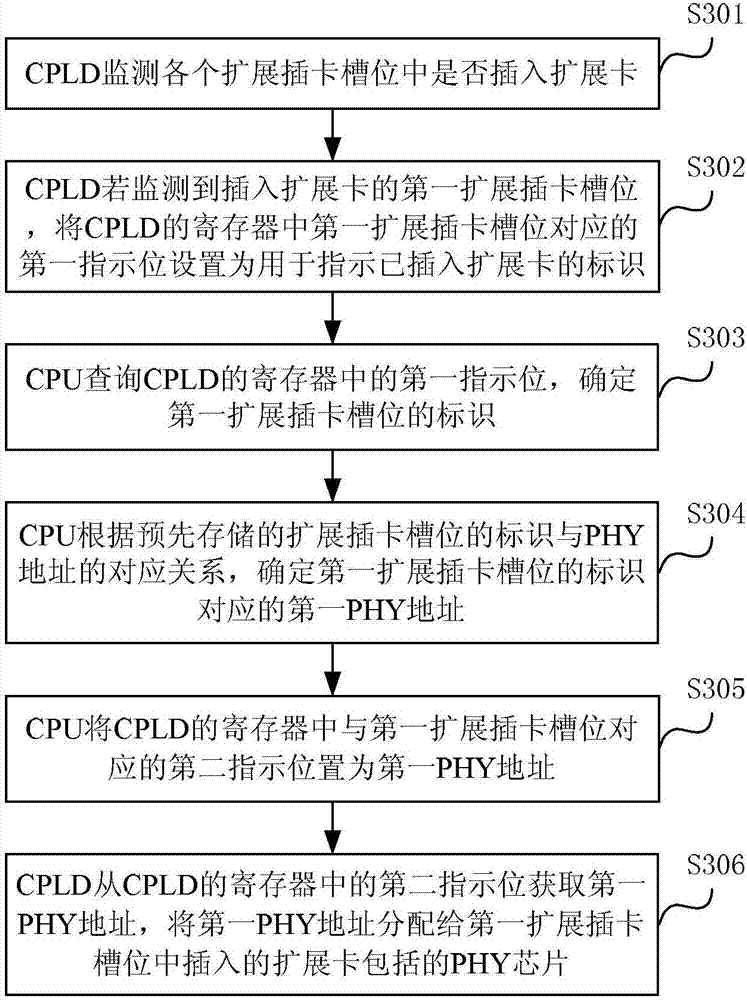

Network device and physical layer address allocation method

The embodiment of the invention provides a network device and a physical layer address allocation method. The network device comprises a CPU, a CPLD and a plurality of expansion card slot positions; the CPLD monitors whether expansion cards are inserted in the expansion card slot positions, a first indicating position corresponding to the first expansion card slot position with an inserted expansion card in a register of the CPLD is set as an identifier used for indicating that the expansion card has been inserted; the CPU determines the identifier of the first expansion card slot position, determines a first PHY address corresponding to the identifier of the first expansion card slot position according to a pre-stored corresponding relation between the identifier of the first expansion card slot position and the PHY address, and sets a second indicating position corresponding to the first expansion card slot position in the CPLD as the first PHY address; and the CPLD obtains the firstPHY address from the register and allocates the first PHY address to a PHY chip contained in the expansion card inserted in the first expansion card slot position.

Owner:NEW H3C SECURITY TECH CO LTD

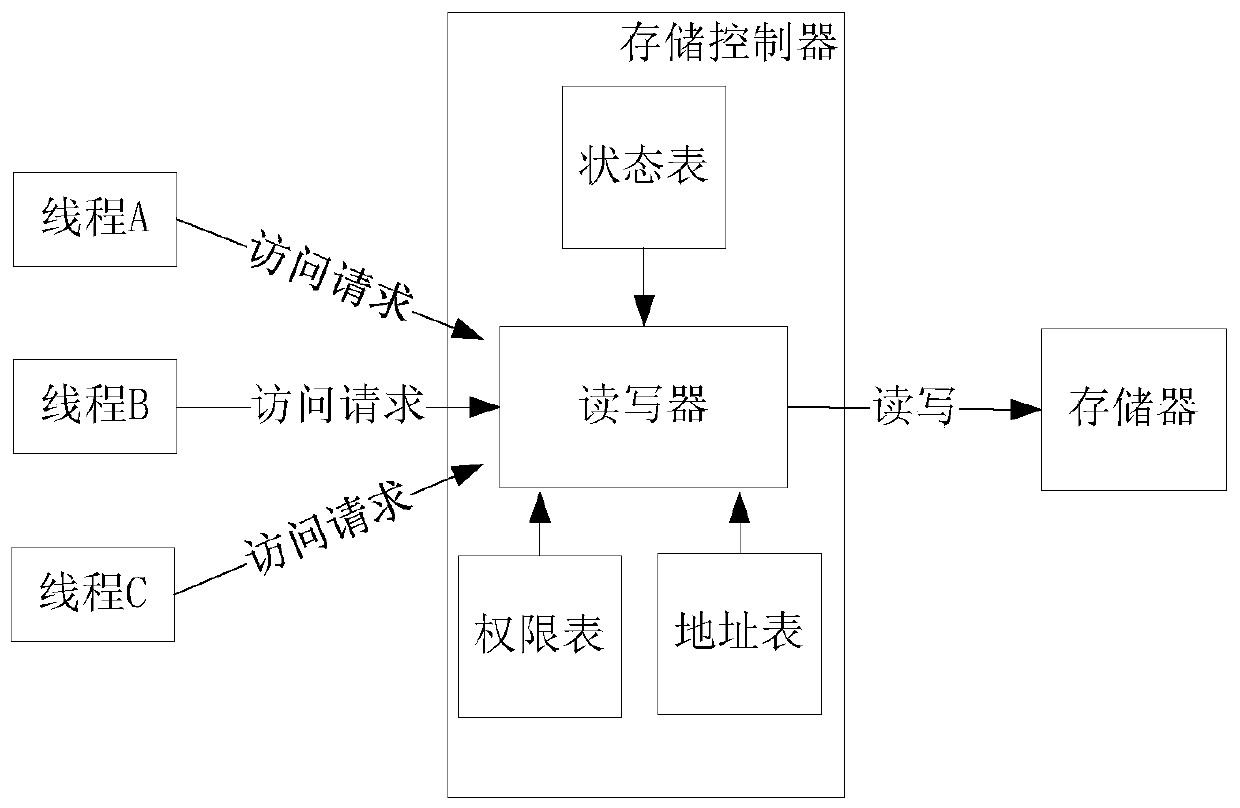

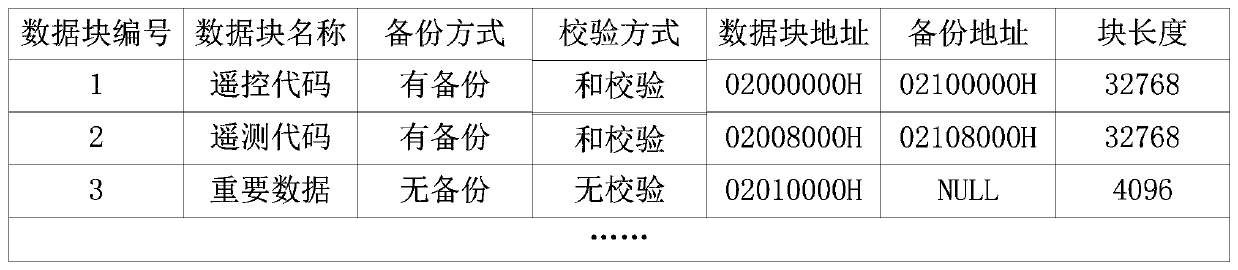

Memory access controller and method of accessing memory

ActiveCN109753248AAvoid access violationsImprove reliabilityInput/output to record carriersMemory controllerReader writer

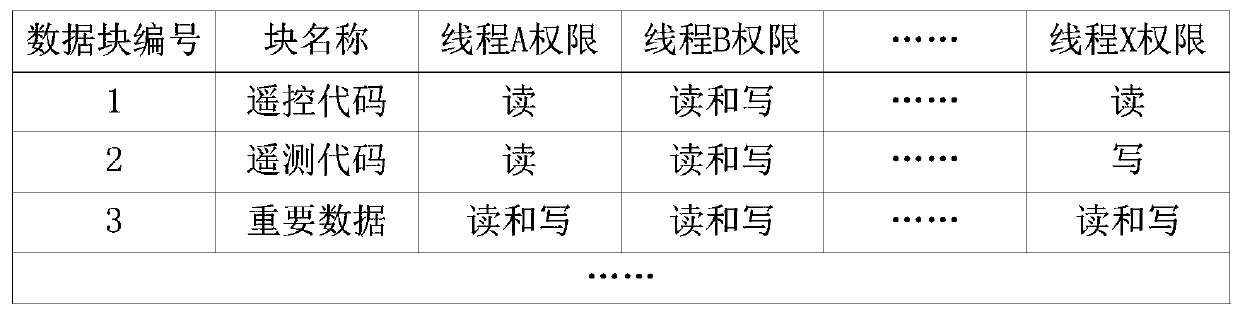

A memory access controller and a method of accessing a memory are provided. According to the invention, the program and the data address are decoupled through the address table. According to the storage access controller and the storage control method, wrong data access is avoided through the permission table, access conflicts are avoided through the state table, wrong data reading is avoided through verification, data reliability is improved through backup, and various technical means are comprehensively applied to perfect the storage access controller and the storage control method. The storage access controller comprises an address table, a permission table, a state table and a reader-writer, the address table records data block addresses, the permission table records the access permission of the threads to the data blocks, and the state table records the states of the data blocks. The reader-writer receives the access request and executes the received access request according to the configuration information of the address table, the authority table and the state table.

Owner:SHANGHAI ENG CENT FOR MICROSATELLITES

Interface access method, display device and electronic equipment

ActiveCN111405213AImplement serial accessAvoid access violationsTelevision system detailsColor television detailsGate arrayDisplay device

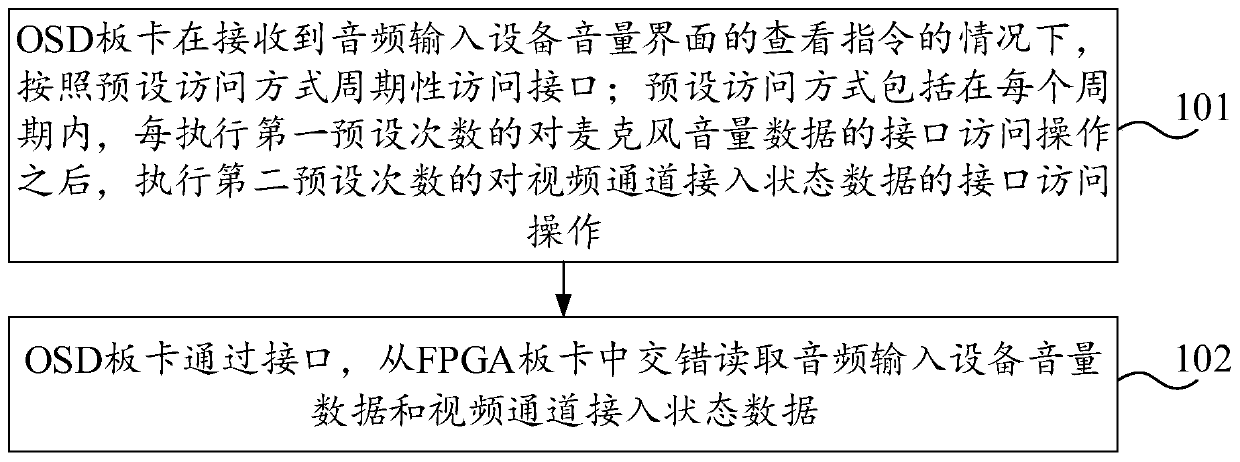

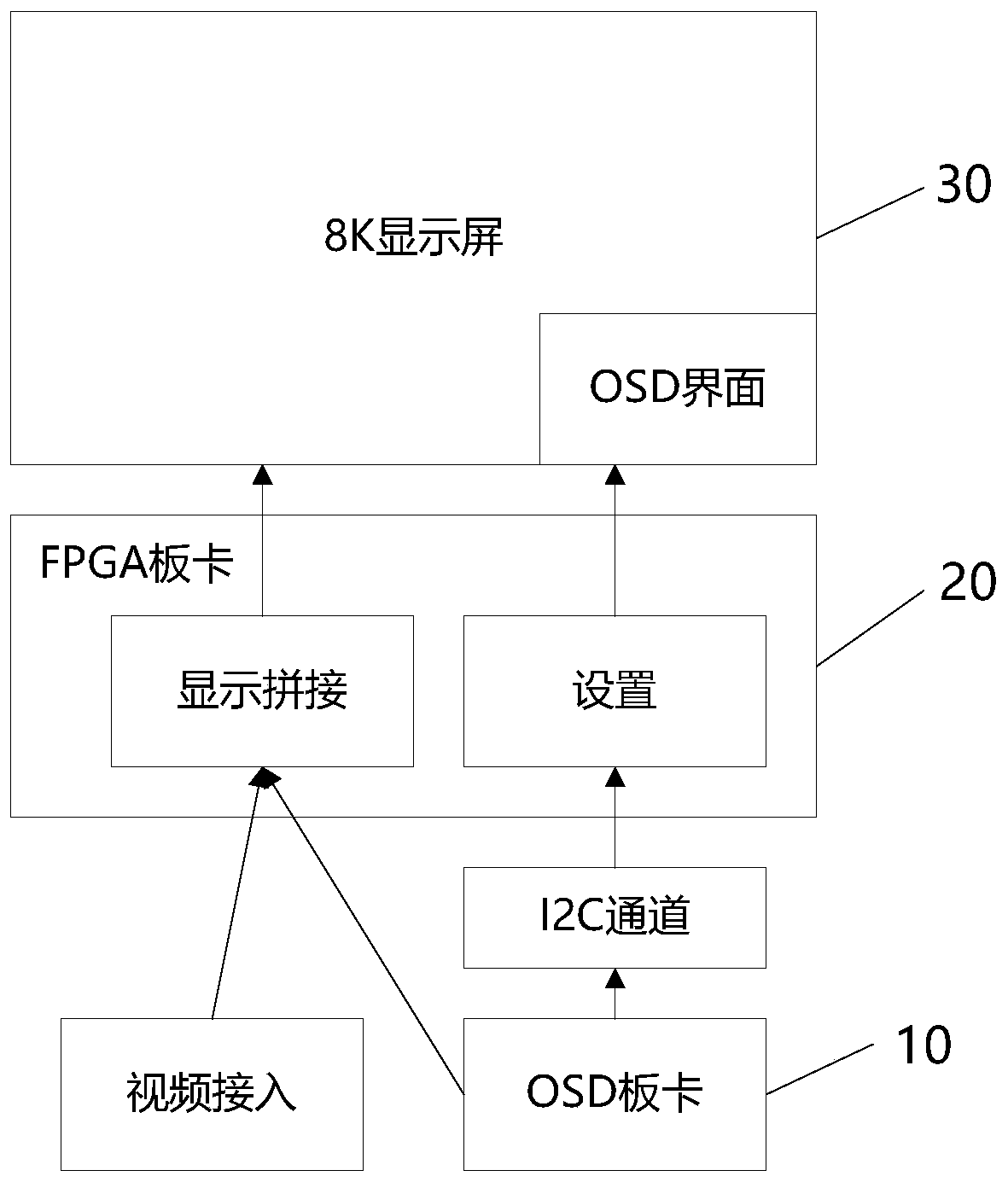

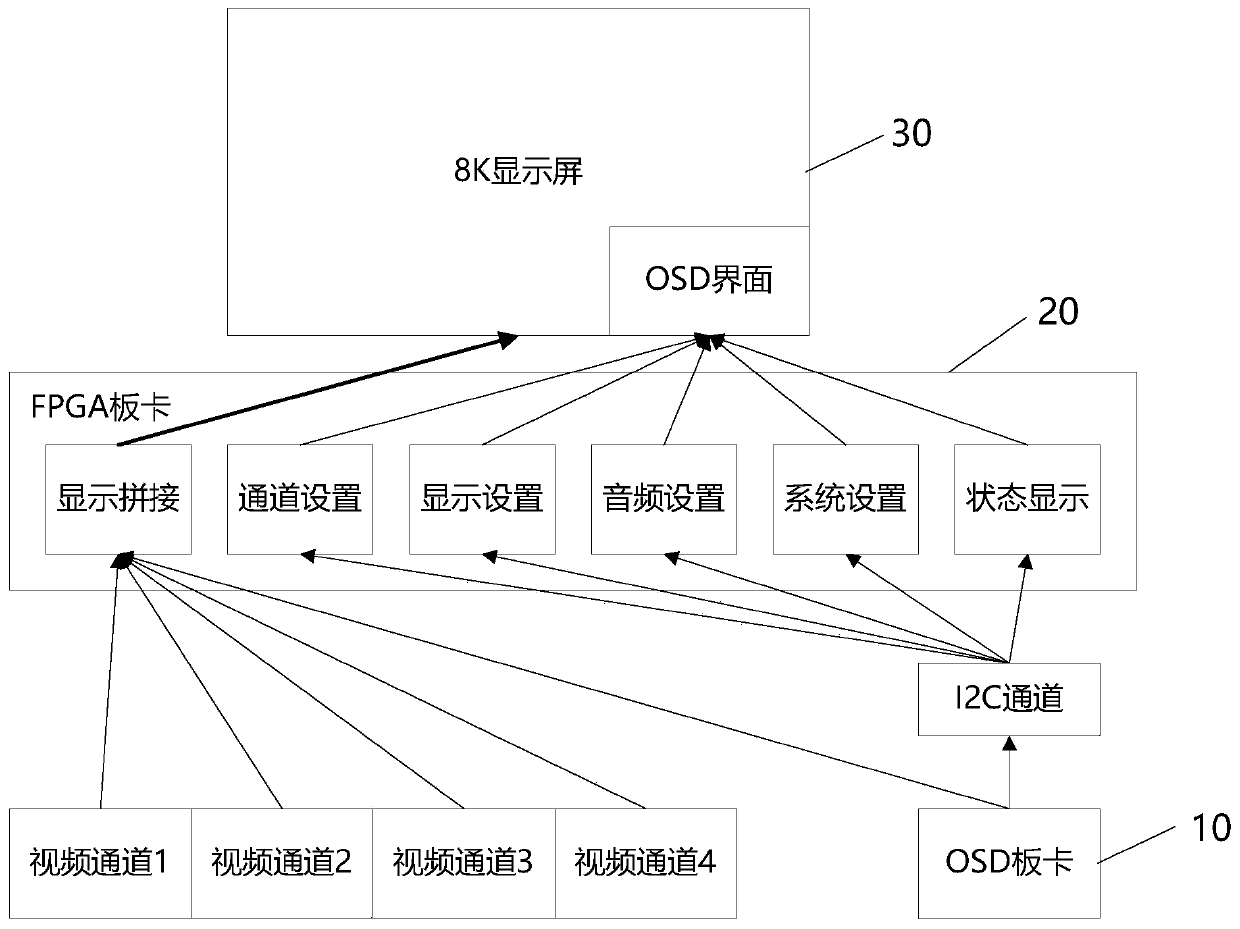

The invention provides an interface access method, a display device and electronic equipment, and relates to the technical field of display. The method comprises the following steps: when a screen menu board card receives a viewing instruction of a microphone volume interface, periodically accessing the interface according to a preset access mode, the preset access mode comprising, in each period,after each execution of an interface access operation on the microphone volume data for a first preset number of times, executing an interface access operation on the video channel access state datafor a second preset number of times; and enabling the screen menu board card to read microphone volume data and video channel access state data from the field programmable gate array board card in a staggered manner through an interface. Thus, serial access of the interface between the screen menu board card and the field programmable gate array board card can be realized, interface access conflicts are avoided, and the real-time performance of microphone volume data and video channel access state data is ensured.

Owner:BOE TECH GRP CO LTD

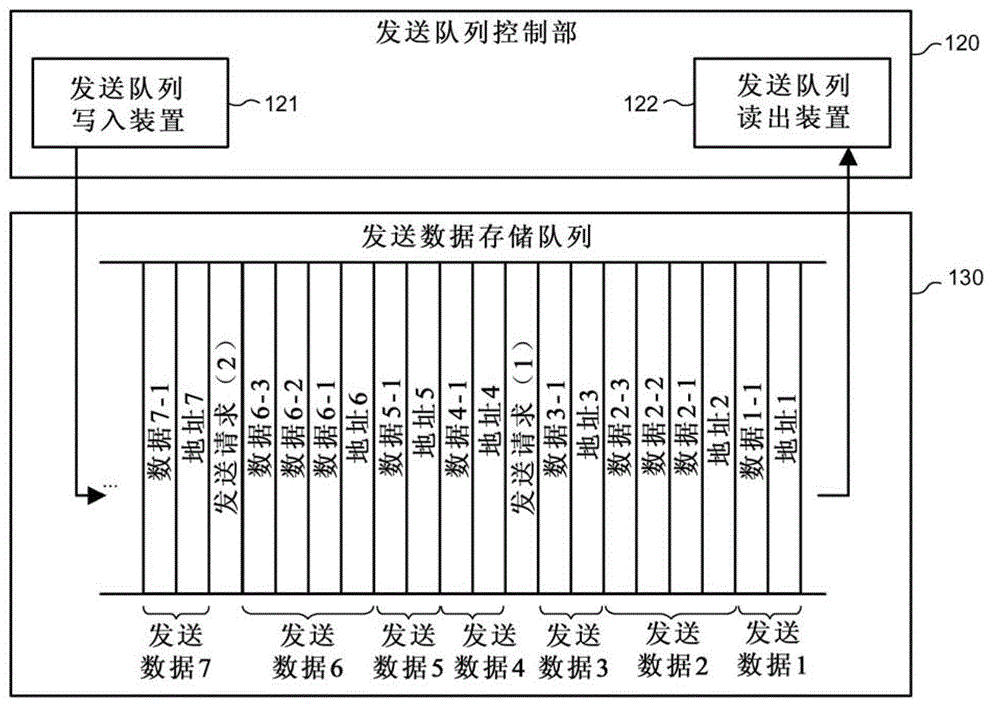

Method for sharing single EDMA (Enhanced Direct Memory Access) channel by multiple cores

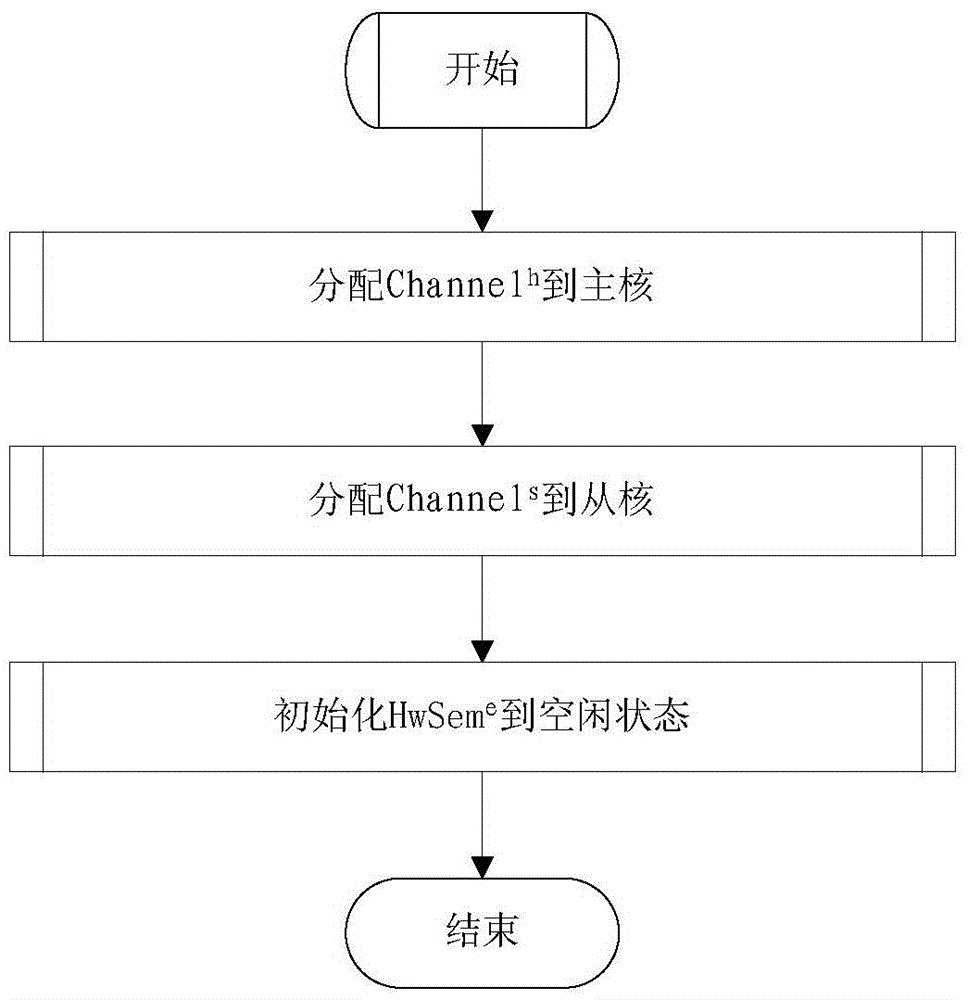

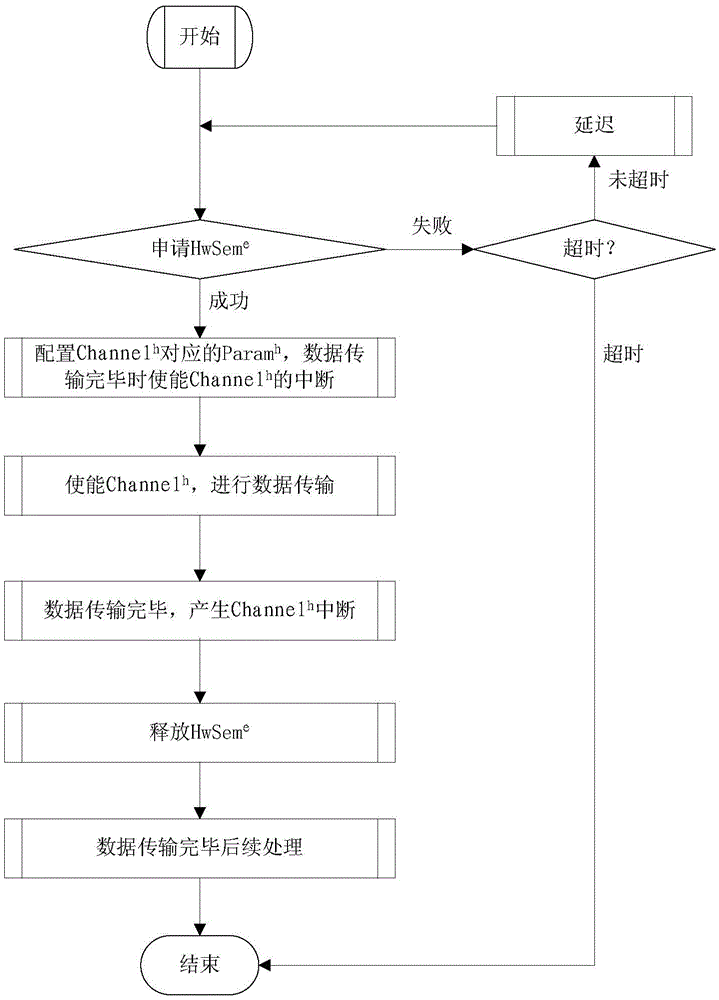

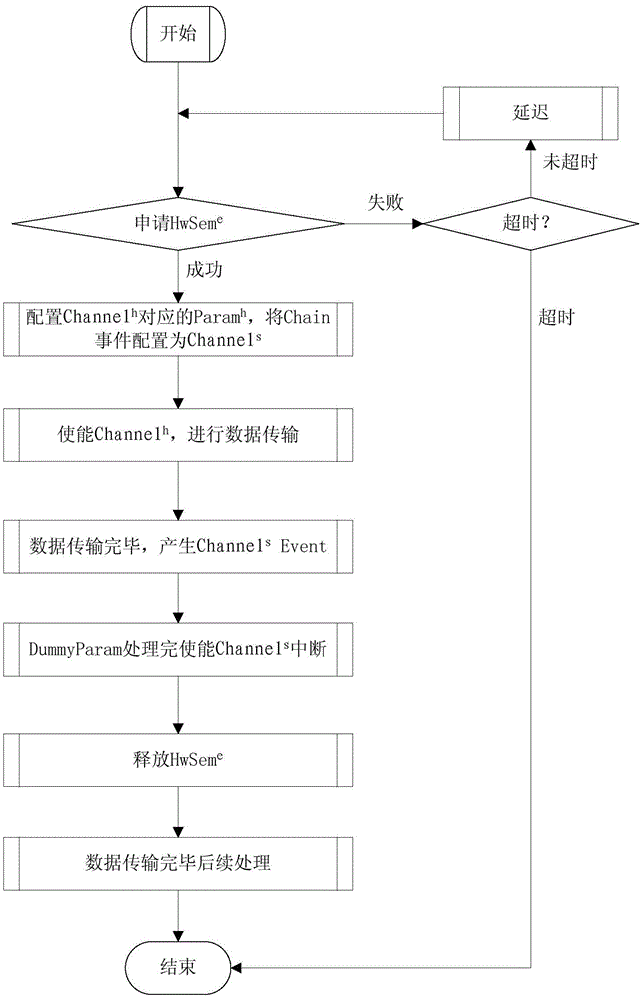

ActiveCN105487991ASimplify the sending processAvoid access violationsElectric digital data processingComputer hardwareDirect memory access

The invention relates to a method for sharing a single EDMA (Enhanced Direct Memory Access) channel by multiple cores. The method comprises the following steps: 1, distributing EDMA Channelh and hardware semaphore HwSemh to a master core, distributing EDMA Channels to slave cores, and initializing the EDMA Channelh, the hardware semaphore HwSemh and the EDMA Channels; 2, applying, by the master core and the slave cores, the EDMA Channelh via the hardware semaphore HwSemh; 3, configuring PaRAM for the master core or the slave cores getting the EDMA Channelh; 4, enabling EDMA to transmit data, and receiving an EDMA interrupt generated after the data is transmitted; and 5, after the data is transmitted, releasing the hardware semaphore HwSemh and PaRAM resources. The method has the advantages that each core can directly transmit data via the EDMA channel, inter-core forwarding is not needed and the like.

Owner:GUANGZHOU HUIRUI SITONG INFORMATION SCI & TECH CO LTD

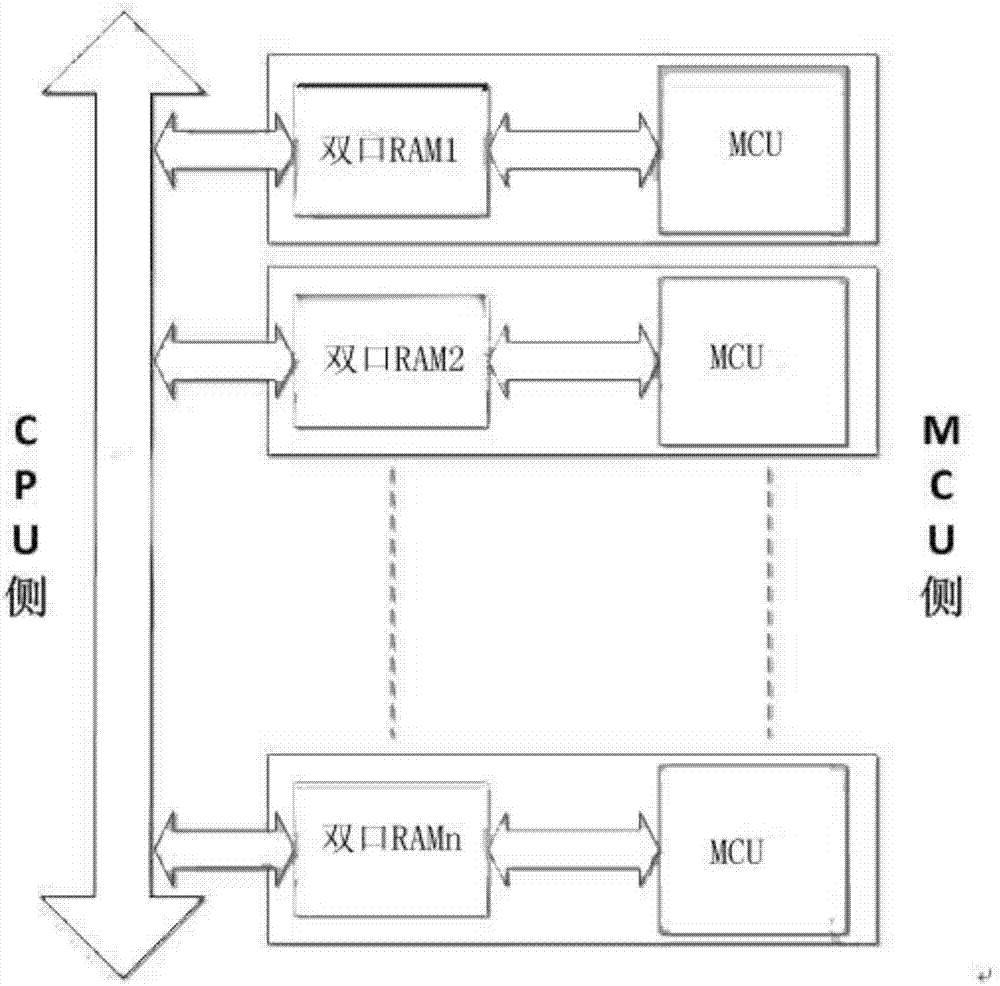

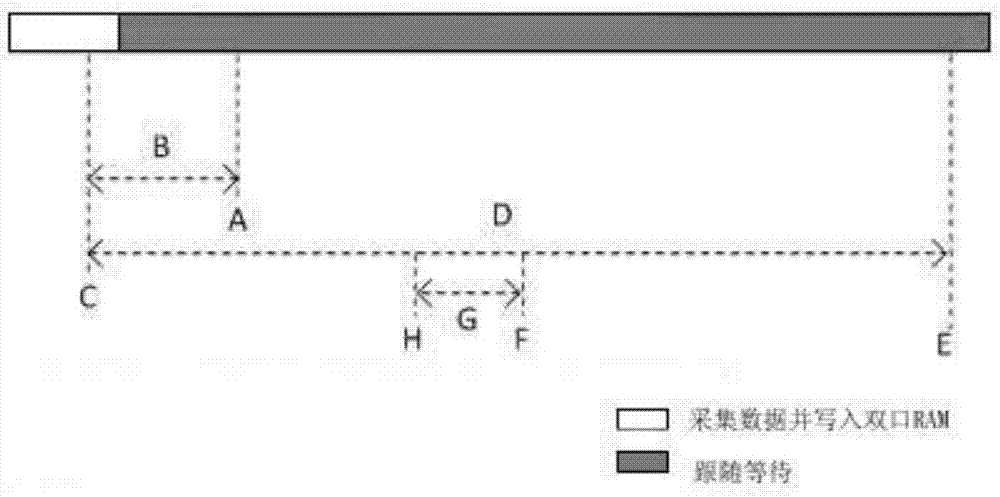

Dual-port RAM following access method

ActiveCN107544927AAvoid access violationsAvoid capture the flagElectric digital data processingAccess methodDual-ported RAM

The invention discloses a dual-port RAM following access method. The dual-port RAM following access method comprises the following steps that A, an MCU constantly detects the state of data written last time in a waiting and follow time period, and when it is detected that a CPU reads the data written last time, a current moment is recorded; B, the moment when the CPU reads data next time is calculated; C, the middle moment between the current moment and the moment when the CPU reads data next time is calculated, and the quit waiting moment of the MCU is calculated, wherein an extended board card prepares data for reading operation of the CPU at the middle moment. By adopting the method, access conflict of a dual-port RAM can be avoided, and the speed of the interaction between the CPU andthe expanded card data can be improved.

Owner:NUCLEAR POWER INSTITUTE OF CHINA

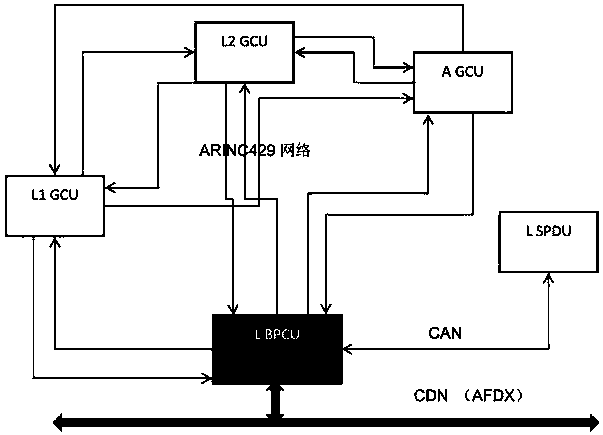

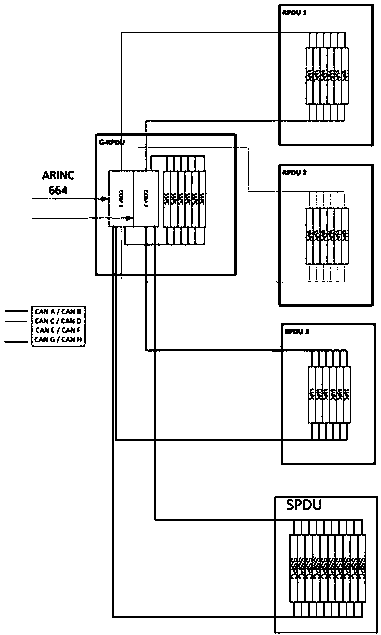

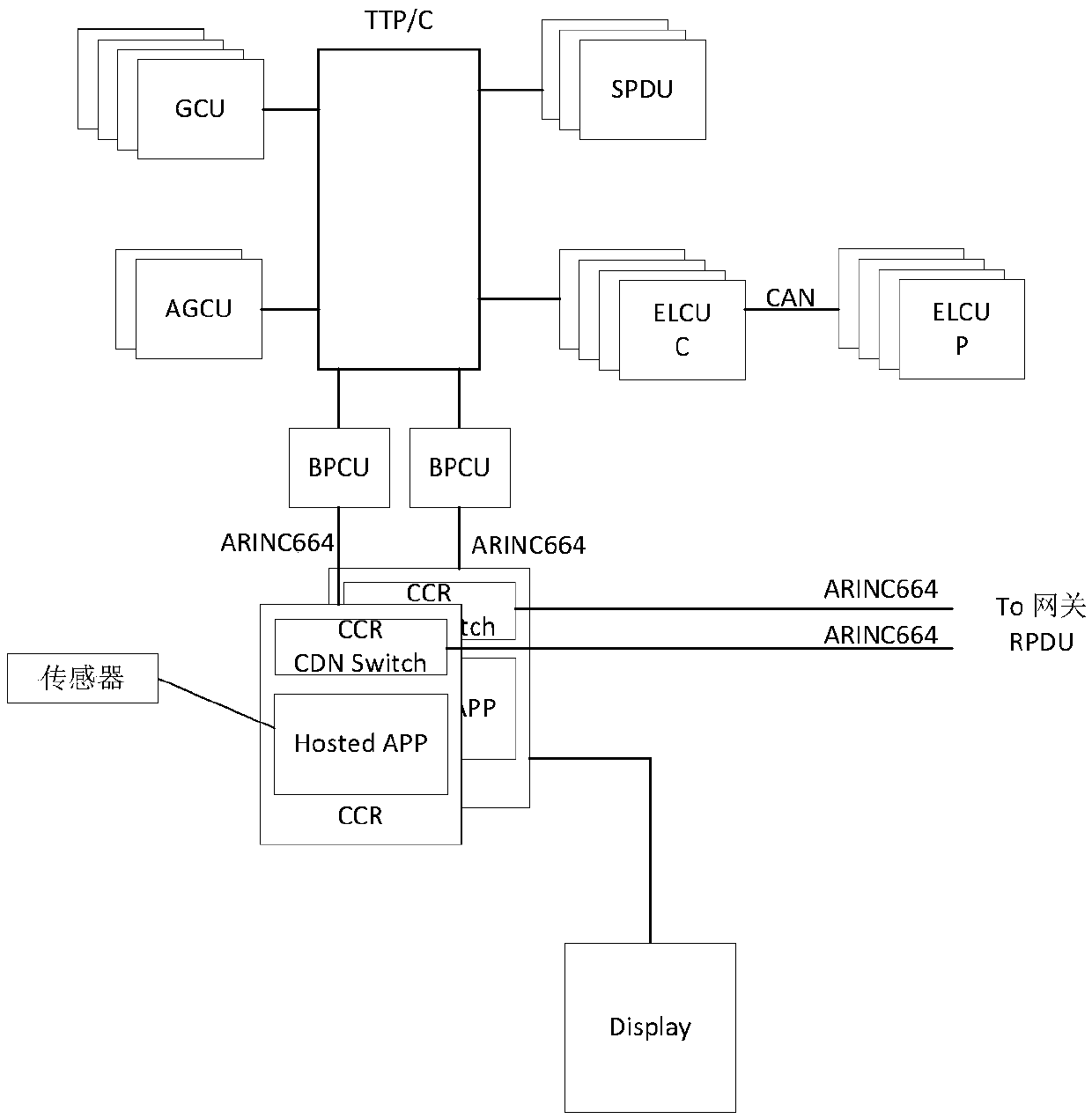

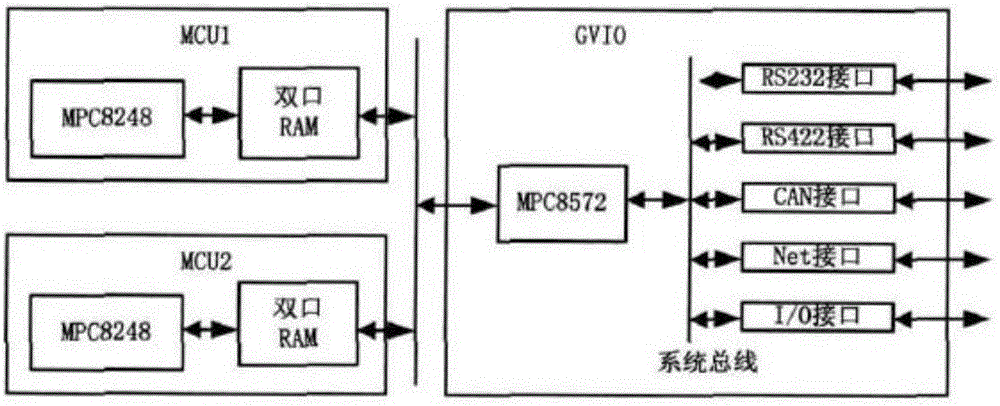

Aircraft power supply system communication architecture

InactiveCN111294376AEnable direct communicationAvoid access violationsBus networksEmbedded systemSource system

The invention discloses an aircraft power supply system communication architecture, and the architecture is characterized in that the architecture is based on a two-stage communication network of AFDXand CAN. The method has the advantages that the hardware overhead is reduced, the product complexity is reduced, the reliability is improved, and meanwhile, the size and the weight of the product arereduced.

Owner:SHANGHAI AVIATION ELECTRIC

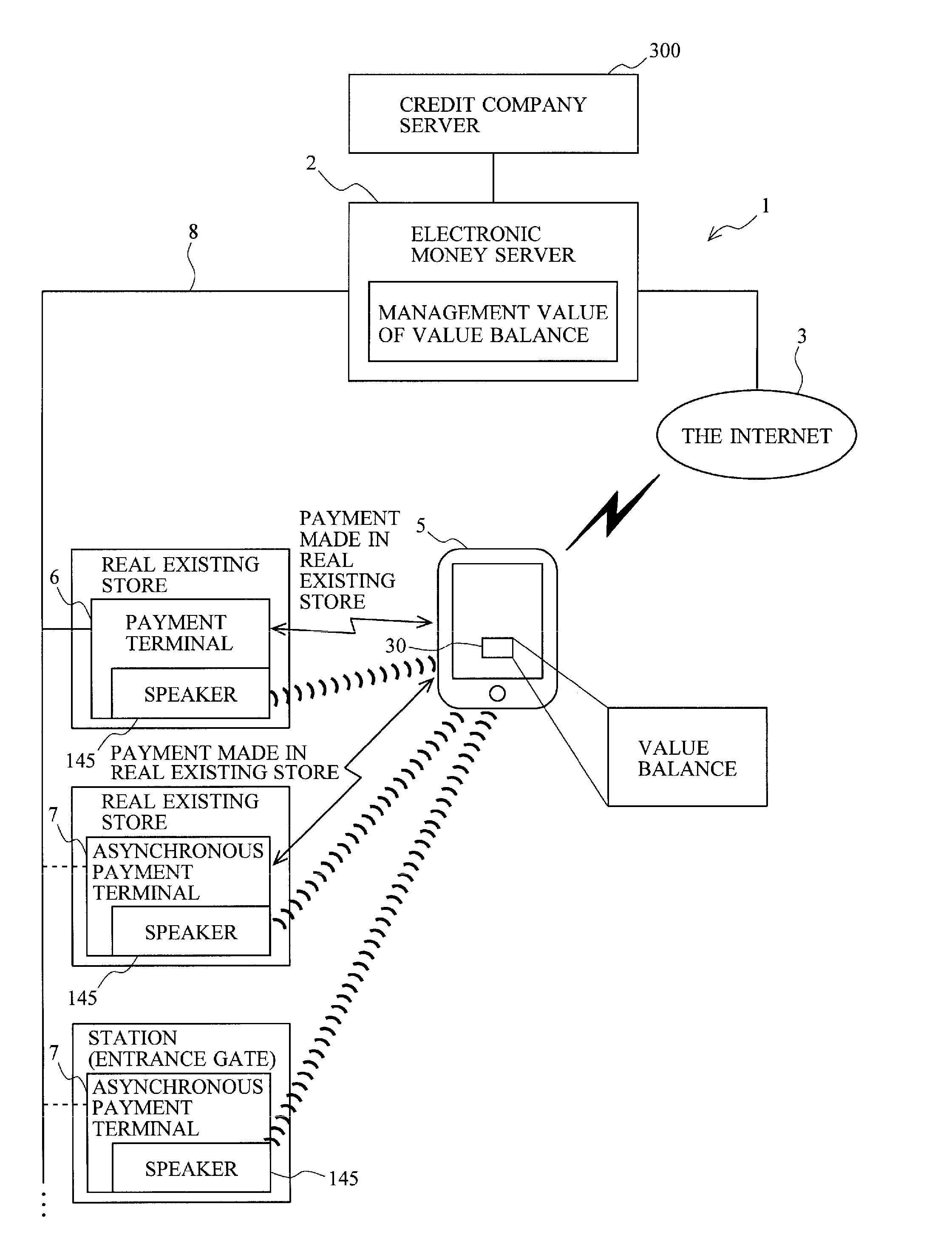

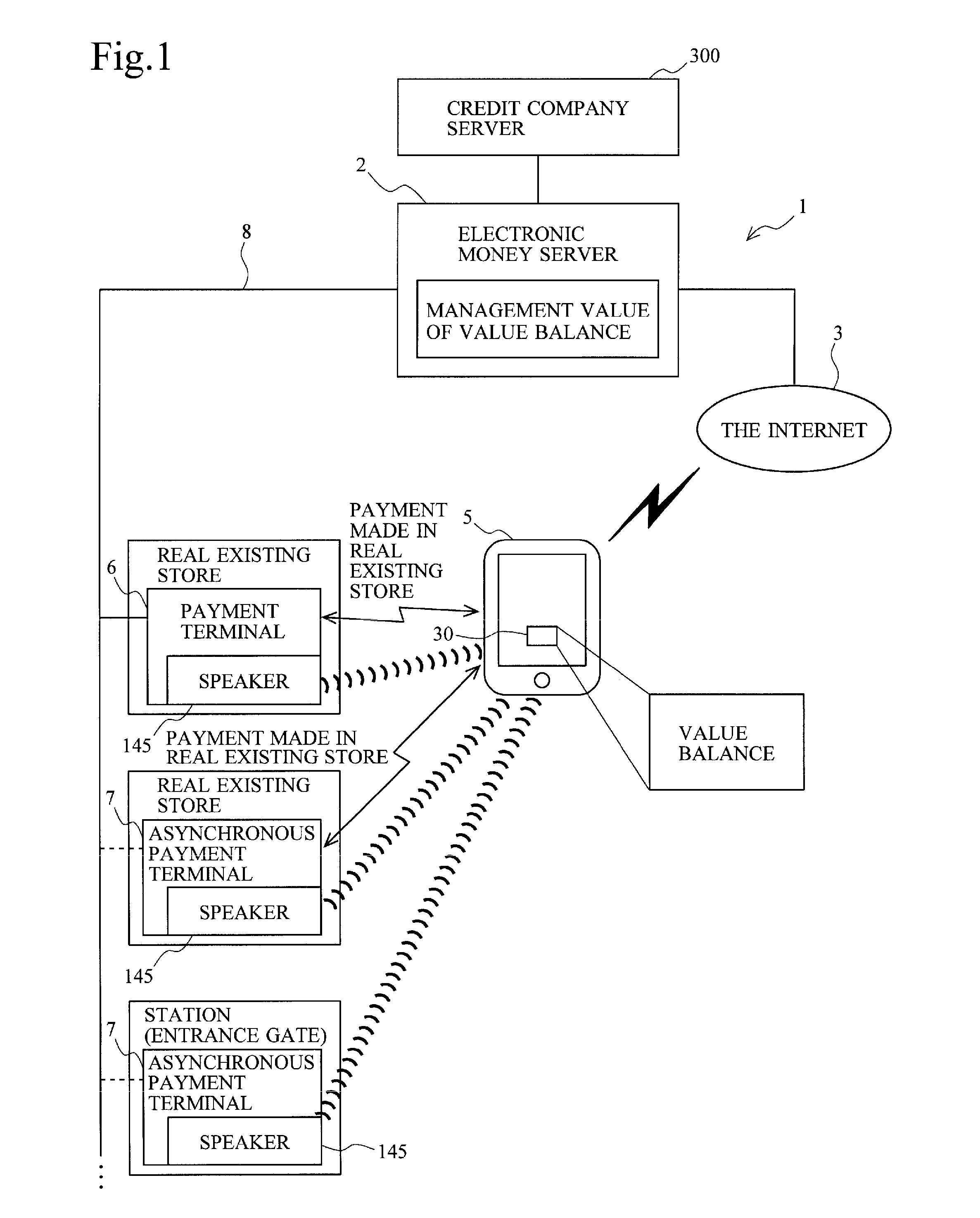

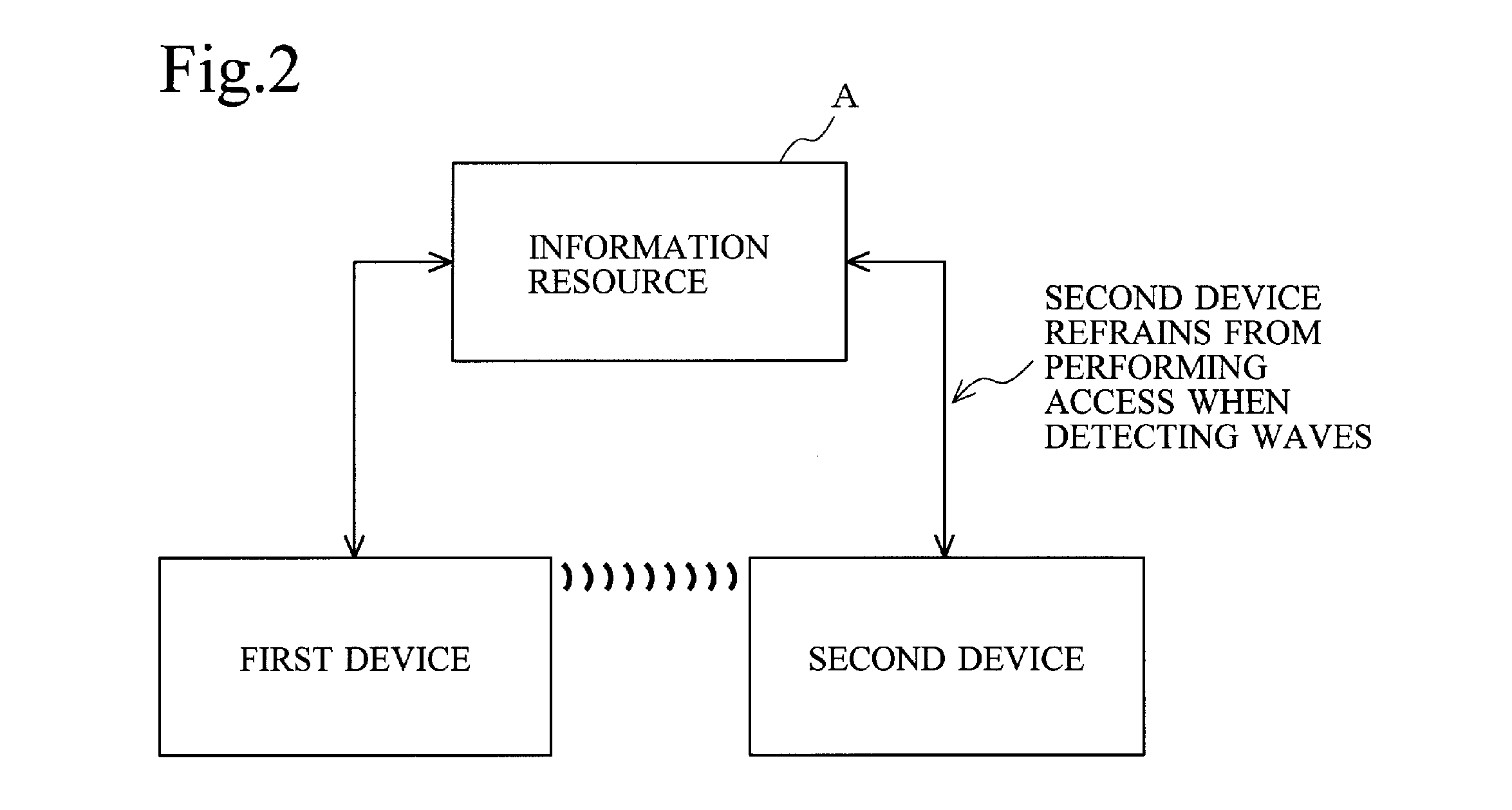

Information access device, computer program product, information processing system, access control system, portable terminal, portable terminal control method, and portable terminal control program product

PendingUS20160196541A1Access conflict be avoidAvoid access violationsFinancePayment architectureControl functionMedia access control

An object is to avoid an access conflict between a plurality of devices that access an IC module.A first device (a payment terminal installed in a store, an entrance gate of a station) and a second device (a portable terminal) can access an IC module that is used in an electronic money system. The second device has the function of receiving (detecting) waves (for example, ultrasound) having a predetermined pattern. The predetermined waves indicate that the first device is accessing the IC module. The predetermined waves may be continuously generated from the first device or may be continuously generated from another device (for example, a device installed near the first device). When the second device detects the waves having the predetermined pattern, the second device refrains from accessing the IC module. This makes it possible to implement autonomous conflict control between a plurality of devices that access the IC module that does not have an adequate conflict control function without providing a special control circuit or the like.

Owner:RAKUTEN GRP INC

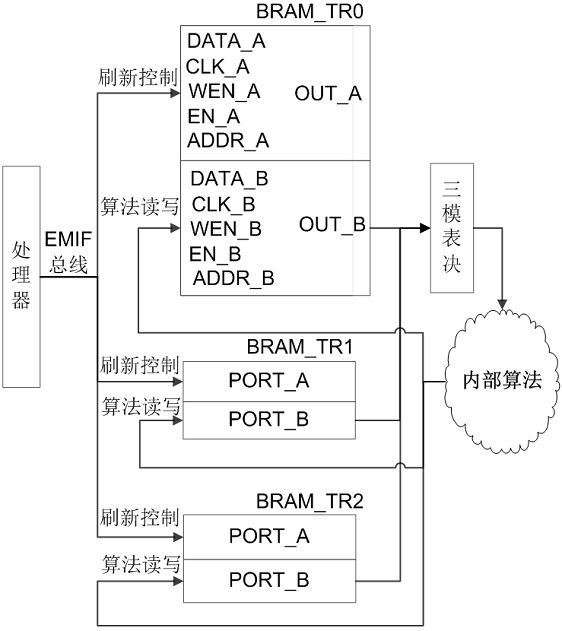

Satellite load FPGA with BRAM and use method thereof

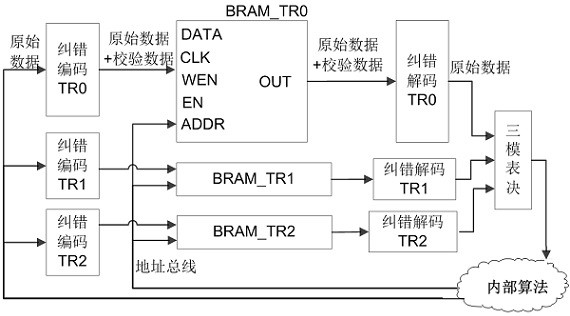

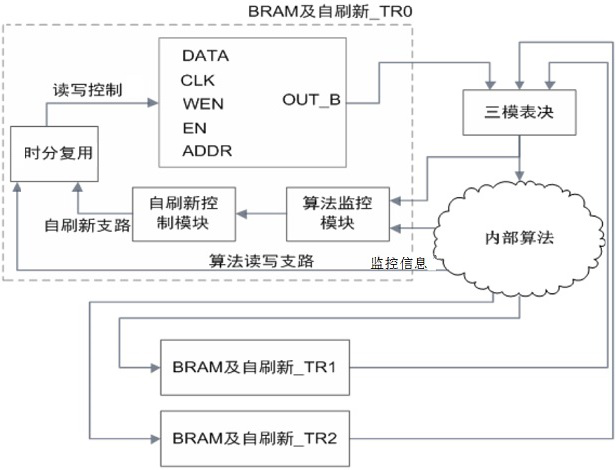

ActiveCN113254252ARealize time-sharing refreshImprove the reliability of radiation resistanceData resettingNon-redundant fault processingMulti processorEngineering

The invention provides a satellite load FPGA with a BRAM and a use method thereof, the satellite load FPGA comprises: an internal algorithm module, a three-mode voting module, the BRAM and a self-refreshing module; the input of the internal algorithm module is correct output data after passing through the three-mode voting module, and the internal algorithm module is used for processing configuration items of the satellite load FPGA; the three-mode voting module is used for acquiring data output by the three-mode BRAM and carrying out three-mode redundancy voting; and the BRAM and the self-refreshing module is used for storing on-orbit parameters and controlling self-refreshing of the on-orbit parameters. According to the satellite load FPGA, the self-refreshing function of the BRAM can be completed without intervention of an external processor, and the problems that a traditional BRAM anti-radiation reinforcement method consumes more resources, and the access conflict risk of the processor is caused can be solved. The problem of satellite load FPGA data errors caused by accumulation of single event upset of the BRAM is solved.

Owner:NAT UNIV OF DEFENSE TECH

Data access method and device, electronic equipment and storage medium

ActiveCN113032805AImprove efficiency in accessing the same dataAvoid access violationsDigital data protectionEnergy efficient computingComputer hardwareData feed

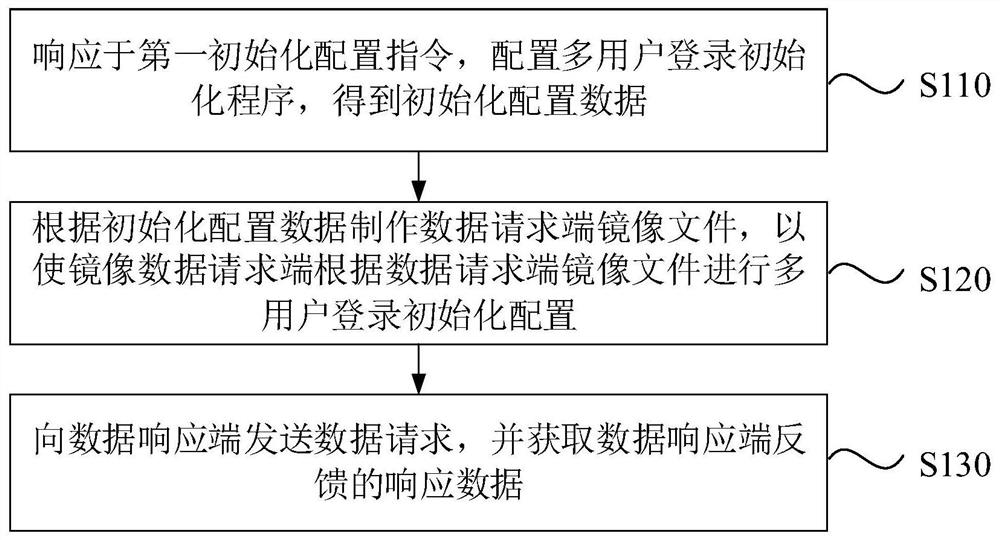

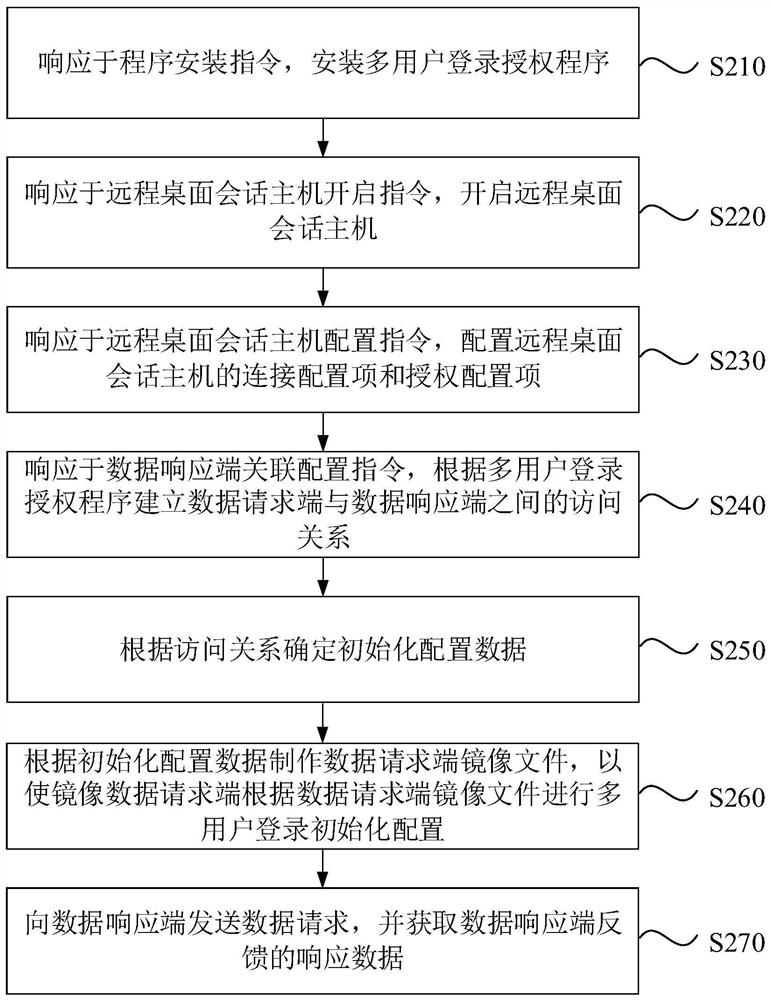

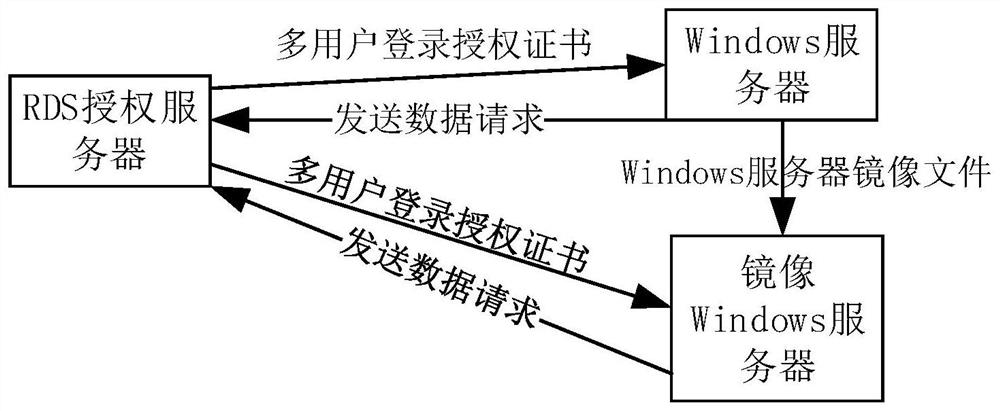

The embodiment of the invention discloses a data access method and device, electronic equipment and a storage medium. The data access method relates to the technical field of Internet, and further relates to cloud computing and virtualization technologies, and comprises the following steps: in response to a first initialization configuration instruction, configuring a multi-user login initialization program to obtain initialization configuration data; making a data request end mirror image file according to the initialization configuration data, so that a mirror image data request end performs multi-user login initialization configuration according to the data request end mirror image file; sending the data request to a data response end, and obtaining response data fed back by the data response end. According to the technical scheme, the access conflict of multiple users to the same data can be avoided, and the efficiency of multiple users to access the same data is improved.

Owner:CCB FINTECH CO LTD

Method for quickly realizing GZIP compression based on hardware and application thereof

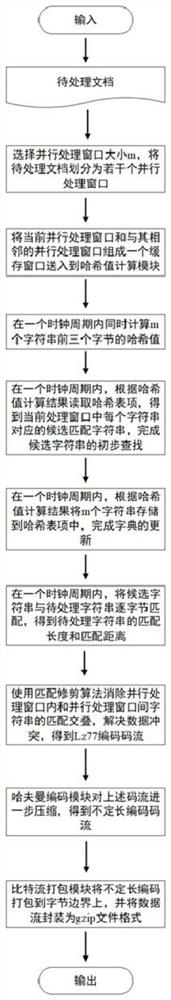

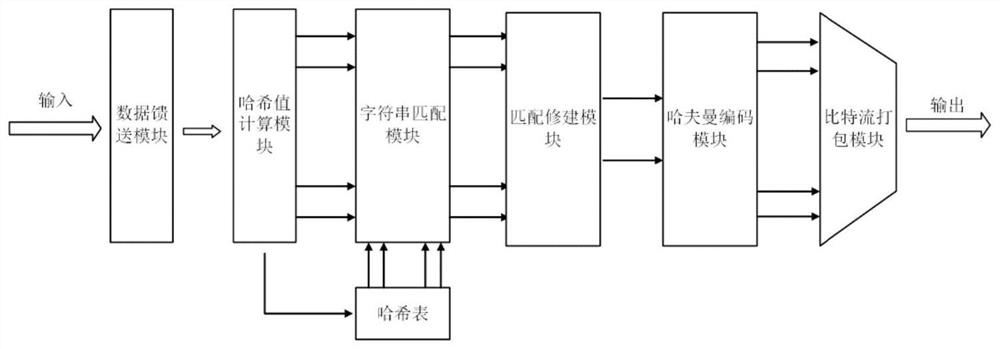

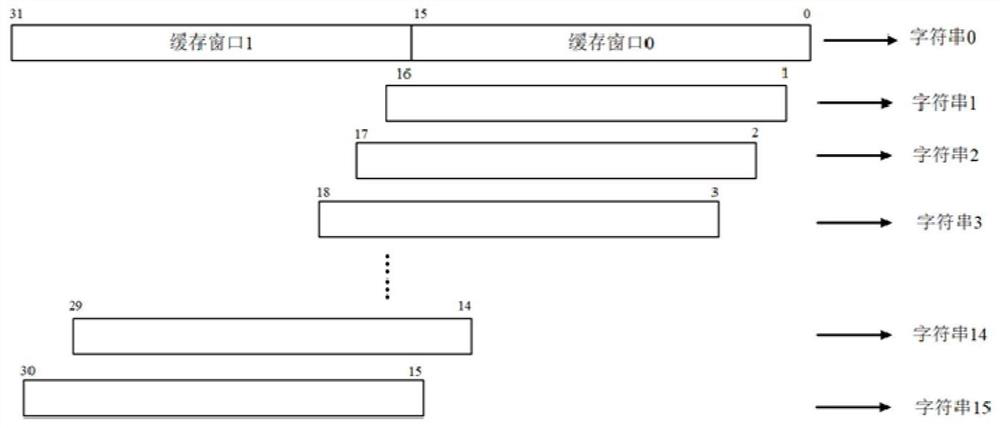

ActiveCN114157305AReduce resource utilizationImprove throughputCode conversionConcurrent computationHigh bandwidth

The invention belongs to the field of data compression, and particularly relates to a method for quickly realizing GZIP compression based on hardware and application thereof, and the method comprises the following steps: dividing a to-be-processed text into a plurality of processing windows with the size of m bytes, carrying out parallel calculation on m character string hash values starting from each byte in one processing window, and taking the hash values as index addresses of a dictionary; storing the current to-be-processed character string into the dictionary, and reading the historical candidate character string to complete the initial matching of the character string; the read historical character string and the current character string to be processed are compared byte by byte to finish fine matching, and the matching length and the matching distance of each character string are obtained. A matching pruning algorithm is introduced to eliminate matching overlapping of character strings in parallel processing windows and between the windows, the dependency between algorithms is solved, and the data parallel processing capacity is improved. According to the invention, a high-bandwidth full-pipeline extensible lossless compression data path suitable for hardware is realized, and the size of a processing window is dynamically adjusted according to the tradeoff among hardware resources, throughput rate and compression rate.

Owner:HUAZHONG UNIV OF SCI & TECH

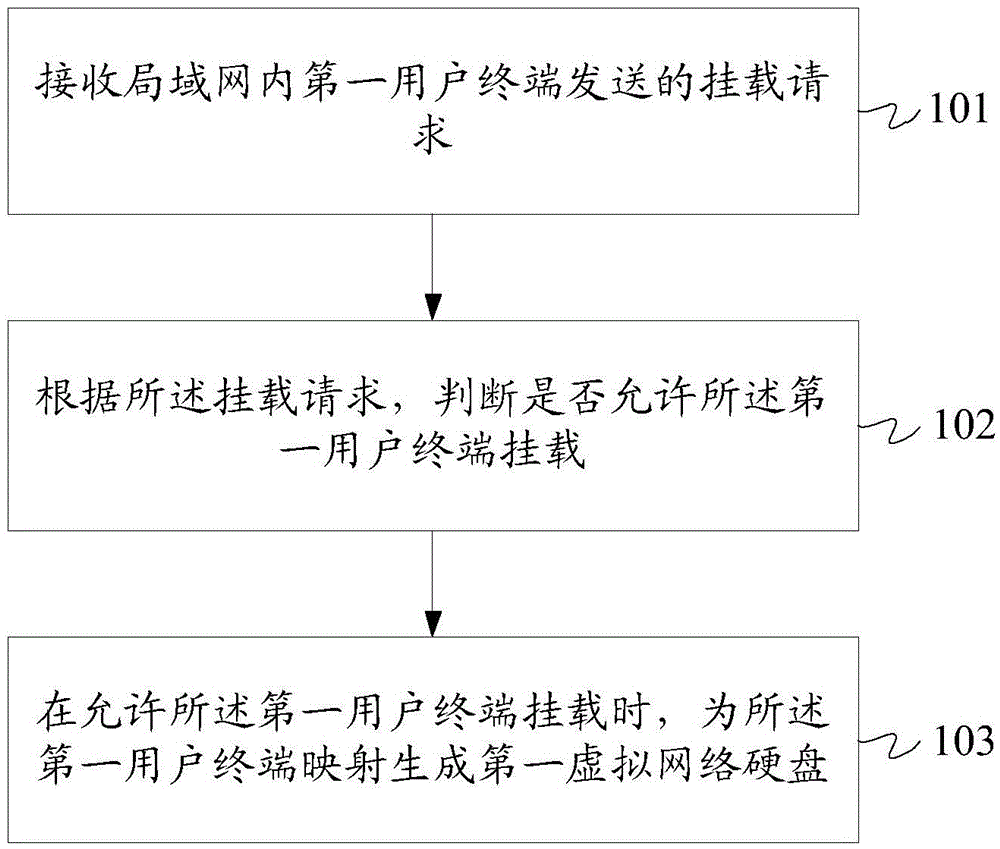

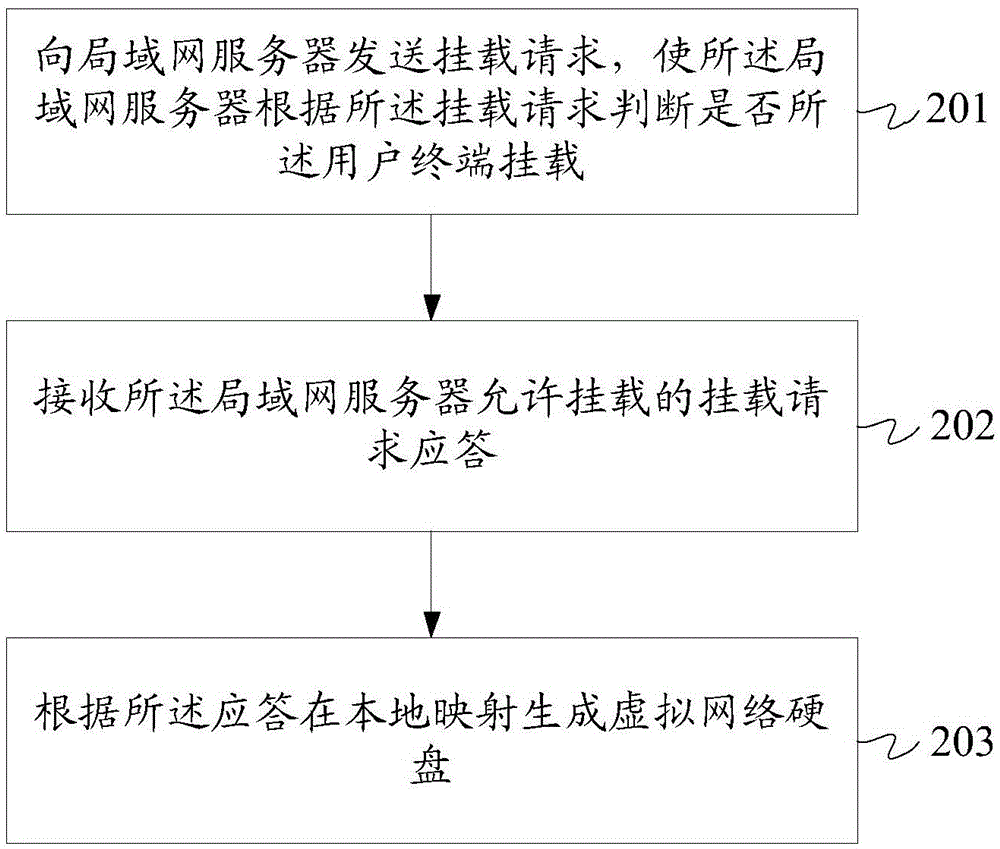

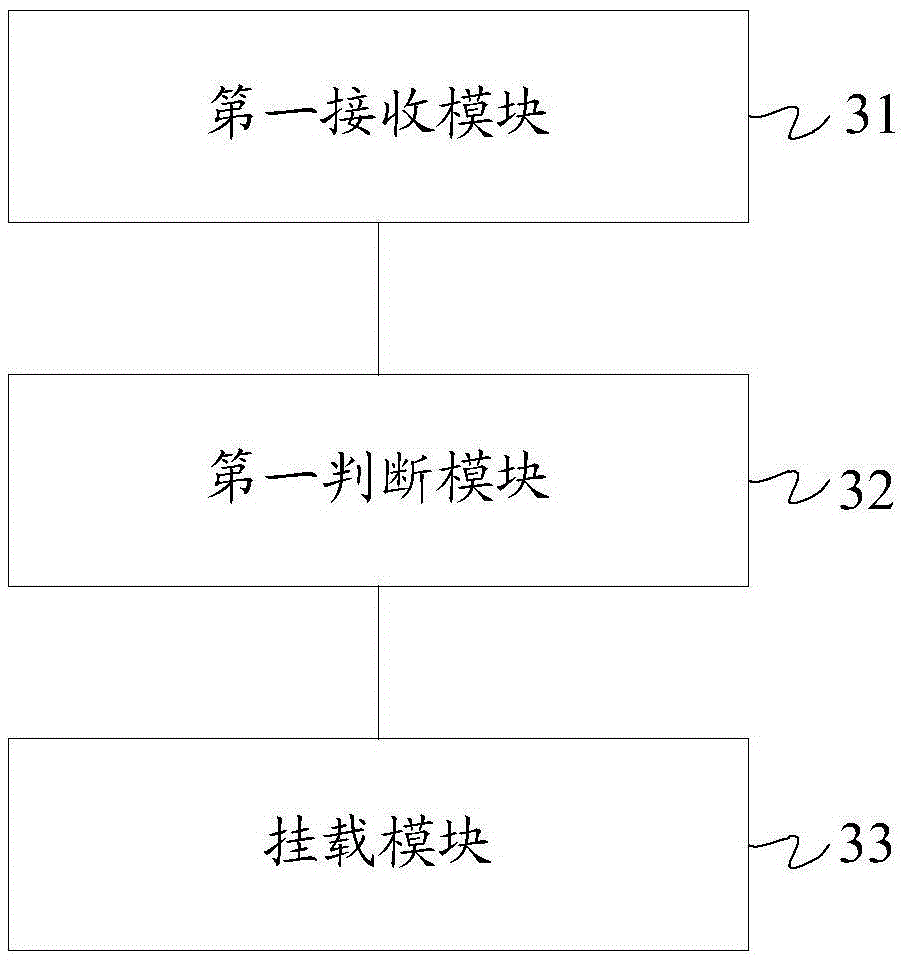

Virtual network hard disk mounting method, local area network server, user terminal and system

InactiveCN106817399AAvoid access violationsEnsure consistencyTransmissionComputer engineeringVirtual network

The invention provides a virtual network hard disk mounting method, a local area network server, a user terminal and a system. The method, which is applied to a local area network server, comprises the following steps: receiving a mounting request sent by a first user terminal in a local area network; judging whether the first user terminal is allowed to mount a virtual network hard disk according to the mounting request; and when the first user terminal is allowed to mount a virtual network hard disk, generating a first virtual network hard disk by mapping for the first user terminal, wherein one virtual network hard disk can be mounted only on one user terminal. Thus, the consistency of data is ensured, and user access conflict is prevented. Moreover, the virtual network hard disk is locally generated by mapping at the user terminal, namely, a complete hard disk is provided locally, so that users can operate data directly.

Owner:ZTE CORP

Redundant system communication method based on double-port RAM

InactiveCN105978776AImprove data exchange rateAvoid access violationsBus networksDependabilityData transmission

The invention discloses a redundant system communication method based on dual-port RAM. Aiming at the problems of slow signal data transmission speed and poor data reliability of vehicle-mounted signal equipment in the prior art, the invention proposes a multi-role-based ring buffer method, taking multiple measures to avoid access conflicts, increasing the data interaction rate of dual-port RAM, and ensuring the security and reliability of data interaction in redundant systems. Data transmission is improved, and the security of the system is also improved.

Owner:冯东瑾

Method and apparatus for management of bus transactions relating to shared resources

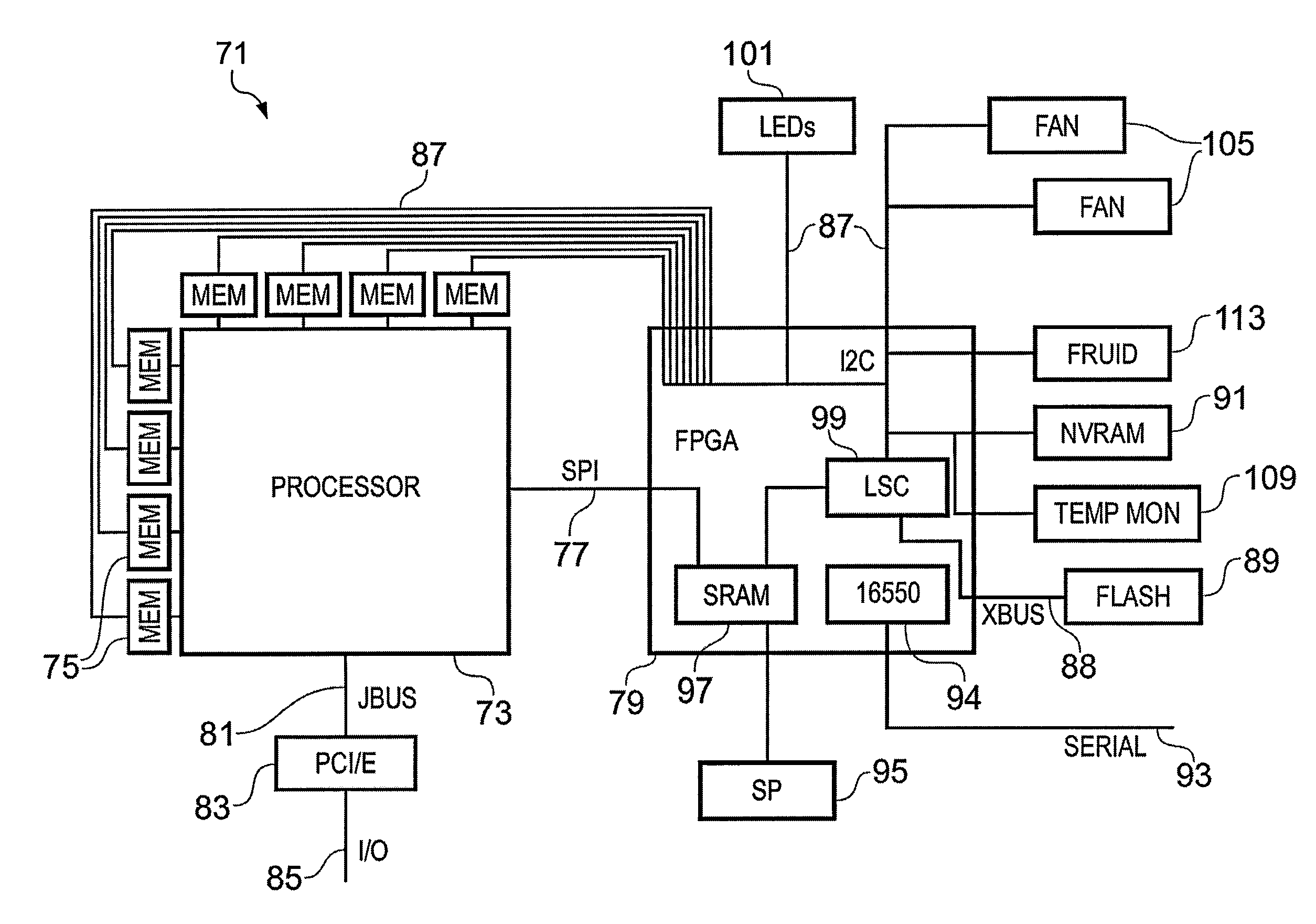

ActiveUS7962721B1Quick updateAvoid access violationsError detection/correctionGeneral purpose stored program computerReal-time computingShared resource

There is provided an information processing apparatus. The apparatus comprises: a processor; at least one I2C device; and a processor support chip. The processor support chip comprises a local service controller and a jointly addressable memory space and has an interface to the processor for the transfer of information therebetween. The processor support chip also has an interface for communication with a service processor; and an I2C interface for communication with the at least one I2C device. The local service controller has exclusive read and write access to the I2C interface; and is operable to maintain a data structure indicating a current value associated with the I2C device in the jointly addressable memory space for access by the processor and the service processor.

Owner:ORACLE INT CORP

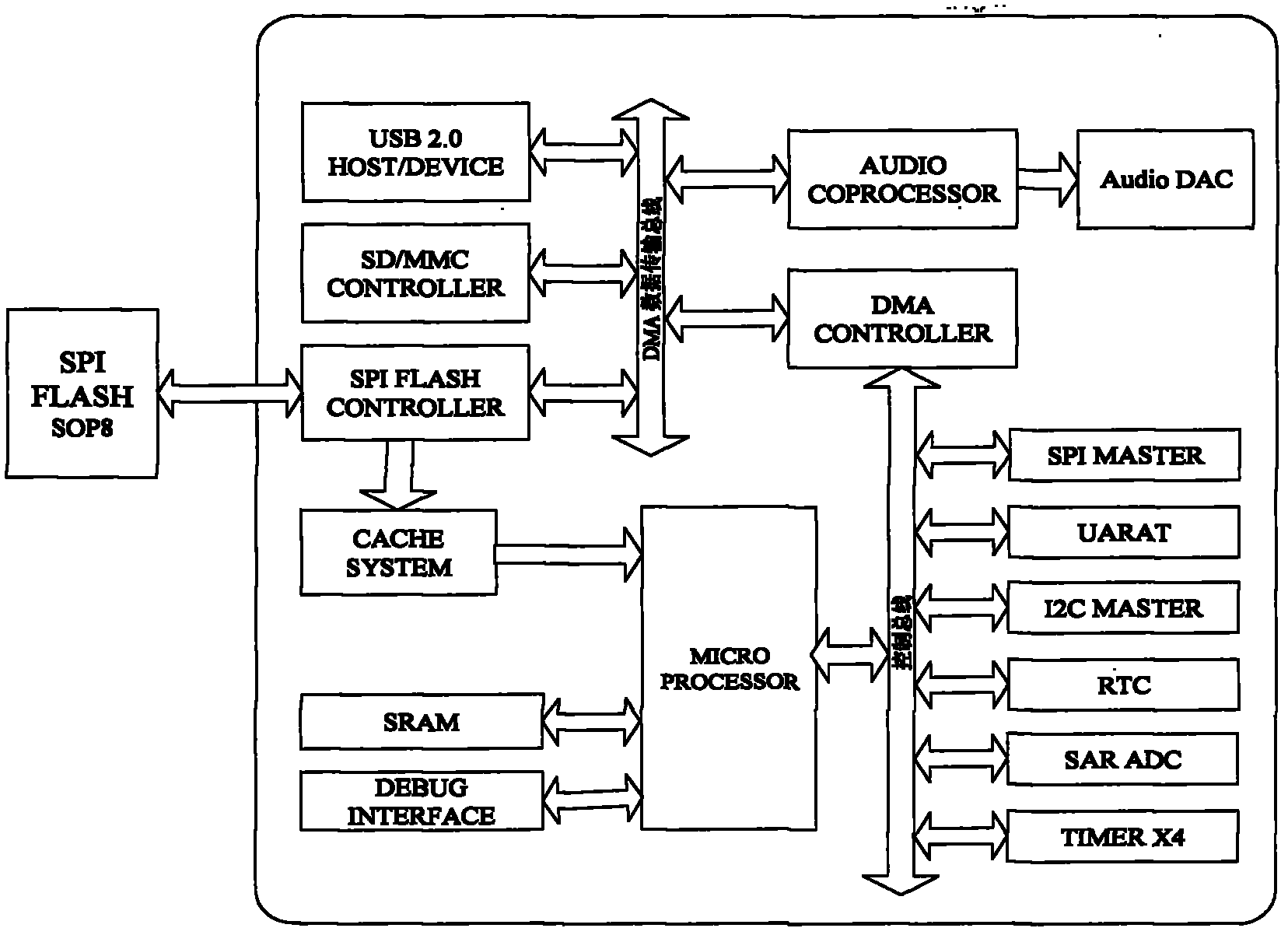

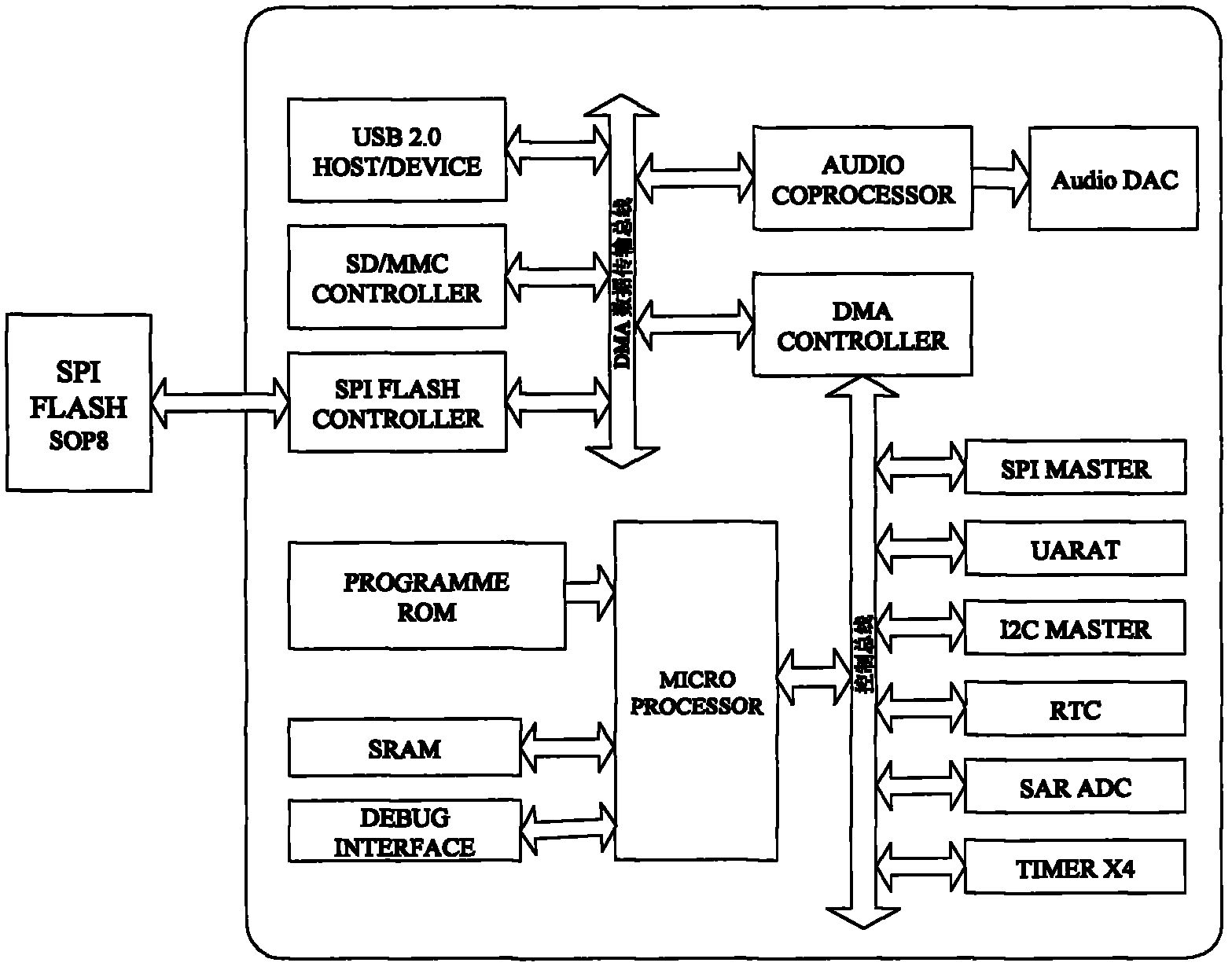

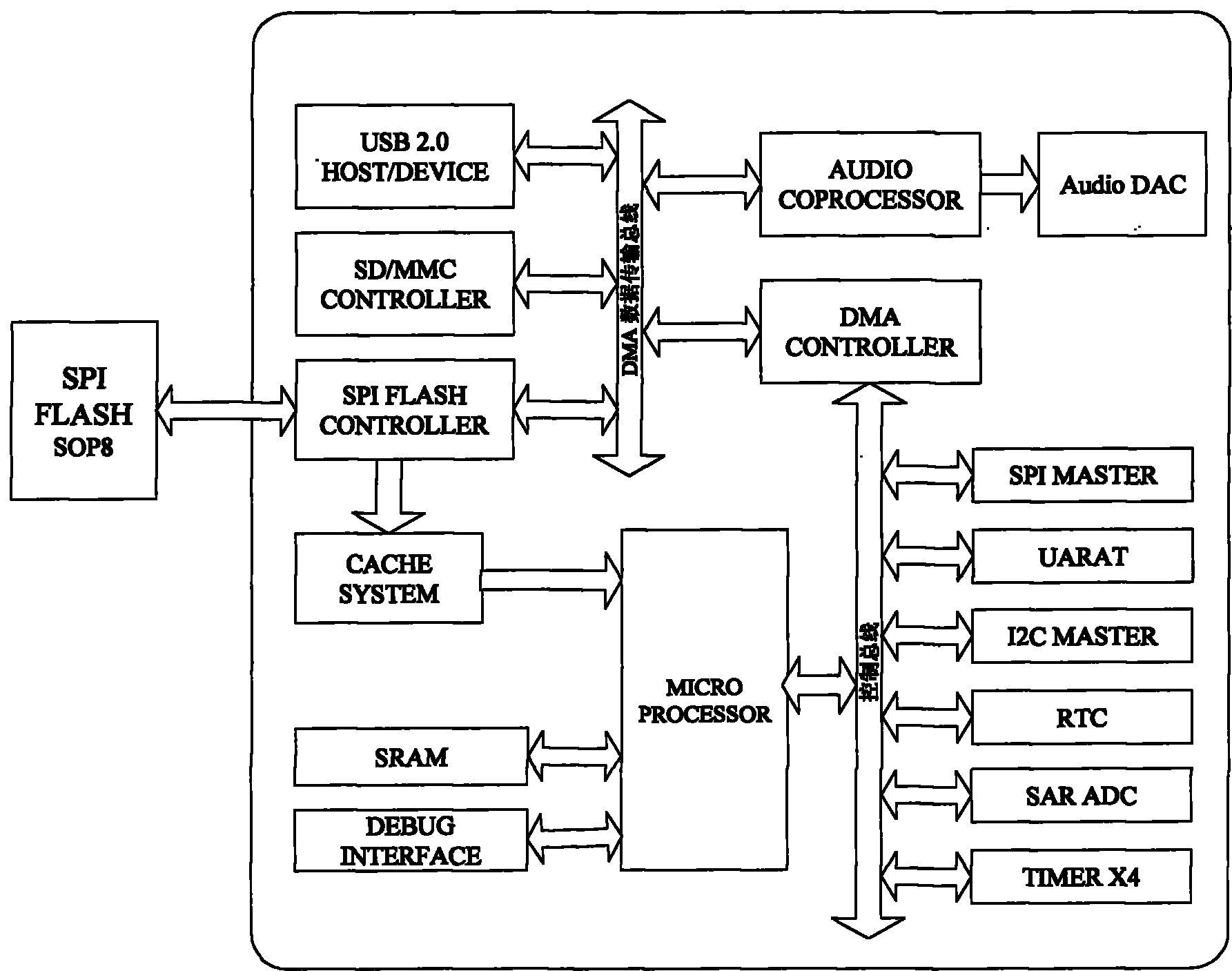

Method for designing voice microprocessor

InactiveCN102043610AAvoid access violationsMachine execution arrangementsCapacity limitApplication software

The invention relates to a method for designing a voice microprocessor, particularly, the program of the voice microprocessor directly operates on a universal serial flash memory chip; the universal serial flash memory chip can be selected in accordance with capacity based on the actual requirement; and compared with the fixed capacity of the program in the voice microprocessor, a user application program is not restricted by the capacity.

Owner:HANGZHOU XINSAI MICRO ELECTRONICS