Satellite load FPGA with BRAM and use method thereof

A payload and satellite technology, which is applied in the field of satellite payload FPGA, can solve the problems of satellite payload FPGA data error and the accumulation of single event flips that are difficult to eliminate, and achieve the effect of solving resource consumption, saving resources, and ensuring correctness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032]In order to make the purpose, technical solution and advantages of the present invention clearer, the technical solution of the present invention will be clearly and completely described below in conjunction with specific embodiments of the present invention and corresponding drawings. Apparently, the described embodiments are only some of the embodiments of the present invention, but not all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

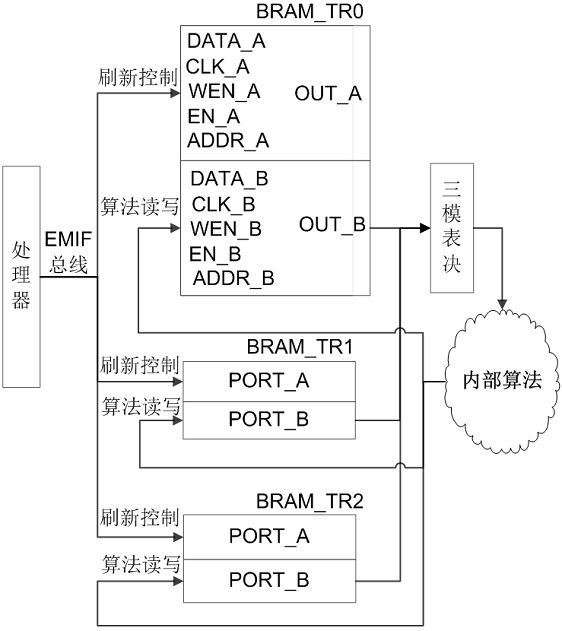

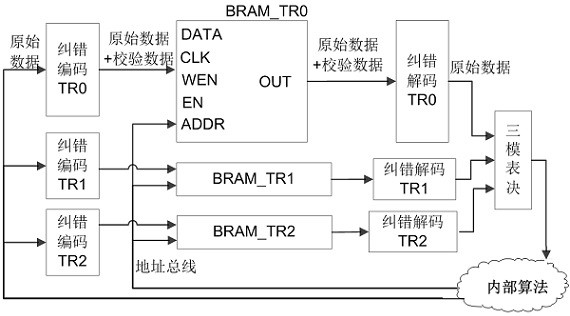

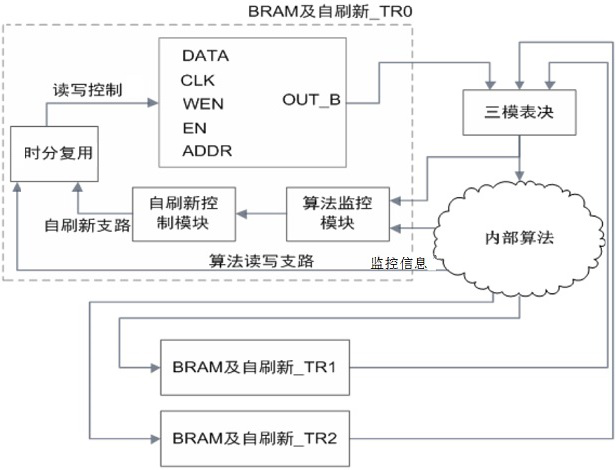

[0033] combine first image 3 A satellite payload FPGA with BRAM is illustrated as one embodiment of the present invention. The satellite load FPGA includes an internal algorithm module, a three-mode voting module, a BRAM and a self-refresh module, wherein:

[0034] The internal algorithm module, whose input is the correct output data after passing through the th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More