Patents

Literature

44results about How to "Shorten execution cycle" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Fairness-based power and channel joint allocation method for cognitive radio system

InactiveCN101626604AHigh QoS support levelImprove fairnessPower managementEnergy efficient ICTQuality of serviceMathematical definition

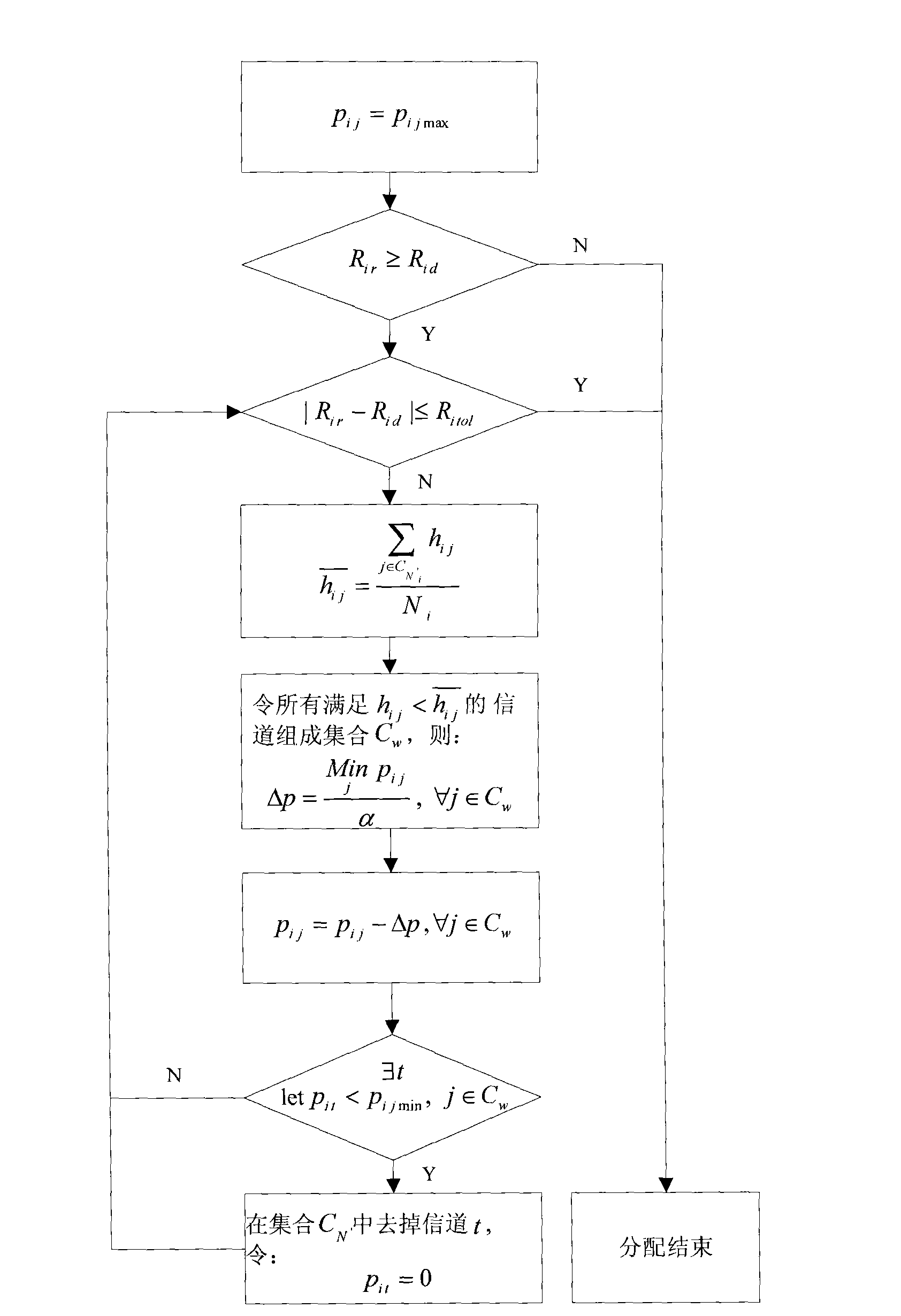

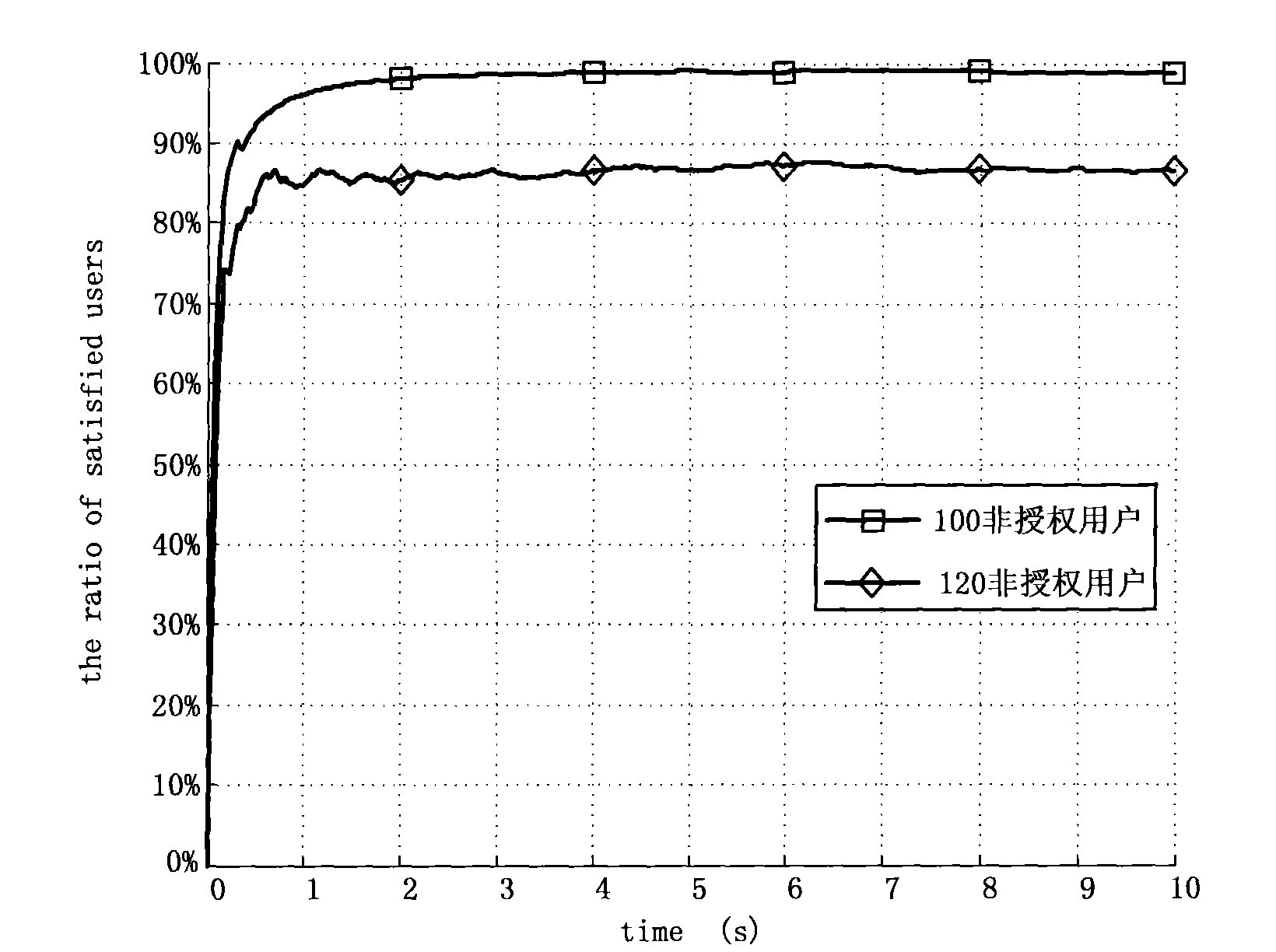

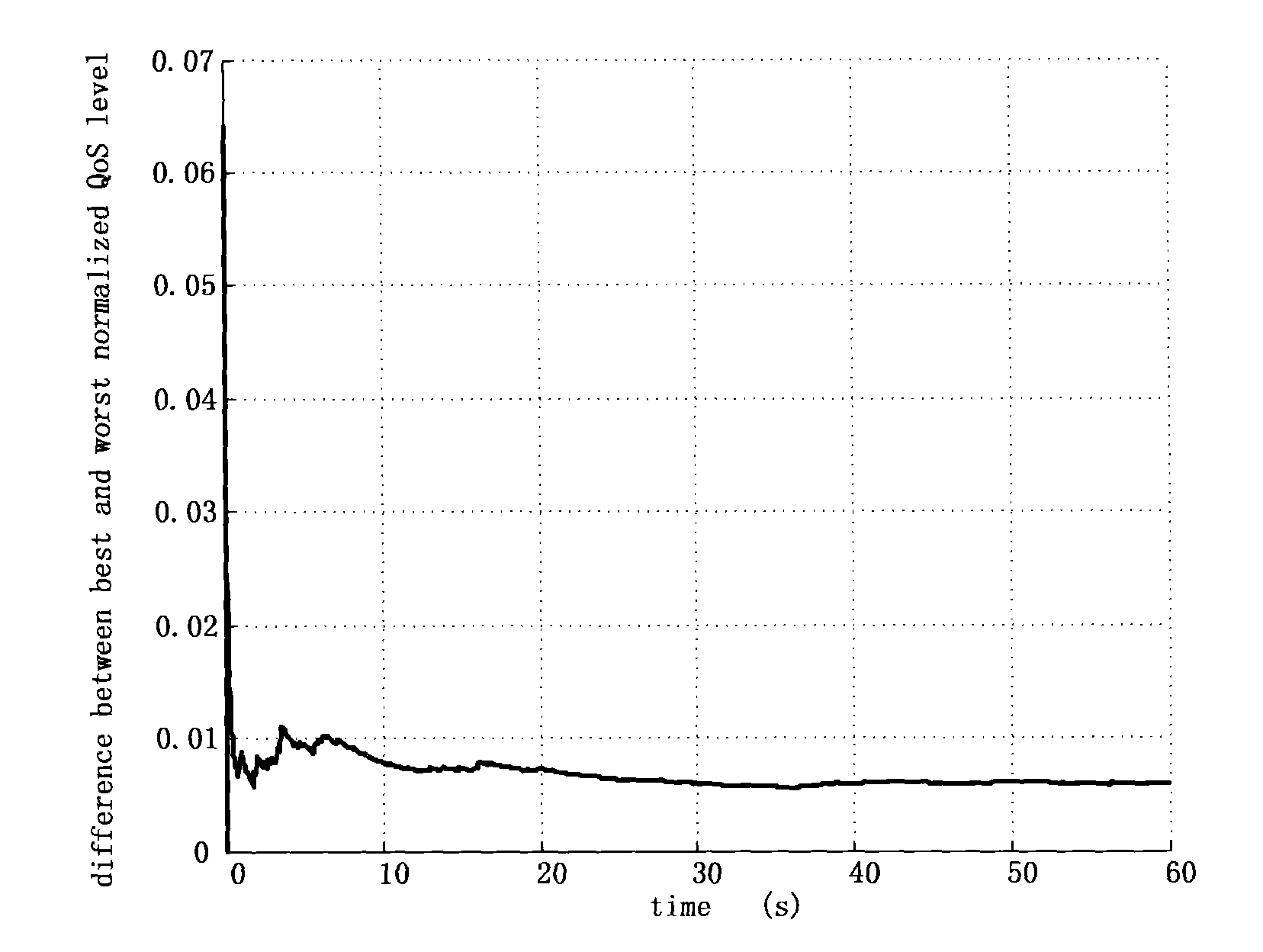

The invention provides a fairness-based power and channel joint allocation method for a cognitive radio system, belongs to the technical field of wireless communication, and in particular relates to power and channel joint allocation used in the cognitive radio system. The invention relates to the power and channel joint allocation method which can meet the requirements of unauthorized users on quality of service (QoS), ensure the fairness and protect the authorized users at the same time. According to different QoS requirements of the unauthorized users, a mathematical definition on the fairness is given. Simultaneously, in order to reduce arithmetic cost and shorten the allocation period, the method divides the whole allocation process into two stages; the first stage is called as the crude allocation, at the stage, the protection of the authorized users is taken as premises, and the maximum resource which can be utilized by each non-authorized user is obtained according to the QoS requirements of the non-authorized users and the fairness; and the second stage is called as the fine allocation, at the stage, a plurality of non-authorized users independently complete the tasks, which can be serially and simultaneously completed by the authorized users, so that the complexity is reduced, the quick power and frequency spectrum allocation can be conveniently realized so as to adapt to the quick time varying characteristics of available frequency spectrum resources in the cognitive radio system, and all authorized users can independently determine the final utilizable resources.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

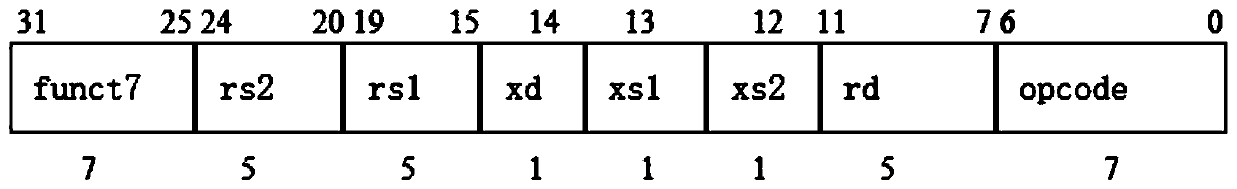

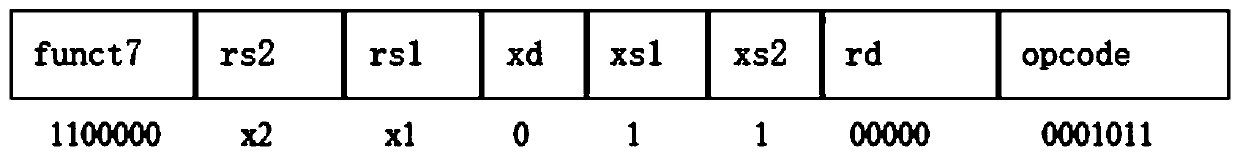

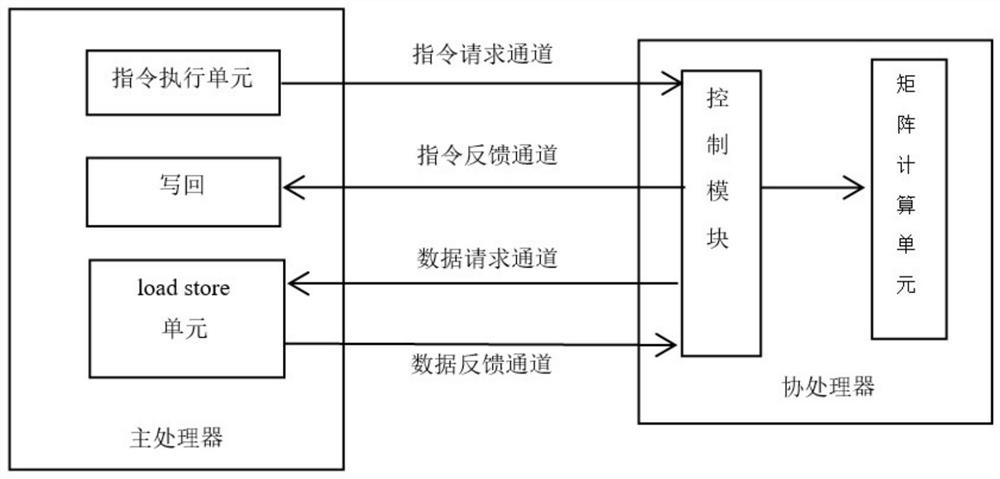

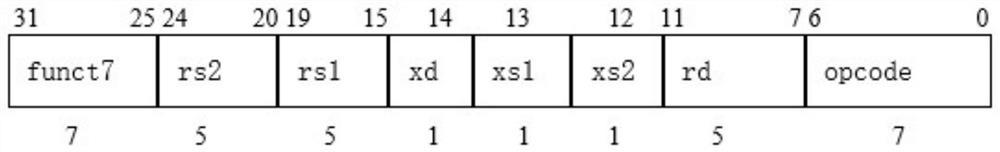

Matrix convolution calculation method, interface, coprocessor and system based on RISC-V architecture

ActiveCN109857460ACalculation speedReduce the number of memory accessesConcurrent instruction executionNeural architecturesExtensibilityProcessor design

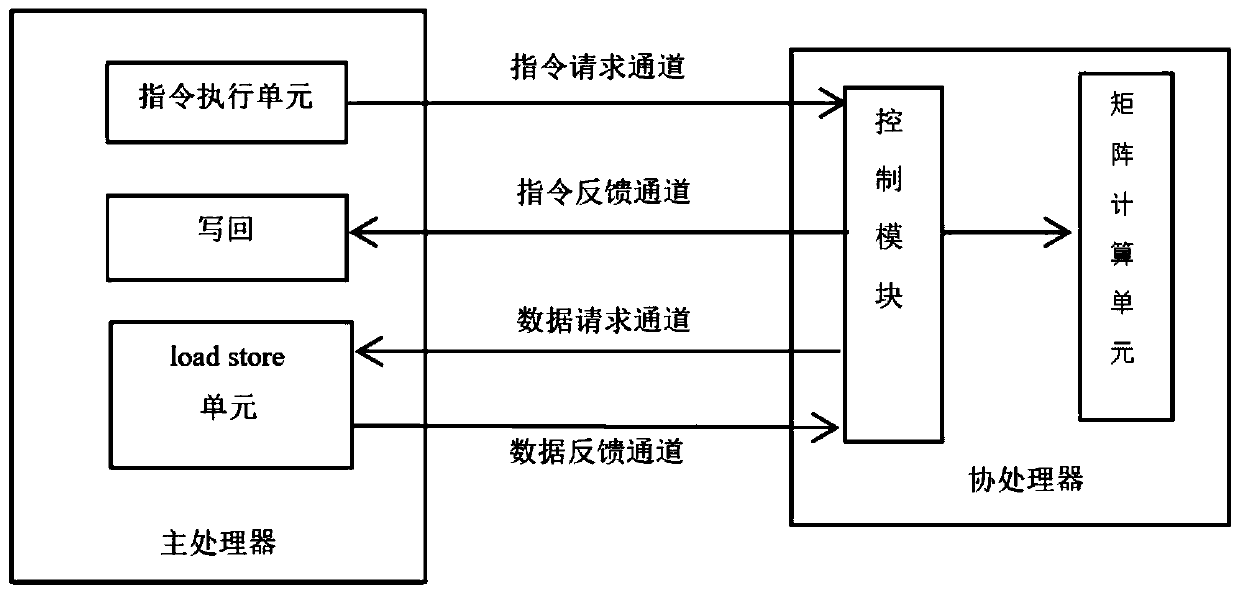

The invention discloses a set based on RISC-. According to the method and system complete mechanism of the instruction, the interface and the coprocessor for matrix convolution calculation of the V instruction set architecture, traditional matrix convolution calculation is efficiently achieved in a software and hardware combined mode, and RISC-is utilized. Extensibility of V instruction sets, a small number of instructions and a special convolution calculation unit (namely a coprocessor) are designed; the memory access times and the execution period of a matrix convolution calculation instruction are reduced, the complexity of application layer software calculation is reduced, the efficiency of large matrix convolution calculation is improved, the calculation speed of matrix convolution isincreased, flexible calling of upper-layer developers is facilitated, and the coding design is simplified. Meanwhile, RISC-is utilized. The processor designed by the V instruction set also has greatadvantages in power consumption, size and flexibility compared with ARM, X86 and other architectures, can adapt to different application scenes, and has a wide prospect in the field of artificial intelligence.

Owner:NANJING HUAJIE IMI TECH CO LTD

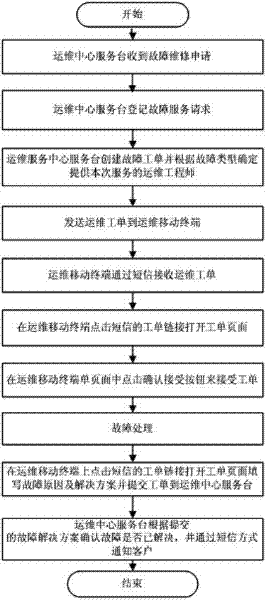

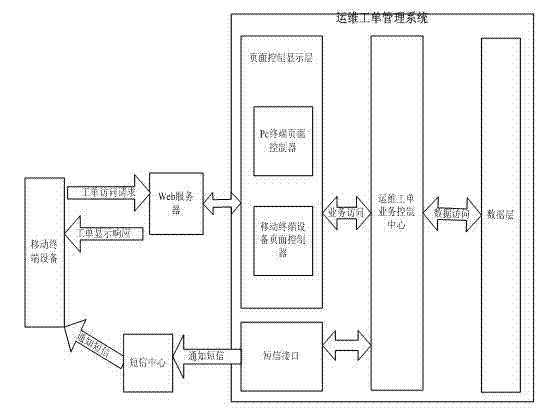

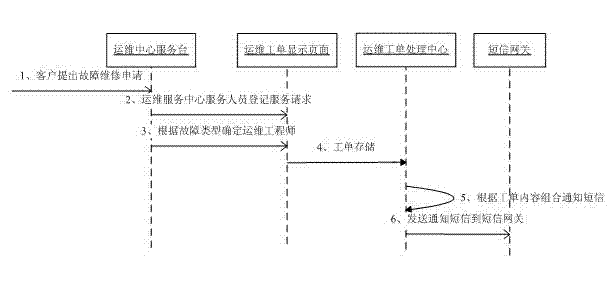

Method and device for processing operation/maintenance work orders based on mobile terminal

InactiveCN102202085AShorten execution cycleReduce time to complete feedbackTransmissionWireless communicationComputer scienceFault handling

The invention discloses a method and device for processing operation / maintenance work orders based on a mobile terminal. The method mainly comprises the following steps: 1) an operation / maintenance center information desk receives fault maintenance application; 2) the operation / maintenance center information desk registers the fault request; 3) the operation / maintenance center information desk creates a work order and determines the operation / maintenance personnel for processing the fault; 4) the operation / maintenance center information desk sends a short message to notify an operation / maintenance mobile terminal; 5) the operation / maintenance mobile terminal receives the notification short message; 6) the work order link of the short message is clicked on the operation / maintenance mobile terminal to open the work order page; 7) a receiving button is clicked on the operation / maintenance mobile terminal to receive the work order; 8) the fault is processed; 9) the work order link in the short message is clicked on the operation / maintenance mobile terminal to open the work order page, a fault solution is filled in, and the work order is submitted; and 10) the operation / maintenance center information desk determines whether the fault is solved according to the submitted fault solution, and notifies the client through a short message. By adopting the method, the operation / maintenance personnel can improve the execution and feedback speed of the work order so as to reduce the execution time of the work order.

Owner:勤智数码科技股份有限公司

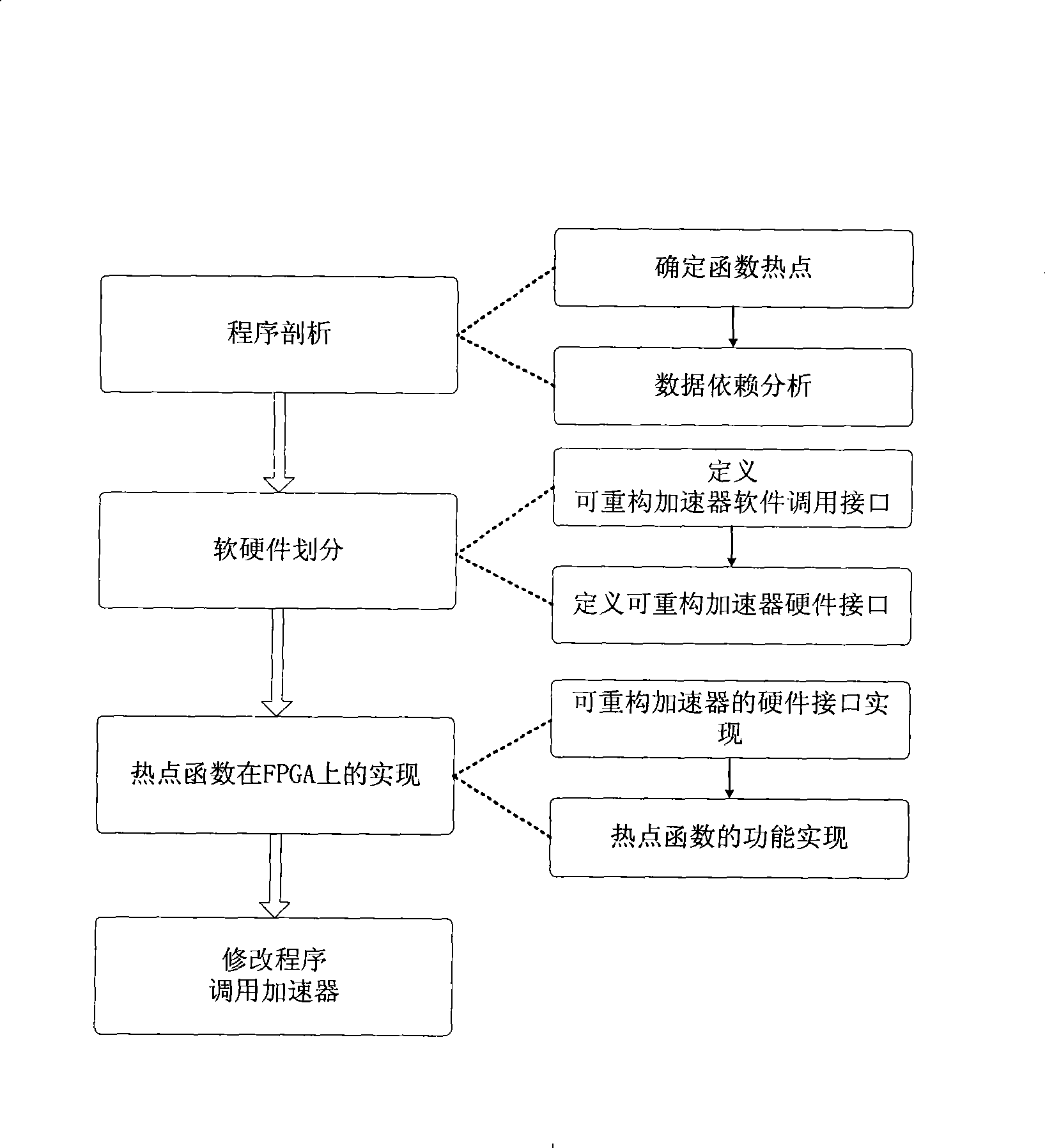

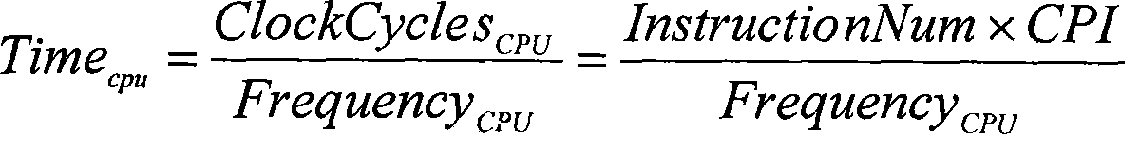

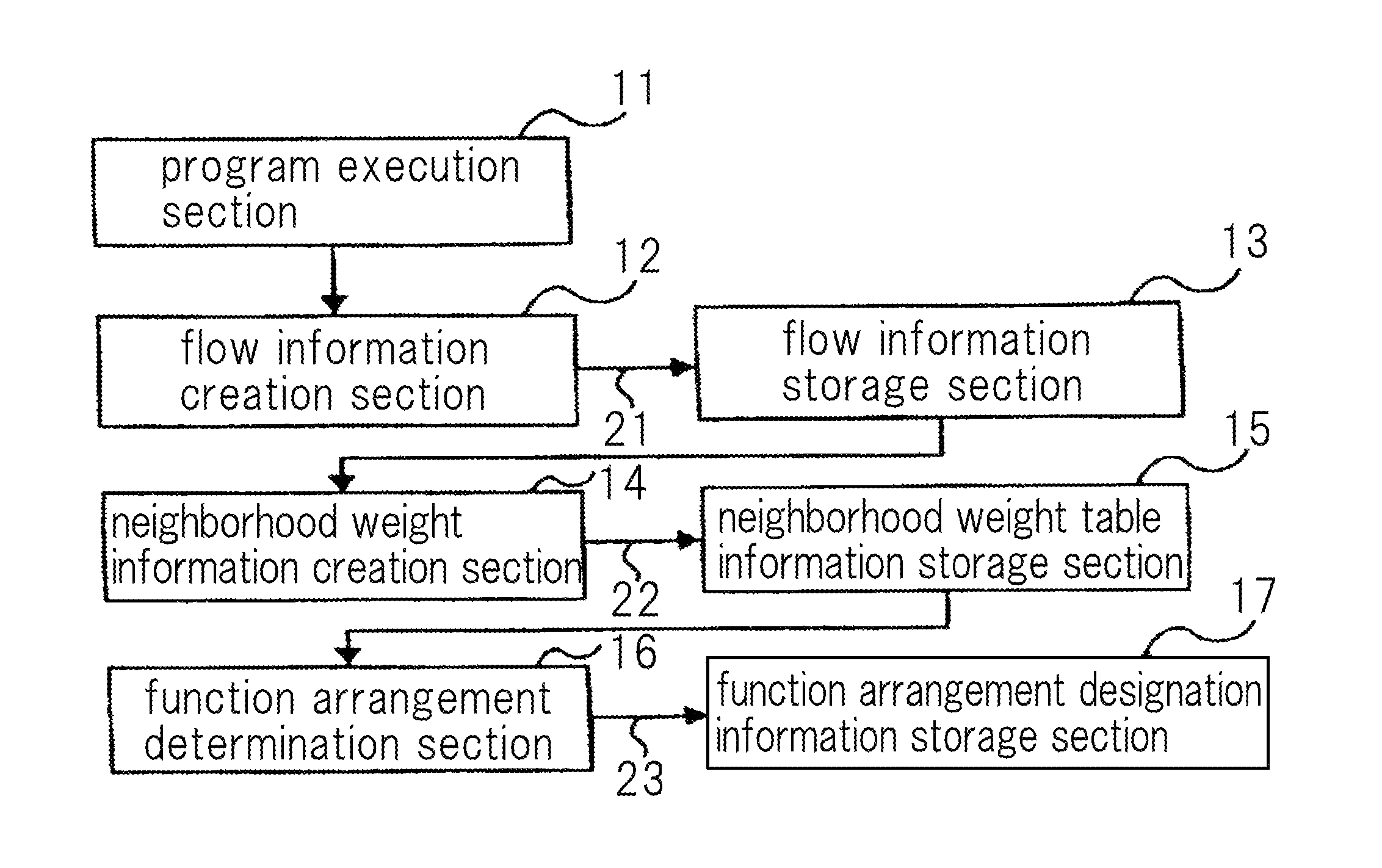

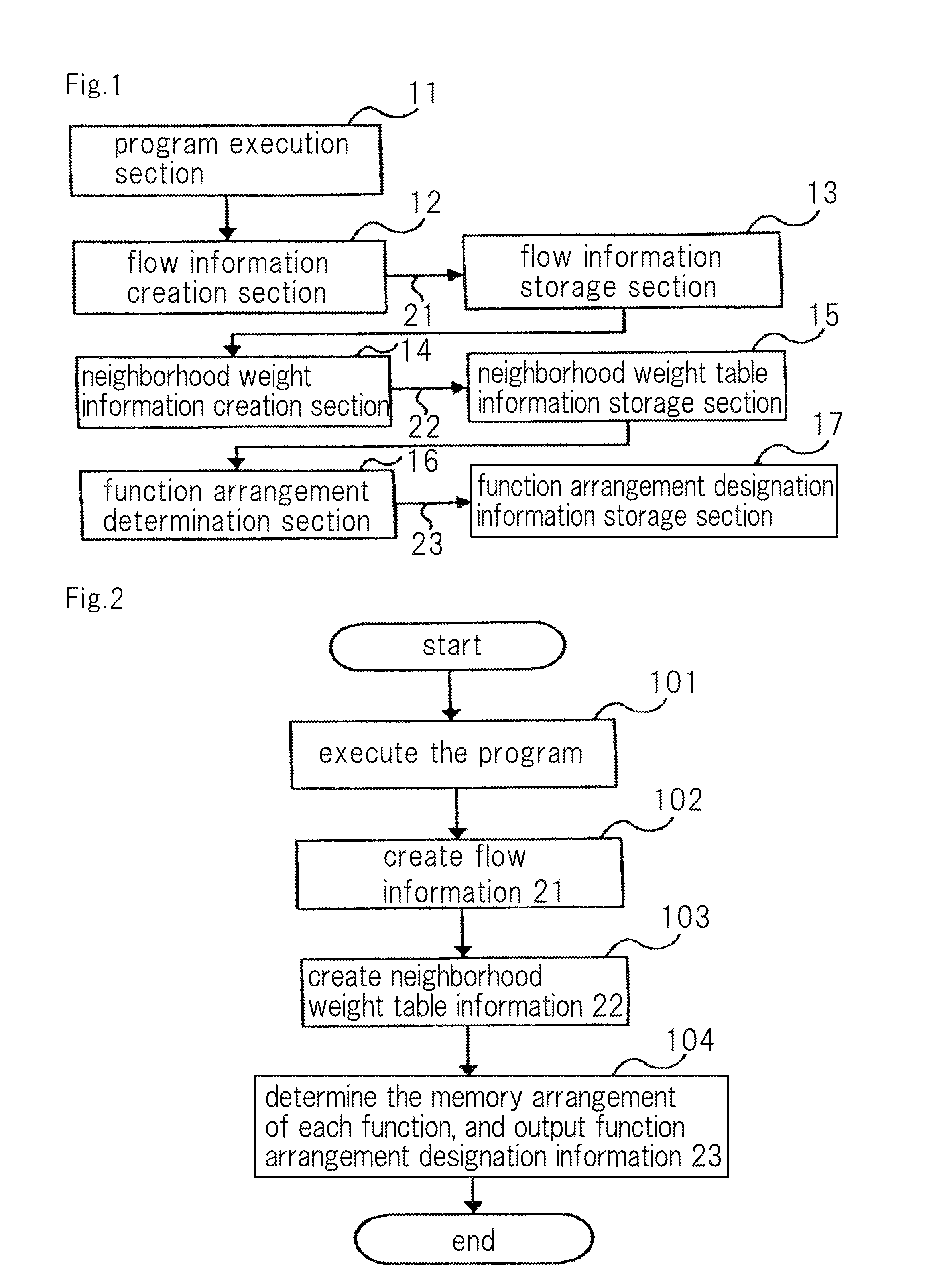

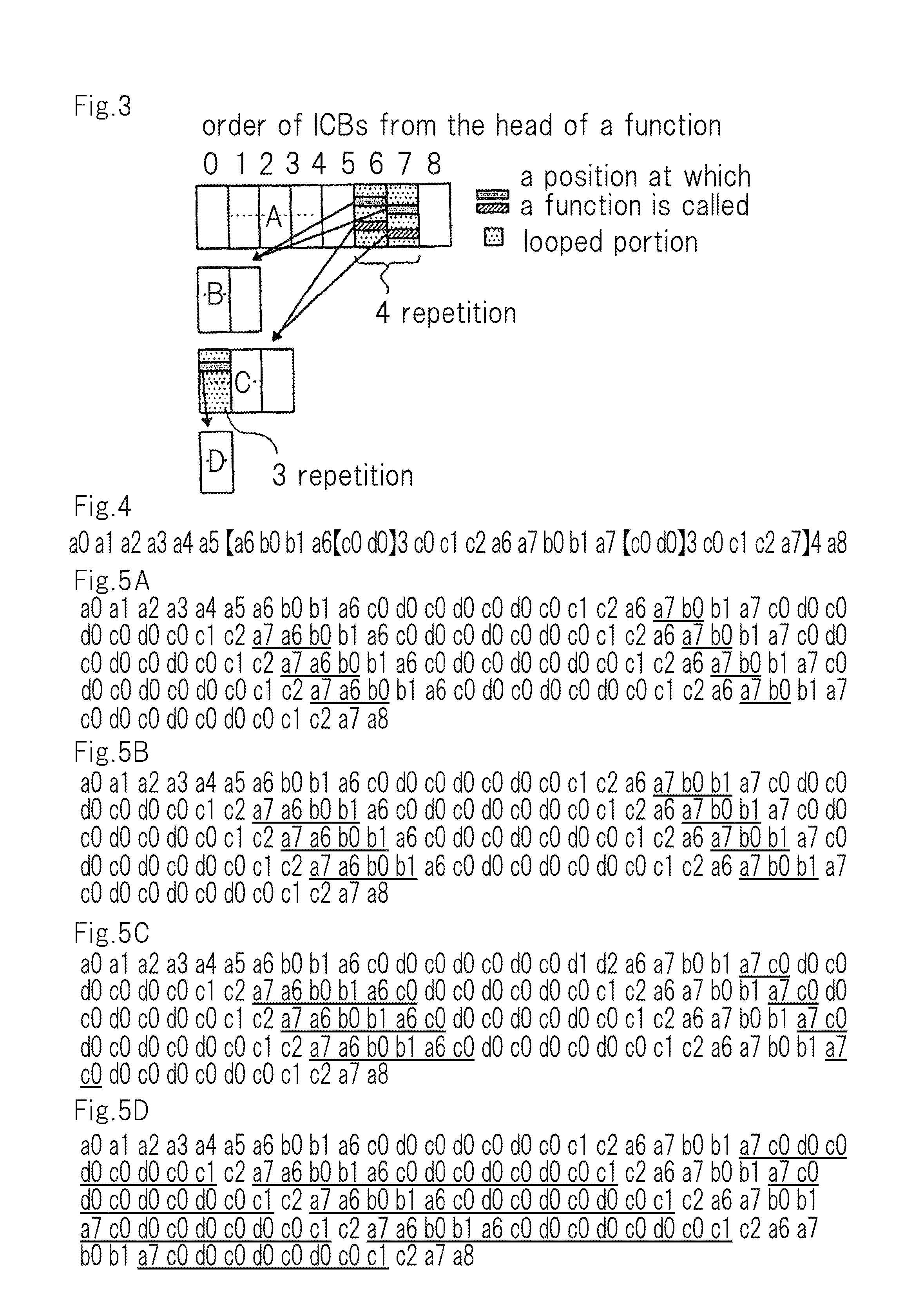

Method for implementing reconfigurable accelerator custom-built for program

InactiveCN101441564AHigh frequencyImprove performanceSpecific program execution arrangementsGeneral purposeGranularity

The invention discloses a method for realizing a reconfigurable accelerator customized for a program. The reconfigurable accelerator customized for the program accelerates the program on an FPGA by arranging the FPGA for the prior general-purpose computer system. The method has a main function of analyzing the program, uses functions to calculate information for the runtime of a granularity sampling program, acquires computing-intensive hot spot functions in the program, realizes the hot spot functions as the reconfigurable accelerator on the FPGA, and modifies call of the hot spot functions in the program into call of the corresponding reconfigurable accelerator to accelerate execution of the hot spot functions. The method uses the reconfigurable accelerator to realize the hot spot functions of the program, improves the total speed-up ratio of the program, uses the FPGA to realize the reconfigurable accelerator, achieves the performance of an approximately applied custom integrated circuit, and simultaneously maintains the flexibility of a general-purpose processor.

Owner:ZHEJIANG UNIV

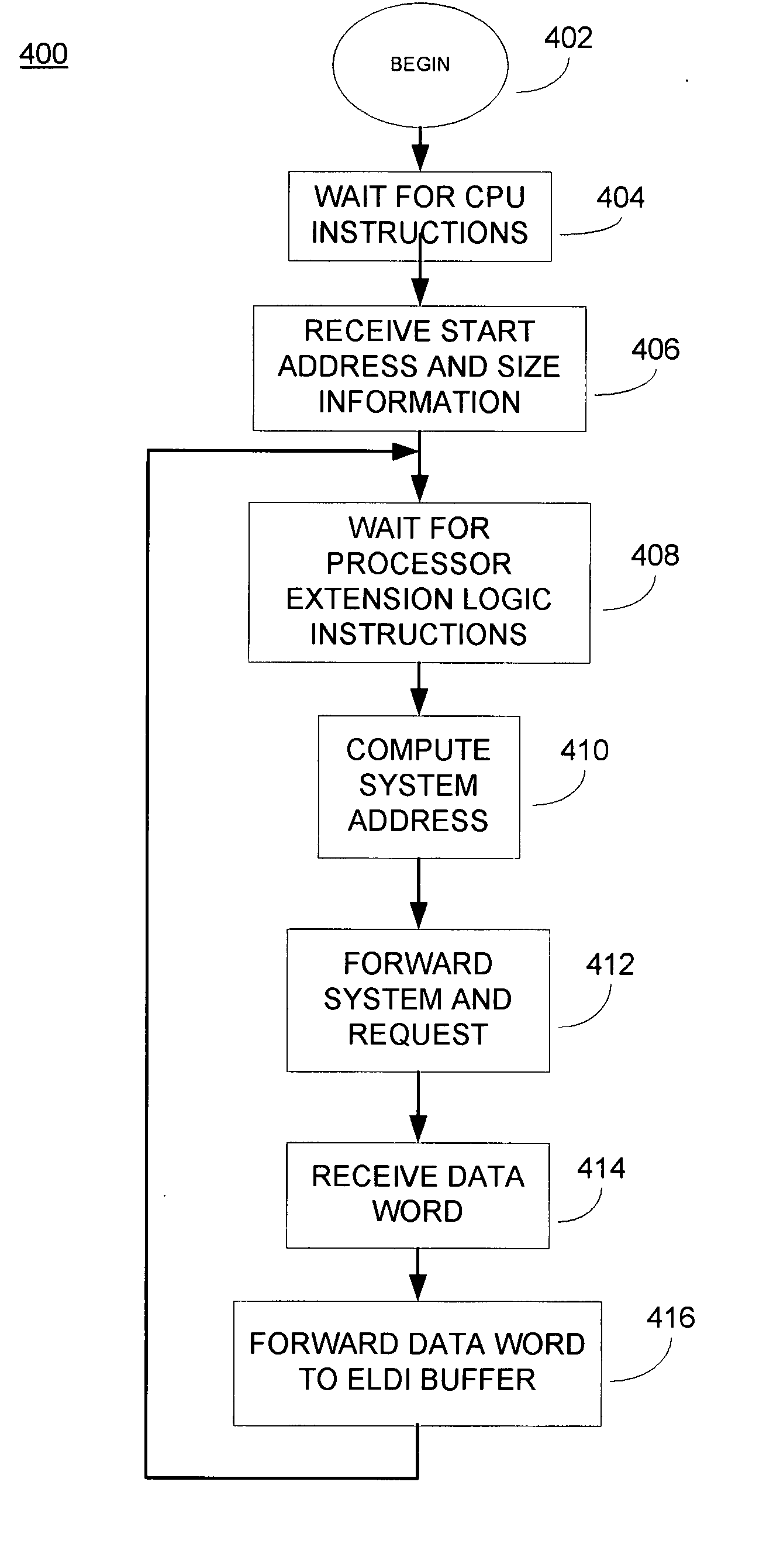

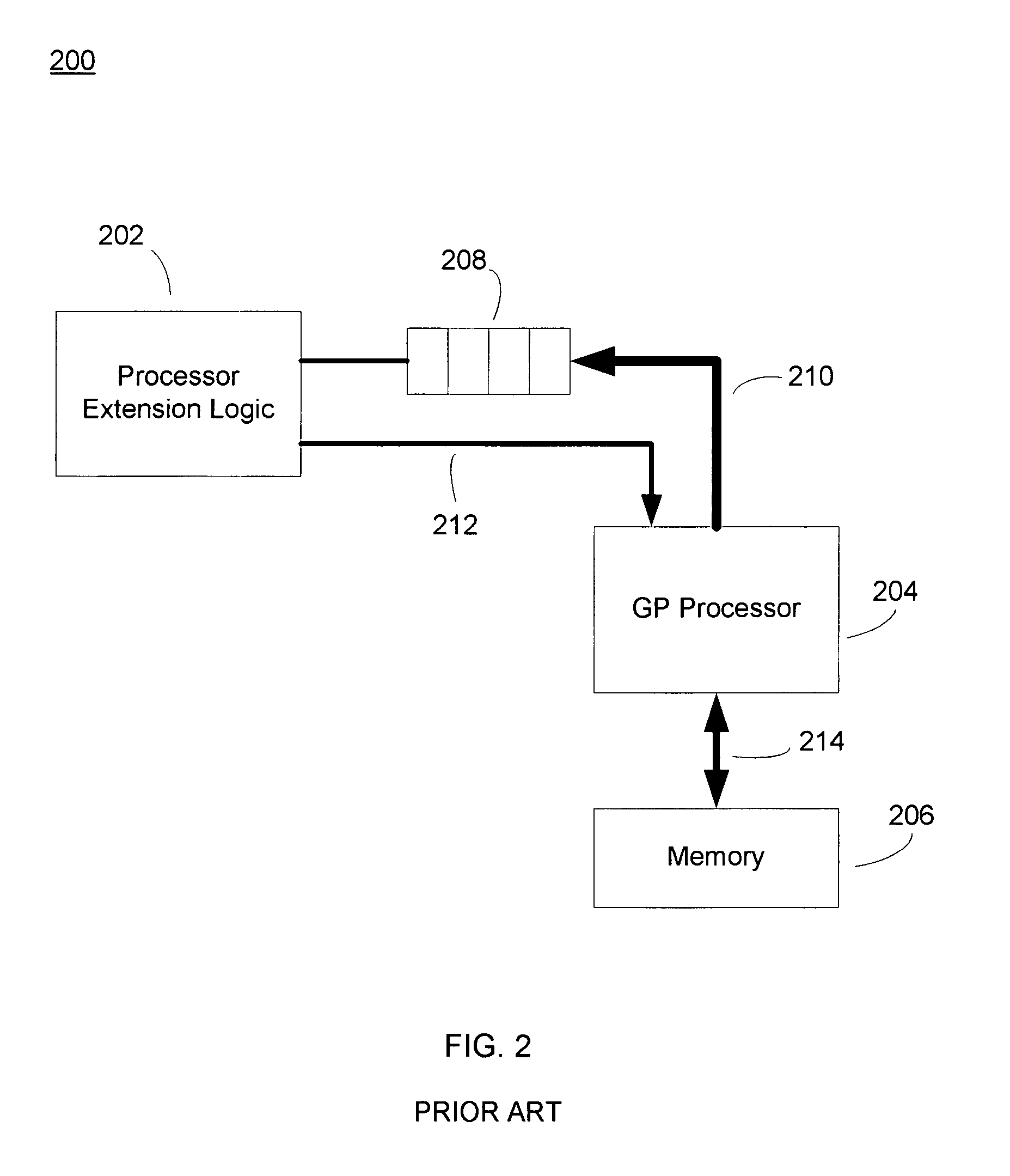

Method and apparatus for improving data and computational throughput of a configurable processor extension

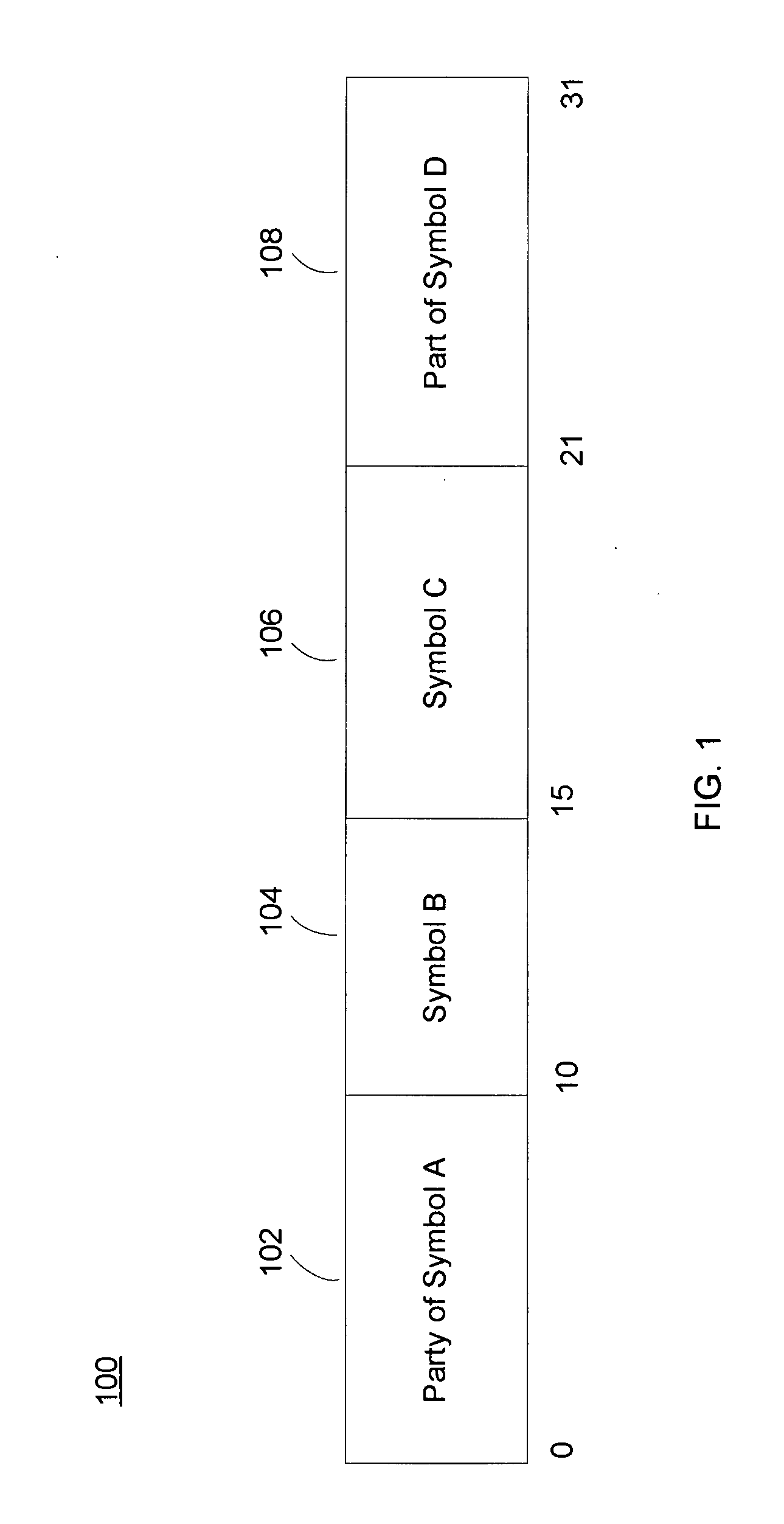

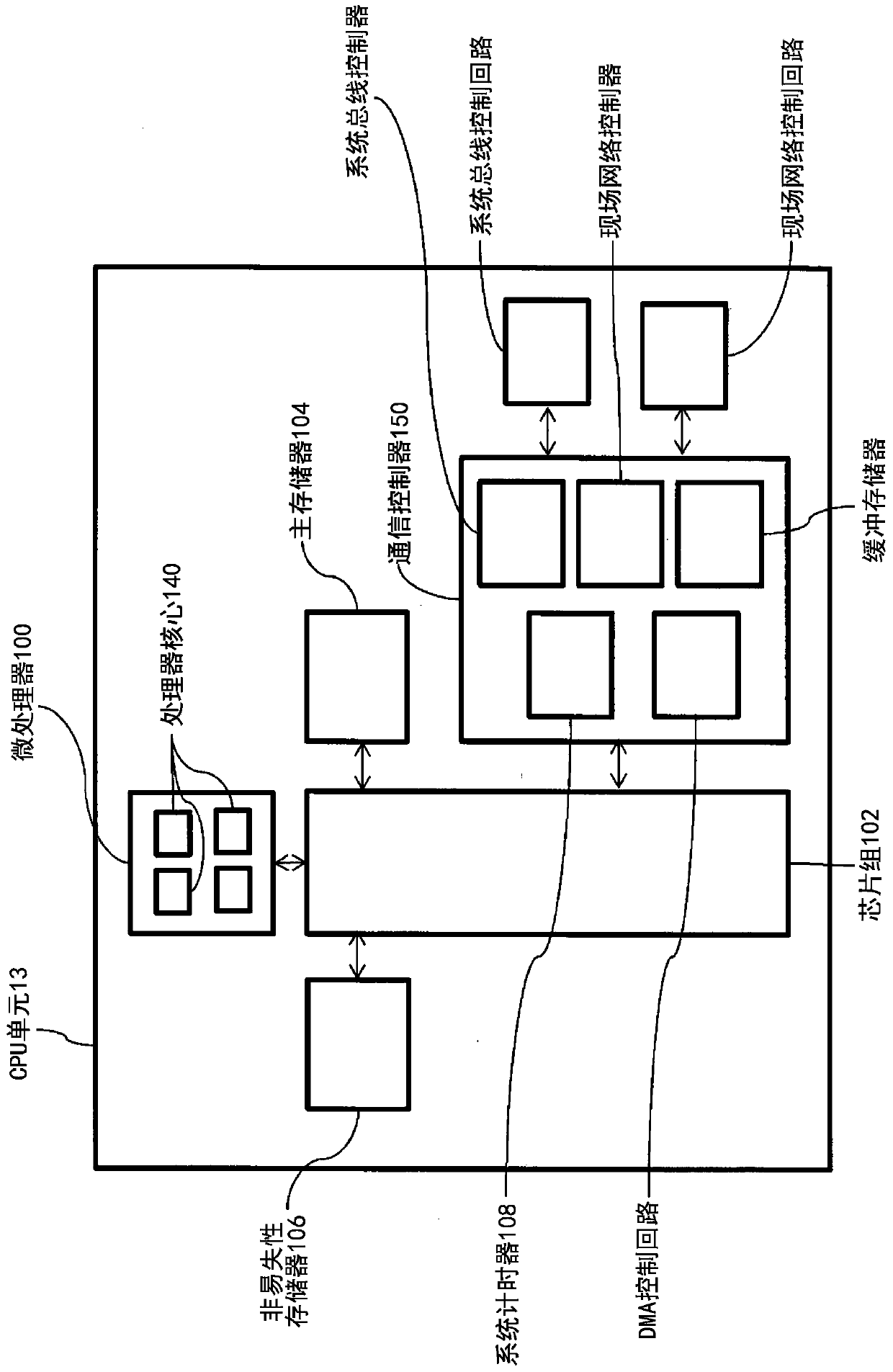

InactiveUS20070250689A1Data augmentationImprove computing throughputGeneral purpose stored program computerSpecific program execution arrangementsDirect memory accessDatapath

Methods and apparatus adapted for enhancing the throughput of a digital processor (e.g., microprocessor, CISC device, or RISC device) through use of a direct memory access (DMA) mechanism. In one embodiment, the processor comprises a “soft” RISC-based processor core that is both user-extensible and user-configurable. The core comprises a functional process or unit (DMA assist) that is coupled to the processor's extension logic and which facilitates throughput by, among other things, ensuring that the CPU and processor extension logic can operate on data in parallel in an efficient manner. In one variant, a parallel datapath (including a buffer) is used in conjunction with the aforementioned DMA assist so as to permit the processor extension logic to efficiently operate in parallel with the CPU.

Owner:ARC INT LTD

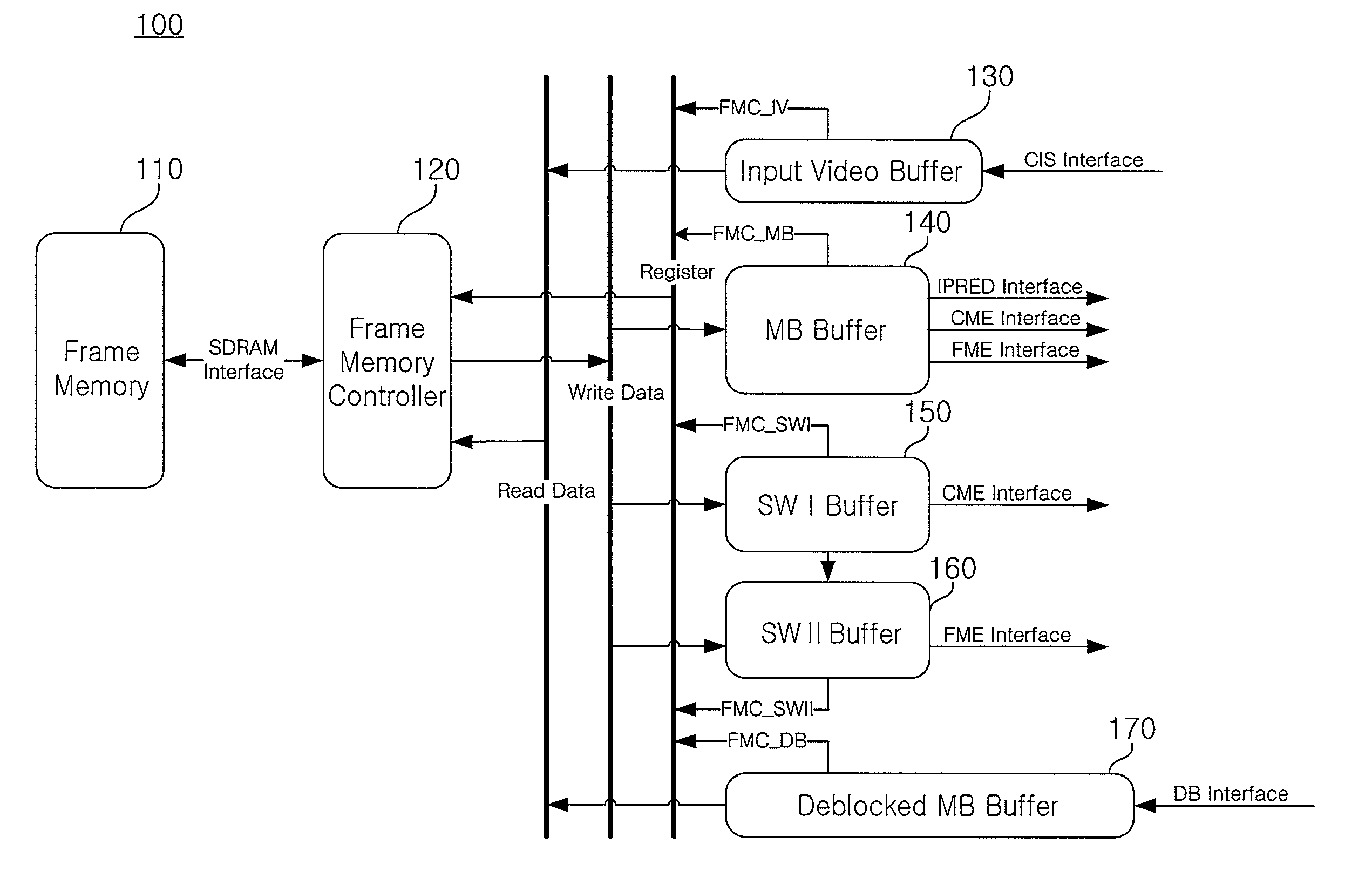

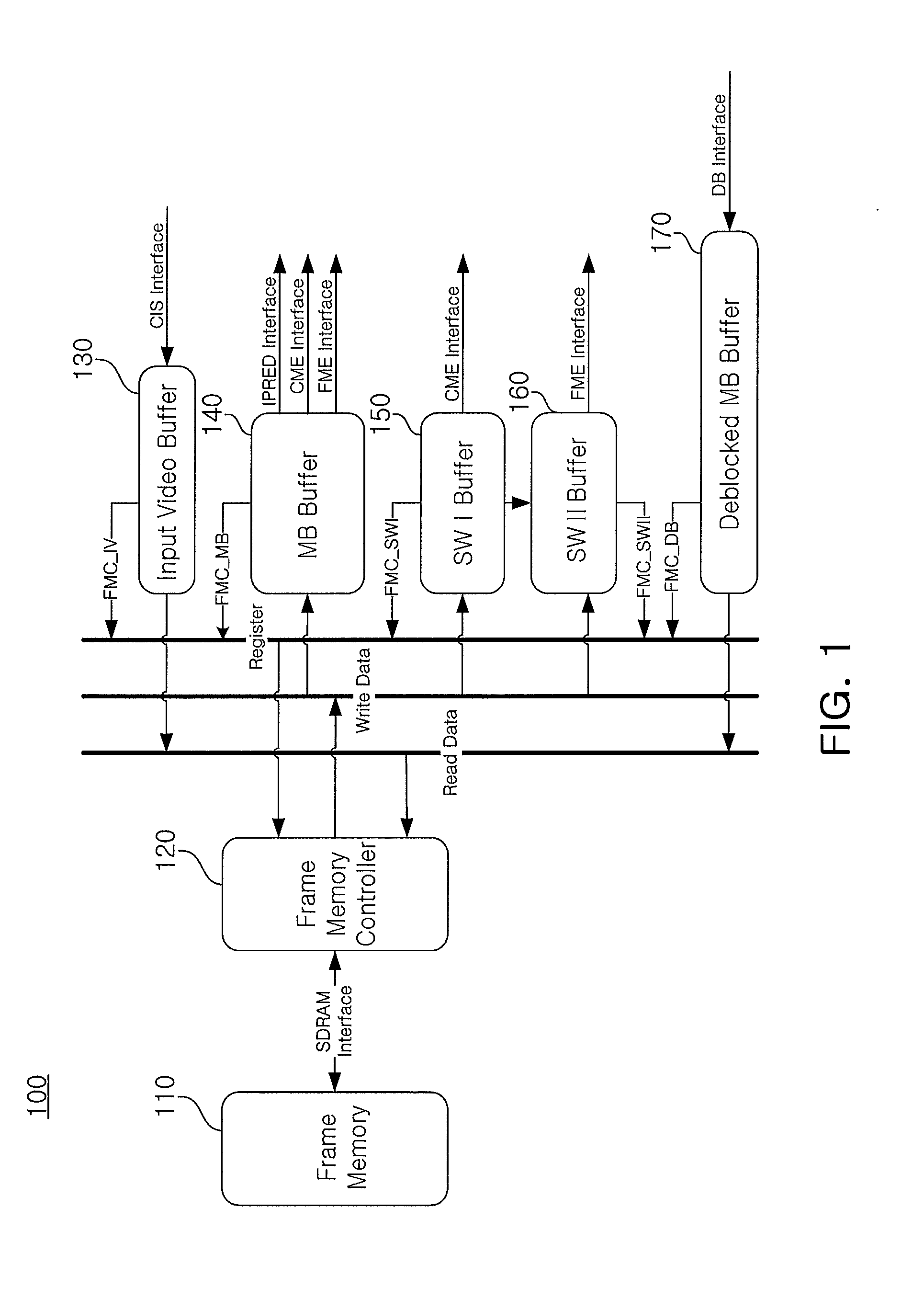

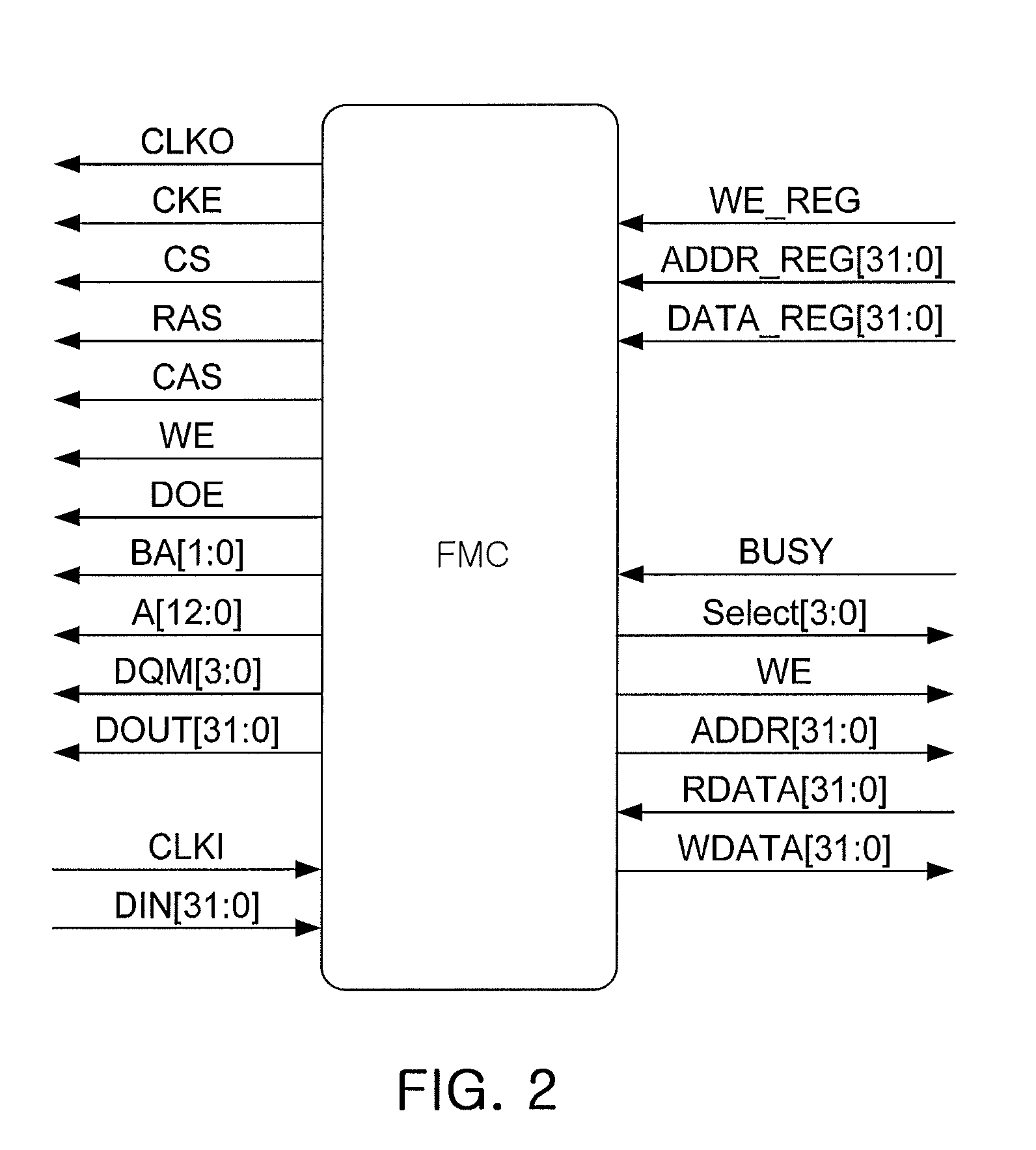

Video processing system

InactiveUS20110135008A1Shorten execution cycleColor television with pulse code modulationColor television with bandwidth reductionMemory controllerPerformance results

A video processing system includes a frame memory, an input video buffer, a macroblock buffer, a first search window buffer, a second search window buffer, a deblocked macroblock buffer, and a frame memory controller. The frame memory stores frame data. The input video buffer stores input data and transfers the input data to the frame memory. The macroblock buffer stores a plurality of macroblocks. The first search window buffer stores a search region of a reference frame for coarse motion estimation. The second search window buffer stores a search region of a reference frame for fine motion estimation. The deblocked macroblock buffer stores the performance results of a deblocking filter. The frame memory controller performs write / read operations on the input video buffer, the macroblock buffer, the first search window buffer, the second search window buffer, the deblocked macroblock buffer and the frame memory.

Owner:ELECTRONICS & TELECOMM RES INST

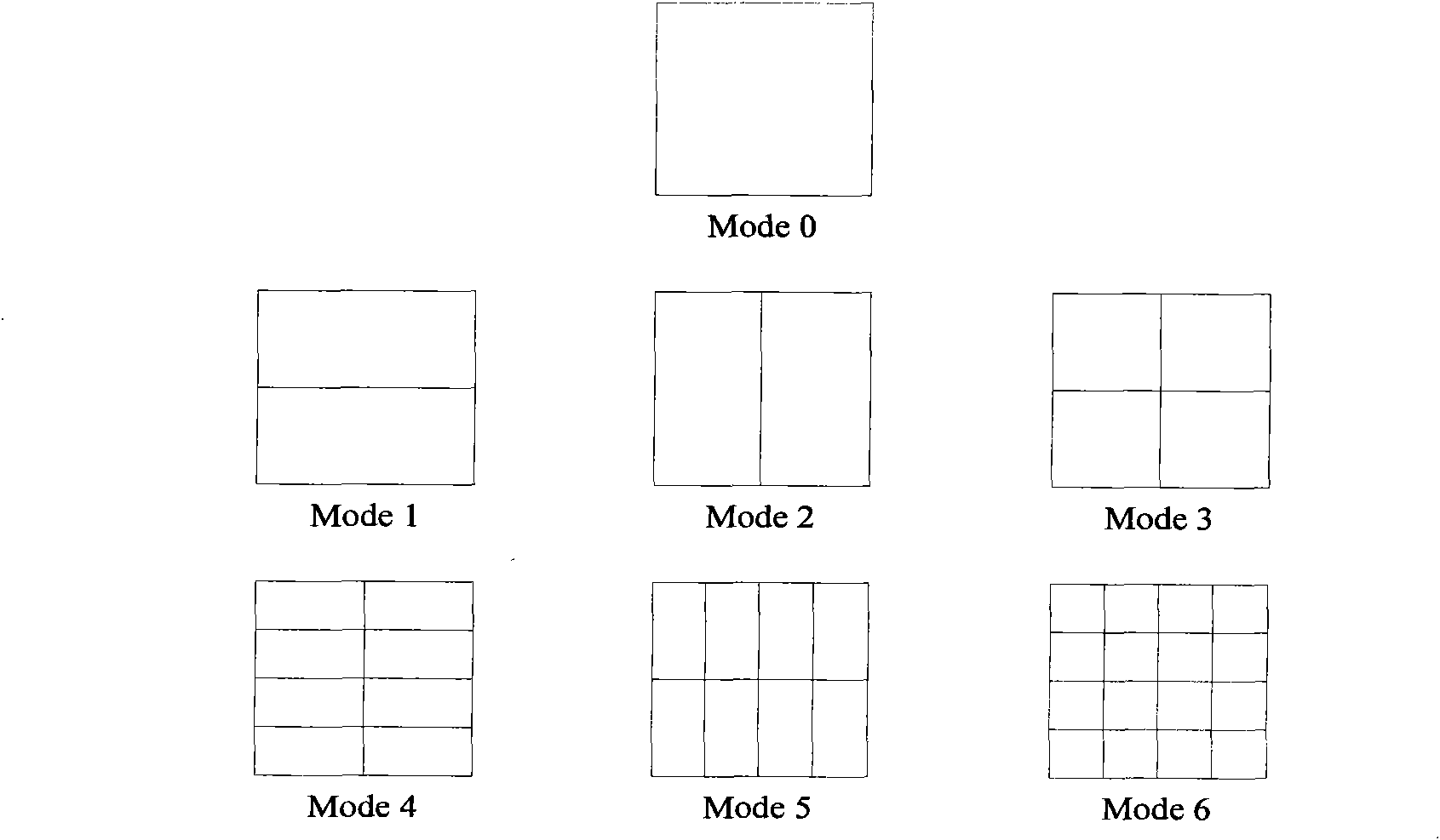

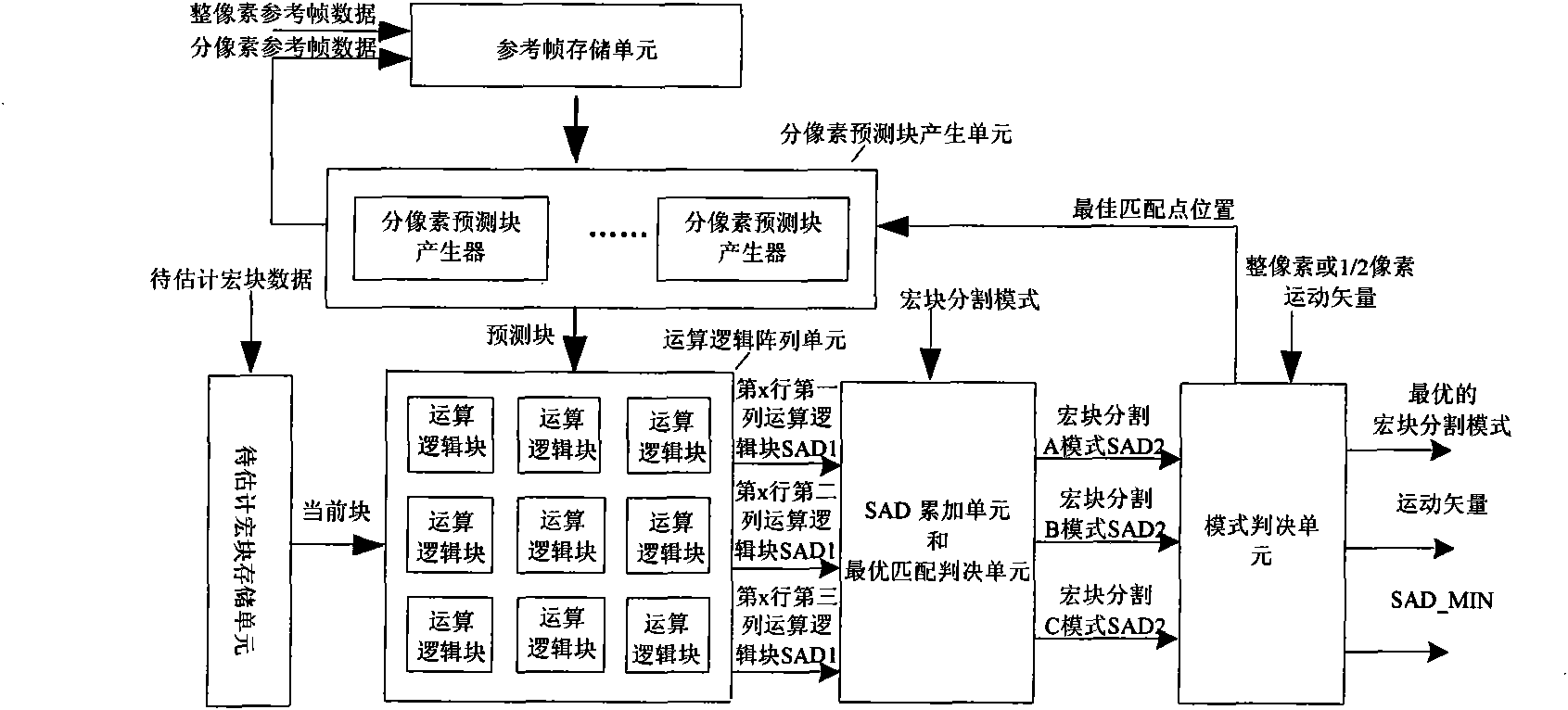

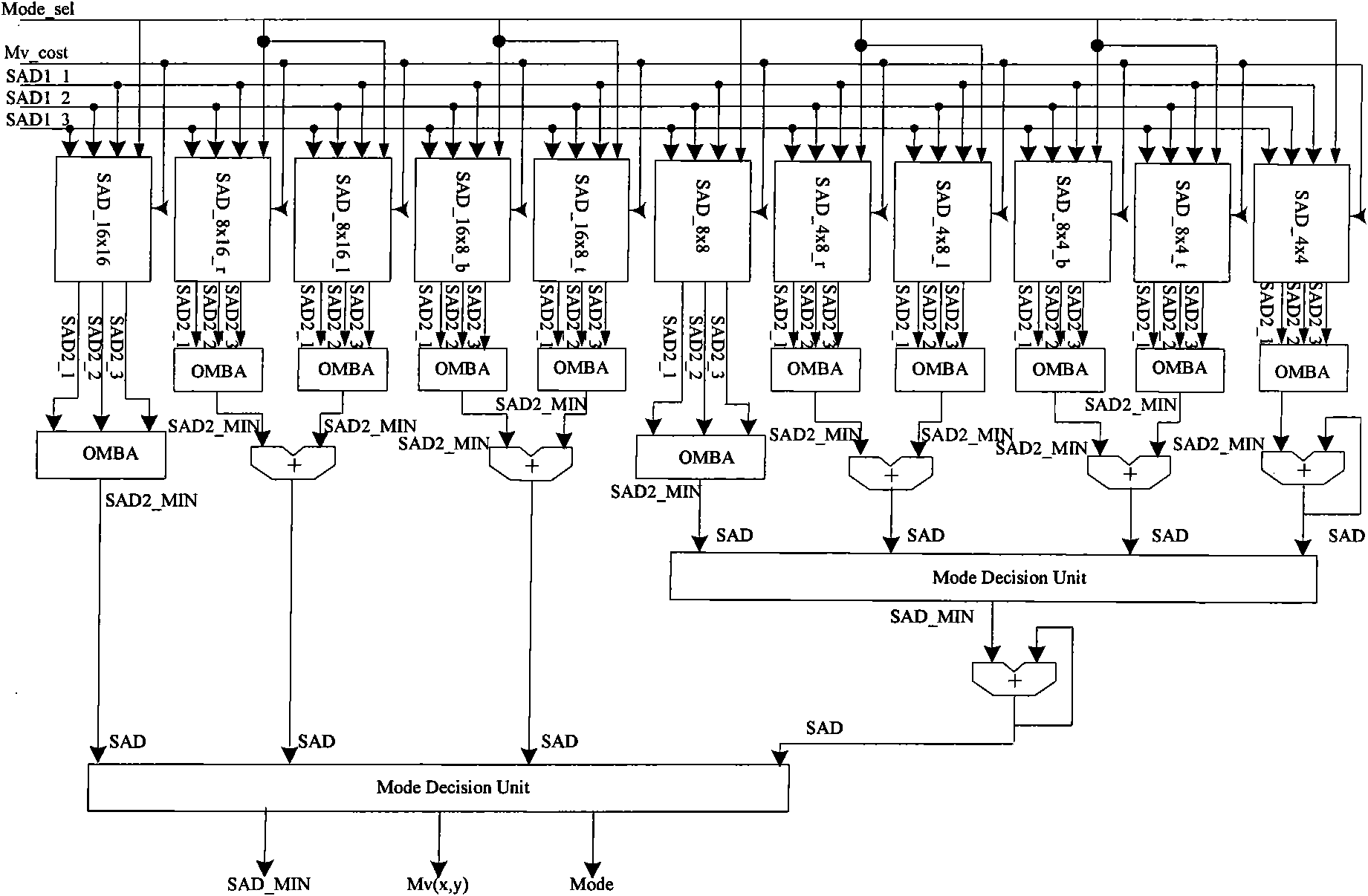

Sub-pixel motion estimation device and method therefor

InactiveCN101600112AGuaranteed real-timeReduce operational complexityTelevision systemsDigital video signal modificationShort cycleStorage cell

The invention provides a sub-pixel motion estimation device and a method therefor; the device comprises a macroblock storage unit to be estimated, a reference frame storage unit, a sub-pixel prediction block generation unit, an arithmetic and logic array unit, an SAD accumulation unit, an optimal matching decision unit and a mode deciding unit, while another pattern of the device comprises the macroblock storage unit to be estimated, the reference frame storage unit, the sub-pixel prediction block generation unit, the arithmetic and logic array unit, the SAD accumulation unit, a mode select unit and the optimal matching deciding unit. The invention balances the search range and the search accuracy of the motion estimation, lowers the calculating complexity, shortens the search time, ensures the instantaneity of a coding system, the whole motion estimation operation is performed in a short cycle, less resources are occupied without damaging the coding performance, little impact is imposed on compression efficiency of an encoder, so that choices can be made by weighing and balancing among performance, power consumption and area of the encoder; in addition, the device and method of the invention have strong versatility and reusability.

Owner:HANGZHOU SILAN MICROELECTRONICS

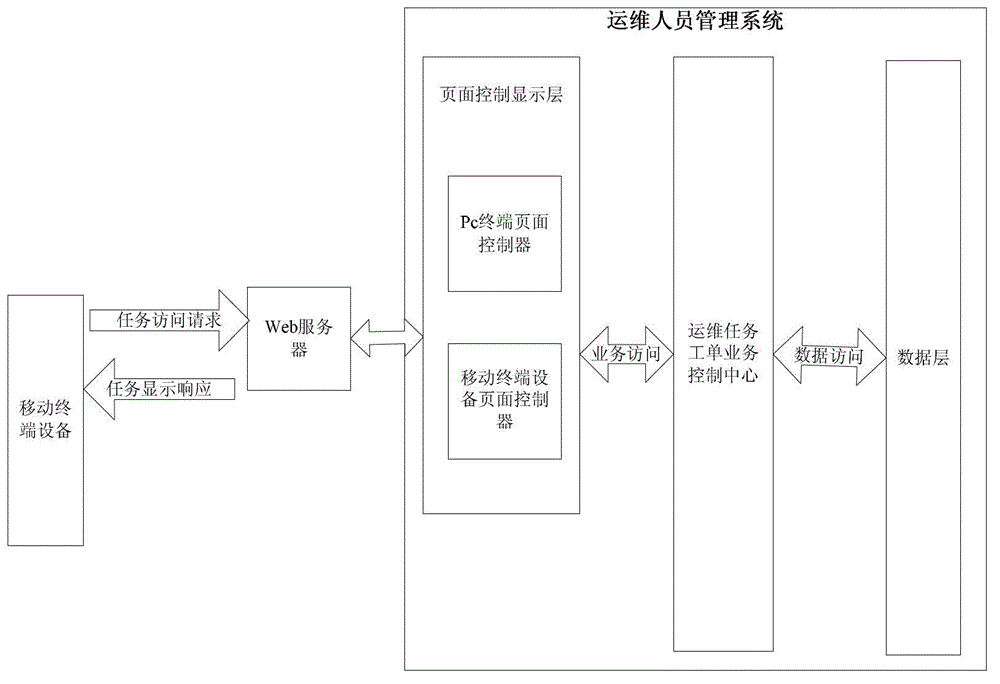

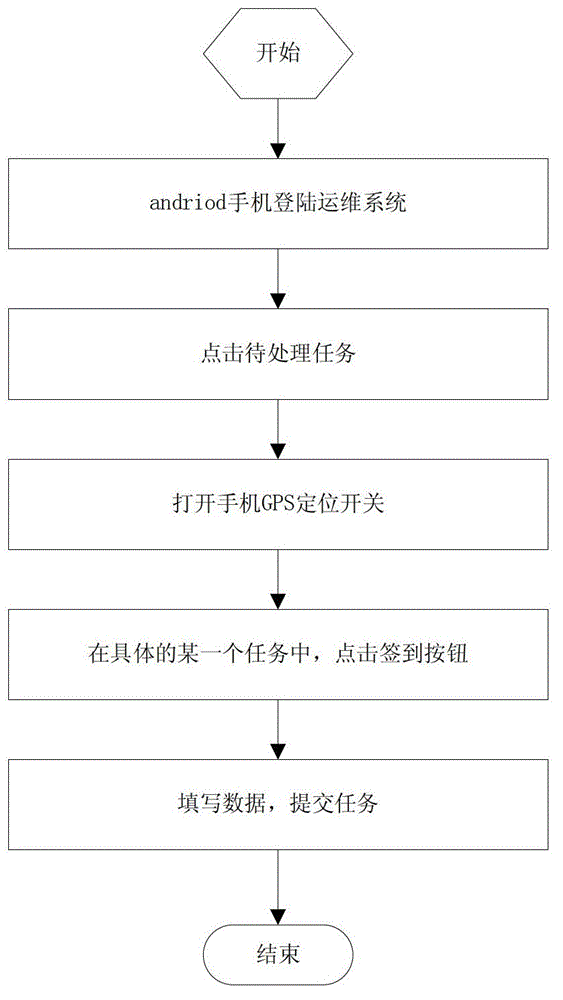

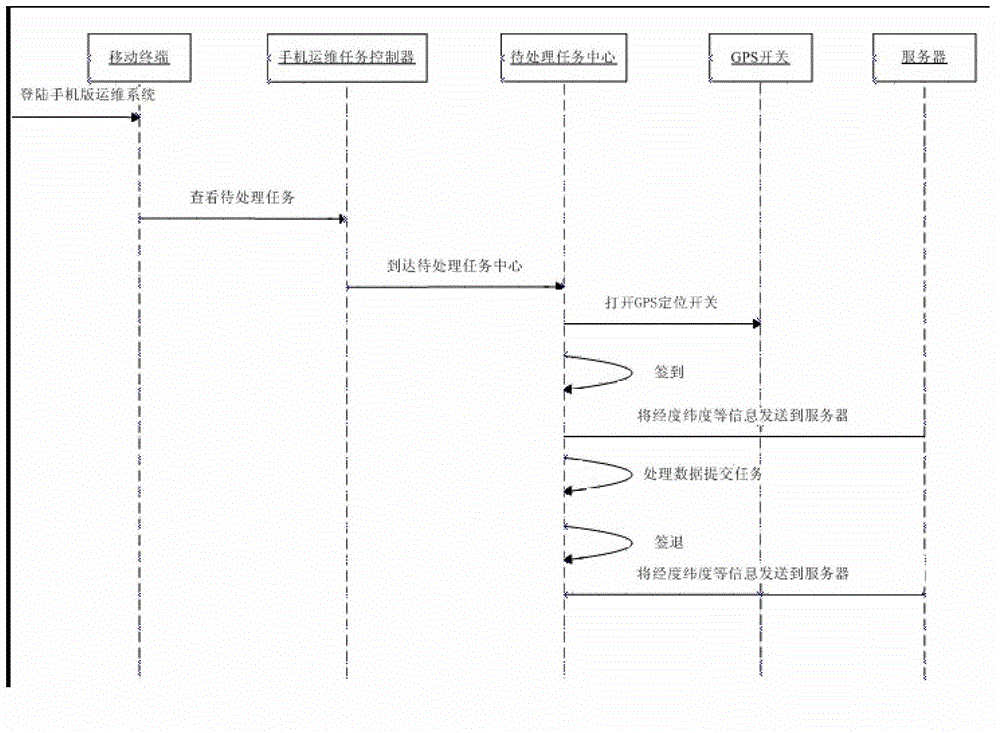

Operation personnel management method and system based on mobile phone GPS positioning

InactiveCN103942744AShorten execution cycleReduce time to complete feedbackData processing applicationsComputer scienceWireless data transmission

The invention discloses an operation personnel management method and system based on mobile phone GPS positioning. The operation personnel management system comprises an operation management center, a wireless data transmission system and a field terminal. Data is transmitted between the field terminal and the operation management center through the wireless data transmission system; the field terminal is an intelligent mobile phone; the intelligent mobile phone is provided with a GPS positioning function; after operation personnel register the system, the operation management center transmits task data to the field terminal; when the operation personnel click a sign-in button, the field terminal intelligent mobile phone automatically obtain such information as longitudes, latitudes, time and the like for transmitting to an operation management center server; in a task, the field terminal intelligent mobile phone transmits data back to the operation management center in real time; and during sign-off, the information as the longitudes, the latitudes, the time and the like is automatically obtained and transmitted to the operation management center. The method and system provided by the invention can assist field operation work with organization and management so as to improve the execution speed of a task work order, improve the transmission accuracy of operation data, and facilitate the management of the field operation personnel.

Owner:勤智数码科技股份有限公司

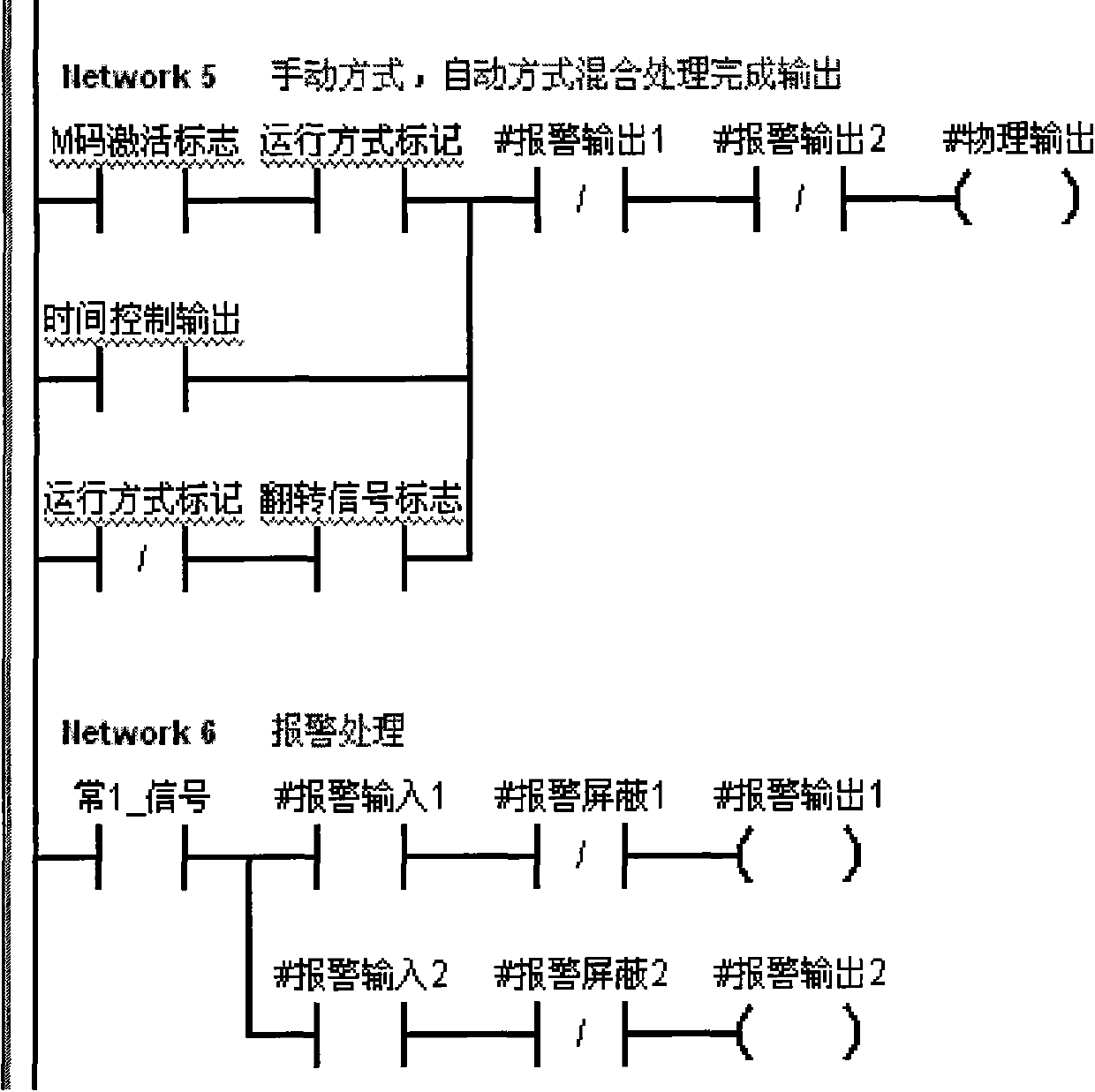

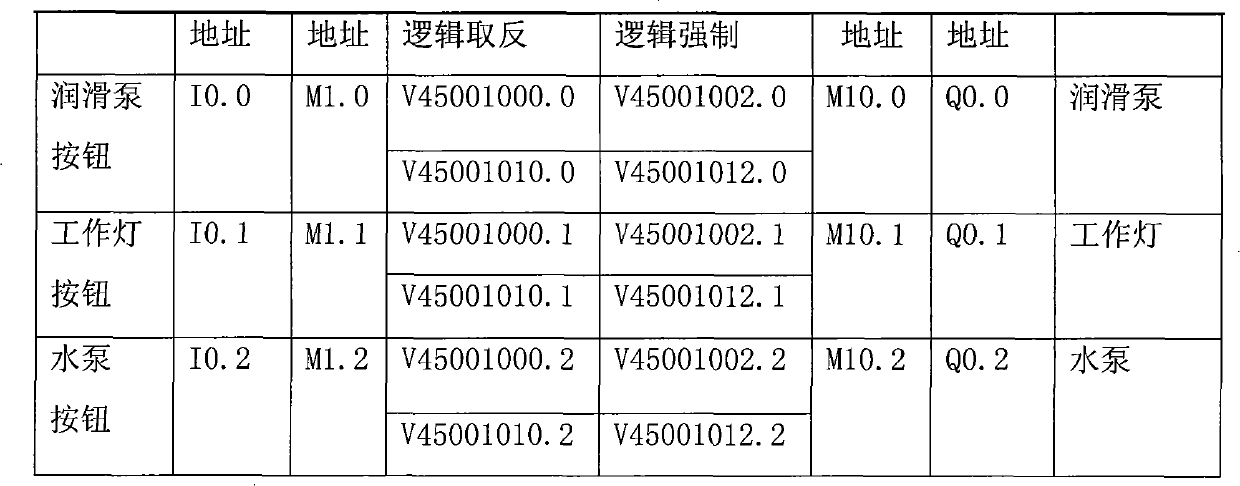

Machining center PLC integration method

InactiveCN101819425AReduce scan timeShorten execution cycleProgramme controlComputer controlMixed programmingPhysical address

The invention relates to a machining center PLC integration method. A function selection module is connected with an input and output filtering processing module, an input and output logic processing module and an internal memory, and controls program contents in a form of byte with the input and output filtering processing module, the input and output logic processing module and the internal memory so as to form a machining center PLC integration system capable of realizing module functions according to needs of the outside. The machining center PLC integration method has the advantages of completely and uniquely mapping physical addresses into the internal memory in the input and output filtering processing module, precisely processing the positive negative logic and forced logic of the physical addresses in the input and output logic processing module, saving scanning time and shortening execution period; and a program control and manual control mixed programming module is a main part of an entire PLC, and the art of programming of the program control and manual control mixed programming module is directly related to the level of integration and also determines the compactness and intensiveness of the logic of the entire PLC.

Owner:宁波恒威机械有限公司

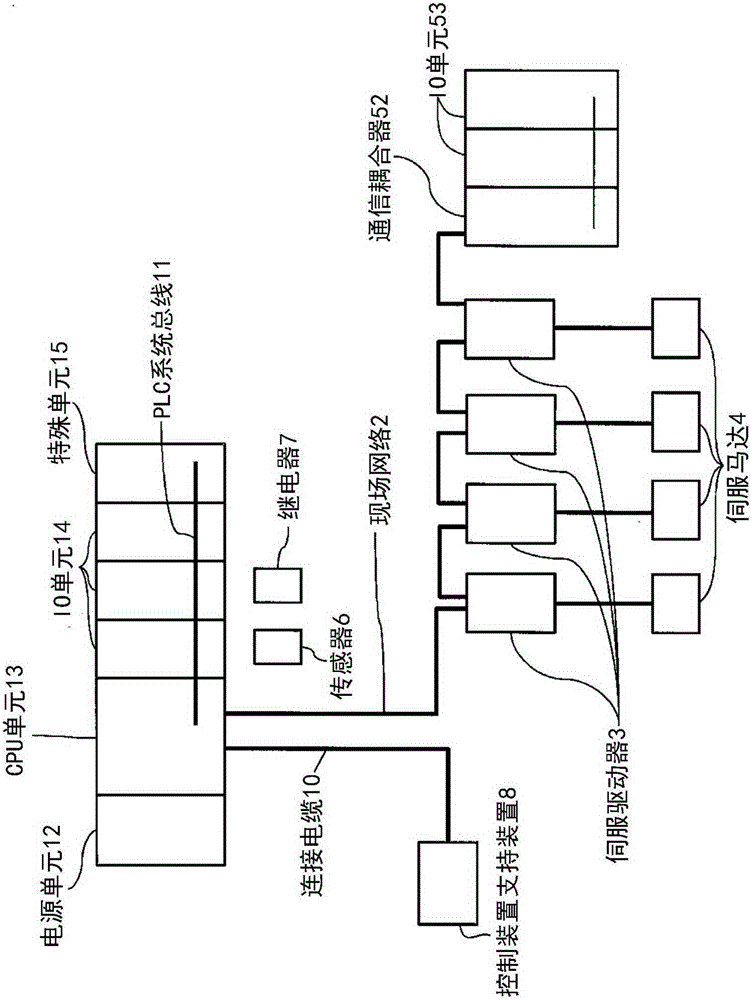

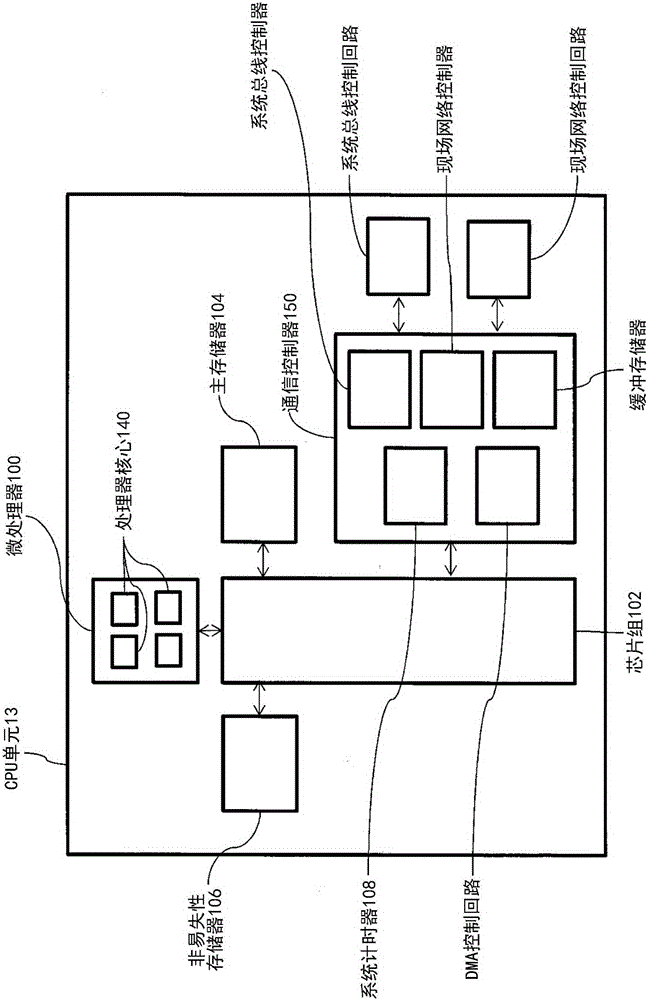

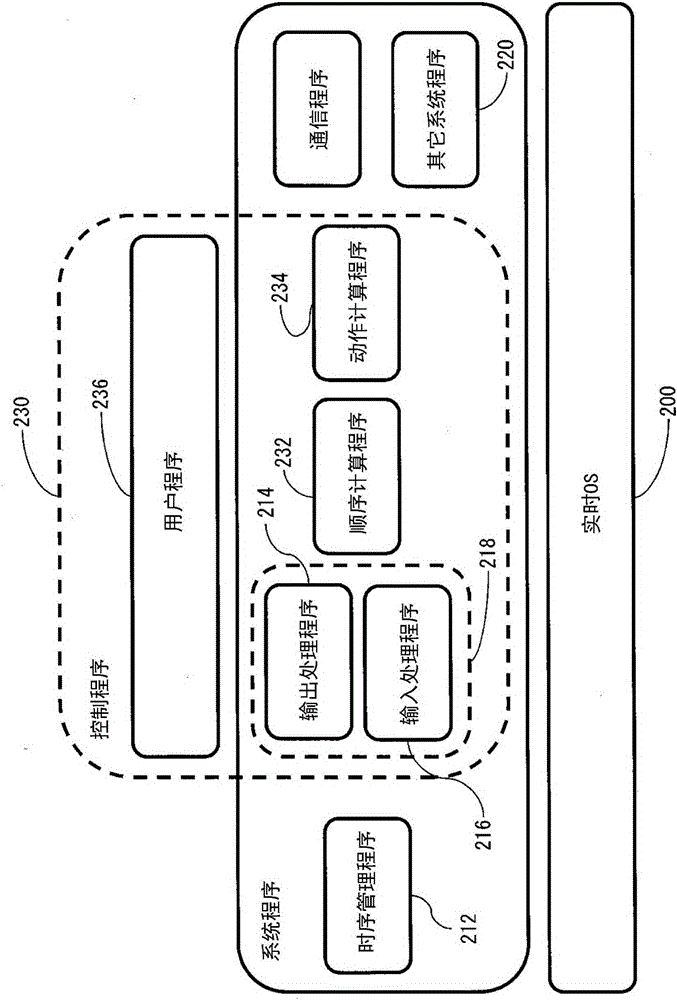

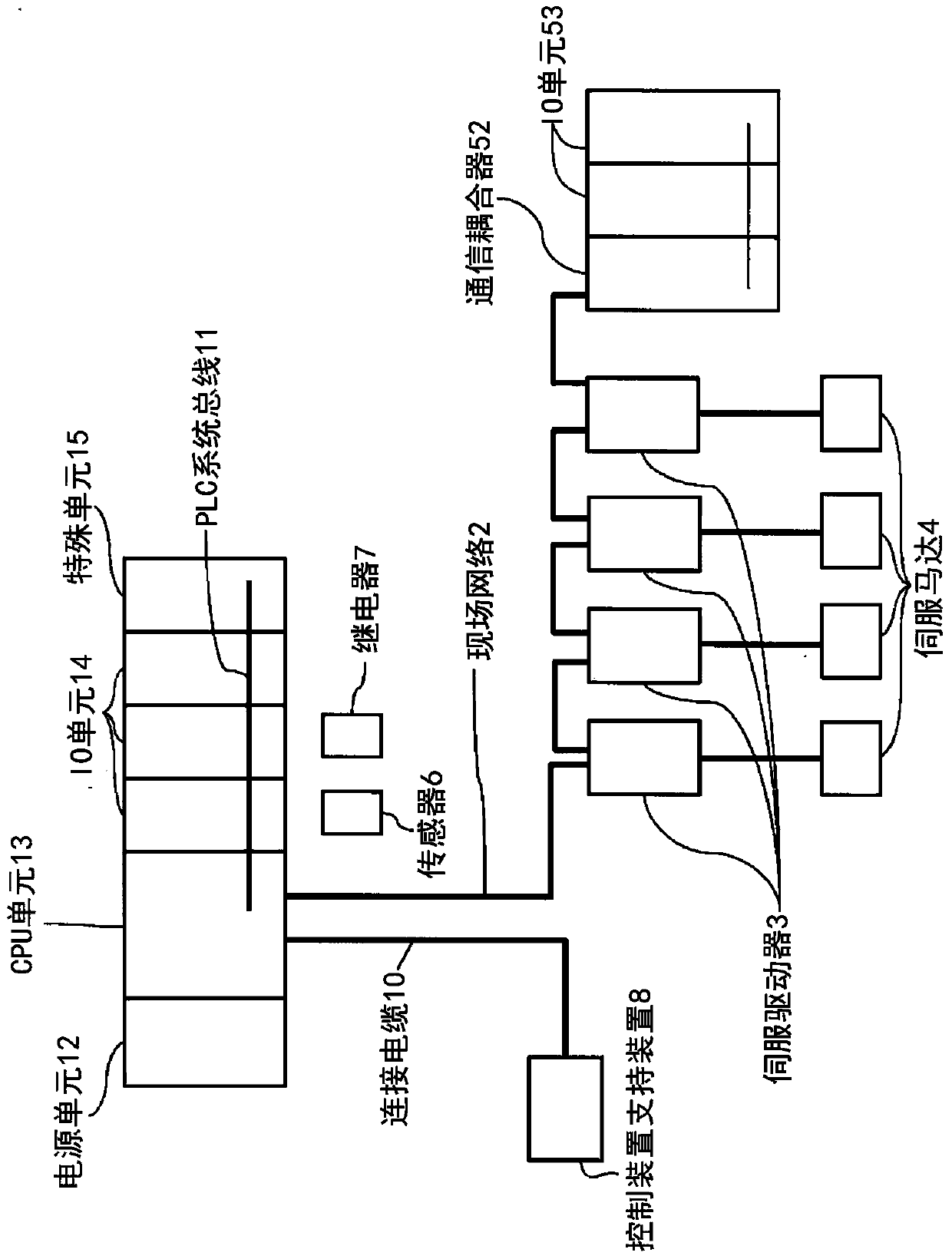

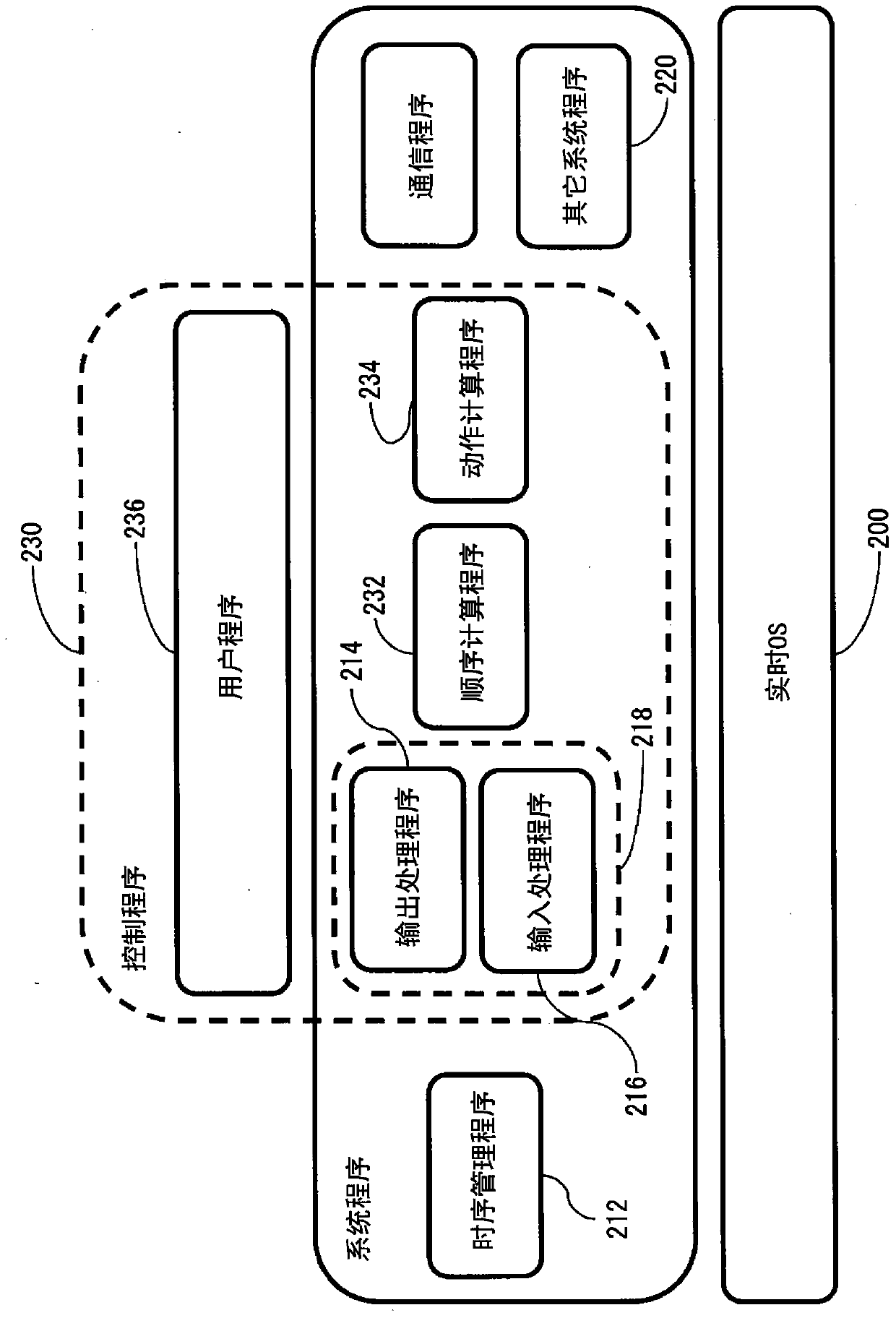

Control apparatus

ActiveCN106020009AReduce I/O timeShorten execution cycleProgramme controlComputer controlParallel computingMotion computation

Provided is a control apparatus that can, by causing multiple control programs that include motion computation programs to be executed in parallel, shorten the execution cycle of control programs that are executed cyclically. A microprocessor (100) is configured to execute multiple control programs in parallel. When executing communication commands included in control programs that are to be executed in parallel, a scheduling program causes the microprocessor to execute the communication commands such that there is no competition between communication processes in a communication controller (150).

Owner:ORMON CORP

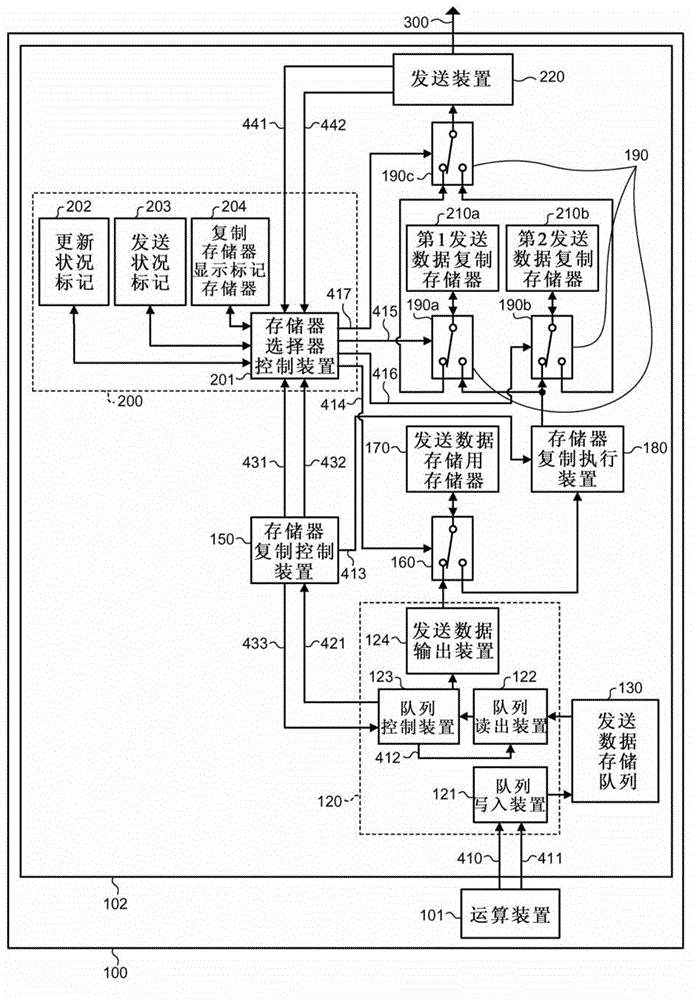

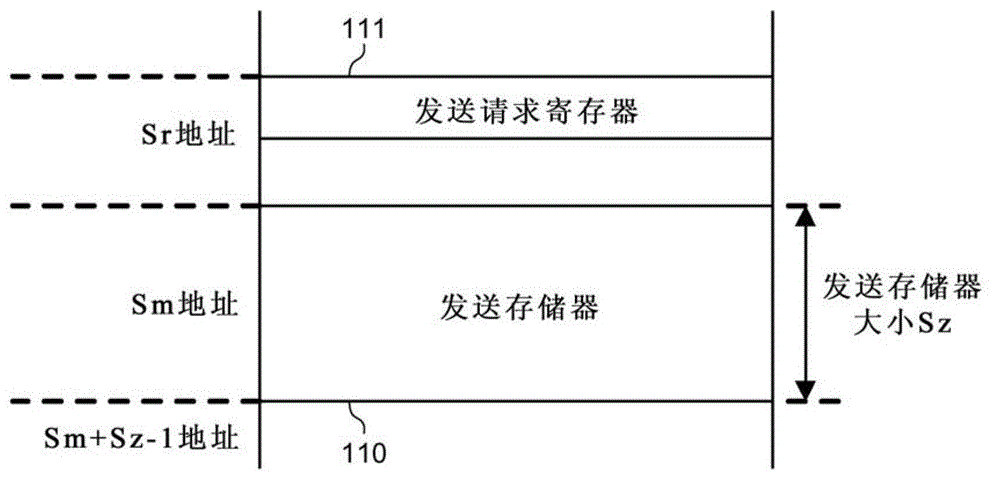

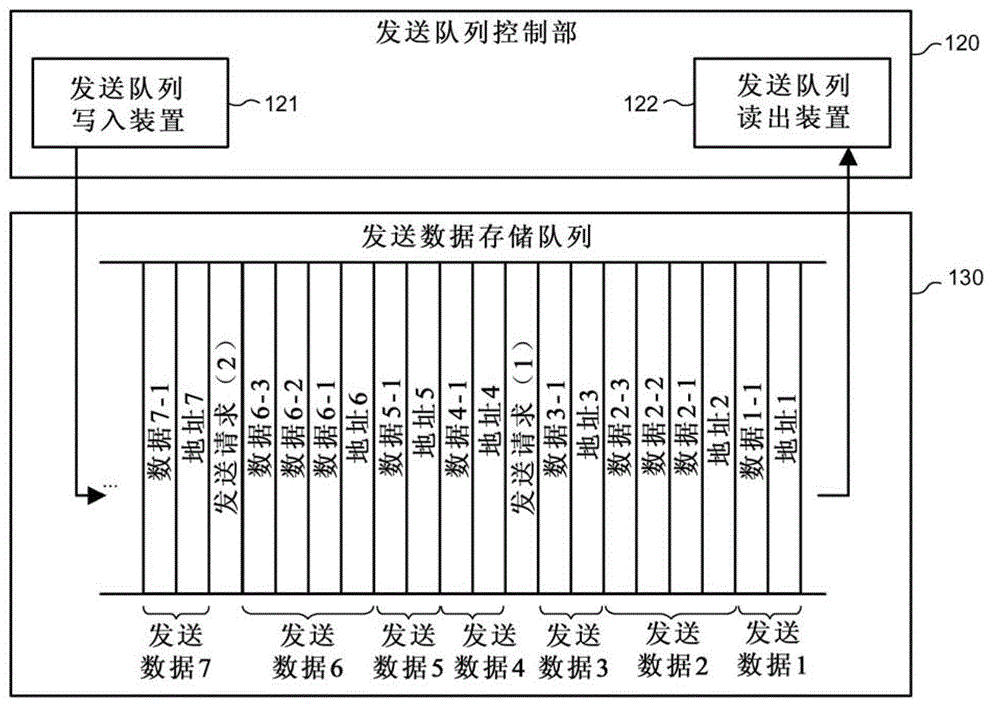

Transmission control device, memory control device, and plc provided with the transmission control device

InactiveCN102754089AGuaranteed simultaneityShorten execution cycleProgramme controlInput/output to record carriersData storingData store

Provided is a transmission control device provided with data store memory into which data is written; a plurality of data copy memories into which the data that have been written into the data store memory are copied; a non-readout copy memory selection means for selecting one of the data copy memories from which the data has not been read out from among the plurality of the data copy memories; a memory copy means for copying the data that has been written into the data store memory into the data copy memory that has been selected by the non-readout copy memory selection means; a readout copy memory selection means for selecting the data copy memory into which the memory copy means has copied the data from among the plurality of data copy memories; and a data output means for reading out the data from the data copy memory that has been selected by the readout copy memory selection means and outputting thereof to the transmission means.

Owner:MITSUBISHI ELECTRIC CORP

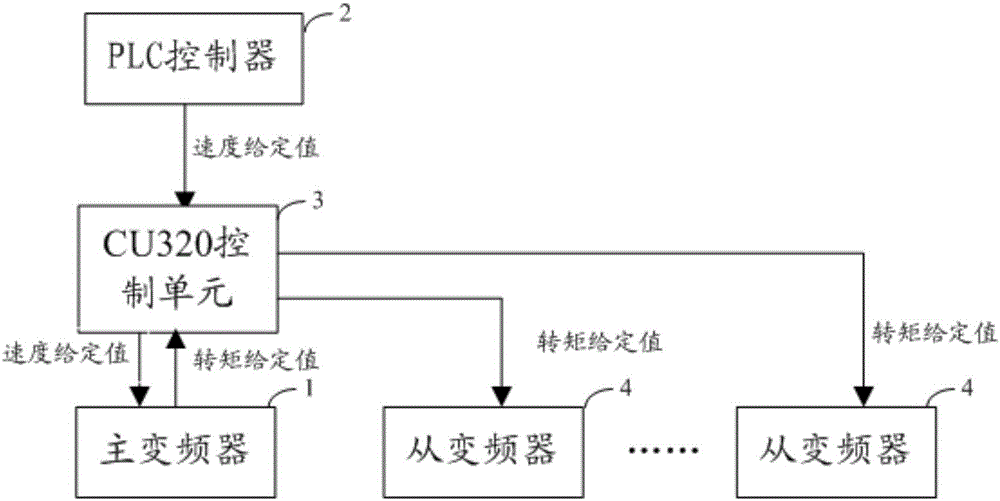

Multi-transmission load balancing control system

InactiveCN106655971AShorten execution cycleIncreased number of controlsAC motor controlMultiple dynamo-electric motors speed regulationElectrical controlFrequency changer

The invention is applicable to the field of electrical control, and provides a multi-transmission load balancing control system. The system comprises a master frequency converter, a plurality of slave frequency converter, a PLC controller, a CU320 control unit and a plurality of motors, the PLC controller controls the communication with the CU320 control unit, and the master and the slave frequency converters communicate with the CU320 control unit and the corresponding motors, wherein the CU320 receives a speed set value sent by the PLC controller and sends the value to the master frequency converter through a Drive-Cliq network, and the master frequency converter calculates a torque set value according to the speed set value and sends the torque set value to the CU320 control unit through the Drive-Cliq network; and the CU320 control unit controls the corresponding motors according to the speed set value and the torque set value. According to the multi-transmission load balancing control system provided by the embodiment of the invention, the load balancing is realized by the CU320 control unit, the execution cycle is a 1ms level, thus the implementation cycle is greatly shortened, the control times within a unit time are increased, and thus the control precision is improved.

Owner:ANHUI MA STEEL AUTOMATION INFORMATION TECH

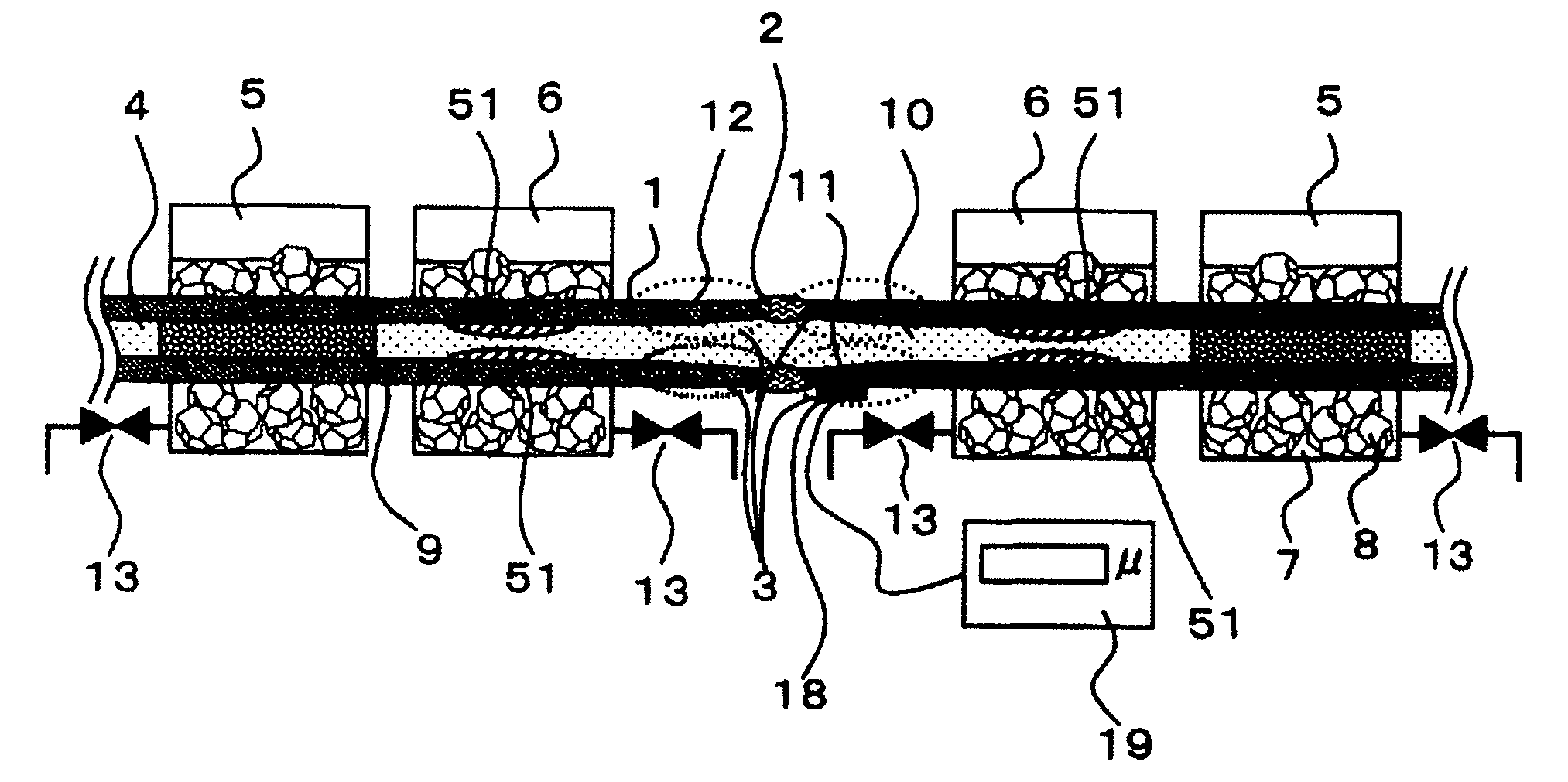

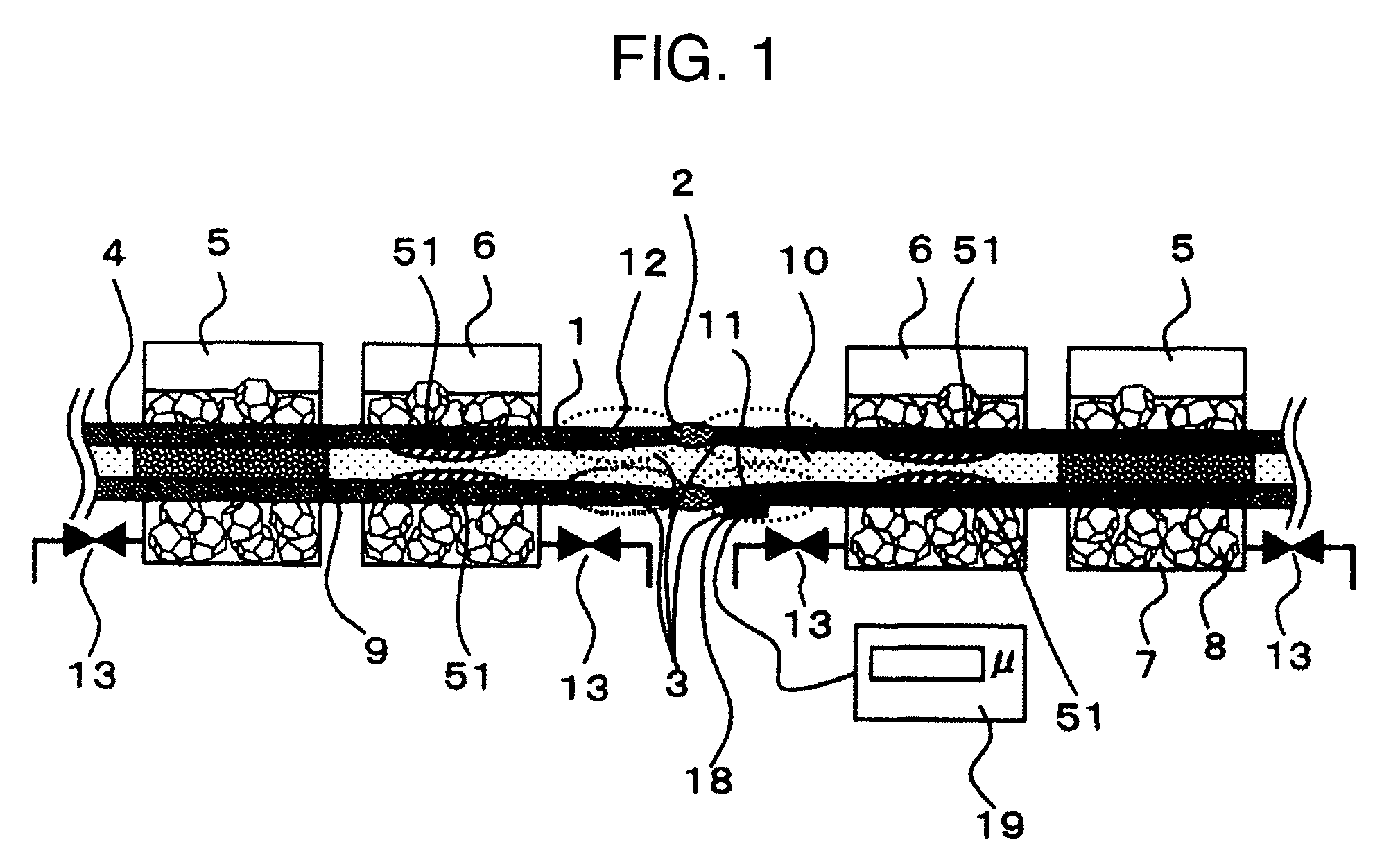

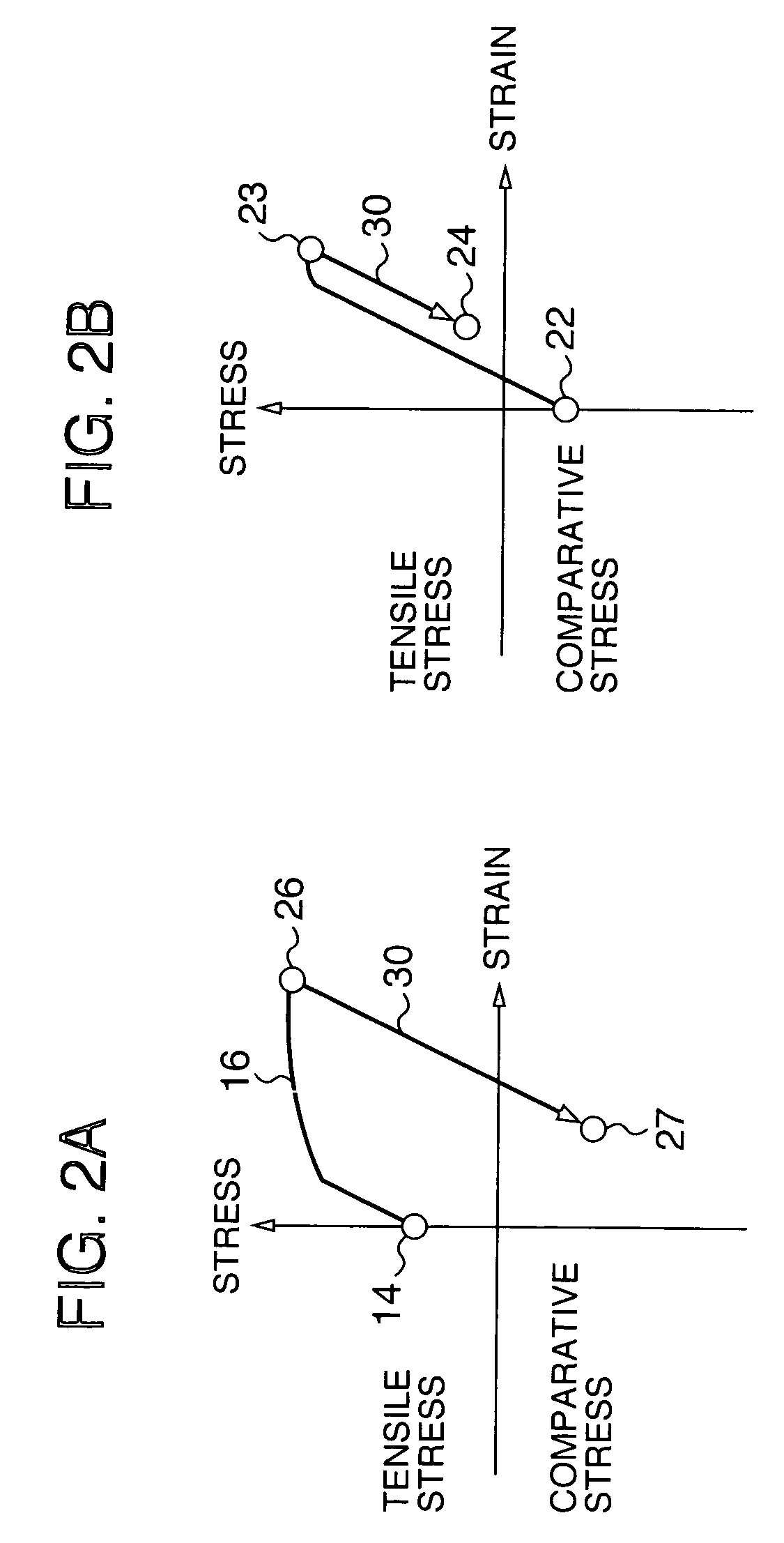

Method for improving residual stress in pipe and apparatus

ActiveUS20060277929A1Improve efficiencyShorten execution cycleDomestic cooling apparatusLighting and heating apparatusSurface coolingEngineering

An method for converting tensile residual stress on an inner surface of a welded part of a pipe to compressive residual stress with use of ice plugs formed by cooling the pipe from the outer surface, comprises the steps of: placing refrigerant containers for forming the ice plugs in the upstream and downstream of a butt-welded part; cooling the outer surface of the pipe to form the ice plugs; and then cooling the outer surface of the pipe with use of at least one refrigerant container for expanding the pipe arranged between the refrigerant containers for forming the ice plugs. When the method is applied to a pipe with a large inside diameter, the method comprises forming the ice plugs at a curved pipe, an elbow or a branch pipe in the upstream and downstream of the butt-welded part.

Owner:HITACHI-GE NUCLEAR ENERGY LTD

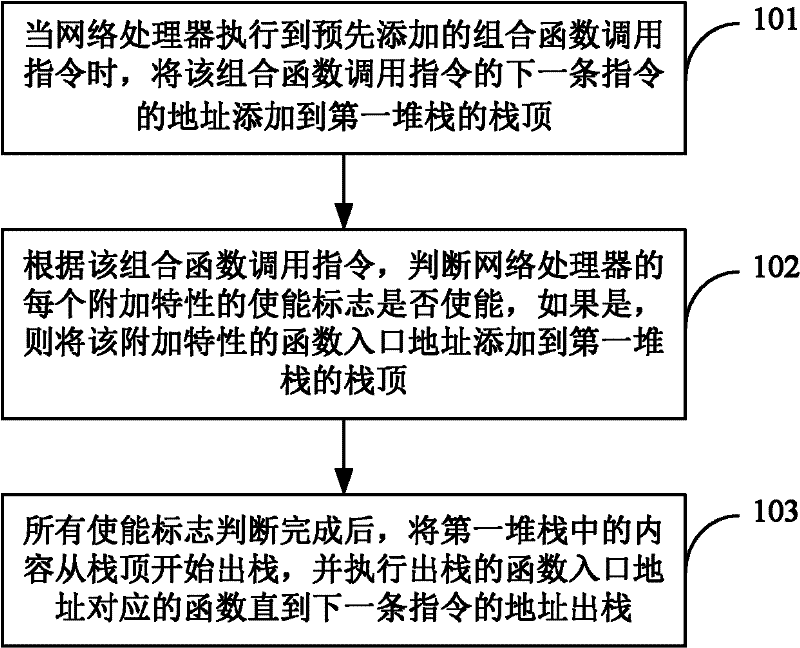

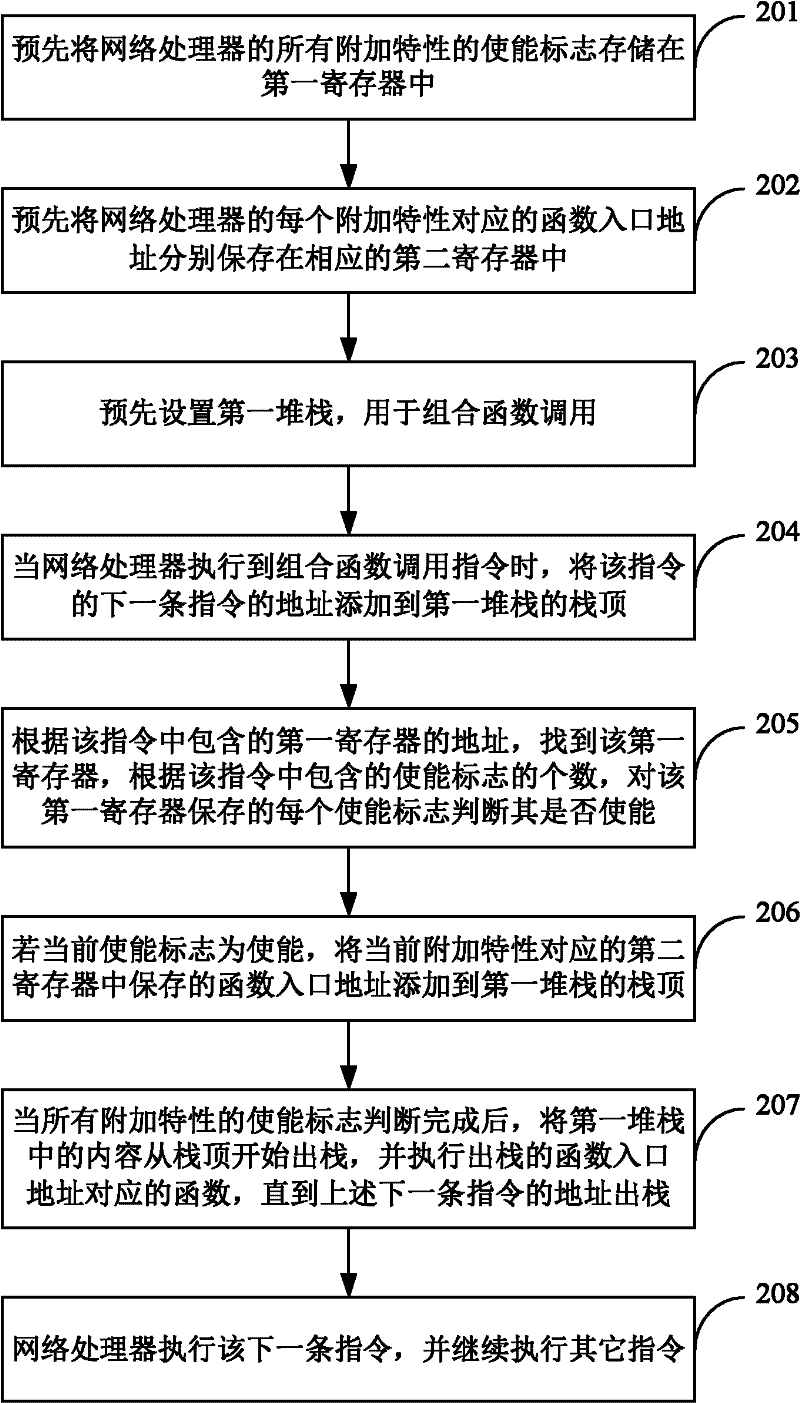

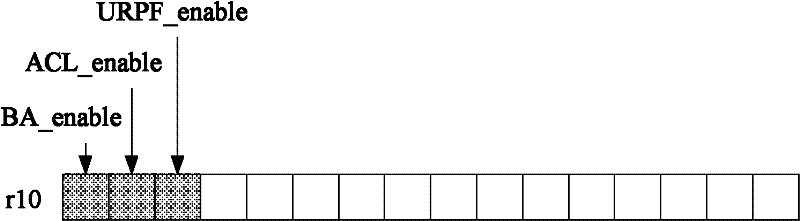

Instruction processing method of network processor and network processor

ActiveCN102292705AShorten execution cycleAny combination is supportedNext instruction address formationSpecific program execution arrangementsParallel computingComposite function

The invention provides an instruction processing method of a network processor and a network processer. The method comprises the steps of when the network processor executes a pre-added composite function, adding the address of a next instruction to the stack top of a first stack, judging whether the enabling signs of each additional characteristic is enabled or not according to a calling instruction of the composite function, if the enabling signs of each additional characteristic is enabled, adding the function entrance address of the corresponding additional characteristic to the stack top of the first stack, when all the enabling signs are judged, poping the function entrance addresses in the first stack from the stack top, and executing the functions to which the poped function entrance addresses correspond, until the address of the next instruction is poped. The network processor comprises a first processing module and a second processing module. In the invention, a judging skip instruction is just needed to be added in a main flow, the functions of all the enabled additional characteristics can be called, saving the instruction execution period substantially, and reducing the effects of main characteristics on the additional characteristics.

Owner:HUAWEI TECH CO LTD

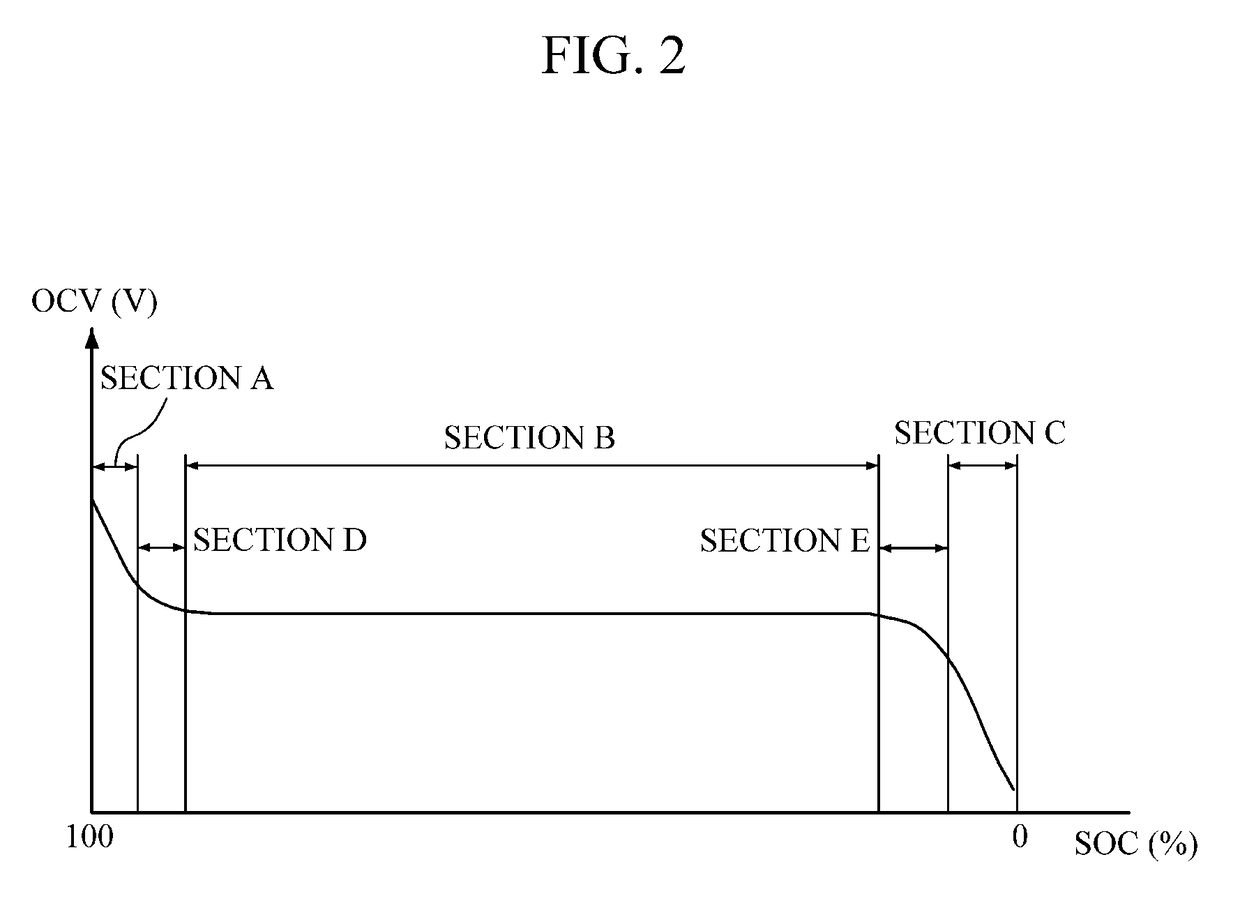

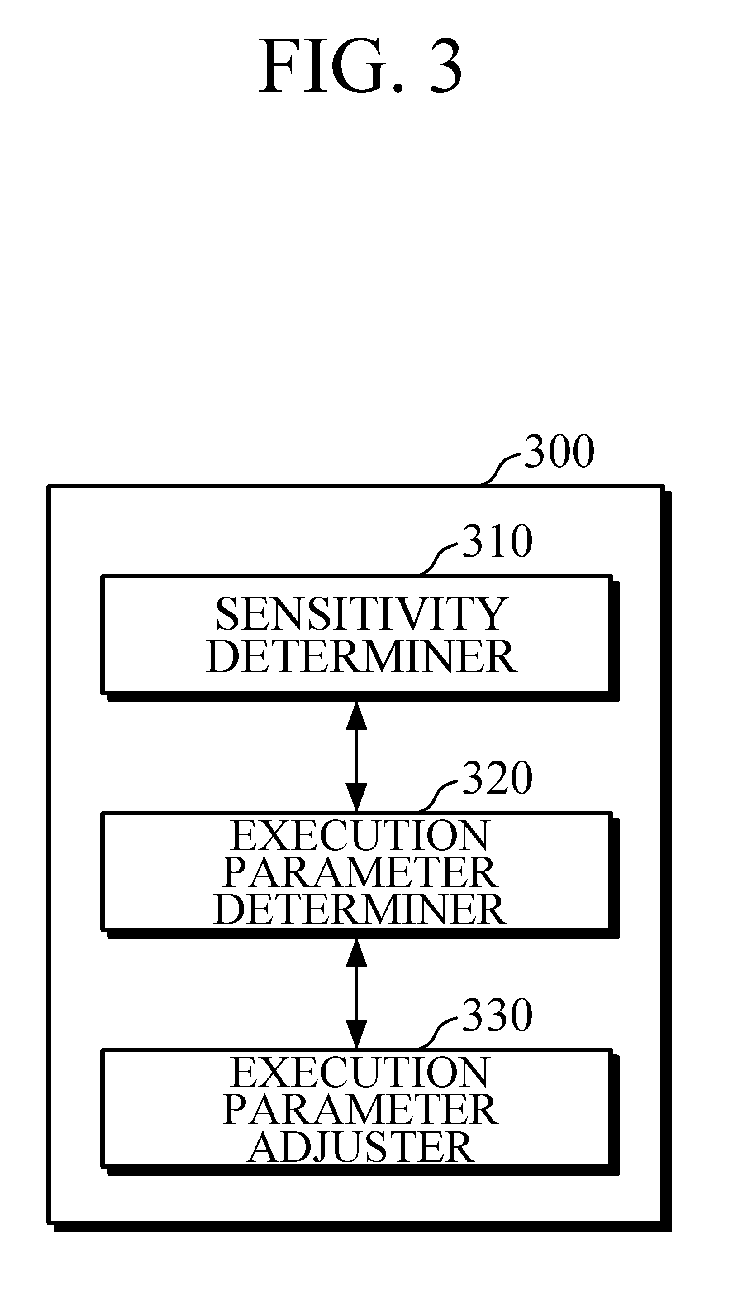

Battery management apparatus and method

ActiveUS20170184679A1Shorten execution cycleIncrease in determined sensitivityElectrical testingEngineeringElectrical and Electronics engineering

Owner:SAMSUNG ELECTRONICS CO LTD

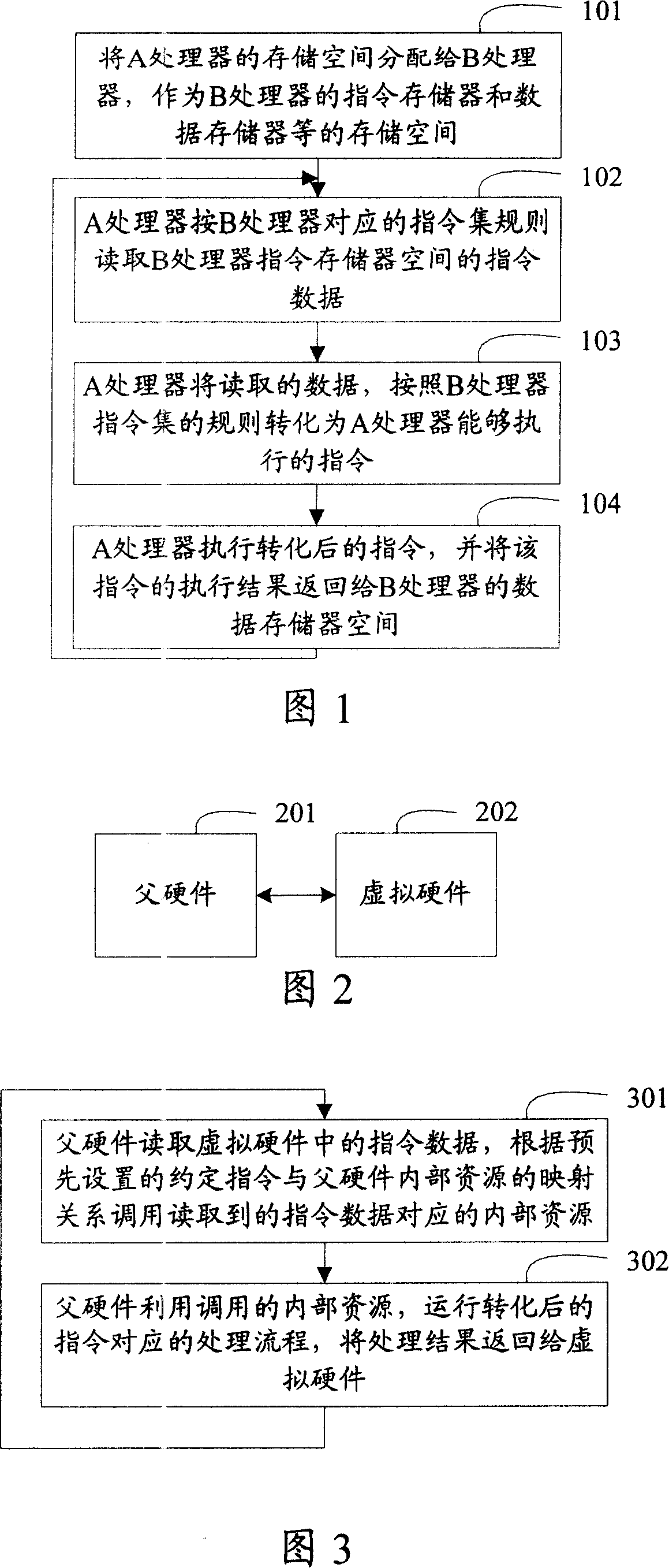

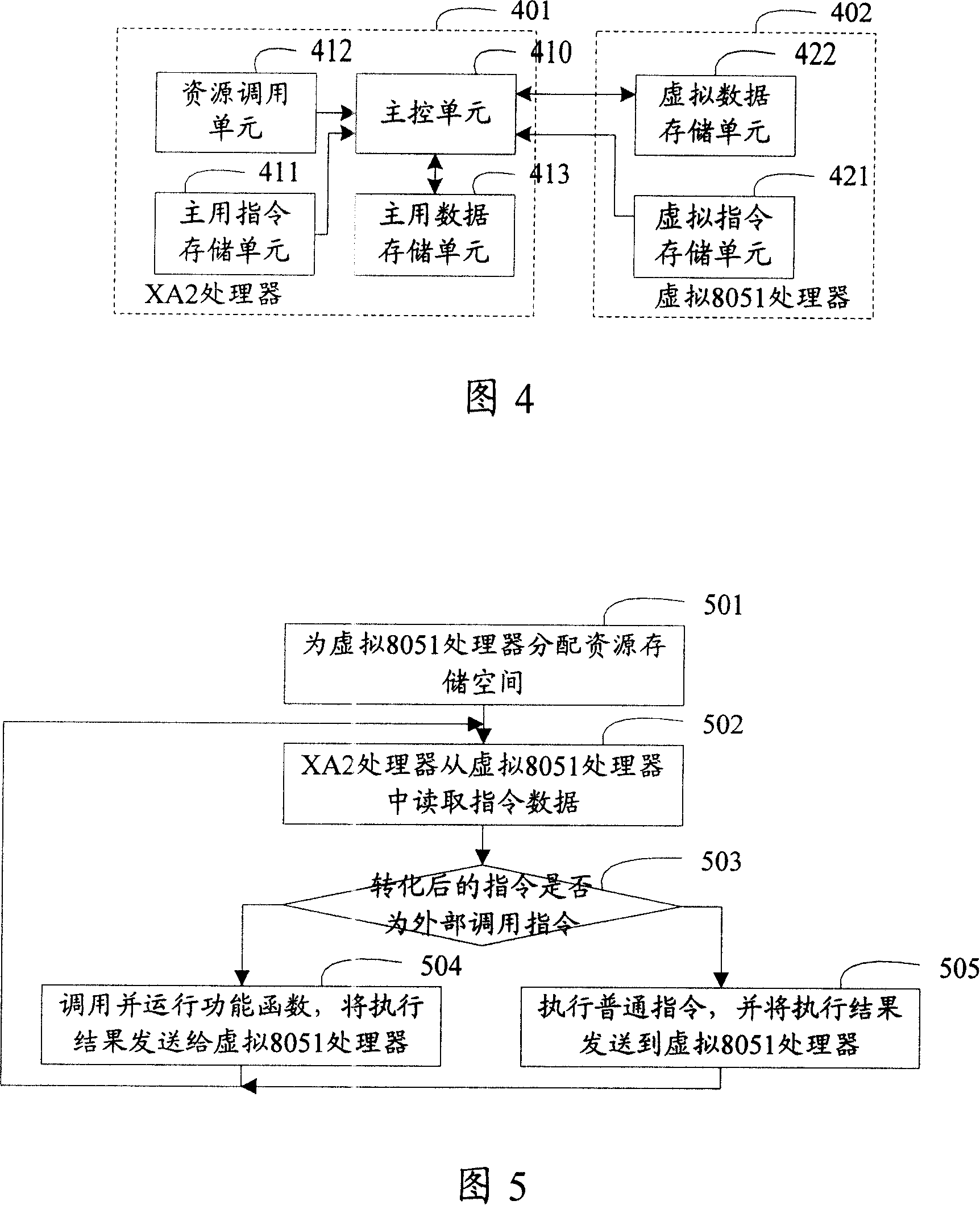

Virtual hardware system and instruction executing method based on virtual hardware system

InactiveCN101154155AFast instruction executionShorten execution cycleMultiprogramming arrangementsConcurrent instruction executionPerformance functionExecution cycle

The invention discloses a virtual hardware system comprising a father hardware and a virtual hardware, wherein, the father hardware reads instruction data from the virtual hardware, operates a processing flow corresponding to the instruction data and sends the processing result to the virtual hardware, and the virtual hardware stores instruction data with mapping relation to the preappointed instruction and receives the processing result from the father hardware. The invention also discloses an instruction execution method based on the virtual hardware. The invention is capable of reading and converting the instruction data of a virtual hardware via the father hardware, calling internal resources, such as performance function and various advanced resources according to the instruction, and utilizing the called internal resources to operate the processing flow corresponding to the instruction, thereby reducing instruction execution cycle and increasing instruction execution speed of the virtual hardware. Moreover, the invention does not need to store the same logic code for realizing the same function in the father hardware and the virtual hardware respectively, thus saving system resources.

Owner:BEIJING SENSESHIELD TECH

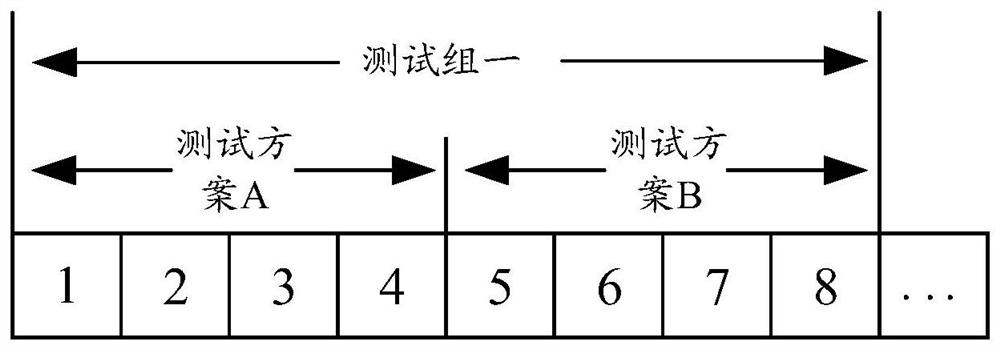

Testing method and device based on network flow, storage medium and electronic equipment

ActiveCN112242911AHigh precisionImprove the efficiency of test executionData switching networksTest efficiencyInternet traffic

The invention provides a testing method and device based on network traffic, electronic equipment and a storage medium and relates to the technical field of computers. The testing method based on thenetwork traffic comprises the following steps: configuring posteriori distribution corresponding to theoretical feedback data of a plurality of test schemes, and executing the following cyclic processuntil test result data corresponding to the plurality of test schemes meet a target condition: the network traffic of the plurality of test schemes is configured through the posteriori distribution and the plurality of test schemes are executed according to the configured network flow and corresponding actual feedback data is determined; updating the posterior distribution according to the actualfeedback data, and determining test result data corresponding to the plurality of test schemes through the updated posterior distribution. According to the method, the test can be ended when the testresult data meets the target condition, a large amount of sample data does not need to be accumulated through network flow, the test period is shortened, the test efficiency is improved, and the testtimeliness is ensured.

Owner:TENCENT TECH (SHENZHEN) CO LTD

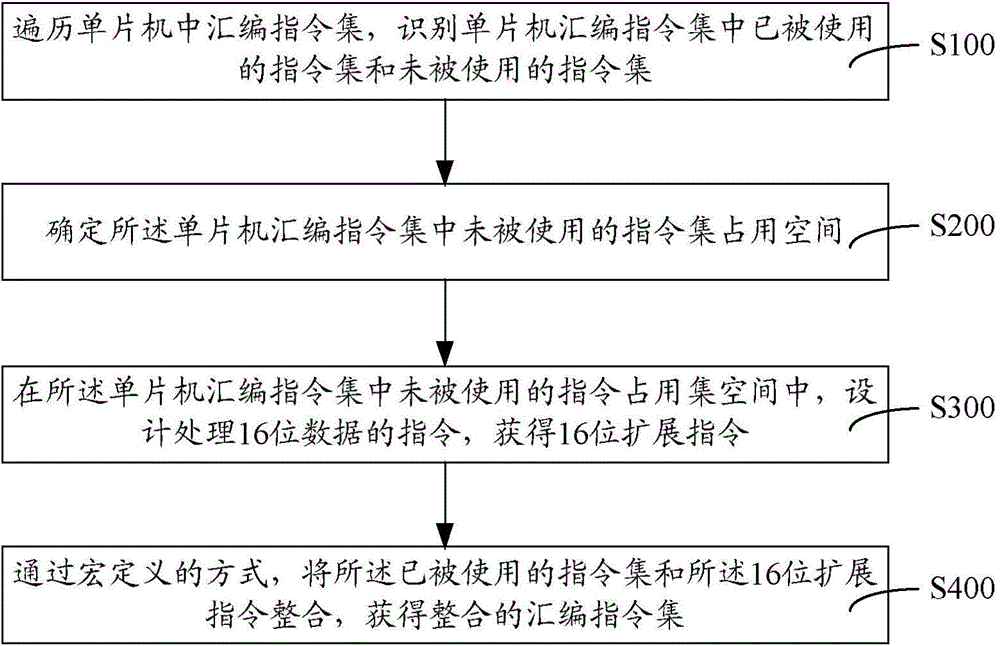

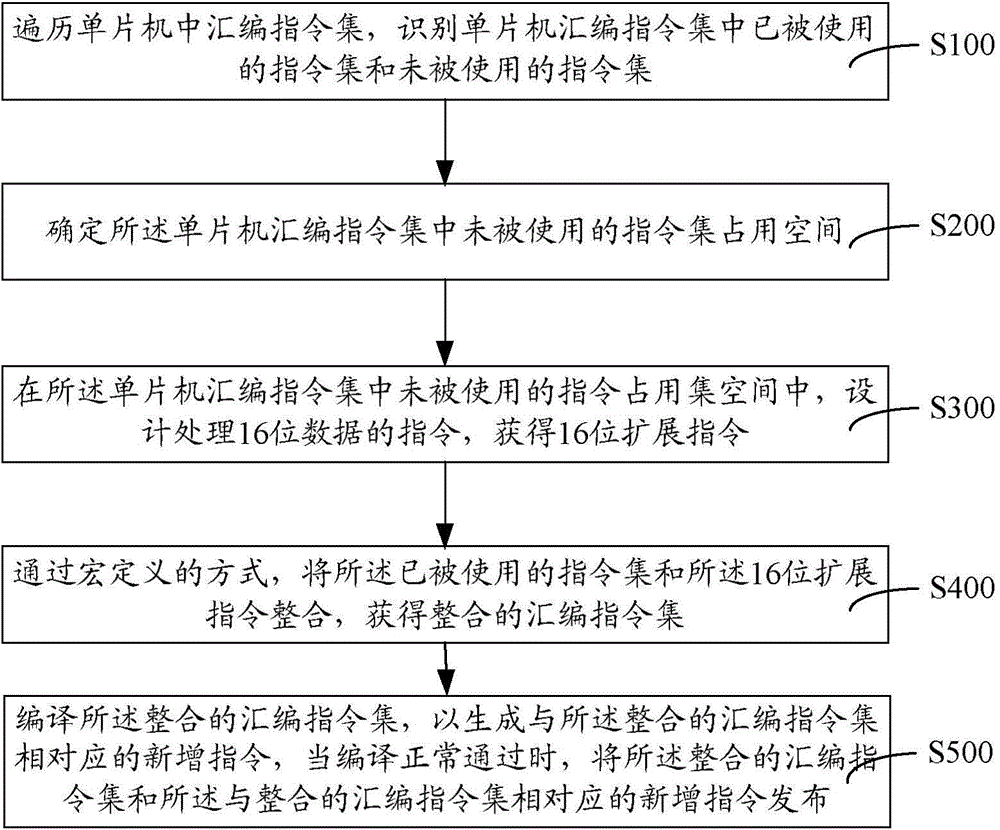

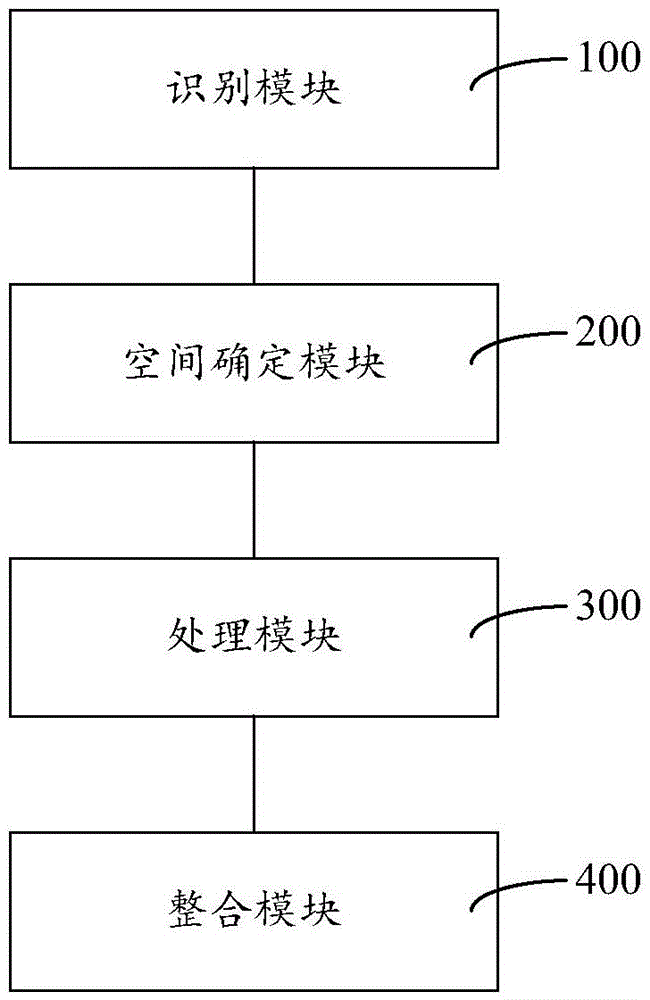

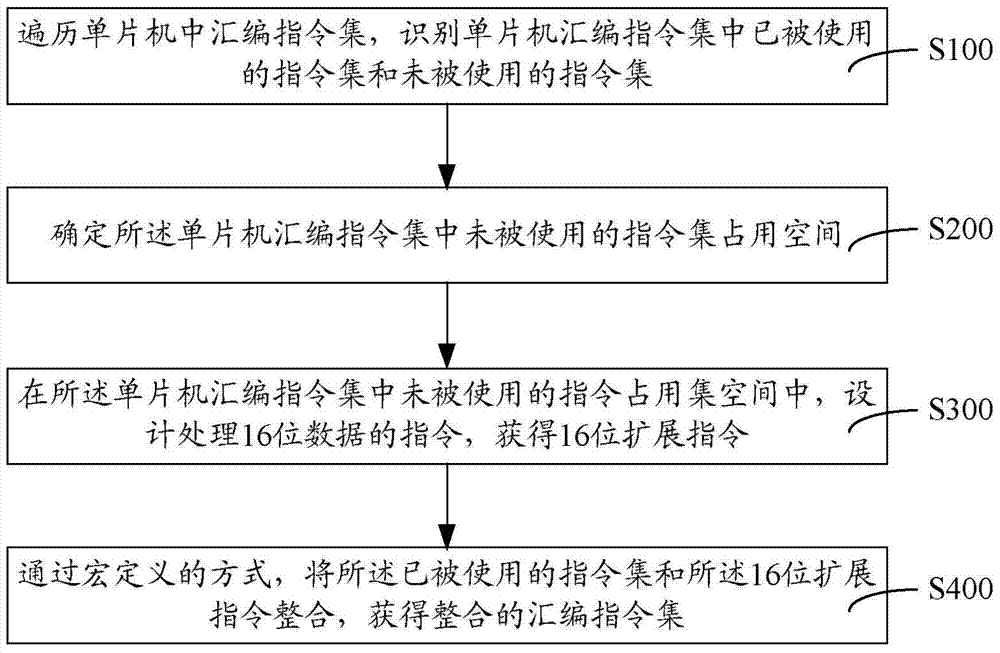

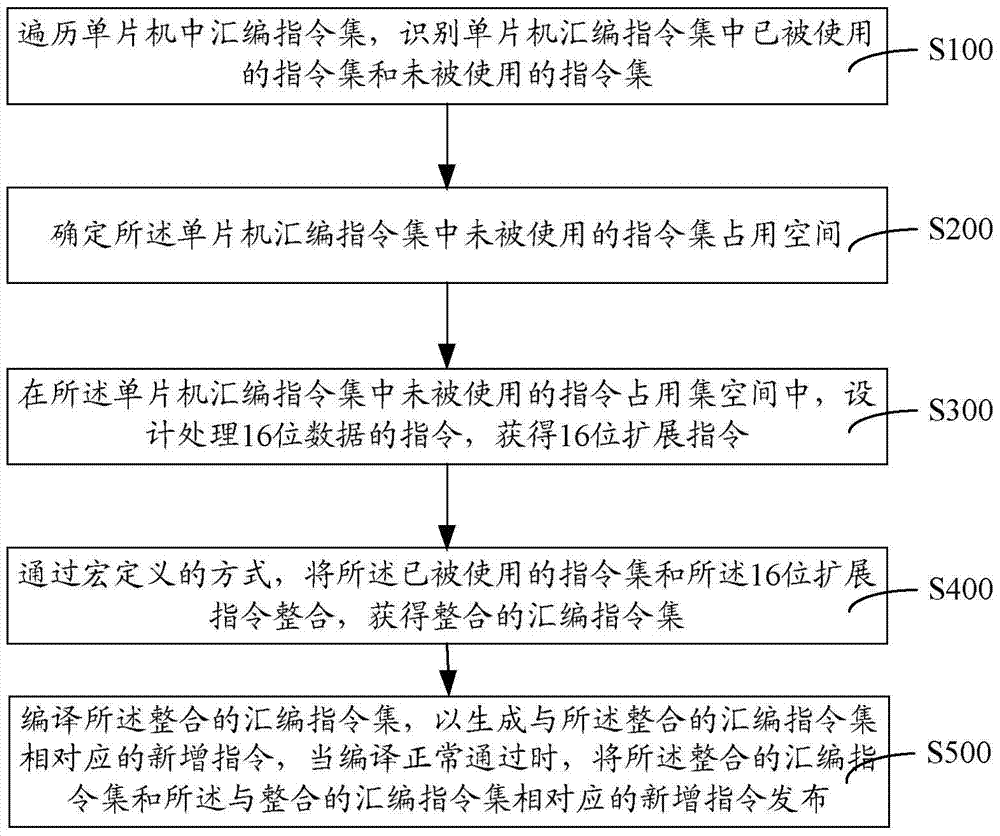

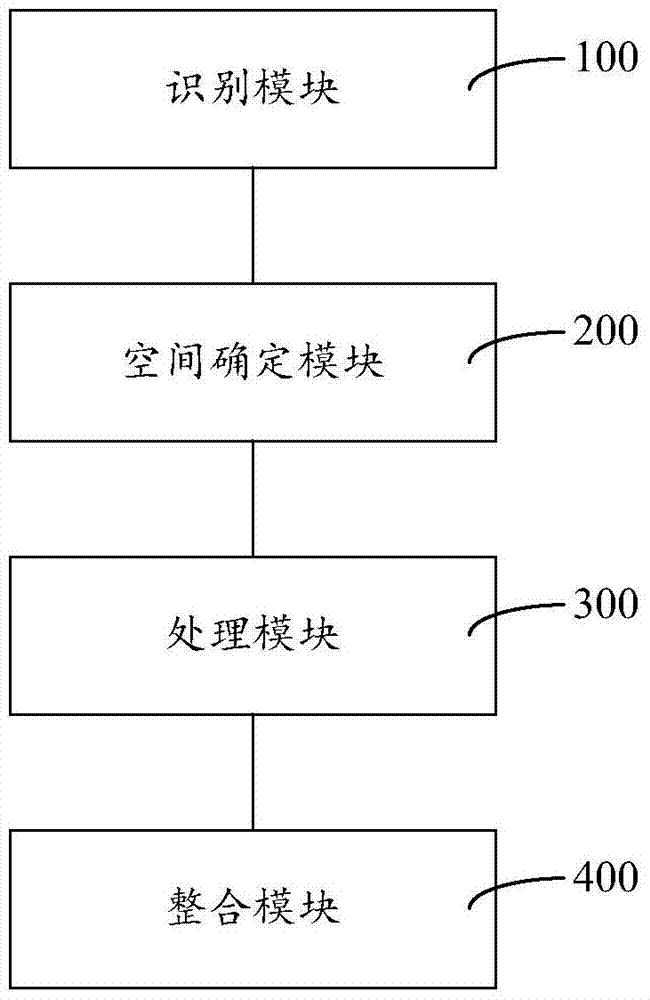

Instruction extension method and system for singlechip microcomputer

ActiveCN104615443AImprove operational efficiencyImprove efficiencySpecific program execution arrangementsMicrocontrollerMicrocomputer

The invention provides an instruction extension method and an instruction extension system for a singlechip microcomputer. The method comprises the following steps: identifying a used instruction set and a non-used instruction set in a singlechip microcomputer assembly instruction set, determining an occupied space of the non-used instruction set in the singlechip microcomputer assembly instruction set, designing an instruction for processing 16-bit data in the occupied space of the non-used instruction set to obtain a 16-bit extension instruction, and integrating the used instruction set and the 16-bit extension instruction by a macro definition mode to obtain an integrated assembly instruction set. In the whole process, an instruction optimizing method aiming at multi-bit data is provided, so that no more instructions for decomposing operation are needed, and the instruction execution period is shortened to 1 period; meanwhile, the usability and the execution efficiency of a code space are improved; under the condition that a 16-bit CPU is not replaced, a demand can be met, and the cost is reduced; furthermore, the multi-bit data processing capacity of an 8-bit CPU is improved, and the operating efficiency of the singlechip microcomputer can be effectively promoted to be further improved.

Owner:ZHUHAI JIELI TECH

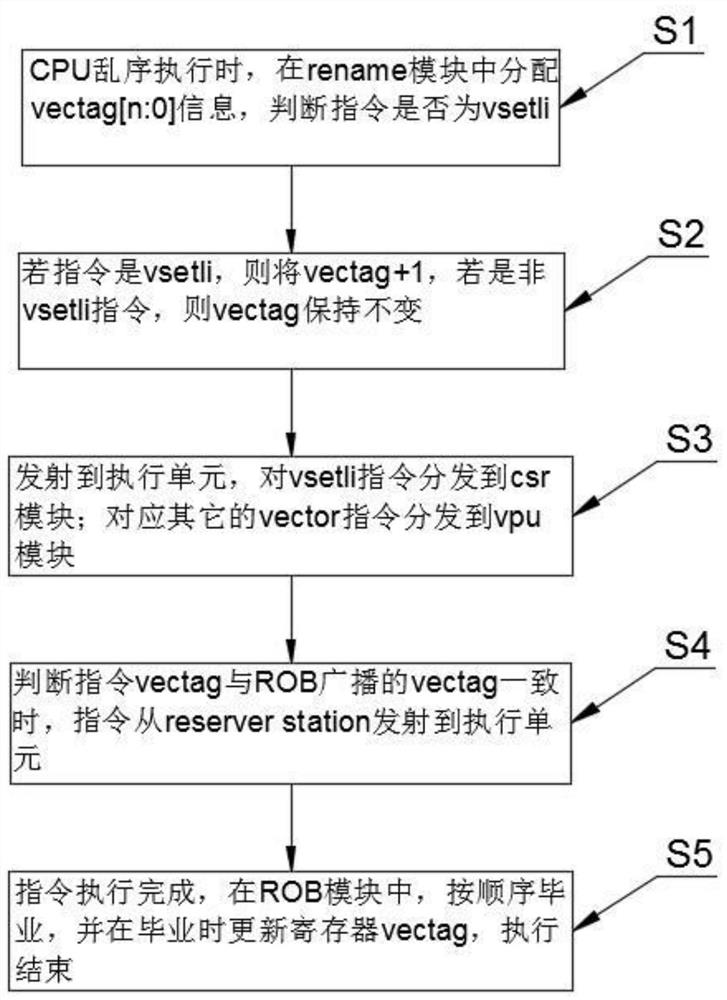

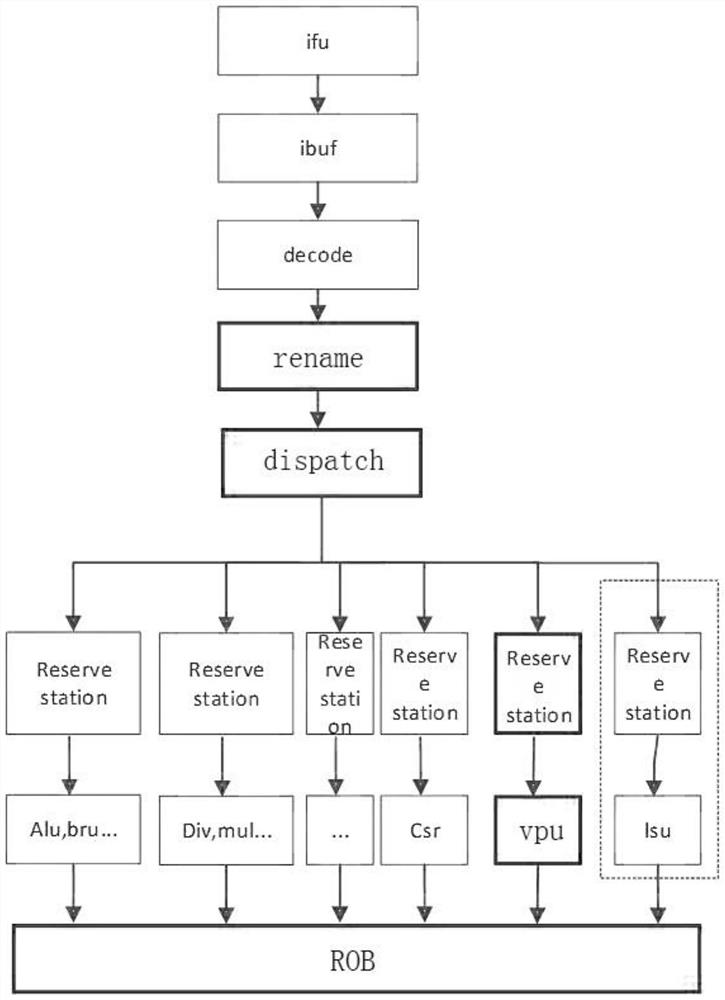

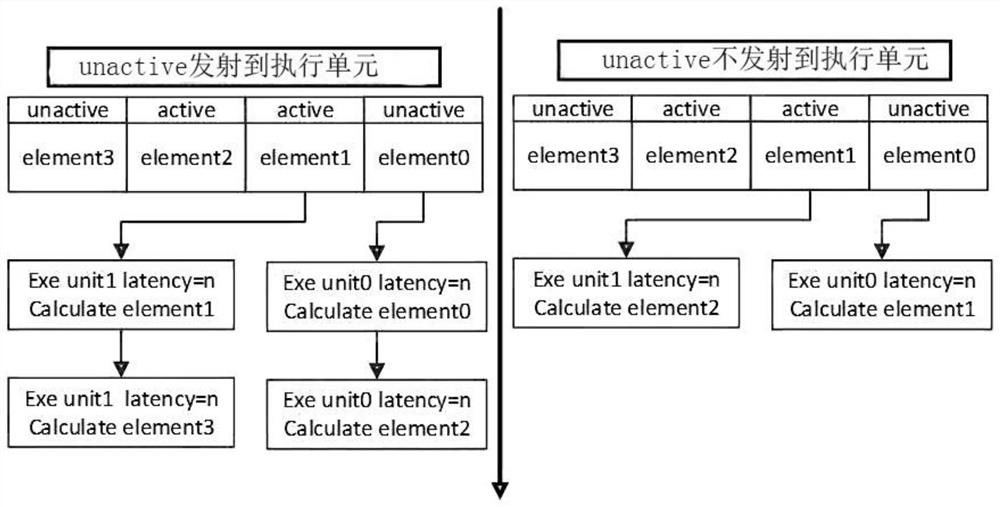

Implementation method and system for vsetli instruction in risv_v vector instruction set

PendingCN113467833AReduce power consumptionShorten execution cycleResource allocationRegister arrangementsOut-of-order executionInstruction set

The invention relates to the technical field of CPUs, in particular to an implementation method and system for a vsetli instruction in a risv_v vector instruction set. The method comprises the steps that: vectag [n: 0] information is distributed in a rename module during out-of-order execution of a CPU, and whether the instruction is vsetli or not is judged; if the instruction is a vsetli instruction, 1 is added to vectag, and if the instruction is a non-vsetli instruction, vectag remains unchanged; the vsetli instruction is transmitted to an execution unit, and the vsetli instruction is distributed to a csr module; corresponding other vector instructions are distributed to a vpu module; when it is judged that the vectag of the instruction is consistent with the vectag broadcasted by an ROB, the instruction is transmitted to the execution unit from a reserver station; and after the instruction execution is completed, graduating is carried out in sequence in the ROB module, the vectag of a register is updated during graduation, and the execution is ended. According to the method, the execution efficiency for a non-vsetl {i} Vector instruction is high. Data is selected in a mask mode, the power consumption is reduced, the execution period can be shortened, and latency is reduced. The method and the system have a very wide market application prospect.

Owner:GUANGDONG STARFIVE TECH LTD

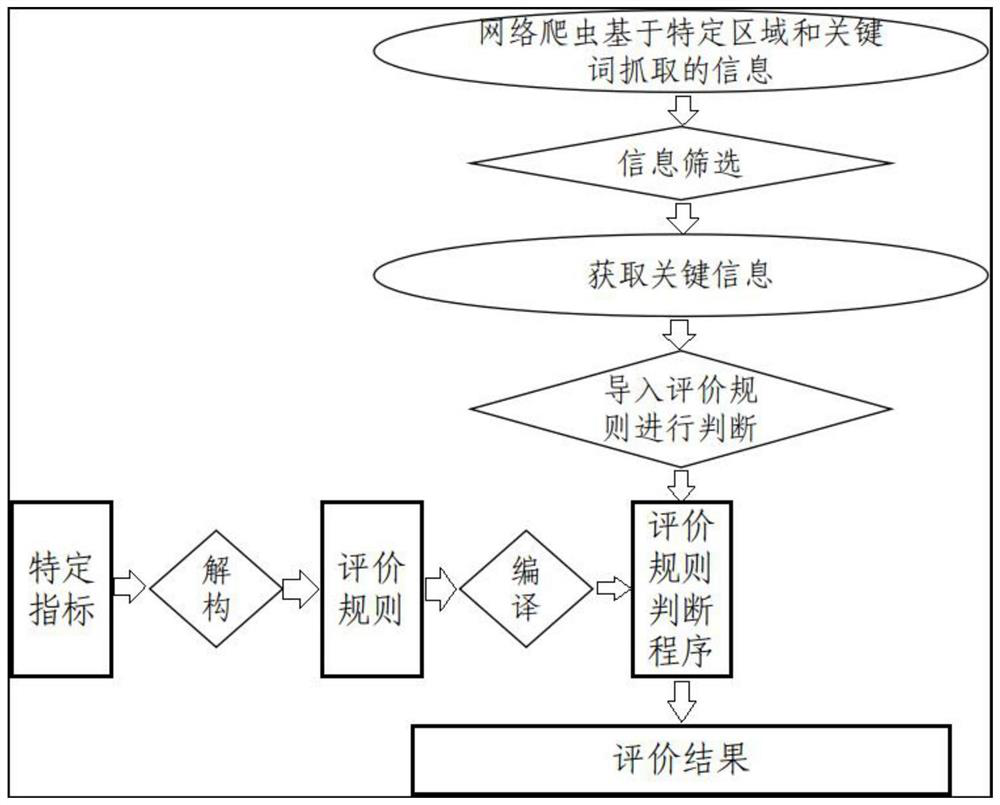

Government affair public evaluation system based on artificial intelligence semantic analysis

InactiveCN111814019ARealize intelligent crawlingAutomatic collectionWeb data indexingSemantic analysisData acquisitionEngineering

The invention discloses a government affair public evaluation system based on artificial intelligence semantic analysis, and relates to the technical field of artificial intelligence semantic analysis. The system comprises a web crawler subsystem and a government affair index management subsystem, wherein the web crawler subsystem comprises a crawler scheduling end, a URL manager, a webpage downloader and a webpage parser; and the government affair index management subsystem comprises an index evaluation factor module, an index framework construction module, an index weight module and an indexhierarchical analysis module. Through a web crawler technology and an artificial intelligence semantic analysis algorithm, intelligent information capture by a computer; automatic data acquisition, automatic matching of evaluation index requirements, automatic judgment and evaluation, automatic data storage, automatic result calculation and reduction of manpower expenditure are realized, and thecost of public government affair third evaluation work is greatly reduced.

Owner:安徽观知天下数字科技发展有限公司

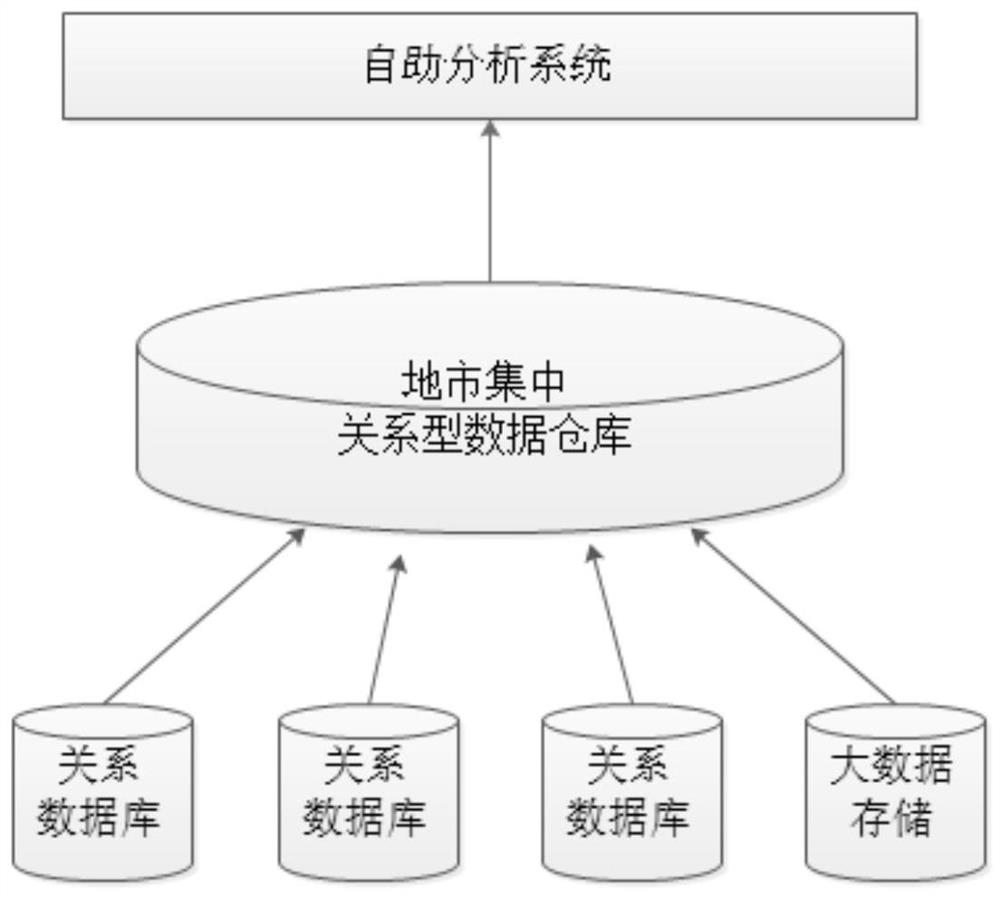

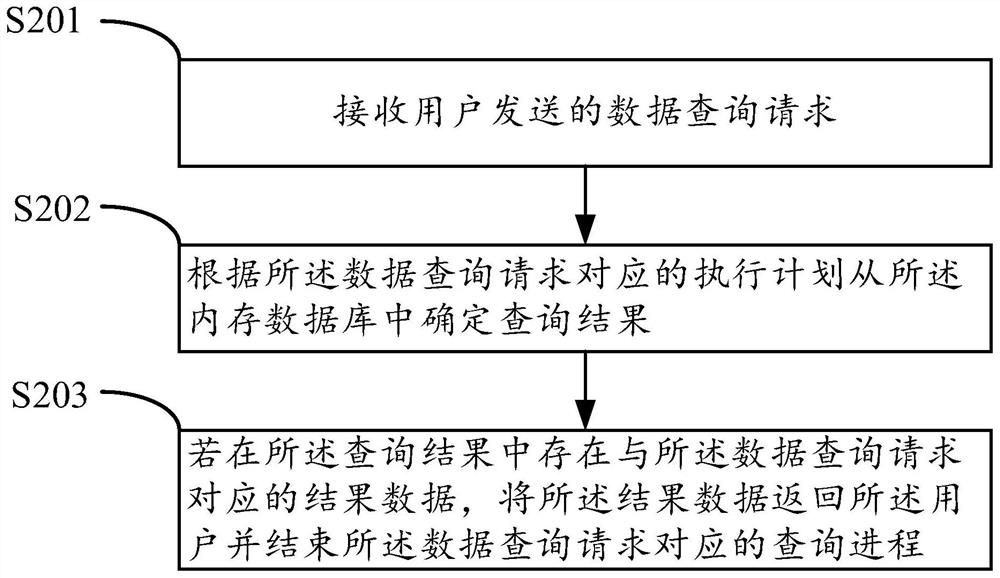

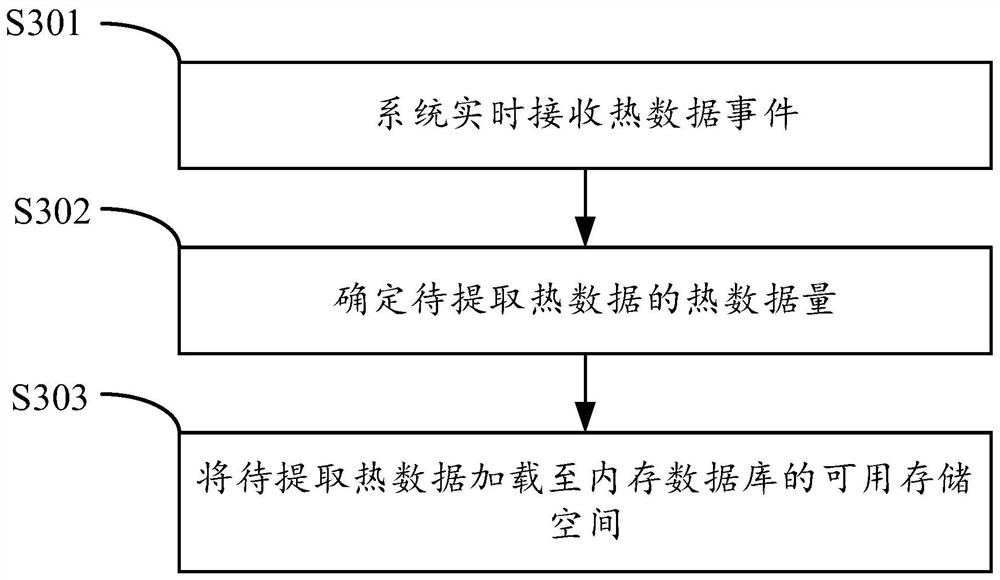

Data query acceleration method and device based on memory computing

InactiveCN111858654AShorten execution cycleImprove interactive experienceDatabase management systemsSpecial data processing applicationsIn-memory databaseExecution plan

The invention discloses a data query acceleration method and device based on memory computing. The method is applied to a system comprising a data warehouse and a memory database. Hot data extracted from the data warehouse is stored in the memory database. The method comprises the following steps: receiving a data query request sent by a user, determining a query result from the memory database according to an execution plan corresponding to the data query request; if result data corresponding to the data query request exists in the query result, returning the result data to the user and ending the query process corresponding to the data query request, thereby shortening the execution period of data query, improving the data query speed in the self-service analysis service system and improving the user interaction experience.

Owner:BORRUI DATA TECH (BEIJING) CO LTD

A runtime access control device and method

The invention discloses a device and method for access control during operation, which relate to information technology, especially information security technology. The device includes a safety device and a guarantee device, and the safety device performs access control on a memory area based on hardware; The security device is based on hardware to ensure that the control state data that makes the security device valid and the specific instruction that makes the security device valid can be set only in a specific state; the security device provides a legal way to cross memory area boundaries, including executing special When a cross-area transfer instruction or an interrupt / exception occurs, it must first be transferred to the transfer area, and then the code in this area performs a boundary switch and transfers to the final target address; especially, if the two are transferred to the common code in the same transfer area Location, the hardware provides identification information to distinguish whether the transfer is caused by the execution of a cross-region transfer instruction or the generation of an interrupt / exception; interrupt return will also cause a cross-region transfer.

Owner:杨力祥

Single-chip computer instruction extension method and system

ActiveCN104615443BImprove operational efficiencyImprove efficiencyConcurrent instruction executionMicrocontrollerCode space

The present invention provides a single-chip computer instruction extension method and system, which can identify the used instruction set and the unused instruction set in the single-chip computer assembly instruction set, and clarify the space occupied by the unused instruction set in the single-chip computer assembly instruction set. In the space occupied by the instruction set, design instructions for processing 16-bit data, obtain 16-bit extended instructions, and integrate the used instruction set and 16-bit extended instructions through macro definition to obtain an integrated assembly instruction set. The whole process provides an instruction optimization method for multi-bit data. It does not need to add more instructions to decompose the operation, and the instruction execution cycle is also shortened to 1 cycle. At the same time, the use efficiency and execution efficiency of the code space are improved. The requirement is met without replacing the 16-bit CPU, the cost is saved, and the multi-bit data processing capability of the 8-bit CPU is improved, which can effectively promote the further improvement of the operating efficiency of the single-chip microcomputer.

Owner:ZHUHAI JIELI TECH

Matrix convolution calculation method, interface, coprocessor and system based on risc-v architecture

ActiveCN109857460BCalculation speedReduce the number of memory accessesConcurrent instruction executionNeural architecturesCoprocessorEngineering

Owner:NANJING HUAJIE IMI TECH CO LTD

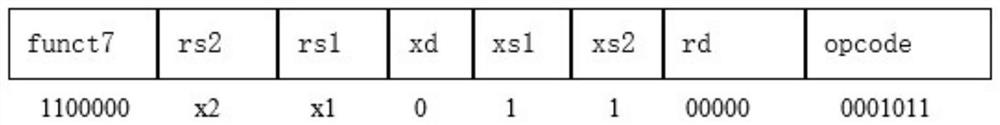

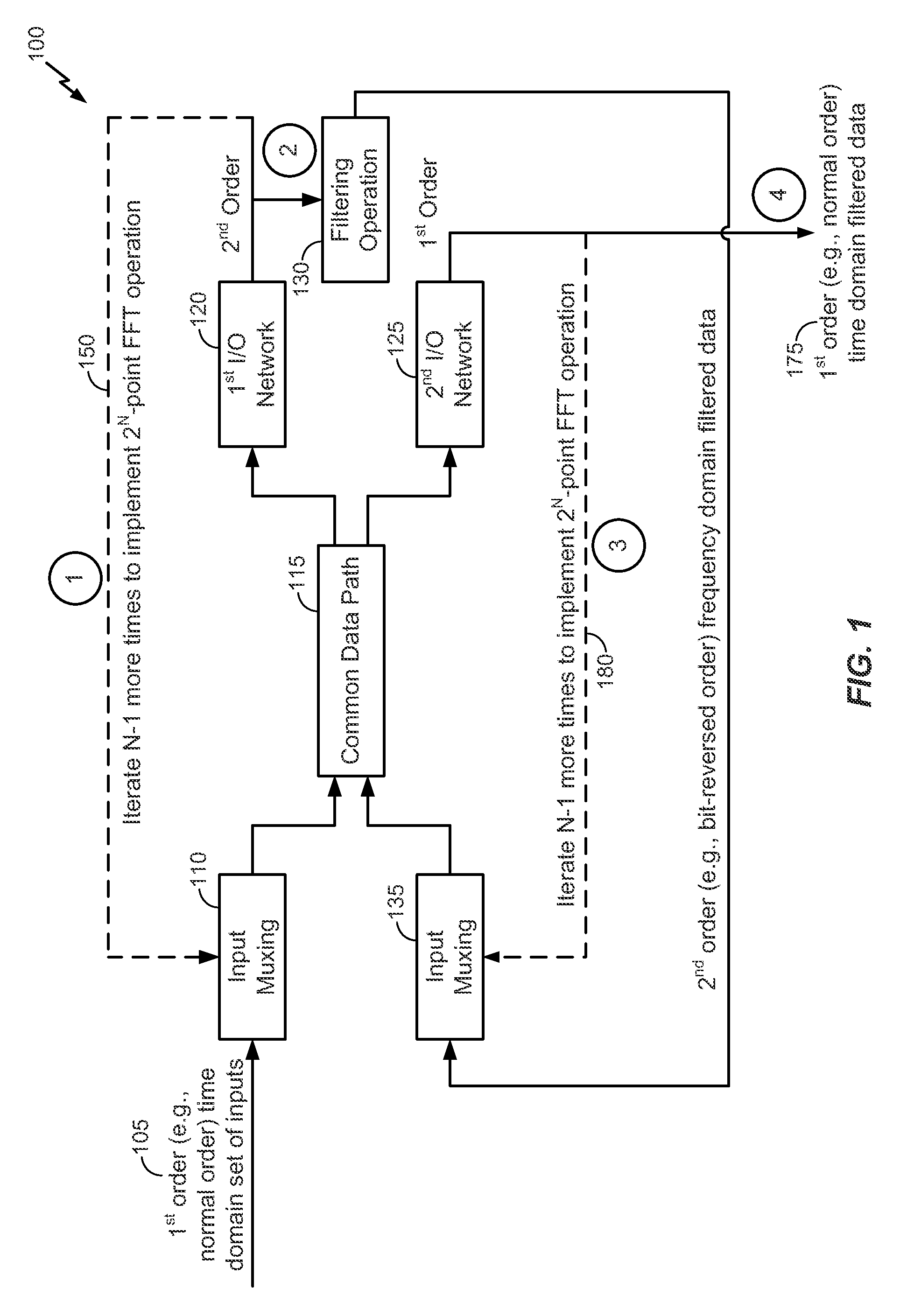

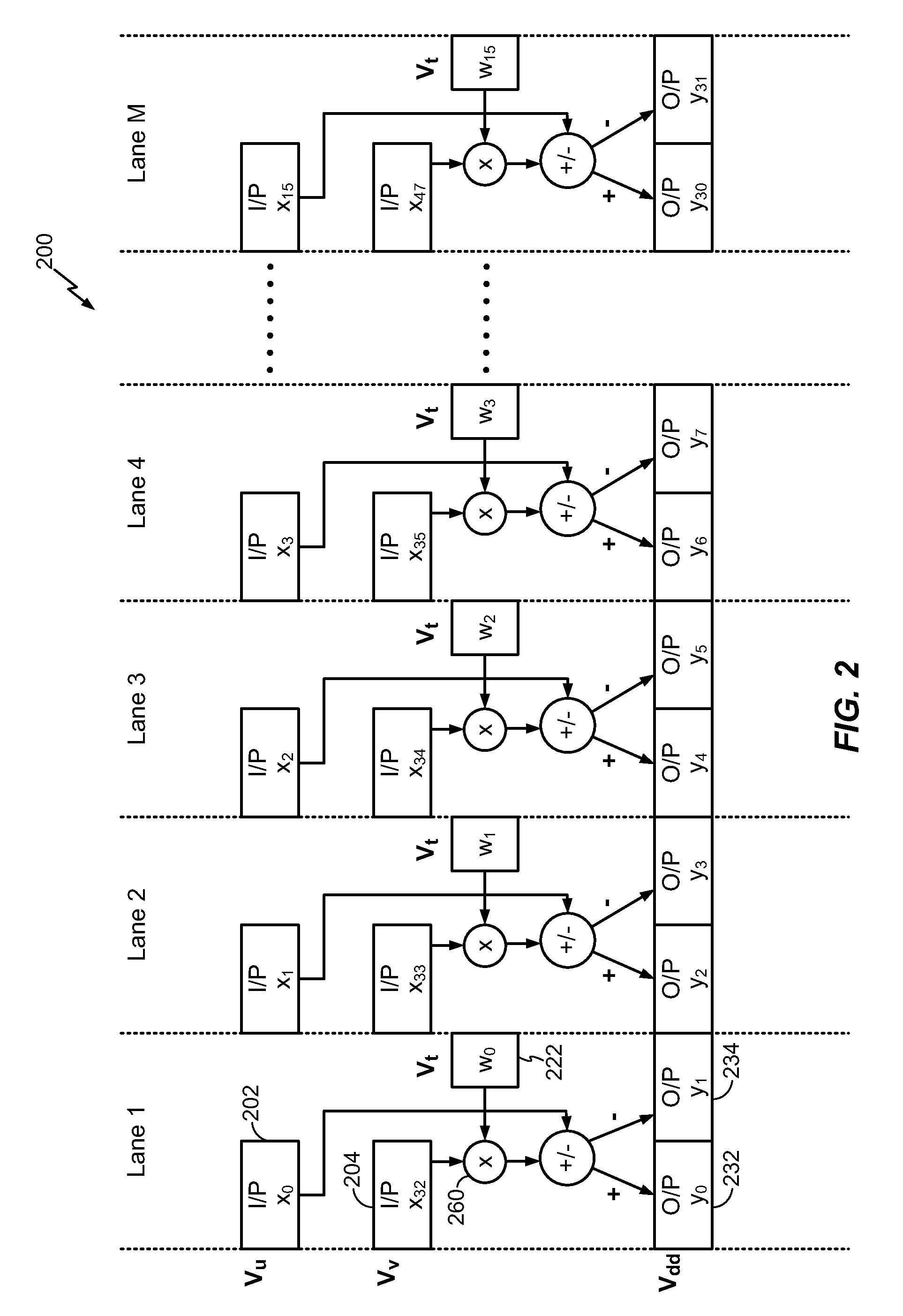

Dual fixed geometry fast fourier transform (FFT)

ActiveUS8787422B2Reduce complexityReduce power consumptionSecret communicationProgram controlTime domainFast Fourier transform

A method includes executing a first instruction at a processor to perform a first fast Fourier transform (FFT) operation on a set of inputs in a time domain to produce data in a frequency domain, where the set of inputs is in a first order and where the data in the frequency domain is in a second order. The method also includes performing an operation on the data in the frequency domain to produce data in the frequency domain, where the data in the frequency domain is in the second order. The method includes executing a second instruction at the processor to perform a second FFT operation on the data in the frequency domain to produce data in the time domain, where the data in the time domain is in the first order.

Owner:QUALCOMM INC

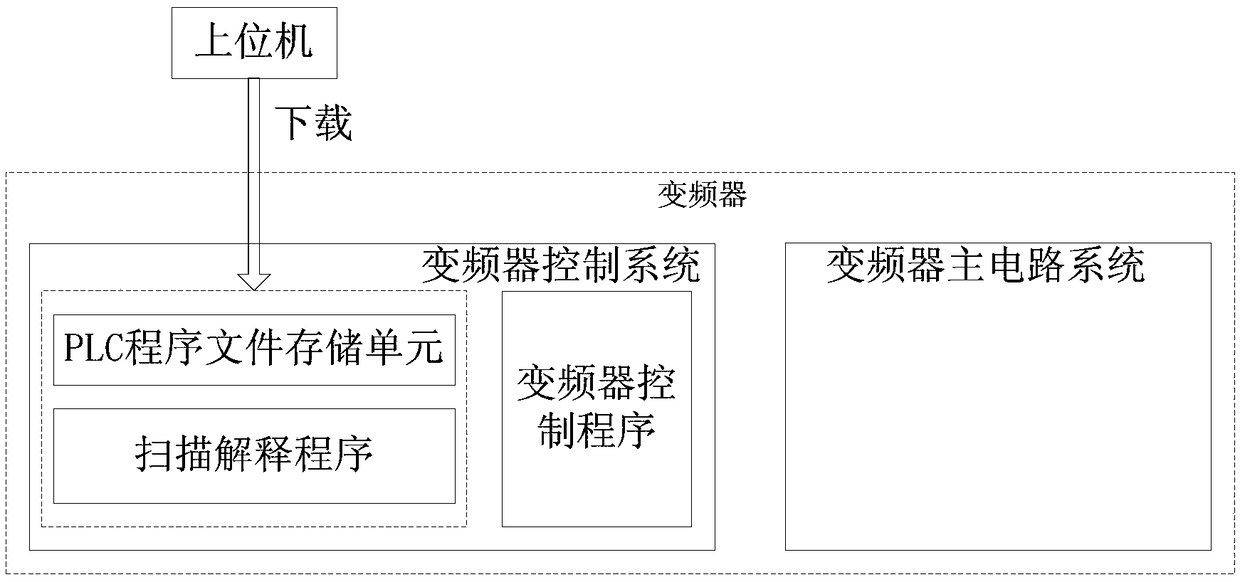

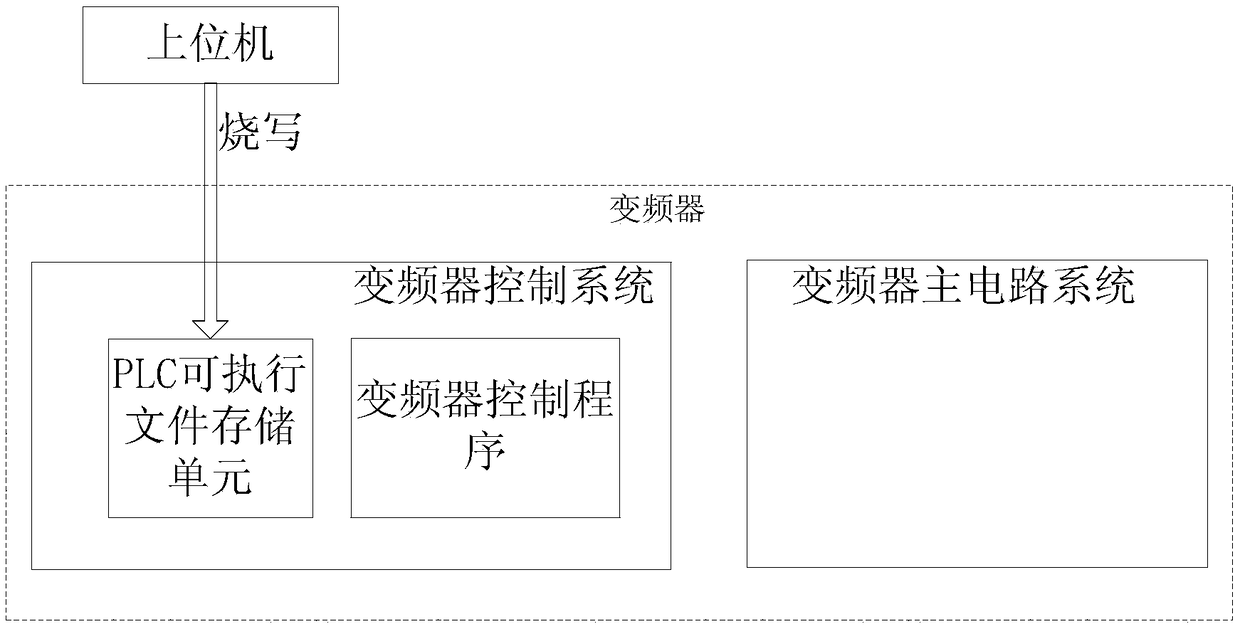

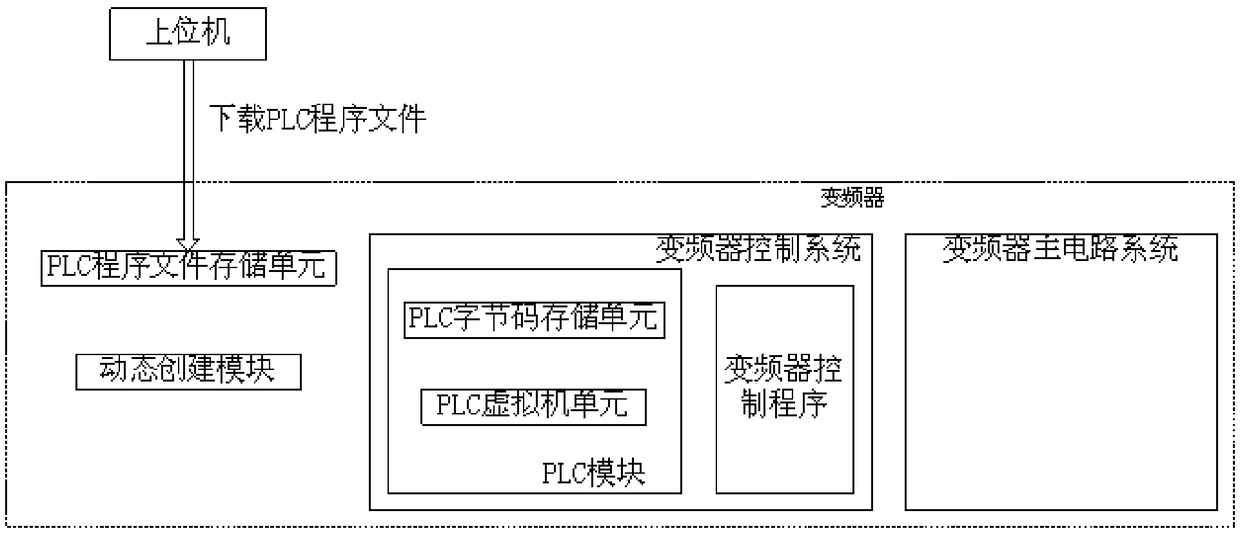

Frequency converter integrated with PLC function and method for realizing integrated PLC function of frequency converter

InactiveCN109213064AShorten execution cycleImprove execution efficiencyProgramme control in sequence/logic controllersFrequency changerControl system

The invention discloses a frequency converter integrated with PLC function. The frequency converter comprises a frequency converter control system. The frequency converter control system comprises a frequency converter control program and a PLC module for executing the PLC function. The PLC module comprises a PLC virtual machine unit for running a PLC byte code and an input signal to obtain a running result, and outputting the obtained running result. The invention also discloses a method for realizing the integrated PLC function of the frequency converter. The frequency converter integrated with the PLC function and the method for realizing the integrated PLC function of the frequency converter can effectively shorten the execution cycle of the PLC control program and improve the execution efficiency of the PLC control program while satisfying the versatility of various types of processors.

Owner:CHANGSHU SWITCHGEAR MFG CO LTD (FORMER CHANGSHU SWITCHGEAR PLANT)

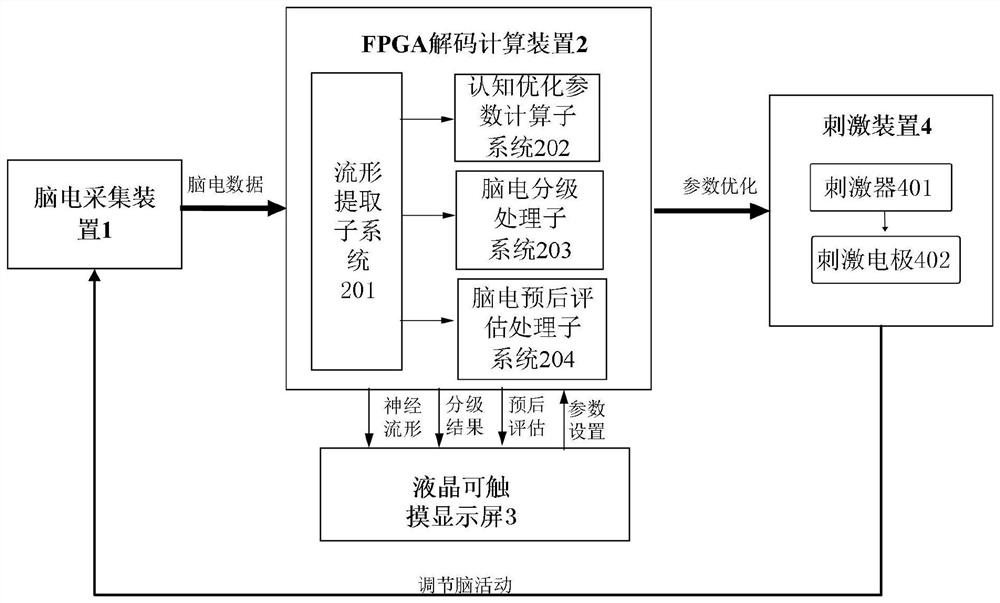

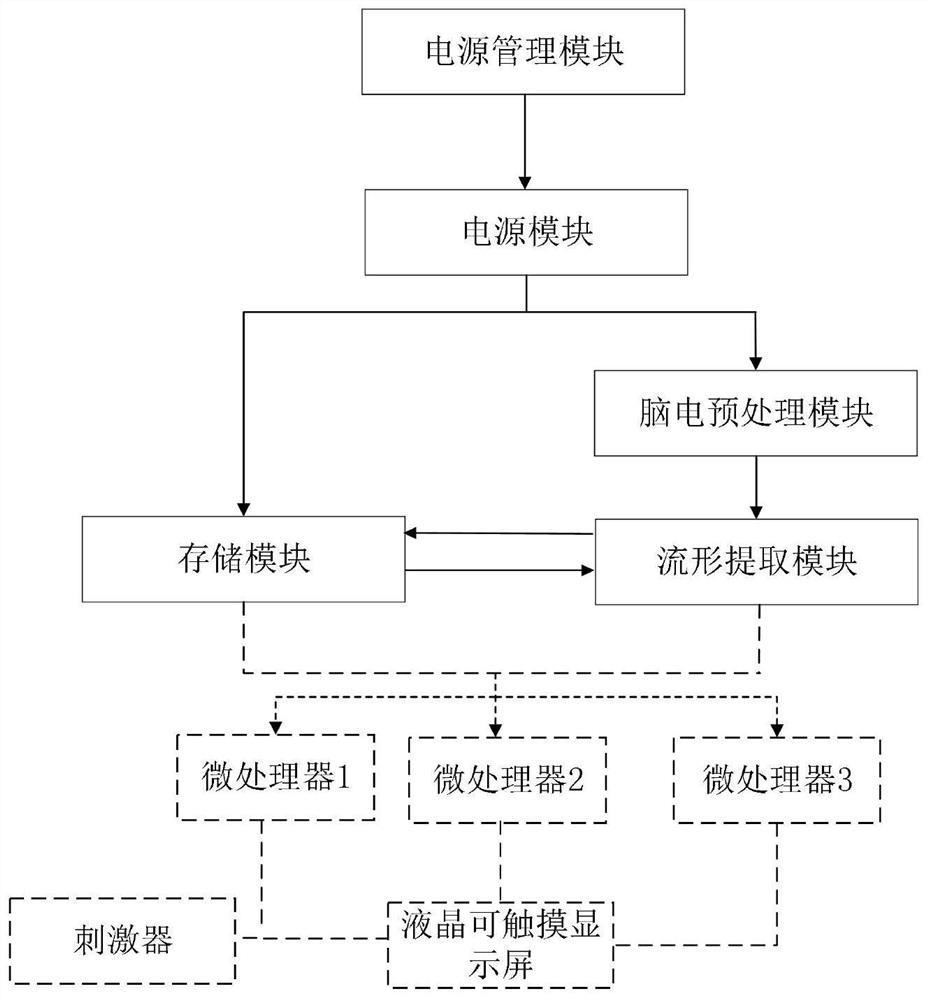

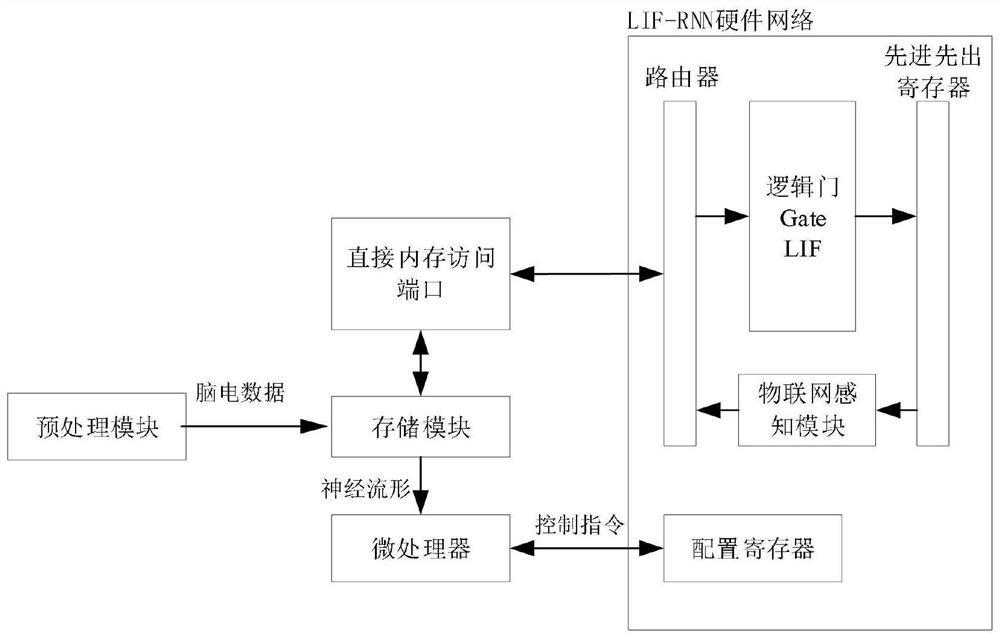

Electroencephalogram grading and prognosis FPGA decoding system based on neural manifold

ActiveCN113112017AImprove stabilityGood nonlinear characteristicsDiagnostic signal processingSensorsComputer visionArtificial intelligence

The invention provides an electroencephalogram grading and prognosis FPGA decoding system based on neural manifold. The system comprises an electroencephalogram acquisition device, an FPGA decoding calculation device, a liquid crystal touchable display screen and a stimulation device. The FPGA decoding calculation device is composed of a manifold extraction subsystem, a cognitive optimization parameter calculation subsystem, an electroencephalogram grading processing subsystem and an electroencephalogram prognosis evaluation processing subsystem which are used for extracting manifolds, calculating stimulation parameters needed for optimizing cognitive functions and conducting grading and prognosis evaluation on electroencephalogram signals respectively. Electroencephalogram grading is carried out, prognosis evaluation is carried out through the change trend of the difference value between the actual neural manifold and the target manifold, the two manifolds, the stimulation parameters and the grading prognosis result are transmitted to a display screen through wires, and the optimal stimulation parameters are transmitted to a stimulation device through a wire for control. According to the system, electroencephalogram automatic grading, prognosis evaluation and brain cognitive function optimization can be achieved.

Owner:TANGSHAN WORKERS HOSPITAL +1

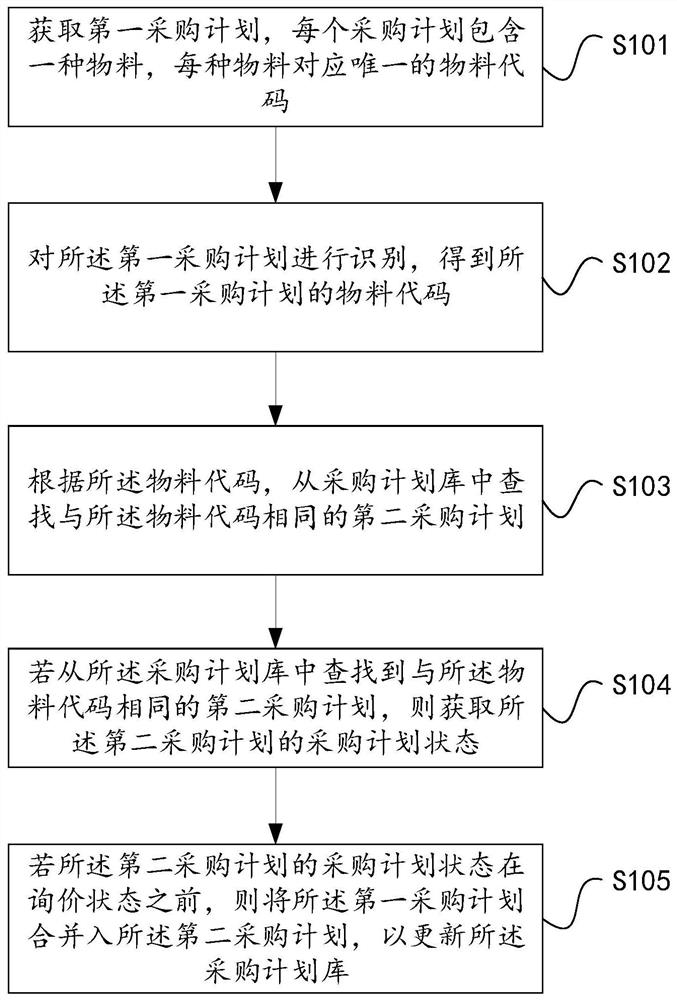

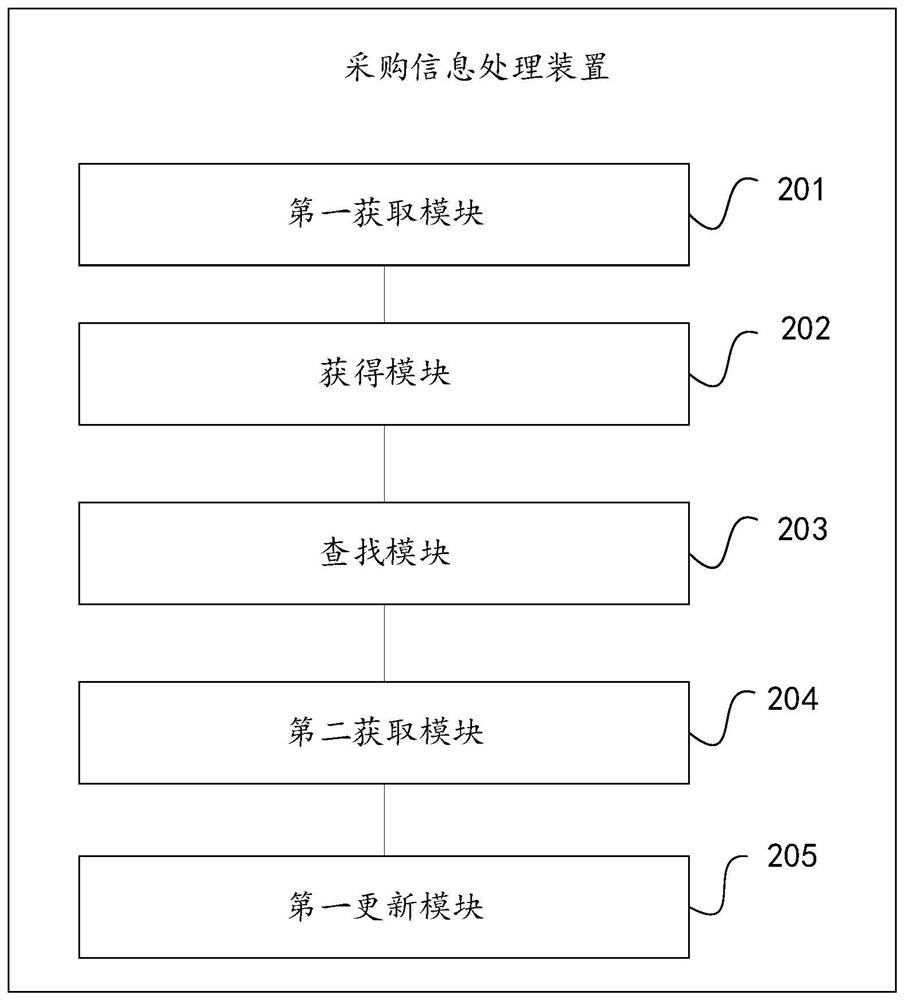

Purchase information processing method and device, electronic equipment and readable storage medium

The invention provides a purchasing information processing method and device, electronic equipment and a readable storage medium. The method comprises the steps of obtaining a first purchasing plan in advance, then identifying the first purchasing plan to obtain a material code of the first purchasing plan, searching a second purchasing plan which is the same as the material code from a purchasing plan library according to the material code, and if the second purchasing plan which is the same as the material code is searched from the purchasing plan library, acquiring a purchasing plan state of a second purchasing plan, and if the purchasing plan state of the second purchasing plan is before the enquiry state, merging the first purchasing plan into the second purchasing plan in the purchasing plan library, and updating the purchasing plan library, so that the new purchasing plan and the existing purchasing plan are merged and purchased together, therefor, the new purchasing plan does not need to continue to wait, the execution period of the new purchasing plan can be shortened, the purchasing plan library can be simpler, and management of the purchasing plan library is facilitated.

Owner:CENT RES INST OF BUILDING & CONSTR CO LTD MCC GRP +1

control device

ActiveCN106020009BReduce I/O timeShorten execution cycleProgramme controlComputer controlMotion computationOperating system

Provided is a control apparatus (1) that can, by causing multiple control programs that include motion computation programs to be executed in parallel, shorten the execution cycle of control programs that are executed cyclically. A microprocessor (100) is configured to execute multiple control programs in parallel. When executing communication commands included in control programs that are to be executed in parallel, a scheduling program causes the microprocessor (100) to execute the communication commands such that there is no competition between communication processes in a communication controller (150).

Owner:ORMON CORP