Matrix convolution calculation method, interface, coprocessor and system based on risc-v architecture

A RISC-V and coprocessor technology, applied in the field of matrix convolution computing, can solve problems such as poor real-time performance, many memory access instructions, and insufficient flexibility, so as to reduce the number of memory accesses and execution cycles, simplify coding design, and improve The effect of calculating speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0091] The technical solution will be described in detail below through a preferred embodiment and in conjunction with the accompanying drawings.

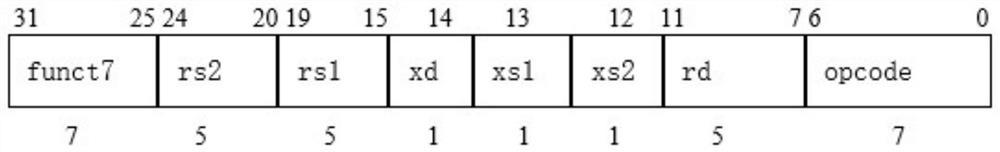

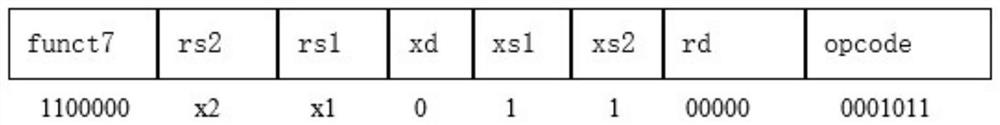

[0092] The invention provides a matrix convolution calculation method based on RISC-V architecture, an RCI interface (RISC-V Coprocessor Interface) for implementing the method, a coprocessor and an overall system. The calculation method includes a custom instruction part based on the RISC-V architecture, which defines the instruction encoding required for the matrix convolution operation.

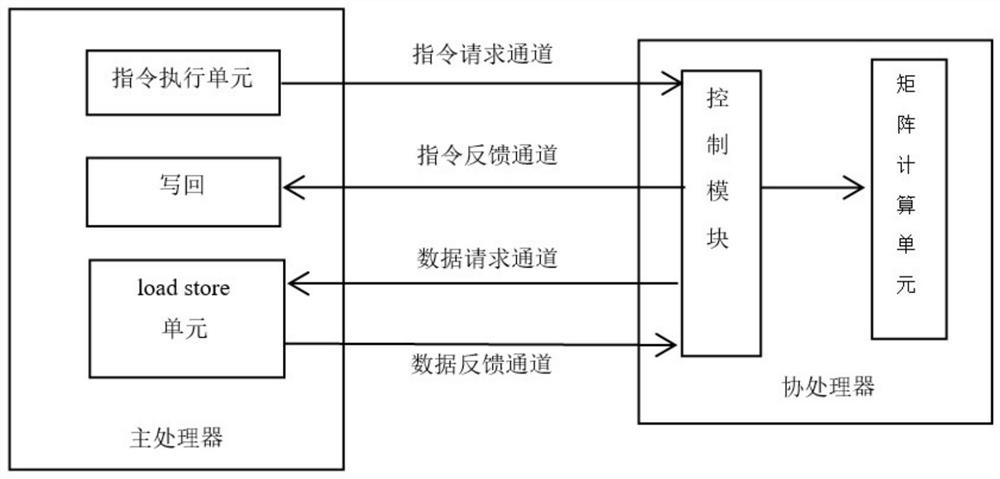

[0093] Such as figure 1 As shown, the matrix convolution computing system based on the RISC-V architecture corresponding to the computing method includes a coprocessor, a main processor, an RCI interface for transmitting requests and feedback between the main processor and the coprocessor, and a user memory for storage;

[0094] The RCI interface defines the data channel, signal, and processing flow between the main processor and the coprocess...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More