Patents

Literature

576 results about "X86" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

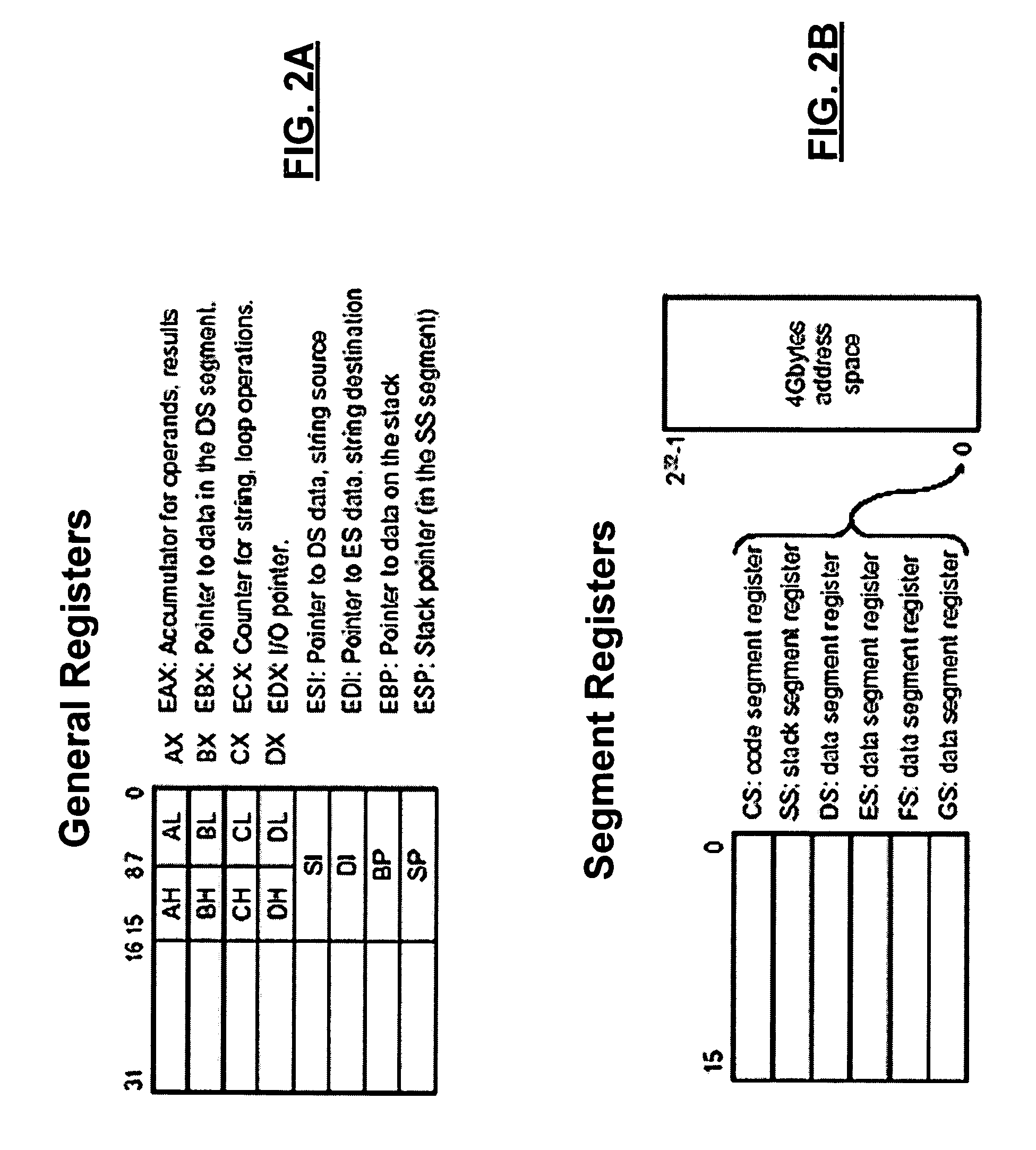

X86 is a family of instruction set architectures initially developed by Intel based on the Intel 8086 microprocessor and its 8088 variant. The 8086 was introduced in 1978 as a fully 16-bit extension of Intel's 8-bit 8080 microprocessor, with memory segmentation as a solution for addressing more memory than can be covered by a plain 16-bit address. The term "x86" came into being because the names of several successors to Intel's 8086 processor end in "86", including the 80186, 80286, 80386 and 80486 processors.

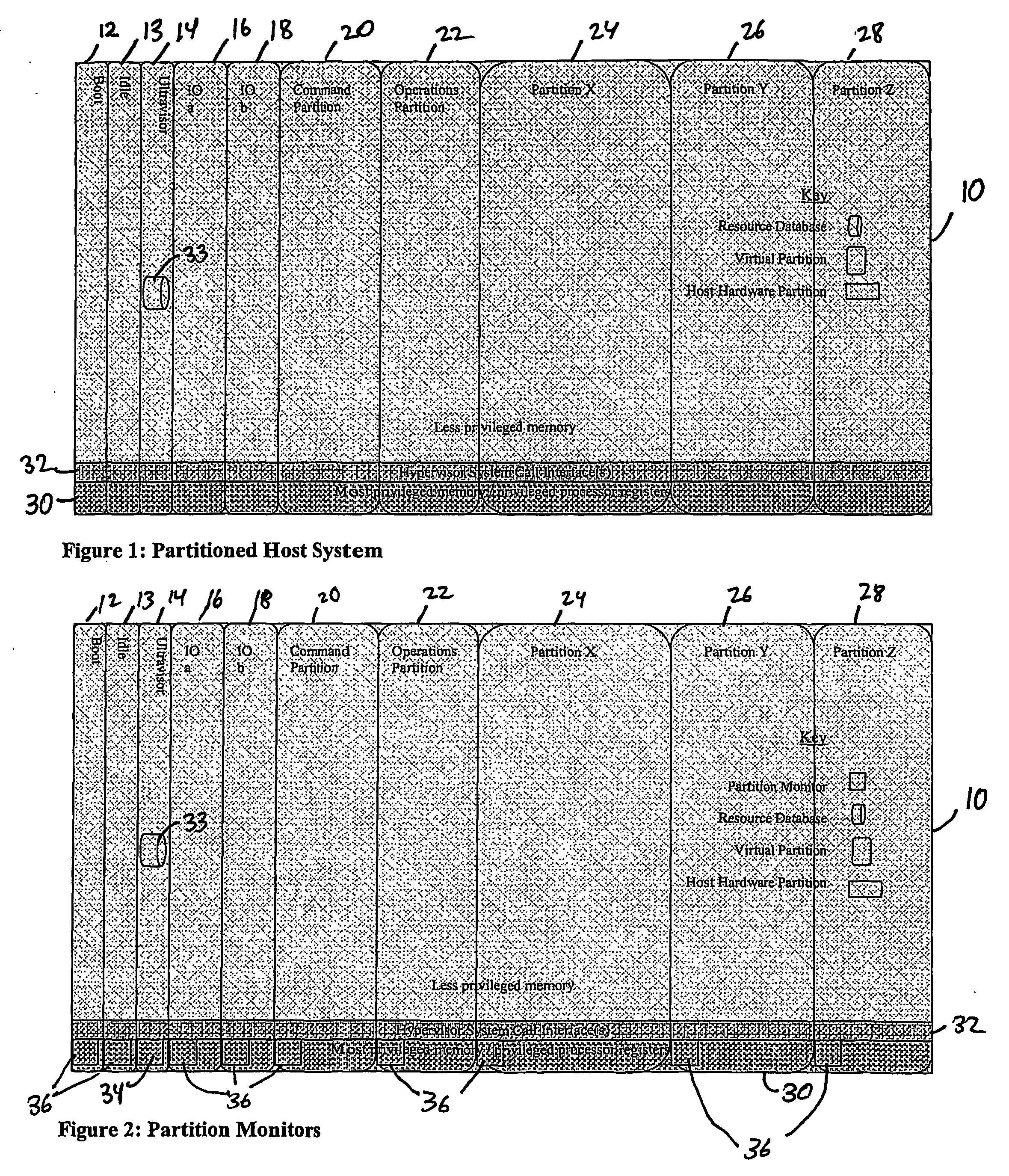

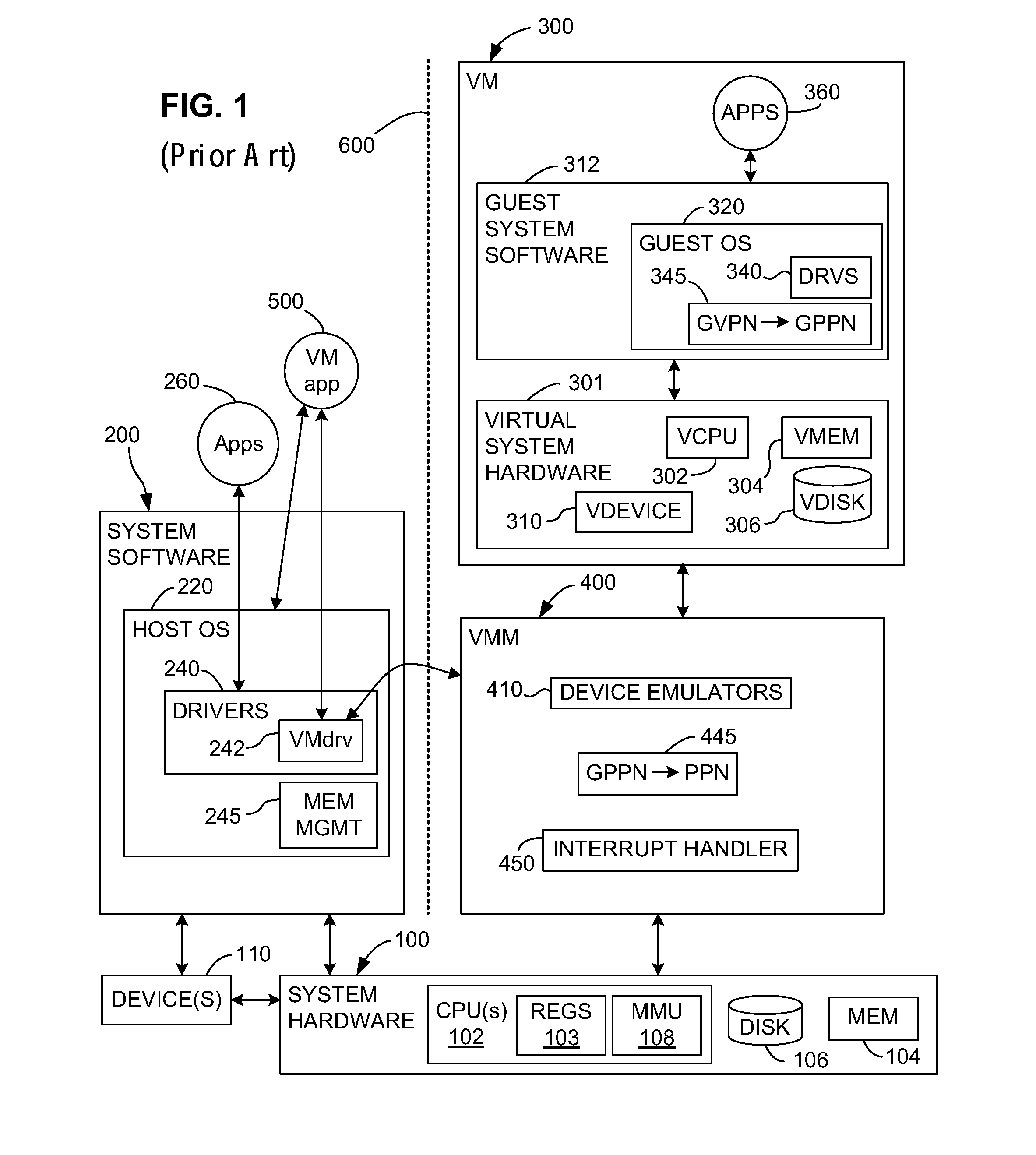

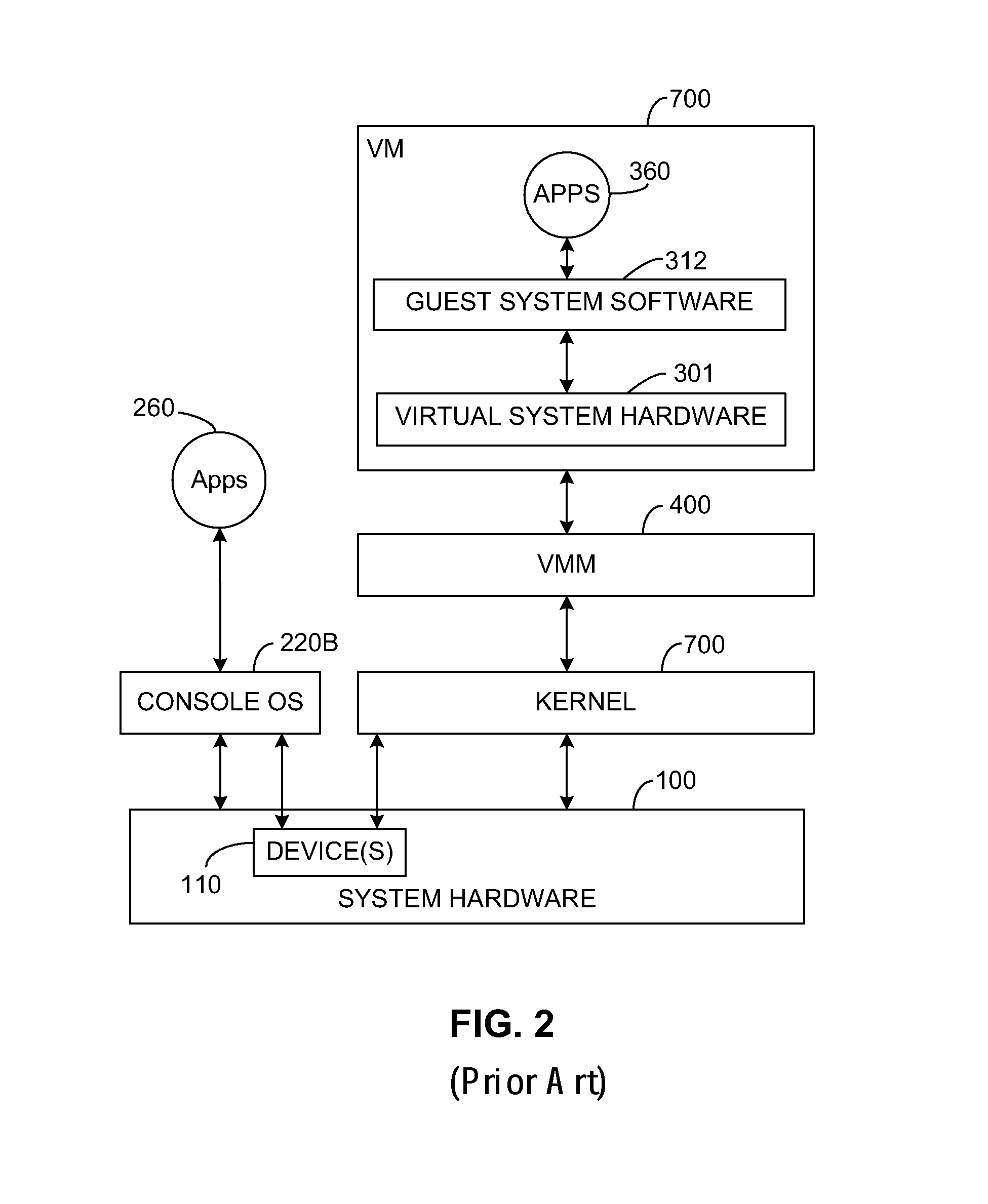

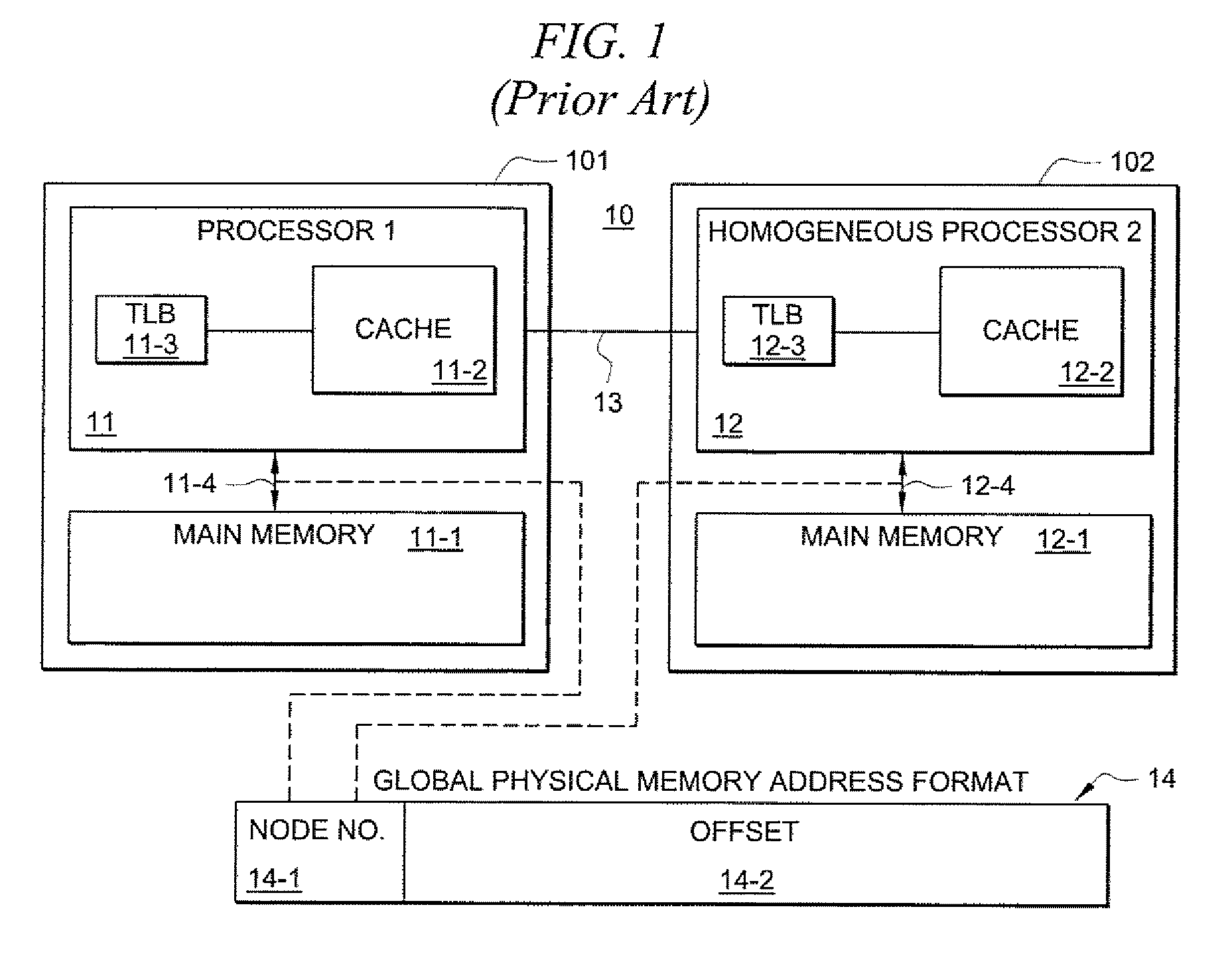

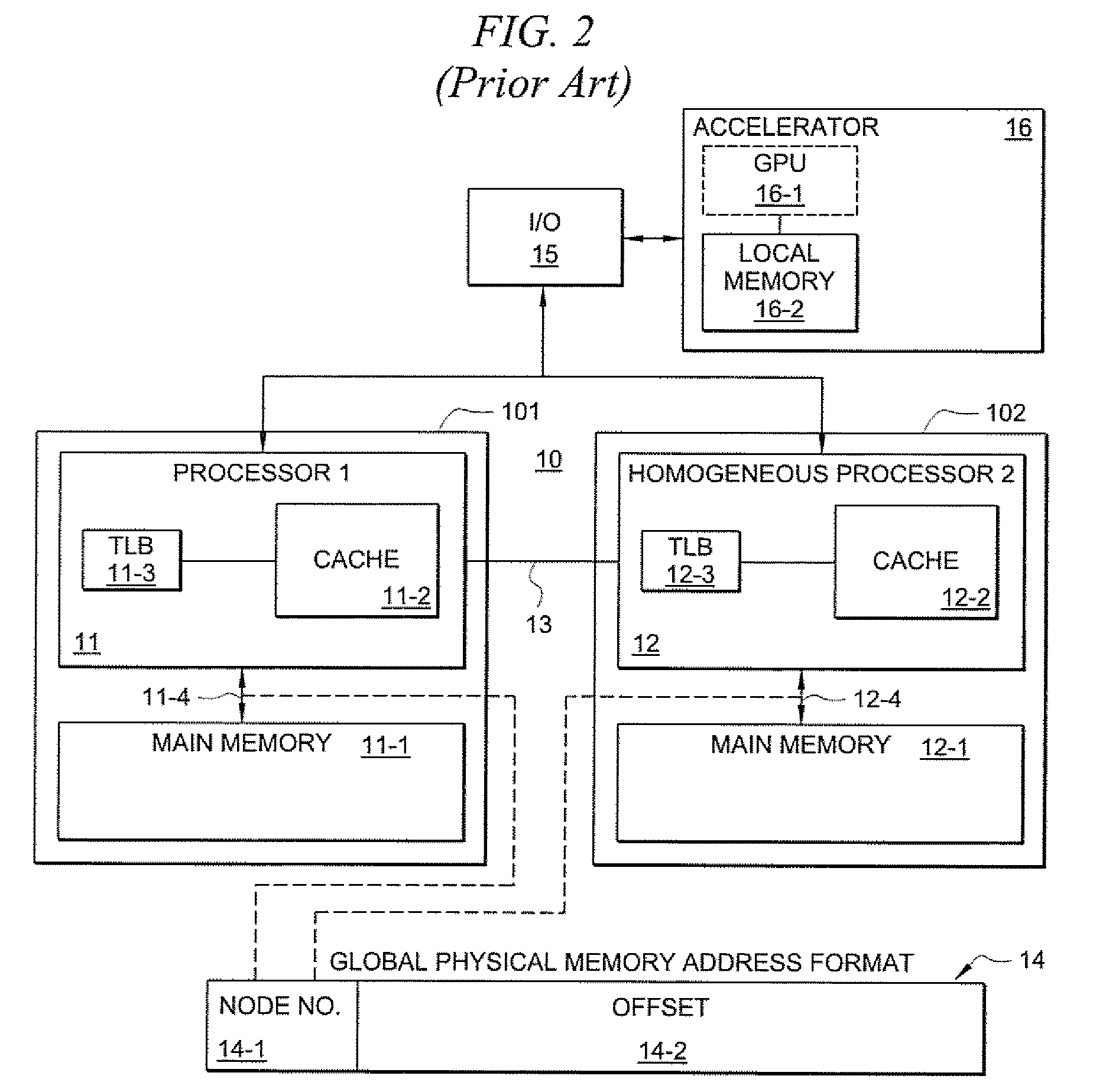

Virtual data center that allocates and manages system resources across multiple nodes

ActiveUS20070067435A1Improve securityExcessive removalError detection/correctionMemory adressing/allocation/relocationOperational systemData center

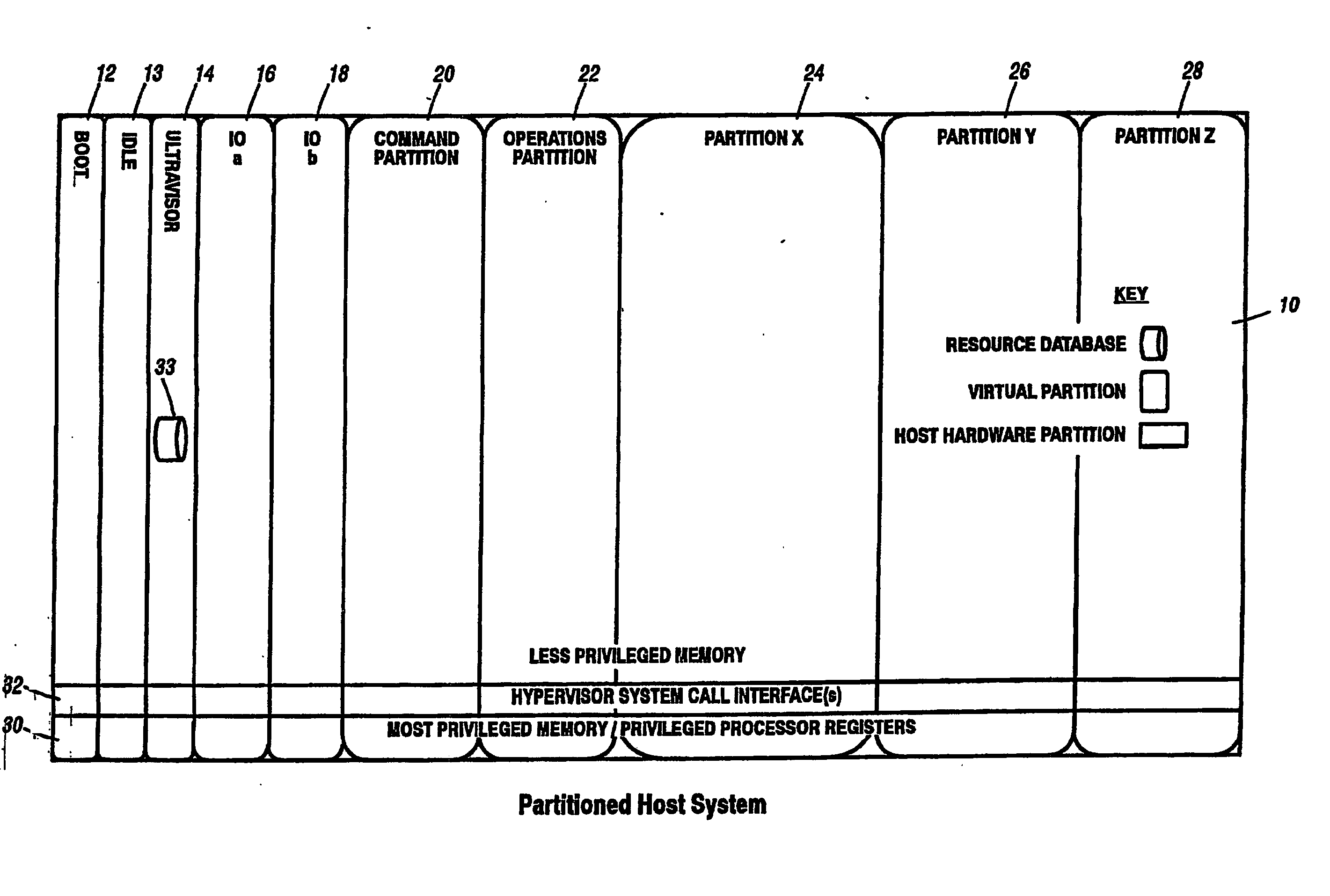

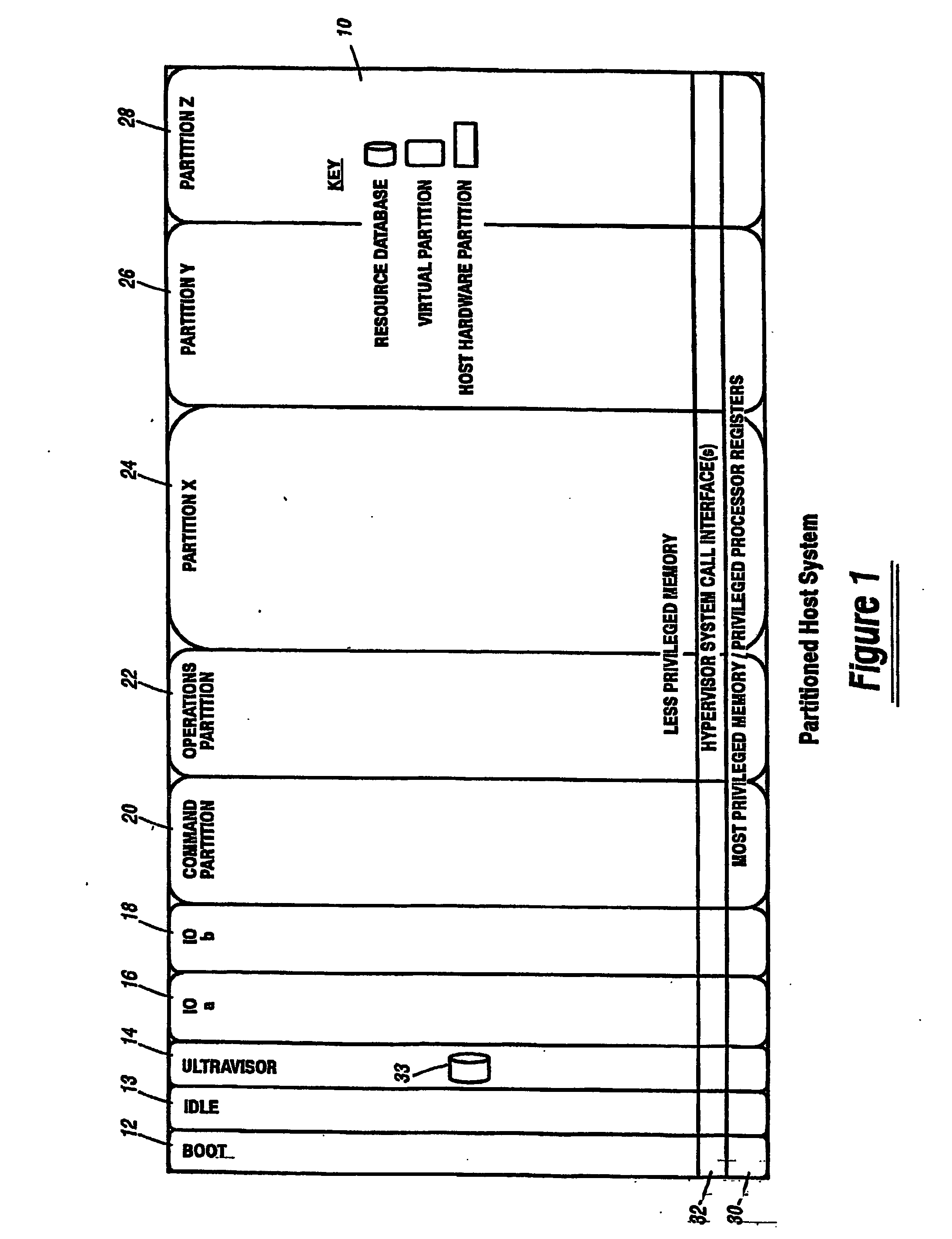

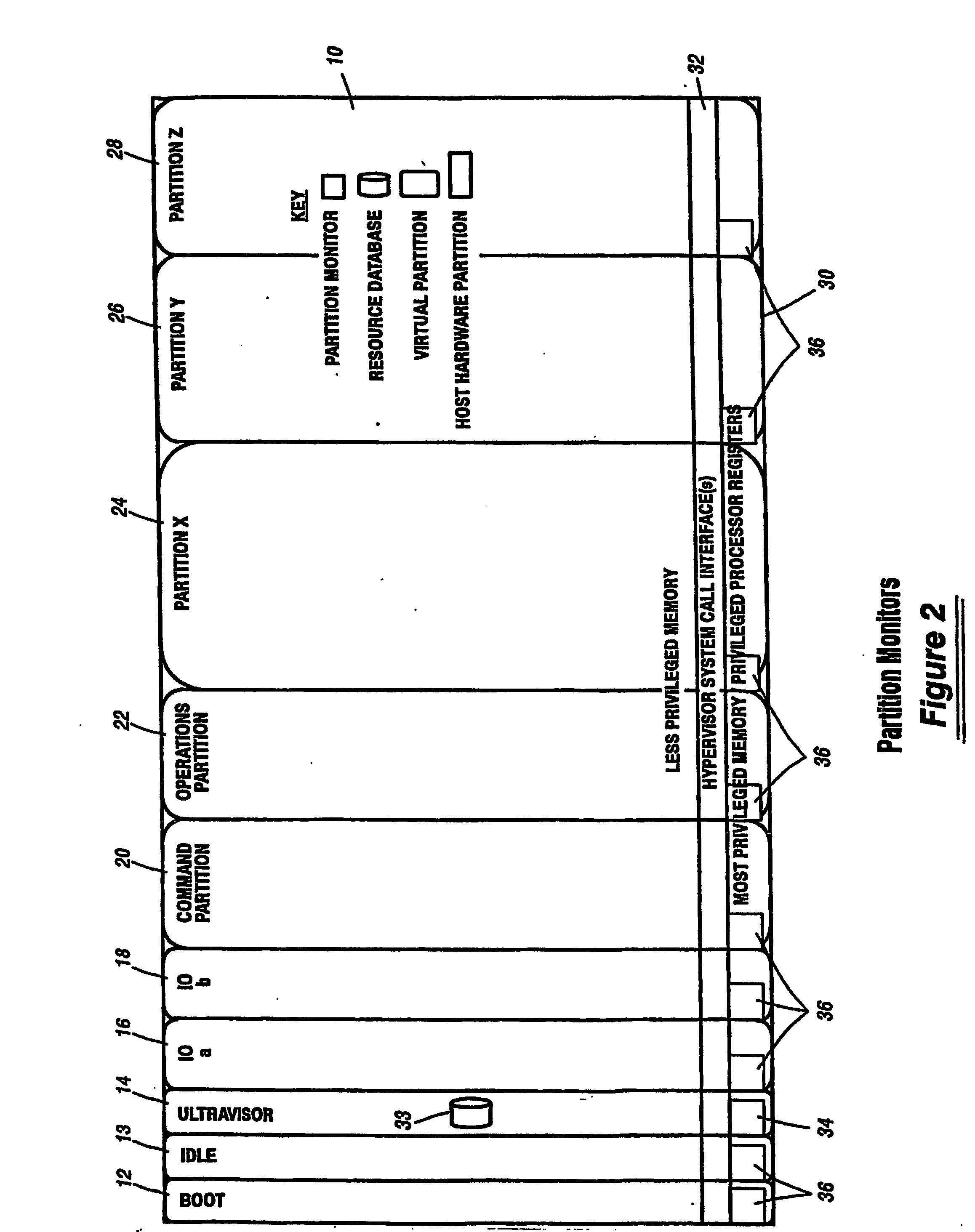

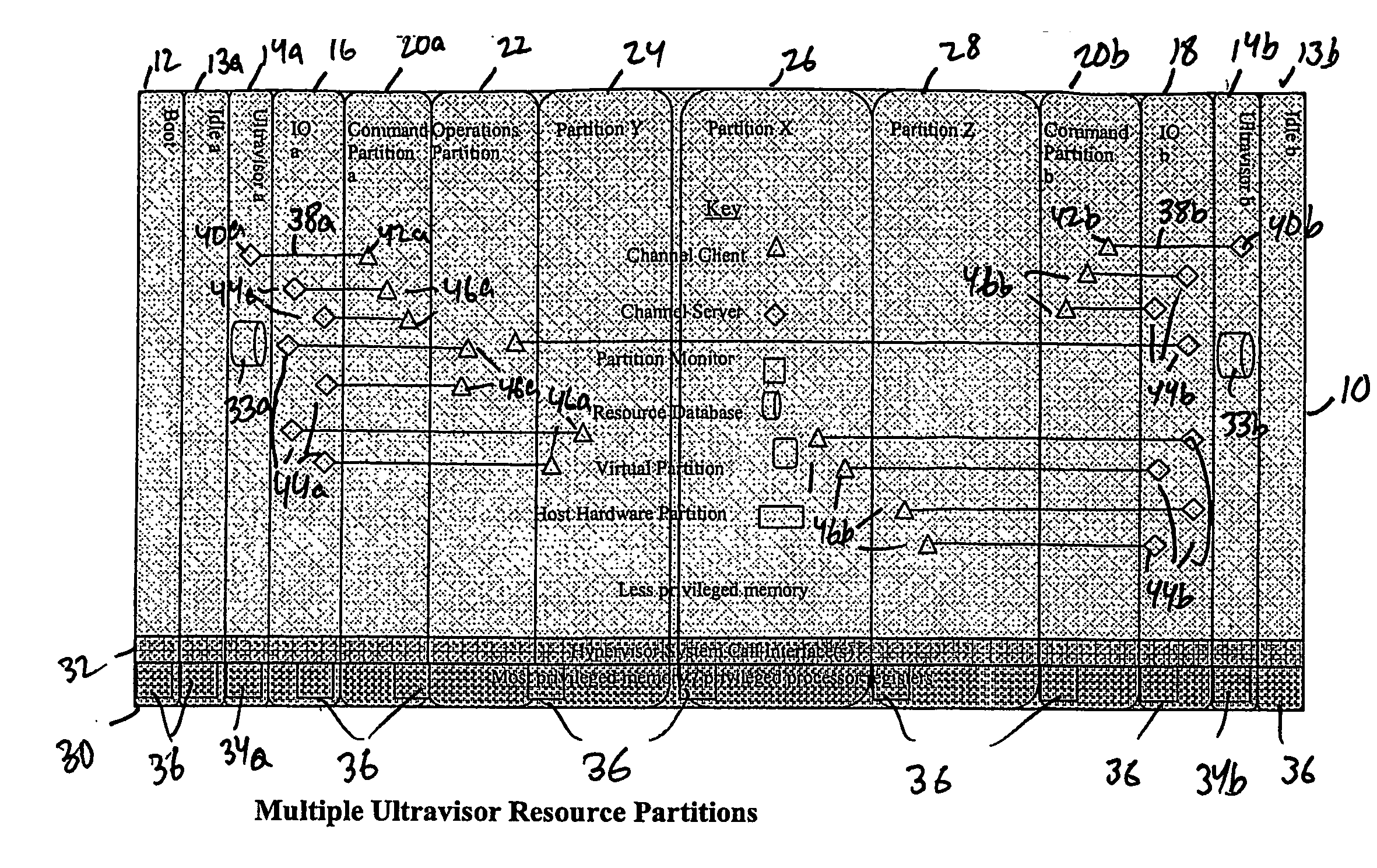

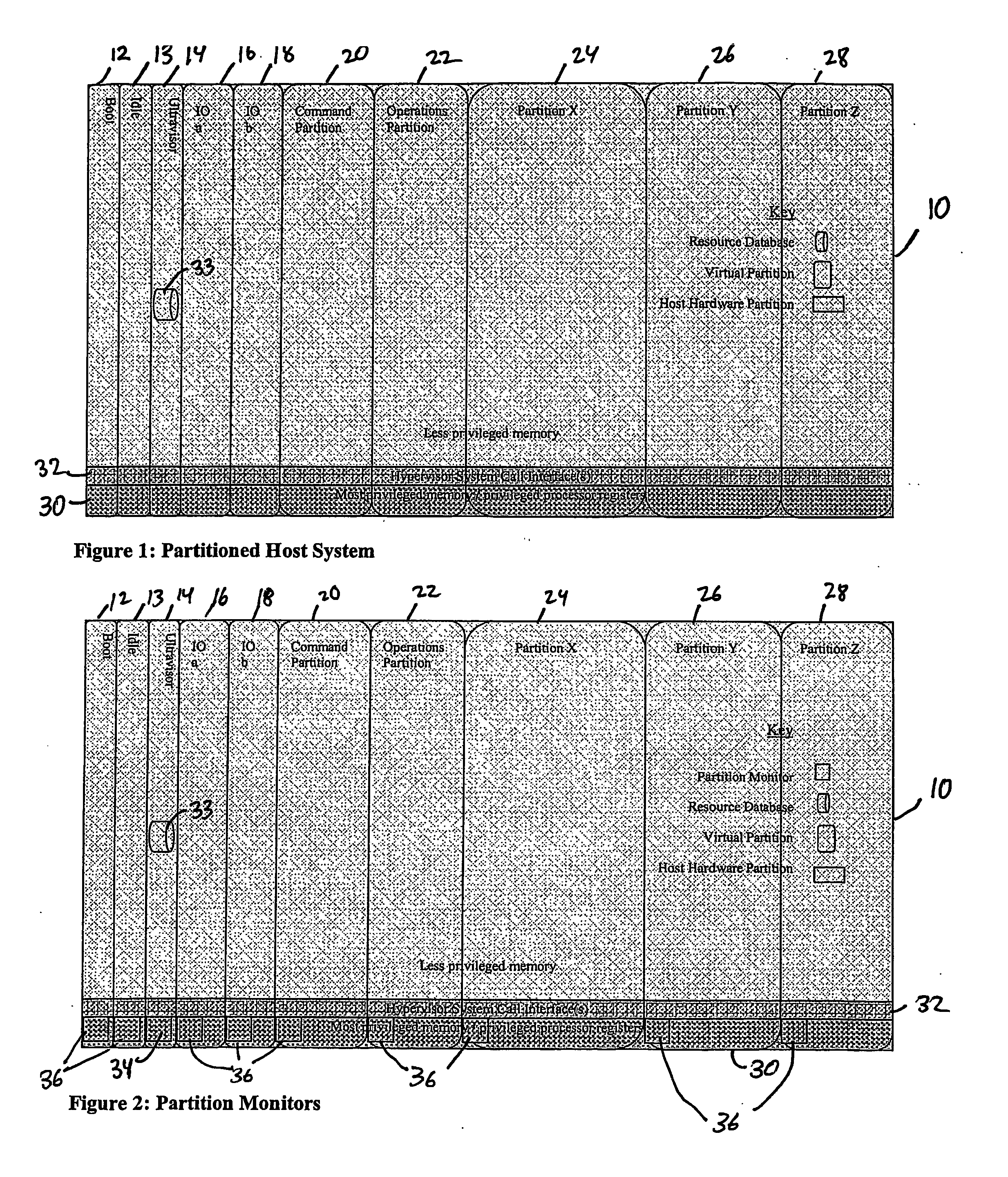

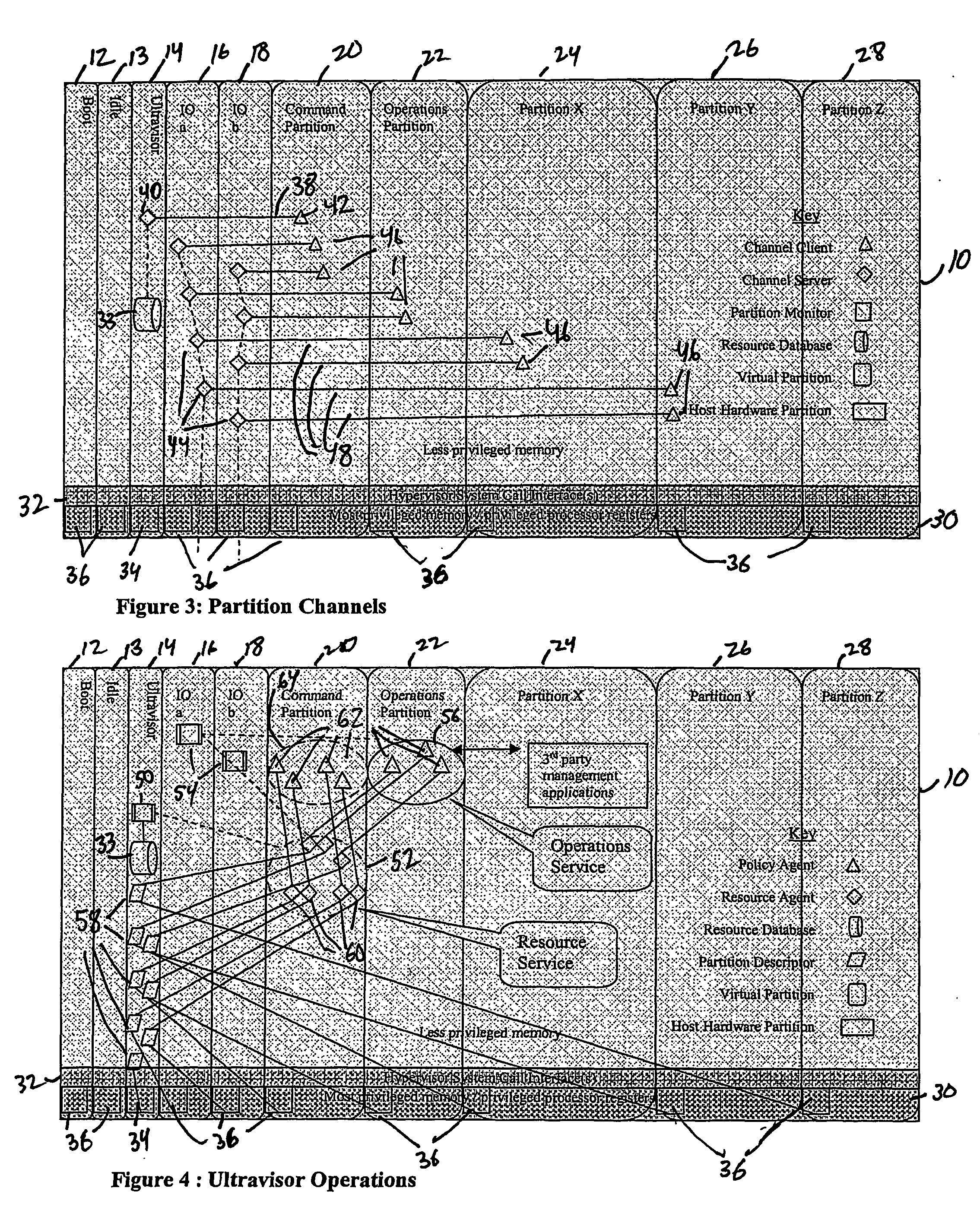

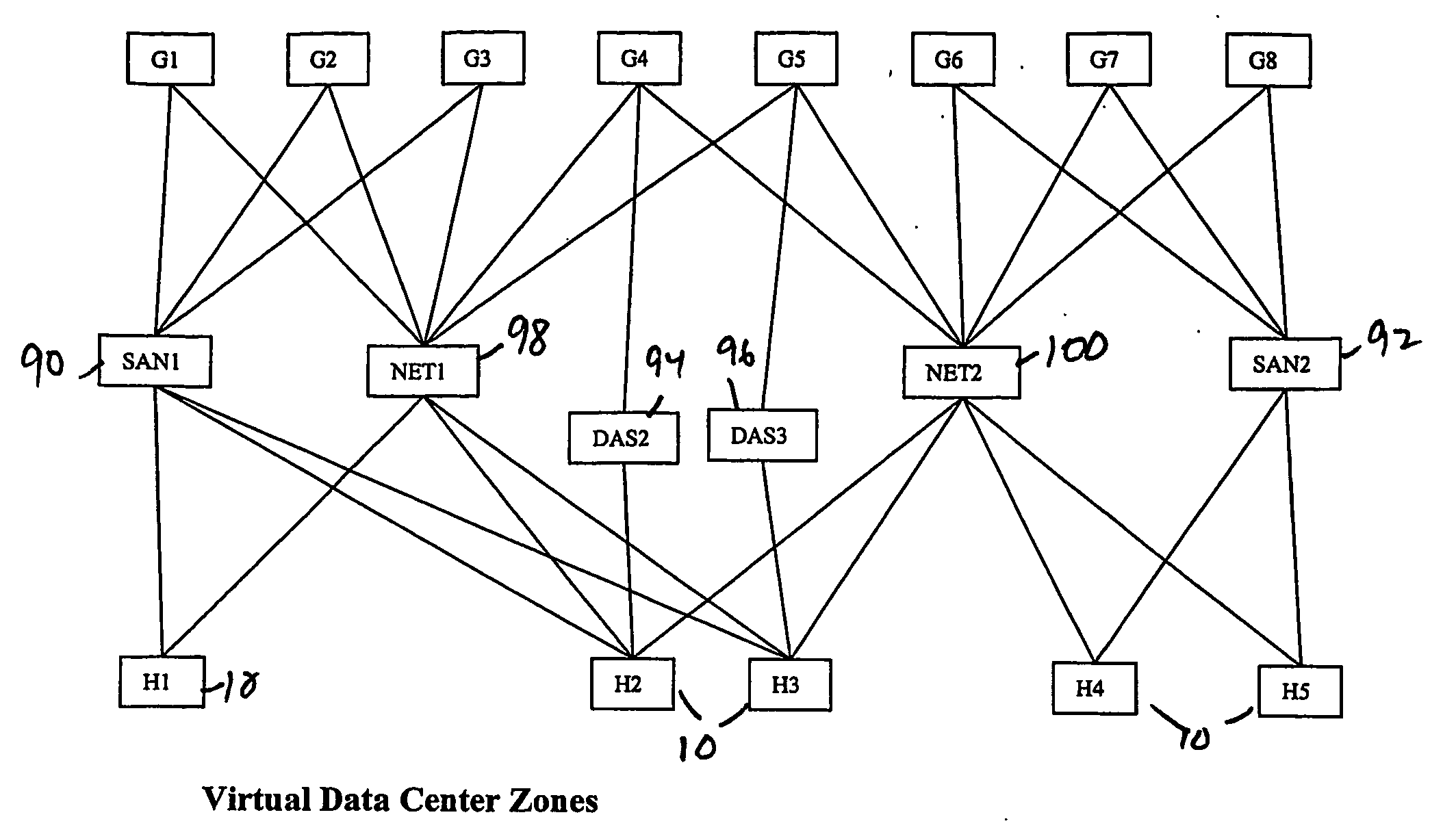

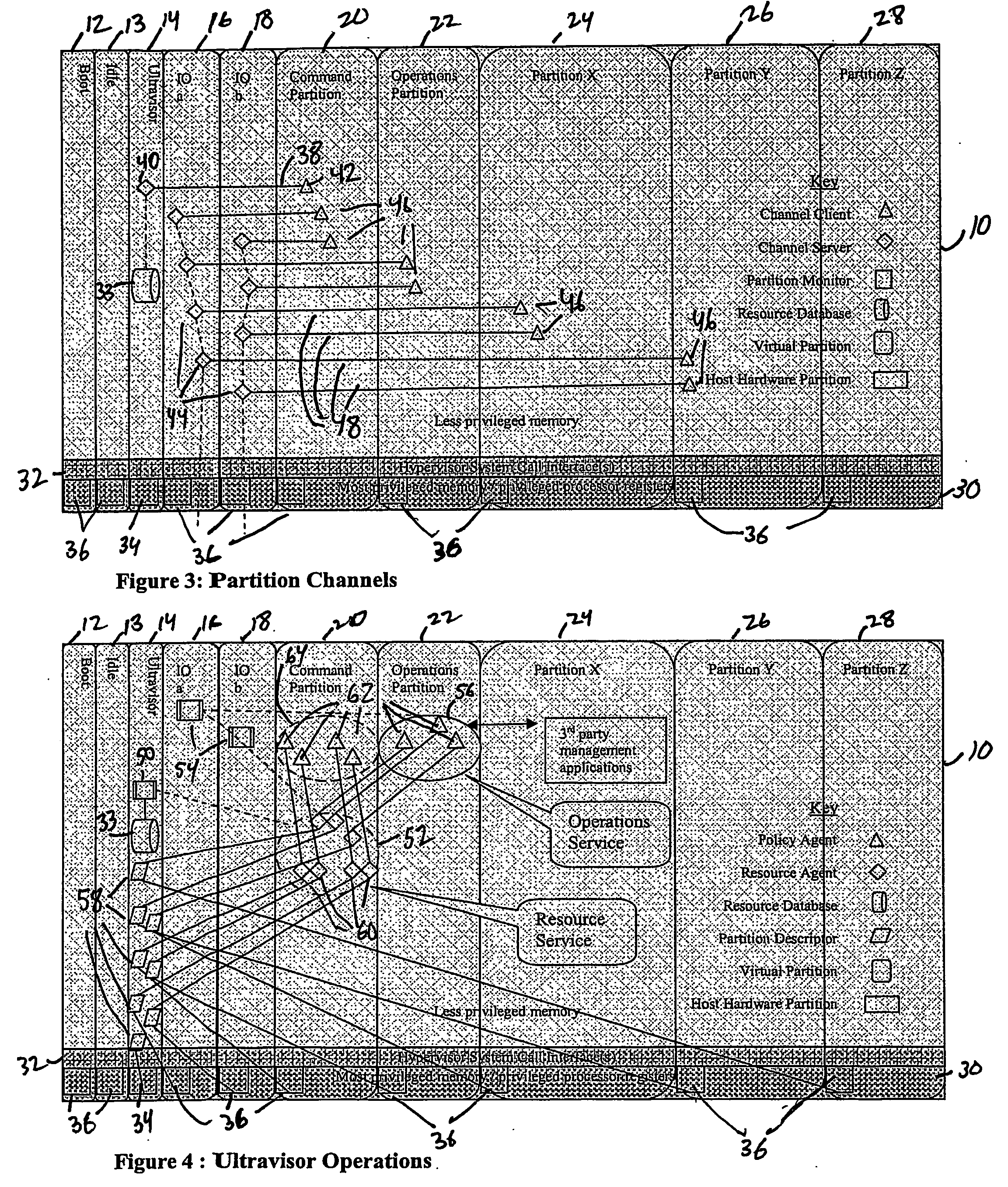

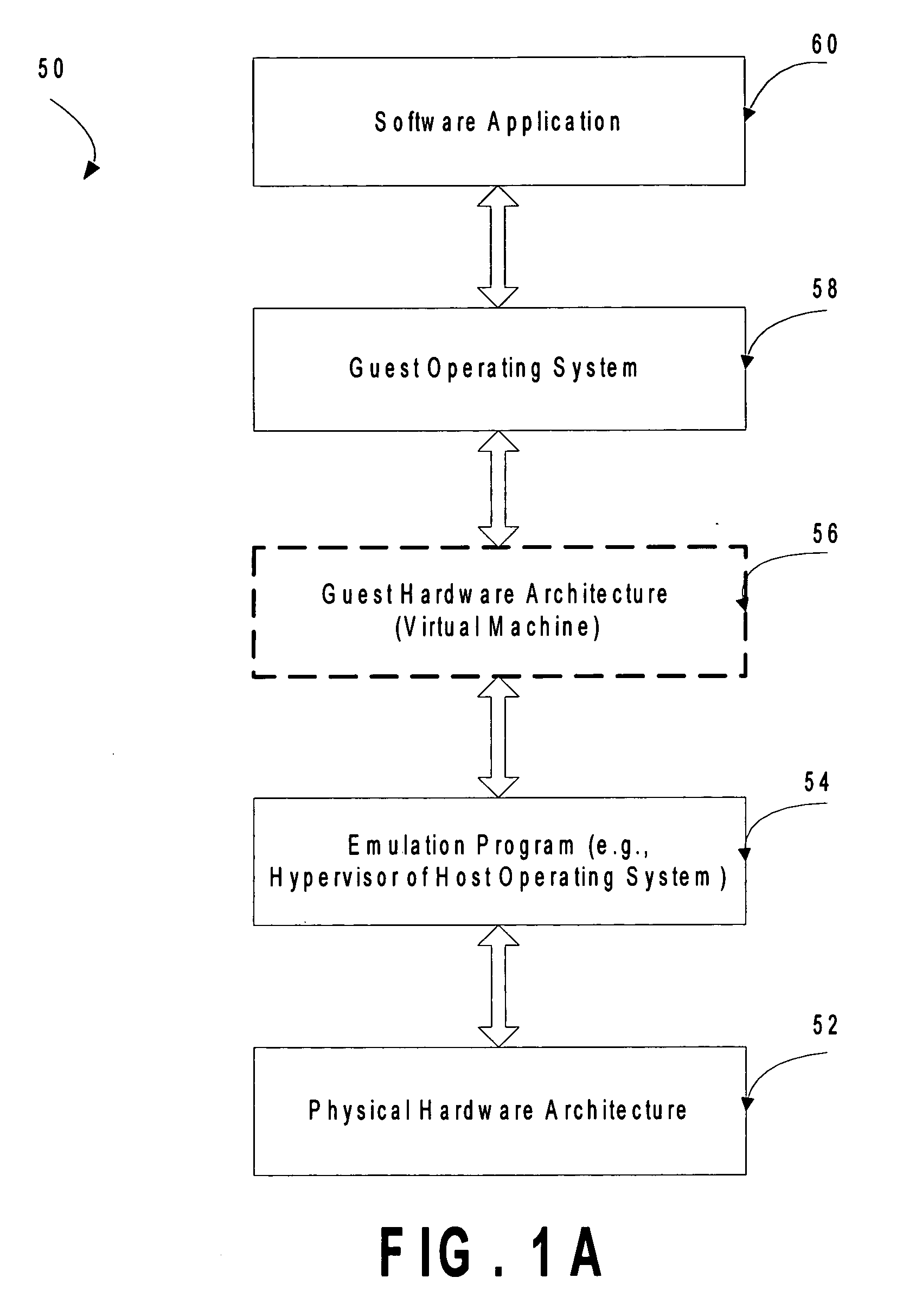

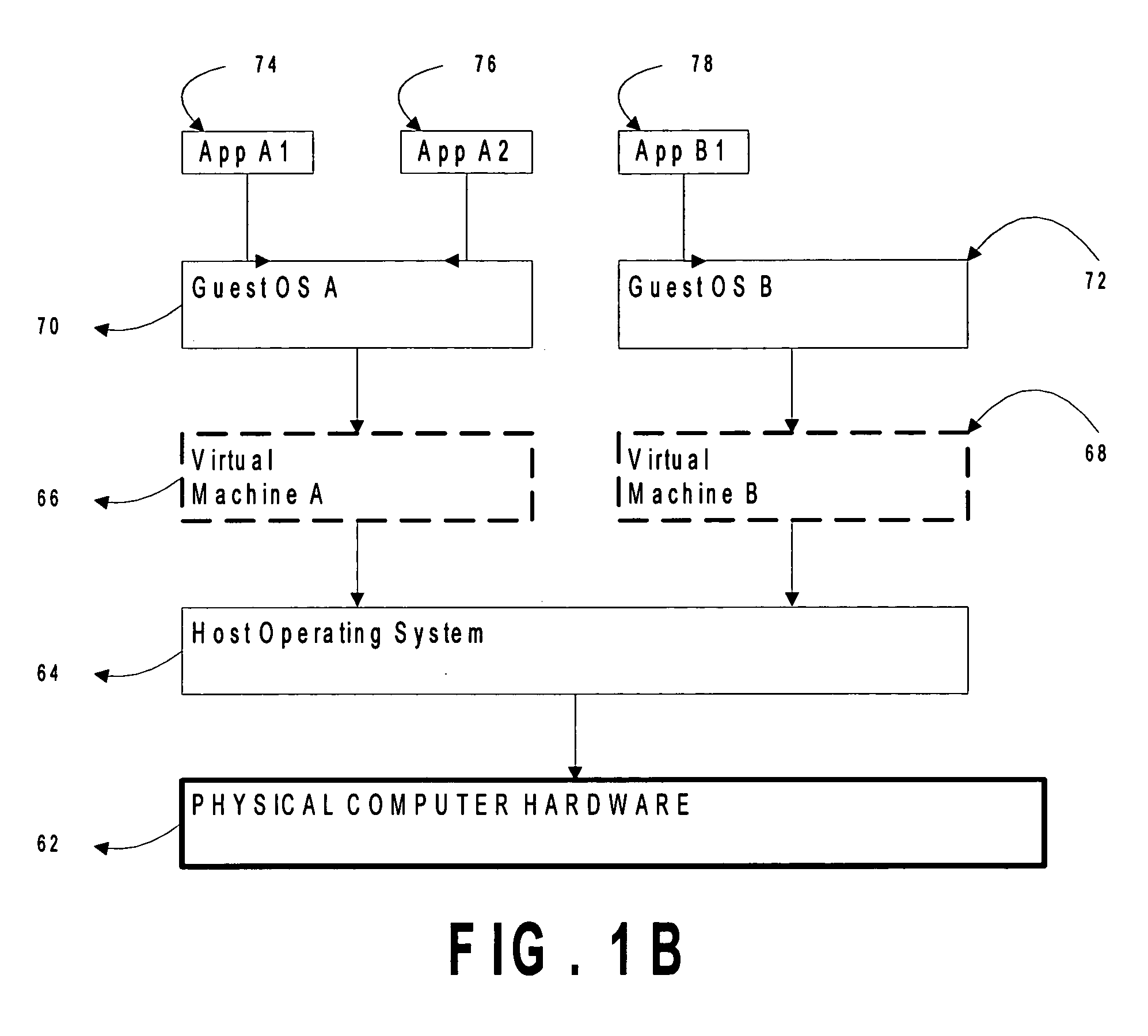

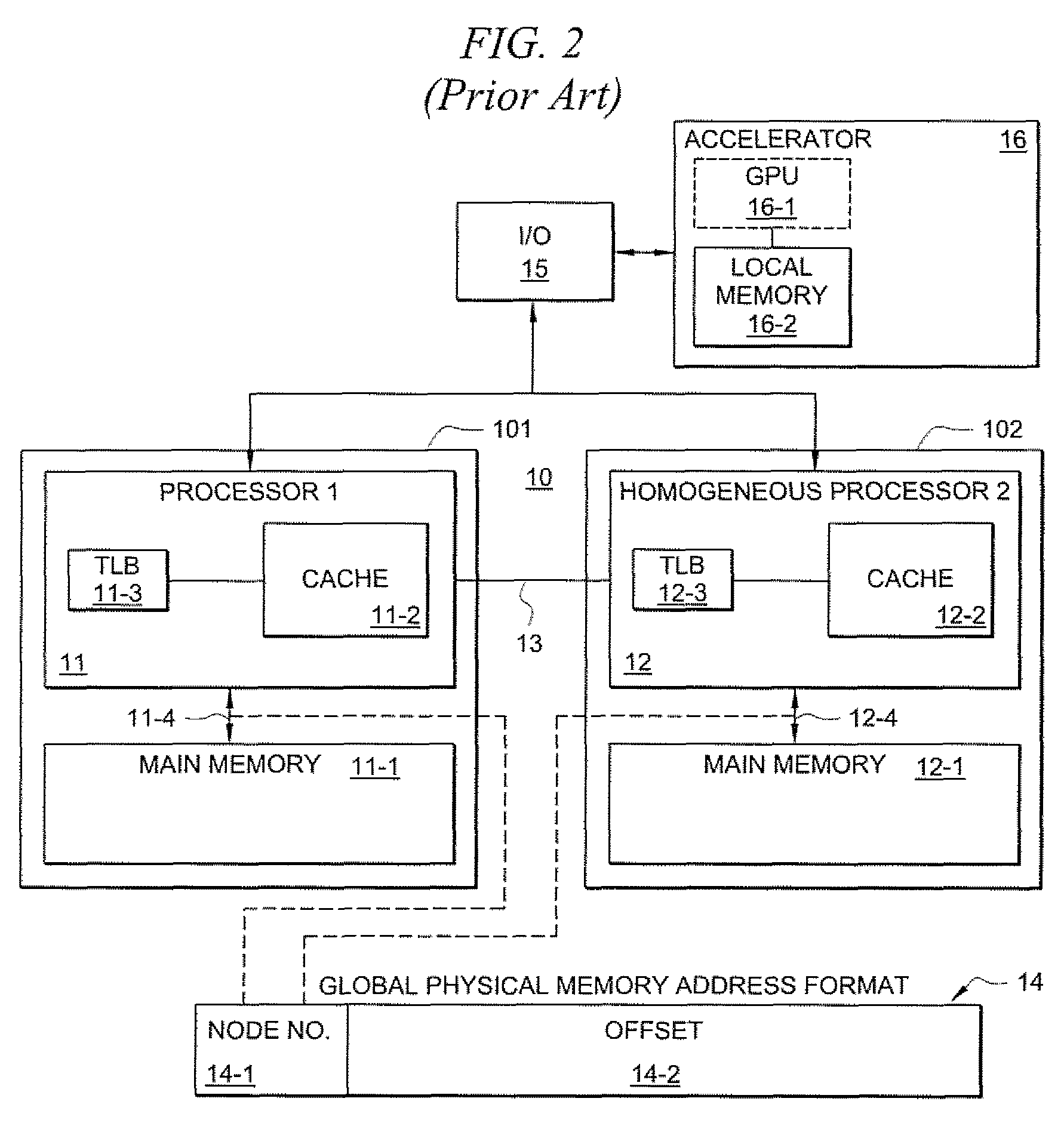

A virtualization infrastructure that allows multiple guest partitions to run within a host hardware partition. The host system is divided into distinct logical or virtual partitions and special infrastructure partitions are implemented to control resource management and to control physical I / O device drivers that are, in turn, used by operating systems in other distinct logical or virtual guest partitions. Host hardware resource management runs as a tracking application in a resource management “ultravisor” partition, while host resource management decisions are performed in a higher level command partition based on policies maintained in a separate operations partition. The conventional hypervisor is reduced to a context switching and containment element (monitor) for the respective partitions, while the system resource management functionality is implemented in the ultravisor partition. The ultravisor partition maintains the master in-memory database of the hardware resource allocations and serves a command channel to accept transactional requests for assignment of resources to partitions. It also provides individual read-only views of individual partitions to the associated partition monitors. Host hardware I / O management is implemented in special redundant I / O partitions. Operating systems in other logical or virtual partitions communicate with the I / O partitions via memory channels established by the ultravisor partition. The guest operating systems in the respective logical or virtual partitions are modified to access monitors that implement a system call interface through which the ultravisor, I / O, and any other special infrastructure partitions may initiate communications with each other and with the respective guest partitions. The guest operating systems are modified so that they do not attempt to use the “broken” instructions in the x86 system that complete virtualization systems must resolve by inserting traps. System resources are separated into zones that are managed by a separate partition containing resource management policies that may be implemented across nodes to implement a virtual data center.

Owner:UNISYS CORP

Computer system para-virtualization using a hypervisor that is implemented in a partition of the host system

ActiveUS20070028244A1Improve securityExcessive removalError detection/correctionMemory adressing/allocation/relocationOperational systemSystem call

A virtualization infrastructure that allows multiple guest partitions to run within a host hardware partition. The host system is divided into distinct logical or virtual partitions and special infrastructure partitions are implemented to control resource management and to control physical I / O device drivers that are, in turn, used by operating systems in other distinct logical or virtual guest partitions. Host hardware resource management runs as a tracking application in a resource management “ultravisor” partition, while host resource management decisions are performed in a higher level command partition based on policies maintained in a separate operations partition. The conventional hypervisor is reduced to a context switching and containment element (monitor) for the respective partitions, while the system resource management functionality is implemented in the ultravisor partition. The ultravisor partition maintains the master in-memory database of the hardware resource allocations and serves a command channel to accept transactional requests for assignment of resources to partitions. It also provides individual read-only views of individual partitions to the associated partition monitors. Host hardware I / O management is implemented in special redundant I / O partitions. Operating systems in other logical or virtual partitions communicate with the I / O partitions via memory channels established by the ultravisor partition. The guest operating systems in the respective logical or virtual partitions are modified to access monitors that implement a system call interface through which the ultravisor, I / O, and any other special infrastructure partitions may initiate communications with each other and with the respective guest partitions. The guest operating systems are modified so that they do not attempt to use the “broken” instructions in the x86 system that complete virtualization systems must resolve by inserting traps.

Owner:UNISYS CORP

Para-virtualized computer system with I/0 server partitions that map physical host hardware for access by guest partitions

InactiveUS20070061441A1Improve efficiencyImprove securityError detection/correctionDigital computer detailsOperational systemSystem call

A virtualization infrastructure that allows multiple guest partitions to run within a host hardware partition. The host system is divided into distinct logical or virtual partitions and special infrastructure partitions are implemented to control resource management and to control physical I / O device drivers that are, in turn, used by operating systems in other distinct logical or virtual guest partitions. Host hardware resource management runs as a tracking application in a resource management “ultravisor” partition, while host resource management decisions are performed in a higher level command partition based on policies maintained in a separate operations partition. The conventional hypervisor is reduced to a context switching and containment element (monitor) for the respective partitions, while the system resource management functionality is implemented in the ultravisor partition. The ultravisor partition maintains the master in-memory database of the hardware resource allocations and serves a command channel to accept transactional requests for assignment of resources to partitions. It also provides individual read-only views of individual partitions to the associated partition monitors. Host hardware I / O management is implemented in special redundant I / O partitions. Operating systems in other logical or virtual partitions communicate with the I / O partitions via memory channels established by the ultravisor partition. The guest operating systems in the respective logical or virtual partitions are modified to access monitors that implement a system call interface through which the ultravisor, I / O, and any other special infrastructure partitions may initiate communications with each other and with the respective guest partitions. The guest operating systems are modified so that they do not attempt to use the “broken” instructions in the x86 system that complete virtualization systems must resolve by inserting traps.

Owner:UNISYS CORP

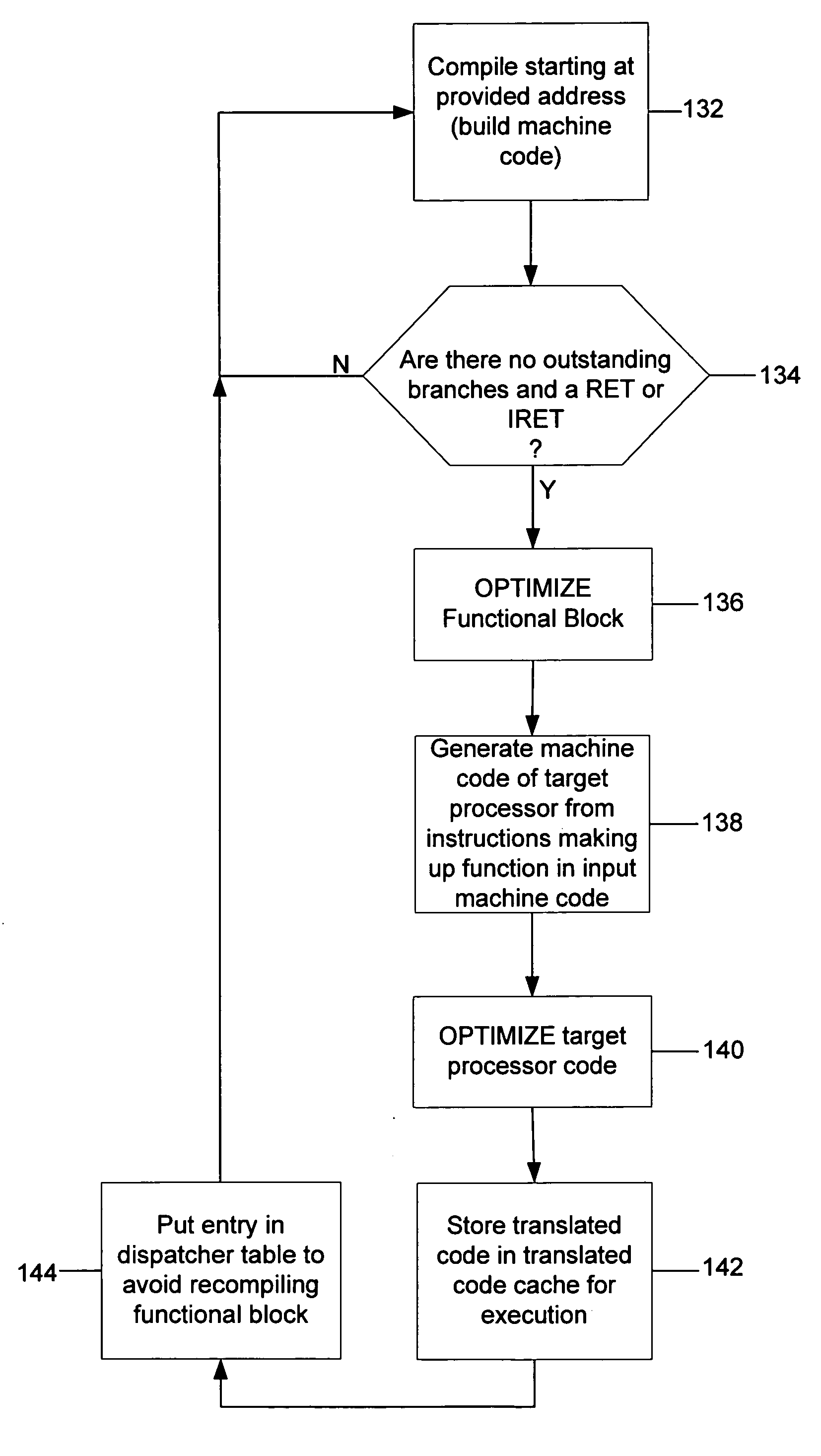

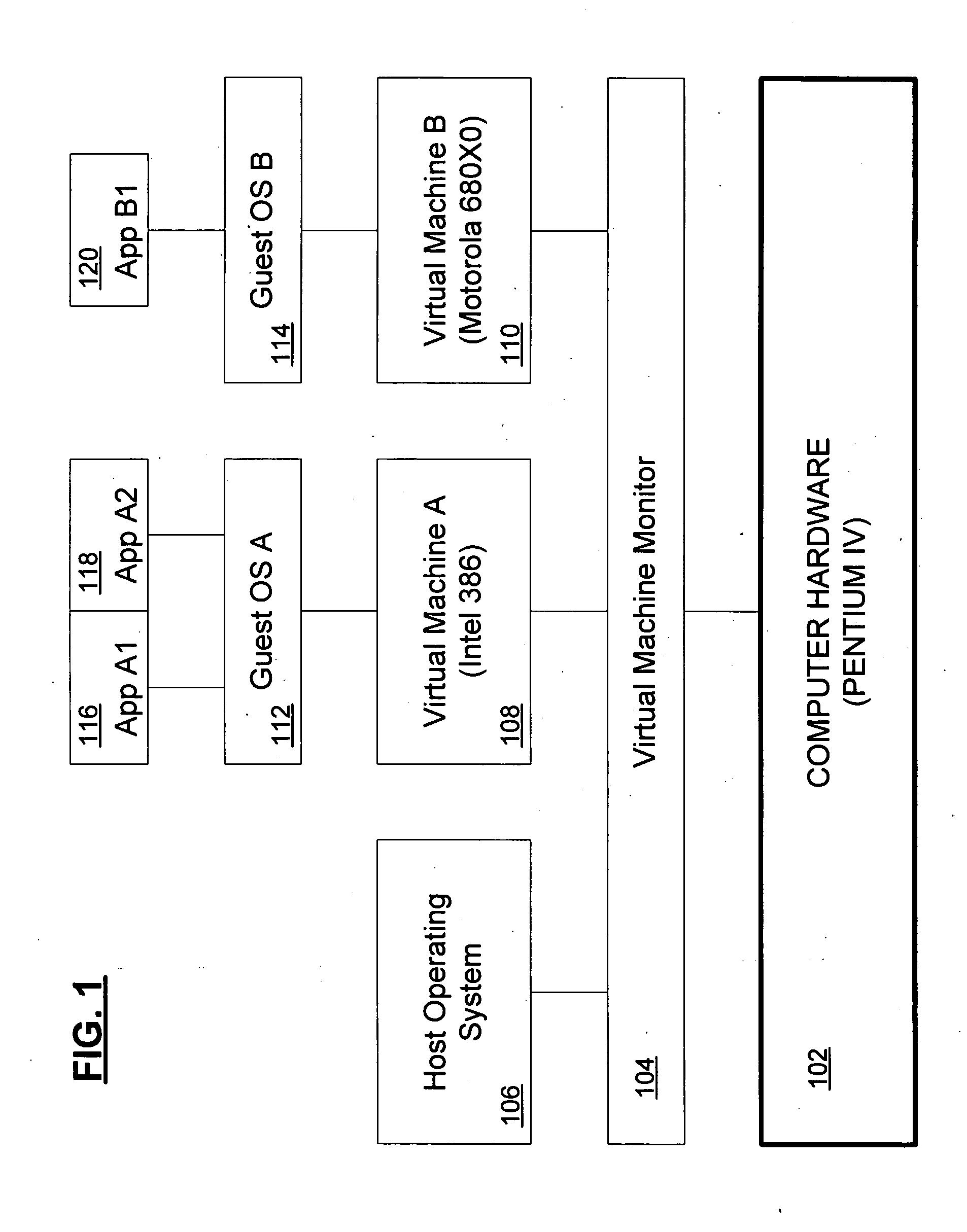

Function-level just-in-time translation engine with multiple pass optimization

InactiveUS20070006178A1Improve translationReduce context switchingBinary to binaryProgram controlCode TranslationSoftware emulation

A JIT binary translator translates code at a function level of the source code rather than at an opcode level. The JIT binary translator of the invention grabs an entire x86 function out of the source stream, rather than an instruction, translates the whole function into an equivalent function of the target processor, and executes that function all at once before returning to the source stream, thereby reducing context switching. Also, since the JIT binary translator sees the entire source code function context at once the software emulator may optimize the code translation. For example, the JIT binary translator might decide to translate a sequence of x86 instructions into an efficient PPC equivalent sequence. Many such optimizations result in a tighter emulated binary.

Owner:MICROSOFT TECH LICENSING LLC

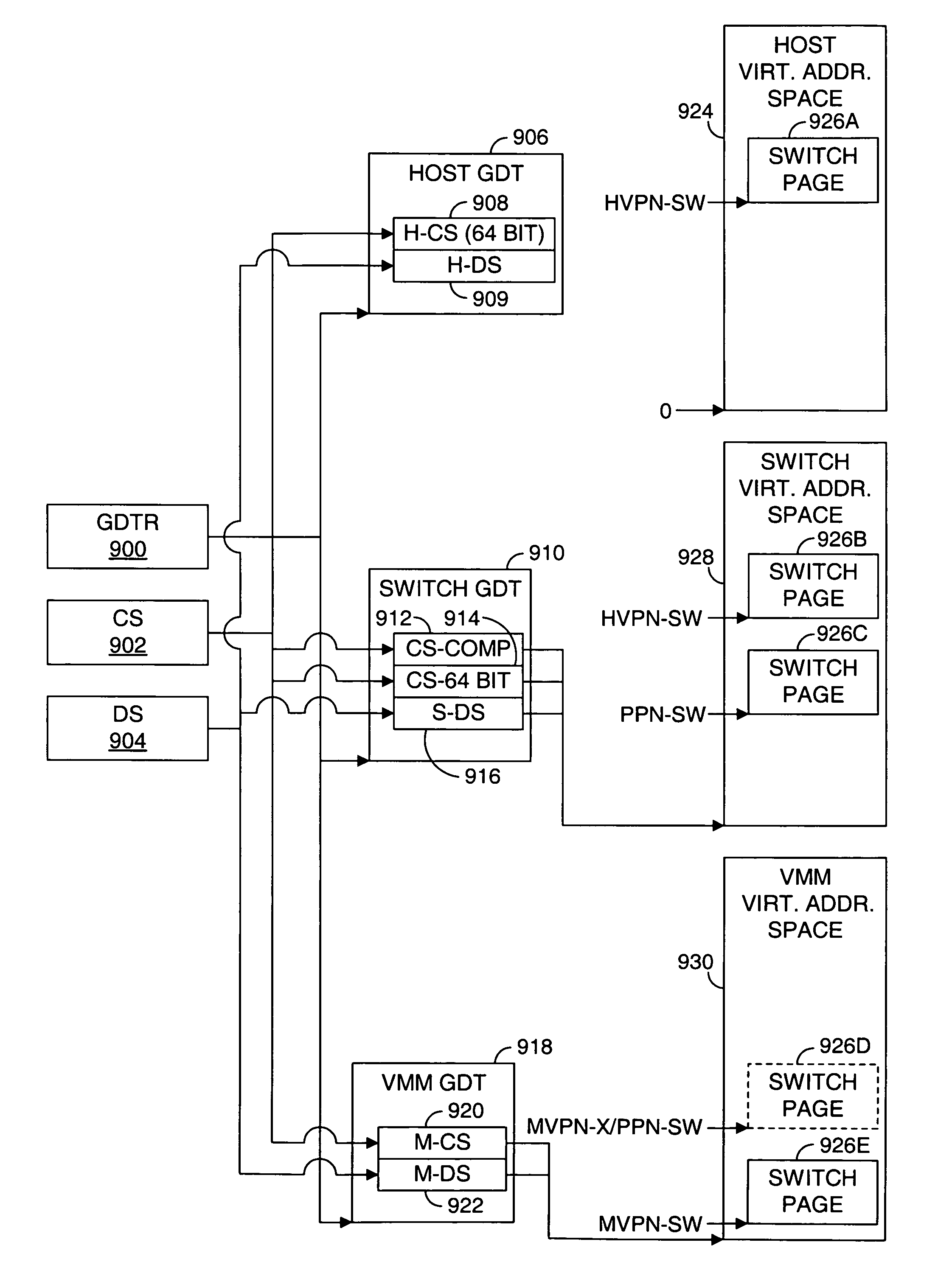

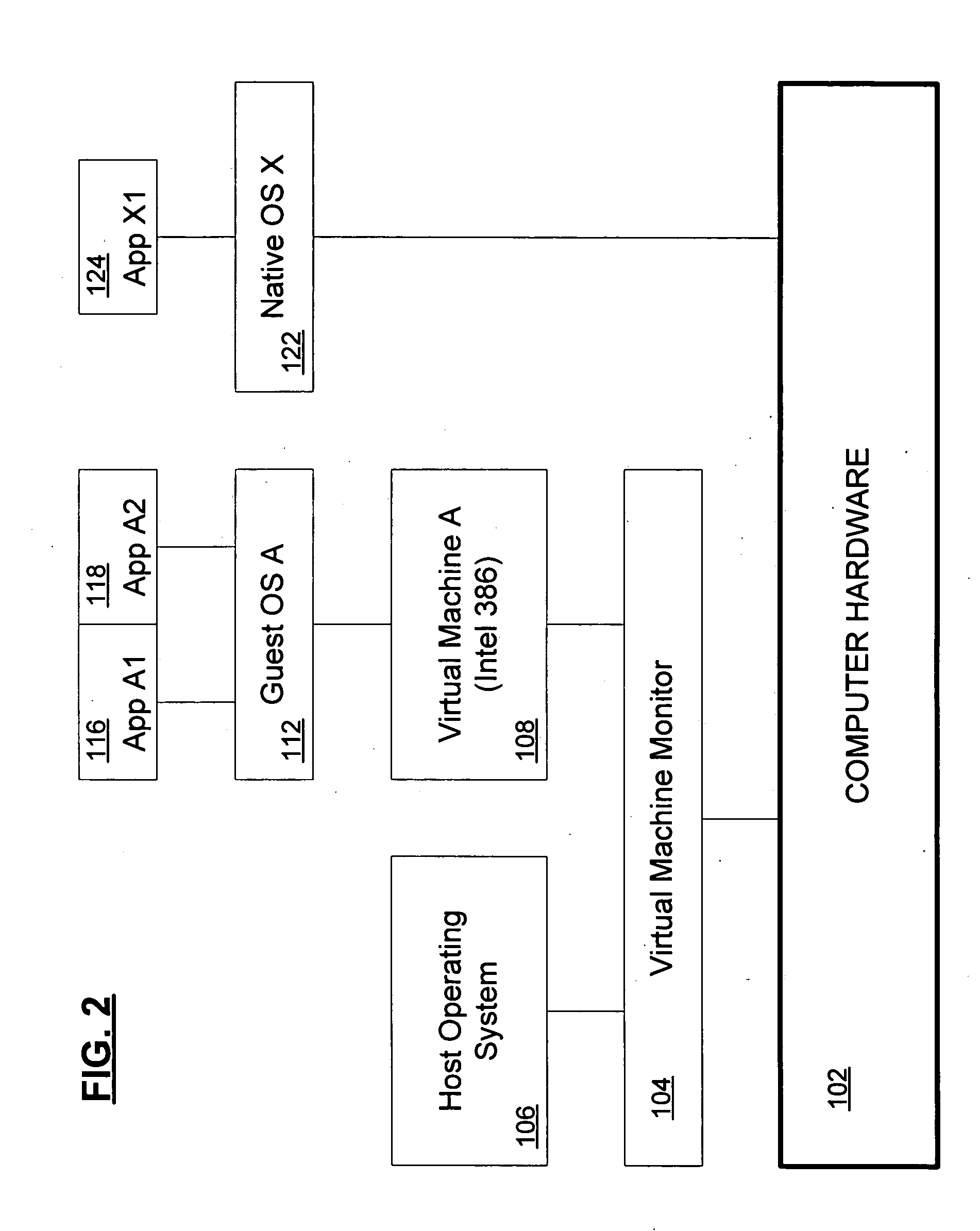

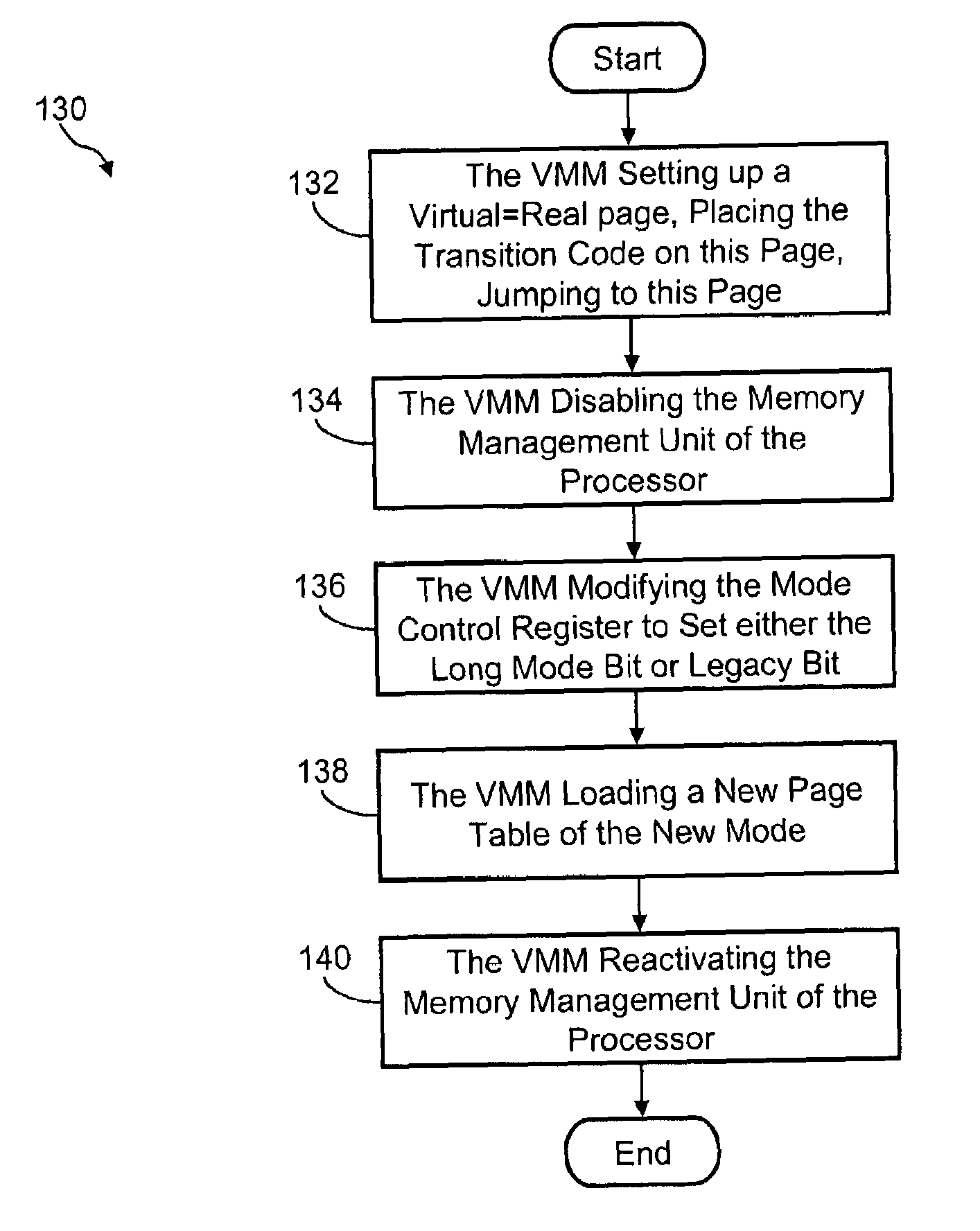

Switching between multiple software entities using different operating modes of a processor in a computer system

ActiveUS7478388B1Restoring contextSoftware simulation/interpretation/emulationMemory systemsLong modeOperational system

A processor has multiple operating modes, such as the long / compatibility mode, the long / 64-bit mode and the legacy modes of the x86-64 microprocessor. Different software entities execute in different ones of these operating modes. A switching routine is implemented to switch from one operating mode to another and to transfer control from one software entity to another. The software entities may be, for example, a host operating system and a virtual machine monitor. Thus, for example, a virtual computer system may comprise a 64-bit host operating system and a 32-bit virtual machine monitor, executing on an x86-64 microprocessor in long mode and legacy mode, respectively, with the virtual machine monitor supporting an x86 virtual machine. The switching routine may be implemented partially or completely in an identity-mapped memory page. Execution of the switching routine may be initiated by a driver that is installed in the host operating system of a virtual computer system.

Owner:VMWARE INC

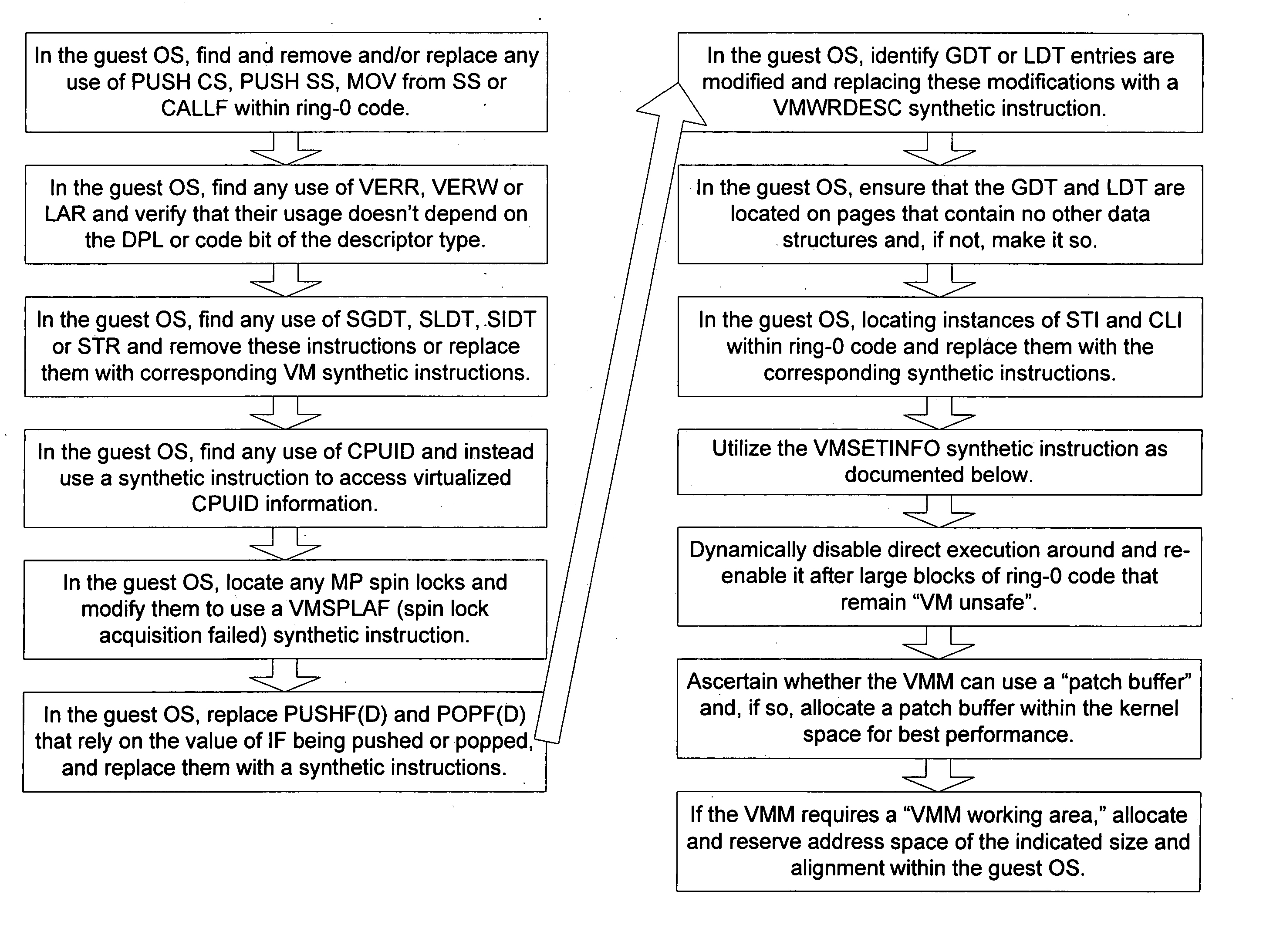

Systems and methods for using synthetic instructions in a virtual machine

ActiveUS20050081199A1Process safetyMuch-improved processor virtualizationDigital computer detailsMultiprogramming arrangementsSafe handlingVirtual machine

The present invention compensates for the shortcomings in x86 processor architectures by providing a set of “synthetic instructions” that cause a trap and thereby provide an opportunity for the virtual machine (VM) to process the instructions safely. By using instructions that are “illegal” to the x86 architecture, but which are nonetheless understandable by a virtual machine, the method of using these synthetic instructions to perform well-defined actions in the virtual machine that are otherwise problematic when performed by traditional instructions to an x86 processor but provide much-improved processor virtualization for x86 processor systems.

Owner:MICROSOFT TECH LICENSING LLC

Systems and methods for improving the x86 architecture for processor virtualization, and software systems and methods for utilizing the improvements

InactiveUS20050076186A1Correct shortcomingGeneral purpose stored program computerSoftware simulation/interpretation/emulationSoftware systemProtected mode

The present invention is directed to improvements to the processor architectures, and more specifically the x86 architecture, to correct shortcomings in processor virtualization. Several embodiment of the present invention are directed to the utilization of at least one virtualization control bit to determine whether the execution of a specific instructions cause a privilege-level exception (e.g., GP0) when executed outside of a privilege ring (e.g., outside of ring-0). Several additional embodiments are directed to the utilization of a virtual assist register to implement at least one virtual assist feature. And several additional embodiments are also directed to utilization of a bit for enabling a virtual protected mode that, when a processor in running in a protected mode, causes said processor, which is otherwise executing as if it is running in protected mode, to execute normally with exceptions to handle special virtualization challenges.

Owner:MICROSOFT TECH LICENSING LLC

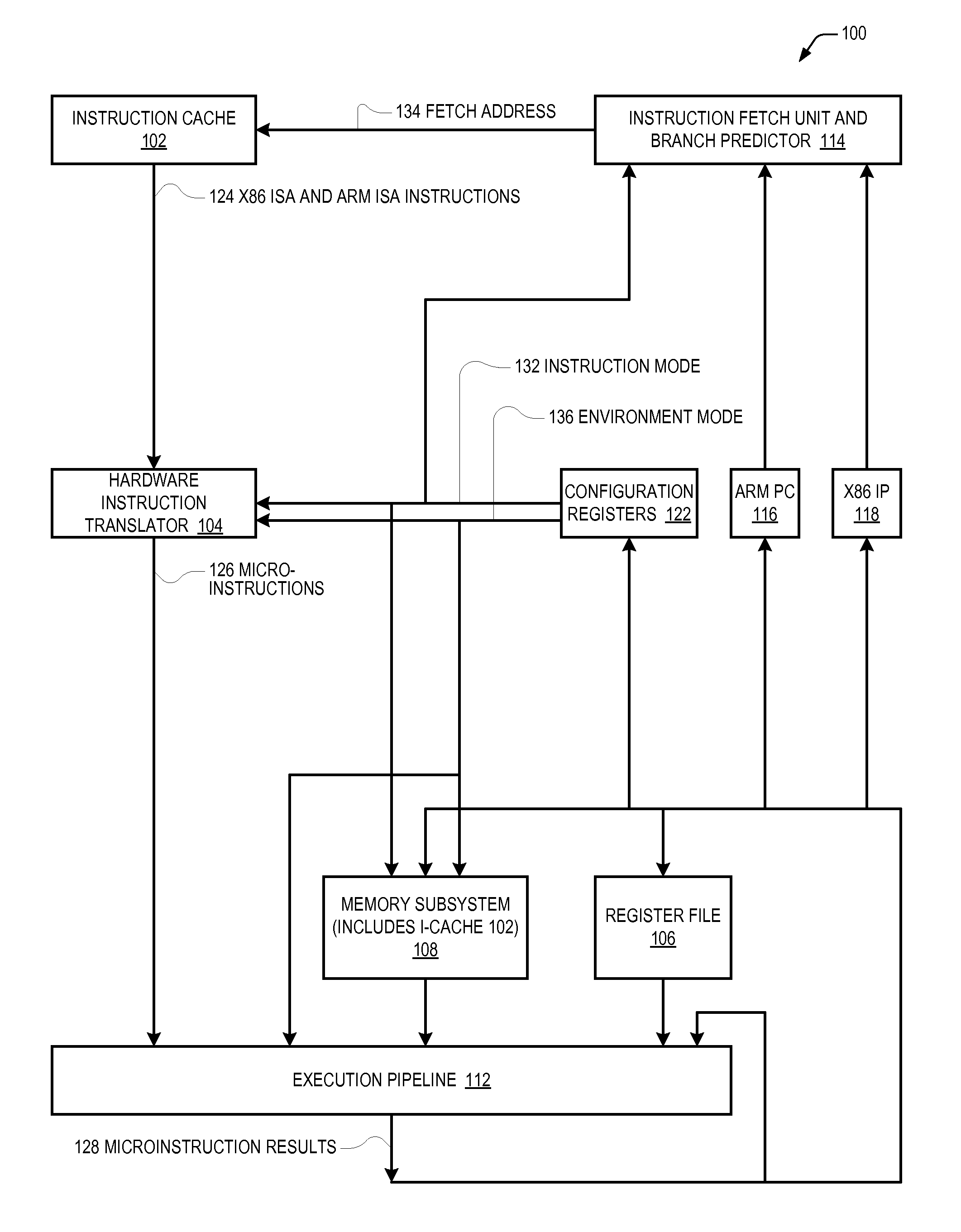

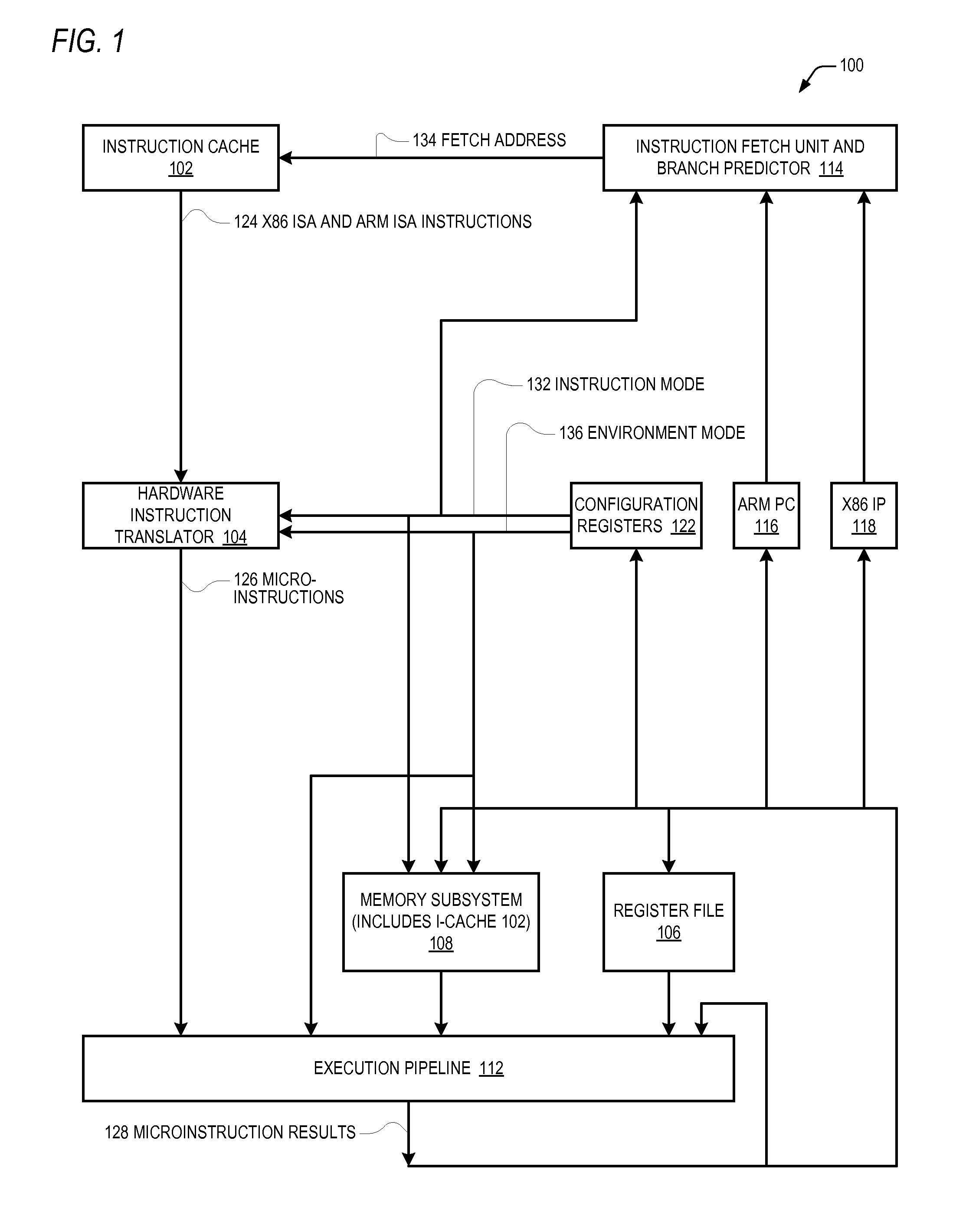

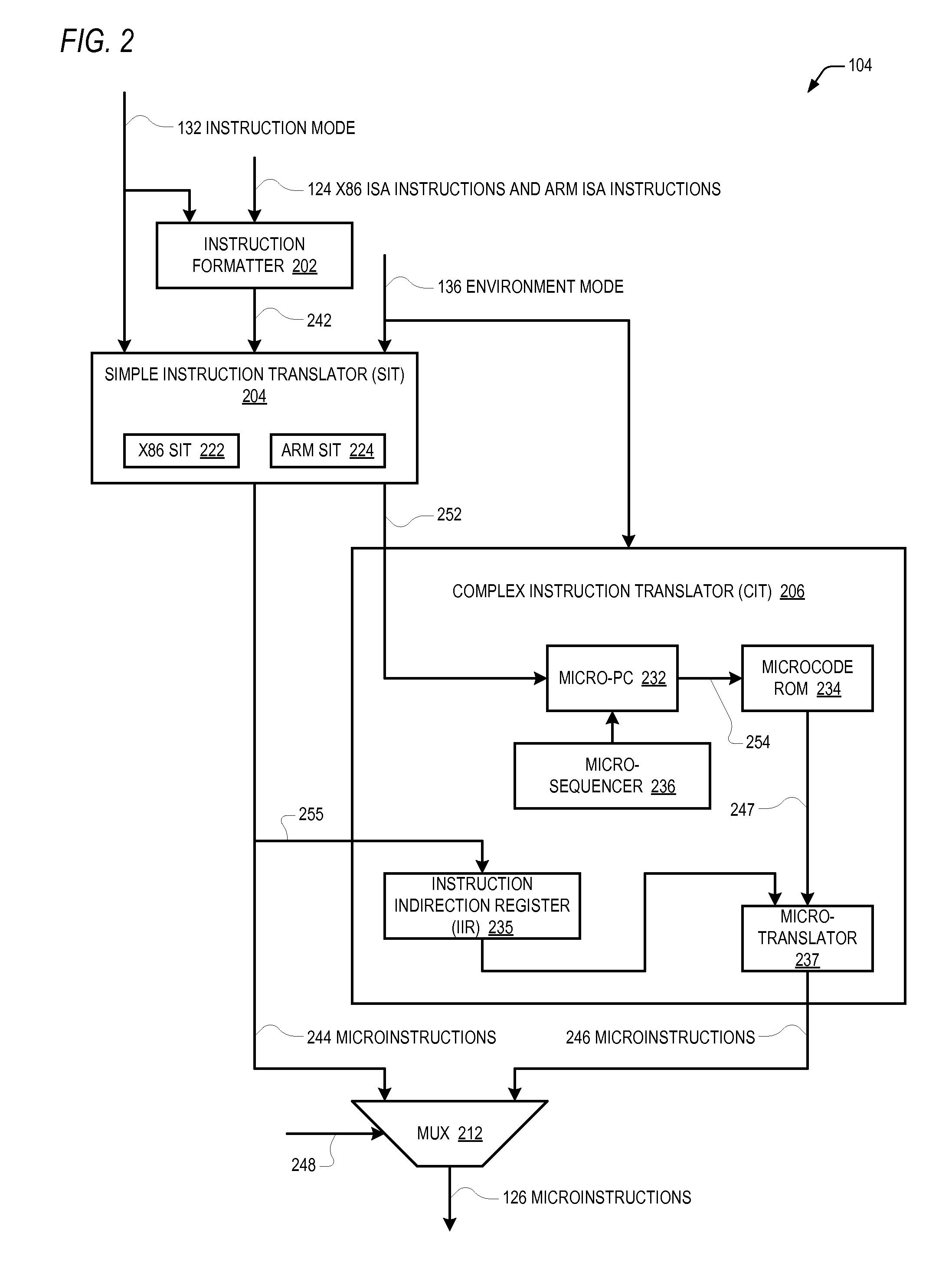

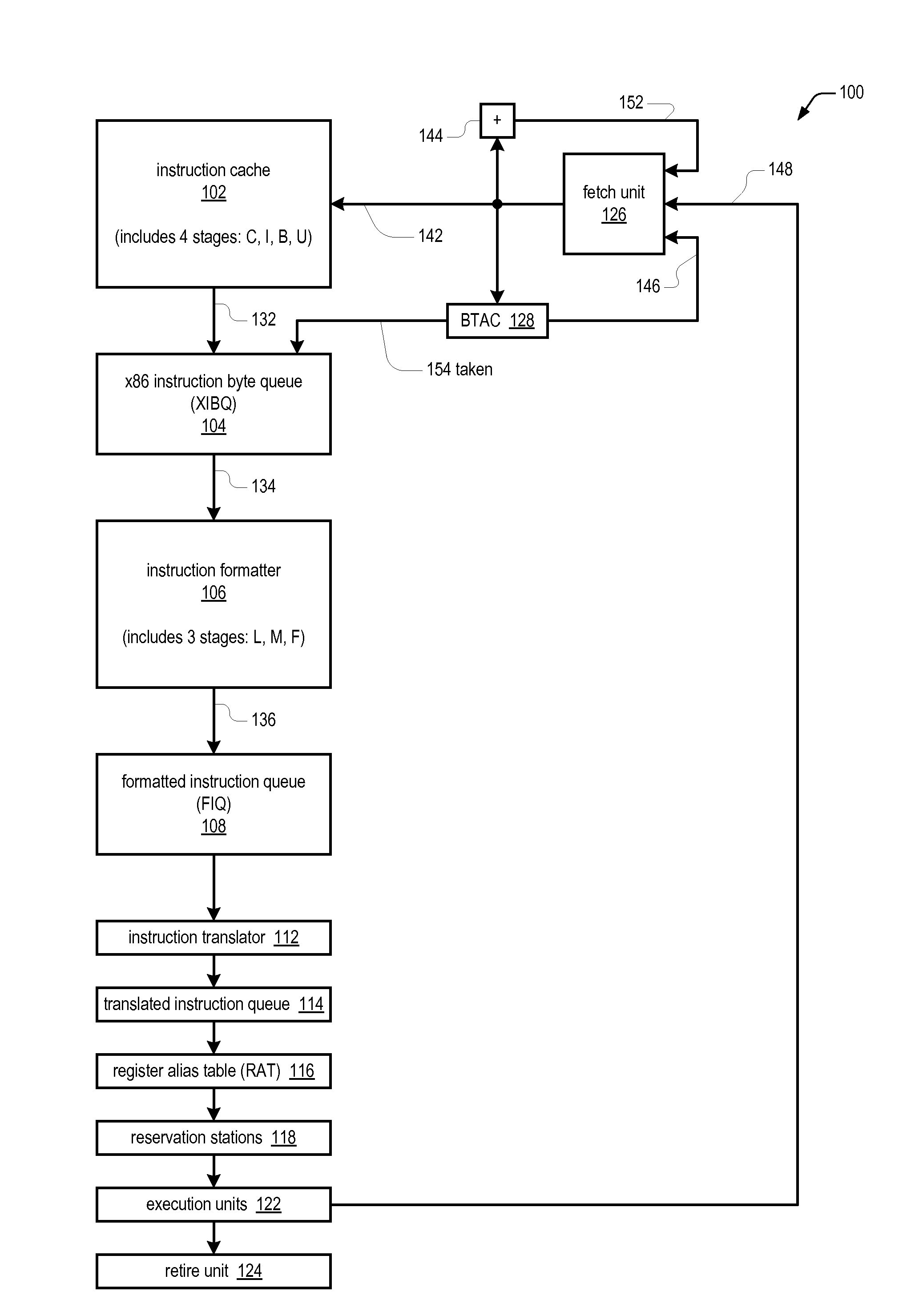

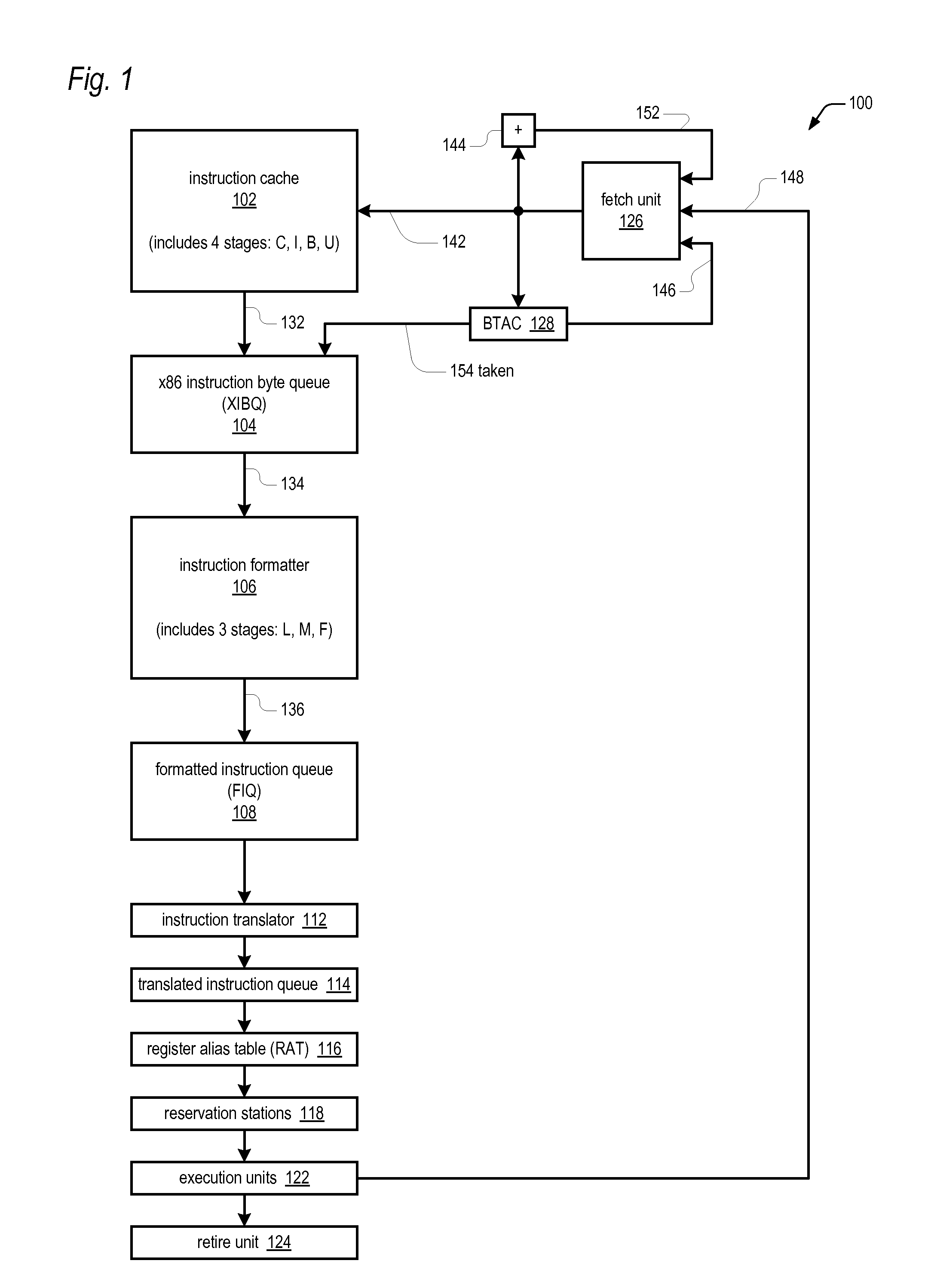

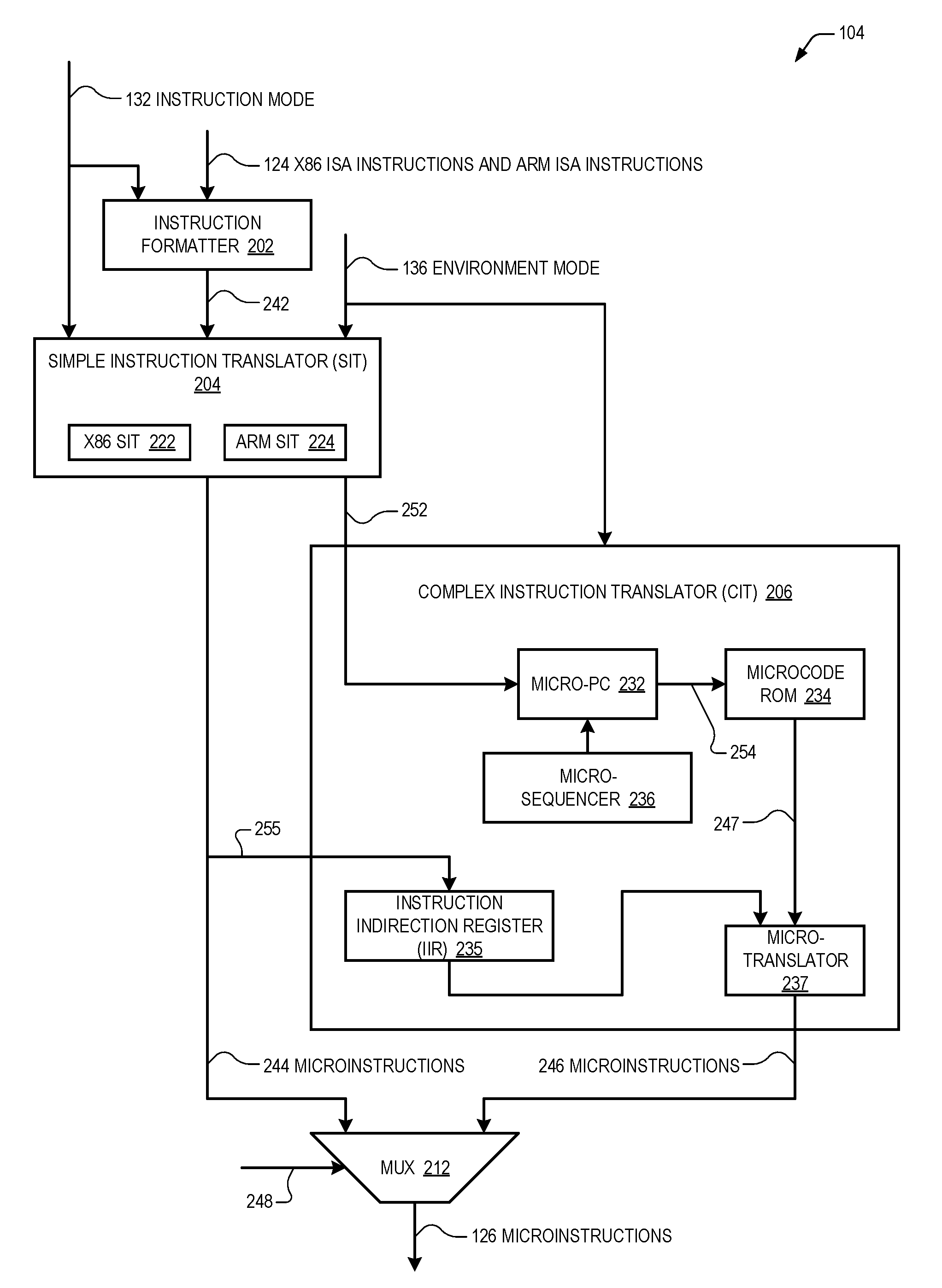

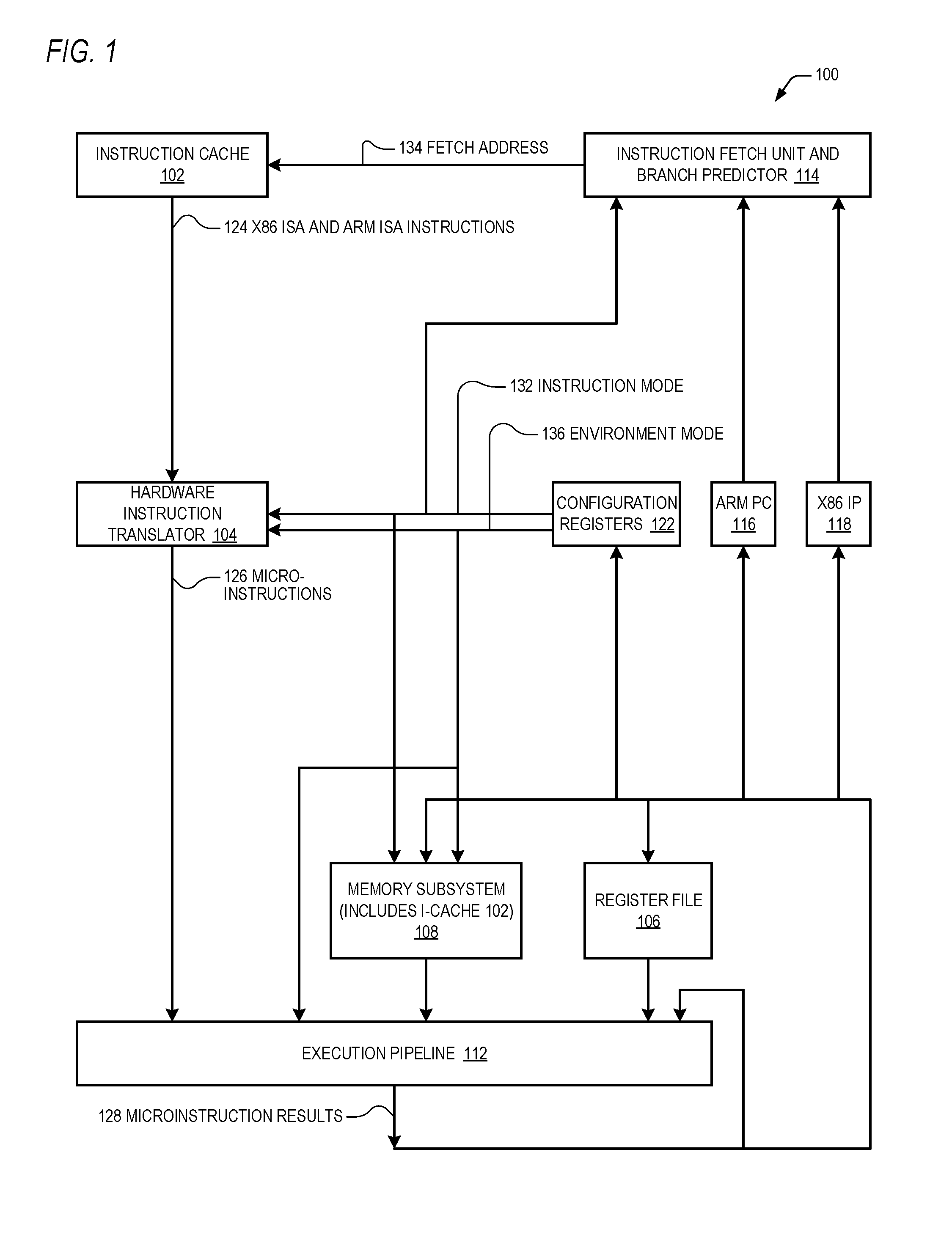

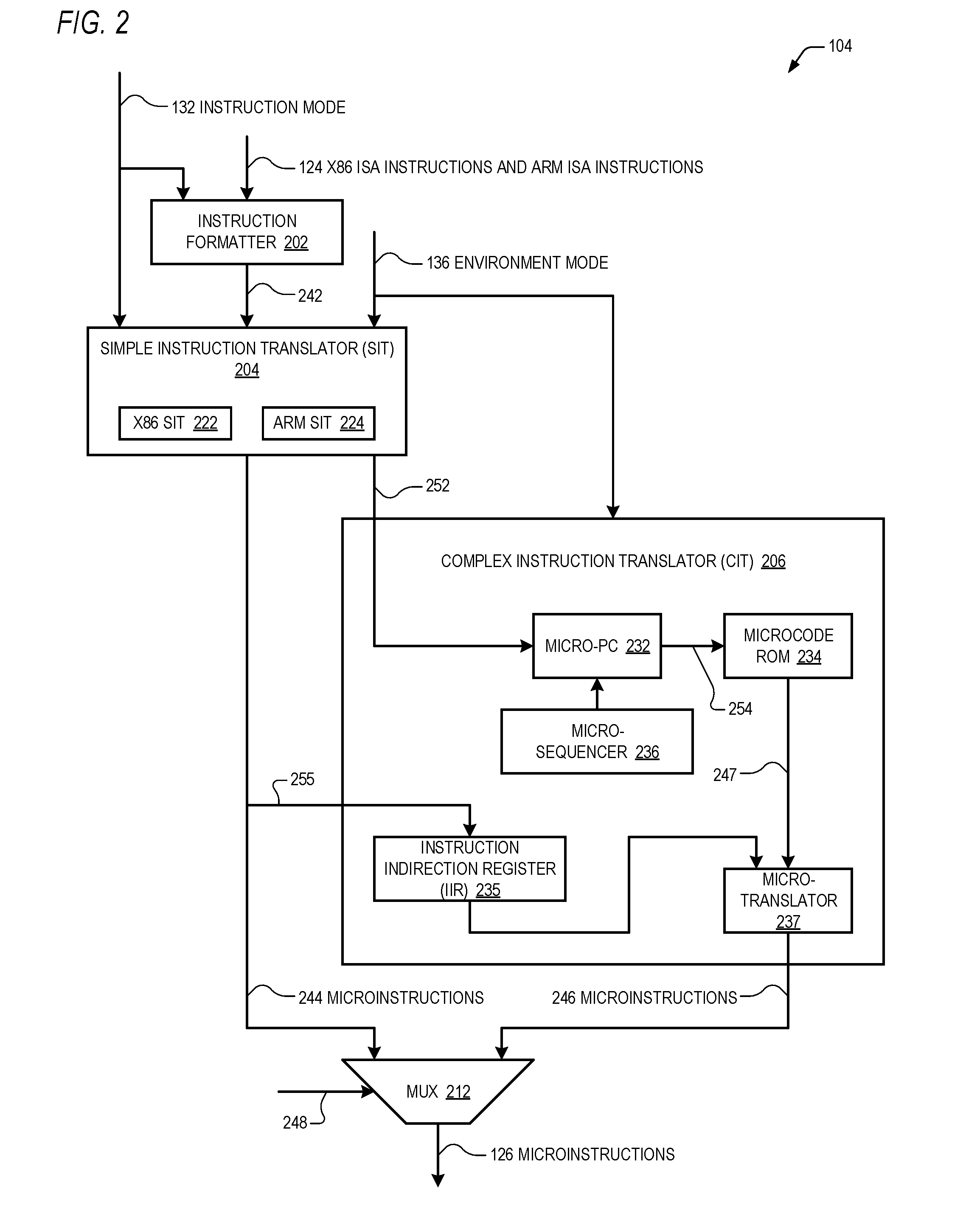

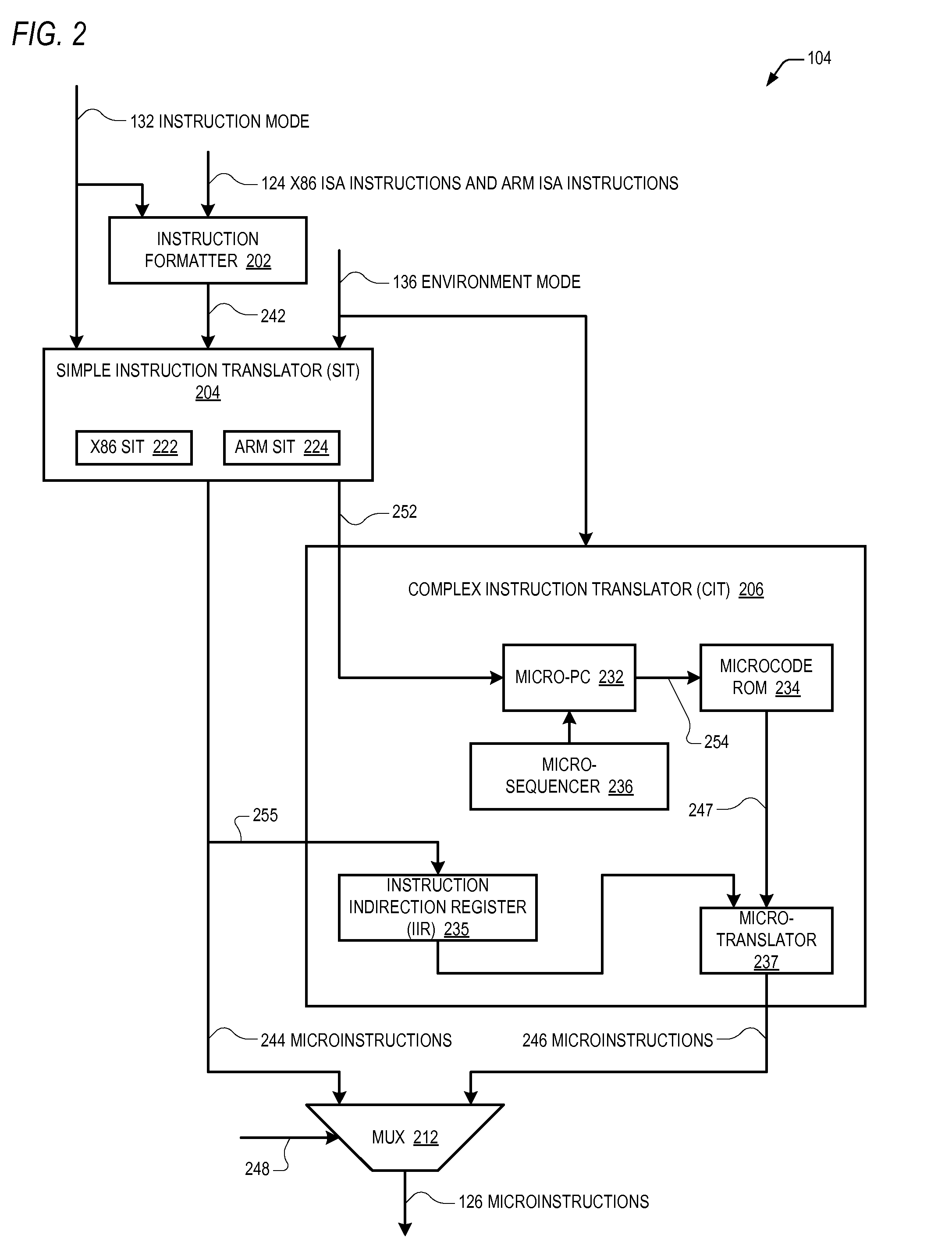

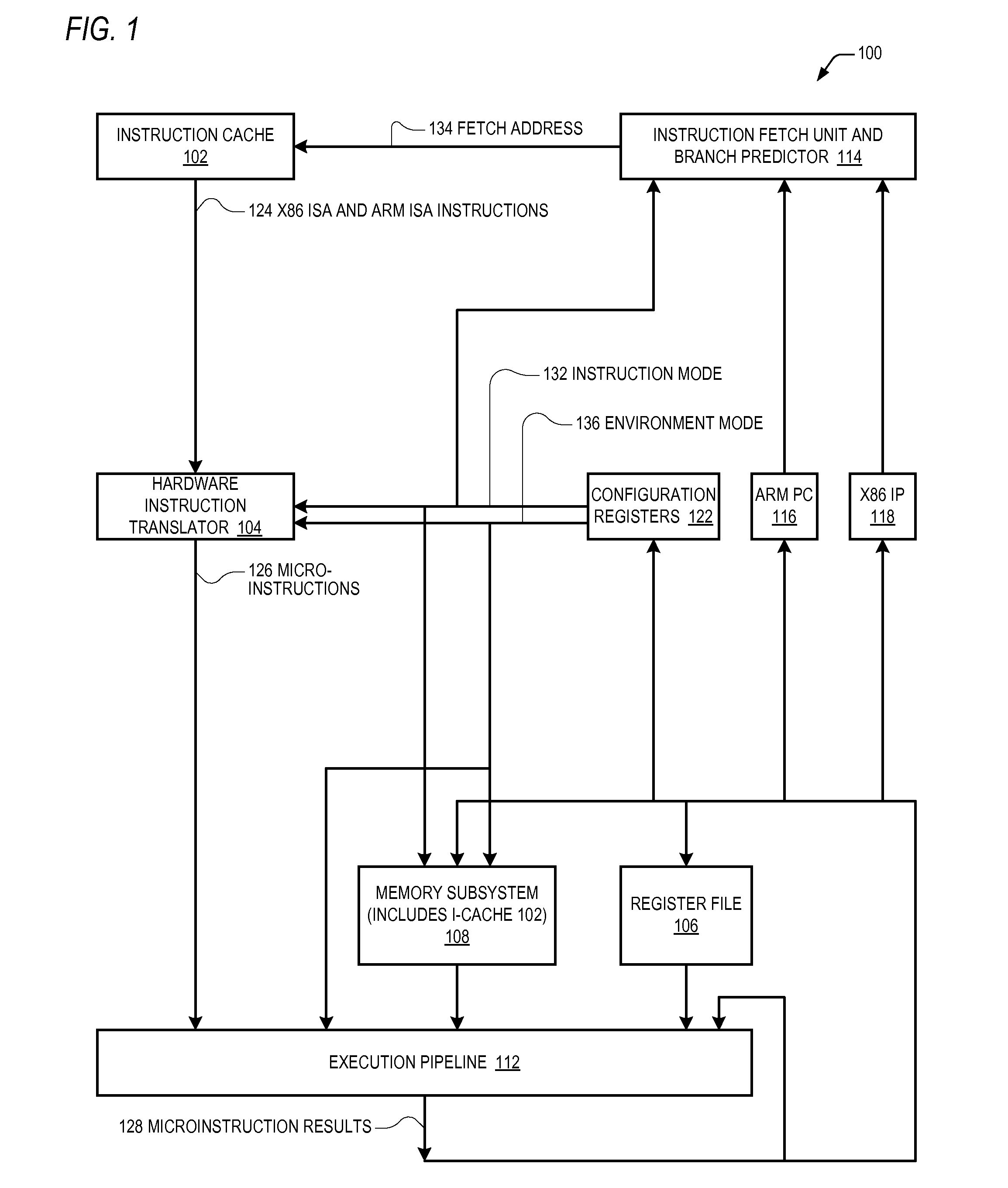

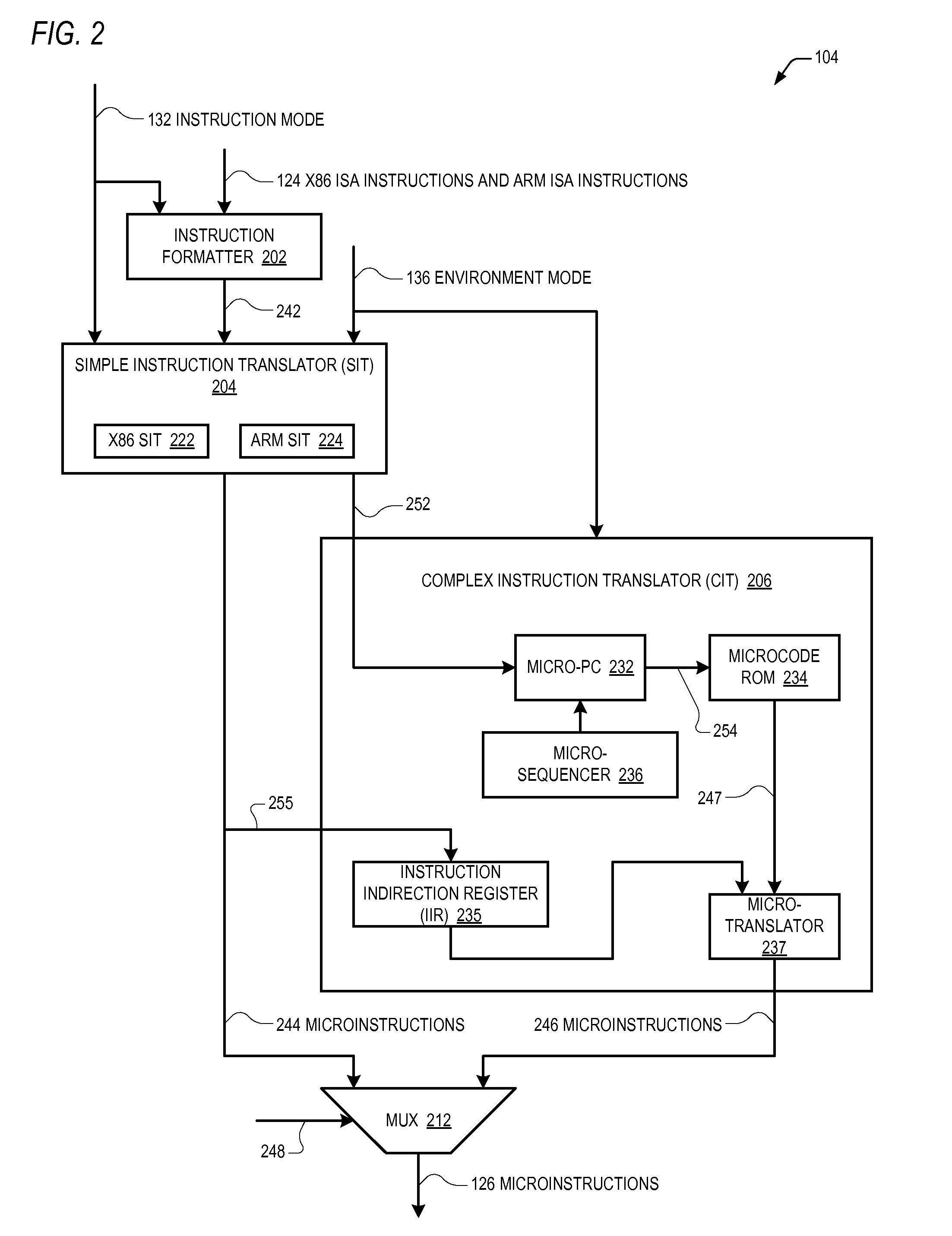

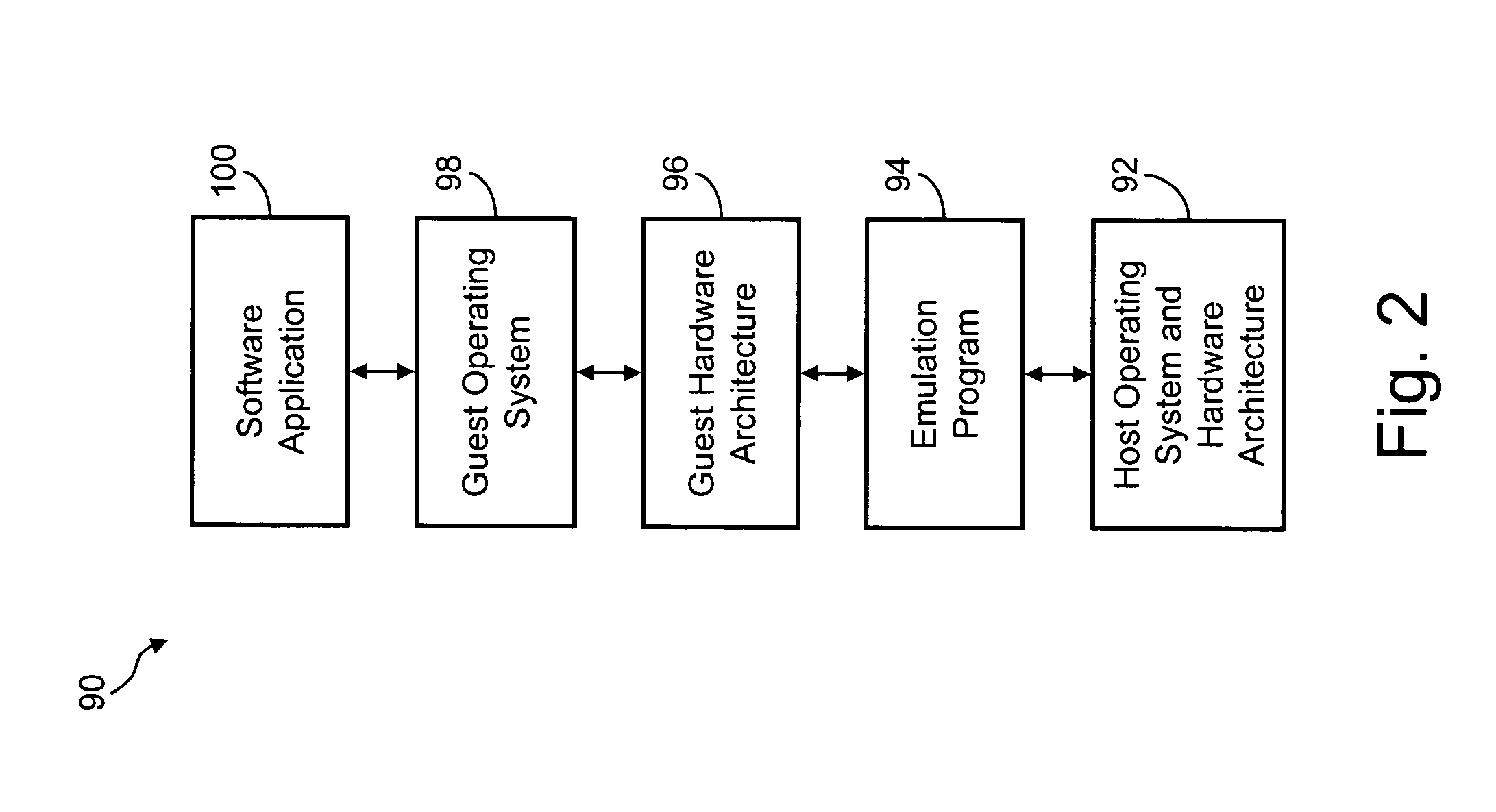

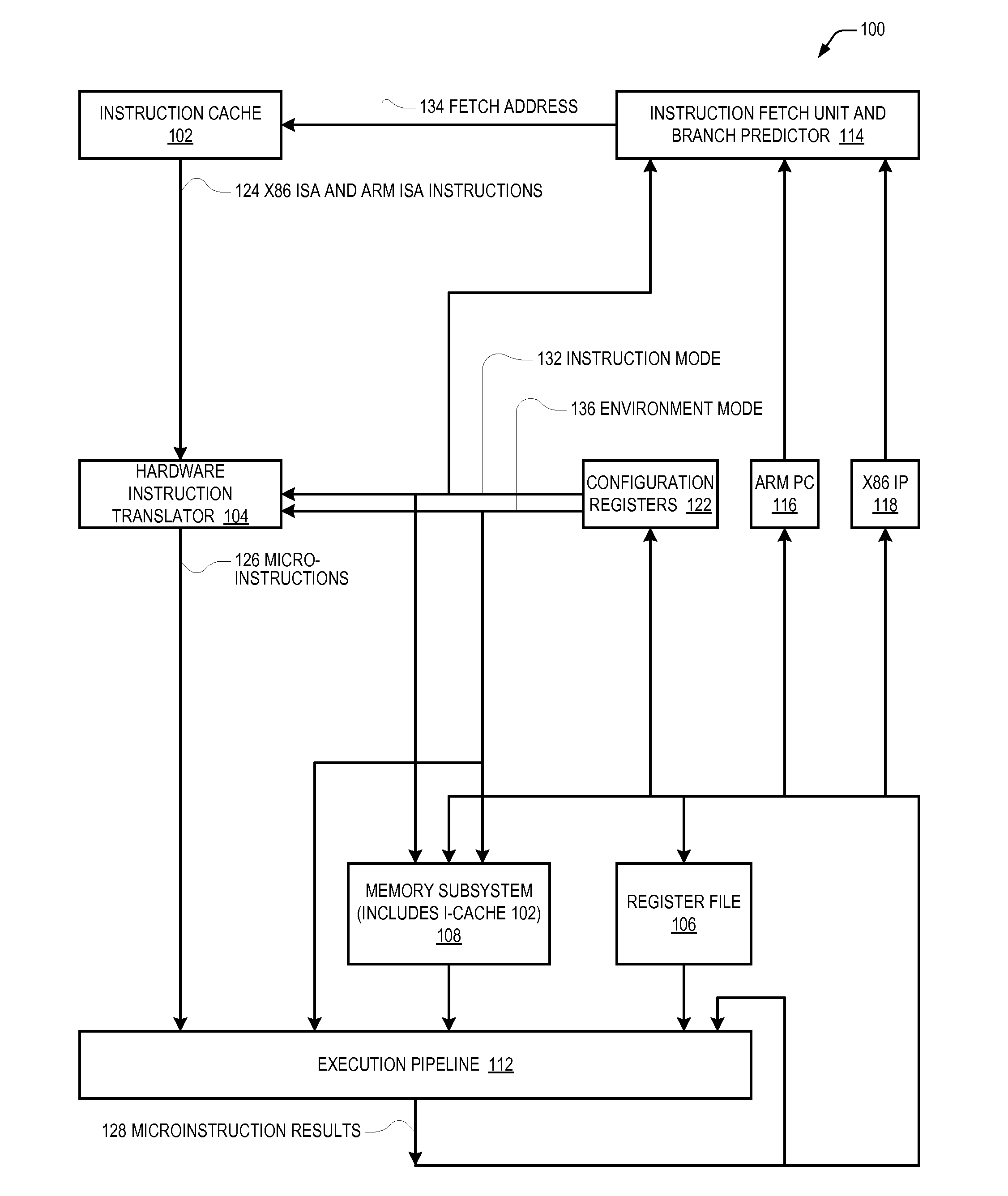

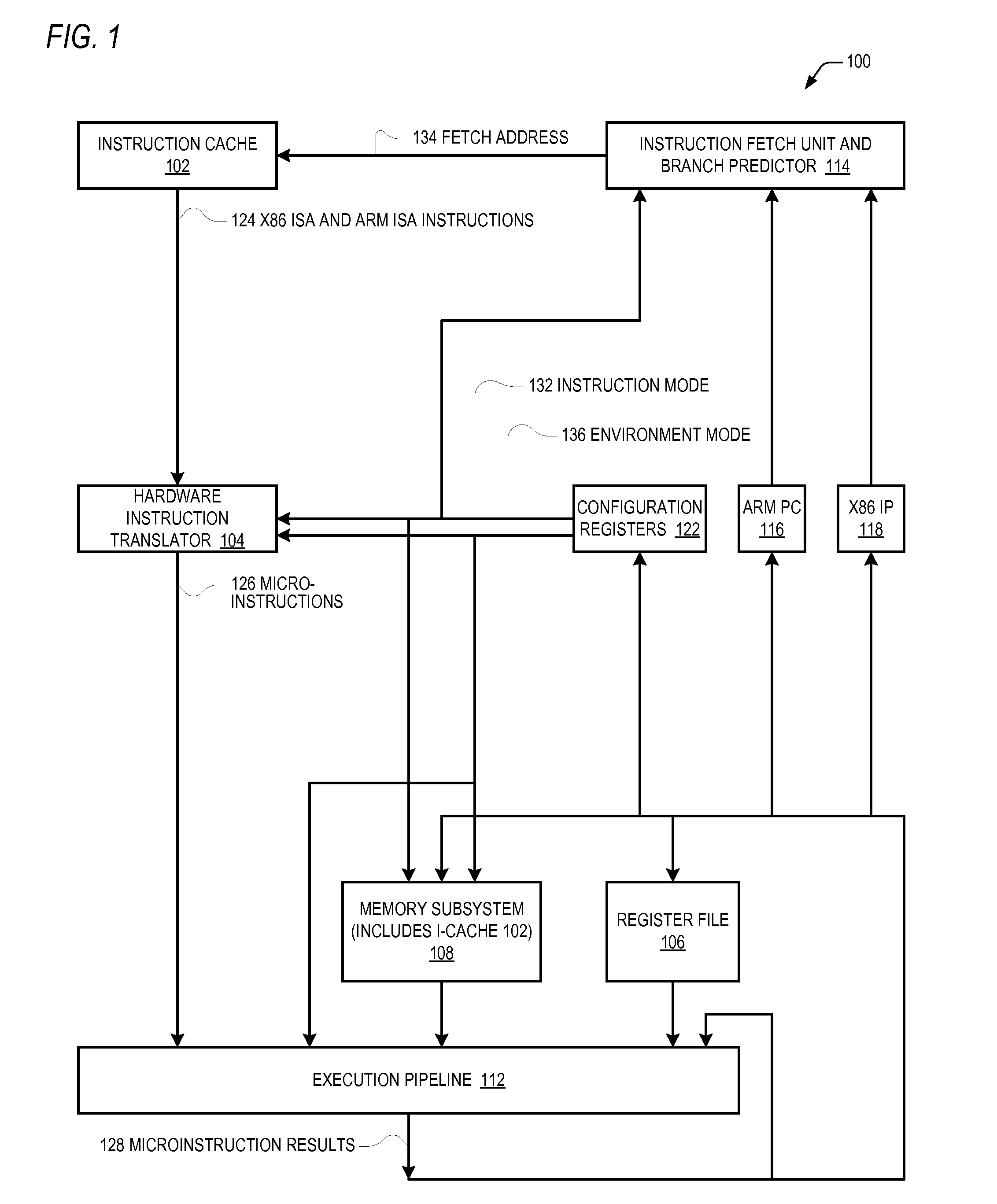

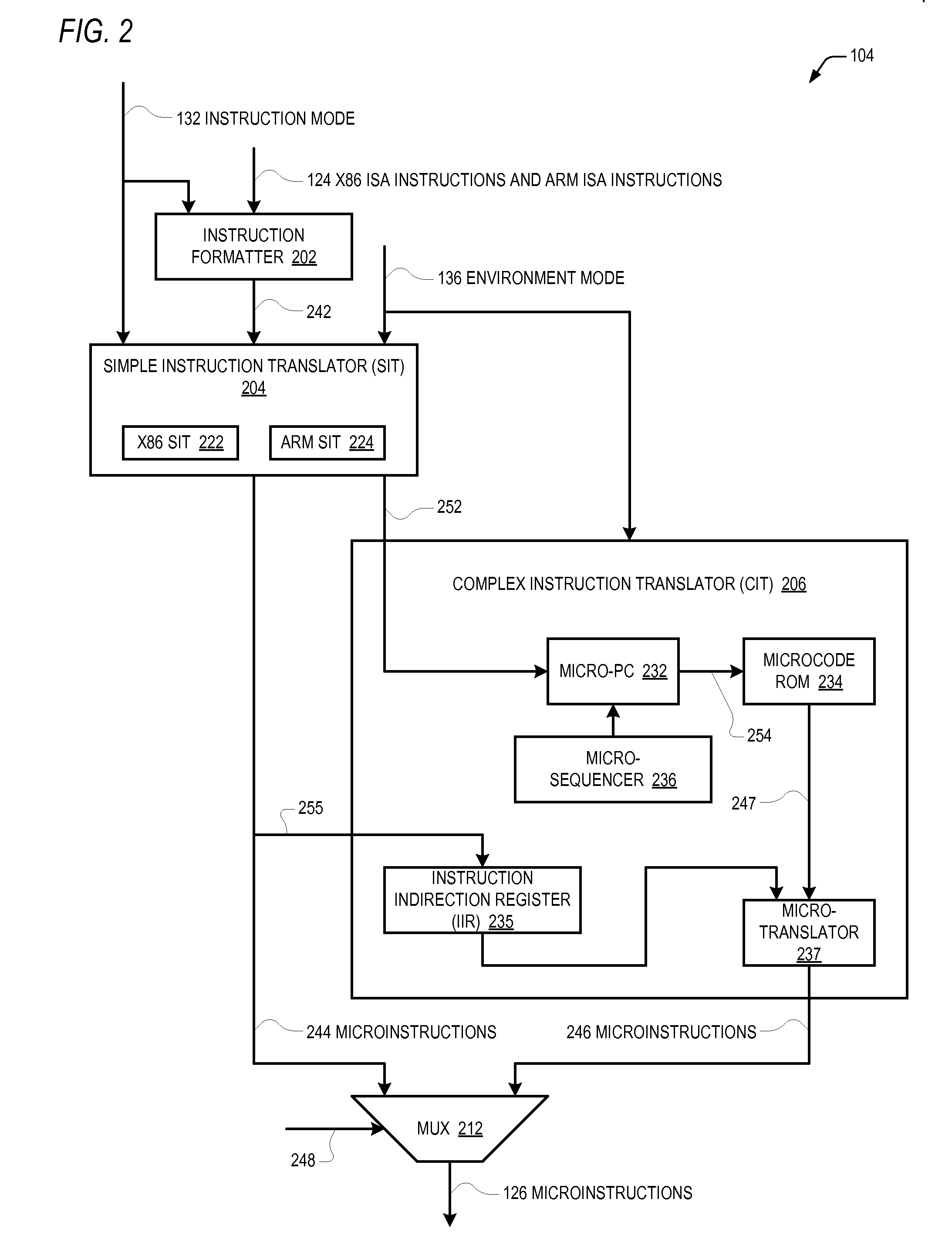

Microprocessor that performs x86 isa and arm isa machine language program instructions by hardware translation into microinstructions executed by common execution pipeline

ActiveUS20120260067A1Instruction analysisRuntime instruction translationComputer architectureProgram instruction

A microprocessor includes a hardware instruction translator that translates x86 ISA and ARM ISA machine language program instructions into microinstructions, which are encoded in a distinct manner from the x86 and ARM instructions. An execution pipeline executes the microinstructions to generate x86 / ARM-defined results. The microinstructions are distinct from the results generated by the execution of the microinstructions by the execution pipeline. The translator directly provides the microinstructions to the execution pipeline for execution. Each time the microprocessor performs one of the x86 ISA and ARM ISA instructions, the translator translates it into the microinstructions. An indicator indicates either x86 or ARM as a boot ISA. After reset, the microprocessor initializes its architectural state, fetches its first instructions from a reset address, and translates them all as defined by the boot ISA. An instruction cache caches the x86 and ARM instructions and provides them to the translator.

Owner:VIA TECH INC

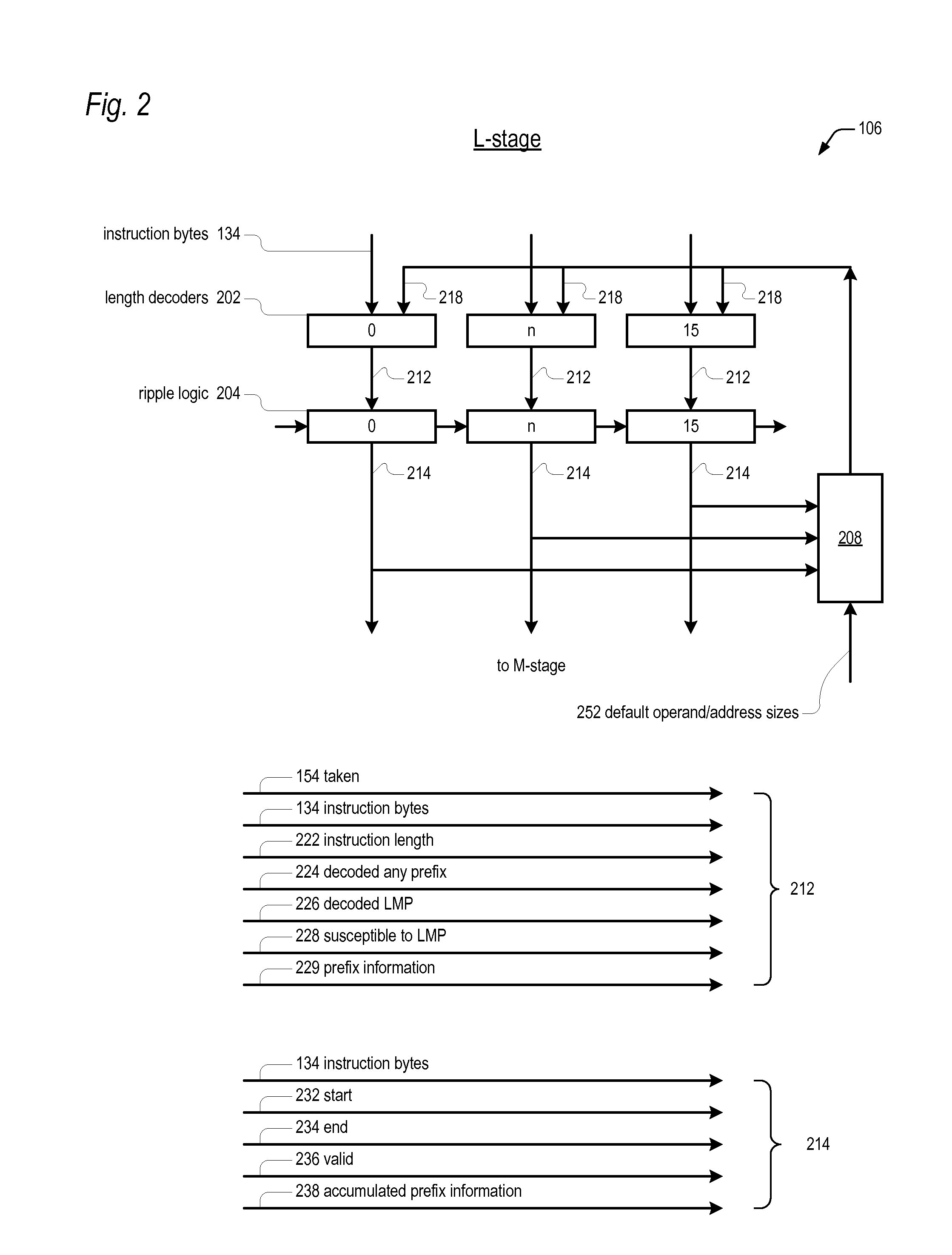

Apparatus for efficiently determining instruction length within a stream of x86 instruction bytes

ActiveUS20100299497A1Efficiently determinedMemory architecture accessing/allocationDigital computer detailsByteCombinational logic

An apparatus efficiently determines the length of an instruction within a stream of instruction bytes processed by a microprocessor having a variable instruction length instruction set architecture. The apparatus includes combinatorial logic associated with each instruction byte of the stream, each configured to receive the associated instruction byte and the next instruction byte of the stream and to generate in response thereto a first length, a second length, and a select control. A multiplexor associated with each of the combinatorial logic selects and outputs one of the following inputs based on the select control received from the combinatorial logic: a zero input and the second length received from the combinatorial logic associated with each of the next three instruction bytes of the stream. An adder associated with each of the combinatorial logic and multiplexor adds the first length and the output of the multiplexor to generate the length of the instruction.

Owner:VIA TECH INC

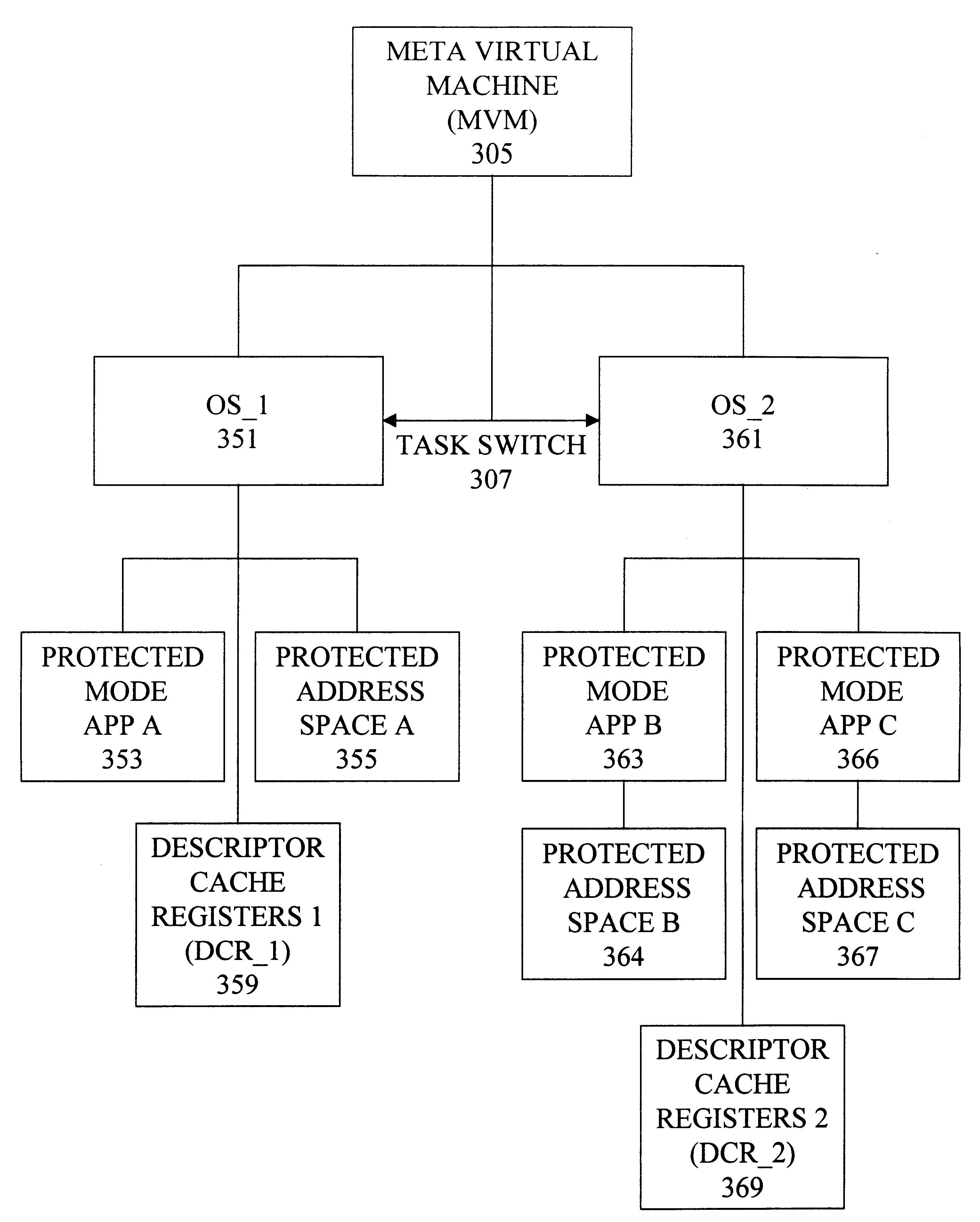

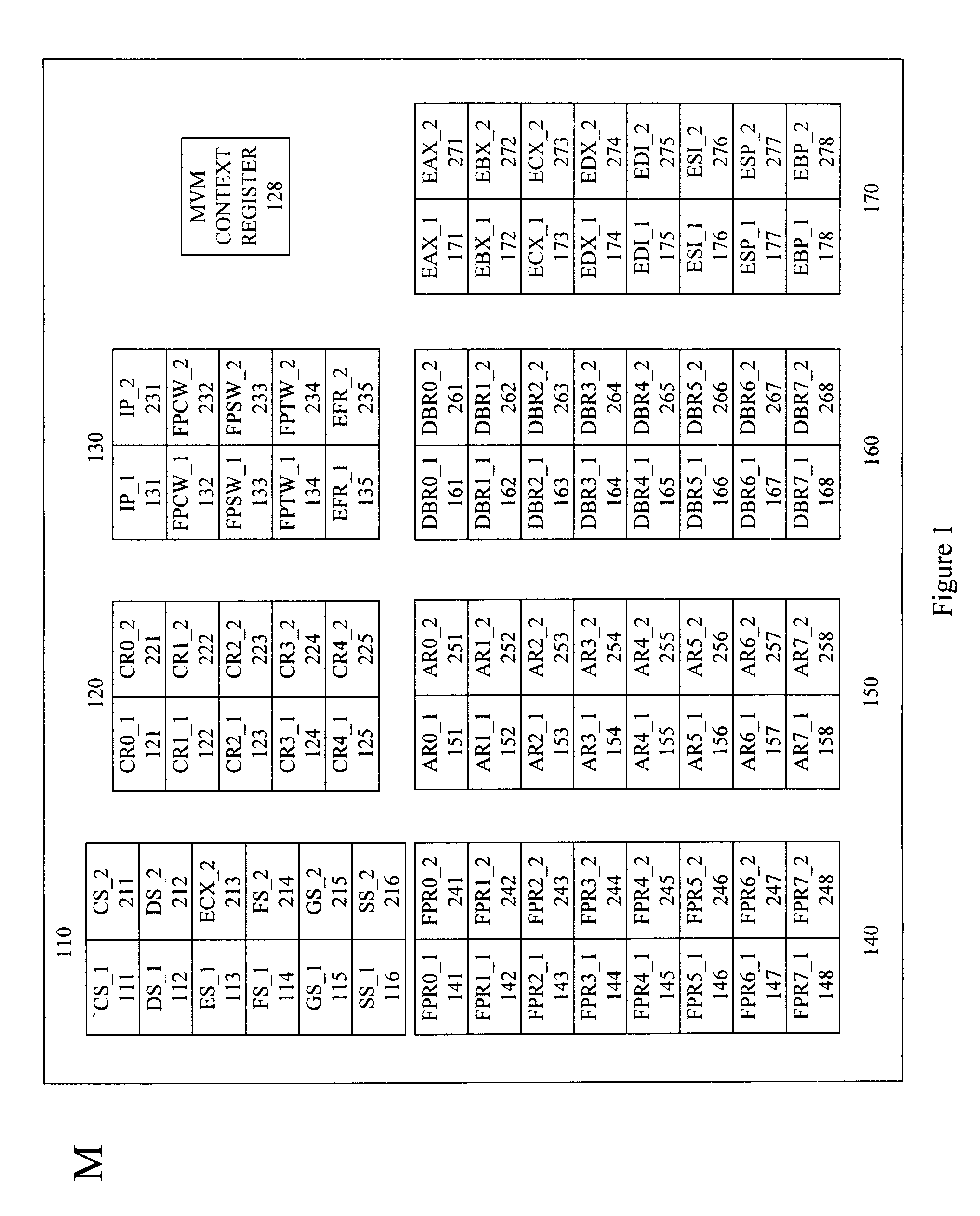

Multiple protected mode execution environments using multiple register sets and meta-protected instructions

InactiveUS6751737B1Volume/mass flow measurementUser identity/authority verificationOperational systemProcessor register

A system is provided that contains multiple control register and descriptor table register sets so that an execution context switch between X86 protected mode operating systems can be performed with minimal processing overhead. Upon receipt of a protected instruction determined to be a meta-protected instruction, the system calls a meta virtual machine (MVM) that performs the functions necessary to shift execution contexts.

Owner:GLOBALFOUNDRIES INC

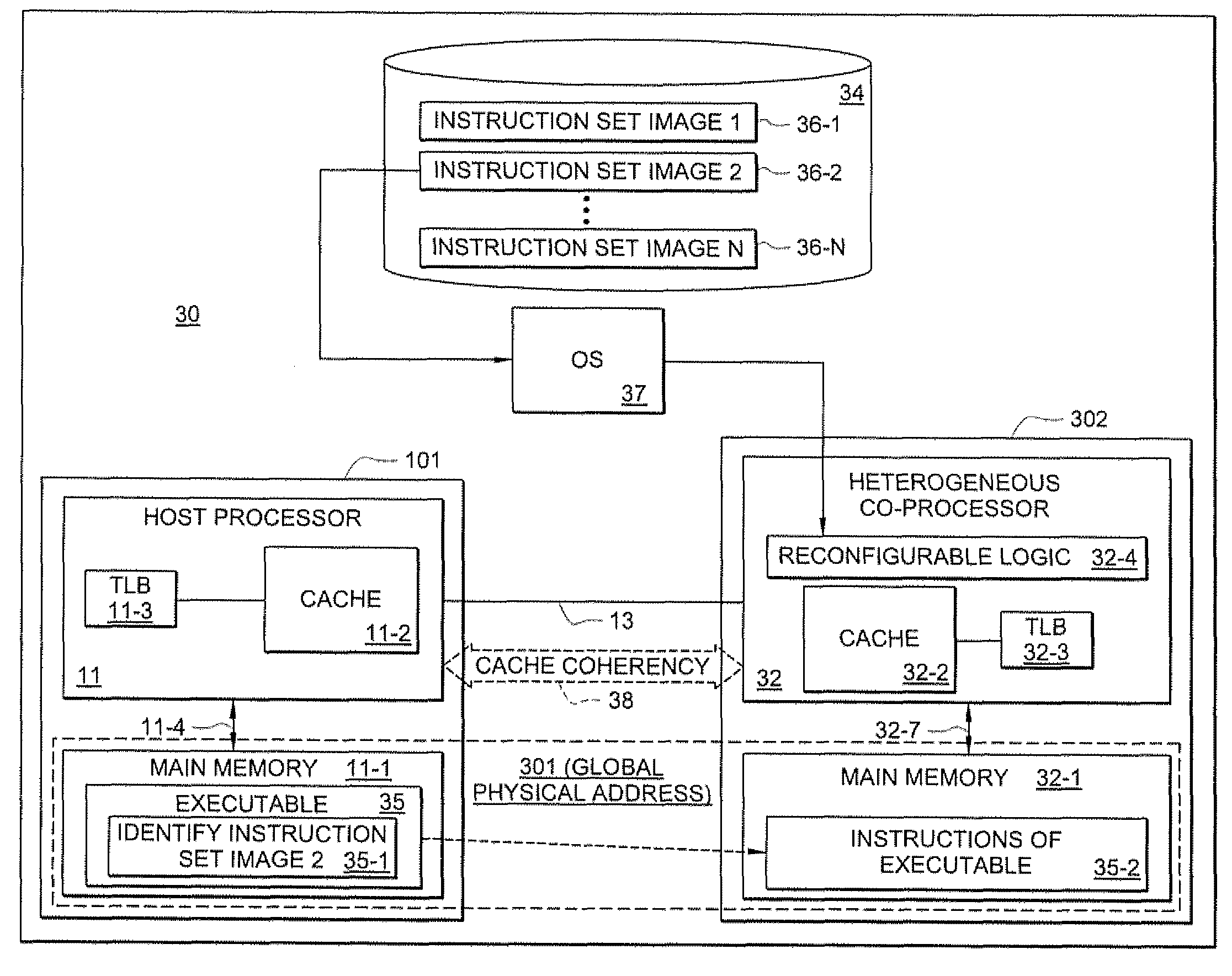

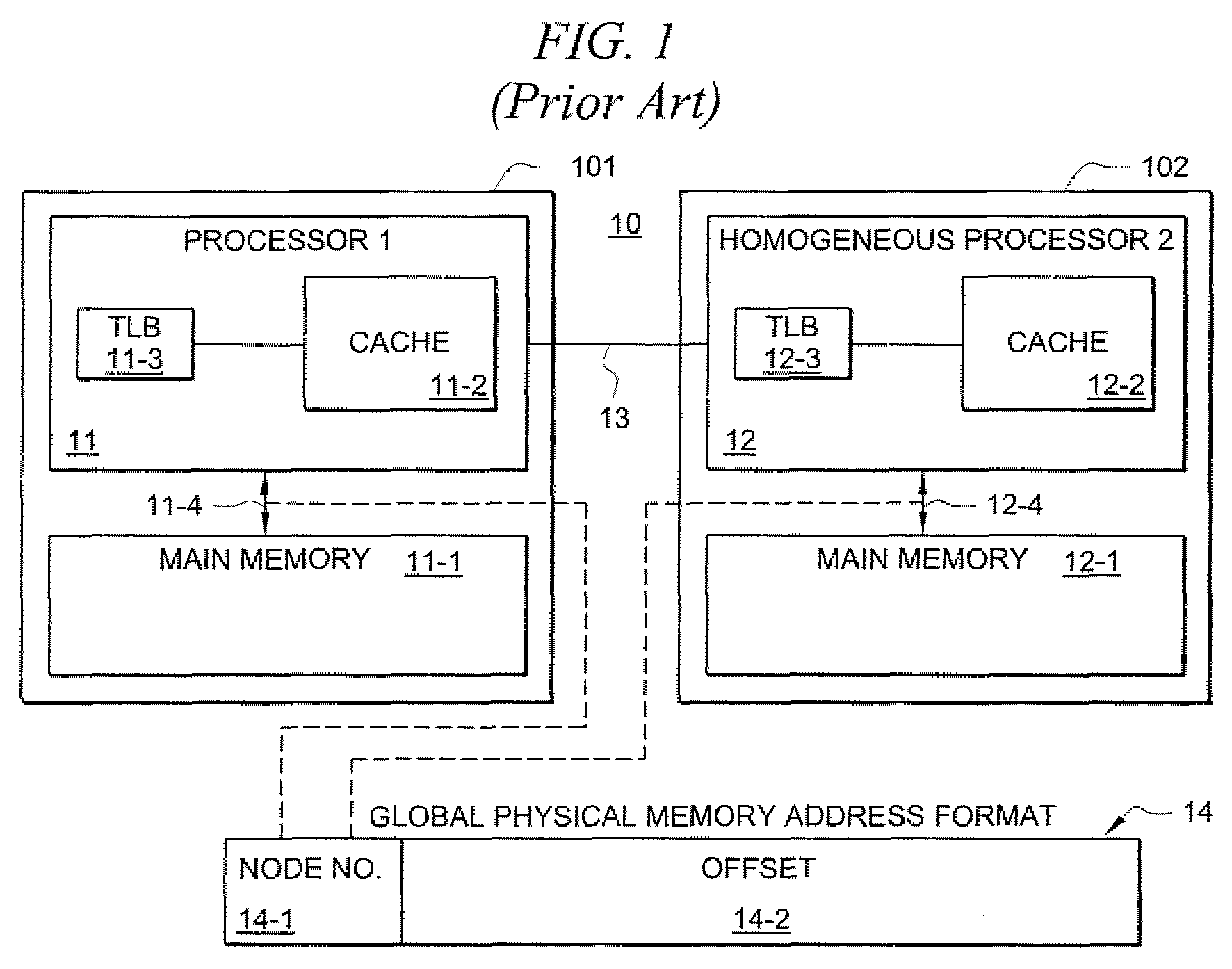

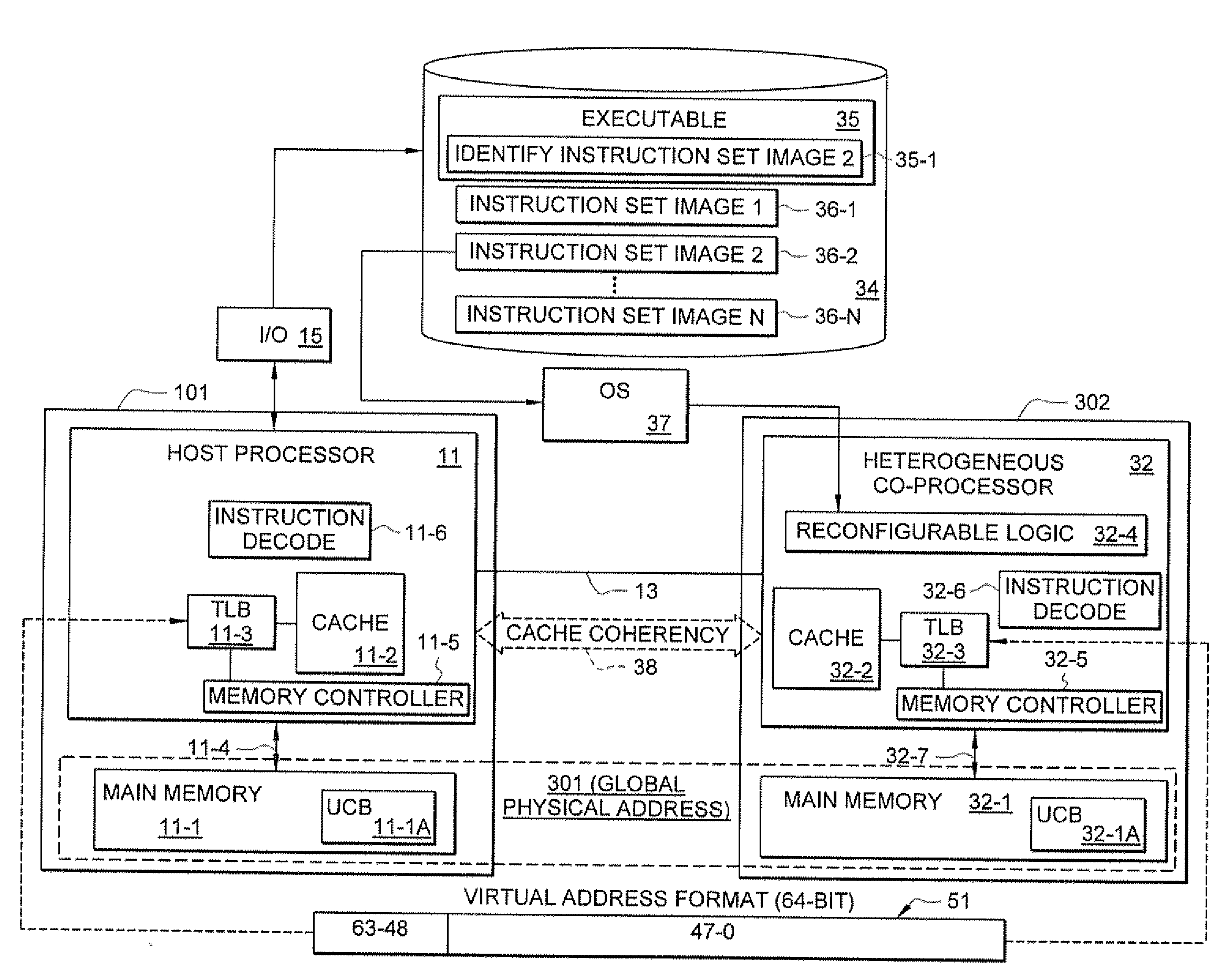

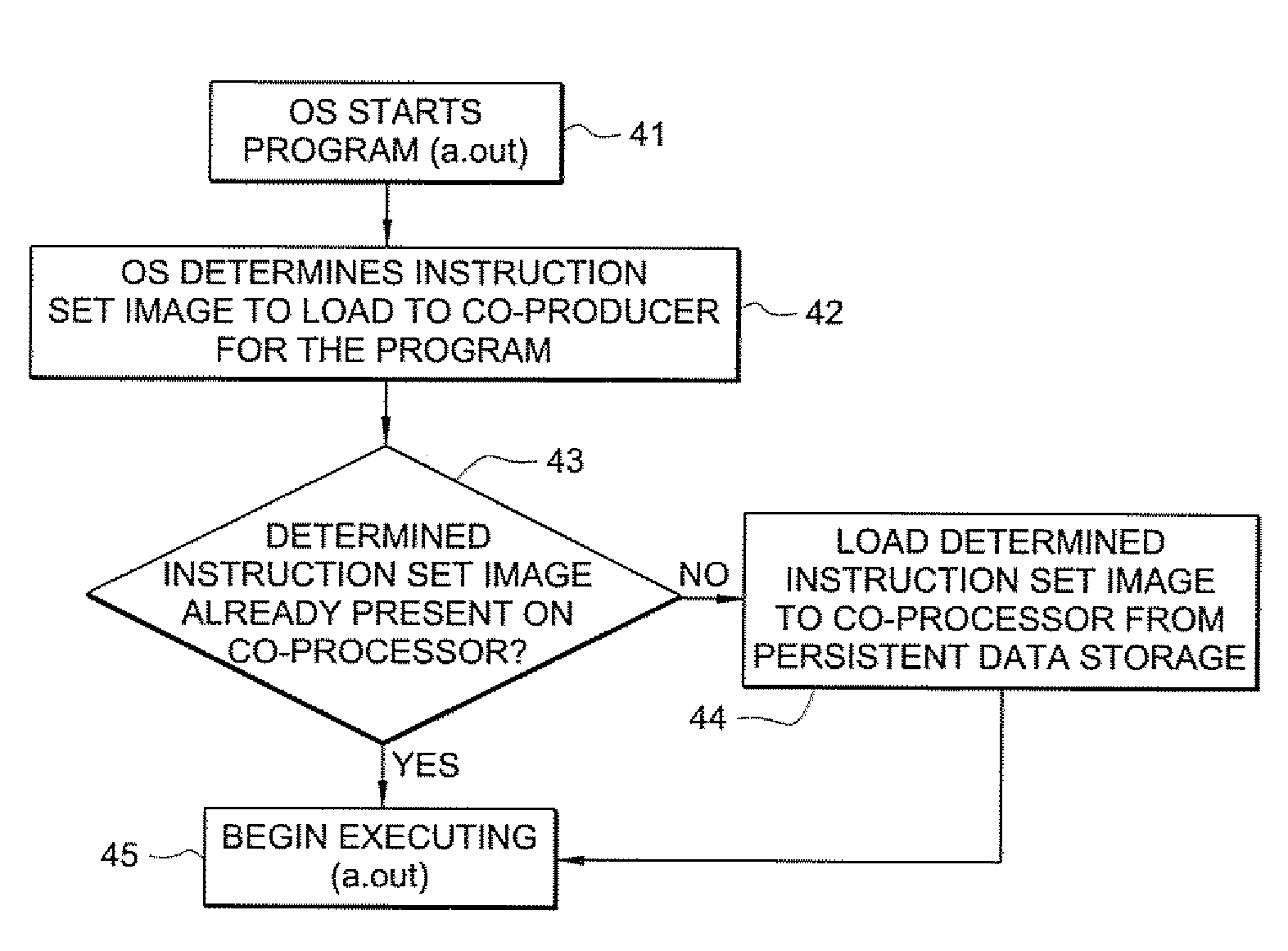

Multi-processor system having at least one processor that comprises a dynamically reconfigurable instruction set

A multi-processor system comprises at least one host processor, which may comprise a fixed instruction set, such as the well-known x86 instruction set. The system further comprises at least one co-processor, which comprises dynamically reconfigurable logic that enables the co-processor's instruction set to be dynamically reconfigured. In this manner, the at least one host processor and the at least one dynamically reconfigurable co-processor are heterogeneous processors having different instruction sets. Further, cache coherency is maintained between the heterogeneous host and co-processors. And, a single executable file may contain instructions that are processed by the multi-processor system, wherein a portion of the instructions are processed by the host processor and a portion of the instructions are processed by the co-processor.

Owner:MICRON TECH INC

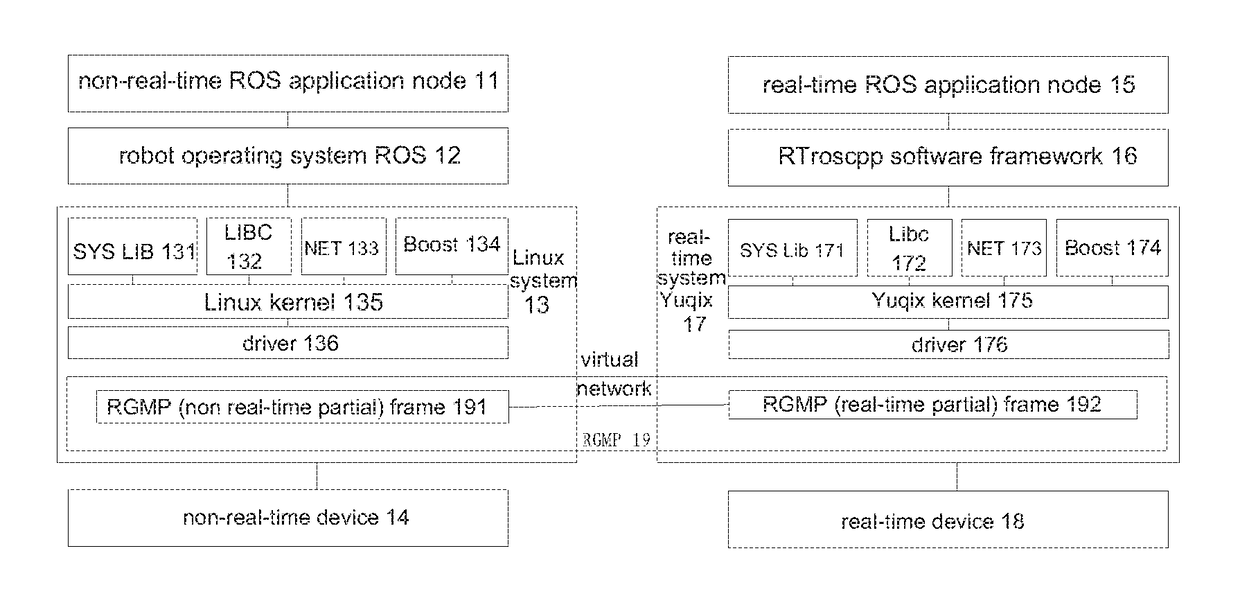

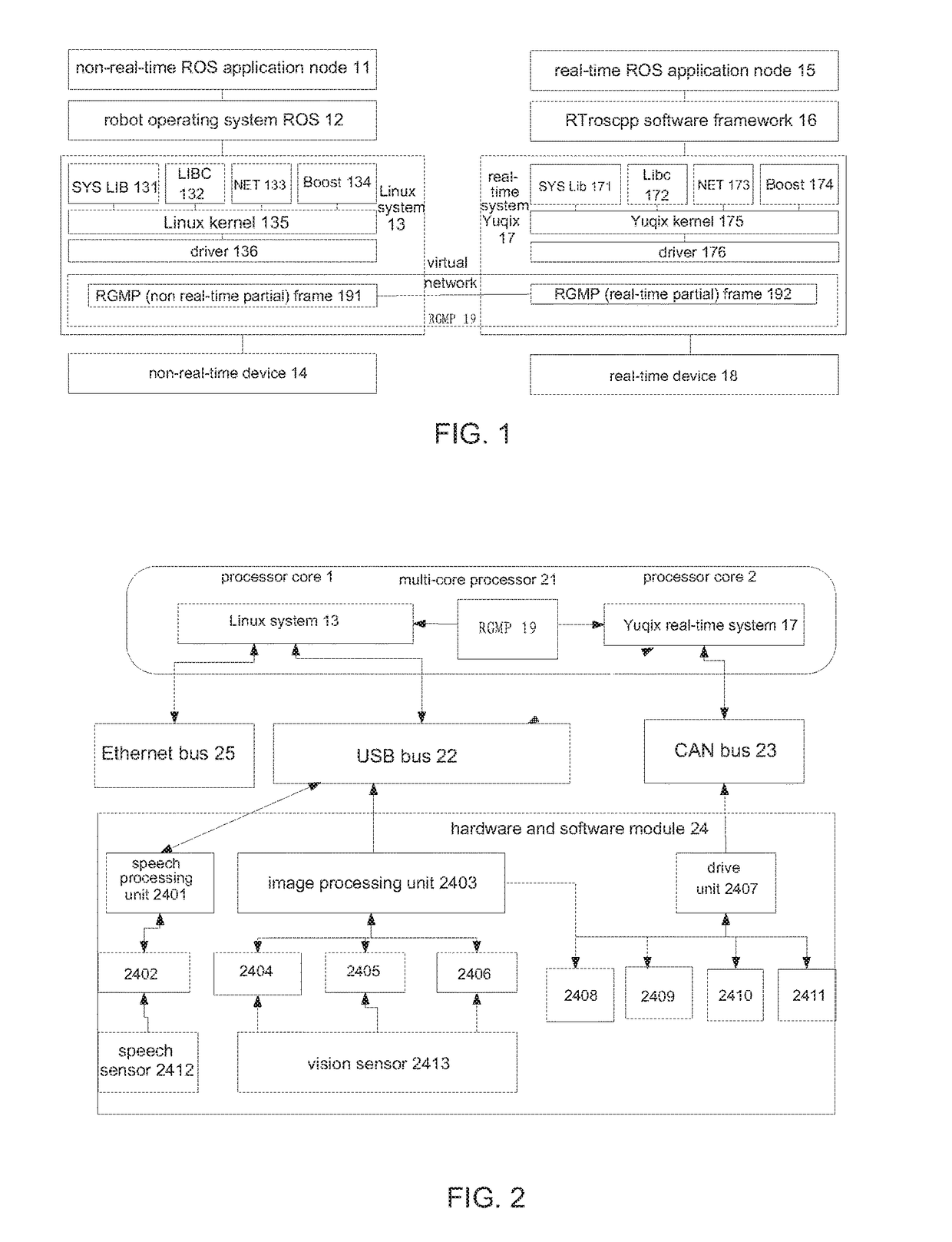

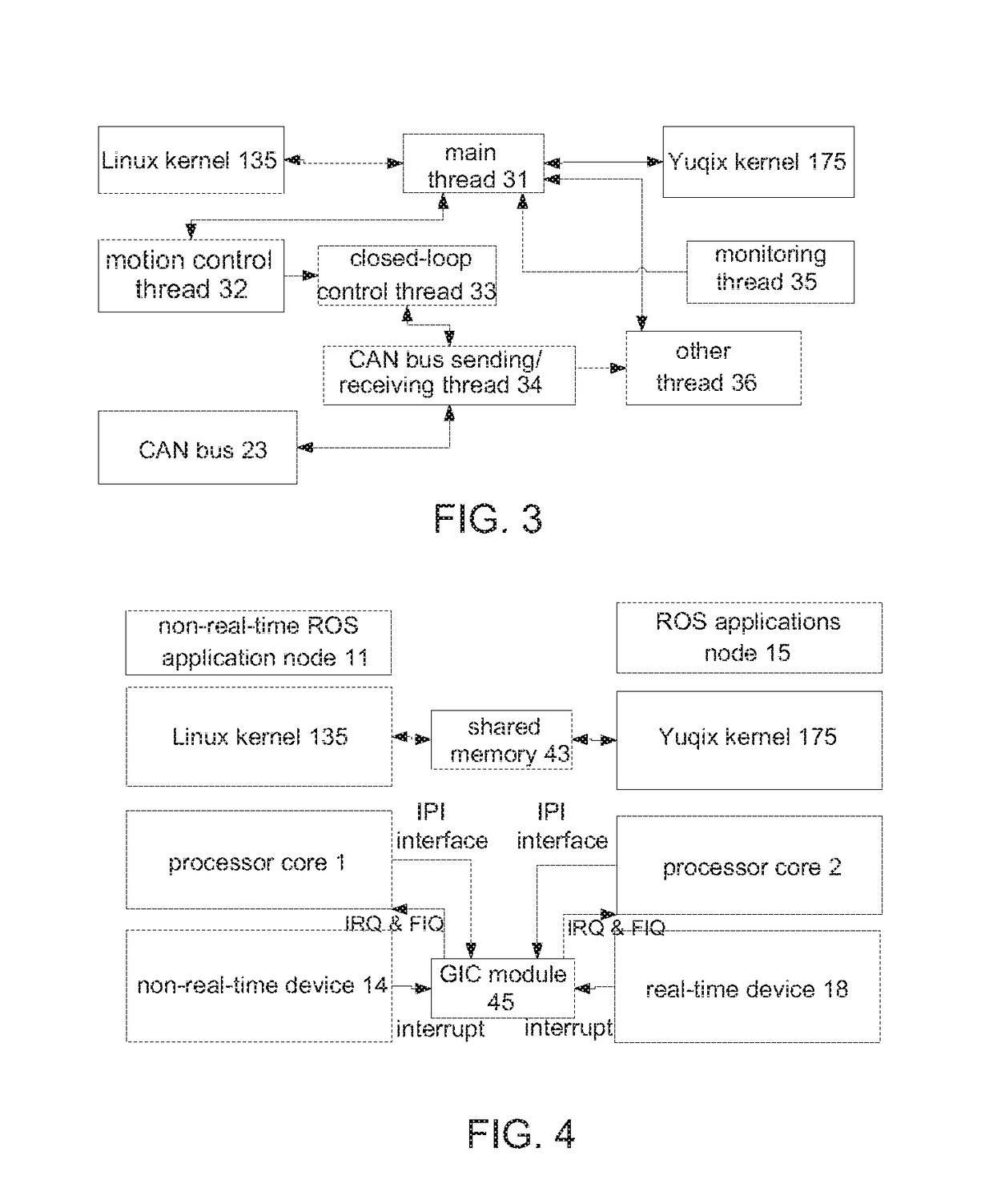

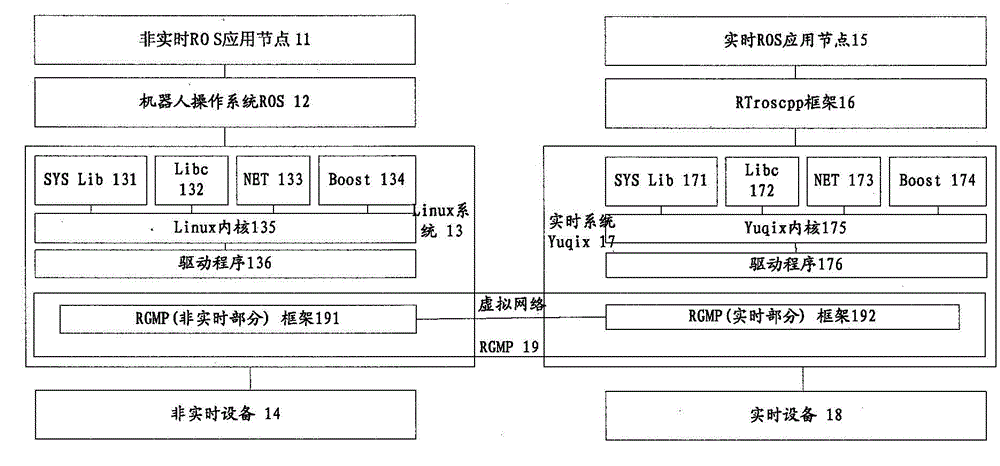

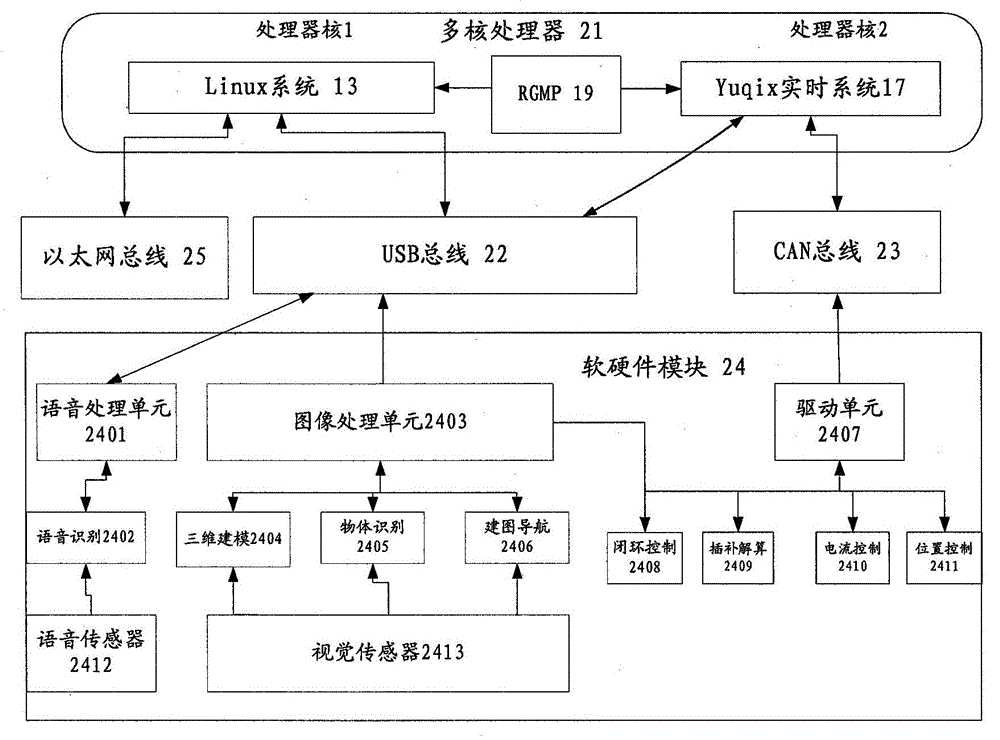

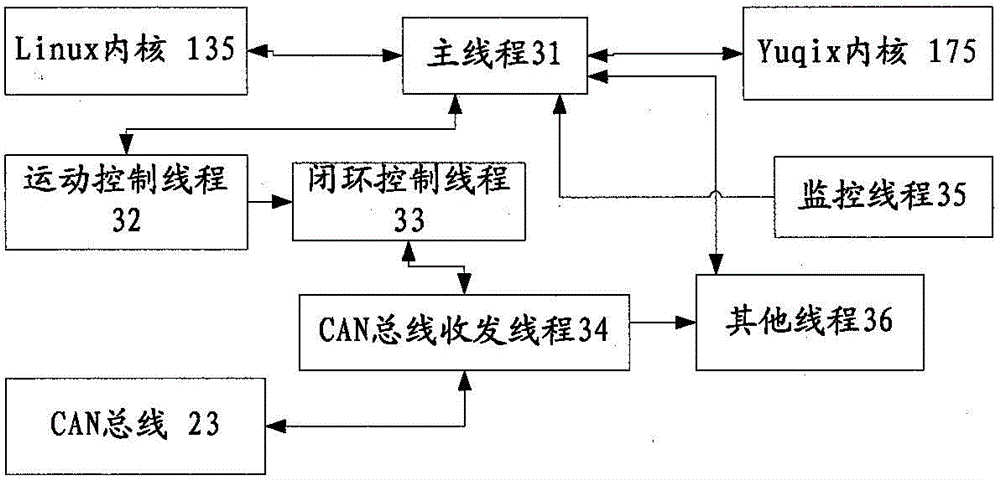

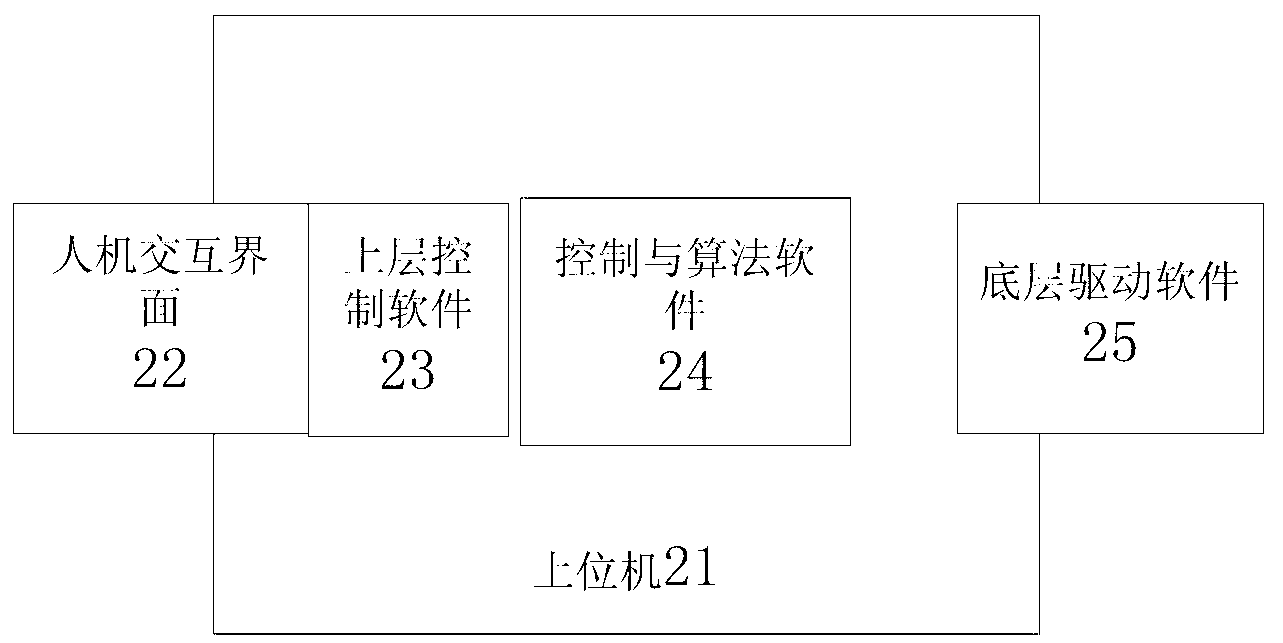

Robotic hybrid system application framework based on multi-core processor architecture

ActiveUS20170203436A1Improve development efficiencyLow costProgramme controlProgramme-controlled manipulatorOperational systemEmbedded operating system

The present invention relates to a robot hybrid system application framework based on a multi-core processor architecture. In the robot system with ARM / X86 multi-core processor as the controller, multi-core parallel processing architecture of the ARM / X86 multi-core processor is used to run the robotic hybrid system application framework comprising real-time operating system, non-real-time operating system and system supporting frame in the whole robot controller, so as to provide improved operating system services. In this application framework, a real-time operating system runs independently in one ARM / X86 core, while several non-real-time operating systems run on other ARM / X86 cores. The operating systems occupy processor resources and peripherals separately and run robotic applications with different real-time requirements. The application program can be used as a unified robot operating system (ROS) application node.

Owner:AUBO BEIJING ROBOTICS TECH CO LTD

Compiler for generating an executable comprising instructions for a plurality of different instruction sets

ActiveUS20090064095A1Software engineeringSpecific program execution arrangementsCoprocessorMulti processor

A software compiler is provided that is operable for generating an executable that comprises instructions for a plurality of different instruction sets as may be employed by different processors in a multi-processor system. The compiler may generate an executable that includes a first portion of instructions to be processed by a first instruction set (such as a first instruction set of a first processor in a multi-processor system) and a second portion of instructions to be processed by a second instruction set (such as a second instruction set of a second processor in a multi-processor system). Such executable may be generated for execution on a multi-processor system that comprises at least one host processor, which may comprise a fixed instruction set, such as the well-known x86 instruction set, and at least one co-processor, which comprises dynamically reconfigurable logic that enables the co-processor's instruction set to be dynamically reconfigured.

Owner:MICRON TECH INC

Compiler for generating an executable comprising instructions for a plurality of different instruction sets

ActiveUS8561037B2Software engineeringSpecific program execution arrangementsMulti processorInstruction set

A software compiler is provided that is operable for generating an executable that comprises instructions for a plurality of different instruction sets as may be employed by different processors in a multi-processor system. The compiler may generate an executable that includes a first portion of instructions to be processed by a first instruction set (such as a first instruction set of a first processor in a multi-processor system) and a second portion of instructions to be processed by a second instruction set (such as a second instruction set of a second processor in a multi-processor system). Such executable may be generated for execution on a multi-processor system that comprises at least one host processor, which may comprise a fixed instruction set, such as the well-known x86 instruction set, and at least one co-processor, which comprises dynamically reconfigurable logic that enables the co-processor's instruction set to be dynamically reconfigured.

Owner:MICRON TECH INC

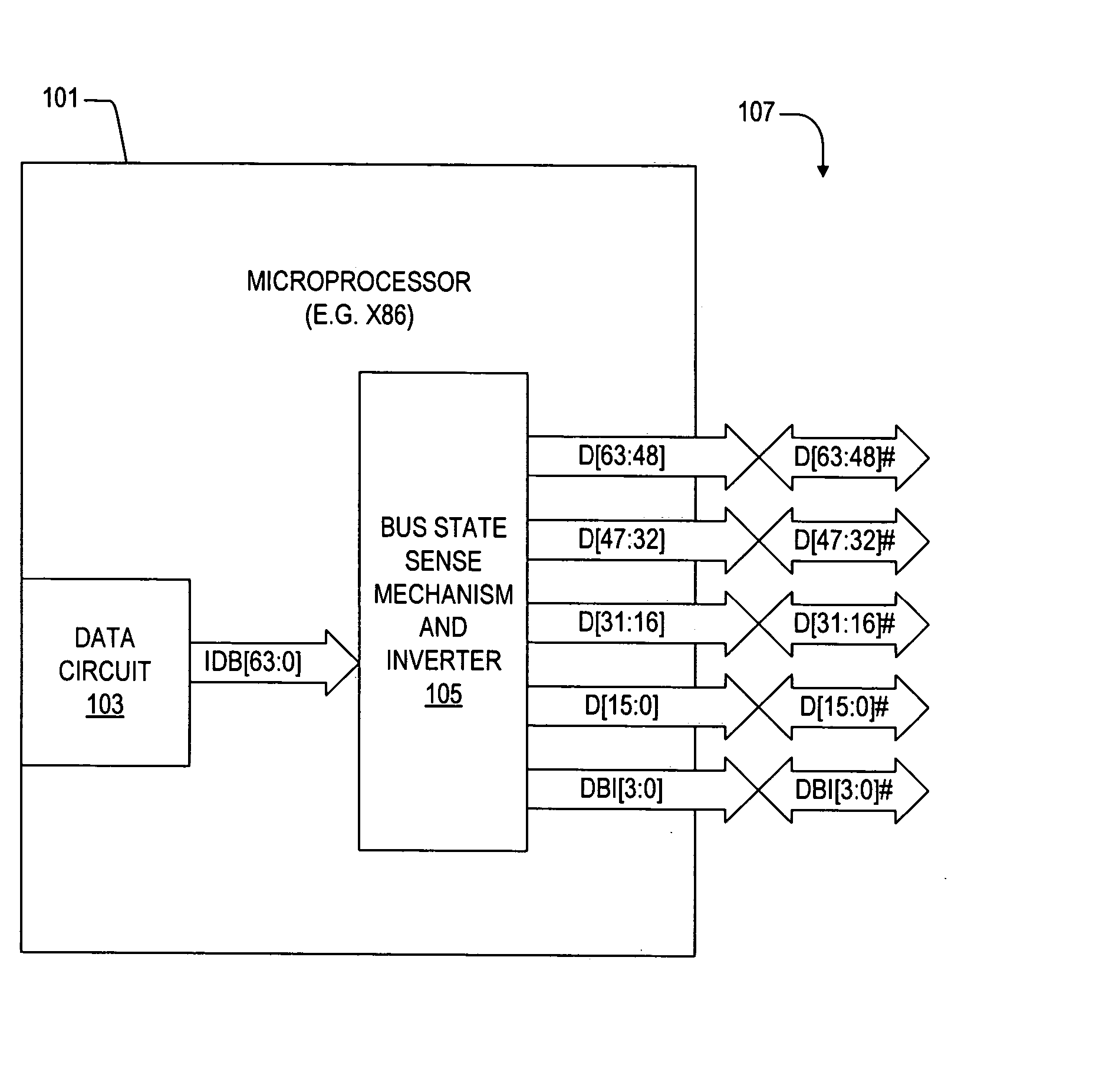

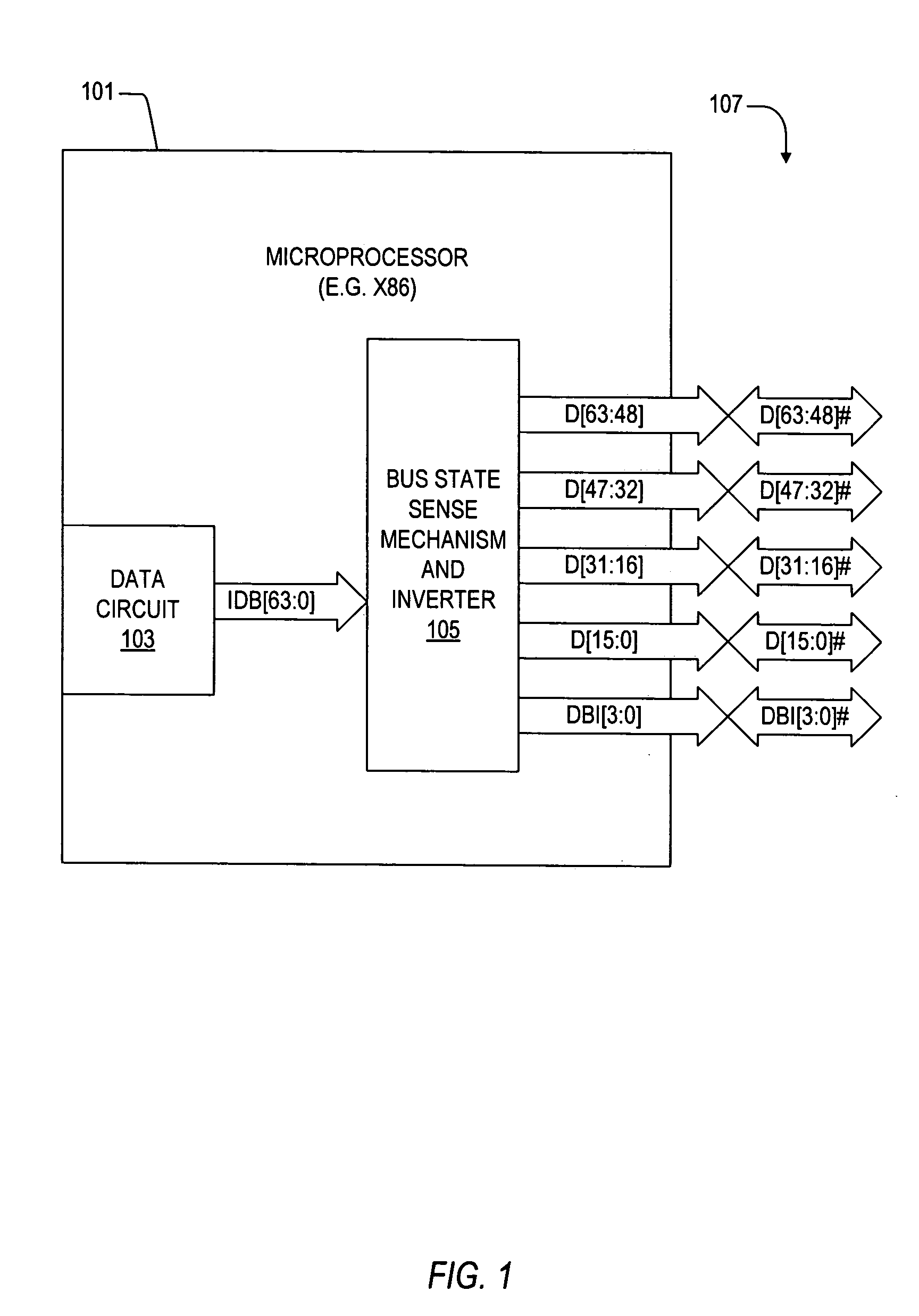

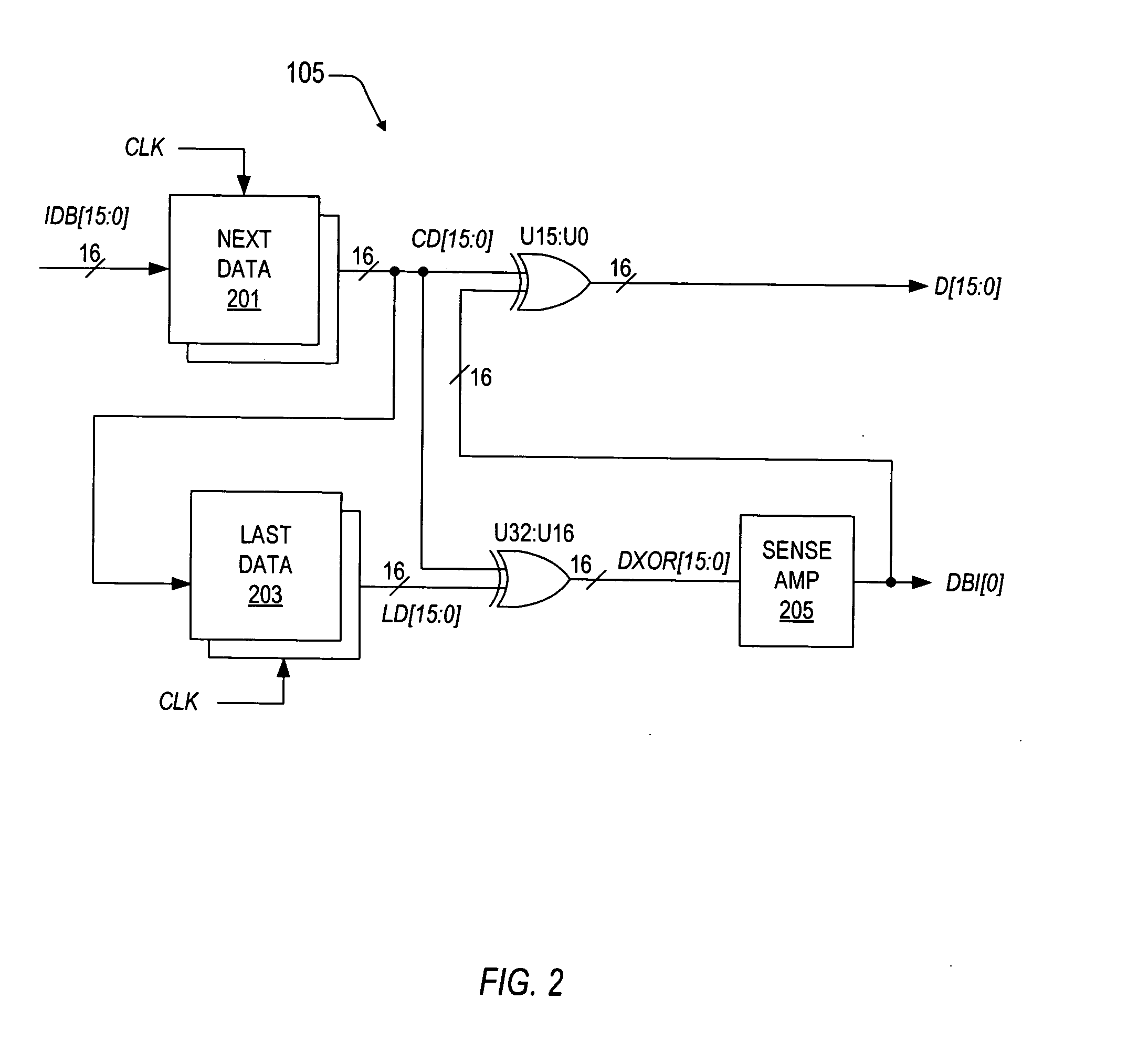

Sense mechanism for microprocessor bus inversion

ActiveUS20050216630A1Digital storageElectric digital data processingData bus inversionMicroprocessor

A sense mechanism for data bus inversion including a first memory device and an analog adder. The first memory device stores bits of the bus in a previous bus cycle. The analog adder compares the bits of the bus in the previous bus cycle with bits of the bus in a current bus cycle and provides a data inversion signal indicative of whether more than half of the bits of the bus have changed state. The analog adder operates as a bus state change sense device which rapidly evaluates bus state changes from one bus cycle to the next. The data inversion signal is used for selectively inverting the data bits of the bus and indicating bus inversion according to data bus inversion operation, such as according to X86 microprocessor protocol.

Owner:VIA TECH INC

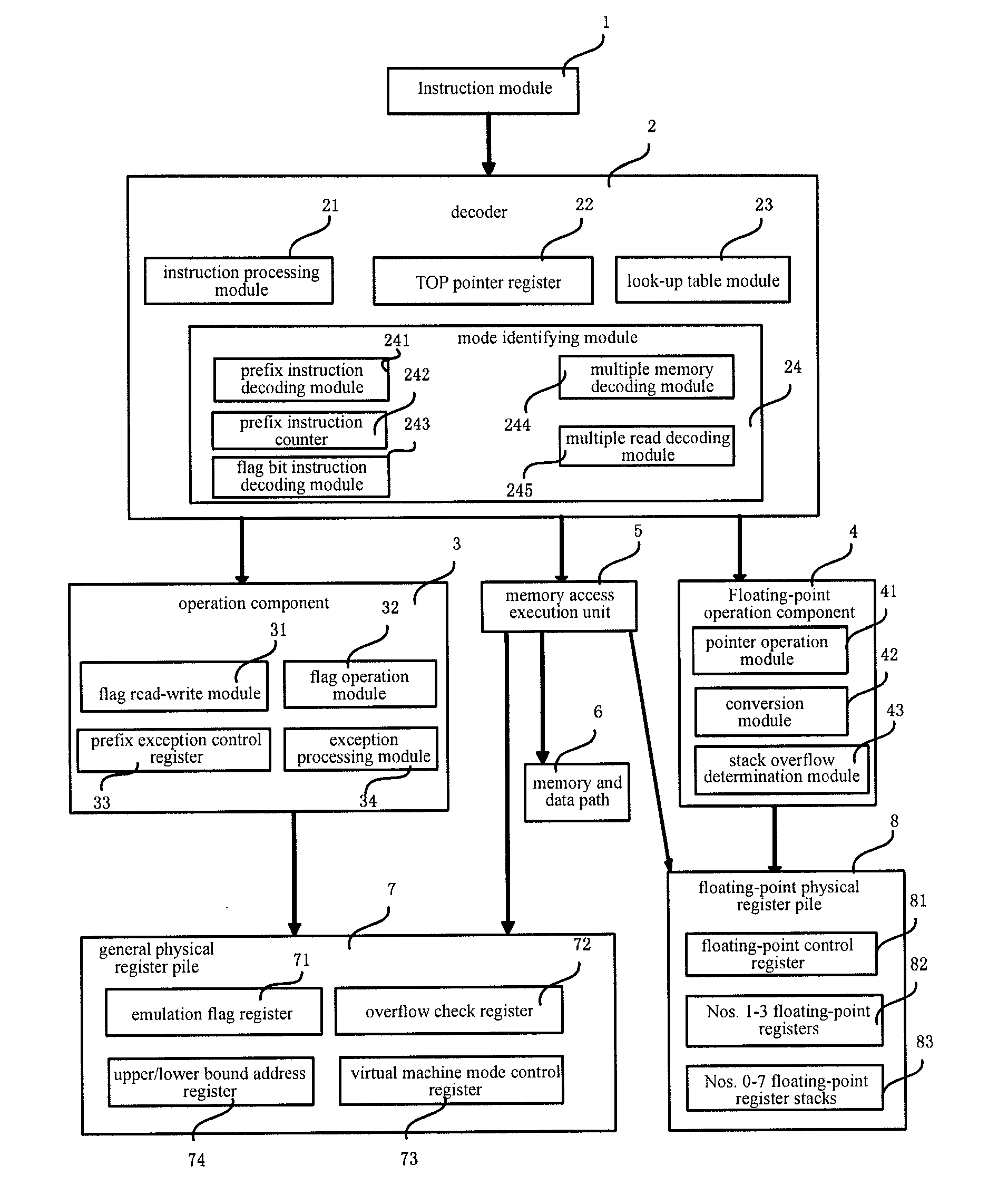

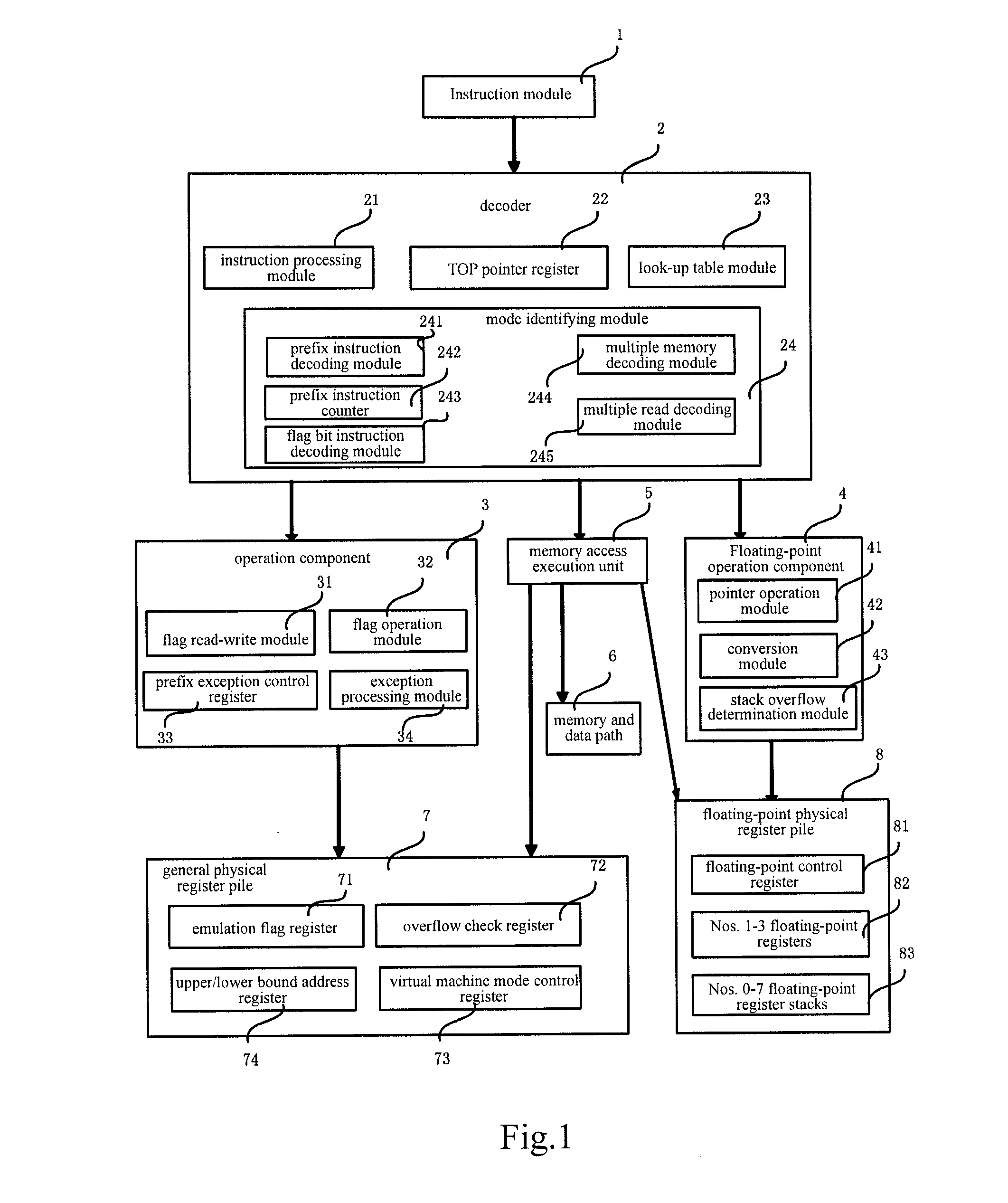

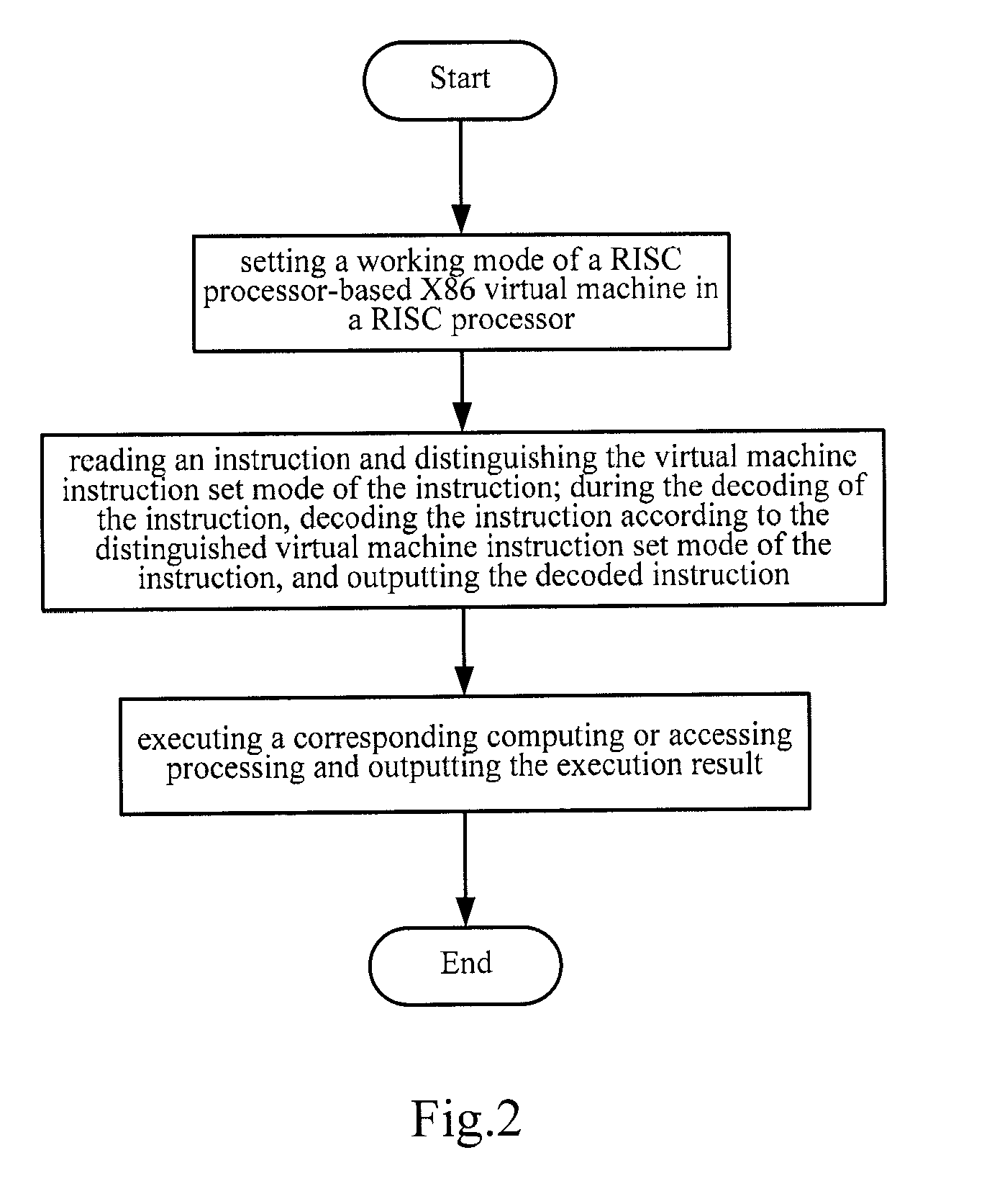

Risc processor apparatus and method for supporting x86 virtual machine

ActiveUS20110035745A1Improve performanceConditional code generationGeneral purpose stored program computerFloating pointInstruction set

A RISC processor apparatus and method for supporting an X86 virtual machine. The RISC processor includes: an instruction module for storing a virtual machine instruction set that supports the X86 virtual machine; a decoder for, during the decoding of an instruction of the virtual machine instruction set, distinguishing the virtual machine instruction set mode of the instruction, decoding the instruction according to the distinguished virtual machine instruction set mode, and outputting the decoded instruction to a fixed-point operation component or a floating-point operation component according to the distinguished virtual machine instruction set mode; the fixed-point operation component for processing the fixed-point instruction of the virtual machine instruction set according to the output of the decoder and outputting the execution result; the floating-point operation component for processing the floating-point instruction of the virtual machine instruction set according to the output of the decoder and outputting the execution result.

Owner:LOONGSON TECH CORP

Microprocessor with arm and x86 instruction length decoders

ActiveUS20160202980A1Memory architecture accessing/allocationInstruction analysisComputer architectureEngineering

A microprocessor natively translates and executes instructions of both the x86 instruction set architecture (ISA) and the Advanced RISC Machines (ARM) ISA. An instruction formatter extracts distinct ARM instruction bytes from a stream of instruction bytes received from an instruction cache and formats them. ARM and x86 instruction length decoders decode ARM and x86 instruction bytes, respectively, and determine instruction lengths of ARM and x86 instructions. An instruction translator translates the formatted x86 ISA and ARM ISA instructions into microinstructions of a unified microinstruction set architecture of the microprocessor. An execution pipeline executes the microinstructions to generate results defined by the x86 ISA and ARM ISA instructions.

Owner:VIA TECH INC

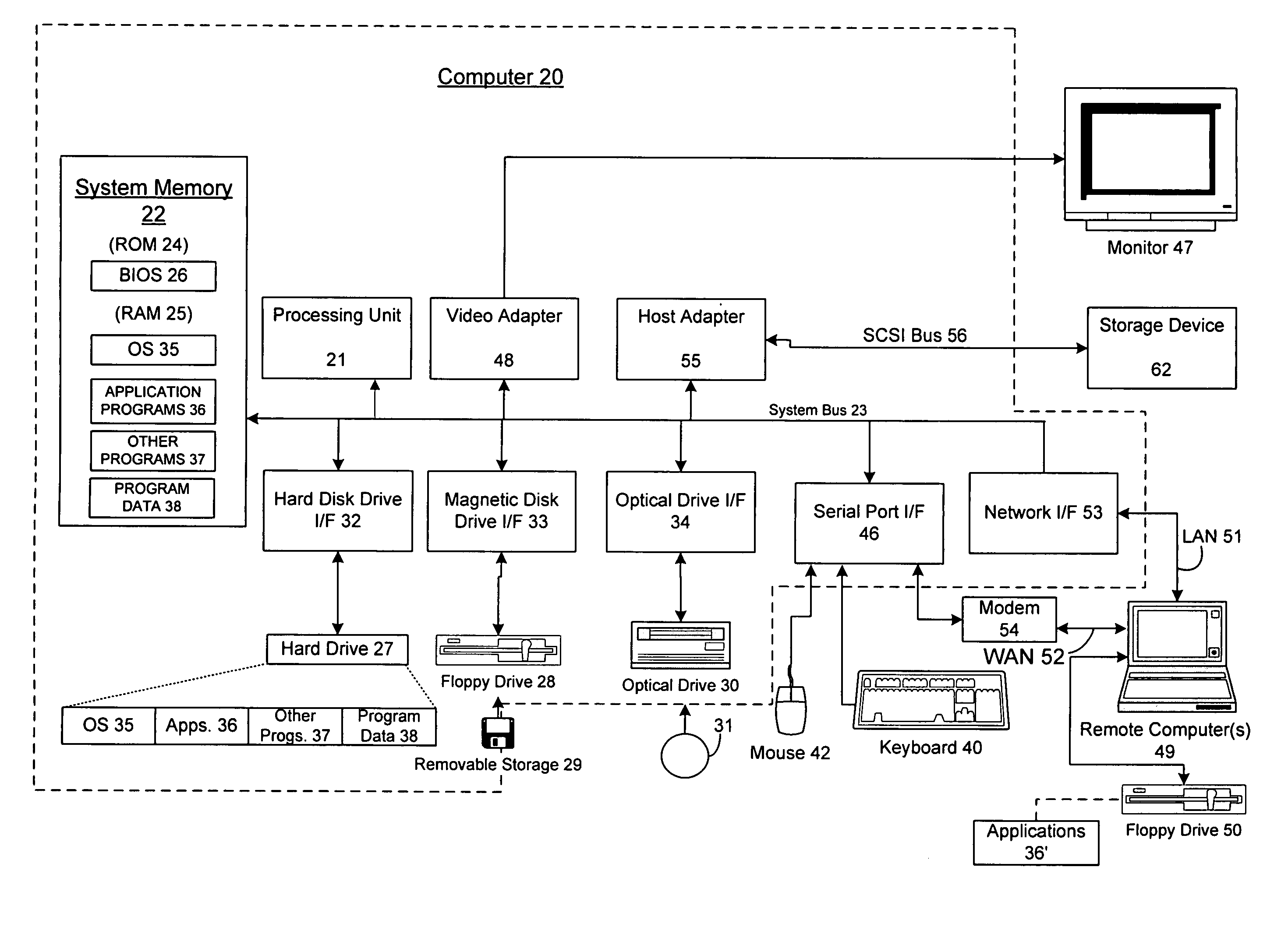

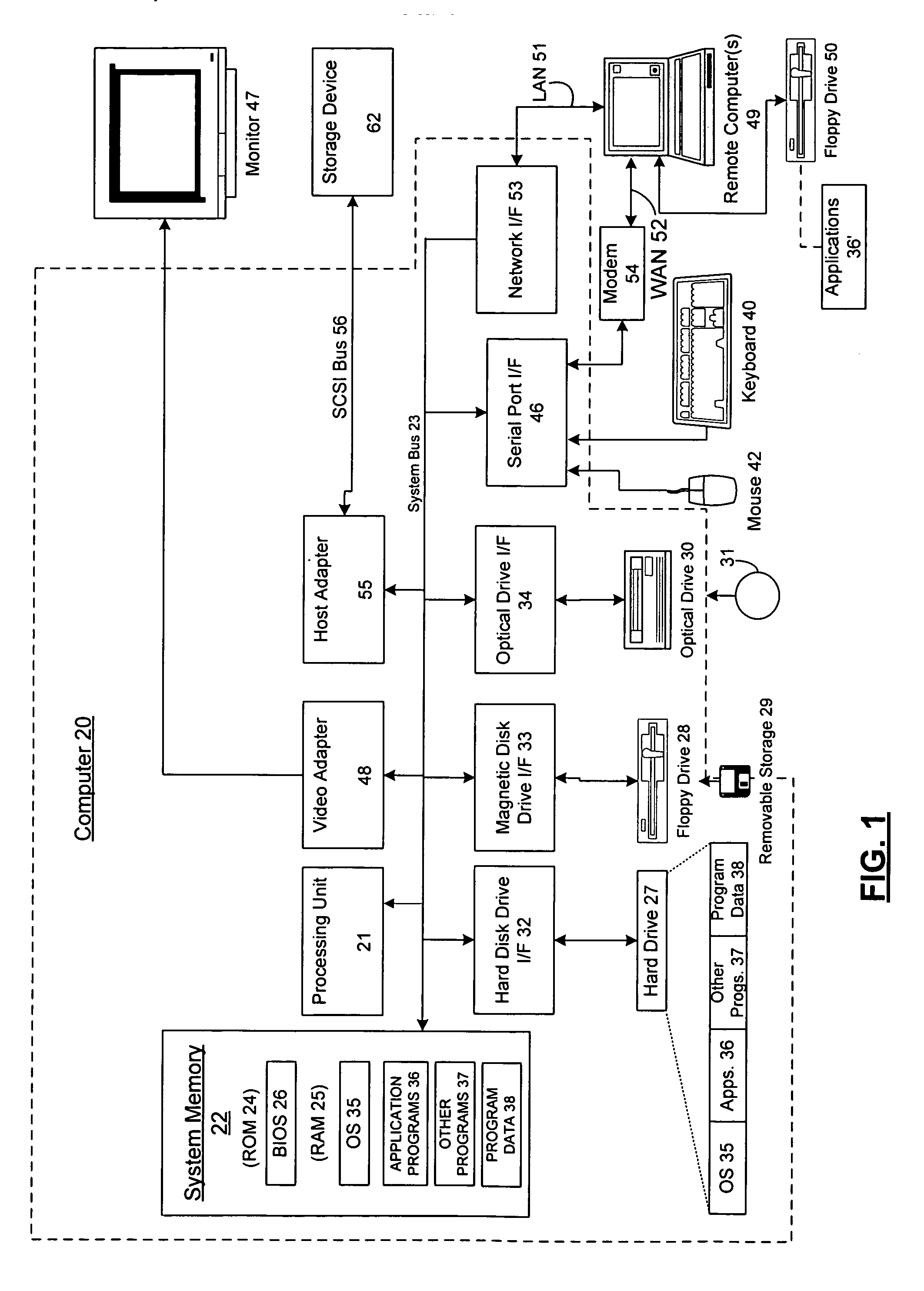

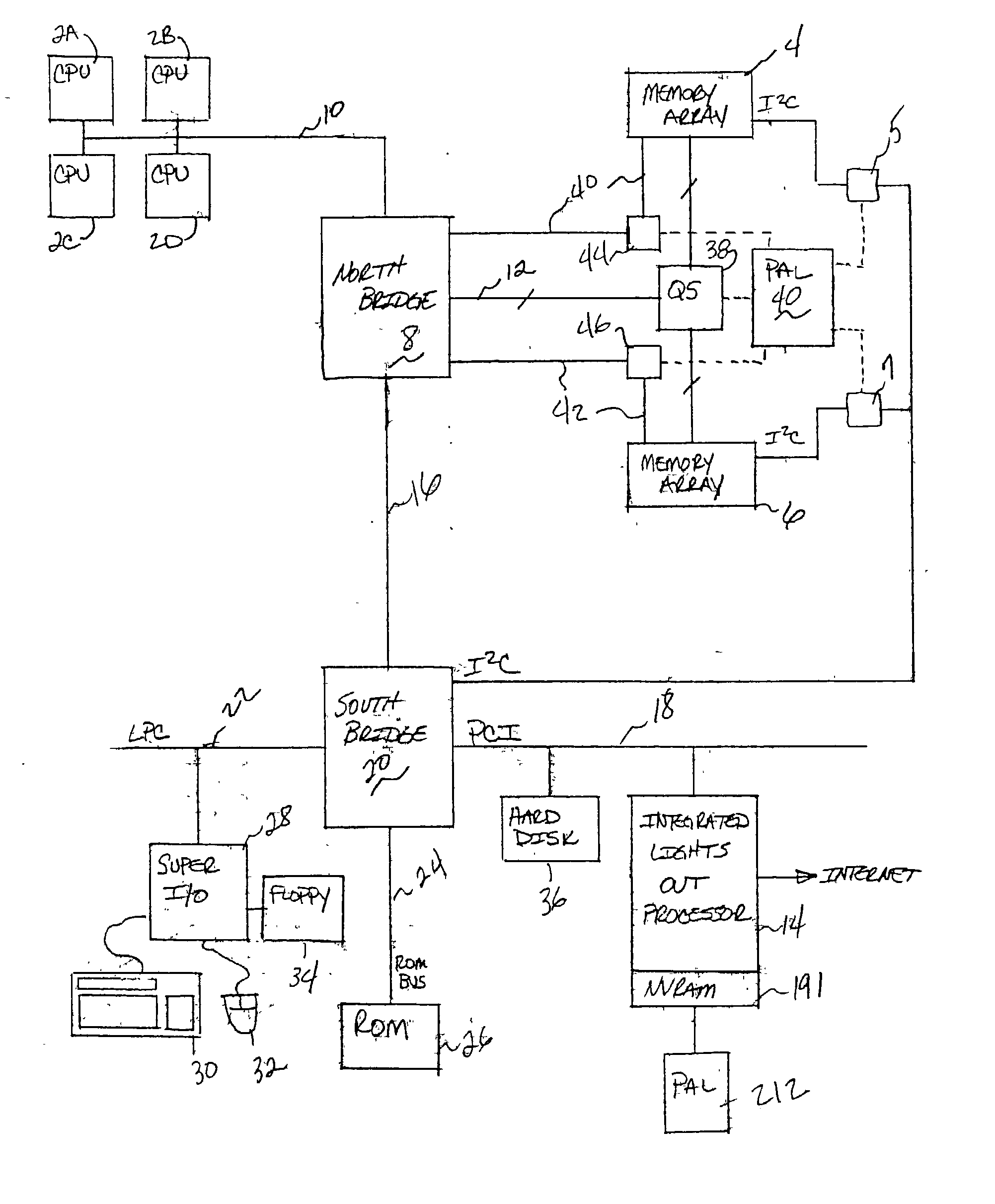

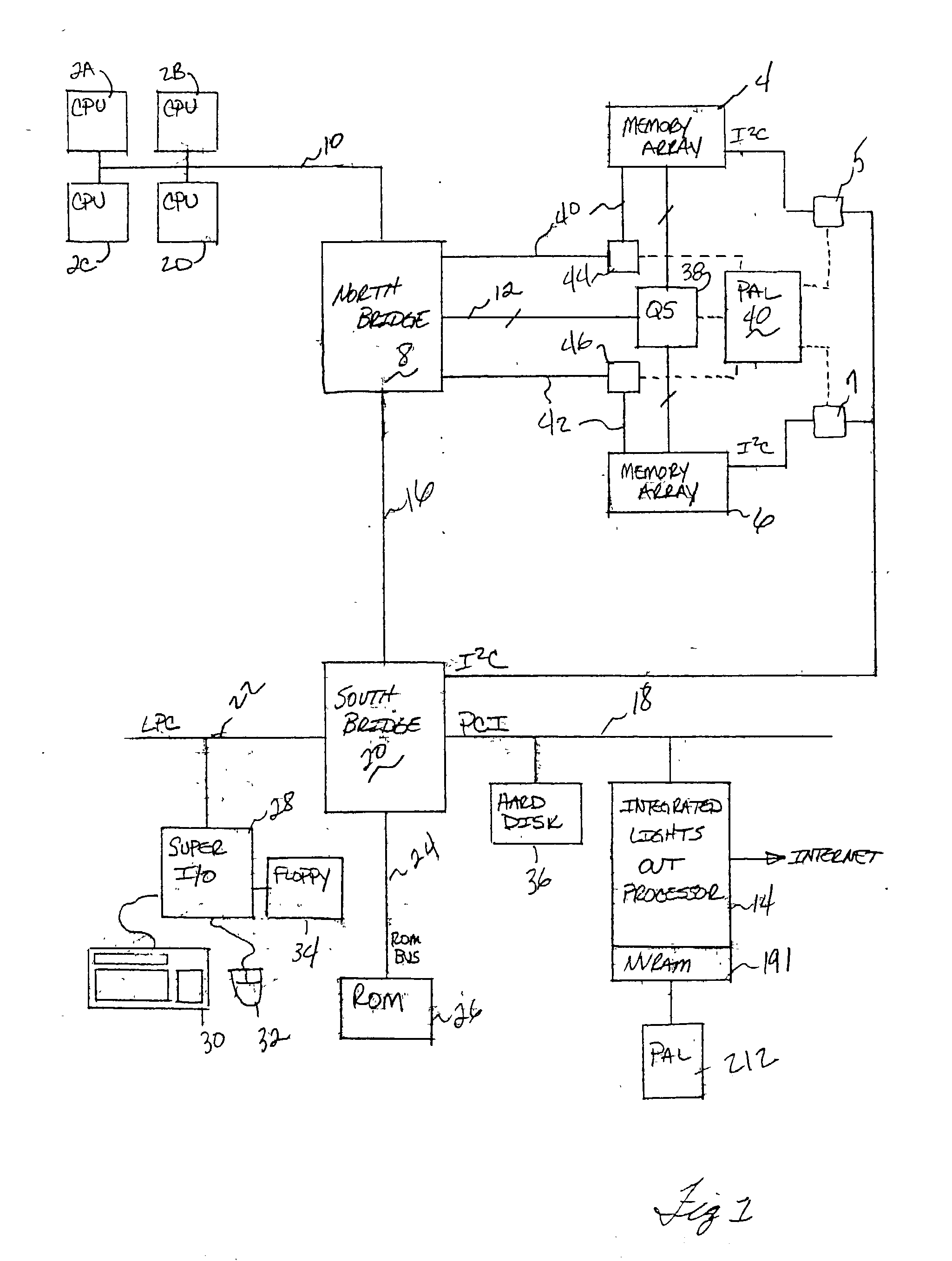

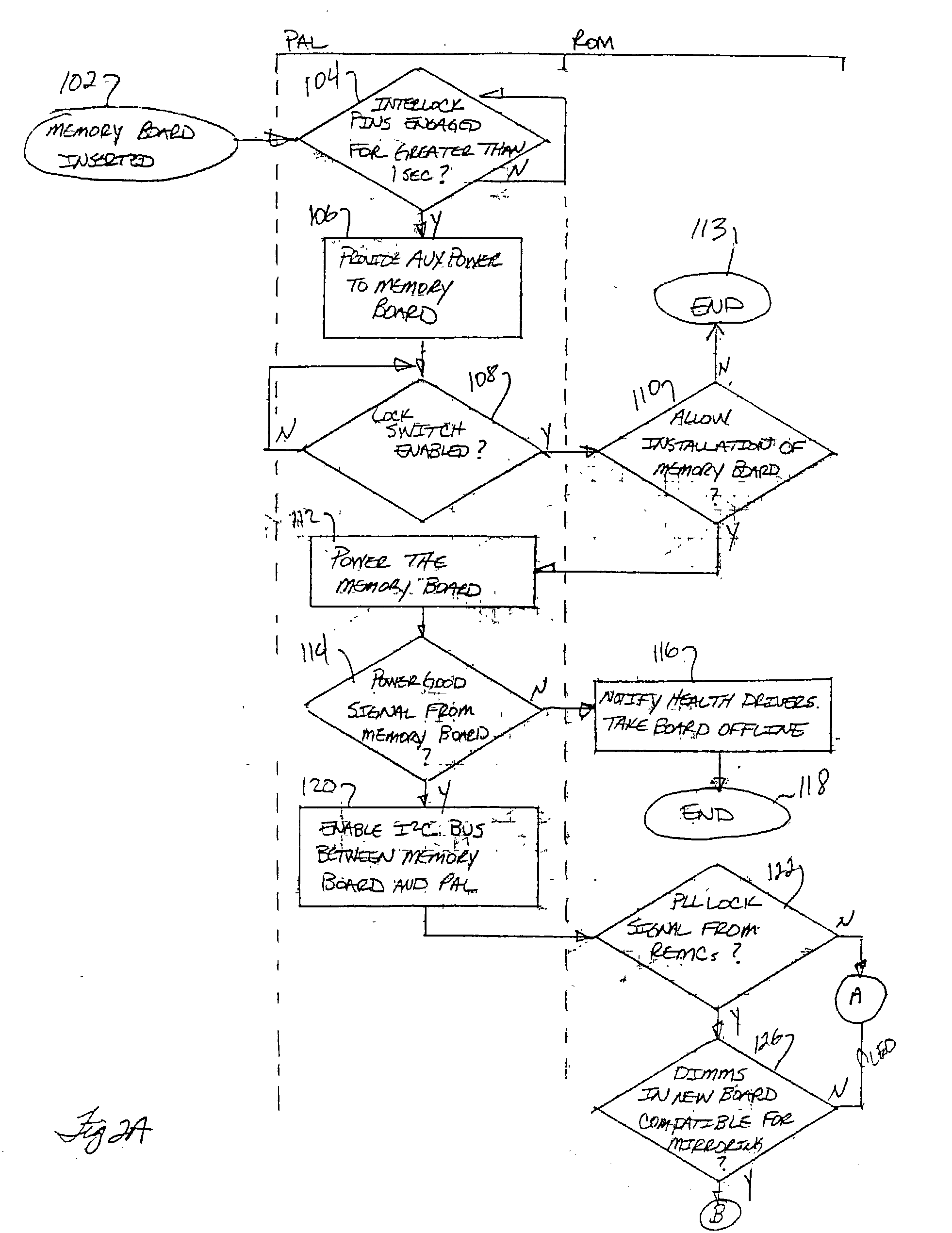

Computer system architecture with hot pluggable main memory boards

InactiveUS20030208654A1Easy accessComponent plug-in assemblagesNon-redundant fault processingOff the shelfOperational system

The specification discloses a server system implementing hot pluggable memory boards in an architecture using X86 processors and off-the-shelf operating system, such as Windows(R) or Netware, which do not support hot plugging operations. Thus, the specification discloses systems and related methods for hot plugging main memory boards transparent to, and without the help of, the operating system. The operating system need only have the ability to recognize additional memory in order to use it. Moreover, the specification discloses a related set of memory error detection and correction techniques, again which are implementing transparent to, and without the help of, the operating system.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

Robotic hybrid system application frame based on multi-core processor architecture

InactiveCN105278940ARun independently of each otherDebug each other independentlySpecific program execution arrangementsFrame basedStructure of Management Information

The invention describes a robotic hybrid system application frame based on a multi-core processor architecture. In a robotic system which takes an ARM (Advanced RISC Machines) / X86 multi-core processor as a controller, a multi-core parallel processing structure of the ARM / X86 multi-core processor is used for operating the robotic hybrid system application architecture consisting of a real-time operating system, non-real-time operating systems and a system supporting frame on a whole robotic controller so as to provide improved operating system service, wherein the real-time operating system, non-real-time operating systems and the system supporting frame simultaneously operate. In the application frame, one real-time operating system independently operates in one ARM / X86 core, meanwhile, a plurality of non-real-time operating systems operate in other ARM / X86 cores, the operating systems mutually individually occupy processor resources and peripherals, robotic application programs with different real time requirements are independently operated, and the application programs can be used (drawing 1) in a uniform ROS (Robotic Operating System) application node form.

Owner:BEIHANG UNIV

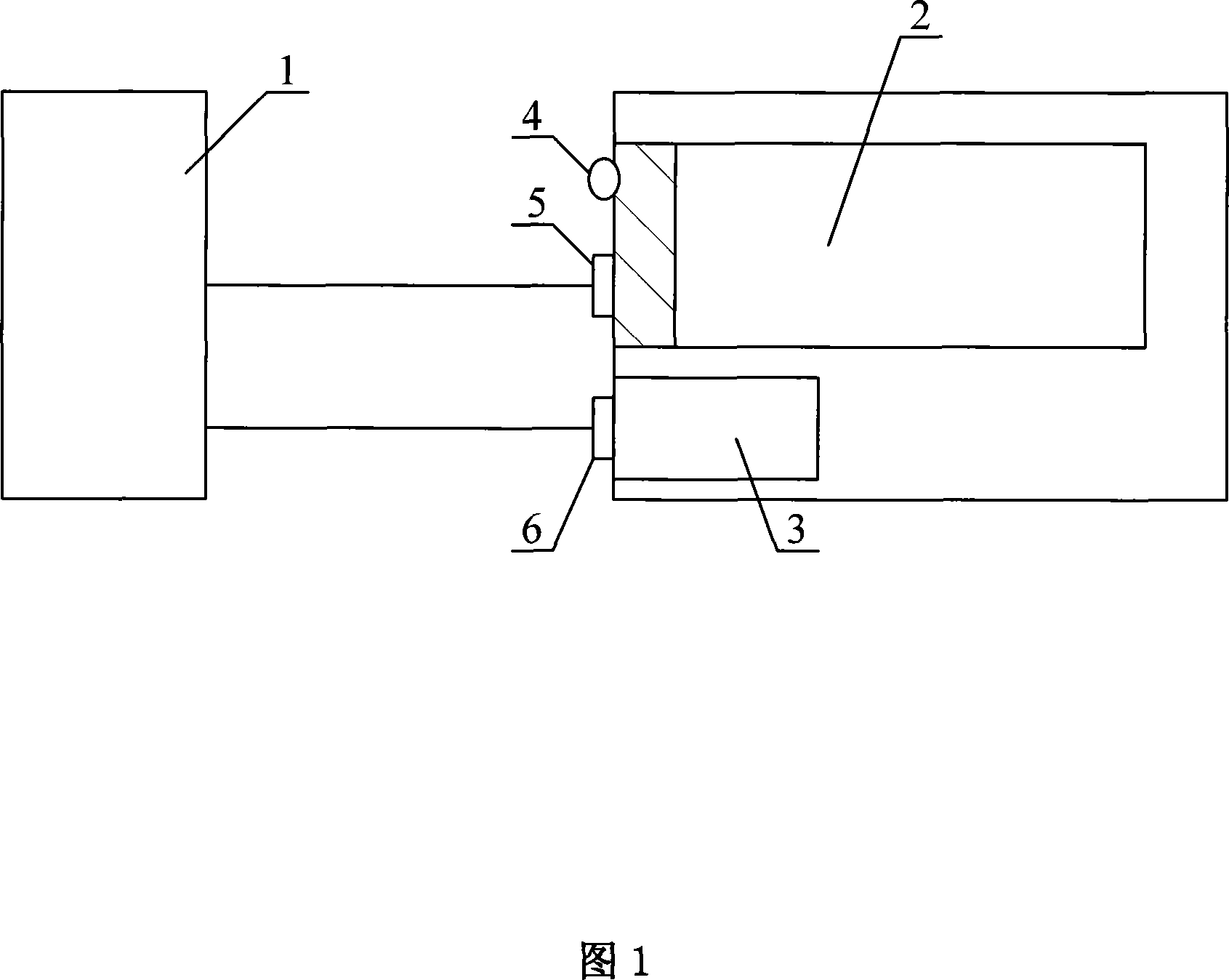

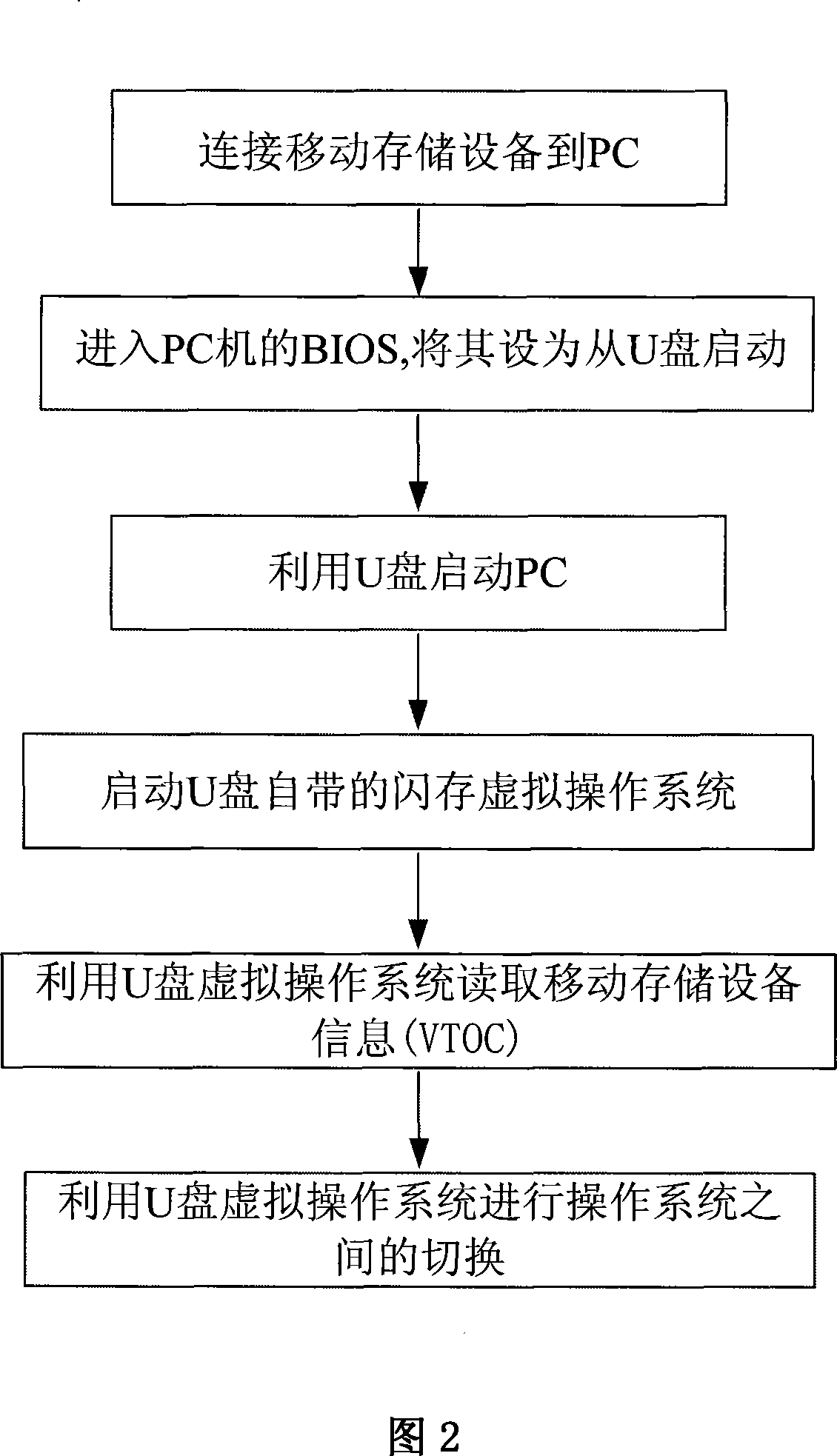

Combined device and method for starting up multiple operation system from mobile memory apparatus

InactiveCN101149685AUnique designFunction increaseProgram loading/initiatingOperational systemMulti language

This invention relates to starting the multi-operating system's aggregate unit and the method from the migration storage device, including: The printed wiring board, who has the external and internal connection posts; Peripheral connection, which connects with external connection post telecommunication; The outer covering using in holding the printed wiring board and the migration storage device; The internal and external connection posts connect with migration storage device's electrical connection and the peripheral connection corresponding, USB dodge saves plate is equipped on the printed wiring board, it has the electrical connection and the USB connection, it's electrical connection connects with the internal post of the printed wiring board. The user may move the multi-operating system from a portable installment, to produce, manage and revise the disk partition, move the multi-language environment in easy, establish and manage the simulation or testing environment, produce and move each kind of database in any X86 platform, and cut-over the operating system but need not to close down and close the application procedure.

Owner:SUZHOU ONE WORLD TECH

Multi-core microprocessor that performs x86 isa and arm isa machine language program instructions by hardware translation into microinstructions executed by common execution pipeline

ActiveUS20120260065A1Program control using stored programsRuntime instruction translationProgram instructionProcessing core

A microprocessor includes a plurality of processing cores each including a hardware instruction translator that translates instructions of x86 instruction set architecture (ISA) machine language programs and Advanced RISC Machines (ARM) ISA machine language programs into microinstructions defined by a microinstruction set of the microprocessor. The microinstructions are encoded in a distinct manner from the manner in which the instructions of the x86 and ARM instruction sets are defined. Each core includes an execution pipeline that executes the microinstructions to generate results defined by the x86 ISA and ARM ISA instructions. Each core uses and associated indicator to determine whether it will boot as an x86 ISA core or an ARM ISA core when reset. The indicators are configurable to indicate that at least one of the cores will boot as an x86 ISA core and at least one other of the cores will boot as an ARM ISA core.

Owner:VIA TECH INC

Systems and methods for running a legacy 32-bit x86 virtual machine on a 64-bit x86 processor

ActiveUS7260702B2Memory architecture accessing/allocationMemory adressing/allocation/relocationMode controlPage table

Owner:MICROSOFT TECH LICENSING LLC

Control register mapping in heterogeneous instruction set architecture processor

ActiveUS20130067199A1Runtime instruction translationDigital computer detailsProgram instructionProcessor register

A microprocessor capable of running both x86 instruction set architecture (ISA) machine language programs and Advanced RISC Machines (ARM) ISA machine language programs. The microprocessor includes a mode indicator that indicates whether the microprocessor is currently fetching instructions of an x86 ISA or ARM ISA machine language program. The microprocessor also includes a plurality of model-specific registers (MSRs) that control aspects of the operation of the microprocessor. When the mode indicator indicates the microprocessor is currently fetching x86 ISA machine language program instructions, each of the plurality of MSRs is accessible via an x86 ISA RDMSR / WRMSR instruction that specifies an address of the MSR. When the mode indicator indicates the microprocessor is currently fetching ARM ISA machine language program instructions, each of the plurality of MSRs is accessible via an ARM ISA MRRC / MCRR instruction that specifies the address of the MSR.

Owner:VIA TECH INC

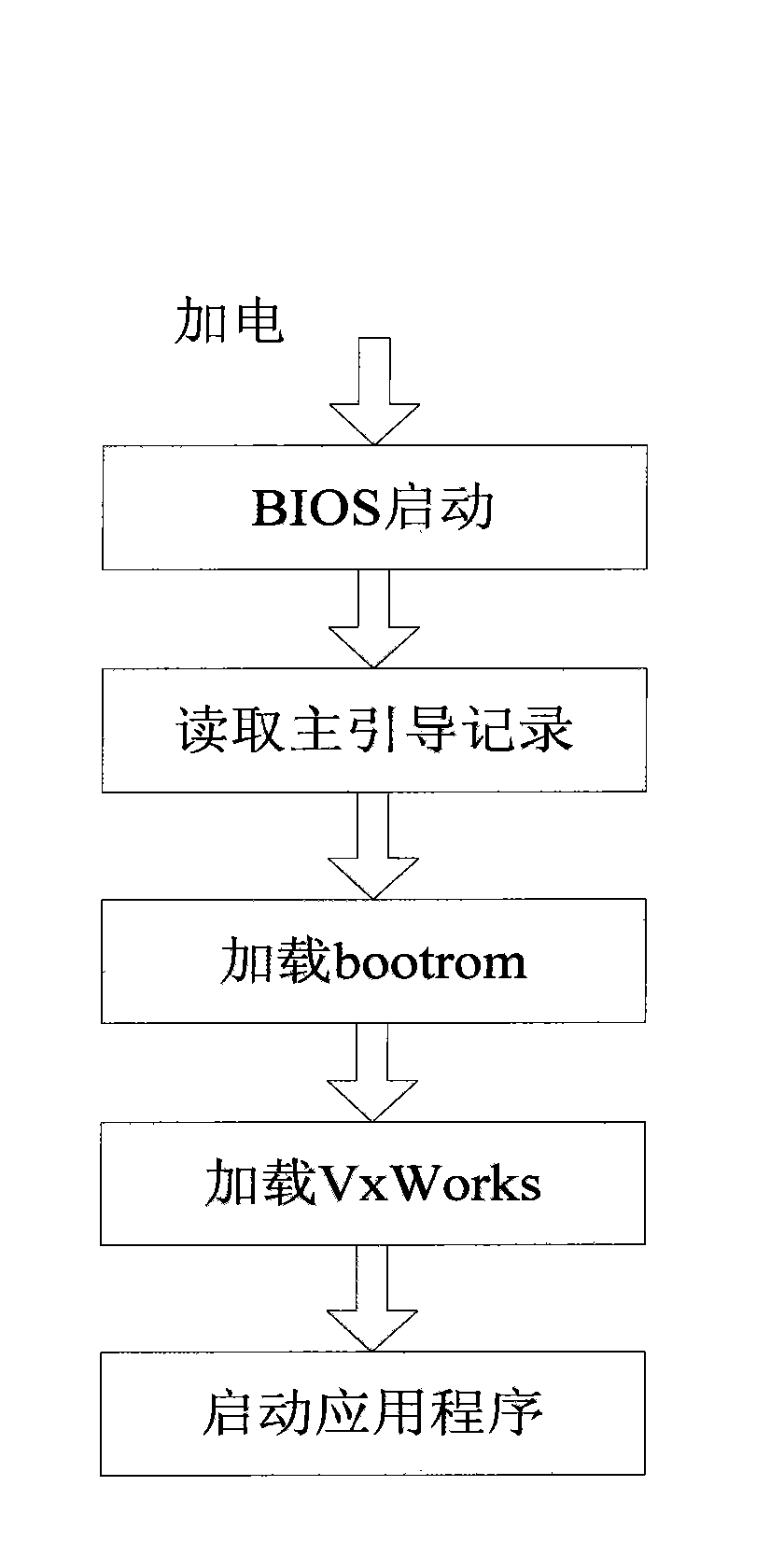

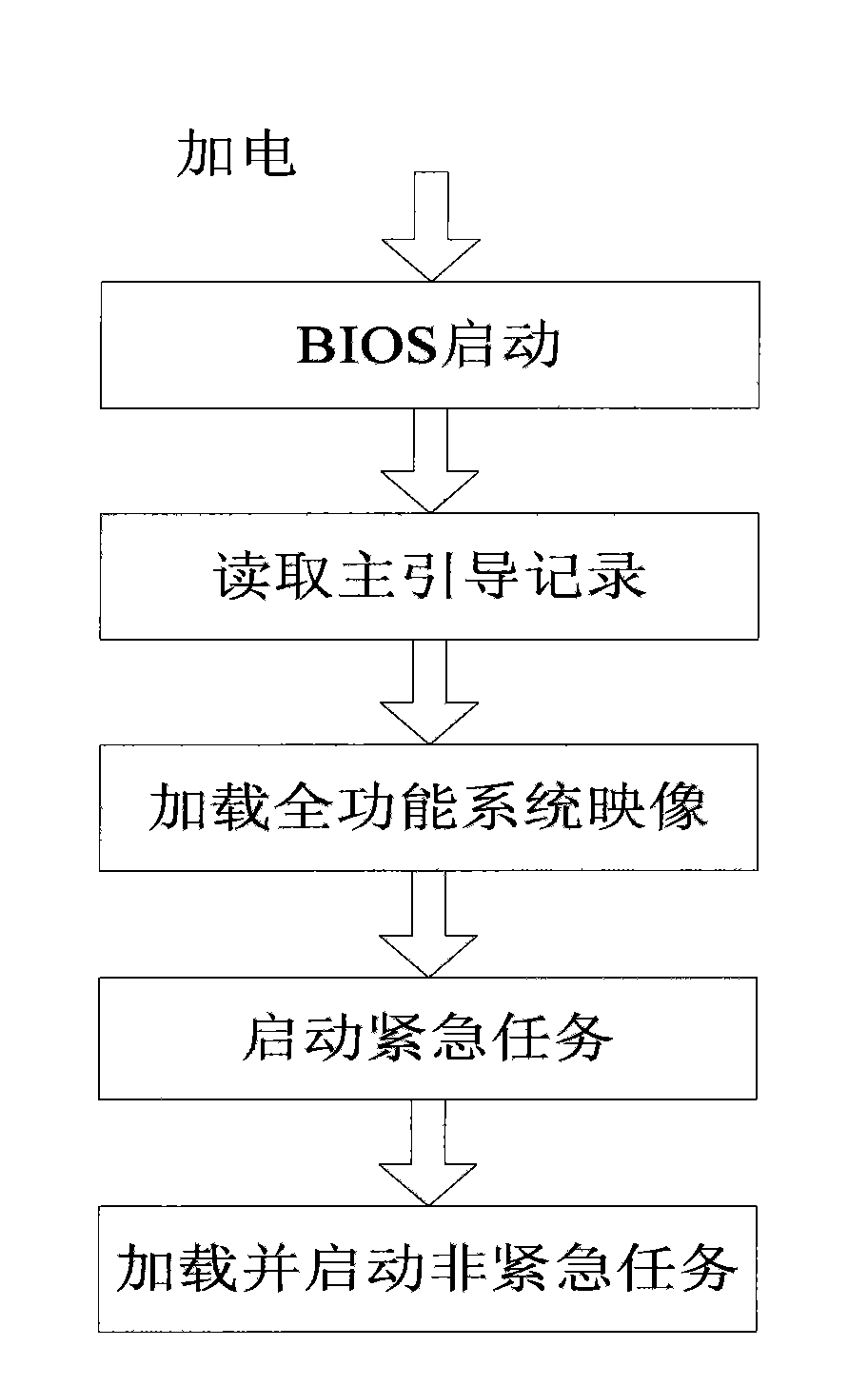

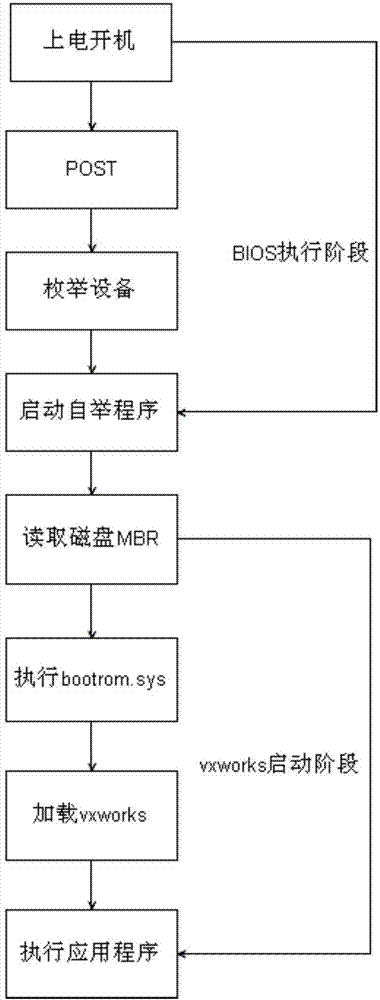

Quick start method of X86 flight control computer

A quick start method of an X86 flight control method belongs to a quick start method of an X86 architecture computer system. For a CPU of an X86 system structure, the initial start stage is generally in the real mode working environment, and the CUP can only access 100MB of memory size, while users can only access 575KB. Normally, a VxWorks system is started through secondary boot, and the application system is started after the operating system is loaded, so that the start needs longer time. In the invention, the VxWorks operating system is cut, the urgent task and the non-urgent task of the application program are directly loaded on to a full function VxWorks system image VxWorks_rom at one time, and simultaneously, the urgent task of the application program is loaded; and by utilizing a linker and a loader of VxWorks, and the symbol table technology, the non-urgent task modules of the operating system and the application program are dynamically loaded after the system is started, thereby greatly improving the start speed of key application program of the flight control computer. The invention provides a realistic application background for the quick start of control computers in the critical safety systems in the field of aerospace and the like.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

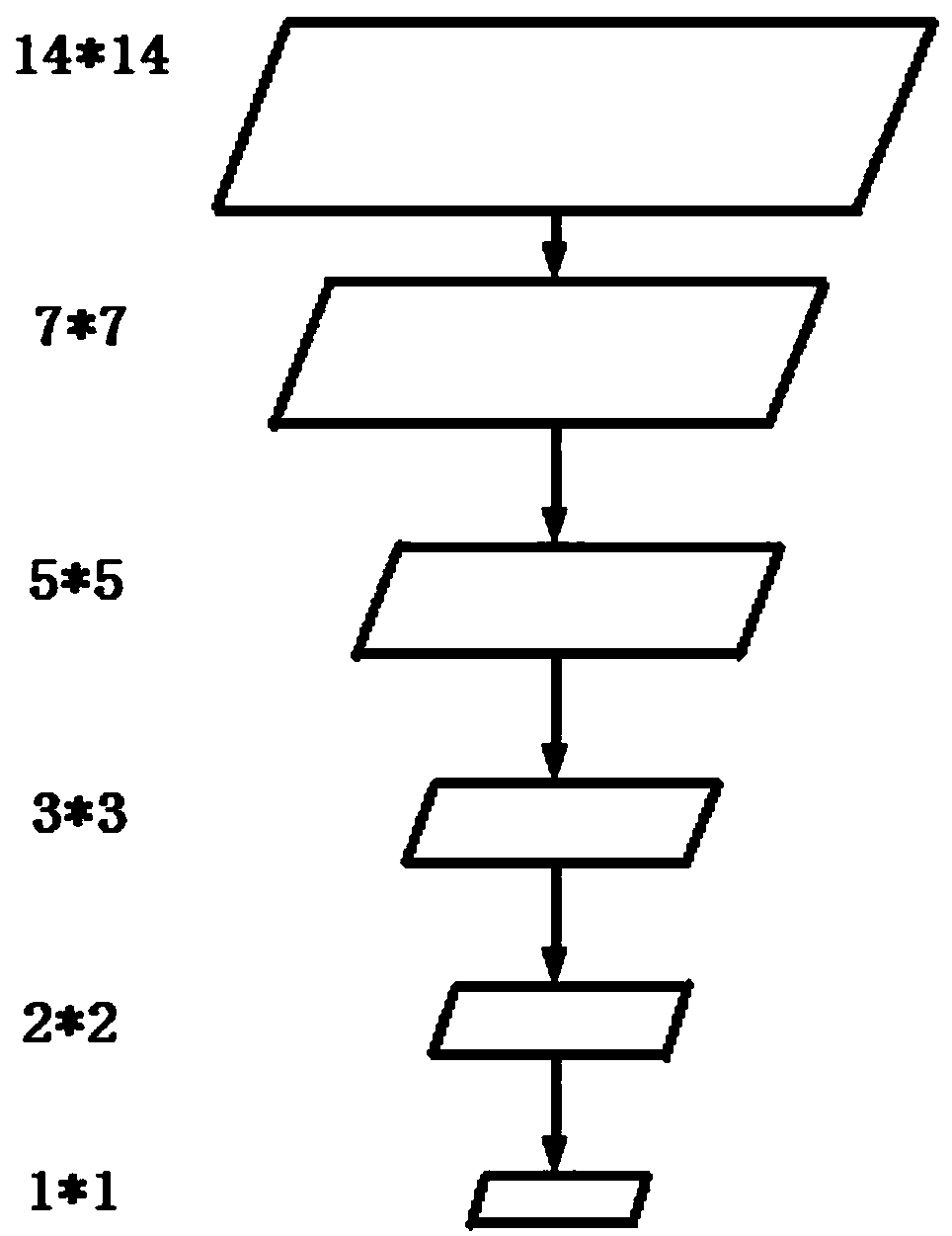

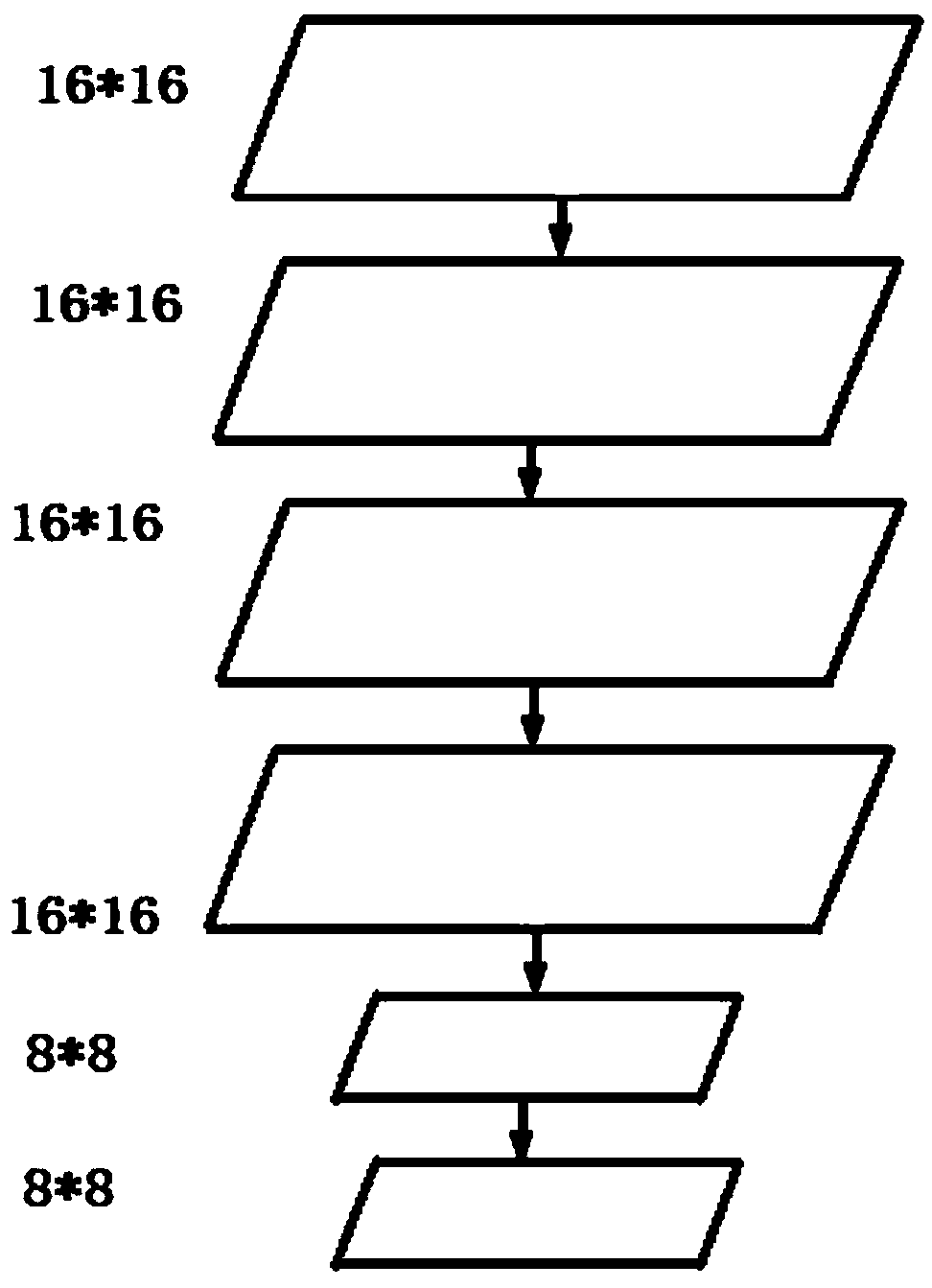

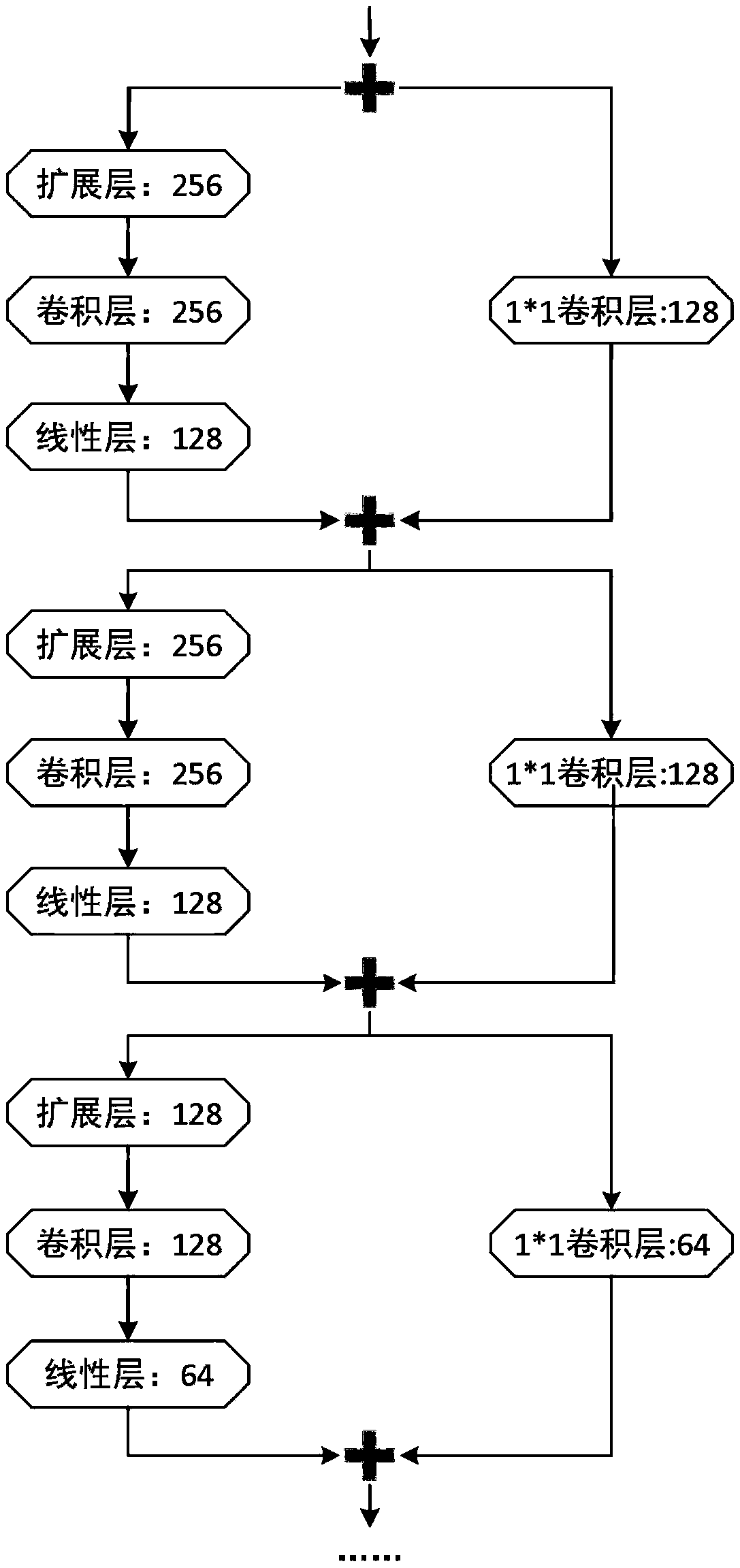

A pedestrian detection method based on depth-supervised learning to extract multi-level features of images

ActiveCN109086678AEnable end-to-end trainingRealize real-time detectionBiometric pattern recognitionNeural architecturesUltrasound attenuationData set

A pedestrian detection method based on depth-supervised learning to extract multi-level features of an image, which comprises the following steps: constructing an infrared pedestrian detection training set and a test data set; a pedestrian detection network based on depth-supervised learning being built on a depth-supervised learning framework Caffe; using RMSprop learning strategy to train the pedestrian detection network, wherein Parameter initialization method is msra, Batchsize size is 48, initial learning rate is 0.025, 5 epochs per iteration, learning rate attenuation is once, attenuation rate is 0.98, after 240000 iterations, the best effect is achieved; aiming at Intel Haswell CPU hardware platform, the forward reasoning phase of pedestrian detection network being optimized and accelerated. The invention does not need a pre-training model, and the pedestrian detection method trained from zero realizes the end-to-end training on the infrared data set, and improves the accuracy of pedestrian detection based on the far-infrared image, which can realize real-time detection based on PC X86 CPU and embedded ARM CPU.

Owner:TIANJIN UNIV

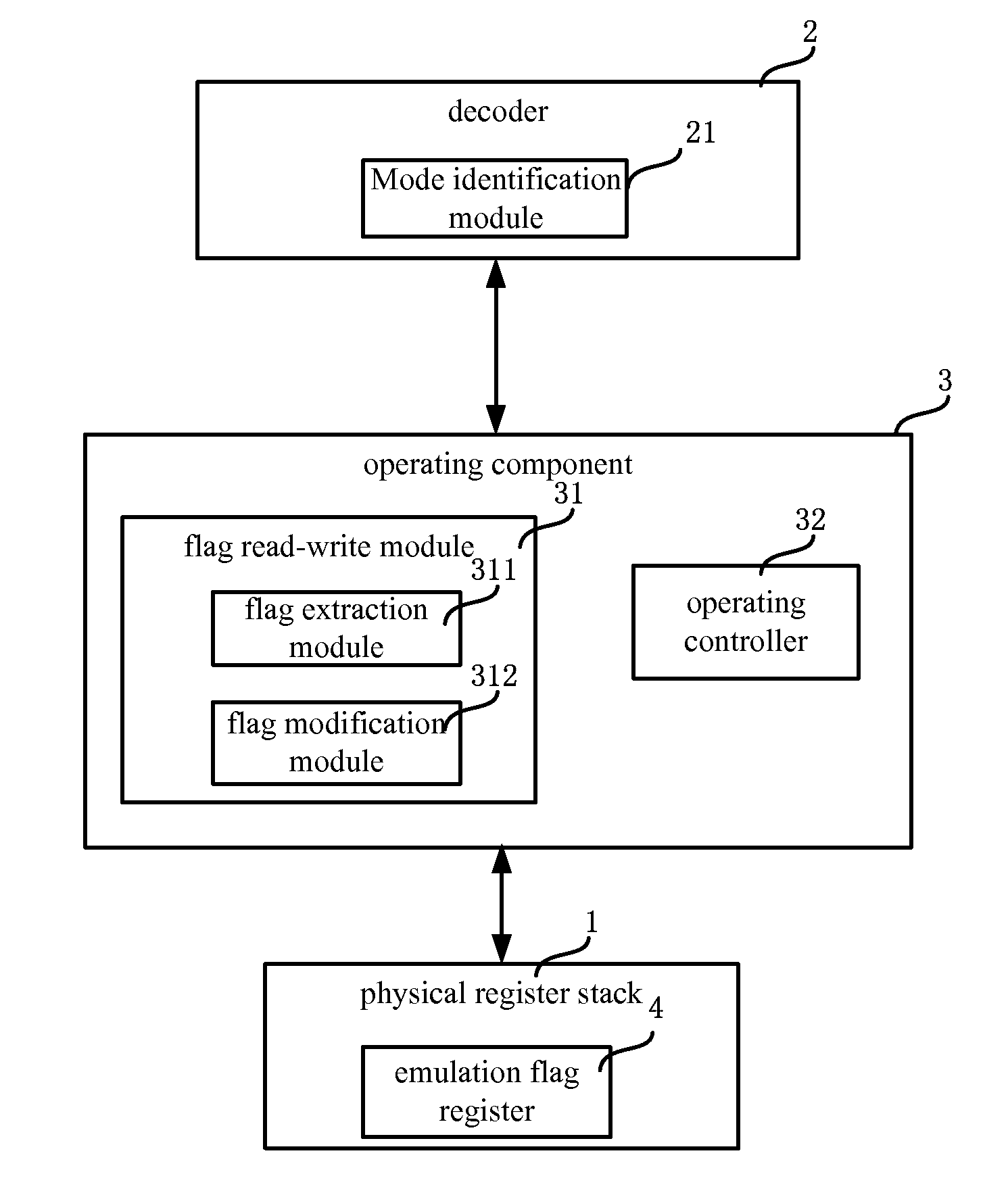

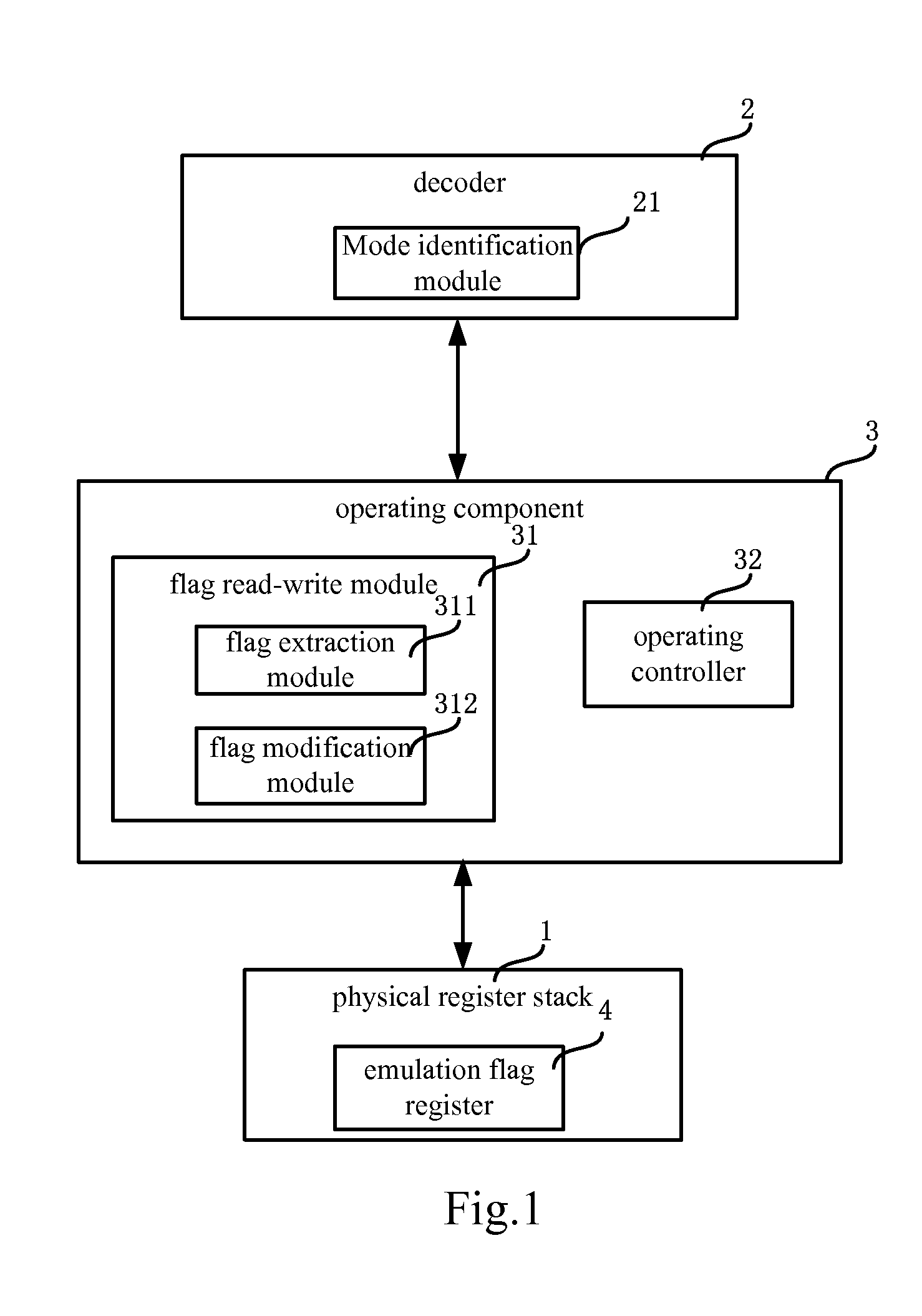

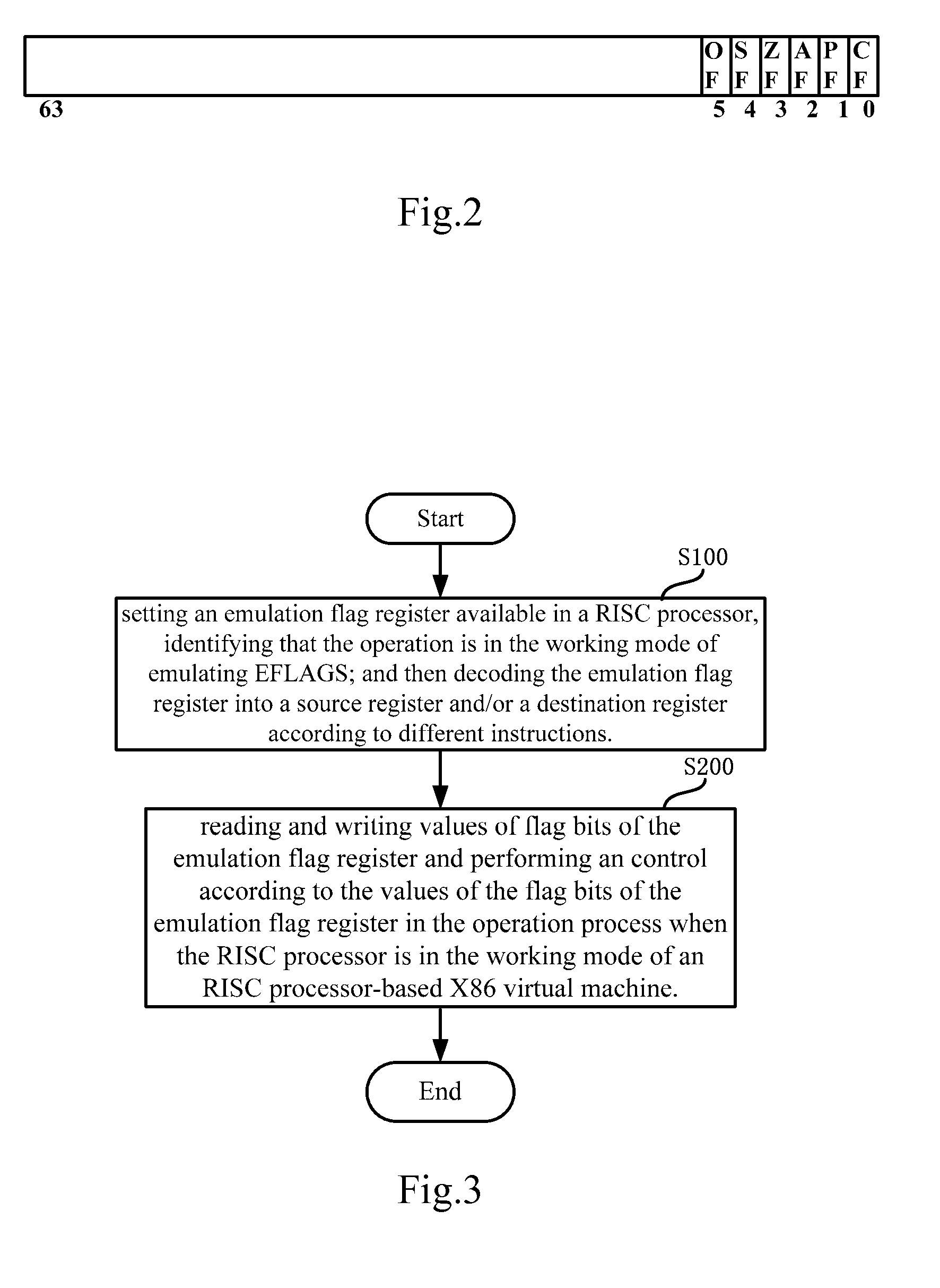

Risc processor and its register flag bit processing method

ActiveUS20100268916A1Improve performanceConditional code generationInstruction analysisProcessor registerFLAGS register

The present invention discloses a RISC processor and a method of processing flag bits of a register in the RISC processor. Said RISC processor comprises a physical register stack, an operating component connected to the physical register stack and an decoder connected to the operating component; the physical register stack comprises an emulation flag register for emulating to realize flag bits of a flag register in a CISC processor; the operating component comprises a flag read-write module for reading and writing the values of the flag bits of the emulation flag register. The operating component further comprises an operating controller for performing an operation control according to the values of the flag bits of the emulation flag register when the RISC processor is in the working mode of X86 virtual machine during an operation process.

Owner:LOONGSON TECH CORP

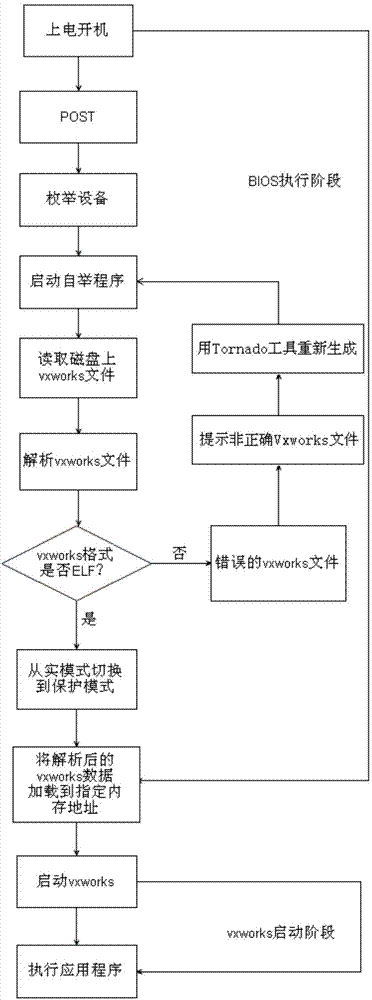

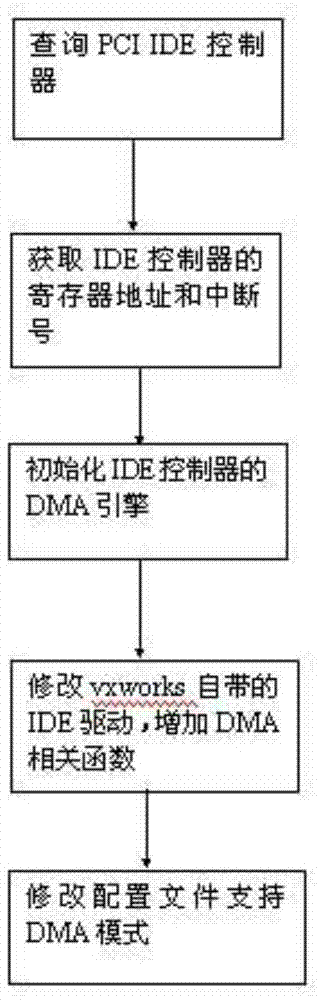

Quick starting optimizing method based on X86 platform Vxworks operation system

ActiveCN103942069AReduce startup timeOptimize execution efficiencyProgram loading/initiatingMemory addressOperational system

The invention discloses a quick starting optimizing method based on an X86 platform Vxworks operation system. The method comprises the following steps of (1) BIOS execution and (2) Vxworks loading and starting. According to the step of BIOS execution, after a computer is powered on and started, POST, initialization setting, execution of resident programs are carried out in sequence, a bootstrap program is started by calling an INT19 file in the system, a Vxworks file in the system is read directly and is analyzed after the bootstrap program is started, then an computer operation mode is switched to a protection mode from a real mode, and data and codes after analysis of the file are uploaded to assigned memory addresses respectively. According to the steps of Vxworks loading and starting, after uploading of the data and uploading of the codes are finished, the data and the codes skip to the position of a memory address e_entry corresponding to an ELF format file header to begin to be executed, the operation system is uploaded and started directly, and application programs are executed. According to the quick starting optimizing method based on the X86 platform Vxworks operation system, the method of uploading the system through bootrom in the prior art is changed, and the starting time is shortened to 3 seconds from original 20 seconds to 30 seconds.

Owner:XIAN RITRONTEK ELECTRONICS TECH

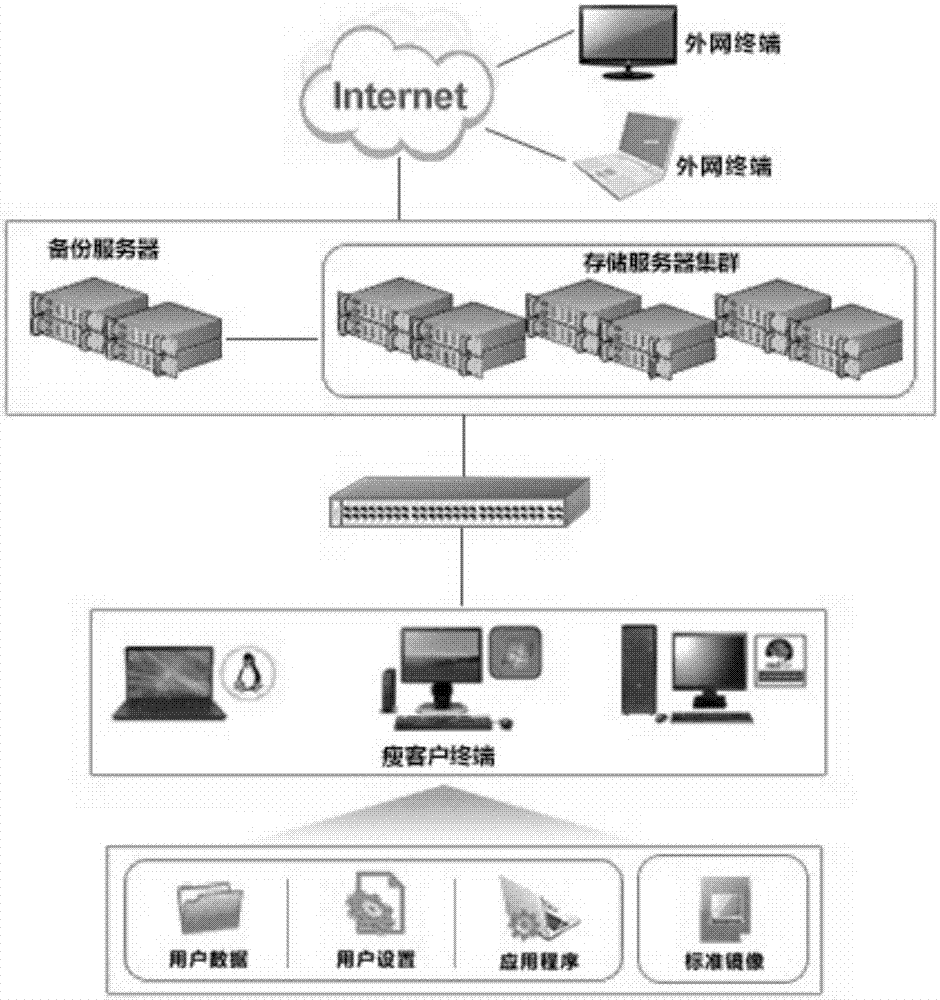

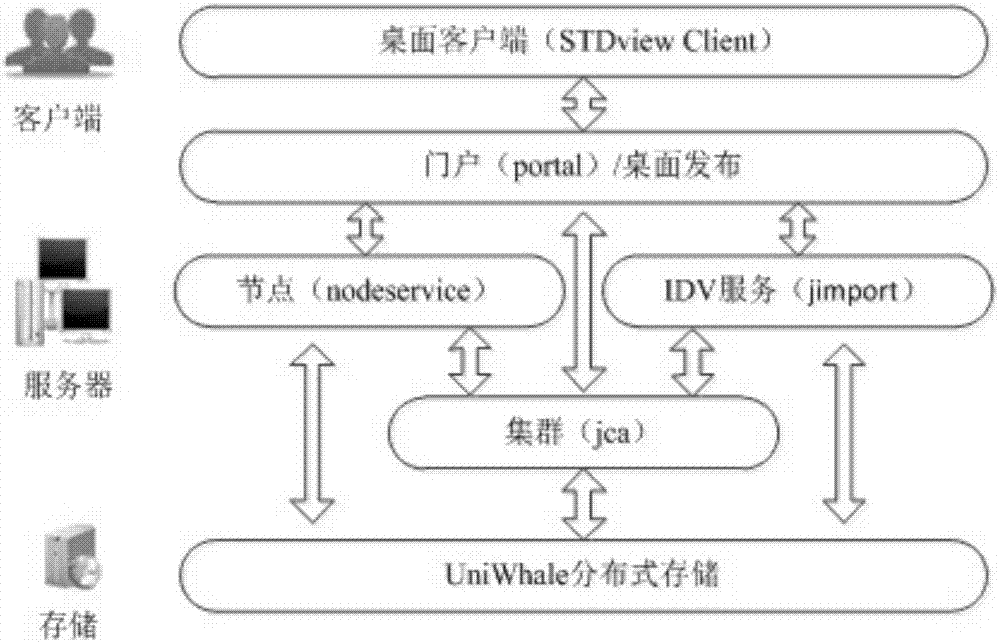

Super-fusion cloud desktop system

InactiveCN107885564AFully experienceSolve resource-intensive problemsDigital data protectionExecution for user interfacesClient-sideThin client

The invention discloses a super-fusion cloud desktop system. The super-fusion cloud desktop system is characterized by comprising a thin client side and a cloud server side, wherein the thin client side is connected with the cloud server side. The super-fusion cloud desktop system is created by adopting a cloud desktop technology, a super-fusion technology, a unified management platform and standard X86 hardware based on the super-fusion concepts of computing, storage, network, server virtualization, desktop virtualization and other resources and technologies. The scheme adopt a novel distributed virtualized technical concept, the user experience obtained by client side (terminal) hardware resources and consistent with a traditional PC is fully utilized while centralized storage and unified management of data resource and safe security are ensured, and the super-fusion cloud desktop system has quicker deployment performance and more excellent performance and is easy to maintain.

Owner:南京斯坦德云科技股份有限公司

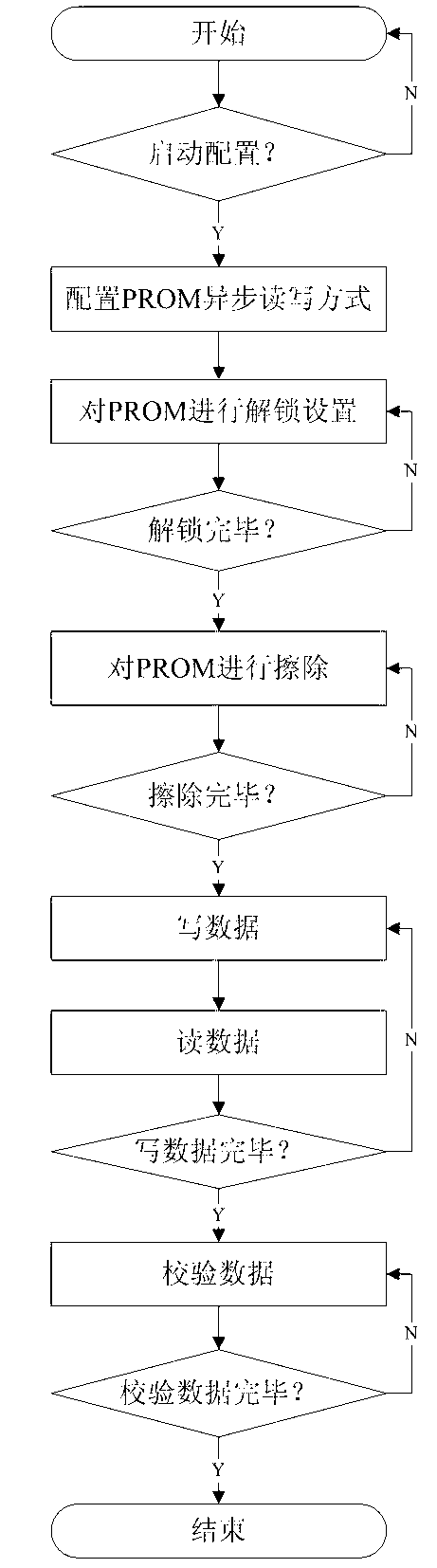

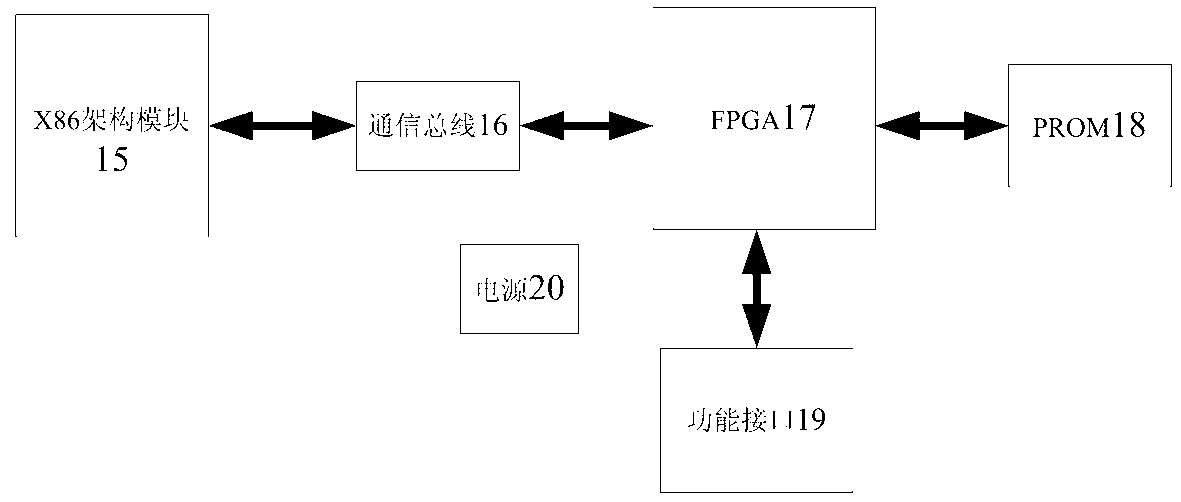

FPGA (field-programmable gate array) program upgrading and online downloading method in digital signal processing platform

ActiveCN102999350AMeet design guidelinesAvoid timeProgram loading/initiatingDigital signal processingInteraction control

The invention provides an FPGA (field-programmable gate array) program upgrading and online downloading method in a digital signal processing platform. The FPGA program upgrading and online downloading method includes two parts of hardware and software, wherein the hardware comprises an X86 architecture module, a communication bus, FPGAs, a PROM (programmable read only memory), functional interfaces and a power supply, wherein the X86 architecture module is connected with the FPGAs through the communication bus, the FPGAs are simultaneously connected with the PROM through special circuit interfaces of the FPGAs, the other functional interfaces of the FPGAs constitute the functional interfaces, and the whole system adopts the power supply for supplying power; and the software mainly comprises programs in an upper computer and the FPGAs in the X86 architecture module, so that human-computer interaction control, upgrading, online downloading and checking of the programs of the FPGAs and the like are realized. According to the method provided by the invention, the characteristics of digital signal processing platforms in the fields of software radio, satellite communication and the like are fully combined to perform program upgrading and updating of the FPGAs, then the programs of the FPGAs are convenient and easy to update and upgrade, the time required for disassembling and assembling products, utilizing a special downloading wire to download and performing other processes can be greatly saved, the design cost is saved, the complexity in design is reduced, and the workload in design is also reduced.

Owner:MIANYANG WEIBO ELECTRONICS

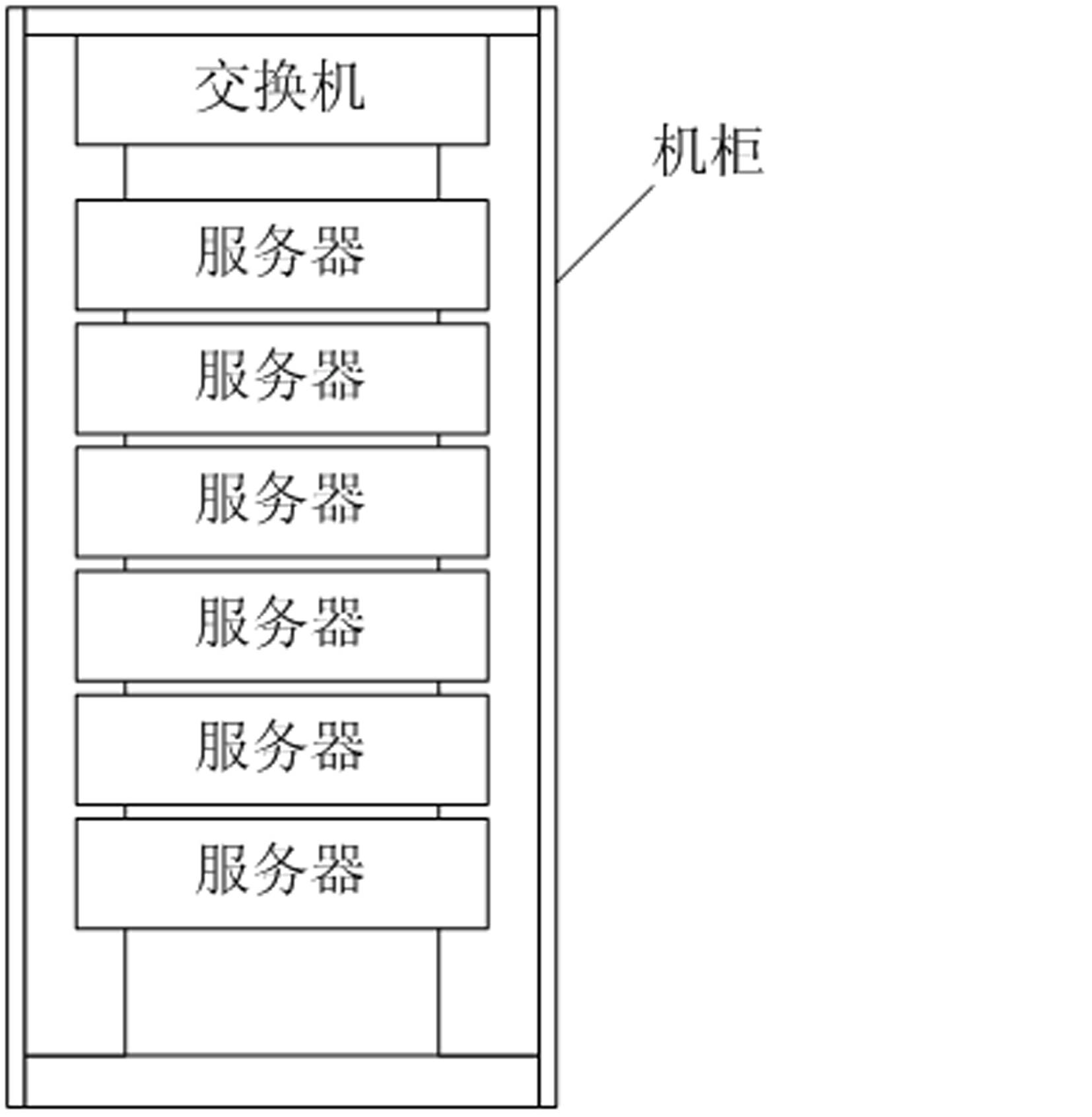

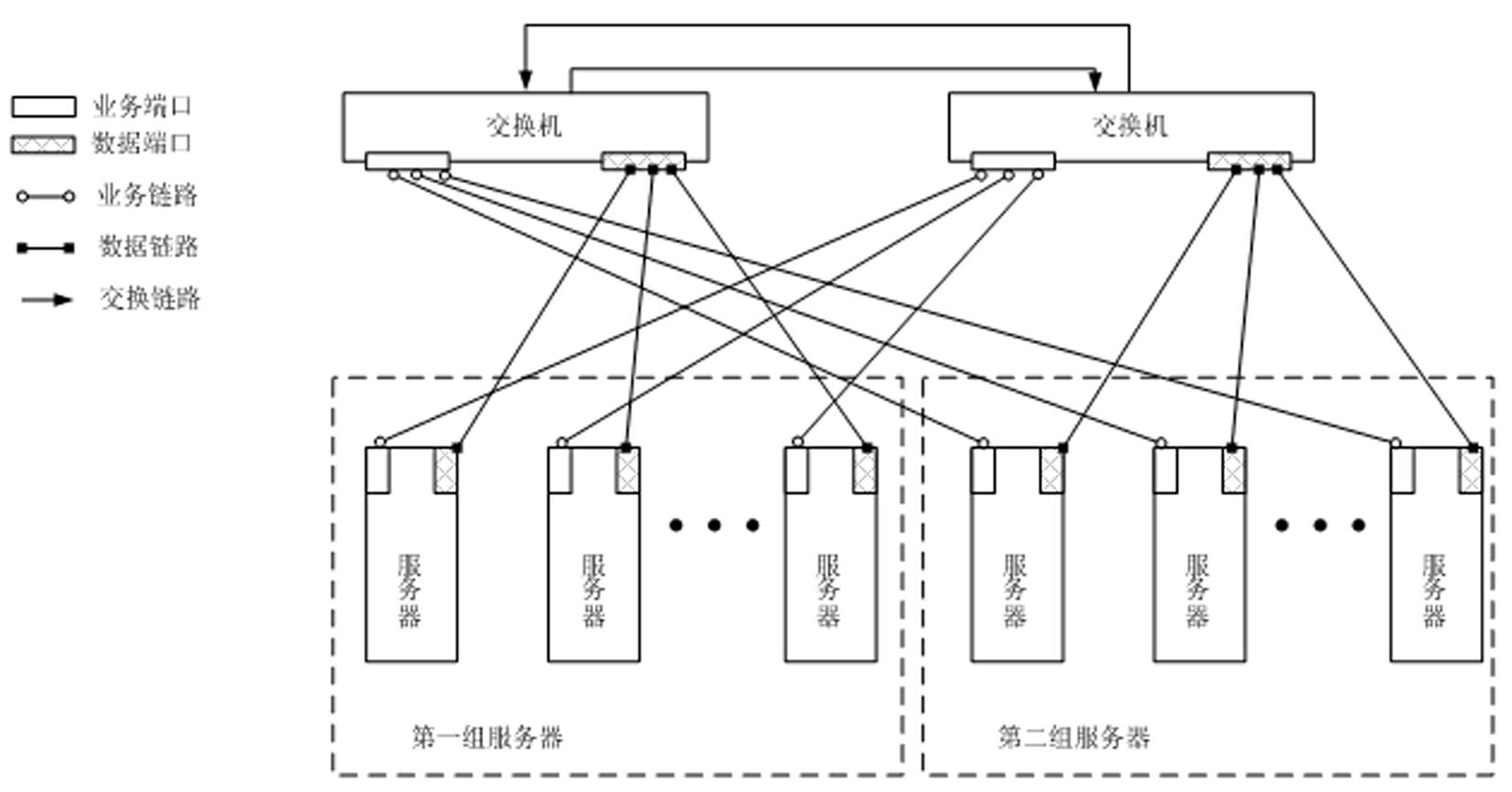

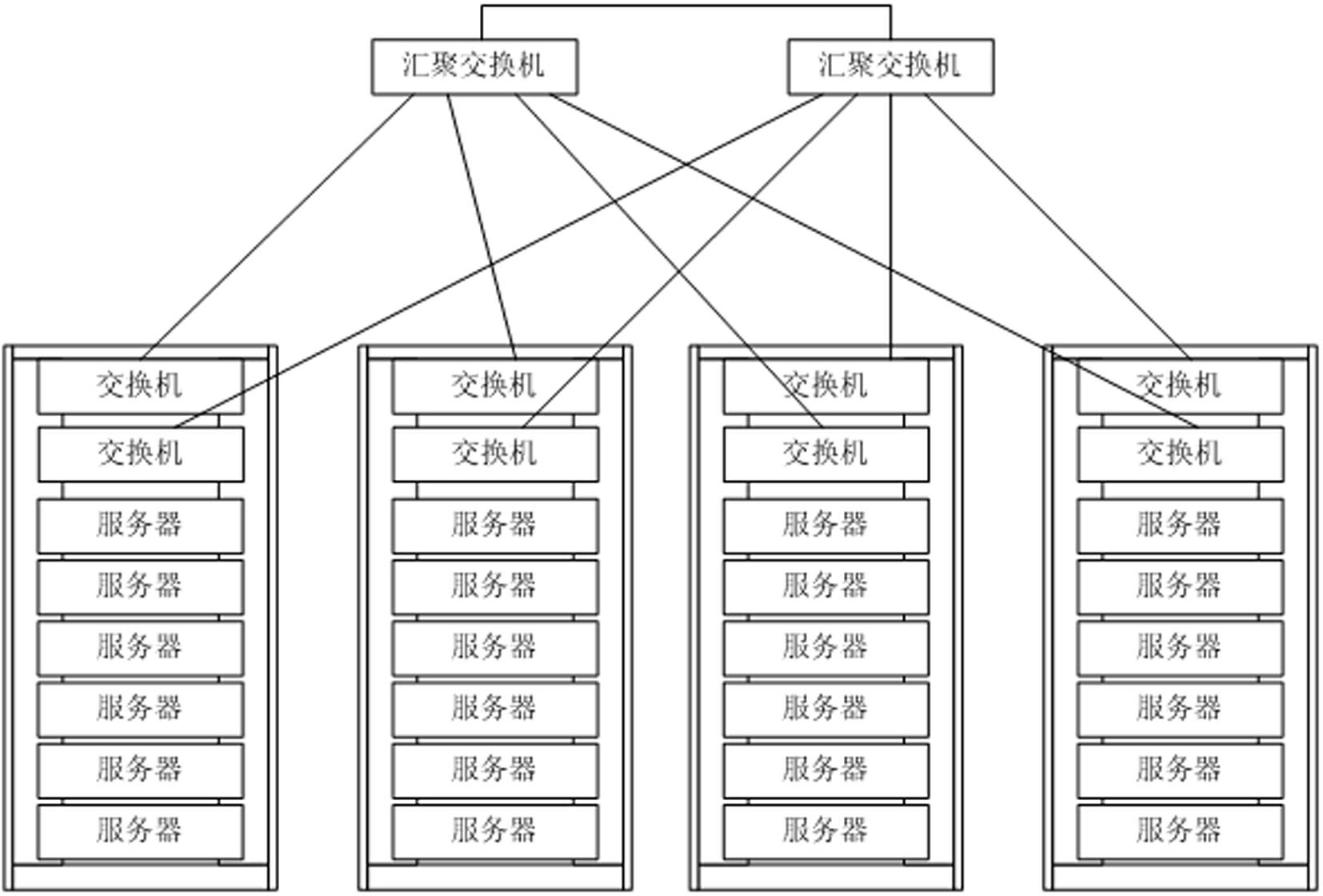

High-performance cluster computing system based on x86PC framework

ActiveCN102546813ALess investmentReduce dispersionDigital data processing detailsTransmissionBusiness dataHigh performance cluster

A high-performance cluster computing system based on an x86 framework PC platform comprises a first access switch and a second access switch, as well as two servers based on the x86 framework PC platform and a computer cabinet for placing the switches and the servers, wherein each server is equipped with a special business data port and a document data port, which are respectively connected with different switches for transmission of both the business data and the document data; and the business data ports and the document data ports are configured in different network segments for expanding I / O (Input / Output) bandwidth.

Owner:北京思特奇信息技术股份有限公司