Patents

Literature

108 results about "Code Translation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

An automated procedure that uses a specialized set of concept descriptors for conversion of the target concept descriptors into executable elements of other code systems with the equivalent semantics.

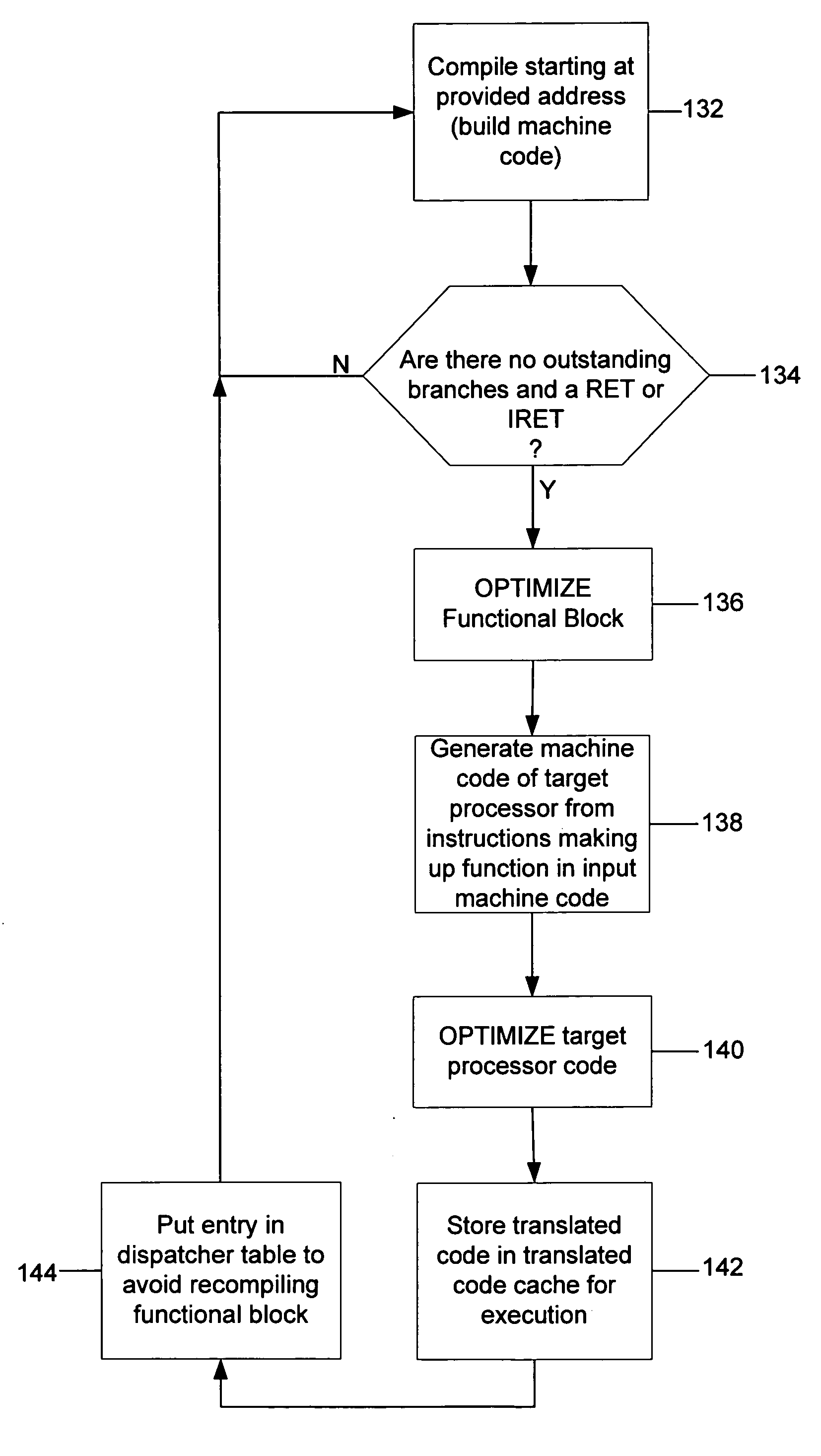

Function-level just-in-time translation engine with multiple pass optimization

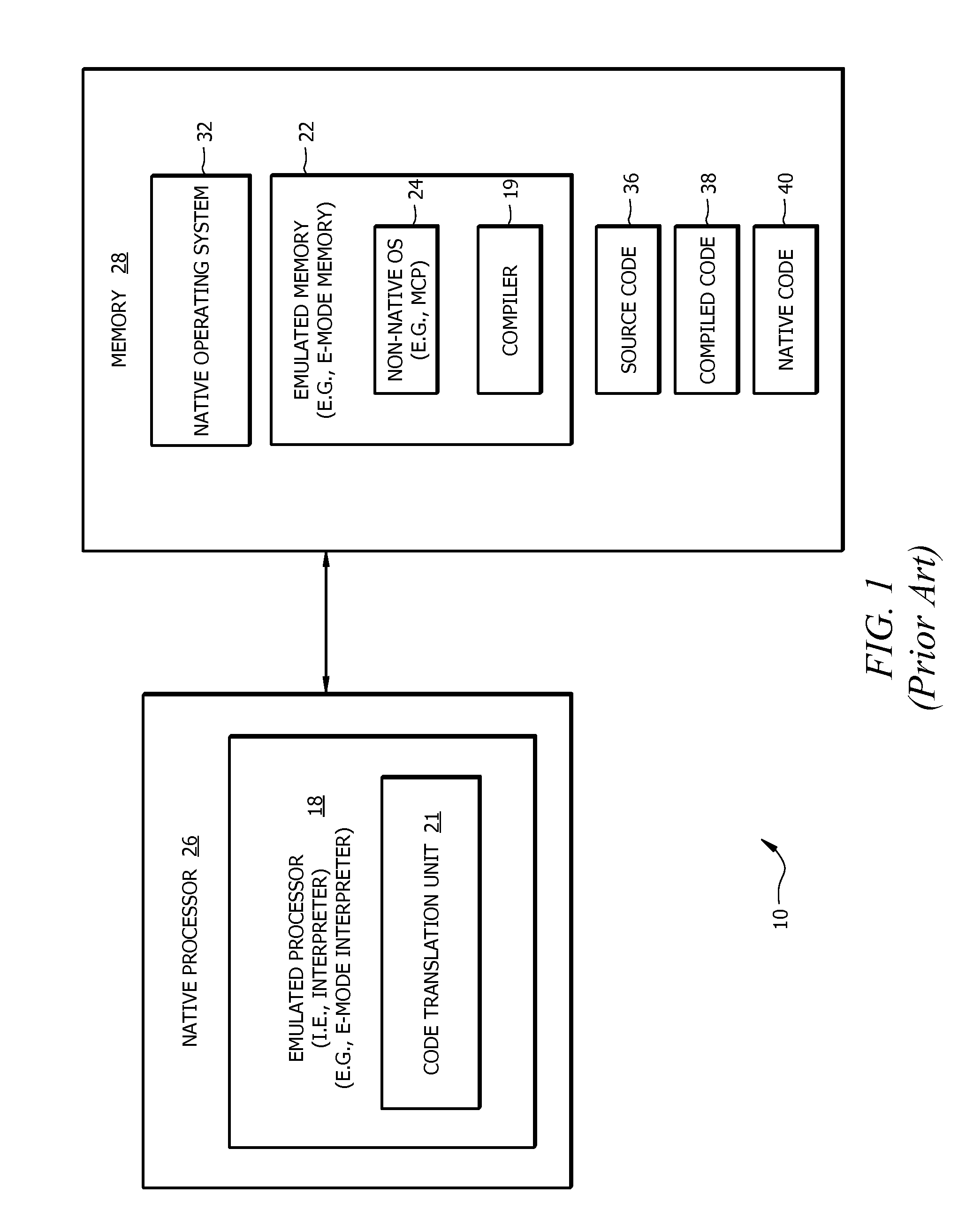

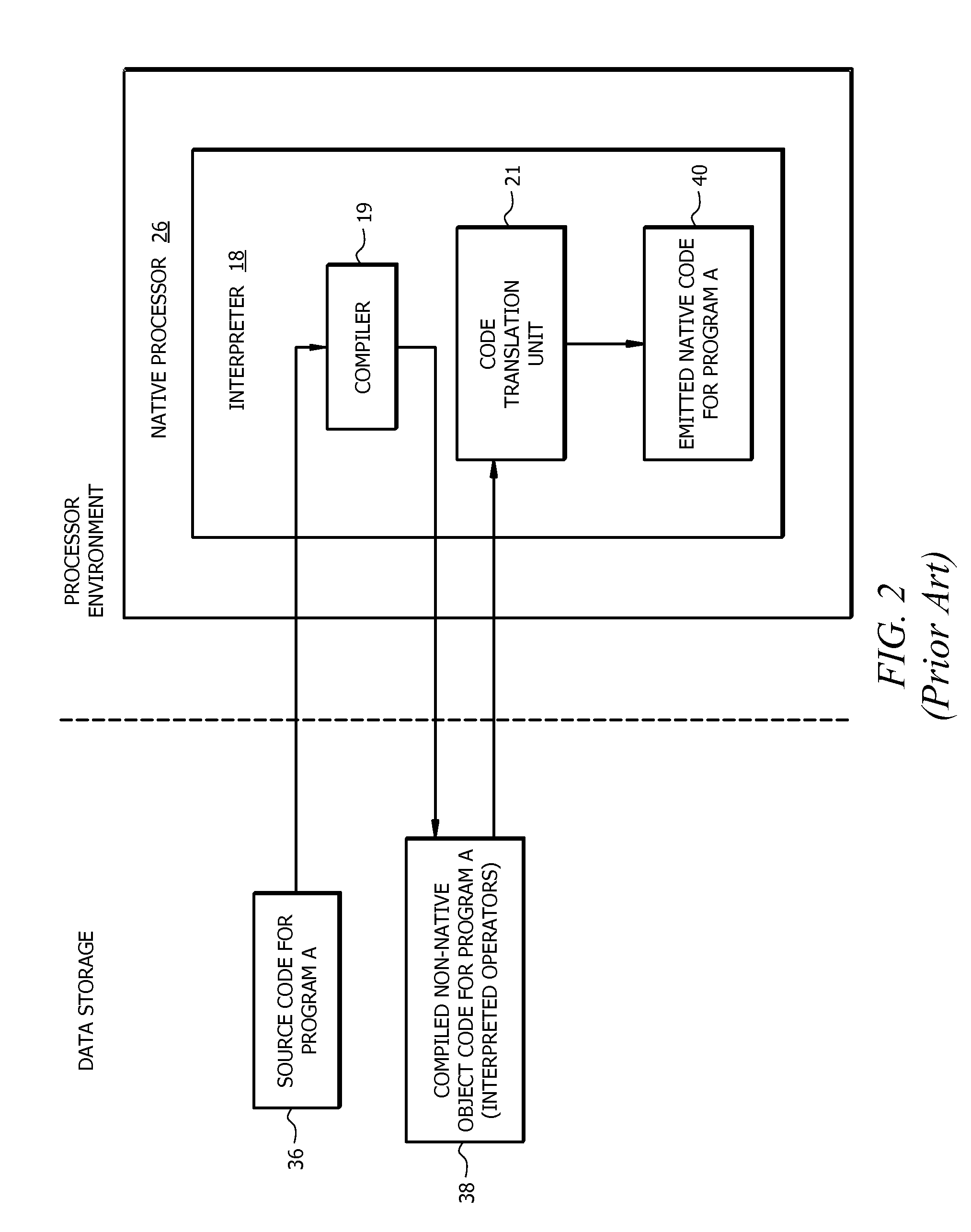

InactiveUS20070006178A1Improve translationReduce context switchingBinary to binaryProgram controlCode TranslationSoftware emulation

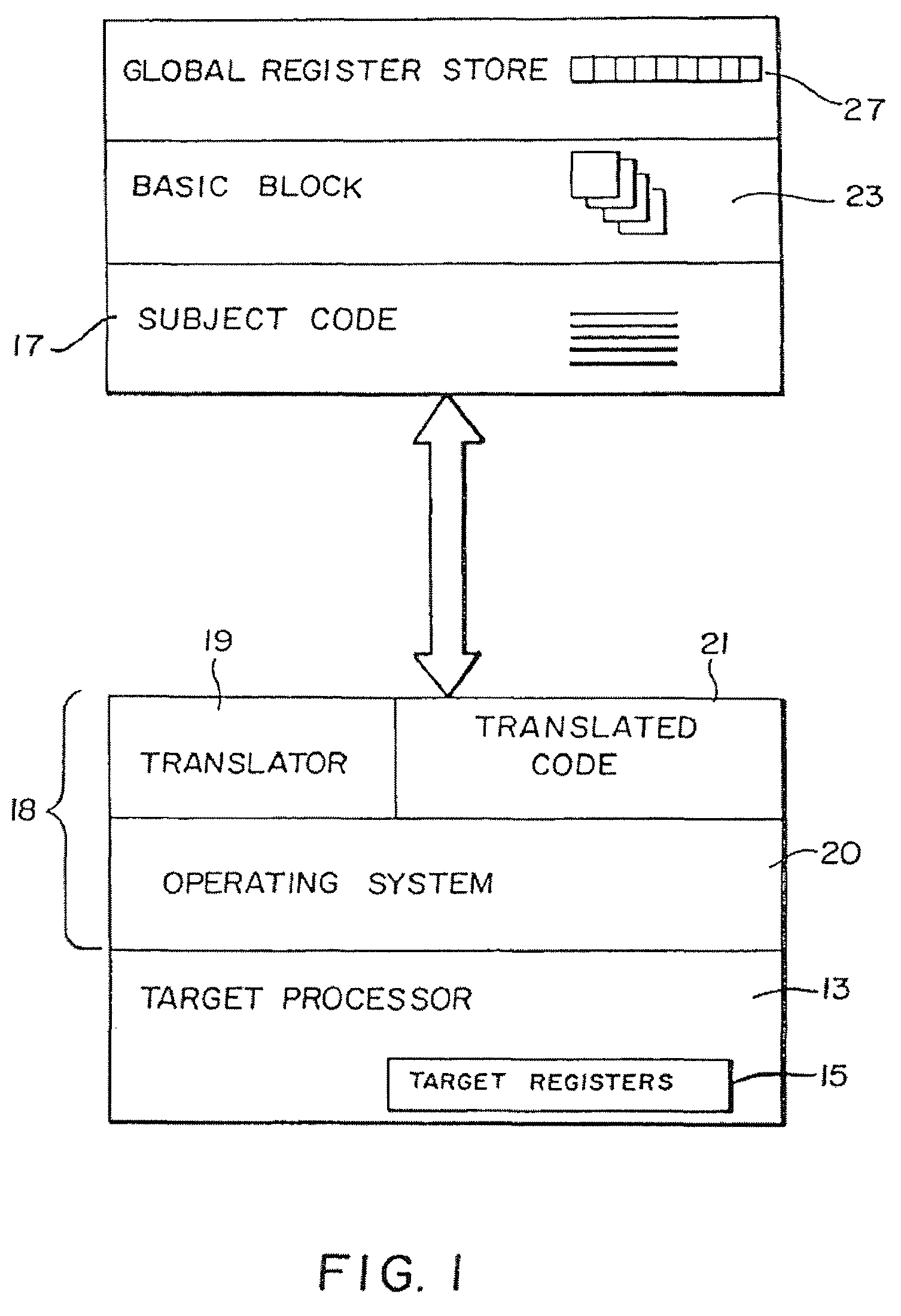

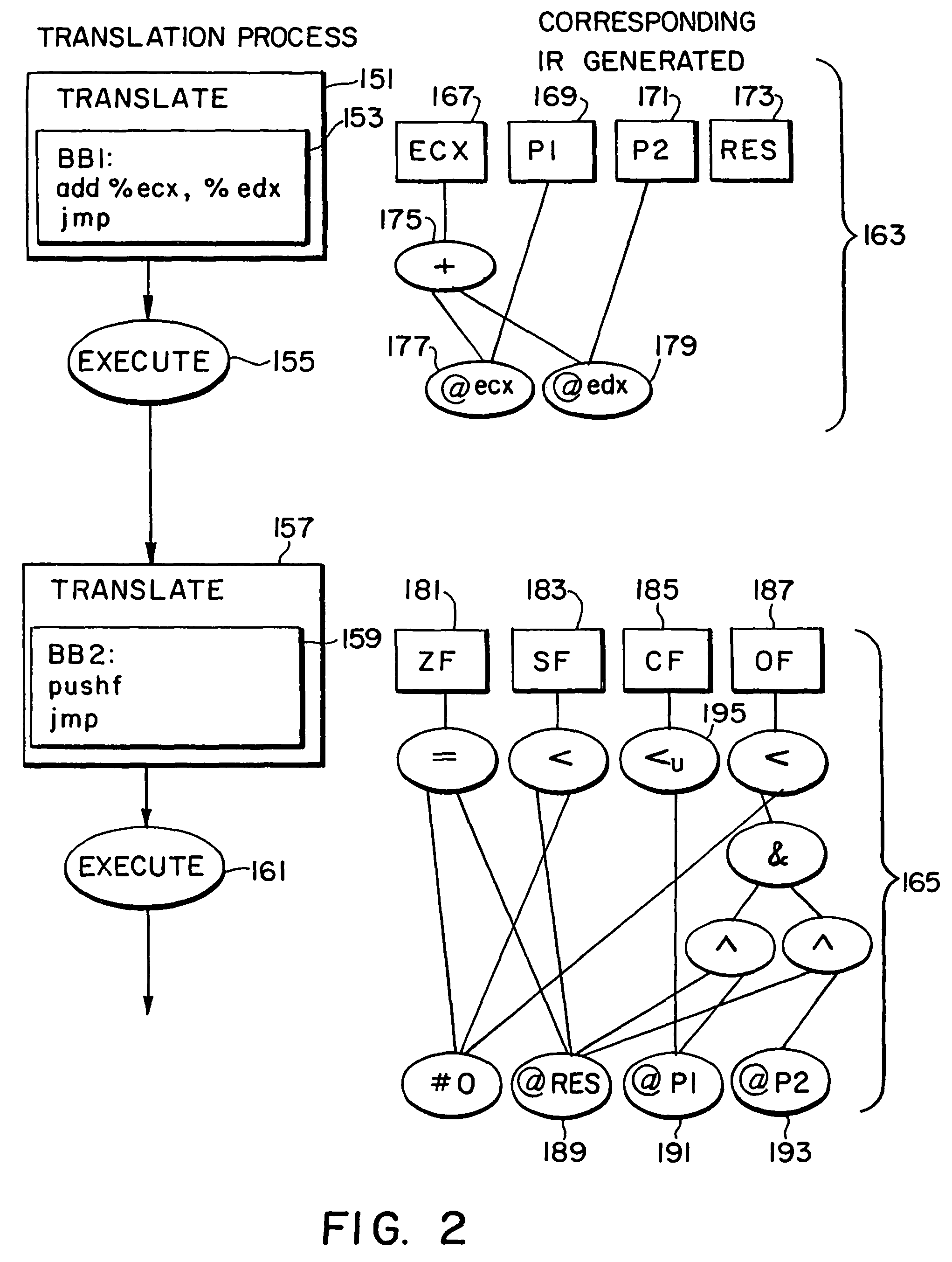

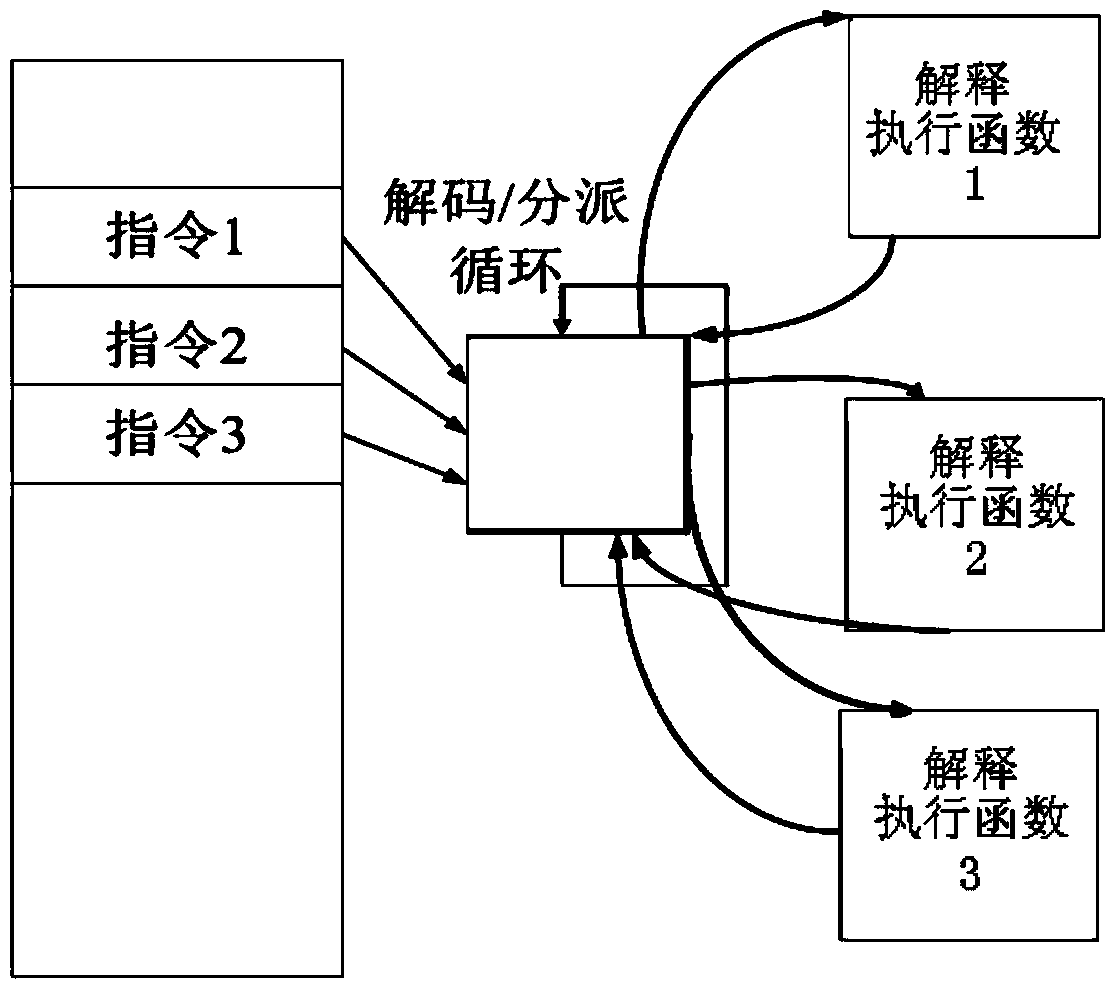

A JIT binary translator translates code at a function level of the source code rather than at an opcode level. The JIT binary translator of the invention grabs an entire x86 function out of the source stream, rather than an instruction, translates the whole function into an equivalent function of the target processor, and executes that function all at once before returning to the source stream, thereby reducing context switching. Also, since the JIT binary translator sees the entire source code function context at once the software emulator may optimize the code translation. For example, the JIT binary translator might decide to translate a sequence of x86 instructions into an efficient PPC equivalent sequence. Many such optimizations result in a tighter emulated binary.

Owner:MICROSOFT TECH LICENSING LLC

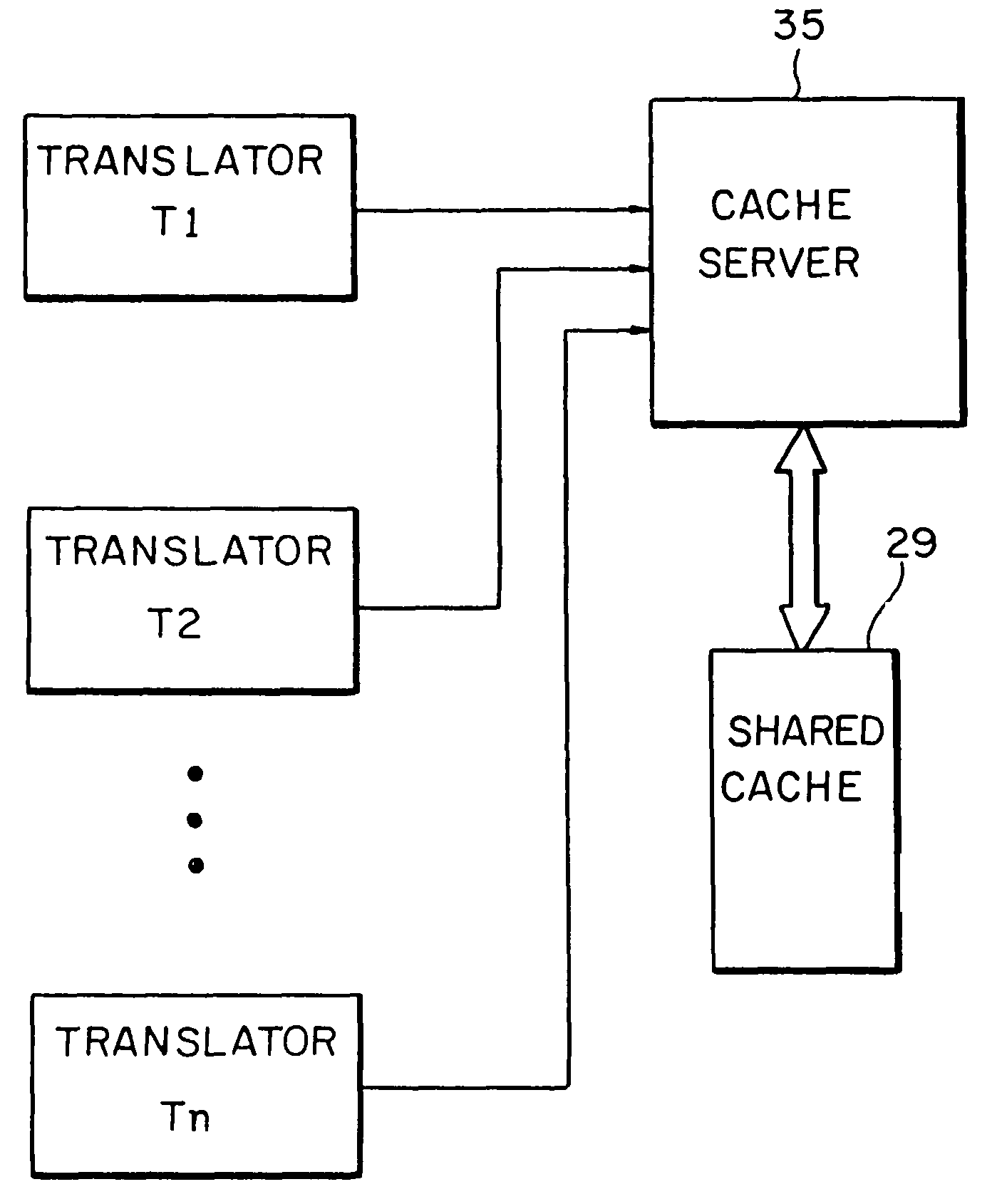

Shared code caching for program code conversion

ActiveUS7805710B2General purpose stored program computerProgram loading/initiatingCode TranslationObject code

Subject program code is translated to target code in basic block units at run-time in a process wherein translation of basic blocks is interleaved with execution of those translations. A shared code cache mechanism is added to persistently store subject code translations, such that a translator may reuse translations that were generated and / or optimized by earlier translator instances.

Owner:IBM CORP

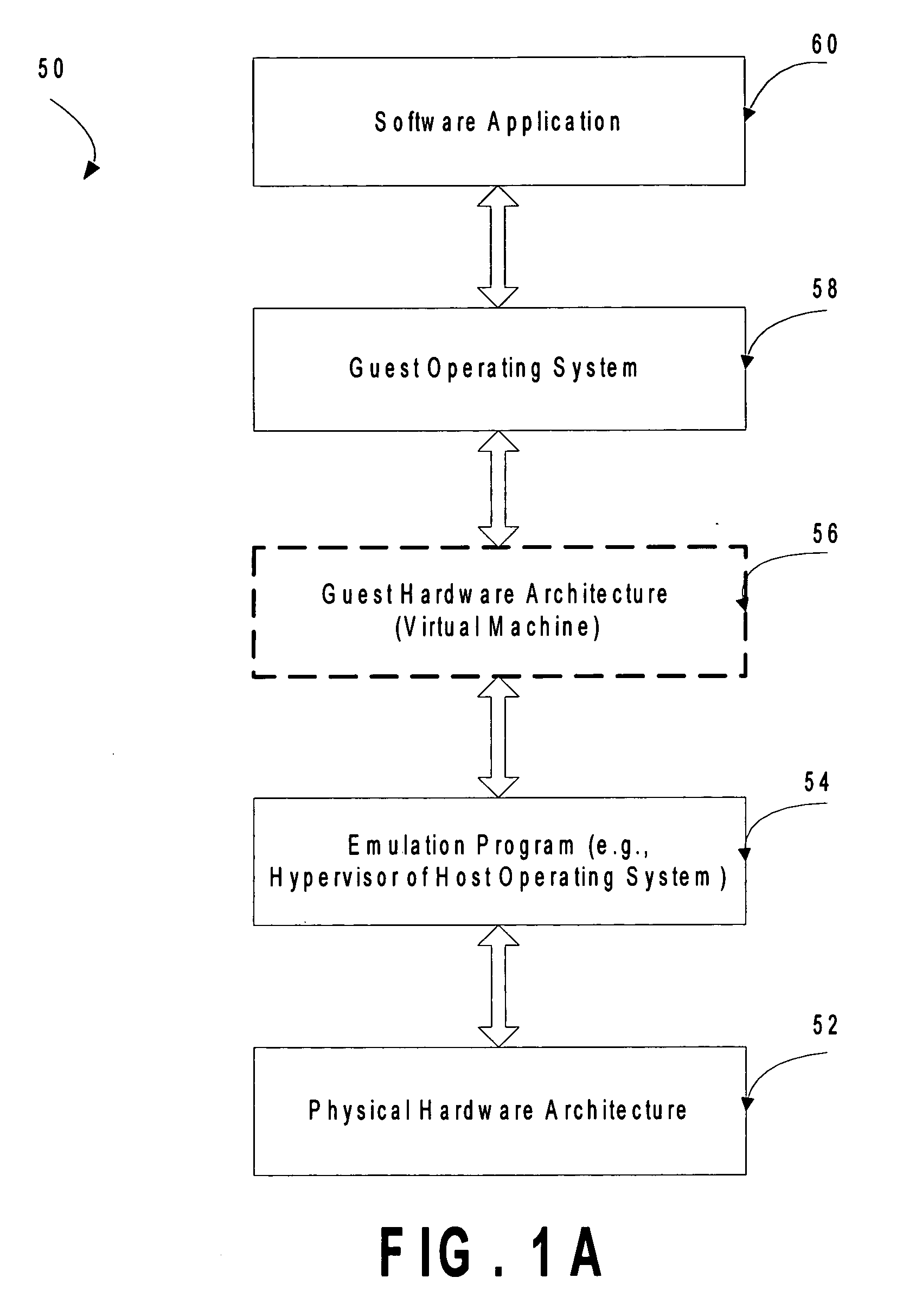

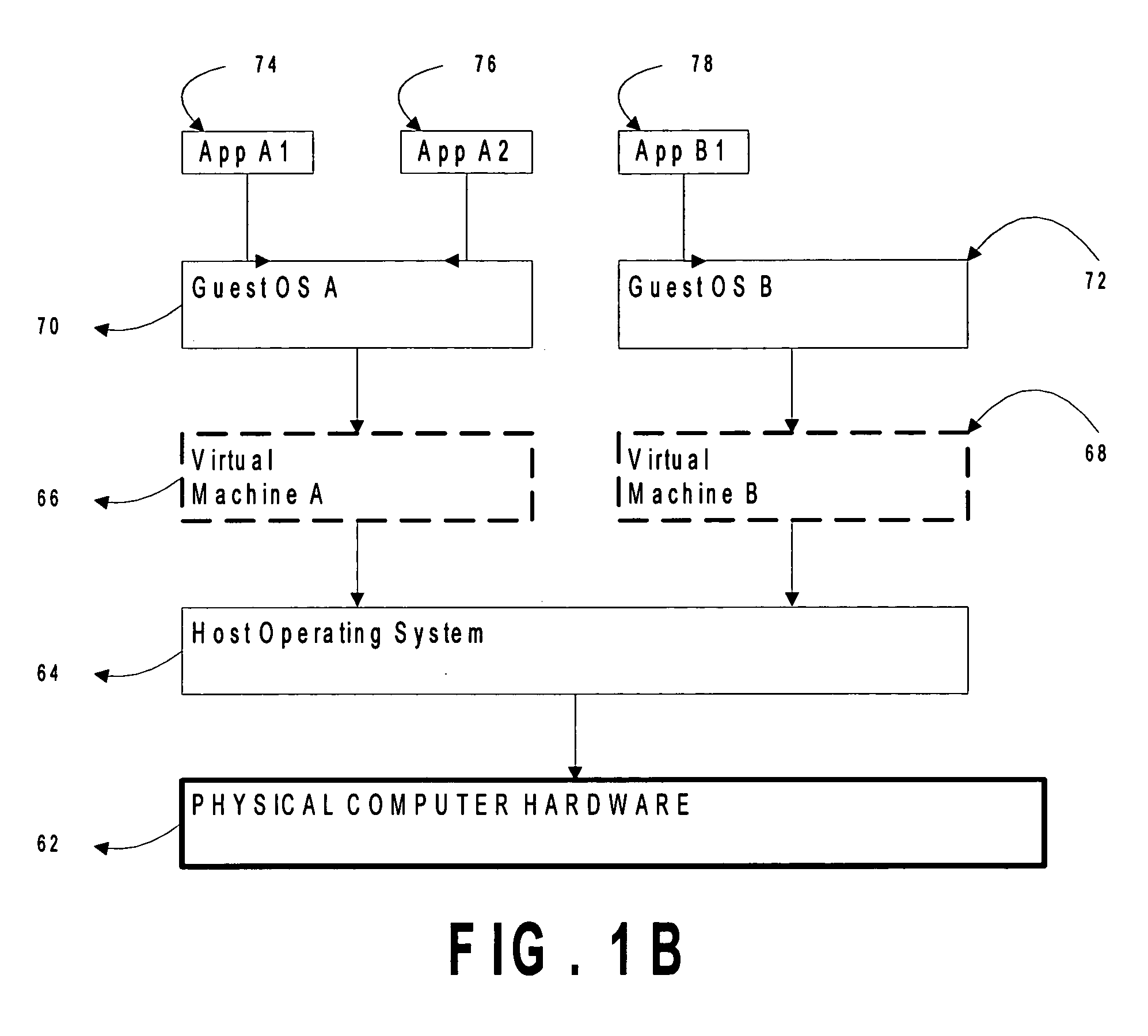

Emulating A Computer Run Time Environment

InactiveUS20090282139A1Multiple digital computer combinationsSoftware simulation/interpretation/emulationOperational systemCode Translation

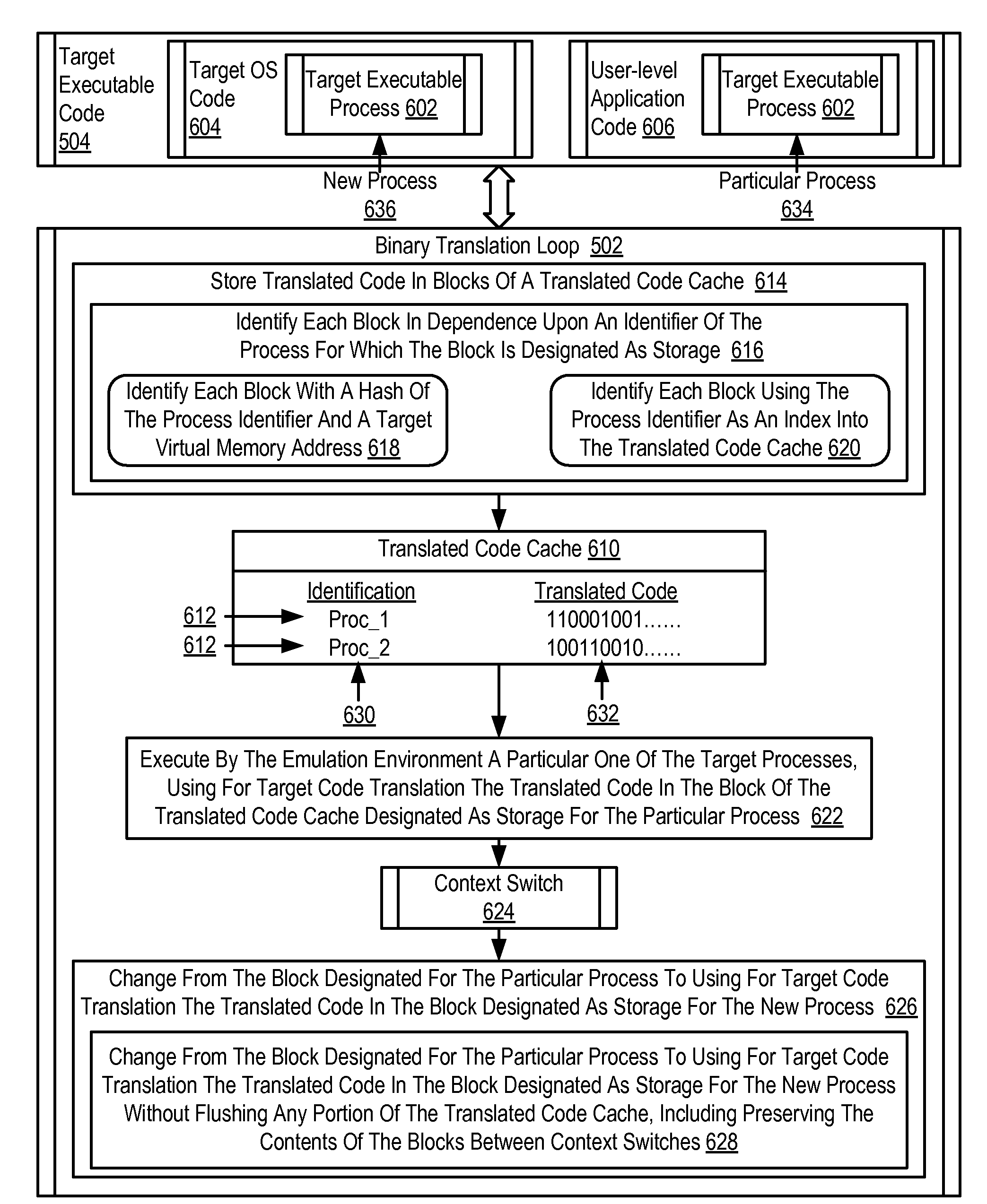

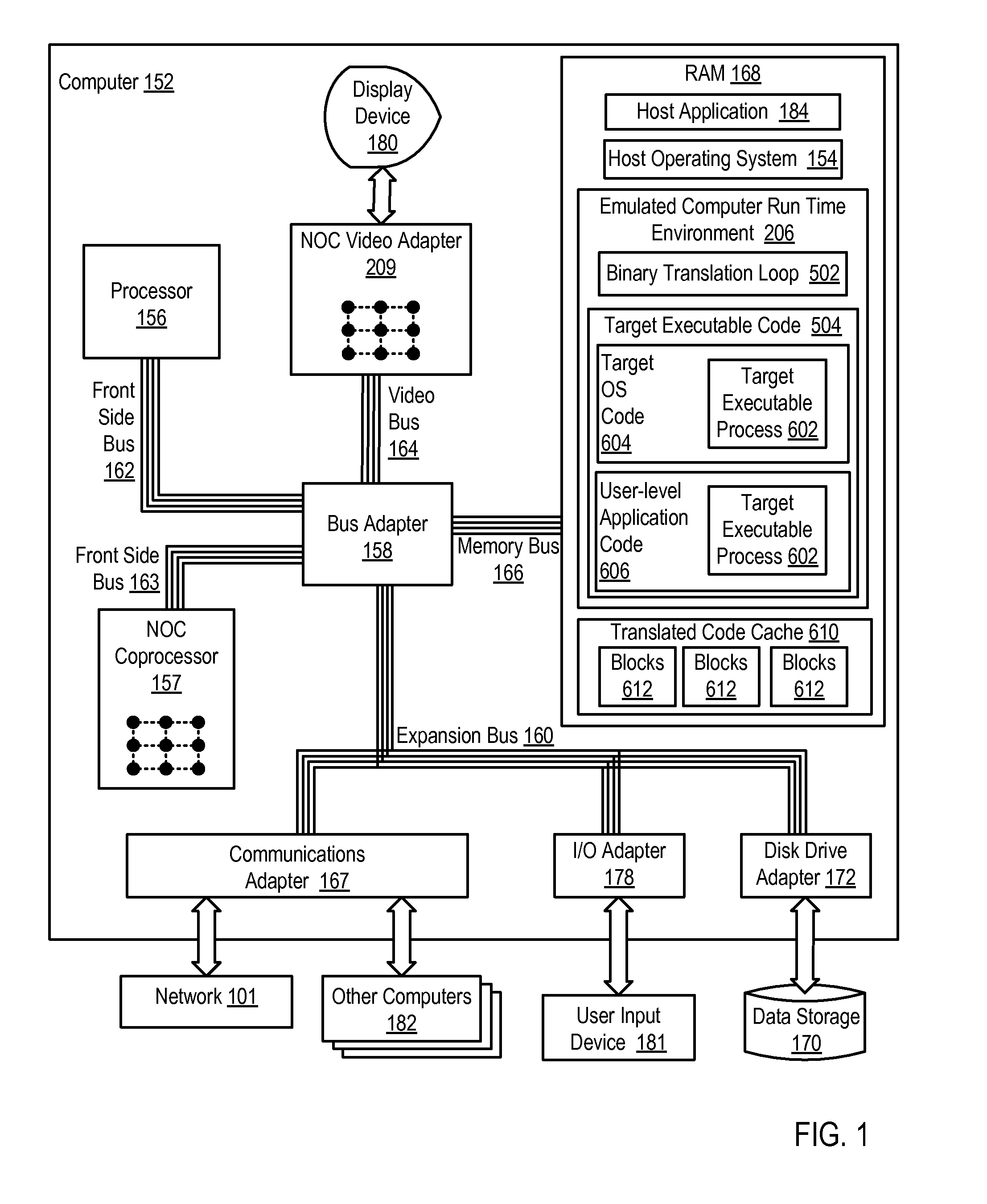

Emulating a computer run time environment including: storing translated code in blocks of a translated code cache, each block of the translated code cache designated for storage of translated code for a separate one of the target executable processes, including identifying each block in dependence upon an identifier of the process for which the block is designated as storage; executing by the emulation environment a particular one of the target executable processes, using for target code translation the translated code in the block of the translated code cache designated as storage for the particular process; and upon encountering a context switch by the target operating system to execution of a new target executable process, changing from the block designated for the particular process to using for target code translation the translated code in the block of the translated code cache designated as storage for the new target executable process.

Owner:IBM CORP

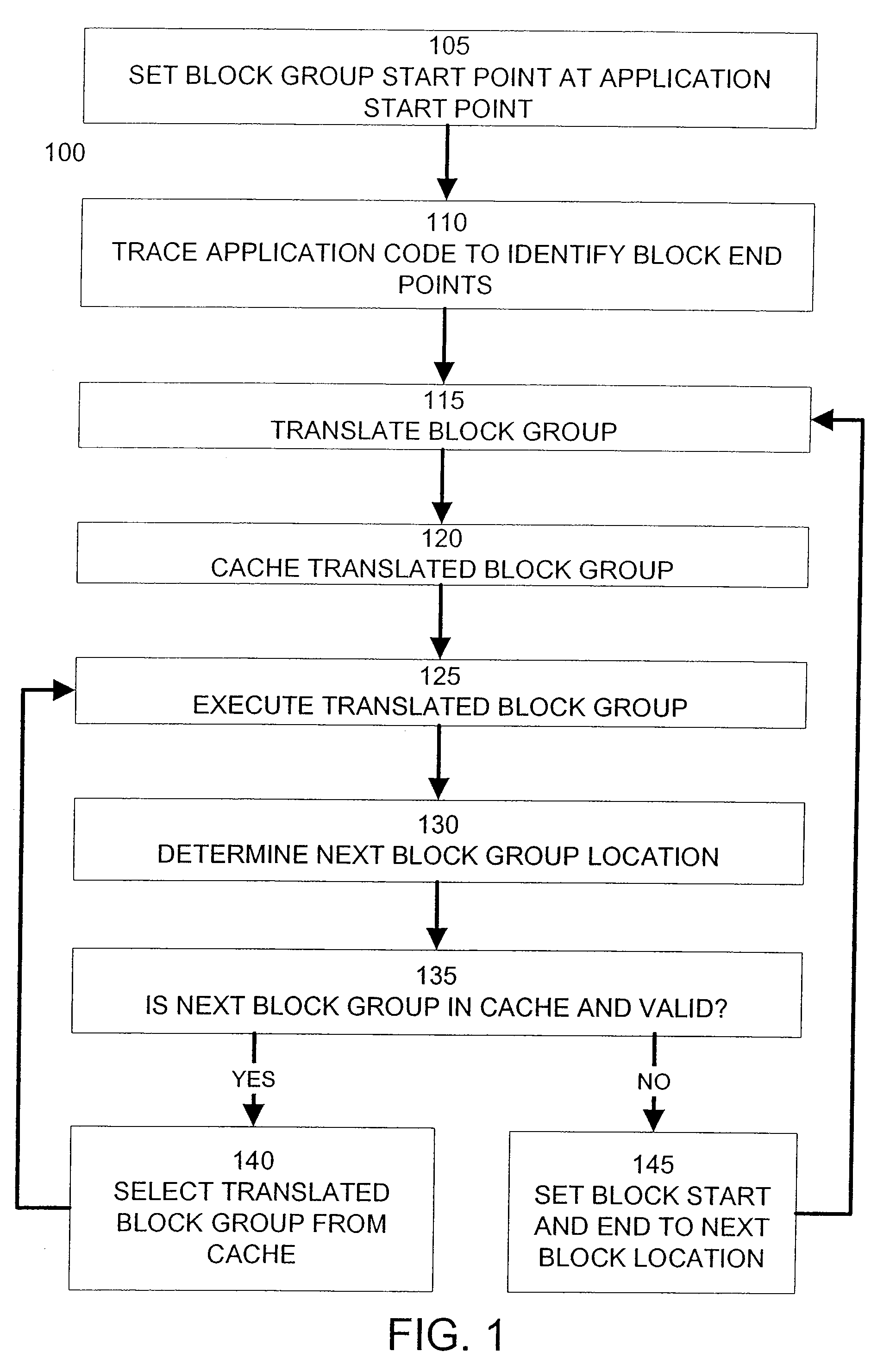

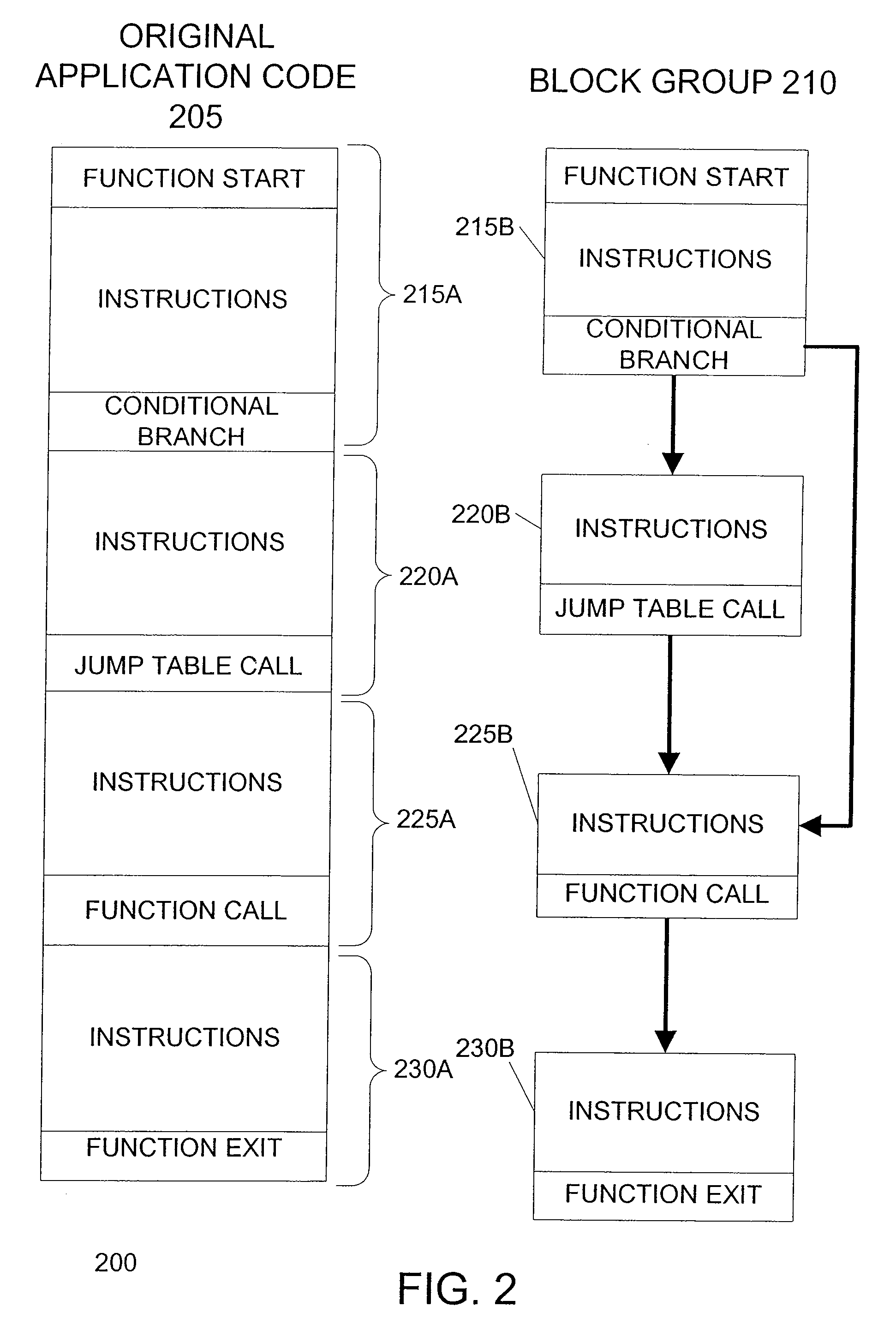

Code Translation and Pipeline Optimization

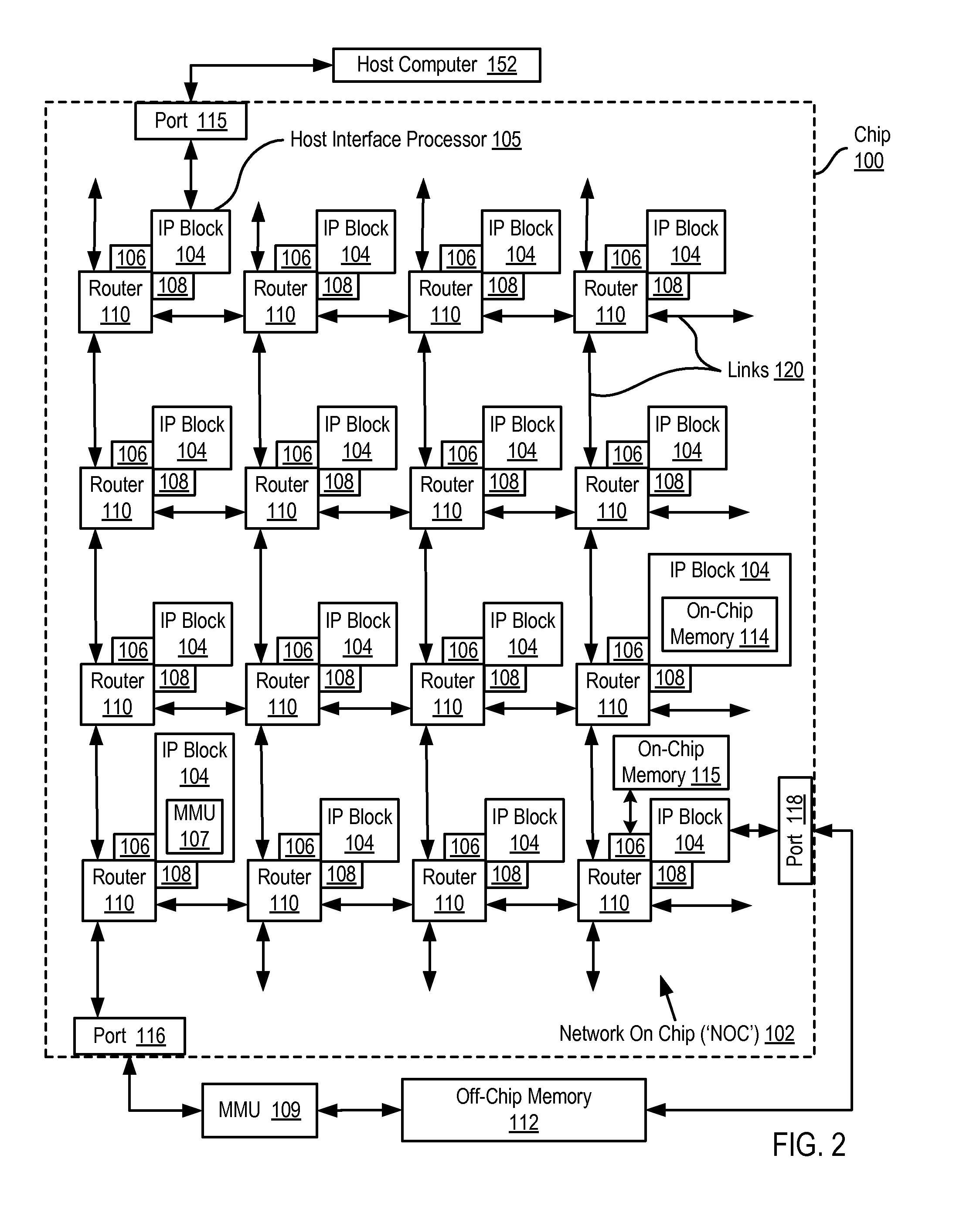

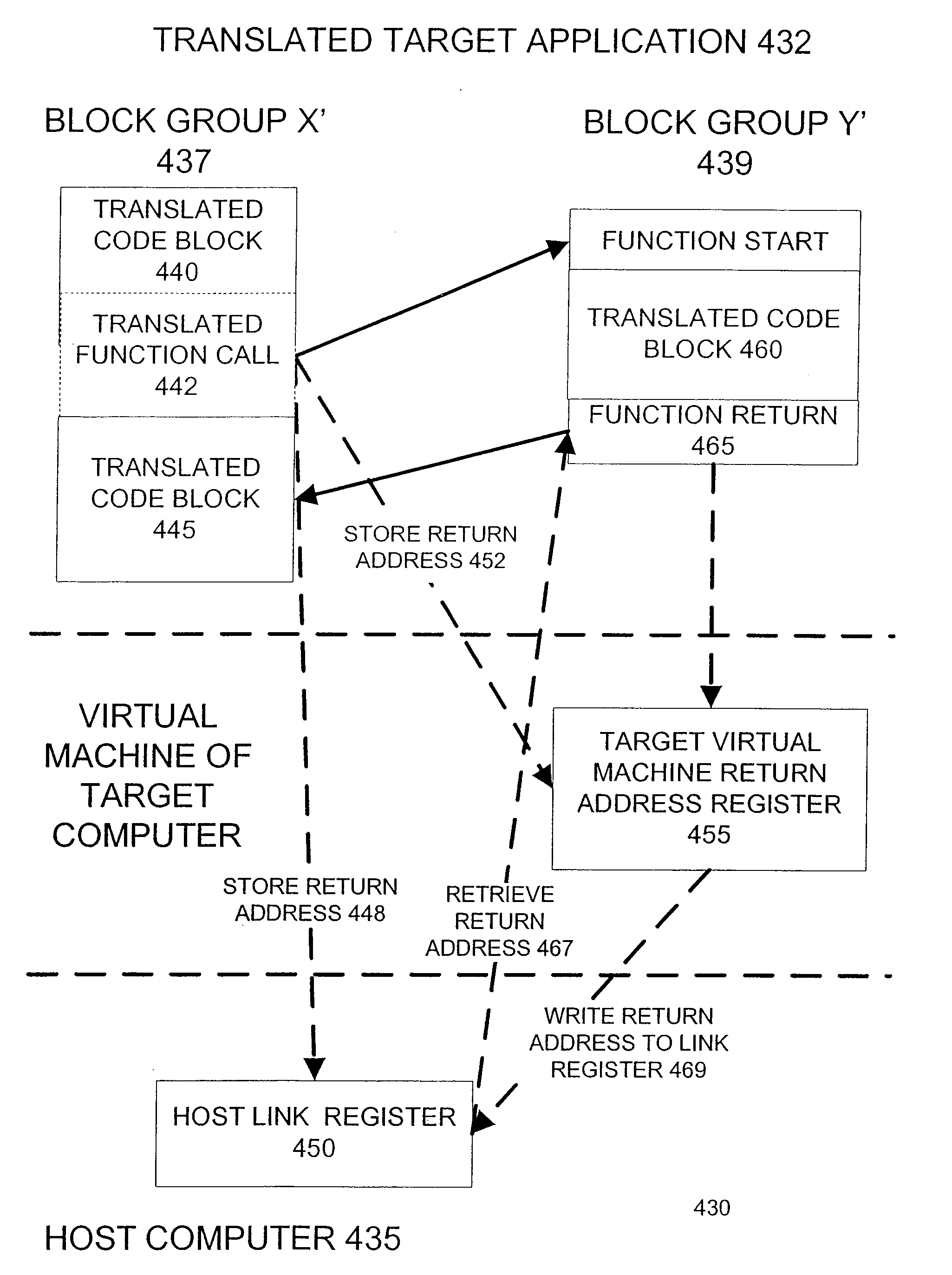

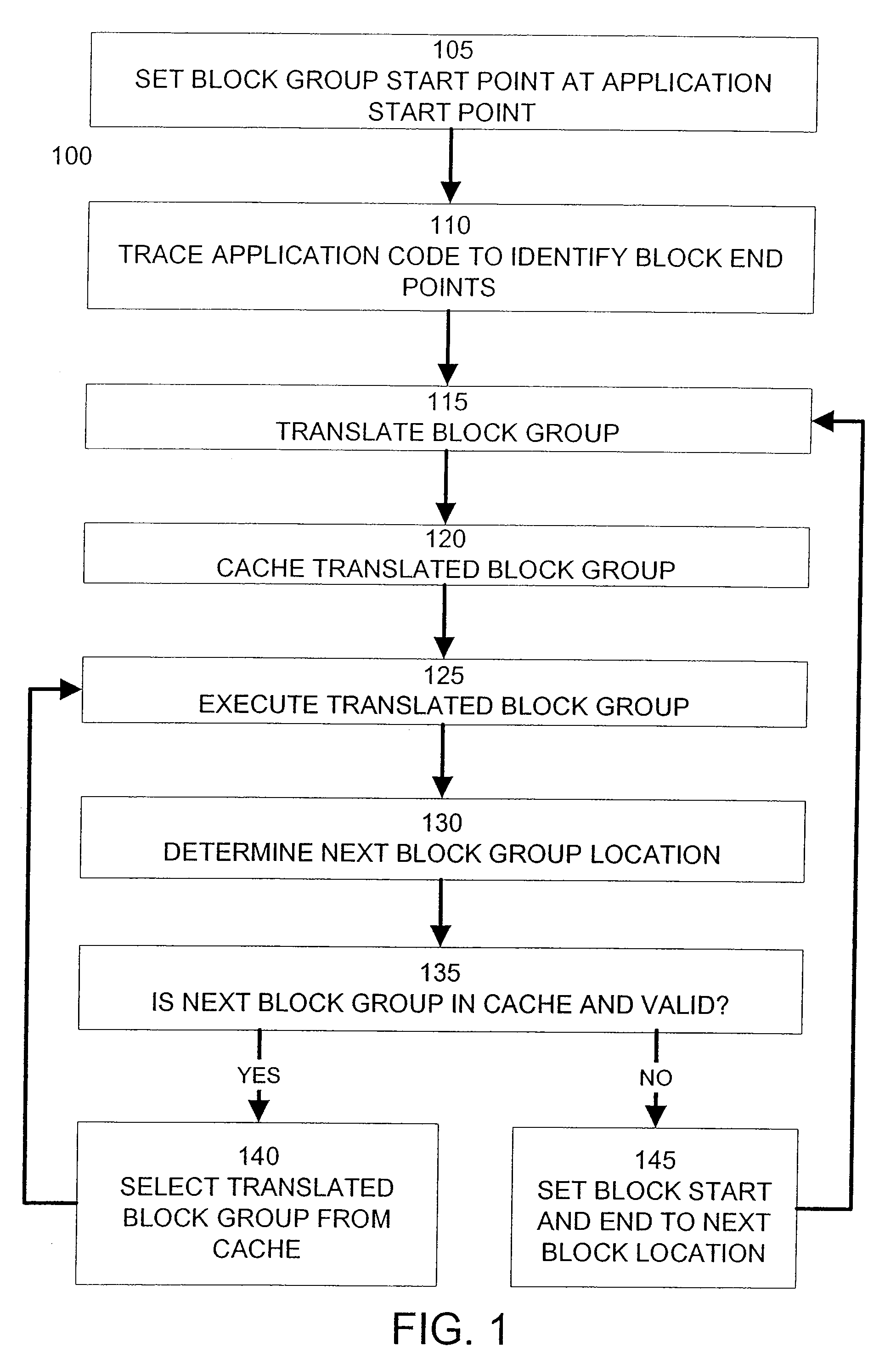

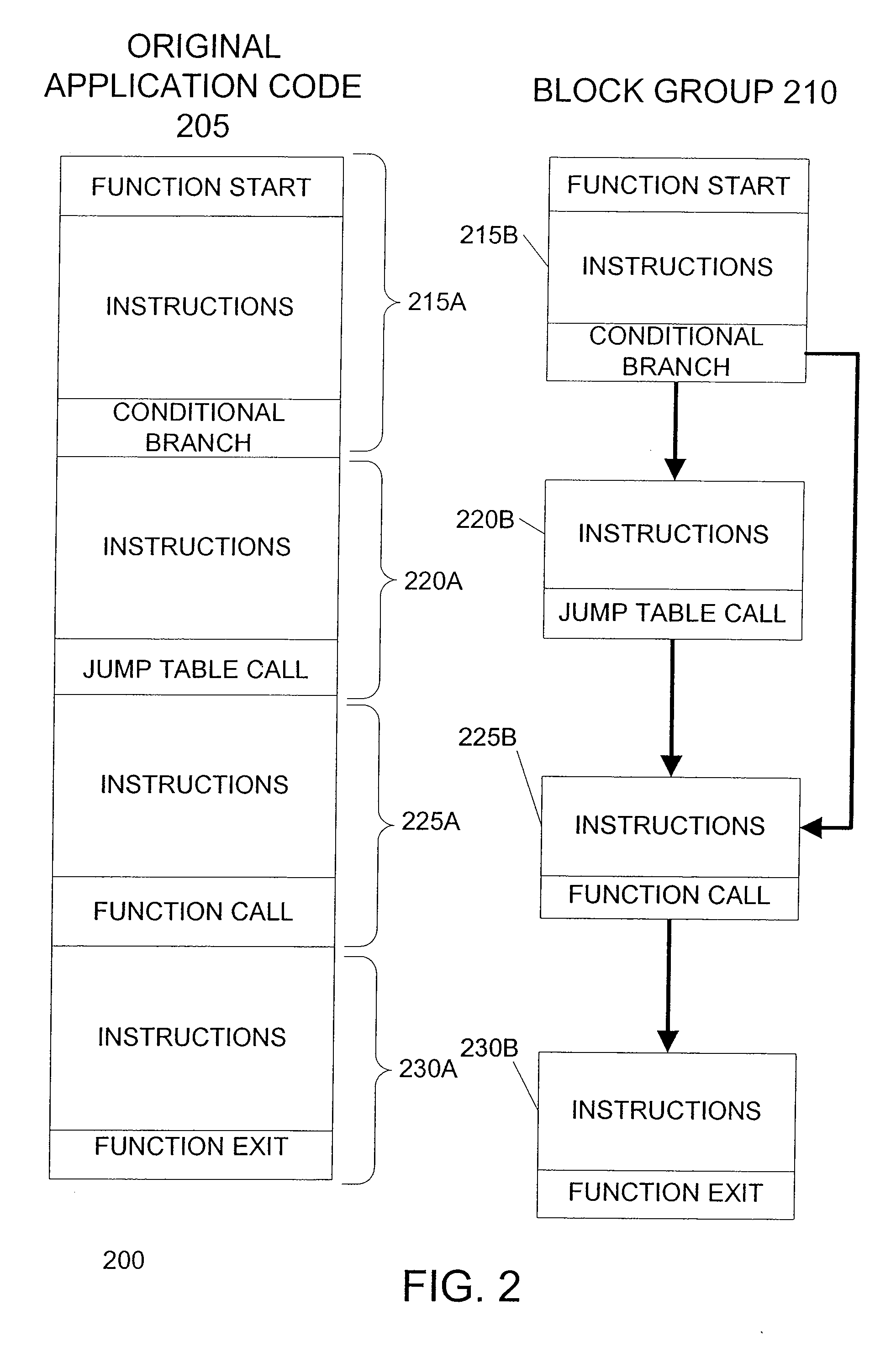

An emulator uses code translation and recompilation to execute target computer system applications on a host computer system. Target application code is partitioned into target application code blocks, and related target application code blocks are combined into block groups and translated. Translated application code block groups are sized to comply with restrictions on branch instruction size. Upon selecting an application code block group for execution, a cache tag is used to determine if a corresponding translated code block group is available and valid. If not, the block group is translated and executed. Sequentially executed translated code blocks are located in adjacent portions of memory to improve performance when switching between translated code blocks. The emulator may use a link register of the host computer system to prefetch instructions and data from translated code blocks. The emulator also takes into account structural hazards in translating instructions.

Owner:SONY COMPUTER ENTERTAINMENT INC

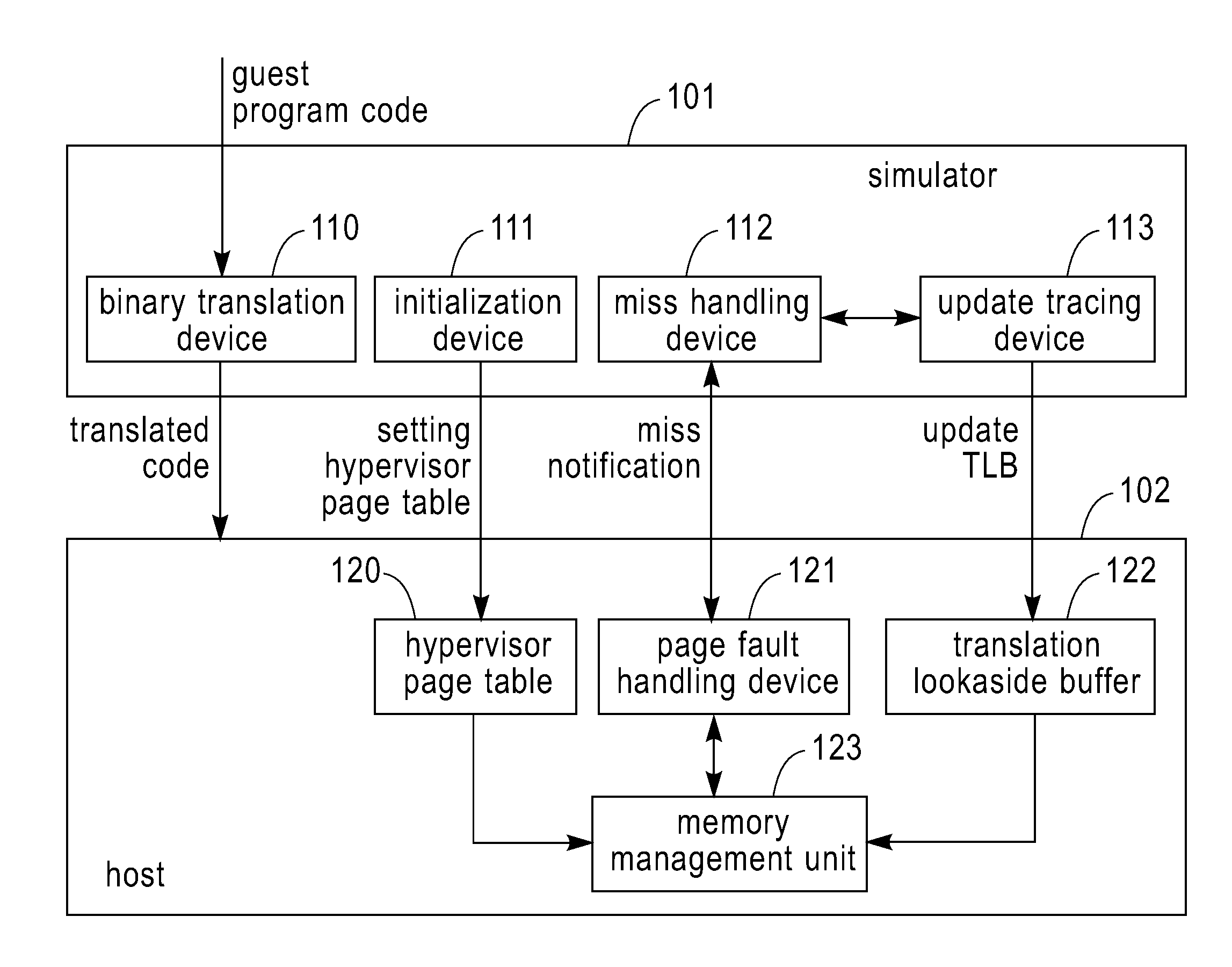

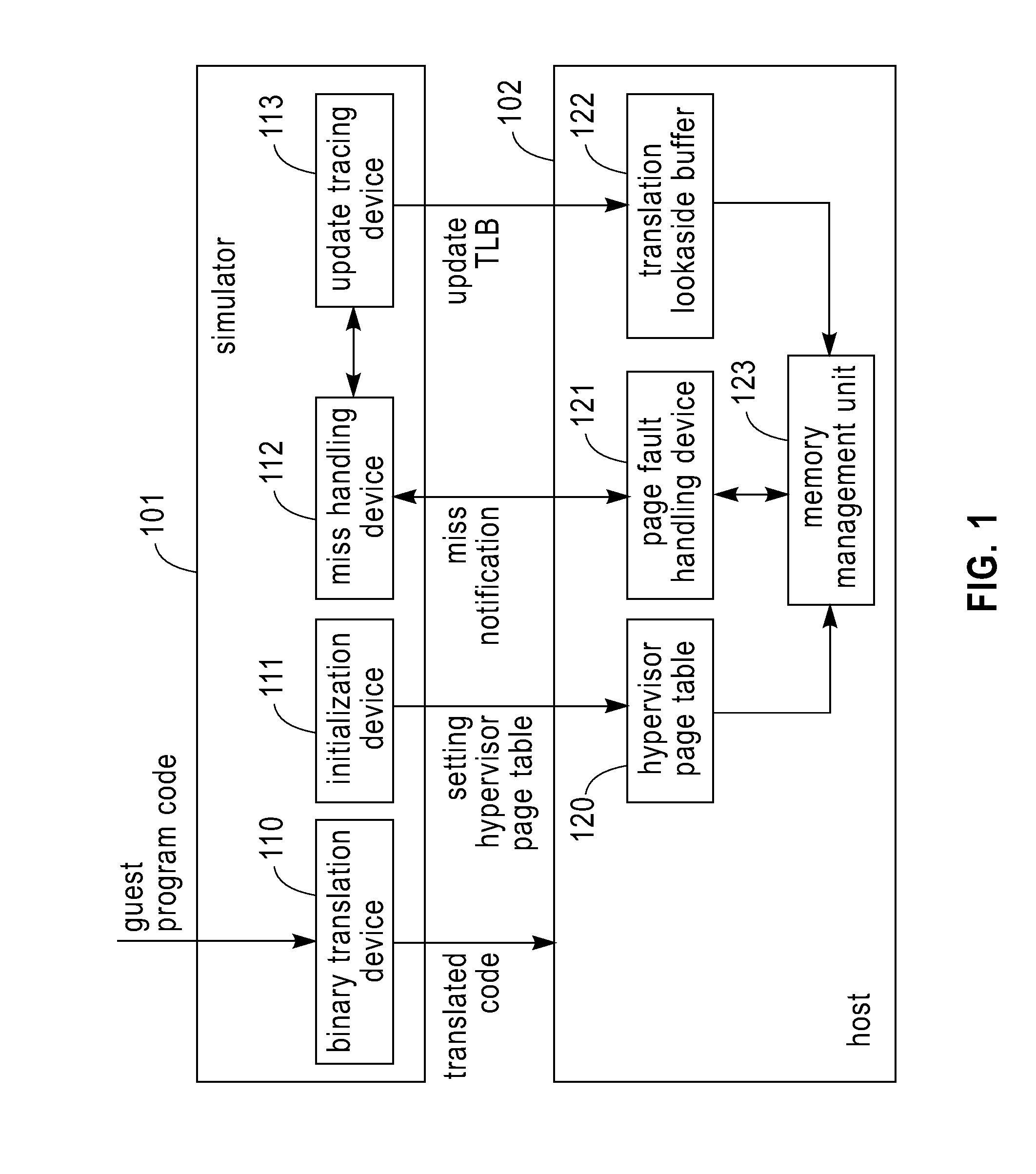

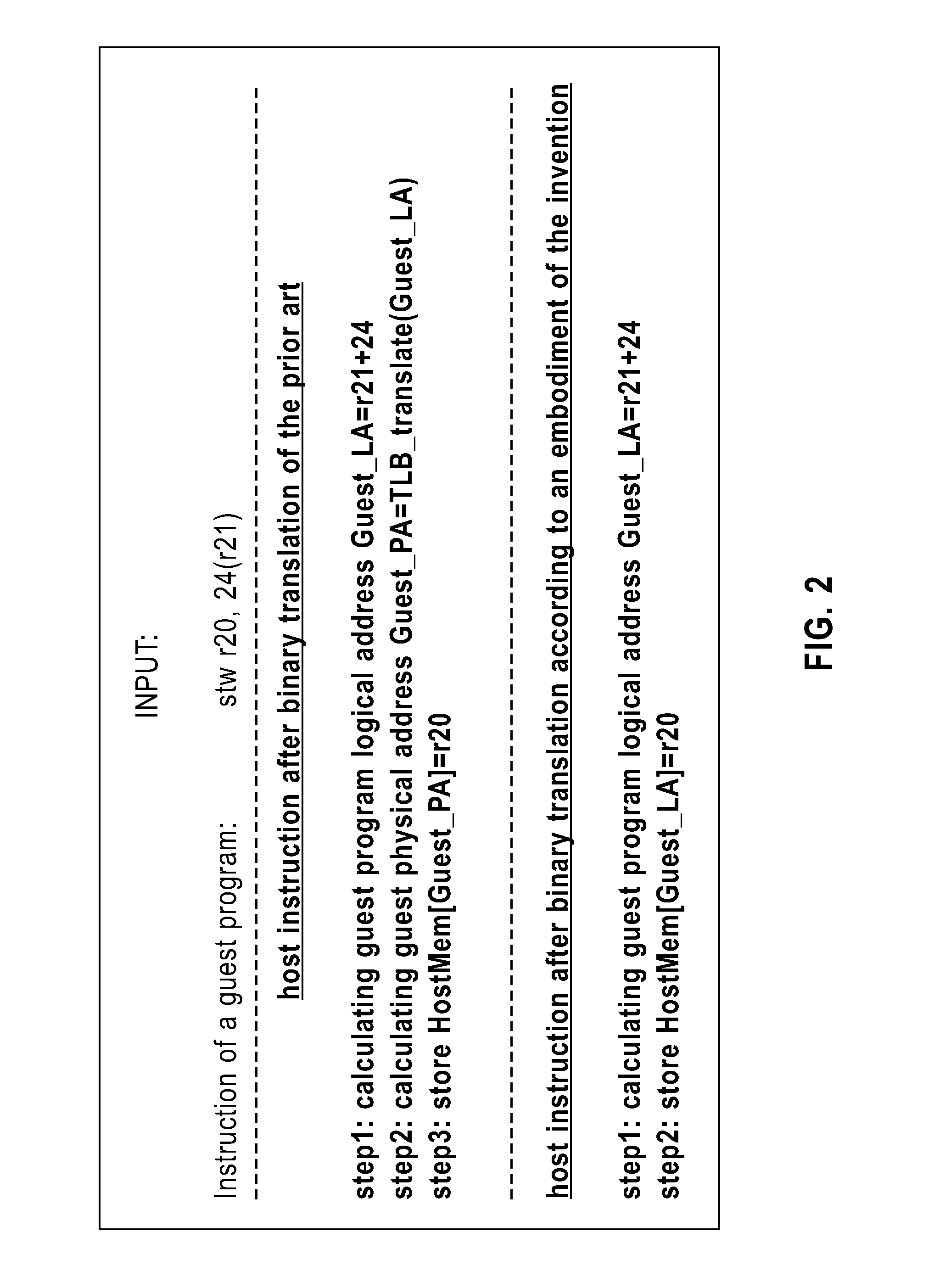

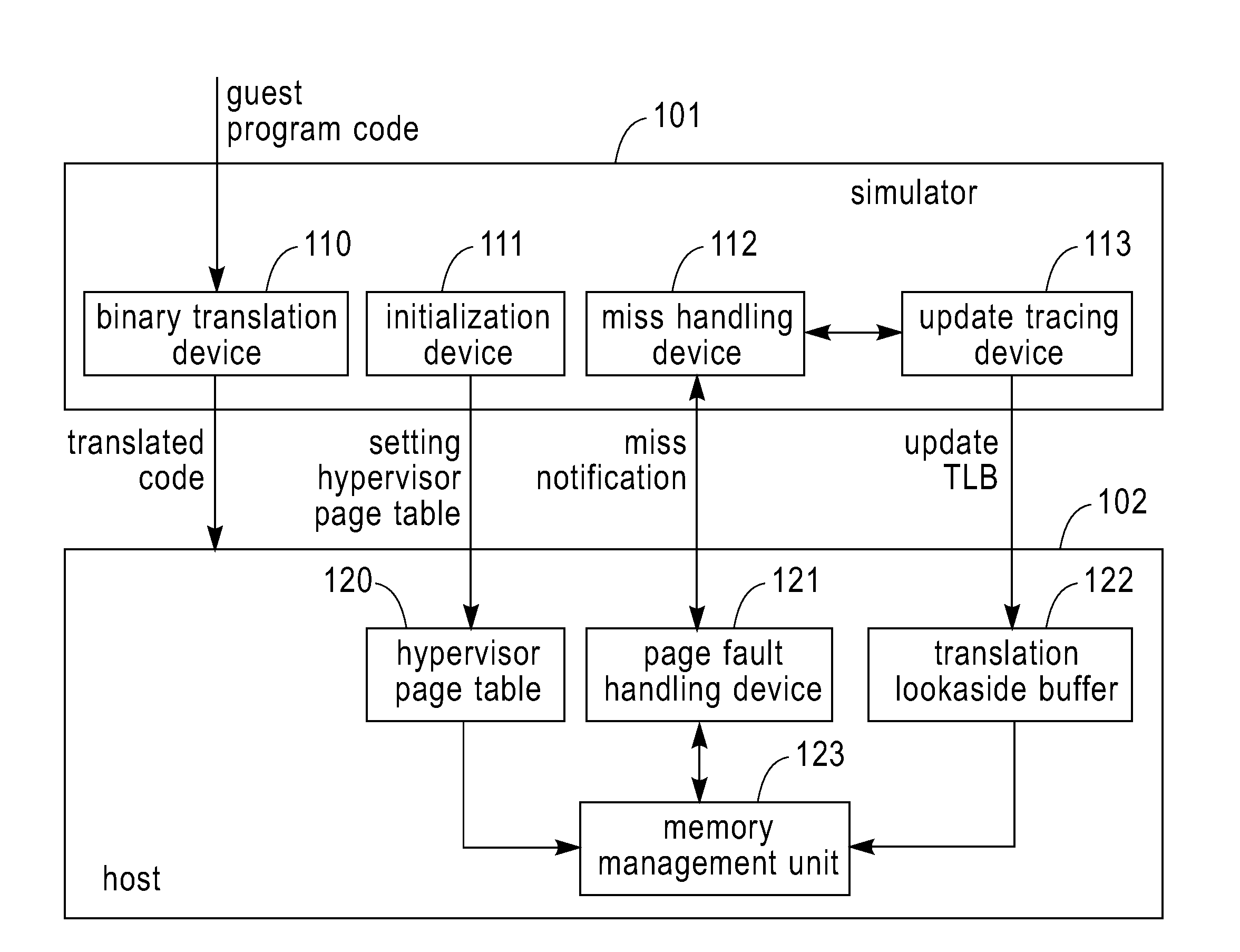

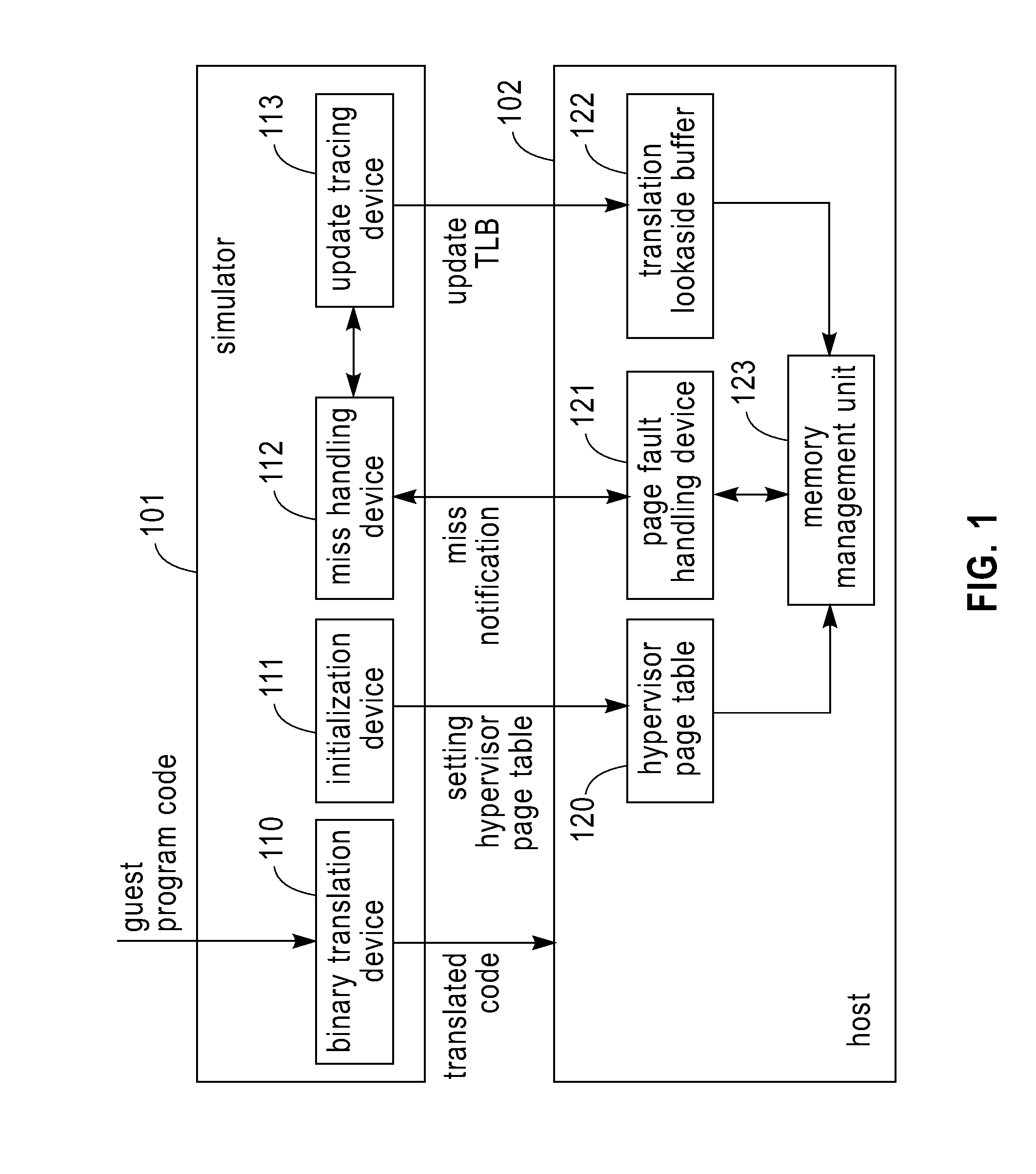

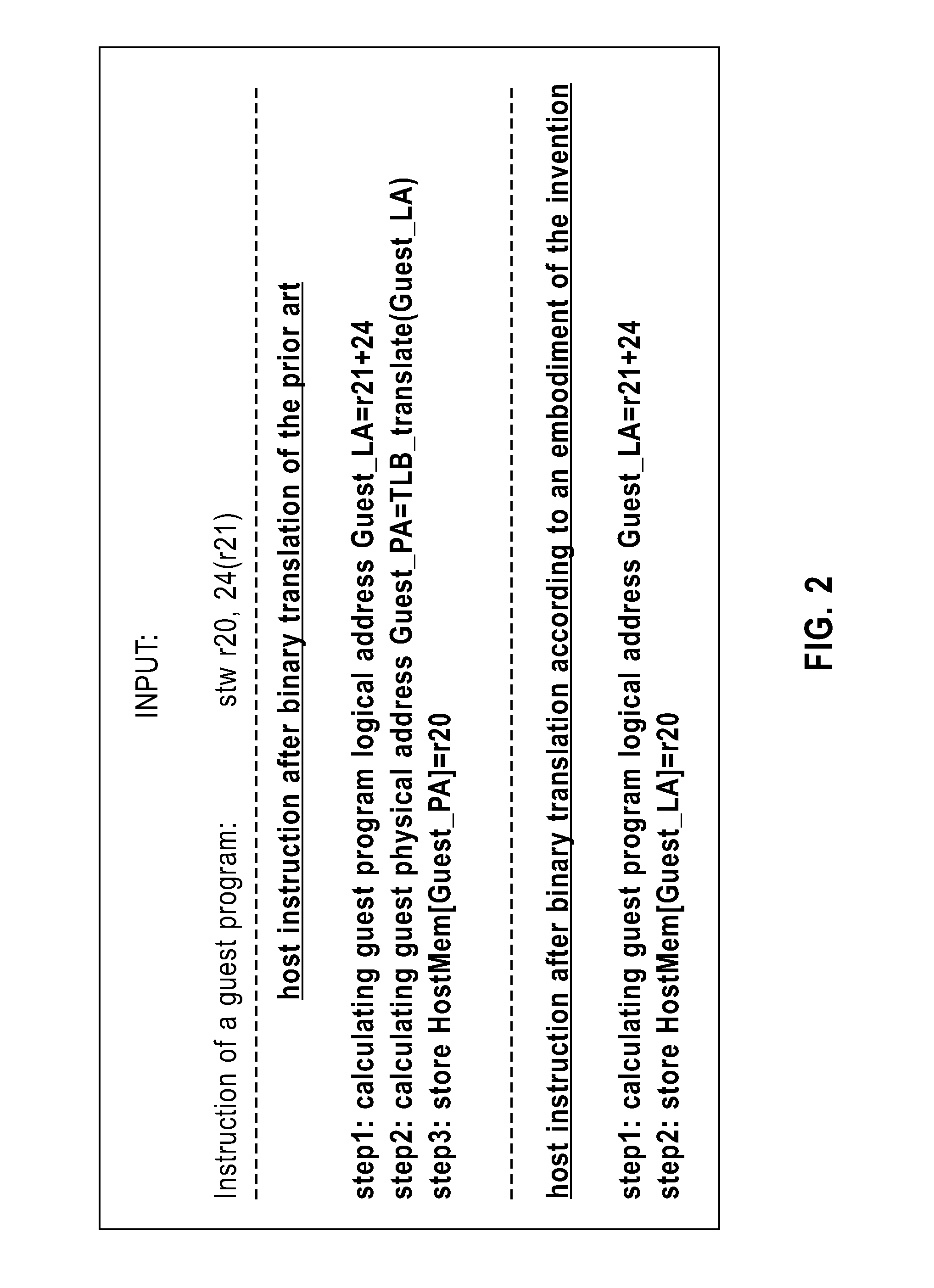

Simulator and simulating method for running guest program in host

ActiveUS20100161875A1Improve executionEfficient executionMemory adressing/allocation/relocationComputer security arrangementsCode TranslationPage table

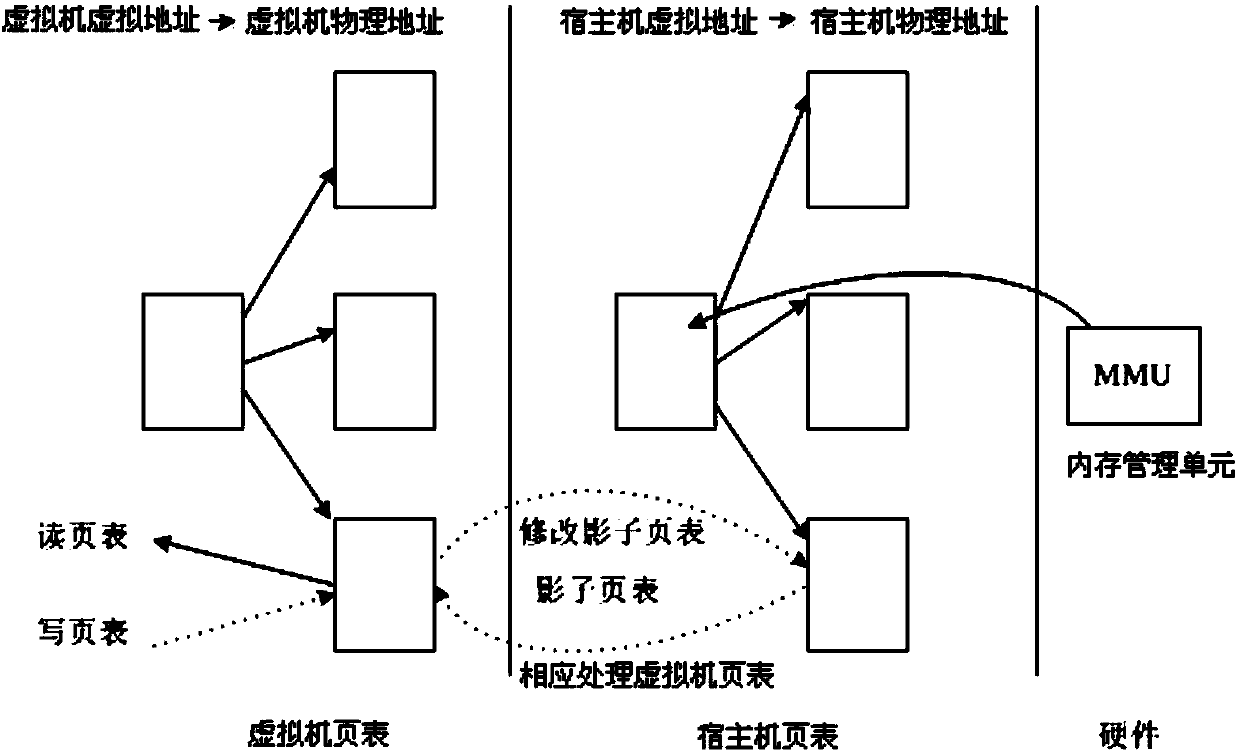

A Simulator and a simulating method for running a guest program in a host are disclosed. The simulator includes: an initialization device configured for setting content of a hypervisor page table in the host, the hypervisor page table mapping a guest physical address space to a host physical address space. The simulator further includes a binary translation device configured for employing a program logical address to perform a memory access in code translation. The simulator also includes a miss handling device configured for updating a guest translation look-aside buffer by treating a miss in a host translation look-aside buffer caused by the execution of the translated code as a miss in the guest translation look-aside buffer, wherein the host translation look-aside buffer is configured to buffer entries for mapping addresses in a guest program logical address space to addresses in the guest physical address space. The simulator further includes an update tracing device configured for, in response to the update to the guest translation look-aside buffer, perform the update to the host translation look-aside buffer. Also disclosed is a method for running a guest program in a host.

Owner:IBM CORP

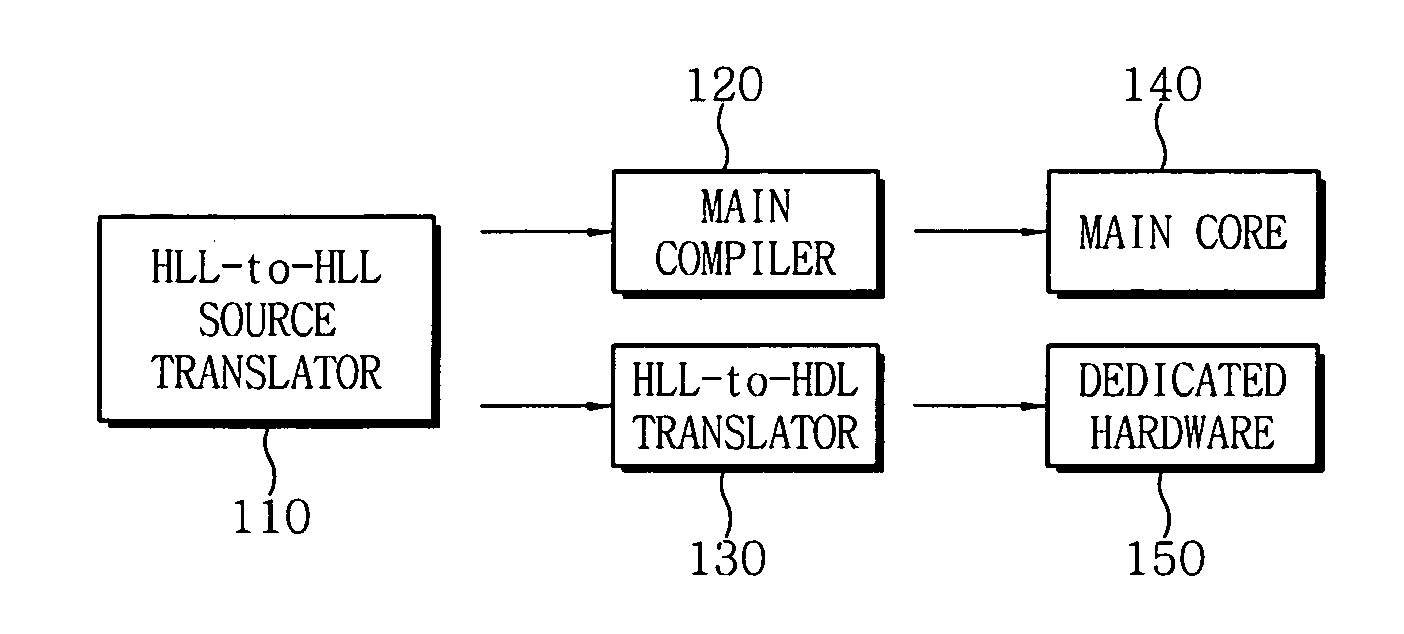

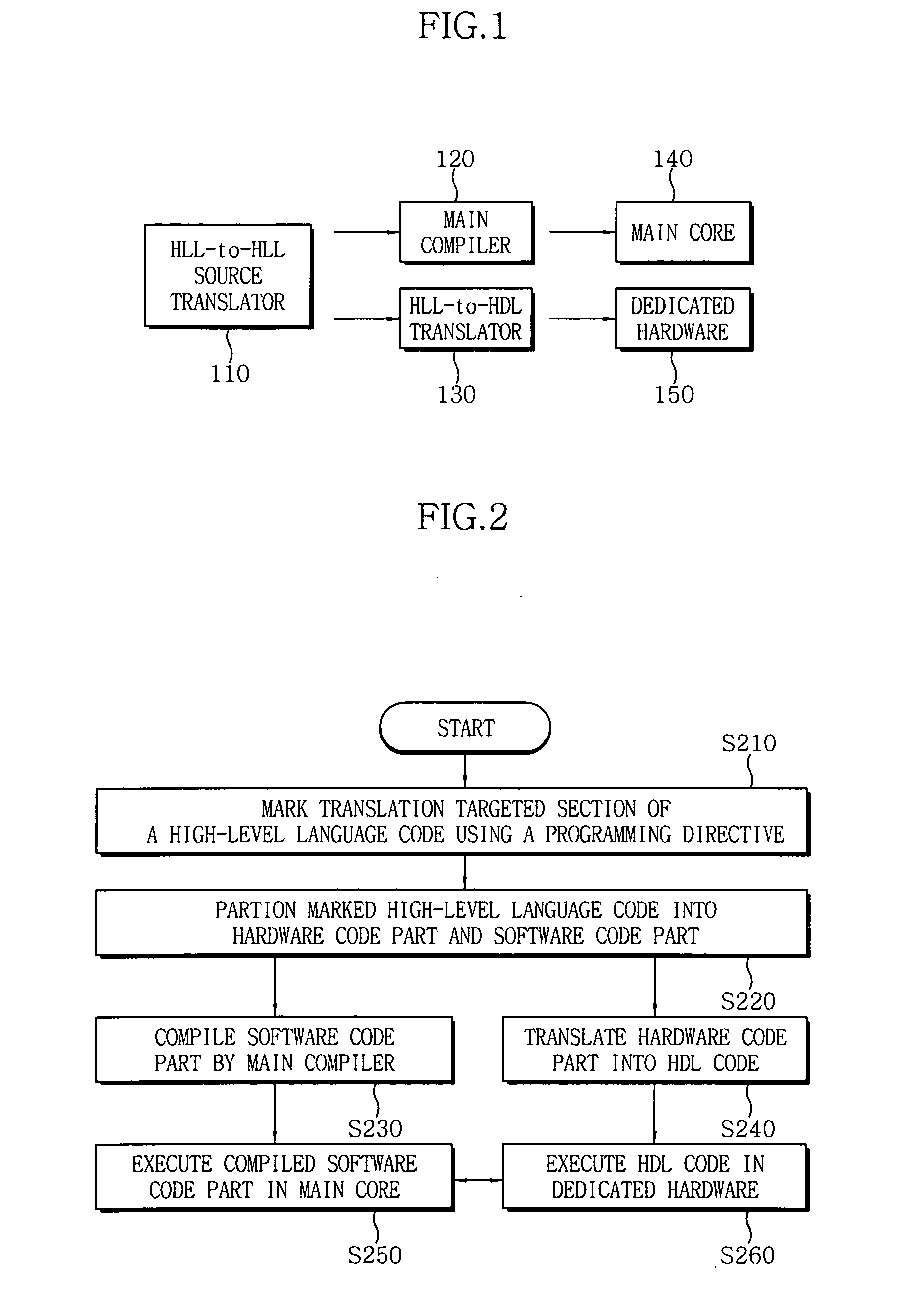

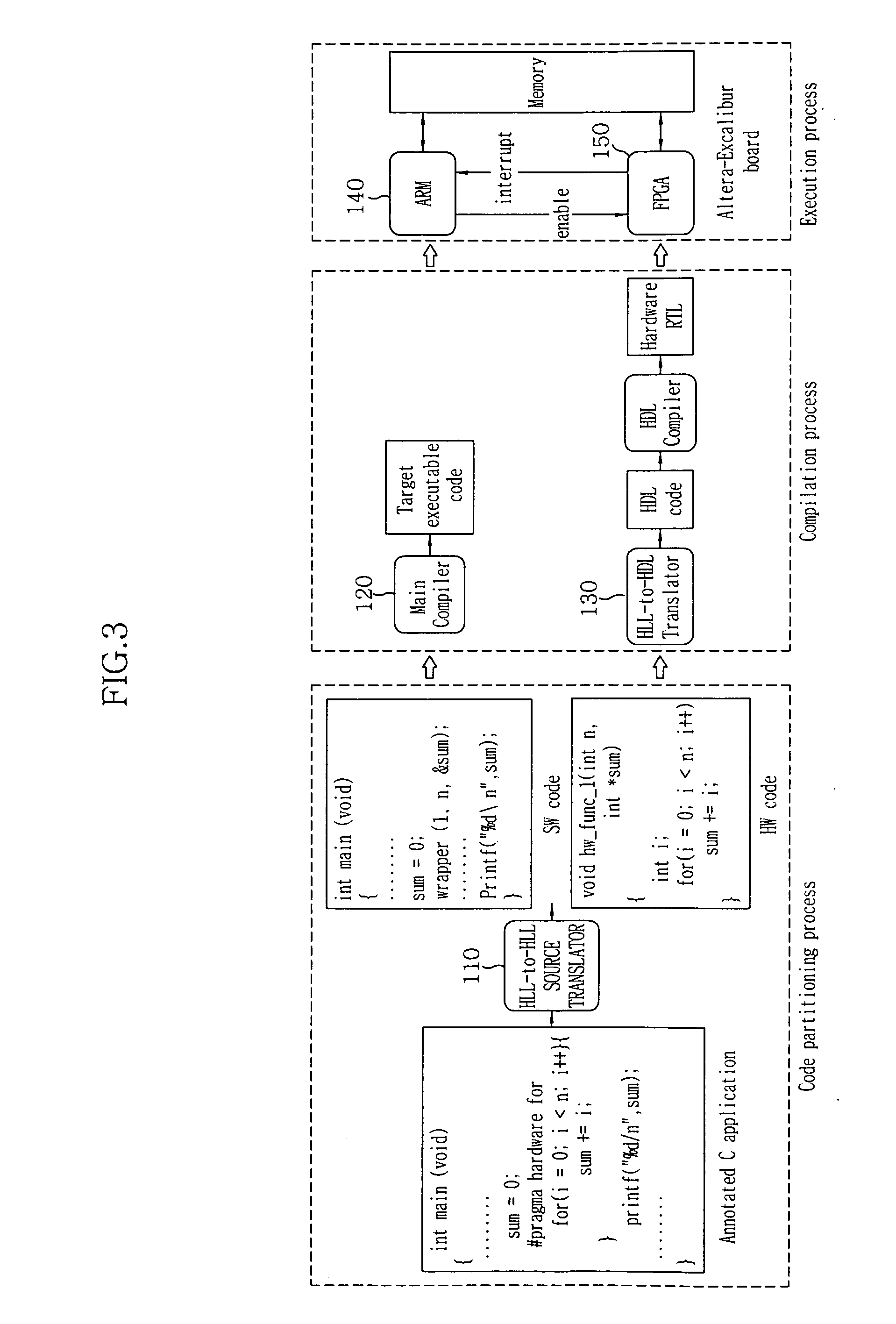

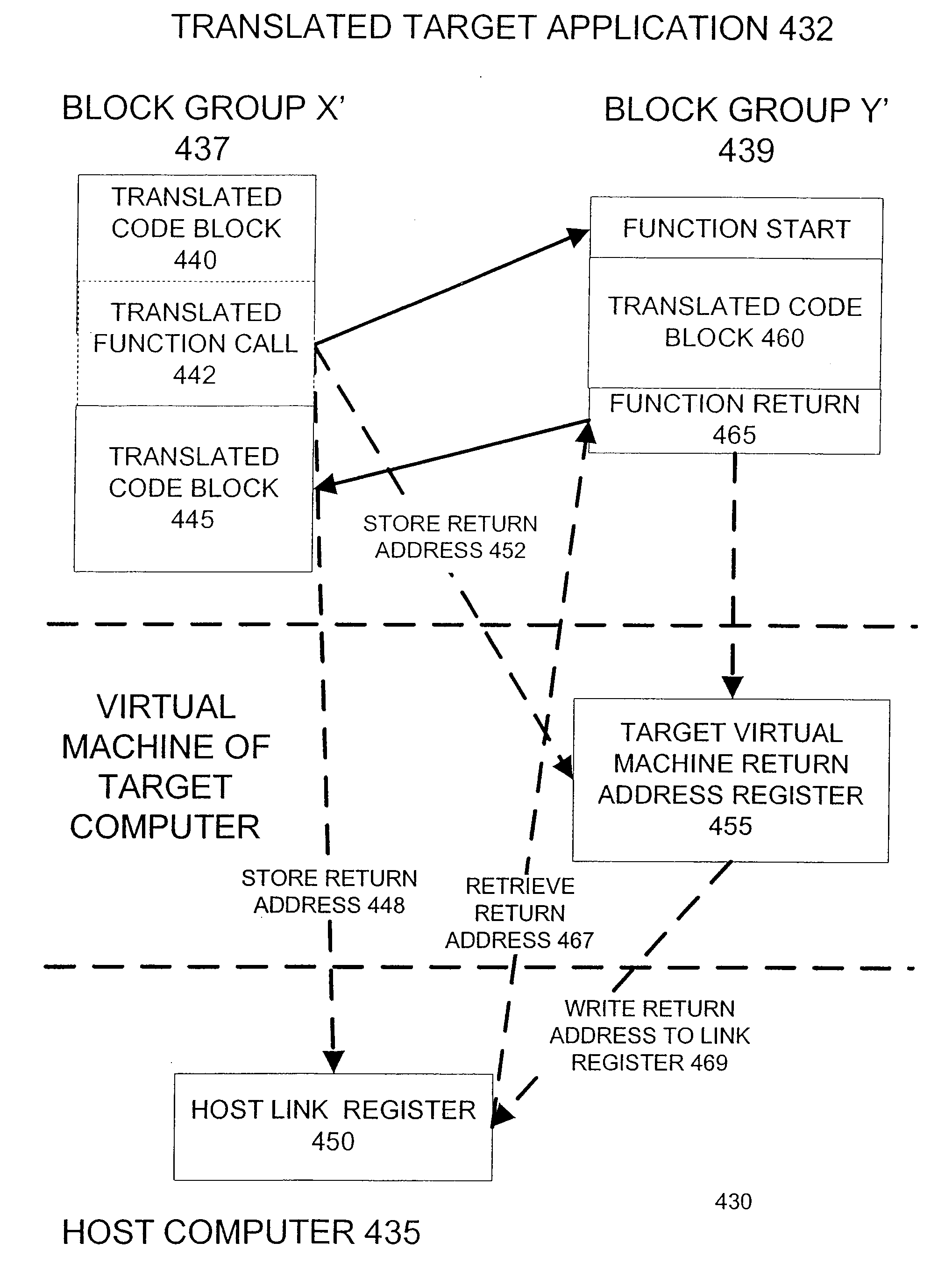

System and method for translating high-level programming language code into hardware description language code

The present invention is directed to a method and system for translating a high-level language (HLL) code such as C, C++, Fortran, Java or the like into a HDL code such as Verilog or VHDL which requires no modification in the original HLL source code, while supporting a cross call between software and hardware, and even recursive calls in hardware. The system includes: a HLL-to-HLL source translator which reads user programming directive from a translation-targeted high-level language code marked with the user directive, and separates the translation-targeted high-level language code into a hardware code part and a software code part; a main compiler which compiles the software code part; a HLL-to-HDL translator which includes the front-end and middle-end of the main compiler and a HDL backend; a main core which executes the compiled software code part; and a dedicated hardware which executes the HDL code.

Owner:KOREA UNIV IND & ACADEMIC CALLABORATION FOUND

Code translation and pipeline optimization

An emulator uses code translation and recompilation to execute target computer system applications on a host computer system. Target application code is partitioned into target application code blocks, and related target application code blocks are combined into block groups and translated. Translated application code block groups are sized to comply with restrictions on branch instruction size. Upon selecting an application code block group for execution, a cache tag is used to determine if a corresponding translated code block group is available and valid. If not, the block group is translated and executed. Sequentially executed translated code blocks are located in adjacent portions of memory to improve performance when switching between translated code blocks. The emulator may use a link register of the host computer system to prefetch instructions and data from translated code blocks. The emulator also takes into account structural hazards in translating instructions.

Owner:SONY COMPUTER ENTERTAINMENT INC

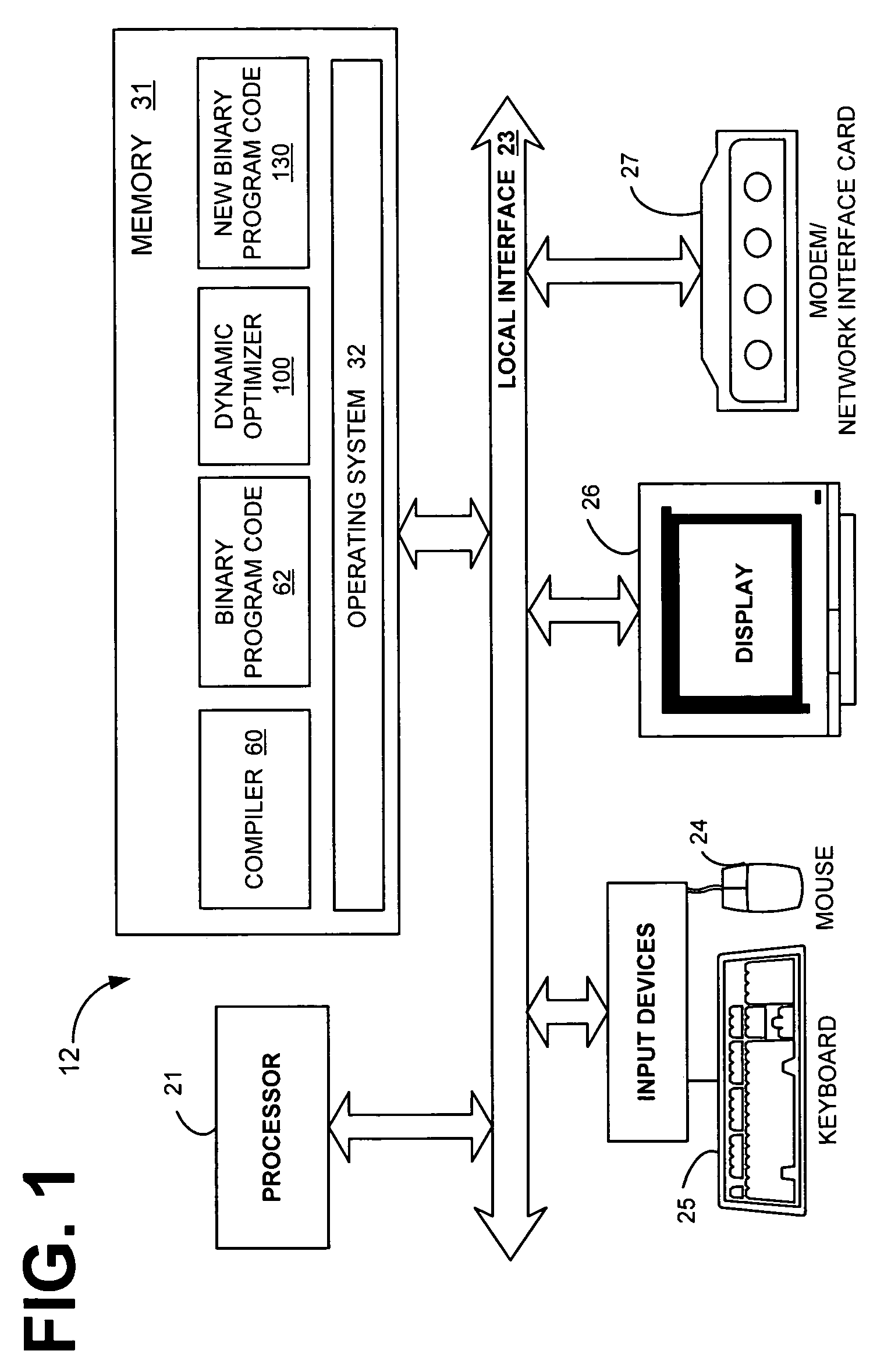

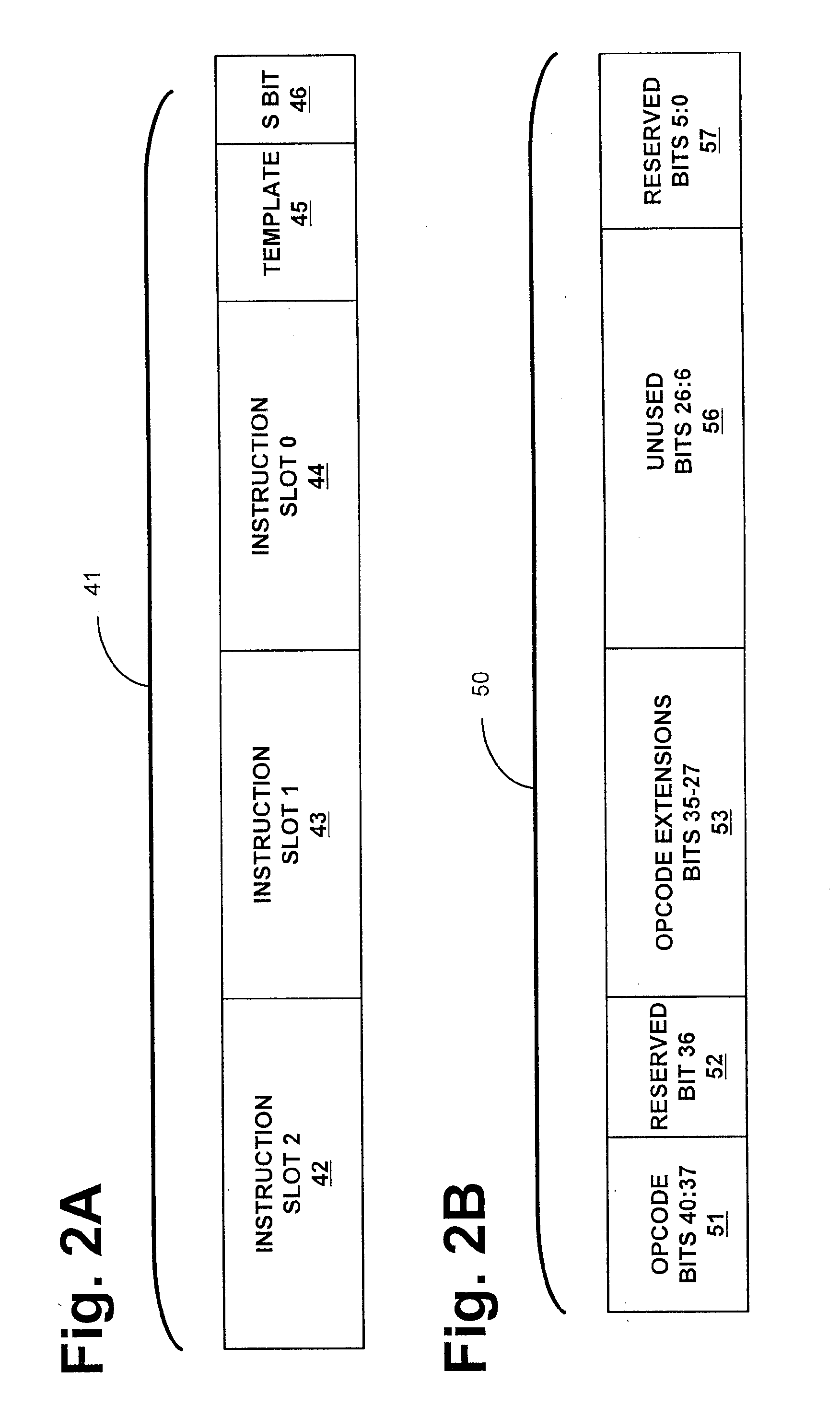

System and method for efficiently passing information between compiler and post-compile-time software

InactiveUS7257806B1Pass efficientlyEliminate time overheadSoftware engineeringInstruction analysisCode TranslationSoftware system

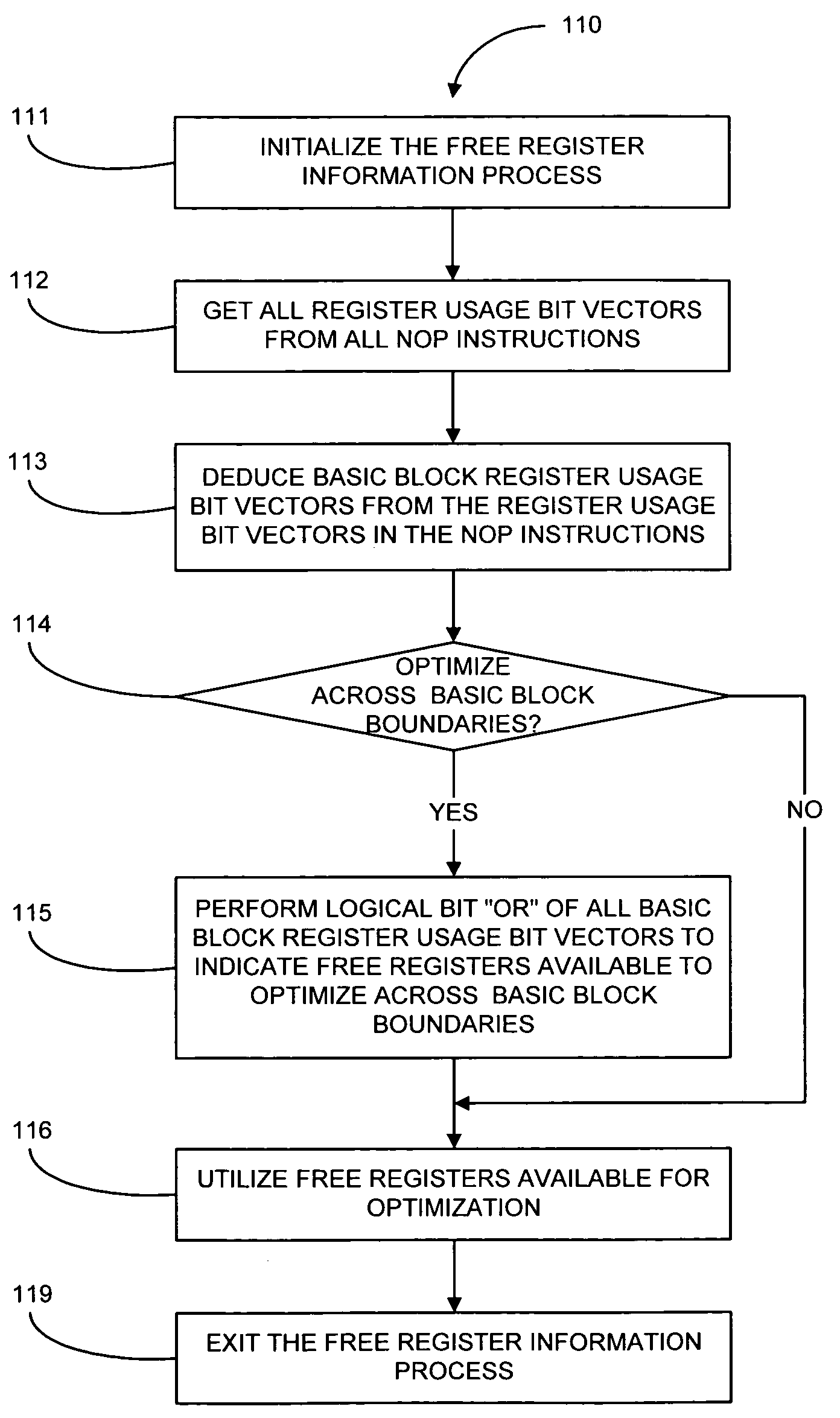

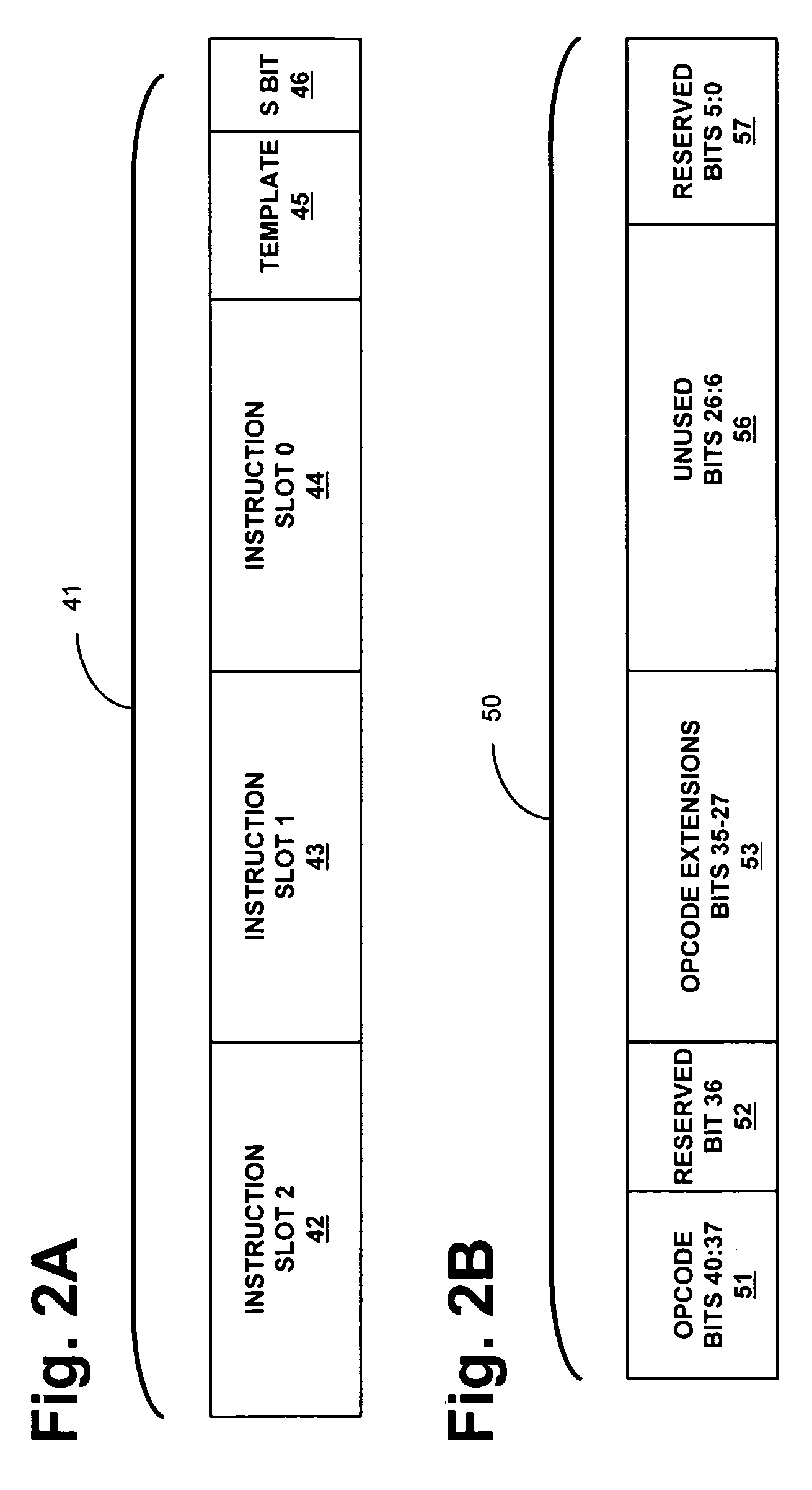

System and method are described for register optimization during code translation utilizes a technique that removes the time overhead for analyzing register usage and eliminates fixed restraints on the compiler register usage. The present invention for register optimization utilizes a compiler to produce a register usage bit vector in a NOP instruction within each basic block (i.e., subroutine, function, and / or procedure). Each bit in the bit vector represents a particular caller-saved register. A bit is set if, at the location of NOP instruction, the compiler uses the corresponding register within that basic block containing the NOP instruction to hold information to be used at a later time. During the translation, the translator examines the register usage bit vector to very quickly determine which registers are free and therefore can be used during the register optimization without the need to save and restore the register values.

Owner:HEWLETT PACKARD DEV CO LP

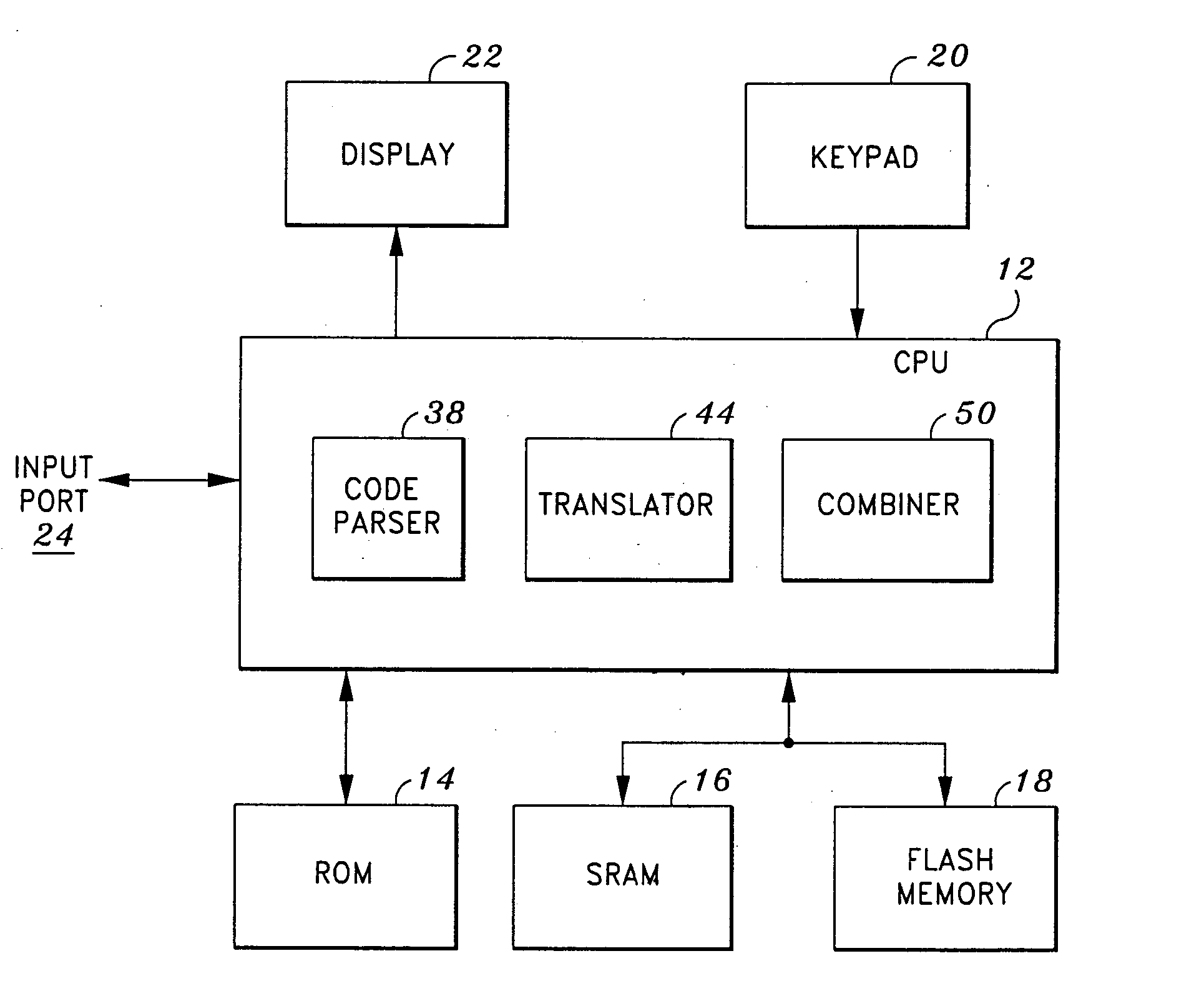

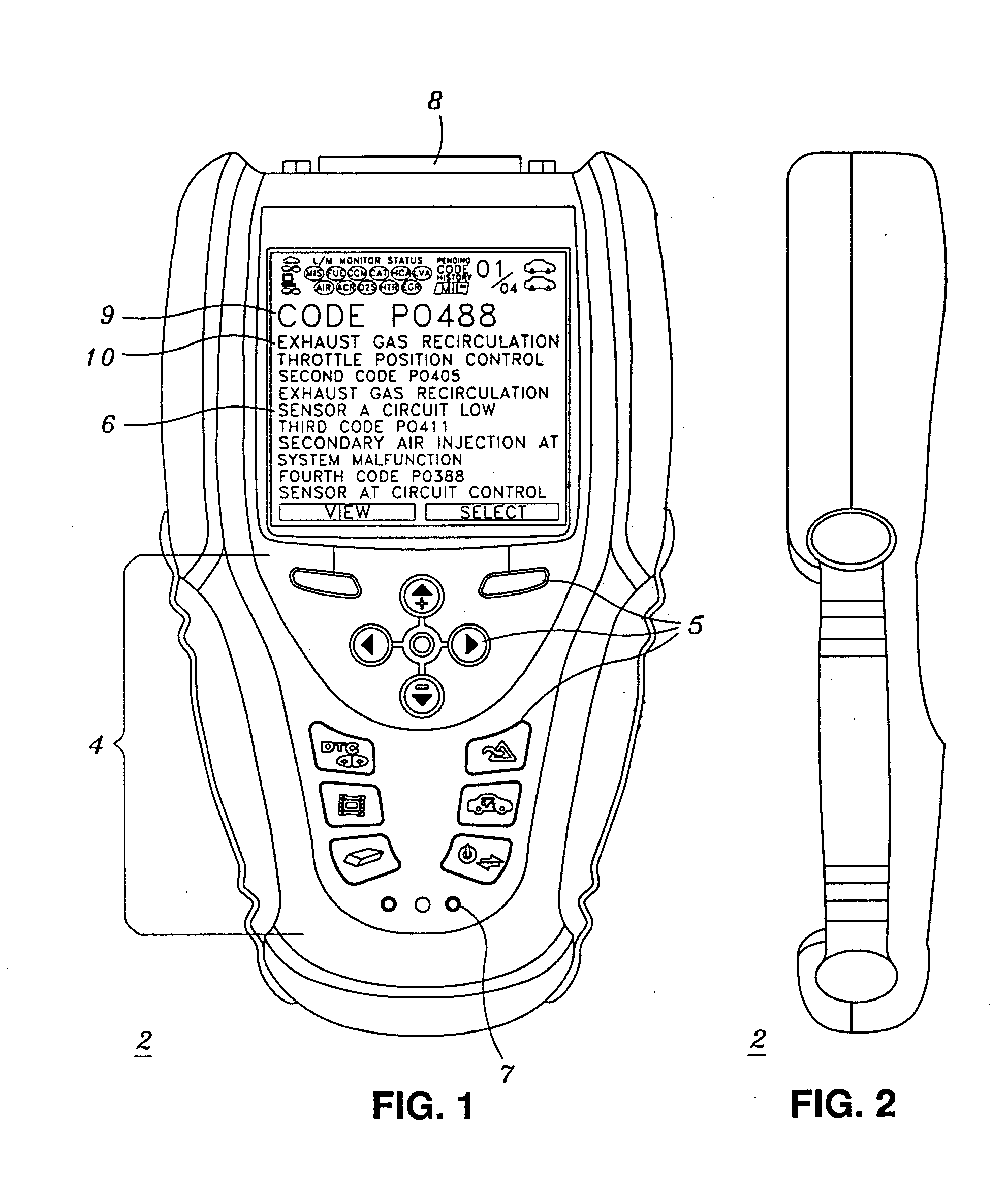

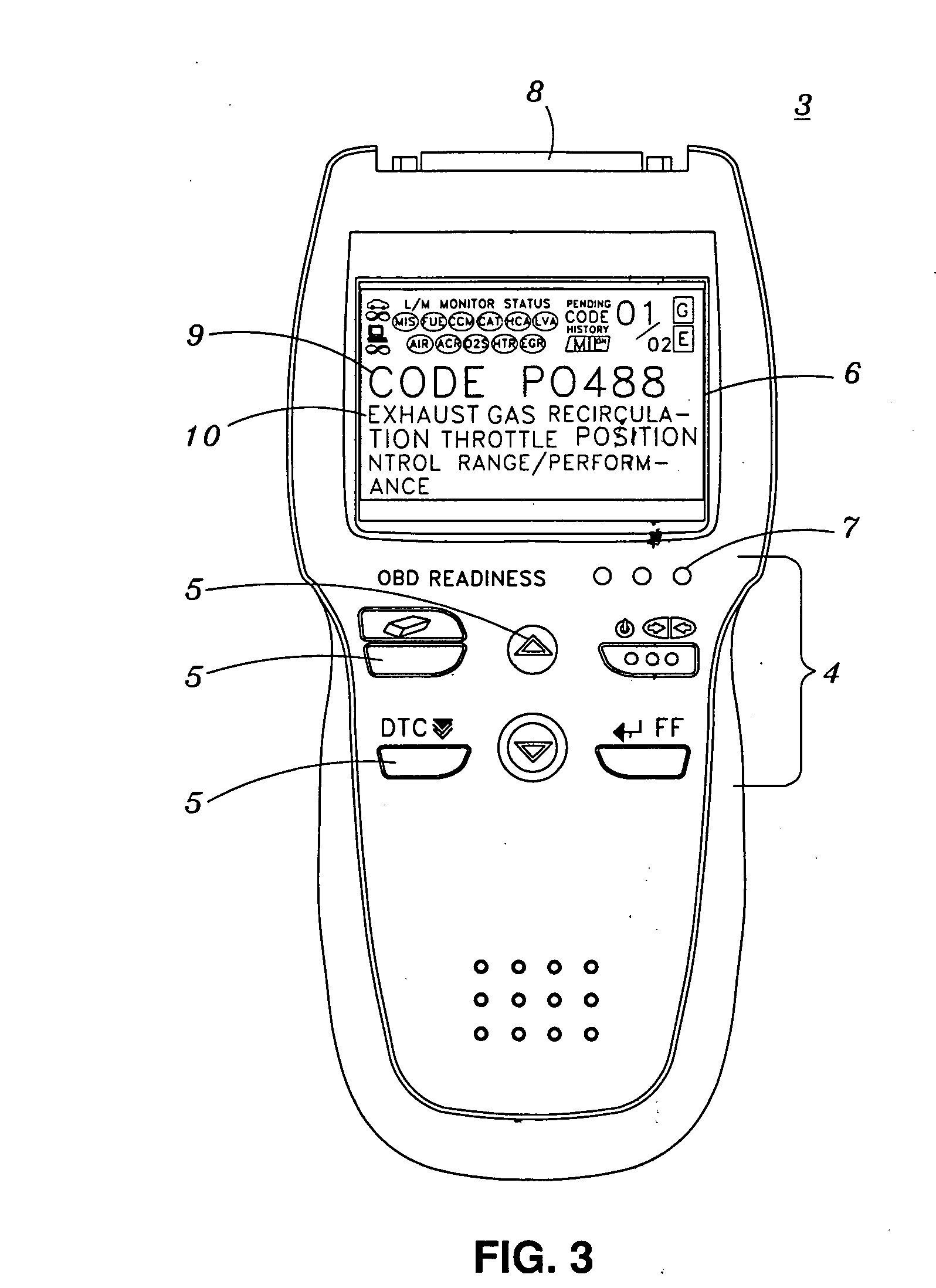

Vehicle diagnostic tool

Owner:INNOVA ELECTRONICS

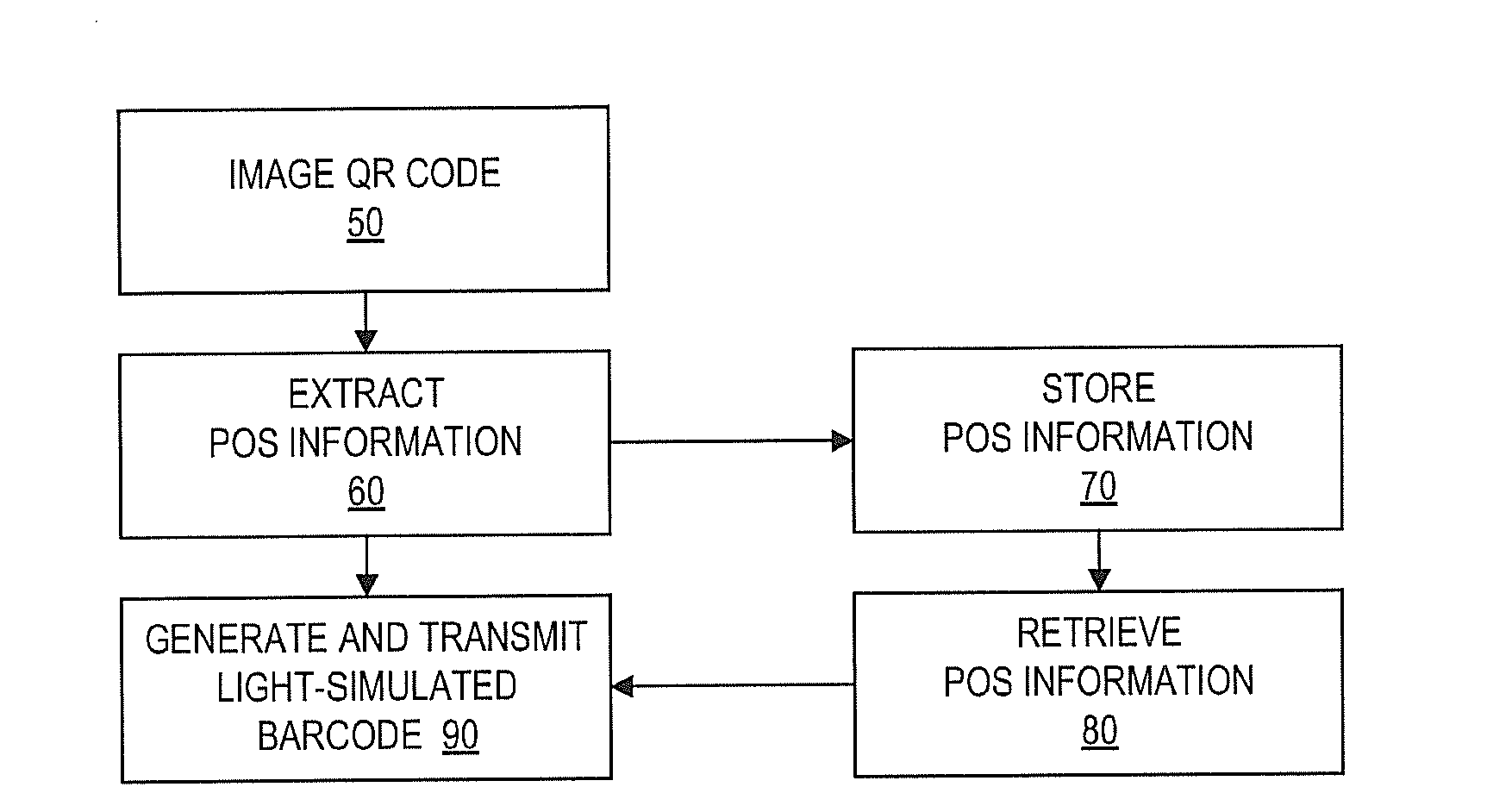

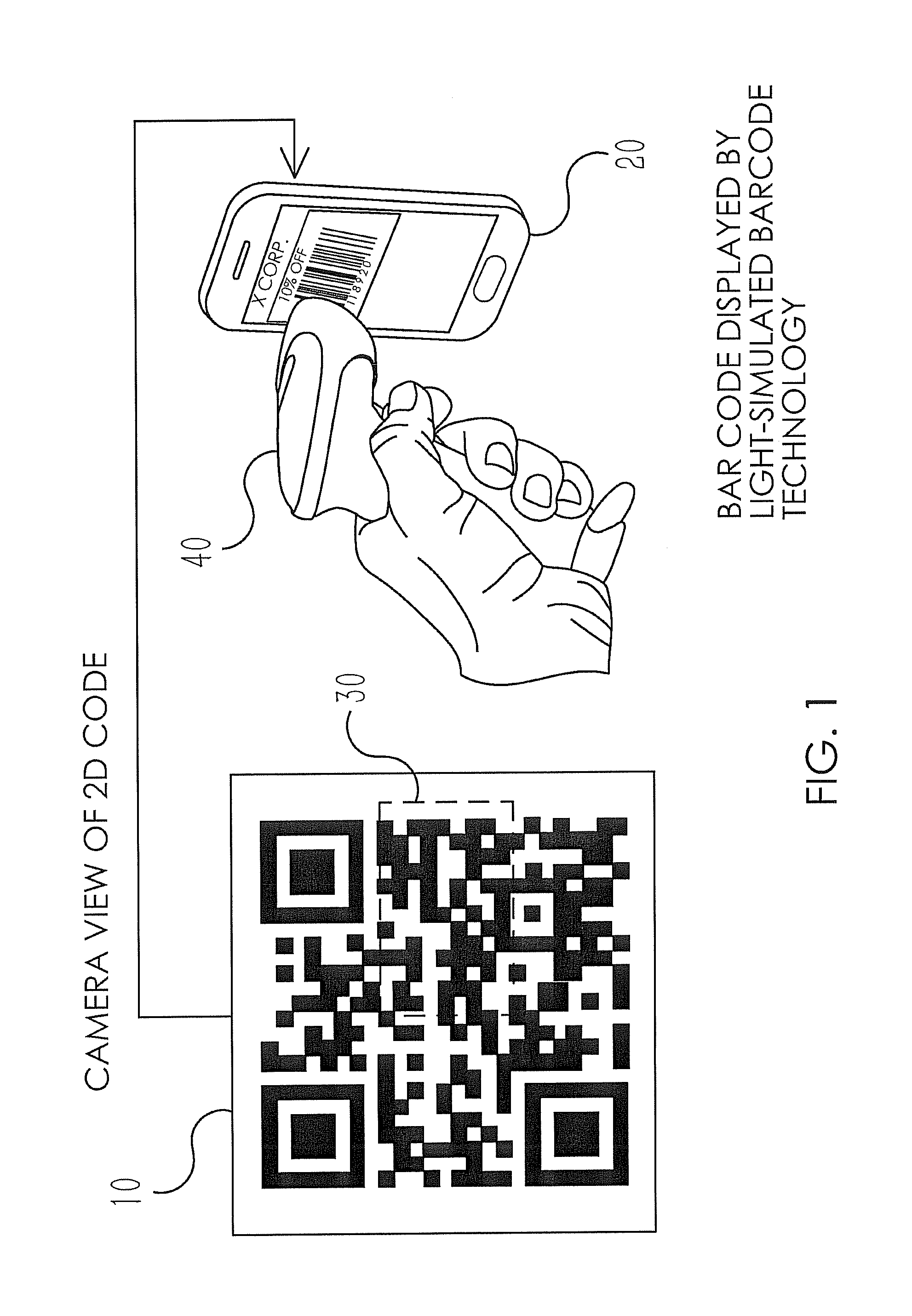

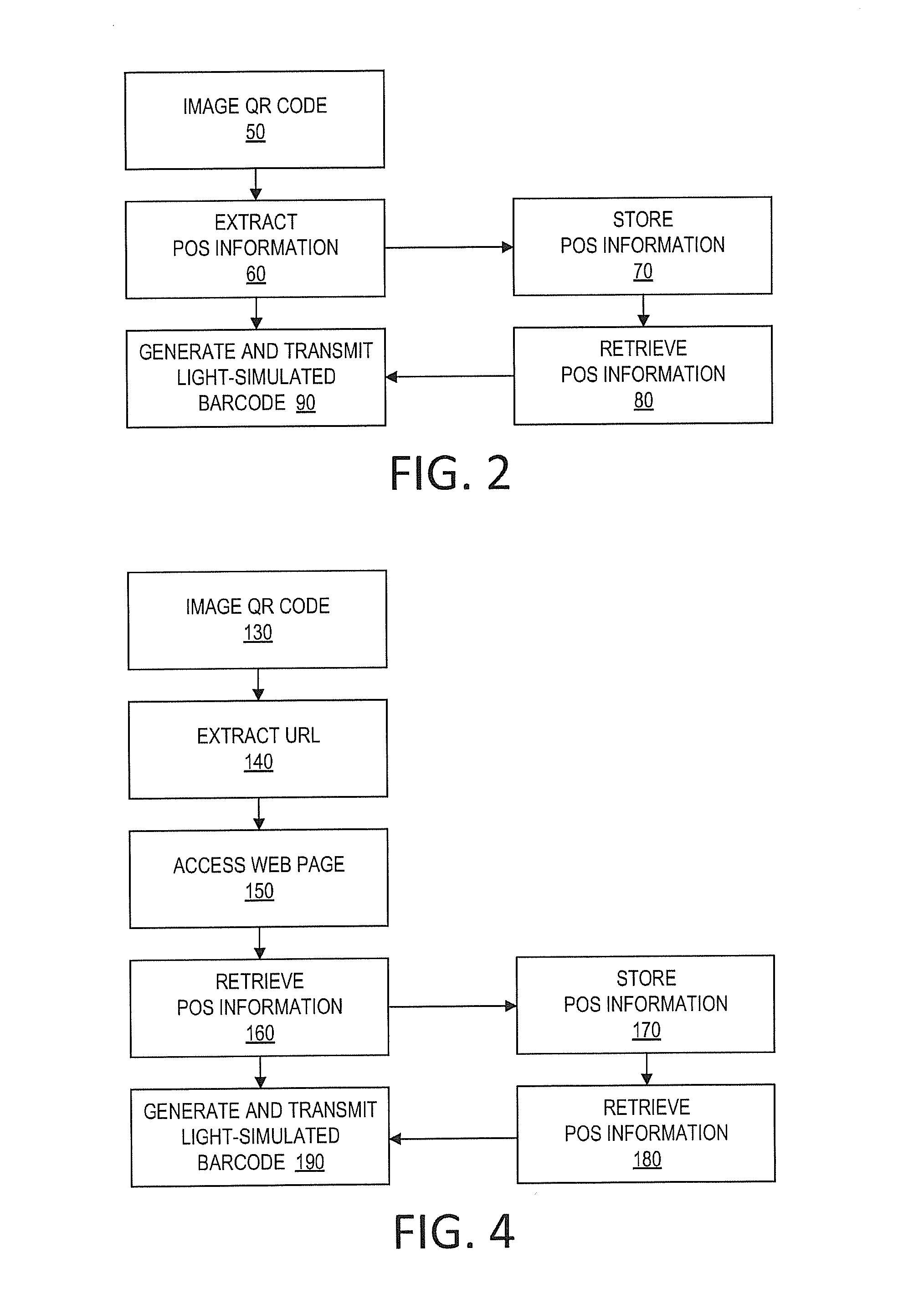

Multi-dimensional code translation

Value documents such as coupons and event tickets that are represented or indexed in the form of QR codes or other types of two-dimensional encoding techniques may be acquired by imaging with a suitably-enabled mobile device, and then translated in the mobile device into a form suitable for presentation as a one-dimensional barcode at a point-of-sale / service using light-simulated barcode technology.

Owner:SAMSUNG ELECTRONICS CO LTD

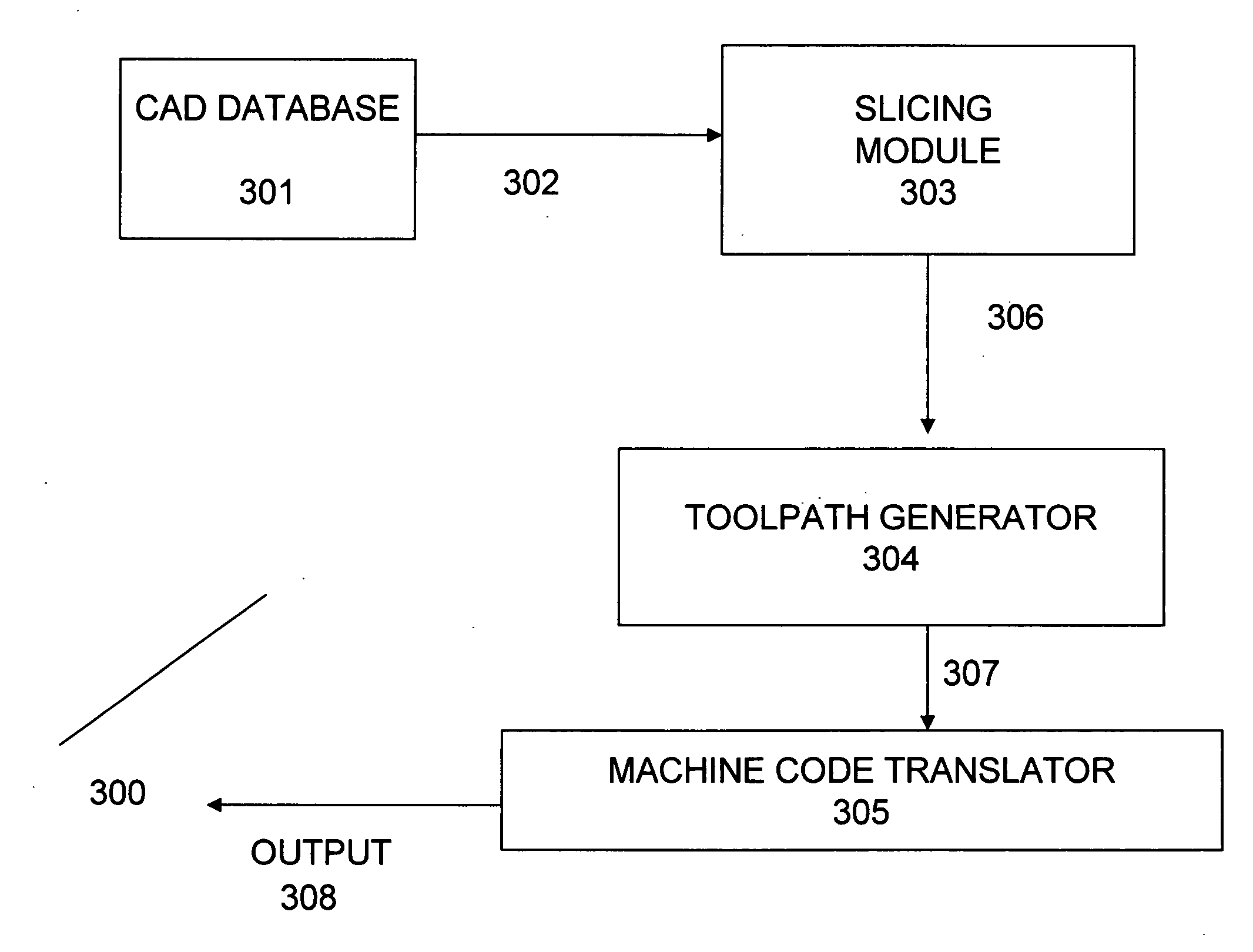

Method and system for toolpath generation

A system and method for toolpath creation is provided. The method includes exporting CAD defined 3-D geometry to a slicing module; slicing the 3-D geometry creating a set of 2-D patterns representing the 3-D geometry; generating vector code from the set of 2-D patterns; and translating the vector code to machine code.

Owner:THE BOEING CO

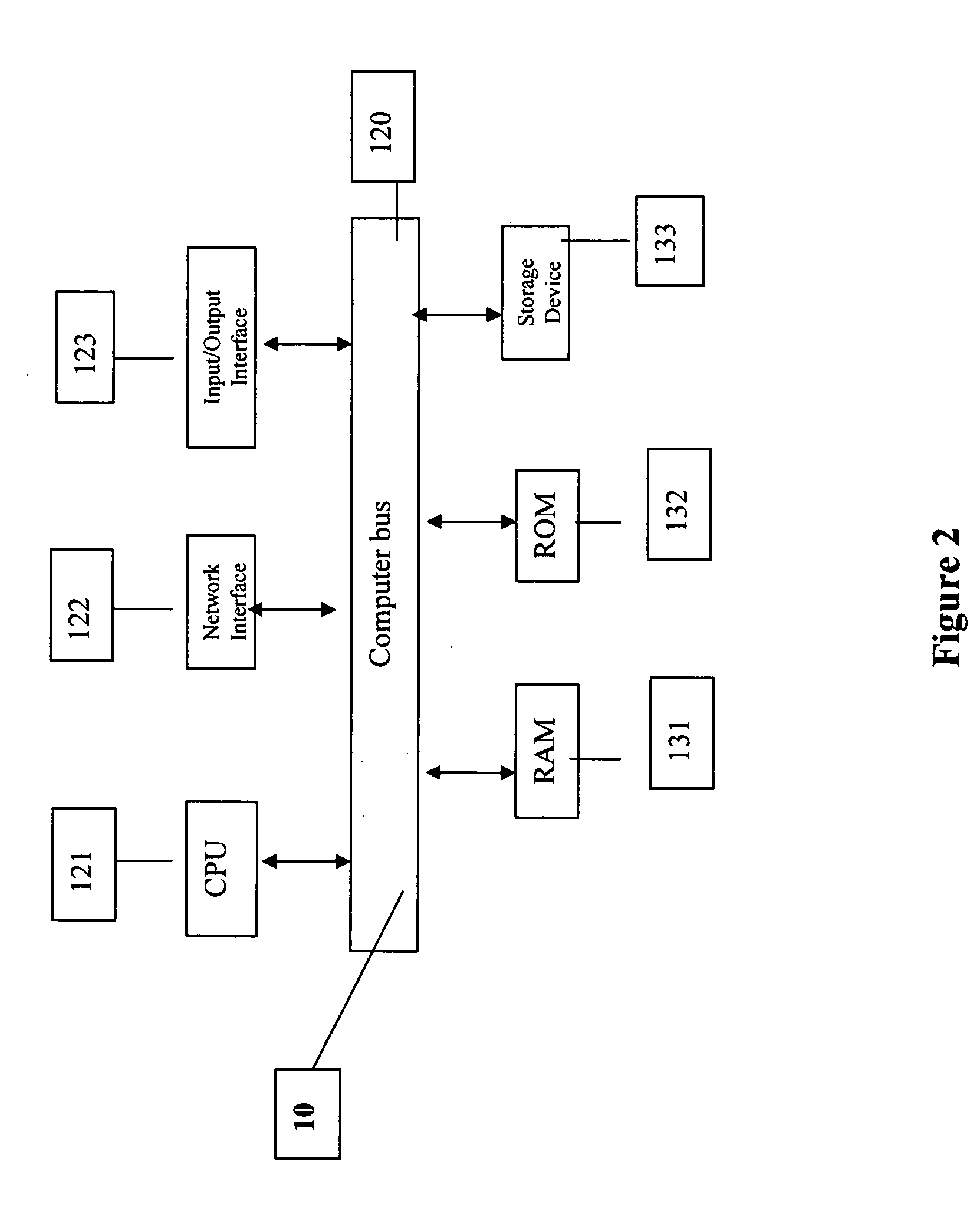

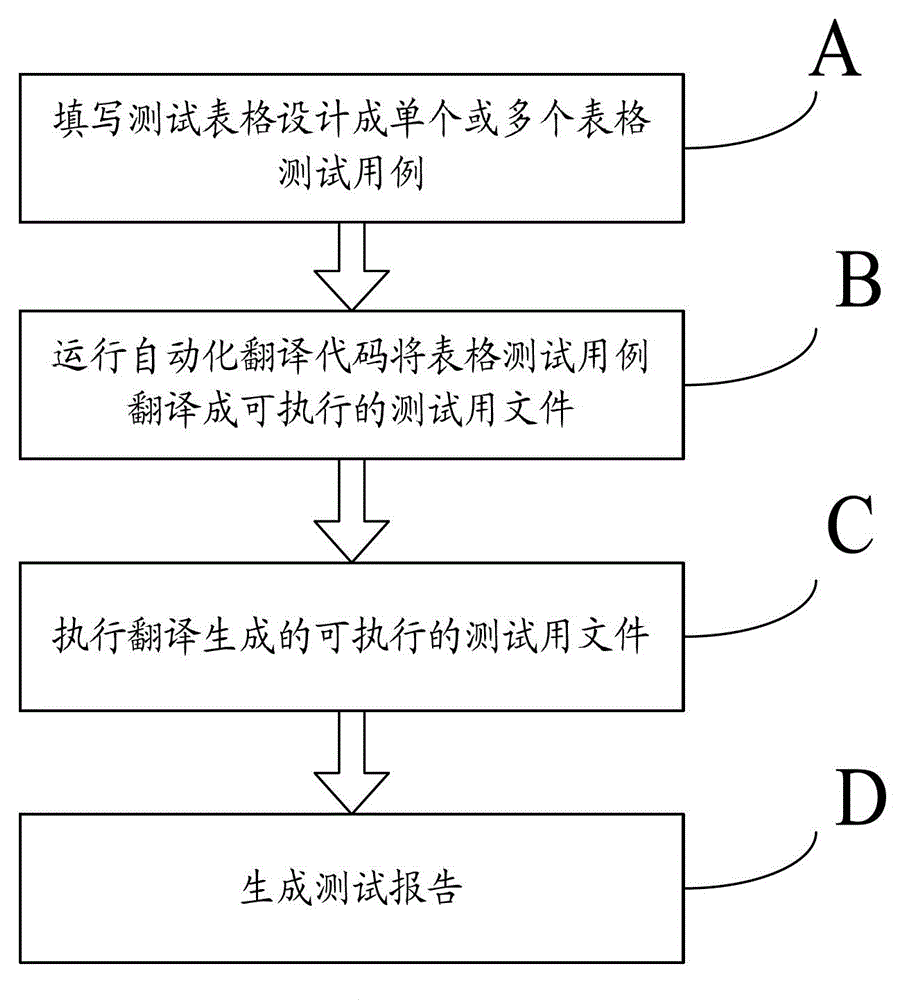

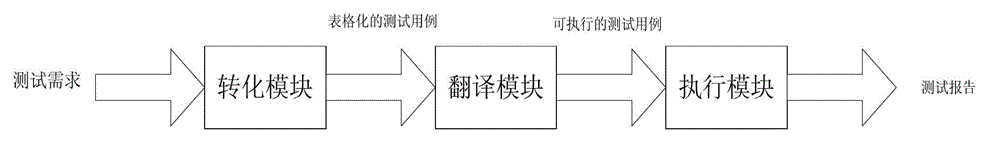

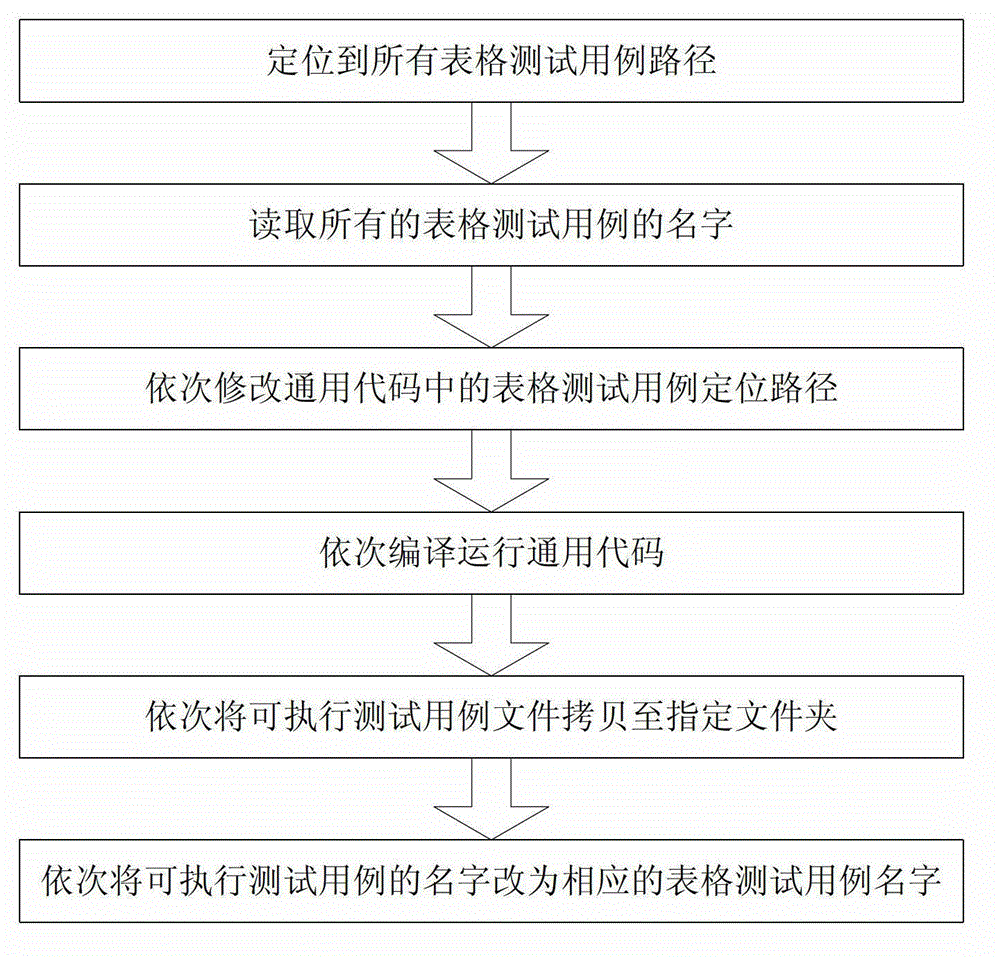

Method and system of electronic control unit (ECU) hardware-in-loop simulation automated testing

ActiveCN103064403AImprove unityImprove regularityElectric testing/monitoringCode TranslationAutomatic testing

The invention discloses a method and a system of electronic control unit (ECU) hardware-in-loop simulation automated testing. The method comprises the following steps: a test form is filled in so that one or a plurality of test form cases, an automation code is run to enable the form test cases to generate executable files for testing, the test is executed, and a test report is generated. An automated interpreter code is needed to design only once and is permanently effective, and an automated testing development engineer is enabled to be out of a lot of test case code translation work. By adoption of a form test case development mode, the method and the system of ECU hardware-in-loop simulation automated testing are simple, efficient, universal and flexible, and cost performance is high and practical. After a lot of form tests are developed by a testing project, corresponding executable test cases are generated by queue with one key and are automatically executed with one key, so that hardware-in-loop (HIL) automated testing of the ECU is achieved in the real sense.

Owner:WEICHAI POWER CO LTD

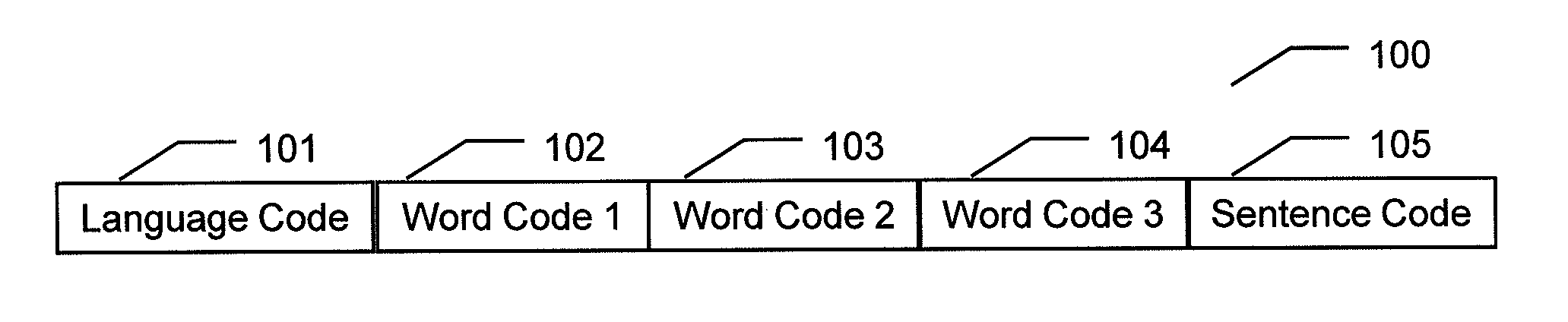

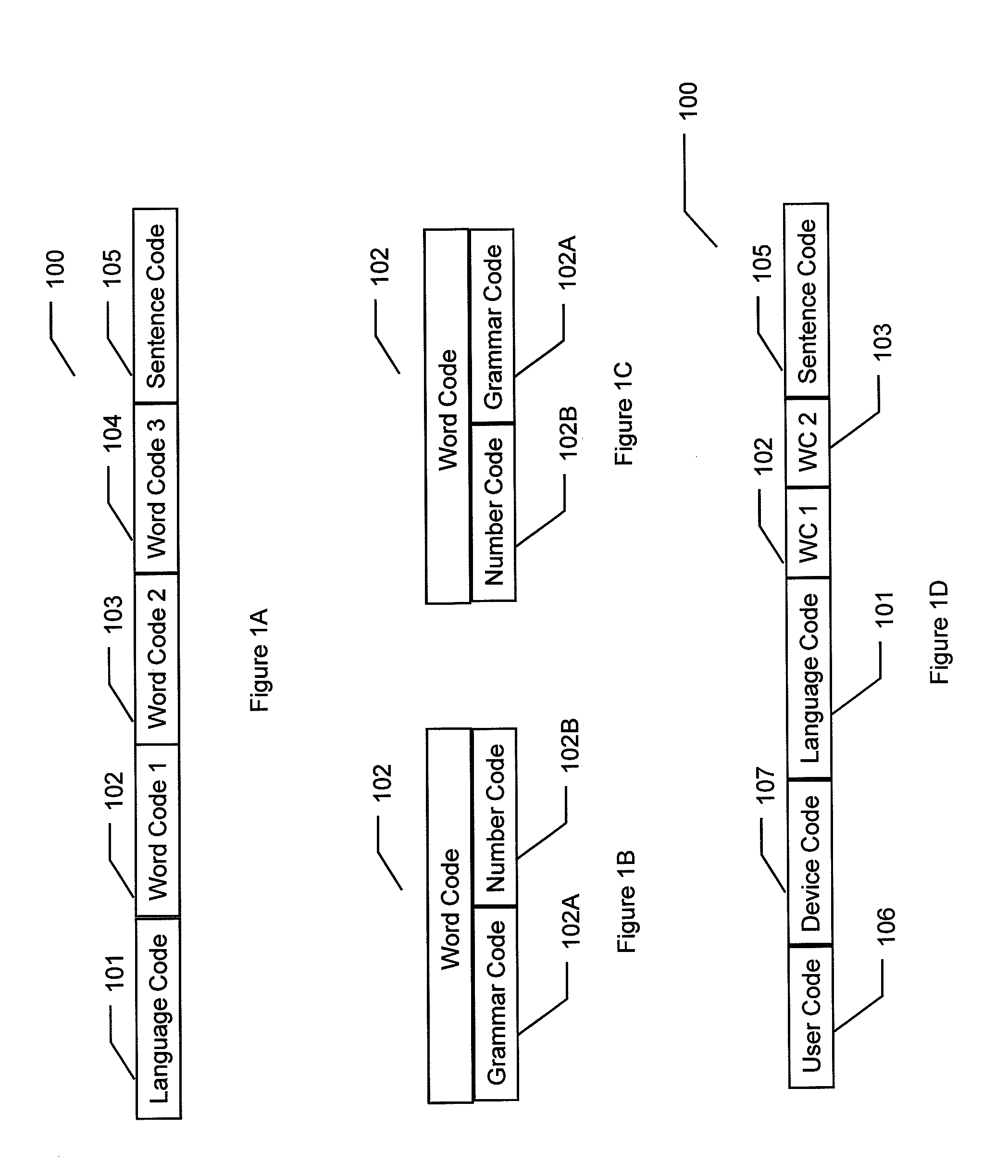

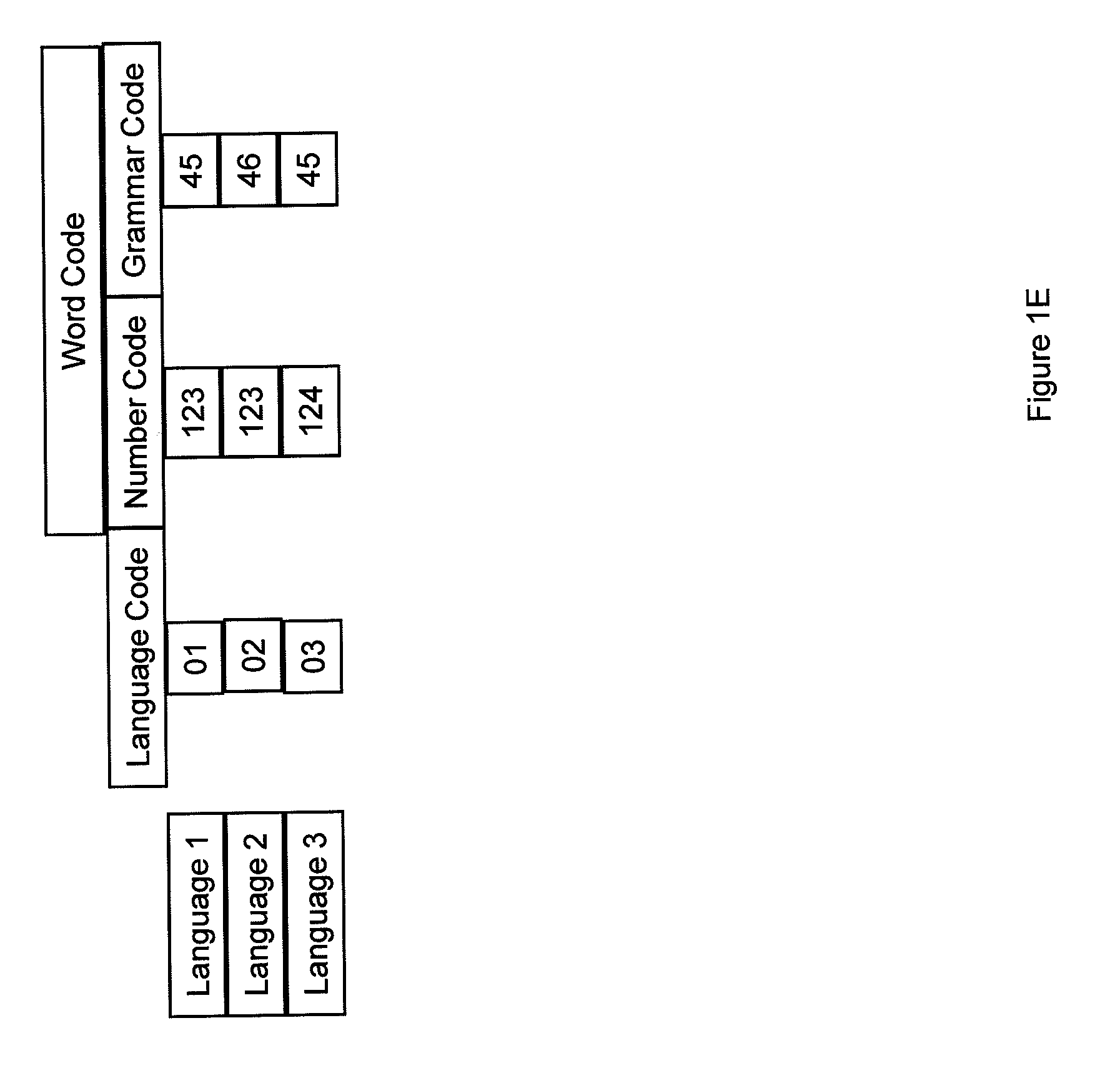

Multiple language translation system

InactiveUS20120209588A1Overcome disadvantagesNatural language translationSpecial data processing applicationsCode TranslationTranslation system

A multiple language translation system is disclosed. A code stream that is transmitted between users comprises a language code indicating the language used, a sentence code indicating a sentence structure, and at least one word code. The word codes are codes representing a word in the language that the language code represents. Each word code comprises a number code representing a unique word and a grammar code indicating grammatical usage the word. During translation of the code stream, the sentence code is used to format the word codes or the words represented by the word codes in a correct sentence. The code stream is translated by identifying the language code and translating the word codes into a second language. The sentence code is then used to arrange the words of the second language into a grammatically correct sentence.

Owner:WU MING YUAN

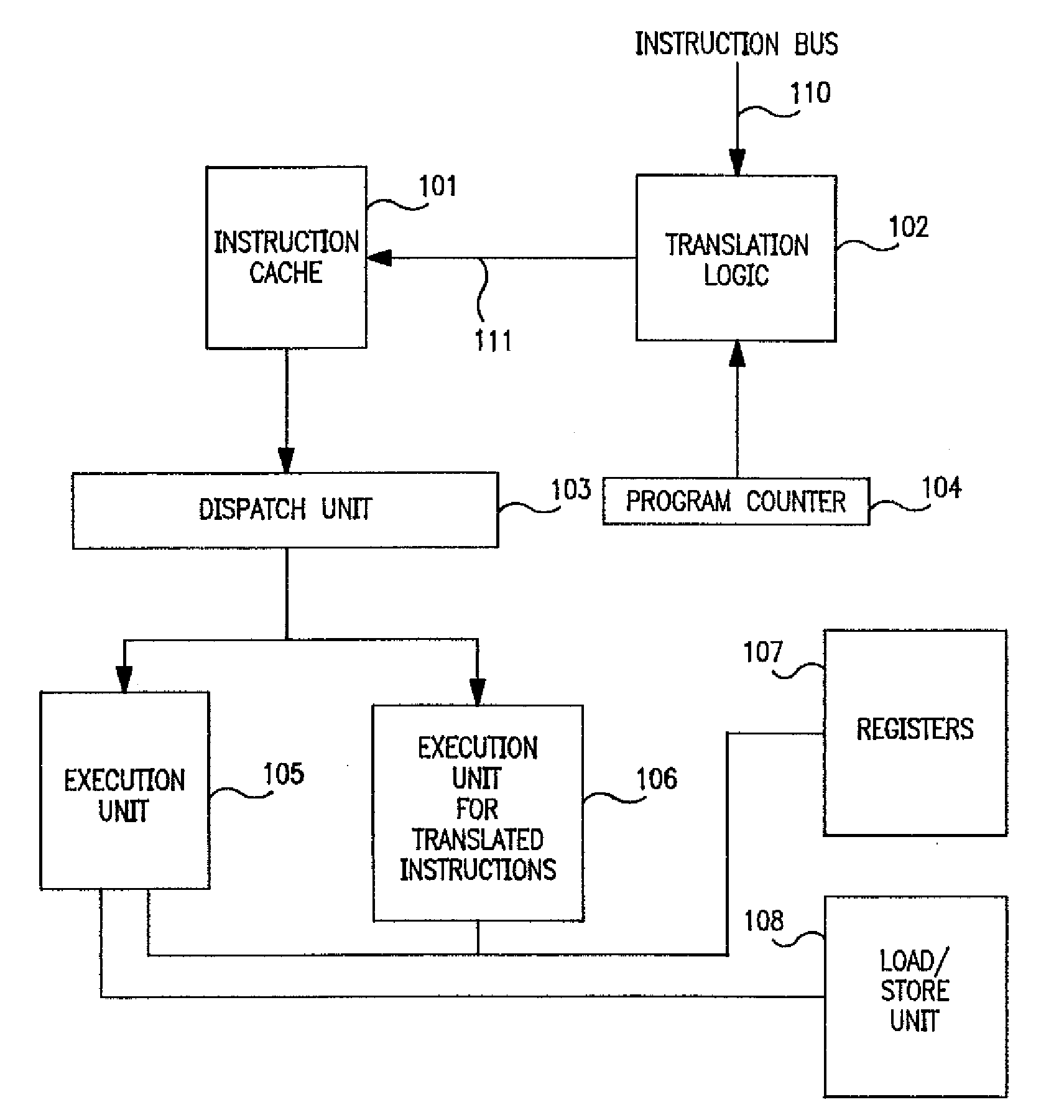

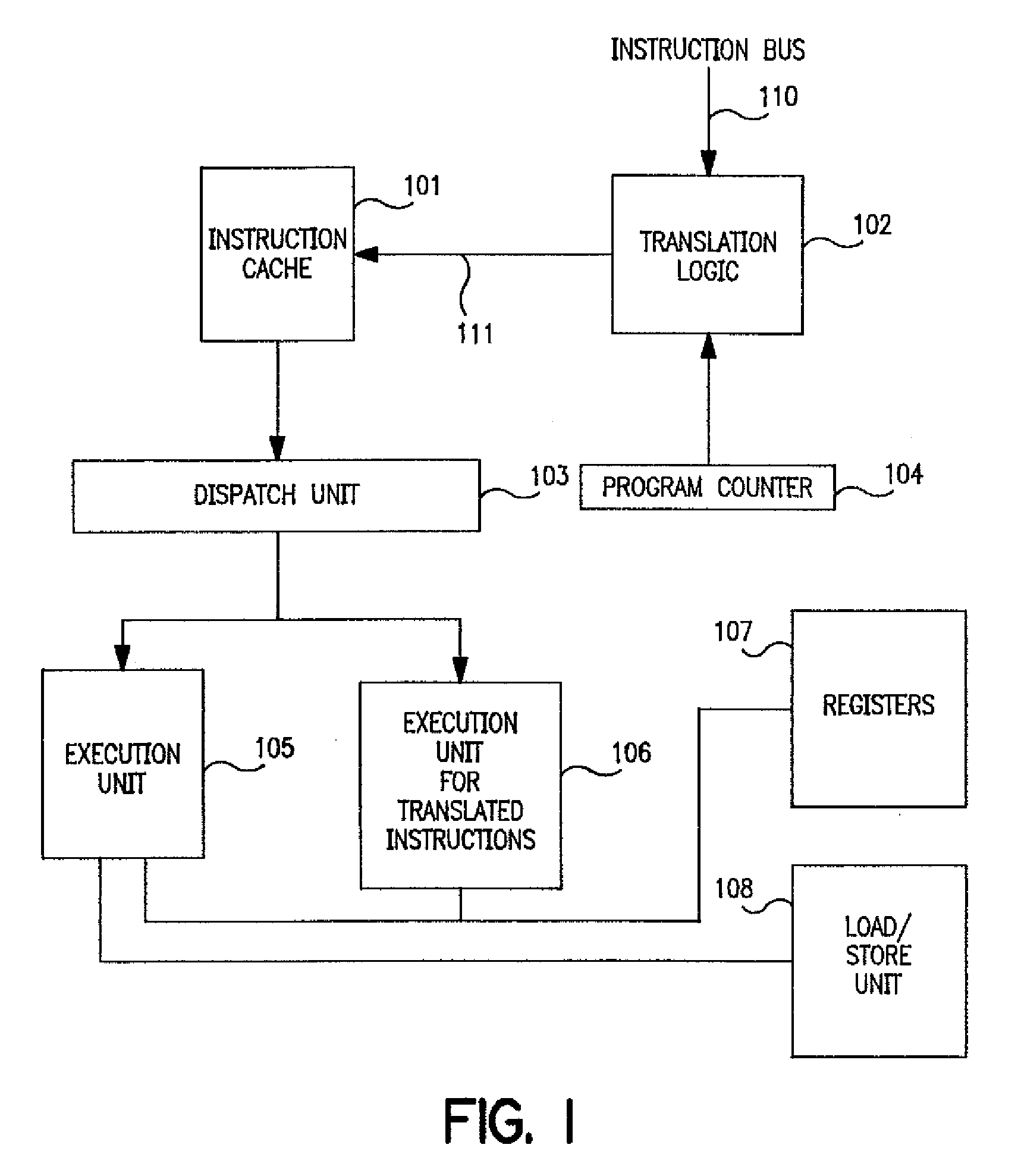

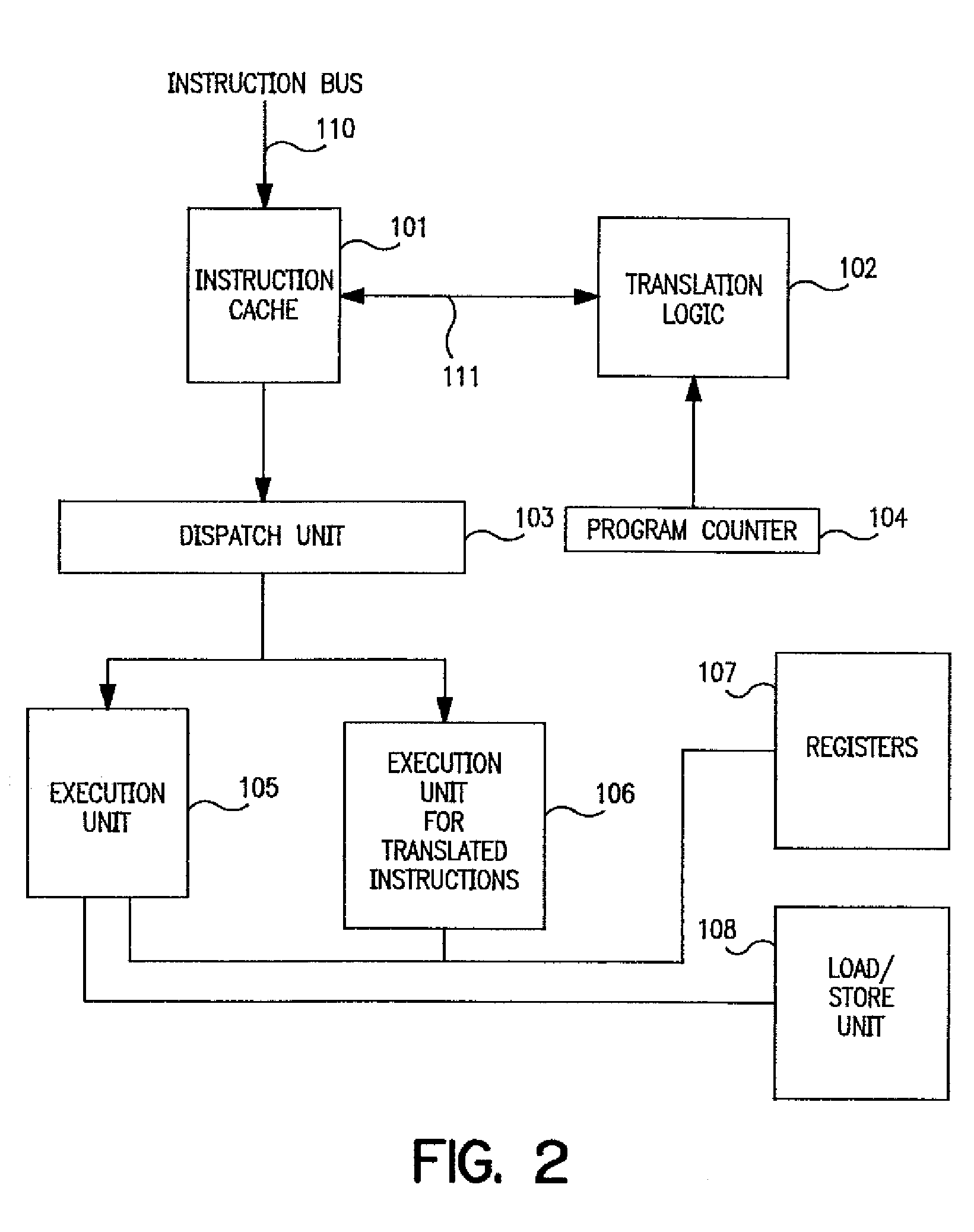

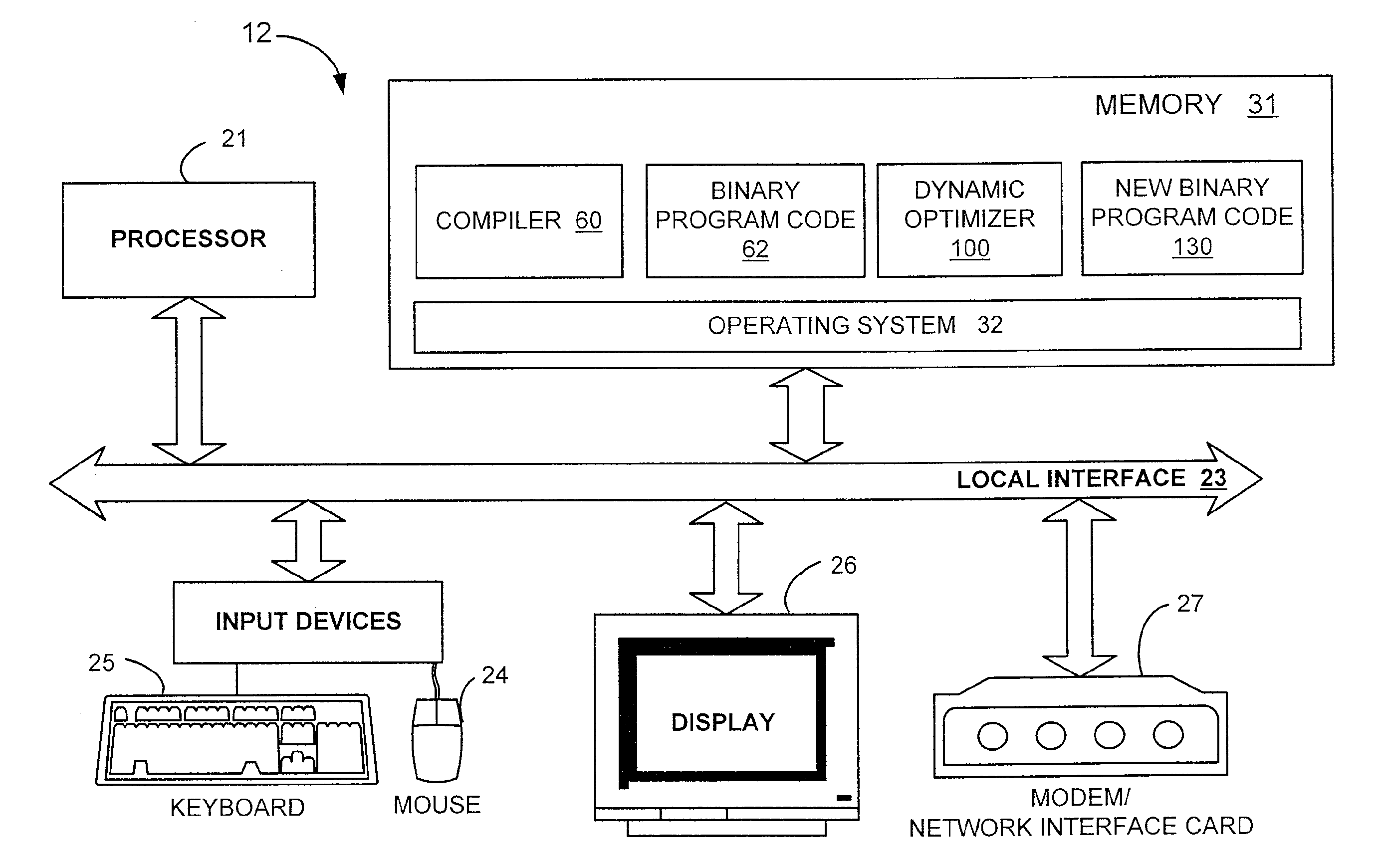

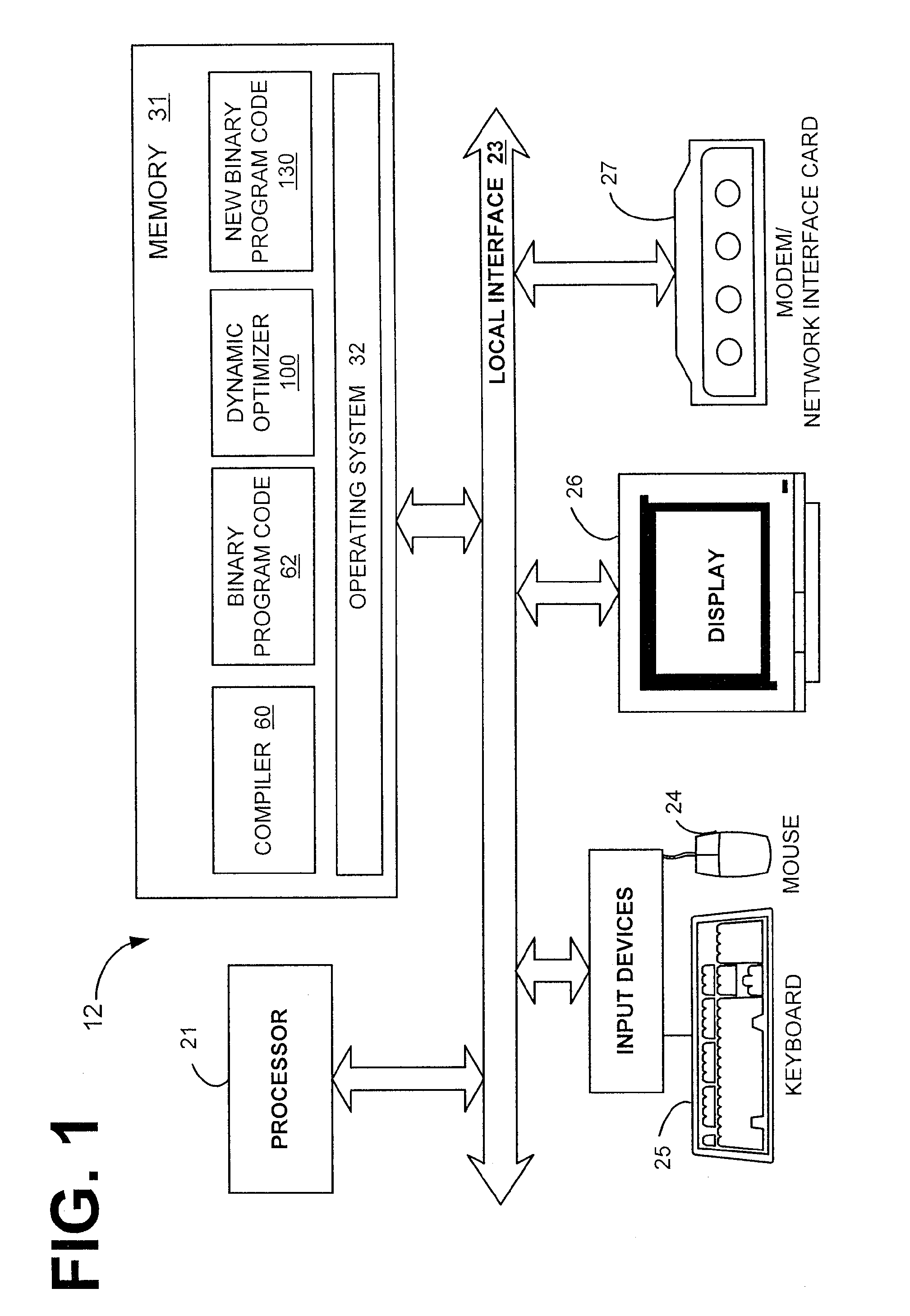

Dynamic object-level code translation for improved performance of a computer processor

InactiveUS20080320286A1Increase the number ofImprove processor performanceRuntime instruction translationDigital computer detailsCode TranslationExecution unit

A system and method for improving the efficiency of an object-level instruction stream in a computer processor. Translation logic for generating translated instructions from an object-level instruction stream in a RISC-architected computer processor, and an execution unit which executes the translated instructions, are integrated into the processor. The translation logic combines the functions of a plurality of the object-level instructions into a single translated instruction which can be dispatched to a single execution unit as compared with the untranslated instructions, which would otherwise be serially dispatched to separate execution units. Processor throughput is thereby increased since the number of instructions which can be dispatched per cycle is extended.

Owner:INT BUSINESS MASCH CORP

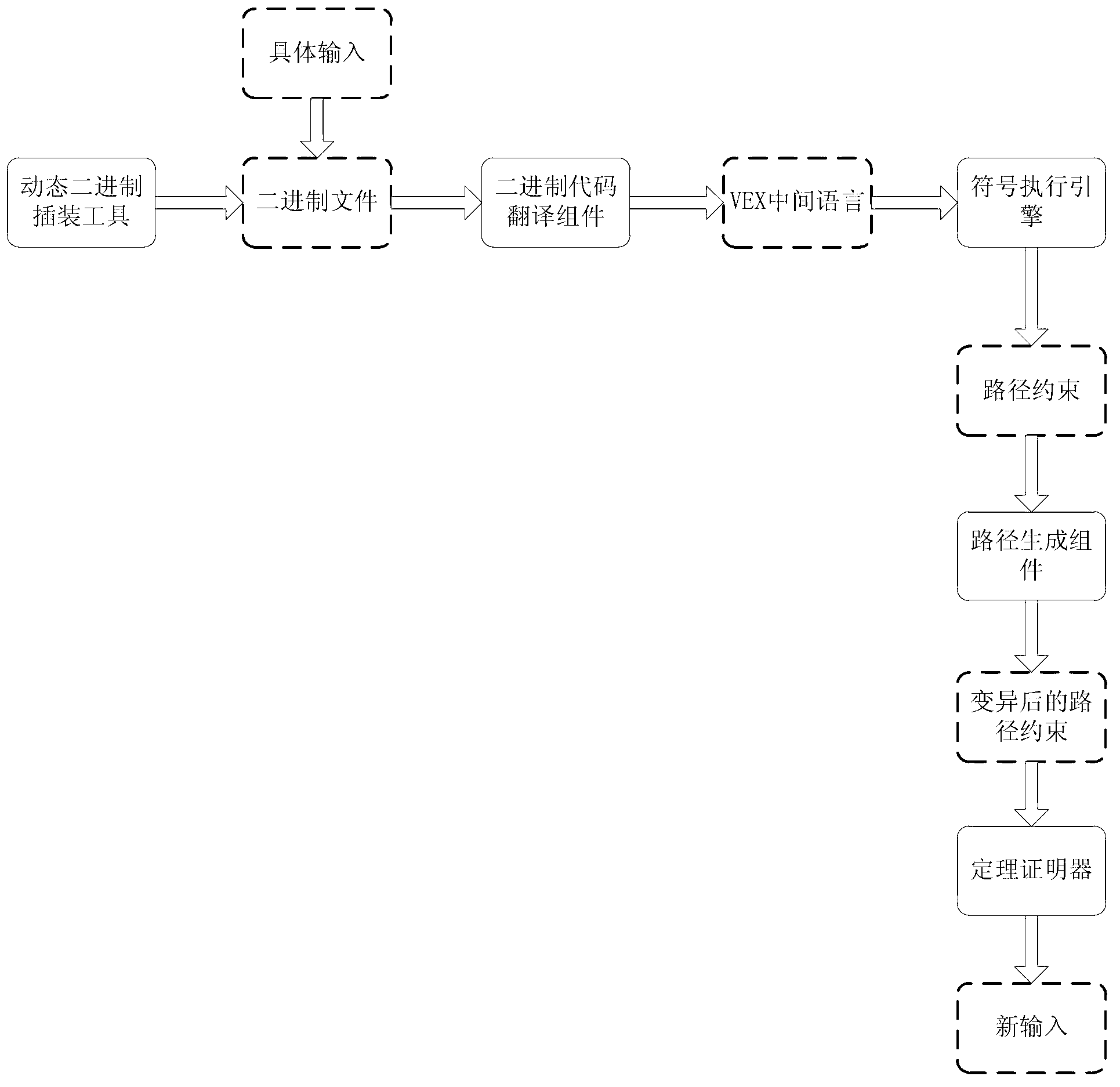

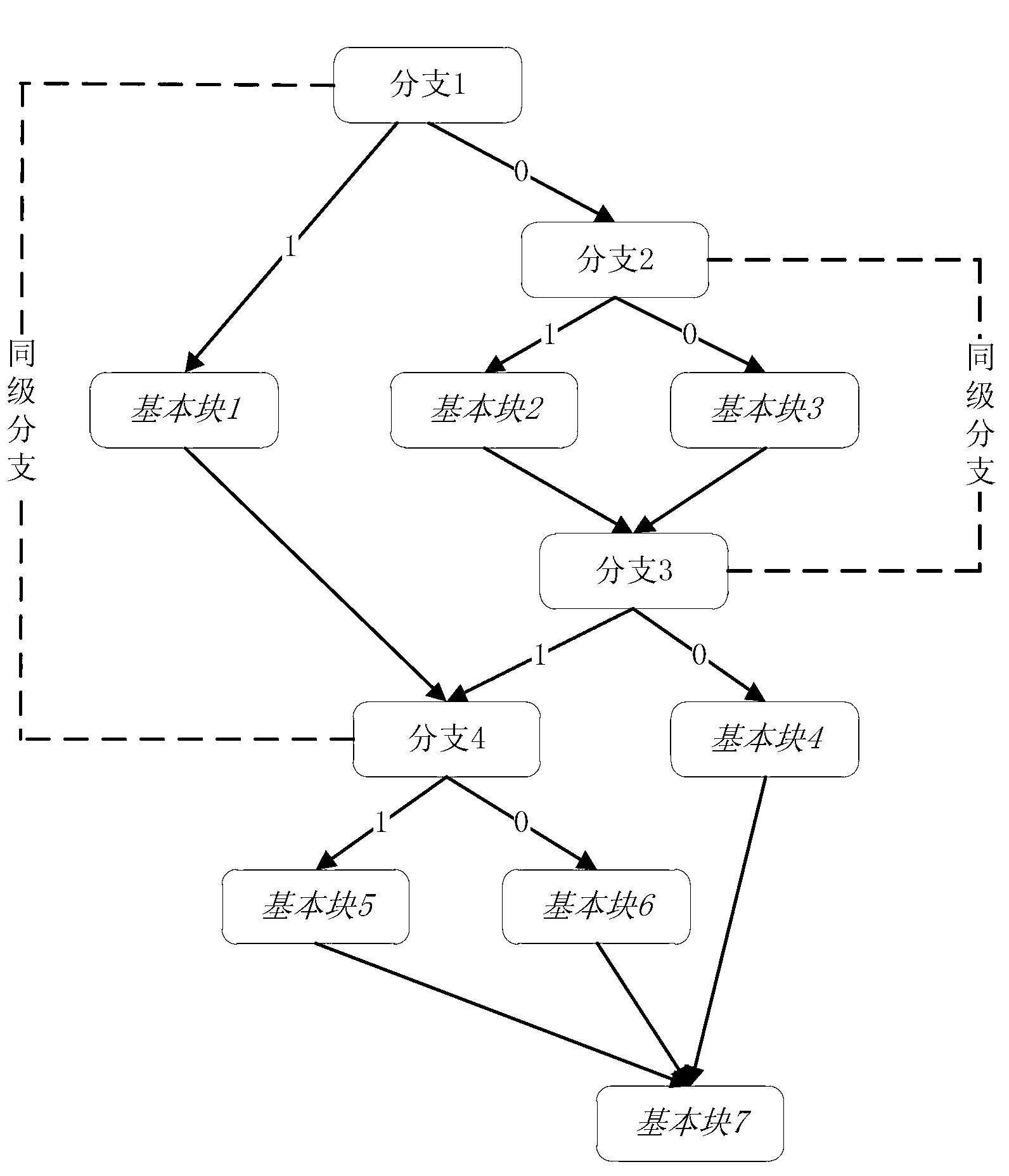

Generation method of dynamic binary code test case

InactiveCN102799529AImprove path coverageSoftware testing/debuggingAlgorithmTheoretical computer science

The invention discloses a generation method of a dynamic binary code test case. The generation method comprises the following steps: a dynamic binary insertion tool is achieved to collect the context information including a register, a memory, a thread, system invoking, base loading and the like in the execution process of the binary code, transmitting such information into a binary code translation assembly, converting the information into an intermediate language, carrying out symbol execution on the intermediate language, disseminating symbol input, and collecting a path constraint depending on the input. And then, inputting the path constraint into a path generation assembly, providing a new in-step branch-path mutation algorithm and a strategy, generating new path constraints as much as possible after each symbol execution, using a theorem prover to solve the new path constraint, obtaining the new input satisfying the path constraint, transmitting the new input to the binary code to carry out specific execution for one time, obtaining new path constraints from the new execution in continuously circular manner, generating new inputs, and improving the cover ratio of the binary code.

Owner:BEIHANG UNIV

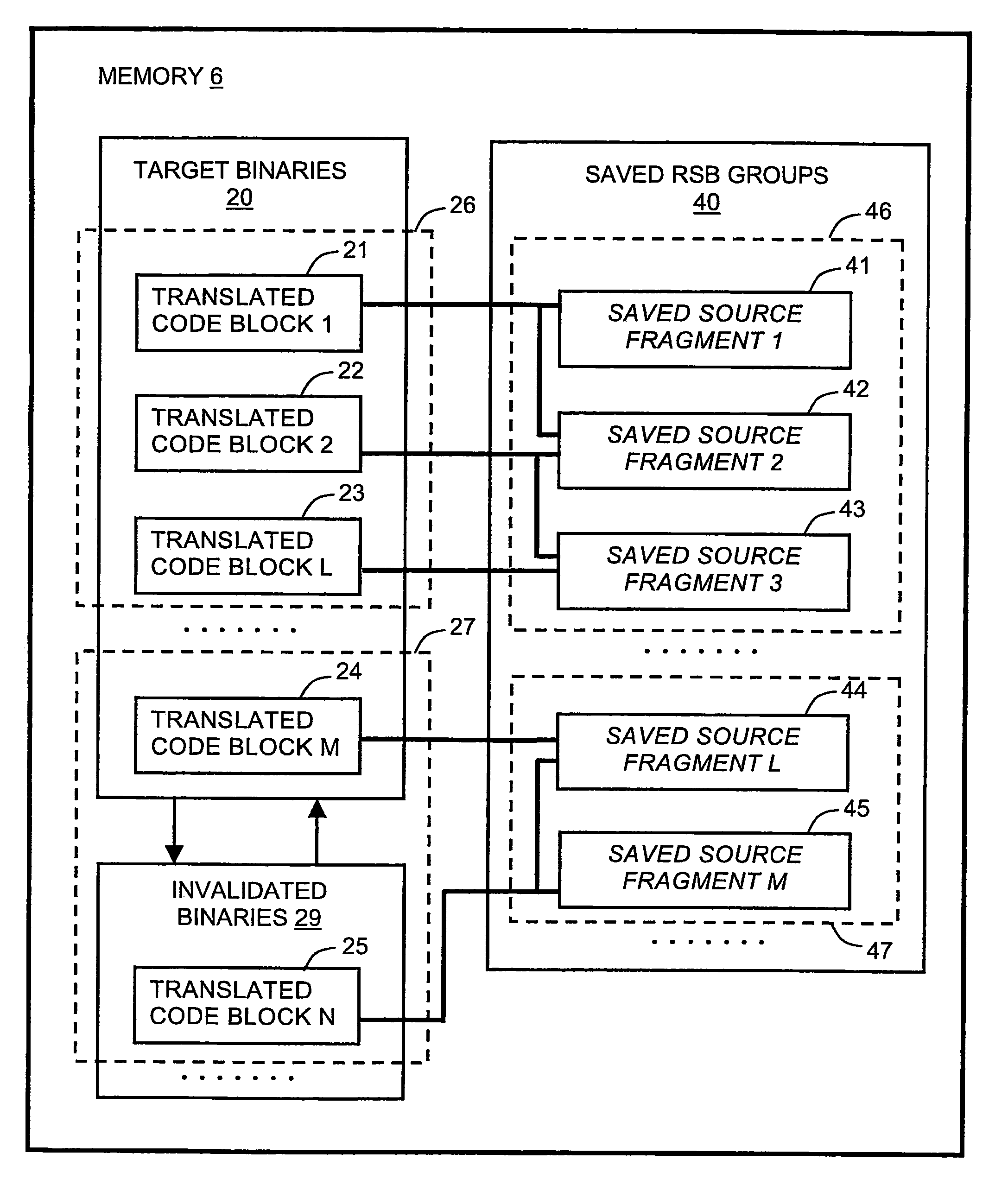

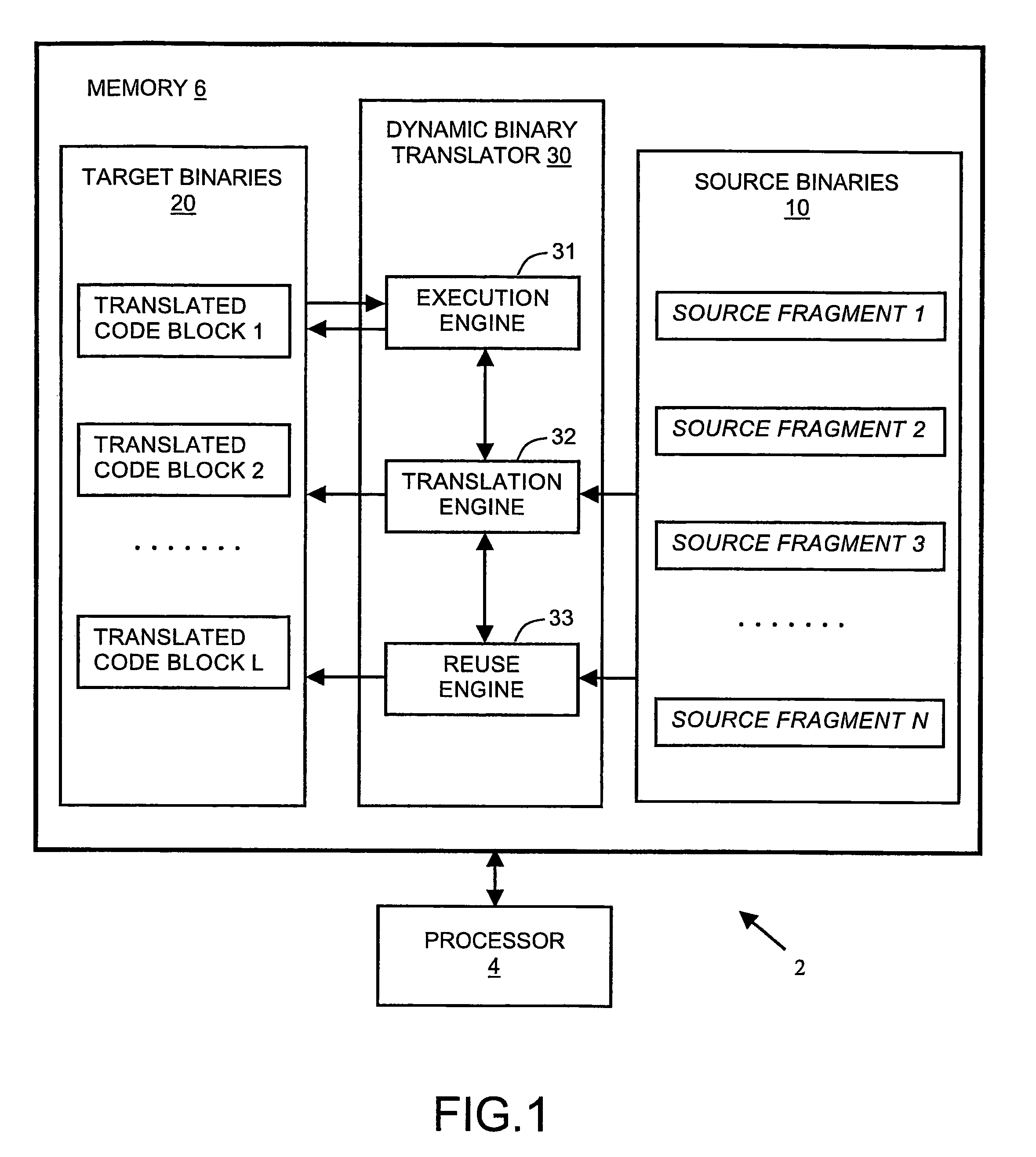

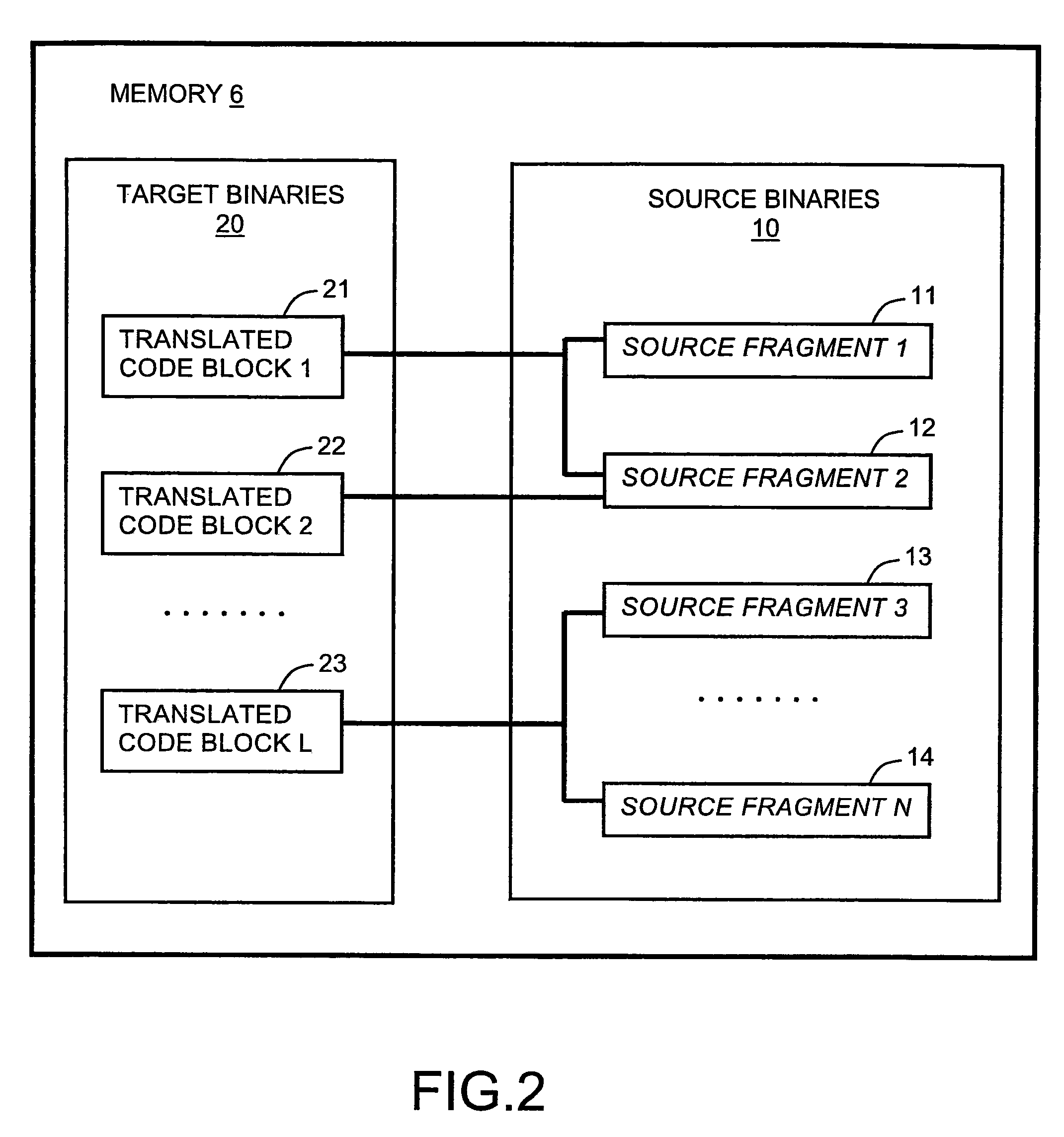

Apparatus, system, and method of dynamic binary translation with translation reuse

InactiveUS7624384B2Specific program execution arrangementsMemory systemsCoding blockCode Translation

Embodiments of the invention disclose a method, apparatus and system of translating a source binary code into a target binary code. The translation according to embodiments of the invention may include determining whether or not a previously translated code block that relates to a source fragment to be currently translated may be reused for execution by a target processor. A reusability status of the previously translated code block may be determined based on a reusability status of a group of previously translated code blocks. In some embodiments, when no previously translated code blocks relating to the currently translated source fragment are found, the source fragment may be translated into a new target code block, which may be executed by the target processor. The new target code block may then be added to a group of previously translated code blocks.

Owner:INTEL CORP

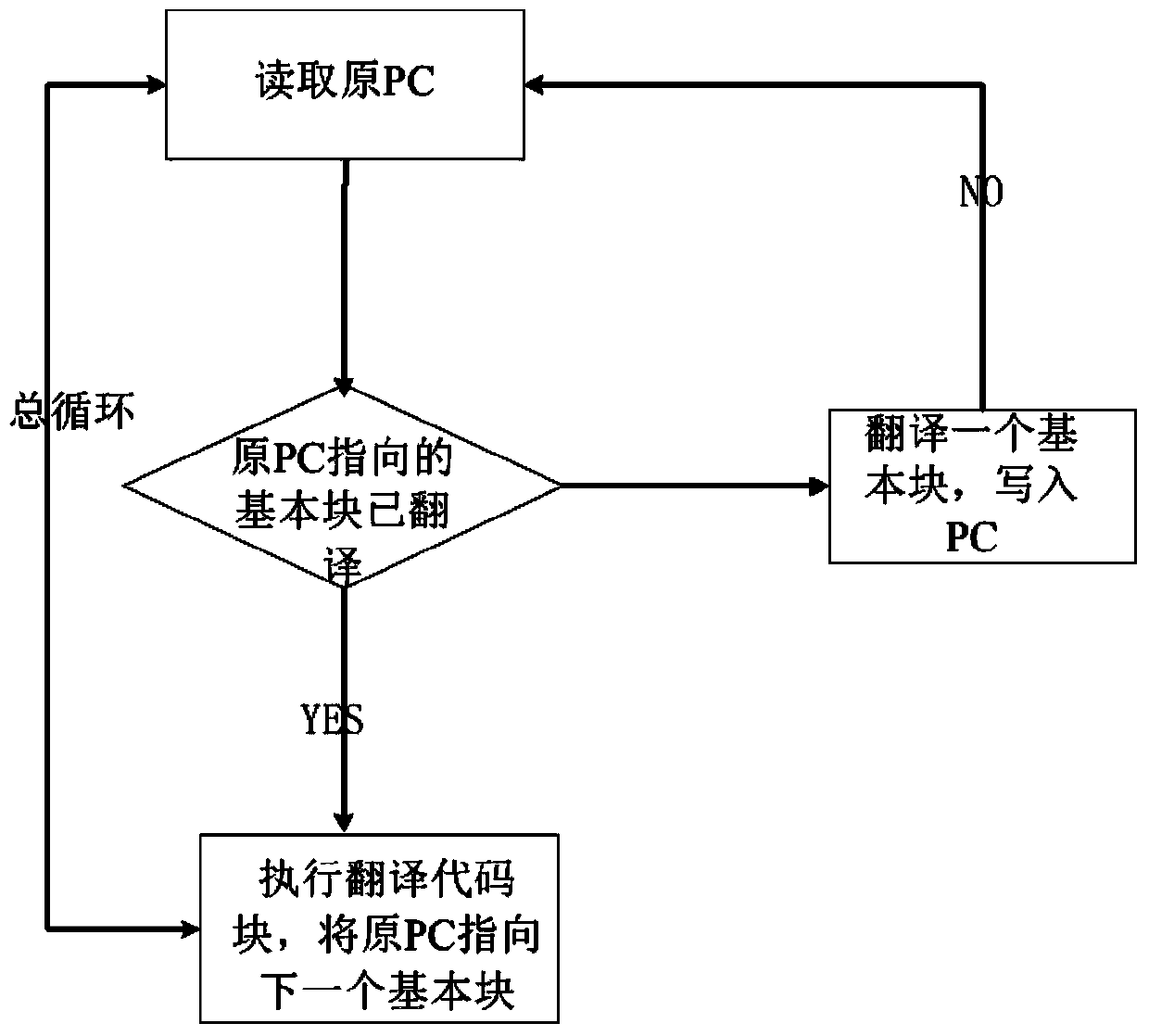

Platform virtualization system

InactiveCN103793260AEase system deploymentRelieve pressureSoftware simulation/interpretation/emulationCode TranslationMemory virtualization

The invention relates to a platform virtualization system comprising a CPU simulator, a memory virtualization module, and an external virtualization module. The CPU simulator reads an X86 architecture code instruction and judges whether an instruction basic block is translated or not; a binary translator is used for translation and comprises a translation engine and an execution engine; the translation engine translates an X86 architecture code into a Loongson platform code; the execution engine prepares the operational context of the Loongson platform code, locates the Loongson platform code corresponding to the X86 architecture code from a Loongson platform code cache and executes the code. The memory virtualization module uses a shadow page-table method. The external virtualization module establishes a corresponding device model for each external device. An X86 architecture virtual machine interacts with the external devices through the device models, thereby discovering and accessing the devices. The platform virtualization system allows information systems not matching with the domestic Loongson hardware platform yet to run in the domestic software-hardware environments in a virtualized manner, and contributions are made for the smooth transition between new and old technical systems in the automatic upgrading process of the information systems.

Owner:INST OF CHINA ELECTRONICS SYST ENG CO +1

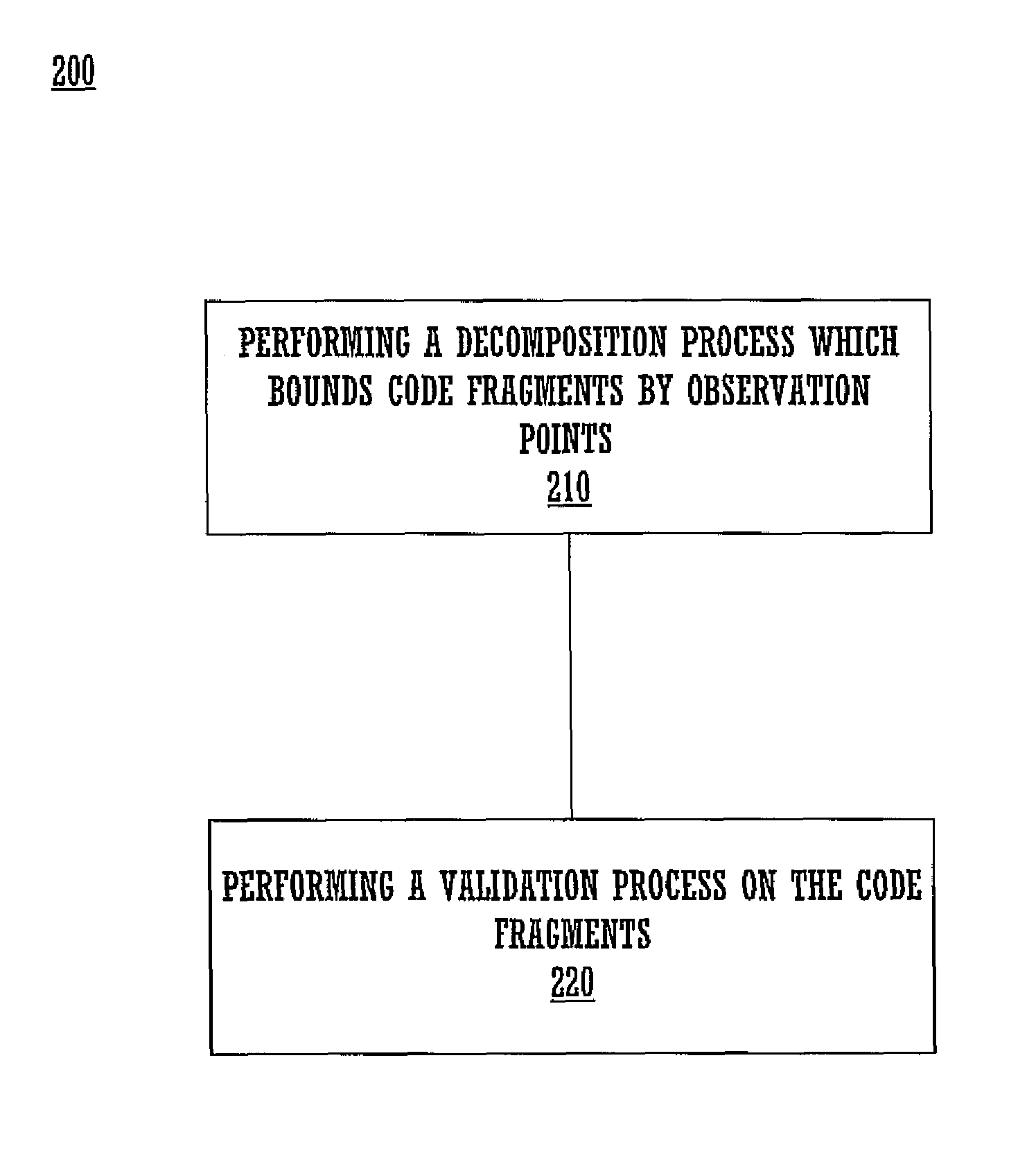

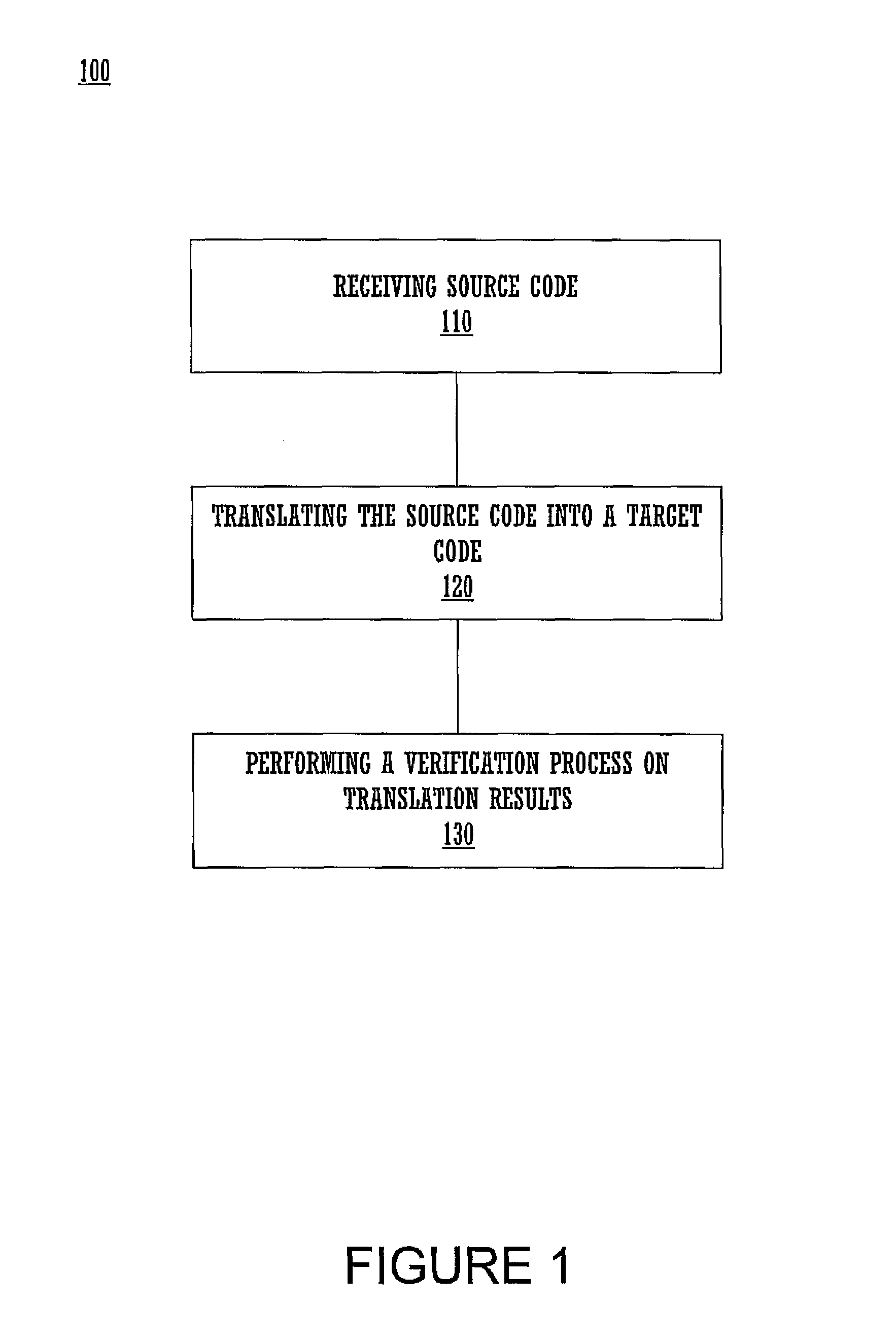

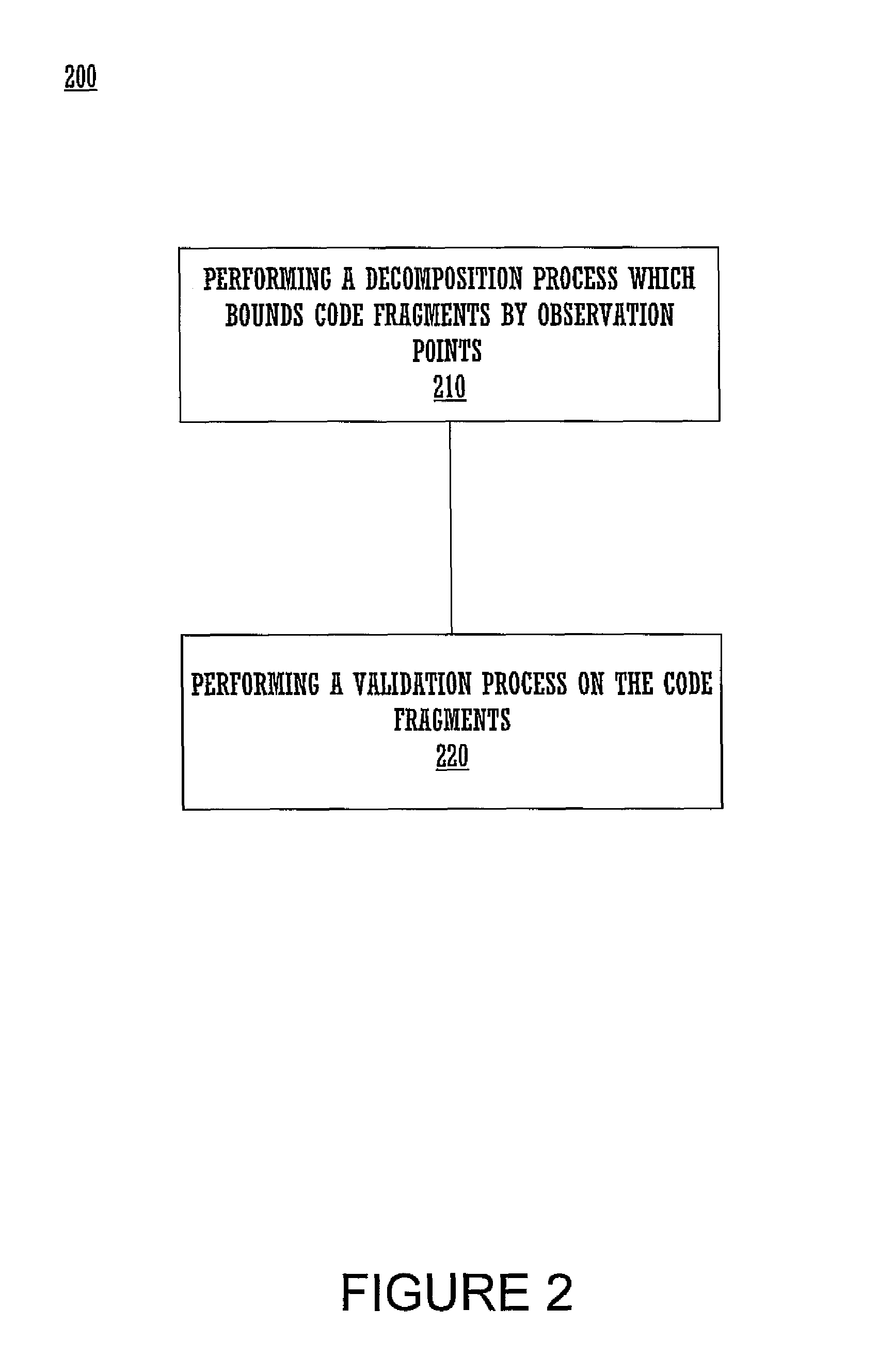

Code translation verification

The present invention translation verification system and method verifies code fragment translations and / or optimizations that are bounded by externally observable information.

Owner:INTELLECTUAL VENTURE FUNDING LLC

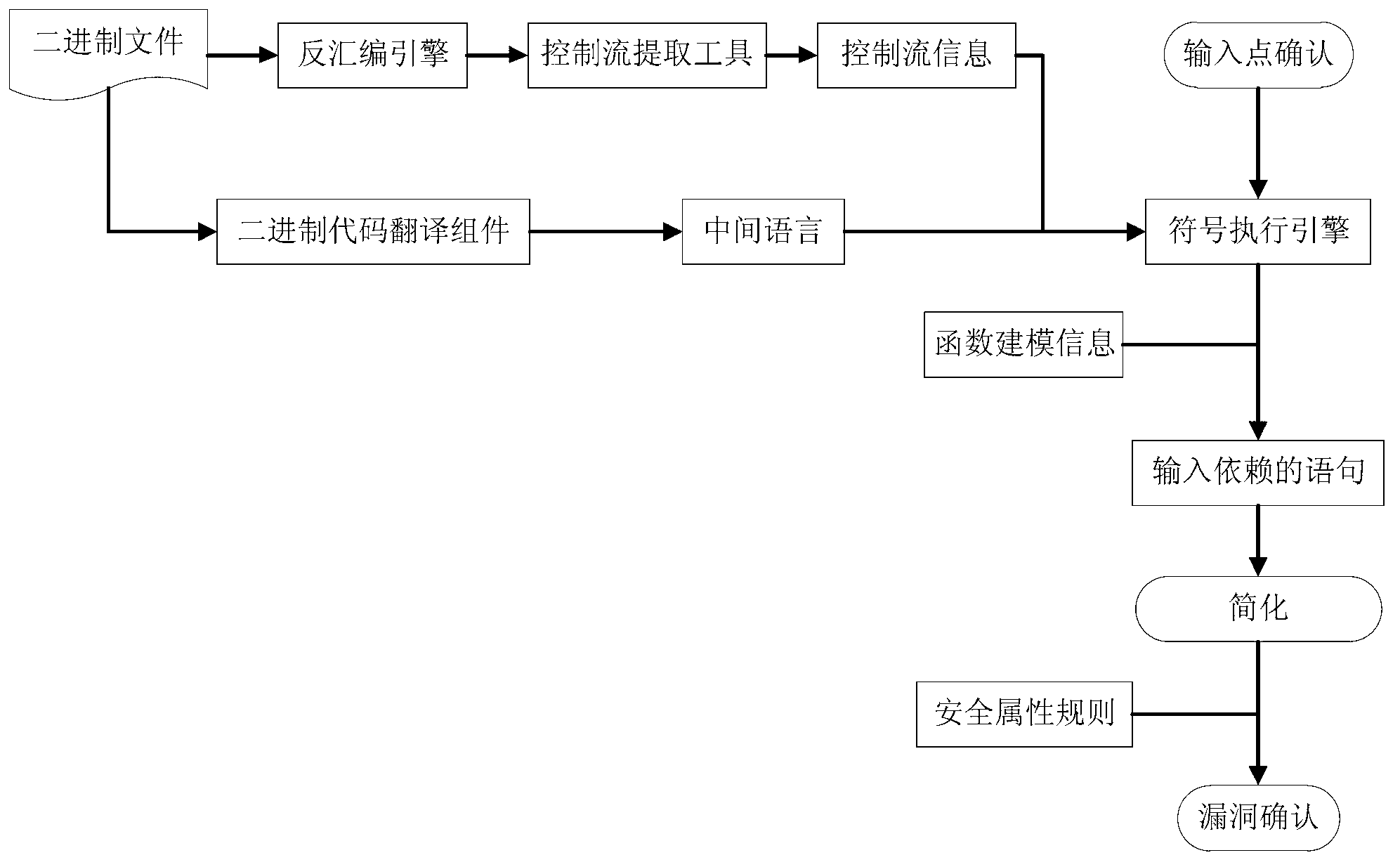

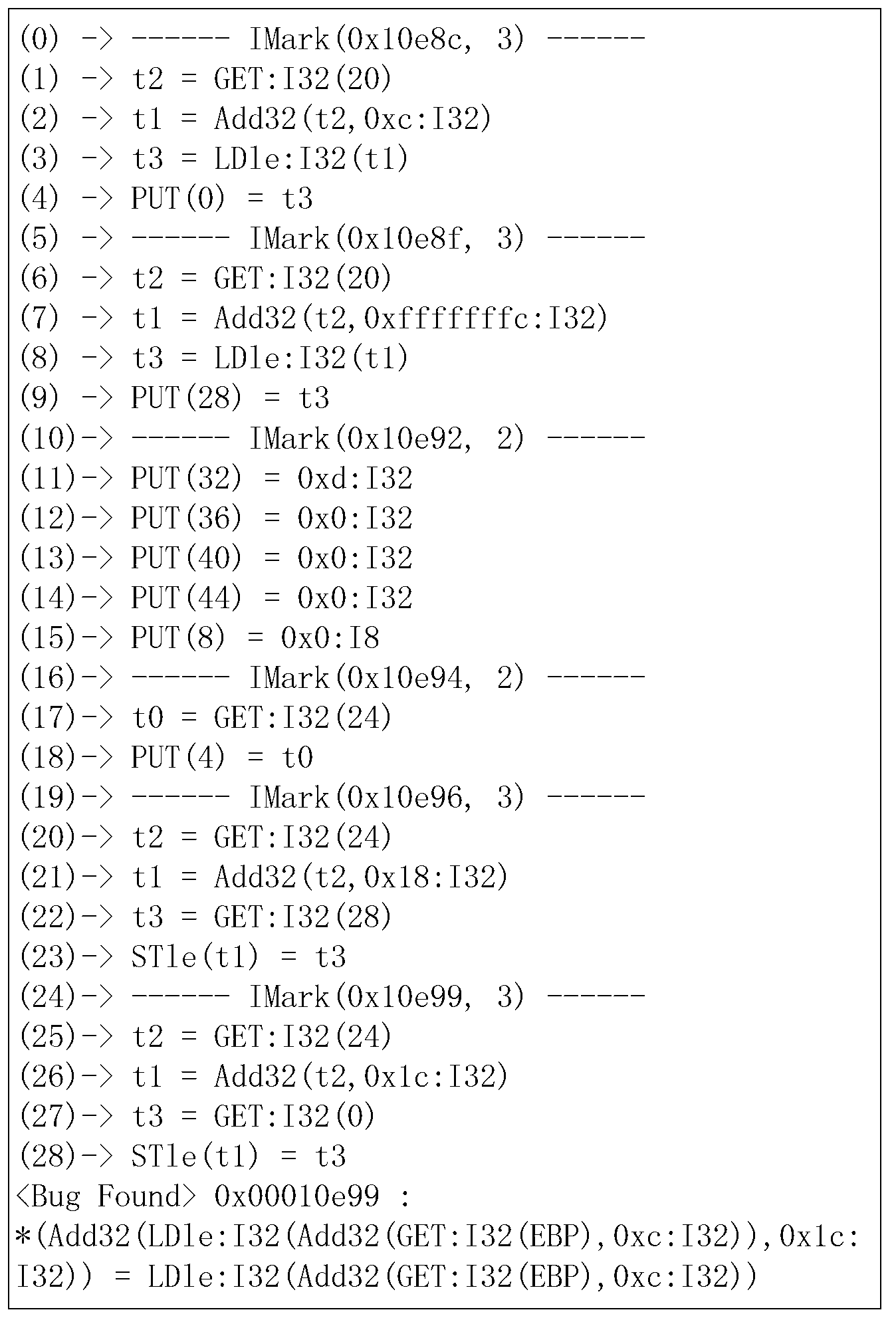

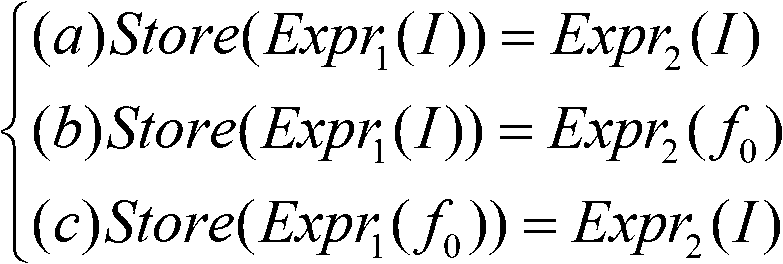

Method for binary code vulnerability discovery on basis of simple symbolic execution

The invention discloses a method for binary code vulnerability discovery on the basis of simple symbolic execution. The method comprises five steps that: firstly, binary codes are translated into an intermediate language with a static single assignment through a binary code translation component; and then, a disassembling engine is used to disassemble the binary codes, the control flow information of the binary codes is extracted, static symbolic execution is carried out in the intermediate language on the basis of the control flow information, an entrance point needs to be determined during the symbolic execution process, an input vector is converted into a symbol, and a called function is modeled. After the symbolic execution process is completed, the statement assembly of the intermediate language which depends on the input vector can be obtained, the statements of an assembly are simplified, and a vulnerability discovery confirmation report is generated after security attribute rules are used to confirm.

Owner:BEIHANG UNIV

Apparatus and method for accurate barcode scanning using dynamic timing feedback

An apparatus and method are described for accurately reading barcodes. For example, one embodiment of an apparatus comprises: a sensor to detect transitions between bars on a barcode having bars with N different widths as the barcode passes by the sensor; a timer to associate a time value with each of the transitions; a delta calculation module to determine a current delta value for a current bar; a bar identification module to compare the current delta value with N delta values stored in a memory, each of the N delta values associated with a different one of N different bar widths, the bar identification module to identify the current bar as being one of the N widths based on a difference between the current delta value and each of the N delta values, the bar identification module to update the memory to include the current delta value as a representative value for the one of the N widths which the current bar is determined to be; and a code translation module to receive a sequence of detected bar widths from the bar identification module and responsively translate the sequence of detected bars into a code.

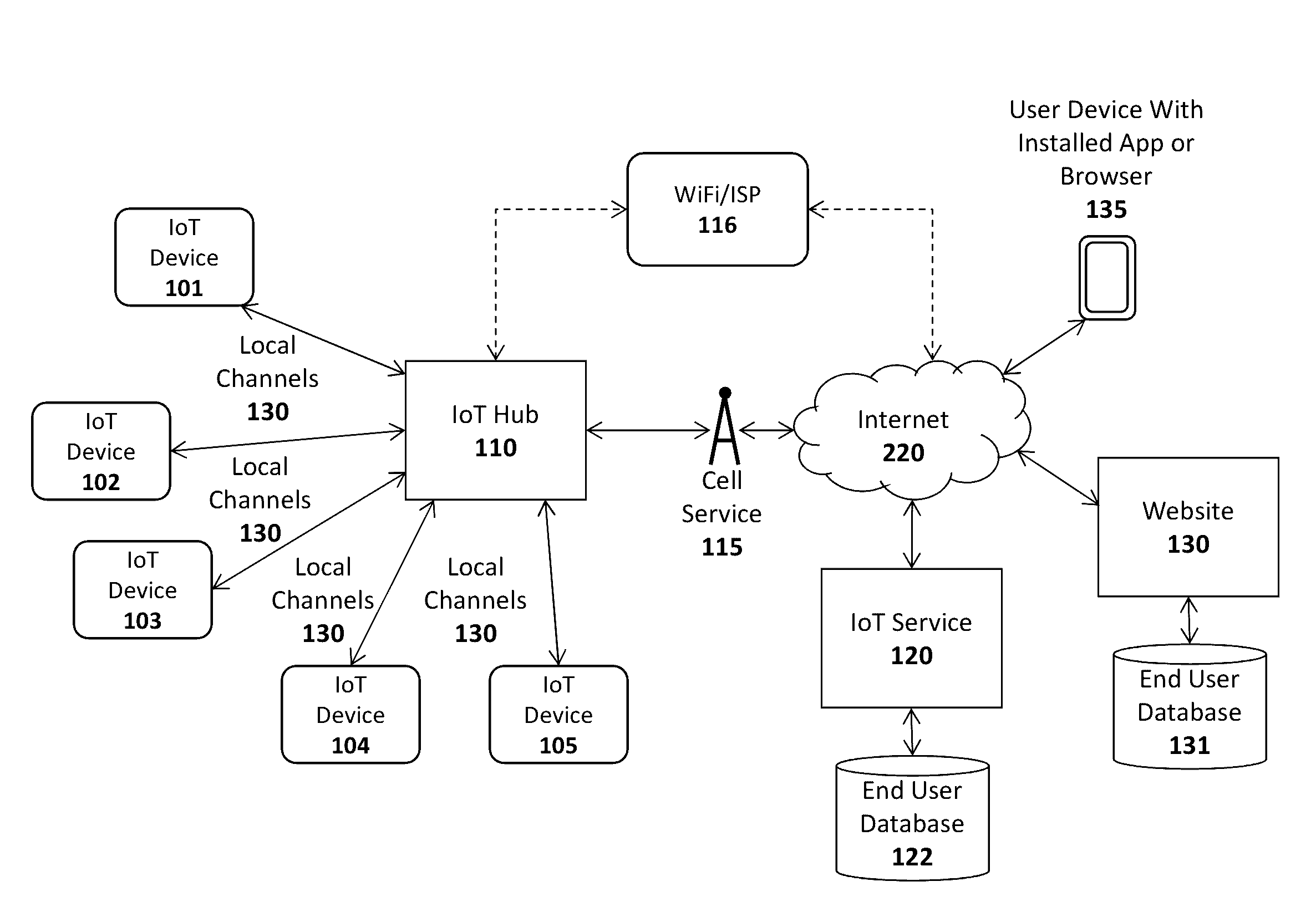

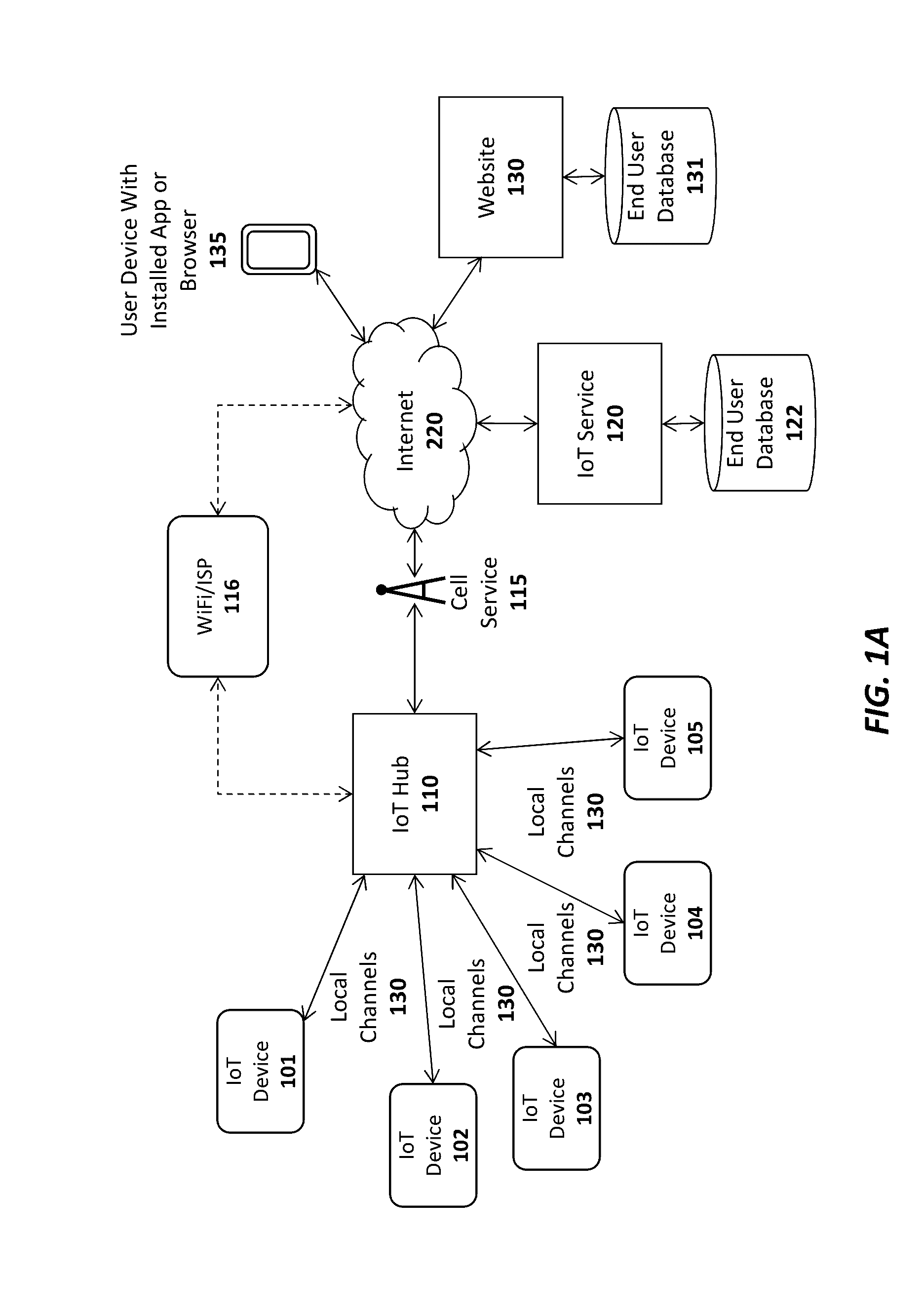

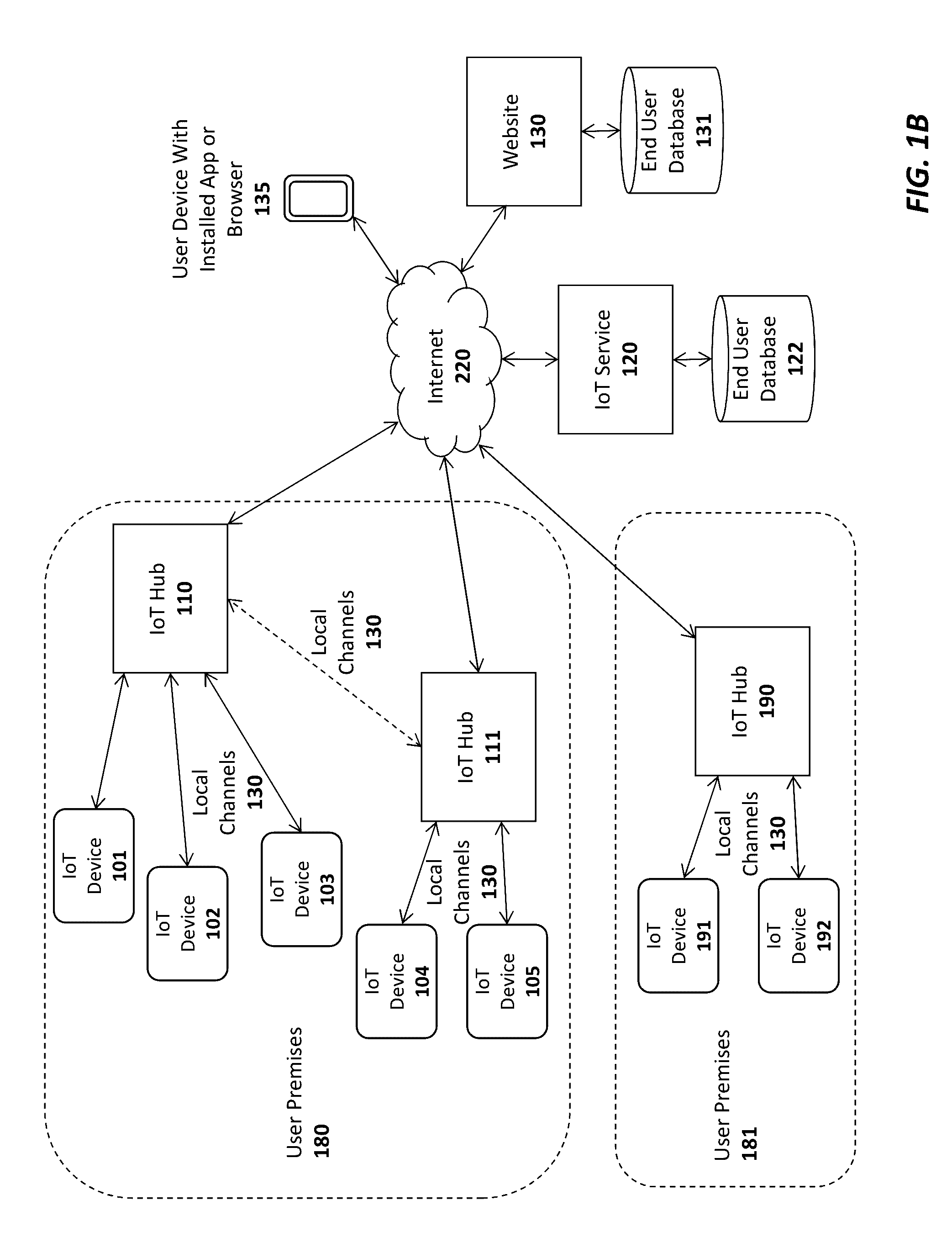

Owner:AFERO

Simulator and simulating method for running guest program in host

ActiveUS8397050B2Improve executionMemory adressing/allocation/relocationComputer security arrangementsCode TranslationPage table

A Simulator and a simulating method for running a guest program in a host are disclosed. The simulator includes: an initialization device configured for setting content of a hypervisor page table in the host, the hypervisor page table mapping a guest physical address space to a host physical address space. The simulator further includes a binary translation device configured for employing a program logical address to perform a memory access in code translation. The simulator also includes a miss handling device configured for updating a guest translation look-aside buffer by treating a miss in a host translation look-aside buffer caused by the execution of the translated code as a miss in the guest translation look-aside buffer, wherein the host translation look-aside buffer is configured to buffer entries for mapping addresses in a guest program logical address space to addresses in the guest physical address space. The simulator further includes an update tracing device configured for, in response to the update to the guest translation look-aside buffer, perform the update to the host translation look-aside buffer. Also disclosed is a method for running a guest program in a host.

Owner:INT BUSINESS MASCH CORP

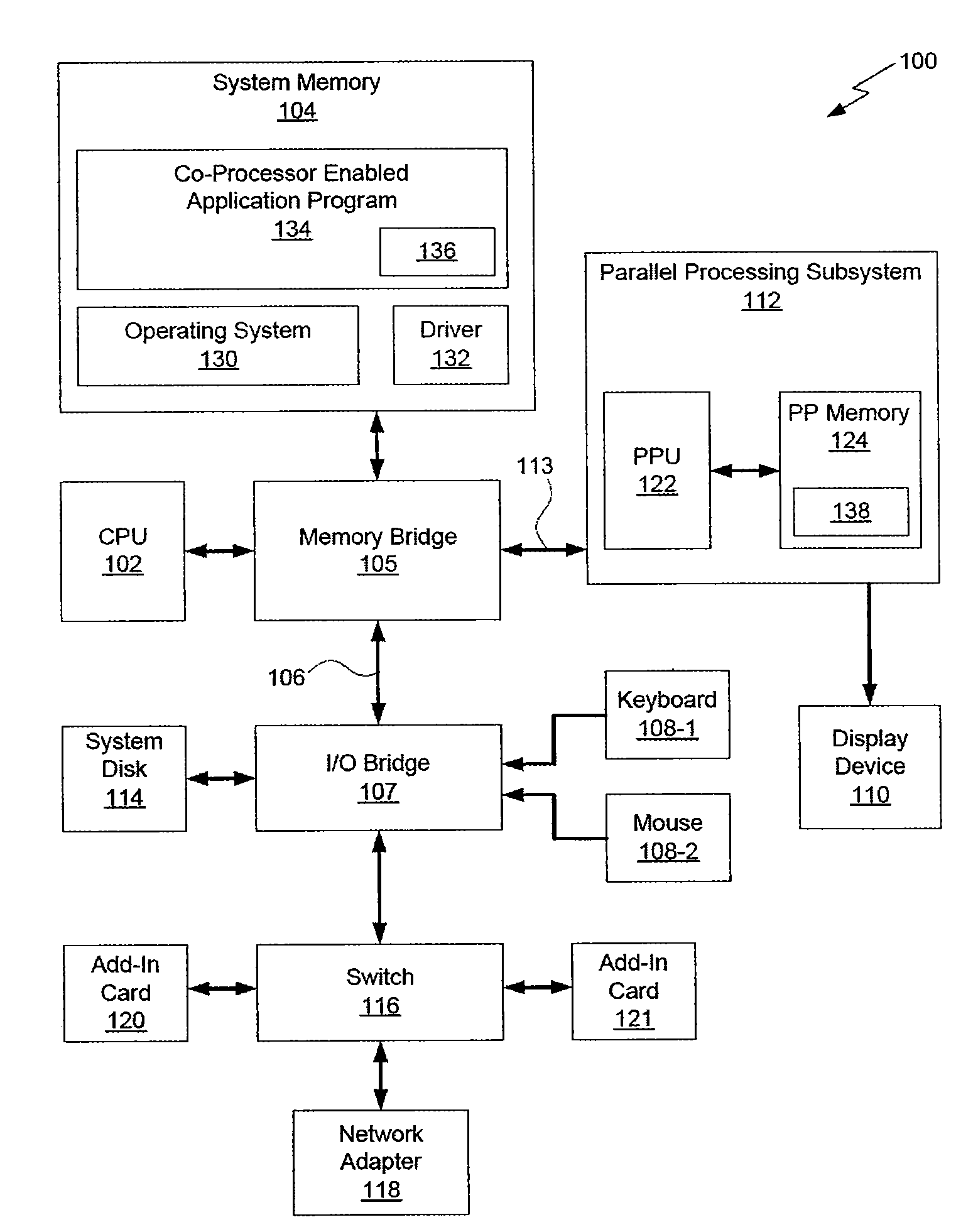

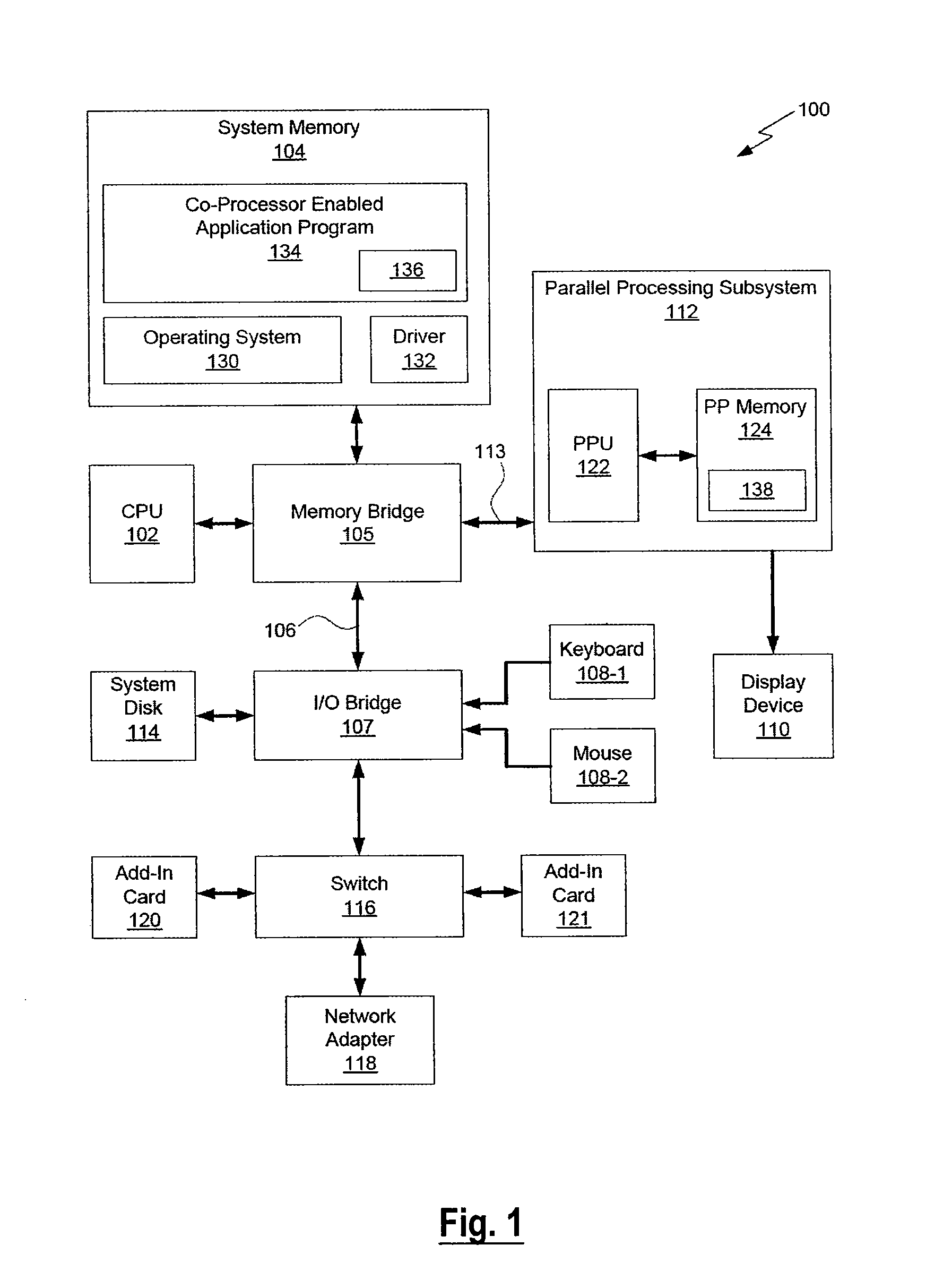

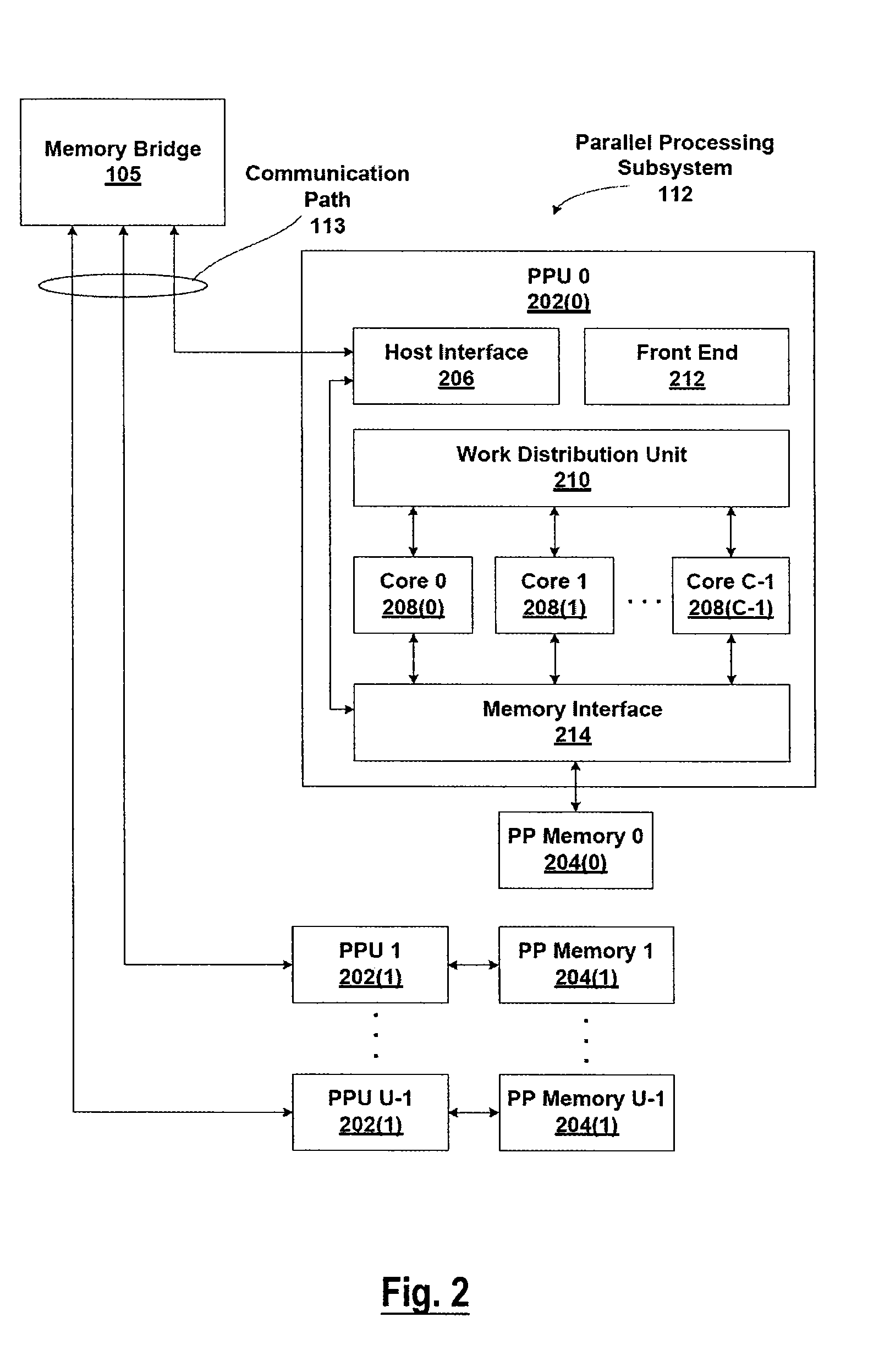

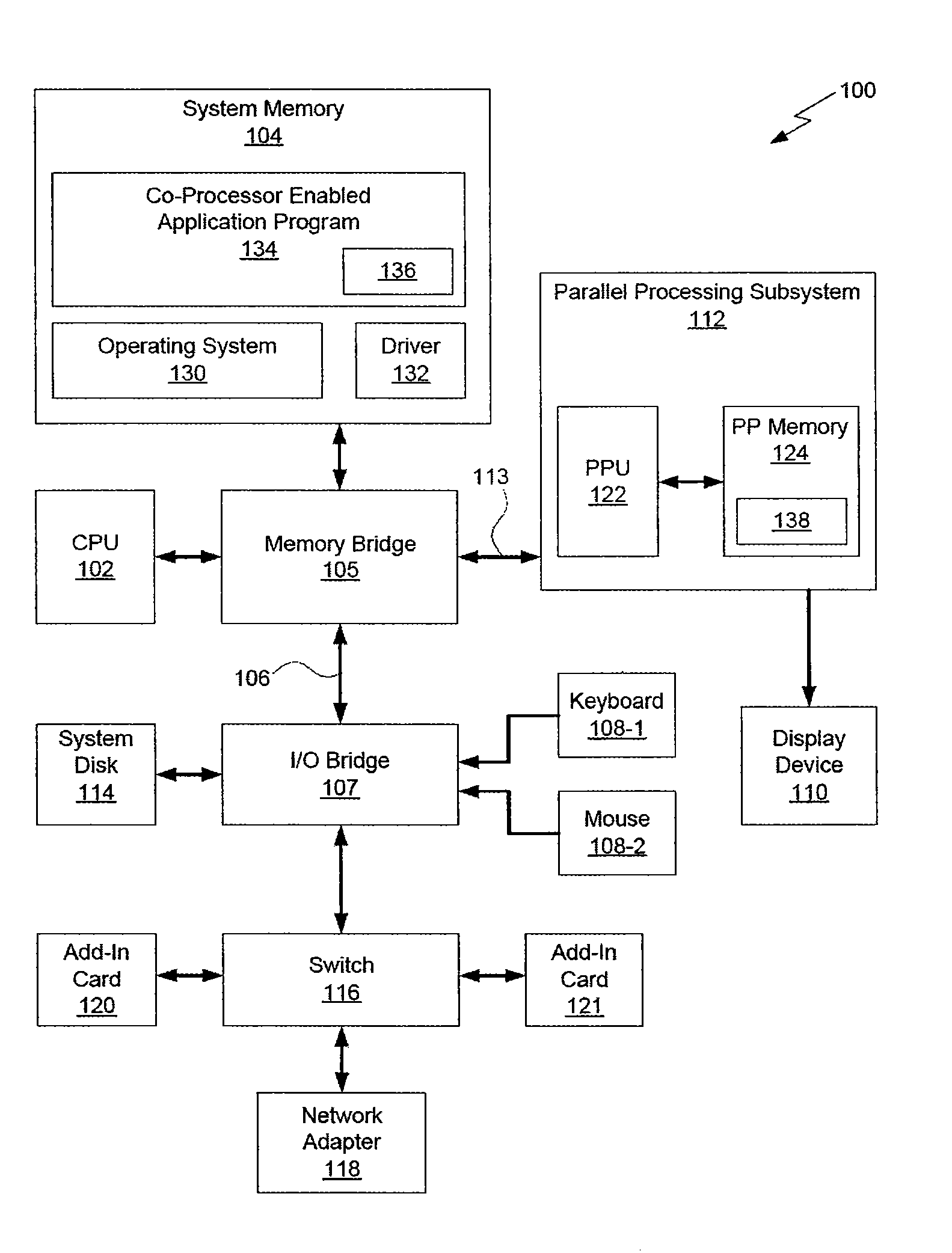

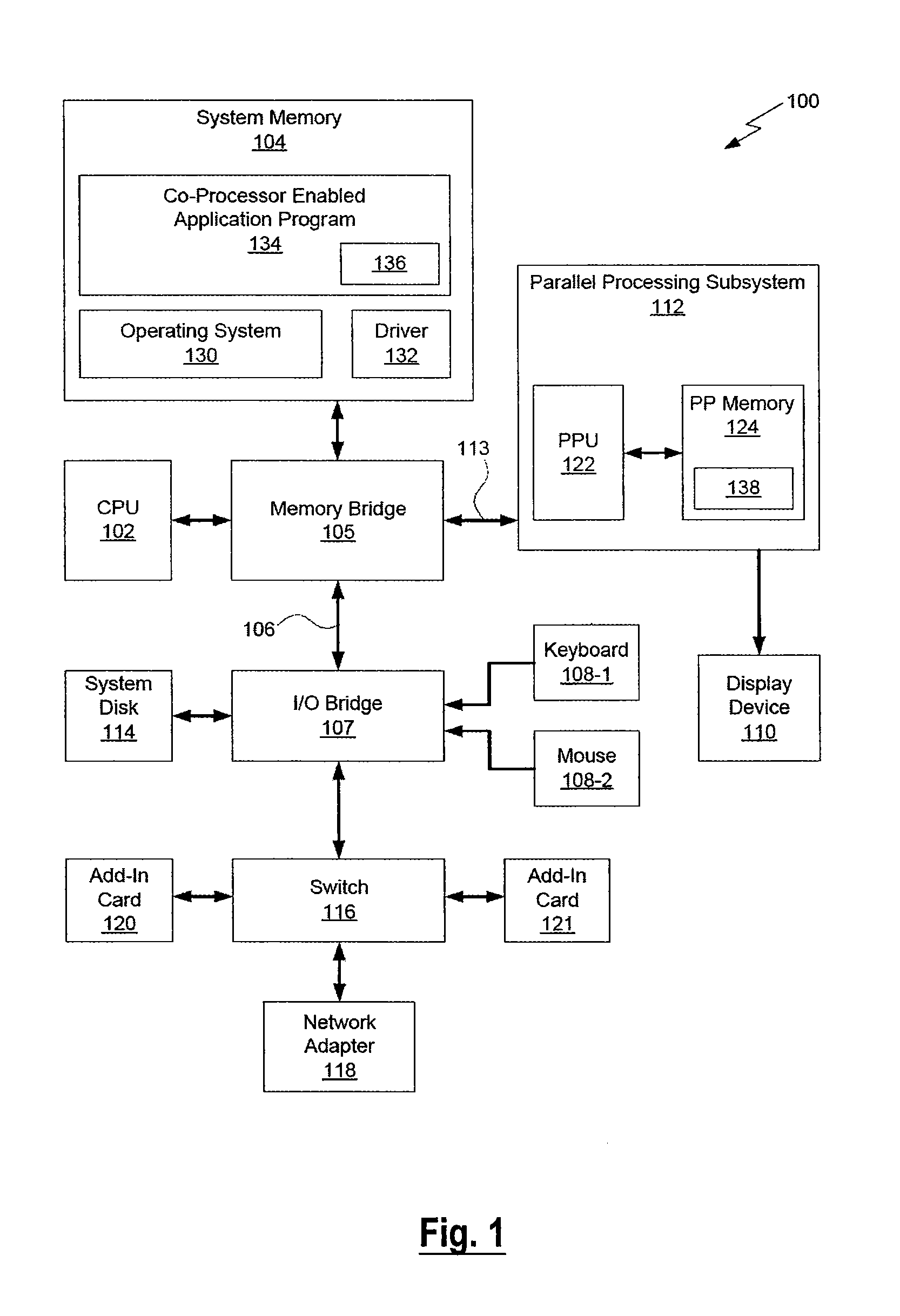

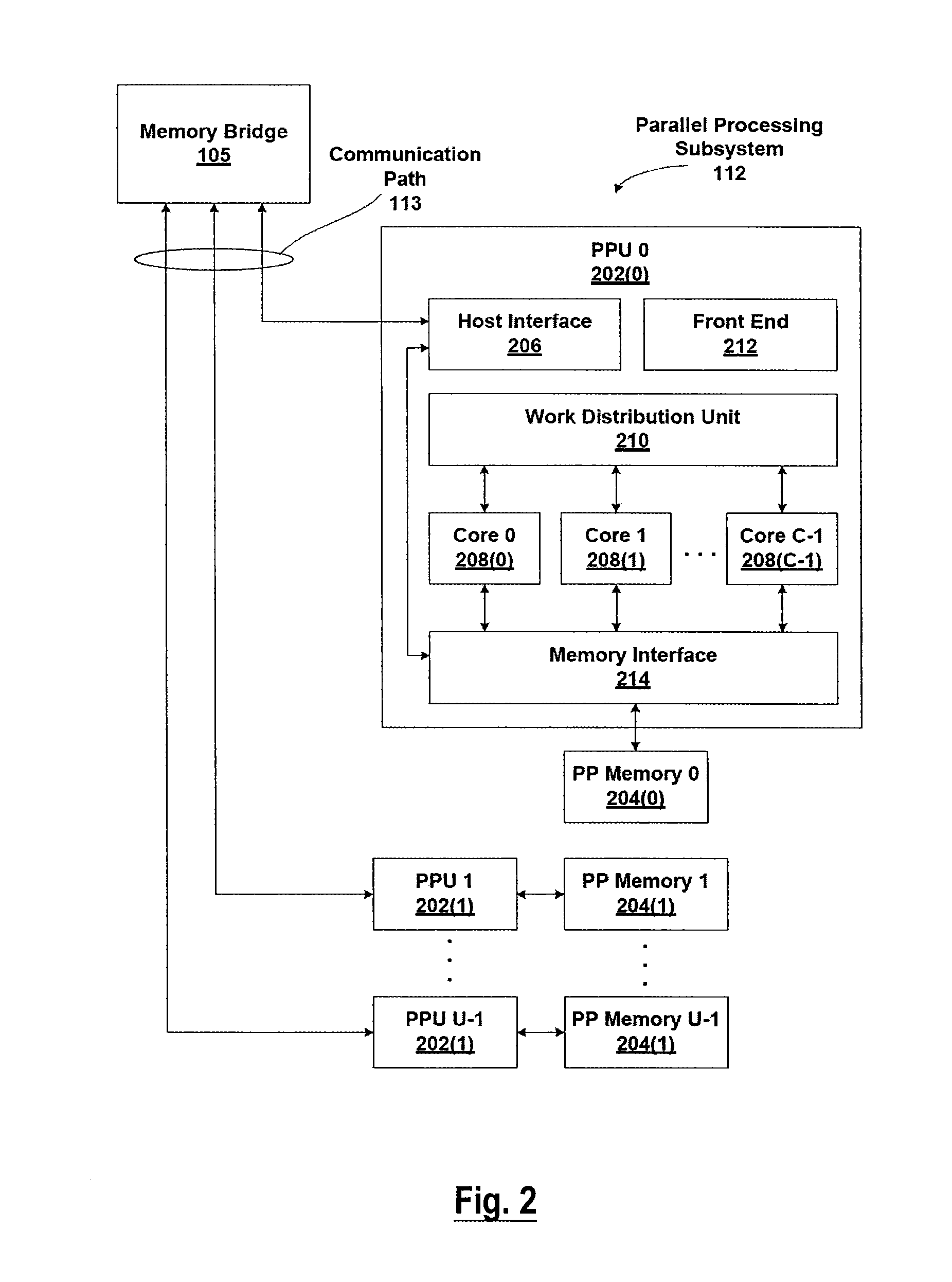

Method And System For Enabling Managed Code-Based Application Program To Access Graphics Processing Unit

ActiveUS20100149193A1Enhanced CUDA parallel processing environmentImprove the processing environmentProcessor architectures/configurationProgram controlInstruction codeCode Translation

One embodiment of the present invention sets forth a method for enabling an intermediate code-based application program to access a target graphics processing unit (GPU) in a parallel processing environment. The method includes the steps of compiling a source code of the intermediate code-based application program to an intermediate code, translating the intermediate code to a PTX instruction code, and translating the PTX instruction code to a machine code executable by the target graphics processing unit before delivering the machine code to the target GPU.

Owner:NVIDIA CORP

Method And System For Enabling Managed Code-Based Application Program To Access Graphics Processing Unit

ActiveUS20100149194A1Enhanced CUDA parallel processing environmentImprove the processing environmentImage data processing detailsArchitecture with multiple processing unitsGraphicsCode Translation

One embodiment of the present invention sets forth a method for enabling an intermediate code-based application program to access a target graphics processing unit (GPU) in a parallel processing environment. The method includes the steps of compiling a source code of the intermediate code-based application program to an intermediate code, translating the intermediate code to a PTX instruction code, and translating the PTX instruction code to a machine code executable by the target graphics processing unit before delivering the machine code to the target GPU.

Owner:NVIDIA CORP

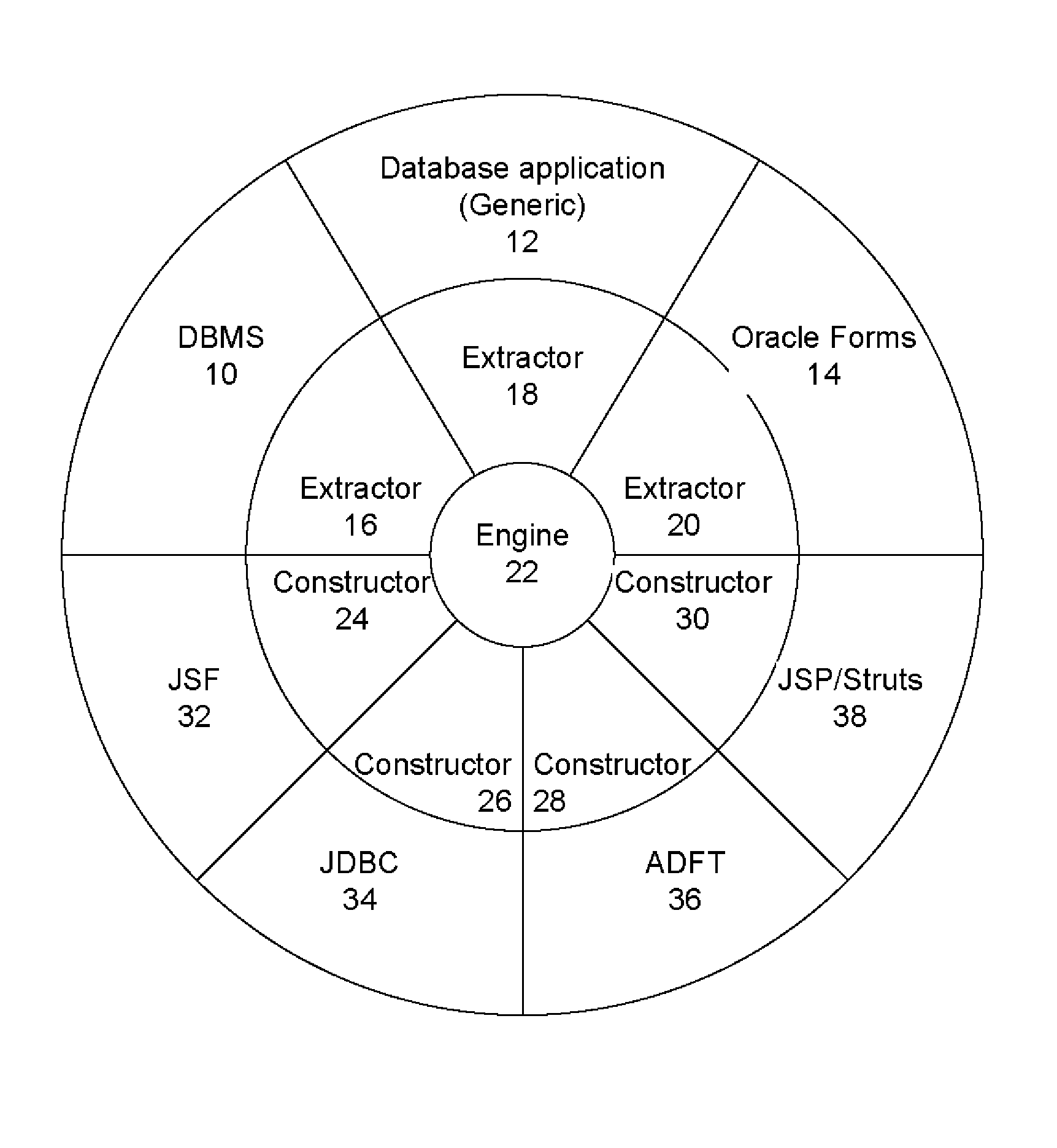

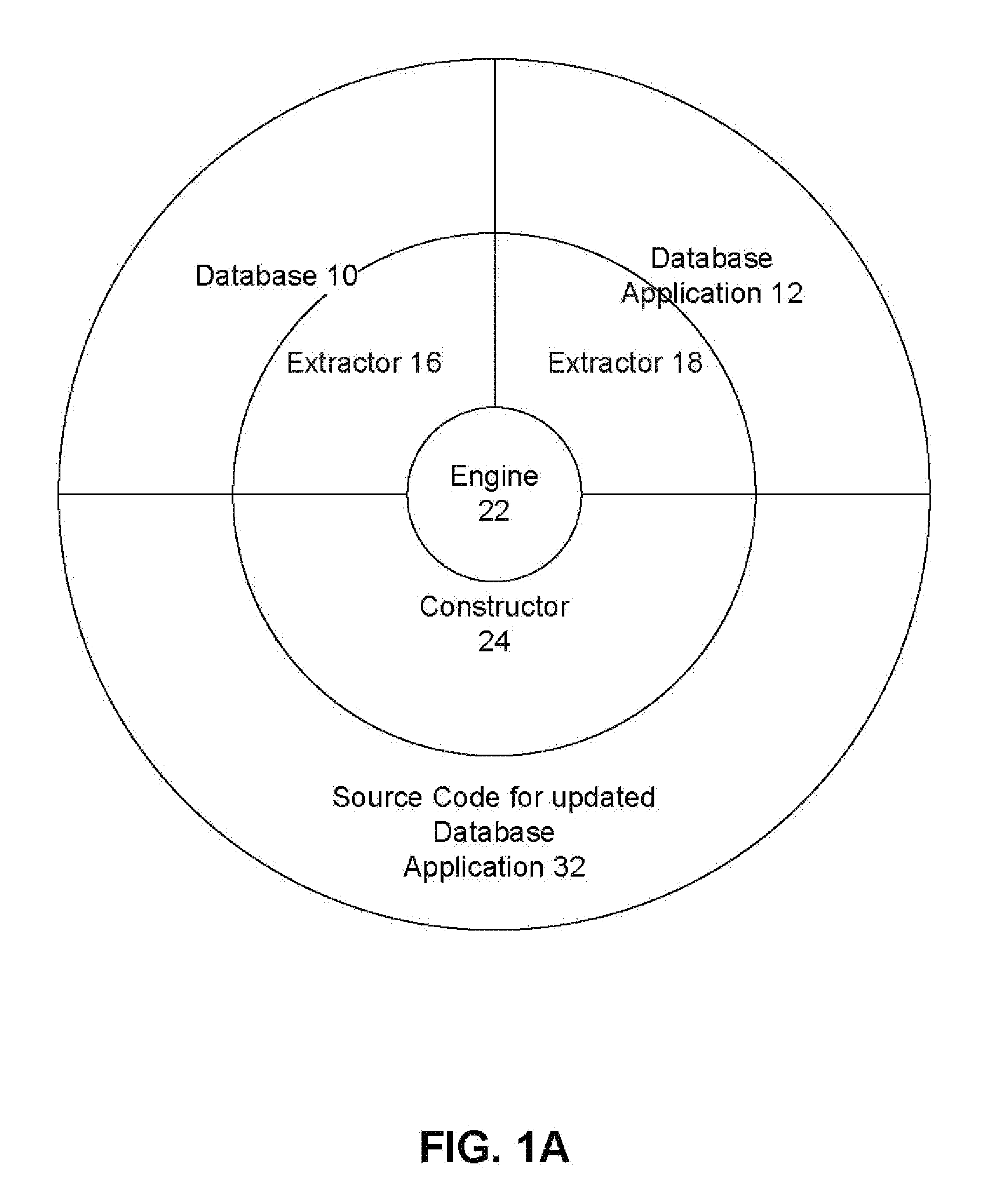

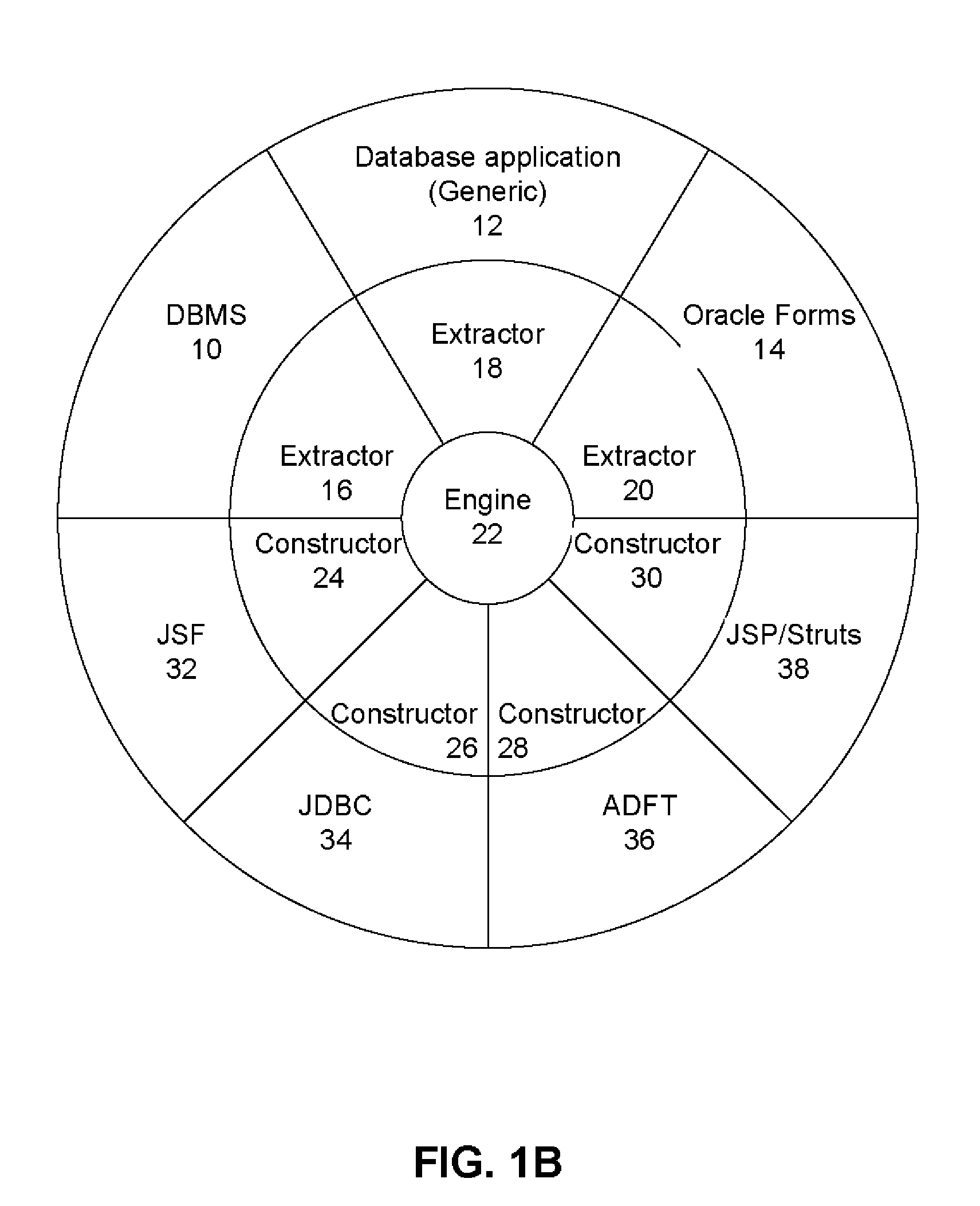

Facilitating database application code translation from a first application language to a second application language

InactiveUS20120124550A1Program code adaptionSpecific program execution arrangementsCode TranslationDatabase application

A method of facilitating code translation from one a first application language to a second application language is provided. This method involves reading information describing the database to a code generation engine and reading database applications associated with the first application language to the code generation engine. The code generation engine may use extractors to generate a database Meta model associated with the first application language and a source database application Meta model associated with the source database application. The code generation engine may then generate second database application code using a code generation engine that applies constructors to the source database application Meta model.

Owner:NOCERA ROBERT +1

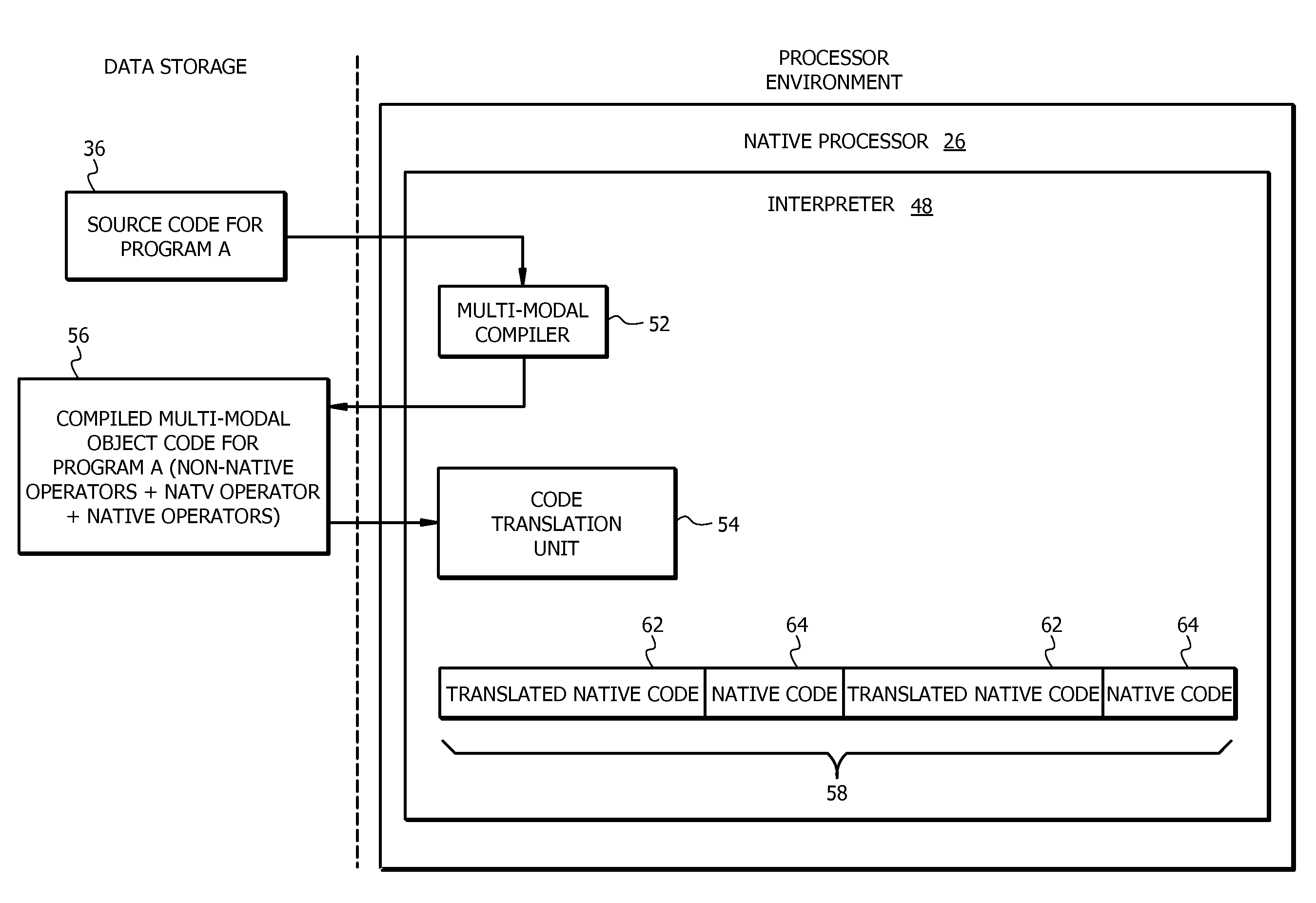

Multi-modal compiling apparatus and method for generating a hybrid codefile

InactiveUS20120143589A1Significant speed improvementImprove performanceSoftware simulation/interpretation/emulationMemory systemsCode TranslationObject code

A non-native, multi-modal compiler and an emulated computing environment for use in a native computing environment. The multi-modal compiler includes a parser configured to parse or divide received source code into a plurality of token elements, whereby at least one statement is recognized from a collection of token elements. The multi-modal compiler also includes a code emitter configured to emit machine code to implement the at least one statement, whereby the emitted machine code is compiled multi-modal object code that includes non-native operators (e.g., E-Mode operators) and NATV operators. The compiled multi-modal object code is configured in such a way that when translated by a code translation unit, the compiled multi-modal object code generates a merged codefile having translated native code segments corresponding to the non-native operators and native code segments corresponding to the NATV operators. The merged codefile is executable by a native processor in the native computing environment.

Owner:UNISYS CORP

Task scheduling method for wireless sensor network node

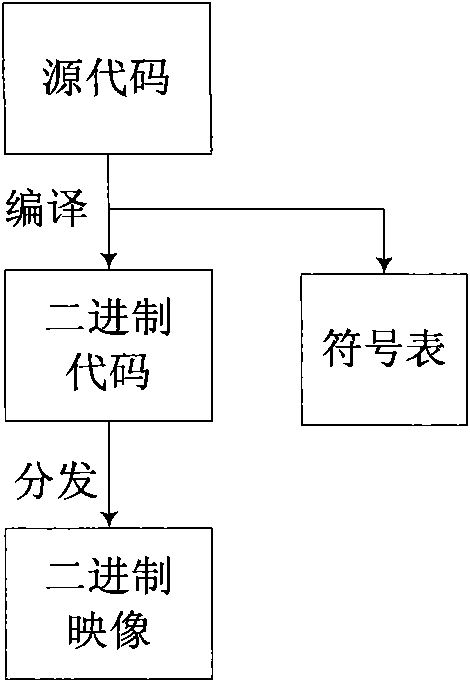

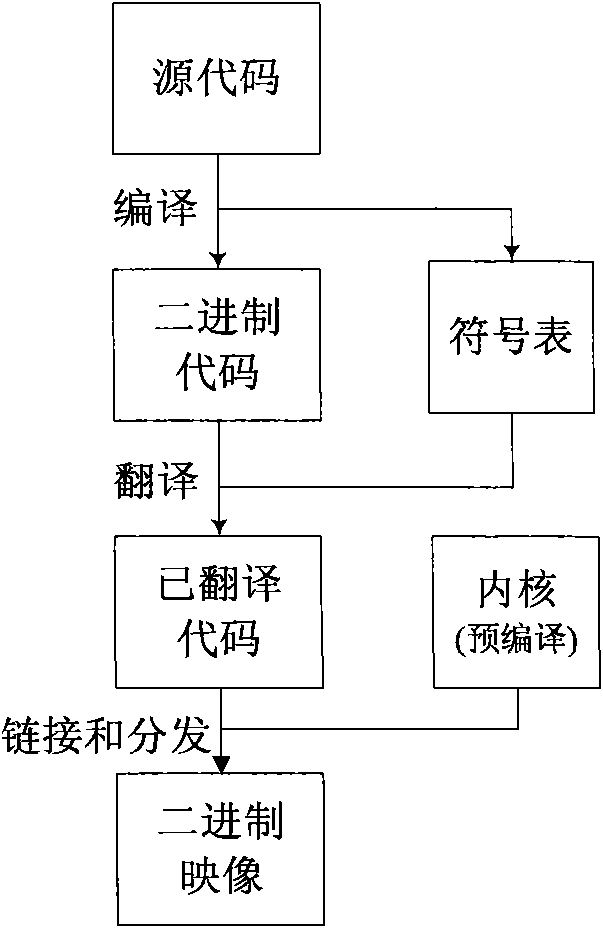

InactiveCN101848549AEfficient translationSmall timeNetwork topologiesCode TranslationOperational system

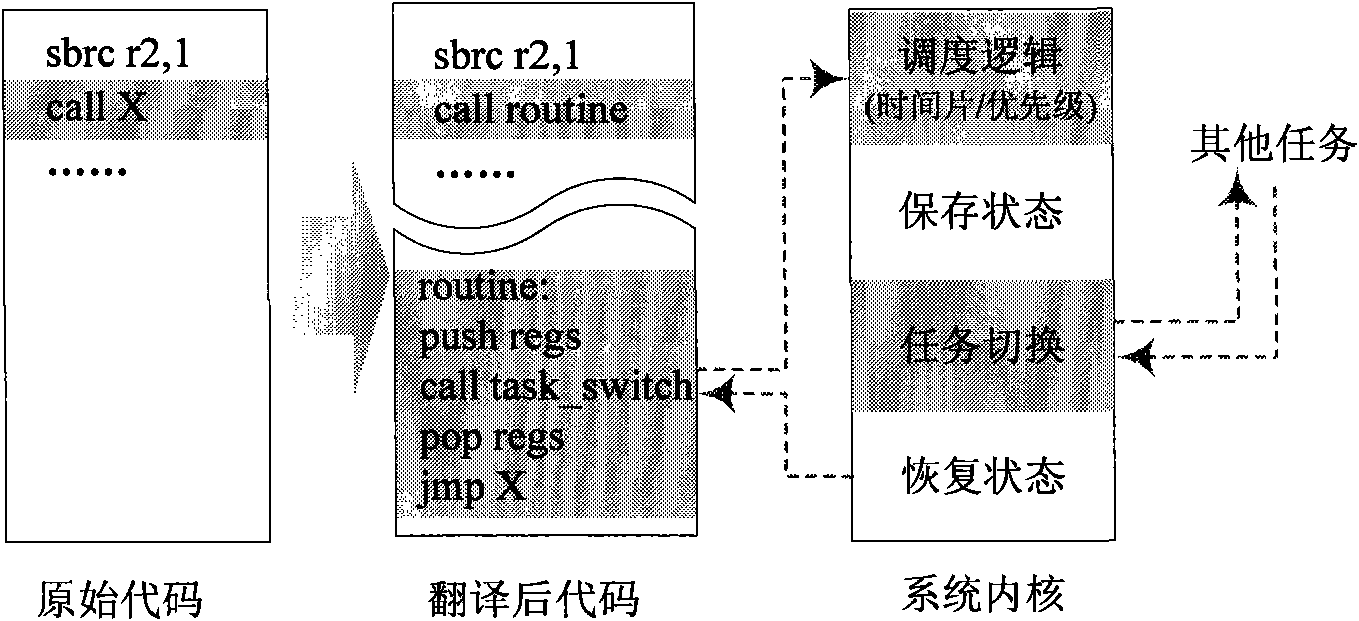

The invention relates to a task scheduling method for a wireless sensor network node. The method is realized based on a special operating system based on a wireless sensor network, wherein the special operating system comprises a binary code translation tool and an operating system kernel, the binary code translation tool runs on a base station node and provides a pretreatment for an application program; the operating system kernel runs on a sensor node and provides a series of kernel services; and the binary code translation tool and the operating system kernel act together to realize preemptive multi-task scheduling in the sensor node. The task scheduling method overcomes defects in the prior art, and realizes functions similar to the time-sharing, concurrent and preemptive multi-task scheduling functions of the traditional operating system. Each task has an independent time slice in the execution process, the information of the time slice is maintained by the operating system, the task does not need to concede the execution right, and the operating system can automatically suspend the task used by the time slice and switch to another task, thereby meeting the multi-task requirement of the application program.

Owner:NAT UNIV OF DEFENSE TECH

System and Method for Efficiently Passing Information Between Compiler and Post-Compile-Time Software

InactiveUS20070226720A1Pass efficientlyEliminate time overheadSoftware engineeringInstruction analysisCode TranslationSoftware system

System and method are described for register optimization during code translation utilizes a technique that removes the time overhead for analyzing register usage and eliminates fixed restraints on the compiler register usage. The present invention for register optimization utilizes a compiler to produce a register usage bit vector in a NOP instruction within each basic block (i.e., subroutine, function, and / or procedure). Each bit in the bit vector represents a particular caller-saved register. A bit is set if, at the location of NOP instruction, the compiler uses the corresponding register within that basic block containing the NOP instruction to hold information to be used at a later time. During the translation, the translator examines the register usage bit vector to very quickly determine which registers are free and therefore can be used during the register optimization without the need to save and restore the register values.

Owner:CHEN DING KAI +1

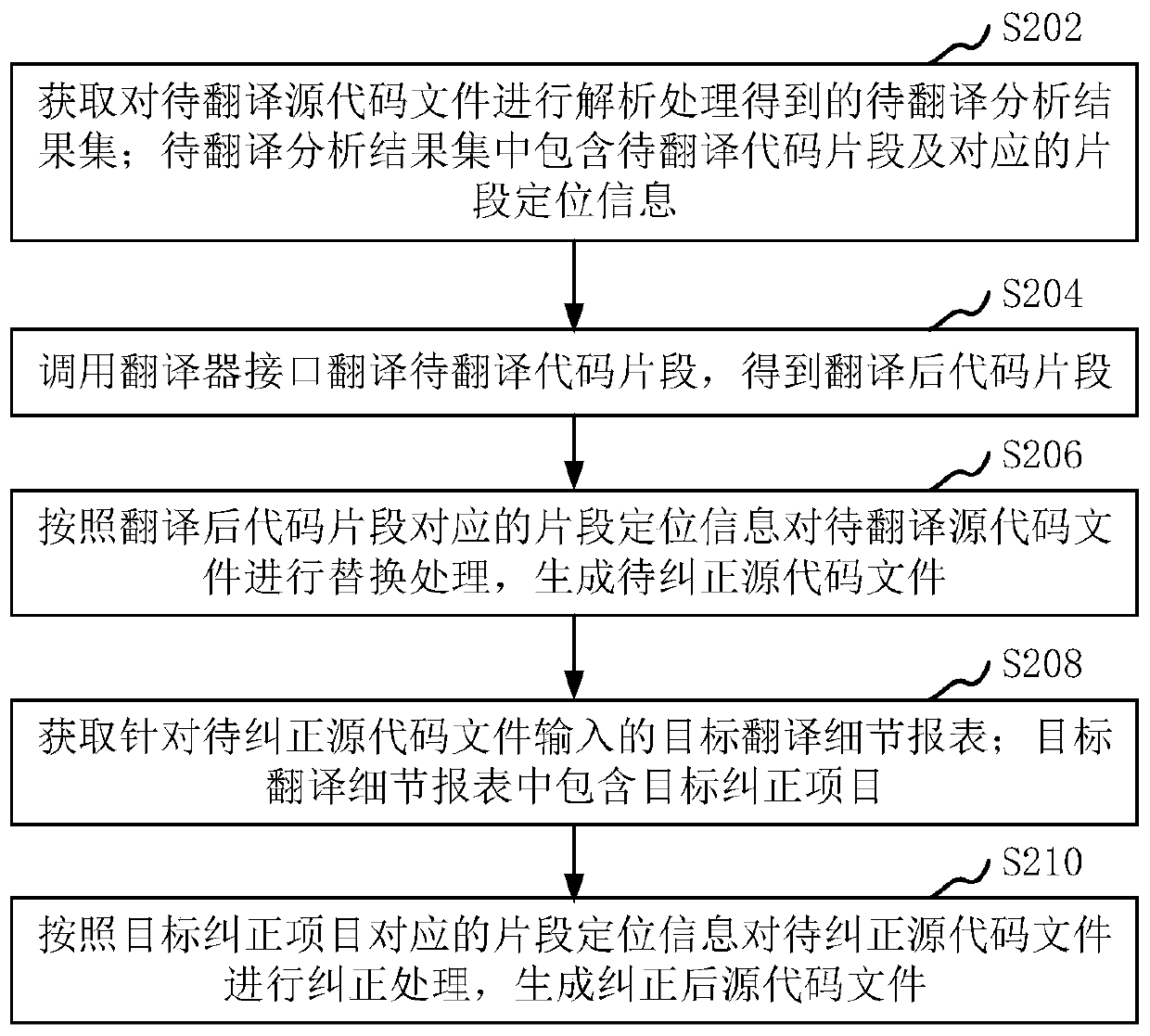

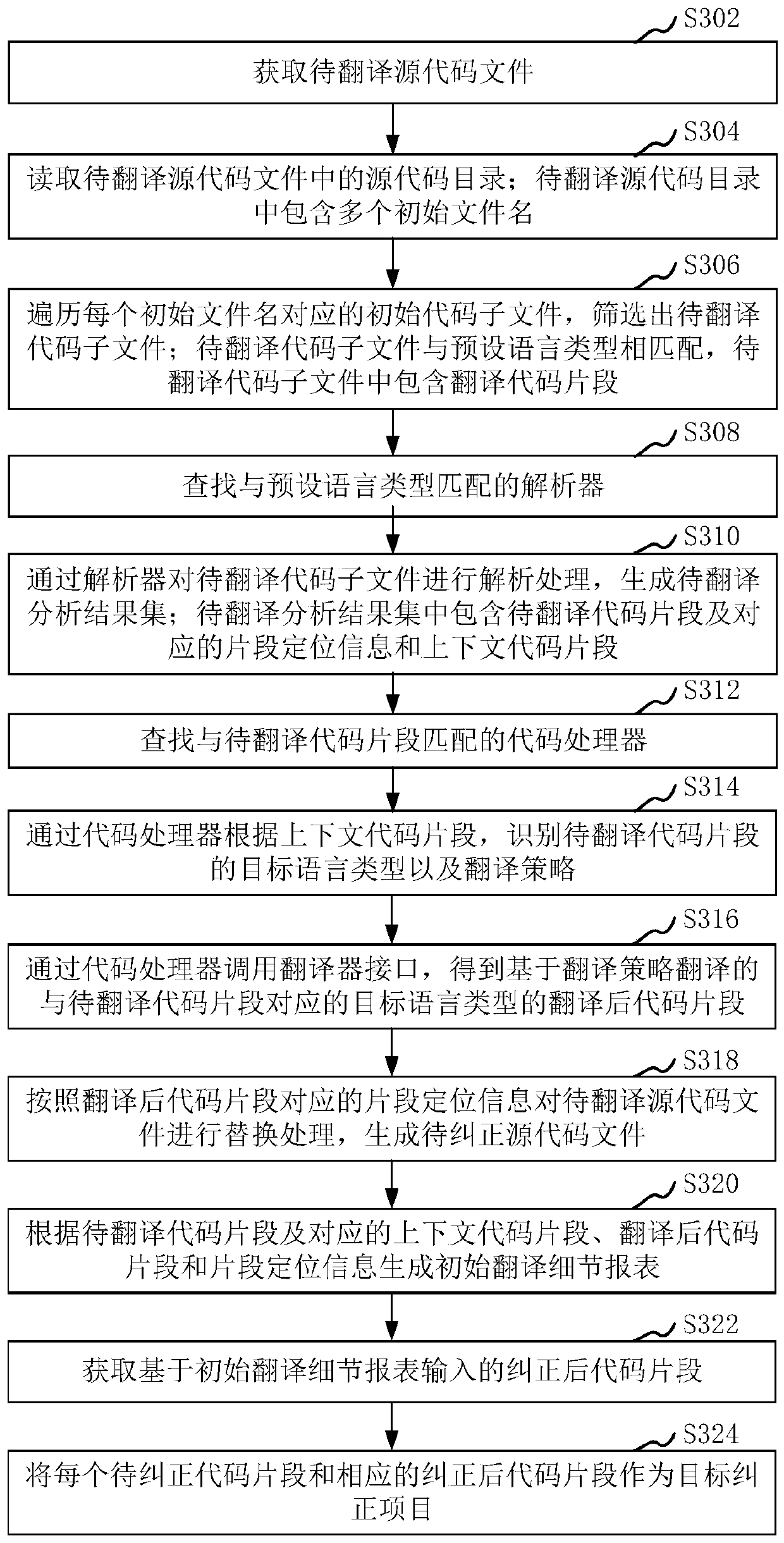

Code translation method and device, computer equipment and storage medium

PendingCN110134404AEnsure comprehensivenessGuaranteed uniformityBinary to binaryCode TranslationSource code file

The invention relates to a code translation method and device, computer equipment and a storage medium. The method comprises the steps of obtaining a to-be-translated analysis result set obtained by analyzing a to-be-translated source code file, wherein the to-be-translated analysis result set comprises a to-be-translated code segment and corresponding segment positioning information; calling a translator interface to translate the to-be-translated code segment to obtain a translated code segment; replacing the to-be-translated source code file according to the fragment positioning informationcorresponding to the translated code fragment to generate a to-be-corrected source code file; obtaining a target translation detail report input for the source code file to be corrected, wherein thetarget translation detail report comprises a target correction item; and correcting the to-be-corrected source code file according to the fragment positioning information corresponding to the target correction item to generate a corrected source code file. By adopting the method, the code translation efficiency can be improved through the code quality tool.

Owner:ONE CONNECT SMART TECH CO LTD SHENZHEN

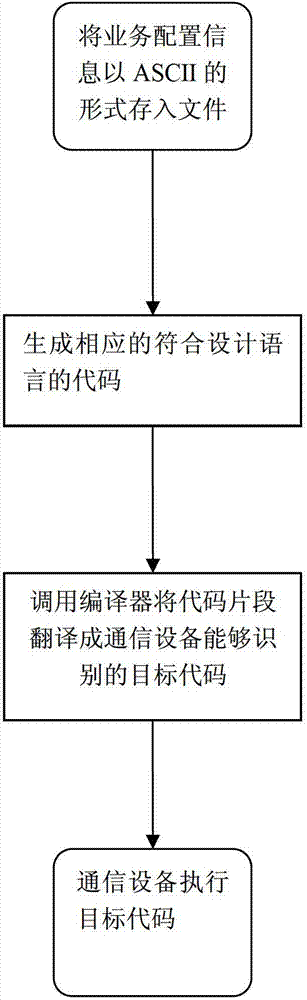

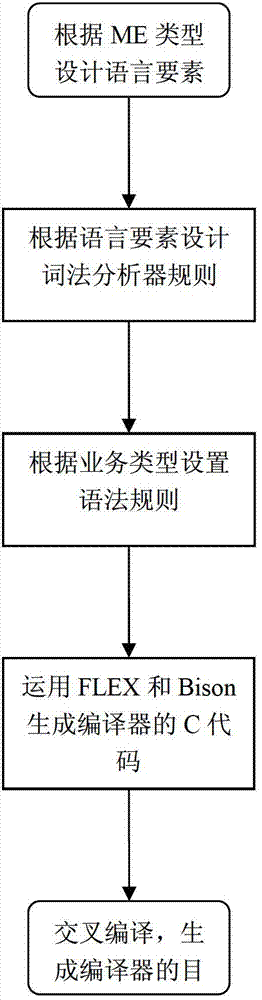

Business analysis method for GPON (Gigabit Passive Optical Network)

ActiveCN103051485ASimplify development workImprove accurate readingMultiplex system selection arrangementsData switching networksCode TranslationObject code

The invention discloses a business analysis method for a GPON (Gigabit Passive Optical Network). The business analysis method comprises the following steps of: on GPON-accessed data communication equipment, collecting ME (Managed Entity) in OMCI (ONT Management and Control Interface) Protocol; selecting attributes and values related to business configuration, and storing the attributes and the values in an ASCII (American Standard Code For Information Interchange) form into a file; generating a corresponding code conforming to a design language; compiling the code into a target cord capable of being recognized by the communication equipment through a compiler; and executing the target code through the communication equipment, and finishing business configuration. The business analysis method has a function that: through the novel language and the compiler, the most complicated analysis part in a business process is split off. When a new business type is generated, only the definition of a programming language needs to be updated, and a complicated analysis process is executed by the compiler generated by FLEX and Bison automatically. Therefore, the development operation of programming personnel can be greatly simplified; and the accuracy, the maintainability, the expandability and the stability of analysis can be improved greatly.

Owner:TAICANG T&W ELECTRONICS CO LTD

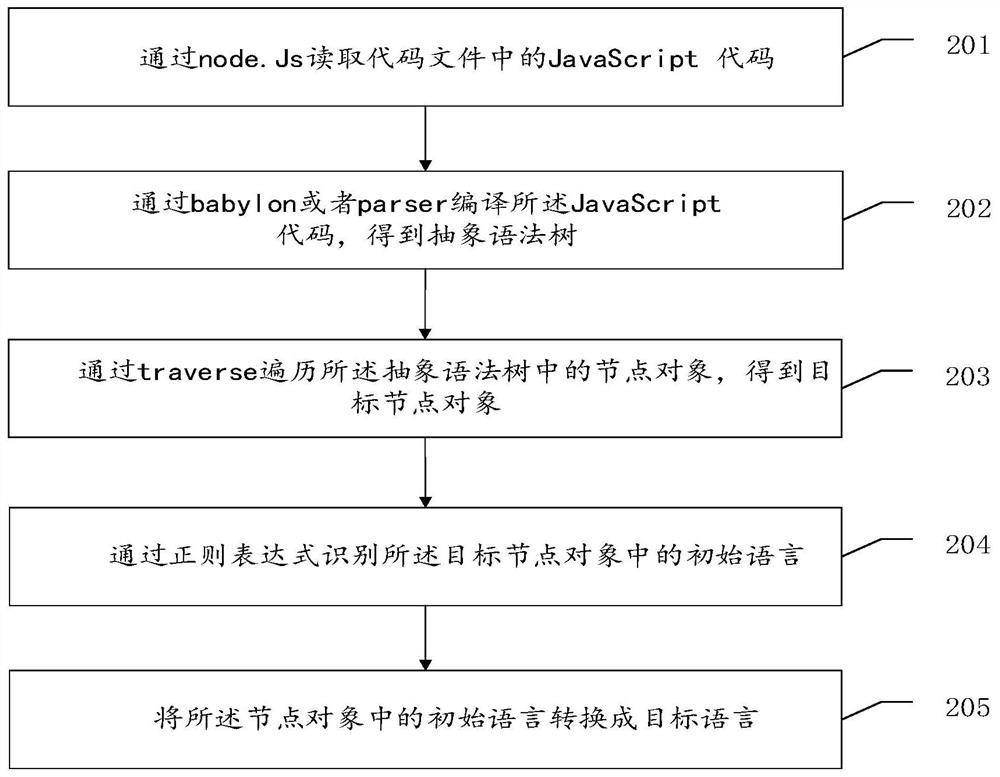

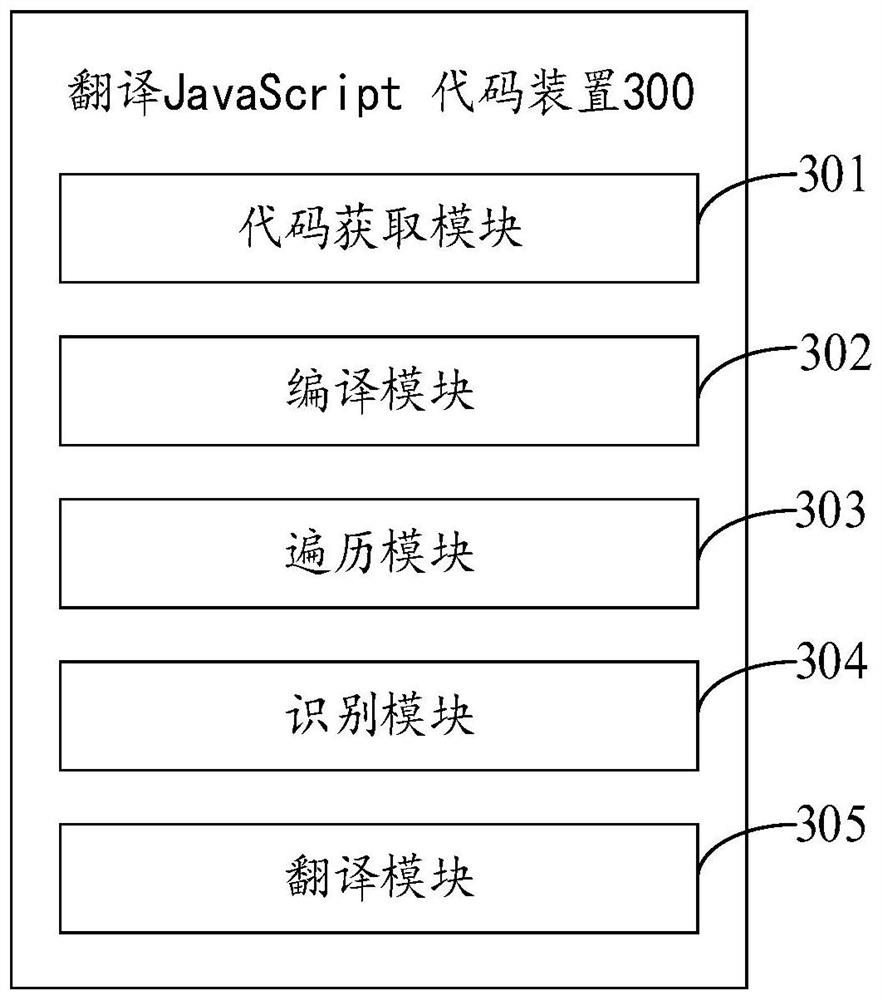

JavaScript code translation method and device, computer equipment and storage medium

PendingCN112015430AAchieve conversionReduce Refactoring CostsNatural language translationCode compilationCode TranslationAbstract syntax tree

The embodiment of the invention belongs to the field of research and development, and relates to a JavaScript code translation method, which comprises the following steps: reading the JavaScript codesin a code file through node.Js; compiling the JavaScript code through a babylon or parser, and obtaining an abstract syntax tree; traversing a node object in the abstract syntax tree through traverseto obtain a target node object; identifying an initial language in the target node object through a regular expression; and converting the initial language in the node object into a target language.In addition, the invention further relates to a blockchain technology, and translation information can be stored in the blockchain. The invention further provides a JavaScript code translation device,computer equipment and a storage medium. And the code reconstruction cost is reduced.

Owner:PINGAN INT SMART CITY TECH CO LTD