Patents

Literature

42 results about "NOP" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In computer science, a NOP, no-op, or NOOP (pronounced "no op"; short for no operation) is an assembly language instruction, programming language statement, or computer protocol command that does nothing.

Method and System of Using One-Time Programmable Memory as Multi-Time Programmable in Code Memory of Processors

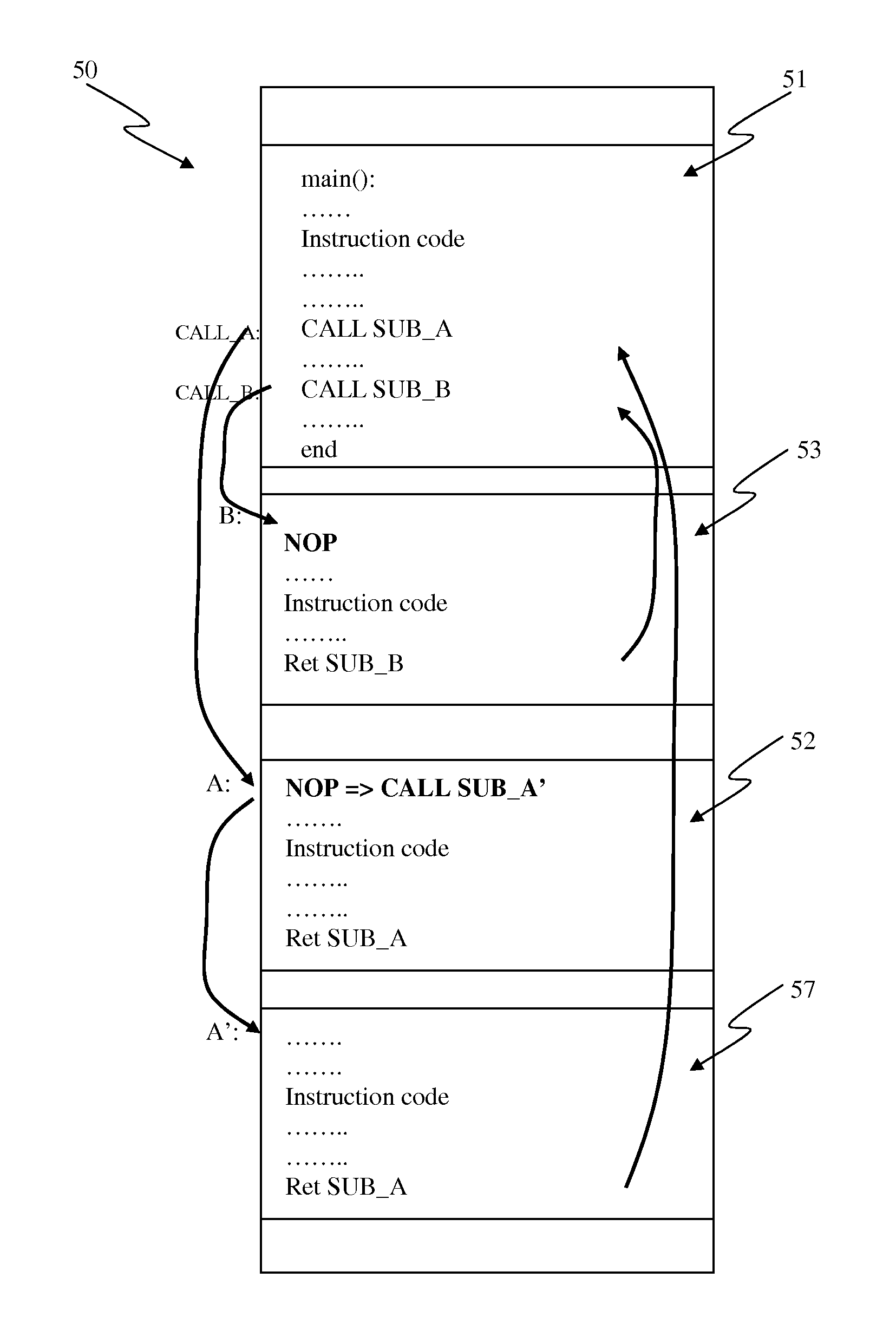

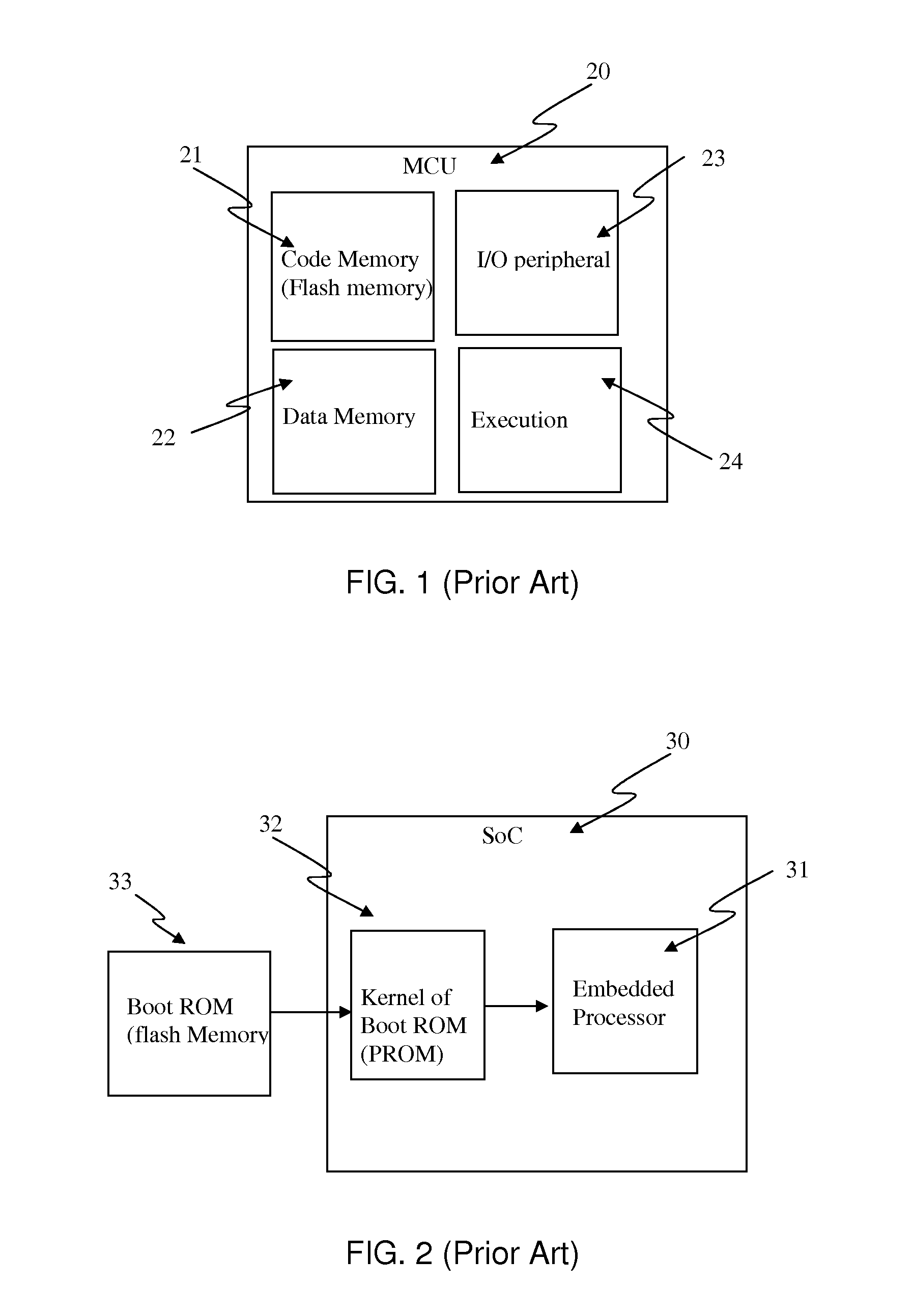

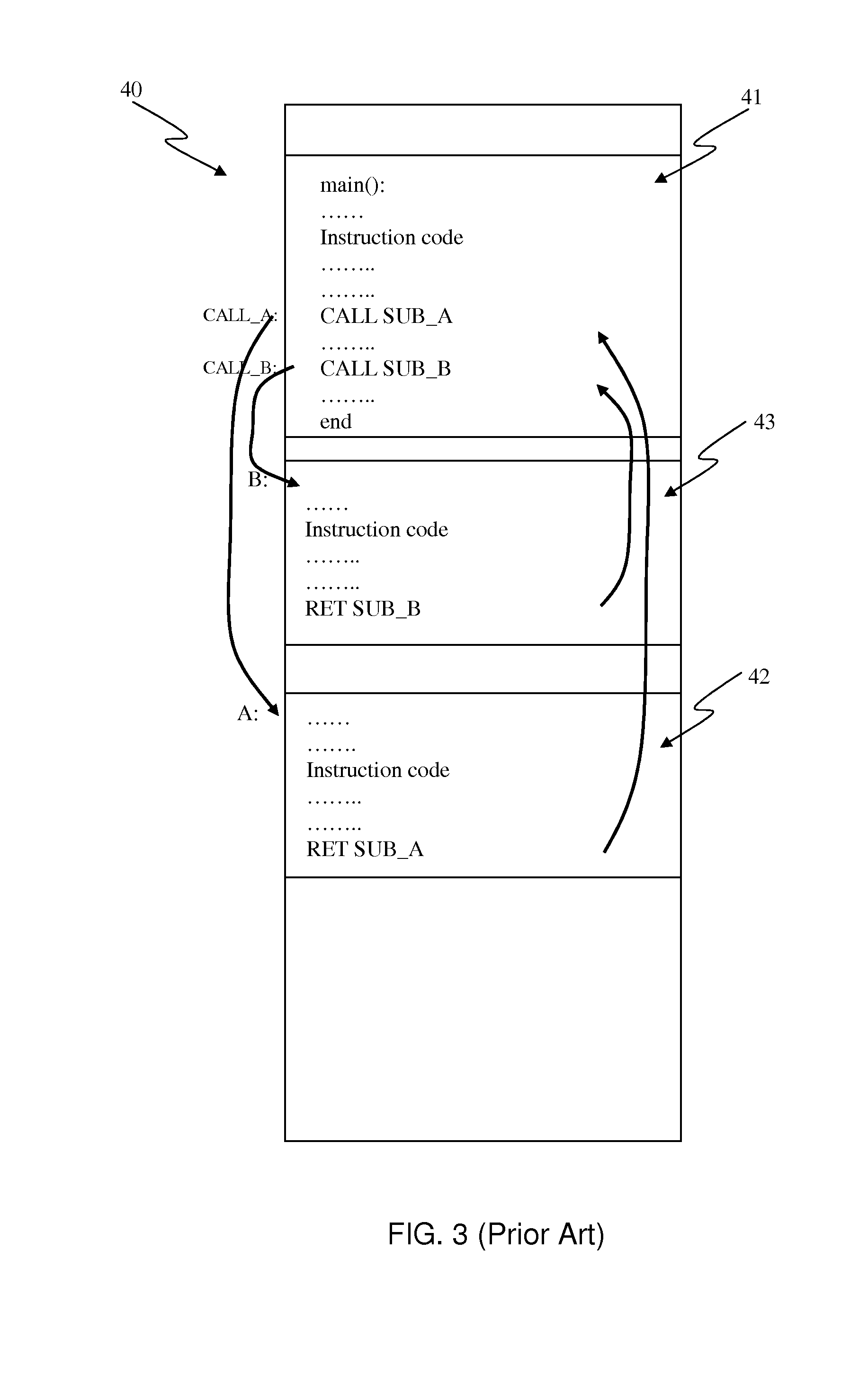

A method, device and system of using an One-Time-Programmable (OTP) memory as an Multiple-Time Programming (MTP) memory equivalent is disclosed. The use of OTP memory in this manner allows code to be updated one or more times and yet remain small in size and relatively easy to process (fabricate). The code can be program code for a processor, such as boot code, boot code kernel or other instruction code. According to one aspect, an OTP memory is able to functionally operate as if it were a MTP memory through intelligent use of NOPs, which are no operations. Subsequently, if a particular subroutine or function in the program code needs to be modified, an instruction (e.g., JUMP instruction) can be programmed into the NOP so that certain existing instructions can be bypassed and the execution of instructions of a new module can be performed.

Owner:ATTOPSEMI TECH CO LTD

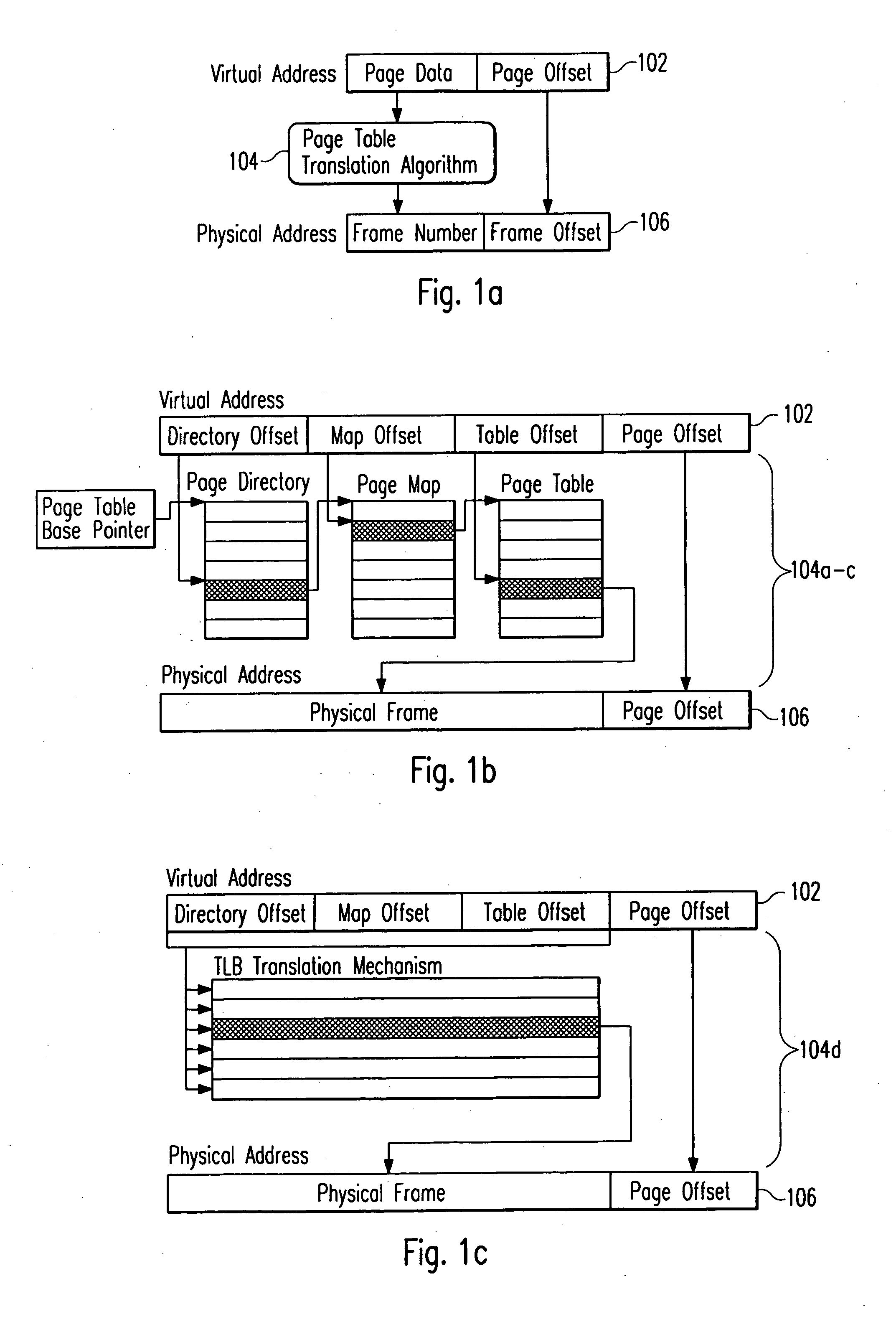

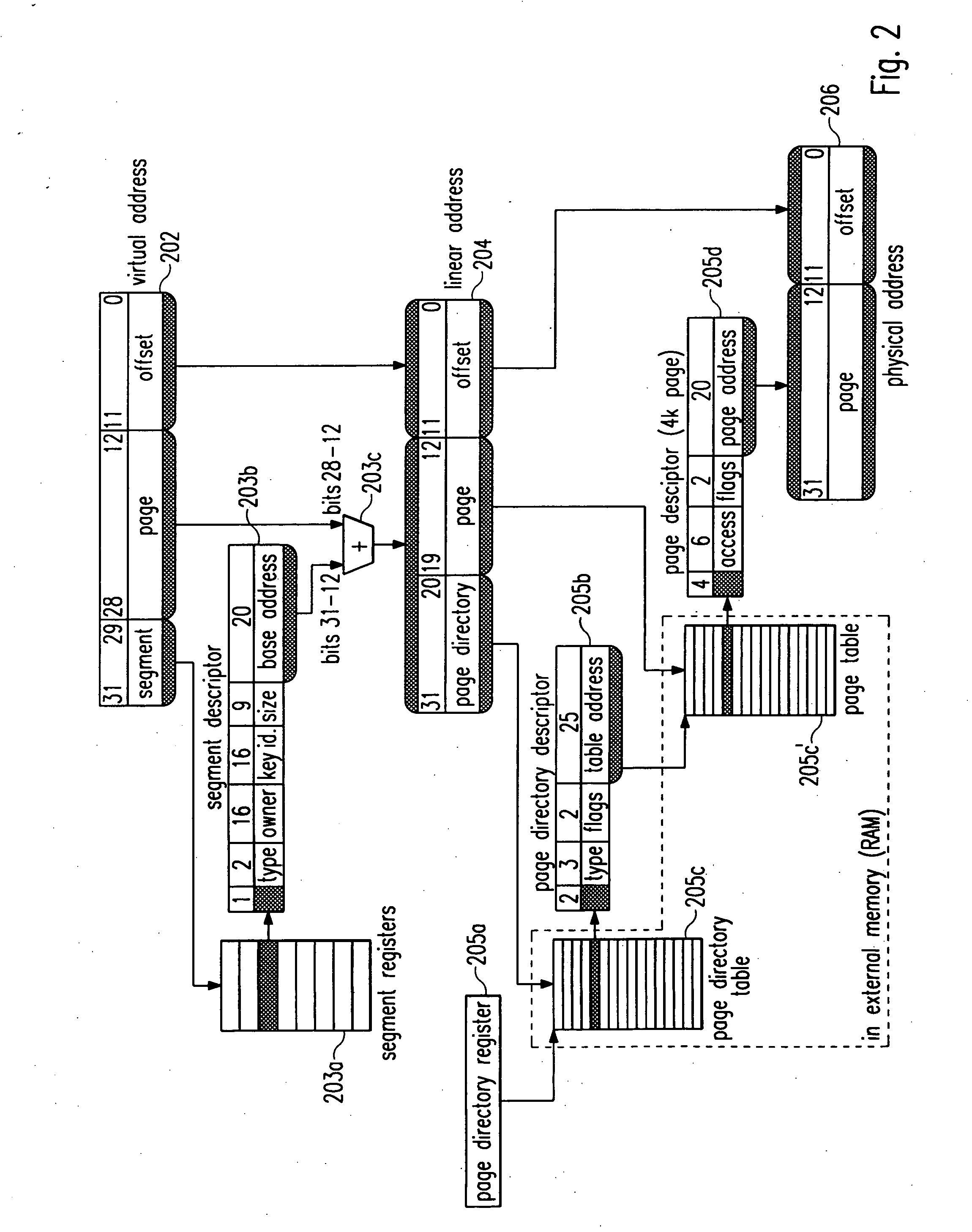

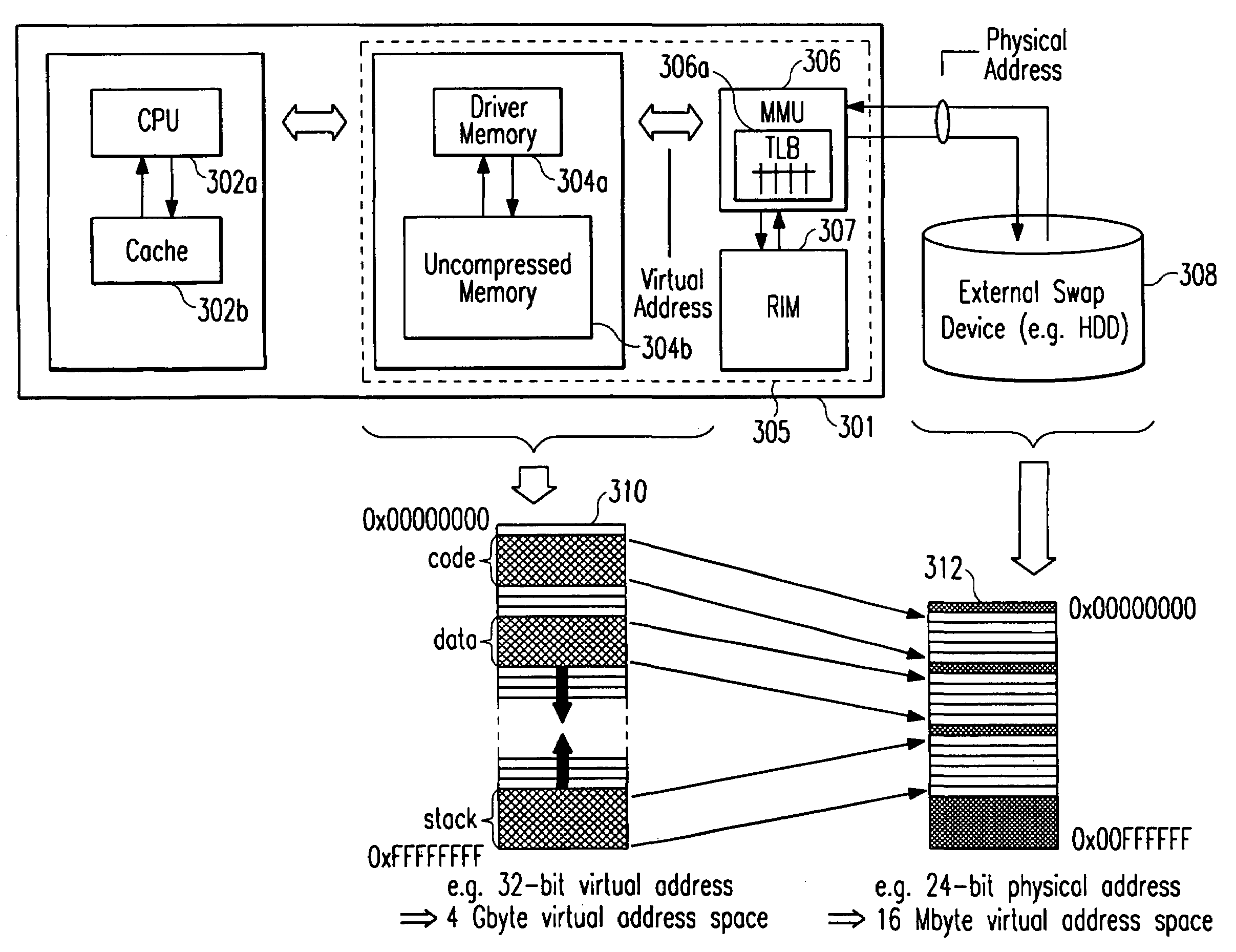

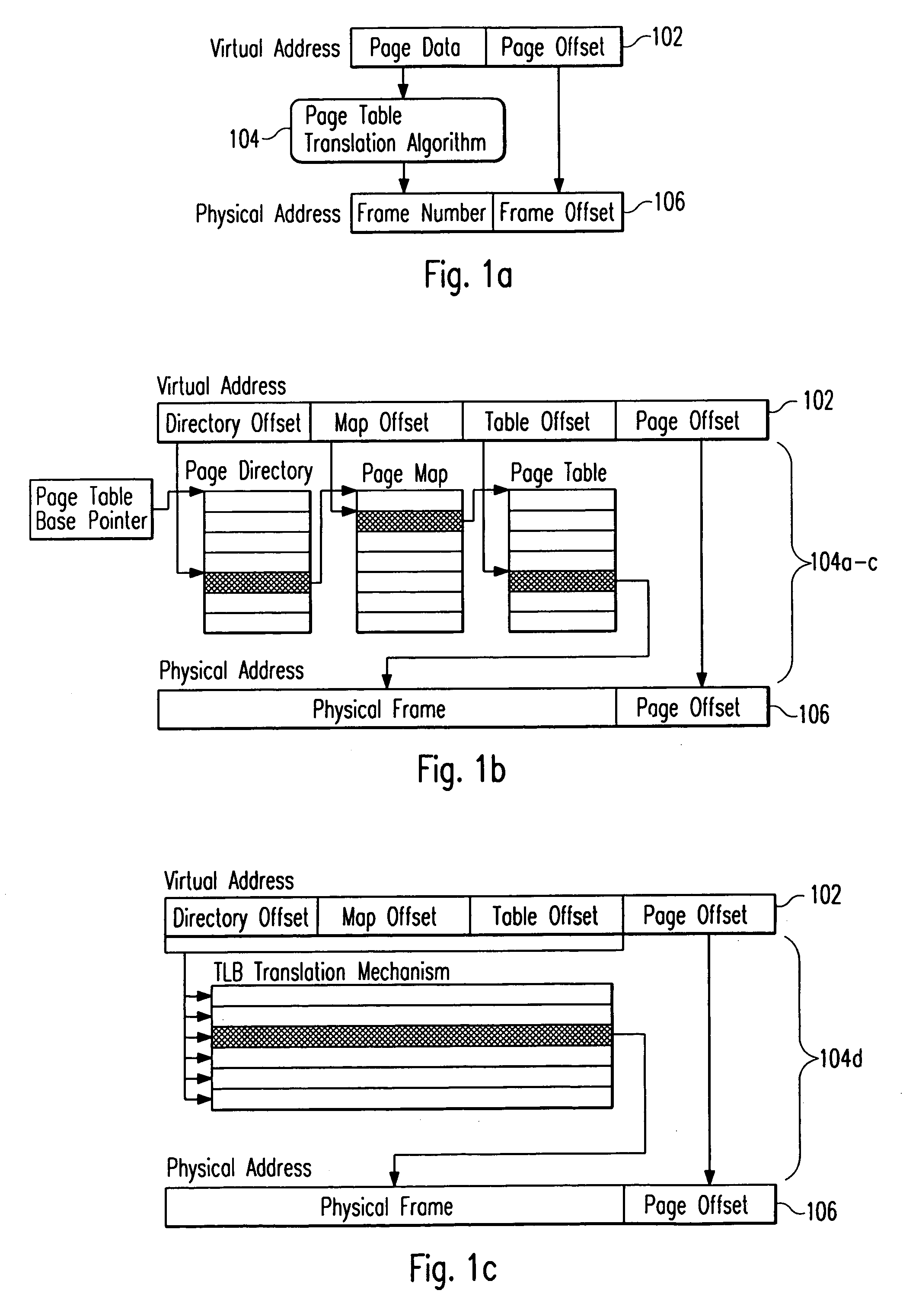

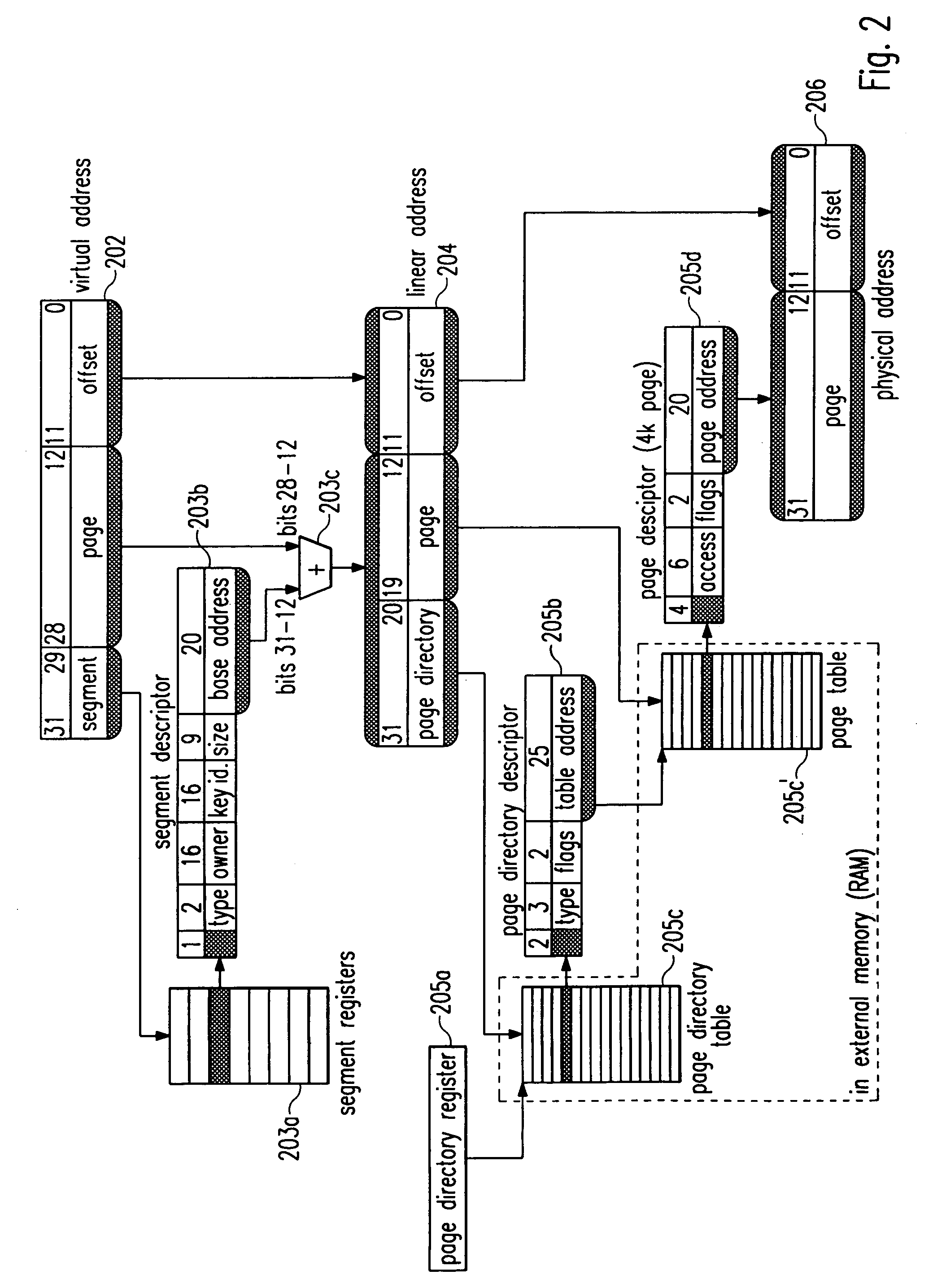

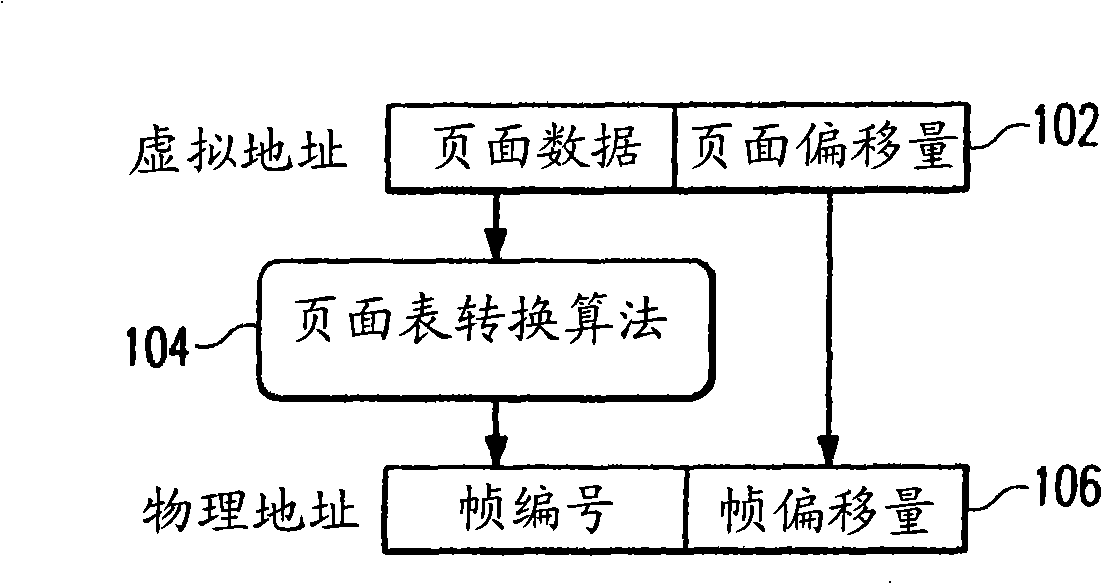

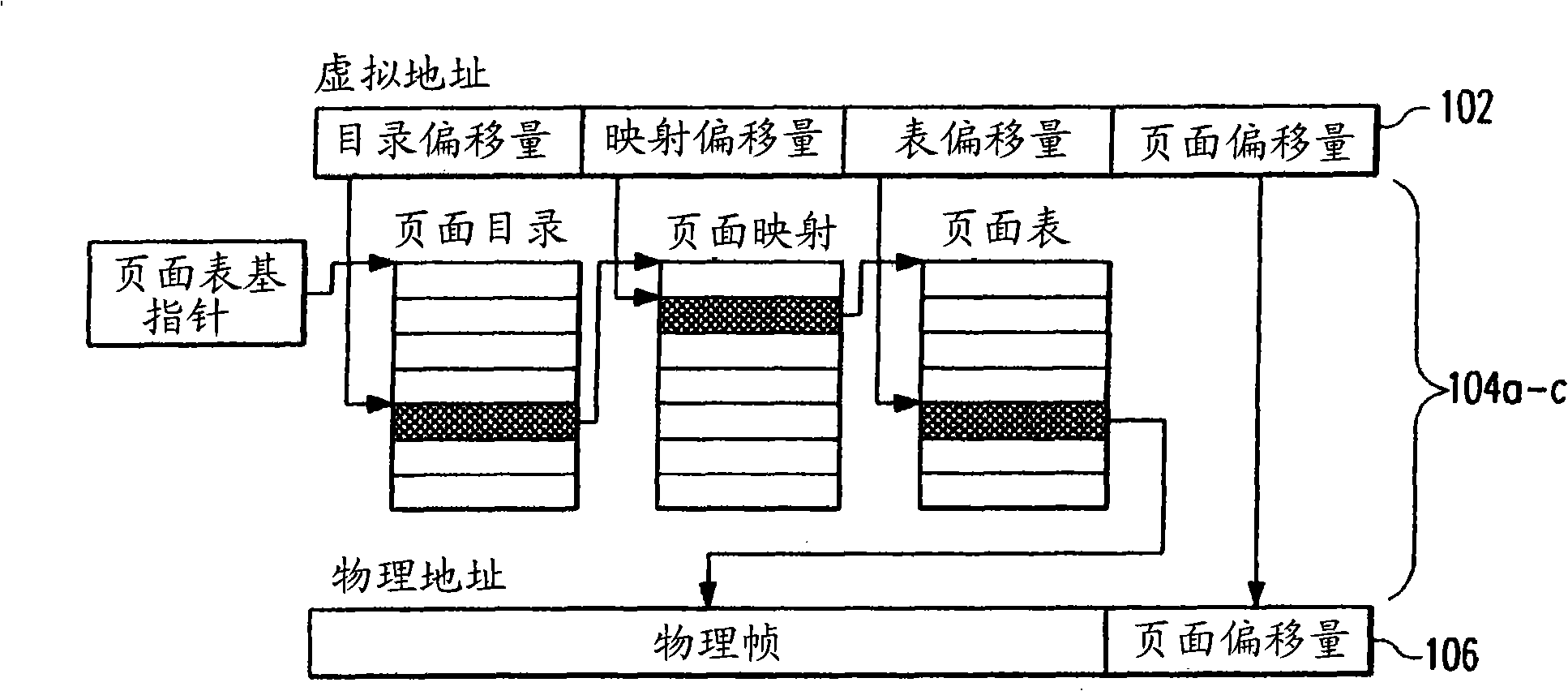

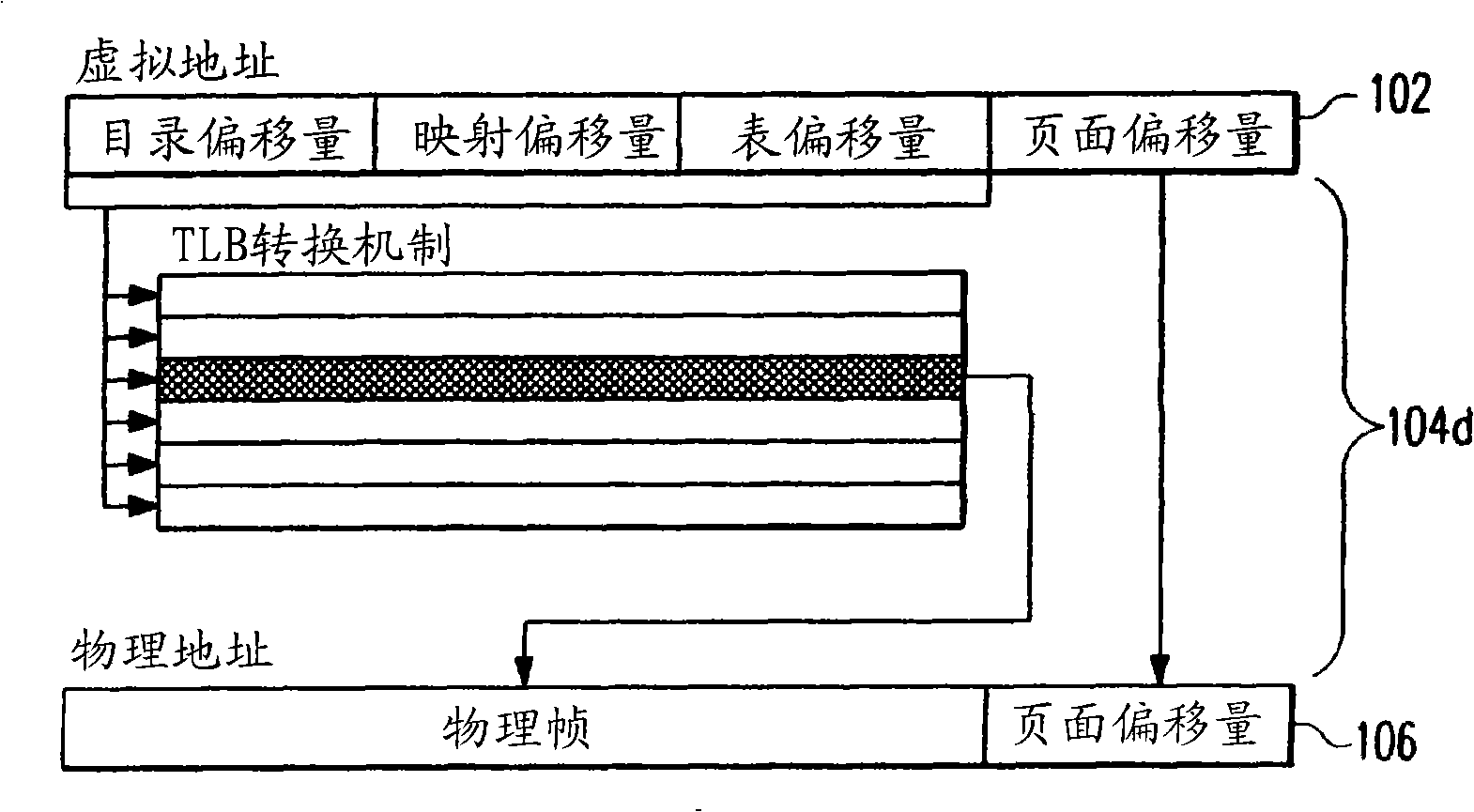

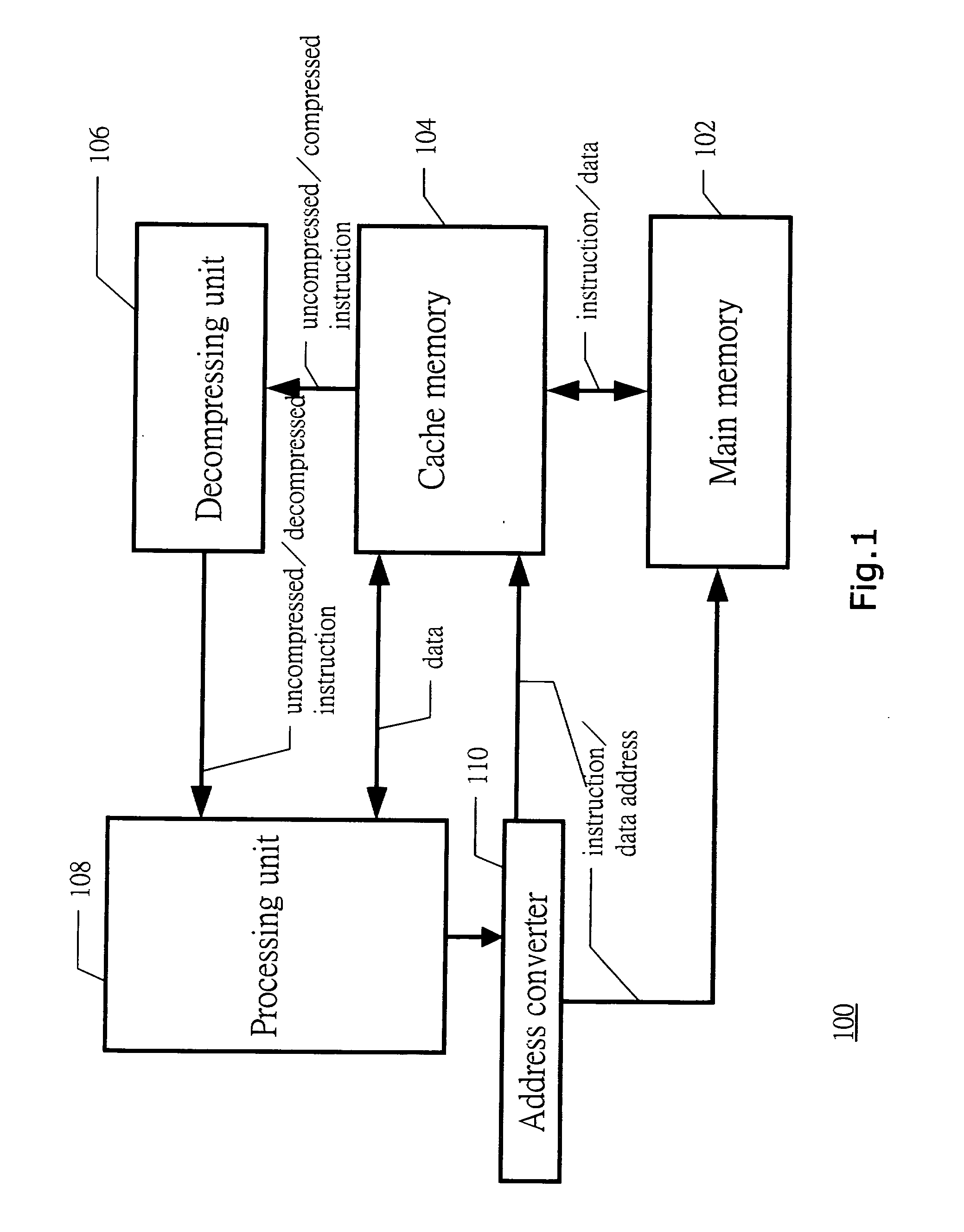

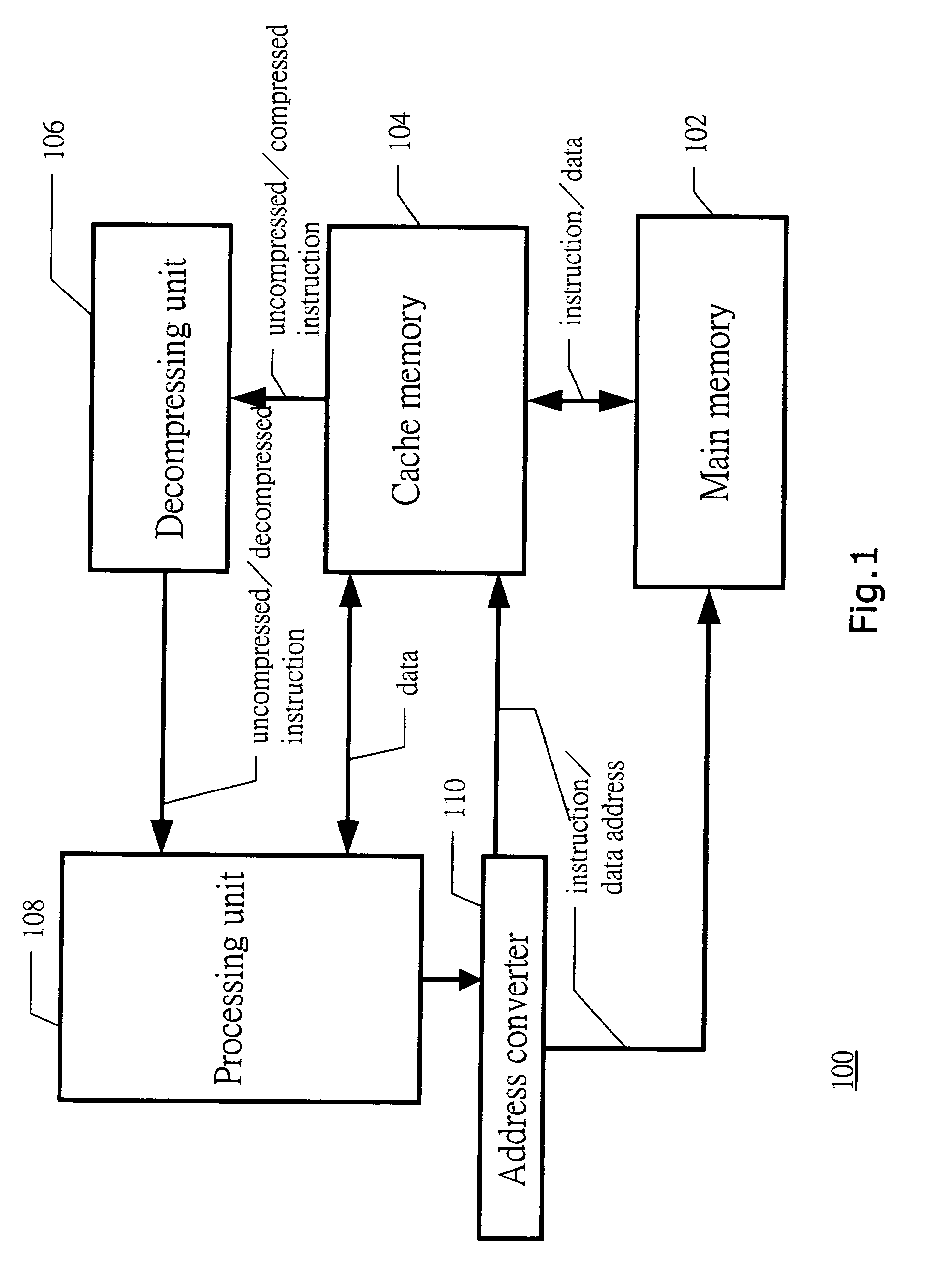

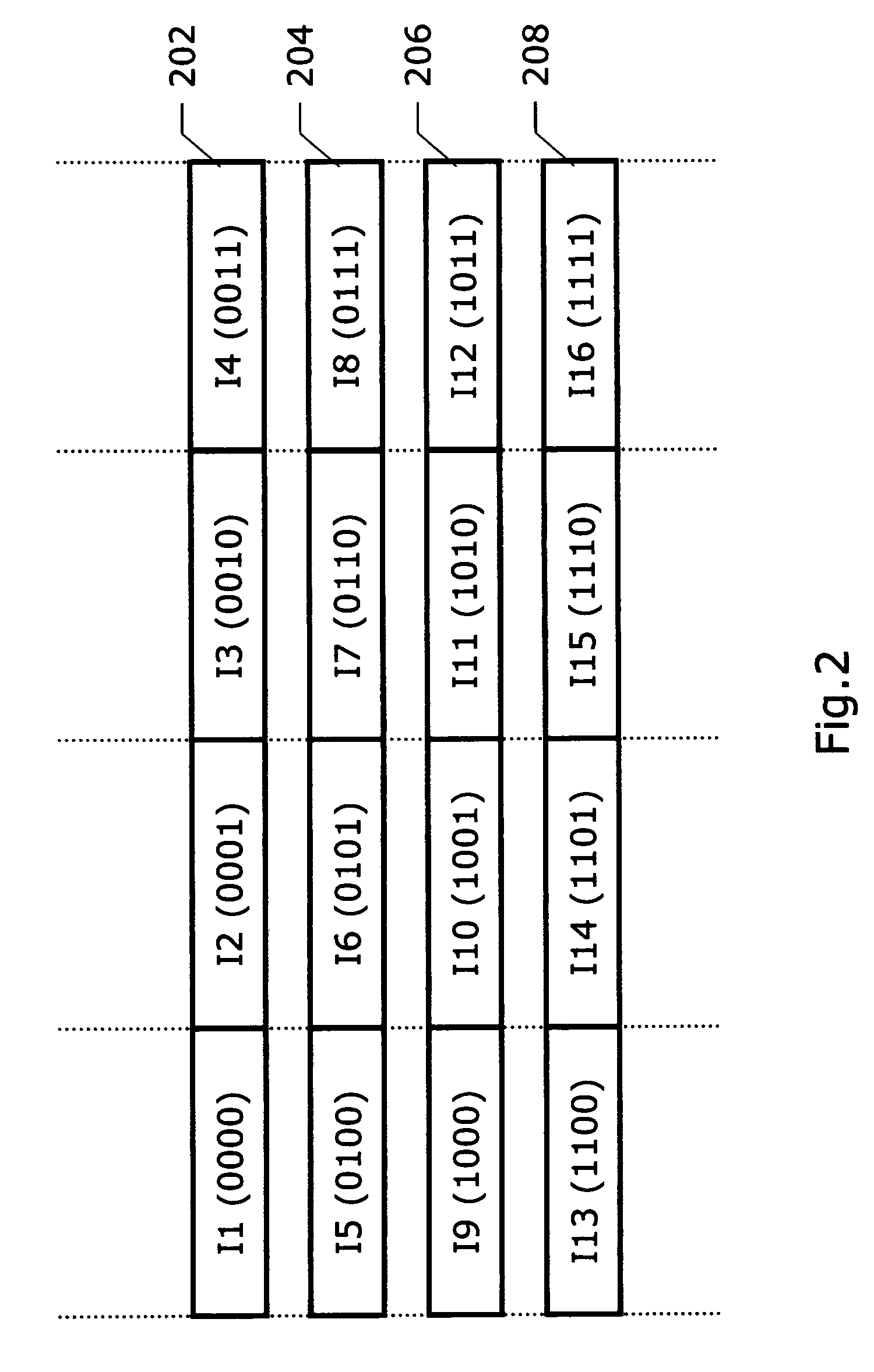

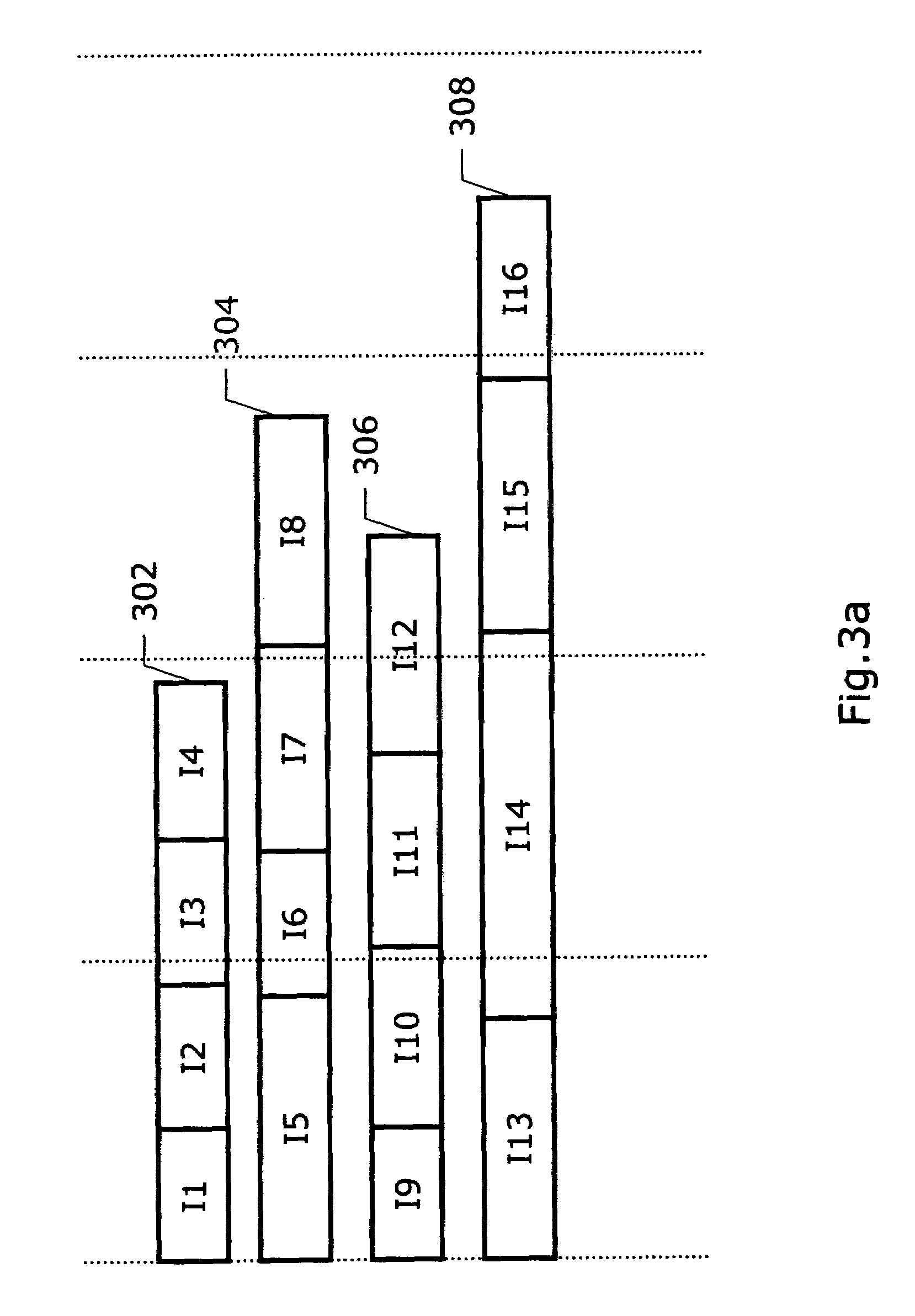

Data compression method for supporting virtual memory management in a demand paging system

InactiveUS20070157001A1Avoid time-consuming index searchAvoid indexMemory architecture accessing/allocationMemory adressing/allocation/relocationData compressionData stream

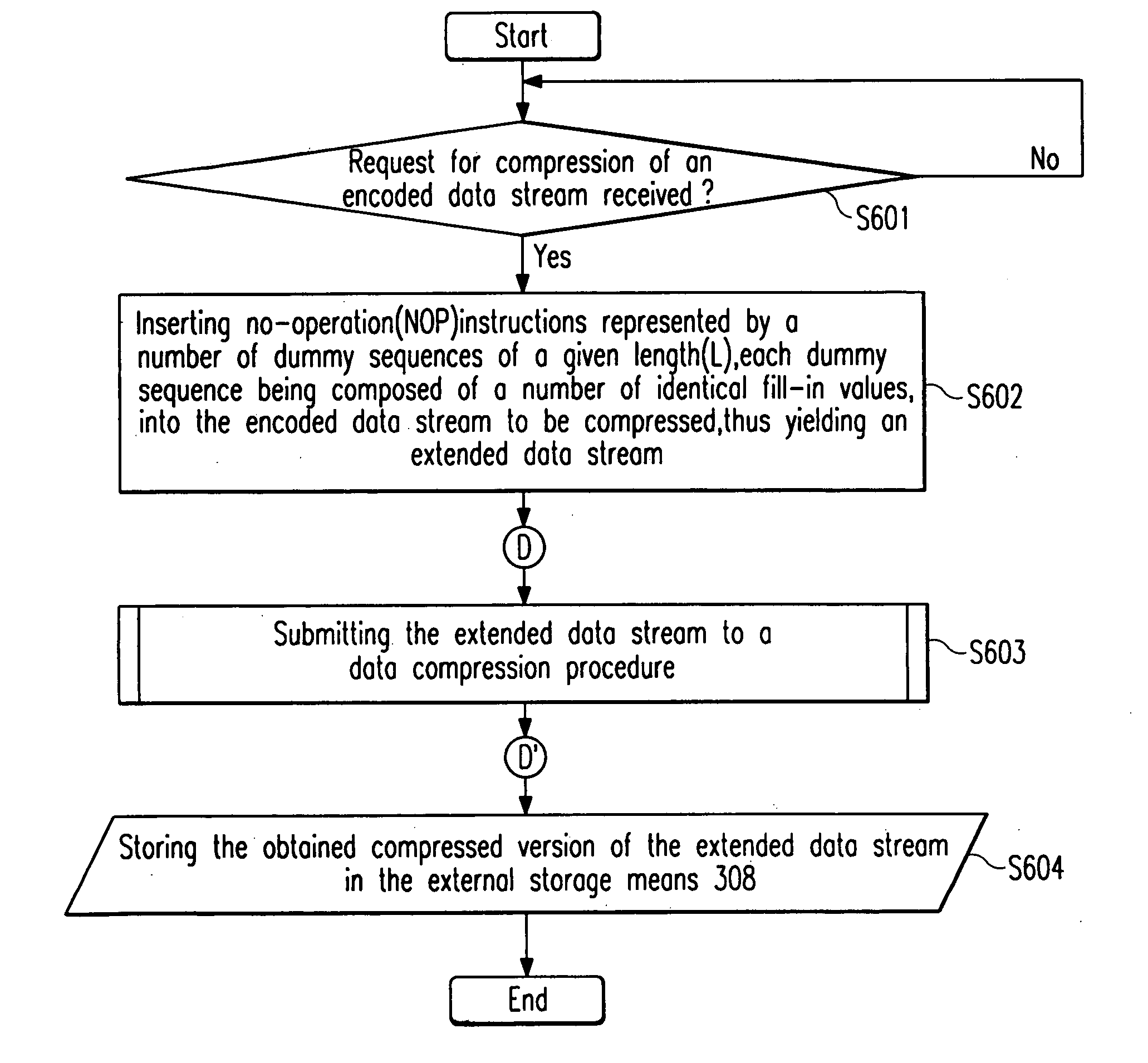

A virtual memory management unit (306) includes a redundancy insertion module (307) which is used for inserting redundancy into an encoded data stream to be compressed, such that after being compressed each logical data block fits into a different one from a set of equal-sized physical data blocks of a given size. For example, said redundancy may be given by no-operation (NOP) instructions represented by a number of dummy sequences of a given length (L) into an encoded data stream to be compressed, each dummy sequence being composed of a number of identical binary or hexadecimal fill-in values.

Owner:SONY ERICSSON MOBILE COMM AB

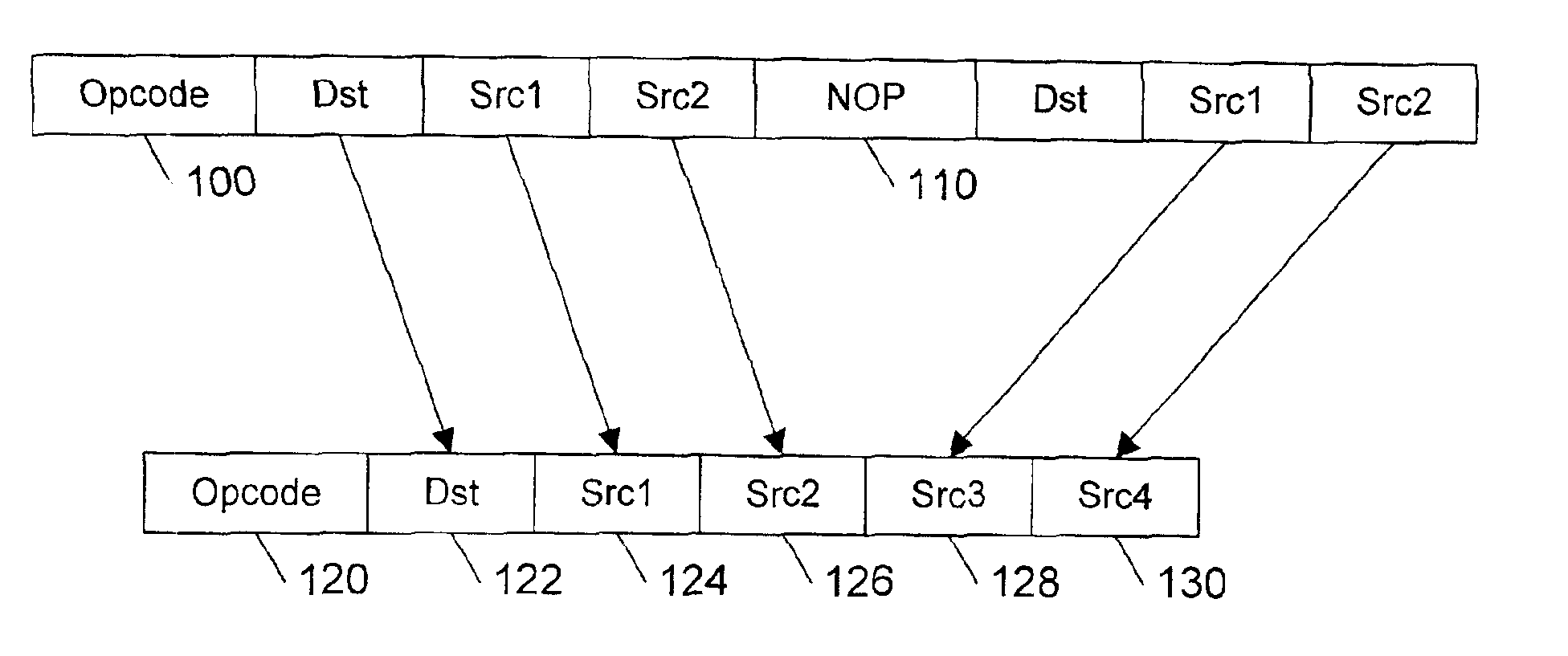

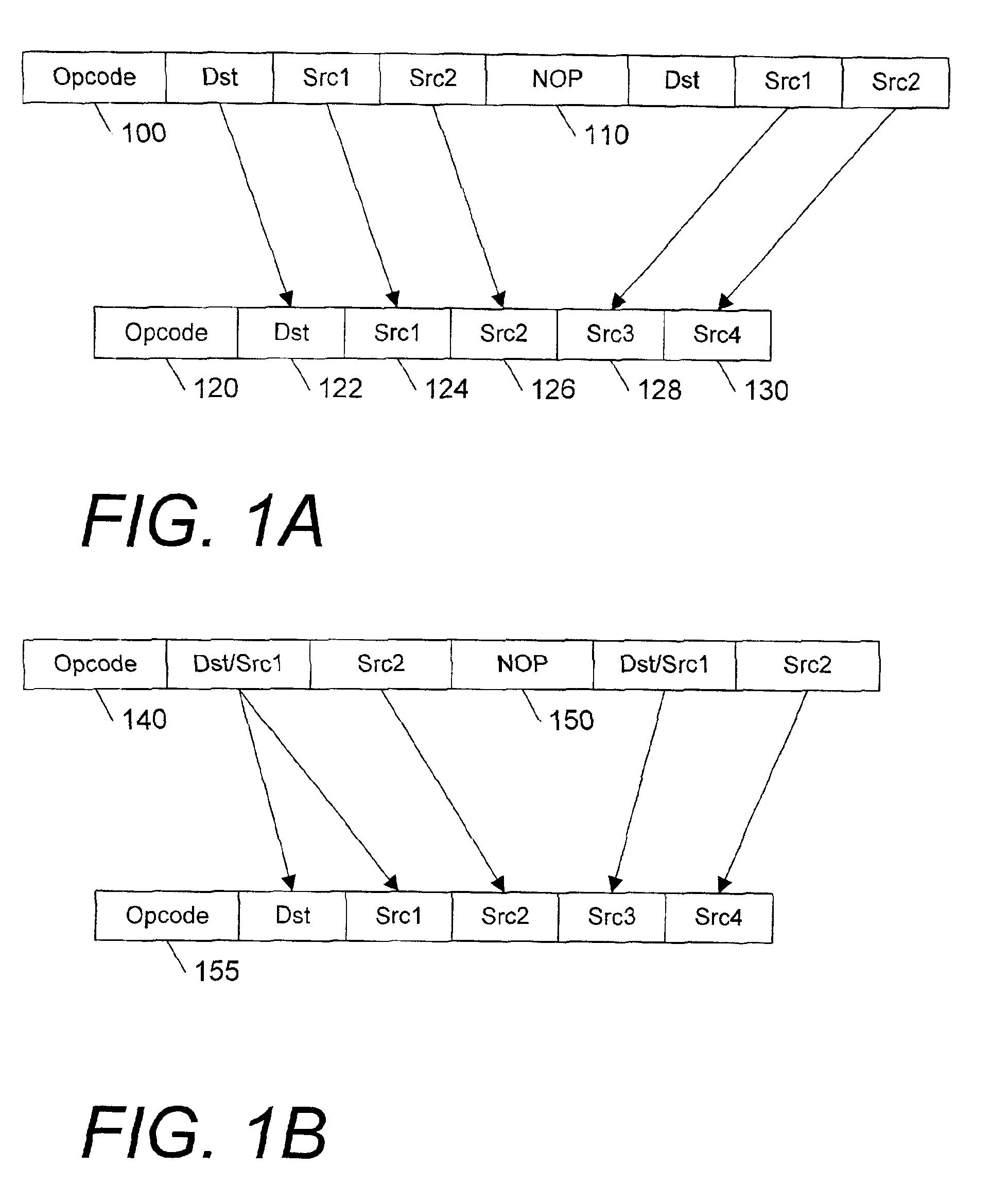

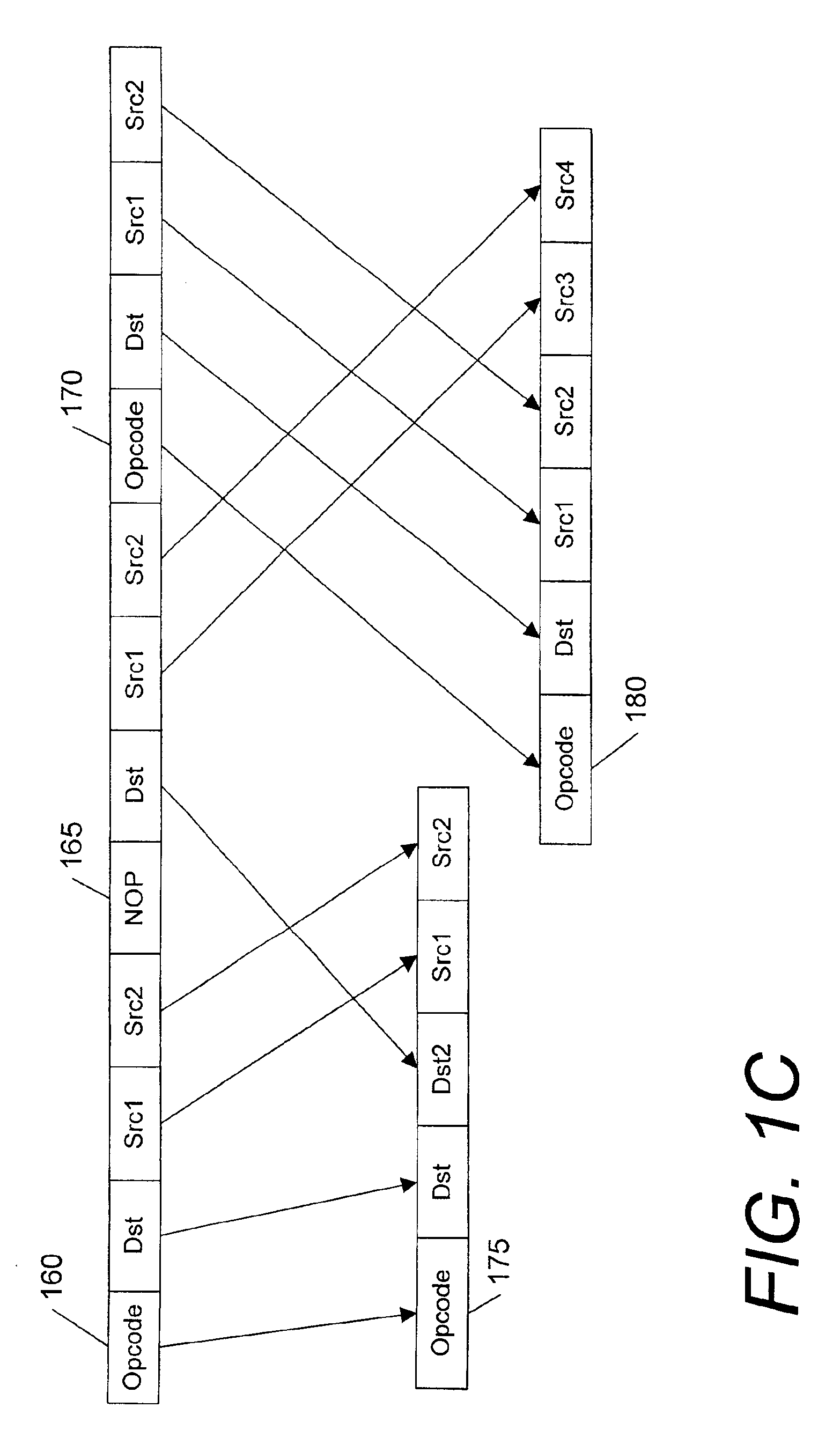

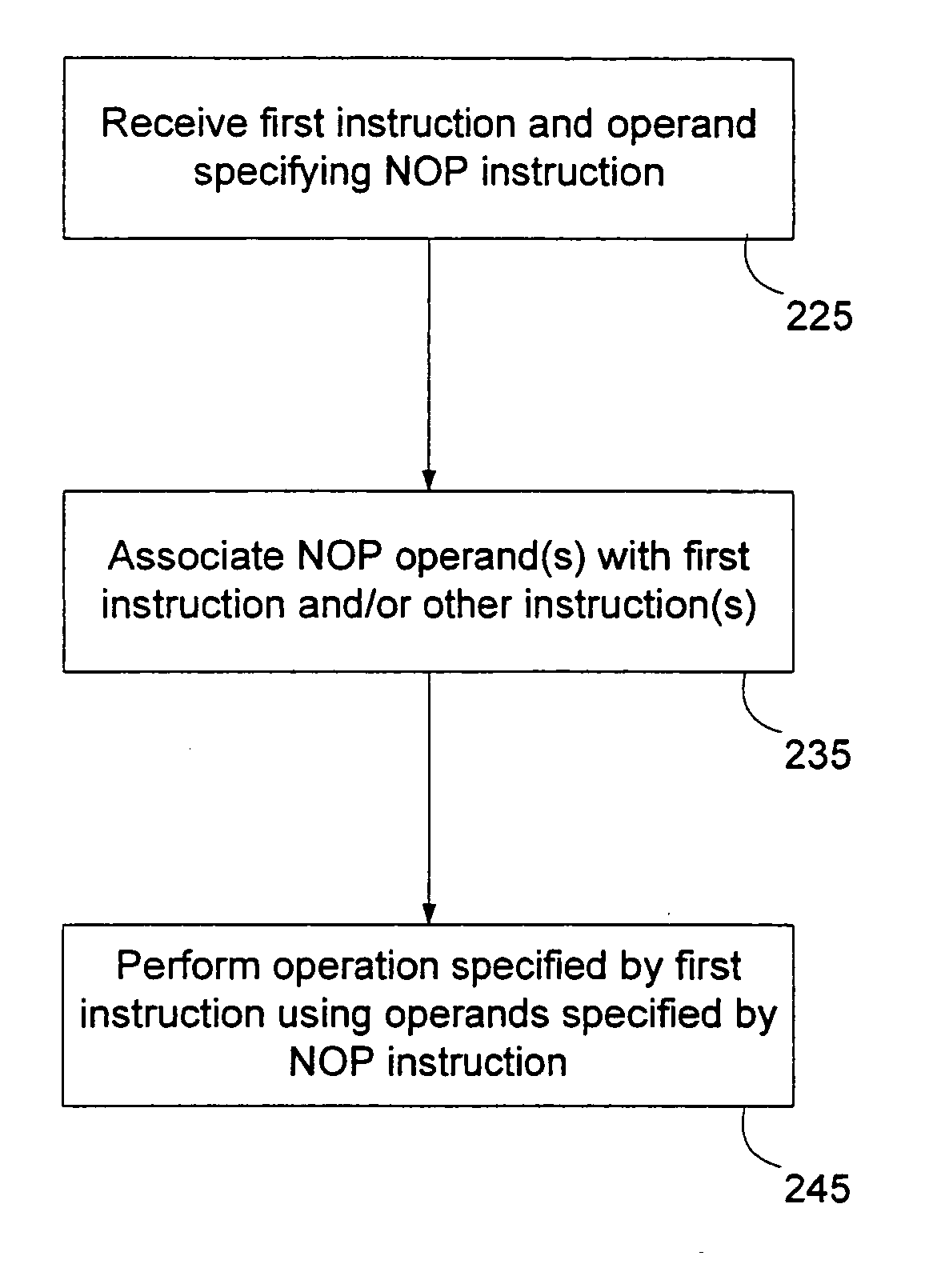

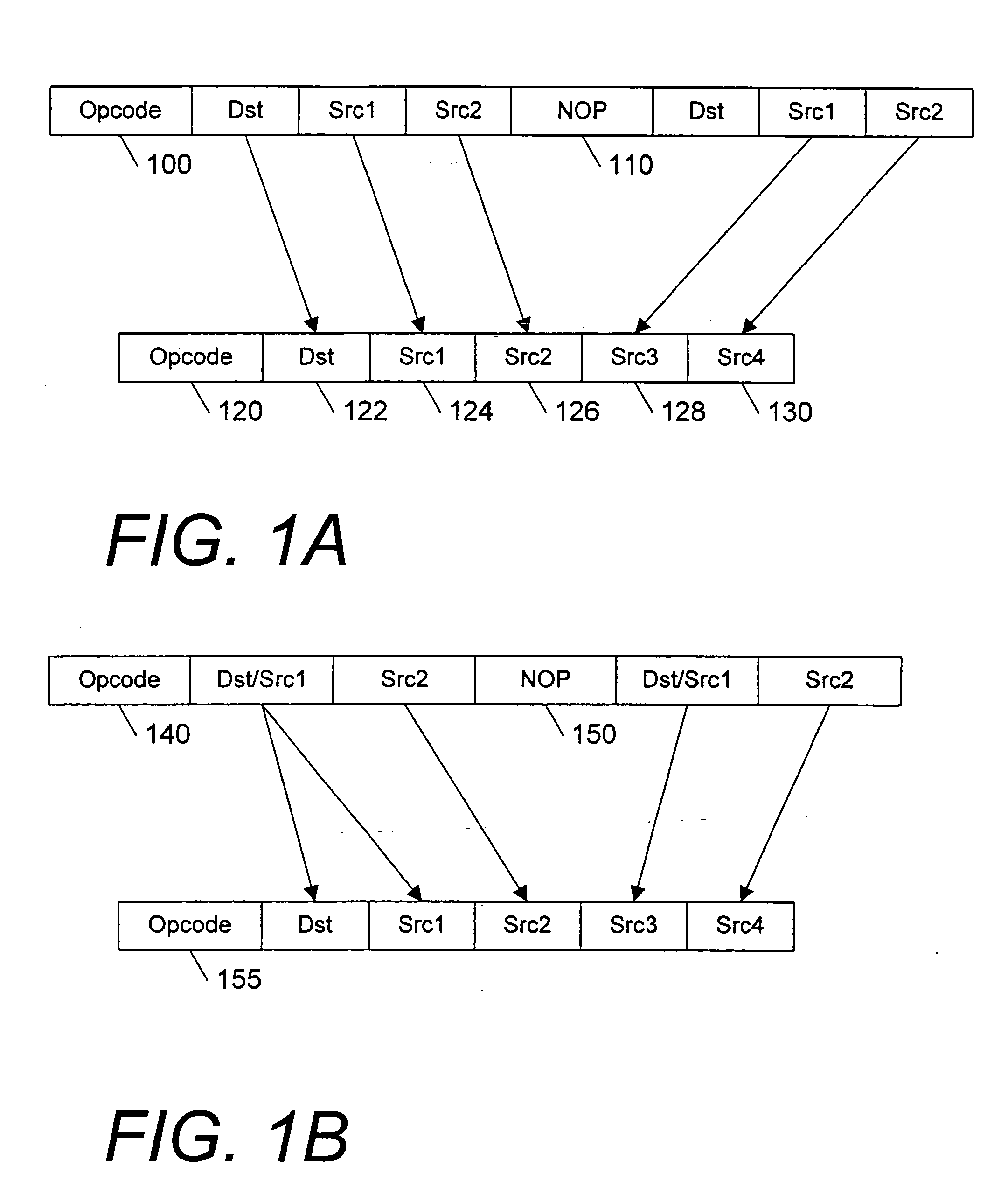

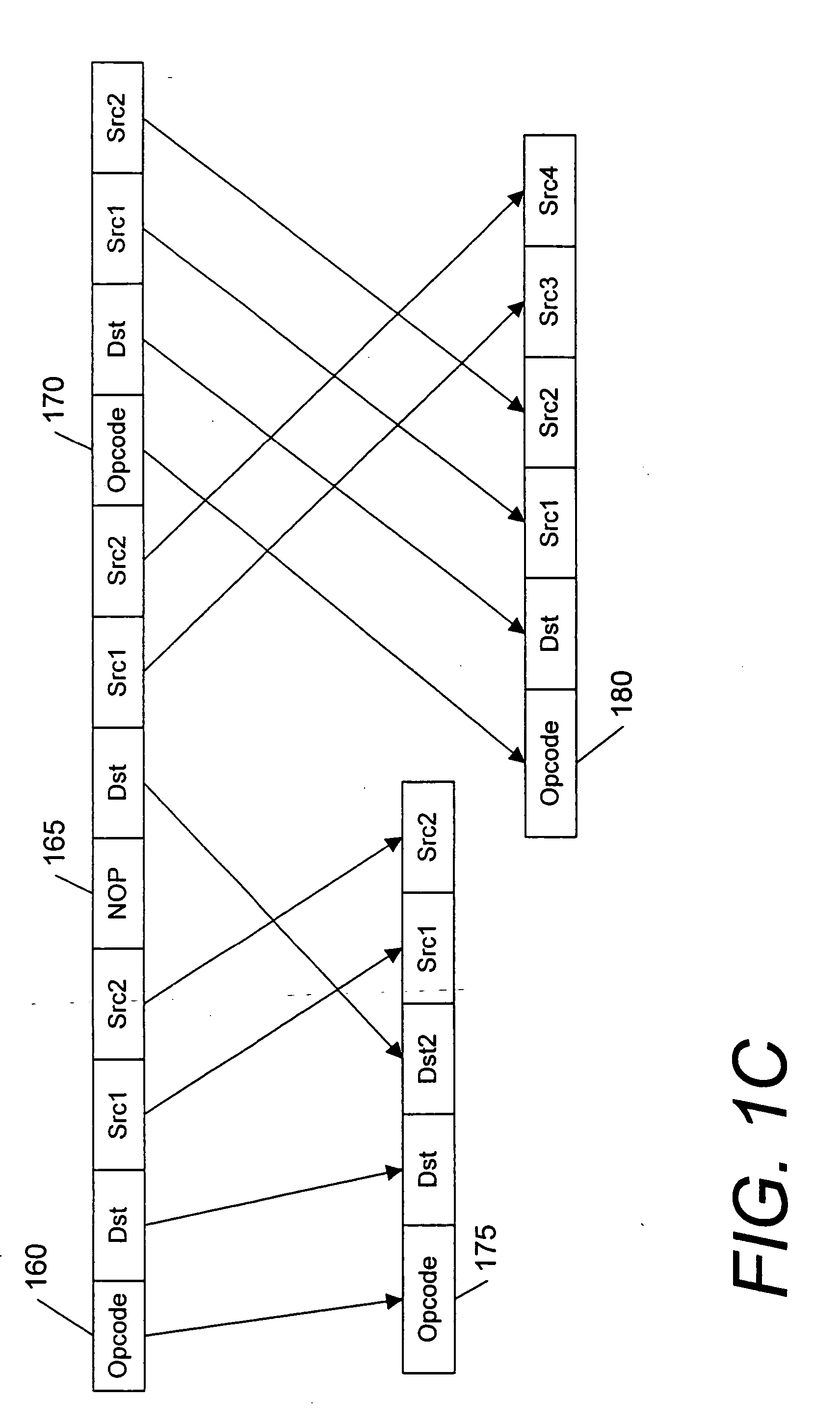

Instruction set extension using operand bearing NOP instructions

Instruction set extension using operand bearing no-operation (NOP) or other instructions. In one embodiment, an apparatus can execute a first instruction with an operand associated with a second instruction. The apparatus includes a decoder to identify an operand associated with the second instruction as being designated for the first instruction. An execution unit executes an operation indicated by the first instruction to operate on the operand associated with the second instruction. The second instruction may occur before or after the first instruction in the program sequence.

Owner:INTEL CORP

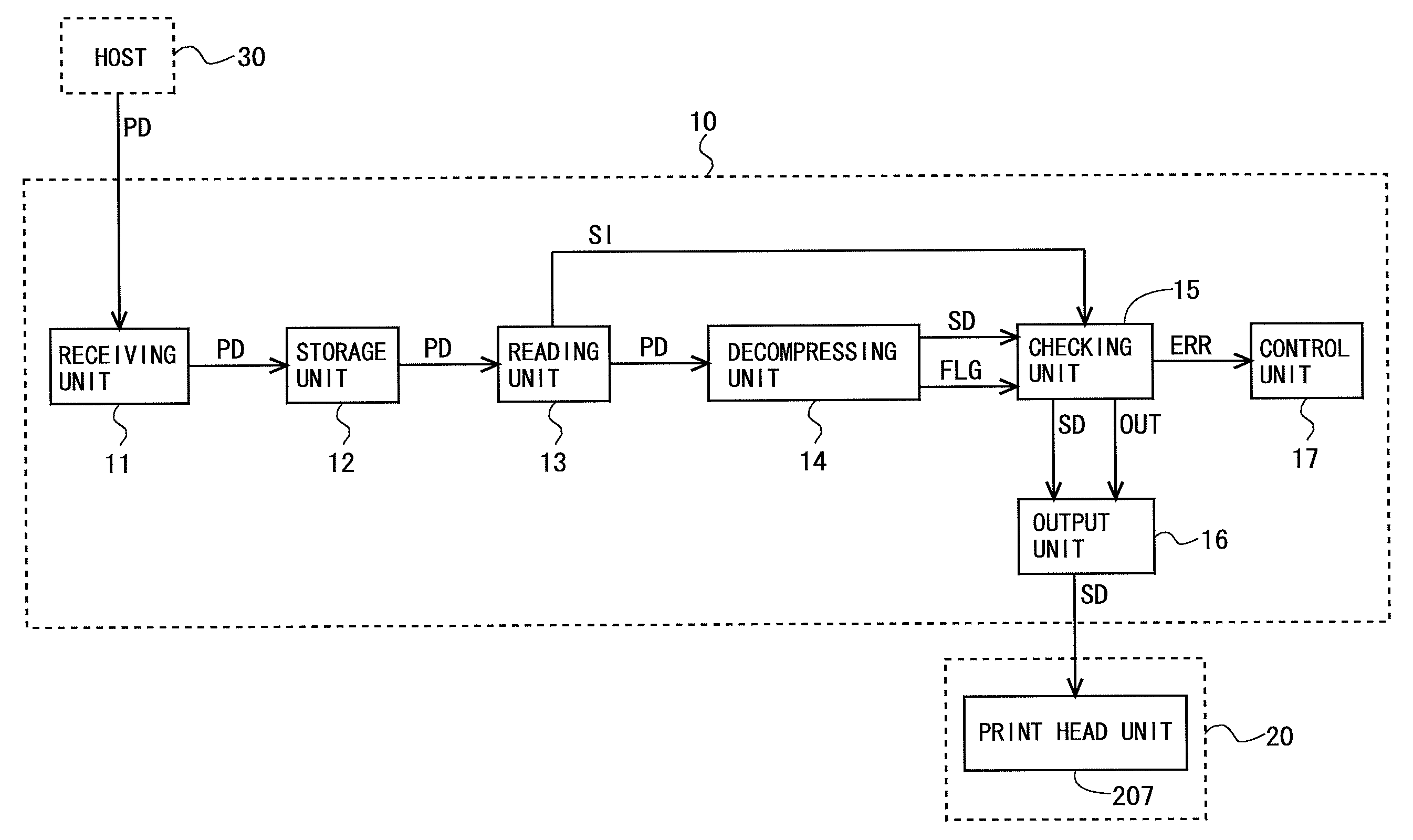

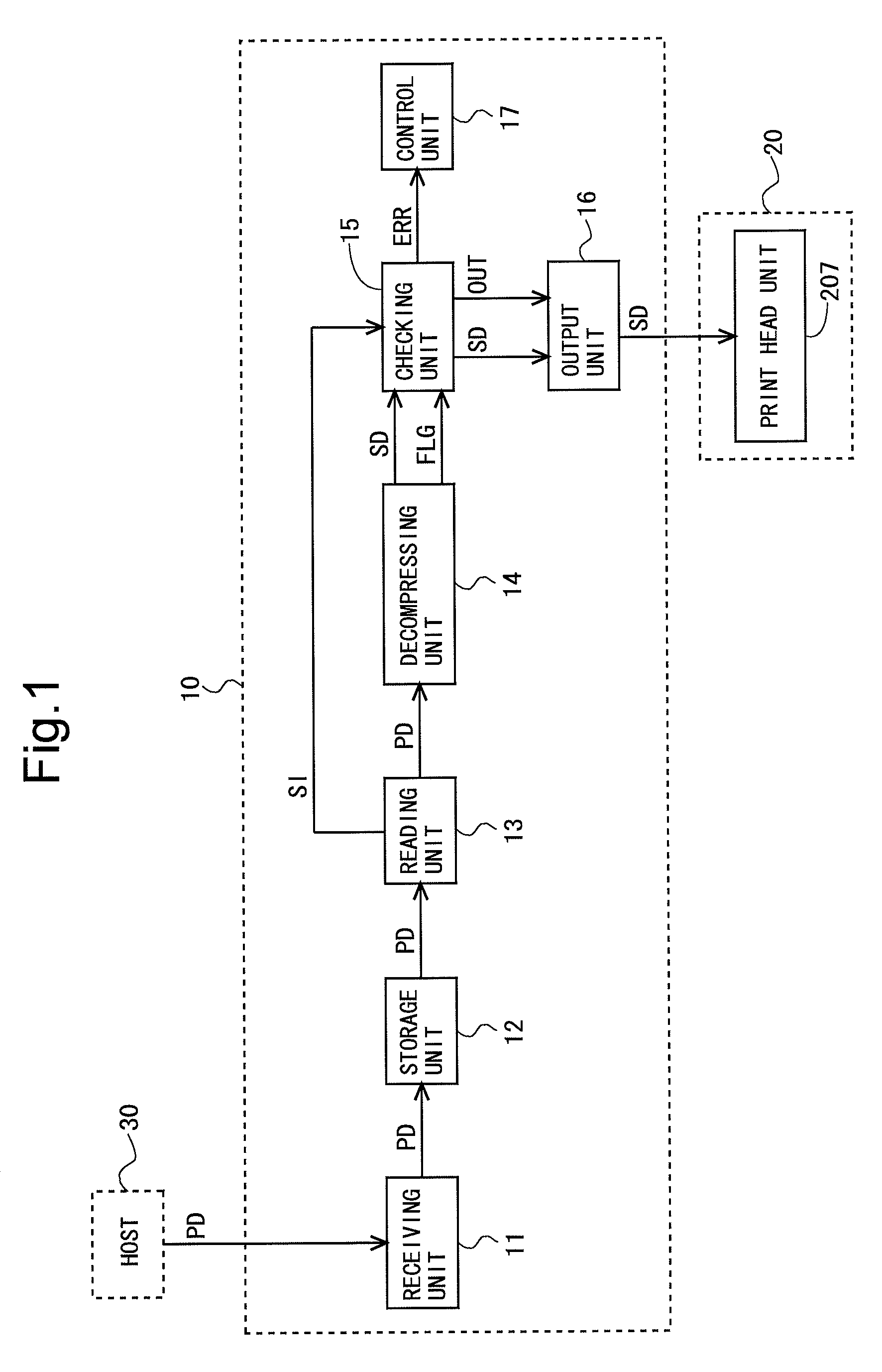

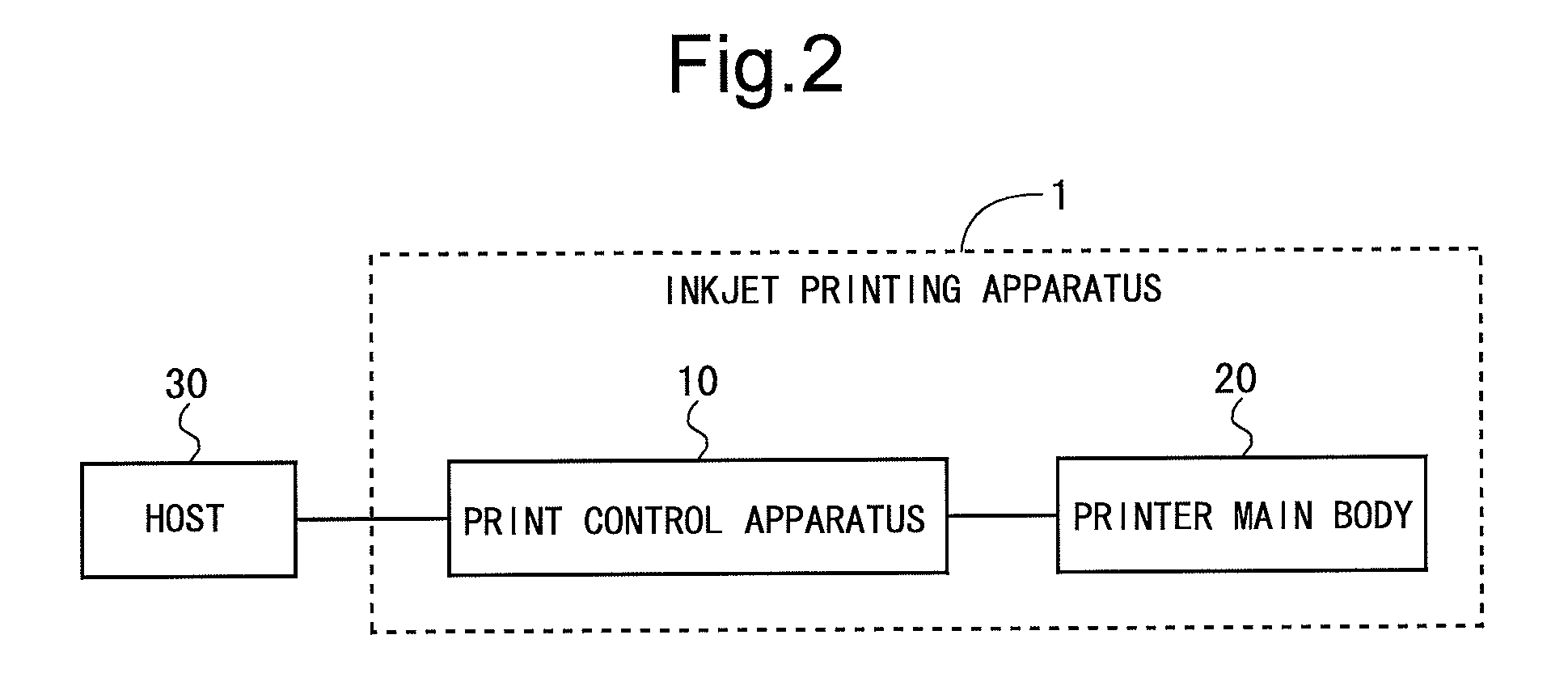

Print control apparatus, inkjet printing apparatus, print control method, and recording medium with data compression/decompression

ActiveUS8964205B2Shorten speedEasy to detectDigitally marking record carriersDigital computer detailsData compressionNOP

Compressed data transmitted to a print control apparatus includes break data having information on a compressed size and a decompressed size for each page. When the compressed data is transferred to a decompressing unit, the break data is converted to NOP data. Information on the decompressed size included in each break data is provided to a checking unit. During a period in which a decompression process is performed, a decompression flag is turned on. The checking unit obtains the actual decompressed size by counting a period in which the decompression flag is turned on, to check whether the decompression process has been normally performed. During a period in which the decompressing unit and the checking unit perform processes for a certain page, a reading unit reads compressed data for the next page.

Owner:DAINIPPON SCREEN MTG CO LTD

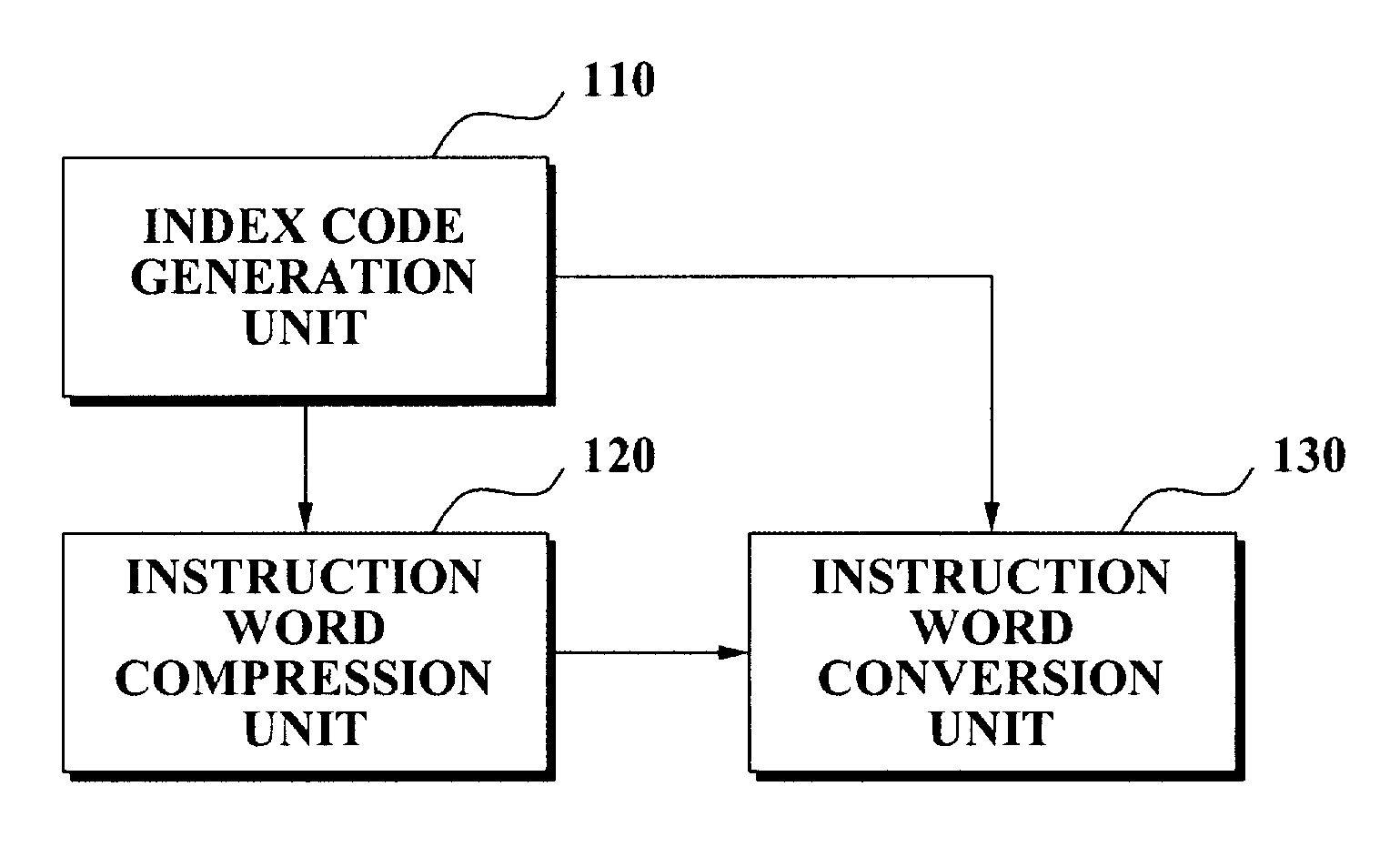

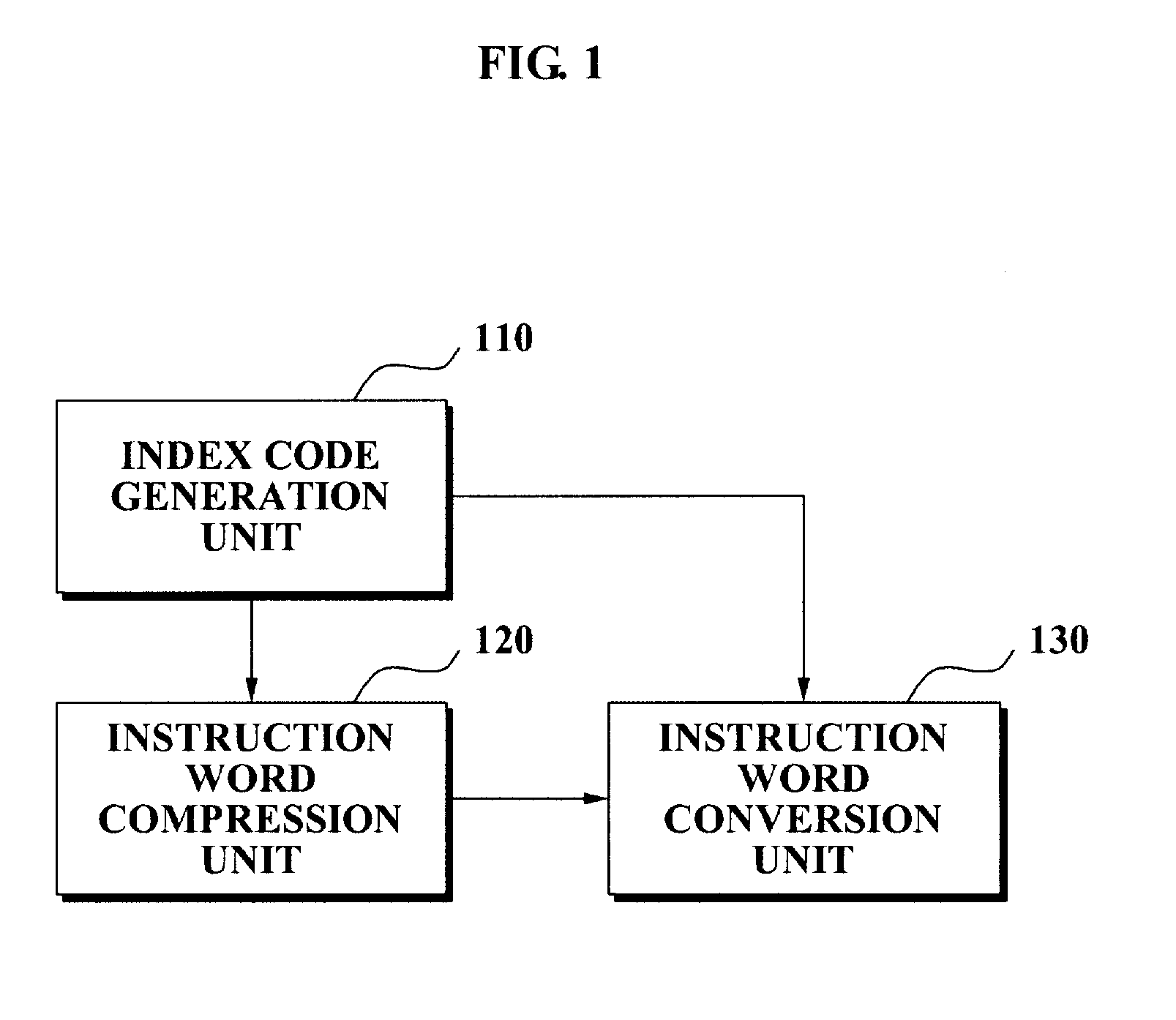

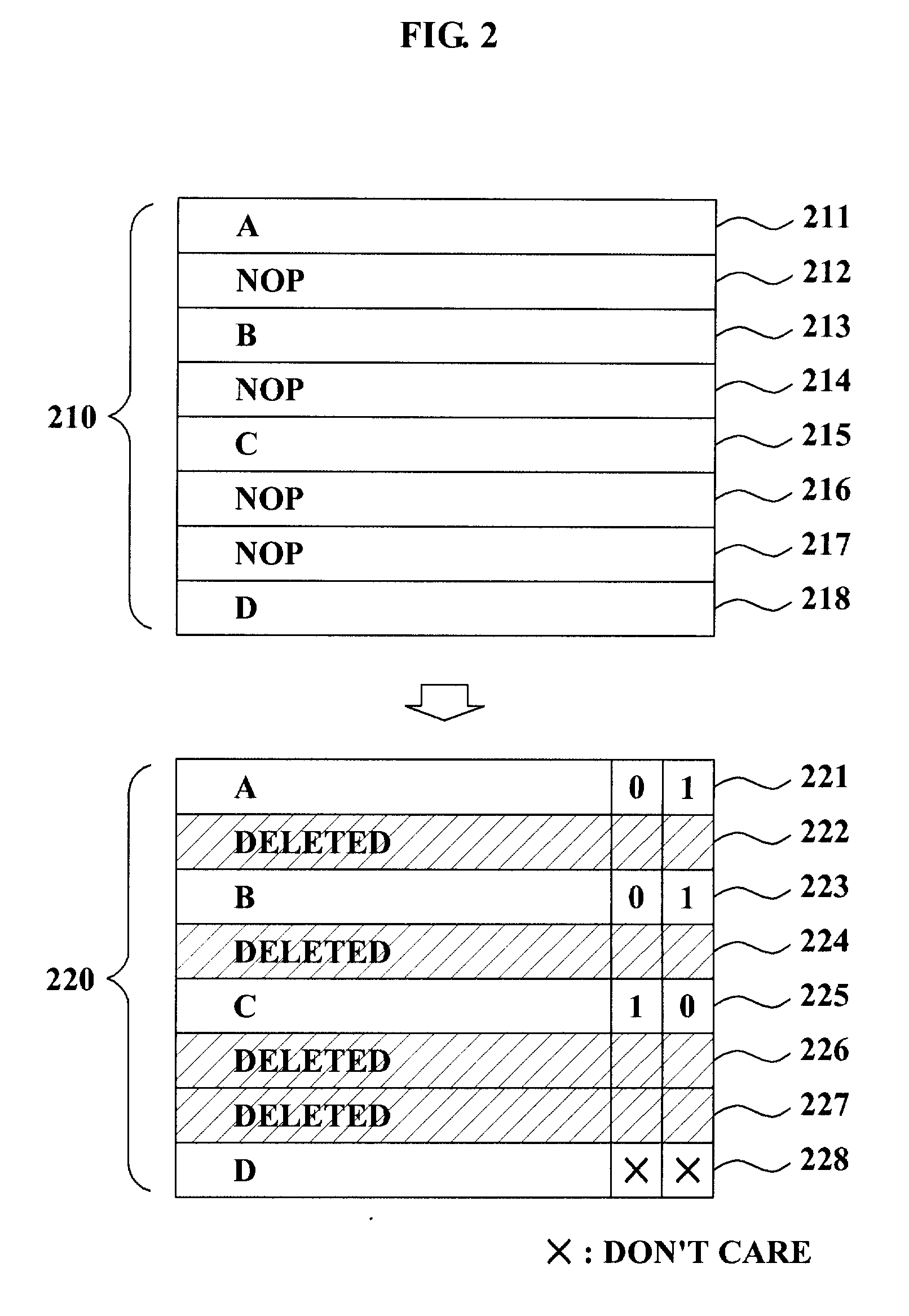

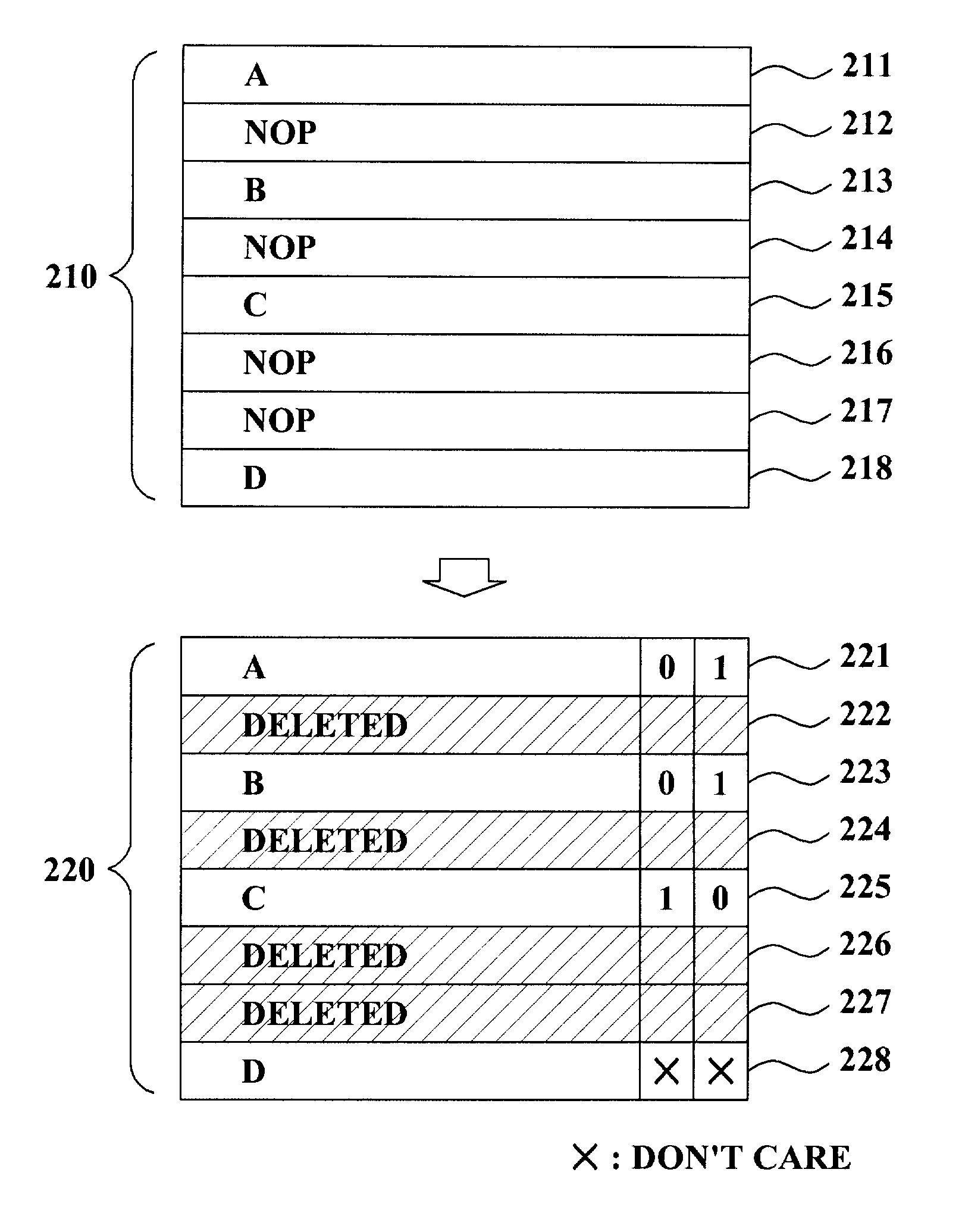

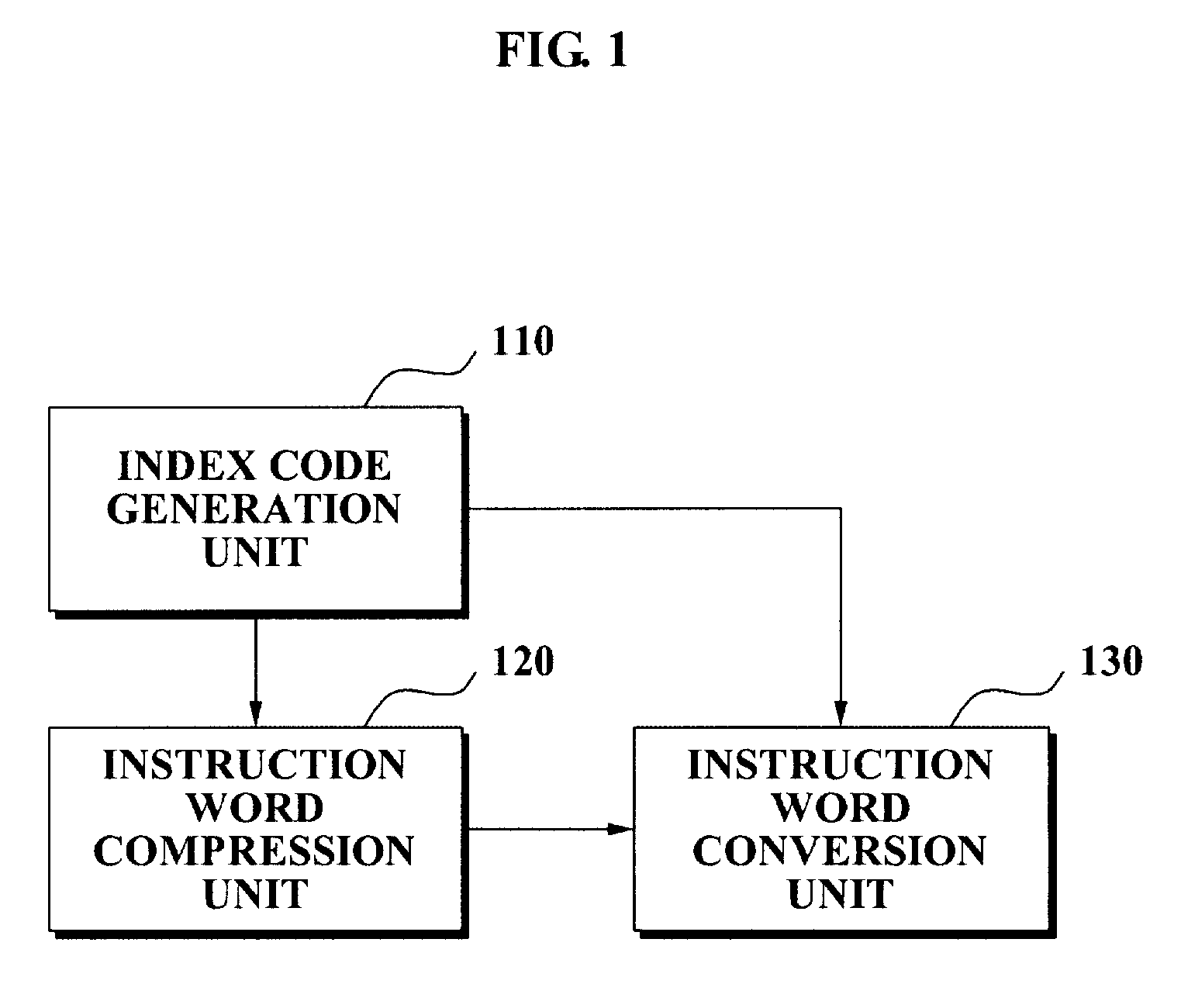

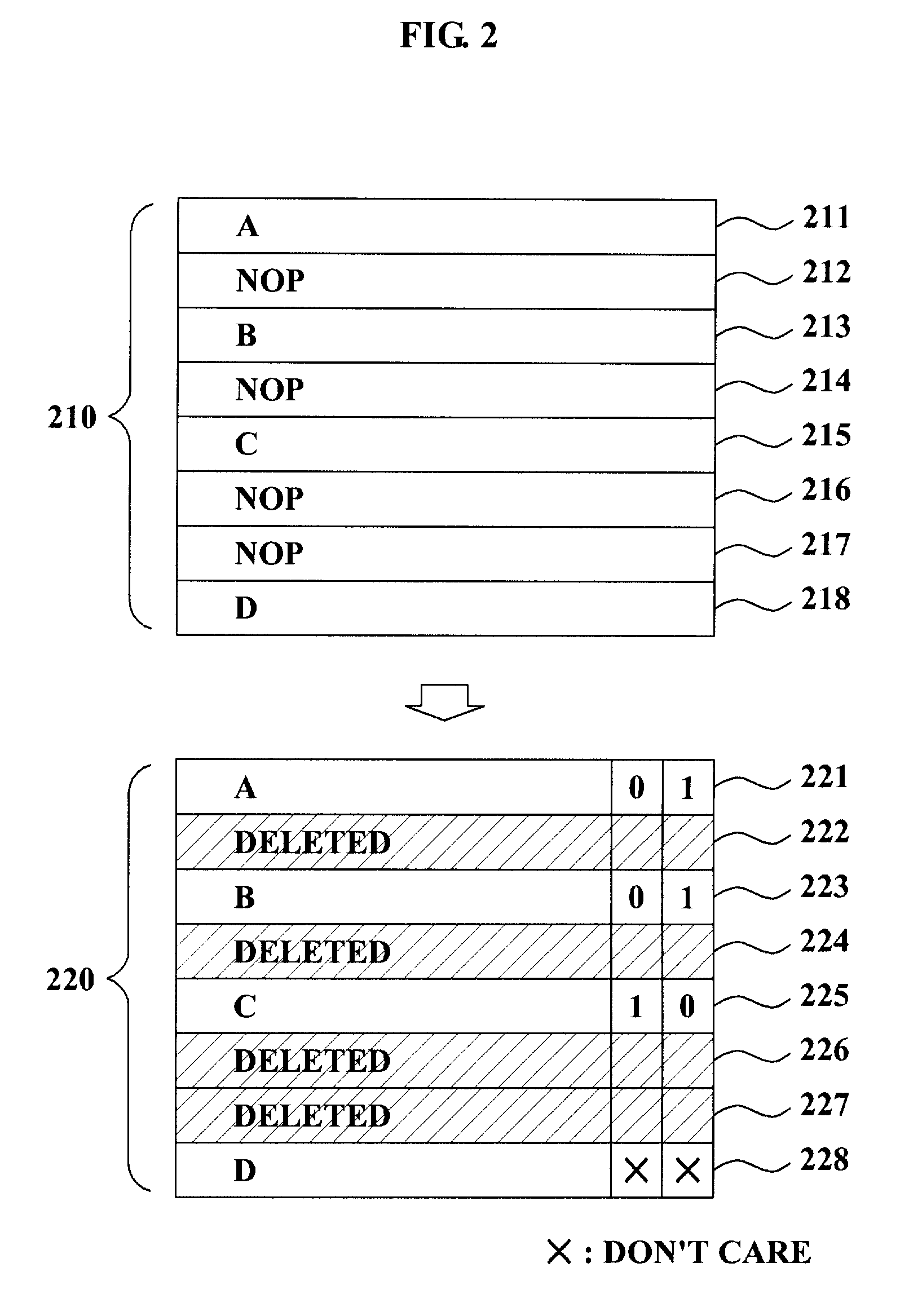

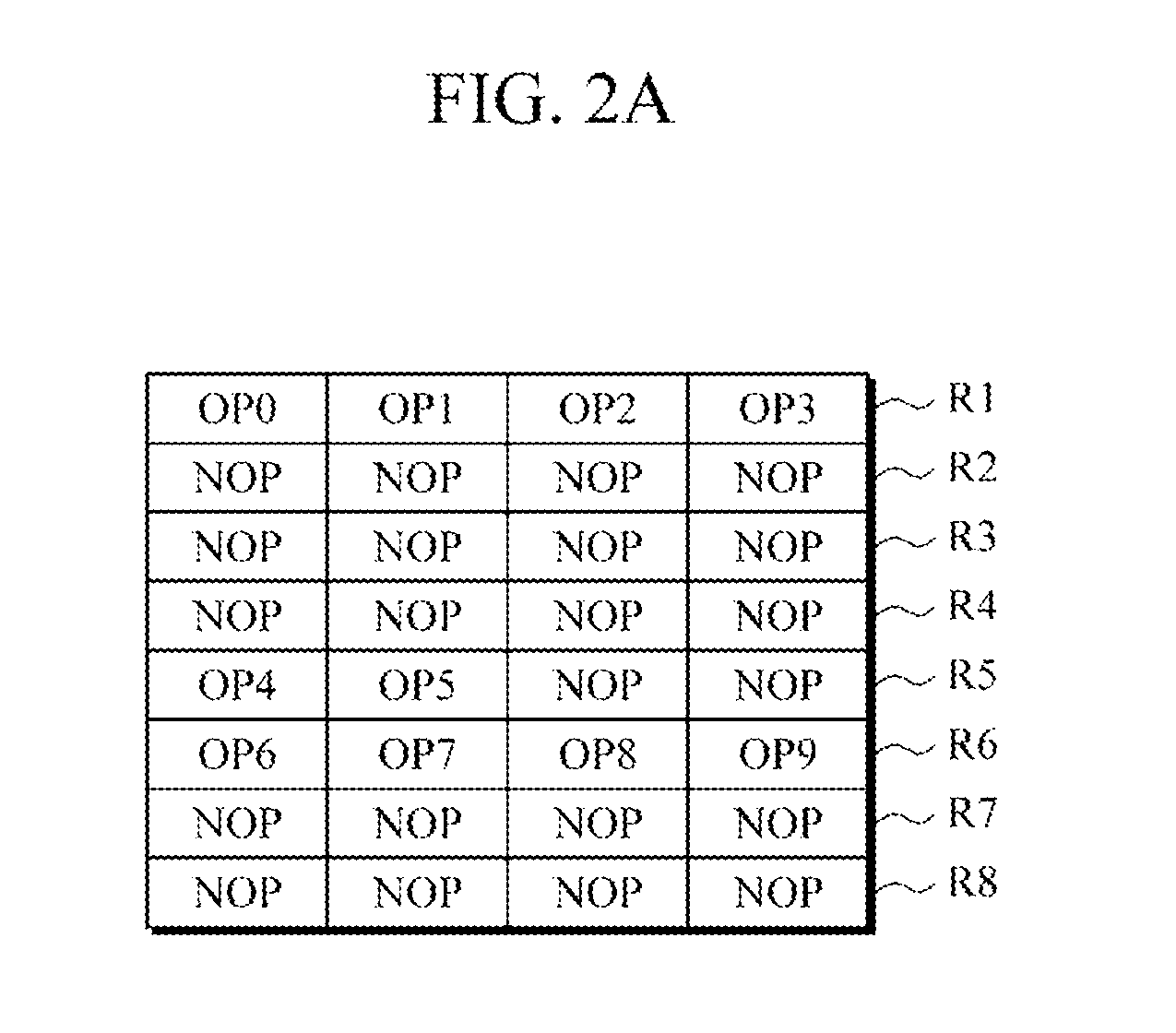

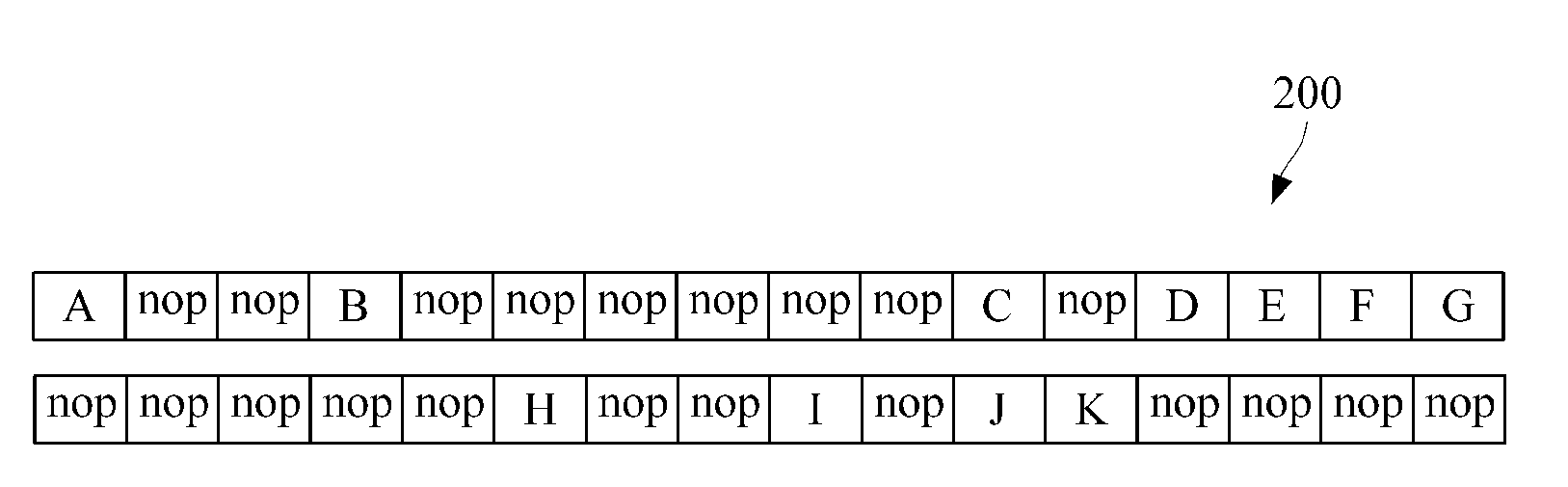

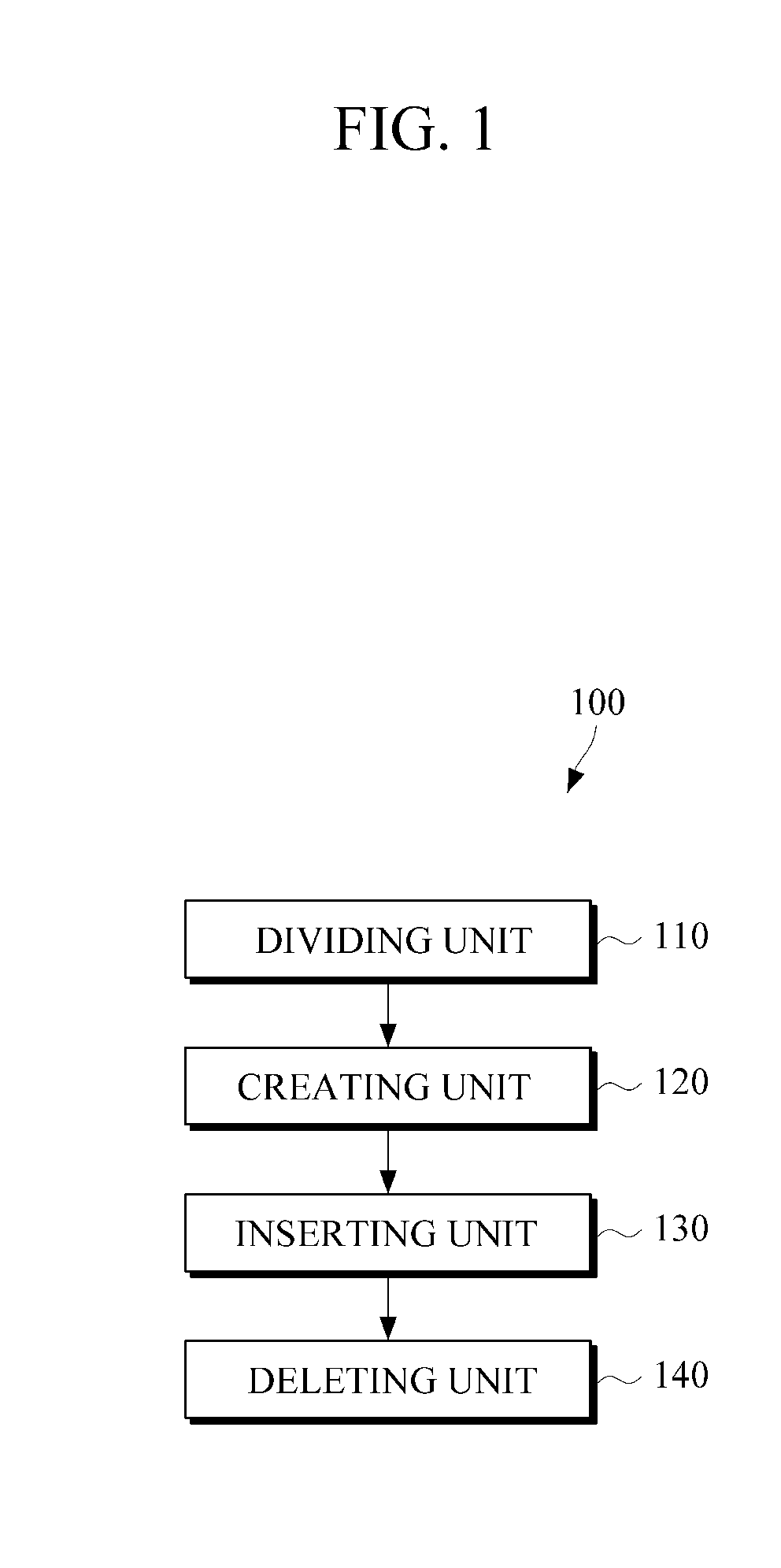

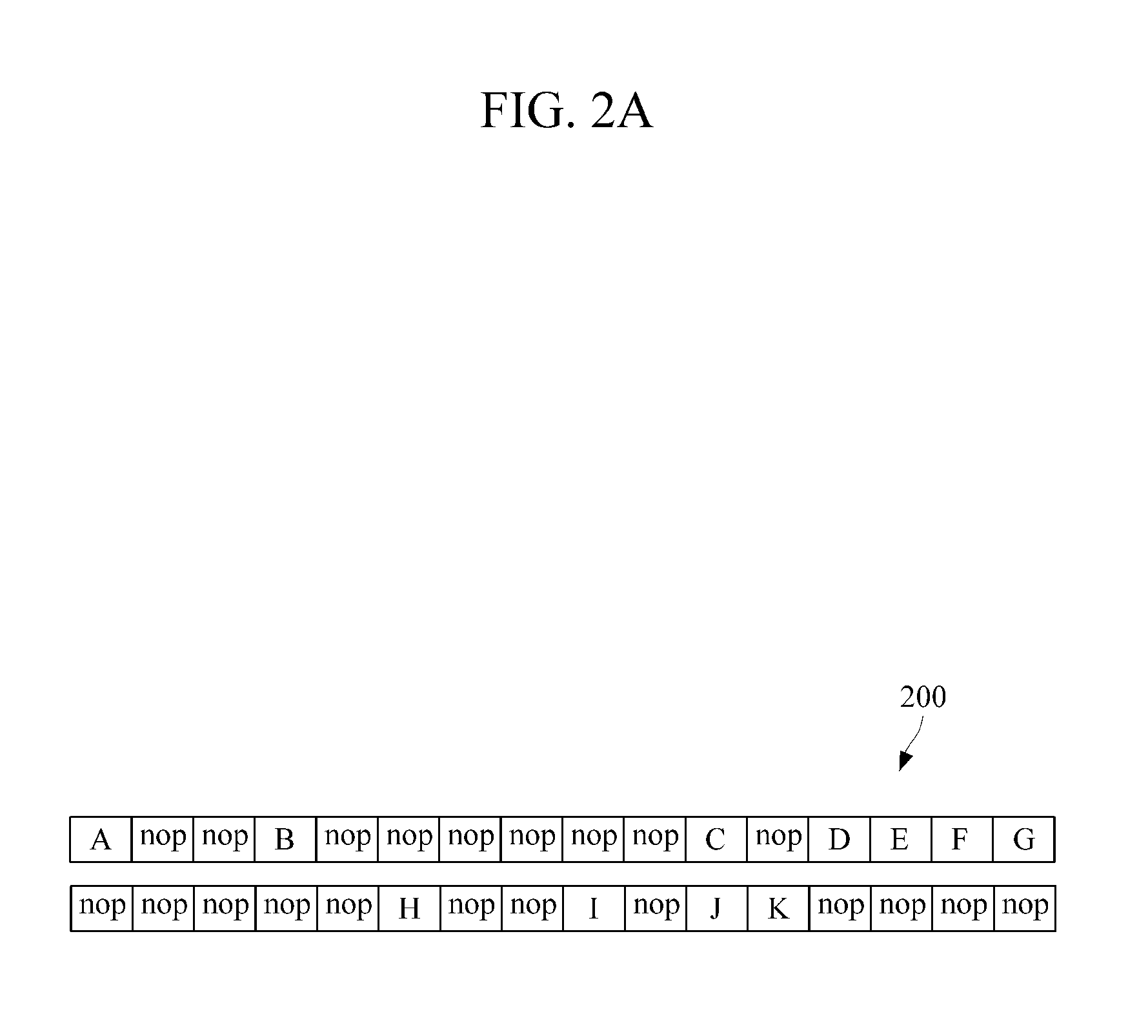

Apparatus for compressing instruction word for parallel processing vliw computer and method for the same

ActiveUS20080235492A1Reduce storage spaceImprove performanceProgram control using stored programsGeneral purpose stored program computerWord groupParallel processing

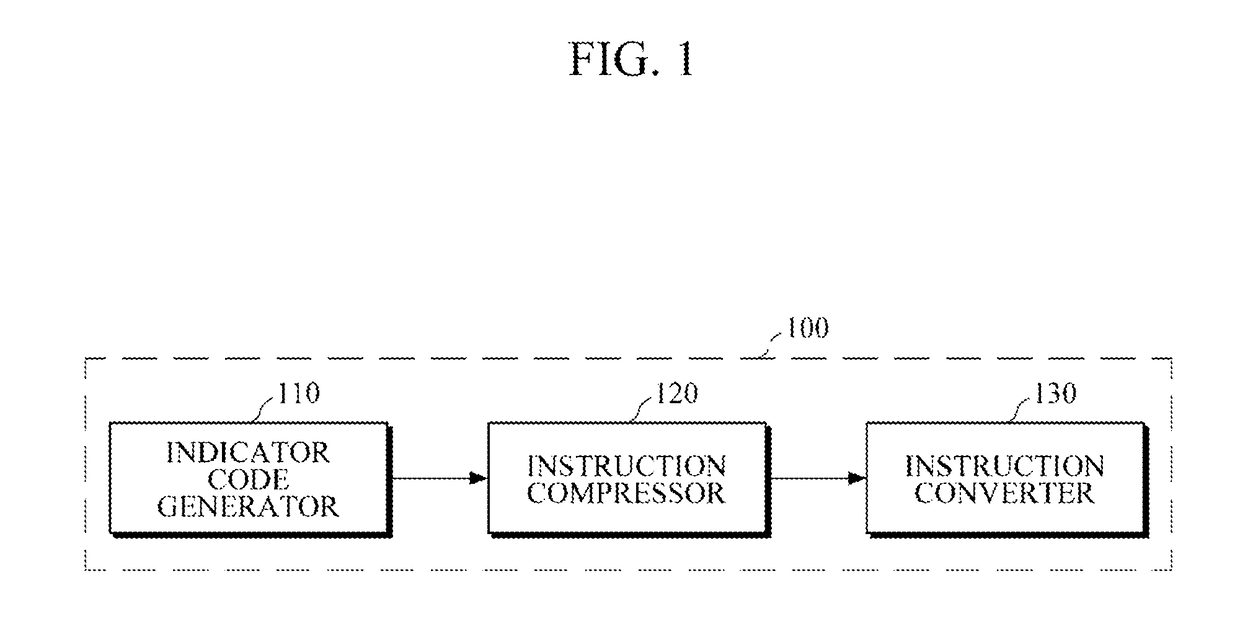

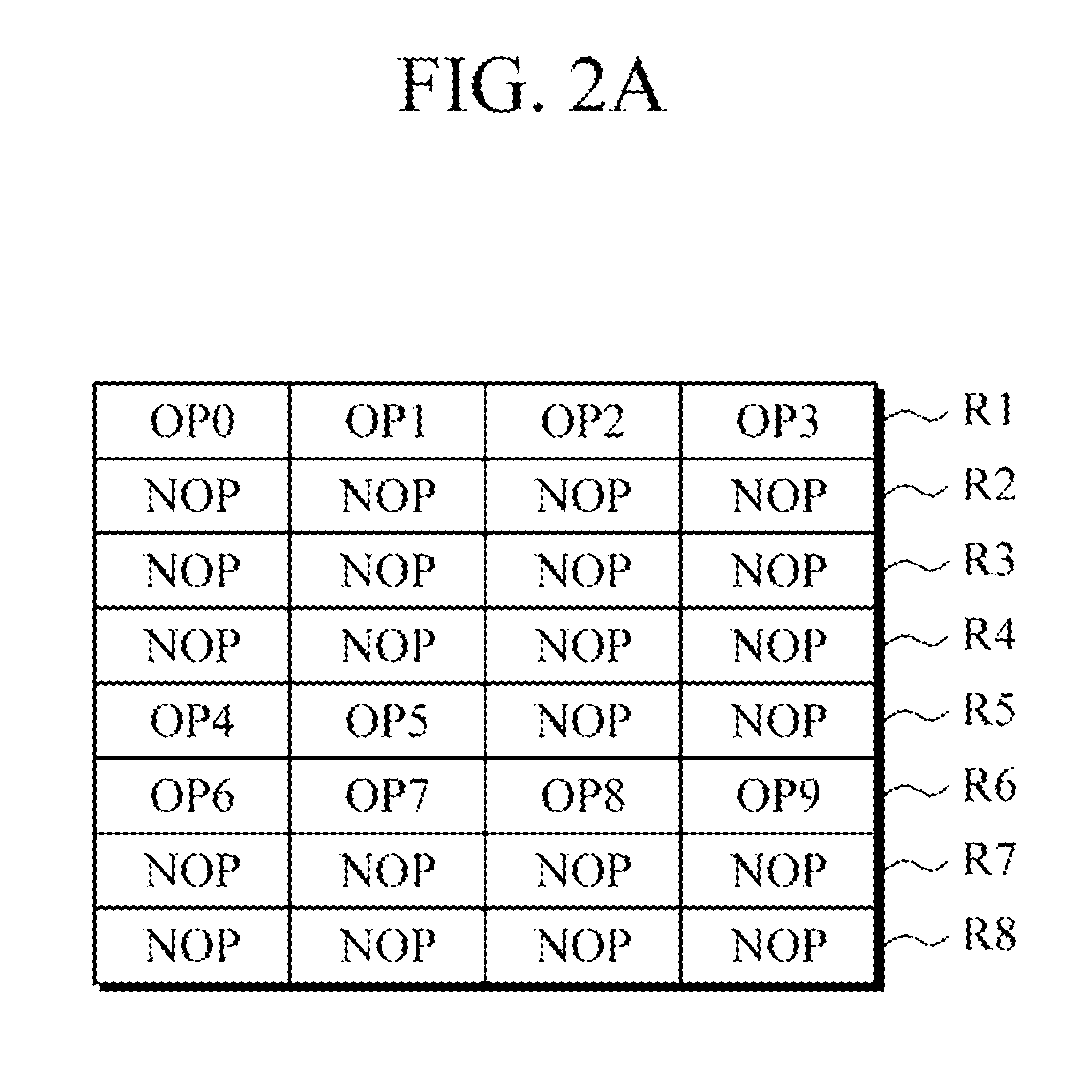

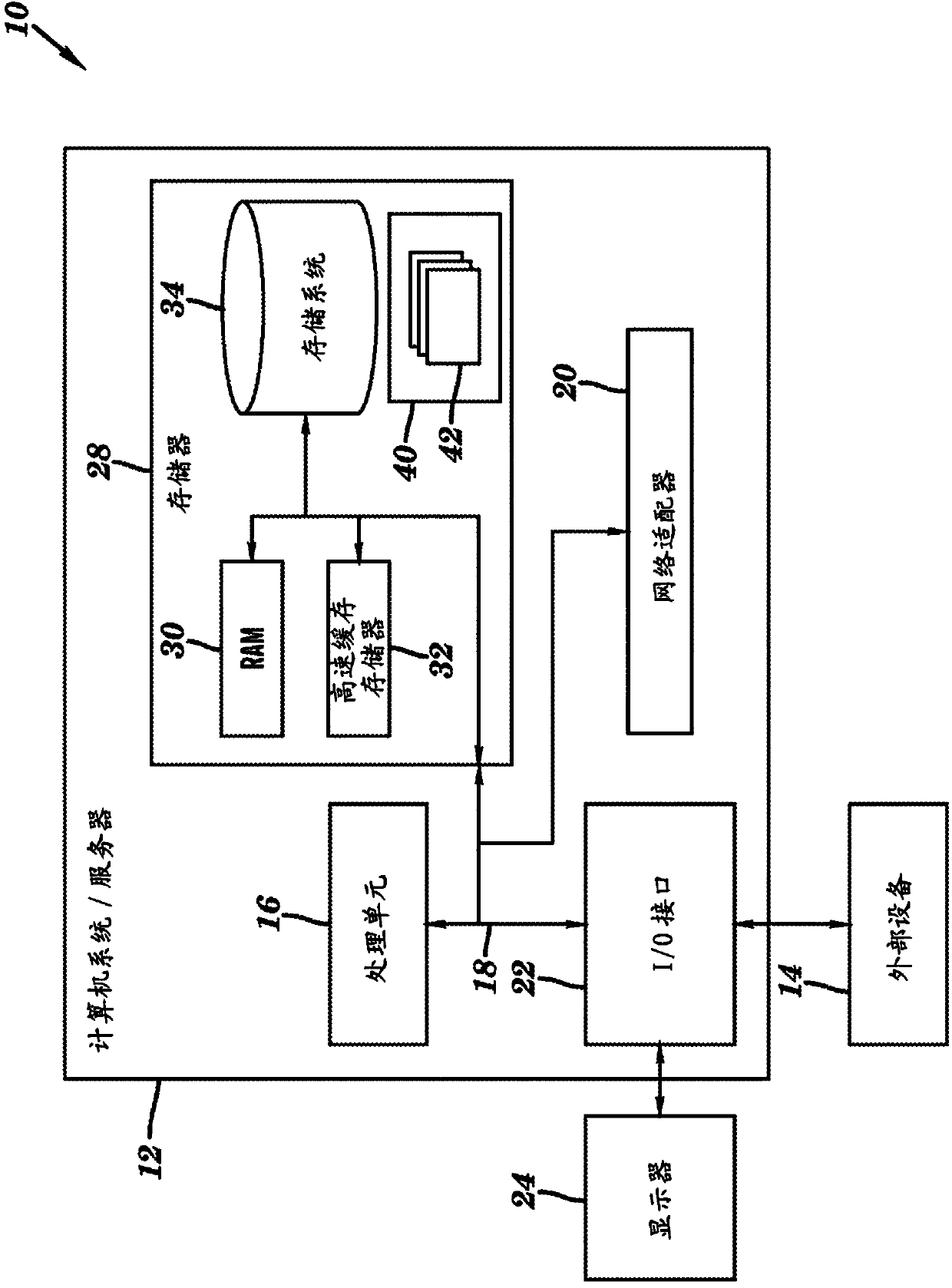

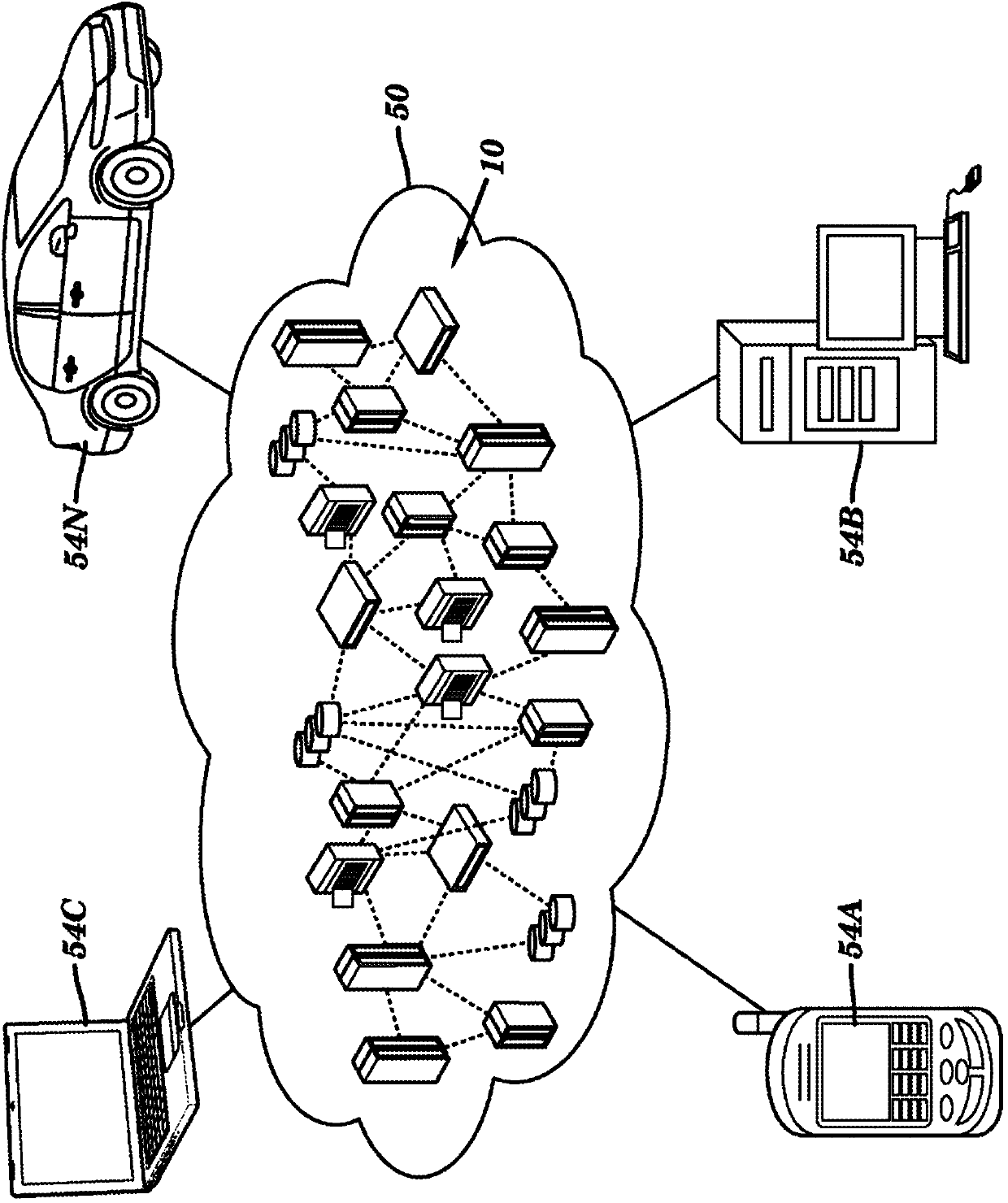

An apparatus and a method are provided for a parallel processing very long instruction word (VLIW) computer. The apparatus includes: an index code generation unit sequentially generating an index code, which is associated with a number of no operation (NOP) instruction word between effective instruction words, with respect to each of instruction word groups to be executed in a VLIW computer; an instruction compression unit sequentially deleting the NOP instruction word which corresponds to the index code with respect to each of instruction word groups; and an instruction word conversion unit converting the effective instruction words to include the index code, the effective instruction words corresponding to the NOP instruction words.

Owner:SAMSUNG ELECTRONICS CO LTD

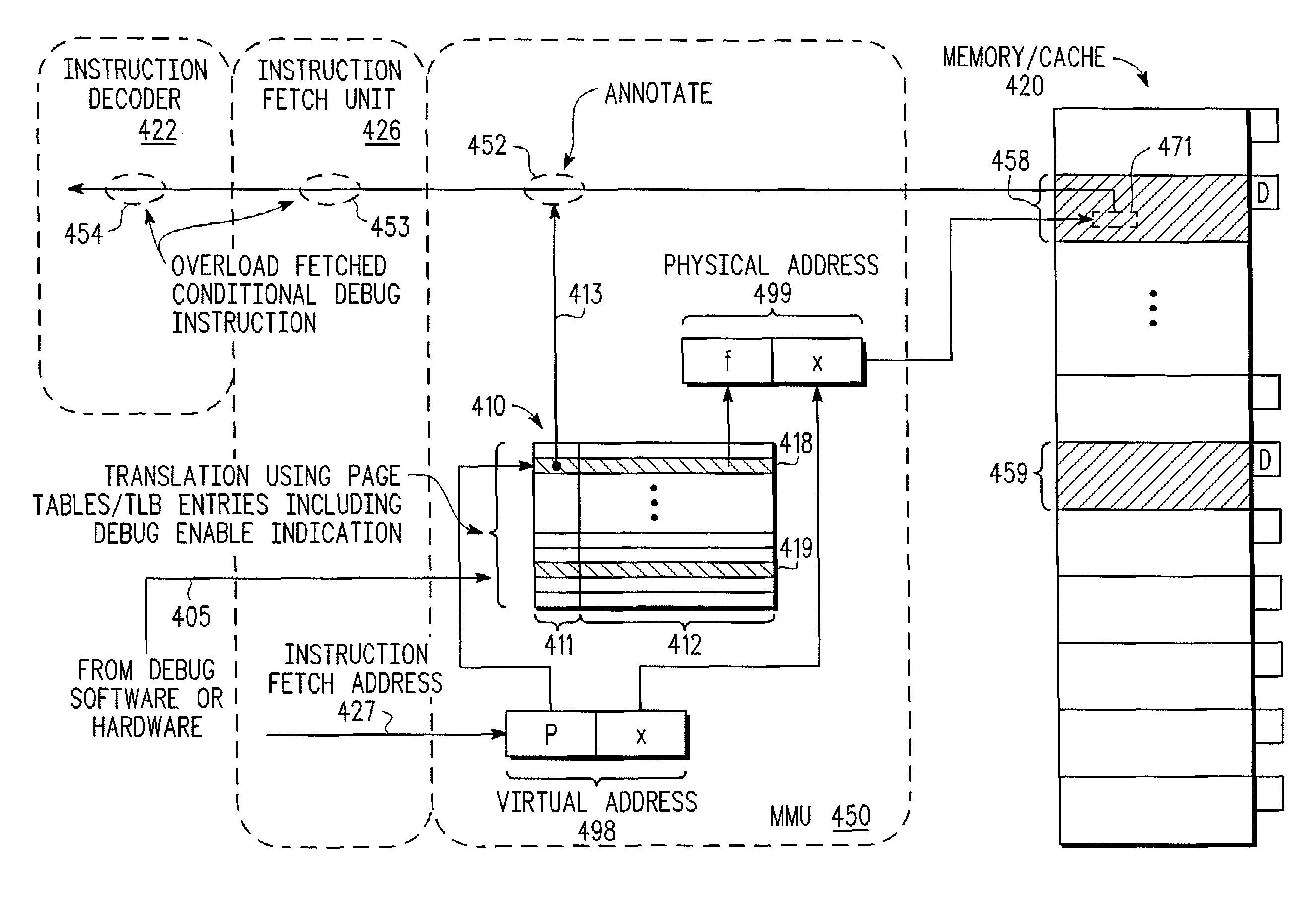

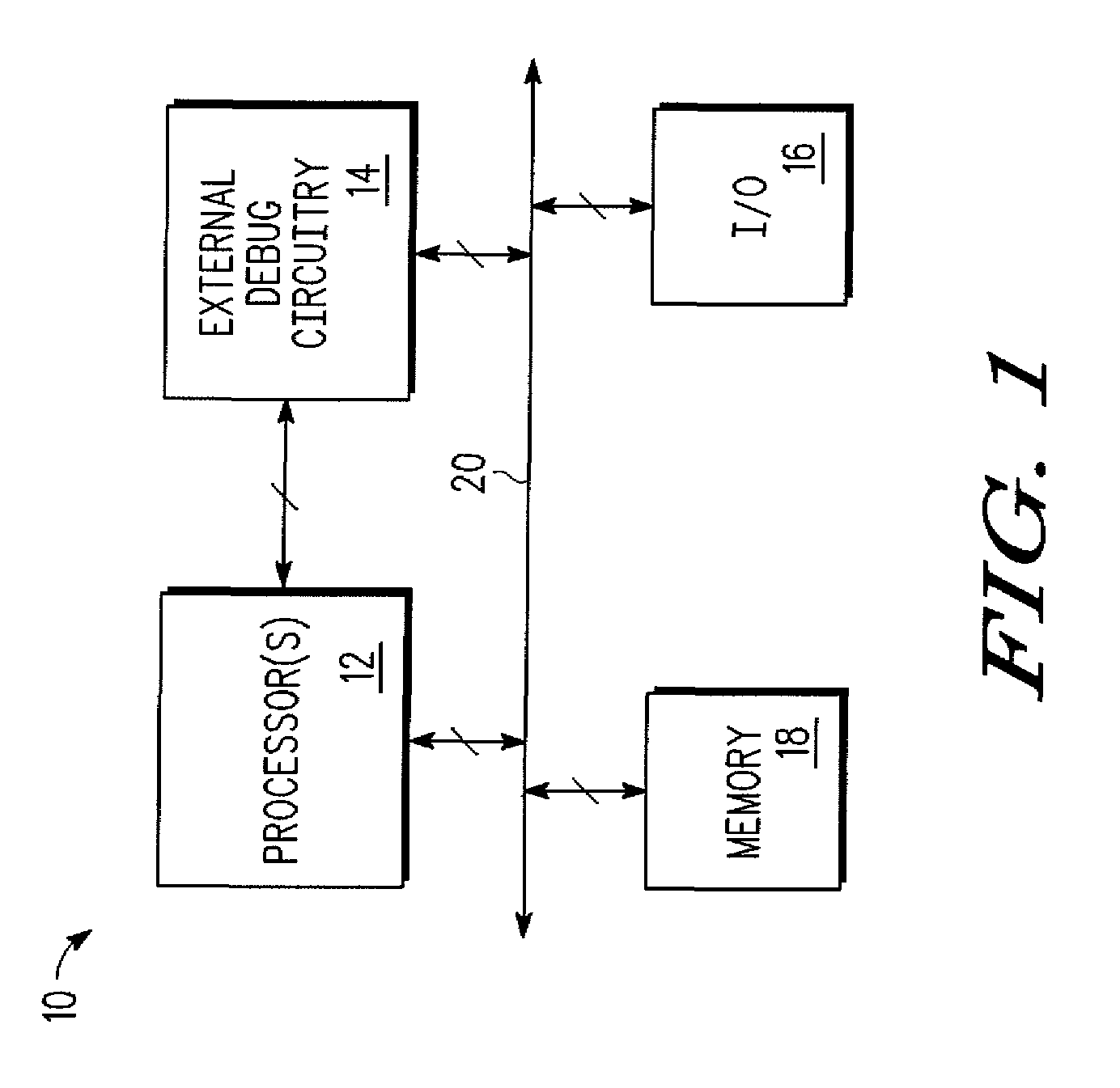

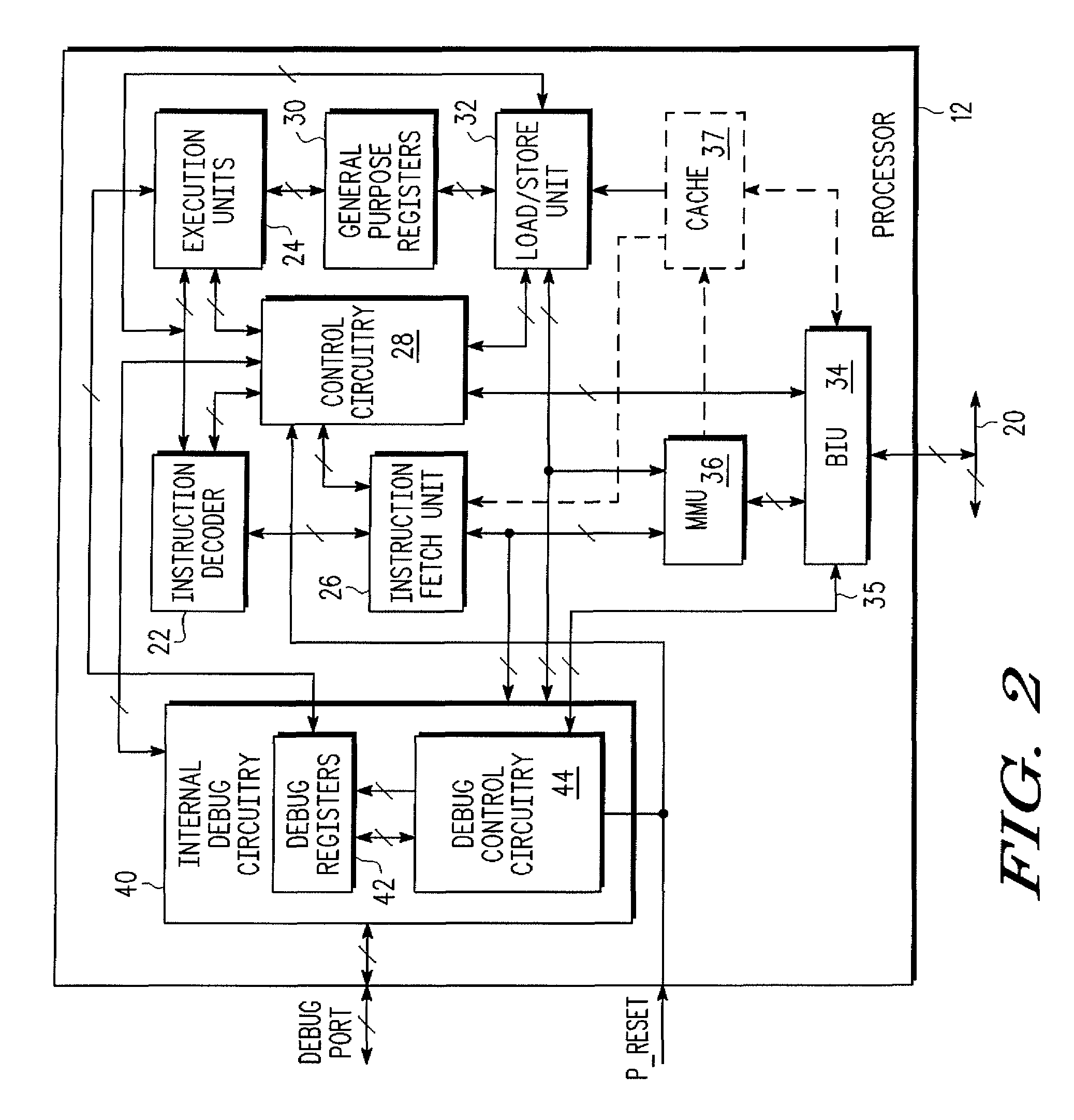

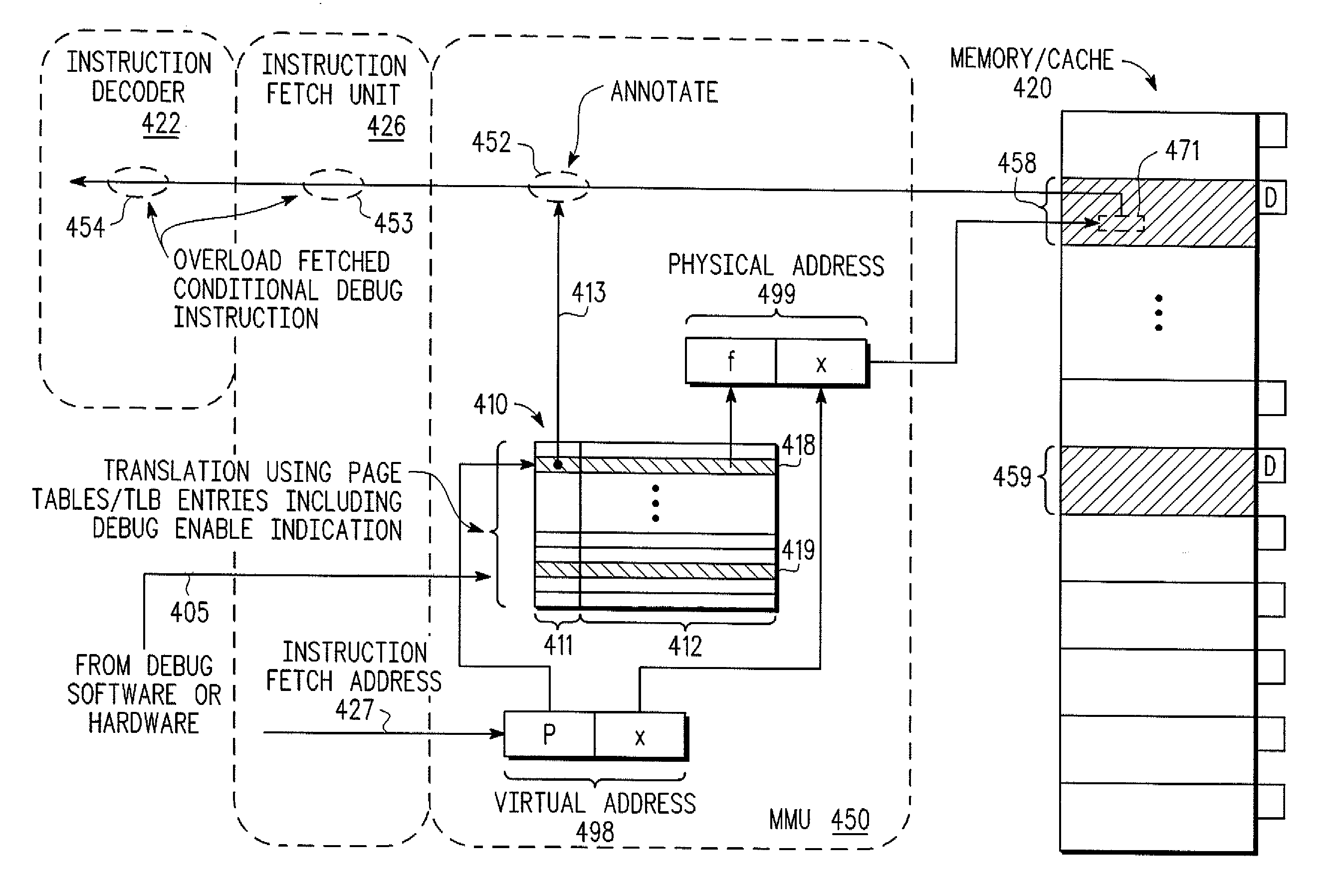

Qualification of conditional debug instructions based on address

A processor implementation supports selection of an execution mode for debug instruction instances based on respective addresses thereof in addressable memory can provide an attractive mechanism for executing debug instructions in a way that allows some instances of the instructions to operate with debug semantics while suppressing other instances by executing them with no-operation (NOP) semantics. In some embodiments, selection of operative execution semantics may be based on attributes of a memory page in which a particular debug instruction instance resides. In some embodiments, portions of an address space may be delimited (e.g., using values stored in bounding registers and addresses of particular debug instruction instances compared against the delimited portions to select appropriate execution semantics. In some embodiments, both types of evaluations may be used in selecting appropriate execution semantics for a particular debug instruction instance.

Owner:SONY CORP +2

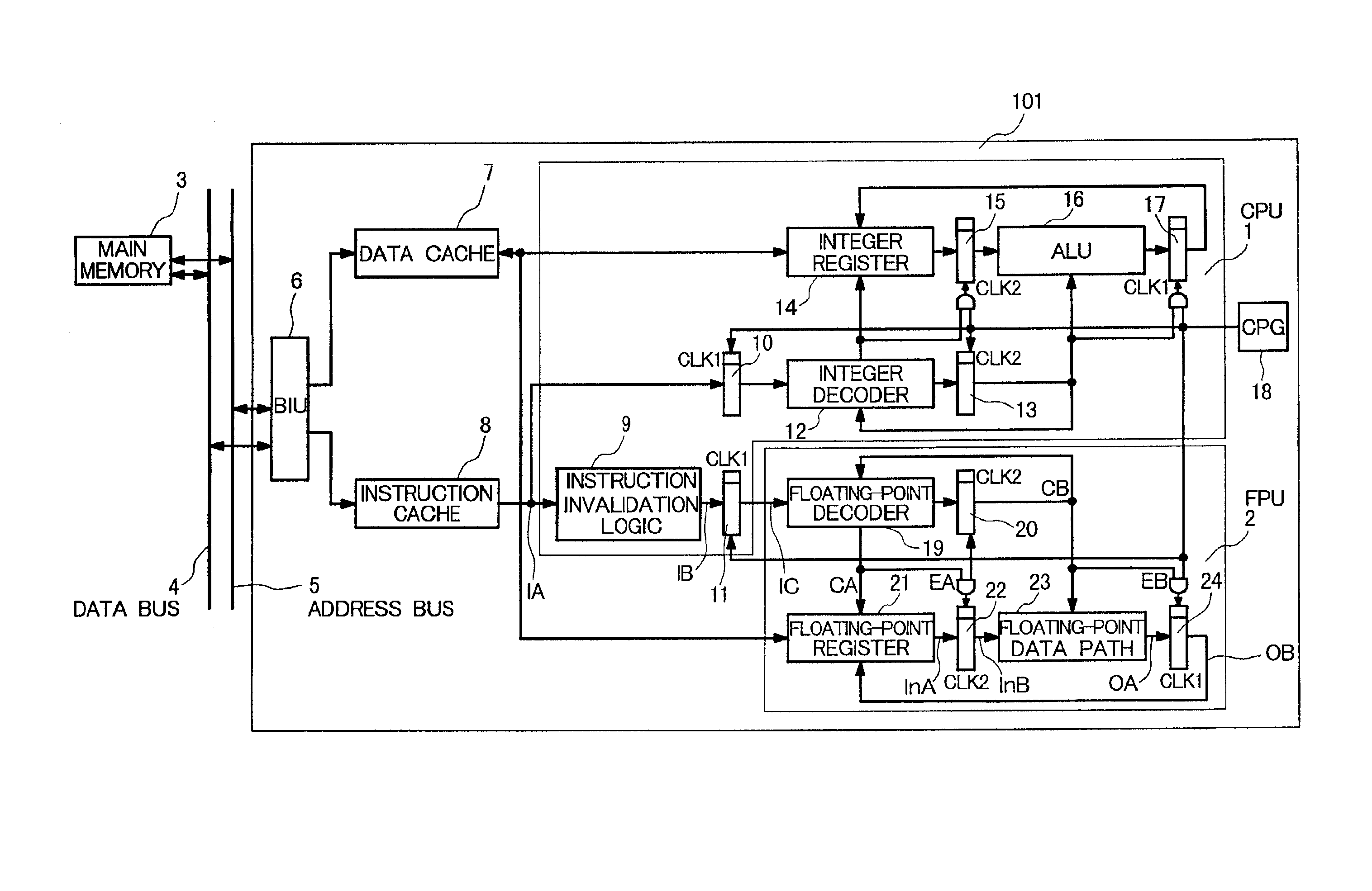

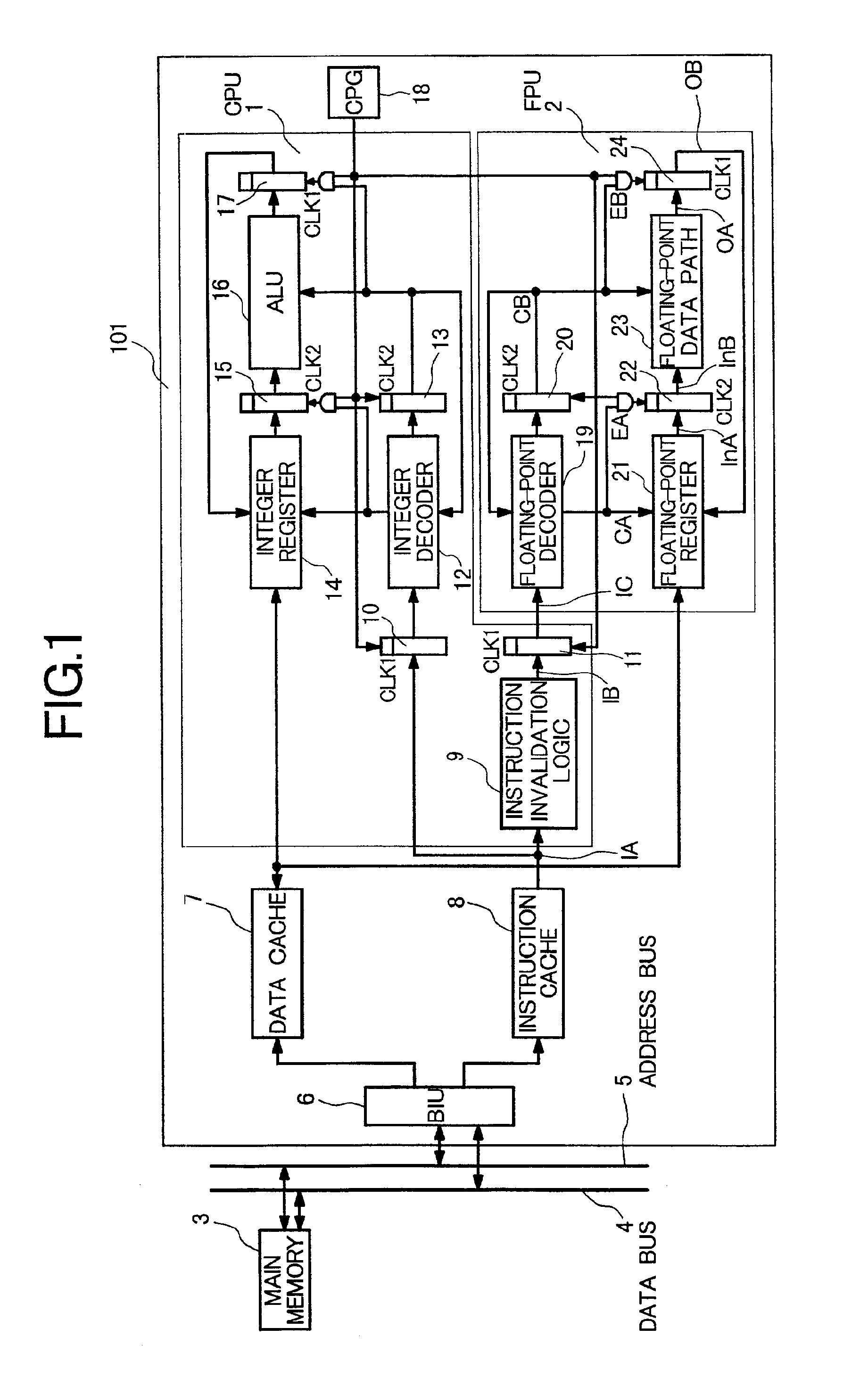

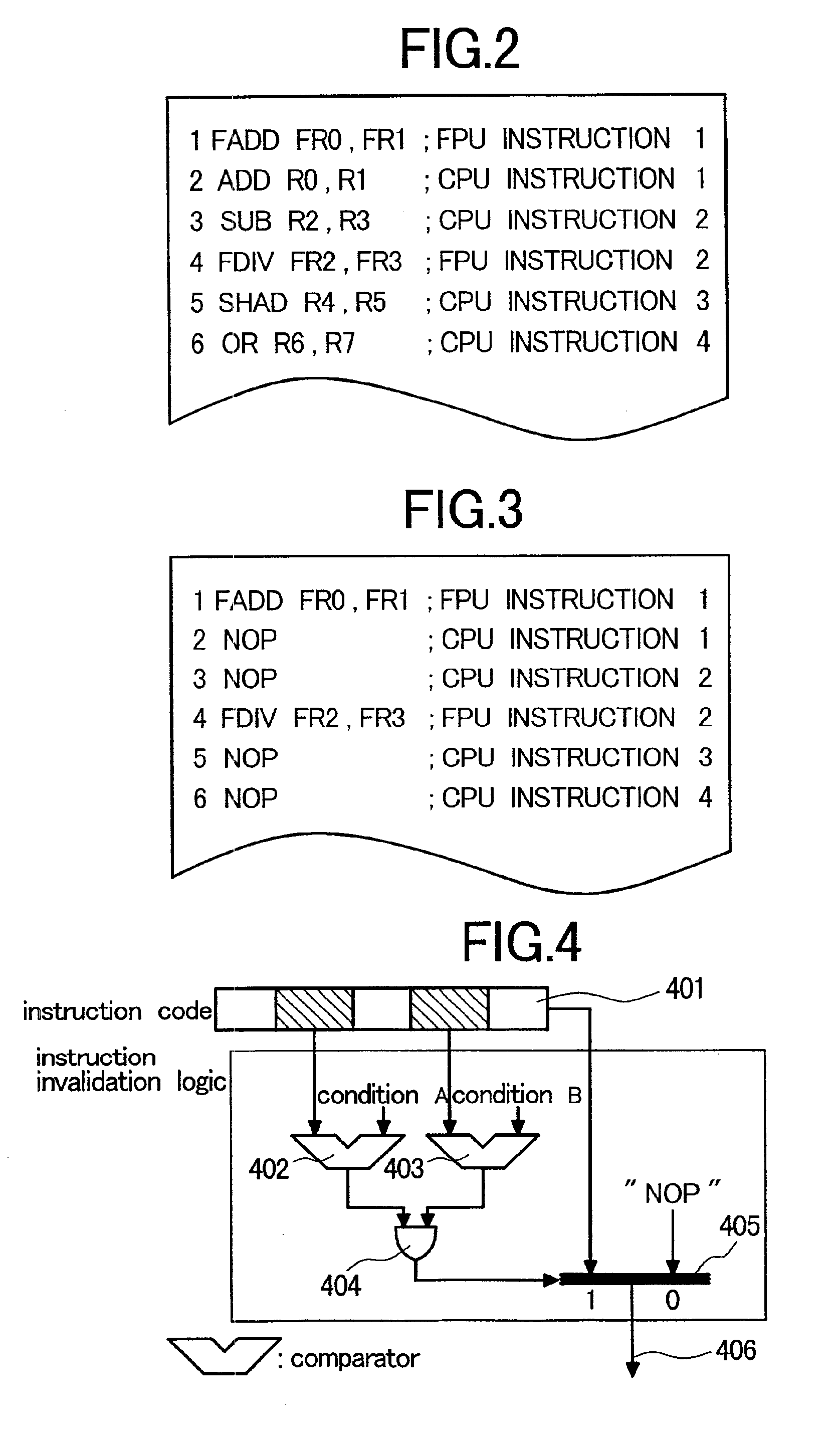

Substituting specified instruction with NOP to functional unit and halting clock pulses to data latches for power saving

InactiveUS6877087B1Reduce switchingTotal current dropEnergy efficient ICTSoftware engineeringProcessor registerParallel computing

A microprocessor to reduce wasteful power consumption of the floating-point unit. An instruction invalidation logic circuit is utilized to substitute the instruction not-to-use-the-floating-point unit, in the instruction string supplied from the instruction cache, with an invalidating instruction, hold that invalidating instruction in the floating-point register, and supply that invalidating instruction to a floating-point decoder in the floating-point unit. In cases when the invalidating instruction was continuous, the power consumption in the floating-point data path as well as the in the floating-point decoder and floating-point register is reduced.

Owner:RENESAS ELECTRONICS CORP

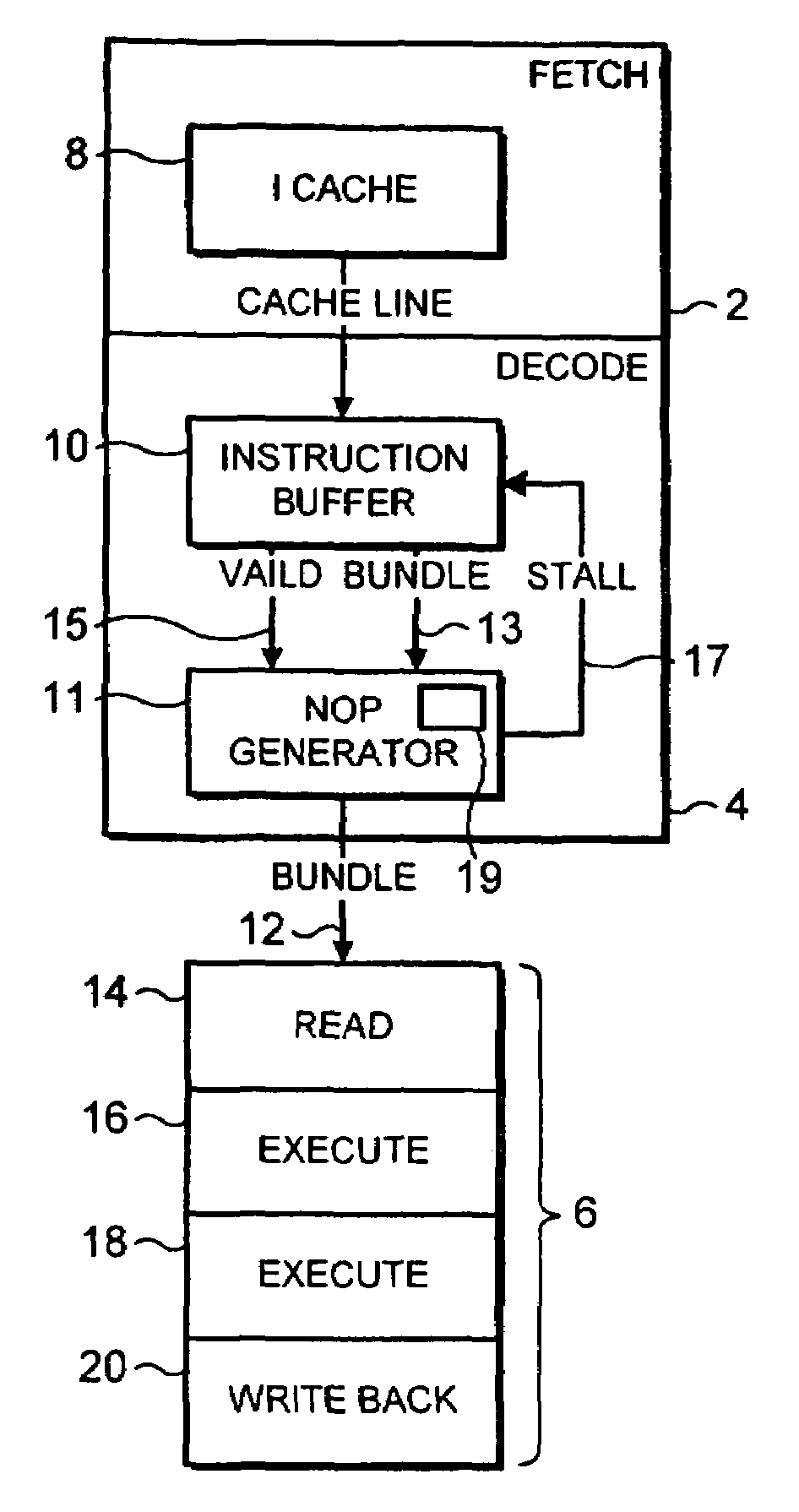

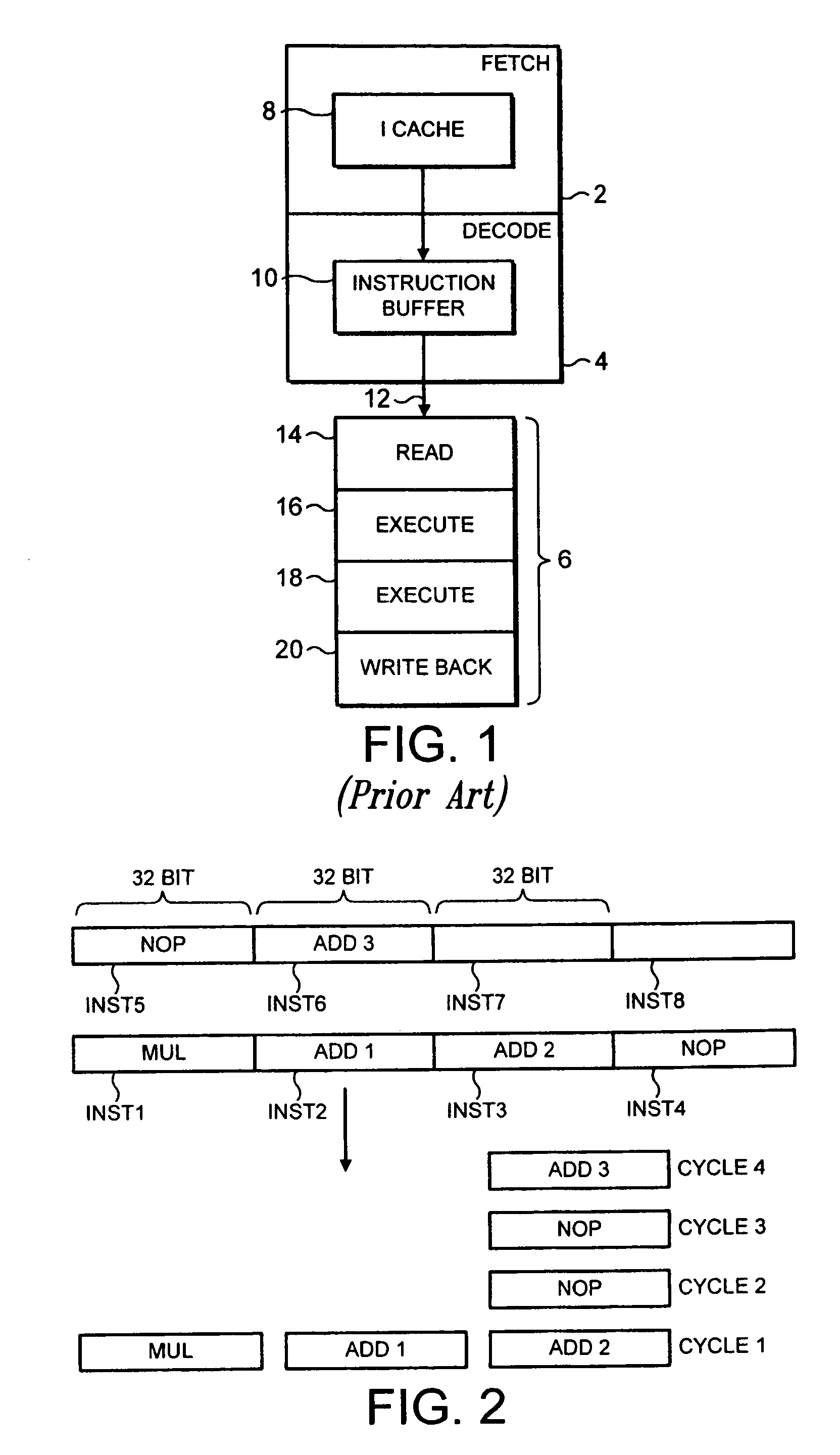

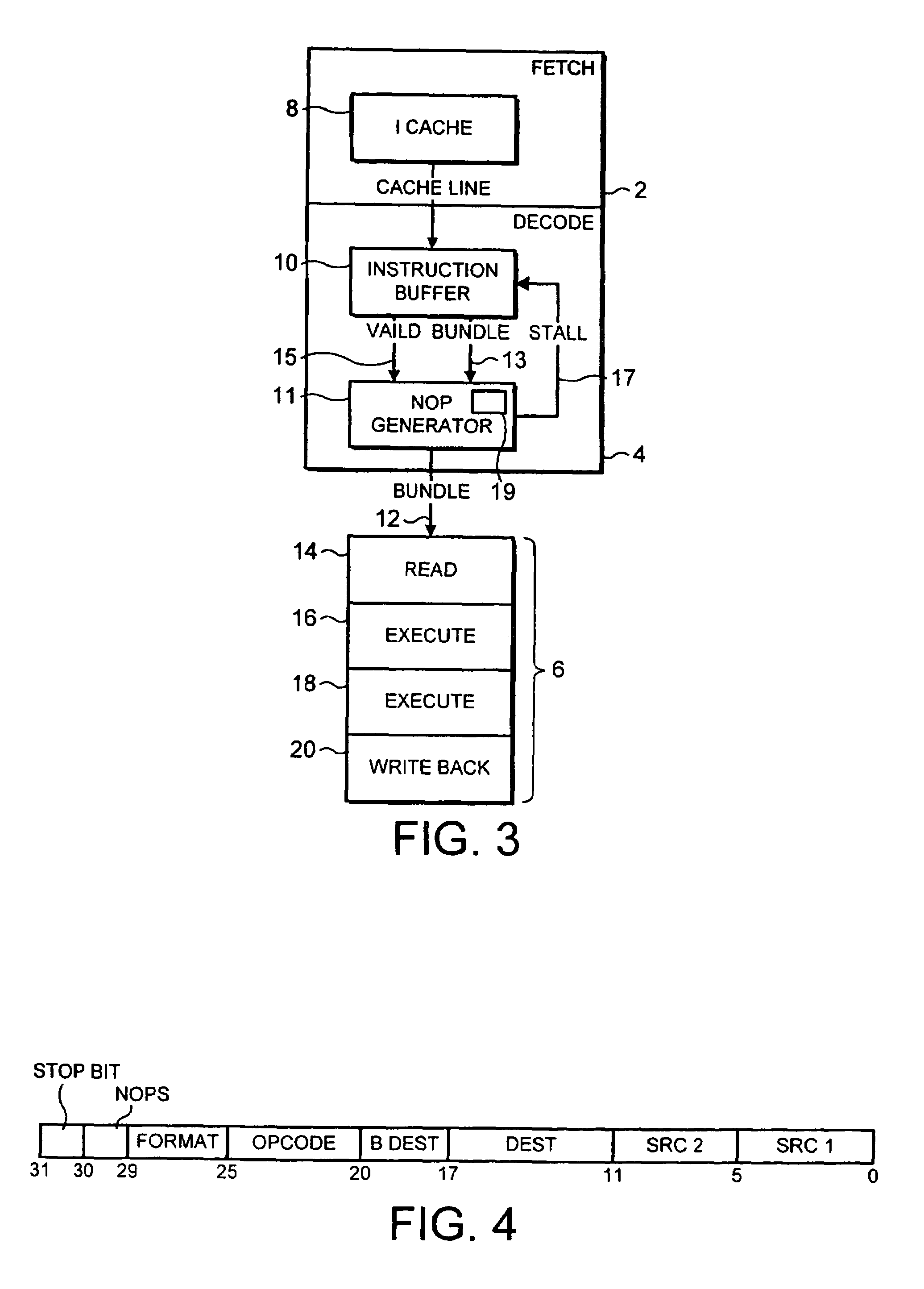

Processor and a method for handling and encoding no-operation instructions

InactiveUS7062634B1Reduce in quantitySuppresses increase in code sizeGeneral purpose stored program computerMemory systemsParallel computingNOP

A processor is described in which the need to encode no-operation instructions (nops) in the program is minimised by providing a device for generating nops in response to information encoded in operative instructions.

Owner:STMICROELECTRONICS LTD

Data compression method for supporting virtual memory management in a demand paging system

InactiveUS7512767B2Avoid indexImprove data performanceMemory architecture accessing/allocationMemory adressing/allocation/relocationData compressionManagement unit

A virtual memory management unit (306) includes a redundancy insertion module (307) which is used for inserting redundancy into an encoded data stream to be compressed, such that after being compressed each logical data block fits into a different one from a set of equal-sized physical data blocks of a given size. For example, said redundancy may be given by no-operation (NOP) instructions represented by a number of dummy sequences of a given length (L) into an encoded data stream to be compressed, each dummy sequence being composed of a number of identical binary or hexadecimal fill-in values.

Owner:SONY ERICSSON MOBILE COMM AB

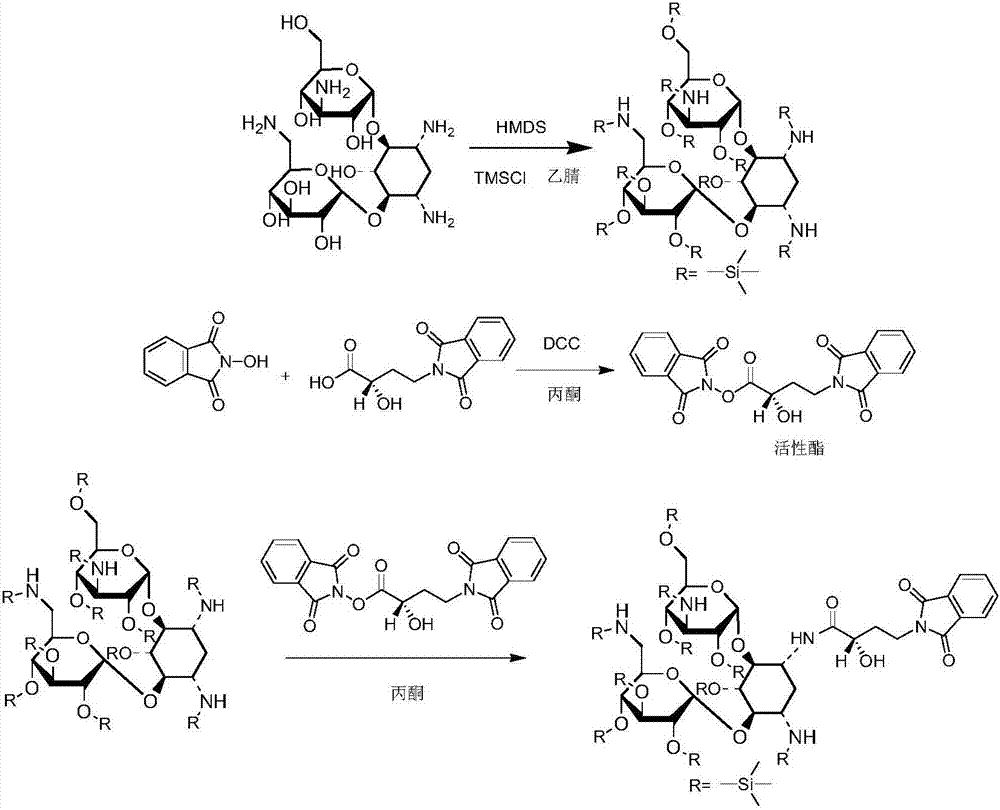

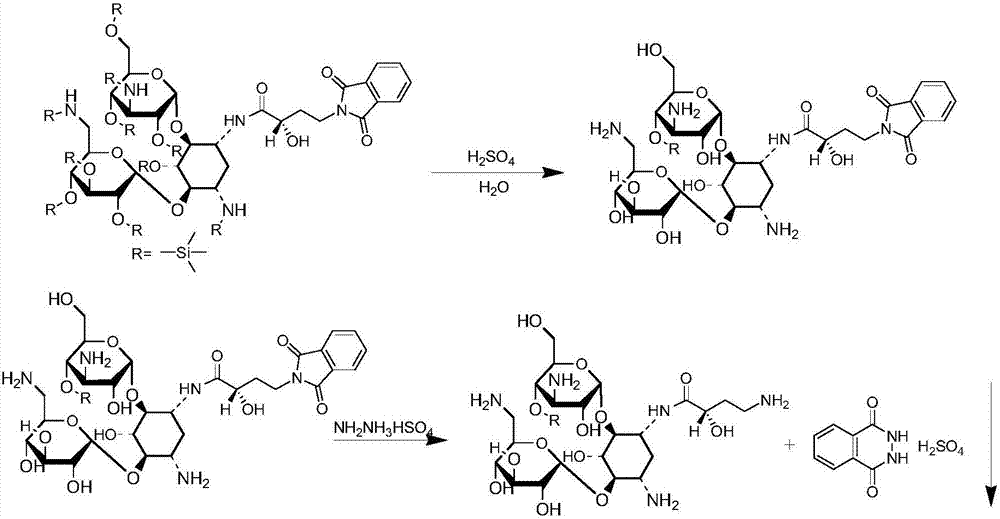

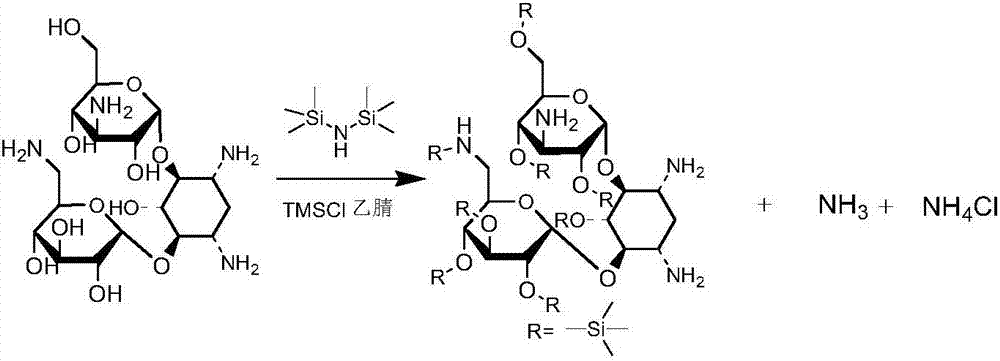

Synthesis method of amikacin

ActiveCN106866755AReduce usageHigh activitySugar derivativesSugar derivatives preparationAmikacinKanamycin

The invention discloses a synthesis method of amikacin. The synthesis method comprises following steps: firstly, a partially silanization protection product of kanamycin A is prepared; dehydration of the partially silanization protection product with PHBA under the action of DCC is carried out so as to obtain a acylated product; the acylated product is subjected to hydrolysis, nitrilase, and column chromatography purification so as to obtain amikacin. According to the synthesis method, NOP is not used, synthesis of an active ester via esterification is avoided, damage on the health of workers is reduced greatly, solid waste generated in production process is reduced greatly, product yield is increased, and the synthesis method is especially suitable for industrialized production.

Owner:山东安信制药有限公司

Qualification of conditional debug instructions based on address

ActiveUS20090235059A1Digital computer detailsSpecific program execution arrangementsParallel computingSemantics

A processor implementation supports selection of an execution mode for debug instruction instances based on respective addresses thereof in addressable memory can provide an attractive mechanism for executing debug instructions in a way that allows some instances of the instructions to operate with debug semantics while suppressing other instances by executing them with no-operation (NOP) semantics. In some embodiments, selection of operative execution semantics may be based on attributes of a memory page in which a particular debug instruction instance resides. In some embodiments, portions of an address space may be delimited (e.g., using values stored in bounding registers and addresses of particular debug instruction instances compared against the delimited portions to select appropriate execution semantics. In some embodiments, both types of evaluations may be used in selecting appropriate execution semantics for a particular debug instruction instance.

Owner:SONY CORP +2

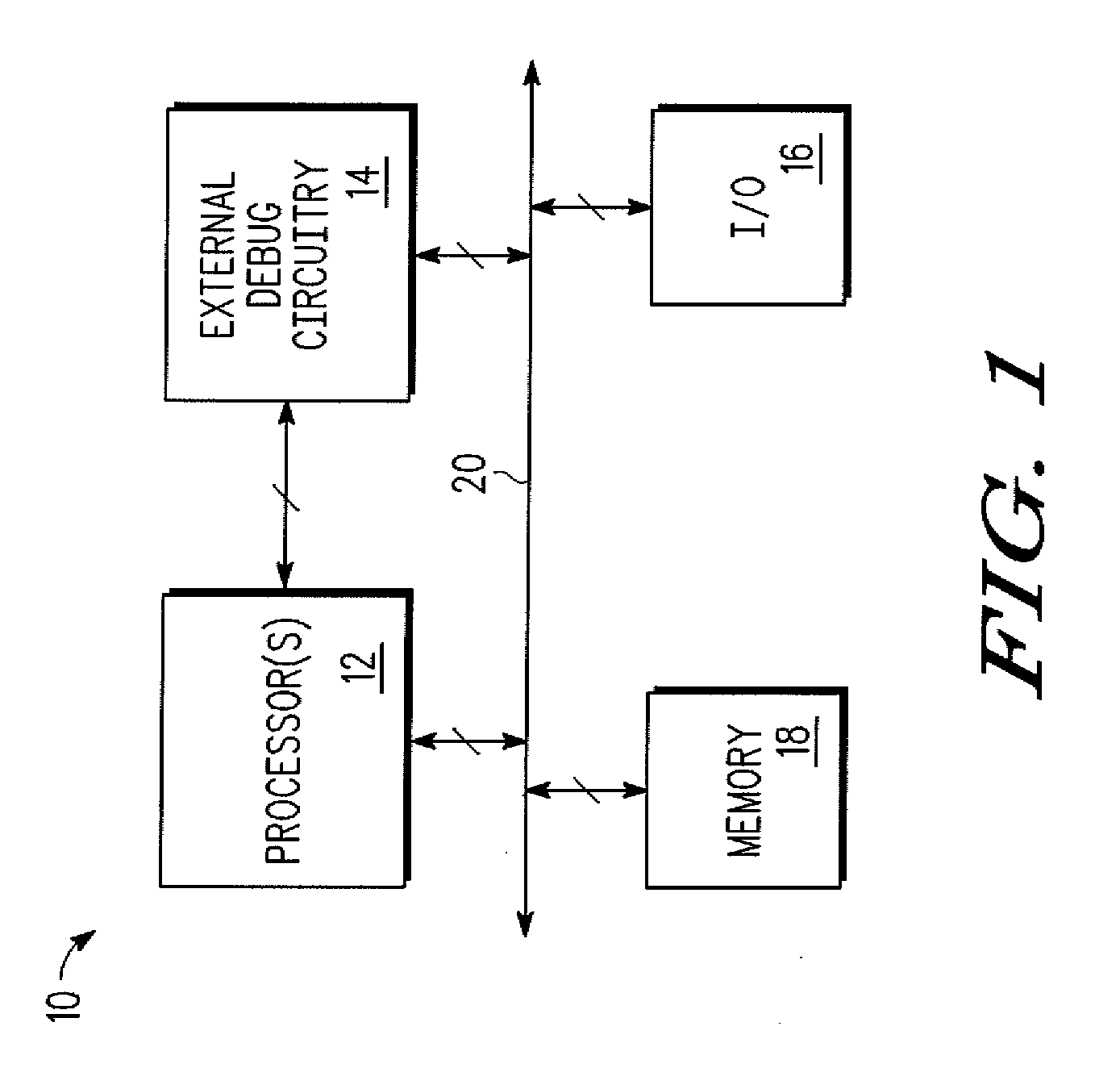

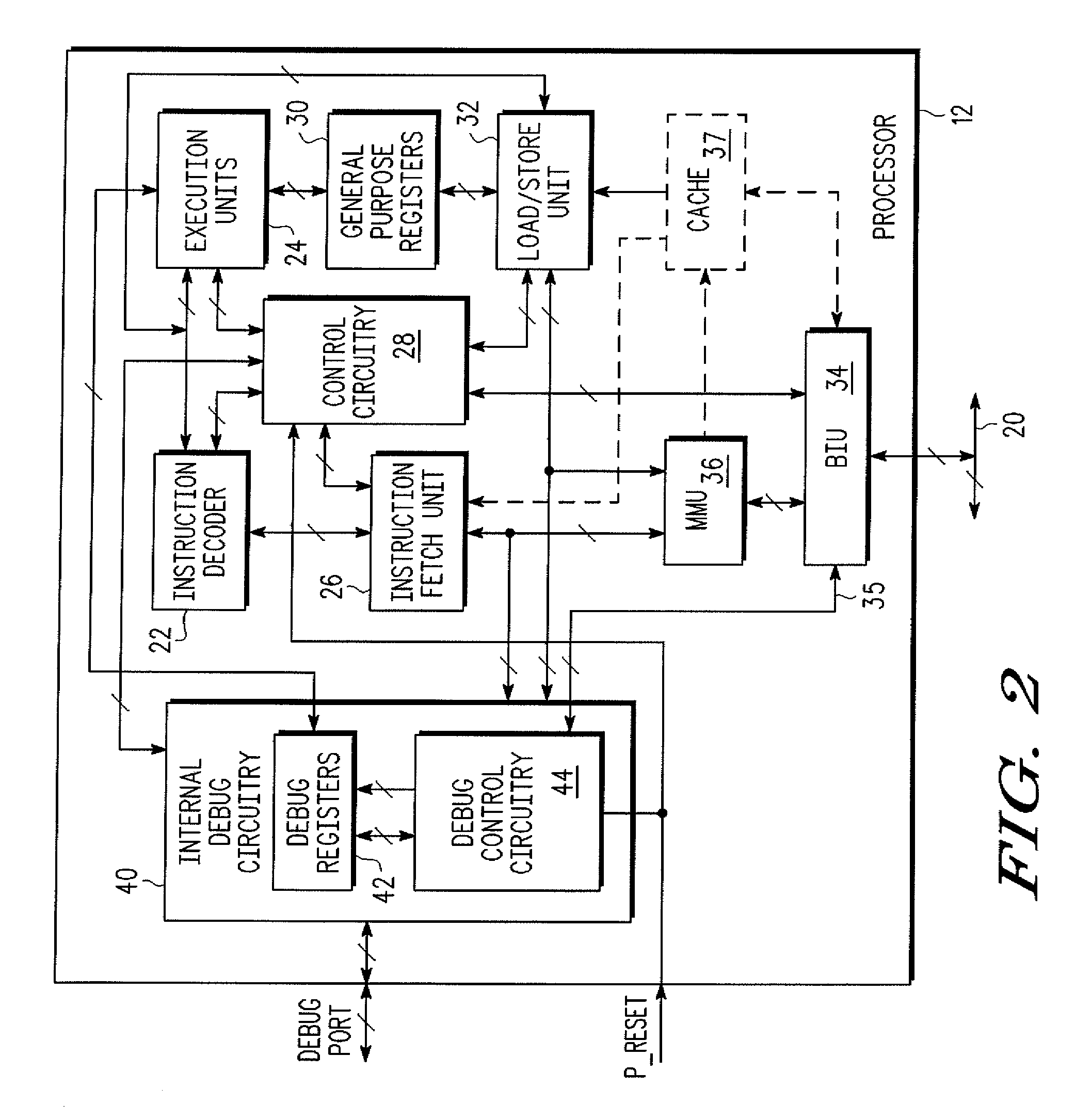

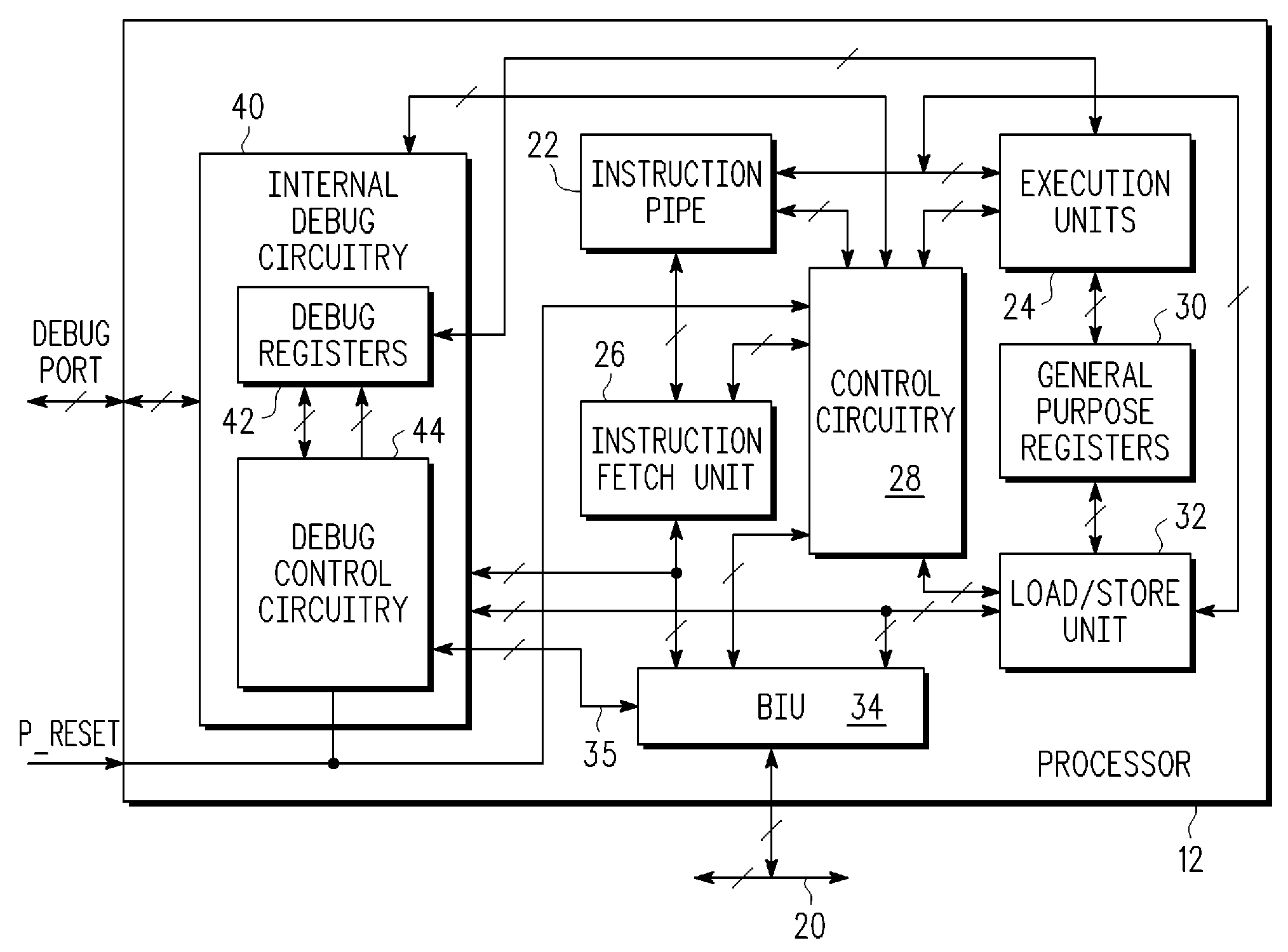

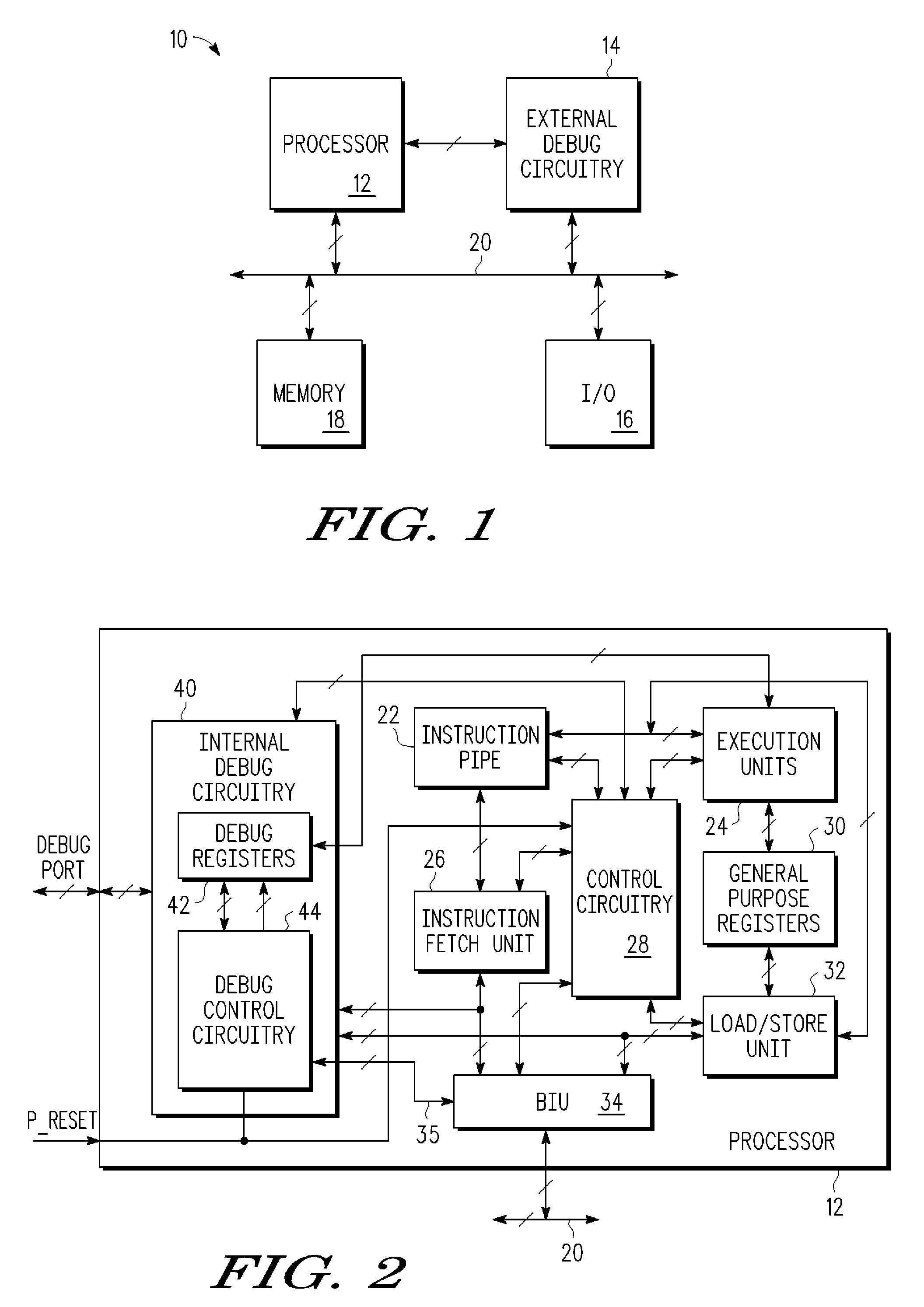

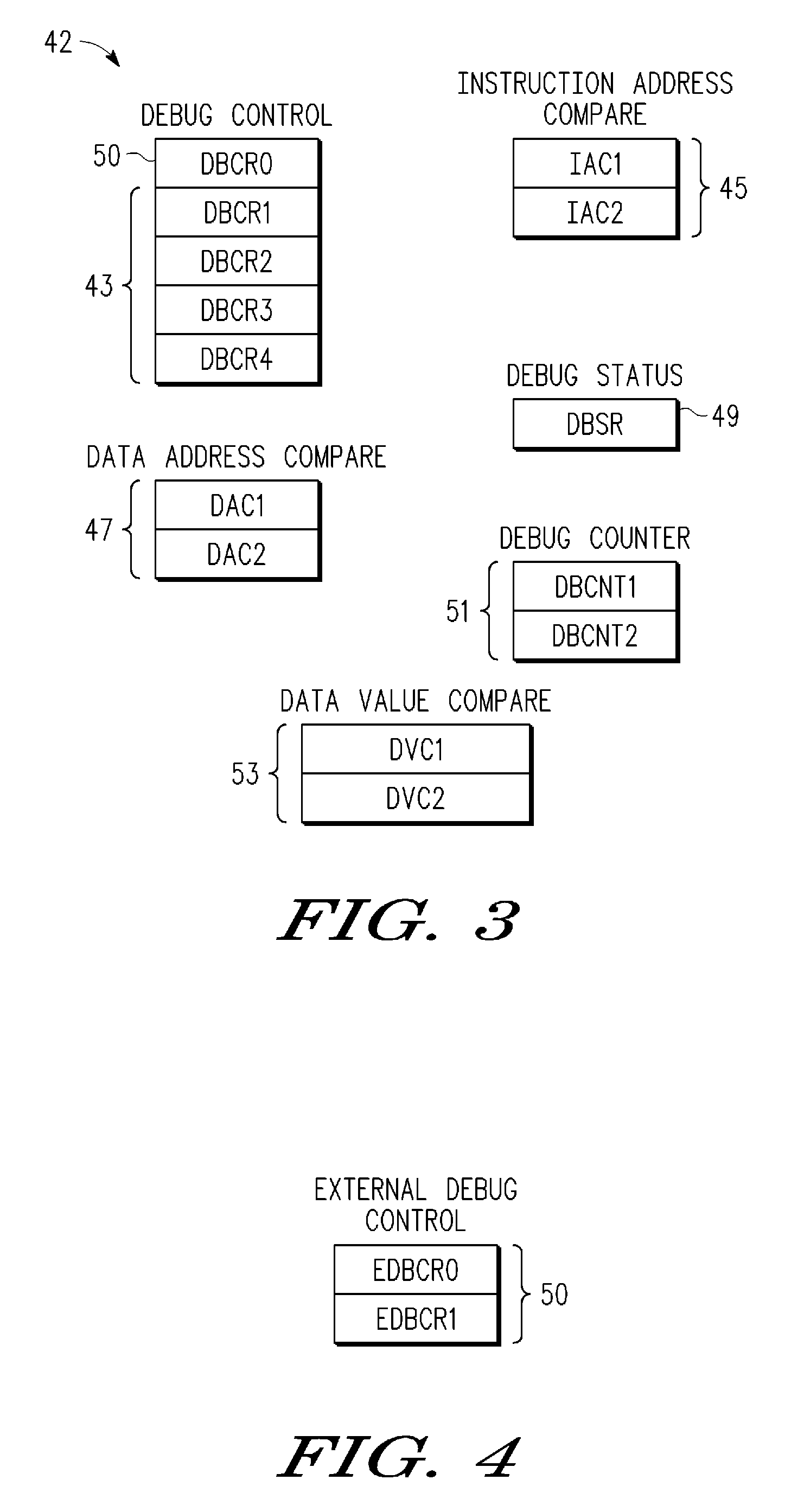

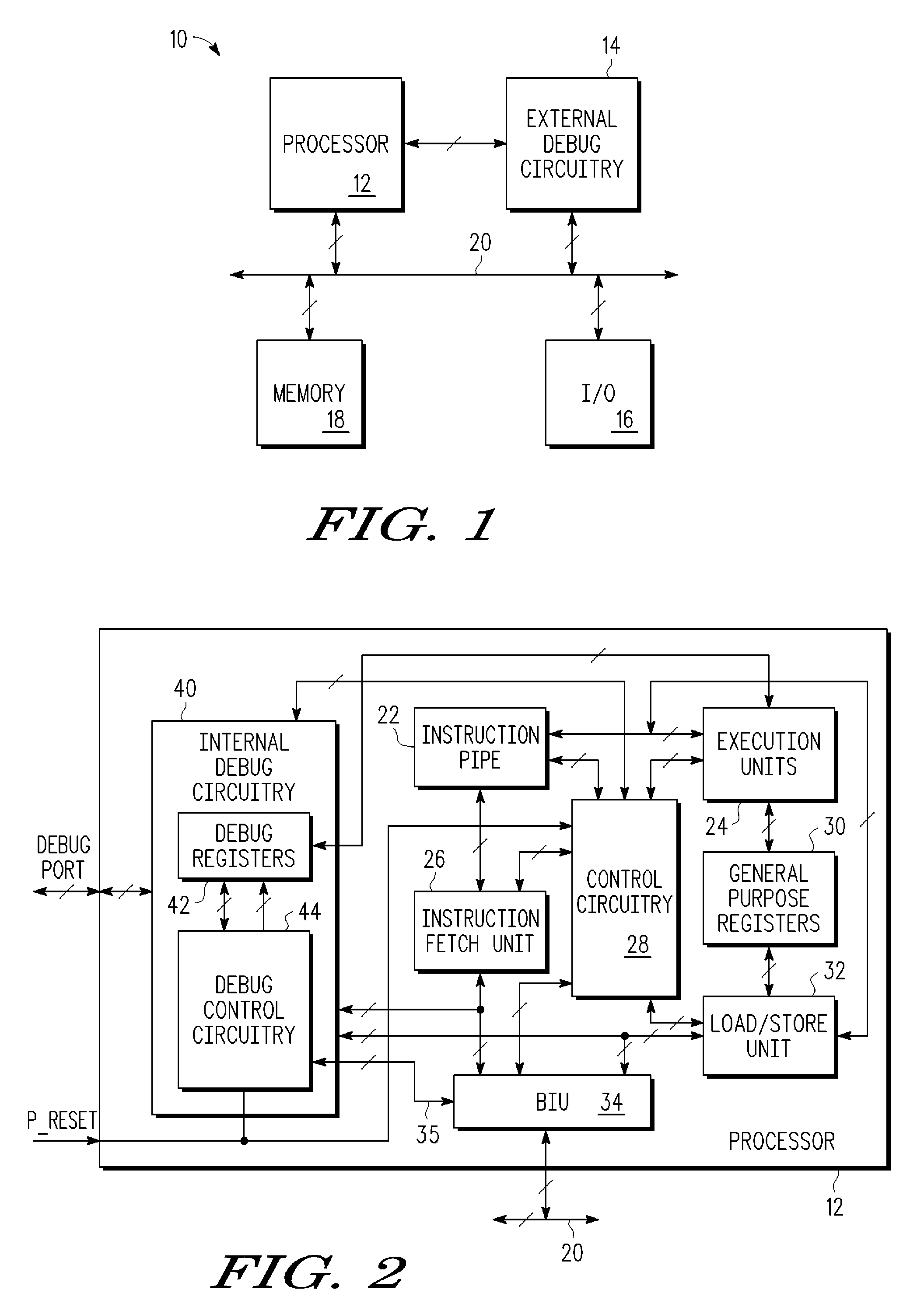

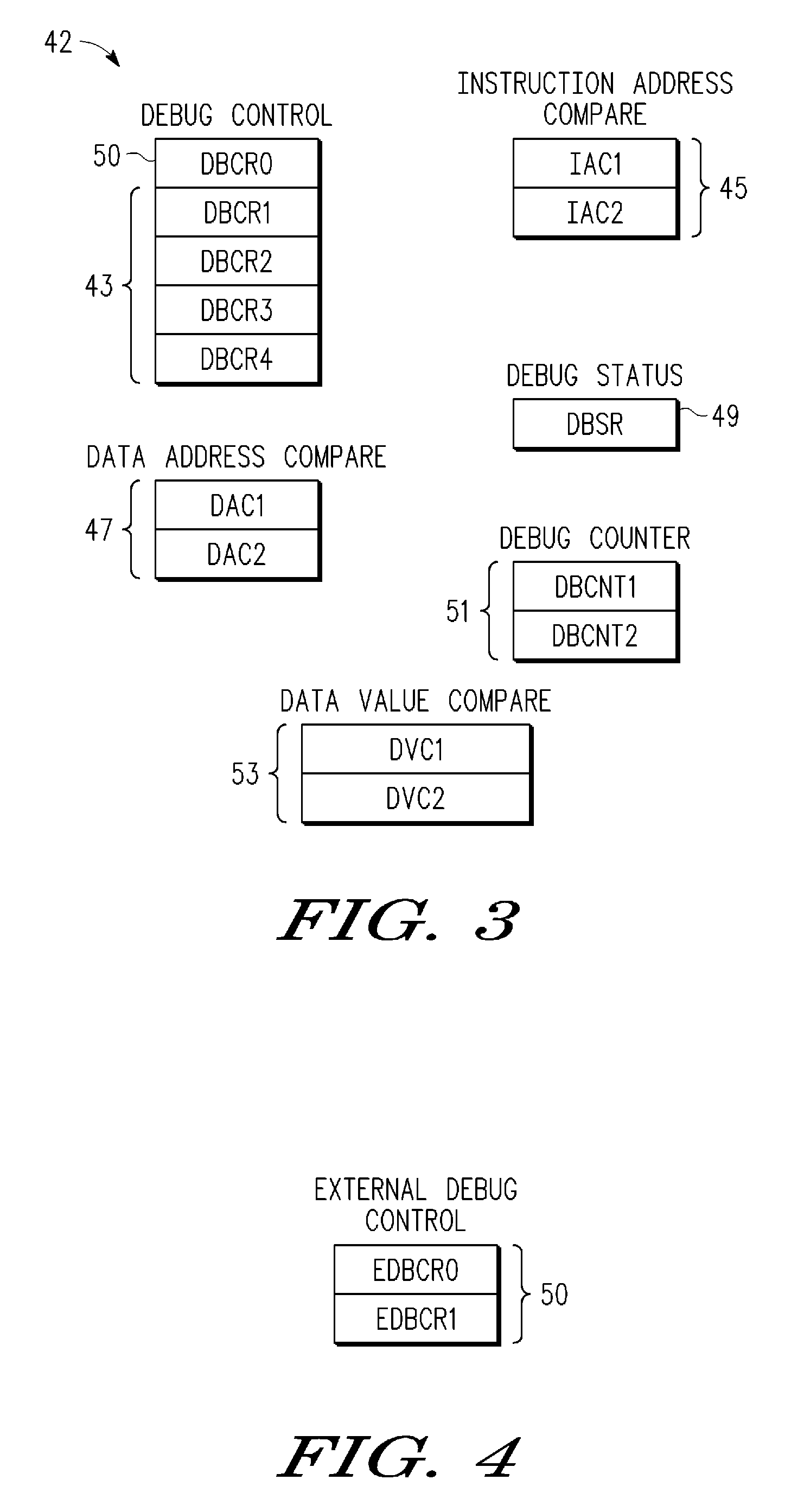

Debug instruction for use in a data processing system

ActiveUS20090100254A1Error detection/correctionDigital computer detailsData processing systemProcessor register

A method includes providing a debug instruction and providing a debug control register field, where if the debug control register field has a first value, the debug instruction executes a debug operation and where if the debug control register field has a second value, the debug instruction is to be executed as a no-operation (NOP) instruction. A data processing system includes instruction fetch circuitry for receiving a debug instruction, a debug control register field, and debug execution control circuitry for controlling execution of the debug instruction in a first manner if the debug control register field has a first value and in a second manner if the debug control register field has a second value, where in the first manner a debug operation is performed and in the second manner no debug operation is performed.

Owner:RAMBUS INC

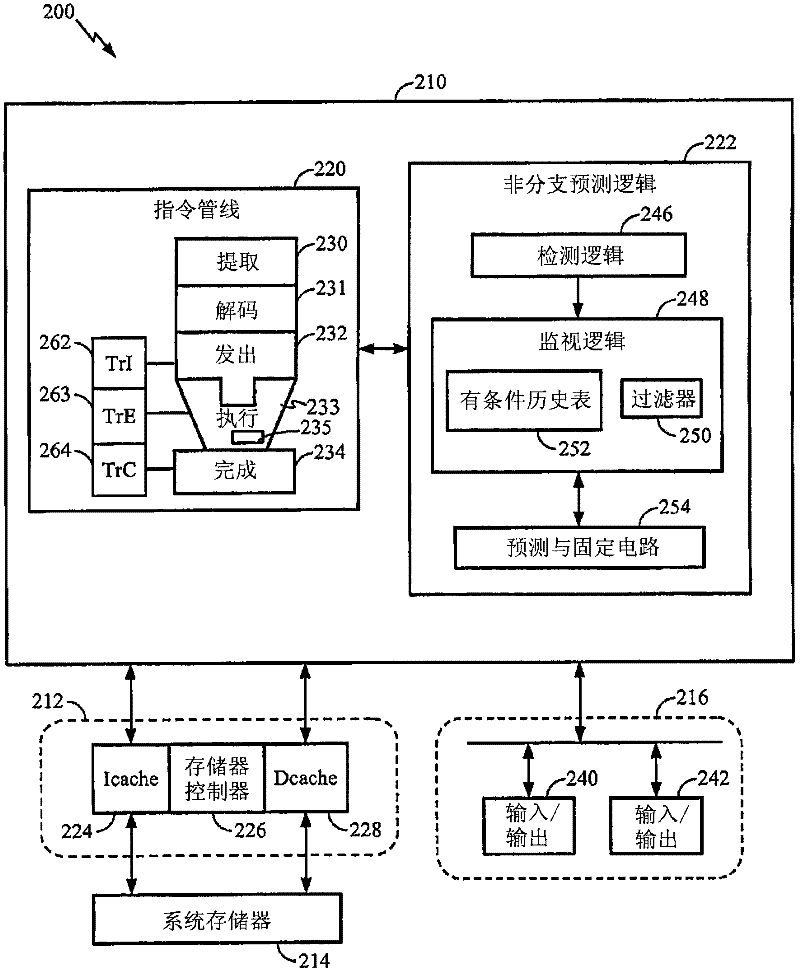

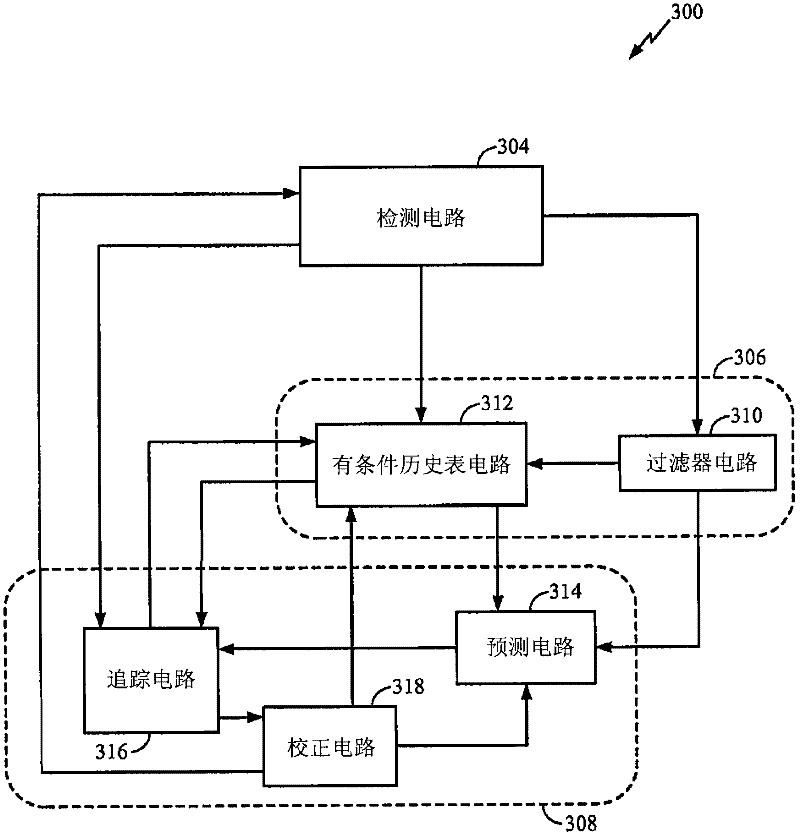

Methods and apparatus to predict non-execution of conditional non-branching instructions

Efficient techniques are described for not executing an issued conditional non-branch instruction. A conditional non-branch instruction is identified as being eligible for a prediction, the prediction indicating that the eligible conditional non-branch (ECNB) instruction would not execute. The ECNB instruction executes as a no operation (NOP) instruction in response to the prediction that the ECNB instruction would not execute. A source operand required for the ECNB instruction to execute is not fetched in response to the prediction to not execute.

Owner:QUALCOMM INC

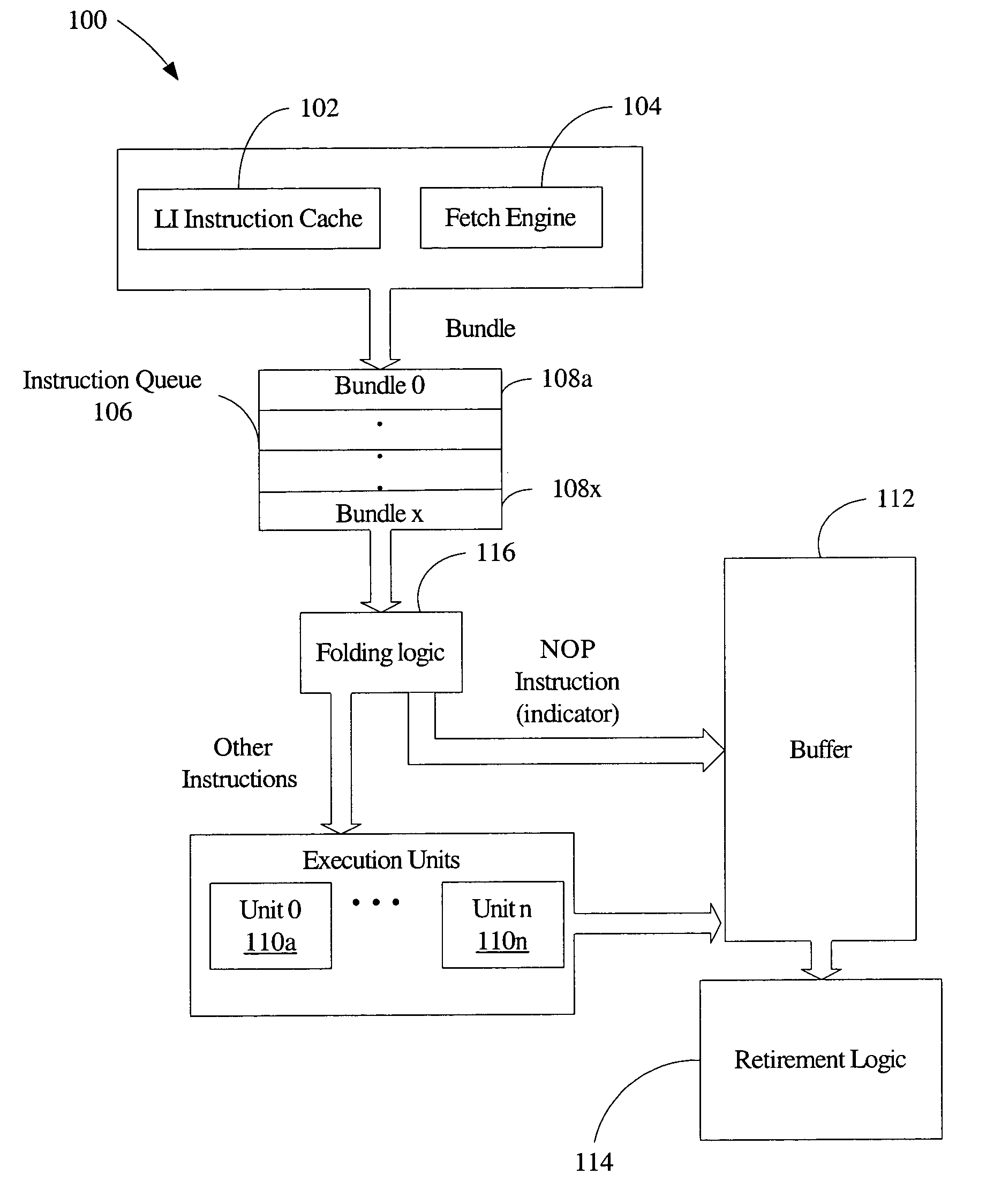

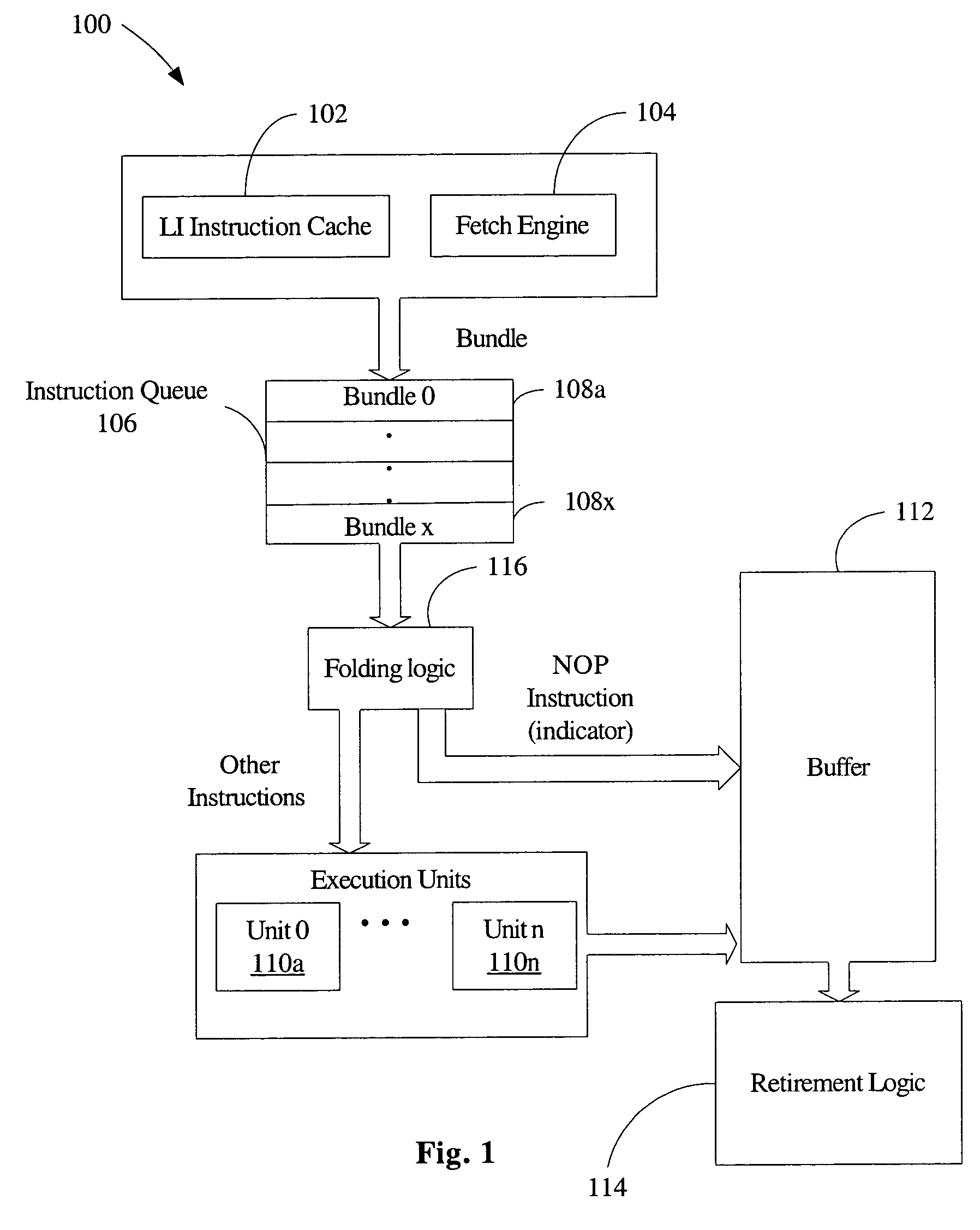

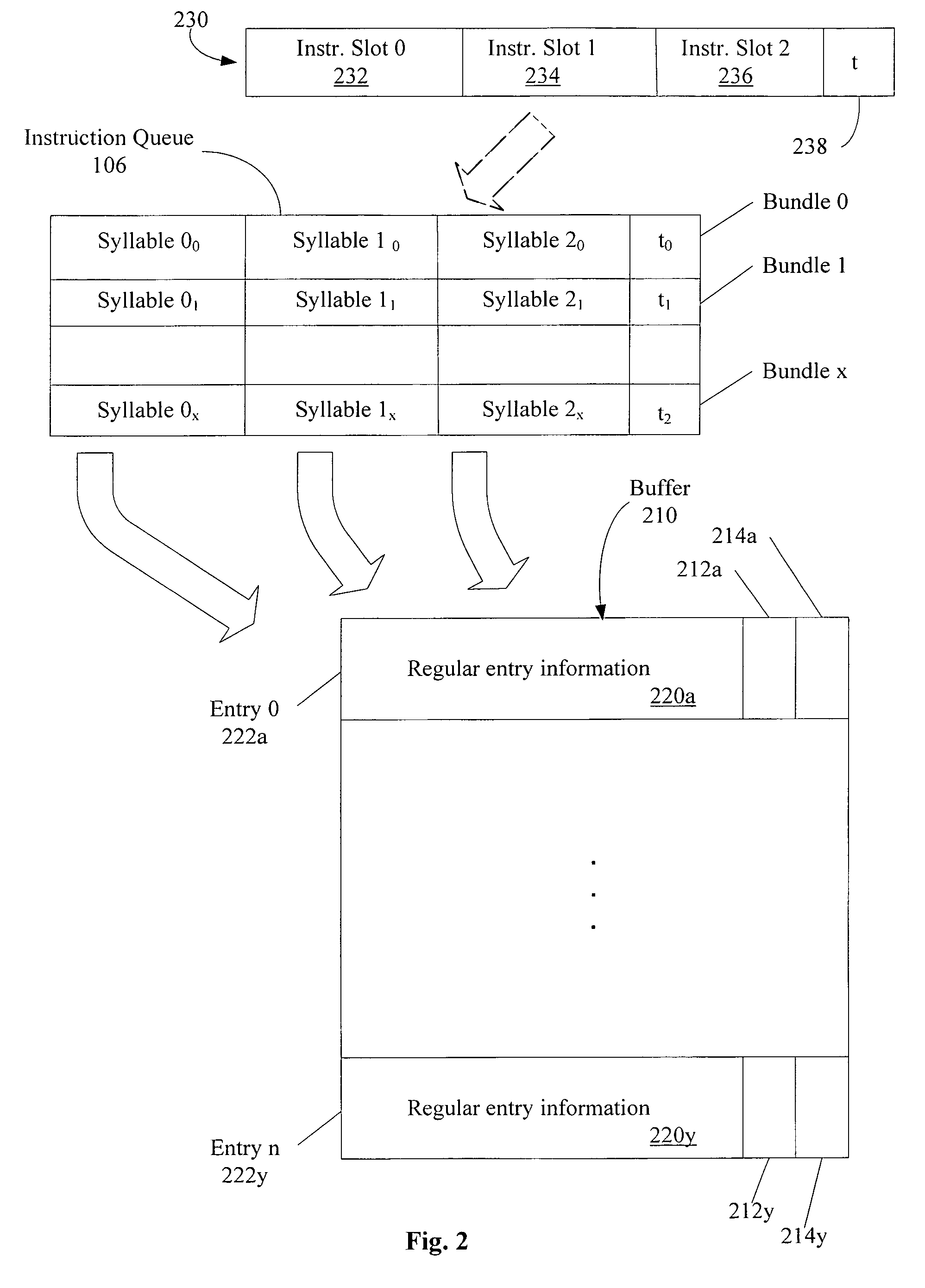

Method and apparatus for NOP folding

InactiveUS7111154B2General purpose stored program computerConcurrent instruction executionNOPInstruction stream

Embodiments of an apparatus, method, and system provide for no-operation instruction (“NOP”) folding such that information regarding the presence of a NOP instruction in the instruction stream is folded into a buffer entry for another instruction. Information regarding a target NOP instruction is thus maintained in a buffer entry associated with an instruction other than the target NOP instruction. For at least one embodiment, NOP information is folded into entries of a re-order buffer.

Owner:INTEL CORP

Data compression method for supporting virtual memory management in a demand paging system

InactiveCN101356509AMemory architecture accessing/allocationMemory adressing/allocation/relocationData compressionIntel HEX

A virtual memory management unit ( 306 ) includes a redundancy insertion module ( 307 ) which is used for inserting redundancy into an encoded data stream to be compressed, such that after being compressed each logical data block fits into a different one from a set of equal-sized physical data blocks of a given size. For example, said redundancy may be given by no-operation (NOP) instructions represented by a number of dummy sequences of a given length (L) into an encoded data stream to be compressed, each dummy sequence being composed of a number of identical binary or hexadecimal fill-in values.

Owner:SONY ERICSSON MOBILE COMM AB

Apparatus for compressing instruction word for parallel processing VLIW computer and method for the same

ActiveUS7774581B2Reduce storage spaceImprove performanceProgram control using stored programsGeneral purpose stored program computerWord groupParallel processing

Owner:SAMSUNG ELECTRONICS CO LTD

Integrated circuit and electronic system and renewable method providing one time programmable (OTP) internal memory configuration

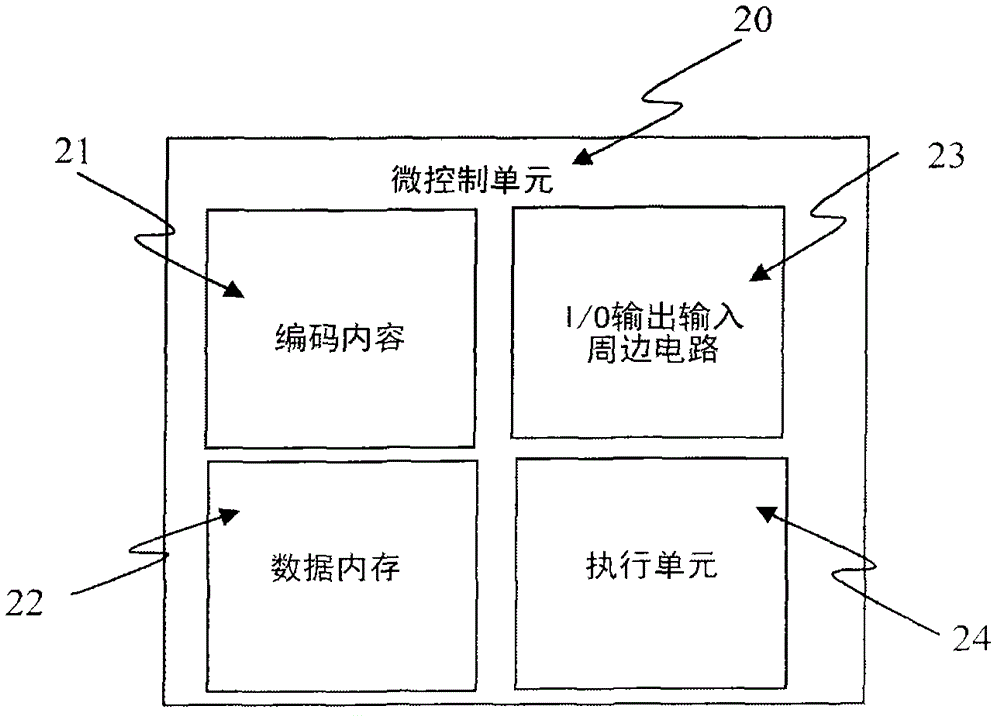

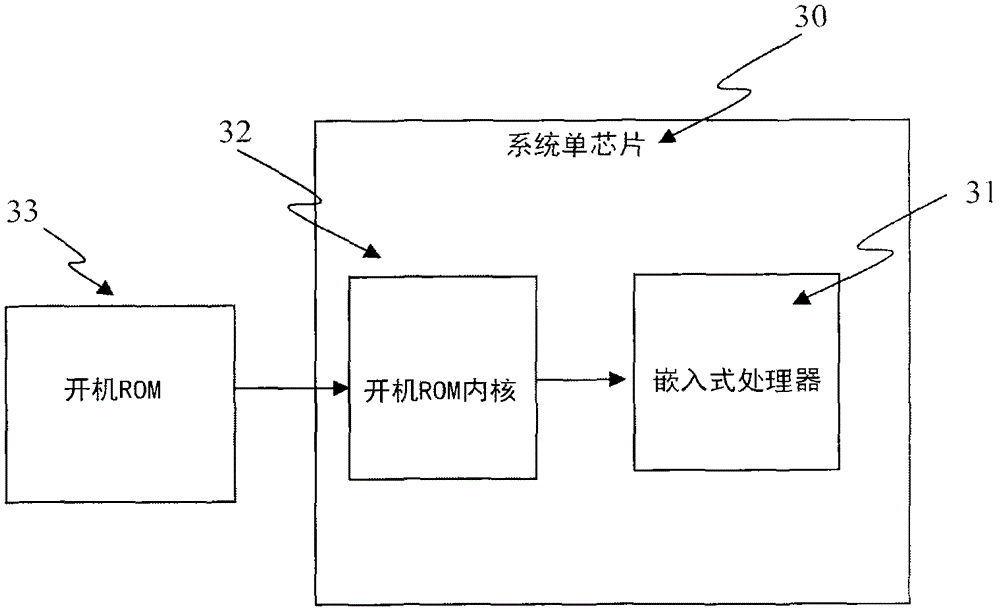

InactiveCN103064654ASmall sizeEasy to processMachine execution arrangementsInternal memoryElectronic systems

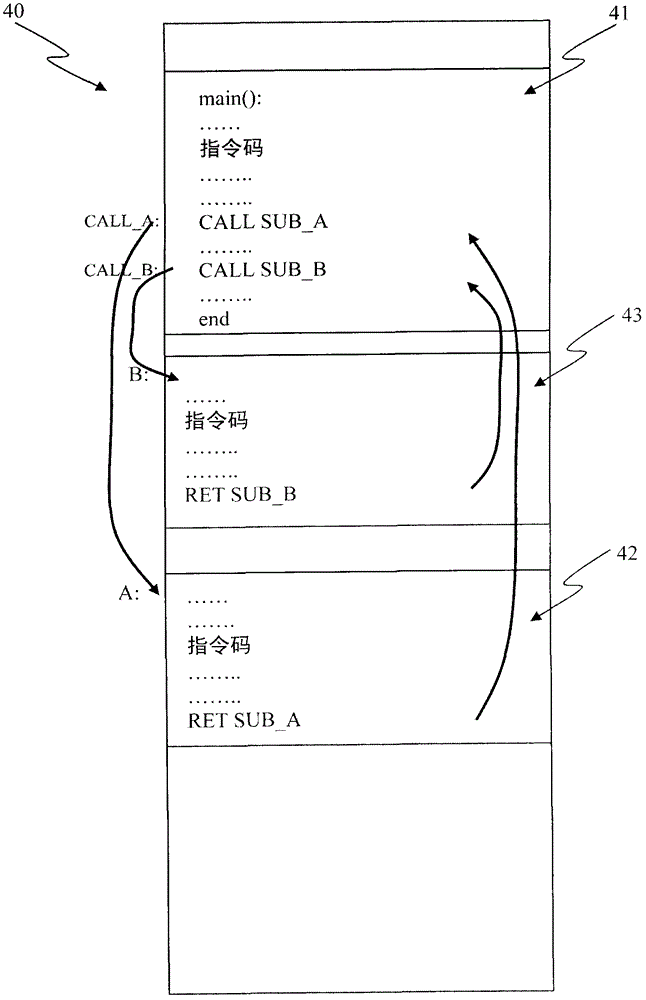

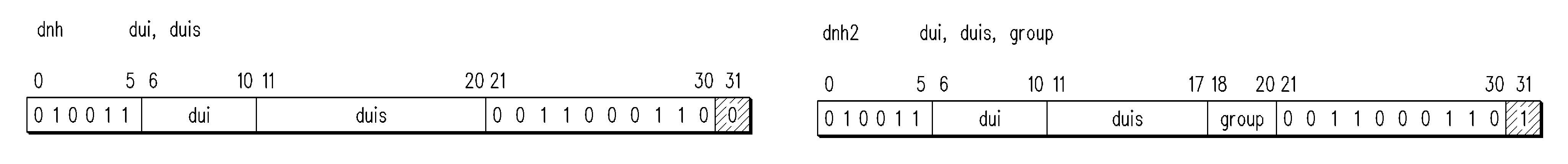

The invention discloses a method, a device and a system which uses a one time programmable (OTP) internal storage as a multi-time programmable (MTP) internal memory configuration. Using the OTP internal memory through the method enables encoding to be renewed one or more times, but the advantages that the size is small and processing and manufacturing can be achieved easily are kept. The encoding can be a procedure code of a processor, such as a startup code, a startup code kernel or other command codes. In a way, one OTP inner memory can be functionally operated like an MTP, and is a No Operations (NOP) command through being intelligentized, and then if a specific subprogram or a function is needed to be modified, a user writes a command (such as a JUMP command) to enter the address of NOP, so that some specifically existing commands are enabled to be bypassed, and a command code of a new module is carried out.

Owner:庄建祥

Debug instruction for use in a data processing system

ActiveUS7689815B2Digital computer detailsSoftware testing/debuggingData processing systemProcessor register

A method includes providing a debug instruction and providing a debug control register field, where if the debug control register field has a first value, the debug instruction executes a debug operation and where if the debug control register field has a second value, the debug instruction is to be executed as a no-operation (NOP) instruction. A data processing system includes instruction fetch circuitry for receiving a debug instruction, a debug control register field, and debug execution control circuitry for controlling execution of the debug instruction in a first manner if the debug control register field has a first value and in a second manner if the debug control register field has a second value, where in the first manner a debug operation is performed and in the second manner no debug operation is performed.

Owner:RAMBUS INC

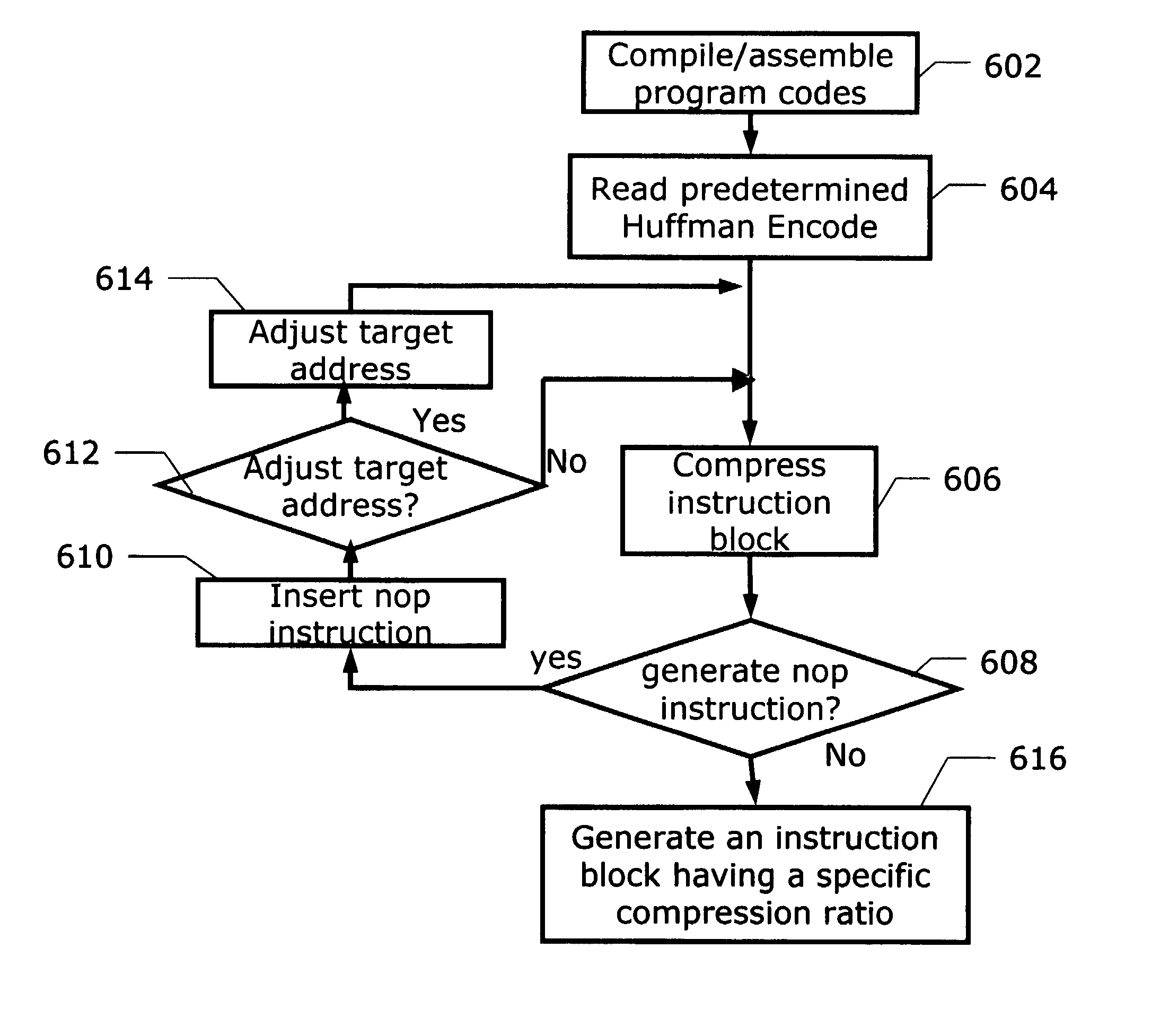

Method for compressing instruction codes

The present invention discloses a method for compressing instruction codes. This method comprises: compressing an instruction block including a plurality of instructions according to Huffman-Encoding technique; determining whether it's necessary to insert no-operation (nop) instructions among the plurality of compressed instructions according to a compression ratio, so as to generate a plurality of new instruction blocks conforming with the compression ratio; if it's necessary to insert nop instructions, inserting nop instructions among the plurality of compressed instructions to form the plurality of new instruction blocks; and repeating the above-mentioned steps until no nop instructions have to be inserted.

Owner:REALTEK SEMICON CORP

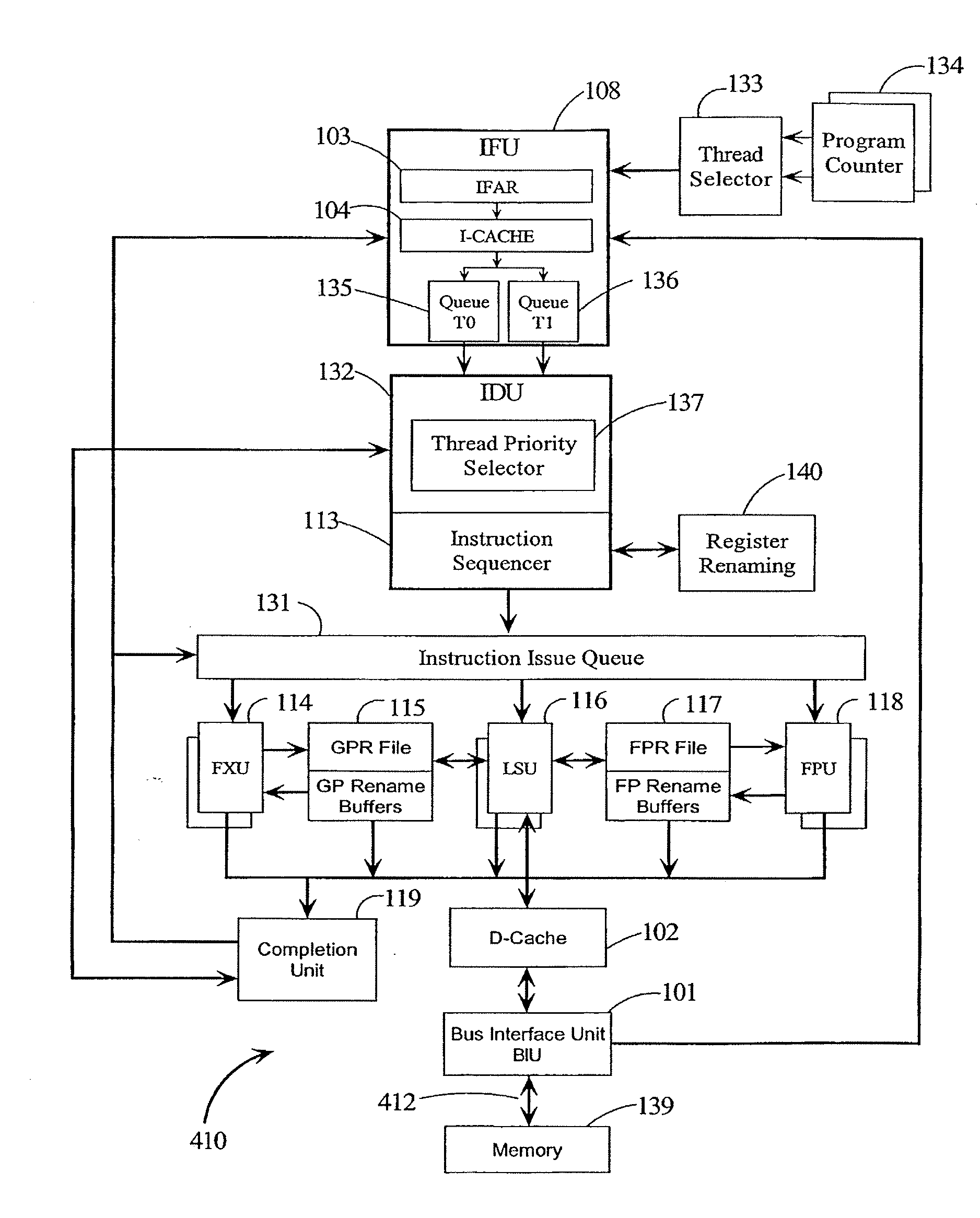

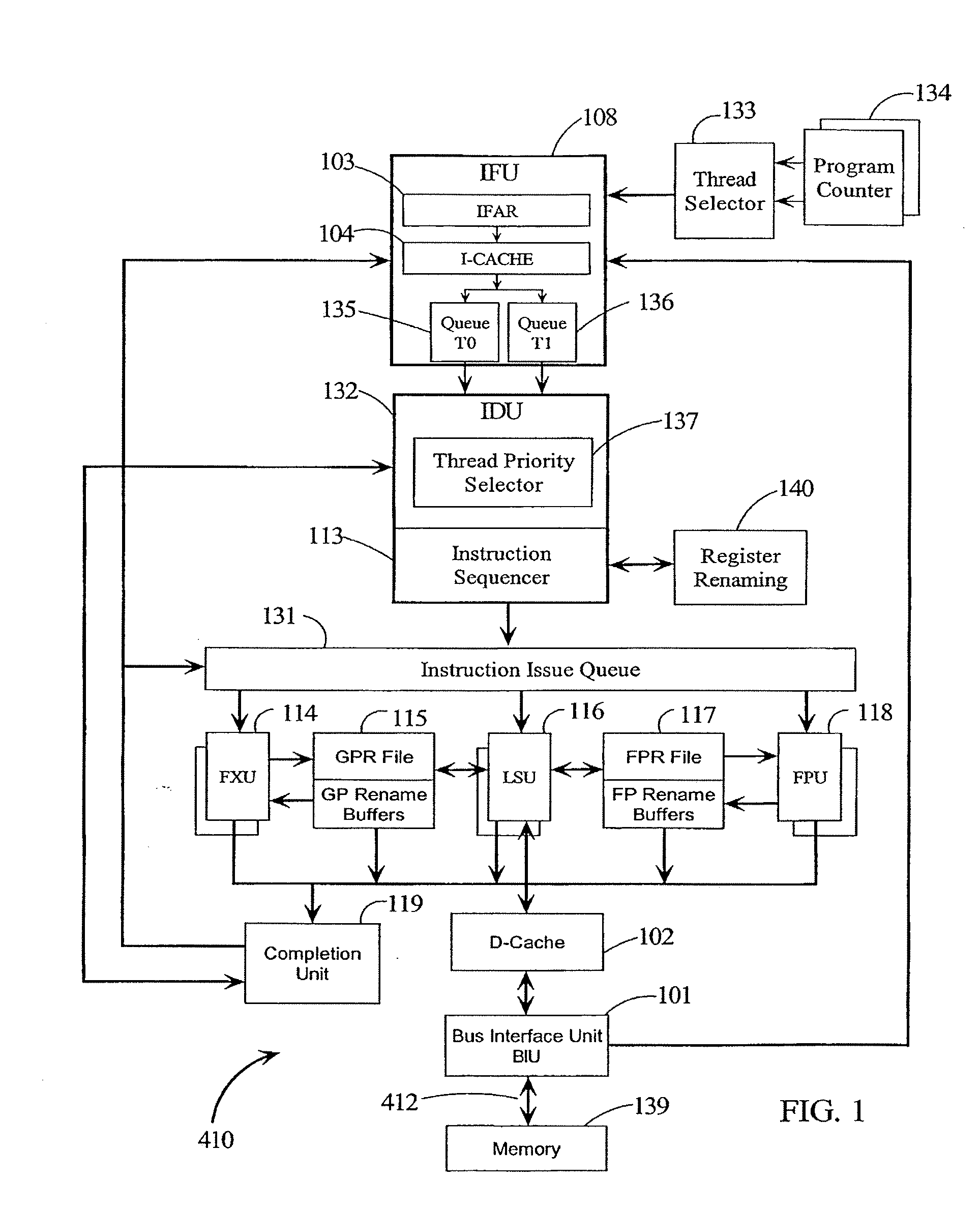

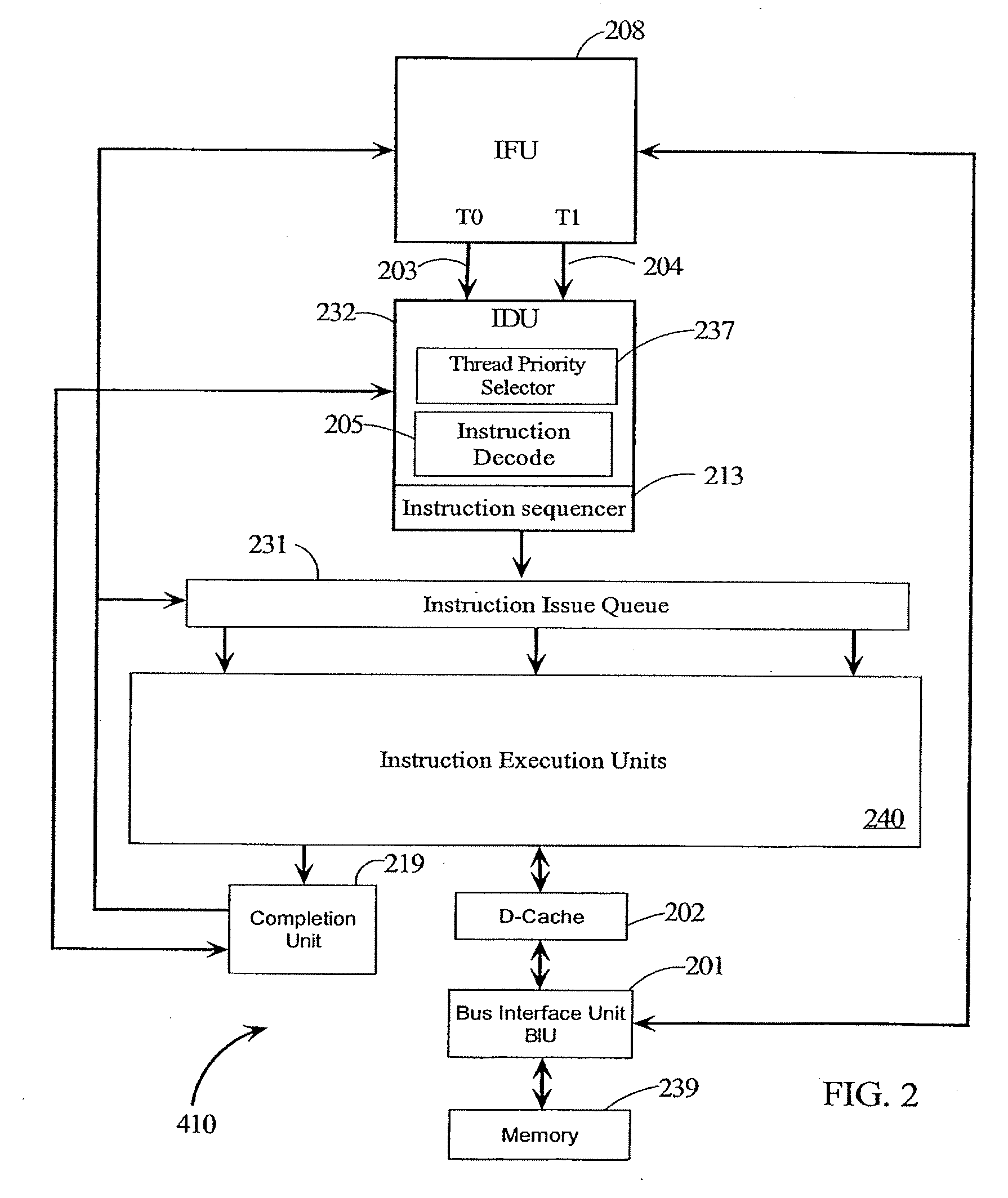

Method For Changing A Thread Priority In A Simultaneous Multithread Processor

InactiveUS20080109640A1Digital computer detailsConcurrent instruction executionParallel computingNOP

An SMT system is designed to allow software alteration of thread priority. In one case, the system signals a change in a thread priority based on the state of instruction execution and in particular when the instruction has completed execution. To alter the priority of a thread, the software uses a special form of a “no operation” (NOP) instruction (hereafter termed thread priority NOP). When the thread priority NOP is dispatched, its special NOP is decoded in the decode unit of the IDU into an operation that writes a special code into the completion table for the thread priority NOP. A “trouble” bit is also set in the completion table that indicates which instruction group contains the thread priority NOP. The trouble bit indicates that special processing is required after instruction completion. The thread priority instruction is processed after completion using the special code to change a thread's priority.

Owner:IBM CORP

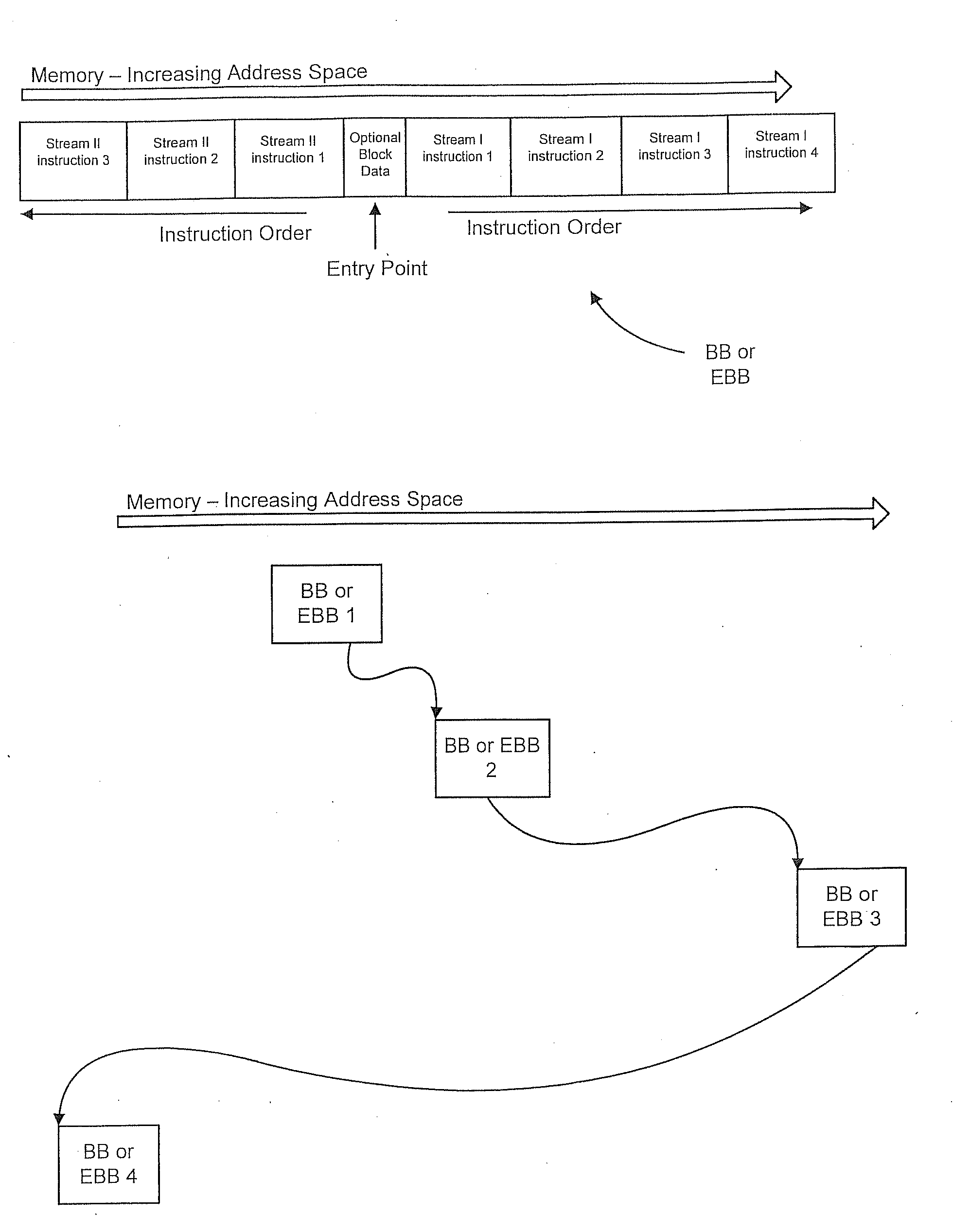

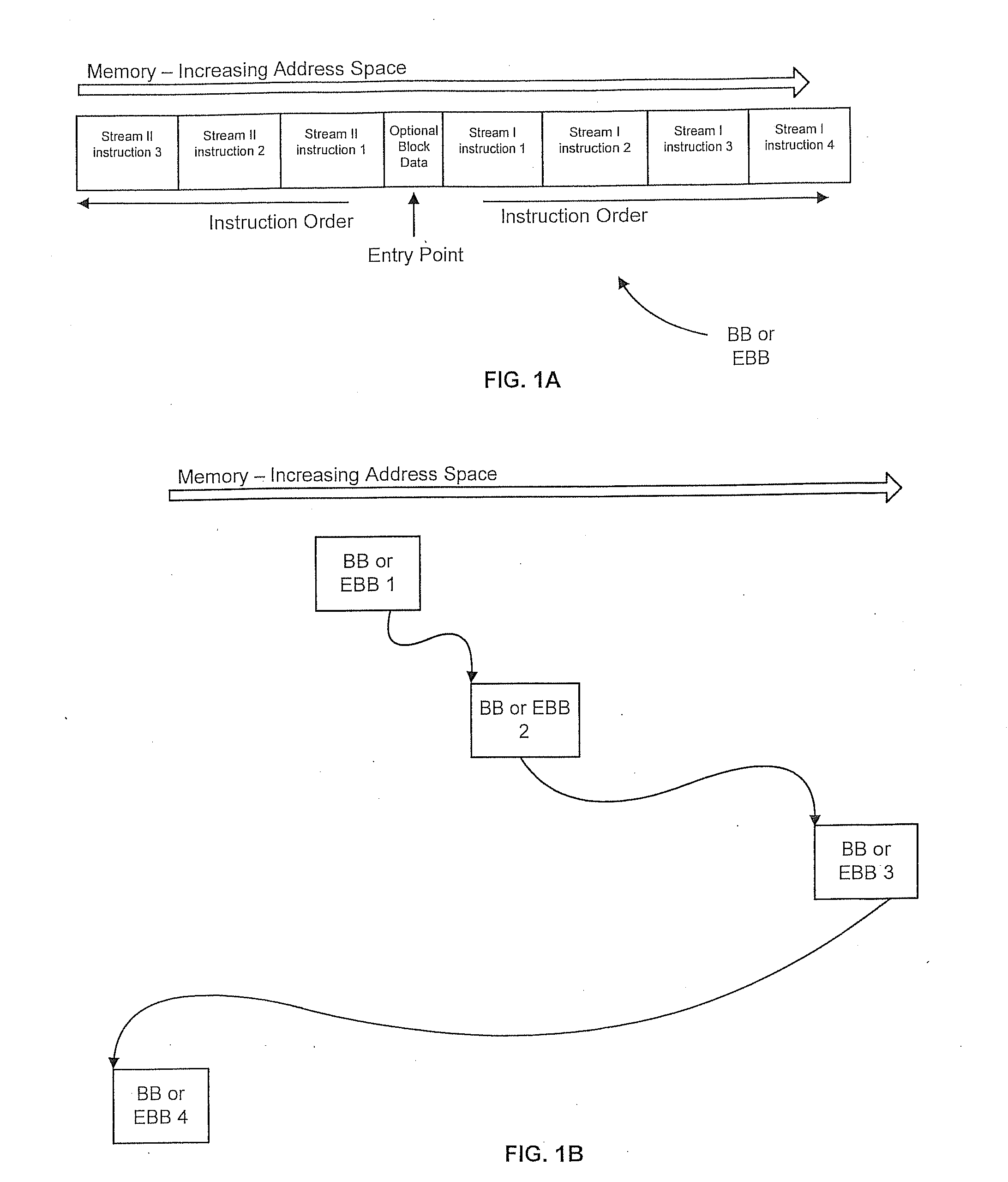

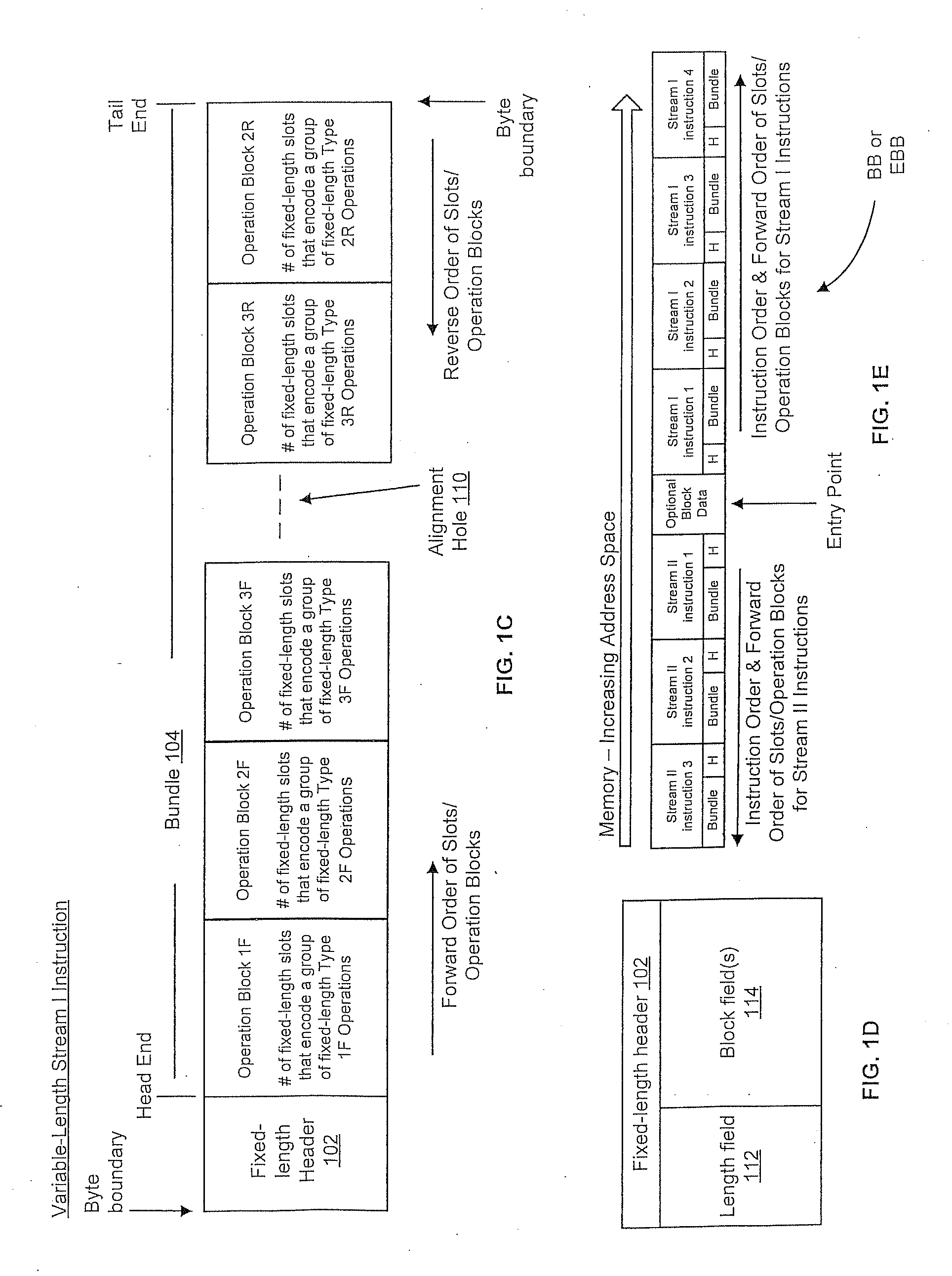

Computer processor employing instructions with elided nop operations

A computer processor that operates on distinct first and second instruction streams that have a predefined timed semantic relationship. At least one of the first and second instruction streams includes variable-length instructions having a header and associated bundle bounded by a head end and a tail end. An alignment hole within the bundle encodes information representing at least one nop operation. The computer processor includes first and second multi-stage instruction processing components configured to process in parallel the first and second instruction streams. At least one of the first and second multi-stage instruction processing components includes an instruction buffer operably coupled to a decode stage. The decode stage is configured to process a variable-length instruction by isolating and interpreting the alignment hole of the variable length instruction in order to initiate zero or more nop operations that follow the timed semantic relationship between the first and second instruction streams.

Owner:MILL COMPUTING

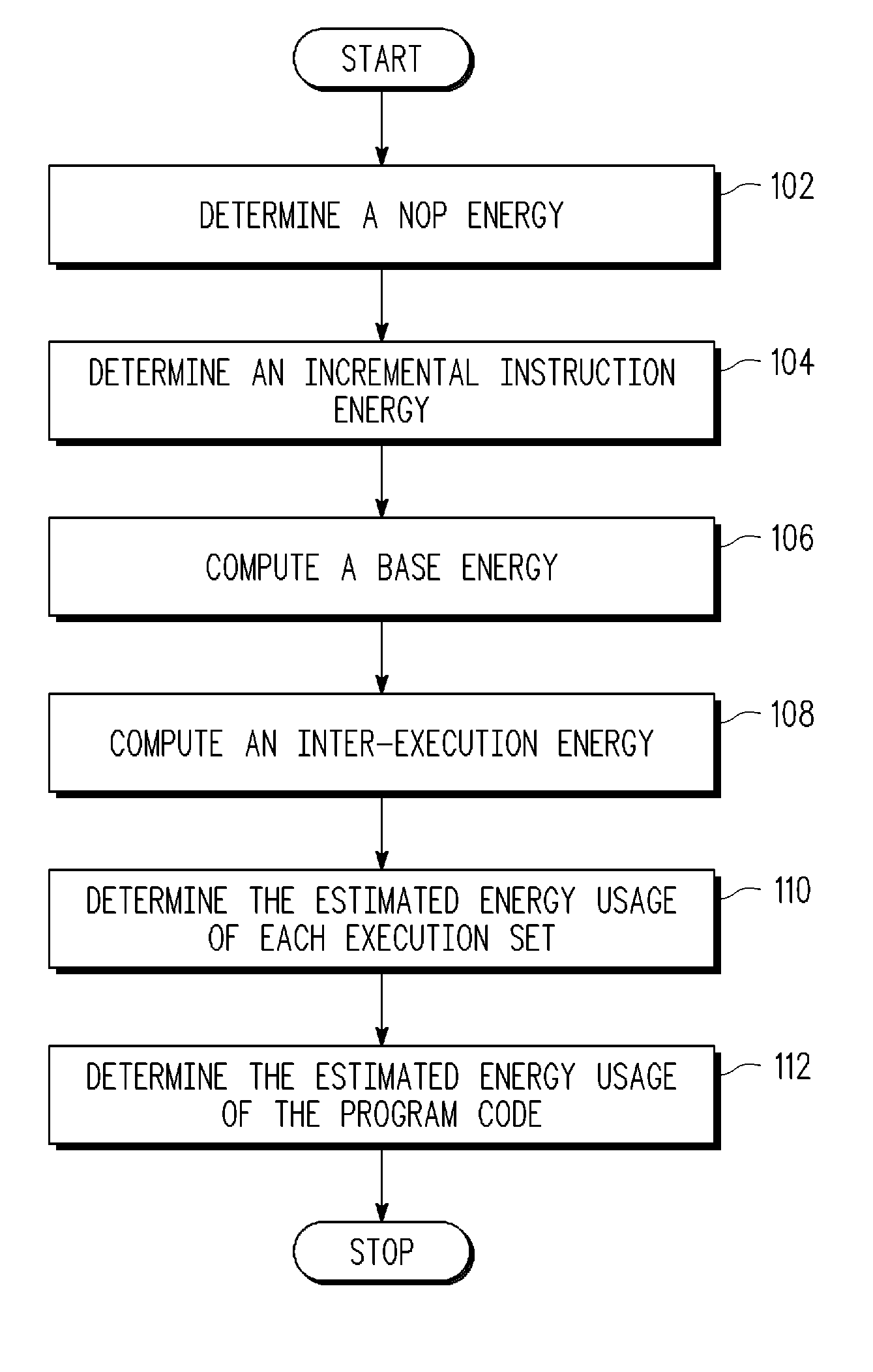

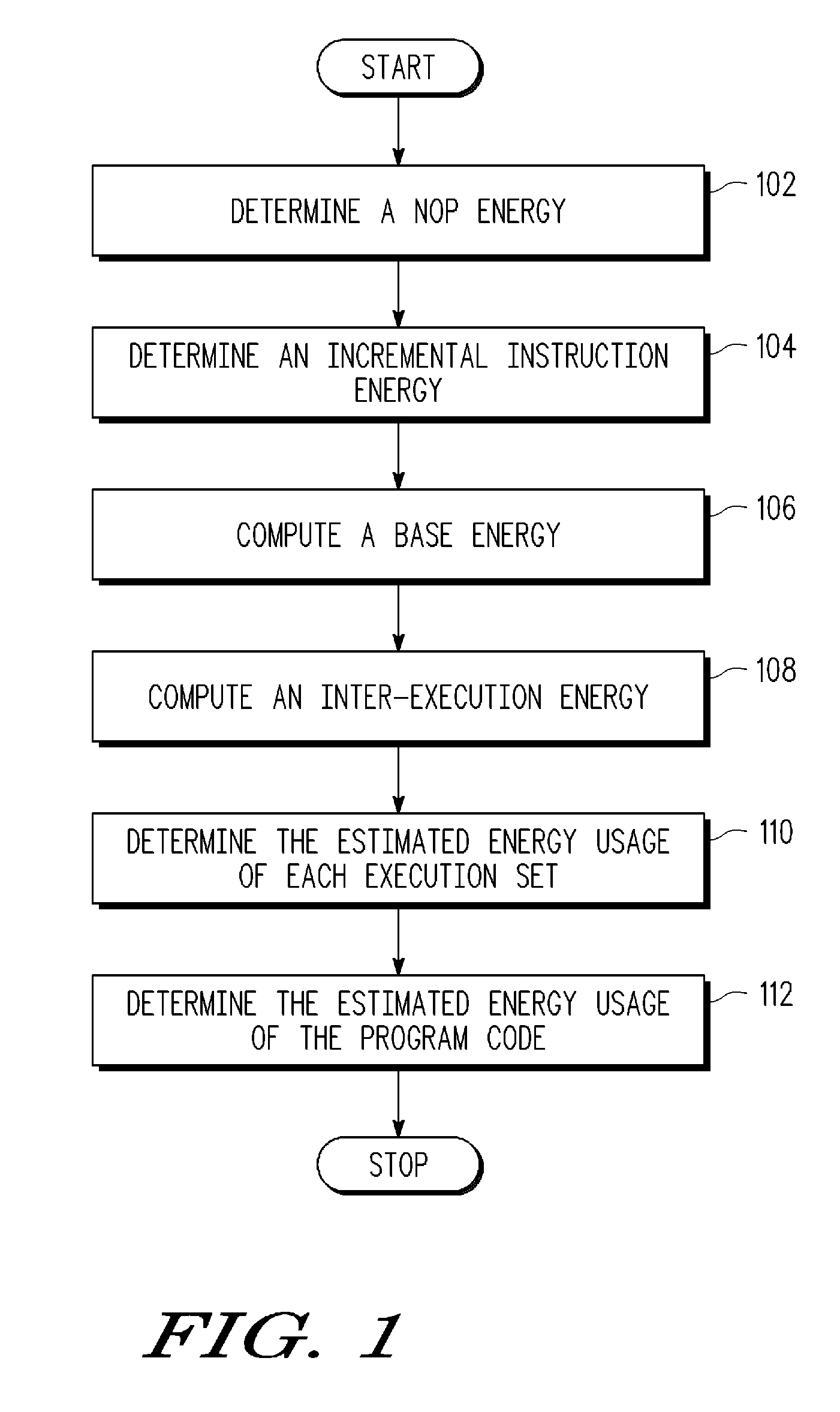

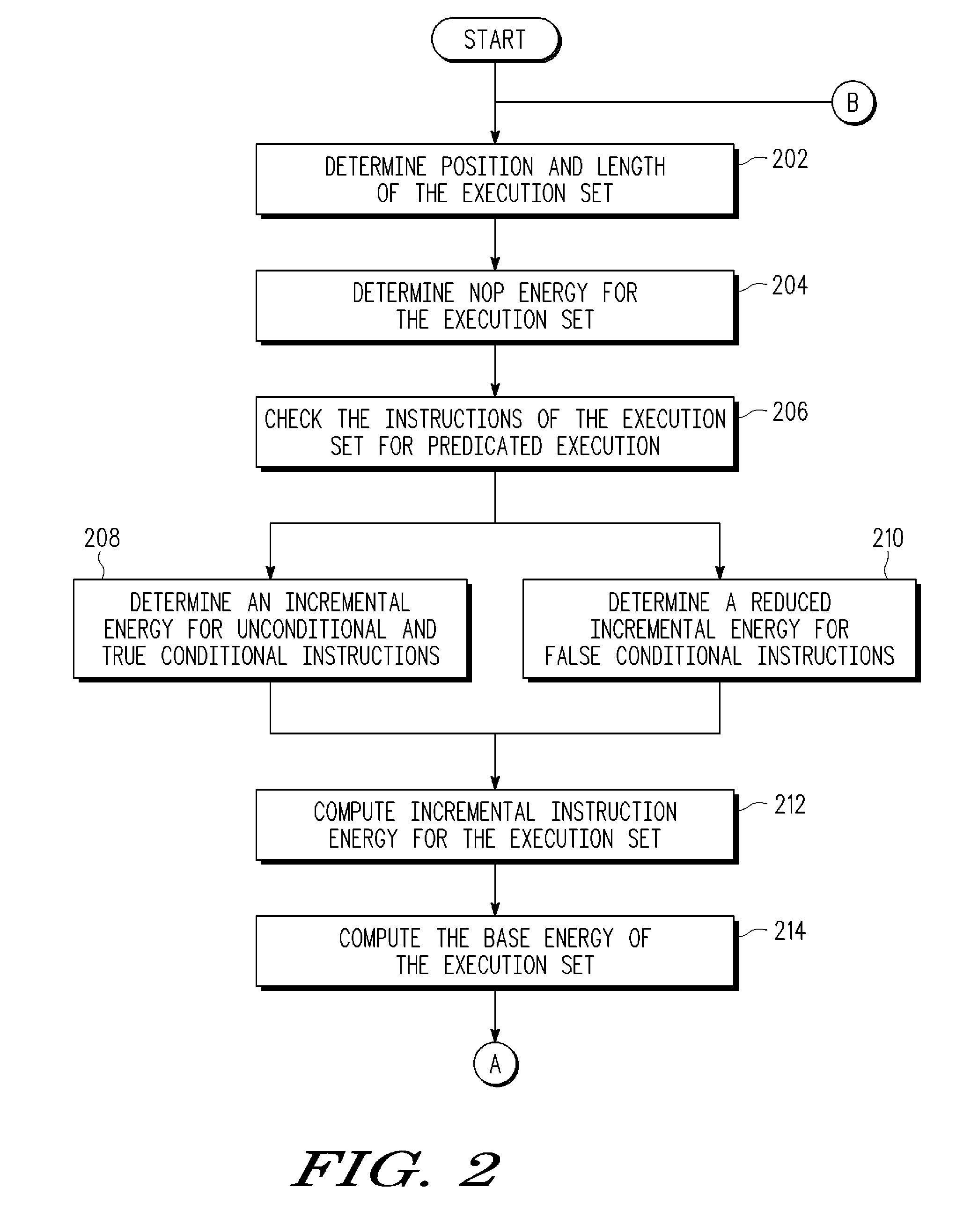

Method for estimating processor energy usage

InactiveUS20070136720A1Digital data processing detailsHardware monitoringNOPVery long instruction word

A method for estimating energy usage of a program code executed by a very long instruction word (VLIW) processor. The program code includes multiple instructions, which are organized as groups referred to as execution sets. The instructions of an execution set are executed simultaneously. A no operation (NOP) energy and incremental instruction energy for each execution set of the program code are determined to compute a base energy of each execution set. An inter-execution set energy of each execution set is then computed. The estimated energy usage of each execution set is determined by adding the corresponding inter-execution set energies to the base energies. A stall energy consumed on account of executing the program code is then computed. Finally, the estimated energy usage of the program code is determined by adding the stall energy to the determined energies of all the execution sets.

Owner:TAIWAN SEMICON MFG CO LTD

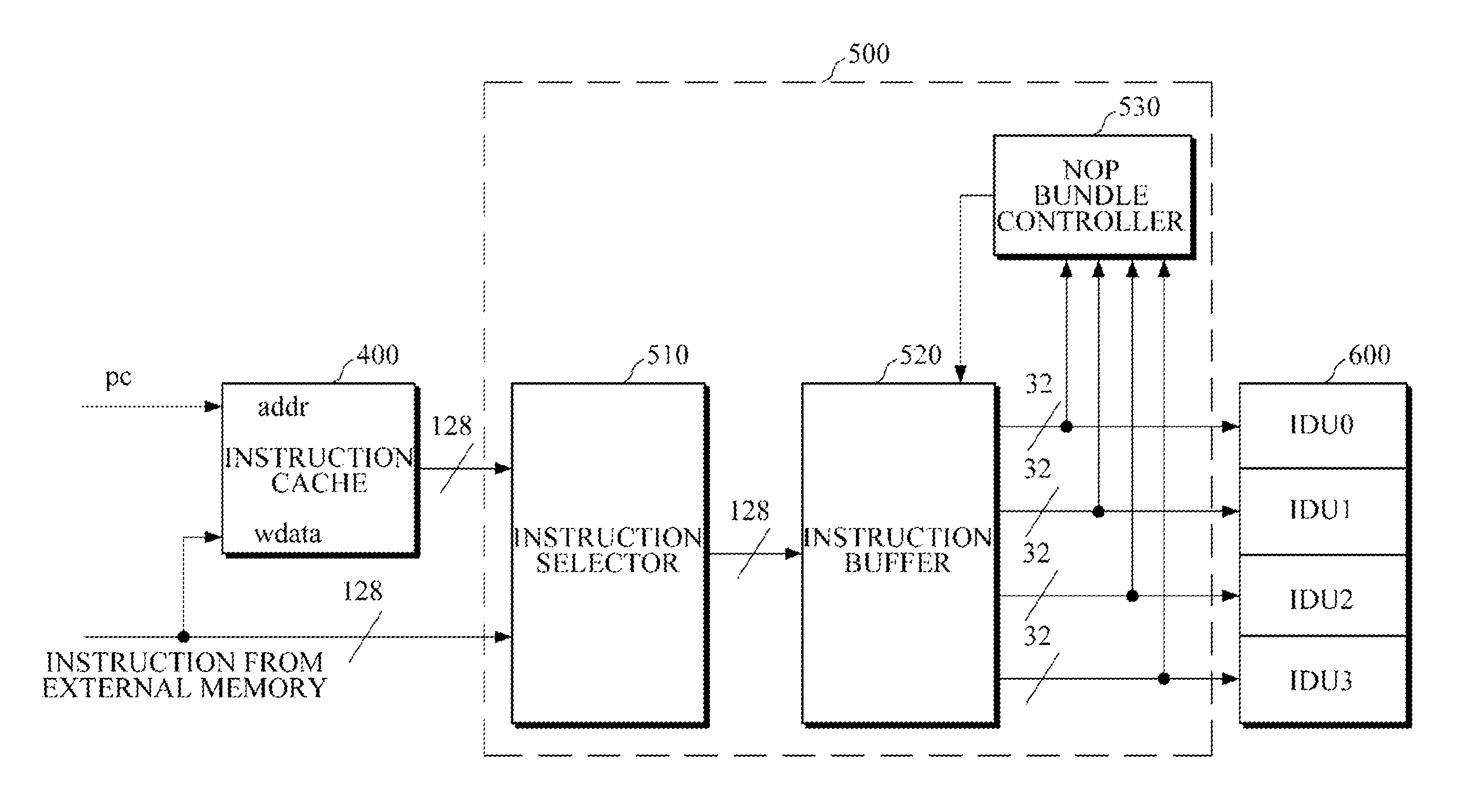

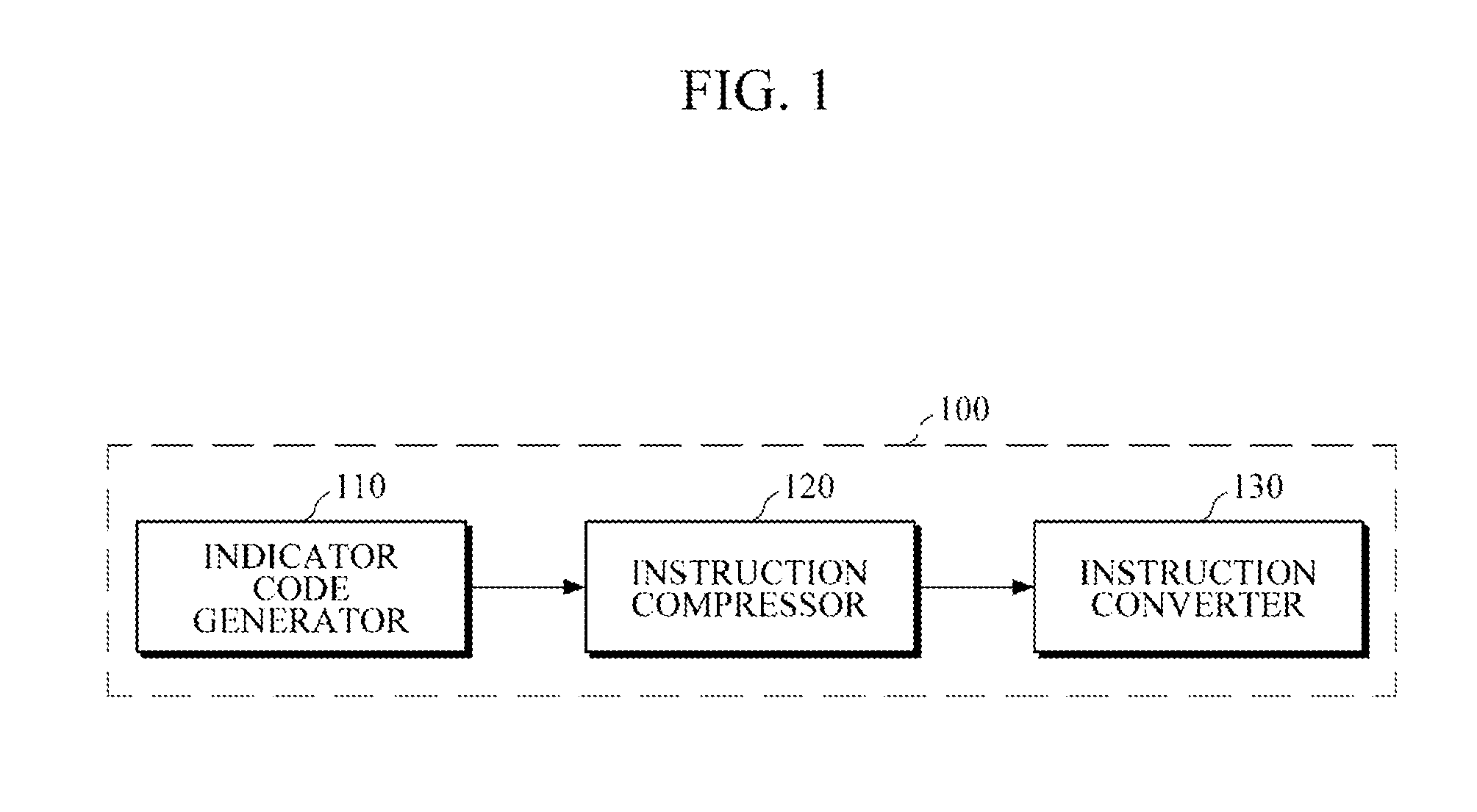

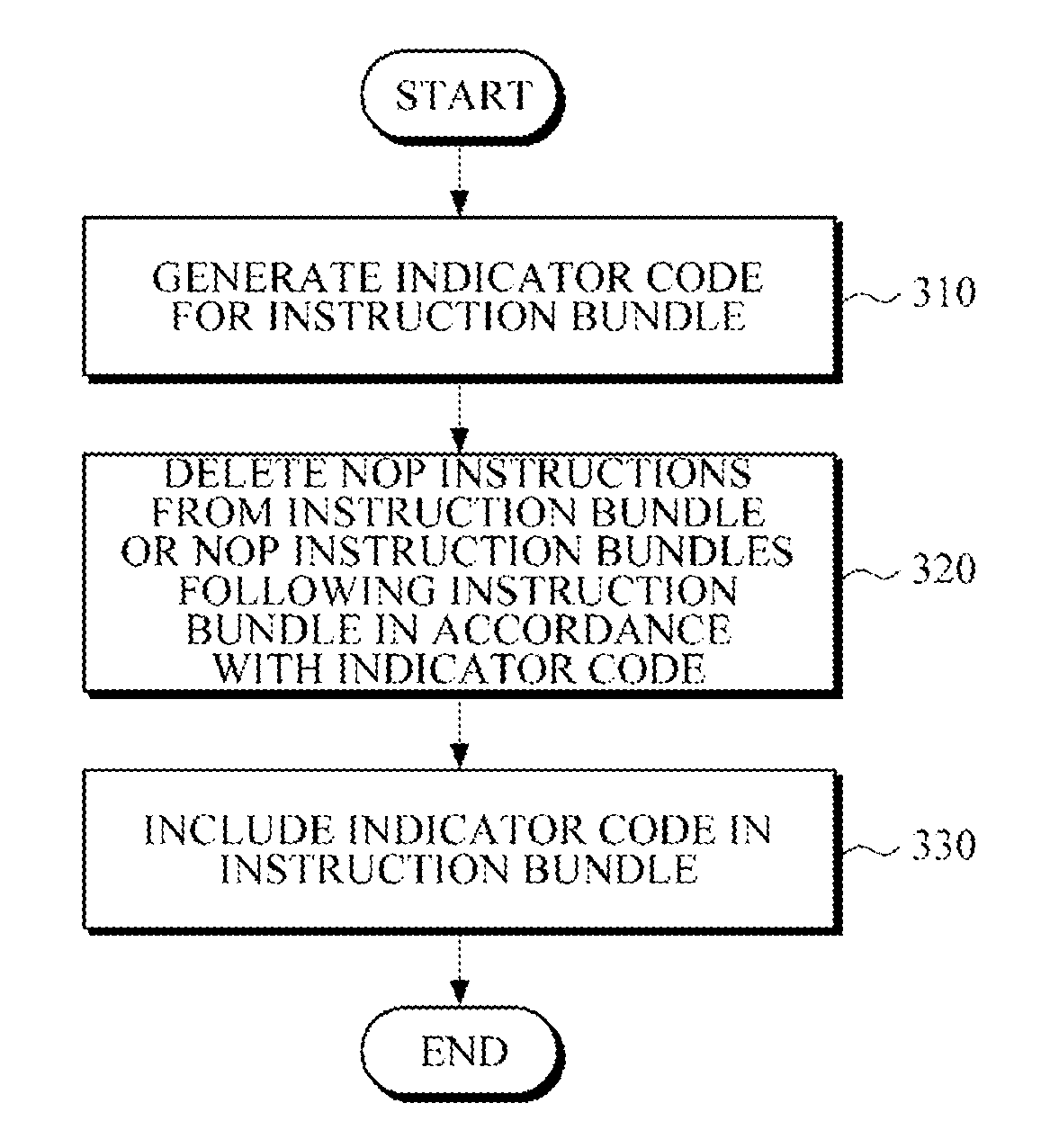

Apparatus and method for compressing instruction for vliw processor, and apparatus and method for fetching instruction

InactiveUS20140317383A1Digital computer detailsConcurrent instruction executionNOPVery long instruction word

Provided are an instruction compression apparatus and method for a very long instruction word (VLIW) processor, and an instruction fetching apparatus and method. The instruction compression apparatus includes: an indicator generator configured to generate an indicator code that indicates an issue width of an instruction bundle to be executed in the VLIW processor, and a number of No-Operation (NOP) instruction bundles following the instruction bundle; an instruction compressor configured to compress the instruction bundle by removing at least one of NOP instructions from the instruction bundle and the NOP instruction bundles following the instruction bundle; and an instruction converter configured to include the generated indicator code in the compressed instruction bundle.

Owner:SAMSUNG ELECTRONICS CO LTD

Apparatus and method for compressing instructions and a computer-readable storage media therefor

InactiveUS20130067207A1Reduce the amount requiredRuntime instruction translationDigital computer detailsParallel processingNOP

Provided is a technique that is capable of efficiently compressing instructions by inserting instruction compression bits into valid instruction bundles and deleting no operation (NOP) instruction bundles. Accordingly, the number of instructions that can be parallel-processed in a processor may be increased.

Owner:SAMSUNG ELECTRONICS CO LTD

Instruction set extension using operand bearing NOP instructions

Instruction set extension using operand bearing no-operation (NOP) or other instructions. In one embodiment, an apparatus can execute a first instruction with an operand associated with a second instruction. The apparatus includes a decoder to identify an operand associated with the second instruction as being designated for the first instruction. An execution unit executes an operation indicated by the first instruction to operate on the operand associated with the second instruction. The second instruction may occur before or after the first instruction in the program sequence.

Owner:INTEL CORP

Apparatus and method for compressing instruction for VLIW processor, and apparatus and method for fetching instruction

InactiveUS9804853B2General purpose stored program computerConcurrent instruction executionNOPVery long instruction word

Owner:SAMSUNG ELECTRONICS CO LTD

Linking code for an enhanced application binary interface (ABI) with decode time instruction optimization

A code sequence made up multiple instructions and specifying an offset from a base address is identified in an object file. The offset from the base address corresponds to an offset location in a memory configured for storing an address of a variable or data. The identified code sequence is configured to perform a memory reference function or a memory address computation function. It is determined that the offset location is within a specified distance of the base address and that a replacement of the identified code sequence with a replacement code sequence will not alter program semantics. The identified code sequence in the object file is replaced with the replacement code sequence that includes a no-operation (NOP) instruction or having fewer instructions than the identified code sequence. Linked executable code is generated based on the object file and the linked executable code is emitted.

Owner:IBM CORP

Maintaining original per-block number of instructions by inserting NOPs among compressed instructions in compressed block of length compressed by predetermined ratio

The present invention discloses a method for compressing instruction codes. This method comprises: compressing an instruction block including a plurality of instructions according to Huffman-Encoding technique; determining whether it's necessary to insert no-operation (nop) instructions among the plurality of compressed instructions according to a compression ratio, so as to generate a plurality of new instruction blocks complying with the compression ratio; if it's necessary to insert nop instructions, inserting nop instructions among the plurality of compressed instructions to form the plurality of new instruction blocks; and repeating the above-mentioned steps until no nop instructions have to be inserted.

Owner:REALTEK SEMICON CORP

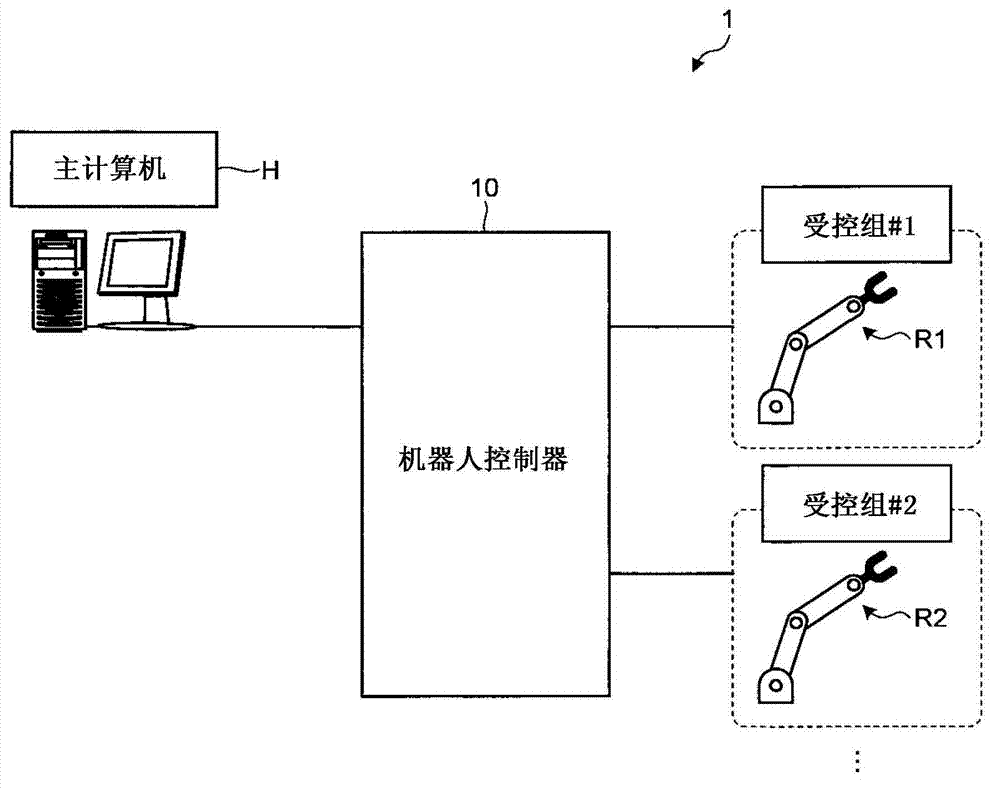

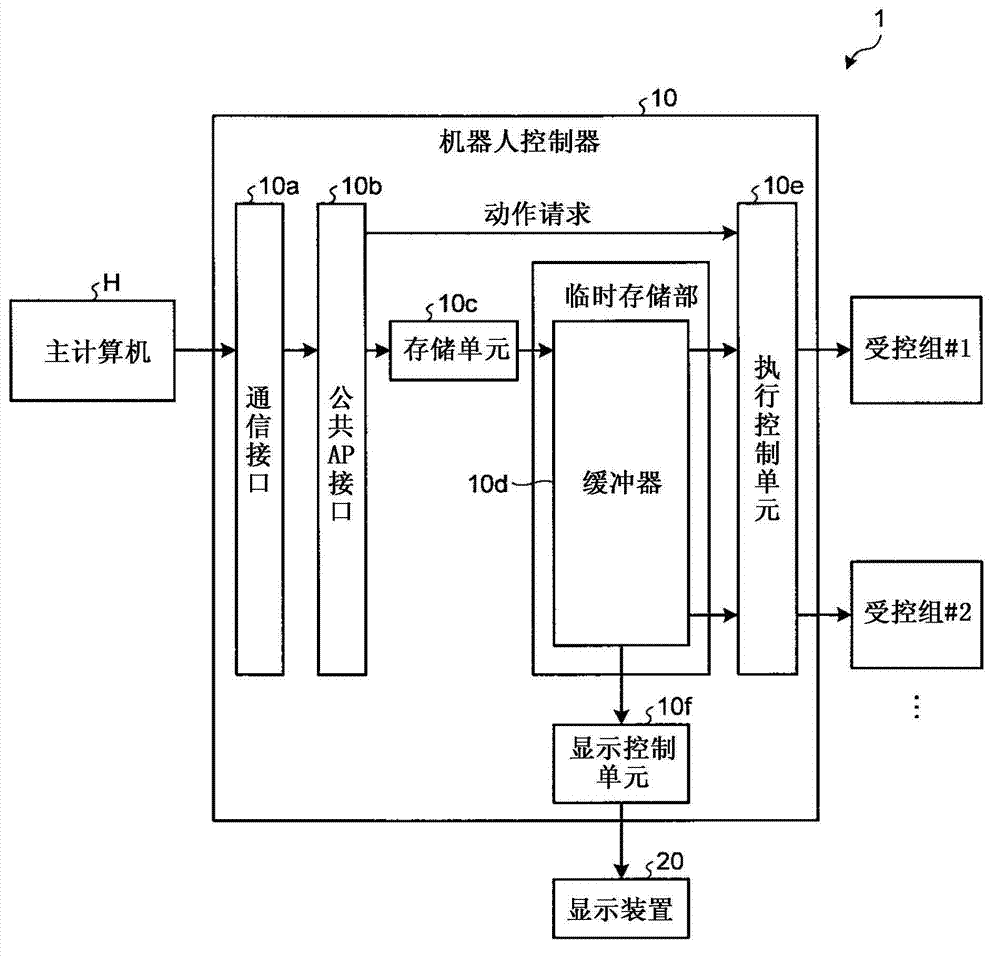

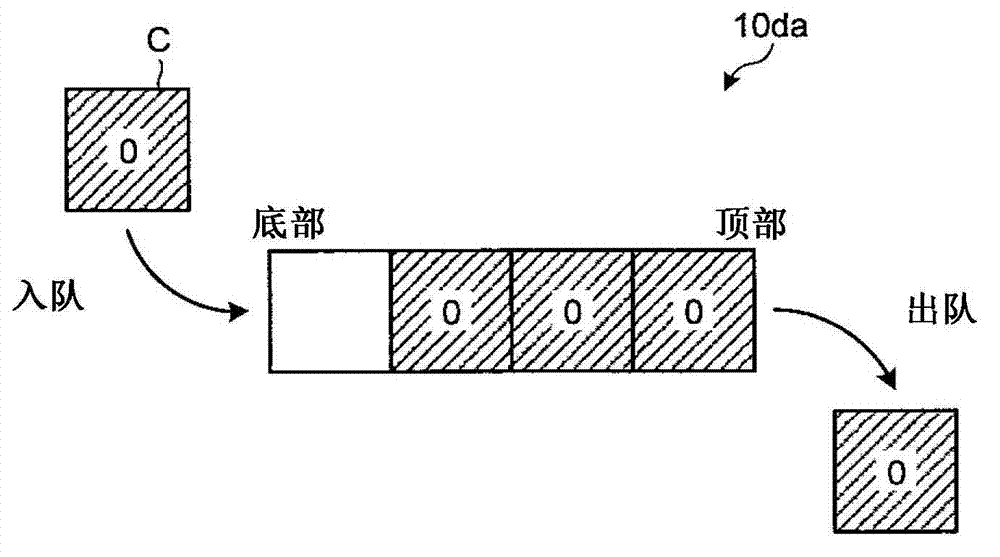

Robot controller and robot system

InactiveCN103770122APrecisely synchronized movementsProgramme-controlled manipulatorSamplingRobotic systemsExecution control

The invention relates to a robot controller and a robot system. The robot controller includes queues, a storage unit, and an execution control unit. The queues are provided for respective controlled groups serving as controlled units. The storage unit stores therein instructions directed to the respective controlled groups, one at a time, from a bottom end of each of the queues. When having accepted a predetermined operation request, the execution control unit simultaneously fetches the instructions directed to the controlled groups, one for each of the controlled groups at a time, from tops of the queues, and makes all of the controlled groups simultaneously start the operations based on such instructions. If there is any controlled group to which no corresponding instruction exists, the storage unit stores therein a no-operation instruction (NOP). If the fetched instruction is the no-operation instruction (NOP), the execution control unit keeps the controlled group from operating until an instruction is fetched next time.

Owner:YASKAWA DENKI KK

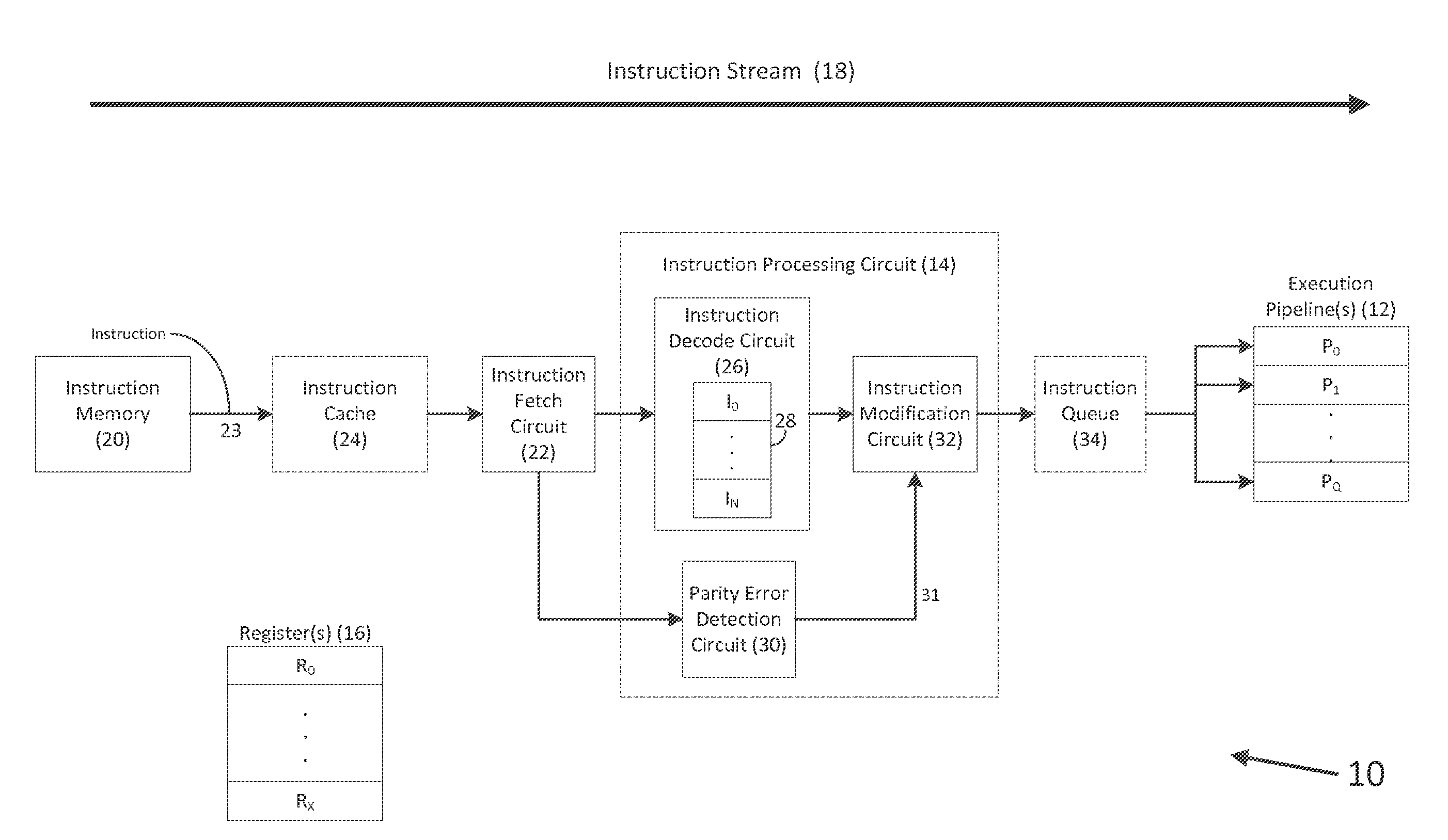

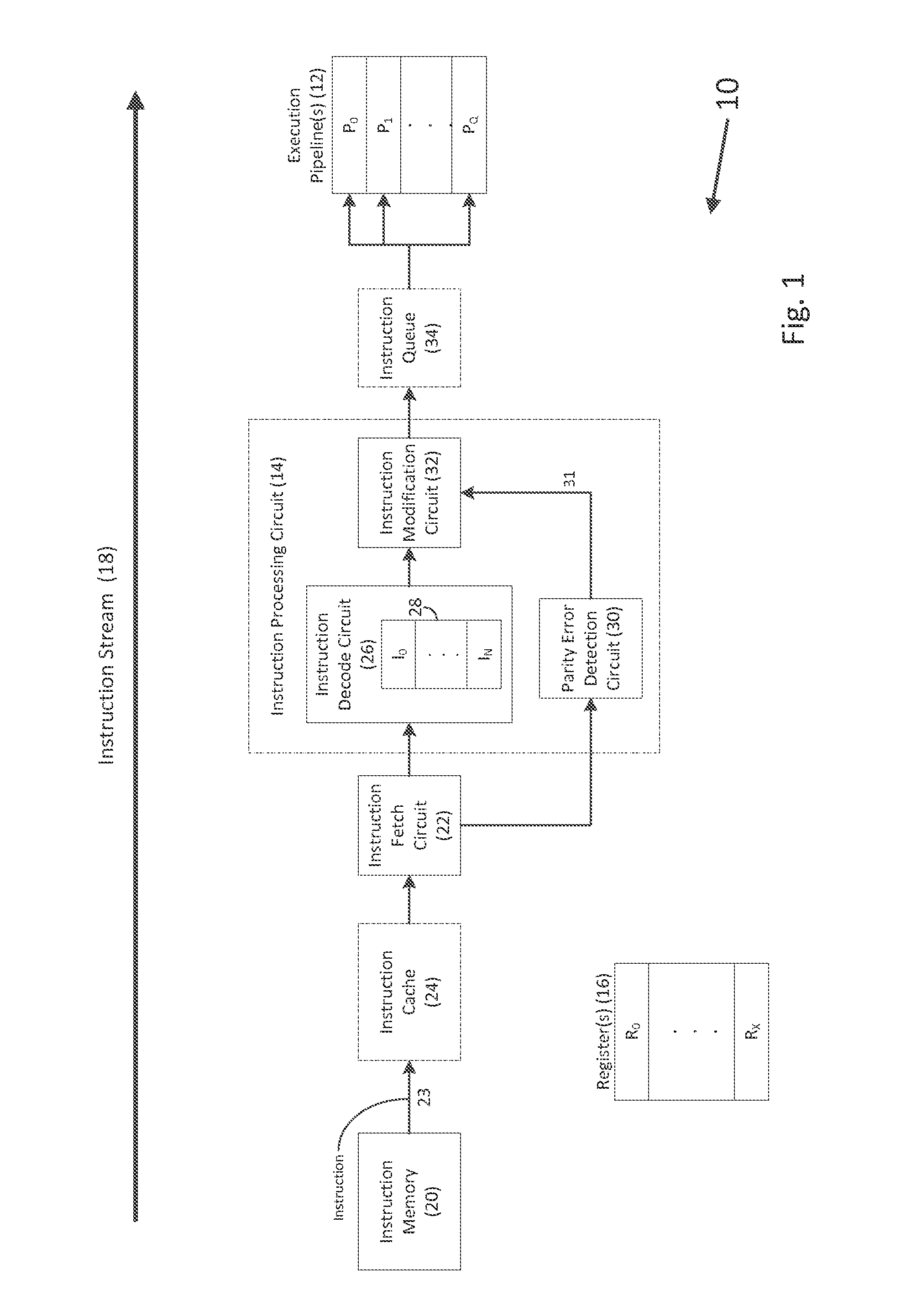

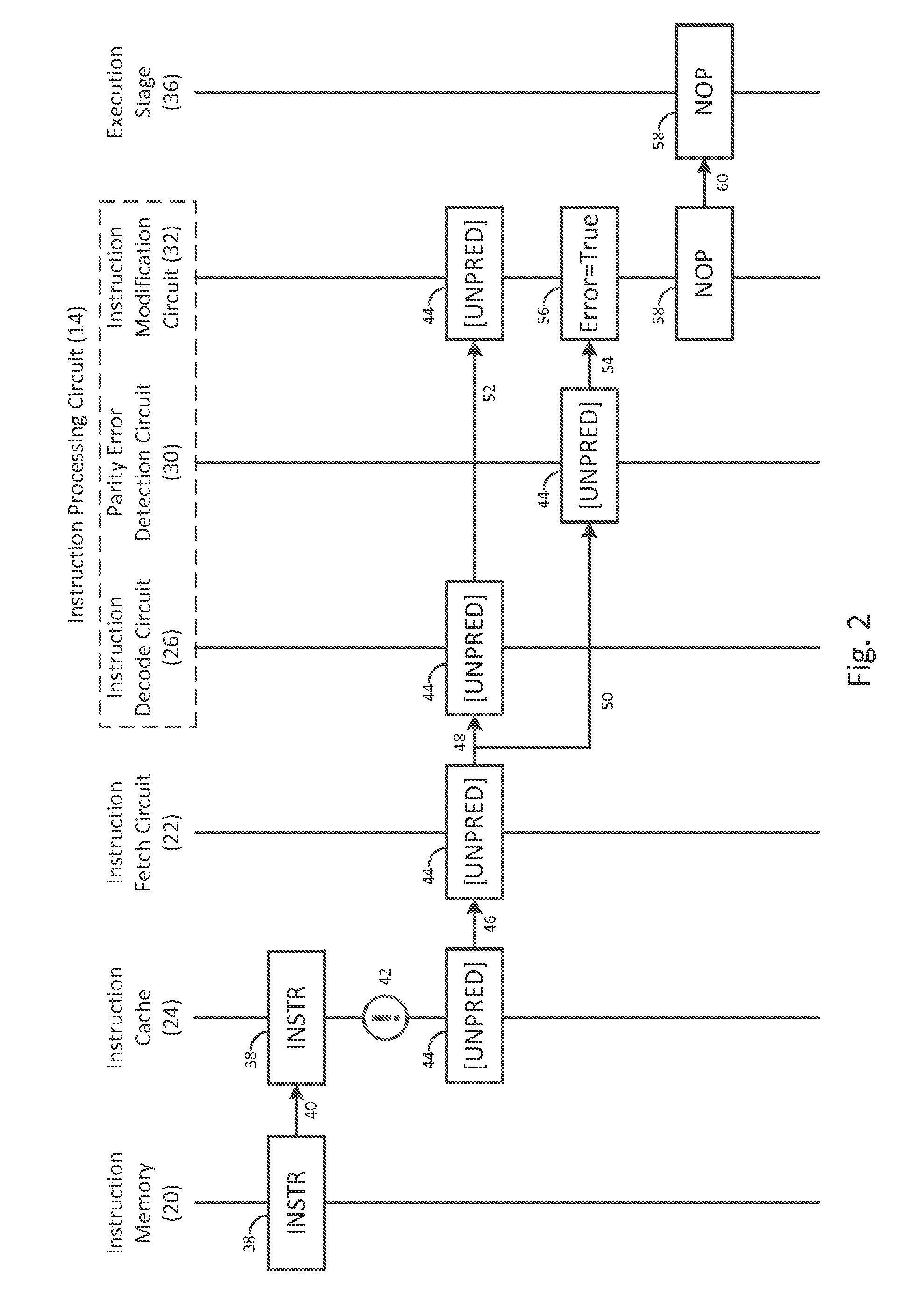

Preventing execution of parity-error-induced unpredictable instructions, and related processor systems, methods, and computer-readable media

InactiveUS20130326195A1Preventing executionReduce the possibilityError detection/correctionInstruction analysisProcessing InstructionParallel computing

Preventing execution of parity-error-induced unpredictable instructions, and related processor systems, methods, and computer-readable media are disclosed. In this regard, a method for processing instructions in a central processing unit (CPU) is provided. The method comprises decoding an instruction comprising a plurality of bits, and generating a parity error indicator indicating whether a parity error exists in the plurality of bits prior to execution of the instruction. If the parity error indicator indicates that the parity error exists in the plurality of bits, one or more of the plurality of bits are modified to indicate a no execution operation (NOP), without effecting a roll back of a program counter of the CPU and without re-decoding the instruction. In this manner, the possibility of the parity error causing an inadvertent execution of an unpredictable instruction is reduced.

Owner:QUALCOMM INC